## Development of edge-emitting Si/SiGe based optical sources operating in the visible and near visible range wavelength for sensing and communication applications

Kingsley Ogudo

### ► To cite this version:

Kingsley Ogudo. Development of edge-emitting Si/SiGe based optical sources operating in the visible and near visible range wavelength for sensing and communication applications. Optics / Photonic. Université Paris-Est, 2018. English. NNT: 2018PESC1060. tel-01935507

## HAL Id: tel-01935507 https://theses.hal.science/tel-01935507

Submitted on 26 Nov 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ PARIS-EST

École Doctorale MSTIC Mathématiques, Sciences et Technologies de l'Information et de la Communication

### Ph.D. THESIS

In order to obtain the title of Doctor of Science Specialty: Electronics, optoelectronics and systems

Defended on June 26th, 2018

Kingsley Aisaboluokpea OGUDO

# Development of edge-emitting Si/SiGe based optical sources operating in the visible and near visible range wavelength for sensing and communication applications

Final Version September 15, 2018

### JURY:

| Reviewers:                                      |                                     |

|-------------------------------------------------|-------------------------------------|

| Laurent Vivien, Directeur de recherche          | C2N, Orsay (France)                 |

| Hongwu Li, Professeur des Universités           | IETR, Université de Nantes (France) |

| Thesis Director:                                |                                     |

| Anne-Laure BILLABERT, Maitre de conférences HdR | ESYCOM-Le Cnam (France)             |

| Advisors:                                       |                                     |

| Jean-Luc POLLEUX, Professeur Associé            | ESYCOM-ESIEE (France)               |

| Lukas SNYMAN, Professor                         | UNISA (South Africa)                |

| Examiners:                                      |                                     |

| Mihai Lazar, Chargé de Recherche                | AMPERE, Centrale/INSA Lyon (France) |

| Elodie Richalot, Professeur des Universités     | ESYCOM, UPEM (France)               |

### ABSTRACT

We propose a low cost full-silicon optical links utilizing 650 – 850 nm propagation wavelengths. The creation of large-scale opto-electronic integrated circuits and optical data "highways" in CMOS integrated circuitry, utilizing Si CMOS compounds, have been envisioned and hold much promise [1] - [3] The latest attempts for realizing optoelectronic systems in CMOS technology have until now mainly been focused on utilizing wavelengths at 1550 nm [4] - [6], mainly because of the ease of design and fabrication of waveguides in this wavelength regime.

However, no effective high-speed optical sources and Si detectors are available at this 1550nm wavelength. Today solutions to overcome the problem are mostly focused on the integration of group III-V elements based optical sources on Silicon through molecular bonding [7a] – [7b]. If optical sources, detectors, waveguides, and sensors could be realized on the same Si CMOS chip at, say, 750 nm wavelength, various low power consuming, light and miniature on-chip-based micro-photonic systems could be designed and realized. While Silicon optical sources may not yet be at the required performance level for very-high speed communications, the low cost "all-silicon" opto-electronic systems still remain a great grail. These sources could lead to new field that could be appropriately named "Si photonic microsystems" opening the route to on-chip optical interconnect, new sensing applications and products especially for the medical, biomedical optics, optical interconnect and bio-photonics field. These systems also do not require ultrahigh frequency bandwidths to transmit, and the emission powers of our avalanche Si light-emitting diodes (LEDs) may be sufficient to sustain the operation of such systems.

This PhD thus deals with low cost SiGe/Si optical links using Microwave-Photonics devices such as, Bipolar integrated SiAvLED, Silicon Nitride and Silicon Oxide optical waveguides, SiGe HPTs, Si and SiGe/Si LEDs. It focuses on the development of edge emitting Si Av LED and Si/SiGe LED with the intention to combine and integration of micron-scale optical sources, optical waveguides and SiGe HPT detectors on the same chip to form a complete communication link for various applications involving short wavelength links (750nm to 950nm).

The progress provided by this PhD to previous works could be synthesized as below:

- Development of edge-emitting Si/SiGe based optical sources operating in the visible and near visible range wavelength

- Design and development of silicon nitride based optical waveguides operation in the sivible range wavelength

- The integration of Si/SiGe Optical source, silicon nitride based waveguide and the Si/SiGe HPT based detector were all integrated and aligned on the same silicon chip, in an industrial based technology, to form complete on-chip micro-optical links at 750nm wavelength, with a SiGe radio frequency (RF) 0.35µm bipolar process.

- The optical source and waveguide alignment, through localising the LED emitting region leading to full links structures

- Full silicon optical links designed: The experimental validation and characterisation of the link structures both in DC bais analysis and RF analysis

- Waveguide functionality realized using R-Soft simulation software suit. Good height alignment while using un-intended available layers, leading to optical coupling from the source through the designed optical waveguide to the detector.

- A series of second generation of on-chip optical communication links of 50µm length, utilizing 650 – 850 nm propagation wavelengths, have been designed and realized in SiGe bi-polar technology process. Micron dimensioned optical sources, waveguides and detectors were all integrated on the same chip to form a complete communication on-chip micro-optical links. Avalanche based Si LEDs (Si Av LEDs), Schottky contacting Si Av LED and Si/SiGe LED, TEOS densification strategies, Silicon-Nitride based waveguides, and state of the art SiGe bipolar detector technologies were used as key design strategies.

- R-soft simulation software (Beam Prop) was used as a mathematical capable simulation tool to model various Silicon-Nitride optical waveguide structures, before the designing, the fabrication, characterisation and testing of the device. Various device structures were modeled, simulation iterations were performed on several optical waveguide designed structures before the device design, and the devices were tested experimentally.

- ADS simulation was used to simulate the two-port equivalent circuit network of the device links for the analysis of RF parasitic capacitance, as a result of substrate and oxide RF coupling (high and low pass kind of filters)

- The fabrication of edge emission Si/SiGe LEDs. It has been fabricated using the 80 GHz SiGe2RF Telefunken GmbH SiGe Bipolar technological processes, which is crucial to be implemented for ultra-low-cost silicon, based IMWP systems. One key aspect of this research is to implement a Si Av LEDs in such a commercial technology without the addition of masks and processing steps. We modify the design layout geometries for different bias configurations in order to obtain different efficient emission point in the source structure. This approach ensures a straight compatibility with SiGe circuits on the same chip, and makes the Si and SiGe Avalanche LEDs directly integrated into an

industrial foundry. The Telefunken SiGe2-RF Bipolar Silicon Germanium process technology exhibits fT up to 80GHz and fmax up to 90GHz. This makes this technology able to provide circuits working above 10GHz and potentially up to 60 GHz in some configurations. This RF bipolar technology allows the production of wafers with applications in high-speed cellular, devices used in high performance standard RF in various applications. As in the SiGe1RF technology of Telefunken used to create the LEDs sources and the SiGe detector, the Germanium content is high with values in the range of 20-25% and might be almost vertical pillars column block structure with the base. This process is a 0.8µm lithography double polysilicon heterojunction bipolar technology. The minimum emitter size on the layout is of 0.8x1.4µm2 for vertical NPN HBT transistors, which provides actual size after processing of  $0.5 \times 1.1 \mu m^2$  due to lateral spacers. This technology leads to two LEDs types: one with a selectively implanted collector (SIC) NPN LEDs and the other one without. The difference between them is the additional mask required by the SIC-transistor, influencing the high frequency performances and static characteristics. This option allows transition frequency (fT) to reach the 80GHz value for SIC transistors, against only 50GHz for non-SIC transistor, with fmax of up to 90GHz in both cases. This process technology also offers PNP transistors, diodes (PN, Zener, ESD, Varactor and Schottky) and passive devices such as inductors capacitors and resistors. In the frame of our relation with Telefunken, a Non-Disclosure Agreement (NDA) has been signed and no information about the detailed process cross-section can be given.

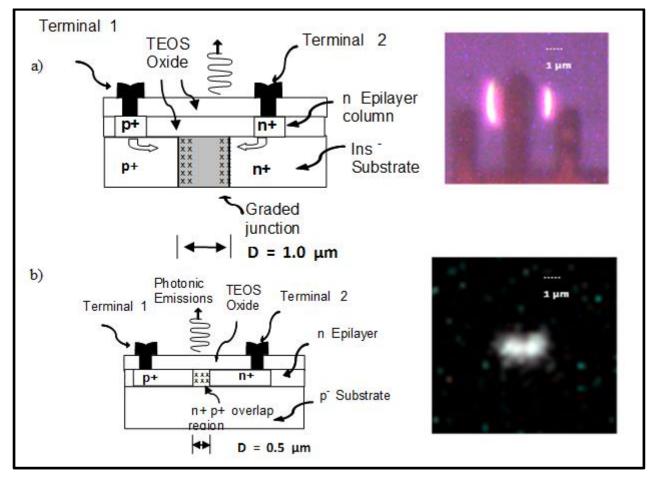

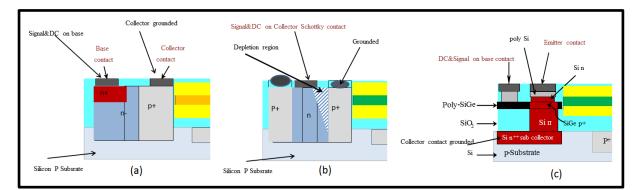

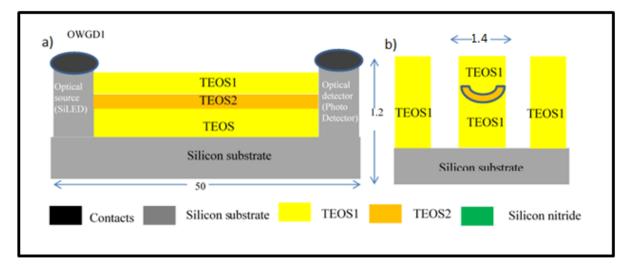

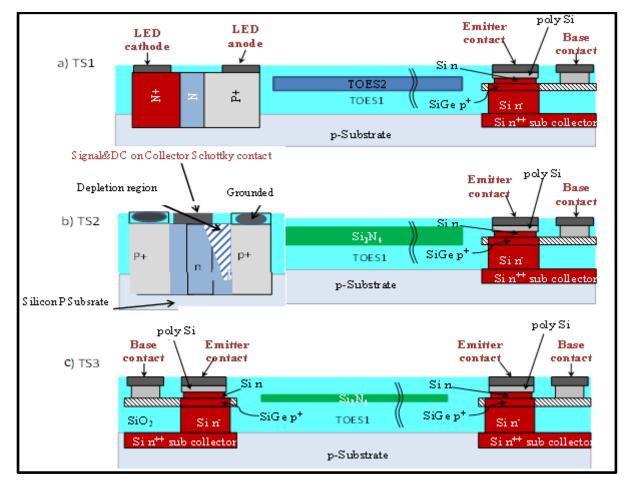

The fabrication of Edge emitting LED topologies: The descriptions of the optical source LEDs structures, three different optical source structures were designed utilizing the 0.35micron RF bipolar technology, each with different configuration source structures, different waveguide structures, but with the same basic SiGe detector structure in the optical links. The optical source was designed with an n+-n p+ columnar structure located laterally on the P-type silicon substrate of very high resistivity. The regions between the elevated source and detector structures were filled with plasma deposited oxide. The columnar structures were all of micron dimension, such that the structures were composed of 1µm cube substructures. The regions were doped accordingly as made available by the process. The regions were appropriately electrically contacted during experimental measurements on the fabricated device on the wafer in order to reverse bias the first p+ n junction. Upon reverse biasing, the depletion region penetrates through to the n+ region in order to strengthen and unify the electric field in the lowly doped n region. The light emission would occur near the surface region of the middle n region and extend more or

less laterally across the whole region. The region between the Si Av LED source and SiGe detector were filled with normal TEOS plasma deposited oxide as part of the available process procedure. The middle layer was subsequently interfaced laterally to the optical light emission region, and the waveguide implemented here was (OWGD1). Appropriate air slots were made on the sides of the waveguide in order to minimise laterally induced oxide parasitic capacitance.

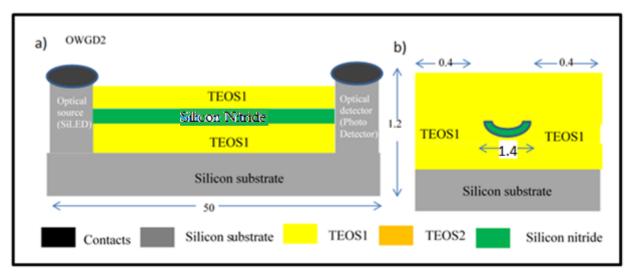

- In the second test structure of the LEDs source was designed in the same basic lateral columnar structure for the optical source as in the first design, but strategic design of a rectangular Schottky configuration contact of Aluminum on n-Silicon is fabricated in the columnar structure middle lowly doped n region on the optical source. The two p+ columnar regions were grounded as required by the RF probe bias during measurement process, and the DC and modulation RF signal was applied on the Schottky contact. Positive voltage bias placed the Schottky contact in forward bias mode and caused a triangular depletion region towards the p+ region of the LED optical source, thereby reverse biasing the p+ n region. This configuration drastically reduces the total depletion region volume and hence reduces depletion layer capacitance. The elongated and uniform electric field region and its associated minimized capacitance would hence enable ultrahigh modulation frequencies. Since small dimensions in µm were used and the light emission processes are impact ionization and avalanche related aid.

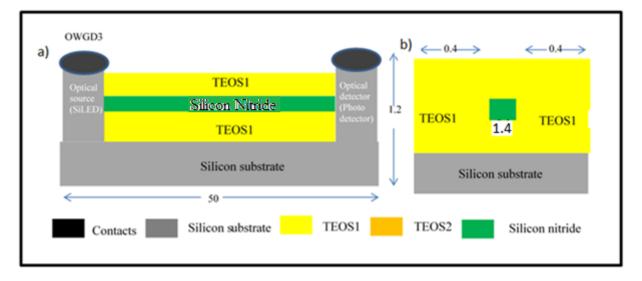

- In a third design, a vertical cubical columnar HPT structure was designed to function as an optical source. The emitter-base n+ (SiGe) which contained 20% of Germanium was placed in reverse bias and in the avalanche regime. The emitter/base terminals were shorted in order to initially simplify the operation of the optical source device to function as an optical emission source, and bias is placed on the bottom contact of collector region. Because of layout and process design and processing limitations, the emitter n+ region is grounded. The SiGe detector structure of this nature has a transition frequency of up to 80GHz, it was assumed that when it was utilized as optical source by reverse biasing base-collector junction in avalanche reverse bias mode, the structure could attain similar operational frequency with optical emissions following this modulation frequency.

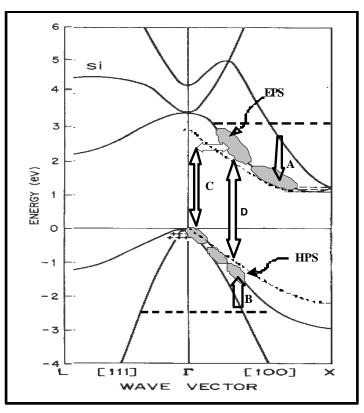

- On the same third design configuration, the optical source was operated in a forward bias configuration during experimental measurements, such that emitter n+ p (SiGe) junction is in forward bias mode. In this configuration, the emitter n+ p (SiGe) region is grounded and negative voltage bias of 2V is applied to the p+ SiGe base region. Electrons were injected from the n collector region and the carriers were energized through conduction transfer

through the low doped n region of the collector. When these carriers are injected in the SiGe base region, they would contain enough energy in order to then transfer electrons from the L valley to the T band structure valley of SiGe. With 20% Germanium doping, the emitted wavelength for this design is expected to be below 1000nm emission wavelength. The very small columnar conduction regions, used in the optical sources in this configuration, would reduce depletion layer capacitance and the subsequent carrier's transit time in the device.

- The work of this PhD is supported by substantial progress that has been made in the field of Si p-n junctions emitting visible light diode when operated in reverse breakdown avalanche mode [15] - [21]. Recently, Si CMOS light emitting sources appeared with much higher efficiencies by implementing two and three junctions Si CMOS injection avalanche LEDs that emit in the spectrum range of 450 to 750 nm [22] - [23]. They can be integrated with ease in standard CMOS circuits. Various prototypes have been realized. Their operating voltage (8V), and current (80  $\mu$ A to 1 mA) are low. They emit from an area of  $1 \times 1 \ \mu\text{m}^2$  between 10 and 100 nW. The internal light emission levels are much higher by a factor of 0.3. Particularly promising technology, which uses defect and surfaceassisted transitions in these types of LEDs, has recently been identified and developed by our group [24] - [26]. Our Si avalanche-based LEDs operate optimally at 650 to 850 nm, and although the optical emission power of Si avalanche- LEDs is still low, about 90nW, they can reach modulation speeds into the GHz range. Since Si LEDs and Si detectors are both available, and can be integrated with relative ease into the proposed SiGe/Si technology, the most challenging part of following this route to realize on-chip micro optical link at 750nm with silicon is, hence, to develop appropriate optical waveguide technology in this 450-850nm wavelength regime that can be integrated into Si CMOS integrated circuitry.

- In this context, the important objectives of this study concern the development of edge emitting Si Av LED & Si/SiGe LED and the understanding of physical integration of Si LEDs and SiGe LEDs, optical waveguide. In addition, to be Bi/CMOS compatible optical detector and the proposal of integrating all on the same silicon chip to form a complete onchip optical links at 750nm for optical intra/interconnect and the characterization of the design on-chip optical links.

- Developing full Silicon on-chip optical links in the near visible at 450nm-850nm. Exploring industrial SiGe/Si foundries Compatibility with further circuit integration (bipolar, BiCMOS), with high speed capabilities Low cost technology. Source and

waveguide alignment compatibility. Finally, on-chip microwave photonics links have been fabricated and characterized using a SiGe Bipolar technology process.

- The purpose of this research was, then, (1), to design, develop edge emitting Si Av LED, Si/SiGe LED design optical waveguides, detailed simulations of the viability of the waveguides for realization of micro-photonic structures in 1.2µm and 0.35µm for optical link in SiGe/Si integrated circuitry at mainly 750nm operating wavelengths were conducted; (2) to demonstrate the possible performance of the design waveguides at 750nm; (3) to demonstrate and realize second iteration optical link in SiGe/Si integrated circuitry at 750 nm experimentally; and (4) The design, fabrication and characterization of the first on-chip microwave photonic links at near-visible wavelength ( $0.65-0.85\mu m$ ). All those structures are fabricated into an 80 GHz Telefunken GmbH SiGe/Si HBT technological processes. The full optical link combines Silicon, SiGe based Avalanche Light Emitting Devices (Si Av LEDs), Silicon-Nitride based, and silicon oxide (TEOS) based waveguides, and SiGe Heterojunction Bipolar Photo-Transistors (HPT). Such device could permit hosting microfluidic systems, on chip data communication and bio-chemical analysis applications and to propose potential applications for some first iteration Bipolar or CMOS based micro-photonic systems and micro-opto- electro-mechanical systems (MOEMS) and (MEMS).

- Best performances of the designed on-chip optical links show a conversion loss as low as 30dB from source to detector with up to 500MHz in cut off frequency. The good alignment and the good efficiency of each device are then clearly achieved. Higher frequency performances are also envisaged from preliminary measurements.

- Compared to international contributions, the work has been accepted for publication in the proceedings of three international conferences. From this work, three journals articles were published in a state-of-the-art ISI accredited scientific journals (JM3-SPIE) and (IEEE JQE) in the USA. A further article is currently submitted to IEEE Journal of Material Engineering (JME). One patent was granted on this work in Korea, after extensive provisional and International Protocol Collaboration Treaty (PCT) patenting.

## RÉSUMÉ

#### Résumé en français :

Nous proposons une étude des liaisons optiques en technologie intégralement silicium à faible coût pour des longueurs d'onde de transmission définies dans la plage 650 à 850 nm. La création de circuits intégrés optoélectroniques à grande échelle et de voies de données optiques dans les circuits intégrés CMOS, utilisant des composés CMOS, a été envisagée et semble prometteuse [1] - [3]. Les derniers efforts pour réaliser des systèmes optoélectroniques en CMOS ont focalisé sur l'utilisation des longueurs d'onde à 1550 nm [4] - [6], principalement en raison de

la facilité de conception et de fabrication de guides d'ondes dans cette gamme de longueurs d'onde.

Cependant, aucune source optique efficace à grande vitesse et aucun détecteur en Silicium ne sont disponibles à cette longueur d'onde de 1550 nm. Aujourd'hui, les solutions pour surmonter le problème sont principalement axées sur l'intégration de sources optiques basées sur des éléments réalisés en semi-conducteur III-V, sur le silicium par liaison moléculaire [7a] - [7b]. Si des sources optiques, des détecteurs, des guides d'ondes et des capteurs pouvaient être réalisés sur la même puce Si CMOS à une longueur d'onde de 750 nm, divers systèmes micro-photoniques légers et miniaturisés basés sur puce pourraient alors être conçus et réalisés. Tandis que les sources optiques au silicium ne sont peut-être pas encore au niveau des performances requises pour les communications à très haut débit, les systèmes optoélectroniques "tout-silicium" à faible coût restent malgré tout un excellent point de départ d'étude. Ces sources pourraient déboucher sur un nouveau domaine qui pourrait s'appeler «microsystèmes photoniques Si» ouvrant la voie à l'interconnexion optique sur puce, nouvelles applications et produits de détection notamment pour l'optique médicale, biomédicale, optique et bio-photonique. Ces systèmes ne nécessitent pas non plus de bande passante à très haute fréquences pour émettre, et les puissances d'émission de nos diodes électroluminescentes (DEL) à avalanche peuvent être suffisantes pour assurer le fonctionnement de tels systèmes.

Ce doctorat traite donc des liaisons optiques SiGe/Si à faible coût en utilisant des dispositifs photoniques-microondes tels que les DEL à avalanche en silicium intégrées bipolaires, les guides d'ondes optiques en Nitrure de silicium et Oxyde de silicium, les phototransistors à hétérojonction SiGe, et les DELs en Si et SiGe/Si. Nous nous sommes concentrés sur le développement de DELs à avalanche en Silicium, et DEL Si / SiGe à émission par la tranche avec l'intention de combiner et d'intégrer des sources optiques de taille micrométriques, des guides d'ondes optiques et des

détecteurs phototransistor à hétérojonction en SiGe sur la même puce pour former une liaison de communication complète pour diverses applications impliquant des liaisons à courtes longueurs d'onde de l'ordre de 750 nm à 950 nm.

La valeur ajoutée apportée par les travaux issus de ce doctorat par rapport aux travaux antérieurs fournis par l'équipe peut être synthétisée comme suit:

- Développement de sources optiques en Si/SiGe à émission par la tranche et fonctionnant dans la gamme de longueur d'ondes du visible et du proche visible.

- Conception et développement d'un guide d'ondes optique à base de nitrure de silicium opérant dans la gamme d'ondes visible.

- L'intégration de source optique Si/SiGe, d'un guide d'ondes à base de nitrure de silicium et d'un détecteur de type phototransistor Si/SiGe ont été intégrées et alignées sur la même puce de silicium, dans une technologie industrielle, pour former une liaison photoniquemicrooondes complète sur puce à la longueur d'onde de 750nm, en utilisant la technologie bipolaire SiGe 0.35 µm pour les fréquences microondes.

- L'alignement de la source optique et du guide d'ondes, grâce à la localisation de la région émettrice de DEL conduit à des structures d'une liaison complète.

- La conception de liaisons optiques tout silicium: la validation expérimentale par la caractérisation des structures des liaisons en analyse DC continue et analyse dynamique RF.

- La réalisation de la fonctionnalité de guide d'ondes à l'aide du logiciel de simulation R-Soft. Un bon alignement de la hauteur, tout en utilisant des couches disponibles non prévues, ont conduit à un bon couplage optique de la source à travers le guide d'onde optique conçu initialement pour le détecteur.

- Une série de liaisons de communication optique sur puce de deuxième génération d'une longueur de 50 µm, utilisant des longueurs d'onde de propagation de 650 à 850 nm, a été conçue et réalisée en technologie bipolaire SiGe. Des sources optiques, des guides d'ondes et des détecteurs de dimensions microniques ont tous été intégrés sur la même puce pour former une communication complète sur les liaisons micro-optique. Les DELs à avalanche en Silicium (Si Av), une DEL à avalanche en Silicium à contact Schottky et des DELs Si/SiGe, les stratégies de densification TEOS, des guides d'ondes à base de nitrure de silicium et les détecteurs en technologie bipolaire SiGe ont été utilisés comme stratégies de conception clés.

Le logiciel de simulation R-soft (Beam Prop) a été utilisé comme outil de simulation mathématique pour modéliser différentes structures de guides d'ondes optiques nitrure de silicium, et a été une aide à la conception, et ce avant la fabrication, la caractérisation et le test du dispositif. Différentes structures de dispositifs ont été modélisées, des itérations de simulation ont été réalisées sur plusieurs structures de guides d'ondes optiques avant la réalisation du dispositif, et les dispositifs ont été testés expérimentalement.

- La simulation ADS a été utilisée pour simuler le réseau de circuits équivalents à deux ports des connexions des dispositifs et plus particulièrement pour l'analyse de la capacité parasite RF dû au couplage RF du substrat et de l'oxyde (filtres passe-haut et passe-bas).

- La fabrication de DEL Si / SiGe à émission par la tranche a utilisé les processus technologiques SiGe2RF Telefunken GmbH SiGe Bipolar à 80 GHz, ce qui est crucial pour les systèmes photoniques microondes intégrés à base de silicium à très bas coût. Un aspect clé de cette recherche est de mettre en œuvre une DEL à avalanche en Silicium dans une telle technologie industrielle sans l'ajout de masques et d'étapes de traitement. Nous avons donc seulement modifié les géométries de disposition de conception pour différentes configurations de polarisation afin d'obtenir différents points d'émission optique efficaces hors de la structure de la source optique. Cette approche assure une compatibilité directe avec les circuits SiGe sur la même puce, et fait que les DEL Si et Avalanche SiGe sont directement intégrées dans une fonderie industrielle. La technologie de procédé industrielle Germanium Bipolaire Silicium/Germanium de Telefunken présente des f<sub>T</sub> allant jusqu'à 80GHz et fmax jusqu'à 90GHz. Cela rend cette technologie capable de fournir des circuits fonctionnant au-dessus de 10 GHz et potentiellement jusqu'à 60 GHz dans certaines configurations. Cette technologie bipolaire RF est utilisée pour les applications dans les réseaux cellulaires à haut débit, dans les dispositifs hautes performances standards. Comme dans la technologie SiGe<sup>1</sup>RF de Telefunken utilisée pour créer les sources de DEL et le détecteur SiGe, la teneur en germanium est élevée avec des valeurs de l'ordre de 20-25% et pourrait être une structure de colonne quasi verticale vis-à-vis de la base. Ce procédé est une technologie bipolaire à hétérojonction à double polysilicium de  $0.8 \mu m$  de lithographie. La taille minimale de l'émetteur sur le réseau est de 0,8x1,4µm<sup>2</sup> pour les transistors HBN NPT verticaux, ce qui donne une taille réelle après le traitement de  $0.5x1.1\mu m^2$  en raison des espacements latéraux nécessaires. Cette technologie conduit à deux types de DEL : l'un avec des DELs NPN à collecteur sélectivement implanté (SIC) et l'autre sans. La différence entre eux est le masque supplémentaire requis par le transistor SIC, influençant les performances à hautes fréquences et les caractéristiques statiques. Cette option permet à la fréquence de transition ( $f_T$ ) d'atteindre la valeur de 80GHz

pour les transistors SIC, contre seulement 50GHz pour les transistors non-SIC, avec un  $f_{max}$  allant jusqu'à 90GHz dans les deux cas. Cette technologie de processus offre également des transistors PNP, des diodes (PN, Zener, ESD, Varactor et Schottky) et des dispositifs passifs tels que des condensateurs inductances et des résistances. Dans le cadre de notre relation avec Telefunken, un accord de non-divulgation (NDA) a été signé et aucune information sur la section transversale détaillée du processus ne peut être donnée dans ce manuscrit.

- Une étude a été menée sur la fabrication de différentes topologies de DEL à émission par la tranche : Les descriptions de trois structures de sources optiques DEL différentes ont été conçues en utilisant la technologie bipolaire RF 0,35 µm, chacune avec différentes structures de configuration de source, différentes structures de guides d'ondes, mais avec la même structure de base du détecteur SiGe. La source optique a été conçue avec une structure de type colonne n<sup>+</sup>-np <sup>+</sup> située latéralement sur le substrat de silicium de type P de très haute résistivité. Les régions entre les structures de source positionnée en hauteur et de détecteur ont été remplies d'oxyde déposé par plasma. Les structures de type colonne étaient toutes de dimension de l'ordre du micromètre, de sorte que les structures étaient composées de sous-structures cubiques de 1 µm. Les régions ont été dopées comme le procédé technologique le permettait. Les régions ont été polarisées électriquement de manière appropriée au cours de mesures expérimentales sur le dispositif fabriqué sur la plaquette afin de polariser en sens inverse la première jonction p<sup>+</sup> n. Lors d'une polarisation inverse, la région d'appauvrissement pénètre alors dans la région  $n^+$  afin de renforcer et d'unifier le champ électrique dans la région n faiblement dopée. L'émission de lumière se produit près de la région de surface de la région du milieu n et s'étend plus ou moins latéralement dans toute la région. La région entre la source de la DEL à avalanche en Silicium et le détecteur SiGe a été remplie d'oxyde déposé par plasma TEOS normal dans le cadre de la procédure de traitement disponible. La couche intermédiaire a ensuite été interfacée latéralement à la région d'émission de lumière optique, et le guide d'ondes mis en œuvre ici était celui nommé OWGD1. Des fentes d'air appropriées ont été réalisées sur les côtés du guide d'ondes afin de minimiser la capacité parasite d'oxyde induite latéralement.

- Dans la seconde structure de test de la source DEL, celle-ci a été conçue dans la même structure de type colonne latérale basique que pour la source optique de la première conception, mais la conception stratégique d'une configuration rectangulaire Schottky d'Aluminium sur n-Silicium est fabriquée dans la structure de type colonne peu dopée au milieu de la région n de la source

optique. Les deux régions p<sup>+</sup> de type colonne ont été polarisées à la masse comme c'est nécessaire pendant le processus de mesure à l'aide d'une pointe RF. Le signal DC et le signal RF de modulation ont été appliqués aux contacts Schottky. La polarisation par une tension positive du contact de Schottky induit un mode de polarisation directe et provoqu une région d'appauvrissement triangulaire vers la région p<sup>+</sup> de la source optique de DEL, polarisant ainsi en inverse la région p<sup>+</sup>n. Cette configuration réduit considérablement le volume total de la zone de déplétion et réduit ainsi la capacité de la couche de déplétion. La région de champ électrique allongée et uniforme et la minimisation de sa capacité associée doit permettre des fréquences de modulation ultra-élevées. Depuis, de petites dimensions micrométriques ont été utilisées et les processus d'émission de lumière sont l'ionisation par impact et le phénomène d'avalanches.

- Dans une troisième conception, une structure de phototransistor à hétérojonction verticale cylindrique a été conçue pour fonctionner comme une source optique. L'émetteur-base n<sup>+</sup> (SiGe) qui contient 20% de Germanium a été placé en polarisation inverse et dans le régime d'avalanche. Les bornes d'émetteur/base ont été court-circuitées afin de simplifier initialement le fonctionnement du dispositif source optique pour fonctionner en tant que source d'émission optique, et une polarisation est placée sur le contact inférieur de la région de collecteur. En raison de la conception et du procédé et des limitations de traitement, la région de l'émetteur n<sup>+</sup> est mise à la masse. La structure de détecteur SiGe de cette nature a une fréquence de transition allant jusqu'à 80GHz, on a supposé que lorsqu'elle était utilisée comme source optique par polarisation inverse de la jonction base collecteur, soit en mode de polarisation inverse, la structure peut atteindre en condition émission optique, une fréquence de modulation opérationnelle du même ordre de grandeur.

- Sur cette même troisième configuration de conception, la source optique a été utilisée dans une configuration de polarisation directe pendant les mesures expérimentales, de sorte que la jonction de l'émetteur n<sup>+</sup>p (SiGe) est en mode de polarisation directe. Dans cette configuration, la région de l'émetteur n<sup>+</sup>p (SiGe) est mise à la masse et une polarisation de tension négative de 2V est appliquée à la région de la base p<sup>+</sup> en SiGe. Des électrons ont été injectés à partir de la région du collecteur n et les porteurs ont été excités par transfert de conduction à travers la région n faiblement dopée du collecteur. Lorsque ces transporteurs sont injectés dans la région de la base en SiGe, ils contiennent suffisamment d'énergie pour ensuite transférer les électrons de la vallée L à la vallée de la structure en bande T de SiGe. Avec 20% de dopage du germanium, la longueur d'onde émise pour cette conception devrait être inférieure à la longueur

d'onde d'émission de 1000 nm. Les très petites régions de conduction en colonnes, utilisées dans les sources optiques dans cette configuration, permettent de réduire la capacité de la couche d'appauvrissement et le temps de transit de la porteuse dans le dispositif.

- Le travail de cette thèse a été possible grâce aux progrès substantiels qui ont été réalisés dans le domaine des diodes à émission de lumière visible par des jonctions Si p-n fonctionnant en mode avalanche dès lors qu'elles sont polarisées en inverse au-delà de la tension d'avalanche [15] - [21]. Récemment, les sources lumineuses Si CMOS sont apparues avec des rendements beaucoup plus élevés en mettant en œuvre des DEL à avalanche à deux et trois jonctions Si CMOS qui émettent dans la gamme spectrale de 450 à 750 nm [22] - [23]. Un fort inrétêt est qu'elles peuvent être intégrées facilement dans les circuits CMOS standards. Divers prototypes ont été réalisés. Leur tension de fonctionnement (8V) et leur courant ( $80\mu A$  à 1mA) sont faibles. Ils émettent sur une surface de  $1 \times 1 \ \mu m^2$  entre 10 et 100 nW. Les niveaux d'émission de lumière interne sont augmentés d'un facteur de 0,3. Une technologie particulièrement prometteuse, qui utilise des défauts et des transitions assistées par la surface dans ces types de DEL, a récemment été identifiée et développée par notre groupe [24] - [26]. Nos DEL à base de phénomène à avalanche en Silicium fonctionnent de manière optimale entre 650 et 850 nm, et bien que la puissance d'émission optique des diodes à avalanche Si soit encore faible, environ 90 nW, elles peuvent atteindre des vitesses de modulation dans la gamme des GHz. Puisque les détecteurs Si et Si sont tous les deux disponibles et peuvent être intégrés relativement facilement dans la technologie SiGe/Si proposée, l'aspect le plus difficile pour suivre cette voie pour réaliser une liaison micro-optique sur puce à 750 nm avec du silicium est donc de développer une technologie de guide d'ondes optique appropriée dans ce régime de longueur d'onde de 450 à 850 nm qui peut être intégré dans les circuits intégrés Si CMOS.

- Dans ce contexte, les objectifs importants de cette étude concernent le développement de la DEL en Si à avalanche et la DEL en Si/SiGe à émission par la tranche et la compréhension de l'intégration physique des DEL Si et DEL SiGe avec les guide d'ondes optiques. En outre, un point crucial est d'être un détecteur optique compatible Bi/CMOS et de permettre l'intégration de tous ces élemnts sur une même puce de silicium pour former une liaison optique sur puce complète à 750 nm pour l'intra/interconnexion optique et la caractérisation des liaisons optiques de conception sur puce.

- Une étude du développement de liaisons optiques complètes sur silicium dans le proche visible à 450 nm-850 nm est présentée grâce à l'exploration de fonderies industrielles SiGe/Si en s'assurant une compatibilité avec l'intégration de circuits supplémentaires (bipolaire, BiCMOS), avec des capacités à haute vitesse technologie à faible coût. Une compatibilité d'alignement des sources et guides d'ondes a été étudiée. Enfin, des liaisons photoniques microondes sur puce ont été fabriquées et caractérisées en utilisant un procédé de technologie SiGe Bipolaire.

- Le but de ces travaux de recherche était donc (1) de concevoir, développer des diodes électroluminescentes Si à avlanche, des DELs Si/SiGe, mener des simulations sur la viabilité des guides d'ondes pour la réalisation de structures micro-photoniques en 1.2µm et 0,35 µm pour la liaison optique dans les circuits intégrés SiGe/Si à des longueurs d'onde de fonctionnement de 750nm principalement; (2) pour démontrer la performance possible des guides d'ondes de conception à 750 nm; (3) pour démontrer et réaliser une deuxième liaison optique d'itération dans un circuit intégré SiGe/Si à 750 nm expérimentalement; et (4) la conception, la fabrication et la caractérisation des premières liaisons photoniques hyperfréquences sur puce à une longueur d'onde quasi visible (0,65-0,85 µm). Toutes ces structures sont fabriquées dans un processus technologique 80 GHz de la fonderie Telefunken GmbH SiGe/Si HBT. La liaison optique complète associe des dispositifs d'émission de lumière par le phénomène à avalanche à base de SiGe (Si Av), à base de silicium-nitrure et à base d'oxyde de silicium (TEOS), et des transistors photoélectriques bipolaires à hétérojonction (HPT). Un tel dispositif permettrait d'héberger des systèmes microfluidiques, des applications de communication de données sur puce et d'analyse biochimique et de proposer des applications potentielles pour certains systèmes micro-photoniques bipolaires ou à base de CMOS et des systèmes micro-optoélectromécaniques (MOEMS) et MEMS.

- Les meilleures performances des liaisons optiques intégrées sur puce indiquent une perte de conversion aussi faible que 30 dB de la source au détecteur avec une fréquence de coupure allant jusqu'à 500 MHz. Le bon alignement et la bonne efficacité de chaque appareil sont alors clairement atteints. Des performances plus élevées sont également envisagées à partir des mesures préliminaires.

- Par rapport aux contributions internationales, le travail a été accepté pour publication dans les actes de trois conférences internationales. De plus, trois articles de revues ont été publiés dans

des revues scientifiques à la pointe de la technologie accréditée par l'ISI (JM3-SPIE) et (IEEE JQE) aux États-Unis. Un autre article est actuellement soumis à l'IEEE Journal of Material Engineering (JME). Un brevet a été délivré pour ce travail en Corée, après de nombreux brevets délivrés provisoirement et en vertu du Traité de collaboration au Protocole international (PCT).

## ACKNOWLEDGEMENT

With special thanks and gratefulness to the following people:

1) Prof. LW Snyman, for his critical wisdom that directed the flow of my curiosity in Opto-electronics engineering and guided me throughout this study.

2) Dr JL. Polleux from University of Paris Est, ESIEE in France who helped me to find a way in the available materials of SiGe Opto-electronic integrated circuitry design and on the topic of Microwave Photonics RF measurements. At different stages of the project, many people supplied me with information; I would like to thank Prof T. Bourouina from ESIEE France for facilitating the optical micrograph pictures of the devices.

3) Dr Anne-Laure BILLABERT from Le CNAM, ESYCOM Paris, who is the director of the thesis, who gave technical input on the analysis and interpretation of the measurement of the optical design waveguides.

4) Dr D Schmieder from Tshwane University of technology RSA. Many thanks for his timeless input and advice with respect to R-soft Simulation software functionalities.

5) The University of Paris Est, ESIEE is thanked for allowing me to use their optical communication characterization facilities as well as the assistance to the study by Dr Carlos VIANA, Jacopo Nanni and Zerihun Tegegne during the initial phases of the study.

6) Many thanks to my family for their spiritual and moral support offered to me, and still offering to me during the cause of my study and beyond. God bless you all.

7) Thank to the following people for their countless prays and moral support: My Mother, Thereza Imeomonde Ogudo; my brother Mr. Ehis C. Ogudo; my sister Mrs Grace Akhimien; my wife Mrs Beatrice E. Ichipi Ogudo.

Last but not the least, I would like to thank those academics, consultants, practicing managers, journalists and other researchers whose work I cited throughout the thesis, without their openness to share knowledge and expertise, writing this thesis would have been very difficult, if not impossible.

## DEDICATION

This study is dedicated to: Almighty God for the strength and guidance He gave me; my mother Theresa Imeomonde Ogudo, my wife Beatrice E. Ogudo, my son Christian Ogudo, my brothers, my sister, my in-law Peter Akhimien, my uncle Godwin Idiovo (aka General) and my pastor WF Kumuyi for their love and prayers during my studies.

# LIST OF ABBREVIATIONS AND ACRONYMS

| 2D     | Two dimensions                           |

|--------|------------------------------------------|

| 3D     | Three dimensions                         |

| APDs   | Avalanche photo detector                 |

| CAD    | Computer aid design                      |

| CMOS   | Complementary Metal Oxide Semi-conductor |

| EPIC   | Electronic-photonic integrated circuit   |

| FDTD   | Finite-Difference Time-Domain            |

| FEOL   | Front end of line                        |

| IMWP   | Integrated MicroWave Photonics           |

| LED    | Light Emitting Diode                     |

| LOCOS  | Local oxidation of silicon               |

| MEMS   | Micro-electro-mechanical systems         |

| MOEMS  | Micro Opto-electro Mechanical Sensor     |

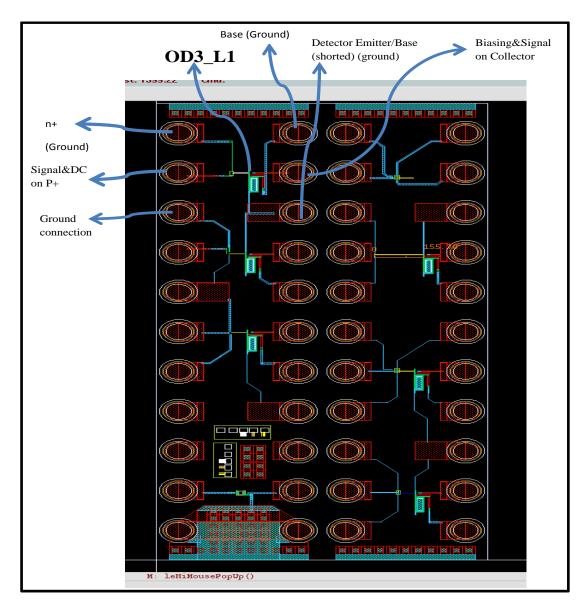

| OD3_L1 | Optical die 3 Layout 1                   |

| OD3_L2 | Optical die 3 Layout 2                   |

| OD3_L6 | Optical die 3 Layout 6                   |

| OEIC   | Opto-electronic Integrated Circuit       |

| OLTS1  | Optical link test structure one          |

| OLTS2  | Optical link test Structure two          |

| OLTS3  | Optical link test Structure three        |

| PMI    | Physical Model Interface                 |

| SLD    | Semi-conductor Laser Diode               |

| SOI    | Silicon-on-insulator                     |

| TEOS   | Tetra-Ethyl-Ortho-Silicate               |

| TS1    | Test structure one                       |

| TS2    | Test structure two                       |

| TS3    | Test structure three                     |

| UPML   | Uniaxial perfectly matched layer         |

|        |                                          |

# TABLE OF CONTENT

| ABSTRACT                                                              | i     |

|-----------------------------------------------------------------------|-------|

| RÉSUMÉ                                                                | vii   |

| Résumé en français :                                                  | vii   |

| ACKNOWLEDGEMENT                                                       | XV    |

| DEDICATION                                                            | xvi   |

| LIST OF ABBREVIATIONS AND ACRONYMS                                    | xvii  |

| TABLE OF CONTENT                                                      | xviii |

| TABLE OF FIGURES                                                      | xxii  |

| LIST OF TABLES                                                        | xxvi  |

| GENERAL INTRODUCTION:                                                 |       |

| CHAPTER 1 State Of The Art                                            |       |

| 1.1 Introduction                                                      |       |

| 1.2 Optical Properties of CMOS Integrated Circuit Structures.         |       |

| 1.3 Si CMOS Avalanche LEDs                                            |       |

| 1.4 SiGe/Si Silicon HPT bipolar technology                            | 41    |

| 1.5 The research Problem statement                                    |       |

| CHAPTER 2: SiGe LED Technology: Edge-emitting topologies              |       |

| 2.1 Introduction                                                      |       |

| 2.2 Light emission mechanisms in Silicon                              |       |

| 2.3 Si Avalanche LEDs Fabrication: Edge emitting topologies           |       |

| 2.4 Proposed Si and SiGe Avalanche LEDs                               | 49    |

| 2.5 Description of the SiGe/Si HPT structure                          | 52    |

| 2.6 Conclusion                                                        | 60    |

| CHAPTER 3: On-chip Optical Waveguides Design and links Configurations | 61    |

| 3.1 Introduction                                                                  |

|-----------------------------------------------------------------------------------|

| 3.1.1 On-chip optical waveguide link design considerations                        |

| 3.1.2 The three different waveguide structures designed                           |

| 3.2 Design of full Silicon Complete On-Chip Optical Links                         |

| 3.2.1 Complete Design of On-Chip Optical Links                                    |

| 3.2.2 Optical link test structure 1 (OLTS1)                                       |

| 3.2.3 Optical link test structure 2 (OLTS2)                                       |

| 3.2.4 Optical link test structure 3 (OLTS3)                                       |

| 3.2.5 Optical link test structure 3 (OLTS3-FB)                                    |

| 3.3 Design Layouts of the On-Chip Optical Links Devices                           |

| 3.4 R-SOFT CAD Software Simulation of the Designed Waveguides                     |

| 3.4.1 Simulations of the optical waveguide Design 1 (OWGD1)                       |

| 3.4.2 Simulations of optical waveguide Design 2 (OWGD2)                           |

| 3.4.3 Simulations of optical waveguide Design 3 (OWGD3) 80                        |

| 3.5 RF Substrate Coupling Considerations in Device On-Chip Optical Links at 750nn |

|                                                                                   |

| 3.5.1 RF parasitic results for Design test structure 1 (OLTS1)                    |

| 3.5.2 RF parasitic results for Design test structure 2 (OLTS2)                    |

| 3.5.3 RF parasitic result for design test structure 3 (OLTS3)                     |

| CHAPTER 4: Reverse biased Avalanche LED based Optical Links                       |

| 4.1 Introduction                                                                  |

| 4.1.1 Device testing, experimental measurement, results interpretation and device |

| characterisation                                                                  |

| 4.1.2 Calibration of the measuring equipment                                      |

| 4.1.3 Optical probing configuration on OLTS1                                      |

| 4.1.4 Test procedures and Parameters                                              |

| 4.1.5 MATLAB main program for DC biasing and RF signal supply to device 101       |

| 4.1.6 DC biasing test conditions and compliance values for OLTS1 10                   |

|---------------------------------------------------------------------------------------|

| 4.1.7 RF test results analysis and compliance values                                  |

| 4.1.8 DC bias analysis and characterization of test structure 1 (OLTS1) 103           |

| 4.1.9 RF power analysis and characterization of test structure 1 (OLTS1) 104          |

| 4.2 Experimental Realisations and Results for OLTS2 105                               |

| 4.2.1 Optical probing configuration on device 2(OLTS2)                                |

| 4.2.2 Test procedures and objectives:                                                 |

| 4.2.3 DC bias analysis and characterization on test structure 2 (OLTS2) 108           |

| 4.2.4 RF power analysis and characterization of test structure 2 (OLTS2) 109          |

| 4.3 Experimental Realisations and Results for OLTS3                                   |

| 4.3.1 Optical probing configuration on device 3 (OLTS3-RB)                            |

| 4.3.2 Procedures and test objectives                                                  |

| 4.3.3 DC bias analysis and characterization of optical link structure OLTS3 113       |

| 4.3.4 RF power analysis and characterization of test structure 3 (OLTS3) 114          |

| CHAPTER 5: Forward biased LED based Optical Links                                     |

| 5.1 Introduction                                                                      |

| 5.1.1. Optical probing configuration on device 3 (OLTS3-FB)                           |

| 5.1.2 Procedures and test objectives                                                  |

| 5.1.3 DC bias analysis and characterization of the optical link structure OLTS3-FI    |

|                                                                                       |

| 5.1.4 RF power analysis and characterization of test structure 3 (OLTS3-FB) 12        |

| 5.1.5 Implementation of the optical links 12                                          |

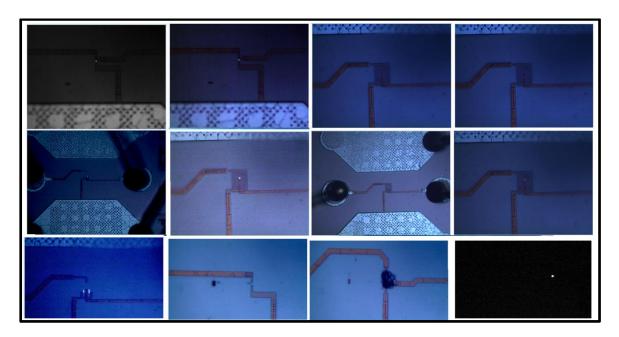

| 5.1.6 Galleries' of bright field micrograph of top illumination of our LEDS 12'       |

| 5.1.7 Localization of the optical LEDs source point for optical coupling optimization |

|                                                                                       |

| CHAPTER 6: Conclusion                                                                 |

| APPENDICES                                                                            |

| I. Potential applications of the developed technology                                 |

|---------------------------------------------------------------------------------------|

| II. Scientific publications that emanated from this work                              |

| International Journal Article Published:                                              |

| International conference presentations and published conference proceedings articles: |

|                                                                                       |

| Chapter in a book:                                                                    |

| III. MATLAB Code Appendices                                                           |

| Appendix A: The MATLAB code developed for the initialization of variable and          |

| biasing the optical source and the detector145                                        |

| Appendix B: The algorithm for the DC biasing and launching the voltage and current    |

| values to the optical link device structures through the Agilent B1500A               |

| Semiconductors extractor                                                              |

| Appendix C: Main program for DC biasing and RF input power supply to device 149       |

| Appendix D: Program for launching the current and voltage values to device 154        |

| IV. References                                                                        |

# TABLE OF FIGURES

| Figure 1: CMOS integrated circuit structure                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

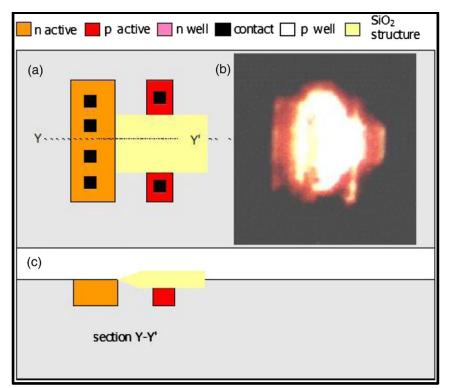

| Figure 2: Si LED integrated in CMOS integrated circuit technology as an optical source [110]. 35                                                                                                                                                                            |

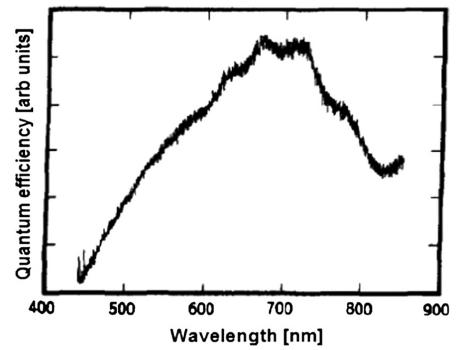

| Figure 3: Emitted spectrum as of a 5x1-µm line width, CMOS integrated CMOS avalanche LED [111]                                                                                                                                                                              |

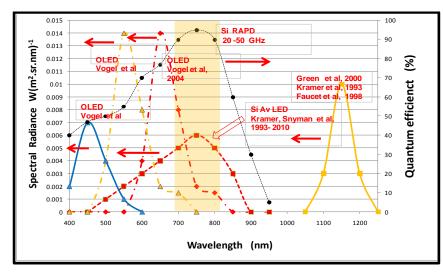

| Figure 4: Spectral Characteristics of Si avalanche-based light emitting device (Si Av LED) and comparison with the spectral detection range [79]                                                                                                                            |

| Figure 5: Electro-optical interfaces realized in 0.35µm technology with standard CMOS design and processing procedures (a) graded junction p+ n n+ RF bi-polar developed (b) p+ n+ overlap device unit 0.5µm dopant developed [119]                                         |

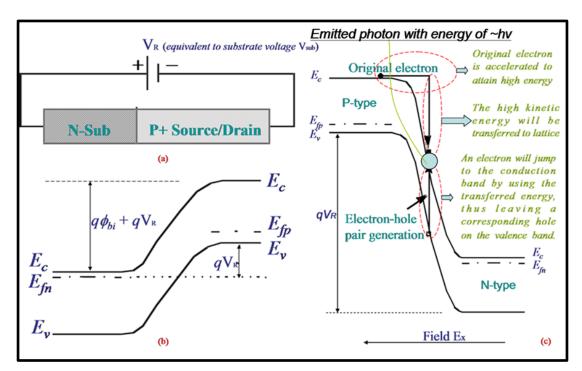

| Figure 6: Energy band scheme for the impact ionization process for an electron in a reverse biased pn silicon junction                                                                                                                                                      |

| Figure 7: Energy distribution of populations of electrons and holes in the conduction band and valence band of silicon for various excitation conditions, momentum changes, and possible subsequent photonic transitions                                                    |

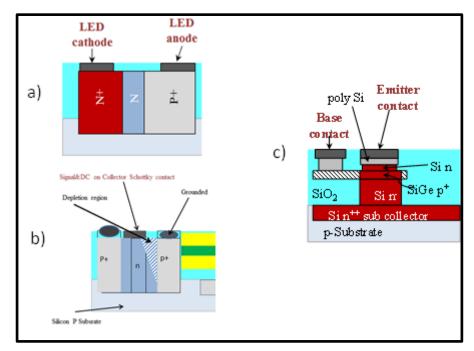

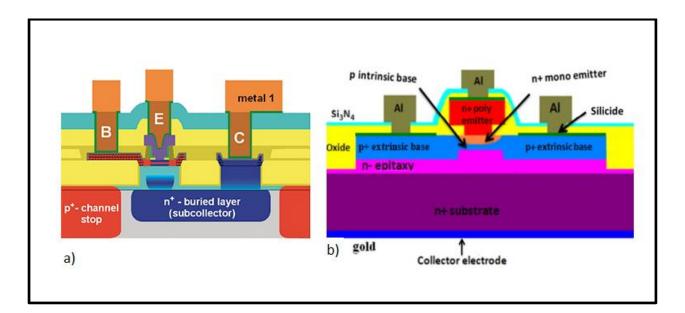

| Figure 8: Schematic cross-section of Si and SiGe LEDs designed into Telefunken SiGe technology<br>                                                                                                                                                                          |

| Figure 9: The schematic of the three different Si based Av LEDs to be implemented in SiGe2RF Telefunken GmbH technology for full on chip optical link system; a) Si Av N+NP+ columnar, b) SiGe-N+PN- with collector contact and c) SiGe-N+P without collector contact       |

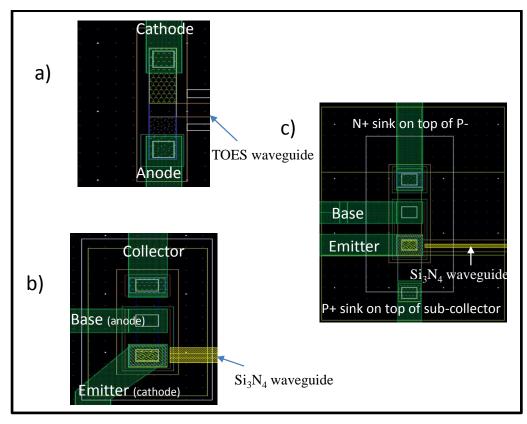

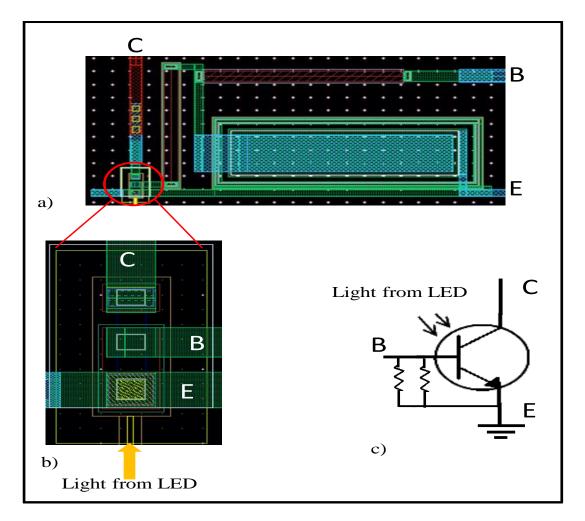

| Figure 10: The layout of the three different Si based Av LEDs implemented in SiGe2RF Telefunken<br>GmbH technology for full on chip optical link system; a) Si Av N+NP+ columnar, b) SiGe-N+PN-<br>LED with collector contact and c) SiGe-N+P LED without collector contact |

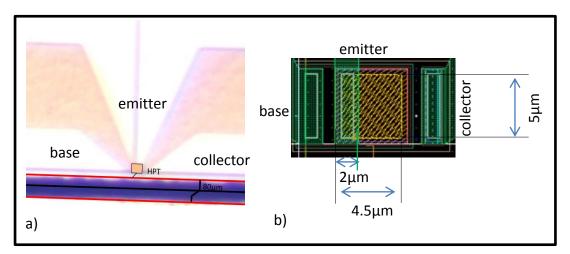

| Figure 11: a) Microscopic picture of the edge SiGe HPT, b) Layout of structure along with its dimensions                                                                                                                                                                    |

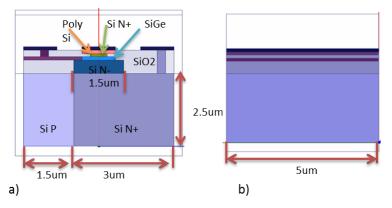

| Figure 12: Basic simplified structure of SiGe/Si HPT used for simulation                                                                                                                                                                                                    |

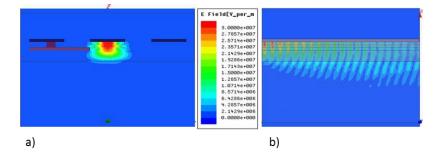

| Figure 13: The magnitude of the electric field evaluated by HFSS at 850nm. a) at the input port, b) along the propagation axis                                                                                                                                              |

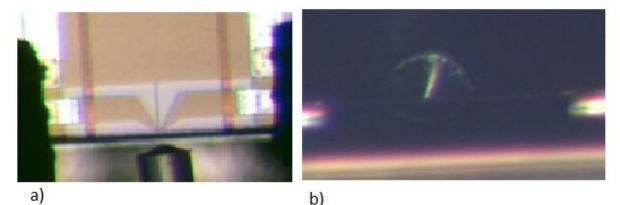

| Figure 14: a) Top view microscopic picture of the device under test and the optical probe pointing                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| on the edge side of the HPT. b) Microscopic picture taken from 45° mirror                                                                             |

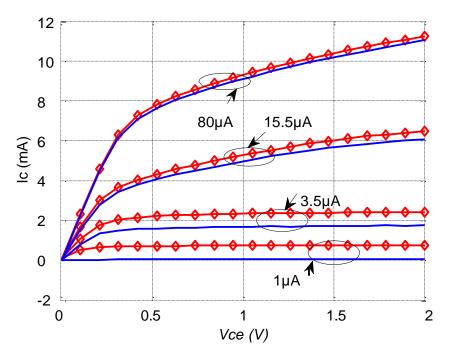

| Figure 15: Ic-Vce curve of edge illuminated SiGe HPT with light (red curves with mark) and under dark condition (blue curves) for different Ib values |

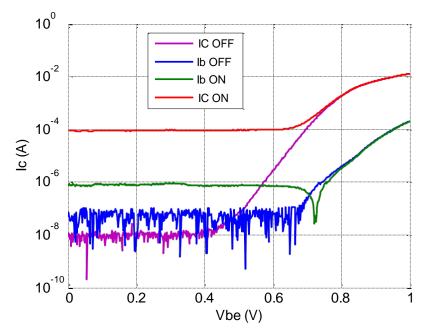

| Figure 16: Gummel plot of edge illuminated SiGe HPTs with 1.14mW optical beam at 850nm and without light illumination                                 |

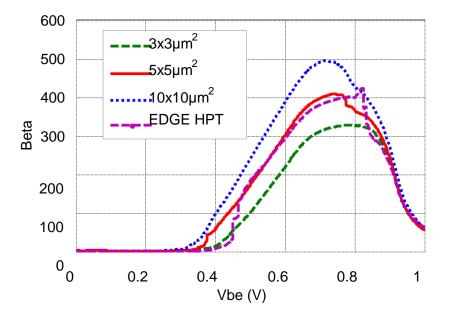

| Figure 17: Comparison of the DC current gain from the edge-HPT or top-HPTs of various optical window sizes in dark conditions                         |

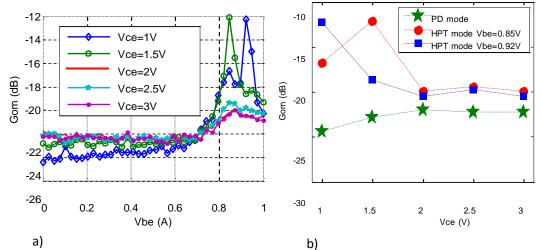

| Figure 18: Opto-microwave gain: a) versus Vbe at different Vce, b) versus Vce in PD mode and HPT mode (Vbe=0.85V and 0.92V)                           |

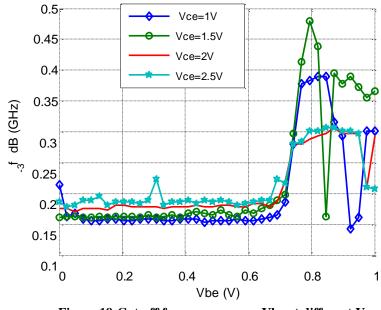

| Figure 19:Cut-off frequency versus Vbe at different Vce                                                                                               |

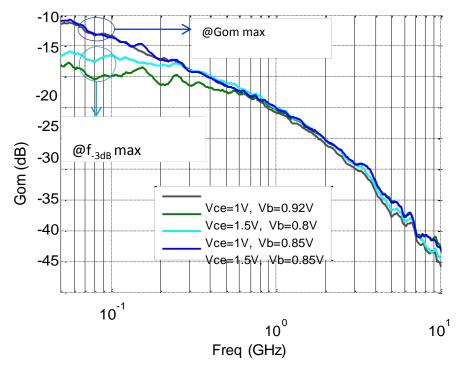

| Figure 20: Opto-microwave gain versus frequency at low frequency Gom and cut-off frequency peak biasing conditions                                    |

| Figure 21: Schematic cross Section of a SiGe2 NPN HPT                                                                                                 |

| Figure 22: Waveguide structure (a) Side view section (b) Cross-sectional view                                                                         |

| Figure 23: Waveguide structure for design 2 (a) Side view section (b) Cross-sectional view 67                                                         |

| Figure 24: Waveguide structure for design 3 (a) Side view section (b) Cross-sectional view 68                                                         |

| Figure 25: The schematic of the detector used at the receiver side of the full optical link                                                           |

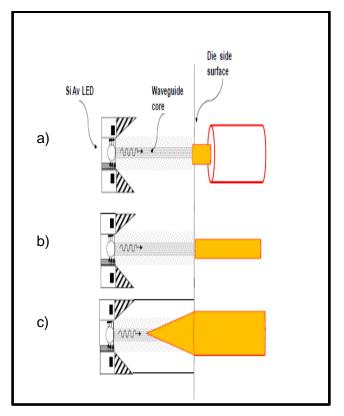

| Figure 26: Basic designs of the optical links using Si and SiGe Av LED, waveguides and SiGe-                                                          |

| based detectors with a) Design test structure 1 (OLTS1), b) Design test structure 2 (OLTS2) and c)<br>Design test structure 3 (OLTS3)                 |

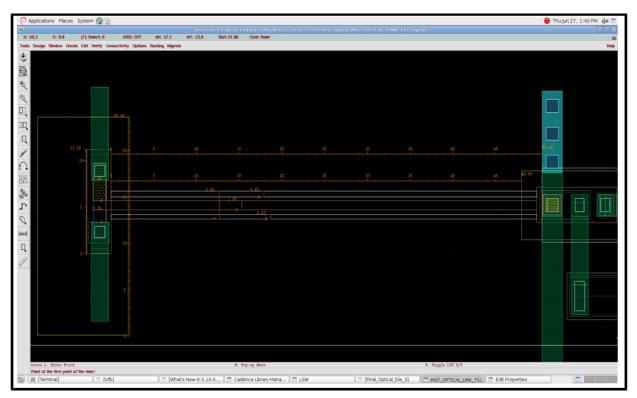

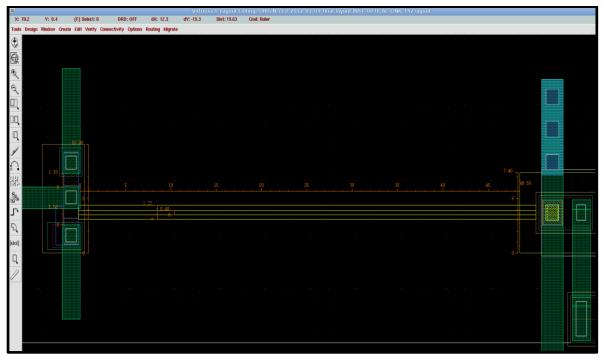

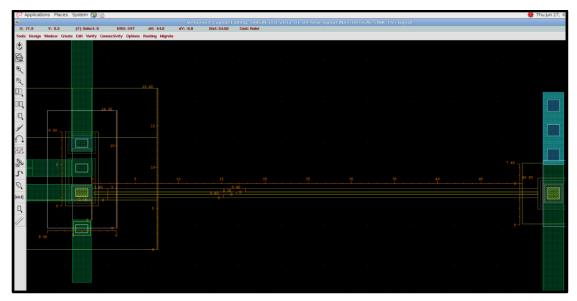

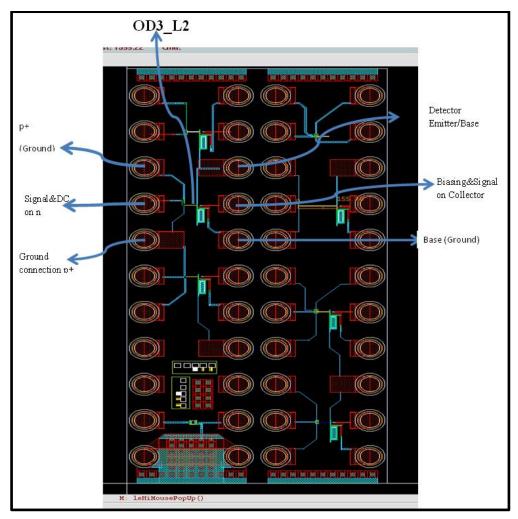

| Figure 27: Top view test structure 1 circuitry layout (OLTS1)                                                                                         |

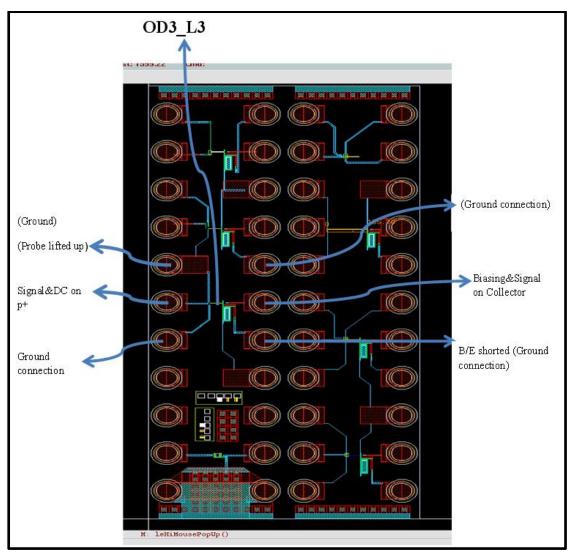

| Figure 28: Top view test structure 2 circuitry layout (OLTS2)                                                                                         |

| Figure 29: Top view test structure 3 circuitry layout (OLTS3)                                                                                         |

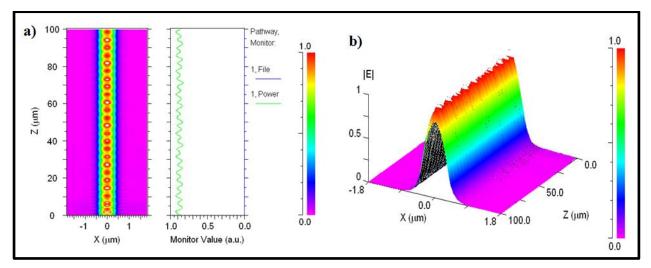

| Figure 30: Waveguide simulation results for design 1 (a) Contour Map (XZ), (b) height-coded E-<br>field                                               |

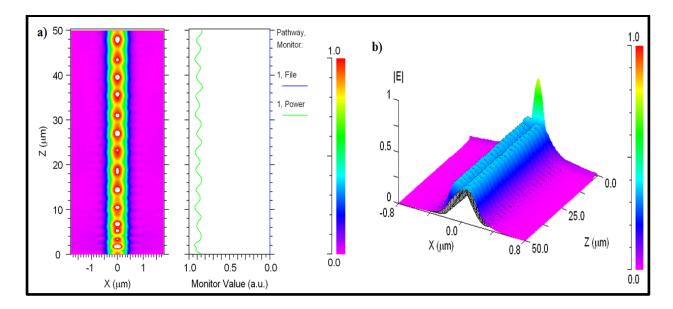

| Figure 31: Waveguide simulation results for design 2 (a) Contour Map (XZ), (b) height-coded E-<br>field                                               |

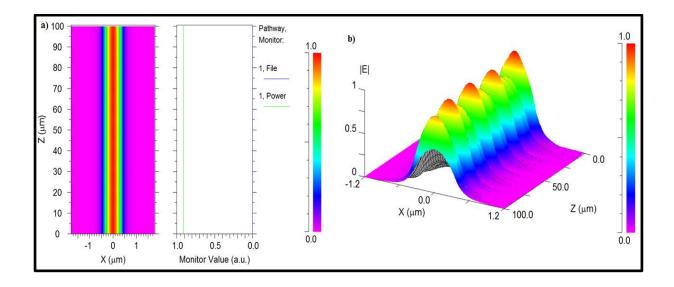

| Figure 32: Waveguide simulation results for design 3 (a) Contour Map (XZ), (b) height-coded E-<br>field                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

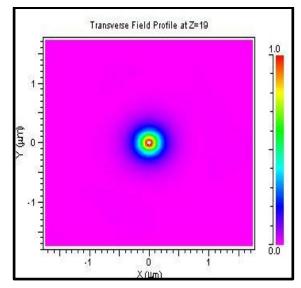

| Figure 33: Transverse field profile for a Silicon-Nitride based waveguide with a core of $0.2 \ \mu m$ diameter Silicon-Nitride embedded in a 1 $\mu m$ diameter silicon oxide cladding |

| Figure 34: Sample of Symbol Table Editor (a) Top list (b) Bottom list                                                                                                                   |

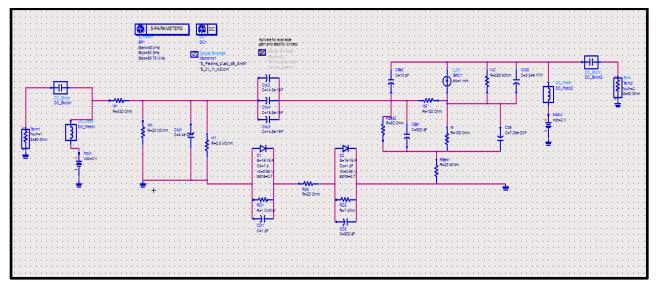

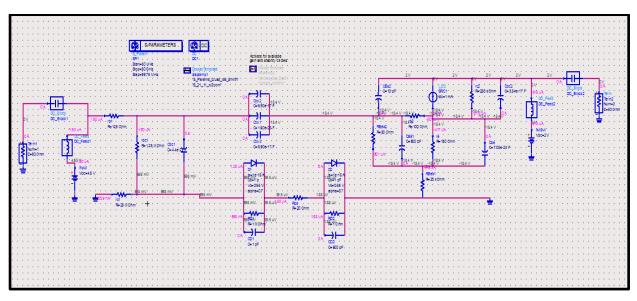

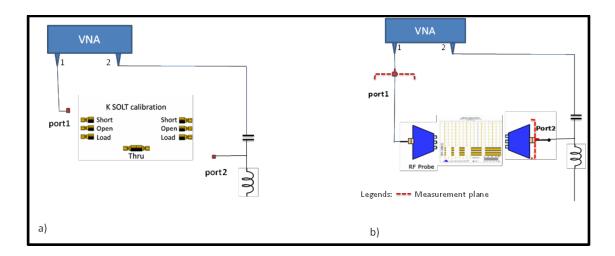

| Figure 35: Optical link topology two-ports network model of (OLTS1)                                                                                                                     |

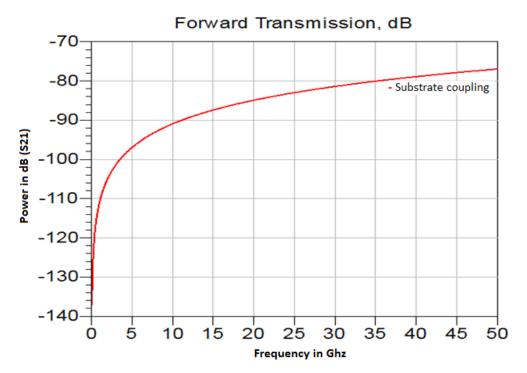

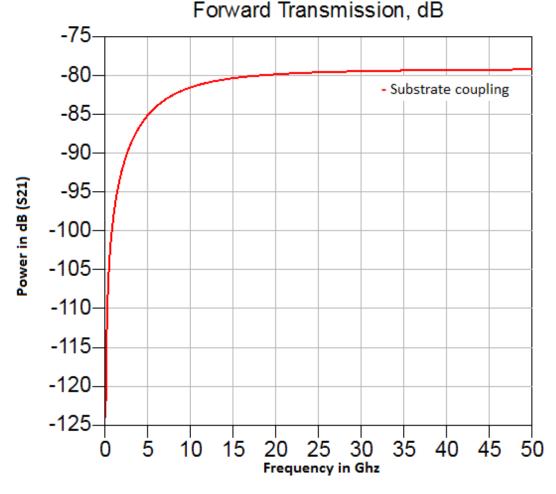

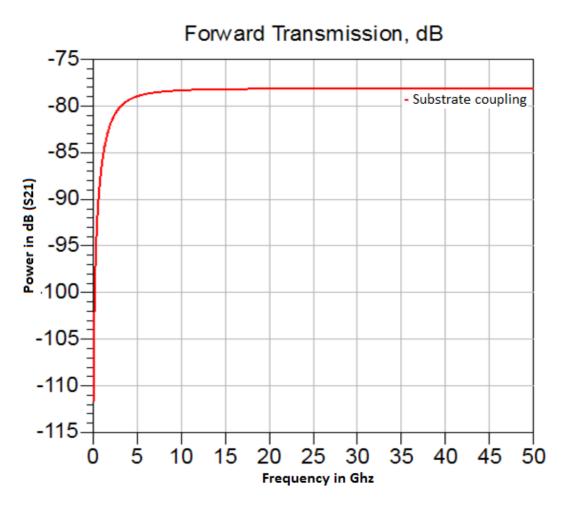

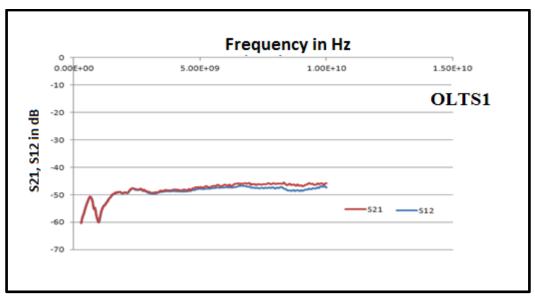

| Figure 36: Substrate coupling analysis of OLTS1 device design 1                                                                                                                         |

| Figure 37: Optical link topology two-ports equivalent network circuit for OLTS2                                                                                                         |

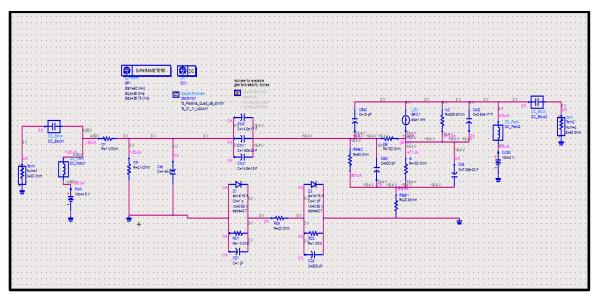

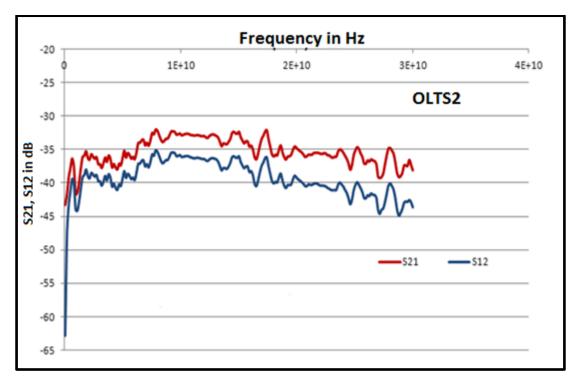

| Figure 38: Substrate coupling analysis of OLTS2 device design 2                                                                                                                         |

| Figure 39: Optical link two-port equivalent network circuit for OLTS3                                                                                                                   |

| Figure 40: Substrate coupling analysis of OLTS3 device design 3                                                                                                                         |

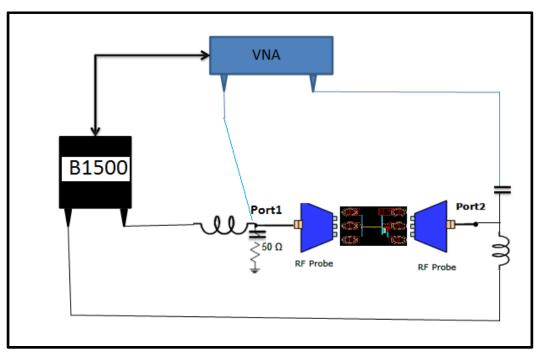

| Figure 41: The opto-microwave measurement test set setup. The device under test includes the optical link device, the bias tee probes                                                   |

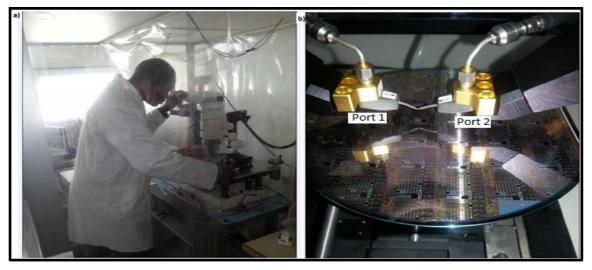

| Figure 42: Experimental characterization setup (a) Test bench photo picture (b) Zoomed wafer containing devices under test                                                              |

|                                                                                                                                                                                         |

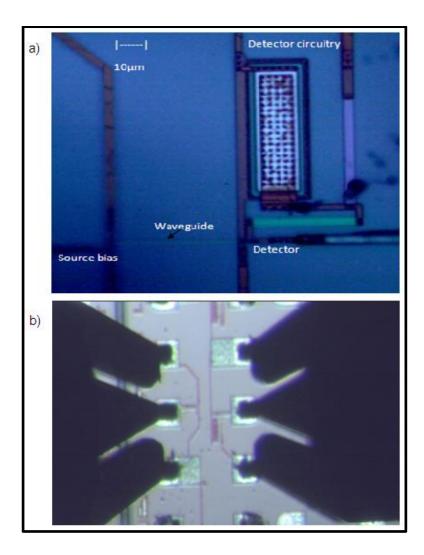

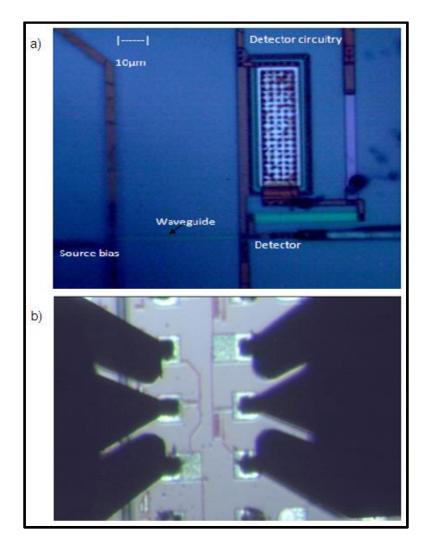

| Figure 43: (a) Microscopic picture of the optical link device (b) Microscopic picture of G-S-G probe connection on one of the devices during measurement                                |

|                                                                                                                                                                                         |

| probe connection on one of the devices during measurement                                                                                                                               |

| probe connection on one of the devices during measurement                                                                                                                               |

| probe connection on one of the devices during measurement                                                                                                                               |

| probe connection on one of the devices during measurement                                                                                                                               |

| probe connection on one of the devices during measurement                                                                                                                               |

| probe connection on one of the devices during measurement                                                                                                                               |

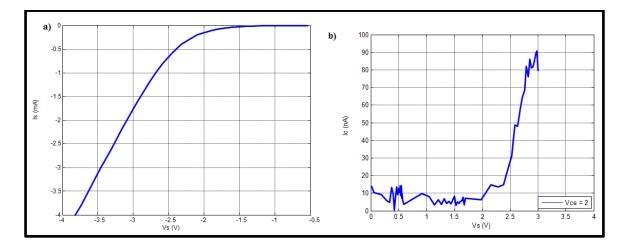

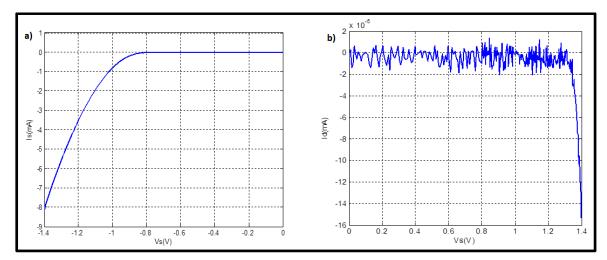

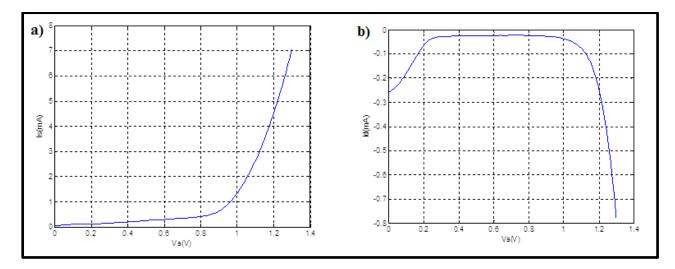

| Figure 52: DC IV Curves for OLTS3 (a) reverse bias Optical source IV curve (b) Detector optical link response when source was activated for OLTS3                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

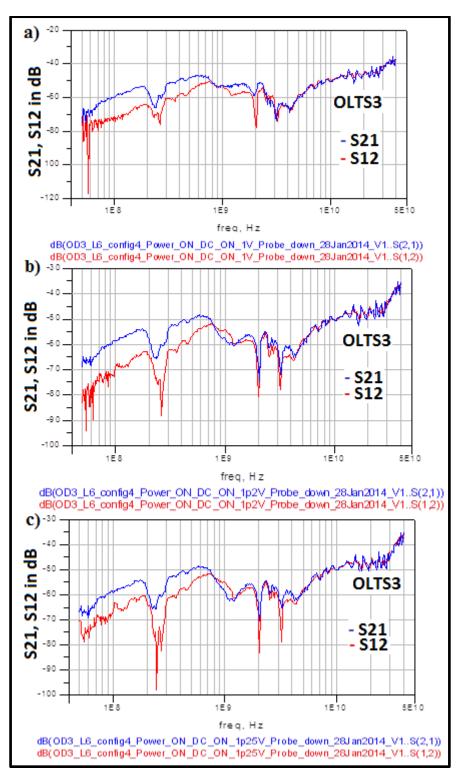

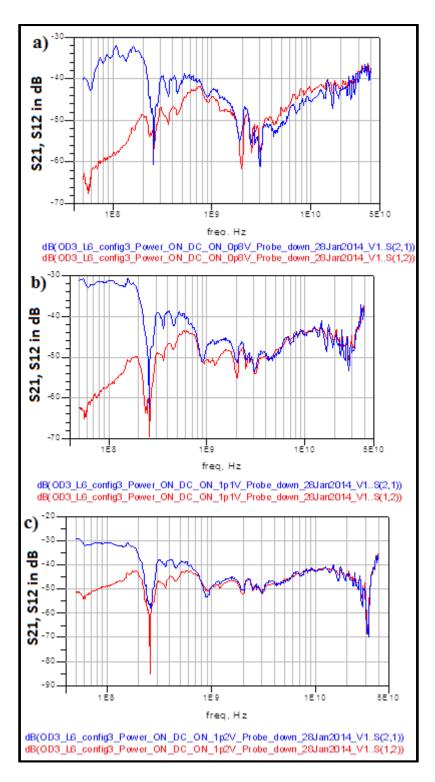

| Figure 53: RF coupling results for the realized on-chip micro-optical link for OLTS3-RB at 1V, 1.2V and 1.25V different bias voltage conditions                                                                                       |

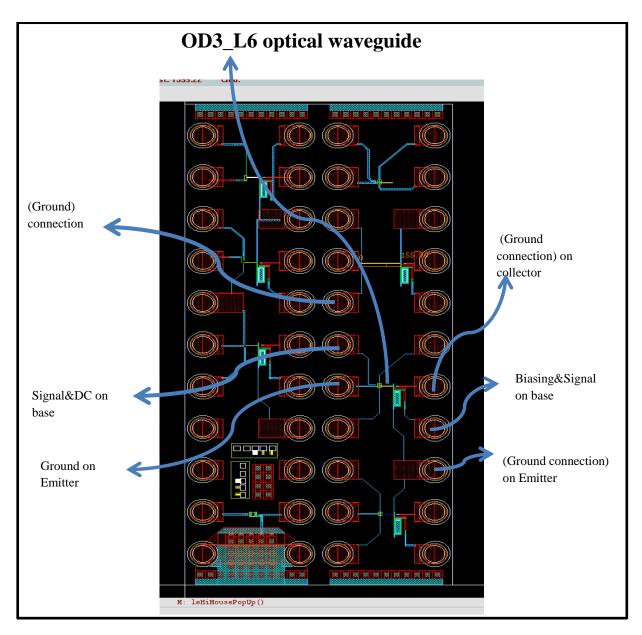

| Figure 54: Device topology layout viewed with cadence design software (OD3_L6-FB) 118                                                                                                                                                 |

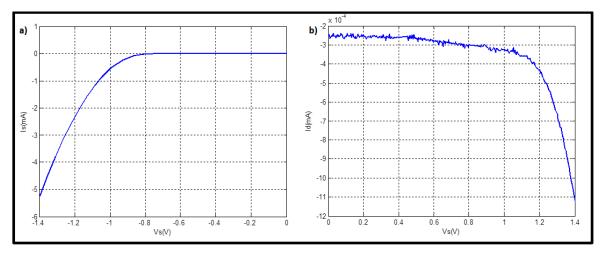

| Figure 55: DC IV Curves for OLTS3 (a) Forward bias Optical source IV curve (b) Detector optical link response when source was activated for OLTS3                                                                                     |

| Figure 56: RF coupling results for the realised on-chip micro-optical link for OLTS3-FB at different bias voltage (0.8V, 1.1V & 1.2V) conditions                                                                                      |

| Figure 57: : (a) Microscopic picture of the optical link device (b) Microscopic picture of G-S-G probe connection on one of the devices during measurement                                                                            |

| Figure 58: Microscopic picture of bright spot LEDs optical source points of some of the devices                                                                                                                                       |

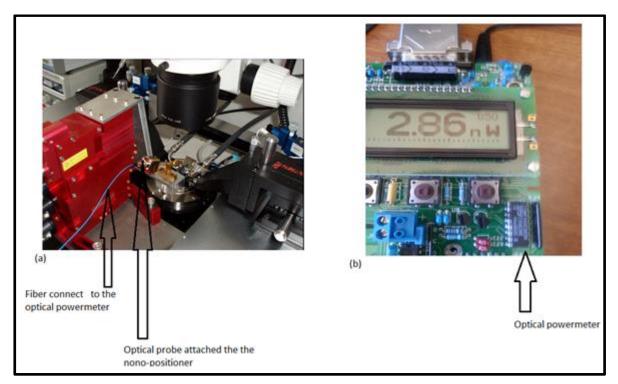

| Figure 59: Experimental bench setup of edge emitting LEDs. (a) Photograph of the bench. b)<br>Picture of the optical power meter                                                                                                      |

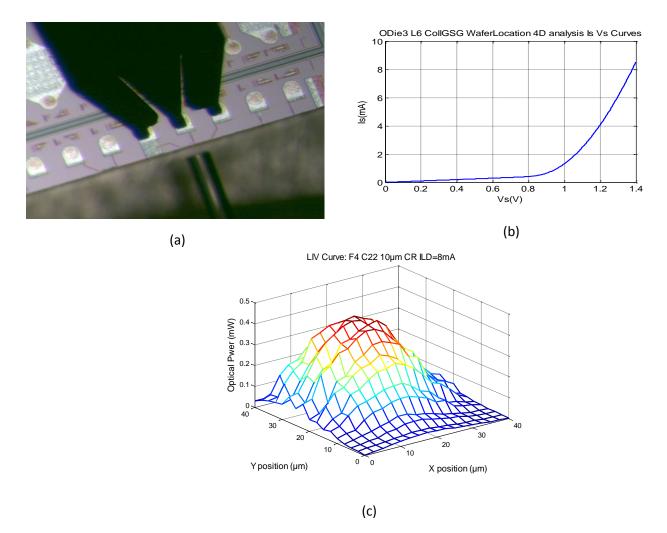

| Figure 60: (a) Top view microscopic picture of the device under test and the optical probe pointing<br>on the edge side of the LED source (b) IV bias curve of the device under test (c) LIV power<br>measurement curve of the device |

| Figure 61: Schematic presentations of potential application of the developed technology in the optical interconnect environment, utilizing a 0.35 µm SiGe process technology                                                          |

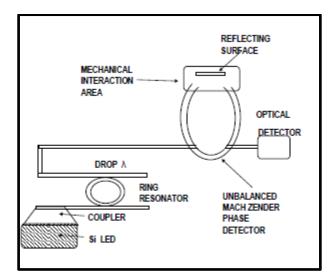

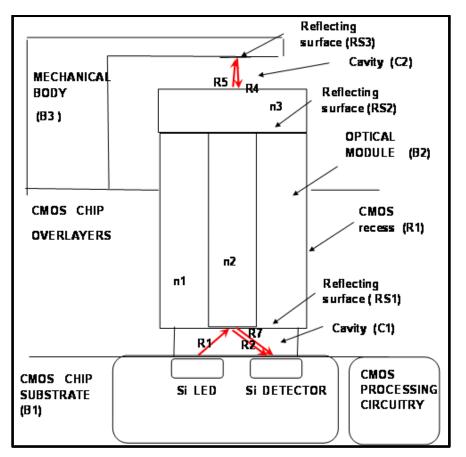

| Figure 62: Conceptual MOEMS sensor device suitable for integration in CMOS IC using all monolithically IC technology (Snyman&Ogudo et al, 2015)                                                                                       |

| Figure 63: Conceptual MOEM sensor device that is suitable for integration in CMOS IC 142                                                                                                                                              |

# LIST OF TABLES

| Table 1: Optical Properties of CMOS ICs at 750 nm.                                 |              |

|------------------------------------------------------------------------------------|--------------|

| Table 2: Properties of the materials used in HFSS simulator                        | 54           |

| Table 3: Optical wave guiding on structures                                        | 65           |

| Table 4: The possible combination of the on-chip full optical link                 | 71           |

| Table 5: Layers colour coded index                                                 | 76           |

| Table 6: DC biasing test conditions and compliance values for OLTS1                | 101          |

| Table 7: Test control parameters                                                   | 102          |

| Table 8: Measured results (RF analysis)                                            | 102          |

| Table 9: DC biasing test conditions and compliance values for OLTS2                | 107          |

| Table 10: Control parameters                                                       | 107          |

| Table 11: Measured results (RF analysis)                                           | 108          |

| Table 12: DC test biasing condition and compliance values for OLTS3                | 112          |

| Table 13: Control parameters                                                       | 113          |

| Table 14: Measured results (RF analysis)                                           | 113          |

| Table 15: DC test biasing condition and compliance values for OLTS3-FB             | 119          |

| Table 16: Control parameters                                                       | 119          |

| Table 17: Measured results (RF analysis)                                           | 120          |

| Table 18: Results summary of the designed optical links test structures (OLTS1, OL | TS2 & OLTS3) |

|                                                                                    |              |

## **GENERAL INTRODUCTION:**

Currently, optical communications and opto-electronic integrated circuits are designed, developed and realized by utilizing group "III-V" semiconductors, such as gallium arsenide and associated compounds. They form the basis of a mature and quite complex technology. A deficiency is that these technologies cannot be integrated into silicon (Si) and mainstream complementary metal–oxide–semiconductor (CMOS) integrated circuit technology with ease. A series of viable Si light-emitting technologies have recently become available that enable the integration of light sources directly into Si CMOS or Bipolar technology e.g. [7]. The creation of large-scale opto-electronic integrated circuits and optical data "highways" in CMOS integrated circuitry, utilizing Si CMOS compounds, have been envisioned and hold much promise [8] - [11]. The latest attempts for realizing optoelectronic systems in CMOS technology have until now mainly been focused utilizing wavelengths at 1550 nm [12] - [14], mainly because of the ease of design and fabrication of waveguides in this wavelength regime, and compatibility to telecommunication bands.

However, neither effective high-speed Si optical sources, nor Si detectors, are available at this 1550nm wavelength. If optical sources, detectors, waveguides, and sensors could be realized on the same Si CMOS chip at, say, 750 nm wavelength, various on-chip-based micro-photonic systems can be design and realized. Achieving these goals can lead to diverse low cost "all-silicon" opto-electronic systems, which will be the "smarter" and more "intelligent" CMOS chips of the future. These systems could lead to a new field that could be appropriately named "Si CMOS photonic microsystems" and lead to new products especially for the medical, biomedical optics, optical interconnect and bio-photonics field. These systems also do not require ultrahigh frequency bandwidths to transmit, and the emission powers of our tailored designed avalanche Si light-emitting diodes (AvSiLEDs) may be sufficient to sustain the operation of such systems. The main objective of my research was, therefore, to design optical waveguides and Bi/CMOS compatible optically and directly integrate the sources, Silicon-Nitride waveguides, TEOS waveguide and the detectors all in the same silicon chip substrate for optical interconnect and communication sensors on chip at 750nm wavelength using SiGe/Si RF Bipolar processing platform. This would have benefits in terms of manufacturing cost reduction, miniaturization, the simplification of packaging requirements and perhaps also of low total power operation requirements for such a system.

The work of this PhD is supported by substantial progress that has been made in the field of Si p–n junctions emitting visible light diode when operated in reverse breakdown avalanche mode [15] - [21]. Recently, Si CMOS light emitting sources appeared with much higher efficiencies by implementing two and three junctions Si CMOS injection avalanche LEDs that emit in the spectrum range of 450 to 750 nm [22] - [23]. They can be integrated with ease in standard CMOS circuits. Various prototypes have been realized. Their operating voltage (8V), and current (80  $\mu$ A to 1 mA) are low. They emit from an area of 1 × 1  $\mu$ m<sup>2</sup> between

10 and 100 nW. The internal light emission levels are much higher by a factor of 0.3. Particularly promising technology, which uses defect and surface-assisted transitions in these types of LEDs, has recently been identified and developed by our group [24] - [26]. Our Si avalanche-based LEDs operate optimally at 650 to 850 nm, and although the optical emission power of Si avalanche- LEDs is still low, about 90nW, they can reach modulation speeds into the GHz range. Since Si LEDs and Si detectors are both available, and can be integrated with relative ease into the proposed SiGe/Si technology, the most challenging part of following this route to realize on-chip micro optical link at 750nm with silicon is, hence, to develop appropriate optical waveguide technology in this 450-850nm wavelength regime that can be integrated into Si CMOS integrated circuitry.

In this context, the important objectives of this study concern the development of edge emitting Si Av LED & Si/SiGe LED and the understanding of physical integration of Si LEDs and SiGe LEDs, optical waveguide. In addition, to be Bi/CMOS compatible optical detector and the proposal of integrating all on the same silicon chip to form a complete on-chip optical links at 750nm for optical intra/interconnect and the characterization of the design on-chip optical links.

Developing full Silicon on-chip optical links in the near visible at 450nm-850nm. Exploring industrial SiGe/Si foundries Compatibility with further circuit integration (bipolar, BiCMOS), with high speed capabilities Low cost technology. Source and waveguide alignment compatibility. Finally, on-chip microwave photonics links have been fabricated and characterized using a SiGe Bipolar technology process.

The purpose of this research was, then, (1), to design, develop edge emitting Si Av LED, Si/SiGe LED design optical waveguides, detailed simulations of the viability of the waveguides for realization of microphotonic structures in 1.2µm and 0.35µm for optical link in SiGe/Si integrated circuitry at mainly 750nm operating wavelengths were conducted; (2) to demonstrate the possible performance of the design waveguides at 750nm; (3) to demonstrate and realize second iteration optical link in SiGe/Si integrated circuitry at 750 nm experimentally; and (4) The design, fabrication and characterization of the first on-chip microwave photonic links at near-visible wavelength (0.65-0.85µm). All those structures are fabricated into an 80 GHz Telefunken GmbH SiGe/Si HBT technological processes. The full optical link combines Silicon, SiGe based Avalanche Light Emitting Devices (Si Av LEDs), Silicon-Nitride based, and silicon oxide (TEOS) based waveguides, and SiGe Heterojunction Bipolar Photo-Transistors (HPT). Such device could permit hosting microfluidic systems, on chip data communication and bio-chemical analysis applications and to propose potential applications for some first iteration Bipolar or CMOS based micro-photonic systems and micro-opto- electro-mechanical systems (MOEMS) and (MEMS). This PhD document is divided in six chapters. The following section gives a brief overview of how this thesis is presented:

#### **Chapter 1: State of The Art**

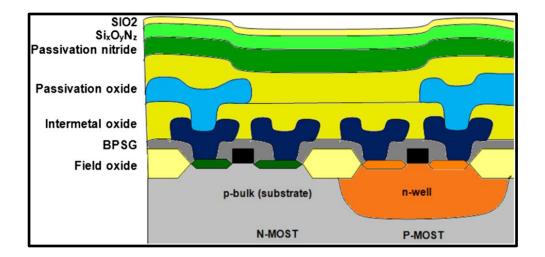

*On-chip optical link considerations*: This chapter presents more background on the motivation that leads to the study of this on-chip optical link technologies. In this chapter, we investigated the optical properties of CMOS IC structure and design as potential structure layers; such as Silicon-Nitride and the oxides layers that can be use as optical waveguides. The research problem statement are highlighted and discussed; which leads to the comparison of different available optical sources, optical waveguides and the design and fabrications complexity with corresponding development cost factors associated with various propagation wavelength utilizing CMOS technology. Lastly, we present the state of the art, SiGe/Si HPT bipolar technology and their compatibility with CMOS technology, and the possible integration with Silicon-Nitride optical waveguide and SiAvLEDs as offer by bipolar technology process at 750nm to form on-chip optical link communication and other optical integrated system applications directly onto CMOS chip.

#### Chapter 2: SiGe LED Technology: Edge-emitting topologies

This chapter focuses on SiGe LEDs, SiAvLEDs and SiGe edge-emitting LED design layout geometries for the different bias configurations of our three different designs. This chapter presents a brief description of the light emission mechanism in silicon and the energy bandgap scheme for the impact ionization process for an electron in a reverse biased pn silicon junction. The layout structure of the three Silicon-based LEDs designed from SiGe2RF Telefunken technology are presented in this chapter. The description of the Si/SiGe HPT detector layout structure and dimensions as implemented in the optical links is also presented in this chapter. Lastly, the proposed integration of the optical sources, the designed optical waveguides and the detector on the same chip to form a full RF-Bipolar on-chip optical links is highlighted. While bipolar, this SiGe technology is thought to be straightforward transposable to SiGe/Si BiCMOS technologies.

### Chapter 3: On-chip optical waveguide design and links configurations

*On-chip optical waveguide link design strategies*: This chapter presents the different optical waveguides design strategies, the theoretical competency about optical waveguides with respect to modes, loss, dispersion and effect of waveguide material characteristics on these parameters especially for  $Si_3N_4$  and SiON. Three different waveguide strategies are proposed. In addition to the waveguide characteristic, it will be important to select the best strategy to get them efficiently coupled from the edge to LED and photodetectors and to reduce the intrinsic height misalignments. The role of the substrate and parasitics coupling are also key issues to properly address. The two main sections are then considered:

• *R-Soft CAD software simulation of the designed waveguides (Isotropic/hemispherical source)*: The simulation results with R-soft software of three proposed optical waveguides designed are presented.

Silicon oxide waveguides using TEOS layers, Silicon-Nitride  $(Si_3N_4)$  waveguides with V-groove design and Silicon-Nitride waveguides with narrower nitride core are considered. Simulation results, the viability and validation of the designed waveguides are highlighted. This chapter also presents the design waveguide simulation results and the interpretations of the simulation results as obtained.