### New Protection Strategies for Integrated Circuits Jean-Michel Cioranesco

### ▶ To cite this version:

Jean-Michel Cioranesco. New Protection Strategies for Integrated Circuits. Cryptography and Security [cs.CR]. Université Panthéon-Sorbonne - Paris I, 2014. English. NNT: 2014PA010022 . tel-01936697

### HAL Id: tel-01936697 https://theses.hal.science/tel-01936697v1

Submitted on 27 Nov 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. U-PANTHÉON - SORBONNE - 1

## Thèse de doctorat

## Discipline : Informatique

présentée par

## Jean-Michel CIORANESCO

## Nouvelles Contre-Mesures pour la Protection de Circuit Intégrés

## New Protection Strategies for Integrated Circuits

dirigée par David NACCACHE

### Soutenue le 18 décembre 2014 devant le jury composé de :

| M. David NACCACHE          | Université Paris 1 | directeur  |

|----------------------------|--------------------|------------|

| M. Christof PAAR           | RUB                |            |

| M. Pierre Paradinas        | CNAM               |            |

| M. Jean-Jacques QUISQUATER | UCL                | rapporteur |

| M. Christophe ROSENBERGER  | ENSICAEN           | rapporteur |

| M. Camille SALINÉSI        | Université Paris 1 |            |

| M. Marc WATIN-AUGOUARD     | Général d'Armée    |            |

### Remerciements

Cela a été un grand honneur pour moi de travailler sous la direction de David Naccache. Je le remercie de m'avoir accordé sa confiance en acceptant la direction de cette thèse et me faisant découvrir le monde si passionnant de la cryptographie. Merci de m'avoir donné les clés pour comprendre quelques-uns de ses secrets. L'aide, les encouragements et les conseils que David n'a pas cessé de me prodiguer tout au long de mon travail de recherche ont été essentiels dans l'élaboration de cette thèse. Je lui exprime toute ma reconnaissance.

Je remercie chaleureusement Messieurs Jean-Jacques Quisquater et Christophe Rosenberger qui ont bien voulu accepter de rapporter sur ce travail.

Mes plus vifs remerciements s'adressent aussi à Monsieur Camille Salinési pour avoir accepté de présider le jury, ainsi qu'à Messieurs Christof Paar, Pierre Paradinas et le Général Marc Watin-Augouard qui me font l'honneur de participer au jury.

Je voudrais maintenant me tourner vers mes collègues et vers mes coauteurs. Merci à tous pour votre amitié et collaboration !

Toute ma reconnaissance, pour sa confiance et ses conseils, à Monsieur Yazid Sabeg sans qui ma vie professionnelle n'aurait pas pris l'orientation qu'elle a aujourd'hui.

Ma gratitude va aussi à Altis Semiconductor, fonderie française de semi-conducteurs, qui a permis de donner un caractère appliqué à mes recherches. Je remercie tout particulièrement l'équipe des doctorants, Roman Korkikian, Guilherme Ozari, Nicolas Champetier, Elhadi Amirouche, Rodrigo Portella et Simon Cogliani pour leur soutien. Je tiens à remercier Fabrice Nogueira et Fabien Lepape de l'équipe du failure analysis pour leurs conseils, ainsi que Laurent Dulau, Raymond Ribas et Raymond Fillipi pour nos échanges autour du design analogique. Une pensée également pour les managers d'Altis, Franck Morier, Brahim Belgacem, Arnaud Salomon, Gianmaria Mazzucheli et Pascal Louis. Je tiens également à adresser mes remerciements à l'équipe de Secure IC, dont Sylvain Guilley et Jean-Luc Danger, pour leur collaboration. Une mention particulière pour Hervé Chabanne et Vincent Despiegel de la société Morpho que je remercie pour nos échanges. Une pensée pour tous ceux que je n'ai pas pu nommer mais qui se reconnaîtront.

Mes vifs remerciements à la société Rambus et son département Cryptography Research, pour l'opportunité professionnelle qu'ils m'ont donnée. Je remercie Ron Black et Craig Hampel pour leur confiance.

Enfin, je voudrais remercier mes parents pour leur soutien sans failles, ma femme Chloé et mon fils Joseph à qui cette thèse est dédiée.

### Résumé :

La sécurité matérielle, préoccupation primordiale de nos jours, concernait au départ certaines applications très spécifiques, essentiellement bancaires, grâce à l'avènement des cartes à puce. Mais aujourd'hui, les domaines d'application de la cryptographie embarquée sont très divers et de plus en plus nombreux. Ils vont des domaines très spécialisés comme par exemple, le domaine médical, à ceux grand public avec, comme cas particulier universellement connu, les téléphones intelligents. Ces derniers se retrouvent au croisement de toutes les applications personnelles, avec un besoin évident de confidentialité des données et également de sécurité d'accès des moyens de paiement.

Les attaques matérielles invasives (celles qui ont comme résultat des circuits modifiés, souvent de façon irrémédiable) ont fait de tous temps partie de l'environnement industriel. La recherche d'innovation associée à la compétition, a constamment poussé les industriels à analyser les produits de leurs concurrents et à en faire une retro-conception pour comprendre leur fonctionnement. Ce qui fut vrai pour la mécanique, l'est également pour l'électronique. La retro-conception de circuits électroniques permet d'identifier des solutions technologiques ou des conceptions de circuits spécifiques, afin de les implémenter.

Dans le cas de la sécurité embarquée et des algorithmes cryptographiques utilisés, le secret à récupérer est double. En premier lieu, trouver de quelle façon a-t-on conçu et implémenté un circuit spécifique à un algorithme cryptographique; deuxièmement trouver les clés secrètes utilisées pour le chiffrement ou la signature. Il s'agit donc de comprendre une architecture mais également de récupérer des données. Ces clés secrètes sont le plus souvent gravées dans une mémoire non volatile, ce qui permet à un attaquant capable de sonder cette mémoire ou de l'analyser optiquement, de récupérer le secret, on parle alors d'*attaques invasives*. Une deuxième classe d'attaques permettant de récupérer le secret d'une puce électronique, est celle des *attaques par canaux cachés*. Ces attaques, afin de récupérer des secrets, utilisent l'analyse de certaines grandeurs physiques, telle que la consommation de courant par exemple.

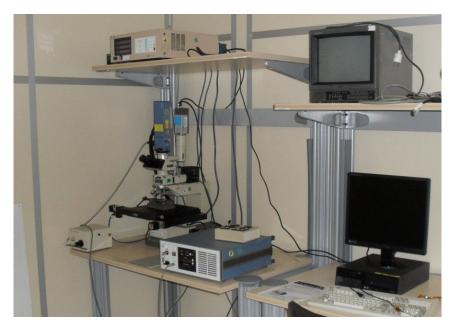

Les attaques invasives (qu'on peut caractériser comme sophistiquées) requièrent non seulement des attaquants experts en semi-conducteurs mais aussi un matériel hautement spécialisé et (par conséquent) onéreux. Ces attaques sont généralement réservées aux laboratoires de fonderies de silicium ou aux centres de recherche qui possèdent les équipements nécessaires pour les réaliser. Les techniques employées pour cette classe d'attaques découlent de celles utilisées dans les laboratoires d'analyses de défauts et de tests des circuits intégrés. Le but premier de ces laboratoires est la mise en évidence de défauts dans les circuits lors de la production, le deuxième étant de tester leur bon fonctionnement et de les déboguer si nécessaire.

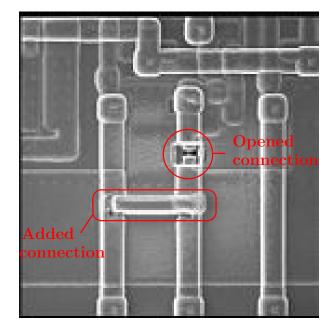

L'équipement des laboratoires d'analyses de défauts permet la mise à nu des circuits encapsulés sans les affecter, d'enlever la couche de passivation ou de certaines couches

de métaux pour l'analyse optique, ou même d'enlever ou d'ajouter certaines parties d'un circuit grâce à l'utilisation d'un FIB. Ces techniques, destinées à l'origine à des tests de qualité lors de la production de semi-conducteurs, ont été détournées de leur utilisation première et servent désormais aux attaques invasives. La première utilisation malveillante de ces outils est la retro-conception. Dans un univers technologique très compétitif, les différents acteurs d'un même marché analysent des produits concurrents afin de comprendre les solutions utilisées pour résoudre un problème donné et de détecter d'éventuelles violations des droits de brevet. Dès lors que les produits sécurisés sont apparus, l'intérêt des ingénieurs et observateurs pour la retro-conception a fortement augmenté. Prenons l'exemple des cartes téléphoniques à unités qui étaient la norme de la fin du siècle précédent. Les unités étaient représentées physiquement sur le circuit de la carte par des fusibles d'une échelle d'une centaine de micromètres. Au fur et à mesure de la conversation téléphonique, les fusibles étaient grillés en leur appliquant un courant nominal donné. La possibilité de modifier le circuit et de court-circuiter un fusible permettrait de créer une carte à utilisation illimitée. Bien heureusement, les outils nécessaires à un tel exploit sont réservés à des entités de grande ampleur. Mais la menace, bien réelle, continue de grandir avec la généralisation des cartes à puce.

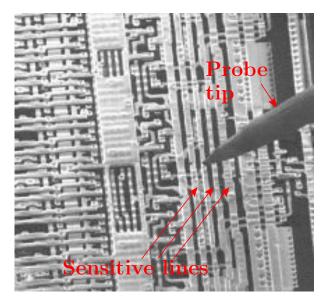

Les laboratoires de tests, quant à eux, ont pour mission de déboguer les circuits sortant de la production. Les circuits peuvent être testés au niveau des tranches des semiconducteurs, ils ne sont alors pas découpés et sont sondés directement. Les tests interviennent également après la mise en boitier où divers logiciels peuvent être téléchargés dans le circuit. Les techniques de tests peuvent être biaisées à des fins malveillantes puisqu'elles permettent de sonder un circuit sur des lignes de métaux qui ne sont pas destinées à communiquer vers l'extérieur. Ceci peut par exemple, permettre de sonder une ligne transportant les clés secrètes de l'algorithme de chiffrement. Un test de fabrication d'une puce requiert l'inclusion d'un circuit spécifique, la chaîne de scan, qui permet au testeur d'accéder à toutes les portes logiques du circuit afin de vérifier leur bon fonctionnement. Bien sûr, cette fonctionnalité constitue une menace pour la sécurité embarquée si elle n'est pas implémentée correctement. Un concepteur de circuit peut par exemple, concevoir un algorithme de chiffrement avec une clé secrète archivée dans une mémoire non volatile à laquelle seul l'algorithme pourrait accéder. Mais plus tard, dans l'intégration des différents blocs formant le circuit intégré, un autre ingénieur peut insérer une chaîne de scan par un logiciel, sans se soucier des contraintes de sécurité d'une partie du circuit, en rendant ainsi les clés secrètes accessibles par la chaîne de scan. De nombreuses attaques utilisant ce vecteur ont été rapportées. Il faut remarquer que l'inclusion d'une chaîne de scan dans un circuit sécurisé fait partie des problèmes les plus difficiles à résoudre. Une solution consiste notamment à utiliser un BIST pour scanner la partie sécurisée du circuit.

Contrairement au cas des attaques invasives, la mise en place d'attaques utilisant une chaîne de scan est facile à mettre en œuvre car généralement, elle ne nécessite pas de matériel très onéreux. Par ailleurs, très souvent les chaînes de scan sont désactivées

après les tests, au moyen de fusibles. Dans cette situation, la reconnexion de la chaîne de scan est rendue possible soit en appliquant du courant aux deux bouts du fusible, soit en utilisant une machine à faisceau d'ions focalisés (FIB) pour effectuer un dépôt de métal et reconnecter ainsi la partie brulée du fusible.

Les attaques par canaux cachés furent introduites à la fin du dernier siècle sous la forme d'analyse de la consommation de courant d'un circuit intégré et d'analyse temporelle de l'exécution d'un algorithme. Les attaques par canaux cachés font référence à l'utilisation de différentes grandeurs physiques comme source d'information. L'exemple de la consommation de courant illustre bien cette classe d'attaques. La technique actuelle des semi-conducteurs est caractérisée par le fait que les données qui ont été manipulées peuvent être corrélées avec la consommation de courant. Une observation de cette consommation permet donc d'obtenir certaines informations sur l'opération cryptographique qui a eu lieu. L'utilisation de la technique de filtrage analogique ou/et digitale, des techniques statistiques et des transformées de Fourier, rend l'analyse de la consommation de courant efficace.

Un exemple « frappant », illustrant bien le concept de canal caché cette fois-ci dans le monde physique et non pas dans celui des circuits, est l'utilisation des sons émis par les différentes touches d'un clavier pour déchiffrer des frappes. Chaque touche a un son correspondant à une fréquence particulière. Si un attaquant peut enregistrer et transférer dans le domaine fréquentiel les sons émis par les touches d'un clavier en créant une bibliothèque de ces sons, il sera par la suite capable de lire ce qu'un utilisateur tape sur ce clavier!

Il existe différents canaux cachés dans un circuit intégré, exploitables avec plus ou moins d'efforts. Il est intéressant de mentionner que ces vulnérabilités peuvent concerner la couche matérielle dans le cas d'un circuit à application spécifique (ASIC) ou programmable (FPGA), mais également la couche logicielle embarquée. Ceci est vrai pour la consommation de courant, les émanations électromagnétiques, les injections de fautes, l'analyse des temps d'exécution et autres canaux cachés.

Les méthodes pour contrer les attaques invasives et les attaques par canaux cachés sont nombreuses et nécessitent différentes stratégies en fonction de la menace à contrer. On parle de contre-mesures pour désigner les actions défensives visant à empêcher l'utilisation malveillante d'un circuit imprimé.

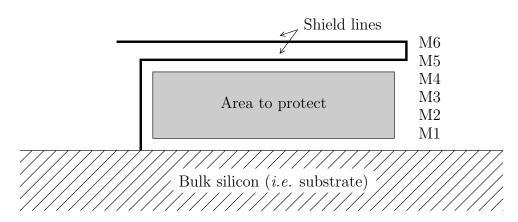

Dans le cas des attaques invasives, les méthodes mises en place pour contrer un attaquant sont généralement coûteuses en surface de puce. Certaines solutions d'encapsulations sécurisées permettent de rendre les attaques plus difficiles à mettre en œuvre mais elles ne font que complexifier la tâche sans éliminer la vulnérabilité. Une autre technique est l'utilisation d'un morceau de circuit fictif visant à perturber l'attaquant dans son effort de retro-conception, en dissimulant les fonctions de la porte logique au niveau de la configuration. La solution la plus répandue pour lutter contre le sondage de certaines lignes logiques dans le circuit est l'utilisation d'un bouclier actif. Un bouclier est composé d'un capteur et d'un petit circuit logique ; le capteur est formé d'un ou plusieurs fils en forme de serpentin s'étendant sur une ou plusieurs couches métalliques supérieures du circuit. Le circuit du bouclier actif détecte toute modification du capteur et est ainsi capable de déceler une éventuelle attaque invasive du circuit intégré en déclenchant un signal d'erreur.

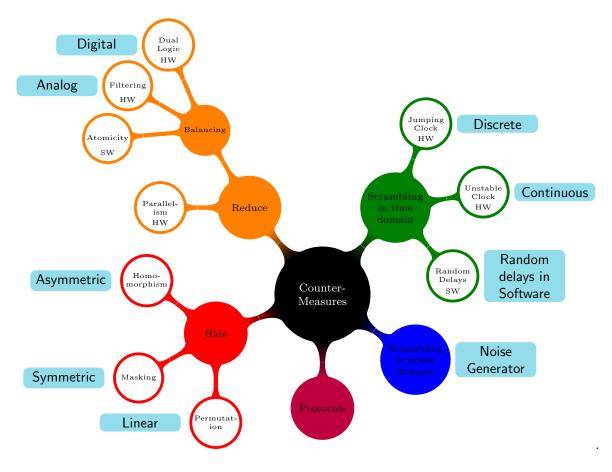

Les contre-mesures concernant les attaques par canaux cachés sont très variées. Elles peuvent être redondantes lorsque l'origine physique de la fuite d'informations est la même, c'est le cas pour la consommation de courant et les émanations électromagnétiques. La stratégie choisie est bien sûr, la mise en place de moyens supprimant cette fuite. Dans le cas de la consommation de courant, les stratégies sont multiples, on peut bien évidemment recourir à l'utilisation d'un brouilleur (sorte de générateur de bruits) et de filtrer la consommation à l'aide d'une alimentation régulée interne à la puce, mais l'efficacité reste limitée. Une autre solution consiste en l'utilisation d'une porte logique balancée, qui consomme la même quantité de courant quelle que soit la donnée manipulée, cette contre-mesure engendre une forte augmentation de la surface du circuit. La meilleure solution reste toujours et encore, la suppression des vulnérabilités à un niveau algorithmique en utilisant par exemple, des techniques de masquage.

L'objectif de cette thèse est de proposer de nouvelles solutions pour protéger les circuits intégrés contre ces attaques physiques.

La première partie décrit les notions d'attaques par canaux cachés, d'attaques invasives et de retro-conception. Plusieurs exemples de ces types d'attaques ont pu être mis en œuvre pendant le travail de recherche de cette thèse, ils sont présentés en détail dans cette partie.

La deuxième partie est consacrée à des propositions de différentes contre-mesures pour contrer des attaques par canaux cachés ayant pour vecteur la consommation de courant. La troisième partie est dédiée à la protection contre les attaques invasives en utilisant divers types de boucliers et capteurs. Nous conclurons ce manuscrit de thèse par la proposition d'un bouclier actif cryptographique inviolable ayant pour but premier de contrer le sondage, mais aussi celui de détecter l'injection de fautes et d'être immunisé contre les analyses par consommation de courant.

#### Descripteurs :

Attaques par canaux cachés, attaques invasives, attaques par fautes, analyse par consommation de courant, circuit intégré, bouclier actif, émanations électromagnétiques, chiffrement sécurisé, sécurité embarquée

### Abstract :

Hardware security awareness was at first limited to very specific applications, mainly focused on the banking industry through the generalization of smart cards. Embedded security applications are now much more diverse, going from medical applications to general public applications. Products such as smartphones, which are at the center of all personal embedded applications, introduced an obvious need for data confidentiality and security in general.

Invasive attacks on hardware have always been part of the industrial scene. Constant research on innovation associated with high competition pushed circuit manufacturers to analyze competitors' products by reverse-engineering and to investigate their functioning. Reverse engineering enables circuit architects to understand technological or design solutions, and eventually to implement them.

In the case of embedded security and cryptography, there are two secrets to recover. First, there is the way designers implemented a specific cryptographic functions, and second, which secret keys are used for encryptions or signatures. There is both an architecture to understand and data to be retrieved. Secret keys are very often stored in a non-volatile memory, which allows an attacker to probe this memory or in some cases to read keys optically. These attacks are called *invasive attacks*. A second class of attacks is that of *side-channel attacks*. These ones are using physical manifestations of a crypto algorithm, such as power consumption, to retrieve a secret.

Invasive attacks form an advance class of attacks that requires a skilled attacker and very specialized and expensive hardware. These attacks are usually only performed by foundry failure analysis lab or research labs that have the tools to perform them. Recently, the business of counterfeiting chips became so profitable that some companies offer as service to reverse engineer and analyze integrated circuits, which is perfectly legal. Techniques used in this class of attacks come from foundries' failure analysis or test laboratory techniques. The goal of these foundries departments is to detect and understand the defects in circuits during manufacturing, then test and debug circuits afterwards.

Laboratory analysis equipments enable to depackage an integrated circuit without altering its functioning, to remove the passivation layer, to remove some metal layers for optical analysis or even to edit circuitry using FIB. These techniques were at first dedicated to the quality tests during manufacturing, but have been diverted to serve invasive attacks. The first malicious use of these tools was done for reverse-engineering. In a very competitive industry environment, different actors of a same market analyze competitive products to understand which solutions have been used to solve a given problem and detect possible patent violations. Since smart cards appeared, the interest in reverse engineering got really higher. Let us take the example of the French phone smart cards that were based on the concepts of credit units, physically represented on the card by fuses of a few hundred micrometer scales. While using the phone card, credits are consumed on the card using a fuse controller that burns fuses one by one. If an attacker would be able to short-circuit one of these fuses, the card would become an unlimited credit card as the fuse could not be burned. Fortunately, the tools needed for such an exploit are reserved for large entities, nevertheless the invasive attack threat exists and will keep growing with the smart card reign. Foundries' test laboratory's mission is to debug circuits exiting production. Circuits can be tested directly on wafers, dies have not been cut-out and they get directly probed on the wafer. Tests are also performed after dies are packaged. Techniques used during the test can be skewed to serve a malicious purpose since they allow an attacker to probe metal lines which are carrying secrets. For example, an attacker could probe a key management system (KMS) key delivery bus carrying keys for an encryption algorithm, which is usually composed of a single wire in case of serial bus, and could read the key out. The test phase of chip manufacturing requires the inclusion of a specific circuit dedicated for testing the correct functioning of logic gates. This functionality is of course, a threat to embedded security if not implemented carefully. A circuit designer can for example, design a cipher algorithm using a secret key stored on a non-volatile memory embedding several countermeasures, but having a DFT engineer inserting a scan-chain into his design without paying attention to security constraints. Then an attacker entering debug mode could read out the secret key. Several attacks using this vector have been documented, and integrating DFT in a secure circuit is a very hard problem to solve. One solution is to build a BIST at the design phase to scan the secure part of the design. On the contrary of invasive attacks, attacks using scan-chain are easier to implement since they do not usually require expensive material. Very often scan-chains are deactivated after test using dedicated fuses. In this case, reconnecting the scan-chain is possible either if a current can be applied on each side of the fuse, or by using a focused ion beam machine (FIB) to reconnect the burnt fuse.

Side-channel attacks were introduced at the end of the last century with power and timing analysis. Side-channel attacks refer to the use of physical parameters to deduce information on a system's architecture and the data being processed. Power analysis is the most studied examples of this class of attacks. The actual CMOS semiconductor technology presents the characteristic that the data which are handled can be correlated with power consumption. An observation of power consumption can reveal information on the cryptographic operation that took place and thus, threaten strong protocols and algorithms. The use of analog filtering, demodulation and digital signal processing combined with statistical methods renders power analysis a very efficient tool to break a cryptosystem.

A very good example of side-channel attacks is the use of sounds to analyze keyboard strokes. On a given keyboard, each stroke creates a different sound in the frequency domain. If an attacker can record sounds of each keystroke and can create a library of these sounds, then he is able to deduce what a user is typing by recording the keyboard sound. Different side-channels can be used on an integrated circuit, accessible

with more or less effort. It is interesting to note that these leakages concerns the hardware layer in the case of an ASIC or FPGA implementation as well as the software layer. This is true in the case of power analysis, electromagnetic emanation, fault injection, timing analysis and other side channels. Countermeasures design specific defensive actions aiming to prevent certain attacks on a chip. Many hardware countermeasures exist against invasive and side-channel attacks and they are very different depending on the threat they address.

In the case of invasive attacks, countermeasures are costly in the chip area. Some products use tempered packaging, which can make attacks more difficult but without eliminating the threat. Another technique is the use of fake circuitry to make reverse engineering harder and hiding logic gate functions at layout level. The most common protection against probing is the use of active shields. A shield is composed of a sensor and a small digital or analog circuit, the sensor is composed of one or several meander shaped wires spreading on one or several metal layers. The active shield circuit purpose is to detect any modification in the sensor and to trigger an error signal.

Side-channel hardware countermeasures are very diverse and can sometimes address different threats when the physical origin of the leak is shared as it is the case for power consumption and electromagnetic analysis. The chosen strategy is of course, to suppress the information leakage. In the case of power consumption, there are multiple strategies; we can for example, use noise generators. Another solution consists in using balanced logic gates that consumed the same amount of power regardless of the data being processed, this countermeasure induces a significant increase in the chip's area. But the best solution remains to suppress leaks at an algorithmic level by using masking techniques, in this case designers need to pay attention how they handle the mask and the data.

The aim of this thesis is to propose new solutions in order to protect embedded circuits against some physical attacks described above. In a first part of the manuscript, we detail the techniques used to achieve side-channel, invasive attacks and reverseengineering. I could implement several of these attacks during my thesis research, they will be detailed extensively. In the second part we propose different hardware countermeasures against side-channel attacks. The third part is dedicated to protection strategies against invasive attacks using active shielding and we conclude this work by proposing an innovative cryptographic shield which is faulty and dpa resistant.

#### Keywords :

Side-channel attacks, invasive attacks, differential power analysis, integrated circuit, active shield, embedded security, cryptography, fault attack

- 12/223 -

## Abreviations

| 2D<br>3D<br>AES<br>ASIC<br>BIST<br>CMOS<br>CFG<br>CPU<br>CRT<br>DFA<br>DFT<br>DIY<br>DLL<br>ECC<br>EDC<br>EDC<br>EDC<br>EDC<br>EMA<br>EMC<br>FIB<br>FPGA<br>GCD<br>GEC<br>HD<br>HF<br>HNO3<br>HODPA<br>HW | 2 Dimensions (circuit)<br>3 Dimensions (circuit)<br>Advanced Encryption standard<br>Application Specific Integrated Circuit<br>Built In Self Test<br>Complementary Metal Oxide Semiconductor<br>Clock Fault Generator<br>Central Processing Unit<br>Chinese Remainder Theorem<br>Differential Fault Attacks<br>Default and Fault Tolerance<br>Do It Yourself<br>Delay-Locked Loop<br>Error-Correcting Code<br>Electromagnetic Analysis<br>Electromagnetic Compatibility<br>Focused Ion Beam<br>Field Programmable Gate Array<br>Great Common Divisor<br>General Error Counter<br>Hamming Distance<br>hydrofluoric Acid<br>High Order Differential Power Analysis<br>Hardware |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HNO3                                                                                                                                                                                                      | fuming Nitric Acid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HW                                                                                                                                                                                                        | Hamming Weight                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IC<br>KMS                                                                                                                                                                                                 | Integrated Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LASER<br>LED<br>LFSR<br>LUT                                                                                                                                                                               | Key Management System<br>Light Amplification by Stimulated Emission of Radiation<br>Light-Emitting Diode<br>Linear Feedback Shift Register<br>Look-up table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Nd :YAG<br>NMOS<br>NVM<br>PA                                                                                                                                                                              | Neodymium-doped Yttrium Aluminium Garnet<br>N-channel Metal Oxide Semiconductor<br>Non Volatile Memory<br>Power Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PLL<br>PUF                                                                                                                                                                                                | Phase Locked Loop<br>Physical Unclonable Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PMOS<br>PRNG | P-channel Metal Oxide Semiconductor<br>Pseudo Random Generator |

|--------------|----------------------------------------------------------------|

| RAM          | Random Access Memories                                         |

| RNG          | Random Number Generator                                        |

| RTL          | Register Transfer Level                                        |

| SCA          | Side-Channel Attack                                            |

| SEM          | Scanning Electron Microscopy                                   |

| SEU          | Single Event Upset                                             |

| SiP          | System in Package                                              |

| SRAM         | Static Random Access Memory                                    |

| SW           | Software                                                       |

| TC           | Target Circuit                                                 |

| PCB          | Printed Circuit Board                                          |

| PCC          | Pearson Correlation Coefficient                                |

| UV           | Ultra Violet                                                   |

## **Table of contents**

### Introduction

| Ι | Sta | te Of   | The Art                                                           | 25 |

|---|-----|---------|-------------------------------------------------------------------|----|

| 1 | Har | dware   | Attacks                                                           | 27 |

|   | 1.1 | Power   | r and Electromagnetic Analysis                                    | 27 |

|   |     | 1.1.1   | Power Analysis                                                    |    |

|   |     |         | 1.1.1.1 Introduction                                              |    |

|   |     |         | 1.1.1.2 Setting-up a DPA bench                                    | 29 |

|   |     |         | 1.1.1.3 Simple Power Analysis - Timing Analysis                   |    |

|   |     |         | 1.1.1.4 Differential Power Analysis                               | 31 |

|   |     |         | 1.1.1.5 Correlation Power Analysis                                | 32 |

|   |     | 1.1.2   | Example of Attack on AES                                          | 34 |

|   |     |         | 1.1.2.1 Correlation Frequency Analysis                            | 38 |

|   |     |         | 1.1.2.2 High Order Power Analysis                                 |    |

|   |     | 1.1.3   | Electromagnetic Analysis                                          | 39 |

|   | 1.2 | Fault . | Attacks                                                           |    |

|   |     | 1.2.1   | Simple luminous radiations                                        | 41 |

|   |     | 1.2.2   | Laser (Light Amplification by Stimulated Emission of Radiation) . | 42 |

|   |     |         | 1.2.2.1 Generalities                                              | 42 |

|   |     |         | 1.2.2.2 Mounting a Laser Fault injection bench                    | 44 |

|   |     |         | 1.2.2.3 Implementation of an attack                               | 46 |

|   |     | 1.2.3   | Voltage Glitch                                                    |    |

|   |     | 1.2.4   | Clock Glitch                                                      | 50 |

|   |     | 1.2.5   | Clock Errors                                                      | 51 |

|   |     | 1.2.6   | Temperature                                                       | 54 |

|   |     | 1.2.7   | Probing Fault Attacks                                             | 55 |

|   |     | 1.2.8   | Electromagnetic Perturbations                                     |    |

|   | 1.3 | Invasi  | ve Attacks                                                        | 57 |

|   |     | 1.3.1   | Reverse Engineering                                               | 57 |

|   |     | 1.3.2   | Optical Analysis                                                  | 61 |

|     | 1.3.3                                         | FIB Circuit Editing                                                                                                                                                                                                                      |

|-----|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Har | dware S                                       | Security Sensors and Countermeasures 65                                                                                                                                                                                                  |

| 2.1 |                                               | ty Error Management                                                                                                                                                                                                                      |

|     | 2.1.1                                         | Global Errors                                                                                                                                                                                                                            |

|     | 2.1.2                                         | Integrity Errors                                                                                                                                                                                                                         |

|     | 2.1.3                                         | Protective actions                                                                                                                                                                                                                       |

| 2.2 | Side-C                                        | Channel Countermeasures Taxonomy       62                                                                                                                                                                                                |

|     | 2.2.1                                         | Power Scrambling 68                                                                                                                                                                                                                      |

|     | 2.2.2                                         | Balancing                                                                                                                                                                                                                                |

|     | 2.2.3                                         | Dummy Cycles                                                                                                                                                                                                                             |

|     | 2.2.4                                         | Parallelism                                                                                                                                                                                                                              |

|     | 2.2.5                                         | Filtering                                                                                                                                                                                                                                |

|     | 2.2.6                                         | Power Jamming                                                                                                                                                                                                                            |

|     | 2.2.7                                         | Protocol                                                                                                                                                                                                                                 |

|     | 2.2.8                                         | Atomicity                                                                                                                                                                                                                                |

|     | 2.2.9                                         | Homomorphism                                                                                                                                                                                                                             |

|     | 2.2.10                                        | Permutation                                                                                                                                                                                                                              |

|     | 2.2.11                                        | Masking                                                                                                                                                                                                                                  |

| 2.3 | Protec                                        | tion against faults                                                                                                                                                                                                                      |

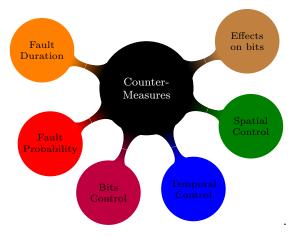

|     | 2.3.1                                         | Fault attacks taxonomy    72                                                                                                                                                                                                             |

|     |                                               | 2.3.1.1 Spatial control                                                                                                                                                                                                                  |

|     |                                               | 2.3.1.2 Temporal control                                                                                                                                                                                                                 |

|     |                                               | 2.3.1.3 Number of bits                                                                                                                                                                                                                   |

|     |                                               | 2.3.1.4 Fault probability                                                                                                                                                                                                                |

|     |                                               | 2.3.1.5 Fault duration                                                                                                                                                                                                                   |

|     |                                               | 2.3.1.6 Effect on bits                                                                                                                                                                                                                   |

|     | 2.3.2                                         | Protection against permanent fault                                                                                                                                                                                                       |

|     | 2.3.3                                         | Protection against transient faults                                                                                                                                                                                                      |

|     | 2.3.4                                         | Protection against frequency or voltage manipulations                                                                                                                                                                                    |

|     |                                               | 2.3.4.1 Protection against frequency manipulations                                                                                                                                                                                       |

|     |                                               | 2.3.4.2 Protection against voltage manipulations                                                                                                                                                                                         |

|     |                                               | 2.3.4.3 Protections against light attacks                                                                                                                                                                                                |

|     |                                               | 2.3.4.4 Generic faults countermeasures                                                                                                                                                                                                   |

| 2.4 | Protec                                        | tion Against Invasive Attacks                                                                                                                                                                                                            |

|     | 2.4.1                                         | Impacting spatial localization                                                                                                                                                                                                           |

|     | 2.4.2                                         | Active shield mechanisms                                                                                                                                                                                                                 |

|     | 2.4.3                                         | Silicon sensitivity                                                                                                                                                                                                                      |

|     | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | Hardware 8<br>2.1 Securi<br>2.1.1<br>2.1.2<br>2.1.3<br>2.2 Side-C<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8<br>2.2.9<br>2.2.10<br>2.2.11<br>2.3 Protec<br>2.3.1<br>2.3<br>2.3.4<br>2.3.2<br>2.3.3<br>2.3.4 |

| II | DPA and EMA Countermeasures                                                                                                                                                                                                                                                                                                                                                                                                       | 79                                                                                                                                 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

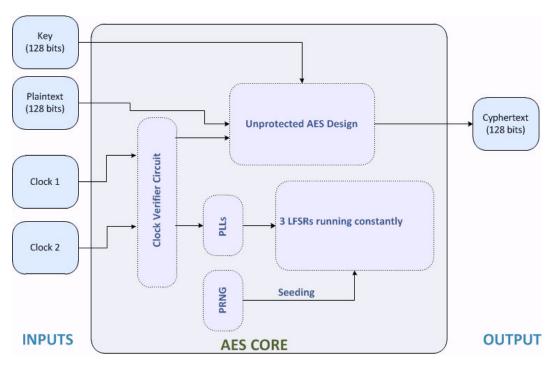

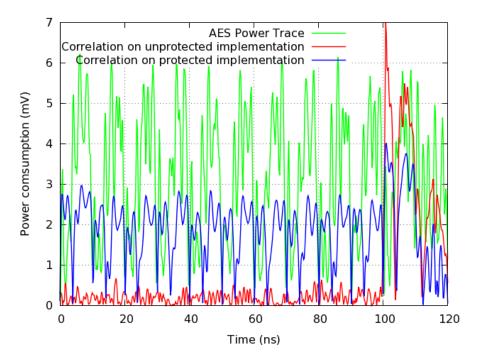

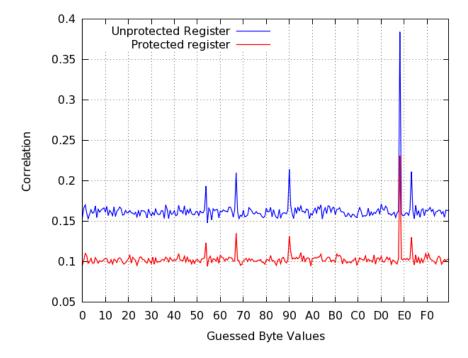

| 3  | 3.1       Introduction                                                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>81</li> <li>82</li> <li>83</li> <li>83</li> <li>84</li> <li>88</li> <li>89</li> <li>91</li> <li>92</li> <li>94</li> </ul> |

| 4  | A Low-Cost Noise Generator4.1 Proposed Design4.2 FPGA implementation                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    |

| 5  | Antagonist registers to reduce data leakage15.1Principle of antagonist register15.2FPGA Implementation15.3Experimental Results1                                                                                                                                                                                                                                                                                                   | .02                                                                                                                                |

| II | Protections Against Invasive Attacks                                                                                                                                                                                                                                                                                                                                                                                              | 07                                                                                                                                 |

| 6  | The Sandwich Capacitors Shield       1         6.1       Introduction       1         6.2       Description of the shield       1         6.2.1       Sandwich Capacitor's Grid       1         6.2.2       Evaluation circuit       1         6.3       Implementation       1         6.3.1       Sandwich Capacitor Design       1         6.3.2       Simulation Results       1         6.3.3       Going to Silicon       1 | 10<br>10<br>11<br>15<br>15                                                                                                         |

| 7  | Random Shielding       1         7.1 Introduction       1         7.2 Overview of Shielding       1         7.3 Requirements of Shielding       1         7.3.1 Manufacturability Requirements for the Shielding       1                                                                                                                                                                                                          | 20<br>24                                                                                                                           |

|   |              | 7.3.1.1 Metal extension beyond a via at end of lines                  |

|---|--------------|-----------------------------------------------------------------------|

|   |              | 7.3.1.2 Metal maximal parallel run length                             |

|   |              | 7.3.1.3 Density considerations                                        |

|   |              | 7.3.1.4 Antennae rules check                                          |

|   |              | 7.3.2 Security Requirements for the Shielding                         |

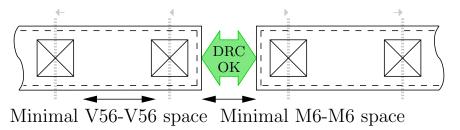

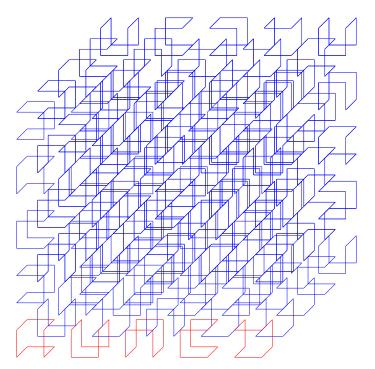

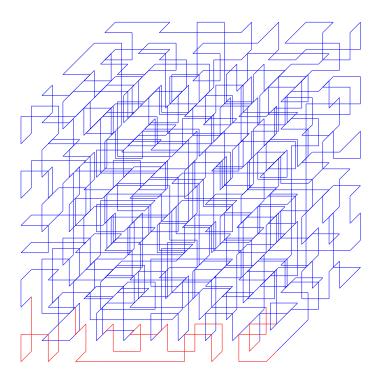

|   | 7.4          | Solution : Dense Random Spaghetti Active Shield                       |

|   |              | 7.4.1 Rationale                                                       |

|   |              | 7.4.2 Comments on the Approach                                        |

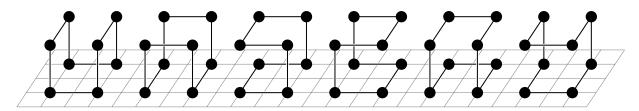

|   |              | 7.4.3 A Small Example                                                 |

|   |              | 7.4.4 Performance on Larger-Scale Circuits                            |

|   |              | 7.4.4.1 Shield Quality                                                |

|   |              | 7.4.4.2 Genetic Algorithms                                            |

|   | 7.5          | Conclusions and Perspectives                                          |

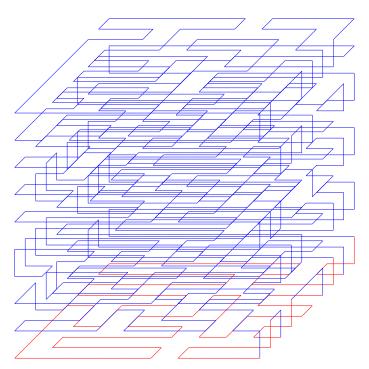

| 8 | Rec          | onfigurable Digital Shielding 139                                     |

| - | 8.1          | Introduction                                                          |

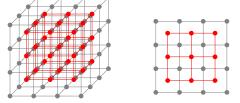

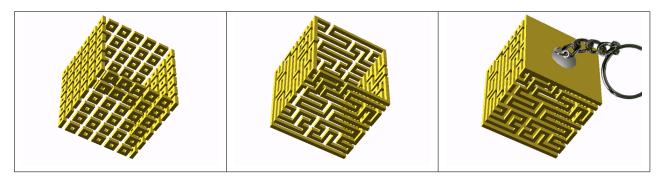

|   | 8.2          | Generating Random 3D Hamiltonian Circuits                             |

|   |              | 8.2.1 General Considerations                                          |

|   |              | 8.2.2 Odd Size Cubes                                                  |

|   | 8.3          | A Toolbox for Generating 3D Hamiltonian Cycles                        |

|   |              | 8.3.1 From Two to Three Dimensions                                    |

|   |              | 8.3.2 Random Cube Association                                         |

|   |              | 8.3.3 Cycle Stretching                                                |

|   |              | 8.3.4 Constraining Existing Hamiltonian Circuitfinding Algorithms 152 |

|   |              | 8.3.5 Branch-and-Bound                                                |

|   |              | 8.3.6 Rewriting 3D Moore Curves                                       |

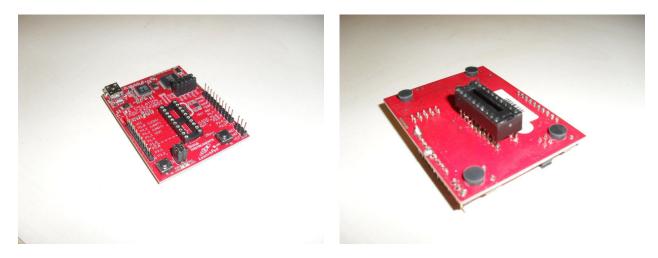

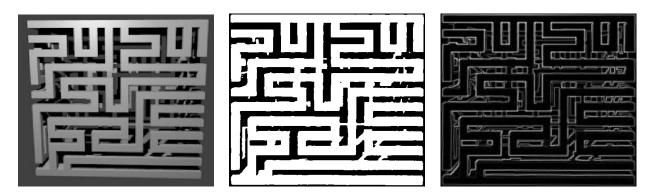

|   | 8.4          | Silicon Experiments                                                   |

|   |              | 8.4.1 Experimental Pre-Silicon Models                                 |

|   |              | 8.4.2 Going To Silicon                                                |

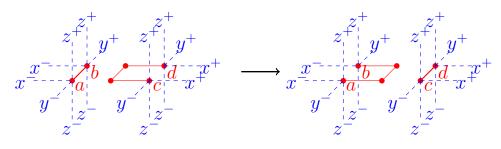

|   | 8.5          | Dynamically Reconfigurable 3D Hamiltonian Circuits                    |

|   |              | 8.5.1 Reconfigurable 3D Mazes                                         |

|   |              | 8.5.2 Description of the Dynamic Grid and the Integrity Verification  |

|   |              | Scheme                                                                |

|   |              | 8.5.3 Vulnerability to Focused Ion Beam (FIB) Attacks                 |

|   |              | 8.5.4 Vulnerability to backside FIB attacks                           |

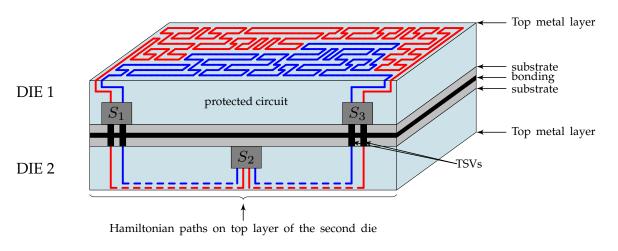

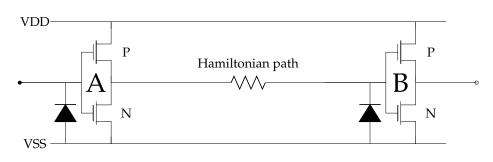

|   |              | 8.5.5 Improvement thanks to SIP technology                            |

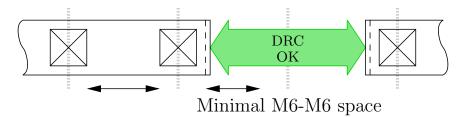

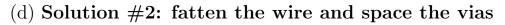

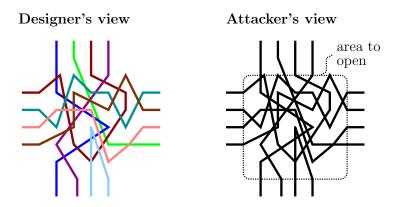

|   |              | 8.5.6 Manufacturing constraint                                        |

|   | 8.6          | Perspectives and Open Problems                                        |

| 9 | <b>Cry</b> ] | otographic Shielding 173                                              |

|   | 9.1          | Introduction                                                          |

|   |              |                                                                       |

|    | 9.2<br>9.3 | Cryptographically Secure Shield       17         9.2.1       Rationale       17         9.2.2       Structure       17         9.2.2.1       Logic Level       17         9.2.3       Connexion to the System       17         9.2.3       Connexion to the System       17         9.3.1       Layout Level       17         9.3.2       Area       18         9.3.3       Power       18 | 4<br>6<br>8<br>9<br>9<br>2 |

|----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| C  | onclu      | usion 18                                                                                                                                                                                                                                                                                                                                                                                   | 5                          |

| Ta | ble o      | f Figures 19                                                                                                                                                                                                                                                                                                                                                                               | 4                          |

| Aŗ | openo      | lix 19                                                                                                                                                                                                                                                                                                                                                                                     | 5                          |

| A  |            | <b>ng Hamiltonian Totems as Passwords19</b> Visual passwords                                                                                                                                                                                                                                                                                                                               | -                          |

|    |            | Hamiltonian Totems                                                                                                                                                                                                                                                                                                                                                                         | 8<br>0<br>2<br>4           |

## Bibliography

213

- 20/223 -

# Introduction

Nowadays, hardware trust and security play a important role because integrated circuits (IC) are present in many critical infrastructures as financial, military, health, etc. Many cryptographic IPs are integrated to assure the security of ICs. But, these cryptographic IPs, in their turn, can be attacked.

Side-channel attacks (SCA) on an integrated circuit performing cryptographic operations are a hot topic of embedded security. These threats can be classified in three categories : non-invasive, semi-invasive and invasive attacks.

- Non-invasive attacks are characterized by the fact that the chip does not suffer any physical modification, its functionality remains intact. These attacks require very little hardware and are fairly inexpensive to achieve, therefore, they are a huge problem of IC security. Such an attack can take several forms. It can use the implantation of the algorithm to monitor the timing of certain executions (example timing). Another very common threat that we will develop extensively relates to power consumption and electromagnetic emanation observation. Other form of non-invasive attacks relates to injecting fault through the chips pads (input, clocks, power supply) by glitching the signals at precise timing. The goal is to perturb the functioning of the system by external means as for instance, peaks of tension in power supply or changes of temperature [8].

- In the case of semi invasive attacks, the chips packaging is removed on its surface but the silicon remains untouched. The attacker does not have any direct contact with the surface of the integrated circuit. In this class of attacks one can find techniques allowing reading the contents of a memory cell without direct probing [84]. Some attack scenarios by fault injection are also considered to be semi-invasive [90, 89]. Semi-invasive attacks require less competence and less investment in material than the invasive ones but they still require access to chemicals and advance knowledge on decapsulation. This scenario is also very common in electromagnetic analysis, where decapsulating the chip allows near field probe to capture emissions in a more localized manner. On the other hand, on a modern integrated chip, it is not obvious to locate the best place for performing an attack.

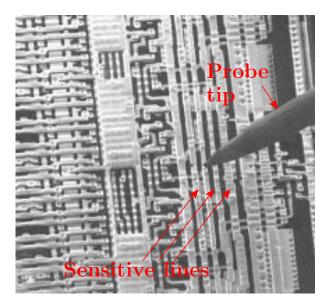

• Invasive attacks are a less common attack scenario as they require very advanced knowledge and equipment on integrated circuits. An attack is invasive when the attacker has the possibility to modify physically the chip. Thus the attacker can gain direct access to the cryptographic system at various stage of its computation. An invasive attack begins usually by removing circuits packaging, technique known as « depackaging » (see Figure 7). The package serves as a protection for the IC and its bonding, allowing simple connections to the PCB. Very often one uses fuming nitric acid (HNO3) to dissolve the packaging without damaging the chip inside and hydrofluoric acid (HF). Then, thanks to a probing station, the attacker can have direct access to top layer metal lines of the circuit and observe directly the signals which transport the data. Recently advanced techniques based on focused ion beam (FIB) have been used to modify a circuitry [46]. Invasive attacks are generally very efficient but in return, they require not only a high competence of the attacker but also very expensive equipment [60, 89]. They also serve to clone chips which contain PUFs.

This thesis is organized in three chapters. In the first chapter we will review the state of the art in hardware attacks. In the second chapter we will then propose some HW DPA countermeasures. And in the third chapter we will propose invasive attacks countermeasures.

# Part 1 State Of The Art

## 1 Hardware Attacks

## **1.1** Power and Electromagnetic Analysis

- 1.1.1 Power Analysis

- 1.1.1.1 Introduction

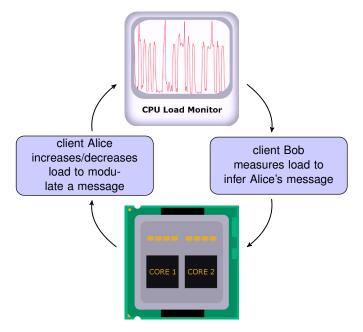

Differential Power Analysis (DPA) is a non-invasive attack that uses the biases power consumption of hardware devices to access keys and other secret information. Effective countermeasures are needed to protect keys and prevent attackers from using DPA for fraud, piracy, cloning, reverse engineering and espionage. In this paper we will present a protection circuit aiming using amplitude and time domain noise generation to hide the cryptographic algorithm signature. Power analysis was first introduced by P. Kocher [59], he discovered that the analysis of computers or microchip power consumption provide information about the operation they process. This is precisely one of the reasons why an hardware implementation of a cryptosystem might be vulnerable.

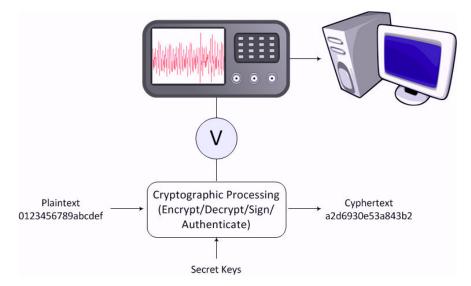

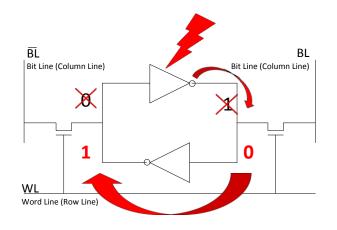

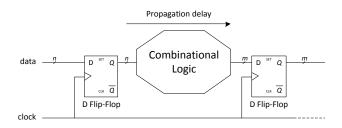

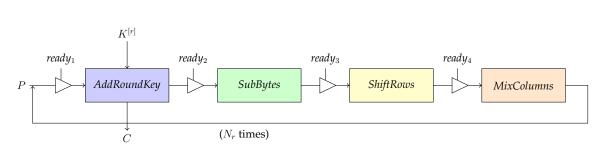

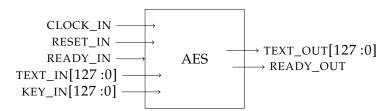

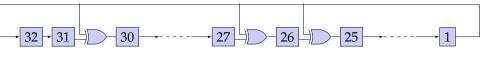

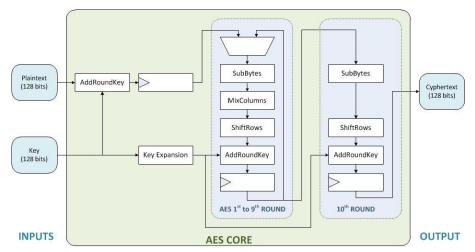

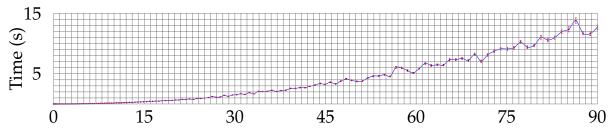

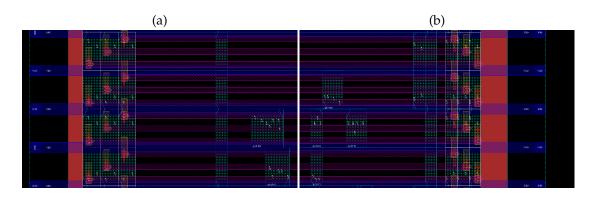

FIGURE 1.1 – schematic principle of power analysis

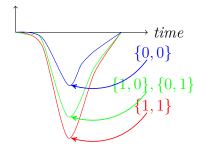

Side channel attacks have proven that a hardware implementation of a strong algorithm does not necessarily imply a secure cryptosystem, many studies [58, 59, 66] have shown that information leaks through power consumption or electromagnetic emanations. Transistors are voltage controlled gates, when a current is applied to the gate, current flows across the substrate and thecharge is delivered to the rest of the circuit. Arrangement of transistors is forming logic gates, and arrangement of gates forms a complex circuit; transistors also serve to create registers which are the mean to store data in the circuit between operations. Whenever a register is changing state, switching from  $1 \rightarrow 0$  or  $0 \rightarrow 0$ , it involves a certain power consumption.

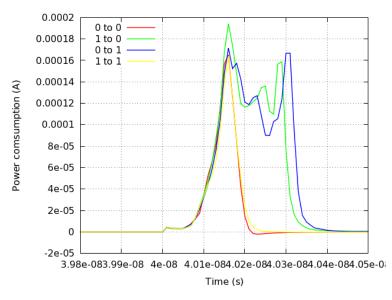

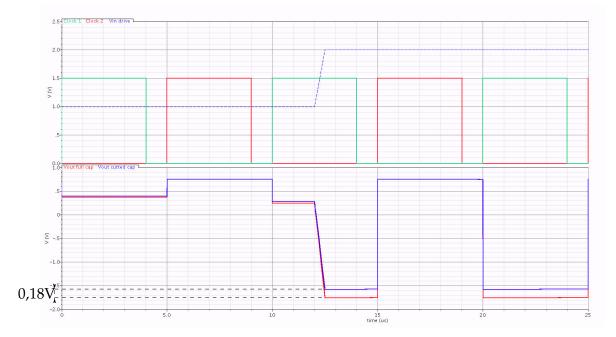

FIGURE 1.2 - Power consumption of a register for the four different possible switches

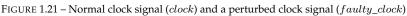

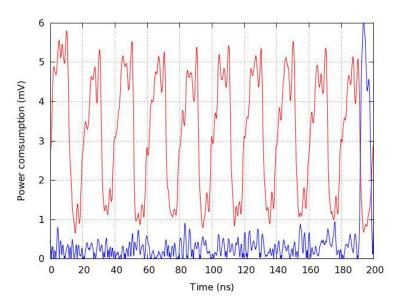

Figure 1.2 presents the differences in power consumption when a register is switching states. We simulate a one bit register with reset in a 130nm library, and we observe that the power consumption is different according to the value which is stored. As registers switches are directly linked to the data manipulated by the cryptographic algorithm, an attacker can use statistical tools on the power signatures to retrieve the secret key of a cryptographic algorithm. The overall power consumption of the chips

secret key of a cryptographic algorithm. The overall power consumption of the chips reflects the activity of all individual transistors, including registers, and is correlated to the computation being performed. In this paper we will investigate the idea of using secured registers in cryptosystems, I.E. registers that consume the same power regarding the data manipulated. Secured register would suppress the power leakage source and thwart Power Attacks.

- 28/223 -

### 1.1.1.2 Setting-up a DPA bench

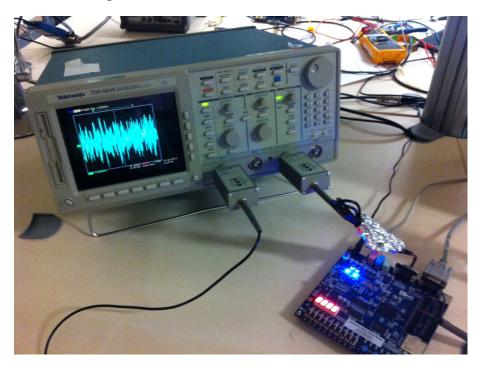

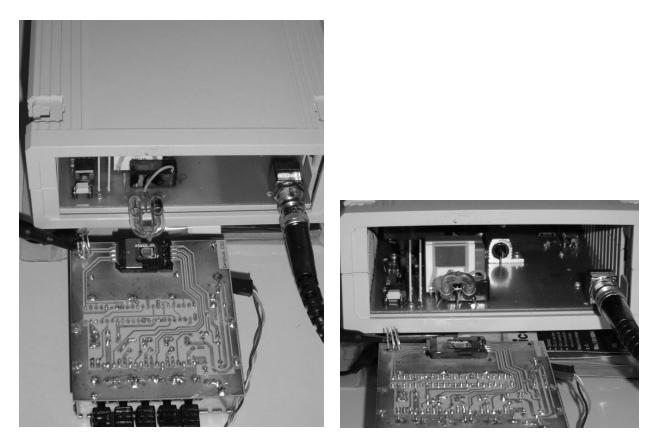

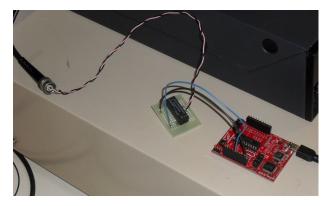

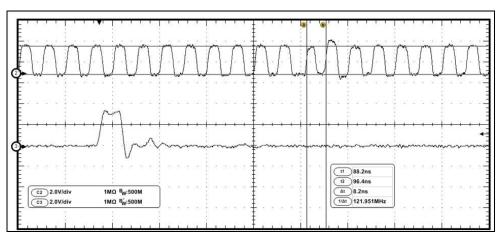

A dpa platform can be set-up with regular lab equipment. For our setup we are using the following equipment :

- A computer for data acquisition and post-processing

- An FPGA board or a micro controller to load HW and SW designs to analyze. Development boards have usually their power supply pins easily accessible on the PCB, a common practice is to analyze the current flowing through a shunt resistor placed on the power supply. It is a better practice to measure power consumption after the power regulator as it is filtering part of the meaningful information. The board will be programmed by the computer through USB interface, but it also needs to receive encryption command. We achieved this using serial interface (RS232) and a UART interface in the FPGA.

- An oscilloscope with a sampling rate higher than the device operating frequency and trigger capability 1.3. In our setup, when encryption is launched on the FPGA, a trigger signal is issued in the RTL on one pin which is connected to the oscilloscope trigger input. This enables to start data acquisition at the same exact point of encryption, we thus avoid the need of aligning traces during post-processing. In device analysis, misalignment is a major issue which is overcome in our setup.

- A voltage probe that enable us to measure the current passing through the shunt resistor. (or an EM probe)

FIGURE 1.3 – DPA bench using an oscilloscope to acquire power traces from a HW cryptosystem running on FPGA

The DPA analysis is performed in two distinct steps :

• **Data Acquisition :** The bench computer is running an acquisition software. This software is composed of several part. First it contains the FPGA compiler and programmer that enables programming the HW design to the FPGA using USB and then the JTAG debug chain. This tool allows us to synthesize our design to the FPGA.

The second part is composed of a C code which send an encryption request to the FPGA through RS232. For instance our AES design was receiving as input the 128 bit plain-text appended to the 128 bit key. Once the encryption is terminated, the design is sending back the cipher through this same RS-232. In the RTL design, we create a state for starting encryption which triggered a flag on a pin of the FPGA board. We connected this pin to the trigger input of an oscilloscope. When the oscilloscope receives an input trigger, he starts the acquisition of the measured signals for a defined number of sample. We adjusted the number of samples plus an offset to match the region of the encryption we want to capture. Once acquired the trace is dumped to the PC, in our case the oscilloscope was using a GPIB interface.

This process achieves the acquisition of one sample composed of a plain-text, a key, a cipher-text and a power trace. This process is automated to be repeated again and again to achieve several hundred of thousands of encryptions.

• Data Post Processing : Once the captured a sufficient number of traces, this data needs to be post processed. The first thing to do is needed is to realign traces. Fortunately, due to our HW trigger, traces were sufficiently aligned to post-process them without realignment. Realignment is a complex process, first a reference trace is chosen and some characteristic points are selected, usually peaks of power related to an operation. According to these characteristic, traces are analyzed one by one, and offset so that the chosen points are aligned.

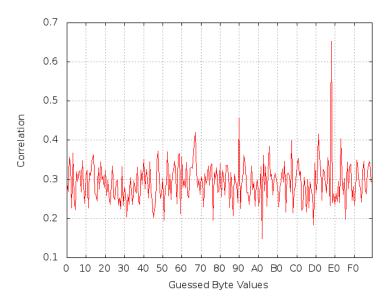

After alignment, one needs to build a power model to correlate power with computed data. The principle of power modeling is to predict the power consumption given a key guess, for each trace correspond one value of predicted power. This power model is then correlated with actual power consumption. We can also sort traces according to a selected bit and a key guess.

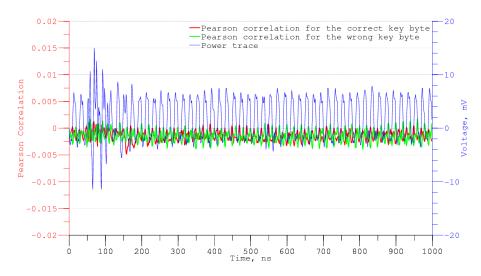

Correlation curve or dpa curve that will present a spike are of course very likely to correspond to a correct key bit or byte guess. The process is then iterated to retrieve the all keys.

### 1.1.1.3 Simple Power Analysis - Timing Analysis

Simple power Analysis is based on the sole observation of a cryptographic device power consumption. It can be performed using very little equipment, a simple oscilloscope

- 30/223 -

and voltage probe to monitor a chip's power consumption. It is a first approach on a black box attack to identify the type of algorithm or implementation we're dealing with by counting the number of rounds. On simpler algorithm SPA allows to disclose secret data by direct observation of power curves and identifying meaningful patterns. SPA involves understanding data being manipulated by the sole observation of power consumption over time.

For unprotected implementation, a single trace can be enough to get information on a cryptosystem. The famous example of RSA modular exponentiation [58] shows that a single power trace of an unprotected information can potentially reveal the secret key. This information can be done by observing the amplitude of the power consumption, or as in the RSA example it can be done by using the timing of an execution.

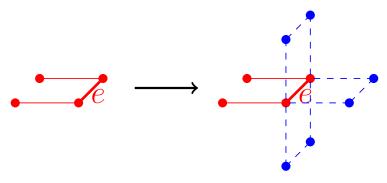

#### 1.1.1.4 Differential Power Analysis

Differential Power Analysis as it was introduced is a rather simple but efficient way of showing a power leakage. The principle is to capture a certain amount of power traces from a given crypto operation using the same secret. DPA is traditionally operated on input bits, but there are many other ways power leakage can be proved. Let us take a given algorithm, we perform a certain amount of operations using the same secret, usually a secret key, and we capture the corresponding power traces. We then select one of the input bits of the algorithm and we separate the traces in two subsets according to the value of this input bit, "0" or "1". We then take the difference of the mean of the two subsets, and we obtain what is called a DPA trace. This trace is flat but presents some spikes where the selected input bit is used, this allows us to prove there is a leak and tells us where and how the input bit is used.

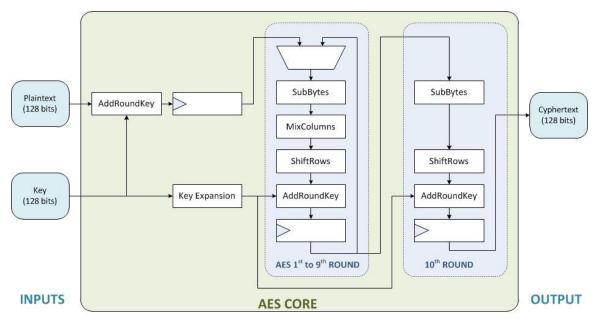

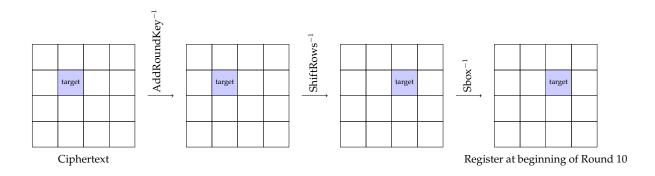

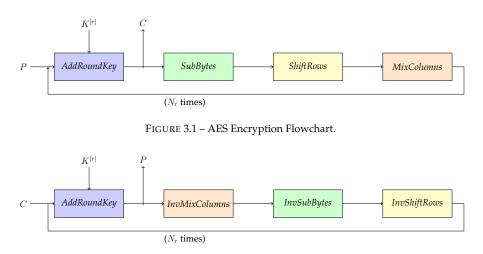

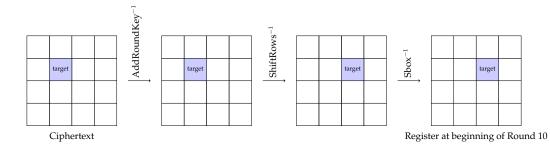

This principle allowed us to prove there is information leaked in the power trace, but it can also be used to retrieve the secret key. Let us use the same principle but with a key hypothesis. We take the example of AES 128bit. We have a set of traces T and a ciphertext C encrypted using the same unknown key K. Let us make an hypothesis on a key byte  $K_i$ , in the last round of AES the last operation is Sbox and then XOR Key, we call D the input of the Sbox, they verify the following equation :

$$C_i = Sbox(D_i) \oplus K_i.$$

We know the ciphertext C and we guessed the i-th byte of the key  $_i$ . We can then revert the equation and compute the corresponding intermediate byte  $D_i$  according to our key guess,

$$D_i = Sbox^{-1}(C_i \oplus K_j)$$

We select one bit in the byte *i* of the intermediate, and we separate traces in two subsets according to the values of this bit. We then trace the DPA curve, and if a spike is present,

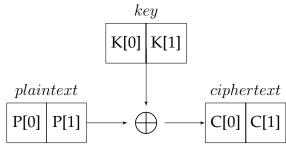

FIGURE 1.4 – Simple cipher example

there is a chance we guessed correctly the byte or parts of the bits of the key. With iteration, and guessing all bytes of the key, we can then retrieve the overall AES key.

### 1.1.1.5 Correlation Power Analysis

Correlation Power Analysis is based on the same principle, but uses a statistical test to determine correlation between power and data. To understand how CPA works, it is important to spend some time on power modeling. Let us take the example of a simple padding encryption, the key is simply XORed to the text 1.4.

In sequential circuits, data intermediates and outputs are stored in registers. When data is written to C[i] it will consume power proportionally to the data value. Depending on attacker's knowledge on the preceding state of the register, different power models are used. The most used power models are the Hamming Weight model and the Hamming Distance model. The Hamming Weight is very useful when the preceding states of the register are unknown. It is basically counting the number of ones in a set of registers. Figure 1.5 represents this power model applied to our simple XOR encryption example. On the contrary, when the preceding state of registers is known or can be guessed, we use the Hamming Distance, which computes the number of changing bits in a set of registers. An example of use of Hamming Distance to compute a power model is given in section 1.1.2.

We then apply this simple power model to the example given on Figure 1.4. We start with a key guess of  $K = \{0, 0\}$ , it is necessary to build a different power model for every key guess. We obtain the power model displayed on Figure 1.6.

Given a key guess, the Power Model we obtain predicts the power consumption of the encryption operation (Figure 1.4) according to the input plaintext. The goal is now to correlate the predicted power consumption with the real power consumption acquired through an oscilloscope. In some case when the preceding state of registers is known, we can use the Hamming Distance between the preceding state and the predicted state to mount a power model (cf. 1.1.2).

power

| Plaintext  | Cyphertext | Power Model    |

|------------|------------|----------------|

| $\{0, 0\}$ | $\{1, 0\}$ | $1\varepsilon$ |

| $\{1, 0\}$ | $\{1, 1\}$ | $2\varepsilon$ |

| $\{0,1\}$  | $\{0, 0\}$ | $0\varepsilon$ |

| $\{1,1\}$  | $\{0, 1\}$ | $1\varepsilon$ |

FIGURE 1.5 - Building a power model based on Hamming weight

| # | Plaintext  | Plaintext $\oplus$ K | Power Model |

|---|------------|----------------------|-------------|

| 1 | $\{0, 0\}$ | $\{0, 0\}$           | 0           |

| 2 | $\{0, 1\}$ | $\{0, 1\}$           | 1           |

| 3 | $\{1, 0\}$ | $\{1, 0\}$           | 1           |

| 4 | $\{1, 1\}$ | $\{1, 1\}$           | 2           |

FIGURE 1.6 – Power model corresponding to key guess  $K = \{0, 0\}$

A single trace contains too much noise to be correlated as is, we need to use a batch of multiple encryptions to perform an efficient attack. Multiple statistical tools exist to correlate real power consumption with the predicted one, they are called distinguisher. We will introduce here the most used distinguisher which is the Pearson correlation coefficient. The following formula gives the Pearson correlation between two population x and y :

$$\rho_{xy} = \frac{cov(x,y)}{\sigma_{xx}.\sigma_{yy}} = \frac{E(xy) - E(x).E(y)}{\sigma_{x}.\sigma_{y}},$$

where *cov* is the covariance,  $\sigma_x$  is the standard deviation of x ,  $\mu_x$  is the mean of x , and E is the expectation.

If we apply the formula to a batch of *n* samples, we obtain

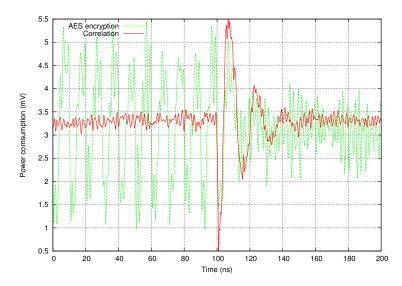

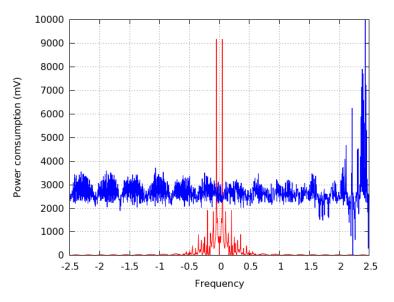

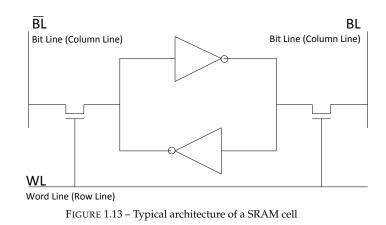

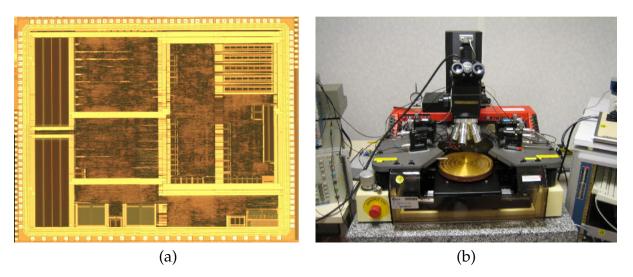

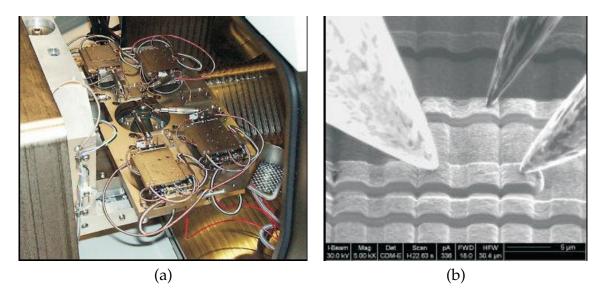

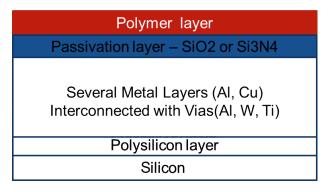

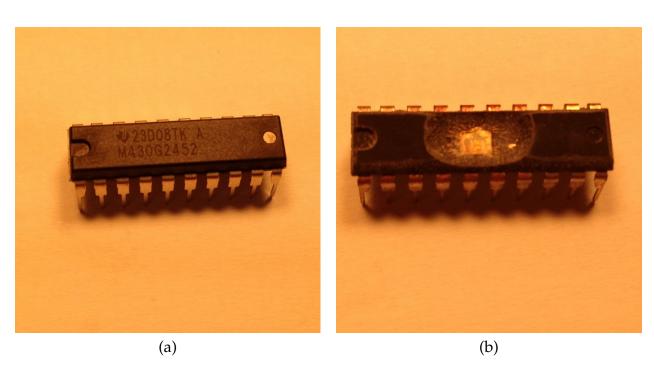

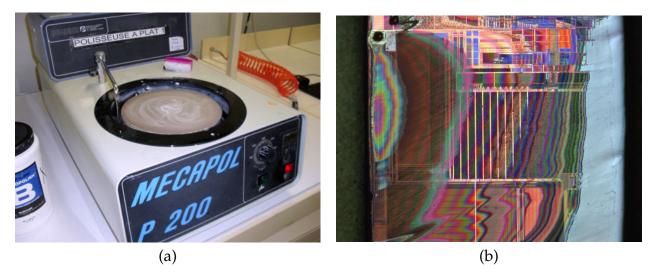

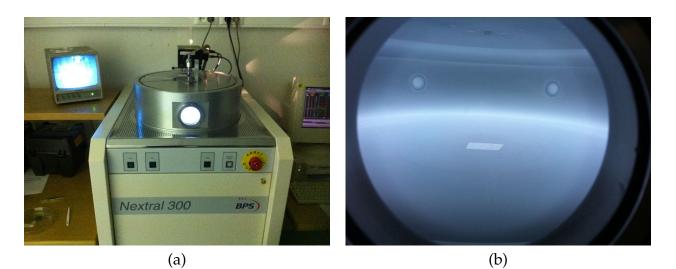

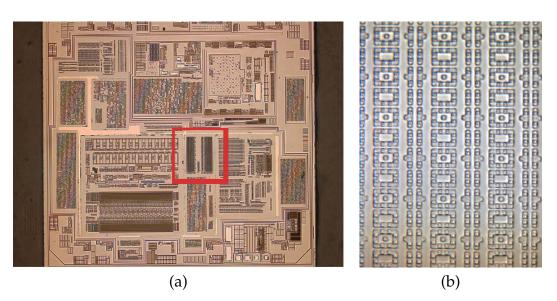

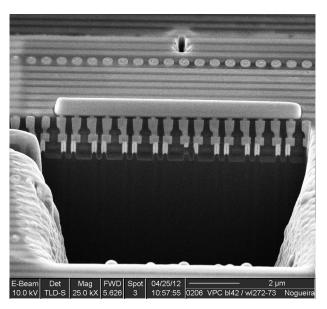

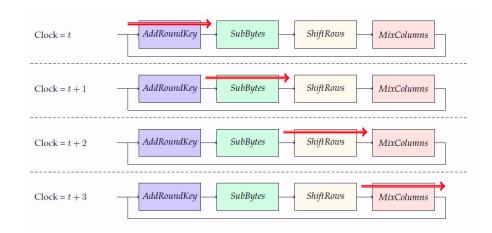

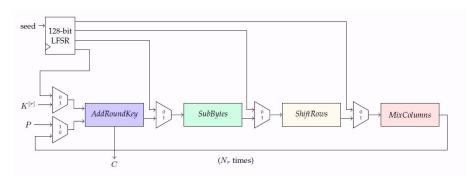

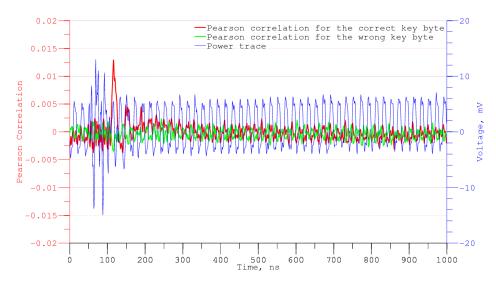

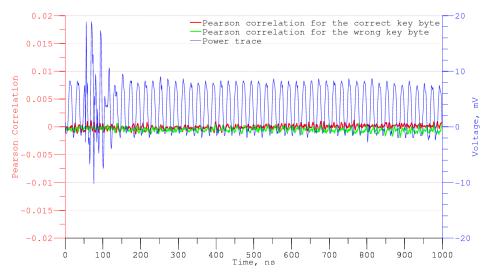

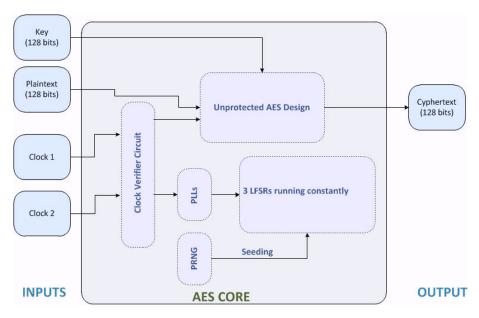

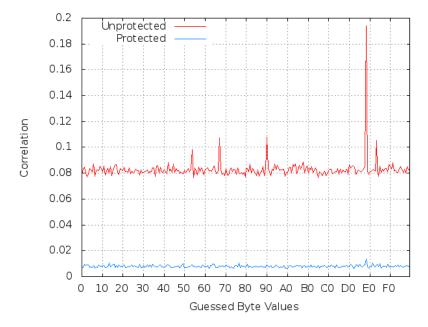

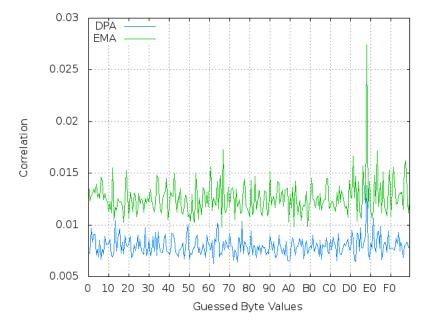

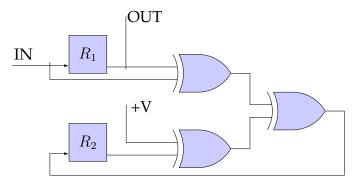

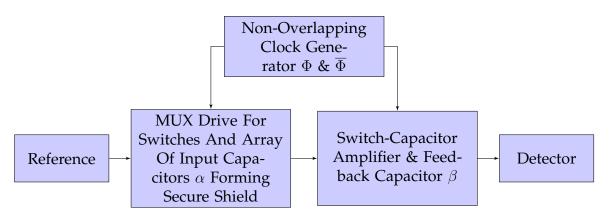

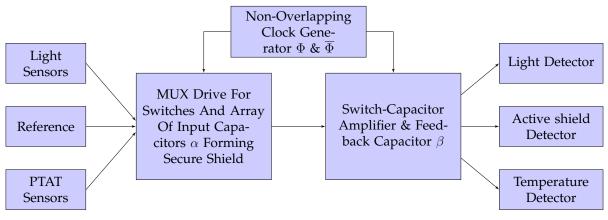

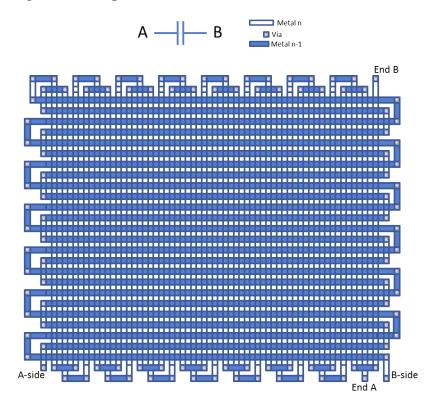

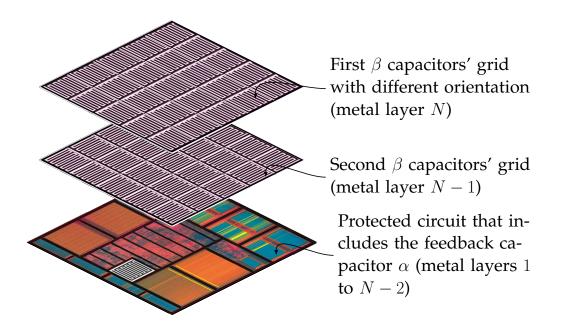

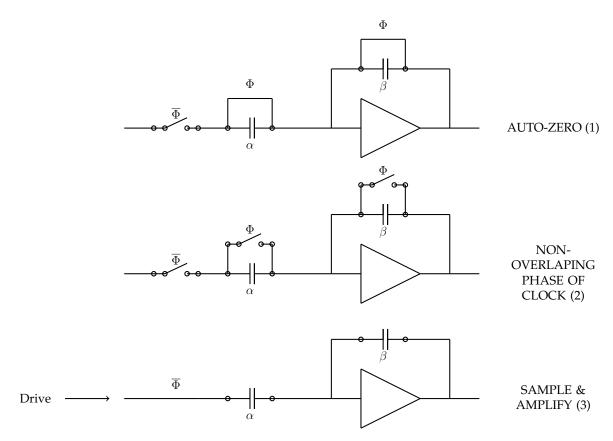

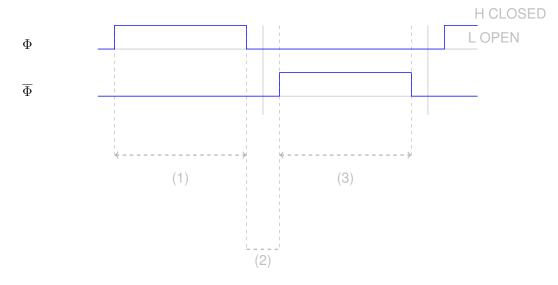

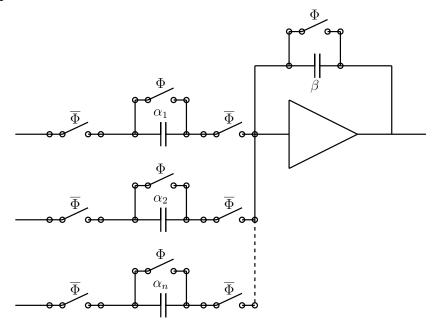

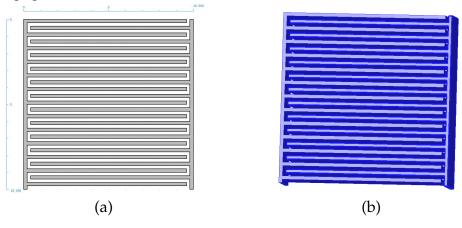

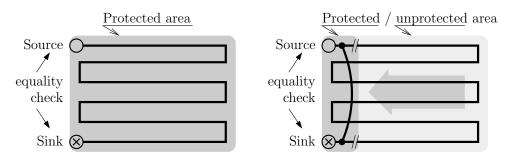

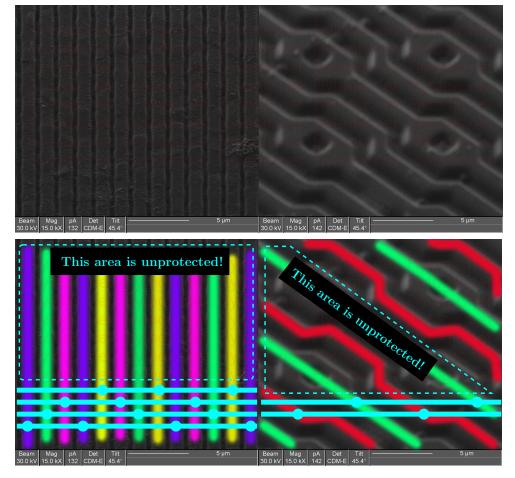

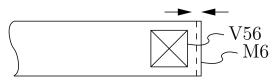

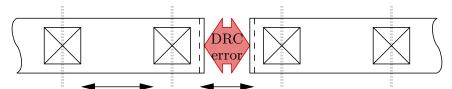

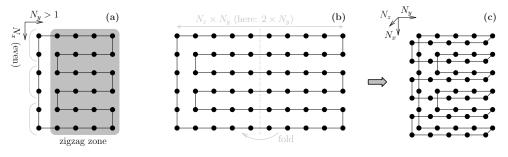

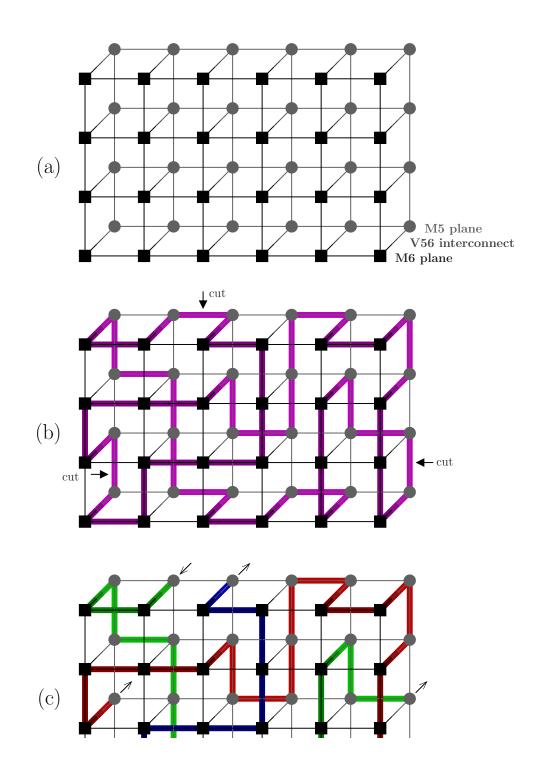

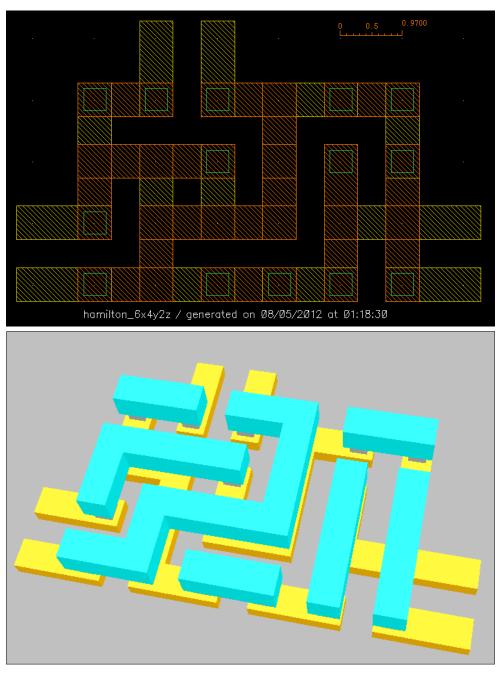

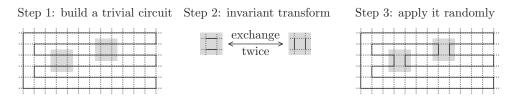

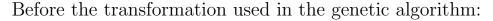

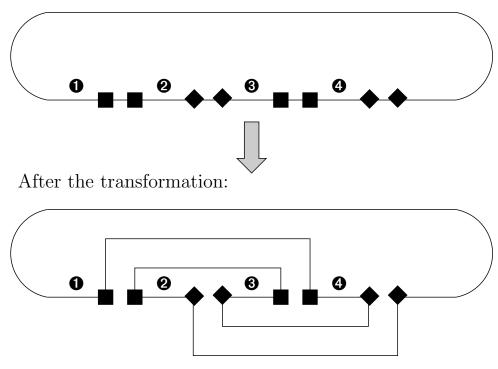

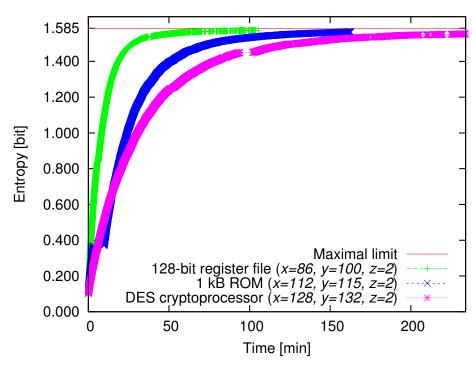

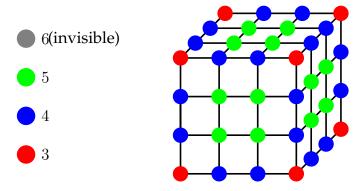

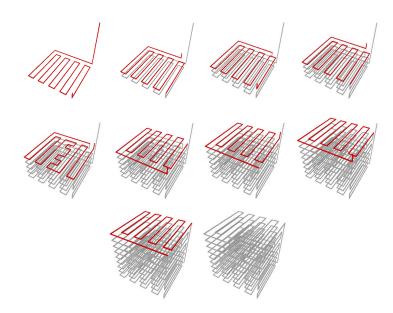

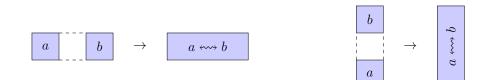

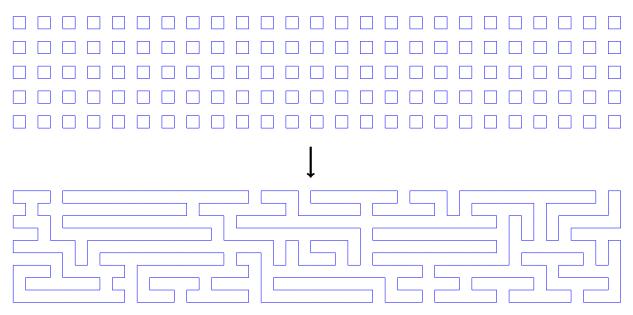

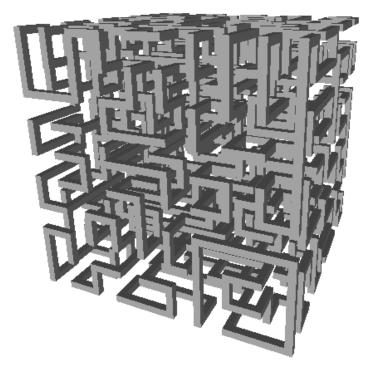

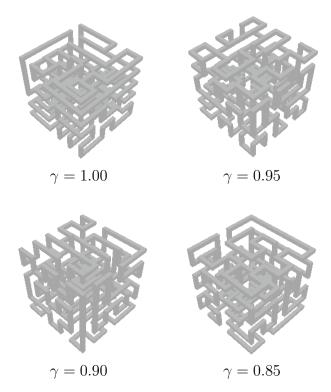

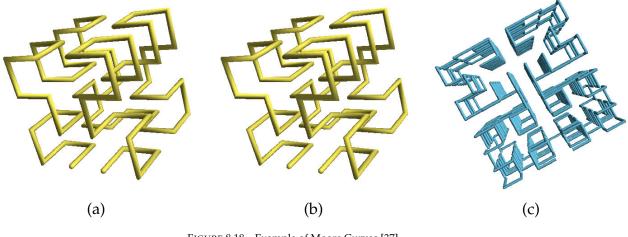

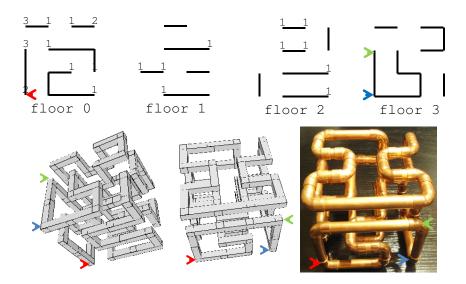

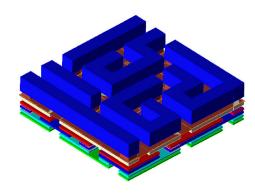

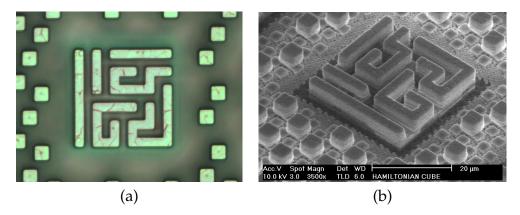

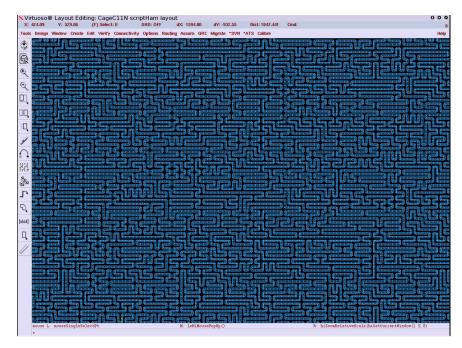

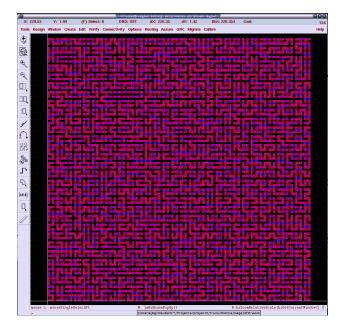

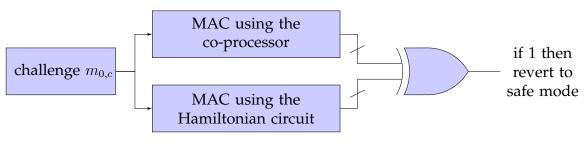

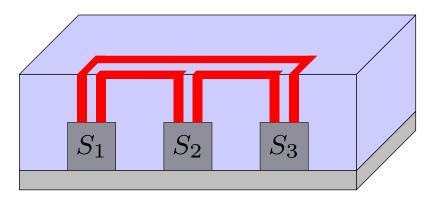

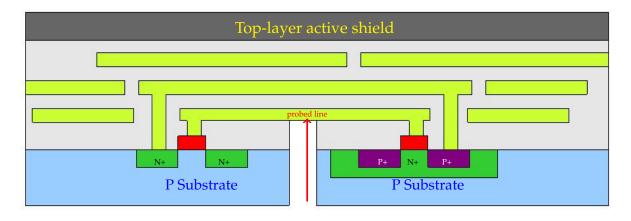

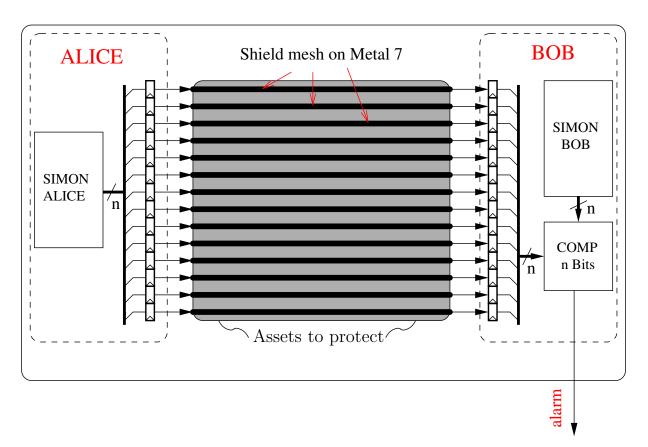

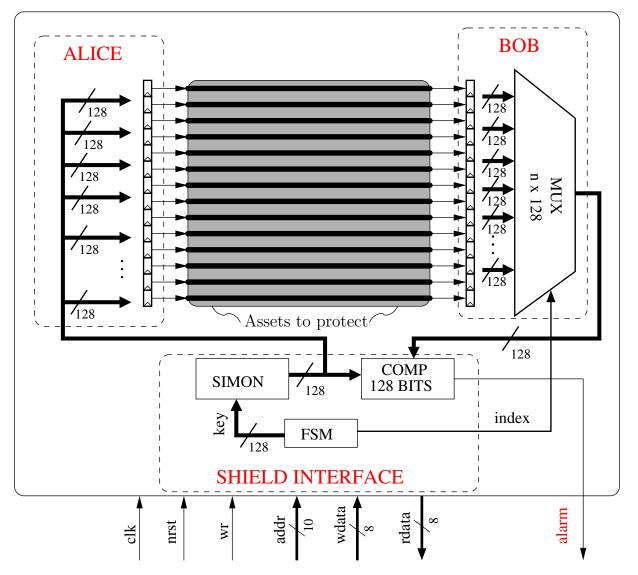

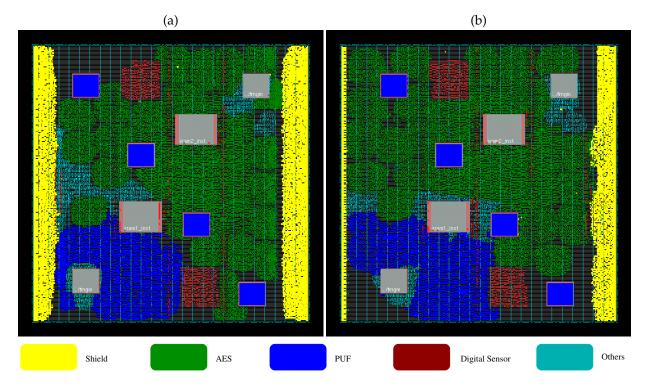

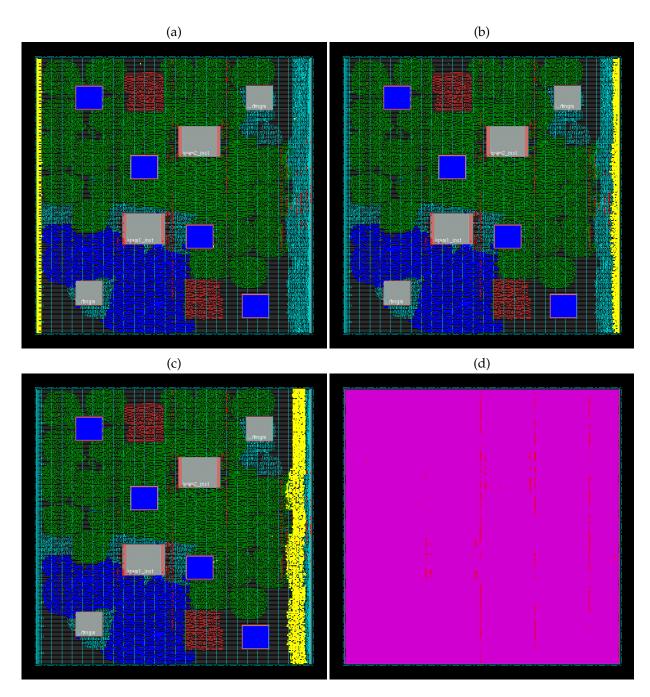

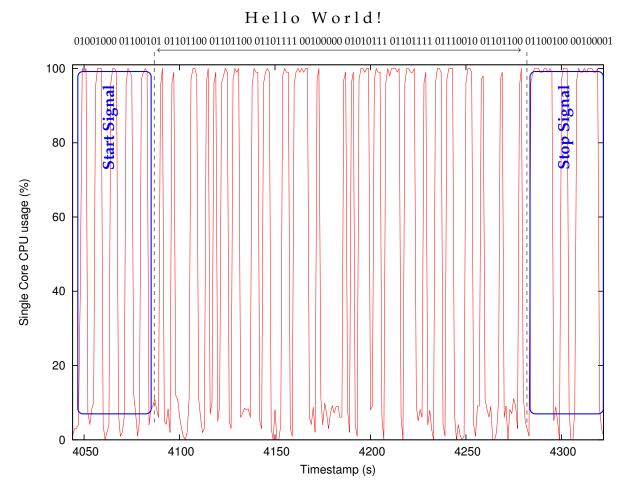

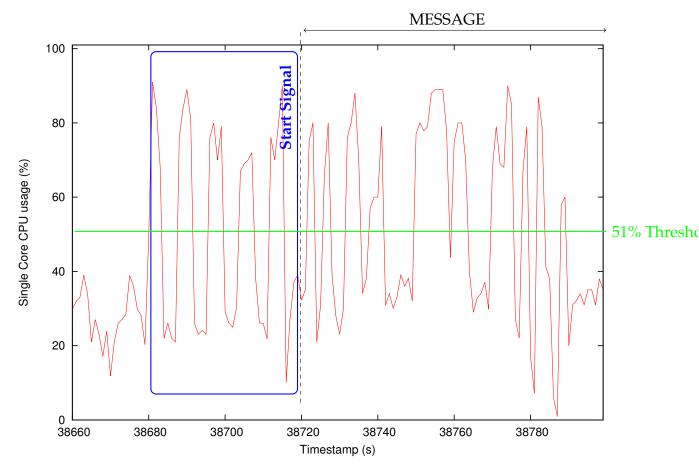

$$\rho_{xy} = \frac{n \sum_{i=1}^{n} x_i y_i - \sum_{i=1}^{n} x_i \sum_{i=1}^{n} y_i}{\sqrt{n \sum_{i=1}^{n} x_i^2 - (\sum_{i=1}^{n} x_i)^2} \sqrt{n \sum_{i=1}^{n} y_i^2 - (\sum_{i=1}^{n} y_i)^2}}$$