# Performance Analysis Strategies for Task-based Applications on Hybrid Platforms

Vinícius Garcia Pinto

# ▶ To cite this version:

Vinícius Garcia Pinto. Performance Analysis Strategies for Task-based Applications on Hybrid Platforms. Distributed, Parallel, and Cluster Computing [cs.DC]. Universidade Federal do Rio Grande do Sul - UFRGS; UGA - Université Grenoble Alpes, 2018. English. NNT: . tel-01962333

# HAL Id: tel-01962333 https://theses.hal.science/tel-01962333

Submitted on 14 Jan 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Communauté UNIVERSITÉ Grenoble Alpes

# THÈSE

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

préparée dans le cadre d'une cotutelle *entre la Communauté Université Grenoble Alpes* et *l'Universidade Federal do Rio Grande do Sul*

Spécialité : Informatique

Arrêté ministériel : le 6 janvier 2005 – 25 mai 2016

Présentée par

# Vinícius GARCIA PINTO

Thèse dirigée par Arnaud LEGRAND et Nicolas MAILLARD préparée au sein des Laboratoire d'Informatique de Grenoble et Grupo de Processamento Paralelo e Distribuído dans l'École Doctorale Mathématiques, Sciences et Technologies de l'Information, Informatique et Programa de Pós-Graduação em Computação

# Stratégies d'analyse de performance pour les applications basées sur tâches sur plates-formes hybrides

Thèse soutenue publiquement le **30 octobre 2018**, devant le jury composé de :

M. Philippe O. A. NAVAUX Professeur, Universidade Federal do Rio Grande do Sul, Président M. Alfredo GOLDMAN VEL LEJBMAN Professeur, Universidade de São Paulo, Rapporteur M. Gaël THOMAS Professeur, Telecom SudParis, Rapporteur M. Mathieu FAVERGE Maître de conférences, Institut Polytechnique de Bordeaux, Examinateur M. Gerson Geraldo HOMRICH CAVALHEIRO Professeur, Universidade Federal de Pelotas, Examinateur M. Bernd MOHR Chargé de Recherche, Forschungszentrum Jülich, Examinateur M. Arnaud LEGRAND Chargé de Recherche, Laboratoire d'Informatique de Grenoble, Directeur de thèse M. Nicolas MAILLARD Professeur, Universidade Federal do Rio Grande do Sul, Directeur de thèse

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

VINÍCIUS GARCIA PINTO

# Performance Analysis Strategies for Task-based Applications on Hybrid Platforms

Thesis prepared under a *co-tutelle* agreement and presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science at the Federal University of Rio Grande do Sul and the University Grenoble Alpes

Advisor (UFRGS): Prof. Dr. Nicolas Maillard Advisor (UGA): Prof. Dr. Arnaud Legrand

Porto Alegre October 2018 Pinto, Vinícius Garcia

Performance Analysis Strategies for Task-based Applications on Hybrid Platforms / Vinícius Garcia Pinto. – Porto Alegre: PPGC da UFRGS, 2018.

178 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2018. Advisor (UFRGS): Nicolas Maillard; Advisor (UGA): Arnaud Legrand.

1. Performance analysis. 2. Task-based applications. 3. Hybrid platforms. 4. Trace visualization. I. Maillard, Nicolas. II. Legrand, Arnaud. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PPGC: Prof. João Luiz Dihl Comba Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

### ACKNOWLEDGMENTS

First I would like to thank CAPES (Brazilian Federal Agency for Support and Evaluation of Graduate Education) for the financial support during these years. I also would like to thank Inria (French National Research Institute for the Digital Sciences) for giving me access to their incredible technical, physical and personnel infrastructure. Additionally, I would like to thank the Institute of Informatics at the Federal University of Rio Grande do Sul and the Grenoble Informatics Laboratory (LIG) at the University Grenoble Alpes.

I would like to thank my advisors Arnaud Legrand and Nicolas Maillard. Nicolas, thank you for opening me the doors of the academic world and for encouraging me to conduct this Ph.D. in an international cooperation context. Arnaud, I am so grateful for having the chance to work with you. I really appreciate your ability to formulate new hipothesis and solutions even after we show you the same result for the tenth time, and, of course, always taking care of the reproducibility aspects. You are a source of inspiration and motivation in my incipient career as a researcher. Finally, I would like to thank Lucas Mello Schnorr. Lucas, even if it has not been possible to include you as my official co-advisor due to bureaucratic formalities, you have spared no efforts to help me, and I am very thankful for your all support with very nice insights and encouragements. I am sure that this work would not be the same without your endless list of suggestions and improvements.

I would like to thank Samuel Thibault, Luka Stanisic and Vincent Danjean who are my co-authors on several papers in the subject of this thesis. Vincent was also my first contact in France, and I am thankful not only for your technical support but also with your academic support with the formalities and paperwork for administrative stuff.

I would like to thank all my colleagues from GPPD and POLARIS/DATAMOVE teams. I really appreciate your company during all these years, not only in the technical discussions but also in the lunch (or sometimes procrastination) time. I would like to thank, in particular, my colleagues from offices 205 (INF), B116 (INRIA) and 434 (IMAG) for tolerating me during these years.

I would like to thank the members of the jury committee: Alfredo Goldman Vel Lejbman, Gaël Thomas, Mathieu Faverge, Gerson Geraldo Homrich Cavalheiro, Bernd Mohr and Philippe Olivier Alexandre Navaux for accepting the invitation, for the nice discussion and their valuable suggestions. I would like to warmly thank my parents for all their support and patience. I also would like to thank Leandro and my sister, Larissa, who was my inspiration to embrace this crazy and challenging adventure called the academic career.

Finally, I would like to thank my lovely fiancee, Franciele Cordeiro, for being beside me (on both sides of the Atlantic) during all this long journey. I couldn't have done this work without you, your support, your suggestions, your courage, and your patience. Thank you for sharing your life and your knowledge with me.

## ABSTRACT

Programming paradigms in High-Performance Computing have been shifting toward taskbased models that are capable of adapting readily to heterogeneous and scalable supercomputers. The performance of task-based applications heavily depends on the runtime scheduling heuristics and on its ability to exploit computing and communication resources.

Unfortunately, the traditional performance analysis strategies are unfit to fully understand task-based runtime systems and applications: they expect a regular behavior with communication and computation phases, while task-based applications demonstrate no clear phases. Moreover, the finer granularity of task-based applications typically induces a stochastic behavior that leads to irregular structures that are difficult to analyze.

In this thesis, we propose performance analysis strategies that exploit the combination of application structure, scheduler, and hardware information. We show how our strategies can help to understand performance issues of task-based applications running on hybrid platforms. Our performance analysis strategies are built on top of modern data analysis tools, enabling the creation of custom visualization panels that allow understanding and pinpointing performance problems incurred by bad scheduling decisions and incorrect runtime system and platform configuration. By combining simulation and debugging, we are also able to build a visual representation of the internal state and the estimations computed by the scheduler when scheduling a new task.

We validate our proposal by analyzing traces from a Cholesky decomposition implemented with the StarPU task-based runtime system and running on hybrid (CPU/GPU) platforms. Our case studies show how to enhance the task partitioning among the multi-(GPU, core) to get closer to theoretical lower bounds, how to improve MPI pipelining in multi-(node, core, GPU) to reduce the slow start in distributed nodes and how to upgrade the runtime system to increase MPI bandwidth. By employing simulation and debugging strategies, we also provide a workflow to investigate, in depth, assumptions concerning the scheduler decisions. This allows us to suggest changes to improve the runtime system scheduling and prefetch mechanisms.

**Keywords:** Performance analysis. task-based applications. hybrid platforms. trace visualization.

# Estratégias de Análise de Desempenho para Aplicações baseadas em Tarefas em Plataformas Híbridas

#### **RESUMO**

No contexto da Computação de Alto Desempenho, a utilização de modelos de programação baseados em paralelismo de tarefas é cada vez mais frequente uma vez que estes são capazes de se adaptar mais facilmente à supercomputadores que utilizam arquiteturas híbridas. O desempenho das aplicações baseadas em tarefas depende fortemente de heurísticas de escalonamento dinâmicas e da habilidade destas em explorar os recursos de computação e comunicação.

Infelizmente, as estratégias de análise de desempenho tradicionais não são adequadas à análise de ambientes de execução dinâmicos e de aplicações baseadas em tarefas. Estas estratégias esperam, em geral, um comportamento relativamente regular com alternância de fases de computação e comunicação enquanto as aplicações baseadas em tarefas não apresentam estruturas tão bem definidas. Além disso, o assincronismo e a granularidade mais fina das aplicações baseadas em tarefas induz comportamentos estocásticos que levam à estruturas naturalmente irregulares que são difíceis de analisar.

Nesta tese, nós propomos estratégias de análise de desempenho que exploram simultaneamente a estrutura da aplicação, características do escalonador e informações da plataforma. Nós mostramos como nossas estratégias podem ajudar à compreender e resolver problemas de desempenho não triviais em aplicações baseadas em tarefas executadasm em plataformas híbridas. Nossas estratégias de análise de desempenho são construídas sobre ferramentas de análise de dados modernas e genéricas, o que possibilita a criação de visualizações específicas e adaptadas. Estas visualizações permitem a compreensão e a identificação de problemas de desempenho ocasionados por decisões de escalonamento impróprias bem como por configurações incorretas do ambiente de execução e da plataforma. Por meio da combinação de técnicas de simulação e depuração com visualizações especificamente desenvolvidas para representar o estado interno do escalonador e suas estimativas, nós mostramos como é possível avaliar certas hipóteses sobre a pertinência das decisões de escalonamento.

Nós validamos nossa propostas por meio da análise de rastros de execução de uma fatorização de Cholesky implementada com o ambiente de execução StarPU e executada com diferentes plataformas híbridas (CPU/GPU). Nossos estudos de caso mostram como melhorar a partição das tarefas entre diferentes núcleos CPU e GPUs para se aproximar dos limites inferiores teóricos, como melhorar o pipeline das operações MPI entre diferentes nós (*multicore* e multi-GPUs) para acelerar o início da aplicação, e como melhorar o ambiente de execução para aumentar a largura de banda MPI. O emprego de estratégias de simulação e depuração, nos fornece uma abordagem que permite examinar, em detalhes, as decisões de escalonamento bem como de propor melhorias nos mecanismos de escalonamento e *prefetch* do ambiente de execução.

**Palavras-chave:** análise de desempenho, aplicações baseadas em tarefas, plataformas híbridas, visualização de rastros.

# Stratégies d'analyse de performance pour les applications basées sur tâches sur plates-formes hybrides

## ABSTRACT

Dans le cadre du calcul haute performance, l'utilisation d'un modèle de programmation basé sur un parallélisme de tâche est de plus en plus courant. Cette approche permet de s'adapter plus facilement aux super-ordinateurs utilisant des architectures hybrides. La performance d'applications à bases de tâches dépend fortement des heuristiques d'ordonnancement dynamiques sous-jacente et de leur capacité à exploiter les ressources de calcul et de communication.

Malheureusement, les stratégies d'analyse de performance traditionnelles ne sont pas adaptées à l'analyse de supports d'exécution dynamiques et d'applications basées sur des tâches. Ces stratégies supposent en général un comportement relativement régulier avec des alternances de phases de calcul et de communication alors que les applications basées sur des tâches ne présentent pas de structures aussi précises. Par ailleurs, l'asynchronisme et la granularité plus fine des applications basées sur des tâches induit des comportements stochastiques qui donnent lieu à des structures naturellement irrégulières qui sont difficiles à analyser.

Dans cette thèse, nous proposons des stratégies d'analyse de performance qui exploitent à la fois la structure de l'application, des caractéristiques de l'ordonnancement et des informations de la plate-forme. Nous présentons comment nos stratégies peuvent aider à comprendre et résoudre des problèmes de performance non triviaux dans des applications basée sur des tâches qui s'exécutent sur des plates-formes hybrides. Nos stratégies d'analyse de performance sont construites à l'aide d'outils d'analyse de données génériques et modernes, ce qui permet de créer des vues spécifiques et adaptées. Ces vues permettent la compréhension et l'identification de problèmes de performances occasionnés par de mauvaises décisions d'ordonnancement ou bien des configurations incorrectes du support d'exécution et de la plate-forme. En combinant des techniques de simulation et de débogage à des vues spécifiquement développées pour représenter l'état interne de l'ordonnançeur et qui le conduisent à prendre ses décisions, nous avons montré qu'il était possible d'évaluer certaines hypothèses sur la pertinence de ses choix.

Nous validons notre proposition en analysant de nombreuses traces d'exécutions d'une factorisation de Cholesky implémenté avec le support d'exécution StarPU et exécutée

sur différentes plates-formes hybrides (CPU/GPU). Nos études de cas montrent comment améliorer la partition des tâches entre les différents cœurs et GPUS pour s'approcher des bornes inférieures théoriques, comment améliorer le pipeline des opérations MPI entre les différents nœuds (multi-coeurs et multi-GPUs) pour accélérer le démarrage de l'application, et comment améliorer le support d'exécution pour augmenter la bande passante MPI. L'emploi des stratégies de simulation et débogage, nous fournissons une approche permettant d'examiner, en détail, les décisions d'ordonnancement et ainsi de proposer des améliorations des mécanismes d'ordonnancement et de prefetch du support d'exécution.

**Keywords:** analyse de performance, parallélisme de tâche, plates-formes hybrides, visualisation de trace.

# LIST OF FIGURES

| Figure 1.1  | The layout of a current parallel computer with a multicore processor         |      |

|-------------|------------------------------------------------------------------------------|------|

| and a       | a manycore accelerator device                                                | 23   |

| Figure 1.2  | Two current parallel computers                                               | 24   |

| Figure 1.3  | The basis of the proposed analysis strategies.                               | 26   |

| -           | The layout of a hypothetical accelerator                                     |      |

| Figure 2.2  | Evolution of the use of accelerators in TOP500 systems                       | 32   |

| Figure 2.3  | An example of recursive tasks in Cilk.                                       | 35   |

| Figure 2.4  | A pseudo-code illustrating how to express dependencies in Cilk and           |      |

|             | 1MP                                                                          |      |

| Figure 2.5  | An example of task description in ParSEC                                     | 39   |

| Figure 2.6  | A pseudo-code of tasks definition in OmpSs                                   | 40   |

| Figure 2.7  | An example of XKaapi task with multiple implementations                      | 42   |

| Figure 2.8  | An example of StarPU codelet                                                 | 43   |

| Figure 2.9  | An example of the current hardware and software stack                        | 47   |

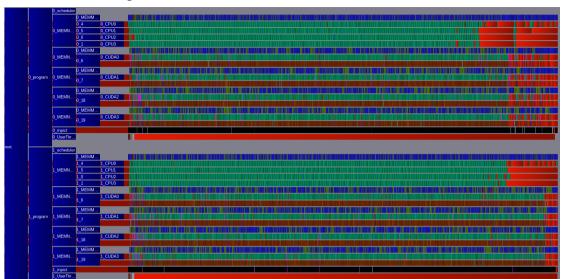

| Figure 3.1  | A StarPU-MPI trace visualized with ViTE.                                     | 51   |

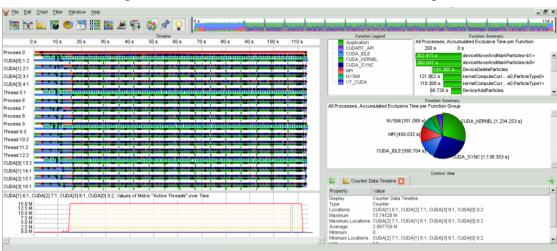

| Figure 3.2  | Visualization of an OTF2 trace in Vampir.                                    | 52   |

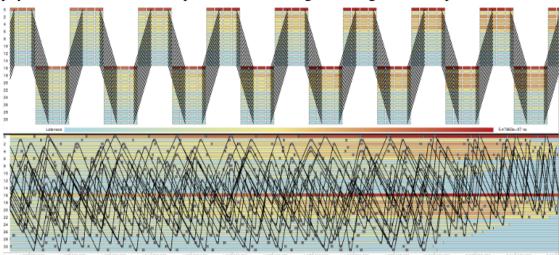

| Figure 3.3  | A comparison between logical and physical views in Ravel                     | 53   |

| Figure 3.4  | Visualization of communication arrows in Vampir and in Brendel's Edge        |      |

| Bund        | lling Approach                                                               | 54   |

| Figure 3.5  | Summarized views of communications in Vampir and Brendel's pro-              |      |

| pose        | d strategy                                                                   | 54   |

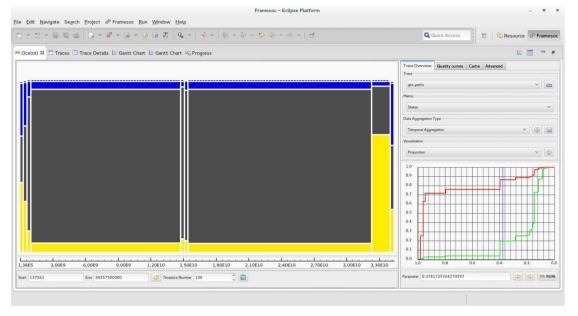

| Figure 3.6  | An Ocelotl aggregated view in FrameSoc.                                      | 56   |

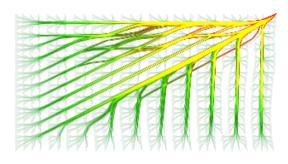

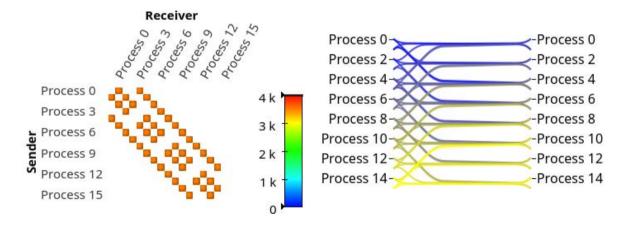

| -           | An example of the trace visualization with dependencies proposed by          | 57   |

| -           | gen et al. (2015)                                                            |      |

| U           | An example of the DAG-based visualization proposed by DAGViz                 |      |

| 0           | The Delay Spotter representation of delays in the DAG.                       | 60   |

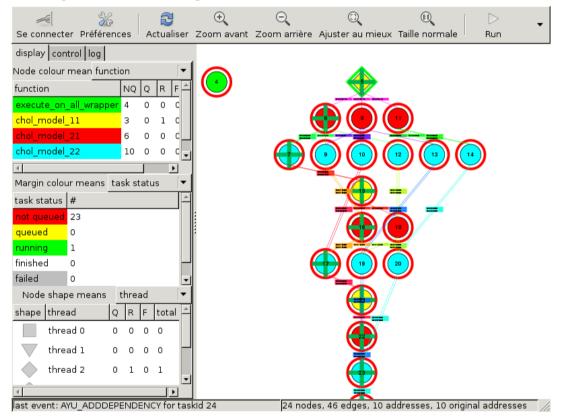

| -           | ) A Temanejo view of a task-based program running with the StarPU me system. | 61   |

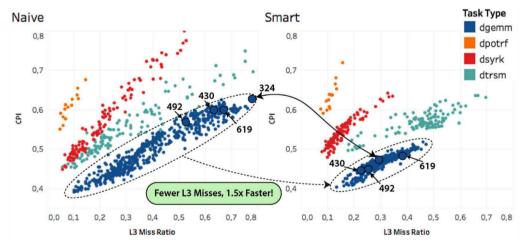

|             | Per-task Performance vs L3 Miss Ratio correlation computed by Task-          |      |

|             | ht.                                                                          | 62   |

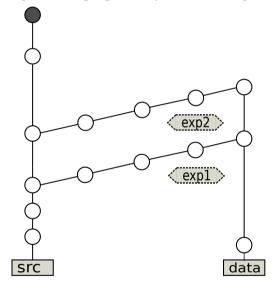

| Figure 4 1  | Git branching scheme proposed by Stanisic, Legrand, and Danjean (2015)       | 0 70 |

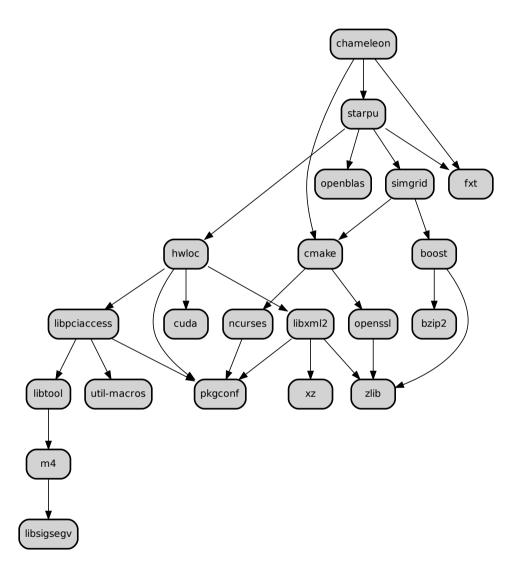

|             | A graph with software dependencies of the Chameleon Solver                   |      |

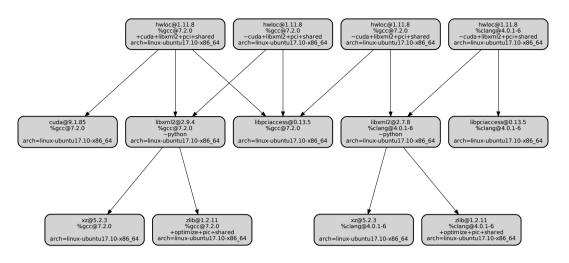

|             | Example of multiple installs of a package in Spack.                          |      |

| -           | Fragment of an execution log containing Spack package state                  |      |

| 1 1guie 4.4 | Tragment of an execution log containing spack package state                  | 15   |

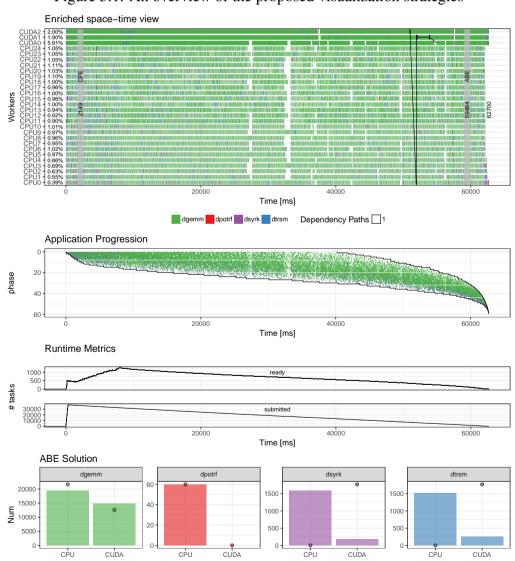

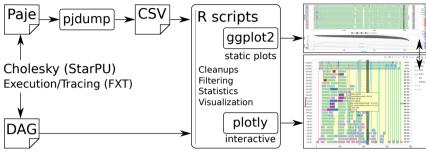

|             | An overview of the proposed visualization strategies                         |      |

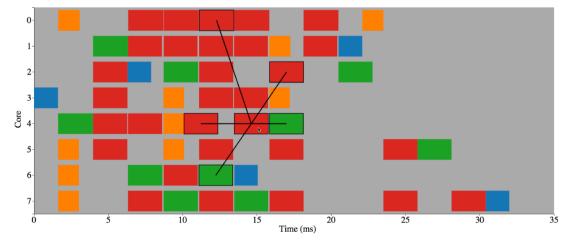

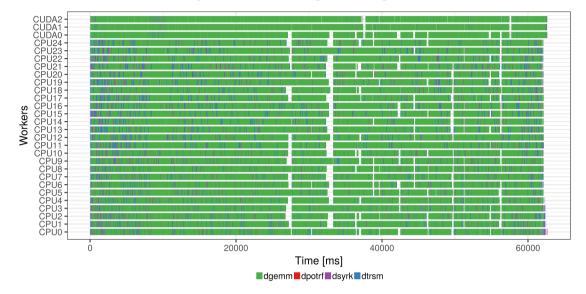

| 0           | A basic space-time plot                                                      |      |

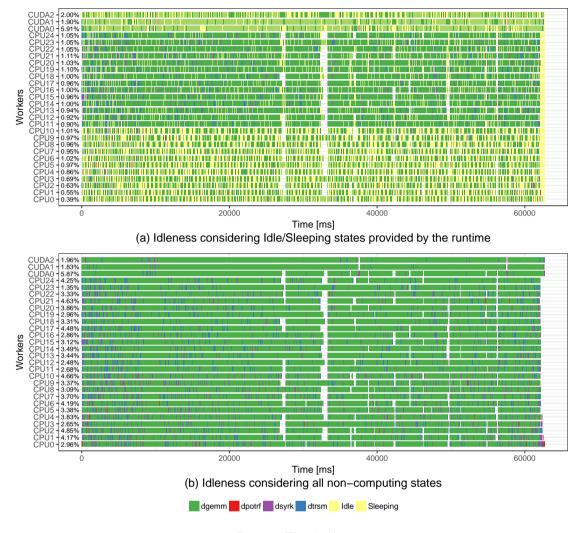

| U           | Enriched space-time view with idleness quantification.                       | 82   |

| -           | Enriched space-time view with highlighting of tasks with anomalous ion.      | 83   |

|             | Space-time view with CPE and ABE bounds                                      |      |

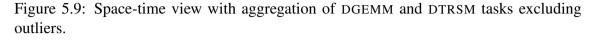

| -           | Space-time view with aggregation of DGEMM tasks with duration smaller        |      |

|             | 100 ms.                                                                      | 86   |

|             | Space-time view with aggregation of DGEMM and DTRSM tasks with               |      |

|             | ion smaller than 100 ms                                                      | 87   |

|             |                                                                              |      |

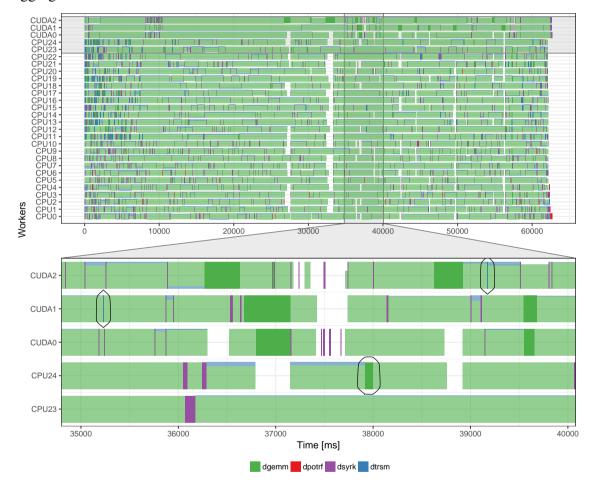

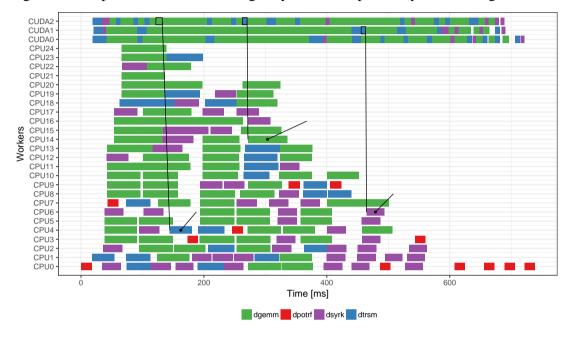

| Figure 5.8 Space-time view with aggregation of DGEMM and DTRSM tasks with duration smaller than 100 ms (excluding some tasks) |

|-------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.9 Space-time view with aggregation of DGEMM and DTRSM tasks exclud-                                                  |

| ing outliers                                                                                                                  |

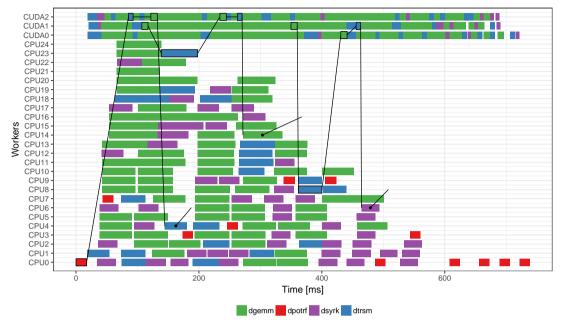

| Figure 5.10 Space-time view with all dependencies of some selected tasks                                                      |

| Figure 5.11 Space-time view showing only the last dependency of a some given                                                  |

| tasks                                                                                                                         |

| Figure 5.12 Space-time view with the backward dependency chain of some se-                                                    |

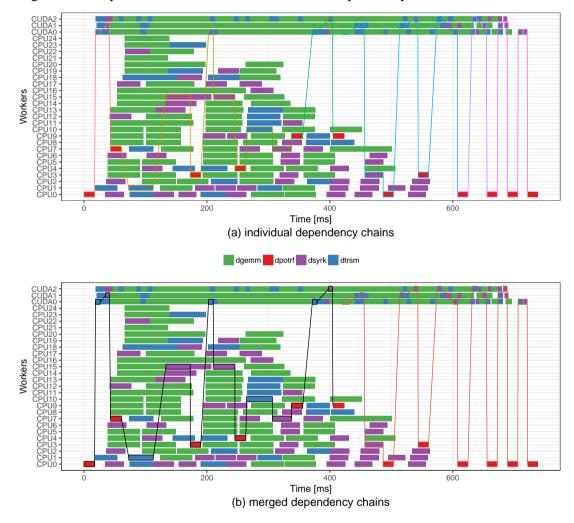

| lected tasks                                                                                                                  |

| Figure 5.13 Space-time view with the backward dependency chain of DPOTRF tasks.                                               |

|                                                                                                                               |

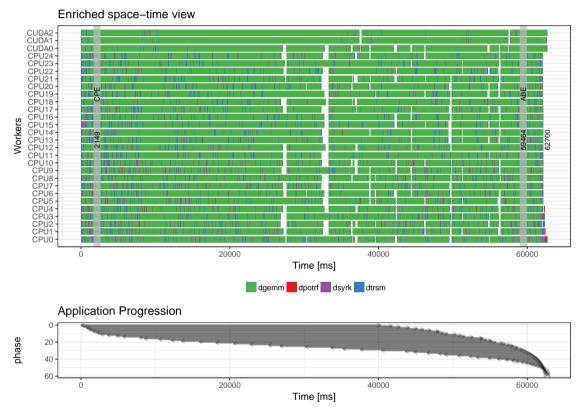

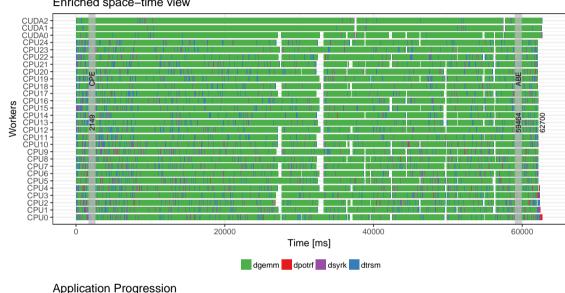

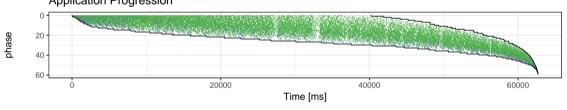

| Figure 5.14 Space-time view with application progression                                                                      |

| Figure 5.15 Space-time view and the additional progression panel populated with                                               |

| tasks                                                                                                                         |

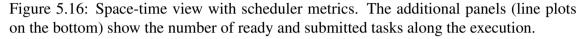

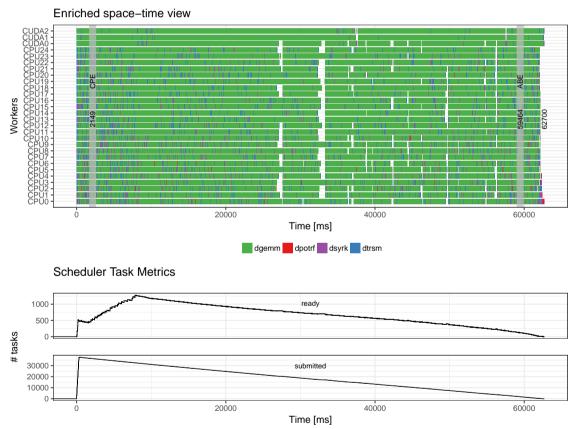

| Figure 5.16 Space-time view with scheduler metrics                                                                            |

| Figure 5.17 Space-time view with CPE and ABE bounds                                                                           |

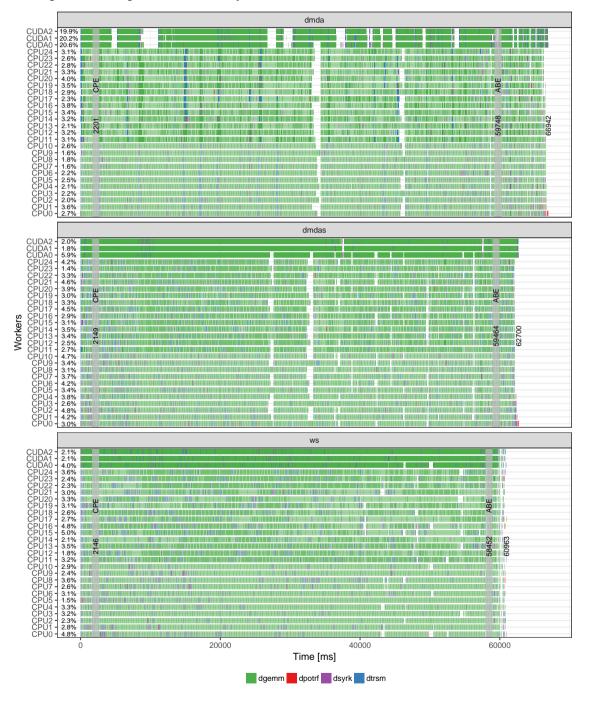

| Figure 5.18 Comparing views from three executions using different schedulers101                                               |

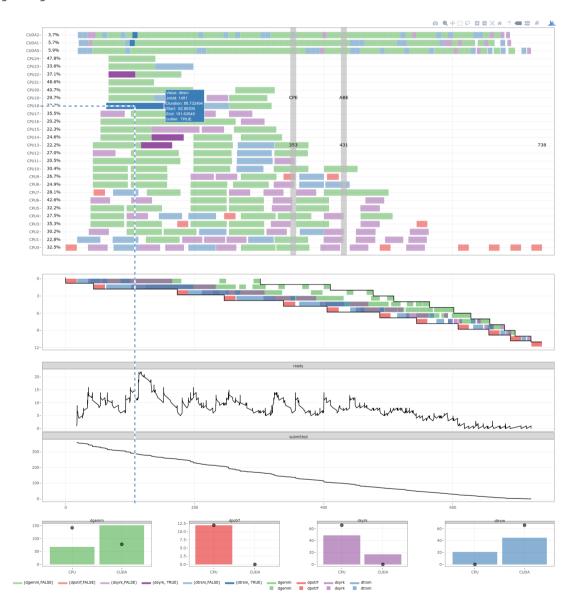

| Figure 5.19 Screenshot of an interactive view generated with plotly                                                           |

| Figure 5.20 A simplified workflow with the steps to generate views from applica-                                              |

| tion execution traces                                                                                                         |

| Figure 5.21 A fragment of a StarPU execution trace in CSV format after conversion                                             |

| from FxT and Pajé                                                                                                             |

| Figure 5.22 Task dependencies information obtained from the application DAG                                                   |

| provided by StarPU106                                                                                                         |

|                                                                                                                               |

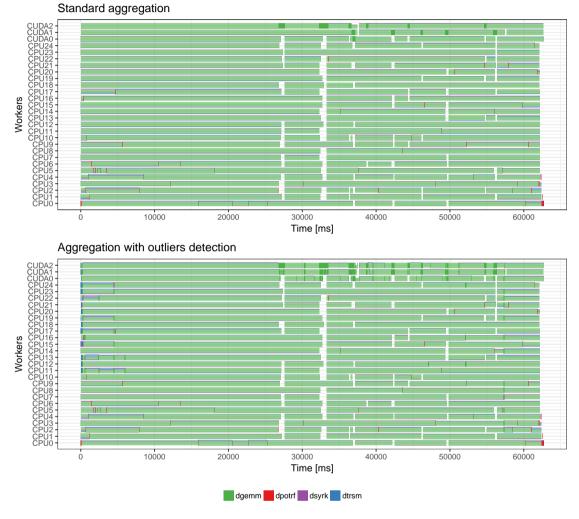

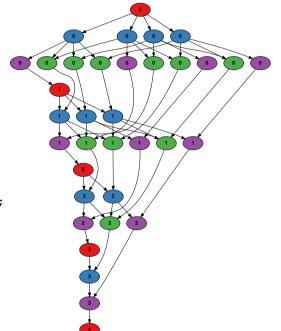

| Figure 6.1 The pseudo-code of the tiled Cholesky decomposition and its corre-                                                 |

| sponding DAG for $N = 5$ 112                                                                                                  |

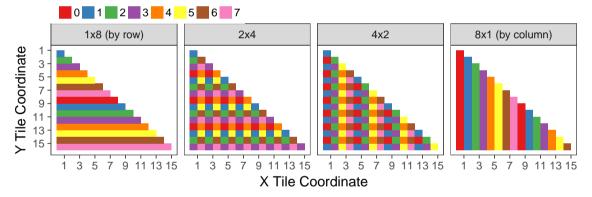

| Figure 6.2 Different static partitioning schemes for DTRSM tasks as dictated by the P113                                      |

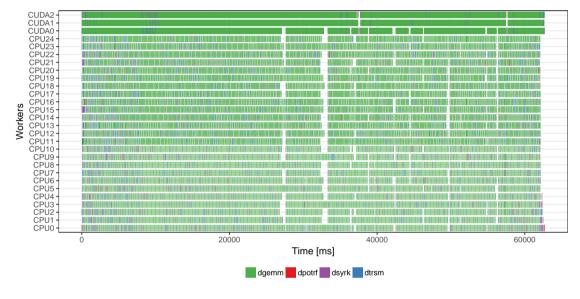

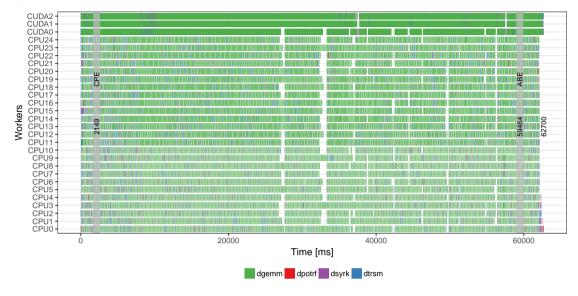

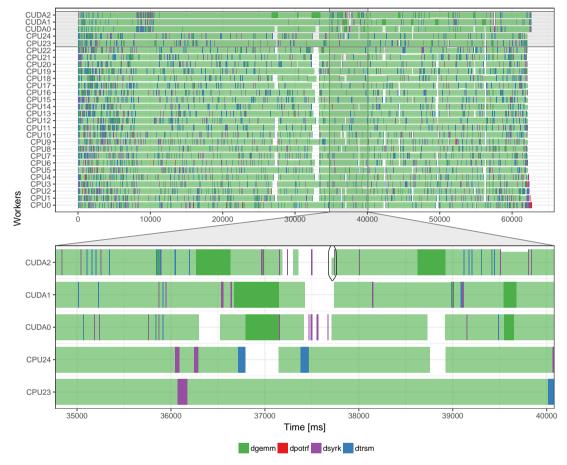

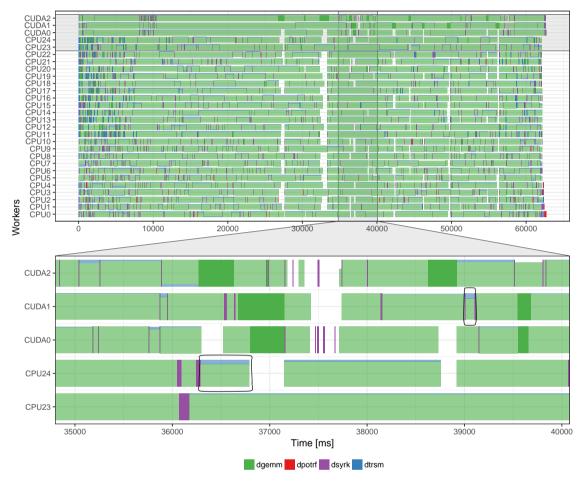

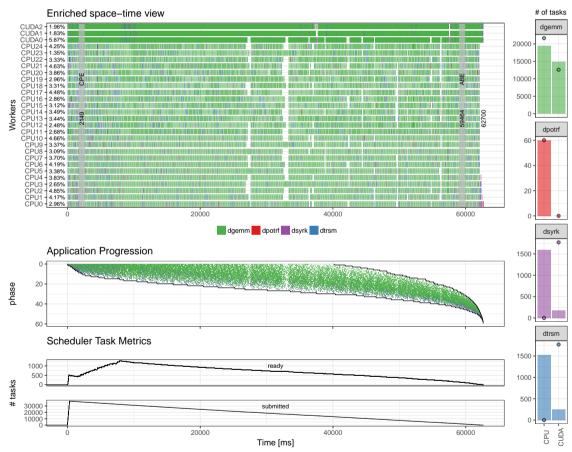

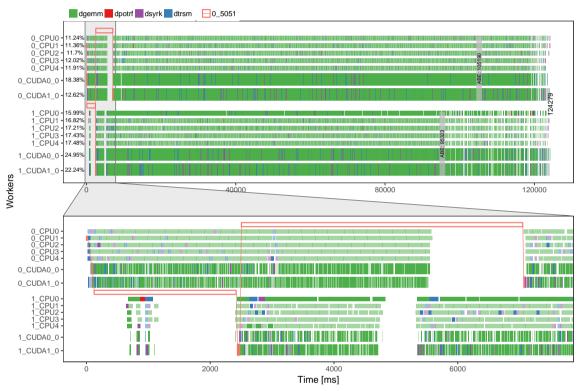

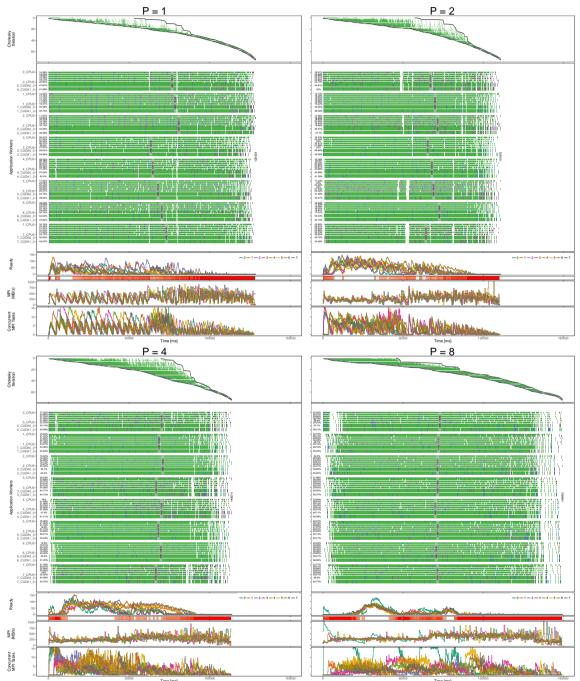

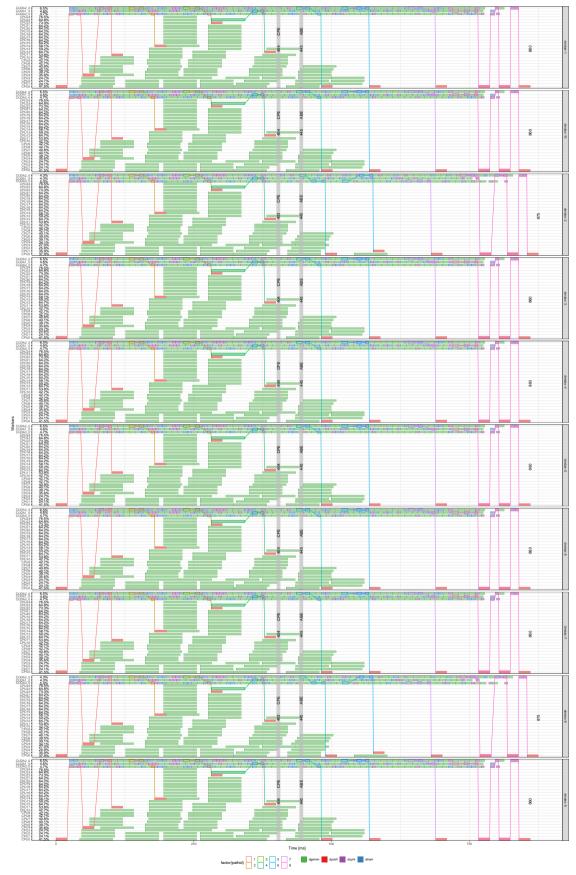

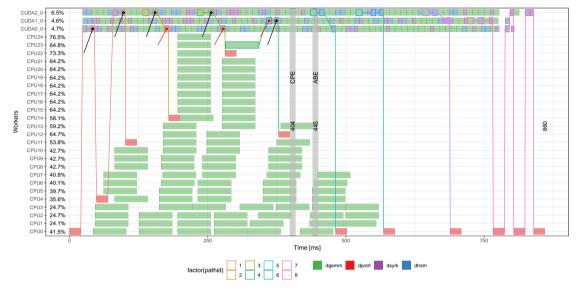

| Figure 6.3 Composite View of a Cholesky factorization with a large matrix (60×60                                              |

| tiles of 960×960) executed with the DMDAS scheduler                                                                           |

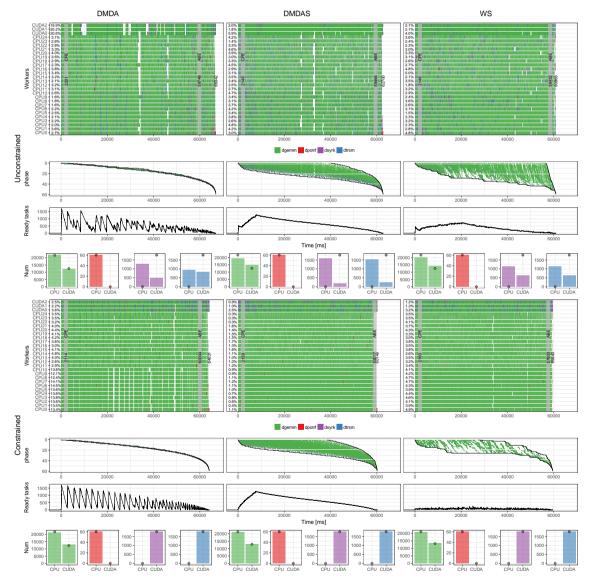

| Figure 6.4 Comparison view of six executions of the Cholesky factorization120                                                 |

| Figure 6.5 Space-time view of a Cholesky factorization with a small matrix (12×12                                             |

| tiles of 960×960) executed with the DMDAS scheduler                                                                           |

| Figure 6.6 Comparison view of six executions of the Cholesky factorization for a                                              |

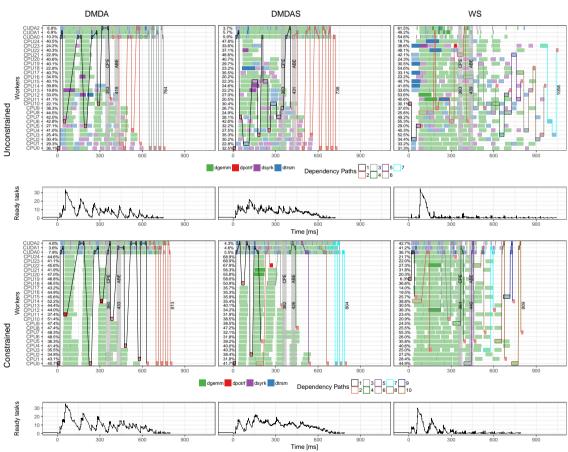

| matrix of 12×12 tiles of size 960×960                                                                                         |

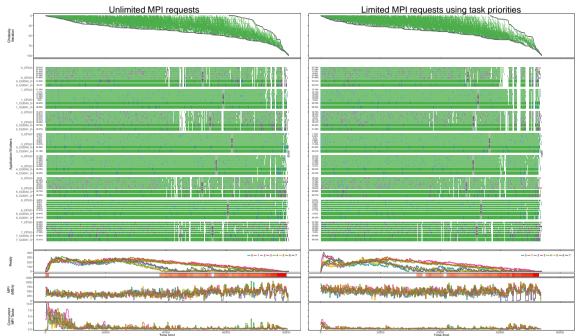

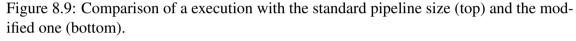

| Figure 6.7 StarPU-MPI multi-node execution of the Cholesky factorization with a                                               |

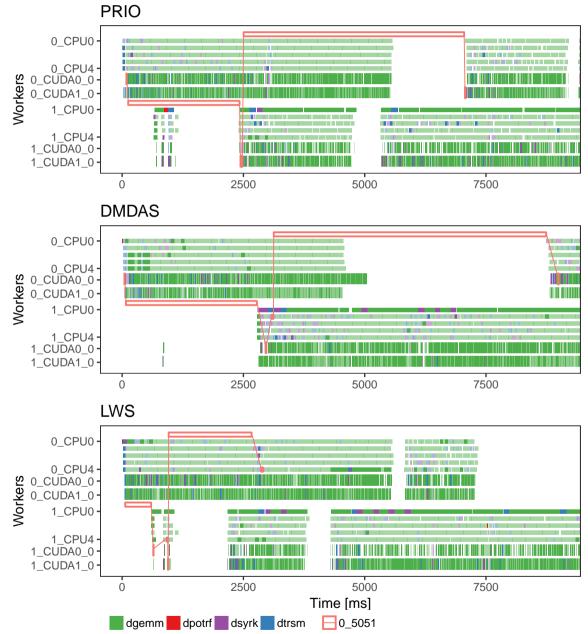

| matrix of 75×75 tiles of 960×960 using PRIO scheduler                                                                         |

| Figure 6.8 The first 8000ms of three StarPU-MPI multi-node executions of the                                                  |

| Cholesky factorization with a matrix of 75×75 tiles of 960×960128                                                             |

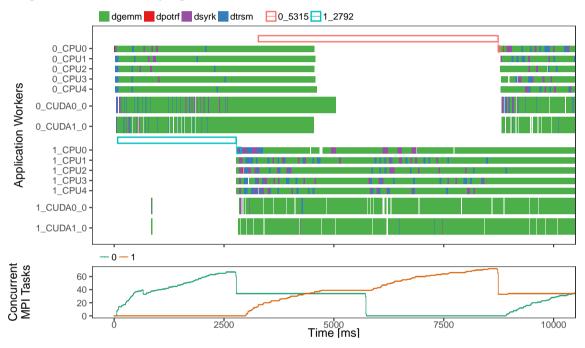

| Figure 6.9 The first 10000ms of a StarPU-MPI multi-node execution of the Cholesky                                             |

| factorization with a matrix of 75×75 tiles of 960×960 using the DMDAS                                                         |

| scheduler                                                                                                                     |

| Figure 6.10 Comparison of two StarPU-MPI multi-node executions of the Cholesky                                                |

| factorization with a matrix of $75 \times 75$ tiles of $960 \times 960$ using LWS scheduler,                                  |

| P=1                                                                                                                           |

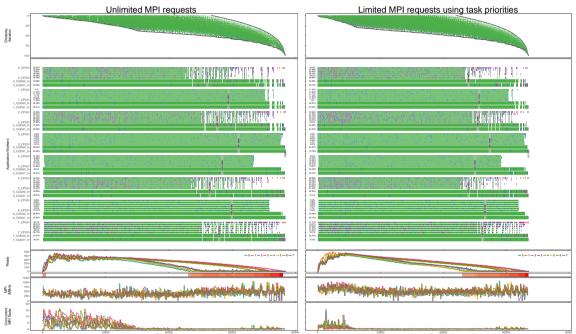

| factorization with a matrix of 75×75 tiles of 1440×1440 using LWS scheduler. 133                                              |

| Figure 6.12 Comparison of two StarPU-MPI multi-node executions of the Cholesky                                                |

| factorization with a matrix of 100×100 tiles of 960×960 using LWS scheduler                                                   |

| and P=2                                                                                                                       |

| 1 - 2                                                                                                                         |

| Figure 6.13 Comparison of two StarPU-MPI multi-node executions of the Cholesky factorization with a matrix of 100×100 tiles of 960×960 using DMDAS scheduler and P=2.                                                                                                                                                                         | 137 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

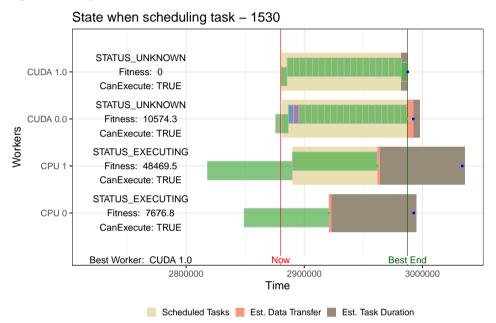

| Figure 7.1 A space-time view representing the execution of a Cholesky factor-<br>ization (matrices with 12×12 tiles of 960×960) with highlighted potencial<br>scheduling mistakes                                                                                                                                                             | 140 |

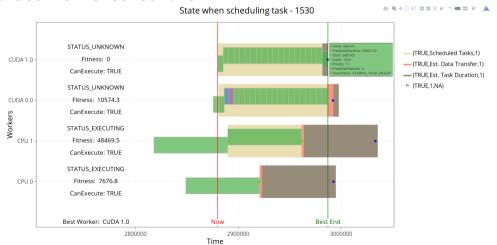

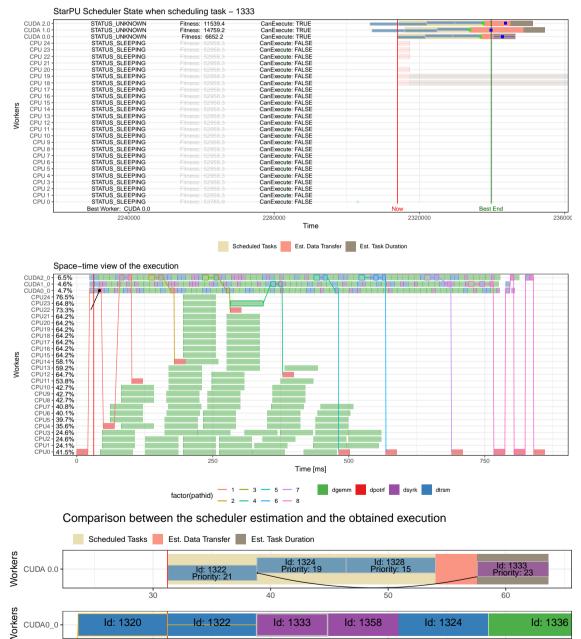

| Figure 7.2 A visual representation of the internal state of the StarPU DMDAS scheduler when scheduling a DSYRK task with ID 13331                                                                                                                                                                                                             | 145 |

| Figure 7.3 Screenshot of a Web interactive view of the StarPU scheduler state gen-<br>erated with plotly1                                                                                                                                                                                                                                     | 145 |

| <ul> <li>Figure 8.1 The space-time view of ten simulated (StarPU+SimGrid) executions of the Cholesky factorization (matrices with 12×12 tiles of 960×960)1</li> <li>Figure 8.2 Space-time view with markers (black pins) to indicate representative delayed tasks. The scheduling state of these tasks will be investigated in the</li> </ul> | 148 |

| next sections                                                                                                                                                                                                                                                                                                                                 | 149 |

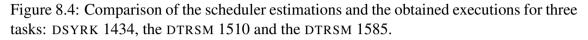

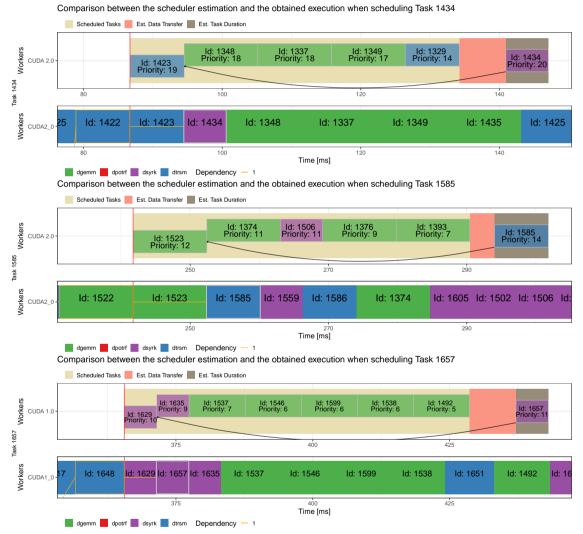

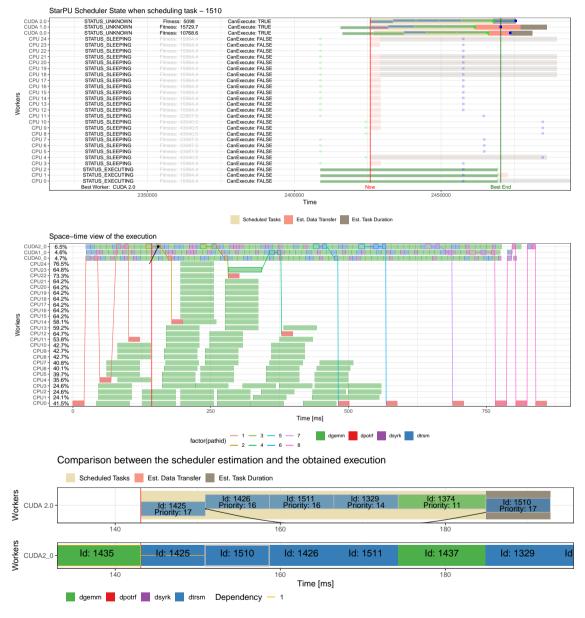

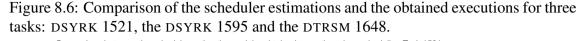

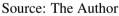

| scheduling step of the DSYRK task 1333 and the obtained execution1<br>Figure 8.4 Comparison of the scheduler estimations and the obtained executions                                                                                                                                                                                          | 151 |

| for three tasks: DSYRK 1434, the DTRSM 1510 and the DTRSM 15851<br>Figure 8.5 A comparison between the estimations computed by StarPU during the                                                                                                                                                                                              | 152 |

| scheduling step of the DSYRK task 1510 and the obtained execution                                                                                                                                                                                                                                                                             |     |

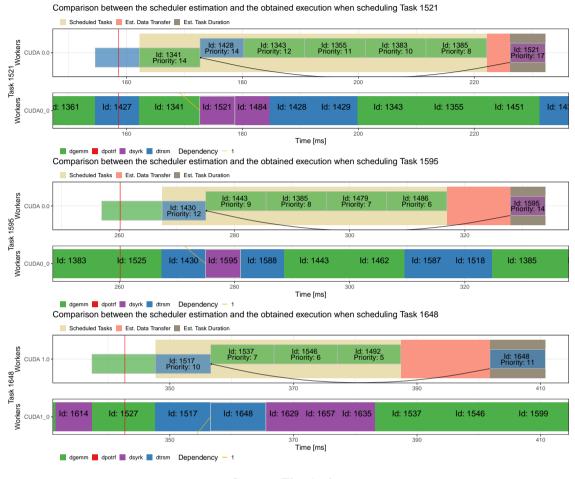

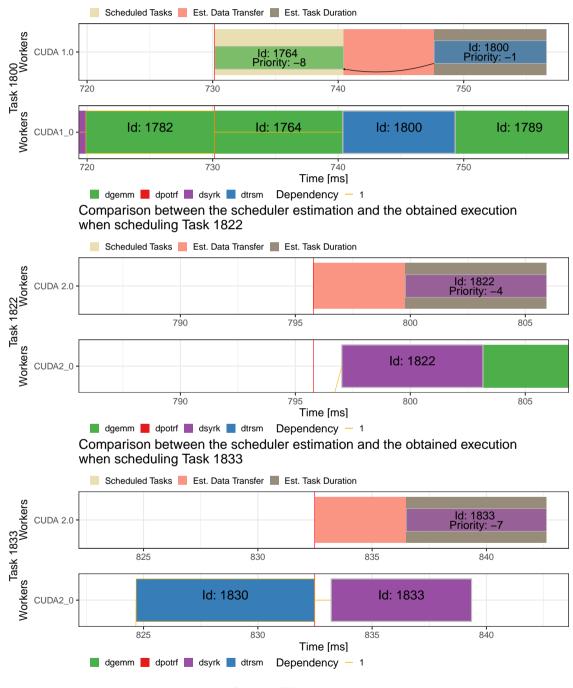

| for three tasks: DSYRK 1521, the DSYRK 1595 and the DTRSM 16481<br>Figure 8.7 Space-time view with markers (black pins) to indicate representative<br>delayed tasks in the end of the execution. The scheduling state of these tasks                                                                                                          | 154 |

| will be investigated in the next sections                                                                                                                                                                                                                                                                                                     | 155 |

| for three tasks: DSYRK 1800, the DSYRK 1822 and the DTRSM 1833                                                                                                                                                                                                                                                                                |     |

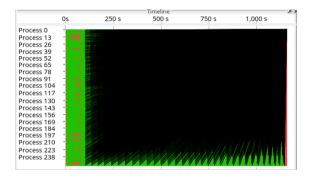

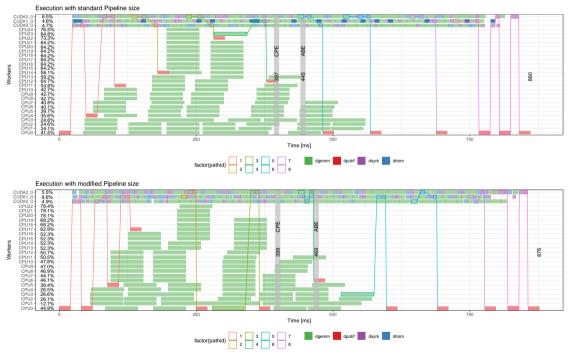

| Figure 9.1 Visualization of a task-based application executed with the OmpSs run-<br>time system                                                                                                                                                                                                                                              | 161 |

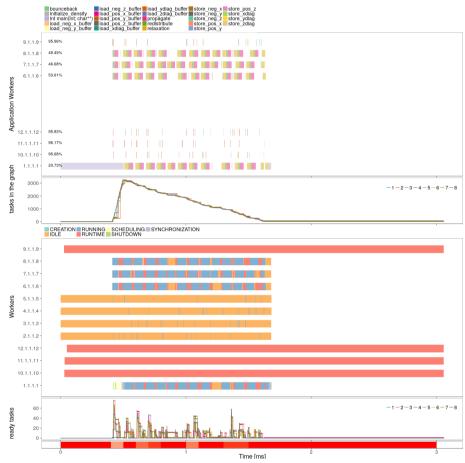

| Figure 9.2 An overview of a Cholesky execution on the Intel Xeon Phi platform<br>with a matrix of 60×60 tiles of 960×960 using the DMDAS scheduler                                                                                                                                                                                            | -   |

# LIST OF TABLES

| Table 3.1 Visualization tools and common features                            | 64  |

|------------------------------------------------------------------------------|-----|

|                                                                              |     |

| Table 6.1 Summary of the hardware/software configuration of the experimental |     |

| platforms used to collect execution traces.                                  | 110 |

| Table 6.2 Summary of workloads                                               | 114 |

| -                                                                            |     |

## LIST OF ABBREVIATIONS AND ACRONYMS

- ABE Area Bound Estimation

- BSP Bulk-Synchronous Parallel

- CFD Computational Fluid Dynamics

- CPE Critical Path Estimation

- CPI Cycles Per Instruction

- CPU Central Processing Unit

- DBF Distributed Breadth First

- DSL Domain-Specific Language

- DMDA Deque Model Data Aware

- DMDAS Deque Model Data Aware Sorted

- DOI Digital Object Identifier

- FLOPS Floating Point Operations Per Second

- GPU Graphical Processing Unit

- HEFT Heterogeneous Earliest Finish Time

- HPC High-Performance Computing

- ILP Instruction-Level Parallelism

- IPC Instructions Per Cycle

- IQR InterQuartile Range

- ISA Instruction Set Architecture

- LML Lightweight Markup Language

- LWS Locality Work Stealing

- MIC Many Integrated Core

- MPI Message Passing Interface

- NUMA Non-Uniform Memory Access

- OTF Open Trace Format

- PPE PowerPC Processor Element

- PTG Parameterized Task Graph

- SPE Synergistic Processor Element

- WF Work First

- WS Work Stealing

# LIST OF ALGORITHMS

| 1 Computation of task groups | 89 |

|------------------------------|----|

|------------------------------|----|

# CONTENTS

| 1 INTRODUCTION                                                                                              |    |

|-------------------------------------------------------------------------------------------------------------|----|

| 1.1 Objectives and Contributions                                                                            | 25 |

| 1.2 Research Context                                                                                        |    |

| 1.3 Thesis Outline                                                                                          |    |

| 2 CONTEXT                                                                                                   |    |

| 2.1 Hybrid HPC Architectures                                                                                |    |

| 2.2 Programming Hybrid Architectures                                                                        | 32 |

| 2.2.1 Task-Based Programming                                                                                |    |

| 2.3 Runtime Systems for Task-Based Parallel Programming                                                     |    |

| 2.3.1 PaRSEC                                                                                                |    |

| 2.3.2 OmpSs                                                                                                 |    |

| 2.3.3 XKaapi                                                                                                |    |

| 2.3.4 StarPU                                                                                                |    |

| 2.3.5 Discussion                                                                                            |    |

| 2.4 Chapter Summary                                                                                         |    |

| 3 STATE OF THE ART                                                                                          |    |

| 3.1 Traditional BSP-based Visualization                                                                     |    |

| 3.1.1 <i>ViTE</i>                                                                                           |    |

| 3.1.2 Paraver                                                                                               |    |

| 3.1.3 Vampir                                                                                                |    |

| 3.1.4 Ravel                                                                                                 |    |

| 3.1.5 Edge Bundling extension for Vampir                                                                    |    |

| 3.1.6 FrameSoc/Ocelotl                                                                                      |    |

| 3.2 Task-oriented Visualization                                                                             |    |

| 3.2.1 Execution Traces with Dependencies                                                                    |    |

| 3.2.2 DAGViz                                                                                                |    |

| 3.2.3 Delay Spotter                                                                                         |    |

| 3.2.4 Temanejo                                                                                              |    |

| 3.2.5 TaskInsight                                                                                           |    |

| 3.3 Discussion                                                                                              |    |

| 3.4 Chapter Summary                                                                                         |    |

| 4 METHODOLOGY                                                                                               |    |

| 4.1 A Reproducible Report                                                                                   |    |

| 4.2 Generating Input Data                                                                                   |    |

| <ul><li>4.2.1 Git and Org-mode Strategy</li><li>4.2.2 Handling Complex Software Stacks with Spack</li></ul> |    |

| 4.2.2 Handling Complex Software Stacks with Spack                                                           |    |

| 4.2.5 Rebuilding the Software Stack                                                                         |    |

| 4.2.4 Storage of Large Files in GIT                                                                         |    |

| 5 PROPOSED VISUALIZATIONS STRATEGIES                                                                        |    |

| 5.1 Enriched Space-time View                                                                                |    |

| 5.1.1 Idleness                                                                                              |    |

| 5.1.2 Outliers or Task Duration Anomalies                                                                   |    |

| 5.1.2 Outlets of Task Duration Attomates                                                                    |    |

| 5.1.4 Aggregation                                                                                           |    |

| 5.1.5 Dependencies                                                                                          |    |

| 5.2 Additional Views                                                                                        |    |

| 5.2.1 Application Progression                                                                               |    |

| 5.2.2 Scheduler Task Metrics                                                                      | 97   |

|---------------------------------------------------------------------------------------------------|------|

| 5.2.3 ABE Solution                                                                                | 98   |

| 5.3 Comparing Views                                                                               | 99   |

| 5.4 Interactive Views                                                                             |      |

| 5.5 Input Description                                                                             |      |

| 5.6 Discussion                                                                                    |      |

| 5.7 Chapter Summary                                                                               |      |

| 6 RESULTS ON VISUALIZATIONS STRATEGIES                                                            |      |

| 6.1 Experimental Setup                                                                            |      |

| 6.1.1 Platforms                                                                                   |      |

| 6.1.2 Application                                                                                 |      |

| 6.2 Case Study: Changing Schedulers on Hybrid Nodes                                               |      |

| 6.2.1 Workload <i>L</i> - Cholesky Factorization of $60 \times 60$ tiles of size $960 \times 960$ |      |

| 6.2.2 Workload <i>S</i> - Cholesky Factorization of 12×12 tiles of size 960×960                   |      |

| 6.3 Case Study: Multi-node Executions with Starpu-MPI                                             |      |

| 6.3.1 Slow-start in Remote Nodes                                                                  |      |

| 6.3.2 Idle Periods During the Computation                                                         |      |

| 6.3.3 StarPU-MPI Data Distribution Strategies                                                     |      |

| 6.4 Chapter Summary                                                                               |      |

| 7 PROPOSED DEBUG STRATEGIES                                                                       |      |

| <ul><li>7.1 A Representative Example</li><li>7.2 Methods and Materials</li></ul>                  |      |

| 7.2.1 Performance Models                                                                          |      |

| 7.2.1 Performance Wodels                                                                          |      |

| 7.2.2 StarPO/Singrid sinulated executions                                                         |      |

| <ul><li>7.2.3 Starr O Scheduler Internals</li></ul>                                               |      |

| 7.2.5 StarPU Modifications                                                                        |      |

| 7.3 A Visual Representation of the Scheduler State                                                |      |

| 7.4 Chapter Summary                                                                               |      |

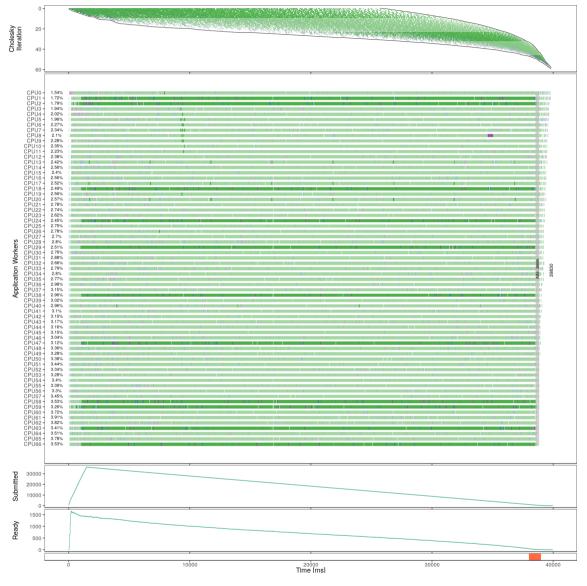

| 8 RESULTS ON DEBUG STRATEGIES                                                                     |      |

| 8.1 Experimental Setup                                                                            |      |

| 8.2 Investigating Scheduling Decisions in the First Half of the Execution                         |      |

| 8.3 Investigating Scheduling Decisions at the End of the Execution                                |      |

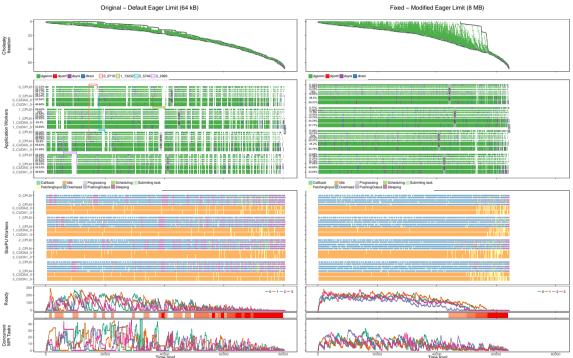

| 8.4 Experiments with Modified Pipeline Size                                                       |      |

| 8.5 Chapter Summary                                                                               |      |

| 9 CONCLUSIONS AND PERSPECTIVES                                                                    | .159 |

| 9.1 Conclusions                                                                                   |      |

| 9.2 Perspectives                                                                                  |      |

| 9.2.1 Analysis of other task-based applications and runtime systems                               |      |

| 9.2.2 Performance Anomalies on Xeon Phi Knights Landing architecture                              |      |

| 9.2.3 StarVZ                                                                                      |      |

| 9.3 Publications                                                                                  |      |

| 9.3.1 Accepted                                                                                    |      |

| 9.3.2 Other accepted publications during the Ph.D.                                                |      |

| BIBLIOGRAPHY                                                                                      | .165 |

## **1 INTRODUCTION**

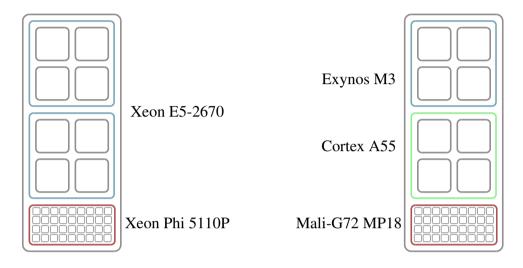

Computer architectures have experienced a paradigm shift in the last years. The stagnation in the processor frequency has led the adoption of other ways to fulfill the ever-growing need for computation power. The combination of multicore processors with accelerator devices has been a prevalent approach to fulfill these performance requirements. Figure 1.1 represents a common layout of current parallel computers including multiple cores associated with an accelerator device disclosing a multilevel and heterogeneous parallelism.

For a long time, the applicability of parallel computers had been limited to restricted domains, mainly concerning High-Performance Computing (HPC) research and scientific applications, e.g., climate modeling, energy research, data analysis, and simulations. However, the recent paradigm shift has put the parallelism in the essence of almost all computing devices. This way, taking only a layout of the architecture as the one of Figure 1.1, it is no longer possible to distinguish a TOP500-ranked supercomputing node from a high-end smartphone.

Figure 1.1: The layout of a current parallel computer with a multicore processor and a manycore accelerator device. The larger boxes represent multicore processors with its powerful cores based on sophisticated control logic and complex cache hierarchy. The smaller ones represent accelerator cores which are simpler but more numerous.

Source: The Author

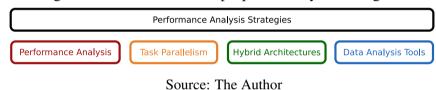

Figure 1.2 illustrates the architecture of two current parallel computers. Both are octa-core systems enhanced with accelerator devices. However, despite the conceptually similar architecture, they have extremely contrasting purposes. The first (right) is a node

Figure 1.2: Two current parallel computers. On the left, a node of the *Cascade* system, ranked in the position 69 in the June 2018 Top500 list. This system has an octa-core Intel Xeon E5-2670 at 2.6GHz with an Intel Xeon Phi 5110P as an accelerator. On the right side, a Samsung Galaxy S9 smartphone using a heterogeneous ARM processor with four M3 cores at 2.7GHz and four Cortex-A55 cores at 1.8GHz with a GPU Mali-G72 as an accelerator.

Source: The Author

of the #69 most powerful system in the last Top500 list <sup>1</sup>, while the second one (left) is a Galaxy S9<sup>2</sup> smartphone produced by Samsung.

Although parallel computers have become mainstream, with hybrid platforms widespread from supercomputing centers to ordinary citizens' pockets, the software stack is not fully prepared to efficiently exploit this multilevel parallelism. The paradigm shift in the hardware has exposed the limitations of traditional tools for programming and analyzing applications running on parallel platforms. Indeed, these limitations come from the context on which these tools were designed, i.e., homogeneous parallel computers used in HPC and scientific domains.

Programming hybrid platforms is complex. The common strategy based on the use of traditional tools (e.g., MPI, pthreads, OpenMP) to program parallel applications in a hybrid hardware is becoming unfeasible and potentially problematic. Efficiently programming such machines achieving portable and scalable performance has become extremely challenging since the use of explicit programming models demands a huge effort to develop and maintain the application (ASANOVIC et al., 2009). Even when successful, this development flow results in a code that is tightly coupled to the target

<sup>&</sup>lt;sup>1</sup>https://www.top500.org/system/178250

<sup>&</sup>lt;sup>2</sup>https://www.gsmarena.com/samsung\_galaxy\_s9-8966.php

hardware, which is not desirable in the hybrid scenario where the accelerator's technology is changing fast, e.g., Cell Broadband Engine Architecture (2006), Graphics Processing Unit (2007), Xeon Phi (2013) (DONGARRA et al., 2017).

The pressure on parallel programming tools has contributed to the popularization of the task-based programming model. While the traditional parallel programming paradigm relies on low-level abstractions like threads and explicit synchronizations, the task-based model describes the application in terms of dependent sequential (or parallel) tasks. Explicit synchronizations are replaced by tasks dependencies that can be, in several cases, inferred automatically from data access. The task-based model is implemented by several programming models: OpenMP 4 (OPENMP..., 2013), OmpSs (DURAN; AYGUADÉ, et al., 2011), PaRSEC (BOSILCA, George et al., 2012), XKaapi (GAU-TIER, T. et al., 2013), StarPU (AUGONNET, Cédric et al., 2011).

Despite the growing availability of tools to program and execute task-based applications on hybrid platforms, there are very few analysis tools with a focus on such kind of parallel applications. One of the main reasons is that the burden of getting the maximum performance from the machine shifts from the application to the runtime developer, who implements a given scheduling heuristic. Usually, developers rely on already-established analysis tools since highly-summarized metrics, e.g., makespan, speedup, and efficiency, are too simplistic to allow understanding performance issues in such scenario. However, existing tools that are capable of giving insights to developers, such as Paraver (PILLET et al., 1995), Vite (COULOMB et al., 2009), and others (KNÜPFER et al., 2008; ISAACS, K. E. et al., 2014; BRENDEL et al., 2016; PAGANO et al., 2013), are unsuited to runtime developers because assumptions and performance bottlenecks are different from classical parallel programs and because the traces of task-based applications can be much richer (e.g., with task-dependencies or information about the state of the scheduler) than the ones of standard MPI or classical OpenMP applications.

#### **1.1 Objectives and Contributions**

Considering the previously discussed scenario, the main objective of this thesis is to **provide appropriate performance analysis strategies for task-based applications executing on hybrid platforms supported by dynamic runtime systems**. We believe that, with a complex hardware/software stack, a meaningful analysis strategy should take into account:

- application aspects (e.g., algorithm structure, finer granularity, task dependencies)

- **platform specification** (e.g., heterogeneous processing and communication capabilities)

- runtime system state (e.g., dynamic scheduling, internal metrics)

In order to fulfill these requirements, our approach is anchored on the four topics shown in Figure 1.3. First, we build on well-established **Performance Analysis** concepts, such as execution traces and timeline views. Second, we exploit both characteristics of **Task Parallelism**, such as data dependencies and dynamic scheduling and of **Hybrid Architectures** such as heterogeneous processing power. Finally, we rely on modern **Data Analysis Tools**, such as R language and its libraries, to read, combine and process execution traces in order to obtain visual representations of the application execution.

## Figure 1.3: The basis of the proposed analysis strategies.

Our main contributions are the following:

- a set of performance analysis strategies to meet the requirements of task-based applications supported by dynamic runtime systems;

- an incremental approach where enrichments to standard visualizations and synchronized extra panels are developed and incorporated on-demand;

- case-study analyses demonstrating how to achieve performance improvements on already optimized task-based applications.

The complex hardware/software stack also emphasizes the need to employ reproducible approaches. Therefore, we also employ a reliable experimental methodology based on Git, Org-mode, Spack, and Zenodo. This methodology enables us to make available a companion dataset containing the source-code and the results data of our experiments. Our extensions to the Git and Org-mode workflow proposed by Stanisic, Legrand, and Danjean (2015) and the availability of experiments data can be considered as additional contributions of this thesis.

#### **1.2 Research Context**

The present work is conducted under the context of a joint Ph.D. between the Graduate Program in Computer Science (PPGC) of the Institute of Informatics at the Federal University of Rio Grande do Sul (UFRGS) in Brazil and the Doctoral School on Mathematics, Information Sciences and Technologies, and Computer Science (ED-MSTII) of the University Grenoble Alpes (UGA) in France. Besides, this work is involved in the context of the International Associated Laboratory in High Performance and Ubiquitous Computing (LICIA).

At UFRGS, this research is developed under the supervision of Nicolas Maillard in the Research Group on *Parallel and Distributed Processing* (GPPD) and at UGA under the supervision of Arnaud Legrand in the team on *Performance Evaluation and Optimization of Large Infrastructures and Systems* (POLARIS) of the Grenoble Informatics Laboratory (LIG). In addition to my official advisors, this work is developed in a strong cooperation with:

- Lucas Mello Schnorr from UFRGS about performance analysis techniques and StarPU-MPI applications. Lucas has been, in practice, a co-supervisor of this thesis;

- Samuel Thibault from University of Bordeaux about the StarPU runtime system;

- Luka Stanisic from Max Planck Computing and Data Facility about performance analysis of StarPU applications;

- Vincent Danjean from University Grenoble Alpes about task-based programming.

#### **1.3 Thesis Outline**

The remainder of this text is structured as follows:

- Chapter 2 presents background concepts of the hardware and software stack of current HPC platforms. First, we present an overview about the multi-level parallelism of the architecture. Second, we discuss programming strategies for hybrid architectures with emphasis on task-based programming.

- In Chapter 3 we present the state of the art of performance analysis tools. We discuss both traditional BSP-based approaches and Task-oriented ones.

- Chapter 4 presents some steps to make this work more transparent and repro-

ducible. This comprises the use of literate programming to write this report and how we keep track of experiments data.

- In **Chapter 5** we detail the proposed visualization strategies to analyze task-based applications.

- Chapter 6 presents our results when analyzing applications with the proposed strategies. We present two case studies, the first one on a single hybrid node and the second on a hybrid cluster.

- In **Chapter 7** we detail our debug-based performance analysis strategies. These strategies are useful for understanding specific scheduler decisions that cannot be totally explained using only the strategies presented in Chapter 5.

- Chapter 8 presents our results when analyzing executions with the proposed debug strategies. We present an investigation of the StarPU scheduler state for a set of tasks that seem to be delayed due to potential scheduling mistakes.

- Chapter 9 presents the conclusions and perspectives of this thesis.

## **2 CONTEXT**

For a long time, parallelism has been a major strategy to increase the processing power of computing systems. Low-level techniques such as the Instruction Level Parallelism (HENNESSY; PATTERSON, 2017) were incorporated into the hardware design, and are now widespread in almost all CPU architectures. These hardware-managed techniques have delivered the benefits of parallelism with no cost in terms of software development. In contrast, the exploitation of parallelism in other levels of the hardware/software stack was restricted to HPC researchers and scientific applications developmers.

This community has developed successful programming tools such as the Message Passing Interface (MPI) to handle the communication among computing nodes and OpenMP to handle shared memory platforms. MPI (GROPP; LUSK; SKJELLUM, 2014) is a *de facto* standard for parallel programming in distributed memory. Using MPI, processes can communicate by exchanging messages, e.g., paired send/receive messages or collective communications. OpenMP (CHAPMAN et al., 2008) is a collection of compiler directives and library functions to enable shared-memory multi-thread programming. Its directives were initially designed to parallelize loop-based algorithms, but recent versions also include support for other designs (e.g., sections, tasks). Classical parallel programs are commonly designed following the concepts of SPMD (Single Program Multiple Data) and BSP (Bulk-Synchronous Parallel) models. SPMD programs run the same code on a set of computing units; each computing unit uses its unique identifier to know on which part of the problem it should work (FOSTER, 1995; SOTTILE; MATTSON; RASMUSSEN, 2009). BSP programs are designed as a series of super-steps (VALIANT; G., 1990), i.e., each computing unit performs some local computation, these computations are followed by a communication phase and finally by a synchronization one. Despite the popularity of these approaches, the emergence of computing nodes with massive multicore processors and enhanced with accelerators has exposed the limitations of such strategies.

In this chapter, we discuss the hardware and software stack of current HPC hybrid platforms. First, in Section 2.1 we address the parallelism of HPC platforms, from the low-level ILP techniques to the multicore processors and accelerators used by the powerful computing systems today. Section 2.2 presents the principles of task-based programming. Finally, Section 2.3 presents some runtime systems that enables task-based parallel programming on hybrid platforms.

#### 2.1 Hybrid HPC Architectures

Parallelism has been exploited for a long time in computer architectures to achieve performance gains. Several parallelism techniques are employed inside the processor architecture to overlap the execution of instructions and decrease the time required to perform the whole computation, what is known as Instruction-Level Parallelism (ILP). Most of these techniques such as pipelining, register renaming and use of multiple redundant functional units are transparent to programmers since to their point of view the results are exactly the same of a sequential execution (HENNESSY; PATTERSON, 2017). Current processors also support another low-level parallelism features like vectorial instructions (*SIMD* extensions) which are more or less transparent to programmer since they are exploited by the compiler, automatic (YAZDANPANAH, 2017) or guided by directives (INTEL, 2017a), or included in high-performance libraries (WANG et al., 2014).

The paradigm shift from sequential processors to multicore chips has disclosed another parallelism layer to programmers. In contrast to the ILP where the parallelism was almost entirely handled by the hardware, in the multicore model, the software must be upgraded to take advantage of the computational power provided by multicore architecture (ASANOVIC et al., 2009). Since the number of cores continues to increase significantly in new hardware generations, the programming tools should provide a way to express the parallelism independently of the actual number of cores. This way, the software can still scale in future processors with higher core counts. Programming tools for multicore processors will be discussed in Section 2.2.

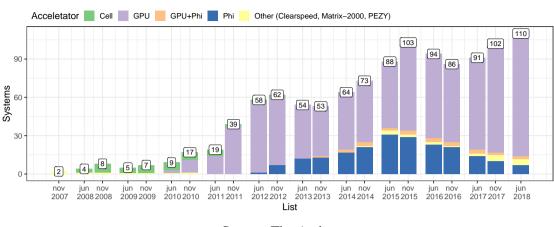

To fulfill the ever-growing need for computation power of High-Performance Computing applications, current HPC platforms are hybrid machines that rely not only on mainstream multicore processors but also in specialized accelerators. These devices are attached to the main system providing massive computational power with a reduced cost. For this reason, accelerated nodes are the main technology used by the powerful HPC platforms, e.g., 110 of the fastest supercomputers listed in the June 2018 Top500 list (MEUER et al., 2014) have nodes enhanced with some accelerator device, as shown in Figure 2.2.

Despite the computational power provided by hybrid machines, efficiently exploit both multicore CPUs and accelerators is challenging. Accelerator devices have very different design and requirements. Usually, they provide massive parallelism through a higher number of simplified cores. In comparison with a CPU, the design of an accelFigure 2.1: The layout of a hypothetical accelerator. Green boxes represent computing units (cores), orange ones the control system and blue ones the memory hierarchy.

Source: The Author

erator favors the computing units rather than control and memory systems as illustrated by the hypothetical accelerator layout of Figure 2.1. Some accelerator technologies are based on specialized instruction sets, which means that they require proper compiler and programming tools (NVIDIA, 2017b). The particular memory hierarchy requires some low-level operations and/or optimizations that normally are transparent in CPU architectures (NVIDIA, 2017a; JEFFERS; REINDERS, J., 2013).

The Figure 2.2 shows the growing use of accelerators devices in the systems ranked in the Top500 list. On the one hand, this series shows that accelerated nodes are becoming commonplace in the HPC landscape, but, it also shows that accelerators technology changes fast. A decade ago, the dominant technology was the Cell Broadband Engine Architecture (CHEN et al., 2007), a heterogeneous multicore chip composed of one PowerPC core (PPE) and eight simple cores (SPE) specialized for SIMD instructions. Then, the advent of CUDA (SANDERS; KANDROT, 2010) and OpenCL (STONE; GO-HARA; SHI, 2010; GASTER, 2012) technologies has facilitated the use of GPU cards for general purpose processing. More recently, Intel has introduced the Many Integrated Core architecture (MIC) (DURAN; KLEMM, 2012), an accelerator technology based on the x86 instruction set, commonly referred by its product name: Xeon Phi (JEFFERS; REINDERS, J., 2013).

Early generations of accelerator devices have presented some limitations that are being addressed in the recent versions. The performance gap between single and double precision was one of these issues. Single precision operations were from 8 up to 14 times

Figure 2.2: Evolution of the use of accelerators in TOP500 systems.

faster than double precision ones in first generations of Cell and Tesla GPUs. In newer GPUs, this gap was reduced by a factor between 2 and 3 (DONGARRA et al., 2017). The device memory size and bandwidth were also limitations for several applications, but these issues were reduced either by hardware improvements or by software solutions. The bidirectional ring interconnection of Xeon Phi devices was also a source of performance disturbances that were reduced in the new Knights Landing version that uses a 2D mesh interconnection (JEFFERS; REINDERS, J.; SODANI, 2016).

The evolution of accelerators technology has promoted them from a trend to a solid approach for HPC platforms. This was achieved by reducing limitations while keeping their good ratio FLOP per money and increasing performance within the same power budget.

#### 2.2 Programming Hybrid Architectures

The development of a software stack that allows to efficiently exploit hybrid architectures has become a major challenge in HPC research. The multiple levels of parallelism in the same system, each level comprising generally different memory and processor technologies make the use of classical programming tools ineffective. Traditional parallel programming tools were designed for homogeneous environments and normally target one level of parallelism. Using them in a hybrid platform implies combining several tools, for example, MPI to communicate the nodes, OpenMP to exploit the parallelism of multicore processors and CUDA/OpenCL to manage the GPUs used as accelerators.

The use of different models with no native integration frequently results in non-

portable applications, readability problems in the code and hand-tuned optimizations. Achieving good performance with this strategy is challenging, and comes with a considerable programming effort. Despite that, a minor platform update, such as adding a new accelerator device, may require redoing all the tuning and optimization steps. In the near future, the advent of platforms with higher core counts and complex memory hierarchies will make intractable the use of such low-level strategies.

One promising approach to manage the heterogeneity of the hardware is the use of an abstraction layer. This layer acts as a middleware between the user application and the low-levels libraries that manage the hardware. This way, it is possible to design the algorithm without considering the hardware aspects. The algorithm is described in terms of tasks and its iterations. These tasks could have dependencies that are someway provided by the programmer. All other operations, such as synchronizations, resource allocation, memory transfers, and load balancing are delegated to a runtime system. To handle the heterogeneity, each task can have multiple implementations to target the different hardware of each processing unit.

In the remainder of this section, we will first present a discussion about the concept of a task and its support on parallel programming tools and then how state-of-the-art tools are using this model to handle hybrid HPC platforms.

#### 2.2.1 Task-Based Programming

The concept of divide a sequential problem in some independent portions of work, which can be executed in parallel, was initially proposed in the 1990s. One of the first parallel programming tools to support this task-based parallelism was Cilk (BLUMOFE, Robert D et al., 1996), originally developed as an open source software at MIT (GROUP, 2017) and now a deprecated feature of Intel C and C++ compilers (INTEL, 2017b).

In this model of parallelism, each task can perform an asymmetrical amount of sequential work and the total number of tasks is, in general, much bigger than the number of physical processing resources. A huge amount of tasks with small granularity provides more flexibility to the scheduler, resulting in a parallel program that is not tightly coupled to the target hardware. The tasks dependencies are expressed in a *fully strict* design, which means that a parent task waits for its direct successors (BLUMOFE, Robert D et al., 1996).

Since tasks are defined without considering the target hardware, task-based tools

rely on an intermediary software layer to provide good performance. This layer consists of a dynamic runtime system which is responsible for handling task scheduling, load balancing, and tasks synchronization. In Cilk, the runtime system is based on a work-stealing scheduling policy, a distributed strategy where an idle processor can steal tasks from another one (BLUMOFE, R. D.; LEISERSON, C. E., 1994).

With the advent of multicore processors in the 2000s, the task-based parallelism was adopted by other programming models such as OpenMP, with **pragma omp task** and **pragma omp task wait** directives of version 3.0 (OPENMP..., 2008), and Intel Threading Building Blocks (TBB) (REINDERS, James, 2007). The task-based paradigm was also implemented by several experimental tools focusing on different hardware platforms: distributed memory (GAUTIER, Thierry; BESSERON; PIGEON, 2007; DINAN et al., 2009; MOR; MAILLARD, 2011), heterogeneous processors (BENDER; RABIN, 2000), GPUs (CEDERMAN; TSIGAS, 2011; TOSS; GAUTIER, Thierry, 2012), Hybrid Nodes(AUGONNET, Cédric et al., 2011; PINTO, Vinicius Garcia; MAILLARD, 2012; PINTO, Vinicius Garcia, 2013; GAUTIER, Thierry; FERREIRA LIMA, et al., 2013)

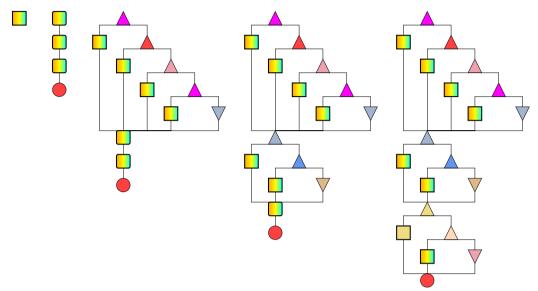

The synchronization primitive **sync** introduced by Cilk to express dependency relationships among tasks, as well its OpenMP equivalent pragma omp  $taskwait^{1}$ , are appropriate to algorithms with a recursive structure. This is the case of several classical divide and conquer applications used to illustrate how Cilk works such as the Fast Fourier Transform, the Merge Sort algorithm or the Strassen method for matrix multiplications. Figure 2.3 illustrates an example of a recursive algorithm in Cilk. This structure rapidly generates a huge number of tasks, and the Cilk steal semantics quickly distribute the workload among the workers. On the other hand, for other algorithm structures such as loop-based ones this strategy may incur in performance bottlenecks. Figure 2.4 illustrates different ways of declaring dependencies in Cilk and OpenMP. The sync (Fig. 2.4(a)) and taskwait (Fig. 2.4(b)) synchronization primitives create a dependency with all the previously submitted tasks. In this example, the DSYRK task of the first iteration of for loop on line 11 actually depends only on the first DTRSM in the previous loop (line 5). Ideally, the first DSYRK could be executed at the same time of all the remaining DTRSM  $(i \ge 2)$ . Nevertheless, the synchronization point of line 10 forces it to wait for all the DTRSM tasks. This kind of bottleneck is avoided when the task dependencies are

<sup>&</sup>lt;sup>1</sup>Although similar, the Cilk **spawn-sync** and OpenMP *task-taskwait* primitives have different behavior. In general terms both **spawn** and **omp task** primitives are used to submit new tasks. However, in Cilk, a **spawn** call starts the execution of the new task and pushes the continuation of the parent task to a queue. For more information, see concepts of *fast/slow* clones and *work-first* discussed by Frigo, Charles E. Leiserson, and Randall (1998) and Guo et al. (2009).

| 1<br>2 | cilk void | <pre>OptimizedStrassenMult(REAL *C, REAL *A, REAL *B,</pre>                                   |

|--------|-----------|-----------------------------------------------------------------------------------------------|

| 3      |           | uint RowWidthA, uint RowWidthB) {                                                             |

| 4      | uint 🤇    | QuadSize = MatSize >> 1;                                                                      |

| 5      | • • •     |                                                                                               |

| 6      | spawn     | <pre>OptimizedStrassenMult(M2, A11, B11, QuadSize,<br/>QuadSize, RowWidthA, RowWidthB);</pre> |

| 7      | spawn     | OptimizedStrassenMult(M5, S1, S5, QuadSize, QuadSize, QuadSize, QuadSize);                    |

| 8      | spawn     | OptimizedStrassenMult(T1sMULT, S2, S6, QuadSize,<br>QuadSize, QuadSize, QuadSize);            |

| 9      | spawn     | OptimizedStrassenMult(C22, S3, S7, QuadSize,<br>RowWidthC, QuadSize, QuadSize);               |

| 10     | spawn     | OptimizedStrassenMult(C11, A12, B21, QuadSize,<br>RowWidthC, RowWidthA,RowWidthB);            |

| 11     | spawn     | OptimizedStrassenMult(C12, S4, B22, QuadSize,<br>RowWidthC, QuadSize, RowWidthB);             |

| 12     | spawn     | OptimizedStrassenMult(C21, A22, S8, QuadSize,<br>RowWidthC, RowWidthA, QuadSize);             |

| 13     | sync;     |                                                                                               |

| 14     |           |                                                                                               |

| 15     | }         |                                                                                               |

Figure 2.3: An example of recursive tasks in Cilk.

Source: Amended from (GROUP, 2017)

expressed in function of the data access.

Since the use of global task dependencies (**spawn-sync** model) can lead to performance bottlenecks, current HPC task-based tools rely on data dependency strategies. This design consists in declaring the access mode (**read**, **write**, **read-write**) for each piece of data accessed by the task. Then, the tasks are submitted in a sequential way. From this information (submission order and access mode), a runtime system can build a task dependency graph. Data dependency models are referred by different names in the literature, such as *data-flow* model (GAUTIER, T. et al., 2013), *sequential task flow* (STF) (AGULLO, Emmanuel et al., 2016) and *superscalar* (DONGARRA et al., 2017). The last one comes from its similarity with superscalar processors which analyzes the sequential instructions flow to identify which ones do not depend on others and, consequently, can be executed in parallel.

In the data dependency model, tasks are created with non-blocking calls. In this design, a task is possibly not ready for execution at the moment of its creation. Task dependencies are automatically inferred and managed by the runtime system. Once all the dependencies are solved, the task is marked as ready for execution. This is differ-

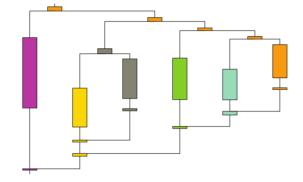

for (k = 0; k < N; k++) { 1 for (k = 0; k < N; k++) { 2 #pragma omp task 3 spawn dpotrf(A[k, k], ...); dpotrf(A[k, k],  $\ldots$ ); 4 #pragma omp taskwait sync; 5 for (i = k+1; i < N; i++) { for (i = k+1; i < N; i++) { 6 #pragma omp task 7 spawn dtrsm(A[i, k], dtrsm(A[i, k], 8 A[k, k], ...); A[k, k], ...); 9 } } 10 #pragma omp taskwait sync; 11 for (i = k+1; i < N; i++) { for (i = k+1; i < N; i++) { 12 #pragma omp task 13 spawn dsyrk(A[i, i], dsyrk(A[i, i], 14 A[i, k], ...); A[i, k], ...); 15 **for** (j = k+1; j < i; j++) { **for** (j = k+1; j < i; j++) { 16 #pragma omp task 17 spawn dgemm(A[i, j], dgemm(A[i, j], 18 A[i, k],A[i, k],A[j, k], ...); 19 A[j, k], ...); 20 } } 21 } } 22 #pragma omp taskwait sync; 23 }

Figure 2.4: A pseudo-code illustrating how to express dependencies in Cilk and OpenMP (a) Cilk (b) OpenMP Tasks

(c) OpenMP Tasks with Data Dependencies

```

for (k = 0; k < N; k++) {

1

2

#pragma omp task depend(inout:A[k, k])

3

dpotrf(A[k, k], \ldots);

4

for (i = k+1; i < N; i++) {

5

#pragma omp task depend(in:A[k, k]) depend(inout:A[i, k])

6

dtrsm(A[i, k],

7

A[k, k], ...);

8

}

9

for (i = k+1; i < N; i++) {

10

#pragma omp task depend(in:A[i, k]) depend(inout:A[i, i])

11

dsyrk(A[i, i],

12

A[i, k], ...);

13

for (j = k+1; j < i; j++) {

14

#pragma omp task depend(in:A[i, k], A[j, k])

15

depend(inout:A[i, j])

16

dgemm(A[i, j],

17

A[i, k],

18

A[j, k], ...);

19

}

20

}

21

}

```

ent from the global task dependencies model used by Cilk and OpenMP where a task is always ready for execution at its creation time. Version 4 of the OpenMP standard has extended the task model of version 3 to support data dependencies. The code of Figure 2.4(c) illustrates how these dependencies are declared in an OpenMP program. Since task creation calls are non-blocking, this code will generate a pool of tasks. When a given task is completed, the runtime enables its successors in the dependency graph which allows finer synchronizations. This also gives more flexibility to the scheduler thanks to the availability of a greater number of tasks ready for execution. In the code example of Figure 2.4(c), the DPOTRF task of second iteration (k = 2) can be executed just after the end of three tasks from the previous iteration (one DPOTRF, one DTRSM and one DSYRK), while in the **spawn-sync** model, it should wait for all the tasks of the previous iteration.

#### 2.3 Runtime Systems for Task-Based Parallel Programming

One of the major features of the task parallelism model is the possibility of designing an algorithm without considering architecture implementation details. Since the tasks are consistent, e.g., with no access to global variables, and their dependencies are correctly described, it is possible to postpone their implementation. This abstraction is also very useful to handle the heterogeneity of the hardware. For example, a programmer can provide multiple implementations for the same task in order to target different hardware architectures. Once all these implementations respect a common interface they can be switched without major consequences.

In this context, programmers have no control over which implementation of the task will be actually executed; they just provide the algorithm (the tasks and its dependencies) and the implementations. During the execution, an intermediary layer, the runtime system, will choose which implementation execute depending on several factors, such as the resource's availability and the provided task implementations.

Several parallel programming tools have been developed in recent years following the concepts of task-parallelism and runtime-taken decisions. In the rest of this section, we will present some of them.

# 2.3.1 PaRSEC

PaRSEC (Parallel Runtime Scheduling and Execution Controller), formerly know as DAGuE (BOSILCA, George et al., 2012), is a runtime system for task-based programming in distributed hybrid architectures. This tool provides automatic data transfers among workers by analyzing the access mode of each piece of data used by the task. PaR-SEC has a simple distributed scheduler that implements a basic work stealing strategy.