# Spiking neural networks based on resistive memory technologies for neural data analysis

Thilo Werner

## ▶ To cite this version:

Thilo Werner. Spiking neural networks based on resistive memory technologies for neural data analysis. Human health and pathology. Université Grenoble Alpes, 2017. English. NNT: 2017 GREAS028. tel-01969946

# HAL Id: tel-01969946 https://theses.hal.science/tel-01969946

Submitted on 4 Jan 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité : Nano-Electronique et Nano-Technologies

Arrêté ministériel : 25 mai 2016

Présentée par

## Thilo WERNER

Thèse dirigée par **Dr. Blaise YVERT** codirigée par **Dr. Barbara DE SALVO**

préparée au sein du CEA-Leti et Braintech lab Inserm & UGA U1205

dans l'Ecole Doctorale Ingénierie pour la Santé, la Cognition et l'Environnement

# Réseaux de neurones impulsionnels basés sur les mémoires résistives pour l'analyse de données neuronales

Thèse soutenue publiquement le « 10 juillet 2017 », devant le jury composé de :

M Damien QUERLIOZ

DR, CNRS, Rapporteur

M Abdelkader SOUIFI

Prof., INSA, Rapporteur

M Thierry BARON

DR, CNRS, Président

M Jean-Michel PORTAL

Prof., CNRS, Examinateur

**M Blaise YVERT**

DR, Inserm, Directeur de thèse

**Mme Barbara DE SALVO**

DR, CEA-Leti, Co-directeur de thèse

Mme Elisa VIANELLO

Dr. Ing., CEA-Leti, Encadrant de thèse

### **ABSTRACT**

Title:

Spiking Neural Networks based on Resistive Memory Technologies for Neural data analysis

he central nervous system of humankind is an astonishing information processing system in terms of its capabilities, versatility, adaptability and low energy consumption. Its complex structure consists of billions of neurons interconnected by trillions of synapses forming specialized clusters. Recently, mimicking those paradigms has been attracting a strongly growing interest, triggered by the need for advanced computing approaches to tackle challenges related to the generation of massive amounts of complex data in the Internet of Things (IoT) era. This has led to a new research field, known as cognitive computing or neuromorphic engineering, which relies on so-called non-von-Neumann architectures (brain-inspired) in contrary to von-Neumann architectures (conventional computers). In this thesis, we explore the use of resistive memory technologies such as oxide vacancy based random access memory (OxRAM) and conductive bridge RAM (CBRAM) for the design of artificial synapses that are a basic building block for neuromorphic networks. Moreover, we develop an artificial spiking neural network (SNN) based on OxRAM synapses dedicated to the analysis of spiking data recorded from the human brain with the goal of using the output of the SNN in a brain-computer interface (BCI) for the treatment of neurological disorders. The impact of reliability issues characteristic to OxRAM technology on the system performance is studied in detail and potential ways to mitigate penalties related to single device uncertainties are demonstrated. Besides the already well-known spike-timing-dependent plasticity (STDP) implementation with OxRAM and CBRAM which constitutes a form of long term plasticity (LTP), OxRAM devices were also used to mimic short term plasticity (STP). The fundamentally different functionalities of LTP and STP are put in evidence.

### Résumé en français

#### Titre:

Réseaux de neurones impulsionnels basés sur les mémoires résistives pour l'analyse de données neuronales

e système nerveux central humain est un système de traitement de l'information stupéfiant en termes de capacités, de polyvalence, d'adaptabilité et de faible consommation d'énergie. Sa structure complexe se compose de milliards de neurones, interconnectés par plusieurs trillions de synapses, formant des grappes spécialisées. Récemment, l'imitation de ces paradigmes a suscité un intérêt croissant en raison de la nécessité d'approches informatiques avancées pour s'attaquer aux défis liés à la génération de quantités massives de données complexes dans l'ère de l'Internet des Objets (IoT). Ceci a mené à un nouveau domaine de recherche, connu sous le nom d'informatique cognitive ou d'ingénierie neuromorphique, qui repose sur les architectures dites non-von-Neumann (inspirées du cerveau) en opposition aux architectures von-Neumann (ordinateurs classiques). Dans cette thèse, nous examinons l'utilisation des technologies de mémoire résistive telles que les mémoires à accès aléatoires à base de lacunes d'oxygène (OxRAM) et les mémoires à pont conducteur (CBRAM) pour la conception de synapses artificielles, composants de base indispensables des réseaux neuromorphiques. De plus, nous développons un réseau de neurones impulsionnels artificiel (SNN), utilisant des synapses OxRAM, pour l'analyse de données impulsionnelles provenant du cerveau humain en vue du traitement de troubles neurologiques, en connectant la sortie du SNN à une interface cerveau-ordinateur (BCI). L'impact des problèmes de fiabilité, caractéristiques des OxRAMs, sur les performances du système est étudié en détail et les moyens possibles pour atténuer les pénalités liées aux incertitudes des dispositifs seuls sont démontrés. En plus de l'implémentation avec des OxRAMs et CBRAMs de la bien connue plasticité fonction du temps d'occurrence des impulsions (STDP), qui constitue une forme de plasticité à long terme (LTP), les dispositifs OxRAM ont également été utilisés pour imiter la plasticité à court terme (STP). Les fonctionnalités fondamentalement différentes de la LTP et STP sont mises en évidence.

#### **ACKNOWLEDGEMENTS**

ertainly, I would not have been able to achieve the results presented in this PhD thesis without the help of numerous people. Therefore, it is my desire to express my deep gratitude to all those who have supported me during the last three years, both professionally as well as personally.

First, I would like to thank my PhD director Blaise Yvert for directing me through this 'exotic' project bridging neuroscience, electrical engineering and machine learning by consistently questioning the status quo, proposing several new ideas and also for his optimistic advices when I struggled with from time to time. Moreover, I am grateful to Barbara de Salvo for the co-direction of this PhD project. Her constant very professional and strategic support as well as fruitful technical discussions helped a lot to steer the work in a successful direction. My special thanks go to Elisa Vianello, my daily advisor, for always being there when I needed assistance, for constantly pushing me to give my best and for her patience with me and my perfectionism. Our countless and sometimes late discussions on neuromorphic subjects brought up a 1000 ideas (more or less) and I will never forget her valuable reminder that 'Research is frustrating!' when I was unsatisfied with the progress of my work. I also want to thank Olivier Bichler from CEA-LIST who assisted me a lot in debugging the code of their special purpose neural network simulator software that I was using (and messing up occasionally).

I am glad I have been able to meet, work and share break times with the people in our lab such as Brigitte, Cathy, Christelle, Eric, Etienne, Gabriel, Gabriele, Khalil, Laurent, Luca, Sabine, Remi, Sophie and Veronique. Of course there are also several people from other labs who helped me with the electrical characterization setup or supported me with expert advice in domains where I did not have enough expertise myself. Among them, I would like to thank especially: Alain Lopez, Carlo Cagli, Denis Blachier and Niccolo Castellani from LCTE as well as Elisabeth Delevoye from DSYS.

Then, there is a great number of interns, PhD students and post-docs that I am thankful to have met and who helped a lot to keep up the social life and reduce the stress level with coffee breaks and nice activities outside of work. In the naive hope not to forget anyone, I want to give my gratitude to the following people: Adam, Amine, Angelica, Annalisa, Anthonin, Blend, Boubacar, Cecile, Daesok, Daniele, Denys, Florent, Giuseppe, Jeremy, Julia, Julien, Loic, Luc, Maria, Marie, Marinela, Marios, Martin, Mouhamad, Mourad, Natalija, Paul, Rana, Selina, Thanasis, Thomas and Vincent. Just as important as people at work to share some creative breaks with are of course 'non-involved' people from the 'outside-of-work' world and I definitely owe finishing this thesis partly to the following people: Alan, Alexia, Daniel, Felipe, Felix, Joana, Johana, Lucy, Ning, Oscar, Pierre, Sebastien, Sholpan and Stephane.

Finally, I want to thank my family for always supporting me in following my ideas and achieving my goals as well as for motivating me when I was doubtful. Continuing my thesis is among the previously mentioned people strongly due to my girlfriend Julia who accompanied me

through this journey of the last three years which was perhaps not quite easy at times but she ever managed to bring me back into equilibrium when it was necessary. Last but definitely not least, I need to mention Marios. He persistently supported me personally when I was close to giving up and he kept listening to my complaints over and over. Therefore, I will be forever in those people's debt and I want to thank them greatly.

## **AUTHOR'S DECLARATION**

declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

| SIGNED:                                 | Www  | DATE: | 08/10/2017 |  |

|-----------------------------------------|------|-------|------------|--|

| ~ I G I I I I I I I I I I I I I I I I I | <br> |       |            |  |

$I\ walk\ slowly\ but\ I\ never\ walk\ backward.$  Abraham Lincoln

# TABLE OF CONTENTS

|    |       |         |                                                              | Page |

|----|-------|---------|--------------------------------------------------------------|------|

| Li | st of | Tables  | i                                                            | xiii |

| Li | st of | Figure  | es es                                                        | xv   |

| In | trodi | uction  |                                                              | 3    |

| 1  | Bas   | ics for | Neuromorphic devices                                         | 7    |

|    | 1.1   | Neuro   | oscience                                                     | . 7  |

|    |       | 1.1.1   | The central nervous system                                   | . 7  |

|    |       | 1.1.2   | Neurons                                                      | . 8  |

|    |       | 1.1.3   | Synapses                                                     | . 10 |

|    |       | 1.1.4   | Electrophysiological techniques to record the brain activity | . 14 |

|    |       | 1.1.5   | Recording of single neurons                                  | . 16 |

|    |       | 1.1.6   | State-of-the-art spike sorting techniques                    | . 17 |

|    |       | 1.1.7   | Brain-computer interfaces                                    | . 19 |

|    |       | 1.1.8   | Neural prostheses                                            | . 20 |

|    | 1.2   | Memo    | ory technologies for data storage                            | . 21 |

|    |       | 1.2.1   | Overview                                                     | . 21 |

|    |       | 1.2.2   | Emerging Non-Volatile Memory technologies                    | . 22 |

|    |       |         | 1.2.2.1 Phase change memory                                  | . 23 |

|    |       |         | 1.2.2.2 Resistive Random Access Memory                       | . 24 |

|    |       |         | 1.2.2.3 Magnetic Random Access Memory                        | . 28 |

|    |       |         | 1.2.2.4 Ferroelectric Random Access Memory                   | . 30 |

|    |       | 1.2.3   | Three-dimensional integration concepts                       | . 30 |

|    |       | 1.2.4   | Comparison                                                   | . 31 |

|    | 1.3   | Emerg   | ging NVM in Neuromorphic Systems                             | . 32 |

|    |       | 1.3.1   | Application of NVM in synapses                               | . 33 |

|    |       |         | 1.3.1.1 PCM synapses                                         | . 33 |

|    |       |         | 1.3.1.2 OxRAM synapses                                       | . 35 |

|    |       |         | 1313 CBRAM synapses                                          | 36   |

# TABLE OF CONTENTS

|   |      |          | 1.3.1.4     | MRAM synapses                                            | 37 |

|---|------|----------|-------------|----------------------------------------------------------|----|

|   |      |          | 1.3.1.5     | FeRAM synapses                                           | 38 |

|   |      | 1.3.2    | Neurom      | orphic concepts based on NVM synapses                    | 38 |

|   |      |          | 1.3.2.1     | Spiking Neural Networks based on emerging NVM            | 39 |

|   |      |          | 1.3.2.2     | Formal Neural Networks based on emerging NVM             | 40 |

|   | 1.4  | Applio   | eations of  | Neuromorphic Networks                                    | 40 |

| 2 | Goa  | l of thi | is work     |                                                          | 43 |

| 3 | Syn  | apse b   | ased on l   | RRAM                                                     | 45 |

|   | 3.1  | Requi    | rements t   | o mimic biological synapses                              | 45 |

|   | 3.2  | Electr   | ical analy  | sis of Resistive RAM                                     | 46 |

|   |      | 3.2.1    | Static IV   | <i>I</i> analysis                                        | 48 |

|   |      | 3.2.2    | Resistar    | nce variability                                          | 51 |

|   |      | 3.2.3    | Resistar    | nce margin                                               | 51 |

|   |      | 3.2.4    | Switchir    | ng variability                                           | 53 |

|   |      | 3.2.5    | Endurar     | nce                                                      | 54 |

|   |      | 3.2.6    | Filamen     | tary vs. non-filamentary switching                       | 59 |

|   |      | 3.2.7    | Retentio    | on for ultra-low programming currents                    | 61 |

|   | 3.3  | Synap    | se design   |                                                          | 62 |

|   |      | 3.3.1    | Synapse     | based on filamentary RRAM                                | 63 |

|   |      | 3.3.2    | Synapse     | based on non-filamentary RRAM                            | 65 |

|   |      | 3.3.3    | Probabil    | istic Spike-Timing-Dependent Plasticity for RRAM synapse | 65 |

|   |      | 3.3.4    | From Ox     | RAM variability to synaptic variability                  | 66 |

|   | 3.4  | Summ     | nary        |                                                          | 67 |

| 4 | Spil | king N   | eural Ne    | twork for spike sorting                                  | 69 |

|   | 4.1  | Motiv    | ation for s | spike sorting                                            | 70 |

|   | 4.2  | Spike    |             | ystem                                                    |    |

|   |      | 4.2.1    |             | approach                                                 | 70 |

|   |      | 4.2.2    | -           | ata encoding                                             | 71 |

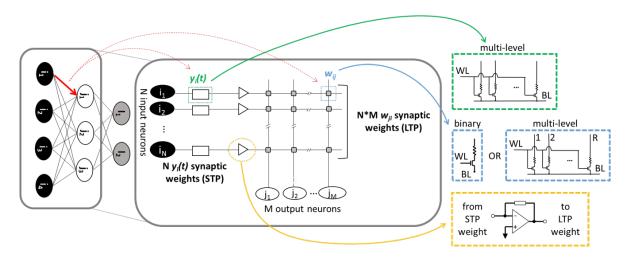

|   |      | 4.2.3    | Spiking     | neural network architecture                              |    |

|   |      |          | 4.2.3.1     | Input layer of SNN                                       | 76 |

|   |      |          | 4.2.3.2     | Output layer of SNN                                      | 77 |

|   |      | 4.2.4    | -           | design                                                   | 78 |

|   |      | 4.2.5    |             | rvised learning by Spike-Timing-Dependent Plasticity     | 79 |

|   |      | 4.2.6    | -           | level description                                        |    |

|   | 4.3  | -        | _           | al data                                                  |    |

|   | 4.4  | Perfor   | mance .     |                                                          | 81 |

| Bi | bliog | graphy                                                            | 143 |

|----|-------|-------------------------------------------------------------------|-----|

| A  | App   | oendix B: Publications                                            | 141 |

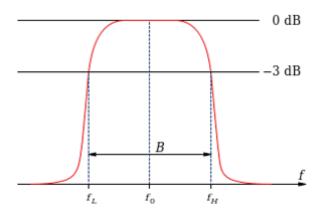

| A  | App   | oendix A: Band-pass filtering                                     | 139 |

| 7  | Con   | nclusions and Perspectives                                        | 135 |

|    | 6.7   | Summary                                                           | 134 |

|    |       | <b>P</b>                                                          | 131 |

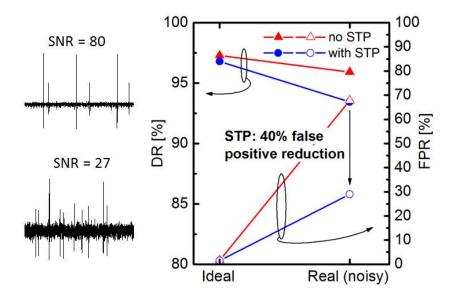

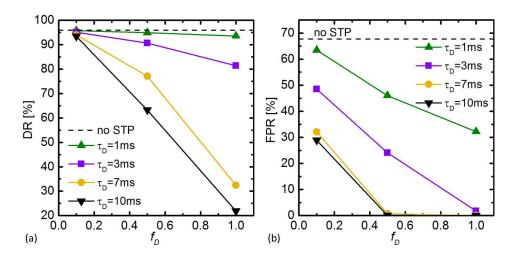

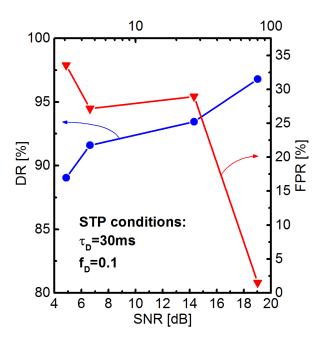

|    |       | 6.6.2 Spike detection in noisy brain signals                      | 130 |

|    |       | 6.6.1 Visual processing with highly noisy input data              | 126 |

|    | 6.6   | Short Term Plasticity in Spiking Neural Networks                  | 125 |

|    | 6.5   | Synapse implementation with OxRAM arrays                          | 121 |

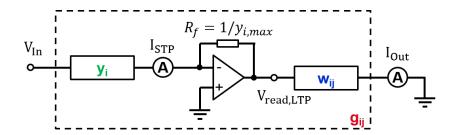

|    | 6.4   | Compound synapse featuring Short and Long Term Plasticity         | 119 |

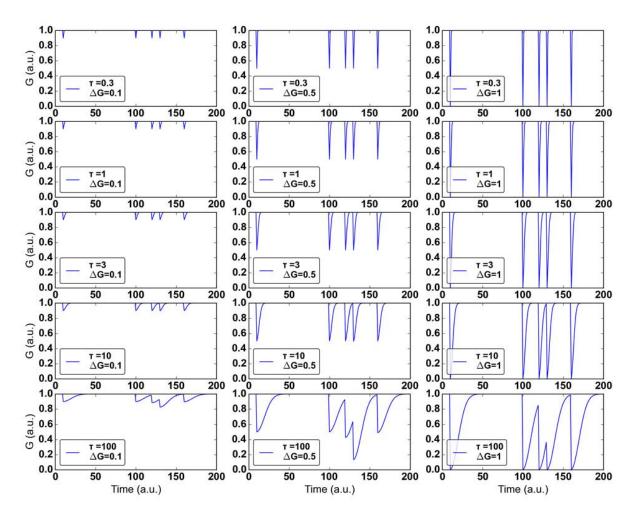

|    | 6.3   | Emulation of Short Term Plasticity using RRAM                     | 114 |

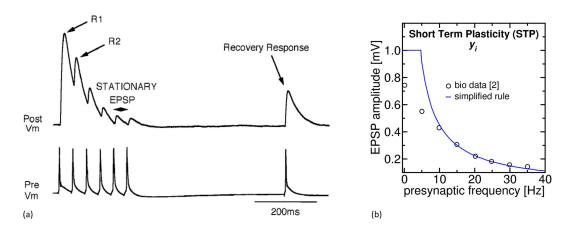

|    | 6.2   | Tsodyks-Markram model                                             | 113 |

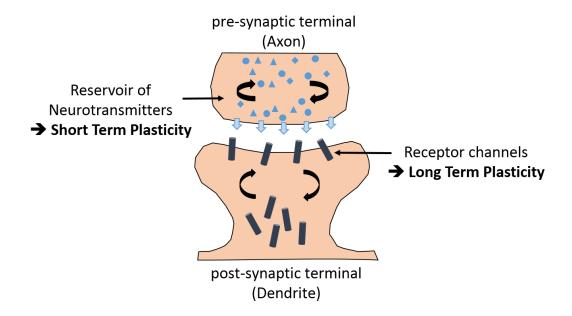

|    | 6.1   | Biological synapse review                                         | 112 |

| 6  | Sho   | ort-Term Plasticity                                               | 111 |

|    | 5.4   | Summary                                                           | 109 |

|    |       | 5.3.5 Learning time                                               | 107 |

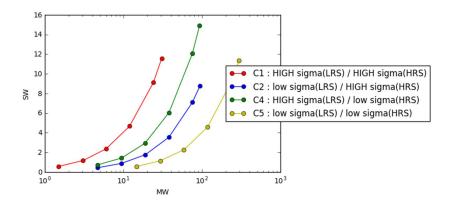

|    |       | 5.3.4 Synaptic granularity                                        | 107 |

|    |       | 5.3.3 Memory window dependence                                    | 104 |

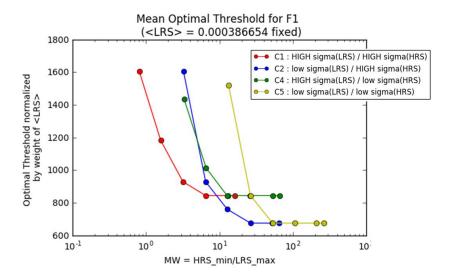

|    |       | 5.3.2 Threshold dependence                                        | 102 |

|    |       | 5.3.1 Reliability                                                 | 99  |

|    | 5.3   | Effects of synaptic variability on SNN in Detection tasks         | 96  |

|    |       | 5.2.1 Reliability                                                 | 94  |

|    | 5.2   | Effects of synaptic variability on SNN in Classification tasks    | 93  |

|    |       | 5.1.1 OxRAM operation for synapses                                | 92  |

|    | 5.1   | Artificial synapse implementation with RRAM technology            | 91  |

| 5  | Syn   | aptic variability in Spiking Neural Networks                      | 91  |

|    | 4.5   | Summary                                                           | 89  |

|    |       | 4.4.5 Qualitative comparison to standard spike sorting techniques | 88  |

|    |       | 4.4.4 Versatility                                                 | 86  |

|    |       | 4.4.3 Power consumption                                           | 84  |

|    |       | 4.4.2 Reliability                                                 | 84  |

|    |       | 4.4.1 Functionality                                               | 82  |

# LIST OF TABLES

| Тав | P. P.                                                                                | age |

|-----|--------------------------------------------------------------------------------------|-----|

| 4.1 | Leaky Integrate Fire (LIF) neuron parameters of the 2-layer spiking neural network   |     |

|     | used for spike sorting of extracellular spiking data                                 | 76  |

| 4.2 | Spiking Neural Network (SNN) statistics                                              | 85  |

| 4.3 | Spiking Neural Network (SNN) power metrics                                           | 86  |

| 4.4 | Quantitative evaluation of spike sorting on different biological datasets            | 87  |

| 4.5 | Qualitative comparison of Spike-Timing Depending Plasticity (STDP) based Spike       |     |

|     | sorting (this work) with standard approaches (template matching, PCA)                | 88  |

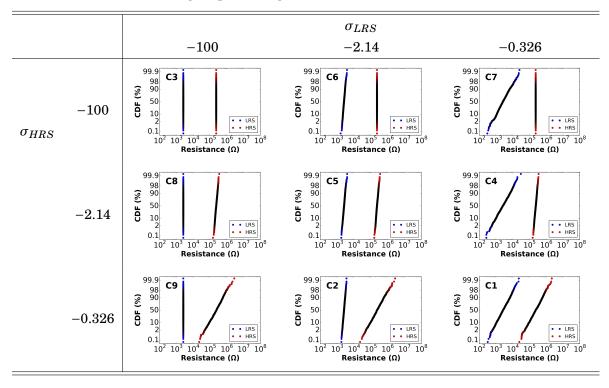

| 5.1 | LRS and HRS test conditions for OxRAM based synapses used to simulate Spiking        |     |

|     | Neural Network for visual signal processing                                          | 99  |

| 6.1 | Statistics of SNN based applications for unsupervised car or spike detection for the |     |

|     | highest noise levels: Cars: 40%, Spikes: SNR=2.7                                     | 133 |

| 6.2 | Energy estimation of SNN based applications for unsupervised car or spike detection  |     |

|     | for the highest noise levels: Cars: 40%, Spikes: SNR=2.7                             | 134 |

# LIST OF FIGURES

| Fig | URE P                                                                                                                                                                                                                                                                                                                                                                                             | age |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

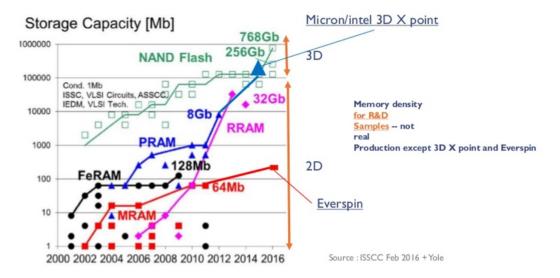

| 0.1 | Evolution of storage capacity of several memory technologies: NAND Flash, phase change memory (PRAM), resistive memory (RRAM), ferroelectric memory (FeRAM) and magnetic memory (MRAM).                                                                                                                                                                                                           | 5   |

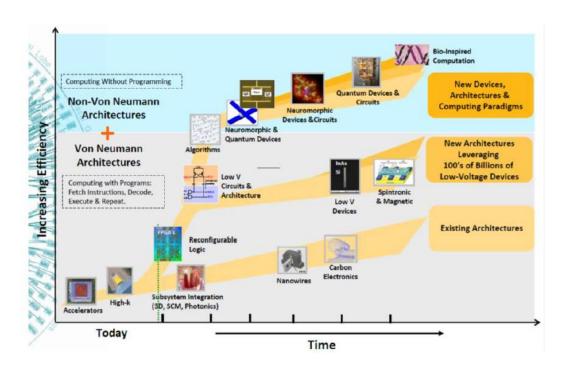

| 0.2 | Prospected computing and technology roadmap based on von-Neumann and non-von-Neumann architectures. Source: IBM                                                                                                                                                                                                                                                                                   | 6   |

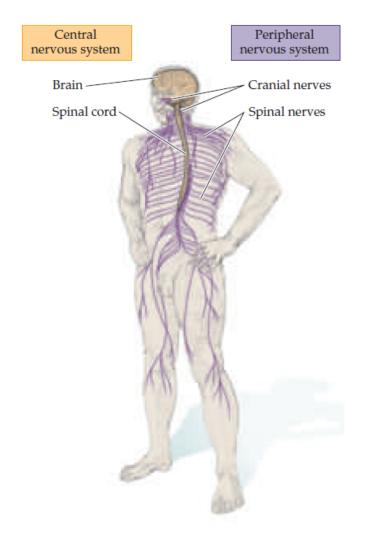

| 1.1 | Schematic illustration of location of central nervous system (CNS) and peripheral nervous system (PNS) in human body. Note that the CNS consists of both brain and spinal cord. Figure taken from [1].                                                                                                                                                                                            | 9   |

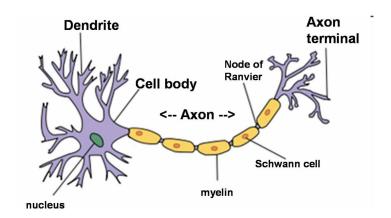

| 1.2 | Structural illustration of a cortical neuron consisting of three main parts: the dendrites, soma and axon                                                                                                                                                                                                                                                                                         | 10  |

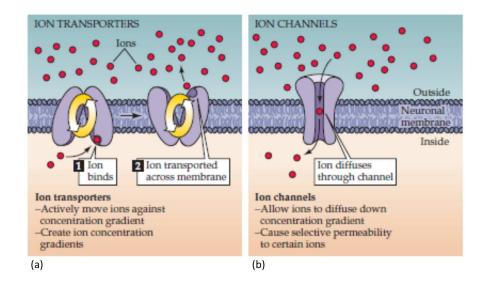

| 1.3 | Illustration of a neuronal cell membrane. (a) Active ion transporters move certain species of ions in one preferable direction resulting in concentration gradients. (b) Ion channels permeable for certain species allow to equalize concentration gradients. Source: [1]                                                                                                                        | 10  |

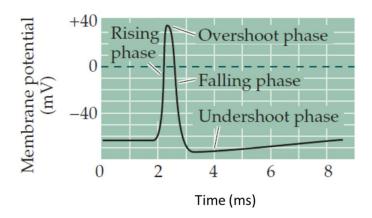

| 1.4 | Schematic internal voltage of a neuron during the emission of an action potential (spike). Normally, a neuron lies at an internal resting potential of around $-65~mV$ which can be changed by synaptic inputs. If a threshold at around $-40~mV$ is reached, a rapid depolarization reaches to approximately $+40~mV$ followed by the rapid repolarization to the resting potential. Source: [1] | 11  |

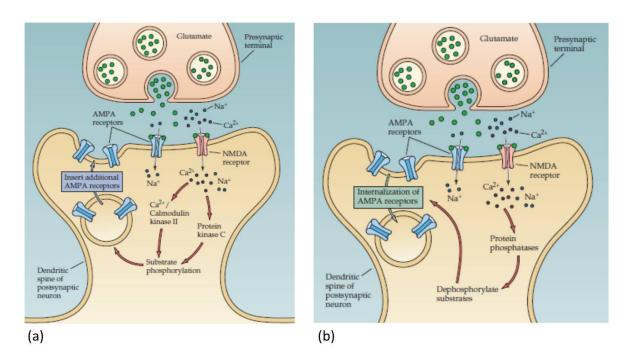

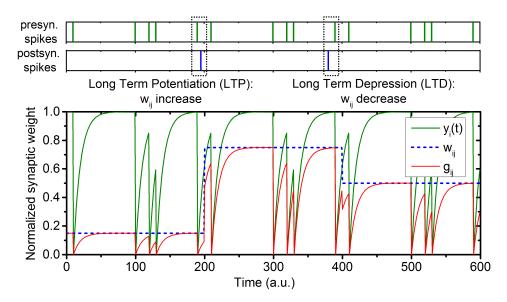

| 1.5 | Schematic illustration of (a) Long-term potentiation (LTP) and (b) Long-term depression (LTD). The synaptic efficacy (strength) depends on the density of so-called AMPA receptors. Accordingly, LTP or LTD are due to an increased or decreased density of AMPA receptors. Source: [1]                                                                                                           | 13  |

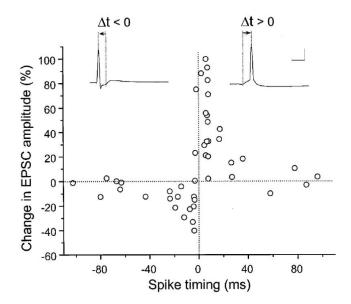

| 1.6  | Experimental spike-timing-dependent plasticity found by Bi and Poo [2]. If a post-synaptic neuron spikes after (before) a pre-synaptic neuron, so that $\Delta T > 0$ ( $\Delta T < 0$ ), their synapse is potentiated (depressed) in an LTP or LTD manner. This change of synaptic strength is expressed by the changed excitatory post-synaptic current (EPSC). A positive change, i.e. an increased EPSC means the synapse has become stronger whereas a negative change, i.e. a decreased EPSC indicates a weakened synaptic strength | 14 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

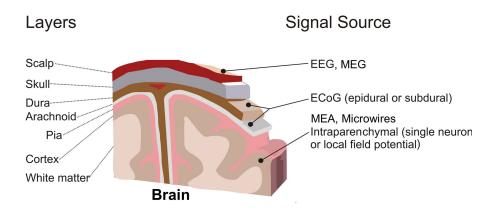

| 1.7  | Overview of brain metrology techniques and their characteristic localization                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15 |

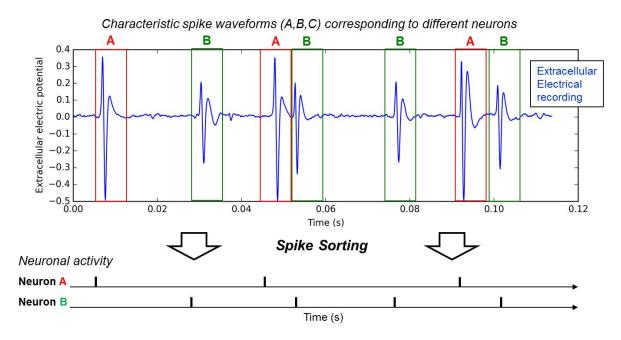

| 1.8  | Schematic illustration of spike sorting from an extra-cellular electrical signal. Different spike waveforms are identified and associated to individual neurons. This allows to extract the spiking activity of single neurons from a multiplexed recording                                                                                                                                                                                                                                                                               | 16 |

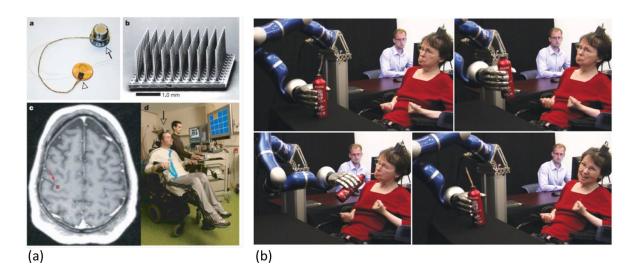

| 1.9  | Selected brain-computer interface cased studies. Two tetraplegic patients were cortically implanted with multi-electrode arrays (left) and a dedicated setup was used for the signal treatment. (a) The subject is able to move a cursor thanks to harnessing his brain signals. (b) The extracted information allowed this subject control a robotic arm to grasp a bottle and drink independently. Source: [3] [4]                                                                                                                      | 20 |

| 1.10 | Overview of state-of-the-art (blue) and emerging (green) memory technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

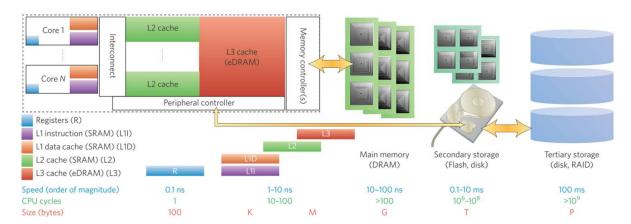

| 1.11 | Memory hierarchy of conventional von-Neumann architectures constructed according the speed of the different technologies. Source: [5]                                                                                                                                                                                                                                                                                                                                                                                                     | 22 |

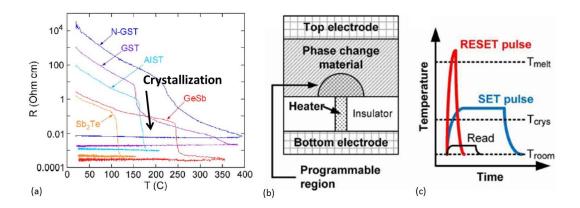

| 1.12 | (a) Resistance as a function of temperature for major phase change materials. When a material in amorphous state is heated up, a crystalline phase will form at some temperature resulting in a significantly lower electrical resistance. (b) Typical integration of a phase change material in a mushroom cell for memory application. (c) Characteristic programming pulses to trigger conversion into crystalline (Set) or amorphous phase (Reset). Source: [6]                                                                       | 23 |

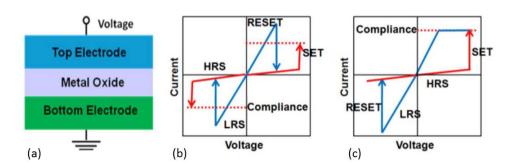

| 1.13 | (a) Basic structure of a RRAM cell. (b) Unipolar and (c) Bipolar device operation. Source: [7]                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25 |

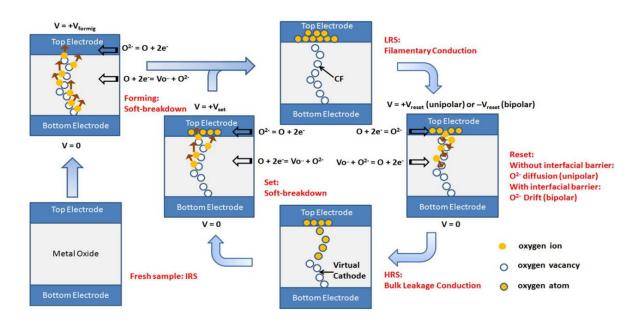

| 1.14 | Illustration of basic physical mechanism involved in switching oxide vacancy based Random Access Memory. Source: [7]                                                                                                                                                                                                                                                                                                                                                                                                                      | 26 |

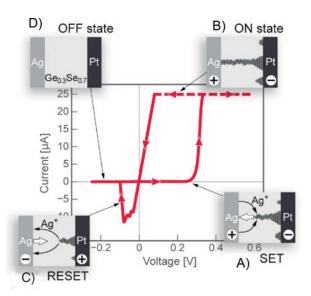

| 1.15 | Illustration of basic physical mechanism involved in switching conductive bridge Random Access Memory. Source: [8]                                                                                                                                                                                                                                                                                                                                                                                                                        | 27 |

| 1.16 | Basic structure of a MRAM cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28 |

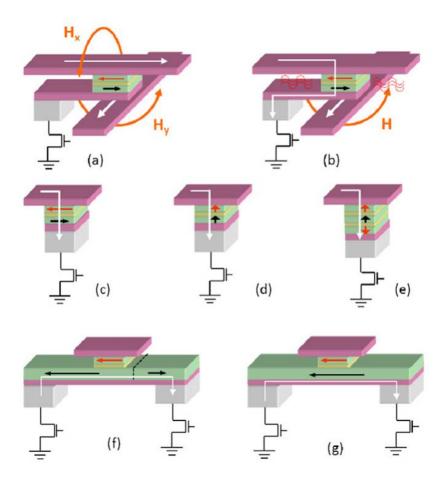

| 1.17 | Overview of current MRAM technologies: (a) Toggle, (b) Thermally assisted MRAM, (c) in-plane STT-RAM, (d) and (e) perpendicular STT-RAM with single and double reference layers (f) domain wall propagation MRAM (g) Spin orbit torque MRAM.                                                                                                                                                                                                                                                                                              |    |

|      | Source: [9]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29 |

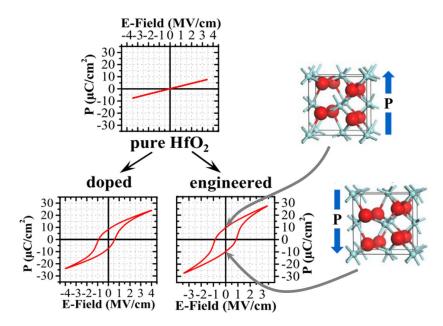

| 1.18 | Principal mechanism of ferroelectric materials. Depending on the orientation of the crystal structure (note the red atoms), the material exhibits a spontaneous electrical                                                                                                                                                                                                                                                            |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30 |

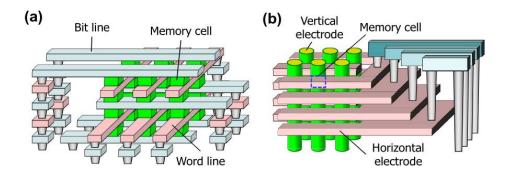

| 1.19 | (a) 3D cross-point and (b) vertical RRAM (VRRAM) integration architectures. Source: [12]                                                                                                                                                                                                                                                                                                                                              | 31 |

| 1.20 | Comparison of most important emerging non-volatile memory technologies. Source: [13]                                                                                                                                                                                                                                                                                                                                                  | 32 |

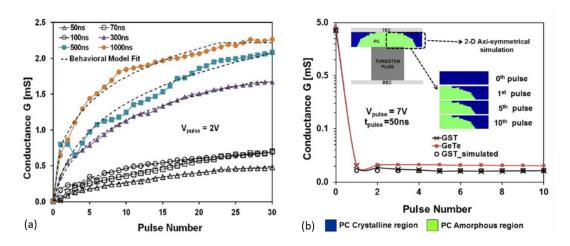

|      | (a) Gradual crystallization of PCM cell upon application of identical set pulses. (b) Abrupt amorphization of PCM cell upon application of identical reset pulses. Source:  [14]                                                                                                                                                                                                                                                      | 34 |

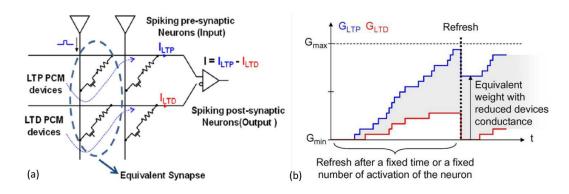

| 1.22 | (a) The 2-PCM synapse design. Both LTP and LTD device use gradual crystallization in order to achieve a progressive potentiation and depression of the synaptic weight which corresponds to $I$ . (b) Refresh algorithm to prevent saturation of synaptic weights. LTP and LTD devices are reset and the previous synaptic weight is restored by gradually programming the device which was stronger before the refresh. Source: [15] | 34 |

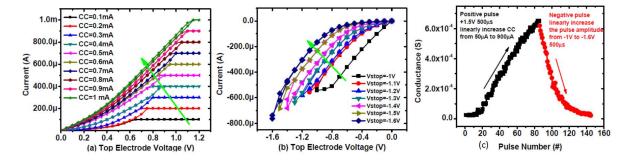

| 1.23 | Gradual programming of OxRAM cell by increasing the (a) current compliance (CC) and (b) reset voltage (Vstop). (c) Gradual potentiation and depression achieved by tuning the programing conditions. Source: [16]                                                                                                                                                                                                                     | 35 |

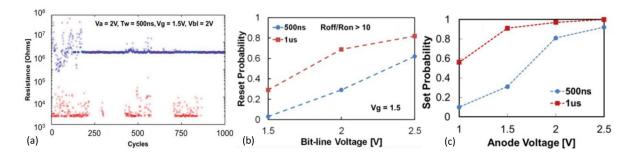

| 1.24 | (a) Probabilistic programming is shown for a CBRAM cell. For a number of cycles, the Set pulses fail to switch the device into LRS. This phenomenon can be used to extract (b) Reset and (c) Set probabilities. Source: [17]                                                                                                                                                                                                          | 37 |

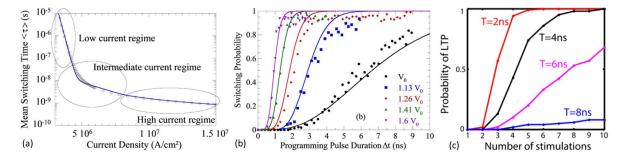

| 1.25 | (a) Switching time as a function of the applied current density in a MRAM cell. Switching probability as a function of (b) applied programming time and (c) delay between programming pulses. Source: [18] [19]                                                                                                                                                                                                                       | 37 |

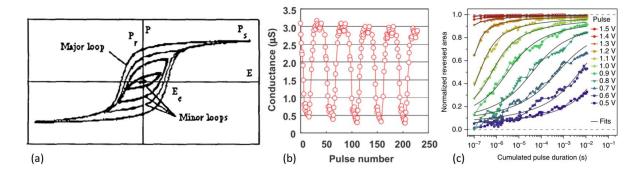

| 1.26 | (a) Hysteresis loop of ferroelectric polarization indicating gradual polarization change. (b) Gradual conductance change observed in a FeFET. (c) Ratio of switched polarization area as function of the cumulated pulse time showing gradual changes. Source: [20]                                                                                                                                                                   |    |

|      | [21] [22]                                                                                                                                                                                                                                                                                                                                                                                                                             | 38 |

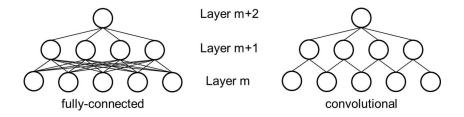

| 1.27 | Schematic illustration of fully-connected neural network (FCNN) and convolutional neural network (CNN)                                                                                                                                                                                                                                                                                                                                | 40 |

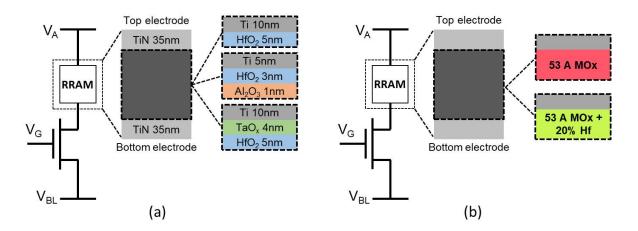

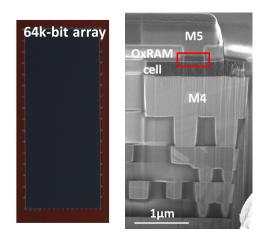

| 3.1  | Schematic of 1-Transistor-1-Resistor ( $1T1R$ ) co-integration. Overview of device structure and different material compositions analysed for this study for (a) OxRAM and (b) CBRAM.                                                                                                                                                                                                                                                 | 47 |

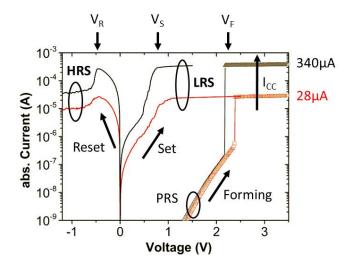

| 3.2  | Schematic switching of 1-Transistor-1-Resistor (1 $T1R$ ) co-integrated RRAM devices. RRAM IV characteristics (here for $Al_2O_3/HfO_2$ OxRAM device) for Forming (symbols) and Set/Reset (solid lines, 30 cycles averaged). Operation is shown for different                                                                                                                                                                         |    |

|      | programming gurrents (PC)                                                                                                                                                                                                                                                                                                                                                                                                             | 17 |

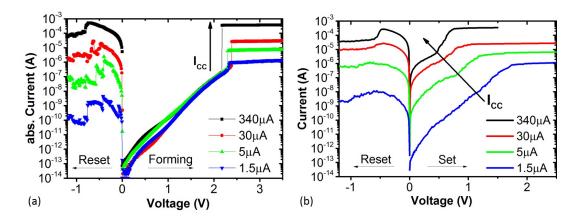

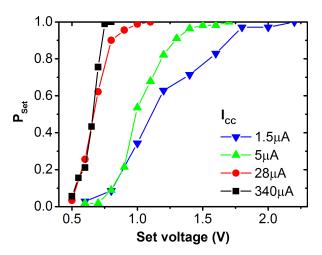

| 3.3  | IV characteristics (shown for $Al_2O_3/HfO_2$ OxRAM) for (a) Forming/1 <sup>st</sup> Reset and (b) Set/Reset. Operation is shown for $I_{CC}$ (i.e. current compliance) ranging from 1.5 $\mu A$ to 340 $\mu A$ . Note the shift of the Set IV curve towards higher voltages for reduced $I_{CC}$ .                                                                                                                                                                                                                                                                                                                                                        | 49 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

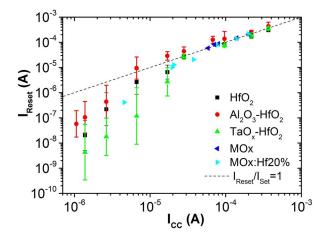

| 3.4  | Reset current ( $I_{Reset}$ ) as a function of $I_{CC}$ for OxRAM and CBRAM material compositions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49 |

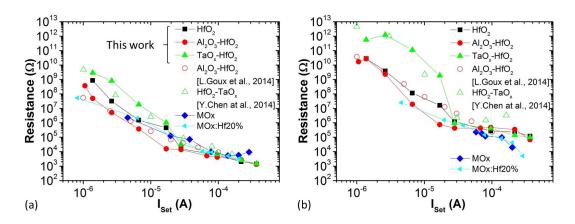

| 3.5  | (a) LRS and (b) HRS as a function of $I_{CC}$ for different oxide materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50 |

| 3.6  | (a) IV characteristic of doped $MO_x$ CBRAM operated using $I_{CC}=4.5\mu A$ and (b) corresponding resistance values for Low and High Resistance States (LRS and HRS) for 30 switching cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50 |

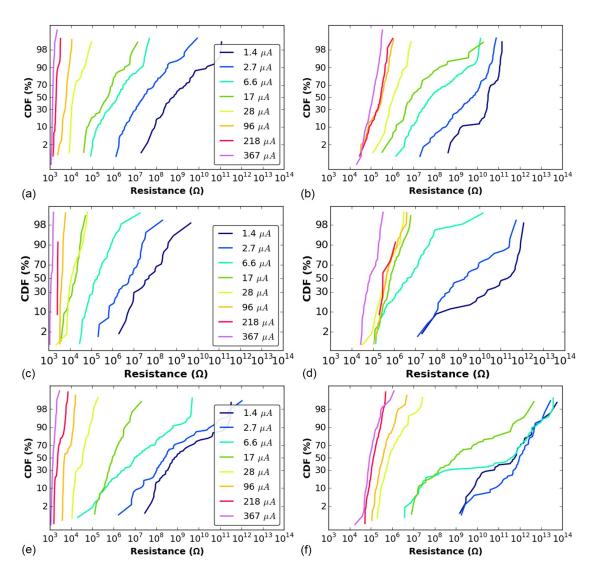

| 3.7  | Cumulative distribution functions (CDF) of Low Resistive State (LRS) and High Resistive State (HRS) as function of the current compliance ( $I_{CC}$ ) for different OxRAM materials: (a) LRS and (b) HRS for $5nm\ Hf\ O_2$ (c) LRS and (d) HRS for $1nm\ Al_2O_3/3nm\ Hf\ O_2$ (e) LRS and (f) HRS for $5nm\ Hf\ O_2/4nm\ TaO_x$ . Note the shift and widening of the CDF in both LRS and HRS for reduced $I_{CC}$                                                                                                                                                                                                                                       | 52 |

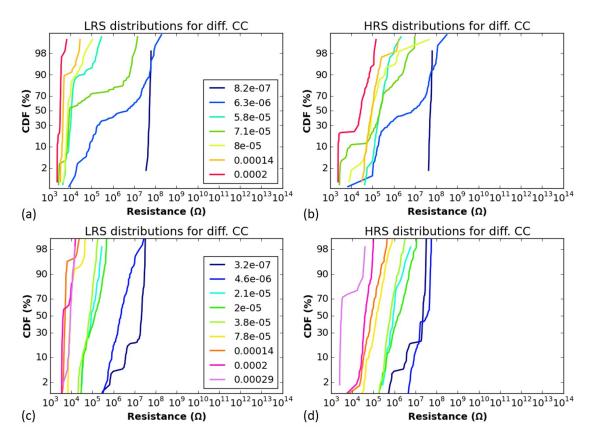

| 3.8  | Cumulative distribution functions (CDF) of Low Resistive State (LRS) and High Resistive State (HRS) as function of the current compliance ( $I_{CC}$ ) for different CBRAM materials: (a) LRS and (b) HRS for undoped $MO_x$ (c) LRS and (d) HRS for $20\% Hf - MO_x$ . Note the shift and widening of the CDF in both LRS and HRS for reduced $I_{CC}$ .                                                                                                                                                                                                                                                                                                  | 53 |

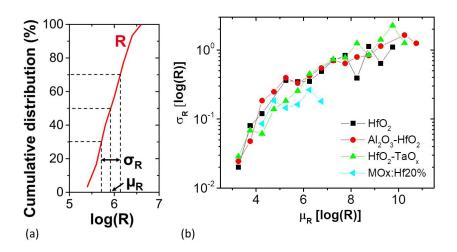

| 3.9  | (a) Variability $(\sigma_R)$ as a function of programmed mean resistance $(\mu_R)$ . (b) $\mu_R$ and $\sigma_R$ extraction methodology from experimental resistance distribution of 30 cycles for one device                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54 |

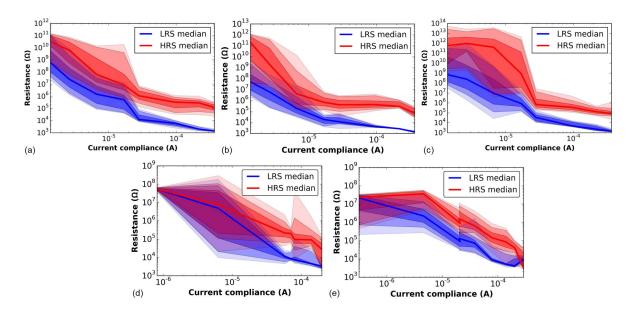

| 3.10 | LRS and HRS as a function of the current compliance $(I_{CC})$ for (a) $5nm\ HfO_2$ , (b) $1nm\ Al_2O_3/3nm\ HfO_2$ and (c) $5nm\ HfO_2/4nm\ TaO_x$ . The bold lines show the geometrical mean values of LRS and HRS, the shaded areas represent different confidence intervals of the experimental sample, i.e. $1\sigma$ , $2\sigma$ and $3\sigma$                                                                                                                                                                                                                                                                                                       | 54 |

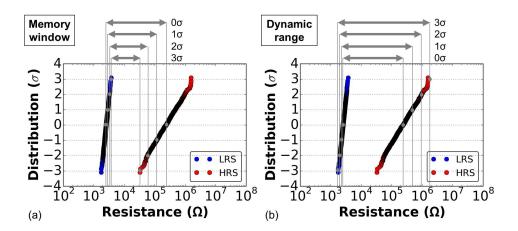

| 3.11 | The extraction of (a) the memory window (MW) and (b) the dynamic range for different confidence intervals ( $\sigma$ ) is schematically illustrated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55 |

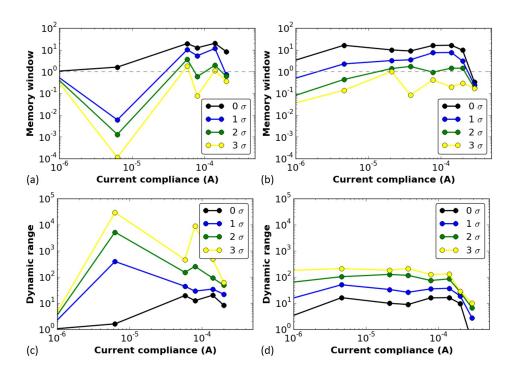

| 3.12 | Memory window as function of $I_{CC}$ for (a) $5nm\ HfO_2$ , (b) $1nm\ Al_2O_3/3nm\ HfO_2$ and (c) $5nm\ HfO_2/4nm\ TaO_x$ . The different lines correspond to different confidence intervals of the experimental sample, i.e. $0\sigma$ , $1\sigma$ , $2\sigma$ and $3\sigma$ . The dashed lines represent a MW of 1, i.e. LRS and HRS distributions blend into each other. Dynamic range as function of $I_{CC}$ for (a) $5nm\ HfO_2$ , (b) $1nm\ Al_2O_3/3nm\ HfO_2$ and (c) $5nm\ HfO_2/4nm\ TaO_x$ . The different lines correspond to different confidence intervals of the experimental sample i.e. $0\sigma$ , $1\sigma$ , $2\sigma$ and $3\sigma$ | 55 |

| 3.13 | Memory window as function of $I_{CC}$ for (a) undoped $MO_x$ and (b) $20\%Hf - MO_x$ . The different lines correspond to different confidence intervals of the experimental sample, i.e. $0\sigma$ , $1\sigma$ , $2\sigma$ and $3\sigma$ . The dashed lines represent a MW of 1, i.e. LRS and HRS                                                                                                                                                                                               |                                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|      | distributions blend into each other. Dynamic range as function of $I_{CC}$ for (a) undoped $MO_x$ and (b) $20\%Hf:MO_x$ . The different lines correspond to different confidence                                                                                                                                                                                                                                                                                                                |                                 |

| 3.14 | intervals of the experimental sample, i.e. $0\sigma$ , $1\sigma$ , $2\sigma$ and $3\sigma$                                                                                                                                                                                                                                                                                                                                                                                                      | <ul><li>56</li><li>57</li></ul> |

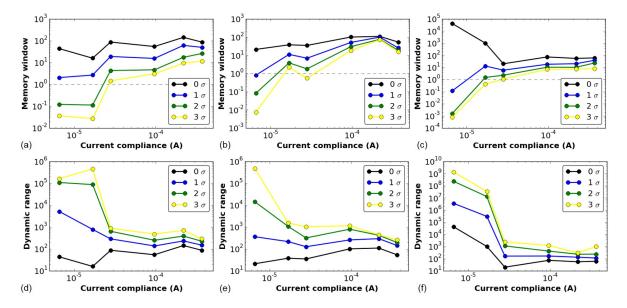

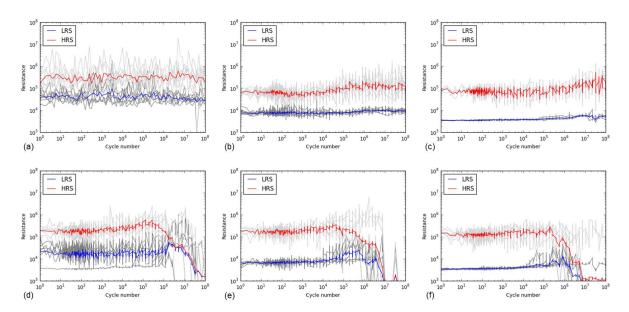

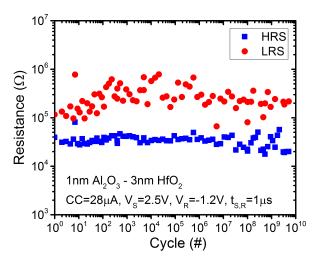

| 3.15 | $HfO_2$ endurance test using pulsed programming with $V_S=2.5V$ and $t_{Set,Reset}=1\mu s$ and a variation of current compliance $I_{CC}$ and reset voltage $V_R$ : (a) $I_{CC}=30\mu A$ , $V_R=-1.2V$ , (b) $I_{CC}=85\mu A$ , $V_R=-1.2V$ , (c) $I_{CC}=135\mu A$ , $V_R=-1.2V$ , (d) $I_{CC}=30\mu A$ , $V_R=-1.5V$ , (e) $I_{CC}=85\mu A$ , $V_R=-1.5V$ , (f) $I_{CC}=135\mu A$ , $V_R=-1.5V$ . The single devices LRS and HRS are represented in grey lines while the mean LRS and HRS are |                                 |

|      | shown in blue and red                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57                              |

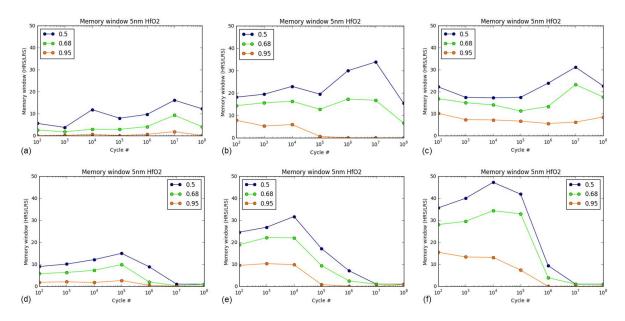

| 3.16 | Memory window (MW) for different distribution intervals ( $\sigma$ ) of $HfO_2$ endurance test using pulsed programming with $V_S=2.5V$ and $t_{Set,Reset}=1\mu s$ and a variation of current compliance $I_{CC}$ and reset voltage $V_R$ : (a) $I_{CC}=30\mu A$ , $V_R=-1.2V$ , (b) $I_{CC}=85\mu A$ , $V_R=-1.2V$ , (c) $I_{CC}=135\mu A$ , $V_R=-1.2V$ , (d) $I_{CC}=30\mu A$ , $V_R=-1.5V$ ,                                                                                                |                                 |

|      | (e) $I_{CC} = 85\mu A$ , $V_R = -1.5V$ , (f) $I_{CC} = 135\mu A$ , $V_R = -1.5V$                                                                                                                                                                                                                                                                                                                                                                                                                | 58                              |

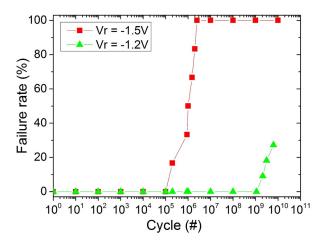

| 3.17 | Endurance failure rate of RRAM as a function of the reset voltage $V_R$ . Early HRS failure rate is induced by high $V_R$                                                                                                                                                                                                                                                                                                                                                                       | 58                              |

| 3.18 | Endurance failure rate of RRAM as a function of the reset voltage $V_R$ . Early HRS failure rate is induced by high $V_R$                                                                                                                                                                                                                                                                                                                                                                       | 59                              |

| 3.19 | $TaO_x/HfO_2$ endurance for pulsed operation using (a) $I_{CC}$ = 5 $\mu A$ , $V_{Set}$ = 3 $V$ , $V_{Reset}$ = $-1.5~V$ , $t_{Set/Reset}$ = 10 $\mu s$ (no resistance window) and (b) $I_{CC}$ = 30 $\mu A$ , $V_{Set}$ = 2.5 $V$ ,                                                                                                                                                                                                                                                            |                                 |

| 3.20 | $V_{Reset} = -1.5 \ V$ , $t_{Set/Reset} = 1 \ \mu s$ (1 decade median-median resistance window) Abrupt Set of single $TaO_x/HfO_2$ device obtained by applying 100 identical Set pulses                                                                                                                                                                                                                                                                                                         | 60                              |

|      | with $I_{CC}$ = 30 $\mu A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60                              |

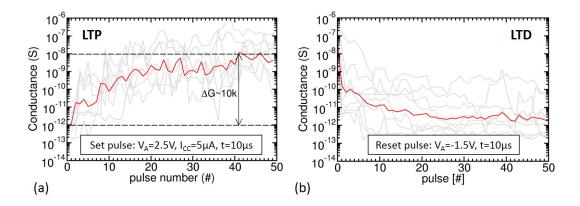

| 3.21 | (a) Long Term Potentiation (LTP) and (b) Long Term Depression (LTD) of $10 \ TaO_x/HfO_2$ devices (grey) obtained by application of 50 identical Set and Reset pulses with                                                                                                                                                                                                                                                                                                                      |                                 |

| 3.22 | $I_{CC} = 5 \ \mu A$ . Geometric mean over all devices is also shown (red)                                                                                                                                                                                                                                                                                                                                                                                                                      | 61                              |

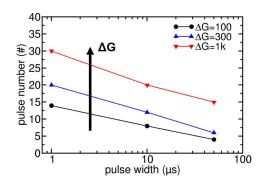

|      | certain ratio $\Delta G$ is shown as a function of the pulse duration for $\Delta G = 100$ , $\Delta G = 300$ and $\Delta G = 1000$ . $I_{CC} = 5 \ \mu A$                                                                                                                                                                                                                                                                                                                                      | 62                              |

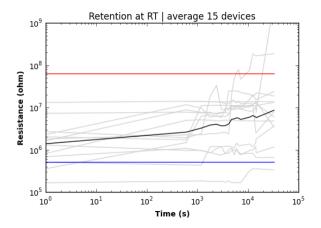

| 3.23 | Data retention of $15x~1nm~Al_2O_3/3nm~HfO_2$ devices programmed into LRS using $I_{CC}=6.5\mu A$ . The test was performed at room temperature. Blue and red lines represent the average LRS or HRS levels. Grey lines show the single device behaviour and                                                                                                                                                                                                                                     |                                 |

|      | black the mean value of all devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62                              |

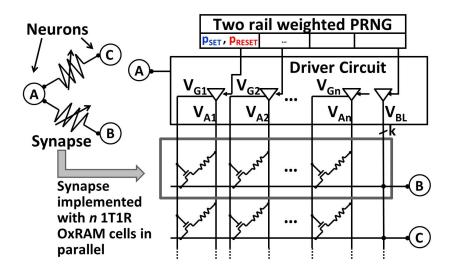

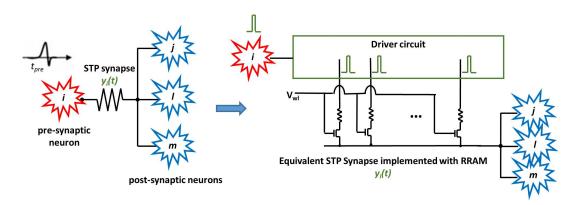

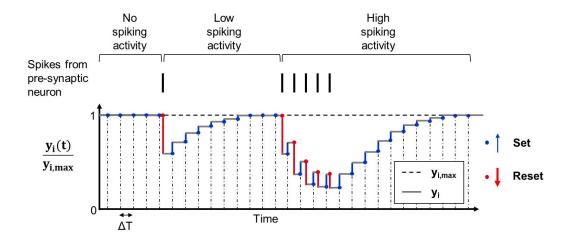

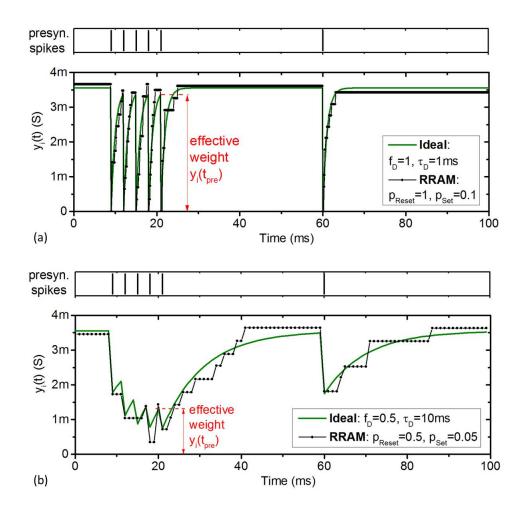

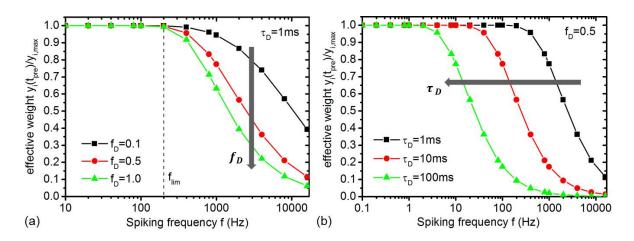

| 3.24 | Multi-cell synapse concept. Each equivalent synapse consists of a series of 1T1R                                                                                      |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | integrated RRAM devices, i.e. the corresponding synaptic weight is the sum of device conductances. A driver circuit including a pseudo random number generator (PRNG) |    |

|      | is used to enable gradual tuning of the synaptic weight, thus overcoming the typical                                                                                  |    |

|      | abrupt switching characteristic of RRAM shown in figure 3.20                                                                                                          | 64 |

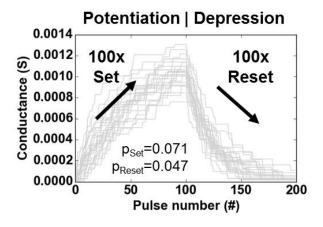

| 3.25 | Potentiation and Depression for 20 synapses each based on 20 OxRAM devices using                                                                                      |    |

|      | a pseudo random number generator (PRNG) for the application of Set and Reset pro-                                                                                     |    |

|      | gramming pulses with $p_{Set}$ and $p_{Reset}$ . OxRAM devices are fitted using experimental                                                                          |    |

|      | data from figure 3.15 (a)                                                                                                                                             | 64 |

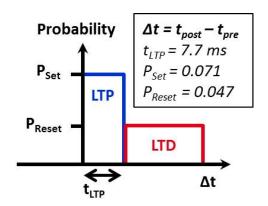

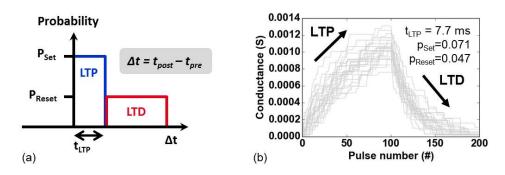

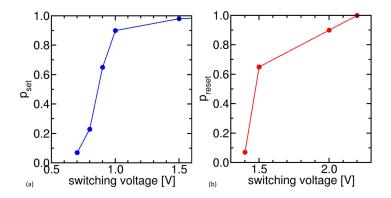

| 3.26 | Probabilistic learning rule used for online learning in our SNN inspired by spike                                                                                     |    |

|      | timing dependent plasticity (STDP). Set and Reset probabilities, $p_{Set}$ and $p_{Reset}$ as well as the LTP time window $t_{LTP}$ are indicated                     | 66 |

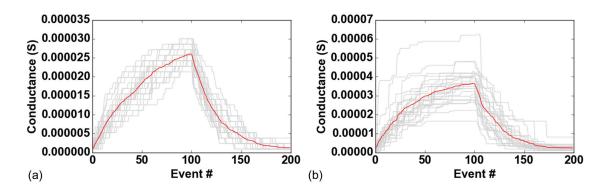

| 3 97 | Representation of synaptic evolution for 100 events of potentiation and depression each                                                                               | 00 |

| 0.21 | for synapses based on (a) OxRAM operated at $I_{CC} = 340\mu A$ and (b) OxRAM operated                                                                                |    |

|      | at $I_{CC}=30\mu A$ . The OxRAM was based on a $1nm~Al_2O_3/3nm~HfO_2$ dielectric. Each                                                                               |    |

|      | grey line represents one synapse based on 20 OxRAM devices. The average synaptic                                                                                      |    |

|      | weight evolution is shown in red                                                                                                                                      | 67 |

|      |                                                                                                                                                                       |    |

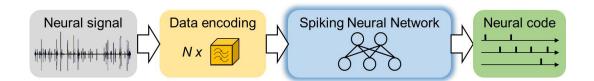

| 4.1  | Overall schematic of spike sorting approach based on data encoding by $N$ band-pass                                                                                   |    |

|      | filters and a spiking neural network. The approach aims to extract the neural code                                                                                    |    |

|      | from electrical neural signals                                                                                                                                        | 71 |

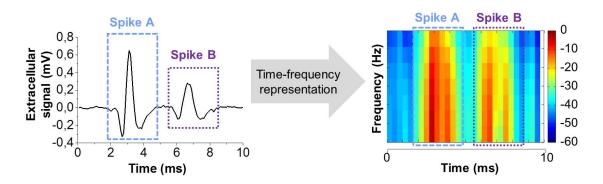

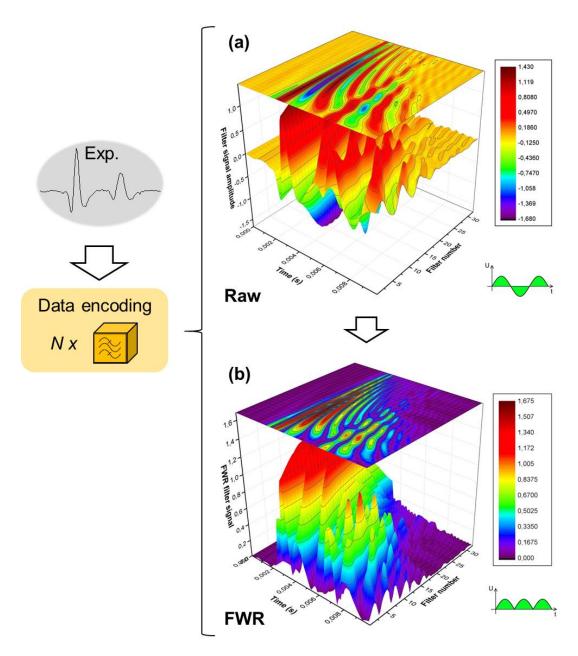

| 4.2  | Signal encoding for spike sorting paradigm based on continuous time-frequency de-                                                                                     |    |

|      | composition of the analog extracellular signal (ES). Different spike shapes (here Spike                                                                               |    |

|      | A and B) exhibit distinct patterns in the spectrogram. These 'finger prints' are used to                                                                              |    |

|      | distinguish between different spike shapes                                                                                                                            | 72 |

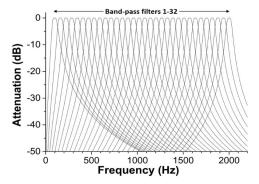

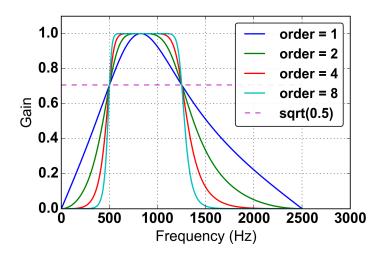

| 4.3  | Band-pass filter characteristics for 32 order 2 Butterworth filters equally distributed                                                                               |    |

|      | between 100 $Hz$ and 2000 $Hz$ . The bandwidth for each filter is $B = 60 Hz$ . This filter                                                                           |    |

|      | set is used to pre-process biological spiking data.                                                                                                                   | 73 |

| 4.4  | Band-pass filter output signals from 32 filters applied to a 10ms long signal (see figure                                                                             |    |

|      | 4.2). (a) The raw continuous filter responses are shown as a function of the time which                                                                               |    |

|      | are then full-wave rectified resulting in signals shown in (b)                                                                                                        | 74 |

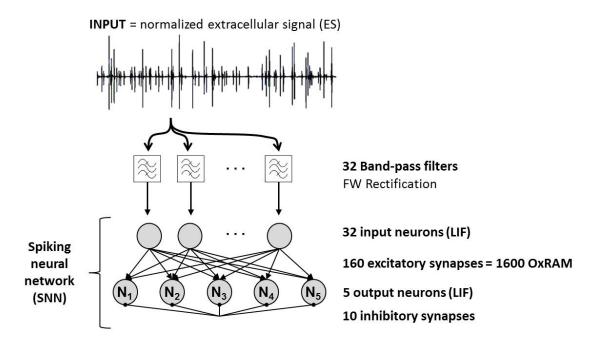

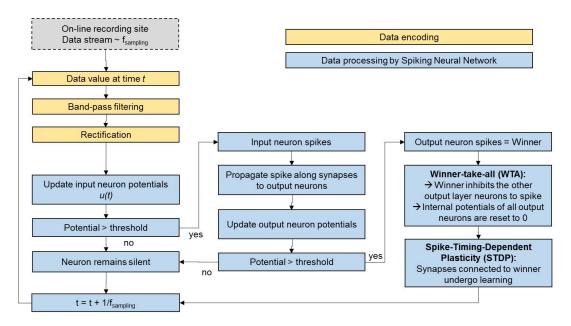

| 4.5  | Functional schematic of spike sorting system based on a Spiking Neural Network.                                                                                       |    |

|      | The extracellular signal (ES) is fed through 32 frequency band-pass filters which are                                                                                 |    |

|      | connected one-to-one to the input layer of the SNN. Synapses are based on OxRAM                                                                                       |    |

|      | devices. Output neurons are interconnected by inhibitory synapses to feature the                                                                                      |    |

|      | winner-take-all principle which allows them to become selective to different input                                                                                    |    |

|      | spike shapes.                                                                                                                                                         | 75 |

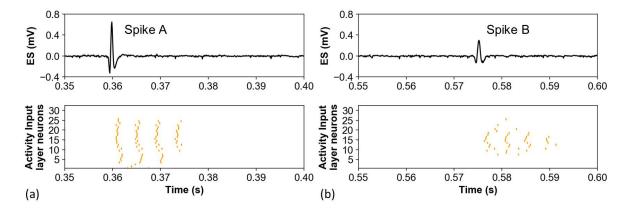

| 4.6  | Recorded extracellular (ES) signals (black) and representation of frequency bands by                                                                                  |    |

|      | input neurons (orange) for (a) Spike A and (b) Spike B                                                                                                                | 77 |

| 4.7         | (a) Probabilistic learning rule used for online learning in our SNN inspired by spike                                                                                                                  |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|             | timing dependent plasticity (STDP). Set and Reset probabilities, $p_{Set}$ and $p_{Reset}$ as                                                                                                          |    |

|             | well as the LTP time window $t_{LTP}$ are indicated. (b) Long Term Potentiation (LTP)                                                                                                                  |    |

|             | and Long Term Depression (LTD) for 20 synapses each based on 20 OxRAM devices                                                                                                                          |    |

|             | using $p_{Set}$ and $p_{Reset}$ . OxRAM devices are fitted using experimental data from figure                                                                                                         |    |

|             | 3.19                                                                                                                                                                                                   | 80 |

| 4.8         | Schematic algorithm of the proposed spike sorting system                                                                                                                                               | 80 |

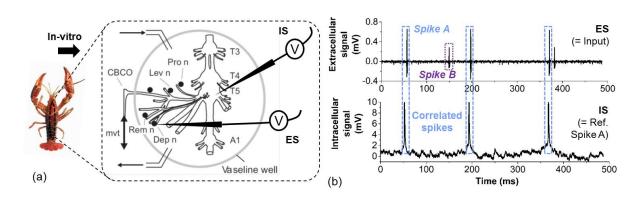

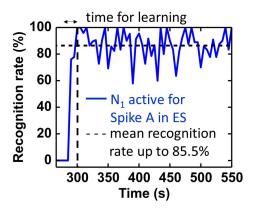

| 4.9         | (a) Illustration of the experiment used to obtain real biological data. The crayfish is                                                                                                                |    |

|             | dissected and two electrodes are used in-vitro, one intracellular electrode inside a                                                                                                                   |    |

|             | motor neuron in the T5 ganglion and one extracellular positioned against a depressor                                                                                                                   |    |

|             | nerve ('Dep'). (b) The extracellular signal (ES, short sequence shown) contains two                                                                                                                    |    |

|             | different spike shapes, labelled as Spike A and Spike B. The intracellular signal (IS)                                                                                                                 |    |

|             | contains spiking events matching only Spike A of the ES                                                                                                                                                | 82 |

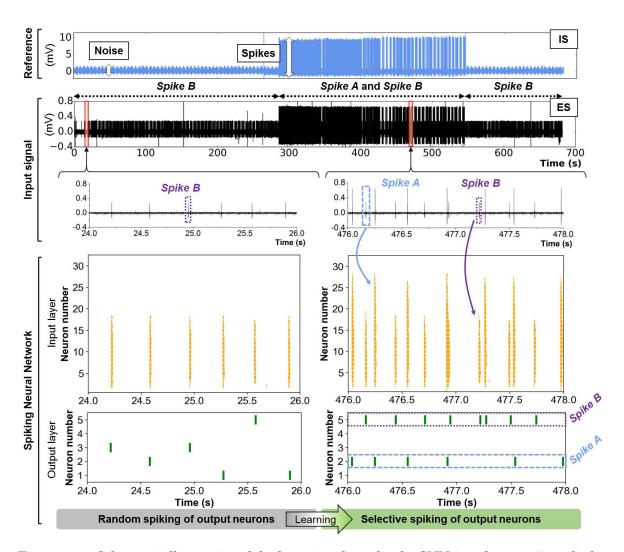

| 4.10        | Schematic illustration of the learning phase for the SNN (see figure 4.5) applied on the                                                                                                               |    |

|             | biological data (see figure 4.9). Initially, the SNN is untrained for new input spikes (in                                                                                                             |    |

|             | the ES signal) and output neurons spike randomly. Due to online learning, different                                                                                                                    |    |

|             | output neurons become gradually selective to certain input spike patterns                                                                                                                              | 83 |

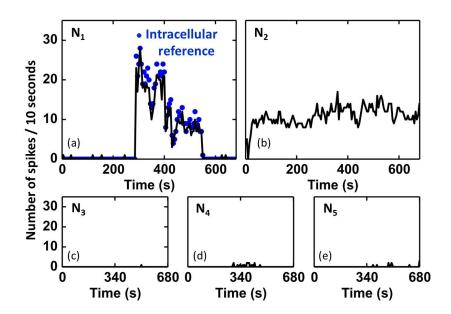

| 4.11        | Activity of SNN output neurons during 681 s of continuous input signal. Activity is                                                                                                                    |    |

|             | plotted as the number of spikes in time intervals of 10 seconds. $N_1$ activity matches                                                                                                                |    |

|             | well with the intracellular reference (blue dots), i.e. $N_1$ detects Spike A. $N_2$ seems to                                                                                                          |    |

|             | be selective to Spike B, however, no reference data is available for verification                                                                                                                      | 84 |

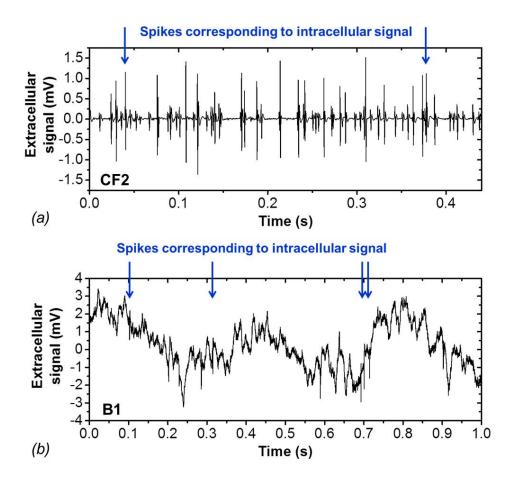

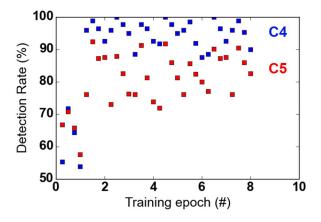

| 4.12        | Temporal evolution of recognition rate of Spike A by $N_1$ . A mean recognition rate                                                                                                                   |    |

|             | of 86.4% (dashed line) is reached within 15 seconds starting from the first Spike A $$                                                                                                                 |    |

|             | occurence                                                                                                                                                                                              | 85 |

| 4.13        | Sequences of real biological spiking data used for verification of Spike Sorting system,                                                                                                               |    |

|             | recorded in (a) in-vitro crayfish [23] and (b) in-vivo implanted rat hippocampus [24].                                                                                                                 |    |

|             | Intracellular recordings were simultaneously obtained and provide the ground truth                                                                                                                     |    |

|             | for valid quantification of the spike recognition rate for the labeled spikes (blue arrows).                                                                                                           | 87 |

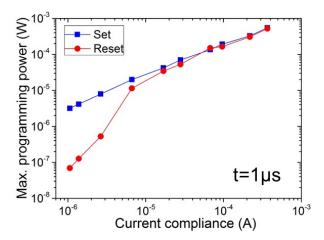

| <b>5</b> 1  | Estimation of maximum programming payon of OvPAM (1 nm Al. O. /2 nm HfO.) or                                                                                                                           |    |

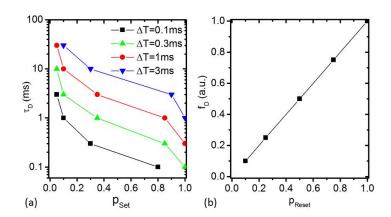

| 5.1         | Estimation of maximum programming power of OxRAM $(1nm\ Al_2O_3/3nm\ HfO_2)$ as a function of the current compliance                                                                                   | 92 |

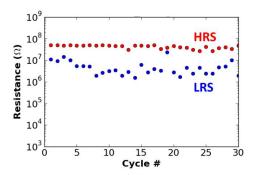

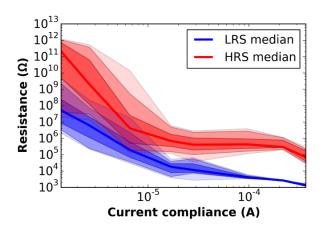

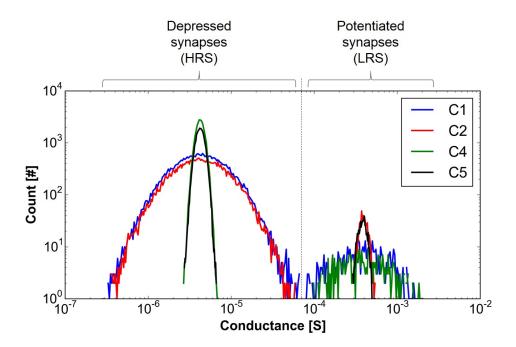

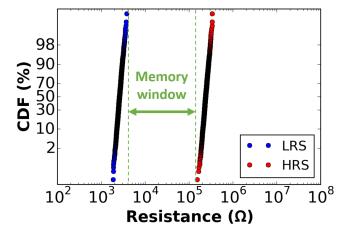

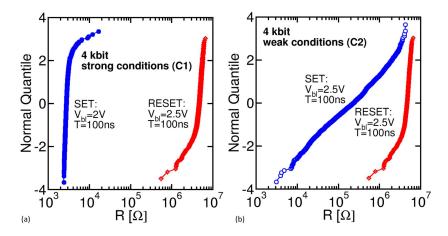

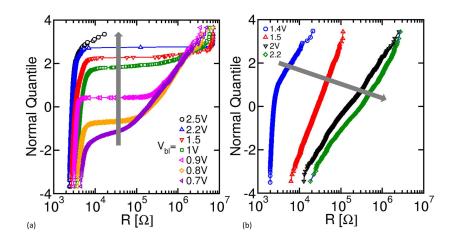

| 5.2         | Experimental LRS and HRS distributions as a function of the current compliance                                                                                                                         | 94 |

| <b>J.</b> ∠ | (CC) for 1T1R OxRAM devices $(1nm Al_2O_3/3nm HfO_2)$ . Set and reset voltages were                                                                                                                    |    |

|             | 2.5V and $-1.2V$ The bold lines mark $Median$ for both LRS and HRS, the shaded                                                                                                                         |    |

|             | areas include 95% of the samples, i.e. reflect the distribution at $2\sigma$                                                                                                                           | 93 |

| 5 2         | -                                                                                                                                                                                                      | 90 |

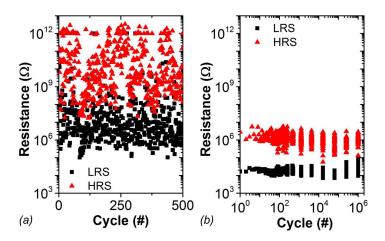

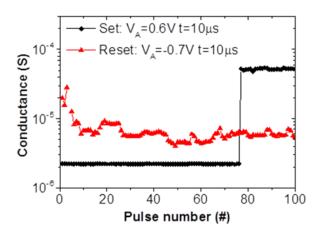

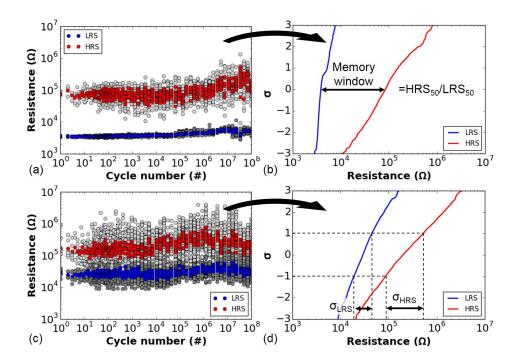

| 5.3         | (a) $HfO_2$ endurance test using a $I_{CC}=135\mu A$ and (b) extracted $\sigma$ for LRS and HRS.<br>(c) $Al_2O_3/HfO_2$ endurance test using a $I_{CC}=30\mu A$ and (d) extracted $\sigma$ for LRS and |    |

|             |                                                                                                                                                                                                        |    |

|             | HRS. The extraction of the memory window (MW) and variabilities $\sigma_{LRS}$ and $\sigma_{HRS}$ is illustrated in (b) and (d)                                                                        | 95 |

|             |                                                                                                                                                                                                        |    |

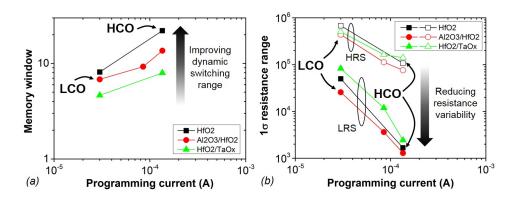

| 5.4  | (a) Median-to-median memory window (MW) for the three tested OxRAM materials as a function on the $I_{CC}$ . (b) Resistance variability $\sigma_{LRS,HRS}$ of the three tested OxRAM materials depending on the PC. Two device approaches are chosen as indicated in the graphs: Low Current OxRAM ('LCO', $Al_2O_3/HfO_2$ , $PC=30\mu A$ ) and High Current OxRAM ('HCO', $HfO_2$ , $PC=135\mu A$ )                                                                                                                                                   | 96   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

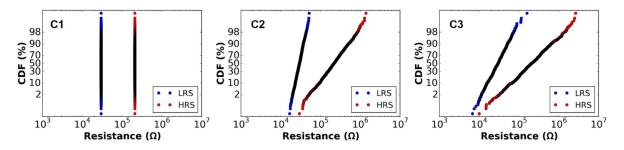

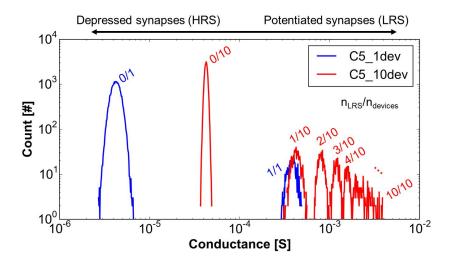

| 5.5  | LRS and HRS distributions of test conditions for SNN of Fig.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 96   |

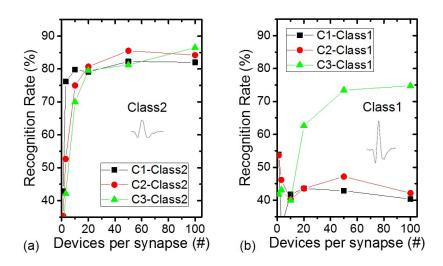

| 5.6  | Overall Recognition Rate of spike sorting SNN as a function of number of devices per synapses and for different conditions $C1-C3$                                                                                                                                                                                                                                                                                                                                                                                                                     | 97   |

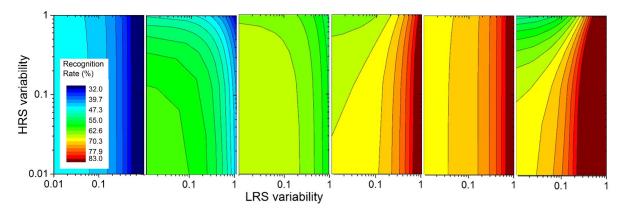

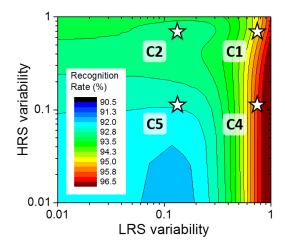

| 5.7  | Recognition rate of SNN used for neural spike classification as a function of LRS and HRS variability. Synaptic redundancy accounts to (a) 1, (b) 5, (c) 10, (d) 20, (e) 50 and (f) 100. Note that these results were obtained for using the same set of parameters, i.e. neuron threshold etc                                                                                                                                                                                                                                                         | 97   |

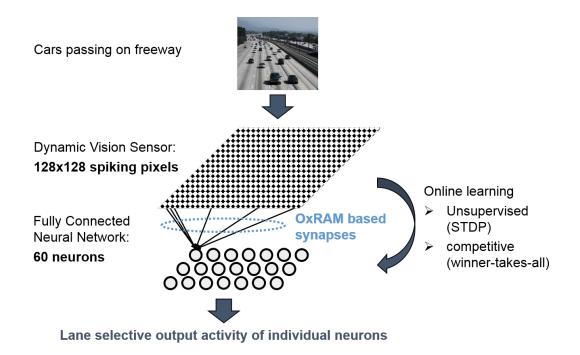

| 5.8  | Two-layer Spiking Neural Network used for unsupervised detection of cars in different traffic lanes                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98   |

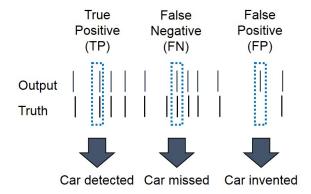

| 5.9  | The reference activity (blue) is compared to the activity of the corresponding output neurons (red) to calculate the number of True Positives (TP), False Negatives (FN) and False Positives (FP)                                                                                                                                                                                                                                                                                                                                                      | 98   |

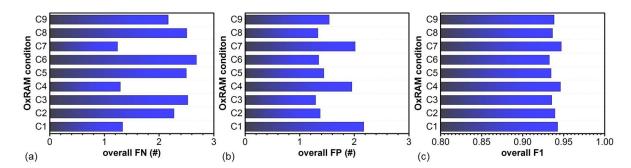

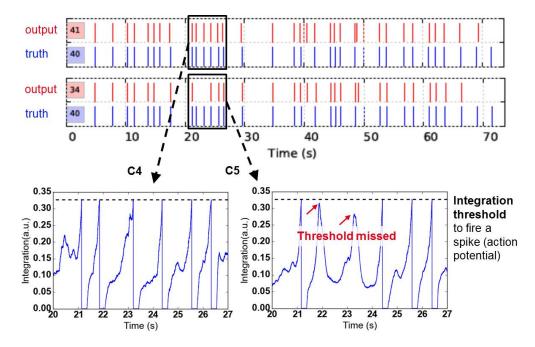

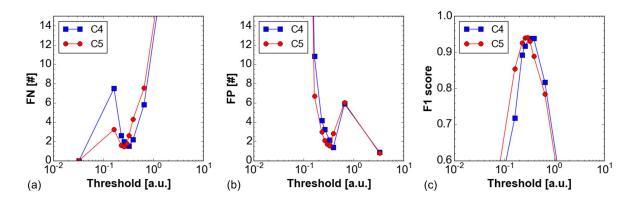

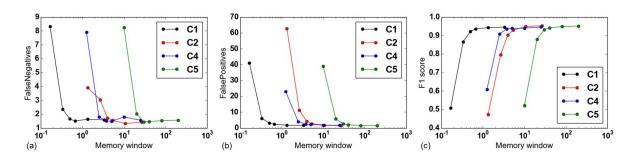

| 5.10 | (a) False Negatives (FN), (b) False Positives (FP) and (c) F1 score for the different OxRAM conditions (see figure 5.10). All numbers are averaged over the six traffic lanes. Note that FN and FP shall be as low as possible while F1 has to be maximized (i.e. converge to 1)                                                                                                                                                                                                                                                                       | 100  |

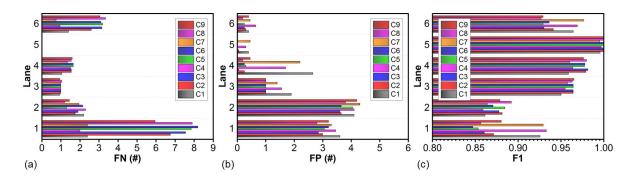

| 5.11 | (a) False Negatives (FN), (b) False Positives (FP) and (c) F1 score for the different OxRAM conditions (see figure 5.10) for the six traffic lanes. Note that FN and FP shall be as low as possible while F1 has to be maximized (i.e. converge to 1)                                                                                                                                                                                                                                                                                                  | 101  |

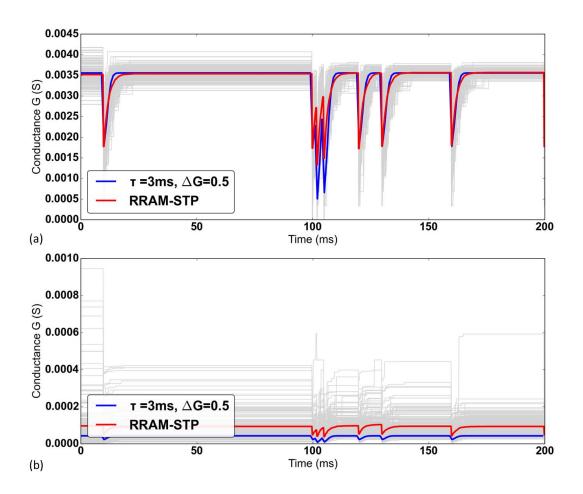

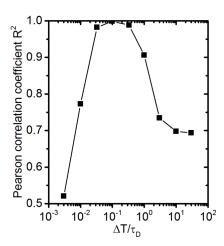

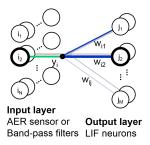

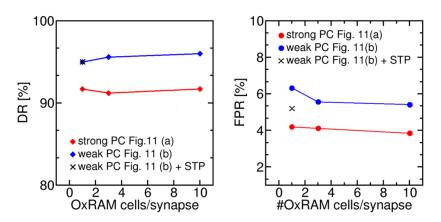

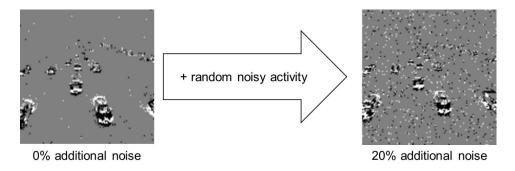

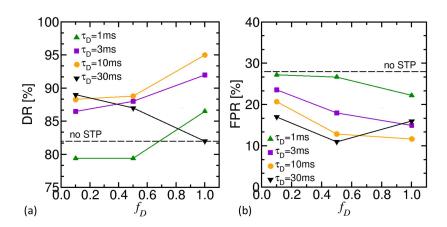

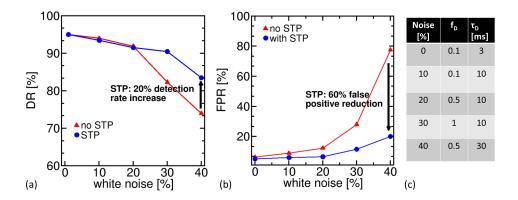

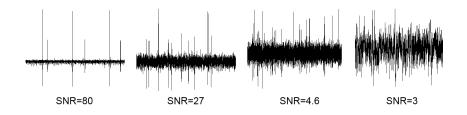

| 5.12 | Recognition rate of car detection SNN (figure 5.8) as a function of LRS and HRS variability of the OxRAM devices used for the implementation of the SNN synapses                                                                                                                                                                                                                                                                                                                                                                                       | 101  |