## Hardware Acceleration for Homomorphic Encryption

Joël Cathebras

#### ▶ To cite this version:

Joël Cathebras. Hardware Acceleration for Homomorphic Encryption. Hardware Architecture [cs.AR]. Université Paris Saclay (COmUE), 2018. English. NNT: 2018SACLS576. tel-02001901

### HAL Id: tel-02001901 https://theses.hal.science/tel-02001901

Submitted on 31 Jan 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Hardware Acceleration for Homomorphic Encryption

Thèse de doctorat de l'Université Paris-Saclay préparée à Université Paris-Sud

Ecole doctorale n°580 sciences et technologies de l'information et de la communication (STIC)

Spécialité de doctorat : Mathématiques et Informatique

Thèse présentée et soutenue à Palaiseau, le 17 décembre 2018, par

#### JOËL CATHÉBRAS

Composition du Jury:

**Lionel Torres**

Professeur, Université de Montpellier,

LIRMM Président

Lilian Bossuet

Professeur, Université Jean-Monnet de Saint-Etienne,

Laboratoire Hubert Curien Rapporteur

Arnaud Tisserand

Directeur de recherche CNRS.

Lab-STICC Rapporteur

Caroline Fontaine

Chargée de recherche CNRS,

CNRS & ENS Cachan, LSV Examinateur

Mariya Georgieva

Associate researcher,

EPFL & Inpher, Inc. Examinateur

**Renaud Sirdey**

Directeur de recherche,

Commissariat à l'Énergie Atomique (CEA), List Directeur de thèse

**Alexandre Carbon**

Ingénieur Chercheur,

Commissariat à l'Énergie Atomique (CEA), List Encadrant

Nicolas Ventroux

Chef de laboratoire,

Commissariat à l'Énergie Atomique (CEA), List Co-Encadrant

Peter Milder

Associate professor, Stony Brook University,

Department of ECE Invité

## Contents

| $\mathbf{R}$ | Remerciements |         |                                                               |    |  |  |  |

|--------------|---------------|---------|---------------------------------------------------------------|----|--|--|--|

| $\mathbf{R}$ | ésum          | é en fr | rançais                                                       | 9  |  |  |  |

| In           | trodi         | uction  |                                                               | 21 |  |  |  |

| 1            | Rev           | view of | homomorphic encryption and its practicability                 | 27 |  |  |  |

|              | 1.1           | Introd  | $\operatorname{uction}$                                       | 27 |  |  |  |

|              |               | 1.1.1   | Technical introduction to homomorphic encryption              | 27 |  |  |  |

|              |               | 1.1.2   | Basic notions for homomorphic encryption                      | 27 |  |  |  |

|              | 1.2           | State   | of the art of homomorphic cryptography                        | 29 |  |  |  |

|              |               | 1.2.1   | History towards FHE                                           | 29 |  |  |  |

|              |               | 1.2.2   | Four generations of FHE schemes                               | 30 |  |  |  |

|              |               | 1.2.3   | Additional considerations and positioning                     | 32 |  |  |  |

|              | 1.3           | The L   | earning With Errors (LWE) problem and its ring variant (RLWE) | 33 |  |  |  |

|              |               | 1.3.1   | The LWE problem                                               | 33 |  |  |  |

|              |               | 1.3.2   | The LWE problem over rings                                    | 35 |  |  |  |

|              | 1.4           | Homo    | morphic encryption in practice                                | 37 |  |  |  |

|              |               | 1.4.1   | Mitigating data expansion impact                              | 37 |  |  |  |

|              |               | 1.4.2   | Choosing an HE scheme and a plaintext space                   | 40 |  |  |  |

|              | 1.5           | Impler  | mentation of RLWE-based schemes                               | 41 |  |  |  |

|              |               | 1.5.1   | Positioning on hardware implementation                        | 41 |  |  |  |

|              |               | 1.5.2   | Hardware implementation issues                                | 42 |  |  |  |

|              |               | 1.5.3   | Related works on hardware implementation                      | 43 |  |  |  |

|              | 1.6           | Conclu  | usion and positioning of this thesis                          | 46 |  |  |  |

| 2            | Def           | inition | of an acceleration strategy for the FV scheme                 | 47 |  |  |  |

|              | 2.1           | The F   | an and Vercauteren (FV) SHE scheme                            | 47 |  |  |  |

|              |               | 2.1.1   | Preliminaries                                                 | 47 |  |  |  |

|              |               | 2.1.2   | Cryptosystem primitives                                       | 48 |  |  |  |

|              |               | 2.1.3   | Security assumptions                                          | 49 |  |  |  |

|              |               | 2.1.4   | Correctness w.r.t. noise growth                               | 49 |  |  |  |

|              |               | 2.1.5   | FV parameter sets                                             | 52 |  |  |  |

|              |               | 2.1.6   | Concluding remarks                                            | 53 |  |  |  |

|              | 2.2           | Profili | ng and hardware implementation strategy                       | 53 |  |  |  |

|              |               | 2.2.1   | Experimental description                                      | 53 |  |  |  |

|              |               | 2.2.2   | Profiling results                                             | 54 |  |  |  |

|   |     | 2.2.3 Analysis w.r.t. existing implementation strategies                   |

|---|-----|----------------------------------------------------------------------------|

|   | 2.3 | Exploration of the RNS/NTT coupled approach                                |

|   |     | 2.3.1 Simplified arithmetic through RNS                                    |

|   |     | 2.3.2 NTT-based polynomial ring multiplications in RNS                     |

|   |     | 2.3.3 Feasibility of the coupled approach                                  |

|   |     | 2.3.4 Concluding remarks on the RNS/NTT coupled approach 62                |

|   | 2.4 | The full RNS variant of FV                                                 |

|   |     | 2.4.1 RNS base extension and RNS scale-and-round for FV 63                 |

|   |     | 2.4.2 Additional optimization                                              |

|   |     | 2.4.3 Profiling                                                            |

|   | 2.5 | Conclusion                                                                 |

|   | 2.6 | Annexes: details on FV primitives                                          |

| 3 | Aut | omatic generation of multi-field NTT architectures 71                      |

|   | 3.1 | Related works and strategy motivation                                      |

|   | 3.2 | From SPIRAL DFT towards multi-field NTT designs                            |

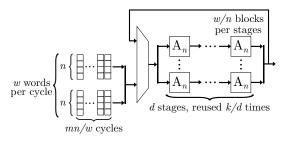

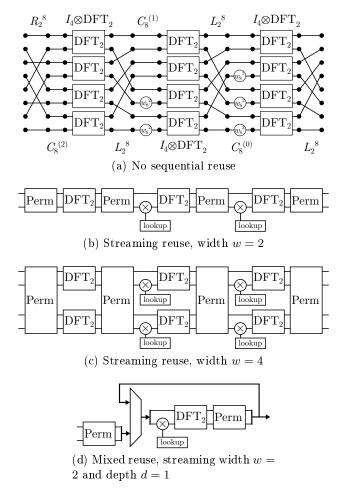

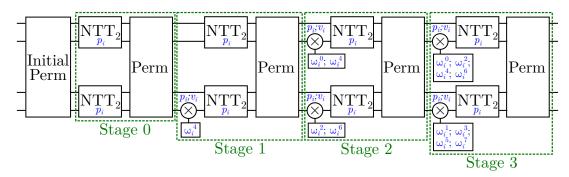

|   |     | 3.2.1 Initial streaming DFT structure                                      |

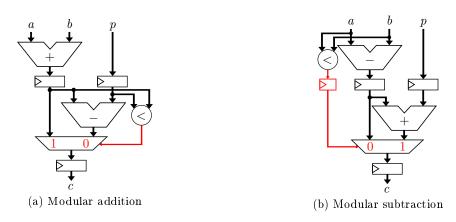

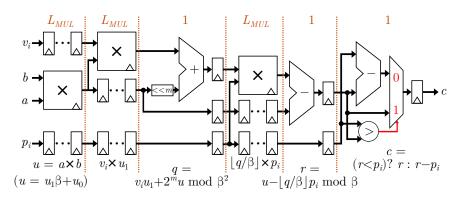

|   |     | 3.2.2 Finite-field arithmetic                                              |

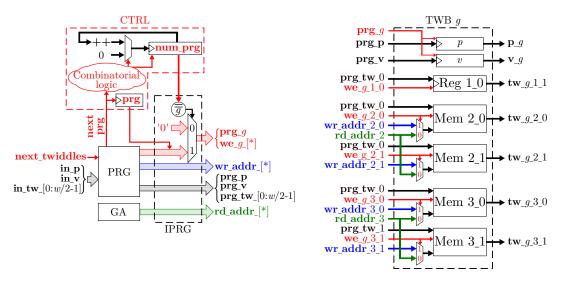

|   |     | 3.2.3 Modification of twiddle factors handling                             |

|   | 3.3 | Proposition of a multi-field NTT design                                    |

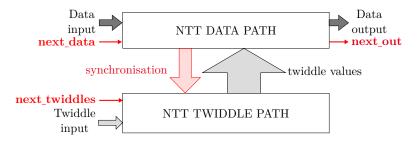

|   |     | 3.3.1 Design overview                                                      |

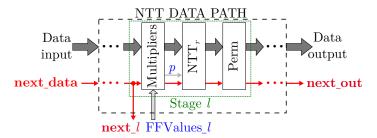

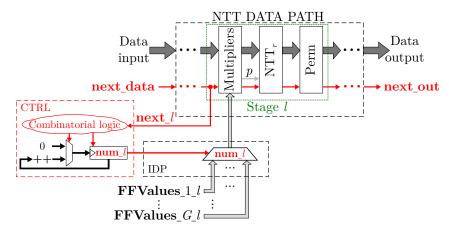

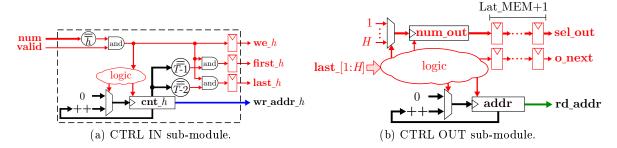

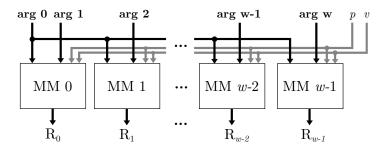

|   |     | 3.3.2 Data path                                                            |

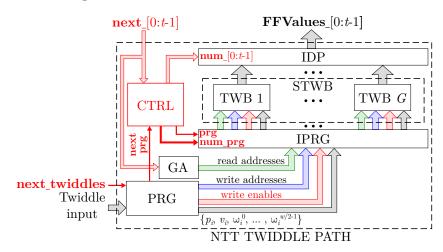

|   |     | 3.3.3 Twiddle path                                                         |

|   | 3.4 | Synthesis results and comparisons                                          |

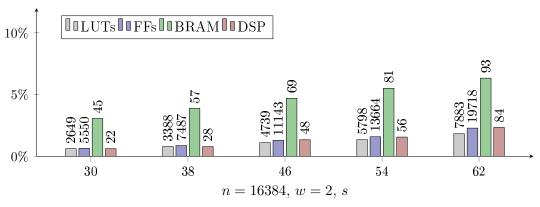

|   |     | 3.4.1 Overhead of the twiddle path                                         |

|   |     | 3.4.2 Comparisons with a straightforward storage of twiddle factor sets 87 |

|   | 3.5 | Conclusion                                                                 |

| 4 | On- | the-fly computation of NTT twiddle factors 91                              |

|   | 4.1 | On the issue of generating multiple twiddle factor sets                    |

|   |     | 4.1.1 Reminders on twiddle factors                                         |

|   |     | 4.1.2 Throughput requirement                                               |

|   |     | 4.1.3 Recurrence relationship for a single set generation                  |

|   | 4.2 | Data-flow oriented twiddle factor set generator                            |

|   |     | 4.2.1 Design overview                                                      |

|   |     | 4.2.2 Computing the twiddle sets                                           |

|   |     | 4.2.3 Sorting the twiddle sets                                             |

|   |     | 4.2.4 Remarks                                                              |

|   | 4.3 | Choice of a recurrence relationship                                        |

|   |     | 4.3.1 General problem presentation                                         |

|   |     | 4.3.2 An optimized recurrence relationship                                 |

|   |     | 4.3.3 Adapting the generic design                                          |

|   | 4.4 | Synthesis results and comparisons                                          |

|   |     | 4.4.1 Study of the hardware cost                                           |

|   |     | 4.4.2 Comparisons with an external storage                                 |

|   | 4.5 | Conclusion 106                                                             |

| 5  | Exploration of a hybrid strategy for the full RNS variants of FV |         |                                                   |     |  |  |  |

|----|------------------------------------------------------------------|---------|---------------------------------------------------|-----|--|--|--|

|    | 5.1                                                              | Propos  | sal of a hybrid computing system                  | 109 |  |  |  |

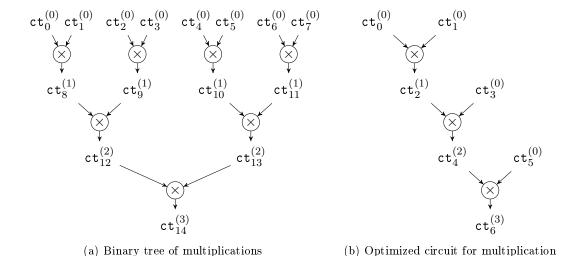

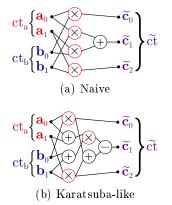

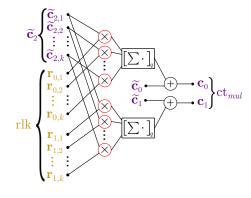

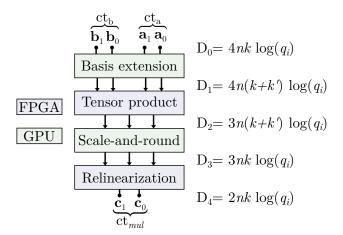

|    |                                                                  | 5.1.1   | Computation details for ciphertext multiplication | 110 |  |  |  |

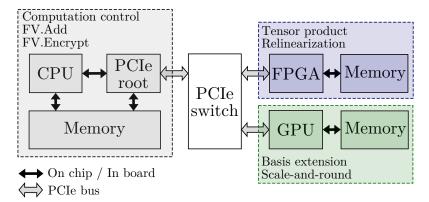

|    |                                                                  | 5.1.2   | Study of the communication requirements           | 112 |  |  |  |

|    |                                                                  | 5.1.3   | Hybrid system overview                            | 114 |  |  |  |

|    | 5.2 GPU acceleration of RNS specific functions                   |         |                                                   |     |  |  |  |

|    |                                                                  | 5.2.1   | The implemented algorithms                        | 115 |  |  |  |

|    |                                                                  | 5.2.2   | Implementations, comparisons and perspectives     | 116 |  |  |  |

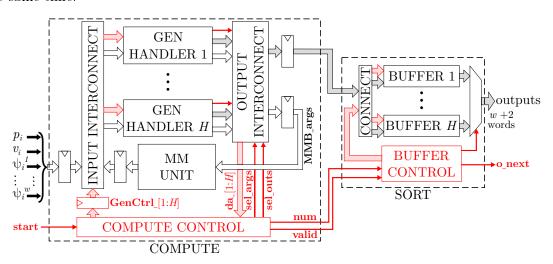

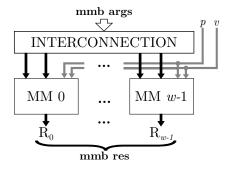

|    | 5.3                                                              | Explor  | ration of efficient RPM designs                   | 119 |  |  |  |

|    |                                                                  | 5.3.1   | Reminder of previous chapters                     | 119 |  |  |  |

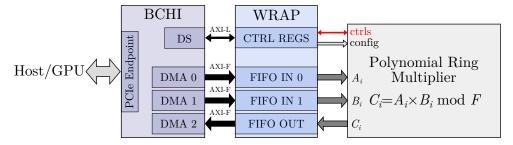

|    |                                                                  | 5.3.2   | Hardware design of an RPM through NWC             | 120 |  |  |  |

|    |                                                                  | 5.3.3   | Proof-of-concept implementation                   | 122 |  |  |  |

|    |                                                                  | 5.3.4   | Projections over FV's parameter sets              | 123 |  |  |  |

|    |                                                                  | 5.3.5   | Concluding remarks                                | 127 |  |  |  |

|    | 5.4                                                              | Conclu  | sion                                              | 128 |  |  |  |

| Co | nclu                                                             | sions a | and perspectives                                  | 131 |  |  |  |

| Pe | rson                                                             | al bibl | iography                                          | 135 |  |  |  |

| Bi | bliog                                                            | graphy  |                                                   | 137 |  |  |  |

## Remerciements

Maintenant que ce travail de thèse est terminé, je mesure ce qu'il doit à la présence de nombreux acteurs, et puisque j'en ai la possibilité, j'aimerais qu'ils trouvent ici l'expression de ma gratitude.

Celle-ci va en premier lieu à mon employeur et à mon unité de rattachement, sans qui je n'aurais pas effectué ce travail, le Commissariat à l'Énergie Atomique (CEA) et le Département Architecture Conception et Logiciels Embarqués (DACLE) du Laboratoire d'Intégration des Systèmes et Technologies (LIST), qui ont financé mes travaux et qui ont mis à ma disposition le matériel pour les mener à bien.

Merci à Arnaud Tisserand d'avoir jugé mon travail avec bienveillance et intérêt lors de mon jury à mi-parcours, puis d'avoir accepté d'en être rapporteur en vue de sa soutenance. J'ai été honoré de la confiance qu'il m'a manifesté en me donnant l'opportunité de présenter mes travaux au séminaire sécurité des systèmes électroniques embarqués de Rennes.

J'aimerais également remercier Lilian Bossuet d'avoir accepté d'être rapporteur de ce travail, de l'avoir examiné avec bienveillance, et de m'avoir fait l'honneur de le trouver pertinent.

Je souhaite remercier Lionel Torres, que je sais par ailleurs très occupé, de m'avoir fait l'amitié d'accepter de participer à ce jury et de le présider. Merci également à Caroline Fontaine et Mariya Georgieva d'avoir apporté dans ce jury une expertise cryptographique supplémentaire et d'avoir jugé ce travail digne d'intérêt.

Enfin, je souhaite exprimer un remerciement tout particulier à Peter Milder pour la collaboration que nous avons eu pendant trois ans et pour sa participation en vidéoconférence à mon jury de thèse. J'espère que nous aurons l'occasion de travailler de nouveau ensemble.

Ma reconnaissance va également à mon encadrement pour sa présence tout au long de ces trois ans. Je veux en premier lieu remercier mon directeur de thèse Renaud Sirdey. Merci Renaud pour nos nombreux échanges qui ont grandement contribué à mon épanouissement dans mon sujet de recherche, et merci tout particulièrement pour le calme avec lequel tu as tempéré mon sur-perfectionnisme et mon manque de confiance en moi.

Je souhaite également remercier Nicolas Ventroux, chef du LCE, et Alexandre Carbon pour m'avoir accueilli dans leur équipe et confié ce sujet de thèse. Merci pour votre présence et votre soutien, pour vos relectures attentives, et pour m'avoir encouragé à valoriser la forme tout autant que le fond.

J'aimerais remercier toutes les personnes avec qui j'ai partagé, de près ou de loin, mon quotidien professionnel pendant ces trois ans. Beaucoup restent anonymes dans ces lignes mais ont contribué à ma bonne intégration dans ce cadre de travail. Certaines y ont participé plus directement et j'aimerai ici les remercier: Marie-Isabelle, Colette, Sandra et Murièle pour

leur précieux soutien, qu'il soit administratif ou logistique; Mickaël pour sa disponibilité pour résoudre les petits problèmes informatiques du quotidien; Renaud pour toute l'expérience d'intégration d'IP qu'il m'a partagé. Je désire aussi exprimer ma gratitude à Khaliff pour son écoute et son aide précieuses en conception FPGA (son domaine d'expertise). Merci également à Thierry pour son intérêt et son expérience scientifiques qui ont enrichi à plusieurs reprises mes réflexions, et à Jean-Marc pour ses bon-plans et son aide bienvenue plus d'une fois.

Je n'oublie pas mes collègues doctorants : compagnons de voyages, de petits ou de grands pots, de profondes ou de légères discussions, de galères inattendues, d'aide mutuelle et de rédactions endiablées. Merci Julien, Vincent, Johannes, Jason, Gabriel et Guillaume, c'est un plaisir d'avoir appris à vous connaître petit à petit. Les gentils stagiaires sont aussi à l'honneur ici : merci Aurore, Fabio et Thibault pour votre présence colorée à la dynamique sympathique. Une mention particulière à Aurore et Jason pour vos relectures efficaces et bienvenues. Ma gratitude s'exprime également à tous les collègues avec qui j'ai partagé un bureau et qui ont su apprécier les expressions singulières de ma joie et de ma fatigue.

J'aimerais remercier enfin les personnes impliquées d'une autre manière dans ces trois années de ma vie. En premier lieu mes parents et mes frères qui ont vécu, sans (trop) rechigner, les montagnes russes de mon moral. Merci Paul, Charles et Raphaël d'avoir composé avec mes disponibilités éparses et de me faire la joie de votre amitié depuis si longtemps. Merci Ludivine pour ta compagnie et les formules voyage dont nous avons le secret. Merci Simon et Robin pour vos relectures aux temps forts de rédaction.

Enfin, je souhaite également remercier toutes les personnes qui ont pensé à moi pendant ces cinq derniers mois. Je ne saurais vous citer tous, mais sachez que vos messages et/ou votre présence à ma soutenance me sont allés droit au cœur.

Pour conclure, j'aimerais remercier deux personnes qui sont des jalons singuliers de ma vie : merci François-Xavier pour ton amitié et nos échanges vivifiants; merci Marie-Émeline pour ta présence offerte simplement et pour tout ce qui en naît.

## Résumé en français

#### Introduction

Les technologies numériques se sont très vite imposées comme essentielles au fonctionnement des sociétés actuelles, et cette tendance ne semble pas sur le point de s'inverser. L'accès croissant des pays en développement à ces technologies, la forte proportion d'utilisateurs au sein des jeunes générations, ainsi que le confort qu'elles apportent au quotidien, sont autant de raisons de croire qu'elles ne disparaîtront pas dans un avenir proche. La diffusion des technologies du numérique pose la question de la confidentialité des données et conduit à la recherche de réponses techniques aidant à protéger la vie privée (voir, par exemple, le concept de Privacy-by-Design [1]). Cette thèse entend contribuer à ces enjeux, en considérant notamment le domaine de la cryptologie.

Science du secret au sens étymologique du terme, l'objet d'étude de la cryptologie est plus vaste que la simple confidentialité de l'information. Son but est de proposer des outils et de bonnes pratiques pour garantir l'intégrité, l'authenticité et la confidentialité des informations à protéger. À cette fin, elle est divisée en deux disciplines : la cryptographie et la cryptanalyse. La cryptographie est consacrée à la protection de l'information, et la cryptanalyse consiste à retrouver l'information ainsi protégée. Cette opposition permanente est une source de perfectionnement des outils cryptographiques [2, 3]. Dans cette thèse, notre intérêt s'oriente davantage vers la cryptographie, mais il faut garder à l'esprit que ces deux disciplines ne doivent pas être considérées indépendamment.

Face à l'augmentation des coûts de maintenance des infrastructures informatiques, le marché des services informatiques centralisés connaît une forte croissance. Par exemple, l'essor de la virtualisation et des réseaux à très haut débit permet à des entités spécialisées de fournir des espaces de stockage et de la puissance de calcul à d'autres entités dont le numérique n'est pas le cœur de métier. La question de l'externalisation de données confidentielles, que ce soit pour leur stockage et/ou leur traitement, est donc pertinente. La cryptographie classique (symétrique et asymétrique) ne permet que de sécuriser l'échange et le stockage des informations. Mais il est également nécessaire de garantir la confidentialité des données pendant les traitements.

En 1978, Rivest, Adleman et Dertouzos introduisirent la notion de cryptographie homomorphe qui permettrait de tels services. Le principe est d'avoir un processus de chiffrement qui préserve une structure entre le domaine chiffré et le domaine clair, permettant ainsi de définir des opérations dans le domaine chiffré à effet équivalent aux opérations usuelles sur les clairs. Ce n'est qu'à la fin des années 2000 que la cryptographie homomorphe a véritablement émergé avec une première solution théorique. Depuis, de nombreux travaux de recherche ont permis de se rapprocher d'une mise en application de ce nouveau type de cryptographie. D'une part, ces travaux simplifient les constructions mathématiques sous-jacentes aux schémas de chiffrement homomorphe, et d'autre part, ils explorent des optimisations algorithmiques pour profiter d'implémentations plus efficaces.

Néanmoins, ce paradigme cryptographique semble induire intrinsèquement des complexités mémoire et calculatoire importantes. Par exemple, un chiffré homomorphe est environ  $10^5$  fois plus grand que la donnée qu'il chiffre, et une opération dans le domaine chiffré est environ  $10^6$  fois plus lourde que son équivalente claire. En conséquence, les acteurs impliqués dans la recherche sur la mise en application de cette nouvelle cryptographie ont besoin d'optimisations supplémentaires telles que l'accélération matérielle.

#### Cette thèse

La cryptographie homomorphe est un domaine encore en éclosion. Bien que de nombreuses applications soient à l'étude, peu ont le mérite d'être pratiquement explorées, et encore moins sont déjà réalisables à grande échelle. Néanmoins, la recherche progresse rapidement vers son utilisation en dehors des laboratoires, et nous espérons que certaines des contributions associées à cette thèse pourront aider ce développement.

La problématique. L'objectif principal de la recherche sur la cryptographie homomorphe est de définir des schémas de chiffrement pour lesquels il y a un équivalent dans le domaine chiffré pour tout traitement applicable sur des données. Cet objectif est appelé chiffrement entièrement homomorphe (FHE: Fully Homomorphic Encryption). Le fait qu'il se soit écoulé près de trente ans entre l'introduction du concept et la première construction théorique d'un schéma n'est pas un hasard. En effet, deux problèmes théoriques se recoupent.

Le premier est la difficulté de trouver des expressions de problèmes mathématiques, assurant la sécurité des schémas, qui permettent de construire des opérations équivalentes. Le second est la présence nécessaire, aussi pour des questions de sécurité, d'un bruit de chiffrement. L'amplitude du bruit dans les chiffrés augmente avec les opérations dans le domaine chiffré. Au-delà d'un certain seuil, le processus de déchiffrement cesse de fonctionner.

Avec les recherches qui ont suivi la première construction théorique d'un schéma FHE, certaines solutions intermédiaires ont rapproché la cryptographie homomorphe d'un usage concret. De même, la recherche sur l'accélération matérielle de ces solutions intermédiaires doit faire face à deux difficultés principales. La première est la variété des schémas proposés : en moins de dix ans, quatre générations de schémas ont déjà été proposées. Ainsi, les avantages et inconvénients des schémas n'ont pas pu être pleinement et objectivement comparés sur une période de temps si courte. Il en résulte donc un positionnement plus qualitatif dans le choix des schémas à considérer pour une accélération matérielle. La deuxième difficulté est que le paramétrage de ces schémas est fortement dépendant de l'application à réaliser dans le domaine chiffré. Cela est dû principalement à la croissance du bruit de chiffrement, qui exige que les paramètres soient correctement dimensionnés. Ainsi la stratégie d'accélération doit être suffisamment flexible pour rester pertinente avec l'accroissement des paramètres.

Contributions scientifiques. Au cours de ce travail, nous avons surtout abordé la question de la dynamique des paramètres. La littérature a proposé les éléments de base sur lesquels reposent nos contributions, à savoir d'une part l'utilisation du système modulaire de représentation (RNS : Residue Number System) pour s'attaquer à la complexité apportée par l'arithmétique des grands nombres entiers, et d'autre part l'utilisation des transformées de

Fourier sur corps finis (NTT: Number Theoretical Transform) pour réduire la complexité algorithmique asymptotique de la multiplication polynomiale. Sur cette base, nous soutenons que l'association du RNS et de la NTT permet de définir des architectures hybrides de calcul, qui promettent une accélération significative des traitements dans le domaine chiffré. Cette thèse résulte d'une analyse approfondie du chiffrement de Fan et Vercauteren (FV), ainsi que des travaux sur la résolution des principales difficultés à combiner la représentation RNS et la multiplication de polynôme par NTT pour des grands paramètres.

Nos principales contributions sont les suivantes. Tout d'abord, nous avons analysé l'approche couplée RNS/NTT et théoriquement validé sa faisabilité jusqu'à de très grands ensembles de paramètres. Deuxièmement, nous avons exploré l'accélération GPU de certains algorithmes spécifiques au RNS, grâce à l'utilisation et à la poursuite des travaux de Bajard et al. [4] et Halevi et al. [5] pour adapter complètement FV au RNS. Troisièmement, nous avons conçu et mis en œuvre un accélérateur orienté flux de données pour des multiplications de polynômes résiduels efficaces et étudié sa capacité à passer à l'échelle.

Cette dernière contribution fait l'objet d'une attention particulière afin de surmonter certains problèmes de conception qui limitaient auparavant la faisabilité de l'approche couplée RNS/NTT pour des grands paramètres. En particulier, nous proposons une solution pour précalculer localement les valeurs nécessaires aux opérations de NTT, sans impact sur les performances. Ceci est obtenu grâce à deux contributions : la conception d'un circuit de NTT changeant ses corps finis de définition à la volée, et la conception d'un générateur de facteur de rotation pour les NTT sur les différents corps finis. Enfin, pour répondre à la question de la grande variation des paramétrages en fonction des différentes applications du chiffrement homomorphe, la génération automatique des descriptions HDL (Hardware Description Language) de nos circuits a été explorée.

#### État de l'art et positionnement

Les chiffrements homomorphes sont capables d'effectuer des opérations sur des données chiffrées sans les déchiffrer au préalable. Cette capacité vient du choix d'un homomorphisme comme fonction de déchiffrement d'un schéma. La définition d'un homomorphisme met directement en évidence la caractéristique désirée : il s'agit d'une correspondance conservant une certaine organisation entre deux structures algébriques du même type (groupes, anneaux, corps...). En considérant l'espace des clairs et l'espace des chiffrés comme des structures algébriques, un homomorphisme consiste alors à avoir une équivalence entre certaines opérations dans les domaines chiffré et clair.

On qualifie de partiellement homomorphe (Partial Homomorphic Encryption: PHE) un chiffrement dont l'ensemble des fonctions évaluables est restreint à un sous-ensemble des fonctions internes sur l'ensemble des clairs. Par exemple, si la fonction de déchiffrement est un homomorphisme de groupe additif (resp. groupe multiplicatif), alors seules les fonctions composées d'additions (resp. de multiplications) auront un équivalent dans l'ensemble des chiffrés. On parlera de chiffrement presque homomorphe (Somewhat Homomorphic Encryption: SHE) lorsque la fonction de déchiffrement est un homomorphisme d'anneaux, c'est à dire qu'il leur est possible d'évaluer à la fois des additions et des multiplications dans le domaine chiffré, mais que ces chiffrement sont limités en opération dans le domaine chiffré par l'accroissement du bruit de chiffrement. Enfin, on parlera de chiffrement complètement homomorphe (Fully Homomorphic Encryption: FHE) si toutes les fonctions internes de l'ensemble des clairs appartiennent à l'ensemble des fonctions évaluables dans le domaine chiffré.

Analyse de l'état de l'art des chiffrements homomorphes. L'effervescence de la recherche autour de la cryptographie homomorphe peut être déroutante pour qui s'intéresse à des considérations pratiques telles que la sécurité et la performance. La première génération résulte de la première construction de schéma complètement homomorphe proposé par Gentry en 2009 avec l'introduction d'une opération de réamorçage (bootstrapping) très coûteuse. La deuxième améliore la gestion du bruit des schémas en évitant de passer par l'opération de réamorçage, et introduit ainsi la notion de chiffrement homomorphe par niveau (L-FHE: Leveled Fully Homomorphic Encryption). La troisième génération est une simplification conceptuelle de la deuxième génération et propose des schémas homomorphes par niveau structurellement plus simples. Enfin, la quatrième génération réintroduit une opération de réamorçage plus performante. Cette fois, c'est chaque opération sur les chiffrés qui réamorce le bruit.

Lorsque l'on s'intéresse à la maturité des schémas, il semble que ceux qui sont construits sur les variantes du problème mathématique LWE (et en particulier ceux basés sur RLWE) soient actuellement les plus équilibrés en termes de sécurité et d'efficacité. En effet, les améliorations de la deuxième génération, puis des troisième et quatrième générations, dépendaient principalement de l'apparition du problème de l'apprentissage avec erreurs (LWE : Learning With Errors). Les schémas basés sur LWE manipulent des matrices et/ou des vecteurs d'entiers modulaires. La variante RLWE (Ring-LWE) manipule des matrices et/ou des vecteurs de polynômes modulaires. La quatrième génération construit également ses schémas sur des variantes du problèmes LWE. Cependant, son schéma le plus prometteur (TFHE [6]) a choisi une structure algébrique légèrement différente des autres pour améliorer les performances de ses primitives. Il manipule des polynômes à coefficients réels modulo un. Par conséquent, ce schéma n'est pas confronté aux mêmes problématiques d'implémentation et nécessite des approches différentes des schémas basés sur RLWE.

Au moment de notre positionnement, la littérature nous a amené à considérer que les schémas construits sur RLWE sont ceux qui se rapprochent le plus d'une utilisation concrète. En particulier, les schémas FV [7] 2ème génération) et SHIELD [8] 3ème génération) sont bien acceptés par la communauté. Notre étude de l'état de l'art de l'implémentation du chiffrement homomorphe s'est donc concentrée sur les problèmes propres à ce type de schémas.

Analyse des stratégies d'implémentation existantes. Le choix de considérer les implémentations matérielles pour les chiffrements homomorphes était un parti pris de cette thèse. Ceci se justifie par les limitations en performance que l'on expérimente avec des implémentations purement logicielles. Ainsi, notre étude s'est focalisée sur les problématiques d'implémentation matérielle et l'état de l'art associé.

Le problème principal concerne la taille importante des paramètres des schémas RLWE, nécessaire pour des raisons de sécurité et d'exactitude. Ce problème se complique en considérant en plus la dynamique des paramètres due aux contraintes applicatives. Pour en avoir une petite idée, le degré des polynômes manipulés peut atteindre plusieurs dizaines de milliers, et la taille de leurs coefficients peut atteindre plusieurs centaines de bit. Par conséquent, les complexités mémoire et calculatoire des opérations sous-jacentes sont particulièrement importantes. Ces opérations sont des multiplications de polynômes, des réductions modulaires de polynômes, des additions de polynômes, des opérations de mise à l'échelle et d'arrondi, et des réductions modulaires.

Notre analyse de la littérature nous a fait constater la difficulté de proposer une approche cohérente qui puisse englober toutes les dimensions de la problématique d'implémentation.

Par exemple, les approches de multiplication de polynômes les plus flexibles permettent, au détriment de complexités asymptotiques moins intéressantes, de simplifier les opérations de mise à l'échelle et de réduction modulaire. Ces approches ne trouvent leur justification que jusqu'à une certaine taille de paramètres. Au contraire, les approches de multiplication de polynômes basées sur la transformée de Fourier sur corps fini (NTT: Number Theoretical Transform), qui ont à ce jour la meilleure complexité asymptotique connue, sont plus complexes à mettre en œuvre.

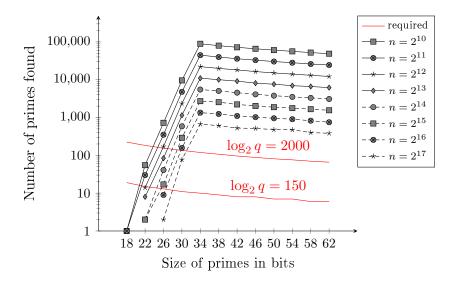

Une première difficulté est due au routage des coefficients pour les algorithmes de transformée de Fourier itératifs. Une deuxième difficulté concerne la gestion des facteurs de rotation des NTT. Lorsque les paramètres du schéma grossissent, l'espace mémoire requis pour ces facteurs (resp. le coût de communication pour les acheminer) augmente fortement le coût matériel (resp. la bande-passante nécessaire). Une troisième difficulté concerne la gestion des très grands coefficients. Sur cette question, l'approche la plus prometteuse semble être l'utilisation d'une représentation non-positionnelle des nombres appelée RNS (Residue Number System). Cependant, bien que le couplage du RNS avec les approches par NTT est théoriquement valide, le choix de la base de représentation RNS est restreint par les contraintes d'existence des NTT. Ainsi, certains choix permettant de faire de l'arithmétique modulaire à bas coût ne sont pas possibles. À cela s'ajoute la difficulté de faire efficacement les opérations de mise à l'échelle et d'arrondi en représentation RNS.

Au regard de toutes ces problématiques, il nous a semblé plus important de rechercher une approche d'accélération flexible plutôt que dédié à la performance brute. Pour cela, nous avons limité l'étude de cas à un schéma homomorphe spécifique, afin de proposer une approche qui tienne compte, autant que possible, de toutes les dimensions du problème.

**Positionnement.** Après avoir étudié les différentes générations de chiffrements homomorphes, nous avons concentré notre étude sur les schémas homomorphes par niveau basés sur le problème RLWE. Ce choix implique que les paramètres dimensionnants dépendent de l'application à effectuer dans le domaine chiffré. L'approche d'accélération matérielle devra donc tenir compte de la dynamique des paramètres.

Ce positionnement a été suivi d'une analyse des différentes approches d'implémentation matérielle pour l'accélération de la cryptographie homomorphe. Cette analyse pose la question de la définition d'une stratégie d'implémentation qui prenne en compte toutes les dimensions du problème de complexité mémoire et calculatoire provenant de la dynamique des paramètres. Cette stratégie devrait être suffisamment flexible pour améliorer la performance du schéma L-FHE tout en évitant les spécialisations prématurées qui ne sont pas adaptées à la dynamique des paramètres.

Afin de définir une telle stratégie à la lumière des travaux connexes, nous avons choisi de faire une étude approfondie du schéma homomorphe FV. Ce dernier est plutôt bien accepté par la communauté de recherche autour du chiffrement homomorphe. Par conséquent, la suite de notre travail s'est concentrée sur l'accélération matérielle du chiffrement FV.

#### Analyse du chiffrement FV

L'analyse approfondie du schéma FV en vue de son accélération matérielle nous a introduit aux problématiques concrètes du choix des paramètres. Dans un premier temps, nous avons présenté ses primitives, les structures algébriques manipulées, ainsi que les équations d'accroissement du bruit. Les paramètres dimensionnants que sont le degré des polynômes et la

taille des coefficients ont un impact majeur dans cet accroissement du bruit, surtout lors des multiplications de chiffrés. De même, ils ont un impact important sur la difficulté du problème RLWE sous-jacent assurant la sécurité du schéma. Les travaux de thèse de Guillaume Bonnoron [9] présentent une méthode de dérivation des paramètres prenant en compte tout ces aspects, ainsi que des exemples concrets de paramètres. À partir de cette vue d'ensemble, la problématique générale des schémas homomorphes par niveau est compréhensible. Afin d'évaluer des applications de taille conséquente dans le domaine chiffré, les paramètres augmentent considérablement. Ainsi, la restriction de l'éventail des paramètres n'est pas possible sans considérer des cas particuliers d'utilisation du schéma FV.

Après la présentation du schéma et de ses paramètres, l'étape suivante consiste à identifier et à quantifier les goulots d'étranglement de la performance des opérations homomorphes avec FV. Le profilage d'une application homomorphe typique a quantifié la complexité dominante des multiplications de chiffrés et des opérations de relinéarisation. Les opérations sous-jacentes de multiplication de polynômes et de mise à l'échelle sont les principales opérations limitant les performances. Sur la base de notre analyse des travaux de l'état de l'art sur ces problématiques, nous avons choisi d'explorer la faisabilité de l'approche couplée RNS/NTT pour l'accélération du crypto-calcul avec FV. Après une présentation détaillée du RNS et des multiplications de polynômes par NTT dans notre contexte, nous avons pu faire une liste de toutes les contraintes à prendre en compte pour l'utilisation conjointe de ces deux approches. L'étude de ces contraintes se termine par une validation théorique et pratique de l'approche couplée.

Une problématique particulière de l'utilisation de la représentation RNS est celle de l'opération de mise à l'échelle. Les travaux concomitants de Bajard et al. [4] et de Halevi et al. [5] ont décrit des méthodes efficaces pour en améliorer la performance dans le cas de FV. L'analyse du profilage présenté par Halevi et al. [5] affine notre propre profilage. Il oriente concrètement notre stratégie d'implémentation matérielle vers l'accélération des multiplications de polynômes résiduels, des opérations d'extension de base RNS, et des opérations de mise à l'échelle en RNS. En raison de la complexité dominante des multiplications de polynômes, nous nous sommes donc concentrés principalement sur leur accélération.

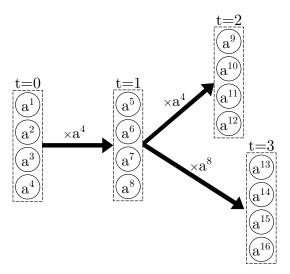

Les opérations de NTT, qui servent de briques de base aux algorithmes de multiplication de polynômes, sont assez difficiles à paralléliser en raison d'accès mémoires complexes. Cela rend les grandes NTT peu adaptées aux architectures SIMD génériques telles que les GPU. Notre choix est donc d'explorer des solutions d'accélération s'appuyant sur du matériel dédié pour ces opérations.

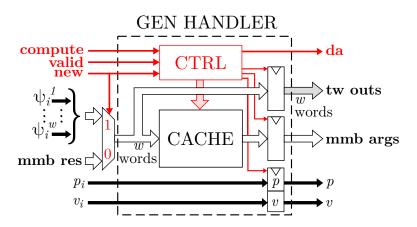

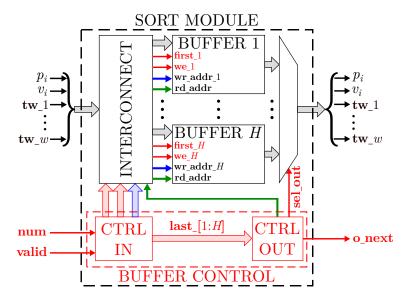

Étant donné les problèmes d'implémentation mis en évidence par les travaux connexes quant à la gestion des facteurs de rotation, notre stratégie consiste à générer et utiliser à la volée ces différents ensembles de facteurs. Ceci exige de s'attaquer à deux problématiques principales de conception. La première est de pouvoir générer efficacement des circuits de NTT multi-corps. Il s'agit de circuits de NTT capables d'effectuer des transformées sur différents corps finis sans impact significatif sur les performances. La seconde est la conception d'un générateur d'ensembles de facteurs de rotation pour les différents corps finis définis par la base RNS. Il faut que cette génération soit sans conséquences lourdes sur le coût du matériel et sur le débit des opérations de NTT.

#### Proposition de circuits de NTT multi-corps

Les problématiques de conception de circuits de NTT sont structurellement les mêmes que celles des transformées de Fourier discrète (DFT : Discrete Fourier Transform). Or, le domaine du traitement du signal a déjà beaucoup contribué à l'implémentation matérielle des DFT. Nous avons en particulier considéré que le projet SPIRAL [10] constitue un point de départ particulièrement intéressant pour automatiser la conception de circuit de NTT. En effet, le projet SPIRAL porte sur l'automatisation du développement logiciel et matériel pour le traitement du signal.

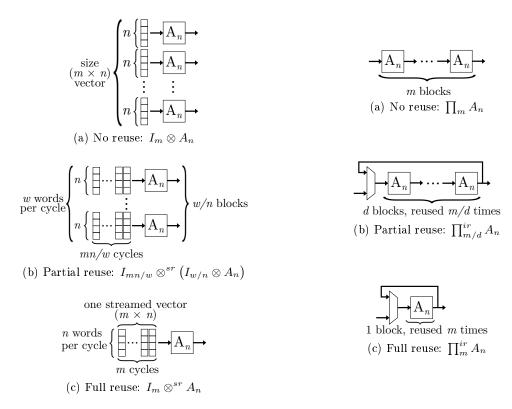

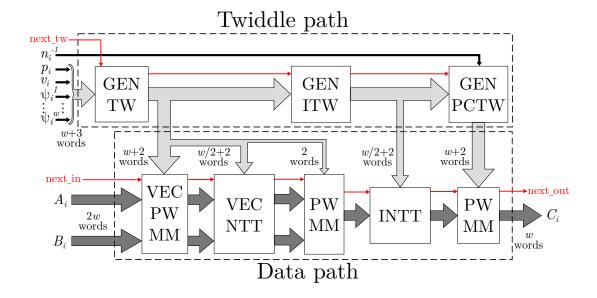

La perspective à moyen terme est de pouvoir concevoir rapidement des circuits de NTT selon des contraintes de coût matériel et de performance de calcul. Cela permettra à un concepteur de systèmes d'ajuster les performances de ses opérateurs de NTT en fonction des exigences applicatives et des autres éléments du système. Au cours de cette thèse, seuls les circuits en flot-de-données complètement déroulés (fully-streaming) ont été étudiés et adaptés en circuit de NTT multi-corps. En raison de contraintes de temps, nous nous sommes concentrés sur ce type d'architectures qui offre les débits les plus élevés. C'est en effet ce qui est principalement requis par notre contexte applicatif.

L'adaptation de SPIRAL pour la génération de NTT consiste en la génération de circuits de DFT dans lesquels l'arithmétique complexe est remplacée par de l'arithmétique modulaire et les facteurs de rotation complexes sont remplacés par les facteurs de rotation du corps fini considéré. Dans le cas d'une DFT, SPIRAL précalcule les facteurs de rotation et les stocke dans des mémoires non-programmables (ROM) à la génération du circuit. Cette approche convient à la DFT, car les facteurs de rotation ne sont pas susceptibles de changer. Cependant, notre cas applicatif nous impose de trouver un moyen de reprogrammer ces facteurs de rotation sans impact majeur sur le débit du circuit de NTT. En effet, le corps fini de définition de la NTT est différent pour chaque canal RNS (chaque élément de la base RNS), et ainsi les ensembles de facteurs de rotation sont différents.

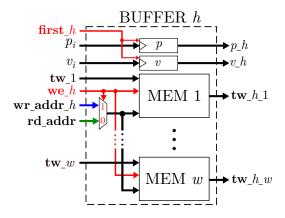

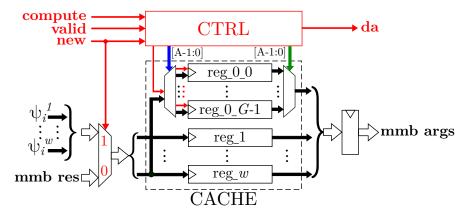

Définition d'une NTT multi-corps. La répartition des facteurs de rotation au sein du circuit de NTT est connue par le générateur SPIRAL. Plutôt que d'implémenter les mémoires des facteurs de rotation directement dans le chemin de données du circuit de NTT, nous proposons de dissocier ces mémoires de ce dernier, afin de les rendre programmables. Nous définissons la notion de banque de facteurs de rotation, qui consiste en la concaténation de toutes les mémoires, initialement dans le chemin de données, et stockant un unique jeu de facteurs de rotation pour un corps fini spécifique. En plus des facteurs de rotation, une telle banque stocke les autres valeurs spécifiques au corps fini, comme l'élément associé de la base RNS.

Pour éviter de réduire le débit du circuit de NTT lors de la reprogrammation d'une banque de facteurs de rotation, notre solution s'appuie sur un ensemble de G banques différentes. Ces G banques vont être successivement accédées par le chemin de données et reprogrammées avec un nouvel ensemble de facteurs de rotation. Ce nombre G est lié au nombre maximum de canaux RNS pouvant être simultanément présents dans le chemin de données. Si nous notons T le débit du chemin de données (nombre de cycles d'horloge entre deux transformées) NTT et  $lat_{NTT}$  sa latence, l'architecture comporte  $G = \lceil lat_{NTT}/T \rceil + 1$  banques différentes. Notre solution s'accompagne de la définition d'un module de reprogrammation des banques de facteurs qui garantie un débit de reprogrammation adapté à celui du circuit de NTT.

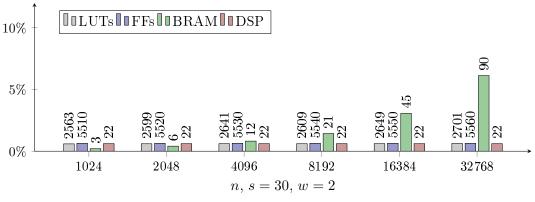

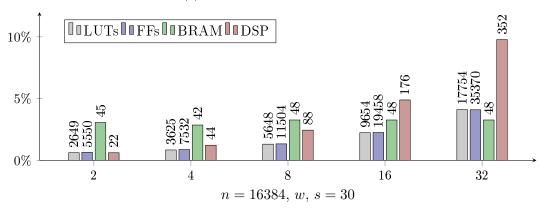

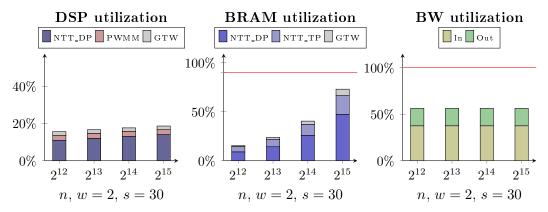

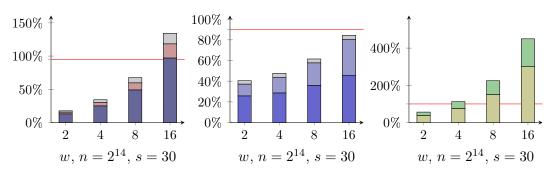

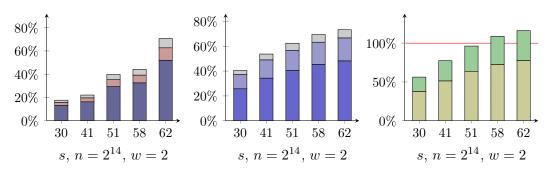

Analyse de notre contribution. Notre proposition de circuit NTT multi-corps implique un surcoût matériel par rapport à un circuit de NTT défini pour un unique corps fini. Ce surcoût est principalement dépendant du nombre G de banques de facteurs instanciées. Les modules contrôlant les accès et la programmation des banques ont un impact relativement faible sur la consommation de ressources matérielles. Pour les paramétrages considérés dans cette thèse, G était toujours égal à quatre. Ce surcoût qu'implique notre solution n'est pas très important par rapport aux avantages qu'il apporte dans notre contexte.

Pour mettre en évidence ces avantages, nous comparons la manipulation de notre gestion de facteurs de rotation à la volée avec une stratégie de stockage local présente dans l'état de l'art. Elle consiste à stocker tous les facteurs de rotations, pour tous les canaux RNS, dans des mémoires non-programmables (ROM) initialisées à la génération du circuit. L'avantage d'utiliser notre approche se concrétise avec l'accroissement des tailles de paramètres du schéma FV. La taille des bases RNS (nombre de corps finis différents) et le degré des polynômes (nombre de facteurs de rotation pour chaque corps fini) augmentent de manière significative. Notre traitement à la volée des ensembles de facteurs de rotation réduit de 20% à 90% les éléments de mémorisation effectivement instanciés pour fournir le même résultat. Ceci permet à notre approche d'être praticable pour des jeux de paramètres de FV significativement plus grands que l'état de l'art (profondeur multiplicative de 30 avec une sécurité de 128-bit).

Notre gestion des facteurs de rotation à la volée permet d'envisager des multiplieurs de polynômes en représentation RNS à haut débit. Néanmoins, à elle seule, cette gestion à la volée ne fait que déporter le problème du stockage de ces facteurs de rotation. Ils devront être acheminés vers le circuit de NTT multi-corps d'une manière ou d'une autre. Dans le cas où les facteurs sont stockés à l'extérieur de l'accélérateur (mémoire du processeur hôte par exemple), il faut s'attendre à une diminution des performances effectives à cause des communications plus lourdes. En effet, l'opérateur de NTT devra recevoir les ensembles de facteurs de rotation en plus des données utiles. Afin de ne pas impacter ces temps de communications, notre stratégie consiste à générer à la volée ces ensembles de facteurs.

#### Génération à la volée des facteurs de rotations

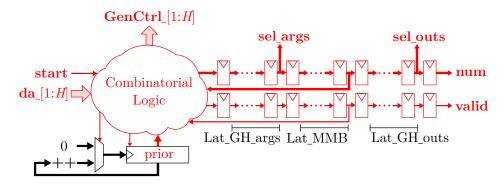

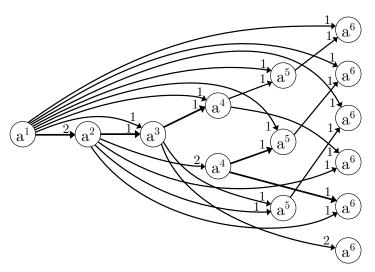

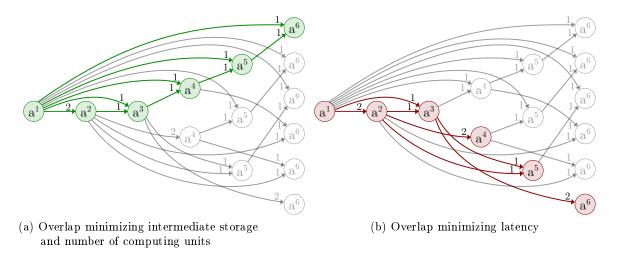

Après avoir proposé une approche pour générer des circuits de NTT multi-corps avec SPIRAL, la deuxième problématique que nous abordons est celle de la génération des ensembles de facteurs de rotation. Nous proposons dans cette thèse des générateurs de ces ensembles qui respectent les exigences de débit de nos circuits de NTT multi-corps. La problématique consiste donc en la génération des puissances d'éléments de différents corps finis pour laquelle notre contexte impose un débit minimal.

La première difficulté se situe dans le choix d'une méthode de génération. Cette difficulté tient à la fois de la dépendance entre les éléments d'une séquence de puissances à générer et de la latence des multiplicateurs modulaires qui produisent de nouveaux éléments. Ainsi, certaines bulles inévitables se produisent dans la génération d'un seul ensemble de facteurs de rotation. La méthode choisie impactera significativement la latence d'une génération, et le coût matérielle pour la mener à bien.

La deuxième difficulté se situe dans le respect du débit minimal requis entre les générations des différents ensembles. Du fait des inévitables bulles dans la génération d'un unique ensemble de facteurs, la génération séquentielle de ces ensembles ne permet pas d'atteindre le débit requis.

Ainsi, nous proposons des solutions qui répondent à ces difficultés. Premièrement, nous formalisons une solution pour respecter le débit requis par le circuit de NTT multi-corps entre deux ensembles de facteurs de rotation consécutifs. Cette première proposition consiste en une solution d'ordonnancement de multiples générations d'ensembles autours d'une unique ressource de calcul. Deuxièmement, nous proposons un choix de relation de récurrence pour la génération de chacun des ensembles de facteurs. Cette relation de récurrence permet de minimiser l'espace de stockage intermédiaire requis tout en minimisant la latence de chaque génération pour la quantité de ressources de calcul disponible.

Analyse de notre contribution. La génération à la volée des ensembles de facteurs de rotation permet d'alléger les communications entre une zone de stockage externe à l'accélérateur et ce dernier. Pour quantifier cet allègement des communications, nous avons comparé notre approche à une stratégie de stockage externe similaire à certains travaux de l'état-de-l'art. Les métriques de comparaisons sont les empreintes mémoires et les bandes passantes requises pour alimenter un circuit de NTT multi-corps. L'empreinte mémoire est définie ici comme la quantité de mémoire utilisée par un programme hôte pour utiliser l'accélérateur de NTT considéré.

L'empreinte mémoire des facteurs de rotation pour la stratégie de stockage externe va de 19,2 koctets à 2,6 Moctets en fonction des jeux de paramètres considérés. Notre stratégie de génération de ces facteurs requiert quand à elle seulement 2,2 koctets au maximum.

En considérant un circuit de NTT cadencé à 200MHz, la stratégie de stockage externe demande au moins 0,75 Goctets/s de bande passante entre l'espace de stockage et l'accélérateur pour les seuls facteurs de rotation. Avec notre générateur, la bande passante nécessaire pour acheminer les éléments initiaux des générations est de maximum 15 koctets/s.

De pair avec notre proposition de circuits de NTT multi-corps, notre générateur de facteurs de rotation permet la conception de circuits de multiplication de polynômes résiduels à haut débit à base de NTT. Dans le contexte de l'accélération matérielle du chiffrement FV, cela ouvre des perspectives intéressantes pour la définition d'une accélération matérielle efficace. En s'appuyant sur notre analyse générale du chiffrement FV, nous présentons une proposition d'architecture système utilisant nos blocs matériels de base pour l'accélération matérielle de la version complètement RNS de FV.

# Exploration d'une accélération hybride pour l'approche couplé ${ m RNS/NTT}$

L'analyse du chiffrement FV menée au début de cette thèse a mis en évidence la nécessité d'accélérer à la fois les opérations de mise à l'échelle en RNS et les multiplications de polynômes résiduels. Cela s'explique par la stratégie d'accélération choisie se basant sur l'approche couplée de la représentation RNS et des multiplications de polynômes basées sur la NTT. La représentation RNS s'attaque à la complexité induite par les grands coefficients, et les approches de convolution par NTT s'attaquent à la complexité induite par le grand degré des polynômes.

Parmi les contributions de cette thèse, nous avons présenté des blocs de base pour l'accélération matérielle des opérations de multiplication de polynômes résiduels. Le choix du matériel dédié pour ces opérations est motivé par la difficulté d'exploiter le parallélisme d'une NTT sur

des architectures SIMD génériques en raison d'accès complexes aux données. Contrairement à la NTT, les fonctions spécifiques au RNS intègrent un parallélisme trivial par rapport au degré des polynômes. Ce parallélisme est facilement exploitable avec des architectures SIMD génériques comme les GPU. Ainsi, notre réflexion considère l'exploration d'une architecture hybride de calcul pour l'accélération du crypto-calcul avec FV. Les fonctions spécifiques au RNS sont accélérées par un GPU, et l'arithmétique polynomiale par un co-processeur dédié.

En plus d'étudier le gain obtenu par l'accélération hybride sur chacune des opérations accélérées, nous nous sommes également intéressés à la problématique de la communication entres les unités de calcul du système. En effet, le flot d'opérations, imposé par la structure des primitives de FV, requiert des échanges continus de données entre le GPU et le co-processeur. Quantifier ces échanges au regard des performances de chacune des unités de calcul est la première étape pour dimensionner un bus système pertinent. Au regard des quantités de données, notre première proposition d'interconnexion s'appuie sur un bus PCIe.

Analyse de notre contribution. Lors d'un stage effectué dans le cadre de cette thèse, l'accélération GPU des fonctions spécifiques au RNS a été explorée. Pour les plus petits jeux de paramètres, le temps passé en communication entre l'hôte et le GPU est plus important que les calculs eux-mêmes. Même pour l'ensemble le plus large, le temps consacré aux communications est non-négligeable. Néanmoins, même avec des temps de communication importants, les opérations spécifiques au RNS bénéficient d'une accélération significative. Pour une implémentation concrète de cette architecture hybride, cela indique que les communications entre les différentes unités de calcul devront être gérées finement pour qu'elles limitent au minimum les performances.

A partir de nos briques de base de NTT multi-corps et de générateur de facteurs de rotations, nous avons fait une proposition de co-processeur pour la multiplication de polynômes résiduels. Nos briques de base permettent la faisabilité de cet accélérateur même pour des grands jeux de paramètres. Notre accélérateur permet une accélération significative de ces multiplications de polynômes par rapport à l'implémentation de Halevi et al. [5], en étant au moins 22 fois plus rapide pendant la multiplication de chiffrés et au moins 4 fois plus rapide lors de l'opération de relinéarisation. De plus, cette accélération reste pertinente avec la croissance des jeux de paramètres, soit de 22 à 31 fois plus rapide pendant la multiplication de chiffrés et de 4 à 9 fois plus rapide pour la relinéarisation.

Pour motiver la pertinence de notre système de calcul hybride, nous avons ensuite estimé l'accélération obtenue pour le calcul d'une opération de multiplication de chiffrés et relinéarisation avec FV. Le tableau 1 présente ces projections pour différents jeux de paramètres. Ces paramètres sont caractérisés par la profondeur multiplicative accessible par les chiffrés. Le temps de communication pour les accès GPU a été pris en compte. Notre système permet d'envisager une multiplication de données chiffrées jusqu'à 14 fois plus rapide qu'une version logicielle bien optimisée (Halevi et al. [5]). Cette accélération réduit le temps de multiplication de chiffrés à 62 ms pour les paramètres permettant une capacité d'évaluation d'une profondeur multiplicative de 30, et à 21 ms pour une profondeur multiplicative de 20. Néanmoins, ces projections sont obtenues en faisant des hypothèses simplificatrices sur les communications et les entrelacements avec d'autres opérations sous-jacentes comme les additions de polynômes résiduels. Ces résultats prospectifs motivent cependant le perfectionnement de l'accélérateur dédié pour l'arithmétique polynomiale ainsi que la réalisation d'un prototype du système hybride de calcul.

Table 1: Projection de l'accélération obtenue avec notre proposition de système hybride de calcul pour la primitive FV.Mul&Relin. Les colonnes RNS regroupent les opérations spécifiques au RNS. Les colonnes RPM regroupent toutes les opérations de multiplication de polynômes requises par l'opération FV.Mul&Relin.

| P              | aram     | eters      | s Timing basis from [5] |       |       |       | Our hybrid system |                |       |       |

|----------------|----------|------------|-------------------------|-------|-------|-------|-------------------|----------------|-------|-------|

| $\overline{L}$ | n        | $\log_2 q$ | Total                   | RNS   | RPM   | Misc. | Total             | speedup        | RNS   | RPM   |

| 1              | $2^{11}$ | 54         | 3.6                     | 1.3   | 2.2   | 0.1   | 0.67              | $\times 5.37$  | 0.51  | 0.06  |

| 5              | $2^{12}$ | 108        | 12.7                    | 3.8   | 8.6   | 2     | 3.28              | imes 3.87      | 1.05  | 0.23  |

| 10             | $2^{13}$ | 216        | 57.6                    | 14.4  | 41.8  | 2.6   | 7.13              | $\times 8.08$  | 3.32  | 1.21  |

| 20             | $2^{14}$ | 432        | $\bf 252$               | 71.3  | 175.3 | 2.2   | 20.7              | imes 12.17     | 11.17 | 7.33  |

| 30             | $2^{15}$ | 594        | 887                     | 233.1 | 630.6 | 2.6   | 61.21             | $\times 14.49$ | 33.14 | 25.47 |

#### Conclusion et perspectives

Les recherches pour du crypto-calcul efficace se poursuivent. Tout au long de cette thèse, nous avons cherché à prendre en compte la complexité de l'implémentation du chiffrement homomorphe. Cette complexité est premièrement celle du choix du chiffrement à considérer pour une accélération matérielle. Notre analyse de l'état de l'art nous a orienté vers les schémas homomorphes basés sur le problème RLWE, et en particulier le schéma FV. Deuxièmement, le choix de la stratégie d'accélération doit prendre en compte de nombreux éléments. Le plus important à notre avis est la grande variété des paramétrages qui implique la nécessité d'une stratégie d'accélération flexible. En ce sens, nous avons choisi une stratégie couplant la représentation des nombres en RNS et la multiplication de polynômes par NTT. Nos contributions montrent en particulier la possibilité d'avoir des circuits de NTT multi-corps avec une génération locale des facteurs de rotation, pour un coût matériel peu sensible aux variations des paramètres de FV.

Au cours de ce travail, nous avons ouvert la voie à la conception d'une architecture de microserveur pour le crypto-calcul avec FV. Nous avons commencé à explorer les problématiques de communication qui se poseraient dans un tel système. Quelques pistes pourraient être intéressantes à explorer dans le cas où l'interconnexion PCIe proposée dans cette thèse serait insuffisante. Par exemple, en explorant l'intégration du GPU et du matériel dédié pour l'arithmétique polynomiale plus près de la mémoire du CPU. En restant dans une approche multi-SoC, nous pourrions considérer l'interface Coherent Accelerator Processor Interface (CAPI) d'IBM. Pour une approche plus intégrée en un single-SoC hétérogène, nous pourrions explorer l'UltraPath Interconnect (UPI) d'Intel. Enfin, tant qu'à considérer la conception d'un ASIC, il serait intéressant d'examiner certaines technologies spécifiques telles que l'intégration de mémoire 3D.

La problématique de conception de système de communication à faible latence et haut débit se retrouve dans d'autres domaines, notamment ceux dont les performances de calcul dépendent davantage de la quantité de données à traiter que des calculs eux-mêmes. De ce point de vue, l'accélération du chiffrement homomorphe est similaire à l'accélération du traitement d'images et de vidéos à la volée.

## Introduction

#### Digital technologies at the heart of our lives

It is no secret that digital technology has very quickly established itself as essential to the functioning of developed societies. And this trend does not seem to be about to reverse. A first impress of this can be obtained looking at the number of internet subscribers that increased from 400 millions to 3.2 billions between 2000 and 2015 [11]. In particular, developing countries play an important role in this growth. Considering then that the part of internet users in the younger generations is significantly larger than for older's ones [12], we can assume that the internet population will continue to grow. More generally, the ease brought by these technologies for many daily tasks gives another reason to believe that they will not disappear in the near future.

These technologies bring with them many economic, societal and cultural opportunities. For instance, specialized medical care brought by massive data collection [13]. But they can also be the source of misuses and imbalances in each of these dimensions. An example of this is the 2015 spy toy controversy [14]. This is only one example among others of abusive data collection of persons who neither have the knowledge of this collection, nor the ability to protect themselves from it. Many of these issues are being addressed by the political sphere and by national and international entities (for example, the 2018 revision of the french law *Informatique et Libertés* [15]. Addressing the moral question of the proper use of these technologies results in legal delimitation expressing the rights and responsibilities of each party. For instance, see the note from the *Commission Nationale de l'Informatique et des Libertés* (CNIL) on the control of Internet use at work [16].

However, the legal sphere only provides a guarantee of judicial sanction for the misuse of technology. It should not be forgotten that a person who deliberately wants to abuse these technologies is able to do so. Let us recall the obvious: this is deeply linked to individual morals that legal sphere cannot entirely control, and the only solution to solve this problem is to encourage personal moral reflection and healthy questioning. Nevertheless, the existence of this misuse can have a serious impact on society. Therefore, as far as possible, some means must be found to prevent the upcoming of abuses, and why not within technology itself.

In this thesis, we are interested in the question of data privacy that arises with this technologies. In particular, in the technical answers that help to protect this privacy (for instance, see the concept of Privacy-by-Design [1]). But before considering any answer, let's try to deepen our knowledge of the issues.

#### The question of data privacy

It is not a trivial reflection to consider the reasons and limits within which the privacy of data must be guaranteed. Without wishing to contribute to this reflection, we would like to list some common cases in which data privacy is considered important or even essential.

A first case, and we believe it is essential, is the right of every human being to have its intimacy respected (Article 12 of United Nations Universal Declaration of Human Rights, Article 9 of the French Civil Code ...).

Another case is the protection of sensitive information. Some examples of such are: the precise location of a nuclear arsenal, or critical diplomatic discussions. If the privacy of the data carrying this type of information is not guaranteed, the safety of people is at risk.

The last case we are discussing here concerns the economic field. Namely, the competitive advantages provided by certain technical knowledge and/or expertise that are materialized by an accumulation of data. In most cases, a company's competitive advantages help it to remain profitable, and thus enable it to meet certain needs of its employees.

These common cases are only examples of where data privacy is indeed important. They nonetheless indicate that it would be irresponsible not to look for ways to prevent data misuse. Indeed, although a technical solution cannot be a cure to the underlying problem, it can nevertheless be an aid to the prevention of greater ills. In this thesis, we are interested in a technical answer called *cryptology*.

#### Cryptology: a technical answer to data privacy

Cryptology is, in its etymological meaning, the science of secrecy. Its subject of study is larger than the simple confidentiality of information. Its purpose is to propose some tools and best practices to guarantee integrity, authenticity and privacy of information to protect.

Historically, the secrecy of information was more closely related to art than science. And its uses were more or less restricted to the military and political spheres. With the advent of digital technologies, the need to protect information changed scale and cryptology democratized itself.

In practice, this science is divided into two disciplines: cryptography and cryptanalysis. Cryptography is about protecting information (etymologically: writing of a secret), and cryptanalysis is about analyzing the secret (etymologically: analysis of the secret). The first seeks to protect information and the second to discover it. This permanent opposition is a source of improvement and refinement of cryptographic tools [2, 3]. In this thesis, we are more interested in the cryptography field, but we hope the reader understands that these two disciplines should not be considered independently.

Securing the exchange of information. The basic principle of cryptography is to scramble information to make it unreadable or uninterpretable to unauthorized persons. This is called an *encryption* process and the resulting information is *encrypted*. This masking of exchanged information is done using a secret element shared by the right holders called a *secret key*. The same secret element is also used to retrieve the original information from the encrypted domain. This is called a *decryption* process. Encryption and decryption are usually called the *primitives* of a cryptographic scheme. This common secret is actually the basis of what we call *symmetric cryptography*. Some examples of symmetric cryptographic schemes are DES, AES, Trivium, etc..

With the advent of telecommunication, the issue of exchanging this common secret arose. Indeed, the secret had itself to transit through telecommunication channels that are insecure. In the 1970s, this problem gave rise to the notion of asymmetric cryptography. In that case, the information is scrambled using a public element called a public key, and the information is

retrieved using a private key. The security of the information is based on some mathematical problems that are hard to solve in the general case but that become easier with a trapdoor. In a nutshell, the public key creates an instance of a mathematical problem by scrambling the information, and the private key is the trapdoor given to a right holder to solve the mathematical problem and hence to retrieve the information. Asymmetric cryptography is less efficient than its symmetric counterpart with respect to communication cost. This is due to an inherent growth in information size while scrambling that does not occur in symmetric cryptography. In practice, asymmetric cryptography is used for secret sharing and authentication protocols but not for the proper exchange of information. Some examples of asymmetric cryptographic schemes are RSA and ElGamal.

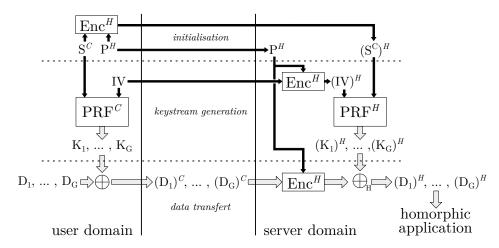

Preserving privacy during data processing. Faced with the constant increase in the cost of maintaining IT infrastructures, the market for centralized IT services is growing rapidly. The question of outsourcing the storage and processing of private data is therefore highly relevant. Symmetric and asymmetric cryptography only allow to secure the exchange and storage of information. But what is required in this case is to guarantee the confidentiality of the data also during their processing.

In 1978, Rivest, Adleman and Dertouzos introduced the notion of homomorphic cryptography that would allow such data processing. The principle is to have a decryption process that preserves some structure between the encrypted and clear domains allowing the definition of equivalent operations. It is only in the late 2000s that homomorphic cryptography has truly emerged with a theoretical solution.

Since then, many research works have improved the practicality of this new type of cryptography. Firstly, by theoretical simplifications of these cryptographic schemes, and secondly, by algorithmic optimizations for efficient implementations.

Nevertheless, this cryptography paradigm seems to have inherently large memory and computational complexities. To give an idea of the order of magnitude, an homomorphic ciphertext is around  $10^5$  times larger than the data it encrypts, and an operation in the encrypted domain is around  $10^6$  times heavier than its clear counterpart. As a result, the actors involved in research on the practicality of this new cryptography are in needs of further optimizations such as dedicated hardware acceleration.

The principle of hardware acceleration is to build a dedicated computing architecture for the realization of a specific task. This has to be considered in opposition to a general purpose computing architecture, which is designed to be efficient in the average case of algorithmic needs for a wide variety of applications. This thesis is a contribution for designing such dedicated hardware architectures for homomorphic encryption acceleration.

#### This thesis

Homomorphic cryptography is a field that is still emerging. Although many applications are being considered, few have the merit of being explored, and even fewer are already feasible on a large scale. Nevertheless, research is making fast-paced progresses towards its use outside the laboratories. And we hope that some of the contributions associated to this thesis may help this development.

Before mentioning our scientific contributions, we will detail a bit the general problematic of homomorphic cryptography and that of its hardware acceleration. From this we will present the results of our work.

#### The problematic

The main goal of research on homomorphic cryptography is to define an encryption scheme that has encrypted equivalents for all the operations that can be applied on data. This goal is referred to as *Fully Homomorphic Encryption* (FHE). The fact that it took almost 30 years between the introduction of the concept and the first theoretical construction of an FHE scheme is no coincidence. Indeed, two intersecting theoretical problems exist.

The first is the difficulty of finding expressions of mathematical problems that allow homomorphic encryption schemes to be constructed. Just like for asymmetric cryptography, these mathematical problems ensure the security of the schemes. But they also influence the algebraic structures of the cleartext and ciphertext spaces, and hence the construction of equivalent operations.

The second is the necessary presence of an encryption noise. But the noise amplitude in the ciphertexts grows with operations in the encrypted domain. Above a certain noise threshold, the decryption process stop working.

With the research that followed the first theoretical construction of an FHE scheme, some intermediate solutions brought the usages of homomorphic encryption close to being practical at large scale. Nevertheless, the research on hardware acceleration for these schemes has to cope with two main issues.

The first is the variety of scheme propositions. In less than 10 years, four generations of schemes have already been proposed. Hence, their respective maturities and advantages could not be fully and objectively compared over such a short period of time. And of course, each has its own algebraic characteristics which makes difficult, if not impossible, the definition of a computing architecture that would accelerate homomorphic encryption in general. The result is therefore a more qualitative positioning in the choice of schemes to consider for hardware acceleration. During the preparation of this thesis, our analysis of the state-of-the-art of homomorphic cryptography made us consider a particular scheme named after its authors Fan and Vercauteren (FV). It appears as one of the main representatives of the second generation of HE schemes and is well accepted in the FHE community.

The second problematic is that the most mature HE schemes from our point of view have their parameterization dependent on the applications to be performed in the encrypted domain. And of course, it would have been too easy if the parameter ranges were small. This is due to the schemes' noise growth which requires the noise gauge to be sized properly. In the case of the FV scheme, the handled elements are polynomials with large degree and large coefficients. Both degree and coefficients get significantly larger with the noise absorption capacity.

#### Scientific contributions

During this work, we have particularly addressed the issue of the wide range of the sizing parameters. The literature has proposed the basic elements upon which are built our contributions. Namely, the use of Residue Number System (RNS) to tackle the complexity brought by large integer arithmetics, and the use of Number Theoretical Transforms (NTT) to reduce the asymptotic complexity of polynomial multiplications. Building on this, we argue that the coupled approach of RNS and NTT allows the definition of hybrid computing systems, which promise a significant acceleration of encrypted-domain computing with the FV scheme.

This thesis results from the in-depth analysis of FV as well as contributions to solve the main difficulties of combining the use of RNS and NTT for large parameters.

Our main contributions are therefore the following. First, an analysis of the RNS/NTT-coupled approach and a theoretical validation of its feasibility up to very large parameter sets. Second, the exploration of GPU acceleration of some RNS specific algorithms brought by concomitant works for the full adaptation of FV to RNS. Third, the design and a proof-of-concept implementation of a data flow oriented hardware for efficient residue polynomial multiplications, and the study of its capability to scale.

This last contribution is the subject of particular attention in order to overcome certain design problems that have previously limited the feasibility of the coupled approach at large scale. In particular, we propose a solution to locally pre-compute the values necessary for NTT computations without impacting the operations' throughput. This is achieved with two contributions: the design of a fully-streaming multi-field NTT, and the design of a twiddle factor set generator. Finally, to take into account the issue of significant changes in FV parameters w.r.t. an application, the automatic generation of RTL descriptions for the proposed designs has been explored.

#### Outline of this document

This document begins by positioning our work within the state-of-the-art of homomorphic encryption acceleration. First, we identify a subset of well-accepted schemes at the time of this thesis begun, and present their implementation issues. It is followed by a discussion on the existing solutions and related works addressing these issues. The first chapter ends with our arguments in favor of our decision to make the FV scheme the subject of an in-depth study to propose a hardware acceleration strategy consistent with the wide ranges of its parameters.

In the second chapter, the FV encryption scheme is detailed. The study of its performance profile orients us towards an implementation strategy based on the RNS representation and NTT-based polynomial multiplications. This strategy is theoretically validated for the wide spectrum of FV parameters. Analyzing closely the related work on a fully RNS version of FV allowed us to refine this strategy by addressing both RNS specific functions and NTT-based Residue Polynomial Multiplication (RPM).

The third and fourth chapters provide details on basic hardware blocks for the efficient design of NTT-based RPM. Both concern the problem of managing pre-computed values for NTT. The third chapter deals more specifically with the automatic generation of RTL circuits for data-flow multi-field NTTs with a particular focus on the handling of the twiddle factor sets. The fourth chapter presents an on-the-fly generation approach of these twiddle factors satisfying the throughput requirements imposed by the NTT circuits.

Based on the analysis and contributions of previous chapters, the fifth chapter presents our proposal of an hybrid computing system for the acceleration of FV. Firstly, the GPU acceleration of RNS-specific functions is studied. Secondly, an architecture's proposal for RPMs is detailed. Together these two studies allow a performance projection for an hybrid GPU/FPGA computing system.

Finally, a general conclusion summarizes the present work and offers perspectives.

## Chapter 1

# Review of homomorphic encryption and its practicability

This chapter presents a review of homomorphic cryptography and its implementations. The primary objective is to position ourselves within the research activity around Homomorphic Encryption (HE). As far as possible, we present the elements that make our qualitative choices understandable. The second objective is to introduce the notions that appear in the various discussions in this document as arguments for our choices.

After having introduced the basic notions of homomorphic encryption, a state of the art of the HE schemes is presented, and our positioning is expressed. The detailed presentation of the LWE and RLWE problems makes it possible to present the research for using HE in practice. Finally, we highlight the implementation issues that must be addressed and we summarize the related works on this matter.

#### 1.1 Introduction

#### 1.1.1 Technical introduction to homomorphic encryption

HE schemes are able to perform operations on encrypted data without decrypting them first. This ability comes from choosing a homomorphism as the decryption function of the encryption scheme. The definition of a homomorphism directly highlights the desired feature: it is a *structure-preserving map* between two algebraic structures of the same type (groups, rings, fields ...). Considering the plaintext space and the ciphertext space as algebraic structures, having a homomorphism is then to have a map that expresses an equivalence between some operations in the encrypted and clear domains.

To summarize, a HE scheme has its decryption function to be a homomorphism. Given an algebraic operation  $\circ$  over the ciphertext space and an algebraic operation \* in the plaintext space, the decryption function is a homomorphism for these operations if and only if:

$\operatorname{Dec}(\operatorname{\mathtt{ct}}_1 \circ \operatorname{\mathtt{ct}}_2) = \operatorname{Dec}(\operatorname{\mathtt{ct}}_1) * \operatorname{Dec}(\operatorname{\mathtt{ct}}_2)$ , for all  $\operatorname{\mathtt{ct}}_1, \operatorname{\mathtt{ct}}_2$  in ciphertext space.

It is said that an equivalent of \* exists in the ciphertext space by decryption homomorphism.