# Réalisation de cellules solaires intégrées par oxydation localisée d'un substrat de silicium fritté poreux

Youssouf Boye

# ▶ To cite this version:

Youssouf Boye. Réalisation de cellules solaires intégrées par oxydation localisée d'un substrat de silicium fritté poreux. Autre. Université d'Orléans, 2016. Français. NNT: 2016ORLE2083. tel-02003388

# HAL Id: tel-02003388 https://theses.hal.science/tel-02003388

Submitted on 1 Feb 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# UNIVERSITÉ D'ORLÉANS

# ÉCOLE DOCTORALE ENERGIE, MATERIAUX, SCIENCES DE LA TERRE ET DE L'UNIVERS

LABORATOIRE GREMI

THÈSE présentée par : Youssouf BOYE

soutenue le : 12 février 2016

pour obtenir le grade de : Docteur de l'université d'Orléans

Discipline/ Spécialité : Science des matériaux

# Réalisation de cellules solaires intégrées par oxydation localisée d'un substrat de silicium fritté poreux

THÈSE dirigée par :

Mr Éric Millon Professeur, Université d'Orléans

**RAPPORTEURS:**

Mme Daniele Blanc-Pelissier Chargée de recherche, CNRS Lyon

Mr Abdelilah Slaoui Directeur de recherche, CNRS Strasbourg

JURY:

Mr Mustapha Lemiti Professeur, Université de Lyon

Mme Danièle Blanc-Pélissier Chargée de recherche, CNRS Lyon Mr Abdelilah Slaoui Directeur de recherché, CNRS Strasbourg

Mr Esidor Ntsoenzok Professeur, Université d'Orléans (Président)

Mr Éric Million Professeur, Université d'Orléans

Mr Alain Straboni Professeur, Université de Poitiers & PDG de S'Tile

## Remerciements

Ces travaux de thèse ont été réalisés dans le cadre d'une convention CIFRE entre l'entreprise S'Tile sise à Poitiers et le laboratoire GREMI (Groupement de Recherche sur l'Énergétique des Milieux Ionisés) d'Orléans.

J'aimerais tout d'abord adresser mes remerciements à madame Chantal Leborgne, professeur de l'Université d'Orléans et directrice du laboratoire GREMI de m'avoir accueilli au GREMI. J'exprime mes chaleureux remerciements et une vive reconnaissance à mes deux encadrants : à mon directeur de thèse monsieur Éric Million, et à mon responsable industriel monsieur Alain Straboni, président du directoire de la société S'Tile. Merci pour votre disponibilité, pour la confiance que vous m'avez accordée tout au long de cette thèse, ainsi que pour les précieux conseils dont j'ai pu bénéficier de votre part. J'ai énormément apprécié votre rigueur scientifique sans oublier vos valeurs humaines. Je renouvelle mes remerciements à Mr Alain Straboni, qui, tout au long de ces années passées au sein de son entreprise, m'a transmis la passion du solaire photovoltaïque.

Mes sincères remerciements à tous les membres du jury d'avoir accepté d'évaluer mes travaux, à mes rapporteurs, Mme Danièle Blanc-Pélissier et Mr. Abdelilah Slaoui, pour les remarques enrichissantes que vous avez pu apporter et pour votre rigueur scientifique.

Je remercie chaleureusement mes chers collègues de S'Tile : Alioune Sow, Guocai Sun, Gaëtan Lorrillère Antoine Malinge Yves Salinesi, Eden Terraz, Bertille Sionneau, David Gaud, David André, Tomo Skelo, Mathilde Duprat, sans oublier la stagiaire Célia Pérou. Merci pour votre sympathie et votre bonne humeur.

J'adresse également mes remerciements à tous les membres du Gremi, plus particulièrement à l'équipe Procédé Plasma Laser, dirigée par Mr. Éric Millon. J'exprime ma reconnaissance à Agnès Petit pour son professionnalisme, sa disponibilité, sa gentillesse et je la remercie de m'avoir initié au MEB du Gremi.

Que ma famille trouve à travers ces quelques lignes, ma profonde gratitude ; merci pour tout le soutien que vous m'avez apporté. À ma femme Alicia, merci pour tous les efforts et tous les sacrifices dont tu as fait preuve durant toutes ces années. À mon fils Issa, pour tout le bonheur que j'ai pu ressentir depuis que tu es venu au monde, merci d'avoir enchanté mes nuits pendant ces années de thèse (ironie). Merci à tous mes amis, à tous ceux qui me sont chers.

Je dédicace ces travaux à ma chère maman.

Réalisation de cellules solaires intégrées par oxydation localisée d'un substrat de silicium fritté poreux

Résumé

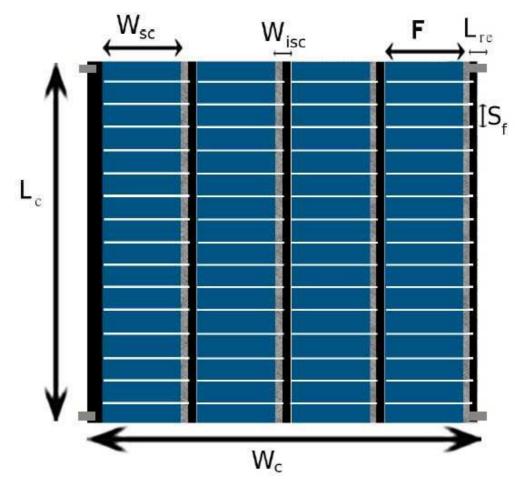

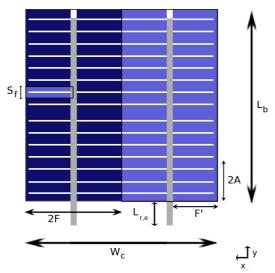

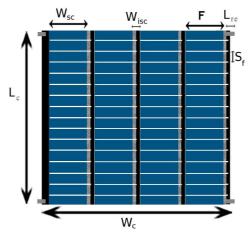

Les travaux de recherche menés dans cette thèse s'inscrivent dans le cadre de la réalisation de la technologie cellule solaire intégrée (i-Cell), qui est une technologie innovante de fabrication de cellules solaires à hauts rendements de conversion et à bas coût de production. L'i-Cell consiste en la réalisation de plusieurs cellules élémentaires ou sous-cellules, en feuilles minces de silicium cristallin purifié, qui sont connectées en série sur un substrat de Si fritté bas coût. La technologie i-Cell permet en effet la réduction du coût de la plaquette grâce à la faible épaisseur des feuilles de silicium et grâce à l'utilisation de substrats issus du frittage de poudres de silicium.

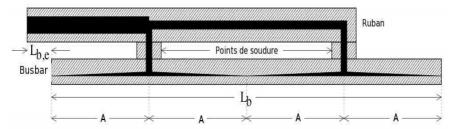

Dans une telle structure la fonction photovoltaïque est assurée par la feuille mince de surface alors que le transport du courant et la fonction mécanique sont gérés par le substrat fritté ce qui permet de réduire les coûts de fabrication de la cellule. En effet, à l'instar des couches minces, on peut décomposer la couche active en cellules de faibles surfaces et ainsi produire sur une surface standard (156 x 156 mm²), une cellule dans laquelle circule un faible courant qui permet de réduire fortement la consommation des métaux précieux au sein de la cellule (Argent) et entre les cellules du module (Cuivre). En outre, la configuration des cellules à i-Cell permet de s'affranchir des busbars en Ag traditionnellement utilisés dans les technologies silicium. Ceci présente l'avantage d'éviter le masquage de la lumière et donc d'augmenter la puissance de la cellule.

Ce travail de thèse s'articule sur deux axes de recherche principaux. Le premier est orienté sur l'étude de la cinétique d'oxydation thermique de substrats de silicium frittés poreux. Le deuxième axe concerne la réalisation du substrat fritté intégré et la réalisation des premiers prototypes d'i-Cells sur ces derniers. Ce travail a permis de démontrer la faisabilité de l'i-Cell et de réaliser des prototypes d'i-Cell sur le substrat fritté intégré. Des rendements de conversion PV supérieurs à 18% ont été ainsi obtenus.

Mots clés: Cellule intégrée, substrat fritté intégré, oxydation thermique du Si fritté poreux

# Realization of integrated solar cell by localized oxidation of a porous sintered silicon substrate

#### **Abstract**

The research work conducted in this thesis are within the framework of the realization of the integrated solar cell technology (i-Cell), which is an innovative solar cell technology with a high conversion efficiency and a low cost production. The i-Cell consists of the realization of several elementary cells or sub-cells, in purified crystalline silicon thin foils, which are connected in series on a low cost sintered silicon substrate. In fact, the i-Cell technology allows the reduction of the cost of the wafer thanks to the low thickness of the silicon foils and through the use of substrates obtained from the sintering silicon powders.

In such a structure, the photovoltaic function is provided by the thin purified Si foil on the surface. Whereas both the current transport and the mechanical function are provided by the sintered silicon substrate – thin allows to reduce the cell manufacturing costs. In fact, just like thin films, we can decompose the active layer in small cell surfaces and thus produce, on a standard surface (156 x 156 mm²), a low current cell that greatly reduces the consumption of precious metals within the cell (Silver) and between the cells within the module (Copper). Furthermore, the configuration of cells in the i-Cell technology permits to eliminate the use of Silver busbars traditionally used in the Si solar cell technologies. This offers the advantage of avoiding the masking light and thus increases the power of the i-Cell.

This thesis work focuses on two main axes of research: The first axis relates to the study of the kinetics of thermal oxidation of porous sintered silicon substrates. The second axis of research focuses on the realization of the "integrated sintered substrates", which consists of the realization of local conductive zones on the insulating porous sintered substrate, and the fabrication of the first i-Cells prototypes on them. This work demonstrated the feasibility of i-Cell and produced prototypes of i-Cell on the integrated sintered substrate. High photovoltaic conversion efficiencies, greater than 18%, were obtained.

*Keywords*: Integrated solar cell (i-Cell), integrated sintered substrate, thermal oxidation porous of sintered Si.

# Table des matières

| Remerciements                                                                                  | 2  |

|------------------------------------------------------------------------------------------------|----|

| Résumé                                                                                         | 4  |

| Abstract                                                                                       | 5  |

| Table des matières                                                                             | 6  |

| Introduction générale                                                                          | 10 |

| Chapitre I : Etude bibliographique des technologies de cellules solaires photovoltaïques       | 15 |

| I.1.1 La situation énergétique mondiale                                                        | 16 |

| I.1.2 Perspective à moyen et long terme : Évolution de la demande énergétique mondiale         | 16 |

| I.2. La production d'électricité dans le monde                                                 | 17 |

| I.2.1. La part des énergies renouvelables dans la production d'électricité dans le monde       | 18 |

| I.2.2. Le marché mondial du photovoltaïque                                                     | 19 |

| I.2.3 Fonctionnement d'une cellule solaire photovoltaïque en silicium                          | 21 |

| I.2.3.1 Historique du solaire photovoltaïque                                                   | 21 |

| I.2.3.2. Principe de fonctionnement                                                            | 22 |

| I.2.3.3. Caractéristiques courant-tension d'une cellule solaire                                | 23 |

| I.2.3.4. Modélisation électrique d'une cellule solaire :                                       | 26 |

| I.2.3.5. Facteurs limitant le rendement d'une cellule                                          | 28 |

| I.2.4 Les différentes filières de fabrication de plaquettes de silicium avec sciage (kerfloss) | 35 |

| I.2.4.1 Le silicium monocristallin :                                                           | 36 |

| I.2.4.2 Le silicium multicristallin:                                                           | 38 |

| I.2.4.3. Les techniques de sciage                                                              | 39 |

| I.2.5 Les technologies de fabrication de plaquette sans sciage (Kefless)                       | 42 |

| A- Les technologies rubans :                                                                   | 42 |

| B- Les technologies Smart-Cut & SLiM-Cut                                                       | 46 |

| I.2.6. Les principales technologies de fabrications de cellules solaires                       | 47 |

| I.2.6.1 Les principaux types de cellules à base de silicium cristallin                         | 48 |

| I.2.7 Conclusion du chapitre I                                                                 | 61 |

| Bibliographie du chapitre 1                                                           | 62              |

|---------------------------------------------------------------------------------------|-----------------|

| Chapitre II : Évolutions technologiques de la société S'Tile et contexte              | 70              |

| II.1 Motivations                                                                      | 71              |

| II.2 Présentation et historique de la société S'Tile                                  | 71              |

| II.3. État de l'art : Évolutions technologiques de S'Tile                             | 72              |

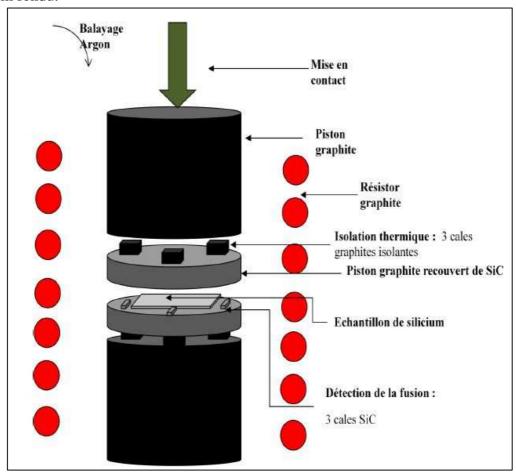

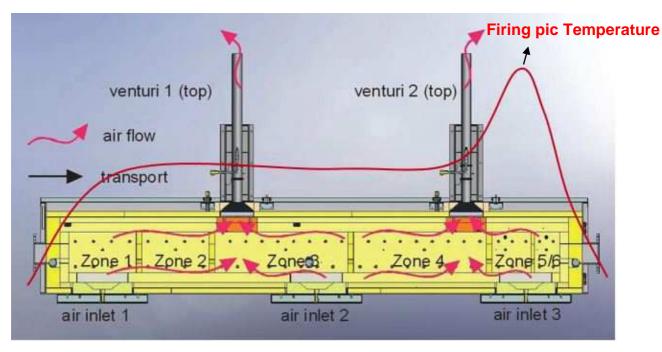

| II.3.1. Le procédé de frittage de poudres de silicium                                 | 72              |

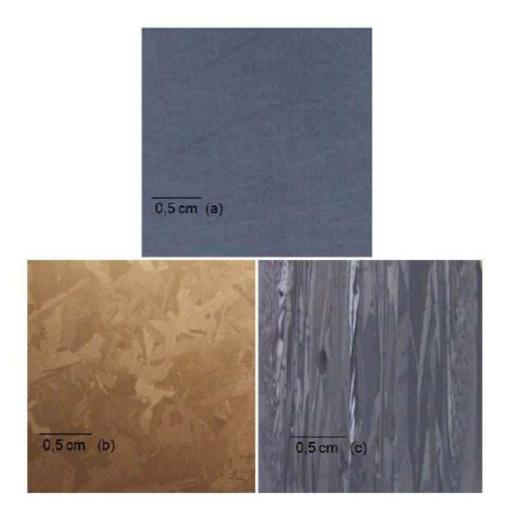

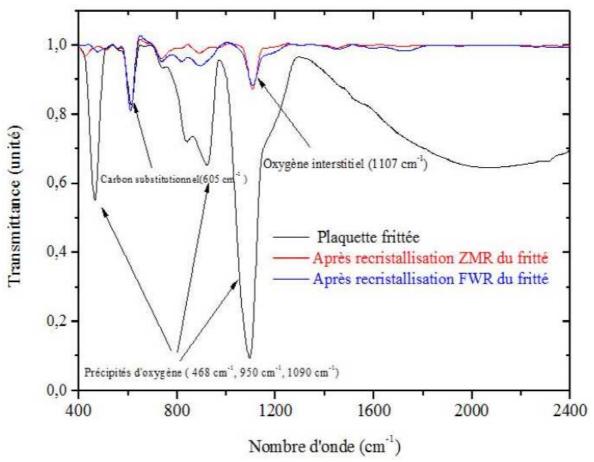

| II.3.2. Les procédés de recristallisation des plaquettes frittées                     | 81              |

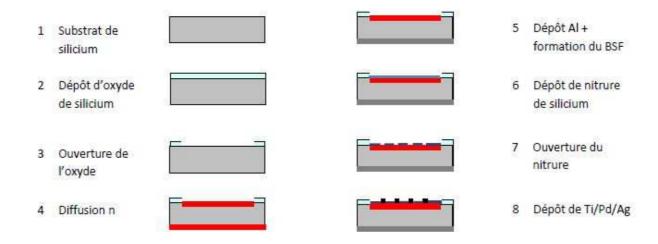

| II.3.3. Les technologies S'Tile de réalisation de cellules solaires sur substrats rec | cristallisés 90 |

| II.4. Conclusion du chapitre II                                                       | 100             |

| Bibliographie du chapitre II                                                          | 101             |

| Chapitre III : Étude de l'oxydation thermique du silicium fritté poreux               | 105             |

| III.1 Introduction                                                                    | 106             |

| III.2. L'oxydation thermique du silicium                                              | 107             |

| III.2.1. Généralités                                                                  | 107             |

| III.2.2. Rôles de l'oxyde de silicium SiO <sub>2</sub>                                | 107             |

| III.2.3. Processus chimique d'oxydation thermique du silicium                         | 107             |

| III.2.4. Oxydation du silicium poreux                                                 | 110             |

| III.3. Oxydation thermique du silicium fritté                                         | 113             |

| III.3.1. Protocole expérimental                                                       | 114             |

| III.3.2. Mise en œuvre de l'oxydation thermique du silicium fritté                    | 121             |

| III.3.3. Résultats et discussions                                                     | 122             |

| III.4. Conclusion du chapitre III                                                     | 139             |

| Bibliographie du chapitre III                                                         | 141             |

| Chapitre IV : Le procédé de réalisation de la cellule intégrée (i-Cell)               | 145             |

| IV.1 Introduction                                                                     | 146             |

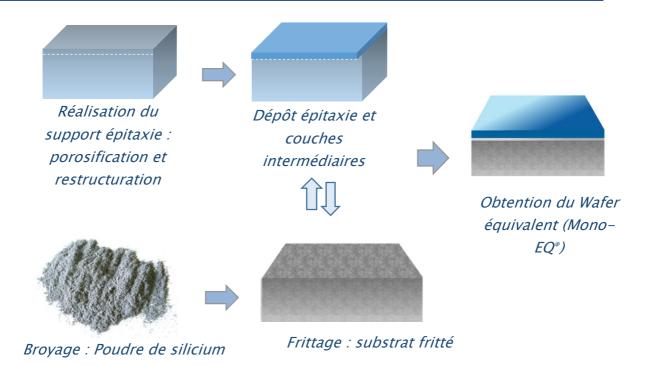

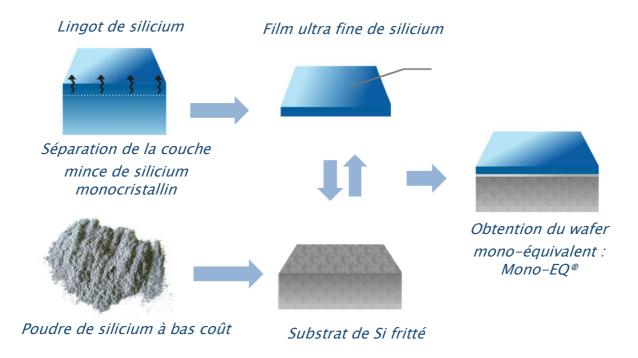

| IV.2. La réalisation du wafer Mono-EQ® (Mono-Équivalent)                              | 147             |

| IV.2.1. Le procédé de fabrication du wafer Mono-EQ®                                   | 147             |

| IV.2.2 Réalisation de cellule solaire sur wafer Mono-EQ® - Transfert de couche        | épitaxiée150    |

| IV.3. La cellule solaire intégrée (i-Cell)                                            | 156             |

| IV.3.1. Structure de la cellule intégrée « i-Cell »                                | 156        |

|------------------------------------------------------------------------------------|------------|

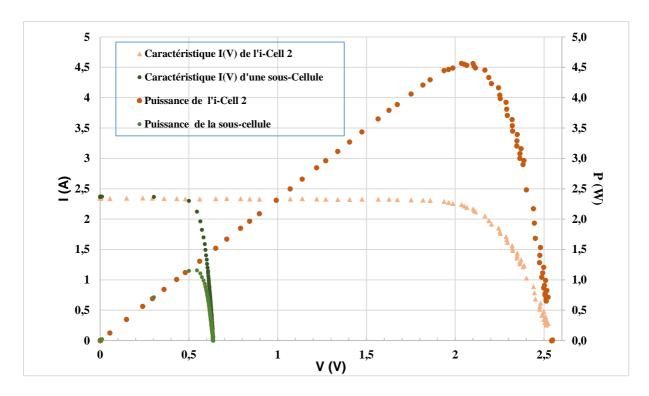

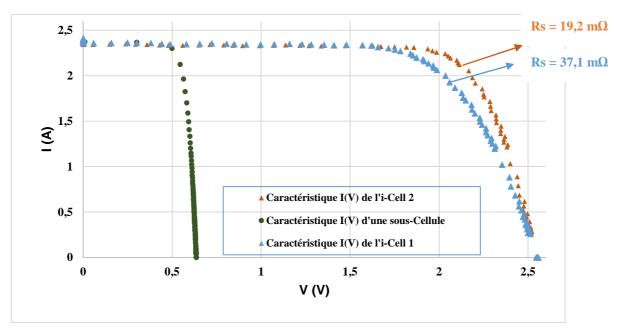

| IV.3.2. Caractéristiques I(V) d'une cellule intégrée :                             | 160        |

| IV.3.3. Économies de matériaux précieux réalisées dans l'i-Cell :                  | 161        |

| IV.3.4. Calcul des coûts de productions d'i-Cell                                   | 162        |

| IV.3.5. Évaluation de pertes de puissance dans une i-Cell :                        | 163        |

| IV.3.6. Réalisation du substrat fritté intégré                                     | 167        |

| IV.3.7. Résultats et discussions                                                   | 170        |

| IV.3.8. Réalisation de prototypes i-Cell sur substrat fritté intégré               | 175        |

| IV.3.9. Résultats de mesures des performances des premiers prototypes d'i-Cells ré | alisés 177 |

| IV.4. Conclusions du chapitre IV                                                   | 180        |

| Bibliographie du chapitre IV                                                       | 182        |

| Conclusion générale et perspectives                                                | 184        |

| ANNEXES                                                                            | 188        |

| ANNEXE I : Techniques de caractérisations utilisées                                | 189        |

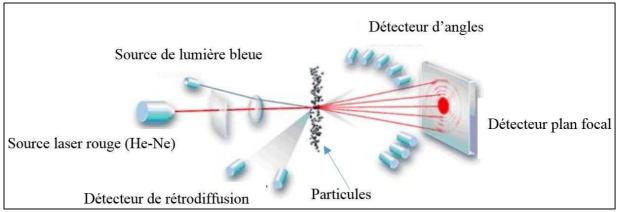

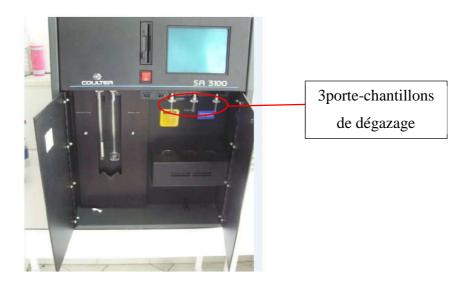

| A-I.1. Techniques de caractérisations microstructurales des poudres                | 189        |

| A-I.2. Techniques de caractérisations des substrats de Si frittés                  | 191        |

| ANNEXE II : Le modèle de Deal & Grove                                              | 195        |

| A-II-1 Représentation du modèle :                                                  | 195        |

| ANNEXE III : Calculs théoriques des pertes de puissance dans la cellule intégrée   | 200        |

| A-III.1. Introduction                                                              | 200        |

| A-III.2. Modélisation électrique d'une cellule solaire, les résistances parasites  | 200        |

|                                                                                    |            |

| A-III.3. Calculs des pertes pour une cellule solaire de structure classique        | 201        |

| A-III.3. Calculs des pertes pour une cellule solaire de structure classique        |            |

# Introduction générale

La forte croissance économique et l'explosion démographique que subit le monde engendrent une surexploitation des énergies fossiles. L'utilisation massive de cette source d'énergie constitue la principale source de pollution et de rejet des gaz à effet de serre dans l'atmosphère. Ceci a des conséquences directes et néfastes sur l'homme et son environnement.

Afin de lutter efficacement contre le changement climatique et réduire nos émissions de gaz à effets de serre, il est essentiel de développer les énergies renouvelables, qui sont des sources d'énergies propres et inépuisables, et d'augmentation la part de celles-ci dans le mix énergétique électrique. Cela passe notamment par l'essor de la filière du solaire photovoltaïque (PV), qui permet de convertir durablement et efficacement le rayonnement solaire en énergie électrique.

Malgré les avancées technologiques et la croissance spectaculaire du marché du solaire photovoltaïque cette dernière décennie, le coût de production des modules solaires constitue encore un obstacle pour une production à très grande échelle et pour aller vers la parité vers des territoires de plus en plus étendus. Le silicium est le matériau de base utilisé dans plus de 90% des systèmes PV actuels, grâce notamment à sa disponibilité naturelle, sa non toxicité, et ses propriétés photoélectriques indéniables. Sa maturité industrielle, et surtout son rapport efficacité de conversion/prix, font qu'il se distingue comme le plus intéressant par rapport à d'autres matériaux employés dans ce domaine.

La réduction du coût de production des modules solaires standard en silicium mono ou multicristallin passe inévitablement par la réduction du coût de la plaquette et de la cellule. Cette dernière représente en effet plus de 60% du coût du module final, à cause notamment du coût de purification du silicium, mais surtout de la perte considérable de matériau lors de l'étape de découpe des lingots en plaquettes de silicium. 50% du silicium est en effet perdu lors de cette étape. Par ailleurs, les techniques de sciages utilisées consomment une quantité conséquente d'abrasifs, qui sont des matériaux très chers.

Afin de contourner l'étape de sciage des lingots, une étape très énergivore et très couteuse, plusieurs technologies de fabrication de plaquette se sont développées ces dernières années. Parmi elles, la technologie séduisante de tirage de rubans. C'est d'ailleurs dans la même approche que la société S'Tile a proposé sa technologie innovante de fabrication de plaquettes

de silicium directement par frittage de lits de poudre de silicium. Cette méthode permet de s'affranchir de l'étape de sciage et de l'utilisation de silicium raffiné.

Plusieurs technologies et concepts de réalisation de cellules ont été développés dans différents travaux de recherches antérieurs à cette thèse. Ces dernières incluent généralement une étape de recristallisation totale ou partielle du substrat fritté. Les limites technologiques liées à la qualité cristalline du substrat fritté recristallisé ainsi qu'aux procédés utilisés présentent un frein à l'obtention de cellules solaires à haut rendement de conversion. Cependant, en conservant son procédé innovant de fabrication de substrat de silicium par frittage de poudre de silicium, S'Tile s'est orienté vers une technologie alternative plus simple, permettant de s'affranchir des étapes de recristallisation. Ce nouveau concept de fabrication de wafers, appelés wafers Mono-EQ<sup>®</sup> (Mono-Équivalent) consiste à rapporter une feuille mince (quelques dizaines de microns) de silicium monocristallin sur le substrat de silicium fritté bas coût. Il présente en effet, un meilleur potentiel de rendement de conversion que les technologies antérieures car la cellule est réalisée directement sur la feuille mince de silicium monocristallin. Les principaux résultats de cellules issus de ce concept sont présentés sur le quatrième chapitre de ce manuscrit.

Les travaux entrepris au cours cette thèse s'inscrivent dans le cadre de l'activité de recherche et développement de la technologie innovante de fabrication de cellules solaires à hauts rendements de conversion et à bas coût. Ce type de cellules, appelées cellules solaires intégrée ou i-Cell [1] (pour integrated Solar Cell), permet à la fois de réduire les coûts liés à l'élaboration de la plaquette, notamment par le frittage de lits de poudres de silicium de qualité métallurgique, mais également le coût du procédé de fabrication de la cellule par la réduction de l'utilisation des matériaux précieux tels que l'argent (Ag) pour les métallisations et le cuivre (Cu) pour l'assemblage en module. En effet, l'élément métallique (Ag) utilisé pour la métallisation (busbars et fingers) des cellules solaires dans les procédés standards, représente plus de la moitié du coût de production de la cellule.

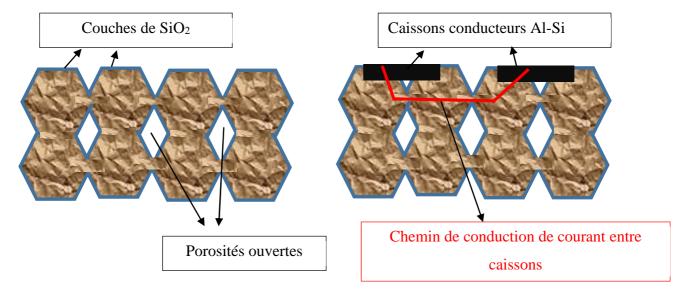

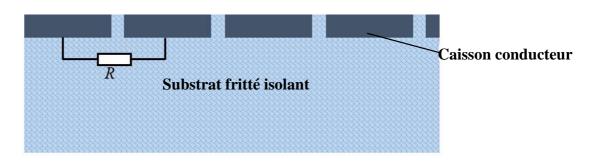

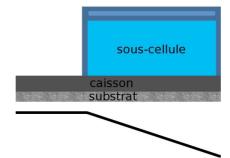

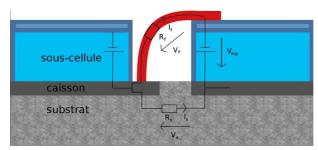

Ainsi, la cellule intégrée (i-Cell) proprement dite est constituée de différentes sous-cellules ou cellules élémentaires connectées en série sur un « substrat de silicium fritté intégré » poreux et électriquement isolant, sur lequel des zones de conduction locales y ont été préalablement intégrées par inclusion d'éléments métalliques. « Le substrat fritté intégré » combine une double fonction, il fait office de support et d'électrodes en face arrière des différentes sous-cellules de la future i-Cell.

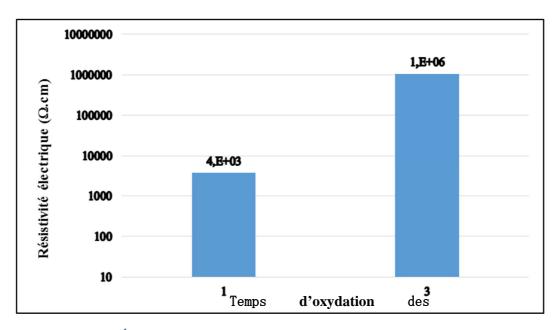

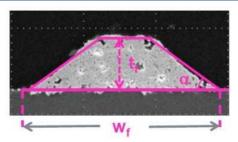

Le principal challenge pour la production d'i-Cells à coûts réduits réside dans l'élaboration de substrats frittés suffisamment isolants à partir de poudre de silicium de qualité métallurgique (UMG), nettement moins chère que la poudre de qualité solaire, qui est beaucoup plus raffinée. Pour cela, plusieurs solutions ont été proposées au cours de cette thèse, notamment par l'oxydation thermique de substrats de silicium frittés pour intégrer la phase isolante dans ces derniers. Les substrats frittés ont été délibérément rendus poreux afin de faciliter la perméation de l'agent oxydant dans les canaux de porosités.

Cette thèse s'articule autour de deux axes principaux : le premier axe de recherche porte sur l'étude de cinétique d'oxydation du substrat de silicium fritté poreux, tandis que le second est consacré à l'étude de l'intégration de zones de conductions locales ou « caissons conducteurs » qui servirons d'électrode face arrière de la future i-Cell. Des prototypes d'i-Cells ont été réalisés et présentés dans le second axe de recherche.

Ce manuscrit est scindé en quatre chapitres.

- Le premier chapitre décrit le contexte énergétique actuel et l'importance de l'augmentation de la part du solaire PV dans le mix énergétique. Il aborde également la physique du fonctionnement de la cellule solaire. Un état de l'art sur les principales technologies de cellules solaires, notamment les technologies de fabrications cellules solaires sur des wafers sans sciage (kerfless) bas coût, dans lequel s'inscrit le contexte de cette thèse.

- Le second chapitre passe en revue les travaux antérieurs concernant les évolutions et les limites technologiques de la cellule solaire de S'Tile, dont le frittage de poudre de silicium est le point de départ. Cette étude a permis de situer ces travaux de thèse dans cette évolution technologique et d'en assurer la continuité en levant/contournant les limites pour une production de cellules solaires à haut rendement et bas coût réalisées sur substrat fritté.

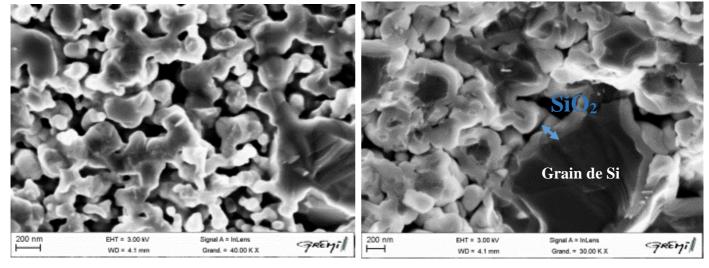

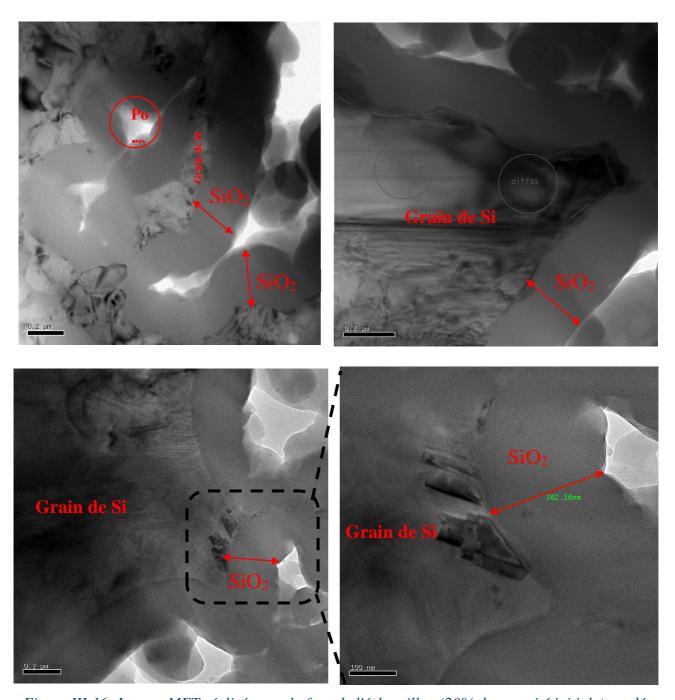

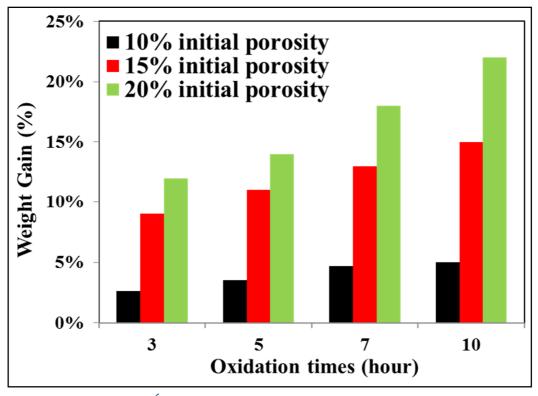

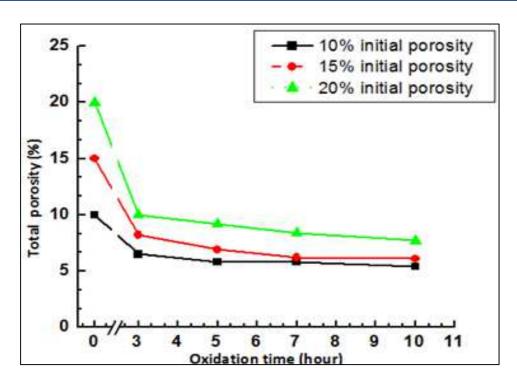

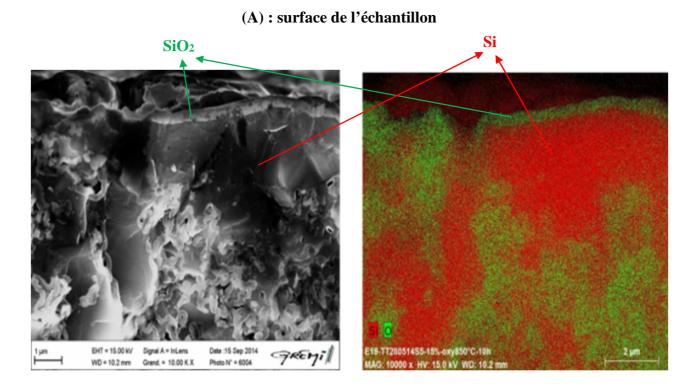

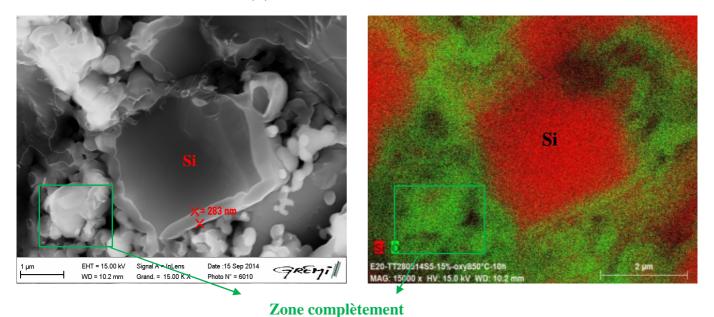

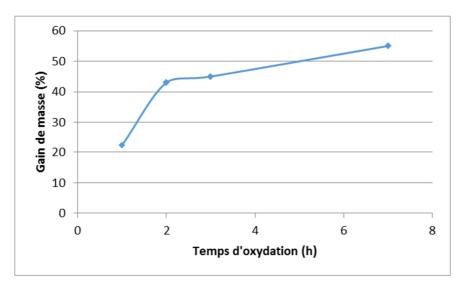

- Le troisième chapitre est consacré à l'étude de l'oxydation thermique du substrat de silicium fritté poreux. L'étude de l'influence des différents paramètres tels que la porosité initiale du substrat, de la température d'oxydation, et du temps sur la cinétique d'oxydation y est présentée et discutée. Des études microstructurales réalisées par microscopies électroniques à l'université d'Orléans ont permis de mettre en évidence la croissance de l'oxyde de silicium au sein des canaux de porosités.

- Le quatrième chapitre présente une description détaillée de la structure de la cellule intégrée (i-Cell), une liste d'avantages et d'inconvénients de la technologie cellules intégrées y est dressée et comparée à la technologie de cellules classiques tant sur le plan économique que technologique. Dans la dernière partie de ce chapitre, après avoir étudié et réalisé le « substrat

fritté intégré », qui joue un rôle essentiel dans le fonctionnent de l'i-Cell, nous avons présenté les résultats montrant les caractéristiques et les performances des premiers prototypes de cellules intégrées réalisées sur ce dernier.

|          | ,                        |            |           |         |         |         |           |          |                 |   |

|----------|--------------------------|------------|-----------|---------|---------|---------|-----------|----------|-----------------|---|

| Chanitus | $I \cdot E_{+i} \cdot J$ | a hihliaan | anhiana   | dog too | haalaai | a da aa | Iliilaa a | lainea   | photovoltaïaue. | a |

| Chapure  | г. слиас                 | ะ กเกแดยก  | ирпиане в | ues tec | molovie | s ae ce | uuues so  | naires i | тоюуонаначе     |   |

Chapitre I : Étude bibliographique des technologies de cellules solaires photovoltaïques

# I.1.1 La situation énergétique mondiale

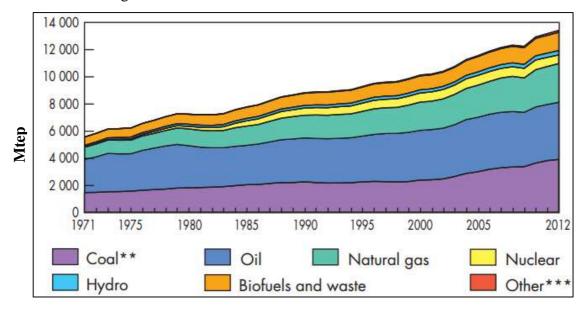

La demande énergétique mondiale a maintenu une très forte croissance au cours de ces dernières décennies. Selon l'Agence Internationale de l'Énergie (AIE), la production mondiale d'énergie primaire à atteint la barre de 13 371 millions de tonnes équivalent pétrole (Mtep) en 2012 [2]. Il est intéressant de voir comment cette consommation d'énergie primaire a évolué dans le temps depuis ces dernières années. La Figure I-1 montre cette croissance ainsi que la contribution de chaque source d'énergie. On notera que la demande est essentiellement satisfaite par les énergies fossiles à plus de 80 %. Cette situation montre la forte dépendance mondiale aux énergies carbonées.

Figure I-1: Évolution de la production mondiale d'énergie primaire et répartition par source d'énergie en (Mtep) [2]

# I.1.2 Perspective à moyen et long terme : Évolution de la demande énergétique mondiale

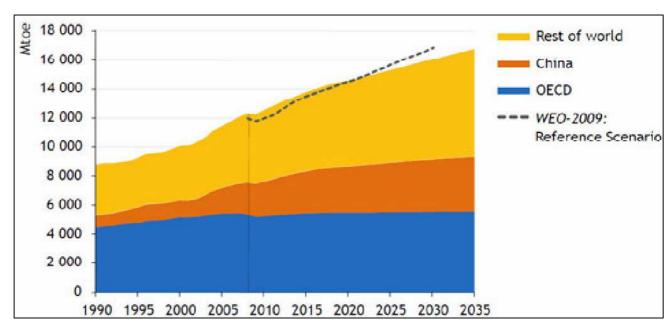

Sous l'effet de l'accroissement de la population mondiale, estimé à 9 à 10 milliards d'habitants à l'horizon 2050, des efforts des pays en voie de développement pour combler leur décalage économique et du maintien d'une légère croissance de la demande énergétique dans les pays développés : la demande d'énergie primaire poursuit sa croissance mais sa répartition géographique se modifie. La Figure I-2 montre l'évolution de cette consommation par grande zone économique depuis 1990 ainsi que les prévisions d'évolution. La prévision WEO (Word Energy Outlook), en pointillé, est comparée à la courbe établie par l'AIE et en est très proche, on notera que seuls les pays de l'OCDE ont une consommation à peu près stabilisée [3].

Figure I-2: Évolution (depuis 1990) de la consommation d'énergie primaire par zone géographique [3]. (Mtoe = Mtep)

D'ailleurs, si l'on rajoute la part du nucléaire dans les énergies fossiles, on remarquera que plus de 87% de la consommation énergétique est d'origine non renouvelable. Ainsi, l'utilisation massive des énergies fossiles pour les années à venir engendrerait d'importantes émissions des gaz à effet de serre et l'augmentation de la température du globe.

A ce rythme, les experts tablent sur une croissance moyenne de l'ordre de 1,7% par an pour les prochaines décennies, ce qui pourrait doubler les besoins énergétiques de la planète à l'horizon 2050 soit une consommation de 20 000 Mtep.

#### I.2. La production d'électricité dans le monde

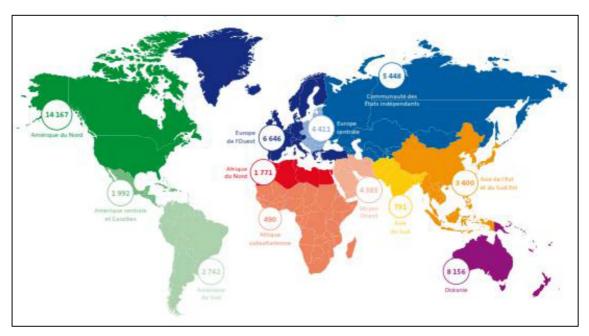

L'énergie électrique représente un facteur indispensable pour le développement économique dans le monde entier. En effet, le progrès technologique dans l'industrialisation et dans le confort de la vie moderne explique l'augmentation de son importance. La production d'électricité par nombre d'habitants permet donc d'avoir une idée claire concernant les écarts de développements entre les différentes régions du monde (figure I-3). Cependant, en 2012, l'Amérique du Nord était la région où on produisait le plus d'électricité (14167 KWh/hab/an.), ce qui représentait approximativement le double de la production de l'Europe de l'Ouest (6646 KWh/hab/an.), plus de 3 fois plus que l'Europe centrale (4411 KWh/hab/an), plus de 4 fois plus qu'en Asie de l'Est et du Sud-Est (3400 KWh/hab/an), encore 8 fois plus qu'en Afrique du Nord (1771 KWh/hab/an) et de l'ordre de 30 fois plus qu'en Afrique subsaharienne (490 kWh/hab/an) (Observ'ER, 2013).

Figure I-3: Production d'électricité en kWh par habitant en 2012 (Source : Observ'ER, 2013)

# I.2.1. La part des énergies renouvelables dans la production d'électricité dans le monde

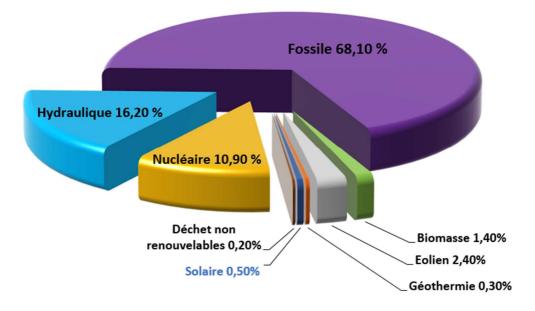

La production d'électricité renouvelable a atteint 20,8% de la production d'électricité mondiale en 2012 (4699,2 TWh). Les combustibles fossiles restent les plus utilisés pour la production de l'électricité mondiale (68,1%) comme le montre la figure I-4.

Figure I-4 : Répartition de la production d'électricité dans le monde en 2012. (Source: Observ'ER, 2013)

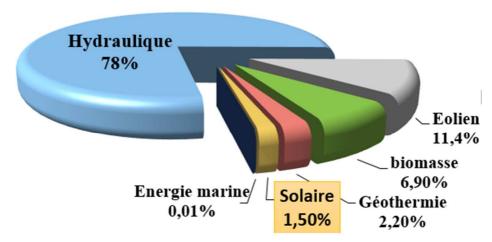

Les sources qui représentent les énergies renouvelables sont : l'hydroélectricité qui contribue à 78% en 2012, l'énergie éolienne (11,4%), la biomasse (6,9%), le solaire (2,2%), la géothermie (1,5%) et les énergies marines (0,01%), (voir figure I-5.).

Figure I-5: Répartition de la production mondiale d'électricité d'origine renouvelable en 2012. (Source: Obser'ER 2013).

Il est important de rappeler que la part du solaire dans les graphiques ci-dessus regroupe les deux principales technologies. La technologie des panneaux photovoltaïques dans laquelle on utilise les propriétés des semi-conducteurs qui génèrent un courant électrique en présence de la lumière. La seconde technologie est celle des centrales solaires thermiques et thermodynamiques, qui consiste à utiliser des miroirs pour concentrer le rayonnement solaire sur un point focal permettant d'avoir des températures très élevées allant de 400 à 1000°C pour produire l'électricité.

#### I.2.2. Le marché mondial du photovoltaïque

Malgré la croissance du marché photovoltaïque dans le monde, la production électrique développée par les panneaux photovoltaïques reste encore très faible dans les mix électriques nationaux. A titre d'exemple, durant l'année 2013, la production photovoltaïque allemande a permis de satisfaire 5,3% de la consommation intérieure électrique. Pour la France, l'énergie photovoltaïque générée, durant les mois de juillet et août 2013, ne représente que 1,5% de la production électrique nationale. Selon l'EPIA, et suivant la croissance du marché actuel, l'énergie photovoltaïque pourrait satisfaire 8% de la demande électrique dans l'Union Européenne en 2020 et 15% en 2030.

#### I.2.2.1 Classement des meilleurs producteurs mondiaux de cellules et modules PV

Comme le montre le tableau I-1, la production mondiale de cellules/panneaux solaires PV est largement dominée par le marché chinois. En effet, la Chine compte le plus grand nombre de producteurs ainsi que les plus importants en termes de volume de production. Les producteurs chinois occupent les six premières places dans le Top 10 des premiers producteurs mondiaux. Utilisant des technologies issues des laboratoires universitaires australiens, ces sociétés ont choisi massivement le silicium cristallin et sont présentes sur toute la chaine de valeur. Ainsi, leur production de cellules solaires est réservée à la fabrication de modules dans leurs propres lignes de fabrication. La production annuelle dépasse en moyenne les 2,5 GW et atteint plus de 3 GW pour le duo en tête du classement que sont **Trina Solar** et **Yingli Green** en 2014. Cependant il faudrait noter aujourd'hui que la grande majorité de la production chinoise est destinée à la demande intérieure, à travers de grands projets d'installation PV. La plupart de ces entreprises chinoises du top 5 commercialisent aujourd'hui des modules de rendement de conversion moyen entre 14 et 16 %.

Tableau I-1: Top 10 des producteurs mondiaux de cellules et de modules solaire PV en 2014. (Source : PVTECH & Renewable Energy)

| Rang  | Entreprises     | Pays  | Technologie                           | Production cellules, modules (GW) |

|-------|-----------------|-------|---------------------------------------|-----------------------------------|

| 1     | Trina Solar     | Chine | (Mono, Multi) Cristallin              | 3,6                               |

| 2     | Yingli green    | Chine | (Mono, Multi) Cristallin              | 3,3                               |

| 3     | Canadian solar  | Chine | (Mono, Multi) Cristallin              | 2,9                               |

| 4     | Jinko solar     | Chine | (Mono, Multi) Cristallin              | 2 ,7                              |

| 5     | JA Solar        | Chine | (Mono, Multi) Cristallin              | 2,4                               |

| 6     | Renesola        | Chine | Multi Cristallin                      | 2,3                               |

| 7     | Sharp solar     | Japon | Multi Cristallin Couches mince (a-Si) | 1,9                               |

| 8     | First solar     | USA   | Couches minces (CdTe)                 | 1,8                               |

| 9     | Hanwha SolarOne | Corée | Multi Cristallin                      | 1,4                               |

| 10    | SunPower        | USA   | Mono Cristallin                       | 1,3                               |

| 10 ex | Kyocera         | Japon | Multi Cristallin                      | 1,3                               |

Les Japonais **Sharp Solar** et **Kyocera** bénéficieraient toujours de la réputation de leurs marques respectives sur leur marché national, ce qui leur aurait permis de rester dans le Top 10 avec une production annuelle respective d'environ 1,9 GW et 1,3 GW. A côté de ces deux gros producteurs japonais, bien que n'étant pas dans le Top 10, la société **Sanyo** se taille une bonne part avec une production de 1,2 GW en cellules et modules. Avec l'entrée sur le marché de leur modules HIT (Heterojunction with Intrinsic Thin-layer), **Sanyo** s'est installé sur le créneau des cellules et modules à très haut rendement. Comme pour la Chine, la production japonaise de cellules PV est consommée par la demande nationale, dopée par les grands projets solaires initiés par l'état, depuis le tsunami à l'origine de l'accident de Fukushima.

L'Américain **SunPower** qui produit aussi des modules à très haut rendement (>20 %) à partir de cellules solaires de très bonne qualité est entré dans le Top 10, ex-aequo avec **Kyocera** en 10e position. A l'inverse on trouve aussi aux USA, le fabricant de modules en couches minces **First Solar** (8e) qui, avec 1,8 GW de production annuelle, commercialise des modules en couches minces au CdTe avec des rendements d'environ 13-14 %.

À côté de ces géants Asio-américains, des entreprises européennes basées principalement en Allemagne résistent à la concurrence chinoise en misant sur la qualité de leurs produits. Parmi ces compagnies, on peut citer **SolarWorld**, leader européen avec une capacité de production supérieure à 1GW.

## I.2.3 Fonctionnement d'une cellule solaire photovoltaïque en silicium

## I.2.3.1 Historique du solaire photovoltaïque

L'effet physique qui sous-tend le photovoltaïque a d'abord été observée par Alexandre Edmond Becquerel [4,5] en 1839, quand il a produit un courant en exposant des électrodes d'argent au rayonnement dans un électrolyte. L'effet a été décrit plus en détail par Adams et Day en 1877 [6]. Ils ont observé que l'exposition des électrodes de sélénium à un rayonnement produit une tension électrique, leur permettant ainsi de produire un courant électrique. Du point de vue historique, ces différents effets sont découverts expérimentalement au cours du XIXe siècle. Ce n'est qu'en 1905, qu'Albert Einstein proposa une théorie qui explique les phénomènes photoélectriques en introduisant le concept de la dualité onde-corpuscule des photons. Dans sa théorie, A. Einstein démontre que l'énergie d'un photon est entièrement transférée à un électron du matériau et que le courant photoélectrique est proportionnel au nombre de photons, donc au flux lumineux [7].

L'effet a été ensuite mis en suspens jusqu'à la découverte du transistor et l'explication de la physique de la jonction PN par Shockley [8] en 1948 et Bardeen et Brattain [9] en 1949, l'année qui a marqué le début de l'ère de la technologie des semi-conducteurs. Quelques années plus tard, en 1954 Chapin et al [10] ont développé la première cellule solaire à base de silicium cristallin, qui a eu un rendement de 6% dans les laboratoires Bell Telephone aux USA (devenus aujourd'hui Alcatel-Lucent Bell Labs). Ce rendement a été amélioré rapidement jusqu'à atteindre à 10%. La première utilisation viable pour cellules solaires était pour des applications spatiales. L'engouement pour l'utilisation de l'énergie solaire photovoltaïque pour des installations terrestres n'a vu le jour qu'en 1973 avec le choc pétrolier. Ainsi, la première maison avec une installation photovoltaïque a vu le jour en 1973 à l'Université de Delaware aux USA. À partir de cette période, de nombreuses institutions de recherche et développement ont été installées dans le monde entier, dont la majorité a été subventionnée par des fonds publics. Aujourd'hui, l'énergie photovoltaïque est à la disposition des entreprises et des particuliers et les panneaux photovoltaïques ont des rendements de conversion avoisinant les 20%.

# I.2.3.2. Principe de fonctionnement

L'effet photovoltaïque est le processus physique qui consiste à transformer l'énergie lumineuse en énergie électrique. Dans ce qui nous intéresse, le matériau est un semi-conducteur, le silicium qui est le matériau de base le plus utilisé, dans plus de 90% des systèmes photovoltaïques actuels.

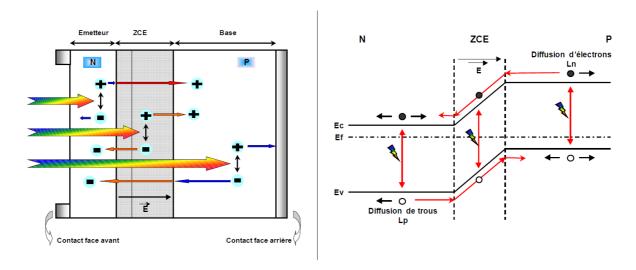

L'absorption de la lumière dans un matériau semi-conducteur génère des paires électrons trous (excitation d'un électron de la bande de valence vers la bande de conduction) créant une tension et/ou un courant électrique. Pour que ces charges puissent être collectées par un circuit extérieur, il faut pouvoir les séparer au sein du matériau. Dans le cas d'une cellule solaire en silicium, la structure utilisée pour permettre cette séparation peut être la jonction PN ou une hétérojonction. Le champ électrique créé à la jonction de la zone N et de la zone P autorise la séparation de la paire électron-trou, les porteurs diffusent ensuite vers les extrémités de la cellule entrainant l'apparition d'une tension aux bornes de cette dernière. Les schémas du principe de fonctionnement d'une cellule solaire sont représentés Figure I-6.

Figure I-6: Structure d'une cellule photovoltaïque (schéma de gauche) et diagramme de bande correspondant (schéma de droite)

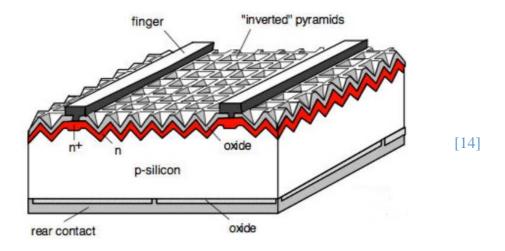

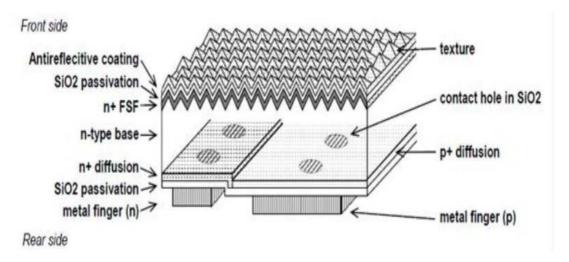

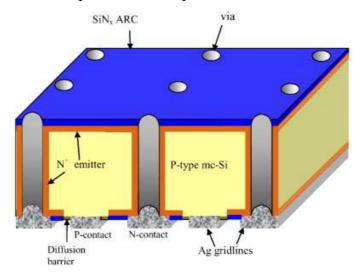

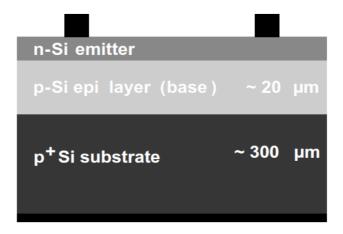

Une cellule solaire standard en silicium est constituée d'un substrat de type P, la base (dont les porteurs de charge majoritaires sont les trous) et d'une zone en face avant fortement dopée n+, appelée émetteur (où les porteurs majoritaires sont les électrons). La jonction de ces deux zones va entraîner la création de la zone de charge d'espace (ZCE). C'est dans cette zone que les porteurs sont séparés. Les charges positives (trous) minoritaires dans l'émetteur, si elles arrivent au bord de la ZCE, sont entrainées par le champ E puis se retrouvent dans la base où elles sont majoritaires. Le phénomène inverse se produit pour les électrons, minoritaires dans la base. Enfin, les contacts métalliques permettent la collecte des charges vers le circuit extérieur : ils se présentent sous forme de grille sur la face avant, et généralement pleine plaque sur la face arrière.

#### I.2.3.3. Caractéristiques courant-tension d'une cellule solaire

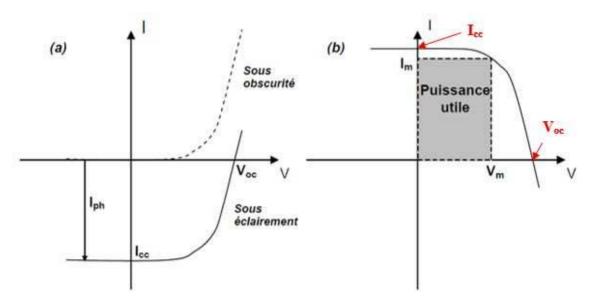

*Sous éclairement*, les photons incidents vont générer des paires électron-trou dont le comportement va différer selon la zone d'absorption :

- ➤ Dans la zone de charge d'espace (ZCE) engendrée par la juxtaposition de la jonction P-N, les paires électron-trou créées sont dissociées par le champ électrique. Les électrons sont accélérés puis injectés dans la zone N (émetteur) et les trous dans la zone P (base). Un photocourant de génération est ainsi crée.

- Dans les zones de base et d'émetteur, les porteurs minoritaires générés (trous dans l'émetteur et électrons dans la base) vont diffuser vers la ZCE; s'ils atteignent cette dernière avant de se recombiner, ils sont injectés dans la zone N pour les électrons et

dans la zone P pour les trous et deviennent majoritaires. Un photocourant de diffusion est créé.

Ces deux contributions s'ajoutent pour donner le photocourant de porteurs minoritaires résultant I<sub>ph</sub>. Il est proportionnel à l'intensité lumineuse.

Sous obscurité, le courant dans une telle structure de type jonction P-N est appelé courant d'obscurité, exprimé par la formule suivante :

$$I_{obs} = I_S \left[ \exp\left(\frac{qV}{nkT}\right) - 1 \right]$$

(I.1)

Avec:

q: La charge élémentaire = 1,6.10<sup>19</sup> (C)

V : Tension aux bornes de la jonction (V)

n : Coefficient d'idéalité de la jonction

k: Constante de Boltzmann = 1.38.10<sup>-23</sup> (J.K<sup>-1</sup>)

T: Température (K)

$I_S$ : Courant de saturation inverse de la jonction PN (A)

Le courant d'obscurité  $I_{obs}$  correspond au courant de la diode  $I_d$ , il résulte de la polarisation de la jonction.

Ainsi le courant délivré sur une charge par une cellule solaire photovoltaïque sous éclairement se traduit par la formule suivante :

$$I(V) = I_{ph} - I_{obs} (V)$$

(I.2)

Soit:

$$I(V) = I_{ph} - I_S \left[ \exp\left(\frac{qV}{nkT}\right) - 1 \right]$$

(I.3)

Sous éclairement, la caractéristique I(V) d'une cellule photovoltaïque idéale est donc la superposition d'un générateur de courant d'intensité  $I_{ph}$  et de la caractéristique de la diode sous obscurité. La cellule produit donc de l'énergie. Par convention on inverse l'axe des courants comme illustré dans la Figure I-7.

Figure I-7: (a) caractéristiques courant-tension de la cellule photovoltaïque sous obscurité et sous éclairement et (b) la représentation conventionnelle de la courbe I(V)

À partir de la caractéristique I(V) sous éclairement de la cellule photovolta $\ddot{i}$ que on déduit les paramètres propres à la cellule et notamment :

- ➤ I<sub>CC</sub>: Courant de court-circuit (obtenu pour V=0)

- ➤ V<sub>CO</sub>: Tension de circuit ouvert (obtenu pour I=0)

- ➤ I<sub>m</sub>: courant à la puissance maximale de fonctionnement de la cellule photovoltaïque

- ➤ V<sub>m</sub>: Tension à la puissance maximale de fonctionnement de la cellule photovoltaïque

- > FF: Facteur de forme,

$$FF = \frac{V_m I_m}{V_{co} I_{cc}} \tag{I.4}$$

η: rendement de conversion de la cellule représente le rapport de la puissance électrique

maximale fournie sur la puissance solaire incidente.

$$\eta = \frac{V_m I_m}{\phi_i S} = \frac{FF.V_{co}.I_{cc}}{\phi_i S}$$

(I.5)

Avec  $\phi_i$ : flux d'éclairement reçu par unité de surface ; S : surface de la cellule photovoltaïque.

Ces paramètres électriques varient avec l'intensité lumineuse, la convention est d'utiliser pour les tests sous éclairements les conditions d'ensoleillement AM 1.5 soit 1000 W/m² et une température de 25°C. La puissance maximale sera alors exprimée en Watt-crête (*Wc*) afin de spécifier que les mesures ont été réalisées sous les conditions standards.

# I.2.3.4. Modélisation électrique d'une cellule solaire :

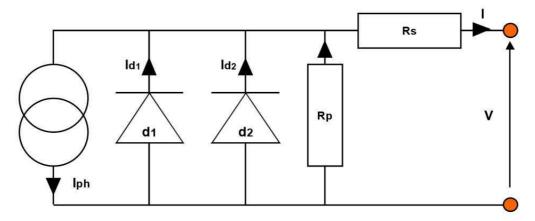

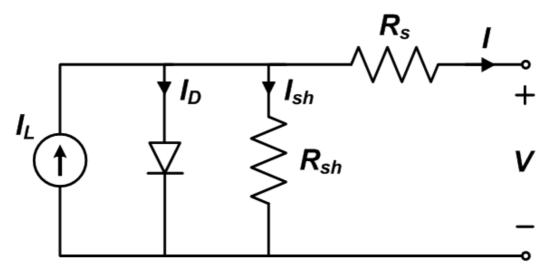

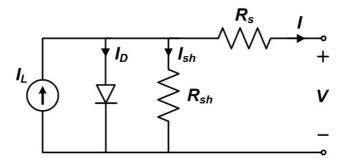

L'analogie entre le fonctionnement d'une cellule solaire photovoltaïque sous éclairement et celui d'un générateur de courant, produisant un courant I<sub>ph</sub> auquel se soustrait le courant de la diode en polarisation directe, n'est que la représentation simplifiée du fonctionnement de la cellule. En effet, afin de tenir compte des différentes limitations de la cellule, un modèle à deux diodes a été introduit comme illustré sur la Figure I-8 [36].

Figure I-8: Modélisation électrique d'une cellule solaire photovoltaïque [36].

Ce modèle met en évidence les différents paramètres de la cellule solaire :

- Le générateur de courant : délivrant le courant I<sub>ph</sub> correspond au courant photogénéré.

- ➤ La résistance série R<sub>s</sub>: elle prend en compte la résistivité propre aux contacts entre les différentes régions constitutives de la cellule, à savoir l'émetteur, la base et les contacts métalliques. Ce terme doit idéalement être le plus faible possible pour limiter son influence sur le courant de la cellule. Ceci peut être réalisé en optimisant le contact métal/semi-conducteur, et en diminuant la résistivité du matériau utilisé. Cependant, un dopage trop élevé entraine une augmentation de la recombinaison des porteurs.

- ➤ La résistance parallèle R<sub>p</sub>: également connue sous le nom de résistance de courtcircuit, elle traduit l'existence de shunts à travers l'émetteur, causés par des défauts. Ceci est

le cas lorsque la diffusion des contacts métalliques à hautes températures perce l'émetteur. Elle peut aussi être due à un court-circuit sur les bords de la cellule. Cette valeur devra être la plus élevée possible.

- ➤ La diode d₁: Elle modélise la diffusion des porteurs dans la base et l'émetteur. Son influence sera d'autant plus grande que le matériau présentera une bonne longueur de diffusion.

- ➤ La diode d₂: Elle modélise la génération/recombinaison des porteurs dans la zone de charge d'espace (ZCE).

En effet, l'équation (I-3) néglige les effets parasites dus aux différentes résistances précitées ci-dessus. En prenant en compte les résistances série et parallèle, le courant au sein de la cellule photovoltaïque se traduit par la relation :

$$I(V) = I_{ph} - I_{s1} \left( \exp\left(\frac{q(V + IR_s)}{n_1 k T}\right) - 1 \right) - I_{s2} \left( \exp\left(\frac{q(V + IR_s)}{n_2 k T}\right) - 1 \right) - \frac{V + IR_s}{R_p}$$

(I-6)

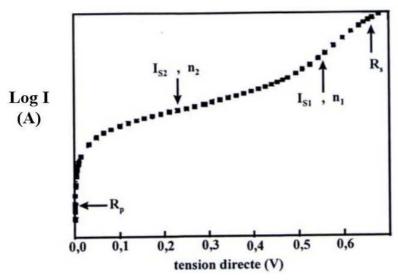

À partir des caractéristiques I(V) de la cellule réelle sous obscurité Figure I-9, il est possible d'accéder aux paramètres du modèle.

Le premier terme de l'expression  $(I_{ph})$  correspond au courant photogénéré.

Le terme  $I_{s1}$  traduit le courant de génération/recombinaison de porteurs au sein de la ZCE.  $I_{s1}$  est le courant de la saturation dans la ZCE. Il est souvent appelé courant de fuite, puisque le courant résultant de cette diode est un courant tunnel, ou un courant de recombinaison via un défaut dans la ZCE. Quant à  $n_1$ , c'est le facteur d'idéalité traduisant les générations/recombinaisons, il est généralement égal à 2.

Le terme  $I_{s2}$  correspond au courant de diffusion dans les zones quasi neutres (émetteur, base) de la diode PN ;  $I_{s2}$  est le courant de saturation dû à la diffusion des porteurs dans ces zones.  $n_2$  Représente le facteur d'idéalité traduisant cette diffusion, il est généralement égal à 1.

Figure I-9: Caractéristiques I(V) d'une cellule photovoltaïque sous obscurité

## I.2.3.5. Facteurs limitant le rendement d'une cellule

En pratique la conversion d'énergie lumineuse en énergie électrique dans une cellule solaire n'est pas complète. Le rendement de conversion est limité par des pertes que l'on peut scinder en deux catégories : les pertes fondamentales ou intrinsèques, liées à la nature du matériau et les pertes technologiques, liées à la technologie employée [11].

# I.1.2.4.1 Pertes fondamentales

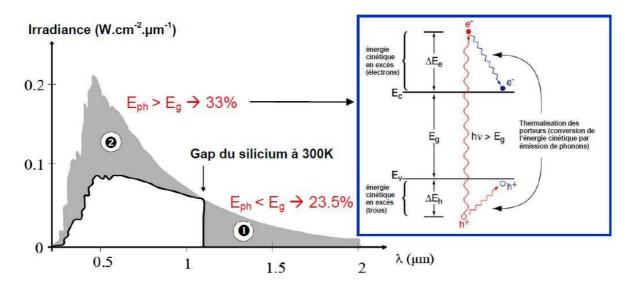

Absorption incomplète des photons: les photons possédant une énergie inférieure à celle de la bande interdite (E<Eg) ne fournissent pas assez d'énergie pour faire passer un électron de la bande de valence (BV) à la bande de conduction (BC). Ils ne contribuent donc pas à la création de paires électron-trou, leur énergie sera alors perdue. Sous éclairement AM 1.5, ces pertes sont évaluées à environ 23.5% (Zone 1 dans la figure I-10) [12].

Figure I-10: Principales pertes intrinsèques pour une cellule photovoltaïque en silicium. La zone (1) correspond aux pertes des photons de faibles énergies  $(E_{ph} < E_g)$ . (2) represente les pertes dues à l'énergie excédentaire des photons. Tandis que l'insert (à droite), illustre le phénomène de thermalisation [13]

*Excès d'énergie des photons*: les photons dont l'énergie est supérieure à celle de la bande interdite ne génèrent qu'une seule paire électron-trou. L'énergie en excès est dissipée sous forme de chaleur par le phénomène de thermalisation (insert Figure I-10). Sous éclairement AM 1.5, ces pertes représentent environ 33% sur le rendement de la cellule en Silicium.

Facteur de forme FF: Les expressions I(V) sont régies par les équations de Boltzmann faisant intervenir l'exponentielle ( $\exp \frac{qV}{kT}$ ). Par conséquent, la courbe I(V) ne peut donc avoir une forme rectangulaire. Dans le cas d'une cellule idéale, le FF ne dépasserait pas 0.89 [13–15] et vaudrait 1 si la caractéristique I(V) était rectangulaire.

Facteur de tension : la tension de circuit ouvert  $V_{OC}$  devrait correspondre à la tension correspondante à l'énergie du gap (Eg/q). En pratique, la tension d'une cellule ne correspond qu'à une fraction de la tension du gap. Cette différence est principalement due aux recombinaisons Auger, qui limitent le  $V_{OC}$  à 0,650 V pour une cellule solaire épaisse, et à 0,720 V pour une cellule de 20  $\mu$ m [11,14].

# I.1.2.4.2 Pertes technologiques:

Les pertes évoquées ci-dessus (mis à part cellules liées au facteur de forme FF) sont toutes dues à des contraintes physiques intrinsèques aux matériaux, elles ne peuvent donc être évitées dès

lors qu'il s'agit d'une cellule en silicium cristallin. Elles ramènent le rendement maximal théorique à 29 % [16].

D'autres pertes liées à la technologie de fabrication peuvent également limiter le rendement de la cellule, il est donc possible de les améliorer en optimisant le procédé de fabrication. Ces pertes sont d'ordre optiques, résistives et par recombinaisons de porteurs.

Les pertes optiques : Elles proviennent de photons qui ne sont pas absorbés par le silicium, malgré leur énergie supérieure au gap. Elles ont un effet majoritairement sur le courant de court-circuit.

- Les pertes par réflexion : Le silicium possède un indice de réfraction très élevé (n= 4 à 650 nm), ce qui entraine une réflexion importante en surface. Le coefficient de réflexion R peut être amélioré par des traitements de surface générant des réflexions multiples et par l'élaboration de la couche d'antireflet.

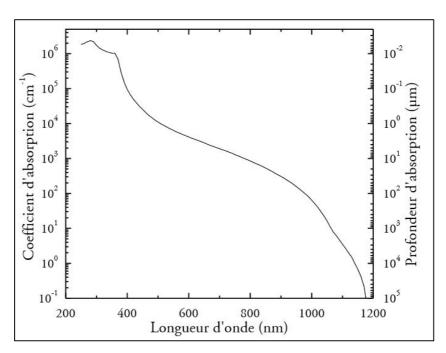

- Les pertes par défaut d'absorption : Les photons de grandes longueurs d'onde (faibles énergies) ne sont pas absorbés sur une épaisseur de l'ordre de l'épaisseur de la cellule (Figure I-11). Une partie de ces photons peuvent donc traverser la cellule sans être absorbés. Cela signifie que le silicium est partiellement transparent pour ces photons. Ce phénomène est d'autant plus important que la cellule est très fine (<100μm) ; un confinement optique (réflecteur arrière) peut alors être utilisé afin de minimiser ces pertes.

- Le taux d'ombrage: La collecte des porteurs en face avant d'une cellule commerciale standard est assurée par une grille de métal. Cette grille n'étant pas transparente, elle engendre des zones d'ombrages sur la cellule où aucun photon ne pourra pénétrer. En revanche, si les dimensions des métallisations sont trop petites, cela créera des pertes résistives, il faut donc chercher un compris.

Figure I-11: coefficient absorption et profondeur de pénétration de la lumière dans le silicium cristallin en fonction de la longueur d'onde à 300 K [13].

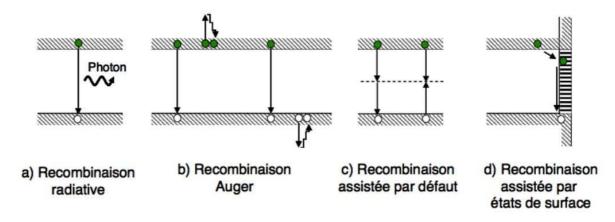

Les pertes par recombinaison une fois que la paire électron-trou est créée par absorption d'un photon, les porteurs de charges doivent migrer vers la ZCE et vers les zones de collecte de la cellule. En chemin, il peut arriver qu'un électron recombine avec un trou. Les porteurs de charges seront alors perdus, et ne participeront pas à la génération de courant. Il existe différents mécanismes de recombinaison, entrainant la recombinaison de la paire électron-trou en surface ou en volume [15].

#### Les recombinaisons en volume, on distingue 3 mécanismes principaux :

- La recombinaison radiative : Un électron de la bande de conduction se recombine avec un trou de la bande de valence pour donner lieu à une émission de photon, dont l'énergie est égale à celle du gap. Le gap du silicium étant indirect, on considère que le mécanisme de recombinaison radiative est négligeable par rapport aux autres mécanismes de recombinaison.

- La recombinaison Auger: Ce mécanisme de recombinaison met en jeu un phénomène à trois particules: un électron de la bande de conduction se recombine avec un trou de la bande de valence, transférant l'énergie excédentaire à une troisième particule, soit située dans la bande de conduction soit dans la bande de valence. L'influence de ce type de recombinaison est d'autant plus importante que le niveau de dopage est élevé [17] ou le flux incident important.

La recombinaison Shokley Read Hall (SRH): Les défauts présents dans le substrat (impuretés, dislocations) créent des niveaux d'énergies discrets dans la bande interdite [18]. Ces niveaux représentent des sites de forte recombinaison. Les électrons passent d'abord de la bande de conduction au niveau discret, puis dans la bande de valence pour s'y recombiner avec un trou. Pour cette raison, il faut éviter absolument l'apparition de défauts cristallins et des impuretés dans une cellule solaire. Les joints de grains sont également des zones de fortes recombinaisons par ce mécanisme.

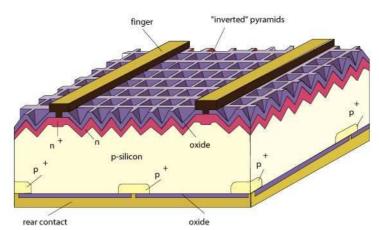

<u>Les recombinaisons en surface</u> sont également de type SRH, elles sont dues aux défauts cristallographiques présents à la surface. La discontinuité du réseau cristallin cause la présence d'un grand nombre de liaisons pendantes, qui créent de nombreux niveaux intermédiaires dans la bande interdite. Ces défauts sont passivés de deux façons : les états d'interface peuvent être en grande partie éliminés grâce à la neutralisation des liaisons pendantes par l'ajout d'une couche diélectrique de passivation qui assure la continuité des liaisons atomiques. On peut aussi, en réalisant un effet de champ, repousser les électrons du voisinage de la surface ; ceux-ci ne peuvent donc pas s'y recombiner. Ceci est réalisé par un dopage localement plus élevé (Front- ou Back Surface Field), ou bien par un diélectrique qui contient des charges fixes de charges opposées à celles des porteurs photo-générés.

Figure I-12: Représentation des différents mécanismes de recombinaisons [15].

Notons que les recombinaisons radiatives et Auger sont des recombinaisons intrinsèques au matériau, c'est-à-dire qu'elles ne dépendent pas du procédé de fabrication mais du semi-conducteur lui-même. En revanche, les recombinaisons SRH sont extrinsèques, elles dépendent de la qualité du procédé mis en jeu, elles peuvent donc être évitées ou minimisées.

Lorsque les charges se recombinent avant d'avoir atteint la ZCE, il y aura une diminution de la tension de circuit ouvert  $V_{CO}$  via le courant de saturation  $I_{s1}$ , ainsi que du courant de court-circuit  $I_{cc}$ . Lorsqu'elles ont lieu dans la ZCE, elles auront un effet sur le courant de saturation  $I_{s2}$ . Ces deux paramètres ont également un effet direct sur le facteur de forme FF [19].

Les pertes résistives : Le rendement de la cellule est également affecté par les pertes résistives affectant notamment la résistance série  $R_s$ ; celles-ci sont dues aux pertes par effet joule rencontrées lorsque le courant traverse des zones de résistivité non nulle. C'est le cas dans l'émetteur, dans la base et dans les métallisations. Le deuxième type de pertes résistives est la dissipation dans la résistance parallèle  $R_p$ , due aux courants de fuites court-circuitant la cellule. Par exemple, c'est le cas si la jonction n'est pas correctement ouverte aux bords de la cellule, ou si la métallisation traverse localement l'émetteur. La modélisation d'une cellule solaire photovoltaïque (Figure I-8) ainsi que l'expression de I(V) qui en découle (Équation I-6 dans section I.1.2.4.2), sont donc rendues possibles en tenant compte des résistances séries  $R_S$  et parallèles  $R_P$ .

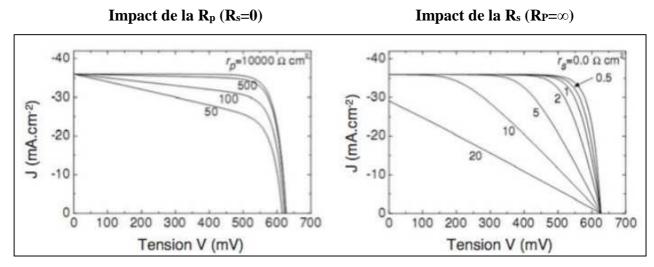

La figure I-13 permet de mettre en évidence l'influence des deux résistances RS et R<sub>P</sub> sur la caractéristique I(V) de la cellule sous éclairement.

Figure I- 13: Mise en évidence de l'influence des résistances parasites sur les caractéristiques I(V) sous éclairement [15].

## I.1.2.4.3 Réduction des pertes :

Nous venons de voir que différents mécanismes de pertes sont liés à la technologie de fabrication utilisée. Nous allons maintenant présenter les différents procédés mis en place dans les chaines de production de cellules solaires standards industrialisées permettant de limiter ces

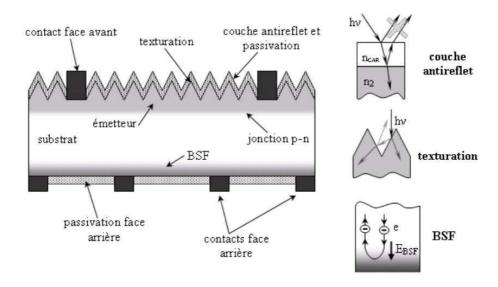

pertes. La Figure I-14 illustre l'architecture de la cellule solaire standard ainsi que les fonctions des principales étapes pour la réduction des pertes technologiques.

➤ Couche antireflet : Afin de réduire la réflexion de lumière incidente, une couche antireflet (CAR), généralement un diélectrique, est déposée sur la face avant de la cellule. son principe est basé sur les interférences destructives des faisceaux lumineux dans les couches diélectriques minces (cf Figure I-14). Dans le procédé standard le nitrure de silicium SiN<sub>x</sub> est généralement utilisé, il possède un indice moyen de 2 dans le visible et d'épaisseur voisine de 75 nm. En incidence normale, la condition d'interférences destructives se traduit par :

$$d_{car} = \frac{(2N+1)\lambda}{4n_{car}} \tag{I-7}$$

Où  $d_{car}$  est l'épaisseur de la couche antireflet, N un nombre entier positif,  $\lambda$  la longueur d'onde considérée et  $n_{car}$  son indice optique. Cette expression correspond à la condition de d'interférences destructives pour laquelle on obtient une annulation des faisceaux réfléchis à l'interface air/CAR et CAR/semi-conducteur.

Différentes CAR sont utilisées dans le photovoltaïque, à savoir SiN<sub>x</sub>, TiO<sub>2</sub>, SiO<sub>2</sub>, ZnS, etc,... [13]. Dans les technologies des cellules à très haut rendement, un e double CAR (deux diélectriques différents) est utilisée.

Fexturation de surface : Afin de minimiser la réflectivité de la lumière sur la surface de la cellule, il convient de créer des reliefs micrométriques, généralement en forme de pyramides si le silicium est de type monocristallin. La longueur d'onde de la lumière incidente étant inférieure aux structures réalisées, les rayons incidents suivent les lois de l'optique géométrique comme schématisé sur la Figure I-14. Le procédé de texturation de surface le plus utilisé pour le silicium monocristallin est l'attaque chimique à l'hydroxyde de potassium (KOH), créant des rugosités de formes pyramidales et de dimensions caractéristiques allant de 5 à 10 μm. Tandis que pour le silicium polycristallin un mélange d'acide est généralement utilisé pour la texturation de surface.

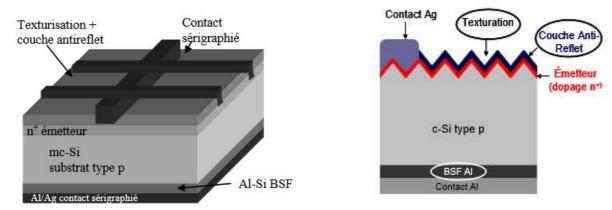

Figure I-14: Structure de la cellule photovoltaïque standard (à gauche). Les insertions (à droite) schématisent les rôles respectifs de la couche antireflet, la texturation et le BSF [15].

➤ Le champ de surface arrière (BSF): Le champ électrique arrière BSF (Back Surface Field) consiste à créer une barrière de potentiel (par exemple, une jonction P+/P) sur la face arrière de la cellule pour assurer une passivation. La barrière de potentiel, générée par la différence de niveau de dopage entre la base et le BSF tend à confiner les porteurs minoritaires dans la base. Les porteurs minoritaires sont ainsi tenus à l'écart de la face arrière où leur vitesse recombinaison est très élevée.

ightharpoonup Passivation de surface : la surface des semi-conducteurs est le siège d'une densité importante de défauts (liaisons pendantes, impuretés, etc..) induisant des pertes considérables liées aux phénomènes de recombinaisons de surfaces. La passivation de surface consiste à améliorer les qualités électroniques de la surface et du volume du matériau en neutralisant les effets de ces défauts électriquement actifs. Différentes couches de passivation sont utilisées dans le photovoltaïque ; les plus utilisées sont l'oxyde thermique de (SiO<sub>2</sub>) et le nitrure de silicium hydrogéné (SiN<sub>x</sub> :H).

## I.2.4 Les différentes filières de fabrication de plaquettes de silicium avec sciage (kerfloss)

#### Le silicium cristallin

Le silicium cristallin reste aujourd'hui le matériau le plus utilisé dans l'industrie du photovoltaïque. En effet, les technologies cristallines représentent plus de 90% du marché mondial de modules photovoltaïques. Cependant, plus de 95% des plaquettes de silicium cristallin sont fabriquées par tirage et découpe de lingots. Cette méthode engendre non

seulement une perte considérable de matière première (environ 50%) [20], mais les coûts de production et énergétiques restent colossaux. On distingue le procédé Czochralski (Cz) ou fusion de zone (Fz) produisant des plaquettes de silicium monocristallin et le procédé de solidification directionnelle pour la production de plaquettes de silicium multicristallin.

#### I.2.4.1 Le silicium monocristallin:

Les procédés Czochralski (Cz) et de fusion de Zone (Fz) permettent d'obtenir des plaquettes de silicium monocristallin de très haute pureté.

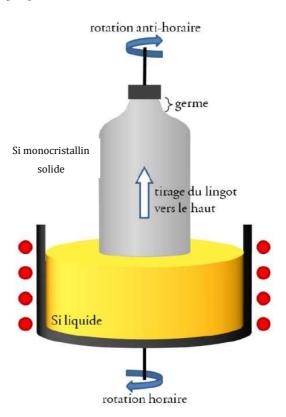

➤ Le procédé Cz, schématisé sur la figure I-15, découvert en 1916 par le scientifique polonais Jan Czochralski. Il consiste à plonger un germe froid de silicium monocristallin dans un bain de silicium purifié légèrement surfondu dans un creuset en quartz [21], le silicium du bain est épitaxié sur ce germe en reproduisant sa structure monocristalline. Le lingot est alors tiré verticalement vers le haut avec une rotation simultanée et dans le sens opposé par rapport au creuset. La vitesse de tirage dépend du diamètre du lingot, et varie entre 40 et 10 cm/h pour des diamètres de 20 à 140 mm [21].

Figure I-15: Procédé Czochralski (Cz) de croissance de lingot

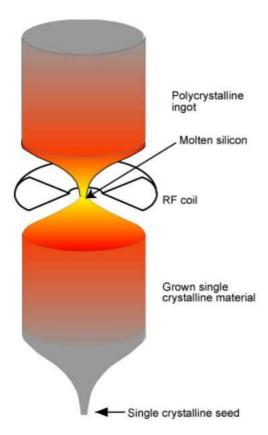

➤ Le procédé fusion de zone (Fz), schématisé sur la figure I-16, consiste quant à lui, à faire fondre localement un lingot cylindrique de silicium multicristallin très pur à l'aide d'un chauffage par induction, un monocristal est ainsi tiré à partir de la zone fondue. Contrairement au procédé Cz, le procédé Fz présente l'intérêt de ne pas utiliser de creuset, qui est une source de contamination en oxygène, carbone ...etc pouvant dégrader les performances des cellules solaires. Cependant son coût reste très élevé pour une production de cellules solaires à grande échelle.

Figure I-16: Procédé Fz de croissance de lingots. (Source : pveducation.org)

Ces procédés permettent d'obtenir des lingots de section circulaire, dotés d'excellentes qualités électroniques avec un potentiel de rendements de conversions photovoltaïques élevés. Les flancs des lingots sont ensuite découpés pour obtenir une forme pseudo-carrée permettant une meilleure compaction des cellules solaire dans les modules. Cette étape de découpe et de sciage des lingots en plaquettes, engendre d'ailleurs des pertes considérables, environ 50 % du matériau.

### I.2.4.2 Le silicium multicristallin:

Le silicium multicristallin est fabriqué principalement à partir de sources de matériaux moins raffinés, ou à partir de rebuts de l'industrie de la micro-électronique. Il existe différents procédés permettant d'obtenir le silicium multicristallin parmi lesquels on distingue les différentes techniques de solidifications directionnelles et la technologie tirage de rubans. Cette dernière sera présentée dans la section : fabrication de plaquettes sans sciage.

#### La solidification directionnelle:

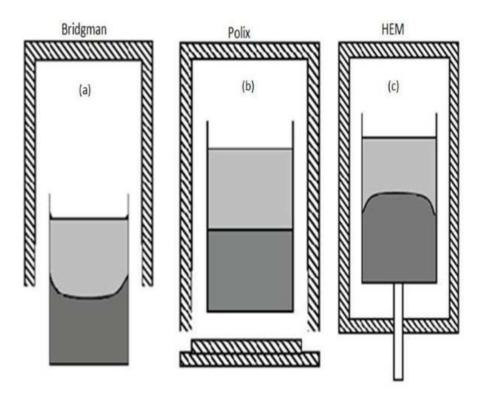

La solidification directionnelle est la méthode la plus utilisée pour la fabrication de plaquettes de silicium (multicristallin). Son principe est montré sur la figure I-17. Elle consiste à réaliser une solidification dirigée du silicium fondu contenu dans un creuset, dont les parois sont généralement constituées de silice. La solidification peut durer jusqu'à 50 heures pour des lingots d'une masse comprise entre 300 et 450 kg. Il existe différentes méthodes de solidification directionnelle telles que : la méthode de croissance Bridgman dans laquelle, le creuset se déplace dans le four à gradient de température (figure I-17. a). Dans la méthode et POLIX et HEM (Heat Extraction Method) [22], le creuset reste fixe (silicium fondu par induction) et un gradient de température s'établit entre le haut et le fond. La méthode POLIX et HEM se différencient selon la manière d'extraire la chaleur. Dans la méthode HEM, l'extraction de la chaleur se réalise localement en bas du creuset figure I-17. b et c). Ce qui permet de garder une structure cristallographique homogène. On distingue également le procédé EMC (Electromagnetic Casting), une technique de coulée continue électromagnétique en creuset froid. Elle consiste à verser du silicium liquide à débit constant dans une lingotière via un répartiteur. Le silicium refroidit est ensuite tiré vers le bas de l'installation à l'aide d'un jeu de rouleaux. Ce procédé a été développé par le laboratoire SIMAP-EPM à Grenoble. L'entreprise EMIX, aujourd'hui filiale du groupe FerroAtlántica, fabrique des plaquettes de silicium par cette technique.

Figure I-17: les principales méthodes de solidification directionnelle [21].

Les procédés de solidifications directionnelles présentent l'intérêt d'intégrer le phénomène de ségrégation, conduisant à une accumulation de la plupart des impuretés métalliques (fer, chrome et nickel...) en haut du lingot solidifié.

### I.2.4.3. Les techniques de sciage

Les extrémités des lingots obtenus sont éliminées par sciage car elles représentent un siège d'accumulation des impuretés. Les lingots sont ensuite découpés verticalement en briques de section carrée, correspondant à la surface de la cellule finale. Les briques sont sciées en fines tranches de silicium appelées *wafer*s. Nous décrirons ci-dessous les deux principales techniques de sciages permettant d'obtenir ces wafers.

# A- Le sciage annulaire

La technique de sciage annulaire, ou ID (*Inner Diameter*) pour « *scie à diamètre intérieur* », est la technique la plus ancienne utilisée industriellement. Son principe est représenté sur la figure I-18. La scie est constituée d'une fine lame d'acier revêtue par un abrasif (diamant) sur le tranchant interne. Elle est maintenue par un dispositif permettant de l'entrainer en rotation.

Le bloc de silicium à scier est ensuite placé au centre de la lame et remonte à une faible vitesse. Une plaquette de silicium (wafer) est ainsi obtenue.

Figure I-18: principe de sciage annulaire (scie à diamètre intérieur) [23]

Cette technique permet d'obtenir des plaquettes de quelques dixièmes de millimètres d'épaisseur avec un bon état de surface et des problèmes de casses assez réduits. En revanche, les plaquettes sont sciées une à une et sont assez épaisses. Compte-tenu de l'épaisseur de la plaquette obtenue (environ 300 µm), le principal problème reste la perte de matière, aussi appelée *kerf loss*, estimée à environ 310 à 350 µm. En raison de la forte perte de matière première, et la faible cadence de production, cette technique a été abandonnée afin de s'orienter vers la technique de sciage à fil [23].

### B- Le sciage à fils

Afin de minimiser les pertes liées à l'utilisation de la technique de sciage annulaire (scie à diamètre intérieur) et d'augmenter la productivité, les recherches se sont orientées vers la technique de sciage à fil. Cette technique a été introduite pour les applications photovoltaïque au milieu des années 80 [24].

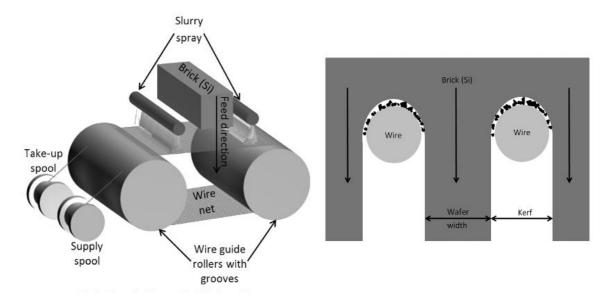

Le principe de cette technique est présenté sur la figure I-19. Un fil d'acier est déroulé d'une bobine émettrice et tiré sur deux rouleaux de guidage au minimum. Les rouleaux de guidage possèdent des rainures disposées à distance constante, correspondant à l'épaisseur désirée de la plaquette. Le fil traverse chacune des rainures du rouleau pour former un réseau complet de fil ou nappe. Un fil d'une longueur allant jusqu'à 800 km est de nouveau enroulé sur une bobine.

Une suspension généralement composé d'un mélange de carbure de silicium (SiC) et de polyéthylène glycol (mélange appelé Slurry), est appliqué par des buses sur le réseau de fils en déplacement et génère une abrasion mécanique. La brique de silicium, collée sur un support, est entrainée dans le réseau de fils recouvert de suspension. Les fils, dont le diamètre se situe entre 120 et 140 µm, se déplaçant à une vitesse de 10 à 15 m/s dans la brique, permettant ainsi de la scier en une seule étape, jusqu'à 3000 plaquettes environs. La découpe de la brique de silicium en plaquette de 160 à 200 µm dure 6 heures environs [25]. Les grains d'abrasif (SiC) sont emprisonnés entre le fil et la brique de silicium, ce qui engendre des pertes de fragments de matière. Ces fragments seront ensuite mélangés à la solution de découpe et donc perdus.

Figure I-19: Schéma du sciage à fils avec abrasifs. a) schéma du principe de sciage. b) illustration du sciage de plaquettes par le passage de la brique de silicium à travers les fils d'acier revêtus d'abrasifs [26].

La technique de sciage à fils avec Slurry génère environ 50% de perte de matériau. Cette perte résulte essentiellement de l'épaisseur du fil et de la suspension lors du sciage. En effet, l'étage de sciage représente un élément déterminant dans le coût de fabrication de la cellule solaire photovoltaïque. Les coûts de fabrication sont d'autant plus bas que l'épaisseur des plaquettes est fine et la perte de matériau faible.

#### I.2.5 Les technologies de fabrication de plaquette sans sciage (Kefless)

# A- Les technologies rubans :

Nous présentons les procédés de fabrication de plaquettes de silicium par tirage de rubans les plus connus. Les procédés silicium ruban sont très séduisants sur le plan technologique. Ils combinent l'étape de cristallisation et de mise en forme du silicium, et présentent l'avantage de minimiser la perte de matière. La consommation du silicium est également divisée par deux (8 g par  $W_c$  contre 16 g par  $W_c$ ). La technologie ruban consiste à produire directement des plaquettes minces (< 200  $\mu$ m) de silicium multicristallin, à partir d'un bain de silicium fondu, par capillarité ou par croissance sur un film ou une maille de carbone. Suivant la direction, nous rencontrons essentiellement deux types de cristallisations : la cristallisation verticale, où les procédés EFG (Edge-defined Film-Fed Growth) et SR (String Ribbon) sont les deux exemples représentatifs ; et la cristallisation horizontale, par exemple, les technologies RGS (Ribbon Growth on Substrate) et CDS (Crystallization on Dipped Substrate).

#### 1- la cristallisation verticale:

Dans ce type de cristallisation, la chaleur du silicium fondu est évacuée par conduction à travers la partie déjà solidifiée de l'échantillon. Le ruban de silicium est tiré de bas en haut à partir d'une réserve de silicium fondu. L'interface liquide-solide est perpendiculaire à la direction de tirage du ruban. Ce type de cristallisation permet d'obtenir de longs grains de quelques millimètres dans la direction du tirage.

### 1.1- La technologie EFG (Edge-defined Film-Fed Growth)

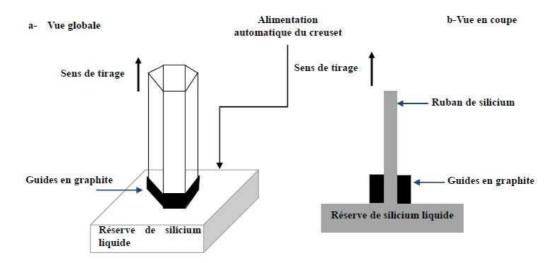

Cette technologie, dont le principe est présenté sur la figure I-20, a été développée par Mobil Tyco et RWE Solar [27,28]. Le silicium est fondu dans un creuset en graphite continuellement rempli durant toute l'opération. Le silicium est alors tiré, de bas en haut à partir du creuset. La forme finale de la plaquette est régie par les forces capillaires de deux guides en graphite (figure I-20b). La vitesse de tirage est comprise entre 1 et 2 cm/min [27]. Afin d'augmenter la cadence de production, un tube octogonal de silicium est tiré, 8 plaquettes sont ainsi obtenues à la fois figure I-20a. Un laser de haute puissance est ensuite utilisé pour couper l'octogone en plaquettes avec les dimensions désirées. Des grains de quelques millimètres de largueur sont ainsi obtenus, et ont la particularité d'être plus grands dans le sens de la longueur. G. Hahn et P. Geiger ont démontré un rendement record de 16,7% sur une cellule de 4 cm² avec la technologie EFG [29]. Ce rendement record a été obtenu grâce à l'utilisation des techniques non industrielles de

lithographies et d'évaporations pour la réalisation des contacts. RWE Schott Solar commercialise des plaquettes de silicium multicristallin produites par la technique EFG [10, 11,47].

Figure I-20: La technologie EFG. a- vue globale du tirage du tube octogonal. b- Vue en coupe [20].

# 1.2- La technologie SR (String Ribbon)

La technologie SR a été introduite aux USA il y a plus de 10 ans par Evergreen. Une unité de production exploitant la technologie SR a été installée en Allemagne par Ever-Q ces dernières années. Ever-Q était une entité issue d'un partenariat associant Q-cells, Evergreen Solar et Renewable Energy Corporation (REC). Cette entité est devenue par la suite SOVELLO en 2005. Ce dernier a continué de produire des plaquettes par la technique SR avant de faire faillite en 2012.

La figure I-21 schématise le principe de la technique SR. Comme dans la technique EFG, le silicium est fondu dans un creuset en graphite continuellement rempli pendant toute l'opération. Le phénomène physique est basé sur la tension de surface. Deux fils résistant à de très hautes températures sont transportés à travers le silicium fondu. Le silicium cristallise alors de bas en haut entre les deux fils. La vitesse de tirage est de l'ordre de 1 cm/min [27]. La taille des grains peut atteindre des valeurs de l'ordre du centimètre.

Figure I-21: La technologie String Ribbon (SR) [20].

# 1.3- La technologie RST de Solarforce $^{TM}$

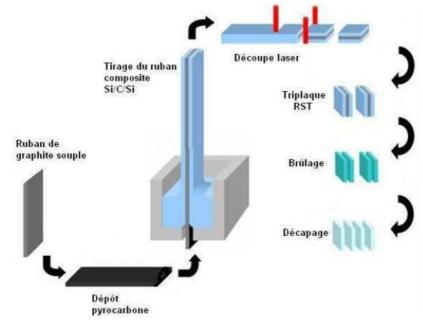

Le principe du procédé RST de Solarforce<sup>TM</sup> est présenté sur la figure I-22. Un ruban de graphite souple est utilisé comme substrat. Ce ruban, après avoir été découpé, purifié et recouvert d'une pellicule de pyrocarbone, passe à travers un creuset contenant le silicium fondu. Le silicium cristallise le long du ruban de carbone à la sortie du creuset. Les rubans silicium-carbone-silicium obtenus sont alors découpés par laser, et le carbone est éliminé par brulage sous oxygène. Des rubans minces (60 – 120 μm) d'épaisseur sont ainsi obtenus. Un rendement de conversion photovoltaïque supérieur à 14% a été démontré [30].

Figure I-22: Principe de la technologie SRT de Solarforce<sup>TM</sup>

#### 2- la cristallisation horizontale :

Dans ce type de cristallisation, le ruban de silicium est tiré sur un substrat étranger, à partir d'une réserve de silicium fondu. Une partie de la chaleur se dissipe dans le substrat étranger, et le silicium en contact cristallise instantanément. Des grains colonnaires, de quelques centaines de micromètres, sont créés à partir du substrat [20].

### 2.1- La technologie RGS (Ribbon Growth on Substrate)

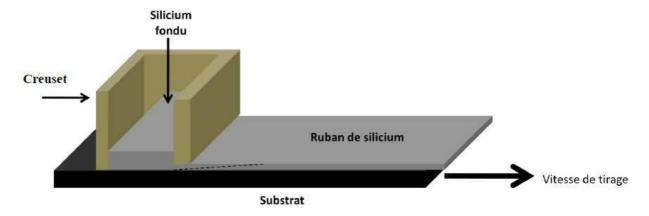

La méthode RGS, développée par Bayer AG dans les années 90, a fait en 2005, l'objet d'une coopération entre ECN, Deutsche Solar Energy et Sunergy Investco. Le principe de la méthode RGS est montré sur la Figure I-22 [20].

Figure I-22: La technologie RGS (Ribbon growth on Substrate) [21].

Le substrat est maintenu à une température en dessous de celle de fusion. Il se déplace à grande vitesse sous un creuset rempli de silicium fondu. L'échantillon est formé à la sortie du creuset. Celui-ci est alors refroidi par le substrat et se détache automatiquement grâce à la différence de coefficients de dilation thermique entre le silicium et le substrat. La vitesse de tirage peut atteindre des valeurs d'environ 600 cm/min [31]. La taille des grains obtenus par cette technique est de l'ordre de quelques centaines de micromètres et peut atteindre le millimètre. En utilisant le procédé standard de sérigraphie (contacts métalliques), le plus haut rendement obtenu avec les cellules élaborées à partir de cette technique est autour de 13,1% [32].

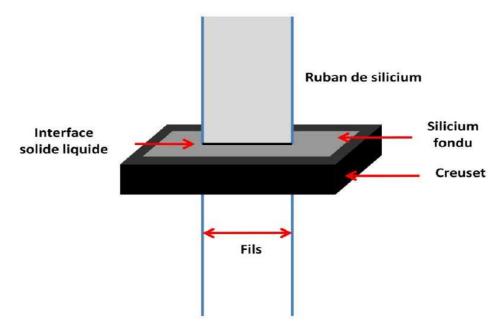

### 2.2- La technologie CDS (Crystallization on Dipped Substrate)

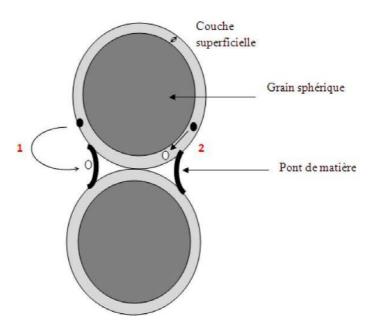

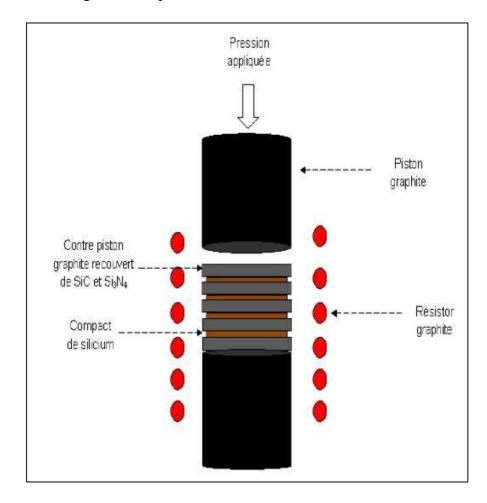

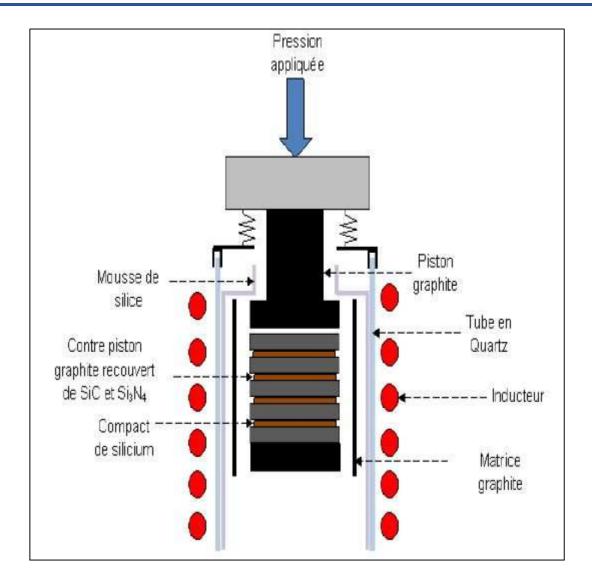

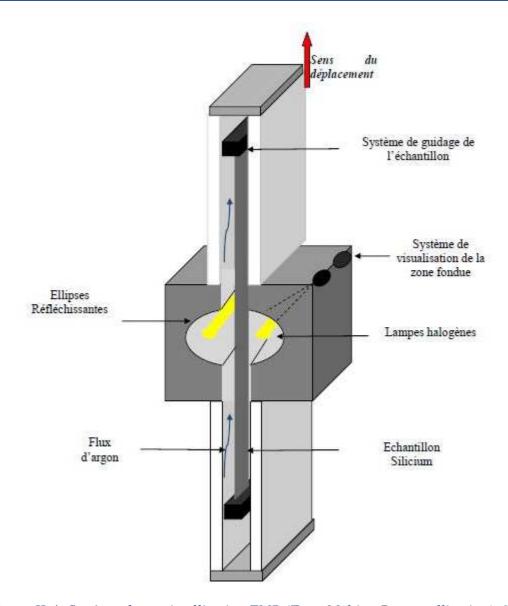

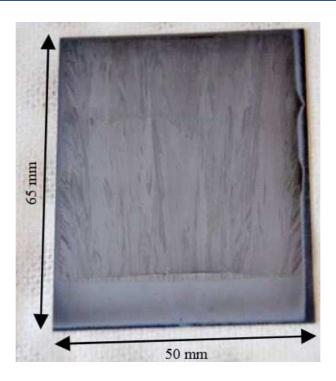

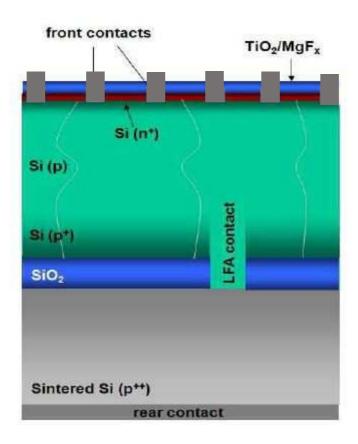

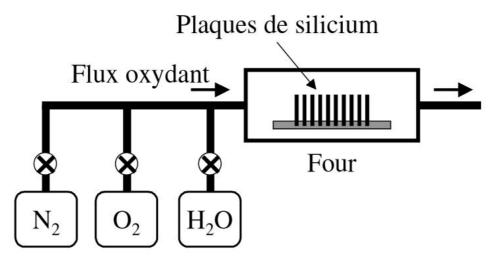

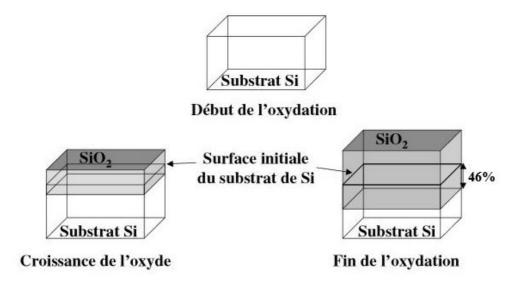

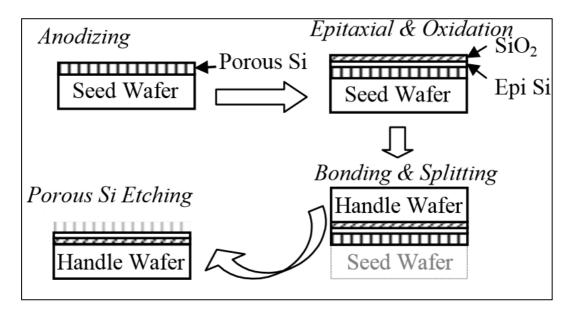

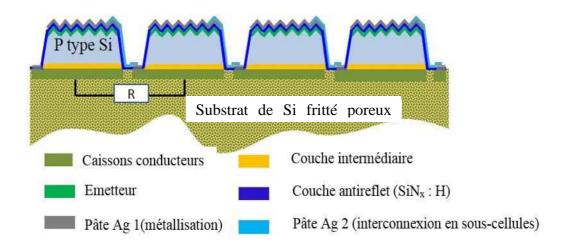

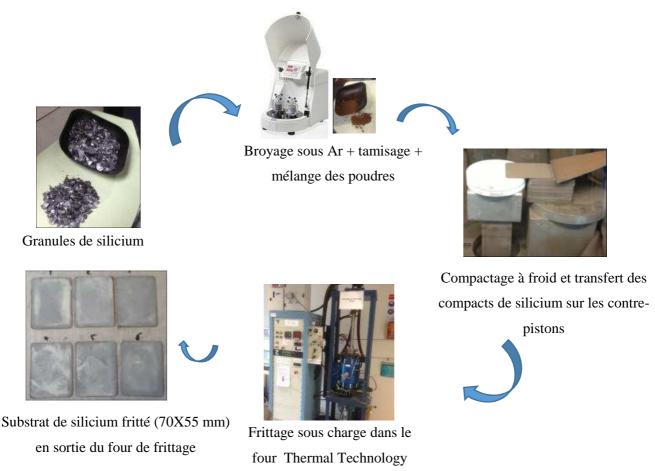

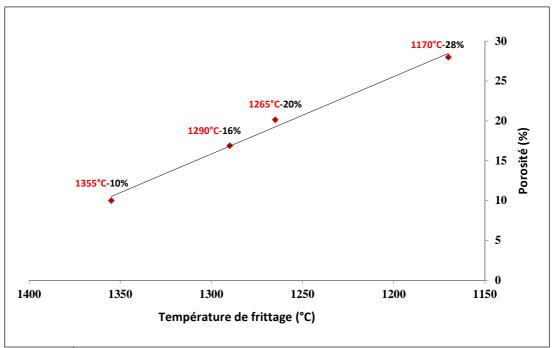

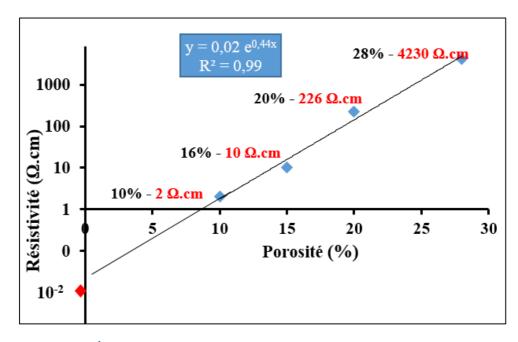

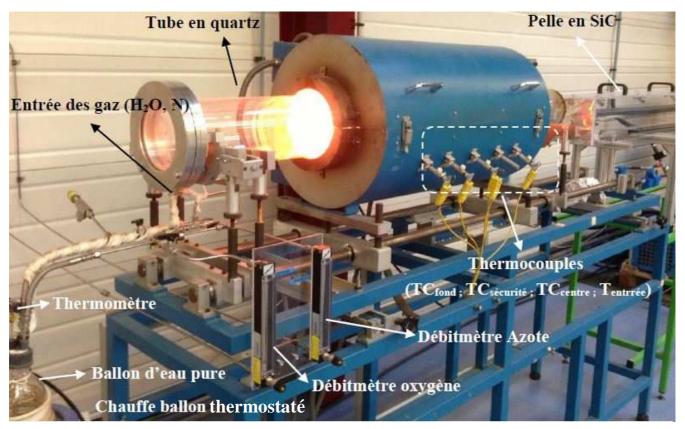

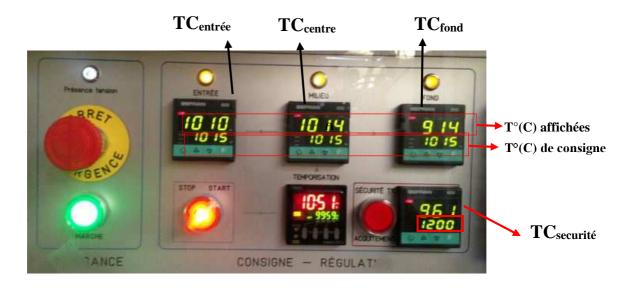

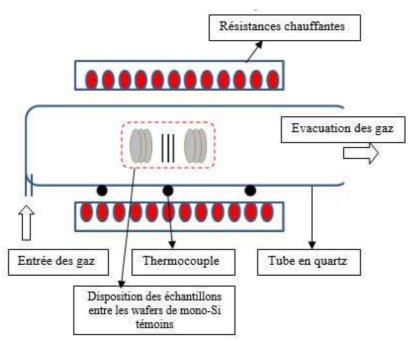

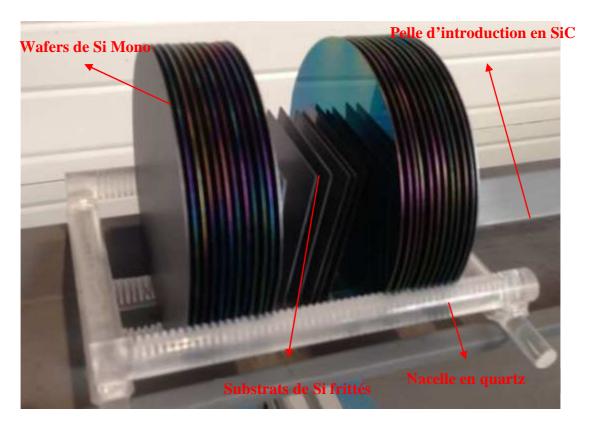

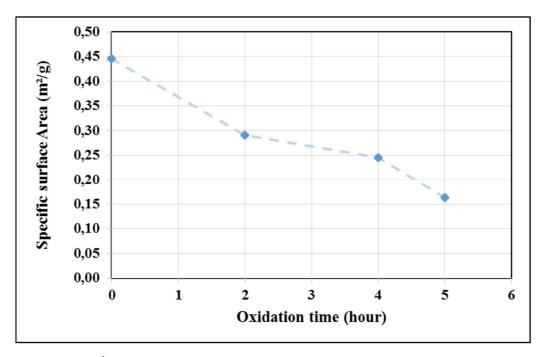

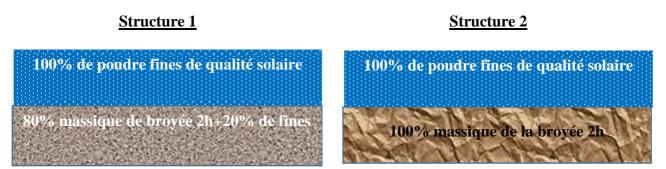

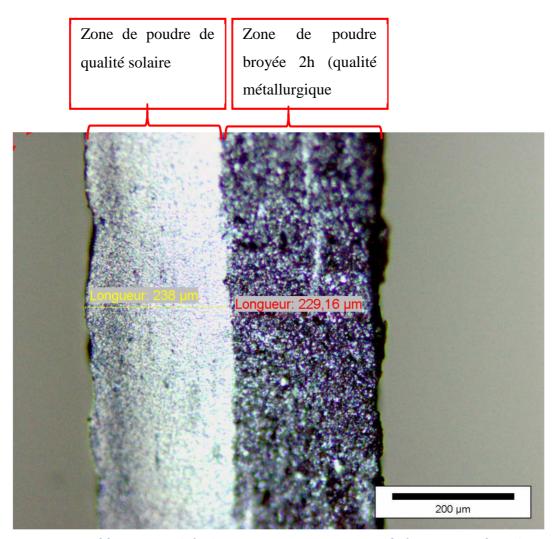

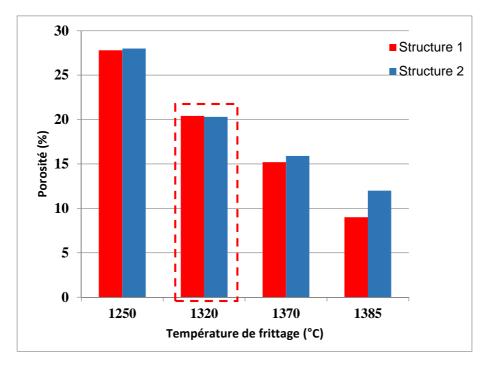

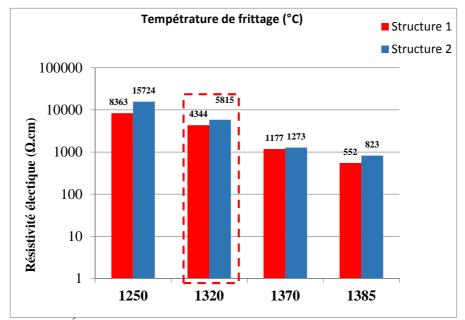

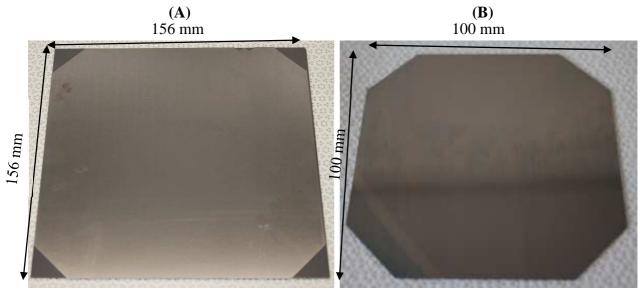

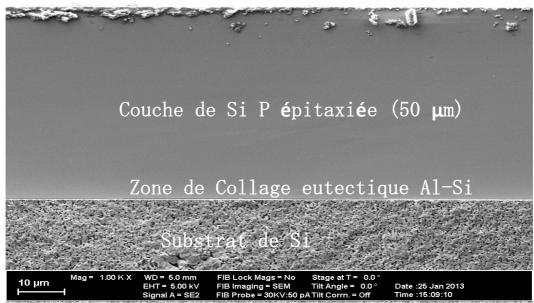

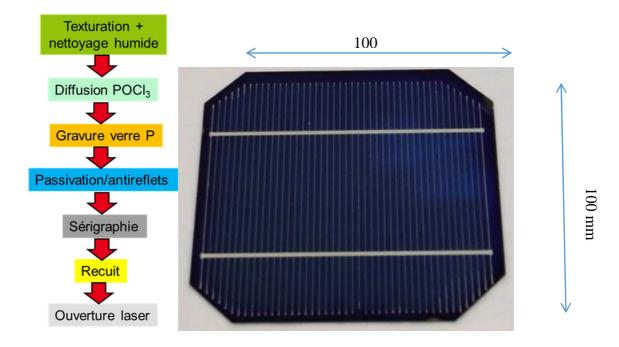

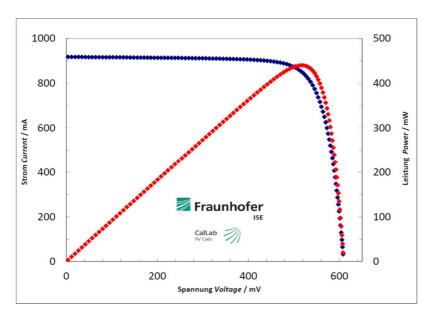

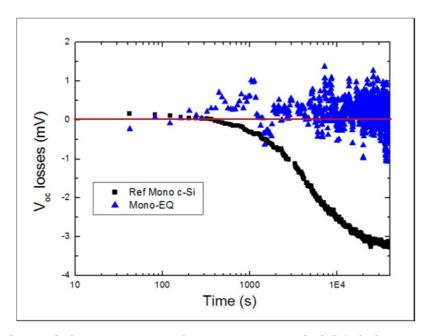

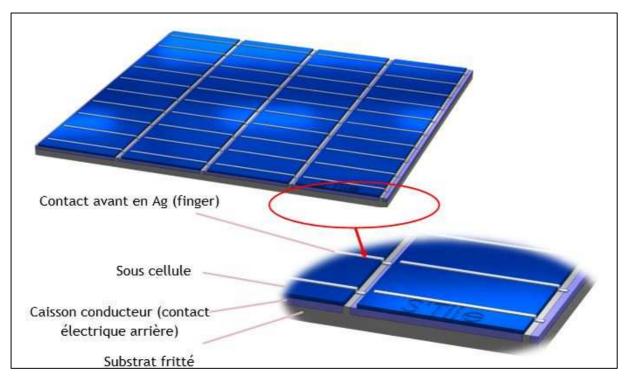

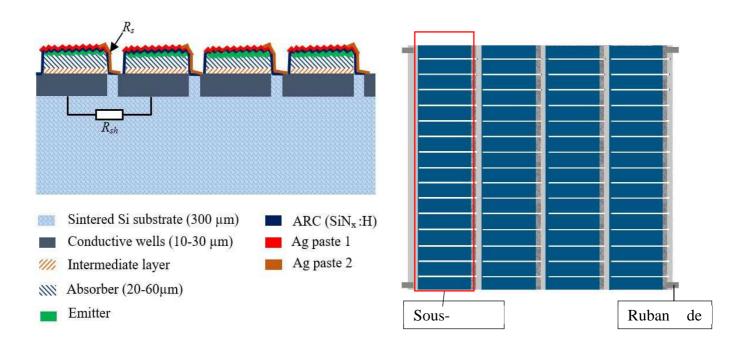

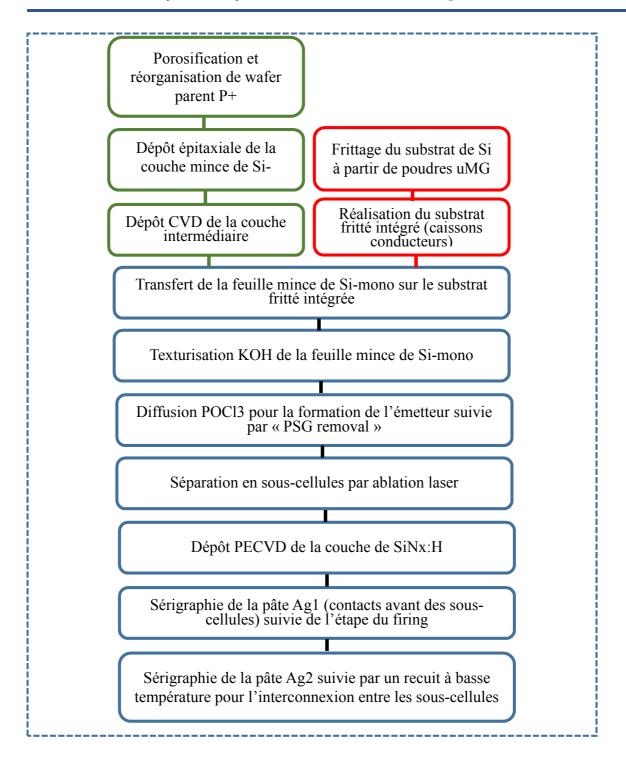

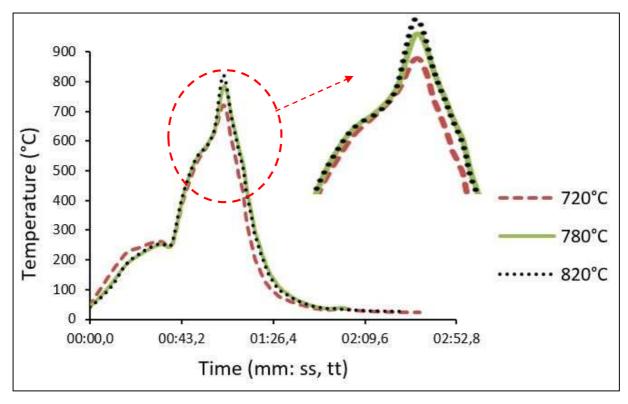

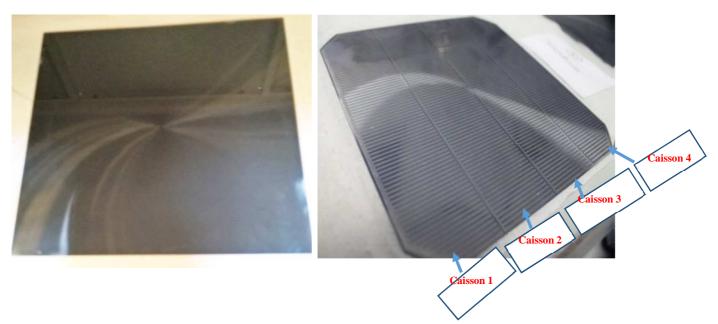

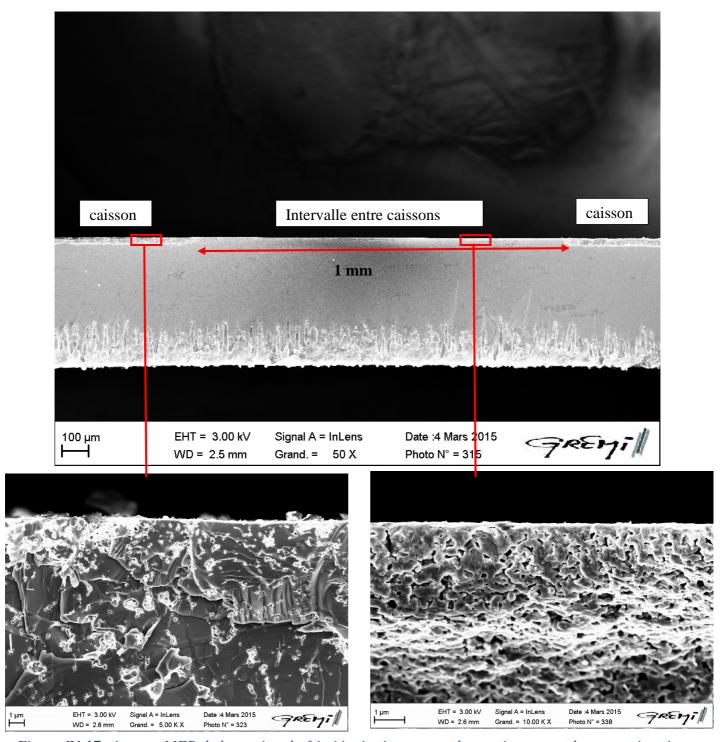

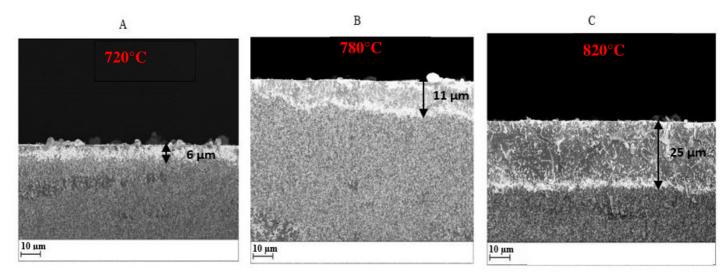

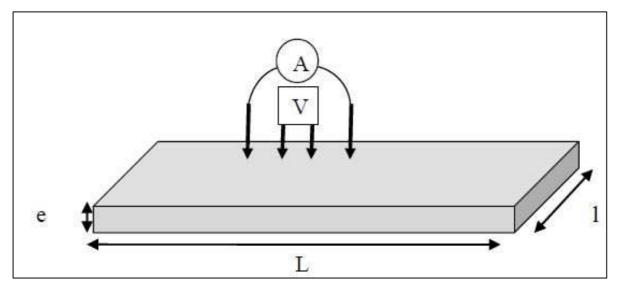

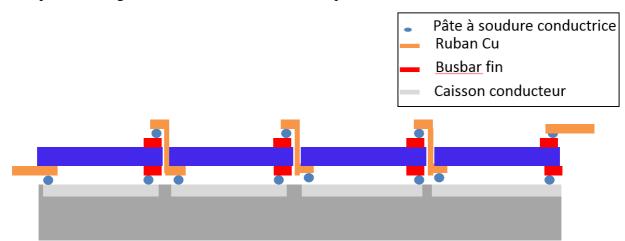

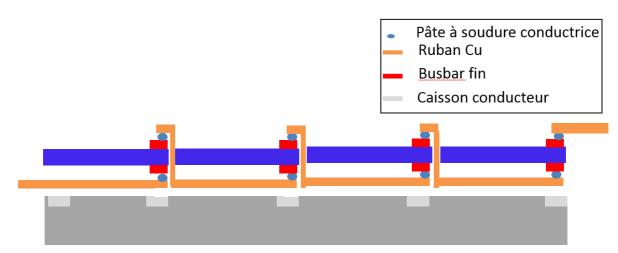

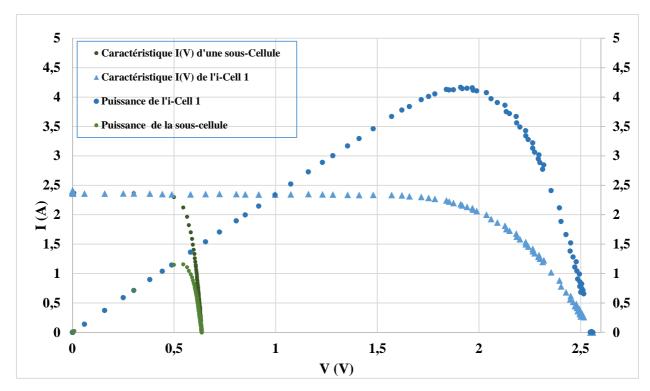

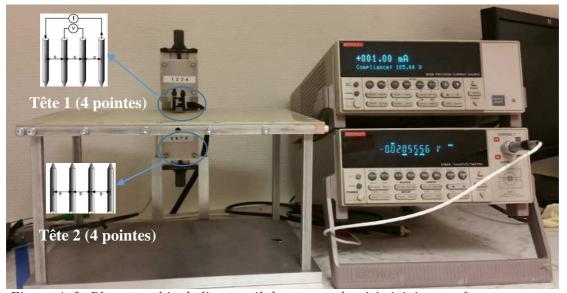

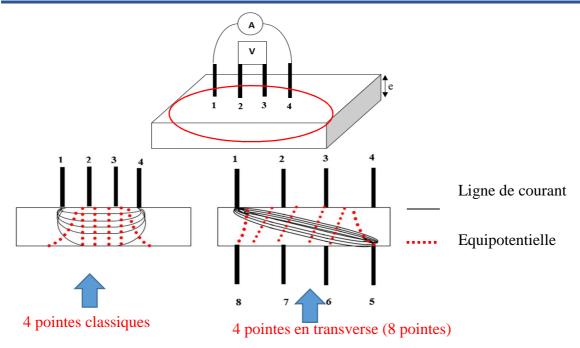

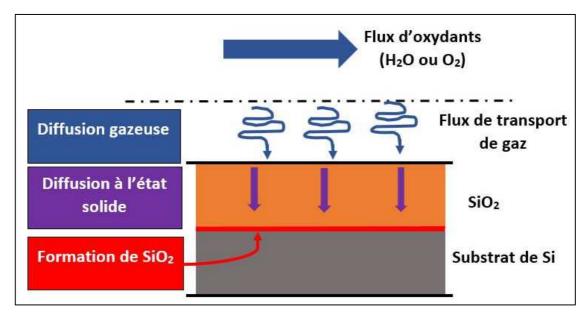

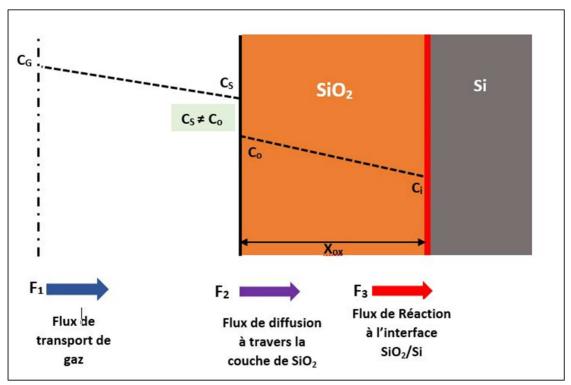

On peut recenser d'autres technologies basées sur le principe de cristallisation horizontale, parmi elles, on rencontre par exemple, la méthode CDS (Crystallization on Dipped Substrate). Cette dernière a été développée par SHARP depuis 1997 [20]. Le principe consiste à plonger