# Power amplifier design for 5G applications in 28nm FD-SOI technology

Florent Torres

### ▶ To cite this version:

Florent Torres. Power amplifier design for 5G applications in 28nm FD-SOI technology. Electronics. Université de Bordeaux, 2018. English. NNT: 2018BORD0064. tel-02057987

### HAL Id: tel-02057987 https://theses.hal.science/tel-02057987

Submitted on 5 Mar 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE PRÉSENTÉE

POUR OBTENIR LE GRADE DE

# DOCTEUR DE L'UNIVERSITÉ DE BORDEAUX

# ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGÉNIEUR SPÉCIALITÉ ÉLECTRONIQUE

### Par Florent TORRES

# Power Amplifier Design for 5G Applications in 28nm FD-SOI Technology

Sous la direction de : Eric KERHERVE & Andreia CATHELIN

Soutenue le 18 mai 2018

### Membres du jury :

| M.   | Raymond QUERE      | Professeur                       | Université de Limoges, France       | Président             |

|------|--------------------|----------------------------------|-------------------------------------|-----------------------|

| M.   | Andreas KAISER     | Directeur de recherche           | ISEN, Lille, France                 | Rapporteur            |

| M.   | Piet WAMBACQ       | Professeur                       | IMEC, Brussel, Belgium              | Rapporteur            |

| M.   | Sven MATTISSON     | Dr., Design Senior<br>Expert     | Ericsson, Lund, Sweden              | Examinateur           |

| Mme. | Nathalie DELTIMPLE | Maître de<br>Conférence HDR      | Bordeaux INP, France                | Examinateur           |

| M.   | Eric KERHERVE      | Professeur                       | Bordeaux INP, France                | Directeur de thèse    |

| Mme. | Andreia CATHELIN   | Dr. HDR, Design<br>Senior Expert | STMicroelectronics, Crolles, France | Co-Directeur de thèse |

### Titre: Développement d'un amplificateur de puissance pour des applications 5G en technologie 28nm FD-SOI

Résumé: Le futur réseau mobile 5G est prévu pour être déployé à partir de 2020, dans un contexte d'évolution exponentielle du marché de la téléphonie mobile et du volume de données échangées. La 5G servira de levier à des applications révolutionnaires qui permettront l'émergence du monde connecté. Dans ce but, plusieurs spécifications pour le réseau sont attendues même si aucun standard n'est encore défini et notamment une faible latence, une consommation d'énergie réduite et un haut débit de données. Les bandes de fréquences traditionnellement utilisées dans les réseaux mobiles ne permettront pas d'atteindre les performances visées et plusieurs bandes de fréquences millimétriques sont à l'étude pour créer un spectre complémentaire. Cependant, ces bandes de fréquence millimétriques souffrent d'une forte atténuation dans l'air et dans les matériaux de construction. Plusieurs techniques vont être implémentées pour outrepasser ces limitations dans les zones urbaines denses comme le backhauling, FD-MIMO et beamforming phased array. Ces techniques entraînent l'utilisation d'un grand nombre de transmetteurs dans les stations de bases et dans les dispositifs de l'utilisateur final. La technologie CMOS offre d'indéniables avantages pour ce marché de masse tandis que la technologie FD-SOI offre des performances et fonctionnalités additionnelles. L'amplificateur de puissance est le bloc le plus critique à concevoir dans un transmetteur et consomme le plus d'énergie. Afin d'adresser les challenges de la 5G, plusieurs spécifications concernant la puissance consommée, la linéarité et le rendement sont attendues. Les variations de l'environnement dans les beamforming phased array et le contexte industriel nécessitent des topologies robustes alors qu'une reconfigurabilité au niveau de l'amplificateur de puissance est bénéfique dans le cas de circuits adaptatifs. Cette thèse adresse ces challenges en explorant la conception d'un amplificateur de puissance reconfigurable et robuste pour des applications 5G en intégrant des techniques de design spécifiques et en mettant en avant les avantages de la technologie 28nm FD-SOI pour la reconfigurabilité.

#### Title: Design of power amplifier for 5G applications in 28nm FD-SOI technology

Abstract: The 5G future mobile network is planned to be deployed from 2020, in a context of exponential mobile market and exchanged data volume evolution. The 5G will leverage revolutionary applications for the advent of the connected world. For this purpose, several network specifications are expected notably low latency, reduced power consumption and high data-rates even if no standard is yet defined. The frequency bands traditionally used for mobile networks will not permit the needed performances and several mmW frequency bands are under study to create a complementary frequency spectrum. However, these mmW frequency bands suffer from large attenuation in building material and in free-space. Therefore, several techniques will be implemented to tackle these limitations in dense urban areas like backhauling, FD-MIMO and beamforming phased array. This is leading to a large number of transceivers for base stations and end-user devices. CMOS technology offers undeniable advantages for this mass market while FD-SOI technology offers additional features and performances. The power amplifier is the most critical block to design in a transceiver and is also the most power consuming. To address the 5G challenges, several specifications concerning power consumption, linearity and efficiency are expected. The environment variations in beamforming phased array and the industrial context drive the need for robust topologies while power amplifier reconfigurability is benefic in a context of adaptive circuits. This thesis addresses these challenges by exploring the conception of a robust and reconfigurable power amplifier targeting 5G applications while integrating specific design techniques and taking advantage of 28nm FD-SOI CMOS technology features for reconfigurability purposes.

#### Unité de recherche

Université de Bordeaux, Laboratoire IMS, CNRS UMR 5218, Bordeaux INP, 351 cours de la Libération, 33405 Talence

### **Acknowledgements**

I would like to start this manuscript by acknowledging the people that had an important role and positive impact during this PhD.

First, I would like to express my gratitude to my supervisors, Eric Kerhervé from IMS Laboratory and Andreia Cathelin from STMicroelectronics. Their precious help, support, technical knowledge and trust have been crucial for me to complete this PhD.

This thesis has been realized in the frame of the joint laboratory between STMicroelectronics, Crolles, and the IMS Laboratory, Bordeaux. During these 3 years I met and collaborated with many amazing people.

I would like to thank all the members, permanent and students, from the Conception group at the IMS Laboratory and particularly from the CSH team managed by Nathalie Deltimple. It has been a pleasure to work with all of you and I am glad to have now such good friends. I will not provide a list of names here, it would definitely be too long!

I would also like to thank Simone Dang Van, Aurore Bousseau and Fabienne Prevot for their support in logistic and administrative related questions. A special thanks to Magali De Matos for her technical help during the circuit measurements.

A part of this thesis has also been realized in Crolles and I had the pleasure to meet very nice and interesting people. Many thanks to all the PhD student that I met there for the good time in Savoy! Of course, special mention to my amazing flatmates for the great memories!

I am also grateful to Philippe Cathelin and all the people I collaborated with from STMicroelectronics for the technical discussions. Thanks to Pascale Maillet-Condoz for her administrative support.

Of course, during these years, the support of my relatives has been extremely important. I will never be grateful enough for all the support I received from my family and friends. All of this wouldn't have been possible without you!

I would like to specially thanks Sophie, who shares my life, for her unconditional support and understanding during these 3 years. Many thanks to your family also. And finally, thank you for following me in Scandinavia for an exciting new chapter of our life...

*In memory of my Dad,*

# **Table of Contents**

| Table | of I   | lustrations                                           | 10 |

|-------|--------|-------------------------------------------------------|----|

| Gene  | ral II | ntroduction                                           | 17 |

| Chap  | ter I  | The Road to 5G Power Amplifier Design                 | 19 |

| l.1   | 50     | 6: Future global wireless network                     | 20 |

| l.1.  | 1      | Generalities                                          | 20 |

| l.1.  | 2      | Frequency considerations                              | 23 |

| l.1.  | 3      | Technical solutions to leverage 5G                    | 25 |

| l.1.  | 4      | Overview of potential 5G modulations and waveforms    | 31 |

| l.1.  | 5      | CMOS technology for 5G                                | 34 |

| 1.2   | Pc     | ower Amplifier theory                                 | 36 |

| 1.2.  | 1      | Power amplifier generalities                          | 36 |

| 1.2.  | 2      | PA classes of operation                               | 40 |

| 1.2.  | 3      | Parameters for modulated signals                      | 45 |

| 1.2.  | 4      | PA for 5G: Specifications                             | 49 |

| 1.3   | m      | mW PA state of the art                                | 51 |

| 1.3.  | 1      | State of the art before circuit design                | 52 |

| 1.3.  | 2      | State of the art after circuit design                 | 59 |

| 1.4   | Co     | onclusion                                             | 68 |

| Chap  | ter II | : mmW PA design methodology in 28nm FD-SOI technology | 71 |

| II.1  | 28     | nm FD-SOI technology overview                         | 73 |

| II.1  | .1     | Active devices                                        | 73 |

| II.1  | .1     | Body Biasing                                          | 75 |

| II.1  | .2     | Back end of line                                      | 77 |

| II.2  | Pc     | ower Amplifiers topologies at mmW frequencies         | 79 |

| II.2  | .1     | Choice of operating classes at mmW frequencies        | 79 |

| II.2  | .2     | Different implementation topologies available         | 80 |

| II.2  | .3     | Power amplifier reconfigurability discussion          | 84 |

| II. | .3 P    | Power cells topologies at mmW frequencies                                    | 87           |

|-----|---------|------------------------------------------------------------------------------|--------------|

|     | II.3.1  | Common-source topology                                                       | 87           |

|     | 11.3.2  | Cascode topology                                                             | 89           |

| П.  | 4 I     | mpedance matching                                                            | 91           |

|     | 11.4.1  | Theoretical aspects                                                          | 91           |

|     | 11.4.2  | Possible implementations at mmW frequencies                                  | 95           |

| П.  | .5 E    | M CAD tools for mmW design modeling                                          | 98           |

|     | II.5.1  | Passive devices modeling                                                     | 98           |

|     | 11.5.2  | Optimization of the EM simulation tools for fast and accurate prototyping    | ; <b>112</b> |

| П.  | .6 S    | tability considerations                                                      | 117          |

|     | II.6.1  | Linear stability                                                             | 118          |

|     | 11.6.2  | Non-Linear stability                                                         | 121          |

| П.  | .7 [    | Design optimization techniques                                               | 122          |

|     | 11.7.1  | Power combining                                                              | 123          |

|     | 11.7.2  | Neutralization capacitance theory                                            | 129          |

| II. | .8 0    | Conclusion - Design flow of mmW PA design                                    | 132          |

| Cl  | hapter  | III: Reconfigurable balanced mmW PA implementation in 28nm FD-SOI technology | nology137    |

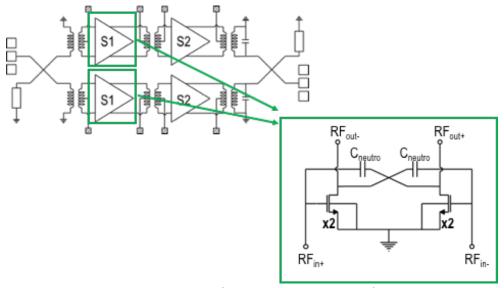

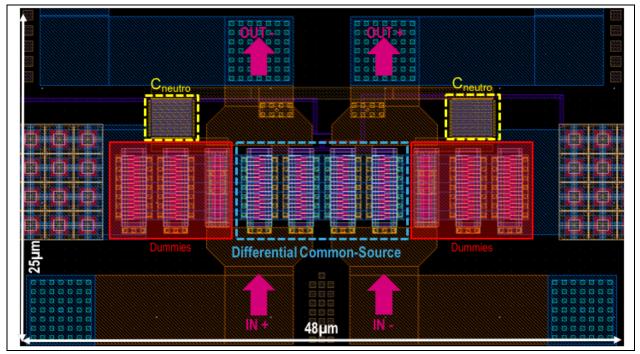

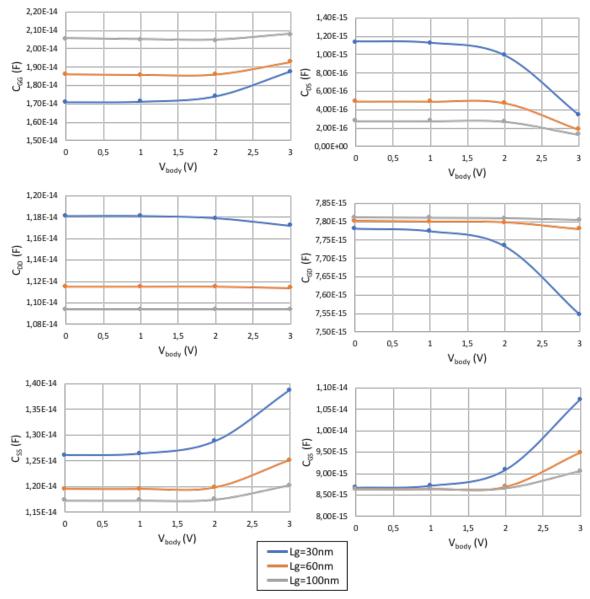

| Ш   | .1 A    | Active devices                                                               | 139          |

|     | II.1.2  | Dimensioning                                                                 | 140          |

|     | III.1.1 | Layout optimization strategy                                                 | 143          |

| Ш   | .2 P    | Power Amplifier topology                                                     | 145          |

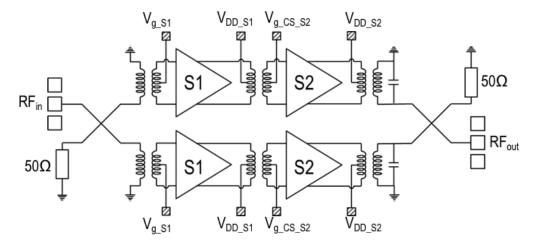

|     | III.2.1 | Choice of overall topology                                                   | 145          |

|     | III.2.2 | Balanced topology implementation                                             | 147          |

| Ш   | .3 S    | tages design                                                                 | 153          |

|     | III.3.1 | Design and implementation of S <sub>2</sub> stage                            | 153          |

|     | III.3.2 | Design and implementation of S <sub>1</sub> stage                            | 158          |

| Ш   | .4 I    | mpedance matching network implementation                                     | 160          |

|     | III.4.1 | Output matching network optimization strategy                                | 160          |

|     | 111.4.2 | Inter-stage and input matching                                               | 164          |

| Ш   | .5 F    | Robust integration and reliability                                           | 167          |

|    | III.5.:            | 1     | ESD protection                                                        | 168 |

|----|--------------------|-------|-----------------------------------------------------------------------|-----|

|    | III.5.2            | 2     | Electromigration                                                      | 169 |

|    | III.5.3            | 3     | Safe operating area                                                   | 170 |

|    | III.5.             | 4     | Ground return path optimization                                       | 170 |

| Ш  | .6                 | Me    | asurements setup                                                      | 172 |

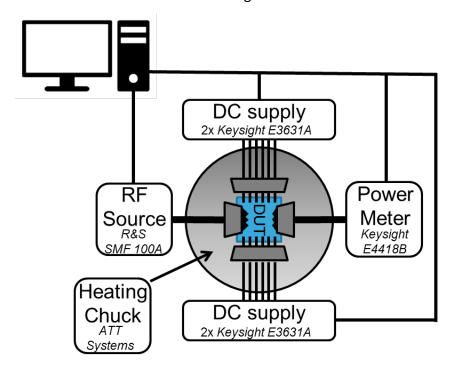

|    | III.6.:            | 1     | Small-signal analysis test bench                                      | 172 |

|    | III.6.2            | 2     | Large-signal measurements test bench                                  | 173 |

| Ш  | .7                 | Me    | asurements at optimal operating point                                 | 174 |

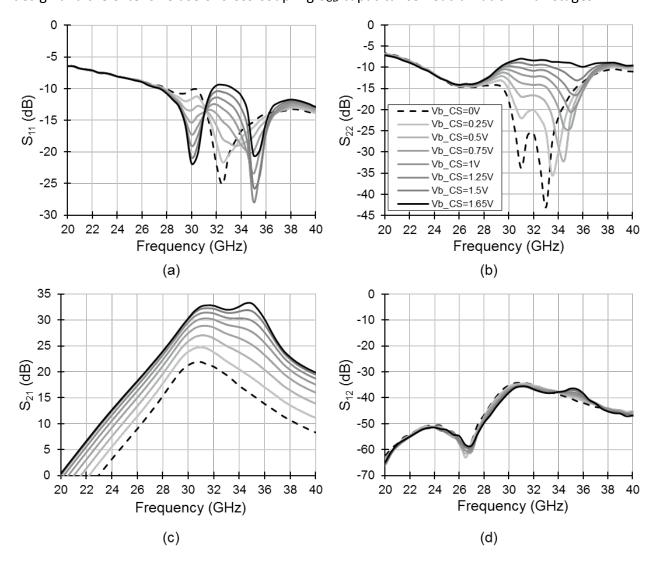

|    | III.7.:            | 1     | Small-signal measurements with body biasing tuning.                   | 175 |

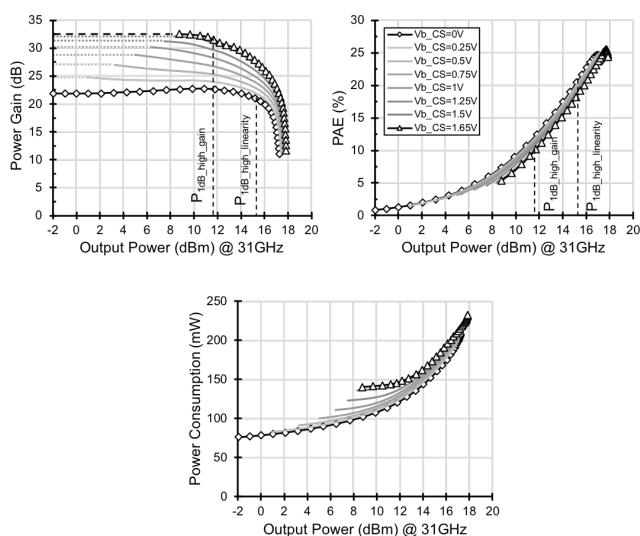

|    | III.7.             | 2     | Large-signal measurements with body biasing tuning                    | 177 |

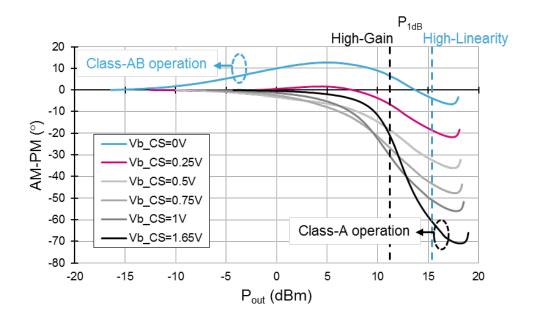

|    | III.7.3            | 3     | AM-PM measurements with body biasing tuning                           | 179 |

|    | III.7.             | 4     | Measurements over frequency range                                     | 181 |

| Ш  | .8                 | Pov   | ver Amplifier behavior for temperature variations                     | 182 |

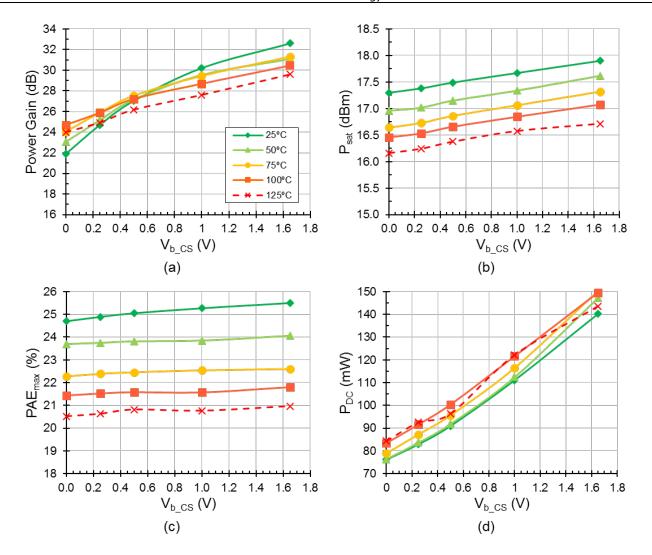

|    | III.8.:            | 1     | Large-signal measurements from 25°C to 125°C with body biasing tuning | 182 |

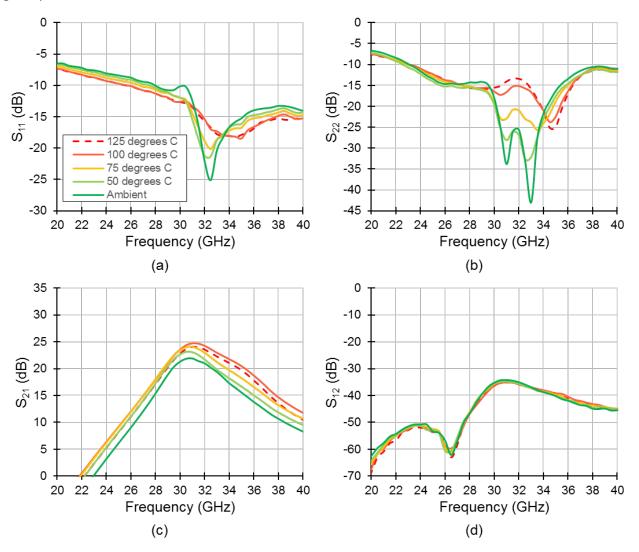

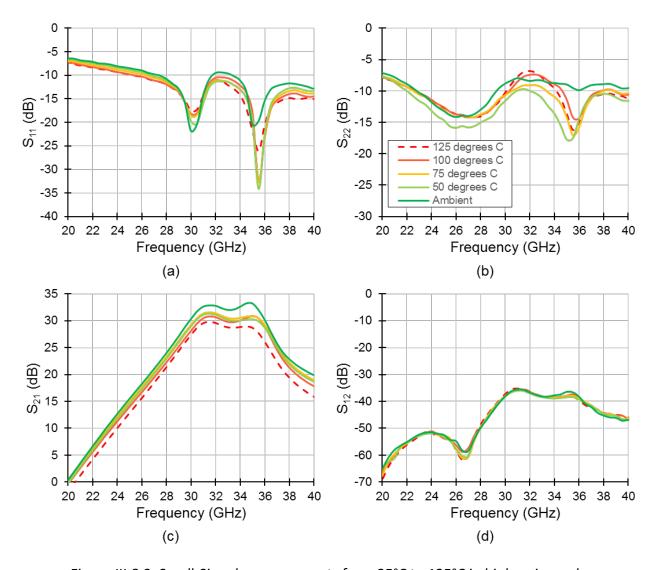

|    | III.8.2            | 2     | Small-signal measurements from 25°C to 125°C                          | 184 |

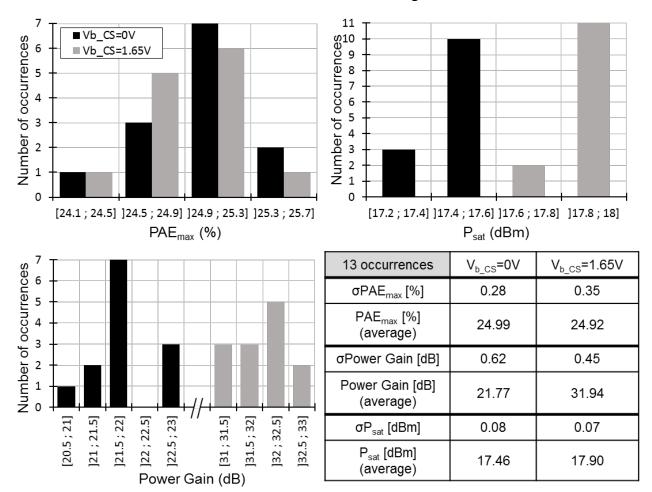

| Ш  | .9                 | On-   | wafer variability statistical study                                   | 187 |

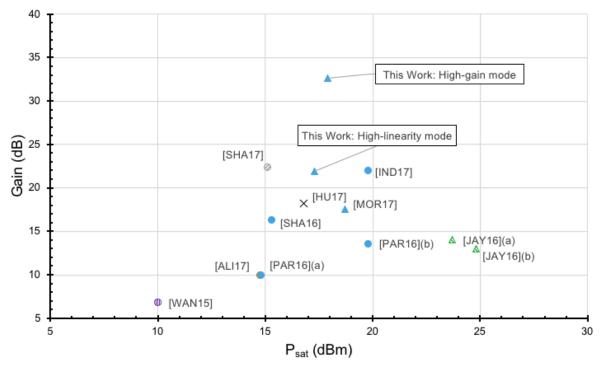

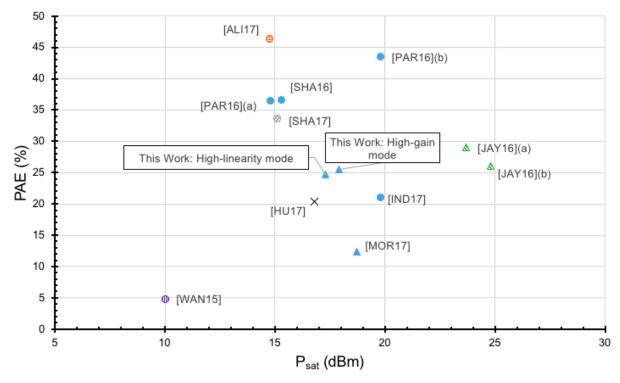

| Ш  | .10                | Con   | nparison and discussion regarding mmW PA state of the art             | 189 |

| Ш  | .11                | Pov   | ver amplifier core performances extraction                            | 196 |

| Ш  | .12                | Con   | nclusion                                                              | 199 |

| Ш  | .13                | Per   | spective: Wideband and reconfigurable 90° hybrid coupler              | 200 |

|    | III.13             | 3.1   | Lateral ground planes placement exploration                           | 200 |

|    | III.13             | 3.2   | Tunable and wideband 90° Hybrid coupler design                        | 203 |

| G  | enera              | al Co | onclusion & Perspectives                                              | 207 |

|    | Conc               | clusi | on                                                                    | 207 |

|    | Pers               | pect  | ives                                                                  | 209 |

| Bi | bliog              | raph  | ıy                                                                    | 213 |

| Li | st of <sub>l</sub> | publ  | lications                                                             | 223 |

| G  | lossaı             | ry    |                                                                       | 225 |

# Table of Illustrations

# Figures

| Figure I.1.1: Mobile telecommunications market 2014-2020 (data sources: [ERI15], [CIS16]                  | )21 |

|-----------------------------------------------------------------------------------------------------------|-----|

| Figure I.1.2: 5G expected specifications (may vary depending on the use-case)                             | 23  |

| Figure I.1.3: Atmospheric attenuation versus frequency (based on [WEL09])                                 | 24  |

| Figure I.1.4: 5G expected frequency spectrum                                                              | 25  |

| Figure I.1.5: Penetration losses in several materials depending on frequency [GLO15]                      | 26  |

| Figure I.1.6: Losses induced by material penetration at 28GHz, 39GHz and 73GHz [NOK16].                   | 26  |

| Figure I.1.7: Cell-dimensioning illustration                                                              | 27  |

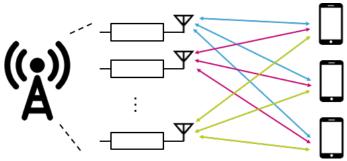

| Figure I.1.8: Massive-MIMO concept                                                                        | 28  |

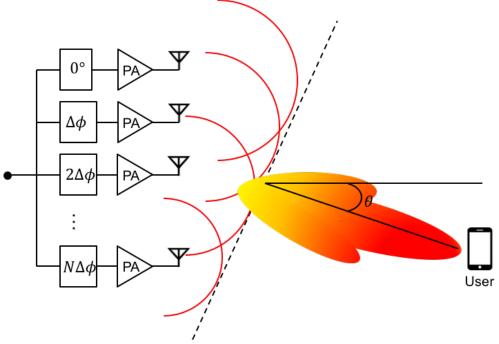

| Figure I.1.9: Beamforming concept                                                                         | 29  |

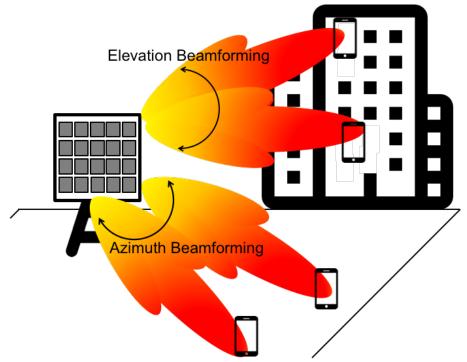

| Figure I.1.10: Full dimension MIMO concept                                                                | 30  |

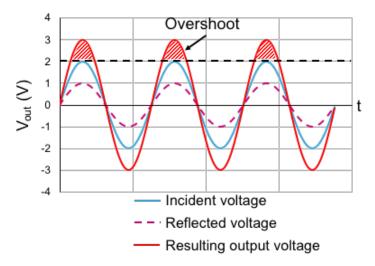

| Figure I.1.11: Constructive combination of incident and reflected waves illustration                      | 31  |

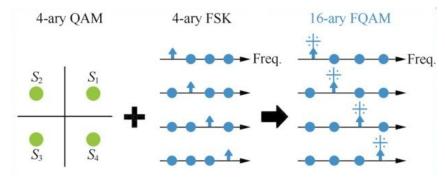

| Figure I.1.12: 16-ary FQAM illustration [SAM15]                                                           | 32  |

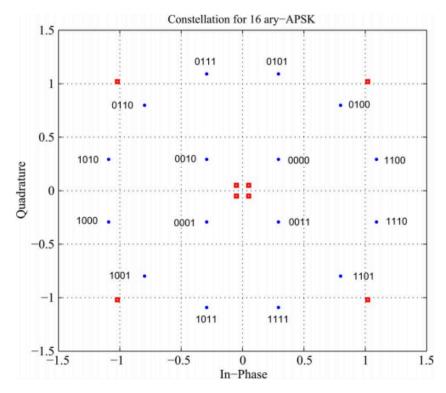

| Figure I.1.13: 16-ary APSK illustration [LI15]                                                            | 32  |

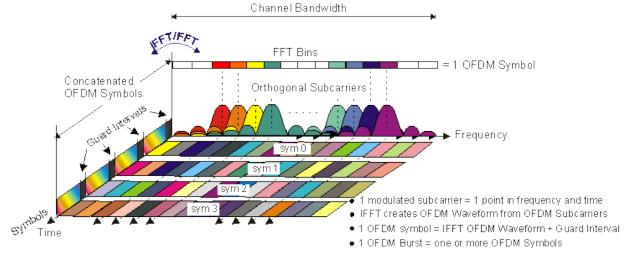

| Figure I.1.14: Frequency and time domains OFDM representation [KEY17]                                     | 33  |

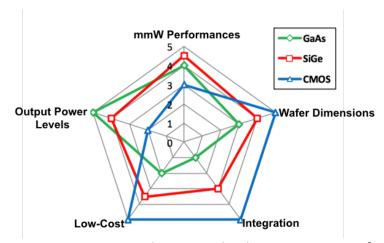

| Figure I.1.15: GaAs, SiGe and CMOS technologies comparison [LAR15-2]                                      | 35  |

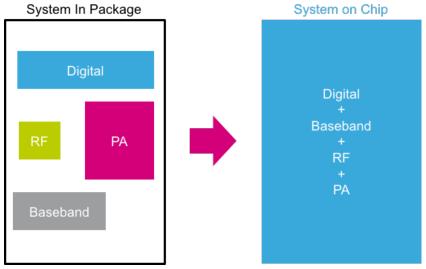

| Figure I.1.16: System on Chip compared to System in Package                                               | 35  |

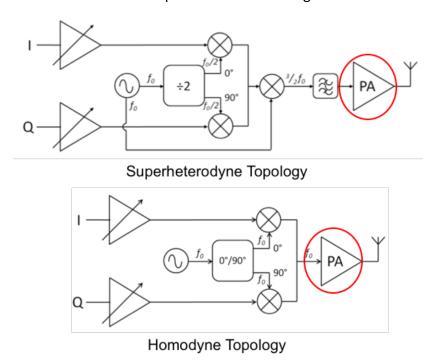

| Figure I.2.1: Power amplifier in different transmitter topologies                                         | 36  |

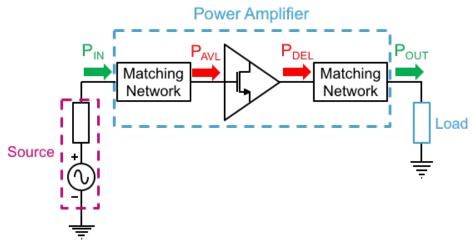

| Figure I.2.2: Different powers involved in a power amplifier                                              | 37  |

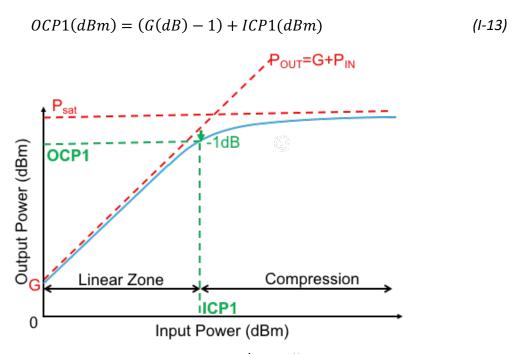

| Figure I.2.3: P <sub>OUT</sub> VS P <sub>IN</sub> , ICP1/OCP1 illustration                                | 39  |

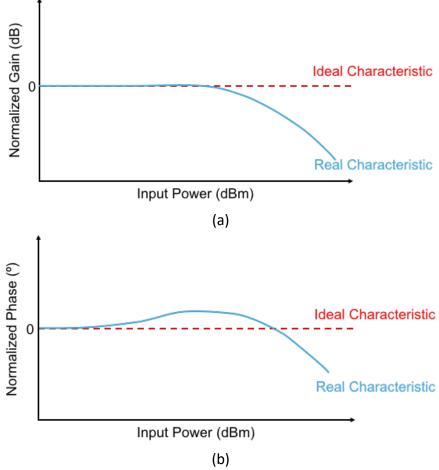

| Figure I.2.4: AM-AM (a) and AM-PM (b) conversions illustration                                            | 40  |

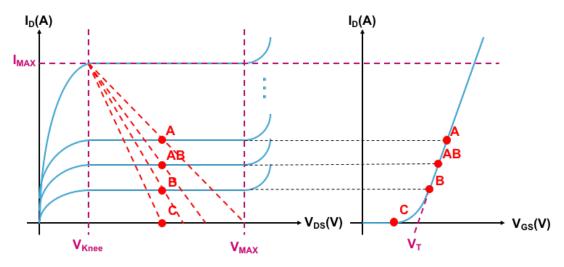

| Figure I.2.5: $I_D = f(V_{DS})$ and $I_D = f(V_{GS})$ characteristics with sinusoidal operating classes   | 42  |

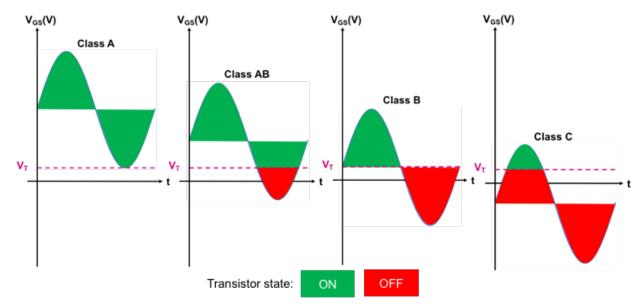

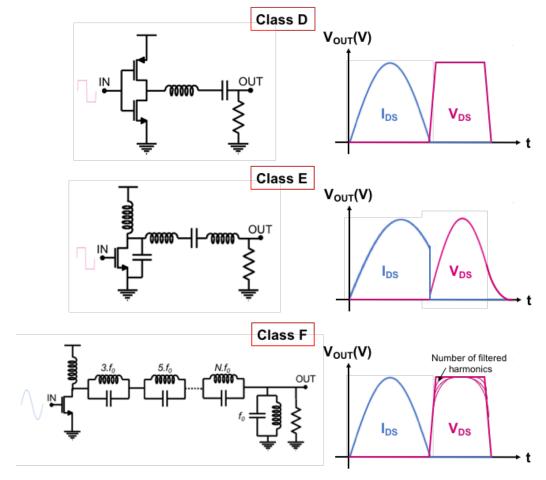

| Figure I.2.6: Transistor conduction zones in different sinusoidal operating classes                       | 43  |

| Figure I.2.7: Switched operating classes amplifiers and waveforms                                         | 45  |

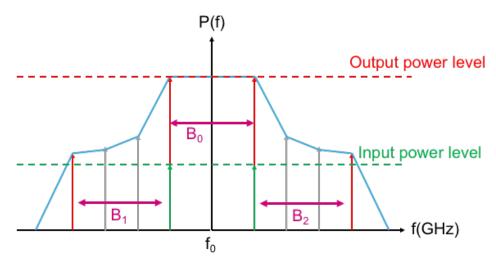

| Figure I.2.8: Adjacent channel leakage ratio illustration                                                 | 46  |

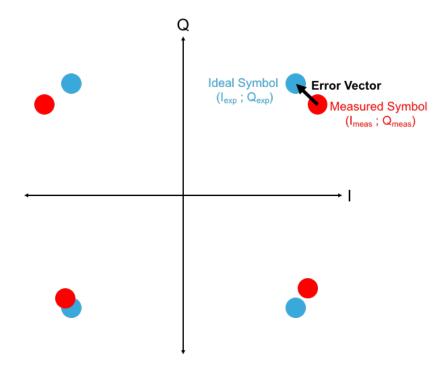

| Figure I.2.9: Error vector illustration                                                                   |     |

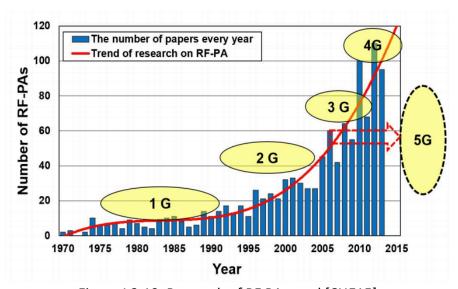

| Figure I.2.10: Research of RF PA trend [CHE15]                                                            | 49  |

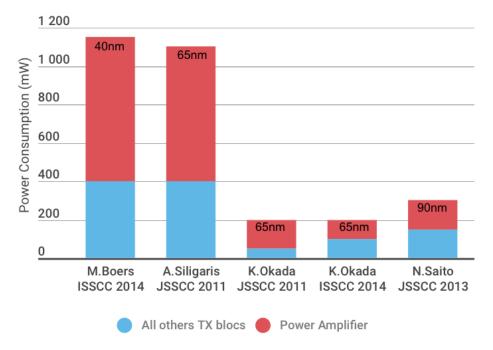

| Figure I.2.11: Power consumption in 60GHz transmitters state of the art                                   | 50  |

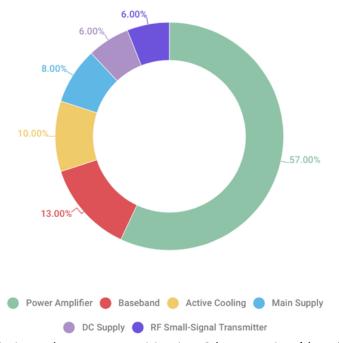

| Figure I.2.12: Dissipated power repartition in 4G base station (data from [AUE11])                        | 50  |

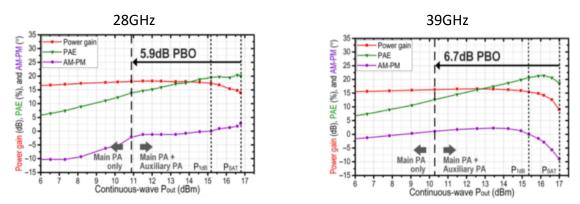

| Figure I.3.1: Bi-band power amplifier scheme [WAN15]                                                      | 52  |

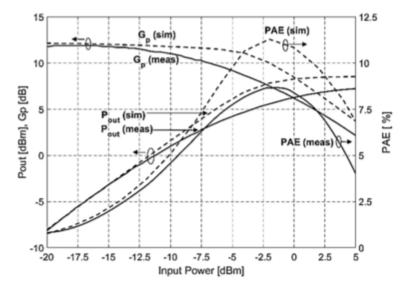

| Figure I.3.2: Bi-band power amplifier performances [WAN15]:                                               | 53  |

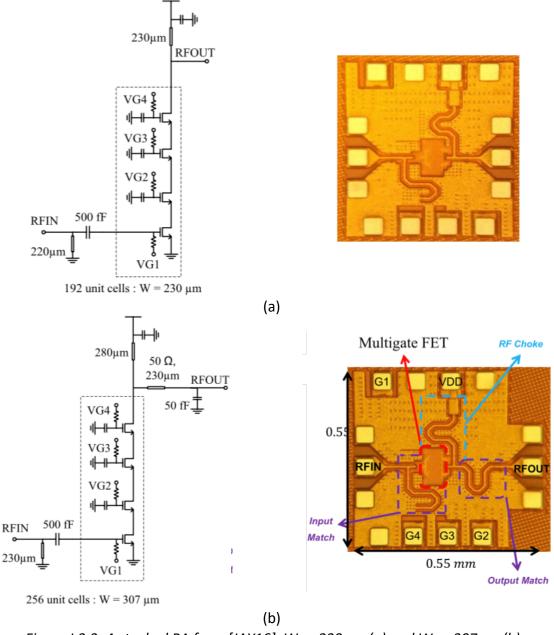

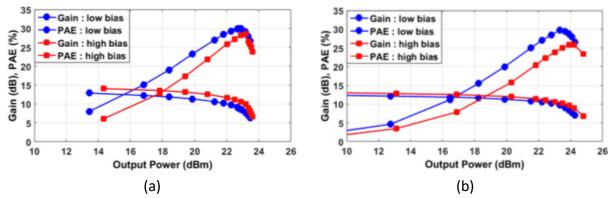

| Figure I.3.3: 4-stacked PA from [JAY16], W <sub>tot</sub> =230μm (a) and W <sub>tot</sub> =307μm (b)(b)   | 54  |

| Figure I.3.4: CW performances of 4-stacked PA from [JAY16], $W_{tot}$ =230 $\mu$ m (a) and $W_{tot}$ =30. |     |

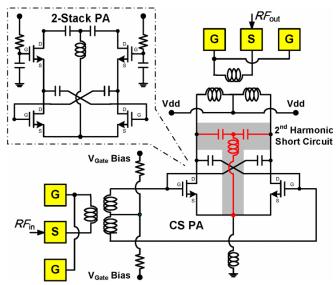

| (b)                                                                                                       |     |

| Figure I.3.5: Common-source and 2-stack PA topologies from [PAR16]                                        | 55  |

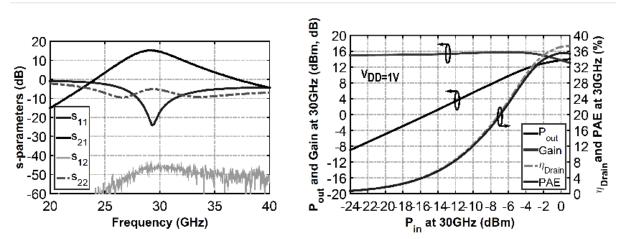

| Figure 1.3.6: CW performances of common-source and 2-stack PA topologies from [PAR16]       | .56  |

|---------------------------------------------------------------------------------------------|------|

| Figure I.3.7: 2-stages differential common-source PA from [SHA16]                           | .56  |

| Figure I.3.8: S-parameters and CW performances of 2-stages differential common-source PA    |      |

| from [SHA16]                                                                                | .57  |

| Figure I.3.9: Power amplifier from [LAR15]: photomicrograph (a) and scheme (b)              | .58  |

| Figure I.3.10: CW performances of the reconfigurable PA presented in [LAR15]                | .59  |

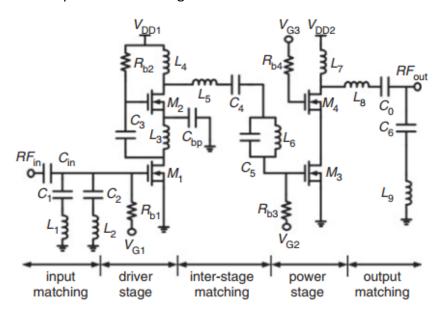

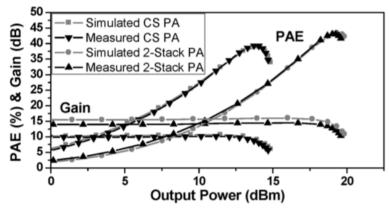

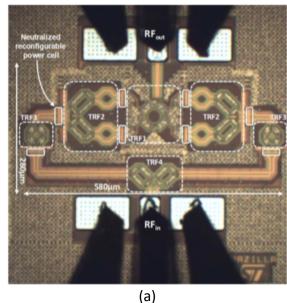

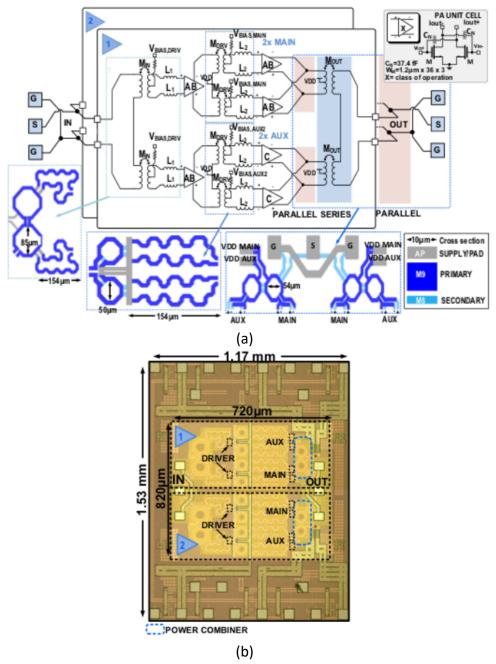

| Figure I.3.11: Power amplifier from [HU17]: scheme (a) and photomicrograph (b)              | .60  |

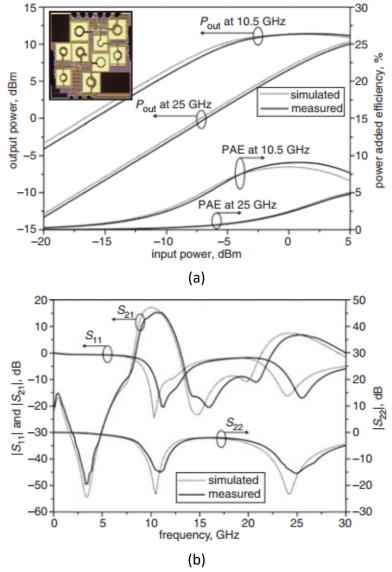

| Figure I.3.12: Power amplifier from [HU17], CW performances                                 | .61  |

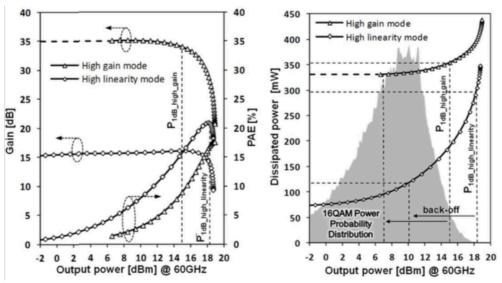

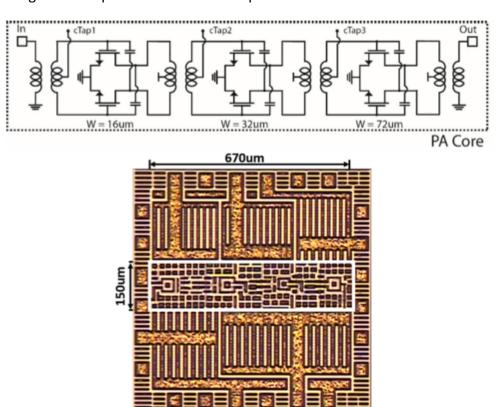

| Figure I.3.13: Power amplifier from [IND17]: scheme (a) and photomicrograph (b)             | .62  |

| Figure I.3.14: Power amplifier from [IND17], CW performances                                | .63  |

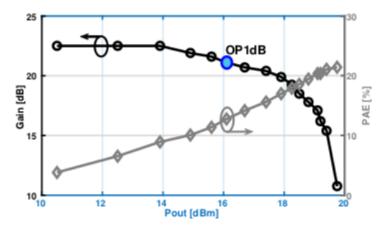

| Figure I.3.15: Power amplifier from [SHA17]: scheme (a) and photomicrograph (b)             | .64  |

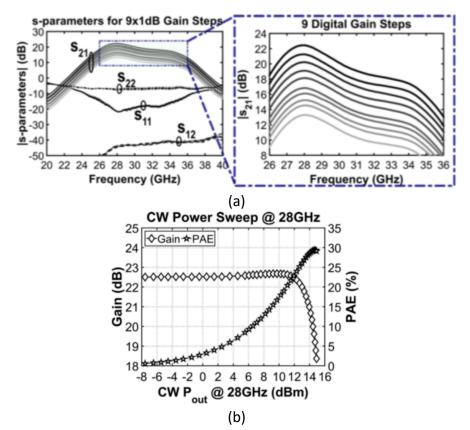

| Figure I.3.16: Power amplifier from [SHA17]: S-parameters with reconfigurable gain (a) and  |      |

| 28GHz CW performances (b)                                                                   | .65  |

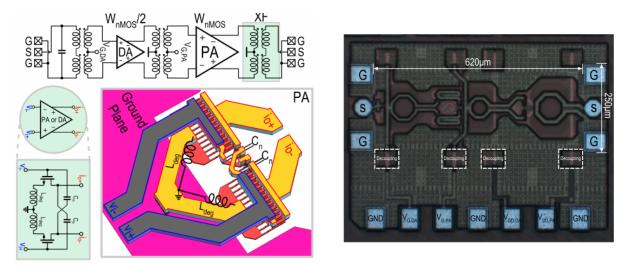

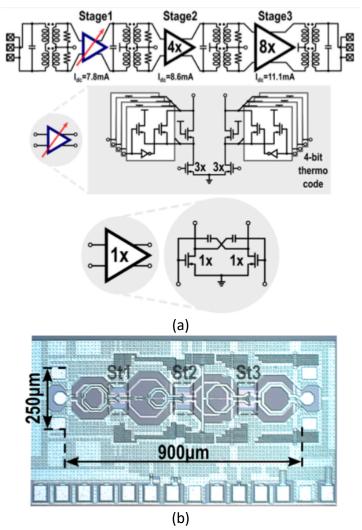

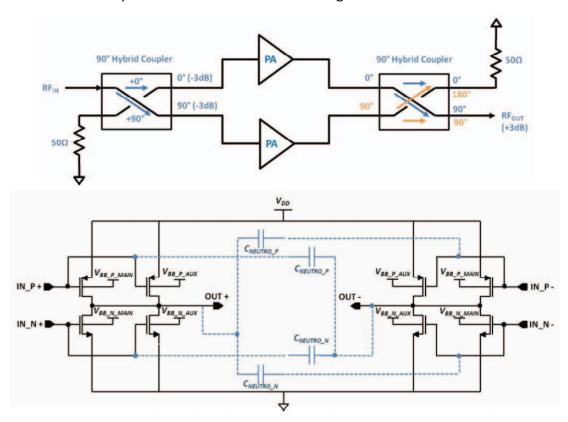

| Figure I.3.17: Self-contained power amplifier from [MOR17]: overall and power-cell topology | .66  |

| Figure I.3.18: Self-contained power amplifier from [MOR17]: CW performances                 | .66  |

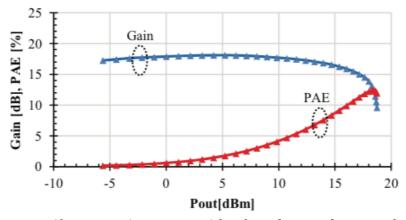

| Figure I.3.19: Power amplifier from [CAL17]: scheme and photomicrograph                     | .67  |

| Figure I.3.20: Power amplifier from [CAL17]: CW performances at 71GHz                       | .68  |

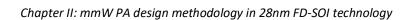

| Figure II.1.1: Cross section of regular Bulk CMOS technology VS 28nm UTBB FD-SOI CMOS       |      |

| technology transistors [CAT17]                                                              | .74  |

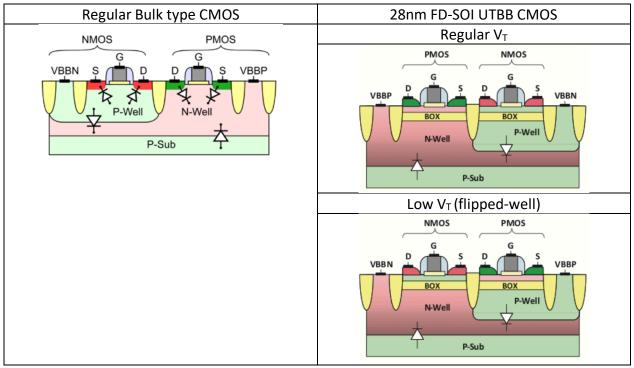

| Figure II.1.2: $I_D=f(V_{DS})$ characteristic comparison between 28nm Bulk and 28nm FD-SOI  |      |

| technologies [LAR15-2]                                                                      | . 75 |

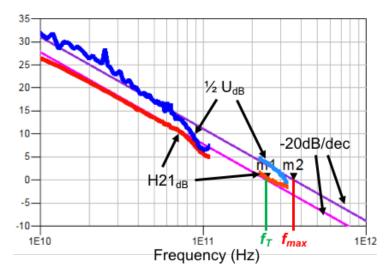

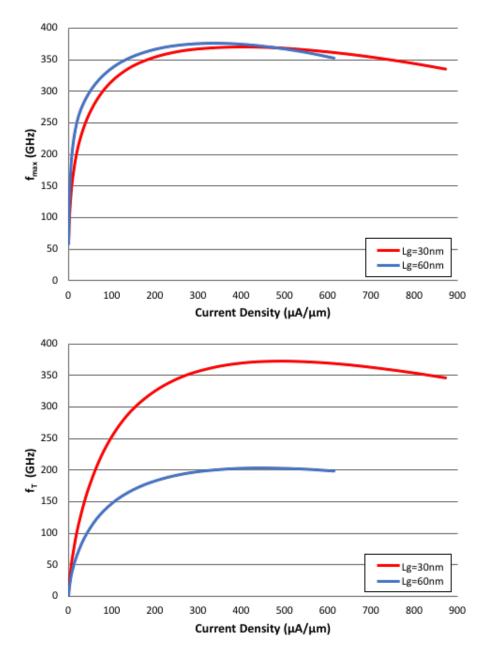

| Figure II.1.3: Measured $f_T$ and $f_{max}$ for full BEOL LVT NMOS transistor [GUI17]       | . 75 |

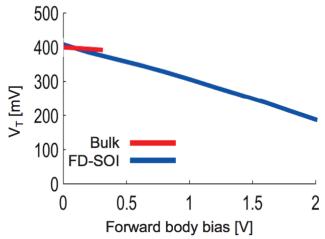

| Figure II.1.4: Forward body biasing induced VT variation comparison between Bulk and 28nm   | FD-  |

| SOI technologies [CAT17]                                                                    | .77  |

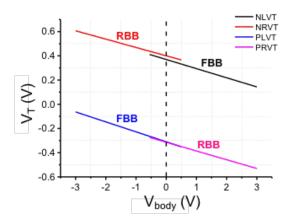

| Figure II.1.5: $V_T$ achievable range with NMOS and PMOS LVT and RVT transistors at minimum |      |

| gate length in 28nm FD-SOI [CAT17]                                                          | .77  |

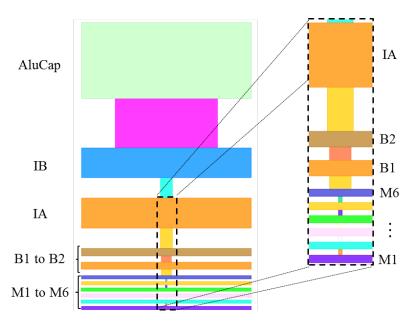

| Figure II.1.6: 10 metal layers 28nm FD-SOI CMOS technology back-end-of-line                 | . 78 |

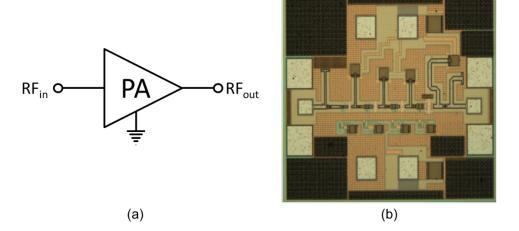

| Figure II.2.1: Single-ended topology scheme (a) and implementation example [DEM10] (b)      | .81  |

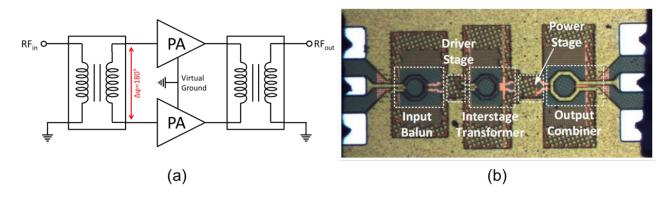

| Figure II.2.2: Differential topology scheme (a) and implementation example [XIA17] (b)      | .81  |

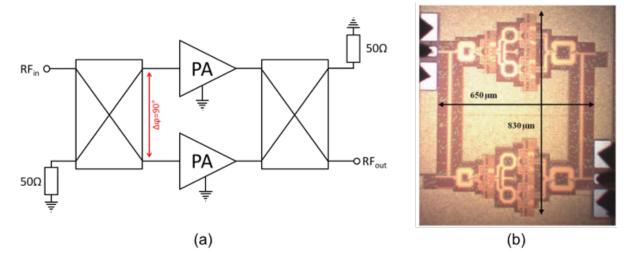

| Figure II.2.3: Balanced topology scheme (a) and implementation example [MOR17] (b)          | .83  |

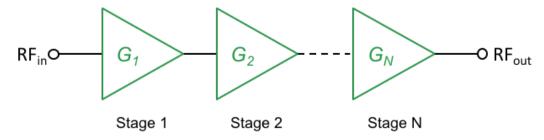

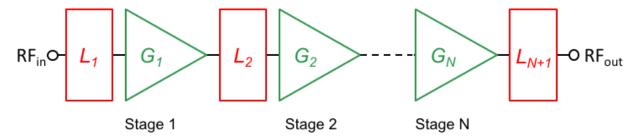

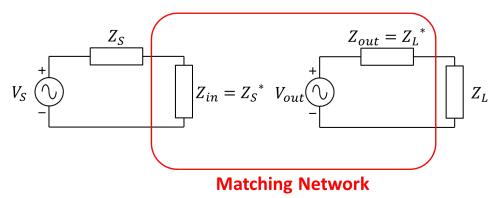

| Figure II.2.4: Ideal multi-stage amplification path                                         | .83  |

| Figure II.2.5: Multi-stage amplification path with lossy matching networks                  | .84  |

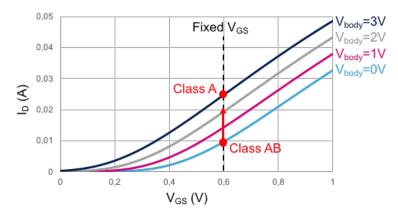

| Figure II.2.6: Operating class shifting induced by body biasing                             | .85  |

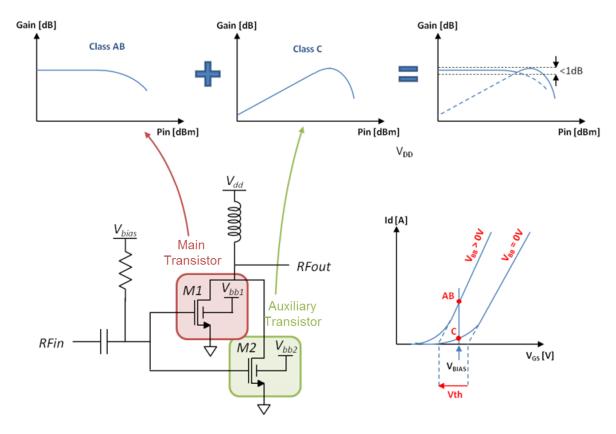

| Figure II.2.7: Body-biasing enabled pseudo-Doherty operation [MOR17-2]                      | .85  |

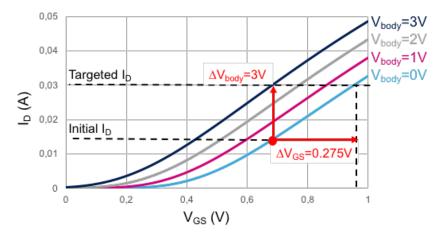

| Figure II.2.8: $V_{GS}$ and $V_{body}$ dynamic comparison for fixed $I_D$ level target      | .86  |

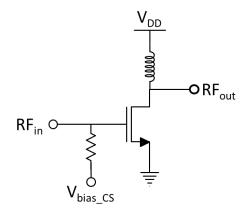

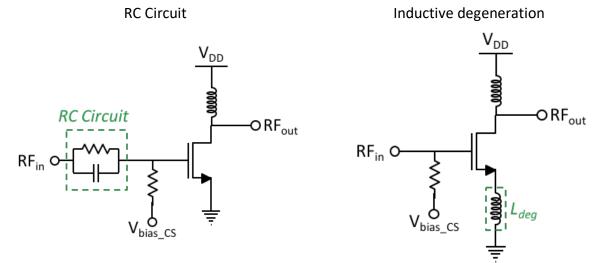

| Figure II.3.1: Common-source topology scheme                                                |      |

| Figure II.3.2: Common-source stabilization techniques                                       | .89  |

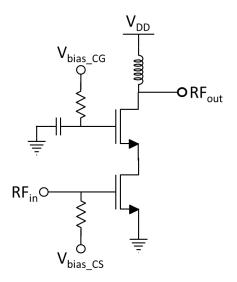

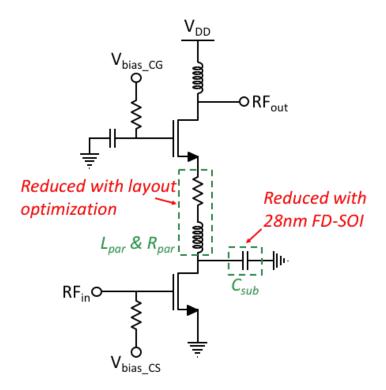

| Figure II.3.3: Cascode topology scheme                                                      |      |

| Figure II.3.4: Cascode inter-stage parasitic elements illustration                          | .90  |

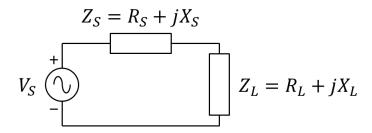

| Figure II.4.1: Active source loaded by a passive load scheme                                         | 91  |

|------------------------------------------------------------------------------------------------------|-----|

| Figure II.4.2: Matching network illustration                                                         | 93  |

| Figure II.4.3: Generic power amplifier scheme with matching networks at the input, output a          |     |

| inter-stage                                                                                          | 93  |

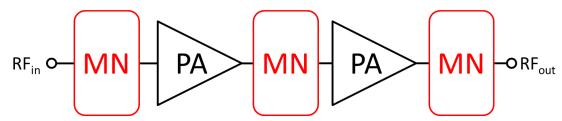

| Figure II.4.4: Load-pull setup and results illustration                                              | 94  |

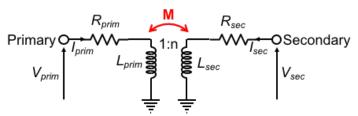

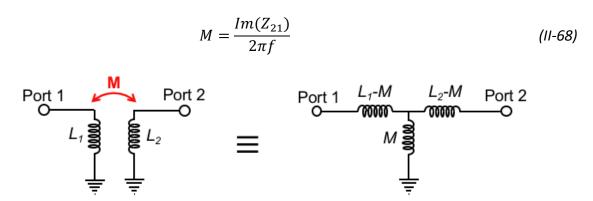

| Figure II.4.5: Simplified transformer model                                                          | 96  |

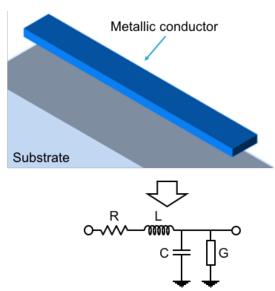

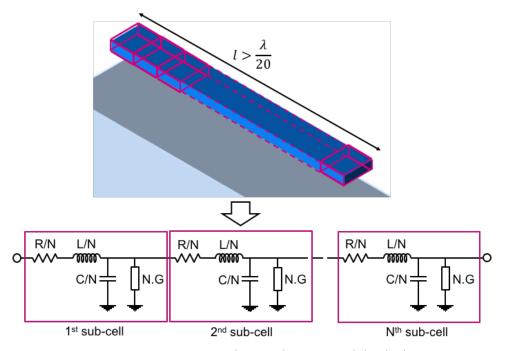

| Figure II.5.1: Transmission line equivalent RLCG model illustration                                  |     |

| Figure II.5.2: Transmission line and RLCG model sub-division                                         | 101 |

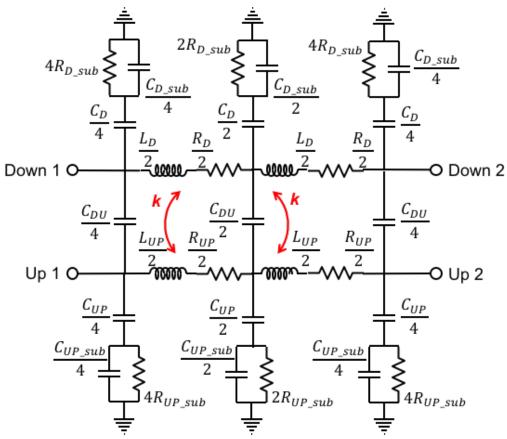

| Figure II.5.3: Lumped model for 28nm FD-SOI transformer prototyping adapted from [LEI11]             | 102 |

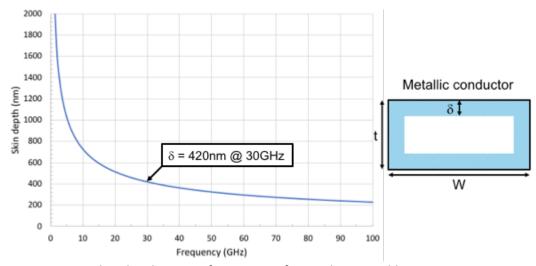

| Figure II.5.4: Skin depth versus frequency of IA and IB metal layers in 28nm FD-SOI                  | 107 |

| Figure II.5.5: Equivalent oxide permittivity simplification                                          | 108 |

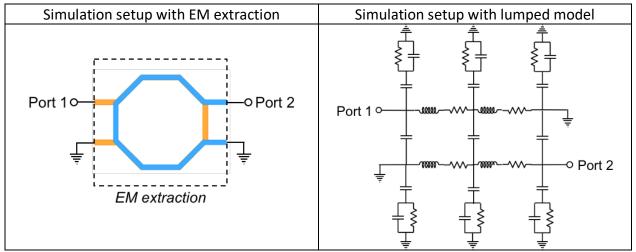

| Figure II.5.6: Transformer two-ports EM simulation setup                                             | 109 |

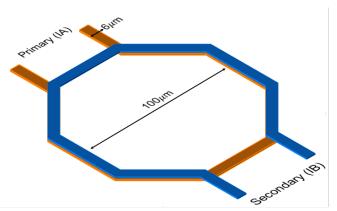

| Figure II.5.7: Designed transformer for EM simulations and model comparison                          | 109 |

| Figure II.5.8: Simulation setup for comparison between lumped model and EM simulations               | 110 |

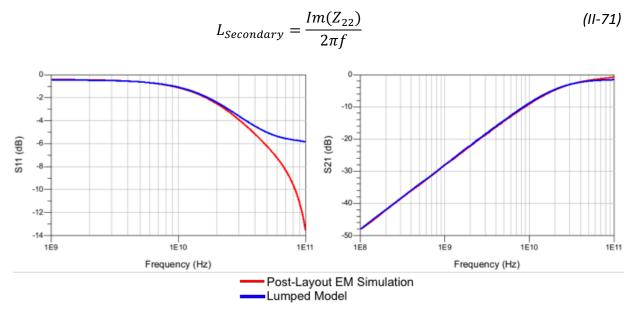

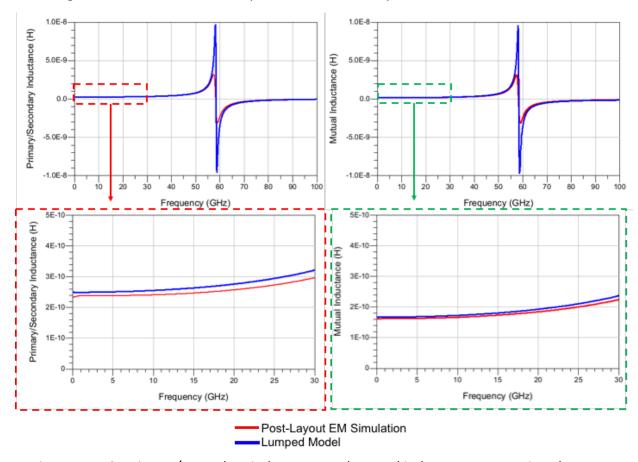

| Figure II.5.9: S21 and S11 comparison between lumped model and EM simulations                        | 111 |

| Figure II.5.10: Primary/secondary inductance and mutual inductance comparison between                |     |

| lumped model and EM simulations                                                                      | 111 |

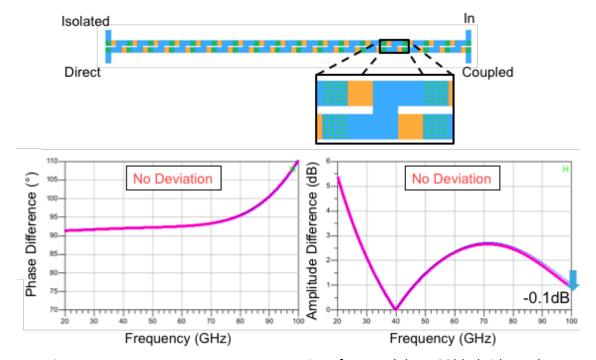

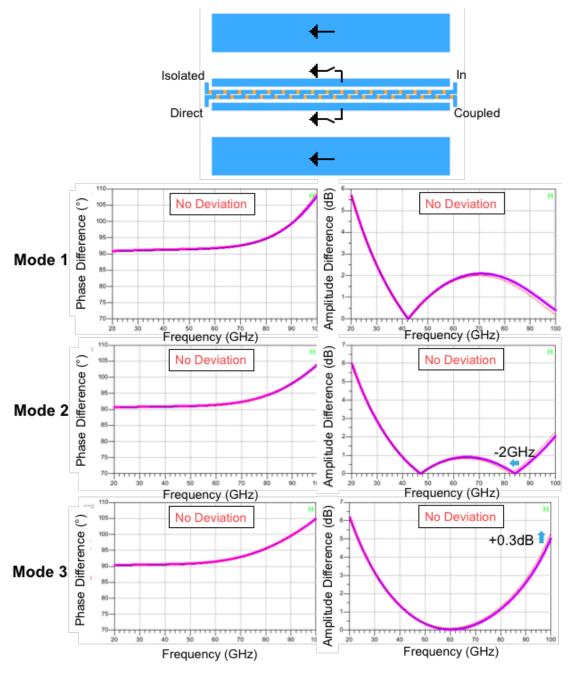

| Figure II.5.11: Momentum setup comparison for standalone 90° hybrid coupler                          | 114 |

| Figure II.5.12: Momentum setup comparison for tunable 90° hybrid coupler: results                    | 116 |

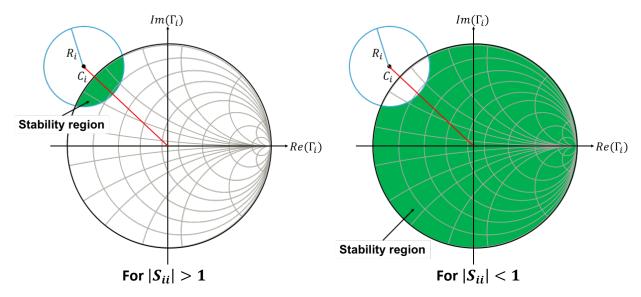

| Figure II.6.1: Stability circles illustration                                                        | 120 |

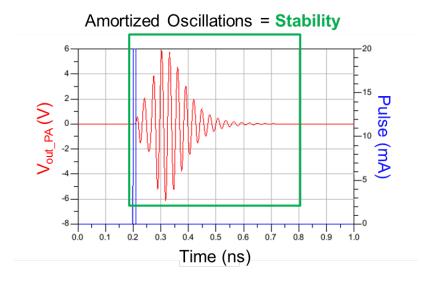

| Figure II.6.2: Amortized oscillations resulting from a pulse excitation                              | 121 |

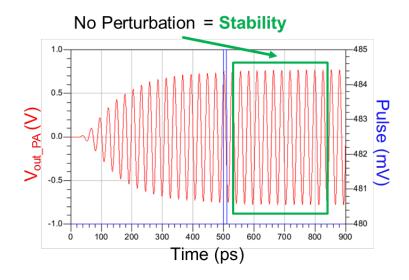

| Figure II.6.3: No perturbations resulting from a pulse excitation                                    | 122 |

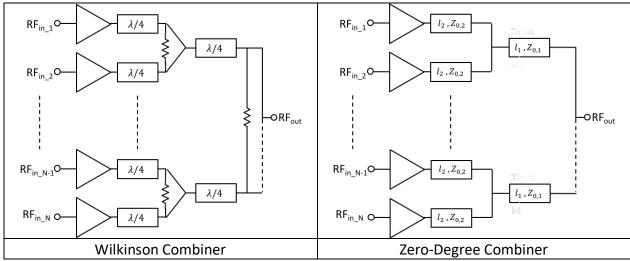

| Figure II.7.1: Wilkinson and Zero-degree combiners block schemes                                     | 123 |

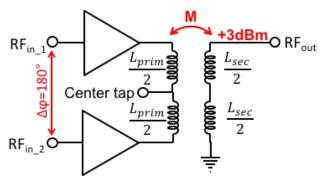

| Figure II.7.2: Differential-to-single power combining through balun                                  | 124 |

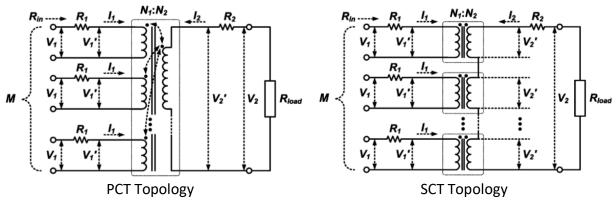

| Figure II.7.3: PCT and SCT topologies block schemes [AN08]                                           | 124 |

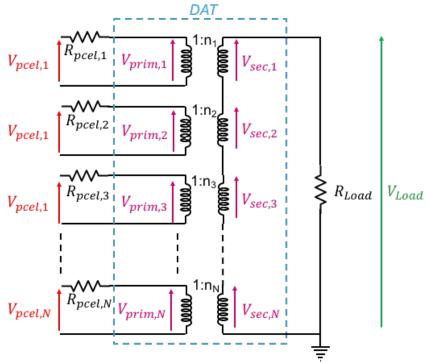

| Figure II.7.4: DAT schematic                                                                         | 125 |

| Figure II.7.5: Combining through 90° hybrid coupler                                                  | 127 |

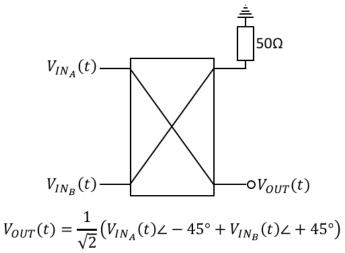

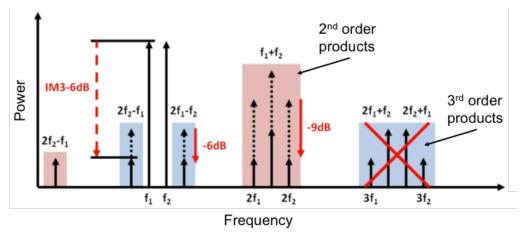

| Figure II.7.6: Intermodulation products comparison between classical and balanced topology           | у   |

| [MOR17]                                                                                              | 128 |

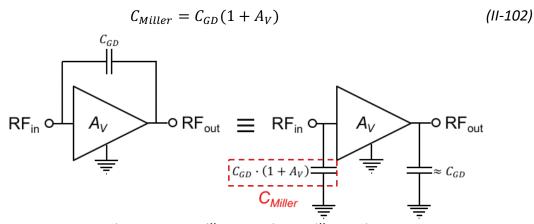

| Figure II.7.7: Miller capacitance illustration                                                       | 129 |

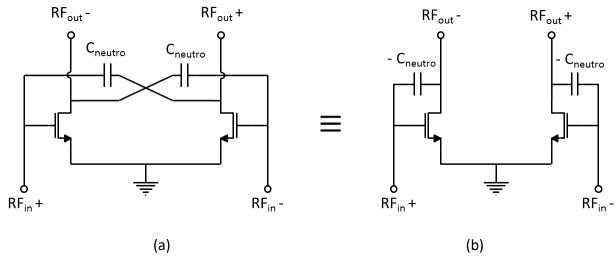

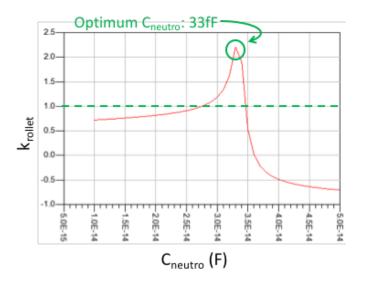

| Figure II.7.8: CS stage with C <sub>neutro</sub> (a) acting as negative parallel capacitance (b)     | 130 |

| Figure II.7.9: Small-signal equivalent scheme of cross-coupled differential common-source st         | _   |

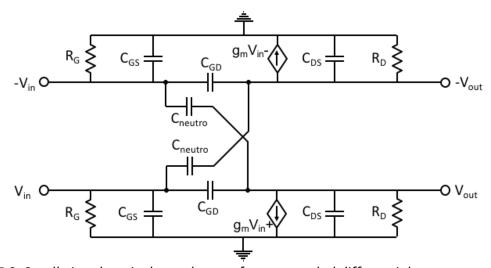

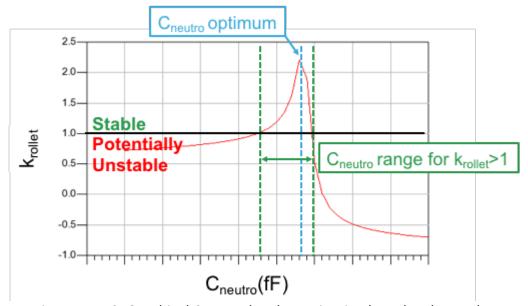

| Figure II.7.10: Graphical C <sub>neutro</sub> value determination based on k <sub>rollet</sub> value |     |

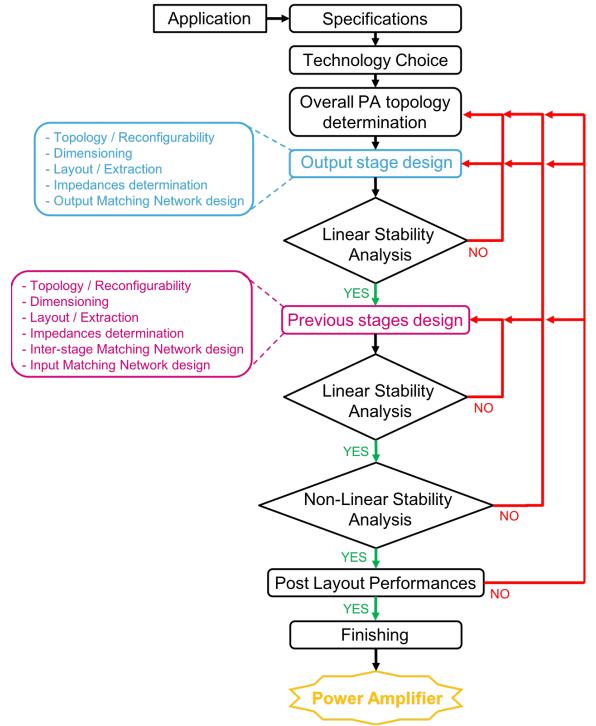

| Figure II.8.1: Complete design flow of a mmW power amplifier in deep sub-micron CMOS                 |     |

| technology                                                                                           | 133 |

| Figure III.1.1: Different transistors topologies                                                     | 140 |

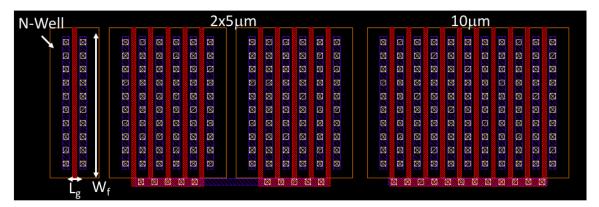

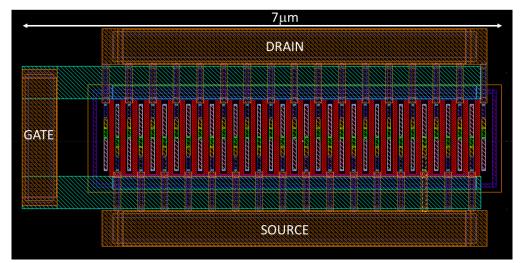

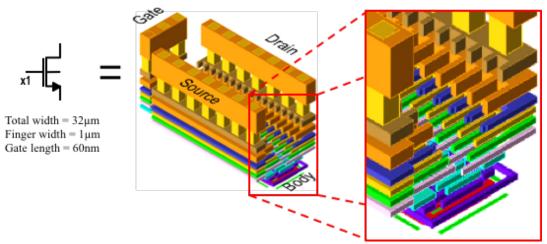

| Figure III.1.2: Layout view of designed elementary cell                                              | 141 |

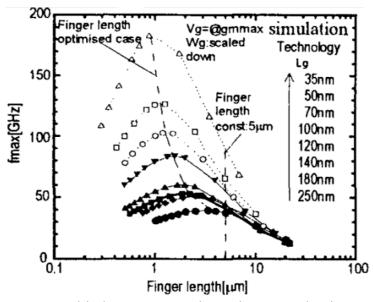

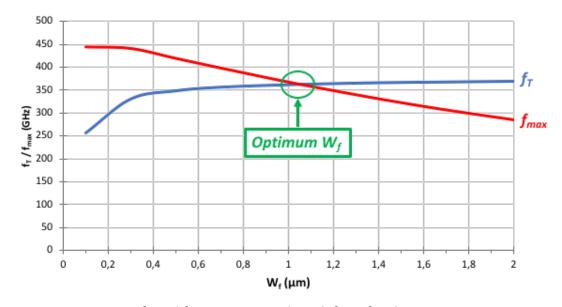

| Figure III.1.3: Finger width determination depending on technology nodes [MOR99]                     | 141 |

| Figure III.1.4: $f_T$ and $f_{max}$ versus gate length for a fixed 400 $\mu$ m transistor        | 142    |

|--------------------------------------------------------------------------------------------------|--------|

| Figure III.1.5: $f_T$ and $f_{max}$ comparison between gate length of 60nm and 30nm (DK 2.7)     | 143    |

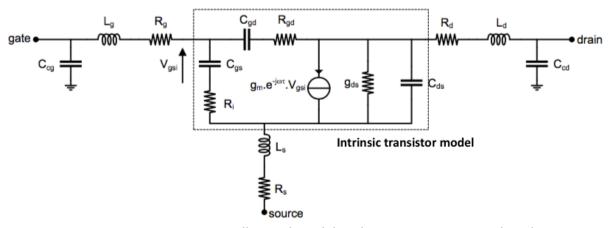

| Figure III.1.6: Intrinsic transistor small-signal model with interconnections induced parasition | c at   |

| high frequency [LAR15-2]                                                                         | 144    |

| Figure III.1.7: 3D view of elementary transistor cell optimal layout                             | 145    |

| Figure III.2.1: Designed balanced power amplifier overall topology targeting 5G and SoC          |        |

| integration challenges                                                                           | 147    |

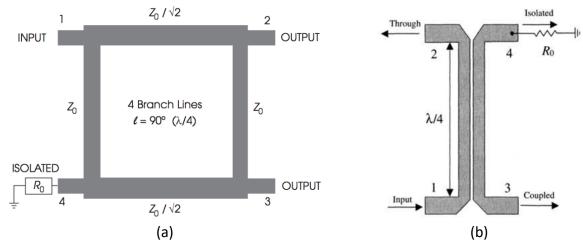

| Figure III.2.2: Branch-lines (a) and coupled-lines coupler (b) illustration [BRE07]              | 147    |

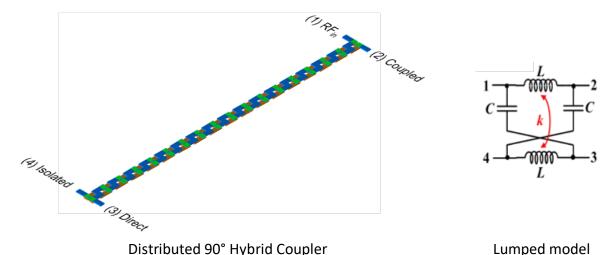

| Figure III.2.3: Quadrature hybrid coupler and simplified lumped elements model                   | 148    |

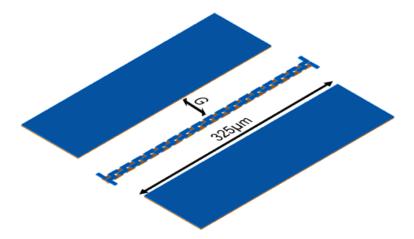

| Figure III.2.4: Unitary twisted cell                                                             | 149    |

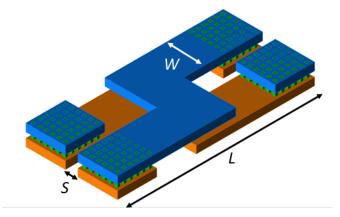

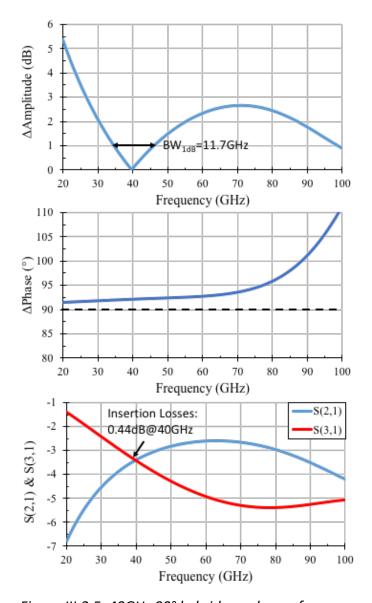

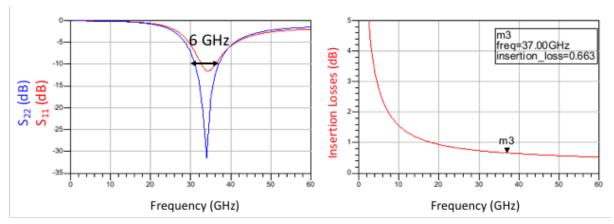

| Figure III.2.5: 40GHz 90° hybrid coupler performance                                             | 151    |

| Figure III.2.6: $50\Omega$ ballast resistor design                                               | 152    |

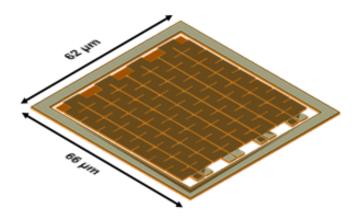

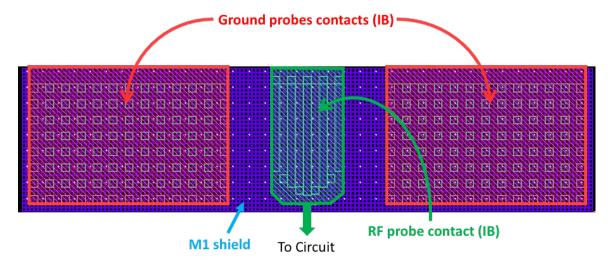

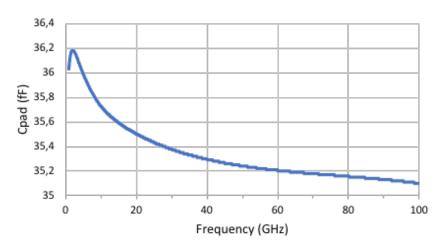

| Figure III.2.7: Layout view of implemented shielded RF pad                                       | 153    |

| Figure III.2.8: RF pad capacitance to ground estimation (EM simulation)                          |        |

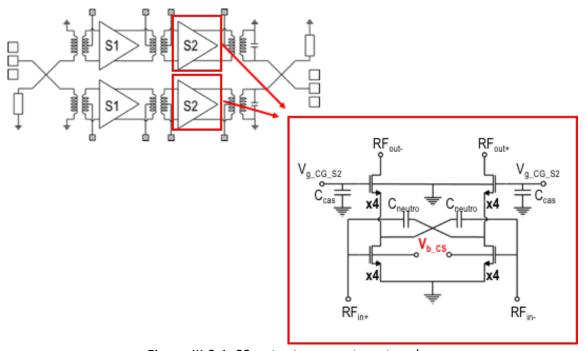

| Figure III.3.1: S2 output power stage topology                                                   |        |

| Figure III.3.2: S2 stage C <sub>neutro</sub> determination                                       | 155    |

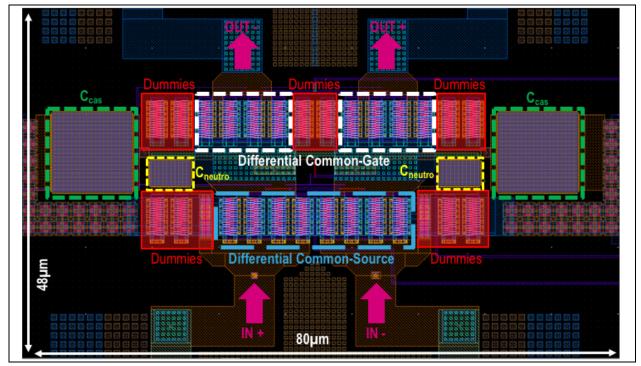

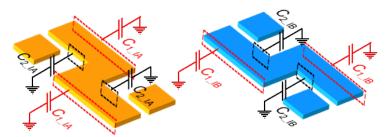

| Figure III.3.3: S2 output power stage layout                                                     |        |

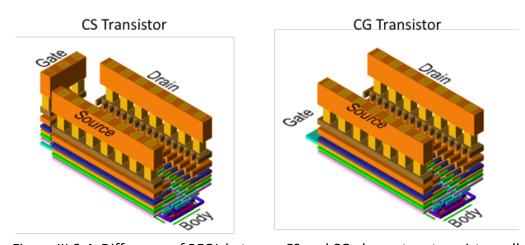

| Figure III.3.4: Difference of BEOL between CS and CG elementary transistor cells                 | 157    |

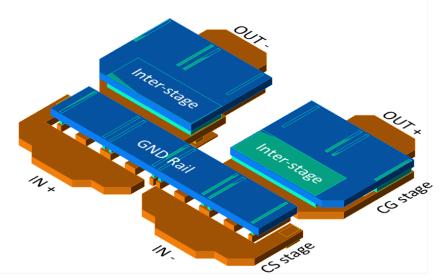

| Figure III.3.5: Interconnections in the cascode stage                                            |        |

| Figure III.3.6: S1 driver power stage topology                                                   |        |

| Figure III.3.7: S1 driver power stage layout                                                     | 160    |

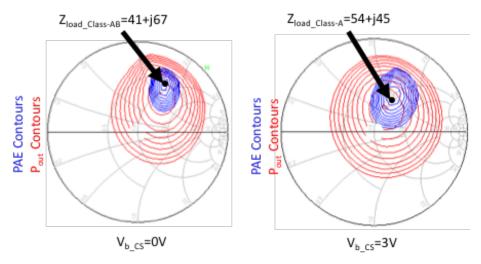

| Figure III.4.1: Active device intrinsic capacitances evolution versus body biasing simulations   |        |

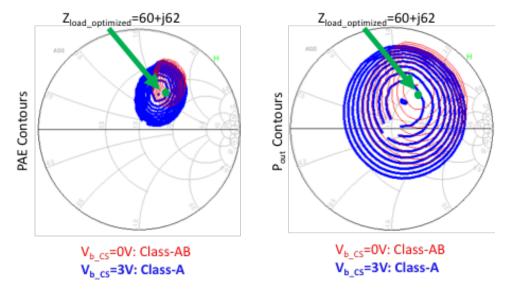

| Figure III.4.2: Load-pull for extreme body-biasing conditions of OV and 3V and associated o      | ptimal |

| differential impedances                                                                          | 162    |

| Figure III.4.3: Optimum output load determination strategy illustration                          | 163    |

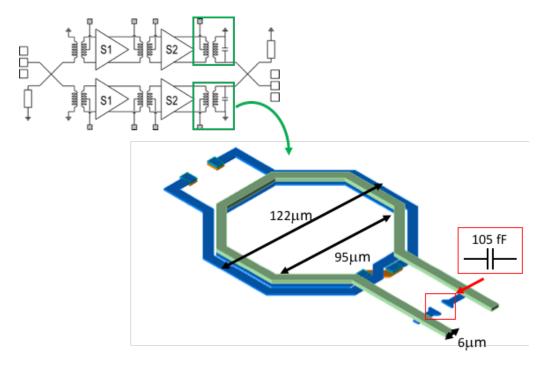

| Figure III.4.4: Output matching network balun with associated dimensions                         | 164    |

| Figure III.4.5: Output balun performances                                                        | 164    |

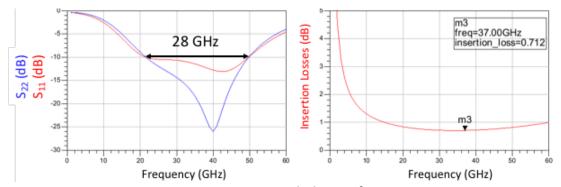

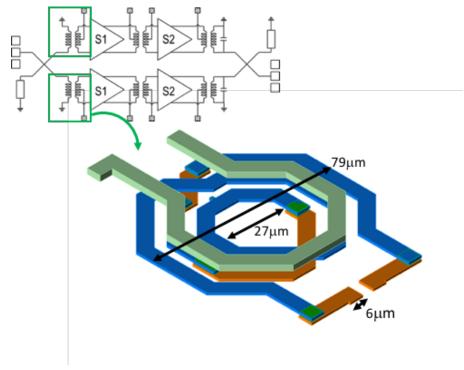

| Figure III.4.6: Inter-stage matching network 3D view and dimensions                              | 165    |

| Figure III.4.7: Inter-stage matching network post-layout performances                            | 166    |

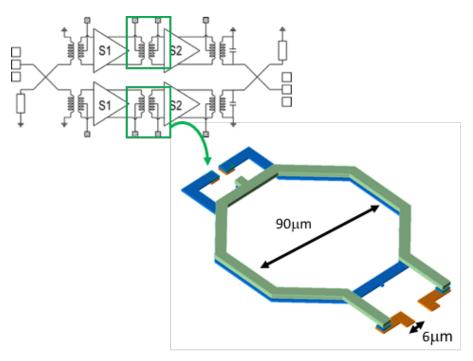

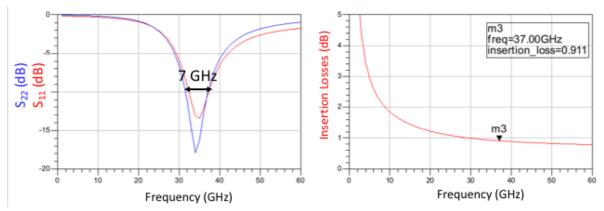

| Figure III.4.8: Input matching network 3D view and dimensions                                    | 167    |

| Figure III.4.9: Input matching network post-layout performances                                  | 167    |

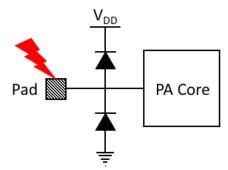

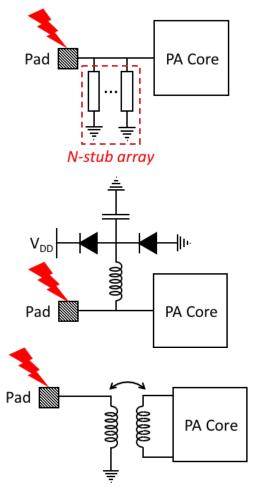

| Figure III.5.1: Diode-based ESD protection                                                       |        |

| Figure III.5.2: Several ESD protection usable at mmW frequencies on RF paths                     | 169    |

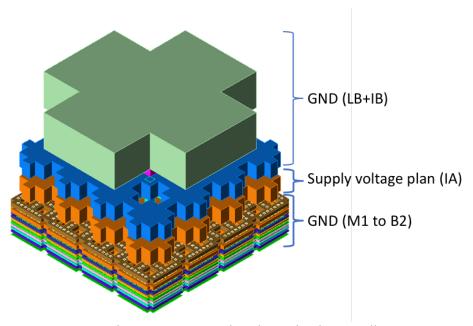

| Figure III.5.3: Elementary ground and supply planes cell 3D view                                 |        |

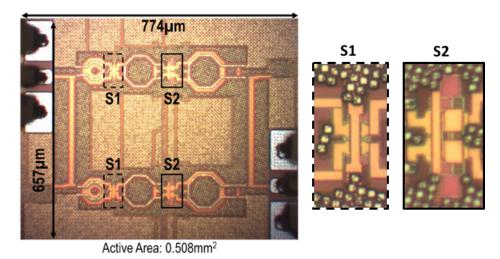

| Figure III.6.1: Manufactured power amplifier photomicrograph                                     |        |

| Figure III.6.2: Small-signal measurements test bench                                             |        |

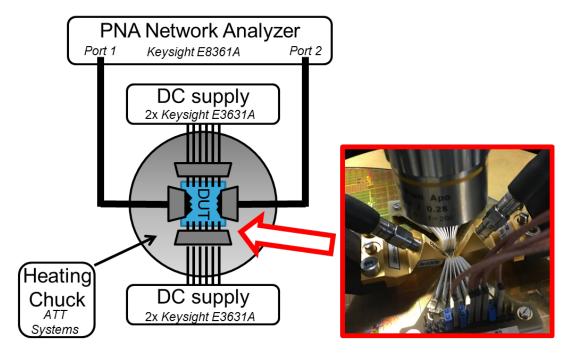

| Figure III.6.3: Large-signal measurements test bench                                             |        |

| Figure III.7.1: Measured S-Parameters with body biasing continuous tuning                        |        |

| Figure III.7.2: Large-signal measurements: Gain (a), PAE (b) and Power consumption (c) with                   |     |

|---------------------------------------------------------------------------------------------------------------|-----|

| body biasing tuning variation from 0V to 1.65V                                                                | 178 |

| Figure III.7.3: AM-PM versus $P_{out}$ measurements at 31GHz with body biasing tuning from 0V                 | to  |

| 1.65V                                                                                                         | 180 |

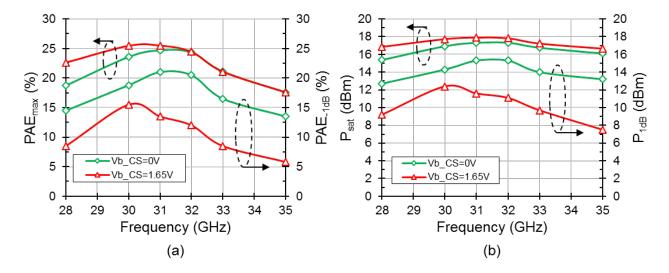

| Figure III.7.4: Large-signal measurements: $PAE_{max}/PAE_{-1dB}$ (a) and $P_{sat}/P_{1dB}$ (b) in extreme mo | des |

| from 28GHz to 35GHz                                                                                           | 182 |

| Figure III.8.1: Large-Signal measurements at 31GHz from 25°C to 125°C                                         | 184 |

| Figure III.8.2: Small-Signal measurements from 25°C to 125°C in high-linearity mode                           |     |

| Figure III.8.3: Small-Signal measurements from 25°C to 125°C in high-gain mode                                | 186 |

| Figure III.9.1: Statistical PAE $_{max}$ , power gain and $P_{sat}$ measurements over 13 on-wafer             | 188 |

| Figure III.10.1: State of the art comparison: power gain level versus P <sub>sat</sub>                        | 193 |

| Figure III.10.2: State of the art comparison: PAE versus P <sub>sat</sub>                                     | 194 |

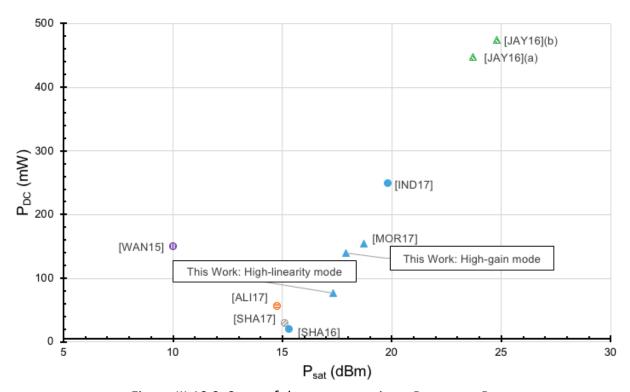

| Figure III.10.3: State of the art comparison: P <sub>DC</sub> versus P <sub>sat</sub>                         | 194 |

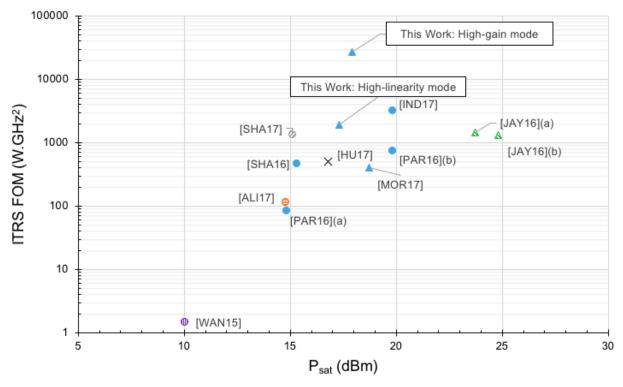

| Figure III.10.4: State of the art comparison: ITRS FOM versus P <sub>sat</sub>                                | 195 |

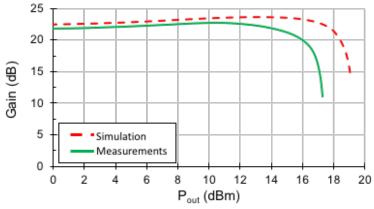

| Figure III.11.1: Gain measurements versus simulations with driver C <sub>neutro</sub> =20fF                   | 197 |

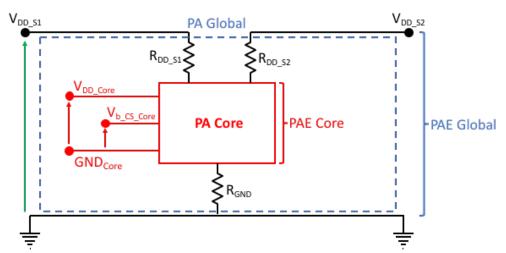

| Figure III.11.2: Power amplifier core and access resistances                                                  | 197 |

| Figure III.11.3: PAE comparison between measurements and simulations featuring $R_{VDD\_S2}$ are              | nd  |

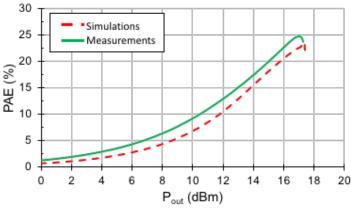

| <i>R<sub>GND</sub></i>                                                                                        | 198 |

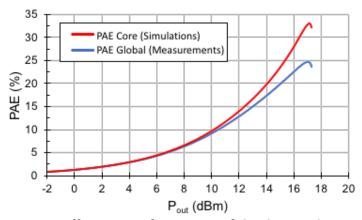

| Figure III.11.4: Core efficiency performances of the designed power amplifier                                 | 198 |

| Figure III.13.1: 3D view of 90° hybrid coupler layout with lateral ground planes                              | 200 |

| Figure III.13.2: Capacitances added on unitary cell                                                           | 201 |

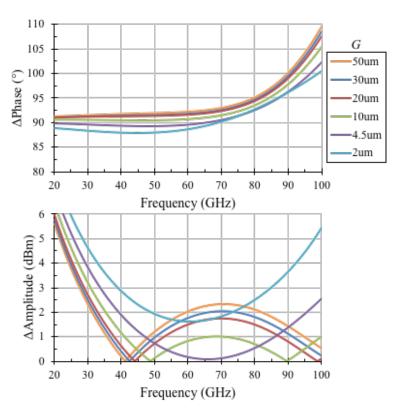

| Figure III.13.3: Small-signal simulations for several ground planes distances from coupler                    | 202 |

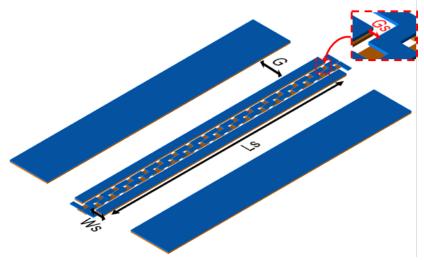

| Figure III.13.4: 3D view of tunable multimode 90° hybrid coupler layout                                       | 204 |

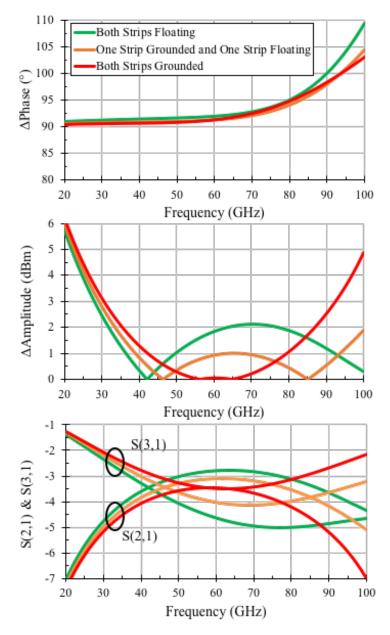

| Figure III.13.5: Tunable Multimode 90° hybrid coupler simulated performances                                  | 206 |

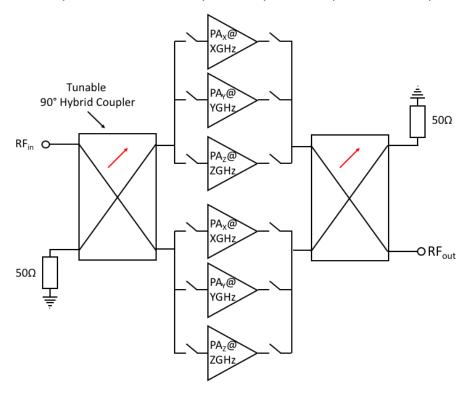

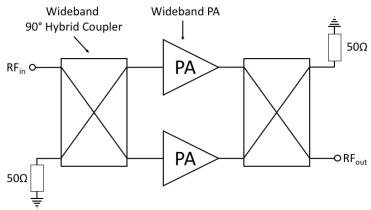

| Figure IV.2.1: Balanced frequency switched PA illustration                                                    | 210 |

| Figure IV.2.2: Balanced wideband PA illustration                                                              | 211 |

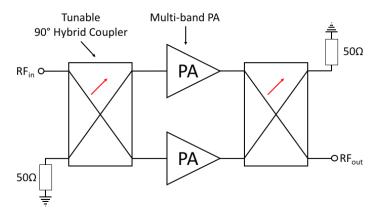

| Figure IV.1.3: Balanced multi-band PA illustration                                                            | 211 |

# Table of Illustrations

# **Tables**

| Table I.1.1: Cell dimensioning and characteristics (data source: [QOR17])                                                      | 27     |

|--------------------------------------------------------------------------------------------------------------------------------|--------|

| Table I.2.1: Definition of the different powers involved in a power amplifier                                                  | 37     |

| Table I.2.2: Theoretical efficiency achievable by operating classes                                                            | 45     |

| Table I.4.1: Specifications to achieve with the power amplifier designed during the thesis                                     | 69     |

| Table II.1.1: 28nm FD-SOI CMOS technology transistors body biasing mode, limits and nomin                                      | nal    |

| voltage                                                                                                                        | 76     |

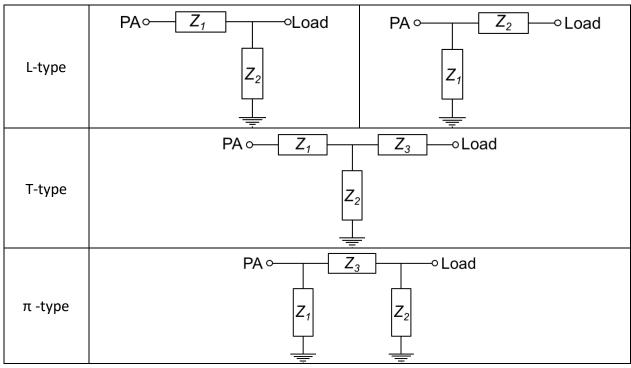

| Table II.4.1: L-type, T-type and $\pi$ -type matching networks block schemes                                                   | 95     |

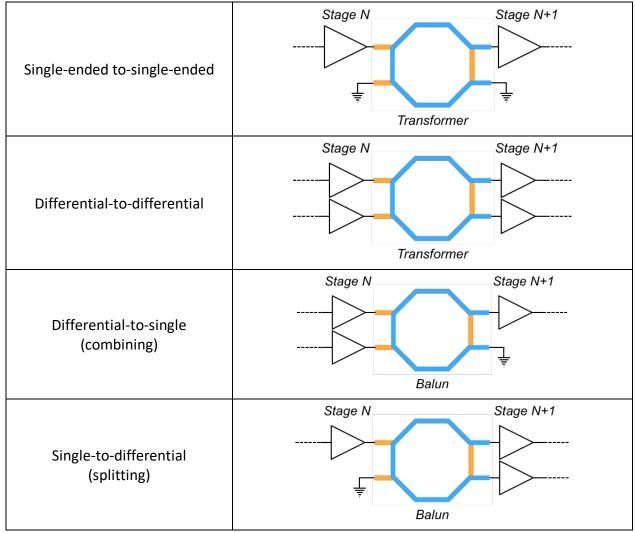

| Table II.4.2: Different inter-stage matching networks achievable with transformers and balu                                    | ıns 98 |

| Table II.5.1: Technological and geometrical parameters definitions used in the model                                           | 104    |

| Table II.5.2: $K_R$ HF resistances weighing factor depending on transformer topology [LEI11]                                   | 106    |

| Table II.5.3: $K_1$ and $K_2$ values depending on transformer geometry [MOH99]                                                 | 107    |

| Table II.5.4: $\mathcal{E}_{IA\text{-}Sub}$ , $\mathcal{E}_{IB\text{-}Sub}$ and $\mathcal{E}_{IA\text{-}IB}$ parameters values | 108    |

| Table II.5.5: Geometrical parameters of the designed transformer                                                               | 110    |

| Table II.5.6: Momentum setup comparison for standalone 90° hybrid coupler: simulation                                          |        |

| resources                                                                                                                      | 115    |

| Table II.5.7: Momentum setup comparison for standalone 90° hybrid coupler: simulation                                          |        |

| resources                                                                                                                      | 116    |

| Table II.6.1: Stability depending on $k_{rollet}$ and $\Delta$ values                                                          | 118    |

| Table III.4.1: S1 and S2 stages optimum impedance values                                                                       | 165    |

| Table III.7.1:Optimal operating point                                                                                          | 175    |

| Table III.10.1: mmW PA state of the art comparison table                                                                       | 192    |

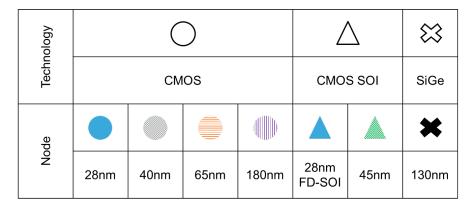

| Table III.10.2: Technology classification used in Figures IV-14 to IV-17                                                       | 193    |

| Table III.13.1: Added capacitances for several gap distances                                                                   | 203    |

| Table III.13.2: Geometrical parameters                                                                                         | 204    |

| Table III.13.3: Comparison with 90° hybrid coupler state of the art                                                            | 205    |

| Table IV.1.1: Large-signal measurements versus targeted values                                                                 | 208    |

| Table IV.2.2: mmW frequency bands under study for 5G complementary spectrum                                                    | 209    |

### General Introduction

We are at the dawn of a revolution in the telecommunication industry. The next generation of mobile network, the 5G, is planned to be deployed in 2020 and contrary to its predecessors it will not be a mobile-centroid network. Therefore, challenging specifications are expected to leverage new applications that will connect people, things, and the world. No standard is available before 2019 but we already know that to achieve the targeted specifications, mmW frequency bands allocation will be necessary. To overcome these high frequencies limits and leverage 5G, new design techniques will be implemented at base stations and end-user devices. The telecommunication industry is actually working on transceivers for mmW 5G and while GaAs, GaN and SiGe technologies have been used for mobile communications, the targeted mass market drives the need for high performances and low-cost integration that FD-SOI CMOS technology can offer.

In any transceiver, the power amplifier design is challenging. In deep sub-micron processes for telecommunication field at mmW frequencies, this is a critical block that has to be designed carefully. In addition, the 5G specifications impose challenging requirements at power amplifier level. This CIFRE thesis, realized in the frame of the ST-IMS common laboratory is targeting several goals:

- The specifications for power amplifier design featuring state of the art performances around 30GHz to address the 5G challenges.

- A power amplifier design solution meeting these specifications and implemented in 28nm FD-SOI technology.

- The exploration of the 28nm FD-SOI technology for RF and mmW applications, with industrial implementation margins.

This manuscript is composed of three chapters.

The first chapter is defining the context of this thesis and presents the mobile telecommunications market evolutions leading to the 5G emergence. To define the power amplifier specifications for 5G leveraged applications, we provide complete overviews of the expected frequency spectrum, potential modulations, and technological solutions to enable high-data rates in dense urban areas. In addition, important power amplifier parameters and performances are defined. The 5G mmW PA challenges are then discussed. A complete state of the art shows the PA design trends for the frequency of interest and highlights the actual limitations that this thesis target to overcome. Therefore, at the end of this first chapter, the thesis goals concerning performances are clearly exposed.

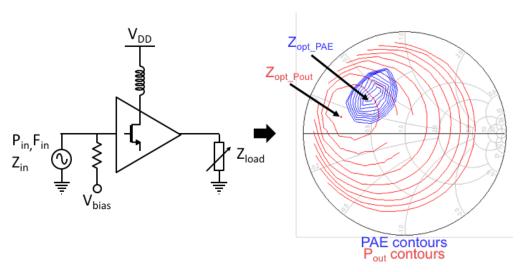

The second chapter presents a design flow for mmW 28nm FD-SOI power amplifiers. The specificities of this technology and the reconfigurability offered by the body-bias capability are discussed.

Then the possible overall PA architectures and amplification stages topologies are exposed. While general mmW impedance matching, stability, and design techniques enhancement are provided, this technology requires specific passive design approach. For this purpose, a specific model for transformer design is proposed. EM simulation tools optimization for fast and accurate prototyping is also discussed to complete a step-by-step design flow and give directions to designers. Indeed, accurate EM simulations in deep submicron technologies at high frequencies is mandatory and time-consuming due to the design elements small dimensions.

The third chapter describes the design and measurements of a balanced power amplifier targeting the 5G challenges in 28nm FD-SOI CMOS process and following the design flow defined in Chapter II. It exposes the design and layout choices, optimizations and margins for a robust integration with gain reconfigurability. The balanced topology choice, providing robustness to output antenna impedance variations, and its implementation are explained. The power-stage is featuring the first reconfigurable cascode implemented in 28nm FD-SOI. This reconfigurability achieves continuous wide range fine gain tuning and dynamic class switching. An output load impedance determination strategy is explored to avoid the performances degradation generally induced by dynamic class switching. On-wafer probing measurements have been conducted exhibiting state of the art level performances over a 5G frequency range. Robustness to temperature ranges up to 125°C and local process variability is also explored. A comparison with the state of the art is provided. This power amplifier has demonstrated the best in class ITRS FOM over the targeted frequency range. Finally, a novel reconfigurable and wideband design for 90° hybrid coupler is explored for future works. This manuscript is concluded by research perspectives for balanced power amplifiers architectures reducing multi-band transceivers complexity and costs by using this new coupler design.

# Chapter I: The Road to 5G Power Amplifier

# Design

### - Table of Contents -

| I.1   | 5G: | Future global wireless network                     | .20 |

|-------|-----|----------------------------------------------------|-----|

| 1.1.1 | L   | Generalities                                       | .20 |

| 1.1.2 | 2   | Frequency considerations                           | .23 |

| 1.1.3 | 3   | Technical solutions to leverage 5G                 | .25 |

| 1.1.4 | ŀ   | Overview of potential 5G modulations and waveforms | .31 |

| 1.1.5 | 5   | CMOS technology for 5G                             | .34 |

| 1.2   | Pov | ver Amplifier theory                               | .36 |

| 1.2.1 | _   | Power amplifier generalities                       | .36 |

| 1.2.2 | 2   | PA classes of operation                            | .40 |

| 1.2.3 | 3   | Parameters for modulated signals                   | .45 |

| 1.2.4 | ŀ   | PA for 5G: Specifications                          | .49 |

| 1.3   | mm  | W PA state of the art                              | .51 |

| 1.3.1 | _   | State of the art before circuit design             | .52 |

| 1.3.2 | 2   | State of the art after circuit design              | .59 |

| 1.4   | Con | iclusion                                           | .68 |

# Chapter I: The Road to 5G Power Amplifier Design

### I.1 5G: Future global wireless network

### I.1.1 Generalities

The mobile communication revolution started in the early 1980's with the first Motorola DynaTAC mobile phone. At that time, the communication was analogic and the mobile phone was only used to phone. This was the first generation of mobile network, the 1G, paving the way for the future of telecommunications. The next decades have seen the apparition of new usages and new mobile network generations. With the 2G, using GSM, GPRS, EDGE and CDMA standards, this is the beginning of text messages and early mobile "Internet" connection. With the 3G in the 2000's, the UMTS/HSPA/CDMA2000 standards leveraged multimedia usages. It was possible to browse the World Wide Web, send emails, stream music, send videos thanks to way higher datarates compared to the previous generation. The first smartphones are appearing, diversifying the usages. However low data-rates around 3.1Mbps were reached in 3G. This exponential multimedia usage drove the need for higher data-rates. The phones are now smart and multitask, the 4G is birthed, leveraged by LTE and then LTE-Advanced standards. This is the current mobile network that we use in our everyday life.

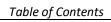

The smartphone has entered our lives and from this time the mobile market presents an uninterrupted growth. In their mobility report, the analysts from Ericsson [ERI15] are making projections about the market evolutions concerning the broadband mobile subscriptions. An evolution of more than +110% in 2020 compared to 2015 is expected, with more than 7 billion broadband mobile subscriptions all over the world, leveraged by the emergence of smartphone in Asian countries. Meanwhile, the analysts from Cisco [CIS16], are expecting more than 11 billion mobile network connected objects in 2020 and more than 24 billion IP network connected objects in 2019. For both cases the part of smartphones and machine-to-machine (M2M) connections in these numbers is the highest. The evolution of the smartphone market and the democratization of high definition mobile video streaming will drive an explosion of the data traffic, with a 10 times higher monthly data-traffic level in 2020 compared to 2015. The emergence of the connected world with the Internet Of Things (IOT) explains the increasing number of M2M connections. The 5G infrastructure Public and Private Partnership [5GPPP] expects the emergence of the connected world to "connect over 7 trillion wireless devices serving over 7 billion people". This mobile market evolution is illustrated in Figure I.1.1.

Figure I.1.1: Mobile telecommunications market 2014-2020 (data sources: [ERI15], [CIS16])

Furthermore, in the future connected world, a real revolution concerning the usages is planned. Everything and everybody will be connected, anywhere, anytime. The transportations become smart and safer with autonomous vehicles and transportation networks monitoring, optimization and security. The City becomes smart, safer. The flux and resources are monitored and managed thanks to the IOT with for example drinking water constant and automated quality check. The houses become connected too, allowing higher safety, a better resources management and is easier to use thanks to home automation. Furthermore, the industry will be connected too and the IOT will play an important role for that. Virtual and augmented reality will

open the way for new entertainment and business opportunities. These technologies will also allow the E-Health era with remote surgery, real-time remote patient monitoring. These are just some examples of the endless capabilities offered by the connected world.

The emergence of these new usages drives the need to rethink the mobile network actually centered on the smartphone usage and to propose a new network architecture, interoperable with existing networks to enable this connected world. As Nokia stated "Driven by the enormous increase in mobile data traffic and flourishing user demands, we need to look beyond 4G". This is in this context that the 5G, the next generation of mobile network is emerging, with a first deployment planned for 2020.

While no standard is yet available, the expected usages are drawing the contours of needed 5G network specifications [AND14] and are discussed in the following paragraph.

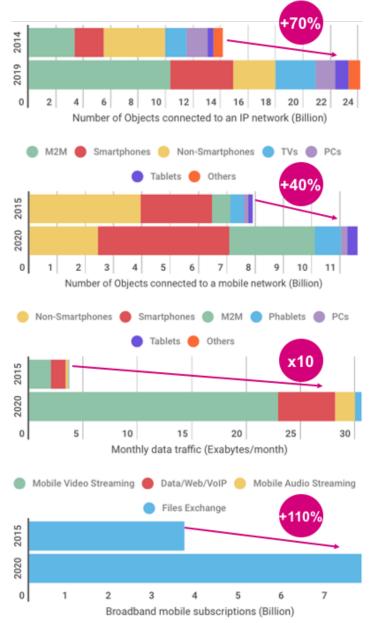

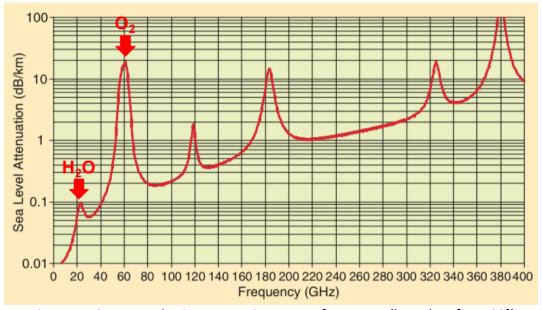

In fact, with the huge increase of data usage, higher data-rates are expected with around 10Gbps downlink speed to allow ultra-HD video streaming and instant access to any content, making the Internet more tactile [FET14]. This notion of real-time tactile Internet [ITU14] is also extremely important for critical applications such as autonomous transportations and remote surgery. For these applications, a maximum system latency of 1ms is expected. The huge deployment of IOT with wireless sensors networks is driving the need for low power usages with battery lifetime of more than 10 years to be efficient. Another important point is the network ubiquity, leading to a network coverage 1000 times higher than in 2010 for constant quality [PIE15] and reliability of service for the user. Finally, while a collective awareness about environment and natural resources preservation is taking place, a decrease by 90% of the 5G network energy consumption is expected, limiting both operating costs and environmental impact. These specifications are summarized in the Figure I.1.2. It is noticeable that these specifications are not fixed and will depend on the different use-cases.

Figure I.1.2: 5G expected specifications (may vary depending on the use-case)

### I.1.2 Frequency considerations

The past and actual mobile network generations are using several frequency bands depending on the region of the world, managed by the International Communications Union. Traditionally, the frequency bands allocated for mobile networks are located under 3.6GHz. These frequencies are beneficial in term of signal propagation. This is easily illustrated by the free-space path loss formula (I-1) and (I-2), derived from Friis equation [FRI46], where higher wavelength  $\lambda$  is leading to lower attenuation in free space.

$$Attenuation = \left(\frac{4\pi \cdot d}{\lambda}\right)^2 \tag{I-1}$$

$$Attenuation (dB) = 20 \log \left(\frac{4\pi \cdot d}{\lambda}\right)$$

(I-2)

These long distance achievable communications made the frequency bands under 3.6GHz very popular throughout the years for multiple applications and this is leading now to a spectral congestion. This issue is sometimes referred as "beachfront effect" and the crowded sub-3.6GHz spectrum cannot handle the needs of 5G network [AND14].

Furthermore, these frequency bands offer a limited bandwidth, incompatible with the targeted data-rates. In fact, the relation between channel capacity *C* (the maximum achievable data-rate) and bandwidth in a noiseless channel is given by the Nyquist formula (I-3) with *M* the number of signal levels and *BW* the bandwidth in Hz. It is noticeable that higher bandwidth is leading to higher achievable data-rate.

$$C(bps) = 2 \cdot BW \cdot \log_2(M) \tag{I-3}$$

The same assessment can be done regarding the Shannon-Hartley formula (I-4) from [SHA49], where the channel capacity C is function of the bandwidth and SNR (Signal-to-Noise Ratio) in a noisy channel.

$$C(bps) = BW \cdot \log_2(1 + SNR) \tag{I-4}$$

The conventional sub-3.6GHz spectrum is not sufficient to leverage 5G and a complementary spectrum is needed. The unlicensed frequency band around 5GHz is a solution but will not be sufficient to achieve the required high data-rates.

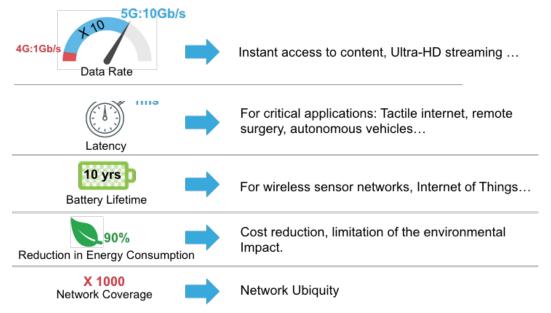

Therefore, a complementary spectrum in the mmW frequencies appears as a good solution to overcome these limits. In fact, wide frequency bands are available, allowing high data-rates. However, these bands suffer from strong attenuation in free space and several mmW frequency bands suffer from air attenuation as they correspond to peak absorption of  $O_2$  (60GHz) and  $O_2$  (23GHz) [UKTI88]. The atmospheric attenuation at sea level in function of the frequency is available in Figure I.1.3 from [WEL09].

Figure I.1.3: Atmospheric attenuation versus frequency (based on [WEL09])

This strong attenuation made the mmW frequencies unsuitable for mobile communications and so these bands are free from any spectral congestion issue. They are ideal to leverage 5G as recent technology enhancements can overcome the attenuation [RAP13] and are discussed in the following section.

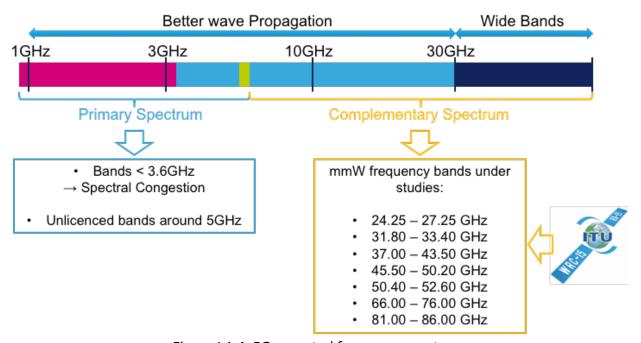

No standard for 5G will emerge before 2019 during the World Radiocommunication Conference (WRC-19) organized by the International Communications Union (ITU) and so no mmW frequency spectrum is yet allocated for 5G at this day. However, several mmW frequency bands are under studies by the 5G industrial actors since ITU WRC-15 conference [WRC15]. The expected 5G frequency spectrum is summarized in Figure I.1.4.

Figure I.1.4: 5G expected frequency spectrum

### I.1.3 Technical solutions to leverage 5G

As we expose previously, one of the main challenges of 5G is to achieve high data-rates and network coverage even in dense urban areas.

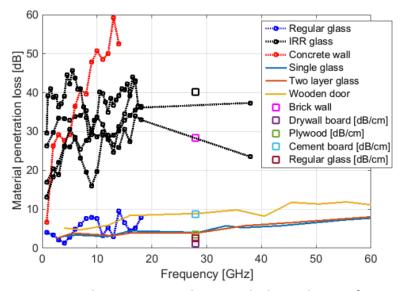

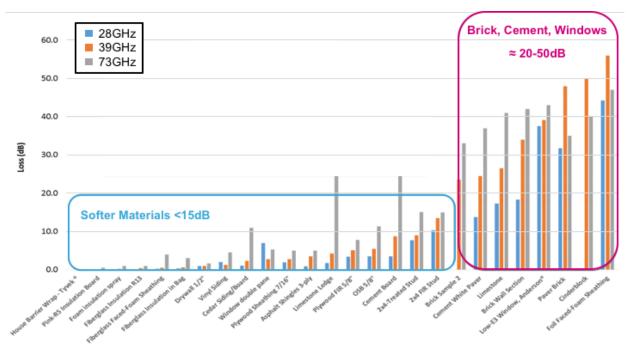

In dense urban areas, the mmW frequencies used to achieve high data-rates are suffering from natural path-loss attenuation and atmospheric peak absorption as we stated previously but also from the attenuation in the different materials encountered in this environment. Several material attenuation values are available in Figure I.1.5 [GLO15] and Figure I.1.6 [NOK16].

Figure I.1.5: Penetration losses in several materials depending on frequency [GLO15]

Figure I.1.6: Losses induced by material penetration at 28GHz, 39GHz and 73GHz [NOK16]

To overcome this issue and allow a higher network capability, the densification of active nodes is a solution but is not the only solution under study. Several technical solutions are studied from the use of small-cells [LAY14] and backhaul [TAO15] to massive MIMO (multiple-input multiple-output) [GAO15] and adaptive beamforming [CHE16]. This section presents a brief overview of the technical solutions that can leverage 5G.

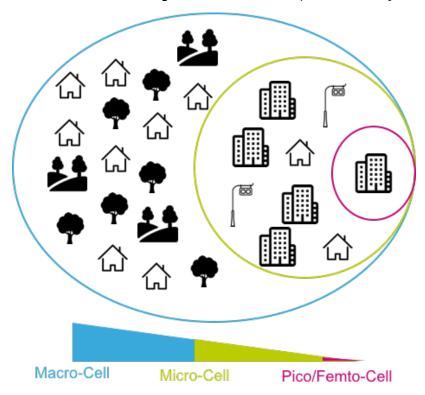

The cell-scaling is fundamental for 5G as it allows several coexistent network layers depending on the environment. The use of small-cells architectures (micro, nano and femto cells) in addition to macro-cells will allow a significant increase in data-rates and efficiency by allowing short range communications and base station complement in dense urban areas with frequency re-use and limited power consumption. The cell dimensioning and the use-case scenario differ regarding the environment and while the small-cells will be advantageous in urban area it will have no interest in rural areas where macro-cells are more adapted. The cell dimensioning and the characteristics concerning power, parallel device number and range are available in Table I.1.1 and illustrated in Figure I.1.7. The characteristics of small-cells communication make the mmW frequencies totally suitable in this case.

|            | Range<br>(radius, km) | Number of users (simultaneous) | Output power<br>(W) | Locations      |

|------------|-----------------------|--------------------------------|---------------------|----------------|

| Macro-cell | 8 to 30               | >2000                          | 10 to >50           | Outdoor        |

| Micro-cell | 0.2 to 2              | 100 to 2000                    | 1 to 10             | Indoor/Outdoor |

| Pico-cell  | 0.1 to 0.2            | 30 to 100                      | 0.25 to 1           | Indoor/Outdoor |

| Femto-cell | 0.01 to 0.1           | 1 to 30                        | 0.001 to 0.25       | Indoor         |

Table I.1.1: Cell dimensioning and characteristics (data source: [QOR17])

Figure I.1.7: Cell-dimensioning illustration

The connection between small-cells is the principle of backhaul. It consists of very short, high data-rates and high capacity signal bouncing in space. With a smart implementation of small-

cells using backhaul in a city (for example in traffic lights or floor lamps), the backhauling can provide high-speed data link at mmW frequencies by avoiding the losses encountered in a base-station-to-end-user direct communication through buildings and other obstacles. It allows multipath possibilities, base station decluttering and ensures a constant quality of service even in case of several nodes failures.

However, base station level optimization is also needed to address the 5G challenges. The concept of Massive MIMO consists in the implementation of large antennas arrays in base stations to allow a large number of simultaneous connections of spatially separated devices with the same quality of service. This technique allows spectral efficiency enhancement without base station densification. A better energy efficiency is also expected as large antenna arrays gain allows lower transmission power levels. The Figure I.1.8 illustrates the concept of Massive MIMO.

Figure I.1.8: Massive-MIMO concept

Beamforming is also a technology expected to leverage 5G conjointly with Massive MIMO. Beamforming is a technique actually used in defense and satellites applications. It consists on the combination of signal in an antenna array to electrically orient a beam without needing any antenna mechanical movement, enabling higher reliability of systems. In a beamforming array, composed by *N* amplification cells, a phase shift is induced by phase shifter in each amplification path, to dynamically, quasi-instantaneously and spatially control the beam orientation and so concentrate the transmitted power to a desired position. This principle is illustrated in Figure I.1.9.

Figure I.1.9: Beamforming concept

Furthermore, the use of multiple amplification paths in base station for beamforming is interesting in term of reliability of service. If one path is under failure, the other paths can overcome this issue.

The use of beamforming technique in massive MIMO array allows an interesting spatial feature, referred as Full Dimension MIMO [NAM13], [KIM14], allowing 3D MIMO communications as illustrated in Figure I.1.10. While this technique has the advantage to provide high number of connections in urban and rural areas, large antenna and amplification system arrays present the disadvantage of being costly.

Figure I.1.10: Full dimension MIMO concept

Furthermore, it is notable that while all the antenna and amplification paths will be the same in this kind of base station, the environmental condition can differ from a circuit to another depending on its position on the array or environmental conditions. This can lead to differences into antenna impedances and can be critical at the amplification path systems output. This kind of mismatch can induce standing wave issue caused by the reflection of a wave by the load. The amplitude of the reflected wave is function of  $\Gamma_L$ , the reflection coefficient of the load (I-5).

$$V_{Reflected} = \Gamma_L \cdot V_{Incident} \tag{I-5}$$

It is possible to quantify the "quality" of the matching with the Voltage Standing Wave Ratio (VSWR), a low value corresponding to a poor matching. The VSWR can be estimated with the equation (I-6).

$$VSWR = \frac{1 + |\Gamma_L|}{1 - |\Gamma_L|} \tag{1-6}$$

Depending on the phase conditions of both reflected and incident waves, a destructive or constructive combination between waves can be obtained. A destructive combination reduces the voltage swing at the amplifier output and can degrade the performances of the overall amplification chain. However, constructive combination enhances the voltage swing at the amplifier output and can dramatically degrade the power amplifier, depending on the amplitude

and the duration of this phenomenon. This effect is illustrated in Figure I.1.11. Therefore, security margins are necessary over the output swing to overcome the power amplifier degradation in case of mismatch.

Figure I.1.11: Constructive combination of incident and reflected waves illustration

### I.1.4 Overview of potential 5G modulations and waveforms

5G required specifications will not only be achieved with new network architectures. New modulations and waveforms schemes are also under study to achieve these specifications in terms of coverage, speed and multi-service abilities to meet the needs of several use-cases. In this section we provide an overview of some 5G candidate modulations and waveforms that have been identified [NEK16], [MED17], [CAI17]. The use of MIMO architectures impose a specific suitability concerning inter-cell interferences while the use of multiple frequency bands requires suitability to flexible and dynamic band allocation.

Concerning the modulation schemes, recent work shows that high-order Quadrature Amplitude Modulations (QAM) are allowing satisfying performances to fit with the 5G needs [KIM16]. However, the inter-cell interferences in dense urban areas induced by small-cells, backhauling, FD MIMO and their coexistence motivated the researches for non-conventional QAM modulations. Frequency Quadrature Amplitude Modulation (FQAM) [HON13], hybrid between Frequency Shift Keying (FSK) and QAM modulations has recently been explored for 5G applications. An example of FQAM modulation scheme can be found in Figure I.1.12, from [SAM15]. FQAM is particularly advantageous in terms of performances notably concerning frame-error-rate [GSM14] and transmission rates for edge-users [HON14]. Furthermore, these performances enhancement are achieved with no complexity increase as the architecture of an OFDM FQAM transceiver is similar to a classical OFDM architecture [NEK16]. However high peak-to-average power ratio (PAPR) is also achieved with FQAM.

Figure I.1.12: 16-ary FQAM illustration [SAM15]

Amplitude Phase Shift Keying modulation (APSK) [MER15] is a hybrid between ASK and PSK and has recently been studied for 5G. An example of APSK constellation diagram is available in Figure I.1.13 from [LI15]. This modulation, coupled with advanced channel coding and demodulation algorithms has demonstrated interesting performances in terms of channel capacity [IMT15]. In [GAZ11] and [BAL12], it has been illustrated that APSK modulation shows a lower PAPR than conventional QAM with the power back-off benefit for power amplifiers. While complex algorithms used for this modulation are leading to higher transceiver complexity, the PAPR reduction achievable with constellation optimization makes this modulation particularly interesting for 5G.

Figure I.1.13: 16-ary APSK illustration [LI15]

In addition to modulation schemes, adapted waveforms are also important. The required specifications drove the need for waveforms that are able to handle multi-frequency spectrum, multiple use-cases with enhanced spectral efficiency and lowered out-of-band emissions to avoid interferences while limiting the power consumption. For this purpose, multi-carrier modulations are being studied. Orthogonal Frequency-Division Multiplexing (OFDM) [CHA66] is actually used in LTE/LTE-Advanced standards and is a strong candidate for 5G. It offers the benefice of being easily integrated in MIMO systems with no added transceiver complexity. OFDM consists in the use of multiple subcarriers within the same channel. The subcarriers are orthogonal to each other's. Therefore, the subcarriers can overlap with no interference. However, guard intervals in the time domain are necessary to avoid multi-path delay induced inter-symbol interferences at the receiver. Cyclic prefix [BIN90] is generally used in OFDM (CP-OFDM) to reduce these intersymbol interferences. It consists in the prefixing of each symbol by the end part of the same symbol. However, spectral efficiency and out-of-band leakage must be improved to meet the needs of 5G and avoid the use of guard-bands. Figure I.1.14 illustrates the principle of OFDM.

Figure I.1.14: Frequency and time domains OFDM representation [KEY17]

For this purpose, several enhancements of OFDM waveform have been recently studied:

- Filtered-OFDM [ABD15] is performing an optimization over out-of-band leakage through sub-carrier filtering in the frequency domain and is lowering the guard-band consumption. Furthermore, the need for global synchronization system can be relaxed compared to classical OFDM topology [ZHA15].

- Windowed-OFDM is very similar to Filtered-OFDM. It is performing an out-of-band leakage reduction through non-rectangular windows use in the time domain. Therefore, side-lobes reduction is achieved [LUO14] and synchronization requirements can be relaxed [NEK16].

- Unique Word-OFDM [HUE10] is a variant of OFDM that achieves improved bit-errorrate and out-of-band emission performances compared to CP-OFDM [ONI10], [RAJ13].

It consists in the use of a non-random unique-word deterministic sequence as guard-band and does not depend on the transmitted data, contrary to random cycle prefix. Therefore, the symbol duration is not extended. Furthermore, this OFDM variant can be used for synchronization and channel estimation [HOF10].

- Universal Filtered-OFDM [WIL14] allows the use of multiple signal layers with the users separated by their interleavers. This is improving cross-talk and multi-path robustness for multiple access channel. It consists in the filtering of sub-carriers blocks. Compared to CP-OFDM, inter-symbol interferences are reduced and the spectral efficiency is improved thanks to guard-band reduction.

However, maximum spectral efficiency is still not achieved and solutions like FBMC waveforms [BEL10] have been proposed for 5G but make the transceivers architectures more complex. Finally, high PAPR is still achieved with OFDM based waveforms and complex modulation schemes that could be used for future wireless networks, compared with single-carrier waveforms due to large signal envelope fluctuations [ROH99]. PAPR reduction for complex modulation schemes and waveforms is actually a trend in the literature to address the 5G challenges [LAA15], [BUL14], [BEN17].

### I.1.5 CMOS technology for 5G

In the previous sections we highlighted that the future mobile network will be defined by the use of small-cells to densify the network. A huge increase of smartphone number and data use, Massive MIMO phased array for beamforming and power consumption reduction are also expected. This mass market requires production costs limitation and high integration capacities for both active network nodes, base stations and end-user devices.

The III-V semiconductors technologies like GaN or GaAs and silicon based SiGe are offering high power capabilities. However, their integration capacity is limited and the production costs are higher compared to CMOS technology. In addition, transceivers in III-V technologies suffer from high power consumption due to high supply voltage levels. At the contrary, CMOS technologies present a high capacity of integration while they are low cost in terms of production. A comparison between GaAs, SiGe and CMOS technology is available in Figure I.1.15.

Figure I.1.15: GaAs, SiGe and CMOS technologies comparison [LAR15-2]

Nevertheless, the downscaling in CMOS technologies made them more adapted for digital circuits. This downscaling, offering lower gate-length, gate oxide thickness and supply voltages allows higher die density, faster devices and reduced power consumption. Recent progresses have been made to allow successful implementation of RF circuits and complete transceivers on CMOS technologies, offering promising performances in deep sub-micron technologies.

With advanced technologies like CMOS SOI, it is possible to integrate both high-speed digital and RF parts to leverage System On Chip (SOC) [CHA99] integration (Figure I.1.16) and so lowering the production cost of communication systems.

Figure I.1.16: System on Chip compared to System in Package

However, the power amplifier remains a bottleneck for SoC integration in advanced deep sub-micron technologies. In fact, the CMOS technology suffers from low transistor breakdown voltages that limit the achievable output power compared to III-V technologies. Nevertheless, the use of Massive MIMO phased-arrays reduce the need for high output power with multi-path

amplification on emitters, as the power is distributed over a wide range of systems. Therefore, the specifications over transmitted power are relaxed. Furthermore, the contribution of power amplifier to overall device power consumption, in both user-end and actual base station, is very large and has to be reduced while high linearity levels are expected. The challenges of CMOS amplifiers for 5G and SoC applications that this thesis addresses are developed in Section I.2.4.

# I.2 Power Amplifier theory

# I.2.1 Power amplifier generalities

In all RF transceiver architectures, the power amplifier is the last element of the transmission chain just before the antenna (Figure I.2.1) and remains challenging to design as a malfunction or degradation impacts critically the overall transmitter performances. In order to achieve power amplifier performance analyses and comparison with the state of the art, several figures of merits can be used and are depicted in the following section.

Figure I.2.1: Power amplifier in different transmitter topologies

First of all, before detailing these different PA performances, it is primordial to be familiar with the different parameters that will be used for calculations. The Figure I.2.2 summarizes these parameters while Table I.2.1 gives their definition.

Figure I.2.2: Different powers involved in a power amplifier

| Name             | Definition                                          |  |

|------------------|-----------------------------------------------------|--|

| P <sub>IN</sub>  | Power delivered by the source                       |  |

| P <sub>AVL</sub> | Power available at the input of the power amplifier |  |

| P <sub>DC</sub>  | Power consumed by the power amplifier               |  |

| P <sub>DEL</sub> | Power delivered by the power amplifier              |  |

| P <sub>OUT</sub> | Power delivered to the load                         |  |

Table I.2.1: Definition of the different powers involved in a power amplifier

From these parameters it is then possible to define the following power amplifier performances.

#### Power added efficiency

The power added efficiency (PAE) is a primordial parameter for power amplifier designed to target mobile networks applications. It links the device input and output power levels with the overall power consumption and so traduces the power amplifier efficiency. This parameter is calculated with (I-7).

$$PAE = \frac{P_{OUT} - P_{IN}}{P_{DC}} \tag{I-7}$$

Several power added efficiency values are interesting to determine when it comes to power amplifier analysis. The  $PAE_{max}$ , corresponding to peak efficiency, is generally used for comparison with the state of the art. However, with complex modulation schemes, the amplifier tends to operate at a certain back-off from maximum output power. The PAE at back-off is so an interesting parameter to enhance. Furthermore, the efficiency at  $P_{1dB}$ , developed in the following section, is also an important comparison point.

Another efficiency parameter can be used, the drain efficiency  $\eta_D$ , but does not take the input power into account in the calculation. This parameter is not preferred for analysis of power amplifiers operating in sine classes. However, it is possible to use it to define efficiency of power amplifier showing different waveforms at the input and output. It is also an interesting parameter to characterize single transistors. Its formula is given in (I-8).

$$\eta_D = \frac{P_{OUT}}{P_{DC}} \tag{I-8}$$

#### Power Gain

The power gain is the parameter that traduces the power amplifier ability to produce output power from a certain amount of power at its input. Several definitions of power gain are available and differs depending on the definition of input power. The definition of the power gain that is used in this work is the transducer gain. It offers the best definition in our case as it takes into account the losses and mismatch induced by matching networks, corresponding to the amplifier in its implementation environment. This power gain can be calculated with the equation (I-9).

$$G = G_{tr} = \frac{P_{OUT}}{P_{IN}} \tag{I-9}$$

Generally, the input and output powers are expressed in dBm, then the power gain becomes (I-10):

$$G(dB) = G_{tr}(dB) = P_{OUT}(dBm) - P_{IN}(dBm)$$

(I-10)

#### Linearity

The linearity is a fundamental parameter for PA operating in communication networks. It traduces the power amplifier ability to amplify a signal without distortion. Several parameters evaluate the linearity of a power amplifier.

#### 1dB compression point

If we consider a continuous-wave signal (CW) applied at the input of a power amplifier, the output power will be defined by (I-11) and (I-12):

$$P_{OUT} = G \times P_{IN} \tag{I-11}$$

$$P_{OUT}(dBm) = G(dB) + P_{IN}(dBm)$$

(I-12)