# Terminaisons verticales de jonction remplies avec des couches diélectriques isolantes pour des application haute tension utilisant des composants grand-gap de forte puissance

Thi Thanh Huyen Nguyen Bui

#### ▶ To cite this version:

Thi Thanh Huyen Nguyen Bui. Terminaisons verticales de jonction remplies avec des couches diélectriques isolantes pour des application haute tension utilisant des composants grand-gap de forte puissance. Electronique. Université de Lyon, 2018. Français. NNT: 2018LYSEI061. tel-02061320

# HAL Id: tel-02061320 https://theses.hal.science/tel-02061320

Submitted on 8 Mar 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre NNT: 2018LYSEI061

#### THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein de (INSA de Lyon)

Ecole Doctorale EEA N° 160 (Électronique, Électrotechnique, Automatique)

Spécialité/ discipline de doctorat : Génie électrique

Soutenue publiquement le 12/07/2018, par : **(Thi Thanh Huyen BUI)**

# Terminaisons verticales de jonction remplies avec des couches diélectriques isolantes pour des application haute tension utilisant des composants grand-gap de forte puissance

Devant le jury composé de :

LEFEBVRE, Stéphane Professeur, SATIE, Paris Président

GHEERAERT, Etienne Professeur, Institut NEEL, Grenoble Rapporteur LEFEBVRE, Stéphane Professeur, SATIE, Paris Rapporteur ISOIRD, Karine Maitre de conférences, LAAS, Toulouse Examinateur LAZAR, Mihai Chargé de recherche CNRS, INSA de Lyon, Villeurbanne AUGE, Jean-Louis Maitre de conférences, INSA de Lyon, Villeurbanne Examinateur

MOREL, Hervé Directeur de recherche CNRS, INSA de Lyon Directeur de thèse

# Département FEDORA – INSA Lyon - Ecoles Doctorales – Quinquennal 2016-2020

| SIGLE     | ECOLE DOCTORALE                                                                                                                                                                                           | NOM ET COORDONNEES DU RESPONSABLE                                                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СНІМІЕ    | CHIMIE DE LYON  http://www.edchimie-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage secretariat@edchimie-lyon.fr INSA: R. GOURDON                                                              | M. Stéphane DANIELE Institut de recherches sur la catalyse et l'environnement de Lyon IRCELYON-UMR 5256 Équipe CDFA 2 Avenue Albert EINSTEIN 69 626 Villeurbanne CEDEX directeur@edchimie-lyon.fr               |

| E.E.A.    | ÉLECTRONIQUE, ÉLECTROTECHNIQUE, AUTOMATIQUE http://edeea.ec-lyon.fr Sec.: M.C. HAVGOUDOUKIAN ecole-doctorale.eea@ec-lyon.fr                                                                               | M. Gérard SCORLETTI<br>École Centrale de Lyon<br>36 Avenue Guy DE COLLONGUE<br>69 134 Écully<br>Tél: 04.72.18.60.97 Fax 04.78.43.37.17<br>gerard.scorletti@ec-lyon.fr                                           |

| E2M2      | ÉVOLUTION, ÉCOSYSTÈME, MICROBIOLOGIE, MODÉLISATION  http://e2m2.universite-lyon.fr  Sec.: Sylvie ROBERJOT  Bât. Atrium, UCB Lyon 1  Tél: 04.72.44.83.62  INSA: H. CHARLES  secretariat.e2m2@univ-lyon1.fr | M. Philippe NORMAND UMR 5557 Lab. d'Ecologie Microbienne Université Claude Bernard Lyon 1 Bâtiment Mendel 43, boulevard du 11 Novembre 1918 69 622 Villeurbanne CEDEX philippe.normand@univ-lyon1.fr            |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-SANTÉ  http://www.ediss-lyon.fr Sec.: Sylvie ROBERJOT Bât. Atrium, UCB Lyon 1 Tél: 04.72.44.83.62 INSA: M. LAGARDE secretariat.ediss@univ-lyon1.fr                            | Mme Emmanuelle CANET-SOULAS INSERM U1060, CarMeN lab, Univ. Lyon 1 Bâtiment IMBL 11 Avenue Jean CAPELLE INSA de Lyon 69 621 Villeurbanne Tél: 04.72.68.49.09 Fax: 04.72.68.49.16 emmanuelle.canet@univ-lyon1.fr |

| INFOMATHS | INFORMATIQUE ET MATHÉMATIQUES http://edinfomaths.universite-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage Tél: 04.72.43.80.46 Fax: 04.72.43.16.87 infomaths@univ-lyon1.fr                    | M. Luca ZAMBONI Bât. Braconnier 43 Boulevard du 11 novembre 1918 69 622 Villeurbanne CEDEX Tél: 04.26.23.45.52 zamboni@maths.univ-lyon1.fr                                                                      |

| Matériaux | MATÉRIAUX DE LYON http://ed34.universite-lyon.fr Sec.: Marion COMBE Tél: 04.72.43.71.70 Fax: 04.72.43.87.12 Bât. Direction ed.materiaux@insa-lyon.fr                                                      | M. Jean-Yves BUFFIÈRE INSA de Lyon MATEIS - Bât. Saint-Exupéry 7 Avenue Jean CAPELLE 69 621 Villeurbanne CEDEX Tél: 04.72.43.71.70 Fax: 04.72.43.85.28 jean-yves.buffiere@insa-lyon.fr                          |

| MEGA      | MÉCANIQUE, ÉNERGÉTIQUE, GÉNIE CIVIL, ACOUSTIQUE http://edmega.universite-lyon.fr Sec.: Marion COMBE Tél: 04.72.43.71.70 Fax: 04.72.43.87.12 Bât. Direction mega@insa-lyon.fr                              | M. Jocelyn BONJOUR INSA de Lyon Laboratoire CETHIL Bâtiment Sadi-Carnot 9, rue de la Physique 69 621 Villeurbanne CEDEX jocelyn.bonjour@insa-lyon.fr                                                            |

| ScSo      | ScSo* http://ed483.univ-lyon2.fr Sec.: Viviane POLSINELLI Brigitte DUBOIS INSA: J.Y. TOUSSAINT Tél: 04.78.69.72.76 viviane.polsinelli@univ-lyon2.fr                                                       | M. Christian MONTES Université Lyon 2 86 Rue Pasteur 69 365 Lyon CEDEX 07 christian.montes@univ-lyon2.fr                                                                                                        |

#### Résumé:

Le développement de l'énergie renouvelable loin des zones urbaines demande le transport d'une grande quantité d'énergie sur de longues distances. Le transport d'électricité en courant continu haute tension (HVDC) présente beaucoup d'avantages par rapport à celui en courant alternatif. Dans ce contexte il est nécessaire de développer des convertisseurs de puissance constitués par des composants électroniques très haute tension, 10 à 30 kV.

Si les composants en silicium ne peuvent pas atteindre ces objectifs, le carbure de silicium (SiC) se positionne comme un matériau semiconducteur alternatif prometteur.

Pour supporter des tensions élevées, une région de "drift", relativement large et peu dopée constitue le cœur du composant de puissance. En pratique l'obtention d'une tension de blocage effective dépend de plusieurs facteurs et surtout de la conception d'une terminaison de jonction adaptée.

Cette thèse présente une méthode pour améliorer la tenue en tension des composants en SiC basée sur l'utilisation des terminaisons de jonctions : Deep Trench Termination. Cette méthode utilise une tranchée gravée profonde en périphérie du composant, remplie avec un matériau diélectrique pour supporter l'étalement des lignes équipotentielles.

La conception de la diode avec cette terminaison a été faite par simulation TCAD, avec deux niveaux de tension 3 et 20 kV. Les travaux ont pris en compte les caractéristiques du matériau, les charges à l'interface de la tranchée et les limites technologiques pour la fabrication.

Ce travail a abouti sur la fabrication de démonstrateurs et leur caractérisation pour valider notre conception. Lors de la réalisation de ces structures, la gravure plasma du SiC a été optimisée dans un bâti ICP de manière à obtenir une vitesse de gravure élevée et en conservant une qualité électronique de l'état des surfaces gravées. Cette qualité est confirmée par les résultats de caractérisation obtenus avec des tenues en tension proches de celle idéale.

**Mots-Clés:** Carbure de silicium, Terminaisons verticales, Deep Trench Termination, Gravure profonde, Simulation Sentaurus.

#### **Abstract**

The development of renewable energy away from urban areas requires the transmission of a large amount of energy over long distances. High Voltage Direct Current (HVDC) power transmission has many advantages over AC power transmission. In this context, it is necessary to develop power converters based on high voltage power electronic components, 10 to 30 kV. If silicon components cannot achieve these objectives, silicon carbide (SiC) is positioned as a promising alternative semiconductor material.

To support high voltages, a drift region, relatively wide and lightly doped is the heart of the power component. In practice obtaining an effective blocking voltage depends on several factors and especially the design of a suitable junction termination.

This thesis presents a method to improve the voltage withstand of SiC components based on the use of junction terminations: Deep Trench Termination. This method uses a trench deep etching around the periphery of the component, filled with a dielectric material to support the spreading of the equipotential lines.

The design of the diode with this termination was done by TCAD simulation, with two voltage levels 3 and 20 kV. The work took into account the characteristics of the material, the interface charge of the trench and the technological limits for the fabrication.

This work resulted in the fabrication of demonstrators and their characterization to validate the design. During the production of these structures, plasma etching of SiC has been optimized in an ICP reactor so as to obtain a high etching rate and maintaining an electronic quality of the state of etched surfaces. This quality is confirmed by the results of characterization obtained with blocking voltage close to the ideal one.

# Table des matières

| 17 | ABLE | DES M  | <b>MATIÈRES</b>                                 | viii |

|----|------|--------|-------------------------------------------------|------|

| L  | ISTE | DES FI | GURES                                           | xii  |

| L  | ISTE | DES TA | ABLEAUX                                         | xix  |

| In | ITRO | DUCTI  | ON GÉNÉRALE                                     | 1    |

| 1  | Int  | RODU   | ction sur le SiC et les techniques de terminai- |      |

|    | SON  | I POUI | R LES COMPOSANTS DE PUISSANCE                   | 5    |

|    | 1.1  | Propi  | riétés du SiC                                   | 6    |

|    |      | 1.1.1  | Structure cristalline et polytypes du SiC       | 7    |

|    |      | 1.1.2  | Propriétés mécaniques et thermiques du SiC      | 8    |

|    |      | 1.1.3  | Propriétés électroniques du SiC                 | 8    |

|    | 1.2  | Тесни  | NOLOGIE DE FABRICATION SIC                      | 14   |

|    |      | 1.2.1  | Croissance de couches épitaxiales               | 15   |

|    |      | 1.2.2  | Dopage du SiC                                   | 16   |

|    |      | 1.2.3  | Contacts métalliques sur SiC                    | 17   |

|    |      | 1.2.4  | Gravure SiC                                     | 17   |

|    |      | 1.2.5  | Passivation                                     | 18   |

|    |      | 1.2.6  | Packaging                                       | 20   |

|    | 1.3  | Tenui  | e en Tension                                    | 21   |

|    |      | 1.3.1  | Définition du claquage par avalanche            | 21   |

|    |      | 1.3.2  | Résistances spécifiques à l'état passants       | 25   |

|    |      | 1.3.3  | Optimisation du couple "épaisseur / dopage"     | 27   |

|    | 1.4  | Тесни  | NIQUE DE TERMINAISON                            | 28   |

|   |     | 1.4.1 | Anneaux de garde (Anneaux diviseurs de champ)                  | 30 |

|---|-----|-------|----------------------------------------------------------------|----|

|   |     | 1.4.2 | Extension de jonction implantée (JTE)                          | 32 |

|   |     | 1.4.3 | Plaque de champ                                                | 34 |

|   |     | 1.4.4 | Couche semi-résistive SIPOS                                    | 36 |

|   |     | 1.4.5 | Technique RESURF                                               | 36 |

|   |     | 1.4.6 | Technique de terminaison en biseau ou MESA                     | 37 |

|   |     | 1.4.7 | Technique Deep Trench Termination (DT2)                        | 39 |

|   | 1.5 | Conc  | LUSION                                                         | 42 |

| 2 | Co  | NCEPT | ION D'UNE DIODE PIN EN SIC AVEC UNE PROTEC-                    |    |

|   | TIO | n DT2 | 2                                                              | 45 |

|   | 2.1 | Intro | DUCTION                                                        | 45 |

|   | 2.2 | Le lo | GICIEL SENTAURUS                                               | 46 |

|   |     | 2.2.1 | Sentaurus Structure Editor                                     | 46 |

|   |     | 2.2.2 | Sentaurus Device                                               | 48 |

|   | 2.3 | Struc | CTURE D'UNE DIODE DE PUISSANCE                                 | 49 |

|   | 2.4 | Fonc  | TIONNEMENT D'UNE DIODE                                         | 51 |

|   |     | 2.4.1 | Diode à l'équilibre                                            | 51 |

|   |     | 2.4.2 | Fonctionnement en direct                                       | 52 |

|   |     | 2.4.3 | Fonctionnement en inverse                                      | 53 |

|   | 2.5 | Dimei | NSIONNEMENT D'UNE COUCHE "DRIFT" POUR LA TENUE EN              |    |

|   |     | TENSI | ON 3 KV                                                        | 54 |

|   | 2.6 | Conc  | eption de la protection périphérique DT2 d'une diode           |    |

|   |     | PıN 3 | кV                                                             | 55 |

|   |     | 2.6.1 | Présentation de la terminaison mesa                            | 56 |

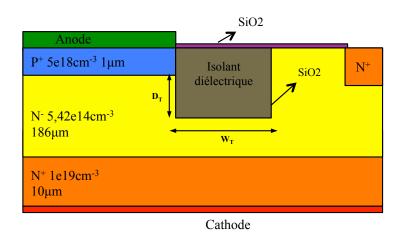

|   |     | 2.6.2 | Structure simulée de la terminaison DT2 simulée                | 57 |

|   |     | 2.6.3 | Influence de l'angle de gravure                                | 58 |

|   |     | 2.6.4 | Influence de la profondeur et largeur de gravure               | 60 |

|   |     | 2.6.5 | Influence du matériau isolant pour remplir la tranchée         | 62 |

|   |     | 2.6.6 | Terminaison de jonction à tranchée profonde avec une plaque de |    |

|   |     |       | ahamp                                                          | 6- |

|   |     | 2.6.7  | Terminaison de jonction à tranchée profonde avec une couche      |     |

|---|-----|--------|------------------------------------------------------------------|-----|

|   |     |        | JTE autour de la tranchée                                        | 66  |

|   |     | 2.6.8  | Optimisation de la dose pour la couche JTE                       | 68  |

|   |     | 2.6.9  | Propriétés électriques de l'interface SiC/diélectrique           | 7º  |

|   |     | 2.6.10 | Influence des charges à l'interface                              | 77  |

|   |     | 2.6.11 | Conclusion                                                       | 81  |

|   | 2.7 | Conc   | eption d'une protection périphérique DT2 pour une                |     |

|   |     | DIODE  | PiN 25kV                                                         | 82  |

|   |     | 2.7.1  | Influence de la profondeur et de la largeur de gravure           | 83  |

|   |     | 2.7.2  | Terminaison de jonction à tranchée profonde avec une couche      |     |

|   |     |        | JTE autour de la tranchée                                        | 84  |

|   |     | 2.7.3  | Terminaison de jonction à tranchée profonde avec une couche      |     |

|   |     |        | JTE autour de la tranchée + SiO2 + diélectrique dans la tranchée | 86  |

|   |     | 2.7.4  | Terminaison de jonction qui utilise la packaging comme une ter-  |     |

|   |     |        | minaison                                                         | 87  |

|   |     | 2.7.5  | Conclusion                                                       | 89  |

|   | 2.8 | Conc   | LUSION                                                           | 91  |

| 3 | Réa | ALISAT | ion d'une protection périphérique DT2 pour                       |     |

| J |     |        | NT SIC                                                           | 93  |

|   | 3.1 |        | DUCTION                                                          | 93  |

|   | 3.2 |        | ure profonde du SiC                                              | 95  |

|   | J   | 3.2.1  | Mécanismes de gravure plasma dans le SiC et réacteurs            | 95  |

|   |     | 3.2.2  | Synthèse des études précédentes au laboratoire sur la gravure    | ,,, |

|   |     |        | plasma du SiC                                                    | 103 |

|   |     | 3.2.3  | Optimisation du procédé de gravure profonde du SiC dans un       |     |

|   |     |        | bâti ICP                                                         | 108 |

|   | 3.3 | Proce  | essus technologique pour les diodes SiC PiN DT2 3kV et           |     |

|   |     |        | CTÉRISATION ÉLECTRIQUE                                           | 116 |

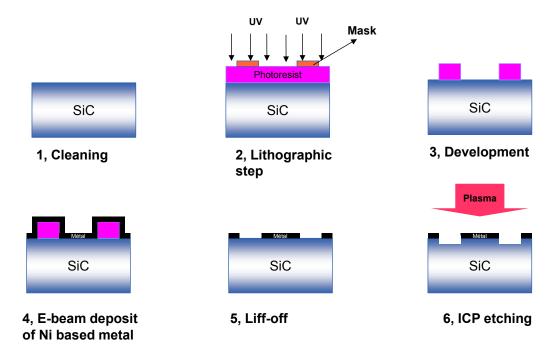

|   |     | 3.3.1  | Nettoyage de surface                                             | 116 |

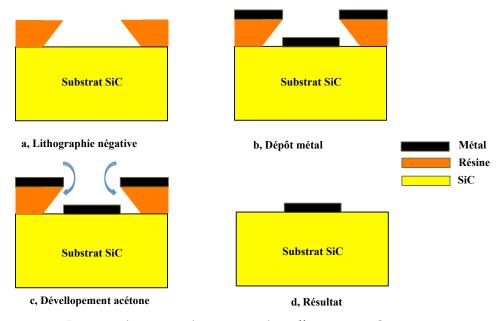

|   |     | 3.3.2  | Photolithographie classique UV                                   | 117 |

|       | 3.3.3  | Technique "liff-off"                          | 120 |

|-------|--------|-----------------------------------------------|-----|

|       | 3.3.4  | Dépôt du masque métallique                    | 122 |

|       | 3.3.5  | Gravure du SiC avec le réacteur ICP           | 122 |

|       | 3.3.6  | Dépôt de parylenne dans les tranchées         | 123 |

|       | 3.3.7  | Caractérisation électrique des diodes SiC DT2 | 124 |

| 3.4   | Conc   | LUSION DU CHAPITRE 3                          | 125 |

| Conc  | LUSIO  | n générale et Perspectives                    | 129 |

| Вівці | OGRAP: | HIE                                           | 133 |

# Liste des figures

| 1.1  | "Paire" SiC (Raynaud 2007)                                      | 7  |

|------|-----------------------------------------------------------------|----|

| 1.2  | Séquence d'empilement des principaux polytypes de SiC           |    |

|      | (Tournier 2007)                                                 | 8  |

| 1.3  | Évolution de la concentration intrinsèque en fonction de la     |    |

|      | température, en tenant compte de la variation de $E_g$ avec la  |    |

|      | température (Raynaud 2007)                                      | 10 |

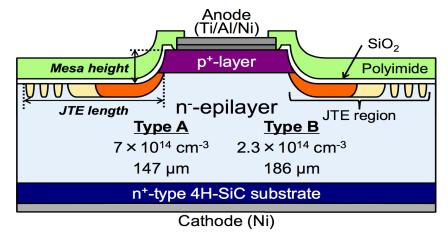

| 1.4  | Structure de composant SiC protégé par JTE avec les couches     |    |

|      | de passivation y compris les paramétres technologiques          |    |

|      | (Diaham et al. 2009)                                            | 19 |

| 1.5  | Module d'électronique de puissance standard                     | 20 |

| 1.6  | Accélération et multiplication des porteurs dans une zone de    |    |

|      | charge d'espace                                                 | 22 |

| 1.7  | Extension de charge d'espace, les coordonées et limites di-     |    |

|      | mensionnelles                                                   | 23 |

| 1.8  | Dépendance des coefficients d'ionisation en fonction du         |    |

|      | champ électrique du SiC-4H (Nguyen 2011)                        | 25 |

| 1.9  | Évolution des intégrales d'ionisation des trous et des élec-    |    |

|      | trons en fonction de la tension appliquées sur une jonction     |    |

|      | en polarisation inverse                                         | 26 |

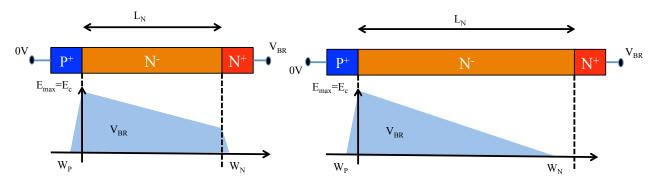

| 1.10 | Répartition du champ électrique au claquage dans une diode      |    |

|      | $P^+N^-N^+$ : jonction plane en limitation de charge d'espace   |    |

|      | (tronquée)(a,) et jonction plane infinie (b,) (non tronqu/'ee). | 28 |

| 1.11 | Distribution de champ électrique dans une structure avec un     |    |

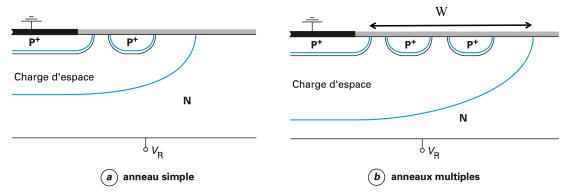

|      | anneau flottant (Leturcq 2000)                                  | 30 |

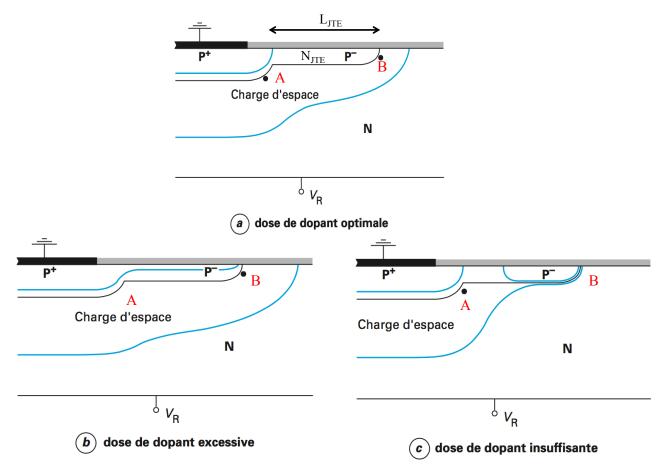

| 1.12 | Extensions de jonction implantées. Influence de la dose de          |    |

|------|---------------------------------------------------------------------|----|

|      | dopant dans la zone P (Leturcq 2000)                                | 33 |

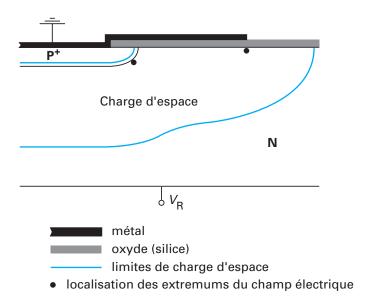

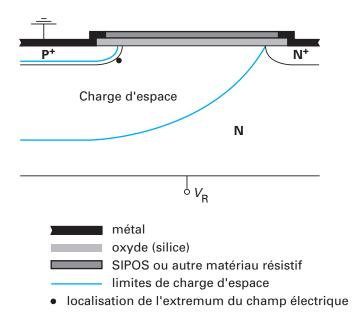

| 1.13 | Protection par plaque de champ (Leturcq 2000)                       | 35 |

| 1.14 | Plaque de champ résistive (SIPOS) (Leturcq 2000)                    | 37 |

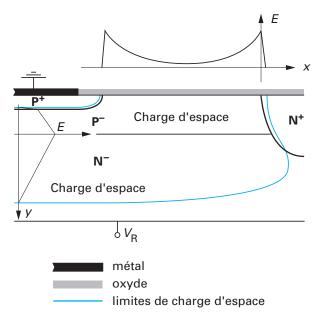

| 1.15 | Terminaison "Resurf" (Leturcq 2000)                                 | 38 |

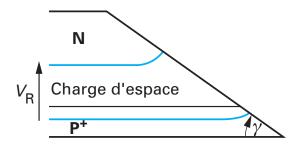

| 1.16 | Terminaison biseau positif (Leturcq 2000)                           | 38 |

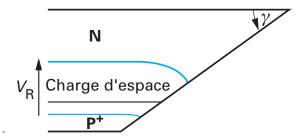

| 1.17 | Terminaison biseau negatif (Leturcq 2000)                           | 39 |

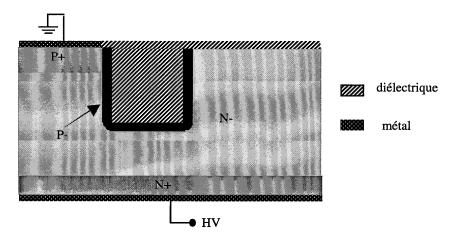

| 1.18 | Techniuqe de termination de jonction à tranchée profonde et         |    |

|      | couche JTE $P^-$ autour de la tranchée (Dragomirescu 2001)          | 40 |

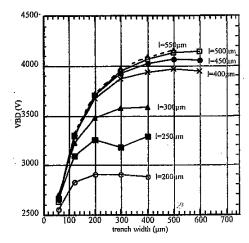

| 1.19 | Tenue en tension en fonction de largeur et profondeur de la         |    |

|      | tranchée (Dragomirescu 2001)                                        | 41 |

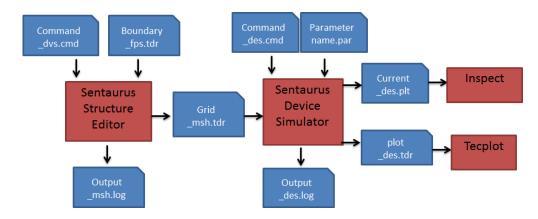

| 2.1  | Diagramme pour simuler la structure d'un composant semi-            |    |

|      | conducteur                                                          | 47 |

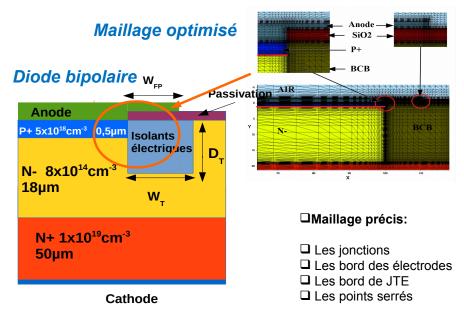

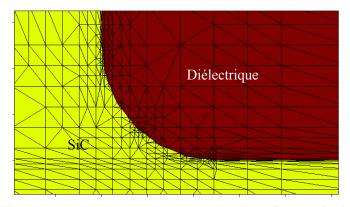

| 2.2  | Maillage optimisé de la structure simulée, vue globale de la        |    |

|      | protection périphérique                                             | 48 |

| 2.3  | Maillage optimisé de la structure simulée à l'interface             |    |

|      | SiC/diélectrique                                                    | 48 |

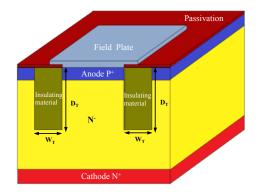

| 2.4  | Structure 3D d'une diode bipolaire de puissance avec tranchée.      | 50 |

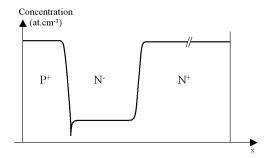

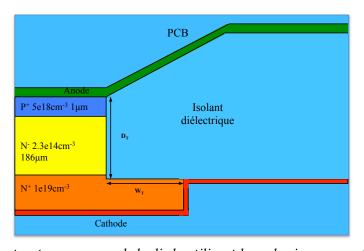

| 2.5  | Structure d'une diode bipolaire de puissance                        | 51 |

| 2.6  | Allure du profil de dopage                                          | 51 |

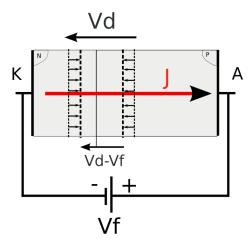

| 2.7  | Extension des Z.C.E à l'équilibre ( $V_f$ = 0) et sous polarisation |    |

|      | directe $(V_f \neq 0) \dots \dots \dots \dots \dots \dots$          | 52 |

| 2.8  | Extension des Z.C.E à l'équilibre ( $V_f$ = 0) et sous polarisation |    |

|      | inverse $(V_f \neq 0)$                                              | 53 |

| 2.9  | Tension de claquage en fonction du dopage et de l'épaisseur         |    |

|      | de la zone de "drift"                                               | 55 |

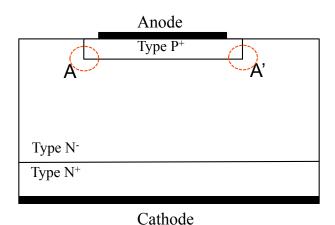

| 2.10 | Structure diode planar                                              | 56 |

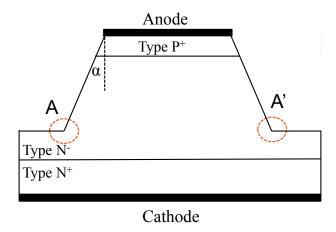

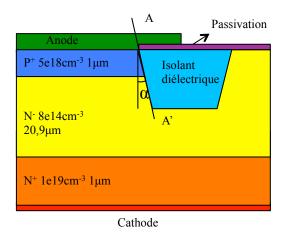

| 2.11 | Terminaison diode mesa                                              | 57 |

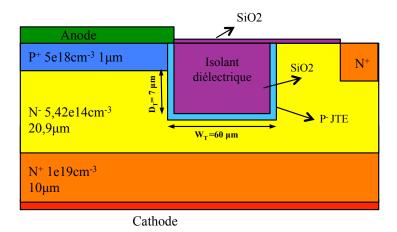

| 2.12 | Structure simulée avec une terminaison DT2                          | 58 |

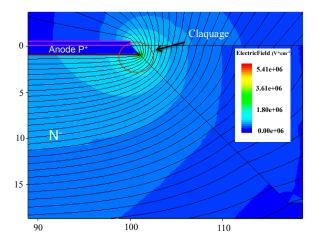

| 2.13 | Structure gravure positive                                          | 59 |

| 2.14 Distribution des équipotentielles au moment claquage                | 59 |

|--------------------------------------------------------------------------|----|

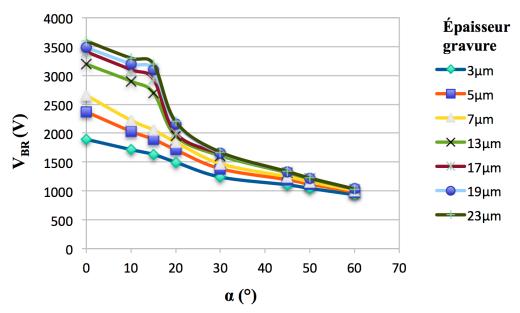

| 2.15 Tenue en tension Vbr en fonction de $\alpha$ pour différents épais- |    |

| seur de gravure                                                          | 60 |

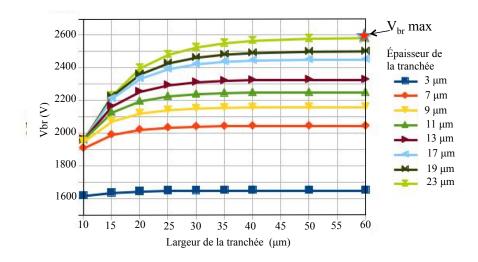

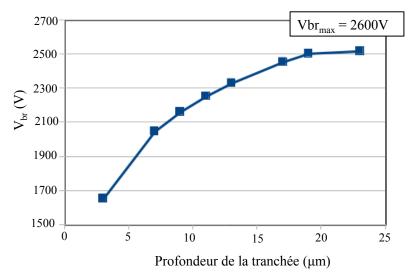

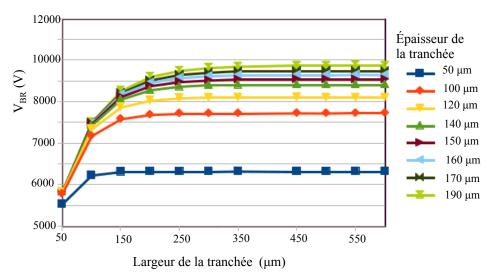

| 2.16 La tenue en tension en fonction de la largeur et l'épaisseur        |    |

| de la tranchée (remplie par SiO2)                                        | 61 |

| 2.17 La tenue en tension en fonction de la profondeur de la tran-        |    |

| chée (remplie du $SiO_2$ ; largeur de la tranchée $W_T$ = 60 $\mu$ m) .  | 62 |

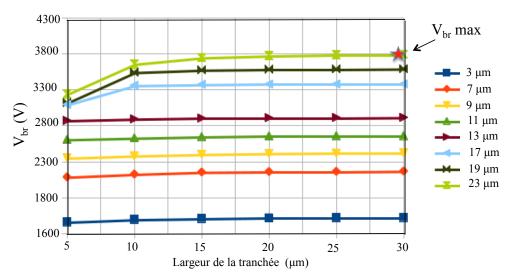

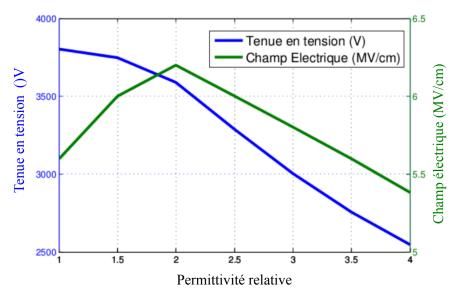

| 2.18 La tenue en tension en fonction de la largeur et l'épaisseur        |    |

| de la tranchée (remplie par vide)                                        | 64 |

| 2.19 La tenue en tension en fonction de la constante diélectrique        |    |

| pour une tranchée optimale                                               | 65 |

| 2.20 La tenue en tension en fonction de la constante diélectrique        |    |

| pour une tranchée optimale                                               | 66 |

| 2.21 DT2 avec JTE                                                        | 67 |

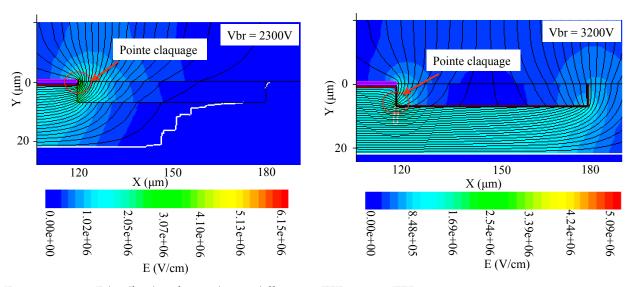

| 2.22 Distribution des équipotentielles sans JTE et avec JTE              | 67 |

| 2.23 Distribution des équipotentielles dans le cas d'une JTE avec        |    |

| un dopage trop faible                                                    | 68 |

| 2.24 Distribution des équipotentielles dans le cas d'une JTE avec        |    |

| un dopage optimal                                                        | 68 |

| 2.25 Distribution des équipotentielles dans le cas d'une JTE avec        |    |

| un dopage trop grand                                                     | 69 |

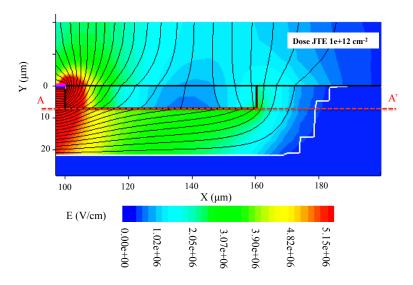

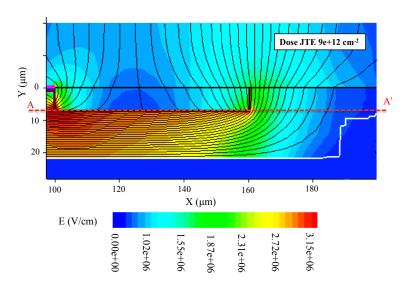

| 2.26 Coupe latérale du module du champ électrique au moment              |    |

| du claquage                                                              | 70 |

| 2.27 La tenue en tension en fonction de profondeur et la dose de         |    |

| couche JTE (largeur de la tranchée 20 $\mu$ m)                           | 71 |

| 2.28 La tenue en tension en fonction de profondeur et la dose de         |    |

| couche JTE (largeur de la tranchée 60 $\mu$ m)                           | 72 |

| 2.29 Schéma des mécanismes piégeage, dépiégeage, recombinai-             |    |

| son, génération.                                                         | 73 |

| 2.30 Densité états interface en fonction de énergy dans le SiC           |    |

| band gap pour SiC-4H, SiC-6H (Saks et al. 2000)                          | 74 |

| 2.31 | Les différents types de charges et leurs localisations. Re-                     |    |

|------|---------------------------------------------------------------------------------|----|

|      | marque : les états d'interface sont qualifiés de défauts in-                    |    |

|      | trinsèques                                                                      | 76 |

| 2.32 | Influence de l'insertion de charges fixes sur la tenue en ten-                  |    |

|      | sion de la diode DT2                                                            | 77 |

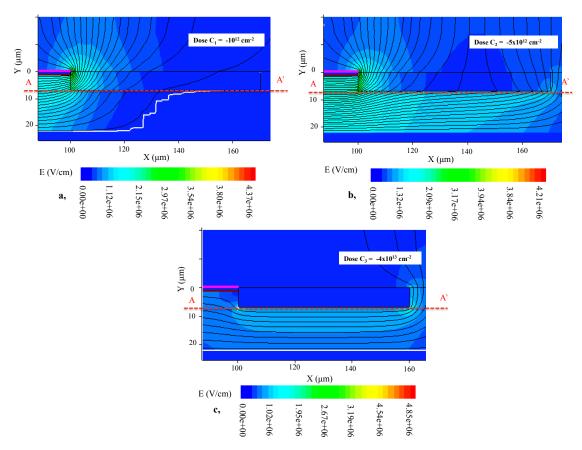

| 2.33 | Distribution des équipotentielles dans le cas $C_1 = -10^{12}$                  |    |

|      | $cm^{-2}$ , $C_2 = -5x10^{12} cm^{-2}$ et $C_3 = -4x10^{13} cm^{-2}$            | 78 |

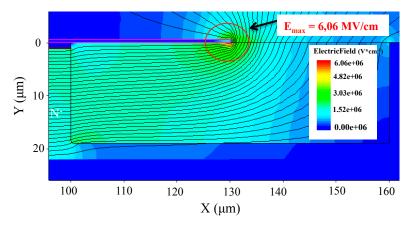

| 2.34 | Distribution de champ dans le SiC en fonction de la concen-                     |    |

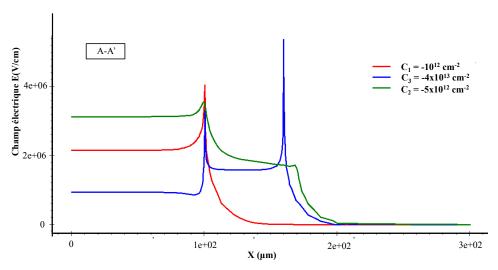

|      | tration de charges négatives                                                    | 80 |

| 2.35 | Distribution du champ électrique pour une dose de C <sub>3</sub>                |    |

|      | $=-4x10^{13} cm^{-2}. \ldots \ldots \ldots \ldots \ldots \ldots$                | 80 |

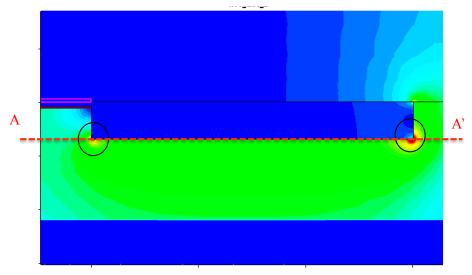

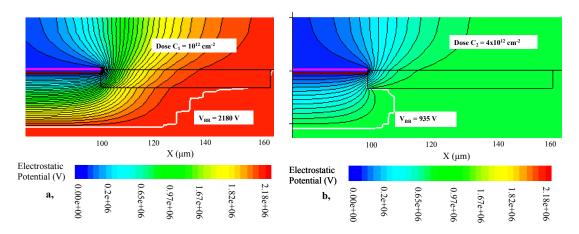

| 2.36 | Distribution des équipotentielles dans le cas $C_1 = 1x10^2$                    |    |

|      | $cm^{-2}$ , $C_2 = 4x10^{12} cm^{-2} \dots \dots \dots \dots \dots \dots \dots$ | 81 |

| 2.37 | Structure diode PiN 25kV avec JTE modulée (Niwa et al. 2012a)                   | 83 |

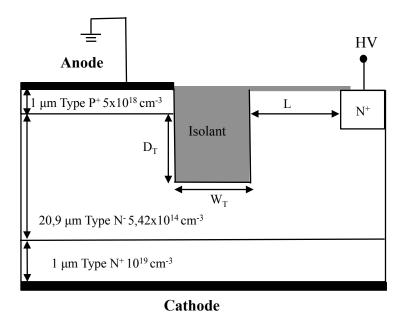

| 2.38 | Structure de la diode PiN 25kV avec la tranchée remplie par                     |    |

|      | l'isolant                                                                       | 83 |

| 2.39 | La tenue en tension en fonction de la largeur et l'épaisseur                    |    |

|      | de la tranchée (remplie par SiO2)                                               | 84 |

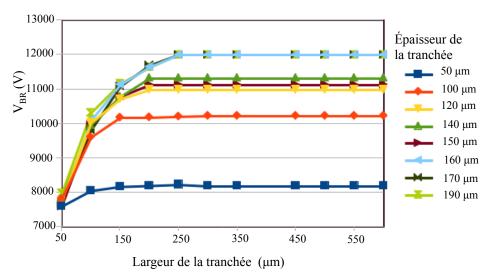

| 2.40 | La tenue en tension en fonction de la largeur et l'épaisseur                    |    |

|      | de la tranchée (remplie par BCB)                                                | 85 |

| 2.41 | Structure diode PiN 25kV DT2 et JTE                                             | 85 |

| 2.42 | Structure diode PiN 25kV DT2 et JTE. Courrant de fuite lors                     |    |

|      | de l'arrêt de la simulation (à gauche) et répartition du champ                  |    |

|      | électrique (à droit)                                                            | 86 |

| 2.43 | Structure diode PiN 25kV DT2 et JTE, SiO2                                       | 87 |

| 2.44 | Distribution du champ électrique au moment de claquage                          |    |

|      | dans la diode 25 kV avec DT2, JTE et SiO2                                       | 88 |

| 2.45 | Le structure nouveau de la diode utilisant le packaging                         |    |

|      | comme terminaison                                                               | 88 |

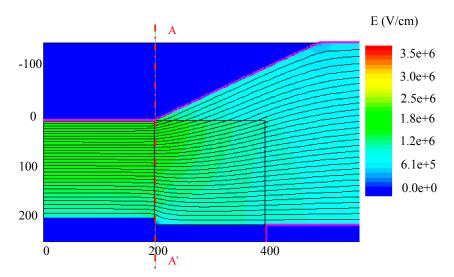

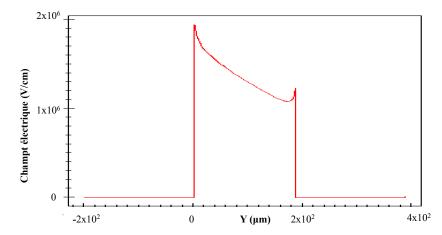

| 2.46 | Distribution des équipotentielles au claquage pour la diode                     |    |

|      | utilisant le packaging comme terminaison                                        | 90 |

| 2.47 | Distribution du champ électrique AA' pour la diode utilisant   |      |

|------|----------------------------------------------------------------|------|

|      | le packaging comme terminaison                                 | 90   |

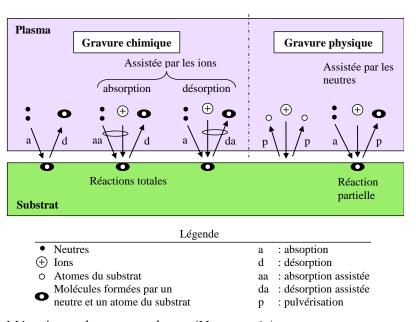

| 3.1  | Mécanismes de gravure plasma (Vang 2006a)                      | 96   |

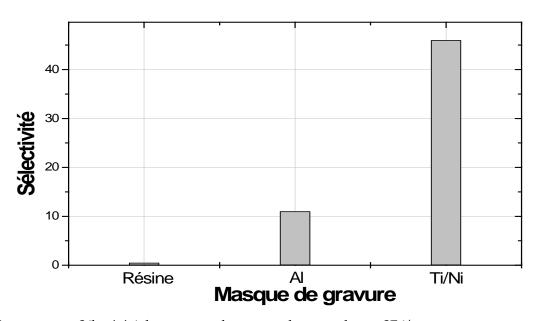

| 3.2  | Sélectivité des masques de gravure dans un plasma SF6/02 .     | 99   |

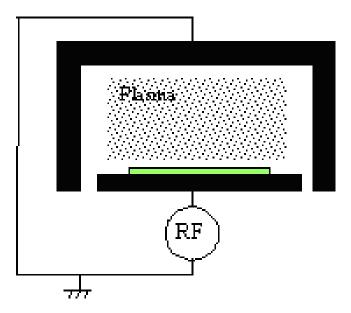

| 3.3  | Réacteurs plasmas RIE (Vang 2006b)                             | 100  |

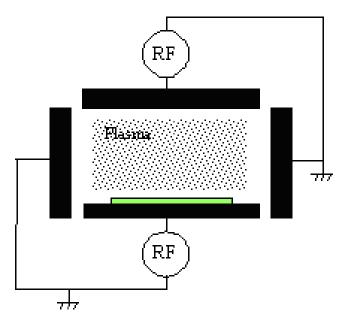

| 3.4  | Réacteurs plasmas ICP (Vang 2006b)                             | 102  |

| 3.5  | Bâtis de gravure plasma utilisés sur la plateforme Nano-       |      |

|      | lyon dans les études précédentes au laboratoire : RIE Nextral  |      |

|      | NEE110 (à gauche), Oxford NGP80 (à droite)                     | 103  |

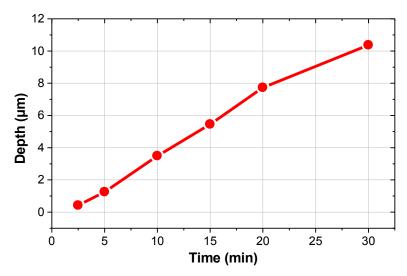

| 3.6  | Courbe expérimentale profondeur de gravure RIE avec            |      |

|      | $SF_6/O_2$ à 250 W en fonction de la durée (Lazar et al. 2006) | 104  |

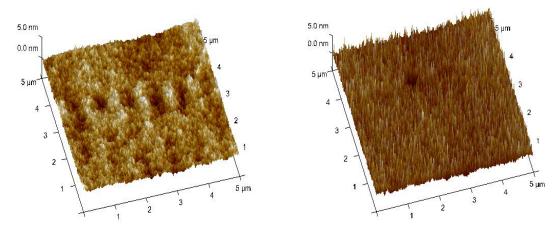

| 3.7  | Images AFM qui présentent la rugosification de la surface      |      |

|      | du SiC après des gravures RIE à 250 W durant 10 min (a) et     |      |

|      | 20 min (b) (Lazar et al. 2006)                                 | 105  |

| 3.8  | L'influence de la pression du réacteur RIE sur la vitesse de   |      |

|      | gravure et sur la sélectivité du masque nickel avec un plasma  |      |

|      | $SF_6/O_2$ à une puissance de 250 W (Morel et al. 2005)        | 106  |

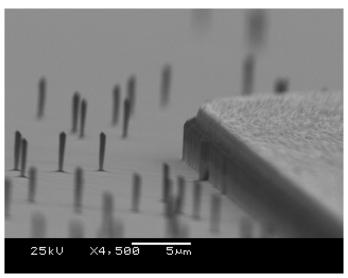

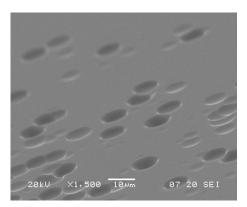

| 3.9  | Images MEB sur des échantillons SiC-4H gravés avec un          |      |

|      | plasma RIE $SF_6/O_2$ à 100 W avec la présence du phéno-       |      |

|      | mène de "trenching" (à gauche) et à 250 W sans "trenching"     |      |

|      | (à droite) (Simescu et al. 2010)                               | 106  |

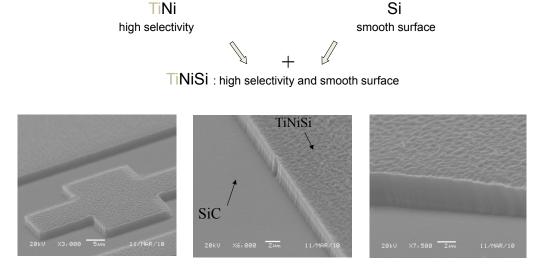

| 3.10 | Micromasking produit par le dépôt de particules en prove-      |      |

|      | nance du masque métallique (Lazar et al. 2011)                 | 107  |

| 3.11 | Images MEB de surfaces gravées très lisses et avec des motifs  |      |

|      | serrés obtenus en utilisant un masquage Ni/Si (Laariedh 2013)  | .108 |

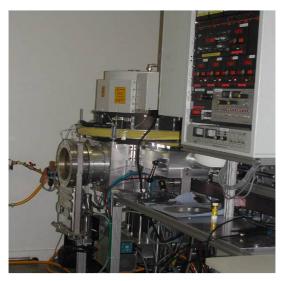

| 3.12 | Image du bâti ICP ETREM utilisé dans cette étude               | 109  |

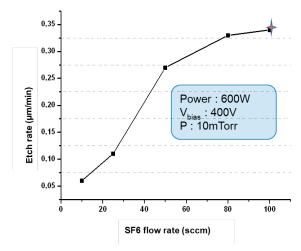

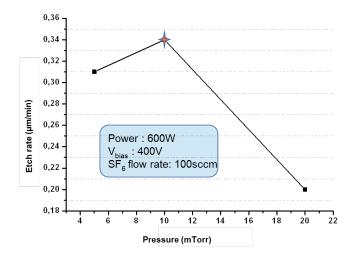

| 3.13 | Optimisation des paramètres de gravure ICP avec plasma         |      |

|      | SF6 pour la réalisation de tranchées profondes en SiC. In-     |      |

|      | fluence du débit de SF6                                        | 110  |

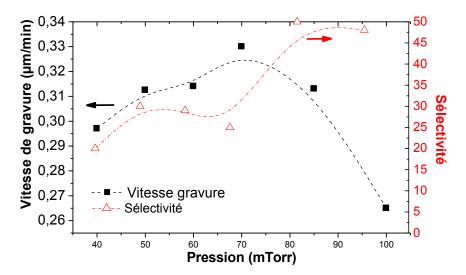

| 3.14 | Optimisation des parametres de gravure icr avec plasma                  |     |

|------|-------------------------------------------------------------------------|-----|

|      | SF <sub>6</sub> pour la réalisation de tranchées profondes en SiC. In-  |     |

|      | fluence de la pression                                                  | 111 |

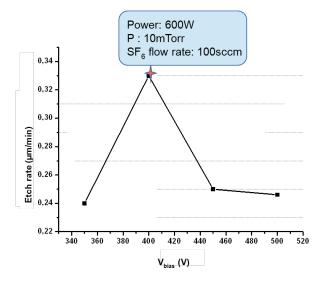

| 3.15 | Optimisation des paramètres de gravure ICP avec plasma                  |     |

|      | SF6 pour la réalisation de tranchées profondes en SiC. In-              |     |

|      | fluence du bias, tension de polarisation du port-échantillon            |     |

|      | RF2                                                                     | 111 |

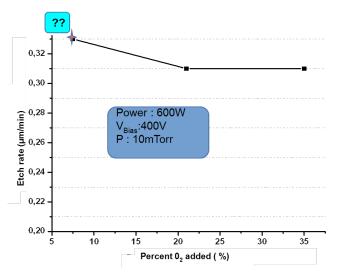

| 3.16 | Optimisation des paramètres de gravure ICP avec plasma                  |     |

|      | SF <sub>6</sub> pour la réalisation de tranchées profondes en SiC. In-  |     |

|      | fluence du taux d'oxygène                                               | 112 |

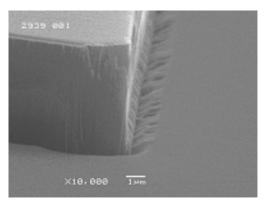

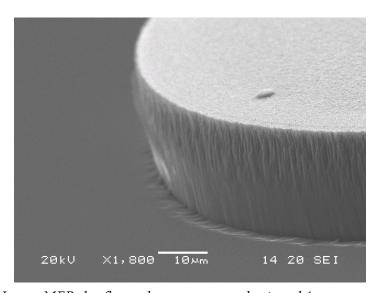

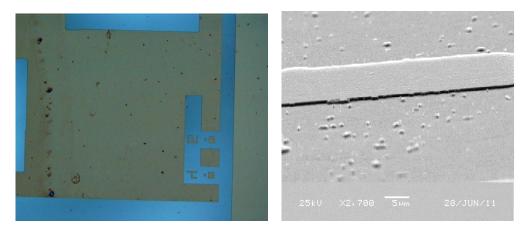

| 3.17 | Image MEB des flancs de gravure pour les tranchées $\approx$ 23 $\mu$ m |     |

|      | que nous avons réalisé avec le procédé ICP                              | 113 |

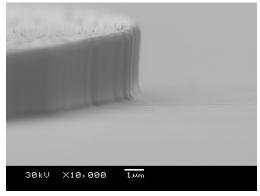

| 3.18 | Image MEB sur une zone révélatrices de défauts et une                   |     |

|      | image plus globale d'un plot gravé sur une surface partielle-           |     |

|      | ment utilisée sur une étape technologique précédente                    | 114 |

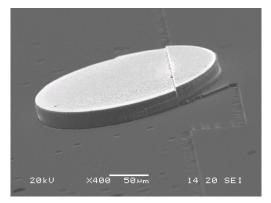

| 3.19 | Process photolithographie avec des résines positives et néga-           |     |

|      | tives                                                                   | 118 |

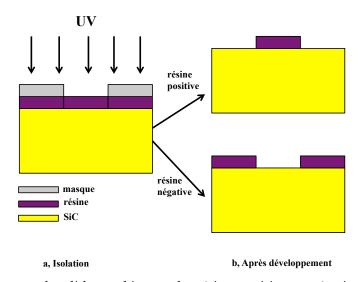

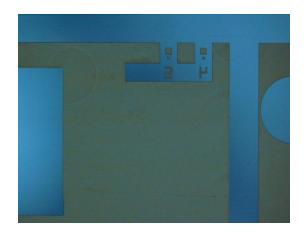

| 3.20 | Images prises avec microscope optique : a) masque Cr-verre              |     |

|      | sale avant nettoyage, b) report de ces saletés sur nos échan-           |     |

|      | tillons. Laariedh (2013)                                                | 120 |

| 3.21 | Images prises avec microscope optique d'un masque Cr-                   |     |

|      | verre après nettoyage Laariedh (2013)                                   | 120 |

| 3.22 | Images prises avec microscope optique d'un masque Cr-                   |     |

|      | verre après nettoyage.                                                  | 121 |

| 3.23 | Présentation schématique des étapes technologiques pour la              |     |

|      | fabrication des diodes SiC PiN DT2                                      | 123 |

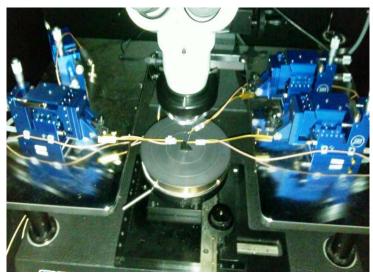

| 3.24 | Test sous pointes avec le banc Signatone S-1160 du labora-              |     |

|      | toire d'une puce SiC                                                    | 125 |

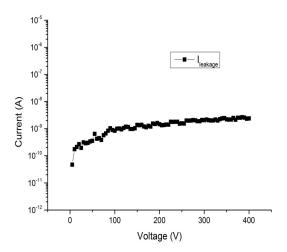

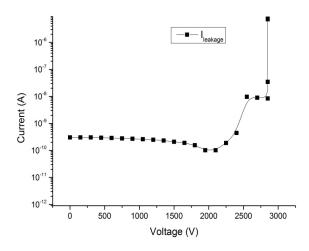

| 3.25 | Test en inverse des diodes SiC DT2 avant le dépôt de parylène.          | 125 |

| 3.26 | Tenue en tension de 3 kV sur les diodes SiC DT2 obtenue                 |     |

|      | après dépôt de parylène                                                 | 126 |

# Liste des tableaux

| 1.1 | Variation du gap en fonction de la température                    | 9  |

|-----|-------------------------------------------------------------------|----|

| 1.2 | Paramètres $N_C$ , $N_V$ et $n_i$ calculés à 300 K (Raynaud 2007) | 10 |

| 1.3 | Énergies d'activation des principaux dopants (Raynaud 2007)       | 11 |

| 1.4 | Paramétres $N_C$ , $N_V$ et $n_i$ calculés à 300 K (Raynaud 2007) | 12 |

| 1.5 | Les constantes pour calculer les coefficients d'ionisation pour   |    |

|     | SiC-4H                                                            | 23 |

# Introduction générale

Ujourd'hui, le développement très rapide de l'énergie renouvelable pose un problème pour transporter une grande quantité d'énergie sur des longues distances ou par cables, car les centrales qui produisent l'énergie renouvelable sont souvent loin des zones urbaines, comme les centrales éoliennes offshore, hydrauliques, solaires, thermiques... Dans ce domaine, le transport d'électricité par un courant continu haute tension (HVDC) présente beaucoup d'avantages par rapport à celui en courant alternatif (HVAC).

D'abord, un avantage économique vient de la réduction des pertes. Pour les lignes aériennes de transport électricité, sans effet de peau, la résistance en courant continu des lignes est plus faible qu'en courant alternatif. En plus, la puissance réactive n'existe pas en courant continu, donc il n'y a pas de pertes Joule dues au transport de la puissance réactive. Le courant est donc seulement limité par les capacités thermiques des conducteurs. Le système de ligne de transmission en courant continu ne nécessite que 2 conducteurs au lieu de 3, donc le coût pour construire est aussi diminué. Toutefois, le courant continu haute tension implique des postes de conversion aux deux extrémités pour se raccorder aux réseaux alternatifs.

D'un point de vue distribution sur longues distances, l'HVDC est l'unique possibilité pour transporter de l'électricité dans des câbles enterrés ou sous-marins sur des distances supérieures à environ 100 km. Les câbles AC ont en effet un comportement capacitif. Leurs charges et décharges finissent par consommer l'intégralité du courant disponible à

cause de la valeur capacitive très grande du câble. Autrement dit la puissance transportée par le câble devient intégralement réactive, et donc finit par empêcher le transport de la puissance active, qui est recherchée. Afin de réduire cet effet capacitif, on installe dans les liaisons classiques en courant alternatif des réactances de compensation, ce qui est coûteux. Par contre en courant continu, aucune puissance réactive n'est produite dans le câble, et l'intérêt du continu, qui en est exempt, croît avec la distance de transport.

Un autre avantage important de la technique HVDC réside dans le problème de la connexion des réseaux avec deux fréquences différentes, par exemple 50 Hz et d'autres à 60 Hz. Une station en courant continu haute tension permet d'échanger de l'énergie entre les deux réseaux sans les connecter directement et donc en évitant la propagation des instabilités d'un réseau à l'autre. De manière plus générale, la stabilité des réseaux est améliorée, le flux d'énergie s'interrompant si une instabilité ou un défaut est détecté d'un côté de la liaison, qui ne se propage donc pas.

Pour les lignes aériennes, les lignes HVDC n'ont pas besoin de compensation sur des longues distances. La stabilité de la tension mais aussi la stabilité de la centrale ne sont pas menacées, les pertes en lignes sont également réduites. Le contrôle de la transmission d'énergie est plus facile.

En dehors de toute considération technique, le choix économique d'utiliser ou pas du courant continu pour une liaison de grande longueur dépend en particulier de trois paramètres :

- le coût supplémentaire des stations de conversion

- les pertes de ces stations de conversion

- les pertes en ligne

Il en résulte donc une longueur de ligne au-delà de laquelle un projet de ligne à courant continu est rentable. On estime en général cette longueur à 500 km environ pour une ligne aérienne et 10 à 50 km pour une ligne par cables.

En parallèle avec le développement du système HVDC, il faut se focaliser aussi sur le développement du convertisseur électronique de puissance, qui est constitué par des composants électroniques utilisés en forte puissance. L'histoire de l'électronique de puissance a commencé depuis des années 1960 avec des composant en silicium (Si). Les premières diodes de puissance apparaissent en 1956. Ensuite au début des années 1970, des transistors bipolaires et thyristors sont arrivés. Le thyristor - GTO, le transistor MOS et l'IGBT sont développés dans les années 80-90. Les composants en silicium sont limités dans les applications industrielles à 3.5 kV, 6.5 kV voire 8 kV selon les cas. La limite pratique est une marge de tension par rapport à l'emballement thermique. Un système de refroidissement thermique efficace est donc indispensable. Les besoins existent pour les futures applications à haute tension (traction, réseau...) surtout pour des composants à très haute tension, c'est à dire 10 kV, 15 kV voire 30 kV. Le silicium ne pourra pas atteindre ces objectifs. Le carbure de silicium (SiC) se positionne comme un candidat très prometteur pour ces objectifs à haute tension.

Le carbure de silicium est un matériau semi-conducteur grand gap, qui possède de bonnes propriétés physiques telles qu'une importante largeur de bande d'énergie interdite, une bonne mobilité, et une bonne conductivité thermique. Il permet d'obtenir des composants fonctionnant dans des conditions de hautes températures, hautes fréquences, et fortes puissances en milieu hostile. Le laboratoire Ampère fait des recherches depuis plusieurs dizaines d'années sur le SiC, y compris des recherches sur le domaine des composants haute tension et très haute tension (au delà de 10 kV) appliqué pour les transmissions HVDC.

Les travaux de recherche présentés ici se situent dans ce contexte. Pour supporter des tensions élevées, une région relativement large et peu do-

BUI Thi Thanh Huyen/ "Terminaison verticales de jonction remplies avec des couches diélectriques isolantes pour des application haute tension utilisant des composants grand-gap de forte puissance" - Thèse INSA de Lyon - AMPERE

pée est utilisée pour permettre à la zone de charge d'espace de s'étendre suffisamment. Cette région, dont la désignation générique est la zone de "drift", constitue le coeur du composant de puissance. La tension de blocage théorique du composant est définie par le dopage et l'épaisseur de la zone de "drift". Cette tension théorique est limitée essentiellement par le mécanisme d'avalanche. Par contre en pratique l'obtention d'une tension de blocage effective proche de la valeur théorique dépend de plusieurs facteurs : courant inverse, dont l'origine principale est la génération thermique dans la zone de charge d'espace, contournement de la jonction par claquage prématuré intervenant sur les bords, courants de fuite superficiels. La conception de terminaisons de jonction adaptées, la passivation, la concentration des centres de génération-recombinaison...sont d'autres facteurs. Enfin, il faut prévoir que la tenue en tension définie en régime statique peut être altérée en régime transitoire par l'effet de la charge d'espace des porteurs en transit, avec, en certains cas, des conséquences destructives (avalanche dynamique) (Leturcq 2000).

Dans cette thèse, nous voulons présenter une méthode pour améliorer la tenue en tension des composants en SiC basée sur l'utilisation des terminaisons de jonctions : Deep Trench Termination. Cette méthode utilise une tranchée gravée profonde au niveau périphérique du composant, avec un matériau diélectrique remplissant la tranchée pour supporter toutes les lignes équipotentielles.

Chapitre

# Introduction sur le SiC et les techniques de terminaison pour les composants de puissance

Près d'un siècle après la découverte des propriétés semi-conductrices du SiC en 1907, le silicium est toujours le semi-conducteur le plus utilisé du fait de son développement technologique et de ses propriétés électriques et physiques. Mais avec l'évolution des besoins en électronique de puissance de plus en plus exigeants, le silicium a atteint ses limites physiques exploitables dans l'électronique de puissance nécessitant de forts courants et de hautes tensions. Précisément, il n'est plus fiable du point de vue électrique au delà de 200 °C à 600 V et connaît de sérieuses défaillances de son environnement et du matériau à partir de 500 °C. De plus, ses propriétés physiques montrent qu'il n'est pas possible de maintenir une forte tenue en tension en inverse avec une faible chute de tension à l'état passant et une commutation rapide notamment dans les conditions extrêmes (hautes températures, radiation et milieux chimiques...). On a

deux solutions pour résoudre ce probléme : améliorer la conception du composant, ou trouver un autre matériau qui peut remplacer le silicium.

Ainsi, une solution est d'employer un matériau grand-gap qui semble mieux approprié. Les propriétés physiques de ce matériau (champ électrique critique, conductivité thermique élevée, vitesse de saturation des porteurs importante...) en font un matériau bien adapté pour l'électronique de haute puissance, haute température et haute fréquence. Parmi ces matériaux grand-gap, le SiC, le diamant et le GaN sont des candidats avec les propriétés les plus attractives, mais ils ont encore des limites en termes de disponibilité de substrats et de maturité de la technologie qui font qu'aujourd'hui ces semi-conducteurs sont moins avancés que le silicium. Toutefois, ces dernières années 1990-2016, la maturité technologique du SiC a permis de réaliser une gamme assez large de composants de puissance (diode, transistors bipolaires, JFET, MOSFET, IGBT...). Une filière SiC est en train d'émerger sur les différents continents. Les plus avancées sont CREE Research aux États-Unis, devenu Wolfspeed, INFINEON et STMicroelectronics en Europe, Rohm, Mitsubishi, CRIEPI et Toyota au Japon. Le premier composant de puissance en SiC disponible sur le marché en 2001 par les sociétés Microsemi et Infineon technologies a été la diode Schottky. Aujourd'hui, des MOSFET 1700 V - 50 A sont disponibles. Les MOSFET 6,5 kV - 50 A sont en phase d'industrialisation.

Dans ce premier chapitre, nous rappelons les principales propriétés du SiC. Un état de l'art des technologies de fabrication SiC, la notion de la tenue en tension de composant et les méthodes de protection périphérique réalisées sur le SiC sont ensuite présentés.

## 1.1 Propriétés du SiC

Le carbure de silicium est un matériau ancien, trouvé dans les météorites et qui n'existe pas à l'état naturel sur la terre. La synthèse du matériau présente cependant beaucoup de difficultés : la température mise en jeu

lors de la synthèse est très élevée, le nombre de polytypes important (près de 200) et leurs conditions d'obtention sont très sensibles aux conditions de température et de pression. Nous rappelons dans un premier temps les propriétés principales du SiC.

## 1.1.1 Structure cristalline et polytypes du SiC

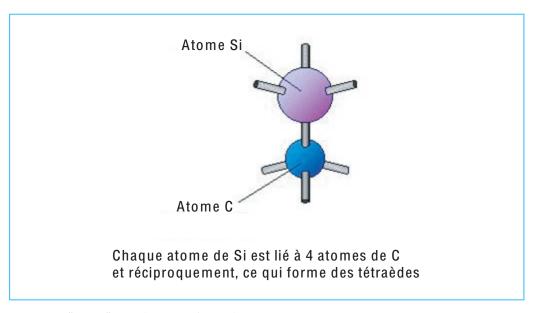

Le carbure de silicium est un matériau cristallin formé par l'empilement alterné de plans compacts de paires C-Si (Fig 1.1). Les différentes séquences d'empilement de ces plans donnent des cristaux différents appelés polytypes. On dénombre plus de 200 polytypes pour le SiC.

FIGURE 1.1 - "Paire" SiC (Raynaud 2007)

Selon la notation de Ramsdell (Raynaud 2007), les polytypes sont nommés par NX, où N est le nombre de couches constituant la période et X désigne la structure cristallographique : H (hexagonale), R (rhomboédrique) ou C (cubique). Les plus intéressants sont les polytypes 6H, 4H, et 3C car ils présentent les propriétés particulièrement recherchées dans la fabrication des composants de puissance.

La figure 1.2 suivante présente la structure de base du SiC et les séquences d'empilement des principaux polytypes de SiC (Tournier 2007).

Aujourd'hui, tous les composants de puissance industrialises utilise du 4H.

Figure 1.2 – Séquence d'empilement des principaux polytypes de SiC (Tournier 2007)

#### 1.1.2 Propriétés mécaniques et thermiques du SiC

Le carbure de silicium possède une énergie de liaison élevée Si-C ( $\sim$  6 eV) permettant d'obtenir une grande stabilité chimique et physique à haute température (jusqu'à 1300°C), ainsi qu'une grande résistance aux radiations. Cela permet l'utilisation des composants SiC dans des environnements hostiles tels que les installations nucléaires ou spatiales. De plus, il a aussi une très bonne conductivité thermique, elle est comparable à celle du cuivre, qui permet une meilleure évacuation de la chaleur au sein des composants, favorisant la montée en puissance ou en fréquence des composants.

## 1.1.3 Propriétés électroniques du SiC

### 1.1.3.1 Énergie de la bande interdite

Le SiC est un semi-conducteur à bande d'énergie interdite indirecte. Sa valeur de bande interdite ( $E_{gap}$ ) est de l'ordre de 3 eV, environ trois

fois celle du silicium. Le gap décroit linéairement en température comme indiqué dans le Tableau 1.1 (Raynaud 2007).

Tableau 1.1 – Variation du gap en fonction de la température

| Polytypes | $E_g$ à oK(eV) | $E_g$ en fonction de T(K)             |

|-----------|----------------|---------------------------------------|

| SiC-6H    | 3,02           | 2,925-3,3x 10 <sup>-4</sup> (T - 300) |

| SiC-4H    | 3,26           | 3,165-3,3x 10 <sup>-4</sup> (T - 300) |

| SiC-3C    | 2,37           | 2,2-5,8x 10 <sup>-4</sup> (T - 300)   |

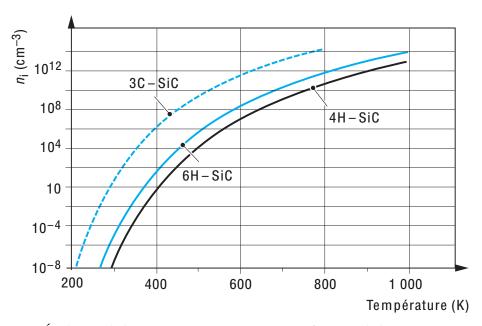

# 1.1.3.2 Concentration des porteurs intrinsèques et densités d'états

La concentration des porteurs intrinséques  $n_i$  de SiC est extrêmement faible comparée à celle du Silicium, en raison du grand gap de ce matériau. C'est un paramètre important car il détermine la limite supérieure de la température de fonctionnement des composants. En plus, il conditionne pour une bonne part l'intensité des courants de fuite en inverse des jonctions bipolaires ou Schottky. Ce paramètre est lié à la largeur de la bande interdite ainsi qu'aux densités effectives d'états de la bande de conduction  $N_C$  et bande de valence  $N_V$ :

$$n_i = \sqrt{N_V N_C} exp(\frac{-E_g}{2kT}) \tag{1.1}$$

Avec:

$$N_C = 2M_C \left(\frac{2m_{dos,n}KT\pi}{h^2}\right)^{\frac{3}{2}}$$

(1.2)

Et:

$$N_V = 2M_V \left(\frac{2m_{dos,p}KT\pi}{h^2}\right)^{\frac{3}{2}} \tag{1.3}$$

Où:

—  $M_C$ ,  $M_V$ : nombre de minima équivalents dans les bandes de conduction et de valence

- $m_{dos,n}$ ,  $m_{dos,p}$ : masses effectives de densité d'états des électrons et des trous

- K : constante de Boltzmann

- h : constante de Planck

La concentration  $n_i$  à température ambiante est indiquée dans le tableau 1.2.

Tableau 1.2 – Paramètres  $N_C$ ,  $N_V$  et  $n_i$  calculés à 300 K (Raynaud 2007)

| Polytypes                 | SiC-6H                 | SiC-4H                 | SiC-3C                 |

|---------------------------|------------------------|------------------------|------------------------|

| $N_C$ (cm <sup>-3</sup> ) | 8,65x 10 <sup>19</sup> | 1,68x 10 <sup>19</sup> | 1,56x 10 <sup>19</sup> |

| $N_V$ (cm <sup>-3</sup> ) | 3,3x 10 <sup>19</sup>  | 3,3x 10 <sup>19</sup>  | 3,3x 10 <sup>19</sup>  |

| $n_i  (cm^{-3})$          | 1,44x 10 <sup>-5</sup> | 6,12x 10 <sup>-8</sup> | 7,54                   |

D'après la figure 1.3 (Raynaud 2007), on voit l'évolution de la concentration intrinsèque en fonction de la température, en tenant compte de la variation de  $E_g$  avec la température. Lorsqu'elle dépasse le dopage de la région faiblement dopée le composant ne peut plus fonctionner. Pour le SiC-6H et 4H, la concentration intrinsèque reste très inférieure, aux dopages généralement utilisés (>  $10^{14} \ cm^{-3}$ ). Par conséquent, le SiC fonctionne en régime extrinsèque jusqu'à 1000 K (700 °C) ou plus.

Figure 1.3 – Évolution de la concentration intrinsèque en fonction de la température, en tenant compte de la variation de  $E_g$  avec la température (Raynaud 2007).

## 1.1.3.3 Énergie d'activation et ionisation incomplète des dopants

L'énergie d'activation est la différence d'énergie entre le niveau discret introduit par l'impureté et la bande de conduction pour les impuretés donneuses et la bande de valence pour les impuretés dopantes acceptrices. Pour le SiC, l'énergie d'activation des dopants est bien supérieure à celle observée dans le Si pour un même dopant. Pour SiC, à température ambiante tous les dopants ne sont pas ionisés. Ce point de "gel des porteurs" (" freeze-out of carriers ") peut être observé que vers 100 K, dans le cas du Si. Nous parlons alors d'ionisation incomplète des dopants. Cette propriété du SiC influence de façon significative les caractéristiques des composants, car elle peut conduire à une augmentation de la résistance série et à une diminution de l'injection des porteurs. Le pourcentage de dopants ionisés à une température donnée dépend peu de la compensation et diminue avec l'augmentation du dopage. Les énergies d'activation des principaux dopants et les calculs du pourcentage de dopants ionisés sont présentés dans la tableau 1.3.

|              | ,            |                 |       |             |          |              |       |

|--------------|--------------|-----------------|-------|-------------|----------|--------------|-------|

| TT 11        | r .          | 1/ 1' 1'        | 1     |             | 1 1      | /D 1         | \     |

| 12012211 1 2 | = $+1100010$ | oe a actimation | noc 1 | nvincinaliv | annante  | I K ALIMALIA | 20071 |

| iabicau 1.3  | - LILLIYIL   | es d'activation | uco L | σιιιισμαία  | uopuilis | (1Xuy/iuuu   | 200// |

| Impuretés | Polytypes     | SiC-6H            | SiC-4H        | SiC-3C          |

|-----------|---------------|-------------------|---------------|-----------------|

| Azote     | Sites occupés | С                 | С             | C et Si         |

|           | Énergies      | $E_{dh} = 81$     | $E_{dh} = 52$ | $E_{dk} = 56,5$ |

|           |               | $E_{dk1} = 138$   | $E_{dk} = 92$ |                 |

|           |               | $E_{dk2} = 142$   |               |                 |

| Aluminium | Sites occupés | Si                | Si            | Si              |

|           | Énergies      | $E_{ah} = 239$    | $E_a = 191$   | $E_a = 254$     |

|           |               | $E_{ak1.2} = 249$ |               |                 |

- On note  $E_{dhi}$  et  $E_{dKi}$  les énergies d'activation des donneurs dans les i sites hexagonaux (indices h) et j sites cubiques (indice k) respectivement.

- On note  $E_{ahi}$  et  $E_{aki}$  les énergies d'activation des accepteurs dans ces mêmes sites hexagonaux et cubiques.

#### 1.1.3.4 Mobilité des porteurs

La mobilité des porteurs est importante si l'on veut déterminer les résistances des couches de SiC que l'on utilise pour réaliser des composant. Les calculs théoriques de la mobilité des porteurs nécessitent de résoudre l'équation de transport de Boltzmann, ce qui se fait généralement dans le cadre de l'approximation du temps de relaxation. Alors, on peut calculer le tenseur de conductivité en fonction du champ électrique, et par la suite la mobilité. Ces calculs demeurent valables pour le SiC, en adaptant les paramètres. La mobilité sous champ faible, que l'on appelle par la suite mobilité  $\mu$  est définie par :

$$v = \mu F \tag{1.4}$$

Où : v est la vitesse des porteurs et F est le champ électrique. La mobilité sous fort champ électrique F peut être décrite comme suit :

$$\mu = \frac{\mu_{LF}}{\left(1 + \left[\frac{\mu_{LF}.F}{v_{sat}}\right]^{\alpha}\right)^{\frac{1}{\alpha}}}$$

(1.5)

avec :  $\mu_{LF}$  est la mobilité sous champ faible décrite ci-dessus et  $v_{sat}$  est la vitesse de saturation de porteurs.

Les valeurs des paramètres  $\alpha$  et  $v_{sat}$  dans les directions parallèles et orthogonales à l'axe sont présentées dans le tableau 1.4 (Raynaud 2007). Ces valeurs sont soit théoriques, déterminées par des simulations de type Monte-Carlo (MC), soit expérimentales.

| Tableau 1.4 – . | Paramétres 1 | $N_C$ , $I$ | $N_V$ et 1 | $\iota_i$ calc | culés à : | 300 K | ( ( ŀ | Kaynaua | . 2007, | ) |

|-----------------|--------------|-------------|------------|----------------|-----------|-------|-------|---------|---------|---|

|-----------------|--------------|-------------|------------|----------------|-----------|-------|-------|---------|---------|---|

| Polytypes                   | SiC-6H              | SiC-6H                | SiC-4H                 | SiC-4H                |

|-----------------------------|---------------------|-----------------------|------------------------|-----------------------|

|                             | expérimental        | simulation MC         | expérimental           | simulation MC         |

| $\alpha \perp (MC)$         | 1,09                | 0,9                   | 0,825                  | 0,84                  |

| $\alpha$ // (MC)            |                     | 1,4                   |                        | 1,11                  |

| $v_{sat} \perp (cm.s^{-1})$ | 2 x 10 <sup>7</sup> | 1,9 x 10 <sup>7</sup> | 2,08 x 10 <sup>7</sup> | 2,1 x 10 <sup>7</sup> |

| $v_{sat} // (cm.s^{-1})$    |                     | $6 \times 10^6$       |                        | 1,7 x 10 <sup>7</sup> |

#### 1.1.3.5 Champ critique

Le champ électrique de claquage du SiC ( $\sim 2.5$  MV/cm) est environ 10 fois plus élevé que celui du Silicium ( $\sim 0.2$  MV/cm).

La tension de claquage pour une diode plane "non-punch-through" (NPT) de surface infinie est donnée par :

$$V_B = \frac{E_C W_B}{2} = \left(\frac{q N_D}{2\varepsilon}\right) W_B^2 \tag{1.6}$$

On voit bien que, avec la même valeur de tenue en tension, l'épaisseur de la région de désertion  $W_B$  sera environ 10 fois plus mince que pour le silicium, et le dopage  $N_D$  sera environ 100 fois plus élevé (équation 1.6). Ainsi, il en résulte une diminution de la taille du composant donc du système de refroidissement par rapport à ceux des composants Si. Par contre, si l'on fixe la taille du composant, le champ critique élevé confère une tensions de blocage plus élevée et un meilleur compromis entre la tenue en tension avec la résistance à l'état passant.

$$R_{ON} = \frac{W_B}{q\mu_n N_D} = \frac{4V_B^2}{\varepsilon \mu_n E_C^3} \tag{1.7}$$

Le champ de claquage est donné par la formule :

Pour le polytype 4H (Konstantinov et al. 1997):

$$F_c = \frac{2,49.10^6}{1 - 0,25lg(N_{D,A}/10^{22})}$$

(1.8)

Pour le polytype 4H (Raghunathan et Baliga 1999) :

$$F_c = 1,64.10^4.(N_D/10^6)^{1/7}$$

(1.9)

Pour le polytype 6H (Raghunathan et Baliga 1999)

$$F_c = 1,52.10^4.(N_D/10^6)^{1/7}$$

(1.10)

#### 1.1.3.6 Coefficients d'ionisation

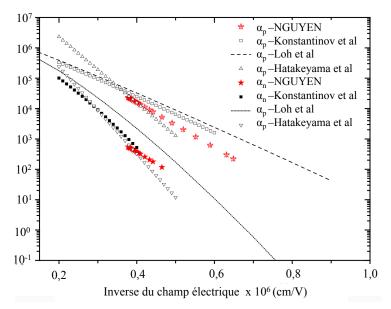

Les coefficients d'ionisation préssentent l'aptitude des atomes du cristal semi-conducteur à s'ioniser sous l'effet de l'impact d'un électron ou d'un trou chaud (c'est-à-dire fortement énergétique). En effet, sous polarisation inverse, des porteurs minoritaires sont injectés dans la zone de charge d'espace, qui subit un champ électrique intense. Ces porteurs peuvent acquérir une énergie cinétique important, si leur libre parcours moyen est assez long, et peuvent ioniser les atomes du réseau lors de collisions avec eux sur le chemin, et ensuite libérer un autre porteur. Celui-ci, étant également balayé par le champ électrique, il contribue à augmenter le courant de fuite. Selon l'énergie mise en jeu lors du choc collisionnel, les porteurs libres qui en résultent peuvent eux-mêmes contribuer à ioniser d'autres atomes. Ce phénomène cumulatif s'appelle la multiplication par avalanche, la quelle peut conduire au claquage du composant. Peu de travaux ont été publiés concernant les coefficients d'ionisation des électrons et des trous en SiC. Les valeurs des coefficients d'ionisation dans le SiC-4H obtenues par Konstantinov en 1997 (Konstantinov et al. 1997) sont largement utilisées dans les simulateurs pour la conception des composants de puissance en SiC jusqu'à maintenant.

#### 1.2 Technologie de fabrication SiC

Les performances des composants en SiC obtenues ne sont pas seulement liées à la technologie de fabrication, mais d'abord liées à la qualité des substrat SiC. Jusqu'à maintenant, la qualité des substrats s'est bien améliorée, mais il reste quand même de nombreux défauts. Les deux familles principales de défauts sont les défauts étendus (les micropipes, les dislocations, les fautes d'empilement dans le plan de base) et les défauts ponctuels. Parmi eux, les défauts micropipes (Hofmann *et al.* 1999) et les dislocations (Blumenau *et al.* 2003) causent un grand impact sur la propriétés mécaniques et surtout électriques du composant. Tout d'abord, la

méthode de "Lely" (Anthony 1958), basée sur la condensation de SiC, permit de faire croître des couches de SiC relativement pures et présentant une faible densité de défauts. La taille du substrat est petite, ce qui rend le rendement d'utilisation de wafer faible, le coût global du composants élevé. D'un point de vue technique, les calibres en courants et en tensions des composants restaient petits.

En 1978 fut montrée une nouvelle méthode dérivée de celle de Lely (Tairov et Tsvetkov 1978) pour obtenir des substrats plus grands en introduisant un germe de SiC monocristallin dans la chambre de croissance. Les vapeurs ne se condensent plus alors de manière aléatoire sur la paroi en graphite mais sur le germe refroidi qui conditionne, par là même, une orientation préférentielle tout au long de la nucléation. En imposant un gradient de température à l'intérieur du réacteur, on constate une amélioration de la qualité des cristaux. Plus récemment, Cree a annoncé en 2012 la commercialisation de la nouvelle génération de substrats de 6 pouces (150 mm) (Cree 2012). Aujourd'hui les micropipes ne sont plus un problème : ils représentent moins de 3 % des sources de défaillances pour des rendements de production de l'ordre de 80 %.

Les différentes techniques et moyens de fabrication employés pour SiC sont similaires à ceux existants pour la filière silicium. Elles ont fait l'objet de développements et optimisations afin d'être adaptées aux spécificités du SiC. Dans le cadre de notre travail, les étapes technologiques importantes sont l'épitaxie, les procédés de dopage, la gravure, le contact ohmique, la passivation et le packaging. Elles révèlent toutes d'une grande complexité. Ells seront abordées par la suite.

### 1.2.1 Croissance de couches épitaxiales

Comme le dopage des substrats SiC est à un niveau élevé (supérieur à  $10^{17}$  cm $^{-3}$ , des couches épitaxiales réalisées à un dopage contrôlé, de type P ou N, sont nécessaires pour assurer les caractéristiques des composants. Ces croissances épitaxiales sont en général des homoépitaxies sur des sub-

strats SiC et dans une moindre mesure, des croissances hétéroépitaxiales sur des substrats silicium. Les méthodes les plus utilisées sont celles par CVD (Chemical Vapor Deposition) en utilisant des gaz comme le silane  $(SiH_4)$  et le propane  $(C_3H_8)$  ou le méthane  $(CH_4)$  ainsi que des précurseurs pour introduire des dopants. Ces croissances se réalisent en général dans des réacteurs verticaux à des températures assez élevées, 1500 à 1600 °C dans le cas des homoépitaxies. Une légère désorientation des substrats est utilisée (off-axis) afin de préservé le polytype du susbtrat. Ces dernières années des progrès importants sur les composants SiC ont été faits grâce à l'amélioration de la qualité des couches épitaxiales. Ceci s'est produit aussi grâce à l'amélioration de la qualité des substrats SiC, en réduisant les densités des défauts (micropipes, dislocations) et en utilisant des méthodes pour éviter la migration de ces défauts vers les couches épitaxiales.

## 1.2.2 Dopage du SiC

Par rapport au silicium ou d'autres semiconducteurs classiques, le dopage sélectif du SiC ne peut pas être réalisé par diffusion des impuretés à cause de leurs coefficients de diffusion trop faibles. Ainsi, le dopage localisé dans le SiC se réalise en général par implantation ionique. Pour guérir les défauts créés dans le réseau cristallin du SiC et activer les dopants, c'est-à-dire les faire migrer dans des sites substitutionnels, il est nécessaire de réaliser des recuits à très haute température, typiquement autour de 1700 °C. Les dopants utilisés pour doper le SiC sont l'azote et le phosphore pour créer des couche de type N ainsi que l'aluminium et plus rarement le bore pour créer des couches de type P. Les énergie d'ionisation de l'azote et l'aluminium pour le SiC sont données dans le tableau 1.3. Remarquons les valeurs assez élevées de celles pour l'aluminium,  $\sim 200$ meV, qui sont la raison des difficultés pour créer des couches de SiC type P à faible résistivité. Au laboratoire AMPERE plusieurs thèses ont été menées pour étudier et optimiser le dopage par implantation ionique comme celles de Laurent Ottaviani (Ottaviani 1999) et Mihai Lazar(Lazar 2002).

D'autres méthodes alternatives de dopage ont été étudiées comme celle par croissance VLS (Vapeur-Liquide-Solide) (Sejil *et al.* 2017).

## 1.2.3 Contacts métalliques sur SiC

Sur les semiconducteurs à large bande interdite, la réalisation des contacts ohmique est en général difficile à cause des désaccords entre les travaux de sortie des métaux et les affinités électroniques ou les travaux de sortie des semiconducteurs. Dans le cas du SiC c'est surtout le contact ohmique sur le type P qui pose des soucis. Pour les contacts sur le SiC de type N on utilise des métallisations à base de nickel et des résistances spécifiques de contact assez faibles, de l'ordre de  $10^{-6} \Omega cm^2$  sont obtenus après un recuit de quelques minutes à rampe de montée rapide jusqu'à 1000 °C. Dans le cas du SiC de type P, des alliages plus complexes sont utilisés, à base d'aluminium, titane et nickel. Des recuits à rampes rapides à plusieurs paliers sont utilisés jusqu'à 800 ou même 1000 °C pour obtenir des résistances spécifiques assez élevées autour de  $10^{-4}~\Omega~cm^2$  en général et pour les meilleures autour de  $10^{-5}$   $\Omega$   $cm^2$ . Au laboratoire AMPERE, récemment, des études dans le cadre de plusieurs thèses ont été conduites sur les contacts ohmiques réalisées sur le SiC de type. (Laariedh 2013) (Abi Tannous 2015).

# 1.2.4 Gravure SiC

Parmi les étapes technologies pour la fabrication des composants dans les circuits intégrés, la gravure constitue l'une des étapes clefs les plus importantes afin de créer les motifs et les zones actives, la protection périphérique du composant, révéler certains défauts du matériau ou de rafraîchir les surfaces dans les procédés technologiques... Dans notre cas, on s'intéresse à la gravure du SiC pour la mise en place de la protection de type mesa. En général, la gravure se fait soit en voie humide, soit en voie sèche en fonction du matériau gravé et de la conception de composant.

Pour graver du SiC, la gravure sèche par "plasma" est choisie, car, contrairement au silicium, le SiC est un matériau "difficile" à graver à cause de ses excellentes propriétés de résistance chimique et mécaniques (inertie chimique). De plus, la gravure plasma est strictement anisotrope et a une grande sélectivité par rapport au masque utilisé. De ce fait, elle présente des avantages qui répondent aux exigences de la diminution des dimensions critiques des motifs (quelques dizaines de nanomètres) et aussi aux qualités des surfaces gravées (sans contamination, sans dommages cristal-lins...).

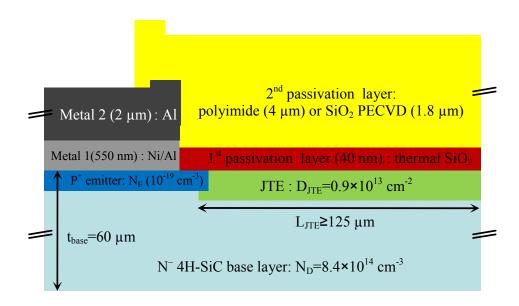

#### 1.2.5 Passivation

Les dispositifs haute tension, lors du fonctionnement peuvent rencontrer des limitations liées aux propriétés électriques de leur environement. Par exemple, pour une diode verticale en polarisation en inverse, un champ électrique élévé apparait en surface du composante. Ce champ peut conduire au claquage externe de la structure par contournement du champ électrique. Pour réduire le champ éléctrique et aussi le risque de contournement en surface de composant, on dépôse une couche d'isolant possédant un champ électrique de claquage supérieur à celui de l'air... On l'appelle "couche de passivation", la plus répandue est l'oxyde de silicium  $SiO_2$ . Elle sert à la fois à passiver les états de charge présents à l'interface avec le semi-conducteur, mais aussi à protéger cette interface de toute contamination pouvant être une source de défaillance dans le temps. Dans la suite, on détaille respectivement les passivations primaire et secondaire.

# 1.2.5.1 Passivation Primaire

La couche de passivation primaire  $SiO_2$  est obtenue via une oxydation thermique (quelques 100 nm) à très haute température (> 1000 °C). Cette couche possède généralement un très fort champ de rupture de l'ordre de 10 - 12 MV. $cm^{-1}$  (Jones et Jones Stephen 2002), (Yano *et al.* 2005). Les densités de charges à l'interface sont très faibles (de l'ordre de  $10^{10}$   $cm^{-2}$  dans le

cas du Si, beaucoup plus élevées dans le cas du SiC), ce qui perturbent peu la répartition des équipotentielles à l'intérieur du semiconducteur (Yano *et al.* 2005). Cette couche de passivation permet de réduire fortement le niveau des courants de fuite des composants semiconducteurs sous polarisation inverse.

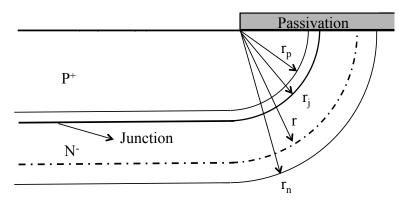

FIGURE 1.4 – Structure de composant SiC protégé par JTE avec les couches de passivation y compris les paramétres technologiques (Diaham et al. 2009)

# 1.2.5.2 Passivation Secondaire

C'est la couche de passivation déposée au desuss de la couche primaire avec un dépôt plus épais (plusieurs micromètres d'épaisseur) de manière conforme. Elle doit posséder une excellente propriété diélectrique, un champ de rupture élevé et aussi être capable de supporter les dilatations thermiques sur des dispositifs de grandes dimensions. Cette couche peut être soit des matériaux inorganiques ( $SiO_2$  et/ou  $Si_3N_4$ ) déposés par CVD (Chemical Vapor Deposition), soit des polymères organiques ou les gels silicones. Les plus répandus sont des polymères comme le polyimide (Nuttall *et al.* 2003).

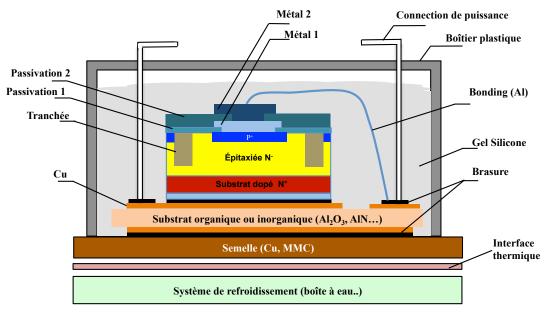

## 1.2.6 Packaging

La puce semi-conductrice est un élément actif d'un module de puissance. Pour le protéger et isoler de son environnement, un packaging (ou boîtier) est indispensable. Le packaging doit évacuer la chaleur que la puce dissipe et transmettre les courants via les terminaux de connection au reste du circuit (bonding). Par exemple, sur la Fig 1.5, les différents éléments de packaging sont présentés. La puce semi-conductrice est brasée sur un subtrat céramique métalisé. Le substrat céramique est ensuite fixé sur une semelle. Les deux parties, subtrat céramique métalisé et semelle, jouent le rôle d'un support mécanique et assurent et le transfert thermique vers l'extérieur. Des fils de bonding assurent les connections électriques à l'intérieur. Les connections vers l'extérieur sont faites par les brasures sur la partie métalisation du substrat céramique. Enfin, l'assemblage est mis en boîtier, lequel est rempli d'un gel silicone (encapsulation), pour protéger les constituants du module de puissance.

Figure 1.5 – Module d'électronique de puissance standard

# 1.3 Tenue en Tension

La tenue en tension d'un composant de puissance est l'une de ses caractéristiques les plus importantes. Elle est définie par la tension que les deux contacts principaux (ou une jonction bloquante du dispositif) peut supporter sous polarisation inverse. Cette jonction, en règle générale, est fortement asymétrique. L'une des deux régions, relativement large et peu dopée souvent désignée par le terme générique de "drift", doit permettre à la zone de charge d'espace de s'étendre suffisamment. La couche de "drift" est souvent homogène, de type N de préférence au type P pour des raisons qui tiennent à la plus forte mobilité des électrons ou aux impératifs de la technologie. Elle constitue la région centrale du composant. Les profils types à considérer dans l'étude de la tenue en tension des composants de puissance sont donc des successions  $P^+NN^+$  et  $P^+NP^+$  (ou les successions complémentaires  $N^+PP^+$  et  $N^+PN^+$ )(Leturcq 2000).

La tenue en tension théorique est définie essentiellement par le mécanisme d'avalanche. Elle dépend pricipalement de l'épaisseur et du dopage de la couche de "drift" qui tient la tenue en tension, le gradient de concentration d'impuretés dans le cas de jonctions très "graduelles". Mais en fait, la tenue en tension effective est différente de la valeur théorique et cela dépend aussi de plusieurs facteurs comme la méthode de protection périphérique, le type de jonction (plane, cylindrique ou sphérique), le contrôle de la nature et de la concentration des centres de génération - recombinaison, la passivation de la surface du composant...Tout d'abord, nous allons détailler le mécanisme d'avalanche dans le volume du composant.

# 1.3.1 Définition du claquage par avalanche

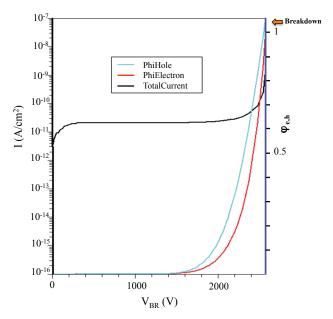

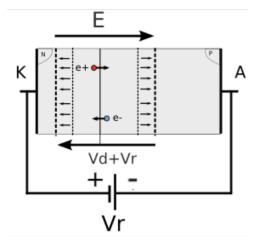

Dans une jonction PN polarisée en inverse règne de part et d'autre un champ électrique intense. Lorsque le champ électrique devient suffisamment important, sous l'effet de ce champ, les porteurs sont accélérés dans la zone de charge d'espace. Ils acquièrent de l'énergie pour ioniser les atomes du réseau et ainsi créer des paires électron-trou, qui accélérées à leur tour peuvent provoquer l'ionisation d'autres atomes. On dit alors qu'il y a une multiplication par avalanche des porteurs (Fig 1.6). Le claquage par avalanche survient lorsque le phénomène de multiplication s'emballe, le courant de fuite tend théoriquement vers l'infini. La tension de claquage est déterminée pour une valeur de courant de fuite donnée. On considère parfois que ces conditions sont satisfaites lorsque l'intégrale d'ionisation est égale à unité (Sze et Gibbons 1966) :

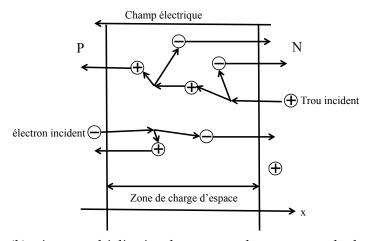

Figure 1.6 – Accélération et multiplication des porteurs dans une zone de charge d'espace.

$$I_{n} = \int_{r_{n}}^{r_{p}} \alpha_{n} exp \left[ -\int_{r}^{r_{p}} (\alpha_{n} - \alpha_{p}) dr' \right] dr = 1$$

(1.11)

$$I_{p} = \int_{r_{n}}^{r_{p}} \alpha_{p} exp \left[ -\int_{r_{n}}^{r} (\alpha_{p} - \alpha_{n}) dr' \right] dr = 1$$

(1.12)

Où:

- r est la coordonnée d'espace  $(r_p < r < r_n)$ .

- $r_p$  et  $r_n$  sont les limites des charges d'espace dans les zones N et P.

- $\alpha_n$  et  $\alpha_p$  sont les coefficients d'ionisation des électrons et des trous.

Ces coefficients  $\alpha_n$  et  $\alpha_p$  sont les paramètres fondamentaux permettant de décrire le mécanisme d'avalanche. Ils représentent le nombre probable de collisions d'ionisation que subit un porteur incident, trou ou électron, sur une unité de longueur de parcours. Une première expression appro-

Figure 1.7 – Extension de charge d'espace, les coordonées et limites dimensionnelles.

chée, largement utilisée par le passé, qui permet d'expliciter la relation entre les coefficients d'ionisation et le champ électrique (Chynoweth 1958), est donnée par la forme exponentielle suivante :

$$\alpha_{n,p} = A_{n,p} exp\left(-\frac{B_{n,p}}{F}\right) \tag{1.13}$$

Où:

- F : champ électrique

-  $A_{n,p}$ ,  $B_{n,p}$ : des constantes, les valeurs proposées par divers auteurs sont données dans le tableau 1.5.

Tableau 1.5 – Les constantes pour calculer les coefficients d'ionisation pour SiC-4H.

|                   | Auteur 1                    | Auteur 2             | Auteur 3             | Auteur 4    | Auteur 5    | Auteur 6    |

|-------------------|-----------------------------|----------------------|----------------------|-------------|-------------|-------------|

| $A_n$             |                             | $1,98x10^6$          | $2,78x10^6$          | $1,76x10^8$ | $0,46x10^6$ | $4,1x10^5$  |

| $A_n$ $(cm^{-1})$ |                             |                      |                      |             |             |             |

| $B_n$             |                             | $(9,46x10^6)^{1,42}$ | $(1,05x10^7)^{1,37}$ | $3,3x10^7$  | $1,78x10^7$ | $1,67x10^7$ |

| (V/cm)            |                             |                      |                      |             |             | '           |

| $A_p$             | $3,25 \pm 0,3$              | $4,36x10^6$          | $3,51x10^6$          | $3,41x10^8$ | $1,56x10^7$ | $1,63x10^7$ |

| $(cm^{-1})$       | $x10^{6}$                   |                      |                      |             |             | ·           |

| $B_{p}$           | $1,79 \pm 0,4$              | $(1,14x10^7)^{1,06}$ | $(1,03x10^7)^{1,09}$ | $2,5x10^7$  | $1,72x10^7$ | $1,67x10^7$ |

| (V/cm)            | $1,79 \pm 0,4$<br>$x10^{7}$ |                      |                      |             |             |             |

Auteur 1 : (Raghunathan et Baliga 1997)

Auteur 2 : (Ng *et al.* 2003)

Auteur 3 : (Loh *et al.* 2008)

Auteur 4 : (Hatakeyama *et al.* 2004)

Auteur 5 : (Nguyen et al. 2012) - Thèse au laboratoire AMPERE

BUI Thi Thanh Huyen/ "Terminaison verticales de jonction remplies avec des couches diélectriques isolantes pour des application haute tension utilisant des composants grand-gap de forte puissance" - Thèse INSA de Lyon - AMPERE

#### Auteur 6: (Konstantinov et al. 1998)

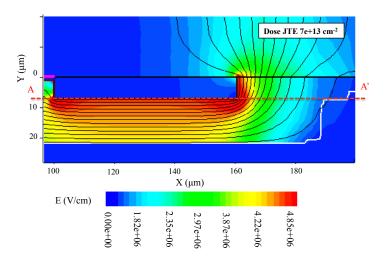

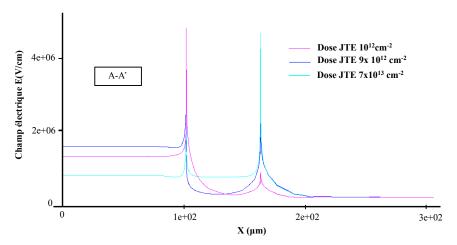

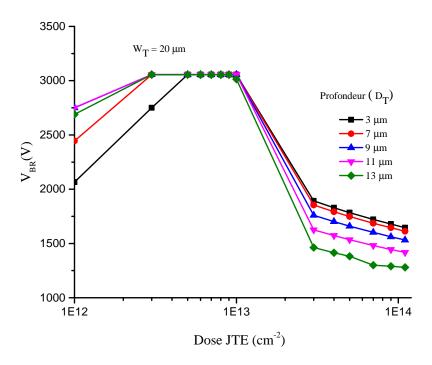

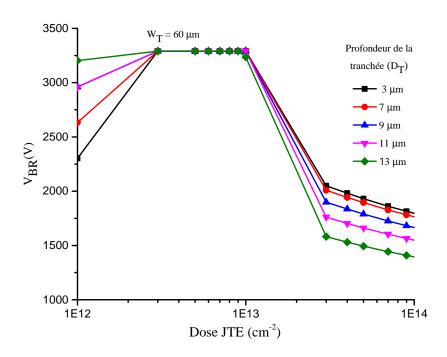

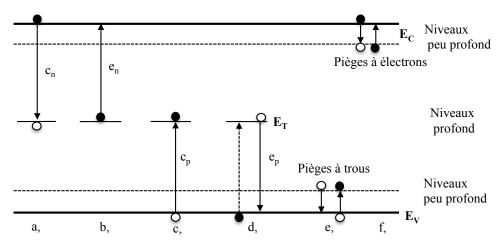

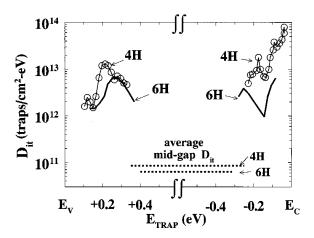

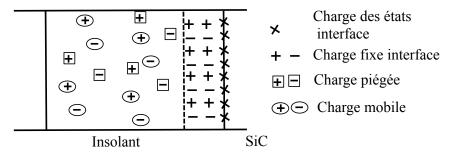

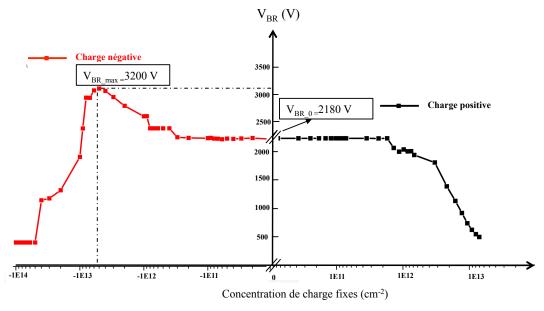

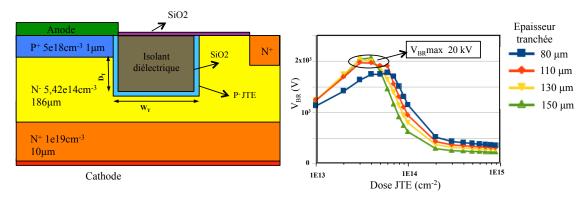

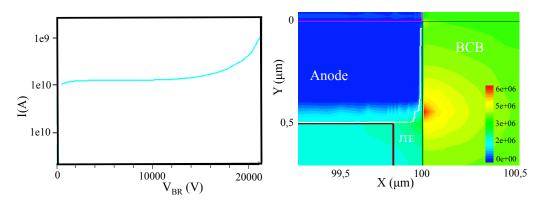

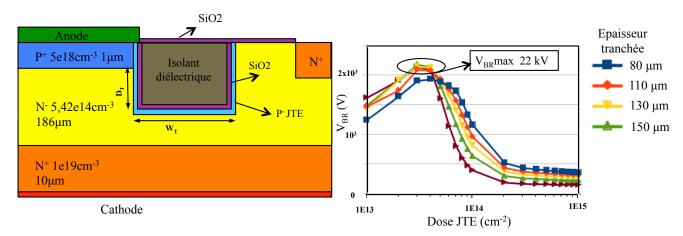

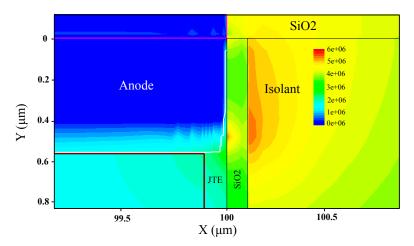

La dispersion de ces valeurs est liée principalement à la détermination expérimentale sur des échantillons et au fait, plus fondamental, que les valeur " $\alpha_{n,p}$ " sont probablement fonction d'autres paramètres que le seul champ électrique. Ces paramètres ont été ensuite vérifiés par une comparaison des résultats expérimentaux avec ceux de simulations et un bon accord a été observé. L'inconvénient majeur de la formualtion (équation 1.13) est qu'elle est délicate à intégrer pour le calcul dans les équations 1.11, 1.12).