# Software-level analysis and optimization to mitigate the cost of write operations on non-volatile memories

Rabab Bouziane

#### ▶ To cite this version:

Rabab Bouziane. Software-level analysis and optimization to mitigate the cost of write operations on non-volatile memories. Performance [cs.PF]. Université de Rennes, 2018. English. NNT: 2018REN1S073. tel-02089718

# HAL Id: tel-02089718 https://theses.hal.science/tel-02089718

Submitted on 4 Apr 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

#### L'UNIVERSITE DE RENNES 1

COMUE UNIVERSITE BRETAGNE LOIRE

ECOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies

de l'Information et de la Communication

Spécialité : (voir liste des spécialités) Informatique

Par

## Rabab BOUZIANE

Software-level Analysis and Optimization to Mitigate the Cost of Write Operations on Non-Volatile Memories

Thèse présentée et soutenue à Rennes, le 07 décembre 2018

Unité de recherche : Inria

Thèse N°:

#### Rapporteurs avant soutenance:

Christine ROCHANGE Professeur, université Paul Sabatier, Toulouse

Pierre BOULET Professeur, université de Lille

#### Composition du Jury :

Président : Sandrine BLAZY Professeur, Université de Rennes 1

Examinateurs : Sandrine BLAZY Professeur, Université de Rennes 1

Maître de Conférence INSA Lyon

Kevin MARQUET Maître de Conférence, INSA Lyon

Dir. de thèse: Erven ROHOU Directeur de Recherche Inria, Centre Inria Rennes-Bretagne Atlantique

Co-dir. de thèse : Abdoulaye GAMATIÉ Directeur de Recherche CNRS, LIRMM, Montpellier

Invité(s)

Prénom Nom Fonction et établissement d'exercice

## **Abstract**

Traditional memories such as SRAM, DRAM and Flash have faced during the last years, critical challenges related to what modern computing systems required: high performance, high storage density and low power. As the number of CMOS transistors is increasing, the leakage power consumption becomes a critical issue for energy-efficient systems. SRAM and DRAM consume too much energy and have low density and Flash memories have a limited write endurance. Therefore, these technologies can no longer ensure the needs in both embedded and high-performance computing domains. The future memory systems must respect the energy and performance requirements. Since Non Volatile Memories (NVMs) appeared, many studies have shown prominent features where such technologies can be a potential replacement of the conventional memories used on-chip and off-chip. NVMs have important qualities in storage density, scalability, leakage power, access performance and write endurance. Many research works have proposed designs based on NVMs, whether on main memory or on cache memories. Nevertheless, there are still some critical drawbacks of these new technologies. The main drawback is the cost of write operations in terms of latency and energy consumption. Ideally, we want to replace traditional technologies with NVMs to benefit from storage density and very low leakage but eventually without the write operations overhead.

The scope of this work is to exploit the advantages of NVMs employed mainly on cache memories by mitigating the cost of write operations. Obviously, reducing the number of write operations in a program will help in reducing the energy consumption of that program. Many approaches about reducing writes operations exist at circuit level, architectural level and software level. We propose a compiler-level optimization that reduces the number of write operations by eliminating the execution of redundant stores, called silent stores. A store is silent if it's writing in a memory address the same value that is already stored at this address. The LLVM-based optimization eliminates the identified silent stores in a program by not executing them.

Furthermore, the cost of a write operation is highly dependent on the used NVM and its non-volatility called retention time; when the retention time is high then the latency and the energetic cost of a write operation are considerably high and vice versa. Based on this characteristic, we propose an approach applicable in a multi-bank NVM where each bank is designed with a specific retention time. We analyze a program and we compute the worst-case lifetime of a store instruction. The worst-case lifetime will help to allocate data to the most appropriate NVM bank.

# Acknowledgements

Firstly, I would like to express my sincere gratitude to my advisor M. Erven ROHOU for the continuous support of my Ph.D study. Beside my advisor, I would like to thank M. Abdoulaye GAMATIE for his co-supervision.

A special thanks to my parents, my brother, my sister and my friends for supporting me throughout writing this thesis. Thanks for all your encouragement!

I dedicate this work to my Dad who is my inspiration in life.

# **Contents**

| Ał       | strac | t       |                                                               | i   |

|----------|-------|---------|---------------------------------------------------------------|-----|

| Ac       | knov  | vledgei | ments                                                         | iii |

| 1 Resumé |       |         |                                                               |     |

| 2        | Intro | oductio | on                                                            | 5   |

|          | 2.1   | Conte   | xt and problematic                                            | 5   |

|          |       | 2.1.1   | Challenges facing traditional memory technologies             | 6   |

|          |       | 2.1.2   | Challenges facing emerging NVMs technologies                  | 7   |

|          | 2.2   | Thesis  | objectives                                                    | 7   |

|          | 2.3   | Contri  | butions                                                       | 9   |

|          | 2.4   | Outlin  | ue                                                            | 10  |

| 3        | Ener  | rgy con | sumption in today's computing systems                         | 11  |

|          | 3.1   | The is  | sue of energy consumption                                     | 11  |

|          | 3.2   | Dealin  | ng with energy consumption issue                              | 12  |

|          |       | 3.2.1   | Compiler optimizations                                        | 13  |

|          |       | 3.2.2   | Dynamic voltage and frequency scaling (DVFS)                  | 14  |

|          |       | 3.2.3   | Power modes                                                   | 14  |

|          |       | 3.2.4   | Microarchitectural techniques                                 | 15  |

|          |       | 3.2.5   | Circuit level techniques                                      | 16  |

|          | 3.3   | Energy  | y consumption issue in emerging NVMs                          | 17  |

|          |       | 3.3.1   | Quick introduction to NVMs basic features                     | 17  |

|          |       |         | Magnetic Tunnel Junction Device                               | 19  |

|          |       | 3.3.2   | Dealing with energy consumption issues related to NVM caches  | 22  |

|          |       |         | Software-level optimizations via compiler techniques          | 22  |

|          |       |         | Architecture-level designs                                    | 24  |

|          |       |         | Circuit-level approaches                                      | 29  |

|          | 3.4   | Empir   | ical energy evaluation for STT-RAM caches with compiler opti- |     |

|          |       | mizati  | one                                                           | 30  |

|   |      | 3.4.1    | Typical loop optimizations: tiling and permutation              | 31         |

|---|------|----------|-----------------------------------------------------------------|------------|

|   |      | 3.4.2    | Experimental setup                                              | 32         |

|   |      | 3.4.3    | Impact of code optimization on performance and energy           | 33         |

|   |      |          | Observations                                                    | 34         |

|   | 3.5  | Why      | advocating software-level techniques for mitigating the energy- |            |

|   |      | issue    | on NVMs?                                                        | 36         |

| 4 | Red  | undan    | t memory write elimination                                      | 39         |

|   | 4.1  |          | luction                                                         | 39         |

|   | 4.2  | Relate   | ed Work                                                         | 40         |

|   |      | 4.2.1    | Profiling-based approaches                                      | 41         |

|   |      | 4.2.2    | Static Analysis approaches                                      | 41         |

|   | 4.3  | Silent   | -store elimination                                              |            |

|   |      | 4.3.1    | Definition and general principle                                | 42         |

|   |      | 4.3.2    | Implementation                                                  | 43         |

|   |      | 4.3.3    | Micro-architectural and compilation considerations              | 44         |

|   | 4.4  | Profit   | ability threshold                                               | 47         |

|   | 4.5  | Prelir   | minary evaluation based on a cycle-accurate simulator           | 48         |

|   |      | 4.5.1    | Application to a simple example                                 | 49         |

|   |      | 4.5.2    | Optimization profitability w.r.t. number of silent stores       | 51         |

|   | 4.6  | Comp     | orehensive evaluation based on an analytic approach             | 54         |

|   |      | 4.6.1    | Distribution of silent stores                                   | 54         |

|   |      | 4.6.2    | Impact of the silent-store elimination                          | 55         |

|   | 4.7  | Towa     | rds relaxed silent-stores                                       | 60         |

|   | 4.8  | Concl    | usion                                                           | 62         |

| 5 | Vari | iable re | etention times in a multi-bank NVM                              | 65         |

|   | 5.1  | Introd   | luction                                                         | 65         |

|   | 5.2  | Explo    | iting variable data retention times                             | 66         |

|   | 5.3  | Motiv    | vation for $\delta$ -WCET Estimates                             | 67         |

|   |      |          | Performance debugging                                           | 68         |

|   |      |          | Energy-efficiency                                               | 69         |

|   | 5.4  | Worst    | -Case stores lifetimes                                          | 70         |

|   |      | 5.4.1    | Motivational Example                                            | 71         |

|   |      | 5.4.2    | Related work                                                    | <b>7</b> 3 |

|   |      |          | WCET estimation techniques                                      | <b>7</b> 3 |

|   |      |          | Background: the Heptane Tool                                    | 74         |

|   |     | 5.4.3   | Proposed Methodology                     | 75 |

|---|-----|---------|------------------------------------------|----|

|   |     |         | $\delta$ -WCET Estimation                | 76 |

|   |     |         | Linking $\delta$ -WCET to NVM Allocation | 78 |

|   | 5.5 | Valida  | ation on Mälardalen Benchmark-suite      | 80 |

|   |     | 5.5.1   | Experimental setup                       | 80 |

|   |     | 5.5.2   | Architectural setup for IoT domain       | 81 |

|   |     | 5.5.3   | Lifetimes Evaluation on Benchmarks       | 85 |

|   |     | 5.5.4   | Gain evaluation                          | 87 |

|   | 5.6 | Concl   | usion                                    | 89 |

| 6 | Con | clusion | ,                                        | 93 |

| U | Con | Clusioi | L                                        | 93 |

|   | 6.1 | Achie   | ved results                              | 93 |

|   | 6.2 | Perspe  | ectives                                  | 94 |

# **List of Figures**

| 1.1 | Élimination des silent stores: le code d'origine ecrit val à l'adresse de x;                       |    |

|-----|----------------------------------------------------------------------------------------------------|----|

|     | Le code transformé charge d'abord la valeur à l'adresse x et la compare                            |    |

|     | à la valeur à écrire. Si elle est égale, l'exécution du store est annulée                          | 2  |

| 1.2 | L'implementation de l'optimization dans LLVM                                                       | 2  |

| 1.3 | Gain d'énergie en fonction du seuil de silentness des applications                                 |    |

|     | Rodinia et de leur rapport $r=\alpha_W/\alpha_R$ associé, où $\alpha_W$ et $\alpha_R$ représentent |    |

|     | respectivement les couts des opérations d'écritures et de lectures                                 | 3  |

| 1.4 | Outil Heptane étendu avec l'analyse $\delta$ -WCET                                                 | 4  |

| 1.5 | Économies d'énergie basées sur deux configurations différentes par                                 |    |

|     | rapport à une mémoire STT-RAM ayant une non-volatilité de 4,27                                     |    |

|     | années                                                                                             | 4  |

| 2.1 | Memory hierarchy model                                                                             | 7  |

| 3.1 | Typical memory access latency (Intel Xeon i7-5600U, 2.6 GHz)                                       | 12 |

| 3.2 | Comparison of traditional memory and NVM technologies [122]                                        | 18 |

| 3.3 | Magnetic tunnel junction (a) Parallel state, (b) Anti-parallel state, (c)                          |    |

|     | Equivalent circuit                                                                                 | 20 |

| 3.4 | Relaxing the non-volatility of STT-RAM [102], dotted border is the                                 |    |

|     | optimal scenario and black line is representing the comparison to SRAM                             | 21 |

| 3.5 | Extract of modified syr2k code                                                                     | 30 |

| 3.6 | Evaluated loop optimization and parallelization                                                    | 32 |

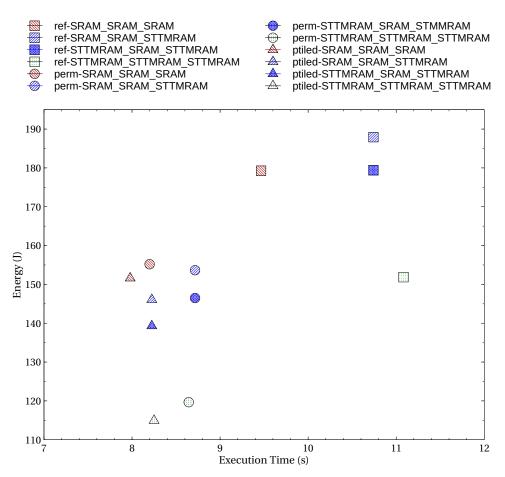

| 3.7 | Performance/energy trade-off with 4 Cortex-A15 cores operating at                                  |    |

|     | 1.0 GHz. The reference case, denoted as ref-* is the syr2k-omp program.                            |    |

|     | The other programs are optimized version of syr2k-omp                                              | 35 |

| 4.1 | Silent store elimination: original code stores val at address of x; trans-                         |    |

|     | formed code first loads the value at address of x and compares it with                             |    |

|     | the value to be written, if equal, the branch instruction skips the store                          |    |

|     | execution.                                                                                         | 43 |

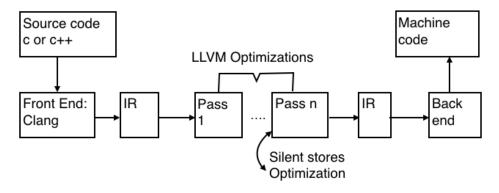

| 4.2 | Implementation of the optimization in LLVM                                                         | 43 |

| 4.3  | Design of the compilation framework                                                     | 4  |

|------|-----------------------------------------------------------------------------------------|----|

| 4.4  | A superscalar execution: the original sequential code is transformed                    |    |

|      | to exploit parallelism by hiding the new instructions added by our                      |    |

|      | transformation                                                                          | 45 |

| 4.5  | Example of predicated execution                                                         | 46 |

| 4.6  | Silent store elimination: (a) original code stores val at address of x; (b)             |    |

|      | transformed code first loads the value at address of x and compares it                  |    |

|      | with the value to be written, if equal, the branch instruction skips the                |    |

|      | store execution; (c) when the instruction set supports predication, the                 |    |

|      | branch can be avoided and the store made conditional                                    | 46 |

| 4.7  | Dedicated kernel. The volatile keyword forces the compiler to keep                      |    |

|      | the memory access on x, while other variables may be promoted to                        |    |

|      | registers. The assignment in the loop repeatedly writes the same value                  |    |

|      | 0 to the same memory location                                                           | 50 |

| 4.8  | Determination of the profitability threshold of silent store elimination.               | 52 |

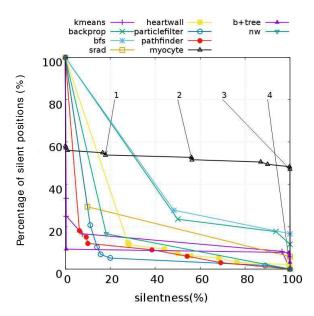

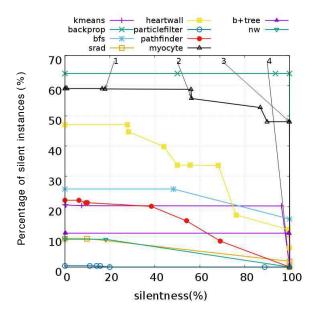

| 4.9  | Percentage of silentness on the basis of the percentage of static positions             |    |

|      | in the code                                                                             | 55 |

| 4.10 | Percentage of silentness on the basis of the percentage of silent in-                   |    |

|      | stances in the code                                                                     | 56 |

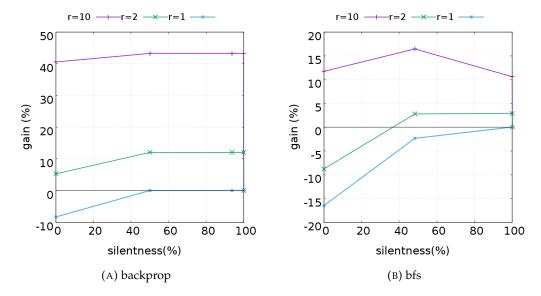

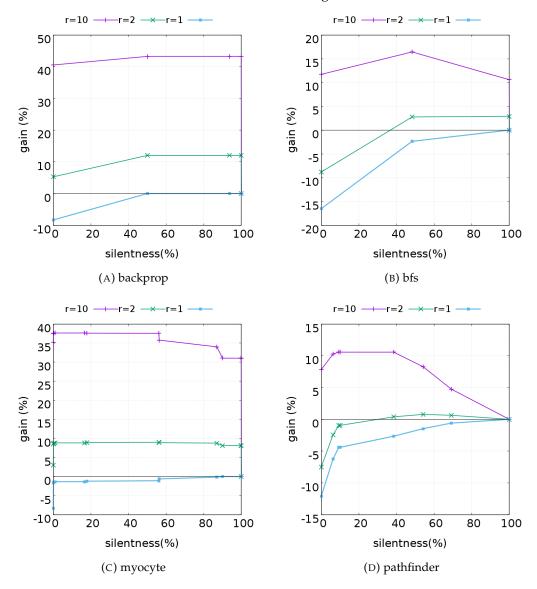

| 4.11 | Energy gain according to the silentness threshold of Rodinia applica-                   |    |

|      | tions, and their associated $r = \alpha_W/\alpha_R$ ratio: most sensitive applications. | 58 |

| 4.12 | Energy gain according to the silentness threshold of Rodinia appli-                     |    |

|      | cations, and their associated $r = \alpha_W/\alpha_R$ ratio: marginally sensitive       |    |

|      | applications                                                                            | 59 |

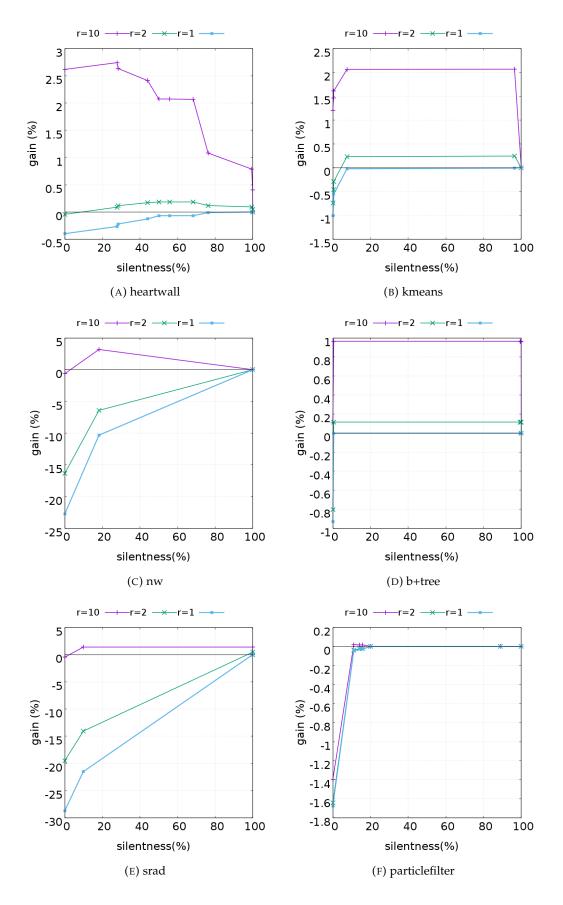

| 4.13 | Binary representation of floating-point numbers as defined by IEEE                      |    |

|      | 754 – 32-bit floats. The mantissa (or significant) is 24-bit long. The two              |    |

|      | values differ only by their last 3 bits                                                 |    |

|      | Checking for Relaxed Silent-Stores                                                      |    |

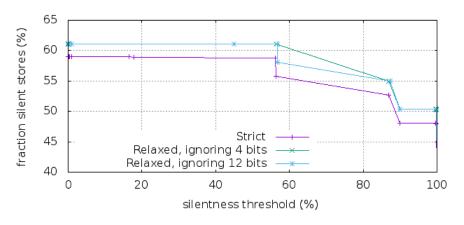

| 4.15 | Strict vs. relaxed silent-stores – Rodinia/myocyte                                      | 6  |

| 5.1  | Examples of cache memory configurations comparing SRAM and STT-                         |    |

|      | RAM [106]                                                                               | 66 |

| 5.2  | Examples of cache memory configurations comparing SRAM and STT-                         |    |

|      | RAM [106]                                                                               | 67 |

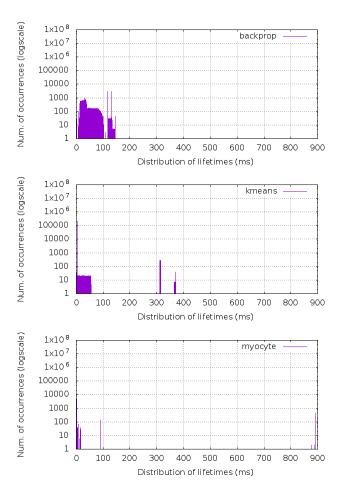

| 5.3  | Data lifetime distributions for <i>backprop</i> , <i>kmeans</i> and <i>myocyte</i>      | 68 |

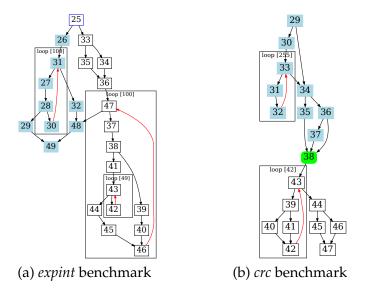

| 5.4  | Motivation for $\delta$ -WCET on sample control-flow graphs                             | 69 |

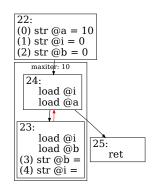

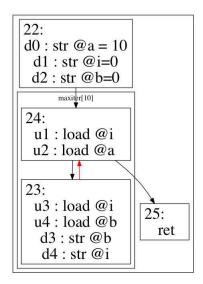

| 5.5  | A sample program (a), with its associated Control Flow Graph - CFG               |    |

|------|----------------------------------------------------------------------------------|----|

|      | (b). The loop iterates ten times. <b>ANNOT_MAXITER</b> is a macro that           |    |

|      | stores this information in a dedicated ELF section of the binary, re-            |    |

|      | trieved by the Heptane tool [27] and attached to the CFG                         | 70 |

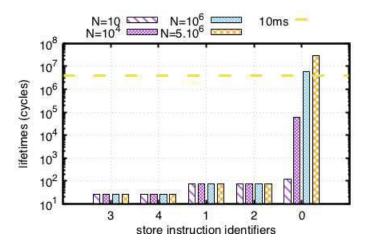

| 5.6  | Duration of the lifetimes created by each store instruction, for different       |    |

|      | numbers of iterations of the loop, and 10 ms threshold, for the example          |    |

|      | shown in Figure 5.5.                                                             | 71 |

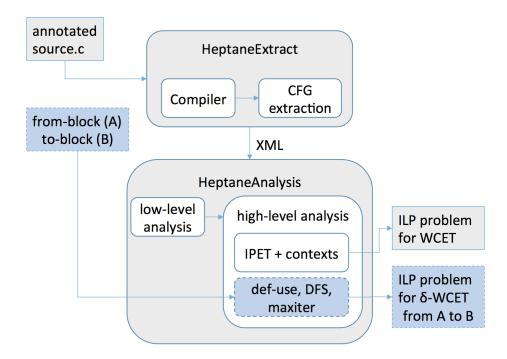

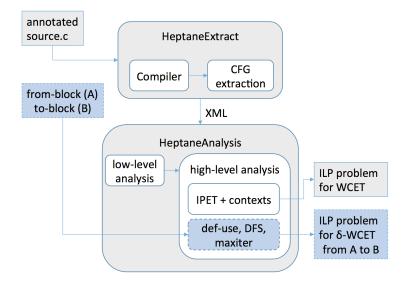

| 5.7  | Heptane tool extended with $\delta$ -WCET analysis (blue dashed-box com-         |    |

|      | ponents added by current work)                                                   | 75 |

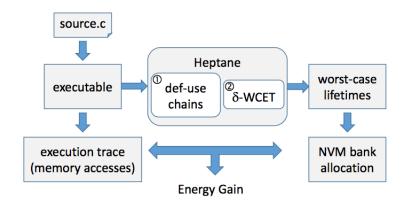

| 5.8  | Sketch of our framework (input: C code)                                          | 76 |

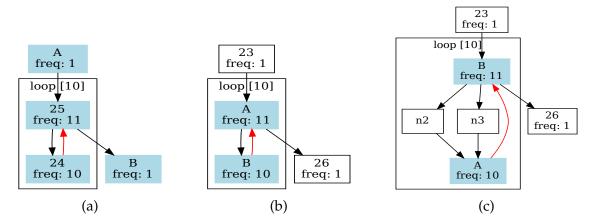

| 5.9  | Handling of maxiter                                                              | 78 |

| 5.10 | Example of reaching definitions                                                  | 79 |

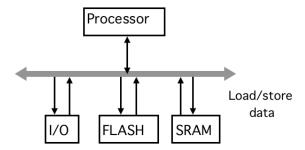

| 5.11 | MCU containing a processor, SRAM, embedded Flash, and programmable               |    |

|      | I/O peripherals                                                                  | 80 |

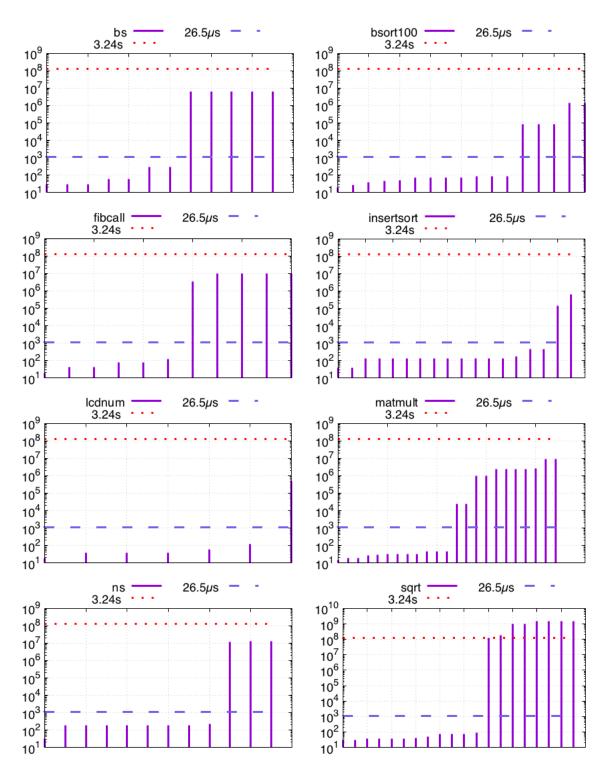

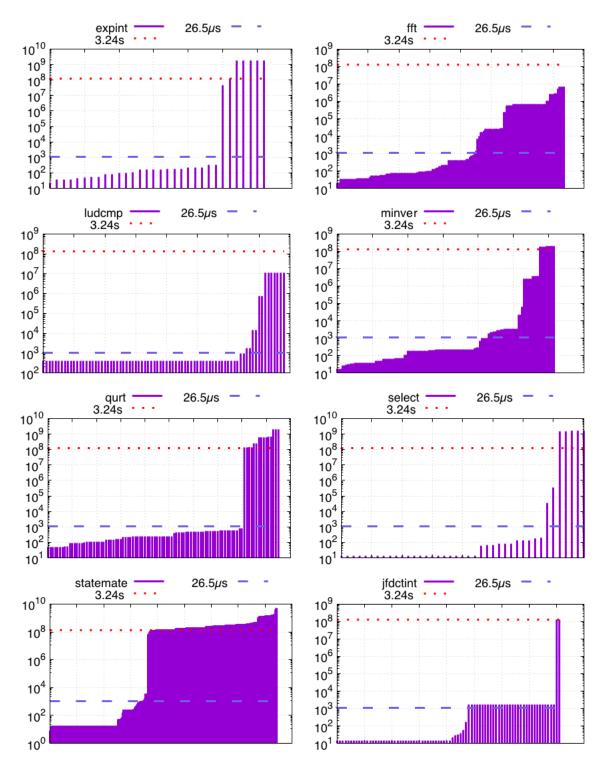

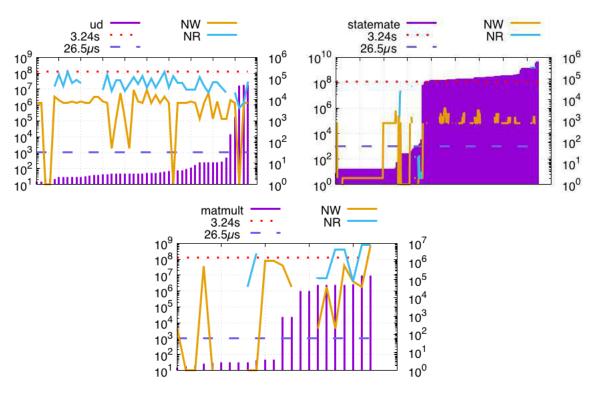

| 5.12 | Worst-case lifetimes of static store instructions for write-light work-          |    |

|      | loads from the Mälardalen benchmark-suite: the X and Y axes respec-              |    |

|      | tively represent the write occurrences and their corresponding worst-            |    |

|      | case lifetime in cycles at 40 MHz. Two duration thresholds are made              |    |

|      | explicit along the Y axis (26.5 µs and 3.24 s)                                   | 82 |

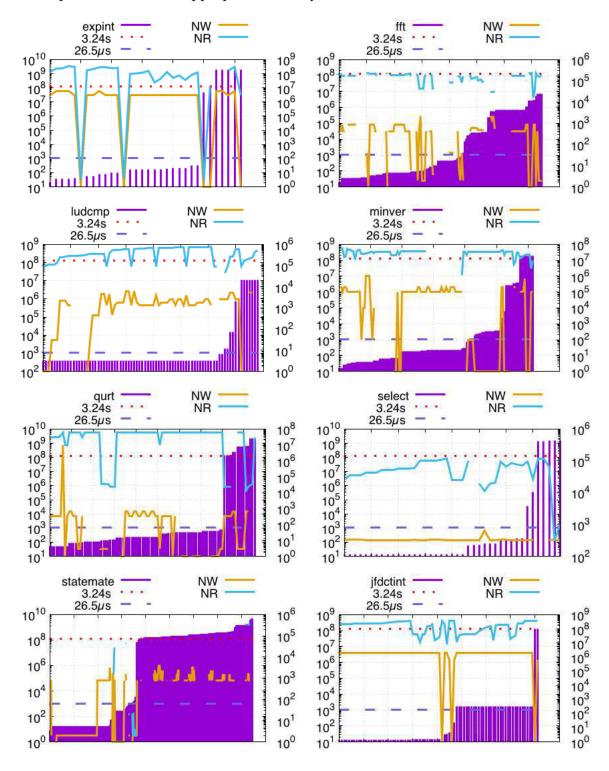

| 5.13 | Worst-case lifetimes of static store instructions for write-light work-          |    |

|      | loads from the Mälardalen benchmark-suite: the X and Y axes respec-              |    |

|      | tively represent the write occurrences and their corresponding worst-            |    |

|      | case lifetime in cycles at 40 MHz. Two duration thresholds are made              |    |

|      | explicit along the Y axis (26.5 µs and 3.24 s)                                   | 83 |

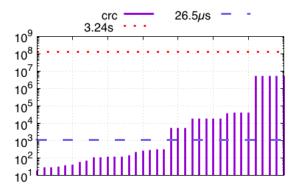

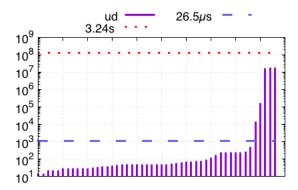

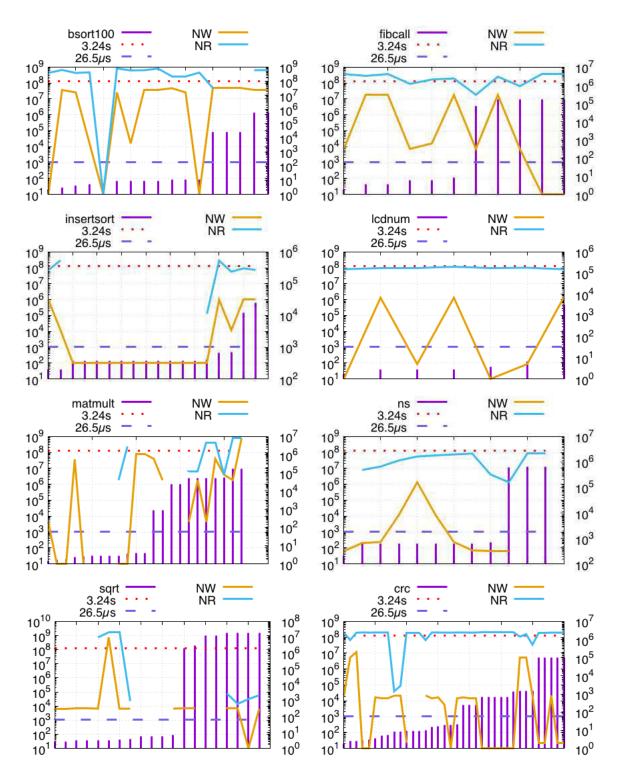

| 5.14 | Worst-case lifetimes of static store instructions for write-intensive work-      |    |

|      | loads from the Mälardalen benchmark-suite: the X and Y axes respec-              |    |

|      | tively represent the write instructions and their corresponding worst-           |    |

|      | case lifetime in cycles at 40 MHz. Two duration thresholds are made              |    |

|      | explicit along the Y axis (26.5µs and 3.24s).                                    | 84 |

| 5.15 | Worst-case lifetimes of static store instructions for write-intensive work-      |    |

|      | loads from the Mälardalen benchmark-suite: the X and Y axes respec-              |    |

|      | tively represent the write instructions and their corresponding worst-           |    |

|      | case lifetime in cycles at 40 MHz. Two duration thresholds are made              |    |

|      | explicit along the Y axis (26.5µs and 3.24s).                                    | 85 |

| 5.16 | Lifetime distribution in <i>sqrt</i> for different values of MAXITER (i.e., N) . | 86 |

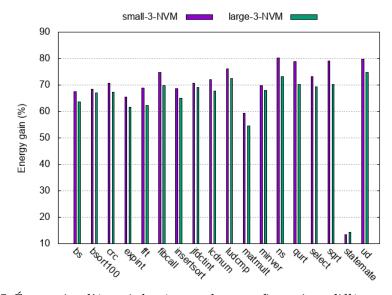

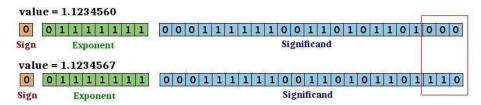

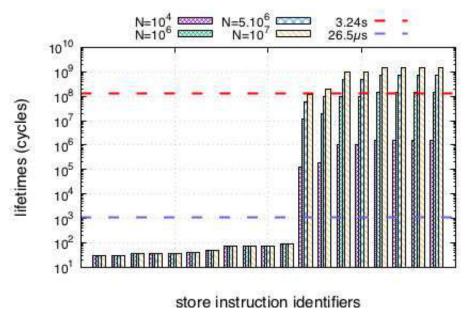

| 5.17 | Energy savings based on Tables 5.3 and 5.2 setup w.r.t. a 4.27 yr STT-  |    |

|------|-------------------------------------------------------------------------|----|

|      | RAM memory                                                              | 88 |

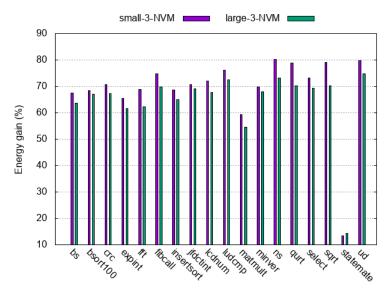

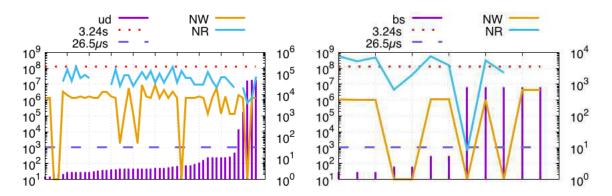

| 5.18 | Plots showing how many times each static store instruction has been     |    |

|      | executed (NW) and how many times the stored value has been read         |    |

|      | (NR), before getting rewritten. X, Y-left and Y-right axes respectively |    |

|      | correspond to store identifiers, lifetimes in cycles and thresholds for |    |

|      | NR and NW                                                               | 89 |

| 5.19 | Plots showing how many times each static store instruction has been     |    |

|      | executed (NW) and how many times the stored value has been read         |    |

|      | (NR), before getting rewritten. X, Y-left and Y-right axes respectively |    |

|      | correspond to store identifiers, lifetimes in cycles and thresholds for |    |

|      | NR and NW                                                               | 90 |

| 5.20 | Plots showing how many times each static store instruction has been     |    |

|      | executed (NW) and how many times the stored value has been read         |    |

|      | (NR), before getting rewritten. X, Y-left and Y-right axes respectively |    |

|      | correspond to store identifiers, lifetimes in cycles and thresholds for |    |

|      | NR and NW                                                               | 91 |

| 5.21 | Plots showing how many times each static store instruction has been     |    |

|      | executed (NW) and how many times the stored value has been read         |    |

|      | (NR), before getting rewritten. X, Y-left and Y-right axes respectively |    |

|      | correspond to store identifiers, lifetimes in cycles and thresholds for |    |

|      | NR and NW                                                               | 92 |

# **List of Tables**

| 3.1 | Example thermal factors $\Delta$ for a range of retention times at 300K [102] | 21 |

|-----|-------------------------------------------------------------------------------|----|

| 3.2 | Some important approaches for minimizing/avoiding write operations            | 24 |

| 3.3 | Some important approaches for mitigating the cost of writes at archi-         |    |

|     | tectural level                                                                | 25 |

| 3.4 | Some important approaches at circuit-level                                    | 29 |

| 4.1 | Relative energy cost of write/read in literature                              | 48 |

| 4.2 | 32 KB SRAM and STT-RAM memory estimation with NVSim                           | 48 |

| 4.3 | Evaluations of dedicated kernel: execution of original code with full         |    |

|     | SRAM L1 cache (ref.); execution of original and optimized codes with          |    |

|     | full STT-RAM L1 cache.                                                        | 50 |

| 4.4 | Number of loads in Rodinia benchmarks profiled with gem5 before               |    |

|     | and after optimization (only stores with 60 $\%$ silentness probability are   |    |

|     | transformed)                                                                  | 51 |

| 4.5 | Number of stores in Rodinia benchmarks profiled with gem5 before              |    |

|     | and after optimization (only stores with 60 $\%$ silentness probability are   |    |

|     | transformed)                                                                  | 52 |

| 4.6 | Energy gain projection w.r.t. specific NVM technologies.                      | 53 |

| 4.7 | Fraction of silent stores (strict and relaxed) at selected silentness thresh- |    |

|     | olds – Rodinia/myocyte)                                                       | 61 |

| 5.1 | Two 512 KB NVM memory retention times [45]                                    | 72 |

| 5.2 | 4 MB NVM memory retention times [106]                                         | 86 |

| 5.3 | 32 KB NVM memory retention times [106]                                        | 87 |

# Chapter 1

# Resumé

La consommation énergétique est devenue un défi majeur dans les domaines de l'informatique embarquée et haute performance. Différentes approches ont été étudiées pour résoudre ce problème, entre autres, la gestion du système pendant son exécution, les systèmes multicœurs hétérogènes et la gestion de la consommation au niveau des périphériques.

Cette étude cible les technologies de mémoire par le biais de mémoires non volatiles (NVMs) émergentes, qui présentent intrinsèquement une consommation statique quasi nulle. Cela permet de réduire la consommation énergétique statique, qui tend à devenir dominante dans les systèmes modernes. L'utilisation des NVMs dans la hiérarchie de la mémoire se fait cependant au prix d'opérations d'écriture coûteuses en termes de latence et d'énergie.

Dans un premier temps, nous proposons une approche de compilation pour atténuer l'impact des opérations d'écriture lors de l'intégration de STT-RAM dans la mémoire cache. Une optimisation qui vise à réduire le nombre d'opérations d'écritures est implémentée en utilisant LLVM afin de réduire ce qu'on appelle les *silent stores*, c'est-à-dire les instances d'instructions d'écriture qui écrivent dans un emplacement mémoire une valeur qui s'y trouve déjà. Cela rend notre optimisation portable sur toute architecture supportant LLVM. La validation expérimentale montre des résultats prometteurs selon le niveau de *silentness* des instructions d'écritures dans les benchmarks étudiés. Certaines considérations de conception sont analysées au niveau de la compilation et de la microarchitecture afin de tirer le meilleur parti de l'optimisation.

Le principe de l'implementation est inspiré par le travail initial de Lepak et al. [54] sur l'élimination des *silent stores* à travers des mécanismes matériels, pour améliorer le speedup sur une architecture monoprocesseur et réduire le trafic sur le bus de données sur une architecture multiprocesseur. Nous considérons une variante de compilation de cette optimisation. Notre approche consiste à transformer un code

donné en insérant des *vérification de silentness* avant chaque operation d'écriture qui a été identifiée comme potentiellement *silent*, comme décrit sur la Fig.1.1. La vérification comprend les instructions suivantes:

- 1. une instruction de lecture à l'adresse de l'écriture,

- 2. une instruction de comparaison, pour comparer la valeur écrite à la valeur déjà écrite,

- 3. une branche conditionnelle pour ignorer l'opération d'écriture si nécessaire.

FIGURE 1.1: Élimination des silent stores: le code d'origine ecrit val à l'adresse de x; Le code transformé charge d'abord la valeur à l'adresse x et la compare à la valeur à écrire. Si elle est égale, l'exécution du store est annulée.

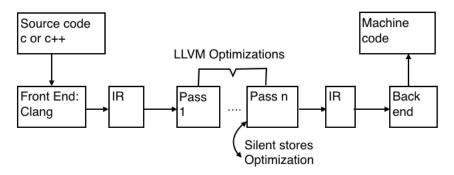

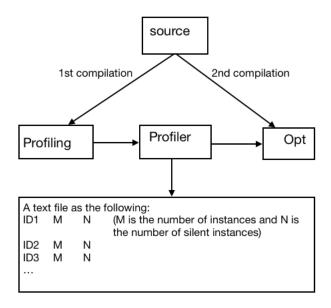

Nous avons implémenté la transformation ci-dessus dans LLVM en utilisant la représentation intermédiaire du code, décrit sur la Fig.1.2. L'approche est accomplie en deux étapes : un profiling des *silent stores* basé sur les accès mémoire observés, suivi par l'application de l'optimisation uniquement sur les *silent stores* qui sont *silent* à une certaine *probabilité* donnée et qui exprime combien de fois une opération d'écriture est *silent*. Une opération d'écriture qui est *silent* et qui est souvent exécutée aura un haut niveau de *silentness* et sera donc bénéfique pour une telle optimisation.

FIGURE 1.2: Implementation de l'optimization dans LLVM

Cette approche est validée dans la suite de benchmarks de Rodinia et des réductions significatives d'énergie dynamique de la mémoire (jusqu'à 42%) sont observées

en fonction des charactéristiques des programmes et de la technologie NVM. La figure 1.3 représente le gain énergétique de deux programmes Rodinia.

FIGURE 1.3: Gain d'énergie en fonction du seuil de silentness des applications Rodinia et de leur rapport  $r = \alpha_W/\alpha_R$  associé, où  $\alpha_W$  et  $\alpha_R$  représentent respectivement les couts des opérations d'écritures et de lectures.

Dans un second temps, nous proposons une approche qui s'appuie sur l'analyse des programmes pour estimer des *pire temps d'exécution partiaux*, dénomés  $\delta$ -WCET. À partir de l'analyse des programmes,  $\delta$ -WCETs sont déterminés et utilisés pour allouer en toute sécurité des données aux bancs de mémoire NVM avec des temps de rétention des données variables. L'analyse  $\delta$ -WCET calcule le WCET entre deux endroits quelconques dans un programe, comme entre deux blocs de base ou deux instructions. Ensuite, les pires durées de vie des variables peuvent être déterminées et utilisées pour décider l'affectation des variables aux bancs de mémoire les plus appropriées.

L'implementation de cette partie a été faite sur Heptane, comme décrit sur la Fig.1.4, qui est un outil d'estimation statique de WCET. À partir d'un CFG, Heptane génère un problème ILP suite à une série d'analyses. Ce problème ILP est ensuite résolu en utilisant un solveur comme Cplex ou lp\_solve. Le concept de notre approche se base sur l'utilisation du def-use (reaching definitions) qui permet d'identifier pour une opération d'écriture, toutes les opérations de lecture qui lui correspondent. Cela permet de construire un sous-graphe du CFG initial du programme. Ce sous-graphe représentera par la suite le graphe que Heptane va traiter et un nouveau problème ILP est généré pour le calcul du  $\delta$ - WCET.

Notre approche est validée dans la suite de benchmarks de Mälardalen et des

FIGURE 1.4: Outil Heptane étendu avec l'analyse  $\delta$ -WCET.

réductions significatives d'énergie dynamique de la mémoire (jusqu'à 80% et 66% en moyenne, comme présentés sur Fig.1.5) sont observées en fonction des charactéristiques des programmes.

FIGURE 1.5: Économies d'énergie basées sur deux configurations différentes par rapport à une mémoire STT-RAM ayant une non-volatilité de 4,27 années.

# **Chapter 2**

# Introduction

#### 2.1 Context and problematic

The trade-off between performance and energy consumption is one of the most challenging issues in embedded systems and high-performance systems. The ideal design would be a design providing the best computing performance while reducing as much as possible the energy consumption. As the integration of new functionalities requires high performance, the number of cores started increasing to meet the requirements. Advanced cache memory architectures including several levels have been a way to hide memory latency and to enable fast memory accesses, improving thus the performance. The current conventional memory technology used for both cache memory and registers is SRAM because of the short data access latency it provides compared to other technologies. However, as technology scales down, the leakage power in CMOS technology of the widely used SRAM-based cache gets increased, which is a major issue to energy-efficiency. An energy-efficient system refers in this work to a system where the amount of energy (in Joules) used by a program to achieve a computation is minimized. Hence, we don't consider the conventional definition which is the number of flops/watt for HPC systems or MIPS/watt.

Emerging Non-Volatile Memories (NVMs) are technologies that envisage addressing the energy consumption issue in future systems. In contrary to the traditional memory technologies that are volatile such as SRAM and DRAM, NVMs present prominent opportunities in favor of power consumption reduction by their almost zero leakage power and their non-volatility. Nevertheless, these emerging NVMs have shown critical drawbacks as well.

In the following, the challenges facing the conventional memory technologies are introduced. In addition, the challenges facing the emerging NVMs are presented. In Section 2.2, the objectives of this thesis are presented and in Section 2.3, the contributions are briefly presented.

#### 2.1.1 Challenges facing traditional memory technologies

Traditional memories such as SRAM, DRAM and Flash have faced during the last years critical challenges related to what modern computing systems required: high performance, high storage density and low power. Memory system has become an important contributor in the overall energy consumption of modern on-chip architectures. As the traditional processor-memory gap is continuously increasing, which refers to the growing increase in number of processor cycles to get data from offchip memory into the CPU, the imbalance between processor and memory speed is currently a drawback in modern computer system performance. The improvement of processor speed is much faster than the DRAM's one. The performance of the processor-memory interface is defined by two parameters: the latency and the bandwidth. The latency is the time between the memory request and its reply (request service), while the bandwidth, also called throughput, is the rate at which data is transferred to or from the memory system. The problem of the growing performance gap between the processor and DRAM is a latency problem. In order to deal with it, cache memory was introduced between the microprocessor and the memory based on SRAM, as a way to hide memory latency.

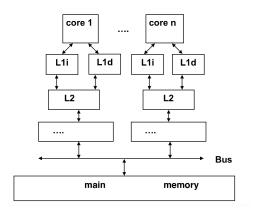

SRAM is widely used in on-chip memories close to the CPU, such as Scratchpad Memory (SPM), L1 cache and L2 cache. It is characterized by its rapid access latency less than 10 ns and by its endurance (number of write operations) which can go up to 10<sup>18</sup>. Modern high performance Chip Multiprocessor (CMP) systems include large on-chip cache hierarchies, e.g., L1, L2, L3,... cache levels, as illustrated in Figure 2.1. Since SRAM suffers from the leakage power that makes it an energy hungry technology, an important part of the overall energy consumption comes from the multi-level on-chip cache hierarchy. In fact, as technology scales down, the leakage power in CMOS technology of the widely used SRAM-based cache gets increased, which degrades the system energy-efficiency. This motivates the need of efficient memory power management techniques able to address the issue.

Researches about the emerging NVM technologies have made a significant progress in recent years. With the attractive features of these emerging technologies, NVMs have the potential to replace the traditional memory technologies. Their high storage density, low leakage and scalability, make them very good candidates to replace the application of conventional SRAM, DRAM and Flash.

FIGURE 2.1: Memory hierarchy model

#### 2.1.2 Challenges facing emerging NVMs technologies

Although many of the emerging NVM technologies are considered as mature technologies, they still suffer from an important downside which is their expensive write operations. Writing on an NVM is consuming both in latency and energy. Hence, this could neutralize the static energetic gain obtained thanks to the low leakage of such technologies. Therefore, the application of NVMs for on-chip memory needs effective techniques for mitigating their costly write operations in order to take advantages of NVMs features. Many previous works have proposed to employ new NVM technologies, such as PCM and STT-RAM, to replace the application of conventional SRAM, DRAM and Flash. Many approaches studied the application of STT-RAM and PCM in different ways: fist-level cache, middle or last level cache, hybrid caches with different technologies at the same cache level, e.g SRAM + STT-RAM, or at different cache levels, e.g SRAM(L2)+STT-RAM(L3). Different cache management techniques for energy saving have been proposed addressing the issue of expensive write operations: minimizing/avoiding the number of writes, cache partitioning, reducing refresh operations...

## 2.2 Thesis objectives

Through this thesis, we want to leverage the role of compiler optimizations and software analysis to take advantage of the NVMs features, mainly their low leakage. The current work aims to fill the gap between known compile-time techniques and successful NVM integration in upcoming energy-efficient computer architectures.

Compilers, traditionally, are not directly exposed to energy aspects. However, with all the weight given to energy consumption, it is worthy to investigate how the

compiler optimizations could have tremendous impacts on the overall energy consumption. Energy considerations are relatively recent in compilation, which is traditionally focusing more on size and speed. As the main factor for activity on processor and memory systems, software has a significant effect on the energy consumption of the entire system. Still, developing new power-aware compiler optimizations and combining them with performance-oriented compiler optimizations is the focus of several researches. As software execution corresponds to performing operations on hardware, as well as accessing and storing data, it requires power dissipation for computation, storage and communication. Beside the fact that the energy consumed during execution is very important, reducing the code size and thus, the storage cost of a program, is the classical goal of compilers. The energy cost of executing a program relies on the machine code and the target machine. Therefore, for a target architecture, energy cost is bound to machine code and consequently to compilation. Hence, it is the compilation process itself that strikes energy consumption.

Traditional optimizations on SRAM-based memories such as common subexpression elimination, partial redundancy elimination, silent stores elimination or dead code elimination, increase the performance of a program by reducing the computations during program execution [79, 2]. Memory optimizations play with latency and data placement. Optimizations such as loop tiling and register allocation try to keep data closer to the processor in order be accessed more faster. Memory optimizations contribute also in reducing energy consumption. Loop tiling tries to keep a value in an on-chip cache instead of an off-chip memory and register allocation optimization try to allocate data in a register instead of the cache. Both techniques allow to save power/energy due to reduced switching activities and switching capacitance [39].

In the wake of what was said above, the main directions involved in this thesis are related to compilation opportunities and software analysis, as the following:

- Evaluating the use of NVM-based cache memory: can we replace the SRAM-based caches by NVM-based caches? How traditional optimizations that have shown interesting results on SRAM-based caches, will behave with these new emerging technologies?.

- Energy-efficiency improvement by addressing the asymmetric nature of NVM's

access: read and write latencies are asymmetric and write operations have an

energetic cost higher than the SRAM's one. To mitigate this drawback, the

number of write operations on NVM should be reduced.

2.3. Contributions 9

Reducing energy consumption via retention time relaxation: the cost of write operation (latency and energy) is related to the retention time which is the non volatility time. The higher is the retention time, the higher is the cost of a write operation. We studied a multi-retention NVM that has different banks with different retention times.

#### 2.3 Contributions

In this work, we address the general question of improving system energy-efficiency by applying compile-time analysis and optimization techniques in presence of NVMs (here, Spin Transfer Torque RAM – STT-RAM, since STT-RAM are quite mature as test chips already exist [33, 81] and show reasonable performance at device level compared to SRAM) within memory hierarchy. The NVMs properties offer complementary advantages for meeting the performance and power consumption requirements.

We explore *compile-time analyses and optimization* and *software analysis*, as a possible alternative to leverage the low leakage current inherent to emerging NVM technologies for energy-efficiency. A major advantage is the flexibility and portability across various hardware architectures enabled by such an approach, compared to the hardware-oriented techniques found in literature. Our proposal is inspired by some existing techniques such as the silent store elimination technique introduced by Lepak et al. [55] and worst-case execution time analysis techniques [113].

The two main contributions are considered as follows:

- As writes on NVMs are generally more expensive than reads, we advocate a compile-time optimization by consistently reducing the number of writes on memory. Here, writes identified as redundant are eliminated, i.e.: when a strictly or approximately identical value is overwritten in the same memory location, respectively referred to as *strict and relaxed silent stores*. We discuss the effectiveness of this first direction from the architecture and compiler viewpoints, in "R. Bouziane, A. Gamatié, E. Rohou. How could compile-time program analysis help leveraging emerging NVM features?. EDIS 2017" [11], see Chapters 4 and 5 and "R.Bouziane, A.Gamatié, E.Rohou. Compile-Time Silent-Store Elimination for Energy Efficiency: an Analytic Evaluation for Non-Volatile Cache Memory. RAPIDO'18" [12], see Chapter 4.

- Given the possibility of relaxing the data retention time of NVMs, we leverage

a design-time analysis on the lifetime of program variables so as to map them

on NVM memory banks with customized retention capacities. This enables to

accommodate NVM features with program execution requirements while favoring energy-efficiency, in "R. Bouziane, A. Gamatié, E. Rohou. Energy-Efficient Memory Mappings based on Partial WCET Analysis and Multi-Retention Time STT-RAM. RTNS'18" [13], see Chapter 5.

#### 2.4 Outline

The reminder of this thesis is organized as follows:

In Chapter 3, we review the issue of energy consumption in traditional technologies and in the emerging NVMs.

In Chapter 4, we present our silent stores elimination approach that eliminates the execution of silent stores in a program.

In Chapter 5, we present our worst-case data lifetimes methodology to allocate each store in a program to the appropriate bank in multi-retention and multi-bank NVMs.

Finally, in Chapter 6, we present a conclusion and some perspectives.

# **Chapter 3**

# Energy consumption in today's computing systems

#### 3.1 The issue of energy consumption

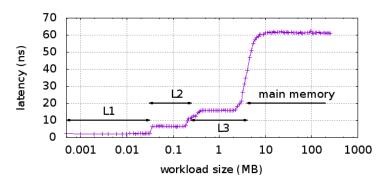

The performance gap between processor's performance and memory speeds has been constantly growing in modern computer systems. State-of-the-art processors from both high-performance computing domain (e.g., Intel Xeon) and embedded computing domain (e.g., ARM Cortex-A57 processor) are able to provide their target applications with high on-chip compute power. At the same time, implemented memory systems do not show similar improvements as the cost of the access to usual off-chip main memory is hardly mitigated. This is often referred to as the *memory wall* problem in literature. The design and management of the memory system, from registers to remote memories hosted on input/output devices, is therefore an important challenge to address for enabling high system performance. Figure 3.1 illustrates the typical access latency growth across the memory hierarchy by considering the *Imbench* benchmark [72]. Here, as long as the memory accesses reach larger size memories (e.g., main memory), the duration of data retrieval increases accordingly.

Different approaches can be considered for addressing the performance issue related to the memory system. The organization of the memory hierarchy into multiple levels reduces as much as possible the access to the memory levels requiring high latency, e.g., the main memory. Software-level techniques can also mitigate the aforementioned memory access bottleneck. In particular, compile-time optimizations contribute in improving data locality in programs. Typically, it is the case of loop tiling or loop fusion transformations [4], which favor a majority of accesses to lower cache levels such as L1 or L2 caches. More generally, compilation techniques aim to improve the performance of programs by reducing as much as possible the usual

FIGURE 3.1: Typical memory access latency (Intel Xeon i7-5600U, 2.6 GHz).

costly memory accesses.

Beyond the performance issue pointed out previously regarding the memory access, it is obvious that the energy-efficiency of a system is also concerned. Indeed, higher access latency inevitably induces higher dynamic and static power consumption. The mitigation of the memory access bottleneck is therefore beneficial to the system energy-efficiency. On the other hand, as the static power consumption is becoming dominant over the dynamic power consumption in advanced chip technology nodes, an aggressive power reduction can be reached by considering memory technologies such as NVMs. A main advantage of NVMs is that they have a quasizero static power consumption thanks to their negligible leakage current. Therefore, potential optimization techniques for NVMs should mainly target their **dynamic** activity, characterized by their high read/write latency and power consumption, compared to classical SRAM and DRAM technologies. While it is a commonplace to consider quasi-similar costs for read and write accesses in the latter technologies, it is not the case with NVMs where the cost of a write often is several times bigger than that of a read. The gap about these costs varies according to the NVM technology parameters, which determine their degree of non volatility [101]. As a matter of fact, decreasing the data retention time of NVMs reduces the latency and energy related to their access. In addition, it decreases the gap between the read/write costs.

## 3.2 Dealing with energy consumption issue

The techniques for managing power consumption are involved at different levels. Although it has been studied for a long time in hardware, energy optimization is more recent in software. In the following, some memory and compiler optimizations are presented, followed by other techniques applied at the architectural level and circuit-level. For sake of brevity, only few works are cited here. The objective of this

section is to provide an overview of the existing techniques without covering the details.

#### 3.2.1 Compiler optimizations

At the software-level, many directions have been conducted into compiler techniques. Yang et al. [117] studied the contribution of compiler optimizations to energy reduction. They investigated the impact of low-level loop optimizations; such as loop unrolling and software pipelining, and high-level loop optimizations; such as loop permutation and tiling, in terms of performance and power trade-offs. They showed that loop unrolling reduces execution time through effective exploitation of ILP from different iterations and results in energy reduction. Loop transformation such as loop permutation, loop tiling and loop fusion contribute significantly to energy reduction, by reducing the total execution time and the total main memory activities (due to improved cache locality).

Kandemir et al. [41] studied the effect of loop transformations in multi-bank memory architectures with low-power operating modes. They investigated how these transformations can be tuned to take into account the banked nature of the memory structure and the existence of low-power modes. They implemented three loop transformation techniques (loop fission/fusion, linear loop transformations and loop tiling) adapted to multi-bank memory. They showed that the modified loop transformations result in large energy savings in both cacheless and cache-based system.

Stirb et al. [125] presented a new loop optimization called loop fusion designed for LLVM and studied its impact on both performance and energy consumption. Loop fusion merges two successive loops by adding the content of the second loop into the first loop and deleting the second loop. The two loops must have the same number of iterations and there should be no code between the two loops. Moreover, there should be no data dependencies between the two loops. They showed that the fusion of two loops cuts in half the number of threads that would be otherwise required to execute them. By decreasing the number of threads, the parallelization overhead is reduced, thus the energy consumption is decreased.

Mehta et al.[73] investigated the effect of loop unrolling, software pipelining and recursion elimination on CPU energy consumption. Then, they proposed a novel compiler technique that reduces energy consumption by proper register labeling during the compilation phase. The idea behind this technique is to reduce the energy of the processor by reducing the energy of the instruction register and the register file

decoder by encoding the register labels such that the amount of switching in those structures is minimized.

Ramanujam et al.[95] addressed the problem of estimating the amount of memory needed for transfers of data in embedded systems. Their technique estimates the number of distinct array accesses and the minimum amount of memory in nested loops, and reduces this number through loop-level transformations.

#### 3.2.2 Dynamic voltage and frequency scaling (DVFS)

DVFS is a technique for altering the voltage and/or frequency of a computing system based on performance and power requirements. For CMOS circuits, dynamic power is related with voltage and frequency as  $P = C \times V^2 \times f$  where C is the effective load capacitance, V the supply voltage and f the clock frequency. Thus, by changing the voltage and frequency, the power dissipation of the processor can be managed, according to workload at run-time to reduce dynamic power and save energy.

Hua et al. [31] studied saving energy in embedded systems using DVFS. Since supporting a large number of voltage levels causes overhead, their approach investigated the optimal number of voltage levels and their values to implement on the multiple-voltage system for achieving energy efficiency. They showed that systems with 3 or 4 voltages are almost as systems with more voltage levels. DVFS technique can be applied to scheduled applications for energy reduction. DVFS uses slack times in the schedule to slow down processes and save energy.

In real time systems, DVFS technique is strongly related to tasks scheduling. The timing deadlines must be respected. Since reducing the frequency will lead to an increase in the execution time, which may make a task not finishing its execution before its deadline. Hence, many works have studied power-aware scheduling based techniques. Kianzad et al. [47] presented a framework called CASPER (combined assignment, scheduling, and power-management) which is based on genetic algorithm to integrate task scheduling and voltage scaling under a single iterative optimization loop. Their technique generates a schedule such that deadline constraints are respected and the power consumption is minimized and distributes the slack time proportionally to different tasks.

#### 3.2.3 Power modes

In embedded systems, a set of operating modes is provided in order to save energy. Different modes consume different amount of power and have different transition time to return back to the normal mode. The lower is the power mode, the higher is

the transition time and vice versa. Therefore, switching from one mode to another should be done carefully. Otherwise, the transition time may have a negative impact on systems with timing constraints.

Li et al. [56] proposed an approach for modeling and selecting the power modes for the optimal system-power management of embedded systems under timing and power constraints. Their approach determines the schedule of mode transitions such that the system can meet its power and timing constraints.

Niu et al. [80] proposed a technique to save both leakage and dynamic energy in hard real-time system scheduled by the earliest deadline first (EDF) strategy. To balance the dynamic and leakage energy consumption, higher-than-necessary processor speeds may be required when executing real-time tasks, which can result in a large number of idle intervals. In order to use these idle times, they proposed a technique that can effectively merge these scattered intervals into larger ones by making the coming tasks delayed as much as possible, without causing any deadline miss. Large idle intervals lead to reduced mode transition overhead, since the processor can stay in either idle or active state continuously for longer time.

#### 3.2.4 Microarchitectural techniques

At the architectural level, Kaxiras et al.[44] presented a method to reduce cache leakage energy consumption by turning off cache lines that likely will not be used again. The authors were able to reduce L1 cache leakage energy by 5x for certain benchmarks with no overhead impact on performance. Zhang et al. [120] proposed a highly-configurable cache architecture for facilitating dynamic reconfiguration to save energy in embedded systems. The cache can be configured by software to be direct-mapped, two-way, or four-way set associative, using a technique they call way concatenation, having very little size or performance overhead. They showed that the proposed cache architecture reduces energy caused by dynamic power compared to a way-shutdown cache.

Hajimiri et al. [25] presented cache reconfiguration and code compression to improve both performance and energy efficiency of embedded systems. For a single-level cache hierarchy, their technique carries out an exhaustive research for the best configuration to minimize energy consumption though an exploration of the cache by varying different parameters such as line size, associativity and total size; and simulating each one of the resultant configuration. The code compression scheme is combined with cache reconfiguration, since code compression improves performance

by reducing memory traffic and bandwidth usage. Hence, the performance loss due to the cache reconfiguration can be neutralized.

Tsai et al.[107] proposed a memory structure called Trace Reuse (TR) Cache to serve as an alternative source for instruction delivery. Through an effective scheme to reuse the retired instructions from the pipeline back-end of a processor, the TR cache presents improvement both in performance and power efficiency by achieving a higher instruction rate.

Some researchers have used scratchpad memory for saving energy in embedded systems. Scratchpad memory refers to on-chip SRAM that is mapped into an address space disjoint from the off-chip memory but connected to the same address and data buses. Compared to off-chip memory, both cache and scratchpad allow much faster access. The main difference between the cache and scratchpad is that the cache access may lead to either hit or miss, while the scratchpad guarantees a single-cycle access time. Steinke et al. [103] proposed a new software technique which supports the use of an on-chip scratchpad memory by dynamically copying program parts into it and then executes the program from the scratchpad itself. This reduces the access to cache and therefore leads to saving of energy. The set of selected program parts are determined with an optimal algorithm using integer linear programming.

Benini et al. [7] presented their design of application specific memory to save energy in embedded systems. Their technique consists on mapping most frequently accessed locations onto a small memory (ASM). This small memory can be placed on-chip and be very close to the processor, thus, the access to it will cost less than accessing large memory. Their technique does not use cache. The use of such a memory instead of a traditional cache is advantageous because memory accesses become less energy consuming. The memory architecture that implements the proposed scheme exploits an ad hoc decoder that maps processor addresses onto ASM addresses. Such a decoder manages the communication with the processor by signaling whether or not the current address is accessing an ASM location. Their local memory and decoding logic ensure that most frequently accessed data are stored in a small number of contiguous memory addresses.

#### 3.2.5 Circuit level techniques

At the circuit-level, Powel et al.[91] proposed an approach to reduce the leakage energy dissipation in instruction caches. They propose, gated-Vdd, a circuit-level technique to gate the supply voltage and reduce leakage in unused SRAM cells. Ye et al.[119] developed a method of transistor stacking in order to reduce leakage

energy consumption while maintaining high performance. Leakage reduction is achieved with minimal overheads in area, power and process technology. Lee et al.[53] proposed a new method that uses a combined approach of sleep-state assignment and threshold voltage (Vt) assignment in a dual-Vt process. They were the first to combine these two methods. By combining Vt and sleep-state assignment, leakage current is reduced since the circuit is in a known state in standby-mode and only transistors that are off need to be considered for high-Vt assignment.

So far, various directions have been investigated in order to reduce energy consumption on conventional memory technologies. However, the emerging NVMs technologies with the features of low leakage power and high density, present new ways of addressing the memory leakage power consumption issue.

## 3.3 Energy consumption issue in emerging NVMs

In this section, we introduce the characteristics of the emerging NVMs, in particular STT-RAM and we present some important research directions devoted for energy consumption in architectures using NVMs.

#### 3.3.1 Quick introduction to NVMs basic features

For the last few decades, computer memory systems have been studied based on characteristics, such as technology, volatility and speed. The classical memory technologies that have been traditionally used for their high speed like SRAM for caches and DRAM for main memory are volatile memories. In the other hand, memories like magnetic disks for data storage and low speed/low energy flash memory that are used in embedded systems, are non-volatile memories

With the increasing concern about energy consumption in both embedded and high-performance systems, new memory technologies have appeared, such as Phase-Change RAM (PCRAM), Spin-Transfer Torque RAM (STT-RAM) and Resistive RAM (RRAM), that present prominent features and open new opportunities for improving the energy-efficiency of computer systems. Indeed, their very low leakage power, makes them very good candidates for optimized energy consumption, as studied in both academia and industry [77]. NVMs have zero standby power, high density and non-volatility. However, they also have the following limitations:

- Relatively long and asymmetric access latencies,

- High dynamic power consumption for write operations,

| Feature               | SRAM               | DRAM              | Disk              | Flash             | STT-RAM          | PCRAM                            | RRAM                              |

|-----------------------|--------------------|-------------------|-------------------|-------------------|------------------|----------------------------------|-----------------------------------|

| Cell size             | >100F <sup>2</sup> | 6-8F <sup>2</sup> | 2/3F <sup>2</sup> | 4-5F <sup>2</sup> | 37F <sup>2</sup> | 8-16F <sup>2</sup>               | >5F <sup>2</sup>                  |

| Read latency          | <10 ns             | 10-50 ns          | 8.5ms             | 25 μs             | <10 ns           | 48 ns                            | <10 ns                            |

| Write latency         | <10 ns             | 10-60 ns          | 9.5 ms            | 200 μs            | 12.5 ns          | 40-150 ns                        | 10 ns                             |

| Energy per bit access | >1 pJ              | 2 pJ              | 100-1000 mJ       | 10 nJ             | 2 pJ             | 100 pJ                           | 0.02 pJ                           |

| Leakage power         | High               | Medium            | High              | Low               | Low              | Low                              | Low                               |

| Endurance             | >1015              | >1015             | >1015             | 104               | >1015            | 10 <sup>5</sup> -10 <sup>9</sup> | 10 <sup>5</sup> -10 <sup>11</sup> |

| Non volatlitly        | No                 | No                | Yes               | Yes               | Yes              | Yes                              | Yes                               |

| Scalability           | Yes                | Yes               | Yes               | Yes               | Yes              | Yes                              | Yes                               |

FIGURE 3.2: Comparison of traditional memory and NVM technologies [122].

• Limited write endurance.

Current NVM technologies have different performance, energy and endurance properties as shown in Figure 3.2. For instance, PCRAM and RRAM, have limited endurance that is much lower than SRAM and DRAM. However, with current technology, STT-MRAM has an endurance similar to SRAM, making it conceivable to design cache hierarchies in non-volatile technologies, including the first level.

From a comparative view, we observe the following:

- Compared to SRAM and DRAM, PCM and STT-RAM have four main advantages: higher storage density, lower leakage power, better scalability and non-volatility,

- Compared to Flash, PCM and STT-RAM have better access performance and better write endurance,

- PCM has higher storage density and STT-RAM has better access performance and better write endurance.

Thus, using NVM can enable significantly larger caches which will lead to fewer cache misses and consequently reduced cache miss rate. Therefore, the NVMs performance will be better than the performance on SRAM-based caches. Using NVMs can also reduce the leakage energy, hence reducing the total energy consumption. Since PCM and STT-RAM are presenting prominent features to replace the traditional memory technologies such as SRAM, DRAM and Flash, many research works have been studying the usage of STT-RAM in cache memories and PCM in ScratchPad memories and in main memory.

Nevertheless, the emerging NVMs have one drawback which is their high write overhead in terms of latency and power consumption, especially compared with their counterpart SRAM. This makes NVMs a priori less favorable for write-intensive workloads. Therefore, a straightforward use of NVMs in place of SRAM would inevitably lead to a performance degradation and dynamic power increase that would in turn become energy-detrimental despite the leakage power saving.

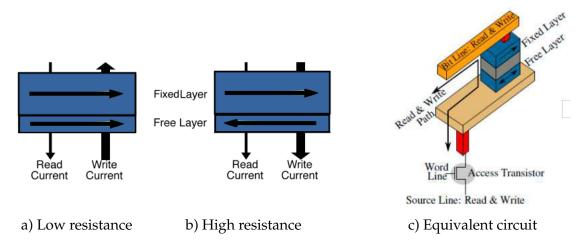

In this work, we focus on a typical emerging NVM technology which is **STT-RAM**. STT-RAM uses a **Magnetic Tunnel Junction (MTJ)** as the memory storage. We focus on this technology to pursue the rest of this work. Nevertheless, as we mainly address a common feature to all types of NVMs which is the access asymmetry, we assume the applicability of our approaches to all NVMs.

#### **Magnetic Tunnel Junction Device**

Unlike charge-based memories such as DRAM, STT-RAM uses Magnetic Tunnel Junction (MTJ) [123] as the information carrier and store data in the form of change in physical state. Each MTJ contains two ferromagnetic layer, *hard* layer and *free* layer, separated by an oxide barrier layer. The magnetization direction of the *hard* layer is fixed, while the one of the *free* layer can be changed by passing a spin-polarized current flowing through the MTJ.

When the polarities of the two layers are aligned, which represents the parallel state, electrons that have a polarity anti-parallel to the two layers (*fixed* and *free*) can move easily through the MTJ, while electrons with the same polarity as the two layers are dispersed. Inversely, when the two layers have anti-parallel polarities, which represents the anti-parallel state, electrons are largely dispersed by one of the two layers, whether their polarity is parallel or anti-parallel, leading to higher resistance. These low and high resistances are used to represent different logic value, [23].

Based on the current direction, i.e the spin of the electrons in the free layer, the spin polarity of the *free* layer will be either parallel or anti-parallel to the *hard* layer's one. Depending on whether the free layer is parallel or anti-parallel to the magnetic orientation of the hard layer, as shown in Figures 3.3(a) and 3.3(b), respectively, the applied voltage can lead to low or high current. This is due to the asymmetry of the current needed to switch the MTJ from the parallel state to the anti- parallel state and inversely [43].

The transition from the parallel to the anti-parallel state requires more current than the transition in the other way. Based on this feature, a value ('0' or '1') is stored in an STT-RAM cell, using the following logic, see Figure 3.3(c):

FIGURE 3.3: Magnetic tunnel junction (a) Parallel state, (b) Anti-parallel state, (c) Equivalent circuit

- when writing '1' into the STT-RAM cell, a positive voltage is applied between the source-line (SL) and the bit-line (BL), which will therefore produce a high-resistance state.

- when writing a '0' into the STT-RAM cell, a negative voltage is applied between the SL and the BL, which will therefore produce a low-resistance state.

As the *free* layer needs no current to maintain its state, MTJs have no inherent leakage current. The MTJ is usually modeled as a current-dependent resistor in the circuit schematic.

STT-RAM uses spin transfer torque to change the direction of the free layer by passing an important and directional write current through the MTJ. The switching process is managed by a random thermal process, meaning that the free layer could change state at any time. However, the MTJ magnetic properties and design are conceived in order to make this event improbable [102]. Performing a write requires that the write current is maintained for a certain amount of time, to guarantee that the free layer has changed state.

The thermal stability of the MTJ is the feature that determines the predicted time of a random bit-flip. The expected time is what we call the retention time. When the stability is high, the random bit-flips are unlikely to happen which makes write operations difficult and therefore high currents are required.

The stability is estimated by the thermal factor,  $\Delta$  and the retention time T of a MTJ is determined by  $\Delta$ , such as:

$$T = \frac{1}{f_0} e^{\Delta}$$

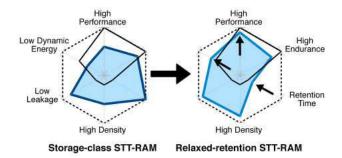

FIGURE 3.4: Relaxing the non-volatility of STT-RAM [102], dotted border is the optimal scenario and black line is representing the comparison to SRAM

where  $f_0$  is the thermal attempt frequency.

For that reason, the thermal instability can lead to data loss which reduces the retention time. As wee see in Table 3.1, the lower is  $\Delta$ , the lower is the retention time which means when the  $\Delta$  decreases, the data loss is rapid.

In another part, studies have also shown that the working temperature has also an impact on data retention time. When the temperature increases, the retention time decreases exponentially [106]. Increasing the temperature from 300K to 350K allows to reduce the retention time to less than a month [96].

Figure 3.4 shows the impact of relaxing the retention time on energy and performance. Shorter retention times can be obtained by reducing the area of the *free* layer of the MTJ, making a significant write power saving as the cost of writing to a cell becomes less expensive [106].

Therefore, as a write operation to an NVM requires changing the physical state of the NVM, the cost of this write will be high since it consumes larger time and energy than a read operation, showing the read/write asymmetry of such technologies. In the same direction, the write-latency and energy cost of  $1 \rightarrow 0$  transition are higher than that the ones of  $0 \rightarrow 1$ , leading to 0/1 write asymmetry [9].

| Data retention time | Δ     |

|---------------------|-------|

| 10 years            | 40.29 |

| 1 year              | 37.99 |

| 1 month             | 35.52 |

| 1 week              | 34.04 |

| 1 day               | 32.09 |

| 1 hour              | 38.91 |

| 1 minute            | 24.82 |

| 1 second            | 20.72 |

TABLE 3.1: Example thermal factors  $\Delta$  for a range of retention times at 300K [102]

#### 3.3.2 Dealing with energy consumption issues related to NVM caches

We discuss in this section some important approaches addressing energy consumption of caches designed with emerging NVMs. The common point between these approaches is to overcome the shortcomings of such technologies. We present here some compiler-level approaches, followed by architectural-level approaches. Then, some works that exploit reducing the retention time are presented. Tables 3.2, 3.3 and 3.4 present an overview of different approaches targeting NVMs at different level, software/compiler, architecture and circuit, respectively.

#### Software-level optimizations via compiler techniques

Chen et al. [17] proposed an SRAM-STT-RAM hybrid cache design which aims to minimize the number of writes to the STT-RAM. Their cache management technique uses the compiler to provide static hints to guide initial data placement such that the write-intensive data are placed into SRAM and the rest of data are placed into STT-RAM. Knowing that the compiler hints may be inaccurate due to lack of runtime information, the authors used hardware-support to correct the inaccurate hints provided by the compiler. Thus, if a write-intensive block is placed in the STT-RAM, it is moved to SRAM and replaced by an SRAM block that contains a less write intensive data.

In hybrid caches, many approaches considered employing migration based policy to mitigate the drawbacks of NVMs. Migration techniques employ additional reads and writes to ensure the data movement, therefore penalizing the performance and energy efficiency of STT-RAM based hybrid cache. For that purpose, Li et al. [62] proposed a migration-aware compilation for STT-RAM-based hybrid cache, by rearranging data layout to reduce the overhead of migrations. In [64], they addressed this issue through a compilation method called migration-aware code motion where data access patterns are changed in memory blocks in order to minimize the overhead of migrations.

Li et al. [65] proposed a compiler-assisted approach, called preferred caching, to reduce the overhead due to migration in hybrid caches. Their technique consists on giving migration-intensive memory blocks the preference for the SRAM part of the hybrid cache. The authors proposed a data assignment technique to improve the efficiency of preferred caching.

Li et al. [63] proposed two compilation-based approaches to improve the energy efficiency and performance of STT-RAM-based hybrid cache by reducing the migration overheads. The first approach, called migration-aware data layout, is proposed

to reduce the migrations by rearranging the data layout. The second approach, called migration-aware cache locking, is proposed to reduce the migrations by locking migration-intensive memory blocks into SRAM part of hybrid cache. The authors showed that the combination of these two techniques can reduce furthermore migrations.

Hu et al. [30] presented an approach based on region partitioning in order to generate optimized data allocation. A program is divided into regions and before executing each region, a data allocation is generated, which is suitable for the region. Li et al. [67] proposed a software dispatch, a cross-layer approach to distribute data to appropriate memory resources based on an application's data access characteristics. They presented an SRAM-STT-RAM hybrid cache design to increase cache capacity and mitigate the limited write endurance problem of STT-RAM. They used compiler and operating system support to migrate the write intensive data from STT-RAM to SRAM. The compiler identifies the write reuse patterns of heap data objects such as linked structures and arrays and inserts instructions to guide the hardware to perform the migration dynamically.

Hu et al. [29] targeted embedded chip multiprocessors with scratchpad memory (SPM) and non volatile main memory. They exploited data migration and recomputation in SPM so as to reduce the number of writes on main memory. Goswami et al. [22] implemented an SRAM-STT-RAM hybrid share memory in GPU. Using STT-MRAM in shared memory design, dynamic power, leakage power and area are reduced. They proposed an additional SRAM based shared memory area that can be configured using software level APIs to behave as cache or RAM to reduce STT-RAM access. Using compiler assistance, last SRAM cache eviction data is forwarded to the next level of memory avoiding STT-RAM.

Li et al. [69] presented a dual-mode STT memory cell to design a configurable L1 cache architecture termed C1C to mitigate read performance barriers with technology scaling. Guided by application access characteristics discovered through novel compiler analyses, the proposed cache adaptively switches between a high performance and a low-power access mode.

Recently, researchers proposed to improve the write performance of STT-RAM by relaxing its non-volatility property. To avoid data loss resulting from volatility, refresh schemes are proposed. However, refresh operations consume additional energy. Li et al. [61] proposed to reduce the number of refresh operations through re-arranging program data layout at compilation time. Rodriguez et al.in [97] presented the steps for designing an STT-RAM-based multi-retention scratchpad and a