# Etude et conception analogique d'architectures d'acquisition acoustique très faible consommation pour applications mobiles

Anthony Baltolu

#### ▶ To cite this version:

Anthony Baltolu. Etude et conception analogique d'architectures d'acquisition acoustique très faible consommation pour applications mobiles. Electronique. Université de Bordeaux, 2018. Français. NNT: 2018BORD0339. tel-02090818

### HAL Id: tel-02090818 https://theses.hal.science/tel-02090818

Submitted on 5 Apr 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE PRÉSENTÉE POUR OBTENIR LE GRADE DE

### **DOCTEUR DE**

### L'UNIVERSITÉ DE BORDEAUX

### ÉCOLE DOCTORALE SCIENCES PHYSIQUES ET DE L'INGÉNIEUR SPÉCIALITÉ ÉLECTRONIQUE

Par Anthony BALTOLU

## ETUDE ET DESIGN ANALOGIQUE D'ARCHITECTURES D'ACQUISITION ACOUSTIQUE TRES FAIBLE CONSOMMATION POUR APPLICATIONS MOBILES

Sous la direction de : Jean-Baptiste BEGUERET (co-directeur : Dominique DALLET)

Soutenue le 14/12/2018

#### Membres du jury:

| M. BEGUERET Jean-Baptiste | Professeur de l'université de Bordeaux    | Directeur         |

|---------------------------|-------------------------------------------|-------------------|

| M. DALLET Dominique       | Professeur de Bordeaux INP                | Co-directeur      |

| M. MALOBERTI Franco       | Professeur de l'université de Pavia       | Rapporteur        |

| M. BARTHELEMY Hervé       | Professeur de l'université Sud Toulon Var | Rapporteur        |

| M. CHALET Frédéric        | Ingénieur chez NXP Semiconductors         | Examinateur       |

| M. TARIS Thierry          | Professeur de Bordeaux INP                | Président du jury |

**Titre :** Etude et conception analogique d'architectures d'acquisition acoustique très faible consommation pour applications mobiles

**Résumé :** Les récentes avancées technologiques des microphones de type microsystème électromécanique (MEMS) leurs permettent une utilisation sur une large gamme d'amplitudes sonores. Leur niveau de bruit ayant baissé, il devient possible de capter des sons provenant d'une distance plus lointaine, tandis que l'augmentation de leur pression acoustique maximale leur permet de ne pas saturer dans un environnement très bruyant de type concert ou évènement sportif. Ainsi le système électronique de conversion analogique-numérique connecté au microphone devient l'élément limitant les performances du système d'acquisition acoustique. Un besoin de nouvelles architectures de conversion analogique-numérique ayant une plage dynamique augmentée se fait donc ressentir. Par ailleurs, ces microphones étant de plus en plus utilisés dans des systèmes fonctionnant sur batterie, la contrainte de limitation de la consommation devient importante.

Dans la bande de fréquences audio, les convertisseurs analogiques-numériques de type sigmadelta sont les plus aptes à obtenir une grande résolution combinée à une faible consommation. Ils sont divisés en deux grandes familles: ceux à temps discret utilisant principalement des circuits à capacités commutées, et ceux à temps continu utilisant des circuits classiques. Cette thèse se concentre sur l'étude et la conception de chacun des deux types de convertisseurs sigma delta, en insistant sur la faible consommation, le faible coût de production (surface occupée) et la robustesse du circuit, cela en vue d'une production de masse pour équipements portables.

La conception d'un convertisseur analogique numérique de type sigma-delta à temps discret a été réalisé, ce dernier atteignant un rapport signal sur bruit de 100 décibels sur une bande de 24kHz, pour une puissance consommée de seulement 480µW. Pour limiter la consommation, de nouveaux amplificateurs à base d'inverseurs sont utilisés, et dont la robustesse contre les variations du procédé de fabrication ou de la température a été améliorée. Les spécifications ont été définies grâce au développement d'un modèle de haut-niveau précis, ce qui permet d'éviter le surdimensionnement tout en atteignant les performances voulues. Enfin, un grand ratio de suréchantillonnage a été choisi afin de réduire l'espace utilisé par les capacités commutées, minimisant le coût de fabrication.

Après une étude théorique de l'équivalence entre les modulateurs sigma-delta à temps discret et à temps continu, ainsi que des spécificités propres aux modulateurs à temps continu, une réalisation de ces derniers a été effectuée. Celui-ci atteint un rapport signal sur bruit de 95 décibels sur une bande de fréquence de 24kHz, tout en consommant 142µW. Pour réduire la consommation ainsi que l'espace utilisé, un filtre de boucle du second-ordre a été réalisé avec un seul amplificateur, et le quantificateur fait aussi office d'intégrateur grâce à l'utilisation d'une structure d'oscillateurs contrôlés en tension. Ce quantificateur à base d'oscillateurs est réalisé par des cellules numériques, réduisant la consommation et l'espace utilisé, mais est hautement non-linéaire. Cette non-linéarité a été prise en compte par des choix architecturaux afin de ne pas réduire les performances finales du modulateur.

**Mots-clés**: modulateur, sigma-delta, convertisseur analogique-numérique, audio, faible consommation, capacités commutées, temps continu, temps discret, quantificateur-intégrateur

Title: Study and analog design of low-power acoustic acquisition systems for mobile applications

**Abstract:** The recent technological advances in microelectromechanical system (MEMS) microphones allow them to be used on a large sound amplitude range. Due to their lower noise level, it becomes possible to capture sound from a faraway distance, while their increased acoustic overload point gives them the ability to capture sound without saturation in a loud environment like a concert or a sport event. Thus, the electronic analog / digital conversion system connected to the microphone becomes the limiting element of the acoustic acquisition system performance. There is then a need for a new analog / digital conversion architecture which has an increased dynamic range. Furthermore, since more and more of these microphones are used in battery-powered devices, the power consumption limitation constraint becomes of high importance.

In the audio frequency band, the sigma-delta analog / digital converters are the ones most able to provide a high dynamic range combined to a limited power consumption. They are split in two families: the discrete-time ones using switched-capacitors circuits and the continuous-time ones using more classical structures. This thesis concentrates on the study and the design of both of these two types of sigma-delta converters, with an emphasis on the low-power consumption, the low production cost (area occupied) and the circuit robustness, in sight of a mass production for portable devices.

A discrete-time sigma-delta modulator design has been made, the latter reaching a signal to noise ratio of 100dB on a 24kHz frequency bandwidth, for a power consumption of only  $480\mu W$ . To limit the power consumption, new inverter-based amplifiers are used, with an improved robustness against the variations of the fabrication process or the temperature. Amplifier specifications are obtained thanks to an accurate high-level model developed, which allows to avoid over-design while ensuring that the wanted performances are reached. Finally, a large oversampling ratio has been used to reduce the switched-capacitors area, lowering the modulator cost.

After a theoretical study of the equivalence between discrete-time and continuous-time modulators, and of continuous-time modulators specificities, a design of the latter has been made too. It reaches a signal to noise ratio of 95dB on a 24kHz bandwidth, while consuming  $142\mu W$ . To reduce the power consumption and the occupied area, a second-order loop filter is implemented using a single amplifier, and the quantizer uses a VCO-based structure that provides inherently an integrating stage. The VCO-based quantizer is made using digital cells, lowering the consumption and area, but is highly non-linear. This non-linearity has been handled by architectural choices to not influence the final modulator performances.

**Keywords:** sigma-delta, modulator, analog digital converter, audio, low-power, switched-capacitors, discrete-time, continuous-time, VCO-based, quantizer, low-area

Laboratoire de l'Intégration du Matériau au Système – UMR 5218 IMS

351 Cours de la libération, 33405 Talence cedex, France

## Résumé français

## I – Brève introduction aux convertisseurs sigmadelta

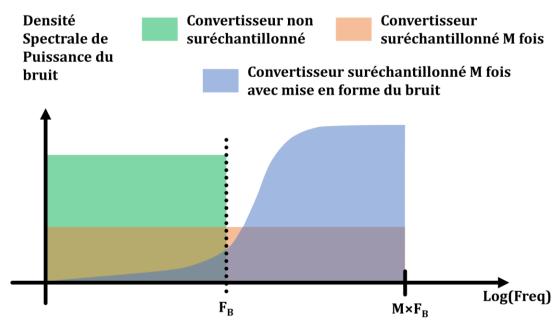

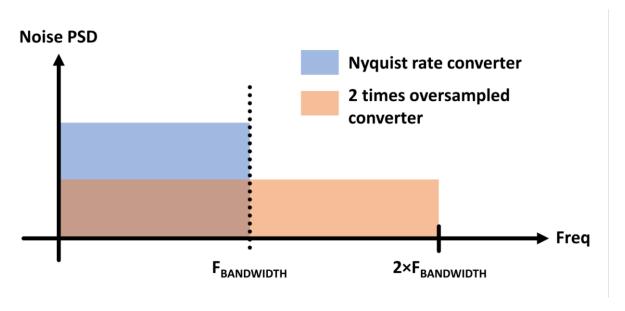

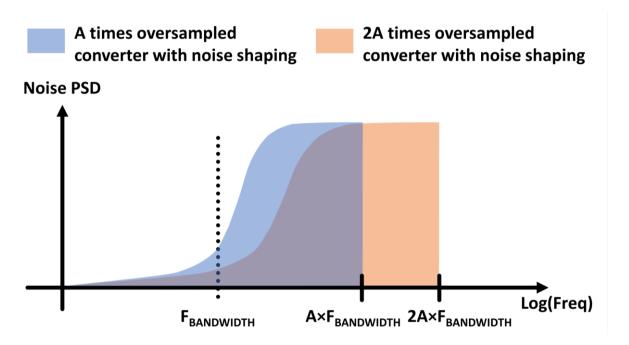

Les convertisseurs analogique-numérique de type sigma-delta combinent deux concepts pour atteindre une haute résolution. Le premier est le suréchantillonnage : en échantillonnant M fois plus vite que la fréquence d'échantillonnage nécessaire donnée par la théorie de Shannon-Nyquist, l'erreur de quantification est distribuée sur une plus grande plage spectrale, diminuant alors sa puissance dans la largeur de bande du signal F<sub>B</sub>. Le second concept est la mise en forme du bruit de quantification : grâce au suréchantillonnage, le système travaille sur une plage spectrale beaucoup plus grande que nécessaire, il devient alors possible de « donner une forme » au bruit de quantification, qui consiste à diminuer sa puissance dans la bande du signal F<sub>B</sub> et l'augmenter hors bande, la puissance totale restant inchangée. Ces deux concepts combinés, illustrés par la figure I-1, sont assez puissants pour obtenir une grande résolution même en utilisant un quantificateur simple bit.

**Figure I-1** Effets du suréchantillonnage et du concept de mise en forme sur le bruit de quantification restant dans la bande du signal F<sub>B</sub>

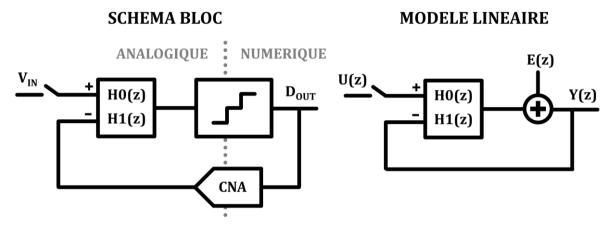

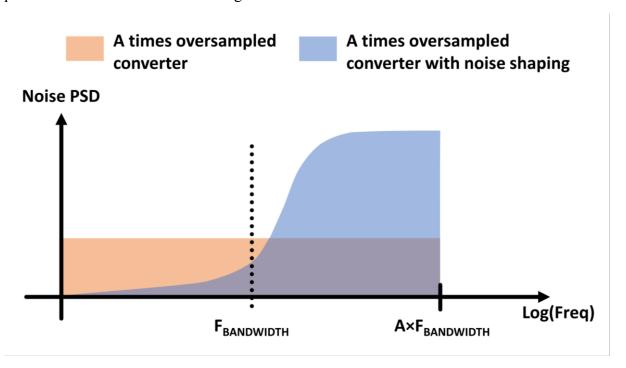

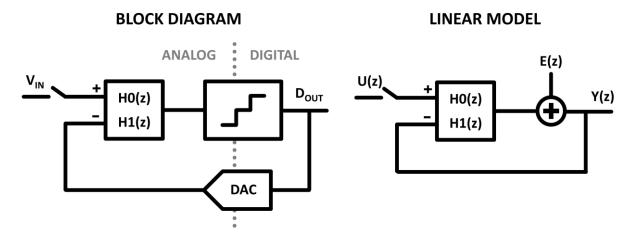

Le schéma bloc d'un modulateur sigma-delta à temps discret est donné en figure I-2, avec son modèle linéaire. C'est un système hybride analogique-numérique rebouclé, composé d'un échantillonneur en entrée à une fréquence  $F_E$ , d'un filtre qui permet la mise en forme du bruit de quantification, d'un quantificateur et d'un convertisseur numérique-analogique pour former la boucle de retour. Le quantificateur étant un élément non-linéaire il est modélisé par l'addition d'une erreur de quantification. La sortie du modulateur Y(z) est fonction du signal d'entrée U(z), de l'erreur de quantification E(z) ainsi que des fonctions de transfert du filtre pour le signal d'entrée et le signal issu de la boucle de retour, respectivement  $H_0(z)$  et  $H_1(z)$ . La relation est donnée dans l'équation suivante :

$$Y(z) = \frac{H_0(z)}{1 + H_1(z)} U(z) + \frac{1}{1 + H_1(z)} E(z)$$

(I-1)

Deux fonctions de transfert remarquables peuvent être dérivées : la fonction de transfert entre le signal d'entrée et la sortie, nommée STF(z), et la fonction de transfert entre le bruit de quantification et la sortie, nommée NTF(z):

$$STF(z) = \frac{H_0(z)}{1 + H_1(z)}, \qquad NTF(z) = \frac{1}{1 + H_1(z)}$$

(I-2)

Pour mettre en forme correctement le bruit de quantification comme montré en figure I-1, la fonction de transfert NTF(z) doit être proche de zéro pour les fréquences basses, ce qui requiert un fort gain à ces fréquences pour le filtre  $H_1(z)$ . Concernant la fonction de transfert STF(z), elle ne doit pas changer le signal à basse fréquences et ainsi avoir un gain unitaire, ce qui impose un fort gain à la fois à  $H_0(z)$  et à  $H_1(z)$ . Ce besoin de fort gain à basse fréquence explique pourquoi les filtres des modulateurs font appel à des intégrateurs.

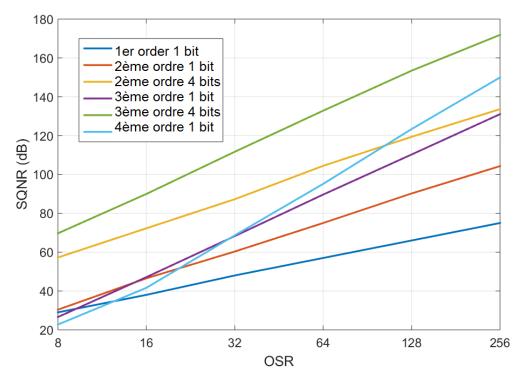

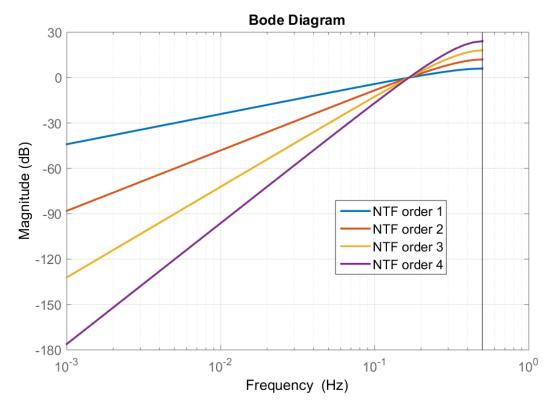

Figure I-2 Schéma bloc et modèle linéaire d'un modulateur sigma-delta

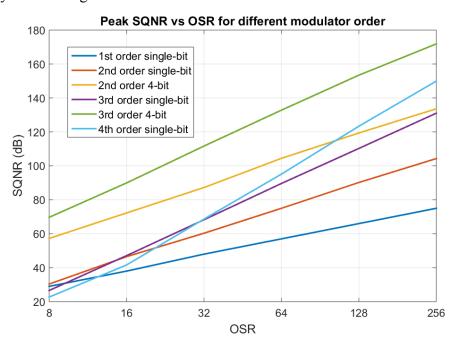

Le nombre d'intégrateurs mis en cascade détermine l'ordre du filtre de mise en forme, un ordre élevé rejetant plus fortement le bruit de quantification hors de la bande de fréquences du signal utile. L'ordre du filtre est ainsi le deuxième paramètre définissant la résolution du modulateur avec le ratio de suréchantillonnage. Cependant un ordre de filtre supérieur à 2 peut entrainer une instabilité du modulateur car une phase de -180° peut être atteinte alors que le filtre fournit toujours du gain dans le système rebouclé, saturant l'entrée du quantificateur. C'est pourquoi les modulateurs d'un ordre supérieur à 2 utilisent une NTF dont le gain à hautes fréquences est limité, de manière à ne jamais saturer l'entrée du quantificateur, perdant un petit peu de performance dans leur propriété de mise en forme du bruit quantification. Le troisième et dernier paramètre influant sur la résolution obtenue par le modulateur est le nombre de bits utilisés dans le quantificateur, qui augmente la résolution de 6dB par bit ajouté, comme dans le cadre de convertisseurs non suréchantillonnés. Le graphique I-3 montre le rapport signal sur bruit de quantification (SQNR) maximal atteignable par un modulateur en fonction de son ratio de suréchantillonnage (OSR) pour différents ordres du filtre de boucle et différents nombres de bits dans le quantificateur. Ainsi l'on peut voir qu'augmenter l'ordre du modulateur permet d'atteindre de meilleures résolutions, seulement à fort OSR pour les modulateurs d'ordre élevé à cause des problèmes de stabilité qui limitent l'efficacité de la mise en forme du bruit. Augmenter le nombre de bits du quantificateur aide à atteindre une forte résolution à faible

OSR, grâce à leur bruit de quantification intrinsèquement inférieur, ce qui relâche aussi le problème de stabilité des modulateurs d'ordre élevé.

**Figure I-3** Rapport signal sur bruit de quantification maximal atteignable pour un modulateur en fonction de son ratio d'échantillonnage, son ordre et du nombre de bits de son quantificateur

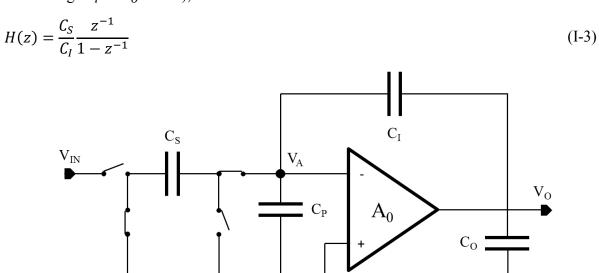

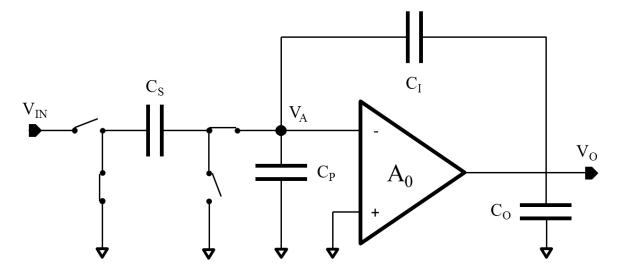

Le schéma d'un intégrateur à temps discret réalisé à l'aide de capacités commutées est donné en figure I-4 durant sa phase d'intégration, où  $A_0$  est son gain DC,  $C_S$  la capacité d'échantillonnage,  $C_I$  la capacité d'intégration,  $C_O$  la capacité de charge et  $C_P$  la capacité parasite sur le nœud  $V_A$ . En considérant un intégrateur parfait (gain  $A_0$  infini, capacités parasites et de charge  $C_P$  et  $C_O$  nulles), sa fonction de transfert est la suivante :

Figure I-4 Schéma d'un intégrateur à temps discret réalisé à l'aide de capacités commutées

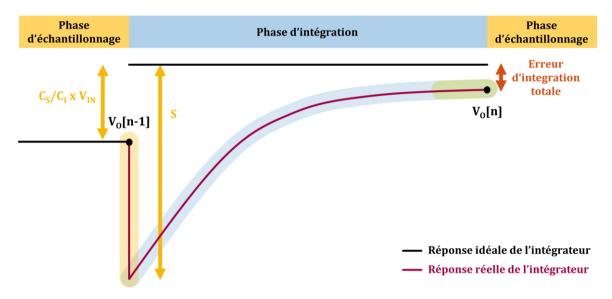

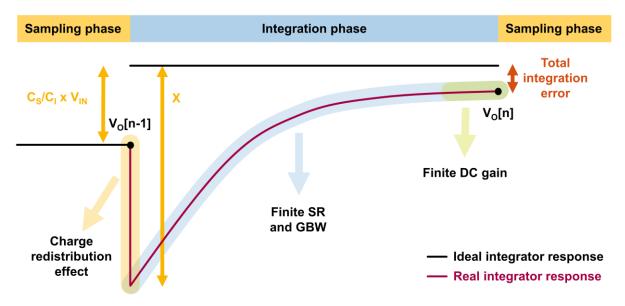

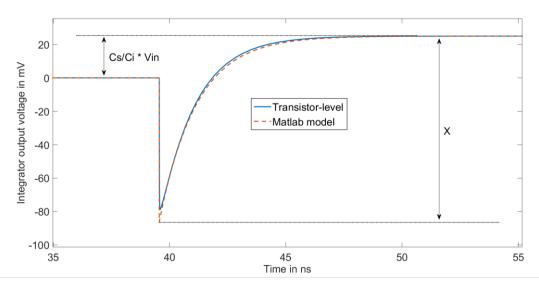

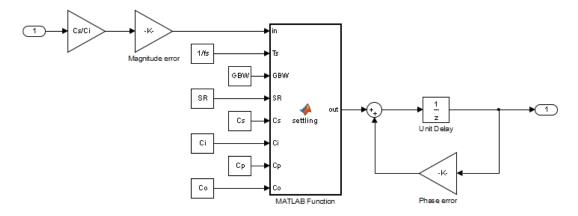

Un intégrateur analogique n'étant jamais idéal, plusieurs effets doivent être pris en compte durant sa phase d'intégration pour s'assurer que ceux-ci ne viennent pas nuire aux performances du modulateur, et ainsi définir des spécifications pour les intégrateurs. Un modèle de reproduction précise de la réponse d'un intégrateur pendant sa phase d'intégration a été élaboré, permettant de s'assurer du bon fonctionnement du modulateur sans sur-dimensionner l'amplificateur, afin de réduire sa consommation au maximum. La figure I-5 montre la réponse d'un intégrateur analogique durant la phase d'intégration.

Figure I-5 Réponse de la tension de sortie de l'intégration durant la phase d'intégration

Au démarrage de celle-ci on connecte la capacité d'échantillonnage au reste de l'intégrateur et, avant même que l'amplificateur ne réagisse, une redistribution des charges dans toutes les capacités de l'intégrateur se produit. Cet effet perturbe le nœud  $V_O$  qui part, dans un premier temps, dans le sens opposé à son résultat final, augmentant la charge à délivrer par l'amplificateur durant la période d'intégration comme le montre la partie jaune du nœud  $V_O$  sur la figure I-5. La marche d'intégration n'est plus la tension échantillonnée multipliée par le rapport des capacités d'échantillonnage et d'intégration, mais une valeur notée S définie par l'équation suivante :

$$S = \frac{C_S}{C_I} \times V_{IN} \times \left(1 + \frac{C_I}{C_S + C_P + C_O \times \left(1 + \frac{C_S + C_P}{C_I}\right)}\right)$$

(I-4)

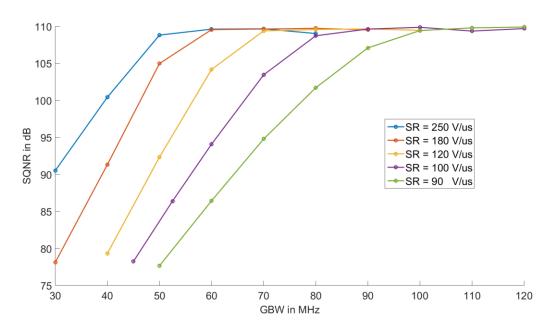

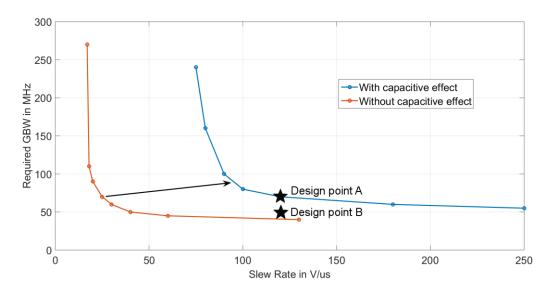

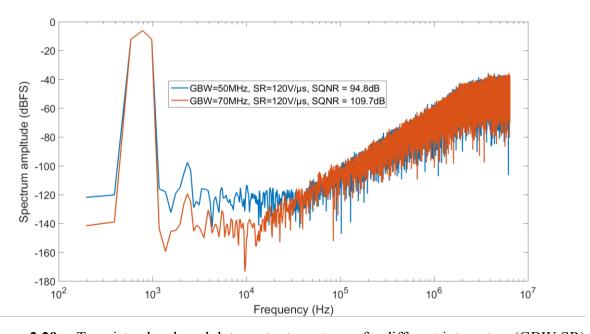

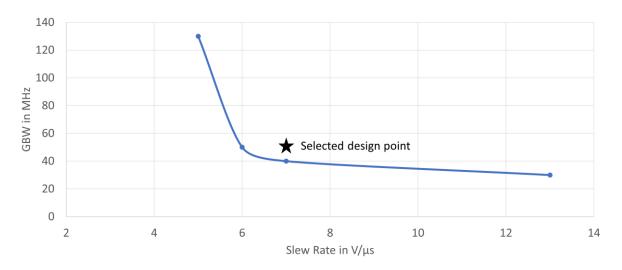

Ensuite l'amplificateur réagit et commence à délivrer du courant pour ramener le nœud  $V_O$  vers sa valeur finale (partie bleu de  $V_O$  sur la figure I-5), et sa réponse peut être de trois types : linéaire, dans ce cas le produit gain bande définit la réponse et l'erreur d'intégration à un instant T ; partiellement linéaire, dans ce cas l'amplificateur est limité par son courant de polarisation et fournit un courant constant jusqu'à ce qu'un comportement linéaire soit possible ; et enfin le cas où l'amplificateur a un courant de polarisation trop faible et est limité par celui-ci durant toute la période d'intégration. L'erreur d'intégration finale dépend alors de la marche d'intégration S, du produit gain bande de l'amplificateur (noté GBW) ainsi que de son slew rate (noté SR). Ce dernier est la valeur maximale de variation du nœud  $V_O$  par unité de temps, qui dépend du courant de polarisation de l'amplificateur. Selon les trois types de réponse, l'erreur

en fin de phase d'intégration  $\varepsilon$  est définie par les équations ci-dessous, où  $T_{SLEW}$  représente la durée pendant laquelle la réponse de l'amplificateur est limitée par son courant de polarisation. Un  $T_{SLEW}$  négatif ou nul équivaut à une réponse linéaire de l'amplificateur et l'erreur dépend d'une exponentielle négative, pouvant devenir négligeable avec un grand produit gain bande. Un  $T_{SLEW}$  inférieur à la phase d'intégration (équivalent à la moitié d'une période d'horloge T) produira une erreur d'intégration dépendante d'une exponentielle négative, pouvant être minimisée par un produit gain bande élevé. Enfin, si le  $T_{SLEW}$  dépasse une demie période d'horloge, l'erreur est linéaire et impacte grandement les performances du modulateur.

$$\varepsilon = \begin{cases} -S \times e^{-2\pi \times GBW \times \frac{T}{2}}, & T_{SLEW} \leq 0\\ -(S - SR \times T_{SLEW}) \times e^{-2\pi GBW \times \left(\frac{T}{2} - T_{SLEW}\right)}, & 0 < T_{SLEW} < \frac{T}{2} \\ -\left(S - SR \times \frac{T}{2}\right), & T_{SLEW} \geq \frac{T}{2} \end{cases}$$

(I-5)

$$T_{SLEW} = \frac{S}{SR} - \frac{1}{2\pi \times GBW} \tag{I-6}$$

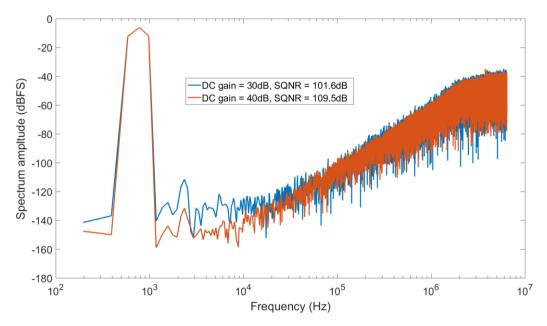

Enfin, après le produit gain bande et le slew rate, une dernière spécification peut entrainer une erreur d'intégration : le gain DC de l'amplificateur. Ce dernier détermine la valeur finale vers laquelle la réponse de l'amplificateur tend si le produit gain bande et le slew rate sont assez élevés pour entrainer une erreur négligeable. La loi de conservation des charges entre les phases d'échantillonnage et d'intégration permet de définir la fonction de transfert de l'intégrateur en tenant compte du gain fini :

$$H_{REELLE}(z) = \frac{C_S}{C_I} \times \frac{\frac{A_0}{1 + A_0 + (C_S + C_P)/C_I} z^{-1}}{1 - \frac{1 + A_0 + C_P/C_I}{1 + A_0 + (C_S + C_P)/C_I} z^{-1}}$$

(I-7)

Une erreur de magnitude est introduite, qui peut être compensée en ajustant le ratio des capacités, mais aussi une erreur de phase traduisant le fait qu'une partie de la charge intégrée est perdue à chaque cycle, plus difficile à compenser et obligeant le gain DC à avoir une valeur élevée.

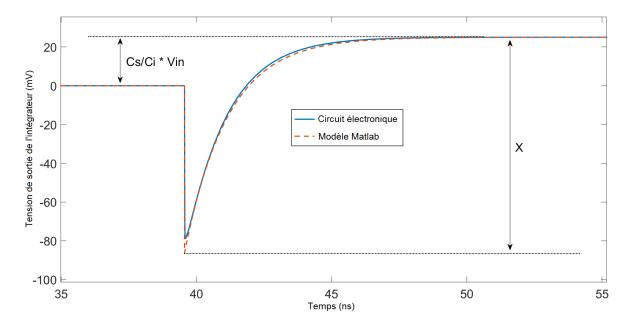

Ce modèle permet ainsi de définir des spécifications précises pour les amplificateurs qui composent les intégrateurs. Ces dernières ne dépendent que de la valeur de composants passifs (valeurs de capacités) et de spécifications du modulateur (fréquence d'horloge par exemple). Ainsi les performances du modulateur peuvent être assurées sans sur-dimensionner les intégrateurs, bénéficiant à la consommation. La figure I-6 illustre la précision du modèle où la réponse de l'intégrateur est comparée à celle d'un circuit électronique ayant les mêmes spécifications et valeurs de capacités. La seule différence entre les deux réponses est l'effet de redistribution des charges qui est plus lissée sur un circuit électronique dû à la résistance non-nulle des commutateurs.

Figure I-6 Comparaison de la réponse du modèle et d'un circuit électronique

## II – Design d'un modulateur à temps discret atteignant 103dB de plage dynamique

Dans le cadre de notre contexte lié à l'acquisition audio, le modulateur doit atteindre un rapport signal sur bruit de 100dB avec une consommation la plus faible possible tout comme une faible occupation d'espace. Les spécifications utiles pour définir l'architecture du modulateur sont données en table II-1.

**Table II-1** Spécifications du modulateur utilisées pour définir son architecture

| Spécification                                | Valeur | Unité   |

|----------------------------------------------|--------|---------|

| Tension de référence                         | 1.5    | V       |

| Largeur de bande du signal (F <sub>B</sub> ) | 24     | kHz     |

| Consommation (P)                             | 480    | $\mu W$ |

| Niveau de bruit ramené à l'entrée            | 7.5    | μV      |

| Plage dynamique (D)                          | 103    | dB      |

| Rapport signal sur bruit                     | 100    | dB      |

| Rapport signal sur bruit et distorsion       | >95    | dB      |

| Rapport signal sur bruit de quantification   | 110    | dB      |

| $FOM_S = D + 10log_{10}(F_B/P)$              | 180    | dB      |

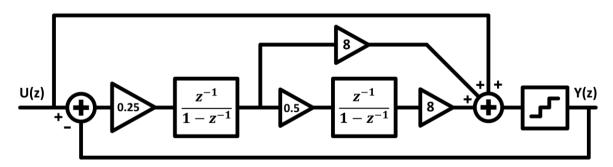

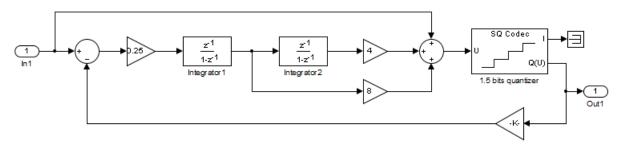

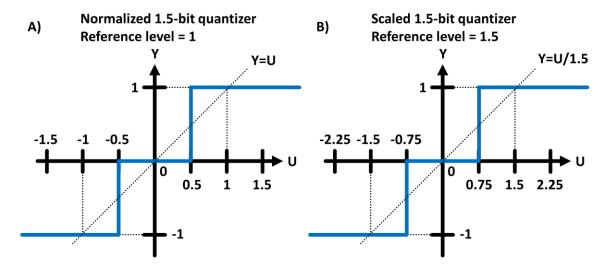

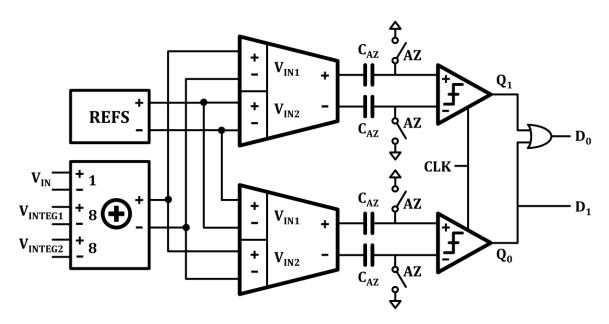

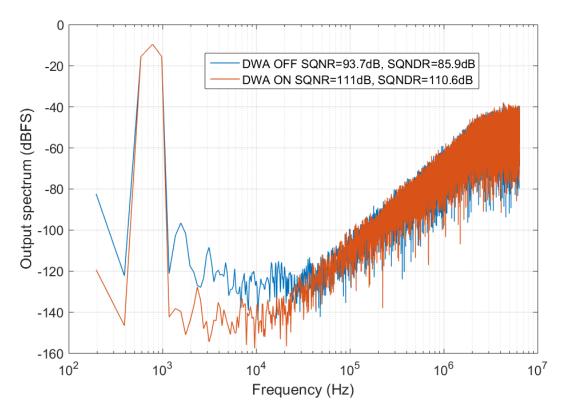

L'architecture choisie est un modulateur d'ordre 2, utilisant un quantificateur à trois niveaux (1,5 bits) et un ratio de suréchantillonnage de 256, donnant un rapport signal sur bruit de quantification de 110dB. Un quantificateur de 1,5 bits est utilisé pour atteindre la résolution voulue sans augmenter l'ordre du modulateur, et cela pour plusieurs raisons : il n'y a pas de problème de stabilité particulier à prendre en compte, et il permet de réduire l'amplitude du

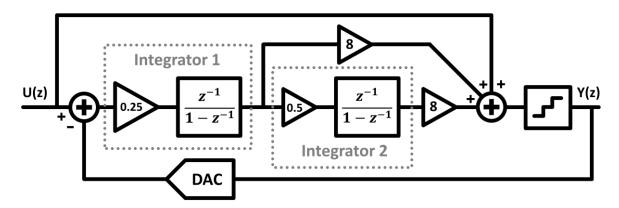

signal de sortie des intégrateurs, comme le fait un quantificateur multi-bits. Contrairement à ce dernier, un quantificateur sur trois niveaux simplifie largement l'algorithme de gestion des éléments du CNA de retour, lui permettant de conserver sa linéarité avec un faible surplus de consommation. Un grand ratio de suréchantillonnage est utilisé, afin de réduire l'espace occupé par les capacités qui représentent généralement la majorité de l'espace d'un modulateur à temps discret. Le modèle linéaire du modulateur est donné en figure II-1 :

Figure II-1 Modèle linéaire du modulateur à temps discret développé

La contrainte de bruit permet de définir la valeur des capacités d'échantillonnage de chaque étage d'intégration, celles-ci sont de 2,3pF pour le premier intégrateur et de 150fF pour le second. Les spécifications dynamiques de chaque intégrateur sont ensuite définies grâce au modèle présenté en section I.

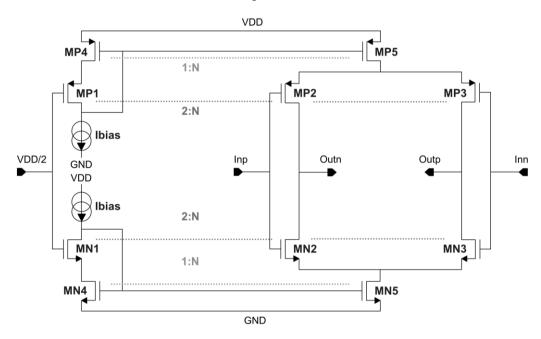

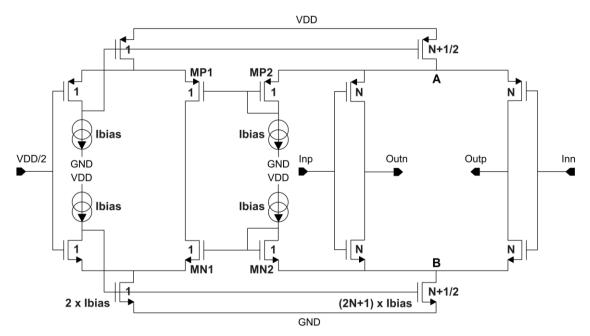

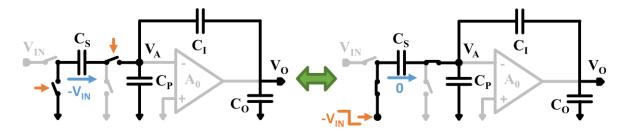

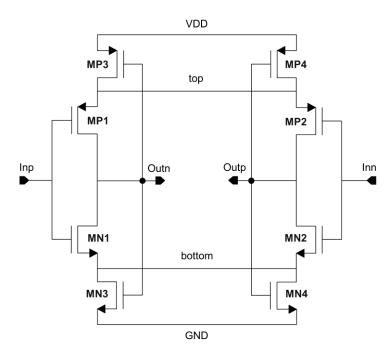

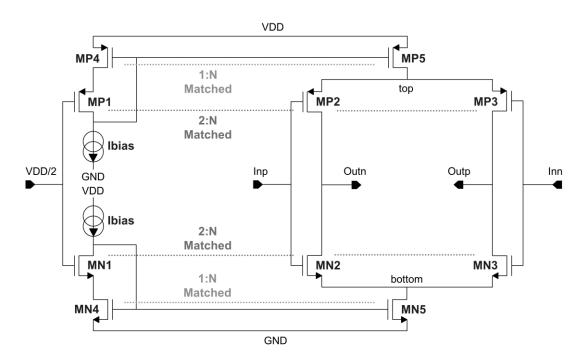

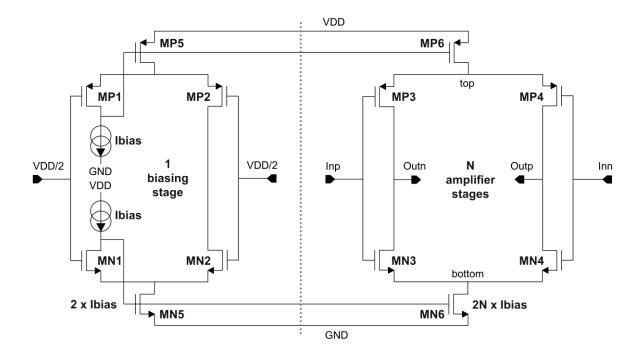

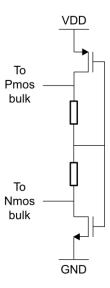

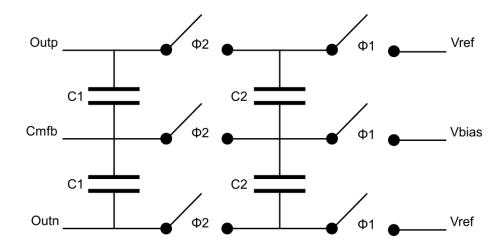

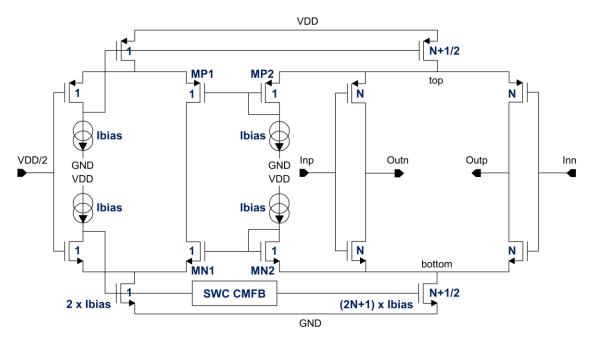

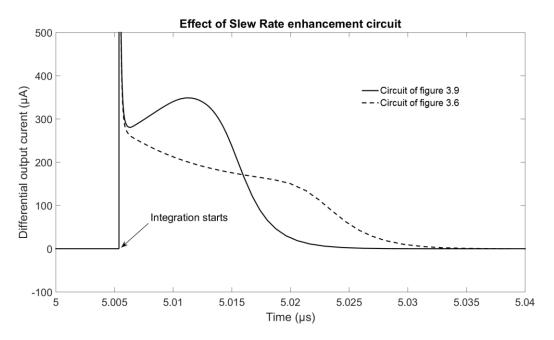

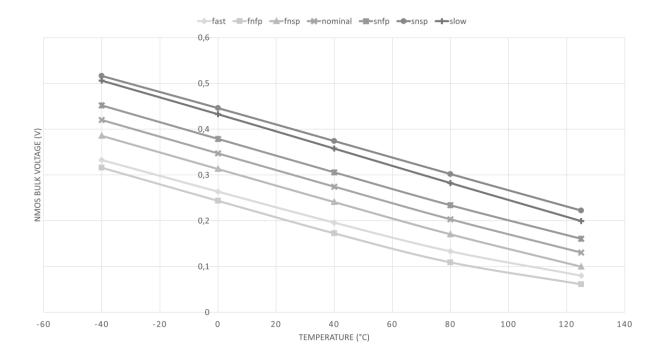

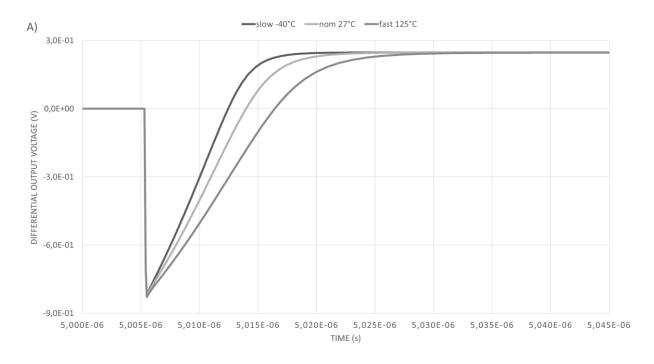

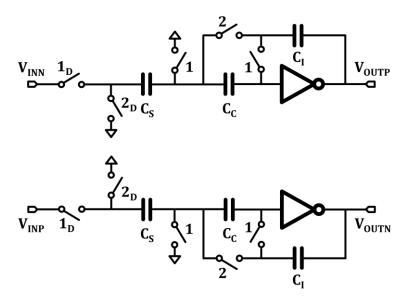

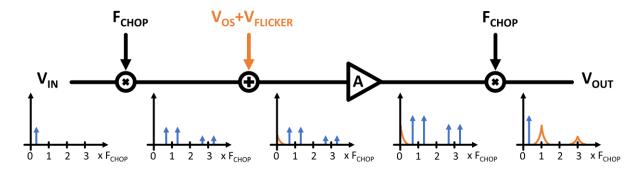

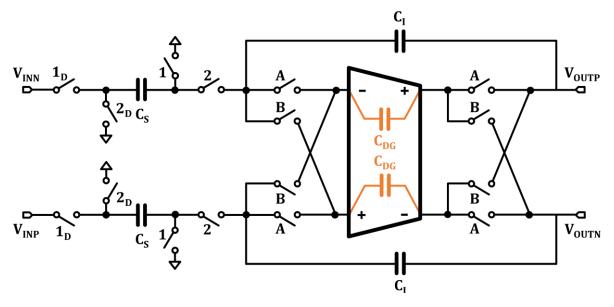

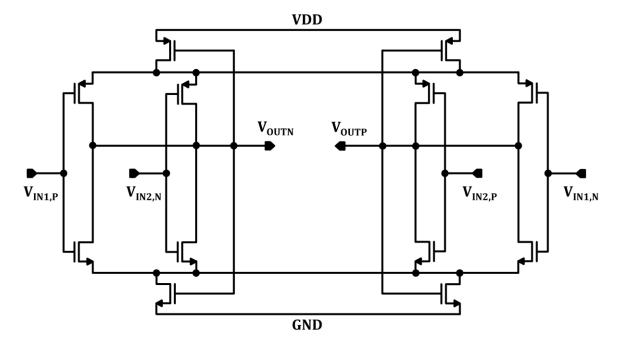

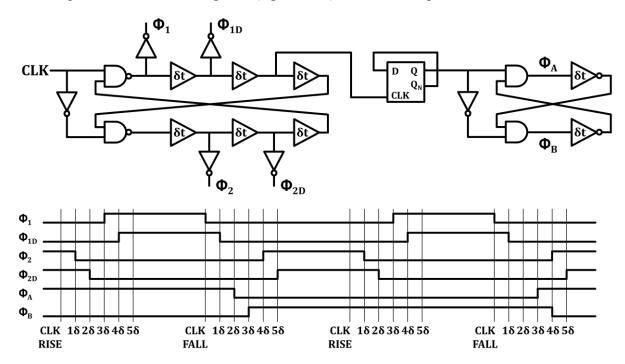

Les amplificateurs de classe AB sont particulièrement adaptés pour les circuits à capacités commutées de faible consommation. Ils présentent un courant de polarisation dynamique en fonction du signal d'entrée, ainsi ils procurent un fort slew rate en début de phase d'intégration, puis retournent à un courant de polarisation réduit le reste du temps. Parmi les amplificateurs de classe AB, ceux à base d'inverseurs ont la plus faible consommation grâce à leur unique branche de courant, les rendant particulièrement attractifs pour l'application souhaitée. Cependant, les amplificateurs inverseurs sont sensibles aux variations de tension d'alimentation, de procédé de fabrication ou de température, ce qui rend le point de polarisation variable sur une large plage et leur consommation mal maitrisée. Pour remédier à ce problème tout en conservant les propriétés dynamiques (classe AB) des amplificateurs inverseurs, le circuit présenté en figure II-2 est utilisé. Un miroir de courant fournit un courant de polarisation en utilisant des transistors dans leur régime linéaire (faible tension drain-source) afin de conserver le fonctionnement en class AB. Cela s'explique de la façon suivante : lorsqu'une assez large tension est appliquée en entrée de l'amplificateur, comme c'est le cas lors du début de la phase d'intégration des circuits à capacités commutées, les inverseurs sont dans des états opposés. Les transistors MN2 et MP3 sont passants et linéaires tandis que les transistors MN3 et MP2 sont bloqués. Ainsi la tension du nœud à la source du transistor MP3 chute tandis que celle du nœud à la source du transistor MN2 monte. Cela augmente les tensions drain-source des transistors de polarisation linéaires MN5 et MP5 : ceux-ci fonctionnent comme une résistance, une plus grande tension correspondant à un plus fort courant. A la fin de la période d'intégration, les entrées retrouvent leur position d'origine autour de la moitié de la tension d'alimentation, et le système retrouve alors le courant défini par l'étage de polarisation. Une modification présentée en figure II-3 permet d'amplifier le fonctionnement en classe AB de cet amplificateur en mettant l'étage de polarisation lui aussi dynamique. Pour cela, l'idée est de détecter les variations des nœuds A et B qui se produisent en début de phase d'intégration, pour augmenter le courant de polarisation jusqu'au retour à la normale. Cette fonction est expliquée côté NMOS mais le raisonnement est le même côté PMOS. Un transistor MN2 est connecté en diode ce qui lui permet sur sa tension de grille de monitorer les variations de tension de sa source. Ainsi lorsque sa tension de source augmente, sa tension de grille aussi, augmentant la tension de grille du transistor MN1 de l'étage de polarisation. Comme la même chose se produit du côté PMOS, un plus grand courant passe dans la branche MP1-MN1, augmentant le courant de l'étage de polarisation, ce qui se répercute ensuite sur l'étage d'amplification. En combinant ces deux techniques, l'amplificateur à base d'inverseurs réalisé permet d'avoir un fonctionnement en classe AB tout en ayant un point de polarisation contrôlé, permettant une architecture robuste, à faible consommation et performante.

**Figure II-2** Amplificateur à base d'inverseurs avec polarisation utilisant des transistors linéaires

Figure II-3 Amplificateur à base d'inverseurs avec étage de polarisation dynamique

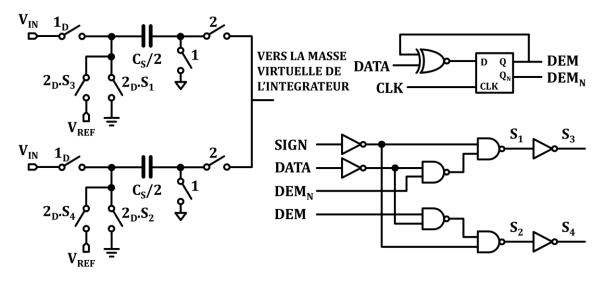

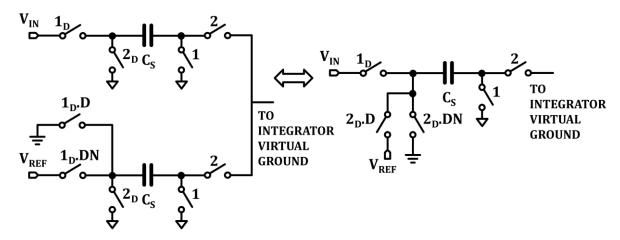

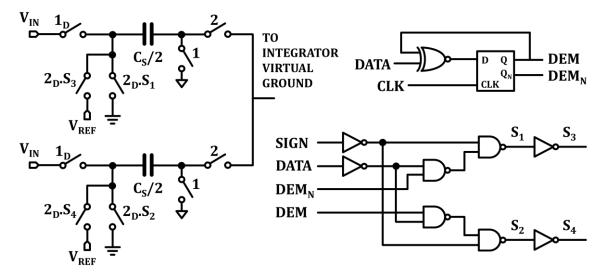

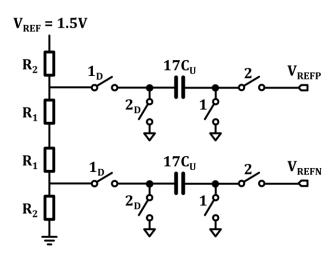

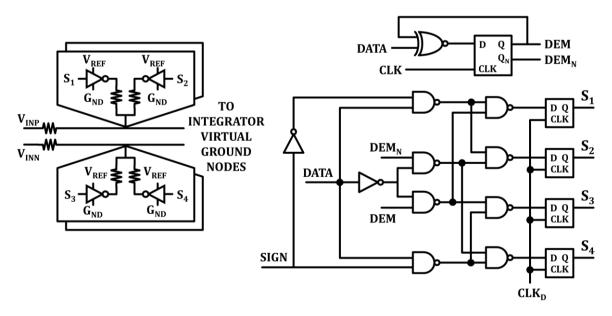

Pour minimiser l'espace occupé par les capacités ainsi que la consommation du modulateur, le CNA présent dans la boucle de retour du modulateur réutilise les capacités d'échantillonnage plutôt que d'en avoir des dédiées. Comme le CNA présente trois niveaux, les capacités d'échantillonnage sont coupées en deux pendant la phase d'intégration : elles sont connectées toutes deux à la tension de référence ou à la masse pour sortir les niveaux « 1 » ou « -1 », tandis que l'une est à la masse et l'autre à la tension de référence pour former le niveau intermédiaire « 0 ». Afin de conserver la linéarité du CNA, les capacités sont alternées à chaque fois que le niveau « 0 » doit être activé et la commande des commutateurs est fournie par un circuit logique simple. L'implémentation du CNA au travers de la capacité d'échantillonnage est présentée en figure II-4 (représentation non différentielle). Les signaux de commande du CNA à trois niveaux sont représentés par un bit de signe (état à « 0 » pour un signe positif, « 1 » pour un signe négatif) et un bit de donnée, correspondant à un code en complément à 2.

Figure II-4CNA à trois niveaux réutilisant la capacité d'échantillonnage

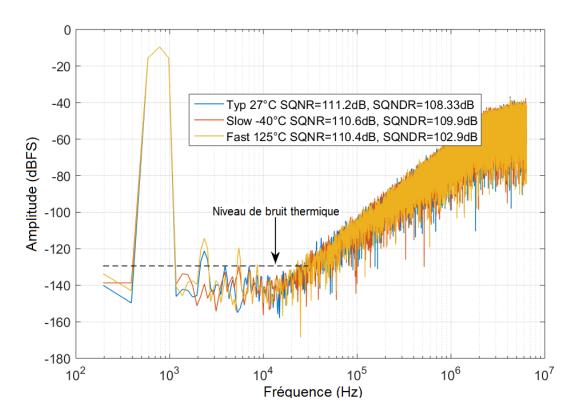

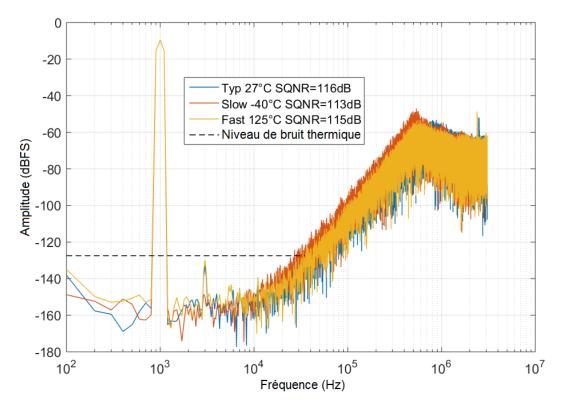

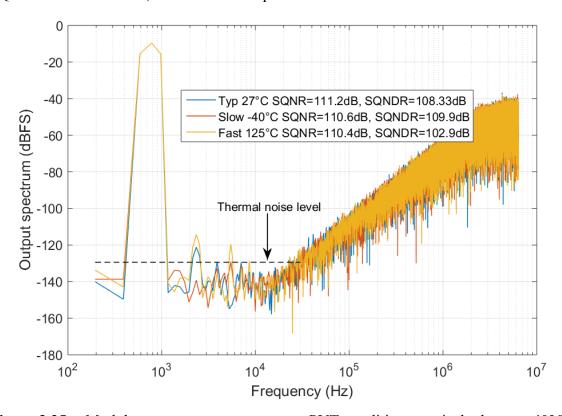

Le modulateur réalisé atteint 110dB de rapport signal sur bruit de quantification pour un signal d'entrée à -3dBFS sur une bande de fréquence de 24kHz. En tenant compte du bruit thermique, simulé à 7.5μVrms à l'entrée sur la même bande audio, le rapport signal sur bruit est de 100dB. Le spectre du signal de sortie du modulateur est donnée en figure II-5. Trois courbes sont affichées, celle d'un procédé de fabrication typique à 27°C, ainsi que les extremums : procédé fast à 125°C et procédé slow à -40°C, les trois atteignant 110dB de rapport signal sur bruit de quantification (SQNR). La distorsion est un peu plus élevée à 125°C mais toujours dans les spécifications, cela est dû à la résistance des commutateurs qui est non-linéaire en fonction du signal échantillonné. Ce modulateur atteint ces performances pour une consommation totale de 480μW, ce qui lui donne une figure de mérite FOM<sub>S</sub> de 180dB, le plaçant ainsi parmi les meilleurs modulateurs audio à temps discret de la littérature. L'utilisation d'amplificateurs à base d'inverseurs a permis d'obtenir une faible consommation, tandis qu'un grand ratio de suréchantillonnage, conjugué à un CNA réutilisant les capacités d'échantillonnage permettent de réduire l'espace occupé (plus faible surface que l'état de l'art) et de produire à faible coût, répondant ainsi à la problématique de recherche.

Figure II-5Spectre de sortie du modulateur pour trois corners différents

Table II-2 Table des performances et comparaison avec l'état de l'art

|                      | Ce<br>Travail | [16]  | [17]  | [20]  | [21]  | [22]  | [33] | [34]  |

|----------------------|---------------|-------|-------|-------|-------|-------|------|-------|

| Techno (nm)          | 140           | 180   | 180   | 180   | 160   | 350   | 130  | 90    |

| Année                | 2017          | 2011  | 2012  | 2009  | 2016  | 2013  | 2012 | 2004  |

| Ordre                | 2             | 4     | 3     | 3     | 3     | 4     | 4    | 3     |

| F <sub>B</sub> (kHz) | 24            | 25    | 50    | 20    | 20    | 20    | 20   | 20    |

| F <sub>E</sub> (MHz) | 12.288        | 1.6   | 3.2   | 4     | 11.29 | 2.4   | 2.5  | 4     |

| OSR                  | 256           | 32    | 32    | 100   | 282   | 60    | 62   | 100   |

| Référence (V)        | 1.5           | 1     | 1.5   | 0.7   | 1.8   | 1.5   | 0.5  | 0.6   |

| DR (dB)              | 103           | 93    | 94    | 85    | 109   | 92.6  | 85   | 88    |

| SNR (dB)             | 100           | 92.5  | -     | 84    | 106   | -     | 82.4 | 85    |

| SNDR (dB)            | 98            | 92    | 88.9  | 81    | 103   | 87.9  | 81.7 | 81    |

| Conso (µW)           | 480           | 58    | 140   | 22    | 1120  | 140   | 35.2 | 140   |

| Aire (mm²)           | 0.084         | -     | 0.49  | 0.715 | 0.16  | 0.207 | 0.57 | 0.18  |

| FOMs (dB)            | 180           | 179.3 | 179.5 | 174.5 | 181.5 | 174   | 173  | 169.5 |

## III — Théorie des modulateurs à temps continu et leurs spécificités

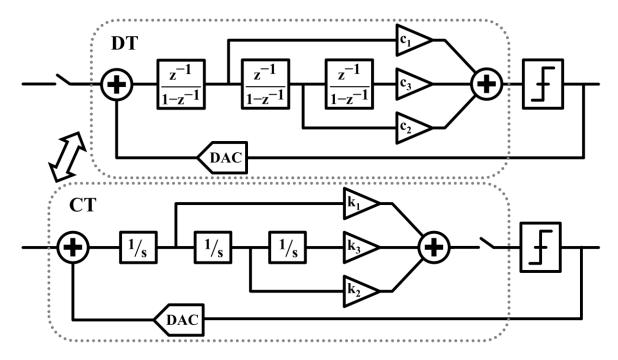

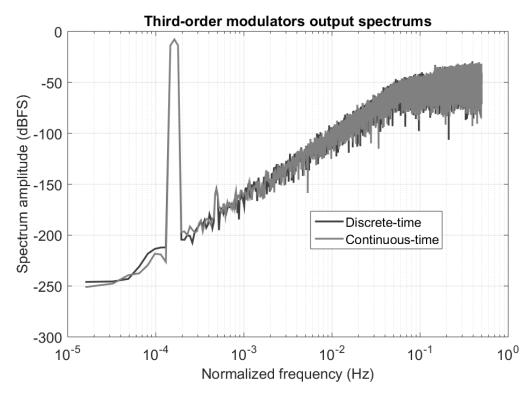

Cette section présente les connaissances théoriques nécessaires à la synthèse d'un modulateur sigma-delta à temps continu, ainsi que les spécificités de ces derniers par rapport à ceux à temps discret précédemment étudiés. Pour réaliser un modulateur à temps continu, on commence par

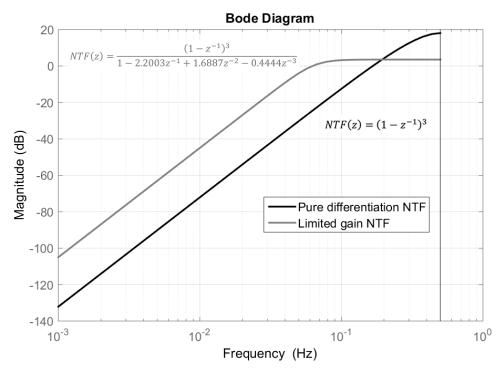

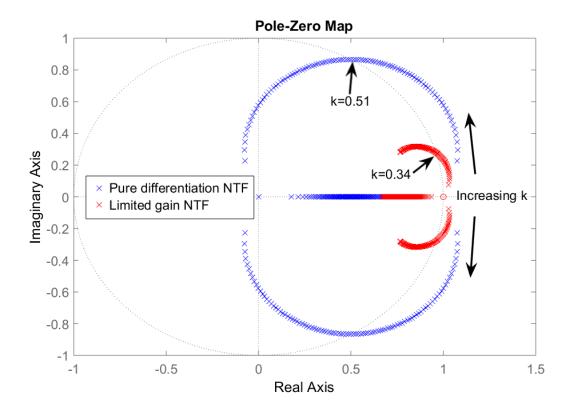

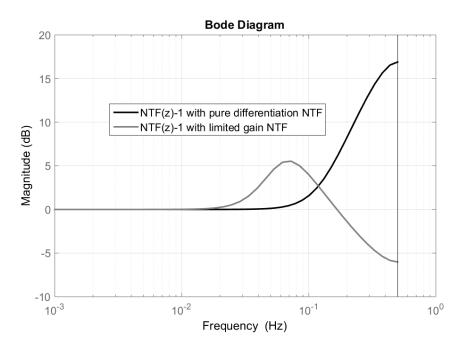

définir un modulateur à temps discret dont les performances satisfont les spécifications requises. Ensuite, en utilisant la méthode d'invariance de la réponse impulsionnelle, on synthétise la boucle de retour CNA – filtre de boucle - échantillonneur pour qu'elle ait la même réponse impulsionnelle que la boucle de retour du modulateur discret. Prenons l'exemple d'un modulateur à temps discret du troisième ordre ayant pour fonction de transfert du bruit de quantification  $NTF_D(z)$  définie ci-dessous et dont on souhaite synthétiser l'équivalent continu. Travaillons premièrement avec un modulateur normalisé (période d'échantillonnage  $T_E$  de 1s).

$$NTF_D(z) = \frac{(1-z^{-1})^3}{1 - 2.2003z^{-1} + 1.6887z^{-2} - 0.4444z^{-3}}$$

(III-1)

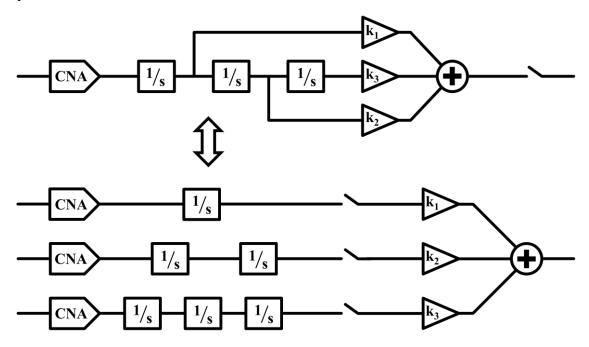

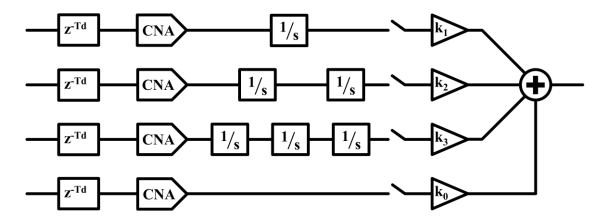

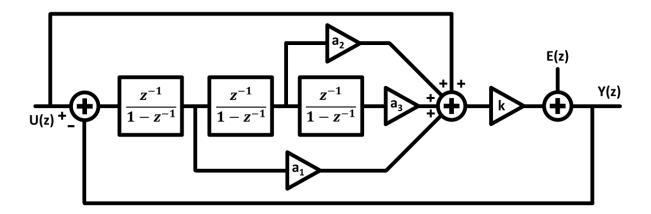

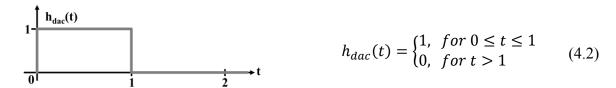

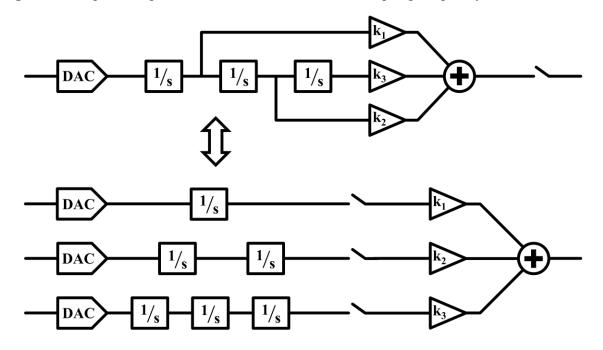

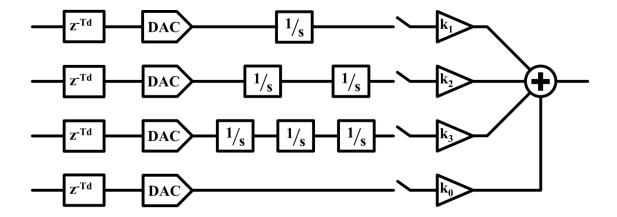

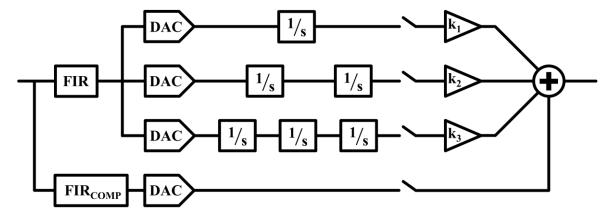

La boucle de retour peut être décomposée comme la somme de trois chemins d'ordre d'intégration différent comme montré en figure III-1. Calculons par la méthode d'invariance de la réponse impulsionnelle l'équivalent discret de chacun de ces chemins, en commençant par celui du premier ordre. Le CNA a une réponse impulsionnelle de type échantillonneur-bloqueur idéal donnée par l'expression ci-dessous :

$$h_{CNA}(t) = \begin{cases} 1, & pour \quad 0 \le t \le 1\\ 0, & pour \quad t > 1 \end{cases}$$

(III-2)

Cette réponse est ensuite intégrée pour donner la réponse du chemin du premier ordre :

$$h_{1}(t) = \begin{cases} \int_{0}^{t} 1 \times dt, & for \ 0 \le t \le 1 \\ h_{1}(1) + \int_{1}^{t} 0 \times dt, & for \ t > 1 \end{cases} = \begin{cases} t, & pour \ 0 \le t \le 1 \\ 1, & pour \ t > 1 \end{cases}$$

(III-3)

On échantillonne ensuite cette dernière toutes les  $T_E$  secondes  $(h_{1d}(n) = h_1(nT_E))$ :

$$h_{1d}(n) = \begin{cases} n, & for \ n \in \{0,1\} \\ 1, & for \ n > 1 \end{cases} = \begin{cases} 0, & for \ n = 0 \\ 1, & for \ n \ge 1 \end{cases}$$

(III-4)

Et l'on prend la transformée en z pour obtenir la fonction de transfert discrète équivalente :

$$H_1(z) = \sum_{n=0}^{\infty} h_{1d}(n) z^{-n} = \sum_{n=1}^{\infty} z^{-n} = \frac{z^{-1}}{1 - z^{-1}}$$

(III-5)

En intégrant  $h_1(t)$  encore une et deux fois, on obtient respectivement  $h_2(t)$  et  $h_3(t)$  donnant la réponse impulsionnelle des deux autres chemins d'intégration. De manière analogue, en échantillonnant ces réponses et en prenant la transformée en z on obtient les fonctions de transfert discrètes équivalentes suivantes :

$$H_2(z) = \frac{0.5z^{-1} + 0.5z^{-2}}{(1 - z^{-1})^2}, \qquad H_3(z) = \frac{\frac{1}{6}z^{-1} + \frac{4}{6}z^{-2} + \frac{1}{6}z^{-3}}{(1 - z^{-1})^3}$$

(III-6)

Il ne manque plus qu'à additionner les transformées en z obtenues avec les coefficients de poids pour obtenir la réponse totale du chemin de retour :

$$H(z) = k_1 H_1(z) + k_2 H_2(z) + k_3 H_3(z)$$

(III-7)

Cela donne la fonction de transfert du bruit de quantification NTF(z) suivante :

$$NTF(z) = \frac{(1 - z^{-1})^3}{1 + \left(k_1 + \frac{k_2}{2} + \frac{k_3}{6} - 3\right)z^{-1} + \left(3 - 2k_1 + \frac{4k_3}{6}\right)z^{-2} + \left(k_1 - \frac{k_2}{2} + \frac{k_3}{6} - 1\right)z^{-3}}$$

(III-8)

Par identification avec  $NTF_D(z)$  donnée en (III-1), on déduit alors la valeur des coefficients  $k_1$ ,  $k_2$  et  $k_3$  qui sont respectivement 0,6703, 0,2441 et 0,0440. En utilisant ces coefficients, le modulateur à temps continu que l'on voulait synthétiser est équivalent à celui de référence à temps discret.

**Figure III-1** Décomposition du CNA – filtre de boucle en chemins de différents ordres d'intégration

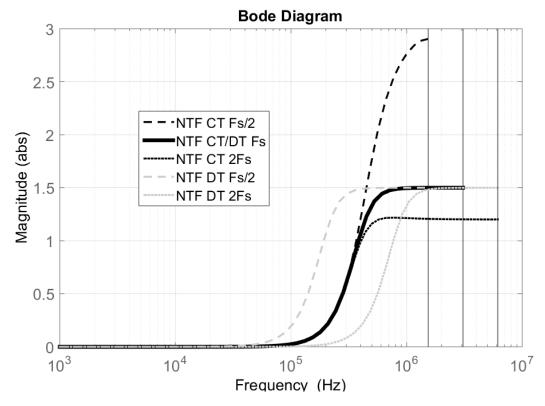

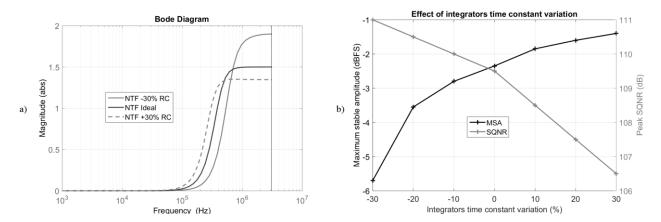

Les modulateurs à temps continu ont des intégrateurs à constante de temps fixe contrairement à ceux discrets dont la constante de temps est fonction de la fréquence d'horloge. Ainsi un modulateur à temps continu n'est adapté que pour une fréquence d'horloge particulière. Le modulateur normalisé présenté utilise une fréquence d'horloge de 1Hz, en changeant celle-ci par  $F_E$ , les intégrateurs auront un signal  $F_E$  plus petit à chaque échantillonnage. Pour retrouver le comportement correct des intégrateurs au cours d'une période d'échantillonnage, leur constante de temps doit alors augmenter et être égale à  $F_E$ .

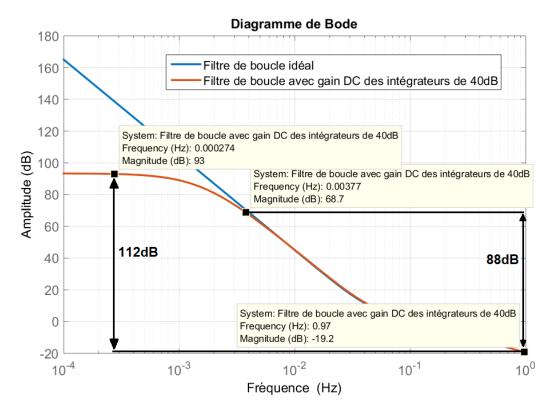

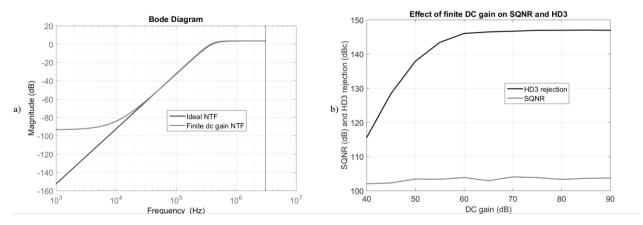

Le principal avantage d'un modulateur sigma-delta à temps continu est sa propriété de filtre anti-repliement. En effet, le signal entrant est échantillonné en sortie du filtre de boucle, aussi ce dernier fait alors office de filtre anti-repliement car il est constitué d'intégrateurs qui ont une réponse fréquentielle passe-bas. La figure III-2 montre la réponse en fréquence idéale du filtre de boucle du modulateur de troisième ordre synthétisé auparavant, ainsi que celle du filtre de boucle utilisant des intégrateurs de gain DC fini et égal à 40dB. En considérant que ce modulateur a un taux de suréchantillonnage de 128, on peut voir que la performance minimum du filtre anti-repliement est donnée par les repliements à des fréquences proches de la bande passante du signal, on obtient dans notre cas 88dB de réjection. Pour des repliements plus basse fréquence, la rejection est meilleure car les intégrateurs ont plus de gain, cependant elle devient limitée lorsque l'on atteint les gains DC de chacun des intégrateurs à 112dB.

**Figure III-2** Réponse en fréquence d'un filtre de boucle idéal et d'un filtre avec gain DC fini, ainsi que l'évaluation des performances anti-repliement du filtre

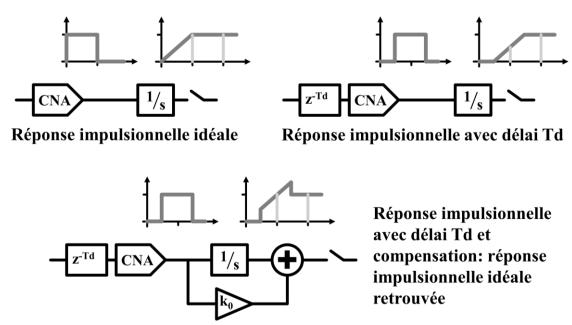

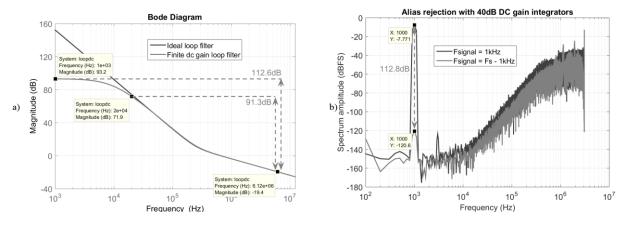

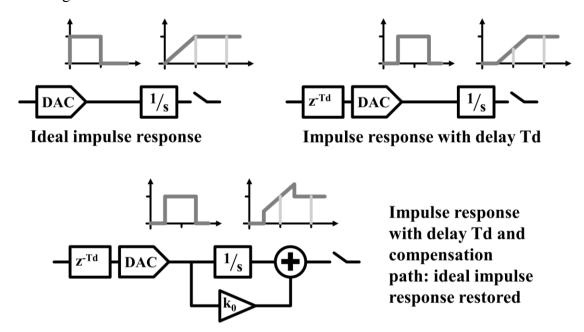

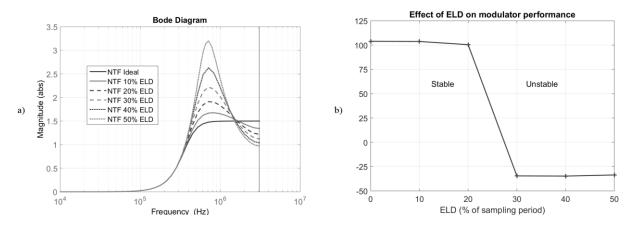

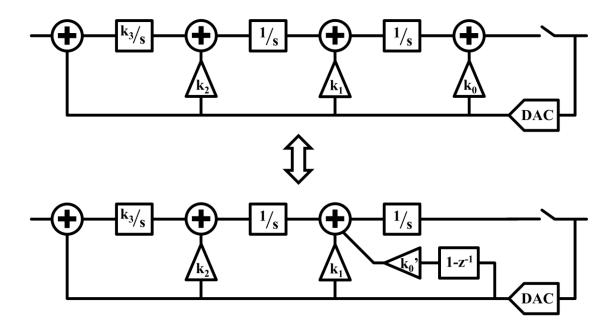

Les modulateurs à temps continu sont sensibles à l'exactitude de temps. Un délai dans la boucle de retour change sa réponse impulsionnelle : celle-ci ne sera plus équivalente, après transformée en z, à la fonction de transfert discrète que l'on voulait synthétiser et peut rendre le modulateur instable. Cela est illustré en figure III-3, où une compensation possible du délai est le rajout d'un chemin non intégrateur dans la boucle de retour, avec le coefficient  $k_0$  adapté.

**Figure III-3** Modification de la réponse impulsionnelle avec l'ajout d'un délai et compensation du délai pour retrouver une réponse impulsionnelle idéale

Un délai minimum est requis par les composants analogiques entre l'instant où l'on échantillonne le signal en entrée du quantificateur, et l'instant où le quantificateur donne une valeur qui fait changer le CNA de la boucle de retour. En considérant un délai d'une demipériode d'échantillonnage, on peut déterminer la valeur du coefficient  $k_0$  de manière analogue à celle faite pour déterminer  $k_1$ ,  $k_2$  et  $k_3$ ; en utilisant la méthode d'invariance de la réponse impulsionnelle. On se base sur le diagramme de la boucle de retour suivant :

Figure III-4 Décomposition de la boucle de retour avec compensation du délai

Le CNA, retardé d'une demi-période, a la réponse impulsionnelle suivante :

$$h_{CNAD}(t) = \begin{cases} 0, & pour \ 0 \le t \le 0.5 \\ 1, & pour \ 0.5 \le t \le 1.5 \\ 0, & pour \ t > 1.5 \end{cases}$$

(III-9)

De manière analogue à précédemment et en utilisant la réponse impulsionnelle retardée du CNA, on détermine alors les fonctions de transfert discrètes de chacun des chemins de la boucle de retour :

$$H_{0D}(z) = z^{-1}, \qquad H_{1D}(z) = \frac{0.5z^{-1} + 0.5z^{-2}}{(1 - z^{-1})}$$

$$H_{2D}(z) = \frac{0.125z^{-1} + 0.75z^{-2} + 0.125z^{-3}}{(1 - z^{-1})^2}$$

$$H_{3D}(z) = \frac{\frac{1}{48}z^{-1} + \frac{23}{48}z^{-2} + \frac{23}{48}z^{-3} + \frac{1}{48}z^{-4}}{(1 - z^{-1})^3}$$

(III-10)

En prenant la somme pondérée, on obtient la fonction de transfert de la boucle de retour complète :

$$H_D(z) = k_0 H_{0D}(z) + k_1 H_{1D}(z) + k_2 H_{2D}(z) + k_3 H_{3D}(z)$$

(III-11)

Ce qui conduit à la fonction de transfert du bruit de quantification suivante :

$$NTF_D = \frac{\left(1-z^{-1}\right)^3}{1 + \left(k_0 + \frac{k_1}{2} + \frac{k_2}{8} + \frac{k_3}{48} - 3\right)z^{-1} + \left(-3k_0 - \frac{k_1}{2} + \frac{5k_2}{8} + \frac{23k_3}{48} + 3\right)z^{-2} + \left(3k_0 - \frac{k_1}{2} - \frac{5k_2}{8} + \frac{23k_3}{48} - 1\right)z^{-3} + \left(-k_0 + \frac{k_1}{2} - \frac{k_2}{8} + \frac{k_3}{48}\right)z^{-4}}$$

(III-12)

L'ajout d'un délai dans la boucle de retour augmente l'ordre de la NTF qui est maintenant du quatrième ordre. La compensation ajoute un degré de liberté supplémentaire au système lui

permettant alors d'annuler le terme d'ordre 4 de la NTF. Par identification avec (III-1), on obtient alors les valeurs de coefficients suivantes :  $k_0 = 0.3666$ ,  $k_1 = 0.7979$ ,  $k_2 = 0.2661$  et  $k_3 = 0.0440$ . On remarque que les valeurs des coefficients  $k_1$  et  $k_2$  sont aussi impactées par l'ajout d'un délai de boucle. D'autres méthodes de compensation sont aussi présentées dans le corps de la thèse.

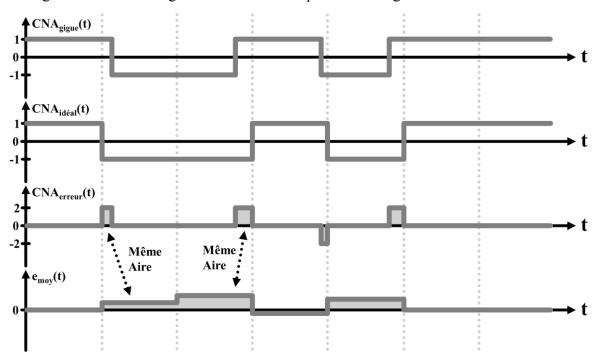

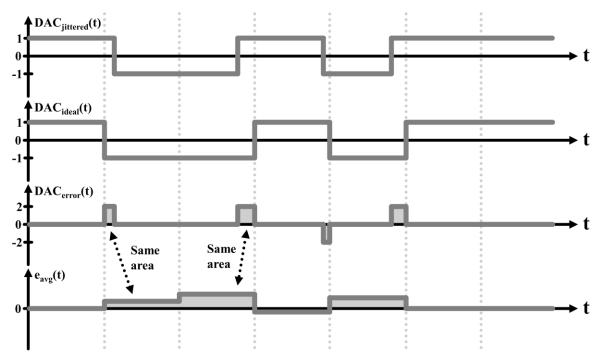

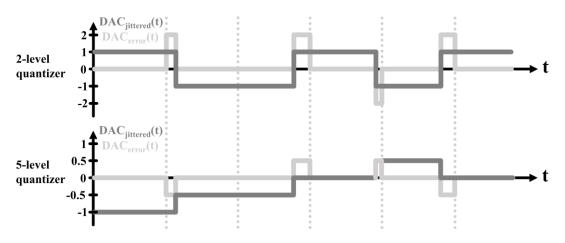

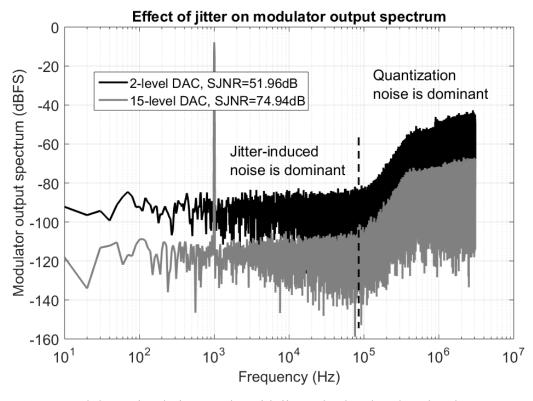

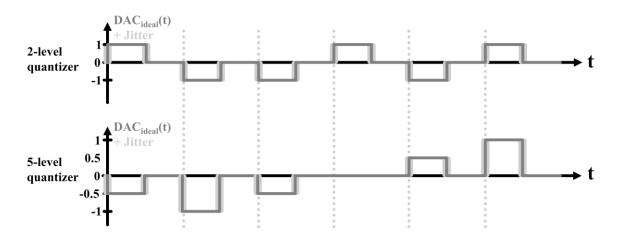

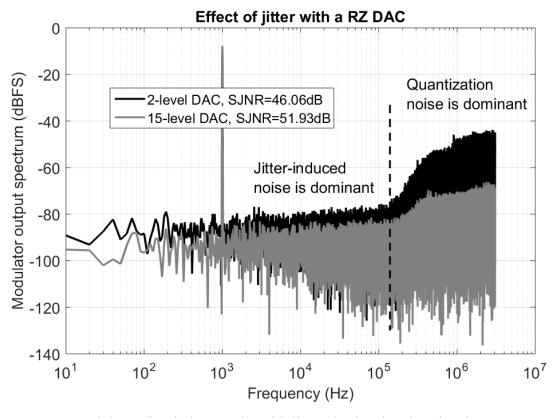

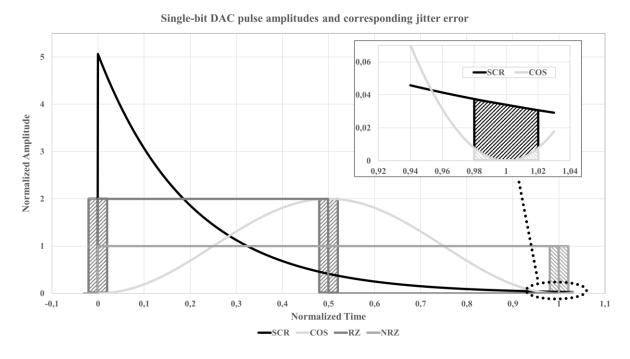

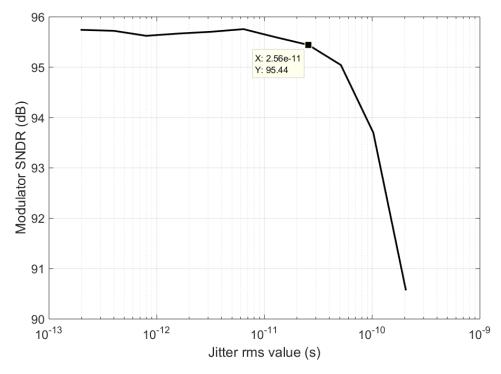

D'autres effets temporels peuvent affecter la résolution du modulateur : le phénomène de gigue sur l'horloge entraine une incertitude sur le moment où le CNA va changer de valeur. Ainsi deux données consécutives du CNA peuvent ne pas avoir de durée exactement égale, entrainant une variabilité sur la durée de chaque valeur de sortie du CNA. L'erreur introduite est dépendante de plusieurs facteurs comme la gigue de l'horloge, le codage du CNA ou la fréquence de l'horloge  $F_E$ , venant ajouter du bruit au signal d'entrée et réduisant la résolution du modulateur. Prenons l'exemple d'un CNA utilisant un codage de non-retour-à-zéro, qui suit une séquence de données y(n): son signal de sortie peut être décomposé comme la somme d'un signal idéal et d'un signal d'erreur comme présenté en figure III-5.

**Figure III-5** Effet de gigue sur l'horloge du CNA introduisant une erreur et détermination de l'erreur moyennée sur une période

L'erreur introduite dépend de la différence entre nouvelle et précédente valeurs du CNA ainsi que de la variation de durée entre les deux valeurs, que l'on représentera par une séquence aléatoire j(n). Moyennant cette erreur sur une période, on obtient la relation suivante :

$$e_{moy}(n) = (y(n) - y(n-1)) \times \frac{j(n)}{T_E} = \delta y(n) \times j(n) \times F_E$$

(III-13)

La puissance du signal d'erreur injecté à l'entrée du modulateur dû à l'effet de gigue est :

$$\sigma_e^2 = \sigma_{\delta y}^2 \times \sigma_j^2 \times F_E^2 \tag{III-14}$$

Ce dernier peut être modélisé comme un signal aléatoire de variance donnée par l'équation (III-14). Réduire la puissance du signal d'erreur pour une certaine variance de gigue donnée

peut être réalisé en diminuant la fréquence d'horloge du modulateur, mais cela revient à réduire sa résolution par la même occasion. Une autre solution consiste à réduire la variance du signal  $\delta y(n)$  qui est la différence entre deux données consécutives de y(n). Pour réaliser cela, un quantificateur et un CNA multi-bits doivent être utilisés dans le modulateur. Puisque  $\delta y(n)$  est égal soit à zéro (quand deux données consécutives sont égales) soit à la taille d'un bit de poids faible, plus on utilise de niveaux de quantification plus la sensibilité du modulateur à l'effet de gigue diminue. D'autres implémentations du CNA sont plus sensibles à l'effet de gigue comme le codage retour-à-zéro, et d'autres moins sensibles comme un CNA à capacités commutées, c'est pourquoi un modulateur à temps continu est plus sensible qu'un modulateur à temps discret.

## IV – Design d'un modulateur à temps continu ayant 16 bits de résolution

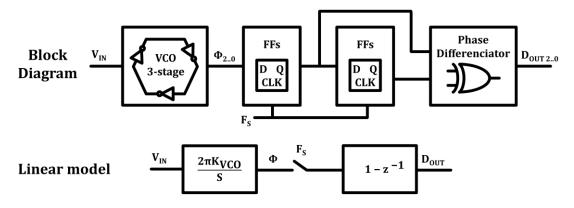

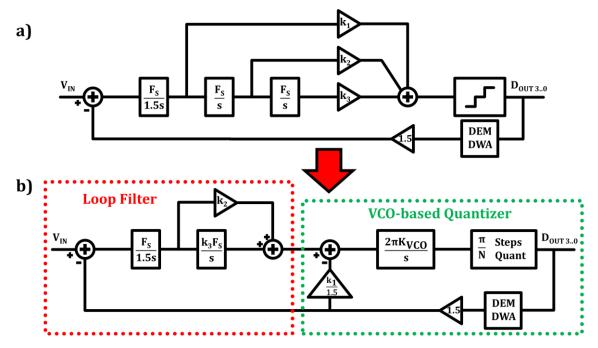

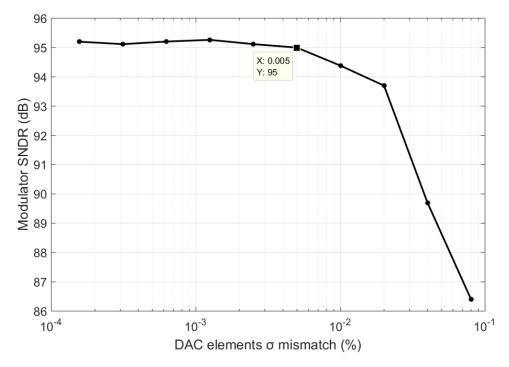

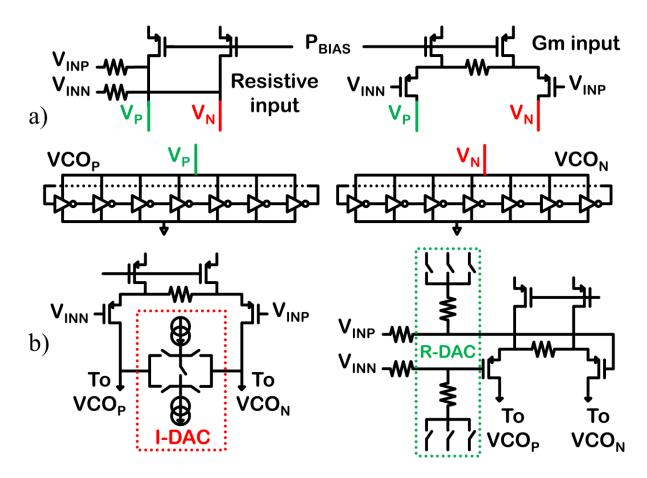

L'étude de l'état de l'art des modulateurs audio à temps continu montre que les concepts les moins consommateurs d'énergie combinent plusieurs fonctions dans un seul bloc de base : un double intégrateur n'utilisant qu'un seul amplificateur ou un quantificateur possédant une fonction d'intégrateur du premier ordre. Parmi ces quantificateurs, un type est utilisé dans des modulateurs à temps continu de fréquences plus élevées que l'audio : le quantificateur à base d'oscillateur contrôlé en tension. Ce dernier permet d'obtenir une quantification multi-bits, tout en y ajoutant certains bénéfices : une implémentation basée sur des cellules numériques (faible espace occupé et faible consommation), et opération intrinsèque d'intégration en utilisant la phase de l'oscillateur comme signal de sortie. De plus, grâce à leur implémentation numérique, la quantification peut se faire quasi-instantanément sur un front d'horloge, diminuant le délai de retour de boucle. Ce type de quantificateur permet de simplifier l'architecture du modulateur, mais apporte aussi certains défauts. La grande non-linéarité des oscillateurs contrôlés en tension limite leur application à des résolutions moyennes, c'est pourquoi ils sont principalement utilisés dans des modulateurs à temps continu de large bande de fréquence du signal où la résolution souhaitée est plus faible qu'en audio. Enfin, ces derniers sont sensibles aux variations de procédé de fabrication et de température, ce qui rend leur gain de conversion tensionfréquence variable et peut poser problème dans le cas d'un intégrateur où la constante de temps doit être fixe. Un modulateur à temps continu utilisant un quantificateur à base d'oscillateurs en tension est réalisé, atteignant 16 bits de résolution et dont les défauts du quantificateur ont été pris en compte par des choix architecturaux.

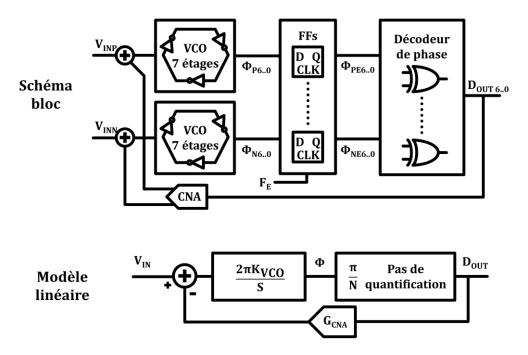

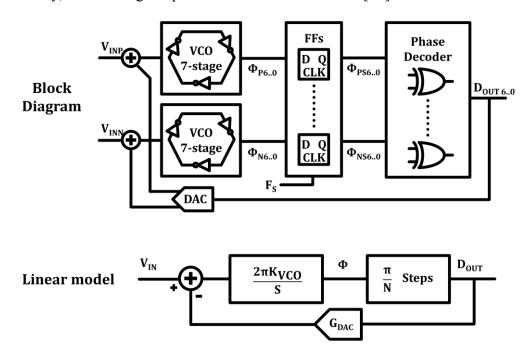

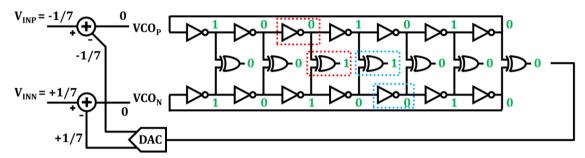

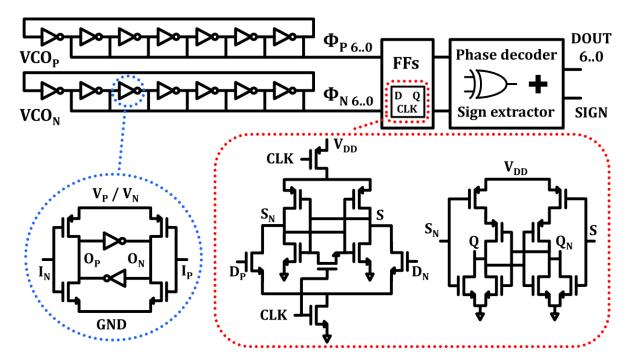

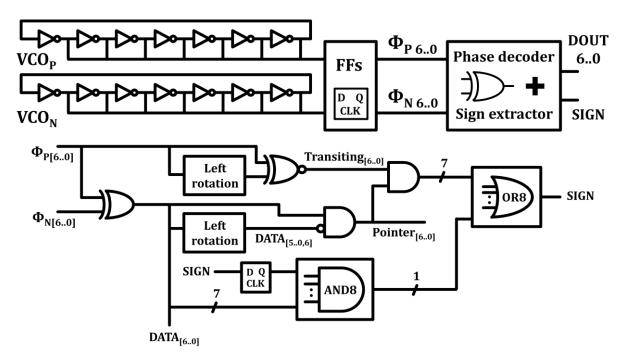

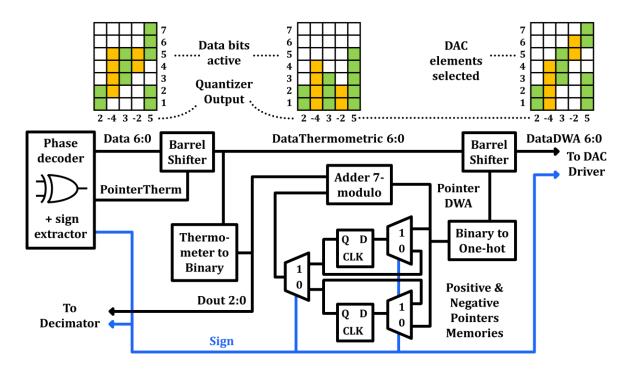

Commençons dans un premier temps par comprendre le fonctionnement d'un quantificateur à base d'oscillateurs contrôlés en tension. Celui-ci est expliqué à l'aide de la figure IV-1 présentant le schéma bloc et le modèle linéaire du quantificateur-intégrateur. Deux oscillateurs contrôlés en tension convertissent une différence de tension en une différence de fréquence à travers un gain  $K_{VCO}$ . La différence de fréquence fait augmenter ou diminuer continuellement la différence de phase entre les deux oscillateurs selon son signe. La position des phases de chaque oscillateur est échantillonnée à l'aide de bascules et un décodeur de phase quantifie la différence de phase avec un nombre prédéfini de valeurs de quantification équitablement réparties sur l'intervalle  $[0, \pi]$  ou  $[-\pi, \pi]$  selon les implémentations. La phase étant l'intégrale

de la fréquence multipliée par un facteur  $2\pi$ , ce quantificateur réalise intrinsèquement un intégrateur parfait. Une boucle de retour est nécessaire pour s'assurer que la différence de phase reste dans l'intervalle de quantification choisi.

**Figure IV-1** Schéma bloc et modèle linéaire d'un quantificateur-intégrateur utilisant des oscillateurs contrôlés en tension

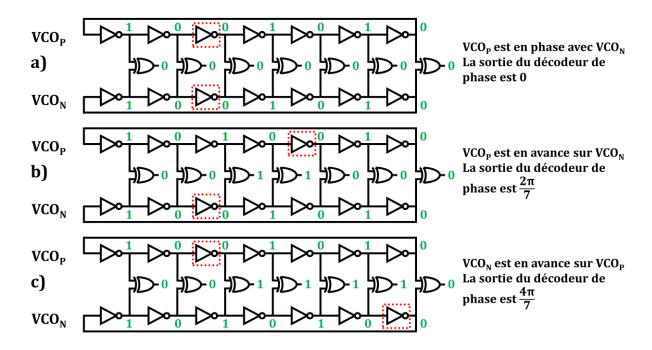

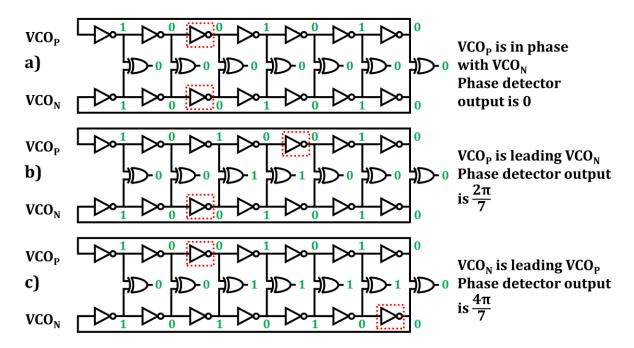

La figure IV-2 explique le fonctionnement du décodeur de phase basé sur des portes logiques XOR en utilisant des oscillateurs à 7 phases. Les inverseurs entourés en rouge sont dans un état de transition : leurs grilles viennent de basculer mais leur sortie pas encore. Quand aucune tension différentielle n'est appliquée à l'entrée des oscillateurs, on se retrouve dans le cas a) où la phase des oscillateurs se propage à la même vitesse dans les deux oscillateurs. Toutes les phases sont égales, et la sortie du décodeur de phase est donc 0. Le cas b) est celui d'une tension différentielle positive : l'oscillateur VCO<sub>P</sub> a une fréquence plus élevée que VCO<sub>N</sub>, son inverseur en transition est en avance de deux éléments, comparé à VCO<sub>N</sub>. Le décodeur de phase voit sa sortie avoir deux bits actifs sur sept, la différence de phase est alors de  $2\pi/7$ . Si toutes les phases étaient dans un état opposé, la différence vaudrait alors  $\pi$ . Le cas c) est celui où la tension d'entrée est négative : l'oscillateur VCO<sub>N</sub> est cette fois-ci plus rapide que VCO<sub>P</sub>. Son avance est de 4 éléments, donnant alors une différence de phase de  $4\pi/7$  entre les deux oscillateurs. Le décodeur de phase à base de portes XOR n'est pas capable de définir le signe de la différence de phase : il en donne seulement la valeur absolue qu'il quantifie sur un intervalle  $[0, \pi]$  avec un pas de  $\pi/N$  où N représente le nombre de phases utilisées. Sa sortie est un code thermométrique de la différence de phase, donnant alors N+1 niveaux de quantification. Un circuit logique simple peut être ajouté en complément du décodeur de phase pour définir le signe de la différence de phase. Ainsi, l'intervalle de quantification passe de  $[0, \pi]$  à  $[-\pi, \pi]$  en conservant le même pas de quantification, ce qui permet d'obtenir avec le même système 2N+1 niveaux de quantification. Ce quantificateur, avec son architecture différentielle et un grand nombre de niveaux de quantification qui réduit la tension en entrée des oscillateurs, permet d'obtenir une linéarité de l'ordre de 80dB, et est intégré dans un modulateur à temps continu du troisième ordre.

**Figure IV-2** Principe de fonctionnement du décodeur de phase XOR a) oscillateurs en phase b) VCO<sub>P</sub> en avance c) VCO<sub>N</sub> en avance

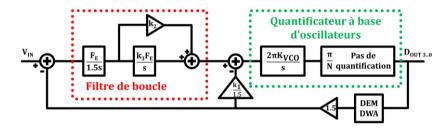

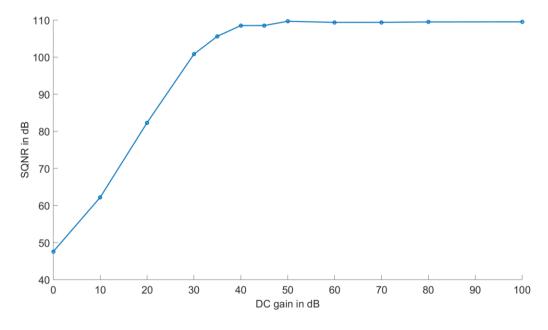

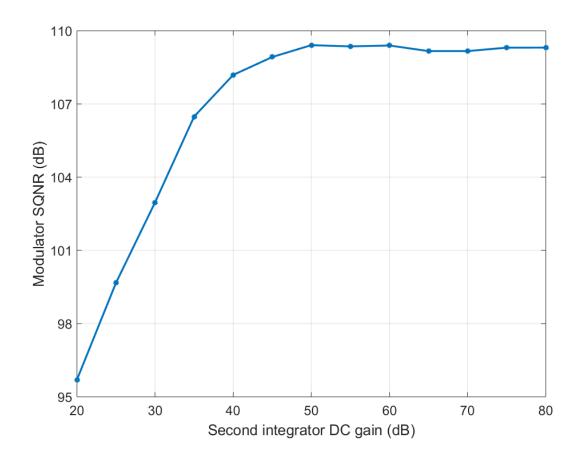

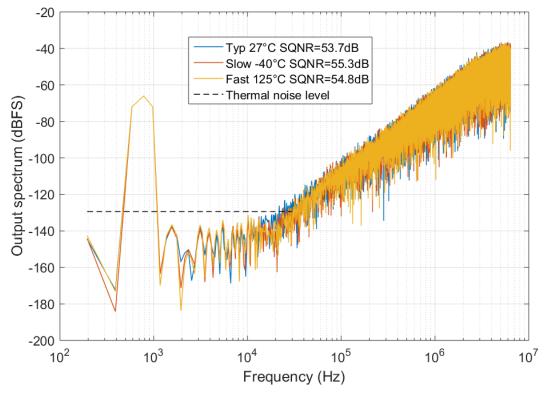

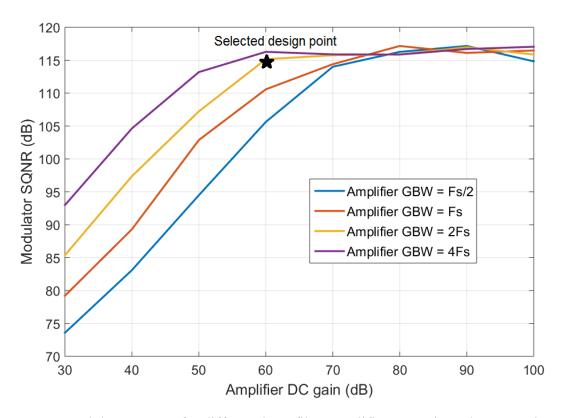

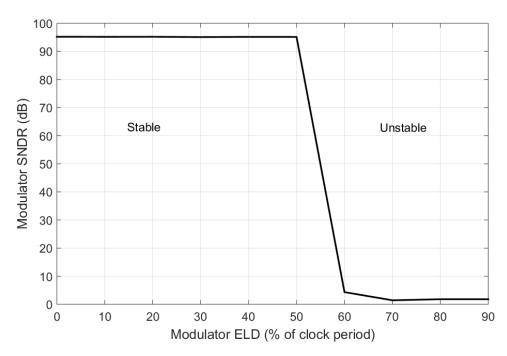

Les spécifications du modulateur à temps continu sont présentées en table IV-1. Comme le quantificateur-intégrateur à base d'oscillateurs est sensible aux variations de procédé de fabrication et à la température, une marge de 20dB est prise entre le bruit de quantification et le bruit thermique. Ainsi, même si la constante de temps de l'intégrateur varie, la marge est assez grande pour assurer les performances du modulateur, sans avoir besoin de calibrer chaque circuit et de compenser ce dernier en température, ce qui ajouterait du coût au produit. Le modulateur réalisé (présenté en figure IV-3) est du troisième ordre, avec un taux de suréchantillonnage de 128 et un quantificateur de 4 bits donnant un rapport signal sur bruit de quantification de 115dB sur une bande de 24kHz. Une NTF à faible gain hors bande est utilisée pour assurer la stabilité du modulateur même en cas de large variation des constantes de temps des intégrateurs. Le filtre de boucle de second ordre rejette la non-linéarité restante du quantificateur-intégrateur afin d'obtenir une haute résolution du modulateur.

Table IV-1 Spécifications du modulateur utilisées pour définir son architecture

| Spécification                              | Valeur | Unité   |

|--------------------------------------------|--------|---------|

| Tension de référence                       | 1.5    | V       |

| Largeur de bande du signal (FB)            | 24     | kHz     |

| Consommation (P)                           | 150    | $\mu W$ |

| Niveau de bruit ramené à l'entrée          | 13     | μV      |

| Plage dynamique (D)                        | 98     | dB      |

| Rapport signal sur bruit                   | 95     | dB      |

| Rapport signal sur bruit et distorsion     | >90    | dB      |

| Rapport signal sur bruit de quantification | 115    | dB      |

| $FOM_S = D + 10log_{10}(F_B/P)$            | 180    | dB      |

Figure IV-3 Modèle linéaire du modulateur à temps continu réalisé

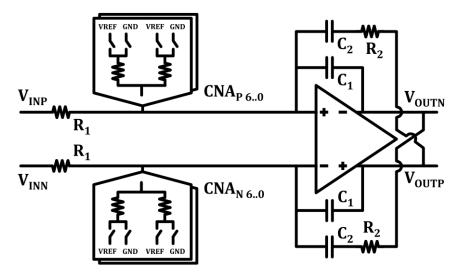

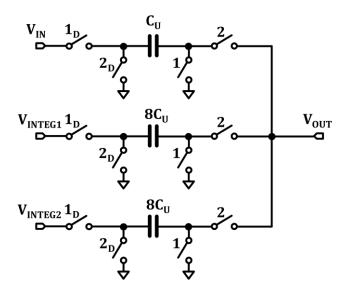

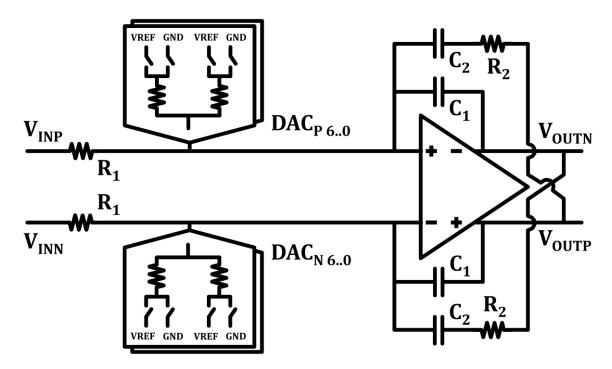

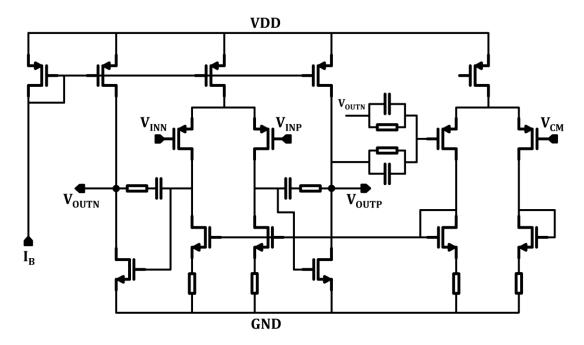

Le filtre de boucle permet, par sa topologie « feedforward », une réalisation utilisant un seul amplificateur comme montré en figure IV-4. Ce dernier utilise un schéma à deux étages classique compensé par une capacité Miller, de façon à obtenir un grand gain DC pour la linéarité du modulateur et la réjection des repliements et des non-linéarités du quantificateur. La fonction de transfert du montage de la figure IV-4 est la suivante :

$$H_F(s) = \frac{-(1 + R_2 C_2 s)}{R_1 (C_1 - C_2) s + R_1 R_2 C_1 C_2 s^2}$$

(IV-1)

En prenant  $C_1 = C_2 = C$ , on obtient :

$$H_F(s) = \frac{-\left(\frac{1}{R_1 R_2 C^2} + \frac{1}{R_1 C} s\right)}{s^2}$$

(IV-2)

Cette équation est maintenant de la même forme que celle du filtre de boucle présenté en figure IV-3 qui est :

$$H(s) = \frac{k_3 F_S^2}{1.5} + \frac{k_2 F_S}{1.5} s \tag{IV-3}$$

Comme la valeur de  $R_1$  est définie par la contrainte de bruit, on peut ensuite définir  $R_2$  et C par identification entre (IV-2) et (IV-3). Le quantificateur-intégrateur utilisé fournit en sortie un code thermométrique de la valeur ainsi qu'un bit de signe. Ces signaux sont particulièrement adaptés pour contrôler un CNA dont les éléments unitaires ont trois niveaux : « -1 », « 0 » et « 1 », réalisés à l'aide d'un duo résistances comme présenté en figure IV-4.

Figure IV-4 Filtre de boucle du second ordre réalisé avec un seul amplificateur

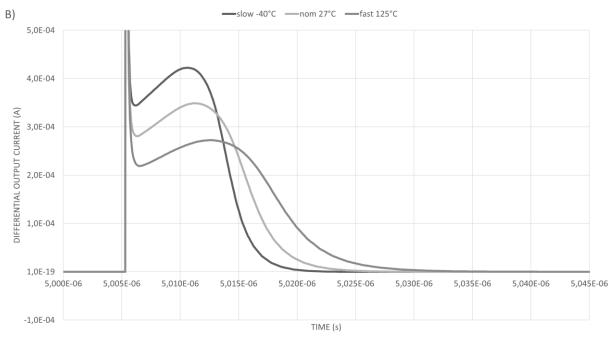

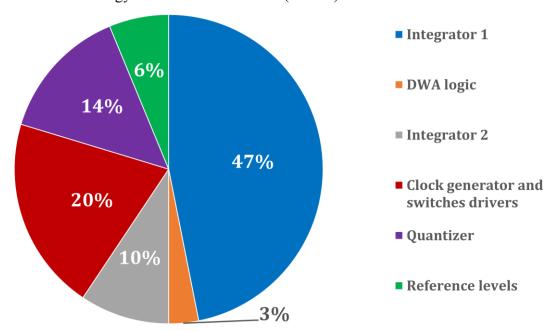

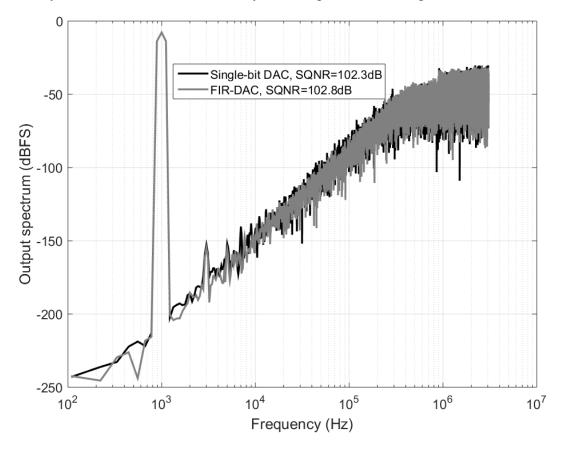

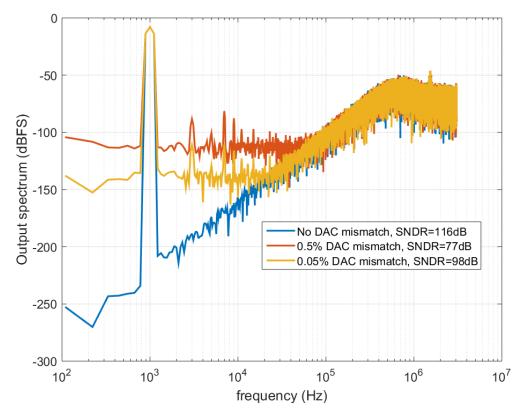

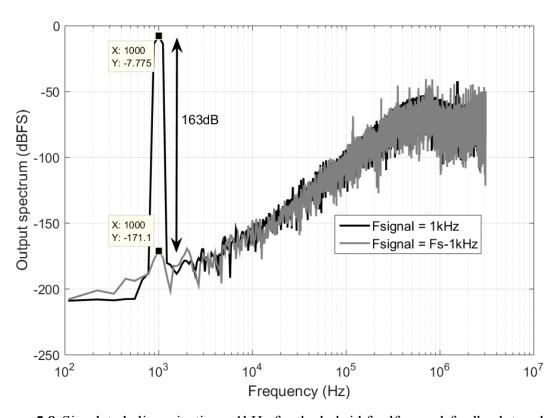

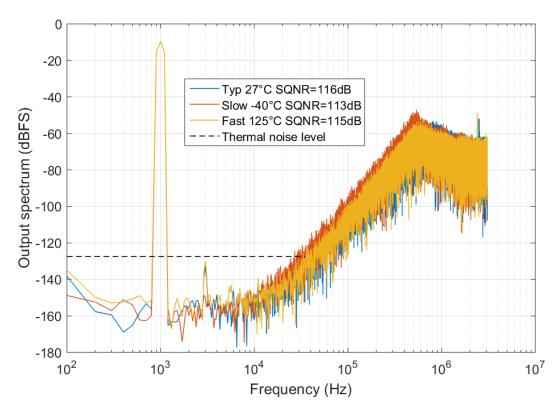

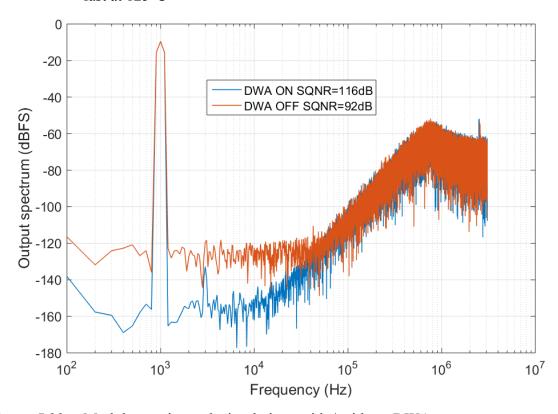

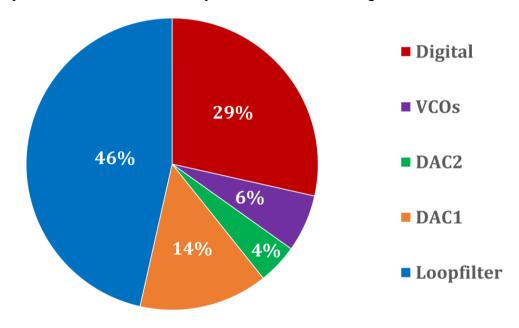

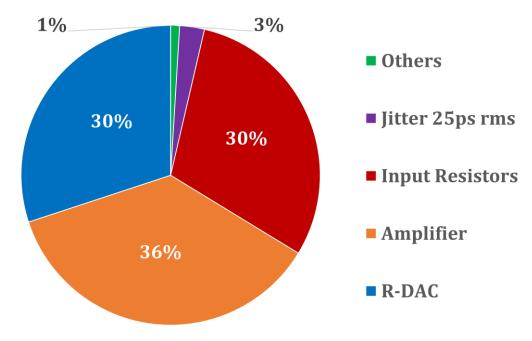

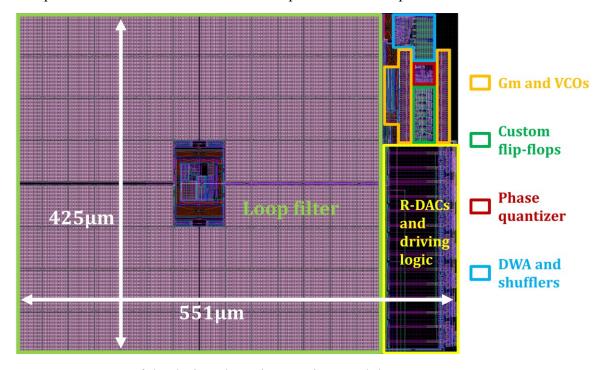

Le modulateur réalisé en technologie 140nm atteint un rapport signal sur bruit de quantification (SQNR) de 116dB en condition typique et de 113dB dans le pire cas sur une bande de 24kHz, comme montré en figure IV-5. Les choix architecturaux faits pour limiter la sensibilité aux variations de process et de température sont donc validés. Concernant la linéarité, l'autre point faible de l'utilisation d'un quantificateur à base d'oscillateurs, le troisième harmonique se situe sous le niveau de bruit thermique simulé, ce qui n'entraine donc pas de baisse de résolution du modulateur, validant là aussi les choix effectués. Ces performances sont atteintes pour une consommation de 142µW et sont résumées en table IV-2 où elles sont aussi comparées avec l'état de l'art.

Figure IV-5 Spectre de sortie du modulateur pour trois corners différents

**Table IV-2** Table des performances et comparaison avec l'état de l'art

|                      | This<br>work | [50]  | [51]  | [53]  | [39]  | [45]  | [63]  | [64]  |

|----------------------|--------------|-------|-------|-------|-------|-------|-------|-------|

| Techno (nm)          | 140          | 180   | 180   | 65    | 160   | 28    | 40    | 65    |

| Année                | 2018         | 2014  | 2016  | 2016  | 2016  | 2015  | 2011  | 2015  |

| Ordre                | 3            | 3     | 3     | 3     | 3     | 2     | 2     | 3     |

| F <sub>B</sub> (kHz) | 24           | 24    | 24    | 25    | 20    | 24    | 24    | 24    |

| FE (MHz)             | 6.144        | 6.144 | 6.144 | 6.4   | 3     | 24    | 6.5   | 3.072 |

| OSR                  | 128          | 128   | 128   | 128   | 75    | 500   | 135   | 64    |

| Référence (V)        | 1.5          | 1.8   | 1.8   | 1     | 1.6   | 3.3/1 | 1.2   | 1.1   |

| DR (dB)              | 98           | 103   | 103.6 | 103   | 103.1 | 100.6 | 102   | 88    |

| SNR (dB)             | 95           | 98.9  | 99.3  | 100.1 | -     | 100.6 | -     | -     |

| SNDR (dB)            | 95           | 98.2  | 98.5  | 95.2  | 91.3  | 98.5  | 90    | 85    |

| Conso (µW)           | 142          | 280   | 280   | 800   | 390   | 1130  | 500   | 121   |

| Aire (mm²)           | 0.232        | 1.25  | 1     | 0.256 | 0.21  | 0.022 | 0.05  | 0.6   |

| FOMs (dB)            | 180.3        | 182.3 | 183   | 177.9 | 180   | 173.9 | 178.8 | 171   |

### V - Conclusion

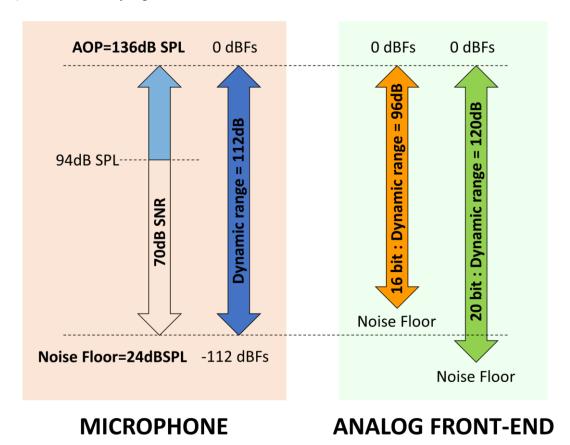

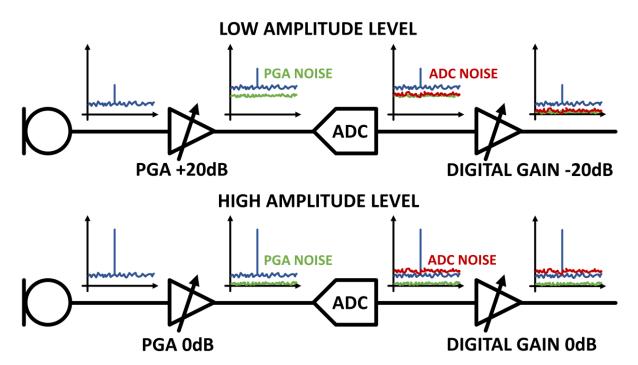

Pour répondre à la problématique d'un système d'acquisition audio à grande plage dynamique (d'environ 120dB), faible consommation et faible coût de production, une architecture composée d'un amplificateur à gain variable et d'un convertisseur analogique numérique à plage dynamique plus faible (de 100dB) est sélectionnée. La recherche s'est concentrée sur la conversion analogique numérique de faible consommation et faible espace occupé. Pour atteindre de hautes résolutions, deux convertisseurs sigma-delta (un à temps discret et l'autre à temps continu) ont été développés.

Le convertisseur sigma-delta à temps discret utilise des amplificateurs à base d'inverseurs pour obtenir une faible consommation. Un nouveau schéma d'amplificateur est présenté de manière à corriger les défauts de l'amplificateur inverseur et le rendre robuste aux variations de température et du procédé de fabrication, afin de contrôler sa consommation. Un taux de suréchantillonnage élevé est utilisé permettant de réduire la taille des capacités afin de réduire l'espace occupé. Dans le même esprit, le CNA de la boucle de retour est intégré aux capacités d'échantillonnage, bénéficiant à l'espace occupé et à la consommation de l'amplificateur en réduisant la capacité de charge. Ce modulateur atteint les performances de l'état de l'art, une figure de mérite FOMs de 180dB, témoin d'une très bonne efficacité énergétique.

Le convertisseur sigma-delta à temps continu utilise un quantificateur-intégrateur à base d'oscillateurs contrôlés en tension. Les oscillateurs transforment la différence de tension en une différence de fréquence, et la phase instantanée (intégrale de la fréquence) est échantillonnée et quantifiée pour former l'opération d'intégration. L'avantage de ce type de quantificateur est l'augmentation de l'ordre du modulateur ainsi que son implémentation utilisant des cellules numériques simples, pour un faible espace occupé et une faible consommation. Un filtre de boucle du second ordre permet de rejeter les non-linéarités des oscillateurs, et est réalisé à l'aide d'un montage à amplificateur unique pour diminuer la consommation. Le modulateur est donc composé de seulement deux sous blocs, ce qui lui permet d'atteindre les performances de l'état de l'art (FOM<sub>S</sub> de 180.3dB) tout en utilisant une implémentation pour moitié numérique, ce qui est bénéfique pour le transfert dans des technologies plus fines (réduction de l'espace occupé et de la consommation).

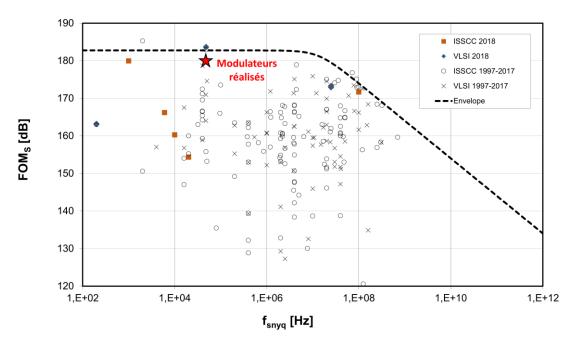

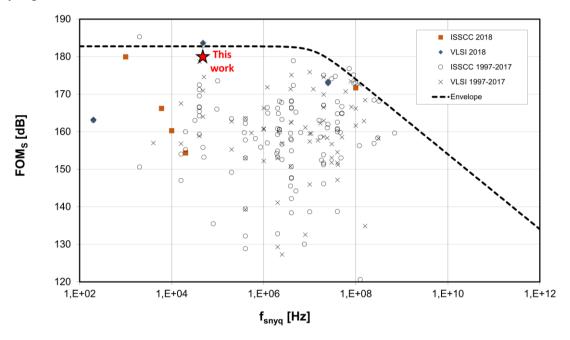

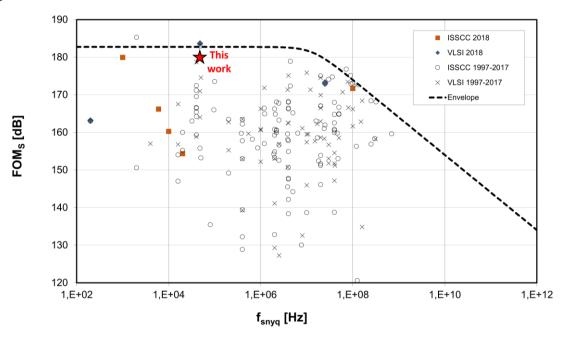

Les figures de mérite de 180dB atteintes par les modulateurs réalisés les placent parmi l'état de l'art dans le comparatif de convertisseurs analogiques/numériques de Boris Murmann [4] comme on peut le voir sur la figure V-1. Ce dernier a été modifié pour ne tenir compte que des modulateurs sigma-delta et la définition de la figure de mérite FOM<sub>S</sub> utilise la formule originelle employant la plage dynamique plutôt que le rapport signal sur bruit et distorsion.

Figure V-1 Placement des modulateurs sur le comparatif des CAN de Murmann

## **Contents**

| List of figures                                                                 | 27  |

|---------------------------------------------------------------------------------|-----|

| Chapter 1: Introduction                                                         |     |

| 1.1 Motivation                                                                  | 31  |

| 1.2 Contributions                                                               | 33  |

| 1.3 Organization                                                                | 33  |

| Chapter 2: Discrete-time modulators and integrators non-idealities modeling     | 35  |

| 2.1 Discrete-time modulators theory                                             | 36  |

| 2.1.1 First-order modulator                                                     | 37  |

| 2.1.2 Second-order modulator                                                    | 39  |

| 2.1.3 Higher-order modulators                                                   | 44  |

| 2.2 Modeling integrator non-idealities                                          | 50  |

| 2.3 Conclusion                                                                  |     |

| Chapter 3: A 103dB DR 2 <sup>nd</sup> order discrete-time sigma-delta modulator | 59  |

| 3.1 Modulator specifications                                                    | 60  |

| 3.1.1 First integrator sizing                                                   | 61  |

| 3.1.2 Second integrator sizing                                                  | 62  |

| 3.2 Integrators design                                                          | 64  |

| 3.3 Summation circuit, quantizer and clocks generator design                    | 77  |

| 3.4 Simulation results                                                          | 82  |

| 3.5 Conclusion                                                                  | 86  |

| Chapter 4: Continuous-time modulators: theory and specificities                 | 87  |

| 4.1 Continuous-time to discrete-time equivalence                                | 88  |

| 4.2 Integrators time constant                                                   | 92  |

| 4.3 Finite DC gain and anti-aliasing property                                   | 93  |

| 4.4 Excess loop delay: effect and compensation                                  | 95  |

| 4.5 Clock jitter in continuous-time modulators                                  | 99  |

| 4.6 FIR feedback DAC in CT modulators                                           | 104 |

| 4.7 Conclusion                                                                  |     |

| Chapter 5: A 16-bit audio continuous-time sigma-delta modulator using a VCO-b   |     |

| quantizer                                                                       |     |

| 5.1 Principle of a VCO-based quantizer                                          |     |

| 5.2 Modulator specification and definition                                      |     |

| 5.3 Modulator design                                                            |     |

| 5.3.1 Second-order loop filter and tri-level elements DAC design                |     |

| 5.3.2 VCO-based quantizer design and interface                                  |     |

| 5.4 Simulation results                                                          |     |

| 5.5 Conclusion                                                                  |     |

| Chapter 6: Conclusion                                                           | 132 |

| Publications                                                                    | 134 |

| References                                                                      | 135 |

| Annendiy                                                                        | 141 |

## List of figures

| Figure 1.1              | New generations microphones need extended dynamic range analog front-ends                              |

|-------------------------|--------------------------------------------------------------------------------------------------------|

| T1                      |                                                                                                        |

| Figure 1.2              | Programmable low-power analog front-end to cover microphone dynamic                                    |

| Figure 2.1              | range                                                                                                  |

| Figure 2.1              |                                                                                                        |

| Figure 2.2              | Effect of noise shaping on remaining in-band noise power                                               |

| Figure 2.3              | Generic sigma-delta modulator block diagram and linear model                                           |

| Figure 2.4              | Effect of doubling the OSR on noise shaping response 38                                                |

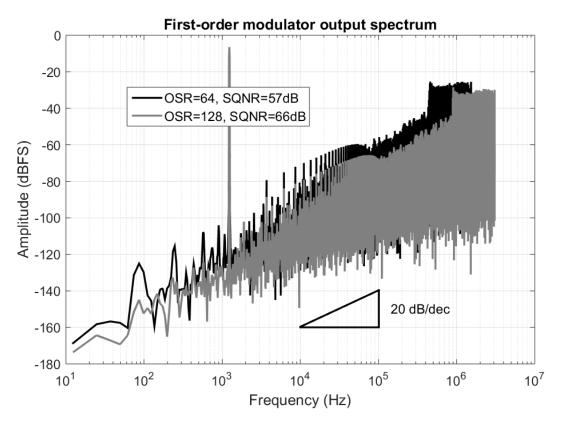

| Figure 2.5              | Output spectrums of audio (24kHz bandwidth) first-order modulators for                                 |

| Eigene 2.6              | different OSR values 39                                                                                |

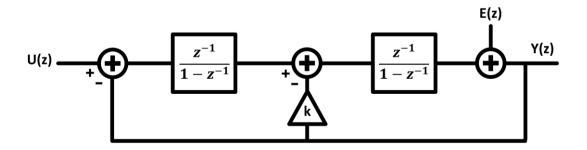

| Figure 2.6              | Second-order modulator linear model using a Cascade of Integrators with                                |

| E: 2.5                  | multiple FeedBack (CIFB) structure 40                                                                  |

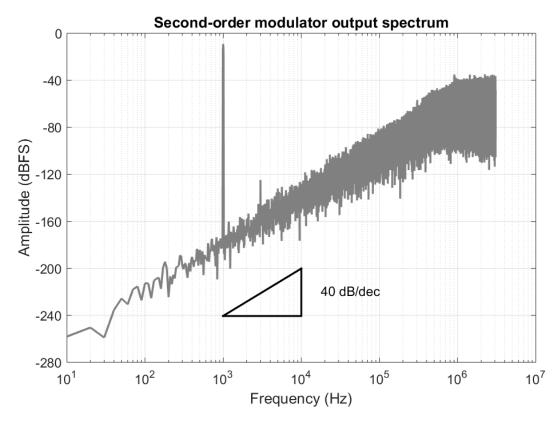

| Figure 2.7              | Second-order modulator output spectrum: SQNR=90dB over 24kHz for an                                    |

| E: 2.0                  | OSR of 128 40                                                                                          |

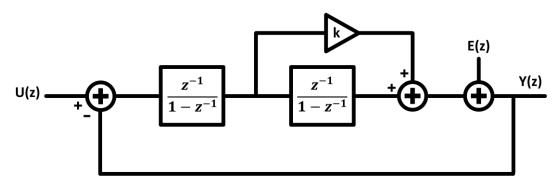

| Figure 2.8              | Second-order modulator linear model using a Cascade of Integrators                                     |

| E: 2.0                  | FeedForward (CIFF) structure 41                                                                        |

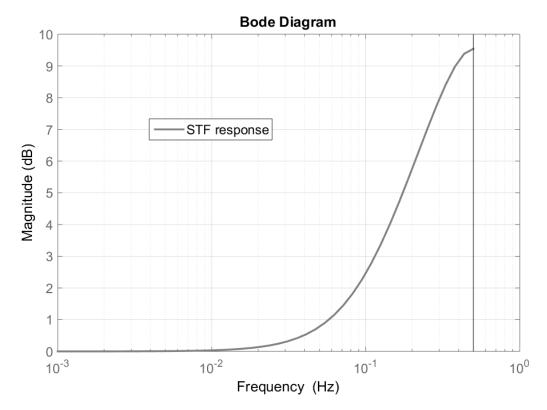

| Figure 2.9              | STF frequency response of a second-order modulator using a CIFF structure 42                           |

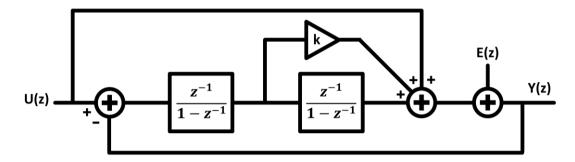

| Figure 2.10             | Second-order modulator using a CIFF structure with input feedforward 42                                |

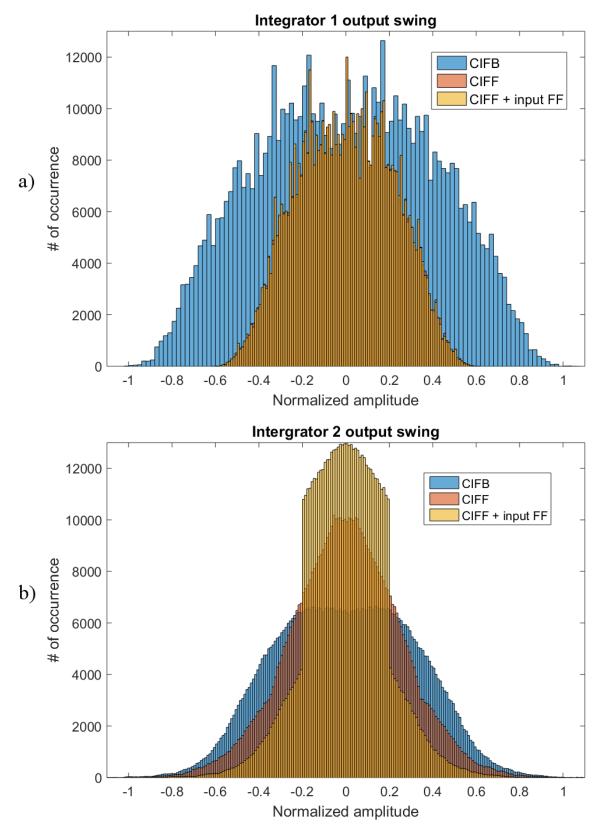

| Figure 2.11             | Comparison of integrators output swing for the three different structures a) first                     |

| F: 0.10                 | integrator, b) second integrator 43                                                                    |

| Figure 2.12             | Comparison of NTF frequency responses for different orders                                             |

| Figure 2.13             | Single-bit quantizer with undefined gain and 3-bit quantizer with unity gain . 45                      |

| Figure 2.14             | Third-order modulator NTFs frequency responses: ideal differentiation and                              |

| E: 2 15                 | limited gain                                                                                           |

| Figure 2.15             | Third-order modulator linear model with undefined quantizer gain                                       |

| Figure 2.16             | Pole-zero plot of third-order NTFs: pure differentiation and limited gain NTFs                         |

| Eigung 2 17             | in function of quantizer gain k                                                                        |

| Figure 2.17             | Frequency responses of NTF(z)-1 for both third-order NTFs: pure                                        |

| Eigung 2 10             | differentiation one and limited gain one                                                               |

| Figure 2.18             | <del>-</del>                                                                                           |

| Eigung 2 10             | in function of the oversampling ratio                                                                  |

| Figure 2.19             | Switched-capacitor integrator during its integration phase                                             |

| Figure 2.20 Figure 2.21 | Capacitive charge redistribution effect occurring at the starting time of the                          |

| rigure 2.21             | integration phase                                                                                      |

| Figure 2 22             | Comparison of integrator output voltage between transistor-level circuit and                           |

| Figure 2.22             | matched parameters model                                                                               |

| Figure 2 22             | Linear SIMULINK model of the second-order modulator with 1.5-bit quantizer                             |

| Figure 2.23             | •                                                                                                      |

| Figure 2.24             | and an OSR of 256                                                                                      |

| Figure 2.24             |                                                                                                        |

| Figure 2.25             | and SR) and capacitances values (C <sub>S</sub> , C <sub>I</sub> , C <sub>P</sub> and C <sub>O</sub> ) |

| Figure 2.25             |                                                                                                        |

| Figure 2.26             | Simulated modulator SQNR in function of its integrators GBW and SR 56                                  |

| Figure 2.27 | Minimum required GBW in function of SR value to not degrade modulator performance and effect of the capacitive charge redistribution effect on the |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|             | specification requirements                                                                                                                         |    |

| Figure 2.28 | Transistor-level modulator output spectrums for different DC gain integrato                                                                        |    |

|             |                                                                                                                                                    | 57 |

| Figure 2.29 | Transistor-level modulator output spectrums for different integrators                                                                              |    |

|             | (GBW,SR) couples                                                                                                                                   |    |

| Figure 3.1  | Second order 1.5-bit modulator linear model and coefficient scaling                                                                                |    |

| Figure 3.2  | Modulator SQNR in function of second integrator DC gain                                                                                            |    |

| Figure 3.3  | Minimum required GBW in function of SR value for second integrator to no                                                                           |    |

|             | degrade modulator performance                                                                                                                      |    |

| Figure 3.4  | Self-biased inverter-based amplifier                                                                                                               |    |

| Figure 3.5  | First biasing attempt using linear transistors to mirror current                                                                                   |    |

| Figure 3.6  | Proposed biasing solution using linear transistors to mirror current                                                                               | 67 |

| Figure 3.7  | Bulk voltage generation circuit used to control the threshold voltage of inverters                                                                 | 68 |

| Figure 3.8  | Switched-capacitor common-mode feedback circuit                                                                                                    |    |

| Figure 3.10 | Comparison of output currents of figure 3.6 and figure 3.9 circuits                                                                                |    |

| Figure 3.11 | NMOS bulk voltage versus process and temperature generated by figure 3.7                                                                           |    |

| 1.8.1.0.1.1 | circuit                                                                                                                                            |    |

| Figure 3.12 | PVT simulation results during the integration phase of A) output voltage B)                                                                        |    |

|             | output current                                                                                                                                     | 73 |

| Figure 3.13 | Nagaraj integrator using inverters as amplifier                                                                                                    | 74 |

| Figure 3.14 | Chopper modulation principle                                                                                                                       | 74 |

| Figure 3.15 | Switched-capacitor integrator with chopper modulation and parasitic                                                                                |    |

|             | capacitance C <sub>DG</sub>                                                                                                                        | 75 |

| Figure 3.16 | Main feedback DAC reusing the sampling capacitance concept                                                                                         | 75 |

| Figure 3.17 | Split sampling capacitor to make a tri-level DAC during the integration pha                                                                        | se |

|             | and switches control signals generation (single-ended version shown)                                                                               | 77 |

| Figure 3.18 | Passive switched-capacitor summation circuit.                                                                                                      | 78 |

| Figure 3.19 | 1.5-bit quantizer A) normalized B) scaled for 1.5V reference                                                                                       | 78 |

| Figure 3.20 | 1.5-bit quantizer reference level generation                                                                                                       | 79 |

| Figure 3.21 | 1.5-bit quantizer and summation circuit block diagram                                                                                              | 80 |

| Figure 3.22 | Schematic of the dual difference pre-amplifiers used in 1.5-bit quantizer                                                                          | 80 |

| Figure 3.24 | Schematic of the clock phases generator and its associated timing diagram                                                                          | 81 |

| Figure 3.25 | Modulator output spectrums over PVT conditions: typical, slow at -40°C an                                                                          | ıd |

|             | fast at 125°C                                                                                                                                      |    |

| Figure 3.26 | Modulator output spectrums under mismatch conditions with and without the                                                                          |    |

|             | implemented DWA algorithm                                                                                                                          |    |

| Figure 3.27 | Modulator output spectrums over PVT conditions for a -60dBFS input signa                                                                           |    |

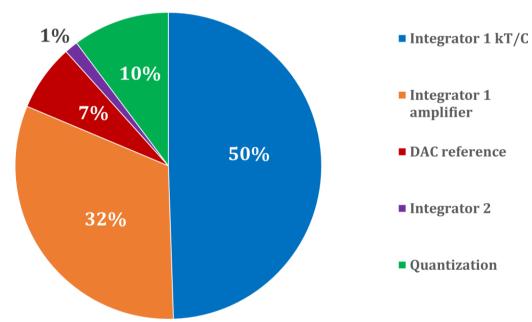

| Figure 3.28 | Modulator power consumption split                                                                                                                  |    |

| Figure 3.29 | Modulator input-referred noise power split                                                                                                         |    |

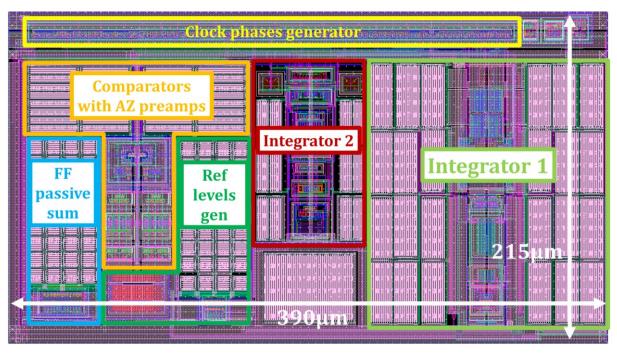

| Figure 3.30 | Layout of the designed modulator                                                                                                                   |    |

| Figure 3.31 | Placement of the discrete-time modulator on Murmann's ADC survey                                                                                   |    |

| Figure 4.1  | Equivalent discrete-time and continuous-time implementations of modulato                                                                           |    |

| 8           | with NTFp                                                                                                                                          | 88 |

| Figure 4.2                | Impulse response of a NRZ DAC with 1Hz sampling frequency                                                                           | 39             |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Figure 4.3                | Decomposition of DAC + loop filter in different integrating order paths 8                                                           | 39             |

| Figure 4.4                | Output spectrums of ideal discrete-time modulator and synthesized continuou                                                         | s-             |

|                           | time one                                                                                                                            | <b>)</b> 1     |

| Figure 4.5                | Effect of the clock frequency variation on both continuous-time and discrete-                                                       |                |

| S                         | time NTFs.                                                                                                                          |                |

| Figure 4.6                | Effect of integrators time constant variation on a) NTF b) maximum stable                                                           |                |

| J                         | amplitude (MSA) and reachable SQNR                                                                                                  | <del>)</del> 3 |

| Figure 4.7                | Effect of the integrators finite DC gain on a) NTF b) SQNR and harmonic                                                             |                |

| 8                         | performance                                                                                                                         | <b>)</b> 4     |

| Figure 4.8                | Alias rejection determined by a) loop filter frequency response b) modulator                                                        |                |

| 8                         | simulation                                                                                                                          | 94             |

| Figure 4.9                | Effect of ELD on a first-order loop filter impulse response and the                                                                 |                |

| 8                         | compensation method.                                                                                                                | 95             |

| Figure 4.10               | Effect of ELD on a) 3 <sup>rd</sup> order NTF b) maximum reachable SQNR                                                             |                |

| Figure 4.11               | Equivalent diagram of DAC + loop filter in presence of ELD and its                                                                  | _              |

| 8                         | compensation path                                                                                                                   | 96             |

| Figure 4.12               | Alternative ELD compensation method to avoid an extra summation node at                                                             |                |

| 1.841.0 1/12              | loop filter output                                                                                                                  | 98             |

| Figure 4.13               | Jittered NRZ DAC waveform and determination of the one-period averaged                                                              | , 0            |

| inguit iiit               | DAC error                                                                                                                           | 00             |

| Figure 4.14               | Influence of NRZ DAC LSB size on introduced jitter error amplitude                                                                  |                |

| Figure 4.15               | Modulator simulation results with jittered 2-level and 15-level NRZ DACs                                                            |                |