## Study of synergistic effects in integrated circuits subjected to ionizing and neutral radiation in space

Thomas Borel

#### ▶ To cite this version:

Thomas Borel. Study of synergistic effects in integrated circuits subjected to ionizing and neutral radiation in space. Electronics. Université Montpellier, 2018. English. NNT: 2018MONTS040. tel-02096790

## HAL Id: tel-02096790 https://theses.hal.science/tel-02096790

Submitted on 11 Apr 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE MONTPELLIER

## En Électronique - Composants et Systèmes

École doctorale Information, Structures et Systèmes (I2S)

Unité de recherche IES - UMR5214

Étude des effets de synergie dans les circuits intégrés soumis à l'environnement spatial de rayonnements ionisants et neutres

### Présentée par Thomas BOREL Le 27 Novembre 2018

Sous la direction de Pr. Laurent DUSSEAU et Dr. Alain MICHEZ

### Devant le jury composé de

| Laurent DUSSEAU,   | Professeur,           | Université de Montpellier        | Directeur de thèse    |

|--------------------|-----------------------|----------------------------------|-----------------------|

| Alain MICHEZ,      | Maître de Conférence, | Université de Montpellier        | Co-Encadrant de thèse |

| Jean-Luc AUTRAN,   | Professeur,           | Aix-Marseille Université         | Rapporteur            |

| Laurent BECHOU,    | Professeur,           | IMS Bordeaux                     | Rapporteur            |

| Jérôme BOCH,       | Professeur,           | Université de Montpellier        | Examinateur           |

| Salvatore DANZECA, | Ingénieur,            | CERN                             | Examinateur           |

| Bruno AZAÏS,       | Expert DGA,           | Direction Générale de l'Armement | Examinateur           |

| Éric LEDUC,        | Ingénieur,            | Microchip Technology Nantes      | Membre Invité         |

## **Abstract**

Tout composant envoyé dans l'espace est soumis à de nombreuses contraintes (radiations, température) qui peuvent conduire à une défaillance de l'ensemble du système. Dans un avenir proche, ces contraintes deviendront de plus en plus critiques à mesure que les agences spatiales développeront des missions visant d'autres planètes, telles que Jupiter, pour lesquelles la contrainte radiative est extrême. Dans ce travail, deux types d'effets dûs aux radiations sont étudiés : les effets cumulatifs et les effets transitoires. L'un correspond à la dégradation induite par les radiations au cours du temps, tandis que l'autre correspond à un événement ponctuel qui peut se produire à tout moment lorsque le système est dans l'espace. Pour garantir le bon fonctionnement en vol, des normes de qualification des composants électroniques ont été élaborées par différentes agences spatiales. Toutes ces normes précisent que les effets cumulatifs et transitoires doivent être vérifiés à l'aide de composants intacts pour chaque essai. Par conséquent, les effets cumulatifs sont traités séparément des effets transitoires, alors qu'il y a une forte probabilité qu'ils apparaissent simultanément pendant une mission spatiale. L'étude des effets de synergie est alors le thème principal de cette thèse.

Sur un amplificateur opérationnel bipolaire, la réponse de sortie du composant due à un événement transitoire est directement liée aux paramètres internes du composant, qui varient sous l'effet des radiations. A l'aide d'une comparaison entre trois amplificateurs opérationnels différents partageant la même référence, l'impact du design sur la dégradation due aux radiation est étudié.

Récemment, des défaillances imprévues ont été reportées pour lesquelles le mode de défaillance semblait indiquer qu'une structure de protection contre les décharges électrostatiques (ESD) était en cause. Par conséquent, pour comprendre si ces protections peuvent causer des défaillances inattendues, la dégradation des « Gate Grounded n-MOSFET » (GGnMOS) est également étudiée.

Any system sent to space is submitted to many constraints (radiations, temperature) which may lead to a failure of the whole system. In a close future, these constraints will become more and more critical as the space agencies are developing missions aiming at others planets such as Jupiter for which the radiative constraint is extremely harsh. In this work, two types of radiation effects are studied: the cumulative effects and the transient effects. One corresponds to the radiation-induced degradation over time, while the other corresponds to a punctual event that can happen at any time when the system is in space. To ensure a proper functioning of a system sent to space, qualifications standards for electronic components have been developed by different space agencies. All of these standards specify that the components must be tested for cumulative and transient effects, using pristine components for each test. Therefore, cumulative effects are treated separately from transient effects, while there is a significant probability that they will appear simultaneously during a space mission. The study of the synergistic effects is then the main frame of this thesis.

On a bipolar operational amplifier, the output response of the component due to a transient event is directly related to the internal parameters of the component, which vary over time once in space. Through a comparison between three different operational amplifier sharing the same reference, the impact of the design over the degradation is explained.

Lately, some unexpected failures were reported for which the failure mode seemed to indicate that an Electrostatic Discharge (ESD) protection structure was involved. Therefore, to understand if those protections may cause some unexpected failures, the degradation of gate grounded n-MOSFET (GGnMOS) will be investigated next.

# Acknowledgements

During those years, had the chance to perform my Ph.D. in two different laboratory. For one part in the Institute of Electronics and Systems (IES) of Montpellier, in France, within the RADIAC team, and for another part at the European Organization for Nuclear Research (CERN), in Switzerland, within the Engineering department. Throughout those different localizations, I had the chance to encounter countless number of people that led helped me, directly or indirectly, to the success of this Ph.D. I would like here to thank them all, those that I will mention below and those that I might have forgotten.

Firstly, I would start to express my sincere gratitude to my Ph.D. Director Laurent DUSSEAU and my Ph.D. co-supervisor Alain MICHEZ for their continuous support, for their patience, motivation, and immense knowledge, and without whom, it would have been more difficult.

I would like to thanks also the two reviewers of my manuscript Jean-Luc AUTRAN and Laurent BECHOU that have accepted to take some time off their busy schedule to correct my work. In addition, I also would like to thanks the other members of the jury to attend my Ph.D. defense.

I would like to thanks the French Directorate General of Armaments (Direction Générale de l'Armement, DGA) for supporting my work and Bruno AZAIS for his supervision.

I would like to thanks the European Organization for Nuclear Research (CERN) and particularly Marcus BRUGGER that allowed me to perform a part of my Ph.D. in this wonderful organization that is CERN, and Salvatore DANZECA for his supervision and his help all along my time over there.

I would like to thanks Microchip Technology Nantes and especially Séverine FURIC, Eric LEDUC, and David TRUYEN for their technical support and their kindness. Their implication in my work have greatly contributed to the success of this Ph.D.

I would like to thanks all my colleagues from the RADIAC team for the good mood and help, and all the others, present and past, Ph.D. students (Pierre K., Pierre P., Alexandre, Arthur, Samir, Kimmo, Salvo, Ygor, Israel, Flavien, Wang, Matthias C., Mathias R., Axel, Rachid, Clovis) with whom I spend very good moments at RADIAC.

I would like to thanks all my CERN colleagues (Georgios, Rudy, Alessandra, Matteo, Chiara, Riccardo, Craig, Gilles, Paul, Raffaello, Salvatore, Giulia, Lucian, Jorge, Adrian, Gabriele), which I have met along this journey, for their friendship and kindness and for the good work environment.

In addition, I would like to thanks all the amazing peoples that I have met during my time at CERN and Geneva, that have enormously supported me without even knowing it (Alexandre, Elena, Safiah,

Roberto, Dimitri, Ines, Arnaud, Vipin, Miriam, Ahmed, Pedro, and others that I might not remember for now).

I would like to thanks all my others very good friends from Montpellier (Viyas, Andrey, Lorena, Alex, Titouan, Craig, Mohan, Wilfried, Aomer, Nico, ... and some of the people I mentioned earlier, and all those that I have forgotten).

And last but not least, I want to thanks my family that have been around during all those years and supported me in my crazy idea to start this Ph.D. It would not have been possible without them.

# **Table of Contents**

| Abstract                                                                           | 3  |

|------------------------------------------------------------------------------------|----|

| Acknowledgements                                                                   | 5  |

| Table of Contents                                                                  | 9  |

| General Introduction                                                               | 15 |

| Chapter I : Introduction                                                           | 19 |

| I.1. Introduction                                                                  | 21 |

| I.2. The different radiative environments                                          | 22 |

| I.2.1. The natural radiative space environment                                     | 22 |

| I.2.1.1 The radiation belts                                                        | 22 |

| I.2.1.2 The cosmic rays                                                            | 23 |

| I.2.1.3 The solar wind                                                             | 24 |

| I.2.1.4 The solar flares                                                           | 25 |

| I.2.2. The man-made radiative space environment: exoatmospheric nuclear explosions | 26 |

| I.2.3. The man-made radiative terrestrial environment: The particle accelerators   | 26 |

| I.3. Cumulative radiation effects on electronic devices                            | 29 |

| I.3.1. The total ionizing dose                                                     | 29 |

| I.3.1.1 The concept of Total Ionizing Dose                                         | 29 |

| I.3.1.2 Photon-Matter interaction                                                  | 29 |

| I.3.1.3 Degradation mechanism of the dose on the materials                         | 30 |

| I.3.2. The Displacement damage dose                                                | 31 |

| I.3.2.1 Displacement Damage mechanism                                              | 31 |

| I.3.2.2 Displacement damage on electronic devices                                  | 33 |

| I.4. The bipolar transistor                                                        | 35 |

| I.4.1. Working principle                                                           | 35 |

| I.4.2. The sensitivity of bipolar transistor to TID and DD                         | 36 |

| I.4.2.1 Effect of the TID on bipolar structures                                    | 36 |

| I.4.2.2 Effect of the DD on bipolar structures                                     | 38 |

| I.4.3. Sensitivity to TID or DD depending on the transistor structure              | 38 |

| I.5. The MOSFET transistor                                                       | 40          |

|----------------------------------------------------------------------------------|-------------|

| I.5.1. Working principle                                                         | 40          |

| I.5.2. The sensitivity of MOSFET transistor to TID                               | 41          |

| I.6. State of art of the synergistic effects studies                             | 44          |

| I.7. Conclusion                                                                  | 46          |

| I.8. References                                                                  | 47          |

| Chapter II : Comparative study of bipolar operational amplifiers subjected to TI | D and DD 51 |

| II.1. Introduction                                                               | 53          |

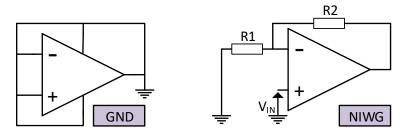

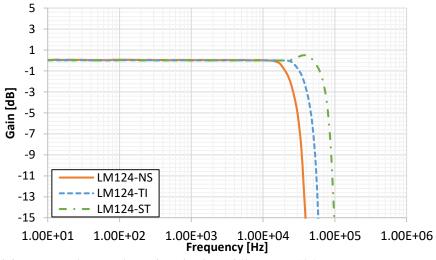

| II.2. Presentation of the previous results                                       | 54          |

| II.2.1. Presentation of the previous research                                    | 54          |

| II.2.2. Presentation of the experiments performed                                | 55          |

| II.2.2.1 Devices under test                                                      |             |

| II.2.2.2 Experimental details                                                    |             |

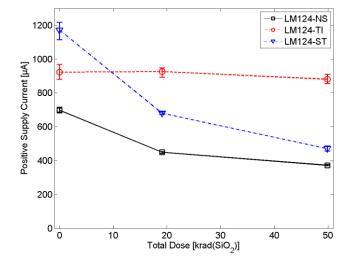

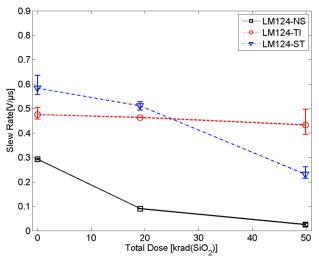

| II.2.2.3 Experimental results                                                    | 56          |

| II.2.3. Problematic                                                              | 60          |

| II.2.3.1 Unexpected degradation of the slew rate                                 | 60          |

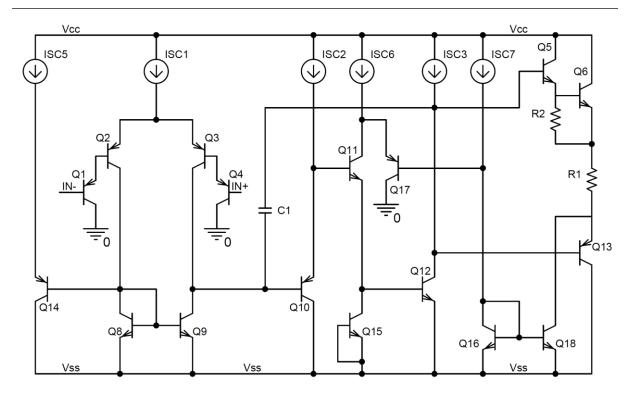

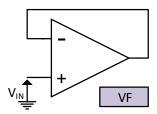

| II.3. Circuit level analysis                                                     | 61          |

| II.3.1. Description of the internal electrical schematic of the LM124            | 61          |

| II.3.1.1 The differential stage                                                  | 61          |

| II.3.1.2 The amplification stage                                                 | 62          |

| II.3.1.3 The output stage                                                        | 62          |

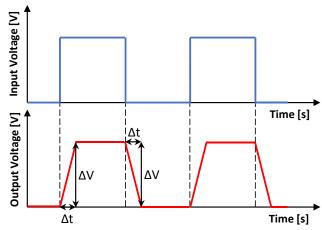

| II.3.2. Description of the slew rate mechanism                                   | 63          |

| II.3.2.1 The positive slew rate:                                                 | 63          |

| II.3.2.2 The negative slew rate:                                                 |             |

| II.3.3. Degradation scenarios                                                    | 65          |

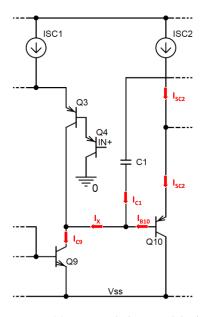

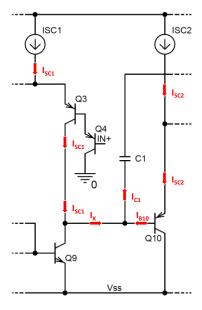

| II.3.3.1 The increase of the base current of Q10                                 | 65          |

| II.3.3.2 Disequilibrium of the current source values                             | 67          |

| II.3.3.3 Disequilibrium of the regulation pair (Q10-Q14)                         |             |

| II.3.3.4 Capacitor undersized                                                    | 71          |

| II.3.3.5 Conclusion of the different degradation scenarios                       |             |

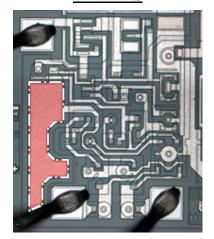

| II.4. Die analysis and measurements                                              | 73          |

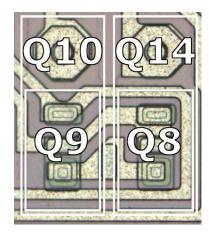

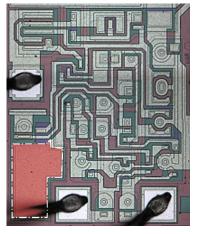

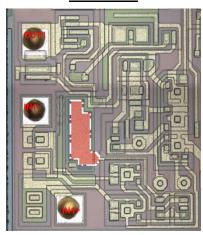

| II.4.1. Microphotography of the LM124                                            | 73          |

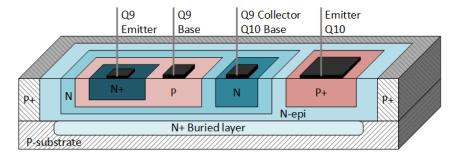

| II.4.2. Different bipolar transistor structures                            | 73  |

|----------------------------------------------------------------------------|-----|

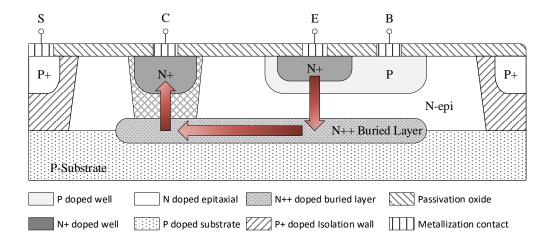

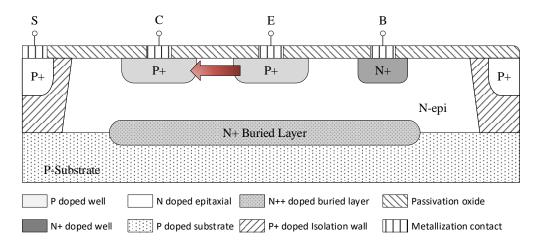

| II.4.2.1 Vertical-NPN and Vertical-PNP structures                          | 73  |

| II.4.2.2 Lateral-PNP structure                                             | 74  |

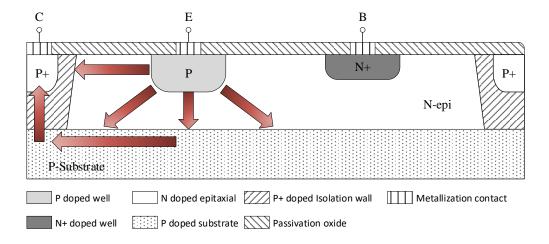

| II.4.2.3 Substrate-PNP structure                                           | 75  |

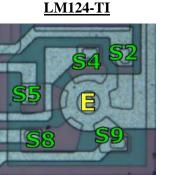

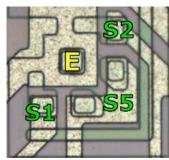

| II.4.3. LM124 die layout analysis                                          | 75  |

| II.4.3.1 Structure of the transistor Q10                                   | 75  |

| II.4.3.2 Capacitor                                                         | 76  |

| II.4.3.3 Stabilization transistors                                         | 79  |

| II.4.3.4 Current sources                                                   |     |

| II.5. Discussion                                                           | 81  |

| II.5.1. Conclusion on the degradation                                      | 81  |

| II.5.2. Impact on the Radiation hardness Assurance                         | 82  |

| II.6. Conclusions                                                          | 83  |

| II.7. References                                                           | 85  |

| Chapter III: Study of the sensitivity of ESD protection structure GGnMOS   | 89  |

| III.1. Introduction                                                        | 91  |

| III.2. Causes and consequences of an Electrostatic Discharge               | 93  |

| III.2.1. Electrostatic charge generation                                   | 93  |

| III.2.2. Cause of an Electrostatic Discharge                               | 93  |

| III.2.3. Consequences of an Electrostatic Discharge on integrated circuits | 94  |

| III.2.4. Electrostatic discharge models                                    | 95  |

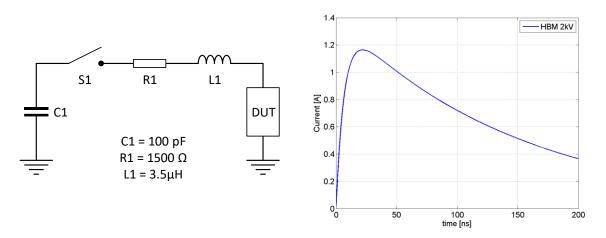

| III.2.4.1 The HBM model                                                    | 95  |

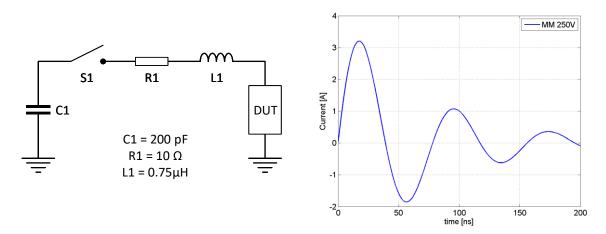

| III.2.4.2 The MM model                                                     | 95  |

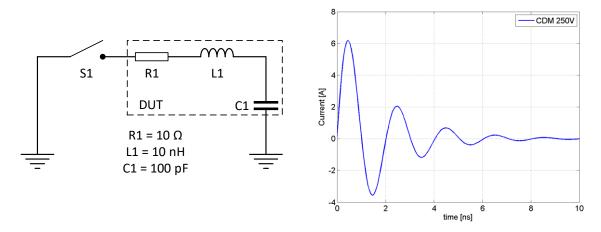

| III.2.4.3 The CDM model                                                    | 96  |

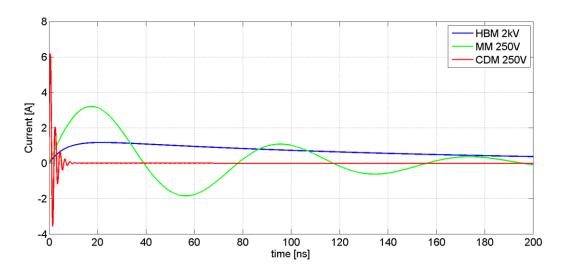

| III.2.4.4 Comparison between the three models                              | 97  |

| III.3. Protection against an electrostatic discharge event                 | 99  |

| III.3.1. Generalities                                                      | 99  |

| III.3.2. Different types of ESD protection                                 | 99  |

| III.3.2.1 Passives ESD protections                                         | 99  |

| III.3.2.2 Actives ESD protections                                          | 100 |

| III 3.3 Ideal FSD protection design                                        | 102 |

| III.3.3.1 Working principle of an ideal ESD protection                      | 102 |

|-----------------------------------------------------------------------------|-----|

| III.3.3.2 Ideal specifications for an ESD protection                        | 102 |

| III.3.3.3 Id-Vd characteristic of an ideal ESD protection with snapback     | 103 |

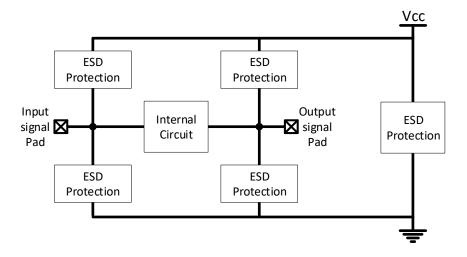

| III.3.4. Implantation strategy of an internal active ESD protection         | 104 |

| III.3.5. types of internal actives ESD protection                           | 105 |

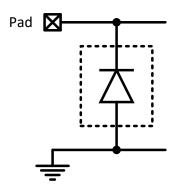

| III.3.5.1 The Diode                                                         | 105 |

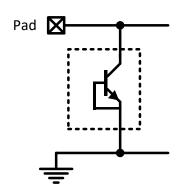

| III.3.5.2 The bipolar NPN transistor                                        | 106 |

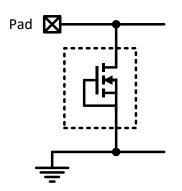

| III.3.5.3 The NMOS transistor (or GGnMOS)                                   | 106 |

| III.3.5.4 The Thyristor (or SCR)                                            | 107 |

| III.3.6. Characterization method of ESD protections                         | 107 |

| III.3.6.1 Standard characterization method: Transmitted Line Pulse          | 107 |

| III.3.6.2 Alternative characterization method: DC measurement               | 108 |

| III.3.7. Selection of the ESD protection candidate                          | 109 |

| III.4. Evaluation of the ESD protection of a MRAM memory                    | 111 |

| III.4.1. Context                                                            | 111 |

| III.4.2. DUT Characterization                                               | 111 |

| III.4.2.1 Devices Under Test                                                | 111 |

| III.4.2.2 Power supply input characterization                               | 112 |

| III.4.3. Radiation testing                                                  | 114 |

| III.4.3.1 Experimental details                                              | 114 |

| III.4.3.2 Experimental results                                              | 115 |

| III.5. Conclusion                                                           | 119 |

| III.6. References                                                           | 120 |

| Chapter IV : Study of MOSFET Based Structure with Total Ionizing Dose       | 123 |

| IV.1. Introduction                                                          | 125 |

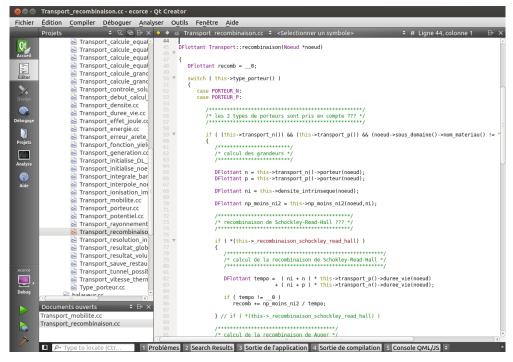

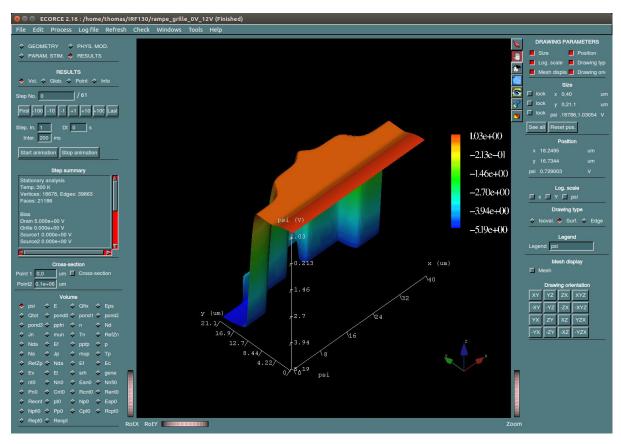

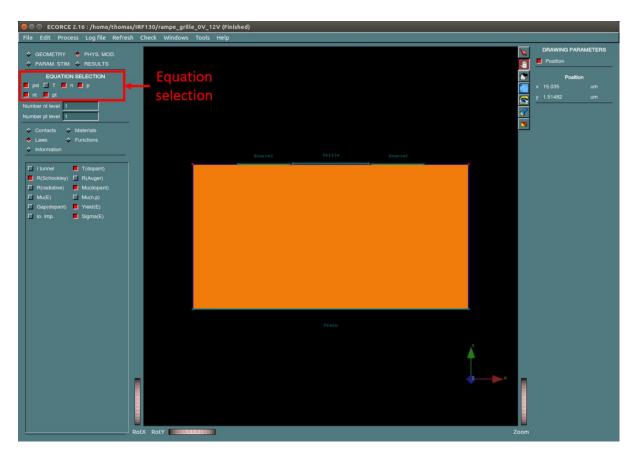

| IV.2. Simulations with ECORCE software                                      | 127 |

| IV.2.1. Presentation                                                        | 127 |

| IV.2.2. Physical model                                                      | 129 |

| IV.2.2.1 Drift-Diffusion equations (Poisson, holes and electrons transport) | 129 |

| IV.2.2.2 Trapping-Detrapping equations for the oxides                       | 131 |

| IV.2.2.3 Heating equations (temperature calculation)                        | 134 |

| IV.2.2.4 Selections of the physical laws                                    | 134 |

| IV.2.3. Numerical discretization methods                                    | 135 |

|-----------------------------------------------------------------------------|-----|

| IV.2.4. Dynamic meshing                                                     | 136 |

| IV.2.4.1 Theory of the dynamic meshing                                      | 136 |

| IV.2.4.2 Example of the dynamic meshing                                     | 139 |

| IV.3. Study on the degradation of a LDMOS structure                         | 143 |

| IV.3.1. Introduction                                                        | 143 |

| IV.3.2. Experimental details and results                                    | 144 |

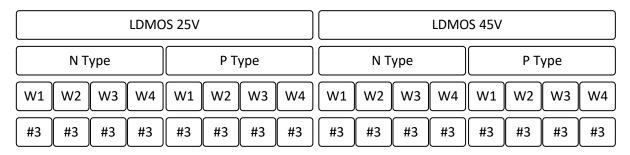

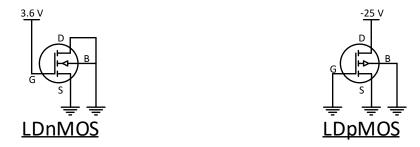

| IV.3.2.1 Devices under test                                                 | 144 |

| IV.3.2.2 Total Ionizing Dose Irradiation                                    | 144 |

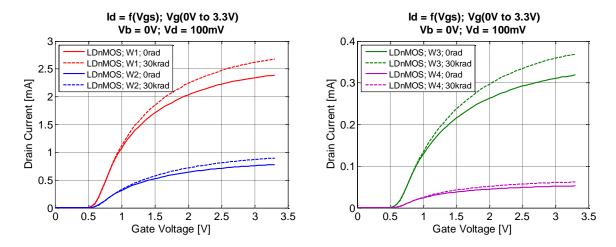

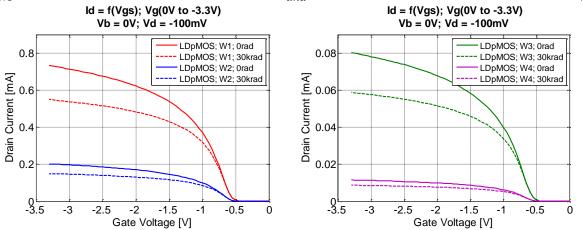

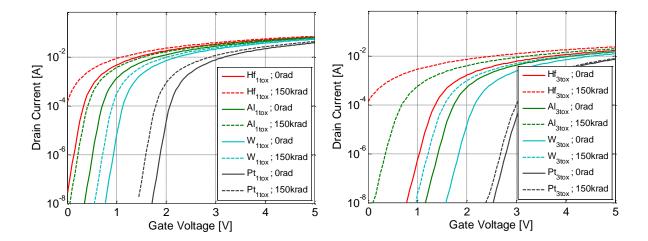

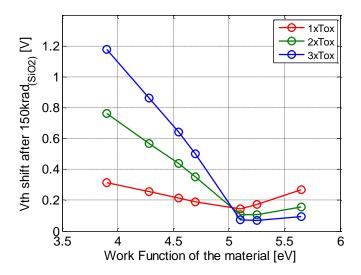

| IV.3.2.3 Experimental Results                                               | 145 |

| IV.3.3. Simulation model                                                    | 146 |

| IV.3.3.1 Device structure                                                   | 146 |

| IV.3.3.2 Simulations                                                        | 147 |

| IV.3.3.3 Adjustment of the simulation model to fit the experimental results | 148 |

| IV.3.4. Simulation results                                                  | 152 |

| IV.3.4.1 Trapped charges distribution inside the oxides                     | 152 |

| IV.3.5. Conclusion on the degradation of the LDMOS structures               | 153 |

| IV.4. Study of the degradation of a GGnMOS structure                        | 155 |

| IV.4.1. Introduction                                                        | 155 |

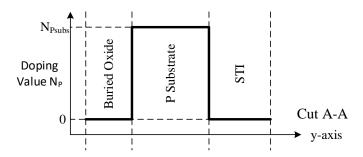

| IV.4.2. Simulation model                                                    | 156 |

| IV.4.2.1 Device structure                                                   | 156 |

| IV.4.2.2 Simulation                                                         | 157 |

| IV.4.3. Theoretical degradation Analysis                                    | 157 |

| IV.4.3.1 Degradation hypothesis                                             | 157 |

| IV.4.3.2 Degradation of the gate oxide with TID                             | 158 |

| IV.4.3.3 Degradation of the ESD triggering voltage with TID                 | 160 |

| IV.4.4. Degradation analysis with TCAD simulations                          | 161 |

| IV.4.4.1 Current leakage analysis                                           | 161 |

| IV.4.4.2 Analysis of the ESD triggering voltage                             | 164 |

| IV.4.5. Conclusion on the degradation of the GGnMOS                         | 170 |

| IV.5. Conclusion.                                                           | 173 |

| IV.6. References                                                            | 174 |

| General Conclusion                           | 177 |

|----------------------------------------------|-----|

| Publications and communication by the author | 181 |

## General Introduction

Any system sent to space is submitted to many constraints (radiations, temperature) which may lead to a failure of the whole system. In a close future, these constraints will become more and more critical as the space agencies are developing missions aiming at others planets such as Jupiter for which the radiative constraint is extremely harsh [1], [2].

In order to ensure the proper functioning of space systems, several methods have been developed to be included in the design flow. In the frame of a Radiation Hardness Assurance (RHA) process, all activities are undertaken to ensure that the electronics and materials of a space system operate according to their design specifications after exposure to the space radiation environment

The increasing cost of electronic components designed to be resistant to radiation (radiation-hardened) and the budgetary restriction of the space agencies, cause industrial enterprises to make use of more and more COST components (Component Off The Shelf). In addition, the fast development of the technologies drives a constant improvement in the design, leaving no room for radiation-hardened components that is sometimes older and less performant.

The utilization of COTS component into radiation electronic design gives larger opportunities by the large scale of performances and functionality. The lower cost of those components gives the possibility to create a wider span of systems with higher performances. However, depending on the application, a qualification of the component used is required.

Several standards, civilian and military, were developed, to give instructions on how to qualify a COTS component for space application [3], [4], [5], [6]. COTS are sometimes also used for others applications, none space related, but for systems evolving in a radiative environment. All of these standards specify that the components must be tested for cumulative and transients effects, using pristine components for each test. Therefore, cumulative effects are treated separately from transient effects, while there is a significant probability that they will appear simultaneously during a space mission. The synergy between these two types of effects, which is not taken into account by the test standards, is then a potential cause of vulnerability that could force equipment manufacturers to use prohibitive safety margins, increasing development costs. In this study, the synergistic effect is investigated to understand which effect is more sensitive to the combination of different effects.

Lately, some unexpected failures were reported for which the failure mode seemed to indicate that an Electrostatic Discharge (ESD) protection structure was involved. Indeed, the particles emitted by the sun, the plasmas of electrons in some orbits or an intentional electron burst can cause a voltage

difference between two surfaces and can create ESDs in space. On the ground, the maintenance of systems under radiation can also be subject to ESD caused by the contact between the operator and the electronic system.

In order to extend the knowledge on which synergistic effects can cause an unexpected degradation of an electronic component or system, in space or others radioactive environment, the RADIAC group of the IES (Institut d'Electronique et des Systèmes) at the University of Montpellier has investigated synergistic effect through different Ph.D. programs. Three different PhDs have already demonstrated the impact of this synergistic effect that occurs on bipolar devices evolving in a radiative environment, submitted to total ionizing dose and displacement damage, which could be subject to Single Event Transients (SET) or Transient Radiative Effects on Electronics (TREE), caused by natural events or intentional events [7], [8], [9].

Following of these studies, this Ph.D. subject proposes to investigate another type of synergistic effects that may affect future electronics systems and provide hints on how the test standards should evolve to take into account the associated threats.

In this manuscript, two different phenomena involving to synergistic effects are presented. The first section investigates the radiation-induced degradation of three operational amplifiers forms different manufacturers sharing the same reference but exhibiting a very different behavior under irradiation. The second section presents the synergistic effect TID-ESD that has never been studied before. The goal of this work is: (1) to understand if the ESD protection used inside integrated circuits may be responsible for some unexplained failure at IC level and (2), if after long-term exposure to a radiative space environment, the protection structure is still able to protect an electronic component from an ESD.

The first chapter presents an overview of different radiative environments originating from natural and manmade sources, in space and on the ground. The physical mechanisms causing the degradation of electronic components due to cumulative effects are explained along with their impact on bipolar and MOSFET technologies.

The second chapter aims at showing how a physical mechanism, i.e. the displacement damage-induced degradation at transistor level in an integrated circuit may cause an unexpected response at circuit level and how this effect may be amplified due to a slight modification in the design. This work is a sequel to the work done by F. Roig on the degradation of LM124 operational amplifiers designed by three different manufacturers [10], [11]. In this previous work, a large amount of experimental data was collected that could not be exploited in the time frame of a single Ph.D. Program. The present work focuses on some unexpected results and aims at understanding why slight changes in the structures affect so significantly the degradation of these operational amplifiers.

The third chapter initiates the first investigation ever made on a new synergistic effect that may occur between the radiation-induced degradation and ESD. The first part of this chapter will explain how ESD is created, what damage it may induce and the different methods developed over the years to protect integrated structures to ESDs. Next, to understand if those protections may cause some unexpected failures, the degradation of gate grounded n-MOSFET (GGnMOS) will be investigated on a component endowed with these protections using a black box approach.

In the last part, an analysis at structure level is performed. Thanks to Microchip Technology Nantes, we had access to technological data of GGnMOS structures that we have used to do some TCAD simulations with the TCAD software ECORCE developed at the University of Montpellier. Since no irradiation results were available on the actual GGnMOS structures and no standalone structures were available, Laterally Diffused MOSFETs (LDMOS) sharing a very similar internal structure were used as test structures. The results of the LDMOS structure have been used to formulate some assumptions on the degradation of the GGnMOS structure. Eventually, through simulations and theoretical analysis, the degradation of those structures to total ionizing dose is presented and some possible methods to increase their robustness are proposed.

#### References

- [1] S. Bourdarie, "Comparative Earth and Jovian Space Environment," *Short Course NSREC*, Paris (France), 2014.

- [2] J. Boch and P. C. Adell, "Dose and Dose-Rate Effects in Micro-Electronics: Pushing the Limits to Extreme Conditions," *Short Course NSREC*, Paris (France), 2014.

- [3] ESCC Basic Specification No.22900 issue 4 and Total Dose Steady-State Irradiation Test Method. (2010, Octobre) ESA. [Online]. https://escies.org

- [4] Single Event Effects Test Method and Guidelines ESCC Basic Specification No.25100 issue 1. (2002, Octobre) [Online]. https://escies.org

- [5] EIA/JEDEC Standard. Test procedure for the measurement of Single Event Effects in Semiconductor Devices from Heavy Ion Irradiation. (1996, Décembre) [Online]. www.jedec.org.

- [6] MIL-STD 883J Method1017.3. Neutron Irradiation. (2013, Juin) [Online]. http://www.dscc.dla.mil/downloads/milspec/docs/mil-std-883/std883.pdf

- [7] N. J.-H. Roche, "Caractérisation et modélisation de l'influence des effets naturels cumulés de l'environnement spatial sur le niveau de vulnérabilité de systèmes spatiaux soumis aux effets transitoires naturels ou issus d'une explosion nucléaire," Thèse de l'université Montpellier 2, 2010.

- [8] F. Roig, "Etude et Modélisation des Effets de Synergie Issus de l'Environnement Radiatif Spatial Naturel et Intentionnel sur les Technologies Bipolaires Intégrées," Thèse de l'université Montpellier 2, 2014.

- [9] M. Bernard, "Etude des Effets de Synergie DOSE ASET dans les Circuits Linéaires en Technologie Bipolaire Embarqués en Environnement Radiatif Natural Spatial," Thèse de l'université Montpellier 2, 2007.

- [10]F. Roig *et al.*, "Modeling and Investigations on TID-ASETs Synergistic Effect in LM124 Operational Amplifier from Three Different Manufacturers," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 6, pp. 4430–4438, Dec. 2013.

- [11]F. Roig et al., "Impact of Neutron-Induced Displacement Damage on the ATREE Response in LM124 Operational Amplifier," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 3043–3049, Dec. 2014.

# Chapter I: Introduction

| I.1. Introduction                                                                  | 21 |

|------------------------------------------------------------------------------------|----|

| I.2. The different radiative environments                                          | 22 |

| I.2.1. The natural radiative space environment                                     | 22 |

| I.2.1.1 The radiation belts                                                        | 22 |

| I.2.1.2 The cosmic rays                                                            | 23 |

| I.2.1.3 The solar wind                                                             | 24 |

| I.2.1.4 The solar flares                                                           | 25 |

| I.2.2. The man-made radiative space environment: exoatmospheric nuclear explosions | 26 |

| I.2.3. The man-made radiative terrestrial environment: The particle accelerators   | 26 |

| I.3. Cumulative radiation effects on electronic devices                            | 29 |

| I.3.1. The total ionizing dose                                                     | 29 |

| I.3.1.1 The concept of Total Ionizing Dose                                         | 29 |

| I.3.1.2 Photon-Matter interaction                                                  | 29 |

| I.3.1.3 Degradation mechanism of the dose on the materials                         | 30 |

| I.3.2. The Displacement damage dose                                                | 31 |

| I.3.2.1 Displacement Damage mechanism                                              | 31 |

| I.3.2.2 Displacement damage on electronic devices                                  | 33 |

| I.4. The bipolar transistor                                                        | 35 |

| I.4.1. Working principle                                                           | 35 |

| I.4.2. The sensitivity of bipolar transistor to TID and DD                         | 36 |

| I.4.2.1 Effect of the TID on bipolar structures                                    | 36 |

| I.4.2.2 Effect of the DD on bipolar structures                                     | 38 |

| I.4.3. Sensitivity to TID or DD depending on the transistor structure              | 38 |

| I.5. The MOSFET transistor                                                         | 40 |

| I.5.1. Working principle                                                           | 40 |

| L5.2 The sensitivity of MOSEET transistor to TID                                   | 41 |

| I.6. State of art of the synergistic effects studies | 44 |

|------------------------------------------------------|----|

| I.7. Conclusion                                      | 46 |

| I.8. References                                      | 47 |

#### I.1. INTRODUCTION

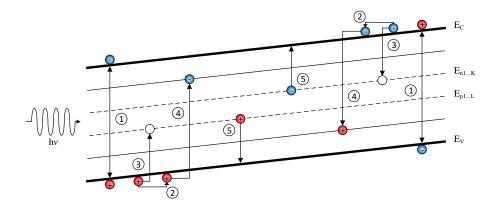

Electronics embedded in systems submitted to radiation are subject to an alteration of their physical parameters. These modifications are still today the cause of a large number of failure of electronic systems in space. The radioactive space environment is one among the most frequently studied environment, in which it is nowadays vital to use electronics and yet, its effect induced on the matter is not fully understood. Radiation effects may be sorted in two different categories known as the cumulative effects and the single event effects.

The cumulative effects usually cause a modification of the electrical parameters over time by trapping charges into the insulators or modifying the crystal lattice of a component. Its degradation can result in a modification of the triggering voltage of a transistor or an increase in the current leakage of a component for example.

The single event effects are caused by a single particle that interacts locally in an integrated circuit but it can also be transmitted to the entire circuit or system, and its effect can be temporary or permanent. Several types of single event effects are known and each one of them induces a very specific modification or degradation on a single component.

In order to use electronics components in a radioactive environment, qualification tests standards recommend a study of the degradation of cumulative effects and single event effects only by using pristine components. However, in some cases, the response to a single event effect can vary depending on the ionizing dose already accumulated and may lead to a different response compared to what was expected.

In order to prove the importance of studying the degradation of the cumulative and single event effects together, we are investigating in this document the importance of taking into consideration the synergistic effects.

The first part of this chapter is dedicated to present different radioactive environments that embedded electronics system can meet. Both natural and man-made environment in space or on the ground act differently on the electronics, thus, different impact on a system is to be expected. Then, the two different cumulative effects induced by radiation on the matter are presented. Then, to understand how the radiation acts on the electronics, two main technologies of components, known as bipolar and MOSFET used in electronics are presented with their expected radiation induced-degradation. In the end, a short state of art on the synergistic effects studies already performed is presented. It will present the previous Ph.D. led on this subject and the different synergistic effects already studied.

#### I.2. THE DIFFERENT RADIATIVE ENVIRONMENTS

#### I.2.1. THE NATURAL RADIATIVE SPACE ENVIRONMENT

Any objects sent to space are submitted to specific constraints modifying its physical and electrical parameters. The natural radiative environment originates from four different sources known as the radiation belts, the cosmic rays, the solar wind and the solar flares. Those radiations are the cause of several failures of objects sent to space. Beside the natural radiative space environment, some others environment created by the human have to be taken into account because they can be also very critical for electronics systems.

#### I.2.1.1 The radiation belts

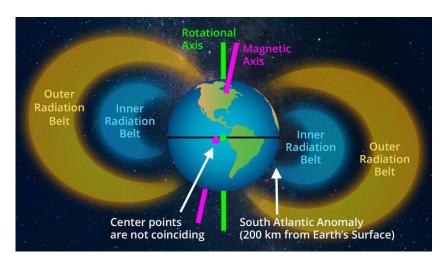

The radiation belts were introduced for the first time in 1958 by the scientist James Alfred Van Allen after analyzing the data obtained by the satellites Explorer 1 and Explorer 3 [1]. This radiation belts, called as Van Allen belts, act as a charge particles shield induced by the magnetic field surrounding our planet. Because of the Earth's magnetic field, most of the particles sent by the outer source toward Earth are deflected or trapped inside these radiation belts, protecting the earth from the radiations. The radiation belts consist of two donuts shaped region, called the inner belt and the outer belt, containing high energetic radiations. They are mainly composed of electrons and protons. An artistic representation of the radiation belts is represented in Figure 1.

Figure 1: Artistic representation of the Van Allen belts surrounding the Earth. Credit: [2]

The inner belt evolves approximatively between 1,500 km and 13,000 km above the ground and is mainly composed of protons of few hundreds of MeV and electrons ranging between 1 MeV and 10 MeV. The outer belt evolves approximatively between 19,300 km and 40,200 km above the ground and is mainly composed of electrons with an energy between 0.04 MeV and few MeV and protons ranging between 1 MeV and 5 MeV [3], [4].

Because of these radiation belts, any spacecraft sent into space is submitted to irradiations, which will damage onboard electronics. In order to estimate the shielding needed to protect a satellite in development, different models were created by ESA and NASA. The empirical models AP8 and AE8, respectively corresponding to the Trapped Proton Model and the Trapped Electrons Model, are among the most used models by the different space agencies [5]. They contain two derivate models for minimum solar activity and maximum solar activity, known as AP8MIN, AP8MAX, AE8MIN and AE8MAX [3].

The space area is divided into three different orbits in which the satellites can evolve:

The lowest orbit area is the LEO for Low Earth Orbit. This orbit evolves between the Kármán line [6] and the beginning of the first radiation belt, between 160 km and 2,000 km. In this orbit, various types of satellites evolve for different missions like communications (ex: Iridium phones system), CubeSat, the International Space Station, and many others. Because of the low altitude, the energy required to send a satellite in this orbit a lot smaller compared to the others orbits, and less power is required to the communicate with Earth. Thus, the LEO orbit contains more spacecraft than any other orbits.

The MEO, standing for Medium Earth Orbit evolves between 2000 km and 35,786 km above sea level. The most common missions of the satellites in this region are for navigation, communication, and geodetic/space environment science [7]. Despite the very wide area, most of the satellites are positioned between 20,200 km and 20,650 km. Unlike the LEO, the MEO directly lies within the highest energetic protons of the radiations belts. Thus, any satellites sent in this orbit needs to be designed with adapted electronic and proper shielding.

The last existing orbit is the GEO orbit, which stands for geostationary orbit. This orbit, positioned at an altitude of exactly 35,786 km, allows for a full revolution in exactly one day. Because of this particularity, a satellite sent on this orbit will have a relatively static position at ground level [7]. The satellites sent on this orbit are not only submitted to high-energy protons and electrons but to heavy ions, and electrons plasma.

Depending on the satellite's mission, a specific orbit has to be selected and the satellite will be submitted to a range of radiations, as defined by the trapped particles models AP8 and AE8. Therefore, any satellites sent to space needs to have its own environmental study.

#### I.2.1.2 The cosmic rays

The cosmic rays are highly energetic radiation coming from distant galaxies, stars, supernovas, etc. with an energy starting from 100 MeV up to  $10^{21} \text{MeV}$  for the highest energy [8]. They are composed of 1% heavy ions, 2% of electrons, 12% of helium and 85% of protons [9].

The galactic cosmic rays were discovered by Victor Franz Hess in 1912 by using three enhanced-accuracy electrometers at an altitude of 5,300 meters in a free balloon flight [10].

Due to their high energy, there is no efficient way to protect an electronic device from them. However, because the flux is very low, the interaction's probability with an electronic component is low. It is then often neglected for the radiation-induced damage estimation [11].

#### I.2.1.3 The solar wind

This phenomenon was first introduced to the community by the German astronomer Ludwig Biermann in 1951 in his article "*Kometenschweife und solare Korpuskularstrahlung*" (in English: Comet tails and solar corpuscular radiation). His discovery, based on the study and observation of comet, conclude that no matter whether a comet is headed towards or away from the Sun, its tail always points away from the Sun. Biermann postulated that this happens because the Sun emits a steady stream of particles that pushes the comet's tail away [12].

The solar wind is a plasma stream consisting essentially of ions and electrons that are ejected from the Sun's upper atmosphere. Because of the low energy, most of the particle can be stopped with an appropriate shielding.

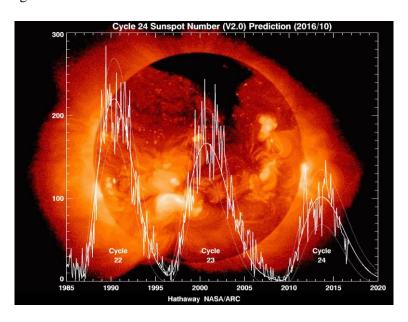

Figure 2: Solar activity recorded since 1985 up to now [13]

It is understood that the sun activity evolves following a cyclic pattern known as the solar activity. It varies following a pattern of 11 years with seven years of high activity and four years of low activity as presented in Figure 2 [14]. Depending on this activity, the particles emitted by the solar wind will be more or less energetic. Therefore, depending on the launch date, satellites may have to be designed to be more robust against radiation to survive to a high solar activity, and some missions are sometimes delayed to be sent during a low solar activity.

#### I.2.1.4 The solar flares

Compared to the solar wind that constantly emits particles, a solar flare is an unpredictable phenomenon caused by the rupture of the sun's magnetic field lines, ejecting at very high speed and high energy particles such as protons and ions. The energy range of those particles are not as high as the cosmic rays, but can still reach few hundreds of MeV for the protons and few tens to hundreds of MeV for the ions. A picture representing a solar flare is presented in Figure 2.

Figure 3: Picture representing a coronal mass ejection from the sun. The earth is represented on the same picture for scale [15].

When a solar flare occurs, the particle shower can last from hours to a couple of days depending on the intensity of the flare. Moreover, because the particles ejected have not the same mass, speed or energy, the first particles reaching the Earth's proximity are the light particles like the electrons, which reach a speed close to the speed of light and take around 8 minutes to reach the firsts satellites. Others particles like heavy ions or protons can take several hours or days to reach the Earth's outer space.

After a solar flare, the amount of trapped particle inside the radiation belts increases, protecting with higher efficiency the earth from others particles, but the environment is then more dangerous for the satellites. This increased amount of trapped particles is observable at the earth's poles as aurora borealis.

#### I.2.2. THE MAN-MADE RADIATIVE SPACE ENVIRONMENT:

#### EXOATMOSPHERIC NUCLEAR EXPLOSIONS

In the case of an exoatmospheric nuclear explosion, that can be provoked intentionally with a weapon, two types of radiation-induced effects caused by radiation to any electronic systems within the range of the explosion: the directs effects and indirect effects.

The direct effects are caused by the nuclear explosion itself. Any satellite within range will be submitted to a large spectrum of high-energy radiations composed of  $\gamma$ -rays, neutrons, and x-rays. The x-rays are among the most energetic particle that can be over 100 times higher than the  $\gamma$ -rays [16]. However, because of its penetration power into the matter, the  $\gamma$ -rays causes more damages [17].

The indirect effects are caused by the particles emitted during the nuclear explosion that are trapped inside the Van Allen belts which, after the explosion, will stay inside the belts, causing an increase of the trapped particles or to the creation of artificial radiation belts. For example, following the series of exoatmospheric nuclear experiments accomplished by the USA and the USSR in the late 50's and early 60's, a series of at least 10 satellites successively failed (7 in 7 months), among which TELSTAR, TRANSIT 4B, TRAAC, and ARIEL, and a number of other ones were impaired such as OSO-1 (Orbiting Solar Observatory) due to the modification of the radioactive space environment [4].

# I.2.3. THE MAN-MADE RADIATIVE TERRESTRIAL ENVIRONMENT: THE PARTICLE ACCELERATORS

Many facilities offer particles accelerators developed for science studies or medical purposes. CERN in particular is known for its Large Hadron Collider (LHC), the most energetic and the longest accelerator on the planet.

LHC's radiative environment consists of a mixed field of particles composed of charged and neutral hadrons (protons, pions, kaons, and neutrons), photons, electrons and muons [18]. This complex field is due to particles generated by the collision proton-proton (or ion-ion) in the experimental areas, the distributed and direct beam losses (protons, ions) around the machine caused by some particle of interacting with the pipes, and the beam interacting with the residual gas inside the vacuum [18], [19].

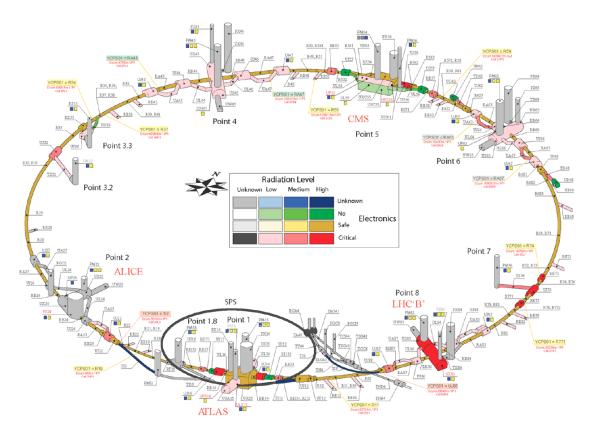

Figure 4: Representation of the radiation level all along the LHC tunnel. A color scale defines the criticality of the electronic depending on the expected radiation.

As presented in Figure 15, the LHC environment is very versatile and it can change a lot depending on the position inside the tunnel. In this picture, the color scale defines the level of radiation depending on the criticality of the electronics inside the LHC. For example, in all the tunnels, the dose expected is high but the electronics systems are not critical. Thus, most of the electronics used are COTS components. In comparison, some areas like the point 1, 2, 5 and 8 host a lot of electronics used to control the beam for the collisions. Therefore, the harsh radiation environment jeopardizes the control of the beam and hardened components have to be used.

A large part of CERN's accelerator control systems are not explicitly designed to be radiation hardened or radiation tolerant but are still exposed to a certain level of radiation that depends on their position in the tunnel [20]. Thus, most of the electronics placed inside the radioactive LHC environment have to be tested to radiation whereas the electronic for the critical areas are often radiation-hardened components.

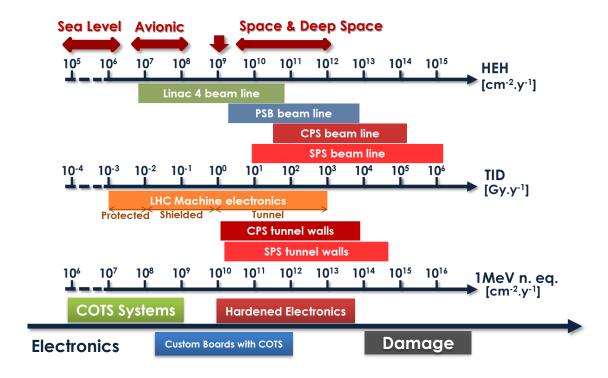

Figure 5: Usage of the electronic depending on the radiation levels inside the different tunnels of the CERN [19]

Figure 5 describes the utilization of the electronics inside the different CERN's tunnels depending on the doses, fluencies and High Energy Hadrons (HEH). As presented on this figure, not all the electronic used inside the CERN's facilities are designed with hardened components. Some systems placed inside the protected areas, for example, may be designed with an only board designed with COST component, but most of the system has to be designed with a custom board with COTS tested to radiation or radiation hardened components.

# I.3. CUMULATIVE RADIATION EFFECTS ON ELECTRONIC DEVICES

#### I.3.1. THE TOTAL IONIZING DOSE

#### I.3.1.1 The concept of Total Ionizing Dose

The Total Ionizing Dose or TID is a cumulative effect that induces an energy deposition, by ionization of the matter causing a generation of electron-hole pairs. This ionization is caused either by the interaction of high-energy photons, by charged particles such as protons, electrons and sometimes heavy ions with atoms of the target material [9], [11], [21]. The TID corresponds to a certain quantity of energy deposited per mass unit:

$$D = \frac{\Delta E}{\Delta m} \qquad \text{with } 1Gy = \frac{J}{kg} \qquad Equation I.3-1$$

Where D is the ionizing dose expressed in Gray [Gy],  $\Delta E$  corresponds to the energy deposited expressed in Joules [J], and  $\Delta m$  to the mass expressed in kilograms. The *Gray* unit is defined in the standards international system of unit since 1985, nevertheless, the previously used unit called the *rad* for *Radiation Absorbed Dose* is still used to quantify a dose degradation of the electronic component. One Gray corresponds to 100 rad.

Another parameters qualifying the TID is the dose rate. This unit expressed in [rad.s<sup>-1</sup>] or [Gy.h<sup>-1</sup>] corresponds to the energy deposit per time unit:

$$D' = \frac{\Delta D}{\Delta t}$$

Equation I.3-2

Depending on the technology, the dose rate can be a key parameter. Indeed, for bipolar technologies, the reduction of the dose rate increases the degradation of the component for the same TID level. This principle, called Enhance Low Dose Rate Sensitivity, has been largely studied in [22]–[26], however, this latter will not be discussed in this manuscript.

#### I.3.1.2 Photon-Matter interaction

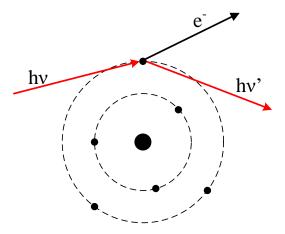

TID radiation testing is usually performed with  $^{60}$ Co  $\gamma$ -rays source. A  $^{60}$ Co source produces a constant emission of  $\gamma$ -photons of 1.17 MeV and 1.33 MeV that interact with the matter mainly by Compton Effect [27]. As represented in Figure 6, during an interaction by Compton Effect, a part of the incident photon's energy, hv, is transferred to a peripheral electron and ejected it from its orbit. The initial photon passes then from an initial energy hv to a lower energy hv', with the difference corresponding to the

energy transferred to the electron [28]. The remaining photon, if it still has enough energy can interact with another electron from another atom, etc.

Figure 6: Representation of a Compton Effect

Even if  $\gamma$ -rays are not presents in the space environment, its controllability and penetration into the matter makes it a good source of radiation testing [29].

#### I.3.1.3 Degradation mechanism of the dose on the materials

Due to their intrinsic properties, the insulating material of electronic devices is the most sensitive part to ionizing dose. Its low charge density makes any electrical conduction impossible. Injection of additional charges will then modify, all along the dose accumulation, the electrical properties of the insulator [30]. Depending on the component's technology, the silicon oxide (SiO<sub>2</sub>) plays a role more or less important.

The MOSFET technology uses the electric field generated inside the gate oxide, by applying a potential on the gate contact, and acts on the substrate to create a conduction channel. Because silicon oxide of the MOSFET generates this electric field, any modification of its electrical parameters would affect the electric field generated for the same voltage applied and modify the voltage threshold of the component [31], [32]. Nowadays, MOSFET's gate oxide tend to be as thin as possible, in order to increase their performances by reducing the amount of defects inside the oxide and manufacture a highly homogenous structure. The reduction of gate oxide thickness has been astonishingly successful so that oxides with a thickness of roughly 20 Å are being manufactured [33].

Bipolar technology does not use the silicon oxide for the same reason as the MOSFET technology. Because of their structure, the silicon oxide is only used to protect the component from any external contamination (dust, light, UVs, etc.). Therefore, the quality of those oxides is often bad and does not affects the electrical properties of the component. No thickness reduction or increase in the quality is performed since that would increase unnecessarily the cost for a similar result.

Although the impact of the radiation affects all oxides based on the same fundamental mechanism, the radiation-induced degradation is completely different on BJTs and MOSFETS. Therefore, the studies of their degradation is considered separately.

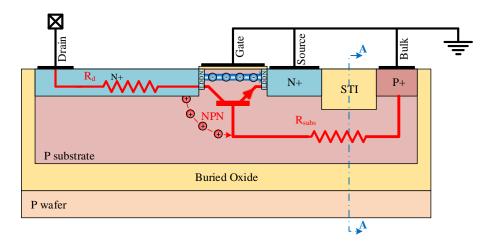

The various physical phenomena detailing the entire process, i.e. from the initial deposition of energy by ionizing particles to the creation of defects in silicon oxide, can be broken down into four steps that are the electron-hole pair creation, the initial recombination, charge drift into the oxide and defect creation into the oxide and at the interface [34].

When an oxide is under irradiation, electron-hole pairs are created in the dielectric [31], releasing a kinetic energy that ionizes the matter. Just after the ionization, a large part of the electron-hole pairs created will be immediately recombined. Depending on the electric field into the oxide, the fractional yield of the electron-hole pairs varies [30], [35]. The remaining electrons are pushed outside the oxide, leaving the holes, which have a much lower mobility, trapped inside the oxide. The fraction of electron-hole pairs that escape the initial recombination is called the electron-hole yield. The holes that escaped the initial recombination will slowly move toward the higher potential with a speed that depends on the temperature, the electric field, the oxide thickness and the holes distribution inside the oxide [34]. When the holes get closer to the Si/SiO<sub>2</sub> interface, a part of the holes are recombined with the electrons of the substrate, and some other will react with hydrogen passivated Si dangling bonds to create interface traps at the Si/SiO<sub>2</sub> interface [36], [37]. During the hole drift and/or trapping, protons can be liberated in the bulk or near-interfacial SiO<sub>2</sub>, leading to a modification of the potential under the oxide. In the end, fractions of the holes are trapped at defect sites near the Si/SiO<sub>2</sub> interface [36], [38].

#### I.3.2. THE DISPLACEMENT DAMAGE DOSE

#### I.3.2.1 Displacement Damage mechanism

The Total Non-Ionizing Dose or Displacement Damage is the result of nuclear interactions between a particle and the matter, causing lattice defects. It can be caused by several types of particle such as the neutrons, protons and heavy ions. Their interaction with a semiconductor material causes a creation of defects in the crystal lattice, leading to the reduction of the mobility, and increase the quantity of traps [39].

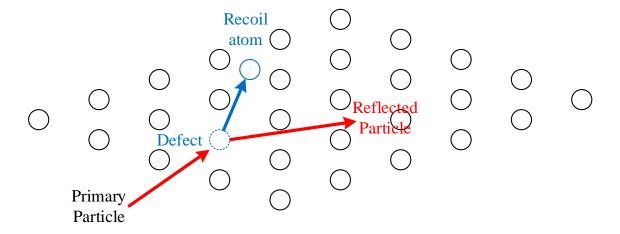

Silicon wafer used to manufacture the electronic component are created in a very specific way that organizes the silicon lattice close to a crystalline lattice. Therefore, when a particle interacts with this lattice, it creates a disorder in the silicon lattice. A representation of the displacement damage effect is represented in Figure 7. When the particle interacts with an atom from the silicon lattice, a part of its energy is transferred to this atom, displacing it somewhere else in the lattice. If the incident particle still

has enough energy, it will continue its travel inside the silicon lattice and will eventually interact with other atoms.

Figure 7: Representation of the mechanism of defect creation onto the silicon lattice. Displacement damage is caused by a displacement of atoms.

The empty space left to create a defect, while the recoiling atom will stay in the middle of the lattice as an interstitial particle. The combination of the defect and the interstitial atom is called a Frenkel pair [40], [41]. These defects result in the creation of energy levels in the forbidden band of the semiconductor, which influences the conductivity of this material.

A displacement defect occurs when an atom of the target material is displaced from its initial location by radiative energy particles, and produce a permanent degradation [40], [41].

When a particle interacts with the silicon lattice, the first atom to be displaced is called the Primary Knocked-on Atom (PKA). Depending on the type of interaction or the energy of the incident particle, two different situations can happen.

In the first case, if the energy exchange between the particle and the atom is too low, only the atom will be displaced. It is usually the case for the interaction with low energy particle because only the Rutherford or Coulomb diffusion occurs.

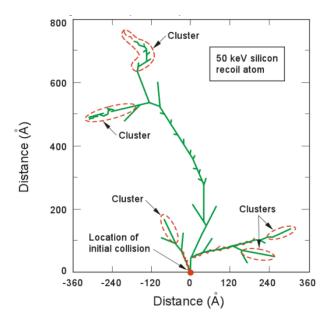

In the second case, if the exchange between the particle and the atom is high, the displaced atom will gain a high energy and in turn, will interact with others particle, etc. In this case, a large number of successive collision can be produced leaving a defect trail in the silicon lattice creating a cluster of defects. An example of a cascade is shown in Figure 8 for a silicon atom with a recoil energy of 50 keV produced by a 1MeV neutron. Clusters are similar to a cluster of displacement defects.

Figure 8: Cascade of defects calculated with a PKA of 50 keV produced by a 1MeV neutron into a silicon lattice [42]

#### I.3.2.2 <u>Displacement damage on electronic devices</u>

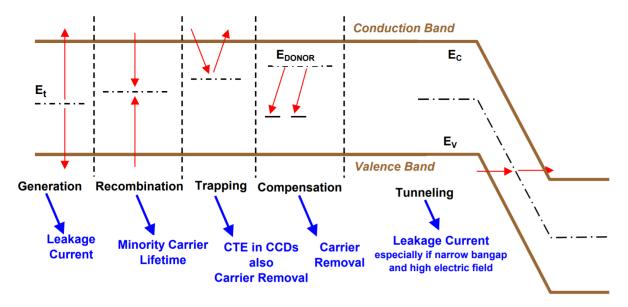

Figure 9: Electrical effects on a semiconductor material induced by the presence of energy levels in the band gap due to displacement damage[43].

After the creation of the defects, when the particle is stabilized and stop moving, it can interact with the electronic devices following five different processes that are presented in Figure 9 [38], [43], [44].

• The electron-hole pair recombination happens by the emission of an electron in the conduction band and a hole in the valence band. This mechanism leads to an increase in the leakage current in silicon material.

- The electron-hole pair recombination is explained by the trapping of a positive carrier with a negative carrier. Due to the proliferation of these traps within the band and due to displacement damage, the life of minority carriers is reduced.

- Trapping of carrier temporary. That will eventually be reemitted in its band after certain duration.

- The doping compensation is explained by trapping of the predominant carriers inside the traps, reducing the doping value of the area.

- The tunneling effect describes a particle going through the valence band up to the conduction band. This phenomenon is mainly caused by a modification of the band slope. More the electric field is high; more the particle will cross the bands easily. The tunneling effect causes an increase in the leakage current. This case is more relevant to MOSFET technologies.

#### I.4. THE BIPOLAR TRANSISTOR

#### I.4.1. WORKING PRINCIPLE

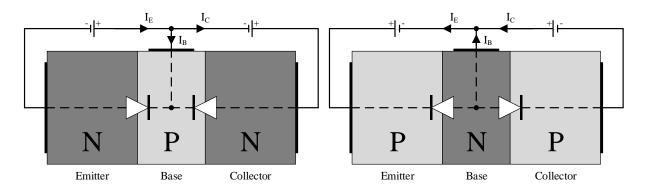

The bipolar transistor (or Bipolar Junction Transistor) was introduced to the community in 1948 by the Bell Telephone Laboratories [45]. It consists of three semiconductors layers stacked together with the two layers on the extremity of the same type (n or p) and one layer of the opposite type in-between. As represented in Figure 10, the NPN bipolar transistor is composed of two N doped semiconductors separated with a P doped semiconductor, and for the PNP transistor consists in two P doped semiconductor departed by an N doped semiconductor. For both components, form the left to the right, those layers are named the emitter, the base, and the collector. Those blocs consist in two PN junctions top to top for the NPN transistor and back to back for the PNP transistor. If we take the example of the NPN transistor, the doping value of the emitter is every time higher than the one of the collector because the emitter area emits the electrons that are collected by the collector.

Figure 10: Representation of an NPN bipolar transistor on the left and a PNP bipolar transistor on the right.

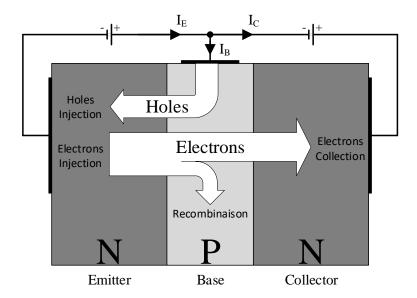

When the diode between the base and the emitter is biased in forward mode, the majority carriers (electron for the case of the NPN) are injected from the emitter to the base. A part of the electrons injected is recombined with the holes present inside the base, but because of the low thickness of the base, the rest of the electrons injected are pushed toward the depletion area of the base-collector junction. The electrons that have reached the base-collector junction without being recombined are accelerated by the electric field of the depletion area of the diode in reversed bias mode. The higher the voltage of the base collection junction, the larger the depleted area will be and will accelerate the electrons. A simplified representation of this mechanism is presented in Figure 11.

Figure 11: Representation of the transistor effect mechanism occurring on the normal operation of an NPN bipolar transistor

The current gain of the transistor corresponds to the ratio between the collector current and the base current.

$$\beta = \frac{I_C}{I_B}$$

Equation 1.4-1

This gain is one of the main parameters of the bipolar transistors, defining its performances. Depending on the application, it ranges from 20 to 100 for high power applications and from 100 to 800 for the low power applications.

Integrated bipolar transistors exist in four different structures that can be used for specific purposes:

- Vertical NPN transistor (VNPN)

- Vertical PNP transistor (VPNP)

- Lateral PNP transistor (LPNP)

- Substrate PNP transistor (SPNP)

Besides their shape, each structure differs by their current flow. Those structures are presented in more detail in the section II.4.2.

#### I.4.2. THE SENSITIVITY OF BIPOLAR TRANSISTOR TO TID AND DD

#### I.4.2.1 Effect of the TID on bipolar structures

As presented before, ionizing radiation results in an increase of charges and defects inside the oxides, and creation of interface traps impinging on the mobility of the holes or electrons. Each one of those

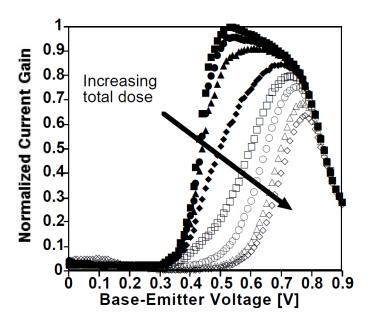

effects acts on bipolar transistor in a different way, but, the main parameter degraded by irradiation is the current gain  $\beta$  [36], [46]–[48]. Figure 12 represents the current grain degradation depending on the base-emitter voltage for different total accumulated dose with, on the top left the curve before irradiation and on the bottom right, the curve after irradiation. As observed the gain current exhibits the most important decrease for the lower base-emitter voltages compared to the higher base-emitter voltage that does not show such a large degradation.

Figure 12: Normalized current gain vs. base-emitter voltage for an NPN bipolar transistor irradiated to various TID values [49].

This degradation can be explained by an increase of the base current of the bipolar transistor resulting from an increase of the recombination rate caused by a larger depletion region and the increase of the surface recombination speed [50] while the collector current remains roughly constant.

It is important to note that depending on the particle used to irradiate the component, the degradation will be different. For example, protons cause a TID and DD degradation on the component, so the radiation-induced degradation between proton and  $\gamma$ -rays or electrons will be different [51].

Besides the current gain degradation, an integrated bipolar structure can show a device-to-device or collector-to-emitter leakage current caused by radiation-induced degradation of the isolation oxides, deep trench and buried oxides [52]–[54].

As explained in the previous section, four different bipolar structures exist and all of them are often used as integrated bipolar transistor. Then, because the radiation-induced trapped charges degrade the component by impacting on the current flow, different sensitivities to TID are to expect for the different bipolar transistors structures.

#### I.4.2.2 Effect of the DD on bipolar structures

The first studies related to the radiation-induced degradation caused by displacement damage date back to the 60s. In their work, Messenger and Spratt developed an equation able to describe the degradation of the current gain amplification caused by neutron irradiation [55]–[57].

$$\frac{1}{\beta} = \frac{1}{\beta_0} + \frac{K \Phi_n}{2\pi f_T}$$

Equation I.4-2

Where  $\beta$  corresponds to the current gain,  $\beta_0$  to the current gain before irradiation,  $\Phi_n$  to the neutron fluence and K to constant of proportionality [49]. To summarize, the Equation I.4-2 describes that the base current is inversely proportional to the minority-carrier lifetime in the emitter-base depletion region or the neutral base. The same equation can be used to describe the displacement damage induced by other particles such as the heavy ions, protons, and electrons.

# I.4.3. SENSITIVITY TO TID OR DD DEPENDING ON THE TRANSISTOR STRUCTURE

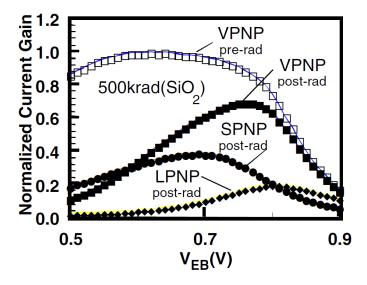

As explained before, most of the species trapped into the oxide are holes, thus, the resultant impact of those trapped charges will affect the component differently if it is an N-type or a P-type. Moreover, considering the current flow in each type of structure (lateral or vertical) the effect of the trapped charges on the current flow will be also different. Figure 13 presents the sensitivity of different types of bipolar transistors depending on their structure for a total dose of 500 krad<sub>(SiO2)</sub>. This graphic, presented by Schmidt *et al.* in [58], describes that lateral bipolar transistors are more sensitive to TID than vertical structures because the current flux passes close to the passivation oxide for the lateral and into a buried layer for the vertical structures.

Figure 13: Comparison of post-irradiation current gain for three different types of PNP BJTs [58]

Like the radiation-induced degradation caused by ionizing dose, it is important to note that depending on the structure of the bipolar transistor, different degradations are expected with the displacement damages because the current flows for each structure are different. For example, Barnaby *et al* [46], [59] and Rax *et al*. [60] showed that the degradation of Vertical NPN, Vertical PNP, and Substrate PNP transistors are more important with proton and neutron irradiations compared to ionizing irradiation. Those irradiations simultaneously degrade the surface recombination velocity, the net positive oxide charge and the collector-region lifetime, which is a very sensitive parameter for bipolar technologies. As a result, both particles will subsequently cause an increased degradation of the current gain.

# I.5. THE MOSFET TRANSISTOR

#### I.5.1. WORKING PRINCIPLE

The MOSFET transistor (Metal Oxide Semiconductor Field Effect Transistor) is nowadays one of the most commonly used transistors inside electronic components. The first idea of a MOSFET structure comes back to the year 1925 when it was patented by Julius Edgar Lilienfeld. Only 35 years after, in 1959, the first transistor was designed by Dawon Kahng and Martin M. Atalla at Bell Labs.

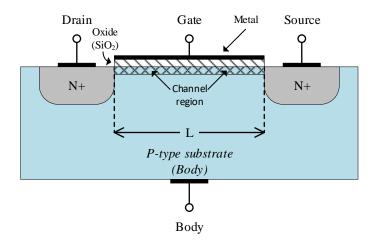

A simplified structure of a MOSFET transistor is presented in Figure 14. Its construction relatively simple is composed of two wells of the same type inside a silicon called the drain and the source (doped n for the N-MOS and p for the P-MOS), separated by the substrate of an opposite doping. Because of this structure, the current is blocked between the two wells. The gate added between the two wells is placed on the top of the silicon and is separated by a silicon oxide insulator. With this topology, no current passes by direct conduction through the channel. Only the generated electric field, by attracting the holes or electrons depending on the type of component (N-channel or P-channel), creates a channel allowing the conduction between the drain and the source.

Figure 14: Simplified structure of an n-type MOSFET transistor

Several topologies of MOSFET transistors exist depending on their applications, but to sum up, the aim of the MOSFET is to be able to control the current flow between the source and drain by varying the gate voltage.

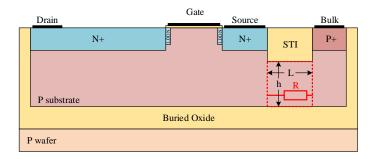

In this thesis, two different topologies of MOSEFT transistors such as the GGnMOS (Gate Grounded N-MOSFET) and LDMOS (Laterally Diffused MOSFET) will be studied. Those two structures are presented in details in Chapter 3 and Chapter 4.

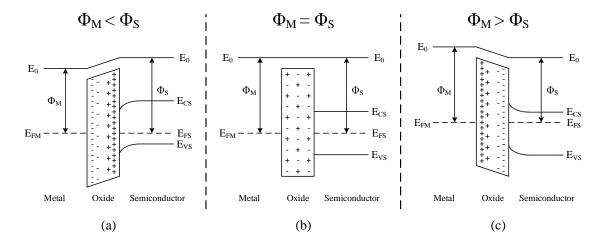

# I.5.2. THE SENSITIVITY OF MOSFET TRANSISTOR TO TID

As explained before, the ionizing dose creates trapped charges into the oxide that moves from one side to another depending on the electric field inside the oxide. Those charges, while moving into the oxide, can be recombined or create defects by moving close to the interface, which changes the behavior of the component. On a MOSFET transistor, the typical radiation-induced degradation modifies the threshold voltage of the component and will then increase the drain leakage current. In a general case, the traps are created by a weak atomic link that creates holes traps [61].

A trapped charge into the oxide can be mobile, fixed, trapped inside the oxide or trapped at the Si/SiO<sub>2</sub> interface. The mobile charges and trapped charges are located into the entire volume and the interface traps are mostly located close to the Si/SiO<sub>2</sub> interface. This placement is mainly caused by the repartition of the electric field into the oxide during the irradiation. Positive electric field into the oxide will push the holes toward the Si/SiO<sub>2</sub> interface increasing the degradation of the parameters of the transistor.

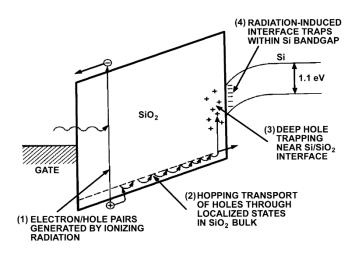

Figure 15: Representation of the four main degradation mechanism induced by ionizing radiation into a MOS structure with a positive biasing [62].

A representation of the four main mechanisms of degradation is presented in Figure 15. At first, ionizing radiation creates an electron-hole pair (1). The positive electric field generated by the voltage biasing at the gate pushes the holes toward the Si/SiO<sub>2</sub> interface by successive hoping (2), whereas the electrons will be pushed toward the gate contact. Once the holes have reached the Si/SiO<sub>2</sub> interface a part of them are trapped into deep traps (3), leading to a long-term trapping and some others generate interface traps within the Si band gap (4). Throughout all the irradiation, a continuous flow of holes is trapped, by flowing the four mechanisms presented. Over time, the increase of those trapped charges increase the impact on the shift of the threshold voltage of the MOSFET transistor. Furthermore, for the same irradiation, if the electric field in the oxide is higher because the holes will move faster toward the Si/SiO<sub>2</sub> interface, the quantity of recombined charges will be reduced. This lead to an increase in the

quantity of charges trapped and interface traps close to the interface. Consequently, the threshold shift will be higher.

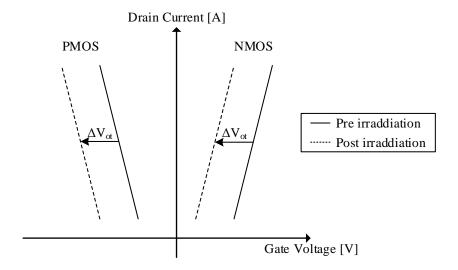

The total shift of the voltage threshold is caused by the increase of the charges inside the oxide  $(Q_{ot})$  and the charges trapped at the interface  $(Q_{it})$ .

Figure 16: Representation of the impact of the positive trapped charges into the oxide on the characteristics of the MOSFET transistors.

The trapped charges inside the oxide can be positive or negative and its density is labeled  $N_{OT}$ . In the silicon oxide, the trapped electrons, because of their mobility higher than the holes, are evacuated by the metal contact. For the trapped holes, that are slower, moves gradually toward the  $Si/SiO_2$  interface, therefore, the trapped charges inside the oxide is mainly positive. It is this last phenomenon that causes an alteration of the electrical characteristics of the electronic components such as the negative and parallel drift of the current-voltage characteristic of the MOSFET transistor. A representation of the variation of the MOSFET characteristics caused by the positive trapped charges inside the oxide is shown in Figure 16.

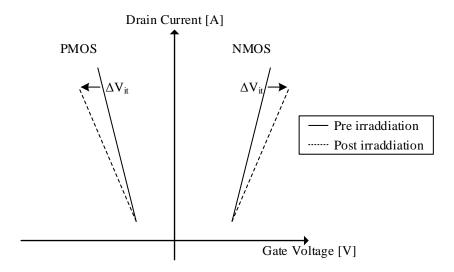

The interface traps density is labeled  $N_{IT}$ . They interact with the carrier inside the silicon by slowing down their mobility while crossing the channel. Therefore, as presented in Figure 17, this mobility reduction modify the MOSFET characteristic slope.

Figure 17: Representation of the impact of the interfaces traps on the characteristics of the MOSFET transistors.

In addition, in order to separate one component to another, shallow trench or deep trench are sometimes implemented as a separation wall between the components in order to avoid current to pass from one component to another and maybe disturb their normal operation. Radiation induced degradation on those oxides can lead to a creation of the path through them, increasing then the leakage current of the component.

# I.6. STATE OF ART OF THE SYNERGISTIC EFFECTS STUDIES

Synergistic effects have been studied for more than ten years in the RADIAC (RADIAtion and Components) research group of the IES of the University of Montpellier. Several Ph.D. programs were dedicated to the investigation of different synergistic effects in collaboration with different civilian and military institutions such as the French Alternative Energies and Atomic Energy Commission (CEA, stands for *Commissariat à l'Énergie atomique et aux Énergies alternatives* in French), the French Directorate General of Armaments (DGA, stands for *Direction Générale de l'Armement* in French), the National Centre for Space Studies (CNES, stands for *Centre national d'études spatiales* in French) and Thales Alenia Space (TAS).

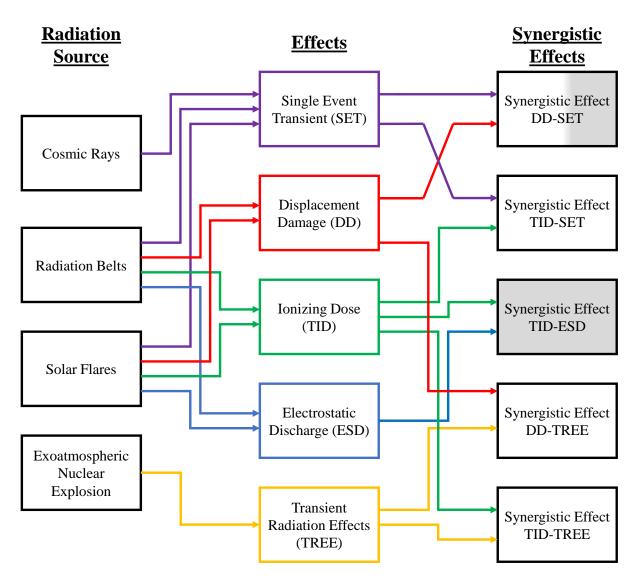

Figure 18: Presentation of different synergistic effects studied on this series of PhD

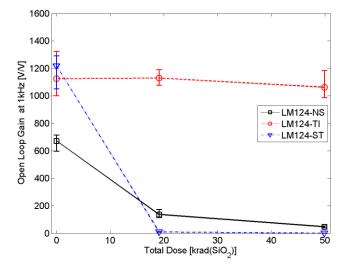

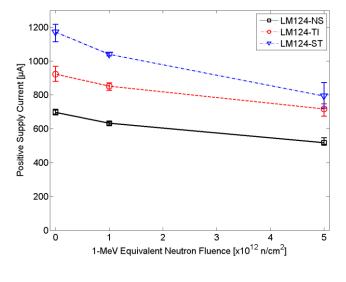

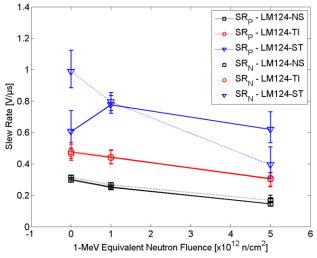

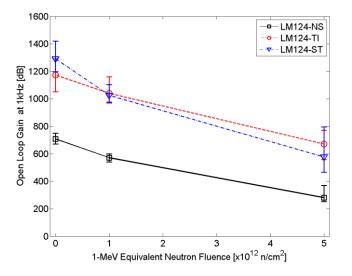

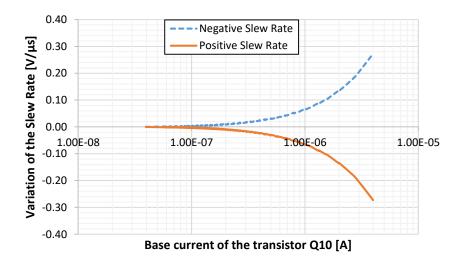

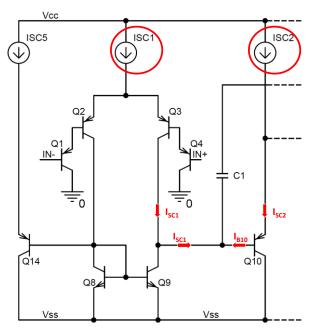

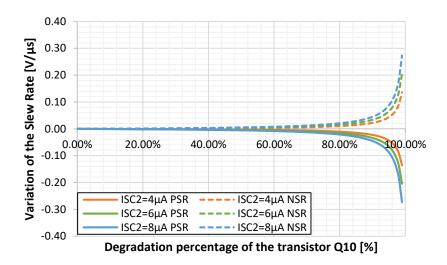

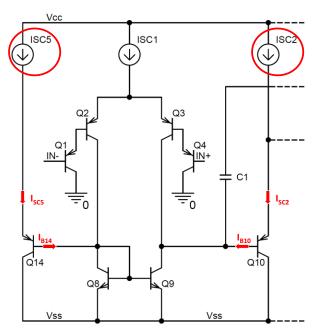

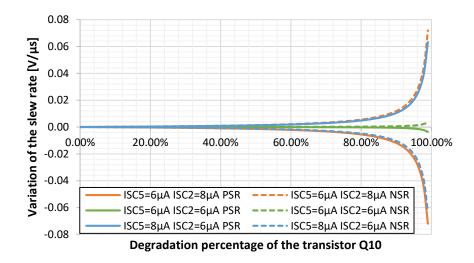

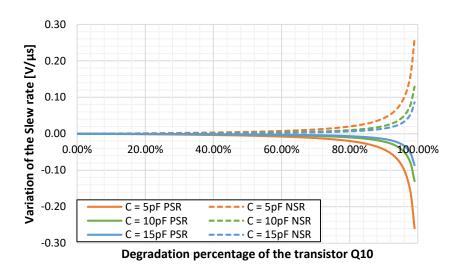

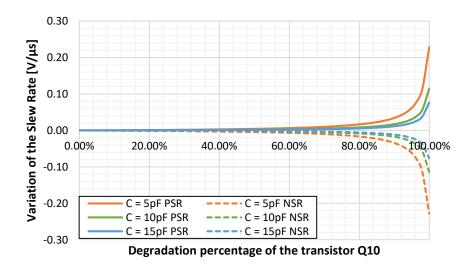

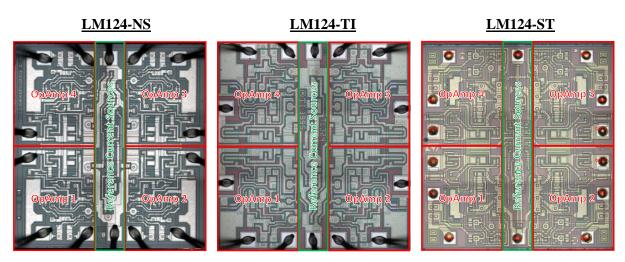

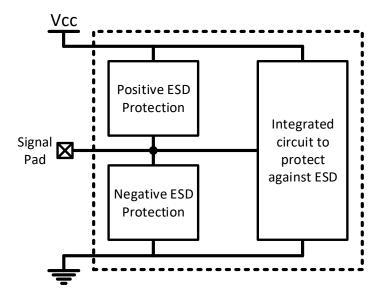

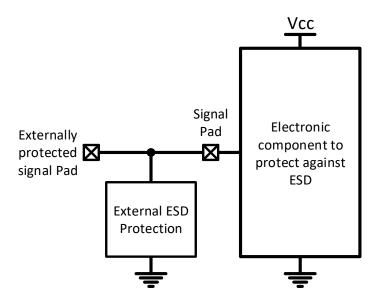

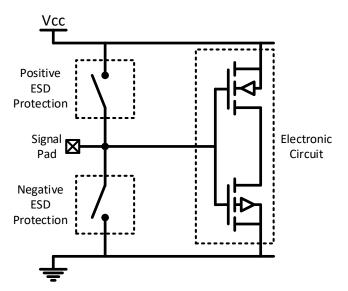

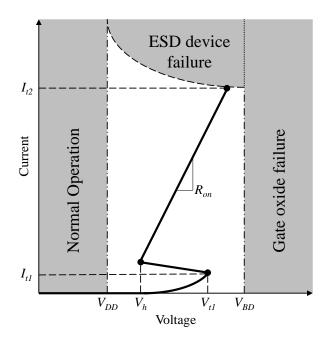

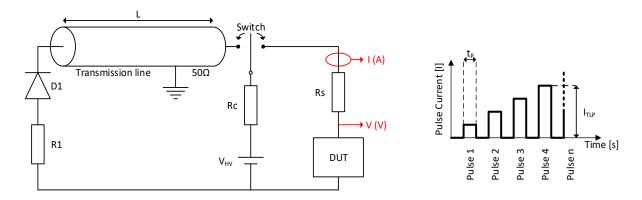

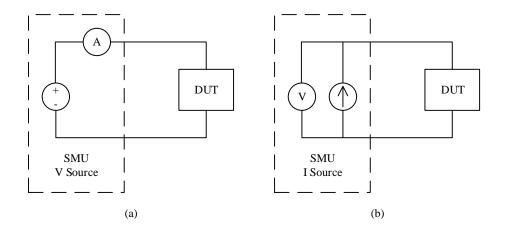

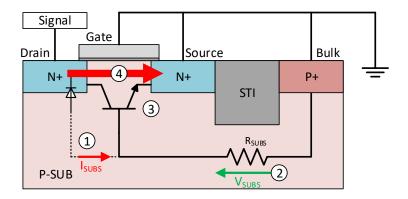

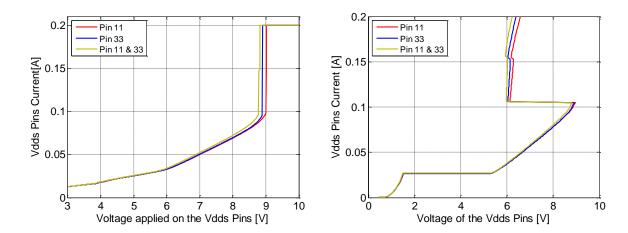

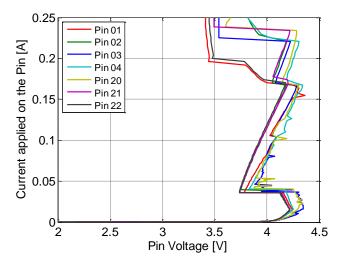

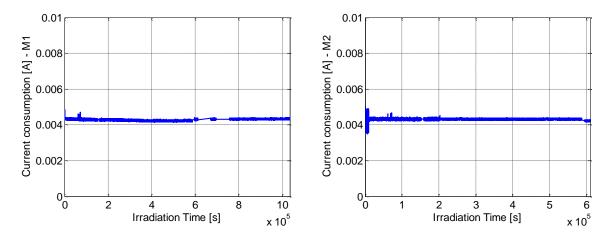

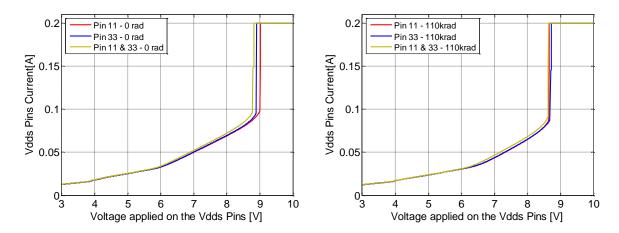

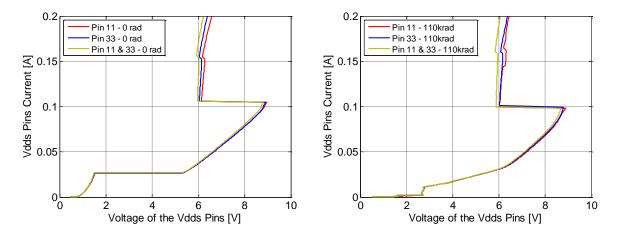

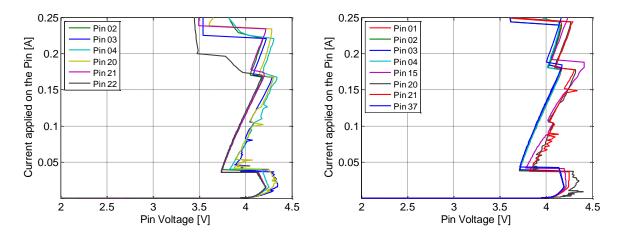

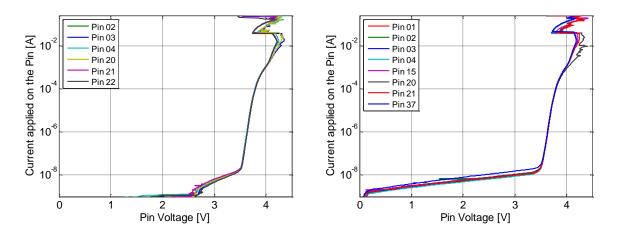

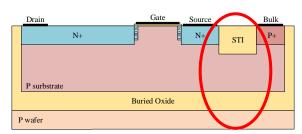

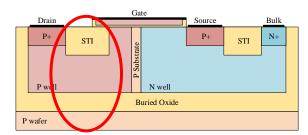

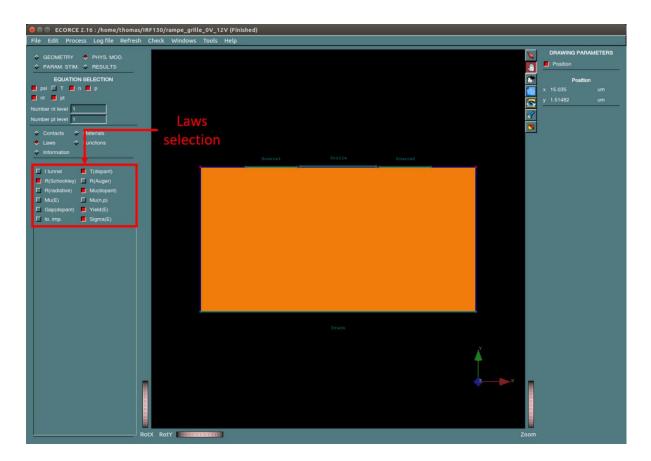

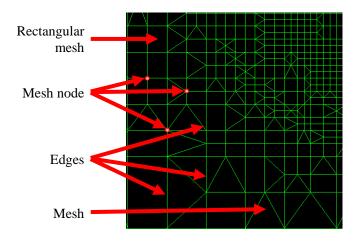

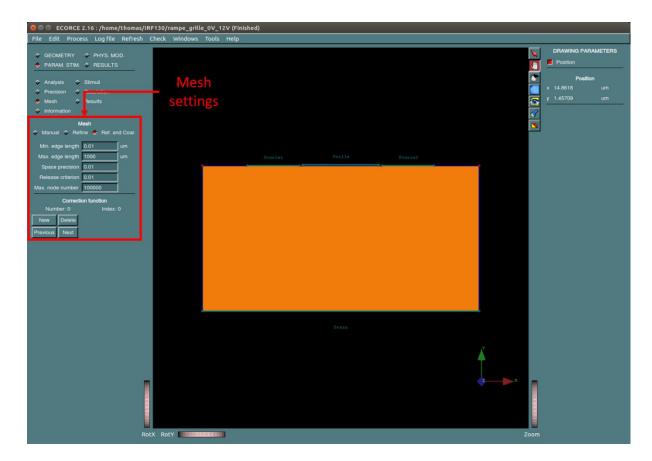

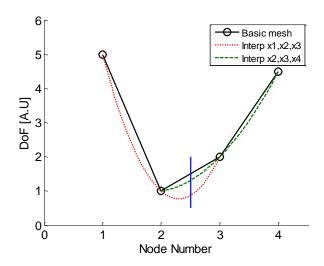

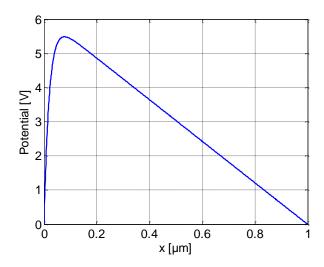

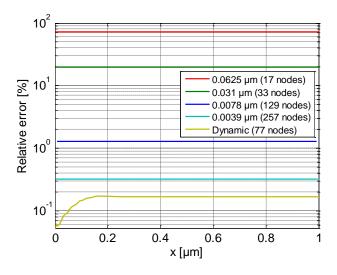

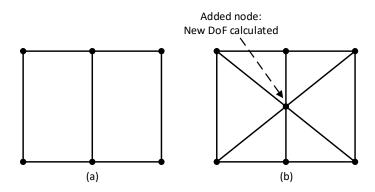

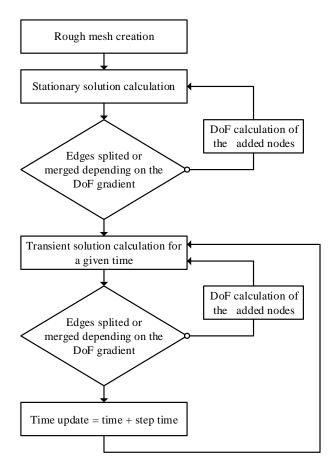

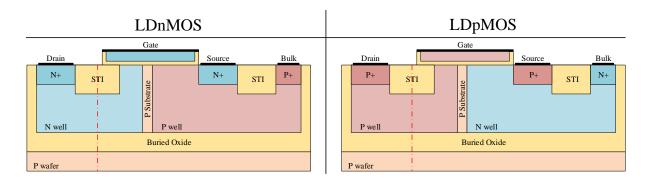

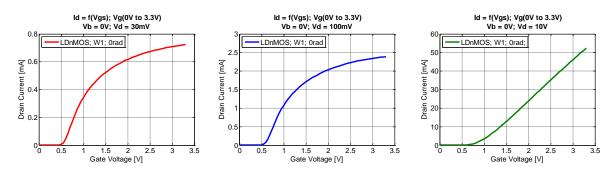

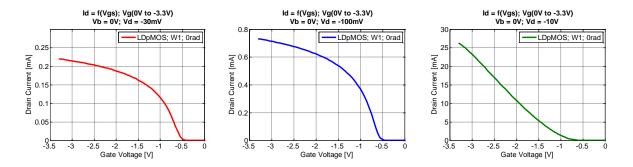

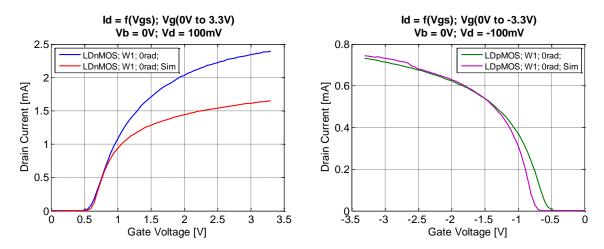

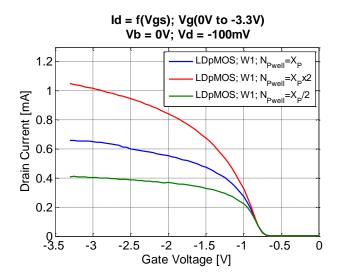

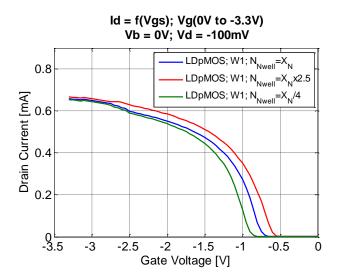

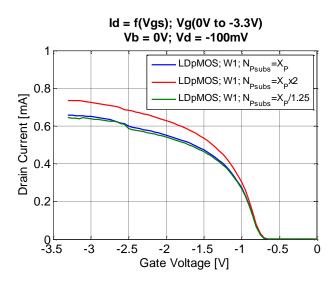

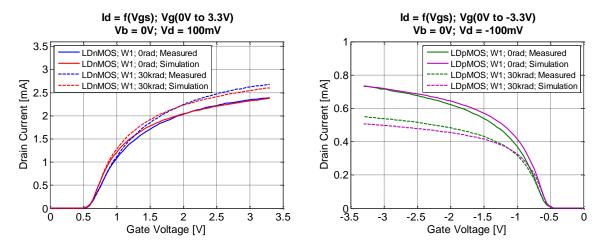

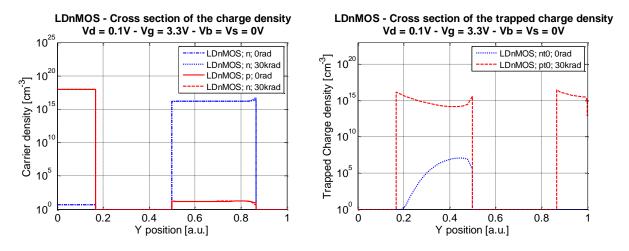

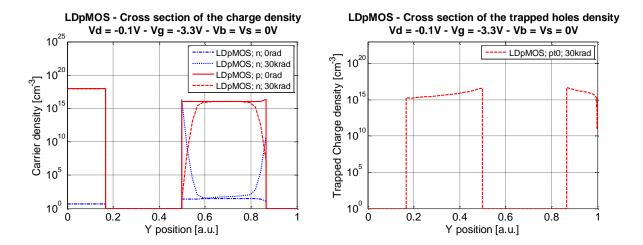

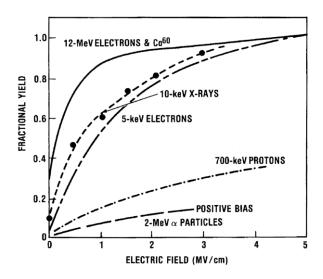

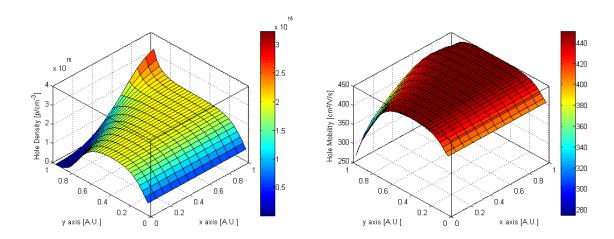

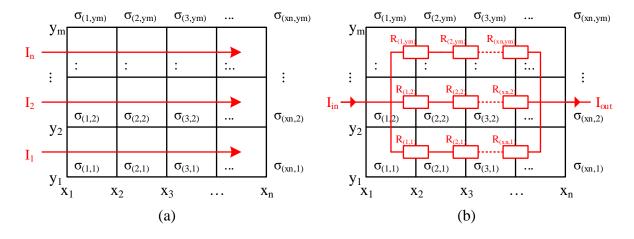

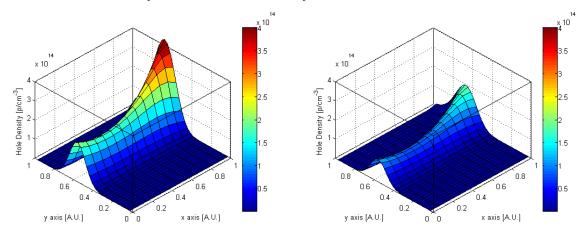

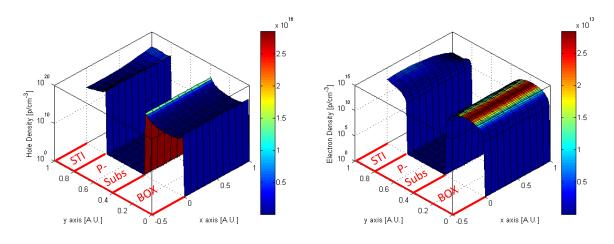

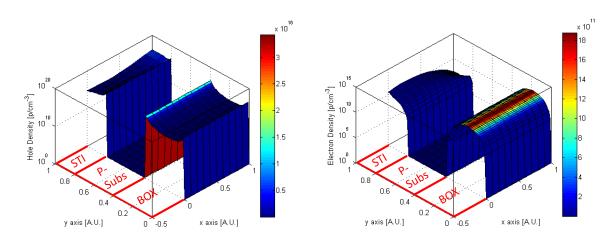

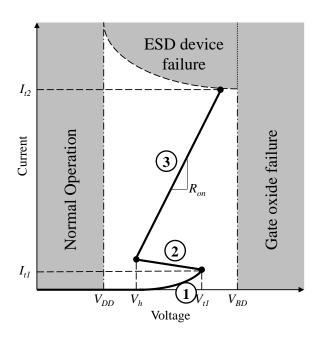

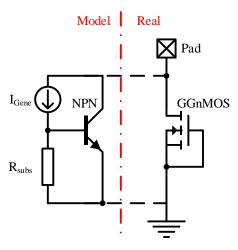

M. Bernard initiated this topic by investigate the synergistic effect between the TID and the SEE on a bipolar voltage comparator [63]. N. Roche extended the research of the synergistic effects by studying