# Methods for protecting intellectual property of IP cores designers

Brice Colombier

#### ▶ To cite this version:

Brice Colombier. Methods for protecting intellectual property of IP cores designers. Micro and nanotechnologies/Microelectronics. Université de Lyon, 2017. English. NNT: 2017LYSES038. tel-02109304

## HAL Id: tel-02109304 https://theses.hal.science/tel-02109304

Submitted on 24 Apr 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre NNT: 2017LYSES038

#### THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein de l' Université Jean Monnet, Saint-Étienne

**Ecole Doctorale 488 Science Ingénierie Santé**

### Spécialité / discipline de doctorat :

Micro-électronique

Soutenue publiquement le 19/10/2017, par : **Brice Colombier**

## Méthodes pour la protection de la propriété intellectuelle des concepteurs de composants virtuels

#### Devant le jury composé de :

| Torres, Lionel        | Professeur | LIRMM               | Président             |

|-----------------------|------------|---------------------|-----------------------|

| Güneysu, Tim          | Professeur | Université de Brême | Rapporteur            |

| Coussy, Philippe      | Professeur | Lab-STICC           | Rapporteur            |

| Chotin-Avot, Roselyne | MCF        | LIP6                | Examinatrice          |

| Le Gal, Bertrand      | MCF        | IMS                 | Examinateur           |

| Bossuet, Lilian       | Professeur | LaHC                | Directeur de thèse    |

| Hély, David           | MCF        | LCIS                | Co-encadrant de thèse |

| Fischer, Viktor       | Professeur | LaHC                | Invité                |

# A thesis submitted for the degree of Doctor of Philosophy from University of Lyon

Doctoral School of Science, Engineering and Health no 488

**Topic : Microelectronics**

# Methods for protecting intellectual property of IP cores designers

By: Brice Colombier

Under the supervision of Lilian Bossuet, Maître de conférences, HDR, and co-supervision of David Hély, Maître de conférences.

Thesis jury: Lilian Bossuet LaHC, France

Roselyne Chotin-Avot LIP6, France Philippe Coussy Lab-STICC, France

Viktor Fischer LaHC, France

Tim Güneysu University of Bremen, Germany

David Hély LCIS, France

Bertrand Le Gal IMS, France

Lionel Torres LIRMM, France

**Defense date:** October 19<sup>th</sup>, 2017

Cette thèse a été financée par la Région Auvergne-Rhône-Alpes

# Remerciements

$\mathring{A}$  ajouter dans la version finale du manuscrit

# **Table of contents**

## **Notations**

| In | trodi | action                                                                     | 1         |

|----|-------|----------------------------------------------------------------------------|-----------|

| 1  | Thr   | eats and protections for design data                                       | 13        |

|    | 1.1   | Parties involved in the design process and their roles                     | 15        |

|    | 1.2   | Threats on design data                                                     | 18        |

|    | 1.3   | Summary: association between parties and threats                           | 20        |

|    | 1.4   | Threat models                                                              | 21        |

|    | 1.5   | Design data protection methods                                             | 24        |

|    | 1.6   | Summary                                                                    | 56        |

|    | 1.7   | High-level requirements for a secure remote activation scheme              | 57        |

|    | 1.8   | SALWARE IP protection module                                               | 57        |

| 2  | Cor   | nbinational logic locking                                                  | <b>59</b> |

|    | 2.1   | Definition                                                                 | 61        |

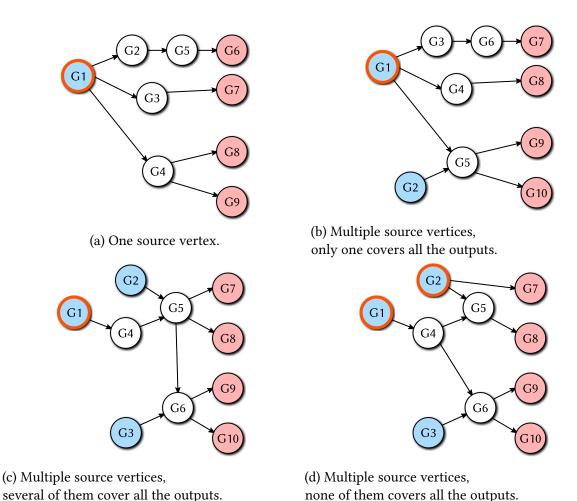

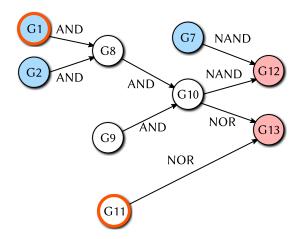

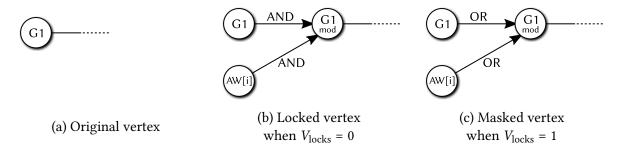

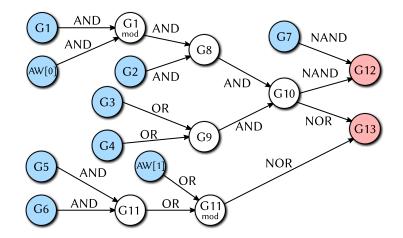

|    | 2.2   | Selection of the place of insertion                                        | 66        |

|    | 2.3   | Experimental results                                                       | 71        |

|    | 2.4   | Discussion                                                                 | 75        |

|    | 2.5   | Conclusion                                                                 | 81        |

| 3  | Cen   | strality indicators for efficient and scalable combinational logic masking | 83        |

|    | 3.1   | Definition                                                                 | 85        |

|    | 3.2   | A proposal for a masking efficiency evaluation metric                      | 85        |

|    | 3.3   | Selection of the place of insertion                                        | 87        |

|    | 3.4   | Experimental results                                                       | 96        |

|    | 3.5   | Possible improvements                                                      | 103       |

|    | 3.6   | A priori evaluation of the masking potential                               | 105       |

|    | 3.7   | Attacks aiming at recovering the activation word                           | 105       |

|    | 3.8   | Conclusion                                                                 | 106       |

| 4  | Kev   | reconciliation protocols for error correction of silicon PUF responses     | 109       |

|              | 4.1     | Similarities between reconciliation in quantum key distribution and reliable |     |

|--------------|---------|------------------------------------------------------------------------------|-----|

|              |         | shared key generation from a PUF response                                    | 111 |

|              | 4.2     | Error correction based on multiple parity checks and binary searches         | 112 |

|              | 4.3     | BINARY protocol                                                              | 113 |

|              | 4.4     | CASCADE protocol                                                             | 116 |

|              | 4.5     | Parameters of the CASCADE protocol                                           | 117 |

|              | 4.6     | Implementation                                                               | 122 |

|              | 4.7     | Experimental results                                                         | 124 |

|              | 4.8     | Security: attacks and countermeasures                                        | 132 |

|              | 4.9     | Discussion                                                                   | 134 |

|              | 4.10    | Conclusion                                                                   | 135 |

| 5            | Con     | aplete hardware/software infrastructure IP for design protection             | 137 |

|              | 5.1     | Integration into EDA tools                                                   | 139 |

|              | 5.2     | Hardware platform: HECTOR board                                              | 146 |

|              | 5.3     | Overall hardware implementation results                                      | 147 |

|              | 5.4     | Software interface                                                           | 149 |

|              | 5.5     | Illustrative example                                                         | 151 |

|              | 5.6     | Use case                                                                     | 152 |

|              | 5.7     | Conclusion                                                                   | 153 |

| Co           | nclu    | sion                                                                         | 155 |

| Pu           | blica   | tions and communications                                                     | 163 |

| Bi           | bliog   | raphy                                                                        | 167 |

| <b>A</b> 1   | nner    | ndices                                                                       | 183 |

| <b>4 3</b> J | PPCI.   |                                                                              | 103 |

| Ex           | amp     | les of graphs found in graph analysis for combinational logic locking        | 183 |

| Lis          | st of l | Figures                                                                      | 187 |

| Lis          | st of T | Γables                                                                       | 191 |

# Sommaire

#### **Notations**

| In | trodu | ction                                                                      | 7         |

|----|-------|----------------------------------------------------------------------------|-----------|

| 1  | Mena  | aces sur les données de conception et méthodes de protection               | 13        |

|    | 1.1   | Acteurs impliqués dans le processus de conception et leur rôle             | 15        |

|    | 1.2   | Menaces sur les données de conception                                      | 18        |

|    | 1.3   | Résumé : liens entre acteurs et menaces                                    | 20        |

|    | 1.4   | Modèles de menace                                                          | 21        |

|    | 1.5   | Méthodes de protection des données de conception                           | 24        |

|    | 1.6   | Résumé                                                                     | 56        |

|    | 1.7   | Caractéristiques requises pour un système d'activation à distance sécurisé | 57        |

|    | 1.8   | Module de protection de la propriété intellectuelle SALWARE                | 57        |

| 2  | Verre | ouillage de la logique combinatoire                                        | <b>59</b> |

|    | 2.1   | Définition                                                                 | 61        |

|    | 2.2   | Sélection du lieu d'insertion                                              | 66        |

|    | 2.3   | Résultats expérimentaux                                                    | 71        |

|    | 2.4   | Discussion                                                                 | 75        |

|    | 2.5   | Conclusion                                                                 | 81        |

| 3  | Indic | cateurs de centralité pour le masquage logique combinatoire efficace et    |           |

|    | adap  | table                                                                      | 83        |

|    | 3.1   | Définition                                                                 | 85        |

|    | 3.2   | Proposition pour une métrique d'évaluation de l'efficacité du masquage     | 85        |

|    | 3.3   | Sélection du lieu d'insertion                                              | 87        |

|    | 3.4   | Résultats expérimentaux                                                    | 96        |

|    | 3.5   | Améliorations possibles                                                    | 103       |

|    | 3.6   | Évaluation a priori du potentiel de masquage                               | 105       |

|    | 3.7   | Attaques visant à retrouver le mot d'activation                            | 105       |

|    | 20    | Conclusion                                                                 | 107       |

| 4  | Prot   | ocoles de réconciliation de clés pour la correction des erreurs dans les            |     |

|----|--------|-------------------------------------------------------------------------------------|-----|

|    | répo   | onses des PUFs                                                                      | 109 |

|    | 4.1    | Similarités entre la réconciliation en distribution quantique de clés et la généra- |     |

|    | 4.2    | tion fiable de clé à partir d'une réponse de PUF                                    | 111 |

|    |        | dichotomique                                                                        | 112 |

|    | 4.3    | Protocole BINARY                                                                    | 113 |

|    | 4.4    | Protocol CASCADE                                                                    | 116 |

|    | 4.5    | Paramètres du protocole CASCADE                                                     | 117 |

|    | 4.6    | Implémentation                                                                      | 122 |

|    | 4.7    | Résultats expérimentaux                                                             | 124 |

|    | 4.8    | Sécurité : attaques et contre-mesures                                               | 132 |

|    | 4.9    | Discussion                                                                          | 134 |

|    | 4.10   | Conclusion                                                                          | 135 |

| 5  | Infr   | astructure matérielle/logicielle complète pour la protection des données            |     |

|    | de c   | onception                                                                           | 137 |

|    | 5.1    | Intégration aux outils de conception électronique                                   | 139 |

|    | 5.2    | Plateforme matérielle : carte HECTOR                                                | 146 |

|    | 5.3    | Résultats d'implémentation matérielle globaux                                       | 147 |

|    | 5.4    | Interface logicielle                                                                | 149 |

|    | 5.5    | Exemple illustratif                                                                 | 151 |

|    | 5.6    | Cas d'utilisation                                                                   | 152 |

|    | 5.7    | Conclusion                                                                          | 153 |

| C  | onclu  | sion                                                                                | 159 |

| Pı | ublica | tions et communications                                                             | 163 |

| Bi | ibliog | raphie                                                                              | 166 |

| A  | nnex   | ces                                                                                 | 183 |

## Acronyms

**ASIC** application-specific integrated circuit.

AW activation word.

**BEOL** back end of line.

**CC**0 combinational 0 controllability.

CC1 combinational 1 controllability.

**CMOS** complementary metal-oxide-semiconductor.

**CO** combinational observability.

**CRP** challenge-response pair.

**DFF** D flip-flop.

**DIP** distinguishing input pattern.

**EDA** electronic design automation.

**EEPROM** electrically-erasable programmable read-only memory.

**FEOL** front end of line.

**FPGA** field-programmable gate array.

**FSM** finite-state machine.

**HDL** hardware description language.

**IP** intellectual property.

**LPN** Learning parities with noise.

LUT look-up table.

**NVM** non-volatile memory.

**OTP-NVM** one-time programmable non-volatile memory.

**PoS** Product-of-Sums.

**PUF** physical unclonable function.

**RO-PUF** ring oscillator PUF.

**ROM** read-only memory.

**SoC** System on Chip.

**SoP** Sum-of-Products.

**SRAM** static random access memory.

**TERO** transient effect ring oscillator.

**TERO-PUF** transient effect ring oscillator PUF.

# **Notations**

- $[X]_K$  Ciphertext obtained after symmetric encryption of the plaintext X with the key K.

- $[X]_K^{-1}$  Plaintext obtained after symmetric decryption of the ciphertext X with the key K.

- HD(A, B) Hamming distance between A and B.

- A[i] i<sup>th</sup> bit of vector A.

## Introduction

According to the World Semiconductor Trade Statistics (WSTS), the sales of the semiconductor market reached almost \$340 billion in 2016<sup>1</sup>. This ever-changing industry is characterised by a vigorous competitiveness, a steadily increasing complexity and a strong market pull. One of the main problems facing this industry today is the protection of design intellectual property rights. This is mainly due to the multiplicity of actors involved in the design, production and marketing of electronic products. In order to understand where the issue comes from, a historical and economical overview of the semiconductor industry is necessary.

#### Historical and economical context

Moore's law, first published in 1965 [Moo65] and revised in 1975 [Moo75] states that the number of transistors that can be integrated on a unit area of integrated circuit doubles every two years. So far, even though a slight slowdown has been observed in recent years, the microelectronics industry followed this law. This is possible by making transistors smaller and smaller, 10nm being the technology node achieved in 2017<sup>2,3</sup>. Such a constant decrease is due to a strong market pull, which led customers to request more and more sophisticated, powerful and small devices.

A corollary of Moore's law is Rock's law, which states that the cost of a fabrication plant for integrated circuits doubles every four years. This emerges directly from the decreasing size of the transistors, making them harder and harder to manufacture. The cost of manufacturing plants now reaches tens of billion dollars<sup>4,5</sup>. With such considerable investments, control over

<sup>&</sup>lt;sup>1</sup>Global Semiconductor Sales Reach \$339 Billion in 2016 http://www.semiconductors.org/news/2017/02/02/global\_sales\_report\_2015/global\_semiconductor\_sales\_reach\_339\_billion\_in\_2016/

<sup>&</sup>lt;sup>2</sup>Samsung Starts Industry's First Mass Production of System-on-Chip with 10-Nanometer FinFET Technology. http://news.samsung.com/global/samsung-starts-industrys-first-mass-production-of-system-on-chip-with-10-nanometer-finfet-technology

<sup>&</sup>lt;sup>3</sup>Intel Finds Moore's Law's Next Step at 10 Nanometers. http://spectrum.ieee.org/semiconductors/devices/intel-finds-moores-laws-next-step-at-10-nanometers

<sup>&</sup>lt;sup>4</sup>China's Tsinghua Unigroup to build \$30 billion Nanjing chip plant. http://www.reuters.com/article/us-tsinghua-plant-idUSKBN1532ED

<sup>&</sup>lt;sup>5</sup>Samsung Breaks Ground on \$14 Billion Fab. http://www.eetimes.com/document.asp?doc\_id=1326565

fabrication plants rose to a national priority in USA<sup>6,7</sup>, since most of the foundries are now located in Asia. Another consequence of this increasing up-front investment is the market domination of existing large corporations, where five of them (Intel, Samsung, Qualcomm, Broadcom, and SK Hynix) hold 41% of the marketshares in 2016<sup>8</sup>. The top two companies, Intel and Samsung, use the historical *Integrated Device Manufacturer* (IDM) model. A single company accomplishes the design, manufacturing and selling of the integrated circuit. However, the next two, Qualcomm and Broadcom, use the *fabless* model. As the name suggests, *fabless* companies do not own any fabrication facility. Instead, they rely on manufacturing plants own by third parties. Those companies, specialised in integrated circuits manufacturing, are called *foundries*. They are more and more important in the semiconductor industry, exceeding 50 billion dollars in sales in 2016, with an 11% increase compared to 2015<sup>9</sup>. Together, fabless designers and foundries form a new business model [Hod11], that appeared in the 1980s, when the process was split into two parts: design and manufacturing.

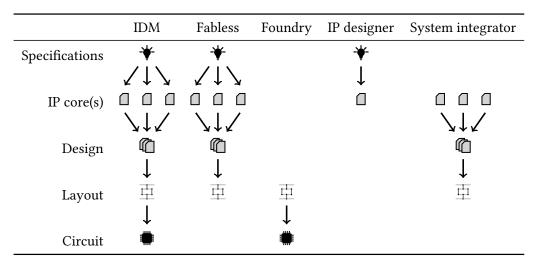

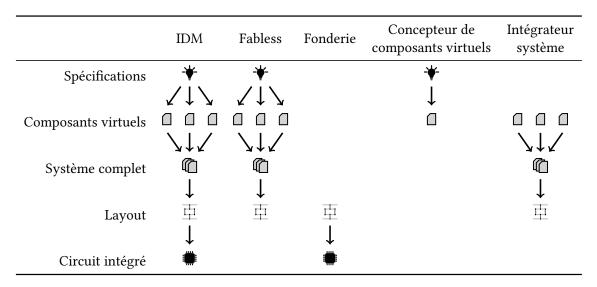

Semiconductors being a very competitive market, shorter and shorter time to market has been required. In conjugation with a strong market pull, the alloted time to design integrated circuits reduced significantly. In order to keep-up with this trend, integrated circuits designers massively switched to a design-and-reuse paradigm, also called core-based design [GZ97]. In this framework, a complex design is split into smaller functional blocks of manageable complexity. Thus two new types of companies appeared in the design process, dividing it further. Intellectual property (IP) providers design individual IP cores, implementing a precise function. For instance, one can find JPEG encoder or Ethernet controller IP cores. Those IP cores are typically purchased by system integrators, who integrate them into a single modular design. The different types of companies taking part in the design of an integrated circuit are shown in Figure 1. Of course, such a strict division does not perfectly match reality. For instance, a fabless designer might develop some IP cores in-house and purchase others from third party IP core providers.

The next section focuses on IP cores, detailing how they are distributed and the threats associated to this business model.

## IP cores distribution and business model

Following the global transition from an industrial economy to a knowledge economy [Dru69], the semi-conductor industry now relies heavily on the exchange and monetisation of intellectual

<sup>&</sup>lt;sup>6</sup>Can the White House Make America's Chip Industry Great Again? http://www.technologyreview.com/s/602768/can-the-white-house-make-americas-chip-industry-great-again/

$<sup>^7 {\</sup>rm Trump}$  team backs call for crackdown on China over semiconductors. http://www.ft.com/content/bca04dfede67-11e6-9d7c-be108f1c1dce

<sup>&</sup>lt;sup>8</sup>Five Suppliers Hold 41% of Global Semiconductor Marketshare in 2016. http://www.icinsights.com/data/articles/documents/938.pdf

<sup>&</sup>lt;sup>9</sup>Pure-Play Foundry Market Surges 11% in 2016 to Reach \$50 Billion! http://www.icinsights.com/data/articles/documents/945.pdf

Figure 1 – Semiconductor companies and their respective positions in the integrated circuit design process.

property for the design of integrated circuits. Practically, IP cores are not provided alone but can come with application-specific integrated circuit (ASIC) synthesis scripts, field-programmable gate array (FPGA) place & route scripts, simulation scripts, testbenches, software models, test vectors, documentation, etc. Much like software companies, IP cores design companies now make the headlines for mergers and acquisitions worth millions of dollars. For instance, Intel acquired Altera and NXP was acquired by Qualcomm in the last two years. As stated in a recent research bulletin by IC Insights<sup>10</sup>, "The dollar value of merger and acquisition agreements in 2015 and 2016 were both about eight times greater than the \$12.6 billion annual average of M&A announcements in the five previous years (2010-2014)".

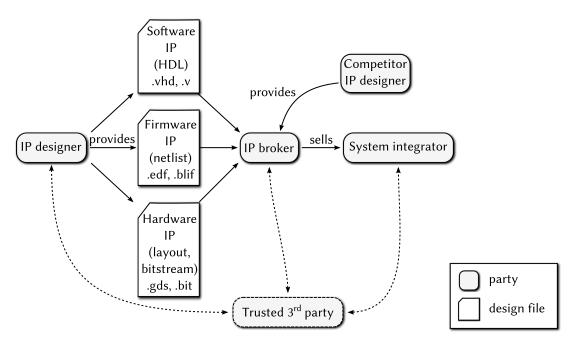

Designers directly sell their IP cores to system integrators or rely on an intermediate IP broker. Those IP brokers, such as ChipEstimate<sup>11</sup>, Design-And-Reuse<sup>12</sup> or CAST<sup>13</sup>, maintain large catalogues of IP cores from multiple designers. System integrators then purchase IP cores from the brokers or from the designers directly. This is very similar to the way software products are sold.

However, even though the distributions of IP cores and pieces of software work in a similar way nowadays, their actual usage after distribution is entirely different. Indeed, proprietary pieces of software come with a license, either in the form of a key, a file or a server. Without them, the software cannot be executed. IP cores however, once they are sold by the designer, are much harder to keep control on. The main issue here is that once an IP core has been sold, the IP designer has no way of knowing how many times the IP core is actually instantiated.

This issue comes into great conflict with the knowledge economy principle stated above. Indeed, without knowing the number of IP core instances, IP designers must adopt a licensing

<sup>10 2015-2016</sup> deals dominate semiconductor M&A ranking. http://www.icinsights.com/data/articles/documents/946.pdf

<sup>&</sup>lt;sup>11</sup>http://www.ipcatalog.com

<sup>&</sup>lt;sup>12</sup>http://www.design-reuse.com

<sup>&</sup>lt;sup>13</sup> http://www.cast-inc.com

model with upfront payment. In this model, an IP designer demands a fixed amount of money from a system integrator before selling the IP core. Once it has been sold, the system integrator can instantiate the IP core as many times as needed. There are two issues with this business model. Firstly, it can inhibit small scale purchases for prototyping purposes or for small companies due to a too high initial investment. Secondly, it strongly limits the advantages brought by core-based design, which could benefit greatly from features typically found in software products like an evaluation period or a premium version of the IP core with enhanced performances.

Besides the limitations brought by upfront licensing, the main issue with the designer not knowing how many times the IP core is instantiated is that it can potentially be illegally copied. For example, a system integrator could sell a previously purchased IP core to business associates for a lower price, without the original designer knowing about it.

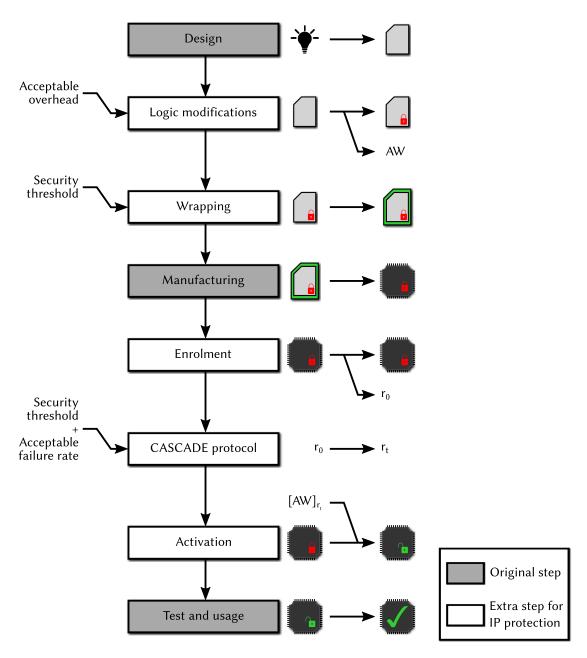

In order to exploit the full potential and benefits of knowledge economy and to prevent illegal copying, a designer must then be able to know how many times a particular IP core has been instantiated. Moreover, by allowing the designer to remotely activate an IP core, pay-per-use licensing would be possible. Finally, with remote activation comes pre-activation mode. If this mode is degraded, illegal copies can be effectively made useless until they are properly activated by the original IP designer. Obviously, such a remote activation scheme should also be secure, so that ill-intentioned users cannot circumvent it and use an illegal copy of the IP core. This is one of the objectives of the SALWARE project.

## **SALWARE** project

The SALWARE project is a 4-year project, supported by the French "Agence Nationale de la Recherche" and by the "Fondation de Recherche pour l'Aéronautique et l'Espace". The title of the project is: "Salutary hardware design to fight against integrated circuit counterfeiting and theft". The name of the project originates from the word malware, which stands for "malicious software", and was turned into salware which stands for "salutary hardware". The aim of the project is to design hardware components that provide intellectual property information and/or allow for remote activation of an integrated circuit or and intellectual property core after manufacturing. The hardware components designed in the framework of the SALWARE project aim at exhibiting the same features as a malware. Namely, they should be stealthy, or lightweight, in order to make the logic resources overhead as low as possible. This is a very strict requirement to make the proposed solution industrially usable. Moreover, they should be efficient at disturbing the operation of the circuit or the IP core, so that illegal copies are essentially useless. Finally, they should be sufficiently hard to remove or circumvent to deter malicious users.

Cédric Marchand, who was another PhD student working in the frame of the SALWARE project, defended his PhD in 2016 [Mar16]. His PhD thesis deals with watermarking, physical

unclonable function (PUF) design and lightweight cryptography implementation, which are essential components for salutary hardware, but more specifically targeted at preventing integrated circuits counterfeiting. This PhD thesis has complementary contributions, which are presented below, focusing more precisely on IP cores.

## **Contributions**

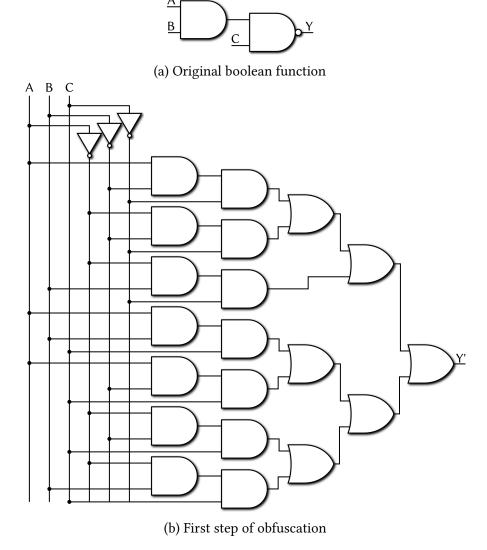

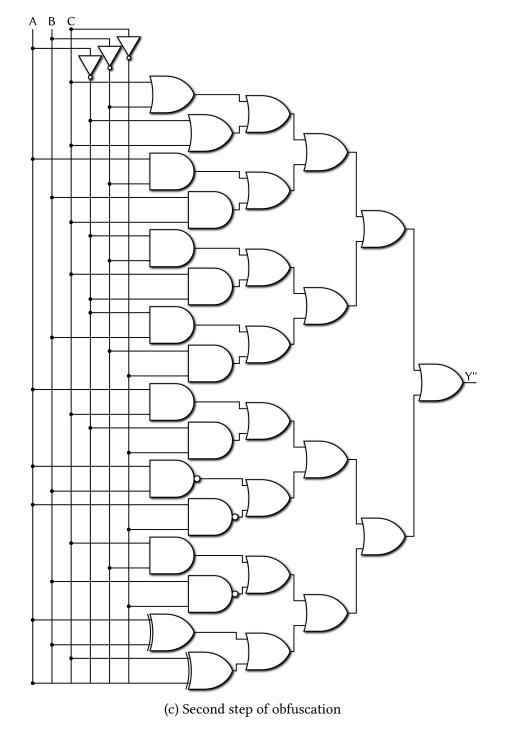

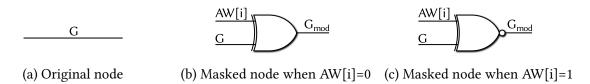

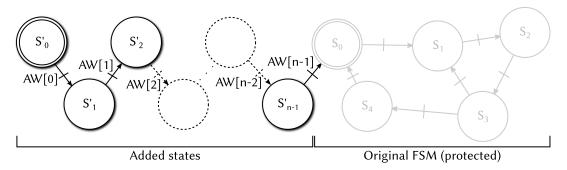

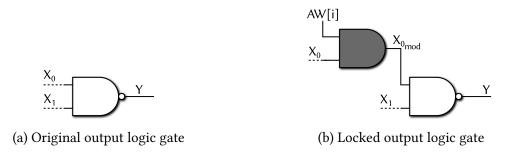

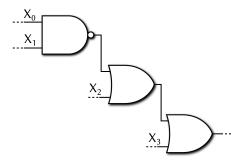

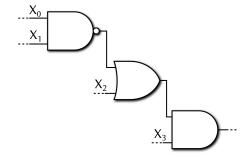

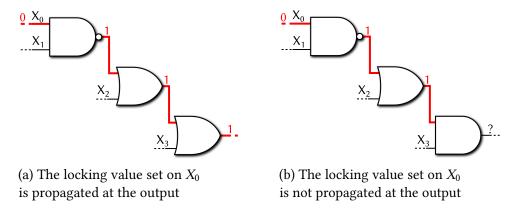

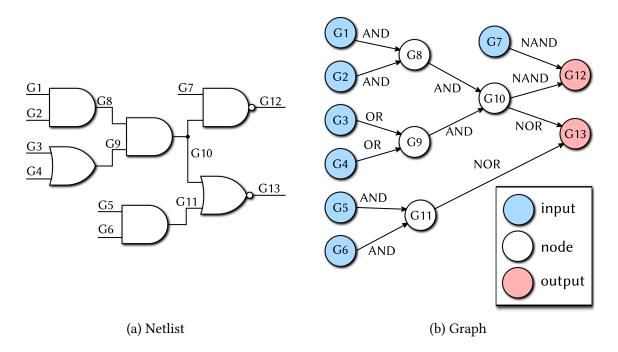

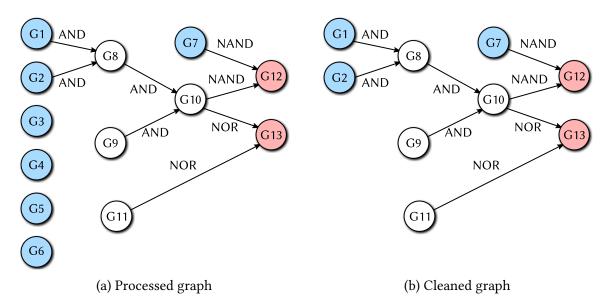

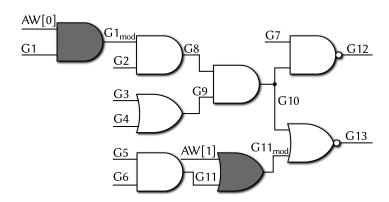

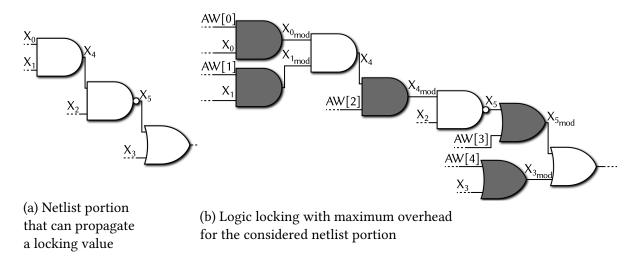

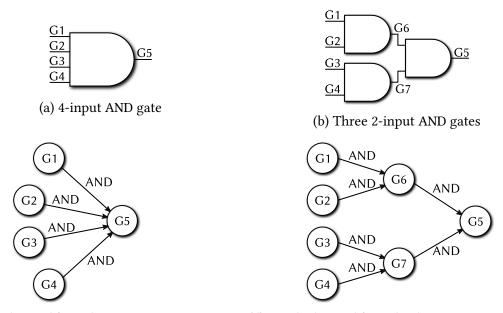

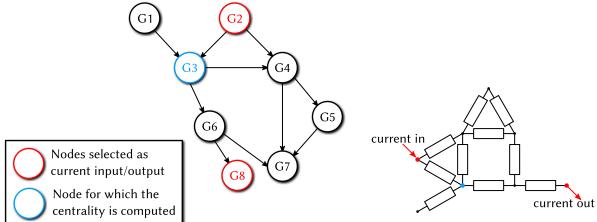

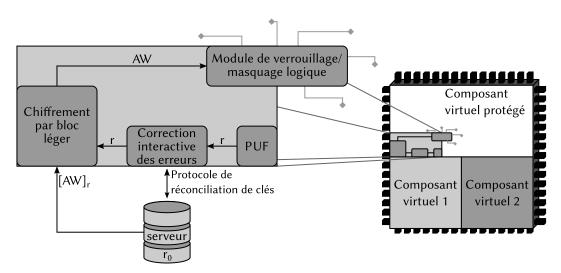

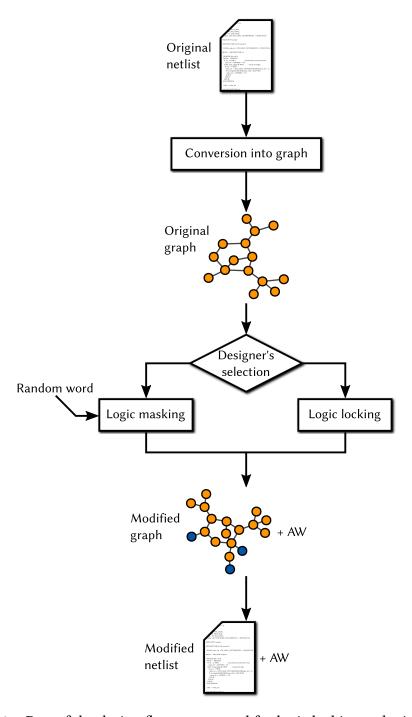

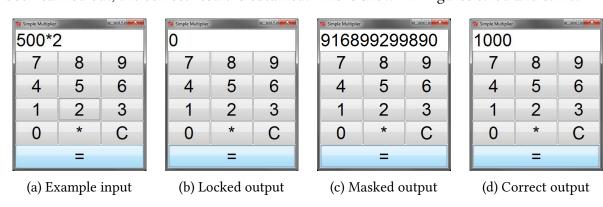

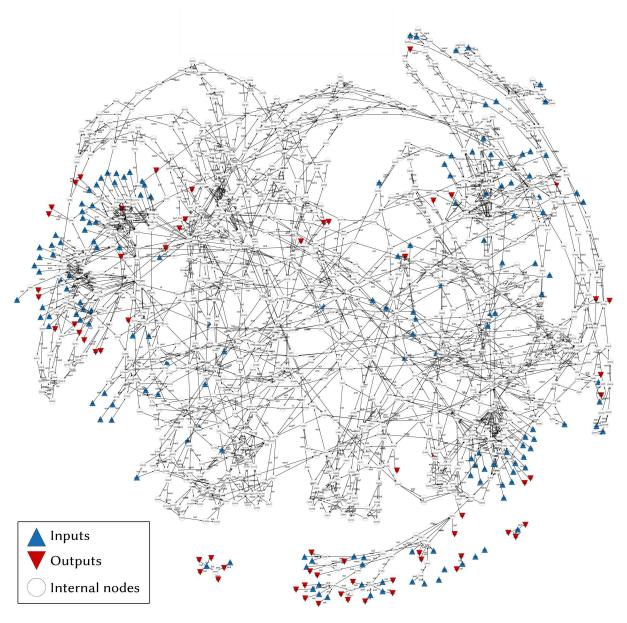

First of all, in order to ensure that a design data protection scheme is efficient, illegal copies must exhibit a very disturbed operation. The first option explored in this thesis to achieve this is to controllably force the outputs of a netlist to a fixed logic level. We call this logic locking. A very efficient algorithm to select the netlist nodes to modify based on the propagation of a controlling value in a graph is presented.

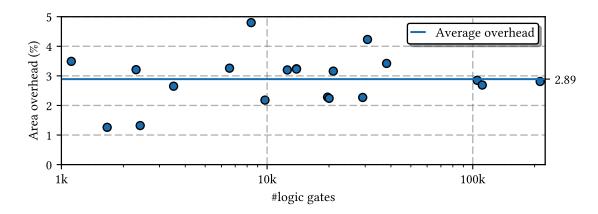

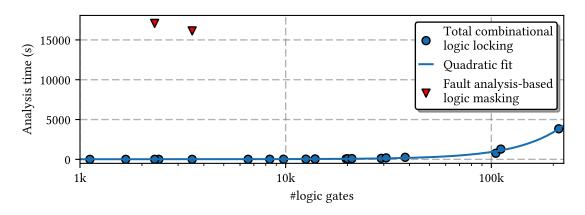

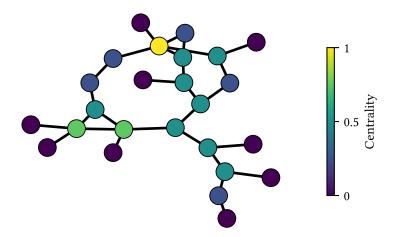

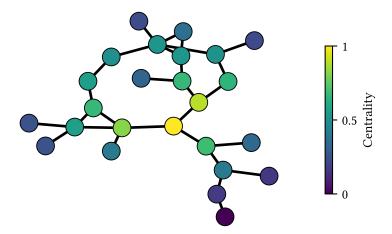

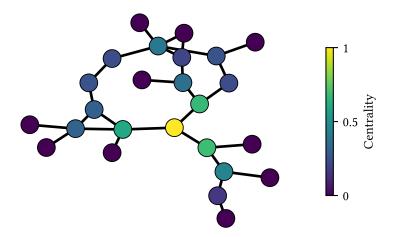

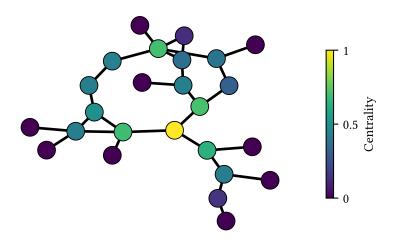

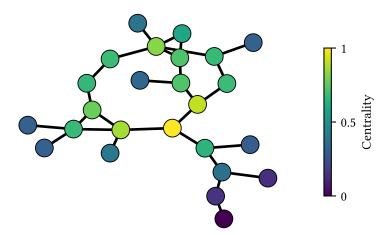

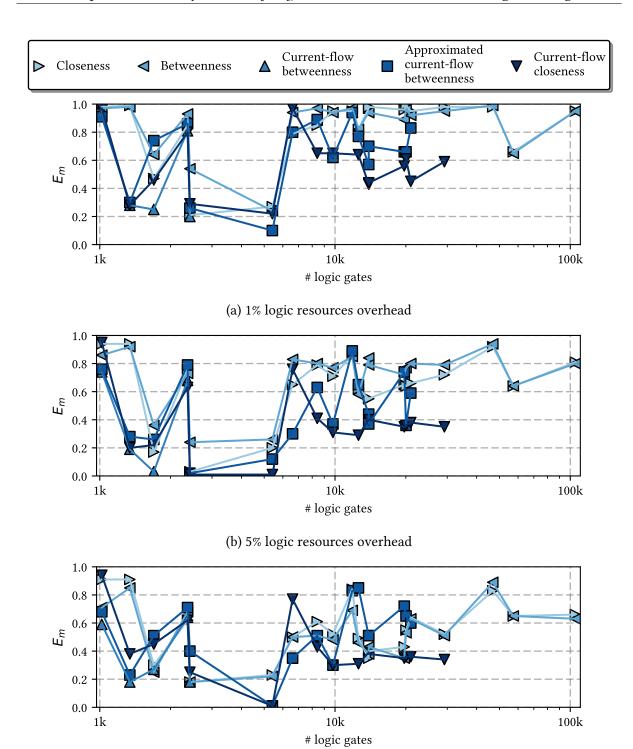

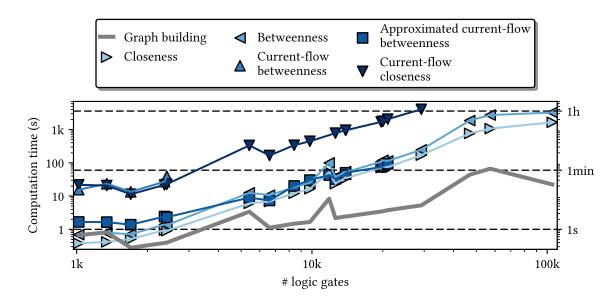

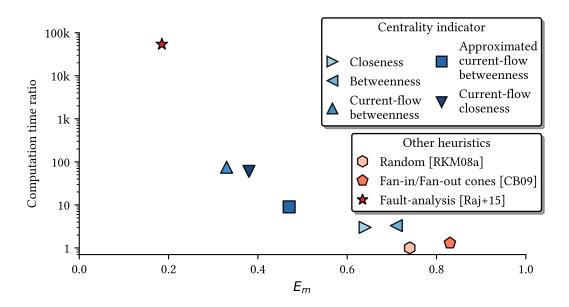

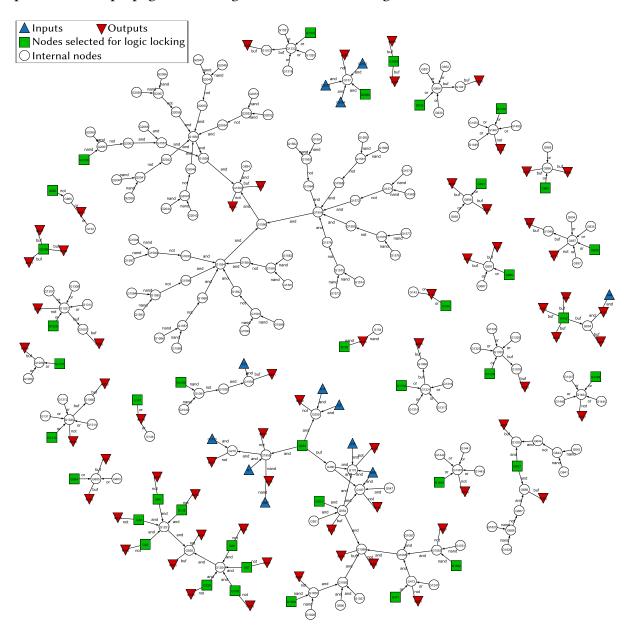

The second option to provide a degraded mode of operation is to disturb the outputs of the netlist by controllably inverting specific internal nodes. We refer to this as logic masking. Specifically, a new method of selection of the nodes to invert based on centrality indicators from graph theory is shown. Compared to state-of-the-art selection heuristics, it scales better to large netlists and efficiently disturbs the circuit operation.

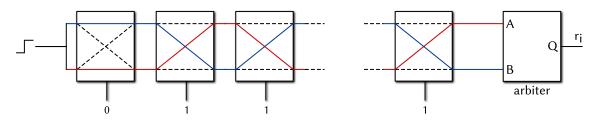

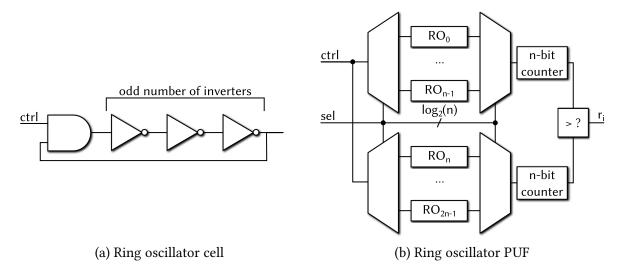

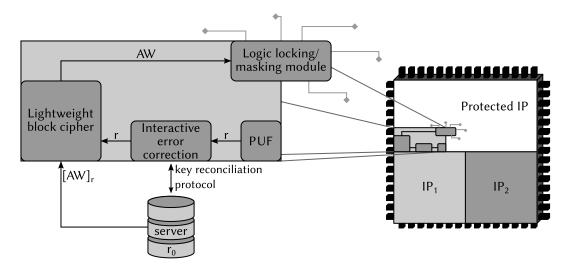

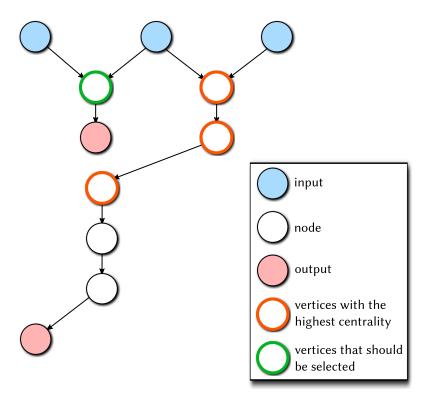

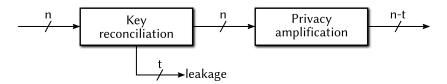

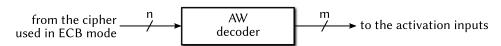

The third contribution of this thesis deals with unique identification of IP core instances using a PUF. PUFs are very interesting primitives since they allow to identify IP core instances by extracting device-specific manufacturing process variations, which are known to be random. However, those PUFs are subject to instability, and the extracted identifiers are not stable enough. To deal with this, we propose an innovative method based on the CASCADE key reconciliation protocol. Originally developed for quantum key exchange, we show that this interactive protocol can be successfully applied to error-correction of silicon PUF responses. Compared to existing error-correcting codes implementations, it is around an order of magnitude more lightweight in terms of required logic resources.

Finally, these contributions and those found in [Mar16] are bundled together in a complete design data protection module. We show that this module fulfils the requirements of a *salware* by being lightweight, secure and efficient at providing different degraded modes of operation for an IP core. Overall, this is an industrially viable solution for IP designers who wish to protect their design data from illegal copying at reduced cost.

## **Outline**

Chapter 1 presents the IP business model which is widely adopted by the semiconductor industry nowadays. We highlight the new threats on design data which emerge from this new business model and provide a detailed threat model. We then provide a state of the art of existing data protection methods for IP cores. We conclude this chapter by giving the requirements for the complete design data protection module and provide a high-level overview of the different

components required to fulfil these requirements. Chapter 2 describes the method based on graph-analysis for combinational logic locking of a netlist. Chapter 3 shows how centrality indicators from graph theory can be used to select the most suited nodes to modify by logic masking. Chapter 4 presents the similarities between two scenarios, quantum key exchange and error-correction for silicon PUF responses. In particular, we show how the CASCADE key-reconciliation protocol can be used to provide lightweight error correction of silicon PUF responses. Finally, Chapter 5 presents the complete hardware/software design data protection module, which is the objective of the SALWARE project.

## Introduction

D'après les Statistiques du Commerce Mondial des Semi-conducteurs, le marché des semi-conducteurs a atteint 340 milliards de dollars de vente en 2016<sup>14</sup>. Cette industrie en évolution constante est caractérisée par une compétitivité intense, une complexité en constance croissance et une forte demande du marché. L'un des principaux problèmes auquel cette industrie doit aujourd'hui faire face est la protection des droits de propriété intellectuelle sur les données de conception. Cela est dû majoritairement à la multiplicité des acteurs impliqués dans la conception, la production et la commercialisation de produits électroniques. Afin de comprendre d'où vient le problème, un aperçu de l'industrie des semi-conducteurs d'un point de vue historique et économique est nécessaire.

## Contexte historique et économique

La loi de Moore, publiée pour la première fois en 1965 [Moo65] puis révisée en 1975 [Moo75], dit que le nombre de transistors qui peuvent être intégrés sur une surface unitaire de circuit intégré double tous les deux ans. Jusqu'ici, même si un ralentissement certain a été observé récemment, l'industrie de la micro-électronique a suivi cette loi. Ceci est rendu possible en réduisant de plus en plus la taille des transistors, 10nm étant le nœud technologique atteint en 2017<sup>15,16</sup>. Cette diminution constante est due à une forte demande du marché, qui a amené les consommateurs à demander des équipements toujours plus sophistiqués, puissants et petits. Un corollaire de la loi de Moore est la loi de Rock, qui dit que le coût de fabrication d'une usine de fabrication de circuit intégrés double, lui, tous les quatre ans. Ceci est une conséquence directe de la diminution de la taille des transistors, ce qui les rend de plus en plus complexes à fabriquer. Le coût d'une usine de fabrication atteint aujourd'hui des dizaines

<sup>&</sup>lt;sup>14</sup>Global Semiconductor Sales Reach \$339 Billion in 2016 http://www.semiconductors.org/news/2017/02/02/global\_sales\_report\_2015/global\_semiconductor\_sales\_reach\_339\_billion\_in\_2016/

<sup>&</sup>lt;sup>15</sup>Samsung Starts Industry's First Mass Production of System-on-Chip with 10-Nanometer FinFET Technology. http://news.samsung.com/global/samsung-starts-industrys-first-mass-production-of-system-on-chip-with-10-nanometer-finfet-technology

<sup>&</sup>lt;sup>16</sup>Intel Finds Moore's Law's Next Step at 10 Nanometers. http://spectrum.ieee.org/semiconductors/devices/intel-finds-moores-laws-next-step-at-10-nanometers

de milliards de dollars<sup>17,18</sup>. Avec des investissements aussi considérables, avoir la mainmise sur les usines de fabrication est devenu une priorité nationale aux États-Unis 19,20, puisque la plupart d'entre elles sont maintenant situées en Asie. Une autre conséquence de l'augmentation de l'investissement initial requis est la domination du marché par les grandes entreprises existantes. Cinq d'entre elles (Intel, Samsung, Qualcomm, Broadcom et SK Hynix) possèdent ainsi 41% des parts de marché en 2016<sup>21</sup>. Les deux premières, Intel et Samsung, suivent le modèle historique du constructeur d'équipement intégré (Integrated Device Manufacturer ou IDM). Une seule entreprise assure la conception, la fabrication et la vente du circuit intégré. Néanmoins, les deux suivantes, Qualcomm et Broadcom, suivent le modèle fabless. Comme le nom l'indique, les entreprises fabless n'ont pas de moyens de fabrication. Elles s'appuient plutôt sur des entreprises tierces possédant des usines de fabrication. Ces entreprises, spécialisées dans la fabrication de circuits intégrés, sont appelées *fonderies*. Elles sont de plus en plus importantes dans l'industrie de la micro-électronique, dépassant les 50 milliards de dollars de vente en 2016, avec une augmentation de 11% par rapport à 2015 $^{22}$ . Ensemble, les concepteurs fabless et les fonderies forment un nouveau modèle économique [Hod11], apparu dans les années 1980, où le processus global a été séparé en deux : conception et fabrication.

L'industrie des semi-conducteurs étant un marché très compétitif, les délais de commercialisation sont également réduits. Ce phénomène, associé à une forte demande des consommateurs, a réduit de manière significative le temps alloué à la conception des circuits électroniques. Afin de suivre cette tendance, les concepteurs ont rapidement adopté un modèle de conception modulaire [GZ97] basé sur la réutilisation de blocs existants (design-and-reuse). Dans ce cadre, un composant complexe est divisé en blocs fonctionnels de taille plus réduite et de complexité gérable. Ainsi, deux nouveaux types d'entreprises sont apparus dans le processus de conception, le divisant encore. Les concepteurs de composants virtuels conçoivent des modules implémentant une fonction spécifique. Par exemple, on peut trouver des composants virtuels de décodage JPEG ou de contrôle Ethernet. Ces composants virtuels sont typiquement achetés par des intégrateurs système, qui les associent dans un système modulaire. Les différents types d'entreprises prenant part à la conception d'un circuit intégré sont présentés dans la Figure 2. Évidemment une division stricte ne reflète pas parfaitement la réalité. Par exemple, un concepteurs fabless peut concevoir certains composants virtuels en interne et en obtenir d'autres de concepteurs tiers.

$<sup>^{17}\</sup>mathrm{China}$ 's Tsinghua Unigroup to build \$30 billion Nanjing chip plant. http://www.reuters.com/article/us-tsinghua-plant-idUSKBN1532ED

<sup>&</sup>lt;sup>18</sup>Samsung Breaks Ground on \$14 Billion Fab. http://www.eetimes.com/document.asp?doc\_id=1326565

<sup>&</sup>lt;sup>19</sup>Can the White House Make America's Chip Industry Great Again? http://www.technologyreview.com/s/602768/can-the-white-house-make-americas-chip-industry-great-again/

$<sup>^{20} \</sup>mbox{Trump}$  team backs call for crackdown on China over semiconductors. http://www.ft.com/content/bca04dfede67-11e6-9d7c-be108f1c1dce

<sup>&</sup>lt;sup>21</sup>Five Suppliers Hold 41% of Global Semiconductor Marketshare in 2016. http://www.icinsights.com/data/articles/documents/938.pdf

$<sup>^{22}</sup>$  Pure-Play Foundry Market Surges 11% in 2016 to Reach \$50 Billion! http://www.icinsights.com/data/articles/documents/945.pdf

FIGURE 2 – Entreprises de la micro-électronique et leur position respective dans le processus de conception d'un circuit intégré.

La section suivante se concentre spécifiquement sur les composants virtuels, la manière dont ils sont distribués et les menaces associées à ce modèle économique.

## Distribution des composants virtuels et modèle économique

Suivant la transition globale d'une économie industrielle vers une économie de la connaissance [Dru69], l'industrie des semi-conducteurs s'appuie maintenant fortement sur l'échange et la monétisation de la propriété intellectuelle pour la conception des circuits intégrés. En pratique, les composants virtuels ne sont pas fournis seuls mais sont accompagnés de scripts de synthèse pour ASIC, de scripts de placement et routage pour FPGA, de scripts de simulation, de bancs de test, de modèles logiciels, de vecteurs de tests, de documentation, etc. Comme les sociétés de logiciels, les entreprises de conception de composants virtuels font maintenant la une avec des fusions et acquisitions atteignant des milliards de dollars. Par exemple, Intel a acquis Altera et NXP a été racheté par Qualcomm dans les deux dernières années. Comme mis en évidence dans un récent rapport par IC Insights<sup>23</sup>, le montant total des fusions et acquisitions en 2015 et 2016 était environ huit fois supérieur aux 12,6 millions de dollars qui constituaient la moyenne annuelle dans les cinq années précédentes (2010-2014).

Les concepteurs vendent leurs composants virtuels directement aux intégrateurs système ou s'appuient sur des grossistes intermédiaires. Ces derniers, tels que ChipEstimate<sup>24</sup>, Design-And-Reuse<sup>25</sup> ou CAST<sup>26</sup> maintiennent d'importants catalogues de composants virtuels de nombreux concepteurs. Les intégrateurs système acquièrent ensuite les composants virtuels

<sup>&</sup>lt;sup>23</sup>2015-2016 deals dominate semiconductor M&A ranking. http://www.icinsights.com/data/articles/documents/946.pdf

<sup>&</sup>lt;sup>24</sup>http://www.ipcatalog.com

<sup>&</sup>lt;sup>25</sup> http://www.design-reuse.com

$<sup>^{26}</sup>http://www.cast-inc.com$

via ces grossistes ou directement auprès du concepteur. Ce mode de fonctionnement est très proche de la manière dont les logiciels sont vendus.

Néanmoins, même si les moyens de distribution des composants virtuels et des logiciels suivent un modèle similaire de nos jours, leur usage après distribution est entièrement différent. En effet, les logiciels propriétaires sont accompagnés d'une licence, sous forme de clé, de fichier ou de serveur. Sans ces derniers, le logiciel ne fonctionne pas. Les composants virtuels, cependant, une fois qu'ils sont vendus par le concepteur, sont beaucoup plus difficiles à contrôler. Le principal problème vient du fait qu'une fois qu'un composant virtuel a été vendu, le concepteur n'a aucun moyen de savoir combien de fois il sera instancié en pratique.

Ce problème s'oppose de manière directe au principe d'économie de la connaissance mentionné ci-dessus. En effet, puisqu'il ne connaît pas le nombre d'instances du composant virtuel, le concepteur doit se résoudre à adopter un modèle de licence à versement initial. Dans ce modèle, le concepteur demande un montant fixe à l'intégrateur système avant de lui fournir le composant virtuel. Une fois la transaction réalisée, l'intégrateur système peut instancier le composant virtuel autant de fois qu'il le souhaite. Deux problèmes apparaissent dans ce modèle économique. Premièrement, cela empêche les achats en quantité limitée qui peuvent être utiles pour le prototypage ou pour les petites entreprises du fait de l'investissement initial élevé. De plus, cela limite fortement les avantages apportés par la conception modulaire, qui pourrait bénéficier largement de possibilités typiquement présentes dans le domaine du logiciel telles qu'une période d'évaluation ou un version premium du composant virtuel avec des performances plus élevées.

Au delà des limitations induites par ce modèle de licence, le principal problème lorsque le concepteur ne sait pas combien de fois le composant virtuel a été instancié est qu'il peut être potentiellement copié de manière illégale. Par exemple, un intégrateur système pourrait vendre à des associés un composant virtuel qu'il a déjà acheté, à un prix réduit et sans que le concepteur original n'en ait connaissance.

Afin d'exploiter pleinement le potentiel et les avantages de l'économie de la connaissance et pour empêcher la copie illégale, un concepteur doit pouvoir savoir combien de fois un composant virtuel a été instancié. En outre, en permettant au concepteur d'activer à distance le composant virtuel, un modèle de licence basé sur l'usage serait possible. Enfin, permettre l'activation à distance implique la présence de modes de fonctionnement dégradés. Les copies illégales sont ainsi rendues inutilisables et donc inutiles jusqu'à ce qu'elle soient activées par le concepteur original. Évidemment, un tel système d'activation à distance doit également être sécurisé, de manière à ce que des utilisateurs mal intentionnés ne puissent pas le contourner et utiliser une copie illégale du composant virtuel. C'est l'un des objectifs du projet SALWARE.

## Le projet SALWARE

Le projet SALWARE est un projet de quatre ans, financé par l'Agence Nationale de la Recherche et la Fondation de Recherche pour l'Aéronautique et l'Espace. L'intitulé du projet est le suivant : "Conception de matériel salutaire pour lutter contre la contrefaçon et le vol de circuits intégrés". Le nom du projet vient du mot *malware*, qui signifie logiciel malicieux, et qui a été changé en *salware* pour matériel salutaire. L'objectif de ce projet est de concevoir des blocs matériels fournissant des informations de propriété intellectuelle et/ou permettant l'activation à distance d'un circuit intégré ou d'un composant virtuel après fabrication. Les blocs matériels conçus dans le cadre du projet SALWARE présentent les mêmes propriétés qu'un *malware*. Ainsi, ils doivent être discrets, ou légers, afin d'induire un coût supplémentaire en ressources logiques le plus faible possible. Ceci est une exigence très stricte pour rendre la solution proposée applicable dans un contexte industriel. En outre, ils doivent perturber efficacement le fonctionnement du circuit ou du composant virtuel, afin de rendre les copies illégales inutiles. Enfin, ils doivent être suffisamment difficiles à contourner ou à supprimer pour décourager les utilisateurs malveillants.

Cédric Marchand, qui était un autre doctorant travaillant dans le cadre du projet SALWARE, a soutenu sa thèse en 2016 [Mar16]. Sa thèse traitait du *watermarking*, de la conception de fonctions physiques non clonables (*Physical Unclonable Function* ou PUF) et de l'implémentation de cryptographie légère, qui sont des éléments essentiels pour du matériel salutaire mais qui sont plus spécifiquement orientés vers la prévention de la contrefaçon de circuits intégrés. Cette thèse de doctorat a des contributions complémentaires, qui sont présentées ci-dessous, et se concentre plus spécifiquement sur les composants virtuels.

## **Contributions**

En premier lieu, afin de s'assurer qu'un système de protection des données de conception est efficace, les copies illégales doivent présenter un comportement très perturbé. La première option étudiée dans cette thèse pour permettre ceci est de forcer à une valeur logique fixe les sorties d'un composant virtuel, de manière contrôlée. Un algorithme très efficace permettant de sélectionner les nœuds de la netlist à modifier, basé sur la propagation d'une valeur de verrouillage dans un graphe, est présenté.

La seconde option pour fournir un mode de fonctionnement dégradé est de perturber les sorties du composant virtuel en inversant certains nœuds internes. Ceci est appelé masquage logique. Spécifiquement, une nouvelle méthode permettant de sélectionner les nœuds à inverser, basée sur les indicateurs de centralité en théorie des graphes, est proposée. Comparée aux heuristiques de sélection de l'état de l'art, elle s'étend plus efficacement à des composants virtuels de grande taille et altère le fonctionnement du circuit de manière efficace.

La troisième contribution de cette thèse traite de l'identification unique des instances

d'un composant virtuel en utilisant une PUF. Les PUFs sont des primitives très intéressantes puisqu'elles permettent d'identifier individuellement les instances en extrayant les variations apparaissant lors du processus de fabrication, qui sont spécifiques à chaque circuit produit et sont aléatoires. Toutefois, les PUFs présentent une certaine instabilité, et les identifiants extraits ne sont pas suffisamment stables. Pour résoudre ce problème, nous proposons une méthode innovante basée sur le protocole de réconciliation de clés CASCADE. Développé au départ pour l'échange quantique de clés, nous montrons que ce protocole interactif peut être utilisé de manière fructueuse pour la correction des erreurs présentes dans les réponses des PUFs. En comparaison des implémentations existantes de codes correcteurs d'erreurs, cette solution est une ordre de grandeur plus légère en terme de ressources logiques requises.

Enfin, ces contributions et celles de [Mar16] sont assemblées en un système complet de protection des données de conception. Nous montrons que ce système remplit les conditions pour être considéré comme un SALWARE, en étant léger, sûr et efficace pour proposer différents modes de fonctionnement dégradés pour un composant virtuel. Finalement, ceci constitue une solution industriellement viable pour les concepteurs de composants virtuels qui souhaitent protéger leurs données de conception de la copie illégale à moindre coût.

#### Plan

Le chapitre 1 présente le modèle économique associé aux composants virtuels qui a été largement adopté par l'industrie des semi-conducteurs. Nous mettons en évidence les nouvelles menaces pour les données de conception qui émergent de ce nouveau modèle économique et proposons un modèle de menace détaillé. Nous présentons ensuite un état de l'art des méthodes de protection des données de conception pour les composants virtuels. Nous concluons ce chapitre en présentant les caractéristiques souhaitées pour un système de protection des données de conception et donnons un aperçu des différents éléments requis pour mettre en œuvre ces fonctions.

Le chapitre 2 décrit la méthode basée sur l'analyse de graphe pour le verrouillage combinatoire d'un composant virtuel. Le chapitre 3 montre de quelle manière les indicateurs de centralité de la théorie des graphes peuvent être utilisés pour sélectionner les nœuds les plus efficaces pour une modification par masquage logique. Le chapitre 4 présente les similarités entre deux scénarios, l'échange quantique de clés et la correction des erreurs dans les réponses des PUFs. En particulier, nous montrons que le protocole de réconciliation de clés CASCADE peut être utilisé pour fournir une solution légère de correction des erreurs pour les réponses des PUFs. Finalement, le chapitre 5 présente le système logiciel/matériel complet pour la protection des données de conception, ce qui constitue l'objectif du projet SALWARE.

## Chapter 1

## Threats and protections for design data

Following the fragmentation of the semiconductor design process mentioned before, multiple parties now participate and are involved at different stages. Such a multiplicity of actors comes with specific risks for design data. Intellectual property transfers between stakeholders, even though they are necessary to the new business model, are the cause of multiple threats. In order to further understand them, a review of the various parties and their individual role is needed.

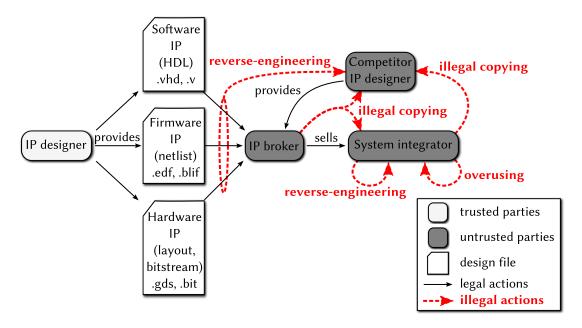

Next, we give a description of the three main threats that can be identified against design data: overproducing, illegal copying and reverse-engineering. We then take the point of view of an IP core designer and identify which of the parties involved in the design process are likely to perform these illegal actions. This leads us to define two threats models, one shared between illegal copying and overproducing and a specific one for reverse-engineering. For each threat model, the attacker's and defender's objectives, capabilities or constraints are detailed.

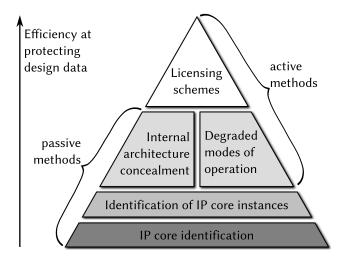

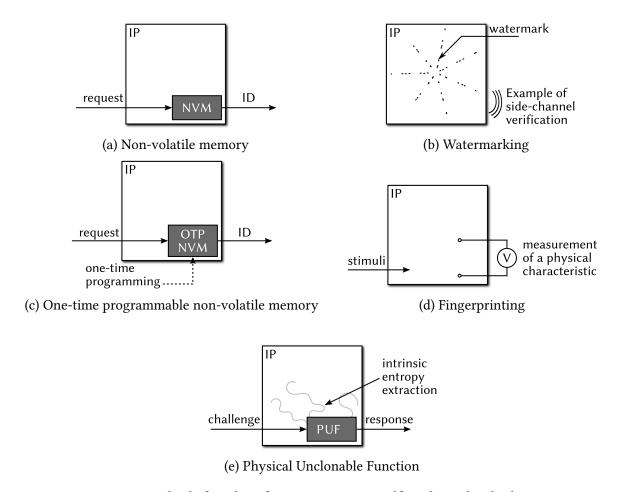

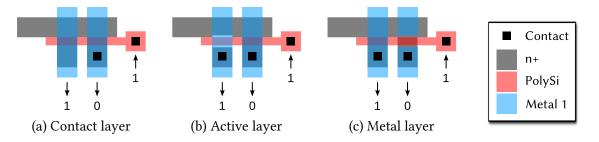

We then give a state-of-the-art of existing methods that aim at the protection of design data. The methods are classified according to their efficiency at providing a complete protection against the aforementioned threats. This ranges from the simple identification of an IP core to thorough licensing schemes. We also present some solutions that are a combination of multiple design data protection methods.

This leads us to propose a set of requirements for a strong, lightweight and usable IP protection scheme. We then present how we propose to implement the features that fulfil these requirements in the SALWARE project.

# Menaces sur les données de conception et méthodes de protection

Suite à la fragmentation du processus de conception de circuits intégrés mentionné précédemment, de nombreux acteurs sont aujourd'hui impliqués à différentes étapes. Cette multiplicité d'acteurs est accompagnée de risques spécifiques pour les données de conception. Les transferts de propriété intellectuelle entre les acteurs, quoique nécessaires au nouveau mode de fonctionnement de l'industrie, sont la cause de multiples menaces. Afin de mieux les comprendre, passer en revue les différents acteurs impliqués et leurs rôles est nécessaire.

Ensuite, nous décrivons les trois menaces principales qui ciblent les données de conception : surproduction, copie illégale et rétro-ingénierie. Nous nous plaçons ensuite du point de vue du concepteur de composants virtuels et identifions quels acteurs impliqués dans le processus de conception sont susceptibles de réaliser ces actions illégales. Cela nous conduit à définir deux modèles de menace, l'un commun à la copie illégale et la surpodcution et l'autre spécifique à la rétro-ingénierie. Pour chaque modèle de menace, les objectifs, les possiblités et les contraintes des attaquants et des défenseurs sont détaillés.

Nous donnons ensuite un état de l'art des méthodes qui visent à protéger les données de conception. Ces méthodes sont classées d'après leur efficacité à fournir une protection complète contre les menaces mentionnées ci-dessus. Cela va de la simple identification d'un composant virtuel à des schémas de licence d'utilisation complets. Nous présentons également quelques solutions qui sont une combinaison de plusieurs méthodes de protection des données de conception.

Cela nous conduit finalement à proposer un ensemble de caractéristiques pour un module de protection des données de conception robuste, léger et utilisable. Nous présentons ensuite comment nous proposons d'implémenter les fonctionnalités satisfaisant à ces exigences dans le cadre du projet SALWARE.

## 1.1 Parties involved in the design process and their roles

Multiple parties are involved in the lifetime of an electronic device. We restrict ourselves to the ones present at design time. Therefore, we do not consider parties in charge of subsequent steps: manufacturing, testing, packaging, supplying, selling, recycling, etc.

#### 1.1.1 IP Designer

The designer of the IP core is the first party to take part in the design process. From the specifications, which can be laid down by a customer, a standard or in-house, an IP core is designed. It consists in describing a hardware implementation of the specifications. Along with the implementation, the designer can supply test vectors, place and route scripts, testbenches, software models, documentation, etc. Together, these parts form the intellectual property material that is referred to as IP core. The actual implementation can come in three main forms:

**Software IP:** the IP core is provided in a hardware description language like VHDL, SystemVerilog or SystemC, before synthesis. This type of IP core offers the advantage of not being dependent on the final hardware target. These descriptions can be done at several levels of abstraction, with the constraint that they must be synthesisable. For example, a VHDL description can go down to the register transfer level, while the SystemC language allows one to do a high-level behavioural description. Software IP is described in a very high-level style, possibly using language features that are close to those of a programming language. However, a soft IP must be synthesisable, otherwise it is closer to a software model.

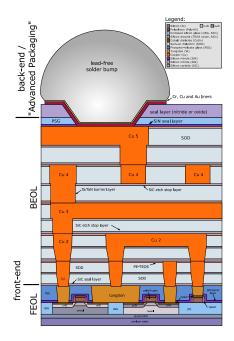

**Firmware IP:** a low level description after synthesis is given, in a netlist format such as EDIF<sup>1</sup>. It may be technology-dependent if the IP core instantiates vendor-specific primitives.

**Hardware IP:** this is the lowest level of abstraction to be found for an IP core. If the target hardware platform is ASIC, then a layout file in the GDS II, OASIS<sup>2</sup> or other format is provided. It directly represents the layout of the design as it will be used for the photo-lithography masks. Conversely, if the design is to be implemented on FPGA, a bitstream file is given. This bitstream file describes how the LUTs, switching matrices and RAM blocks inside FPGA must be configured to achieve the desired logic function.

These three types of IP cores represent different levels of abstraction. Examples of IP core designers are ARM<sup>3</sup>, Dolphin Integration<sup>4</sup>, Intrinsic ID<sup>5</sup> or Rambus<sup>6</sup>.

<sup>&</sup>lt;sup>1</sup>Electronic Design Interchange Format

<sup>&</sup>lt;sup>2</sup>Open Artwork System Interchange Standard

<sup>&</sup>lt;sup>3</sup>http://arm.com

<sup>&</sup>lt;sup>4</sup> http://dolphin-integration.com

<sup>&</sup>lt;sup>5</sup> http://intrinsic-id.com

<sup>&</sup>lt;sup>6</sup>http://rambus.com

#### 1.1.2 Broker

A broker acts as a middleman between designers and system integrators. In order to provide more visibility to third party IP core designers, the broker maintains a catalogue of IP cores, which are classified by category according to the function they implement. For instance, a broker can offer several Ethernet controllers from various designers, reaching various performance targets. Some of these controllers can be low-power while others achieve very high throughput.

From a system integrator point of view, those online catalogues are very helpful. They allow to search and compare the IP cores from different vendors with criteria such as the performance/area/power consumption ratio, the technology node, the foundry, the hardware target, etc. Moreover, the organisations maintaining these catalogues can provide management software for those IP cores. For example, this type of software can manage an IP core repository and provide version control, so that the IP cores can be updated if revisions are done.

Examples of IP core brokers are AnySilicon<sup>7</sup>, ChipEstimate<sup>8</sup>, Design & Reuse<sup>9</sup> or Open-Cores<sup>10</sup>, the latter being specialised in open-source IP cores. It is worth noting that FPGA manufacturers Xilinx<sup>11</sup> and Intel<sup>12</sup> also provide a catalogue of IP cores in their respective electronic design automation (EDA) tools Vivado and Quartus Prime.

### 1.1.3 System integrator

The system integrator purchases IP cores from a broker or directly from designers. These individual IP cores, which achieve a specific function, are then integrated together in a complex, modular system.

For a system integrator, previously mentioned IP core characteristics such as the process node or the foundry are crucial for flawless integration. If an IP core has already been manufactured and validated in silicon, it is said to be "silicon ready". This information is provided by the broker or the designer and is of great help for the system integrator.

Nowadays, most of the designs integrate multiple IP cores. Therefore, the vast majority of electronics design companies are system integrators.

## 1.1.4 Trusted third party

In order to facilitate the interaction between the previously described parties, a trusted third party is sometimes involved. When two parties do not necessarily trust each other but still need to interact, they only need to trust this trusted third party.

<sup>&</sup>lt;sup>7</sup> http://anysilicon.com

$<sup>^8</sup>http://chipestimate.com$

<sup>&</sup>lt;sup>9</sup>http://design-reuse.com

<sup>&</sup>lt;sup>10</sup> http://opencores.org

<sup>&</sup>lt;sup>11</sup> https://www.xilinx.com/

<sup>&</sup>lt;sup>12</sup> https://altera.com/

Sometimes, in the case of IP cores that are meant to be integrated on FPGAs, the hardware manufacturer can act as a trusted third party. For instance, the hardware manufacturer can integrate secret keys given by the designer into the FPGA. These keys can then be used for IP licensing without the system integrator knowing them.

The role of the trusted third party is described in more details in section 1.5.5, dealing with IP licensing schemes.

### 1.1.5 Interaction between parties

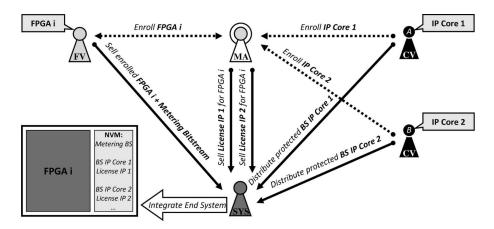

Figure 1.1 shows how the previously described parties interact with one another in the typical semiconductor IP business. Specifically, it depicts how design data is transferred from one party to the other. However, there could be additional relations between these parties. For example, a system designer could request a specific IP to be designed by the IP core designer. A designer could also provide support to the system integrator to assist in the integration of the IP core. However, those relations do not deal with design data transfer.

Figure 1.1 – Design data transfer in the semiconductor IP business.

#### 1.1.6 Business models

Different types of business model can be found in the semiconductor IP market. They developed in the 1980s, when the semiconductor business started shifting to a knowledge economy. Previously, semiconductor devices were simply sold by manufacturers to system integrators who combined them on boards to design a final product. With the dematerialisation of IP cores, more sophisticated business models could emerge [Fab06]:

**Per-use:** In the per-use model, the IP core designer gives the system integrator the right to use the IP in a certain use scope. The scope must be defined very clearly and can consist in a specific project for example.

**Time-based:** The time-based model allows a system integrator to use an IP core as much as needed but only for a limited period of time. If needed, the contract can be later extended if it expired before the project is completed.

**Royalty-based:** In this model, the final price depends on the usage of the IP core. For example, this can be related to the number of manufactured integrated circuits. It can be very advantageous for both sides, since a system integrator can obtain an IP core for a low initial price but the original designer can also get paid significantly more if the final product is successful.

Even though they differ, all those business models have in common to require a transfer of design data. This comes with associated threats, detailed in the next section.

## 1.2 Threats on design data

With the semiconductor IP business model presented come specific threats on design data. This is first visible on Figure 1.1, where all the arrows representing design data transfer are one-way. This graphically conveys the idea that these design data transfers are asymmetrical. The IP designer provides the broker with an IP core, but in return the broker does not provide any intellectual property to the designer. Similarly, when a system integrator purchases an IP core, the intellectual property material is transferred from the IP designer to the system integrator in only one direction. This poses direct threats to design data since such asymmetric transfer gives rise to intellectual property infringements [SEM06; GDT14] which have severe economic and social impacts [Fro11]. These threats are described in the following subsections.

## 1.2.1 Overproducing

The first type of threat, emerging directly from the immaterial nature of IP cores is *overproducing*. It occurs when, in a per-use business model, the system integrator overrides the scope of use which was previously agreed upon. For example, an IP core which was used in a project is reused later in another design without mentioning it to the IP designer. In a time-based business model, this means that a system integrator keeps using an IP core even though the subscription period has elapsed. If royalties are owed by the system integrator to the IP core designer, the actual number of manufactured devices can be underreported to make the final cost lower. Consequently, for all these cases, the number of instances of the IP core reported to the designer does not match reality. This prevents proper billing and compensation.

#### 1.2.2 Illegal copying

The next type of threat is *illegal copying*. This occurs when an IP broker or a system integrator copies an IP core in order to provide it or sell it to another party, unbeknown to the IP core designer. For example, it can be the case if an IP broker charges a system integrator for a certain number of instances of the IP core but in fact reports only half of these instances to the IP core designer. In this case, half of the instances are illegal copies of the IP core since the original designer is unaware of their existence. In large companies, different business units could also share IP cores between projects without reporting it. Finally, a system integrator who obtained an IP core from one designer could sell it to a competitor IP core designer. Similarly to overproducing, these case of illegal copying result in an actual number of IP core instances which is higher that the one reported to the IP core designer, preventing correct billing.

#### 1.2.3 Reverse-engineering

The third threat against design data which can be identified is *reverse-engineering*. This is a direct threat to the intellectual property material itself, since it aims at recovering how a logic function is implemented. Therefore, reverse-engineering intends to find out the processes and techniques to go from the specifications to the implementation of the IP core.

Depending on the form in which the IP core is provided, reverse-engineering it can be more or less demanding. In the case of a soft IP described using a hardware description language, recovering the implementation is much easier than if only a layout is available. Similarly, a bitstream for an FPGA is usually hard to reverse-engineer completely [NR08; BSH12]. However, it is safe to assume that if a motivated attacker has sufficient resources and time, then reverse-engineering is always possible.

Reverse-engineering can also occur later, after the device has been manufactured. From high definition pictures of a delayered chip, automated image recognition software can recover the entire layout [MN08; TJ11; McL11]. More sophisticated imaging devices can be used such as microscopes that use scanning electron, scanning capacitance or X-rays technology [Qua+16]. Using X-rays for example allows an attacker to perform non-destructive reverse-engineering, since the chip is not damaged and can still operate after. On the other hand, a delayered chip is permanently damaged and cannot be used anymore.

In order to go further up in abstraction, recovering the netlist is necessary. This can be done from the bitstream [NR08; BSH12] or the layout. By observing the inputs and outputs of the device, the FSM can also be recovered [Bru+09; Smi+17].

Reverse-engineering can be done by the system integrator. This could help in future designs by not requiring the help of a contract IP core designer anymore. With the knowledge on how to implement a function, this can be done in-house.

A competitor IP core designer could also be interested in the internal architecture of an IP core and attempt to reverse-engineer it. This gives an advantage by reducing design time and

achieving equivalent performance if similar functions must be implemented in the future.

Reverse-engineering can be linked to illegal copying. Indeed, if the reverse-engineering step is successful, the attacker owns a version IP core without the original designer knowing it. The IP core can then be instantiated again, making it an illegal copy.

It is interesting to note that reverse-engineering can also have positive aspects [Qua+16]. It helps in failure analysis and detection. It can also be used to provide intellectual property information and prove that a particular IP core has been instantiated in a device [GDT14]. Moreover, reverse-engineering is often necessary to ensure that a design has not been infected by a hardware Trojan [Xia+16; BFS16]. Finally, this is also a great tool for educational purposes.

# 1.2.4 Limitations bypass

Since IP cores are increasingly following a software-like business model, another type of threat could emerge in the future. Just like pieces of software, IP cores could be distributed in evaluation mode, or offer a premium version with greater performances. So far, only software-assisted manipulations have been demonstrated. For instance, in 2015, a tool was able to disable the hardware locks of processing units of AMD Radeon GPUs<sup>13</sup>. This effectively allows to upgrade a graphics card.

We could not find purely hardware-based attacks, partly because multi-mode IP cores are rare. Therefore, this threat is not addressed in this thesis. However, in view of how well precedented these practises are for software, one can reasonably expect them to apply to IP cores too, once they reach such a level of refinement.

# 1.3 Summary: association between parties and threats

The semiconductor IP business presented in Figure 1.1 can now be extended by showing the different threats on it. Since we aim at providing IP core designers with means of protecting their intellectual property, we should now adopt their point of view when evaluating the trustworthiness of other parties. This is shown in Figure 1.2, in which untrusted parties *from the IP core designer's point of view* are highlighted in dark grey and threats are in red. We considered that the trusted third party, described previously, is indeed trusted. Thus it does not appear in Figure 1.2.

In an attempt to fight these threats, a precise threat model is required. This is presented in the following sections. For each of the previously described threats, a threat model is given, comprising an attacker and a defender model.

<sup>&</sup>lt;sup>13</sup>New tool reawakens disabled hardware in high-end AMD Radeon graphics cards http://www.pcworld.com/article/2960717/components-graphics/new-tool-reawakens-disabled-hardware-in-high-end-amd-radeon-graphics-cards.html

Figure 1.2 – Specific threats to design data in the semiconductor IP business. Trusted and untrusted parties are from the IP designer point of view.

# 1.4 Threat models

# 1.4.1 Threat model for design data exposed to illegal copying/overproducing

The threat model for illegal copying and overproducing is the same. Indeed, the final purpose of illegal copying, after illegal design transfer, is to instantiate the IP core without the designer knowing it. Thus it results in the same consequences as overproducing.

#### 1.4.1.1 Attacker model

**Attacker's objectives** When an attacker aims at carrying out illegal copying or overproducing of an IP core, its objective is to instantiate the IP core more times than agreed with the designer or the broker. From the attacker's point of view, a black box instantiation of a functional IP core is sufficient. Even though some technical characteristics of the core may be required, the knowledge of the internals is not needed to perform the attack.

**Attacker's capabilities** We assume that the attacker can obtain a copy of the IP core in a legal way. He also has the technical resources to instantiate it correctly. Namely, this means that he can obtain all the necessary technical information required such as the process node, the design rules, the foundry, etc.

#### 1.4.1.2 Defender model

**Defender's objectives** The designer's objective here is to prevent the attacker from proceeding to a black box instantiation of the IP core without reporting it to the designer. Practically speaking, the designer wants to know how many instances of the IP core exist. However, this does not prevent black box instantiation as described above. In addition, the defender must be able to control how many instances of the IP core actually operate. The fact to know how many instances of an IP core are operating is commonly referred to as *metering* [Kou11].

**Defender's constraints** From the defender's point of view, the main constraint to defend against illegal copying is the cost of the protection system. Indeed, adding extra components to the IP core in order to protect it increases the logic resources, the power consumption and possibly the latency of the core. This all comes at a cost, either because the IP core layout occupies a larger area and is more expensive to manufacture or because a higher power consumption or latency makes it less competitive. Therefore, the cost of the protection system must not exceed the financial losses caused by illegal copying or overproducing. However, the financial losses suffered by IP core designers can be hard to estimate.

# 1.4.2 Threat model for design data exposed to reverse-engineering

This threat model addresses reverse-engineering when committed with a malicious intent, in contrast with reverse-engineering aiming at educational purposes.

#### 1.4.2.1 Attacker model

Attacker's objectives When an attacker attempts to reverse-engineer an IP core, the aim is to find out how specifications have been implemented in hardware. Namely, this includes revealing the types of logic gates used and the connections between them or the layout patterns on every layer. The objective is to gain knowledge of the practical implementation methods and techniques, in order to reduce time to market for a future in-house design while achieving similar performances to competitor devices.

**Attacker's capabilities** The attacker can access both the digital and physical versions of the IP core. The digital version refers to the computer file which holds the design data. For example, this can be a VHDL, GDS II or bitstream file. The attacker can also have access to a physical implementation of the IP core in an integrated circuit. Depending on the financial support he gets, an attacker can use powerful techniques to recover design information [TJ11]. Some companies, such as Texplained<sup>14</sup> are specialised in providing this type of services.

<sup>&</sup>lt;sup>14</sup> https://www.texplained.com/

#### 1.4.2.2 Defender model

**Defender's objectives** From a defender's perspective, the objective is to conceal the architecture of the IP core. The ideal model for this is a black box, where only the inputs and outputs are visible. However, due to the way IP cores are distributed and supposed to be used, this objective is hard to fulfil.

A more relaxed version, which is at the same time more realistic given today's attackers capabilities, is to make the reverse-engineering as hard and time consuming as possible. Given that the parties who can perform reverse-engineering are the system integrator or a competitor IP designer, the objective of a designer is to make the reverse-engineering process more expensive than in-house development of the IP core.

**Defender's constraints** Similarly to the constraints detailed above for illegal copying and overproducing, the cost of the protection method against reverse-engineering must be lower than the potential financial losses caused by the intellectual property infringement.

As highlighted before, reverse-engineering can have salutary purposes like failure detection or tests. From a practical point of view, a protection against reverse-engineering can make such purposes harder to achieve.

# Conclusion on threats on design data

Due to the emergence of core-based design, overproducing/illegal copying and reverse-engineering have arisen or have been amplified. However, they have slightly different characteristics.

Reverse-engineering is quite a challenging task to perform, and will only become harder with the decreasing size of transistors and their increasing density. In addition, IP designers are more and more aware of this threat and have a large panel of possibilities to fight against it. Nevertheless, the development of automated reverse-engineering tools makes progress too. Therefore, the amount of time taken to reverse-engineer a design is only due to the manual intervention of people which is still required, since not everything can be automated. This still takes a good amount of time and skills. The required tools to physically de-package and process a circuit to reverse-engineer it are costly too. Overall, the potential financial losses for the IP core designer are high, but the increasingly fast time-to-market tends to reduce them if they are restricted to the intellectual property infringement.

Overproducing and illegal copying, on the other hand, do not require much time to be performed by an attacker. Indeed, after obtaining the design, copying it is trivial. However, obtaining it in the first place can cost some money. After the copy has been performed, overproducing a design requires no extra skills than the ones already present in most design houses. Thus the potential losses for the IP designer are much greater. Moreover, these potential losses can also originate from reverse-engineering being used to perform the illegal

copy, beyond the infringement of intellectual property mentioned above. Overall, these are a much more important threat for IP core designers than reverse-engineering. This is summarised in Table 1.1.

|                               | Requirements                  |     |                          | Potential financial losses |  |  |

|-------------------------------|-------------------------------|-----|--------------------------|----------------------------|--|--|

| Threat                        | Time Money (equipment) Skills |     | for the IP core designer |                            |  |  |

| Reverse-engineering           | ••0                           | ••• | ••0                      | ••0                        |  |  |

| Overproducing/Illegal copying | •00                           | ••0 | •00                      | •••                        |  |  |

Table 1.1 – Threats on design data.

In order to fight these threats, many design data protection schemes were developed. They consist in adding specific modules to a design or modifying it directly. These are developed in the following section.

# 1.5 Design data protection methods

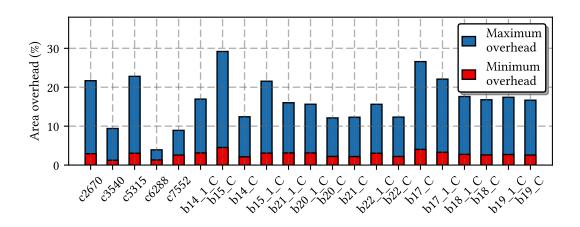

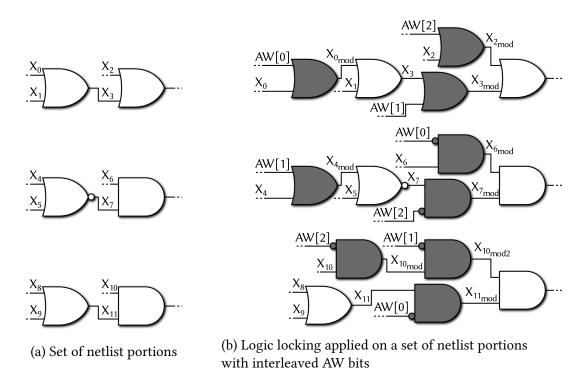

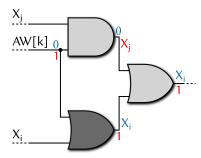

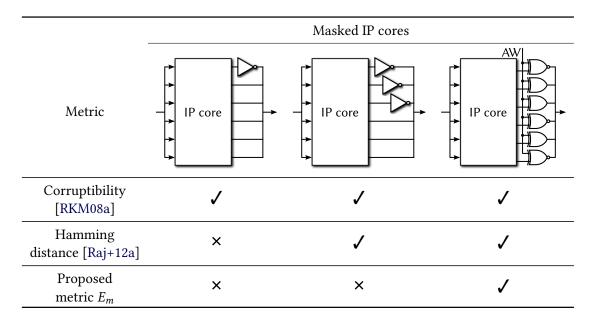

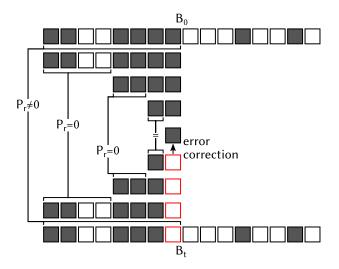

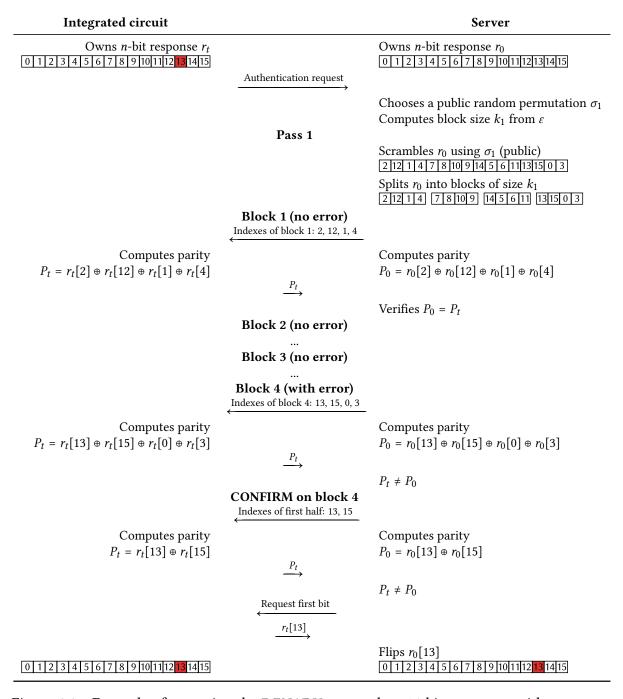

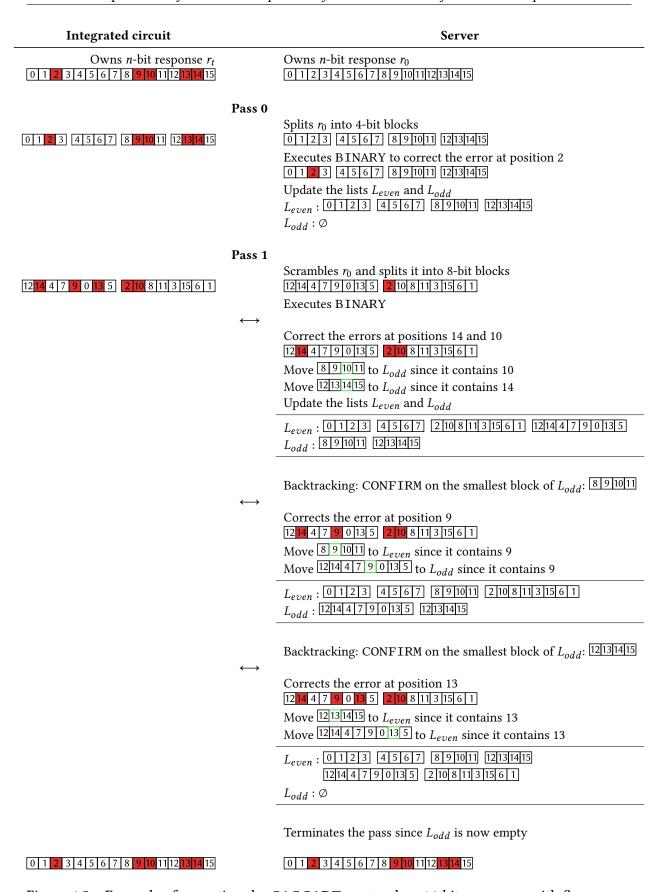

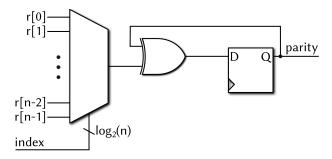

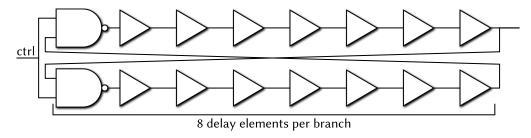

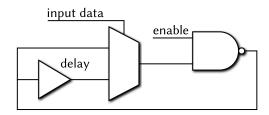

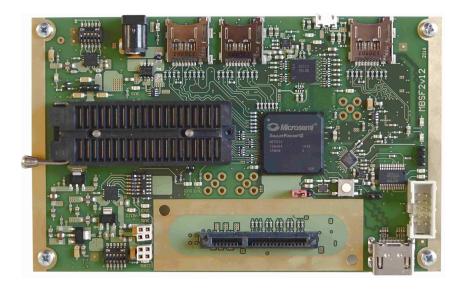

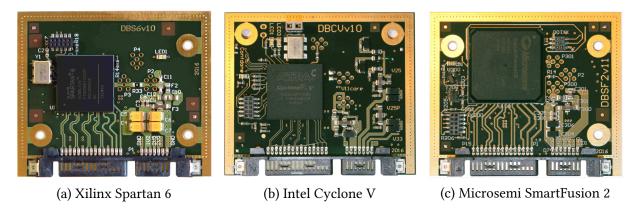

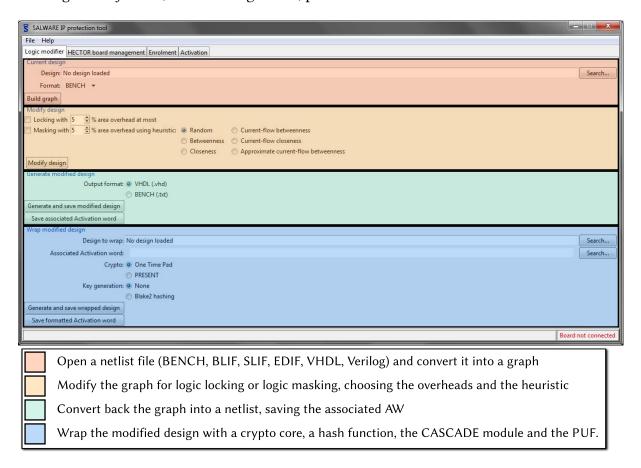

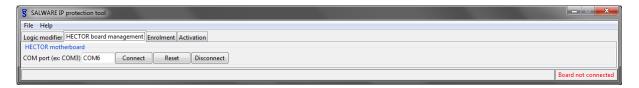

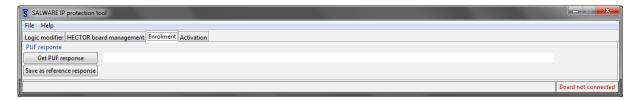

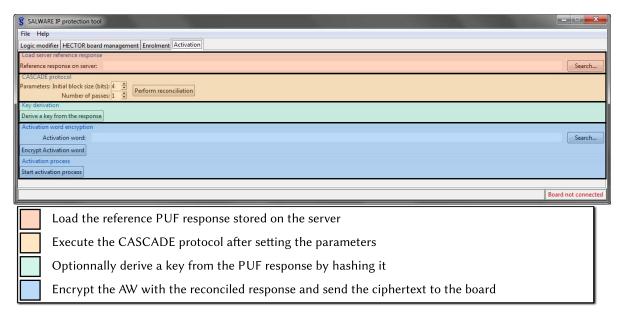

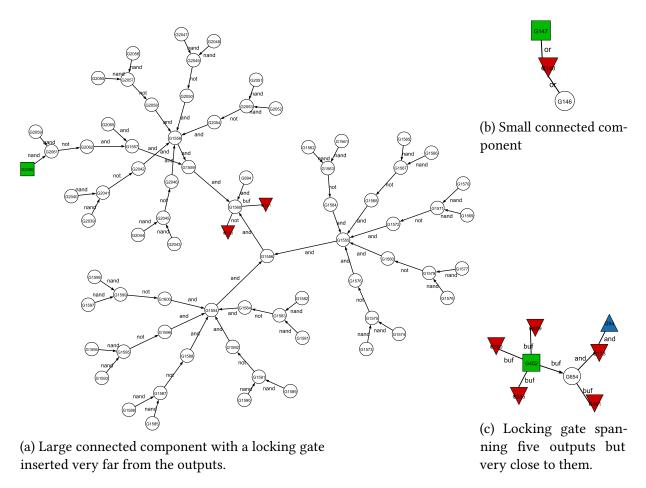

Traditionally, design data protection methods are classified into passive and active methods. Passive protection means allow a designer to detect that an illegal action occurred. For example, by embedding an identifier inside an IP core, a designer who obtained a circuit can extract the identifier and prove that his IP core was instantiated. However, this does not prevent the illegal action to occur. Conversely, active protection means offer the designer a way to actively prevent the illegal action. For example, the circuit can exhibit an erratic behaviour until the correct activation word is fed to it.