## Securing a trusted hardware environment (Trusted Execution Environment)

Mathieu da Silva

#### ▶ To cite this version:

Mathieu da Silva. Securing a trusted hardware environment (Trusted Execution Environment). Micro and nanotechnologies/Microelectronics. Université Montpellier, 2018. English. NNT: 2018MONTS053. tel-02122896

### HAL Id: tel-02122896 https://theses.hal.science/tel-02122896

Submitted on 7 May 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE MONTPELLIER

En SYAM – Systèmes Automatiques et Micro-Electroniques

École doctorale : I2S – Information, Structures et Systèmes

Unité de recherche : LIRMM - Laboratoire d'Informatique, de Robotique et de Micro-électronique de Montpellier

# SECURISATION D'UN ENVIRONNEMENT MATERIEL DE CONFIANCE (TRUSTED EXECUTION ENVIRONMENT)

SECURING A TRUSTED HARDWARE ENVIRONMENT (TRUSTED EXECTION ENVIRONMENT)

### Présentée par Mathieu Da Silva Le 26 novembre 2018

Sous la direction de Bruno Rouzeyre, Giorgio Di Natale et Marie-Lise Flottes

#### Devant le jury composé de

| Bruno Rouzeyre,    | Professeur à l'Université de Montpellier, LIRMM, Montpellier                    | Directeur de thèse |

|--------------------|---------------------------------------------------------------------------------|--------------------|

| Giorgio Di Natale  | Directeur de recherche au CNRS, LIRMM, Montpellier                              | Co-encadrant       |

| Marie-Lise Flottes | Chargé de recherche au CNRS, LIRMM, Montpellier                                 | Co-encadrant       |

| Lilian Bossuet     | Professeur à l'Université Jean Monnet, Laboratoire Hubert Curien, Saint-Etienne | Rapporteur         |

| Lorena Anghel      | Professeur à Grenoble INP, TIMA, Grenoble                                       | Rapporteur         |

| Alberto Bosio      | Professeur à l'ECL, INL, Lyon                                                   | Président          |

| David Hély         | Associate Professor à Grenoble INP, LCIS, Grenoble                              | Membre             |

| Sophie Dupuis      | Maître de conférence à l'Université de Montpellier, LIRMM, Montpellier          | Membre             |

#### **ABSTRACT**

This work is part of the Trusted Environment Execution eVAluation (TEEVA) project (French project FUI n°20 from January 2016 to December 2018) that aims to evaluate two alternative solutions for secure mobile platforms: a purely software one, the Whitebox Crypto, and a TEE solution, which integrates software and hardware components. The TEE relies on the ARM TrustZone technology available on many of the chipsets for the Android smartphones and tablets market. This thesis focuses on the TEE architecture. The goal is to analyze potential threats linked to the test/debug infrastructures classically embedded in hardware systems for functional conformity checking after manufacturing.

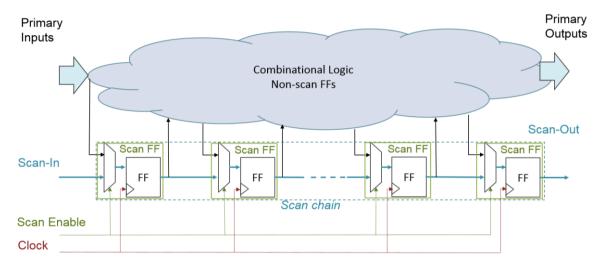

Testing is a mandatory step in the integrated circuit production because it ensures the required quality and reliability of the devices. Because of the extreme complexity of nowadays integrated circuits, test procedures cannot rely on a simple control of primary inputs with test patterns, then observation of produced test responses on primary outputs. Test facilities must be embedded in the hardware at design time, implementing the so-called Design-for-Testability (DfT) techniques. The most popular DfT technique is the scan design. Thanks to this test-driven synthesis, registers are connected in one or several chain(s), the so-called scan chain(s). A tester can then control and observe the internal states of the circuit through dedicated scan pins and components. Unfortunately, this test infrastructure can also be used to extract sensitive information stored or processed in the chip, data strongly correlated to a secret key for instance. A scan attack consists in retrieving the secret key of a crypto-processor thanks to the observation of partially encrypted results.

Experiments have been conducted during the project on the demonstrator board with the target TEE in order to analyze its security against a scan-based attack. In the demonstrator board, a countermeasure is implemented to ensure the security of the assets processed and saved in the TEE. The test accesses are disconnected preventing attacks exploiting test infrastructures but disabling the test interfaces for testing, diagnosis and debug purposes. The experimental results have shown that chips based on TrustZone technology need to implement a countermeasure to protect the data extracted from the scan chains. Besides the simple countermeasure consisting to avoid scan accesses, further countermeasures have been developed in the literature to ensure security while preserving test and debug facilities. State-of-the-art countermeasures against scan-based attacks have been analyzed. From this study, we investigate a new proposal in order to preserve the scan chain access while preventing attacks, and to provide a plug-and-play countermeasure that does not require any redesign of the scanned circuit while maintaining its testability. Our solution is based on the encryption of the test communication, it provides confidentiality of the communication between the circuit and the tester and prevents usage from unauthorized users. Several architectures have been investigated, this document also reports pros and cons of envisaged solutions in terms of security and performance.

#### **RESUME**

Ce travail de thèse a pour cadre le projet Trusted Environment Execution eVAluation (TEEVA) (projet français FUI n°20 de Janvier 2016 à Décembre 2018) qui vise à évaluer deux solutions alternatives de sécurisation des plateformes mobiles, l'une est purement logicielle, la Whitebox Crypto, alors que l'autre intègre des éléments logiciels et matériels, le Trusted Environment Execution (TEE). Le TEE s'appuie sur la technologie TrustZone d'ARM disponible sur de nombreux chipsets du marché tels que des smartphones et tablettes Android. Cette thèse se concentre sur l'architecture TEE, l'objectif étant d'analyser les menaces potentielles liées aux infrastructures de test/debug classiquement intégrées dans les circuits pour contrôler la conformité fonctionnelle après fabrication.

Le test est une étape indispensable dans la production d'un circuit intégré afin d'assurer fiabilité et qualité du produit final. En raison de l'extrême complexité des circuits intégrés actuels, les procédures de test ne peuvent pas reposer sur un simple contrôle des entrées primaires avec des patterns de test, puis sur l'observation des réponses de test produites sur les sorties primaires. Les infrastructures de test doivent être intégrées dans le matériel au moment du design, implémentant les techniques de Design-for-Testability (DfT). La technique DfT la plus commune est l'insertion de chaînes de scan. Les registres sont connectés en une ou plusieurs chaîne(s), appelé chaîne(s) de scan. Ainsi, un testeur peut contrôler et observer les états internes du circuit à travers les broches dédiées. Malheureusement, cette infrastructure de test peut aussi être utilisée pour extraire des informations sensibles stockées ou traitées dans le circuit, comme par exemple des données fortement corrélées à une clé secrète. Une attaque par scan consiste à récupérer la clé secrète d'un crypto-processeur grâce à l'observation de résultats partiellement encryptés.

Des expérimentations ont été conduites sur la carte électronique de démonstration avec le TEE afin d'analyser sa sécurité contre une attaque par scan. Dans la carte électronique de démonstration, une contremesure est implémentée afin de protéger les données sensibles traitées et sauvegardées dans le TEE. Les accès de test sont déconnectés, protégeant contre les attaques exploitant les infrastructures de test, au dépend des possibilités de test, diagnostic et debug après mise en service du circuit. Les résultats d'expérience ont montré que les circuits intégrés basés sur la technologie TrustZone ont besoin d'implanter une contremesure qui protège les données extraites des chaînes de scan. Outre cette simple contremesure consistant à éviter l'accès aux chaînes de scan, des contremesures plus avancées ont été développées dans la littérature pour assurer la sécurité tout en préservant l'accès au test et au debug. Nous avons analysé un état de l'art des contremesures contre les attaques par scan. De cette étude, nous avons proposé une nouvelle contremesure qui préserve l'accès aux chaînes de scan tout en les protégeant, qui s'intègre facilement dans un système, et qui ne nécessite aucun redesign du circuit après insertion des chaînes de scan tout en préservant la testabilité du circuit. Notre solution est basée sur l'encryption du canal de test, elle assure la confidentialité des communications entre le circuit et le testeur tout en empêchant son utilisation par des utilisateurs non autorisés. Plusieurs architectures ont été étudiées, ce document rapporte également les avantages et les inconvénients des solutions envisagées en termes de sécurité et de performance.

#### 1. <u>Introduction</u>

Avec le nombre important d'applications dont sont chargées les smartphones, les opérations critiques, telles que les transactions bancaires ou la gestion des droits numériques (DRM), ont besoin d'être protégées. Une solution existante est d'utiliser un environnement de confiance, le Trusted Environment Execution (TEE), pour réaliser ces opérations confidentielles. Les applications communes sont quant à elles exécutées dans le système d'exploitation du smartphone, par exemple Android. L'objectif de cette thèse est d'évaluer l'architecture TEE face aux menaces liées à l'exploitation des infrastructures de test. Les infrastructures de test sont nécessaires afin d'assurer la qualité d'un produit après fabrication, ainsi que fournir un moyen de debug lorsque le circuit est opérationnel.

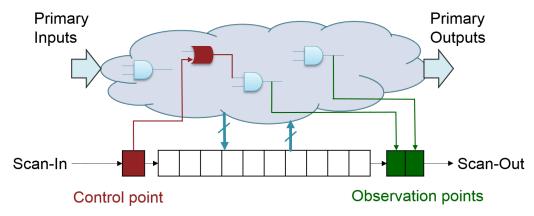

Le test/debug des circuits intégrés est possible grâce à des techniques de design dédiées, appelées Design-for-Testability (DfT). Les chaînes de scan sont la technique de DfT la plus commune. Cette méthode consiste à organiser les bascules du circuit en un/des registre(s) à décalage lorsque le circuit est en mode de test. Ainsi, les états internes du circuit sont contrôlables en utilisant l'entrée série de la chaîne de scan, appelée scan-in, et ils sont observables en utilisant la sortie série de la chaîne de scan, appelée scan-out. En plus des chaînes de scan, plusieurs standards ont été proposés pour faciliter le test des circuits électroniques. Le standard pour tester les cartes électroniques est l'IEEE 1149.1 [8], communément appelé JTAG. Le standard IEEE 1500 [9] a été proposé pour tester les System-on-Chip (SoC). Et le récent standard IEEE 1687 [10], aussi appelé IJTAG, facilite l'accès aux instruments de test embarqués, en définissant un réseau scan reconfigurable.

Ces techniques de conception en vue du test sont nécessaires pour fournir une observation et un contrôle total sur les états internes du système. Elles sont utilisées après la production du circuit intégré pour vérifier son bon fonctionnement. De plus lorsque le circuit est opérationnel, les infrastructures de test assurent le diagnostic en cas de dysfonctionnement du circuit intégré, ainsi qu'un moyen de debugger les applications installées sur le dispositif électronique. Cependant, accéder aux infrastructures de test peut compromettre la sécurité du système. En effet, un attaquant peut exploiter les moyens de test intégrés au circuit afin de voler des informations secrètes. Par exemple, sur des crypto-processeurs, l'observation du contenu des chaînes de scan permet de retrouver la clé secrète. Plusieurs attaques sur l'Advanced Encryption Standard (AES [12]) ont été proposées dans la littérature [13]-[16], appelées attaques scan. L'AES est composé de plusieurs rondes où des opérations de substitution et permutation sont appliquées sur un bloc de données en clair afin d'obtenir le bloc chiffré. Les attaques scan ciblent la première ronde de l'AES quand les données ne sont que partiellement chiffrées. La procédure de l'attaque consiste à passer le circuit en mode test après l'exécution de la première ronde afin de récupérer le contenu du registre de ronde en accédant aux chaînes de scan. L'attaquant procède ensuite à une attaque différentielle en appliquant des paires de texte en clair, puis en calculant la distance d'Hamming entre les deux résultats. Dans certains cas, le résultat du calcul de la distance de Hamming permet à l'attaquant d'identifier un octet de la clé. La stratégie est alors d'essayer plusieurs paires de texte en clair jusqu'à ce que la différence entre les deux résultats permette de déterminer un octet de clé. L'attaquant répète ces étapes pour tous les octets de clé afin de récupérer la clé dans sa totalité.

D'autres attaques existent exploitant les interfaces de test JTAG, IEEE 1500 et IJTAG. Une attaque possible consiste à voler le fichier de configuration d'un FPGA lorsque celui-ci est envoyé par l'interface JTAG [26]. Ce fichier de configuration contient toutes les propriétés intellectuelles du designer. Une autre fonctionnalité du JTAG est le téléchargement de mises-à-jour de firmware. Cette fonctionnalité a été exploitée dans [27] afin de télécharger un firmware corrompu. Ce firmware corrompu permettait à l'utilisateur d'accéder à tout le service payant sur son décodeur TV. Les fonctionnalités de debug offertes par le standard JTAG permettent aussi à un attaquant d'étudier le logiciel installé sur le dispositif afin d'en trouver les failles. Dans [28], une faille a été trouvée dans l'iPhone pour insérer des cartes SIM non autorisées par le fabricant. Dans [29], l'exploitation d'une erreur dans le code a permis de faire fonctionner des jeux sans la vérification DRM sur la console de jeu Xbox 360.

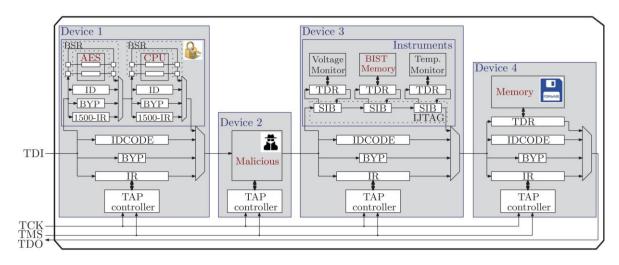

Les attaques exposées jusqu'ici sont réalisées par un utilisateur non autorisé extérieur au circuit. Une autre classe d'attaquant peut être considérée, elle concerne les attaques réalisées par un élément malicieux à l'intérieur du circuit. Une attaque interne au circuit est présentée en [30], consistant à étudier le cas d'un circuit malicieux inséré dans la chaîne JTAG du système électronique. Ce circuit attaquant est alors capable de voler et de modifier les données de test passant à travers lui.

Plusieurs contremesures ont été proposées pour se prémunir des attaques exploitant les infrastructures de test. Une solution utilisée dans l'industrie consiste à déconnecter les chaînes de scan en brûlant des fusibles après le test de fabrication. Cette solution a été privilégiée sur la carte électronique de référence du projet fonctionnant avec le TEE. Le principal inconvénient de cette solution est que les opérations de diagnostic et de debug ne sont plus possibles. De plus, si un attaquant est capable de reconnecter les accès déconnectés à l'aide d'une sonde, cette contremesure devient inefficace.

Une autre contremesure est basée sur une approche alternative de DfT, le Built-In Self-Test (BIST) [36]. Cette technique limite le contrôle et l'observation des chaînes de scan pour le testeur externe, prévenant ainsi contre les attaques scan. Cette solution est intéressante dans le cas des cryptoprocesseurs, car ils sont généralement facilement testables avec des données pseudo-aléatoires [37]—[39]. Cependant, cette contremesure compromet elle aussi la maintenance lorsque le circuit est opérationnel.

Un autre type de contremesures est basé sur un mécanisme de verrouillage des infrastructures de test. Les moyens de test sont déverrouillés après un protocole d'authentification. Ces contremesures garantissent que seuls les utilisateurs autorisés peuvent déverrouiller les fonctionnalités de test soit à l'aide d'un mot de passe [49], [50] ou soit à l'aide de paires de challenge/réponse [51]–[58]. En plus de l'important surcoût en surface et en temps de test impliqués par ces solutions, une gestion de clé est requise afin de partager avec les utilisateurs autorisés le mot de passe ou les paires de challenge/réponse utiles au déverrouillage du mécanisme de protection.

Une autre famille de protections consiste en la détection du comportement d'un attaquant [62], [63]. Au lieu de verrouiller l'accès au test, ces solutions sont basées sur des détecteurs capables de distinguer entre le testeur et un possible attaquant. Ces contremesures ne préviennent uniquement que contre les menaces extérieures au circuit. Les possibles éléments malicieux insérés dans les chaînes de test ne sont pas considérés.

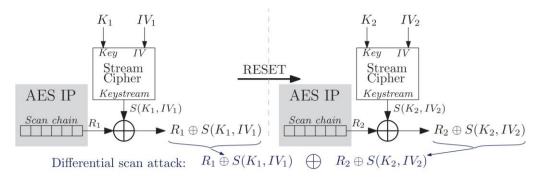

Une dernière catégorie de contremesures repose sur l'encryption du canal de test, ce qui assure la confidentialité des messages échangés entre le circuit et le testeur. L'encryption protège contre les utilisateurs non autorisés ainsi que contre les possibles éléments malveillants insérés dans la chaîne de test. Les attaquants ne sont pas capables de communiquer avec un circuit protégé, ni d'intercepter les communications. Pour encrypter les données de test, deux types de chiffrement peuvent être utilisés : le chiffrement par bloc, et le chiffrement par flot. Le choix entre les deux chiffrements dépend des performances recherchées ainsi que de la sécurité désirée. Dans la littérature ([30], [60] et [61]), le chiffrement préféré pour encrypter le canal de test est le chiffrement par flot. Les chiffrements par bloc ont un coût en surface plus important, et nécessitent d'adapter leur fonctionnement afin de traiter les communications de test qui sont réalisées en série. Néanmoins, les chiffrements par flot peuvent présenter une vulnérabilité de sécurité dans le cas d'une mauvaise implémentation. Nous montrons dans la section suivante que les solutions [30], [60] et [61] présentent cette vulnérabilité.

Dans cette thèse, nous proposons deux contremesures consistant à encrypter le canal de test : une première basée sur le chiffrement par flot, qui n'est pas exposée à la vulnérabilité mentionnée plus haut, une deuxième basée sur le chiffrement par bloc. L'état de l'art des contremesures basées sur l'encryption du canal de test est présenté dans la Section 2. La Section 3 présente les deux solutions proposées. La Section 4 consiste en l'évaluation de ces nouvelles solutions en termes de performance et de sécurité, ainsi qu'à leur comparaison. Finalement, la Section 5 conclut ce résumé concernant les travaux de thèse.

#### 2. Etat de l'art des contremesures basées sur l'encryption du canal de test

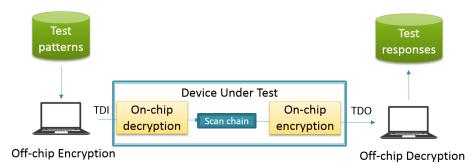

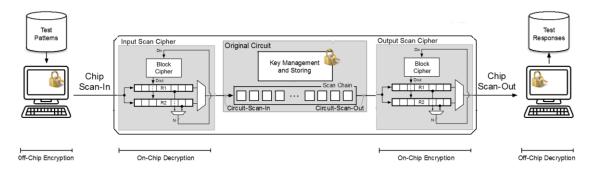

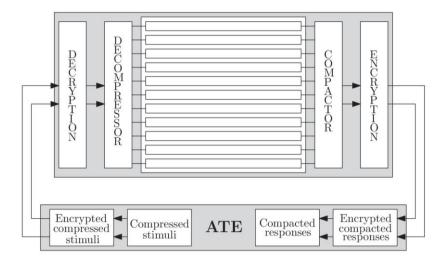

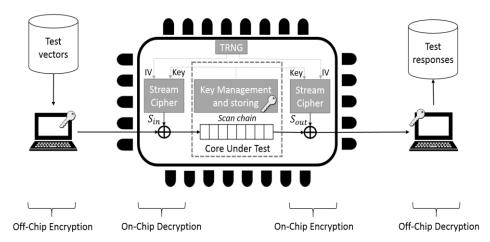

Plusieurs solutions ont été proposées pour assurer la confidentialité des communications dans les infrastructures de test. Dans ces solutions, l'interface de test intègre des chiffrements en entrée et en sortie du canal de test. Le protocole de test s'en retrouve donc légèrement modifié. Premièrement, le testeur encrypte les données de test en dehors du circuit avec la clé secrète partagée avec le circuit. Deuxièmement, les données de test chiffrées sont envoyées au circuit, qui les décrypte à l'aide du chiffrement implanté à l'entrée de son infrastructure de test. Une fois les données de test décryptées, le circuit peut poursuivre les opérations de test. Avant que les réponses de test ne soient envoyées au testeur, le chiffrement implanté en sortie du canal de test se charge d'encrypter les réponses. Le testeur reçoit alors les réponses de test chiffrées, qu'il décrypte en dehors du circuit à l'aide de la clé secrète, puis les compare avec les réponses attendues. Avec ce schéma de communication, les données et les réponses sont gardées confidentielles durant le processus de test. Sans la connaissance de la clé, il n'est pas possible d'observer les états internes du circuit, ni possible de contrôler le circuit pour le mettre dans un état souhaité. De cette façon, il n'y a pas de risques que les données chiffrées soient lues par une tierce personne non autorisée.

Puisque les données dans les infrastructures de test sont transmises en série, la plupart des schémas d'encryption sont basés sur le chiffrement par flot. Les auteurs [30] proposent d'utiliser le TRIVIUM [59] comme chiffrement par flot pour encrypter les communications JTAG. Le TRIVIUM génère un flux de nombre pseudo-aléatoire à partir d'une clé secrète et d'une valeur d'initialisation (IV). Dans [30], l'IV est codé en dur à l'intérieur du circuit grâce à des fusibles programmés au moment

de la fabrication. La clé secrète est quant à elle dérivée d'un challenge envoyé par le testeur. Seul un utilisateur autorisé connaît les paires de challenge/réponse, et donc la clé secrète utilisée pour encrypter les données de test.

La solution proposée en [60] traite le problème de possibles cores malveillants insérés dans les SoCs. La contremesure protège contre le risque qu'un core malveillant vole des données de test passant par le canal de test. Pour ce faire, un chiffrement par flux TRIVIUM encrypte les données de test. La clé secrète est générée aléatoirement par le testeur. Elle est ensuite envoyée au core protégé en utilisant une chaîne de scan dédiée et non visible des autres cores. Concernant l'initialisation du TRIVIUM, les auteurs ne spécifient pas la configuration de l'IV.

Le chiffrement par flot est aussi utilisé en [61] pour encrypter le réseau scan reconfigurable dans le standard IJTAG. Un TRIVIUM décrypte et encrypte les données envoyées et reçues du réseau scan reconfigurable. Le but est de protéger les instruments de test contre le vol de données par un instrument malicieux dans la chaîne de test, ainsi que contre les attaquants extérieurs souhaitant utiliser illégalement les instruments embarqués. Concernant l'initialisation du chiffrement par flux, les auteurs proposent des ensembles uniques de clés et d'IVs pour chaque instrument protégé, mais les auteurs ne mentionnent pas le changement de clé ou d'IV entre chaque session d'encryption.

Or il est essentiel pour assurer une bonne protection de changer la clé secrète ou l'IV entre chaque session d'encryption. Autrement, le chiffrement par flot présente une vulnérabilité appelée « two  $times\ pad$  ». On considère deux réponses de test  $R_1$  et  $R_2$  et un chiffrement par flux qui encrypte ces réponses en sortie de chaîne de test. Pour la première réponse  $R_1$ , le chiffrement par flot génère un flux de bits pseudo-aléatoire, noté S, à partir d'une clé secrète et d'une valeur initiale IV. Le chiffré de la réponse est alors  $R_1 \oplus S$ . La réponse  $R_2$  est obtenue après un reset du circuit, réinitialisant par la même occasion le chiffrement par flot. Si la même clé secrète et la même IV sont utilisées pour encrypter  $R_2$ , alors le chiffré est  $R_2 \oplus S$ . Dans le cas des attaques scan telles que présentées en [13]–[16], l'attaquant procède au XOR entre les deux réponses, donnant comme résultat  $[R_1 \oplus S(K, IV)] \oplus [R_2 \oplus S(K, IV)] = R_1 \oplus R_2$ . L'impact du chiffrement par flot est alors retiré, rendant le circuit vulnérable aux attaques scan. Un attaquant peut donc réaliser des attaques scan même si les réponses de test sont encryptées.

Les contremesures présentées en [30], [60] et [61] sont toutes exposées à cette vulnérabilité, puisque la gestion de l'IV et de la clé secrète n'est pas correcte. La même paire (clé secrète, IV) ne doit pas être utilisée plus qu'une fois pour éviter la génération du même flux pseudo-aléatoire pour différentes encryptions.

#### 3. Proposition de contremesures

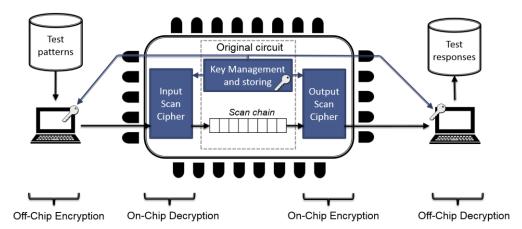

Dans ce chapitre, nous proposons premièrement une contremesure basée sur le chiffrement par flot qui ne présente pas la vulnérabilité des contremesures de l'état de l'art. Nous proposons ensuite une méthode d'encryption de la chaîne de scan basée sur le chiffrement par bloc.

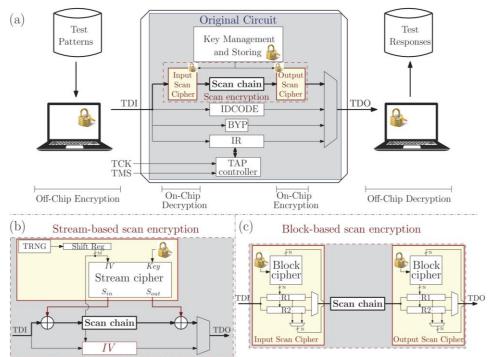

Dans les deux contremesures proposées, un premier chiffrement est implanté en entrée de chaîne de scan en charge de décrypter les patterns de test. Un deuxième chiffrement est implanté en sortie

de chaîne de scan en charge d'encrypter les réponses de test. En plus de l'implémentation des chiffrements, l'encryption du canal de test requiert d'implanter un mécanisme de gestion de clé afin de partager de façon sécurisée la clé secrète entre le circuit et le testeur. Nous supposons que le dispositif électronique doit être protégé des attaques scan, et donc qu'il embarque un ou des crypto-processeur(s). Nous proposons de réutiliser la gestion de clé déjà implantée pour le crypto-processeur ainsi que son stockage sécurisé, pour gérer et stocker la clé encryptant le canal de test. De cette façon, la clé est stockée de façon sécurisée dans le crypto-processeur, et elle est partagée avec les utilisateurs autorisés sans introduire de problèmes spécifiques de gestion de clé.

#### a) Encryption du canal de test avec le chiffrement par flux

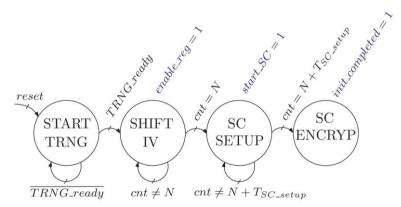

Concernant la contremesure basée sur le chiffrement par flot, la nouveauté de notre approche comparée à l'état de l'art réside dans le fait que l'IV n'est pas une valeur constante, mais qu'elle est générée aléatoirement par un générateur de nombre aléatoire, True Random Number Generator (TRNG). L'utilisation du TRNG garantit de ne jamais réutiliser la même IV pour la génération du flux pseudo-aléatoire. Ainsi, le chiffrement par flot ne présente pas la vulnérabilité two times pad décrite dans la section précédente.

La valeur aléatoire de l'IV doit être connue par le testeur extérieur afin que celui-ci puisse communiquer avec le circuit. Pour rendre la valeur de l'IV accessible à l'extérieur du circuit, une instruction JTAG, appelée *GETIV*, est ajoutée au jeu d'instructions. Lorsque le testeur exécute cette instruction, l'IV générée aléatoirement est envoyée en sortie de l'interface de test. Le testeur n'a plus qu'à lire la valeur de l'IV afin de pouvoir encrypter et décrypter les données de test en dehors du circuit. Il est important de noter que la sécurité de la solution n'est pas compromise en rendant l'IV public, puisque la clé du chiffrement par flot est toujours gardée secrète. Un attaquant n'est pas capable de déchiffrer les communications chiffrées sans la clé secrète.

L'encryption des données de test est réalisée avec le chiffrement par flot TRIVIUM. Un seul TRIVIUM est capable de générer deux flux pseudo-aléatoires : l'un pour décrypter les données arrivant en entrée du canal de test, l'autre pour encrypter les réponses sortant du canal de test. Avant la génération des flux pseudo-aléatoires par le TRIVIUM, une phase d'initialisation est nécessaire pour que le TRNG atteigne une entropie suffisante pour générer un nombre aléatoire. Le chiffrement par flot est lui aussi initialisé. Pendant l'initialisation, les chaînes de scan ne sont pas accessibles, toutes les opérations de test sont considérées comme une instruction *BYPASS*. Une fois la phase d'initialisation achevée, le jeu d'instructions est déverrouillé. Seulement un utilisateur, connaissant la clé secrète et ayant récupéré l'IV générée aléatoirement par le circuit grâce à l'instruction *GETIV*, peut communiquer avec le circuit.

#### b) Encryption du canal de test avec un chiffrement par bloc

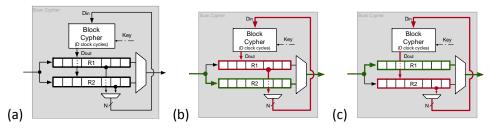

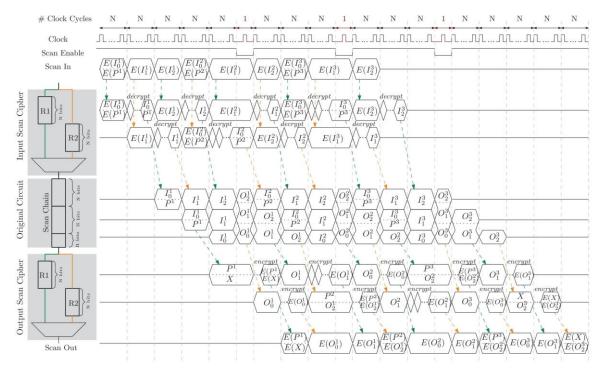

Dans ces travaux de thèse, nous avons aussi proposé une contremesure basée sur le chiffrement par bloc. Nous avons choisi des chiffrements par bloc dits « légers » afin de limiter le coût en surface et en consommation de puissance. Deux chiffrements par bloc légers sont implantés, l'un pour le déchiffrement effectué en entrée du canal de test, et l'autre pour l'encryption effectuée en sortie du canal de test. Chacun des deux chiffrements possède deux registres de rondes afin de réaliser en parallèle l'encryption des données et l'acquisition série des données du canal de test. La réalisation de ces opérations en parallèle permet de ne pas perdre en temps de test.

Puisque les communications de test sont effectuées en série, l'utilisation du chiffrement par bloc implique d'ajouter des données supplémentaires aux données de test initiales afin de former des segments de la taille du bloc encrypté/décrypté. La chaîne de scan est ainsi remplie et vidée segment par segment. Chaque segment est composé d'un bloc de données sur N bits (N représentant la taille du bloc encrypté/décrypté). Quand la chaîne de scan n'est pas multiple de N, la solution fonctionne toujours mais chaque pattern est complété avec des données supplémentaires. En considérant R le reste modulo N de bascules dans la chaîne de scan, il est nécessaire de compléter les données de test par N-R bits. Les données supplémentaires demandent du temps de test additionnel pour que le testeur les envoie dans la chaîne de scan. Le résultat est que cette solution a un surcoût en temps de test dépendant du nombre de pattern nécessaire pour tester le circuit. Ce coût est évalué à N-R coups d'horloge pour chaque pattern de test.

Pour réduire ce coût, une optimisation de la solution a été proposée. Elle consiste à exploiter le temps de test additionnel ajouté à chaque pattern pour améliorer la testabilité du circuit. En effet, en ajoutant N-R bascules scan au circuit, il est possible de les utiliser en tant que points d'observation sur la logique du circuit. Les points d'observation sont une technique de test permettant de propager des signaux « difficilement » observables directement à des bascules scan, sans affecter le temps de test initial. Le but de cette technique est de réduire le nombre de patterns nécessaire pour tester un circuit, tout en préservant le même taux de couverture de fautes.

En conclusion, les deux contremesures proposées permettent de se protéger contre les menaces utilisant l'infrastructure de test, tout en préservant les fonctionnalités de debug et de diagnostic lors de possibles maintenances. C'est un principal avantage comparé à la solution consistant à déconnecter les accès de test. Un autre avantage concerne la réutilisation de la gestion de clé déjà implanté dans le circuit. Les contremesures basées sur un protocole sécurisé utilisant des primitives cryptographiques, comme [49]–[58], ont quant à elles besoin d'avoir une gestion de clé dédiée.

Les deux solutions ont fait l'objet d'une publication dans un journal [69], et à plusieurs présentations à des conférences [70]–[72] ainsi qu'à des workshops [76]–[81]. Dans la section suivante, nous comparons les deux solutions.

#### 4. Evaluation et comparaison des solutions proposées

Les contremesures consistant à encrypter le canal de test sont évaluées par rapport à la protection apportée sur l'infrastructure de test, les coûts en termes d'implémentation et l'intégration de la solution dans un SoC.

#### a) Analyse de sécurité

Concernant la sécurité, le déchiffrement effectué en entrée du canal de test empêche d'écrire une valeur désirée dans la chaîne de scan sans la connaissance de la clé. Le chiffrement effectué en sortie du canal de test empêche l'observation des états internes du circuit, sans avoir réalisé le déchiffrement au préalable. Les possibles éléments malicieux insérés dans les infrastructures de test ne peuvent donc pas voler des données confidentielles. De plus, l'encryption du canal de test permet de se prémunir des attaquants extérieurs au circuit, souhaitant par exemple réaliser des attaques scan [13]–[16] ou

exploiter les fonctionnalités JTAG telles que le debug [28][29], l'accès au réseau IJTAG, ou le téléchargement de firmware [27].

La proposition de contremesure basée sur le chiffrement par flot présente un niveau de sécurité plus important que les solutions proposées dans l'état de l'art. En effet, la mauvaise gestion de clé secrète et d'IV rend les contremesures [30], [60] et [61] vulnérables aux attaques scan. Nous proposons de générer aléatoirement l'IV initialisant le chiffrement par flot afin d'éviter cette vulnérabilité, et par conséquent protéger contre les attaques scan.

Finalement, les deux propositions d'encryption du canal de test (par le chiffrement par flux et par le chiffrement par bloc) protègent contre les menaces liées à l'utilisation de l'infrastructure de test.

#### b) Coûts d'implémentation

En terme de testabilité, l'encryption du canal de test permet de tester le circuit original sans réduire le taux de couverture de fautes. En effet, les patterns du circuit original sont appliqués tels qu'ils sont après leur déchiffrement. Cependant, l'architecture de la solution a besoin d'être testée, sans l'aide des chaînes de scan qui exposeraient les chiffrements implantés aux attaques scan. Nous proposons de tester fonctionnellement les chiffrements en utilisant les patterns dédiés à tester le circuit original. Le test des chiffrements par bloc est facilité par les propriétés de diffusion des algorithmes cryptographiques ([37] et [38]). Concernant le test des chiffrements par flot, le flux de bits pseudo-aléatoire généré par le TRIVIUM est une combinaison des états internes du chiffrement, le rendant facilement testable. Les deux chiffrements, par bloc et par flot, propagent donc facilement les erreurs à leur sortie lorsqu'une encryption est réalisée. Pour valider cette hypothèse, nous avons mené des expérimentations consistant à appliquer la séquence de test de plusieurs circuits sur les chiffrements implantés. Pour tous les circuits considérés, le taux de couverture de fautes dans l'architecture de la contremesure est de 100%. En d'autres termes, les chiffrements implantés sont testés en même temps que le circuit original, sans application de séquence particulière.

Nous avons aussi mené des expérimentations pour évaluer le surcoût en terme de surface et de temps de test dans le cas d'une simple chaîne de scan. Si un TRNG est déjà implanté dans le circuit alors la solution basée sur le chiffrement par flot peut l'utiliser pour générer l'IV, limitant le coût en surface. Dans ce cas, le chiffrement par flot présente une surface moindre (5 408,52  $\mu$ m² pour l'implémentation avec le TRIVIUM) comparée au chiffrement par bloc (9 282.52  $\mu$ m² pour l'implémentation avec le chiffrement par bloc SKINNY). Il est clair aussi que le chiffrement par flot surpasse le chiffrement par bloc en terme de coût en temps de test, à cause du surcoût à chaque pattern pour ce dernier. Ce coût peut cependant être réduit en appliquant l'optimisation consistant à insérer des points d'observation sur le circuit original.

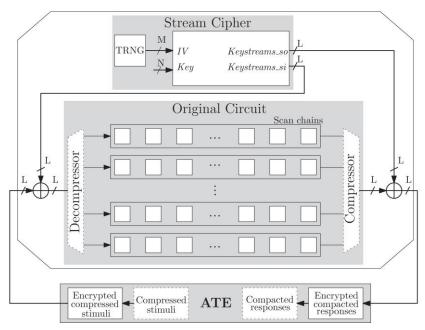

Les deux solutions ne sont pas limitées à une seule chaîne de scan. Nous avons proposé de les étendre pour protéger des chaînes de scan multiples, indépendamment de l'implémentation de techniques de compression. La contremesure basée sur le chiffrement par flot présente un coût plus faible en terme de surface (de 5 553,60  $\mu$ m² à 9 999,60  $\mu$ m² pour l'implémentation avec TRIVIUM) et de puissance consommée (environ 35  $\mu$ W), comparé à la contremesure basée sur le chiffrement par bloc (pour l'implémentation avec SKINNY, environ 10 000  $\mu$ m² pour la surface, et de 128,2  $\mu$ W à 2 232,9  $\mu$ W pour la puissance consommée). Cependant, le nombre limite de chaîne de scan traité par

un chiffrement est plus faible (jusqu'à 32 chaînes de scan) pour la contremesure avec le chiffrement par flot, comparé à la limite de la contremesure avec le chiffrement par bloc (jusqu'à 64 chaînes).

#### c) Intégration dans un SoC

Les infrastructures de test de chacun des cores composant un SoC sont souvent connectées en série les uns après les autres. L'entrée et la sortie série de l'interface de test permet alors d'accéder aux chaînes de scan des différents cores dans le SoC. Quand un core implante des chiffrements en entrée et sortie de chaîne de scan, tous les autres cores de la chaîne de test reçoivent des données encryptées, protégeant ainsi contre les potentiels cores malicieux. L'encryption avec un chiffrement par flux consiste à une opération bit à bit, n'impliquant donc aucun problème d'intégration de la solution dans un design SoC. A l'inverse, l'encryption avec le chiffrement par bloc nécessite d'ajouter des données supplémentaires afin d'avoir des segments de la taille du bloc encrypté. Ces données supplémentaires sont alors reçues par les autres cores du canal de test, pouvant créer des problèmes dans les opérations de test. Par conséquent, le concepteur doit être conscient du problème potentiel de l'intégration dans un SoC de la solution basée sur le chiffrement par bloc. Un moyen pour éviter d'envoyer des données supplémentaires dans la chaîne de test est insérer des bascules dans la chaîne de scan connectées à des points d'observation sur la logique du circuit. De cette façon, la chaîne de scan est multiple de la taille du bloc encrypté. Cependant, l'insertion des points d'observation implique de modifier le circuit original. Il n'est donc pas possible d'appliquer la solution dans le cas d'un core non modifiable.

Pour conclure la comparaison, le choix entre les deux contremesures proposées dépend du circuit original où la protection est implantée : si un TRNG est déjà implanté dans le circuit original, si la longueur de la chaîne de scan est multiple du bloc encrypté, si le circuit original peut être modifié afin d'insérer des points d'observation. Le choix dépend aussi du nombre de chaîne de scan qui doit être encrypté dans le cas de la configuration multiple des chaînes de scan.

La comparaison des deux solutions a fait l'objet d'une soumission au journal *Transactions on VLSI Systems* ainsi qu'une présentation à une conférence [74].

#### 5. Conclusion

Les circuits cryptographiques sont largement répandus pour assurer la confidentialité dans les systèmes électroniques. C'est le cas par exemple dans les smartphones où les opérations d'encryption sont réalisées pour échanger ou stocker des informations confidentielles. Dans ce cadre, les opérations d'encryption sont réalisées dans un environnement de confiance, le TEE. Cependant, cet environnement n'est pas suffisant pour assurer la protection des crypto-processeurs contre des attaques matérielles telles que l'exploitation des infrastructures de test.

Les tests de production des circuits cryptographiques sont obligatoires afin d'assurer la qualité du produit. Il est d'autant plus important de réaliser le test car des défauts physiques sur le circuit peuvent compromettre la sécurité. L'implémentation des techniques de test (chaînes de scan, JTAG, IEEE 1500 et IJTAG) est donc essentielle. Néanmoins, ces infrastructures de test peuvent être un point d'entrée pour un attaquant souhaitant corrompre la sécurité du système. Une contribution de cette thèse

concerne la proposition de nouvelles contremesures consistant à encrypter le canal de test. Plusieurs contremesures basées sur le chiffrement par flot ont été précédemment proposées, mais présentant toutes une faiblesse dans leur implémentation. Nous avons proposé une nouvelle implémentation sans la vulnérabilité des contremesures de l'état de l'art, ainsi qu'une solution basée sur des chiffrements par bloc légers. Le principe de ces contremesures est l'insertion de modules de chiffrement/déchiffrement en amont et en aval du canal de test. L'encryption est effectuée à l'aide d'une clé secrète partagée avec les utilisateurs autorisés grâce à la gestion de clé déjà implantée dans le circuit. Un avantage important est de conserver les fonctionnalités de diagnostic et de debug pour les utilisateurs autorisés.

Dans cette thèse, nous avons aussi évalué et comparé les deux solutions. Les résultats expérimentaux ont montré que l'encryption avec le chiffrement par flot présente un coût plus faible en surface, en temps de test et en puissance consommée, dans le cas où un générateur de nombre aléatoire est déjà implanté dans le circuit. Dans le cas contraire, l'encryption avec le chiffrement par bloc est une bonne alternative, avec une possible optimisation pour réduire le coût en temps de test et faciliter l'intégration dans un design SoC.

#### REMERCIEMENTS

Je souhaiterais remercier plusieurs personnes qui ont contribué par leur aide et par leur soutien à la réalisation de cette thèse. Premièrement, je suis reconnaissant d'avoir eu Bruno Rouzeyre, Marie-Lise Flottes et Giorgio Di Natale pour encadrer ma thèse. Ils m'ont aidé à appréhender le contexte de la thèse, et à mener à bien ces travaux en m'apportant chacun leurs conseils et leurs idées. Les différentes contributions de cette thèse sont le résultat d'une excellente ambiance de travail, propice à réaliser d'intéressantes recherches.

Cette thèse n'aurait pas pu voir le jour sans le financement du projet FUI TEEVA. Je remercie les partenaires du projet que j'ai pu rencontrer à diverses occasions lors de réunions pour leur apport dans la réalisation de cette thèse.

Durant ces trois années, j'ai pu compter sur l'aide de plusieurs personnes en plus de mes encadrants : Sophie Dupuis, qui m'a aidé dans mes travaux et qui a participé à plusieurs publications, et Papa Sidy Ba, un ancien doctorant, qui m'a apporté sa maîtrise des outils Design Compiler et TetraMax utiles aux expérimentations menées dans cette thèse. Je n'oublie pas Emanuele Valea, mon collègue de bureau et ami, avec lequel j'ai collaboré depuis août 2017. Je me considère chanceux d'avoir pu bénéficier de son point de vue perspicace durant ma dernière année de thèse, qui a permis une entraide très efficace pour mener à bien ces travaux et pour les publier.

Je tiens également à remercier Lorena Anghel et Lilian Bossuet d'avoir accepté de rapporter cette thèse. Merci aussi à David Hély et à Alberto Bosio d'avoir accepté de faire partie du jury.

Mes années au LIRMM ont été une formidable expérience, où j'ai reçu un très bon accueil. Je voudrais remercier spécialement Caroline Lebrun, secrétaire du département microélectronique, toujours présente pour m'aider et répondre à mes questions.

Les doctorants du LIRMM ont aussi participé à ce que l'ambiance de travail soit très agréable à travers nos pauses cafés. Je peux même en compter un grand nombre en tant qu'amis, qui ont participé à enrichir ma vie montpelliéraine avec les différentes sorties organisées.

Je tiens finalement à remercier toutes les personnes de mon entourage qui m'ont soutenu durant ces trois ans, amis et famille. Malgré la distance, mes parents et mon frère Florian ont toujours été là pour m'aider dans mon quotidien. Un énorme merci aussi à Sara qui m'a apporté soutien et motivation pour mener à bien cette thèse.

## **CONTENTS**

| Contents    | S                                                                   | 15 |  |  |

|-------------|---------------------------------------------------------------------|----|--|--|

| List of fig | List of figures19                                                   |    |  |  |

| List of ta  | List of tables21                                                    |    |  |  |

| Acronym     | 1S                                                                  | 22 |  |  |

| -           | tion                                                                |    |  |  |

| introduc    |                                                                     | 23 |  |  |

| Chamban     | I Contout                                                           | 27 |  |  |

| •           | I Context                                                           |    |  |  |

|             | roduction to TEEVA project                                          |    |  |  |

| I.2. Te     | st, diagnosis and debug for Integrated Circuits                     | 30 |  |  |

| I.2.a       | Design-For-Testability and test application                         | 31 |  |  |

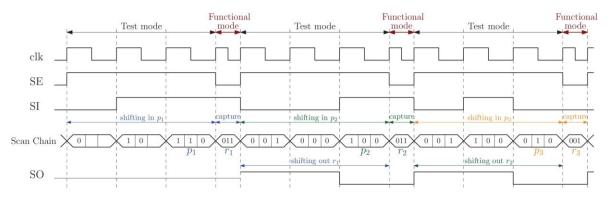

|             | I.2.a.i Scan test procedure for stuck-at faults testing             | 32 |  |  |

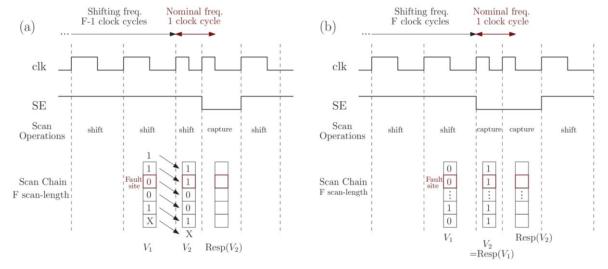

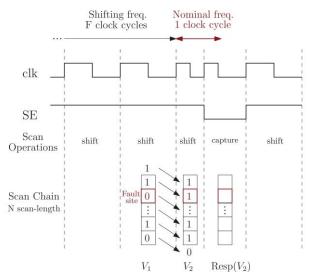

|             | I.2.a.ii Scan test procedure for transition-delay faults testing    | 33 |  |  |

|             | I.2.a.iii Insertion of test points                                  | 34 |  |  |

|             | I.2.a.iv Multiple scan chains                                       | 35 |  |  |

| 1.2.b       | Test standards: JTAG, IEEE 1500 and IJTAG                           | 36 |  |  |

| 1.2.c       | Overview of the Design-for-Debug implemented in ARM designs         | 38 |  |  |

| I.3. Co     | nclusion on test infrastructures                                    | 40 |  |  |

|             |                                                                     |    |  |  |

| Chapter     | II Security threats through test infrastructures                    | 41 |  |  |

| II.1. Th    | reat model related to test infrastructures                          | 42 |  |  |

| II.1.a      | External attacker                                                   | 42 |  |  |

|             | II.1.a.i Scan attacks                                               | 43 |  |  |

|             | II.1.a.ii Intellectual property theft                               | 46 |  |  |

|             | II.1.a.iii Updating a corrupted firmware                            | 46 |  |  |

|             | II.1.a.iv Exploiting the debug facilities                           | 47 |  |  |

|             | II.1.a.v Exploiting the IJTAG network                               | 48 |  |  |

| II.1.b      | Internal attacker                                                   | 49 |  |  |

|             | II.1.b.i Insertion of a malicious component in the test daisy-chain | 49 |  |  |

|             | II.1.b.ii Counterfeit components                                    | 49 |  |  |

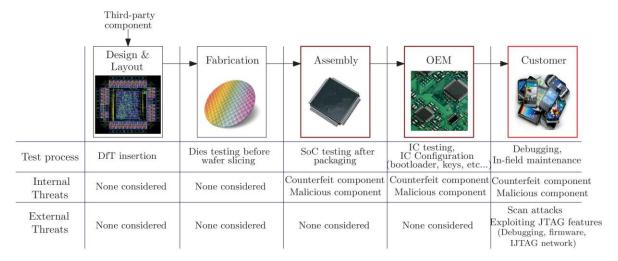

| II.2.  | Th    | reats throughout IC supply chain                                           | 50 |

|--------|-------|----------------------------------------------------------------------------|----|

| II.3.  | Att   | ack report on the reference board of TEEVA project                         | 51 |

| II.    | 2.a   | Discovered attacks on TEE in the literature                                | 51 |

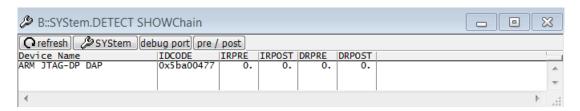

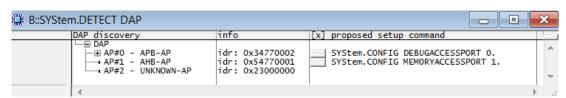

| II.    | 2.b   | Overview of the reference board operating with TEE                         | 52 |

| II.    | 2.c   | Security analysis through JTAG access on the reference board               | 53 |

| II.4.  | Co    | nclusion on attacks using test infrastructures                             | 54 |

| Cla au | 1     |                                                                            |    |

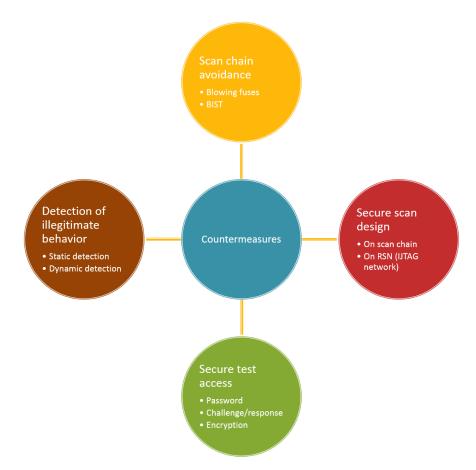

|        |       | III Existing countermeasures against attacks using test interfaces         |    |

|        |       | ssification of the existing countermeasures                                |    |

|        |       | an chain avoidance                                                         |    |

| III.3. | Sec   | cure scan design                                                           | 58 |

| III    | .3.a  | On scan chains                                                             | 58 |

| III    | .3.b  | On Reconfigurable Scan Network (IJTAG)                                     | 62 |

| III.4. | Sec   | cure test access                                                           | 63 |

| Ш      | .4.a  | Password                                                                   | 64 |

| Ш      | .4.b  | Challenge/Response                                                         | 65 |

| Ш      | .4.c  | Encryption of test communication                                           | 69 |

| III.5. | De    | tection of illegitimate behavior                                           | 71 |

| Ш      | .5.a  | Static detection                                                           | 72 |

| III    | .5.b  | Dynamic detection                                                          | 73 |

| III.6. | Eva   | aluation of the existing countermeasures                                   | 74 |

| III.7. | Co    | nclusion on the state-of-the-art countermeasures                           | 79 |

|        |       |                                                                            |    |

| Chap   | ter l | IV Proposed countermeasures based on scan encryption                       | 80 |

| IV.1.  | End   | cryption with symmetric ciphers                                            | 81 |

| IV     | '.1.a | Block ciphers                                                              | 82 |

|        |       | IV.1.a.i Block ciphers limitations                                         | 82 |

|        |       | IV.1.a.ii Application for encrypting test data                             | 83 |

| IV     | '.1.b | Stream ciphers                                                             | 83 |

|        |       | IV.1.b.i Stream ciphers limitations                                        | 83 |

|        |       | IV.1.b.ii Vulnerabilities of existing countermeasures using stream ciphers | 84 |

| IV.2. | Pri   | nciple o   | of proposed scan chain encryption                          | 85    |

|-------|-------|------------|------------------------------------------------------------|-------|

| IV.3. | Pro   | posed      | countermeasure based on block ciphers                      | 86    |

| IV.   | 3.a   | CBC ap     | oplied on single scan chain                                | 86    |

|       |       | IV.3.a.i   | Stuck-at faults testing with CBC                           | 87    |

|       |       | IV.3.a.ii  | Transition-delay faults testing with CBC                   | 88    |

|       |       | IV.3.a.iii | Mode of operations                                         | 89    |

|       |       | IV.3.a.iv  | Optimization of CBC solution                               | 92    |

| IV.   | 3.b   | Extens     | ion to multiple scan chains design                         | 94    |

| IV.4. | Pro   | posed      | countermeasure based on stream cipher                      | 98    |

| IV.   | 4.a   | First pı   | roposal to share the IV from the scan chain                | 99    |

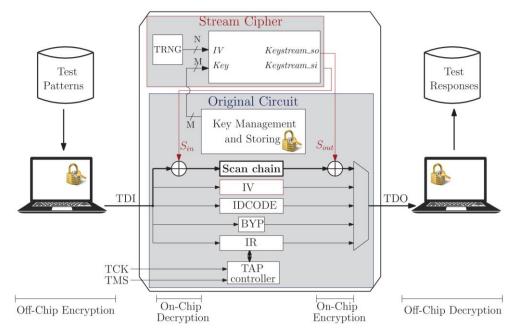

| IV.   | 4.b   | Propos     | sal of CSC integrated in JTAG infrastructure               | 100   |

|       |       | IV.4.b.i   | Wafer testing                                              | 101   |

|       |       | IV.4.b.ii  | Mission mode                                               | 101   |

| IV.   | 4.c   | Implen     | mentation of CSC integrated in JTAG infrastructure         | 102   |

|       |       | IV.4.c.i   | General architecture                                       | 102   |

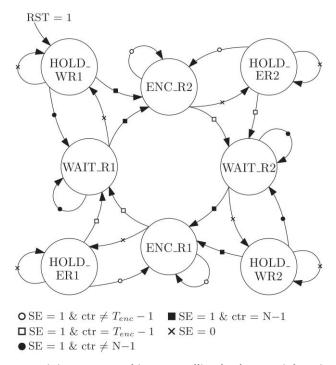

|       |       | IV.4.c.ii  | Control Unit                                               | 104   |

|       |       | IV.4.c.iii | Overheads compared to original JTAG test wrapper           | 105   |

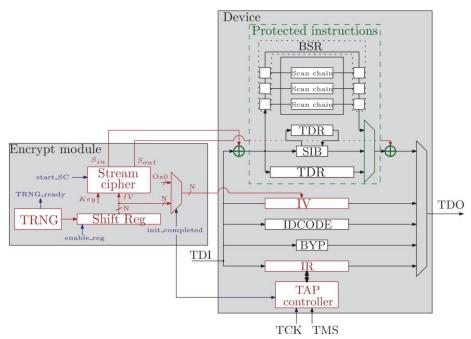

|       |       | IV.4.c.iv  | Extension to multiple scan chains                          | 106   |

| IV.5. | Co    | nclusior   | on the new proposed countermeasures                        | 107   |

| Chap  | ter ' | V Featu    | res and comparison of the two proposed countermeasures     | 108   |

| V.1.  | Glo   | bal adv    | vantages of scan encryption compared to the state-of-the-a | rt109 |

| V.I   | .a    | Security   | y evaluation                                               | 109   |

| V.I   | .b    | Charact    | teristics and costs evaluation                             | 110   |

| V.2.  | lm    | plemen     | tation costs                                               | 113   |

| V.2   | 2.a   | On sing    | le scan chain                                              | 113   |

| V.2   | 2.b   | On mu      | ıltiple scan chains                                        | 114   |

|       |       |            | vevaluation                                                |       |

| V.4.  |       | -          |                                                            |       |

|       |       |            | n of the solutions in a SoC design                         |       |

| v.5.  | Co    | nclusior   | n on the advantages of the proposed countermeasures        | 117   |

|       |       |            |                                                            |       |

| Chan  | ter \ | VI Concl   | lusion                                                     | 118   |

| VI.1   | Contributions             | 119 |

|--------|---------------------------|-----|

| VI.2   | Summary of the comparison | 119 |

| VI.3   | Perspectives              | 121 |

| Biblio | ography                   | 122 |

| Publi  | cations                   | 127 |

## **LIST OF FIGURES**

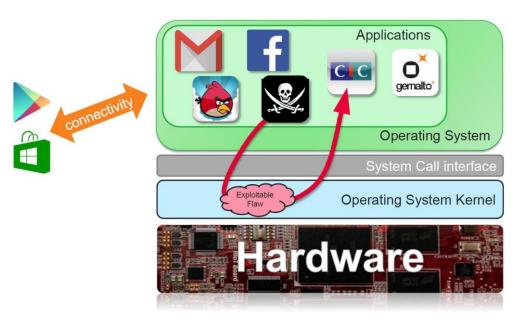

| Figure 1               | Security threats on mobile platforms.                                                                                                                                                     | 28        |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

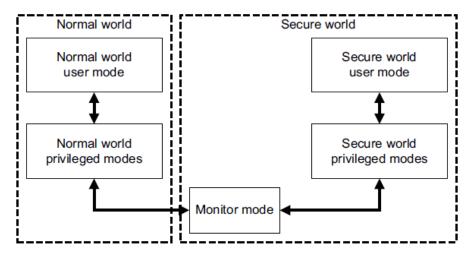

| Figure 2               | Modes in an ARM processor implementing TrustZone [1] technology.                                                                                                                          | 29        |

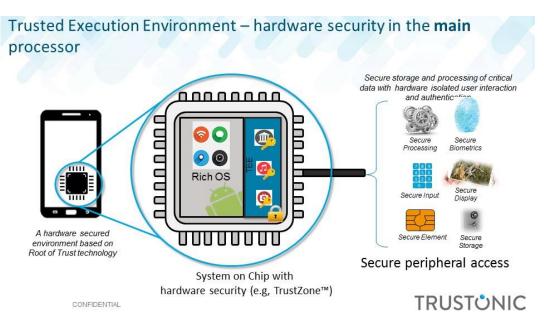

| Figure 3               | Mobile chip operating with the TEE.                                                                                                                                                       | 30        |

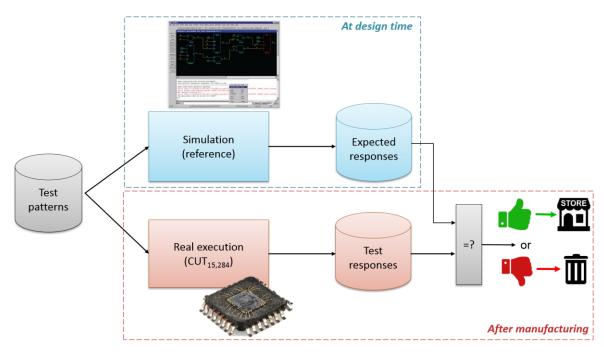

| Figure 4               | Testing principle.                                                                                                                                                                        | 31        |

| Figure 5               | Single scan chain.                                                                                                                                                                        | 32        |

| Figure 6               | Example of scan procedure for testing stuck-at faults.                                                                                                                                    | 32        |

| Figure 9               | Insertion of control points and observation points on a circuit.                                                                                                                          | 35        |

| Figure 7               | (a) Launch-On-Shift (LOS) scheme. (b) Launch-On-Capture (LOC) scheme.                                                                                                                     | 33        |

| Figure 8               | Launch-On Extra-Shift (LOES) scheme.                                                                                                                                                      | 34        |

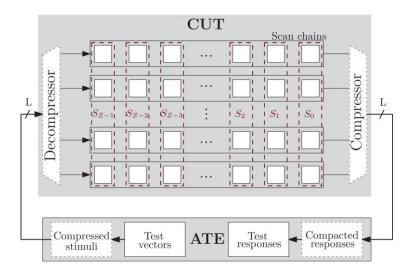

| Figure 10              | Multiple scan design with the possible integration of test compression techniques.                                                                                                        | 36        |

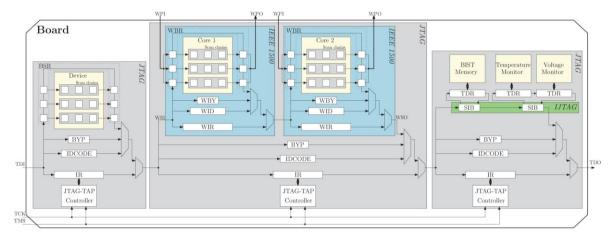

| Figure 11              | JTAG daisy-chained components and integration with IEEE 1500 (blue area) and                                                                                                              |           |

|                        | IJTAG (green area) standards.                                                                                                                                                             | <i>37</i> |

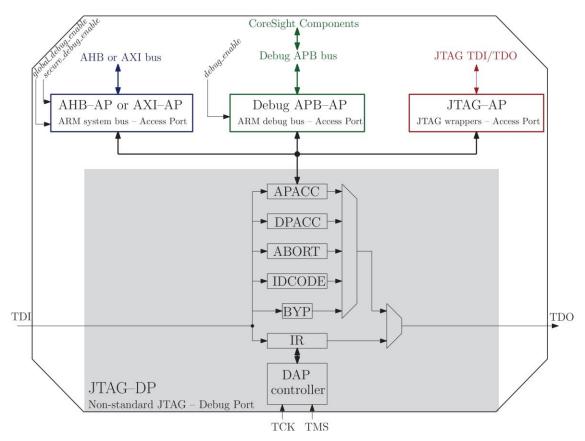

| Figure 12              | Overview of the non-standard JTAG-Debug Port (JTAG-DP) giving 3 accesses to                                                                                                               |           |

|                        | (1) the ARM system bus (AHB or AXI); (2) the ARM debug bus (Debug APB); and                                                                                                               |           |

|                        | (3) the standard JTAG wrappers.                                                                                                                                                           | 40        |

| Figure 13              | JTAG daisy-chained components (Device 1) a SoC containing an AES crypto-core                                                                                                              |           |

|                        | and a CPU, (Device 2) a malicious core, (Device 3) a device with embedded                                                                                                                 |           |

|                        | instruments accessible through an RSN, and (Device 4) a memory contained a                                                                                                                |           |

|                        | firmware.                                                                                                                                                                                 | 42        |

| Figure 14              | Differential scan attack on AES.                                                                                                                                                          | 44        |

| Figure 15              | IC supply chain with the threats of the different actors using the test facilities.                                                                                                       | 50        |

| Figure 16              | Detection with TRACE32 of the JTAG-Debug Port (DP) implemented on the HIKEY                                                                                                               |           |

|                        | board.                                                                                                                                                                                    | 52        |

| Figure 17              | Detection with TRACE32 of the Access Ports (APs) implemented on the HIKEY                                                                                                                 |           |

|                        | board.                                                                                                                                                                                    | 52        |

| Figure 18              | Classification of the countermeasures against the attacks using the test                                                                                                                  |           |

|                        | interfaces.                                                                                                                                                                               | 56        |

| Figure 19              | Scheme of test communication encryption.                                                                                                                                                  | 70        |

| Figure 20              |                                                                                                                                                                                           | 0.4       |

| F: 21                  | Differential scan attack on test data encrypted with stream cipher.                                                                                                                       | 84        |

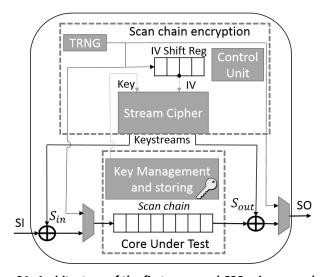

| Figure 21              | Principle of proposed scan chain encryption.                                                                                                                                              | 86        |

| Figure 21<br>Figure 22 |                                                                                                                                                                                           |           |

| _                      | Principle of proposed scan chain encryption.                                                                                                                                              | 86        |

| Figure 22              | Principle of proposed scan chain encryption.  Basic scheme of CBC on a single scan chain configuration.                                                                                   | 86        |

| Figure 22              | Principle of proposed scan chain encryption.  Basic scheme of CBC on a single scan chain configuration.  (a) generic scheme of scan cipher; (b) R1 is used for encryption while R2 shifts | 86<br>87  |

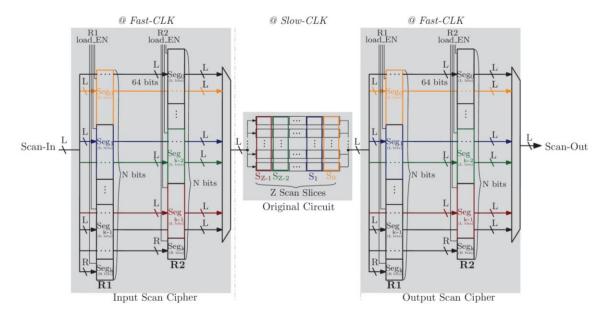

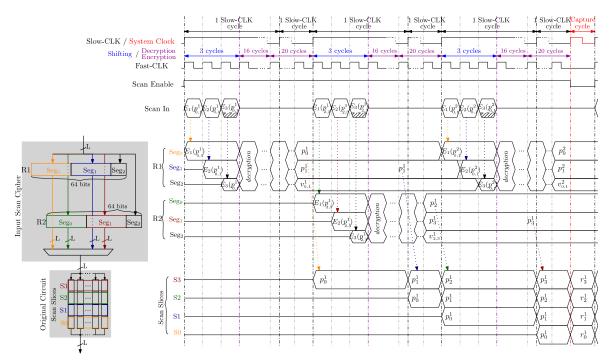

| Figure 26 | Proposed CBC solution applied on L multiple scan chains.                           | 95  |

|-----------|------------------------------------------------------------------------------------|-----|

| Figure 27 | Time diagram of shift operations for the Input Scan Cipher in the case of CBC      |     |

|           | applied on L multiple scan chains.                                                 | 96  |

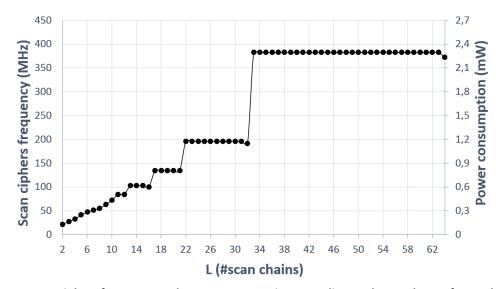

| Figure 28 | Scan ciphers frequency and power consumption according to the number L of          |     |

|           | scan chains (in the case of SKINNY block cipher).                                  | 97  |

| Figure 29 | CBC applied when a test compression method is used.                                | 98  |

| Figure 30 | Principle of the proposed CSC using a random IV.                                   | 98  |

| Figure 31 | Architecture of the first proposed CSC using a random IV.                          | 99  |

| Figure 32 | Basic scheme of CSC on single scan chain integrated in JTAG infrastructure.        | 102 |

| Figure 33 | Detailed architecture of the CSC solution.                                         | 103 |

| Figure 34 | Finite State Machine controlling the initialization procedure of the CSC solution. | 104 |

| Figure 35 | CSC solution applied on L multiple scan chains regardless of test compression.     | 106 |

| Figure 36 | (a) Global architecture of the scan encryption countermeasures. (b) CSC            |     |

|           | implementation. (c) CBC implementation.                                            | 109 |

## **LIST OF TABLES**

| Table 1  | Evaluation of the existing countermeasures (red: drawback, green: benefit).      | <i>78</i> |

|----------|----------------------------------------------------------------------------------|-----------|

| Table 2  | Test time cost of CBC for several circuits.                                      | 91        |

| Table 3  | Impact on number of observation points per flip-flops for test time optimization |           |

|          | on Pipelined AES-128 circuit.                                                    | 92        |

| Table 4  | Cost to use optimized CBC regarding several circuits.                            | 93        |

| Table 5  | Area cost of the proposed CSC compared to the original JTAG wrapper.             | 105       |

| Table 6  | Comparison of the proposed scan chain encryptions to the state-of-the-art (red:  |           |

|          | drawback, green: benefit).                                                       | 112       |

| Table 7  | Area and test time cost of scan encryption with stream cipher and block cipher,  |           |

|          | applied on several circuits.                                                     | 114       |

| Table 8  | Scan encryption with stream cipher and block cipher applied on multiple scan     |           |

|          | chains design.                                                                   | 115       |

| Table 9  | Scan ciphers tested for free.                                                    | 116       |

| Table 10 | Comparison between scan encryption with stream cipher and block cipher.          | 120       |

|          |                                                                                  |           |

## **ACRONYMS**

| AES    | Advanced Encryption Standard           |

|--------|----------------------------------------|

| AHB    | Advanced High-performance Bus          |

| AP     | Access Port                            |

| APACC  | Access Port ACCesses                   |

| APB    | Advanced Peripheral Bus                |

| ATE    | Automatic Test Equipment               |

| ATPG   | Automatic Test Pattern Generator       |

| AXI    | Advanced eXtensible Interface          |

| BIST   | Built-In Self-Test                     |

| BSR    | Boundary Scan Register                 |

| BYP    | Bypass register                        |

| CBC    | Countermeasures Based on Block cipher  |

| CSC    | Countermeasures Based on Stream cipher |

| CTR    | Counter mode                           |

| CUT    | Circuit Under Test                     |

| DAP    | Debug Access Port                      |

| DES    | Data Encryption Standard               |

| DfT    | Design-for-Testability                 |

| DfD    | Design-for-Debug                       |

| DP     | Debug Port                             |

| DPACC  | Debug Port ACCesses                    |

| DRM    | Digital Rights Management              |

| ECC    | Elliptic Curve Cryptography            |

| FF     | Flip-Flop                              |

| FPGA   | Field-Programmable Gate Array          |

| FSM    | Finite State Machine                   |

| GE     | Gate Equivalent                        |

| HMAC   | Keyed-Hash Message Authentication Code |

| IC     | Integrated Circuit                     |

| IDCode | Identification Code register           |

| IJTAG  | Internal JTAG                          |

| IP     | Intellectual Property                  |

| IR     | Instruction Register                   |

| IV     | Initialization Vector                  |

| JTAG   | Join Test Action Group                 |

| LFSR | Linear Feedback Shift Register             |

|------|--------------------------------------------|

| LOC  | Launch-On-Capture                          |

| LOES | Launch-On Extra-Shift                      |

| LOS  | Launch-On-Shift                            |

| LSIB | Locking Segment Insertion Bit              |

| LUT  | LookUp Table                               |

| MAC  | Message Authentication Code                |

| MMU  | Memory Management Unit                     |

| n.s. | not specified                              |

| NS   | Non-Secure                                 |

| OEM  | Original Equipment Manufacturer            |

| os   | Operating System                           |

| PRNG | Pseudo Random Number Generator             |

| PUF  | Physically Unclonable Function             |

| RAM  | Random Access Memory                       |

| REE  | Rich Environment Execution                 |

| RSA  | Ronald Rivest, Adi Shamir, Leonard Adleman |

| RSN  | Reconfigurable Scan Network                |

| SE   | Scan Enable                                |

| SI   | Scan-In                                    |

| SIB  | Segment Insertion Bit                      |

| SKMU | Secret Key Management Unit                 |

| so   | Scan-Out                                   |

| SoC  | System-on-Chip                             |

| TA   | Trusted Applications                       |

| TAP  | Test Access Port                           |

| TCK  | Test Clock                                 |

| TDI  | Test Data Input                            |

| TDO  | Test Data Output                           |

| TDR  | Test Data Register                         |

| TEE  | Trusted Environment Execution              |

| TMS  | Test Mode Select                           |

| TRNG | True Random Number Generator               |

| TRST | Test Reset                                 |

| WBR  | Wrapper Boundary Register                  |

| WBY  | Wrapper Bypass                             |

| WCK  | Wrapper Clock                              |

| WID  | Wrapper Identification register            |

| WIR  | Wrapper Instruction Register               |

| WPI  |                                            |

| WPO | Wrapper Parallel Output |

|-----|-------------------------|

| WSI | Wrapper Serial Input    |

| WSO | Wrapper Serial Output   |

#### INTRODUCTION

The context of this thesis is in the Trusted Environment Execution eVAluation (TEEVA) project, which aims to give a security evaluation of the Trusted Environment Execution (TEE) technology. The TEE is mainly used in mobile platforms to provide a secure environment for the execution of critical-security application, such as bank transactions. The goal of this thesis focuses on the attacks carried out through the test infrastructures, and their countermeasures.

Testing is a mandatory task in the Integrated Circuit (IC) production process to ensure product quality. In the area of digital testing, test procedures require to implement dedicated design for test purposes, called Design-for-Testability (DfT), to reduce efforts for test pattern generation. The most popular DfT method relies on scan chains usage. This approach consists in replacing original registers by serial scan registers, and connecting these scan registers into one or several scan chains. Extra control signals allow shifting in and out test data through the scan chain(s), providing full control and observation of the circuit internal states. Scan design greatly reduces the complexity of the test pattern generation and the overall test application time.

In addition to scan chains, test standards have been proposed to reach the interface of the scan chains for each device in complex ICs. This avoids connecting each device to the external pins. The first test standard to be proposed for board testing is the IEEE Std. 1149.1, also known as JTAG. It offers an interface to the user that relies on the Test Access Port (TAP) controller. The user has the access to a scan network, which connects all the devices on the board in a daisy-chain fashion. The same principle has then been extended to System-on-Chips (SoCs) with the IEEE Std. 1500. This allows testing the internal cores of a SoC equipping them with standardized test wrappers. More recently, the IEEE Std. 1687, also known as IJTAG, has been released to facilitate the access to the hundreds of embedded instruments that are present in nowadays SoCs. The IJTAG is based on a Reconfigurable Scan Network (RSN) that can be properly set by the user according to which instruments he/she wants to reach.

The access to the test infrastructure of the whole SoC by a malicious user represents a very serious security threat. While testability is positively impacted by scan designs thanks to full control and observation of IC internal states, the confidentiality of processed data is unfortunately negatively affected for exactly the same reasons. Indeed, scan attacks exploit facilities offered by the scan chains to retrieve the secret data processed by the device. These attacks target secure circuits implementing a cryptographic algorithm and storing a secret key. They rely on the possibility for hackers to shift out the scan chain content while the circuit state is correlated with the secret, i.e., the key.

Moreover, test infrastructures based on JTAG, IEEE 1500 and IJTAG standards can be exploited for a wide range of attacks. For instance, this is the case when the JTAG interface is used to access the system memory for debugging purposes, allowing an attacker to corrupt the firmware, to steal Intellectual Property (IP), or to find a flaw in the executed program.

Many research works have been dedicated to propose countermeasures against attacks exploiting test infrastructures. The main difficulty in the scan attack prevention stems from the need to maintain

both data security and hardware quality ensured by test, diagnostic and debug activities. The cost of the scan attack prevention in terms of circuit characteristics (power, performances, area), insertion in the design flow, test quality and test time is an important issue. While several solutions have been proposed to prevent scan attacks, no proposal is available for providing both high security and quality in preserving test, diagnostic and debug facilities at low cost and at all cycles of the device lifespan.

The contribution of this thesis is to present a secure, plug-and-play, and cost-efficient mechanism for preventing scan attacks, while providing full control and observation on the scan content for authorized users. The main idea is to maintain the confidentiality of the scan content through encryption/decryption of the test data flowing through the test infrastructures. The encryption can be performed either with block ciphers, or with stream ciphers. The choice of stream vs block cipher is driven by performance and security trade-offs. Because of their smaller footprint, stream ciphers are generally preferred to block ciphers in the literature. Nevertheless, when incompletely implemented, solutions based on stream ciphers are prone to scan attacks and thus have to be completed. This mitigates their interest versus block cipher solutions. In this thesis, we propose two new solutions: one exploiting block ciphers, and another exploiting stream ciphers fulfilling security requirement. We detail the advantages of these solutions compared to the state-of-the-art countermeasures. Moreover, we give a comparison between these two scan encryption countermeasures.

This thesis is divided in six chapters. Chapter I presents the context of the thesis on the security evaluation of the Trusted Environment Execution (TEE) technology with respect to the hardware access provided by the test infrastructures.

Chapter II brings out the security threats from the misuse of test infrastructures. The threat model includes "external attackers" (with unauthorized to access the test interfaces), as well as "internal attackers" (with insertion of malicious core connected to the test infrastructure at design time). A main attack from external attackers is the scan-based attack, exploiting the observation offered by the scan chain in order to steal confidential data, such as the secret key of a crypto-processor. Chapter II also reports our experiments and analysis on the project reference board considering the scan attack, and show that it implements the most common and radical industrial countermeasure consisting in disconnecting the test accesses after manufacture testing. A discussion about limitations in terms of security and debug/diagnostic facilities conclude the chapter.

Furthers scan-attack countermeasures have been developed in the literature. In Chapter III, the state-of-the-art of such countermeasures is presented. We propose a taxonomy according to the target strategy consisting in avoiding the scan chains, modifying the scan chains structures, providing a secure test access, or detecting illegitimate behavior in the use of the test interfaces.

Chapter IV presents a new approach based on the encryption of the test communication, ensuring the confidentiality of the exchanged data between the device under test and the tester. Several architectures are explored using block or stream ciphers with the goal to ensure same testability for the protected circuit than before scan protection.

Chapter V gives a comparison of the proposed solutions in terms of implementation costs, testability evaluation, and integration in a SoC design.

Finally, in Chapter VI we draw some conclusions and perspectives.

## Chapter I

## Context

## Summary

| I.1. Int | troduction to TEEVA project                                      | 28 |

|----------|------------------------------------------------------------------|----|

| I.2. Te  | est, diagnosis and debug for Integrated Circuits                 | 30 |

| I.2.a    | Design-For-Testability and test application                      | 31 |

|          | I.2.a.i Scan test procedure for stuck-at faults testing          | 32 |

|          | I.2.a.ii Scan test procedure for transition-delay faults testing | 33 |

|          | I.2.a.iii Insertion of test points                               | 34 |

|          | I.2.a.iv Multiple scan chains                                    | 35 |

| 1.2.b    | Test standards: JTAG, IEEE 1500 and IJTAG                        | 36 |

| 1.2.c    | Overview of the Design-for-Debug implemented in ARM designs      | 38 |

| I.3. Co  | onclusion on test infrastructures                                | 40 |

|          |                                                                  |    |

#### I.1. Introduction to TEEVA project

This thesis is part of the TEEVA (Trusted Environment Execution eVAluation) project, a FUI project led by Gemalto (FUI n°20 from January 2016 to December 2018) with the following partners Trustonic, Phonesec, EMSE, Laboratoire Hubert Curien and LIRMM. TEEVA tackles the sensitive threats on mobile platforms. Smartphones represent high-value targets for hackers since they contain personal data and are used for mobile payment. The Android platform is a main target for identity theft, or financial data theft. Application stores propose a lot and a wide diversity of applications, such as email, games, social media, and bank applications. Among this large number of applications, some malwares could execute malicious program and steal sensitive data processed by other applications.