# Deep levels characterizations in SiC to optimize high voltage devices

Teng Zhang

#### ▶ To cite this version:

Teng Zhang. Deep levels characterizations in SiC to optimize high voltage devices. Electronics. Université de Lyon, 2018. English. NNT: 2018LYSEI108. tel-02124529

### HAL Id: tel-02124529 https://theses.hal.science/tel-02124529

Submitted on 9 May 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

N°d'ordre NNT: 2018LYSEI108

#### THESE de DOCTORAT DE L'UNIVERSITE DE LYON

opérée au sein de INSA de Lyon

### **Ecole Doctorale** N° ED160 Électronique, Électrotechnique, Automatique

Spécialité de doctorat : Génie Électrique

Soutenue publiquement le 13/12/2018, par : **Teng ZHANG**

### Caractérisations des défauts profonds du SiC et pour l'optimisation des performances des composants haute tension

#### Devant le jury composé de :

Professeur des Universités Labo. LAAS TARTARIN, Jean-Guy Président

TARTARIN, Jean-Guy BI, Jinshun

LOCATELLI, Marie-Laure Chargée de Recherche JUILLAGUET, Sandrine

Maître de Conférences

Professeur des Universités Labo. LAAS Professeur des Universités UCAS, Beijing Labo, L2C

Rapporteur Rapporteur Labo, LAPLACE Examinatrice Examinatrice

PLANSON, Dominique RAYNAUD, Christophe Professeur des Universités INSA de Lyon Maître de Conférences

INSA de Lyon

Directeur de thèse Co- encadrant

#### Département FEDORA – INSA Lyon - Ecoles Doctorales – Quinquennal 2016-2020

| SIGLE     | ECOLE DOCTORALE                                                                                                                                                                                     | NOM ET COORDONNEES DU RESPONSABLE                                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СНІМІЕ    | CHIMIE DE LYON http://www.edchimie-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage secretariat@edchimie-lyon.fr INSA: R. GOURDON                                                         | M. Stéphane DANIELE Institut de recherches sur la catalyse et l'environnement de Lyon IRCELYON-UMR 5256 Équipe CDFA 2 Avenue Albert EINSTEIN 69 626 Villeurbanne CEDEX directeur@edchimie-lyon.fr                 |

| E.E.A.    | ÉLECTRONIQUE,<br>ÉLECTROTECHNIQUE,<br>AUTOMATIQUE<br>http://edeea.ec-lyon.fr<br>Sec.: M.C. HAVGOUDOUKIAN<br>ecole-doctorale.eea@ec-lyon.fr                                                          | M. Gérard SCORLETTI<br>École Centrale de Lyon<br>36 Avenue Guy DE COLLONGUE<br>69 134 Écully<br>Tél : 04.72.18.60.97 Fax 04.78.43.37.17<br>gerard.scorletti@ec-lyon.fr                                            |

| E2M2      | ÉVOLUTION, ÉCOSYSTÈME, MICROBIOLOGIE, MODÉLISATION http://e2m2.universite-lyon.fr Sec.: Sylvie ROBERJOT Bât. Atrium, UCB Lyon 1 Tél: 04.72.44.83.62 INSA: H. CHARLES secretariat.e2m2@univ-lyon1.fr | M. Philippe NORMAND UMR 5557 Lab. d'Ecologie Microbienne Université Claude Bernard Lyon 1 Bâtiment Mendel 43, boulevard du 11 Novembre 1918 69 622 Villeurbanne CEDEX philippe.normand@univ-lyon1.fr              |

| EDISS     | INTERDISCIPLINAIRE SCIENCES-SANTÉ http://www.ediss-lyon.fr Sec.: Sylvie ROBERJOT Bât. Atrium, UCB Lyon 1 Tél: 04.72.44.83.62 INSA: M. LAGARDE secretariat.ediss@univ-lyon1.fr                       | Mme Emmanuelle CANET-SOULAS INSERM U1060, CarMeN lab, Univ. Lyon 1 Bâtiment IMBL 11 Avenue Jean CAPELLE INSA de Lyon 69 621 Villeurbanne Tél : 04.72.68.49.09 Fax : 04.72.68.49.16 emmanuelle.canet@univ-lyon1.fr |

| INFOMATHS | INFORMATIQUE ET MATHÉMATIQUES http://edinfomaths.universite-lyon.fr Sec.: Renée EL MELHEM Bât. Blaise PASCAL, 3e étage Tél: 04.72.43.80.46 Fax: 04.72.43.16.87 infomaths@univ-lyon1.fr              | M. Luca ZAMBONI Bât. Braconnier 43 Boulevard du 11 novembre 1918 69 622 Villeurbanne CEDEX Tél : 04.26.23.45.52 zamboni@maths.univ-lyon1.fr                                                                       |

| Matériaux | MATÉRIAUX DE LYON http://ed34.universite-lyon.fr Sec.: Marion COMBE Tél: 04.72.43.71.70 Fax: 04.72.43.87.12 Bât. Direction ed.materiaux@insa-lyon.fr                                                | M. Jean-Yves BUFFIÈRE INSA de Lyon MATEIS - Bât. Saint-Exupéry 7 Avenue Jean CAPELLE 69 621 Villeurbanne CEDEX Tél : 04.72.43.71.70 Fax : 04.72.43.85.28 jean-yves.buffiere@insa-lyon.fr                          |

| MEGA      | MÉCANIQUE, ÉNERGÉTIQUE, GÉNIE CIVIL, ACOUSTIQUE http://edmega.universite-lyon.fr Sec.: Marion COMBE Tél: 04.72.43.71.70 Fax: 04.72.43.87.12 Bât. Direction mega@insa-lyon.fr                        | M. Jocelyn BONJOUR INSA de Lyon Laboratoire CETHIL Bâtiment Sadi-Carnot 9, rue de la Physique 69 621 Villeurbanne CEDEX jocelyn.bonjour@insa-lyon.fr                                                              |

| ScSo      | http://ed483.univ-lyon2.fr<br>Sec.: Viviane POLSINELLI<br>Brigitte DUBOIS<br>INSA: J.Y. TOUSSAINT<br>Tél: 04.78.69.72.76<br>viviane.polsinelli@univ-lyon2.fr                                        | M. Christian MONTES Université Lyon 2 86 Rue Pasteur 69 365 Lyon CEDEX 07 christian.montes@univ-lyon2.fr                                                                                                          |

<sup>\*</sup>ScSo: Histoire, Géographie, Aménagement, Urbanisme, Archéologie, Science politique, Sociologie, Anthropologie

### Acknowledgement

Sincere appreciation to my advisors Christophe Raynaud and Dominique Planson, as huge hints along with precious guidance and support have been provided which help me to unlock the door to the physics throughout these 3 years of my PhD study that is worshipful.

In addition, I'd like to acknowledge my dear colleges in laboratory Ampère, INSA who helped a lot: R. Caillaud, S. O. Avino, S. Niu, B. Asllani, M. Beye el al., as well as enlightening professors such as B. Allard and G. Bermond. Thanks to my friends of China namely B. Yu, C. Zhou, X. Wang, B. Cuan, X. Jiang, C. Xu, X. Zhu, Y. MA, F. Liu, Y. Li et al. as well for the skylark.

Remarkable acknowledgment to the Labo Ampère, INSA de Lyon, and the CSC also quenching any menace from the "rear" that could come across to me: from delicious menu I appreciate a lot, basic funding for the comfortable lives, to the well-designed curriculum enlarging my knowledge about the fundamental modern theory and keeping my brain CPU lighting for overcoming those struggles that block the road to scientific accomplishment.

At last, I would like to give my sincere and special to my family for supporting the journey for studying in France, the one that had been attracting me a lot, and this footmark I left in Lyon and INSA is so glittering that will never come to the ennui.

### **Abstract**

Due to the increasing appeal to the high voltage, high temperature and high frequency applications, Silicon Carbide (SiC) is continuing attracting world's attention as one of the most competitive candidate for replacing silicon in power electric field. Meanwhile, it is important to characterize the defects in semiconductors and to investigate their influences on power devices since they are directly linked to the carrier lifetime. Moreover, reliability that is also affected by defects becomes an unavoidable issue now in power electrics.

Defects, including point defects and extended defects, can introduce additional energy levels in the bandgap of SiC due to various metallic impurities such as Ti, Fe or intrinsic defects (vacancies, interstitial...) of the cristalline lattice itself. As one of the widely used defect characterization method, Deep Level Transient Spectroscopy (DLTS) is superior in determining the activation energy  $E_A$ , capture cross section  $\sigma$  and defect concentration  $N_T$  as well as the defect profile in the depletion region thanks to its diverse testing modes and advanced numerical analysis.

Determination of Schottky Barrier Height (SBH) has been confusing for long time. Apart from experimental measurement according to I-V or C-V characteristics, various models from Gaussian distribution of SBH to potential fluctuation model have been put forward. Now it was found that these models are connected with the help of flat-band barrier height  $\Phi_{BF}$ . The Richardson plot based on  $\Phi_{BF}$  along with the potential fluctuation model becomes a powerful tool for SBH characterization. SBHs with different metal contacts were characterized, and the diodes with multi-barrier are verified by different models.

Electron traps in SiC were studied in Schottky and PiN diodes, while hole traps were investigated under strong injection conditions in PiN diodes. 9 electron traps and 4 hole traps have been found in our samples of 4H-SiC. A linear relationship between the extracted  $E_A$  and  $\log(\sigma)$  indicates the existence of the intrinsic temperature of each defects. However, no obvious difference has been found related to either barrier inhomogeneity or contact metal. Furthermore, the electron traps near interface and fixed positive charges in the oxide layer were investigated on SiC power MOSFETs by High Temperature Gate Bias (HTGB) and Total Ionizing Dose (TID) caused by irradiation. An HTGB-assist-TID model was established in order to explain the synergetic effect.

Two carrier freeze-out regions were found near 40 K and 100 K that will degenerate the accuracy of traditional capacitance DLTS test. Meanwhile, concentration of certain defects can be reduced by high temperature annealing, that is also a cause to the multi-barrier effect. Special attentions were paid on defects with tiny activation energy at extremely low temperature as well as the abnormal DLTS signal caused by negative-U centers. Irregular switch on DLTS transient (i.e. between capture and emission) is found related to width of detection zone in depletion region.

Future works are mainly focused on interface characterization as well as improvement on trapping models at low temperature. In addition, the stress effect especially introduced by the characterization method should be paid attention as well.

# List of figures

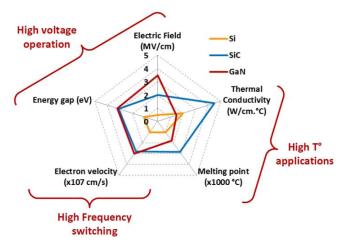

| Figure 1.1. Comparison of material properties of Si, SiC and GaN [3]5                                                            |

|----------------------------------------------------------------------------------------------------------------------------------|

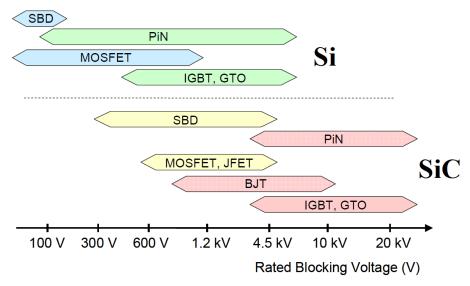

| Figure 1.2. Major territories of individual unipolar and bipolar power devices for Si                                            |

| and SiC in terms of the rated blocking voltage [13]7                                                                             |

| Figure 1.3. Double barrier phenomenon in Schottky diode8                                                                         |

| Figure 1.4. Temperature dependence of forward I-V characteristics for 4H-SiC                                                     |

| rectifier reported in [19]9                                                                                                      |

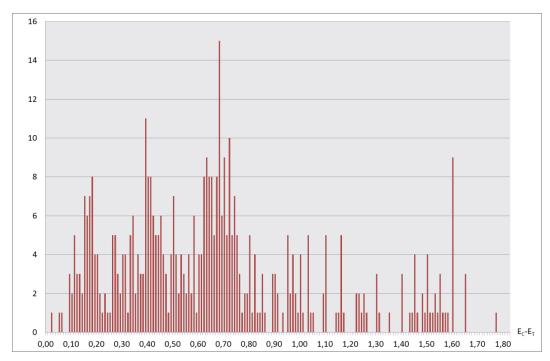

| Figure 1.5. Number of articles which report defects with certain activation energy                                               |

| $(E_C - E_T)$ in 4H-SiC                                                                                                          |

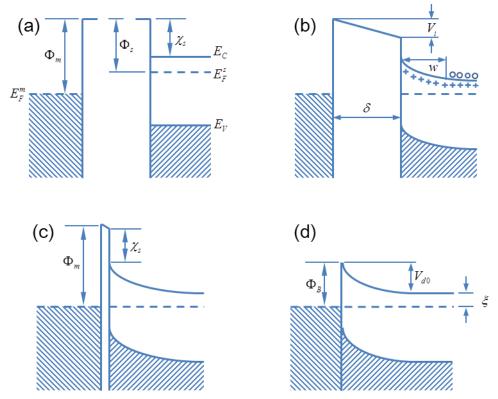

| Figure 2.1. Formation of an ideal Schottky barrier between a metal and an n-type                                                 |

| semiconductor (a) neutral and isolated, (b) electrically connected by a wire, (c)                                                |

| separated by a narrow gap, (d) in perfect contact. Cross and circle marks in (b)                                                 |

| denote donor ion and electron in conduction band respectively16                                                                  |

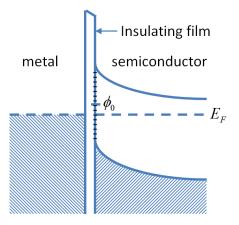

| Figure 2.2. Metal-semiconductor contact with interface states                                                                    |

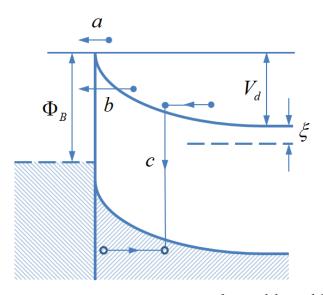

| Figure 2.3. Main current transport processes in a forward-biased Schottky barrier 19                                             |

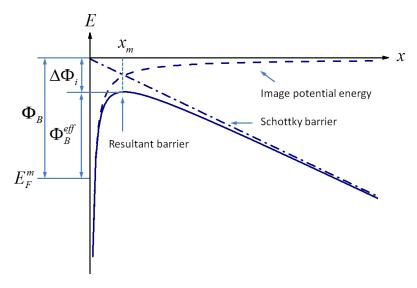

| Figure 2.4. Image-force lowing of SBH                                                                                            |

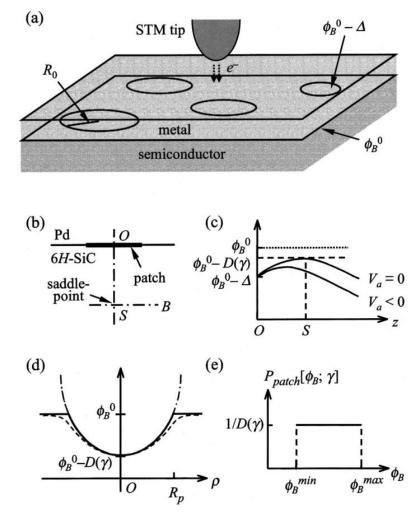

| Figure~2.5.~(a)~Schematic~of~the~Tung~model.~A~random~distribution~of~circular~patches                                           |

| of size $R_0$ and barrier height $\phi_{\!\scriptscriptstyle B}^0-\Delta$ in the otherwise homogeneous background of             |

| SBH $\phi_{\!\scriptscriptstyle B}^{\scriptscriptstyle 0}$ . (b) A patch of size comparable to or smaller than the semiconductor |

| Debye length gives rise to a potential saddle-point S beneath the patch center O.                                                |

| (c) Potential profile along the interface normal (along O-S) for zero applied bias                                               |

| $V_a$ , and for a reverse bias $\ (V_a < 0)$ . Reverse bias reduces the potential maximum                                        |

| (i.e., an increased depth) near S. (d) Lateral profile of the potential maximum                                                  |

| projected normally onto the MS interface. The dashed line is the exact potential,                                                |

| the dash-dot line is Tung's parabolic approximation, and the solid line is the                                                   |

| truncated paraboloid used to calculate the microscopic BHD. (e), Calculated                                                      |

| probability density for a single low-barrier patch of strength $\gamma$ , with                                                   |

| $\phi_B^{\min} = \phi_B^0 - D(\gamma) \text{ and } \phi_B^{\max} = \phi_B^0 \text{ [102]}.$                                      |

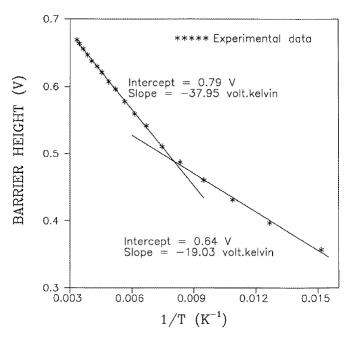

| Figure 2.6. The barrier height obtained from I-V measurements as a function of                                                   |

| inverse temperature in [86]35                                                                                                    |

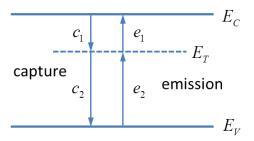

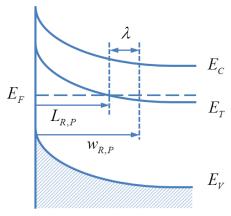

| Figure 3.1. Schematic of electron capture-emission through trap levels40                                                         |

| Figure 3.2. Lambda shift under either reverse bias or pulse voltage42                                                            |

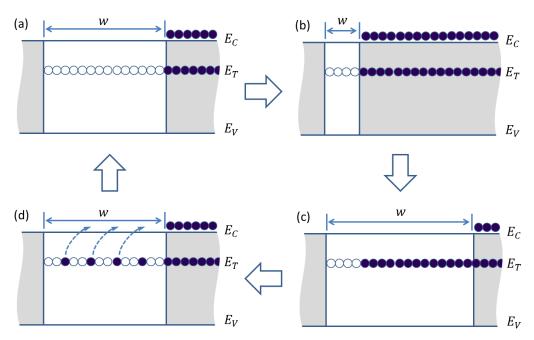

| Figure 3.3. A schematic of the DLTS transient signal generation. (a): Steady state                 |

|----------------------------------------------------------------------------------------------------|

| reverse bias, (b): Applying pulse; (c): Just after removing pulse; (d): Capacitance                |

| transient due to thermal emission of carriers                                                      |

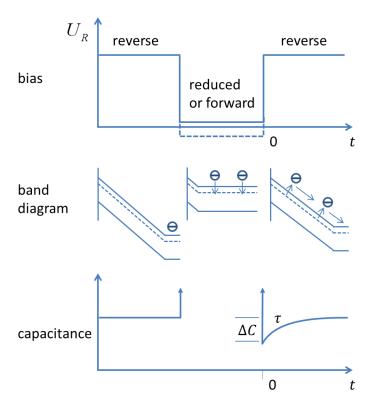

| Figure 3.4. Capacitance and band diagram evolution based on bias condition45                       |

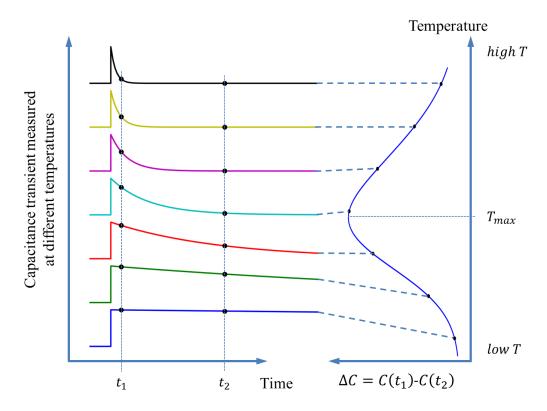

| Figure 3.5. Difference in capacitance between two time points at various temperatures              |

| [113]46                                                                                            |

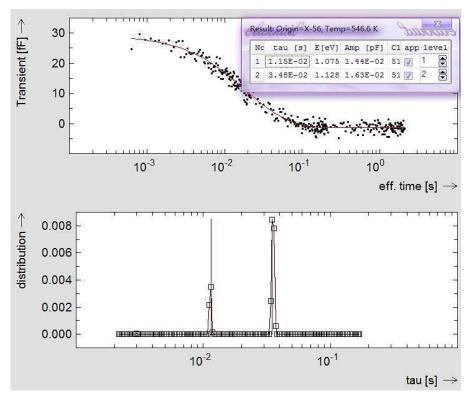

| Figure 3.6. Original capacitance transient signal (upper plot) and its Laplace                     |

| transform spectra (lower plot). Inner table lists the extracted parameters of two                  |

| different levels, where their fitting curve is presented in the upper plot as solid                |

| line                                                                                               |

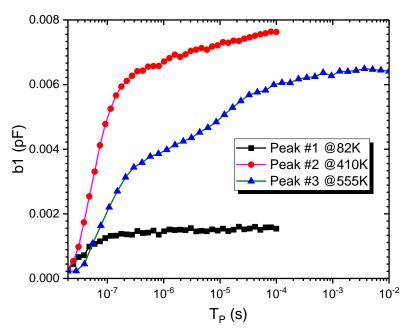

| Figure 3.7. Isothermal DLTS signal (b1) with variation of pulse width logarithmically              |

| on 4H-SiC SBD with metal contact of tungsten. Three signals were measured at                       |

| different temperature marked in the plot53                                                         |

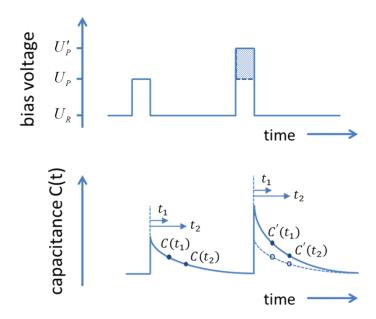

| Figure 3.8. Schematic illustration of pulse shape and capacitance transient in DDLTS               |

| [111]55                                                                                            |

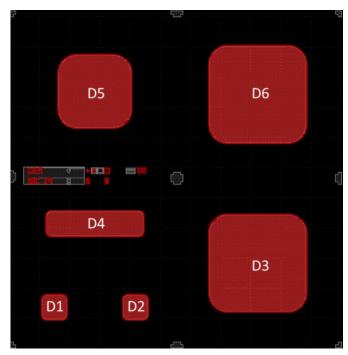

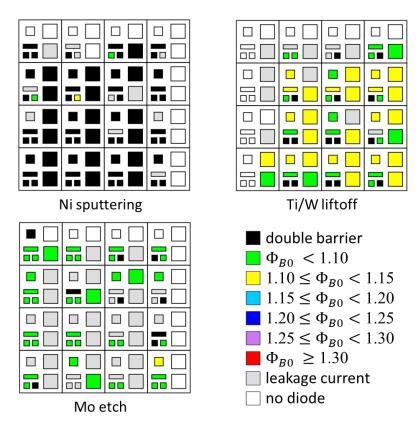

| Figure 4.1. Map of cell of SBD samples, diodes within each cell are labeled from D1 to             |

| D658                                                                                               |

| Figure 4.2. Mapping of barrier height on 3 SBD samples. Those marked "no diode" are                |

| lack of effective diodes due to wafer cutting60                                                    |

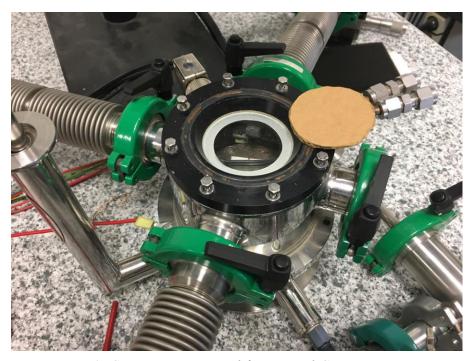

| Figure 4.3. Cryostat system used for I-V and C-V measurements                                      |

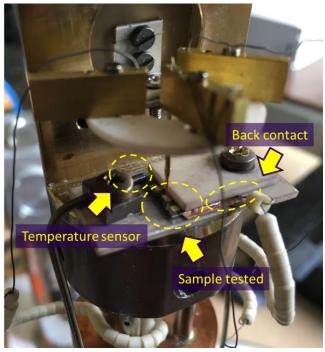

| Figure 4.4. DLTS test system (left) and its inside view on head part for sample                    |

| installation (right)62                                                                             |

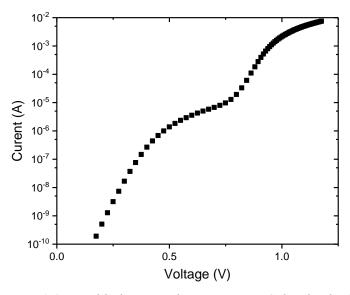

| Figure 4.5. Forward I-V characteristic on diode Ti/W liftoff66                                     |

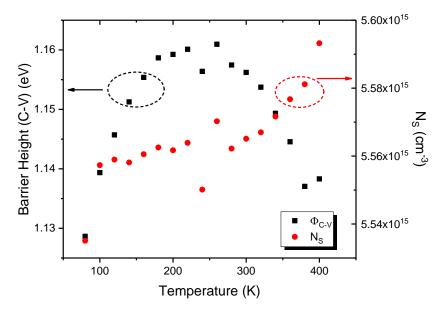

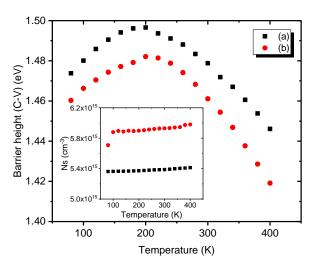

| Figure 4.6. Calculated Schottky barrier height and shallow doping concentration on                 |

| Ti/W liftoff diode based on C-V characterization67                                                 |

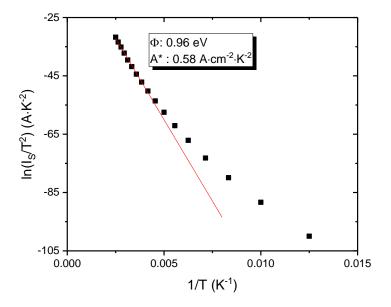

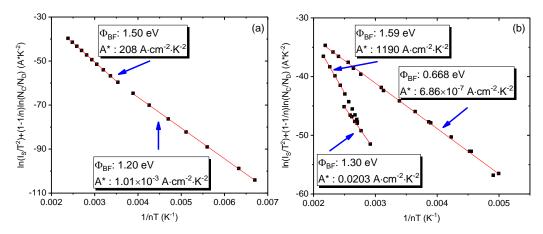

| Figure 4.7. Richardson plot on Ti/W liftoff diode                                                  |

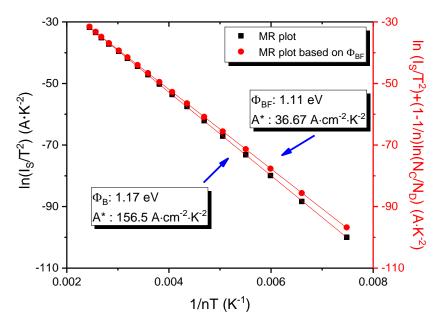

| Figure 4.8. Modified Richardson plot and its modification based on flat-band barrier               |

| height68                                                                                           |

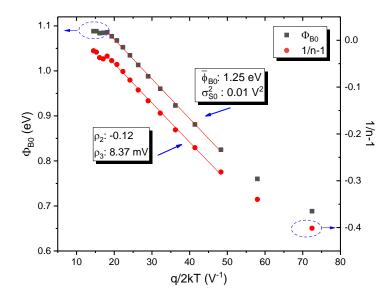

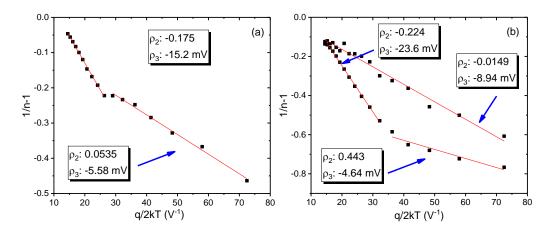

| Figure 4.9. Zero-bias barrier height $\Phi_{B0}$ and $1/n-1$ as a function of $q/2kT$ 69           |

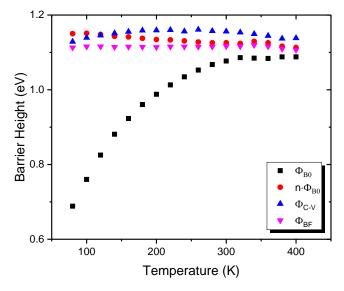

| Figure 4.10. Comparison of zero-bias barrier height $\Phi_{B0}$ , $n\Phi_{B0}$ , SBH determined by |

| C-V $\Phi_{C-V}$ and flat-band barrier height $\Phi_{BF}$ 69                                       |

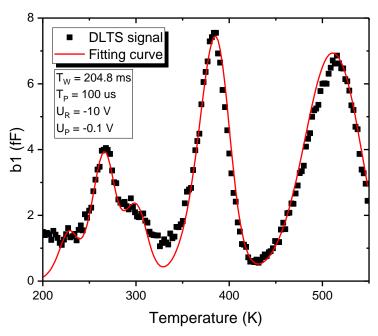

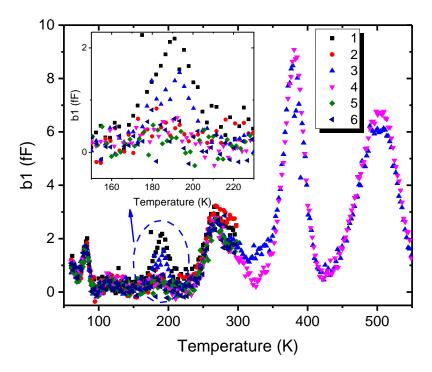

| Figure 4.11. DLTS signal (correlation b1) and the simulation fitting curve according to            |

| the parameters of 6 trap levels extracted by Arrhenius analysis list in Table 4.6                  |

| on Ti/W liftoff diode between 200 K and 550 K                                                      |

|                                                                                                    |

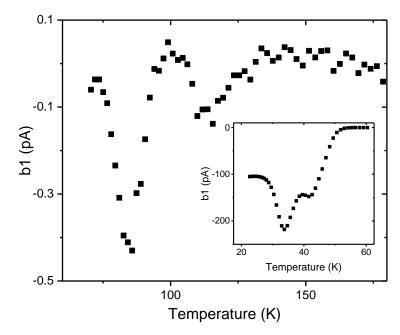

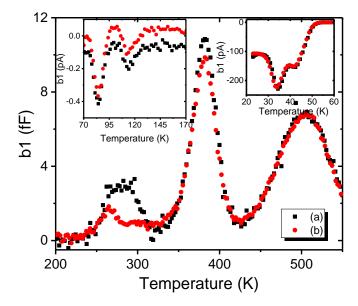

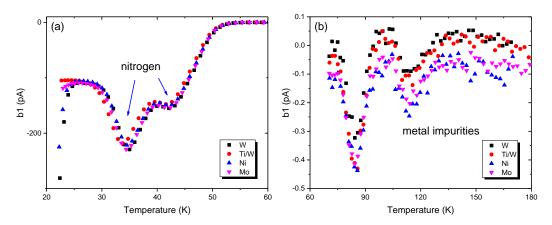

| Figure 4.12. Current DLTS (I-DLTS) signal (correlation b1) on Ti/W liftoff diode from               |

|-----------------------------------------------------------------------------------------------------|

| 70 K to 170 K and between 20 K and 60 K (inner plot), with a period width of                        |

| 204.8 ms71                                                                                          |

| Figure 4.13. Forward I-V characteristics on two diodes (a) and (b) of Mo-etch samples.              |

|                                                                                                     |

| Figure 4.14. Calculated SBH $\Phi_{C-V}$ based on C-V characterization. Inner plot shows            |

| the extracted doping concentration                                                                  |

| Figure 4.15. Modified Richardson plot based on the flat-band barrier height $\Phi_{\mathit{BF}}$ on |

| diode (a) and (b). $n$ and $I_s$ were calculated in the different linear zones of the I-            |

| V curves                                                                                            |

| Figure 4.16. $1/n-1$ as a function of $q/2kT$ on diode (a) and (b)                                  |

| Figure 4.17. DLTS signal (correlation b1) with a period width of 204.8 ms on the                    |

| diodes (a) and (b) of Mo sample between 200 K and 550 K. The inserts are I-                         |

| DLTS spectrum between 20 K and 60 K (top right) and 70 K to 170 K (top left). 75                    |

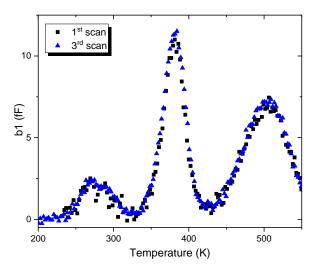

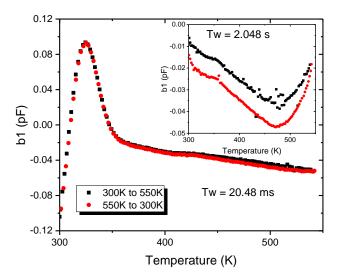

| Figure 4.18. DLTS signal (b1) with a period width $T_{\rm W}$ = 204.8 ms of different scan          |

| cycles on Ti/W sputtering 1 min diode (A)76                                                         |

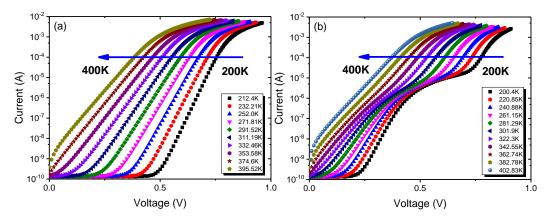

| Figure 4.19. Forward I-V characteristic on diode (A) of Ti/W sputtering 1 min between               |

| 200 K and 400 K measured during the DLTS test of (a) : $1^{st}$ scan and (b) : $3^{nd}$ scan        |

| illustrated in Figure 4.1877                                                                        |

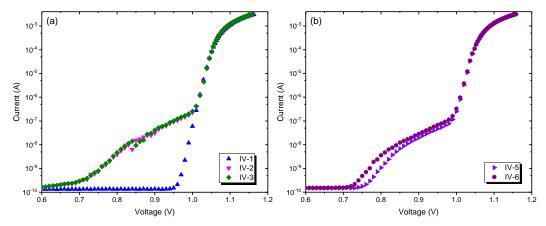

| Figure 4.20. Evolution on forward I-V characteristic due to (a):annealing before DLTS               |

| scan with high temperature and (b) room temperature annealing after high                            |

| temperature DLTS scan on diode (B) of Ti/W sputtering 1 min with labels                             |

| illustrated in Table 4.9                                                                            |

| Figure 4.21. Evolution on forward I-V characteristic due to DLTS scan on diode (B) of               |

| Ti/W sputtering 1 min with labels illustrated in Table 4.979                                        |

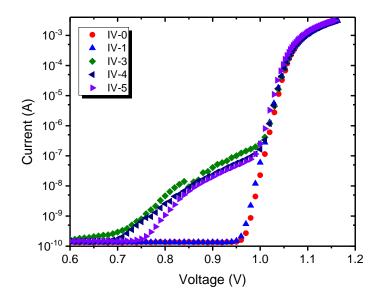

| Figure 4.22. DLTS signal (b1) with a period width $T_{\rm W}$ = 204.8 ms of different scan          |

| cycles on Ti/W sputtering 1 min diode (B). The labels indicate the number of                        |

| DLTS scan cycles (Tempscan) marked in Table 4.9                                                     |

| Figure 4.23. Isothermal DLTS scan with variation of period width $(T_{W})$ from 0.6 ms to           |

| 3 s on diode (B) of Ti/W sputtering 1 min sample. Labels of test number are                         |

| illustrated in Table 4.980                                                                          |

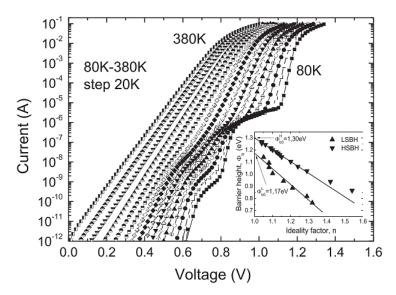

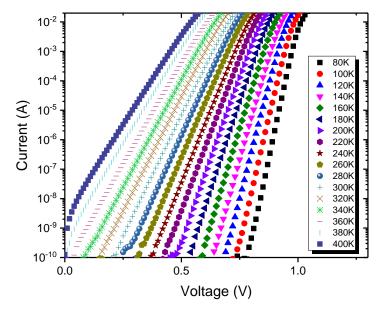

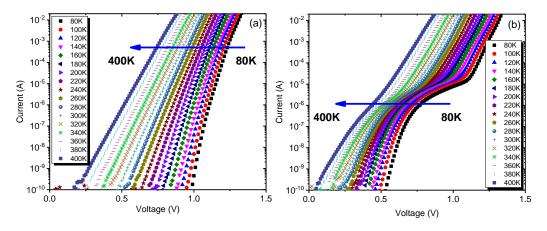

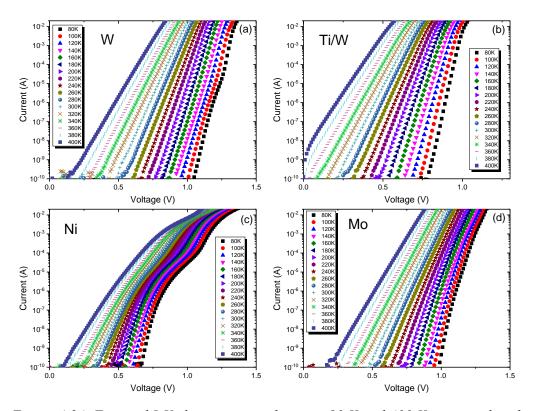

| Figure 4.24. Forward I-V characteristics between 80 K and 400 K measured in the                     |

| cryostat with a step of 20 K on samples of (a): Tungsten (S7); (b):                                 |

| Titanium/Tungsten (S3); (c): Nickel (S2) and (d): Molybdenum (S8). Sample                           |

| descriptions are illustrated in Table 4.1                                                           |

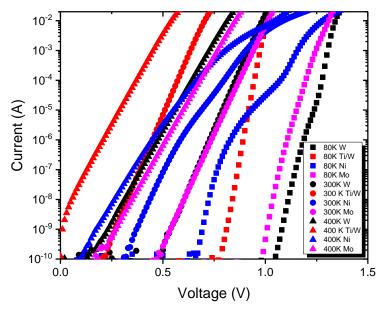

| Figure 4.25. Comparison of forward I-V curve at 80 K, 300 K and 400 K on four SBDs                                  |

|---------------------------------------------------------------------------------------------------------------------|

| with different metal contacts82                                                                                     |

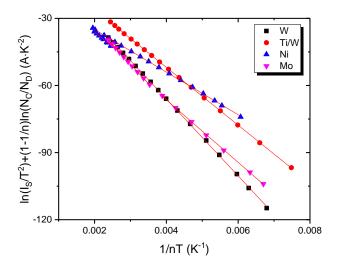

| Figure 4.26. Modified Richardson plot according to flat-band SBH of 4 diodes with                                   |

| different metal contacts                                                                                            |

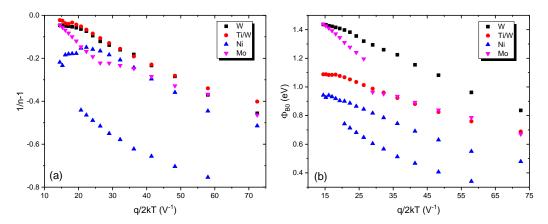

| Figure 4.27. (a): $1/n-1$ as a function of $q/2kT$ (potential fluctuation model) and (b)                            |

| zero-bias barrier height $\Phi_{{\scriptscriptstyle B}0}$ as a function of $q/2kT$ (Gaussian distribution model)    |

| on 4 diodes with different metal contacts83                                                                         |

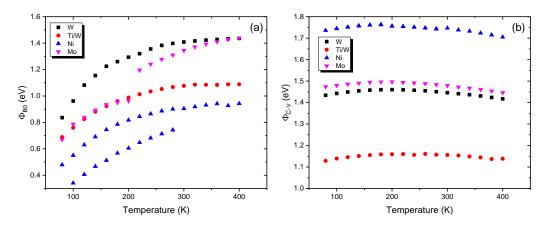

| Figure 4.28. Temperature dependence on (a): zero-bias barrier height $\Phi_{{\scriptscriptstyle B}0}$ and (b): the  |

| SBH extracted from C-V $\Phi_{\text{C-V}}$ of diodes with 4 different metal contacts85                              |

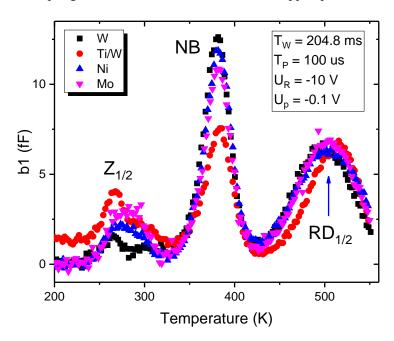

| Figure 4.29. Comparison of DLTS signal (correlation b1) between 200 K and 550 K on                                  |

| 4 diodes with different metal contacts                                                                              |

| Figure 4.30. Comparison of I-DLTS signal (b1) with a period width of 204.8 ms and                                   |

| temperature range (a): 20 K to 60 K and (b): 70 K to 170 K86                                                        |

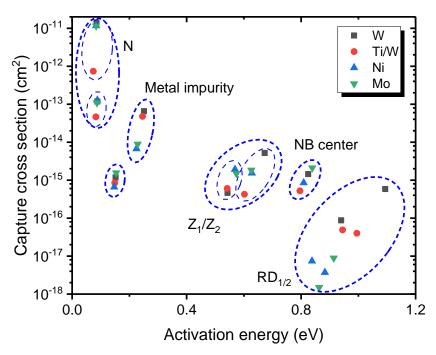

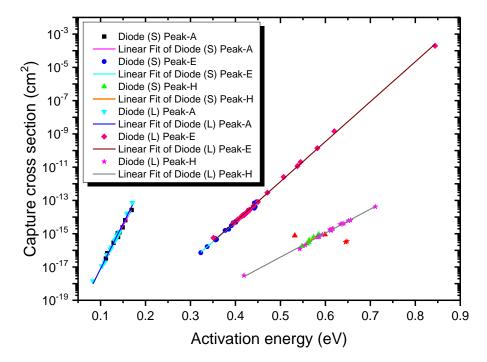

| Figure 4.31. Mapping of defect activation energy compared to the conduction band                                    |

| and its capture cross section with the help of Arrhenius analysis based on DLTS                                     |

| results on 4 diodes with different metal contacts. Those points circled with dash                                   |

| lines are suggested to originate from the same defect labeled beside87                                              |

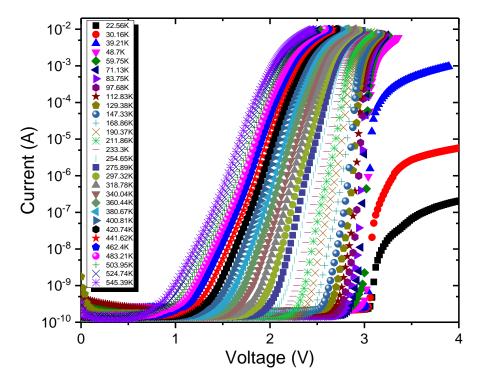

| Figure 5.1. Forward I-V characteristics on diode (L) from 20 K to 550 K90                                           |

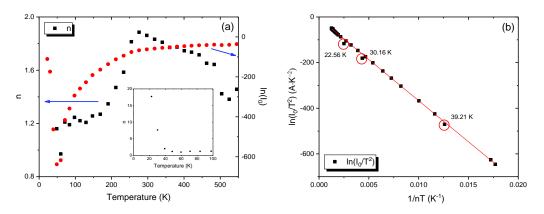

| Figure 5.2. (a): Extracted ideal factor $n$ and saturation current $I_0$ at different                               |

| temperatures according to linear regions with relatively high current illustrated                                   |

| in Figure 5.1. and (b): plot of $\ln \left( I_0/T^2 \right)$ as a function of $1/nT$ . Three points                 |

| marked with red circles were those measured at lowest temperatures (labeled                                         |

| beside the circles) and are not involved in the linear fitting90                                                    |

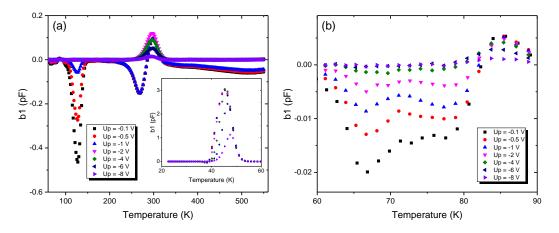

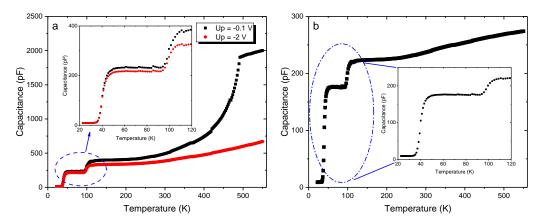

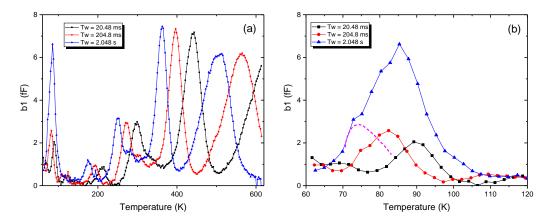

| Figure 5.3. (a): DLTS spectra under different pulse voltages $U_{\scriptscriptstyle P}$ between 20 K and 550        |

| K with $T_W = 204.8$ ms, $U_R = -10$ V, $T_P = 100$ $\mu$ s. (b) shows the same signals with a                      |

| temperature range from 60 K to 90 K92                                                                               |

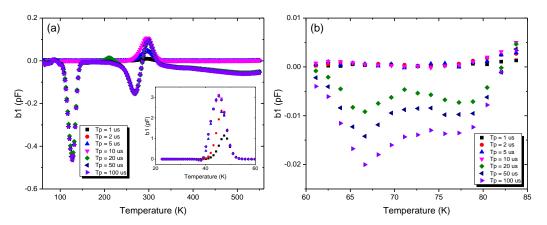

| Figure 5.4. (a) DLTS spectra under different pulse width from 20 K to 550 K with                                    |

| $T_W = 204.8 \text{ ms}, \ U_R = -10 \text{ V}, \ U_P = -0.1 \text{ V}.$ (b) is the same signals with a temperature |

| range from 60 K to 85 K93                                                                                           |

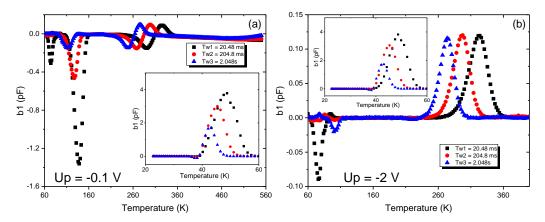

| Figure 5.5. DLTS spectra (20 K $-$ 550 K) with three different period widths for (a):                               |

| strong hole injection with $U_P = -0.1 \text{ V}$ and (b) weak hole injection with $U_P = -2 \text{ V}$ .           |

| Other parameters are as follows: $U_R = -10 \text{ V}$ , $T_P = 100  \mu\text{s}$ . The flat area with no           |

| peak identified above 400 K in (b) are hided for better illustration94                                              |

| Figure 5.6. I-DLTS signal with a period width of 204.8 ms of both weak and strong                 |

|---------------------------------------------------------------------------------------------------|

| injection condition for the PiN diode within the temperature range of (a): 20 $K-$                |

| 60 K and (b): 60 K – 200 K94                                                                      |

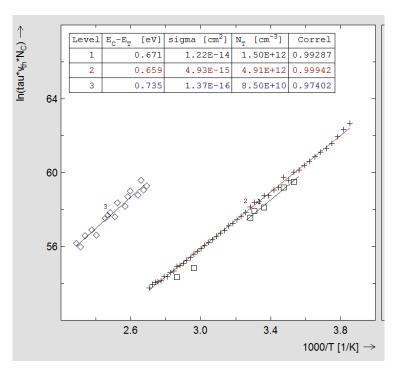

| Figure 5.7. HERA analysis results for the defect between 250 K and 450 K, the                     |

| extracted level 1 and 2 indicate the possible overlap of the trap levels97                        |

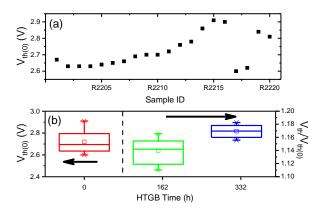

| Figure 5.8. (a): Original threshold voltage for all 20 samples involved in HTGB test              |

| and (b): Dispersion of normalized Vth before (left part) and after HTGB (right                    |

| part), with 10 MOSFETs for each group (162 h or 332 h). The first 10 samples (ID                  |

| R2201 to R2210) belong to 332 h HTGB test and the rest 10 are in the 162 h group                  |

| Normalized $V_{th}$ was separately calculated                                                     |

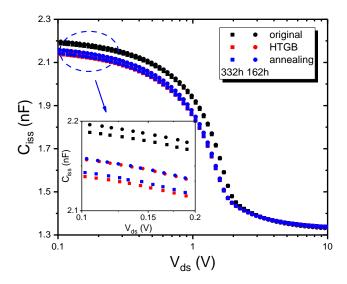

| Figure 5.9. Input capacitance $C_{iss}$ as a function of applied drain-source voltage $V_{ds}$ on |

| 162h-HTGB device (R2217) and 332h-HTGB device (R2207) before and after                            |

| HTGB along with data measured after room temperature annealing for a week.                        |

|                                                                                                   |

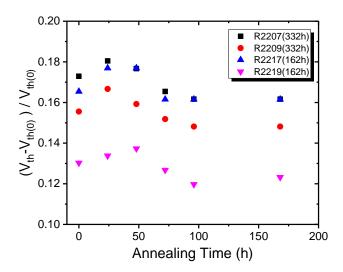

| Figure 5.10. Time dependence of normalized threshold voltage during one week after                |

| HTGB. No bias was added during this annealing at room temperature 101                             |

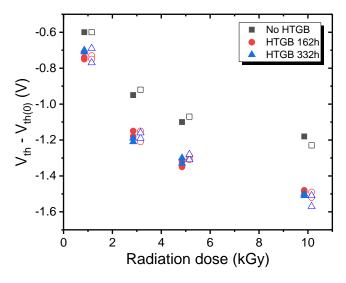

| Figure 5.11. Threshold voltage shift as a function of radiation dose with different               |

| HTGB time, compared to the value right before the radiation experiment. Open                      |

| symbols present data measured after annealing. X-axis is slighted adjusted within                 |

| each TID dose group for better reading101                                                         |

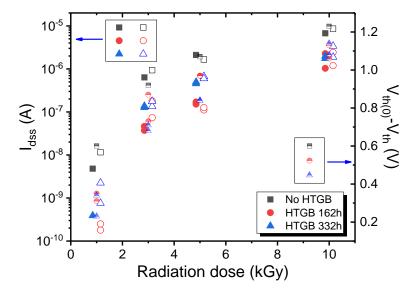

| Figure 5.12. Drain-source leakage current @ $V_{ds} = 1200 \text{ V}$ and the shift on threshold  |

| voltage as a function of radiation dose and HTGB time. Several $I_{\it dss}$ much lower           |

| in 1 kGy group are not shown here. Open symbols present data measured after                       |

| annealing and the half-filled symbols are the threshold shift compared to their                   |

| original values. X-axis is slighted adjusted within each TID dose group for better                |

| reading102                                                                                        |

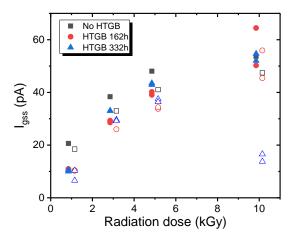

| Figure 5.13. Gate leakage current @ $V_{gs}$ = 22 V as a function of radiation dose and           |

| HTGB time. Open symbols present data measured after annealing. X-axis is                          |

| slighted adjusted within each TID dose group for better reading 103                               |

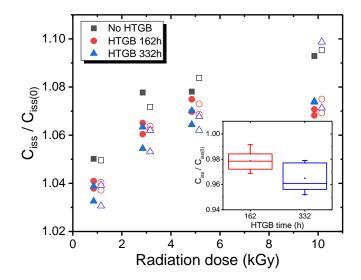

| Figure 5.14. Normalized input capacitance @ $V_{ds} = 0.1$ V as a function of radiation dose      |

| and HTGB time. Open symbols present data measured after annealing. X-axis is                      |

| slighted adjusted within each TID dose group for better reading. The insert shows                 |

| the variation of $C_{iss}$ due to HTGB before TID                                                 |

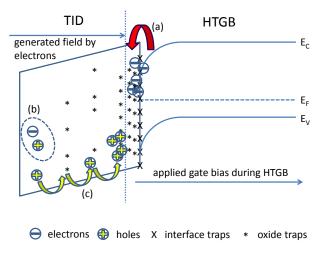

| Figure 5.15. Illustration of band diagram near interface during HTGB (right) and TID              |

| (left), with the marked process (a): electrons directly tunneling and capture (b):                |

| *                                                                                                 |

| electron-hole pairs generation due to irradiation and (c): holes displacement and                                  |

|--------------------------------------------------------------------------------------------------------------------|

| capture104                                                                                                         |

| Figure 5.16. (a): pulse capacitance and (b): reverse capacitance with a bias of -10 V                              |

| measured during DLTS scan between 20 K and 550 K on PiN diode discussed in                                         |

| section 5.1106                                                                                                     |

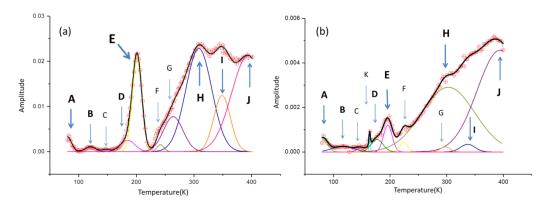

| Figure 5.17. DLTS signal and the peak analysis by Origin on (a): diode (L) with $T_P = 1$                          |

| ms, $T_W = 100$ ms and (b): diode (S) with $T_P = 1$ ms, $T_W = 200$ ms between 80 K and                           |

| 400 K. The sizes of the Alphabets represent the height of each individual peak. 108                                |

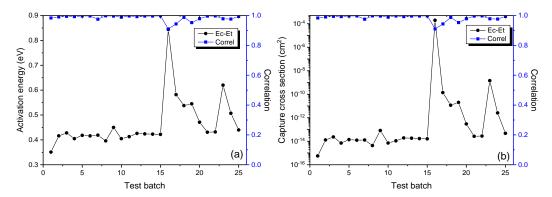

| Figure 5.18. Extracted (a): activation energy relate to conduction band $E_C - E_T$ and (b):                       |

| capture cross section as a function of the test batch with different $T_{p}$ - $T_{W}$                             |

| combinations of peak E on diode (L), along with their correlation on linear fitting                                |

| during Arrhenius analysis                                                                                          |

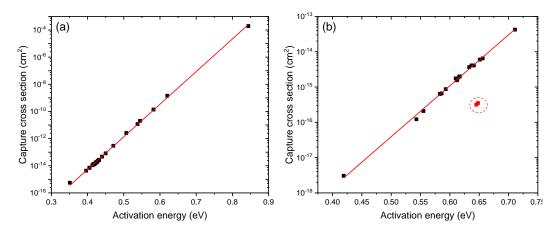

| Figure 5.19. Linear relationship between activation energy and capture cross section of                            |

| (a): peak E and (b): peak H on diode (L). Two points marked red in (b) are                                         |

| suggested to be the error data and are not used in the linear fitting109                                           |

| Figure 5.20. Linear relationship between activation energy and capture cross section of                            |

| all three peaks (A, E, and H) on diode (L) and diode (S). Several points of peak H                                 |

| are suggested to be the error data and are marked red                                                              |

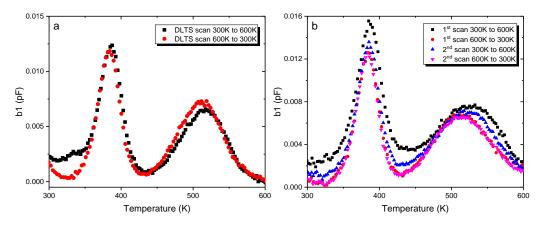

| Figure 5.21. DLTS signal (correlation b1) with a period width of 204.8 ms on (a): Ti/W                             |

| sputtering 1min sample (S4) and (b): Ni sputtering sample (S2) during                                              |

| temperature scan in different directions (heat up or cool down). The waiting time                                  |

| between scan of 300 K – 600 K and 600 K – 300 K is limited to minutes and can be                                   |

| neglected 111                                                                                                      |

| Figure 5.22. Signal DLTS on different correlations (a): a1(Tw/2) and (b): b1M on the                               |

| Ti/W sample with the same scan $300 \text{ K} - 600 \text{ K} - 300 \text{ K}$ as in Figure $5.21(a)112$           |

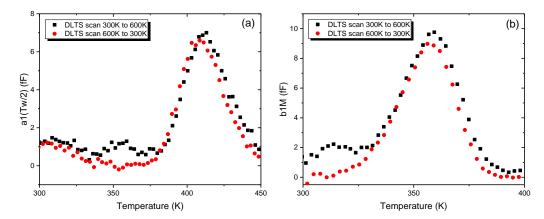

| Figure 5.23. DLTS signal (correlation b1) between 300 K and 550 K on PiN diode                                     |

| discussed in section 5.1 with a period width of 20.48 ms and 2.048 s (top-right                                    |

| plot). Before the DLTS scan 550 K – 300 K, an additional waiting time of 30 min                                    |

| are applied with tiny bias ( $-0.1~\mathrm{V}$ ) right after the heat-up scan ( $300~\mathrm{K}-550~\mathrm{K}$ ). |

| 113                                                                                                                |

| Figure 5.24. DLTS spectra with 3 different period widths on diode Ti/W liftoff (S3)                                |

| between (a): 60 K and 600 K, while (b) is the same signal between 60 K and 120 K                                   |

| in order for better illustration, with $U_R = -10$ V, $U_P = -0.1$ V and $T_P = 100$ $\mu s.114$                   |

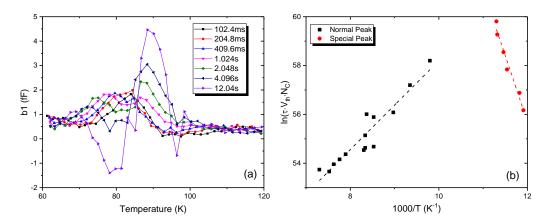

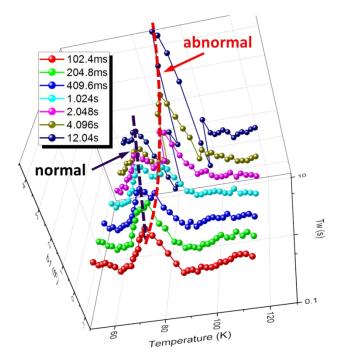

| Figure 5.25. (a): DLTS spectra (b1) between 60 K and 120 K with 7 different period                                 |

| widths on Tungsten diode (S7) and (b) is its Arrhenius plot extracted                                              |

| Figure 5.26. 3D-plot of Figure 5.25(a). The blue and red dash lines indicate the                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------|

| evolution trend on two peaks                                                                                                         |

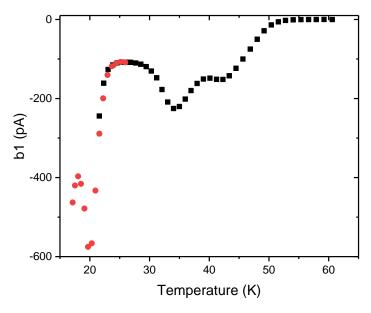

| Figure 5.27. I-DLTS signal (correlation b1) on Ti/W sputtering 1 min sample (S4) at                                                  |

| low temperature. The black squares are that discussed in Chapter 4, while the red                                                    |

| circles are the focus in this section                                                                                                |

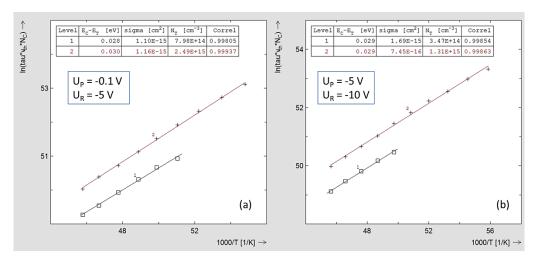

| Figure 5.28. Arrhenius plot from maximum analysis of DLTS on diode S4 at                                                             |

| temperature below 25 K. The pulse width is 5 $\mu s$ and the bias condition on (a) and                                               |

| (b) are listed inside plot. Some points extracted with maximum analysis that do                                                      |

| not belong to these two levels are not shown in the plot                                                                             |

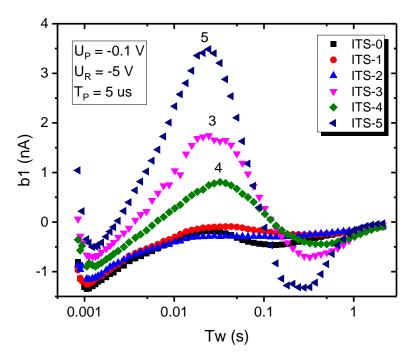

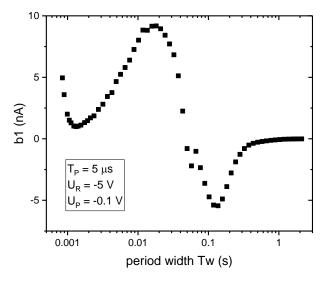

| Figure 5.29. I-DLTS signal (correlation b1) from ITS period scan at 17.35 K on sample                                                |

| S4 with $T_P = 5 \mu s$ , $U_R = -5 V$ and $U_P = -0.1 V$                                                                            |

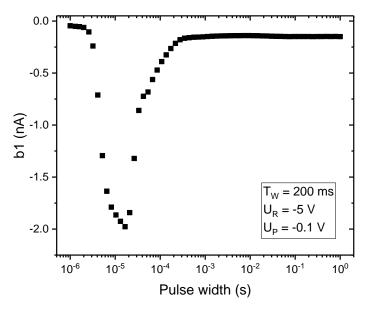

| Figure 5.30. I-DLTS signal (correlation b1)of isothermal variation of $T_p$ at 17.35 K                                               |

| with a fixed period width of 200 ms                                                                                                  |

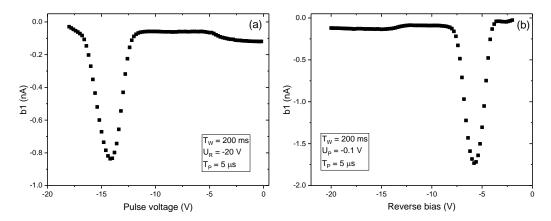

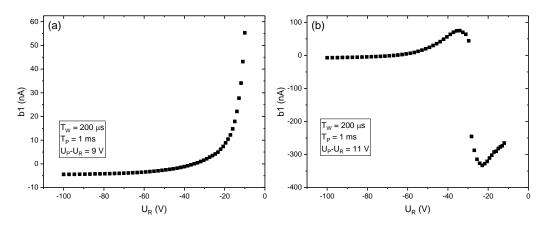

| Figure 5.31. I-DLTS signal (correlation b1)of isothermal variation of (a): $U_P$ and (b):                                            |

| U <sub>R</sub> at 17.35 K                                                                                                            |

| Figure 5.32. I-DLTS signal (correlation b1)of isothermal variation of both $U_{\scriptscriptstyle P}$ and $U_{\scriptscriptstyle R}$ |

| with pulse heights keep constant120                                                                                                  |

| Figure 5.33. I-DLTS signal (correlation b1)of isothermal variation of $T_p$ at 17.35 K                                               |

| with a fixed period width of 1 ms 122                                                                                                |

| Figure 5.34. I-DLTS signal (correlation b1)of isothermal variation of $U_{\scriptscriptstyle P}$ at 17.35 K                          |

| with (a): $U_R = -10$ V and (b): $U_R = -20$ V. The pulse width is 30 $\mu$ s and period                                             |

| width is 1 ms. Inner plot in (a) shows the trap concentration profile calculated                                                     |

| based on results in (a)                                                                                                              |

| Figure 5.35. Left plot: I-DLTS signal (correlation b1)of isothermal variation of $T_p$ at                                            |

| 17.35 K with a fixed period width of 200 µs. And right plot: the measured                                                            |

| transient curve at different $T_p$ in the left plot                                                                                  |

| Figure 5.36. Left plot : I-DLTS signal (correlation b1)of isothermal variation of $U_{\rm R}$ at                                     |

| 17.35 K with a fixed period width of 200 µs. And right plot: the measured                                                            |

| transient curve at different $U_{\scriptscriptstyle R}$ in the left plot                                                             |

| Figure 5.37. Relationship between the observed transient curve and $U_P - U_R$ during the                                            |

| DLTS shown in Figure 5.36. The blue dots surrounded by rad dash square                                                               |

| indicate the measured transient signals which correspond to that in Figure 5.36                                                      |

| with the come label                                                                                                                  |

| Figure 5.38. The maxima and minima voltage illustrated in Figure 5.37 as a function of                                             |

|------------------------------------------------------------------------------------------------------------------------------------|

| pulse voltage used in the DLTS isothermal variation of $U_{\scriptscriptstyle R}$ measures. Different                              |

| voltage sources were used that (a): low voltage module up to 20 V and (b): high                                                    |

| voltage module up to 100 V                                                                                                         |

| Figure 5.39. The maxima and minima voltage illustrated in Figure 5.37 as a function of                                             |

| reverse bias used in the DLTS isothermal variation of $U_{\scriptscriptstyle P}$ measures. Different                               |

| voltage sources were used that (a): low voltage module up to 20 V and (b): high                                                    |

| voltage module up to 100 V                                                                                                         |

| Figure 5.40. I-DLTS signal (correlation b1)of isothermal variation of $U_{\scriptscriptstyle P}$ and $U_{\scriptscriptstyle R}$ at |

| 17.35 K with fixed difference of (a): $U_P - U_R = -9$ V and (b): $U_P - U_R = -11$ V 126                                          |

### List of tables

| Table 1.1. Main Physical Properties of 3C-, 6H-, 4H-SiC, and Si [10, 11]6                                 |

|-----------------------------------------------------------------------------------------------------------|

| Table 1.2. The maximum blocking voltage available for some commercial high power                          |

| SiC devices and their fabricants. Information is updated to August 20187                                  |

| Table 1.3. Classification on defects in crystals10                                                        |

| Table 1.4. Several defects reported in 4H-SiC14                                                           |

| Table 3.1. Comparison of different DLTS modes from our DLTS manual, it marks                              |

| with '+' as good, 'o' as medium and '-' as bad51                                                          |

| Table 4.1. 4H-SiC SBD samples used in this study58                                                        |

| Table 4.2. Size parameters of diodes illustrated in Figure 4.159                                          |

| Table 4.3. Statistics on each sample from the preliminary I-V charactrization60                           |

| Table 4.4. Typical parameters used for capacitance DLTS scan64                                            |

| Table 4.5. Common isothermal DLTS modes64                                                                 |

| Table 4.6. Calculated deep level parameters based on Arrhenius plot by DLTS                               |

| measurement between 200 K and 550 K and those interpretations. The defects are                            |

| indicated by the position of the positive peak shown in Figure 4.1171                                     |

| Table 4.7. Calculated deep level parameters based on Arrhenius plot by I-DLTS                             |

| measurement between 20 K and 170 K and those interpretations. The defects are                             |

| indicated by the position of the negative peak shown in Figure 4.1272                                     |

| Table 4.8. Comparison of the parameters of the Gaussian model and the potential                           |

| fluctuation model. The two parameters $\bar{\Phi}_{B0}'$ and $\sigma_{s0}'^2$ are calculated from the Eq. |

| (2.46) with extraction of the MR plot of Figure 4.15                                                      |

| Table 4.9. Measure steps and addition condition on diode (B) of Ti/W sputtering 1 min                     |

| sample. General measure condition of I-V and DLTS temperature scan are given                              |

| in section 4.2, while that of Isothermal DLTS tests are illustrated in Figure 4.23.                       |

| 77                                                                                                        |

| Table 4.10. Flat-band SBH and effective Richardson constant of diodes with different                      |

| metal contacts extracted from MR plot shown in Figure 4.2683                                              |

| Table 4.11.Parameters in potential fluctuation and Gaussian distribution model of                         |

| diodes with different metal contacts extracted from plots shown in Figure 4.27                            |

| between 80 K and 400 K84                                                                                  |

| Table 5.1. Calculated deep level parameters based on Arrhenius plot by I-DLTS                             |

| measurement between 20 K and 280 K for both strong and week hole injection.                               |

| The defects are indicated by the position of the negative peak shown in Figure 5.6.   |

|---------------------------------------------------------------------------------------|

| 95                                                                                    |

| Table 5.2. Calculated deep level parameters based on Arrhenius plot by C-DLTS         |

| measurement for both strong and weak hole injection. The defects are indicated        |

| by the position of the peak shown in Figure 5.4 and Figure 5.5 with the period        |

| width of 204.8 ms, while the activation energy is related to either conduction band   |

| (electron traps) or valence band (hole traps)96                                       |

| Table 5.3. Trap levels identification. The type C or I indicates the measure used (C- |

| DLTS or I-DLTS), while the (e) or (h) in identification points out the defect type    |

| (electron trap of hole trap)97                                                        |

| Table 5.4. Main electric parameters tested and test condition                         |

| Table 5.5. Maximum time delay between the end of radiation and first characterization |

| following TID test99                                                                  |

| Table 5.6. Activation energies of common SiC doping impurities summarized in [159].   |

|                                                                                       |

| Table 5.7. Calculated trap parameters on average based on Eq. (5.4) along with he     |

| slope and intercept of linear fitting of each peak shown in Figure 5.20110            |

| Table 5.8. Extracted trap parameters on Ti/W and Ni samples with the help of          |

| Maximum (maximum Arrhenius analysis) and HERA analysis                                |

| Table 5.9. Extracted $V_I$ of sample S4 at different temperature according to C-V     |

| analysis measured by DLTS system during the tempscan121                               |

# List of symbols

| A                                    | Richardson constant / Amplitude of transient                      |  |

|--------------------------------------|-------------------------------------------------------------------|--|

| $A^*$                                | Effective Richardson constant                                     |  |

| В                                    | Offset during transient                                           |  |

| C                                    | Capacitance                                                       |  |

| C(t)                                 | Capacitance as a function of time                                 |  |

| C'(t)                                | Capacitance as a function of time after the second pulse of DDLTS |  |

| $\Delta C$                           | Amplitude of capacitance transient                                |  |

| $\Delta C_i$                         | Amplitude of individual capacitance transient                     |  |

| $C_0$                                | Capacitance before transient                                      |  |

| $C_{iss}$                            | Input capacitance of MOSFET                                       |  |

| $C_{\scriptscriptstyle R}$           | Capacitance at reverse bias                                       |  |

| $D^{\scriptscriptstyle +}$           | Positive charge state                                             |  |

| $D^{-}$                              | Negative charge state                                             |  |

| $D^0$                                | Neutral charge state                                              |  |

| $D_n$                                | Diffusion constant of electron                                    |  |

| $D_{\scriptscriptstyle S}$           | Interface states density                                          |  |

| $\mathcal E$                         | Electric field                                                    |  |

| $E_a$                                | Activation energy                                                 |  |

| $\mathcal{E}_{\scriptscriptstyle B}$ | Breakdown field                                                   |  |

| $E_{C}$                              | Energy level of conduction band                                   |  |

| $E_{\scriptscriptstyle F}$           | Fermi level                                                       |  |

| $E_F^m$                              | Fermi level in the metal                                          |  |

| $E_F^s$                              | Fermi level in the semiconductor                                  |  |

| $E_g$                                | Energy gap between conduction band and valence band               |  |

| $E_g^{\it eff}$                      | Measured effective forbidden band gap                             |  |

| $E_g(0)$                             | Energy gap between conduction band and valence band at 0 K        |  |

| $E_{V}$                              | Energy level of valence band                                      |  |

| $F_n$                                | Discrete Fourier Transform                                        |  |

| $\mathcal{E}_{i}$                    | Electric field between metal and semiconductor                    |  |

| $\mathcal{E}_{	ext{max}}$            | Maximum electric field over the barrier                           |  |

| $\mathcal{E}_{_{S}}$                 | Surface electric field                                            |  |

| $E_{T}$                              | Energy level of trap                                              |  |

| I                                    | Current                                                           |  |

| I(t)                       | Current as a function of time                                |

|----------------------------|--------------------------------------------------------------|

| $I_0$                      | Saturation current of p-n junction                           |

| $I_{dss}$                  | Drain-source leakage current of MOSFET                       |

| $I_{gss}$                  | Gate leakage current of MOSFET                               |

| $I_R$                      | Current at reverse bias                                      |

| $I_s$                      | Saturation current of SBD                                    |

| J                          | Current density                                              |

| ${\pmb J}_0$               | Saturation current density of rectifier                      |

| $J_{\it ms}$               | Current density from metal to semiconductor                  |

| $\boldsymbol{J}_r$         | Recombination current density                                |

| $oldsymbol{J}_{sm}$        | Current density from semiconductor to metal                  |

| $oldsymbol{J}_{te}$        | Current density according to thermal emission theory         |

| L                          | Distance intersection Fermi level and trap level             |

| N                          | Number of sampling values                                    |

| $N_{C}$                    | Electron effective density of states                         |

| $N_{\scriptscriptstyle A}$ | Doping concentration of acceptor                             |

| $N_{\scriptscriptstyle D}$ | Doping concentration of donor                                |

| $N_{\scriptscriptstyle S}$ | Shallow doping concentration                                 |

| $N_{\scriptscriptstyle T}$ | Trap concentration                                           |

| $Q_d$                      | Net positive charge in the semiconductor                     |

| $Q_{\scriptscriptstyle m}$ | Negative charge on the surface of metal                      |

| $Q_{ss}$                   | Net positive charge due to interface state                   |

| $R_{on}$                   | On-resistance                                                |

| $R_{\scriptscriptstyle S}$ | Series resistance                                            |

| S                          | Effective surface                                            |

| $S_i$                      | Effective surface of region i.                               |

| T                          | Temperature                                                  |

| $T_0$                      | Parameter involved in $T_0$ effect                           |

| $T_P$                      | Pulse width in DLTS                                          |

| $T_{W}$                    | Period width in DLTS                                         |

| U                          | Energy between donor and acceptor level in negative-U system |

| ${U}_{r}$                  | Recombination ratio                                          |

| $U_{\scriptscriptstyle H}$ | Pulse height in DLTS                                         |

| $U_{P}$                    | Pulse voltage in DLTS                                        |

| $U_P'$                     | Second pulse voltage in DDLTS                                |

| $U_{\scriptscriptstyle R}$ | Reverse bias in DLTS                                                          |

|----------------------------|-------------------------------------------------------------------------------|

| V                          | Bias voltage                                                                  |

| $V_{\scriptscriptstyle R}$ | Breakdown voltage                                                             |

| $V_d$                      | Difference between $\Phi_B$ and $\xi$                                         |

| $V_{d0}$                   | Difference between $\Phi_B$ and $\xi$ at balance condition                    |

| $V_{ds}$                   | Drain-source voltage                                                          |

| $V_{gs}$                   | Gate-source voltage                                                           |

| $V_{_I}$                   | Intersection with x-axis of $1/C^2 \sim V_r$ plot during C-V analysis         |

| $V_{i}$                    | Voltage drop between metal and semiconductor if electrically connected        |

| $V_r$                      | Reverse bias voltage                                                          |

| $V_{_{th}}$                | Gate threshold voltage of MOSFET                                              |

| $X_{n}$                    | Entropy factor during emission process                                        |

| $a_i$                      | Fraction of effective surface of individual region with total contact surface |

| $a_n$                      | Cosine coefficient of Fourier transform                                       |

| $b_n$                      | Sine coefficient of Fourier transform                                         |

| $c_1$                      | Electron capture rate between trap level and conduction band                  |

| $c_2$                      | Electron capture rate between trap level and valence band                     |

| $C_n$                      | Electron capture rate / Complex Fourier coefficient                           |

| $c_n^D$                    | Discrete Fourier coefficients                                                 |

| d                          | Distance where the barrier falls by a value of $kT/q$ from its maximum        |

| $e^{-}$                    | Electron                                                                      |

| $e_{_{1}}$                 | Electron emission rate between trap level and conduction band                 |

| $e_2$                      | Electron emission rate between trap level and valence band                    |

| $e_n$                      | Electron emission rate                                                        |

| f(t)                       | Continuous function of time                                                   |

| $f_{\scriptscriptstyle k}$ | Discrete sampling value                                                       |

| h                          | Planck constant                                                               |

| k                          | Boltzmann constant                                                            |

| l                          | Carrier mean free path                                                        |

| <i>m</i>                   | Free electron mass                                                            |

| m                          | Electron effective mass                                                       |

| n                          | Electron concentration / Ideality factor Concentration of free electrons      |

| $n_0$                      |                                                                               |

| $n_{i}$                    | Electron concentration in intrinsic semiconductor                             |

| $n_{Tc}$                   | Filled traps during the capture process                                       |

| $n_{Te}$                                                        | Filled traps during the emission process                                                            |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| p                                                               | Hole concentration                                                                                  |

| $p_{t}$                                                         | Tunneling probability                                                                               |

| q                                                               | Magnitude of the electron charge                                                                    |

| $t_0$                                                           | Time between end of charging pulse and the first sampling value                                     |

| $\overline{v}$                                                  | Average thermal velocity                                                                            |

| $V_{th}$                                                        | Thermal velocity of carrier                                                                         |

| $V_{th,n}$                                                      | Thermal velocity of electrons                                                                       |

| $v_{s}$                                                         | Saturation drift velocity                                                                           |

| w                                                               | Depletion region width  Effective depletion region width where traps can be detected by DLTS        |

| $W_{e\!f\!f}$                                                   |                                                                                                     |

| $W_P$                                                           | Depletion region width at pulse voltage  Depletion region width at reverse bias                     |

| $W_R$                                                           |                                                                                                     |

| $x_m$                                                           | Position where the maximum value of Schottky potential height is reached<br>Schottky barrier height |

| $\Phi_{\scriptscriptstyle B}$ $ar{\Phi}_{\scriptscriptstyle R}$ | Average of Schottky barrier height                                                                  |

| Ь                                                               | Calculated average of SBH based on $\Phi_{BF}$ and $\rho_2$                                         |

| $ar{\Phi}_{B0}'$ $\Phi_{B0}$                                    | Schottky barrier height at zero bias                                                                |

| $ar{\Phi}_{B0}$                                                 | Average of Schottky barrier height at zero bias                                                     |

| $\Phi_{B0}$ $\Phi_{BF}$                                         | Schottky barrier height on flat-band condition                                                      |

| $\Phi_{Bn,i}$                                                   | Individual constant barrier height of a series of ideal regions                                     |

| $\Phi_{Bn,l}$                                                   | Individual constant barrier with the lowest barrier height                                          |

| $\Phi_{\scriptscriptstyle B}^{\it eff}$                         | Effective Schottky barrier height involving image-force lowering                                    |

| $\Phi_{\scriptscriptstyle C-\scriptscriptstyle V}$              | Schottky barrier height determined by C-V                                                           |

| $\Delta\Phi_i$                                                  | Reduction on barrier height due to image-force lowering                                             |

| $\Phi_{\scriptscriptstyle m}$                                   | Work function of metal                                                                              |

| $\Phi_s$                                                        | Work function of semiconductor                                                                      |

| α                                                               | Effective tunneling constant                                                                        |

| β                                                               | Temperature coefficient of band gap                                                                 |

| $\chi_s$                                                        | Electron affinity of semiconductor                                                                  |

| δ                                                               | Distance between metal and semiconductor                                                            |

| $\mathcal{E}_0$                                                 | Permittivity in the vacuum                                                                          |

| $\mathcal{E}_i$                                                 | Permittivity of the interfacial layer                                                               |

| $\mathcal{E}_{ir}$                                              | Relative permittivity of the interfacial layer                                                      |

| $\mathcal{E}_{s}$                                               | Permittivity of the semiconductor                                                                   |

| $\boldsymbol{\mathcal{E}}_{s}^{\prime}$ | Permittivity of the semiconductor under high frequency                                             |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

| $\phi_0$                                | Neutral level of interface states                                                                  |  |  |

| γ                                       | Temperature coefficient of saturation current in p-n junction                                      |  |  |

| $\mu$                                   | Carrier mobility                                                                                   |  |  |

| $\mu_n$                                 | Electron mobility                                                                                  |  |  |

| $ ho_2$                                 | Linearity coefficient of $\overline{\Phi}_{\scriptscriptstyle B}$ varies with bias voltage         |  |  |

| $ ho_3$                                 | Linearity coefficient of $\sigma_s$ varies with bias voltage                                       |  |  |

| $\sigma$                                | Capture cross section                                                                              |  |  |

| $\sigma_{_n}$                           | Capture cross section of electrons                                                                 |  |  |

| $\sigma_{_p}$                           | Capture cross section of holes                                                                     |  |  |

| $\sigma_{\scriptscriptstyle S}$         | Standard deviation in Gaussian distribution                                                        |  |  |

| $\sigma_{\scriptscriptstyle S}'$        | Calculated standard deviation in Gaussian distribution based on $\Phi_{\rm BF}$ and $\rho_{\rm 3}$ |  |  |

| $\sigma_{{\scriptscriptstyle S}0}$      | Standard deviation in Gaussian distribution at zero bias                                           |  |  |

| au                                      | Time constant                                                                                      |  |  |

| $	au_c$                                 | Capture time constant                                                                              |  |  |

| $	au_e$                                 | Emission time constant                                                                             |  |  |

| $	au_r$                                 | Carrier lifetime within the depletion region                                                       |  |  |

| $\omega_0$                              | Angular velocity involved in Fourier transform                                                     |  |  |

| ξ                                       | Difference between $E_F$ and $E_C$                                                                 |  |  |

| Ψ                                       | Constant parameter in the expression of saturation current of p-n junction                         |  |  |

### Table of contents

| ACKN   | OWLEDGEMENT                                                 | ]          |

|--------|-------------------------------------------------------------|------------|

| ABSTE  | RACT                                                        | 11         |

| LIST C | OF FIGURES                                                  | IV         |

| LIST C | OF TABLES                                                   | XII        |

| LIST C | OF SYMBOLS                                                  | XIV        |

| TABLI  | E OF CONTENTS                                               | XIX        |

| INTRO  | DUCTION                                                     | 1          |

| CHAP   | ΓER 1 START OF ART                                          | 4          |

| 1.1 I  | Background                                                  | 5          |

| 1.1.1  | Development of modern power electronics and its limitation  | 5          |

| 1.1.2  | Silicon carbide (SiC)                                       | $\epsilon$ |

| 1.1.3  | Schottky barrier diodes (SBD)                               | 8          |

| 1.1.4  | Multi-barrier in SBD                                        | 8          |

| 1.2 I  | Reliability and Defects                                     | 10         |

| 1.2.1  | Classification of defects                                   | 10         |

| 1.2.2  | Defects reported in SiC devices                             | 12         |

| CHAP   | ΓER 2 BARRIER HEIGHT DETERMINATION OF SCI                   | ноттку     |

| DIODE  | <b>ES</b>                                                   | 15         |

| 2.1 I  | Energy band diagram and formation of Schottky barrier diode | 16         |

| 2.1.1  | Ideal Schottky contact                                      | 16         |

| 2.1.2 | The effect of interface states                       | 17 |

|-------|------------------------------------------------------|----|

| 2.2   | Current transport mechanisms though Schottky barrier | 19 |

| 2.2.1 | Introduction                                         | 19 |

| 2.2.2 | The diffusion theory                                 | 20 |

| 2.2.3 | The thermionic-emission (TE) theory                  | 20 |

| 2.2.4 | Tunneling and Thermionic-Field Emission (TFE) model  | 21 |

| 2.2.5 | Recombination in the depletion region                | 22 |

| 2.2.6 | Image-force lowering of SBH                          | 23 |

| 2.3   | Measurement of SBH                                   | 25 |

| 2.3.1 | I-V characteristics                                  | 25 |

| 2.3.2 | C-V measurements                                     | 26 |

| 2.4   | Review on SBH models                                 | 27 |

| 2.4.1 | Ideality factor and zero-bias barrier height         | 27 |

| 2.4.2 | $T_0$ effect                                         | 27 |

| 2.4.3 | Gaussian distribution                                | 28 |

| 2.4.4 | Potential Fluctuation model                          | 28 |

| 2.4.5 | Flat-band barrier height                             | 29 |

| 2.4.6 | Modified Richardson plot                             | 29 |

| 2.4.7 | Relationships between different models               | 29 |

| 2.5   | Barrier inhomogeneity in Schottky devices            | 32 |

| 2.5.1 | Introduction                                         | 32 |

| 2.5.2 | Parallel diode model                                 | 32 |

| 2.5.3 | Tung's model                                         | 33 |

| 2.5.4 | Multi Gaussian distribution model                    | 35 |

| СНАР  | TER 3 DEEP LEVELS DETECTION                          | 36 |

| 3.1   | Overview                                             | 37 |

| 3.2   | Electron capture-emission mechanism                  | 38 |

| 3.2.1 | Capture                                              | 38 |

| 3.2.2 | Emission                                             | 39 |

| 3.2.3 | Steady state capture-emission                        | 39 |

| 3.2.4 | Transient                                            | 41 |

| 3.2.5 Limitation on trap detection |                                                       | 42 |

|------------------------------------|-------------------------------------------------------|----|

| 3.3                                | DLTS Principle                                        | 44 |

| 3.3.                               | 1 Basic DLTS principle                                | 44 |

| 3.3.                               | 2 Fourier transform and DLTFS                         | 46 |

| 3.3.                               | 3 HERA DLTS                                           | 48 |

| 3.4                                | Category of DLTS                                      | 50 |

| 3.4.                               | 1 DLTS transient modes                                | 50 |

| 3.4.                               | 2 Isothermal DLTS                                     | 52 |

| 3.4.                               | 3 Other DLTS                                          | 54 |

| СНА                                | PTER 4 EXPERIMENTAL STUDY ON SIC SBD                  | 57 |

| 4.1                                | Sample used in this study                             | 58 |

| 4.1.                               | 1 Overview                                            | 58 |

| 4.1.                               | 2 Preliminary statistics                              | 59 |

| 4.2                                | Measurements setup                                    | 61 |

| 4.2.                               | 1 Hardware setup                                      | 61 |

| 4.2.                               | 2 I-V measurements                                    | 63 |

| 4.2.                               | 3 C-V measurements                                    | 63 |

| 4.2.                               | 4 DLTS measurement                                    | 63 |

| 4.3                                | Experimental results                                  | 66 |

| 4.3.                               | 1 Case study: Ti/W liftoff sample                     | 66 |

| 4.3.                               | 2 Research on diode with multi-barriers               | 72 |

| 4.3.                               | 3 Comparison on samples with different metal contacts | 81 |

| СНА                                | PTER 5 CHARACTERIZATION ON OTHER SAMPLES AND          | ı  |

| DISC                               | CUSSION                                               | 88 |

| 5.1                                | PiN diode                                             | 89 |

| 5.1.                               | 1 Sample overview                                     | 89 |

| 5.1.                               | 2 Experiment setup                                    | 89 |

| 5.1.                               | 3 Static Characterization                             | 89 |

| 5.1.                               | 4 DLTS characterization                               | 91 |

| 5.2  | MOSFET                                                             | 98         |

|------|--------------------------------------------------------------------|------------|

| 5.2. | 1 Introduction                                                     | 98         |

| 5.2. | 2 Experiments setup                                                | 98         |

| 5.2. | 3 Experimental results                                             | 99         |

| 5.2. | 4 Discussion                                                       | 104        |

| 5.3  | Discussion                                                         | 106        |

| 5.3. | 1 Freeze-out effect                                                | 106        |

| 5.3. | 2 Relationship between activation energy and capture cross section | of certain |

| defe | ect level.                                                         | 107        |

| 5.3. | 3 Annealing effect during DLTS                                     | 111        |

| 5.3. | 4 Negative-U center                                                | 113        |

| 5.3. | 5 Behavior at extremely low temperature                            | 117        |

| СНА  | PTER 6 CONCLUSION AND PROSPECTIVE                                  | 127        |

| 6.1  | Conclusion                                                         | 128        |

| 6.2  | Perspective                                                        | 130        |

| REFI | ERENCE                                                             | 131        |

# Introduction

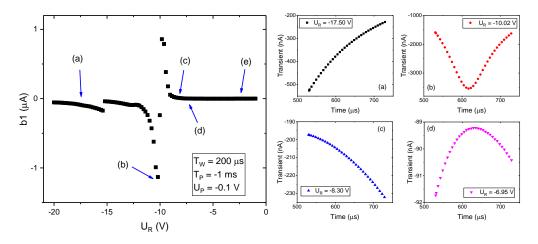

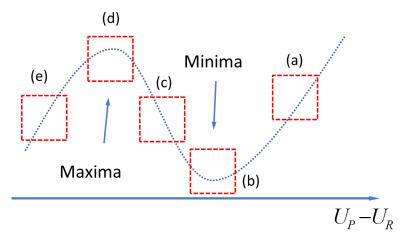

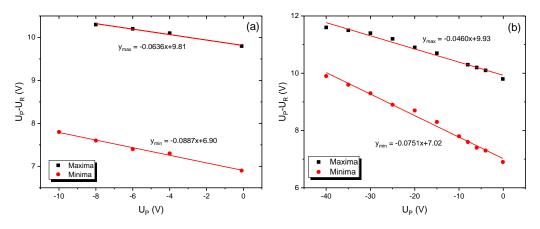

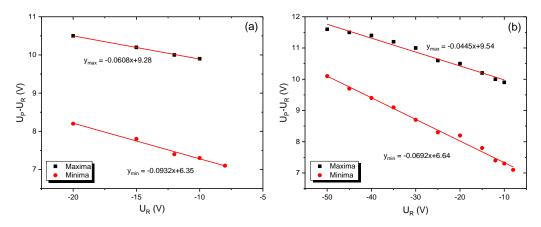

Silicon carbide, as one of the well-known potential substitute materials of silicon in power electrics, has been attracting attention due to its high temperature, high power, and high frequency applications. The mature on large size of SiC wafer as well as cutting process bring hope to the commercial massive production, which in turn speeds up the research on SiC as the material of new generation.