# Strain integration and performance optimization in sub-20nm FDSOI CMOS technology

Rémy Berthelon

## ► To cite this version:

Rémy Berthelon. Strain integration and performance optimization in sub-20nm FDSOI CMOS technology. Micro and nanotechnologies/Microelectronics. Université Paul Sabatier - Toulouse III, 2018. English. NNT: 2018TOU30066 . tel-02132872

# HAL Id: tel-02132872 https://theses.hal.science/tel-02132872v1

Submitted on 17 May 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

En vue de l'obtention du

## DOCTORAT DE L'UNIVERSITÉ DE TOULOUSE

Délivré par : l'Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

## Présentée et soutenue le 26/04/2018 par : RÉMY BERTHELON

Strain integration and performance optimization in sub-20nm FDSOI CMOS technology

## JURY

Sorin Cristoloveanu Olivier Thomas Chantal Fontaine Damien Querlioz Alain Claverie François Andrieu Didier Dutartre Franck Arnaud IMEP-LaHC, Grenoble Im2np, Marseille LAAS, Toulouse Université Paris-Sud CEMES, Toulouse CEA-LETI, Grenoble STMicroelectronics, Crolles STMicroelectronics, Crolles Rapporteur Rapporteur Examinatrice Examinateur Directeur de thèse Co-encadrant de thèse Co-encadrant de thèse Invité

#### École doctorale et spécialité :

SDM : Nano-physique, nano-composants, nano-mesures - COP 00 Unité de Recherche : CEMES/CNRS (UPR 8011)

# Remerciements

Avant de rentrer dans le vif du sujet, je tiens à remercier toutes les personnes qui ont contribué de très près ou de plus loin à ce travail de thèse.

En premier lieu, je tiens à remercier Michel Haond pour m'avoir accueilli dans l'équipe "14FD" de STMicroelectronics, même si cette aventure n'aura duré qu'une petite année... Merci donc à Maud Vinet d'avoir bien voulu me récupérer au CEA-LETI dans son laboratoire LICL, sans quoi cette thèse n'aurait pas pu continuer dans de bonnes conditions. Merci à Franck Arnaud d'avoir pris le relais côté ST, d'avoir participé à ma soutenance et de m'intégrer dans son équipe pour la suite.

Mes remerciements vont ensuite à mes co-encadrants François Andrieu et Didier Dutartre. Merci François pour ton encadrement de très grande qualité. J'ai eu la chance de bénéficier de tes compétences techniques et de ton état d'esprit remarquables. Tu as su me pousser grâce à ton enthousiasme et ton exigence. Merci d'avoir répondu à mes sollicitations permanentes tout en m'accordant une forte autonomie. C'était un réel plaisir d'être ton thésard. Merci Didier pour avoir toujours su porter de l'intérêt à mon travail, entre deux task forces... Ton expertise matériaux et ta pertinence m'ont épaté à de nombreuses reprises. Merci pour la confiance que tu m'as accordée. J'adresse également tous mes remerciements à mon directeur de thèse Alain Claverie. Merci Alain pour ton soutien à distance. Avec un peu de recul, je regrette de ne pas avoir assez "exploité" (je te cite) tes connaissances. Je te remercie également de t'être toujours préoccupé de mon bien-être en tant que thésard.

Je tiens ensuite à remercier tous les membres du jury d'avoir accepté d'évaluer cette thèse, en particulier les rapporteurs qui ont eu le courage de lire ce long manuscrit. Merci donc à Olivier Thomas (je ne suis pas prêt d'oublier la question sur l'effet des gradients de contrainte) et Sorin Cristoloveanu (merci de m'estimer au point de me faire participer à un reviewing). Merci également à Chantal Fontaine d'avoir présidé avec brio la soutenance et enfin à Damien Querlioz de s'être autant intéressé à mes travaux.

A STMicroelectronics, je tiens à remercier toutes les personnes qui étaient rattachées au programme "14FD". En particulier, je remercie Manu Josse pour ses coups de pouce et maitre Olivier Weber pour sa pédagogie à toute épreuve. Un grand merci à Pierre "pp41" Perreau pour la gestion des manips, à Raphaël Bingert pour l'initiation au SPICE ainsi que Pierre Morin pour nos discussions strain. Merci également à l'ensemble de l'équipe PI, en particulier Jérôme Mazurier, Elise Baylac, Manu Richard, Nelly Guillot, Sonar', Manu Petitprez (merci de me former aujourd'hui), Claire Gallon, JC Grenier ... Je remercie également tous les autres intervenants sur le "14FD", notamment: Alexandre Pofelski, Marie-Anne Jaud, Thierry Poiroux, Fabien Rozé, Denis Rideau, Daniel Benoit, Victorien Paredes, Olivier Gourhant... Merci également à "Vince" Barral pour nos échanges sur l'ULPv2 ainsi qu'aux "fiabilistes" (i.e. l'équipe du SOC): coach Mus', CD "minou", CND et Pat'. Enfin, merci mon co-box Nils pour ta maitrise d'IUI mais surtout pour les magnifiques photos que tu prends de moi.

Au CEA-LETI, je remercie l'ensemble du LICL, laboratoire riche techniquement et humainement. Merci Cyrille Le Royer, Yves Morand, Christophe Plantier, garants de l'activité strain. Merci mes co-bureaux Valérie Lapras, une aventurière, et Olivier Rozeau (au revoir Madame). Merci Benoit "spin-up" Bertrand (vive  $IAT_EX!$ ) et Louis "spin-down" Hutin, véritable Wikipedia ambulant (je ne fais que 95% confiance en la validité de tes facts, comme pour Wikipedia...). Merci Laurent "Lolo" Brunet pour la baseline, tes supers manips Coolcube et ta passion pour les trappeurs d'Alaska... Merci Perrine Batude de m'avoir confié la manip SDRASS et pour ton énergie débordante. Merci Bernard Previtali pour les caracs SEM, Claude Tabone pour son amour de la cantine et surtout Laurent Brevard, freerider de l'extrême qui m'a tant aidé sur le suivi des lots au LETI. Je remercie également Claire Fenouillet, Sylvain Barraud, Jean-Pierre Colinge, Hervé Boutry. Au-delà du LICL, tous mes remerciements aux personnes du LETI que j'ai eu la chance de côtoyer. Merci David Cooper (poor Gooner), Nicolas Bernier et Victor Boureau pour les mesures de strain. Merci Denis Rouchon pour notre étude µRaman. Merci Mikael "Mike" Cassé (tu resteras mon premier mentor) et Xavier "Zav" Garros (allez le PSEG!). Merci mon cher "piti": Alain Toffoli (vert de la première heure), Fabienne Allain (on se fait un double paramétrage sur Alisé) et Giovanni Romano ("cosi fan tutte"). Merci Frédérique Glowacki pour nos tentatives désespérées d'oxydation. Merci Shay Reboh pour nos discussions relaxation de SiGe et Comsol. Merci François Triozon pour les simulations NEGF et merci Benoit Matthieu pour nos comparaisons de simus méca. Merci Bastien Giraud, Reda Boumchedda et Jean-Philippe Noel pour les discussions SRAM. Je remercie également Joris Lacord, Jacques Cluzel (et son multimètre nommé "Revient"), Jean-Michel Hartmann, Vincent Mazzocchi, Pascal Besson, Pierrette Rivallin, Virginie Loup, ...

Je tiens également à remercier Joël Eymery, Vincent Favre-Nicollin et Gaëtan Girard pour les mesures à l'ESRF auxquelles j'ai eu la chance d'assister (je suis toujours curieux des résultats). Merci aussi à Gérard "GG" Ghibaudo pour m'avoir accordé du temps, même si je ne faisais pas partie de la horde de thésards qu'il dirige en parallèle.

J'adresse également mes remerciements à tous les thésards/stagiaires (aujourd'hui docteurs pour la plupart) pour tous les bons moments passés durant ces trois années. A ST, merci à la team du midi: Boris "Bob", BASTIEN, Giulio Uno, Giulio Due (je vous laisse débattre qui est qui), Romu "mais mec", Nils (un petit deuxième pour la route), Andrej, Carlos et enfin merci Hassan, ma petite feuille de vigne préférée, pour ta magnifique Megane tuning. Au Leti, un grand merci à la team Padawan du LICL: Alex ("voilà hein CuCube c'est fini"), Lina "Kadura-chan" pour le plus beau wallpaper ever, tes belles idées cadeau et surtout pour les chocobananas, Giulia "Pecorina" la teenager bisounours, Julien et tes talents d'imitateur, Carlos (hala Paris), Jessys (avec un s parce que tu es plusieurs), Loïc, Daphnée, Camila (don't forget: Mathcad is fun, Mathcad is life), Mathilde, Sotiris ( $Ev\chi\alpha\rho\iota\sigma\tau\omega$ )... Merci également à Gaspard pour une première expérience de co-encadrement de stage bien sympathique grâce à toi. Merci Blendissimo for your physics lessons and your stupid 50m-long shots. Pasa la pelota! Enfin, un grand merci à "Tonio" pour tous nos bons moments passés, du LCTE à Hawaii en passant par ton jardin avec cabanon. Bravo à toi pour ton triplé historique en cette saison 2017-2018 (job, bébé, doctorat). Café?

Pour finir, un grand MERCI à tous mes Martinérois. Merci la Fratrie pour fêter les week-ends avec le combo rituel "VnB + on mange où?" et merci pour les vannes inépuisables. Merci à mes beaux-parents Noun' et Momo pour toute votre affection et à la belle-famille au sens large (mon beauf Nico, Agnès et Jean-Marc, Clé "poulet", Elsa, Soso, Mitmit', Marine,...). Je remercie évidemment toute ma famille: Mamychèle (quel courage d'assister à cette ennuyante soutenance), PapyBajeat, TontonLuc, TontonPhi et ses angevins, etc... Je rajoute une tendre pensée pour PapyBernard et MamyJacqueline. Merci Papa, merci Maman, merci pour tout !!! Je termine ces remerciements avec les deux personnes qui me sont les plus chères: Merci Tom, mon petit frère modèle, véritable source d'inspiration quotidienne. Merci Lisa, ma crème de la crème, tout simplement indispensable. A nous le bonheur... "SiGe, il s'appelle SiGe, je suis folle de lui..."

# Contents

| Ir | ntroduction                                                                                                                                                              |    |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 1  | Boosting sub-20nm CMOS technology performance: the relevance of strain                                                                                                   | 9  |  |

|    | 1.1 Introduction to CMOS logic                                                                                                                                           | 10 |  |

|    | 1.1.1 The MOSFET, device at the heart of logic                                                                                                                           | 10 |  |

|    | 1.1.1.a The MOSFET switch                                                                                                                                                | 10 |  |

|    | 1.1.1.b Boolean functions using logic combinatory gates                                                                                                                  | 11 |  |

|    | 1.1.2 The Power/Performance/Area metrics                                                                                                                                 | 12 |  |

|    | 1.1.2.a Power/Performance: the ring-oscillator metrics                                                                                                                   | 12 |  |

|    | 1.1.2.b Area: standard cell design                                                                                                                                       | 14 |  |

|    | 1.1.3 The MOSFET operation and metrics                                                                                                                                   | 15 |  |

|    | 1.1.3.a The MOSFET structure                                                                                                                                             | 15 |  |

|    | 1.1.3.b The MOSFET operation                                                                                                                                             | 16 |  |

|    | 1.1.3.c The MOSFET principal metrics                                                                                                                                     | 17 |  |

|    | 1.1.3.d The effective drive current in an inverter                                                                                                                       | 19 |  |

|    | 1.1.3.e The importance of the electrostatic control $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                          | 20 |  |

|    | 1.1.3.f The performance/leakage trade-off $\ldots$                                                                                                                       | 20 |  |

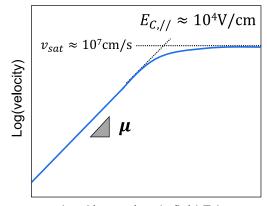

|    | 1.1.3.g The crucial role of carrier mobility $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                   | 21 |  |

|    | 1.2 CMOS technology scaling: the king is dead, long live the king !                                                                                                      | 24 |  |

|    | 1.2.1 The happy scaling, the good old days $\ldots \ldots \ldots$                                         | 24 |  |

|    | 1.2.2 The introduction of goodies $\ldots \ldots \ldots$ | 25 |  |

|    | 1.2.3 The rise of new architectures $\ldots$                                            | 26 |  |

|    | 1.2.3.a The FinFET $\ldots$                                                                                                                                              | 26 |  |

|    | 1.2.3.b The FDSOI technology                                                                                                                                             | 27 |  |

|    | 1.2.3.c Stacked nanosheets                                                                                                                                               | 29 |  |

|    | 1.2.4 The parasitics, key players                                                                                                                                        | 30 |  |

|    | 1.2.5 CMOS scaling: conclusion and perspectives                                                                                                                          | 32 |  |

|    | 1.3 Strain integration in CMOS technologies                                                                                                                              | 34 |  |

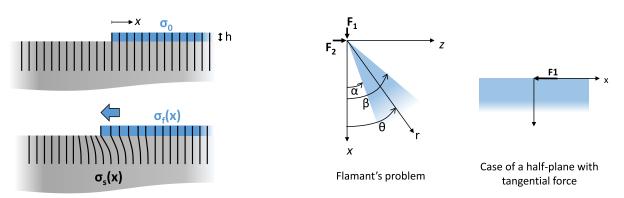

|    | 1.3.1 Theory of elasticity $\ldots$                                                     | 34 |  |

|    | 1.3.2 The impact of strain on Silicon properties                                                                                                                         | 36 |  |

|    | 1.3.2.a Band structure of Silicon                                                                                                                                        | 36 |  |

|    | 1.3.2.b Deformation potential theory                                                                                                                                     | 37 |  |

|          | 1.3.2.c Interaction with confinement $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 4$                                                                                | 10          |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|          | 1.3.2.d Summary                                                                                                                                                                               | 41          |

|          | 1.3.3 Strain integration techniques                                                                                                                                                           | 42          |

|          | 1.3.3.a Locally-introduced strain techniques                                                                                                                                                  | 42          |

|          | 1.3.3.b Globally-introduced strain techniques                                                                                                                                                 | 14          |

|          | 1.3.4 Local Layout Effects                                                                                                                                                                    | 47          |

|          | 1.3.5 Summary on strain integration in CMOS technology                                                                                                                                        | 50          |

|          | 1.4 Conclusion to Chapter 1                                                                                                                                                                   | 50          |

| <b>2</b> | Strained channel MOSFET performance: mobility and access resistance 5                                                                                                                         | 51          |

|          | 2.1 Long channel mobility impacted by strain                                                                                                                                                  | 52          |

|          | 2.1.1 The split-CV technique                                                                                                                                                                  | 52          |

|          | 2.1.2 Impact of strain on long channel mobility                                                                                                                                               | 53          |

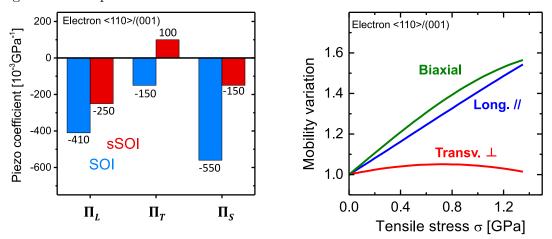

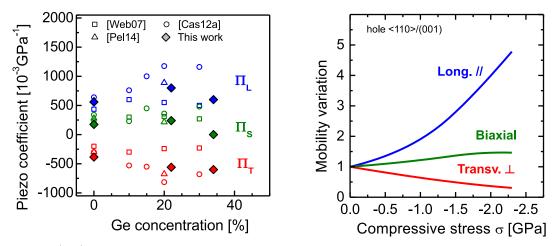

|          | 2.1.3 The piezoresistivity model                                                                                                                                                              | 54          |

|          | 2.2 Short channel mobility and access resistance extraction                                                                                                                                   | 57          |

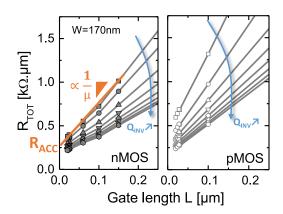

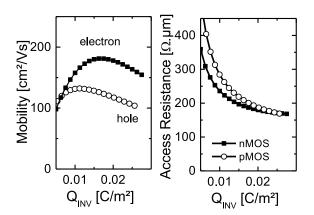

|          | 2.2.1 Total resistance method                                                                                                                                                                 | 57          |

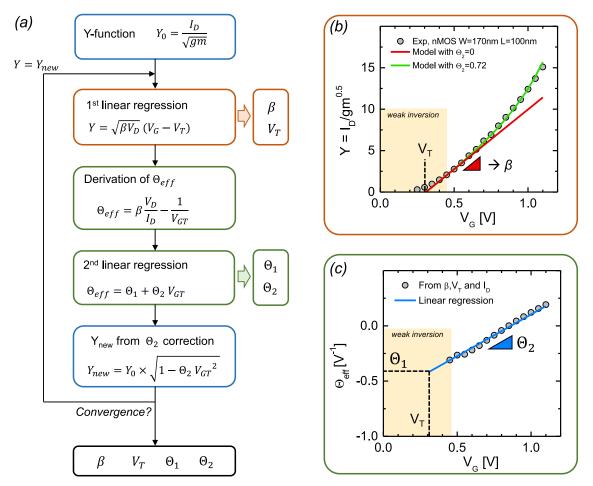

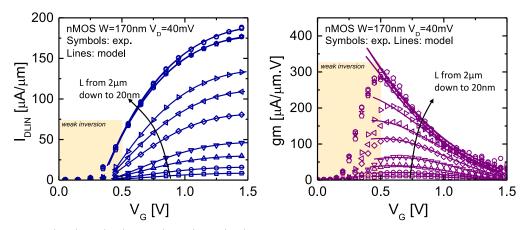

|          | 2.2.2 The Y-function methodology $\ldots \ldots 5$                                          | 58          |

|          | 2.2.2.a Principle                                                                                                                                                                             | 58          |

|          | 2.2.2.b Extraction procedure                                                                                                                                                                  | 59          |

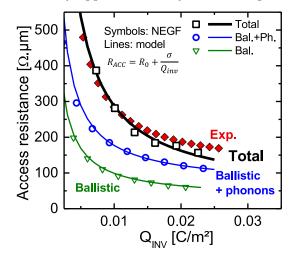

|          | 2.2.2.c Access resistance extraction                                                                                                                                                          | 62          |

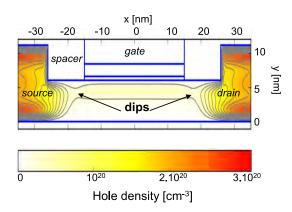

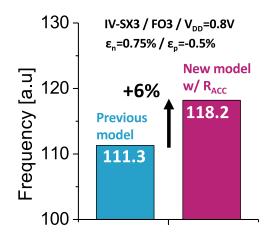

|          | 2.2.3 Adapted Y-function with a new model of access resistance                                                                                                                                | <u> 5</u> 3 |

|          | 2.2.3.a Motivation: the role of the near spacer region $\ldots \ldots \ldots$ | <u> 5</u> 3 |

|          | $2.2.3.b$ New Y-function-based method $\ldots \ldots \ldots$                  | 64          |

|          | 2.2.4 Summary                                                                                                                                                                                 | 66          |

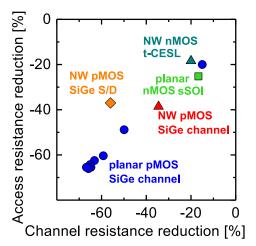

|          | 2.3 The impact of strain on access resistance                                                                                                                                                 | 66          |

|          | 2.3.1 Planar FDSOI $\ldots \ldots \ldots$                                     | 67          |

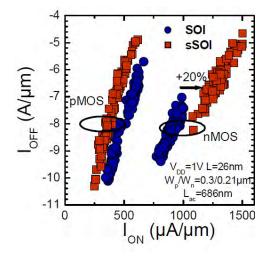

|          | 2.3.1.a Experimental results on sSOI $\ldots \ldots $                                       | 67          |

|          | 2.3.1.b SiGeOI NEGF simulations                                                                                                                                                               | 68          |

|          | $2.3.2$ Nanowires embedding strain $\ldots \ldots \ldots$                     | <u> 59</u>  |

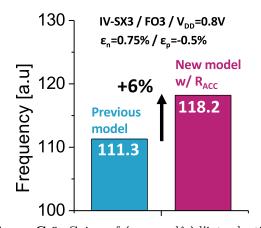

|          | 2.3.3 Summary and SPICE predictions                                                                                                                                                           | 70          |

|          | 2.4 Conclusion to Chapter 2                                                                                                                                                                   | 72          |

| 3        | Strain-induced layout effects in SiGeOI pMOSFETs 7                                                                                                                                            | <b>'</b> 3  |

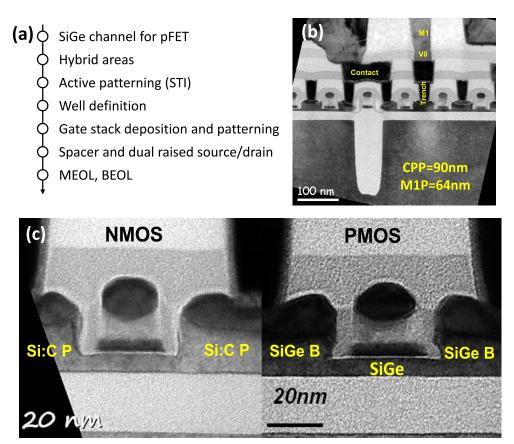

|          | 3.1 FDSOI technologies and devices                                                                                                                                                            | 74          |

|          | 3.1.1 28nm and 14nm FDSOI technologies at a glance                                                                                                                                            | 74          |

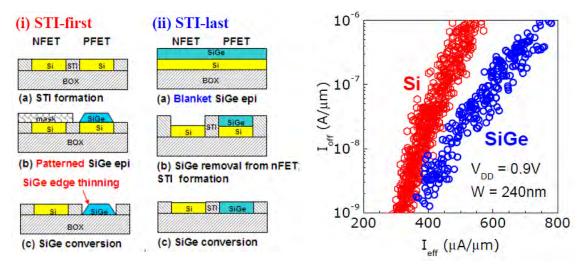

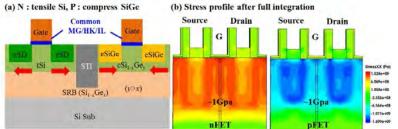

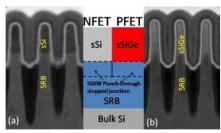

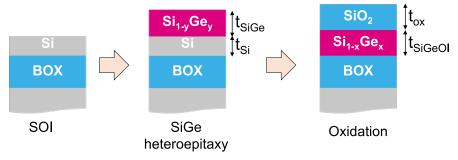

|          | 3.1.2 Integration of SiGe in FDSOI                                                                                                                                                            | 76          |

|          | 3.1.2.a The condensation technique                                                                                                                                                            | 76          |

|          | 3.1.2.b SiGe integration in 14nm FDSOI technology                                                                                                                                             | 79          |

|          | 3.2 Strain measurement, simulation and modeling in patterned SiGeOI                                                                                                                           | 31          |

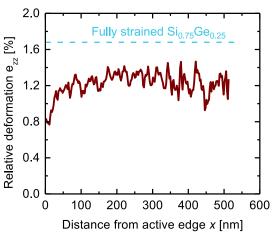

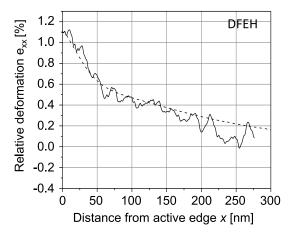

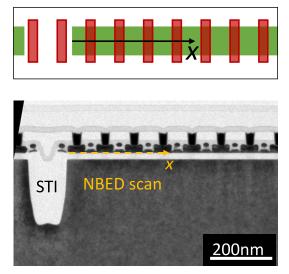

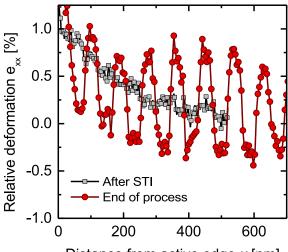

|          | 3.2.1 Nano-Beam Electron Diffraction measurements                                                                                                                                             | 31          |

|   | 3.2.2 Mechanical simulations                                                                                             | 84  |

|---|--------------------------------------------------------------------------------------------------------------------------|-----|

|   | 3.2.2.a Hypotheses and model                                                                                             | 84  |

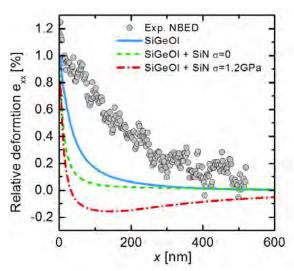

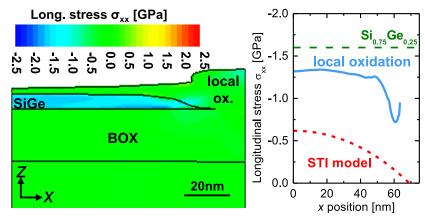

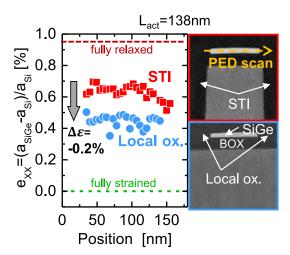

|   | 3.2.2.b Results and discussion $\ldots$ | 85  |

|   | 3.2.3 Stress relaxation compact modeling                                                                                 | 86  |

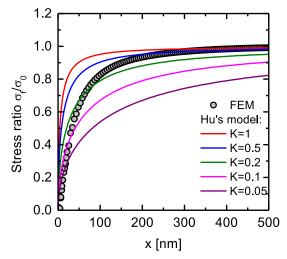

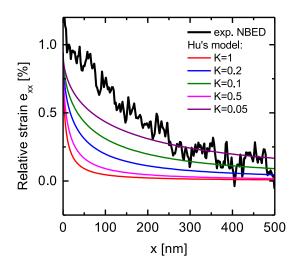

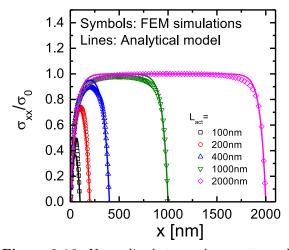

|   | 3.2.3.a Theoretical approach: Hu's model                                                                                 | 86  |

|   | 3.2.3.b Empirical approach: stress from SiGe channel                                                                     | 87  |

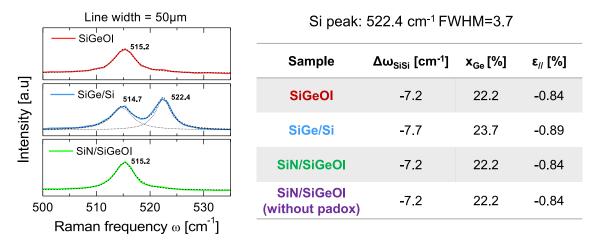

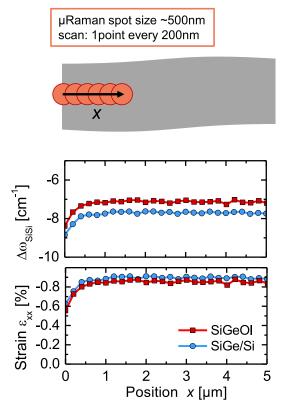

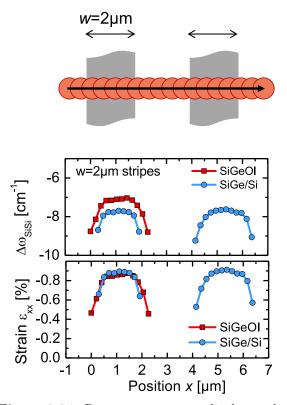

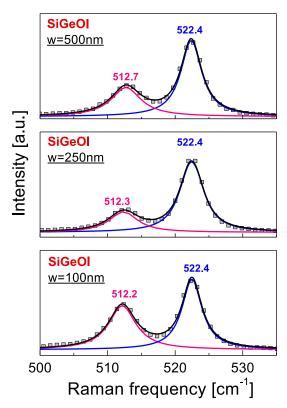

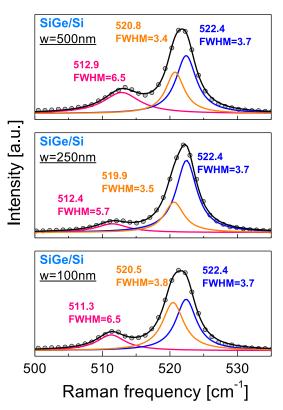

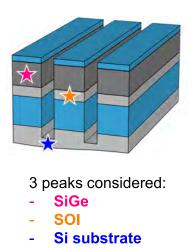

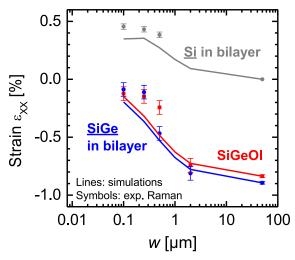

|   | 3.2.4 µRaman measurements                                                                                                | 91  |

|   | 3.2.4.a Experimental details: samples and structures                                                                     | 91  |

|   | 3.2.4.b Pseudomorphic SiGe strain extraction by µRaman                                                                   | 92  |

|   | 3.2.4.c Unidirectional strain relaxation extraction by $\mu$ Raman $\ldots \ldots \ldots$                                | 93  |

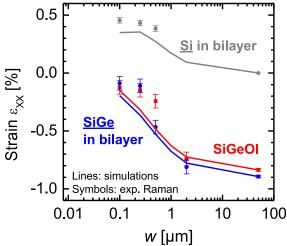

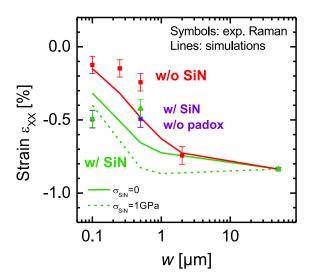

|   | 3.2.4.d Results                                                                                                          | 94  |

|   | 3.2.4.e Conclusion on $\mu$ Raman measurements                                                                           | 98  |

|   | $3.2.5$ Discussion $\ldots$                                                                                              | 99  |

|   | 3.3 Stress from SiGe source/drain: measurements, simulations and modeling $\ldots \ldots \ldots$                         | 100 |

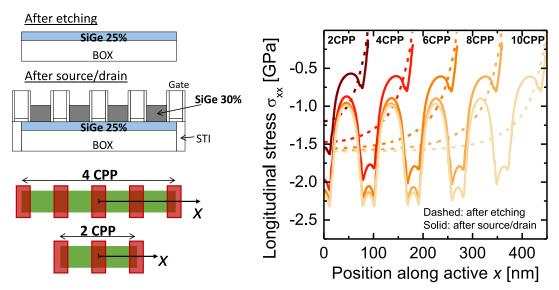

|   | 3.3.1 Additional stress from SiGe source/drain in a non-patterned SiGeOI active layer                                    | 100 |

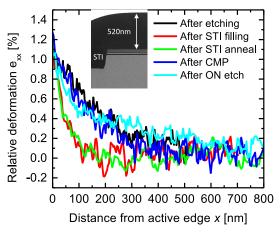

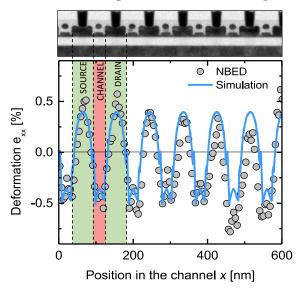

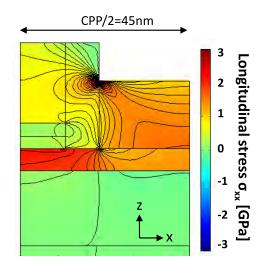

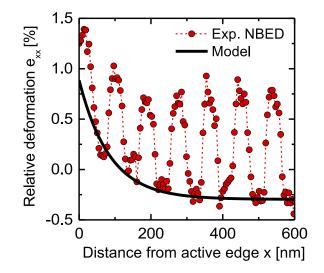

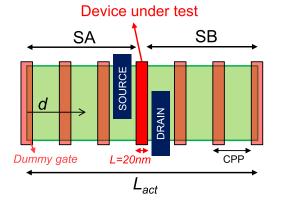

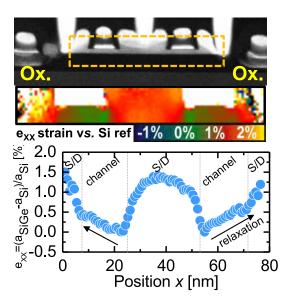

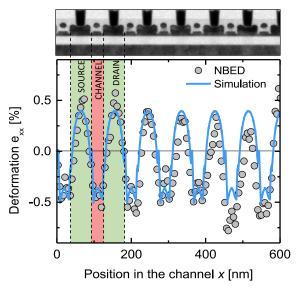

|   | 3.3.1.a NBED measurements and simulations                                                                                | 100 |

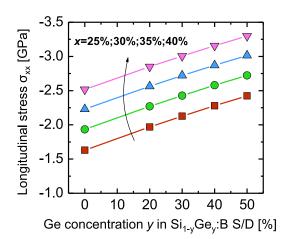

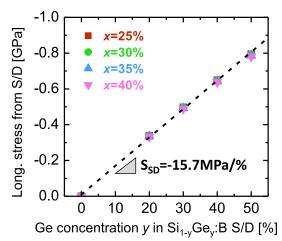

|   | 3.3.1.b The influence of Germanium concentrations                                                                        | 101 |

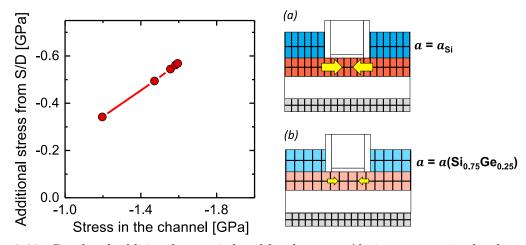

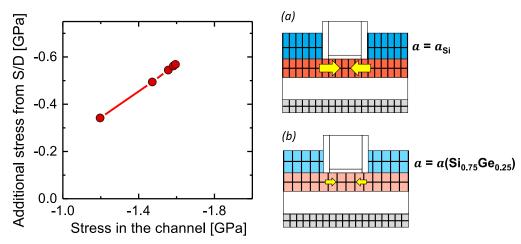

|   | 3.3.2 The impact of SiGeOI relaxation on stress from source/drain                                                        | 102 |

|   | 3.3.3 Stress from SiGe source/drain compact modeling $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                  | 103 |

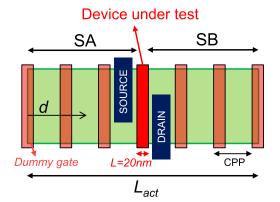

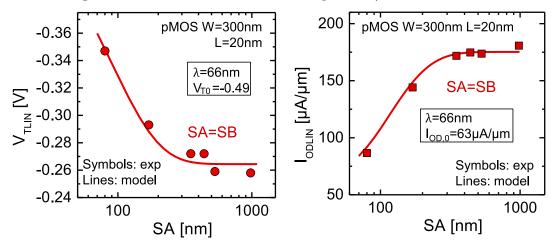

|   | 3.4 Local Layout Effects: electrical results                                                                             | 106 |

|   | 3.4.1 Electrical characteristics modeling                                                                                | 106 |

|   | 3.4.2 28nm SiGeOI results                                                                                                | 107 |

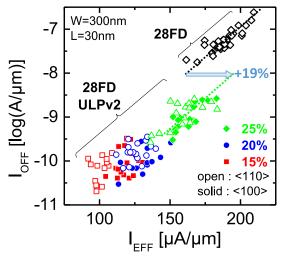

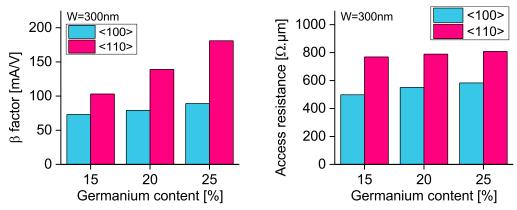

|   | $3.4.2.a$ Impacts of orientation and Germanium concentration on performance $% A^{\prime }$ .                            | 107 |

|   | 3.4.2.b Local layout effects                                                                                             | 109 |

|   | 3.4.2.c Conclusion to 28nm results                                                                                       | 111 |

|   | 3.4.3 14nm SiGeOI results                                                                                                | 112 |

|   | 3.4.3.a Rectangular symmetrical and asymmetrical layouts                                                                 | 112 |

|   | 3.4.3.b Non-rectangular layouts                                                                                          | 116 |

|   | 3.4.3.c Multifinger layouts                                                                                              | 118 |

|   | 3.4.3.d Active narrowing                                                                                                 | 120 |

|   | 3.4.3.e Impact of Germanium concentration                                                                                | 121 |

|   | 3.5 Conclusion to Chapter 3                                                                                              | 124 |

| 4 | Performance boosters for SiGeOI pMOSFETs                                                                                 | 125 |

|   | 4.1 Introduction to chapter 4                                                                                            | 126 |

|   | 4.2 Design solutions                                                                                                     | 127 |

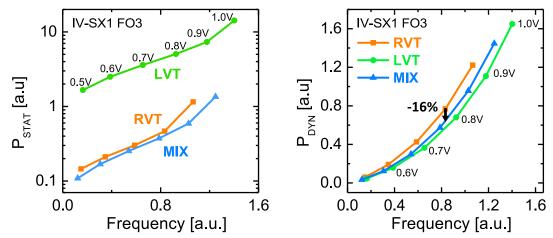

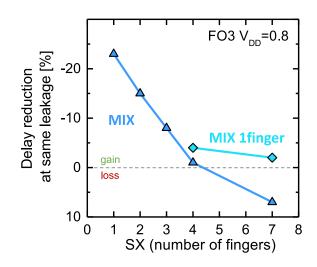

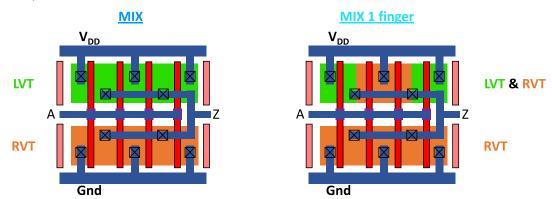

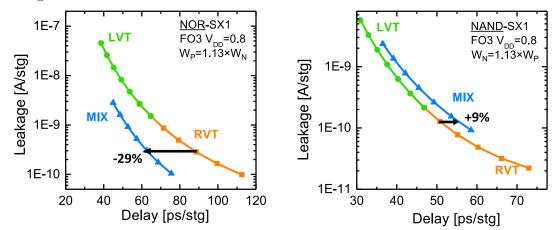

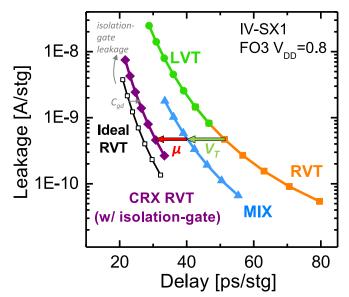

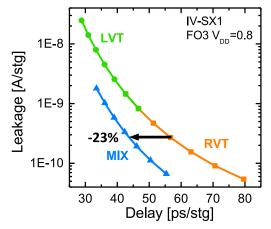

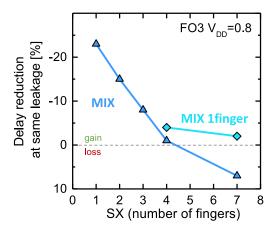

|   | 4.2.1 Intra-cell $V_{\rm T}$ -mixing                                                                                     | 127 |

|   | 4.2.1.a Principle                                                                                                        | 127 |

|   | 4.2.1.b SPICE simulation results                                                                                         | 127 |

|   | 4.2.1.c Mix-VT summary                                                                                                   | 131 |

|   |                                                                                                                          |     |

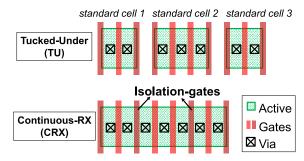

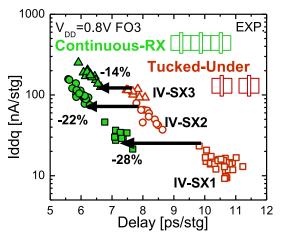

|          | 4.2.2 The continuous-RX design $\ldots$ | 133 |

|----------|--------------------------------------------------------------------------------------------------------------------------|-----|

|          | 4.2.2.a Principle                                                                                                        | 133 |

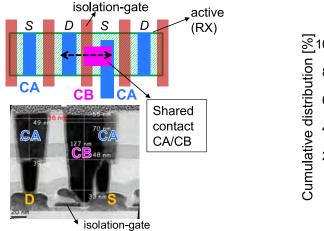

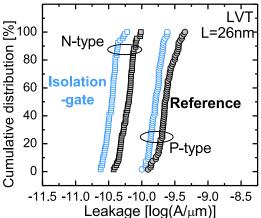

|          | 4.2.2.b Isolation-gate construct                                                                                         | 133 |

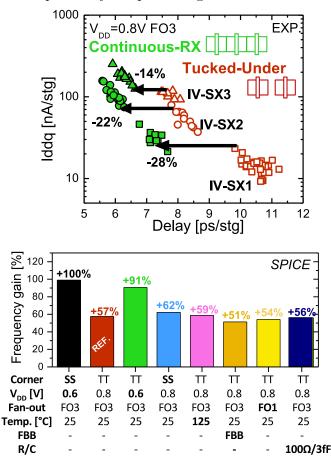

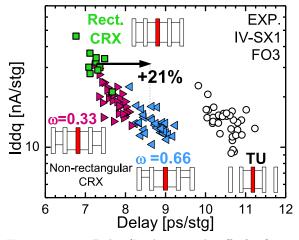

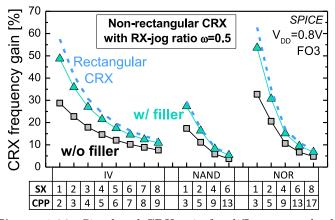

|          | 4.2.2.c CRX performance evaluation                                                                                       | 135 |

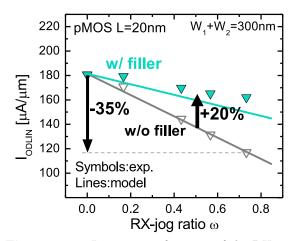

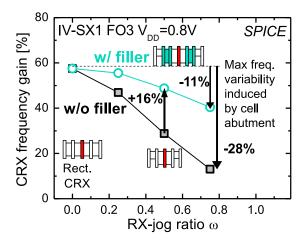

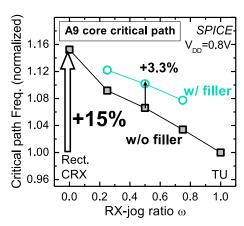

|          | 4.2.2.d The impact of RX-jogs                                                                                            | 136 |

|          | 4.2.2.e The interest of a filler cell                                                                                    | 136 |

|          | 4.2.2.f Continuous-RX: summary                                                                                           | 137 |

|          | 4.2.3 Design solution benchmark                                                                                          | 138 |

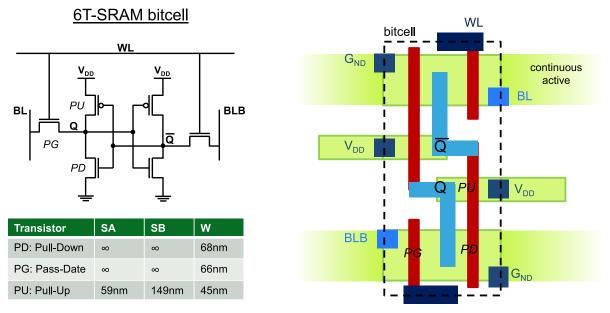

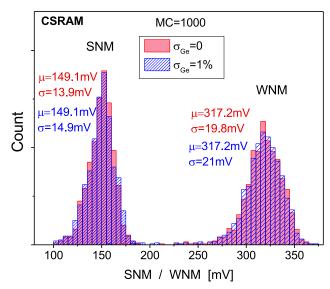

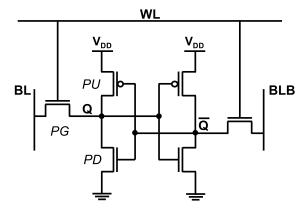

|          | 4.2.4 SiGe introduction in FDSOI SRAM bitcells                                                                           | 140 |

|          | 4.2.4.a Introduction                                                                                                     | 140 |

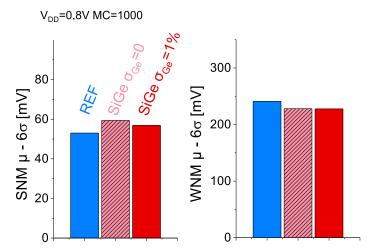

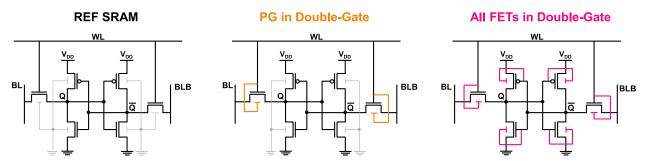

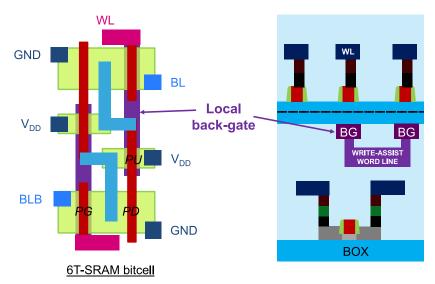

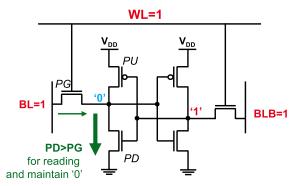

|          | 4.2.4.b SiGe in classical SRAM                                                                                           | 141 |

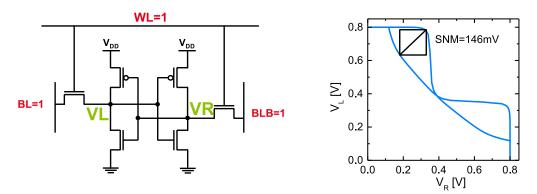

|          | 4.2.4.c Complementary SRAM                                                                                               | 143 |

|          | 4.2.4.d Conclusion                                                                                                       | 145 |

|          | 4.3 Technology solutions                                                                                                 | 147 |

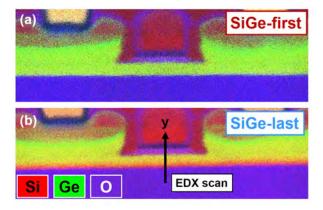

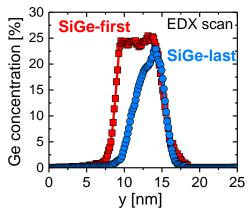

|          | 4.3.1 The SiGe-last approach                                                                                             | 147 |

|          | 4.3.1.a Process integration                                                                                              | 147 |

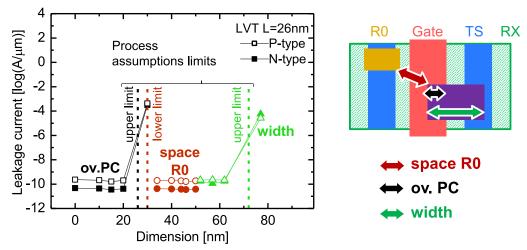

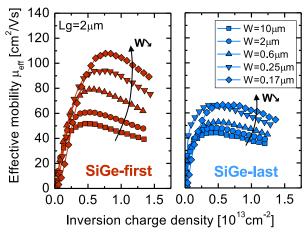

|          | 4.3.1.b Layout effects                                                                                                   | 148 |

|          | 4.3.1.c Experimental performance                                                                                         | 151 |

|          | 4.3.1.d Discussion                                                                                                       | 151 |

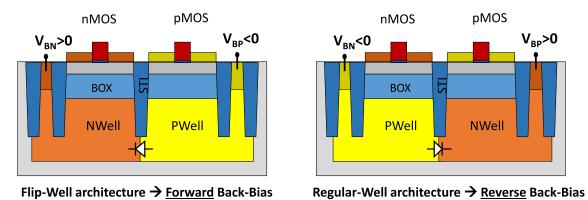

|          | 4.3.2 Dual Isolation by Trenches and Oxidation                                                                           | 153 |

|          | 4.3.2.a Process integration                                                                                              | 153 |

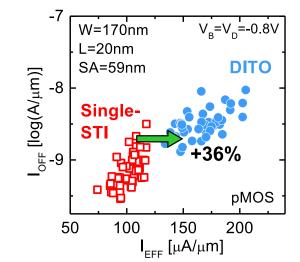

|          | 4.3.2.b Device electrical results                                                                                        | 155 |

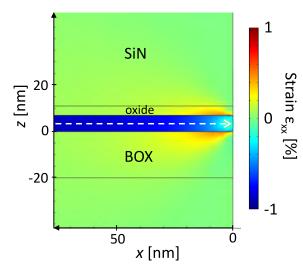

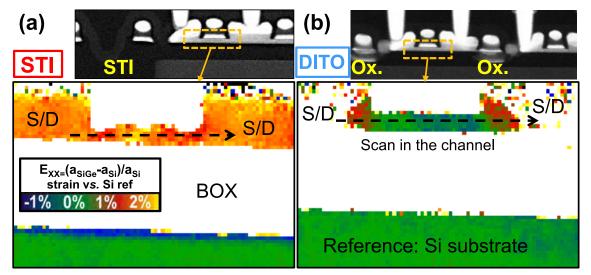

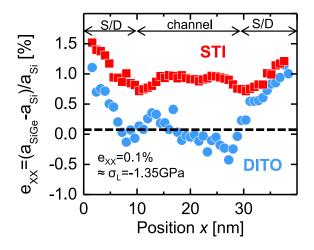

|          | 4.3.2.c Strain characterization                                                                                          | 158 |

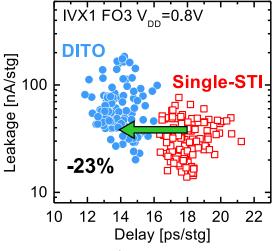

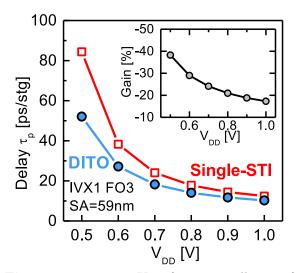

|          | 4.3.2.d Performance                                                                                                      | 160 |

|          | 4.3.2.e Back-biasing enabled by DITO                                                                                     | 161 |

|          | 4.4 Conclusion to Chapter 4                                                                                              | 164 |

| <b>5</b> | Next generation strained FDSOI CMOS devices                                                                              | 165 |

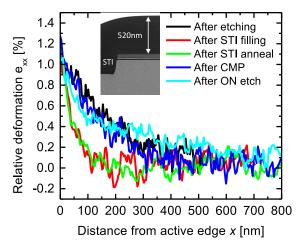

|          | 5.1 Tensile strain from strained-SOI substrate                                                                           | 166 |

|          | 1                                                                                                                        | 166 |

|          | 5.1.2 sSOI Local Layout Effects                                                                                          | 167 |

|          | 5.1.3 Conclusion $\ldots$               | 170 |

|          | 5.2 The BOX-creep technique                                                                                              | 172 |

|          |                                                                                                                          | 172 |

|          | 5.2.2 Mechanical simulations                                                                                             | 172 |

|          |                                                                                                                          | 172 |

|          | 5.2.2.b The BOX-creep mechanism                                                                                          | 174 |

|          | 5.2.2.c Impact of SiN parameters                                                                                         | 174 |

|          | 5.2.2.d The role of pad oxide and layout effect                                                                          | 175 |

|          | 5.2.2.e Compatibility with SiGe channel                                                                                  | 176 |

|          | 5.2.2.f Conclusion on mechanical simulations                                                                             | 178 |

| 5.2.3 Electrical results                                                                                   | 178 |

|------------------------------------------------------------------------------------------------------------|-----|

| 5.2.3.a BOX-creep with tensile LPCVD SiN                                                                   | 178 |

| 5.2.3.b BOX-creep with compressive PECVD SiN                                                               | 180 |

| 5.2.4 Discussion and perspectives                                                                          | 181 |

| 5.3 The SDRASS technique                                                                                   | 184 |

| 5.3.1 Introduction: the STRASS technique                                                                   | 184 |

| 5.3.2 SDRASS principle and experiment details                                                              | 184 |

| 5.3.3 Morphological results                                                                                | 185 |

| 5.3.4 Electrical results                                                                                   | 187 |

| 5.3.5 Conclusion and perspectives                                                                          | 189 |

| 5.4 Dynamic Back-Bias in 3D-monolithic                                                                     | 191 |

| 5.4.1 Introduction to 3D-monolithic                                                                        | 191 |

| 5.4.2 Electrostatic coupling in 3D-monolithic                                                              | 192 |

| 5.4.2.a Experimental results                                                                               | 192 |

| 5.4.2.b 3D 14nm Design-Kit $\ldots$                                                                        | 193 |

| 5.4.3 Performance/Power                                                                                    | 194 |

| 5.4.3.a The role of back-gate extension                                                                    | 194 |

| 5.4.3.b Layouts and environment                                                                            | 194 |

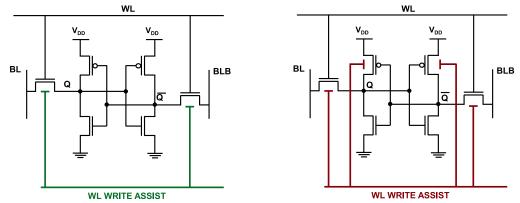

| 5.4.4 6T-SRAM with local back-gate                                                                         | 198 |

| 5.4.4.a Double-gate modes                                                                                  | 198 |

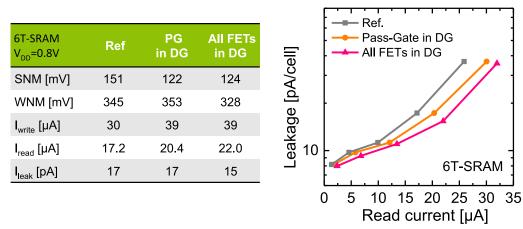

| 5.4.4.b Write-assist technique                                                                             | 200 |

| 5.4.5 Conclusion $\ldots$ | 201 |

| General conclusion                                                                                         | 203 |

| Bibliography                                                                                               | 207 |

|                                                                                                            |     |

| Appendix                                                                                                   | 231 |

| A Hu's model of patterning-induced strain relaxation                                                       | 231 |

| B SRAM static testbench                                                                                    | 233 |

| C Résumé en français                                                                                       | 239 |

| Publications                                                                                               | 265 |

| Abstract                                                                                                   | 268 |

|                                                                                                            |     |

# Symbols and Acronyms

| Symbol                 | Definition                                                      | Unit                       |

|------------------------|-----------------------------------------------------------------|----------------------------|

| α                      | Activity factor                                                 | -                          |

| $\gamma$               | Body factor                                                     | V/V                        |

| $\Delta \omega_{SiSi}$ | Si-Si Raman frequency peak shift                                | $m^{-1}$                   |

| ε                      | Strain                                                          | -                          |

| $\varepsilon_0$        | Permittivity of vacuum                                          | F/m                        |

| $\varepsilon_{Si}$     | Permittivity of Silicon                                         | F/m                        |

| η                      | Viscosity                                                       | Pa.s                       |

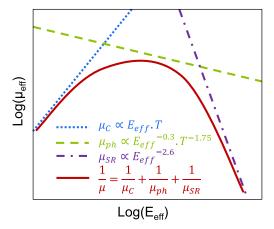

| $	heta_i$              | Mobility attenuation parameters                                 | $\mathrm{V}^{-i}$          |

| $\lambda$ (Chap.2)     | Parameter of access resistance dependence with inversion charge | $\Omega/V$                 |

| $\lambda$ (Chap.3-5)   | Typical relaxation length                                       | m                          |

| $\lambda_0$            | Mean free path                                                  | m                          |

| $\mu_0$                | Low-field mobility                                              | $\mathrm{m}^2/\mathrm{Vs}$ |

| $\mu_B$                | Apparent ballistic mobility                                     | $\mathrm{m}^2/\mathrm{Vs}$ |

| $\mu_{eff}$            | Effective mobility                                              | $\mathrm{m}^2/\mathrm{Vs}$ |

| ν                      | Poisson's ratio                                                 | _                          |

| Ξ                      | Deformation potential                                           | eV                         |

| П                      | Piezoresistive coefficient                                      | $Pa^{-1}$                  |

| σ                      | Mechanical stress                                               | Pa                         |

| $\sigma$ (Chap.2)      | Parameter of access resistance dependence with inversion charge | $\Omega.V$                 |

| τ                      | Relaxation time                                                 | S                          |

| $	au_P$                | Propagation delay                                               | S                          |

| $\phi_f$               | Fermi potential                                                 | eV                         |

| $\phi_M$               | Metal work function                                             | eV                         |

| $\phi_S$               | Semiconductor work function                                     | eV                         |

| $\chi_S$               | Electron affinity                                               | eV                         |

| $\psi_S$               | Surface potential                                               | eV                         |

| ω                      | RX-jog ratio                                                    | -                          |

| $\omega_0$             | Raman frequency peak of Silicon                                 | $\mathrm{m}^{-1}$          |

| $C_d$                  | Drain capacitance                                               | F                          |

| $C_{EFF}$              | Effective capacitance                                           | F                          |

| $C_g$                  | Gate capacitance                                                | F                          |

| $\overline{C_{gc}}$    | Gate-to-channel capacitance                                     | F                          |

| $\overline{C_{ij}}$    | Elastic constants                                               | Pa                         |

|                        | Gate oxide capacitance                                          | F                          |

| $C_w, C_{BE}$      | Wire (or Back-End) capacitance                           | F                     |

|--------------------|----------------------------------------------------------|-----------------------|

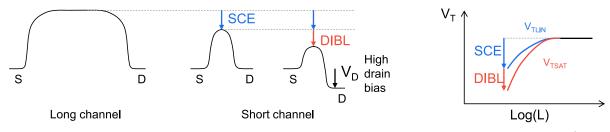

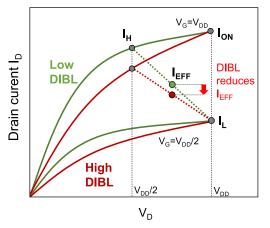

| DIBL               | Drain-Induced Barrier Lowering                           | V or $V/V$            |

| CTE                | Coefficient of Thermal Expansion                         | $\mathrm{K}^{-1}$     |

| E                  | Moung's modulus                                          | Pa                    |

| $E_{//}$           | Longitudinal field                                       | V/m                   |

| $E_C$              | Conduction band energy                                   | eV                    |

| EDP                | Energy Delay Product                                     | J.s                   |

| $E_{eff}$          | Transverse effective field                               | V/m                   |

| $E_G$              | Band gap energy                                          | eV                    |

| EOT                | Equivalent Oxide Thickness                               | m                     |

| $E_V$              | Valence band energy                                      | eV                    |

| Freq, f            | Frequency                                                | Hz                    |

| gm                 | Transconductance                                         | A/V                   |

| ħ                  | Reduced Planck constant                                  | J.s                   |

| $I_{DDQ}$          | Leakage current (also called stand-by or static current) | А                     |

| $I_{DYN}$          | Dynamic current                                          | А                     |

| $I_{EFF}$          | Effective drain current                                  | A (or $\mu A/\mu m$ ) |

| I <sub>LIN</sub>   | Linear drain current                                     | A (or $\mu A/\mu m$ ) |

| I <sub>ODLIN</sub> | Linear drain current at a given gate overdrive           | A (or $\mu A/\mu m$ ) |

| I <sub>OFF</sub>   | OFF-state current or leakage current of a MOSFET         | A (or $A/\mu m$ )     |

| I <sub>ON</sub>    | ON-current or saturation current                         | A (or $\mu A/\mu m$ ) |

| I <sub>th</sub>    | Drain current criterion for threshold voltage extraction | А                     |

| $k, k_B$           | Boltzman constant                                        | J/K                   |

| k                  | Wavevector                                               | -                     |

| L                  | Transistor gate length                                   | m                     |

| $m^*$              | Effective mass                                           | kg                    |

| $m_0$              | Longitudinal mass                                        | kg                    |

| $m_l$              | Transverse mass                                          | kg                    |

| $m_t$              | Rest mass of electron                                    | kg                    |

| $N_A$              | Acceptor impurities concentration                        | $A/cm^3$              |

| $n_i$              | Intrinsic carriers concentration                         | $\mathrm{cm}^{-3}$    |

| $P_{DYN}$          | Dyamic power                                             | W                     |

| $P_{STAT}$         | Static power                                             | W                     |

| $P_{TOT}$          | Total power                                              | W                     |

| q                  | Elementary charge                                        | С                     |

| $Q_{DEP}$          | Depletion charge                                         | С                     |

| $Q_{INV}$         | Inversion charge                                             | $\mathbf{C}$                          |

|-------------------|--------------------------------------------------------------|---------------------------------------|

| R <sub>ACC</sub>  | Access resistance                                            | $\Omega~({\rm or}~\Omega.\mu{\rm m})$ |

| $R_{EFF}$         | Effective resistance                                         | Ω (or $Ω.µm$ )                        |

| $R_{ON}, R_{TOT}$ | ON-resistance in linear regime and at a given gate overdrive | $\Omega~{\rm or}~\Omega/\mu{\rm m}$   |

| $S_{ij}$          | Stiffness constants                                          | $\mathrm{Pa}^{-1}$                    |

| SNM               | Static Noise Margin                                          | V                                     |

| SS                | Subthreshold swing                                           | $\mathrm{mV/dec}$                     |

| $t_{ox}$          | Gate oxide thickness                                         | m                                     |

| VB                | Back-bias voltage (Body voltage)                             | V                                     |

| $v_d$             | Drift velocity                                               | m/s                                   |

| $v_{inj}$         | Injection velocity                                           | m/s                                   |

| $v_{sat}$         | Saturation velocity                                          | m/s                                   |

| $v_T$             | Thermal velocity                                             | m/s                                   |

| VD                | Drain voltage                                                | V                                     |

| $V_{DD}$          | Supply voltage                                               | V                                     |

| $V_{FB}$          | Flat-band voltage                                            | V                                     |

| $V_{\rm G}$       | Gate voltage                                                 | V                                     |

| V <sub>S</sub>    | Source voltage                                               | V                                     |

| V <sub>T</sub>    | Threshold voltage                                            | V                                     |

| V <sub>TLIN</sub> | Threshold voltage in linear regime                           | V                                     |

| V <sub>TSAT</sub> | Threshold voltage in saturation regime                       | V                                     |

| W                 | Transistor width                                             | m                                     |

| WNM               | Write Noise Margin                                           | V                                     |

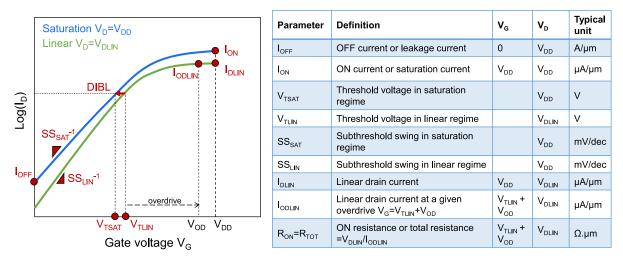

| Acronym  | Definition                                 |

|----------|--------------------------------------------|

| BEOL     | Back-End Of Line                           |

| BOX      | Buried OXide                               |

| CA       | Active contact layer                       |

| CB       | Gate contact layer                         |

| CESL     | Contact Etch Stop Layer                    |

| CMOS     | Complementary Metal Oxide Semiconductor    |

| CMP      | Chemical-Mechanical Planarization          |

| CPP, CGP | Contacted-Poly Pitch, Contacted Gate Pitch |

| CRX      | Continuous-RX                              |

| DDB      | Double-Diffusion Break                     |

|          |                                            |

| DFEH       | Dark Field Electron Hologrpahy                           |

|------------|----------------------------------------------------------|

| DITO       | Dual Isolation by Trenches and Oxidation                 |

| DTCO       | Design/Technology Co-Optimization                        |

| EDX        | Energy-dispersive X-ray spectroscopy                     |

| FBB        | Forward Back-Bias                                        |

| FDSOI      | Fully Depleted Silicon On Insulator                      |

| FEOL       | Front-End Of Line                                        |

| FWHM       | Full Width at Half Maximum                               |

| FO         | Fan-Out                                                  |

| GAA        | Gate-All-Around                                          |

| GP         | Ground Plane                                             |

| HH         | Heavy Holes                                              |

| HVT        | High-VT                                                  |

| IoT        | Internet of Things                                       |

| IV         | Inverter                                                 |

| LH         | Light Holes                                              |

| LLE        | Local Layout Effects                                     |

| LOCOS      | LOCal Oxidation of Silicon                               |

| LPCVD      | Low-Pressure Chemical Vapor Deposition                   |

| LVT        | Low-VT                                                   |

| M1         | First level of metal                                     |

| M1P        | First-level metal pitch                                  |

| MEOL       | Middle-End Of Line                                       |

| MOSFET     | Metal Oxide Semiconductor Field Effect Transistor        |

| NBED, NBD  | Nano-Beam Electron Diffraction                           |

| NEGF       | Non-Equilibrium Green's Function                         |

| nFET, nMOS | n-type Metal Oxide Semiconductor Field Effect Transistor |

| PD         | Pull-Down                                                |

| PECVD      | Plasma-Enhanced Chemical Vapor Deposition                |

| PED        | Precession-Electron-Diffraction                          |

| pFET, pMOS | p-type Metal Oxide Semiconductor Field Effect Transistor |

| PG         | Pass-Gate                                                |

| PPA        | Power/Performance/Area                                   |

| PU         | Pull-Up                                                  |

| RBB        | Reverse Back-Bias                                        |

| RCS        | Remote Coulomb Scattering                                |

| RTO        | Rapid Thermal Oxidation                                  |

| RVT        | Regular-VT                                               |

|            |                                                          |

| RX     | Active area layer                                                 |

|--------|-------------------------------------------------------------------|

| S/D    | Source/Drain                                                      |

| SA, SB | Gate-to-STI distance from left, right, side                       |

| SADP   | Self Aligned Double Patterning                                    |

| SAIPS  | Self-Aligned In-Plane Stressor                                    |

| SCE    | Short Channel Effects                                             |

| SDB    | Single-Diffusion Break                                            |

| SDRASS | Source and Drain from Recrystallization of Amorphized SiGe on SOI |

| SiGeOI | Silicon-Germanium On Insulator                                    |

| SIT    | Sidewall Image Transfer                                           |

| SLVT   | Super-Low-VT                                                      |

| SMT    | Stress Memorization Technique                                     |

| SOI    | Silicon On Insulator                                              |

| SPER   | Solid Phase Epitaxial Regrowth                                    |

| SPICE  | Simulation Program with Integrated Circuit Emphasis               |

| SRAM   | Static Random Access Memory                                       |

| SRB    | Strain-Relaxed Buffer                                             |

| SRS    | Surface Roughness Scattering                                      |

| sSOI   | Strained-SOI                                                      |

| STI    | Shallow Trench Isolation                                          |

| STRASS | Strained Si by Top Recrystallization of Amorphized SiGe on SOI    |

| TEM    | Transmission Electron Microscopy                                  |

| TU     | Tucked-Under                                                      |

| UTBB   | Ultra-Thin Body and Buried oxide                                  |

| XRD    | X-Ray Diffraction                                                 |

|        |                                                                   |

## Introduction

## Context

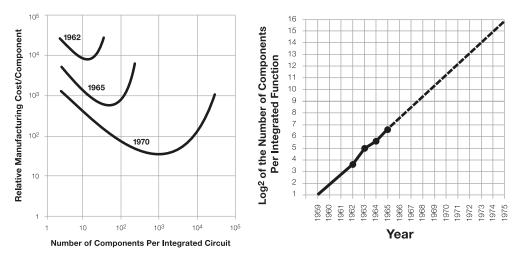

For the past 50 years, the semiconductor industry has known an exponential growth that has affected our everyday life. From the discovery of the transistor effect by W. Shockley, J. Bardeen and W. H. Brattain at the Bell Labs in 1947, the first microprocessor was manufactured by Intel in 1971, embedding around 2300 transistors (Intel 4004). Today, a microprocessor can count more than 7 billion transistors (22-core Xeon Broadwell-E5 from Intel) and the global semiconductor industry sales raised to \$335.2 billion in 2015. Such a growth has been enabled by an aggressive scaling of the integrated circuit dimensions. This so-called "happy scaling" has lost its efficiency to keep reducing the power consumption. Innovations were required, especially during the last decade when physical barriers had to be pushed back. As a result, the technology complexity has increased and different ingredients have been implemented.

In this context, the introduction of new transistor architectures has been necessary to meet the requirements both in terms of density and performance. Especially, the Fully Depleted Silicon On Insulator (FDSOI) technology has appeared as an alternative to the FinFET to succeed the historical planar bulk technologies. FDSOI technology has several strengths such as a good electrostatic control, a low variability and a great back-biasing capability. In addition to the change of transistor architecture, the use of strain as a performance booster has been widely discussed and is today mandatory in advanced technology. The work of this thesis deals with the strain integration in Fully Depleted Silicon On Insulator technology in order to boost and optimize the performance.

#### Manuscript organization

The manuscript is organized as follows:

The **first chapter** details the context of this work. The basics of the Complementary Metal Oxide Semiconductor (CMOS) technology are presented. First, a focus is made on the principle of operation of the field effect transistor, which is the key element for digital computing. Then, the CMOS technology evolution through the well-known scaling is depicted. Finally, the interest of strain integration to boost the performance is discussed.

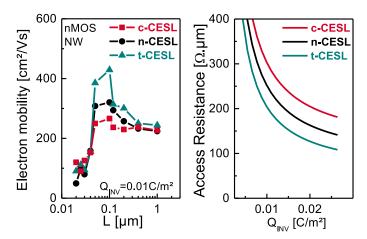

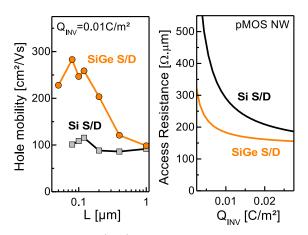

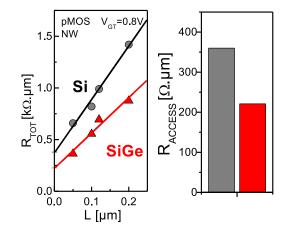

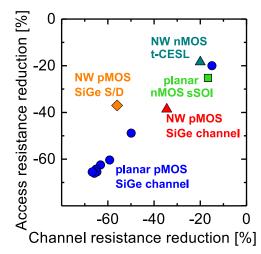

The **second chapter** focuses on the performance of strained devices. In particular, the impact of strain on carrier mobility is investigated. A dedicated attention is paid on the electrical characterization of short channel transistors, emphasizing the crucial role of the access resistance and its strain dependence.

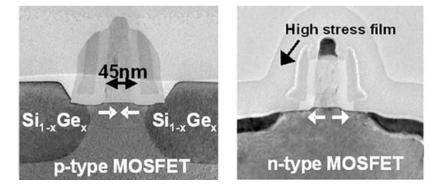

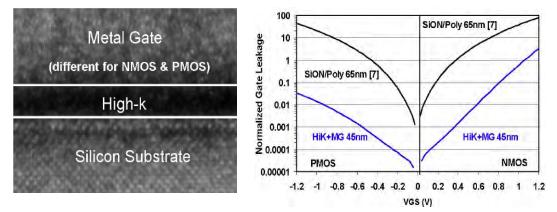

The **third chapter** discusses the use of strained SiGe channel in FDSOI technology. After presenting the FDSOI technology, a focus is made on the strain measurement and modelling in patterned SiGe active areas. An extensive study of the strain-induced layout effects is finally presented.

The **fourth chapter** aims at providing solutions to boost the performance of scaled devices embedding strain. This chapter is splitted into two main parts: design- and technology-based solutions.

In the **fifth and last chapter**, new strain integration techniques in FDSOI technology are investigated. In particular, a focus is made on tensile strain generation. For instance, the BOX-creep technique is assessed though mechanical simulations and experimental results. Finally, the great backbiasing capability of FDSOI technology is evaluated in a dynamic approach enabled by 3D monolithic.

This work has been carried out in STMicrolectronics, Crolles, and in the CEA-LETI, Grenoble.

# CHAPTER 1

# Boosting sub-20nm CMOS technology performance: the relevance of strain

## Contents

| 1.1 | Intro | duction to CMOS logic                                         | 10 |

|-----|-------|---------------------------------------------------------------|----|

| 1   | .1.1  | The MOSFET, device at the heart of logic                      | 10 |

| 1   | .1.2  | The Power/Performance/Area metrics                            | 12 |

| 1   | .1.3  | The MOSFET operation and metrics                              | 15 |

| 1.2 | CMC   | OS technology scaling: the king is dead, long live the king ! | 24 |

| 1   | .2.1  | The happy scaling, the good old days                          | 24 |

| 1   | .2.2  | The introduction of goodies                                   | 25 |

| 1   | .2.3  | The rise of new architectures                                 | 26 |

| 1   | .2.4  | The parasitics, key players                                   | 30 |

| 1   | .2.5  | CMOS scaling: conclusion and perspectives                     | 32 |

| 1.3 | Strai | n integration in CMOS technologies                            | 34 |

| 1   | .3.1  | Theory of elasticity                                          | 34 |

| 1   | .3.2  | The impact of strain on Silicon properties                    | 36 |

| 1   | .3.3  | Strain integration techniques                                 | 42 |

| 1   | .3.4  | Local Layout Effects                                          | 47 |

| 1   | .3.5  | Summary on strain integration in CMOS technology              | 50 |

| 1.4 | Conc  | lusion to Chapter 1                                           | 50 |

In this Chapter, the context of this thesis work is presented. The CMOS logic is first introduced, focusing on the MOSFET principle of operation and the main metrics used for its assessment. Then, the second section provides a brief history of the CMOS technology scaling. Finally, the last section gives some insights about the strain integration in CMOS technology.

## 1.1 Introduction to CMOS logic

The aim of this section is to provide the basics of CMOS logic. Especially, the operation of the Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is presented. First, the use of the MOSFET as a switch to perform logic operations is detailed. Then, the MOSFET metrics and figures of merit are discussed with a particular attention on the crucial role of carrier mobility. Finally, a focus is made on the different metrics of digital CMOS integrated circuits in terms of performance and power consumption.

#### 1.1.1 The MOSFET, device at the heart of logic

#### 1.1.1.a The MOSFET switch

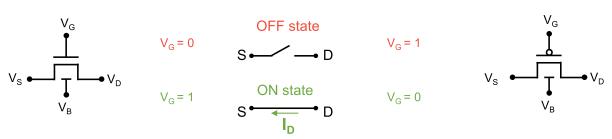

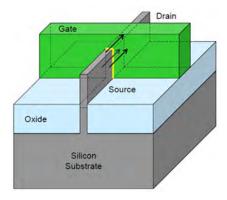

The Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is the key element of integrated circuits. It features 4 terminals which are the Gate (G), the Source (S), the Drain (D) and the Body (B). A schematic of the transistor is given in Figure 1.1. According to the voltage applied on the gate, an electrical current is allowed to flow or not from the source to the drain. As a result, the MOSFET can be considered as a switch between an OFF state and an ON state.

pMOSFET

nMOSFET

Figure 1.1: Schematic of the MOSFET, made of 4 terminals: Gate, Source, Drain and Body. The MOSFET is considered of a switch whose state ON or OFF is controlled by the gate voltage  $V_G$ . An nMOSFET (pMOSFET) is OFF if  $V_G = "0"$  ( $V_G = "1"$ ) and turned ON if  $V_G = "1"$  ( $V_G = "0"$ ), respectively. The n- and p-MOSFETs behave complementary, hence the name CMOS technology.

The MOSFET can either be of n- of p-type depending on the carrier type in the source/drain and body. An nMOSFET (also called nMOS or nFET) consists in n-type source and drain, and a p-type body. The major carrier in the source and drain reservoirs are thus electron. It is the opposite for a pMOSFET, featuring p-type source and drain (hole reservoirs) and n-type body.

The nMOSFET is in OFF state if a "0" is applied on its gate. In this case, it acts as an open switch, i.e. no current flows. On the other hand, if a "1" is applied on the gate, the switch is closed, allowing a current to flow between the source and the drain. It is the exact opposite for the pMOSFET, which is in OFF (ON) state if a "1" ("0") is applied on the gate, respectively. As a consequence, the

nMOSFET and pMOSFET are complementary (hence the CMOS technology). This is summarized in Figure 1.1.

#### 1.1.1.b Boolean functions using logic combinatory gates

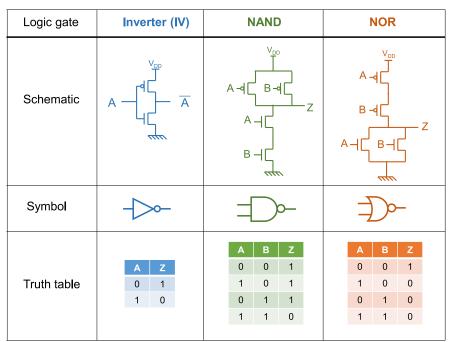

In the CMOS technology, the two types of MOSFET are enjoyed to achieve Boolean functions using logic gates. The most simple logic gate is the inverter. As its name indicates, the inverter output is the inverse of its input. The inverter is made with one nMOS transistor and one pMOS transistor, as shown in Figure 1.2. The nMOS source is connected to the ground ( $G_{ND}$ ) while the pMOS one is connected to the supply voltage  $V_{DD}$ . Both nMOS and pMOS gates are connected to the input (A) and both drains to the output (Z). This way, if the input is "0", the nMOS is OFF and the pMOS ON. The output is thus pulled up to  $V_{DD}$ , i.e. "1". If the input is "1", the pMOS is open (i.e. OFF) and the nMOS is closed (i.e. ON), pulling down the output to "0", since it is connected to the ground. The inverter output is thus well given by  $Z=\overline{A}$ .

Figure 1.2: Schematic, symbol and truth table of inverter, NAND and NOR logic gates. The nMOSFET network is called pull-down because it connects the output to the ground and the pMOSFET network is called pull-up because it connects the output to the supply voltage  $V_{DD}$ . The transistors inside networks are connected in series or in parallel according to the logic function.

Figure 1.2 algo gives the schematic, symbol and truth table of the NAND and NOR 2-input logic gates. The NAND logic gate consists in two pMOSFETs in parallel and two nMOSFETs in series. It is the opposite for the NOR gate. The input A is connected to the gate of one pFET and one nFET and the remaining two gates are connected to the second input B. Let us consider a NOR gate. If either A or B is "1", at least one nFET is ON, creating a path from the ground to the output (i.e. Z="0"). The output is pulled-up to  $V_{DD}$  if and only if both inputs A and B are "0" since the two pMOS transistors are in series.

The pMOSFET network is called the pull-up network because it connects the output to the supply

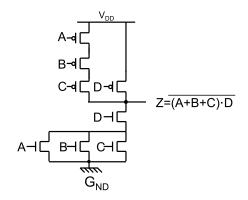

Figure 1.3: Schematic of the OR-AND-INVERT-31 (OAI-31) compound gate. The logic function is achieved by relevantly building the pull-down and pull-up networks. Transistors in series in the pull-up network are in parallel in the pull-down network and vice versa.

voltage  $V_{DD}$  and the nMOSFET network is called the pull-down because it connects the output to the ground  $G_{ND}$ . More complex logic functions can be achieved by using pull-up and pull-down networks made of transistors in series or in parallel. Figure 1.3 shows the example of the compound gate achieving the function  $Z = \overline{(A + B + C) \cdot D}$ . This logic compound gate is called OR-AND-INVERT-31 or OAI-31. In the pull-down network, the 3 inputs A, B and C built in parallel are connected in series with the fourth input D. It is the opposite for the pull-up network. The logic function of OAI-31 could have been achieved with several logic gates such as inverter or NOR. However, it would have required to use more transistors. Hence the interest of relevantly using pull-up and pull-down networks.

#### 1.1.2 The Power/Performance/Area metrics

In this section, a focus is made on the Power/Performance/Area (PPA) metrics. These metrics are of great interest to characterize a CMOS technology <sup>1</sup>.

#### 1.1.2.a Power/Performance: the ring-oscillator metrics

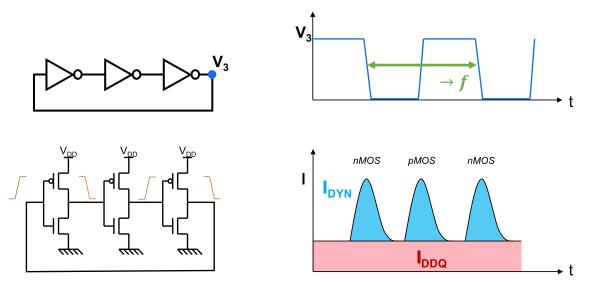

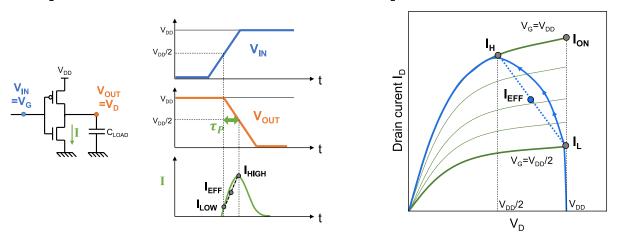

In a digital integrated circuit, the logic gates are used for operating boolean functions. The circuit speed is directly linked to the ability of the logic gates to perform their operation. The ring-oscillator is a device enabling a dynamic characterization [Sai15]. It consists in a circular chain made of an odd number of inverters. Figure 1.4 shows an example with three inverters. The output of the last inverter is connected to the input of the first inverter. This way, the output is not stable as it will oscillate between the "1" and "0" states (i.e.  $V_{DD}$  and  $G_{ND}$ ). The oscillation frequency Freq (or f) depends on the number of inverters N and the propagation delay of each inverter  $\tau_P$ :

$$Freq = \frac{1}{2.N.\tau_P} \tag{1.1}$$

When the inverter is not switching (i.e. input and output are at a fixed value), the current flowing through the inverter is the leakage current  $I_{DDQ}$ . This current is also referred as the stand-by or static current. It is measured through the supply voltage in the quiescent state (hence the name

<sup>1</sup> In addition to the Power/Performance/Area metrics, the Cost, Yield and also Reliability are sometimes also mentioned.

Figure 1.4: (left) symbolic and schematic views of a ring-oscillator made of three inverters. (right) Voltage at the output of the third inverter as a function of time, oscillating between "1" ( $V_{DD}$ ) and "0" ( $G_{ND}$ ) at a frequency f. The current flowing through an inverter is composed of the dynamic current  $I_{DYN}$  and the static current  $I_{DDQ}$ . The dynamic current is the drive current of either the pMOS or the nMOS to load the output capacitance (i.e. the gates from the next level inverter) during a switching and the static current is the leakage when the inverter is not active.

$I_{DDQ}$ ). This leakage current is directly linked to the nMOS and pMOS leakage currents  $I_{OFF}$ , defined in section 1.1.3.

When a stage of inverter is switching because of a change of input, a dynamic current loads the output capacitance. In a ring-oscillator, this dynamic current  $I_{DYN}$  is successively generated by each inverter stage. It flows alternatively through the nMOS (pull-down) and the pMOS (pull-up) according to the switching operation ("0" to "1" or "1" to "0").  $I_{DYN}$  is measured through  $V_{DD}$ <sup>1</sup>. The delay can be expressed as a function of the dynamic current <sup>2</sup>:

$$\tau_P = \frac{V_{DD} \, C_{EFF}}{2 \, I_{DYN}} \tag{1.5}$$

where  $C_{EFF}$  is the effective capacitance to be loaded. This capacitance includes the gate capacitance of the next level inverter (the active part) and all parasitic capacitances (discussed later on in section 1.2.4).

$$-I = C_{EFF} \frac{\mathrm{d}V}{\mathrm{d}t} \tag{1.2}$$

and by defining  $I_{DYN}$  as the average current during the switching and integrating:

$$-I_{DYN}\tau_P = C_{EFF} \int_0^{\tau_P} \frac{\mathrm{d}V}{\mathrm{d}t} dt \tag{1.3}$$

Even though no current flows through V<sub>DD</sub> when the output capacitance is discharged by the nMOS (the current flows through the output to the ground), it is the exact same current that is injected from the supply voltage to load the capacitance. That is why I<sub>DYN</sub> can be measured through V<sub>DD</sub>.

Starting from:

One can also write:

$$\tau_P = R_{EFF} C_{EFF} \tag{1.6}$$

with  $R_{EFF} = \frac{V_{DD}}{2 I_{DYN}}$ .

In terms of power, the dynamic and static powers are deduced from the currents. The dynamic power is given by:

$$P_{DYN} = I_{DYN} V_{DD} = \frac{V_{DD}^2 \cdot C_{EFF}}{2\tau_P}$$

$$\tag{1.7}$$

and the static power by:

$$P_{STAT} = I_{DDQ} V_{DD} \tag{1.8}$$

The total power of a circuit depends on the activity factor  $\alpha$ :

$$P_{TOT} = \alpha P_{DYN} + P_{STAT} \tag{1.9}$$

This activity factor depends on the application. Finally, the Energy-Delay-Product EDP, defined as

$$EDP = E \cdot \tau_P = P_{TOT} \cdot \tau_P \cdot \tau_P \tag{1.10}$$

is a good figure of merit for energy efficient circuits. Its minimum translates the sweet point between consumption and performance.

#### 1.1.2.b Area: standard cell design

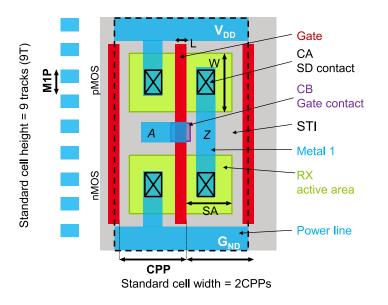

In the previous paragraph, the dynamic power/performance metrics have been presented. In this paragraph, the last term of PPA, i.e. the Area, is discussed by the means of a typical layout of a standard cell. A standard cell consists in a physical implementation of a function operated by transistors. Standard cells include combinatory logic (e.g. inverter, NAND, NOR) and sequential logice or storage (e.g. flipflops) functions. Figure 1.5 shows the layout of the 1-finger inverter standard cell (also called IV-SX1).

The main layers are represented on the layout: active area (RX), gate (or poly, PC), active contact (CA), gate contact (CB), first level of metal (M1). The active areas are isolated from each other by the means of Shallow Trench Isolation (STI). The pMOS and nMOS sources are connected to the power rails (power supply  $V_{DD}$  for pMOS and ground  $G_{ND}$  for nMOS). The function of a standard cell is determined by the way the transistors are connected to each other with the metal lines. In

$$-I_{DYN}\tau_P = C_{EFF}\left[V(\tau_P) - V(0)\right] = C_{EFF}\left[\frac{V_{DD}}{2} - V_{DD}\right] \Leftrightarrow \tau_P = \frac{V_{DD}C_{EFF}}{2I_{DYN}}$$

(1.4)

which leads to:

Figure 1.5: Layout of the 1-finger inverter standard cell. The pMOS and nMOS are designed between the two power rails. The standard cell height is expressed as a function of the number of Metal-1 pitches and its width is expressed as a function of the number of poly pitches (CPPs).

the case of the inverter, the pMOS and nMOS drains are connected to the output. In an integrated circuit, the standard cells are abutted to each other and can be flipped in order to share the power rails.

The area of a standard cell is defined by its height and width. The height is expressed as a function of the number of M1 pitches (M1P), also called tracks<sup>1</sup>, and the width as a function of the number of Contacted Poly Pitches (CPPs). The product M1P×CPP is therefore a good figure of merit of a technology density, i.e. node. The area of the Static Random Access Memory (SRAM) cell (see appendix B) is also a good indicator of a technology density.

In advanced technologies, efforts have been made on the optimization of the standard cell rather than only focusing on the transistor. This is referred as the Design/Technology Co-Optimization (DTCO).

#### 1.1.3 The MOSFET operation and metrics

In the previous section, the MOSFET has been presented as an ideal switch that is used in the CMOS technology to perform logic operations. The aim of this section is to provide some insights about the MOSFET operation and the main metrics used in this work. A more detailed theory and modeling of the MOSFET transistor can be found in [Sko00] and [Hu10].

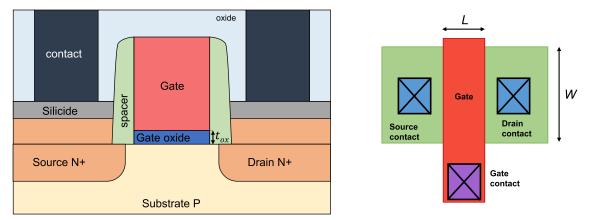

#### 1.1.3.a The MOSFET structure

An illustration of a MOSFET device is shown in Figure 1.6. The control electrode, i.e. the gate, consists in a Metal Oxide Semiconductor (MOS) capacitance, whose geometry is defined according to the gate length L and transistor width W. The gate oxide is characterized by its thickness  $t_{ox}$ , which is crucial for the device performance. The two reservoirs of carrier, i.e. the source and drain,

<sup>1</sup> In a FinFET technology (see section 1.2.3.a), the height of standard cell is a multiple of the fin pitch.

are placed at each side of the gate. Figure 1.6 also shows a typical layout of a transistor. The active area is represented in green and the gate in red.

Figure 1.6: Illustration of typical MOSFET (left) cross-section and (right) top-view, i.e. layout.

#### 1.1.3.b The MOSFET operation

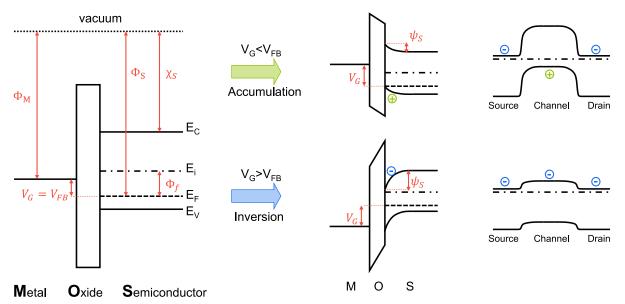

The MOS capacitance can operate in different regimes, according to the potential at the semiconductor/oxide interface  $\psi_s$ , dependent on the gate voltage V<sub>G</sub>. Let us consider a MOS with a p-type semiconductor, which is the case of the nMOSFET. The three regimes are:

- The accumulation ( $\psi_s < 0$ ;  $V_G < V_{FB}$ ). The majority carrier (holes in a p-type substrate) are attracted by the electric field towards the gate. The flat-band voltage  $V_{FB}$  is defined as the gate voltage that must be applied in order to have a flat energy band in the semiconductor, (i.e. no charge in the capacitor). Figure 1.7 shows the band diagram of the MOS structure under flat-band condition and accumulation. The band diagram from the source to the drain is also represented. A barrier of potential prevents the electron to flow from source to drain. The MOSFET is in OFF state.

- The depletion  $(0 < \psi_s < \phi_f; V_G > V_{FB})$ .  $\phi_f$  is the Fermi potential, given by  $\phi_f = \frac{kT}{q} \ln \left(\frac{N_A}{n_i}\right)$  where  $N_A$  is the dopant concentration is the substrate. Under the depletion regime, majority carriers are pushed away from the oxide/semiconductor interface. The charge in the semiconductor is due to the ionized dopants (negative charge in the case of an nMOSFET).

- The inversion  $(\psi_s > \phi_f; V_G >> V_{FB})$  or strong inversion  $(\psi_s > 2 \cdot \phi_f)$ . In inversion, the previously minority carriers become more numerous. In strong inversion, there are more minority carriers (electrons) than majority carriers (holes) in the bulk. A conduction path, called the channel, appears. The electrons are allowed to flow between the source and drain as illustrated in Figure 1.7. The MOSFET is in ON state.

The threshold voltage is defined as the criterion of strong inversion. In the case of the historical planar bulk<sup>1</sup> technology, the threshold voltage is defined by :

$$V_T = V_{FB} + 2\phi_f + \frac{Q_{dep}}{C_{ox}} \tag{1.11}$$

<sup>1</sup>  $\,$  For the threshold voltage of FDSOI MOSFET, see equation 1.31

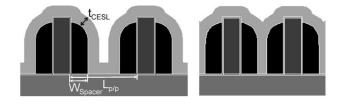

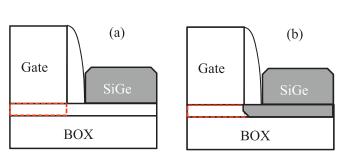

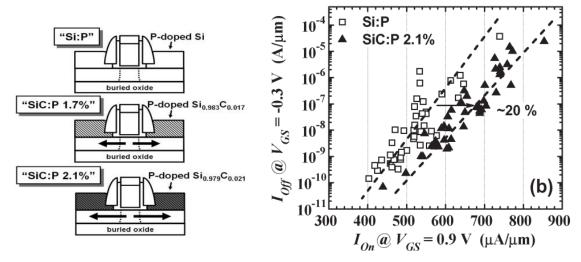

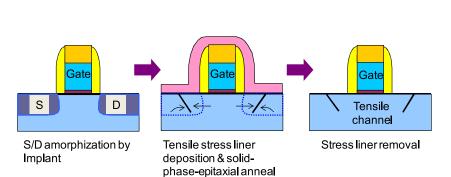

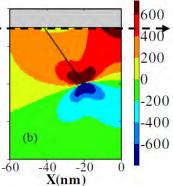

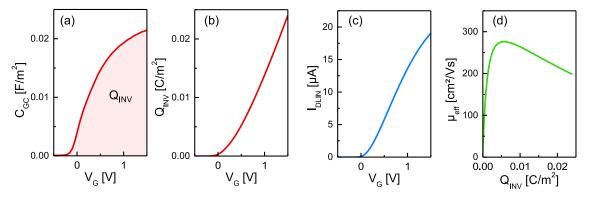

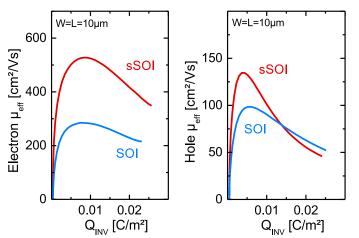

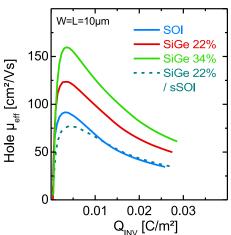

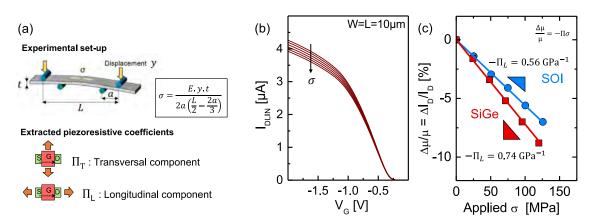

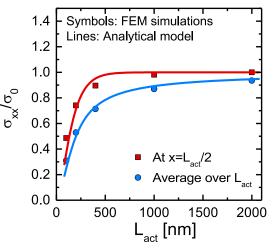

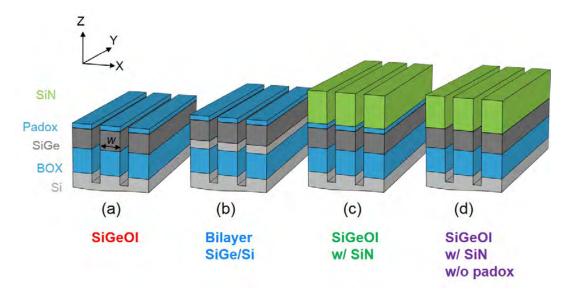

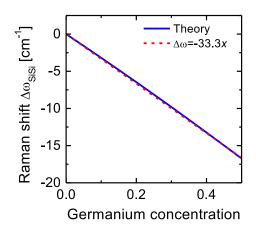

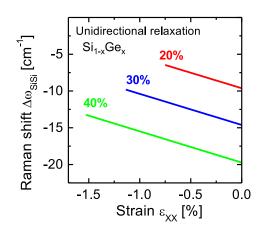

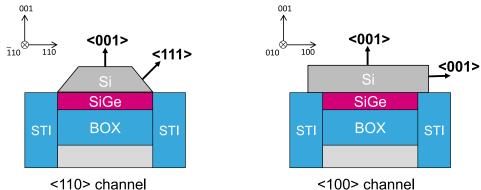

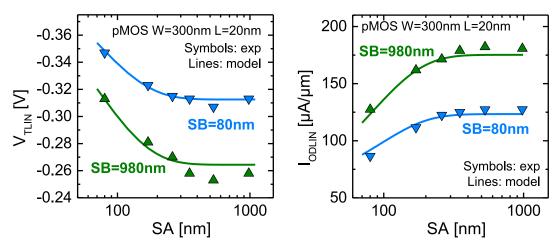

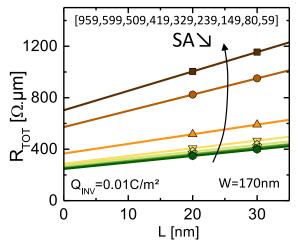

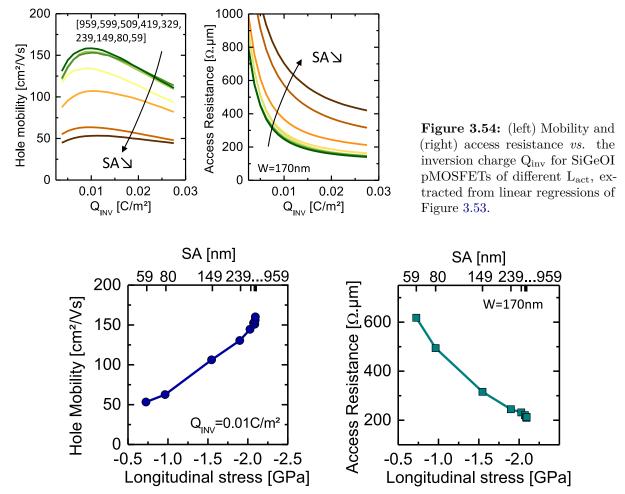

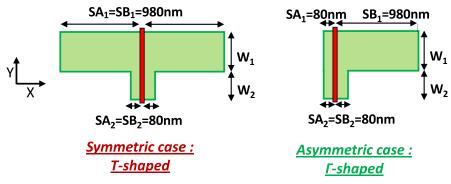

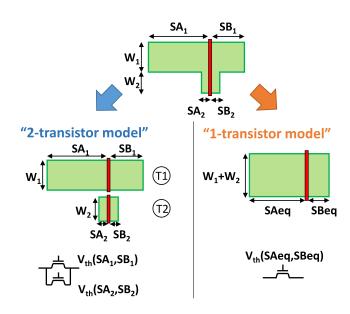

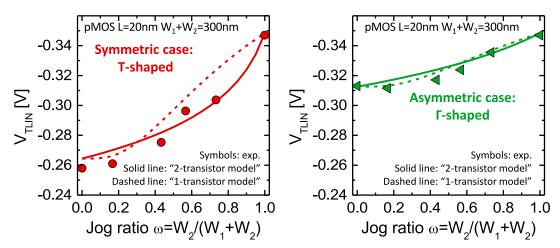

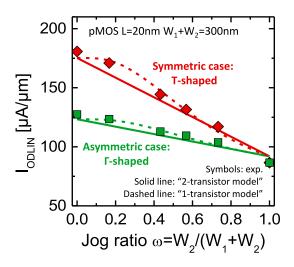

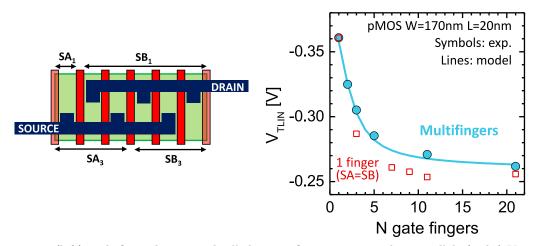

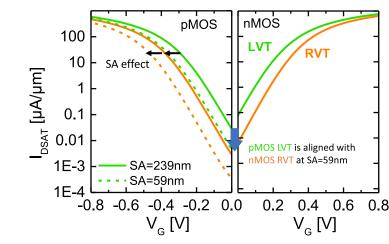

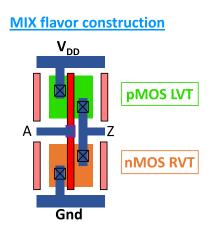

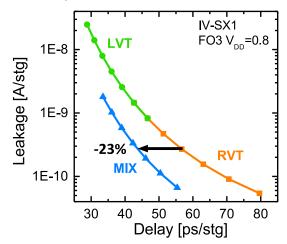

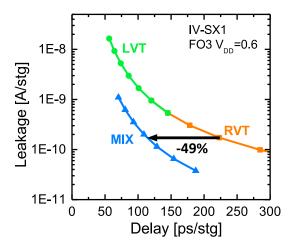

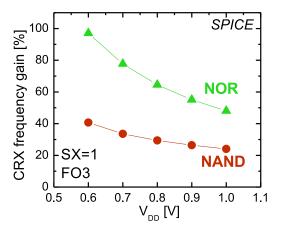

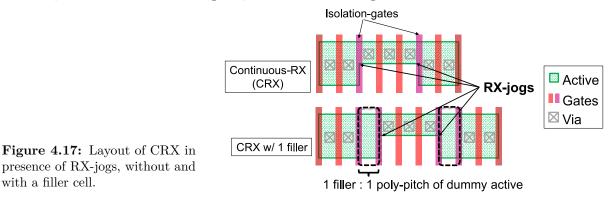

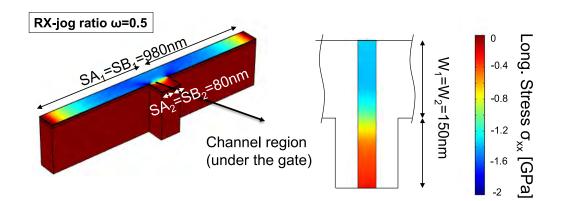

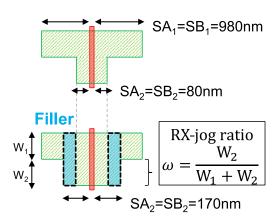

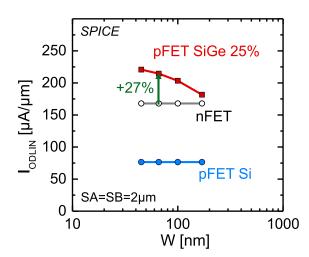

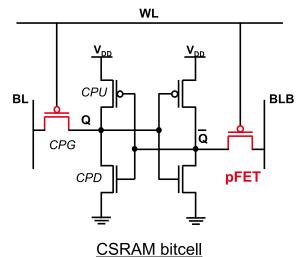

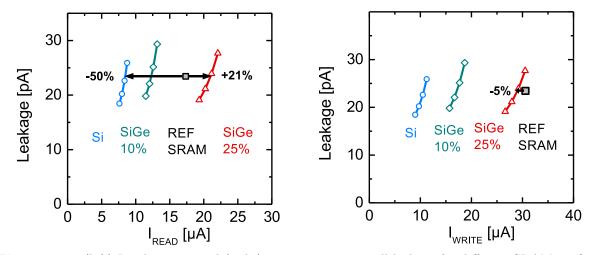

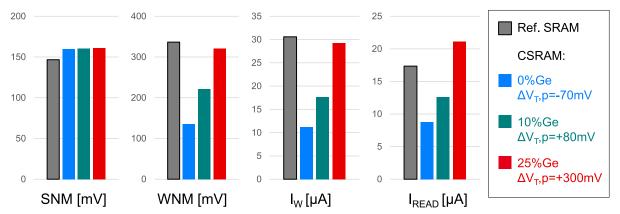

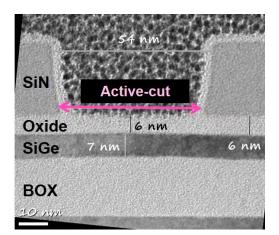

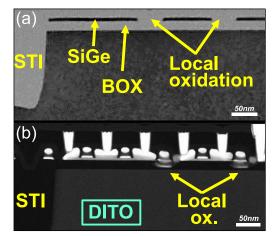

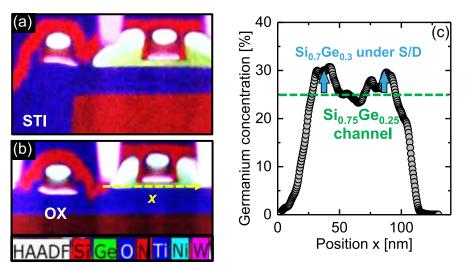

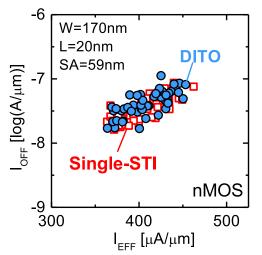

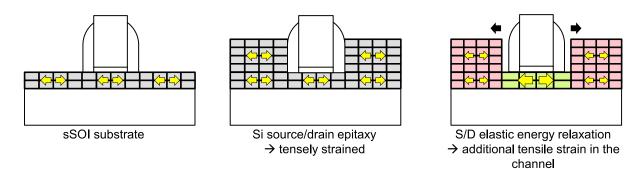

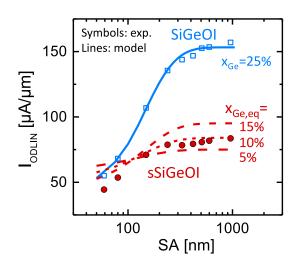

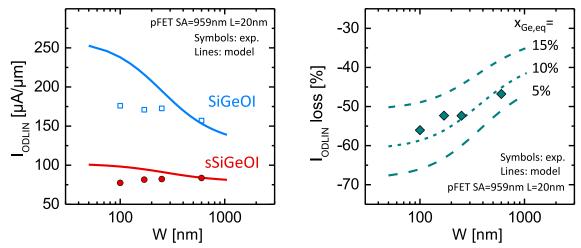

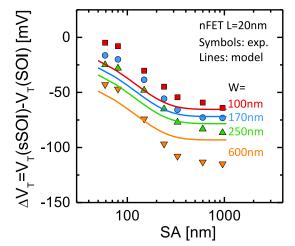

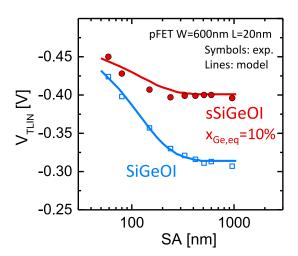

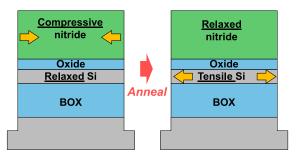

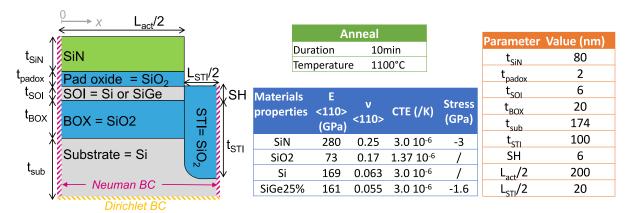

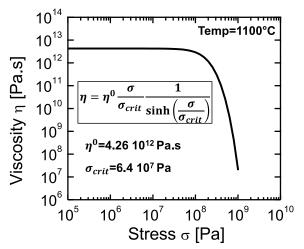

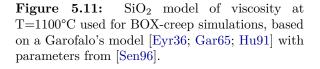

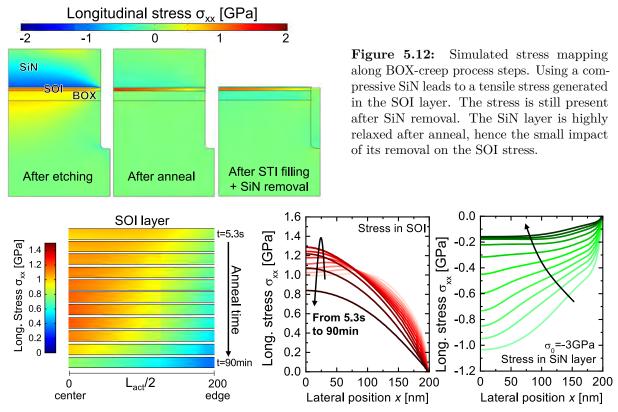

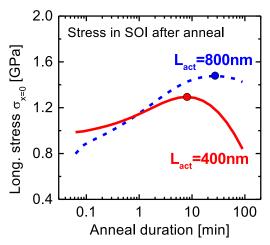

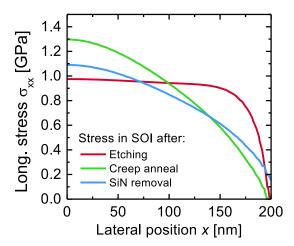

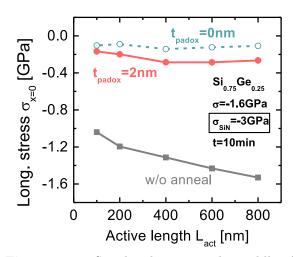

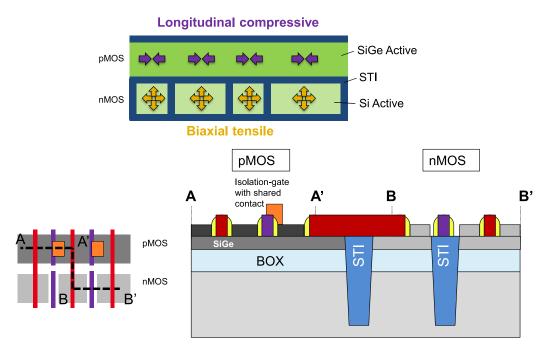

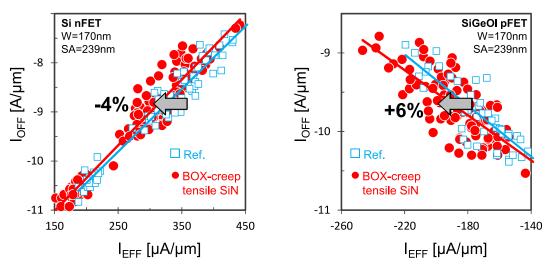

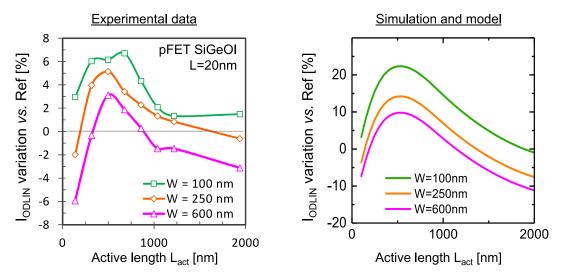

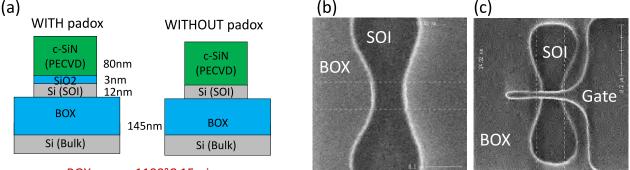

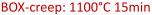

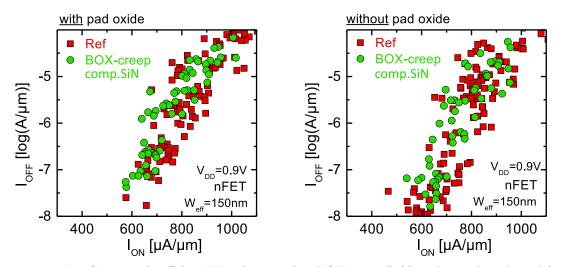

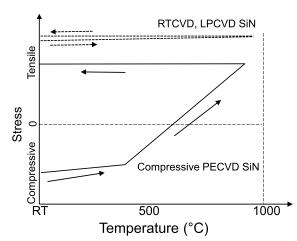

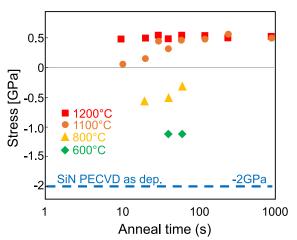

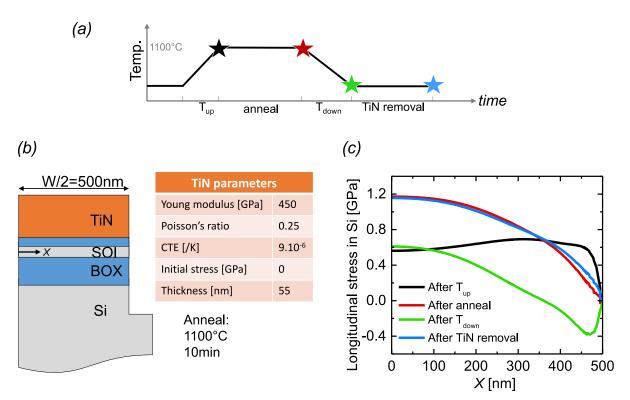

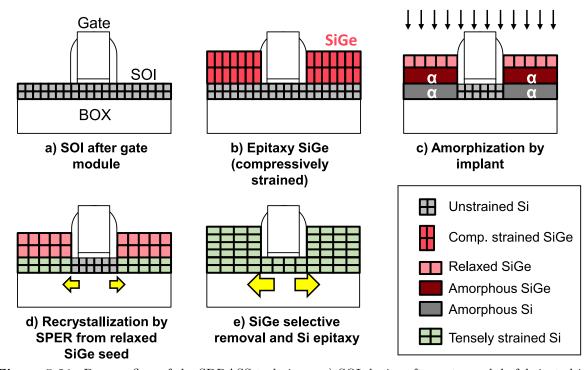

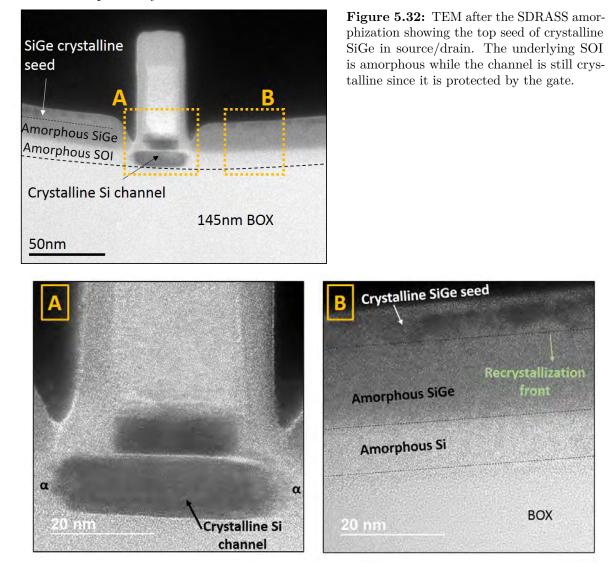

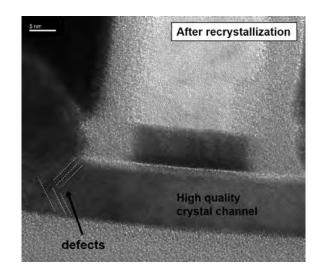

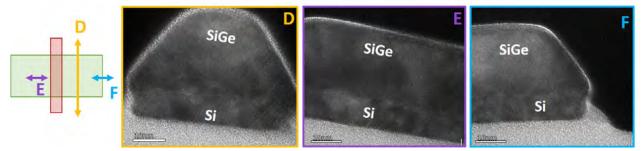

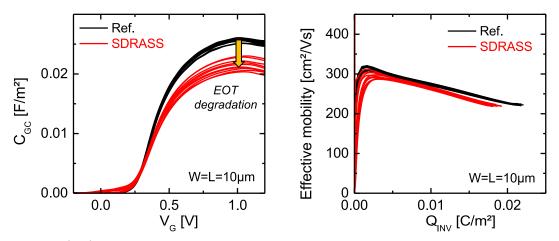

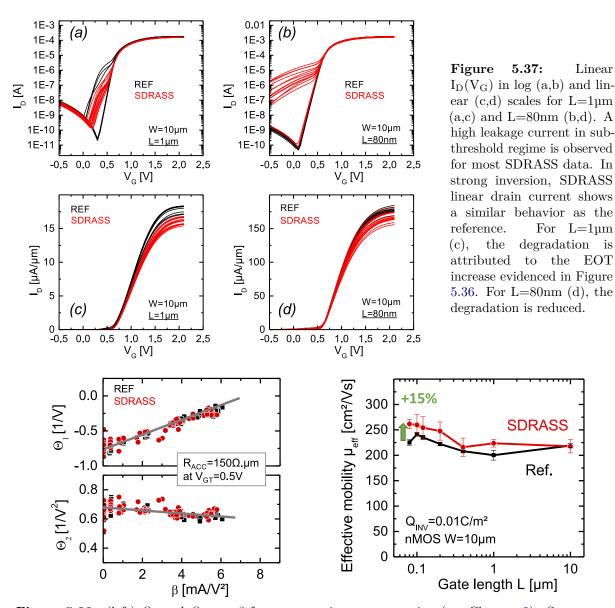

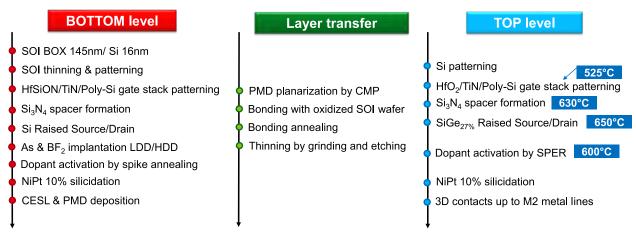

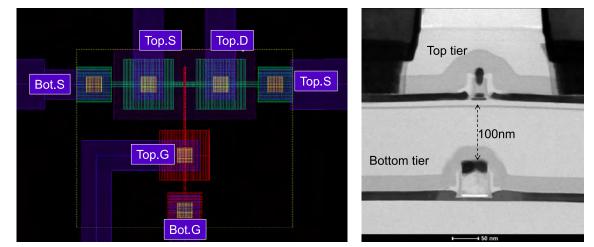

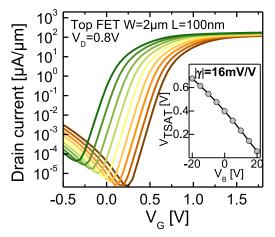

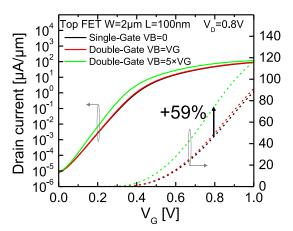

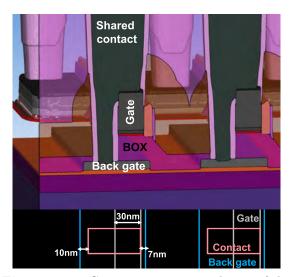

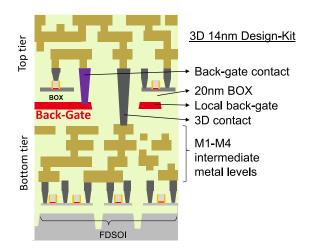

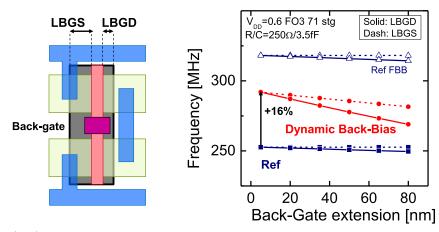

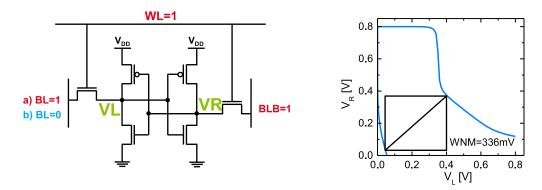

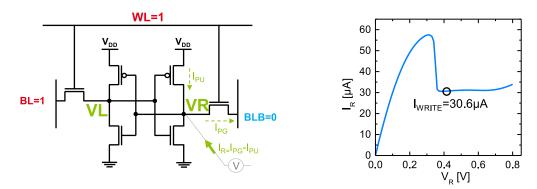

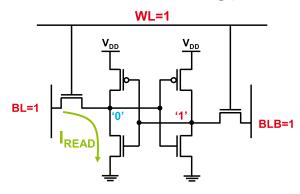

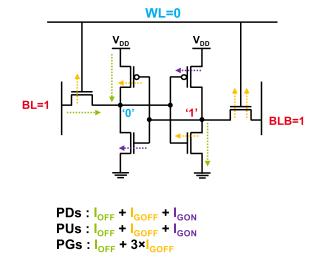

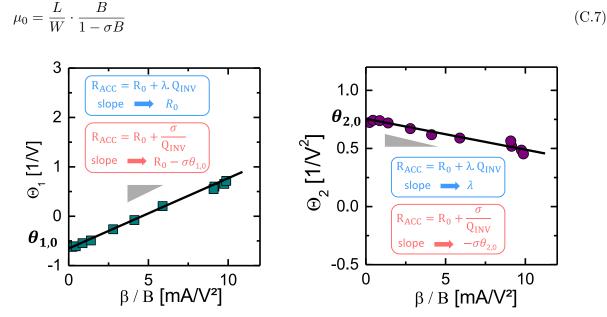

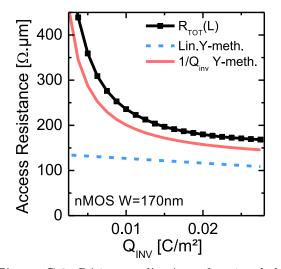

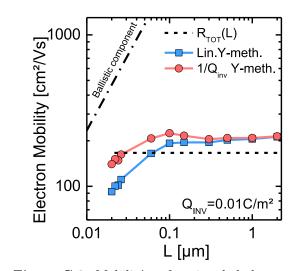

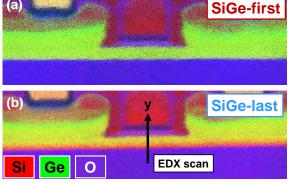

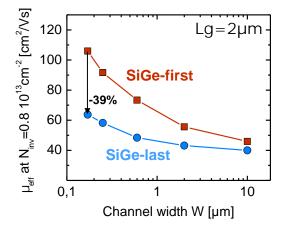

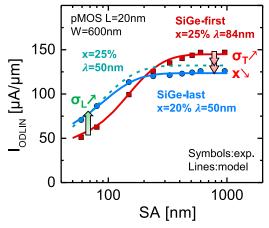

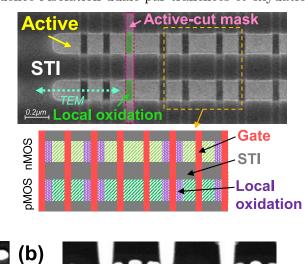

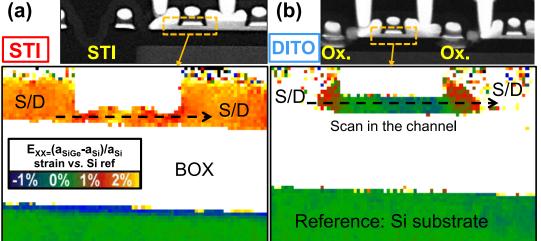

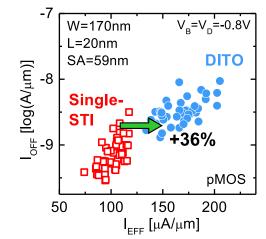

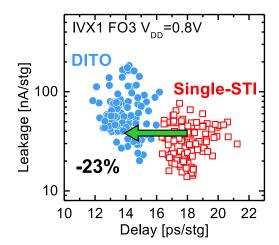

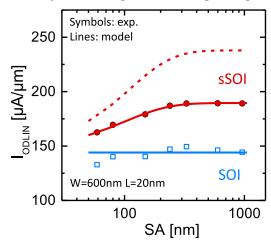

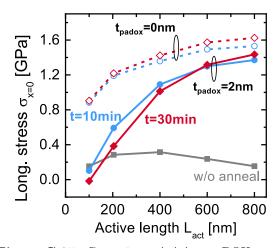

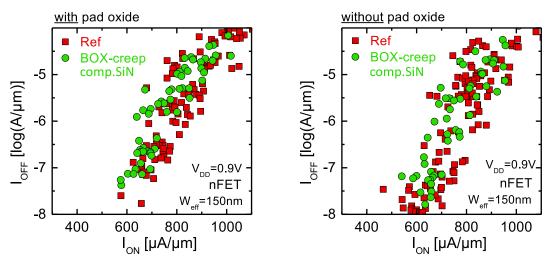

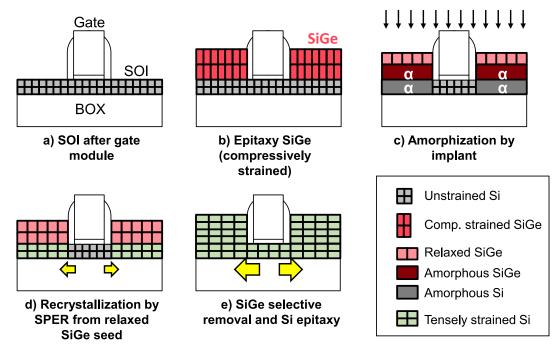

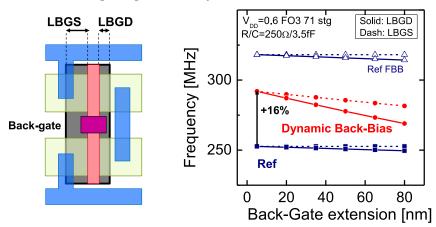

Figure 1.7: (left) Band diagram of the MOS structure under flat band condition.  $\phi_M$  and  $\phi_S$  are the metal and semiconductor work functions, respectively.  $\chi_S$  is the electron affinity.  $\phi_f$  is the Fermi potential.  $E_F$  is the Fermi level.  $E_i$  is the intrinsic Fermi level.  $E_C$  is the bottom of the conduction band and  $E_V$  the top of the valence band. (right) Band diagrams of a MOSFET in (top) accumulation or OFF state, i.e. no current from source to drain, and (bottom) inversion or ON state, i.e. carriers are free to flow from source to drain because of the reduced potential barrier.