# Understanding the performance of mutual exclusion algorithms on modern multicore machines.

Hugo Guiroux

## ▶ To cite this version:

Hugo Guiroux. Understanding the performance of mutual exclusion algorithms on modern multicore machines.. Operating Systems [cs.OS]. Université Grenoble Alpes, 2018. English. NNT: . tel-02133371

## HAL Id: tel-02133371 https://theses.hal.science/tel-02133371

Submitted on 18 May 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Informatique Arrêté ministériel : 25 mai 2016

Présentée par

## **Hugo GUIROUX**

Thèse dirigée par Vivien QUEMA, GRENOBLE INP et codirigée par Renaud LACHAIZE, UNIV. GRENOBLE ALPES préparée au sein du Laboratoire Laboratoire d'Informatique de Grenoble

dans l'École Doctorale Mathématiques, Sciences et technologies de l'information, Informatique

Comprendre la performance des algorithmes d'exclusion mutuelle sur les machines multicoeurs modernes

Understanding the performance of mutual exclusion algorithms on modern multicore machines.

Thèse soutenue publiquement le **17 décembre 2018**, devant le jury composé de :

### **Monsieur TIMOTHY HARRIS**

INGENIEUR, AMAZON A CAMBRIDGE - ROYAUME-UNI, Rapporteur **Monsieur GAËL THOMAS**

PROFESSEUR, TELECOM SUD-PARIS, Rapporteur

### **Monsieur ANDRZEJ DUDA**

PROFESSEUR, GRENOBLE INP, Président

### **Monsieur PASCAL FELBER**

PROFESSEUR, UNIVERSITE DE NEUCHATEL - SUISSE, Examinateur

#### **Monsieur VIVIEN QUEMA**

PROFESSEUR, GRENOBLE INP, Directeur de thèse

### **Monsieur RENAUD LACHAIZE**

MAITRE DE CONFERENCES, UNIVERSITE GRENOBLE ALPES, Examinateur

| We have arranged the whole system as a society of sequential processes whose harmonious cooperation is regulated by explicit mutual synchronization statements.  — Edsger W. Dijkstra. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| To my wife, Justine                                                                                                                                                                    |

|                                                                                                                                                                                        |

|                                                                                                                                                                                        |

|                                                                                                                                                                                        |

## Acknowledgements

First of all, I would like to thank the members of my Ph.D. thesis jury, Dr. Harris, Pr. Thomas, Pr. Duda and Pr. Felber, which have taken the time to examine my work and made meaningful comments and remarks before and during the defense. It was an honour for me to present my work in front of such a prestigious jury. I would also like to thank my two Ph.D. advisors, Renaud Lachaize and Vivien Quéma, for the long hours that we spent together discussing research ideas, profound scientific questions as well as non-scientific related topics. They both taught me to recognize what is a great research paper, to what standards my work should hold and how to make strong and interesting scientific work. They were here to support me during the difficult yet exciting experience that a Ph.D. can be.

Doing this Ph.D. would have been less pleasurable without the member of the ERODS team, with which I had countless discussions. More precisely, I want to thank (in alphabetical order): Maha Alsayasneh, Fabienne Boyer, Thomas Calmant, Matthieu Caneill, Jeremie Decouchant, Amadou Diarra, Didier Donsez, Christopher Ferreira, Soulaimane Guedria, Olivier Gruber, Mohamad Jaafar, Vikas Jaiman, Vincent Lamotte, Vania Marangozova-Martin, Muriel Nguimtsa, Nicolas Palix, Noel de Palma, Albin Petit, Ahmed El Rheddhane and Thomas Ropars. This thesis would not have happened without the financial support of the LIG and the University Grenoble Alpes.

During this three years, I had the chance to do an internship inside the MLE team at Oracle Labs Zurich. This experience brought me a lot and opened my mind to other interesting research topics. First and foremost, I would like to thank Vasileios Trigonakis for being a friend, helping me and advising me when I needed it. Thanks to the MLE team and the Oracle Labs: Matthias Branter, Lucas Braun, Laurent Daynès, Bastian Hossbach, Alexander Ulrich and Alexander Schubert.

A big shout out to all my friends that were here to support me during the three long years. Without you, I would not have done the Ph.D. that I did, even if you were not directly involved in my work. All the week-ends and holidays that we spent together helped me tremendously. A Ph.D. is a long journey, friends and family are the strong foundation that I needed. Thanks to Fairouz Azzoune, Carla Balbo, Perrine Blachon, Yoann Blein, Sandro Chionna, Jeanne Detroye, Aurélie Estermann, Clément Louis, Jennyfer Martinez, Simon Moura, Célia Muffato. Family is important: they provide a safe environment where anyone can talk openly about their feeling without being judged. I would like to thank both my family and my in-laws for their support

## Acknowledgements

throughout the years. A special thank to my sister, who told me to not always take things too seriously and enjoy the life that I had, and to my father, who always gives me invaluable advices and who taught me to always be curious about everything. Finally, a final word for the person that is the most important in my life: Justine. Without you, I would not have done this Ph.D., and I would not have accomplished a lot of things that happened in my life. You were always here to support me and encourage me in everything that I tried to accomplish. You always believed in me, even when I was not. Thank you for everything that you did.

Zurich, 05 January 2019

H.G.

## **Preface**

This thesis presents the research conducted in the ERODS team at Laboratoire d'Informatique de Grenoble, to pursue a Ph.D. in Computer Science from the doctoral school "Mathématiques, Sciences et Technologies de l'Information, Informatique" of the Université Grenoble-Alpes. My research activities have been supervised by Vivien Quéma (ERODS / Grenoble INP) and Renaud Lachaize (ERODS / Université Grenoble Alpes). Some of the works presented in this thesis have been done in collaboration with members of the Distributed Programming Laboratory (LPD) of Ecole Polytechnique Fédérale de Lausanne (EPFL) [69].

This thesis studies and analyzes mutual exclusion lock algorithms on multicore applications running on NUMA multicore machines.

This work led to the following publications (authors are in alphabetical order):

- Hugo Guiroux, Renaud Lachaize, and Vivien Quéma. "Multicore Locks: The Case Is Not Closed Yet". 2016 USENIX Annual Technical Conference, USENIX ATC 2016, Denver, CO, USA, June 22-24, 2016. Ed. by Ajay Gulati and Hakim Weatherspoon. USENIX Association, 2016, pp. 649-662

- Rachid Guerraoui, Hugo Guiroux, Renaud Lachaize, Vivien Quéma, and Vasileios Trigonakis. "Lock – Unlock: Is That All? A Pragmatic Analysis of Locking in Software Systems". ACM Transaction on Computer System (2018) (to appear)

Grenoble, Summer 2018

H.G.

## **Abstract**

A plethora of optimized mutual exclusion lock algorithms have been designed over the past 25 years to mitigate performance bottlenecks related to critical sections and synchronization. Unfortunately, there is currently no broad study of the behavior of these optimized lock algorithms on realistic applications that consider different performance metrics, such as energy efficiency and tail latency. In this thesis, we perform a thorough and practical analysis, with the goal of providing software developers with enough information to achieve fast, scalable and energy-efficient synchronization in their systems. First, we provide a performance study of 28 state-of-the-art mutex lock algorithms, on 40 applications, and four different multicore machines. We not only consider throughput (traditionally the main performance metric), but also energy efficiency and tail latency, which are becoming increasingly important. Second, we present an in-depth analysis in which we summarize our findings for all the studied applications. In particular, we describe nine different lock-related performance bottlenecks, and propose six guidelines helping software developers with their choice of a lock algorithm according to the different lock properties and the application characteristics.

From our detailed analysis, we make a number of observations regarding locking algorithms and application behaviors, several of which have not been previously discovered: (i) applications not only stress the lock/unlock interface, but also the full locking API (e.g., trylocks, condition variables), (ii) the memory footprint of a lock can directly affect the application performance, (iii) for many applications, the interaction between locks and scheduling is an important application performance factor, (iv) lock tail latencies may or may not affect application tail latency, (v) no single lock is systematically the best, (vi) choosing the best lock is difficult (as it depends on many factors such as the workload and the machine), and (vii) energy efficiency and throughput go hand in hand in the context of lock algorithms. These findings highlight that locking involves more considerations than the simple "lock – unlock" interface and call for further research on designing low-memory footprint adaptive locks that fully and efficiently support the full lock interface, and consider all performance metrics.

## Résumé

Une multitude d'algorithmes d'exclusion mutuelle ont été conçus au cours des vingt cinq dernières années, dans le but d'améliorer les performances liées à l'exécution de sections critiques et aux verrous. Malheureusement, il n'existe actuellement pas d'étude générale et complète au sujet du comportement de ces algorithmes d'exclusion mutuelle sur des applications réalistes (par opposition à des applications synthétiques) qui considère plusieurs métriques de performances, telles que l'efficacité énergétique ou la latence. Dans cette thèse, nous effectuons une analyse pragmatique des mécanismes d'exclusion mutuelle, dans le but de proposer aux développeurs logiciels assez d'informations pour leur permettre de concevoir et/ou d'utiliser des mécanismes rapides, qui passent à l'échelle et efficaces énergétiquement.

Premièrement, nous effectuons une étude de performances de 28 algorithmes d'exclusion mutuelle faisant partie de l'état de l'art, en considérant 40 applications et quatre machines multicoeurs différentes. Nous considérons non seulement le débit (la métrique de performance traditionnellement considérée), mais aussi l'efficacité énergétique et la latence, deux facteurs qui deviennent de plus en plus importants. Deuxièmement, nous présentons une analyse en profondeur de nos résultats. Plus particulièrement, nous décrivons neufs problèmes de performance liés aux verrous et proposons six recommandations aidant les développeurs logiciels dans le choix d'un algorithme d'exclusion mutuelle, se basant sur les caractéristiques de leur application ainsi que les propriétés des différents algorithmes.

A partir de notre analyse détaillée, nous faisons plusieurs observations relatives à l'interaction des verrous et des applications, dont plusieurs d'entre elles sont à notre connaissance originales : (i) les applications sollicitent fortement les primitives lock/unlock mais aussi l'ensemble des primitives de synchronisation liées à l'exclusion mutuelle (ex. trylocks, variables de conditions), (ii) l'empreinte mémoire d'un verrou peut directement impacter les performances de l'application, (iii) pour beaucoup d'applications, l'interaction entre les verrous et l'ordonnanceur du système d'exploitation est un facteur primordial de performance, (iv) la latence d'acquisition d'un verrou a un impact très variable sur la latence d'une application, (v) aucun verrou n'est systématiquement le meilleur, (vi) choisir le meilleur verrou est difficile, et (vii) l'efficacité énergétique et le débit vont de pair dans le contexte des algorithmes d'exclusion mutuelle.

Ces découvertes mettent en avant le fait que la synchronisation à base de verrou ne

### Résumé

se résume pas seulement à la simple interface "lock – unlock". En conséquence, ces résultats appellent à plus de recherche dans le but de concevoir des algorithmes d'exclusion mutuelle avec une empreinte mémoire faible, adaptatifs et qui implémentent l'ensemble des primitives de synchronisation liées à l'exclusion mutuelle. De plus, ces algorithmes ne doivent pas seulement avoir de bonnes performances d'un point de vue du débit, mais aussi considérer la latence ainsi que l'efficacité énergétique.

## Contents

| A  | cknov  | wledge   | ments                                    | iii  |

|----|--------|----------|------------------------------------------|------|

| Pı | reface | <b>:</b> |                                          | v    |

| A  | bstrac | ct       |                                          | vii  |

| Re | ésum   | é        |                                          | ix   |

| Li | st of  | figures  |                                          | xii  |

| Li | st of  | tables   |                                          | xii  |

| 1  | Intr   | oductio  | on                                       | 1    |

|    | 1.1    | Multio   | core primer                              | . 1  |

|    | 1.2    | Mutu     | al exclusion                             | . 3  |

|    | 1.3    | Thesis   | s statement                              | . 3  |

|    | 1.4    | Contr    | ibutions                                 | . 4  |

|    | 1.5    | Outlin   | ne                                       | . 5  |

| 2  | Bac    | kgroun   | d                                        | 7    |

|    | 2.1    | Locki    | ng                                       | . 7  |

|    |        | 2.1.1    | Synchronization primitives               | . 7  |

|    |        | 2.1.2    | Categorizing lock algorithms             | . 9  |

|    |        | 2.1.3    | Waiting policy                           | . 25 |

|    | 2.2    | Relate   | ed work                                  | . 27 |

|    |        | 2.2.1    | Lock algorithm implementations           | . 27 |

|    |        | 2.2.2    | Adaptive algorithms                      | . 28 |

|    |        | 2.2.3    | Studies of synchronization algorithms    | . 28 |

|    |        | 2.2.4    | Energy efficiency                        | . 29 |

|    |        | 2.2.5    | Lock-related performance bottlenecks     | . 30 |

| 3  | LiT    |          | brary for Transparent Lock interposition | 31   |

|    | 3.1    | Desig    |                                          | _    |

|    |        | 3.1.1    | General principles                       |      |

|    |        | 3.1.2    | Supporting condition variables           | 33   |

## **Contents**

|     |       | 3.1.3   | Support for specific lock semantics                             | 34      |

|-----|-------|---------|-----------------------------------------------------------------|---------|

|     | 3.2   | _       | mentation                                                       | 36      |

|     | 3.3   | Looku   | ıp overhead                                                     | 36      |

|     | 3.4   | Experi  | imental validation                                              | 37      |

|     | 3.5   | Statist | ical test                                                       | 39      |

| 4   | Stud  | dy      |                                                                 | 41      |

|     | 4.1   | Study'  | 's methodology                                                  | 41      |

|     |       | 4.1.1   | Studied algorithms                                              | 41      |

|     |       | 4.1.2   | Testbed                                                         | 44      |

|     |       | 4.1.3   | Studied applications                                            | 45      |

|     |       | 4.1.4   | Tuning and experimental methodology                             | 47      |

|     | 4.2   | Study   | of lock throughput                                              | 50      |

|     |       | 4.2.1   | Preliminary observations                                        | 50      |

|     |       | 4.2.2   | Main questions                                                  | 53      |

|     |       | 4.2.3   | Additional observations                                         | 61      |

|     |       | 4.2.4   | Effects of the lock choice on application performance           | 63      |

|     | 4.3   | Study   | of lock energy efficiency                                       | 65      |

|     |       | 4.3.1   | Energy-efficiency lock behavior                                 | 65      |

|     |       | 4.3.2   | POLY                                                            | 67      |

|     | 4.4   |         | of lock tail latency                                            | 73      |

|     |       | 4.4.1   | How does tail latency behave when locks suffer from high levels | , ,     |

|     |       | • •     | of contention?                                                  | 73      |

|     |       | 4.4.2   | Do fair lock algorithms improve the application tail latency?   | 74      |

|     |       | 4.4.3   | Do lock tail latencies affect application throughput?           | 74      |

|     |       | 4.4.4   | Implications                                                    | 75      |

|     | 4.5   |         | sis of lock/application behavior                                | 78      |

|     | 13    | 4.5.1   | Summary of the lock/application behavior analysis               | ,<br>78 |

|     |       | 4.5.2   | Guidelines for lock algorithms selection                        | 88      |

| 5   | Con   | clusion | 1                                                               | 95      |

| ,   | 5.1   |         | ns learned                                                      | 96      |

|     | 5.2   |         | e research                                                      | 97      |

| Bil | bliog | raphy   |                                                                 | 100     |

# List of Figures

| 1.1 | A modern multicore NUMA machine                                                                                                                                                                                                   | 2        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1 | Principle of the ttas lock algorithm.                                                                                                                                                                                             | 10       |

| 2.2 | Principle of the MCS lock algorithm                                                                                                                                                                                               | 12       |

| 2.3 | Principle of a Cohort lock algorithm                                                                                                                                                                                              | 14       |

| 2.4 | Principle of the RCL lock algorithm                                                                                                                                                                                               | 18       |

| 2.5 | Principle of the Malth_Spin lock algorithm                                                                                                                                                                                        | 21       |

| 3.1 | Pseudocode for the main wrapper functions of LiTL                                                                                                                                                                                 | 32       |

| 3.2 | Performance comparison of manually implemented locks vs. LiTL                                                                                                                                                                     | 35       |

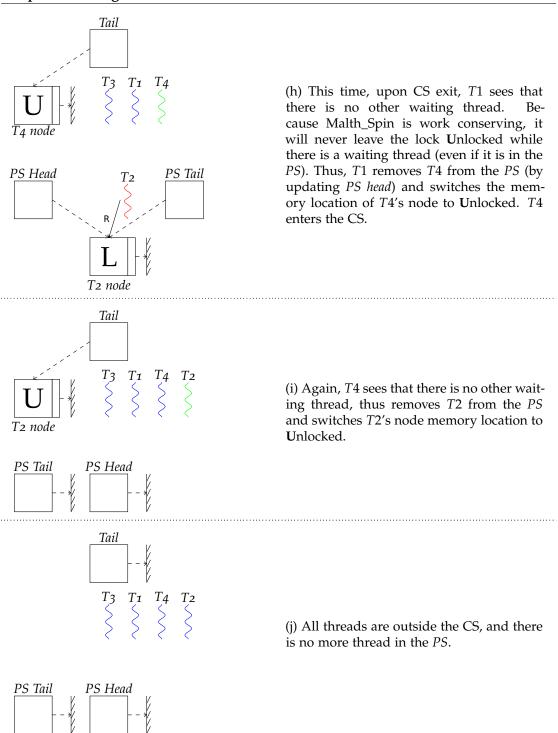

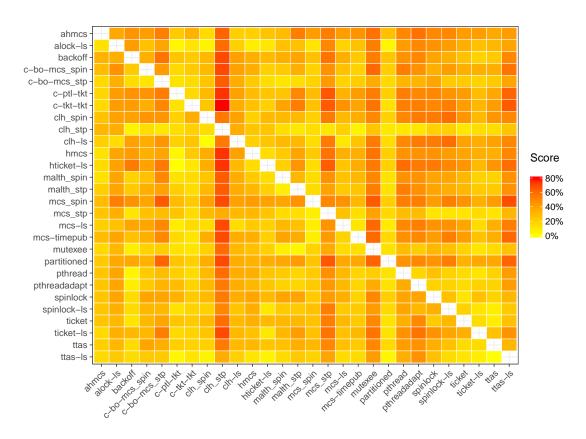

| 4.1 | For each pair of locks ( <i>rowA</i> , <i>colB</i> ) at <i>opt nodes</i> , scores of lock <i>A</i> vs lock <i>B</i> : percentage of lock-sensitive applications for which lock <i>A</i> performs at least 5% better than <i>B</i> | 56       |

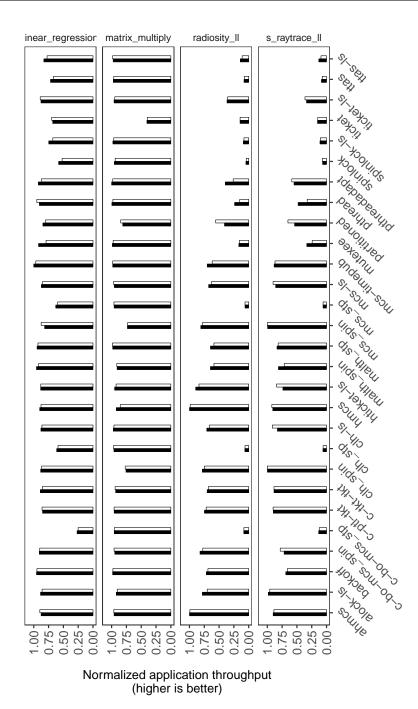

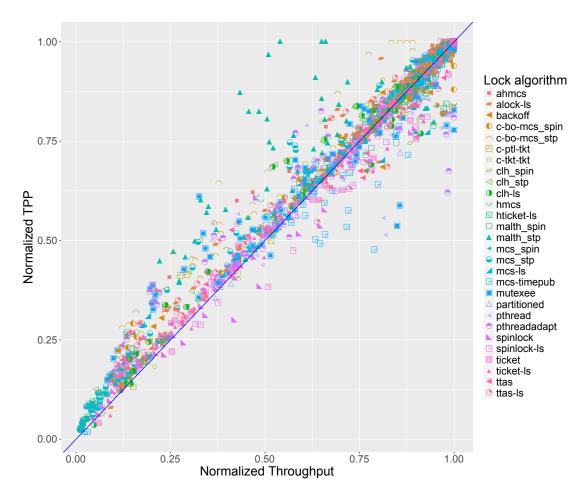

| 4.2 | Correlation of throughput with energy efficiency (TPP) on various lock-<br>sensitive applications with various lock algorithms and various con-<br>tention levels                                                                 | 68       |

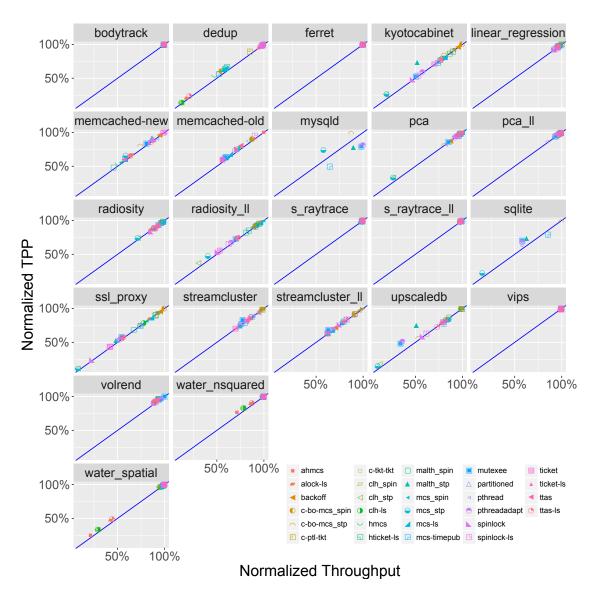

| 4.3 | Correlation of throughput with energy efficiency (TPP) on various lock-<br>sensitive applications at <i>one node</i> for the different lock algorithms                                                                            | 69       |

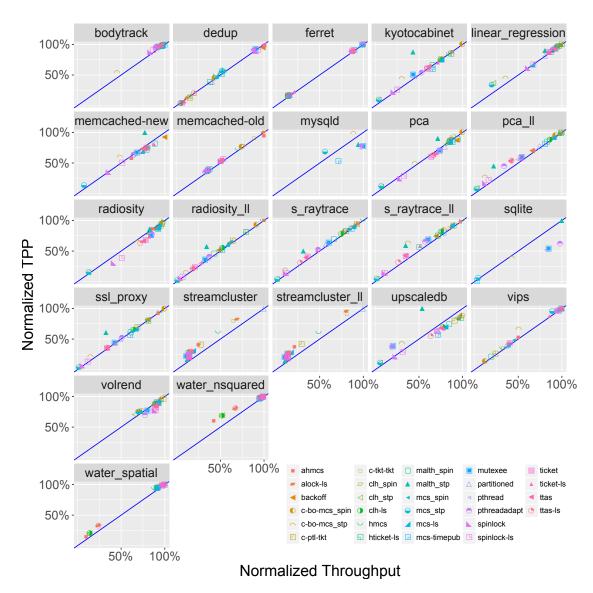

| 4.4 | Correlation of throughput with energy efficiency (TPP) on various lock-<br>sensitive applications at <i>max nodes</i> for the different lock algorithms                                                                           | 70       |

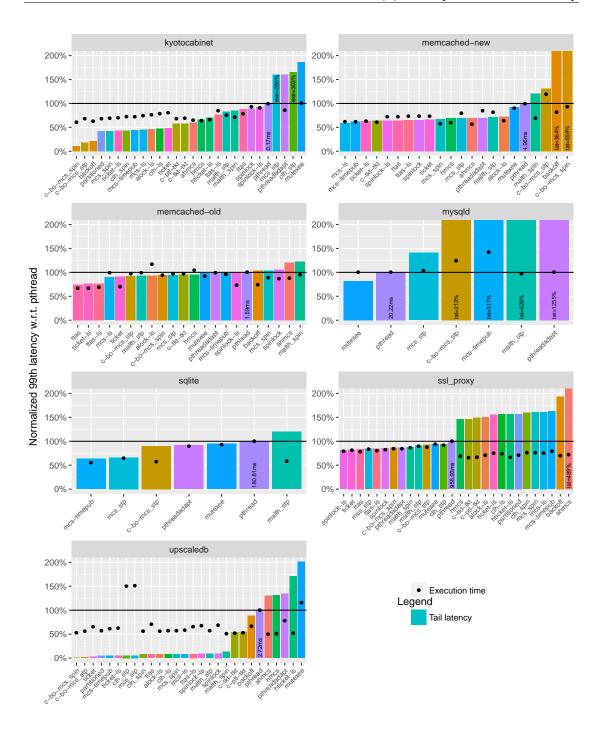

| 4.5 | For each server application, the bars represent the normalized 99th tail latency (w.r.t. Pthread) and the dots execution time (lower is better) normalized (w.r.t. Pthread) of each lock algorithm.                               |          |

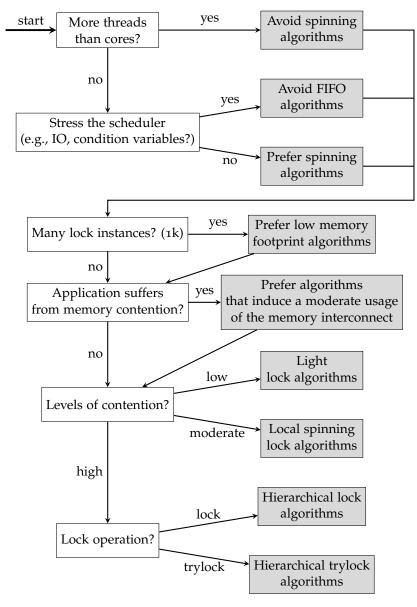

| 4.6 | Steps to follow for the application developer to chose a lock algorithm.                                                                                                                                                          | 77<br>92 |

| 4.0 | steps to follow for the application developer to chose a fock digorithm.                                                                                                                                                          | 92       |

## List of Tables

| 3.1  | Detailed statistics for the performance comparison of manually implemented locks vs. LiTL                                                                                                                                                            | 38 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Percentage of lock pairs ( <i>A</i> , <i>B</i> ) where, if performance with manually implemented locks of A is worse, equals or better than B, it is also respectively worse, equals or better than B with transparently interposed locks using LiTL | 38 |

| 3.3  | Paired Student t-test to compare manually implemented locks vs. LiTL.                                                                                                                                                                                | 39 |

| 4.1  | Lock algorithms summary                                                                                                                                                                                                                              | 43 |

| 4.2  | Hardware characteristics of the testbed platforms                                                                                                                                                                                                    | 44 |

| 4.3  | Real-world applications considered                                                                                                                                                                                                                   | 45 |

| 4.4  | For each application, performance gain of the best vs. worst lock and                                                                                                                                                                                |    |

|      | relative standard deviation                                                                                                                                                                                                                          | 52 |

| 4.5  | Number of applications and number of lock performance sensitive ap-                                                                                                                                                                                  |    |

|      | plications.                                                                                                                                                                                                                                          | 53 |

| 4.6  | For each (lock-sensitive application, lock) pair, performance gain (in %) of                                                                                                                                                                         |    |

|      | opt nodes over max nodes                                                                                                                                                                                                                             | 54 |

| 4.7  | Breakdown of the (lock-sensitive application, lock) pairs according to their                                                                                                                                                                         |    |

| 0    | optimized number of nodes                                                                                                                                                                                                                            | 55 |

| 4.8  | Statistics on the coverage of locks on lock-sensitive applications                                                                                                                                                                                   | 55 |

| 4.9  | For each lock, fraction of the lock-sensitive applications for which the lock yields the best performance for three configurations: <i>one node, max</i>                                                                                             |    |

|      | nodes and opt nodes                                                                                                                                                                                                                                  | 57 |

| 4.10 | For each lock, at <i>max nodes</i> and at <i>opt nodes</i> , fraction of the lock-sensitive                                                                                                                                                          |    |

|      | applications for which the lock is harmful                                                                                                                                                                                                           | 58 |

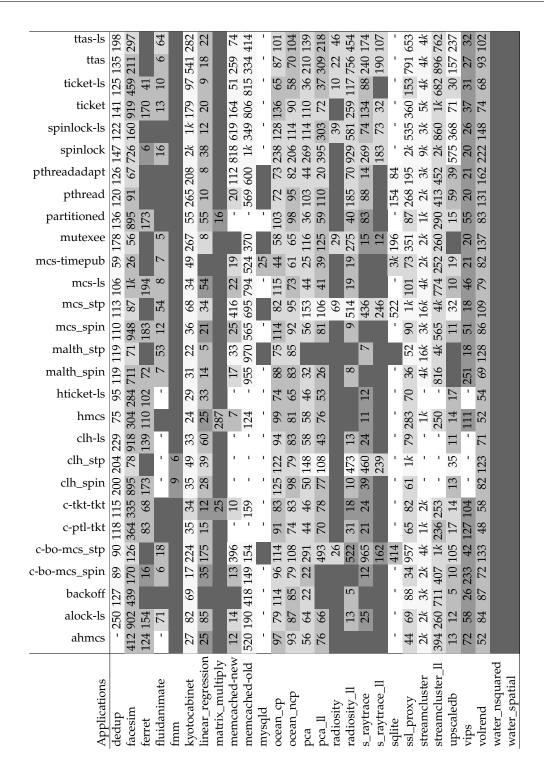

| 4.11 | For each lock-sensitive application, at <i>max nodes</i> , performance gain, (in                                                                                                                                                                     |    |

|      | %) obtained by the best lock(s) with respect to each of the other locks                                                                                                                                                                              | 60 |

| 4.12 | For each lock-sensitive application, percentage of pairwise changes in                                                                                                                                                                               |    |

|      | the lock performance hierarchy when changing the number of nodes                                                                                                                                                                                     | 62 |

| 4.13 | Energy-efficiency gain of <i>opt nodes</i> over <i>max nodes</i> breakdown for lock-sensitive applications                                                                                                                                           | 66 |

| 4.14 | Percentage of lock-sensitive applications for which <i>opt nodes</i> is lower, the                                                                                                                                                                   |    |

|      | same or higher for energy efficiency w.r.t. performance                                                                                                                                                                                              | 66 |

## **List of Tables**

| 4.15 | Pearson correlation coefficient between throughput and TPP for all lock- |    |

|------|--------------------------------------------------------------------------|----|

|      | sensitive applications                                                   | 71 |

| 4.16 | Lock-sensitive application performance bottleneck(s) and lock algorithms |    |

|      | choice advice                                                            | 79 |

| 4.17 | Lock algorithm properties                                                | 89 |

## 1 Introduction

For several decades, processor vendors improved performance by increasing CPU frequency. However, physical limitations such as current leakage causing CPU to heat up limited the increase of frequency over the years. As a consequence, to keep increasing performance, vendors switched to multicore architectures [104].

As of 2018, multicore machines with tens of cores (e.g., 64 cores) are now widespread. While previously reserved to server, multicore processors are now embedded into personal desktop, laptop and even mobiles. Moreover, processor vendors continue to increase the number of cores per socket, with socket up to 64 cores are rumored to become available before 2020 [15].

## 1.1 Multicore primer

Figure 1.1 illustrates a modern multicore machine. Modern multiprocessor machines are composed of several sockets, each one composed of several homogeneous cores. Each of these cores is composed of its own set of registers and components (e.g., memory unit, arithmetic logic unit – ALU), allowing several execution contexts running in parallel. Cores access memory through a hierarchical organization of private and shared caches. Generally, there are one (L1) or two (L1 and L2) private caches per core; a bigger cache (the *last level cache – LLC*, often L3) is shared between the cores of a socket. Finally, data is stored in DRAM and menory accesses go through the memory controller responsible for accesses to the DRAM module where the memory is stored.

Historically, CPU frequency has increased faster than memory frequency, such that cores stall, waiting for their memory accesses to be fulfilled. A (partial) solution is to provide bigger and faster caches, yet this is not always enough, especially as the number of cores on a socket keeps increasing. To distribute the memory load, modern multicore machines are based on a NUMA (Non-Uniform Memory Accesses) architecture. A NUMA machine is composed of several NUMA nodes, each one composed of

Figure 1.1 – A modern multicore NUMA machine.

one socket, one or more memory controllers, upon which one or more DRAM modules are attached. In order to allow any core to have access to the entire available memory, sockets are linked together through a high-speed interconnect (e.g., Intel QuickPath Interconnect [60] or AMD HyperTransport [28]). On such a machine, local memory accesses (i.e., a memory request is served by a cache/DRAM of the same NUMA node as the request core) and remote memory accesses (a memory request is served by a cache/DRAM of a remote NUMA node) do not have the same latency, hence the term *Non-Uniform Memory Access*. Besides, the bandwidth of remote memory accesses is more constrained than the one of local memory accesses.

Because cores rely on caches to improve memory latency, situations might arise where two cores have the same data in their respective private cache, one core modifies its own local copy and the second one does not see the modification: there is a cache coherence problem. To maintain a single, coherent view of the memory, a cache coherency protocol is used<sup>1</sup>. At the granularity of a cache line (generally 64 bytes on a modern machine), each core tracks the status of a given memory location and communicates to other cores when the location is accessed or modified. Maintaining this coherency is costly, because cache lines need to be exchanged between cores, and on NUMA machine this leads to costly exchanges through the interconnect.

<sup>&</sup>lt;sup>1</sup>This thesis only considers ccNUMA (cache-coherent NUMA) SMP machines.

## 1.2 Mutual exclusion

To fully exploit the parallelism exposed by a multicore machine, software is now written from the beginning with concurrency and parallelism in mind, often leveraging frameworks and languages that help developers writing concurrent code. However, efficiently leveraging the available hardware parallelism is often challenging due to bottlenecks that impede multicore scalability. One of the main factor of poor scalability is the consequence of Amdahl's law.

Theoretically, the scalability of a program is dictated by Amdahl's law [7], which states that a program's scalability is always constrained by its sequential parts. These sequential parts are most often due to synchronization: in order to avoid inconsistent states, execution contexts running concurrently must synchronize their access to shared data. The most popular means of synchronization is mutual exclusion via locking: a critical section (i.e., the part of code that needs to be executed atomically) is protected by a lock, serializing accesses to this section. In this context, an efficient way to improve scalability is to reduce the sequential parts as much as possible. Because the time spent inside the lock algorithm protecting the critical section might unnecessarily lengthen the sequential part, studying lock algorithms has been of prime interest to the research community. Over the past 25 years, a plethora of optimized mutual exclusion (mutex) lock algorithms have been designed to mitigate these issues [91, 9, 80, 29, 76, 85, 88, 54, 75, 36, 55, 37, 43, 33, 68, 25, 38, 24, 42, 112, 34, 46, 64, 93]. Application and library developers can choose from this large set of algorithms for implementing efficient synchronization in their software. However, there is currently no detailed study to guide this puzzling choice for realistic applications.

## 1.3 Thesis statement

The most recent and comprehensive empirical performance evaluation on multicore synchronization [33], due to its breadth (from hardware protocols to high-level data structures), only provides a partial coverage of locking algorithms. Indeed, the aforementioned study only considers nine algorithms, does not consider hybrid waiting policies (i.e., what a thread does while waiting for a lock), omits emerging approaches (e.g., load-control mechanism) and provides a modest coverage of hierarchical locks [38, 25, 24], a recent and efficient approach for NUMA architectures. Generally, most of the observations highlighted in the existing literature are based on microbenchmarks and only consider the lock/unlock interface, ignoring other lock-related operations such as condition variables and trylocks. Besides, in the case of papers that present a new lock algorithm, the empirical observations are often focused on the specific work-load characteristics for which the actual lock was designed [61, 72], or mostly based on microbenchmarks [38, 34]. Finally, existing analyses focus on traditional performance metrics (mainly throughput) and do not cover other metrics, such as energy efficiency

and tail latency, which are becoming increasingly important.

In this thesis, we perform a thorough and practical analysis of synchronization, with the goal of providing software developers with enough information to design fast, scalable and energy-efficient synchronization in their systems.

## 1.4 Contributions

The contributions of this thesis are threefold.

The first contribution is a broad performance study (Sections 4.2 to 4.4) on Linux/x86 (i.e., the Linux operating system running on AMD/Intel x86 64-bit processors) of 28 state-of-the-art mutual exclusion lock algorithms on a set of 40 realistic and diverse applications: PARSEC, Phoenix, SPLASH2 benchmark suites, MySQL, Kyoto Cabinet, Memcached, RocksDB, SQLite, upscaledb and an SSL proxy. Among these 40 applications, we determine that performance varies according to the choice of a lock for roughly 60% of them, and perform our in-depth study on this subset of applications. We believe this set of applications to be representative of real-world applications: we consider applications that not only stress the classic lock/unlock interface to different extents, but also exhibit different usage patterns of condition variables, trylocks, barriers and that use different number of locks (i.e., from one global lock to thousands of locks). We consider four different multicore machines and three different metrics: throughput, tail latency and energy efficiency. In our quest to understand the behavior of locking, when choosing the per-configuration best lock, we improve on average application throughput by 90%, energy efficiency by 110% and tail latency 12× with respect to the default POSIX mutex lock (note that, in many cases, different locks optimize different metrics). As we show in this thesis, choosing a well performing lock is difficult, as this choice depends on many different parameters: the workload, the underlying hardware, the degree of parallelism, the number of locks, how they are used, the lock-related interfaces that the application stresses (e.g., lock/unlock, trylock, condition variables), the interaction between the application and the scheduler, and the performance metric(s) considered.

Our second contribution is an in-depth analysis of the different types of lock-related performance bottlenecks that manifest in the studied applications. In particular, we describe nine different lock-related performance bottlenecks. Based on the insights of this analysis, we propose six guidelines for helping software developers with their choice of lock algorithms according to the different lock properties and the application characteristics. More precisely, by answering to a few questions about the considered application (e.g., more threads than cores? blocking syscalls?) and by looking at a few lock-related metrics (e.g., the number of allocated locks, the number of threads concurrently trying to acquire a lock), the developer is able to understand easily and quickly which

lock algorithm(s) to choose or to avoid for his specific use case.

Our third contribution is LiTL², an open-source, POSIX compliant [57], low-overhead library that allows transparent interposition of Pthread mutex lock operations and support for mainstream features like condition variables. Indeed, to conduct our study, manually modifying all the applications in order to retrofit the studied lock algorithms would have been a daunting task. Moreover, using a meta-library that allows plugging different lock algorithms under a common API (such as liblock [72] or libslock [33]) would not have solved the problem, as this still requires a substantial re-engineering effort for each application. In addition, such meta-libraries provide no or limited support for important features like Pthread condition variables, used within many applications. Our approach is a pragmatic one: similarly to what is done by previous works on memory allocators [16, 3, 67, 47], we argue that transparently switching (i.e., without modifying the application) lock algorithms (resp. memory allocators) is an efficient and pragmatic solution.

## 1.5 Outline

This thesis is organized as follows. Chapter 2 introduces our work, gives some background on locking and lock algorithms and discusses related works. Chapter 3 presents LiTL, the library we developed to evaluate the lock algorithms on the studied applications. Chapter 4 studies the throughput, energy efficiency and tail latency of lock algorithms, and performs a detailed analysis explaining, for each of the studied applications, which types of locks work well/poorly and why.

Finally, Chapter 5 concludes this thesis and discusses future research directions that we believe are worth investigating.

<sup>&</sup>lt;sup>2</sup>LiTL: Library for Transparent Lock interposition.

## 2 Background

This Chapter provides the necessary background related to the other chapters of this thesis. We first give a primer of synchronization and locking, as well as describe existing lock algorithms in Section 2.1, then discuss the related work in Section 2.2.

## 2.1 Locking

All modern lock algorithms rely on hardware atomic instructions to ensure that a critical section is executed in mutual exclusion. To provide atomicity, the processor relies on the cache-coherence protocol of the machine to implement an atomic readmodify-write operation on a memory address. Previous work [33] demonstrated that lock algorithm performance is mainly a property of the hardware, i.e., a lock algorithm must take into account the characteristics of the underlying machine. The design of a lock algorithm is thus a careful choice of data structures, lock acquisition/release policies and (potential) load-control mechanisms.

Section 2.1.1 introduces the locking API. Section 2.1.2 proposes a classification of the lock algorithms into five categories. Section 2.1.3 discusses the various waiting policies.

### 2.1.1 Synchronization primitives

Locking is by far the most commonly-used approach to synchronization. Practically all modern software systems employ locks in their design and implementation. The main reason behind the popularity of locking is that it offers an intuitive abstraction. Locks ensure *mutual exclusion*; only the lock holder can proceed with its execution. Executions that are protected by locks are known as *critical sections*. Mutual exclusion is a way to synchronize concurrent accesses to the critical section, i.e., threads synchronize/coordinate to avoid one thread entering the critical section before the other left

it. In addition, *condition variables* allow threads to cooperate within a critical section by introducing a happened-before relationship between them, e.g., for a synchronized queue protected by a lock, inserting an element inside the queue happens before removing the element.

#### Mutual exclusion

**Lock/unlock.** Upon entering the critical section, a thread must acquire the lock via the lock operation. This operation is *blocking*, i.e., a thread trying to acquire a lock instance already held waits until the instance becomes available. When the lock holder exits the critical section, it must call the unlock operation, to explicitly release the lock. How to acquire a lock, what to do while waiting for the lock, and how to release the lock are choices made by a lock algorithm.

**Trylock.** If a lock is busy, a thread may do other work instead of blocking. In this case, it can use the non-blocking trylock operation. This operation has a return code to indicate if the lock is acquired. What a thread does when the trylock does not acquire the lock is up to the software developer, not the lock algorithm. We observe that developers frequently use trylock to implement busy-waiting, in order to avoid being descheduled (the policy used by the Pthread lock algorithm while waiting for a lock) if the lock is already held. This action is useful when the application developer knows that the critical section protected by the lock is short, and thus that there is a high chance for a thread to obtain the lock quickly. If the trylock acquires the lock, the lock holder must call unlock to release the lock.

#### **Conditions variables**

Threads often rely on condition variables to receive notifications when an event happens (e.g., when data is put inside a queue). A thread that wants to wait on a condition variable calls wait while holding a lock. As a consequence, the thread releases the lock and blocks<sup>1</sup>. When the condition is fulfilled, another thread calls signal or broadcast to wake any or all blocked threads, respectively. Upon wake-up (and before exiting from wait), a thread needs to acquire the lock again in order to re-enter the critical section. Efficiently implementing condition variables on top of locks is non-trivial (see Section 3.1.2).

<sup>&</sup>lt;sup>1</sup>Releasing the lock and blocking is atomic, to avoid loosing a signal and being blocked indefinitely.

## 2.1.2 Categorizing lock algorithms

The body of existing work on optimized lock algorithms for multicore architectures is rich and diverse and can be split into the following five categories. The first two categories (competitive and direct handoff succession) are based on the succession policy [34] of the lock algorithm, i.e., how lock ownership is transferred at unlock-time. These two categories are mutually exclusive. The three other categories regroup algorithms that either compose algorithms from the first two categories (hierarchical approaches), change how critical sections are executed (delegation-based approaches), or improve existing locks with load-control mechanisms. Note that overall these categories overlap: a given algorithm can fall into several categories.

### 1) Competitive succession

Some algorithms rely on a competitive succession policy, where the lock holder sets the lock to an available state, and all competing threads might try to acquire it concurrently, all executing an atomic instruction on the same memory address. Such algorithms generally stress the cache-coherence protocol as they trigger cache line invalidations at unlock-time to all cores waiting for the lock, while ultimately only one core succeeds in acquiring it. Competitive succession algorithms might allow *barging*, i.e., "arriving threads can barge in front of other waiting threads" [34], which, for applications sensitive to the fairness between threads (e.g., latency sensitive applications), might lead to unfairness and starvation. Examples of algorithms using a competitive succession policy are simple spinlock [95], Backoff spinlock [9, 80], test and test-and-set (ttas) lock [9], Mutexee lock [42] and standard Pthread mutex locks² [68, 57]. Figure 2.1 illustrates the ttas lock algorithm.

<sup>&</sup>lt;sup>2</sup>Throughout this manuscript, we refer to the GNU C Library implementation of the Pthread mutex lock algorithm.

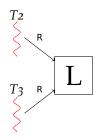

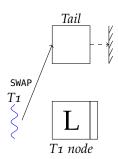

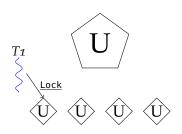

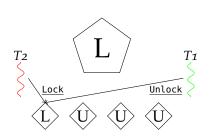

(a) To acquire the lock (the white rectangular box), which is a memory location having the state Unlocked (e.g., its content is 0), thread *T*1 executes an atomic instruction (CAS, *compare-and-set*) to change the lock state from Unlocked to Locked (e.g., changing its content from 0 to 1). Note that *T*1 is in blue to illustrate the fact that it is *outside* the critical section (CS) before executing the CAS instruction.

(b) T1 has the lock and is inside the CS (a thread inside the CS is in green). T2 and T3 both try to acquire the lock. However T1 already holds the lock, thus they wait for the lock to become Unlocked by looping on a memory load (Read) instruction on the location of the lock. A red thread is a thread waiting for a lock.

Figure 2.1 – Principle of the ttas lock algorithm.

(c) Upon the exit of the CS, T1 releases the lock with a memory store (Write), writing Unlocked inside the memory location. Note that on some architectures (e.g., ARM [11]), a memory barrier might be necessary before the write to avoid memory instructions inside the CS to be reordered with instructions outside the CS.

(d) The lock is Unlocked, and *T*1 is outside the CS. Because both *T*2 and *T*3 were waiting for a change of the lock status, they both issue a CAS instruction concurrently, trying to acquire the lock. Due to the semantics of the CAS instruction, only one of the two threads acquires the lock and enters the CS.

(e) *T*2 acquired the lock and is inside the CS. *T*3 still waits for the lock, and will acquire it when *T*2 releases it, unless *T*1 tries to acquire the lock in the meantime. In such a case, for a ttas lock, because arriving threads can barge in front of other waiting threads, *T*3 will be in competition with *T*1 to acquire the lock after *T*2 releases it.

Figure 2.1 – Principle of the ttas lock algorithm (Cont.).

#### 2) Direct handoff succession

Direct handoff locks (also known as queue-based locks) are lock algorithms in which the unlock operation identifies a waiting successor and then passes ownership to that thread [34]. As the successor of the current lock holder is known, it allows each waiting thread to wait on a non-globally shared memory address (one per waiting thread). Then, the lock holder passes ownership with the help of this private memory address, thus avoiding cache line invalidations to all the other competing cores (contrary to the competitive succession policy). This approach is also known to yield better fairness. Besides, this approach generally gives better throughput under contention compared to simpler locks like spinlock: with direct handoff locks, each thread spins on its own local variable, avoiding to send cache line invalidations to all other spinning cores when the lock is acquired/released (contrary to locks based on a global variable). Examples of direct handoff lock algorithms are: MCS [80, 95], CLH [29, 76, 95].

Some algorithms do use a globally shared memory address but still use a direct handoff succession policy. For example, the Ticket lock [91] repeatedly reads a single memory address in a non-atomic fashion, waiting for its turn to come. The Partitioned Ticket lock [36] uses a hybrid solution, where the same memory address can be observed by a subset of the competing threads.

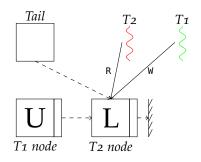

Figure 2.2 illustrates the MCS lock algorithm.

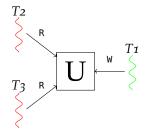

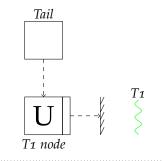

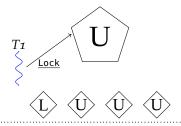

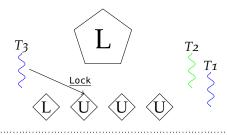

(a) The MCS lock algorithm organizes waiting threads in a single linked list, keeping track of the tail of the list with a pointer. At the beginning, the linked list is empty, i.e., *Tail* points to *nil*. *T*1 wants to acquire the lock, thus it tries to enqueue itself for the lock. *T*1 *node* (for the linked list) contains a memory location on which *T*1 spins while waiting for the lock and by default is Locked, and a pointer to the next element (i.e., the next thread node) of the waiting list. To acquire the lock, *T*1 uses an atomic SWAP instruction, which atomically sets *Tails* to point to *T*1 *node* and retrieves the previous value of *Tail* (here *nil*).

(b) After the *SWAP*, *Tail* points to *T1 node*. Because *Tail* was previously *nil*, there is no other thread waiting for the lock nor inside the CS, thus *T1* enters the CS without waiting (*T1* memory location is **U**nlocked as *T1* does not wait).

(c) Another thread *T2* also wants to acquire the lock, thus it atomically uses SWAP to update the *Tail* pointer so that it points to *T2* node.

Figure 2.2 – Principle of the MCS lock algorithm.

(d) After the SWAP, because *Tail* was not previously *nil* (it pointed to *T1 node*), *T2* sets its node to be the successor of the previous *Tail*, i.e., *T2 node* is the successor of *T1 node*. It also waits (*T2* is in red) for its memory location (that is Locked) to become Unlocked before entering the CS. Note that contrary to a ttas lock (see fig. 2.1), each thread waiting for a MCS lock waits on its private memory location, avoiding cache line invalidations sent to all cores when the lock state changes (with MCS, cache lines are exchanged only between the cores of the unblocked thread and the lock holder).

(e) Upon CS exit, *T*1 sees that it has a successor, thus *T*1 releases the lock by changing the memory location of *T*2 *node* to Unlocked.

(f) *T*2 memory location is **U**nlocked, thus *T*2 enters the CS.

(g) Upon CS exit, *T*2 sees that it has no successor, thus it tries to release the lock by setting the *Tail* pointer back to *nil* using a CAS atomic instruction The CAS is necessary to ensure that both checking that *Tail* points to *T*2 *node* and changing *Tail* execute atomically. Otherwise, another thread might try to acquire the lock while *T*2 releases it (i.e., the other thread switches *Tail* to point to its node and sets itself as the successor of *T*2).

(h) T2 successfully sets Tail to nil, both T1 and T2 are outside the CS.

Figure 2.2 – Principle of the MCS lock algorithm (Cont.).

## 3) Hierarchical approaches

These approaches aim at providing scalable performance on NUMA machines, by attempting to reduce the rate of lock migrations (i.e., cache line transfers between last level caches), which are known to be costly between NUMA nodes. A hierarchical lock tends to give the lock to a thread running on the same NUMA node as the thread holding the lock, improving throughput, at the expense of fairness between threads. This category includes HBO [88], HCLH [75], FC-MCS [37], HMCS [25] and the algorithms that stem from the *lock cohorting* framework [38]. A cohort lock is based on a combination of two lock algorithms (similar or different): one used for the global lock and one used for the local locks (there is one local lock per NUMA node); in the usual  $C-L_A-L_B$  notation,  $L_A$  and  $L_B$  respectively correspond to the global and the node-level lock algorithms. The list notably includes C-BO-MCS, C-PTL-TKT and C-TKT-TKT (also known as HTicket [33]). The *BO*, *PTL* and *TKT* acronyms respectively correspond to Backoff lock, Partitioned Ticket lock, and standard Ticket lock.

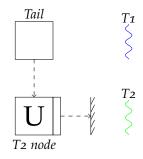

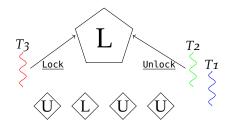

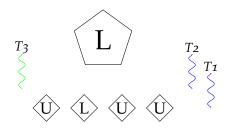

Figure 2.3 illustrates a cohort lock algorithm.

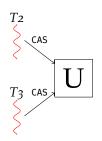

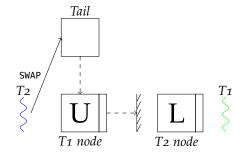

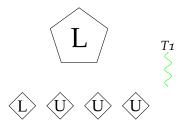

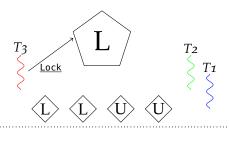

(a) A cohort lock algorithm is a hierarchical lock composed of two different lock algorithms: a global one (represented by a pentagon) and a local one (represented by a rotated square). There are one local lock per NUMA node (here 4) and one global lock. Each lock composing a cohort lock starts in a Ulnocked state. To acquire the cohort lock, *T*1 first locks the local lock attached to the NUMA node on which *T*1 runs (here the left-most one).

(b) *T*1 is the lock holder of its local lock and it tries to acquire the global lock.

(c) T1 has both a local lock and the global lock, it enters the CS.

Figure 2.3 – Principle of a Cohort lock algorithm.

(d) *T*2 also wants to acquire the cohort lock. Because it runs on the same NUMA node as *T*1, *T*2 tries to acquire the same local lock as *T*1. The lock is already taken by *T*1, thus *T*2 waits for the lock to become available.

(e) Upon exit of the CS, *T*1 sees that there is a waiting thread on its local lock, thus it unlocks the local lock, which will be acquired by *T*2. Because *T*1 and *T*2 have the same local lock, *T*1 does not unlock the global lock, but "gives" it to *T*2 (there is no special action here, the global lock "belongs" to a NUMA node, not to a specific thread).

Note that not all lock algorithms can be used for the global/local locks: (i) for the local lock algorithm, it must be possible to know if there is another waiting thread (also known as *cohort detection*), and (ii) the global lock algorithm must support the scenario where the thread locking the lock is not the same as the thread unlocking it (also known as *thread-oblivousness*).

(f) A new thread *T*3 wants to enter the CS. *T*3 does not run on the same node as *T*1 and *T*2, thus it tries to acquire its local lock (the second one on the left) and succeeds.

(g) T3 sees that its NUMA node is not the holder of the global lock, thus it waits for the global lock to be released. Here we see that in the worst case, there are at most N-1 waiting threads on the global lock (where N is the number of NUMA nodes).

(h) Upon CS exit, T2 releases its local lock.

15

(i) Because there is no other waiting thread on the local lock of T2, it releases the global lock, which belongs to T2's NUMA node.

(j) *T*3 acquires the global lock. Because it has both a local lock and the global one, it enters the CS. If there is no other thread that tries to acquire the cohort lock, upon CS exit, *T*3 will first unlock its local lock, then the global one (similarly to the previous step).

Figure 2.3 – Principle of a Cohort lock algorithm (Cont.).

## 4) Delegation-based approaches

Delegation-based lock algorithms are locks in which it is (sometimes or always) necessary for a thread to delegate the execution of a critical section to another thread. The typical benefits expected from such approaches are improved cache locality for the operations within the critical section and better resilience under very high lock contention. This category includes Oyama [85], Flat Combining [55], RCL [72], FFWD [93], CC-Synch [43] and DSM-Synch [43]. Contrary to other algorithms, delegation-based algorithms require critical sections to be expressed as a form of closure (e.g., a function), which is not compatible with the lock/unlock API presented earlier (§2.1.1).

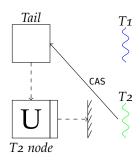

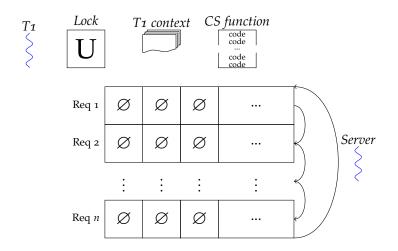

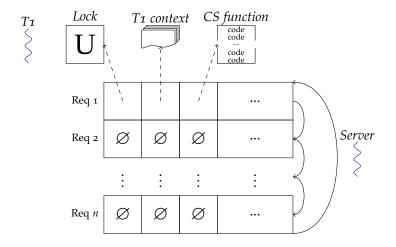

Figure 2.4 illustrates the RCL lock algorithm.

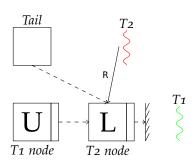

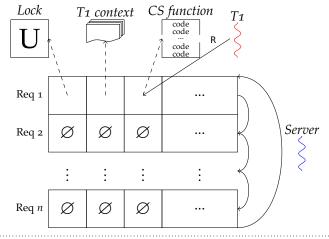

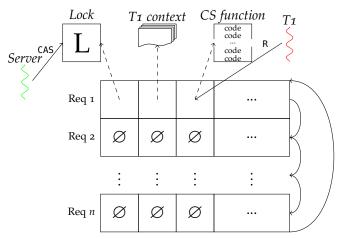

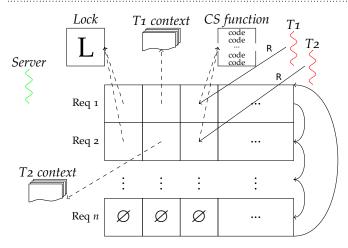

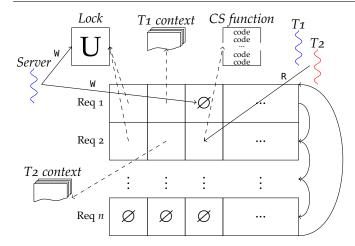

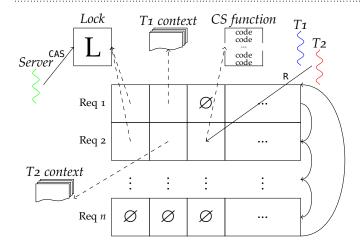

(a) A RCL lock delegates the execution of the CS to a remote thread (the Server). The Server monitors an array of requests (one slot per thread), where each request is composed of a pointer to the lock protecting the CS, a pointer to a structure called the context, which contains the environment (e.g., variables) with which the CS must be executed, and a pointer to the CS function. Each request entry is padded to fit a cache line to avoid false sharing. Note that one of the limitations of RCL is that the CS must be expressed as a function taking a list of arguments (the context), which is not the initial semantics of a POSIX mutex lock. As a consequence, RCL is not transparent w.r.t. the application. The Server continuously scans the array for the slot whose CS function field is not nil, which indicates that a thread wants a CS to be executed.

On this figure, *T*1 wants to execute a CS protected by a lock (by default Unlocked).

(b) After having set up its context, *T*1 writes the *lock*, *context* and *CS function* addresses to their respective pointer fields.

Figure 2.4 – Principle of the RCL lock algorithm.

(c) *T*1 waits for its request to be fulfiled (i.e., waiting for the CS to be executed on its behalf) by waiting for the *CS function* pointer to become *nil*.

Note that the *Server* serializes all CS executions, even if they acquire different locks. However, when two requests use the same lock, only the *Server* acquires the lock (avoiding cache line transfers), the requesting threads wait on their private *CS function* field.

(d) The *Server* sees a new request (*CS function* of *T*1 is not *nil*) and first tries to acquire the lock pointed by the *lock* pointer field. RCL still tries to take the lock atomically in the case of a concurrent thread that did not delegate its CS execution to the *Server*. The *Server* succeeds and enters the CS.

(e) While the *Server* is executing the CS of *T*1, another thread *T*2 requests the execution of the same CS protected by the same lock. It sets up its context, its request fields, and waits on the *CS function* pointer for its request to be fulfilled.

Figure 2.4 – Principle of the RCL lock algorithm (Cont.).

(f) The *Server* finished handling the request of *T*1: it writes *nil* inside *T*1 *CS function* pointer, which unblock *T*1. The *Server* also unlocks the lock.

(g) The *Server* proceeds to the next request and sees *T2*'s one. As a consequence, it atomically acquires the lock, and enters the CS.

(h) Finally, the *Server* finishes *T2*'s request, and writes *nil* to *T2*'s *CS function* pointer to unblock *T2*.

Figure 2.4 – Principle of the RCL lock algorithm (Cont.).

# 5) Load-control mechanisms

This category includes lock algorithms implementing mechanisms that detect situations in which a lock needs to adapt itself. For example, GLS [10] and SANL [112] switches between different lock algorithms to cope with changing levels of contention (i.e., how many threads concurrently attempt to acquire a lock). Other algorithms such as AHMCS<sup>3</sup> [24] and so-called *Malthusian algorithms* like Malth\_Spin and Malth\_STP<sup>4</sup> [34] adapt the locking scheme (i.e., how a lock is acquired/released) depending on the contention level. Finally, some algorithms aim to avoid lock-related pathological behaviors (e.g., preemption of the lock holder to execute a thread waiting for the lock): MCS-TimePub<sup>5</sup> [54] and LC [61] are two examples of such locks.

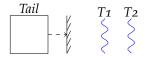

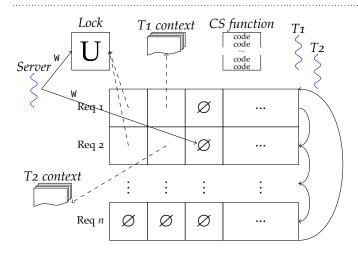

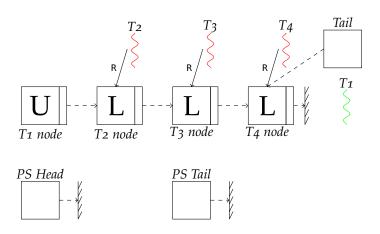

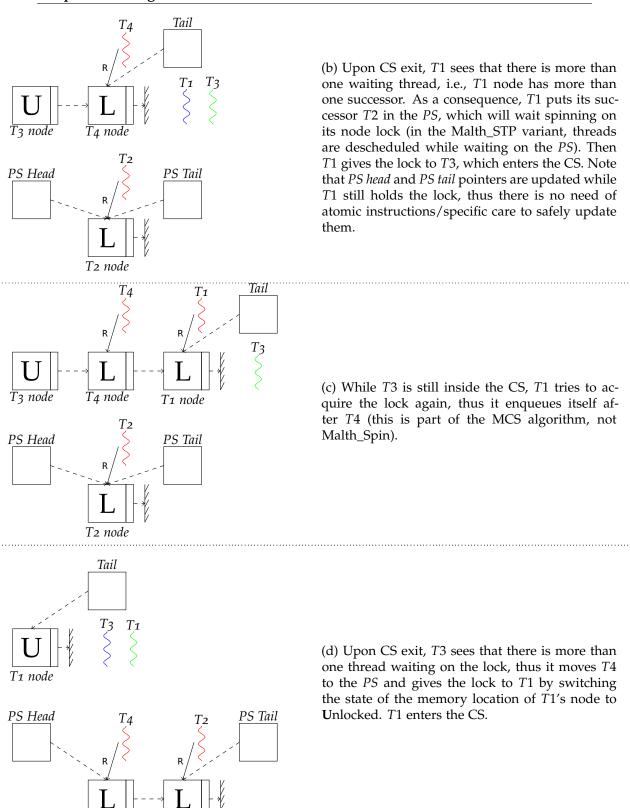

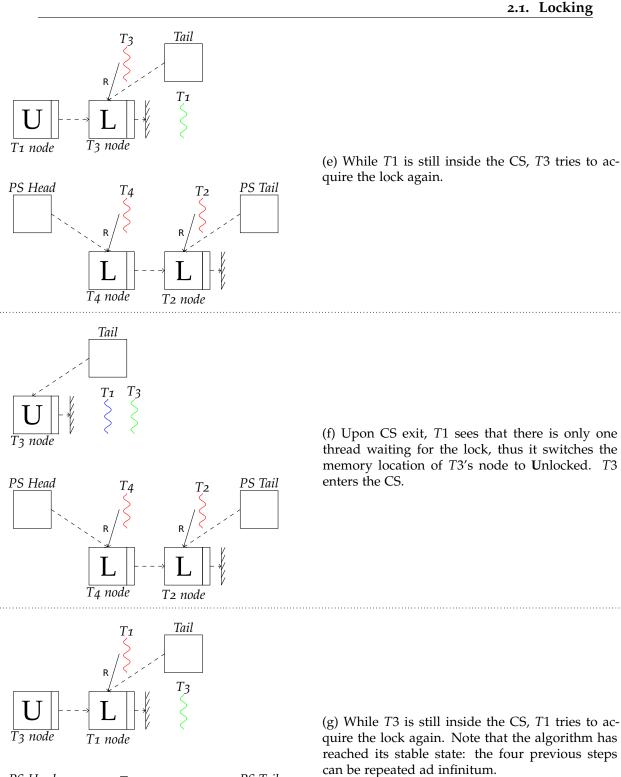

Figure 2.5 illustrates the Malth\_Spin lock algorithm.

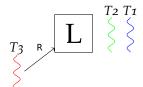

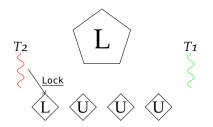

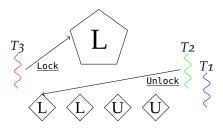

(a) A Malth\_Spin lock algorithm is a modification of the MCS lock algorithm. The idea of Malth\_Spin is to move the surplus of waiting threads into a passive set (PS hereafter), where threads in this set do not compete to acquire the lock. Malth\_spin eventually converges towards the situation where there is at most one thread in the CS, one thread waiting for the lock, and all the other waiting threads are in the PS or outside the CS. The PS is maintained as a double linked list, where the head and the tail of this list are tracked with PS head and PS tail pointers. All modifications to the MCS algorithm are made inside the unlock operation, just before releasing the lock.

In this figure, we start with a MCS lock with three waiting threads (*T*2, *T*3, *T*4) and one thread inside the CS (*T*1). There is no thread in the *PS* yet, i.e., both *PS head* and *PS tail* point to *nil*.

Figure 2.5 – Principle of the Malth\_Spin lock algorithm.

<sup>&</sup>lt;sup>3</sup>The original AHMCS paper [24] presents multiple versions of AHMCS. In this article, the version *without* hardware transactional memory of AHMCS is considered.

<sup>&</sup>lt;sup>4</sup>Malth\_Spin and Malth\_STP correspond to MCSCR-S and MCSCR-STP respectively in the terminology of Dave Dice [34]; still we do not use the latter names to avoid confusion with other MCS locks.

<sup>&</sup>lt;sup>5</sup>MCS-TimePub is mostly known as MCS-TP. Still, we use MC-TimePub to avoid confusion with MCS\_STP.

Figure 2.5 – Principle of the Malth\_Spin lock algorithm (Cont.).

T<sub>4</sub> node

T2 node

Figure 2.5 – Principle of the Malth\_Spin lock algorithm (Cont.).

PS Tail

$T_2$

T2 node

PS Head

T<sub>4</sub> node

Figure 2.5 – Principle of the Malth\_Spin lock algorithm (Cont.).

# 2.1.3 Waiting policy

An important design dimension of lock algorithms is the *waiting policy* used when a thread cannot immediately obtain a requested lock [34]. There are three main approaches.

# **Spinning**

The most straightforward solution for waiting is to continuously check the status of the lock until it becomes available. However, such a policy might waste energy, and the time spent waiting on a core might prevent other descheduled threads from progressing. Processors provide special instructions to inform the CPU microarchitecture when a thread is spinning. For example, x86 CPUs offer the PAUSE instruction<sup>6</sup> that is specifically designed to avoid branch-misprediction, and which informs the core that it can release shared pipeline resources to sibling hyperthreads [34].

In case of a failed lock acquisition attempt, different lock algorithms can use different (and possibly combine several) techniques to lower the number of simultaneous acquisitions attempts and the energy consumption while waiting. Using a fixed or randomized backoff (i.e., a thread avoids attempting to acquire the lock for some time) lowers the number of concurrent atomic instructions, thus the cache-coherence traffic. Hardware facilities can also be used to lower the frequency of the waiting thread's core (DVFS [106]), or to notify the core that it can enter in an idle state to save power (via the MONITOR/MWAIT instructions [42]<sup>7</sup>). Finally, a thread can voluntarily surrender its core in a polite fashion by calling sched\_yield or sleep.

#### Immediate parking

With immediate parking<sup>8</sup>, a thread waiting for an already held lock immediately blocks until the thread gets a chance to obtain the lock<sup>9</sup>. This waiting policy requires kernel support (via the futex syscall on Linux) to inform the scheduler that the thread is waiting for a lock, so that it does not try to schedule the thread until the lock is made available. At unlock-time, the lock holder is then responsible to inform the scheduler that the lock is available.

<sup>&</sup>lt;sup>6</sup>The MFENCE instruction can also be used and is known to yield lower energy consumption than the PAUSE instruction on certain Intel processors [42].

<sup>&</sup>lt;sup>7</sup>On the x86 platform, MONITOR/MWAIT are privileged instructions, which are accessible for locks running in privilegied mode, or via a kernel module [8].

<sup>&</sup>lt;sup>8</sup>In the remainder of this manuscript, we use *blocking* and (*immediate*) parking interchangeably.

<sup>&</sup>lt;sup>9</sup>Some locks use timeouts to bound the time a thread spends in the blocked state in order to improve responsiveness.

# Hybrid approaches

The motivation behind hybrid approaches is that different waiting policies have different costs. For example, the *spin-then-park* policy is a hybrid approach using a fixed or adaptive spinning threshold [63]. It tries to mitigate the cost of parking as the block and unblock operations are expensive (both in terms of energy and performance). The spinning threshold is generally equal to the time of a round-trip context switch. Other techniques mix different spinning policies, such as backoff and sched\_yield [33]. Finally, more complex combinations can be implemented: some algorithms [103, 42] trade fairness for throughput by avoiding to unpark a thread at unlock-time if there is another one currently spinning (also known as *adaptive unlock*).

The choice of the waiting policy is mostly orthogonal to the lock design but, in practice, policies other than pure spinning are only considered for certain types of locks: the direct handoff locks (from categories 2, 3 and 5 above), Mutexee and the standard Pthread mutex locks. However, this choice directly affects both the energy efficiency and the performance of a lock: Falsafi et al. [42] found that pure spinning inherently hurts power consumption, and that there is no practical way to reduce the power consumption of pure spinning. They found that blocking can indeed save power, because when a thread blocks, the kernel can then put the core(s) in one of the low-power idle states [6, 59]. However, the process of blocking is costly, because the cost of the blocking and unblocking operations is high on Linux. Switching continuously between blocking and unblocking can hurt energy efficiency, sometimes even more than using pure spinning policies. Thus, there is an energy-efficiency tradeoff between spinning and parking. Note that we use hereafter the expression *parking policy* to encompass both *immediate parking* and hybrid *spin-then-park* waiting policies.

In this Section, we provided background on locking, proposed a categorization of the existing lock algorithms and discussed the importance of the waiting policy of a lock algorithm. Designing correct and efficient lock algorithms is hard: the number of design choices (e.g. NUMA-aware, succession policy, waiting policy) is large and these choices imply trade-offs. The next Section discusses work around lock algorithm implementations and their effect on performance.

# 2.2 Related work

This thesis aims to understand the performance of existing lock algorithms on modern multicore machines. In this Section, we discuss the large body of work studying the different aspects of lock algorithms. More precisely, Section 2.2.1 presents work studying the implementation of lock algorithms, and previous approaches to transparently replace lock algorithms inside applications. Section 2.2.2 discusses the possibility to dynamically adapt lock synchronization at run-time. Section 2.2.3 considers previous studies of multicore lock algorithms. Section 2.2.4 covers existing works that highlight the importance of energy efficiency for both applications and lock algorithms. Finally, Section 2.2.5 discusses lock-related performance bottlenecks.

# 2.2.1 Lock algorithm implementations

The design and implementation of the LiTL lock library (presented in Chapter 3) borrows code and ideas from previous open-source toolkits that provide application developers with a set of optimized implementations for some of the most-established lock algorithms: Concurrency Kit [4], liblock [73, 71, 72], libslock [33] and lockin [42, 10]. All of these toolkits require potentially tedious source code modifications in the target applications, even in the case of algorithms that have been specifically designed to lower this burden [12, 95, 107]. Moreover, among the above works, virtually none of them provides a simple and generic solution for supporting Pthread condition variables. One noticeable exception is lockin [42, 10], which only requires including a header inside the source code of the application and recompile it linked against a specific shared library. lockin also proposes a condition variable algorithm; still the proposed algorithm does not circumvent the "thundering-herd" effect for all lock algorithms (see Section 3.1.2). The authors of liblock [72] proposed an approach to support condition variables; still we discovered that it suffers from liveness hazards due to a race condition (more details in Section 3.1.2). Indeed, when a thread T calls pthread\_cond\_wait, it is not guaranteed that the two steps (releasing the lock and blocking the thread) are always executed atomically. Thus, a wake-up notification issued by another thread might get interleaved between the two steps and T might remain indefinitely blocked.

Several research works have leveraged library interposition to compare different locking algorithms on legacy applications (e.g., Johnson et al. [61] and Dice et al. [38]). However, to the best of our knowledge, they have not publicly documented the design challenges to support arbitrary application patterns (e.g., condition variables), nor disclosed the corresponding source code and the overhead of their interposition library has not been discussed.

# 2.2.2 Adaptive algorithms

Previous works discuss the possibility to dynamically adapt lock synchronization at run-time. One way is to dynamically switch between lock algorithms depending on the contention level. The work by Lim et al. [70] considers switching among three lock algorithms (TTAS, MCS and a delegation-based one), depending on the level of contention on the lock instance. SANL [112] switches between local and remote (i.e., delegation-based) locking schemes. As explained in Section 2.1.2, delegation-based algorithms require critical sections to be expressed as a form of closure, which is incompatible with our transparent approach (i.e., without source code modification). More recently, Antic et al. [10] proposed GLS, a solution that dynamically switches among three lock algorithms (Ticket, MCS, Pthread mutex), using Ticket at low contention levels, MCS at high contention levels, and Pthread when it detects overthreading (i.e., more threads than cores). While these approaches confirm our observations that there is no one-size-fit-all locking algorithm (more details in Section 4.5), their goal is to make locking easy for a developer, not to choose the best lock algorithm in all cases. Indeed, they only switch among a few different lock algorithms, whereas, as we will show with our study, there are more lock algorithms to consider, making the choice more complex. None of the solutions considers some of the bottlenecks that we observed, like trylock contention, the lock handover effect and bottlenecks related to the memory footprint of a lock instance (§4.5). For example, all solutions embed all the different lock data structures into a unique one, inflating the memory layout of a lock instance: some applications (e.g., dedup) using thousands of lock instances that are good with a classical low memory footprint Ticket algorithm might not be good with the Ticket version of GLS, even if GLS never uses lock algorithms other than Ticket.

A second solution is to monitor the load pattern of the application to detect situations that are subject to pathological behavior. Load control (LC) [61] is a runtime solution, which dynamically reduces the number of threads trying to acquire the lock at the same time, to avoid pathological issues (e.g., lock convoy). LC requires kernel modifications on Linux to measure load accurately and with high resolution ( $\sim 100\mu s$ ). This approach is thus incompatible with our work, where we focus on lock algorithms that do not require code modifications. As we will show later, our work highlights the need for low-memory, complete interface (i.e., lock, trylock, and condition variables), fully adaptive (i.e., from spinlocks all the way to complex HMCS locks) lock algorithms. Yet, none of the existing solutions answer this need.

# 2.2.3 Studies of synchronization algorithms

Several studies have compared the performance of different multicore lock algorithms, from a theoretical angle and/or based on experimental results [9, 80, 65, 19, 95, 33, 71, 38]. Our study (see Chapter 4) encompasses significantly more lock algorithms

and waiting policies. Moreover, the bulk of these prior studies is mainly focused on characterization microbenchmarks, while we focus instead on workloads designed to mimic real applications. Two noticeable exceptions are the work from Boyd-Wickizer et al. [19] and Lozi et al. [72]; still they do not consider the same context as our study. The former is focused on kernel-level locking bottlenecks, and the latter is focused on applications in which only one or a few heavily contended critical sections have been rewritten/optimized (after a profiling phase). For all these reasons, we make observations that are significantly different from the ones based on all the abovementioned studies.

Some related work discusses the choice of synchronization paradigms and lock algorithms [78, 79, 77]. The proposed guidelines are often a subset of our proposed guidelines in Section 4.5.2: because these works only study a smaller set of applications and lock algorithms, they generally do not cover all the cases we observed.

Other synchronization-related studies have a different scope and focus on concurrent data structures, possibly based on other facilities than locks. Gramoli [48] studies different concurrent data structures on micro-benchmarks with multiple synchronization techniques. David el al. [31, 32] evaluate theoretical and practical progress properties of concurrent search data structures. Brown et al. [20] study the performance of hardware transactional memory with microbenchmarks on modern NUMA multicore machines. Finally, Calciu et al. [21] study the tradeoff between message passing and shared memory synchronization on multicore machines. Similarly to us, they advocate that software should be designed to be largely independent of the choice of low-level communication mechanism.

#### 2.2.4 Energy efficiency

Improving energy efficiency in systems and applications has been thoroughly studied in the past. For example, previous works describe user-level [109, 99, 98, 82, 92, 110] and kernel [86] facilities that both manage and predict power consumption. Prior works propose trading performance and/or precision for energy. For example, programming models [13, 94] allow developers to approximate loops to decrease power consumption. Compiler techniques [109, 108] and hardware mechanisms [66] trade off performance for energy. To the best of our knowledge, the work by Falsafi et al. [42] is the only one studying the energy efficiency of lock algorithms. In this thesis, we confirm their findings and validate their POLY<sup>10</sup> conjecture on significantly more lock algorithms and applications (see Section 4.3).

<sup>&</sup>lt;sup>10</sup>POLY stands for "Pareto optimality in locks for energy efficiency".

# 2.2.5 Lock-related performance bottlenecks