# UTBB FDSOI mosfet dynamic behavior study and modeling for ultra-low power RF and mm-Wave IC Design

Salim El Ghouli

### ▶ To cite this version:

Salim El Ghouli. UTBB FDSOI mosfet dynamic behavior study and modeling for ultra-low power RF and mm-Wave IC Design. Micro and nanotechnologies/Microelectronics. Université de Strasbourg, 2018. English. NNT: 2018STRAD015. tel-02136789

## HAL Id: tel-02136789

https://theses.hal.science/tel-02136789

Submitted on 22 May 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## UNIVERSITÉ DE STRASBOURG

# ÉCOLE DOCTORALE MSII ICUBE – UMR7357

THÈSE présentée par :

## Salim EL GHOULI

soutenue le 22 juin 2018

pour obtenir le grade de : Docteur de l'université de Strasbourg

Discipline / Spécialité : Science de l'ingénieur / Micro et Nano électronique

# UTBB FDSOI MOSFET DYNAMIC BEHAVIOR STUDY AND MODELING FOR ULTRA-LOW POWER RF and mmWAVE IC DESIGN

THÈSE dirigée par :

M. LALLEMENT Christophe

Professeur, université de Strasbourg

et codirigée par : M. SALLESE Jean-Michel

Maître d'enseignement et de recherche, École Polytechnique

Fédérale de Lausanne (EPFL), Suisse

**RAPPORTEURS:**

Mme. MANEUX Cristell Professeur, Université de Bordeaux

M. INIGUEZ Benjamin Professeur, Universitat Rovira i Virgili, Tarragona, Spain

**EXAMINATEURS:**

M. HEBRARD Luc Professeur, Université de Strasbourg

M. JUGE André Docteur, STMicroelectronics

# بِسْمِ اللَّهِ الرَّحْمَنِ الرَّحِيمِ وَمَا يُلَقَّاهَا إِلَّا الَّذِينَ صَبَرُوا وَمَا يُلَقَّاهَا إِلَّا ذُو حَظٍّ عَظِيمٍ

"And no one will be granted such goodness except those who exercise patience and selfrestraint, none but persons of the greatest good fortune." Quran, Surat 41, Ver. 35.

To my parents, my wife and my son

## Acknowledgments

I would like to express my sincere gratitude to Christophe Lallement for directing this research work and for his patience, support, and encouragement. Without his supervision this research work would not have been possible.

The interesting ideas treated in this research work would not have been thinkable without the brilliant and instructive suggestions of the co-director Jean-Michel Sallese. I thank him very much for his support, discussions and unique pedagogical guidance.

I'm highly indebted to Michel Minondo, André Juge, Hervé Jaouen, Thierry Poiroux and Patrick Scheer for their daily support and encouragement. In particular, André's bright comments have had a significant impact in almost all aspects of my research work. I would also like to show my gratitude to Frederic Monsieur and Denis Rideau for sharing their physics knowledge and TCAD expertise with me.

I would like to thank Veronique Bessodes and Christophe Bernicot for their unconditional support and advice. Additionally, it has been a great privilege to interact with Frederic Paillardet, Jean-Pierre Blanc, Lionel Vogt, Eric Nercessian, Nicolas Pelloux, and Stephane Le Tual from STMicroelectronics design team.

I would also like to thank Gilles Gouget, Clément Charbuillet, Kanika Sharma, Jean Remy, Benoit Legoix, Vincent Quenette, Frederic Dauge, Benoit Morel, Benjamin Dormieu, Pascal Fonteneau, Michel Buczko, and Sebastien Jan from STMicrolectronics for their collaboration and support. I thank all who in one way or another contributed in the completion of this research work.

Most importantly, I would like to thank my wife Pauline Vettier and my son Ilyas El Ghouli for their permanent support, patience and encouragement without whom this research work would not have been possible. They have truly embellished my life. I'm also thankful to my wife's parents for their permanent support.

I would like to finally express my gratitude to my parents for their immense sacrifices to ensure I received the best possible education. My brothers and sister for their encouragement and patience.

## **Abstract**

This research work has been motivated primarily by the significant advantages brought about by the UTBB FDSOI technology to the Low power Analog and RF applications. The main goal is to study the dynamic behavior of the UTBB FDSOI MOSFET in light of the recent technology advances and to propose predictive models and useful recommendations for RF IC design with particular emphasis on Moderate Inversion regime. After a brief review of progress in MOSFET architectures introduced in the semiconductor industry, a state-of-the-art UTBB FDSOI MOSFET modeling status is compiled. The main physical effects involved in the double gate transistor with a 7 nm thick film are reviewed, particularly the back gate impact, using measurements and TCAD. For better insight into the Weak Inversion and Moderate Inversion operations, both the low frequency g<sub>m</sub>/I<sub>D</sub> FoM and the proposed high frequency y<sub>m</sub>/I<sub>D</sub> FoM are studied and also used in an efficient first-cut analog design. Finally, a high frequency NQS model is developed and compared to DC and S-parameters measurements. The results show excellent agreement across all modes of operation including very low bias conditions and up to 110 GHz.

Key words: Analog and RF, Double-gate FETs, Fully Depleted Silicon-on-Insulator (FDSOI), UTBB, Inversion Coefficient, Transconductance efficiency, g<sub>m</sub> over I<sub>D</sub>, Transadmittance efficiency, Low-Power, Low-Voltage, HF, mm-Wave, NQS, LNA, LNA-MIXER.

## Résumé

Ce travail de recherche a été principalement motivé par les avantages importants apportés par la technologie UTBB FDSOI aux applications analogiques et RF de faible puissance. L'objectif principal est d'étudier le comportement dynamique du transistor MOSFET du type UTBB FDSOI et de proposer des modèles prédictifs et des recommandations pour la conception de circuits intégrés RF, en mettant un accent particulier sur le régime d'inversion modérée. Après une brève analyse des progrès réalisés au niveau des architectures du transistor MOSFET, un état de l'art de la modélisation du transistor MOSFET UTBB FDSOI est établi. Les principaux effets physiques impliqués dans le transistor à double grille avec une épaisseur du film de 7 nm sont passés en revue, en particulier l'impact de la grille arrière, à l'aide de mesures et de simulations TCAD. La caractéristique g<sub>m</sub>/I<sub>D</sub> en basse fréquence et la caractéristique y<sub>m</sub>/I<sub>D</sub> proposée pour la haute fréquence sont étudiées et utilisées dans une conception analogique efficace. Enfin, le modèle NQS haute fréquence proposé reproduit les mesures dans toutes les conditions de polarisation y compris l'inversion modérée jusqu'à 110 GHz.

Mots-clés : Analogique et RF, Double Grille, FDSOI, UTBB, Coefficient d'inversion, Efficacité de la transconductance, g<sub>m</sub> sur I<sub>D</sub>, Efficacité de la transadmittance, faible puissance, faible tension, HF, spectre millimétrique, NQS, LNA, LNA-MIXER.

## Contents

| List of Fi | igures                                          | ii    |

|------------|-------------------------------------------------|-------|

| List of ta | ables and diagrams                              | xiv   |

| List of A  | ppendices                                       | xv    |

| Acronym    | ns and Abbreviations                            | xvi   |

| List of S  | ymbols                                          | xviii |

| Introduc   | tion                                            | 1     |

| Backgro    | ound and Motivation                             | 1     |

| Thesis (   | Outline                                         | 3     |

| Chapter    | 1 State of the Art                              | 7     |

| 1.1 l      | ntroduction                                     | 7     |

| 1.2 L      | JTBB FDSOI technology                           | 10    |

| 1.3        | Device modeling approaches                      | 16    |

| 1.4 L      | JTBB FDSOI compact models                       | 18    |

|            | BSIM IMG                                        |       |

| 1.4.2      | HISIMSOTB                                       | 21    |

| 1.4.3      | UFDG                                            | 21    |

| 1.4.4      | Leti-UTSOI2                                     | 22    |

| 1.5        | Conclusion                                      | 23    |

| Part I DC  | and Small Signal Low Frequency Operation        | 25    |

| Chapter    | 2 DC and Low Frequency description and modeling | 27    |

| 2.1 l   | ntroduction                                                   | 27 |

|---------|---------------------------------------------------------------|----|

| 2.2 L   | JTBB FDSOI MOSFET description and DC operation                | 30 |

| 2.2.1   | C-V characteristic                                            | 31 |

| 2.2.2   | I-V characteristic                                            | 36 |

| 2.3     | DC and low frequency small-signal operation modeling and      |    |

| charact | erization                                                     | 43 |

| 2.3.1   | Long channel DC modeling – a threshold voltage based approach | 44 |

| 2.3.2   | Equivalent low frequency small signal circuit                 | 51 |

| 2.3.3   | DC and low frequency characterization                         | 56 |

| 2.3.4   | Normalization                                                 | 60 |

| 2.4 I   | -V and C-V operations assessment                              | 60 |

| 2.4.1   | I-V operation assessment                                      | 61 |

| 2.4.2   | C-V operation assessment                                      | 64 |

| 2.4.3   | Dynamic operation assessment using UTSOI2 and the equivalent  |    |

| circui  | it 65                                                         |    |

| 2.5     | Operating point information                                   | 69 |

| 2.5.1   | OP information inaccuracy for sub-circuit based MOSFETs       | 70 |

| 2.5.2   | Enhancement proposal                                          | 72 |

| 2.6     | Conclusion                                                    | 77 |

| Chantar | 2 g aver L inverience economent                               | 81 |

| Chapter | 3 $g_m$ over $I_D$ invariance assessment                      | 01 |

| 3.1 l   | ntroduction                                                   | 81 |

| 3.2 g   | g <sub>m</sub> over I <sub>D</sub> based design methodology   | 82 |

| 3.3 l   | nvariance unpredictability using TCAD                         | 83 |

| 3.4 T   | Transconductance efficiency and current normalizations        | 85 |

| 3.5 E   | Experimental results                                          | 88 |

| 3.5.1   | Back gate voltage impact                                      | 89 |

| 3.5.2   | Temperature impact                                            | 93 |

| 3.5.3   | Short channels                                                | 94 |

| 3.5.4   | Drain to source voltage                                       | 97 |

|     | 3.6          | Discussion on g <sub>m</sub> over I <sub>D</sub> invariance                           | 98  |

|-----|--------------|---------------------------------------------------------------------------------------|-----|

|     | 3.7          | Conclusion                                                                            | 99  |

| Pź  | art II F     | ligh frequency Operation                                                              | 101 |

| . ` | u. (         |                                                                                       |     |

| CI  | hapte        | r 4 High Frequency Operation                                                          | 103 |

|     | 4.1          | Introduction                                                                          | 103 |

|     | 4.2          | RF and mm-Wave characterization                                                       | 104 |

|     | 4.3          | High frequency operation modeling                                                     | 108 |

|     | 4.3.         | 1 Simplified front and back Gates models                                              | 110 |

|     | 4.3.         | 2 Channel segmentation                                                                | 115 |

|     | 4.3.         | Complete front and back gates model                                                   | 117 |

|     | 4.4          | RF and mm-Wave FoMs assessment                                                        | 120 |

|     | 4.4.         | 1 Y-parameters                                                                        | 121 |

|     | 4.4.         | 2 Current gain and Transit Frequency FoM                                              | 125 |

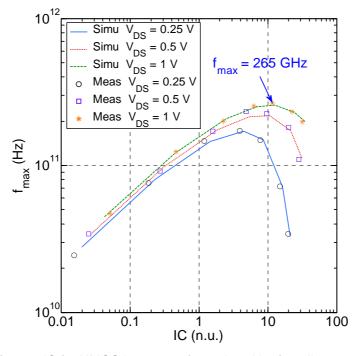

|     | 4.4.         | Mason's gain and maximum oscillation frequency FoM                                    | 128 |

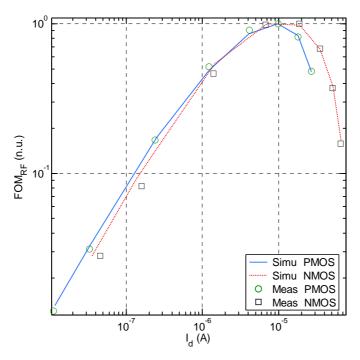

|     | 4.4.         | Performance and power consumption tradeoff FoM                                        | 130 |

|     | 4.5          | Conclusion                                                                            | 131 |

| CI  | hapte        | r 5 Transadmittance efficiency in presence of NQS effects                             | 133 |

|     | 5.1          | Introduction                                                                          | 133 |

|     | 5.2          | Device description and characterization                                               | 134 |

|     | F 0          | ·                                                                                     |     |

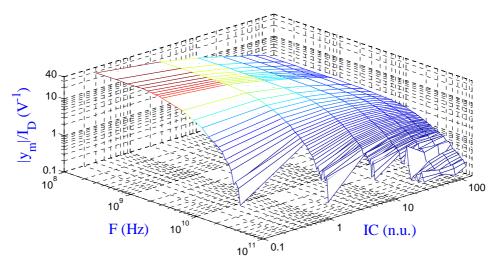

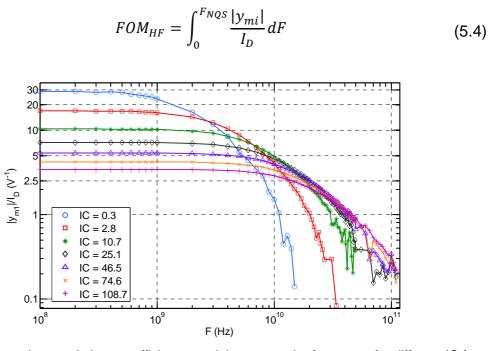

|     | 5.3<br>chann | Frequency dependence of the Transadmittance efficiency in long el UTBB FD SOI MOSFETs | 134 |

|     | 5.4          | Impact of distributed effects along the gate on NQS                                   | 141 |

|     | 5.5          | Onset of NQS effects                                                                  | 148 |

|     | 5.6          | Back gate control                                                                     | 150 |

|     | 5.6.         |                                                                                       |     |

|     | 5.6.         |                                                                                       |     |

|     | 5.7          | Channel Mobility extraction using NQS effect                                          | 153 |

| 5.8     | Discussion                                                 | 155 |

|---------|------------------------------------------------------------|-----|

| 5.9     | Conclusion                                                 | 156 |

| Part II | RF Design application                                      | 159 |

| Chapt   | er 6 RF and mm-Wave design application                     | 161 |

| 6.1     | Introduction                                               | 161 |

| 6.2     | Classical design sizing methods in Analog and RF           | 162 |

| 6.3     | Advantages of UTBB FDSOI technology                        | 166 |

| 6.4     | g <sub>m</sub> over I <sub>D</sub> invariance based method | 167 |

| 6.5     | High frequency performance assessment                      | 169 |

| 6.6     | LNA design using MI Tradeoff in UTBB FDSOI                 | 169 |

| 6.6     |                                                            |     |

| 6.6     | Passives related constraints and Length selection          | 171 |

| 6.6     | 6.3 Width and V <sub>GS</sub> calculations                 | 173 |

| 6.7     | LNA - MIXER                                                | 174 |

| 6.8     | Conclusion                                                 | 176 |

| Gener   | al conclusion                                              | 177 |

| Rese    | earch work results                                         | 177 |

| Pers    | pectives                                                   | 182 |

|         | graphy                                                     |     |

|         | grapity                                                    |     |

| Apper   | ndix A                                                     | 195 |

| Apper   | ndix B                                                     | 201 |

| Apper   | ndix C                                                     | 203 |

| Apper   | ndix D                                                     | 205 |

| Appendix E           | 209 |

|----------------------|-----|

| List of publications | 211 |

| Résumé de thèse      | 213 |

## List of Figures

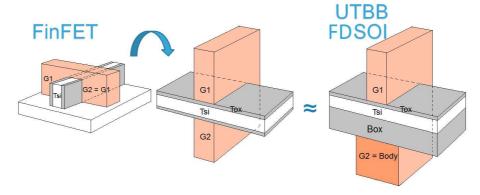

| Fig. | 1.1 FinFET (left) and UTBB FDSOI (right) similarity                                                  | 8    |

|------|------------------------------------------------------------------------------------------------------|------|

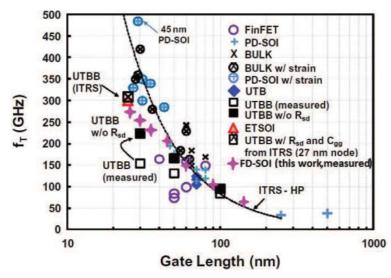

| Fig. | 1.2 Benchmarking transit frequency f <sub>T</sub> for various state-of-the-art MOSFETs versus        |      |

|      | gate length [14].                                                                                    | 8    |

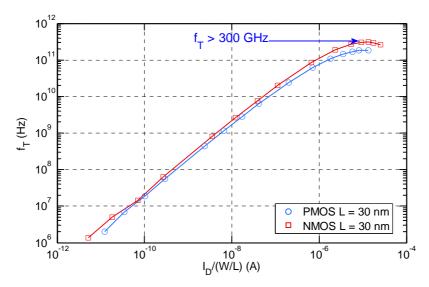

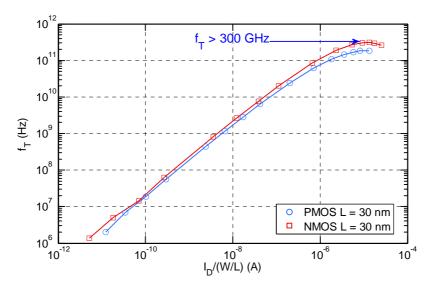

| Fig. | $1.3$ Measured $f_T$ versus normalized drain current $I_D/(W/L)$ for UTBB FDSOI NMOS                 |      |

|      | and PMOS (L = 30 nm, Nf = 20, $W_f$ = 1 $\mu$ m, $V_{DS}$ = 1 $V$ )                                  | 9    |

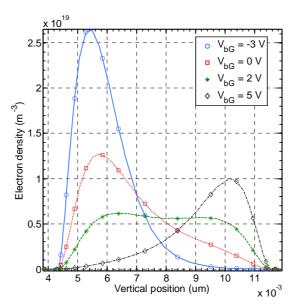

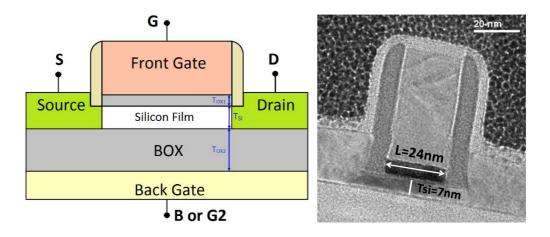

| Fig. | 1.4 Simulated electron density in the silicon film at different back gate voltages $V_{\text{bG}}$   |      |

|      | for a UTBB FDSOI NMOS (L = 1 $\mu m$ & W = 1 $\mu m$ ) in saturation $V_{DS}$ = 1 V and              |      |

|      | strong inversion (at constant $V_{GS} = 1 \text{ V}$ )                                               | . 10 |

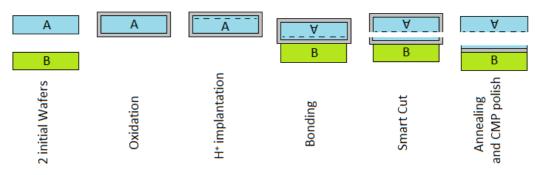

| Fig. | 1.5 UNIBOND fabrication process with Smart Cut                                                       | . 11 |

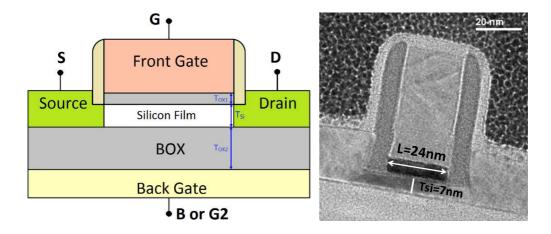

| Fig. | 1.6 Cross section (left) and TEM (right [3]) of the UTBB FDSOI MOSFET                                | . 11 |

| Fig. | 1.7 Cross section comparison between bulk MOSFET (right) and UTBB FDSOI                              |      |

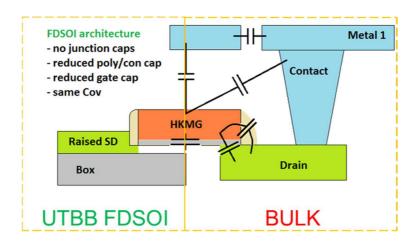

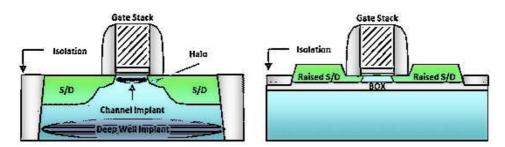

|      | (left)                                                                                               | . 12 |

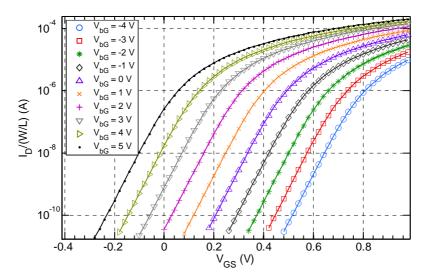

| Fig. | 1.8 Measured and normalized drain current $I_D/(W/L)$ versus front gate voltage $V_{GS}$             |      |

|      | for various back gate voltages $V_{\text{bG}}$ in semi logarithmic scale for $L=1~\mu\text{m},~W=10$ |      |

|      | $\mu m$ at $V_{DS} = 1$ V                                                                            | . 13 |

| Fig. | 1.9 Bulk MOSFET (left) versus UTBB FDSOI MOSFET (right)                                              | . 13 |

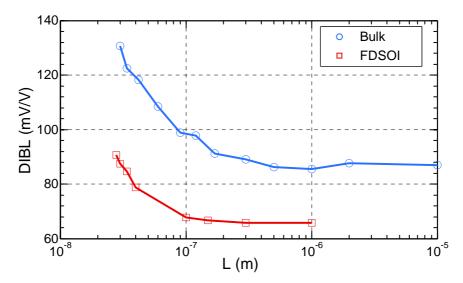

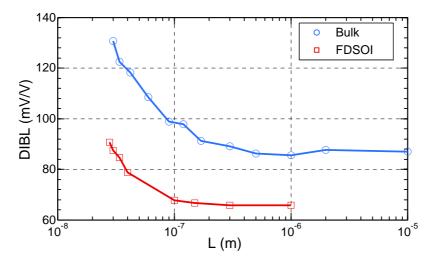

| Fig. | 1.10 Comparison of DIBL between FDSOI 28 nm and bulk 28nm technologies in                            |      |

|      | saturation ( $V_{DS} = 1 \text{ V}$ ) and $V_{bG} = 0 \text{ V}$ .                                   | . 14 |

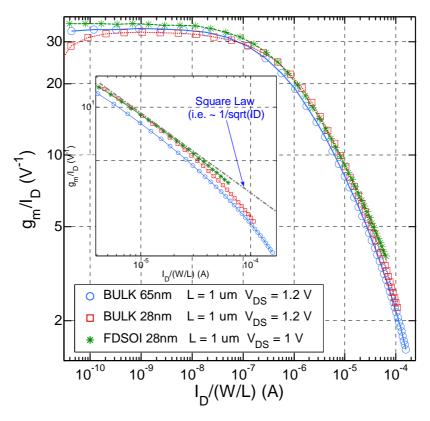

| Fig. | 1.11 Transconductance efficiency $g_m/I_D$ versus normalized drain current $I_D/(W/L)$ for           |      |

|      | long channels in saturation for bulk 65 nm, bulk 28 nm, and UTBB FDSOI 28 nm                         | . 16 |

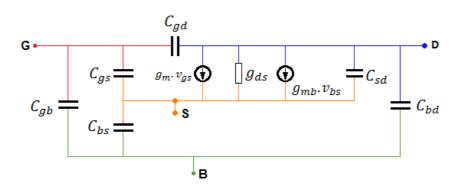

| Fig. | 1.12 Modified Meyer equivalent circuit.                                                              | . 17 |

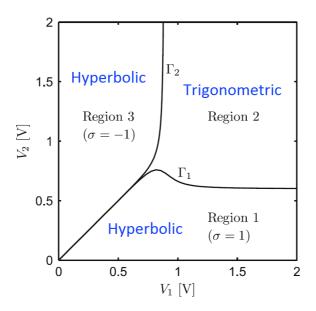

| Fig. | 1.13 Regions of operation on the front and back gates voltages plane for an imref                    |      |

|      | splitting $Vc=0.5V$ , $T_{si}=20$ nm, $T_{ox1}=2$ nm, and $T_{ox2}=40$ nm. $V_1$ and $V_2$ are the   |      |

|      | front and back gate voltages respectively [57]                                                       | . 19 |

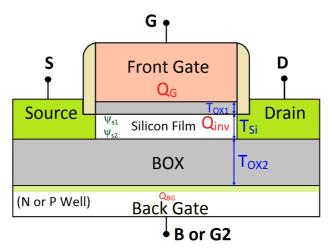

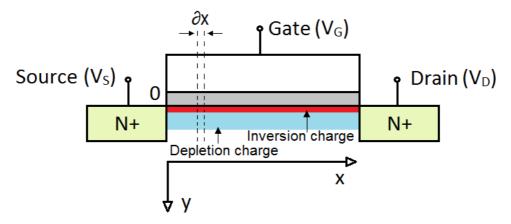

| Fig. | 2.1 UTBB transistor architecture (cross-section) with modeled charges as well as                     |      |

|      | front and back surface potentials                                                                    | .31  |

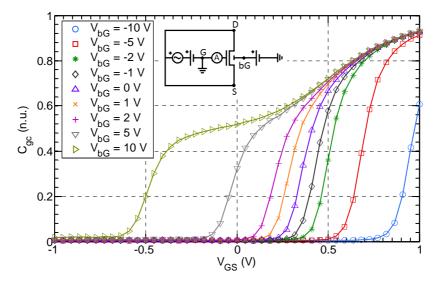

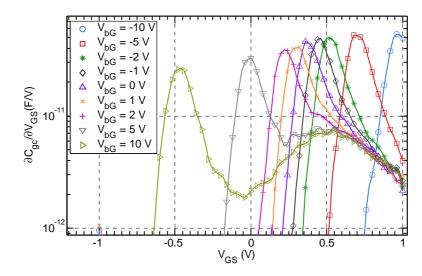

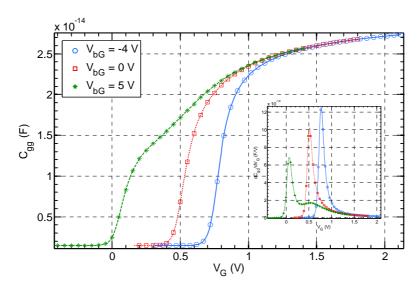

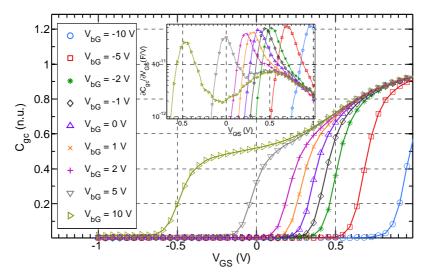

| Fig. | 2.2 Measured and normalized front gate capacitance versus front gate voltage for                                                 |      |

|------|----------------------------------------------------------------------------------------------------------------------------------|------|

|      | various back gate voltages for NMOS and at $V_{DS}=0\ V$ (L = 10 $\mu m,\ W=2\ \mu m,$                                           |      |

|      | MULT = 30). Inset: diagram showing C-V measurement procedure.                                                                    | . 32 |

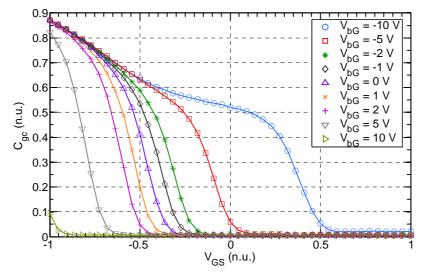

| Fig. | 2.3 Measured and normalized front gate capacitance versus front gate voltage for                                                 |      |

|      | various back gate voltages for PMOS and at $V_{DS}=0\ V$ (L = 10 $\mu m,\ W=2\ \mu m,$                                           |      |

|      | MULT = 30).                                                                                                                      | . 32 |

| Fig. | 2.4 Measured gate capacitance derivatives versus V <sub>GS</sub> for various back gate voltages                                  |      |

|      | for NMOS (L = 10 $\mu m,W$ = 2 $\mu m,MULT$ = 30).                                                                               | . 34 |

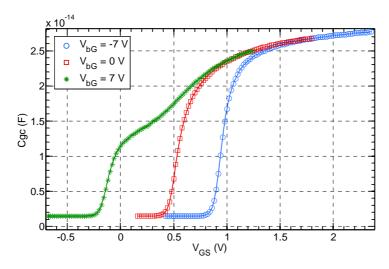

| Fig. | 2.5 TCAD simulations of the gate capacitance versus $V_{GS}$ for three $V_{bG}$ values (-7 V,                                    |      |

|      | 0 V, and 7 V) for $L=1~\mu m$ and $V_{DS}=1~V.$                                                                                  | . 34 |

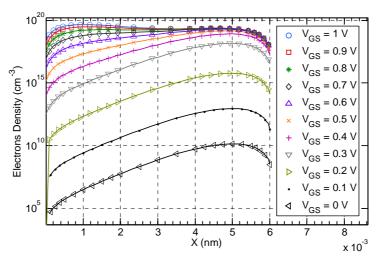

| Fig. | 2.6 Electron concentration versus position in the silicon film for various $V_{\rm GS}$ values                                   |      |

|      | and fixed $V_{bG}=7\ V$ for $L=1\ \mu m$ and $V_{DS}=1\ V.$                                                                      | . 35 |

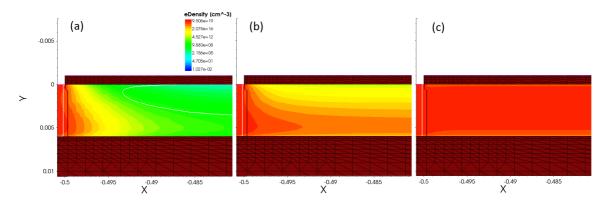

| Fig. | 2.7 Electron concentration using TCAD simulations for fixed $V_{bG} = 7 \text{ V}$ , and (a) $V_{GS}$                            |      |

|      | =0 V, (b) at threshold $V_{GS}=0.3~V$ and (c) $V_{GS}=1~V$ for $L=1~\mu m$ and $V_{DS}=1~V$                                      | . 35 |

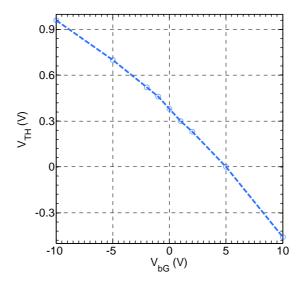

| Fig. | 2.8 Front gate threshold voltage $V_{TH}$ versus back gate voltage $V_{bG}$ for NMOS (L =                                        |      |

|      | $10~\mu m,~W=2~\mu m,~MULT=30)$                                                                                                  | . 36 |

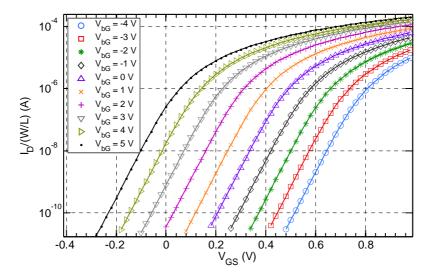

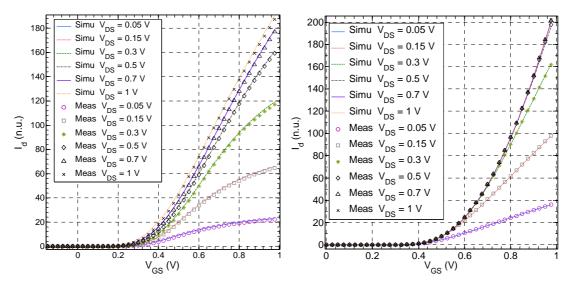

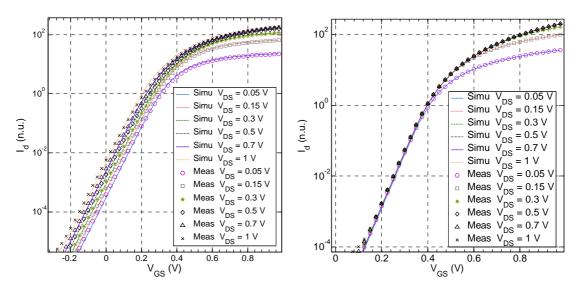

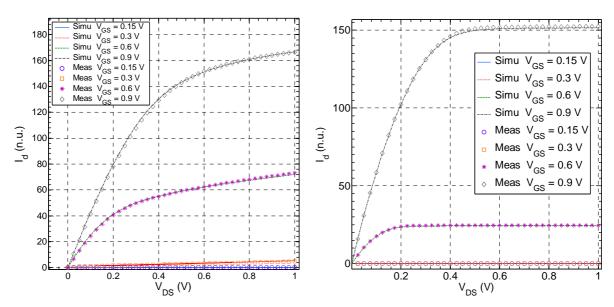

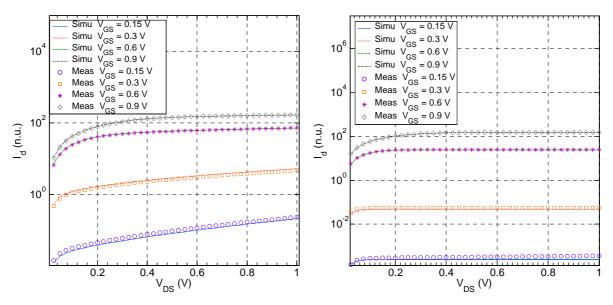

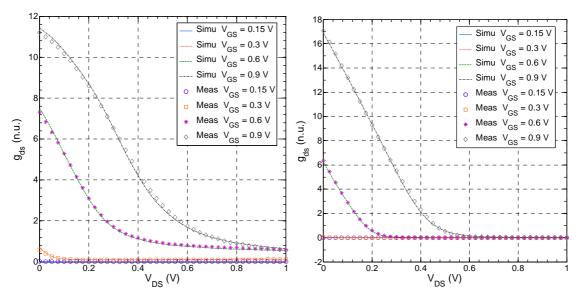

| Fig. | 2.9 Measured and normalized drain current (i.e. $I_D/(W/L)$ ) versus front gate voltage                                          |      |

|      | $V_{GS}$ for $V_{DS}=1~V$ and various back gate voltages for NMOS (L = 1 $\mu m,W$ = 1 $\mu m).$                                 |      |

|      |                                                                                                                                  | . 37 |

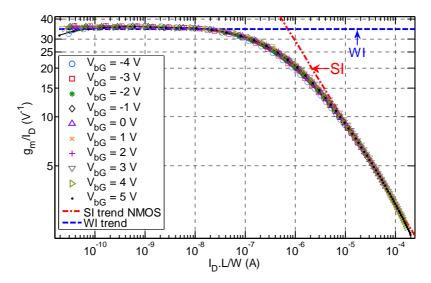

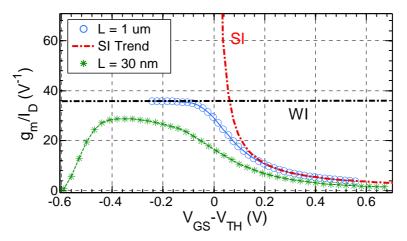

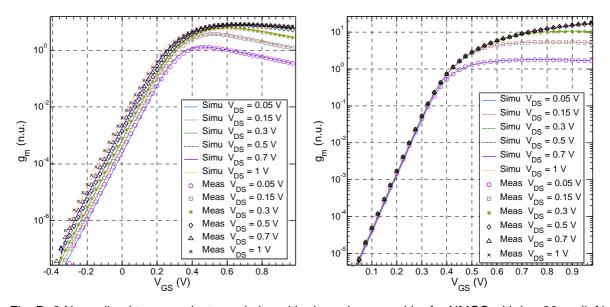

| Fig. | $2.10$ Measured $g_{m}$ over $I_{D}$ characteristics versus normalized drain current $I_{D}/(W/L)$                               |      |

|      | for various back gate voltages $V_{\text{bG}}$ along with the WI and SI trends for NMOS (L =                                     |      |

|      | $1~\mu m,W=1~\mu m,V_{DS}=1~V).$                                                                                                 | . 37 |

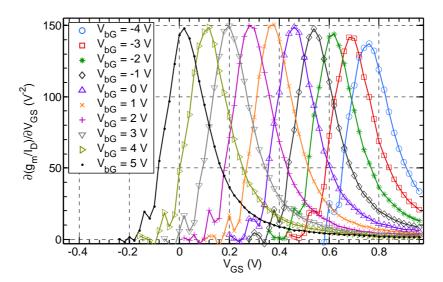

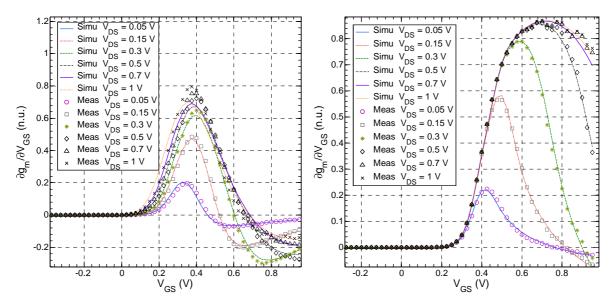

| Fig. | 2.11 Measured $g_m$ over $I_D$ derivative versus front gate voltage for $V_{DS} = 0.05 \ V$ and                                  |      |

|      | various back gate voltages for NMOS (L = 1 $\mu m$ , W = 1 $\mu m$ ).                                                            | . 39 |

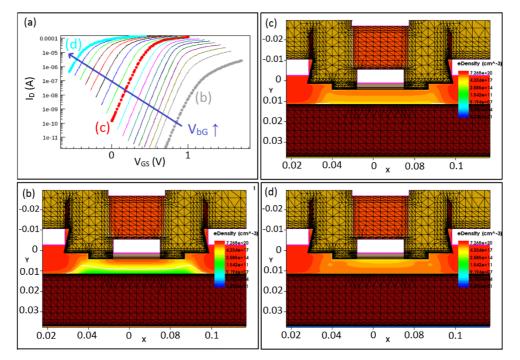

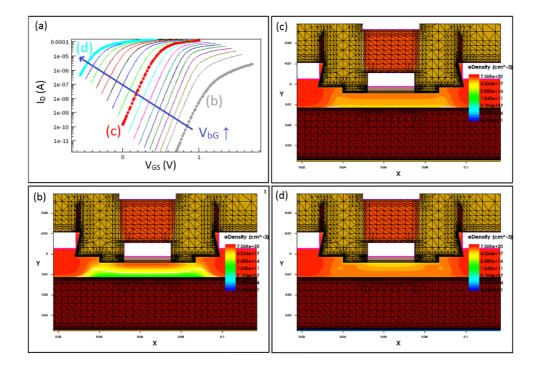

| Fig. | 2.12 TCAD simulations showing the impact of the back gate voltage on carriers                                                    |      |

|      | concentration and consequently on input characteristic $I_{\text{D}}$ - $V_{\text{GS}}$ (a) $I_{\text{D}}$ - $V_{\text{GS}}$ for |      |

|      | various $V_{bG}$ from -10 V to 8 V. (b) channel inversion at the front for negative $V_{bG} =$                                   |      |

|      | -10 V (c) channel inversion in silicon film volume at $V_{bG}=0$ V, and (d) channel                                              |      |

|      | inversion local maximum near the back interface for $V_{bG}=8$ V. Distance unit is                                               |      |

|      | μm                                                                                                                               | . 40 |

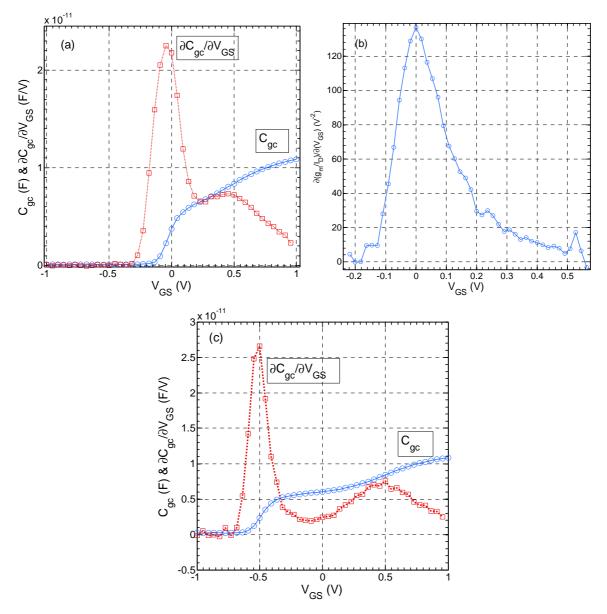

| Fig. | 2.13 TCAD simulations showing (a) $C_{gc}$ and its derivative for $V_{bG}$ = 5 V (b)                                             |      |

|      | derivative of $g_m/I_D$ for $V_{bG}=5$ V, and (c) $C_{gc}$ and its derivative for $V_{bG}=10$ V, $L=$                            |      |

|      | 1 $\mu m$ and $V_{DS} = 1 V$                                                                                                     | . 41 |

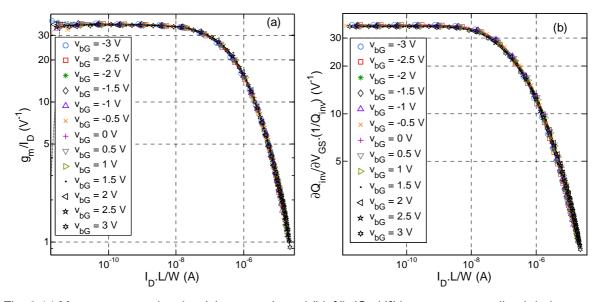

| Fig. | 2.14 Measurements showing (a) $g_m$ over $I_D$ and (b) $\partial (ln(Q_{inv})/\partial V_{GS})$ versus normalized          |      |

|------|----------------------------------------------------------------------------------------------------------------------------|------|

|      | drain current for various $V_{bG}$ values (from -3 V to 3 V) in linear mode ( $V_{DS} = 50$                                |      |

|      | mV).                                                                                                                       | 42   |

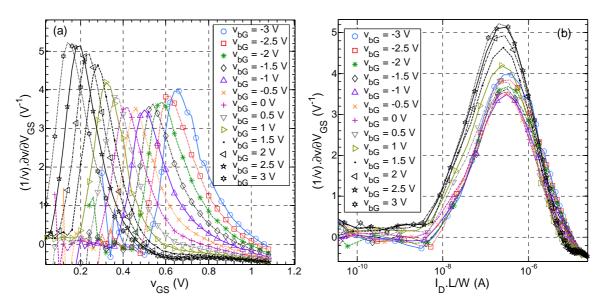

| Fig. | 2.15 Measurements showing the transport term $\partial ln(v)/\partial V_{GS}$ versus gate voltage $V_{GS}$                 |      |

|      | in (a) and normalized drain current in (b) for various $V_{\text{bG}}$ values (from -3 V to 3 V)                           |      |

|      | in linear mode (L = 1 $\mu$ m, W = 1 $\mu$ m)                                                                              | 43   |

| Fig. | 2.16 Cross section of the bulk MOSFET for $V_D = V_S \; (N\text{-type}) \dots$                                             | . 44 |

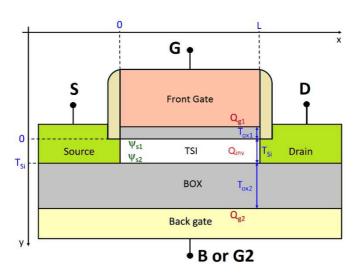

| Fig. | 2.17 FDSOI UTBB transistor architecture (cross-section) with involved charges as                                           |      |

|      | well as front and back surface potentials.                                                                                 | 48   |

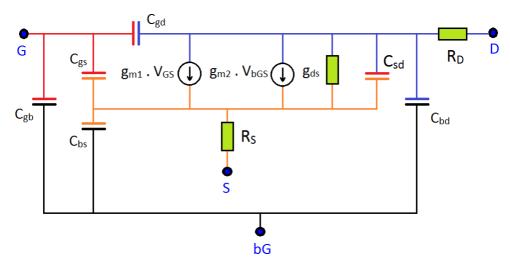

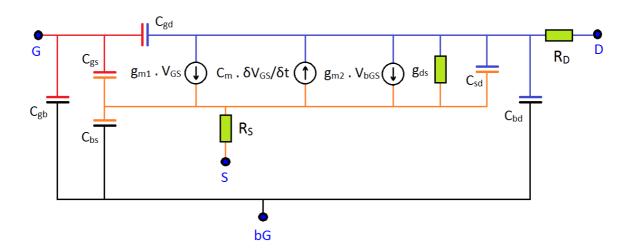

| Fig. | 2.18 Equivalent schematic for small signal and low-frequency operation of the UTBB                                         |      |

|      | FDSOI including series resistances $R_S$ and $R_D$ ( $C_{gd} = C_{gdi} + C_{gde}$ and $C_{gs} = C_{gsi} + \ldots$          |      |

|      | Cgse).                                                                                                                     | 52   |

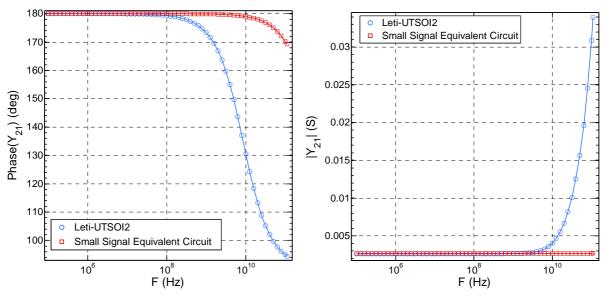

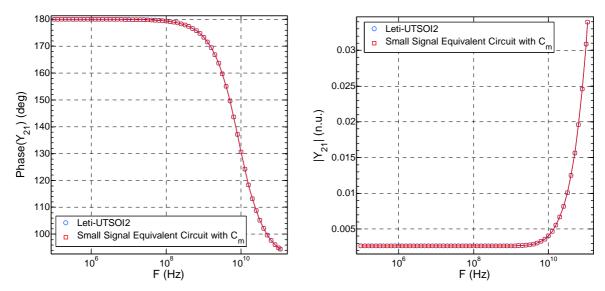

| Fig. | 2.19 NMOS gate to drain transadmittance phase (left) and modulus (right) simulated                                         |      |

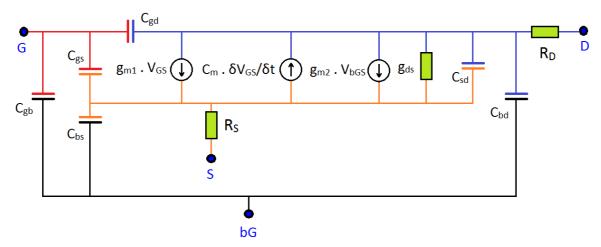

|      | using Leti-UTSOI2 and the small signal equivalent circuit in Fig. 2.18. $L=1\ \mu\text{m},W$                               |      |

|      | = 10 $\mu m,N_F$ = 10, and $V_{GS}=V_{DS}$ = 1 $V_{}$                                                                      | 53   |

| Fig. | 2.20 Equivalent schematic for small signal and quasi-static operation of the UTBB                                          |      |

|      | FDSOI MOSFET including series resistances $R_S$ and $R_D$ ( $C_{\text{gd}} = C_{\text{gdi}} + C_{\text{gde}}$ and $C_{gs}$ |      |

|      | $=C_{gsi}+C_{gse}$ )                                                                                                       | . 54 |

| Fig. | 2.21 NMOS gate to drain transadmittance phase (left) and modulus (right) simulated                                         |      |

|      | using Leti-UTSOI2 and the quasi-static small signal equivalent circuit in Fig. 2.20.                                       |      |

|      | $L=1~\mu m,W=10~\mu m,N_F=10,$ and $V_{GS}=V_{DS}=1~V.$                                                                    | 55   |

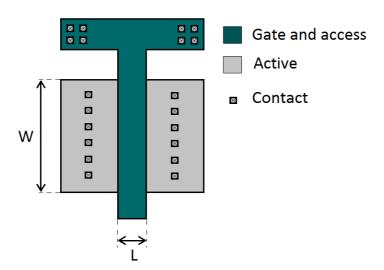

| Fig. | 2.22 DC structure illustration.                                                                                            | 56   |

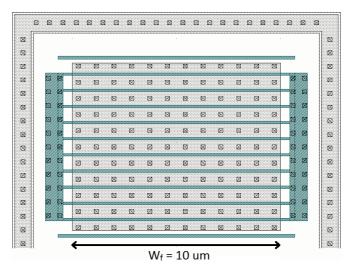

| Fig. | 2.23 RF multi-finger structure with a finger length of $W_{\rm f}$ = 10 $\mu m.$                                           | 57   |

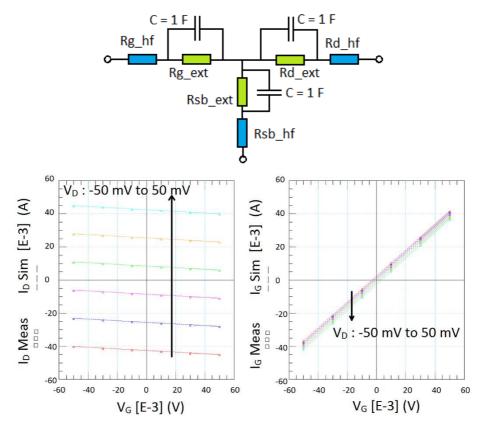

| Fig. | 2.24 (Top) SHORT structure equivalent schematic used to extract parasitic external                                         |      |

|      | resistances Rg_ext, Rd_ext and Rsb_ext (gate, drain and common source and back                                             |      |

|      | gate terminals series resistances respectively, source and back gate being shorted).                                       |      |

|      | (Bottom) an illustration of the performed optimization.                                                                    | 58   |

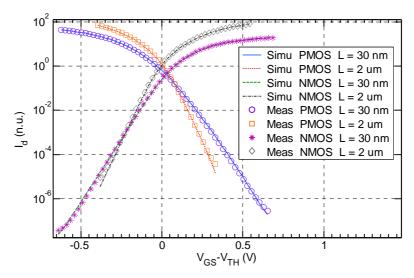

| Fig. | 2.25 Normalized drain current $I_d$ vs. gate voltage overdrive in linear operation $ V_{DS} $                              |      |

|      | = 0.3 V for two NMOS and PMOS lengths (L = 30 nm and 2 $\mu m$ ), $W_f$ = 2 $\mu m$ and                                    |      |

|      | $N_f = 10$ at $T = 25$ °C.                                                                                                 | . 61 |

| Fig. | 2.26 Normalized drain current $I_d$ vs. $V_{GS}$ - $V_{TH}$ in linear operation $ V_{DS}  = 0.3 \ V$ for                   |      |

|      | two NMOS and PMOS lengths (L = 30 nm and 2 $\mu m$ ), $W_f$ = 2 $\mu m$ and $N_f$ = 10 at T                                |      |

|      | $=25^{\circ}\mathrm{C}$                                                                                                    | . 62 |

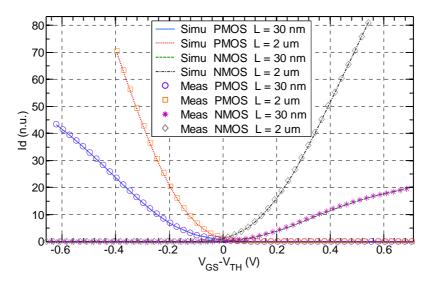

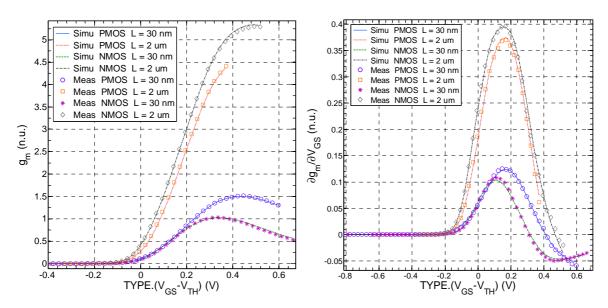

| Fig. 2.27 Normalized transconductance vs. overdrive $V_{GS}-V_{TH}$ in linear operation $\left V_{DS}\right $  |    |

|----------------------------------------------------------------------------------------------------------------|----|

| = 0.3 V for two NMOS and PMOS lengths (L = 30 nm and 2 $\mu m$ ), $W_{\rm f}$ = 2 $\mu m$ and                  |    |

| $N_f = 10$ at $T = 25$ °C.                                                                                     | 62 |

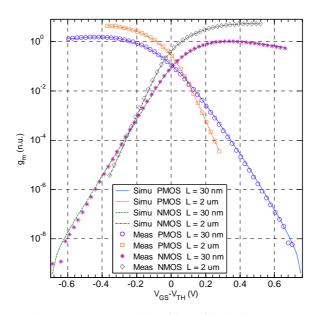

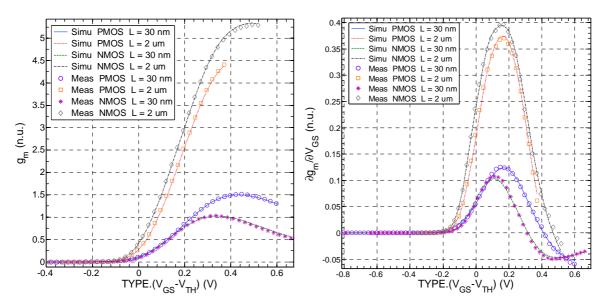

| Fig. 2.28 Normalized transconductance (left) and its derivative (right) vs. gate overdrive                     |    |

| in linear operation $ V_{\rm DS} =0.3~V$ for two NMOS and PMOS lengths (L = 30 nm and                          |    |

| $2~\mu m),~W_f=2~\mu m$ and $N_f=10$ at $T=25^{\circ}C.$                                                       | 63 |

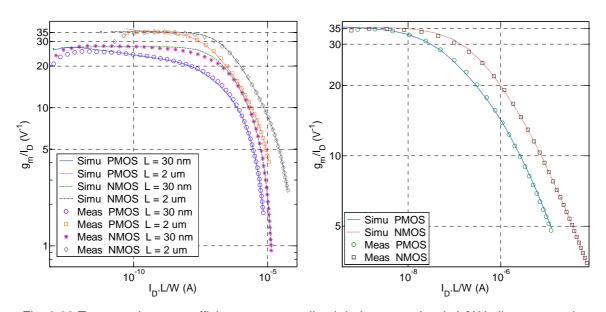

| Fig. 2.29 Transconductance efficiency vs. normalized drain current $I_{\text{d}} = I_{\text{D}}.L/W$ in linear |    |

| operation $ V_{DS} =0.3~V$ for NMOS and PMOS (L = 30 nm, $W_{\rm f}=2~\mu m$ and $N_{\rm f}=10$                |    |

| at T = 25°C) (left). Same for NMOS and PMOS with $L=2\ \mu m$ in saturation is given                           |    |

| (right)                                                                                                        | 64 |

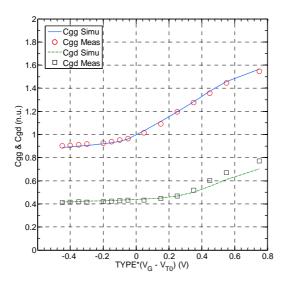

| Fig. 2.30 Normalized $C_{gg}$ and $C_{gd}$ vs. gate voltage overdrive TYPE.(V $_{\!G}-V_{TH})$ in linear       |    |

| mode $ V_D =0.3~V$ for NMOS (L = 30 nm, $W_f=2~\mu m$ and $N_f=10)$ at $T=25^{\circ}C$ and                     |    |

| frequency = 100 MHz.                                                                                           | 65 |

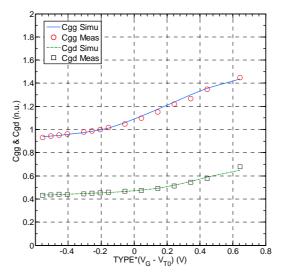

| Fig. 2.31 Normalized $C_{gg}$ and $C_{gd}$ vs. gate voltage overdrive TYPE.(V $_{\!G}-V_{TH})$ in linear       |    |

| mode $ V_D =0.3~V$ for PMOS (L = 30 nm, $W_f=2~\mu m$ and $N_f=10)$ at $T=25^{\circ}C$ and                     |    |

| frequency = 100 MHz.                                                                                           | 65 |

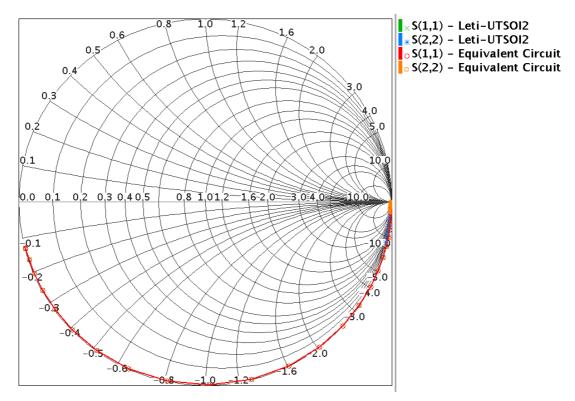

| Fig. 2.32 Smith chart showing the input and output S-parameters simulated using the                            |    |

| proposed equivalent circuit in Fig. 2.18 and the Leti-UTSOI2 of $L=1\ \mu m\ NMOS$                             |    |

| in saturation ( $V_{DS} = 1 V$ )                                                                               | 66 |

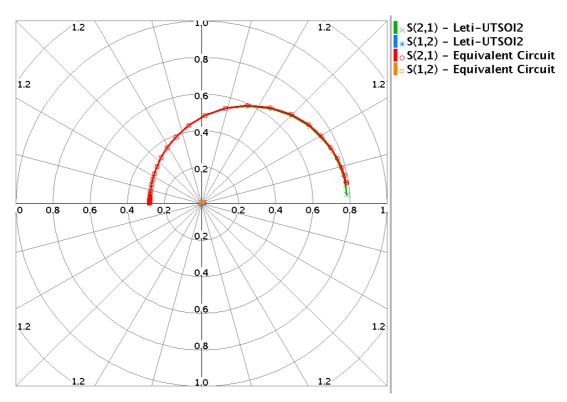

| Fig. 2.33 Polar chart showing the input to output and output to input S-parameters                             |    |

| simulated using the proposed equivalent circuit in Fig. 2.18 and the Leti-UTSOI2 of                            |    |

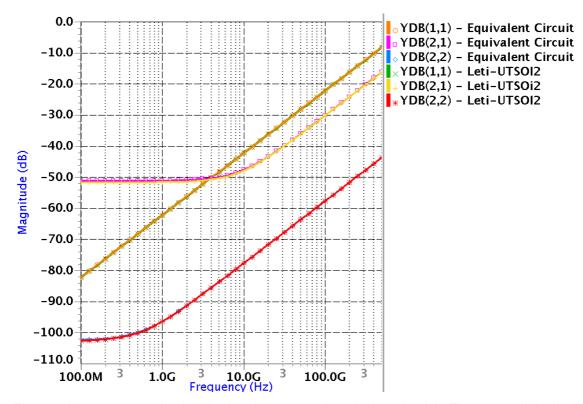

| $L=1~\mu m$ NMOS in saturation ( $V_{DS}=1~V$ )                                                                | 67 |

| Fig. 2.34 Y-parameters simulated using the proposed equivalent circuit in Fig. 2.18 and                        |    |

| the Leti-UTSOI2 of L = 1 $\mu m$ NMOS in saturation (VDS = 1 V)                                                | 67 |

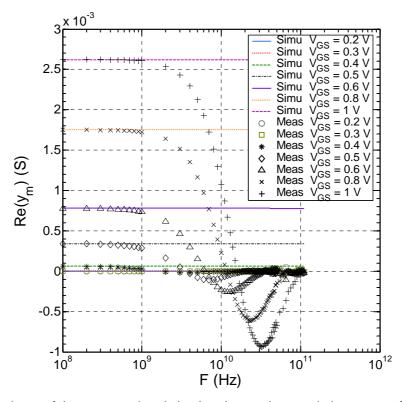

| Fig. 2.35 The real part of the measured and simulated mutual transadmittance $y_{\text{m}}$ of a long          |    |

| channel $L=1\ \mu m$ for various gate to source voltages from WI to SI in saturation                           |    |

| $(V_{DS} = 1 V)$                                                                                               | 68 |

| Fig. 2.36 The phase of the measured and simulated mutual transadmittance $y_m$ of a long                       |    |

| channel $L=1\;\mu m$ for various gate to source voltages from WI to SI in saturation                           |    |

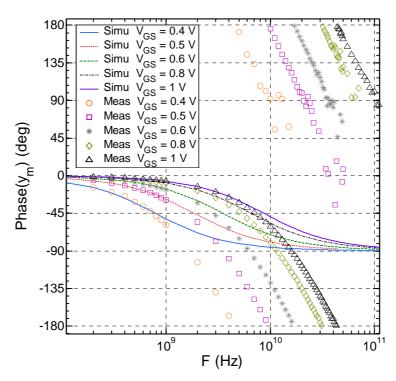

| $(V_{DS} = 1 \ V)$                                                                                             | 69 |

| Fig. 2.37 A sub-circuit example of a RF MOSFET (B instead of bG in bulk)                                       | 71 |

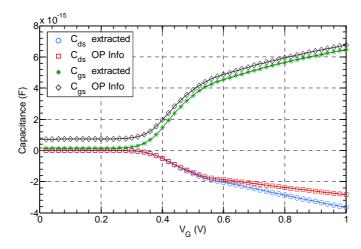

| Fig. 2.38 Comparison of OP Info capacitances and extracted counterparts in saturation                          |    |

| $V_{DS}$ =1V for NMOS (L = 1 $\mu m$ and W = 0.5 $\mu m$ ).                                                    | 71 |

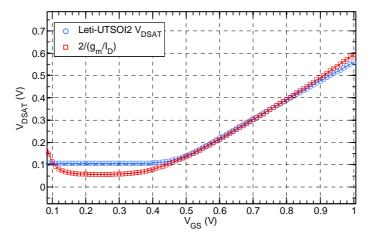

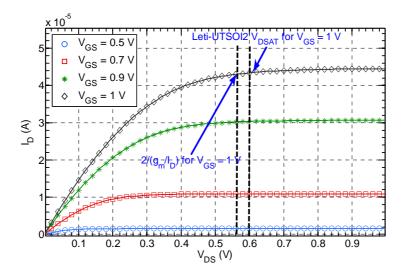

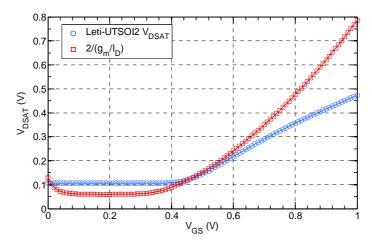

| Fig. | 2.39 Comparison of the Leti-UTSOI2 and 2/(g <sub>m</sub> /I <sub>D</sub> ) expression V <sub>DSAT</sub> values versus                     |      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | $V_{GS}$ in saturation for NMOS and $L=2\mu m$                                                                                            | . 76 |

| Fig. | $2.40~I_D-V_{DS}$ characteristics for various $V_{GS}$ and $L=2~\mu m$ showing two $V_{DSAT}$                                             |      |

|      | definitions (Leti-UTSOI2 and 2/(g <sub>m</sub> /I <sub>D</sub> ) expression).                                                             | . 76 |

| Fig. | 2.41 Comparison of the Leti-UTSOI2 and $2/(g_m/I_D)$ expression $V_{DSAT}$ values versus                                                  |      |

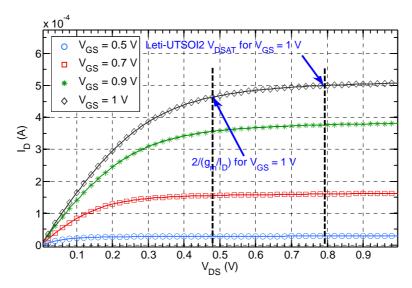

|      | V <sub>GS</sub> in saturation for NMOS and L = 100 nm.                                                                                    | . 77 |

| Fig. | $2.42\;I_D-V_{DS}$ characteristics for various $V_{GS}$ and for $L=100\;nm$ showing two $V_{DSAT}$                                        |      |

|      | definitions (Leti-UTSOI2 and 2/(g <sub>m</sub> /I <sub>D</sub> ) expression).                                                             | . 77 |

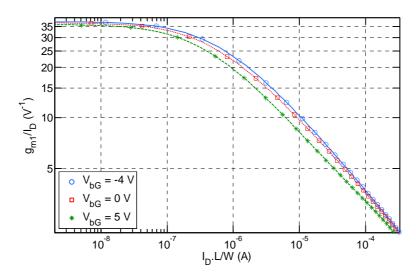

| Fig. | 3.1 $g_{m1}$ over $I_D$ versus normalized drain current ( $I_D$ .L/W) of NMOS ( $L=1~\mu m$ ) in                                          |      |

|      | saturation at $V_{bG} = \{-4 \text{ V}, 0 \text{ V}, 5 \text{ V}\}$ and $T = 25^{\circ}\text{C}$ .                                        | . 84 |

| Fig. | 3.2 Gate capacitance $C_{gg}$ versus front gate voltage $V_G$ of NMOS (L = 1 $\mu m$ ) in                                                 |      |

|      | saturation at $V_{bG} = \{-4\ V,\ 0\ V,\ 5\ V\}$ and $T=25\ ^{\circ}C.$ Inset shows capacitance                                           |      |

|      | derivative $\partial C_{gg}/\partial V_G$ .                                                                                               | . 85 |

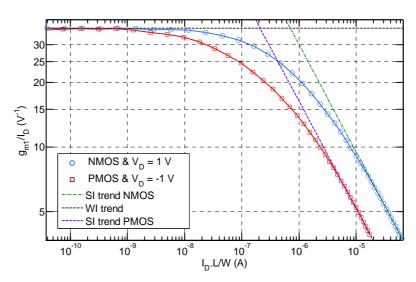

| Fig. | 3.3 Measured $g_{m1}$ over $I_D$ versus square shape drain current ( $I_D$ .L/W) of NMOS and                                              |      |

|      | PMOS (L = 1 $\mu$ m) in saturation at $V_{bG}$ = 0 V and T = 25 °C.                                                                       | . 86 |

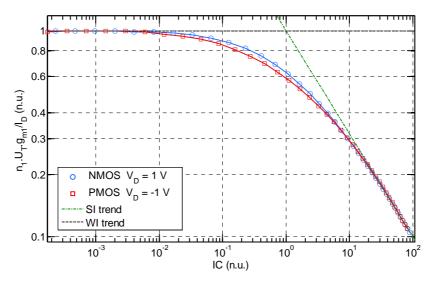

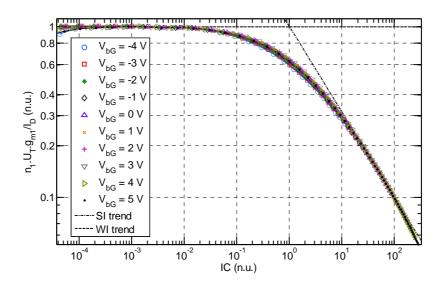

| Fig. | 3.4 Normalized transconductance efficiency versus IC of a NMOS and PMOS (L =                                                              |      |

|      | 1 $\mu m$ ) in saturation at $V_{bG}=0$ V and $T=25$ °C.                                                                                  | . 89 |

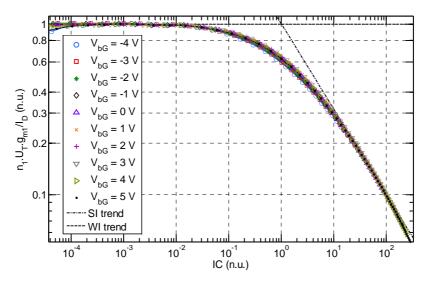

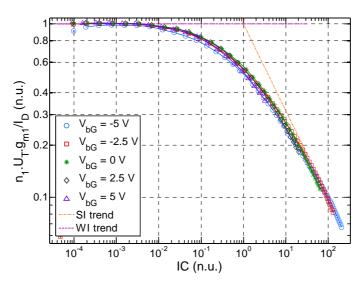

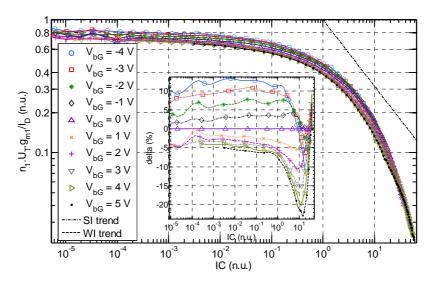

| Fig. | 3.5 Normalized $g_{m1}$ over $I_D$ as a function of the inversion coefficient at different $V_{bG}$                                       |      |

|      | for NMOS (L = 1 $\mu m$ & W = 1 $\mu m$ ) in saturation (VD = 1V) at T = 25 $^{\circ}C$                                                   | . 90 |

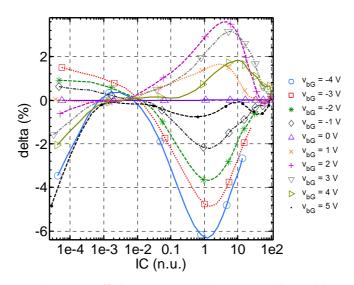

| Fig. | 3.6 Transconductance efficiency curves delta versus $V_{\text{bG}} = 0V$ curve                                                            | . 90 |

| Fig. | 3.7 Normalized $g_{m1}$ over $I_D$ as a function of the inversion coefficient at different $V_{bG}$                                       |      |

|      | for PMOS (L = 1 $\mu m$ & W = 1 $\mu m$ ) in saturation (V $_D$ = -1 V) at T = 25 $^{\circ}C$                                             | . 91 |

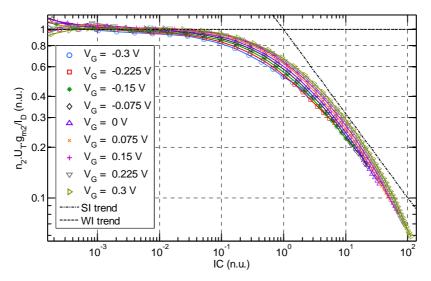

| Fig. | 3.8 Normalized $g_{m2}$ over $I_D$ as a function of the inversion coefficient at different $V_G$                                          |      |

|      | for NMOS (L = 1 $\mu$ m) in saturation (V <sub>D</sub> = 1V) at T = 25°C.                                                                 | . 92 |

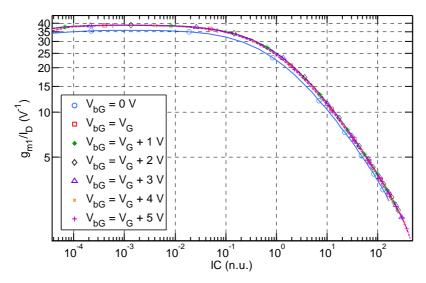

| Fig. | 3.9 Measured g <sub>m1</sub> over I <sub>D</sub> as a function of IC for fixed V <sub>bG</sub> and simultaneous front                     |      |

|      | and back gates sweep with an offset for NMOS (L = 1 $\mu m$ ) in saturation (V <sub>D</sub> = 1V)                                         |      |

|      | at T = 25°C                                                                                                                               | . 93 |

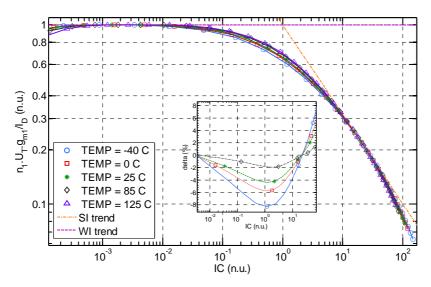

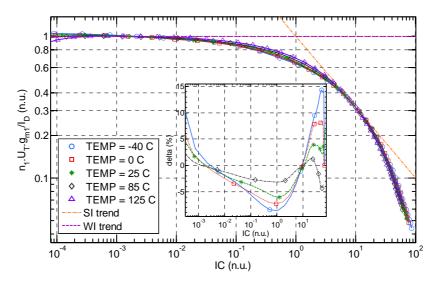

| Fig. | 3.10 n <sub>1</sub> .U <sub>T</sub> .g <sub>m1</sub> /I <sub>D</sub> as a function of the inversion coefficient at different temperatures |      |

|      | for NMOS (L = 300 nm & W = 1 $\mu$ m) in saturation (V <sub>D</sub> = 1V) and V <sub>bG</sub> = 0 V; inset                                |      |

|      | shows delta versus T = 125 °C case.                                                                                                       | . 94 |

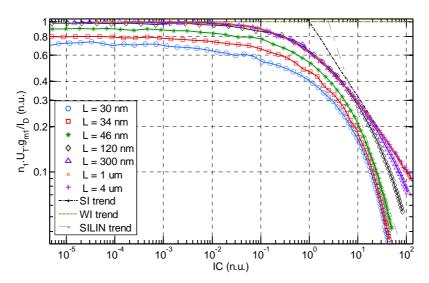

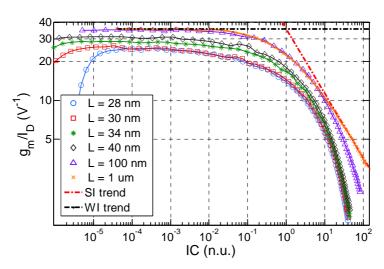

| Fig. | 3.11 Normalized g <sub>m1</sub> over I <sub>D</sub> as a function of the inversion coefficient for different                              |      |

|      | lengths for NMOS (W = 1 $\mu$ m) in saturation (V <sub>D</sub> = 1V) at T = 25°C                                                          | . 95 |

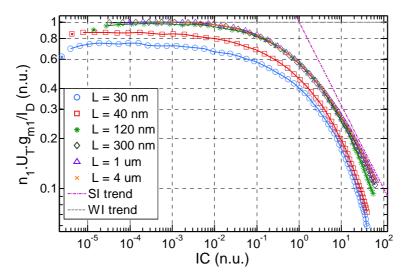

| Fig. 3 | 3.12 Normalized $g_{m1}$ over $I_D$ as a function of the inversion coefficient for different                                             |      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1      | engths for PMOS (W = 1 $\mu$ m) in saturation (V <sub>D</sub> = 1V) at T = 25°C.                                                         | . 95 |

| Fig. 3 | 3.13 Normalized g <sub>m1</sub> over I <sub>D</sub> as a function of the inversion coefficient at different                              |      |

| 7      | $V_{bG}$ for NMOS (L = 30 nm & W = 1 $\mu$ m) in saturation ( $V_D$ = 1 $V$ ) at T = 25 °C                                               | . 96 |

| Fig. 3 | .14 n <sub>1</sub> .U <sub>T</sub> .g <sub>ml</sub> /I <sub>D</sub> as a function of the inversion coefficient at different temperatures |      |

| f      | For NMOS (L = 30 nm & W = 1 $\mu$ m) in saturation (V <sub>D</sub> = 1V) and V <sub>bG</sub> = 0 V; inset                                |      |

| S      | shows delta versus T = 125 °C case.                                                                                                      | . 96 |

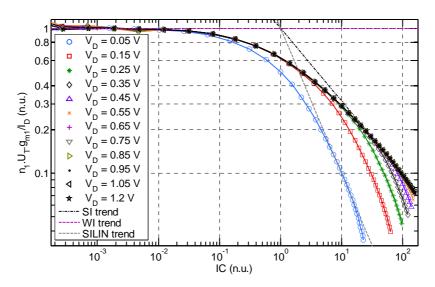

| Fig. 3 | 3.15 Normalized g <sub>m1</sub> over I <sub>D</sub> as a function of the inversion coefficient for different                             |      |

| V      | $V_D$ for NMOS (W = 1 $\mu$ m and L = 1 $\mu$ m) at T=25°C                                                                               | . 97 |

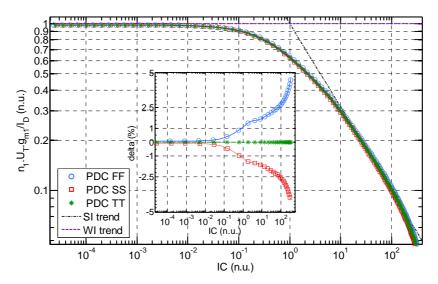

| Fig. 3 | 3.16 NMOS transconductance efficiency as a function of the inversion coefficient                                                         |      |

| f      | For different process corners (L = 1 $\mu$ m & W = 1 $\mu$ m) in saturation (V <sub>D</sub> = 1V) and                                    |      |

| 7      | V <sub>bG</sub> = 0 V; inset shows delta versus typical corner case                                                                      | . 98 |

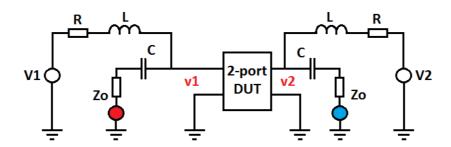

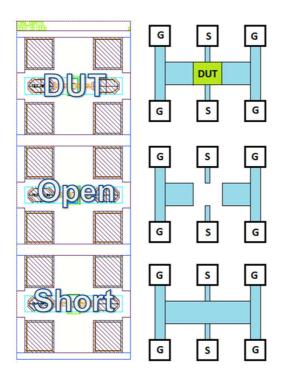

| Fig. 4 | .1 2-port RF structures setup for S-parameters measurement                                                                               | 105  |

| Fig. 4 | .2 2-port test structures using Ground-Signal-Ground probe pads                                                                          | 106  |

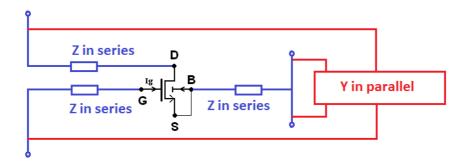

| Fig. 4 | .3 Schematics representing the DUT with parallel and series parasitic elements (B                                                        |      |

| =      | = bG)                                                                                                                                    | 107  |

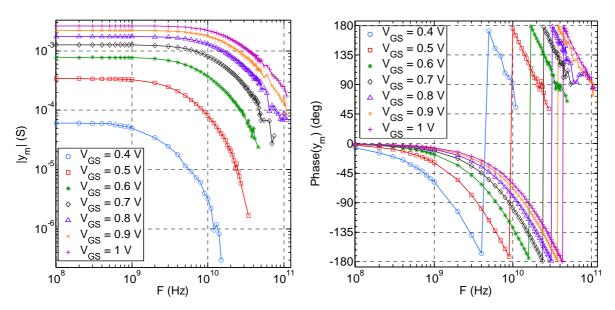

| Fig. 4 | .4 Measured modulus (left) and phase (right) of the mutual transadmittance of an N                                                       |      |

| 7      | Type MOSFET with $L = 1 \mu m$ in saturation ( $V_{DS} = 1 V$ )                                                                          | 109  |

| Fig. 4 | .5 Measured phase of the mutual transadmittance of an N-Type MOSFET with L =                                                             |      |

| 2      | 28 nm in saturation ( $V_{DS} = 1 \text{ V}$ )                                                                                           | 109  |

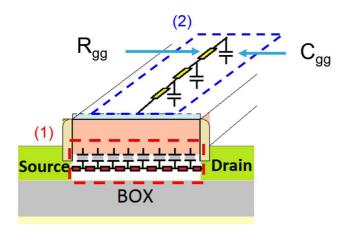

| Fig. 4 | 6 A representation of the two distribution effects in the channel (1) and in the gate                                                    |      |

| f      | inger (2)                                                                                                                                | 110  |

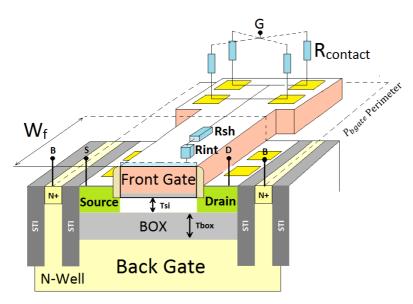

| Fig. 4 | .7 UTBB FDSOI transistor architecture (3D).                                                                                              | 111  |

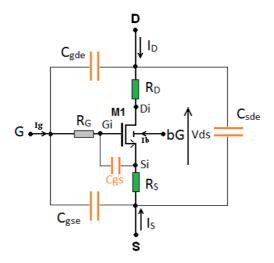

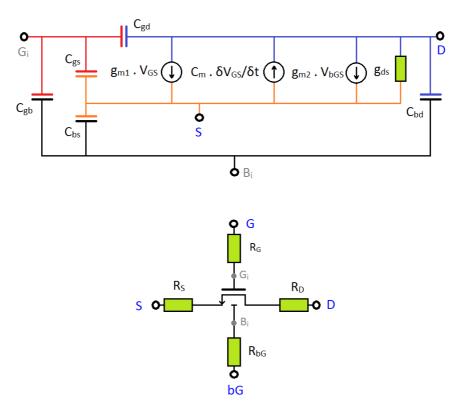

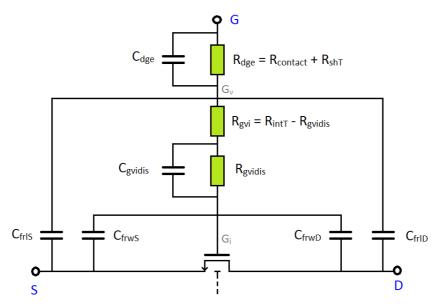

| Fig. 4 | .8 RF equivalent schematic proposal with additional front-gate (Rg) and back-gate                                                        |      |

| (      | R <sub>bG</sub> ) resistances. Top: the core model. Bottom: the complete quasi-static model                                              | 112  |

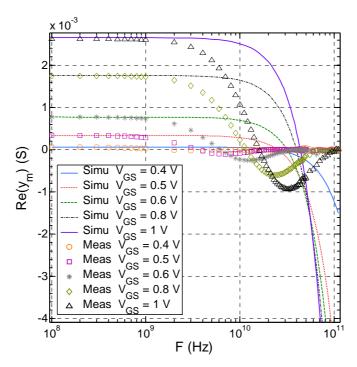

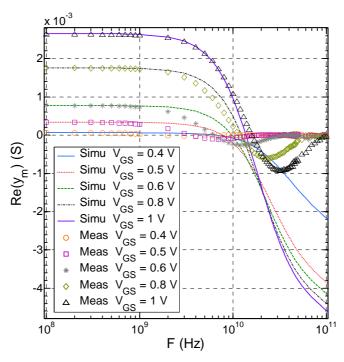

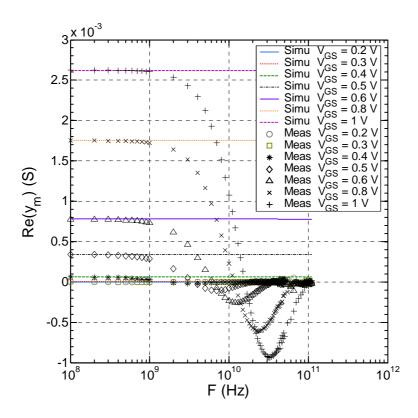

| Fig. 4 | .9 The real part of the measured and simulated mutual transadmittance y <sub>m</sub> of a long                                           |      |

| C      | channel $L = 1 \mu m$ for various gate to source voltages from WI to SI in saturation                                                    |      |

| (      | $V_{DS} = 1 \text{ V}$ ). Model includes simplified front and back gates resistances and ignores                                         |      |

| N      | NQS effect                                                                                                                               | 114  |

| Fig. 4 | .10 The real part of the measured and simulated mutual transadmittance y <sub>m</sub> of a long                                          |      |

| c      | channel $L = 1 \mu m$ for various gate to source voltages from WI to SI in saturation                                                    |      |

| (      | $V_{DS} = 1 \text{ V}$ ). Model includes front and back gates simplified resistances. Front gate                                         |      |

| r      | resistance is tuned for SI.                                                                                                              | 114  |

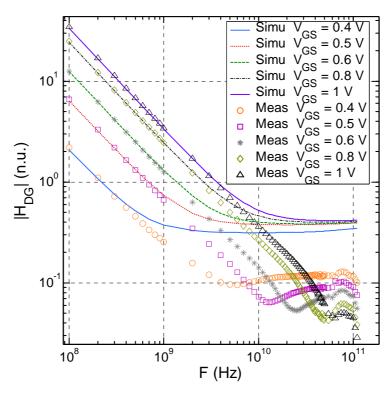

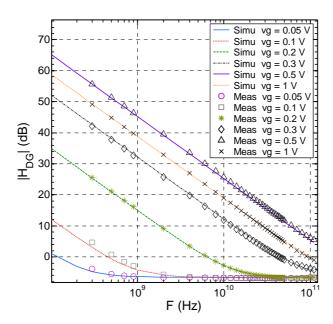

| Fig. 4.11 The modulus of the measured and simulated current gain H <sub>DG</sub> of a long channel           |     |

|--------------------------------------------------------------------------------------------------------------|-----|

| $L=1\ \mu m$ for various gate to source voltages from WI to SI in saturation (V $_{DS}=1$                    |     |

| V). Model includes front and back gates simplified resistances and ignores NQS                               |     |

| effect                                                                                                       | 115 |

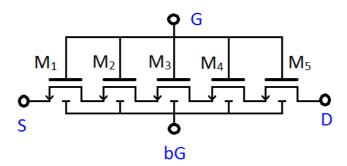

| Fig. 4.12 Channel segmentation using 5 series MOSFETs.                                                       | 116 |

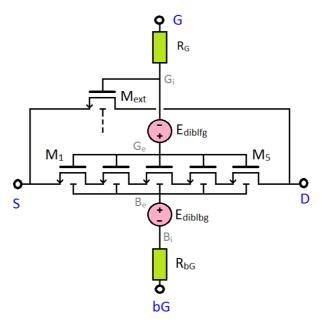

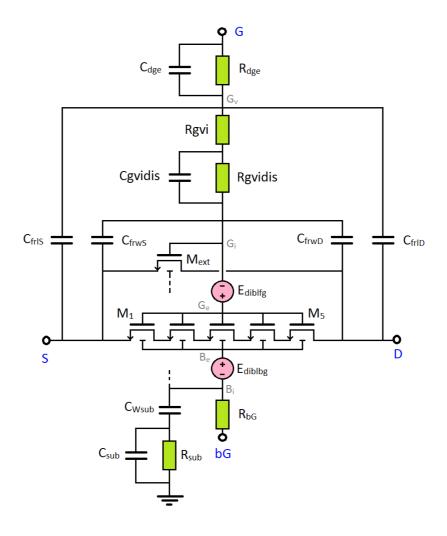

| Fig. 4.13 Non-quasi-static model with simplified gates models.                                               | 117 |

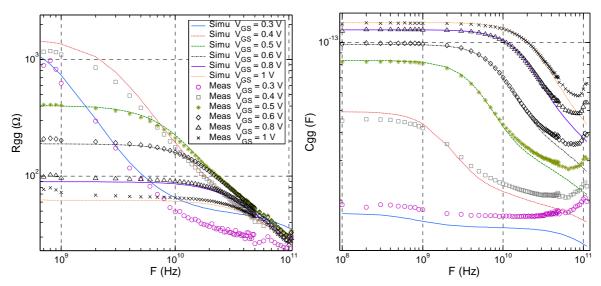

| Fig. 4.14 Gate resistance (left) and gate capacitance (right) vs. frequency for $L=1\ \mu m$                 |     |

| and $Wf = 1 \mu m$ .                                                                                         | 118 |

| Fig. 4.15 Front gate network with series and parallel RC lumped circuits.                                    | 119 |

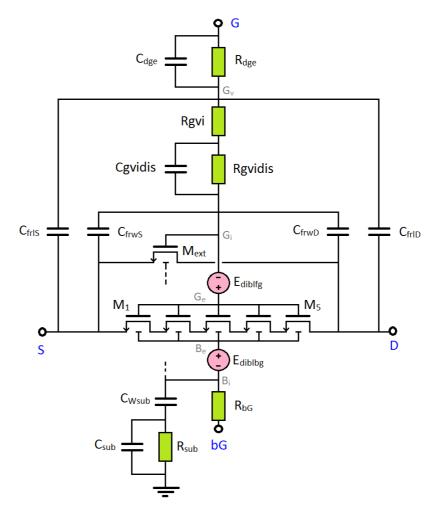

| Fig. 4.16 Complete Non-Quasi-Static model.                                                                   | 120 |

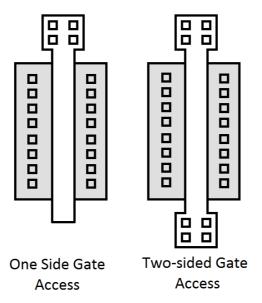

| Fig. 4.17 One side and two side gate access configurations.                                                  | 121 |

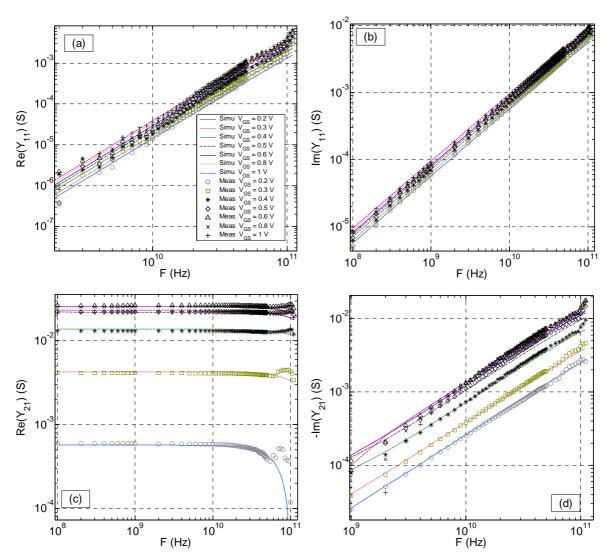

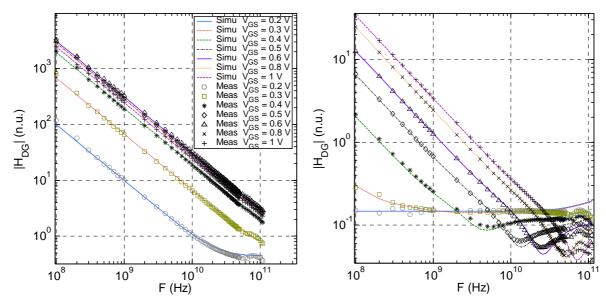

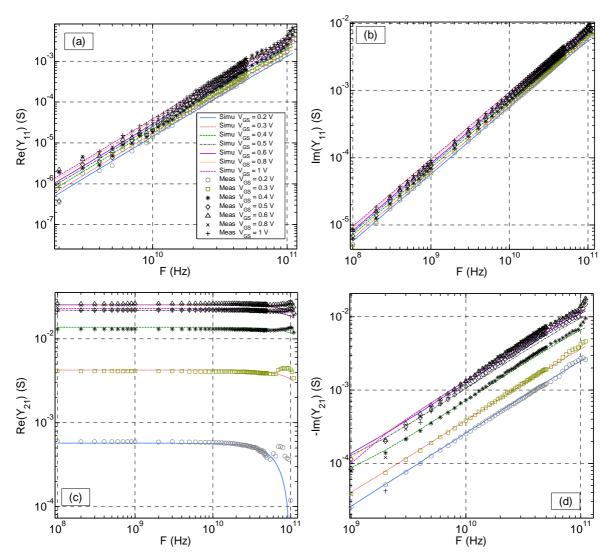

| Fig. 4.18 Simulation and measurements of the input admittance Y <sub>11</sub> and input to output            |     |

| transadmittance Y <sub>21</sub> of a 30 nm long NMOS vs. frequency for various gate to source                |     |

| voltages from WI to SI in saturation ( $V_{DS} = 1 \text{ V}$ )                                              | 122 |

| Fig. 4.19 Simulation and measurements of the input transadmittance Y <sub>11</sub> and input to              |     |

| output transadmittance $Y_{21}$ of 1 $\mu m$ long NMOS vs. frequency for various gate to                     |     |

| source voltages from WI to SI in saturation ( $V_{DS} = 1 \text{ V}$ )                                       | 123 |

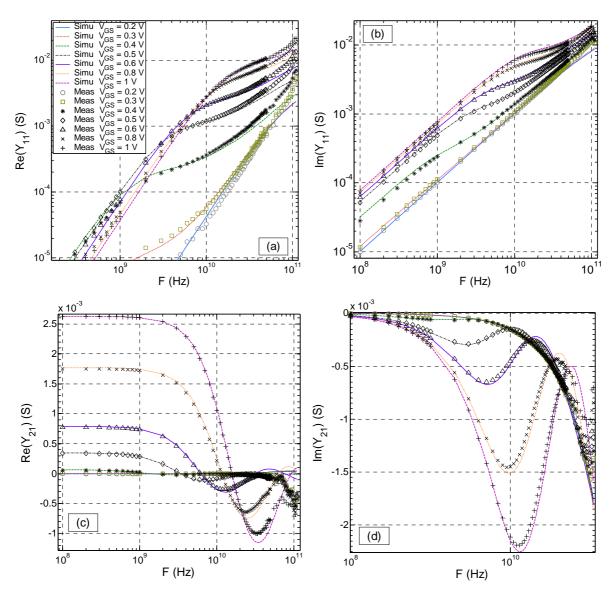

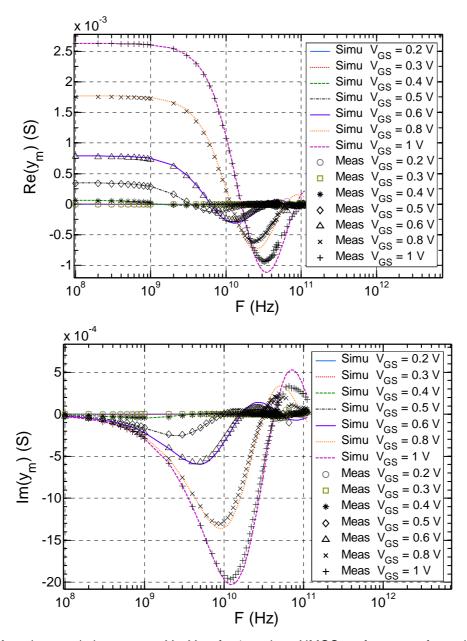

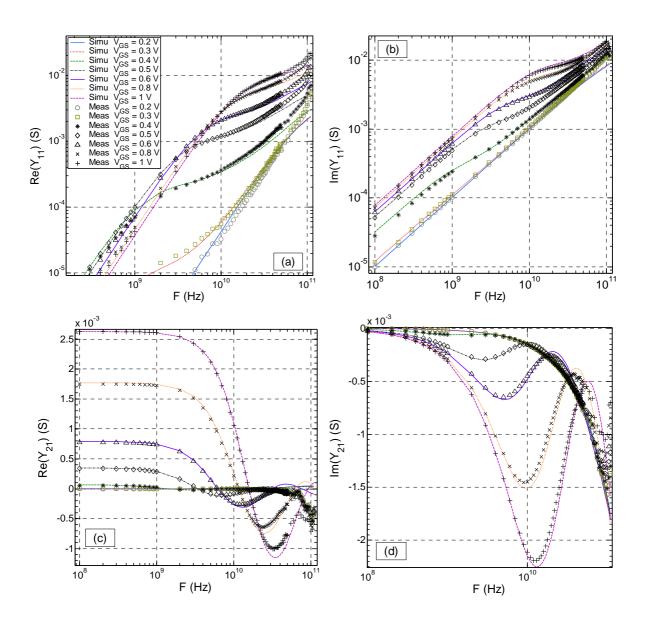

| Fig. 4.20 Mutual transadmittance $y_m = Y_{21}\text{-}Y_{12}$ of a 1 $\mu m$ long NMOS vs. frequency for     |     |

| various gate to source voltages from WI to SI in saturation ( $V_{DS}=1\ V$ )                                | 124 |

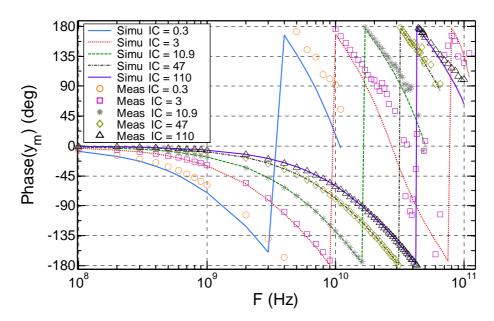

| Fig. 4.21 Measured and simulated mutual transadmittance phase of a 1 µm long NMOS                            |     |

| vs. frequency for various Inversion Coefficients IC from WI to SI in saturation ( $V_{DS}$                   |     |

| = 1 V)                                                                                                       | 125 |

| Fig. 4.22 Small signal current gain ( $ H_{DG} $ ) vs. frequency (F) in linear mode $V_{DS}=0.3\ V$          |     |

| for NMOS (L = 30 nm, $W_f$ = 2 $\mu m$ and $N_f$ = 10) at T = 25 $^{\circ} C.$                               | 126 |

| Fig. 4.23 Current gain $ H_{DG} $ of a 30 nm long (left) and 1 $\mu m$ long (right) N-type                   |     |

| MOSFETs for various gate to source voltages $V_{\text{GS}}$ from WI to SI in saturation ( $V_{\text{DS}}$    |     |

| = 1 V)                                                                                                       | 126 |

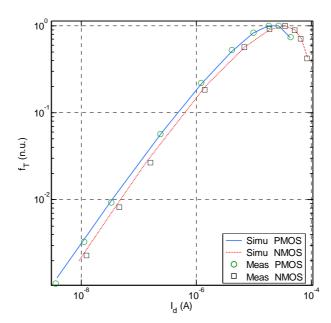

| Fig. 4.24 Normalized transit frequency (f <sub>T</sub> ) vs. normalized drain current $I_d = I_D / (W/L)$ in |     |

| linear mode $ V_{DS} =0.3~V$ for NMOS and PMOS (L = 30 nm, $W_f=2~\mu m$ and $N_f=$                          |     |

| 10) at $T = 25^{\circ}C$                                                                                     | 127 |

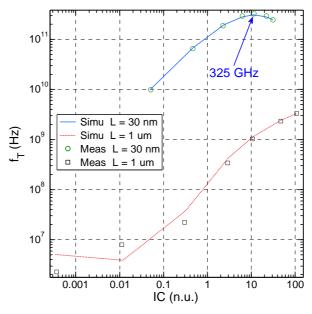

| Fig. 4.25 Transit frequency $f_T$ versus IC of a short (L = 30 nm) and long (L = 1 $\mu$ m) N-               |     |

| type MOSFETs in saturation ( $V_{DS} = 1 \text{ V}$ )                                                        | 127 |

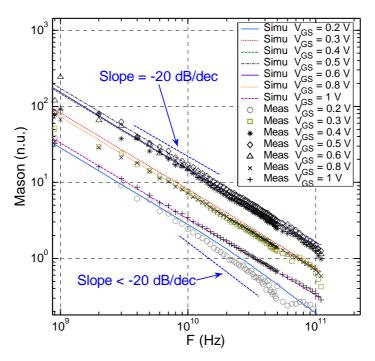

| Fig. 4.26 Mason gain vs. frequency (F) of NMOS (L = 30 nm) for various gate to source                             |   |

|-------------------------------------------------------------------------------------------------------------------|---|

| voltages in linear mode $V_{DS} = 0.25 \ V$                                                                       | 8 |

| Fig. 4.27 Mason gain vs. frequency (F) of NMOS (L = 30 nm) for various gate to source                             |   |

| voltages in saturation mode $V_{DS}=1\ V.$ Model w/o gates resistances (left) and with                            |   |

| the gates networks (right)                                                                                        | 9 |

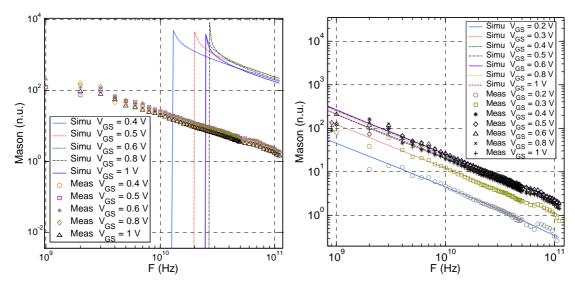

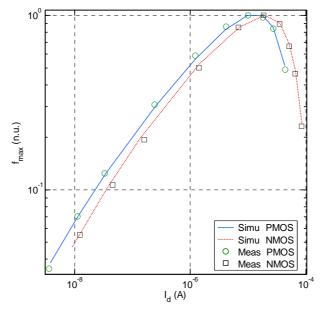

| Fig. 4.28 Normalized $f_{\text{max}}vs.$ the normalized drain current $I_d$ in linear mode $ V_{DS} =0.3~V$       |   |

| for NMOS and PMOS (L = 30 nm, $W_f$ = 2 $\mu m$ and $N_f$ = 10) at T = 25 °C                                      | 9 |

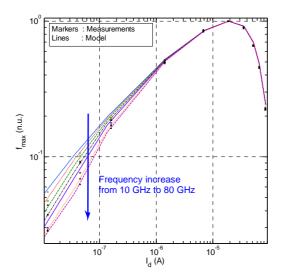

| Fig. 4.29 Normalized $f_{max}$ vs. drain current $I_d$ in linear mode (i.e. $\left V_{DS}\right =0.3~V)$ for NMOS |   |

| and for following frequencies: 10 GHz, 20 GHz, 30 GHz, 40 GHz, 50 GHz, 70 GHz                                     |   |

| and 80 GHz (L = 30 nm, $W_f$ = 2 $\mu m$ and $N_f$ = 10) at T = 25 $^{\circ}$ C                                   | 0 |

| Fig. 4.30 $f_{max}$ vs. IC for NMOS $L=30$ nm for various $V_{DS}$ from linear to saturation                      | 0 |

| Fig. 4.31 FoM RF vs. $I_d$ in linear operation $ V_{DS} =0.3\ V$ for NMOS and PMOS (L = 30                        |   |

| nm, $W_f$ = 2 $\mu m$ and $N_f$ = 10) at T = 25 $^{\circ}$ C                                                      | 1 |

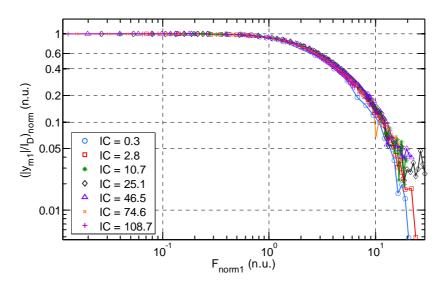

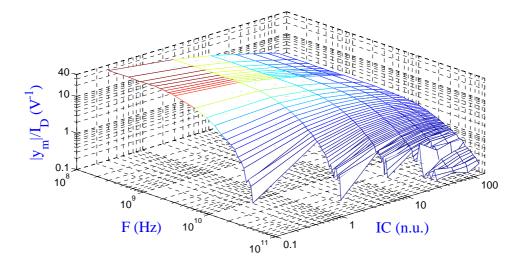

| Fig. 5.1 3-D plot of the measured transadmittance efficiency modulus versus the                                   |   |

| frequency and inversion coefficient IC for $L=1~\mu m$ at $V_{DS}=1~V13$                                          | 5 |

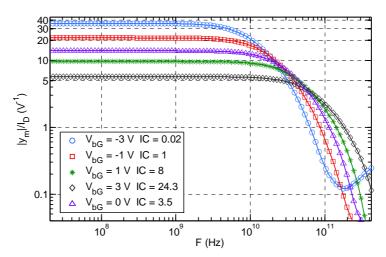

| Fig. 5.2 Measured transadmittance efficiency modulus versus the frequency for different                           |   |

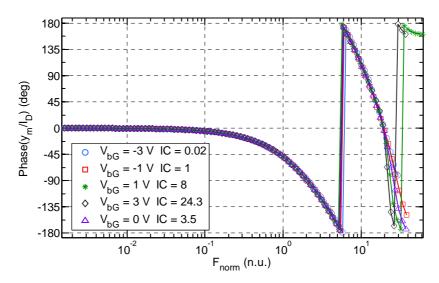

| IC for a NMOS (L = 1 $\mu$ m) in saturation (V <sub>DS</sub> = 1 V) and V <sub>bG</sub> = 0 V                     | 7 |

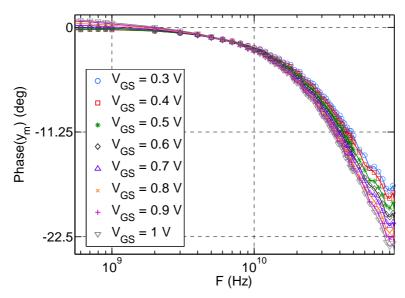

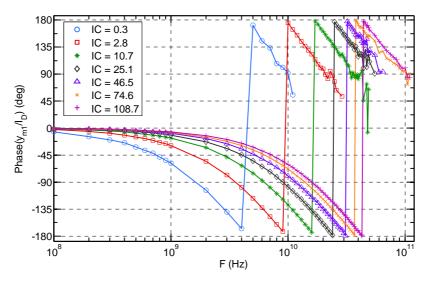

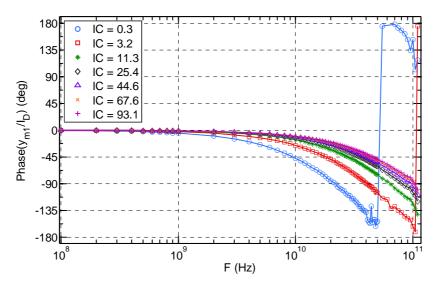

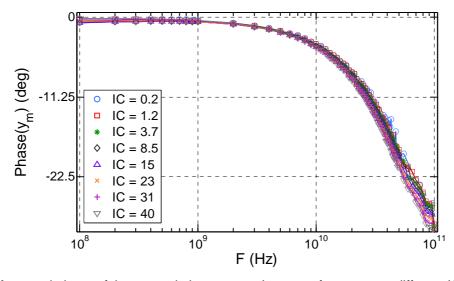

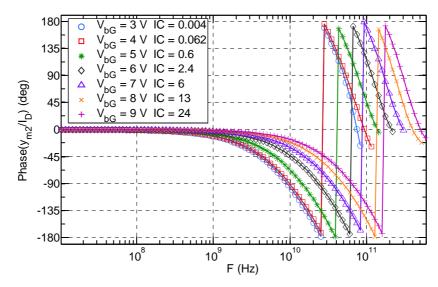

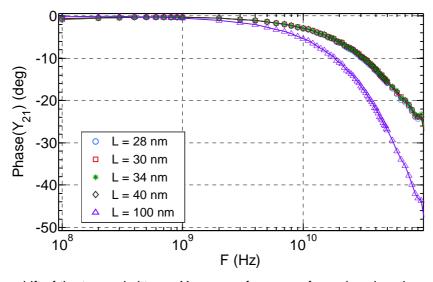

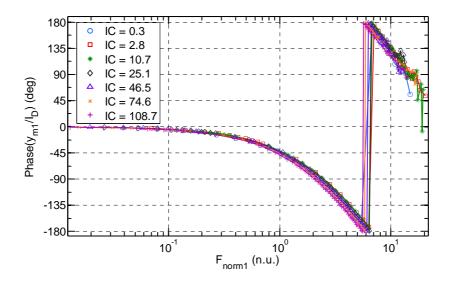

| Fig. 5.3 Measured phase of the transadmittance over I <sub>D</sub> versus frequency at different IC               |   |

| for NMOS (L = 1 $\mu m$ ) in saturation (VDS = 1 V) and VbG = 0 V                                                 | 8 |

| Fig. 5.4 Measured phase of the transadmittance over I <sub>D</sub> versus frequency at different IC               |   |

| for PMOS L = 1 $\mu m$ (left) and L = 300 nm (right) in saturation (V $_{DS}$ = -1 V) and $V_{bG}$                |   |

| = 0 V                                                                                                             | 8 |

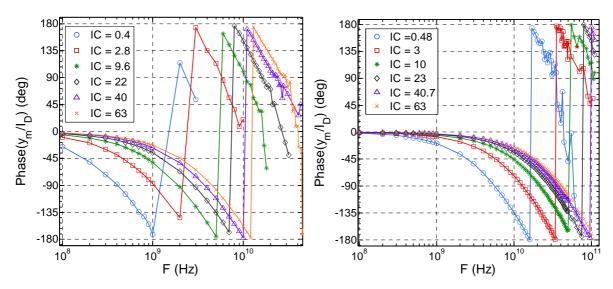

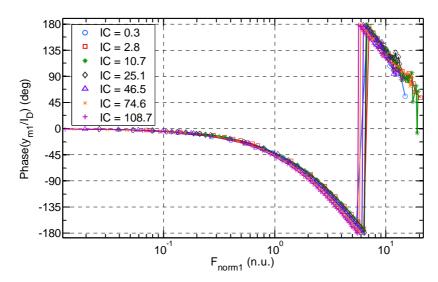

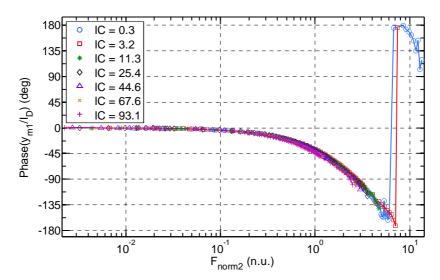

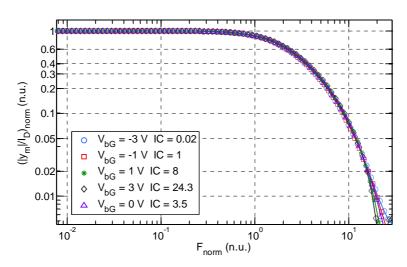

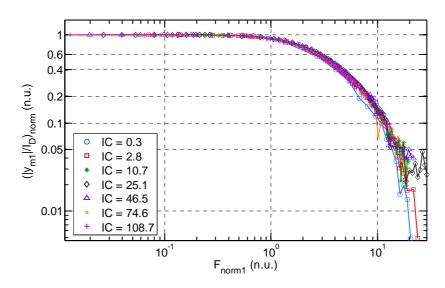

| Fig. 5.5 Normalized transadmittance magnitude over I <sub>D</sub> versus normalized frequency                     |   |

| $F_{norm1}$ at different IC for NMOS (L = 1 $\mu m$ & W = 1 $\mu m$ ) in saturation (V $_{DS}$ = 1 V)             |   |

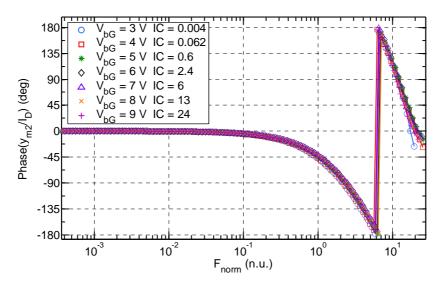

| and $V_{bG} = 0 \text{ V (Measurements)}$                                                                         | 0 |

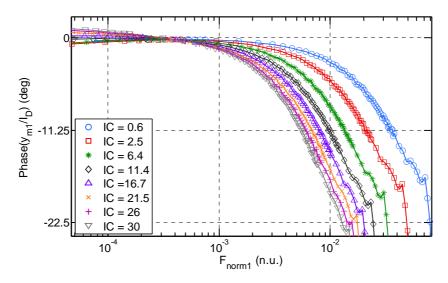

| Fig. 5.6 Phase of the transadmittance over $I_D$ versus normalized frequency $F_{norm1}$ at                       |   |

| different IC for NMOS (L = 1 $\mu m$ & W = 1 $\mu m$ ) in saturation (V $_{DS}$ = 1 V) and V $_{bG}$              |   |

| = 0 V (Measurements)                                                                                              | 1 |

| Fig. 5.7 Phase of the transadmittance over I <sub>D</sub> versus frequency at different IC for NMOS               |   |

| (L = 300 nm & W = 1 $\mu m$ ) in saturation (V_{DS} = 1 V) and V_{bG} = 0 V (Measurements).                       |   |

| 14                                                                                                                | 4 |

| Fig. | 5.8 Phase of the transadmittance over $I_D$ versus normalized frequency $F_{norm1}$ with                      |

|------|---------------------------------------------------------------------------------------------------------------|

|      | constant mobility at different IC for NMOS (L = 300 nm & W = 1 $\mu m)$ in saturation                         |

|      | $(V_{DS} = 1 \text{ V})$ and $V_{bG} = 0 \text{ V}$ (Measurements)                                            |

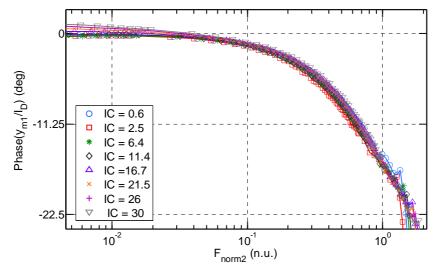

| Fig. | 5.9 Phase of the transadmittance over $I_D$ versus normalized frequency $F_{norm2}$ with                      |

|      | constant mobility at different IC for NMOS (L = 300 nm & W = 1 $\mu m)$ in saturation                         |

|      | $(V_{DS} = 1 \text{ V})$ and $V_{bG} = 0 \text{ V}$ (Measurements)                                            |

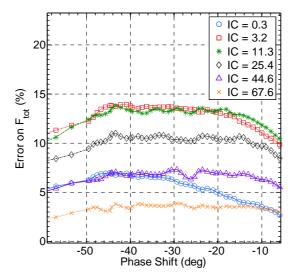

| Fig. | $5.10$ Frequency error versus phase shift after normalization using $F_{tot}$ (IC = $93.1$ is                 |

|      | taken as a reference)                                                                                         |

| Fig. | 5.11 Measured phase of the transadmittance over I <sub>D</sub> versus frequency at different IC               |

|      | for NMOS (L = 28 nm & W = 1 $\mu m$ ) in saturation (V $_{DS}$ = 1 V) and V $_{bG}$ = 0 V                     |

| Fig. | $5.12$ Measured phase of the transadmittance over $I_D$ versus frequency at different IC                      |

|      | for PMOS (L = 28 nm & W = 1 $\mu m$ ) in saturation (V $_{DS}$ = -1 V) and V $_{bG}$ = 0 V 146                |

| Fig. | $5.13$ Phase of the transadmittance over $I_D$ versus the normalized frequency $F_{norm1}$                    |

|      | estimated with a constant mobility at different IC for NMOS ( $L=28\ nm\ \&\ W=1$                             |

|      | $\mu m$ ) in saturation (V <sub>DS</sub> = 1 V) and V <sub>bG</sub> = 0 V (Measurements)                      |

| Fig. | $5.14$ Phase of the transadmittance over $I_D$ versus normalized frequency $F_{norm2}$ with                   |

|      | constant mobility at different IC for NMOS (L = 28 nm & W = 1 $\mu m)$ in saturation                          |

|      | $(V_{DS} = 1 \text{ V})$ and $V_{bG} = 0 \text{ V}$ (Measurements)                                            |

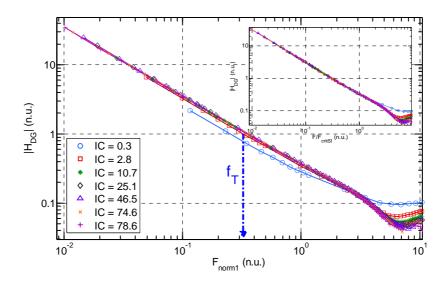

| Fig. | $5.15$ Measured $ H_{\mathrm{DG}} $ versus normalized frequency $F_{\mathrm{norm1}}$ at different IC for NMOS |

|      | (L = 1 $\mu m$ & W = 1 $\mu m$ ), (V $_{DS}$ = 1 V) and V $_{bG}$ = 0 V. Inset shows $ H_{DG} $ versus        |

|      | F/F <sub>critSI</sub> where F <sub>critSI</sub> is given by (5.6).                                            |

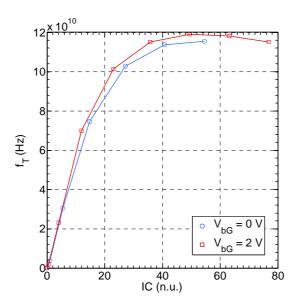

| Fig. | 5.16 Transit frequency $f_T$ versus IC at two different back gate voltages $V_{bG}$ (blue:                    |

|      | $V_{bG}=0\ V$ and red: $V_{bG}=2\ V)$ for NMOS (L = 100 nm) in saturation (V_{DS}=1\ V)                       |

|      | (4-port Measurements)                                                                                         |

| Fig. | $5.17$ Simulated transadmittance efficiency modulus versus frequency at different $V_{\text{bG}}$             |

|      | for NMOS (L = 1 $\mu$ m) in saturation (V <sub>DS</sub> = 1 V) and V <sub>GS</sub> =0.5V (TCAD)               |

| Fig. | 5.18 Normalized transadmittance efficiency modulus versus normalized frequency                                |

|      | $F_{norm}$ at different $V_{bG}$ for NMOS (L = 1 $\mu m)$ in saturation (V_DS=1V) and $V_{GS}=0.5$            |

|      | V (TCAD)                                                                                                      |

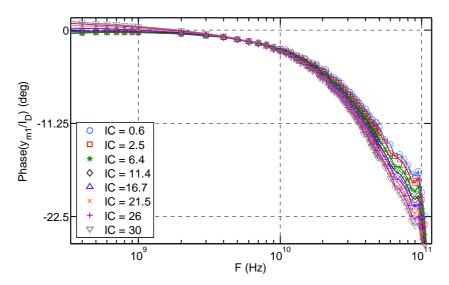

| Fig. | 5.19 Simulated phase of the transadmittance efficiency versus normalized frequency                            |

|      | $F_{norm}$ at different $V_{bG}$ for NMOS (L = 1 $\mu m)$ in saturation (V_DS= 1V) and $V_{GS}=0.5$           |

|      | V (TCAD)                                                                                                      |

| Fig. | 5.20 Simulated phase of the back transadmittance efficiency versus frequency at                              |     |

|------|--------------------------------------------------------------------------------------------------------------|-----|

|      | different $V_{bG}$ for NMOS (L = 1 $\mu$ m) in saturation ( $V_{DS}$ = 1 V) and $V_{G}$ = 0 V (TCAD).        |     |

|      |                                                                                                              | 153 |

| Fig. | 5.21 Simulated phase of the back transadmittance efficiency versus normalized                                |     |

|      | frequency $F_{norm}$ at different $V_{bG}$ for NMOS (L = 1 $\mu$ m) in saturation ( $V_{DS}$ = 1 $V$ ) and   |     |

|      | $V_G = 0 V (TCAD).$                                                                                          | 153 |

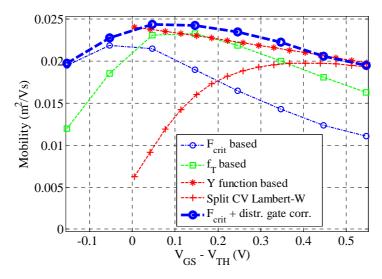

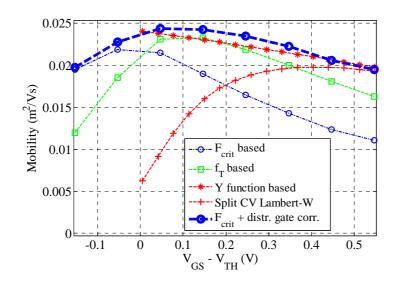

| Fig. | 5.22 Mobility versus gate voltage overdrive for $L = 0.3 \mu m$ extracted using various                      |     |

|      | methods: F <sub>crit</sub> based, f <sub>T</sub> based, classical Y function with iteration, Lambert-W Split |     |

|      | C-V based, and F <sub>crit</sub> based with correction of the distributed gate effect                        | 155 |

| Fig. | 6.1 Square law model and weak inversion exponential model failures to predict                                |     |

|      | measured $g_\text{m}/I_D$ in MI for a long and short channel devices. $V_\text{TH}$ is defined here as       |     |

|      | the $V_{GS}$ at the maximum of $\partial C_{gc}/\partial V_{GS}.$                                            | 163 |

| Fig. | 6.2 Measured gate to channel capacitance normalized using front oxide capacitance                            |     |

|      | $(C_{ox}.W.L)$ with respect to $V_{GS}$ for various $V_{bG}$ and its derivative (Inset) for N-type           |     |

|      | UTBB FDSOI MOSFET                                                                                            | 163 |

| Fig. | 6.3 Comparison of DIBL between FDSOI and bulk in saturation ( $V_{DS}$ =1 $V$ ) and $V_{bG}$                 |     |

|      | = 0 V                                                                                                        | 164 |

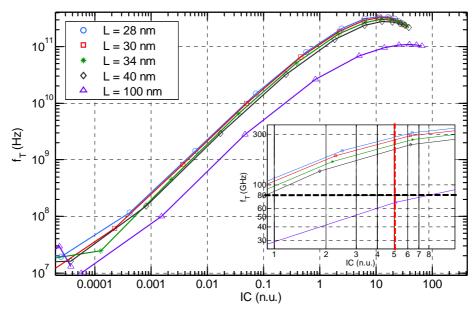

| Fig. | 6.4 Measured f <sub>T</sub> versus IC for various MOSFET lengths in saturation (V <sub>DS</sub> =1V).        |     |

|      | Inset gives a focus on the second part of the MI (1 < IC < 10)                                               | 165 |

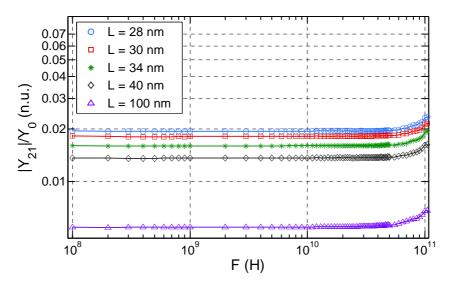

| Fig. | $6.5$ Measured and normalized $\left Y_{21}\right $ versus frequency for various lengths and finger          |     |

|      | length is 1 µm.                                                                                              | 166 |

| Fig. | $6.6$ Phase shift of the transadmittance $Y_{21}$ versus frequency for various lengths and                   |     |

|      | finger length is 1 µm.                                                                                       | 166 |

| Fig. | 6.7 gm over I <sub>D</sub> charts versus IC for several short NMOS along with a longer channel               |     |

|      | (L = 1 μm) for comparison                                                                                    | 168 |

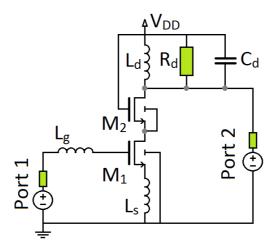

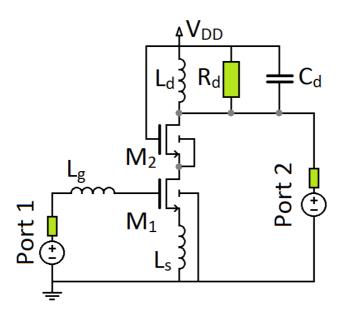

| Fig. | 6.8 LNA cascode circuit.                                                                                     | 170 |

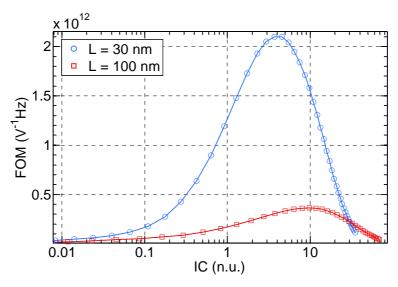

|      | 6.9 FoM versus IC for two lengths.                                                                           |     |

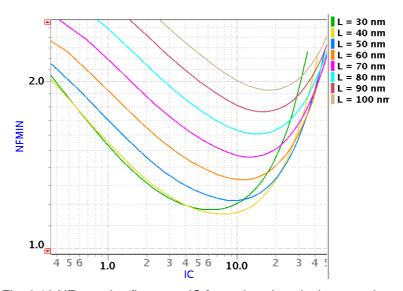

|      | 6.10 NF <sub>MIN</sub> noise figure vs. IC for various lengths in saturation                                 |     |

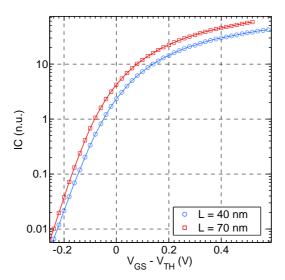

|      | 6.11 Inversion Coefficient vs. gate voltage overdrive for two lengths $L = 40$ nm and                        |     |

|      | L = 70 nm.                                                                                                   | 173 |

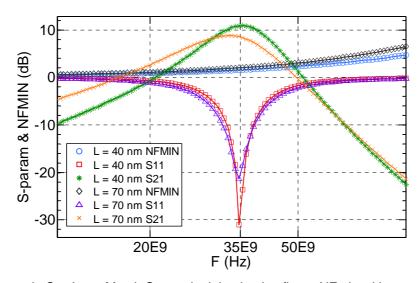

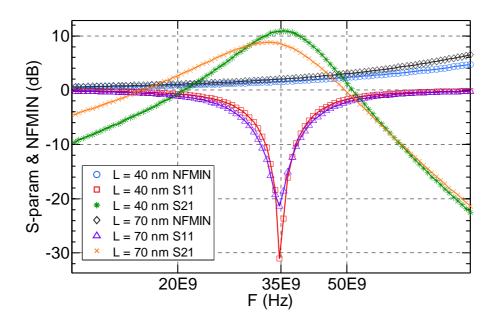

| Fig. | 6.12 Power gain $S_{21}$ , Input Match $S_{11}$ , and minimal noise figure NFmin with respect                |     |

| U    | to frequency for two LNA circuits (first with MOSFET length of 40 nm and second                              |     |

|      | with 70 nm).                                                                                                 | 174 |

|      | ,                                                                                                            |     |

## List of Figures

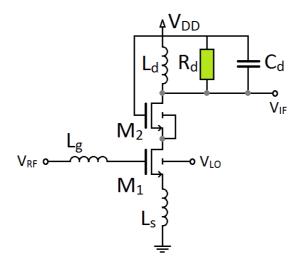

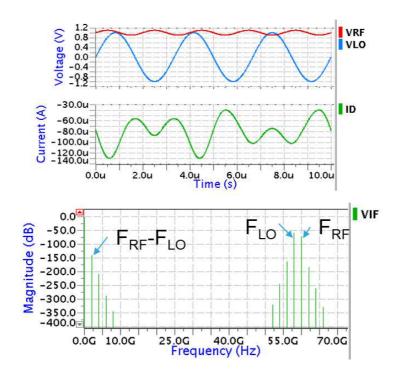

| Fig. | 6.13 The LNA-MIXER circuit                                                             | 175 |

|------|----------------------------------------------------------------------------------------|-----|

| Fig. | 6.14 (top) Time domain input voltages VRF and VLO, and output current I <sub>D</sub> , |     |

|      | (bottom) corresponding spectrum.                                                       | 176 |

## List of tables and diagrams

| Table 1-1 Summary of surface potential calculation models in a DG MOSFET [59]                              | 9  |

|------------------------------------------------------------------------------------------------------------|----|

| Table 2-1 Threshold voltage comparison between the C-V derivative based and g <sub>m</sub> /I <sub>D</sub> |    |

| derivative based methods.                                                                                  | 39 |

| Table 2-2 Summary of the extraction steps                                                                  | 59 |

| Table 2-3 Normalization.                                                                                   | 50 |

| Table 2-4 Operating Point information restricted list proposal for analog design $(B = bG)$ .              |    |

|                                                                                                            | 72 |

| Table 3-1 n <sub>1</sub> factor and I <sub>1</sub> for N-MOSFET and P-MOSFET in saturation and at 25 °C    | 38 |

| Table 4-1 Summary of the expressions used for equivalent circuit parameters extraction                     |    |

| from Y-parameters (source and back gate being tight together in a 2-port) 10                               | )8 |

| Table 6-1 Summary of the two LNAs parameters at $F_0 = 35$ GHz                                             | 73 |

## List of Appendices

| Appendix A | 195 |

|------------|-----|

| Appendix B | 201 |

| Appendix C | 203 |

| Appendix D | 205 |

| Appendix E | 209 |

## Acronyms and Abbreviations

A/D Analog to digital

BSIM Berkeley Short-channel IGFET Model

GBW Gain-Bandwidth

CLM Channel Length Modulation

CMOS Complementary Metal-Oxide-Semiconductor

CS Common-Source

DIBL Drain Induced Barrier Lowering

DUT Device under Test

FDSOI Fully Depleted Silicon on Insulator

FET Field Effect Transistor

FinFET Fin Field Effect Transistor

FoM Figure-of-Merit

GIDL Gate Induced Drain Leakage

GISL Gate Induced Source Leakage

IC Integrated Circuit

MI Moderate Inversion

MOS Metal-Oxide-Semiconductor

MOSFET Metal-Oxide-Semiconductor Field-Effect-Transistor

mm-Wave Millimeter-Wave

LNA Low noise amplifier

NMOS N-type Metal-Oxide-Semiconductor

NQS Non-Quasi-Static

OP Operation Point

PMOS P-type Metal-Oxide-Semiconductor

PSD Power Spectral Density

QS Quasi-Static

RF Radio Frequencies

SCE Sort-Channel Effects

SEM Scanning Electron Microscope

SH Self-Heating

SI Strong Inversion

SOI Silicon on Insulator

T Temperature

TCAD Technology Computer Aided Design

TEM Transmission electron microscopy

UTBB Ultra-Thin-Body and Box

UTSOI Ultra-Thin SOI

VSAT Velocity Saturation

WI Weak Inversion

## List of Symbols

### **Physical constants**

k Boltzmann's Constant in [J.K<sup>-1</sup>]

T Absolute Temperature in [K]  $\mu_0$  Low-field mobility in [m<sup>2</sup>.V<sup>-1</sup>.s<sup>-1</sup>]

#### Geometry

L Channel length in [m]

W Total channel width in [m]

W<sub>f</sub> Single gate finger width in [m]

N<sub>f</sub> Number of gate fingers

M Number of devices in parallel

T<sub>ox</sub> Front gate oxide thickness in [m]

T<sub>si</sub> Silicon film thickness in [m]

T<sub>BOX</sub> Back gate oxide thickness (BOX thickness) (= T<sub>ox2</sub>) in [m]

### **Voltages**

UT Thermodynamic Voltage in (= kT/q) in [V] VD DC drain to source voltage  $(= V_{DS})$  in [V] VG DC gate to source voltage  $(= V_{GS})$  in [V] VbG DC back gate to source voltage in [V]

V<sub>TH</sub> Threshold voltage in [V]

V<sub>DSAT</sub> Drain to source saturation voltage in [V]

V<sub>ov</sub> Gate to source voltage overdrive (= V<sub>G</sub> - V<sub>TH</sub>) in [V]

#### Currents

ID Static drain current flowing into the drain terminal in [A]

$I_d$  Normalized drain current (=  $I_D/(W/L)$ ) in [A]

IC Inversion Coefficient which is also a drain current normalization

I<sub>1</sub> Technology characteristic current for the front gate (= I<sub>spec</sub>) in [A]

I<sub>2</sub> Technology characteristic current for the back gate in [A]

I<sub>□</sub> Square shape drain current in [A]

ION MOSFET ON current (digital applications FoM) in [A]

IOFF MOSFET OFF current (digital applications FoM) in [A]

#### **Conductances and Transconductances**

$g_{m1}$  or  $g_m$  Front gate transconductance in [S]  $g_{m2}$  or  $g_{mb}$  Back gate transconductance in [S]  $g_{ds}$  Output conductance (=  $g_d$ ) in [S]

### Charges

Q<sub>inv</sub> Inversion mobile charge density (= Q<sub>i</sub>) in [C.m<sup>-2</sup>]

Q<sub>I</sub> Inversion charge in [C]

$Q_G$  front gate charge (=  $Q_{g1}$ ) in [C]

Q<sub>D</sub> Drain charge in [C]

Q<sub>S</sub> Source charge in [C]

$Q_{bG}$  Back gate charge for UTBB FDSOI MOSFET (=  $Q_{g2}$ ) in [C]

Q<sub>B</sub> Bulk charge for bulk MOSFETs in [C]

#### Gains in [dB]

H<sub>DG</sub> Current gain

U Unilateral gain or Mason's gain

A<sub>v</sub> Voltage gain

#### **Admittances and Transadmittances**

ym Intrinsic mutual front gate transadmittance in [S]

y<sub>xy</sub> Admittance (x = y) or transadmittance  $(x \neq y)$  in [S] where x and y

are taking the following values: 1 for drain, 2 for gate, 3 for source

and 4 for back gate

#### **Capacitances and Transcapacitances**

C<sub>ox</sub> Oxide capacitance per unit area in [F.m<sup>-2</sup>]

$C_{qs}$ Total gate to source capacitance in [F]  $C_{gsi}$ Intrinsic gate to source capacitance in [F] Extrinsic gate to source capacitance in [F] Case

Gate to drain capacitance in [F]  $C_{gd}$

Cgdi Intrinsic gate to drain capacitance in [F] Extrinsic gate to drain capacitance in [F] Cgde  $C_{\mathsf{sb}}$ Source to back gate capacitance in [F]  $C_{gb}$ Total gate to back gate capacitance in [F]

Cgbi Intrinsic gate to back gate capacitance in [F]

Cgbe Extrinsic gate to back gate capacitance in [F]

$C_{db}$ Drain to back gate capacitance in [F] Drain to source capacitances in [F] Cds

$C_{dg}$ Drain to gate capacitance in [F]  $C_{sg}$ Source to gate capacitance in [F]  $C_{sd}$ Source to drain capacitance in [F]  $C_{bd}$ Back gate to drain capacitance in [F]

Back gate to gate capacitance in [F] Cbg Cbs Back gate to source capacitance in [F]

Gate capacitance, including overlap capacitances in [F]  $C_{gg}$

$C_{dd}$ Drain capacitance in [F]  $C_{ss}$ Source capacitance in [F]

Total back gate capacitance in [F]  $C_{bb}$

$C_{m}$ Intrinsic mutual capacitance related to front gate in [F]

#### Resistances

Rg Gate resistance in  $[\Omega]$

Rs Source series resistance in  $[\Omega]$ Drain series resistance in  $[\Omega]$  $R_D$  $R_{bG}$ Back gate resistance in  $[\Omega]$ Rcontact Contact resistance in  $[\Omega]$

#### **Times and Frequencies**

f⊤ Transit frequency in [Hz]  $\tau_T$  Transit time in [s]

f<sub>max</sub> Maximum oscillation frequency in [Hz]

## Other

$n_1$  Front gate slope factor

n<sub>2</sub> Back gate slope factor

## Introduction

Wireless portable devices improve life by providing quick tracking and diagnostics, and have become ubiquitous over the last few years. The main reasons of this spectacular spread are the low price and high performance. Still, the power-consumption remains one of the major barriers somehow preventing the complete achievement of the wider Network of Things. With the emergence of the Internet of Things (IoT), there has been rising interest in fast, low-cost and low-power Systems-On-Chip (SoCs) to satisfy the thirst for sensing and communicating in a continuous and unnoticeable way. The popularity of these devices and things is due mainly to advances in the semiconductor industry which have promoted low-cost, low-power and high speed Integrated Circuits (ICs) through aggressive scaling [1].

## Background and Motivation

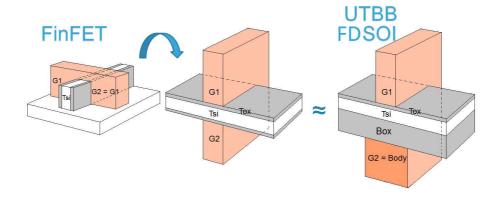

Silicon technology has been driven for years by downscaling dictated by the high-performance integrated digital circuits. Today, further reduction of transistor dimensions is critical due to intrinsic limitations such as short channel effects. To overcome these challenges, semiconductor industry strategies include the use of new materials and revolutionary device architectures such as Multiple-Gate (MG). Moreover, shrinking the thickness of the silicon body is proposed in the case of planar ultra-thin Body and Box (UTBB) fully depleted (FD) Silicon-on-Insulator (SOI) double-gate (DG) MOSFET, and vertical FinFET [2][3][4][5].

The UTBB FDSOI MOSFET is considered as a planar low-cost and a straightforward solution to continue shrinking the CMOS transistor for low power and high-speed Very-Large-Scale Integration (VLSI) circuits [6]. The advantages of the UTBB FDSOI MOSFETs include: steep subthreshold slope (close to the room temperature Boltzmann limit of 60 mV/dec for long channels) thanks to the better control of the channel potential [7], low channel doping and excellent control of short-channel effects (SCE). Both FinFET and UTBB FDSOI MOSFETs allow excellent

channel control for high digital performances [8][9][10]. However, analog and RF performances are affected unevenly.

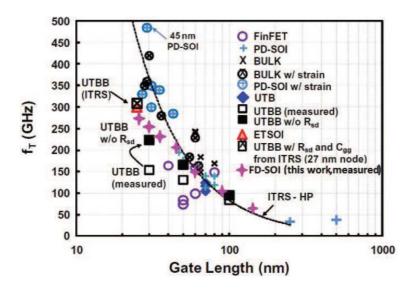

Because of a crowded up-to-5 GHz spectrum with many interferers, some applications such as automotive radar started to tackle the mm-Wave spectrum looking for more bandwidth [11]. Other applications are under active investigation and design in mm-Wave spectrum such as low-power portable radars demonstrated in [12] and high data rate Wireless USB-like communication prospected in [13]. The aforementioned nanoscale CMOS device architectures display very high transit frequencies practically beyond the Millimeter-Wave (mm-Wave) spectrum and can be clearly used for these mm-Wave applications [14][15]. To be ready to take full advantage of the advanced nanoscale CMOS devices, the computer-aided design (CAD) tools have to be updated with accurate descriptions of their behavior in all operation conditions. Therefore, FinFET and UTBB FDSOI MOSFET models for high frequency (HF) and low-voltage (LV) applications are required. The simulation of advanced high precision mixed-mode analog circuits including A/D converters, switched-capacitor circuits, and RF amplifiers requires accurate device models in a large frequency spectrum including mm-Wave. Actually, at high frequency operation, the input signal may have rise or fall times comparable or smaller than the transit time of the transistor. Though all standard compact models, including the advanced Leti-UTSOI2 model, are mainly low frequency quasi-static models with no or simplified high frequency effects.

As mentioned above, low power consumption is one of the main challenges for IoT widespread especially at high frequency operation for RF or mm-Wave communication. High performance rechargeable batteries have already granted a certain degree of autonomy. Moreover, CMOS technology evolution has allowed substantial reduction of power consumption needs in the digital part of the Integrated Circuits (ICs) [16][17]. To further reduce power consumption in the light battery powered devices, high frequency front-end subsystems design has to take into consideration power consumption. Particularly, with the increasing off leakage current that determines the systems stand-by power consumption, power management techniques have to be used and bias conditions have to be lowered. Furthermore, with the very high transit frequencies achieved today in submicron CMOS technologies, the

operating point can be moved towards Weak Inversion (WI) and Moderate Inversion (MI) regimes in order to achieve low drive currents, higher gains and still acceptable operation frequencies [18]. Moderate Inversion operation is increasingly important for low-voltage and low-power CMOS applications since it allows for high transconductance efficiency and low V<sub>DSAT</sub> while maintaining high bandwidth. However, operating MOSFET in MI greatly complicates analog CMOS design as no physically based simple model is available for hand calculation.

This research work has been motivated primarily by the significant advantages brought about by the UTBB FDSOI technology to the Low power Analog and RF applications on the one hand and the interesting physical phenomena occurring in the thin silicon film under the impact of the two independent gates on the other hand. The main goal is to study the dynamic behavior of the UTBB FDSOI MOSFET in light of the recent technology advances and propose predictive models and useful recommendations for RF IC design with particular emphasis on Moderate Inversion regime.

#### Thesis Outline

After a brief review of progress in MOSFET architectures introduced in the semiconductor industry, in **Chapter 1** we go through the list of the advantages of the state-of-the-art UTBB FDSOI technology. We also present two modeling approaches as a basis of our research work. We then describe the existing compact models for quasi-static UTBB FDSOI MOSFET.

Chapter 2 describes the static and low frequency behavior of the UTBB FDSOI MOSFET. The main involved physical effects are reviewed, particularly the back gate impact, using measured data and technology computer-aided design (TCAD) simulations. A threshold based long channel model is compared to the classical bulk model, and a small signal low frequency equivalent circuit is proposed. Two modeling approaches are investigated: the simple enhanced equivalent circuit and an industrial recently proposed compact model namely Leti-UTSOI2 model. The important low frequency Figures-of-Merit are assessed using both models. An enhancement of the classical MOSFET Operating Point Information feature is finally proposed. The

classical feature is intensively used in Analog and RF design CAD despite the severe discussed limitations.

For better insight into the Weak Inversion and Moderate Inversion MOSFET operation, the  $g_m$  over  $I_D$  figure of merit namely the transconductance efficiency is studied in **Chapter 3.** Transconductance efficiency is an essential design synthesis tool for low-power analog and RF applications. The invariance of  $g_m/I_D$  versus normalized drain current curve is analyzed in UTBB FDSOI asymmetric double gate (DG) MOSFET. The Chapter studies the breakdown of this invariance versus back gate voltage, transistor length, temperature, drain to source voltage and process variations. The unforeseeable invariance is emphasized by measurements of a commercial 28 nm UTBB FDSOI CMOS technology, thus supporting the  $g_m/I_D$  based design methodologies usage in double gate UTBB FDSOI transistors sizing.

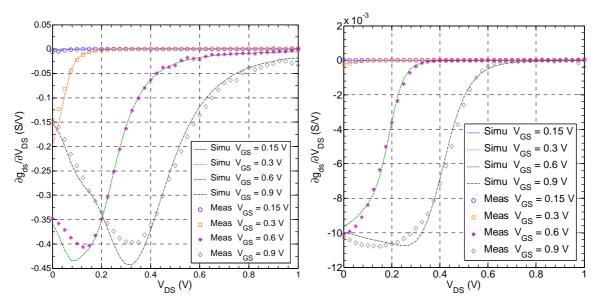

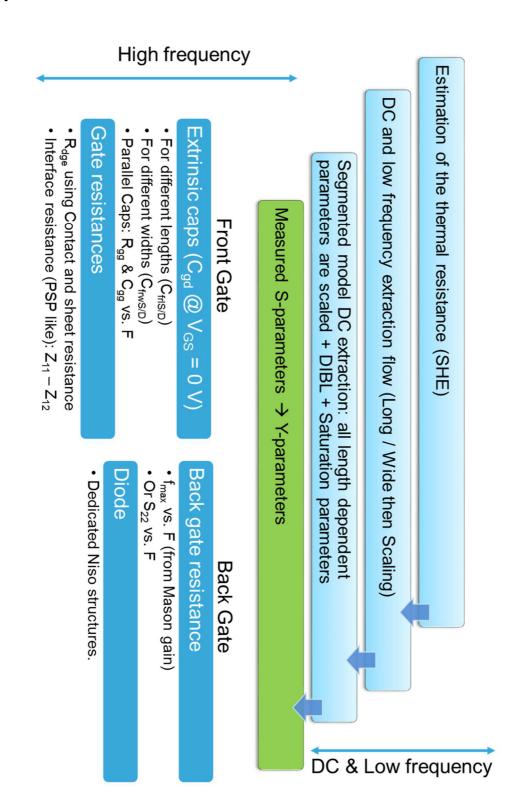

Chapter 4 discusses RF and mm-Wave characterization and modeling of the UTBB FDSOI MOSFET high frequency behavior up to 110 GHz. Various model enhancements are proposed to capture high frequency effects including Non-Quasi-Static (NQS) effect and gate distributed effect. The high frequency UTBB FDSOI model is extended using front and back gates networks. Simulated high frequency figures of merit are assessed and compared to measured data.