## Monitoring of temperature effects on CMOS memories Emna Farjallah

## ▶ To cite this version:

Emna Farjallah. Monitoring of temperature effects on CMOS memories. Other. Université Montpellier, 2018. English. NNT: 2018MONTS091. tel-02139553

## HAL Id: tel-02139553 https://theses.hal.science/tel-02139553

Submitted on 24 May 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE MONTPELLIER

#### En Systèmes Automatiques et Microélectroniques

École doctorale : Information, Structures, Systèmes

Unité de recherche : Laboratoire d'Informatique, Robotique et Microélectronique de Montpellier

# Monitoring des Effets de la Température sur les Mémoires CMOS

## Présentée par Emna FARJALLAH

## Le 27 Novembre 2018

## Sous la direction de Luigi DILILLO

### Devant le jury composé de

| Bruno ROUZEYRE, Professeur, Univ. de Montpellier                  | Président du jury |

|-------------------------------------------------------------------|-------------------|

| Alberto BOSIO, Professeur, Univ. de Lyon                          | Rapporteur        |

| Eduardo Augusto BEZERRA, Professeur, Univ. de Santa Catarina      | Rapporteur        |

| Marco OTTAVI, Professeur, Univ. de Rome Tor Vergata               | Examinateur       |

| Frédéric WROBEL, Professeur, Univ. de Montpellier                 | Examinateur       |

| Hassen AZIZA, Maître de conférences, École polytech' de Marseille | Examinateur       |

| Valentin GHERMAN, Docteur chercheur, CEA LIST                     | Invité            |

| Jean-Marc ARMANI, Ingénieur chercheur, CEA LIST                   | Invité            |

## Monitoring des effets de la température sur les mémoires CMOS

Résumé: La complexité des systèmes électroniques ne cesse d'augmenter, tout comme la tendance actuelle de miniaturisation des transistors. La fiabilité est ainsi devenue un continuel défi. Les environnements hostiles caractérisés par des conditions extrêmes de hautes températures affectent le bon fonctionnement des systèmes. Pour les composants de stockage de données, la température est considérée comme une menace pour la fiabilité. Le développement de techniques de suivi et de contrôle devient ainsi essentiel afin de garantir la fiabilité des mémoires volatiles et non volatiles. Dans le cadre de ma thèse, je me suis intéressée à deux types de mémoires : les mémoires NAND Flash et les mémoires SRAM. Pour contrôler les effets de la température sur les mémoires Flash, une solution basée sur l'utilisation d'un timer a été proposée afin de réduire la fréquence de rafraîchissement tout en continuant à garantir l'intégrité de l'information stockée. De plus, une méthode statistique et une approximation calculatoire basées sur des opérations de vérification périodique ont été proposées afin d'améliorer le taux d'erreurs (RBER) tolérables dans des SSDs de types Entreprise à base de mémoires Flash. Enfin, pour les mémoires SRAM, l'effet de la température sur la vulnérabilité par rapport aux événements singuliers (SEU) a été étudiée. Une étude comparative sur l'apparition des SEU a été menée avec différentes températures pour des cellules standards 6T-SRAM et des cellules de stockage durcies (DICE).

Mots clés: Fiabilité, Contrôle, Température, Mémoires Flash, Rétention, RBER, Rafraîchissement, Mémoires SRAM, DICE, Événements singuliers

## Monitoring of the effects of temperature on CMOS memories

**Abstract:** With the constant increase of microelectronic systems complexity and the continual scaling of transistors, reliability remains one of the main challenges. Harsh environments, with extreme conditions of high temperature and thermal cycling, alter the proper functioning of systems. For data storage devices, high temperature is considered as a main reliability threat. Therefore, it becomes essential to develop monitoring techniques to guarantee the reliability of volatile and non-volatile memories over an entire range of operating temperature. In the frame of this thesis, I focus my studies on two types of memories: NAND Flash memories and SRAMs. To monitor the effects of temperature in NAND Flash memories, a timer-based solution is proposed in order to reduce the refresh frequency and continue to guarantee the integrity of data. In addition, statistical and computational approximation techniques based on periodic check operations are proposed in order to improve the tolerated Raw Bit Error Rate (RBER) in enterprise-class Flash based SSDs. Finally, for SRAM memories, the effect of temperature on Single Event Upset (SEU) sensitivity is studied. A comparative study on SEU occurrence under different temperatures is conducted for standard 6T-SRAM cells and hardened Dual Interlocked Storage Cells (DICE).

**Keywords:** Reliability, Monitoring, Temperature, Flash memories, Retention, RBER, Refresh, SRAM memories, DICE, SEU

### Acknowledgments

This thesis work has been conducted in the Laboratory of Reliability and Sensors Integration (LFIC), part of the CEA Laboratory of Systems and Technologies Integration (CEA-LIST).

Firstly, I would like to thank Eduardo Augusto BEZERRA and Alberto BOSIO who made me the honor to be the reviewers of my PhD thesis. I would also like to thank Marco OTTAVI, Frédéric WROBEL, Bruno ROUZEYRE and Hassen AZIZA who accepted to be part of my jury.

I would like to express my gratitude to Thierry COLETTE and Jean-René LEQUEPEYS, heads to the Department of Architecture, Design and Embedded Software (DACLE) for offering me the opportunity to conduct my thesis work in good conditions in their unit.

My sincere thanks also go to Antoine DUPRET and Tanguy SASSOLAS, heads of the LFIC, who provided me the opportunity to join their team as a PhD student, and who gave me access to the laboratory and research facilities.

I would like to express my sincere gratitude to my thesis director Luigi DILILLO for his crucial support, his insightful knowledge and trust and without whom I would not have achieved this work. I would also like to thank him for his warm welcome each time he received me in the Laboratory of Informatics, Robotics and Microelectronics of Montpellier (LIRMM).

Besides my thesis director, I would like to thank my advisor Valentin GHERMAN for his great help, his availability and his guidance. I would also like to thank him for all the rich scientific discussions we had which made me question my work and become a better researcher.

My sincere thanks goes to my mentor Jean-Marc Armani who provided me with valuable advice, crucial support and trust during the last two years. His guidance and great kindness helped me to overcome the difficulties during this research period and in the writing of this thesis.

I would also like to thank my fellow LFIC labmates for their support and help and for all the stimulating discussions we had. In particular, I am very grateful to Jaume, Esteban, Cyril, Mariem and Wafa for the valuable pieces of advice they gave me especially during this last year. I would also like to thank former labmates who left LFIC for other adventures and who were crucial to my work experience in the laboratory. I am grateful to Baptiste, Arnaud, Clément and Daniel for all the nice moments we shared and pleasant atmosphere they managed to bring to LFIC.

A special thanks goes to Emmanuel from LCE for his cheerfulness, his positive attitude and help. My sincere gratitude goes to Dzila my office labmate, but above all my friend and my confident, who always found the words to cheer me up, who was there for all my ups and downs and whose presence in the LFIC brought joy into my heart.

I mainly owe this achievement to my parents Leila and Jalel and to my sisters Asma and Eya who never doubted in my capacities or stopped encouraging me and who supported me physically and morally in all the crucial times of my life.

Finally, I would like to thank Thibaut for believing in me even when I did not, for his support, his great patience and joyful music. He knew how to cheer me up and I learned to rediscover life through his innocent gaze. Now the world is a better place.

# Contents

| In | trod | uction                                                                                                           | 1              |

|----|------|------------------------------------------------------------------------------------------------------------------|----------------|

| 1  | Ove  | erview of the target memories                                                                                    | 3              |

|    | 1.1  | Reliability fundamentals                                                                                         | 3              |

|    |      | 1.1.1 Reliability and failure rate                                                                               | 3              |

|    |      | 1.1.2 Reliability and Mean-Time-To-Failure                                                                       | 4              |

|    | 1.2  | Temperature effects on semiconductors                                                                            | 5              |

|    |      | 1.2.1 MOSFET threshold voltage                                                                                   | 5              |

|    |      | 1.2.2 MOSFET drain current                                                                                       | 6              |

|    |      | 1.2.3 MOSFET Leakage current                                                                                     | $\overline{7}$ |

|    |      | 1.2.4 Electromigration                                                                                           | 7              |

|    | 1.3  | General introduction to memories                                                                                 | 8              |

|    | 1.4  | NAND Flash memories                                                                                              | 9              |

|    |      | 1.4.1 NAND Flash structure                                                                                       | 10             |

|    |      | 1.4.2 NAND Flash operations                                                                                      | 13             |

|    |      | 1.4.2.1 Read operation $\ldots$                                                                                  | 13             |

|    |      | 1.4.2.2 Program operation                                                                                        | 15             |

|    |      | 1.4.2.3 Erase operation                                                                                          | 16             |

|    |      | 1.4.3 Single vs. multiple level cells                                                                            | 17             |

|    | 1.5  | SRAM memories                                                                                                    | 19             |

|    |      | 1.5.1 SRAM structure                                                                                             | 20             |

|    |      | 1.5.2 SRAM operations                                                                                            | 20             |

|    |      | 1.5.2.1 Read operation $\ldots$ | 20             |

|    |      | 1.5.2.2 Write operation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$         | 21             |

|    |      | 1.5.2.3 Hold phase and cell stability                                                                            | 23             |

|    |      | 1.5.3 Radiation effects on integrated circuits                                                                   | 25             |

|    |      | 1.5.3.1 Particles interaction with matter                                                                        | 25             |

|    |      | 1.5.3.2 Generalities on radiations effects on integrated circuits                                                | 26             |

|    | 1.6  | Conclusion                                                                                                       | 28             |

| 2  | Sta  | te-of-the-art of reliability monitoring techniques                                                               | 29             |

|    | 2.1  |                                                                                                                  | 29             |

|    |      |                                                                                                                  | 29             |

|    |      |                                                                                                                  | 29             |

|    |      |                                                                                                                  | 31             |

|    |      |                                                                                                                  | 31             |

|    |      |                                                                                                                  | 33             |

|   |            | 2.1.1.2.3 Erase disturbs $\ldots$                                                                                    | 34              |

|---|------------|----------------------------------------------------------------------------------------------------------------------|-----------------|

|   |            | 2.1.1.3 Endurance                                                                                                    | 35              |

|   |            | 2.1.1.4 Data retention                                                                                               | 35              |

|   |            | 2.1.2 Reliability improvement techniques in NAND Flash                                                               | 37              |

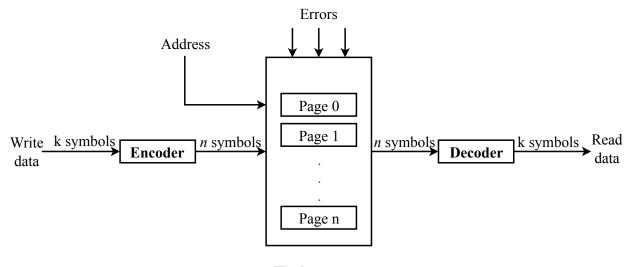

|   |            | 2.1.2.1 Error correction codes                                                                                       | 37              |

|   |            | 2.1.2.1.1 Basics for error correction codes                                                                          | 37              |

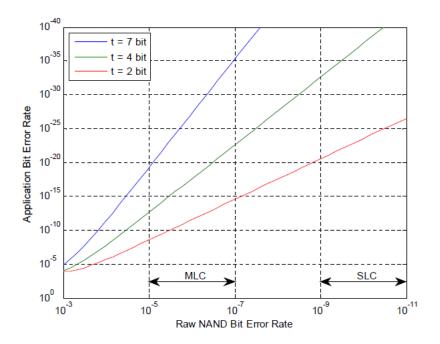

|   |            | 2.1.2.1.2 Metrics of error correction codes                                                                          | 38              |

|   |            | 2.1.2.1.3 Reliability improvement with error correction codes                                                        | 39              |

|   |            | 2.1.2.2 Read operation optimization                                                                                  | 40              |

|   |            | 2.1.2.3 Flash refresh and correction                                                                                 | 42              |

|   | 2.2        | Radiation resilience techniques for SRAM                                                                             | 43              |

|   |            | 2.2.1 Radiation effects on SRAM                                                                                      | 43              |

|   |            | 2.2.1.1 Cumulative dose and single events                                                                            | 43              |

|   |            | 2.2.1.2 Soft errors in SRAM                                                                                          | 44              |

|   |            | 2.2.2 Radiation effects resilience techniques                                                                        | 45              |

|   |            | 2.2.2.1 Radiation shielding                                                                                          | 45              |

|   |            | 2.2.2.2 Components hardening                                                                                         | 45              |

|   |            | 2.2.2.3 System-level hardening                                                                                       | 47              |

|   | 2.3        | Conclusion                                                                                                           | 48              |

| 3 | Det        | a nefresh methodology in Flech SSD based on Ambenius Timen                                                           | 49              |

| ა | 3.1        | a refresh methodology in Flash-SSD based on Arrhenius Timer<br>Endurance and retention issues in NAND Flash memories | <b>49</b><br>49 |

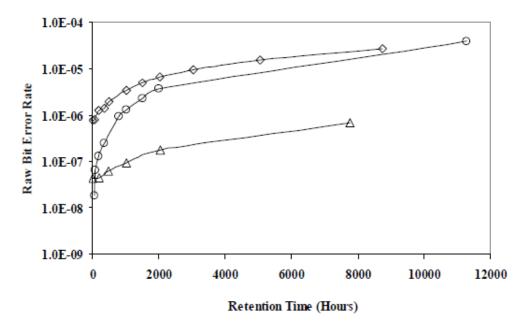

|   | 0.1        | 3.1.1 Retention error rate in NAND Flash                                                                             | 49<br>50        |

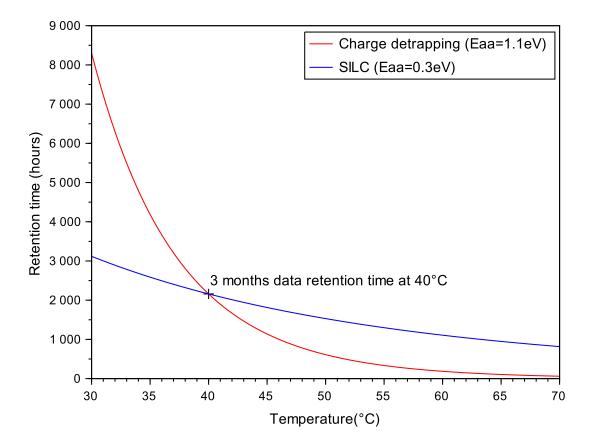

|   |            | 3.1.2 Effect of temperature on retention capability                                                                  | 50<br>51        |

|   |            | 3.1.3 Limitations of conventional refresh schemes                                                                    | 54              |

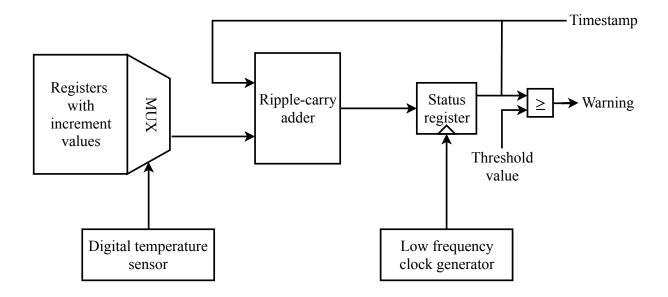

|   | 3.2        | Arrhenius timer purpose                                                                                              | 54<br>54        |

|   | 3.3        | Arrhenius timer structure and operations                                                                             | 55              |

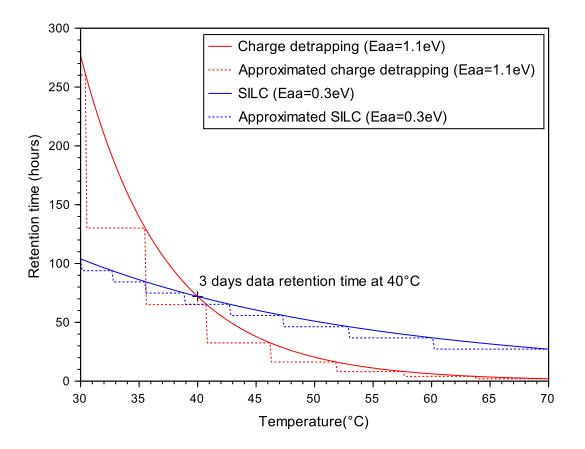

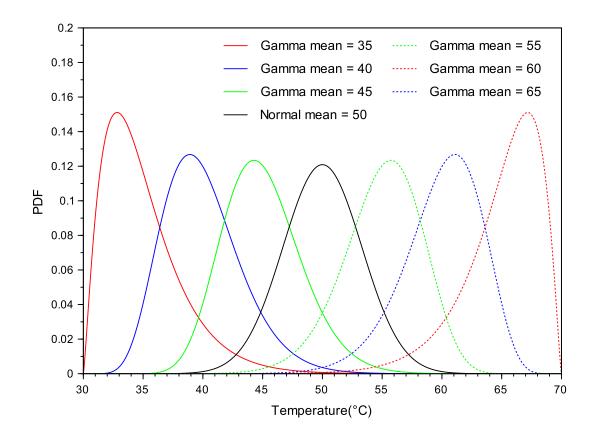

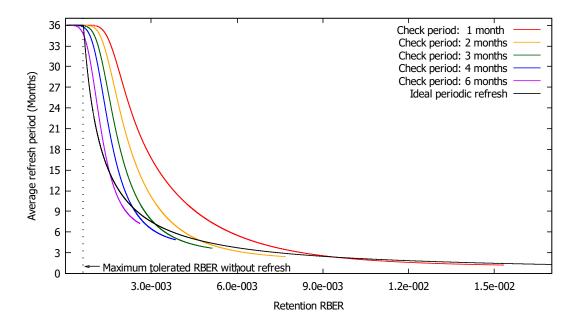

|   | 3.4        | Estimated refresh frequency reductions                                                                               | 59              |

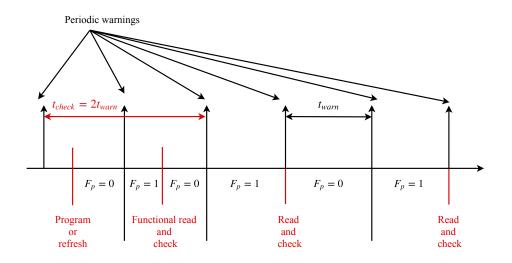

|   | 3.4<br>3.5 | Warning triggering with A-timer and timestamps                                                                       | 62              |

|   | 3.6        | Conclusion                                                                                                           | 64              |

|   | 5.0        |                                                                                                                      | 04              |

| 4 | Imp        | provement of the tolerated raw bit error rate in NAND Flash SSDs                                                     | 67              |

|   | 4.1        | Retention errors detection and rate estimation                                                                       | 67              |

|   |            | 4.1.1 Retention errors detection in MLC NAND Flash                                                                   | 68              |

|   |            | 4.1.2 Statistical background for retention RBER estimation                                                           | 70              |

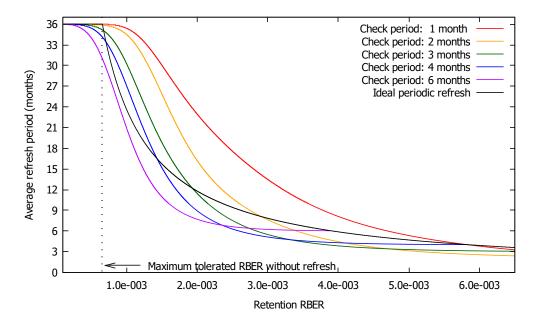

|   | 4.2        | Statistical approach for tolerated RBER improvement                                                                  | 73              |

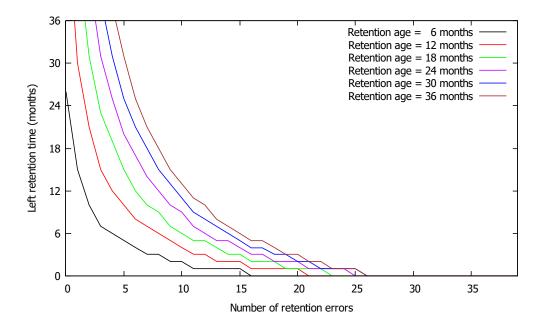

|   |            | 4.2.1 Left retention time estimation                                                                                 | 73              |

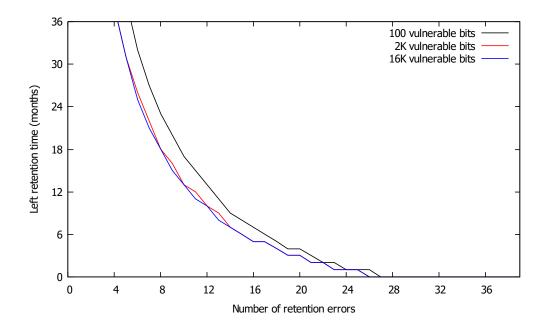

|   |            | 4.2.2 Maximum tolerated retention RBER estimation                                                                    | 77              |

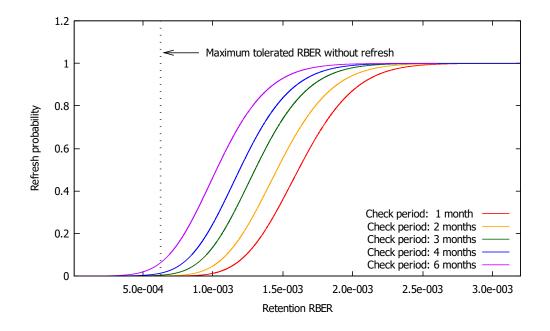

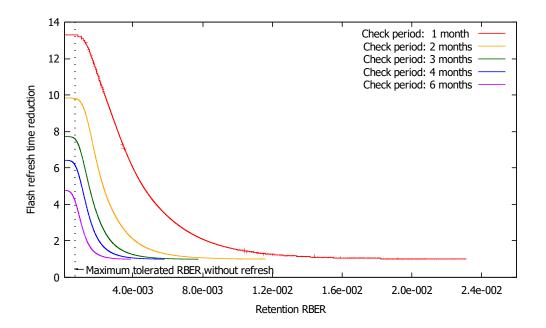

|   | 4.3        | Selective refresh with retention RBER linear approximation                                                           | 79              |

|   |            | 4.3.1 Left retention time estimation with retention RBER linear approximation $\ldots$                               | 81              |

|   |            | 4.3.2 Selective refresh optimization                                                                                 | 82              |

|    |       | 4.3.3 Improvement in the maximum tolerated retention RBER                | 83  |

|----|-------|--------------------------------------------------------------------------|-----|

|    | 4.4   | Conclusion                                                               | 88  |

| 5  | Ten   | perature influence on SEU vulnerability of SRAM cells                    | 91  |

|    | 5.1   | Leakage in SRAM and temperature influence on sensitivity to radiations   | 91  |

|    |       | 5.1.1 SRAM leakage in hold phase                                         | 92  |

|    |       | 5.1.2 Temperature effect on soft error rate in SRAM                      | 92  |

|    |       | 5.1.3 Models of transient current pulses generated by ionizing particles | 93  |

|    | 5.2   | 6T-SRAM and DICE designs                                                 | 95  |

|    |       | 5.2.1 Structure of the simulated 6T-SRAM cells                           | 95  |

|    |       | 5.2.2 Structure of the simulated DICE                                    | 96  |

|    |       | 5.2.3 Transistors dimensioning in the simulated cells                    | 97  |

|    | 5.3   | Simulation setup                                                         | 99  |

|    | 5.4   | Simulation results and analysis                                          | 101 |

|    |       | 5.4.1 6T-SRAM cells results                                              | 102 |

|    |       | 5.4.2 DICE results                                                       | 103 |

|    | 5.5   | Conclusion                                                               | 105 |

| Ge | enera | al conclusion 1                                                          | .07 |

| A  | UB    | ER estimation in case of absence of check operations                     | .09 |

| в  | UB    | ER estimation in case of check operations                                | .11 |

| Bi | bliog | graphy relative to the study 1                                           | .13 |

| Bi | bliog | graphy 1                                                                 | .15 |

# List of Figures

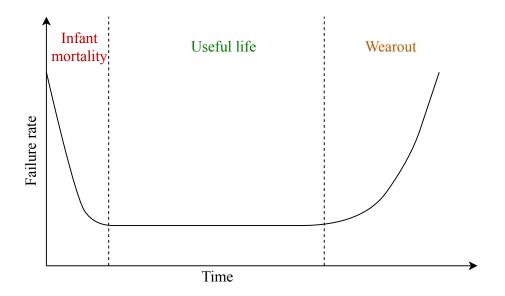

| 1.1  | Failure rate variation with time [1]                                                | 5  |

|------|-------------------------------------------------------------------------------------|----|

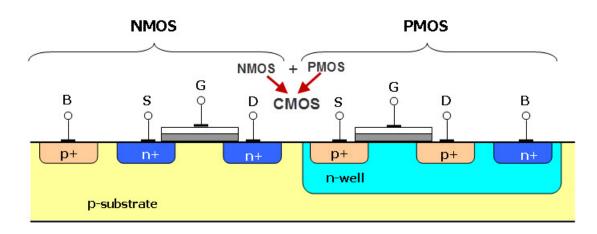

| 1.2  | NMOS and PMOS structures [2]                                                        | 6  |

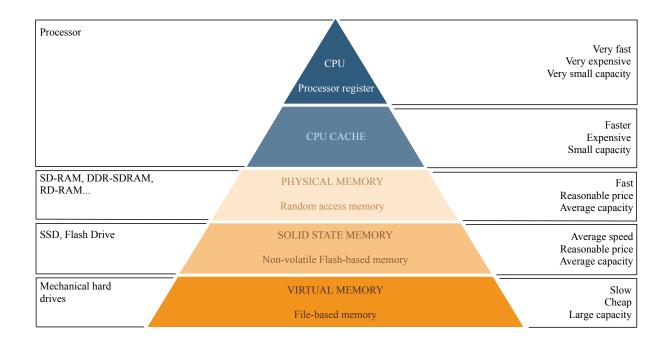

| 1.3  | Simplified computer memory hierarchy                                                | 9  |

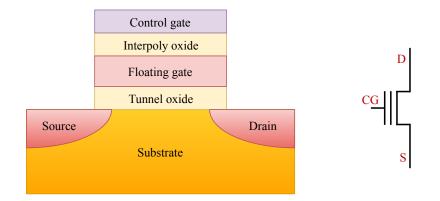

| 1.4  | Schematic of a floating gate transistor and its electric symbol $[3]$               | 10 |

| 1.5  | Threshold voltage distribution of an SLC [3][4]                                     | 11 |

| 1.6  | Comparison of NAND and NOR Flash cells arrangement [5]                              | 12 |

| 1.7  | Schematics of NAND string (left) and NAND array (right) [3]                         | 12 |

| 1.8  | Threshold voltage distribution of an SLC with reference voltages [3]                | 13 |

| 1.9  | Read operation of an erased NAND cell (left) and a programmed NAND cell (right) [3] | 14 |

| 1.10 | NAND block read [3]                                                                 | 14 |

| 1.11 | Programming (left) and retaining charge (right) in a NAND cell [3]                  | 15 |

| 1.12 | NAND block program [3]                                                              | 16 |

| 1.13 | NAND cell erase [3]                                                                 | 17 |

| 1.14 | Multi level storage in NAND Flash memories [3]                                      | 18 |

| 1.15 | NAND storage cells characteristics [3]                                              | 19 |

| 1.16 | 6T-SRAM cell structure [2]                                                          | 21 |

| 1.17 | SRAM array architecture [2]                                                         | 22 |

| 1.18 | Read operation for 6T-SRAM cell [2]                                                 | 23 |

| 1.19 | Write operation for 6T-SRAM cell [2]                                                | 24 |

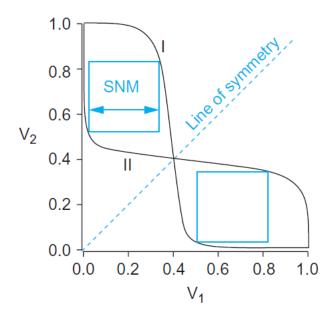

| 1.20 | DC error sources in cross-coupled inverters for hold SNM calculation $[2]$          | 24 |

| 1.21 | Butterfly curve for a 6T-SRAM cell [2]                                              | 25 |

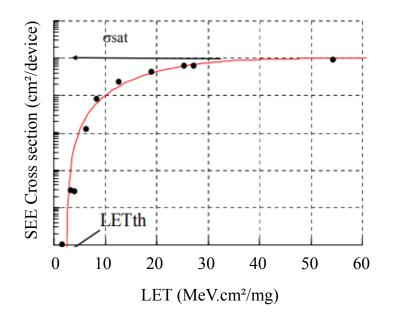

| 1.22 | Typical curve of SEE cross section versus LET (adapted from [6])                    | 27 |

| 2.1  | Threshold voltage variations with cumulative program and erase cycles for SLC and   |    |

|      | MLC Flash memories [4]                                                              | 30 |

| 2.2  | Stress induced leakage current and resulting oxide breakdown [7]                    | 31 |

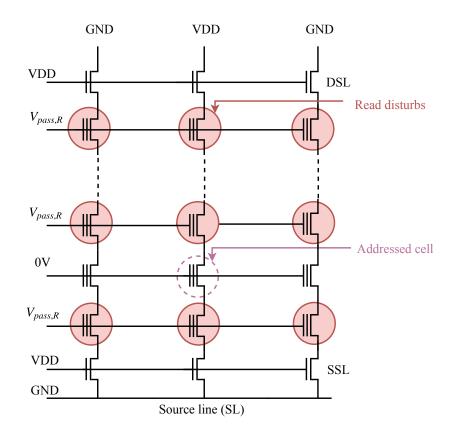

| 2.3  | Potentially disturbed cells by a read operation in a NAND Flash block $[3][8]$      | 32 |

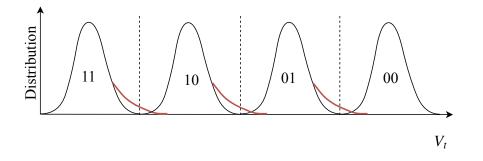

| 2.4  | Impact of read disturbs on the threshold voltage distribution of an MLC $[3]$       | 32 |

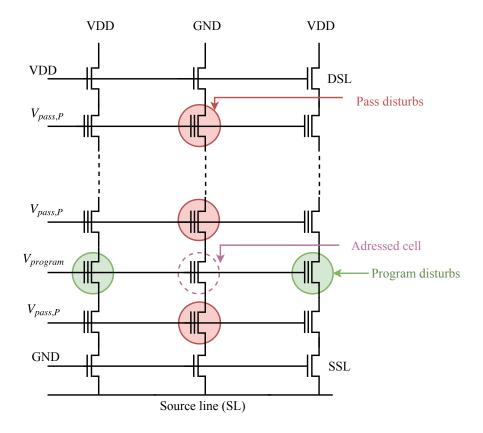

| 2.5  | Pass and program disturbs in a NAND Flash block $[3][8]$                            | 33 |

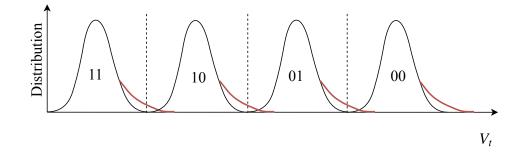

| 2.6  | Impact of program disturbs on the threshold voltage distribution of an MLC $[3]$    | 34 |

| 2.7  | Impact of erase errors on the threshold voltage distribution of an MLC $[3]$        | 34 |

| 2.8  | The threshold voltage distribution of an MLC with retention errors $[3]$            | 36 |

| 2.9  | Encoding and decoding system of ECC in Flash memories [9]                           | 38 |

| 2.10 | Relation between UBER and RBER for binary BCH error correction codes with           |    |

|      | different strenghts and over 512 bytes user data sectors $[7]$                      | 40 |

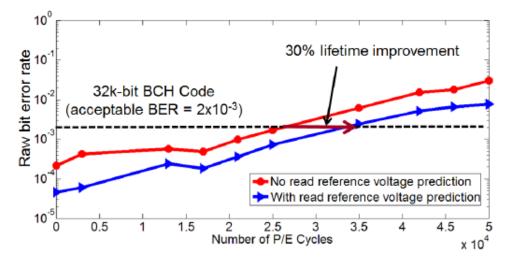

| 2.11 | RBER with and without read reference voltage optimization [10]                      | 41 |

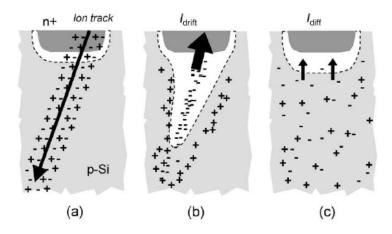

| 2.12         | Generation (a), transport (b) and collection (c) of carriers after a charged particle strike in a reverse biased p-n junction [11]                                                                                                                                    | 45 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

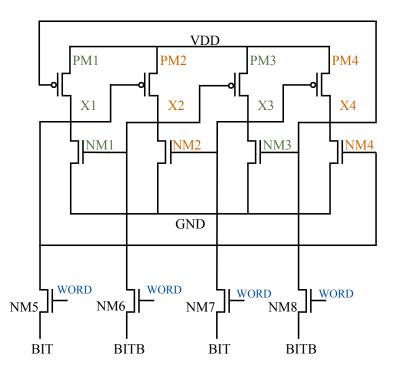

| 2.13         | DICE cell structure [12]                                                                                                                                                                                                                                              | 47 |

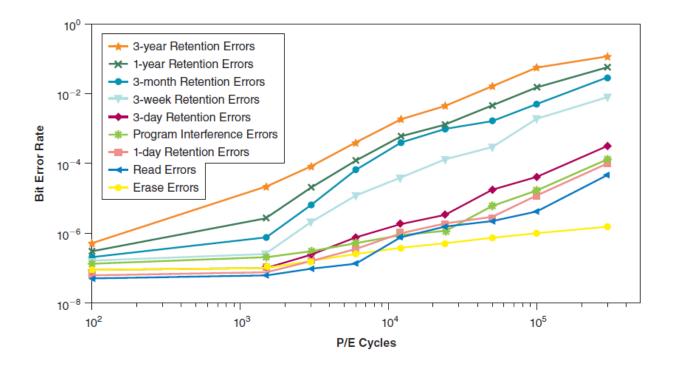

| 3.1          | Error rates variation with P/E cycles for the different types of errors in 3X-nm MLC NAND Flash memories [13]                                                                                                                                                         | 51 |

| 3.2          | Flash memory retention time versus temperature for an enterprise-class SSD respect-<br>ing the JEDEC requirements (JESD218B.01)                                                                                                                                       | 53 |

| 3.3          | Block diagram of A-timer implementation                                                                                                                                                                                                                               | 56 |

| $3.4 \\ 3.5$ | Arrhenius curves approximation that can be achieved by Arrhenius timer<br>Probability density functions of the considered normal and Gamma distributions of                                                                                                           | 57 |

| 3.6          | the operating temperature with a standard deviation of $3.3 ^{\circ}\text{C}$<br>Refresh operations with the use of A-timer warning period $\tau_{warn}$ and the approximated data retention time $\tau_{ret\_app} = 2\tau_{warn}$ considered at a constant operating | 60 |

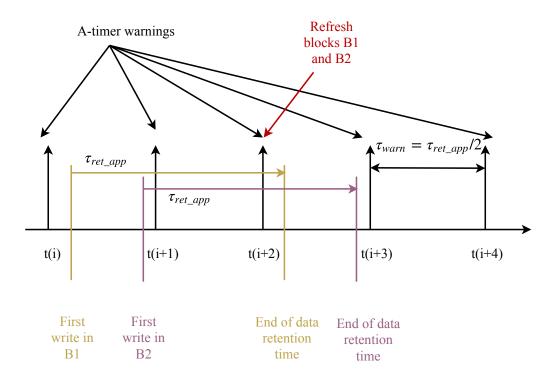

|              | temperature for two arbitrary data blocks B1 and B2                                                                                                                                                                                                                   | 63 |

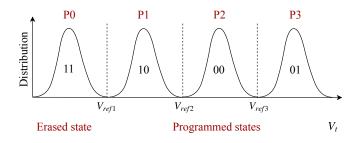

| 4.1          | A logical state encoding of an MLC NAND Flash and the corresponding threshold voltage distribution                                                                                                                                                                    | 68 |

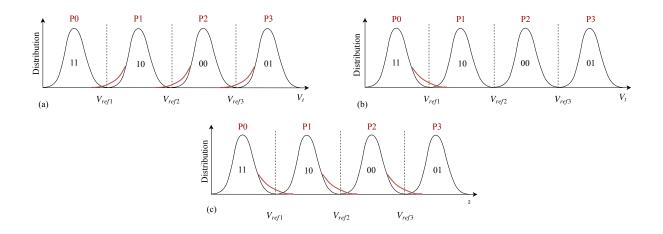

| 4.2          | Effects of retention errors (a) erase errors (b) and read and write disturb errors (c) on the threshold voltage distribution of an MLC NAND Flash memory                                                                                                              | 69 |

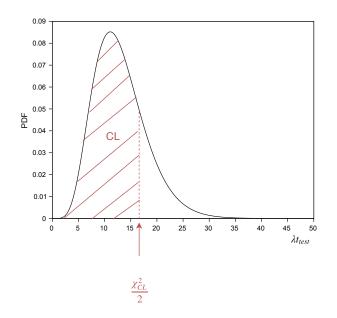

| 4.3          | PDF of Gamma distribution and estimation of $\lambda_{up}$ value corresponding to a confidence level CL                                                                                                                                                               | 72 |

| 4.4          | RBER variation with retention time at room temperature for 10K cycled MLC Flash from different vendors [14]                                                                                                                                                           | 73 |

| 4.5          | Reliable left retention time as a function of $N_{ret}$ at different retention ages                                                                                                                                                                                   | 76 |

| 4.6          | Reliable left retention time as a function of $N_{ret}$ at 36 months of retention age for different values of $N_{vul}$                                                                                                                                               | 77 |

| 4.7          | Refresh probability over a target storage period of 36 months for the refresh scheme of algorithm 1. Flash memory pages with 16 Kb vulnerable bits and an ECC able to correct up to 40 bits $\ldots$                                                                  | 80 |

| 4.8          | Average time between refresh operations for the refresh scheme of algorithm 1 in comparison to a systematic refresh scheme with a fixed refresh frequency. Flash                                                                                                      | 80 |

|              | memory pages with 16 Kb vulnerable bits and an ECC able to correct up to 40 bits.                                                                                                                                                                                     | 80 |

| 4.9          | Management of page flags in order to reduce the number of check operations of algorithms 1 and 2                                                                                                                                                                      | 83 |

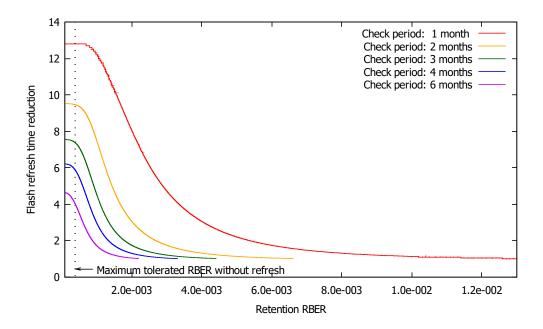

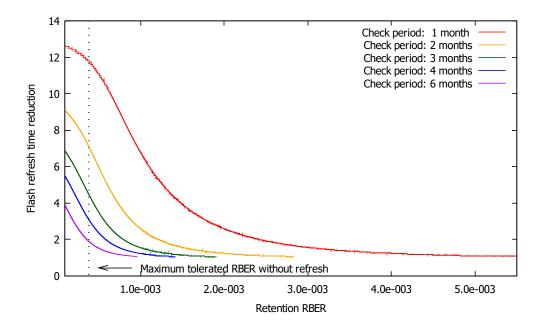

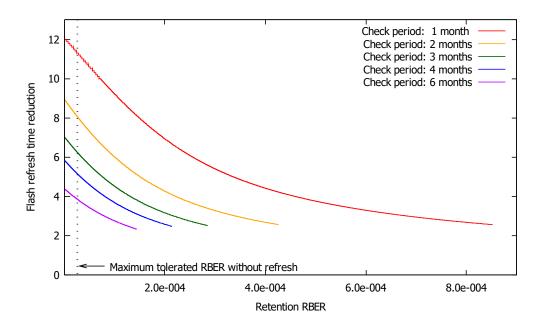

| 4.10         |                                                                                                                                                                                                                                                                       |    |

| 4.11         | memory pages with 16 Kb vulnerable bits and an ECC able to correct up to 40 bits .<br>Access time reductions with respect to a systematic refresh scheme with a fixed refresh frequency. Flash memory pages with 16 Kb vulnerable bits and an ECC able                | 85 |

|              | to correct up to 40 bits                                                                                                                                                                                                                                              | 86 |

| 4.12 | Access time reductions with respect to a systematic refresh scheme with a fixed               |

|------|-----------------------------------------------------------------------------------------------|

|      | refresh frequency. Flash memory pages with 16 Kb vulnerable bits and an ECC able              |

|      | to correct up to 30 bits                                                                      |

| 4.13 | Access time reductions with respect to a systematic refresh scheme with a fixed               |

|      | refresh frequency. Flash memory pages with 16 Kb vulnerable bits and an ECC able              |

|      | to correct up to 20 bits                                                                      |

| 4.14 | Access time reductions with respect to a systematic refresh scheme with a fixed               |

|      | refresh frequency. Flash memory pages with 16 Kb vulnerable bits and an ECC able              |

|      | to correct up to 10 bits                                                                      |

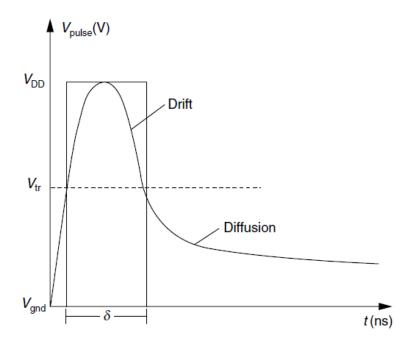

| 5.1  | Transient current pulse shape caused by an $\alpha$ -particle strike with drift and diffusion |

|      | contributions [15]                                                                            |

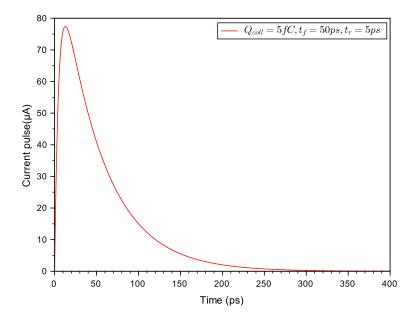

| 5.2  | Example of a double exponential transient current pulse                                       |

| 5.3  | Schematic of the 6T-SRAM cell used in simulations                                             |

| 5.4  | Schematic of the DICE used in simulations                                                     |

| 5.5  | Butterfly curve and SNM calculation for 22 nm 6T-SRAM cell 100                                |

| 5.6  | Examples of minimal current pulses able to flip a 32 nm DICE 102                              |

| 5.7  | Critical charge evolution with temperature for 6T-SRAM cells                                  |

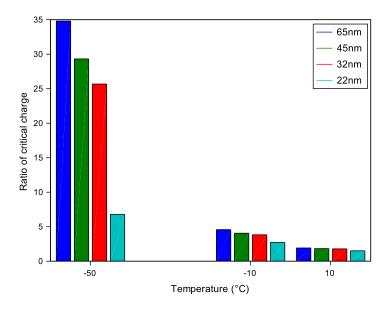

| 5.8  | Critical charge ratio compared to 27 °C for 6T-SRAM                                           |

| 5.9  | Critical charge evolution with temperature for DICE                                           |

| 5.10 | Critical charge ratio compared to 27 °C for DICE                                              |

# List of Tables

| 2.1 | Data retention and endurance relationship for Swissbit SLC and MLC Flash memories at $40 ^{\circ}$ C [4] | 36  |

|-----|----------------------------------------------------------------------------------------------------------|-----|

| 2.2 |                                                                                                          |     |

| 3.1 | Estimated refresh frequency reductions between 30 $^{\circ}\mathrm{C}$ and 70 $^{\circ}\mathrm{C}$       | 61  |

| 4.1 | Retention errors fingerprints of an MLC NAND Flash with the encoding of Fig.4.1 $$ .                     | 70  |

| 4.2 | Maximum tolerated $RBER_{ret}$ in NAND Flash pages when $UBER \leq 10^{-16}$                             | 78  |

| 4.3 | Maximum tolerated $RBER_{ret}$ improvement ratio compared to a no check case in                          |     |

|     | NAND Flash pages                                                                                         | 78  |

| 4.4 | Maximum tolerated $RBER_{ret}$ in NAND Flash pages when $UBER \leq 10^{-16}$                             | 84  |

| 4.5 | Maximum tolerated $RBER_{ret}$ improvement ratio compared to a no check case in                          |     |

|     | NAND Flash pages                                                                                         | 84  |

| 5.1 | Transistors dimensions for 6T-SRAM cells                                                                 | 98  |

| 5.2 | Supply voltages for 6T-SRAM and DICE simulations                                                         | 99  |

| 5.3 | SNM evolution with temperature for 6T-SRAM cells                                                         | 100 |

# Introduction

The continuous demand for electronic and microelectronic systems with higher performance and low power pushes the manufacturers towards technology limits and motivates the search for new physical and architectural solutions. In this context, reliability, which is defined as the probability that a given device or system works properly, is becoming an important matter [1].

Reliability requirements evolve due to the transistor shrinking and the development of emerging technologies based on new materials and technological processes. The interest in reliability is furthermore justified for applications where electronic components operate in harsh environments. These environments present extreme conditions of temperature and vibrations as is the case for automotive applications and oil & gas industries. Furthermore, in aerospace and military domains, electronic equipment may be exposed to ionizing radiation. These harsh conditions increase the probability of failures occurrence. For example, the exposure to high temperatures or to long and repetitive thermal cycles causes electric parameters degradation and physical properties of materials alteration, which results in components deterioration. The International Technology Roadmap for Semiconductors (ITRS), a report published yearly by a group of leading chip manufacturing organizations, evolves to match the needs of the semiconductor industry. In the 2013 edition of ITRS, reliability is referred to as a near-term and long-term challenge for CMOS logic devices, Dynamic Random Access Memories (DRAM) and non-volatile RAM [17].

The automotive industry is the one of the most concerned by exposure of electronic systems to high temperatures. Automotive standards fix the range of ambient operating temperatures from -40 °C to 125 °C. The upper limit may be easily exceeded, depending on the considered location, as is the case for electronic components mounted under the hood [18]. Oil & gas industries are also concerned by high temperature constraints. In fact, drilling operations are usually done at temperatures ranging from 150 °C to 175 °C. Moreover, the decrease of natural reserves along with the technology advances pushed the drilling to greater depths with, as a direct consequence, well temperatures that exceed 200 °C [18]. For aerospace applications, electronic control systems are no longer centralized but more distributed and are, in some cases, in contact with engines. This reduces the interconnection complexity but results in a working temperature going from -55 °C to 200 °C [18].

These industries must insure the proper functioning of their electronic components despite the constraint of high temperature. Reliable data acquisition and storage constitute an important basis for components accurate operations. Volatile or non-volatile data storage mediums should be able to store data correctly through the entire range of operating temperature. For example, the *First High Temperature Electronics Products Survey* of Sandia National Laboratories indicated the industry players interest in data acquisition and storage, particularly in non-volatile memories as Flash memories [19]. Currently, the automotive industry shows a great need for embedded non-volatile memories with high reliability for an extended operating temperature range [20]. As for volatile memories, Static Random Access memories (SRAM) are widely used in integrated circuits

due to their speed and compatibility with standard logic processes. In addition, on-chip SRAM are one of the most important components for high performance system-on-chip (SoC) designed to operate at high temperatures [21][22].

Given all these elements, the target of this thesis is the study of the temperature impact on two types of memories: NAND Flash memories and SRAM. The effects of temperature on reliability are considered with an emphasis on retention for NAND Flash. Statistical and computational solutions aiming to improve the error rate in these memories have also been proposed. In SRAM, the effects of temperature on reliability are considered with an emphasis on resilience to Single Event Upsets (SEU).

This thesis is organized as follows. In the first chapter, an overview of reliability fundamentals and metrics is introduced. It is followed by details on the temperature effects on semiconductors with an emphasis on the electric parameters that impact reliability. Then, a general introduction on memories is given. For NAND Flash memories, the structure and operation are explained. For SRAM, the same study is done and is followed by an overview of radiation effects on integrated circuits.

In the second chapter, state-of-the-art techniques for reliability improvement in NAND Flash and SRAM are exposed. For NAND Flash, data retention and cycling endurance metrics are introduced and followed by a list of monitoring techniques based on the use of error correction codes, read operation optimization and data refresh. For SRAM, radiation effects are explained with emphasis on soft errors. State-of-the-art techniques for radiation effects resilience are finally given.

In the third chapter, the temperature effects on the chosen non-volatile memories, i.e. the NAND Flash memories, are addressed. Here, a timer-based solution is proposed to monitor the effect of temperature on the data retention capability. The timer purpose and working principle are first explained and compared to already existing solutions. The structure of the timer is then detailed. Simulation results related to the improvement of refresh frequency are also given. A final section explains the possible use of the timer with timestamps for warning triggering.

In the fourth chapter, the study of retention in NAND Flash memories is pushed further. Here, a statistical method and a computational approximation are proposed in order to improve the tolerated error rate in NAND Flash-based Solid State Drives (SSD). The two methods are explained with details on the used algorithms. The obtained results related to the error rate and average storage time improvements are also reported. Read and write times reduction resulting from the computational approximation method are detailed in the last section of this chapter.

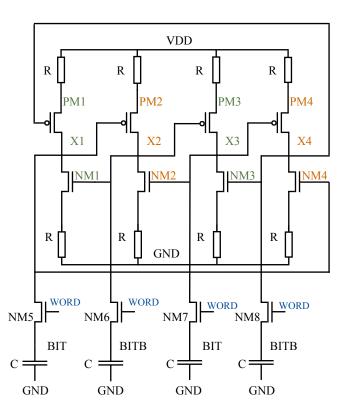

In the fifth chapter, the temperature effects on the chosen volatile memories, i.e. SRAM, are addressed. The combined effects of thermal variations and radiation on SRAM are studied. A comparative study on the occurrence of single event upsets is made for two types of SRAM cells: the classic 6-transistor (6T) cell and the hardened Dual Interlocked Storage Cell (DICE). Here, the current pulses resulting from an ionizing particle strike on the sensitive nodes of the two cells are modeled. Simulation results on the evolution of the critical charge that provokes a bit flip are reported. Final remarks and conclusions are given at the end of this thesis.

## Overview of the target memories

In this chapter, we start by the fundamentals of device and systems reliability. A general study of the temperature effects on the electric parameters of Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFET) is then given. A short overview of the existing memory types is also presented. In particular, we focus on the two memory types studied in this thesis: NAND Flash and SRAM. Considering the NAND Flash memory, we describe its structure and detail its operation. A comparison between Single Level Cells (SLC) and Multi Level Cells (MLC) is also given. For SRAM, the conventional 6 transistor (6T) structure and its operation are explained. In addition, details on the cell stability are introduced with emphasis on noise margin. Finally, the causes of integrated circuits sensitivity to radiations are listed.

#### 1.1 Reliability fundamentals

Over the last decade, the complexity of digital systems has substantially increased due to very large scale integration (VLSI) on chips and technology shrinking. Reliability issues came along and became a concern for both designers and customers. The probability that a system or device performs its intended function without failure under specific environmental conditions and for a specified duration highly depends on the used design and the quality of the components. In this section, we give an overview of device and systems reliability metrics.

#### 1.1.1 Reliability and failure rate

In the sequel, reliability metrics are defined for a population of N identical components or devices which are considered under the same stress conditions during a given period of time t. Stress conditions are caused by environmental parameters such as temperature, humidity, shock or mechanical stress. Consider that F(t) is the number of components that fail to function correctly after the stress process. S(t) is the number of components that resist to stress conditions and continue to function correctly after t. Reliability R(t) is defined as the probability of survival of components to stress conditions and is expressed as follows [1]:

$$R(t) = \frac{S(t)}{N} \tag{1.1}$$

The probability of components failure, also called unreliability is expressed as follows [1]:

$$UR(t) = \frac{F(t)}{N} \tag{1.2}$$

The failure rate FR(t) is by definition the number of components failing per unit of time over the number of surviving components after a period of time t [1]:

$$FR(t) = \frac{1}{S(t)} \frac{dF(t)}{dt}$$

(1.3)

The *bathtub curve* as shown in Fig. 1.1 gives the evolution of the failure rate with time. This curve has been proven adequate to describe the reliability of electronic components and devices. It displays three types of variation zones:

- Infant mortality period which is a starting zone of high failure rate. Design issues or lack of quality control result in defective components when first put in operation. These defects can be minimized by *burn-in* tests where devices are exposed to temperature stress conditions close to the intended operating conditions. In case of devices survival after this test, they are released for actual use and this drastically decreases the *infant mortality probability*.

- Useful life period which is characterized by a constant failure rate. In this zone, failures appear randomly in time as they are generally not related to initial manufacturing or design issues. The failures in this period are the most critical as they occur in the useful life period of the equipment.

- *Wear-out period* where failure rate increases as a result of components aging and deterioration caused by repetitive use.

In case the useful life period is considered where the failure rate is constant and equal to  $\lambda$ , the following equation can be deduced using (1.3) and the fact that R(t) + UR(t) = 1 [1]:

$$\lambda \int_0^t \mathrm{d}x = -\int_1^{R(t)} \frac{\mathrm{d}R}{R} \tag{1.4}$$

and considering the limits of the integration, we get [1]:

$$R(t) = e^{-\lambda t} \tag{1.5}$$

#### 1.1.2 Reliability and Mean-Time-To-Failure

Mean-Time-To-Failure (MTTF) is the average period of time during which a system runs correctly before the occurrence of the first failure. In practical use, it is more adequate to use MTTF than R(t) that gives different values for different operating times. MTTF is given by the following equation [1]:

$$MTTF = \int_0^\infty t\left(-\frac{dR(t)}{dt}\right) dt \tag{1.6}$$

For a constant failure rate (4.1), MTTF can be written as follows [1]:

Figure 1.1: Failure rate variation with time [1]

$$MTTF = \frac{1}{\lambda} \tag{1.7}$$

Therefore, the relation between reliability and MTTF can be expressed as follows [1]:

$$R(t) = e^{-\frac{t}{MTTF}}$$

(1.8)

## **1.2** Temperature effects on semiconductors

Temperature variations at device and circuit levels affect the speed and power in semiconductors. In MOSFETs, temperature has a strong impact on electric parameters that are related to reliability. In this section, an overview of these effects is given and followed by details on electromigration in semiconductor-based devices.

#### 1.2.1 MOSFET threshold voltage

The threshold voltage in a MOSFET is described as follows [23]:

$$V_t = V_{FB} + 2\phi_F + \gamma \sqrt{2\phi_F} \tag{1.9}$$

Figure 1.2: NMOS and PMOS structures [2]

where  $V_{FB}$  is the flat band voltage,  $\phi_F = \phi_T \ln(\frac{N_A}{n_i})$  is the Fermi energy with the thermal voltage  $\phi_T = \frac{kT}{q}$ ,  $N_A$  the substrate doping concentration,  $n_i$  the intrinsic carrier concentration of Si and  $\gamma$  is a body effect parameter. The flat band voltage is defined by  $V_{FB} = \phi_{gs} - \frac{Q_{ss}}{C_{ox}}$  where  $\phi_{gs} = \phi_T \ln(\frac{N_A N_G}{n_i^2})$  is the gate-substrate contact potential,  $N_G$  the gate doping concentration,  $Q_{ss}$  the surface charge density and  $C_{ox}$  the oxide capacitance.

In the threshold voltage expression, the parameters depending on temperature are  $\phi_{gs}$  and  $\phi_F$  and this dependence may be written as follows [24]:

$$\frac{\partial V_t}{\partial T} = \frac{\partial \phi_{gs}}{\partial T} + 2\frac{\partial \phi_F}{\partial T} + \frac{\gamma}{\sqrt{2\phi_F}}\frac{\partial \phi_F}{\partial T}$$

(1.10)

Commonly, a MOSFET is modeled to have a threshold voltage decreasing with temperature increase. This can result in reliability problems in NAND Flash memories if  $V_t$  is significantly decreased by temperature.

#### **1.2.2 MOSFET drain current**

The behavior of drain current  $(I_d)$  in a MOSFET varies with temperature. At a constant drain to source voltage  $(V_{ds})$  and depending on the applied gate voltage  $(V_{gs})$ , a MOSFET is either in ON or OFF state. When  $V_{gs}$  is above the threshold voltage  $V_t$  and the drain is positively biased, a n-channel MOSFET is in ON state and a current  $I_{on}$  flows between the drain and source. This current is approximated by [25]:

$$I_{on} = \mu C_{ox} \frac{W_g}{L_g} (V_{gs} - V_t)^2$$

(1.11)

where  $W_g$  and  $L_g$  are respectively transistor gate width and length,  $C_{ox}$  is the oxide capacitance and  $\mu$  the electron mobility in the channel. For a fixed value of  $V_{gs}$  above  $V_t$ ,  $I_{on}$  decreases with temperature due to the decreasing mobility and the slight decrease of  $V_t$  [25][26]. By decreasing  $V_{gs}$  below  $V_t$ , the current flow in the channel is normally turned off but parasitic electrons create a subthreshold leakage current  $I_{sub}$  highly dependent on temperature.

#### 1.2.3 MOSFET Leakage current

Subtreshold leakage current  $I_{sub}$ , between the source and drain of a MOSFET in the subthreshold region, has an exponential dependence on temperature. The subtreshold leakage current is represented by the Shockley diode model [24][27]:

$$I_{sub} = I_0 \left( e^{\frac{V_{ds}}{\phi_T}} - 1 \right)$$

(1.12)

where  $I_0$  is the reverse saturation current.

The exponential temperature dependence of  $I_{sub}$  comes from the expression of the thermal voltage  $\phi_T = \frac{kT}{q}$ . Also, it should be noted that the subthreshold leakage current is predominant over other forms of leakage current in a MOSFET. This exponential temperature dependence of  $I_{sub}$  threatens the reliability of NAND Flash memories and SRAM operating at high temperatures.

#### 1.2.4 Electromigration

High currents flowing through wires can eventually damage them, and electromigration is the main failure mode. It is caused by the shift of atoms in material under the effect of high-energy electrons. This failure mechanism has an important impact in the case of high current densities where the atoms moving down a wire narrow its width and further increase current density. The narrowing of the wire increases the wire resistance and may result in a delayed signal propagation and eventually a functional failure.

As electromigration can result in system failures, its impact on reliability is measured via the MTTF defined by Black's equation [2][28]:

$$MTTF = A_j J^{-n_j} e^{\frac{E_a}{kT}}$$

(1.13)

where  $A_j$  is a constant related to the wire cross section area, J is the current density,  $n_j$  a constant scaling factor and  $E_a$  the activation energy corresponding to the failure mechanism.

## 1.3 General introduction to memories

Memories are key components for computer and electronic systems since they are used for both data and program instructions storage. The need for different storage capacities depends on the application field. For example, data centers are in the order of Petabytes of storage capacity, personal computers are in the order of hundreds of Megabytes to Gigabytes of memory and embedded systems tend to have smaller amounts of memory, from hundreds of Kilobytes to Megabytes. Different types of memories are used in electronic systems. Each type corresponds to a different technology and has a different storage capacity, power requirements, latency and price. The volatility and the data access mode can also vary from one type of memory to another. For these reasons, each electronic system relies on a mix of the different types of memories.

The pyramidal structure of the computer memory hierarchy is illustrated in Fig. 1.3. On top of the pyramid are central processing unit (CPU) registers that hold words retrieved from CPU caches. Both registers and caches are fast, with smaller storage capacity and higher cost per byte stored. For computer systems, memory is divided in two main groups: the main memory and the mass storage memory. The main memory communicates with the CPU and is usually made out of Random Access Memories (RAM). RAMs have a small access time, an average storage capacity and they are priced reasonably. They are read/write memories accessed for both data storage and retrieval, in contrast to read-only memories (ROMs) only accessed for reading data. RAMs also come in two varieties: Static RAM (SRAM) and Dynamic RAM (DRAM). Mass storage requires relatively cheap data storage devices with large capacities and lower speed. These requirements are met by hard drives using magnetic storage of up to Terabytes of data, and more recently by NAND Flash-based Solid State Drives (SSD). Flash memories are non-volatile, i.e. able to retain data when the power is off, but SRAM and DRAM are both volatile. This gives another classification of memories based on their volatility. The type of data stored in SRAM, DRAM or Flash memories depends on their features and requires some compromises. SRAM are faster than DRAM but cost more and come in less density given a fixed area. Flash memories are non-volatile and less expensive than volatile RAM but they have higher access times [29].

Scaling affects these different types of memories. As transistors shrink, switching speed increases and manufacturing cost decreases. However, scaling introduces new problems related to complexity increase and exacerbation of reliability issues. Moreover, memory designers need to ensure the possible adaptation of existing processes to size reduction. In this context, the Semiconductor Industry Association (SIA) develops the International Technology Roadmap for Semiconductors (ITRS). This roadmap combines the efforts of different companies and researchers to develop compatible process steps and anticipate and challenges related to scaling [30].

The integration limit of Flash memories approaches and new types of emerging memories are starting to replace them [31]. The non-volatility of Flash, the speed of SRAM and the density of DRAM features can be balanced in emerging non-volatile memories such as Spin-Transfer Torque Random Access Memory (STT-RAM), Ferroelectric Random Access memory (FeRAM), Phase-Change Memory (PCM), and Resistive Random Access Memory (RRAM).

Figure 1.3: Simplified computer memory hierarchy

In this report, we focus on NAND Flash memories and SRAM.

## 1.4 NAND Flash memories

Among the different types of memories, NAND Flash technology offers a cost effective solution for applications requiring high density and solid state storage. NAND Flash, together with NOR Flash memories, dominate the market of mass storage non-volatile memories [32].

The first NOR Flash memories were commercialized by Intel in 1988 as a non-volatile storage medium for program codes based on the invention of Flash memory by Dr. Fujio Masuoka from Toshiba. They were then used in the first Flash cards and non-volatile solid state drives. Toshiba then introduced the NAND Flash memories in 1989 characterized by their lower cost per bit and their faster access time [3].

NOR Flash memories have a parallel array architecture that provides a direct access to cells and guarantees a better random performance compared to NAND Flash which have a serial array architecture. The internal structure of NAND Flash, explained in the following, provides a smaller area and a faster write ability compared to NOR Flash, but also results in a degraded access randomness. The lower cost per bit of NAND Flash makes it suitable for low cost mass storage.

In this section, we first introduce the structure of a NAND Flash memory. Then, we detail the read, write and erase operations. A comparison between single level cells and multilevel cells is presented at the end of this section.

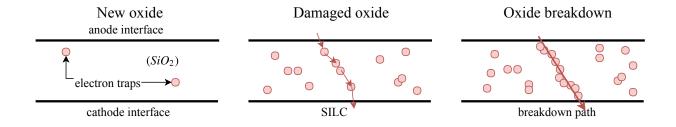

#### 1.4.1 NAND Flash structure

A NAND Flash memory cell is made of a floating gate transistor. This is a particular type of MOS transistors characterized by the presence of two overlapping gates instead of one (Fig. 1.4) [3][31][33][34]:

- A control gate (CG) with a contact providing a gate terminal as in a standard MOS transistor.

- A floating gate (FG) where electrons are stored when the corresponding cell is programmed. They generate a counter electric field partially screening the one produced by the CG. The FG is surrounded by two layers of oxide:

- A tunnel oxide underneath the FG, which is a weak insulator through which electrons tunnel between the FG and the substrate in case of a strong enough voltage differential.

- An interpoly or blocking oxide above the FG, which is a strong insulator that separates the two gates and prevents electrons from passing through the FG to the CG.

Figure 1.4: Schematic of a floating gate transistor and its electric symbol [3]

By applying appropriate voltages on the transistor inputs, electrons can be injected to or extracted from the FG which results in a program or erase operation of the FG transistor. When injected in the FG, electrons remain trapped. Here, a FG transistor is considered in the case of a Single Level Cell (SLC) which is able to store a single bit. The program and erase operations change the transistor threshold voltage and this results in two logic states of the cell: 0 and 1. A programmed cell with a higher threshold voltage corresponds to a logic 0 and an erased cell with a lower threshold voltage corresponds to a logic 1 [3].

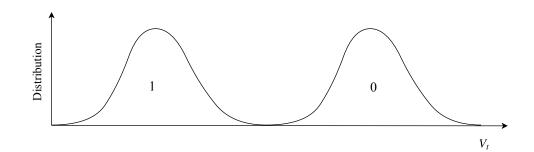

It needs to be noted that environmental and manufacturing sources of variations have an influence on the characteristics of NAND Flash memories as it is the case of any other microelectronic component. The variation sources are: process variation, supply voltage and temperature also known as PVT. These variations are modeled by uniform or normal statistical distributions. Process variations are usually modeled with a Gaussian distribution [2]. In the case of NAND Flash, process variations have an impact on the threshold voltage of FG transistors and the Gaussian distribution is used as an accurate model for Flash cells threshold voltage distributions [10][35]. Fig. 1.5 shows the threshold voltage ( $V_t$ ) distribution in the case of an SLC.

Figure 1.5: Threshold voltage distribution of an SLC [3][4]

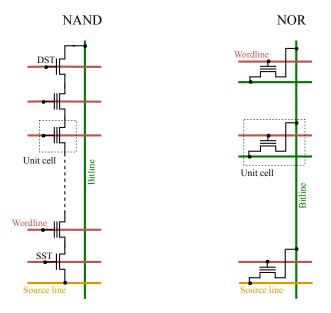

Memory cells are organized in a matrix form in order to minimize the total area. Depending on how FG transistors are connected in the Flash memory array, NOR and NAND Flash memories can be distinguished. Fig. 1.6 shows a comparison of NAND and NOR Flash memory cells arrangement.

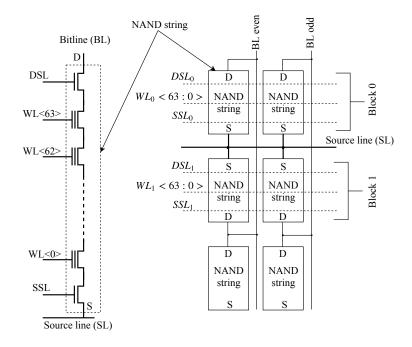

NAND strings are composed of FG transistors connected in series and placed between two selection transistors: a Source Selection Transistor (SST) that connects to the Source Line (SL) and a Drain Selection Transistor (DST) that connects to the bitline (BL) (Fig. 1.6 and Fig. 1.7).

Fig. 1.7 shows a NAND array composed of a series of blocks, a block being the smallest erasable entity. Each block is composed of a group of NAND strings that share the same wordlines (WL) which justifies the simultaneous erase of an entire block.

In a NAND Array, there may be two types of bitlines: even BL and odd BL as shown in Fig. 1.7. Memory cells controlled by the same WL form a logical page and each block contains multiple pages. A page is the smallest addressable unit in read and write operations. Even and odd cells controlled respectively by even and odd BLs, form two different logical pages. Each page is composed of main and spare cells. Main cells are for data storage and spare cells are usually used to store redundant information necessary for the implementation of error correction codes.

Apart from the memory array, a NAND Flash memory needs additional circuitry for read, write and erase operations. A row decoder commands the WLs belonging to a selected NAND string for a read, write or erase operation. BLs are connected to sense amplifiers that convert the current that goes through a memory cell during a read operation into a digital value. Charge pumps, voltage regulators, logic circuits and redundancy structures are also needed for the proper functioning of a NAND Flash memory.

Figure 1.6: Comparison of NAND and NOR Flash cells arrangement [5]

Figure 1.7: Schematics of NAND string (left) and NAND array (right) [3]

#### 1.4.2 NAND Flash operations

#### 1.4.2.1 Read operation

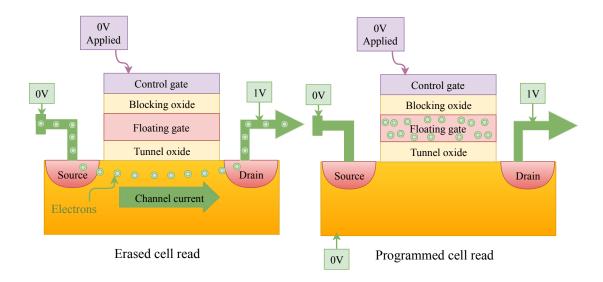

A read operation of a NAND Flash memory is a conductivity test operated on the string corresponding to the cell that needs to be read. Charge presence or absence in the FG respectively inhibit or allow the string conductivity. The string current response is used to distinguish a programmed cell from an erased one.

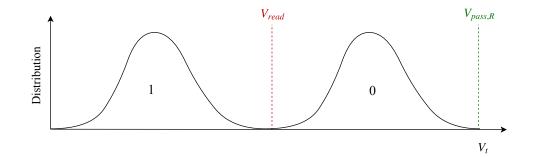

The  $V_t$  distributions of Fig. 1.8 is considered in the case of single level cells [3]. The challenge with the read operation of a cell is that it requires the rest of the corresponding string to be conducting. This needs to be done independently from the state of the cells composing the rest of the string (programmed or erased). For the read operation, these cells need to be driven by a high voltage  $V_{pass,R}$  in order to force their conductivity regardless of their states. This voltage is typically equal to 4–5V. For the read cell, the gate voltage  $V_{read}$  needs to be equal to 0V. Besides, a voltage differential is present between the source and drain of the read cell by the application of adequate voltages on the bitline and on the gates of DST and SST (Drain Selection Line (DSL) and Source Selection Line (SSL), respectively Fig. 1.7) belonging to the string of the read cell [3][8].

Figure 1.8: Threshold voltage distribution of an SLC with reference voltages [3]

If the read cell is erased, electrons are not present in the FG and this provides no interference between the CG and the substrate. The read cell conducts resulting in a current flowing through the whole string which is interpreted as a logic 1 by a sense amplifier. If the read cell is programmed, the charge on the floating gate will inhibit the low voltage applied on the control gate by the generation of a counter electric field that screens the electric field from the CG. The read cell will not conduct and the absence of current on the string will be interpreted as a logic 0 (Fig. 1.9).

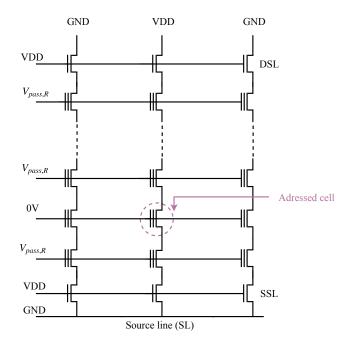

Due to the organization of the NAND Flash array, a cell read operation is achieved by the application of different voltages on the BLs and WLs of the addressed block as it can be seen in Fig. 1.10.

Figure 1.9: Read operation of an erased NAND cell (left) and a programmed NAND cell (right) [3]

Figure 1.10: NAND block read [3]

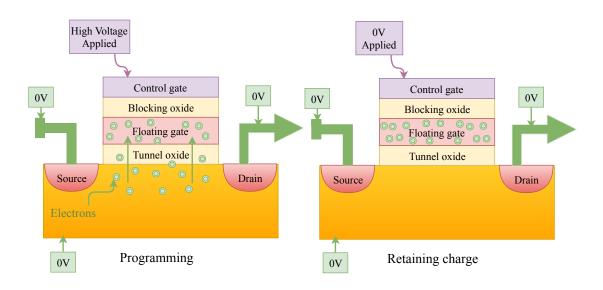

#### 1.4.2.2 Program operation

When programming a NAND cell, a high voltage is applied to the control gate. This results in a high voltage differential and a strong electric field across the gate oxide. With *Fowler-Nordheim* (FN) tunneling that exploits the quantum-effect of electron tunneling, electrons present in the semiconductor substrate will migrate to the FG through the tunnel oxide. But, they are stopped by the blocking oxide from tunneling to the CG. The stronger the electric field, the higher the injection probability and the number of electrons crossing the tunnel oxide. When the program operation is complete, electrons remain trapped in the FG as they do not have enough energy to tunnel back to the transistor channel. When they are present in the FG, electrons generate their own electric field which interferes with the tests of conductivity during read operations and indicate whether the cell is programmed or not (Fig. 1.11).

Figure 1.11: Programming (left) and retaining charge (right) in a NAND cell [3]

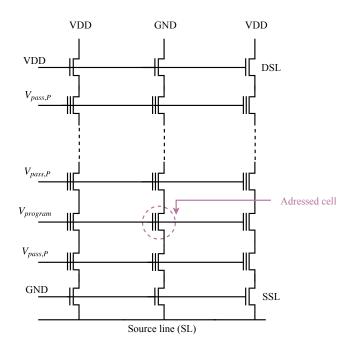

As in the read operation, different voltages need to be applied on the NAND array terminals to insure the programming of the target cell without modifying the neighboring ones. As shown in Fig. 1.12 and in order to trigger the injection of electrons into the FG, the following voltages need to be applied [3][8]:

- $V_{program}$  on the gate of the selected transistor to be programmed. This voltage need to be high enough (20–25V) to extract electrons from the substrate and tunnel them to the FG.

- Supply voltage (VDD) on DSL and ground (GND) on SSL.

- GND on the BL to be programmed.

• VDD on the other inhibited BLs and  $V_{pass,P}$  on the unselected gates.  $V_{pass,P}$  is a moderate voltage (8–10V) that, combined with the VDD applied to the inhibited BLs, results in a *self-boosting* mechanism preventing the cells sharing the same WL as the programmed one from going through an undesired program. This phenomenon is based on the creation of a capacitive coupling that boosts the potential of the unselected cells channel and thus results in a *tunneling inhibition*.

Figure 1.12: NAND block program [3]

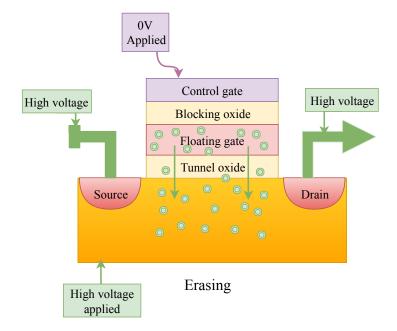

#### 1.4.2.3 Erase operation

Erase operation is based on reversing the *Fowler-Nordheim* mechanism used in program operations. To achieve the electrical erase, the wordlines of the block to be erased need to be biased at 0Vand the substrate needs to be biased with a high voltage (18V). This creates a voltage differential that results in electrons tunneling back to the substrate through tunnel oxide and emptying the FG. To prevent the undesired erase of the unselected blocks that share the same p-well, their corresponding WLs are left floating. With the charged p-well, the floating WLs will see their potential rising due to capacitive coupling and this way, *Fowler-Nordheim* mechanism is inhibited in these blocks (Fig. 1.13) [3][8].

Figure 1.13: NAND cell erase [3]

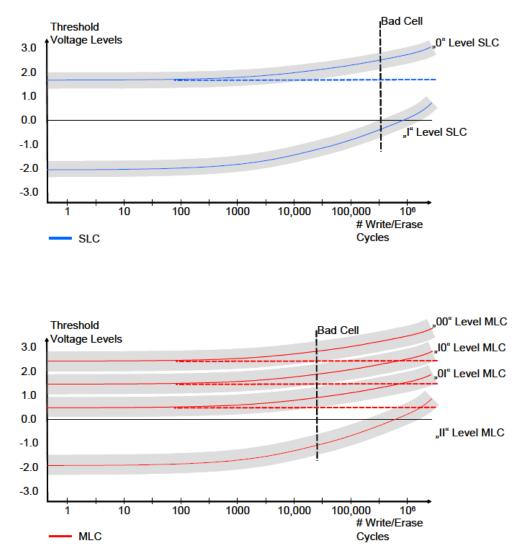

#### 1.4.3 Single vs. multiple level cells

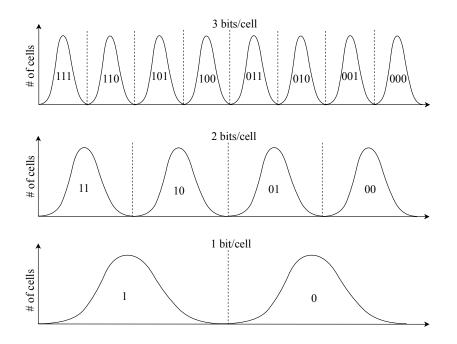

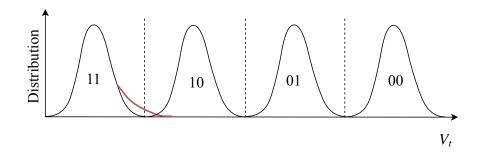

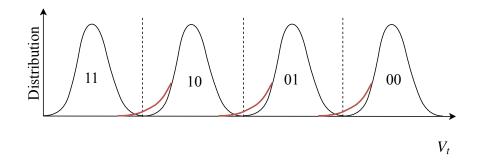

Historically, NAND Flash memories were able to store a single bit per cell, thus the appellation Single Level Cell (SLC). Then, they evolved into Multi Level Cell (MLC) NAND Flash where two or more bits can be stored per cell. The storage of 2 bits per cell is achieved by adapting the amount of stored charge, so that four logic levels are available instead of two. Compared to the case of an SLC, the erased state (logic 11) and the fully programmed state (logic 00) are kept the same with a narrower  $V_t$  range (Fig. 1.14). The two additional programmed states (logic 10 and 01) correspond to a partially charged floating gate (Fig. 1.14). Three, four or more bits can be stored by cells by increasing the number of logic levels to 8, 16 or more. Fig. 1.14 also shows the case of a Triple Level Cell (TLC) able to store three bits per cell [3].

Multi level storage increases the storage capacity without increasing the process complexity. However, it relies on the ability to precisely control the amount of charge injected into the FG in order to set the threshold voltage distributions that correspond to the wanted number of logic levels. A cell able to store n bits should be operated with  $2^n$  logic levels. A high program accuracy and more complex programming algorithms, such as Incremental Step Pulse Programming (ISPP) that programs floating gates iteratively and step by step by injecting small amounts of charge followed by a verify approach, are then necessary to have narrow  $V_t$  distributions and avoid the overlapping

Figure 1.14: Multi level storage in NAND Flash memories [3]

resulting from the multiplication of logic levels. Reading operations are also more complex due to the number of read voltages increase and read margins reduction. Accurate and fast current sensing is then needed [34].

Improved reliability needs to be guaranteed as the higher capacity and lower cost per bit of multi-level storage is compromised by degraded performance and endurance. In fact, multi-level cells tend to wear out faster than SLC due to their higher sensitivity to physical changes in the tunnel oxide layer. Additional reliability problems are experienced due to the multiple variations of the CG voltage and the increased disturbance from neighboring cells [3].

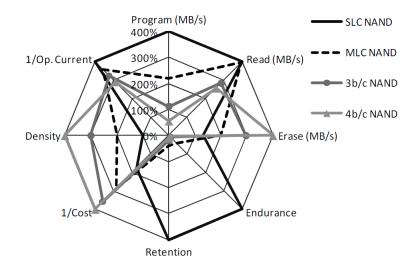

Here, cells able to store only 2 bits are referred to as MLC. As it can be seen in Fig. 1.15, the comparison between SLC, MLC, 3-bit and 4-bit per cell memories show a reduction of endurance, retention, write and read performances and operating current with the increasing number of bits per cell. Erase speed is improved due to larger block sizes. Adequate memories are then chosen depending on the application type and the intended usage. For mass storage applications such as archiving, 4-bit per cell storage may be preferred. For read intensive consumer applications such as Flash memory cards, 3-bit per cell storage can be used. For applications with smaller write performance needs, MLC storage is sufficient. Besides, SLC storage is preferred for reliability demanding applications whether multi level storage is more used for mass storage consumer applications [3].

Figure 1.15: NAND storage cells characteristics [3]

#### 1.5 SRAM memories

SRAM has long been a standard commodity-type product filling memory needs in different applications ranging from consumer electronics to high-end computers. Nowadays, it is mainly used in CPU register files, CPU caches and buffers. The first SRAM chip was released by Intel based on the invention of John Schmidt at Fairchild Semiconductor in 1969. The next year, the first DRAM memory chip was also released by Intel [36].

SRAM uses cells that maintain their state trough feedback, whereas DRAM cells store charge on a floating capacitor through an access transistor. Charges tend to leak in DRAM through the OFF-state access transistor. For this reason, DRAM cells must be refreshed by periodic read and rewrite operations, whereas SRAM cells retain their data as long as power is applied due to the internal feedback.

SRAM has different attractive properties: it is faster and easier to use than DRAM. It is also logically compatible with standard CMOS processes. In addition, technology scaling enabled SRAM size reduction and its dense integration on chips. On the other hand, this introduced problems related to the cost and leakage power consumption. Supply voltage control along with size reduction also made SRAM more vulnerable to soft errors and more precisely to Single Event Upsets (SEU).

In this section, we first introduce the structure of an SRAM with emphasis on the composition of a standard cell. Then, we detail the read and write operations. The fundamentals of cell stability and noise margin are also addressed. Generalities on radiation effects on integrated circuits are presented at the end of this chapter.

## 1.5.1 SRAM structure

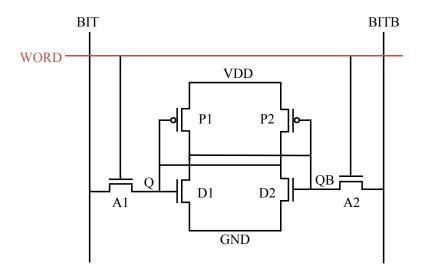

An SRAM is mainly composed by storage cells able to hold data as long as power is applied, and a peripheral circuitry for writing and reading data stored into the cells. Many SRAM Cell designs exist and each involves a different number of transistors ranging from 4 to 12. Here, we consider a 6-transistor (6T) organization, which is the most common design for SRAM cells due to its low leakage and good compactness.

It should be noted that the operations provided by a 6T-SRAM cell can also be accomplished by a standard flip-flop, but a 6T-SRAM cell has the advantage of having an area smaller by an order of magnitude than a flip-flop [37]. This compactness feature is beneficial when memory cells dominate the area as in large RAM arrays. It also results in lower power dynamic consumption. However, compactness is achieved at the expense of a more complex peripheral circuitry [38].

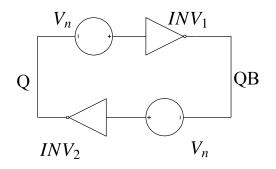

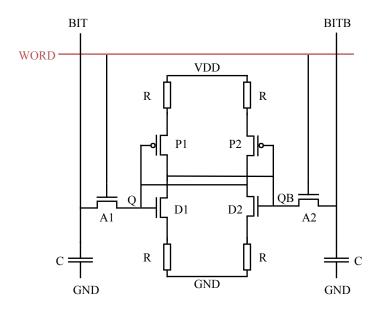

A 6T-SRAM is composed of a pair of weak cross-connected inverters to hold the stored data and two NMOS access transistors enabling the read and write operations as it can be seen in Fig. 1.16. The pair of cross-coupled inverters enables the storage of a single bit, either a logic 1 or 0, set through the voltage difference forced on the bitlines couple, BIT and BITB. During the storage phase, small disturbances caused by noise or leakage can be corrected by the positive feedback of the pair of inverters. These disturbances may be increased by different operating and environmental conditions and eventually result in failures. The wordline signal, WORD in the 6T-SRAM circuit, drives the two NMOS access transistors (A1 and A2) enabling the charge transfer between the cell nodes Q and QB, respectively with BIT and BITB during write and read access cycles. The main challenge with an SRAM cell is to keep its area minimal while ensuring that the cell circuitry is sufficiently weak to be overpowered during a write access, but yet strong enough to keep the stored value correct and not erased during a read access.

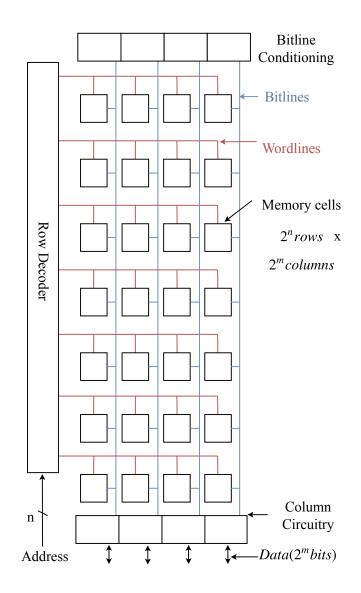

For a 6T-SRAM array, cells are arranged in a matrix form with each cell being accessed for both read and write operations via BIT and BITB and through the access signal WORD. In the case of an SRAM array containing  $2^n$  words of  $2^m$  bits each (Fig. 1.17), bits are stored in 6T-cells via:

- The application of the adequate voltages on BIT and BITB depending on the value of the bit to be stored. Here, the column circuitry and column decoder are involved. It should be noted that column circuitry may contain amplifiers and buffers to sense data.

- The selection of the adequate row of cells to store data via the row decoder. The latter uses the received address to activate the adequate row by asserting the corresponding wordline through the signal WORD.

## 1.5.2 SRAM operations

## 1.5.2.1 Read operation

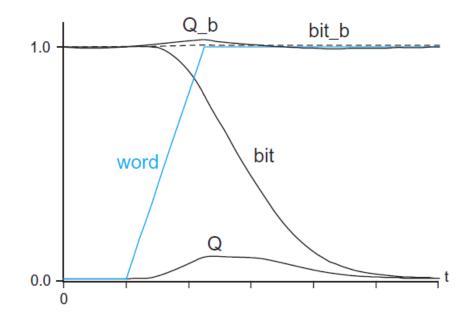

A bit stored in an SRAM cell is read by first precharging the two bitlines high and then leaving them both floating. The signal WORD is raised high and the two NMOS access transistors are

Figure 1.16: 6T-SRAM cell structure [2]

in ON state. This enables the cell nodes Q and QB to transfer the stored data to BIT and its complement on BITB.

Without loss of generality, Q is assumed to store a logic 0 (QB is at logic 1). When WORD is high, BIT is pulled down through A1 and D1 which are in ON state. While BIT is being pulled down, Q tends to slightly rise because of the current flowing through A1 but is ultimately held low by D1 (Fig.1.18). Here, a *read stability* constraint should be met by having D1 stronger than A1. Generally, this constraint is satisfied by fixing the W/L ratio of the transistors used in the pair of inverters such that the nodes Q and QB remain below the switching threshold of P2/D2 and P1/D1 inverters respectively [2][39].

#### 1.5.2.2 Write operation

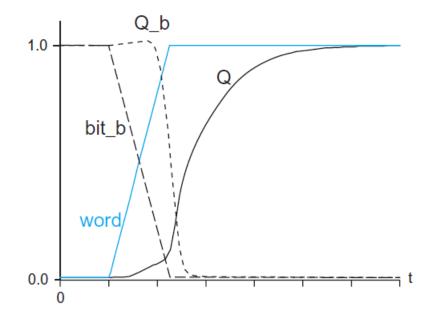

A write operation in a 6T-SRAM cell is done by driving the value to be written and its complement on BIT and BITB, respectively. The wordline WORD is then raised high which puts the two access transistors in ON state and enables the charge transfer between the cell nodes Q–QB, and BIT–BITB, respectively. The new data is then able to overpower the cross-connected inverters of the cell.

Without loss of generality, Q is assumed to be initially set to 0 and we intend to write a 1 in the cell. So, BIT needs to be raised high by a write driver. BITB is pulled down to ground and A1 and A2 are put in ON state through WORD rise. In fact, due to the *read stability* constraint, BIT is unable to raise Q high alone through A1 (A1 wheaker than D1). QB needs to be pulled low through A2. As P2 opposes this operation, P2 needs to be weaker than A2. This is known as *writability*

Figure 1.17: SRAM array architecture [2]

Figure 1.18: Read operation for 6T-SRAM cell [2]

constraint. QB being pulled low, this will put D1 in OFF state and P1 in ON state which will pull Q high as desired (Fig.1.19) [2][39].

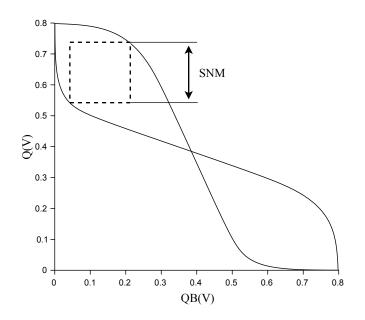

#### 1.5.2.3 Hold phase and cell stability

The 6T-SRAM cell is intended to hold the stored value in the pair of cross-connected inverters as long as the supply voltage is applied. During the hold phase, WORD is pulled low which puts the access transistors in OFF mode. This way, BIT and BITB are disconnected from the cell nodes Q and QB, respectively and the stored data remains unchanged in the cross-coupled inverters.

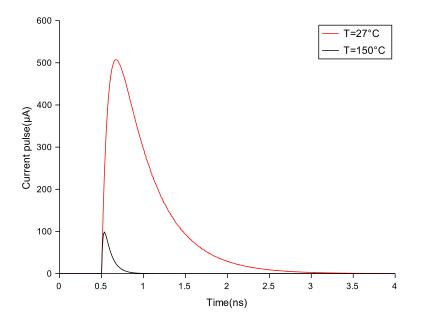

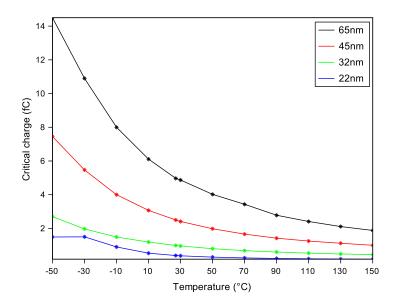

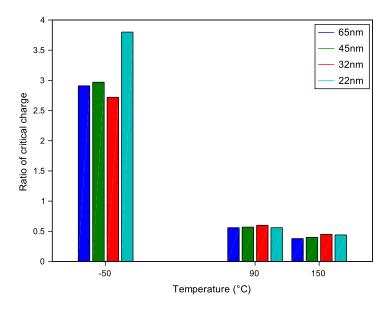

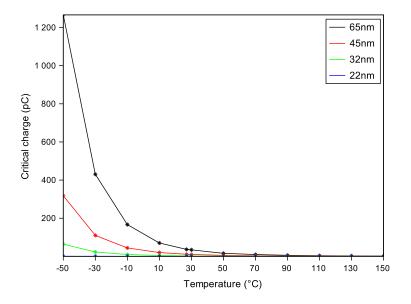

Due to *read stability* and *writability*, transistors must respect several ratio constraints. D1 and D2 must be the strongest among the 6 transistors of the SRAM cell, A1 and A2 must be of intermediate strength and P1 and P2 must be weak. Along with size and design constraints, SRAM cells must be able to function correctly despite voltage, temperature and process variations [40].