# Development of thermally assisted MRAMs: from basic concepts to industrialization

Ioan Prejbeanu

#### ▶ To cite this version:

Ioan Prejbeanu. Development of thermally assisted MRAMs: from basic concepts to industrialization. Condensed Matter [cond-mat]. Université Grenoble Alpes, 2015. tel-02146801

## HAL Id: tel-02146801 https://theses.hal.science/tel-02146801

Submitted on 4 Jun 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **Université Grenoble Alpes**

Mémoire pour obtenir le diplôme de

### Habilitation de Diriger les Recherches

Development of thermally assisted MRAMs: from basic concepts to industrialization

présentée par

### <u>Ioan Lucian Prejbeanu</u>

Ingénieur chercheur CEA

UMR 8191 CEA / CNRS / UJF-Grenoble 1 / Grenoble-INP

INAC, 17 rue des Martyrs, 38054 Grenoble Cedex 9, France

E-mail: <a href="mailto:lucian.prejbeanu@cea.fr">lucian.prejbeanu@cea.fr</a>

#### Membres du jury

- Russell Cowburn Professeur, University of Cambridge, IEEE Distinguished Lecturer 2015, Rapporteur,

- Michel Hehn Professeur, Université de Lorraine / IJL Rapporteur

- Dafiné Ravelosona DR1, CNRS / IEF Rapporteur

- Ahmad Bsiesy Professeur, UGA / EEATS

- Bernard Dieny Directeur de Recherches, SPINTEC / CEA EEATS

- Alain Schuhl Professeur, UGA, Ecole Doctorale de Physique, Directeur CNRS / INP

- Jean-Pierre Nozières DR2, CNRS / SPINTEC invité

Soutenance prévue le 1er septembre 2015

## **Acknowledgments**

#### Jury members:

Russell Cowburn, Michel Hehn, Dafiné Ravesosona, Alain Schuhl, Ahmad Bsiesy, Bernard Diény, Jean-Pierre Nozières

#### Special thanks to:

- Ricardo Sousa, Bernard Dieny, Jean-Pierre Nozières (MRAM team in Spintec), Olivier Redon (LETI), Ken Mackay (Crocus)

- PhDs on thermally assisted MRAMs: Marta Kerekes, Sebastien Bandiera, Erwan Gapihan,

Lucien Lombard, Quentin Stainer, Jérémy Alvarez-Hérault, Giovanni Vinai, Kamil Akmaldinov

- Postdoc: Cristian Papusoi

I would like to thank all my other colleagues from:

- CROCUS Technology: Bertrand Cambou, Jean-Pierre Braun, Céline Portemont, Clarisse Ducruet, Claire Creuzet, Yann Conraux, Jérémy Alvarez-Hérault, Lucien Lombard, Jérémy Pereira, Jong Shin, Julien Vidal, Virgile Javerliac, Mourad El Baraji, Neal Berger, Thierry Chavignier, Corinne Felot, Nathalie Vialle, Julia Auffranc, Jean-Pascal Bost

- SPINTEC: Stéphane Auffret, Bernard Rodmacq, Marie-Thérèse Delaye, Maria Souza, Liliana Buda-Prejbeanu, Vincent Baltz, Jérôme Moritz, Ursula Ebels, Guillaume Prenat, Grégory di Pendina, Catherine Broisin, Rachel Mauduit, Claire Baraduc, Gilles Gaudin, Mihai Miron, Olivier Boulle, Philippe Sabon, Isabelle Joumard, Eric Billiet,

- LETI: Henri Sibuet, Bertrand Delaet, Astrid Astier, Marie-Claire Cyrille, Luca Perniola, Etienne Nowak

- INESC: Paulo and Susana Freitas, Ricardo Ferreira

- Singulus: Juergen Langer, Berthold Ocker, Marco Stenger, Wolfram Maass

- IBM: Daniel Worledge, Anthony Annunziata, Philip Trouilloud

for fruitful discussions and for their contributions to the results presented in this manuscript:

All my family: namely my wife (Liliana), my kids (Elisa & Vlad), my parents (Lucia, Ion), my parents in law (Dochia, RIP Ioan)

This work was performed partially supported by:

- the joint program between Spintec and Crocus

- the French Agence Nationale de la Recherche (ANR RAMAC, PATHOS and EXCALYB)

- the European Commission (NEXT, ERC Adv Grant HYMAGINE).

## **Summary**

In the first part of this manuscript, I will show how thermal assistance can be implemented in field induced switched MTJ to enhance the reliability and the scalability of MRAM. A new self-referenced reading scheme can be implemented in such MTJ in order to obtain a Magnetic Logic Unit that present new logic functionalities compared to standard MRAM. In a second time, I will present the implementation of thermal assistance in MTJ with current induced switching writing scheme. In that case, no field line is required, increasing thus the storage capacity of MRAM cell and decreasing the writing consumption while keeping a satisfying data retention capacity. Ultimately, thermal assistance can be implemented in MTJ with perpendicular magnetization. In that case, thermally induced anisotropy reorientation (TIAR) can be used to decrease the switching power consumption, increase the writing reliability and further improve the scalability of TAS-MRAM down to the 22nm technological node.

**The second part** will be dedicated to the description of my future research projects for the forthcoming years linked mainly to applied aspects of the magnetic tunnel junctions for: sub-20nm scalable MRAMs, hybrid logical circuits and innovative magnetic field sensors.

**Finally** I will present my short bio, my CV, a detailed list of all the PhD supervising activity, as well as a complete list of publications after PhD.

## **Keywords**

- Spintronics

- Tunnel magnetoresistance

- Magnetic tunnel junctions

- MRAM,

- Non-volatile memories

- Magnetic multilayers

- Thin films

- Thermal properties

- Exchange bias

- Perpendicular magnetic anisotropy

## **TABLE OF CONTENTS**

| 1. | INTRODUCTION                                                                            | 5  |

|----|-----------------------------------------------------------------------------------------|----|

|    | 1.1 STATUS OF EMERGING NONVOLATILE MRAM MARKET                                          | 6  |

|    | 1.2 COMPARISON MRAM VS REDOX-RAM                                                        |    |

|    | 1.3 Main applications of MRAM                                                           |    |

|    | 1.5 HISTORICAL CONTEXT OF THIS WORK                                                     |    |

|    | 1.6 DESCRIPTION OF THE MANUSCRIPT                                                       |    |

| 2. | BASICS OF MRAMS                                                                         | 16 |

|    | 2.1 STORAGE FUNCTION: MRAM RETENTION                                                    | 17 |

|    | 2.1.1 Key role of the thermal stability factor                                          | 17 |

|    | 2.1.2 Thermal stability factor for in-plane and out-of-plane magnetized storage layer   | 17 |

|    | 2.2 READ FUNCTION                                                                       | 20 |

|    | 2.2.1 Principle of read operation                                                       | 20 |

|    | 2.2.2 STT induced disturbance of the storage layer magnetic state during read           | 21 |

|    | 2.3 FIRST MRAM GENERATIONS                                                              | 22 |

|    | 2.3.1 Stoner-Wohlfarth MRAM                                                             | 22 |

|    | 2.3.2 Toggle MRAM                                                                       | 25 |

| 3. | THERMALLY ASSISTED MRAMS                                                                | 29 |

|    | 3.1 THERMALLY ASSISTED SWITCHING WORKING PRINCIPLE                                      |    |

|    | 3.2.1 Heating asymmetry vs current polarity                                             | 38 |

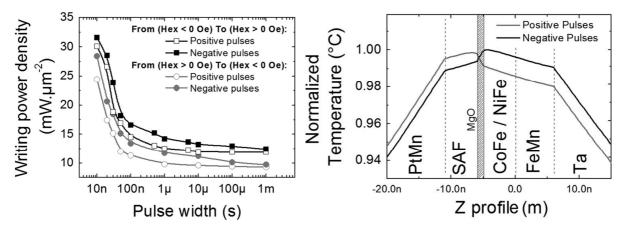

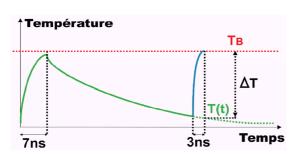

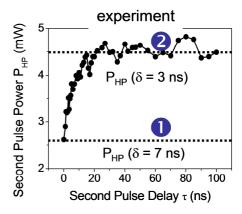

|    | 3.2.2 Heating and cooling dynamics                                                      | 39 |

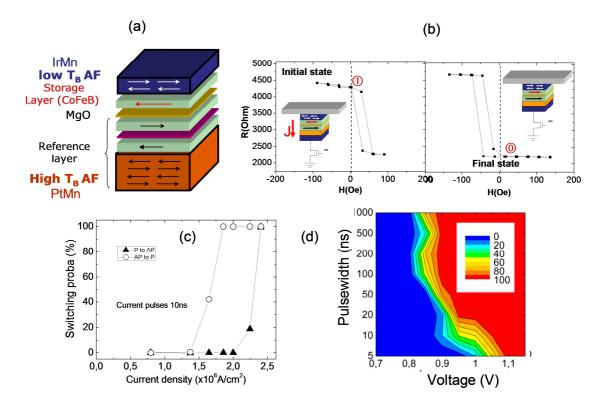

|    | 3.3 DEMONSTRATION OF TAS-MRAM WRITE OPERATION                                           |    |

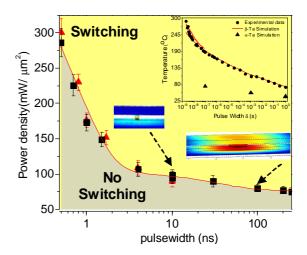

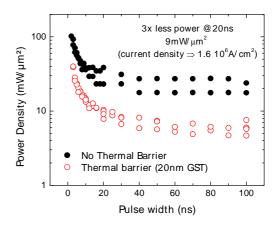

|    | 3.4.1 Minimization of the heating power by using thermal barriers                       | 43 |

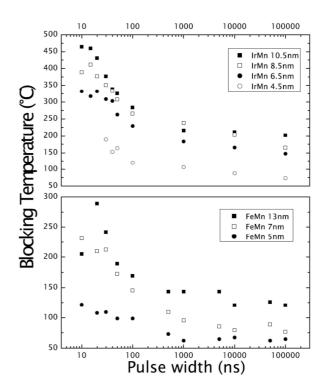

|    | 3.4.2 Minimization of the heating power by using AF materials with low Néel temperature |    |

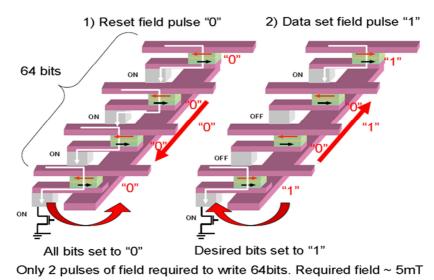

|    | 3.4.3 Minimization of the power consumption by writing strategies                       | 46 |

|    | 3.5 IMPROVED EXCHANGE BIAS PROPERTIES                                                   | 47 |

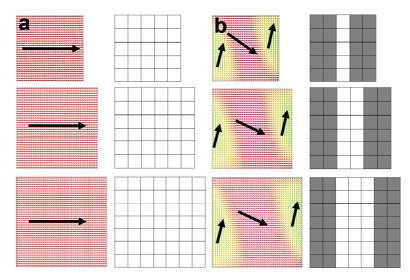

|    | 3.5.1 Impact of the micromagnetic configuration of the ferromagnetic layer              | 47 |

|    | 3.5.2 Impact of the microstructural properties of the antiferromagnetic layer           | 49 |

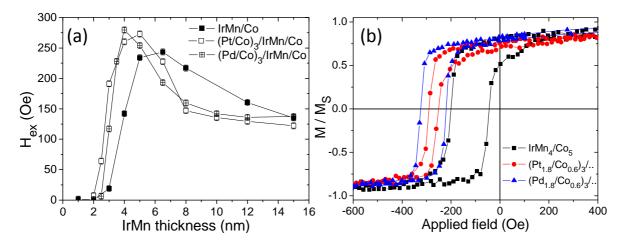

|    | 3.5.3 Use of orthogonal Pt(Pd)/Co)₃/IrMn/Co trilayer structures                         | 49 |

|    | 3.5.4 Cu dusting layer in (Pt(Pd)/Co)3/IrMn/Co trilayers                                | 51 |

|    | 3.6 PROTECTION AGAINST STRAY FIELDS AND WRITE SELECTIVITY                               | 53 |

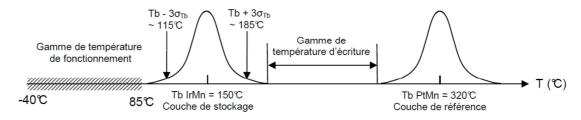

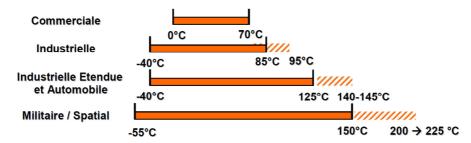

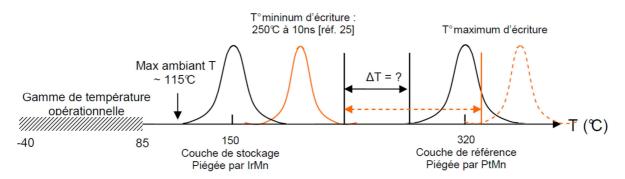

|    | 3.7 TEMPERATURE RANGE                                                                   |    |

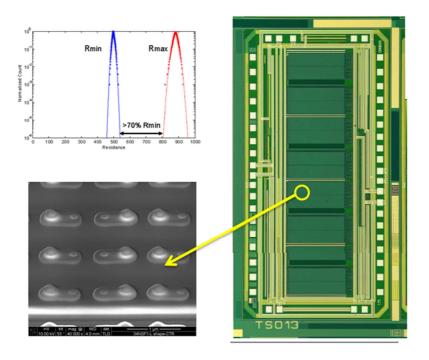

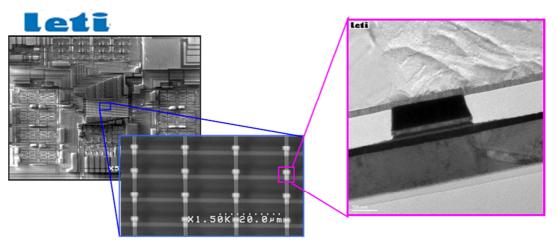

|    | 3.8 INDUSTRIALIZATION OF THE TAS-MRAM TECHNOLOGY                                        |    |

| 4  | SELF REFERENCED TAS MRAM                                                                | _  |

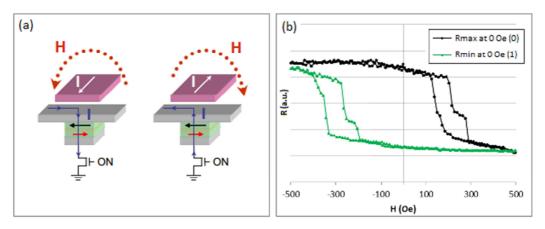

|    | 4.1 Working Principle                                                                   |    |

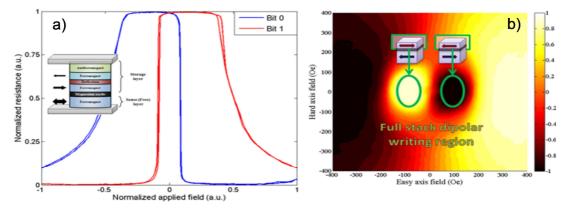

|    | 4.2 DIRECT VS DIPOLAR WRITING                                                           |    |

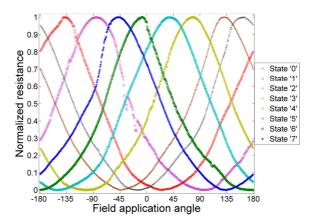

|    | 4.3 Multi-bit storage                                                                   |    |

|    | 4.4. LOGIC FUNCTIONALITIES                                                              | _  |

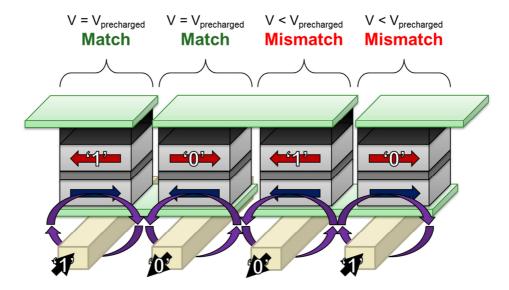

|    | 4.4.1 Match in Place (MiP)                                                              | 68 |

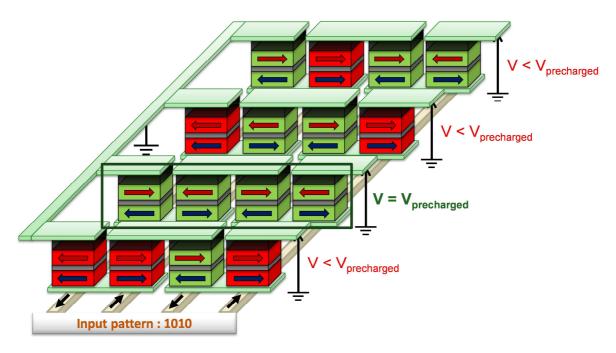

|    | 4.4.2 CAM memories                                                                      | 70 |

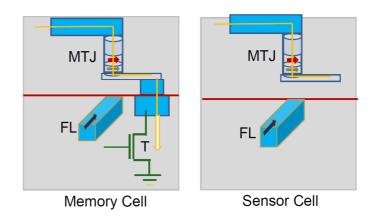

|    | 4.5 MLU-BASED MAGNETIC SENSORS                                                          |    |

|    | 4.6 INDUSTRIALIZATION OF THE MLU TECHNOLOGY                                             |    |

|    | 4.6.1 MLU based embedded memories                                                       |    |

|    | 4.6.2 MLU based Magnetic sensors                                                        | 73 |

|    | 4.7 Conclusions on SR-TAS-MRAM                                                            | 74       |

|----|-------------------------------------------------------------------------------------------|----------|

| 5. | THERMALLY ASSISTED STT-MRAM                                                               | 76       |

|    | 5.1 SPIN-TORQUE-TRANSFER MRAM (STT-MRAM)                                                  | 79       |

|    | 5.1.1 Principle of STT writing                                                            | 79       |

|    | 5.1.2 Considerations of breakdown, write, read voltage distributions                      | 81       |

|    | 5.1.3 Influence of STT write pulse duration                                               | 82       |

|    | 5.2 IN-PLANE STT-MRAM                                                                     |          |

|    | 5.3.1 Proof of concept                                                                    | 84       |

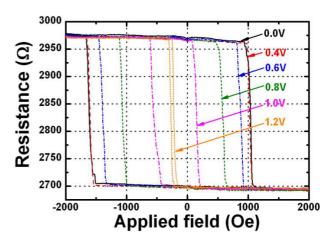

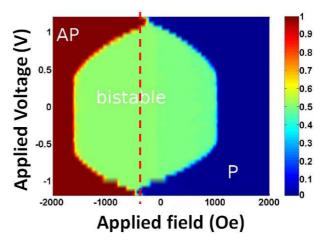

|    | 5.3.2 Bipolar TAS                                                                         | 86       |

|    | 5.4 CONCLUSIONS ON TAS-STT-MRAM                                                           | 90       |

| 6. | ULTIMATE MRAM SCALABILITY: THERMALLY INDUCED ANISOTROPY REORIENTATION                     | 91       |

|    | 6.1 MOTIVATION                                                                            | 94<br>96 |

| 7. | GENERAL CONCLUSIONS                                                                       | 102      |

| 8. | PERSPECTIVES – FUTURE PROJECTS                                                            | 107      |

|    | 8.1 Sub-20nm scalable, low power MRAMs                                                    | . 109    |

|    | 8.1.1 Electric field control EFE-STT-MRAMs                                                | 110      |

|    | 8.1.2 Perpendicular shape anisotropy (PSA) STT- MRAM                                      | 112      |

|    | 8.1.3 Novel approaches to sub-20nm patterning of MTJ stacks                               | 113      |

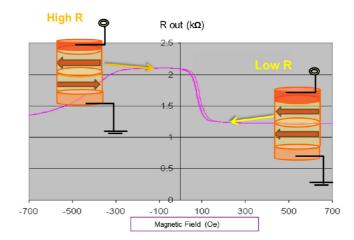

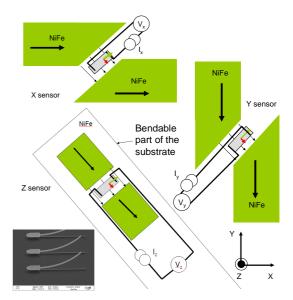

|    | 8.2 MTJ based Magnetic field sensors                                                      | . 114    |

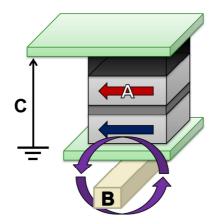

|    | 8.2.1 3D magnetic sensors                                                                 | 115      |

|    | 8.2.2 Tunable sensors                                                                     | 115      |

|    | 8.2.3 Domain wall based magnetic sensors                                                  | 117      |

| G  | LOSSARY OF ACRONYMS                                                                       | 118      |

| Α  | BOUT ME                                                                                   | 119      |

|    | A. CURRICULUM VITAE  B. PHD SUPERVISING  D. LIST OF PUBLICATIONS (AFTER PHD: 2002 - 2014) | . 124    |

|    | 1. JOURNAL ARTICLES (45)                                                                  | 126      |

|    | 2. CHAPTER BOOKS (5)                                                                      | 129      |

|    | 3 PATENTS (38)                                                                            | 130      |

## **PART I**

## 1. INTRODUCTION

| 1.1 STATUS OF EMERGING NONVOLATILE MRAM MARKET | 6  |

|------------------------------------------------|----|

| 1.2 COMPARISON MRAM VS REDOX-RAM               |    |

| 1.3 MAIN APPLICATIONS OF MRAM                  | 8  |

| 1.4 CURRENT AND FUTURE CHALLENGES FOR MRAMS    | 9  |

| 1.5 HISTORICAL CONTEXT OF THIS WORK            |    |

| 1.6 Description of the Manuscript              | 13 |

## 1.1 STATUS OF EMERGING NONVOLATILE MRAM MARKET

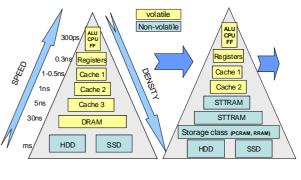

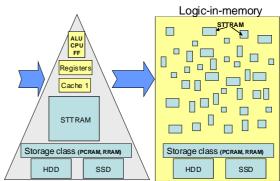

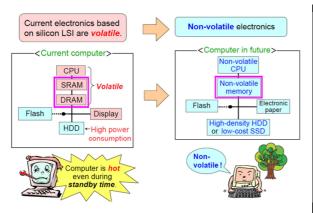

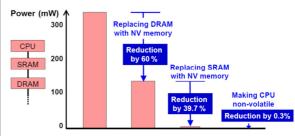

Demand for on-chip memories has been recently increasing due the growth in demand for data storage and the increasing gap between processor and off-chip memory speeds. One of the best solutions to limit power consumption and to fill the memory gap is the modification of the memory hierarchy by the integration of nonvolatility at different levels (storage class memories, DRAM main working memory, SRAM cache memory), which would minimize static power as well as paving the way towards normally-off / instant-on computing (logic-in-memory architectures) (see Figure 1.1). Besides computers, today's portable electronics have become intensively computational devices as the user interface has migrated to a fully multimedia experience. To provide the performance required for these

Figure 1.1: Expected evolution of memory architecture from present hierarchy to logic-in-memory architecture

applications, the actual portable electronics designer uses multiple types of memories:

- a medium-speed random access memory for continuously changing data,

- a high-speed memory for caching instructions to the CPU and

- a slower, nonvolatile memory (NVM) for long-term information storage when the power is removed.

Combining all of these memory types into a single memory has been a long-standing goal of the semiconductor industry, as computing devices would become much simpler and smaller, more reliable, faster and less energy consuming. As a result, advanced NVM chips are expected to see phenomenal growth in the forthcoming years. **MRAM is one of a number of new technologies aiming to become a "universal" memory device applicable to a wide variety of functions.** MRAMs are expected to combine nonvolatility, high speed, moderate power consumption, infinite endurance, and radiation hardness, all at moderate cost and be easy to embed in devices.

Since its inception in the late 1990s, MRAM have however not yet reached large volume applications, with only Toggle switching-based standalone products currently available from Everspin, at the 180 nm technology node <sup>1</sup>.

The more recent advent of spin transfer torque (STT)<sup>2</sup>, however, has shed a new light on MRAM with the promises of much improved performances and greater scalability to very advanced technology node. Indeed, in 2010, the International Technology Roadmap for Semiconductors (ITRS), Emerging Research Devices and Emerging Research Materials Working Groups "identified spin transfer torque MRAM and redox RAM as emerging memory technologies recommended for accelerated research and development leading to scaling and commercialization of nonvolatile

<sup>1</sup> L. Savtchenko, B. Engels, N. Rizzo, M. Deherrera, J.A. Janesky, US6545906 (2001).

<sup>2</sup> J. Slonczewski, "Currents and torques in metallic magnetic multilayers", J.Magn.Magn.Mater.159, L1 (1996); "Excitation of spin waves by an electric current ", 195, L261 (1999).

**RAM to and beyond the 16 nm generation**"<sup>3</sup>. Currently there is an intense research and development effort in microelectronics on these two technologies, one based on spintronic phenomena, the other based on migration of vacancies or ions in an insulating matrix driven by oxidation-reduction potentials. Both technologies could be used for standalone or embedded applications.

As a consequence, MRAM is now viewed as a credible replacement for existing technologies for applications where the combination of nonvolatility, speed, and endurance is key. Several start-up companies (e.g., Everspin Technologies, Grandis, Crocus Technology, Avalanche, Spin-Transfer Technology), large IC manufacturers (e.g., IBM, NEC, Toshiba, Intel, Samsung) and equipment suppliers (e.g., Canon Anelva, Singulus, Applied Materials, TEL) are now actively developing the STTRAM technology and a forthcoming launching of 64Mbit in-plane magnetized STTRAM products was recently announced by Everspin.

#### 1.2 COMPARISON MRAM VS REDOX-RAM

The redox RAMs combine good potential for scaling below 10 nm generation, fast read and write times, (<10 ns) and relatively low write current (in the microampere range). Additionally, these nonvolatile memories should be stackable in three-dimensional architectures called cross-bar architectures and offer multilevel capabilities thanks to the possibility to control the growth/dissolution of the conducting filaments which determines the cell resistance level. However, at this point, they still suffer from a poor understanding of the underlying physical mechanisms so that no predictive model of reliability exists yet for this technology. Finally, their endurance (~10<sup>8</sup> cycles) is sufficient for Flash type applications but not enough for the working memory in microprocessors (which require >10<sup>15</sup> cycles). Therefore, these memory elements seem to be most suited for storage class memory applications (intermediate level between hard disk drives (HDD), solid state drives (SSD) and DRAM) and memristor applications thanks to the possibility that they offer to continuously vary their resistance between a minimum and a maximum value in a hysteretic way. This may open the path to neuromorphic architectures that mimic the working principle of the human brain.

The STT-MRAM appears today as the most credible candidate for DRAM and cache replacement as it combines CMOS compatibility, high retention time (10 years), large endurance (>10<sup>15</sup> cycles), and relatively fast write/read time (1-30ns depending on the architectures). However, this technology is still not yet fully mature, particularly at the smallest dimensions (sub-20 nm). The main issues remain associated with the cell-to-cell variability. This variability is mainly caused by the edge defects generated during patterning of the cells. Whenever the MgO barrier is damaged by the patterning, this yields local changes in the barrier resistance, tunnel magnetoresistance and magnetic anisotropy, i.e., cell retention. Now that the number of laboratories (including major equipment suppliers) working on this technology has substantially increased, technological progress should be faster.

<sup>3</sup> http://www.itrs.net/Links/2010ITRS/2010Update/ToPost/ERD\_ERM\_2010FINALReportMemory Assessment\_ITRS.pdf

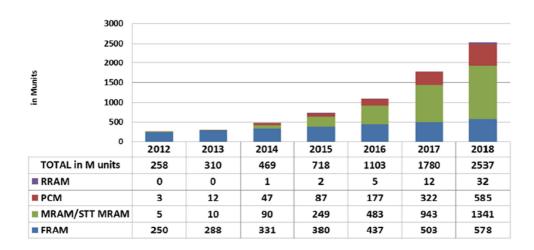

Figure 1.2: Emerging NVM production in Million devices will grow at a CAGR of 46% with MRAM leading the overall production in 2018. PCM will grow also rapidly. ReRAM will just start to emerge in 2017-2018.FRAM will grow at a steady state

#### 1.3 MAIN APPLICATIONS OF MRAM

According to recent market research reports, solid-state memory constitutes a market of over \$50 billion, while the nonvolatile memory (NVM) segment is much smaller. A few computers use NVMs, which retain data when the power is off, in the form of solid-state drives (SSDs) replacing traditional hard disk drives (HDDs). The now ubiquitous smart cell (mobile) phones and other handheld devices also use NVM, but there is a trade-off between cost and performance. The cheapest NVM is Flash memory, which, among other uses, is the basis of small, portable Flash memory sticks. Flash memory, however, is slow and has a limited cyclability of 10<sup>5</sup> cycles, sufficient for a large number of storage applications ranging from memory sticks to digital camera memory to SSDs, but much lower than that of redox-RAM or STT-MRAM.

Besides computers, today's portable electronics have become intensively computational devices as the user interface has migrated to a full multimedia experience. To provide the performance required for these applications, the portable electronics designer uses multiple types of memory: a medium-speed random-access memory for continuously changing data, a high-speed memory for caching instructions to the CPU, and a slower NVM for long-term information storage when the power is removed. Combining all of these memory types into a single memory has been a long-standing goal of the semiconductor industry. With such a memory, computing devices would become much simpler and smaller, more reliable, faster, and less energy consuming.

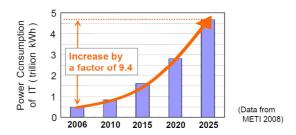

As a result, advanced NVM chips are expected to see phenomenal growth in the next few years, with the global market increasing from \$209 million in 2012 to \$2,028 million by 2018<sup>4</sup> - see Figure 1.2.

This will occur in a number of applications: embedded system-on-chip (SOC) cards; radio-frequency identification (RFID) tags used in goods transported by high-speed detection conveyors; smart airbags used in automobiles; radiation-hardened memory in aerospace and nuclear installations; printed memory platforms (such as smart cards, games, sensors, display, storage-class memory network); and high-end smart mobile phones.

MRAM is one of a number of new technologies aiming to become a "universal" memory device applicable to a wide variety of functions.

<sup>4</sup> YOLE report on Emerging Non Volatile Memories Technologies & Markets (2013)

- As a matter of fact, MRAM can have similar performance to SRAM Cache 3 (switching time ~1 ns) but is nonvolatile.

- It has also similar density to DRAM but at much lower power consumption since there is no need to refresh and with reduced leakage since MRAM can be powered off on standby.

- Besides, it is non-volatile as Flash memory but much faster and suffers no degradation over time. It is this combination of features which makes it so attractive. Some suggest that it could replace SRAM, DRAM, some storage class memories, resulting in instant-on nonvolatile computers and tiny, super-fast and reliable portable devices.

In cell phones, handheld tablet computers, notebooks, personal digital assistants (PDAs), notebooks, and other forms of mobile computing, MRAM is an attractive alternative to deploying both Flash and DRAM since it can save money and space. With software applications residing in memory, mobile devices could rapidly power-up to exactly where they were when they were turned off. In general computing and networking, MRAM can be used to avoid boot-up delays and to provide faster access to hard drives and nonvolatile backup capabilities. At present, BIOS tend to use high cost, low density EEPROM or battery backed-up SRAM – and volatile memory is used to alleviate I/O bottlenecks. In such applications, MRAM could prove much more economical.

**In factory automation systems,** microcontrollers and robots typically employ both RAM and PROMs/Flash. Lower costs will be achieved by replacing these two chips with one MRAM device.

**RFID tags** need low-cost NVM, and a price point that makes MRAM economically viable for RFID applications will almost certainly push MRAM into other cost-sensitive areas.

**For aerospace use,** MRAMs are radiation-hard, meaning that they can withstand ionizing radiation in contrast to most of semiconductor memories based on the capacitor charge. This makes them suitable for use in airplanes (already in Airbus flight controllers), in satellites, and in spacecraft.

**For military use,** the radiation hardness makes them suitable for missiles and perhaps on battlefields where equipment could potentially be exposed to tactical weapons.

MRAM could also be used in **nuclear environment** such as nuclear power plants where conventional CMOS electronics devices fail when exposed to radiation.

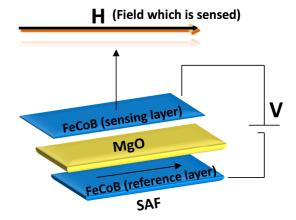

#### 1.4 CURRENT AND FUTURE CHALLENGES FOR MRAMS

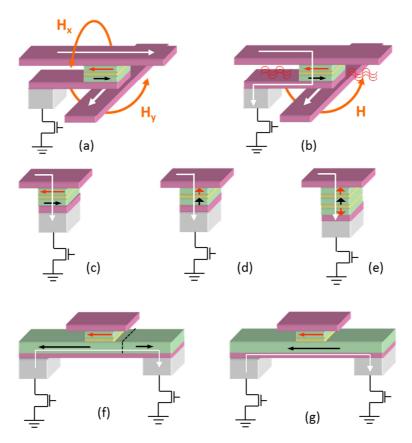

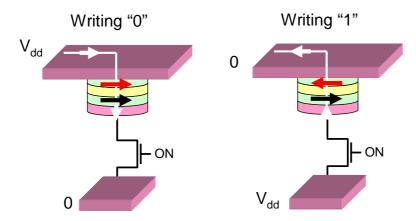

MRAM technologies (*Figure 1.3*) evolved in the last years, benefiting from the progress in spintronics research, namely the tunnel magnetoresistance (TMR) of MgO magnetic tunnel junctions (MTJ)<sup>5</sup>, the STT <sup>6</sup> and the spin orbit torque (SOT) <sup>7</sup> phenomena. The elementary cell of all these MRAM architectures is a MTJ consisting of two ferromagnetic layers separated by a thin insulating barrier and the readout (i.e. determining the magnetic state of the MTJ) is always performed by measuring the MTJ resistance. Between 1996 and 2004, most research and development focused on MRAM written by field (top line in *Figure 1.3*). Until the discovery of STT switching and its gradual implementation in MTJ after 2006, the only known way to manipulate the magnetization of a magnetic nanostructure (here the MTJ storage layer) was indeed with use of a magnetic field. The magnetic field is created by pulses of current flowing in conducting lines located below and above the MTJ. These approaches, which will be described in more detail in the next sections, actually resulted in the commercialization of the first MRAM products (1, 4, 8, and 16 Mbit MRAM chips) by Freescale Semiconductor and its spin-off Everspin Technologies in 2006. **An extension of the initial field written MRAM** (*Figure 1.3a*) is

<sup>5</sup> S. Yuasa et al, "Giant room temperature magnetoresistance in single-crystal Fe/MgO/Fe magnetic tunnel junctions", Nature materials, (2004); S.S.P. Parkin et al, "Giant tunnel magnetoresistance at room temperature with MgO (100) tunnel barriers", Nature Materials, nmat 1256 (2004).

<sup>6</sup> Slonczewski J C 1996, J. Magn. Magn. Mater. 159 L1-L7

<sup>7</sup> I.M Miron. et al., Nature, 476 189 (2011)

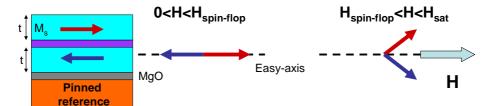

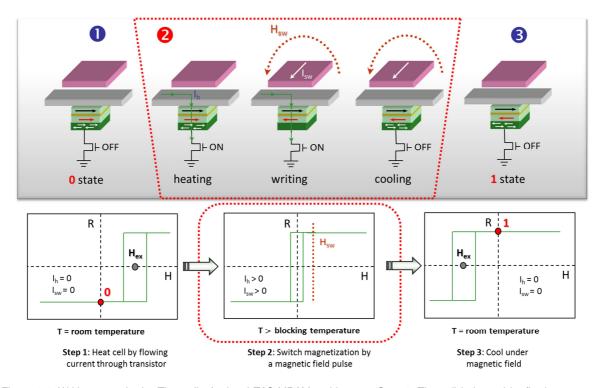

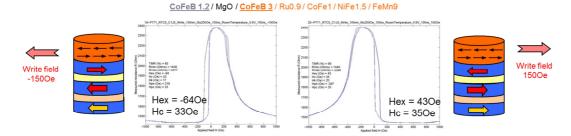

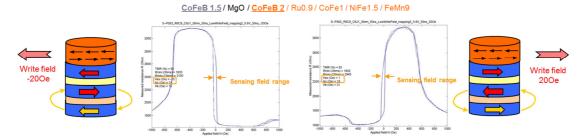

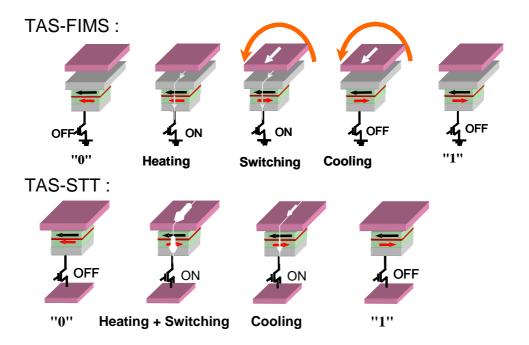

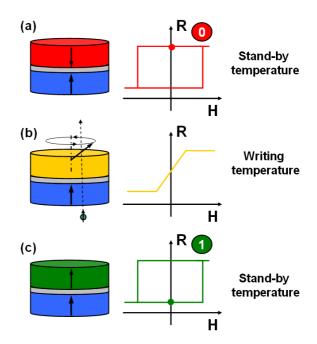

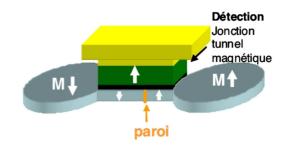

the Thermally Assisted MRAM (TAS-MRAM)<sup>8</sup> (Figure 1.3b), proposed by Spintec and mainly developed by Crocus Technology. In TAS-MRAM, the write selectivity is achieved by a combination of temporary heating of the selected cell produced by the tunneling current flowing through the cell and a single pulse of magnetic field. The power consumption to write these memory elements is significantly reduced compared to conventional field-written MRAM thanks to the possibility of using lower magnetic fields and of sharing each field pulse among several cells so as to write several bits at once. Besides, TAS-MRAM with a soft reference allows introducing new functionalities such as the "Match In Place<sup>TM</sup>", particularly promising for security and routers applications. Field-written technology is robust and is already used in a variety of applications where reliability, endurance, and resistance to radiation are important features, such as in automotive and space applications. However, the down-size scalability provided by field-writing in conventional technology is limited to MTJ dimensions on the order of 60nm×120nm due to electromigration in the conducting lines used to generate the field. In addition, in field-writing, the write field extends all along the conducting line where it is produced and decreases relatively gradually in space, inversely proportional to the distance to this line. As a result, unselected bits adjacent to selected bits may sense a significant fraction of the write field, which may yield accidental switching of these unselected bits.

Since the first observation of STT-induced switching in GMR metallic spin-valve pillars, the interest in using STT as a new write approach in MRAM has increased, motivated by the fact that STT-writing (*Figure 1.3c*) offers a much better down-size scalability than field-writing as the critical current

Fig. 1.3 – Various MRAM technologies: toggle (a), Thermally Assisted MRAM (b), in-plane (c) and (d) out-of-plane magnetized STTRAM, p-STTRAM with double barrier(e), 3-terminal devices based on domain wall propagation (f) and SOT (g)

<sup>8</sup> B. Dieny and O. Redon, patent FR2832542, I.L. Prejbeanu et al, IEEE Trans. Magn 40 2625 (2004); I.L. Prejbeanu, S. Bandiera, J. Alvarez-Herault, R.C. Sousa, B. Dieny and J-P Nozieres Thermally assisted MRAMs: ultimate scalability and logic functionalities J. Phys. D: Appl. Phys. 46 (2013) 074002

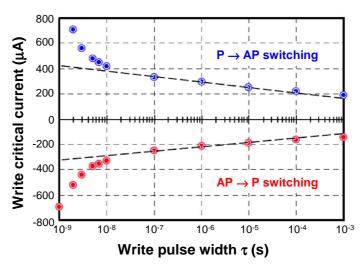

for writing decreases proportionally to the cell area down to a minimum value set by the retention (~15µA). Furthermore, STT provides very good write selectivity since the STT current flows through only the selected cells. The greatest interest is now focused on out-of-plane magnetized STTRAM (p-STTRAM), taking advantage of the perpendicular magnetic anisotropy which exists at the CoFeB/MgO interface (Figure 1.3d)<sup>9</sup>. p-STT-MRAM require significantly less write current than their in-plane counterparts for a given value of memory retention and provide a better stability of the written information. Optimized p-STTRAM stacks will likely comprise two tunnel barriers with antiparallel polarizing layers to maximize anisotropy and STT efficiency (Figure 1.3e). The thermal assistance can also be combined with STT to circumvent a classical dilemma in data storage between the memory writability and its retention<sup>10</sup>. Recently it has been shown that assistance by an electric field may reduce the STT writing critical currents in MTJs<sup>11</sup>. This has been demonstrated in magnetic stacks with perpendicular magnetic anisotropy but the effect is quite weak when using metallic layers due to the electric field screening over the very short Fermi length in metals. An electrically reduced magnetic anisotropy leads to lower energy barrier that is easier to overcome for changing magnetization direction. In principle, voltage control spintronic devices could have much lower power consumption than their current-controlled counterparts provided they can operate at sufficiently low voltage (typically below 1V). Multiferroïc or ferromagnetic semiconductor materials could provide more efficient voltage controlled magnetic properties. 3-terminal MRAM cells written by domain wall propagation (Figure 1.3f) or SOT (Figure 1.3g) were also recently proposed 12 to separate write and read current paths. This can ease the design of non-volatile logic circuits and increase the reliability of the memory. SOT-MRAM offers the same non-volatility and compliance with technological nodes below 22nm, with the addition of lower power consumption (provided the write current density can be further reduced thanks to stack optimization), cache-compatible high speed and improved endurance. The drawback is the increased cell size.

The potential benefits of spin-based memories are especially appealing when viewed in light of the exploding demand for on-chip memories. However, spin-based devices are still in their nascent stages, particularly at the sub-20nm dimensions, and in order to realize their potential, there is a need to strengthen the technology maturity and for advances in circuit designs and innovative architectures.

There is still a need to strengthen the technology maturity and for advances in circuit designs and innovative architectures. The main issues remain associated with the cell to cell variability, TMR amplitude and temperature range. Variability is mainly caused by edge defects generated during patterning of the cells. MgO damages yield local changes in the barrier resistance, TMR and magnetic anisotropy i.e. cell retention. With the increasing number of actors now working on this technology, faster technological progresses can be expected in the near future. Also, implementing self-referenced reading scheme can lead to improved tolerance to process defects. Concerning out-of-plane STTRAM, progresses are needed in the composition of the stack to minimize the write current, maximize the TMR amplitude and improve the temperature operating range. Double barrier MTJ with separately optimized interfacial and bulk properties should allow reaching the requirements for Gb STTRAM at 12nm node (Fig.1.3e). Heusler and  $X_{1-x}Mn_x$  (X = Cr, V, Ge, Ga...) alloys have also already demonstrated their potential for p-STTRAM (low  $M_s$ , large perpendicular anisotropy, low damping)<sup>13</sup> but none of the existing alloys combine all required properties yet.

<sup>9</sup> M. Gajek, J.J. Nowak, J.Z. Sun, P.L. Trouilloud, E.J. O'Sullivan, D.W. Abraham, M.C. Gaidis, G. Hu, S. Brown, Y. Zhu, R.P. Robertazzi, W.J. Gallagher, D.C. Worledge, Appl. Phys. Lett. 100 132408 (2012)

<sup>10</sup> S. Bandiera, R.C. Sousa, M. Marins de Castro, C. Ducruet, C. Portemont, S. Auffret, L. Vila, I.L. Prejbeanu, B. Rodmacq and B. Dieny, Appl. Phys. Lett. 99 202507 (2011)

<sup>11</sup> W.G. Wang et al., Nat. Mater., 11, 64 (2012)

<sup>12</sup> I.M Miron. et al., Nature, 476 189 (2011), P.M. Braganca, J.A. Katine, N.C. Emley et al., IEEE Transactions on Nanotechnology, Volume: 8 Issue: 2 Pages: 190-195 (2009)

<sup>13</sup> H.X. Liu et.al., Appl. Phys. Lett. 101, 132418 (2012)

Progress is also steadily being made in the composition of the stack to maximize the TMR amplitude, (now above 200 %), and in improvements in the temperature operating range (to minimize the decrease of the PMA with operating temperature). The ultimate scalability in STTRAM could be provided by combining thermally/voltage assisted switching and STT. SOT-MRAM can be viewed as a very interesting approach for non-volatile logic and MRAM of improved endurance. Voltage controlled spintronics devices may later yield devices of much reduced power consumption. As a matter of fact, there is lot of room for reducing the power consumption in MRAM technologies considering that the barrier height to insure a 10 year retention of a Gb chip is typically of  $80k_BT \sim 4x10^{-4}fJ$  whereas the energy presently required per STT write event is in the range 50fJ-1pJ.

#### 1.5 HISTORICAL CONTEXT OF THIS WORK

The research of new approaches to making non-volatile memories has been a major activity of SPINTEC since its inception. SPINTEC research laboratory was established in 2000 to specifically work at valuation of upstream work in the areas of nanomagnetism and spintronics. The MRAM team in SPINTEC has proposed alternative MRAM technologies with improved performances (speed, scalability and power consumption) and avoiding problems like the write selectivity, power consumption, electromigration and thermal stability at high densities. Multiple approaches have been pursued in parallel:

- Thermally-Assisted Switching (TAS), as developed by our spin-off Crocus Technology

which has been refined by constant materials improvements and for which lately multi-level

storage has been demonstrated in a "Magnetic Logic Unit" (MLUTM).

- **Spin Transfer Torque (STT)**, which has been improved by reducing the critical switching current and/or allowing reversible switching with a unipolar current.

- The combination of TAS and STT, which has been revisited for perpendicular magnetic tunnel junctions (viewed as the future of STT MRAM) in a new concept dubbed Thermally-Induced Anisotropy Reorientation (TIAR) which provides industry-record writing efficiency.

- Precessional switching (also known as Orthogonal Spin Torque OST), which was initially proposed by Spintec in 2001 and has been finally demonstrated, fulfilling its promises of ultimate speed.

Spintec has been amongst the pioneers in MRAM development and is recognized worldwide as such. Consequently, we have / have had multiple partnerships with laboratories, research centers and companies, through joint R&D projects (ANR, EU), as well as bilateral industry partnerships. A preferred relation exists with Crocus, which led to the onset of a 5 years "joint laboratory" signed in 2013.

Based on patents filed between 2001 and 2005, a new technology of non-volatile magnetic memories, thermally assisted has been demonstrated by Spintec. The originality of this technology stems from the specific writing process that combines a short heating pulse sent through the memory cell (few nanoseconds) with a magnetic field pulse or a spin polarized current. The very convincing results obtained by SPINTEC and LETI in the framework of the NEXT European project between 2001 and 2005 enabled the launch of a start-up Grenoble, Crocus-Technology, which has managed to raise 13.5 Million Euros from venture capitals in 2006. This transaction also received the grand prize of the ANVAR innovation in 2005 and was a finalist EU Descartes Prize in 2006.

Since the first demonstration of the TAS-MRAM concept in 2004, several improvements / variations of this technology have been proposed:

1) By introducing "thermal barriers" based on conductive material of low thermal conductivity, of each side of the tunnel junction, it is possible to confine the heat generated at the insulating barrier in the layers of interest. Thermal barriers allowed dividing the heating current by 2, thus improving largely the consumption of TA-MRAM.

- 2) Building double tunnel junctions, it is possible to design a memory capable of storing more than two bits per cell, thus doubling the storage density of TAS-MRAM. Furthermore, double barrier systems provide another advantage in terms of reliability; they allow reducing the voltage drop across each barrier during write, which significantly reduces the risk of electrical breakdown.

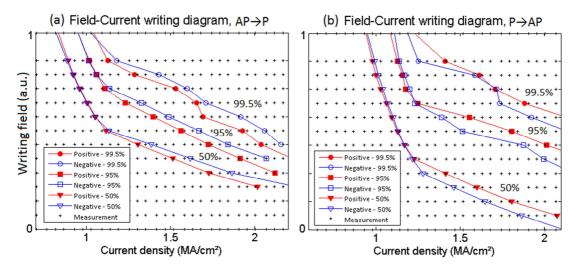

- 3) The concept of heat assistance can be advantageously coupled to writing by spin-polarized current to significantly improve the thermal stability in STT-based systems. The use of spin transfer as writing means offers much better prospects for decreasing sizes than writing magnetic field. Indeed with the spin transfer, the write current decreases as the cell size while in the field writing, the write current rather tends to increase as the size decreases. However, the STT-RAM suffers from the same problem as the MRAM standards in terms of thermal stability for small sizes. TA-STT-RAM concept (Thermally Assisted Spin Transfer Torque RAM) allows to ensure higher MRAM densities while minimizing the write current. In this concept, the same current flowing through the tunnel junction makes heats by Joule effect and exerts magnetic torque by spin transfer torque phenomenon. The concept of TA-STT-RAM was developed within the framework of a bilateral agreement between CEA and Crocus and a ANR 2007 "RAMAC," (Technology Roadmap for Advanced MRAM).

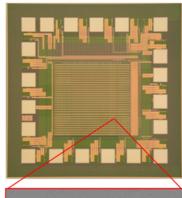

- 4) Recently, the joint R&D teams from Crocus in Spintec developed a self-referenced reading concept which now serves as building block for the company's products. This new concept makes the memory much more tolerant to process variations and very promising for security applications (smart cards, routers, biometrics). Technological advances have enabled obtained Crocus growing dramatically, as evidenced by one of the latest fund-raising 300M€ in 2011 enabling him to go live with one of the first full magnetic back-end fab worldwide.

- 5) In addition, the research work carried out in close collaboration with SPINTEC allowed several advances at the highest international level of research on MRAM: the ultra-low power memories combining writing to the local heating spin polarized current TAS-STT of systems with perpendicular anisotropy.

Spintec laboratory and Crocus Technology represent in Grenoble an excellent example of the coexistence of fundamental study and technological application based on magnetic materials. The connection with the original laboratory is kept alive through a joint Research and Development program (now joint lab) which finances among other research activities the so-called "CIFRE thesis", a PhD with an applicative approach, closely connected with a technological application. The different joint research activities were also financed through several ANR contracts (RAMAC 2007-2010, Pathos 2010-2013, Excalyb 2014-2018)

#### 1.6 DESCRIPTION OF THE MANUSCRIPT

The manuscript is organized in three different parts:

In the first part of this manuscript (chapters 2-7), I will show how thermal assistance can be implemented in field induced switched MTJ to enhance the reliability and the scalability of MRAM. A new self-referenced reading scheme can be implemented in such MTJ in order to obtain a Magnetic Logic Unit that present new logic functionalities compared to standard MRAM. In a second time, I will present the implementation of thermal assistance in MTJ with current induced switching writing scheme. In that case, no field line is required, increasing thus the storage capacity of MRAM cell and decreasing the writing consumption while keeping a satisfying data retention capacity. Ultimately, thermal assistance can be implemented in MTJ with perpendicular magnetization. In that case, thermally induced anisotropy reorientation (TIAR) can be used to decrease the switching power consumption, increase the writing reliability and further improve the scalability of TAS-MRAM down to the 22nm technological node.

#### • Chapter 2

In this chapter I will describe key parameters of the functioning of MRAM memories, including the storage and the read functionalities, as well as a brief description of the first MRAM proposed architectures, based on the combination of orthogonal magnetic fields, either spatially (Stoner – Wohlfarth architecture) or in a time sequence (toggle architecture)

#### • Chapter 3

In order to improve the thermal stability, the write selectivity and the power consumption for MRAM applications, we proposed a new concept, of thermally assisted writing TAS-MRAM. The working principle, the details of the heating processes in a magnetic tunnel junction and the improvements achieved in order to reduce the heating power density, to maximize the retention of the memory will be described in this chapter. These studies have been done during the PhD thesis of Marta Kerekes, Lucien Lombard, Erwan Gapihan and during the postdoc of Cristian Papusoi.

#### Chapter 4

This chapter will deal with the optimization of SR-MRAM for high density storage. Two routes for achieving this will be explored. In the first one we will focus on the reduction of the patterning dimensions of the MTJ, while maintaining manageable power-consumption and data retention properties, with the experimental demonstration of the feasibility of its functionalities. We will then investigate new data encoding methods for multibit operations, from the simulation of their performances to their experimental demonstration. These studies have been done during the PhD thesis of Quentin Stainer

#### • Chapter 5

The problem with the field driven writing of TAS-MRAM cells is still that the magnetic field needs to be generated by a current line with current pulses of a few milliamperes. TAS-MRAM requires a single magnetic field and lower field values compared to the toggle MRAM approach, thus lowering the total power consumption. However, the write field does not scale with cell size and can be at best kept constant, unlike STT-MRAM where the write current scales with cell size. In TAS-MRAM, the heating current is not the bottleneck, since the use of thermal barriers has already demonstrated a heating current density in the 1-2×10°A/cm<sup>2</sup> range, similar to the lowest values of spin transfer torque MRAM cells (STT-MRAM). Alternatively, it is possible to get rid of the field line by still using the thermally assisted concept but combining it with spin transfer torque (STT) to switch an exchange biased storage layer. In this case, the same current flowing through the cell is used both to heat up the cell and switch the storage layer magnetization by STT. It is thus possible to combine the added stability obtained from the exchange biasing to retain the information with the reduction of the current through cell size scaling, since the cell switching occurs at a constant current density, typically in the 10°A/cm² range. These studies have been done during the PhD thesis of Jérémy **Alvarez-Hérault and Antoine Chavent**

#### Chapter 6

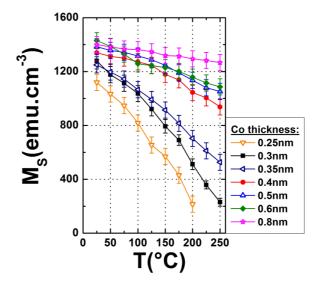

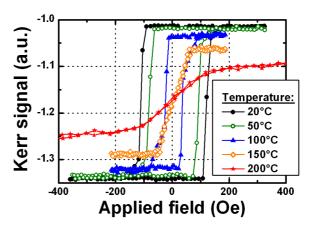

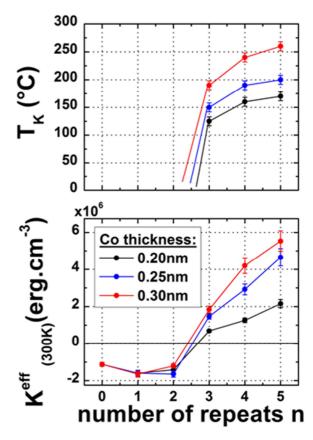

One significant realization towards high density memory cells has been to assist the spin transfer switching of the magnetization of the perpendicular cell. This was achieved by a thermally induced reorientation of the free layer magnetic anisotropy from out-of-plane to inplane. The junction temperature increase is due to the Joule dissipation around the tunnel barrier produced by the same pulse of current which generates the spin transfer torque. It allows the spin transfer torque efficiency to be maximized during write, since the spin polarization of the current is perpendicular to the magnetization of the storage layer. This reduces the STT switching current and suppresses stochastic variations in switching time. This thermal assistance scheme was demonstrated in a MRAM cell designing a magnetic electrode coupled to a Co/Pd multilayer having a strong temperature dependence of the

perpendicular anisotropy. Leading to a temperature at which the magnetization re-orientation in-plane occurs can be adjusted between 90 and 250°C by varying the Co thickness in the 0.2- 0.4nm range. These cells showed thermal stability factors of  $162k_BT$  for a critical current density of  $4.6MA/cm^2$ , a record write efficiency at that time. These studies have been done during the PhD thesis of Sebastien Bandiera.

#### Chapter 7

Will summarize the main conclusions of all these studies and will propose a MRAM roadmap for advanced technological nodes, below 20nm.

The second part of this manuscript will be dedicated to the description of my future research projects for the forthcoming years linked mainly to applied aspects of the magnetic tunnel junctions for: sub-20nm scalable MRAMs, hybrid logical circuits and innovative magnetic field sensors.

#### Chapter 8

This chapter will detail the perspectives of this work as well as some of my future projects, dedicated to applied aspects of the magnetic tunnel junctions for: sub-20nm scalable MRAMs, hybrid logical circuits and innovative magnetic field sensors.

Finally I will give details about my scientific career after the PhD defended end of 2001, including:

- a Curriculum Vitae.

- my main research highlights,

- a detail of the 12 PhDs (co)supervised in this period as well as

- a list of publications including 45 Journal articles, 5 chapter books and 38 patents.

### 2. BASICS OF MRAMS

In this chapter I will describe key parameters of the functioning of MRAM memories, including the storage and the read functionalities, as well as a brief description of the first MRAM architectures, based on the combination of orthogonal magnetic fields, either spatially (Stoner – Wohlfarth architecture) or in a time sequence (toggle architecture)

| 2.1 Storage function: MRAM retention                                                  |    |

|---------------------------------------------------------------------------------------|----|

| 2.1.1 Key role of the thermal stability factor                                        | 17 |

| 2.1.2 Thermal stability factor for in-plane and out-of-plane magnetized storage layer | 17 |

| 2.2 READ FUNCTION                                                                     | 20 |

| 2.2.1 Principle of read operation                                                     | 20 |

| 2.2.2 STT induced disturbance of the storage layer magnetic state during read         | 21 |

| 2.3 FIRST MRAM GENERATIONS                                                            | 22 |

| 2.3.1 Stoner-Wohlfarth MRAM                                                           | 22 |

| 2.32 Toggle MRAM                                                                      | 25 |

#### 2.1 STORAGE FUNCTION: MRAM RETENTION

#### 2.1.1 Key role of the thermal stability factor

In memory applications, a key characteristic is the retention of the memory, i.e. how long the memory chip is capable of keeping the information which has been written in it. The specification depends on the application but is, for instance, on the order of 10 years for mass storage application such as in hard disk drives (HDD). In MRAM, the information may get corrupted by unintended switching of the magnetization of the storage layer due to thermal fluctuations. The failure rate in an MRAM chip of N bits in standby mode can be estimated as follows. The magnetization of the storage layer of the memory cell can be described as a bistable system, the two stable states being separated by an energy barrier  $\Delta E$ .  $\Delta E$  is determined by the magnetic material's properties and the shape and dimensions of the magnetic element, i.e. the MTJ storage layer, as explained below. At a temperature T, the characteristic thermally-activated switching time is given by an Arrhenius law,

$$\tau = \tau_0 \exp\left(\frac{\Delta E}{k_B T}\right),\tag{2.1}$$

where  $k_B$  is the Boltzmann constant and  $\tau_0$  is an attempt time of the order of 1 ns. For a given bit, the probability of not having accidentally switched after a time t is

$$P_{noswitch}(t) = \exp(-t/\tau). \tag{2.2}$$

For N bits, the probability for the set of N bits of not having experienced any switching event after a time t is:

$$P_{noswitch}^{N}(t) = \left[P_{noswitch}(t)\right]^{N} = \exp(-Nt/\tau). \tag{2.3}$$

Consequently, the probability of having experienced at least one switching event after a time t, i.e. the failure rate in standby mode is given by:

$$F(t) = 1 - \exp(-Nt/\tau) = 1 - \exp\left[\frac{-Nt}{\tau_0} \exp\left(-\frac{\Delta E}{k_B T}\right)\right]. \tag{2.4}$$

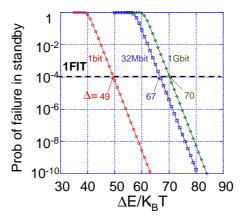

This expression clearly shows that the factor  $\Delta = \frac{\Delta E}{k_B T}$ , often called thermal stability factor, plays a key

role in the failure rate of MRAM chips in standby mode, i.e., memory retention failure. *Figure 2.1* shows the variation of the failure rate during 10 years in standby mode (not during a write or read operation) as a function of the thermal stability factor ( $\Delta$ ) for a 32 Mbit and a 1 Gbit MRAM chip. In order for the probability of experiencing one failure in time (FIT) during 10 years in standby mode to be below an acceptable level of  $10^{-4}$  (this number depends on the whether the application is memory or logic, and on the possible use of error correction codes), the thermal stability factor must be greater than 67 for the 32 Mbit chip and greater than 66 for the 1 Gbit chip. The higher the memory capacity, the larger the thermal stability factor has to be.

#### 2.1.2 Thermal stability factor for in-plane and

Figure 2.1: Failure rate during 10 years in standby mode for MRAM chips of 1 bit, 32 Mbit or 1 Gbit as a function of thermal stability factor.

#### out-of-plane magnetized storage layer

In magnetic materials, the barrier height  $\Delta E$ , which determines the thermal stability factor, is most often created by a magnetic anisotropy which can have different origin. This anisotropy can be of magnetocrystalline origin or can be due to stress or to some electronic hybridization effects taking place at the interfaces in magnetic multilayers. It can be also due to the shape of the patterned magnetic element: a magnetic nanostructure having an elongated shape has an easy axis of magnetization along the long

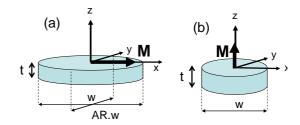

Figure 2.2: Schematic representation of a storage layer with its characteristic dimensions. (a) Case of an in-plane magnetized storage layer with an elliptical prism shape. (b) Case of an out-of-plane magnetized storage layer having the shape of a flat cylinder.

dimension of the structure. Whatever the origin of this anisotropy, it can generally be described by an energy per unit volume  $E_{anisotropy} = -K(\hat{n}\cdot\hat{M})^2$  where  $\hat{n}$  is a unit vector along the easy axis of

magnetization and  $\hat{M}$  is a unit vector parallel to the magnetization direction. The barrier height separating the two opposite stable states along the easy axis direction is then given by  $\Delta E = KV$  where V is the volume of the magnetic nanostructure i.e. the volume of the storage layer in a considered memory cell.

Commonly used in-plane magnetized materials in MRAM have in general relatively weak magnetocrystalline anisotropy. Their magnetic anisotropy mostly originates from their shape. The MTJs, and in particular their storage layers, are patterned in the form of elliptical elements. The barrier height is then given by:

$$\Delta E = \frac{1}{2} \mu_0 (N_y - N_x) M_s^2 V \tag{2.5}$$

where  $N_x$  and  $N_y$  are the storage layer demagnetizing coefficients respectively along the short and long axis of the ellipse,  $M_s$  is the storage layer magnetization, and  $\mu_0$  is the vacuum permeability equal to  $4\pi \, 10^{-7} \, H/m$  (SI).

There are no simple expressions for the demagnetizing coefficients  $N_x$  and  $N_y$  of an elliptical cylinder as a function of its characteristic dimensions (thickness t, width w, length  $A_R w$  where  $A_R$  is the in-plane aspect ratio). These coefficients are functions of elliptic integrals and must be tabulated or numerically calculated 1415. Let's mention that for elliptical cylinders with small thickness t, the structure is often approximated as a uniformly magnetized ellipsoid, for which closed-form solutions exist. Qualitatively, for the purpose of understanding the general influence of the storage layer dimensions, the thermal stability factor  $\Delta$  of in-plane magnetized storage layer can be approximated by:

$$\Delta = \frac{\Delta E}{k_B T} = \frac{\mu_0}{2} \frac{M_s^2 t^2 (A_R - 1) w}{k_B T}.$$

(2.6)

The equation (2.6) shows that for in-plane magnetized system,  $\Delta$  scales with the lateral dimension w (which is typically the technological node), the aspect ratio as  $(A_R-1)$ , square of saturation magnetization  $M_s$ , and square of thickness t. Practically, aspect ratios between 1.5 and 2.5 are used. For larger aspect ratios, the magnetization switching no longer occurs via a coherent rotation of the

<sup>14</sup> J.A. Osborn, Demagnetizing factors of the general ellipsoid, Phys.Rev.67, 351 (1945)

<sup>15</sup> M. Beleggia, M. De Graef, Y.T. Millev, D.A. Goode and G. Rowlands, *Demagnetization factors for elliptic cylinders*, J. Phys. D: Appl.Phys. 38 (2005) 3333

magnetization (i.e., as a whole magnetic block) but proceeds via nucleation of a reversed domain and propagation of domain wall. Therefore, there is no benefit in terms of thermal stability of the magnetization in increasing the aspect ratio above ~2.5. From equation (2.6), one can estimate that the smallest dimensions that an in-plane 2.5 nm thick CoFeB storage layer ( $M_s \approx 10^6 \text{A/m}$ ) can have whilst keeping a thermal stability factor above 70 is of the order of 60 nm× 150 nm.

Perpendicular-to-plane magnetized storage layer (*Figure 2.2*) can in general have better thermal stability than their in-plane counterparts at smaller dimensions because of their much larger intrinsic anisotropy. This is actually one of the reasons why the hard disk drive industry switched from in-plane magnetized magnetic media to perpendicular media in 2004. The perpendicular magnetic anisotropy (PMA) in thin film magnetic materials can have different origins. It can originate from the bulk of the material as in FePt or FePd L1<sub>0</sub> ordered alloys due to a tetragonal distortion of the lattice cell along the growth direction. This bulk anisotropy is usually described by a characteristic energy per unit volume (in J/m³)

$$\mathbf{E}_{anisotropy}^{Bulk} = -K_V (\hat{n} \cdot M)^2 \tag{2.7}$$

where  $\hat{n}$  is a unit vector normal to the plane of the layer. The PMA may also be of interfacial origin due to interfacial electron hybridization or interfacial stress (for instance at Co/Pd, Co/Pt or CoFe/MgO interfaces). This interfacial PMA is usually expressed in terms of a volume energy (in J/m³) as

$$\mathbf{E}_{anisotropy}^{Interface} = -\frac{K_S}{t} (\hat{n} \cdot \hat{M})^2 \tag{2.8}$$

where  $K_{\rm S}$  is the surface energy (J/m²) and t the thickness of the storage layer. However, this PMA is partially counterbalanced by the demagnetizing energy, i.e., the cost of magnetostatic energy required to pull the magnetization of a thin film out of the plane. Indeed, from a pure magnetostatic viewpoint, the thickness of a magnetic thin film is most often its smallest dimension. The direction along the thickness is therefore usually the hard axis of magnetization (in terms of magnetostatics). If the magnetization is nevertheless pulled out of plane by other sources of anisotropy, these other sources must overcome the demagnetizing energy. For an extended thin film, the demagnetizing energy per unit volume is written:

$$E_{demagnetizing} = +\frac{1}{2}\mu_0 M_s^2 (\hat{n} \cdot \hat{M})^2$$

(2.9)

In perpendicular STT-MRAM, the MTJ and therefore its storage layer is usually patterned in the form of a flat cylinder, since there is no longer a need for in-plane shape anisotropy to insure thermal stability of the magnetization. A cylindrical shape allows an increase in areal density. If the width of the cell is larger than 50 nm, the demagnetizing energy expression in equation (2.9) is a sufficiently good approximation. However, for smaller dimensions, it is necessary to take into account the exact values of  $N_x$ ,  $N_y$ ,  $N_z$  demagnetizing coefficients. Since  $N_x + N_y + N_z \approx 1$  and  $N_x = N_y$  due to the cylindrical shape, the demagnetizing energy can be written as:

$$E_{demagnetizing} = +\frac{1}{4}\mu_0 (3N_z - 1)M_s^2 (\hat{n} \cdot \hat{M})^2$$

(2.10)

The total magnetic anisotropy energy per unit volume of the patterned storage layer is then the sum of these various anisotropy contributions:

$$E_{anisotropy} = E_{anisotropy}^{Bulk} + E_{anisotropy}^{Interface} + E_{demagnetizing} = -\left[K_V - \frac{1}{4}\mu_0 (3N_z - 1)M_s^2 + \frac{K_s}{t}\right] (\hat{n} \cdot \hat{M})^2 (2.11)$$

For the storage layer magnetization to remain stable in the out-of-plane direction, the term called the effective anisotropy

$$K_{eff} = K_V - \frac{1}{4}\mu_0 (3N_z - 1)M_s^2 + \frac{K_s}{t}$$

(2.12)

must be positive, meaning that the bulk and interfacial perpendicular anisotropy must exceed the demagnetizing energy. To estimate the thermal stability factor of the storage layer, a cylindrical storage layer of diameter w in a perpendicular MTJ, one must consider which magnetization switching process prevails. In out-of-plane magnetized nanostructures of dimensions typically above 40 nm, magnetization reversal tends to proceed by nucleation of a reversed domain, most often at the edge of the nanostructures and propagation of the domain wall throughout the nanostructure. In this case, the barrier height for reversal is determined by the energy required for the nucleation of the reversed domain. In contrast, for smaller structures (typically below 30 nm in diameter), the magnetization does not have enough space to nucleate a reversed domain and consequently switches as a rigid magnetic block (often called a "macrospin"). In this macrospin approximation, which is valid for technological node below ~30 nm, the thermal stability factor of a cylindrical storage layer of diameter w in a perpendicular MTJ is written:

$$\Delta = \frac{\Delta E}{k_B T} = \frac{\left[ \left( K_V - \frac{1}{4} \mu_0 (3N_z - 1) M_s^2 \right) t + K_s \right] \frac{\pi}{4} w^2}{k_B T}$$

(2.13)

As an example, for a 1.2 nm thick CoFeB storage layer, with typical value of the interfacial anisotropy, a MgO barrier of 1.2.10<sup>-3</sup> J/m², and a magnetization on the order of 1000 kA/m:

- $\Delta = 107 \text{ for } w = 30 \text{ nm},$

- $\Delta$ = 77 for w = 25 nm,

- $\Delta$ = 52 for w = 20 nm, and

- $\Delta$ = 32 for w = 15 nm.

A 10 year retention for a MTJ with  $w \le 20$  nm therefore requires an increase the interfacial anisotropy, a decrease the storage layer thickness while maintaining its TMR amplitude, or a decrease its saturation magnetization.

#### 2.2 READ FUNCTION

#### 2.2.1 Principle of read operation

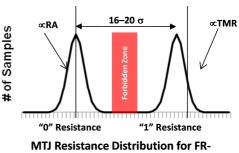

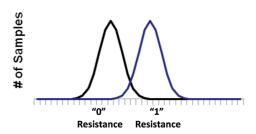

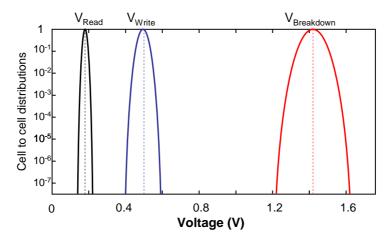

The general principle of the read operation in MTJ-based MRAM consists in exploiting the change of resistance between P and AP magnetic configurations to determine the magnetic state of the junction and therefore the written information. This principle is illustrated in *Figure 2.3*. During read, a small reading current flows through the MTJ to sense its magnetic state from the value of the cell resistance. Usually, the output resistance value is compared to a reference cell whose resistance is the average value of the low and high resistance state (*Figure 2.3c*). To discriminate between the two possible MTJ states in a fast and reliable way, the cell-to-cell distribution of low resistance and high resistance states must be separated by at least  $6(\sigma_{low} + \sigma_{high})$ , where  $\sigma_{low}$  and

$\sigma_{high}$  are respectively the half-width of the distributions of low and high resistance states over an MRAM chip (*Figure 2.3b*).

Figure 2.3: Principle of read operation: (a) During R ratio. The plot The distributions of  $R_{low}$  corresponding to P state a. % of the time for fast and reliable discrimination between the two me chip in 130 nm technology. (c) Example of readout a probability of switching between two cells in opposite magnetic with a reference cell having an intermediate resistance  $(R_{low}+R_{high})/2$ .

V. This choice is motivated by two reasons:

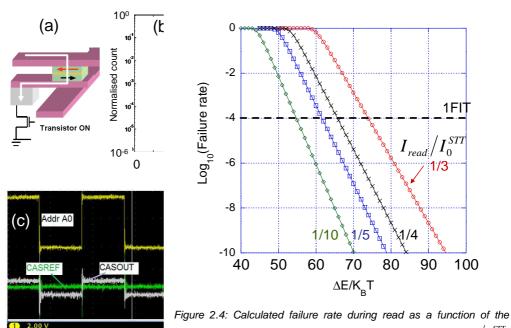

thermal stability factor in standby for several values of the  $I_{read}/I_0^{STT}$  ratio. The plot assumes that 8 bits are read simultaneously during 10 % of the time for 10 years. The dashed line corresponds to an example situation where one failure in time (FIT) would happen in 10 years with a probability of  $10^4$ .

The read current is chosen so that the voltage across the MTJ during read is in the range 0.1 V to 0.2

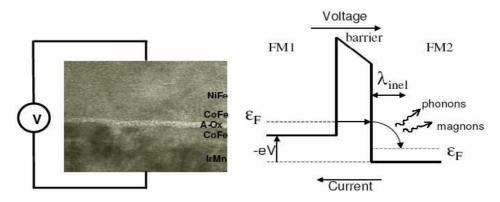

- (a) In MTJs in general and in MgO based MTJ in particular, the TMR amplitude decreases with bias voltage. This TMR decrease versus V is explained by a reduction of the spin polarization as the bias voltage increases due to the fact that the spin filtering mechanism associated with the symmetry of the wave becomes less effective at higher voltage. Also, hot tunneling electrons injected in the receiving electrode after tunneling generate magnetic excitations in the ferromagnetic electrodes which can contribute to depolarize the tunneling current. With read voltage in the range of 0.1 V to 0.2 V, the decrease of TMR compared to the maximum amplitude at very low voltage is no more than 10 % in relative value.

- (b) To avoid spin transfer torque disturbance of the storage layer magnetic state by the read current as explained in the following section (2.2.2).

#### 2.2.2 STT induced disturbance of the storage layer magnetic state during read

Very similarly to the write current in STT-MRAM, the current flowing throughout the MTJ during read, exerts a spin transfer torque effect on the storage layer magnetization. In order to avoid an unwanted writing (or disturbance) during read, the read current must be low enough compared to the STT critical current for switching. The failure rate associated with accidental STT switching of the storage layer magnetization during read can be estimated as follows. Let's consider  $I_0^{STT}$  the STT critical current.

The barrier height for magnetization switching under a read current  $I_{read} < I_0^{STT}$  is decreased due to the STT influence according to the following formula:

$$\Delta E = \Delta E_0 \left( 1 - \frac{I_{read}}{I_0^{STT}} \right)^{\delta}$$

(2.14)

where  $\Delta E_0$  is the barrier height at zero current, as given by the equations (2.5) and (2.12).

This yields the following failure rate during read:

$$F(t) = 1 - \exp\left(-Nt/\tau\right) = 1 - \exp\left[-\frac{Nt}{\tau_0} \exp\left(-\frac{\Delta E}{k_B T} \left(1 - \frac{I_{read}}{I_0^{STT}}\right)^{\delta}\right)\right]$$

(2.15)

Figure 2.4 shows how the read current has to be adjusted with respect to the STT critical current for switching depending on the storage layer thermal stability factor and on the required failure rate. In STT-MRAM, the write voltage on the order of 0.5 V and the read voltage on the order of 0.15 V are typically used, corresponding to a ratio  $I_{read}/I_0^{STT}$  ratio between 1/3 and 1/4.

#### 2.3 FIRST MRAM GENERATIONS

Several large IC manufacturers (Motorola, IBM, NEC, Toshiba, Samsung, ...), attracted by the potential of MRAM as a universal memory, rapidly entered the MRAM arena and started their initial developments with the same write scheme, known as "Stoner-Wohlfarth (SW) approach" or "Field Induced Magnetic Switching approach" (FIMS). Motorola 16 and IBM 17 were the two main industrial players developing in the early 2000s a MRAM architecture based on 1MTJ-1FET per cell and were exploiting this write scheme for the memory encoding.

Two categories of field-induced magnetic switching MRAM (FIMS-MRAM) are described in the following sections:

- 1. MRAM based on the Stoner Wohlfarth model

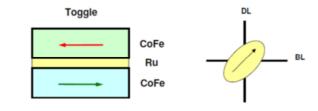

- 2. **The "toggle" MRAM**, an improved version, which succeeded to reach the market in 2006.

#### 2.3.1 Stoner-Wohlfarth MRAM

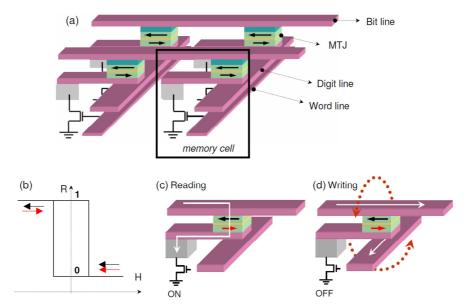

The Stoner-Wohlfarth MRAM (SW-MRAM) was the first developed architecture of MTJ-based MRAM. SW-MRAM consists of an array of MTJs in which each MTJ is connected in series with a selection transistor (*Figure 2.5*). The MTJs are sandwiched between two sets of orthogonal conducting lines (called bit lines and word lines) aimed at creating local magnetic fields on the MTJs storage layer when current flows are sent through them:

- during reading, the selection transistor of the addressed cell is closed, a current flows

through the MTJ and the magnetic state of the memory point is derived from the measured

resistance of the stack.

- during writing, the selection transistor is open: no current flows through the MTJ.

The read operation of the MTJ based class of MRAM was greatly improved compared with all metal technologies (AMR or GMR based). However large capacity chips required both large TMR and narrow distributions of the resistance in the two states (Parallel and Antiparallel configurations). In architectures using mid-point reference cells for the detection of the information stored in the magnetic bits a minimum of 12-sigma is required for multi-megabits arrays between the centers of the distribution of the resistance of high and low resistance states. In the 4Mb demonstrator chip of Motorola published in 2005, over 20-sigma separation was demonstrated thanks to an improved process control of the bit patterning, giving ample read margin. The largest SW-MRAM chips that has

<sup>16</sup> Tehrani S, Engel B, Slaughter JM, Chen E, De Herrera M, Durlam M, Naji P, Whig R, Janesky J, Calder J, Recent developments in Magnetic Tunnel Junction MRAM, IEEE trans. on Mag., 36, N°5, 2752 (2000)

<sup>17</sup> Scheuerlein, R., Gallagher, W., Parkin, S., Lee, A., Ray, S., Robertazzi, R., Reohr, W., *A 10ns Read and Write non-volatile Mmeory Array Using a Magnetic Tunnel Junction and FET Switch in each Cell*, Digest of technical papers, IEEE International Solid State Circuits Conference, 128 (2000)

been produced was the 16Mb chip from the alliance IBM-Infineon<sup>18</sup>, which is also the largest MRAM chip ever fabricated so far. It was built from a 0.18µm CMOS technology with three additional mask levels for the realization of the MRAM elements.

Figure 2.5: (a) Schematic representation of a conventional SW-MRAM architecture containing MTJ cells at the intersection of orthogonal lines and on top of a selection transistor The MTJ are n-plane magnetized with one layer of fixed magnetization pinned along the ellipse long axis ("reference layer," black arrow) and one layer of switchable magnetization having two stable states along the ellipse long axis ("storage layer," red arrow). (b) Typical minor hysteresis loop showing the reversal of the storage layer and two corresponding resistance levels. (c) Reading scheme: transistor is ON and a small electrical current is sent through the junction to measure its resistance (d) Writing scheme: to address the memory element located at the front left of the array, two pulses of current (represented by white arrows) are simultaneously sent in the bit line and word line which cross each other at the addressed memory point. These pulses generate two perpendicular magnetic fields (represented by orange arrows) which add as two vectors at the addressed memory point.

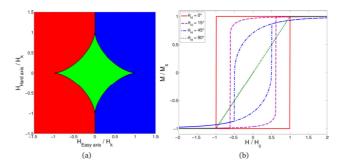

To write at a particular addressed cell, two simultaneous pulses of current are sent in the bit line and world line which cross each other at the addressed MTJ cell. These currents must be adjusted so that the resulting field at the addressed cell is locally large enough to switch its storage layer magnetization in the desired direction while not switching the storage layer magnetization in the other memory points located further along the same bit line or the same world line. In these SW-MRAMs, the write selectivity is thus based on the combination of two orthogonal magnetic fields, one along the easy axis of magnetization, the other along the hard axis. This write principle is based on the so-called Stoner-Wohlfarth switching astroid (*Figure 2.6* which provides a quantitative criterion for magnetization switching in a magnetic nanostructure with uniaxial anisotropy).

To review the principle, a magnetic nanostructure of magnetization  $M_s$  has a uniaxial anisotropy described by an anisotropy energy per unit volume  $K_u$ . This nanostructure is assumed to be sufficiently small so that its magnetization remains homogeneous and therefore can be described in the macrospin approximation. We now assume that the magnetization is initially oriented in one direction along the easy axis of magnetization and that we want to switch it in the opposite direction. This is achieved by applying simultaneously a field along the easy axis of magnetization  $(H_x)$  and another one in the orthogonal direction, i.e., along the hard axis of magnetization  $(H_y)$ . It was demonstrated that in this situation, the condition for switching is that the total field vector of components  $(H_x, H_y)$  must fall out-of the Stoner-Wohlfarth astroid, which is defined by the relationship:

<sup>18</sup> Gallagher, W.J. Abraham, D. Assefa, S. Brown, S.L. De Brosse, J. Gaidis, M. Galligan, E. Gow, E. Hughes, B. Hummel, J. Kanakasabapathy, S. Kaiser, C. Lamorey, M. Maffit, T. Milkove, K. Yu Lu Nowak, J. Rice, P. Samant, M. O'Sullivan, E. Parkin, S.S.P. Robertazzi, R. Trouilloud, P. Worledge, D. Wright, G. See-Hun Yang, *Recent advances in MRAM technology*, Proceedings of the IEEE International Symposium on VLSI Technology, 72 (2005)

$$H_x^{2/3} + H_Y^{2/3} = \left(\frac{2K_u}{M_s}\right)^{2/3}$$

(2.16)

This sets a lower limit to the amplitude of the write field in a SW-MRAM chip. Other memory cells called half-selected bits and located on the active field lines also feel the field created by the current pulse but not the two perpendicular fields simultaneously. They are. In order to avoid half-selected bits to switch, the easy axis field must be lower than the

anisotropy field

$$H_k$$

given by  $H_K = \left(\frac{2K_u}{M_s}\right)$

otherwise this field alone would switch all bits located along the corresponding word line. Thus, taking into account the lower limit set by the SW astroid and upper limit set by the anisotropy field, this defines the

Figure 2.6: (a) Stability regions for the magnetization of a ferromagnet with an easy anisotropy axis at 0°. The red and blue regions correspond to unique possible alignment directions of the magnetization along its easy axis, indicated by the white arrows, while in the green region both directions are concurrently stable. The boundaries of the bistable region constitute the Stoner-Wohlfarth astroid. (b) Normalized magnetization of a macrospin ferromagnet as a function of the external field amplitude and directions, projected on the field application axis directions of the magnetization along its easy axis, indicated by the white arrows, while in the green region both directions are concurrently stable. The boundaries of the bistable

ideal operating window for SW-MRAM. However, in practical devices, several factors actually restrain the size of this operating window:

- The SW astroid in elliptic MTJ of typical dimensions 100 nm × 200 nm is often distorted due to micromagnetic distortions of the magnetization.

- The switching criterion given by the SW astroid is actually valid only at 0 K. For devices

operating at ambient temperature, thermal activation can significantly assist the magnetic

switching so that the operating window must be pushed further away from the theoretical

astroid.

- Due to variability in the patterning process, cell-to-cell distributions in effective

anisotropy field lead to cell-to-cell distribution in the shape and size of the SW astroid.

This imposes stringent conditions on the process of fabrication of the memory elements,

preventing the realization of large memory arrays. This SW write scheme is efficient as long

as all the bits constituting the array have identical or very similar magnetic properties.

No write conditions exist in which all bits could be properly written without writing any half-selected bits. The main parameters ruling the distribution widths are the uniformity of the chemical composition of the MTJ and the accuracy of the patterning process. Any defect or dispersion in the shape of the MTJ immediately results in a broadening of the switching field distribution. Similarly, the correct control of the shape upon scaling is very critical to tightly control the switching distribution. If the switching field of some bits gets too close to the astroid curve, its magnetic stability is reduced and it might be accidentally written due to thermal fluctuations even in the sole presence of the magnetic field along the hard axis. This problem may also occur due to some irreproducibility in the switching process in the magnetic elements. Indeed, it has been observed that upon cycling, the switching field of a single element could vary over a relatively wide range depending on the magnetization reversal mechanism that occurred. These jumps between competing mechanisms are mainly due to the thermal fluctuations that cannot be neglected at room temperature. To prevent this detrimental effect of the thermal fluctuations, specific shapes were designed that proved to yield more repeatable switching process. Element shapes with flat ends have more unpredictable switching mechanisms as either Cstate, S-states or even vortex could develop due to large magnetic charges at their ends. Tapered ends are preferable to minimize magneto-static fields although too sharp ends are difficult to technologically control.

The research and development in this area has been very useful in starting the development of hybrid CMOS/MTJ technology but it did not yield a product because of write selectivity problems and poor down-size scalability. Taking into account all these problems of switching field distributions and thermal fluctuations, the operating region of the SW-MRAM was quite reduced and often bits became inoperable. Industrials had thus to create redundancy bits to replace the defective ones. Due to the technological difficulties to produce a reliable product based on the SW write scheme, several industrials even stepped out the MRAM arena, as Cypress or the IBM/Infineon alliance.

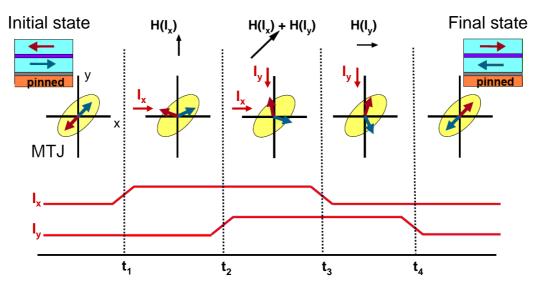

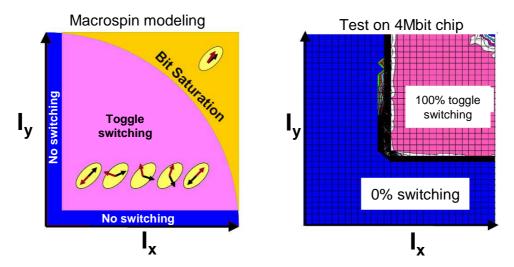

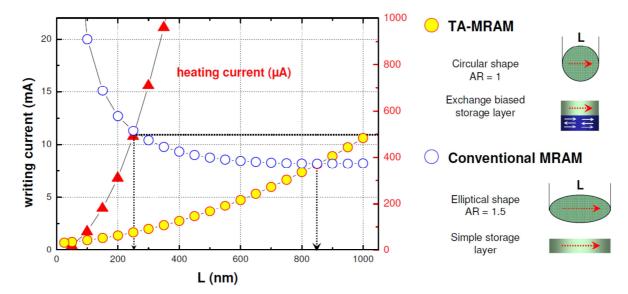

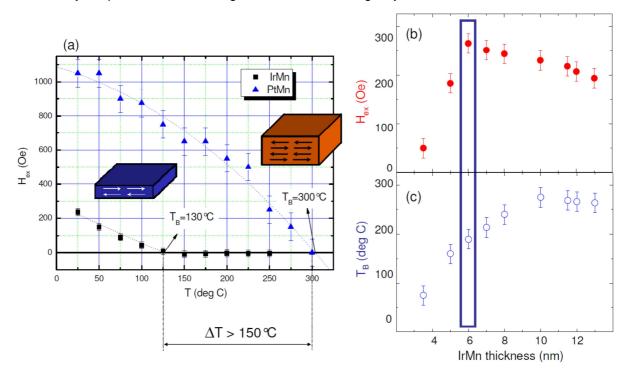

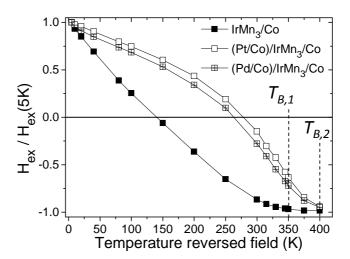

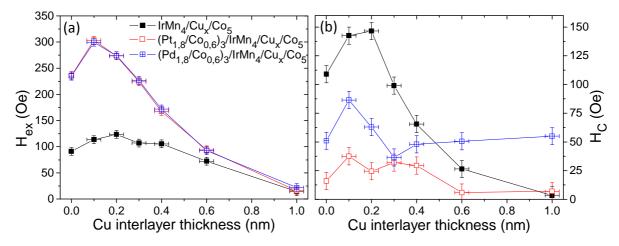

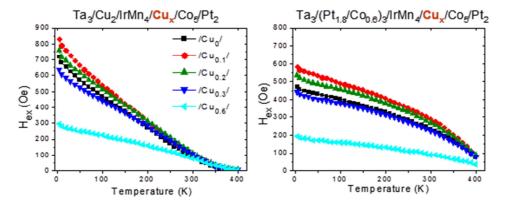

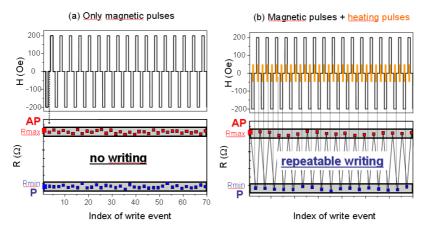

#### 2.3.2 Toggle MRAM