# Substrats innovants pour des composants de puissance à base de GaN

Anthony Cibie

### ▶ To cite this version:

Anthony Cibie. Substrats innovants pour des composants de puissance à base de GaN. Matériaux. Université Grenoble Alpes, 2019. Français. NNT: 2019GREAI014. tel-02163166

# HAL Id: tel-02163166 https://theses.hal.science/tel-02163166

Submitted on 24 Jun 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité: 2MGE: Matériaux, Mécanique, Génie civil,

Electrochimie

Arrêté ministériel : 25 mai 2016

Présentée par

# **Anthony CIBIÉ**

Thèse dirigée par Léa DI CIOCCIO, Ing. Rech. CEA

préparée au sein du CEA-LETI – Laboratoire d'Intégration et de Transfert de Film (LIFT) dans l'École Doctorale I-MEP2 - Ingénierie - Matériaux, Mécanique, Environnement, Energétique, Procédés, Production

# Substrats innovants pour des composants de puissance à base de GaN

Thèse soutenue publiquement le « 8 mars 2019 », devant le jury composé de :

#### **Monsieur Farid Medidoub**

Chargé de Recherche, IEMN - CNRS, Rapporteur

#### **Monsieur Yvon Cordier**

Directeur de Recherche, CRHEA - CNRS, Rapporteur

### **Monsieur Dominique Planson**

Professeur des Universités, INSA Lyon, Président du jury

#### **Madame Julie WIDIEZ**

IGR. CEA. Co-Encadrante de thèse

#### Madame Léa DI CIOCCIO

IGR, CEA, Directrice de thèse

# Remerciements

Je remercie tout d'abord Jean-Sébastien Moulet et Florence Servant de m'avoir accueilli dans le laboratoire d'Intégration et de Transfert de Film (LIFT) au CEA-LETI dans lequel s'est déroulée cette thèse.

Je tiens également à remercier Dominique Planson, Yvon Cordier et Farid Medjdoub d'avoir accepté de faire partie de mon jury de thèse.

Cette thèse n'aurait pas été possible sans ma directrice de thèse Léa Di Cioccio. Merci pour ses conseils et son soutien au cours de ces trois ans, tant du point de vue de la technique que du point de vue personnel. Je remercie bien sûr également mes encadrants. Merci à Lamine Benaissa de m'avoir encadré durant le début de ma thèse pour ses conseils et son soutien. Je te souhaite toute la réussite possible pour ton projet professionnel. Un grand merci également à Julie Widiez d'avoir accepté de m'encadrer pour la dernière année de ma thèse. Sa bonne humeur, ses conseils et son soutien ont été d'une grande aide pour cette troisième et dernière année.

Un grand merci également à tous ceux qui ont contribué à ces travaux de thèse et sans qui je n'aurais rien pu faire. Merci à William Van Den Daele et Stéphane Bécu pour les caractérisations électriques et à Denis Blachier pour les caractérisations thermiques. Je tiens également à remercier Paul-Henri Haumesser pour son aide sur les ECD de cuivre, à Jean-Philippe Colonna pour les simulations sous COMSOL et à Matthew Charles pour tout ce qui était relatif aux épitaxies de GaN des composants que nous avons utilisés. Je remercie également Charlotte Gillot, Jérôme Biscarrat, Yannick Baines pour leur expertise sur les composants GaN. En particulier, je tiens à remercier énormément René Escoffier pour tout le temps qu'il a consacré à m'aider à interpréter les différents résultats de mesures électriques et à les comprendre. Il me reste encore de nombreuses personnes à remercier pour leur aide. Il m'est difficile de faire une liste exhaustive de toutes les personnes qui ont contribué à ces travaux. Aussi je m'excuse par avance auprès des personnes que j'aurais oublié dans ces remerciements, ce n'est pas volontaire... Je remercie notamment Victor Gaude, Pauline Burtin, Stéphane Ballerand, Stephane Litaudon, Marc Zussy, Jean Dijon, Hélène Le Poche, Adeline Fournier, Benoit Thollin.

Cette thèse n'aurait pas été la même sans la bonne humeur et la sympathie de tous les membres du laboratoire dans lequel j'ai travaillé. Ce fut un véritable plaisir de tous vous rencontrer et je m'estime chanceux d'avoir travaillé dans un laboratoire comme le LIFT (et anciennement LSA). Aussi je remercie tous les membres actuels du laboratoire : Thomas, Adrien, Nicolas T., Ismo, Emmanuel A., Emmanuel R., Emmanuelle L., Lucile, Christophe, Thierry S., Christine, Lucie, Ivan, Nicolas B., Amandine, Marie, Thierry F., JS, Béa, Cédric, Chantal, Amal, Selsabil, Paul. Et aussi les anciens : Aurélien, Charlotte, Lyvia, Céline, Emmanuelle G., Etienne, Baptiste, Catherine,

Mickael et Trang. Je n'oublie bien sûr pas Kremena que je remercie énormément pour son aide sur la fin de ma thèse, ton aide a été très précieuse! Et j'oublie encore moins mes camarades de bureau : Jon, Joris et Guillaume que ce fut un plaisir de cotoyer, ça me manquera de ne plus partager un bureau avec vous!

Je tiens également à remercier toute ma famille pour son soutien. Et je terminerais ces remerciements par ma chérie Amandine. Merci à toi d'être à mes côtés et de m'avoir soutenu durant ces moments difficiles.

# Sommaire

| In | trod | uction générale                                                                     | 14 |

|----|------|-------------------------------------------------------------------------------------|----|

| 1  | Cor  | ntexte et pré-requis                                                                | 17 |

|    | 1.1  | Contexte de l'électronique de puissance                                             | 18 |

|    |      | 1.1.1 L'électronique de puissance                                                   | 18 |

|    |      | 1.1.2 Emergence du carbure de silicium SiC et du nitrure de gallium GaN             | 20 |

|    |      | 1.1.3 Exemple du transistor HEMT à base de GaN                                      | 22 |

|    | 1.2  | Limitations du substrat pour l'épitaxie de GaN                                      | 29 |

|    |      | 1.2.1 Méthode de croissance                                                         | 30 |

|    |      | 1.2.2 Contraintes liées à l'hétéroépitaxie                                          | 30 |

|    |      | 1.2.3 Substrats d'épitaxie                                                          | 32 |

|    | 1.3  | Limitations des performances dues au substrat                                       | 36 |

|    |      | 1.3.1 Aspect thermique                                                              | 36 |

|    |      | 1.3.2 Aspect tenue en tension                                                       | 44 |

|    | 1.4  | Approches adoptées lors de la thèse                                                 | 48 |

| 2  | Rer  | oorts de composants de puissance à base de GaN                                      | 52 |

| _  | 2.1  |                                                                                     | 53 |

|    | 2.2  | <b>o</b>                                                                            | 56 |

|    | 2.2  | 2.2.1 Plaques de composants disponibles                                             |    |

|    |      | 2.2.2 Composants de test                                                            |    |

|    |      | 2.2.3 Composants de puissance                                                       | 65 |

|    | 2.3  | Procédé de report adopté                                                            | 65 |

|    | 2.0  | 2.3.1 Description globale du procédé de report                                      | 65 |

|    |      | 2.3.2 Validation morphologique et électrique du procédé de report                   | 71 |

|    | 2.4  | Résultats électriques et analyses                                                   | 76 |

|    | 2.4  | 2.4.1 Impact du report sur la valeur de la résistance du canal                      | 76 |

|    |      | 2.4.1 Impact du Teport sur la valeur de la Tesistance du Canal                      | 77 |

|    |      | 2.4.2 Report de diodes Schottky                                                     | 82 |

|    | 2.5  | Conclusion                                                                          | 88 |

|    | 2.0  | Conclusion                                                                          | 00 |

| 3  |      | actérisations thermiques de composants GaN reportés                                 | 89 |

|    | 3.1  | Objectifs                                                                           | 90 |

|    | 3.2  |                                                                                     | 90 |

|    |      | 3.2.1 Motif de caractérisation de la résistance thermique du canal                  | 90 |

|    |      | 3.2.2 Mesure de résistance thermique du canal de composants GaN reportés            | 92 |

|    | 3.3  | Caractérisation par caméra infra-rouge de l'échauffement de composants GaN reportés | 94 |

|         | 3.3.1 Description de la méthode de caractérisation par caméra infra-rouge          | 94 |

|---------|------------------------------------------------------------------------------------|----|

|         | 3.3.2 Caractérisation par caméra infra-rouge de composants GaN reportés sur cuivre | 97 |

| 3.4     | Conclusion                                                                         | 03 |

| Conclu  | on générale 10                                                                     | )5 |

| Annex   | : Substrat adapté à l'épitaxie du GaN                                              | )8 |

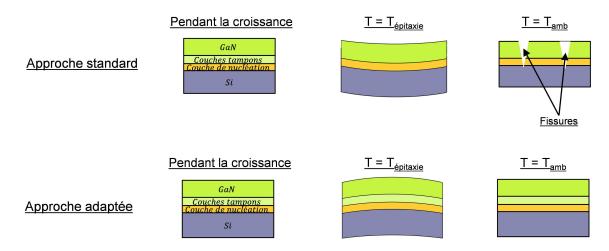

| A.1     | Approche adoptée                                                                   | 09 |

| A.2     | Simulation des substrats évidés                                                    | 11 |

| A.3     | Réalisation expérimentale                                                          | 13 |

| A.4     | Conclusion                                                                         | 14 |

| Bibliog | aphie 11                                                                           | 14 |

# Table des figures

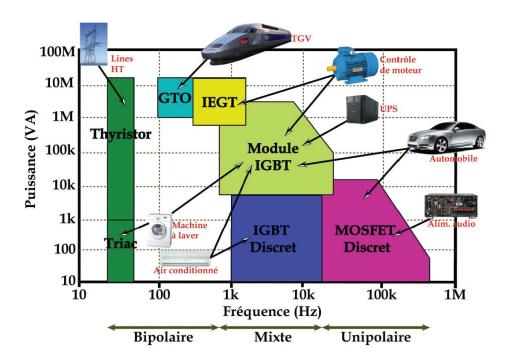

| 1  | Differents domaines d'applications des composants de puissance en 2005 [1]                         | 18 |

|----|----------------------------------------------------------------------------------------------------|----|

| 2  | A gauche : circuit simplifié illustrant le principe du découpage temporel à l'aide d'un            |    |

|    | interrupteur à deux pôles, commutant entre les positions 1 et 2. A droite : variation              |    |

|    | de la tension aux bornes de la charge résistive en fonction du temps et montrant                   |    |

|    | l'impact des commutations de l'interrupteur [2]                                                    | 19 |

| 3  | Structure et symbole d'un transistor NMOS à canal d'inversion [3]                                  | 20 |

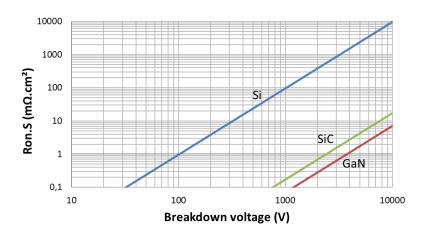

| 4  | Résistance spécifique en fonction de la tension de claquage pour le Si, le SiC (4H)                |    |

|    | et le GaN à température ambiante                                                                   | 21 |

| 5  | Pertes en conduction et en commutation d'un transistor de puissance                                | 21 |

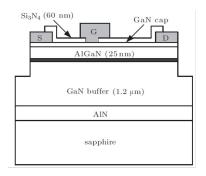

| 6  | Schéma en coupe d'un transistor HEMT à base de GaN. S représente la source, G                      |    |

|    | la grille et D le drain. Le trajet des électrons lorsque le transistor est passant est             |    |

|    | représenté avec le trait en blanc                                                                  | 23 |

| 7  | Vue de dessus d'un transistor HEMT observé au microscope optique. Le trait en                      |    |

|    | blanc montre la localisation de la vue en coupe présentée sur la figure 6                          | 23 |

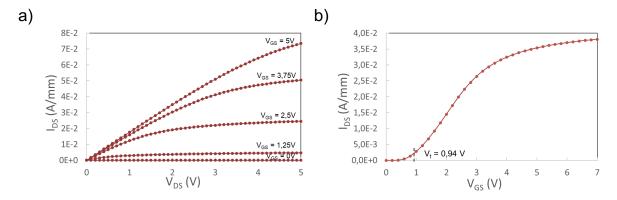

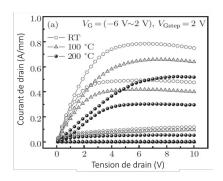

| 8  | Caractéristiques électriques d'un transistor HEMT normally-off GaN sur substrat si-                |    |

|    | licium $(L_q/W_q/L_{qd}=1/100/15 \ \mu m)$ . a) Courbes $I_{DS}(V_{DS})$ pour différentes tensions |    |

|    | de grille $V_{GS}$ . b) Courbes $I_{DS}(V_{GS})$ pour une tension de drain $V_{DS}=0,1~V$          | 24 |

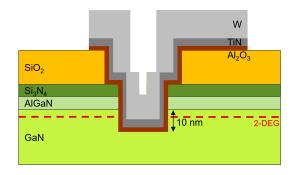

| 9  | Vue en coupe d'une grille avec une structure en « gate recess »                                    | 24 |

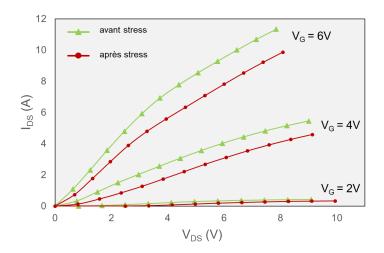

| 10 | Illustration de l'effet de current collapse pour un transistor 10A. Un premier réseau              |    |

|    | I(V) est tracé pour différentes tensions de grille (ici sont représentées les courbes              |    |

|    | pour $V_{GS} = 2V$ ; $4V$ ; $6V$ . La condition de stress est réalisée sous $V_{GS} = -4V$ et pour |    |

|    | $V_{DS}$ allant de 0V à 450V sont appliquées (non représentée ici)                                 | 25 |

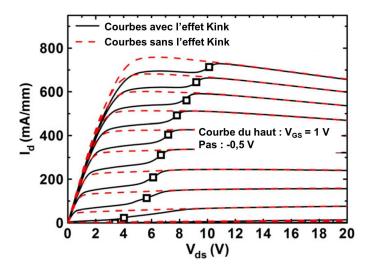

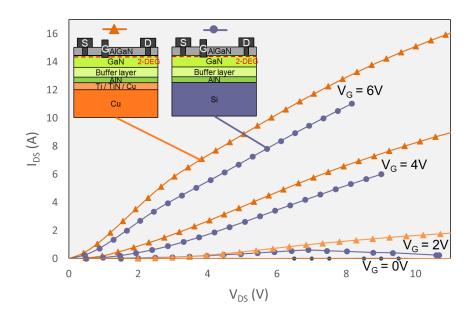

| 11 | Courbes $I_{DS}(V_{DS})$ à différentes valeurs de tensions de grille $V_{GS}$ d'un transistor      |    |

|    | HEMT AlGaN/GaN présentant l'effet Kink (courbes en lignes continues) et sans                       |    |

|    | cet effet Kink (courbes en pointillés) [4]                                                         | 26 |

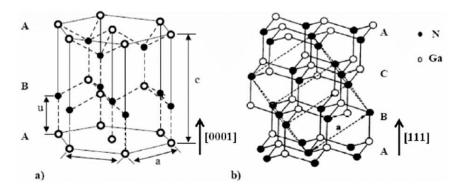

| 12 | Structure wurtzite a) et zinc-blende b) du GaN [5]                                                 | 26 |

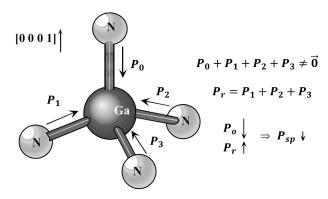

| 13 | Polarisation spontanée dans la structure wurtzite du GaN dans le cas d'une polarité                |    |

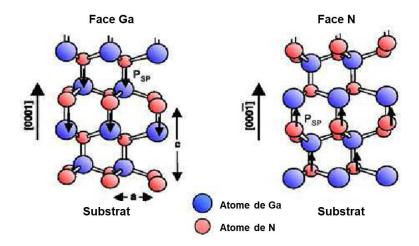

|    | Ga [6]                                                                                             | 27 |

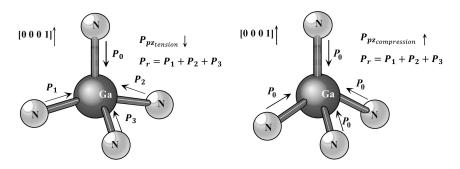

| 14 | Polarité gallium (gauche) et polarité azote (droite) dans le GaN [7]                               | 27 |

| 15 | Direction de la polarisation piézoélectrique dans le cas d'une contrainte en tension               |    |

|    | (gauche) et d'une contrainte en compression (à droite) dans le cas d'une polarité Ga               |    |

|    | [6]                                                                                                | 28 |

| 16 | Création des plans de charges pour une hétérostructure AlGaN/GaN dans le cas                       |    |

|    | d'une polarité Gallium                                                                             | 29 |

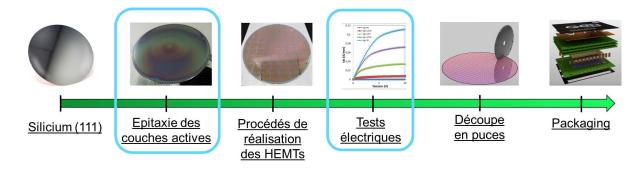

| 17 | Procédé de fabrication de composants de puissance à base de GaN                                    | 29 |

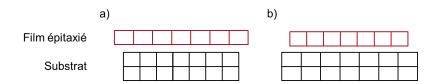

| 18 | Impact du désaccord de maille entre un film épitaxié et un substrat sur le type de contrainte induite dans le film épitaxié. Chaque carré représente schématiquement une maille de côté a. Dans le cas a) on a $a_{substrat} < a_{film}$ d'où un film contraint en compression alors que dans le cas b) on a $a_{substrat} > a_{film}$ d'où un film contraint en tension.                                                          | 30              |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

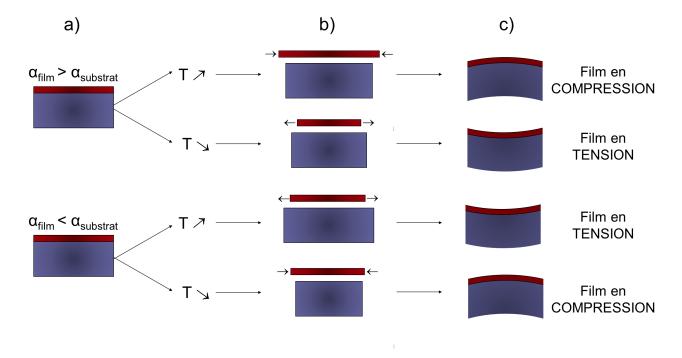

| 19 | Effet d'une variation de température sur la courbure d'une hétérostructure présentant des coefficients de dilatation thermique différents. a) Le film est déposé sans contrainte sur un substrat à une certaine température. b) Si le substrat et le film n'était pas lié, chacun s'étirerait ou se comprimerait différemment suite à une variation de température. Dans le cas réel, le substrat impose au film ses déformations. |                 |

| 20 | c) La contrainte résultante induit une courbure de la structure                                                                                                                                                                                                                                                                                                                                                                    | 31              |

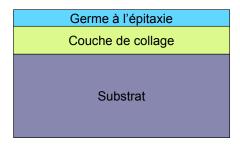

| 21 | Schéma simplifié d'un substrat multicouches. Il est constitué d'un substrat sur lequel est assemblée à l'aide d'une éventuelle couche de collage une couche de germe à                                                                                                                                                                                                                                                             |                 |

| 22 | l'épitaxie                                                                                                                                                                                                                                                                                                                                                                                                                         | 34              |

| 23 | (température ambiante, $100^{\circ}$ C et $200^{\circ}$ C) [8]                                                                                                                                                                                                                                                                                                                                                                     | 36              |

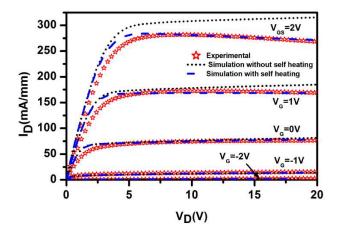

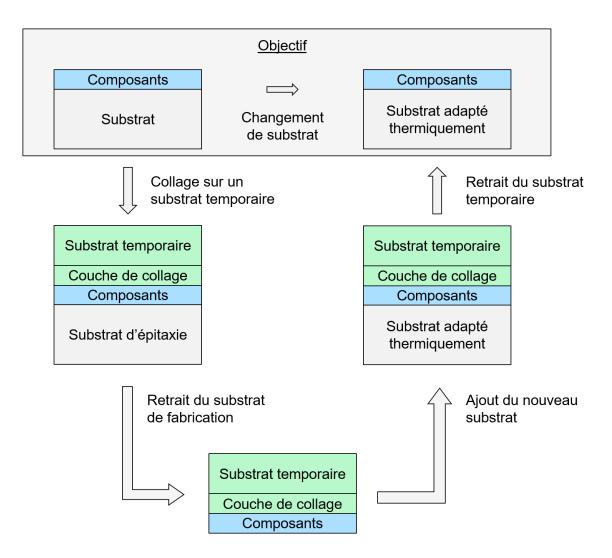

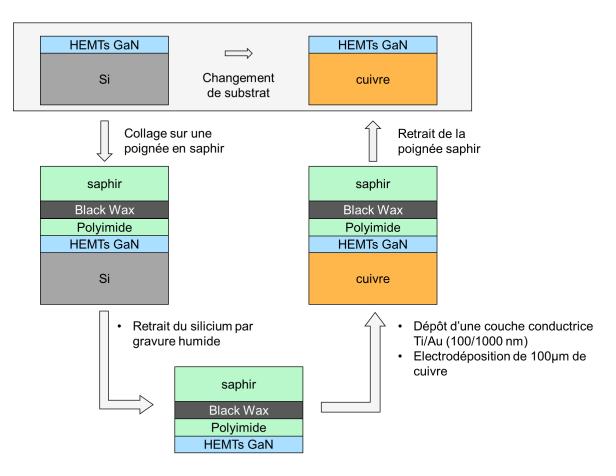

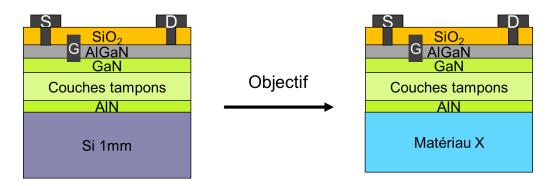

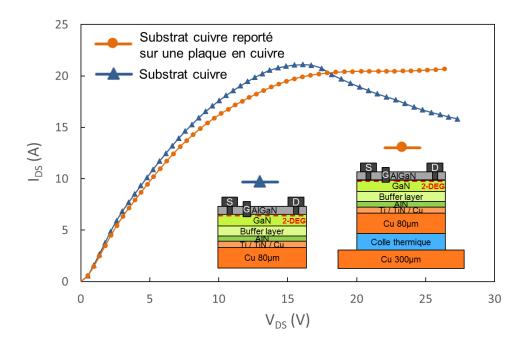

| 24 | simulation sans auto-échauffement et en traits bleus avec auto-échauffement Principe du report de composants sur un substrat plus adapté à partir du substrat de fabrication                                                                                                                                                                                                                                                       | 37<br>38        |

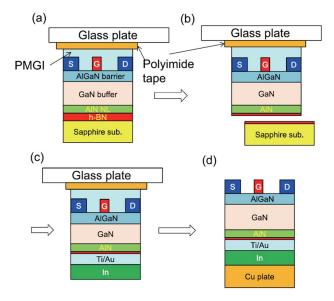

| 25 | Procédé de transfert de HEMTs à base de GaN sur substrat cuivre à partir d'un substrat de fabrication en saphir [10]. (a) Collage temporaire sur une poignée en verre. (b) Détachement du substrat saphir à l'aide d'une fine couche de h-BN préalablement déposée. (c) Dépôt de couche Ti/Au puis de In. (d) Collage par thermocompression                                                                                        | 90              |

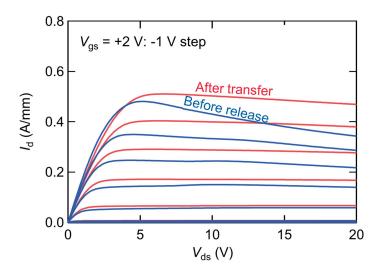

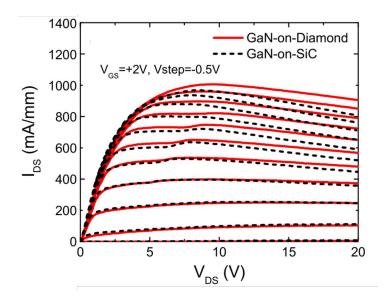

| 26 | de l'ensemble avec une plaque en cuivre. Le substrat en verre est ensuite retiré Caractéristiques I(V) de composants GaN avant report, i.e. sur saphir, et après                                                                                                                                                                                                                                                                   | 39              |

| 27 | report, i.e. sur cuivre [10]                                                                                                                                                                                                                                                                                                                                                                                                       | 40              |

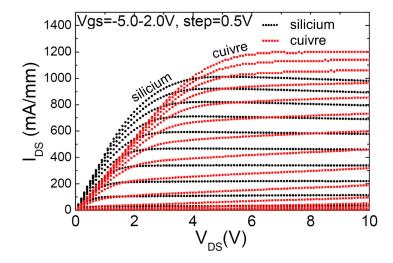

| 00 | substrat silicium [11]                                                                                                                                                                                                                                                                                                                                                                                                             | 41              |

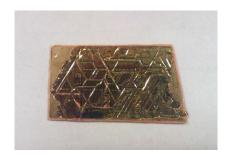

| 28 | Photographie de transistors HEMTs à base de GaN reportés sur substrat cuivre [11].                                                                                                                                                                                                                                                                                                                                                 | 41              |

| 29 | Courbes $I_{DS}$ en fonction de $V_{DS}$ pour des transistors HEMTs sur silicium et après report sur cuivre [11]                                                                                                                                                                                                                                                                                                                   | 42              |

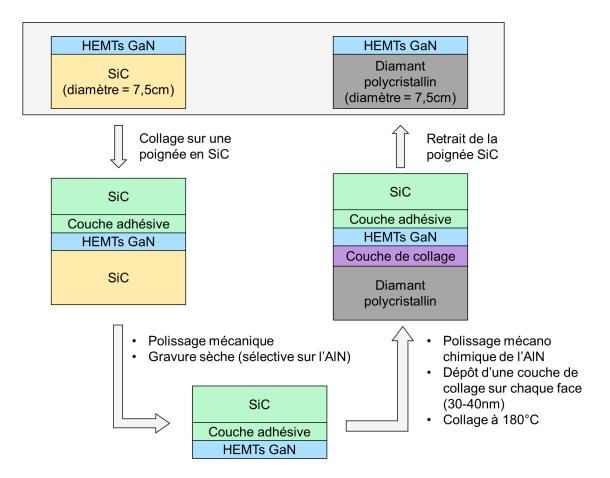

| 30 | Transfert de composants HEMTs à base de GaN sur un substrat en diamant à partir                                                                                                                                                                                                                                                                                                                                                    |                 |

| 31 | d'un substrat SiC [12]                                                                                                                                                                                                                                                                                                                                                                                                             | 43              |

| 32 | rouge) sur substrat diamant [12]                                                                                                                                                                                                                                                                                                                                                                                                   | $\frac{44}{45}$ |

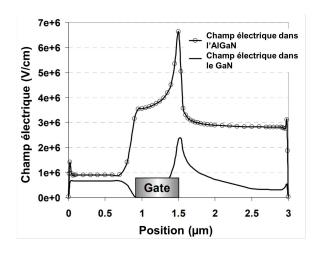

| 33  | Simulation du champ électrique dans un HEMT AlGaN/GaN en polarisation de                                                                                                                                                                            | 45  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 91  | claquage [13]                                                                                                                                                                                                                                       | 45  |

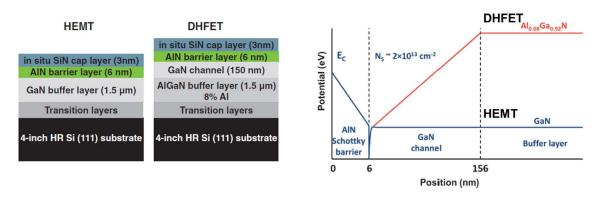

| 34  | schématique des bandes de conduction d'un HEMT AlN/GaN standard (en bleu)                                                                                                                                                                           |     |

|     | et d'un DHFET [14]                                                                                                                                                                                                                                  | 46  |

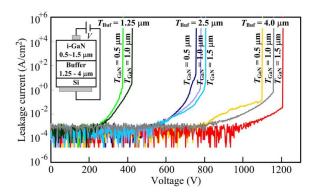

| 35  | Courants de fuites verticales pour différentes épaisseurs de couches tampons et de                                                                                                                                                                  | 10  |

| 00  | GaN en fonction de la tension appliquée. Les couches tampons sont constituées d'une                                                                                                                                                                 |     |

|     | succession de paires $GaN/AlN$ (20/5nm) [15]                                                                                                                                                                                                        | 47  |

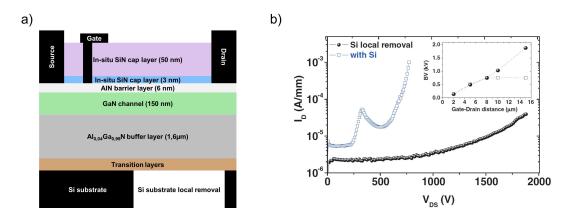

| 36  | a) Schéma en coupe d'un transistor AlGaN/GaN HEMT sur substrat silicium partiellement évidé entre la grille et le drain b) Courant de drain à l'état bloqué $(V_{GS} = 5V)$ avec le silicium (en bleu) et avec le retrait partiel de silicium entre |     |

|     | la grille et le drain (en noir) [16].                                                                                                                                                                                                               | 47  |

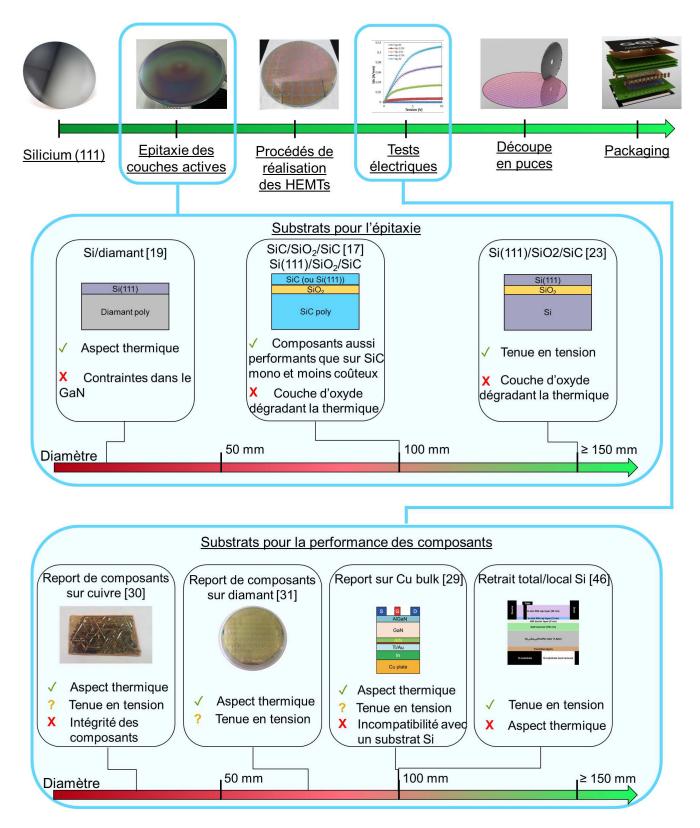

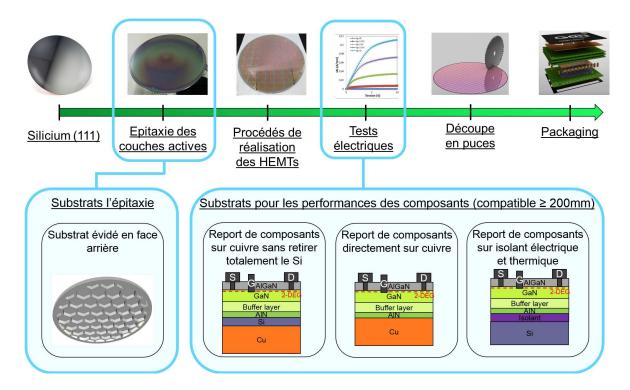

| 37  | Schémas présentant différentes solutions de l'état de l'art aux problématiques d'épi-                                                                                                                                                               |     |

| 20  | taxie et de performances de composants GaN                                                                                                                                                                                                          | 50  |

| 38  | Schémas présentant différentes approches réalisées lors de cette thèse                                                                                                                                                                              | 51  |

| 39  | A gauche : schéma simplifié d'un HEMT (vue en coupe) sur substrat silicium. A droite : HEMT reporté sur un autre substrat après avoir retiré le substrat silicium .                                                                                 | 53  |

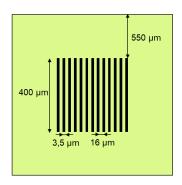

| 40  | A gauche : structure utilisée lors des simulations, les zones en noir correspondent                                                                                                                                                                 | 90  |

| 10  | aux zones de générations thermiques reproduisant l'échauffement des composants                                                                                                                                                                      |     |

|     | de puissance en fonctionnement. A droite : Vue de dessus de la couche d'AlGaN (de                                                                                                                                                                   |     |

|     | $0,3~\mu m$ d'épaisseur) avec les zones d'échauffements en noir. Les schémas ne sont pas                                                                                                                                                            |     |

|     | à l'échelle                                                                                                                                                                                                                                         | 55  |

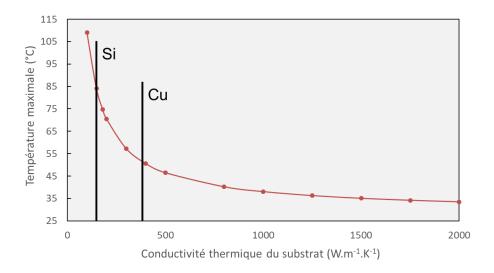

| 41  | Température maximale de l'empilement simulée par éléments finis sous ANSYS                                                                                                                                                                          |     |

|     | en fonction de la conductivité thermique du substrat pour une puissance générée                                                                                                                                                                     |     |

| 4.0 | équivalente à 1W/mm                                                                                                                                                                                                                                 | 56  |

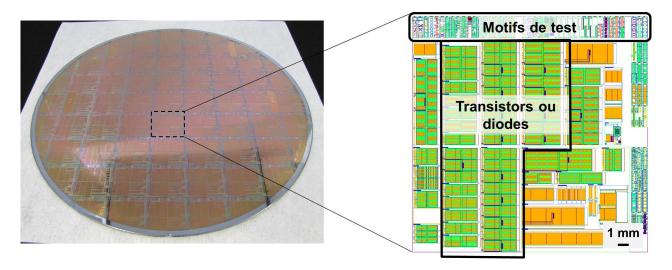

| 42  | A gauche : photographie d'une plaque de 200 mm de diamètre comportant des                                                                                                                                                                           |     |

|     | composants de puissance en GaN réalisés à partir d'une épitaxie de GaN sur un                                                                                                                                                                       |     |

|     | substrat Si(111) de 1 $mm$ d'épaisseur. Un champ de $2, 2 \times 2, 2$ $cm^2$ est encadré en noir. A droite : dessin d'un champ                                                                                                                     | 57  |

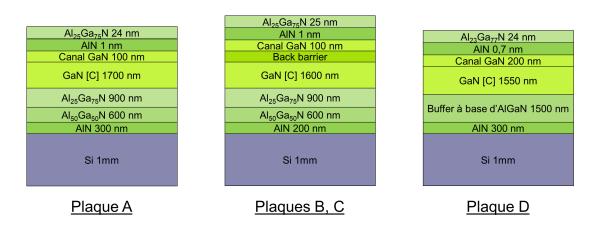

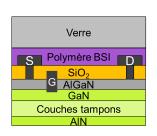

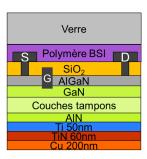

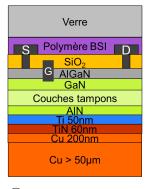

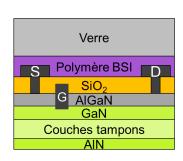

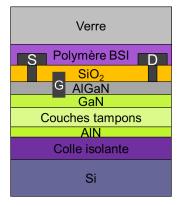

| 43  | Empilements d'épitaxie des plaques de composants utilisées lors de cette thèse                                                                                                                                                                      | 58  |

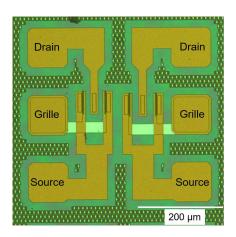

| 44  | Deux transistors de test observés au microscope optique                                                                                                                                                                                             | 59  |

| 45  | Motif TLM à structure linéaire utilisé lors de cette thèse observé au microscope                                                                                                                                                                    |     |

|     | optique                                                                                                                                                                                                                                             | 60  |

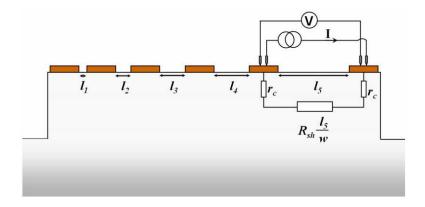

| 46  | Vue en coupe du motif de mesure 4 pointes d'une mesure TLM linéaire. $r_c$ représente                                                                                                                                                               |     |

|     | la résistance du contact, $R_{sh}$ la résistance par carré de couche, $l_i$ la distance entre                                                                                                                                                       |     |

|     | chaque contacts et $w$ la largeur des contacts [17]                                                                                                                                                                                                 | 60  |

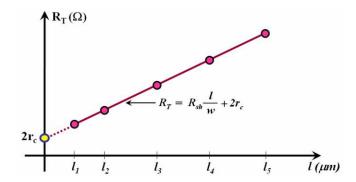

| 47  | Courbe théorique de $R_T(l)$ pour un contact ohmique                                                                                                                                                                                                | 61  |

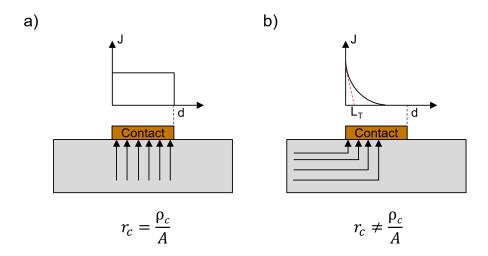

| 48  | Lignes de courant dans le cas d'un contact vertical (a) et dans le cas d'un contact                                                                                                                                                                 |     |

|     | horizontal (b) [18]. A représente l'aire du contact, d la longueur du contact, J la                                                                                                                                                                 |     |

|     | densité de courant passant par le contact, $L_T$ la longueur de transfert, $\rho_c$ résistance                                                                                                                                                      | cc  |

| 49  | spécifique de contact et $r_c$ la résistance de contact                                                                                                                                                                                             | 62  |

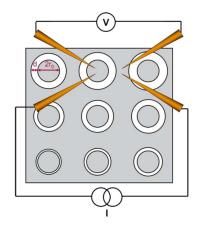

| 49  | et l'isolation [19]                                                                                                                                                                                                                                 | 62  |

| 50  | Schéma d'un motif TLM circulaire [19]                                                                                                                                                                                                               | 63  |

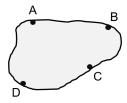

| 51  | Exemple d'échantillon satisfaisant les conditions de Van Der Pauw                                                                                                                                                                                   | 63  |

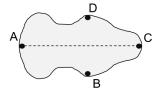

| 52  | Exemple d'échantillon avec un axe de symétrie. Les contacts A et C, ainsi que les                                                                                                                                                                   | - 3 |

|     | contacts B et D, sont symétriques par l'axe tracé en pointillés                                                                                                                                                                                     | 64  |

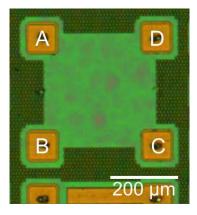

| 53 | Motif Van Der Pauw utilisé lors de cette thèse observé au microscope optique                         | 64  |

|----|------------------------------------------------------------------------------------------------------|-----|

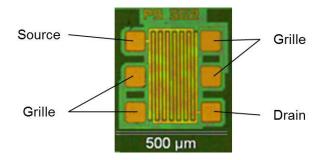

| 54 | a) Image réalisée au microscope optique d'un transistor HEMT 10A à base de GaN.                      |     |

|    | De gauche à droite on voit les contacts de drain, de source et de grille. Les « tâches »             |     |

|    | noires correspondent aux empreintes que laissent les pointes lors des caractérisations               |     |

|    | b) Image réalisée au microscope optique d'une diode Schottky à base de GaN. De                       |     |

|    | gauche à droite, on voit les contacts de l'anode et de la cathode                                    | 65  |

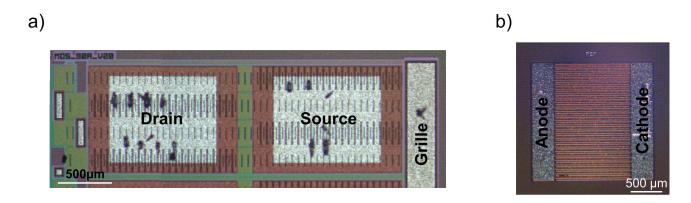

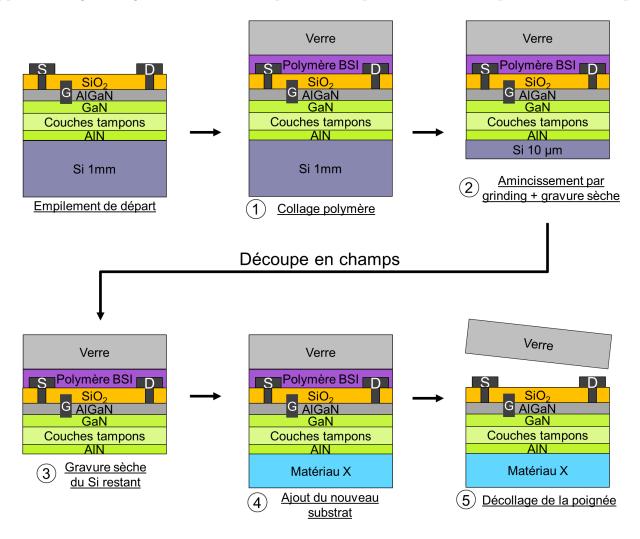

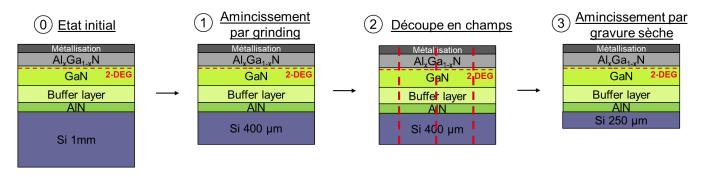

| 55 | Procédé de report utilisé pour remplacer le substrat silicium par un autre matériau.                 | 66  |

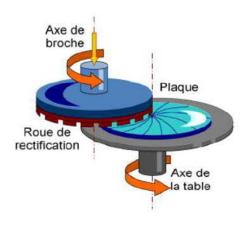

| 56 | Principe de l'amincissement par grinding [20]                                                        | 67  |

| 57 | Dégradation du polymère BSI suite à la gravure sèche de $10 \ \mu m$ de silicium sur des             |     |

|    | champs de $2, 2 \times 2, 2$ $cm^2$                                                                  | 68  |

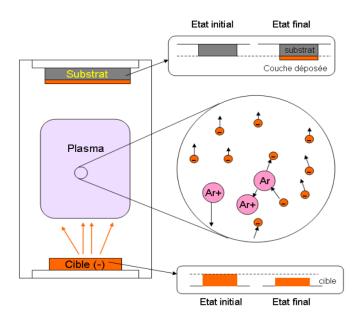

| 58 | Procédé de dépôt du cuivre en face arrière des composants. La première étape                         |     |

|    | consiste en un dépôt physique en phase vapeur d'une couche d'accroche Ti, d'une                      |     |

|    | barrière de diffusion TiN et d'une couche conductrice de Cu permettant l'électrodé-                  |     |

|    | position de cuivre.                                                                                  | 68  |

| 59 | Principe du dépôt de couches minces par pulvérisation cathodique [21]                                | 69  |

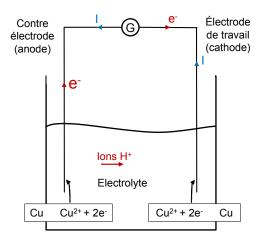

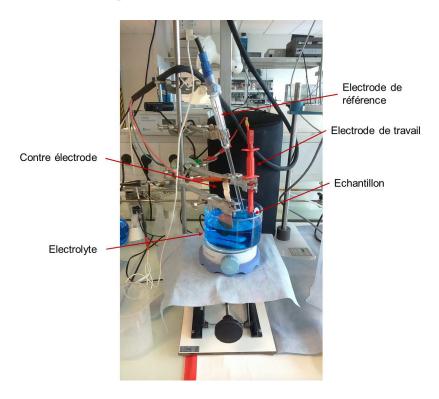

| 60 | Principe de l'électrodéposition dans le cas du cuivre. La contre électrode et l'élec-                |     |

|    | trode de travail sont constituées respectivement d'un morceau de cuivre et de l'échan-               |     |

|    | tillon sur lequel on souhaite réaliser le dépôt et sont placés dans un électrolyte. Une              |     |

|    | source de courant est appliquée pour privilégier les réactions d'oxydation à la contre               |     |

|    | électrode et de réduction à l'électrode de travail                                                   | 70  |

| 61 | Croissance de cuivre par électrodéposition en face arrière des composants                            | 70  |

| 62 | Procédé de report des composants sur un substrat silicium à l'aide d'une colle isolante.             | 71  |

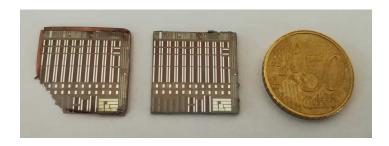

| 63 | Champ de $2, 2 \times 2, 2$ $cm^2$ de composants diodes reportés sur cuivre à gauche et à            |     |

|    | l'aide d'une colle isolante à droite.                                                                | 72  |

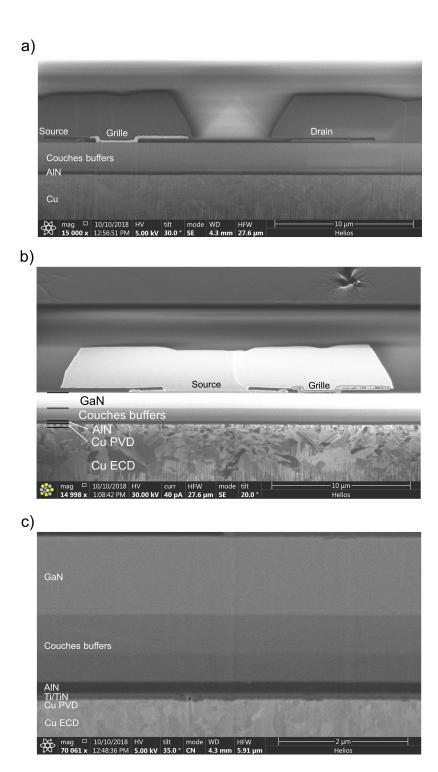

| 64 | Caractérisation FIB-MEB d'un transistor de test reporté sur cuivre. Il s'agit de la                  |     |

|    | plaque D. a) La zone observée comprend les contacts de source, de grille et de drain.                |     |

|    | b) Contact de source et de grille ainsi que les couches d'épitaxie et le substrat cuivre.            |     |

|    | c) Couches d'épitaxie, dépôts PVD de Ti, TiN et Cu et substrat Cu déposé par ECD.                    | 73  |

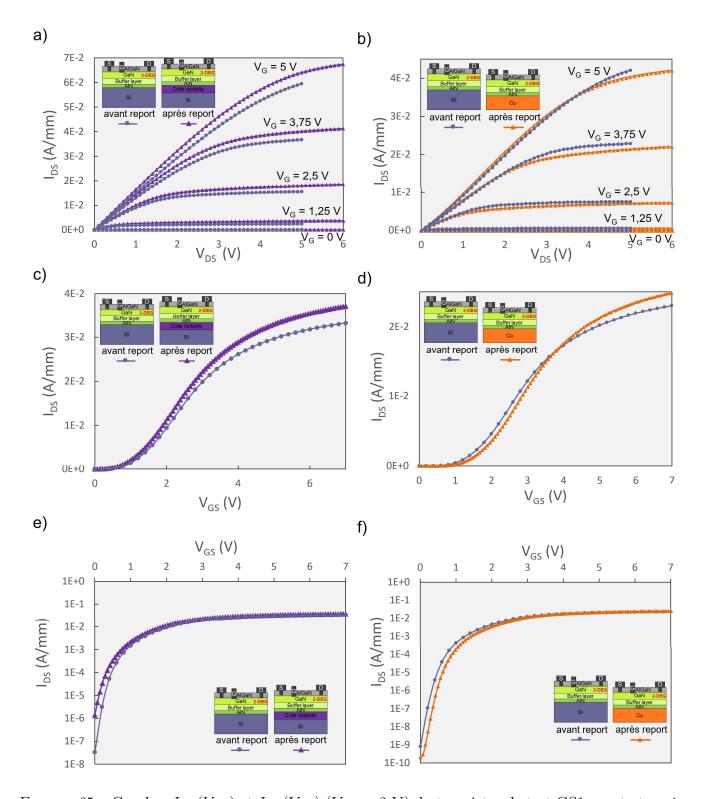

| 65 | Courbes $I_{DS}(V_{DS})$ et $I_{DS}(V_{GS})$ $(V_{DS} = 2 V)$ du transistor de test GS1 avant et     |     |

|    | après report à l'aide d'une colle isolante (report 3, colonne de gauche) et sur cuivre               |     |

|    | (report 1, colonne de droite). a) et b) Courbes $I_{DS}(V_{DS})$ avant et après report               |     |

|    | respectivement sur colle isolante et cuivre. c) et d) Courbes $I_{DS}(V_{GS})$ avant et après        |     |

|    | report. e) et f) Courbes $I_{DS}(V_{GS})$ en échelle semi-logarithmique avant et après report.       | 75  |

| 66 | Procédé d'amincissement effectué pour étudier la réduction de la résistance $R_{sh}$                 |     |

|    | observée lors des différents reports                                                                 | 76  |

| 67 | Courant de drain $(I_{DS})$ à l'état passant d'un transistor HEMT reporté sur cuivre et              |     |

|    | du même transistor avant report (i.e. sur substrat silicium) en fonction de la tension               |     |

|    | de drain $V_{DS}$ pour différentes tensions de grille $V_{GS}$ (0 $V$ , 2 $V$ , 4 $V$ et 6 $V$ ). La |     |

|    | source et le substrat sont reliés à la masse                                                         | 79  |

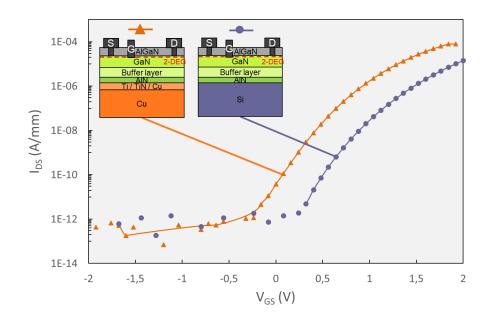

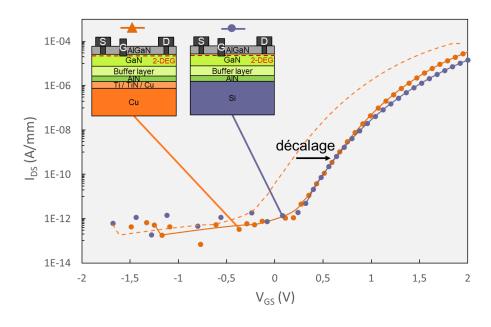

| 68 | Courbes $I_{DS}(V_{GS})$ d'un transistor HEMT avant report (sur silicium) et après report            |     |

|    | (sur cuivre) pour une tension de drain $V_{DS} = 0.5 V$ . Le substrat et la source sont              | 0.0 |

| 00 | reliés à la masse.                                                                                   | 80  |

| 69 | Courbes $I_{DS}(V_{GS})$ d'un transistor HEMT avant report (sur silicium) et après report            |     |

|    | (sur cuivre) pour une tension de drain $V_{DS} = 0.5 V$ . Le substrat et la source sont              | 0.0 |

|    | reliés à la masse.                                                                                   | 80  |

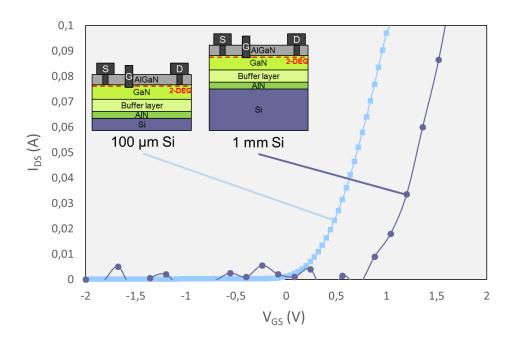

| 70 | Courbes $I_{DS}(V_{GS})$ d'un transistor HEMT sur substrat silicium standart (1 mm d'épaisseur) et après amincissement de ce substrat à 100 $\mu m$ pour une tension de drain $V_{DS} = 0, 5 \ V$ . Le substrat et la source sont reliés à la masse                          | 81       |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

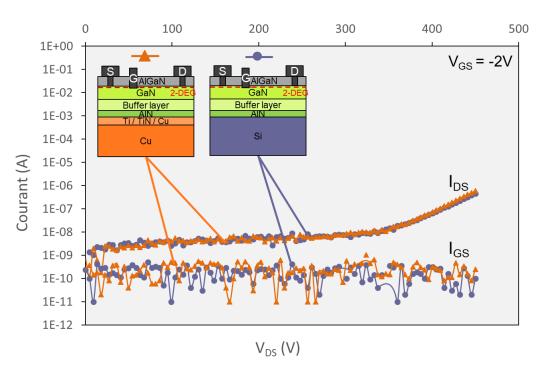

| 71 | Courant de grille $(I_{GS})$ et de drain $(I_{DS})$ à l'état bloqué d'un transistor HEMT reporté sur cuivre et du même transistor avant report, i.e. sur substrat silicium. La tension $V_{DS}$ varie de 0 $V$ à 450 $V$ tandis que qu'une tension de $-2$ $V$ est appliquée |          |

| 72 | sur la grille. La source et le substrat sont reliés à la masse                                                                                                                                                                                                               | 82<br>83 |

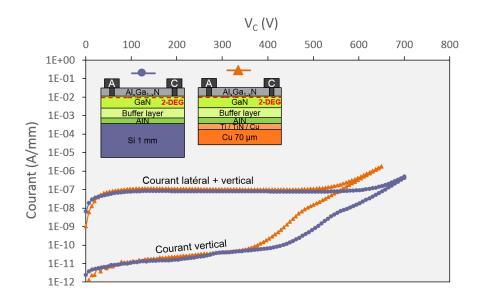

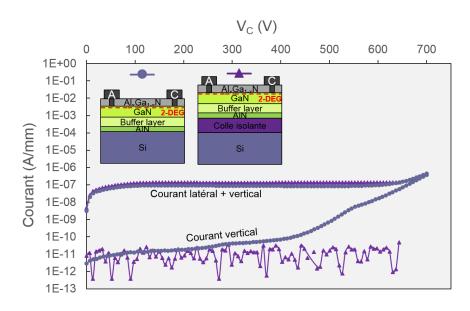

| 73 | Courant à l'état bloqué d'une diode Schottky reportée sur cuivre et du même composant avant report, i.e. sur substrat silicium. La tension à la cathode varie de 0 V à 650 V pour le cas cuivre et de 0 V à 700 V pour le cas silicium. L'anode et le                        |          |

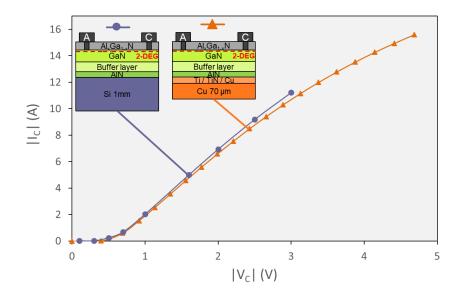

| 74 | substrat sont reliés à la masse                                                                                                                                                                                                                                              | 84       |

| 75 | pour le cas silicium. L'anode et le substrat sont reliés à la masse                                                                                                                                                                                                          | 85       |

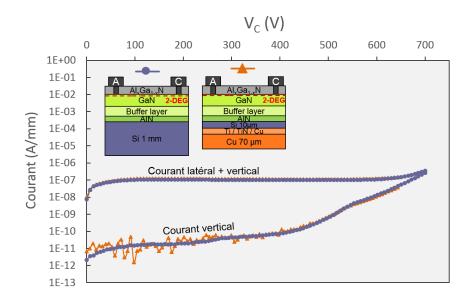

| 76 | le substrat sont reliés à la masse                                                                                                                                                                                                                                           | 86<br>87 |

| 77 | Courant de fuites à l'état bloqué d'une diode Schottky reportée sur substrat silicium à l'aide d'une colle isolante et du même composant avant report sur substrat silicium. L'anode et le substrat sont reliés à la masse                                                   | 87       |

| 78 | Motif PS SG2 pour la mesure de la résistance thermique du canal du transistor observé au microscope optique                                                                                                                                                                  | 90       |

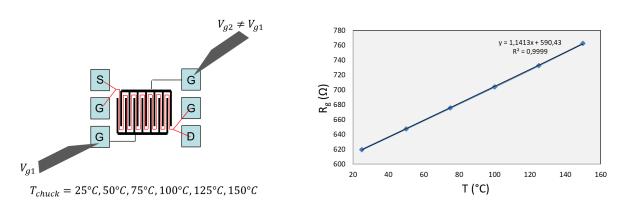

| 79 | A gauche : positionnement des pointes lors de l'étalonnage entre la résistance de la grille $R_g$ et la température du plateau du banc de mesure $T_{chuck}$ . A droite : courbe d'étalonnage $R_g(T)$ ainsi obtenue                                                         | 91       |

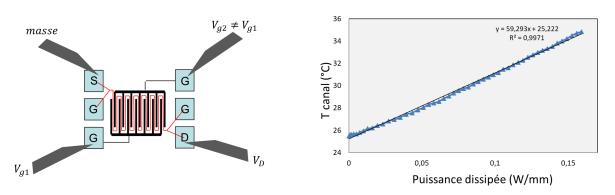

| 80 | A gauche : positionnement des pointes lors de la mesure de la résistance thermique du canal $R_{th}$ . A droite : évolution de la température du canal en fonction de la                                                                                                     |          |

| 81 | puissance dissipée $P$ pour un motif PS SG2 donné                                                                                                                                                                                                                            | 91<br>93 |

| 82 | Banc de caractérisation Signatone WL 350 équipé d'une caméra infrarouge InSb                                                                                                                                                                                                 |          |

|    | pour les mesures de température                                                                                                                                                                                                                                              | 94       |

| 83 | Exemple arbitraire d'une caractérisation thermique d'un composant avec l'approche standard. L'image (a) présente le principe de la mesure : des acquisitions de température sont effectuées avec un pas de temps limité à 10 ms. L'image (b) présente une courbe de température que l'on peut obtenir avec cette méthode : le pas minimum entre chaque acquisition n'est pas compatible pour voir avec précision l'évolution de la température.                                                                                                                                                                                                                             | 95  |

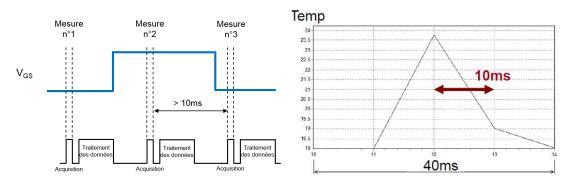

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

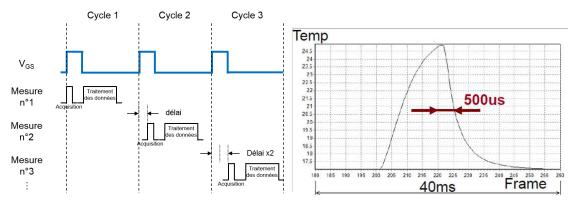

| 84 | Exemple arbitraire d'une caractérisation thermique d'un composant avec l'approche dite « trigger delay ». L'image (a) présente le principe de la mesure : une acquisition est effectuée à chaque cycle, chacune d'elle étant espacée de la précédente par un pas de temps fixe pour couvrir toute l'évolution de la température au cours d'un cycle. L'image (b) présente une courbe de température que l'on peut mesurer avec cette méthode : on obtient alors une évolution plus précise comparée à la méthode présentée précédemment (figure 83a).                                                                                                                       | 96  |

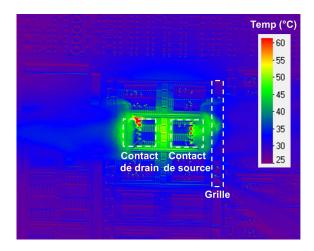

| 85 | Image thermique obtenue à l'aide d'un détecteur infrarouge sur un transistor HEMT polarisé à l'état passant. Les points à 60°C sur les pointes sont un artefact de mesure du au fait que ces dernières se sont légèrement décalées entre la calibration de la                                                                                                                                                                                                                                                                                                                                                                                                               |     |

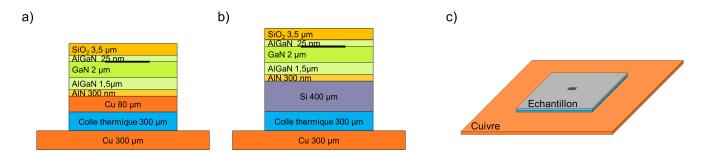

| 86 | caméra et la mesure.  Empilements utilisés lors des simulations sous COMSOL de dissipation thermique.  a) Empilement avec le substrat cuivre. b) Empilement avec le substrat silicium. c)  Vue 3D de l'ensemble. La zone sur laquelle est appliquée la puissance est symbolisée                                                                                                                                                                                                                                                                                                                                                                                             | 97  |

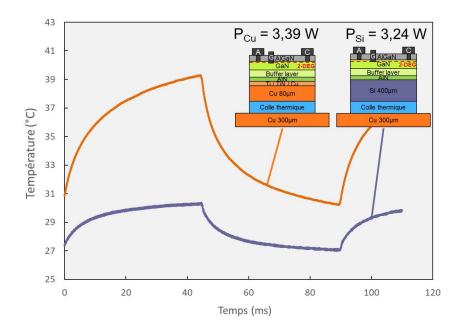

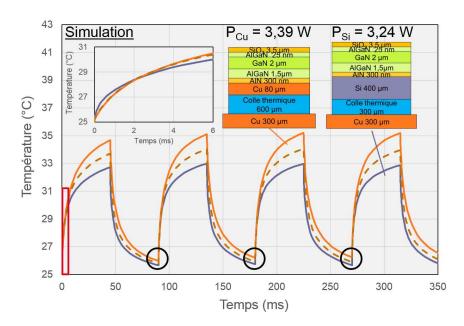

| 87 | par un trait noir dans les images a) et b) et par une surface noire dans l'image c). Evolution de la température de surface en fonction du temps pour des composants HEMTs sur substrat silicium et cuivre. Les composants ont été reportés sur une plaque en cuivre à l'aide d'une colle thermique. Une puissance de 3,39 $W$ et de 3,24 $W$ sont appliqués respectivement sur le composant sur substrat cuivre et silicium pendant 45 $ms$ pour une période de 90 $ms$ . Le pas de la mesure est de 5 $\mu s$ .                                                                                                                                                           | 98  |

| 88 | Simulation de l'évolution de la température de surface en fonction du temps pour des composants HEMTs sur substrat silicium et cuivre. La courbe en pointillés représente le cas du substrat cuivre avec la même épaisseur de colle thermique que celui du subtrat silicium. Le graphe supplémentaire représente un agrandissement de l'évolution de ces température de $0 \ ms$ à $2 \ ms$ et correspond à la zone encadrée en rouge sur les courbes. Une puissance de $3,39 \ W$ et de $3,24 \ W$ sont appliqués respectivement sur le composant sur substrat cuivre et silicium pendant $45 \ ms$ pour une période de $90 \ ms$ . Le pas de la mesure est de $5 \ \mu s$ |     |

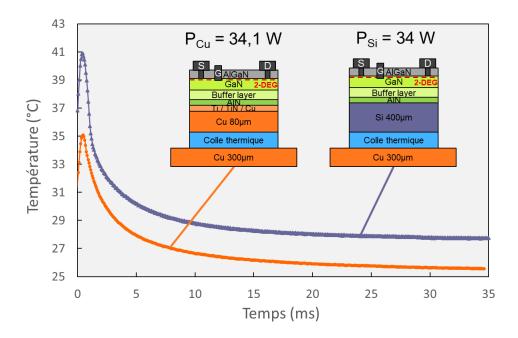

| 89 | Evolution expérimentales de la température de surface en fonction du temps pour des composants HEMTs sur substrat silicium et cuivre. Les composants ont été reportés sur une plaque en cuivre à l'aide d'une colle thermique. Une puissance de $34,1~W$ et de $34~W$ sont appliqués respectivement sur le composant sur substrat cuivre et sur substrat silicium pendant $1~ms$ pour une période de $150~ms$ . Le pas de la mesure est de $70~\mu s$                                                                                                                                                                                                                       | 101 |

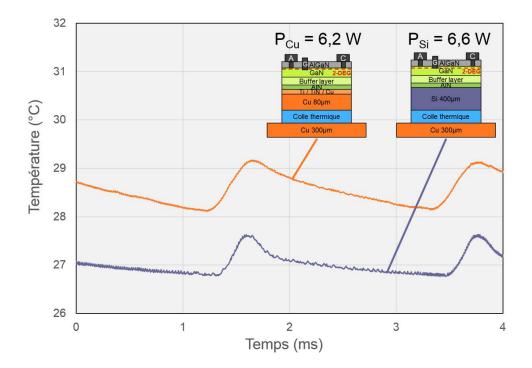

| 90 | Evolution de la température de surface en fonction du temps pour des composants HEMTs sur substrat silicium et cuivre. Les composants ont été reportés sur une plaque en cuivre à l'aide d'une colle thermique. Une puissance de $6,2~W$ et de $6,6~W$ sont appliqués respectivement sur le composant sur substrat cuivre et sur substrat silicium pendant $500~\mu s$ pour une période de $2~ms$ . Le pas de la mesure est                                                                                                                                                                                                                                                 |     |

|    | de 5 $\mu s$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 102 |

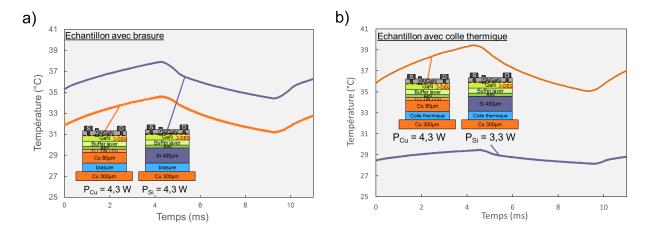

| 91 | a) Evolution expérimentale de la température de surface en fonction du temps pour                  |

|----|----------------------------------------------------------------------------------------------------|

|    | des composants HEMTs sur substrat silicium et cuivre. Les composants ont été re-                   |

|    | portés sur une plaque en cuivre à l'aide d'une brasure. Une puissance de $4,3~W$ est               |

|    | appliquée sur les composants sur substrat cuivre et sur substrat silicium pendant                  |

|    | $5 ms$ pour une période de $10 ms$ . Le pas de la mesure est de $5 \mu s$ . b) Evolution expé-     |

|    | rimentales de la température de surface en fonction du temps pour des échantillons                 |

|    | reportés sur une plaque en cuivre à l'aide d'une colle thermique pour établir une                  |

|    | comparaison. Une puissance de $4,3~W$ et de $3,3~W$ sont appliquées respectivement                 |

|    | sur le composant sur substrat cuivre et sur substrat silicium                                      |

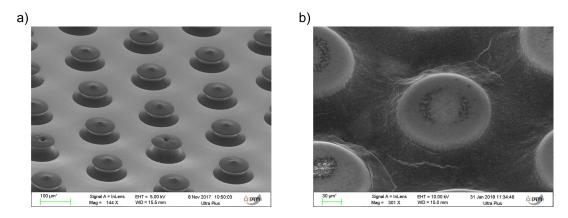

| 92 | a) Observation au MEB de forêts de nanotubes de carbone d'environ 50 $\mu m$ de                    |

|    | hauteur b) Observation au MEB des mêmes forêts de nanotubes de carbone que sur                     |

|    | l'image a) sur lesquels a été réalisé une ECD de cuivre                                            |

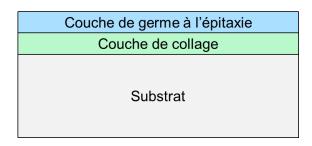

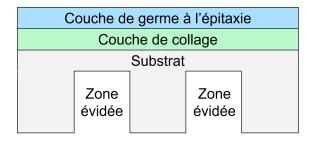

| 93 | Vue schématisée en coupe d'un substrat multicouches                                                |

| 94 | Vue schématisée en coupe de la structure simulée                                                   |

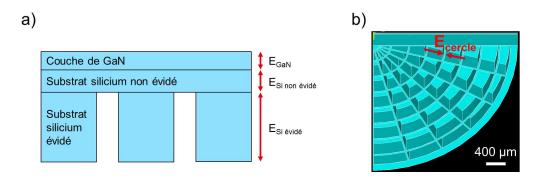

| 95 | a) Vue schématisée en coupe de la structure simulée. b) Vue de dessous d'un substrat               |

|    | évidé simulé. La distance $E_{cercle}$ désigne l'épaisseur des parois circulaires non évidées. 111 |

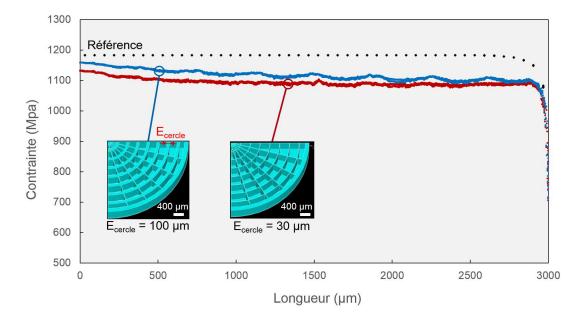

| 96 | Evolution de la contrainte dans la couche de GaN en fonction de la position pour un                |

|    | évidement en motif circulaire. L'épaisseur des cercles non évidés est variable dans                |

|    | ces simulations                                                                                    |

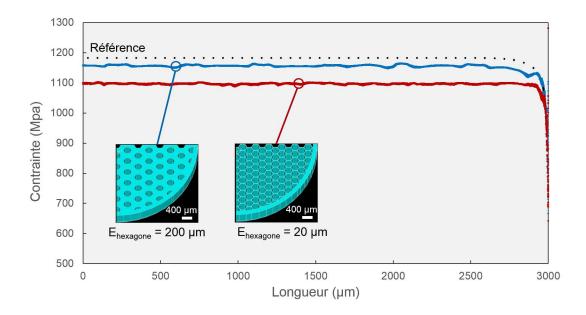

| 97 | Evolution de la contrainte dans la couche de GaN en fonction de la position pour                   |

|    | un évidement en nid d'abeille. L'épaisseur des parois non évidées des hexagones est                |

|    | variable dans ces simulations                                                                      |

| 98 | Face arrière d'une plaque silicium de diamètre 100 $mm$ et d'épaisseur 525 $\mu m$ évidée          |

|    | selon des motifs hexagonaux                                                                        |

# Introduction générale

L'électronique de puissance est une branche de l'électronique ayant une grande importance dans de nombreux domaines d'applications comme l'automobile ou encore l'électroménager. Son objectif est la conversion de l'énergie électrique et elle possède différents enjeux dont on peut citer par exemple les performances, l'efficacité énergétique, l'encombrement ou encore la fiabilité. A l'heure actuelle, ce marché est dominé par les composants à base de silicium. Cependant, de nouveaux matériaux comme la carbure de silicium (SiC) ou le nitrure de gallium (GaN) ont récemment émergé grâce à leurs propriétés physiques intéressantes pour les applications de puissance. Dans ce manuscrit, nous nous concentrerons sur les composants à base de GaN.

Ces composants sont principalement fabriqués sur des substrats d'un matériau différent du nitrure de gallium. En effet, les substrats massifs de GaN sont coûteux et ne sont pas disponibles en grandes dimensions dans le commerce. Parmi les matériaux utilisés pour servir de substrat au GaN, on peut citer notamment le SiC, le nitrure d'aluminium (AlN), le saphir  $(Al_2O_3)$  ou encore le silicium (Si). Dans le cadre de cette thèse, nous avons travaillé avec des transistors HEMTs et des diodes Schottky en GaN sur substrat silicium de diamètre 200 mm. Ces composants ont été fabriqués au sein du CEA-Leti et reflètent la ligne stratégique du Leti à savoir de travailler avec des composants en nitrure de gallium sur substrat silicium pour l'électronique de puissance.

La fabrication de ces composants passe par une étape d'épitaxie des couches actives suivie des procédés de réalisation des composants (implantation, métallisation, etc..). De manière générale, l'utilisation d'un substrat différent du matériau GaN entraîne différentes problématiques au niveau de l'épitaxie liées aux désaccords de maille et de dilatation thermique entre les deux matériaux. De plus, le substrat utilisé peut impacter les performances électriques des composants au niveau de la dissipation thermique ou encore de la tenue en tension. Différentes approches ont été étudiées pour apporter des solutions à ces problématiques. Parmi elles, nous nous pencherons dans ce manuscrit sur des solutions « substrat », autrement dit sur des approches qui s'appuient sur l'utilisation de substrats adaptés pour l'épitaxie et/ou pour les performances des composants. Dans la littérature, dans le cas des performances électriques des composants par exemple, les solutions adoptées ne résolvent généralement qu'une seule de ces problématiques (dissipation thermique par exemple) sans nécessairement améliorer ou mettre en avant l'impact sur les autres aspects (par exemple la tenue en tension). De plus, nous nous concentrerons dans ce manuscrit à la recherche de solutions « substrat » compatibles avec le substrat silicium et utilisant des procédés compatibles avec des substrats de grande dimension ( $\geq 200 \ mm$  de diamètre).

Le chapitre 1 présentera dans un premier temps les raisons pour lesquelles le nitrure de gallium a émergé en tant que candidat pour l'électronique de puissance. Les différentes solutions au niveau du substrat étudiées dans la littérature pour répondre aux problématiques de performances de composants et d'épitaxie seront présentées. Enfin nous conclurons ce chapitre en présentant

l'approche retenue durant cette thèse.

Dans le chapitre 2, nous présenterons l'approche que nous avons choisie pour tenter d'améliorer les performances électriques des composants. Celle-ci consiste, à partir des composants que nous avions à disposition, à remplacer le substrat silicium de fabrication par un substrat cuivre dans le but d'améliorer la dissipation thermique des composants. Nous présenterons ainsi dans ce chapitre les procédés technologiques qui ont été mis en place afin de réaliser ce changement de substrat. Nous nous pencherons également sur les impacts de ces procédés ainsi que du remplacement du substrat silicium par un autre matériau (notamment du cuivre) sur les caractéristiques électriques des composants.

Dans le chapitre 3, nous nous intéresserons à la dissipation thermique des composants reportés sur cuivre. Nous étudierons, à l'aide de mesure par caméra infra-rouge, l'échauffement de ces composants en commutation dans le but de comparer des composants sur substrat silicium avec des composants reportés sur substrat cuivre. Nous mettrons en place des simulations par éléments finis à l'aide du logiciel COMSOL afin d'apporter des interprétations sur les phénomènes expérimentaux observés.

En annexe de ce manuscrit, nous présenterons également une approche substrat innovante pour l'épitaxie qui a été étudiée dans le but de proposer une approche permettant d'utiliser des substrats molybdène et tungstène qui ne pourraient normalement pas être utilisables tels quels en grandes dimensions du fait de leur masse volumique importante. Nous avons choisi de concentrer la présentation écrite de ces travaux de thèse sur le report de composants plutôt que sur cette approche, qui s'est avérée plus compliquée à mettre en place qu'initialement prévu. C'est la raison pour laquelle ces travaux ne seront présentés qu'en annexe.

# Chapitre 1

# Contexte et pré-requis

# Sommaire

| Somman | C              |                                                                      |    |

|--------|----------------|----------------------------------------------------------------------|----|

| 1.1    | Con            | texte de l'électronique de puissance                                 | 18 |

|        | 1.1.1          | L'électronique de puissance $\dots$                                  | 18 |

|        | 1.1.2          | Emergence du carbure de silicium SiC et du nitrure de gallium GaN $$ | 20 |

|        | 1.1.3          | Exemple du transistor HEMT à base de GaN                             | 22 |

| 1.2    | Limi           | itations du substrat pour l'épitaxie de GaN                          | 29 |

|        | 1.2.1          | Méthode de croissance                                                | 30 |

|        | 1.2.2          | Contraintes liées à l'hétéroépitaxie                                 | 30 |

|        | 1.2.3          | Substrats d'épitaxie                                                 | 32 |

| 1.3    | Limi           | itations des performances dues au substrat                           | 36 |

|        | 1.3.1          | Aspect thermique                                                     | 36 |

|        | 1.3.2          | Aspect tenue en tension                                              | 44 |

| 1.4    | $\mathbf{App}$ | roches adoptées lors de la thèse                                     | 48 |

|        |                |                                                                      |    |

# 1.1 Contexte de l'électronique de puissance

# 1.1.1 L'électronique de puissance

De nombreuses applications, comme l'automobile, l'électroménager ou encore les ordinateurs portables, nécessitent une énergie électrique pour fonctionner. Cette énergie peut être fournie à ces systèmes sous une forme (continue ou alternative) différente de celle dont ils ont besoin pour fonctionner. Il faut donc passer par une étape de conversion. Par exemple, un ordinateur portable fonctionnant avec une énergie électrique sous forme continue aura besoin d'un adaptateur pour être branché sur le secteur (forme alternative). C'est dans ce domaine qu'intervient l'électronique de puissance : elle consiste en la conversion de l'énergie électrique en veillant notamment à limiter les pertes de conversion. Elle traite de différents domaines tels que l'électronique grand public, le photovoltaïque ou encore l'automobile. Chacune de ces applications a des exigences différentes en termes de puissance ou de fréquence, qui sont atteintes par différents composants tels que présentés sur la figure 1. Par exemple, les composants de type MOSFET vont adresser des applications (comme l'automobile) nécessitant un fonctionnement à faible puissance (inférieure ou de l'ordre de 10 kW) et à grande fréquence (de l'ordre 100 kHz). Ce marché de l'électronique de puissance est principalement dominé par les composants silicium de type MOSFET, IGBT, etc. Mais comme nous le verrons plus en détail par la suite, de nouveaux matériaux émergent en tant que concurrents potentiels au silicium.

FIGURE 1 – Différents domaines d'applications des composants de puissance en 2005 [1].

Avant de détailler plus précisément le principe de fonctionnement de certains composants de puissance et de comprendre les exigences associées à ces composants, nous allons présenter rapidement la manière dont ils sont utilisés en électronique de puissance. Ce domaine s'appuie sur le principe du découpage temporel. Pour en présenter de manière simplifiée le principe, prenons le cas où nous désirons abaisser la tension continue d'une source pour qu'elle soit adaptée à la tension d'utilisation d'une charge (convertisseur DC/DC). Soit une source de tension continue de

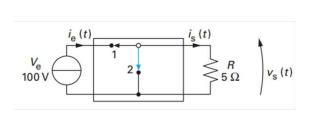

$V_e = 100V$  qui doit fournir en énergie une charge résistive R, tel qu'illustré sur l'image de gauche de la figure 2. L'idée consiste à commuter de manière cyclique un interrupteur entre les états 1 et 2 présentés dans la figure. Dans l'état 1, la source transmet l'énergie à la charge résistive. Dans l'état 2, il n'y a pas d'énergie transmise. Il s'agit d'une phase de roue libre permettant d'assurer la continuité du courant dans la charge et ainsi d'éviter les surtensions dans le cas d'une charge inductive où on a  $(V_s$  et  $I_s$  sont respectivement la tension à ses bornes (en Volt) et le courant (en Ampère) et L son inductance (en Henry)):

$$V_s = L \frac{dI_s}{dt} \tag{1.1}$$

La charge résistive voit ainsi soit une tension égale à  $V_e$  dans l'état 1 soit une tension nulle dans l'état 2 tel que montré dans l'image de droite de la figure 2. Globalement, la charge voit une valeur moyenne comprise entre 0 et  $V_e$  et qui dépend de la durée  $\alpha T_{cycle}$  de l'état 1,  $\alpha$  étant le rapport cyclique du système. Il est donc possible de choisir une tension ciblée en prenant un rapport  $\alpha$  adapté. En réalité, la mise en oeuvre de cette méthode est plus compliquée que telle qu'elle vient d'être décrite. Par exemple, la charge peut ne pas accepter des grandeurs hachées, nécessitant un filtre passe-bas LC en sortie du convertisseur pour lisser la tension. La tension d'entrée et les caractéristiques des composants du convertisseur peuvent varier, imposant l'utilisation d'un système de correction qui régule la tension en sortie en modifiant le rapport cyclique de commutation  $\alpha$ .

FIGURE 2 – A gauche : circuit simplifié illustrant le principe du découpage temporel à l'aide d'un interrupteur à deux pôles, commutant entre les positions 1 et 2. A droite : variation de la tension aux bornes de la charge résistive en fonction du temps et montrant l'impact des commutations de l'interrupteur [2].

Il est intéressant pour la suite de retenir du paragraphe précédant que les transistors de puissance doivent donc jouer le rôle d'interrupteurs de puissance qui commutent entre deux états :

- un état passant où le composant doit laisser passer le courant avec une faible résistance

- un état bloqué où le composant ne doit pas laisser passer le courant malgré une forte différence de potentiel appliquée à ses bornes

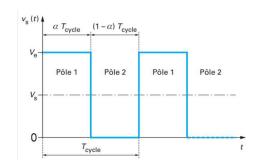

Afin de mieux comprendre ces exigences pour les composants de puissance, nous allons nous intéresser au cas du transistor MOSFET (pour « Metal Oxide Semiconductor Field Effect Transistor » en anglais). Il s'agit d'un transistor à effet de champ constitué d'un contact de source, d'un contact de drain et d'une grille (comme représenté schématiquement dans la figure 3). Il peut être qualifié de NMOS (PMOS) si les porteurs assurant le passage du courant sont des électrons (trous).

L'effet transistor est obtenu en appliquant un potentiel sur la grille ce qui permet de moduler de façon électrostatique la densité de charge dans le canal. En effet, dans le cas d'un canal d'inversion (ou canal surfacique) représenté sur la figure 3 et pour un NMOS, polariser positivement la grille revient à créer un canal de conduction rempli d'électrons mobiles sous la grille (donc de type de porteur opposé aux porteurs majoritaires du substrat), permettant ainsi le passage du courant entre la source et le drain (pour une tension  $V_{DS}$  entre source et drain positive). On peut alors définir la notion de résistance à l'état passant, qui correspond à la résistance que va opposer le canal au passage du courant. Inversement, s'il n'y a pas de canal créé, le courant ne peut pas passer entre la source et le drain et on a un état bloqué. Dans la réalité, des courants de fuites indésirables peuvent passer entre la source et le drain à l'état bloqué, et on parle alors de tenue en tension des composants pour quantifier l'importance de ces fuites de courants.

FIGURE 3 – Structure et symbole d'un transistor NMOS à canal d'inversion [3].

# 1.1.2 Emergence du carbure de silicium SiC et du nitrure de gallium GaN

Comme il a été énoncé précédemment, un transistor de puissance alterne entre des états passants (caractérisés par la résistance à l'état passant  $R_{ON}$ ) et des états bloqués (caractérisés par la tenue en tension des composants).

A l'état passant, la résistance  $R_{ON}$  va induire des pertes par effet Joule en conduction impactant directement le rendement de conversion que l'on veut le plus élevé possible. Il est donc intéressant, pour des applications de puissance, d'avoir des composants avec un  $R_{ON}$  le plus faible possible.

A l'état bloqué, le transistor ne doit pas laisser de courant passer entre la source et le drain. Le dimensionnement des composants est ainsi réalisé pour avoir une tenue en tension compatible avec les applications de puissance visées et dépend directement des propriétés physiques des matériaux utilisés.

Nous avons ainsi des critères permettant de comparer des composants fabriqués à partir de différents matériaux. Nous nous intéressons ici au cas de composants en silicium (Si), carbure de silicium (SiC) et en nitrure de gallium (GaN). La figure 4 présente la résistance spécifique (résistance à l'état passant multipliée par la section de passage du courant) en fonction de la tension de claquage dans le cas de composants unipolaires réalisés à partir de Si, de SiC et de GaN. Pour réduire les pertes en conduction et avoir des composants qui tiennent la tension, il faut donc être dans la zone « en bas à droite » du graphe (i.e. avoir une faible résistance spécifique et une tension de claquage importante). On voit ainsi que les matériaux SiC et GaN présentent une limite théorique plus intéressante pour l'électronique de puissance que le Si.

FIGURE 4 – Résistance spécifique en fonction de la tension de claquage pour le Si, le SiC (4H) et le GaN à température ambiante.

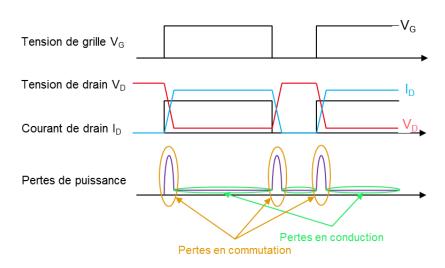

Durant le fonctionnement des composants, il existe d'autres types de pertes que celles de conduction à l'état passant présentées précedemment. En effet, les transistors doivent alterner entre les états passants et bloqués (figure 5). Lors de ces transitions, le courant et la tension aux bornes du transistor ne sont pas simultanément nuls d'où une perte par effet Joule. Il est possible de diminuer ces pertes en ayant une vitesse de commutation la plus grande possible. La mobilité électronique et la vitesse de saturation des électrons deviennent alors des critères pour qualifier la capacité à monter en fréquence pour un matériau donné. Le tableau 1 présente ces valeurs dans le cas du Si, SiC, GaN et du diamant. On voit ainsi que le GaN et le SiC se démarquent du Si de par leurs valeurs élevées de mobilité et de vitesse de saturation des électrons.

FIGURE 5 – Pertes en conduction et en commutation d'un transistor de puissance.

De plus, les composants d'électronique de puissance font passer une grande énergie en fonctionnement. Une partie de cette énergie est dissipée par effet Joule dans le composant, induisant un fonctionnement à haute température. Il est important, pour des raisons de fiabilité et de performances, qui seront détaillées par la suite, de limiter cette température, et donc d'utiliser des matériaux qui ont une bonne conductivité thermique, ce qui est le cas du SiC et encore plus du diamant.

| Matériaux                                    | Si        | 4H-SiC   | GaN                                  | Diamant |

|----------------------------------------------|-----------|----------|--------------------------------------|---------|

| Energie de bande interdite (eV)              | 1,12      | 3,26     | 3,39                                 | 5,47    |

| Champ de claquage (MV/cm)                    | 0,3       | 3        | 3,3                                  | 10      |

| Mobilité électronique $(cm^2/(V.s))$         | 1430 [22] | 950 [23] | bulk : 900 [24]<br>2-DEG : 2000 [25] | 1000    |

| Conductivité thermique (W/(cm.K))            | 1,5       | 3,8      | 1,3                                  | 20      |

| Vitesse de saturation (10 <sup>7</sup> cm/s) | 1         | 2        | 3                                    | 1,1     |

Tableau 1 – Propriétés physiques intrinsèques du Si, 4H-SiC et GaN à température ambiante.

On constate que le diamant est le matériau le plus intéréssant pour l'électronique de puissance. Des composants ont déjà été réalisés à partir de ce matériau [26] [27]. Cependant, les dimensions des substrats en diamant disponibles restent assez limitées. De nombreuses recherches ont donc également été réalisées sur les matériaux SiC et GaN. Dans cette thèse, nous nous concentrons exclusivement sur les composants en GaN qui se démarquent de ceux réalisés en SiC par leur gaz bidimensionnel d'électrons (détaillé dans la suite) qui possède à la fois une forte densité électronique et une valeur de mobilité électronique élevée.

# 1.1.3 Exemple du transistor HEMT à base de GaN

### Principe de fonctionnement :

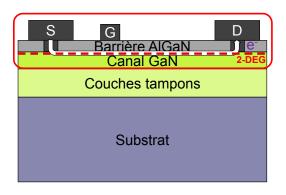

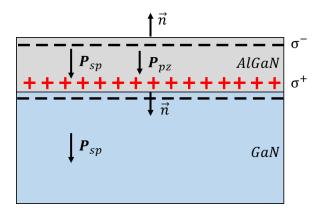

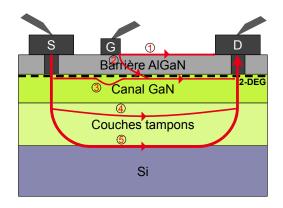

Un HEMT (pour High Eletron Mobility Transistor en anglais) AlGaN/GaN est un transistor constitué d'une grille de type schottky ou MIS (métal isolant semiconducteur) et de deux contacts ohmiques (le drain et la source) tel qu'il est schématisé sur la figure 6. Ces composants sont fabriqués à base de GaN épitaxié sur divers substrats. Ce substrat peut être du GaN massif ( $\leq 50~mm$  dans le commerce), mais également du SiC ( $\leq 150~mm$ ) ou encore du Si ( $\leq 300~mm$ ). Des couches tampons sont présentes afin de permettre une épitaxie des couches actives de bonne qualité et également pour isoler électriquement les composants du substrat. Le transistor en tant que tel ne consiste qu'en l'empilement entouré dans la figure 6 : il se caractérise par son hétérostructure AlGaN/GaN qui permet l'apparition d'un gaz bidimensionel d'électrons (2-DEG pour « two dimensional electron gas »en anglais) qui sert de canal au transistor. Ce gaz 2D d'électrons est la raison pour laquelle les composants GaN se démarquent en termes de performances pour des applications de puissance. Bien que les couches tampons et le substrat n'aient pas un rôle actif dans le fonctionnement du composant HEMT, les performances des composants vont être impactées en fonction des matériaux utilisés. Leurs impacts, et particulièrement ceux du substrat, seront étudiés dans cette thèse.

FIGURE 6 – Schéma en coupe d'un transistor HEMT à base de GaN. S représente la source, G la grille et D le drain. Le trajet des électrons lorsque le transistor est passant est représenté avec le trait en blanc.

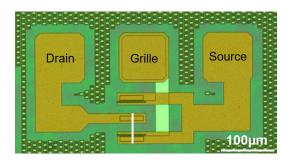

Le schéma en coupe présenté sur la figure 6 ne permet pas d'avoir une vue globale du transistor. En effet, ces composants ont également une dimension en largeur qui leur permet de délivrer des courants plus importants : on peut alors exprimer ce courant en A/mm en divisant le courant total par la largeur du transistor (nommée largeur de grille, notée  $W_g$  et exprimée en mm). La figure 7 présente une vue de dessus d'un transistor HEMT ayant une largeur de grille  $W_g = 100~\mu m$  observé au microscope optique. Le trait blanc permet de visualiser la localisation de la vue en coupe présentée à la figure 6.

FIGURE 7 – Vue de dessus d'un transistor HEMT observé au microscope optique. Le trait en blanc montre la localisation de la vue en coupe présentée sur la figure 6.

L'effet transistor est obtenu en appliquant un potentiel sur la grille. Si cette tension est inférieure à une tension de seuil notée  $V_{th}$ , le gaz 2D d'électrons va être déplété sous la grille, empêchant le courant de passer entre la source et le drain. On parle alors d'état bloqué. La tenue en tension est alors assurée principalement par la zone entre la grille et le drain, expliquant la distance grille-drain bien supérieure à la distance source-grille comme illustré sur la figure 6. A l'inverse, une tension de grille supérieure à  $V_{th}$  permettra au transistor d'être à l'état passant. La figure 8 présente des caractéristiques électriques en statique d'un transistor HEMT AlGaN/GaN ayant une largeur de grille  $W_g = 100 \ \mu m$ , une longueur de grille  $L_g = 1 \ \mu m$  et une distance grille-drain  $L_{gd} = 15 \ \mu m$ . La figure 8.a) présente le courant de drain  $I_{DS}$  en fonction de la tension de drain  $V_{DS}$  pour différentes polarisations de grille  $V_{DS}$ . Le courant  $I_{DS}$  passe par un régime transitoire en fonction de la tension de drain pour arriver ensuite à un régime de saturation (ce régime de saturation est atteint pour les courbes avec une tension de grille  $V_{GS} < 5 \ V$  sur la caractéristique de la figure 8.a) ). De plus, aucun courant ne circule dans le transistor pour une tension  $V_{GS}$  égale à 0 V, ce qui n'est pas le cas pour  $V_{GS} = 1,25 \ V$ , indiquant une tension de seuil  $V_{th}$  positive (ce qui est confirmé par la

figure 8.b) qui représente l'évolution du courant  $I_{DS}$  en fonction de la tension  $V_{GS}$ ). On parle alors de transistors « normally-off ».

FIGURE 8 – Caractéristiques électriques d'un transistor HEMT normally-off GaN sur substrat silicium  $(L_g/W_g/L_{gd}=1/100/15~\mu m)$ . a) Courbes  $I_{DS}(V_{DS})$  pour différentes tensions de grille  $V_{GS}$ . b) Courbes  $I_{DS}(V_{GS})$  pour une tension de drain  $V_{DS}=0,1~V$ .

Sans procédé technologique particulier, la tension de seuil d'un transistor HEMT AlGaN/GaN est négative, ce qui signifie que le transistor est à l'état passant lorsqu'aucune tension n'est appliquée sur la grille, on parle de transistor « normally-on ». Pour des raisons de sécurité dans les circuits de conversion utilisés, il est préférable de travailler avec des transistors « normally-off ». De nombreuses études ont donc été réalisées afin de rendre ces transistors « normally-off » : on peut citer par exemple l'utilisation d'une fine couche barrière d'AlGaN [28], le rajout d'une couche d'AlGaN dopé p au niveau de la grille (ce type de transistor est alors appelé « gate injection transistor » en anglais) [29], l'utilisation d'une couche de GaN dopé p sous la grille [30] ou encore la gravure localisée de la couche barrière d'AlGaN pour que la grille coupe le gaz 2D d'électrons (« gate recess » en anglais) [31] [32]. C'est cette dernière méthode qui est utilisée sur les transistors « normally-off » étudiés dans cette thèse. Une vue en coupe d'une telle grille est présentée sur la figure 9. Pour ces transistors, une gravure de  $10 \ nm$  a été réalisée dans le GaN.

FIGURE 9 – Vue en coupe d'une grille avec une structure en « gate recess ».

# Effet de current collapse :

Nous allons détailler dans cette partie et la suivante des mécanismes de piégeages se produisant dans les composants GaN. Le premier d'entre eux est le « current collapse » (que l'on peut traduire

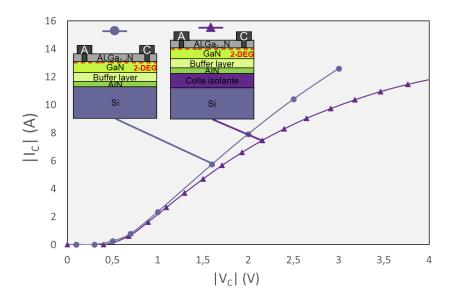

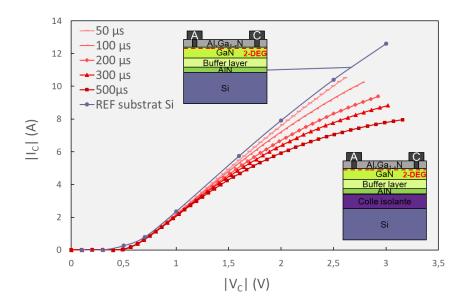

par « effondrement du courant » en français). Ce phénomène se caractérise par une réduction du courant à l'état passant suite à l'application d'un fort potentiel à l'état bloqué sur le drain pour un transistor ou sur la cathode pour une diode. Cet état bloqué va provoquer un piégeage d'électrons issus du canal dans les couches buffers [33] et/ou dans la barrière [34]. Ces électrons piégés, appelés « électrons chauds », vont dépléter le canal ce qui va provoquer une baisse du courant de drain à l'état passant. La figure 10 présente un exemple de cet effet mesuré électriquement sur des composants HEMTs GaN sur substrat silicium. Les courbes  $I_{DS}(V_{DS})$  à l'état passant d'un transistor HEMT sont tracés pour différentes valeurs de la tension de grille  $V_{GS}$  pour un même transistor avant stress (triangles) et après stress (i.e. après passage du transistor à l'état bloqué, ronds). On observe bien une diminution de la valeur du courant à cause de l'effet de current collapse.

FIGURE 10 – Illustration de l'effet de current collapse pour un transistor 10A. Un premier réseau I(V) est tracé pour différentes tensions de grille (ici sont représentées les courbes pour  $V_{GS} = 2V; 4V; 6V$ . La condition de stress est réalisée sous  $V_{GS} = -4 V$  et pour  $V_{DS}$  allant de 0V à 450V sont appliquées (non représentée ici)

#### Effet Kink:

L'effet Kink est un phénomène observé à l'état passant des transistors HEMTs à base de GaN. Il se traduit par une augmentation rapide du courant de drain à faible  $V_{DS}$ . La figure 11 présente cet effet sur une caractéristique  $I_{DS}(V_{DS})$  d'un transistor HEMT à base de GaN. Les caractéristiques en lignes continues présentent les courbes avec l'effet Kink alors que celles en pointillés présentent les courbes « standard ». En réalité, il s'agit d'une réduction du courant de drain à faible valeur de  $V_{DS}$  causée par un piégeage d'électrons dans la couche buffer de GaN réduisant ainsi la densité du gaz 2D d'électrons [4]. Pour une tension  $V_{DS}$  de l'ordre d'une valeur nommée  $V_{kink}$  (illustrée par les carrés dans la figure 11), un dépiégeage de ces électrons se produit et le courant augmente ainsi pour retrouver sa valeur « normale ».