## Impact of 14/28nm FDSOI high-k metal gate stack processes on reliability and electrostatic control through combined electrical and physicochemical characterization techniques

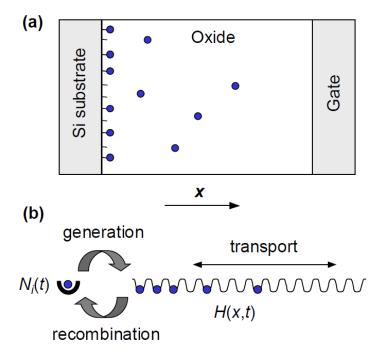

Pushpendra Kumar

## ▶ To cite this version:

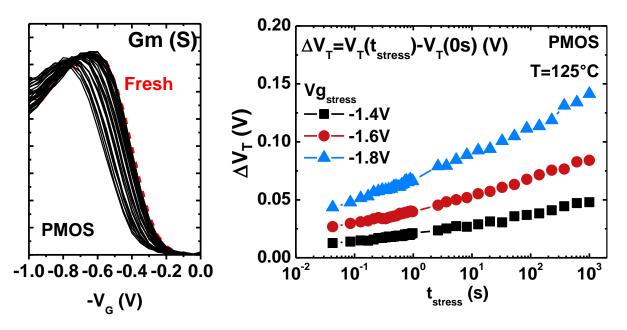

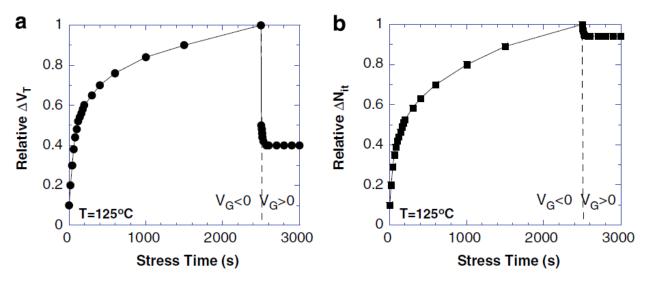

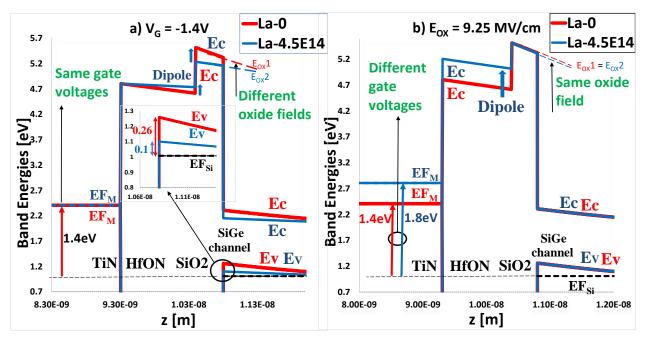

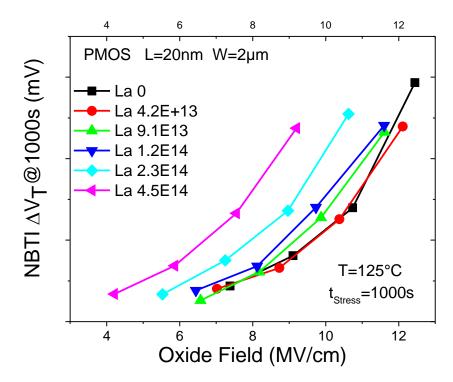

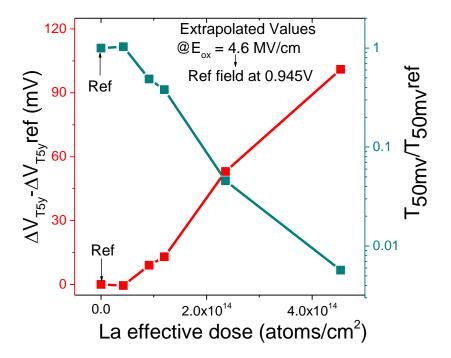

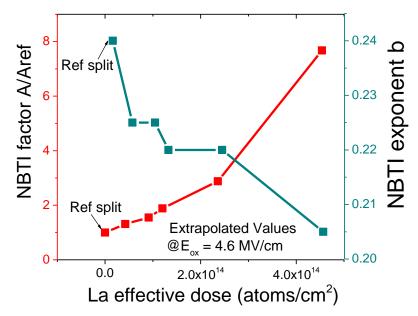

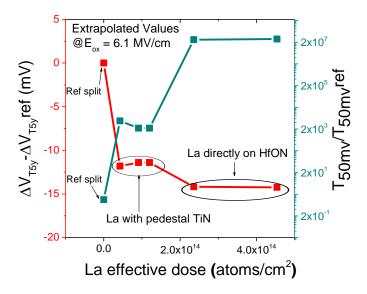

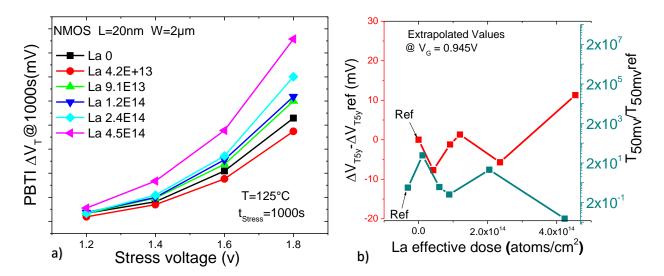

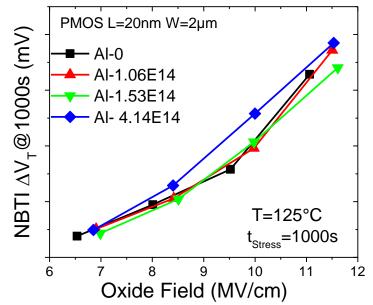

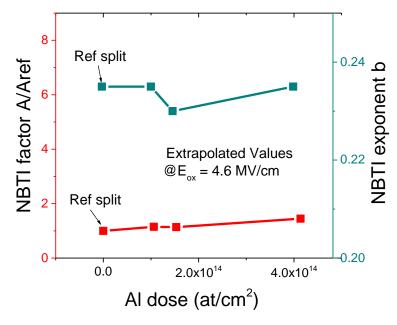

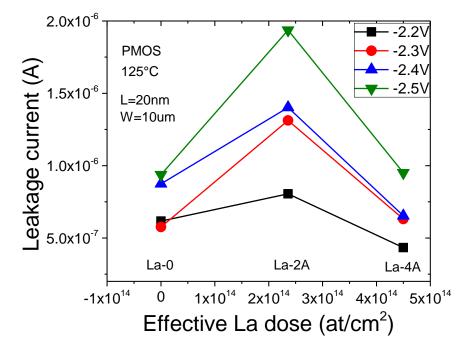

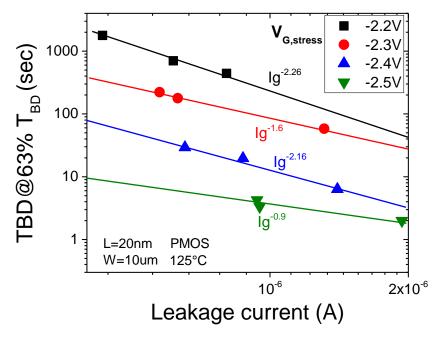

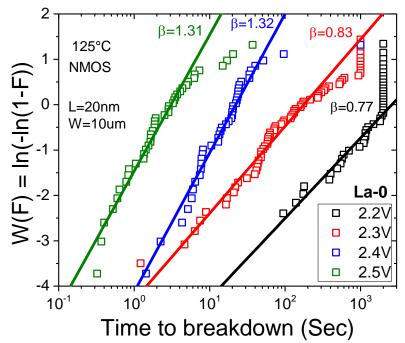

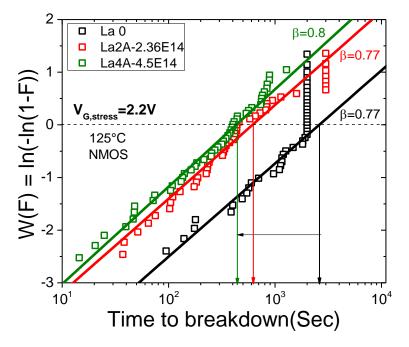

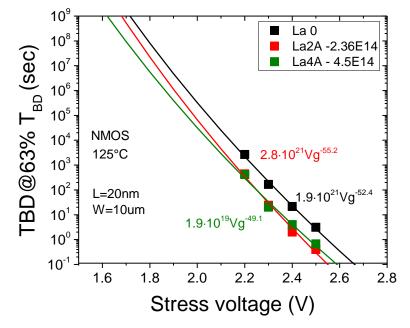

Pushpendra Kumar. Impact of 14/28nm FDSOI high-k metal gate stack processes on reliability and electrostatic control through combined electrical and physicochemical characterization techniques. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2018. English. NNT: 2018GREAT114. tel-02169583

## HAL Id: tel-02169583 https://theses.hal.science/tel-02169583

Submitted on 1 Jul 2019

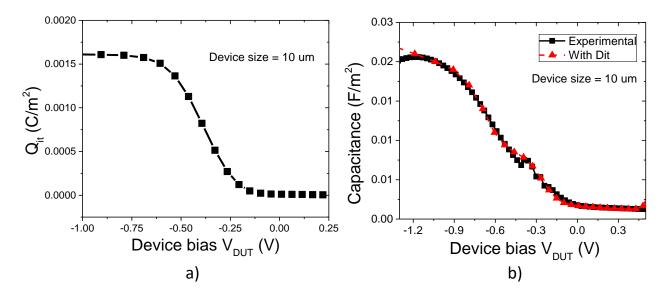

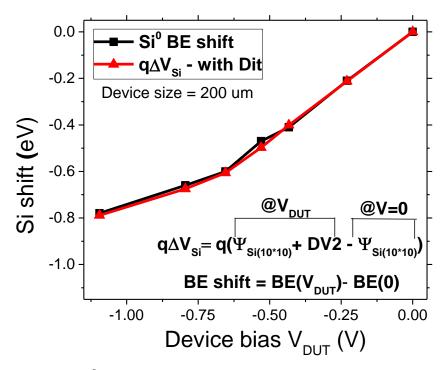

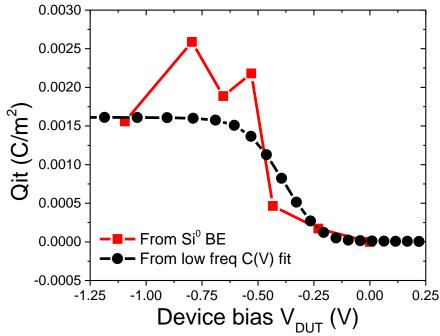

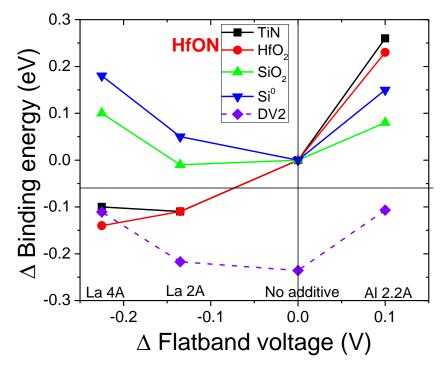

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Communauté UNIVERSITÉ Grenoble Alpes

## THÈSE

Pour obtenir le grade de

## DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

### Spécialité : Nano électronique et nano technologie

Arrêté ministériel : 25 mai 2016

Présentée par

## Pushpendra KUMAR

Thèse dirigée par **Gérard GHIBAUDO** et codirigée par **Charles LEROUX et Florian DOMENGIE**

préparée au sein **de la société STMicroelectronics, du laboratoire** CEA-LETI (Grenoble) et de l'IMEP-LAHC dans l'École Doctorale EEATS

## Impact of 14/28nm FDSOI high-k metal gate stack processes on reliability and electrostatic control through combined electrical and physicochemical characterization techniques

Thèse soutenue publiquement le **19 décembre 2018**, devant le jury composé de :

Mme. Mireille MOUIS DR, CNRS-Grenoble, Président Mme. Nathalie Labat PR, laboratoire IMS, Rapporteur M. Brice GAUTIER PR, INSA-Lyon, Rapporteur M. Charles Leroux ING, CEA-LETI, Examinateur M. Florian Domengie ING, STMicroelectronics, Examinateur Mr Gérard Ghibaudo DR, CNRS Alpes, Directeur de thèse

## Acknowledgements

I would like to thank all the people and the various teams who have contributed to the work presented in this thesis.

First, I would like to thank my supervisors Charles Leroux from CEA-LETI, Florian Domengie from STMicroelectronics, and my PHD director Gerard Ghibaudo from IMEP. Charles helped in building well-planned experiments and their timely completion, his valuable experience and knowledge of device physics and electrical characterization greatly helped in obtaining new and interesting results. Florian's knowledge and experience in process development helped greatly in device fabrication and building of new process for its performance improvements. Gerard's valuable advices and continuous support helped build a well-planned work and this thesis.

Secondly, I would like to thank the Metal R&D/Engineering/Hardware team of STMicroelectronics, with whom I spent half of my time during the PHD thesis. The team helped in device fabrication and in performing some non-standard process steps which were challenging. I would also like to thank the laboratory of electrical characterization (LCTE) of CEA-LETI, where I spent the other half of my thesis, for its help in electrical characterization and device reliability.

Next, I would like to thank the various process development, process integration and physical characterization teams of STMicroelectronics and CEA-LETI, who helped in some way in performing experiments and analysis for this work: Kristell Courouble (high-k), Fabien Deprat (SiGe), Côme de buttet (WET), Yann Escarabajal (Wet), Olivier Gourhant (DIA), Bilel saidi (TT), Francesco Abbate (XRR), Denis Combe (Metal), Delphine Doloy (XRF), Denis Guiheux (XPS), A.Roland, N.Miguel (TEM), Alexia Valery (ASTAR), Patrice Gergaud (XRD), Eugenie Martinez (XPS), Yves Morand, Jean-Michel pedini, Nils Rambal, Claude Tabone. I would like to specially thank Eugenie Martinez from CEA-LETI for her support and contribution in the development of XPS under bias technique.

Lastly, I would like to thank Carlos Suarez-Segovia and Sylvian Baudot, who worked on the development of the sacrificial gate process using which additives were introduced in the devices used in this work.

| General introduction |                                                            |    |  |  |  |

|----------------------|------------------------------------------------------------|----|--|--|--|

| Context              |                                                            | 7  |  |  |  |

| Thesis o             | bjectives and outline                                      | 8  |  |  |  |

| 1. Gate s            | stack technology for 14/28 nm FDSOI MOSFET devices         | 11 |  |  |  |

| 1.1 MC               | DSFET device                                               | 11 |  |  |  |

| 1.1.1                | MOSFET operation                                           | 11 |  |  |  |

| 1.1.2                | Metal-Oxide-Semiconductor gate stack properties            | 15 |  |  |  |

| 1.2 Gat              | te stack fabrication process                               | 19 |  |  |  |

| 1.2.1                | Gate dielectrics                                           | 19 |  |  |  |

| 1.2.2                | Metal gate electrode and deposition techniques             | 21 |  |  |  |

| 1.2.3                | Metal gate integration in 14 nm Fully-Depleted SOI devices | 29 |  |  |  |

| 1.2.4                | Introduction of additives for workfunction engineering     | 29 |  |  |  |

| 1.3 Pro              | cess flow                                                  | 33 |  |  |  |

| 1.3.1                | MOS transistor Process flow                                | 33 |  |  |  |

| 1.3.2                | Process flow simplification for MOS capacitor              | 34 |  |  |  |

| 1.3.3                | Beveled Interlayer Oxide                                   | 35 |  |  |  |

| 1.4 MC               | $GG$ induced $V_T$ variability                             | 36 |  |  |  |

| 1.5 MC               | DSFET reliability                                          | 39 |  |  |  |

| 1.5.1                | Bias temperature instability (BTI)                         | 39 |  |  |  |

| 1.5.2                | Time dependent oxide breakdown (TDDB)                      | 48 |  |  |  |

| 1.6 Co               | nclusion                                                   | 55 |  |  |  |

| 2. Chara             | cterization techniques for the gate stack                  | 56 |  |  |  |

| 2.1 Ele              | ctrical characterization                                   | 57 |  |  |  |

| 2.1.1                | CV measurements and electrical parameters extraction       | 57 |  |  |  |

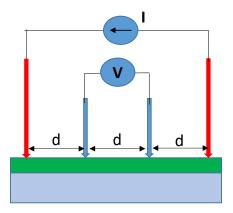

| 2.1.2                | Sheet resistance measurements by four probe method         | 62 |  |  |  |

| 2.2 Ph               | ysicochemical and Stress characterization                  | 63 |  |  |  |

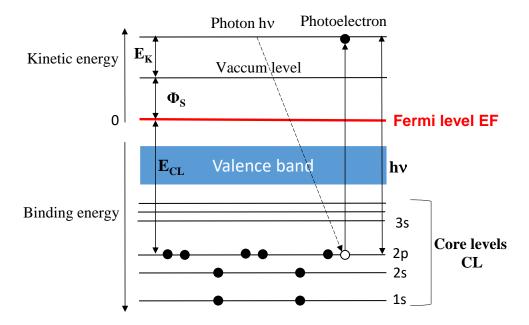

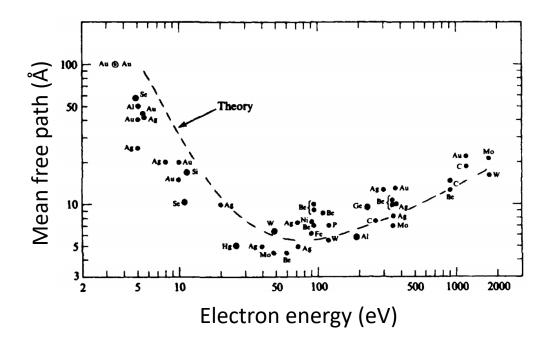

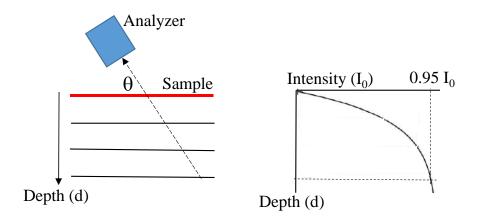

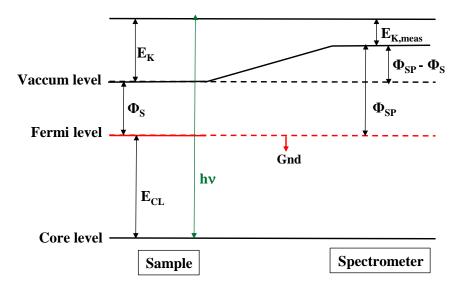

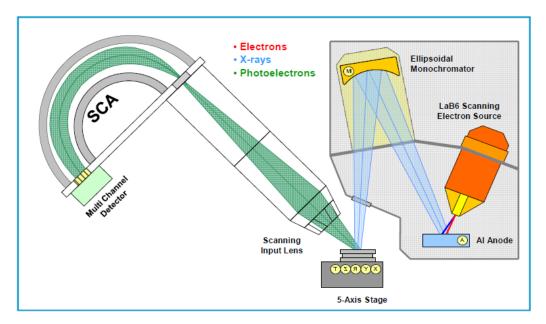

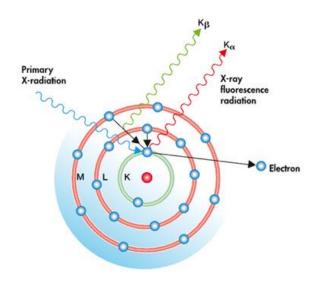

| 2.2.1                | X-ray Photoelectron Spectroscopy (XPS)                     | 63 |  |  |  |

| 2.2.2                | X-Ray Fluorescence (XRF)                                   | 70 |  |  |  |

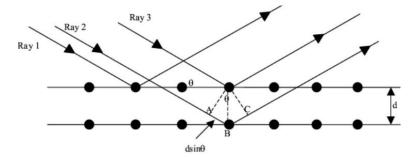

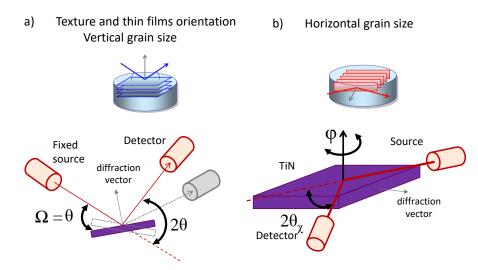

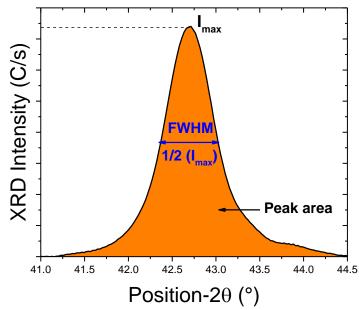

| 2.2.3                | X-Ray Diffraction (XRD)                                    | 71 |  |  |  |

| 2.2.4                | Mechanical stress measurements                             | 75 |  |  |  |

| 2.3 Cor              | nclusion                                                   | 76 |  |  |  |

# Contents

| 3. Impact of La and Al additives on MOSFET reliability                   | 77  |

|--------------------------------------------------------------------------|-----|

| 3.1 Impact of La and Al additives on BTI reliability                     | 77  |

| 3.1.1 Device fabrication                                                 | 77  |

| 3.1.2 Electrical measurements and analysis                               | 78  |

| 3.1.3 Results                                                            |     |

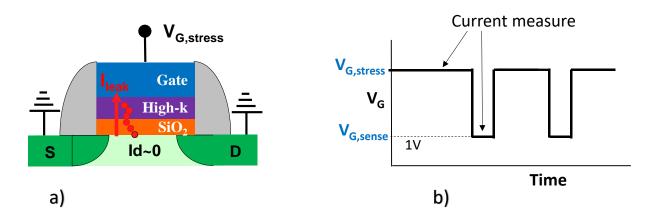

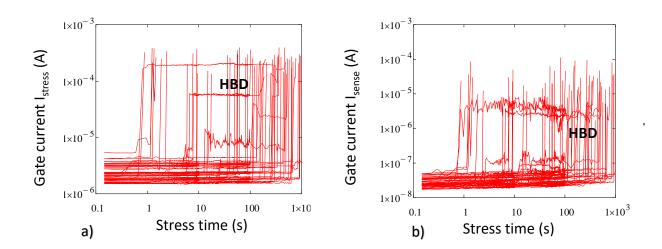

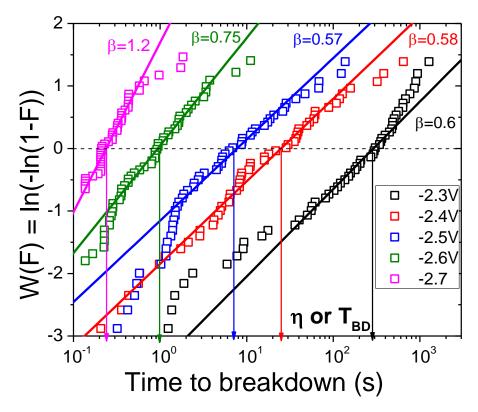

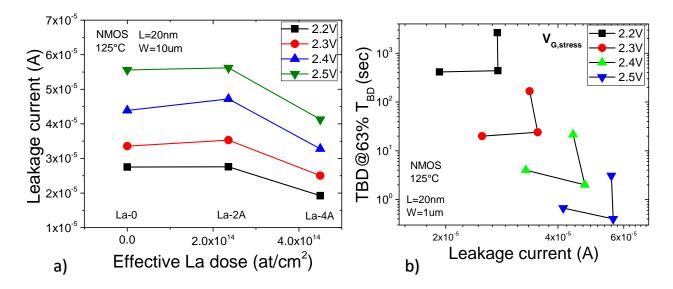

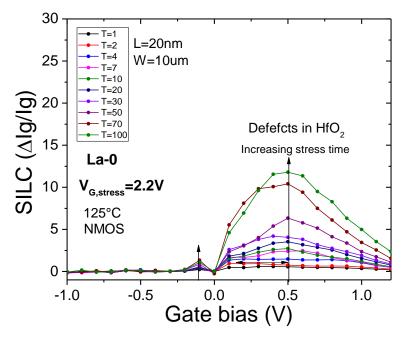

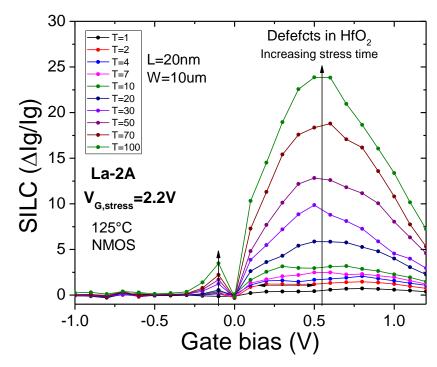

| 3.2 Impact of La and Al additives on TDDB reliability                    | 95  |

| 3.2.1 Electrical measurements                                            | 95  |

| 3.2.2 Results                                                            |     |

| 3.3 Conclusion                                                           | 111 |

| 4. Impact of TiN process on its microstructure and electrical properties |     |

| 4.1 Context                                                              |     |

| 4.2 Device fabrication                                                   | 114 |

| 4.3 Measurements and results                                             | 115 |

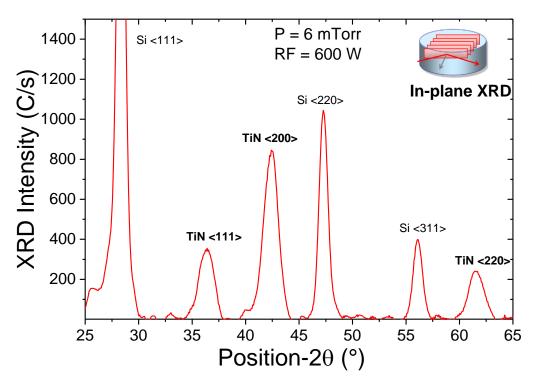

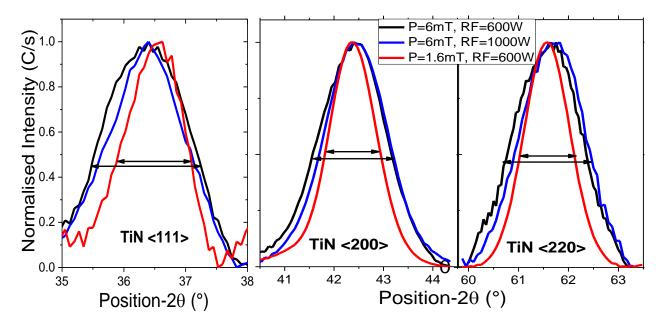

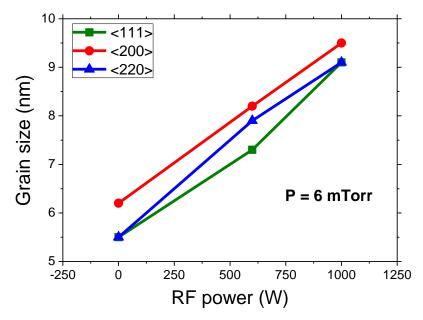

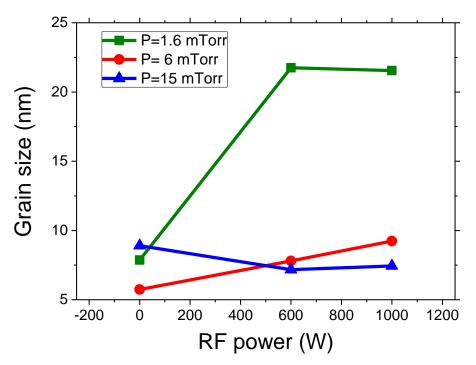

| 4.3.1 In-plane XRD for TiN grain size                                    | 116 |

| 4.3.2 θ-2θ XRD for TiN grain orientation                                 |     |

| 4.3.3 Mechanical stress                                                  |     |

| 4.3.4 Resistivity of TiN films                                           |     |

| 4.3.5 Effective workfunction measurements                                |     |

| 4.3.6 Grain size variation with wafer radius                             |     |

| 4.3.7 Effect of substrate temperature                                    |     |

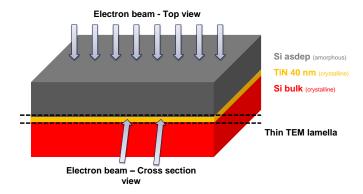

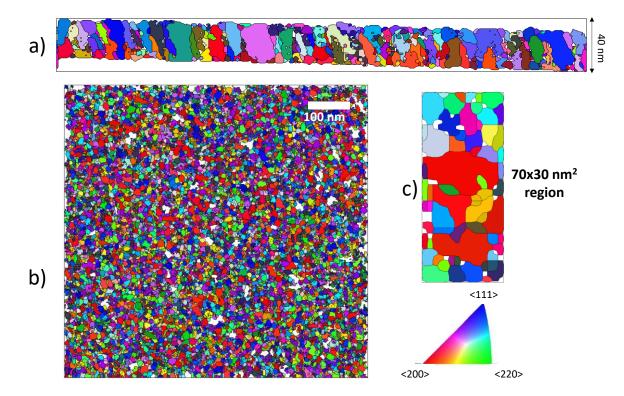

| 4.3.8 TiN grain analysis by ASTAR technique                              | 131 |

| Conclusion                                                               | 134 |

| 5. Study of La and Al diffusion in HKMG stack                            |     |

| 5.1 Introduction to diffusion                                            |     |

| 5.2 Device fabrication                                                   |     |

| 5.3 Results                                                              | 141 |

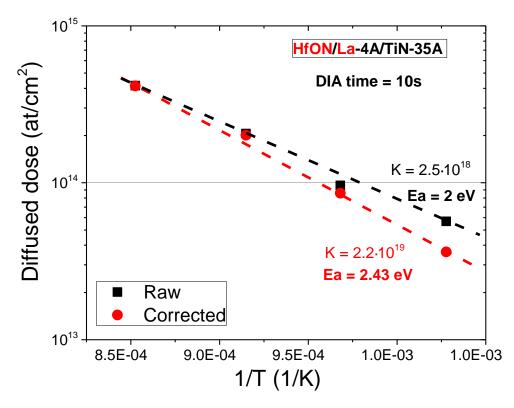

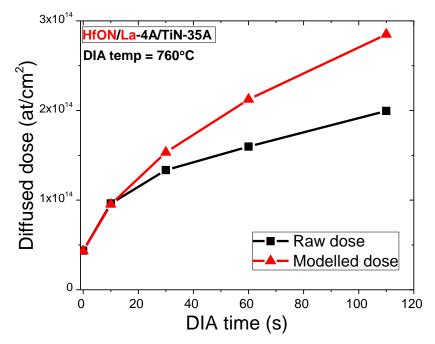

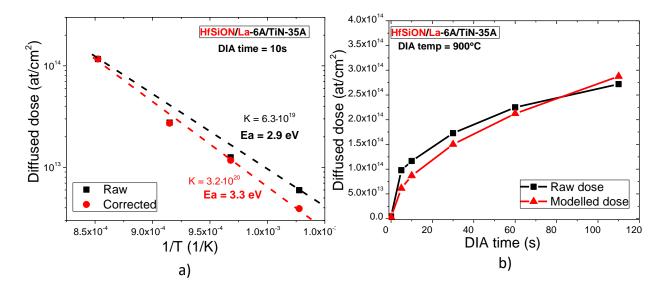

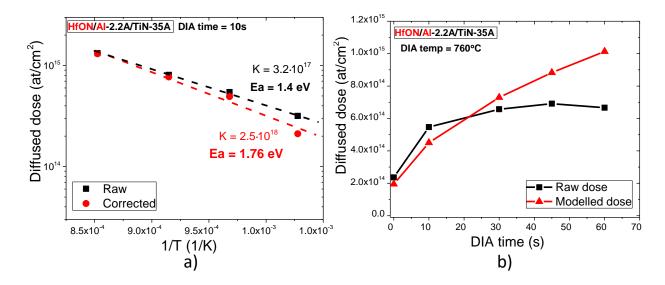

| 5.3.1 Modulation of diffused additive dose by DIA conditions             | 141 |

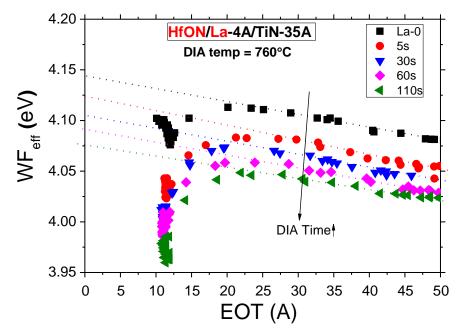

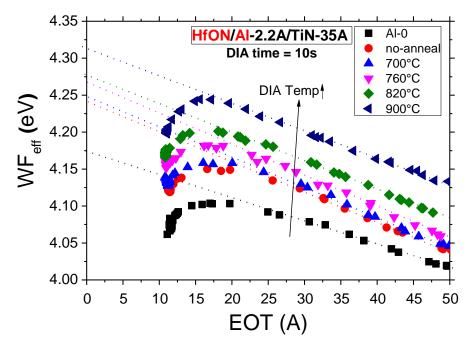

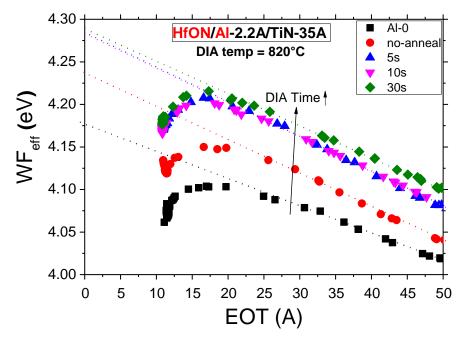

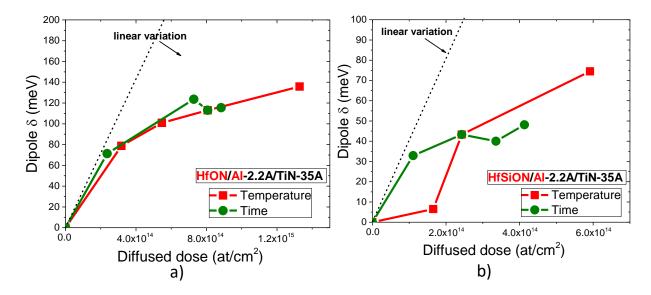

| 5.3.2 Modulation of effective workfunction by DIA conditions             | 149 |

| Conclusion                                                               | 153 |

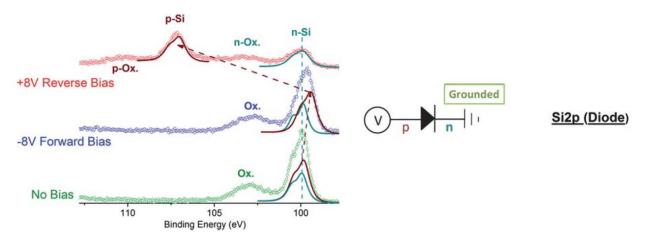

| 6. X-ray Photoelectron Spectroscopy under bias                           | 154 |

| 6.1 State of the art and the need for XPS under bias                     | 154 |

| 6.2 Test structures and their biasing issues                             |     |

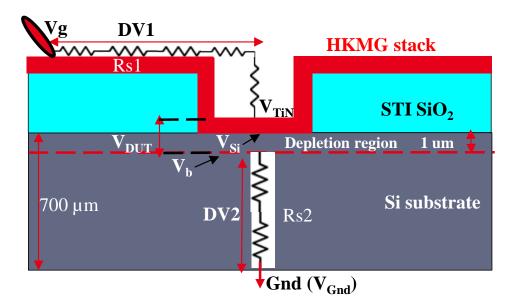

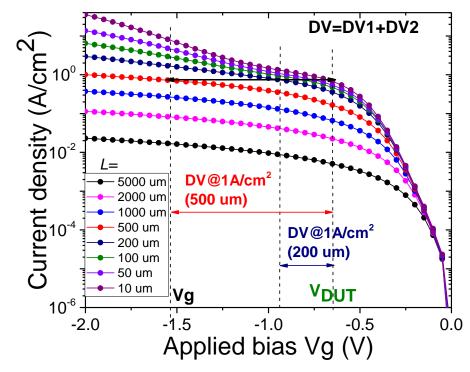

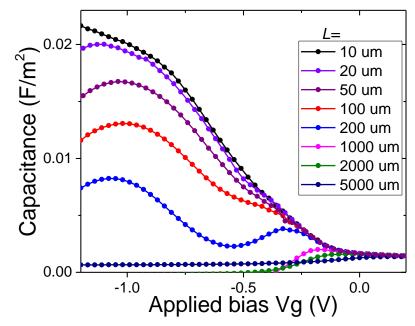

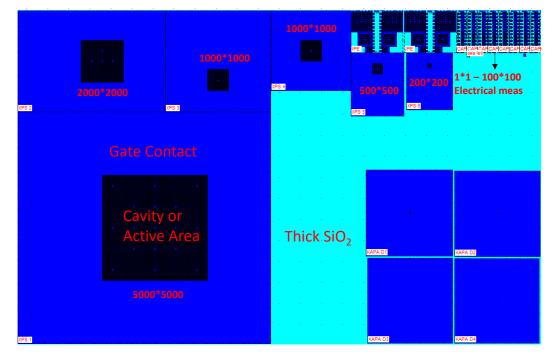

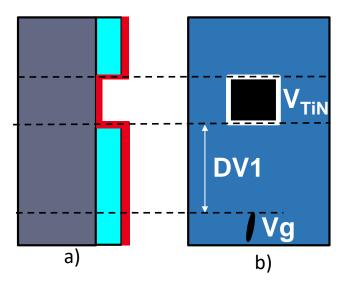

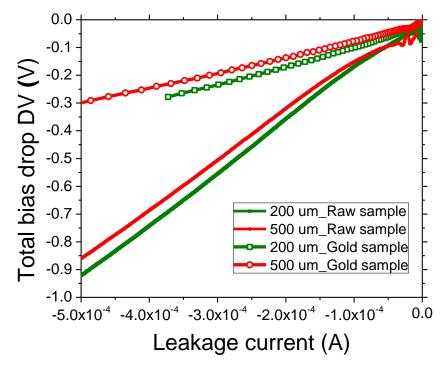

| 6.2.1        | Test structures and their process flow          | 158 |

|--------------|-------------------------------------------------|-----|

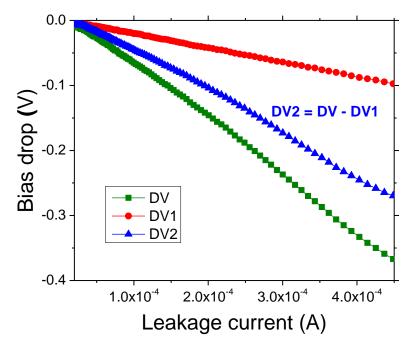

| 6.2.2        | Biasing issues in the test structures           | 159 |

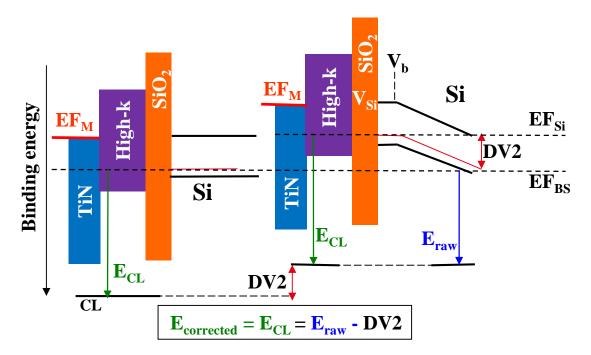

| 6.2.3        | Biasing solutions and electrical modelling      | 161 |

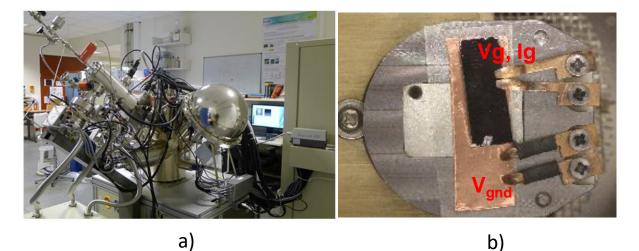

| 6.3 Issu     | ues related to the XPS equipment                | 165 |

| 6.3.1        | Device location                                 | 165 |

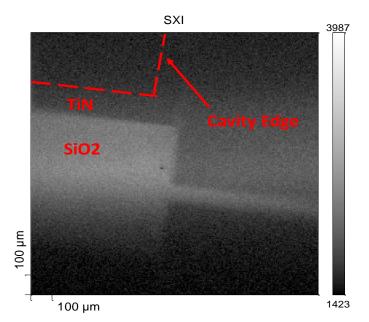

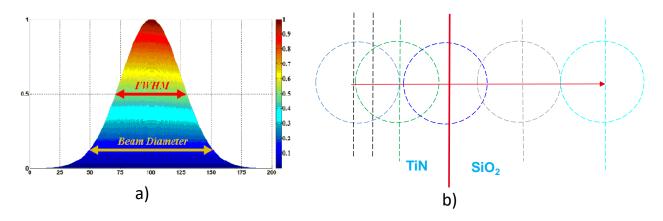

| 6.3.2        | XPS beam position error and size estimation     | 167 |

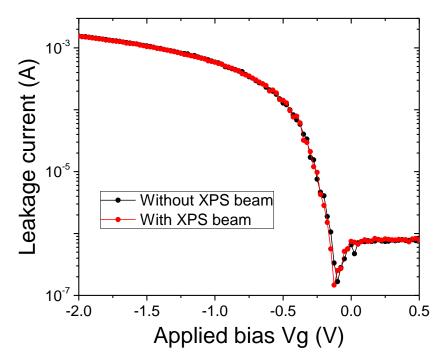

| 6.3.3        | Impact of X-ray beam on the gate stack          | 168 |

| 6.3.4        | Reduction of substrate resistance               | 169 |

| 6.4 XP       | S under bias technique validation               | 170 |

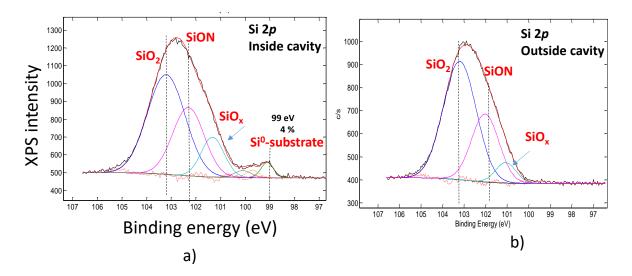

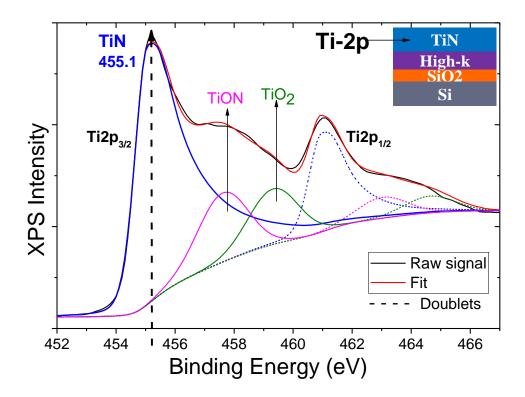

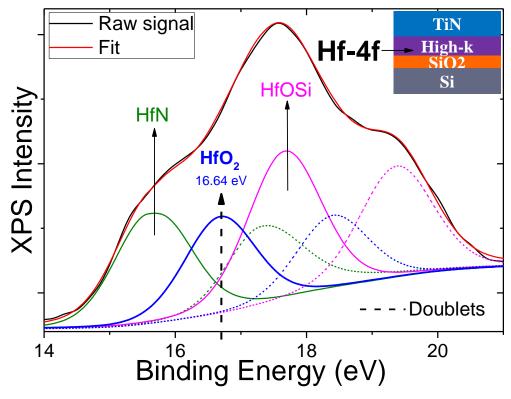

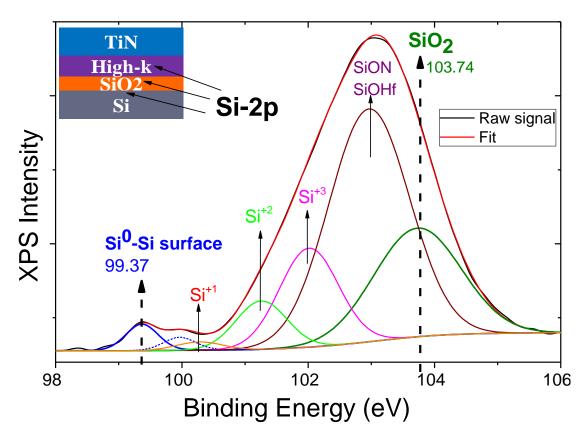

| 6.4.1        | XPS spectra fitting methodology                 | 171 |

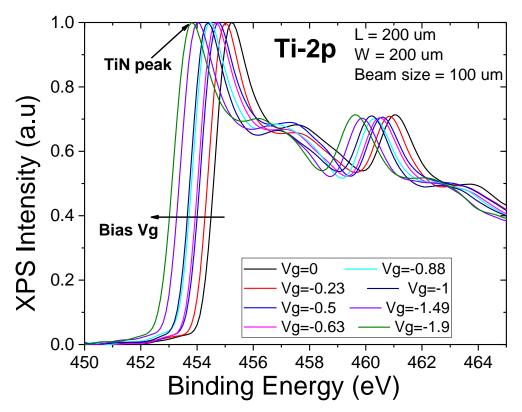

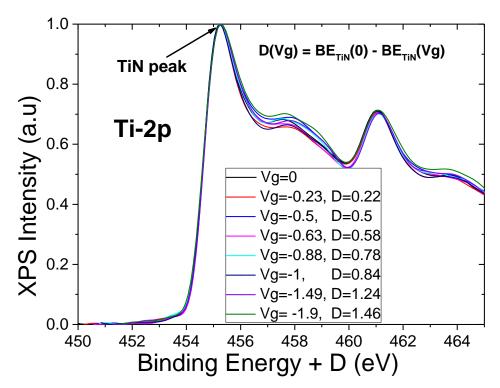

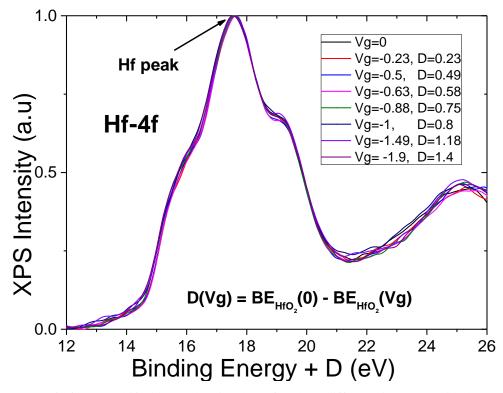

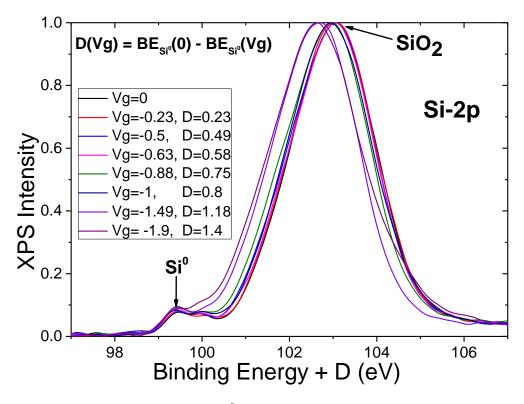

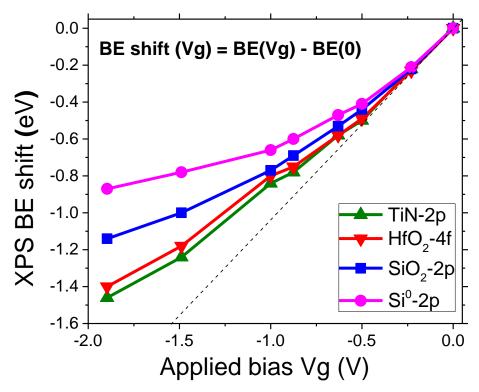

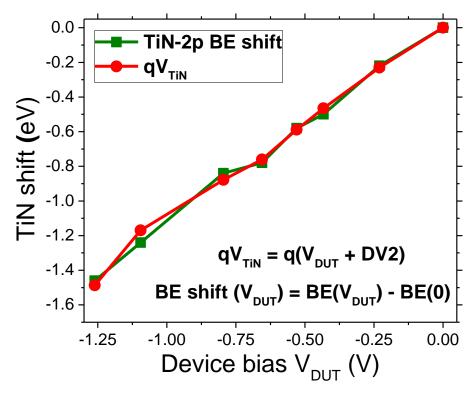

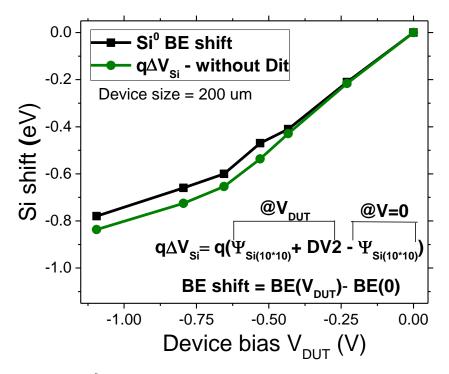

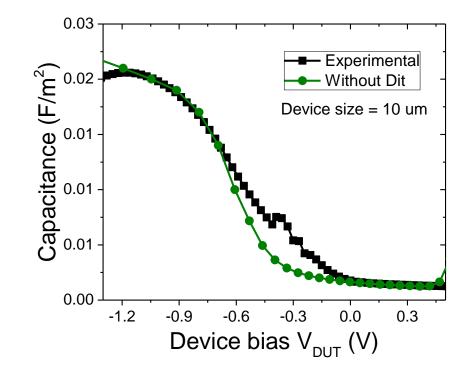

| 6.4.2        | Shift of binding energies with bias             | 173 |

| 6.4.3        | Technique validation                            | 177 |

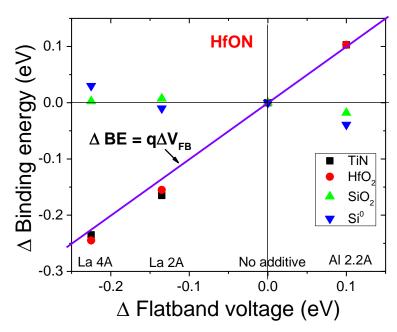

| 6.5 Dip      | oole localization by XPS under bias             |     |

| 6.5.1        | Dipoles related to La and Al addition           |     |

| 6.5.2        | Methodology to reduce experimental difficulties | 187 |

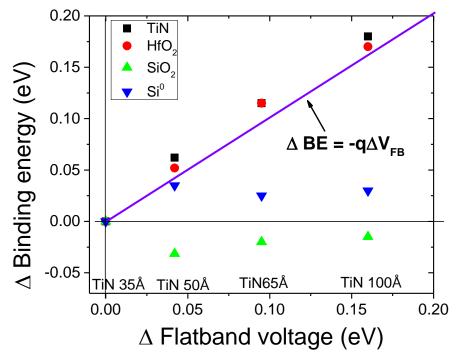

| 6.2.3        | Dipoles related to TiN thickness modulation     |     |

| Conclus      | 191                                             |     |

| Conclusion   | ns and perspectives                             |     |

| List of pub  | lications                                       |     |

| List of Pate | ents                                            |     |

| Annex        |                                                 |     |

## **List of Abbreviations**

MOSFET: Metal Oxide Semiconductor-Field Effect Transistor CMOS: Complementary Metal Oxide Semiconductor FDSOI: Fully Depleted Silicon On Insulator WFeff: Effective workfunction VFB: Flatband voltage HKMG: High-k metal gate STI: Shallow Trench Isolation EOT: Equivalent Oxide Thickness IL: Interfacial Layer ALD: Atomic Layer Deposition **PVD:** Physical Vapor Deposition CMP: Chemical mechanical polishing **RF-PVD: Radio-Frequency Physical Vapor Deposition** S/D: Source-Drain DIA: Drive in anneal C-V: capacitance voltage MGG: Metal gate granularity FCC: Face centered cubic NBTI: Negative Bias temperature instability PBTI: Positive Bias temperature instability TDDB: Time Dependent Oxide Breakdown SILC: Stress Induced Leakage Current HBD : Hard breakdown. SBD : Soft breakdown AHI : Anode hole injection MVHR: multivibrational hydrogen release

XRD: X-Ray Diffraction

XPS: X-ray Photoelectron Spectroscopy

XRF: X-Ray Fluorescence

FWHM: Full width at half maximum

MPE: Multiphonon emission

TBD: time to breakdown at 63% devices

CL: Core level

VB: Valence band

BE: Binding energy

DUT: Device under test

## **General introduction**

## Context

Digital electronic devices have become a necessary part of our daily life, with applications in communications, entertainment, automotive, medical equipment and internet of things. This became possible, and is also described as the second industrial revolution, due to the continuous efforts in research and development to improve the performance of these electronic devices. These devices contain multiple semiconductor chips, each having a specific function. Each of these chips is made of many integrated circuits, containing billions of transistors, which is at the heart of these circuits. The first transistor, called the bipolar transistor (BJT), was developed in 1947 by Bell laboratory researchers John Bardeen, William Shockley and Walter Brattain, for which they received the Nobel prize in physics. Then in 1959, D. Kahng and Mr. Attala invented the first MOSFET (Metal Oxide Semiconductor-Field Effect Transistor). In the beginning, BJT devices were preferred due to their rapid switching speeds, but later MOSFET devices started to dominate the microelectronics industry due to their lower power consumption. Since then, MOSFET's became the key part of the CMOS (Complementary Metal Oxide Semiconductor) technology, used to fabricate logic gates of the integrated circuits.

In order to continually improve electrical performance, reduce power consumption and manufacturing costs of digital devices or circuits, the dimensions of the transistor needs to be reduced. This is known as downscaling, as predicted by the Moore's law in 1965, and involves reducing the transistor and gate oxide dimensions. The performance improvement is due to the increase of transistor channel current, which increases its switching speed. Thus, although the operating principle of the MOSFET is still the same, its size have decreased and its quantity placed on a chip has doubled every two years, as described by the International Semiconductor Technology Roadmap (ITRS). This led to massive technological progress in design and fabrication of integrated circuits, with an ever increasing transistor density, electrical performance and their applications.

However, these technological advances have faced some serious challenges since the 2000's, where the downscaling has resulted in major device physics and process integration issues. Indeed, due to miniaturization of the transistor dimensions and of the gate oxide to the nanometric scale, undesirable effects including some complex quantum phenomena have emerged. These include the high gate leakage current for very thin gate oxides, short channel effects for very small transistors, threshold voltage variability, etc. Increase in the gate leakage current affects transistor reliability and increases its power consumption. Thus, the simple downscaling was no longer sufficient to improve transistor performance.

Therefore, new solutions were proposed to deal with these issues, while still being able to downscale. First was the introduction of the (high-k metal gate) HKMG stack, which replaced the conventional poly-Si/SiO<sub>2</sub> stack. The introduction of the high-k oxide decreases the gate leakage while still keeping the same capacitance density, because a higher oxide thickness can be used.

Moreover, introduction of a metal gate electrode eliminated the polysilicon depletion in gate electrode (thus increasing switching speed), eliminated the Fermi Level pinning with the high-k layer, decreased gate resistance and boron penetration effects. Second is the introduction of the FDSOI (Fully depleted silicon on insulator) substrate, containing an ultra-thin buried oxide. Compared to a bulk substrate, FDSOI reduced the threshold voltage (V<sub>T</sub>) variability, short channel effects and gate leakage current.

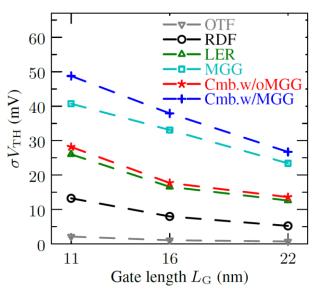

In this context, optimization and tuning of electrical and process parameters, of the MOSFET devices with HKMG stack on FDSOI substrates, becomes very important. V<sub>T</sub> of MOSFET's must be fine-tuned to satisfy certain requirements for specific FD-SOI devices. V<sub>T</sub> is mainly dependent on the parameter known as the effective work function (WF<sub>eff</sub>), which is related to the metal gate work function (WF<sub>M</sub>) and the properties of the high-k layer. In order to fine-tune the WF<sub>eff</sub> of MOSFET's, additives such as Lanthanum (La) and Aluminum (Al) have been introduced inside the HKMG stack by a drive in anneal (DIA) process. However, the impact of these additives on MOSFET reliability is not known. Moreover, even though a limited relationship between diffused dose of these additives and the shift in WFeff has been investigated earlier, a clear understanding and modelling of the diffusion phenomena and effect on the WFeff with the process conditions DIA have not been done. Although some contributions to the V<sub>T</sub> variability are dramatically reduced, especially by the introduction of the FD-SOI substrate, studies have pointed out that the contribution due to the microstructure of the metal gate still remains important, and must be investigated. Lastly, in order to build a full understanding of the CMOS devices and for its further development, a comprehensive knowledge of band-energies of different layers in the gate stack is required, which cannot be extracted from simple electrical measurements. Thus, there is a need to develop a non-destructive characterization technique to measure the band energies of the HKMG stack.

## Thesis objectives and outline

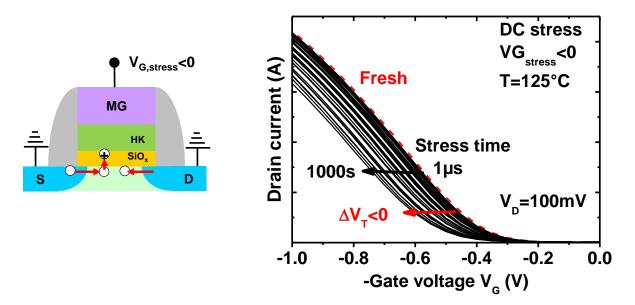

The main objectives of this thesis are to investigate : 1) the effects of La and Al additives on the BTI (bias temperature instability) and TDDB (time dependent oxide breakdown) reliability, 2) the impact of DIA conditions on the diffusion of these additives and device  $WF_{eff}$ , 3) the impact of TiN metal gate deposition conditions on its microstructure in the context of reducing  $V_T$  variability, mechanical properties and device  $WF_{eff}$ , and 4) development of XPS (X-ray Photoelectron Spectroscopy) under bias technique to determine the band energies of the MOSFET HKMG stack.

The first chapter introduces the gate stack technology for a MOSFET device of the 14 and 28 nm FDSOI technology. The working operation of a MOSFET device, its various performance parameters and how they can be tuned by the various charges, interface states and dipoles present in the gate stack are described. Then we discuss on the importance of the different layers consisting the HKMG stack and their processes, i.e. the interlayer, high-k and the metal gate. Special attention has been paid to the deposition of TiN, La and Al by the RF-PVD method, and their various process parameters have been presented. The introduction of La and Al additives for  $V_T$  engineering into the HKMG stack has also been described. Further, we describe the process flow used to manufacture the MOS devices used in this work, as well as its simplification for capacitance devices. An introduction on the various contributions to  $V_T$  variability has been given, and special

attention has been paid to the contribution of the metal gate microstructure. Finally, a brief introduction of the NBTI, PBTI and TDDB reliability has been given, which includes a review of state of the art and the various mechanisms and models that exists presently.

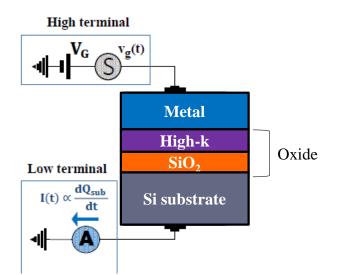

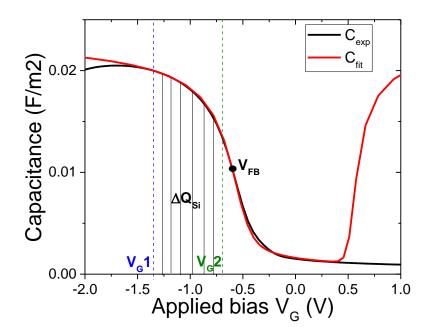

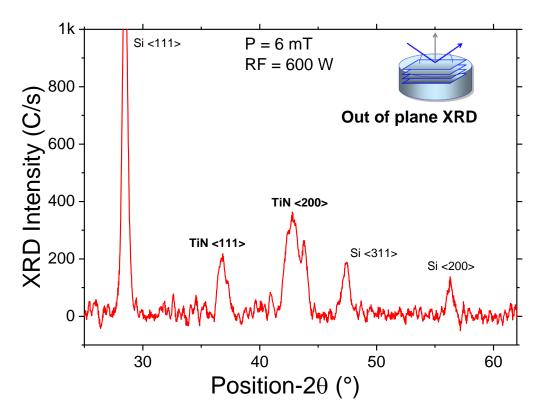

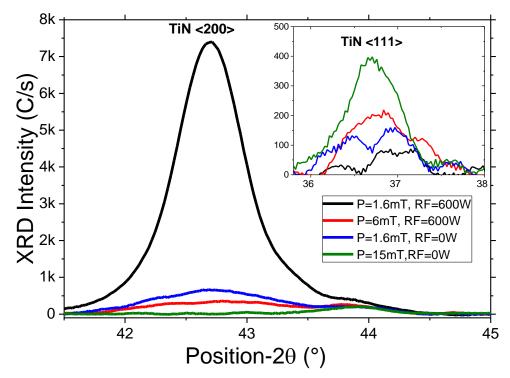

The second chapter introduces the various electrical and physicochemical techniques used in this work to characterize the gate stack. The capacitance voltage (C-V) measurement technique, analytical and automatic method to extract flatband voltage ( $V_{FB}$ ) and equivalent oxide thickness (EOT) from experimental C-V measurements is presented. Moreover, a method to separately extract the charges and dipoles present in the gate stack is presented. Then, the four probe method used to extract sheet resistance of films is described. This chapter also presents the various non-electrical techniques that have been used in this thesis. This includes first the X-ray Photoelectron Spectroscopy (XPS) technique used to obtain the band energies of the gate stack layers, X-Ray Fluorescence (XRF) technique used to measure the additive dose and metal gate elemental composition, and finally the X-Ray Diffraction (XRD) technique used to obtain information on the microstructure of crystalline films by combining the in-plane and out of plane configurations. Lastly, the technique to measure the stress added by the deposition of a film on a Si substrate is presented.

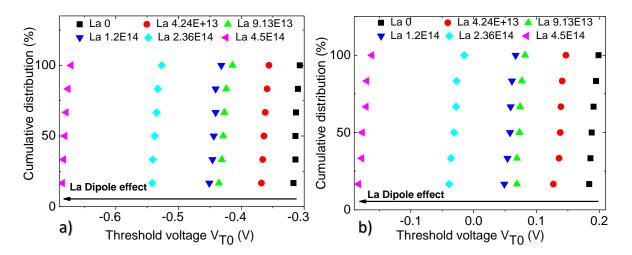

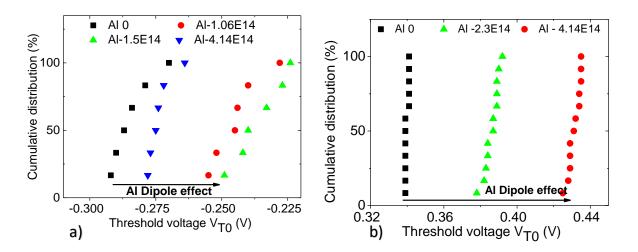

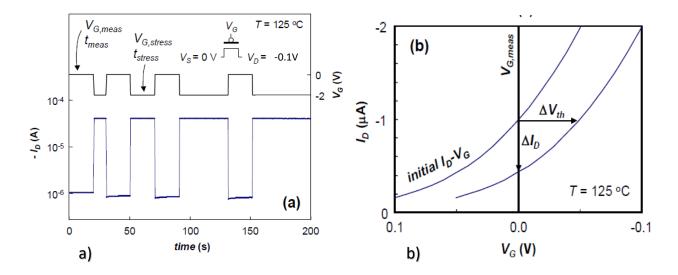

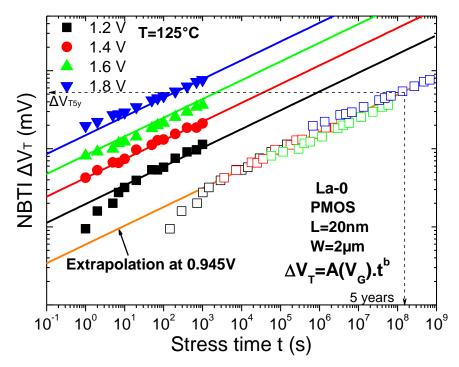

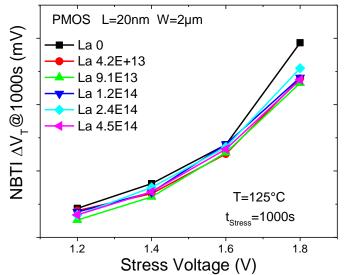

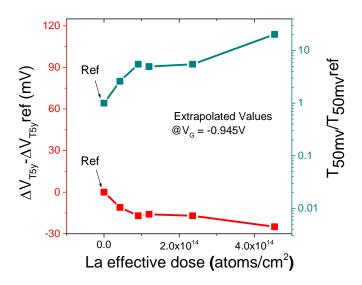

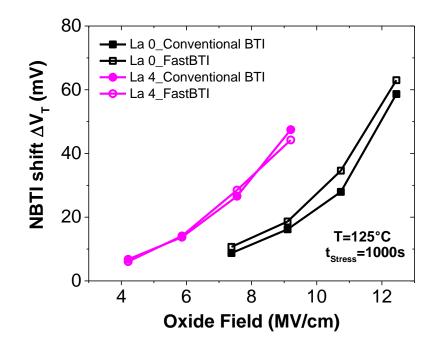

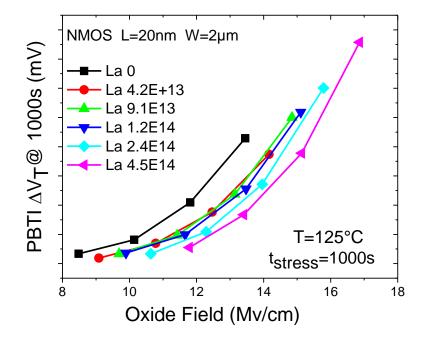

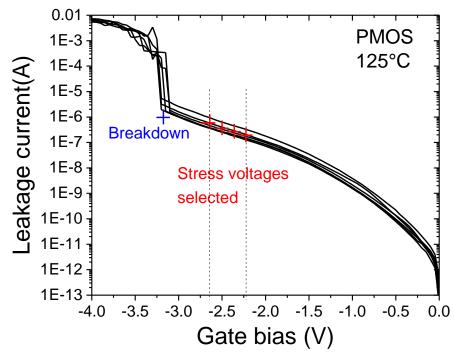

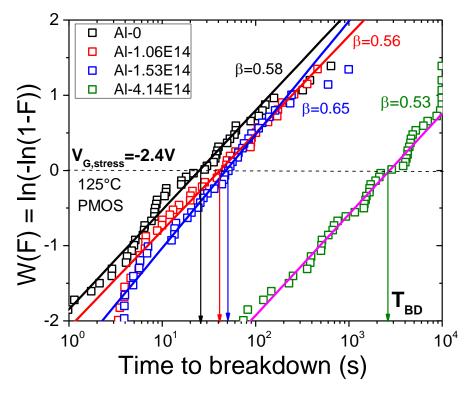

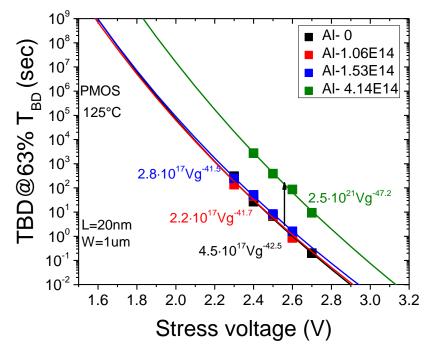

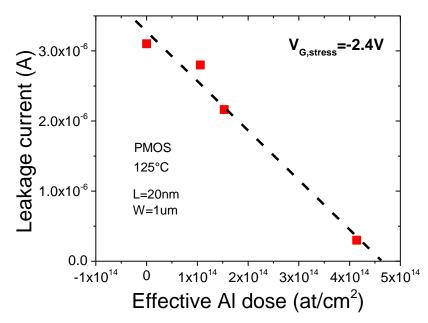

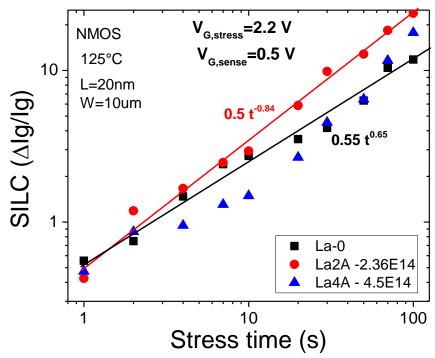

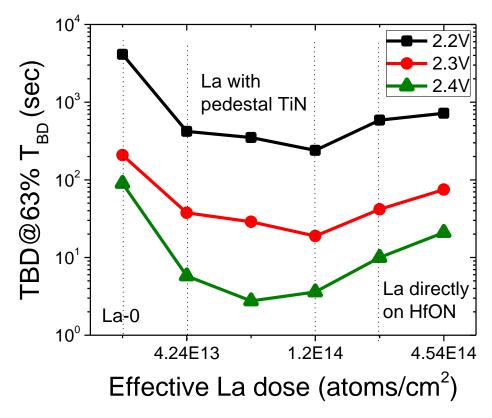

The third chapter is based on the study of the impact of La and Al additives, used for threshold voltage adjustment, on MOSFET BTI and TDDB reliability. This chapter covers first the device fabrication and secondly the test methodology, analysis for NBTI and PBTI  $V_T$  shift, and the role of oxide field on the BTI reliability. Then, results on the role of La and Al additives on BTI life-time and time to failure of the device are studied, and the physical interpretation related to the impact of these additives on the HKMG stack is discussed. Next, the impact of these additives on the TDDB reliability is studied. This covers the electrical measurements for TDDB, time to breakdown detection and their representation on the Weibull distribution scale. Further, the methodology to select the gate stress voltage for TDDB tests is described. Lastly, results on the role of La and Al on NMOS and PMOS time to breakdown have been shown and their explanations by defect creation in the oxide are discussed.

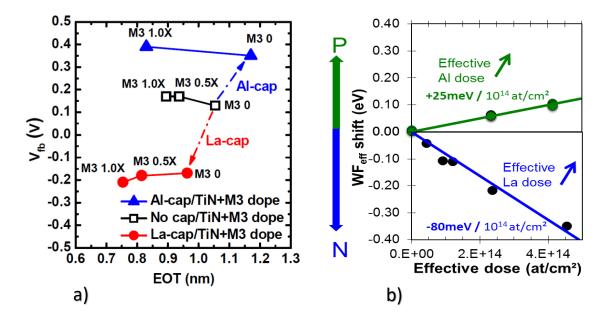

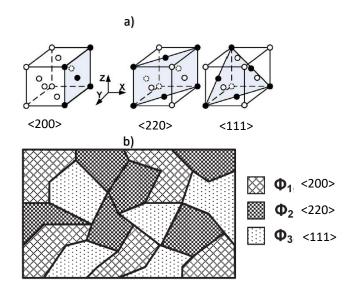

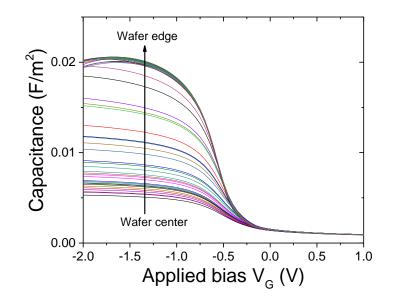

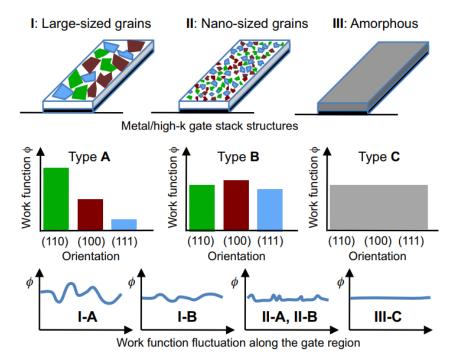

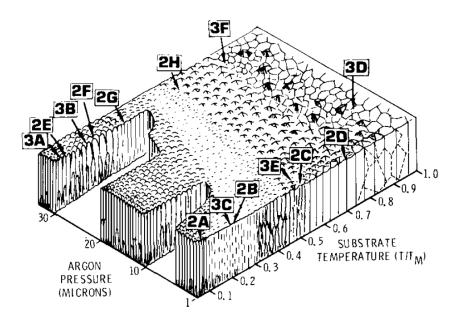

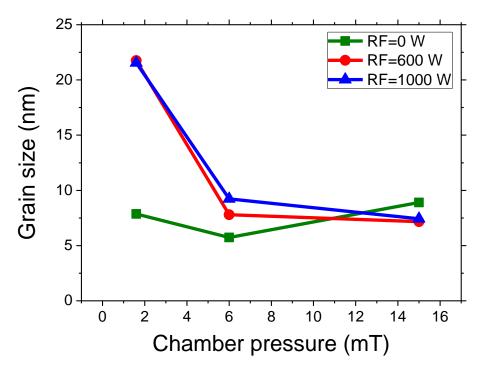

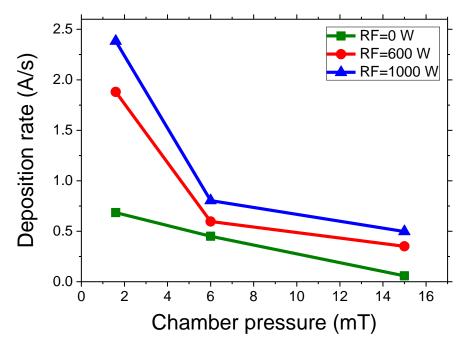

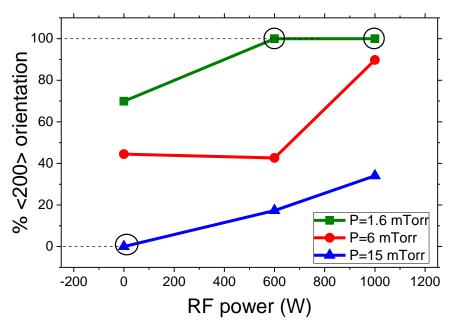

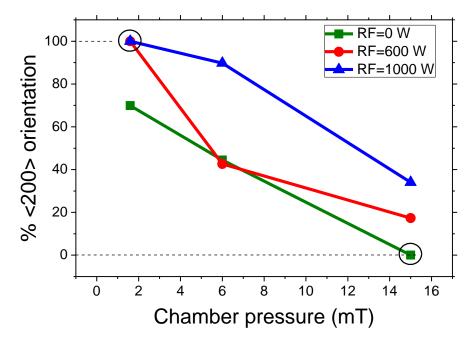

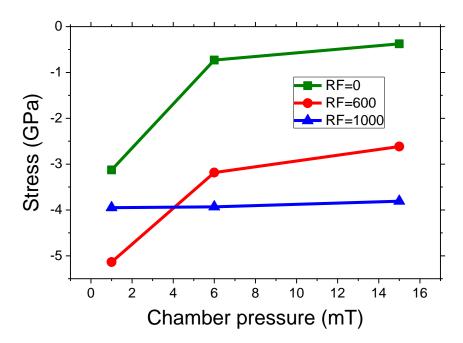

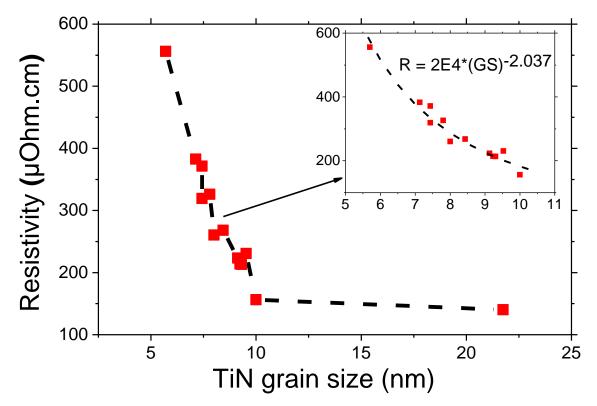

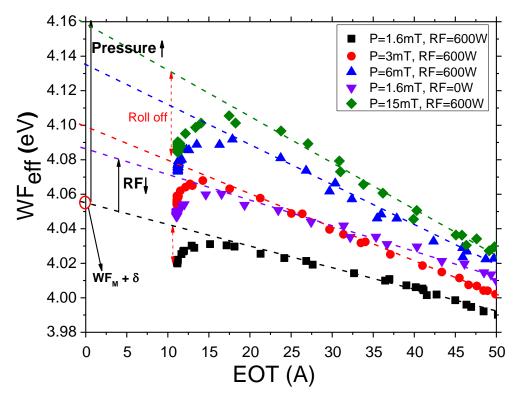

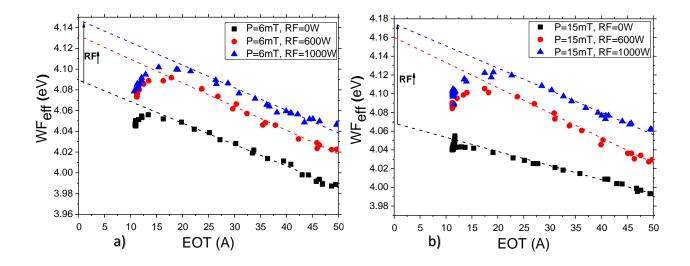

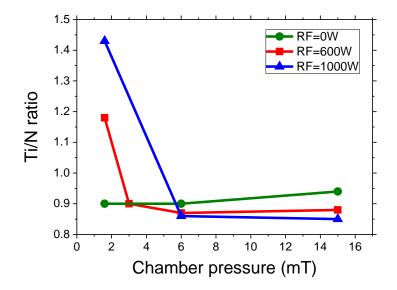

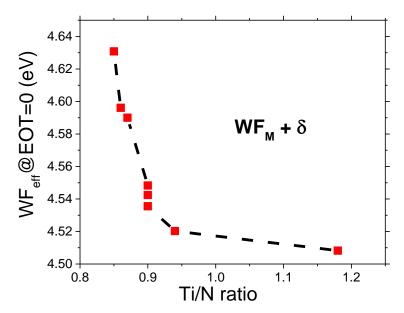

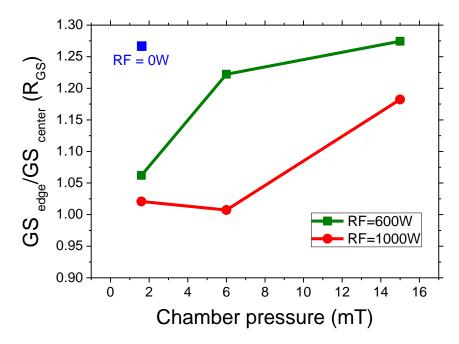

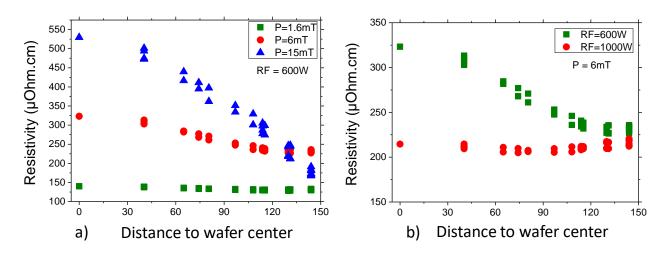

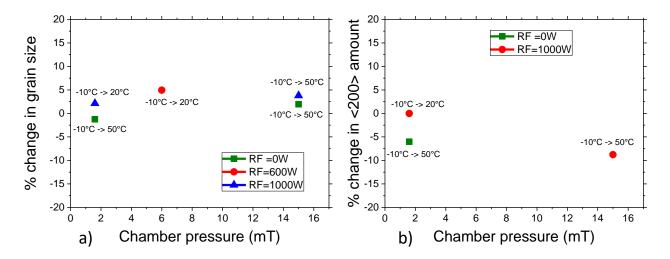

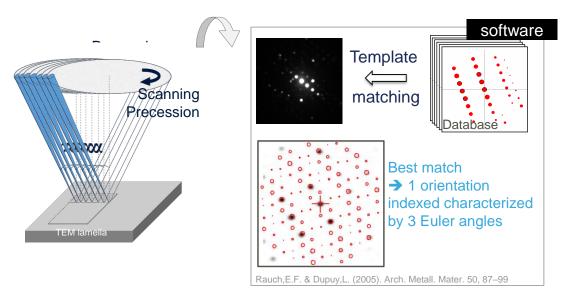

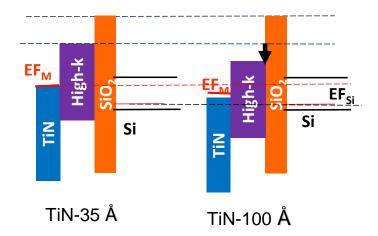

The fourth chapter focuses on the effect of TiN metal gate deposition conditions, chamber pressure and RF power, on physical and electrical properties of MOS device and TiN film itself. First, the need for TiN microstructure modulation in the context of lowering the threshold voltage variability has been stated and then the possible RF-PVD process variations that can achieve this modulation in TiN microstructure are discussed. The HKMG stack process and the two different process flow (or devices) that have been used in this study, to measure physical and electrical properties are presented. Then, the different physical and electrical measurements and the results obtained for variations in RF-PVD chamber pressure and RF power are presented. This includes first the grain size calculated by in-plane XRD measurements and relative percentage of grain orientation calculated by out of plane XRD measurements, and then the mechanical stress and sheet resistance results. Further, the effective workfunction versus EOT and Ti/N ratio results are presented, and the correlation between metal workfunction, dipoles and Ti/N ratio is reported. The effect of TiN process conditions on the wafer non-uniformity of grain size and sheet resistance, and the impact of substrate temperature on the grain size and their relative orientations are also presented. Finally, results on the ASTAR technique for TiN microstructure analysis and comparison of its results with XRD are shown.

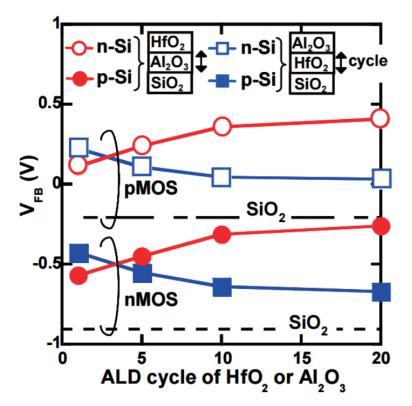

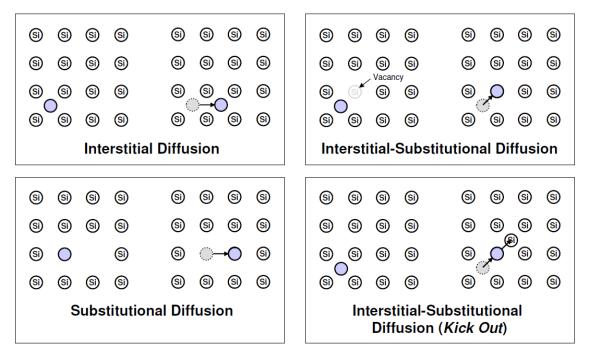

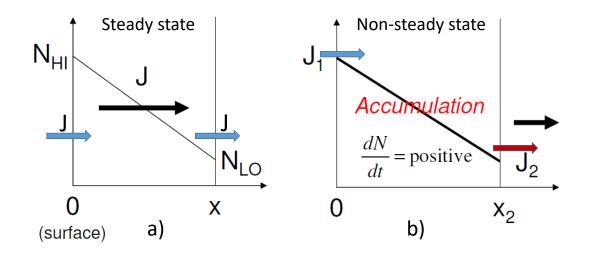

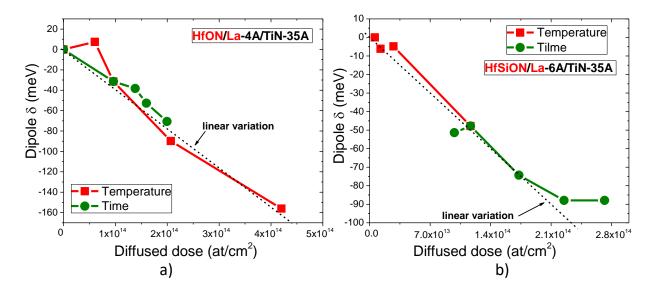

The fifth chapter investigates the diffusion of La and Al additives inside the HKMG stack, with DIA conditions (temperature and time) of the sacrificial gate process. First, the mechanisms and the fundamentals of the diffusion process are described. The sacrifical gate process and the use of two different process flow (or devices) are also introduced, that have been used to study additve diffusion and effective workfunction. Then, the results on diffused dose of La or Al in the gate stack with DIA time and temperature, measured by X-Ray Fluorescence (XRF) technique are presented. This section highlights the main differences between La and Al additive diffusion and different high-k. Finally, the modulation of effective workfunction or additive dipole by the DIA conditions is presented, followed by the correlation between the modulation of dipole and diffused dose by DIA conditions, for the two additives and high-k materials.

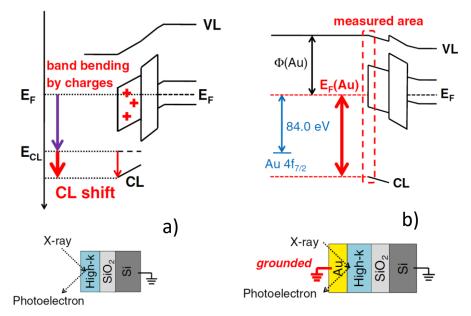

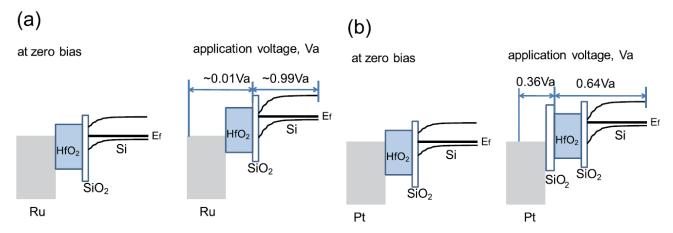

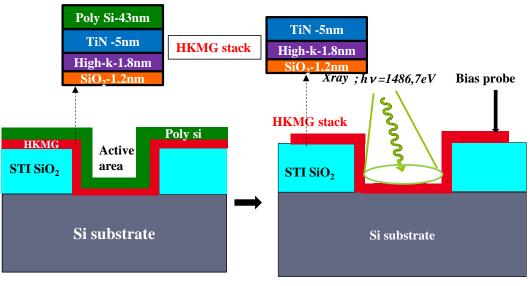

The final chapter focuses on the development and validation of XPS under bias technique to analyze HKMG stack band energies, with the main aim to localize different dipoles. First, the need for this technique is presented and a comparison of its benefits with capacitance measurements is done. The state of the art and the major issue related to the conventional XPS and XPS under bias techniques are also presented. Then, the specific test structures, used to perform XPS under bias measurements, their process flow and the biasing issues occuring in them due to different parasitic serial resistances are discussed. The biasing solutions developed by us using a specific methodology that combines electrical measurements, XPS under bias measurements and modeling on different devices are presented. Further, the various experimental issues, related to XPS equipment and the samples, and their solutions are discussed. This includes the issue of device location inside the XPS equipment, the estimation of the exact size and the position error of the Xray beam, the impact of the X-ray beam on the devices during XPS measurements and the experimental methods employed to decrease the parasitic bias drops in the Si substrate. Then, XPS under bias technique is validated by first developing a procedure to fit the XPS signals from the different layers of the HKMG gate stack, and then comparing the binding energy values obtained from fitting the XPS signals to the values obtained with our electrical modelling. Finally, XPS under bias technique will be used to localize and quantify dipoles related to the addition of La or Al, and dipoles occuring due to TiN gate thickness modulation. A methodology to use XPS measurements at zero bias for estimating the values at the flatband condition will also be presented.

This CIFRE Ph.D. work has been carried out in collaboration with STMicroelectronics in Crolles, the CEA-LETI and the IMEP-LAHC laboratories in Grenoble. Most of the steps in the devices fabrication was conducted at STMicroelectronics, and some at CEA-LETI. Electrical characterizations were performed in the Laboratoire de Caractérisation et Tests Electriques (LCTE) of the CEA-LETI. Physical characterizations were performed at both CEA-LETI and STMicroelectronics. For XPS under bias studies, the test structures and XPS measurements were done at CEA-LETI and at ST.

## 1. Gate stack technology for 14/28 nm FDSOI MOSFET devices

This chapter introduces the gate stack technology for a MOSFET device of the 14 and 28 nm FDSOI technology. Section 1.1 describes the working operation of a MOSFET device and its various performance parameters and how they can be tuned by the various charges, interface states and dipoles present in the gate stack. Section 1.2 describes the need for different layers consisting the HKMG stack and their processes, i.e. the interlayer, high-k and the metal gate. Special attention has been paid to the deposition of TiN, La and Al by the RF-PVD method, and their various process parameters have been discussed. Then, the introduction of La and Al for  $V_T$  engineering into the HKMG stack has been discussed.

Section 1.3 describes the process flow used to manufacture the MOS devices used in this work, and its simplification for capacitance devices. Section 1.4 presents the various contributions to  $V_T$  variability and special attention has been paid to the contribution of the metal gate microstructure to  $V_T$  variability. In section 1.5, a brief introduction of the NBTI, PBTI and TDDB reliability has been given. This describes the state of the art and the various mechanisms and models that exists presently.

## **1.1 MOSFET device**

### **1.1.1 MOSFET operation**

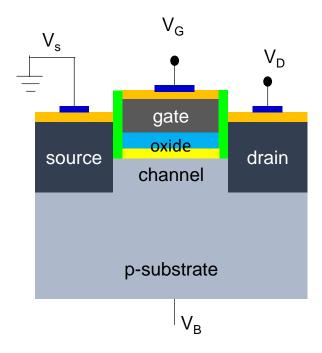

Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) is based on the principle of the field effect [1], which is the modulation of charge density in a material by an electric field applied perpendicularly to its expected flow. In a MOSFET the charge is controlled at the semiconductor surface, called the channel. A MOSFET is a four-terminal device consisting of: source, drain, gate and substrate as shown in Figure 1.1. Modulation of charge carriers in the semiconductor channel is governed by the polarization of gate (V<sub>G</sub>) and substrate (V<sub>B</sub>) through an insulating layer (the dielectric layer) by capacitive coupling. After their generation, carrier's transportation in the channel is controlled by potential difference (V<sub>D</sub>) between the two charge reservoirs (source and drain) establishing a drain current I<sub>D</sub>. The transistor thus behaves like a switch. It is in an 'OFF' state (V<sub>G</sub> = 0 V) for which the current between source and drain is very low and in an 'ON' state for which V<sub>G</sub> is equal to V<sub>D</sub>, allowing the passage of current I<sub>ON</sub>. The threshold voltage (V<sub>T</sub>) is the minimum gate-to-substrate voltage difference that is needed to create a conductive channel between the source and drain terminals.

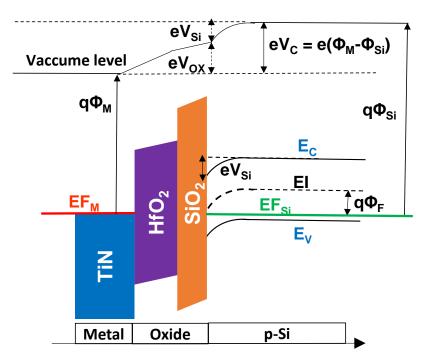

Figure 1.1: Schematic diagram of a four terminal n-MOSFET device

The MOS capacitor is the simplest MOS structure and is composed of a p-type (for NMOS) or n-type (for PMOS) doped silicon substrate, a gate oxide and a metal layer. When the different layers constituting the MOS structure are brought into contact, an alignment of Fermi levels of metal ( $EF_M$ ) and semiconductor ( $EF_{si}$ ) appears. As a result, a unique thermodynamic system is formed which is characterized by a single Fermi level (Figure 1.2). Then, an electrostatic potential, called contact potential ( $V_C$ ), is generated following the alignment of the Fermi levels. It is expressed by:

$$V_{\rm C} = \Phi_{\rm M} - \Phi_{\rm Si}$$

1.1

where  $q\Phi_M$  corresponds to the difference between the metal Fermi level and its vacuum level,  $q\Phi_{Si}$  corresponds to the difference between the semiconductor Fermi level and its vacuum.  $q\Phi_F$  is the difference between the intrinsic Fermi level of silicon and the resulting Fermi level. In addition, a bending of energy bands is directly driven by the contact potential in the semiconductor (V<sub>Si</sub>) and in the oxide (V<sub>OX</sub>) and at V<sub>G</sub> = 0 V their relationship is given by:

$$V_{\rm C} = \Phi_{\rm M} - \Phi_{\rm Si} = -(V_{\rm OX} + V_{\rm Si})$$

1.2

When a gate bias  $V_G$  is applied, then equation 1.2 becomes:

$$V_G = \Phi_M - \Phi_{Si} + V_{OX} + V_{Si}$$

1.3

Figure 1.2: Energy band structure of the stack constituting the MOS capacitor at  $V_G = 0$  (depletion condition)

Assuming that the oxide is perfect (absence of charges), the oxide potential drop  $V_{ox}$  will be linear. So, we can express it using Gauss theorem from the charge  $Q_{Si}$  created in the semiconductor:

$$V_{OX} / T_{OX} = -Q_{Si} / \varepsilon_{ox}$$

1.4

where  $Q_{Si}$  is the charge in the semiconductor and  $T_{Ox}$  is the oxide thickness. The relationship between  $Q_{Si}$  and  $V_{Si}$  can be described by the Poisson equation for electrostatics, according to classical electrodynamics [1]. However, for ultra-thin oxide thicknesses and low field strengths, such interactions are better described by quantum Poisson-Schrodinger simulations described in chapter 2.

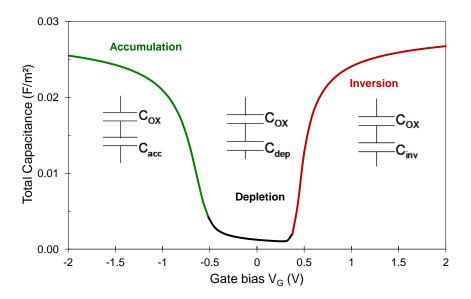

The charges induced in the semiconductor may be of three types: majority carriers, minority carriers and depletion charge. These charges can be controlled by the voltage applied to the gate  $V_G$ , specifically by  $V_{Si}$ . For a p-type semiconductor substrate and with a NMOS transistor, the following regimes occurs depending on the applied  $V_G$ :

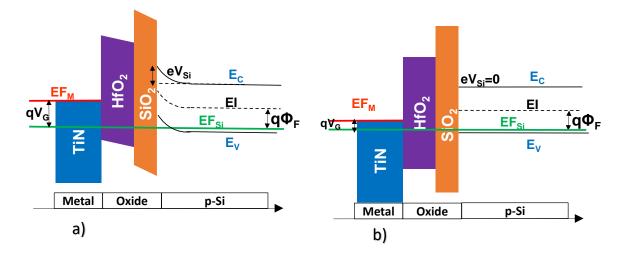

- $V_{Si} < 0$ : Accumulation regime. Majority carriers are attracted to the surface of the semiconductor and their density becomes larger than that in the substrate volume. The transistor is in the "OFF" state (Figure 1.3a).

- $V_{Si} = 0$ : *Flat band condition*. The flat band voltage ( $V_{FB}$ ) is the bias condition of the gate  $V_G$  at which there is no charge in the substrate. At this condition the applied potential  $V_G$  equals the contact potential  $V_C$ . There is no bend bending at the Si interface, i.e  $V_{Si} = 0$ , and the concentrations of minority and majority carriers are constant throughout the substrate (Figure 1.3b).

Figure 1.3: Energy band structure of the stack constituting the MOS capacitor in a) Accumulation condition and b) Flatband condition

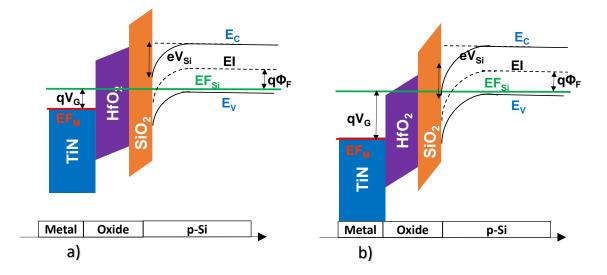

- $0 < V_{Si} < \Phi_F$ : *Depletion regime*. Majority carriers are reduced at the interface and minority carriers starts to increase at the semiconductor interface. An area depleted of carriers is created near the surface (Figure 1.2)

- $\Phi_F < V_{Si} < 2\Phi_F$ : Weak inversion or subthreshold regime. Minority carrier density starts to increase and equals the majority carriers at the surface, but still remains low compared to that of the majority carriers in the substrate volume. Transistor is in the "OFF" state or weak inversion under threshold voltage (Figure 1.4a).

- $2\Phi_F < V_{Si}$ : *Strong inversion regime*. The transistor is in the "ON" state. Minority carrier density becomes greater than the majority carrier concentration in the substrate volume. In this case, a minority carrier channel is formed between the source and the drain on the surface of the semiconductor and is called the inversion channel (Figure 1.4b).

The threshold voltage  $V_T$  of a MOS can be defined as the gate voltage  $V_G$  such that the condition  $V_{Si} = 2\Phi_F$  is satisfied. Thus we obtain as follows:

$$V_{T} = \Phi_{M} - \Phi_{Si} + 2\Phi_{F} - \sqrt{(4\varepsilon_{Si}qN_{Si}\Phi_{F})/C_{OX}}$$

1.5

where,  $\epsilon_{Si}$  is the semiconductor permittivity,  $N_{Si}$  is the substrate doping concentration (cm<sup>-3</sup>) and  $C_{OX}$  is the capacitance per unit area. In fact, if there is one unique  $V_{FB}$  condition corresponding to semiconductor flatband at the interface,  $V_T$  characterizing the onset of the transistor may find several definitions: such as specific surface potential  $V_{Si}$ , certain channel current density at a certain drain voltage  $V_D$ , maximum of transconductance, extrapolation to  $I_D = 0$  etc.

Figure 1.4: Energy band structure of the stack constituting the MOS capacitor in a) Weak inversion and b) Strong inversion condition

The heavily doped (n+ for NFETs and p+ for PFETs) source/drain regions, are used to make an ohmic contact with the conductive channel for  $|V_G| > |V_T|$ , so that a voltage difference between the source and the drain ( $V_{DS}$ ) will result in a current flow ( $I_{DS}$ ) of minority carriers (electrons for NFETs and holes for PFETs) from the positive voltage at the drain terminal to the negative voltage at the source (the polarity and current flow is the contrary for a PMOS). This current flow of minority carriers is also known as drive current and is one of the main MOSFET device performance parameters. In the "OFF" state, the drive current is very small (ideally zero) and in the "ON" state, it is a function of both  $V_G$  and  $V_D$ .

### 1.1.2 Metal-Oxide-Semiconductor gate stack properties

#### Gate dielectric capacitance and equivalent oxide thickness

Capacitance is the ability of a body to store an electrical charge on two electric conductors separated by a dielectric layer. When a potential difference V is applied to the conductors, an electric field develops across the dielectric, causing positive charge (+Q) on one plate and negative charge (-Q) on the other plate. The capacitance C is defined as C = Q/V. In a Metal-Oxide-Semiconductor capacitor, one of the plates is the metal gate and the other is the silicon substrate. The dielectric consists of the gate oxide with a relative permittivity  $\varepsilon_{ox}$  (commonly known as the dielectric constant) and thickness  $T_{OX}$ . Consequently, the gate dielectric capacitance per unit area ( $C_{OX}$ ) can be expressed as follow:

$$C_{OX} = \varepsilon_0 \varepsilon_{ox} / T_{OX}$$

1.6

where  $\epsilon_0 = 8.854.10^{-12} \mbox{ F/m}$  is the vacuum permittivity.

SiO<sub>2</sub> was the industry standard oxide material for MOS capacitance measurements. In order to compare different dielectric materials, and with respect to SiO<sub>2</sub>, the notion of EOT (Equivalent Oxide Thickness) has been introduced. EOT is the equivalent thickness of SiO<sub>2</sub> oxide giving the same capacitance for any dielectric (usually a high-k dielectric) of physical thickness  $T_{OX}$  and dielectric constant  $\varepsilon_{ox}$ . The EOT is given by:

EOT=

$$T_{OX} \epsilon_{sio2}/\epsilon_{ox}$$

1.7

The capacitance is thus given by:

$$C_{ox} = \varepsilon_0 \varepsilon_{sio2} / EOT$$

1.8

The physical measurement of the nanoscale oxide thicknesses is difficult because it evolves during the manufacturing process and physical measurements reach their limit when thickness become close to the nanometer. The extraction of EOT constitutes a more accurate and relevant measurement to exploit the  $V_{FB}$  variations with that of the oxide thickness. We will therefore express various equations in terms of EOT rather than the physical semiconductor oxide thickness.

#### Flat band voltage VFB

The flat band voltage ( $V_{FB}$ ) is the bias condition of the gate  $V_G$  at which there is no charge in the substrate, leading to flat energy bands at the interface ( $V_{Si} = 0$ ,  $Q_{Si} = 0$ ) (Figure 1.3 b). Thus the voltage associated with the applied potential is called the flat band voltage and is expressed as follows:

$$V_{FB} = \Phi_M - \Phi_{Si} + V_{OX}$$

1.9

The term  $V_{OX}$ , at flatband, is 0 for an ideal device (when no oxide charges or interfacial drops are present and Eq. 1.4 applies). For non-ideal cases,  $V_{OX}$  is not equal to 0 and so  $V_{FB}$  is influenced by oxide charges density and interfacial voltage drops such as dipoles. So for real devices it becomes a process dependent parameter, especially in bilayer high-k/SiO<sub>2</sub> oxide structures that are currently being used in advanced MOSFETs.

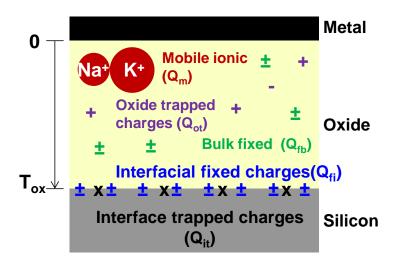

There are generally 4 types of charges possible in a MOSFET device that can affect the  $V_{FB}$  (Figure 1.5):

• The interface fixed charges Q<sub>fi</sub>, that can be located near the Si/SiO<sub>2</sub> interface, high-k/SiO<sub>2</sub> interface, metal/high-k layer [2]. Fixed oxide charges do not move or exchange charge with the underlying silicon and also do not change with the applied voltage.

- Bulk oxide charges Q<sub>bulk</sub> are the charges in the volume of the oxides and consists of the oxide trapped charges (Q<sub>ot</sub>) and the bulk fixed charges (Q<sub>fb</sub>). Like interface fixed charges, these do not move or exchange charge with the underlying silicon [3].

- The interface trapped charges (Q<sub>it</sub>) are positive or negative charges located at the Si/SiOx interface. They are due to structural defects, oxidation-induced defects or dangling bonds at this interface. Unlike fixed charges or trapped charges, interface trapped charges are in electrical communication with the underlying channel and can thus be charged or discharged, depending on the Si surface potential V<sub>Si</sub> [3].

- Mobile ionic charges (Q<sub>m</sub>) are primarily due to positive alkali ions in the oxide such as Na+, K+ and Li+ [4], incorporated during device processing steps.

Figure 1.5: Location of charges in thermally oxidized silicon [4]

The effect of each charge on the  $V_{FB}$  condition depends on its distance from the oxide/silicon interface and can be calculated from Gauss law. Assuming a uniformly distributed charge per unit volume,  $V_{FB}$  shift induced by bulk charges will then vary with the square of its thickness (or EOT) [2].  $V_{FB}$  shift induced by interfacial fixed charges results in a linear modification of the  $V_{FB}$  vs EOT plot for a given oxide.

It has been experimentally demonstrated that  $V_{FB}$  vs EOT plot is described by a straight line for SiO<sub>2</sub> and HfO<sub>2</sub> oxides [2] [5] [6]. Therefore, the impact of bulk charges in the dielectric layers is negligible. Moreover, recent studies have evidenced the independence of  $V_{FB}$  shift with HfO<sub>2</sub> thickness, implying that no isolated fixed charges are present at the HfO<sub>2</sub>/SiO<sub>2</sub> interface or in HfO<sub>2</sub> bulk. Indeed, any charge at HfO<sub>2</sub>/SiO<sub>2</sub> interface or in HfO<sub>2</sub> bulk would lead to increasing  $V_{FB}$  shift when HfO<sub>2</sub> thickness increases [6]. Based on these results, the  $V_{FB}$  equation including the charges at the Si/SiO<sub>2</sub> interface (Q<sub>Si/SiO2</sub>) can be written as [5]:

$$V_{FB} = \Phi_{M} - \Phi_{Si} - Q_{Si/SiO2} (EOT/ \varepsilon_{sio2})$$

1.10

As the threshold voltage is related to the  $V_{FB}$ , charges also directly influence the threshold voltage and most of the performance parameters of MOSFET devices, such as effective mobility, junction leakage, noise, reliability and breakdown voltage in discrete transistors and digital integrated circuits.

#### **Dipole effect**

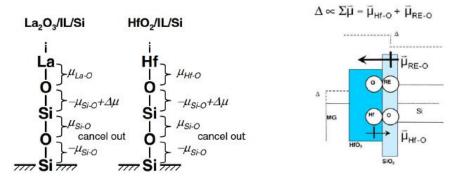

Interface dipoles can be present in the gate stack at the various interfaces, where they generate potential drops ( $\delta$ ) and so their effect on V<sub>FB</sub> is independent of the thickness of the oxides. Several models have therefore been proposed to explain dipoles at various locations in the gate stack, in particular at metal/high-k interface and at high-k/SiO<sub>2</sub>interface. Dipole formation at the interfaces have been mainly explained by these two phenomena

Electronegativity differences: Two materials in contact with each other will have atoms with different electronegativities at their interface. For instance at the interface between SiO<sub>2</sub> and high-k, an atom of oxygen is bonded to an atom of high-k on one side and to an atom of Si on the other. Each bond has a dipole moment μ, which depends on the charge Q carried by the bond and its length d. In bulk high-k or SiO<sub>2</sub>, the dipole moments compensate each other, but at the interface a net dipole moment is created, which is the sum of individual dipole moments. HfO<sub>2</sub> or La<sub>2</sub>O<sub>3</sub> thus creates a dipole in contact with SiO<sub>2</sub> (Figure 1.6). This mechanism has been utilized to explain V<sub>FB</sub> shifts due to dipole at many interfaces. Such as the dipole at the interface between metal gate and high-k dielectrics [7] [8], and also for the case of capping the top surface of the high-k layer with additives such as aluminum [9] or lanthanum [10].

Figure 1.6 Dipole moments associated with HKMG stack interfaces [11][12]

Oxygen vacancy formation: According to this model, difference of oxygen atomic density (σ) at the interface causes deformation and strain at the interface, leading to an increase of free energy of the interface. The free energy of the interface should be therefore minimized by the movement of oxygen from larger σ side to the smaller [10]. As a result, a charge imbalance at the interface is induced by the movement of oxygen as it is negatively charged. This mechanism has been used to explain V<sub>FB</sub> shifts due to dipole at the metal/high-k interface [13] [14], at high-k/SiO<sub>2</sub> interface [15] or at the Si/SiO<sub>2</sub> interface [16].

The final equation of the  $V_{FB}$  combining the effects of all the charges inside the gate stack and dipoles at the interfaces becomes:

$$V_{FB} = \Phi_{M} - \Phi_{Si} - Q_{Si/SiO2} (EOT/\epsilon_{sio2}) + \Sigma \delta$$

1.11

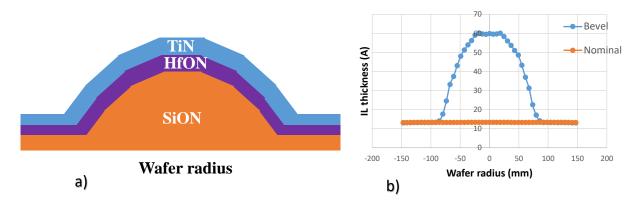

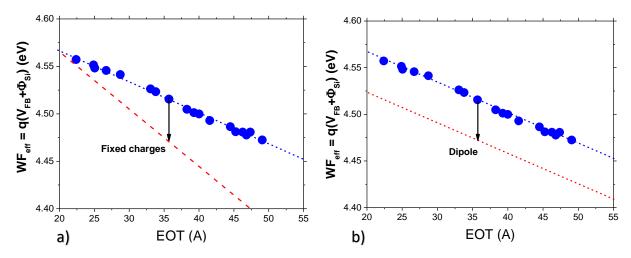

$V_{FB}$  and EOT can be calculated by fitting experimental capacitance voltage curves. The above relationship between  $V_{FB}$  and EOT can be used to extract gate stack charges and dipoles.  $QS_{i/SiO2}$  can be calculated from the slope of the  $V_{FB}$  vs EOT curve and  $WF_M + \delta$  can be estimated from the extrapolated  $V_{FB}$  value at EOT=0 [17]. Practically EOT is modulated along the wafer radius by varying the SiO<sub>2</sub> IL, called as the bevel process (section 1.3.3) which has been developed at STMicroelectronics's 300 mm wafer fab.

#### Metal effective work function

The work function of the metal  $WF_M$  is defined as the minimum energy needed to remove an electron from the metal to a point in the vacuum immediately outside the metal surface. For an ideal device without any charges and dipoles, it is given as follows:

$$WF_M = q\Phi_M = qV_{FB} + q\Phi_{Si}$$

1.12

We have seen that  $V_{FB}$  of real devices can be affected by various process steps that can introduce fixed charges at the interface or in the bulk of oxides and interface dipoles. In this case, equation 1.12 does not hold any longer and the concept of effective work function  $WF_{eff}$  has to be introduced.  $WF_{eff}$  takes into account not only  $q\Phi_M$  but also the  $V_{FB}$  contribution of the charges and dipoles in the gate stack. So the  $WF_{eff}$  is described as:

$$WF_{eff}/q = V_{FB} + \Phi_{Si} = \Phi_M + \Delta V_{FB}, \quad \Delta V_{FB} = -Q_{Si/SiO2} (EOT/\epsilon_{SiO2}) + \Sigma \delta$$

1.13

## **1.2** Gate stack fabrication process

#### **1.2.1 Gate dielectrics**

Gate dielectrics are responsible for the capacitive effect produced in a MOSFET device. Traditionally,  $SiO_2$  has been used as the gate dielectric, but continuous device scaling for future technology nodes required reduction in the thickness (or EOT) of gate dielectrics in order to maintain high drive current and adequate gate capacitance. This scaling of SiO<sub>2</sub> was challenged due to exponential increase in gate leakage currents as the thickness decreased [18].

In order to replace  $SiO_2$  and to overcome these problems,  $SiO_2$  incorporated with nitrogen was proposed to form oxynitrides ( $SiO_xN_y$ ). At the beginning this became an appropriate solution to increase MOSFET performance[19]. Compared to non-nitrided films, the oxynitrides films containing nitrogen atoms increased its diffusion barrier properties, leading them to be more resistant to further oxidation and diffusion of dopants from the gate to the channel and vice versa. Moreover, nitrogen atoms at the Si/SiO<sub>2</sub> interface resulted in the reduction of defect generation and traps in the oxide [20]. In addition, nitrogen increases the dielectric constant of the oxynitride. This increase is linear with the percentage of nitrogen, from  $"SiO_2 = 3.9$  to  $"Si_3N_4 = 7.8$  [21] and thus reduces gate leakage. SiON however reached its limits from the 45nm node because of the weak permittivity and degradation of reliability due to the presence of nitrogen atoms. Gate leakage on SiON dielectrics became superior to specifications recommended by the ITRS.

As an alternative to SiON gate dielectrics, a high permittivity (high-k) material was introduced to continue the aggressive scaling of advanced MOSFETs. Due to its high permittivity a larger thickness can be used, compared to SiON, while keeping the same EOT and thus decreasing the leakage current. The direct deposition of the high-k dielectric on the silicon substrate forms a layer of unintentional silica of poor quality and is detrimental to transistor electrical properties, such as threshold voltage, channel carrier mobility, interface traps and charges in the dielectric [22]. On the other hand, a well-controlled silicon oxide or oxynitride (SiO<sub>2</sub>, SiO<sub>x</sub>, SiON) (interfacial Layer (IL) deposited on Si substrate has excellent surface quality and therefore can reduce or even eliminate the above problems associated with a High-k/Si interface [23].

#### Interlayer dielectric growth

As mentioned above, the electrical properties of MOSFET devices are strongly correlated with structure and defects near and at the  $Si/SiO_2$  interface. High quality ultra-thin oxides films are not easily fabricated with conventional thermal oxidation methods. Therefore, enhanced techniques to grow ultra-thin  $SiO_2$  films with superior quality and performance have been designed and implemented in recent years. As discussed before, SiON has superior electrical properties compared to  $SiO_2$  and so we will focus on the deposition techniques for SiON.

The main fabrication techniques, used for  $SiO_2$  film growth, are the rapid thermal oxidation (RTO), in-situ steam generation (ISSG), rapid thermal chemical vapor deposition (RTCVD) and remote plasma enhanced chemical vapor deposition (RPECVD) [24]. Nitridation of SiO<sub>2</sub> films, formed by RTO or ISSG, by DPN (decoupled plasma nitridation) or RPN (remote plasma nitridation) have been investigated earlier [24]. Nevertheless, nitridation in amonia (NH<sub>3</sub>) is a simple way to introduce relatively high concentrations of nitrogen into SiO<sub>2</sub>. The ultra-thin oxynitride (SiON) films (between 8Å and 12 Å), used in this work as the interlayer dielectric, is fabricated at STMicroelectronics by performing first an enhanced ISSG oxidation of silicon at 800°C, followed by NH<sub>3</sub> nitridation and RTP anneal at 700°C.

### **High-k deposition**

The  $SiO_2$  or SiON dielectrics by themselves are not able to satisfy the gate leakage requirements at the 45 nm node and beyond. The high-k material has to meet several criteria to be considered as a candidate to replace  $SiO_2$ , as listed below. The high-k must:

- Have a high enough dielectric constant

- Have a large conduction and valence band offsets relative to metal Fermi level and to the conduction and valence bands of silicon, as gate leakage decreases with band offsets.

- Form a good quality interface with the channel so as not to degrade mobility

- Have good stability in the different stages of transistor fabrication, meaning retention of the amorphous phase at high temperatures. Indeed, a polycrystalline material could result in grain boundaries acting as current leakage paths.

- Have minimum traps and fixed charges

- Meet the feasibility criteria in industrial conditions (thin layers, short deposit times, low thermal budgets and cost)

- Meet the requirements in terms of reliability

Among the various potential candidates, Hafnium-based dielectrics (HfO<sub>2</sub> and HfSiOx silicates, HfSiON) best meet these criteria [24]. Within the International Semiconductor Development Alliance (ISDA), which included STMicroelectronics and IBM, HfSiON material was selected to succeed SiON in the technological nodes 32 / 28nm. Indeed, HfSiO silicates have better results than HfO<sub>2</sub>, because of better thermal stability, a gain in mobility and a reduction in charge trapping. However, it has been reported that HfO<sub>2</sub> has a higher dielectric constant, about 18-25 [25], compared to about 15 for HfSiO [26]. Moreover, Hf-based gate dielectrics have high band offsets, Ec = 1.5 eV and Ev = 3 eV [25], leading to leakage current densities at least two orders of magnitude lower than SiO<sub>2</sub>. The presence of nitrogen in the film (HfON or HfSiON) enhances the thermal stability relative to HfSiO, leading to amorphous films up to annealing temperatures of 1100°C [27]. This high thermal stability makes these dielectrics suitable for integration into the CMOS process flow, being able to handle the subsequent source and drain high temperature anneals.

Initially, physical vapor deposition (PVD) was used to deposit hafnium-based gate dielectrics [27]. Now, chemical vapor deposition (CVD) or Metal organic CVD (MO-CVD) and atomic layer deposition (ALD) are being used to deposit these layers. This has been done to meet the compositional control and conformality requirements of the films. The CVD or MO-CVD processes, used to deposit HfSiO films, uses metal organic precursors. ALD processes are used to deposit HfO<sub>2</sub> uses hafnium tetrachloride (HfCl<sub>4</sub>) as precursor. Finally, in order to incorporate nitrogen into the films to further increase the dielectric constant, nitridation methods such as Decoupled Plasma Nitridation are currently used. In 14 or 28 nm MOSFET devices fabricated at STMicroelectronics, HfON and HfSiON are deposited over the interlayer dielectric (SiON) by ALD or by MO-CVD respectively in order to keep a high mobility interface, followed by nitridation using DPN and Post-Nitridation Anneal before metal gate deposition. The resulting high-k layer has a thickness between 19Å and 21 Å.

## **1.2.2** Metal gate electrode and deposition techniques

### Choice of gate material

Poly-crystalline silicon (poly-Si) has been used for decades as the gate for MOSFET. It was used for its good electrical conduction properties when doped with impurities. However, poly-Si could not be used for advanced technological nodes and metal gates were introduced for several reasons mentioned below:

• Metal gates eliminate the depletion zone formed at the poly-Si and high-k interface that acts as a parasitic capacitance, and boron penetration effects. This thus reduces the EOT penalty and increases the ON current of the transistors.

- Poly-Si in contact with high-k causes the Fermi level pinning. This causes the modification of the Poly-Si Fermi level due the formation of dipole at the poly-Si and high-k interface [13].

- Surface phonon scattering degrades the electron mobility in the high-k, reducing the speed at which transistors can switch. Introduction of metal gate significantly increases the density of electrons in the gate electrode [28]. Therefore, the higher density of electrons in a metal screen out the vibrations and let current to flow more smoothly, compared to poly-Si gate with lower free electron concentration.

- Metal gates show less resistance compared to Poly-Si gate.

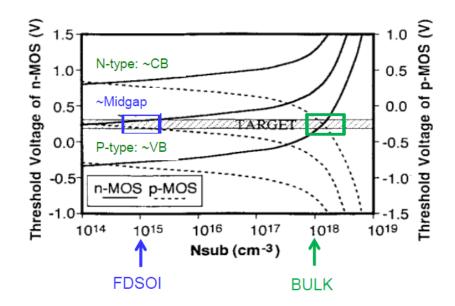

#### **Choice of Metal gate**

The first criteria for the choice of metal gate is its work function  $WF_m$  that determines the threshold voltage of the transistor. Advanced technology nodes requires low threshold voltage for both NFET and PFET devices. The effective work function target depends on the channel doping density [29] (Figure 1.7), as predicted by the term Nsc in Eq. 1.5. According to this, for high doping concentration, metals with workfunction close to the silicon conduction band (CB) or the silicon valence band (VB) are required, for NFETs and PFETs respectively [30]. In contrast, for low doping concentration, the target is almost midgap work functions, like TiN, at only 100 meV from either side of the intrinsic silicon Fermi level. Therefore, in fully depleted silicon on insulator (FD-SOI) devices with undoped Si channel, almost midgap metals will be required for low V<sub>T</sub>, in contrast to bulk technologies [31] [32].

Figure 1.7: Metal work function requirements as a function of channel doping density, to achieve low  $V_T$  for both NFET and PFET devices [29]

The second criteria for the choice of the metal gate is its thermal stability. This means that their microstructure should remain stable and that they do not react with the other layers. During the process of MOSFETs devices, the development of HKMG stack is followed by a high temperature annealing (around 1050°C) for source and drain dopant activation (S-D anneal). This process method is termed as the Gate First approach. Figure 1.8 shows that only the mid-gap metals, including TiN, and high WF<sub>m</sub> metals are thermally stable above 700°C [33]. In contrast, low WF<sub>m</sub> metals, being less electronegative, will tend to form an oxide at high temperature.

| Stability on SiO2 in Former Gas anneal<br>Stability of SiO2 in Former Gas anneal<br>Stability of SiO2 in Former Gas anneal |      |                                |                 |     |                 |                 |                 | 13<br>IIIA | 14<br>IVA |     |                 |    |

|----------------------------------------------------------------------------------------------------------------------------|------|--------------------------------|-----------------|-----|-----------------|-----------------|-----------------|------------|-----------|-----|-----------------|----|

|                                                                                                                            | 3    | > 700℃<br>4 5 6 7 8 9 10 11 12 |                 |     |                 |                 |                 |            | 12        | В   | С               |    |

|                                                                                                                            | IIIB | IVB                            | vв              | -   | VIIB            | -               | viII            |            | IB        | IIB | Al <sup>n</sup> | Si |

|                                                                                                                            | Sc   | Tin                            | Vn              | Cr  | Mn <sup>n</sup> | Fe              | Сор             | Nip        | Cu        | Zn  | Ga              | Ge |

|                                                                                                                            | Y    | Zr <sup>n</sup>                | Nb <sup>n</sup> | Mom | Tc              | Ru <sup>p</sup> | Rh <sup>p</sup> | PdP        | Ag        | Cd  | In              | Sn |

|                                                                                                                            | La   | Hfn                            | Tan             | Wm  | Rep             | Os              | Ir P            | Ptp        | Au        | Hg  | Τl              | Pb |

| $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                   |      |                                |                 |     |                 |                 |                 |            |           |     |                 |    |

Figure 1.8: Characteristics of metals in terms of thermal stability and workfunction, indicated by the gray level for the stability and an indication of N-like or P-like behavior index of each element [33]

Another effect of the high temperature annealing is the diffusion of oxygen from the metal gate towards the pedestal oxide and thus degrading the EOT of the device. This has been observed in particular for P type metals such as tungsten, platinum or rhenium but solubility of oxygen in pure titanium (Ti) is high (10%). In case of a Ti/HfO<sub>2</sub>/SiO<sub>2</sub>/Si stack, annealing even leads to the removal of some interfacial oxide [9]. This is due to the diffusion of oxygen from the pedestal SiO<sub>2</sub>, through the HfO<sub>2</sub>, toward the TiN gate due to the high solubility of oxygen in titanium nitride (TiN) and is called the oxygen scavenging effect. This strong affinity of TiN for oxygen makes it possible to reach EOTs of the order of 1 nm. All the advantages mentioned above (mid gap WF<sub>M</sub>, excellent thermal stability and the scavenging effect), makes TiN almost indispensable in a Gate First integration strategy.

#### Metal gate deposition techniques

TiN metal films are mainly deposited by Atomic Layer Deposition (ALD) and Physical Vapor Deposition (PVD) techniques. ALD is a thin film deposition technique that is based on the sequential use of a gas phase chemical process. ALD makes atomic scale deposition control possible and provides extremely conformal, uniform thickness and low impurity level films. It has successfully been used to deposit TiN films from TiCl<sub>4</sub> and NH<sub>3</sub> precursors [34]. However, despite

these advantages TiN metal gate was not deposited by ALD in our work at STMicroelectronics. The main limitations of ALD were the slow deposition rate and high cost, which has limited its use in the semiconductor industry. However, ALD is becoming the preferred choice for applications that require high global thickness non-uniformity and conformal step coverage, such as for extremely scaled devices with gate last integration scheme. Nevertheless, for our work that uses the gate-first processes, such conformal step coverage is not essential. For this reason, Radio-Frequency PVD (RF-PVD), allowing deposition at room temperature and at higher deposition rates, have been chosen for metal gate applications at STMicroelectronics.

#### **Physical Vapor Deposition**

PVD processes include a variety of thin film deposition methods that are used to deposit thin films atomically by means of fluxes of individual neutral or ionized species. Cathodic arc deposition, electron beam physical deposition, evaporative deposition, pulsed laser deposition and sputter deposition are some examples of physical vapor deposition methods. In our work, TiN metal gate films has been deposited by the sputtering method.

Sputtering is the process of removing surface atoms or molecules from a solid target by the bombardment of ions and involves ejecting those atoms or molecules from a source (target) onto a substrate (silicon wafer). Sputtering, unlike evaporation, does not require melting the metal to be deposited. Therefore, refractory metals such as titanium (Ti) and tungsten (W), that are very difficult to melt, can be used. Sputtering also preserves the original composition of the target material. In addition, sputtering allows the deposition of many different materials by combining materials from solid and gaseous sources, which are introduced into the vacuum chamber either before or during deposition. This form of sputter deposition is called reactive sputter deposition.

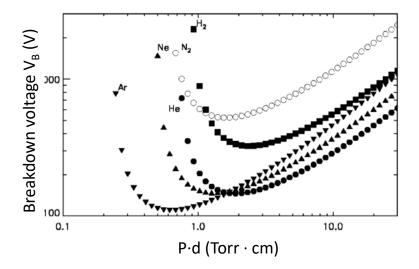

The sputtering process is carried out in a vacuum chamber in order to avoid contaminants to interfere with the deposition process and to establish the pressure required by the sputtering plasma. The high vacuum pumping (in the  $10^{-8}$  Torr range) is done by cryopumps. In a simple DC sputtering system, the target plays the role of the cathode and the substrate, that of the anode. When a DC voltage equal to a voltage known as breakdown voltage (Vb) is applied between both electrodes, a plasma is created. The electrons collide with argon and create positively charged argon ions (Ar+), which are strongly attracted to the negatively charged cathode (the target). The argon ions collide with the target surface and some of them causes surface atoms of the target to be ejected. The sputtered atoms travel to the substrate where they are deposited as a film.

For a given gas, the minimum voltage Vb necessary to create a stream of electron between the electrodes is a function of the product of the pressure (p) and the electrodes gap distance (d) (parameter pd in Fig. 1.9). The curve of voltage versus pd is called Paschen's curve. Examples of Paschen's curves obtained for different gases are shown in Fig. 1.9. The pressure has to be high enough to keep a high density of Ar+ ions in the plasma to sputter the target but low enough to reduce the collisions of the sputtered atoms with Ar atoms. A pressure too low or too high have to be compensated by higher breakdown voltages, as described in Figure 1.9.

Figure 1.9: Paschen curves obtained for Helium, Neon, Argon, Hydrogen and Nitrogen [35]

Sputtering effects can be enhanced by adding magnets behind the cathode to a simple DC sputtering system. In this case, the sputtering rate is improved because the Ar ionization efficiency is enhanced. Electrons are confined because they tend to follow the magnetic field lines, ionizing more argon atoms in their path. In this way, both electron and Ar+ ions density are increased in a DC magnetron system. On one hand, with the increased electron density, Vb can be decreased from 5000 V - 10000 V in a simple DC sputtering system to only 400 V – 800 V in a DC magnetron system. On the other hand, due to the increased density of Ar+ ions, it is possible to lower the sputtering chamber pressure. At lower pressures, the sputtered atoms have fewer collisions on their path to the substrate which results in an increased deposition rate. Finally, the electron confinement in a magnetic field near the target also reduces electron bombardment of the substrate. This results in much less heating of the substrate.

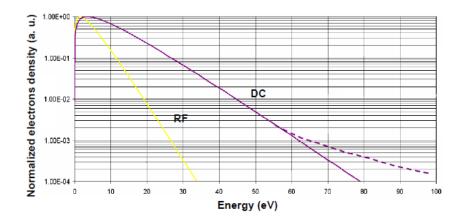

In addition, a Radio Frequency (RF) generator operating at a frequency of 13.56 MHz (standard in industry) can be coupled to a DC power. The main interests of RF-PVD deposition are the reduction of the breakdown voltages and the improvement of film deposition uniformity. Indeed, the voltage needed to ignite the plasma is reduced because oscillating electrons are able to ionize more Ar gas. A direct consequence of the reduction of the breakdown voltage is that the metal atoms are ejected with less energy, limiting the damage that could be caused on the high-k layer by bombardment on the wafer during the plasma sputtering. This is a critical point because any significant damage can be detrimental for gate stack integrity and transistor electrical properties. In addition, less high energetic electrons are provided in a RF sputtering plasma compared to DC plasma for the same density of electrons, as shown in Figure 1.10.

Figure 1.10: Energetic distribution of electrons in RF (yellow) and DC (purple) plasma [36]

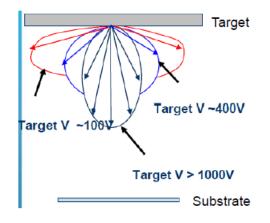

Figure 1.11: Representation of sputtering angle vs. breakdown voltage [36]

The breakdown voltage reduction also allows to increase significantly the sputtering angle of the ejected metal atoms, as shown in Figure 1.11. Consequently, the thickness uniformity can be improved to about 1% for thicknesses < 100 Å.

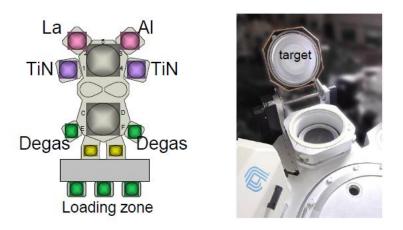

The Endura platform supplied by Applied Materials has been used in this work for TiN metal gate deposition in RF-PVD process chambers (Figure 1.12). Apart from TiN deposition chamber, two other chambers are present to deposit aluminum (Al) and lanthanum (La). Each RF-PVD process chamber contains a target material (Ti, Al, La) for thin films deposition.

Figure 1.12: On the left, Endura platform with 4 RF-PVD chambers for TiN, lanthanum and aluminum deposition. On the right, photo of a deposition chamber

Figure 1.13: Schematic of a RF-PVD chamber used to deposit TiN metal gate layers

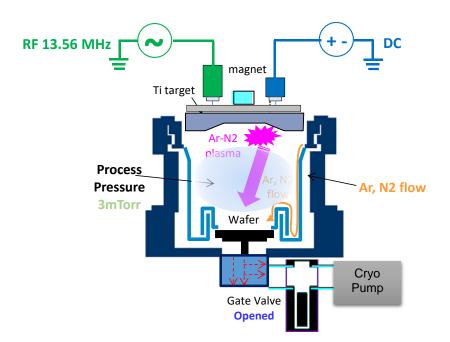

In general, all RF-PVD chambers are composed of a RF generator, a DC power supply, a cryo pump system for ultra-high-vacuum and an Ar mass-flow controller to regulate the argon flow into the chamber. Reactive RF sputter chambers used to deposit TiN contains, additionally, a nitrogen mass-flow controller, as shown in Figure 1.13. The stoichiometry of the deposited thin films can be controlled by adjusting the flow of these gases. The RF and DC power can be controlled by tuning the parameters of their respective generators. The partial pressure of Ar and N<sub>2</sub> gases (and

so the total chamber pressure) can be controlled by the flow of these gases from the respective mass-flow controllers and by adjusting the gate valve position (mid-gate to gate-open positions). In chapter 4, the impact of RF power and partial pressure on TiN properties will be investigated.

#### **TiN films deposition**

TiN is formed by reactive sputtering of a pure Ti target in a nitrogen-containing ambient, typically Ar/N<sub>2</sub>, in a RF-PVD chamber with combined DC and RF generators. Unlike, TiN films deposited by ALD or CVD, the nitrogen and titanium do not combine in the gas phase, but on the surface of the target, chamber walls, and on the wafer. The TiN metal gate layer used in this work is deposited with a gradient profile of nitrogen and its deposition proceeds as follows: first, the Ti target is completely de-nitrided by pure Ar sputtering. Next, during film deposition, the chamber is backfilled with an Ar/N<sub>2</sub> mixture and plasma is initiated with a high volumetric flow rate of nitrogen  $(N_2/(Ar + N_2) = 0.7)$  in order to progressively cover the surface of the target with nitrogen. As a result, only titanium is sputtered from the surface of the target for the first monolayers deposited over the high-k. As nitrogen covers the target surface, TiN begins to sputter and nitrogen composition gradually increases in the TiN film being deposited. At this point, a noticeable drop of the sputter rate occurs due to the decrease in sputtering yield caused by the nitridation of Ti target surface. Accordingly, the deposition rate decreases from 1.6 Å/s to 0.4 Å/s during the TiN deposition with a total pressure of about 3 mTorr and a DC and RF power of 700W and 600W, respectively. A gradient profile of nitrogen into TiN results in better gate leakage and better reliability [37].

#### **Deposition of Aluminum and Lanthanum monolayers**

Al and La monolayers are deposited between the high-k and TiN gate for gate stack work function engineering. These additives forms dipoles at the IL and HK interface and hence modulate the WF<sub>eff</sub>, this topic will be discussed in detail in later sections. While TiN is deposited with combined DC and RF powers, Al and La are deposited with only RF sputtering at smaller deposition rates because desired thicknesses are much thinner (from  $2\text{\AA}$  to  $6\text{\AA}$ ) compared to TiN. RF power and Ar flow conditions are chosen to optimize the deposition rate and the uniformity of the monolayers. Increasing the RF power and reducing the Ar flow results in a higher deposition rate, but an increment of the Ar flow improves the uniformity, as a result of the reduction of deposition rate. In the selected deposition conditions, the deposition rate is extremely low, in the range between 0.1 Å/s and 0.3 Å/s.

### 1.2.3 Metal gate integration in 14 nm Fully-Depleted SOI devices

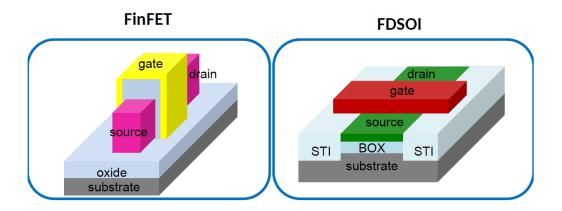

As CMOS technology scales down, two approaches have been pursued by the industry to overcome the fundamental limits of traditional planar bulk transistors. One is the introduction of a Tri-gate or FinFET transistor at the 22 nm/16 nm node [38]. The other is the Fully Depleted Silicon On Insulator (FDSOI) architecture, shown in Figure 1.14, which provides a simplified planar manufacturing process compared to 3-D FinFET technology. Although FinFET architectures offer impressive drive currents per footprint at low supply voltages because of the 3-D conduction channel and excellent electrostatic control, they have high gate and parasitic capacitances, proportional to the 3-D effective width increase, which negatively impacts both the speed and active power consumption [39]. In addition, complexity of FinFET technology has created new challenges for many design teams because their current tools and techniques may not have enabled them to design their IP blocks optimally for FinFET processes, delaying the time to market.

Figure 1.14: Scheme of the FinFET and the Fully-Depleted Silicon-on-Insulator [40].

In contrast, FDSOI technology is derived from bulk design rules and its process technology [41] and the design transfer is thus less complicated. Only few analog parts need to be adopted to the FDSOI technology. It is a planar technology that reuses ninety percent of the process steps used in the bulk counterpart and the overall manufacturing process in FDSOI is 15% less complex, leading to lower cycle time and reduced manufacturing costs. The manufacturing tools for FDSOI are identical to the last generation of bulk processes. FDSOI transistors are manufactured on an ultrathin buried oxide (BOX) layer of 20 nm. Silicon channel thickness is about 6 nm. Shallow Trench Isolation (STI) feature authorizes the lateral insulation between adjacent semiconductor device components.

### **1.2.4** Introduction of additives for workfunction engineering

The effective work function (WF<sub>eff</sub>) values of metal electrodes must satisfy the  $V_T$  requirements of specific devices. In undoped-channel 14nm FD-SOI devices, WF<sub>eff</sub> at only 100 mV from the midgap are required [32] [29], which makes a very fine adjustment of the effective work function of metal electrodes even more necessary.

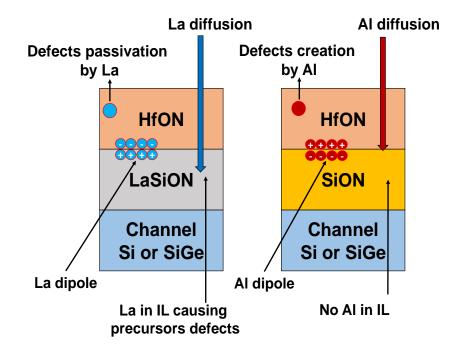

#### Lanthanum (La) for NFETS

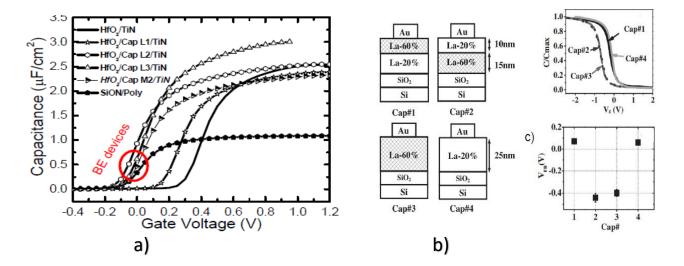

In order to reach the WF<sub>eff</sub> specifications for NFETs, La has been introduced into the gate stack. La<sub>2</sub>O<sub>3</sub> and La-silicate have been studied as alternate gate dielectrics [42][43]. Insertion of La<sub>2</sub>O<sub>3</sub> capping layers deposited above the high-k layer has also been extensively studied [10][44]. Narayanan et al. proposed to insert nanoscale capping layers containing lanthanum into HfO<sub>2</sub>/TiN stacks [10] in a conventional gate first flow (Figure 1.15 a). In this way, lanthanum induced large V<sub>FB</sub> shifts towards N+, from 4.43 eV (without La) to 4.05 eV (with La). However, it is indicated that the La thickness is a critical parameter to optimize, it must be thick enough to shift the WF<sub>eff</sub> towards N+ but not so much that lanthanum near or in the Si/SiO<sub>2</sub> interface degrades the mobility. Narayanan proposed that the WF<sub>eff</sub> shifts can be either due to positively charged mobile oxygen vacancies formed upon the substitution of Hf<sup>4+</sup> in HfO<sub>2</sub> with lower valence La<sup>3+</sup> and/or a dipole at the metal/high-k interface due to differences in electronegativities between La and Hf. In contrast, Yamamoto et al. [45] experimentally evidenced that the most plausible origin for the V<sub>FB</sub> shift is the formation of a dipole layer at the HfLaOx/SiO<sub>2</sub> interface (Figure 1.15 b).

The potential of metallic lanthanum deposited by RF-PVD inserted into TiN metal gate has also been evaluated in the multilayer TiN/La or TiN/La/TiN structure [46][37] [6] [47](Figure 1.16) and in the alloyed TiLaN metal [48]. Apart from the WF<sub>eff</sub> shift, these structures were proposed for another benefit: the interlayer scavenging effect. La ions remove oxygen from the interlayer to decrease the overall EOT of the devices and so suppressed the interlayer growth to extremely small values of around 1nm.

Figure 1.15: a) nFET CVs as a function of increasing La cap thickness showing the Wf<sub>eff</sub> tunability by La [10] and b) Schematic description of MOS capacitors with different La concentration profiles in HfLaOx films, their CV curves and V<sub>FB</sub> values [44]

Figure 1.16: a)  $V_{FB}$  vs. EOT plot for TiN gate with La and Al cap layers [46] and b) Effective workfunction (Wf<sub>eff</sub>) vs La or Al dose diffused inside the gate stack [47]

#### Aluminum (Al) for PFETS

In order to reach the WF<sub>eff</sub> specification for PMOS, Al has been extensively used to shift the WF<sub>eff</sub> towards P+. The introduction of Al<sub>2</sub>O<sub>3</sub> as an alternate high-k dielectric has been studied [49][50][51]. Al<sub>2</sub>O<sub>3</sub> layers has also been incorporated either at the SiO<sub>2</sub>/Hf-based oxide interface or above Hf-based high-k dielectric. When a thin Al<sub>2</sub>O<sub>3</sub> layer was deposited between the SiO<sub>2</sub> and HfO<sub>2</sub> layers, WF<sub>eff</sub> increased up to +900 meV compared to SiO<sub>2</sub> reference [5]. In this work it was proved that this Wf<sub>eff</sub> shift was indeed due to a dipole effect at the SiO<sub>2</sub>/high-k interface. Deposition of a thin Al<sub>2</sub>O<sub>3</sub> layer on the top of HfO<sub>2</sub> or HfSiON also induced an increase of the WF<sub>eff</sub> towards P+, but the shift was smaller (100-200 meV) [52] compared to capacitors with Al<sub>2</sub>O<sub>3</sub> below HfO<sub>2</sub>. The shift towards P+ in a gate-first integration has been explained by the diffusion of Al towards the bottom HfO<sub>2</sub> interface [52][53], creating a dipole layer at the HfO<sub>2</sub>/ SiO<sub>2</sub> interface as for Al<sub>2</sub>O<sub>3</sub> directly deposited at this interface (Figure 1.17).

The introduction of metallic aluminum deposited by RF-PVD and inserted between two TiN layers (TiN/Al/TiN structure) has also been previously studied [46][47][54][55] (Figure 1.16).

Figure 1.17: VFB variations of n-MOS and p-MOS capacitors with HfO2/ Al2O3 dielectrics [53]

### Sacrificial metal gate-first process

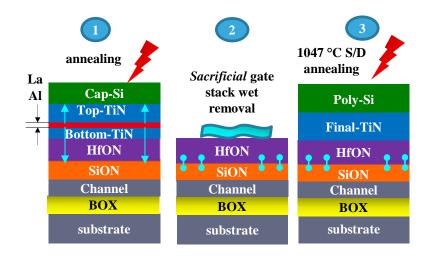

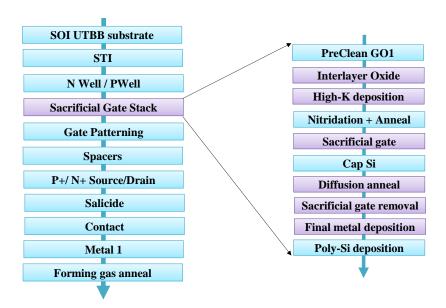

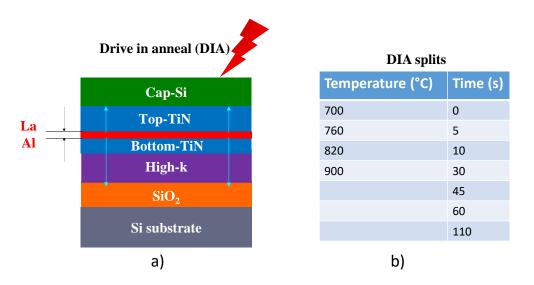

In this work, La and Al additives are introduced into the HKMG stack by the sacrificial gate process. Once interlayer and high-k dielectrics have been deposited on the Si substrate, metal gate containing the additives is deposited following the steps given below, and shown in Figure 1.18.

- 1. First, the sacrificial multi-layer metal gate stack, composed of a TiN layer and monolayers of La or Al additives in between, is deposited in the Endura RF-PVD system described in the section 1.2.2.

- 2. Next, poly-Si is deposited as a capping layer on the top, followed by a thermal treatment under  $N_2$  atmosphere at certain temperature and for a duration, to activate the diffusion of additives into the High-k/SiON stack. This step is called the drive-in-anneal (DIA).

- 3. The sacrificial gate stack is then removed by a chemical wet solution.

- 4. Finally, a poly-Si/TiN electrode without additives is deposited, followed by gate patterning. Later, spike annealing at 1047°C is done, which is responsible of the Source-Drain (S-D) dopant activation.

Figure 1.18: Sacrificial gate-first approach: 1) sacrificial gate deposition and annealing, 2) sacrificial gate stack wet removal and 3) final gate deposition and source-drain annealing

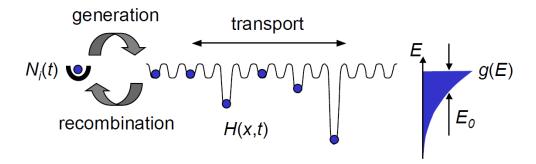

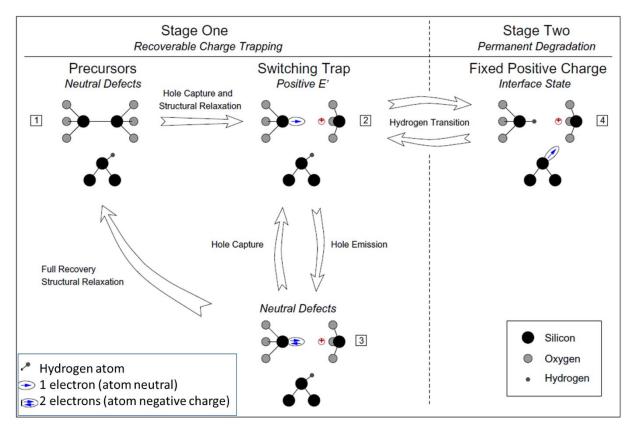

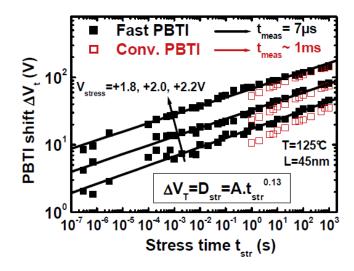

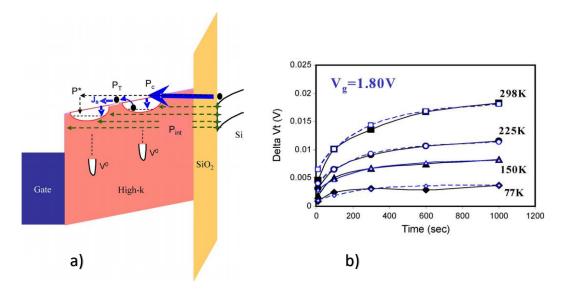

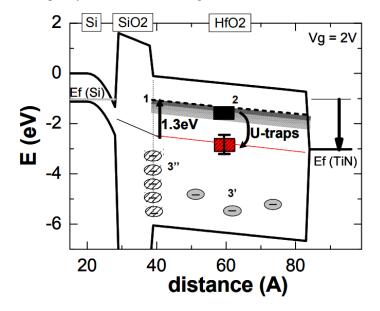

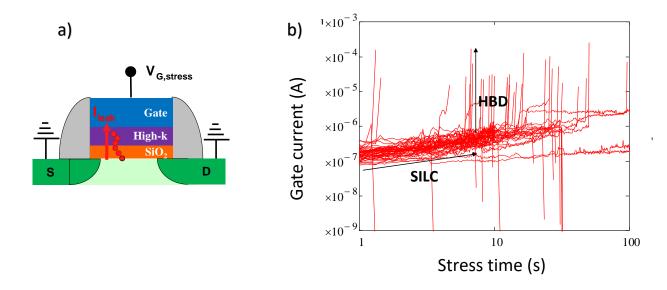

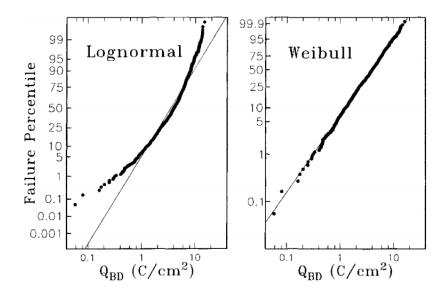

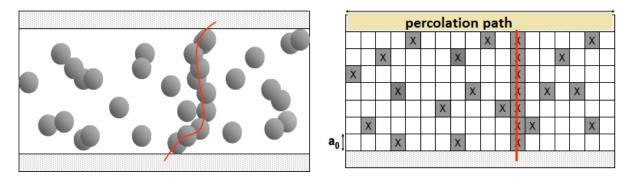

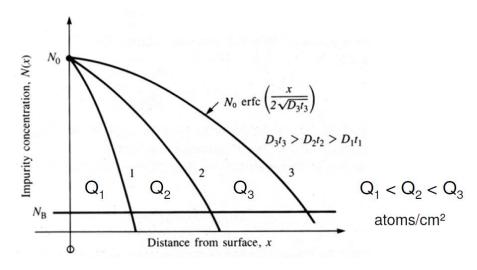

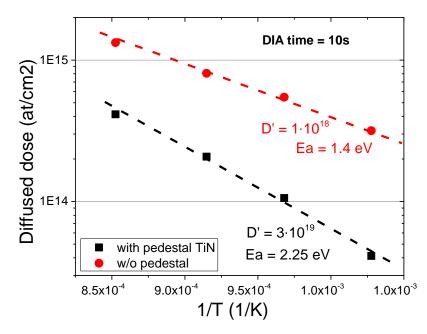

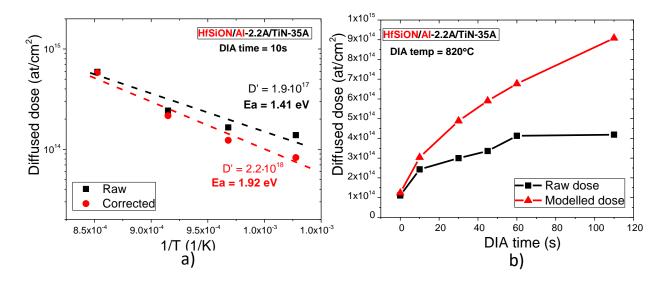

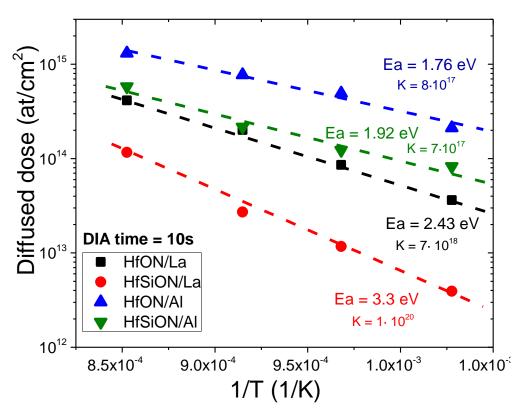

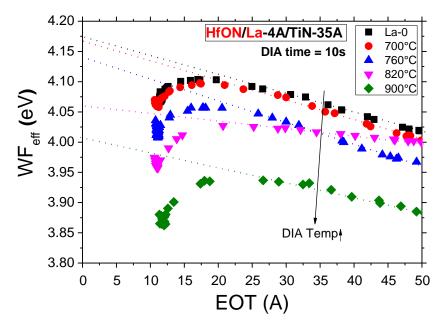

## **1.3 Process flow**