## Cryogenic electronics and quantum dots on silicon-on-insulator for quantum computing

Heorhii Bohuslavskyi

#### ▶ To cite this version:

Heorhii Bohuslavskyi. Cryogenic electronics and quantum dots on silicon-on-insulator for quantum computing. Quantum Physics [quant-ph]. Université Grenoble Alpes, 2018. English. NNT: 2018GREAY080. tel-02183484

## HAL Id: tel-02183484 https://theses.hal.science/tel-02183484

Submitted on 15 Jul 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité: NANOPHYSIQUE

Arrêté ministériel : 25 mai 2016

Présentée par

#### Heorhii BOHUSLAVSKYI

Thèse dirigée par Marc SANQUER et codirigée par Sylvain BARRAUD

préparée au sein du Laboratoire d'Electronique et de Technologie de l'Information (LETI - CEA) dans l'École Doctorale de Physique de Grenoble

## Electronique cryogénique et réalisation de boîtes quantiques sur substrat SOI pour le calcul quantique

# Cryogenic electronics and quantum dots on silicon-on-insulator for quantum computing

Thèse soutenue publiquement le **14 décembre 2018**, devant le jury composé de :

#### **Monsieur Marc SANQUER**

Directeur de Recherche, CEA-INAC, Service de PHotonique ELectronique et Ingénierie QuantiqueS (PHELIQS), Directeur de thèse **Monsieur Sylvain Barraud**

Ingénieur de Recherche, CEA-Leti, Département DCOS, Laboratoire SCME/LICL, Encadrant de thèse

#### Monsieur Michel Pioro-Ladrière

Professeur agrégé, Université de Sherbrooke, Rapporteur

Monsieur Yong Jin Directeur de Recherche, CNRS/C2N, Rapporteur

#### Monsieur Christian Enz

Professeur, École Polytechnique Fédérale de Lausanne, Examinateur

#### Monsieur Gérard Ghibaudo

Directeur de Recherche, IMEP-LAHC - UMR 5130, Président

#### Monsieur Philippe Galy

Directeur Technique, STMicroelectronics, Invité

## Résumé

Cette thèse étudie l'électronique cryogénique et la réalisation de boîtes quantiques (QD) sur substrat SOI pour le calcul quantique. Deux technologies sont proposées pour la démonstration de boîtes quantiques d'électrons (trous). La première s'appuie sur les dispositifs Trigate SOI développés au CEA-LETI et la seconde exploite la technologie FD-SOI 28 nm développée par STMicroelectronics. Dans un premier temps, les dispositifs à doublegrille du LETI sont mesurés à très basse température (60 mK) pour mettre en avant le principe d'exclusion de Pauli pour les premiers trous confinés à l'intérieur des deux QD. Au travers de cette expérience réalisée sur un double QD nous étudions une brique élémentaire permettant à terme l'initialisation et la lecture d'un qubit. Cette expérience a par la suite été étendue à d'autres dispositifs possédant quatre grilles pour lesquels un protocole de mesure est proposé pour la démonstration de deux qubits de spin d'électron. Dans un second temps, nous avons adressé la question du contrôle, de la lecture et de la manipulation des qubits de spin par une électronique pouvant fonctionner à basse température. Les performances digitales et analogiques des transistors FD-SOI ont été étudiées sur une large gamme de température. La réduction de la température montre une nette amélioration de la mobilité des électrons et des trous mais également une plus faible pente sous le seuil (SS) qui s'accompagne également d'une augmentation de la tension de seuil  $(V_{TH})$ . La saturation de la SS pour les faibles températures est expliquée à l'aide d'un modèle analytique développé dans le cadre de cette thèse. En modélisant une queue étroite de densité d'états près des bords des bandes de conduction et de valence et en utilisant la statistique de Fermi-Dirac, un excellent accord est obtenu entre les mesures et le modèle. L'ajout d'une variation exponentielle dans la densité de pièges d'interface permet de reproduire l'évolution de la SS sur plus de 6 décades de courant. Par ailleurs, nous montrons que l'effet d'une polarisation face arrière qui permet d'ajuster la  $V_{TH}$  des transistors FD-SOI pour viser des applications haute performance ou basse consommation fonctionne parfaitement à basse température. La modulation de la  $V_{TH}$  reste la même de 300 K à 4 K pour les grandes et petites longueurs de grille des transistors NMOS/PMOS. Afin de tirer avantage de la technologie FD-SOI et d'évaluer son intérêt pour l'électronique cryogénique, nous avons caractérisé plusieurs oscillateurs en anneaux (RO) jusqu'à 4 K. L'étude a été réalisée en deux temps. Dans un premier temps, l'augmentation de la  $V_{TH}$  à basse température n'a pas été corrigée. Puis, cette augmentation de la  $V_{TH}$  a été corrigée grâce à la polarisation face arrière afin de conserver la même  $V_{TH}$  que celle mesurée à 300 K. Afin de conserver les avantages tirés des plus fortes mobilités des porteurs à basse température, nous montrons que la  $V_{TH}$  doit être corrigée pour réduire significativement le délai de commutation d'une chaine d'inverseurs. Nous montrons qu'à 4 K un régime de fonctionnement optimal alliant à la fois haute performance et basse consommation peut être obtenu avec une tension d'alimentation  $(V_{DD})$  de 0.3 V contre 1 V à 300 K. Cela permet de réduire de façon significative la dissipation statique et dynamique des RO. Un produit Energie-Délai de 6.9 fJ·ps avec un délai par étage de 37 ps sont obtenus à  $V_{DD} = 0.325 \text{ V}$  grâce à l'utilisation de la polarisation face arrière. Pour finir, nous discutons de la dualité des transistors FD-SOI canal court qui peuvent être utilisés soit comme MOS-FET ou comme transistors à électron unique. La présence de QD dans les transistors FDSOI est démontrée avec des caractéristiques proches de celles obtenues avec d'autres architectures (type nanofil) offrant ainsi des perspectives intéressantes pour une future co-intégration d'une électronique cryogénique avec des qubits de spin réalisés à partir d'une même plateforme industrielle.

## Abstract

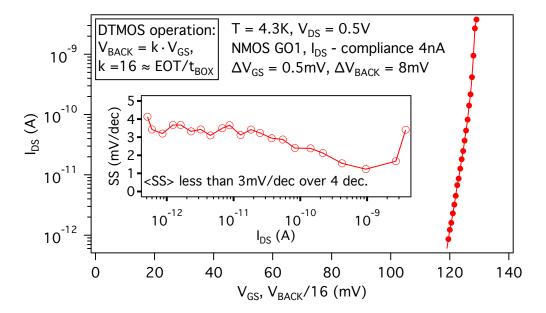

This thesis studies cryogenic electronics and quantum dots on silicon-on-insulator (SOI) for quantum computing. Different types of electron and hole quantum dots are fabricated with Leti's SOI nanowire (NW) and planar 28 nm FD-SOI technology. In the first part, Pauli Spin Blockade (PSB) is studied for the first holes down to 60 mK. We show that it is governed by a strong spin-orbit coupling (SOC). The intradot relaxation rate of 120 kHz was found for the first holes. The access barriers tunability realized with additional gates was proven to be efficient regarding the isolation of qubit from source/drain metallic leads. Following the recent demonstration of electron-dipole spin resonance (EDSR) achieved in electron quantum dots confined in the corners of silicon nanowire (CDs), we deeply investigated quantum dots in several n-type samples under different body-biasing conditions. Based on preliminary cryogenic transport measurements, an operation protocol for a compact two electron spin qubit gate has been proposed.

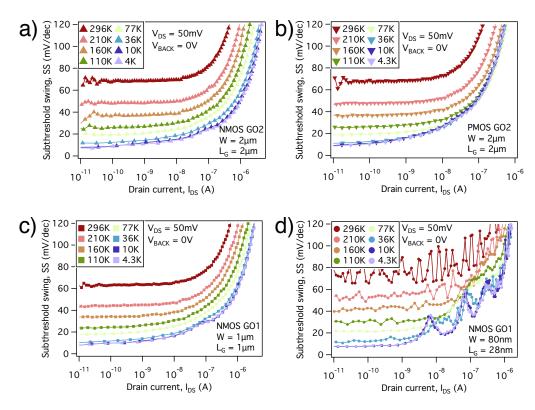

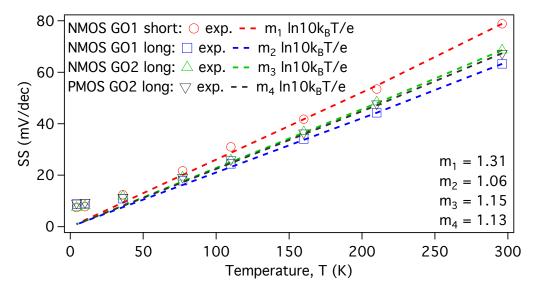

Regarding cryogenic electronics required for efficient control, manipulation and read-out of a large number of qubits, the low temperature digital and analog performance of 28 nm FD-SOI MOSFETs were analyzed from room temperature down to 4 K. Significant improvements in transistor performance are achieved with a clear enhancement of carrier mobility and a strong reduction of subthreshold swing (SS), even for short-channel devices with gate length down to 28 nm. The saturation of the subthreshold swing at low temperature is explained with a new analytical model developed in this thesis. By introducing a narrow tail in the density of states at the edges of the conduction and valence bands and using the Fermi-Dirac statistics, an excellent agreement of SS is achieved between experiments and modeling. The analysis of the  $SS-I_{DS}$  metric under different forward body-biasing (FBB) conditions has revealed that the increased density of interface traps cannot be responsible for the SS saturation at low temperature. By adding a slight exponential variation in the interface trap density, we show that the  $SS-I_{DS}$  curve can be well reproduced over more than 6 decades, paving a way for an efficient cryogenic design of CryoCMOS. In a

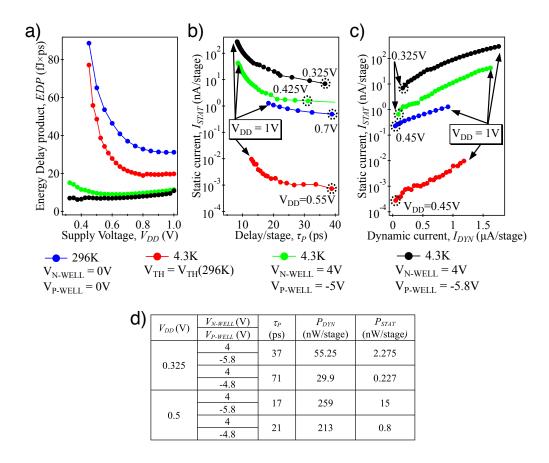

second time, the cryogenic performance of Ring Oscillators (RO) down to 4 K was investigated. We have shown that the optimal supply voltage can be reduced down to 0.3 V. This allows to efficiently reduce the dynamic and static power dissipations. At the same time, a small Energy-Delay product of 6.9 fJ·ps with a delay per stage of 37 ps was achieved at  $V_{DD}=0.325$  V under aggressive FBB.

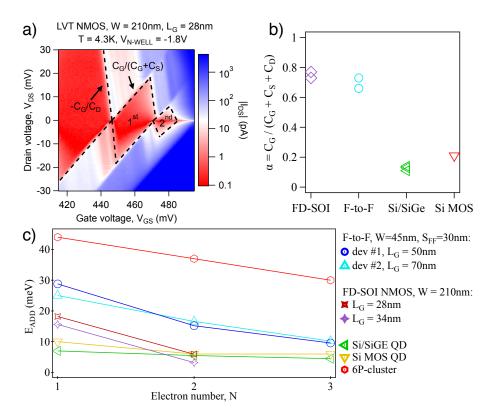

Finally, in the last chapter, the duality of short-channel FD-SOI transistors operation as FETs or SETs is demonstrated at 4 K. By benchmarking the QDs with respect to the common silicon platforms, we show that 28 nm FD-SOI technology has a great potential for both cryogenic electronics and qubits.

## Thesis outline

This thesis consists of six chapters and is organized as follows. Chapter 1, the current challenges towards silicon-based large scale quantum computing are reviewed. We first start with a brief introduction into the physics of quantum bits (qubits) and list the major achievements recently obtained in the silicon spin qubit progress. This includes the realization of a robust silicon electron qubits in purified silicon as well as the demonstration of CMOS compatible electron and hole qubits fabricated on 300 mm silicon substrates using Leti's silicon-on-insulator (SOI) nanowire technology. Then, more sophisticated few-quantum bits experiments are mentioned and the challenges towards many-qubits system regarding the requirements for long-range coupling, advanced solutions for qubit's readout, scalable architectures, purification of natural silicon to improve the spin qubit performance, the optimal temperature of qubit operation and the need of cryogenic electronics to efficiently control qubits. Indeed, a particular attention to cryogenic electronics (CryoCMOS) based on advanced CMOS technologies was a driving force of this thesis.

Then, low temperature experiments on multi-gate nanowire transistors are described in the next chapter 'Silicon Nanowire Technology for Qubits'. First, the fabrication of SOI nanowire multi-gate devices is briefly described. Pauli Spin Blockade (PSB) for the first holes is studied and the role of the spin-orbit coupling is analyzed down to 60 mK. Moreover, electrostatic tunability of access barriers using a p-type device with four gates in series is demonstrated and its importance regarding improvements in hole spin qubit performance is discussed. Then, the electron quantum dots confined in the corners of nanowire (corner dots) are reviewed for all-electrical electron spin control using electron-dipole spin resonance (EDSR). The importance of using a special design with split-gates (Face-to-Face) is emphasised. We study electron corner dots in several n-type devices and discuss the role of disorder and dopants in the channel using addition energy values as the main metric. Our analysis of low temperature stability diagrams is supported with realistic simulations. Finally, by investigating different double

quantum dot (DQD) regimes in a n-type device with four gates, we propose an operation principle for the demonstration of CMOS two-qubit gate, the building block of quantum computers.

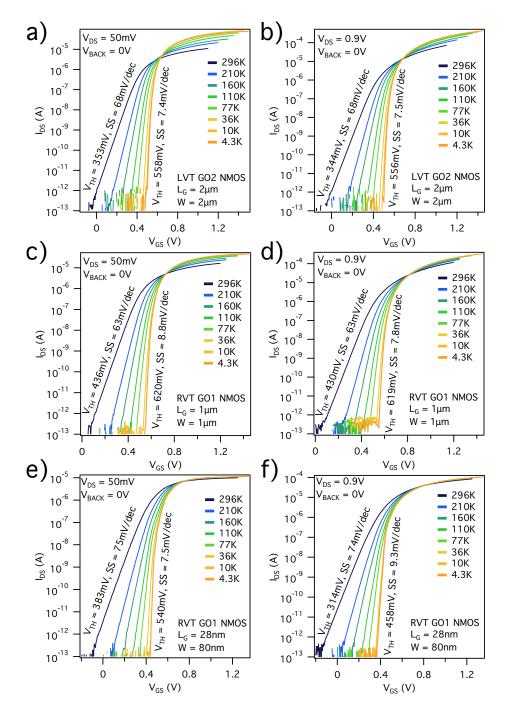

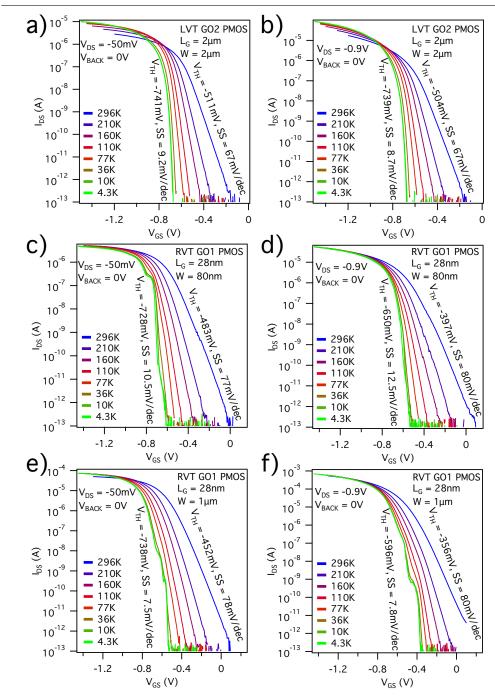

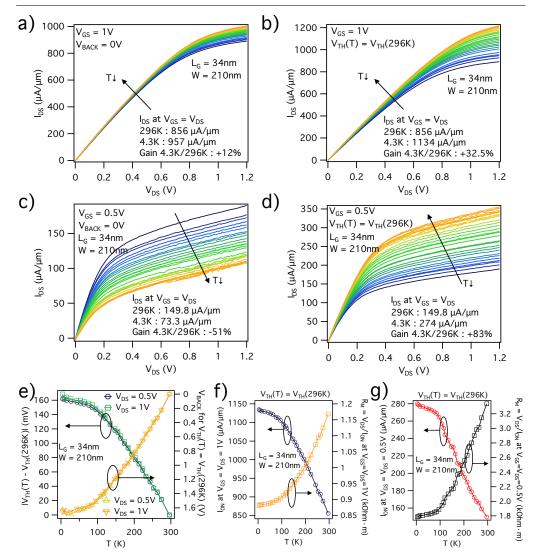

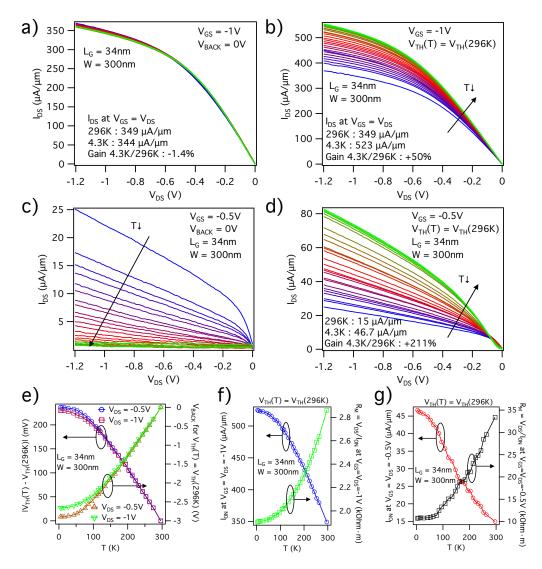

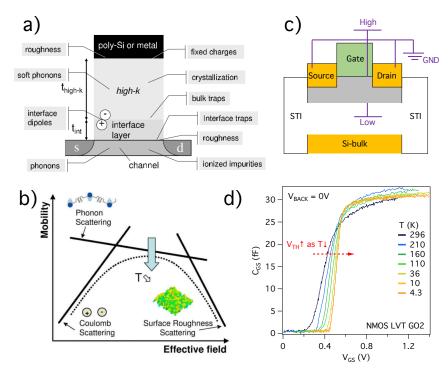

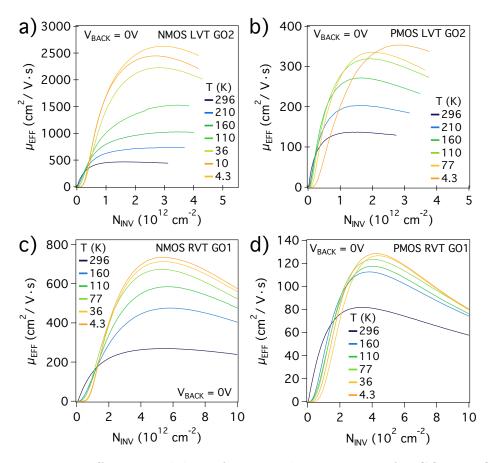

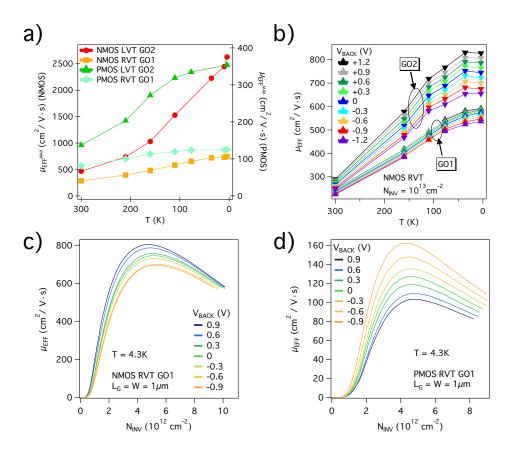

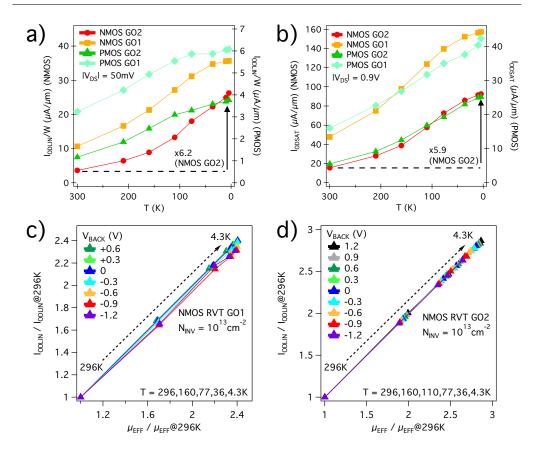

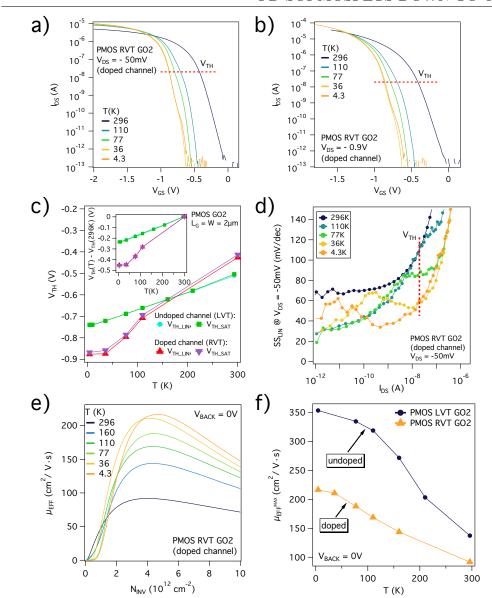

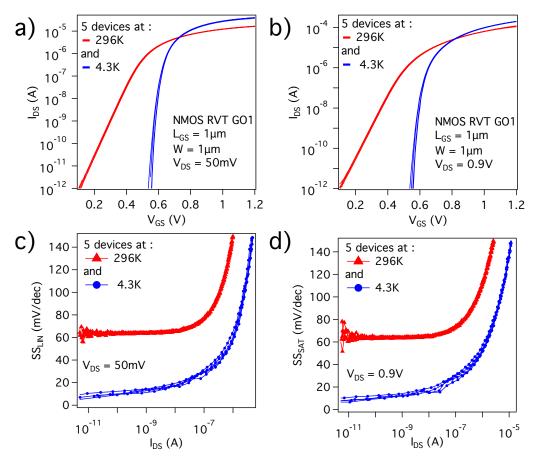

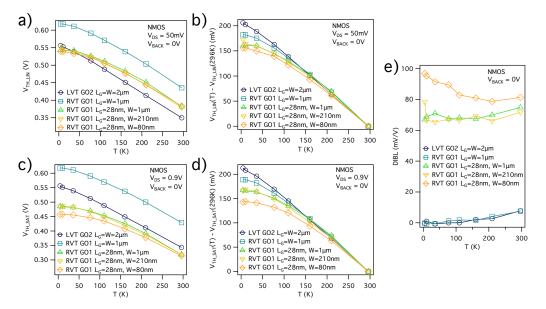

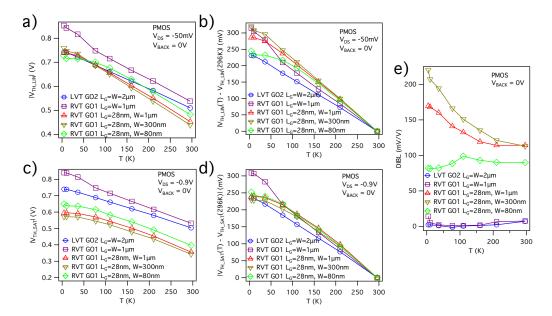

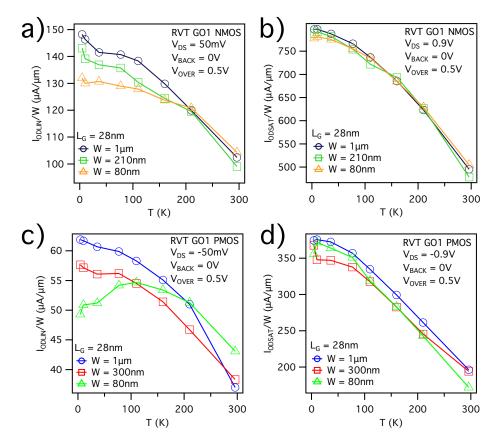

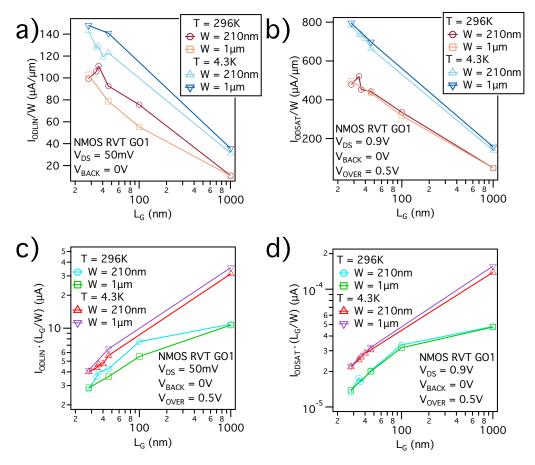

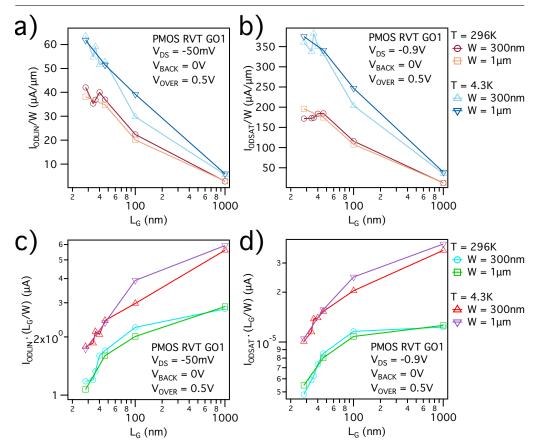

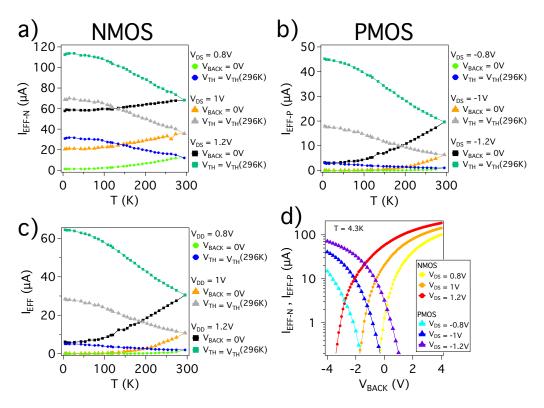

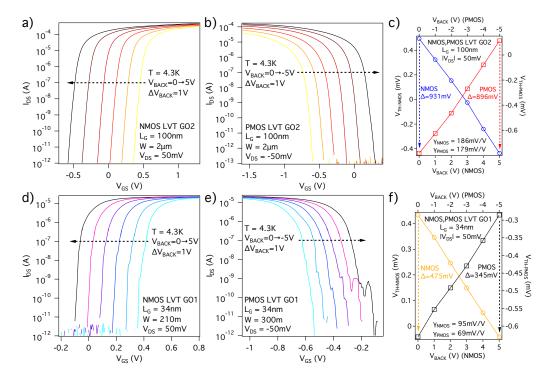

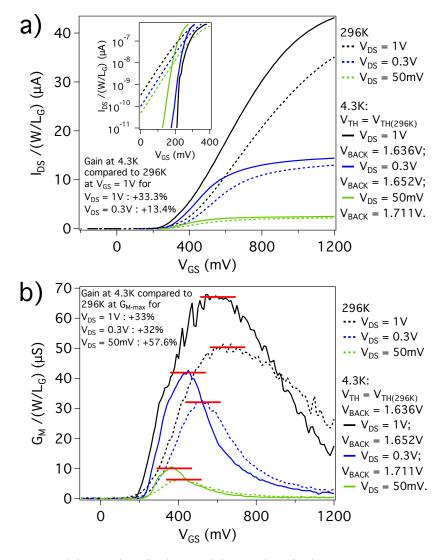

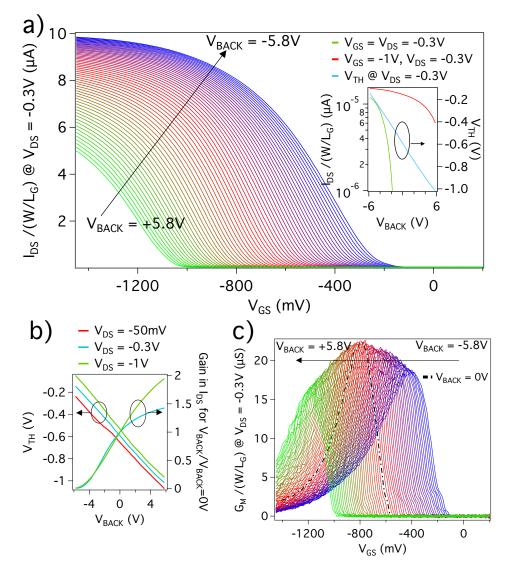

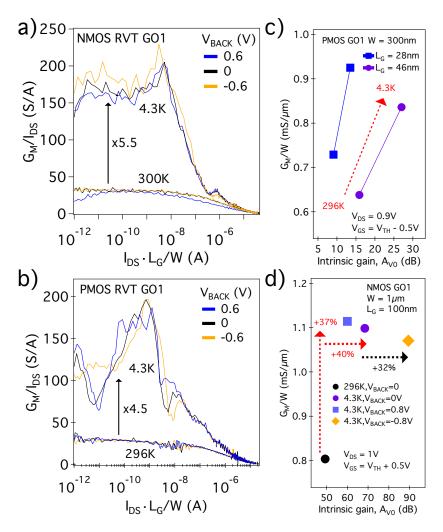

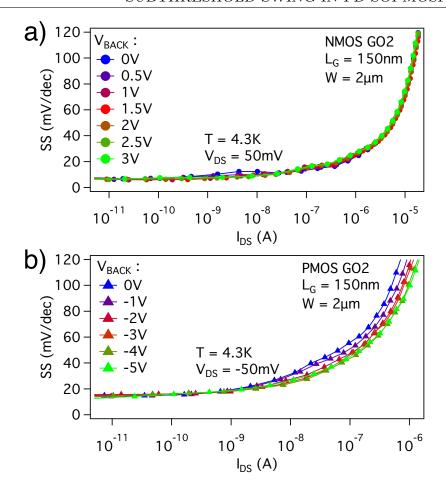

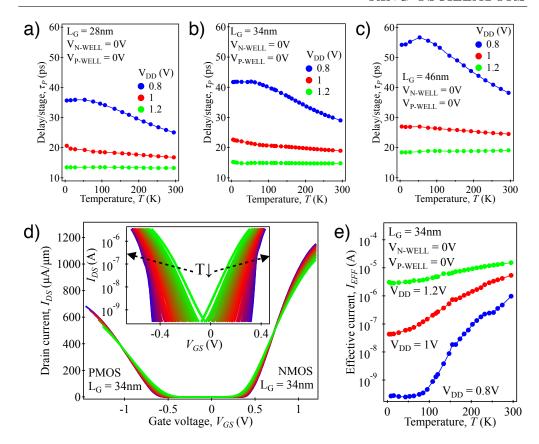

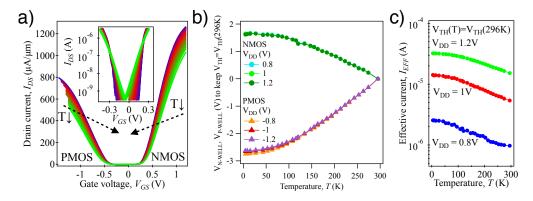

The next chapter summarises the digital and analog performance of 28nm FD-SOI MOSFETs from room temperature down to 4 K. It begins with a description of key features of this commercially available technology and room temperature analysis. Then, transfer  $I_{DS} - V_{GS}$  and output  $I_{DS} - V_{DS}$  characteristics of a large number of isolated devices are given and the low temperature behaviour of FD-SOI is discussed. We investigate the low temperature evolution of the effective mobility  $\mu_{EFF}$  for NMOS and PMOS devices with different gate oxide thickness using the C-V split technique. The effect of channel doping on  $\mu_{EFF}(T)$ , the shift of threshold voltage  $(V_{TH})$  at low temperature, the subthreshold behaviour in terms of  $SS-I_{DS}$  metric are discussed. A variability analysis of long-channel devices is presented and the variability issues associated to a cryogenic operation are mentioned. The overdrive drain currents  $I_{ODLIN}$  and  $I_{ODSAT}$  are discussed for a large set of NMOS and PMOS transistors with short- and long gate length. Then, the body-biasing capability is analyzed down to 4 K. The low temperature behaviour of effective currents of short-channel NMOS and PMOS are reviewed as well as the extended window of body-biasing at low temperature are discussed. An excellent efficiency of body-biasing is demonstrated down to 4 K. The analog performance at 4 K is analyzed.

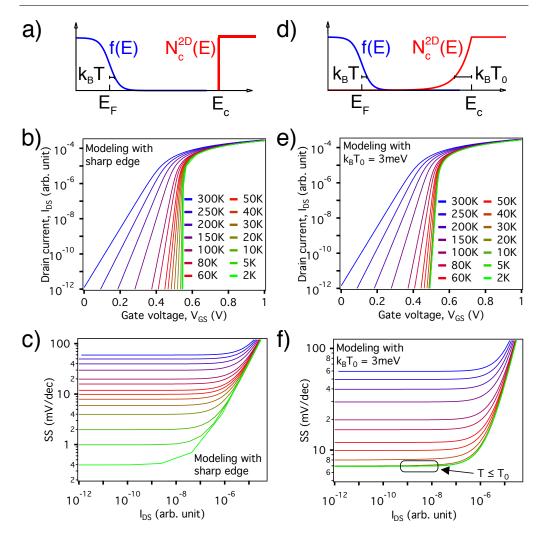

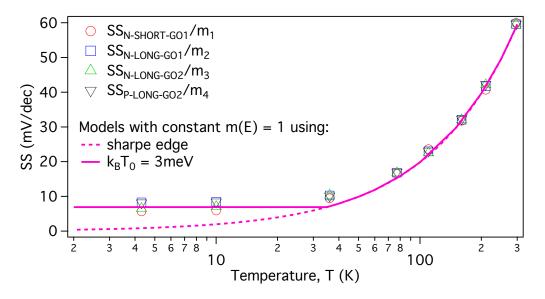

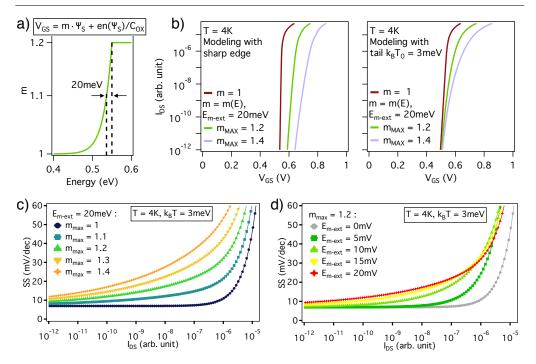

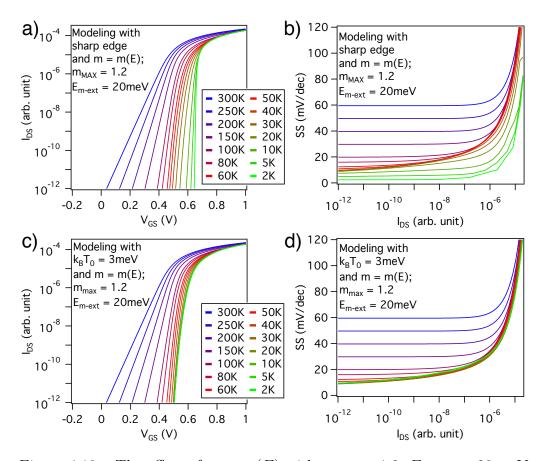

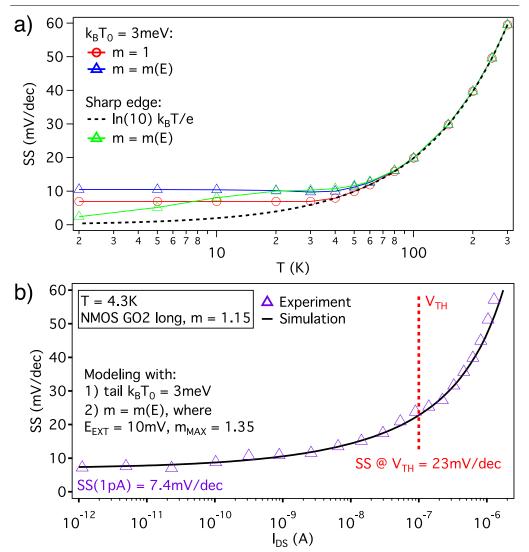

In Chapter 4, the low-temperature saturation of the subthreshold swing (SS) in FD-SOI MOSFETs is discussed. First, we show the saturation of SS(T) for a set of different samples and review the existing theories and approaches used to explain the saturation. Then, by introducing a narrow tail close to the edges of the conductance and valence bands and using the Fermi-Dirac statistics to describe charge carriers, we develop a physics-based model explaining the saturation of SS below 35 K in FD-SOI devices.

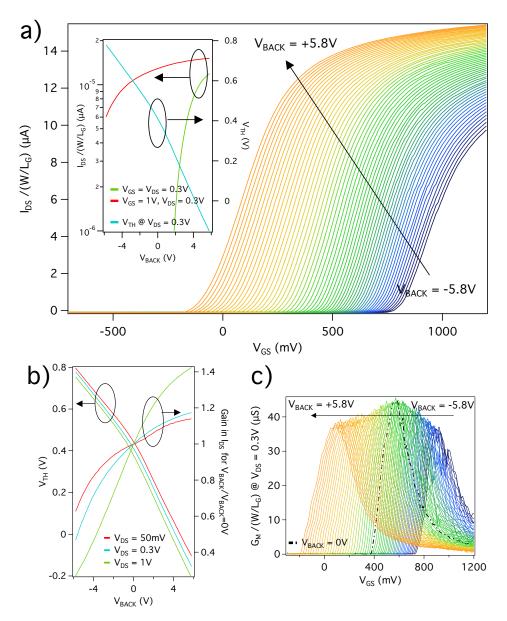

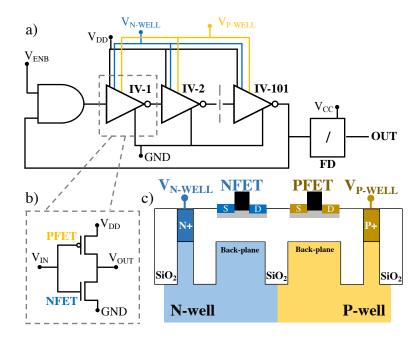

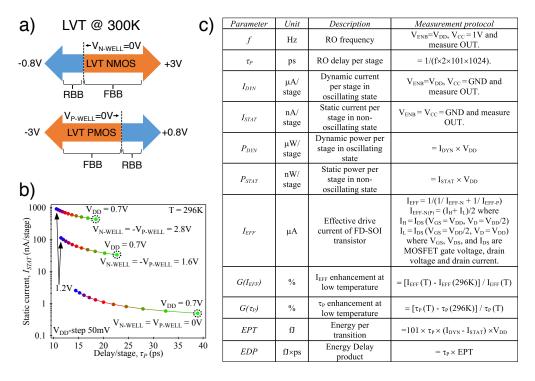

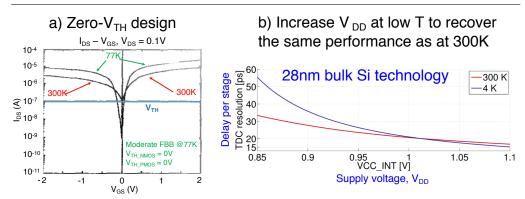

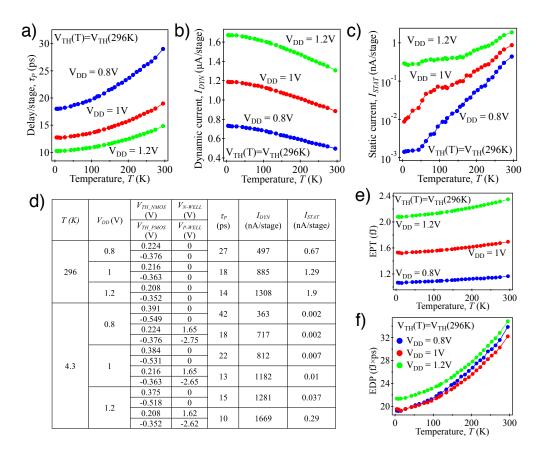

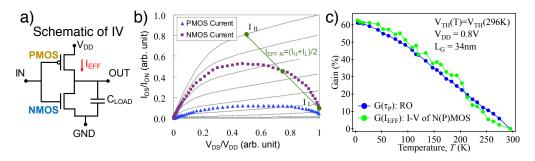

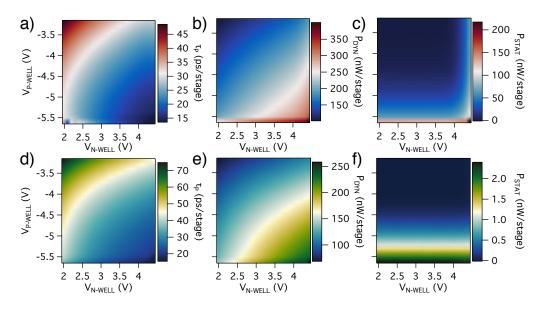

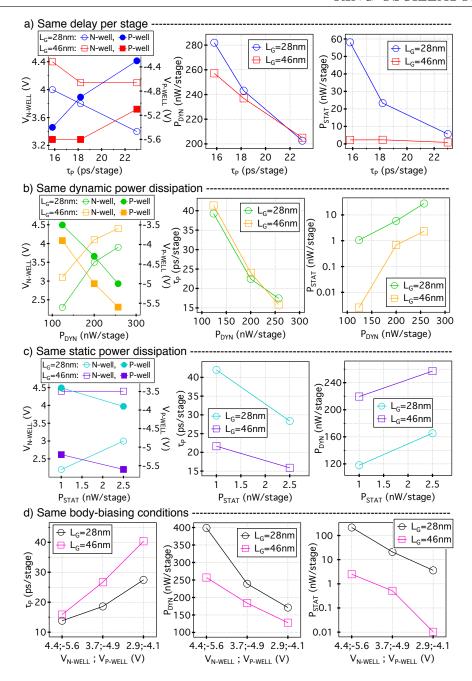

Cryogenic performance of 28 nm FDSOI Ring Oscillators (ROs) is analyzed down to 4 K in Chapter 5. The chapter starts with a description of the circuit, its principle of operation as well as room temperature characterization. Then, a thorough analysis of cryogenic performance of ROs fabricated with different technologies and the existing solutions for optimization of low temperature performance are presented. Two different modes of operation are reviewed. Within the first one the measurements are done without body-biasing having the  $V_{TH}$ -shift attenuating the impact of low temperature mobility enhancement on RO performance. In the second approach, forward body-biasing (FBB) is used to keep  $V_{TH} = V_{TH}(296K)$  of NMOS and PMOS transistors down to 4 K. Then, several metrics are used to analyze the cryogenic performance of ROs, such as the dynamic and static

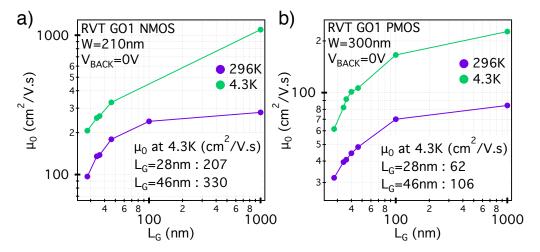

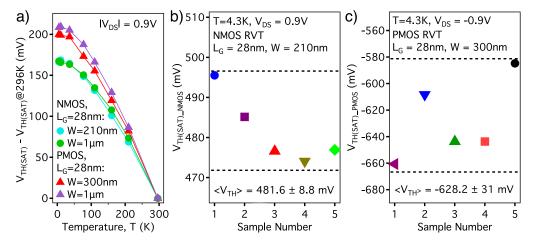

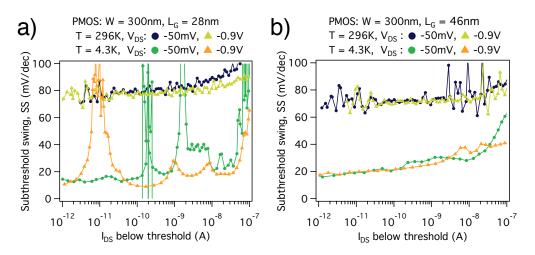

currents  $I_{DYN,STAT}$  (power  $P_{DYN,STAT}$ ), the delay per stage  $(\tau_P)$ , the energy per transition (EPT), the energy-delay product (EDP) under different FBB conditions. We find a good agreement between the low-temperature gain in  $\tau_P$  obtained from the measurement of ROs and the gain estimated using the effective current  $I_{EFF}$  from isolated NMOS and PMOS transistors from 296 K down to 4 K. By exploring very aggressive FBB voltages  $(V_{FBB})$  up to  $\pm 5.8$  V, we show that the performance-power tradeoff can be efficiently managed at 4 K and the supply voltage can be reduced down to  $V_{DD} = 0.325 \text{ V}$  while keeping an excellent performance. We present the low-field mobility ( $\mu_0$ ) comparison between 296 K and 4 K and show that, even for the shortest  $L_G = 28$  nm, the short-channel  $\mu_0(4K)$  is enhanced as compared to room temperature. Then, by comparing the key metrics of ROs with  $L_G = 28$  and 46 nm, we demonstrate that comparable performance can be achieved for these devices thanks to FBB. The variability analysis of short-channel NMOS and PMOS devices is discussed and the choice of optimal temperature for the cryogenic electronics of control based on FD-SOI of 4 K is justified.

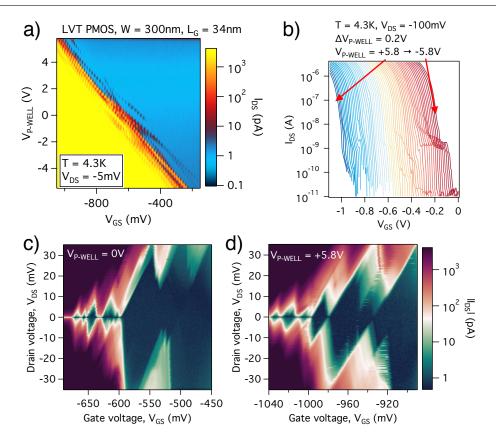

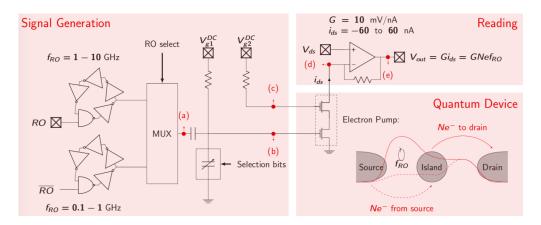

The last chapter describes the duality of short-channel FD-SOI transistors. Here by measuring wide (W=200-300 nm) and short-channel transistors, we show that the same NMOS and PMOS devices can be operated either as field-effect transistors (FETs) or single electron transistors (SETs) depending on the drain voltage  $V_{DS}$  and body-biasing. In two similar NMOS devices, we find almost the same features in 4 K stability diagrams with high addition energies as well as an excellent electrostatic control. By benchmarking different silicon platforms currently used to fabricate robust and efficient quantum dots, we demonstrate the interest of FD-SOI technology for qubit applications. In addition, PMOS short-channel devices were deeply analyzed and the effect of boron dopants diffused from Source/Drain regions is illustrated by using the Coulomb spectroscopy. The chapter ends with a description of a prototype cryogenic circuit recently fabricated using 28 nm FD-SOI which integrates both cryoelectronics and quantum devices.

Finally, we outline the main conclusions and perspectives of this thesis in terms of different silicon quantum dots for spin qubits and cryogenic electronics based on industrial FD-SOI technology.

# Contents

| 1 | Current challenges towards Si-based large scale quantum computing |                                                                                            |            |

|---|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------|

|   | 1.1                                                               | Towards large-scale silicon quantum computing                                              | <b>4</b>   |

|   | 1.1                                                               | Results presented in this thesis with respect to the challenges                            | 7          |

|   | 1.2                                                               | of silicon CMOS quantum computing                                                          | 19         |

| 2 | Silie                                                             | on Nanowire Technology For Qubits                                                          | 20         |

|   | 2.1                                                               | Brief description of Leti's SOI nanowire technology and 300K                               |            |

|   |                                                                   | systematic characterization                                                                | 21         |

|   | 2.2                                                               | Low temperature characterization of PMOS devices: PSB                                      |            |

|   |                                                                   | and the QD tunability                                                                      | 25         |

|   |                                                                   | 2.2.1 Brief review of charge transport through double quan-                                |            |

|   |                                                                   | $\operatorname{tum}  \operatorname{dot}  \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 25         |

|   |                                                                   | 2.2.2 Theory of Pauli Spin Blockade in the presence of                                     |            |

|   |                                                                   | strong SOC                                                                                 | 26         |

|   |                                                                   | 2.2.3 Pauli Spin Blockade for the first holes: Experiment .                                | 27         |

|   |                                                                   | 2.2.4 P-type quantum dots with electrostatically controlled                                |            |

|   |                                                                   | tunnel coupling                                                                            | 37         |

|   | 2.3                                                               | Back-gate tunable QDs and Coulomb spectroscopy of the                                      |            |

|   |                                                                   | first electrons                                                                            | 39         |

|   |                                                                   | 2.3.1 N-type Corner Dots under zero and reverse body-                                      |            |

|   |                                                                   | biasing                                                                                    | 39         |

|   |                                                                   | 2.3.2 Dopant-assisted QDs under forward body-biasing                                       | 44         |

|   | 2.4                                                               | Towards scalable electron spin qubits with Corner Dots                                     | 47         |

|   | 2.5                                                               | Conclusions                                                                                | 48         |

| 3 | Dig                                                               | al and Analog performance of 28 nm FD-SOI MOS-                                             |            |

|   | $\mathbf{FE}^{\prime}$                                            | s down to 4 K                                                                              | <b>5</b> 0 |

|   | 3.1                                                               | Introduction in 28nm Fully Depleted Silicon-on-Insulator tech-                             |            |

|   |                                                                   | nology                                                                                     | 51         |

|   | 3.2                                                               | Transfer and output characteristics down to 4 K                                            | 53         |

|   | 3.3<br>3.4  | Long-channel mobility down to 4 K                                                                                  | 61  |

|---|-------------|--------------------------------------------------------------------------------------------------------------------|-----|

|   | 0.1         | channel PMOS                                                                                                       | 65  |

|   | 3.5         | Long-channel device variability at 4 K                                                                             | 68  |

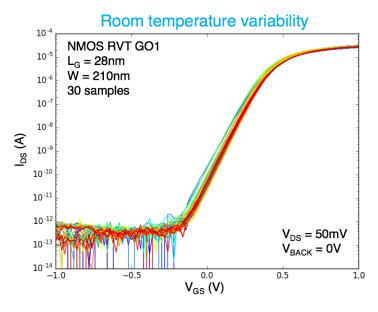

|   | 3.6         | Short-channel devices: the effect of $W$                                                                           | 70  |

|   | 3.7         | Short-channel devices: the effect of $L_G$                                                                         | 73  |

|   | 3.8         | Body-biasing at low temperature                                                                                    | 74  |

|   | 3.9         | Analog performance at 4 K                                                                                          | 77  |

|   | 3.10        | ~ -                                                                                                                | 83  |

| 4 |             | -temperature Saturation of the Subthreshold Swing D-SOI MOSFETs                                                    | 85  |

|   | 4.1         | Experimental evidence of the saturation of SS in FD-SOI                                                            | 96  |

|   | 4.2         | devices                                                                                                            | 86  |

|   | 4.3         | Si and SOI technologies                                                                                            | 91  |

|   |             | band edges and constant $m$                                                                                        | 94  |

|   | 4.4         | Second approach to model $SS(T)$ : disorder-induced tail below band edges and $m = m(E) \dots \dots \dots \dots$ . | 100 |

|   | 4.5         | Cryogenic behavior of $SS$ under body-biasing                                                                      | 104 |

|   | 4.6         | Conclusion                                                                                                         | 106 |

| 5 | Cry         | ogenic Performance of 28 nm FD-SOI Ring Oscillators                                                                | 108 |

|   | 5.1         | Setup used for cryogenic measurements of ring oscillators $$ . $$ .                                                | 109 |

|   | 5.2         | Principle of operation and room temperature performance of RO                                                      | 109 |

|   | 5.3         | Existing solutions for the optimization of cryogenic perfor-                                                       |     |

|   | 5.4         | mance using standard silicon technologies                                                                          | 112 |

|   | <b>.</b> .  | sation                                                                                                             | 114 |

|   | 5.5         | Forward body-biasing compensation of the $V_{TH}$ -shift down to 4.3 K                                             | 117 |

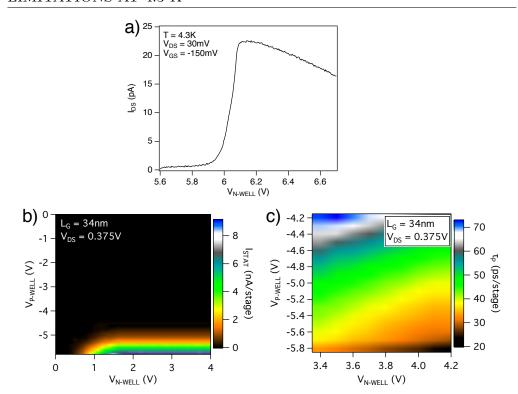

|   | 5.6         | Maximal performance and body-biasing limitations at 4.3 K                                                          | 121 |

|   | 5.7         | Boosting the RO performance with relaxed $L_G$                                                                     | 124 |

|   | 5.8         | Variability, zero- $V_{TH}$ regime, and the optimal temperature                                                    |     |

|   |             | of operation                                                                                                       | 128 |

|   | 5.9         | Conclusions                                                                                                        | 130 |

| 6 | Dua<br>to S | lity of short-channel FD-SOI transistors: from FETs ETs                                                            | 132 |

### CONTENTS

|    | 6.1   | Setups used for low-temperature measurements                          | 133         |

|----|-------|-----------------------------------------------------------------------|-------------|

|    | 6.2   | Conventional CMOS and $Si$ -based MOS structures for quan-            |             |

|    |       | tum computing                                                         | 133         |

|    | 6.3   | FET-to-SET transition in NMOS at 4.3 K                                | 134         |

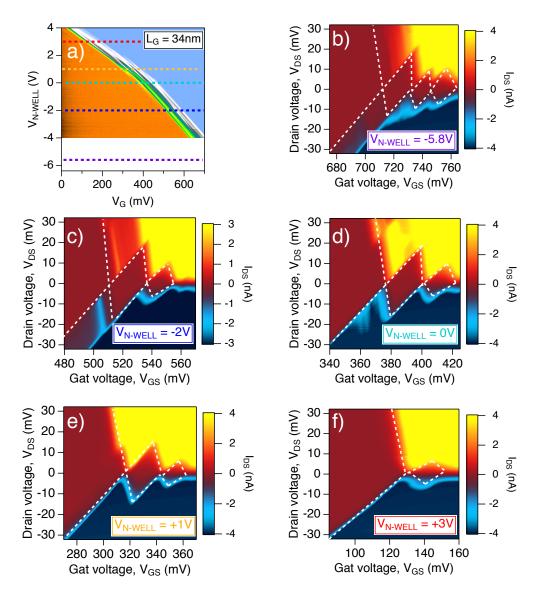

|    | 6.4   | Evolution of <i>n</i> -type quantum dots under different body biasing | 136         |

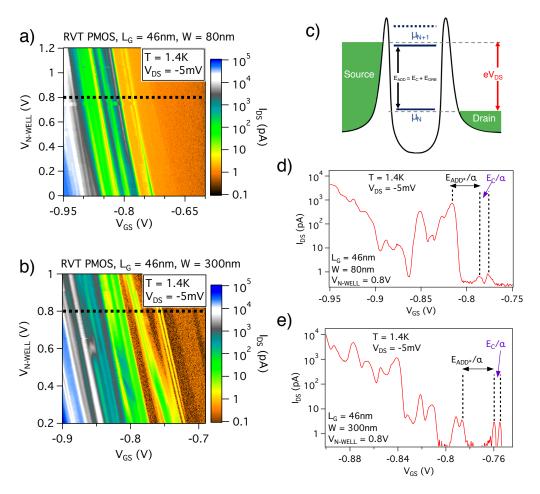

|    | 6.5   | Problems with short- $L_G$ PMOS at 4.3 K and possible solutions       | 143         |

|    | 6.6   | Towards FD-SOI based circuits with quantum devices                    | 147         |

|    | 6.7   | Conclusions                                                           | 148         |

| 7  | Ger   | neral conclusions and Perspectives                                    | 150         |

| Re | efere | nces                                                                  | <b>15</b> 4 |

## Short list of frequent acronyms

Qubit - Quantum bit.

**SOI** - Silicon-on-Insulator.

**FD-SOI** - Fully-Depleted Silicon-on-Insulator.

**28nm FD-SOI** - STMicroelectronics commercial planar process technology.

**PSB** - Pauli Spin Blockade.

**SOC** - Spin-orbit coupling.

SS - Subthreshold Swing.

**EDSR** - Electron-dipole spin resonance.

**QD** - Quantum dot.

**DQD** - Double quantum dot.

CD - Corner dot.

FBB/RBB - Forward and reverse body-biasing.

$V_{FBB}$ ,  $V_{RBB}$  - Forward and reverse body-biasing voltages.

**CryoCMOS** - Cryogenic digital and analog electronics specially designed to control, measure and read-out large-scale qubit systems.

**RO** - Ring oscillator.

FET or MOSFET - Field-effect transistor

**SET** - Single electron transistor.

$I_{ODLIN}$  and  $I_{ODSAT}$  - Overdrive drain current extracted at typically  $V_{GS} - V_{TH} = 0.5$  V and  $V_{DS} = 50$  mV and  $V_{DS} = 1$  V respectively.

**NMOS** / **PMOS** - n- and p-type MOSFETs.

$V_{TH}$  - Threshold voltage of a MOSFET.

$V_{TH-LIN}$ ,  $V_{TH-SAT}$  - Linear and saturation MOSFET threshold voltages extracted at low and high drain voltage (typically at 50 mV and 1 V).

$I_{DYN}$ ,  $P_{DYN}$  - Current and power of a ring oscillator in the dynamic (oscillating) mode.

$I_{STAT}$  ,  $P_{STAT}$  - Current and power of a ring oscillator in the static (stand-by) mode.

$\tau_P$  - Measured delay per stage of a ring oscillator accounting for the number of inverter stages and the frequency divider.

$I_{EFF}$  - Effective current calculated using transfer and output characteristics of N- and PMOS transistors.

$V_{DD}$  - Supply voltage of a ring oscillator.

$\mu_{EFF}$  - Effective mobility of a MOSFET measured using the C-V split technique.

$\mu_0$  - Low-field mobility of a MOSFET extracted using the Y-function method

Face-to-face, F-to-F - A specially designed Leti nanowire transistors with two spilt gates partially covering the channel and placed in front of each other.

- **RCS** Remote Coulomb Scattering.

- **SR** Surface roughness.

- **PS** Phonon scattering.

- **SPS** Soft phonon scattering.

- $I_{ON}$ ,  $I_{OFF}$  Drain current of a MOSFET at high drain voltage (typically  $V_{DS}=1V$ ) and  $V_{GS}=V_{DS}$  and  $V_{GS}=0$  V respectively.

- $E_{ADD}$  Additional energy required to add an additional electron (hole) in a quantum dot.

- **BOX** Buried oxide separating bulk silicon from the channel in the silicon-on-insulator wafer.

- $V_{BACK}$  Backgate voltage. For electrons,  $V_{BACK} > 0$  V becomes  $V_{FBB}$  and  $V_{BACK} < 0$  V is  $V_{RBB}$ .

- **EOT** Equivalent oxide thickness of the  $SiO_2/high \kappa$  gate oxide of Leti and STMicroelectronics transistors which both use high- $\kappa$  metal gate technology.

- **DIBL** Drain-Induced Barrier Lowering.

- RT Room temperature.

- $\mathbf{RVT}$  /  $\mathbf{LVT}$  Regular and low  $V_{TG}$  architectures of 28 nm FD-SOI transistors.

- GO1, GO2 Thin and thick EOT transistors.

- $C_{OX}$  Gate capacitance defined by the geometrical dimensions.

- $C_{Si}$  Semiconductor capacitance.

## Chapter 1

# Current challenges towards Si-based large scale quantum computing

In this chapter a brief review of main ideas behind quantum computing is given. The progress in silicon-based spin qubits with close to conventional CMOS fabrication route is presented. The difficulties associated with scaling up, i.e. increasing the number of qubits with respect to main constraints are mentioned. The interest of co-integration of the qubit layer with cryogenic electronics is justified. Finally, the correspondence between the results presented in this thesis with the challenges of silicon CMOS large-scale quantum computing is established.

# 1.1 Towards large-scale silicon quantum computing

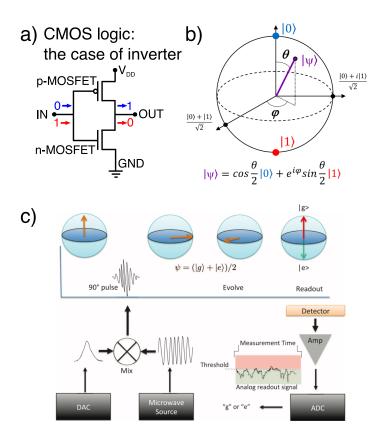

The necessity of quantum computers (QCs) to simulate 'physics' by exploiting the problem of many-particle quantum wavefunction was first foreseen by Richard Feynman in the 80ties [1]. Quantum computing is fundamentally different from the classical binary logic where the information is encoded into bits storing either logical "1" or "0 [2]. This principle is illustrated in Fig.1.1 (a) using a simple inverter. Indeed, the quantum computer composed of quantum bits (qubits) can store exponentially more information than the one using classical binary logic [3]. For instance, to represent n-qubit system one needs to have n quantum and  $2^n$  classical bits. A large number of new quantum algorithms for resolving problems not accessible by standard computers (SCs) has been proposed [4]. The

# CHAPTER 1. CURRENT CHALLENGES TOWARDS SI-BASED LARGE SCALE QUANTUM COMPUTING

following algorithms are of particular interest: (i) Shor's algorithm [5] for integer factorisation (running time  $O(logN)^3$  for QC and exponentially larger  $exp(O(logN)^{1/3}(O(log logN)^{2/3}))$  for SC [6]); (ii) Grover's algorithm [7] for unstructured search problem (nearly quadratic speedup for QC [4]), to calculate dynamical properties by resolving the Schrodinger equation of (interacting) many-body systems which is currently a topic of active research in the fields of quantum chemistry[8], quantum field theory[9], etc. Finally, quantum computing can be efficiently applied for solving large systems of linear [10] and differential equations [11], data fitting [12], and machine learning [13].

Similarly to the binary classical logic, a qubit can be characterized by two states :  $|0\rangle$  (ground state) and  $|1\rangle$  (exited state) as shown in Fig.1.1 (b). However, the difference lays in the quantum nature of qubits systems. The qubit can be in the linear combination of computational basis states leading to the superposition:  $|\psi\rangle = \alpha|0\rangle + \alpha|1\rangle$ . Thus, the qubit can exist in a continuum of states until is measured and  $\alpha^2$ ,  $\beta^2$  give the probability of finding  $|0\rangle$  or  $|1\rangle$  after the measurement. A convenient way to represent a two-level quantum system is to use the Block sphere. Then, the pure states  $|0\rangle$  and  $|1\rangle$  (spin-up and spin-down for spin qubits) point towards the north and south poles of the Block sphere whereas the interior points correspond to the mixed states (see Fig.1.1 (b)).

The famous paper on the requirement for the physical implementation of quantum computation [15] (so-called DiVincenzo criteria) describe a list of necessary condition for realizing the QC: (1) a scalable physical system with well-characterized qubits (few-electron/hole regime, cryogenic temperature, static magnetic field); (2) the ability to initialize the state of the qubits (3) long relevant decoherence ( $T_1$  to corresponding the relaxation from excited to ground state and  $T_2$  describing the dephasing time), much longer than the gate operation time; (4) A universal set of quantum gates (quantum 'XOR' or 'CNOT' gate will be discussed in details); (5) A qubit-specific measurement capability (read-out through spin-to-charge conversion or using a reflectometry technique); (6) The ability of interconvert stationary and flying qubits; (7) The ability to faithfully transmit flying qubits between specified locations. The last two conditions (6-7) are additional to (1-5) and are required for quantum communication protocols and will only partially be addressed in this chapter.

The principle of qubit operation is given in Fig.1.1. A very simplified operation sequence consists in: (i) initializing the qubit in the ground state  $|0\rangle$  (a static magnetic field  $B_0$  splits the lowest energy level by lifting the spin degeneracy), (ii) sending both DC (few mV) and AC (typically from 1 to 10 GHz for silicon spin qubits) signals to detune the quantum dot system

Figure 1.1: (a) Illustration of classical binary logic using an inverter. (b) Qubit representation with a Block sphere formalism. (c) Principle of operation of a qubit. Taken from [14]

and to coherently drive the qubit between  $|0\rangle$  and  $|1\rangle$ , (iii) waiting for the system located in a dephasing environment to evolve, (iv) reading-out the final output and thus determining the Rabi frequency and dephasing times [14]. Finally, typical key parameters used to benchmark different qubit realization are: clock speed, coherence time, the fidelity and speed of single-and two-qubit logic gates, read-out time, susceptibility to crosstalk between qubits, footprint for scalability, architectural complexity (how many gates to define a single qubit, the number of levels of metal gates, etc), the constraints imposed on the control and read-out hardware [14].

Regarding quantum computation with superconducting qubits, this platform uses superconducting Josephson junctions which are usually realized as tunnel junctions in which two superconductors (typically made of aluminum) are separated by an insulating region (oxide layer). Tremendous progress has been achieved in the field of superconducting qubits [16, 17].

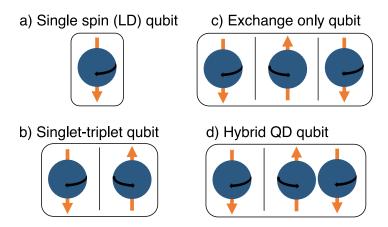

Figure 1.2: Different quantum dot spin qubits.

But, given the possible issues with large scaling-up of macroscopic superconducting systems, we will focus our attention on the semiconductor spin qubits. Furthermore, since there exist several limitations for the gate fidelity and spin coherence times in III-V systems due to a high percentage of nuclear spins in the host material [18, 19], in this section we will focus on silicon-based quantum dot system realizations.

Indeed, tremendous work has been done to make these silicon-based systems compatible with industrial CMOS technology characterized by high-yield, reproducibility and cleanliness [20]. Although initially solid-state quantum qubits were realized through manipulation of a single charge in quantum dot systems [21], it was found advantageous to encode the information into a spin degree of freedom since spin qubit coherence times are much less impacted by charge noise. Particularly long coherence times and high fidelity were recently reported for silicon spin qubits [22–24].

There exist several types of implementations of semiconductor spin qubits based on gate-defined quantum dot systems. For instance, a single spin (Loss-DiVincenzo) qubit is the most compact architecture which is realized with only one quantum dot [25] as shown in Fig.1.2 (a). It requires magnetic manipulation (AC B-field for electrons [22]) or electron-dipole spin resonance EDSR-manipulation with AC E-field only for holes [26] or electrons (depending on the strength of spin-orbit coupling SOC) [27]. Other common qubit implementations schematically shown in Fig.1.2 (b - d) are the following:

- a singlet-triplet qubit which consists of realizing a spin qubit with two quantum dots controlled using one gate voltage, thus having one electric and one magnetic axis [28];

- an exchange only qubit is obtained with three dots and controlled with two gate voltages, having two electric axes [29];

- a hybrid quantum dot qubit which uses two dots controlled with one gate voltage having two electric axes [30].

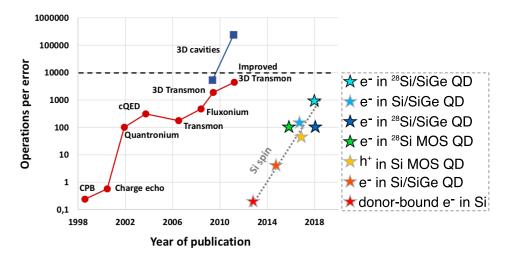

Figure 1.3: Graph adapted from [16], showing the number of operations per error for various implementations of superconducting qubits versus publication year. The added star symbols represent recent demonstrations of Si spin qubits in electrostatically-defined quantum dots. The figure of merit was estimated as the dephasing time  $T_2^*$  divided by the time needed to induce a  $\pi$ -rotation of the spin. Taken from [31].

While Google, IBM and a number of other companies and academic labs have achieved considerable progress in superconducting systems as large as 50 qubits [32], more recently silicon-based electron (hole) spin qubits were demonstrated to operate close to the operation per error threshold or 'Q'-factor as shown in Fig.1.3. Maximizing the Q-factor is crucial for performing robust calculations since it sets an upper bound to the number of operations that can be sequentially performed on a number of qubits for the implementation of quantum error detection protocols [31]. Thus, owing to the silicon spin qubit compatibility with state-of-the-art technologies continuously improved over several decades by the IC manufacturing industry, the stage of the superconducting qubit progress will possibly be achieved and overpassed in the near future.

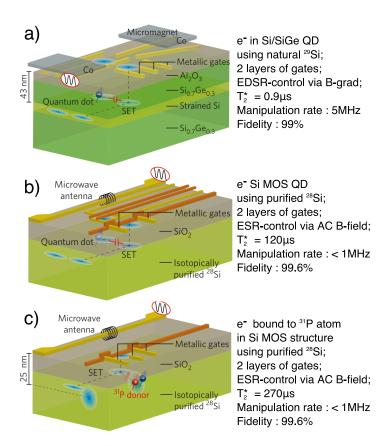

In Fig.1.4 three recent demonstrations of silicon spin qubit architecture are shown. All these architectures were used for electron spin qubit experiments. In Fig.1.4 (a) a single electron was trapped in a natural Si/SiGe

quantum well and a quantum dot was electrostatically formed with gate voltages [33]. Vandersypen and colleagues performed the electron spin manipulation using EDSR-mechanism thanks to an on-chip micromagnet generating an inhomogeneous B-field across the quantum dot. A high fidelity exceeding 99% and long inhomogeneous dephasing time  $T_2^*$  during freeevolution as well as relatively fast qubit manipulation rate were found. In contrast, using isotopically purified  ${}^{28}Si$  in MOS structure with a microwave antenna close to the quantum dot (as shown in Fig.1.4 (b)), Veldhorst and colleagues could achieve much longer  $T_2^*$  and higher fidelity rate [22] due to reduced impact of hyperfine interaction with nuclear spins since approximatively 4.7% of non-zero nuclear spin  $^{29}Si$  is usually present in natural silicon. The manipulation of spin was performed through electron spin resonance (ESR) induced thanks to the microwave antenna generating AC B-field. Finally, Muhonen and colleagues found even larger  $T_2^*$  [34] by using a single electron spin bound to a phosphorus dopant in isotopically purified  $^{28}Si$ , see (as shown in Fig.1.4 (c). The same mechanism of ESR-manipulation using an on-chip microwave antenna was used. In all cases, the spin read-out was performed using a single electron transistor (SET) capacitively coupled to the quantum dot. A common feature of all above-presented architectures is the use of 'planar' geometry, many gates and several layers of metal gates to realize a single qubit. Although these qubit experiments have confirmed the expectation that individual electron spins in silicon can be highly decoupled from their environment and can be controlled coherently with high accuracy, regarding the scalability issues and problematic integration into common CMOS technologies, these architectures are not optimal.

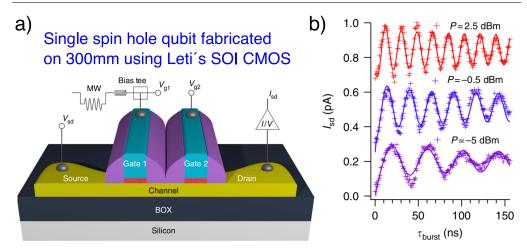

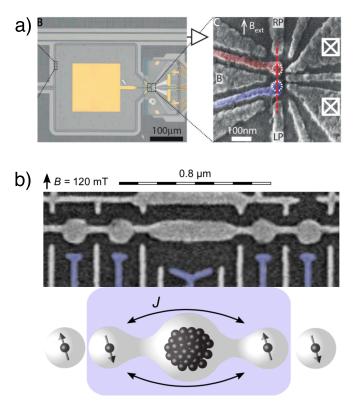

An alternative route based on the fabrication of industry-standard CMOS transistors was proposed to obtain devices with qubit functionality. Fig.1.5 (a) shows a p-type double gate nanowire transistor fabricated on a 300 mm Silicon-on-Insulator wafer. Using hole double quantum dot (DQD) in Pauli Spin Blockade (PSB) configuration, a fast, all-electrical, two-axis control of the first hole spin qubit was demonstrated (see Rabi oscillations in 1.5 (b)). Regarding a common CMOS silicon nanowire fabrication high- $\kappa$  metal gate (HKMG) process [36], the only additional step is the use of electron-beam lithography to obtain sub-100 nm gate pitch and thick 20 nm spacers isolating the DQD from Source/Drain regions. The main difference here is that due to the strong SOC for holes in silicon, no additional micromagnet or microwave lines are needed to produce EDSR-manipulation. Another distinct feature of this architecture lays in its compactness: one gate-confined quantum dot can provide a qubit and the adjacent one can be used for PSB read-out [37]. Despite the obvious advantage regarding the device yield, variability, and reproducibility due to the well-established fabrication pro-

Figure 1.4: Three breakthrough, proof-of-concept electron spin qubit experiments demonstrated in 2014. Adapted from [35]

cess, the qubit functionality was demonstrated in the many-hole regime. However, the first hole-regime which is very difficult to achieve was observed in similar nanowire devices in [38, 39] and in planar Si MOS QDs [40].

Nevertheless, an ultra-compact and very promising hole spin qubit platform was successfully demonstrated with remarkably high manipulation frequency  $f_{RABI} = 85$  MHz and rather moderate dephasing time from Ramsey experiment  $T_2^* = 60$  ns (due to the many-hole region and the presence of boron dopants in the channel).

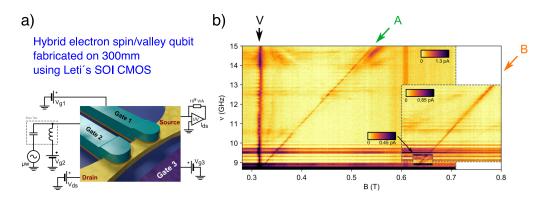

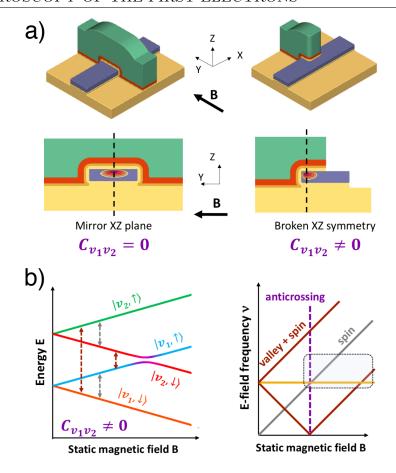

More recently, an experimental demonstration of electric-dipole, spin-valley resonance mediated by intrinsic spin-orbit coupling (SOC) in a silicon electron double QD has been reported [27]. Although SOC is intrinsically weak in silicon, its effect can be enhanced in the corner QDs of an etched SOI device, owing to their reduced symmetry. Then, SOC enables EDSR

Figure 1.5: (a) Simplified 3-dimensional schematic of an SOI nanowire field- effect transistor with two gates (Gate1 and Gate2). Using a bias-T, Gate 1 is connected to a low-pass-filtered line, used to apply a static gate voltage  $V_{g1}$ , and to a 20-GHz bandwidth line, used to apply the high-frequency modulation necessary for qubit initialization, manipulation, and read-out. (b) Rabi oscillations for different microwave power as a function of microwave bursts demonstrating controlled spin rotations. Taken from [26].

on the spin-split doublet of the first, lowest energy valley by mixing the up-spin state of this valley with the down-spin state of the second valley. Importantly, the EDSR Rabi frequency is strongly enhanced near the corresponding anti-crossing, namely when the valley and Zeeman splittings are close enough [27, 41]. In turn, the valley splitting can be efficiently electrically-tuned via body-biasing in such nanowire devices [42]. This tuning is essential in order to enhance the above-described EDSR mechanism for electrons [27]. A signature of Rabi oscillations and thus of the coherent control can be found in [43].

Thus, all-electrical control of a hybrid electron spin/valley qubit, as well as the first hole spin qubit using the same SOI CMOS nanowire technology, have marked an important step towards large-scale quantum computing.

Similarly to the classical binary logic build up from the NOT and AND gates, arbitrary quantum logic can be generated from a small set of quantum gates. Two different realizations of controlled-NOT (CNOT) quantum gates using exchange interaction are shown in Fig.1.7 (a - b). Whereas the demonstration of an efficient CNOT gate for spins in silicon opens a path for multi-qubit algorithms in silicon-based quantum computing (in [44], the

Figure 1.6: (a) Sketch of the sample and measurement setup consisting in the silicon nanowire with the source/drain extensions colored in yellow, the two top gates in green, and the side gate in purple. The gate oxides are colored in orange and the buried oxide (BOX) of the SOI in blue. (b) Color plot of the measured drain current  $I_{ds}$  as a function of the magnetic field B and microwave frequency  $\nu$ . The gates are biased in the spin-blockade regime. Three different measurements are gathered for clarity. EDSR transitions are revealed by oblique straight lines, labeled with letters A and B. Adapted from [27].

resonantly driven gate operation of 200 ns is much shorter than the qubit dephasing time), the complexness of the architecture is significantly increased as compared to the single spin qubits described above.

Alternatively to the spin read-out using single electron transistors (SETs) or quantum point contacts (QPCs) challenging for scalability, gate-coupled radio-frequency (RF) reflectometry has been recently proposed as an alternative approach to qubit read-out [47]. In this read-out technique, the qubit sensing is accomplished by measuring the dispersive response of an electromagnetic RF resonator connected to one of the qubit gates and excited at its resonance frequency. Very recently, significant improvements in RF-based read-out were reported using Si MOS design [48] (average fidelity 73%), dopant-based architecture [49] (average fidelity 83%). In these experiments, resolving the qubit state within single-shot (single measurement) was demonstrated marking another step towards viable read-out method for spin qubits in silicon. A major improvement in RF-based read-out was also reported for the SOI CMOS nanowire platform (using a similar multi-gate device as those used for hole and electron qubits) [50].

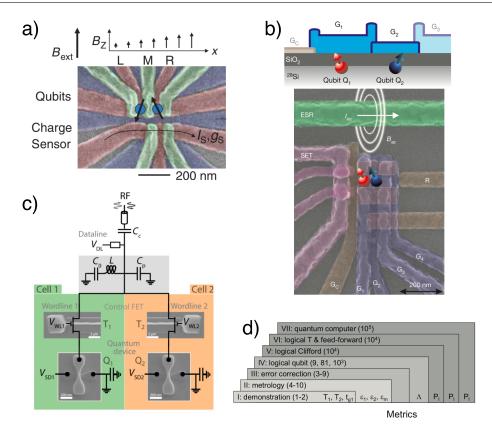

In addition to the single qubit and CNOT gate demonstration, a dynamic random access architecture for efficient read-out of complex quan-

Figure 1.7: (a - b) Implementation of CNOT gates within electron spin qubit architectures using Si/SiGe and Si MOS platforms. Taken from [44] and [23]. (c) An example of a CMOS dynamic random access architecture for radio-frequency read-out of qubit devices. Taken from [45]. (d) Main steps from single qubit demonstration up to the realization of quantum computer with the number of qubits necessary to fulfil each stage's requirements. Taken from [46].

tum circuits was demonstrated at millikelvin temperatures using Leti's SOI CMOS nanowire technology [45]. The circuit divided into cells containing a CMOS quantum dot (QD) and a field-effect transistor that enables selective readout of the QD, as well as charge storage on the QD gate is shown in Fig.1.7 (c). This is analogous to the 1 transistor - 1 DRAM cell approach used in CMOS technologies. Using an RF-resonator, the dynamic read-out of two cells was successfully reported thus paving the way for reducing the number of input lines per qubit and enabling addressing large-scale device arrays.

Fig.1.7 (d) shows the roadmap towards a quantum computer illustrat-

ing the increasing complexity of qubit experiments, described by technology levels I to VII. Numbers in parenthesis show approximate qubit numbers. Errors for 1 qubit, 2 qubits and measurement are described by  $\epsilon_1$ ,  $\epsilon_2$ ,  $\epsilon_m$  which leads to an error suppression factor  $\Lambda$ . The fault-tolerant error correction is achieved when  $\Lambda > 1$  [46]. Here, it is worth mentioning that contrarily to the classical logic where each physical bit corresponds to a single logic bit, in order to achieve high computational tolerance by correcting different type of errors occurring during CNOT operation [51, 52], a quantum logic bit typically consists of several physical qubits (the actual number depends on a particular technology used as well as the error-correcting code and can reach  $10^3$ ).

Although a classical computer can compete up to about 50 qubits, solving relevant problems in quantum chemistry or code-breaking using known quantum algorithms and error correction methods require a large number of physical qubits  $10^6-10^8$  [20, 53, 54]. Thus, adoption of well-established, mature CMOS technologies for fabrication of high-quality, reproducible single qubits seems to be one of the most promising paths towards large-scale quantum computation.

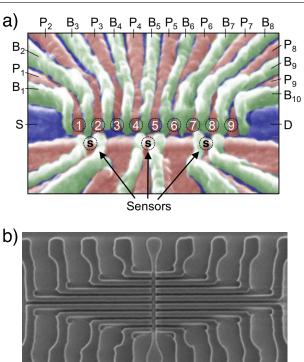

In order for a functional quantum computer to become a reality, different architectures integrating many qubits are currently investigated. In Fig.1.8 (a), a 12-quantum-dot device (for potentially 9 qubits and 3 charge sensors) fabricated on an undoped Si/SiGe heterostructures as a proof of concept for a scalable, linear gate architecture for silicon QDs is shown.

Using this design, similar quantum dots were obtained with approximatively 20% of relative variation of single quantum dot parameters (charging and orbital energies) [56]. Whereas it has marked a major achievement, it is not clear whether such variability is acceptable for large-scale quantum computing. Thus, top-down close-to-industrial CMOS fabrication process with several additional e-beam lithography steps was recently developed at Leti (in theory, the same gate pitch can be achieved using extreme UV lithography which will be brought into production fabrication for the most advanced technological nodes [57]). The left array of 8 Face-to-Face gates can be used to electrostatically define QDs in the corners of nanowire whereas the right array is used for RF read-out [58].

As we already discussed previously, silicon spin qubits in isotopically purified  $^{28}Si$  present remarkably longer, by more than two orders of magnitude,  $T_2^*$  as compared to their natural silicon counterparts. For instance,  $T_2^* = 120\mu$ s for qubits based on Si MOS quantum dots [22],  $140 - 270\mu$ s for qubits based on phosphorus donors [34],  $20\mu$ s for qubits based on  $^{28}Si/\text{SiGe}$  heterostructures [24] for 99.92%  $^{28}Si$  were reported.

Two-qubit CNOT gates fabricated using isotopically purified 99.92%

Figure 1.8: (a) False-color SEM image of a typical overlapping gate design for Si/SiGe electron QDs architecture. A linear array of 9 QDs is formed under plunger gates P1 - P9 and the tunnel couplings are controlled using barrier gates B1 - B10. Quantum dot charge sensing is realized using sensors formed under S1 - S3. Taken from [55] (b) An SEM image after gate etching of one-dimensional array of qubits along Si nanowire using 'Face-to-face' (F-to-F) devices in series recently fabricated on 300 mm wafers by Leti.

$^{28}Si$  also have been demonstrated with high fidelities [24, 23], much better than those based on natural silicon [33, 60]. Recently, qubits based on isotopically purified Si MOS structures on 300 mm wafers covered with a 100 nm thick layer  $^{28}Si$  purified at 99.92% have been reported and long spin relaxation time  $T_1 = 145$  ms has been measured [61].

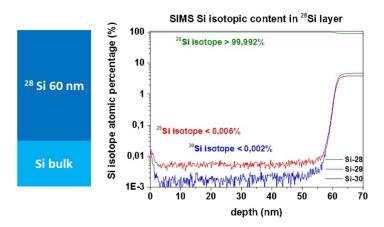

In Fig.1.9, SIMS analysis of  $^{28}Si$  CVD-grown on 300 mm bulk Si substrates demonstrating 99.992% percentage of  $^{28}Si$  is shown [59]. The level of  $^{28}Si$  enrichment reported in this work is larger than in all previous reports concerning silicon qubits and hits the record purification for large-area sili-

#### 99.992% CVD-grown <sup>28</sup>Si on 300mm

Figure 1.9: Secondary ion mass spectrometry measurements of 300 mm wafers fabricated by Leti. Left panel: targeted layer composition. Right panel: SIMS depth profiles of the Si isotopes in the resulting layer. The concentration of the  $^{29}Si$  isotope which contains a nuclear spin 1/2 is less than 0.006% in the top layer and the concentration of the nuclear spin-free  $^{30}Si$  isotope lower than 0.002%. Taken from [59].

con films. In addition, a detailed investigation of the isotopic concentration profile as a function of annealing temperature is given in [59] which allowed to identify the thermal budget range for the successful qubit fabrication on 300 mm using standard CMOS foundries.

Having discussed different single qubit and CNOT gate architectures as well as advanced read-out techniques, another important brick towards large-scale quantum computing is to achieve long-range coupling. There exist a great variety of different strategies to fulfill this long-range coupling requirement. We will focus on the two most promising approaches which are spin-photon coupling with on-chip microwave cavity [62–64] and extended Heisenberg exchange interaction using a quantum mediator [65].

A silicon spin qubit coupled to a superconducting NbTiN resonator reported in [62] is shown in Fig.1.10 (a). In this work, the authors demonstrated that an electron spin can be efficiently coupled to a microwave photon from the resonator. Given large  $\mu$ m-dimensions of the resonator, the coupling of distant qubits separated by less than 100 nm was argued to be possible. Indeed, using this approach, multiple qubits can possibly interact through the same resonator thus providing a route towards scalable networks of spin qubit registers [62, 20].

# CHAPTER 1. CURRENT CHALLENGES TOWARDS SI-BASED LARGE SCALE QUANTUM COMPUTING

Another scalable strategy for long-range qubit interactions is to use intermediate quantum dots to accomplish the coupling between neighboring qubits. In [65], this approach was applied to QDs electrostatically defined in GaAs two-dimensional electron gas and separated by more than 200 nm as shown in Fig.1.10 (b). In theory, the same method can be adopted for silicon QDs if the gate pitch is reduced below 100 nm [20]. Malinowski and colleagues have shown that a many-electron quantum dot (mediator) can be efficiently used for long-range exchange interaction providing another path for scaling large quantum-dot based qubit circuits.

Figure 1.10: Long-range qubit coupling using (a) spin-photon coupling with on-chip superconducting resonator (taken from [62]) and (b) extended Heisenberg exchange interaction via an intermediate quantum dot (taken from [65]).

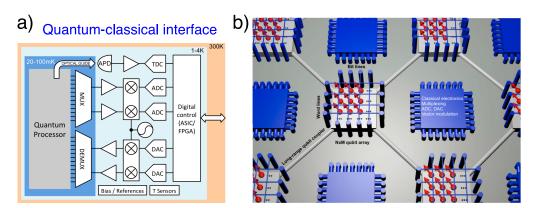

Finally, the qubit control signals and the wiring solutions as explained in [14, 20] require local electronics for running a large number of qubits in parallel. Indeed, connecting  $10^6-10^8$  qubits from sub-100 mK to room temperature voltage source via wires or coaxial lines is hardy achievable as it conflicts with Rent's rule in classical systems and the total number

of pins on a chip [66]. Thus, the most straightforward strategy for CryoElectronics meeting the necessary requirements for qubits (clock speed, resolution, frequency range, memory, power dissipation) [67, 20] is to adopt an existing advanced sub-100 nm CMOS technology (typically  $1-10~\mathrm{GHz}$ frequencies are needed to run silicon spin qubits) to balance cryogenic constraints. In addition, contrarily to III-V semiconductor qubits, in order to be able to couple/decouple adjacent qubits through exchange interaction, silicon spin qubits are denser with a typical 20-100 nm pitch. Thus, if the co-integration of hot spin qubits working at 1-4 K [61] with local electronics is carried out on the same chip, the density requirement imposes using very advanced CMOS technologies [20]. Depending on the actual qubit requirements regarding functionality, power budget, the spacing between qubits different complexity of classical electronics can be realized [68]. Importantly, special attention should be paid to the thermal power dissipation from cryoelectronics defining at which temperature stage the local electronics should reside.

Figure 1.11: (a) A sketch showing the co-integration of qubit physical level and the control and read-out cryogenic electronics. Taken from [67]. (b) An example of qubit arrays with corresponding local electronics placed in the qubit plane for simplicity. Taken from [20].

# 1.2 Results presented in this thesis with respect to the challenges of silicon CMOS quantum computing

From the progress in Si-based quantum computing presented in the previous section, it seems to be clear that a thorough analysis of multi-gate Leti's qubit close-to-industrial architecture with an eventual benchmarking with the most common Si architectures is crucial for advancing towards many-qubit arrays. This is why in Chapter 2 we give a detailed analysis of both n- and p-type quantum dots of different flavor (usual quantum dots centered in the nanowire and corner dots confined in the corners of nanowire) using Leti's SOI nanowire technology. Moreover, the tunability of quantum dots in multi-gate devices using body-biasing is presented. Pauli Spin Blockade for the first holes in a double quantum dot is studied as it is commonly used in qubit read-out schemes. The role of intentionally placed and diffused dopants in the channel is discussed and the main results are supported with tight-binding simulations.

In Chapter 3, the requirements of CMOS cryogenic electronics are discussed. The digital and analog performance of 28 nm FD-SOI isolated transistors is analyzed from 300 K down to 4 K. The saturation of subthreshold swing and threshold voltages are explained by physical modeling in Chapter 4. Chapter 5 is dedicated to the analysis of low-temperature performance of Ring Oscillators fabricated within the FD-SOI technology. Several important conclusions regarding power-performance management at low temperatures are drawn. Finally, a review of the FD-SOI technology for qubit applications is given in Chapter 6 by an extensive analysis of single quantum dots electrostatically defined in conventional short-channel transistors.

## Chapter 2

# Silicon Nanowire Technology For Qubits

This chapter begins with a brief introduction on the fabrication of SOI nanowire multi-gate devices followed by room temperature characterization of a large number (many thousands) of samples.

Then, Pauli Spin Blockade (PSB) for the first holes is studied at different temperatures and the dip-behavior of the leakage current is explained by the spin-orbit interaction mechanism.

Moreover, by measuring a p-type device with four gates in series at low temperature, we demonstrate the electrostatic tunability of access tunnel barriers required to couple/decouple an inner double quantum dot (DQD) from the Source/Drain regions which can be used to improve the hole spin qubit performance.

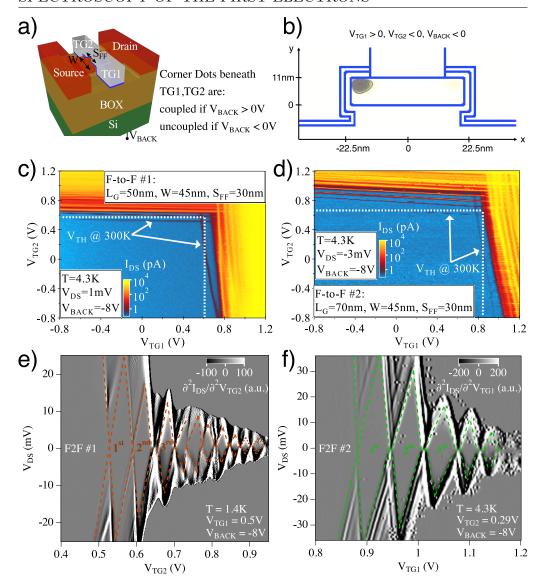

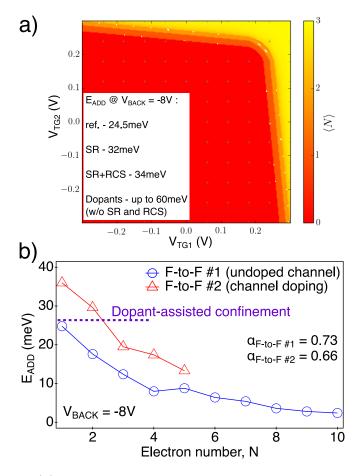

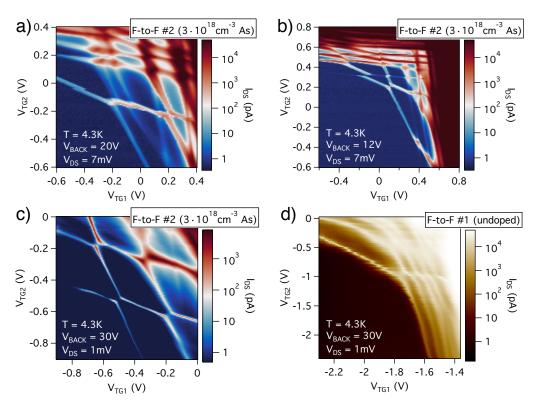

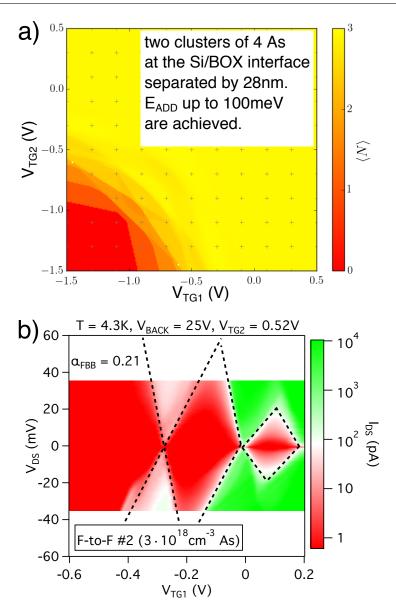

We study quantum dots in using split-gate or the so-called Face-to-Face (F-to-F) geometry and analyze the first electrons confined either in the dots located in the edges of silicon nanowire or on a cluster of dopants under aggressive forward back-biasing (for the device with channel doping).

Our analysis of Face-to-Face devices is supported by realistic simulations based on the effective mass approximation used to compute the electron wavefunctions and addition energies  $E_{ADD}$  as well as the constant interaction method. All the simulations of n-type F-to-F samples were performed by Leo Bourdet (CEA-INAC).

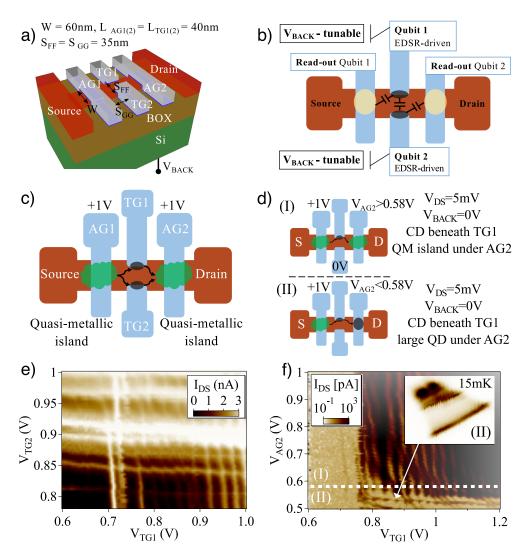

Finally, we propose a four-gate geometry for the realization of a CMOS two-qubit logic gate and investigate different quantum dot configuration within this system.

The results presented in this chapter were partially published in [38, 69–71].

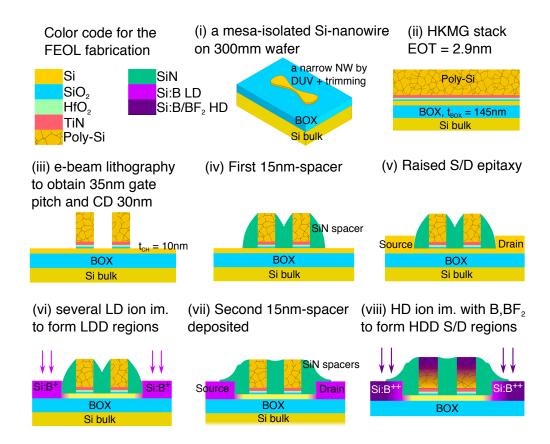

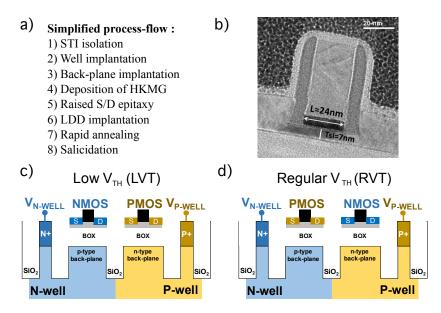

# 2.1 Brief description of Leti's SOI nanowire technology and 300K systematic characterization

The fabrication of multigate nanowire transistors on 300 mm SOI substrate starts with active area patterning. The whole process flow is adopted from [36, 72] with few unconventional fabrication steps such as the use of thick spacers to enhance quantum dot confinement at very low temperature and electron-beam lithography to achieve 30-40 nm spacing between adjacent gates [70]. In the following, the front-end-of-line (FEOL) process is briefly reviewed. [110]-oriented nanowire field-effect-transistors (N- and PMOS) with high- $\kappa$ /metal gate stack were fabricated on (100) SOI wafers with BOX (buried oxide) thickness of 145 nm. The silicon layer is patterned to create nanowires by mesa isolation technique. Each transistor is isolated from each other with the  $SiO_2$  buried oxide of the SOI substrate. Nanowire patterns are defined by deep-UV (193 nm) optical lithography and followed by a resist trimming process in order to shrink the dimensions of nanowires. After the active patterning, a high- $\kappa$ /metal gate is deposited. The high- $\kappa$ oxide is 1.9 nm  $HfO_2$  deposited by chemical vapour deposition technique (CVD) onto thermally-grown  $SiO_2$  of 2.5 nm. This gives the equivalent oxide thickness (EOT) of 2.9 nm. Note that the 2.5 nm of  $SiO_2$  is larger than the usual sub-1 nm value used in advanced CMOS, since we infer a large impact of Remote Coulomb Scattering (RCS) on the low-field mobility [73]. Indeed, in order to improve the stability of quantum dots at very low temperature, pushing this  $SiO_2/HfO_2$  interface further away could be an important point for qubit applications. The atomic layer deposition (ALD) of 5 nm of TiN as the metal gate is followed by doped poly-Si of 50 nm. The gate is wrapped around the channel in the Trigate configuration [36] which guarantees an excellent electrostatic control of field-effect transistors (FETs) including high  $I_{ON}$ , low  $I_{OFF}$ , close-to-60 mV/dec subthreshold swing at room temperature, etc., and single electron transistors (SETs) with high charging energies, close-to-1 lever arm parameter, etc. The silicon film thickness is approximately 10 nm. In practice, nanowire width down to 10 nm can be achieved after active patterning [36], however, for the devices presented in this chapter, a typical width is 25-50 nm.

The role of the silicon nitride (SiN) spacers formed on the sidewalls of the gate is crucial. The first spacer is mainly used to protect the channel during low dose (LD) ion implantation (II) used to form LDD regions providing low access resistances and avoiding semiconductor-metal junctions (Schottky diodes). In addition, to improve access resistance, Si raised

## 2.1. BRIEF DESCRIPTION OF LETI'S SOI NANOWIRE TECHNOLOGY AND 300K SYSTEMATIC CHARACTERIZATION

Source/Drain (t=18 nm) are realized by CVD. Finally, the second spacer consisting of a tetraethyl orthosilicate (TEOS) liner and a nitride layer was fabricated before Source/Drain high dose (HD) implantations, activation spike anneal (to activate the dopants) and silicidation (NiPtSi silicide to obtain low contact ohmic resistances). The FEOL process flow with the main fabrication steps is summarized in Fig.2.1.

To complete the fabrication, tungsten contact and standard Cu backend-of-the-line process flows were used [70]. Thus, the interconnections, the bonding pads were created and the devices were encapsulated in a protective glass.

Some of architectures developed for different qubit experiments are summarized in Fig.2.2. An important progress towards CMOS quantum computing has been recently achieved using Leti's SOI nanowire technology:

- Fig. 2.2 (a) - using the double gate in series, the first CMOS hole qubit

Figure 2.1: Simplified FEOL process flow for a double gate PMOS with the key fabrication steps schematically shown. Adapted from [43].

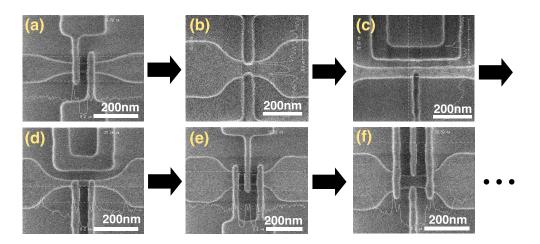

Figure 2.2: (a - f) SEM images of different multi-gate NW transistors used as quantum devices at low temperature. The images were taken after gate patterning (before the first spacer deposition).

was demonstrated [26] as well as the double gate reflectometry technique for an efficient qubit read-out [47]; Pauli Spin Blockade in the few-hole regime at 4 K and 15 mK will be presented in this chapter.

- Fig.2.2 (b) the quantum dots (QDs) formed in the top corners of nanowire, also called Corner Dots (CDs) were extensively characterized at low temperature under different body-biasing conditions [71, 74]. In the light of recent theoretical models of all-electrical control through Electron Dipole Spin Resonance (EDSR) over the spin of electron, these unusual QDs are of great importance for scalable CMOS electron qubits [27, 41]; A thorough analysis of CDs regarding the addition energies  $E_{ADD}$ , lever arm  $\alpha$  and the backgate tunability will be presented in this thesis.

- Fig.2.2 (d) Electrically driven electron spin resonance mediated by spin-valley-orbit coupling in a corner dot was demonstrated [27] as well as Rabi oscillations using PSB spin-selective read-out technique [43].

- Fig.2.2 (e) high-fidelity (above 99% for 1 ms integration time) gate-based spin read-out was demonstrated in [50] using the latched spin block-ade mechanism [75]. In addition, low temperature characterization and tunability of similarly fabricated 4-gates-in-series devices (not shown) will be presented in this chapter.

- Fig.2.2 (f) the F-to-F geometry with additional access gates to locally couple/decouple corner dots (electron spin qubits) will be discussed in this chapter.

One of the key features of our close-to-industrial CMOS fabrication is

### 2.1. BRIEF DESCRIPTION OF LETI'S SOI NANOWIRE TECHNOLOGY AND 300K SYSTEMATIC CHARACTERIZATION

Figure 2.3: Probe station characterization over a 300 mm wafer at 300 K. Statistics over 20 random samples with  $I_{DS}-V_{GS}$  at  $V_{DS}=40$  mV is shown. A low degree of variability is demonstrated for both access (a, b) and F-to-F (c, d) gates in terms of  $V_{TH}$  and SS.

that, at the end, a large amount of quantum devices is available for room temperature (RT) analysis with 300 mm probe station. This preliminary testing at RT allows us to verify the proper operation of different gates and their symmetrical operation.

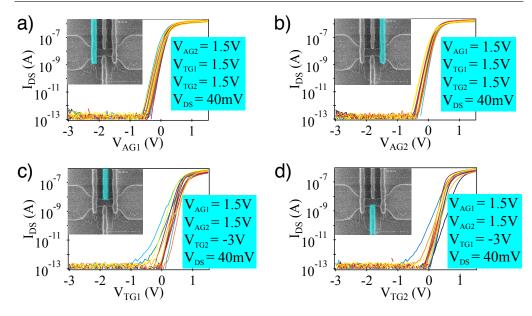

In Fig.2.3 the transfer characteristics  $I_{DS} - V_{GS}$  of a four gate NMOS device at 300 K is shown. The channel width is relaxed to 60 nm as it is required for devices that can host CDs. The gate length  $L_G$  is 40 nm for all four gates and the spacing between gates along the channel and for F-to-F gates is 35 nm. We note, that special measurement sequences were developed in order to have a better understanding of performance of F-to-F or Access gate. For instance, we open all the gates by applying a positive voltage and consecutively sweep the Access gates, see Fig.2.3 (a - b). Testing of the F-to-F gates consists in setting positive voltages to the Access gates and trying to close the channel with one F-to-F gate while sweeping the second one as shown in Fig.2.3 (c - d).

Then, despite the complexness of multi-gate device fabrication, for a set of 20 quantum devices we find a relatively low dispersion in terms of single device variation and an excellent electrostatic control comparable to the single-gate devices [36]. Due to an unintentional misalignment, we observe

a slightly higher degree of variability for F-to-F gates. It should be noted that this variability can be reduced by further optimizing the fabrication process.

# 2.2 Low temperature characterization of PMOS devices: PSB and the QD tunability

### 2.2.1 Brief review of charge transport through double quantum dot

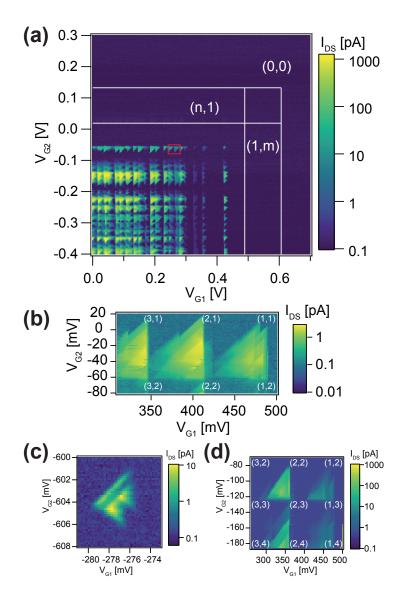

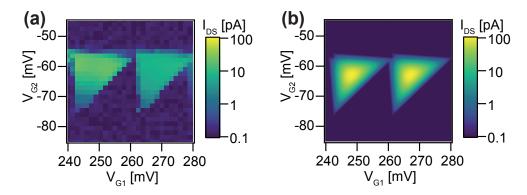

When a double gate devices (see Fig.2.2 (a)) are cooled down to 4 K and below, the so-called stability diagram are typically recorded to probe transport through quantum dots [77]. They are obtained by sweeping the gate voltages and recording the drain current  $I_{DS}$ . In our case, artificial atoms or QDs with discrete energy spectrum are formed due to structural

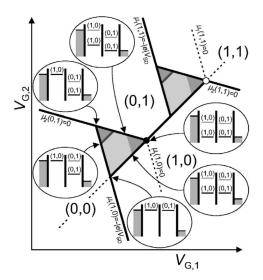

Figure 2.4: A triple points appearing in a DQD system at low temperature for a small  $V_{DS}$ . A triangle is formed from each triple point. Transport through the dot is energetically allowed only within this bias triangle and Coulomb blocked outside. Gray lines and regions in the triangles illustrate  $(V_{G,1}, V_{G,2})$  at which transitions excited-state levels play a role. Electrochemical potentials corresponding to transitions involving an excited state are shown in gray in the level diagrams. Taken from [76].

and electrical confinement. The gate spacers provide the isolation from Source/Drain regions and serve as tunnel barriers and QDs are capacitively coupled to the gates [76]. Then, at low temperature, the phenomenon of Coulomb blockade determines the properties of transport (typically when the thermal energy is much smaller compared to the charging energy). Indeed, the Coulomb repulsion between charge carriers on the QD leads to an energy cost for adding an extra electron/hole to the dot and a precise control over the QD population can be achieved. Due to this charging energy, the charge carriers need to pay in order to tunnel from metallic leads onto a QD. The drain current becomes blocked if the electrochemical potentials within the double quantum dot system are not aligned as shown in Fig.2.4.

In Fig.2.4, a typical signature of transport through a double quantum dot in series is shown. At  $V_{DS}$  of few mV, resonant current through aligned electrochemical potentials results in pairs of triangles outside of which the transport is Coulomb blocked. It should be noted that upon increasing  $V_{DS}$ , the triangle tend to overlap, finally forming a single triangle at sufficiently high drain voltages. When decreasing  $V_{DS}$ , the triangles evolve into triple points.

Moreover, from the stability diagram analysis, the strength of coupling between two quantum dots can be deduced [76]. This coupling is parametrized by the mutual capacitance  $C_{12}$ . Generally, it is important to be able to finely tune this coupling in order to tune two adjacent quantum dots.

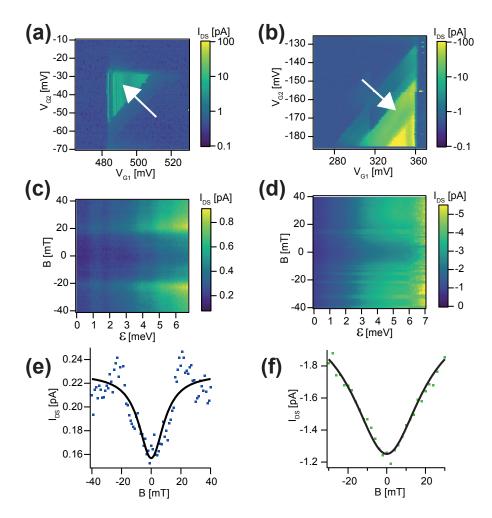

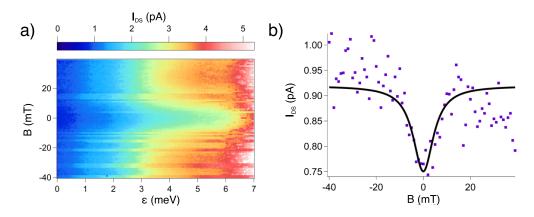

### 2.2.2 Theory of Pauli Spin Blockade in the presence of strong SOC

The Pauli exclusion principle leading to a spin blockade in semiconductor QDs was proven to be a powerful tool for read-out of the spin degree of freedom of single electrons [78, 79, 18]. More recently, PSB read-out technique was successfully used for CMOS electron [43] and hole [26] spin qubits fabricated with Leti's nanowire technology.

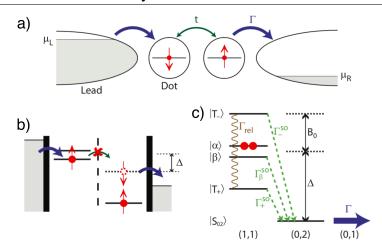

When a DQD is electrostatically tuned in the regime with the (0,2) occupation of QDs (or equivalent charge occupation such as (m, n+2) where m and n are integers) and the transition to (1,1) is probed, depending on whether  $V_{DS}$  is negative or positive, the spin blockade phenomenon might occur when external magnetic field is applied. It can be understood from Fig.2.5 (b): the transition from the energy lowest triplet state T(1,1) to the energetically allowed singlet state S(0,2) is forbidden and the resulting transport is blocked. However, depending on the hosting semiconductor

material, type of charge carriers (electrons, holes), and other parameters, the blockade can be lifted via different relaxation mechanisms. Indeed, depending on the dominant mechanism for mixing of blocked and allowed spin states, one can distinguish different manifestation of PSB. For PSB governed by hyperfine coupling, at zero magnetic field  $B_{ext}$ , a peak in leakage current appears. This is due to nuclear-field induced mixing between the unblocked singlet and the blocked triplet states [80]. Then, the current can be suppressed when a relatively small  $B_{ext}$  of typically few mV is applied. Another well-studied PSB mechanism is so-called spin-flip cotunneling which also manifests a peak at  $B_{ext} = 0$  T. In this case, the second-order tunneling process allowing to exchange an electron with the source reservoir can result in an effective spin flip [81]. This spin relaxation mechanism is also suppressed at finite  $B_{ext}$ . In this case, however, typical critical field can reach few hundreds of mT since it is related to the electronic temperature in the source reservoir [37]. The third commonly reported mechanism of PSB is due to strong spin-orbit coupling (SOC). This mechanism will be studied for the first holes in silicon in the next subsection. Contrarily to electrons in III-V materials [82], electrons in silicon have weak SOC and PSB for them is typically governed either by hyperfine interaction or spin-flip cotunneling. A dip in current at zero  $B_{ext}$  for PSB governed by SOC mechanism can be understood in the following way [83]: by applying external magnetic field, the blocked triplet states start to mix with singlet S(0,2) state and thereby the spin blockade is lifted via relaxation of different triplet states into S(0,2) if magnetic field mixing blocked and unblocked states is applied as shown in Fig.2.5 (c). Another type of relaxation occurs between the blocked states (note that there are four blocked states due to the splitting of  $T_{\pm}(1,1)$  in magnetic field) and is described by  $\Gamma_{rel}$  (relaxation to the ground state) [83].

### 2.2.3 Pauli Spin Blockade for the first holes: Experiment

In this section, we will investigate PSB for the first holes observed at 60 mK and 4 K using a p-type device with double gate in series as shown in Fig.2.2 (a). All the measurements for this samples were done with  $V_{BACK} = 0 \text{ V}$ .

To achieve the base temperature  $T_{base}$  of 60 mK, we cooled down the device in an Air Liquide dilution refrigerator. This cryostat does not have the 1 K pot and the lowest temperature is reached when <sup>4</sup>He is pumped. We used home-made opto-isolated voltage sources to DC bias gates and

Figure 2.5: Double quantum dot in the Pauli Spin Blockade regime. (a) Illustration of transport through a DQD characterized by the strength of the tunnel interdot coupling t and the decay (relaxation) rate of the S(0,2)  $\Gamma$  in PSB. (b) Due to the Pauli exclusion principle, the transport is blocked for S(0,2) - T(1,1) transition. (c) Different energy levels and transition rates for non-spin-conserving interdot coupling. Taken from [83].

transimpedance amplifier to convert current into voltage and then read-out using a commercial digital multimeter. Typical electronic temperature  $T_{el}$  is somewhat higher that  $T_{base}$ . By fitting the Coulomb blockade resonance in similar nanowire devices,  $T_{el}$  was previously found to be around 200 mK. More details on the dilution refrigerator can be found in [84].

Since the proposal of Loss and DiVincenzo in 1998 [25] to make quantum bits based on spins confined in semiconductor quantum dots, substantial progress has been made. First, in III-V materials, where the maturity of growth techniques has allowed the emergence of top-down qubits based on the confinement of a two-dimensional electron gas in GaAs/AlGaAs heterostructures [76], but also bottom-up qubits made from nanowires (InAs or InSb) [85, 86]. In all III-V qubits, the dephasing time is limited by the interaction of the electron spin with the nuclear spins present in the host material [87, 88]. In contrast, silicon presents a low natural abundance of nuclear spins and can even be isotopically purified. It can be used to make electron spin qubits with extremely long dephasing time [89, 90, 33, 22]. An all-electrical control of single dot spin qubit by a single gate voltage microwave signal without the need of local magnetic field gradient would be a clear asset for future developments. Fast and local electrical manipulation using spin-orbit interactions has already been demonstrated in III-V

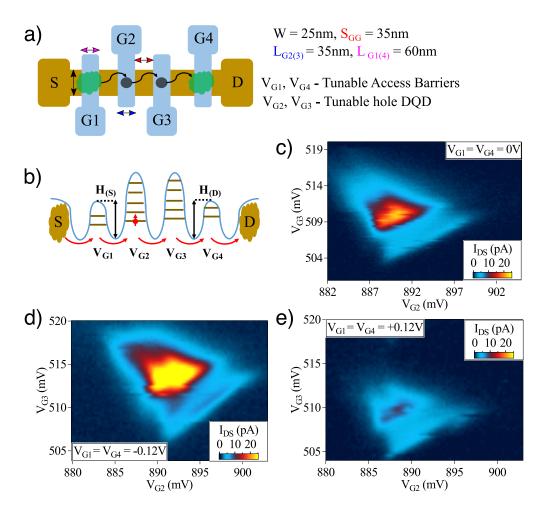

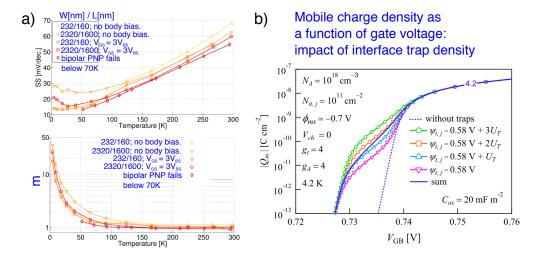

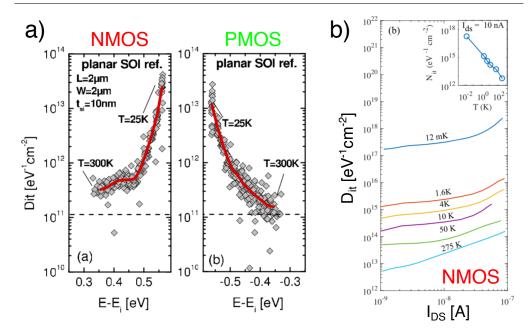

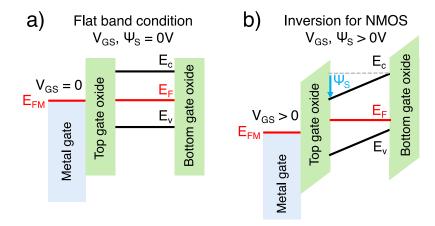

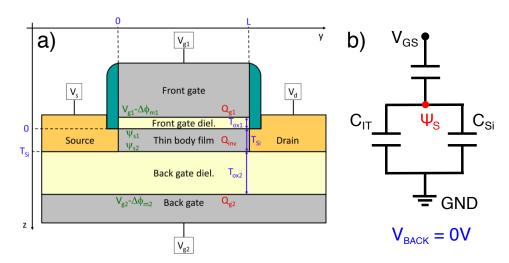

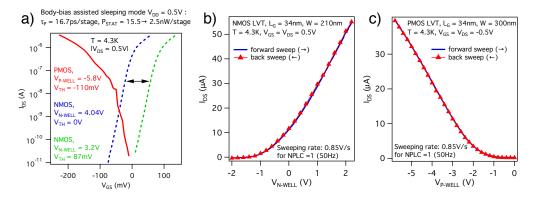

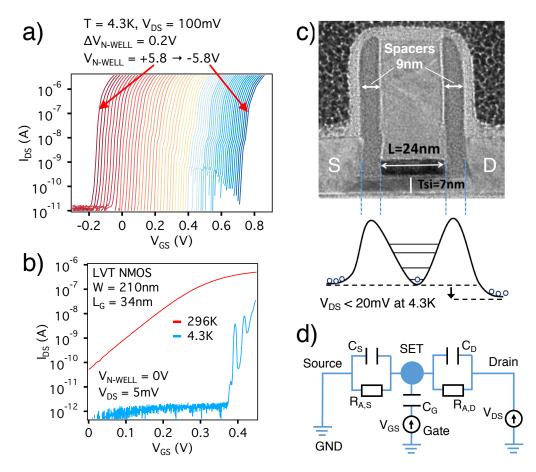

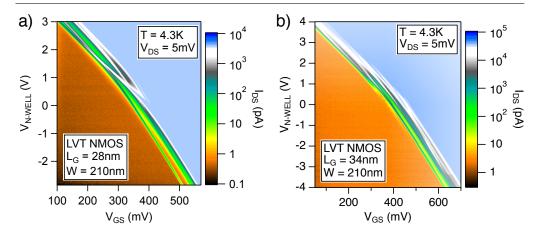

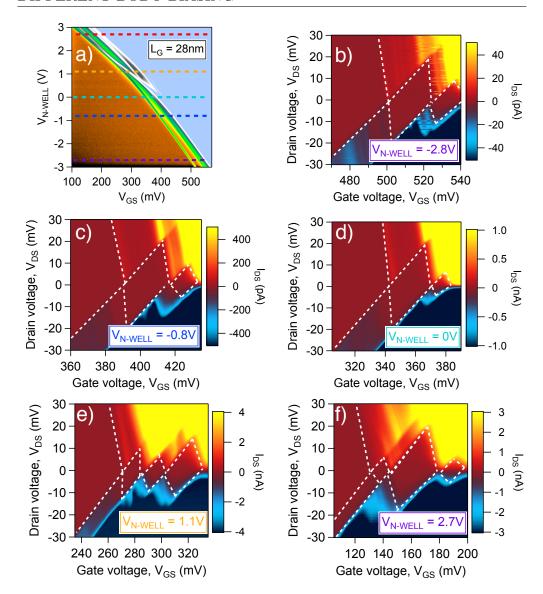

materials [85, 86]. Thus focusing on holes in silicon appears as an appealing strategy since holes present a limited hyperfine interaction [91] as well as a strong spin-orbit interaction (SOC) due to their p-orbital nature. Recent experiments [92, 93] have indeed revealed SOC-related spin properties and a hole spin qubit has even been demonstrated [26]. Here, we present a silicon hole double quantum dot based on the Leti nanowire technology. The device is tunable in the few hole regime in which we investigate Pauli spin blockade, the key ingredient for spin qubits initialization and readout in several qubit implementations [76]. More specifically, we focus on the magnetic field evolution of the leakage current through the device in the PSB regime. It reveals a dip around zero magnetic field linked to spin-orbit mixing [83]. The spin relaxation rates determined from the PSB are comparable with the values extracted for electrons in InAs nanowire double quantum dots [82] and are compatible with the operation of a hole spin-orbit qubit in silicon [26].