## Modeling, Prediction and Optimization of Energy Consumption of MPI Applications using SimGrid

Franz Heinrich

#### ▶ To cite this version:

Franz Heinrich. Modeling, Prediction and Optimization of Energy Consumption of MPI Applications using SimGrid. Modeling and Simulation. Universit\'e Grenoble Alpes, 2019. English. NNT: 2019 GREAM018. tel-02269894

## HAL Id: tel-02269894 https://theses.hal.science/tel-02269894

Submitted on 9 Sep 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Informatique

Arrêté ministériel : 25 mai 2016

Présentée par

#### Franz Christian Heinrich

Thèse dirigée par Arnaud LEGRAND, CNRS

préparée au sein du Laboratoire d'Informatique de Grenoble dans l'École Doctorale Mathématiques, Sciences et technologies de l'information, Informatique

Modélisation, prédiction et optimisation de la consommation énergétique d'applications MPI à l'aide de SimGrid

# Modeling, Prediction and Optimization of Energy Consumption of MPI Applications using SimGrid

Thèse soutenue publiquement le **21 mai 2019**, devant le jury composé de :

#### **Amina GUERMOUCHE**

Maîtresse de Conférences, Télécom SudParis, France, Examinatrice

#### Laurent LEFÈVRE

Chargé de Recherche, Inria / ENS de Lyon, France, Rapporteur

#### Jean-François MÉHAUT

Professeur, Université Grenoble-Alpes, France, Président

#### **Martin Schulz**

Professeur, Technische Universität München, Allemagne, Rapporteur

#### **Arnaud LEGRAND**

Directeur de Recherche, LIG, CNRS, France, Directeur de thèse

## **Abstract**

The High-Performance Computing (HPC) community is currently undergoing disruptive technology changes in almost all fields, including a switch towards massive parallelism with several thousand compute cores on a single GPU or accelerator and new, complex networks.

The energy consumption of these machines will continue to grow in the future, making energy one of the principal cost factors of machine ownership. This explains why even the classic metric "flop/s", generally used to evaluate HPC applications and machines, is widely regarded as to be replaced by an energy-centric metric "flop/watt".

One approach to predict energy consumption is through simulation, however, an accurate simulation of the system is crucial to estimate the energy faithfully. In this thesis, we contribute to the performance and energy prediction of HPC architectures. We propose an energy model which we have implemented in the open source SimGrid simulator. We validate this model by carefully and systematically comparing it with real experiments. We leverage this contribution to both evaluate existing and propose new DVFS governors that are designed to suit the HPC context.

## Résumé

La communauté du calcul haute performance (HPC) est actuellement en pleine mutation, avec des évolutions technologiques majeures telles que le parallélisme massif apporté par des milliers de cœurs de calcul sur un seul accélérateur de type GPU ou bien les réseaux d'interconnexion à très haut débit.

La consommation d'énergie de ces machines est appelée à continuer à croître dans les années à venir, faisant de l'énergie l'un des principaux facteurs de coût. Cela explique pourquoi la métrique classique "flop/s", généralement utilisée pour évaluer les la performance des applications et des infrastructures HPC, est progressivement remplacée par des métriques centrées sur l'énergie comme le "flop/watt".

La simulation est une approche possible pour prédire la consommation d'énergie de ces infrastructures. Cependant, il est nécessaire de mettre en place une simulation fidèle du système pour obtenir une prédiction de performance fiable. Dans cette thèse, nous contribuons à la prédiction de la performance et de la consommation énergétique des architectures HPC. Nous proposons un modèle d'énergie que nous avons implémenté dans le simulateur open source SimGrid. Nous validons ce modèle avec soin en le comparant systématiquement avec des expériences réelles. Nous utilisons cette contribution pour évaluer des algorithmes déjà existant de régulation de la fréquence afin de réduire la consommation énergétique et nous proposons de nouveaux gouvernors DVFS spécialement conçus pour le contexte HPC.

## Acknowledgements

As a student, I heard many stories from and about PhD students and how they had to cope with working on a scientific project for years. Making this experience myself was quite humbling, and I think it is reasonable to say that without the help of many amazing people I would not have managed to achieve results I present in this thesis. I therefore decided to dedicate more space than just the generic one-page acknowledgements to the people that have helped and accompanied me throughout my PhD because I believe that these people have absolutely deserved it.

### My Advisor

▶ Arnaud Legrand At some point during my thesis, Tom said, "After three years as a PhD student, you have no respect left for your advisor." The contrary is true and after 4.5 years of working with you, I find it suprisingly difficult to write these lines because words cannot really convey what this fantastic journey with you means to me personally.

Instead of going into details, I would like to express my admiration for you, not only because of your scientific brilliance and rigor but also because of your great leadership and proximity. I feel the deepest gratitude for all the time and effort it took you to guide me in my endeavour (and the patience that I undoubtedly tested numerous times along the way). Your kindness and politeness that you exhibit when dealing with your PhD students and colleagues have impressed and influenced me and clearly are one of the reasons why your PhD students sometimes have to fight against all the other people that want to collaborate with you!

#### The PhD Committee

▶ Martin Schulz, Laurent Lefèvre, Amina Guermouche and Jean-François Méhaut I am truly honored that all of you, despite having a tight schedule on your own,

accepted to review this manuscript and that you attended my defense. I also highly appreciate your feedback on this work and the discussions that followed my presentation.

### My Team: POLARIS

- ▶ **Tom Cornebize** Be it on business trips or during a private weekend in Aix-lesbains, I've enjoyed spending time with you. Even better, you have been the best intern I have ever had (also the only one): autonomous, good ideas and great rigor. I think your work is highly interesting and I hope you will find enough motivation to keep this high standard!

- ▶ Vincent Danjean Thank you for sharing your huge knowledge of operating systems / Debian with me this has helped me in several cases quite significantly with my research. I have been particularly impressed by the lesson you taught me when you resolved a day-long bug hunt I was on in just a few minutes. Another thing that impressed me is your millionaire's cake. You surely could be one if you started selling it! Thanks for the recipe!

- ▶ Augustin Degomme Your technical knowledge of SMPI is highly appreciated, not only during several debugging sessions where you have helped me out. Thank you for all your efforts and for being the witty, always friendly guy that you are!

- ▶ Nicolas Gast Thanks for telling me about the ADMM algorithm and hence giving me a great idea for a DVFS manager! Also for being the funny, humble and active person that you are. It was a pleasure to work with you!

- ▶ Bruno Gaujal Thanks to you, I can now say that I am somewhat able to understand French people speaking with a slight accent from the south. Besides that, I appreciate your humour but also your knowledge and enthusiasm!

- ▶ Florence Perronin Thanks for being there for the PhD students that seek help, be it scientifically or personally, and your very pleasant company during breaks!

- ▶ Stéphan Plassart Even though you arrived only in late 2016, you quickly became one of the closest colleagues and also a good friend. I don't exaggerate when I say that I was able to improve my French significantly thanks to your corrections and patience during our lunch- and coffee-breaks. I'm glad you listened when things were not working, answered questions on the French system, explained things you

are passionate about (or not... like the CVEC) and showed me Aix-les-bains. We still need to play a first round of golf together soon!

- ▶ Annie Simon The POLARIS team members can consider themselves lucky to have such a caring assistant. I have come to highly appreciate your humour and talking to you was always a more-than-pleasant distraction from my scientific work. You are truly the good soul of this team, and I hope that they get to work with you for a long time to come!

- ▶ Lukas Schnorr Thank you for being a great friend and colleague! I have loved and missed (after your departure) our discussions on reproducibility, experiments and everything else. Getting to know you closer was a real pleasure and not only your professionalism, deep understanding of your domain but also your kindness towards others is what makes you a fantastic teacher. I hope we get to see each other again rather sooner than later!

- ▶ Jean-Marc Vincent Thank you so much for your help with my presentation and your comments on my work. This has undoubtedly prepared me for my defense. It has always been a pleasure to discuss with you, not only because of your humble character, but because you are so knowledgeable in so many fields and always willing to share.

- ▶ Others I would like to thank all the other current and former members of PO-LARIS (Guillaume Huard, Philippe Waille, Pedro Bruel, Bruno Donassolo, Vinìcius Garcia Pinto, Luca Stanisic, our interns and everyone I forgot) for the great time in the lab!

#### POLARIS's Twin-Team: DATAMOVE

The DATAMOVE team shares almost everything with POLARIS: The same corridor, offices, food, events, ...

- ▶ Pierre-François Dutot Thanks for all the information you gave me on Hawaii and wine tasting in France!

- ▶ **Grégory Mounié** Your explanations on OS concepts and your great new ideas on how to debug seemingly unexplicable behaviors have helped me with my scientific work. Additionally, even though my last rehearsal was very spontaneous, you still took the time and helped me by asking great questions and pointing out what remained unclear to you. Thanks for your support!

- ▶ Pierre Neyron Guten Tag! Surprisingly, you are the only member of our teams that constantly claims to be the wrong person to talk to: You reject all blaming when the internet access is broken or when the printer is malfunctioning. The reason for this could be that you *really* are not the right person for this! When it comes to Grid′5000, I can attest that you are not only the right person to talk to, but even extremely helpful, especially when I needed something urgently. You have solved numerous problems quickly and efficiently, and I applaud you here for your CNRS award that you just won. Congrats! If there was another medal for advice on sports / mountains or teaching PhD students nordic skiing, I would highly recommend you for that one as well.

- ▶ Olivier Richard Unfortunately, we have never really worked together, but your funny personality makes you a great person to have around. Thanks for all the discussions, be it in the lab or on business trips!

- ▶ Julio Toss Thanks for helping me settle in Grenoble. Coming in, without speaking any French, was quite unsettling but you have helped me to get started here. It is very unfortunate that you had to leave in 2016 already, but I have not forgotten our trips and our endless org-mode discussions!

- ▶ Brice Videau Thanks a lot for your help with the calibration procedures and explaining the tools I needed to know for debugging. I hope that at some point, we can work on a joint project together!

- ▶ Others I would like to thank everyone else, especially Fanny Dufossé, Bruno Raffin, Denis Trystram, Frédéric Wagner but also Carmen Chan, Tristan Ezequel, Adrien Faure, Nicolas Michon, Michael Mercier, Clement Mommessin, Baptiste Pichot, Millian Poquet, Danilo Santos, Théophile Terraz and Salah Zrigui for the great time in the lab. Every single one of you has helped me in one way or another and made me laugh numerous times!

#### Scientific Collaborations

- ▶ Anne-Cécile Orgerie Thanks for your kindness and your willingness to contribute with hands-on help and great advice on energy-related subjects! Working with you has been very pleasant for me and I hope we will continue to work together in the future.

- ▶ **Professor Martin Quinson** Thank you for hosting me for almost a month in Rennes! Not only during my stay with you, but during the entirety of my thesis, I

have enjoyed your down-to-earth mentality, your humour, kindness and certainly your helpfulness with SimGrid related issues.

- ▶ Sascha Hunoldt Your honesty and ambition is impressive and your comments on my paper have helped me improve it for the second (and accepted) version. I think that the scientific community needs more rigorous researchers like you. Thank you for working with me!

- ▶ **Frédéric Suter** Thank you for all the comments and help with the SimGrid code base. Your efforts and explanations have often saved me from hyperventilating!

### Friends & Family

- ▶ My Family I would like to thank my family and in particular my parents for their support and their help in various ways. It is highly appreciated!

- ▶ Jan-Philipp Kayser, Alexander Kruck, Hajo Trimborn Thank you all for your friendship that cannot be put in a few sentences and the great time we always spend together.

- ▶ **Jeffrey Overbey** All your advice, be it scientific or on grammar and writing, has been highly valuable to me. Besides being a brilliant software engineer and researcher, your company during our travels has been highly appreciated!

- ▶ Samantha Ho You have been there for me even during the roughest of times, and your support has helped me so much. Thank you!

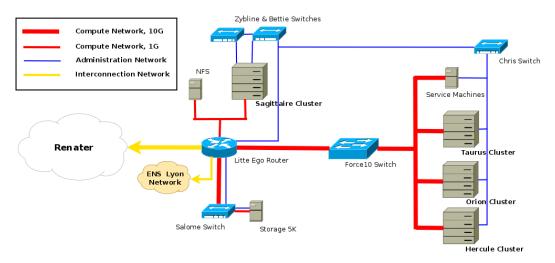

#### Infrastructure

▶ **Grid'5000** Experiments presented in this thesis were carried out using the Grid'5000 testbed, supported by a scientific interest group hosted by Inria and including CNRS, RENATER and several Universities as well as other organizations.

## Contents

| 1 | Intr | oductio | on                                                        | 1  |

|---|------|---------|-----------------------------------------------------------|----|

| 2 | Con  | text    |                                                           | 5  |

|   | 2.1  | High    | Performance Computing (Until) Today                       | 5  |

|   |      | 2.1.1   | Scientific Applications in a Nutshell                     | 5  |

|   |      | 2.1.2   | Architectures: Computation                                | 7  |

|   |      | 2.1.3   | Architectures: Communication                              | 12 |

|   |      | 2.1.4   | Programming paradigms                                     | 14 |

|   | 2.2  | High    | Performance Computing Tomorrow: Exascale Computing        | 19 |

|   |      | 2.2.1   | Applications                                              | 20 |

|   |      | 2.2.2   | Architectures: Computation                                | 23 |

|   |      | 2.2.3   | Architectures: Communication                              | 28 |

|   |      | 2.2.4   | Programming Paradigms                                     | 30 |

|   | 2.3  | Concl   | usion                                                     | 31 |

| 3 | Rela | ated Wo | ork                                                       | 33 |

|   | 3.1  | Simul   | ation Based Performance and Energy Prediction             | 33 |

|   | 3.2  | Concl   | usion                                                     | 35 |

| 4 | The  | SimGr   | rid Project                                               | 37 |

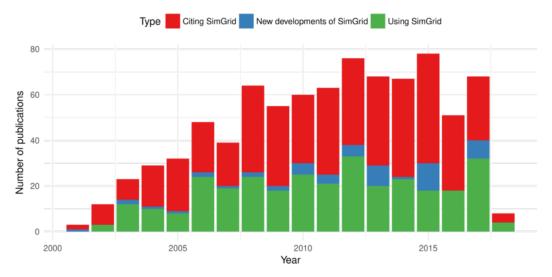

|   | 4.1  | Overv   | view of the SimGrid Project                               | 37 |

|   |      | 4.1.1   | History and Impact                                        | 37 |

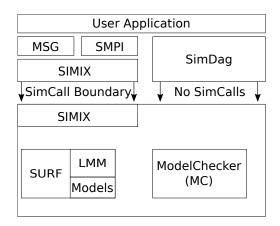

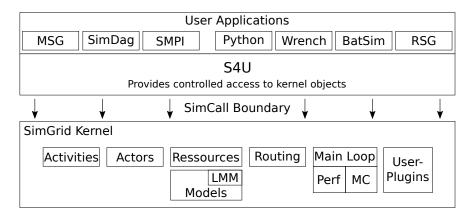

|   |      | 4.1.2   | Software Architecture                                     |    |

|   |      | 4.1.3   | Software Engineering                                      |    |

|   | 4.2  | A Ger   | neral Introduction to SimGrid                             |    |

|   |      | 4.2.1   | Modeling Virtual Resources                                | 41 |

|   |      | 4.2.2   | Modeling Applications                                     | 45 |

|   | 4.3  | SMPI    | Simulating MPI Applications                               |    |

|   |      | 4.3.1   | Emulation of MPI code                                     |    |

|   |      | 4.3.2   | Modeling of MPI Communications                            | 52 |

|   |      | 4.3.3   | Scalability                                               | 53 |

|   | 4.4  | Runti   | me Support (StarPU-SimGrid): Simulating Dynamic GPU-based |    |

|   |      | Appli   | cations                                                   | 57 |

|   | 4.5  | Contr   | ibutions to the SimGrid Project                           | 58 |

|   |                                               | 4.5.1                                       | Platform description                    | 58                                      |

|---|-----------------------------------------------|---------------------------------------------|-----------------------------------------|-----------------------------------------|

|   |                                               | 4.5.2                                       | PAPI support                            | 59                                      |

|   |                                               | 4.5.3                                       | Privatization                           | 59                                      |

|   |                                               | 4.5.4                                       | Energy plugin                           | 60                                      |

|   |                                               | 4.5.5                                       | DVFS plugin                             | 60                                      |

|   |                                               | 4.5.6                                       | Load Balancing                          | 60                                      |

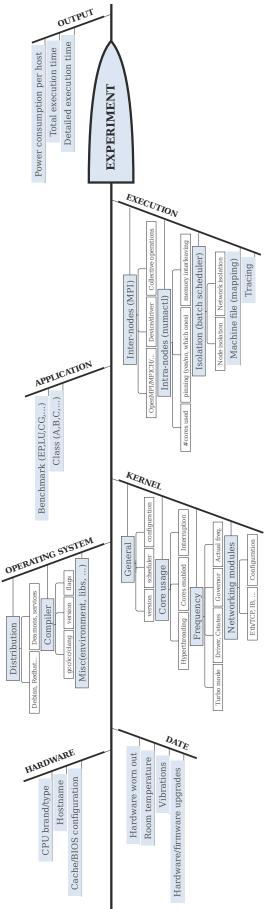

| 5 | Exp                                           | erimen                                      | tal Methodology                         | 63                                      |

|   | 5.1                                           | Exper                                       | imental Setup                           | 63                                      |

|   | 5.2                                           | Factor                                      | rs Influencing the Experimental Results | 63                                      |

|   |                                               | 5.2.1                                       | Hardware                                | 65                                      |

|   |                                               | 5.2.2                                       | Date                                    | 65                                      |

|   |                                               | 5.2.3                                       | Operating System / Software Stack       | 67                                      |

|   |                                               | 5.2.4                                       | Kernel                                  | 67                                      |

|   |                                               | 5.2.5                                       | Application                             | 70                                      |

|   |                                               | 5.2.6                                       | Execution                               | 70                                      |

|   |                                               | 5.2.7                                       | Output                                  | 71                                      |

|   |                                               | 5.2.8                                       | Data Analysis                           | 71                                      |

|   | 5.3                                           | Netwo                                       | ork Calibration                         | 72                                      |

|   |                                               | 5.3.1                                       | Network                                 | 72                                      |

|   |                                               | 5.3.2                                       | Hardware Limitations                    | 72                                      |

| 6 | Con                                           | tributi                                     | on: Modeling Multi-Core CPUs            | 73                                      |

|   | 6.1                                           | Proble                                      | em                                      | 73                                      |

|   | 6.2                                           | _                                           | sed Solution                            |                                         |

|   | 6.3                                           | Perfor                                      | rmance Evaluation / Effectiveness       | 79                                      |

|   | 6.4                                           | Limita                                      | ations                                  | 80                                      |

|   |                                               | 6.4.1                                       | Technical limitations                   | 80                                      |

|   |                                               | 6.4.2                                       | Scaling limitations                     |                                         |

|   |                                               | 6.4.3                                       | Future Work                             | 82                                      |

|   |                                               |                                             |                                         |                                         |

| 7 | Con                                           | tributi                                     | on: Modeling Intra-Node Communications  | 83                                      |

| 7 | <b>Con</b> 7.1                                | Proble                                      | em                                      |                                         |

| 7 |                                               | Proble                                      |                                         | 83                                      |

| 7 | 7.1                                           | Proble<br>Soluti                            | em                                      | 83<br>83                                |

| 7 | 7.1<br>7.2                                    | Proble<br>Soluti<br>Perfor                  | emon                                    | 83<br>83<br>85                          |

| 8 | 7.1<br>7.2<br>7.3<br>7.4                      | Proble<br>Soluti<br>Perfor<br>Limita        | em on                                   | 83<br>83<br>85<br>85                    |

|   | 7.1<br>7.2<br>7.3<br>7.4                      | Proble Soluti Perfor Limita tributie        | em on                                   | 83<br>83<br>85<br>85<br><b>89</b>       |

|   | 7.1<br>7.2<br>7.3<br>7.4                      | Proble Soluti Perfor Limita tributie        | em on                                   | 83<br>83<br>85<br>85<br>89              |

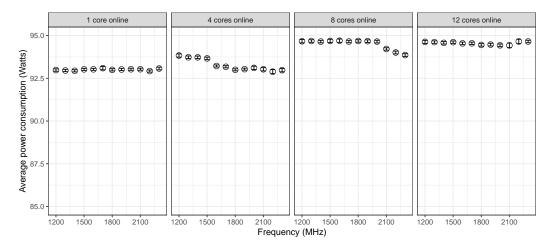

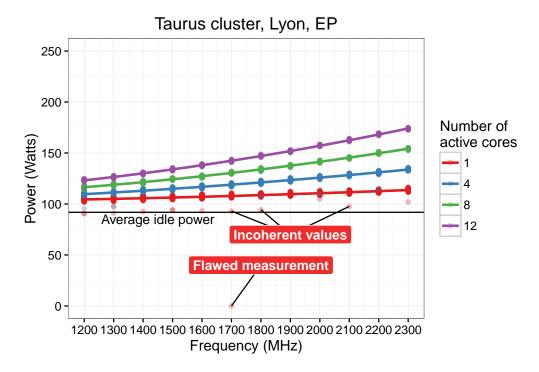

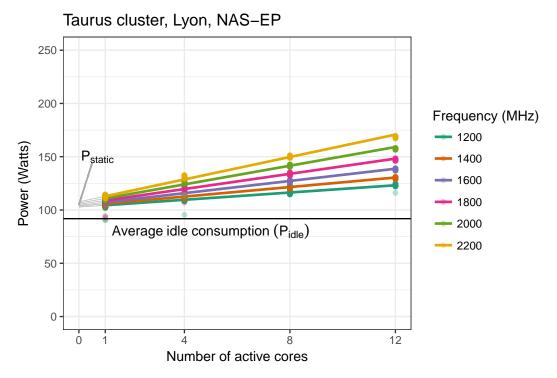

|   | 7.1<br>7.2<br>7.3<br>7.4<br><b>Con</b><br>8.1 | Proble Soluti Perfor Limita tributie        | em on                                   | 83<br>83<br>85<br>85<br><b>89</b><br>92 |

|   | 7.1<br>7.2<br>7.3<br>7.4<br><b>Con</b><br>8.1 | Proble Soluti Perfor Limita tributie Proble | em on                                   | 83<br>83<br>85<br>85<br>89<br>92<br>94  |

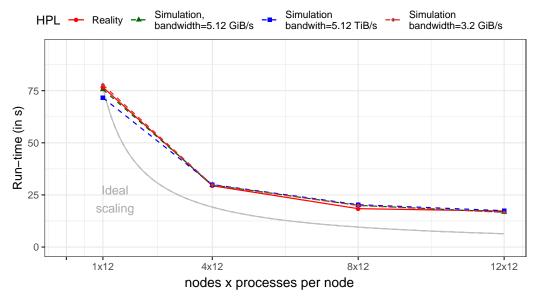

|     | 8.4    | Use Ca   | ase: Capacity Planning for HPL                           | . 101 |

|-----|--------|----------|----------------------------------------------------------|-------|

|     | 8.5    | Limita   | tions                                                    | . 102 |

|     |        | 8.5.1    | Model Limitations                                        | . 102 |

|     |        | 8.5.2    | Experimental Limitations                                 | . 104 |

|     | 8.6    | Conclu   | usions                                                   |       |

| 9   | Con    | tributio | on: Optimizing the Power Consumption With DVFS           | 107   |

|     | 9.1    | Conte    | xt                                                       | . 107 |

|     |        | 9.1.1    | Iterative Applications                                   | . 107 |

|     |        | 9.1.2    | DVFS, a Means to Reduce the Power Consumption of HPC     |       |

|     |        |          | Applications                                             | . 109 |

|     | 9.2    | Relate   | d Work                                                   | . 115 |

|     |        | 9.2.1    | Adagio (Application Level DVFS)                          | . 115 |

|     |        | 9.2.2    | Load Balancing with Adaptive MPI (AMPI)                  | . 117 |

|     |        | 9.2.3    | Residual Load Imbalance                                  |       |

|     | 9.3    | Contri   | butions                                                  | . 119 |

|     |        | 9.3.1    | DVFS Governor: AdagioImproved                            | . 120 |

|     |        | 9.3.2    | DVFS Governor: Lagrange                                  | . 122 |

|     | 9.4    | Perfor   | mance Evaluation/Effectiveness                           |       |

|     |        | 9.4.1    | DVFS/Adagio/AdagioImproved/Lagrange                      | . 126 |

|     |        | 9.4.2    | Efficiency Comparison DVFS / Load Balancer               |       |

|     | 9.5    | Limita   | tion and Future Work                                     |       |

|     |        | 9.5.1    | Unavailable Frequencies and More Complex Architectures . | . 129 |

|     |        | 9.5.2    | Current Limitations of Our Implementation                | . 130 |

|     | 9.6    | Conclu   | usions                                                   | . 131 |

| 10  | Con    | clusion  | and Future Work                                          | 133   |

|     | 10.1   | Thesis   | Summary                                                  | . 133 |

|     | 10.2   | Limita   | tions                                                    | . 134 |

|     |        | 10.2.1   | Model Limitations                                        | . 134 |

|     |        | 10.2.2   | Application Limitations                                  | . 136 |

|     |        | 10.2.3   | Experimental Limitations                                 | . 136 |

|     | 10.3   | Future   | e Work                                                   | . 137 |

|     |        | 10.3.1   | Extending the Work of this Thesis                        | . 137 |

|     |        | 10.3.2   | SimGrid                                                  | . 138 |

|     |        | 10.3.3   | Joint Work with the SimGrid Userbase                     | . 140 |

| Bil | bliogi | raphy    |                                                          | 141   |

Introduction

Over the past few decades, High-Performance Computing (HPC) has supported a great number of scientific discoveries in both academic and industrial contexts. Today, a continuously growing number of researchers from largely different fields have come to appreciate the computational power provided by supercomputers for their studies of intricate and important questions that were often formerly infeasible, such as climate change or the molecular structure of human diseases. In the industrial world, an increasingly fierce global competition and faster innovation cycles require researchers and engineers to rely on complex simulations to test and optimize products and materials in order to gain an advantage over the competition.

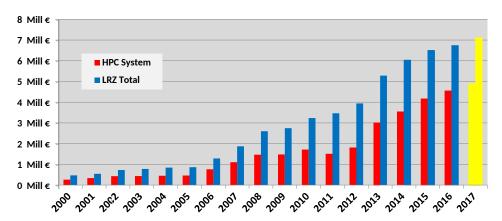

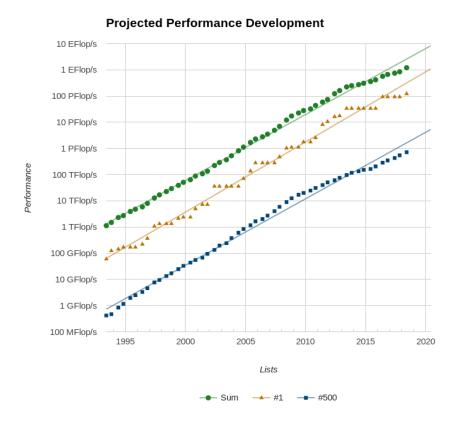

Both worlds have in common that their science is often limited by the existing technology and algorithmic solutions that do not support computations at the desired level of detail. Continuing the development of machines and algorithms is therefore a necessity to provide researchers with the needed computational power. Today, the race to exascale, i.e., the next generation of supercomputers, is in full swing. Alas, to achieve a performance on the order of  $1 \times 10^{18} \, \mathrm{flop/s}$  sustainably, a disruptive technology change in almost all fields, including hardware (computation units, networks), software (e.g., batch schedulers) and user applications is required. With a much greater number of computation cores, possibly in the hundreds of millions or even billions, exascale machines are expected to deliver high performance at the cost of a much higher power consumption than today's machines. For this reason, energy is expected to become the main optimization goal since power contributes greatly to the total cost of operation. This can be easily understood when considering Germany as an example: 1 kW h was priced at 0.07 € in 2000 but has since more than doubled and cost 0.157 € in 2016 [Sho+17, Chapter I]. Increasing electricity prices in combination with growing machine sizes have caused power expenditures to grow incessantly. This is illustrated in Figure 1.1, which compares the yearly total electricity cost of the Leibniz-Rechenzentrum (LRZ) in Garching near Munich, Germany, to the cost incurred by its HPC system.

To reduce future spendings on electricity or at least keep increases to an acceptable minimum, efforts to improve power efficiency must be undertaken. With the abovementioned cost for 1 kW h, a constant power reduction of 1 MW would

have saved 1,375,320 € in 2016 and even more today. It is therefore important to improve general hardware efficiency but also to reconsider how these platforms are used and programmed. Significant time is spent running tests on production platforms and moving these tests away from the machines will improve system efficiency ("science-per-watt"), but not necessarily the power consumption. It is therefore an important goal to ensure that application developers rely on algorithms that minimize power consumption, for instance by overlaping communication times with computation or by reducing the amount of data movements through improved data locality. Improving the flop/W ratio of an application is not trivial. Application developers must therefore be provided with the right tools and lightweight models that consider power efficiency [Don+11, p. 38].

One possible approach is the optimization and evaluation of applications through simulation. Once the target platform has been modeled, a simulator can estimate an application's performance on that particular machine. This can help to move away not only performance testing but also debugging, since a simulator can be expected to return deterministic results and reproducing a bug can be easier. Besides raw performance estimations, a simulator can also provide further beneficial information, for example, when and where network bottlenecks (bandwidth, congestion) occur. This can be particularly helpful with iterative developments of next-generation machines through co-design, because application developers can assess more quickly what recent developments mean for their application's performance whereas hardware developers can find out what changes (for example, to the network configuration) could speed up targeted applications and what does not (e.g., more nodes or a more expensive network topology).

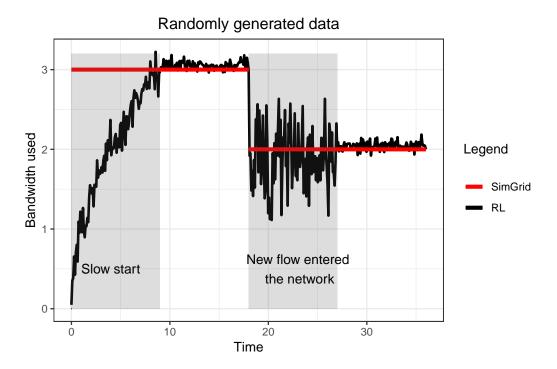

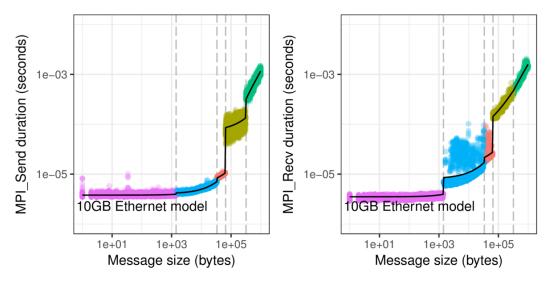

This thesis contributes to the utility of simulation as a mean for building energy efficient applications, with the core contribution being a deliberately simple energy model. To test its accuracy, we implemented a prototype in SimGrid, a simulator that is particularly well suited for faithful simulation of MPI applications thanks to its well-tested network models. Our model computes the energy for every node individually and uses the load of the multi-core processors of each node as a basis for this estimation. The load changes often and the current energy consumption is therefore often recomputed over the entire execution time of the application, making precise performance predictions for applications running on multi-core systems crucial to our approach.

With a well functioning energy model in place, we study in a second contribution the potential (automatic) energy savings of adaptative MPI applications by changing a node's frequency. We implemented several, rather simple governors from the linux kernel but also a previously published application-space governor called Adagio [Rou+09]. We present also some ideas to improve Adagio and finally de-

**Figure 1.1:** The energy bill for data centers has drastically increased since the early 2000s, making energy savings an important goal for hardware vendors and application developers. This statistic shows the increase of the Germany-based Leibniz-Rechenzentrum [Sho+17, Figure 1].

velop our own governor that is based on mathematical optimization. We eventually conclude our study with a comparison to load balancing, which we found to yield significant higher savings for irregular applications.

#### **Thesis Structure**

The remainder of this thesis is structured as follows: Chapter 2 presents the current state of High-Performance Computing and the changes we need to reach a sustainable exaflop-performance. The variety of components, the cost of operating such a machine and the need of application developers to optimize their code for each platform (and energy savings) motivates the work presented in this thesis. Chapter 3 then gives an overview of the existing work, especially simulators developed by other projects. Our own simulator, SimGrid, is introduced in Chapter 4. This chapter emphasizes especially SMPI, a simulator for MPI applications that ships with SimGrid, and the issues that are inherent to "online emulation". Our methodology is outlined in Chapter 5. The first contribution, multi-core modeling for SMPI, is presented in Chapter 6. Inter-node communication has been validated many times with SMPI, but intra-node communication requires some additional effort. Our approach is explained in Chapter 7. Chapter 8 then finally deals with the problem of energy prediction: A key strength of our proposed model, which computes the energy consumption based on the current load, is its simplicity. Our last contribution is presented in Chapter 9 and shows how we studied energy savings obtained through dynamic changes of frequency. This thesis is then concluded by Chapter 10, which also presents future work.

Context 2

High-Performance Computing (HPC) platforms have been developed to satisfy the demand for immense computing power. Adopted by a wide range of scientific domains, HPC has always been subject to change but the evolution over the last decade has been particularly far-reaching.

This chapter gives a general overview of HPC and is structured as follows: Section 2.1 presents the current-state of HPC up to the petaflop-era. Subsequently, Section 2.2 contrasts this with new requirements and developments for the next-generation of HPC (called exascale).

## 2.1 High Performance Computing (Until) Today

### 2.1.1 Scientific Applications in a Nutshell

Not even half a century ago, computational cost caused many scientific problems to be impenetrable, but the advent of computers has given researchers a new instrument that has rendered many of these problems tractable, even though especially the most demanding and challenging problems are limited to the most powerful machines, and hence a small subset of all platforms, because only they can can provide enough resources to satisfy these applications' requirements.

Unsurprisingly, the HPC community consists of researchers from both academia and industry and covers a large variety of fields, such as engineering (e.g., aerodynamics in aviation, material science), geology (oil exploration, earthquakes), meteorology (weather forecasts), medicine (e.g., HIV, brain simulation), biology (e.g., drought-resistance in plants, protein docking), or globally relevant questions such as climate change.

These fields of interest contain profoundly different scientific problems that require computational power, but to investigate them, scientists use very similar approaches: They commonly rely on simulations that model parts of reality with the aid of discretized partial differential equations.

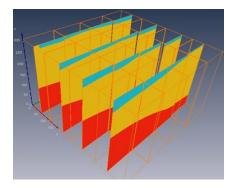

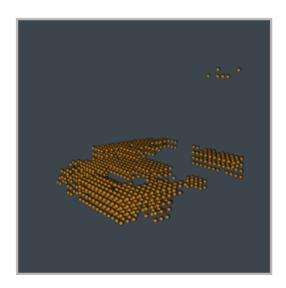

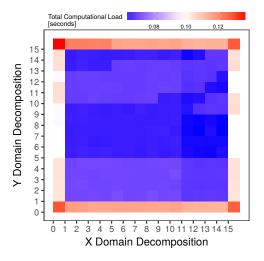

**Figure 2.1:** A domain decomposition of rocky ground used for an earthquake simulation with Ondes3D. The physical domain is cut into cuboids which are evenly assigned to processors.

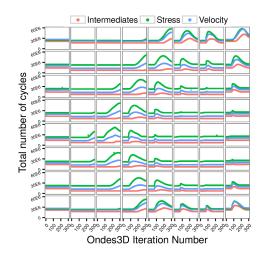

As a consequence, the general structure of HPC applications is mostly regular: The physical domain (i.e., the object of interest), known at the start, is first discretized, i.e., decomposed into a finite amount of smaller elements with an easier geometric shape (cubes, rectangles, ...). Figure 2.1 exemplifies this process with a decomposition into cuboids for a geological problem. Each cuboid is subsequently assigned to a single processor. In a second step, each thus obtained element (part of the initial problem) must be initialized, for instance from observations (e.g., geological composition, depicted in different colors in Figure 2.1) or a random field. In the final step, the simulation is started and computations are applied on a per-element basis.

It is important to note that the resources required by steps two and three depend on the application and the decomposition's resolution. Consider a "relatively" coarse-grained  $1000 \times 1000 \times 1000$  decomposition resolution, with each element containing only five double values. Clearly,  $5 \times 10^9$  values would have to be allocated and initialized, consuming a total of 40 GB of memory. A refined resolution is normally applied to all dimensions and so doubling the resolution will require  $8 \times 40 = 320 \, \mathrm{GB}$  to be allocated.

The resource consumption can therefore explode easily. To mitigate this, the entire domain is typically distributed over several machines (interconnected by a network). With each machine storing just the fraction of the domain that it processes, regular communication between machines in order to exchange data (such as computation results) or for synchronization (if required) becomes inevitable.

The following discussion gives an overview on current HPC node hardware (Section 2.1.2), network setup (Section 2.1.3) and the main programming paradigms for HPC programming (Section 2.1.4).

### 2.1.2 Architectures: Computation

The scale of supercomputers with hundreds or thousands of nodes is too large to be bought by single research entities such as research teams or university departments, even though these machines are normally already built with off-the-shelf components for cost reasons. In most cases, government organizations such as the NSF or the DoE in the U.S. finance the majority of the expenses required for acquisition and maintenance of a supercomputer. Once the production phase has been entered, access to the supercomputer is normally granted to selected researchers after evaluation of their proposed project.

More often than not, HPC nodes are constructed to provide general computational power to as many disciplines as possible and hence do not favor a specific kind of computation over others. In some rare cases, however, supercomputers are explicitly procured for and restricted to a very limited research field (such as daily weather simulations). This restriction implies that application requirements are rather well known in advance and specialization (leading to, e.g., increased performance or lower energy consumption) can thus be justified.

The three generic computational units (CPU, GPU and Many-Core-Coprocessors) found today in HPC nodes are presented in the following discussion.

#### **CPU**

CPUs are considered the "heart" of a computer and can be found in every PC, laptop or server. Their development is a very costly undertaking and requires high-tech knowledge in many fields, such as circuit design and manufacturing.

It is hence not surprising that most HPC systems rely on the well-known x86 architecture, as produced by Intel and AMD, for their main processors.

For several decades, processor frequency used to double every 18-24 months. Alas, a processor's power consumption grows quadratically with the frequency and as a consequence, even limited clock speed increments quickly result in higher heat dissipation and require more costly cooling to prevent damage. Vendors have for this reason turned towards multiplying computation units, e.g., by adding several CPUs to a node or adding more cores to a CPU. Having multiple computation units in the same node means that they share the same address space and can access an application's data that is stored in the system's main memory (RAM) directly, without further transfer over a network.

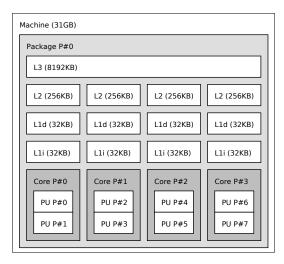

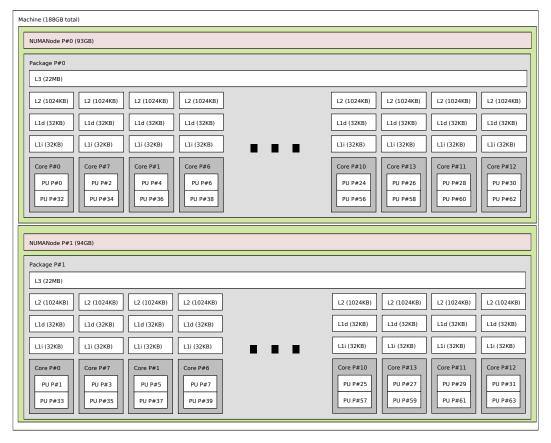

Sharing the main memory between CPUs creates several side-effects: First of all, transferring data from the main memory is very slow and often forces the CPU to wait. To mitigate this, CPUs try to reduce RAM accesses by using a cache hierarchy with different cache sizes and performances per level. Figure 2.2 (page 9) illustrates the cache hierarchies of a commodity laptop bought in 2015 and Figure 2.3 (page 10) a recent HPC node. One can distinguish in total 4 levels of caches:

The first level (L1) cache, exclusive to each core, is typically very fast but also very small with only a few kB. The L1 cache exists for instructions (L1i) and for data (L1d). The second level (L2) cache is still private to each core but its increased size comes at a lower performance. While the L1 caches feature the same size for laptop and HPC node, the L2 cache is already four times larger for each HPC-core than for the laptop. Finally, the third level (L3) cache is shared between all cores of the same CPU and can store several MB of data. The HPC node has an overall larger L3 cache per CPU (22 MB vs. 8 MB), but at the same time it needs to serve in total 16 CPU cores and hence four times more than the corresponding laptop cache. It is thus essential to keep this hierarchy when programming applications. Ensuring both spatial and temporal locality helps to avoid costly cache misses.

All cores can access the main memory to read and write data independently of each other. Therefore, data coherency must be guaranteed among all cores to avoid computations with different values for the same variable. Updates to data stored in RAM must hence trigger an invalidation of any corresponding cached copy. This means that in the worst case, when all cores have a copy in their caches, writing a single value back to RAM requires to broadcast the invalidation to all cache levels of all cores. Consequently, CPU core count scalability is adversely impacted by larger caches and most CPUs have therefore relatively few cores but very large caches, even though the design of their hierarchy (including number and size of caches) can vary.

Privileging caches over main memory greatly contributes to application performance. Over the years, many intricate techniques that help with this have been developed. Cache-prefetching, for instance, reduces the amount of direct memory accesses and cache-misses by intelligently loading data from the main memory into caches before it is actually required.

Unfortunately, even with good cache usage, waiting times for the processor can still occur, for example, when a dependency on a not yet available result of another operation exists.

Instruction Level Parallelism (ILP) aims to reduce waiting times by identifying instructions that can be executed in parallel. Some ILP-based techniques are instruction pipelining, out-of-order execution or speculative execution. The introduction

Figure 2.2: A visual representation of the cache hierarchy and sizes of a workstation laptop as obtained through hwloc-ls.

of HyperThreading has optimized this even further so that significant speed-ups in the future are not to be expected.

Besides the instruction level, the data-level can be exploited for further parallelism, typically through vectorization. The idea is that a single instruction (such as addition or multiplication) must be applied to all vector coordinates. Several extensions of the x86-architecture (e.g., legacy MMX, multiple versions of SSE and the new standard Advanced Vector Extensions (AVX) and its different versions), introduced supplementary registers and operations. The AVX-512 extension provides 32 registers with 16 bit each. These can be used to hold 8 single precision or 4 double precision floating points. To take full advantage of vectorization, the instruction (the operator to be applied) as well as the data must be identified. In some cases, a compiler may be able to automatically determine the instructions and data but data-dependencies are difficult to resolve with certainty, so a compiler may or may not vectorize code correctly. In practice, this has largely remained the programmer's responsibility.

Vectorization is an important performance optimization for scientific applications, as they are well-known to be often regular and therefore can profit frequently from good vectorization.

A CPU's performance is improved by several levels of parallelism (multi-CPU, multi-core, instruction and data-level) and many on-chip features. CPUs are also built to be backward compatible with legacy software (e.g., the new AVX is backwards compatible to SSE), so removing a once introduced feature is difficult.

CPUs have thus a very general nature that makes them well-suited for problems that are not massively parallel.

**Figure 2.3:** A visual representation of the cache hierarchy and sizes of a node as obtained through hwloc-ls.

The following section contrasts CPUs with GPUs, devices that are highly specialized on supporting massive parallelism.

#### **GPU**

The hardware-implementation of the large x86 instruction set and necessary optimizations (e.g., ILP) consume power and space on the die for its transistors. This makes CPUs very complex and forces them to dedicate about 70% of the space (and hence energy) to hardware-internal decoding of the control flow.

For significant performance gains, this share needs to be reduced as much as possible, for instance by removing unnecessary features. As a side-effect, space is released on the die since each core shrinks in size, making it possible to fill in more compute cores. For many general-case applications, the removal of features such as ILP comes at a loss of performance. On the other hand, applications that satisfy some assumptions (e.g., that they are very regular and do not require ILP so much) will receive a large performance boost.

In these special cases, it is hence a good idea to use simplified hardware with more compute units for improved performance. GPUs, originally developed to render 3D scenes in video games, have a lean implementation, a commodity hardware and are massively parallel. Consider for instance Nvidia's flagship GPGPU at the time of writing, the Tesla V100, that comes with 5120 cores.

Unsurprisingly, as GPUs are especially powerful vector machines, an application that is vectorized easily will profit from executing on a GPU as they are expert in rapidly executing the same operation over and over again. Alas, the execution itself is not as seamless as for CPUs, because a GPU does not execute the binary itself. Instead, a programmer needs to use OpenCL [Inc] or CUDA [NVI] to start threads on the device and to transfer all required data in and out. Furthermore, data locality is very important as caches are small (relative to the number of cores) and loading data is hence expensive. Programming GPUs is discussed in more details in Section 2.1.4.

Regardless of elevated requirements for programming (that possibly necessitate extensive and expensive (re-)training), imposed restrictions regarding suitable applications and even high energy consumption (up to  $300\,\mathrm{W}\,\mathrm{s}$ ), GPUs have recently become a common addition to HPC nodes as they are cheap, fast and significantly more energy efficient (when using flop/W as a metric) than CPUs.

#### **Many-Core Chips**

Many Integrated Core (MIC) accelerator cards are the third option and provide a middle way between the general but slow and energy inefficient CPU and the fast but highly specialized GPU. MICs are (like GPUs) add-on chips that communicate over specific busses (e.g., bandwidth-limited PCIe) and they come with their own memory on the chip. They were also widely considered a viable alternative to GPUs after Intel's well-known Xeon Phi was introduced. The Xeon Phi in particular is presented here, since it has been the most popular MIC for a long time, even though the Phi add-on model line has been abandoned today.

The Xeon Phis were the first to support the new vectorization standard AVX-512, implemented for all 48 to 72 cores with 4 threads per core, making up to 288 logical cores available. This is significantly less than the thousands of particularly floating-point oriented cores used by GPUs, but as a trade-off, each MIC core is capable of dealing with control statements much more efficiently.

Unlike GPUs, the Phis run their own Linux-based micro operating system on the chip and must hence be booted. This combined with their support for the x86 architecture allows them to execute binaries directly on the chip. This enables users also to launch individual processes on each core, converting the Phi effectively into a mini-cluster. As another side-effect, this also lowers the entry barrier significantly as applications using the accelerator only need to be written in a commonly used language (plain C, C++ or Fortran) and a specialized compiler (e.g., provided by Intel) will further help the user. Although this is certainly helpful to obtain quick performance boosts, exploiting the chips capacity entirely requires programmers to prepare / rewrite the code in a way that the compiler can identify every optimization potential. It can generally be said that (similar to GPUs) MICs work great with applications that have already been optimized for vectorization.

#### Conclusion

With three very different types of computation units (CPU, GPU, MIC), each exhibiting its own characteristics and advantages, machines can be configured very differently. System vendors tend to add accelerators to more machines and so it is not surprising that the November 2018 edition of the Top500 lists 138 (27.6%) machines as using accelerators.

#### 2.1.3 Architectures: Communication

#### **Network Technology**

Many applications implement intensive communication patterns between processes launched on the same or different nodes in order to send/receive data that is required for further computation or to simply synchronize with others. Messages containing data have no upper size boundary and can reach several GB. For large amounts of data, the transfer time is predominantly determined by the bandwidth, which must hence be large enough. On the other hand, for very small messages (e.g., for synchronization or updates to a few variables), bandwidth is significantly less important as the total transfer time will be very small. Instead, the speed is mostly determined by the network's latency.

In environments such as HPC machines, where distance is relatively small and all routers and switches are under the full control of the data center, latency is mainly influenced by the technology used. Today, it is dominated by Gigabit Ethernet and Infiniband, although some other competitors such as Intel's Omnipath and custom

interconnects exist. Ethernet is used in private networks at home or in professional environments and therefore is a non HPC specific, very low cost solution that uses the entire TCP/IP stack (and all of the overhead it comes with) and can currently reach bandwidths up to  $400\,\mathrm{Gbit/s}$ . On the other hand, Infiniband and OmniPath are proprietary solutions that are specific to HPC and significantly more expensive. What makes them interesting to the HPC community is that the network stack has been reduced by removing parts from the TCP/IP stack that are useful in dynamic and large-scale networks such as the internet but that are not required for a wellcontrolled or (comparatively) simple environment such as a HPC machine. Those parts include loss mechanisms, flow control and routing. Other parts, including 0-copy RDMA and deterministic routing have been specialized.

In some cases (e.g., for Cray machines), when the enormous cost can economically be justified, a custom-tailored interconnect is employed to reduce the latency even further.

Choosing one of these software/hardware stacks also means to a trade-off between cost and performance / power consumption.

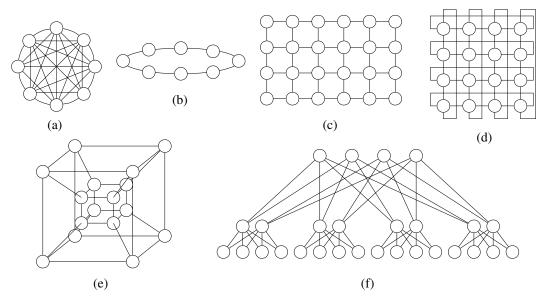

#### **Topology**

Even for small-scale clusters, fully connected networks (Figure 2.4 (a)) are infeasible due to quadratical growth of required cables and ports. (For *n* nodes,  $\frac{n \cdot (n-1)}{2}$  cables and n-1 ports per node are required.) Instead, nodes are connected through intermediate routers / switches and form a physical topology. Over the years, many topologies have been used in HPC, some of which are illustrated in Figure 2.4, including meshes (c), multidimensional tori (d), hypercubes (e), fat-trees (f) and clos-networks. Researchers evaluate a topology by looking at several properties, such as simple and very fast routing algorithms (i.e., quick computation of the shortest path between two nodes), bisection bandwidth, diameter, scalability and cost. When setting up a physical network, it is important to find a good balance between these properties to guarantee good performance for as many types of applications as possible, since changing the topology is either impossible or very difficult as this requires physical reconfiguration. The best topology for a given application often depends on its implemented communication patterns and may not be the perfect fit for other applications.

**Figure 2.4:** Several classic network topologies. Shown are: (a) fully connected network, (b) ring, (c) mesh, (d) torus, (e) hypercube and (f) fat-tree [CLR08, Figure 3.1].

#### **Observations**

An application's performance certainly depends on its own communication patterns but is also impacted by network technology and topology. The former is generally under control of the researcher whereas the latter is provided by the machine vendor and normally cannot be re-configured arbitrarily.

The multitude of technologies makes it necessary to determine the best choice by looking at the mix of applications that are supposed to use the machine. Unfortunately, since there are so many tunable parameters, evaluating / predicting an application's performance on a given network is rather challenging.

## 2.1.4 Programming paradigms

Naturally, scientists want their applications to run even faster and increasing the parallelism is often a promising approach to achieve this. To support this parallelism, more compute units need to be added and hardware needs to be updated, for instance by moving to heterogeneous nodes (i.e., CPU + accelerator).

Efficient usage of heterogeneous machines with several interconnected nodes, each possibly containing one or more multi-core CPUs and other specialized components such as GPUs, MICs etc., is a difficult undertaking that often requires profound knowledge of the underlying hardware and problem. Consider a simple matrix-multiplication: Moving it from the main CPU to an accelerator may speed-up the

*algorithm* itself; however, the data must be moved to the accelerator first, causing an overhead. For somewhat small matrices, this may overall result in a slow-down.

The rapid innovation and development cycles of hardware make it very difficult if not impossible for manpower-limited research-teams to implement proper support for each type of hardware. But also the software itself may pose problems: A software's architecture may have been designed years ago, without now emerging technologies in mind. It may hence require significant refactoring efforts to even implement basic support for massive parallelism.

Furthermore, programmers do not only want to exploit the parallelism that is today available *intra-node*, they also want to use interconnected nodes to distribute computations across several nodes (*inter-node*). It is common to rely on different paradigms that aid programmers with these two tasks.

#### Inter-node

For a given problem, sequential algorithms are often already known or easier to come up with than parallel algorithms. A natural approach for the development of a parallel algorithm is hence to parallelize the sequential algorithm by distributing data among all nodes so that every node can start computing as quickly and as much as possible. When the computation requires data that is only available on other nodes, inter-node communication based on message passing can be used to retrieve this data.

The Message Passing Interface (MPI) standard [For] has been developed by the MPI-Forum for this purpose. It is freely available in its most recent version 3.1 at the time of writing. Open source implementations are actively developed and released by several projects, such as Open MPI [Gab+04], MVAPICH [LWP04] and MPICH [Gro02], but proprietary implementations exist as well, e.g., IntelMPI.

MPI abstracts the complexity of the network by providing a well-defined API to the user that includes standard send/recv operations, numerous collective communication operations (broadcast, all-to-all, ...) but also advanced features such as buffered sends, 0-copy RDMA etc., while making little to no comments on *how* to concretely implement them.

Another great benefit of MPI are so-called *virtual topologies*. These (logical) topologies allow algorithm designers and programmers to define a notion of relationship (neighborhood) among processes. This is not inherently necessary, because every

process can always send a message to every other process, but it permits algorithm designers to structure the program more cleanly, giving them a better view of the communication patterns. Programmers, on the other hand, can implement the computation patterns more easily. Rank ids have no longer to be cumbersomely calculated by (for example) their position in the network but all communication partners are stored in the topology. Collective communications can also be applied to virtual topologies and can therefore be more readily used, leading to a more high-level programming style. Structuring the communication relieves the network and hence improves the overall performance as well.

Lastly, the runtime itself may benefit from declaring virtual topologies as this can help with mapping the processes to the computational units on all nodes.

#### Intra-node

Multi-core CPUs are now commonly found in each node and can be exploited by a parallel application. All cores provide unified (but not necessarily uniform) access to the same main memory whereas their caches are (on some levels) private and shared on others.

An application can take advantage of a multi-core CPU in several ways: Firstly, if the application is already parallelized with MPI, one or more MPI-processes can be started on each of the cores. However, processes do not share the same memory address space and consequently, making data from one process available to another may incur additional copies / transfers even though the data is available in a cache that both processes can access. This remains even true if the values are already stored in the memory.

Secondly, if the application is fully sequential and re-writing is not an option, developers can substitute libraries with existing multi-threaded versions (e.g., Intel's Math Kernel Library (MKL) for BLAS algorithms).

Finally, the application can be (re-)written using threads, but this is cumbersome and error-prone due to low-level programming. A more high-level approach is to parallelize using the OpenMP (Open Multi-Processing) standard's #pragma annotations for C, C++ and Fortran, which is natively supported by some compilers, for example GCC since version 5 Unlike MPI, OpenMP relies exclusively on threads and creates and manages threads for the user. Alas, good performance results can often only be obtained after thorough tuning of the application and parameters.

Unlike MPI, OpenMP can only be used to parallelize an application on the same node as there is no notion of data transfer. Still, data can be shared between threads directly through the memory, as their address space is shared. For this reason, MPI can (theoretically) replace OpenMP but not vice versa. Nevertheless, with their concepts being very different, it is difficult to know whether MPI performs better than OpenMP on a particular platform. Many scientific application developers have therefore resorted to maintaining an MPI-only and an MPI+OpenMP version. In the latter case, it is a common practice to launch one MPI process per socket which in turn starts OpenMP threads on every core of that socket.

#### **GPU programming**

It was already mentioned in the last section that multi-core CPUs can be exploited without any modifications to the code by using multi-threaded libraries, such as MKL. This is also true for GPUs, if the library in question supports GPU offloading. Otherwise, substantial development needs to be done in order to incorporate the data transfer from and to the GPU as well as kernels that can be executed on the GPU's cores. Since Nvidia is the most common supplier for high-performance GPUs, this is most commonly done through its proprietary API called *CUDA* that integrates with C, C++ and Fortran, although many other languages are also supported through third-party wrappers. CUDA only supports Nvidia GPUs, so the Open Compute Language (OpenCL), which comes with the benefit of additional support for other devices, is a viable alternative that is already used by simulations as this portability allows applications to run also on machines with other devices, AMD GPUs.

As a consequence, it is the programmer's responsibility to handle communication with other nodes through MPI and node-internal communication with GPUs via CUDA. Furthermore, exploiting the massive parallelism of a GPU is not an easy feat, as it requires first of all to keep the load high enough on each node to occupy all GPU cores. Secondly, this data must also be granular enough to assign a piece of work to every core. Further tuning options exist that are known to be important for performance, for instance the number of threads (for oversubscription) or streams.

Scientists from application domains such as physics and biology are often not familiar with these new concepts and have to undergo further training before making modifications to their applications. Since it is difficult to predict the outcome of their modifications, implementing accelerator support in their application may be postponed as long as possible.

#### **MIC**

Older code-bases can often exploit MICs without rewriting the code through linked libraries, similar to GPUs and multi-core CPUs. MKL, developed by Intel, is used for BLAS functionality and supports exploitation of many-core chipsets for several (but not all) operations. However, not all supported operations, such as matrix-multiplication, are always executed on the accelerator as MKL determines whether the parameter size is large enough to offset the penalty for transferring the data to the MIC.

As mentioned before, a MIC can also be used as a mini-cluster by directly launching MPI processes on its cores, even though generally with very limited amounts of RAM available (with a few GB of high-bandwidth RAM normally significantly less but much faster RAM than the host node). As a consequence, computations requiring massive amounts of data cannot be executed on the MIC without transferring data from and to the host's main memory (or other nodes). Messages from and to processes outside of the MIC must pass through the PCIe bus and this extra traversal increases latency. Although this is negligible for large messages, it can add significantly to the time it takes a small message to arrive. With bandwidth being limited as well, however, the PCIe bus can become a bottleneck when all cores are sending large (i.e., bandwidth-intensive) messages.

Running MPI on MICs directly therefore causes a topology that has largely differing cost for sending messages: Sending messages to other processes running on the same MIC is significantly less expensive than using first the bus and then the network. Furthermore, due to the little on-card memory, sending large messages must take into account whether the receiver is on a MIC and can actually receive (store) this message.

With all these constraints, it is in practice rather uncommon for MICs to be a plug-in solution. Like GPUs, programmers need to consider MICs and their properties when writing code that is supposed to exploit a MICs capabilities completely. This implies that significant effort for rewriting an application may be required.

#### Conclusion

Programmers want to make an optimal choice so that their application can be executed at optimal performance. Unfortunately, the multitude of libraries and programming frameworks on the one hand side and hardware on the other hand

makes it very difficult to predict in advance what performance can be expected from a choosen software/hardware stack.

## 2.2 High Performance Computing Tomorrow: Exascale Computing

We have seen in Section 2.1 the components the HPC community relies on to build machines that can operate sustainably at the petascale ( $1 \times 10^{15}$  operations per second) level. Scientists can exploit this immense computational power in many ways, e.g., by adding more detail to their scientific model or by increasing the decomposition's resolution. Currently, scientists are still limited by technology and by improving the machines further, questions that cannot be resolved at this time become feasible. For this reason, the HPC community races to develop exascale machines (1  $\times$  10<sup>18</sup> operations per second) but at the same time, several issues thwart quick development. First and foremost, the physical size of today's fastest machines already fills entire machine rooms and so increasing a machine's performance by adding 10 times more nodes cannot work due to space constraints. The second problem is that the energy consumption of an exascale machine with possibly billions of computation cores would be infeasible if no measures to reduce the consumption are taken. Initially, the U.S. Department of Energy proposed the threshold for exascale systems to be at most 25 MW for financial and political reasons [Don+11, p. 4], but environmental and practical reasons (e.g., redundant power supply, cost for diesel or battery aggregates, ...) certainly exist as well. Today, this threshold is expected to be set more realistically around 30 MW to 40 MW. Thirdly, all previously presented issues persist and become even more challenging for exascale: Rigid applications will not scale, heterogeneous nodes will be more difficult to manage as they will exhibit even more massive parallelism and the network will experience unprecedented levels of contention due to message exchanges and largely increased amounts of data.

Profound technology changes are necessary to move from (sub-)petascale to exascale. It has been estimated that this current overhaul of technology is comparable in disruptiveness to the major transition in the 90's that saw vector computing replaced with parallel computing [Don16, Section 4.2.4].

The following sections follow the same pattern as the above discussion. First, applications are discussed in Section 2.2.1, followed by computation units in Section 2.2.2. Communication and networks are discussed in Section 2.2.3 and, finally, programming for exascale is presented in Section 2.2.4.

## 2.2.1 Applications

For sustained exascale performance, developers will be forced to take on a more active role when it comes to managing and optimizing an applications execution. New responsibilities include now load balancing and resilience design. Co-design, on the other hand, is an important paradigm that will be required to be applied during development of the machine and application for successful exascale performance.

#### **Load Balancing**

Applications running on petascale machines already have to deal with load balancing to obtain maximum throughput. Unfortunately, it is not always clear *why* a load imbalance exists. Processes/threads could be idle waiting for data from another process, maybe because the network exhibits a bottleneck and is overly congested, or have just fewer computations to do. In the future, higher core- and thread-counts (expected to reach even billions [Don+11, Section 3.1]), required for exascale performance, will exacerbate this problem.

Load imbalance is rarely easy to fix through modifications to the source code, as it is often inherent to applications, both regular and irregular, and amplified by hardware variability.

In the case of regular applications, algorithm designers frequently begin with sequential algorithms that are then parallelized, requiring large synchronizations through collective communications. Nowadays prevalent complex node architectures (e.g., CPU + accelerator) can be the cause as well since managing all important aspects (e.g., parameters such as block size) can be difficult using only MPI + OpenMP.

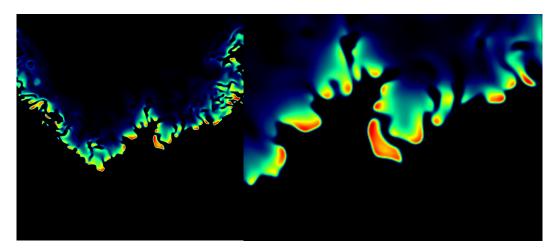

For irregular applications that mix different models (e.g., different gasses in turbulent combustion or changing layers of rock/soil in geology), load balance deteriorates even more: Physical effects depend on local conditions and exhibit different behavior in non-uniform conditions. For example, when simulating combustion, turbulent conditions cause local variations in the fuel-air ratio which causes the burning velocity to change locally. This, in turn, causes cellular flames (depicted in Figure 2.5), a highly irregular state. This irregularity explains why these applications seemingly can never have enough compute power: in 2011, a time frame as small as  $1.9\,\mathrm{ms}$  of methane-combustion in a gas-turbine was simulated using MPI and took over  $1.3\times10^6\,\mathrm{million}$  core hours (using a total of  $16\,384\,\mathrm{cores}$ ) [MDV11, p. 1346].

**Figure 2.5:** An illustration of (simulated) cellular flames where temperatures differ locally due to differences in burning velocity. The right picture highlights that parts of the flame can have highly irregular shapes and can be detached from the rest [Day+09].

Even with a thousand times more computational power than petascale machines, exascale machines will still not be powerful enough for many of today's scientific questions as time complexity increases exponentially with the time and space order of the underlying physics. The full simulation of a gas turbine combustor, for instance, is expected no earlier than 2045 and only if machine floprates continue to grow linearly.

With the immense cost of running a simulation at the exascale, many scientists see these platforms mostly as a means to run hundreds of *petascale* simulations at the same time instead of running one simulation at the exascale.

#### Resilience

Tens of thousands of nodes, hundreds of millions of cores and billions of threads lead to a low mean-time between failures for exascale machines, maybe even as low as  $30 \, \mathrm{min}$  [Cap+14, Section 2.2]. Each of these may have various and unforeseeable reasons and are not limited to any level of the stack. They may occur at the data center level (e.g., fatal outages), hardware level (e.g., hardware failure), or even bugs on the software level (e.g., operating system, support libraries, ...). Each failure can potentially be catastrophic for the execution of a job in the sense that the application needs to restart completely, implying full loss of already achieved progress. It is therefore desireable to implement strategies that make an application resilient against failures. This allows an application to terminate correctly, even though intermittent failures occurred.

A popular approach to mitigate full loss is to checkpoint(-restart) the application [Cap+14, Section 4.1.1]. A snapshot of the application state is saved periodically and once a failure has occurred, the application is interrupted and reset to the state saved in the checkpoint. There is still some loss, but it is reduced significantly. To reduce the great cost (e.g., no unreceived messages at the time of checkpointing, heavy IO traffic, ...) it comes with, many variations of this approach have been proposed. In fact, checkpoint-restarting can be so expensive that it can be cheaper to use replication.

Other issues such as memory corruption are more serious, impossible to evade and difficult to recognize, as they occur silently. They are also difficult to recover from, since the corrupt data may not be restorable. Consider high-energy neutrons, stemming from cosmic radiation: They are known culprits for apparently random flips of bits in RAM when sufficiently small circuits are used [Cap+14, Section 2.1]. An application that uses numerically robust algorithms may ignore or even restore corrupt values within a data vector (e.g., a column of a matrix), but control variables such as loop counters are more difficult to deal with and applications are especially vulnerable in this regard. An application may hence crash on a node or enter a deadlock state when a control variable is corrupted.

The MPI standard and consequently most scientific applications are still not ready for fault-tolerance. Progress is stifled by the fact that a best practice has not yet been found; each class of applications seems to work best with a different approach. Plus, a half-baked standardization attempt is feared to come with a performance degradation that is unacceptable to many users or vendors. Significant efforts have been made, however, and ULFM (User Level Fault Mitigation) [Bla+13] is a proposal developed by the MPI Forum's "Fault Tolerance Working Group" that aims to ensure that node failures can no longer cause MPI calls to crash or deadlock the application by waiting for messages from the dead node indefinitely.

Other approaches to save data from being lost include storage of (important) data in multiple locations (possibly with varying levels of quality/redundancy) and algorithm-based fault tolerance (ABFT). ABFT exploits properties of the underlying computational algorithm in a way that faulty data can be restored, e.g., through redundant or supplementary data and further knowledge of the computational structure. This approach is quite limiting with respect to the algorithm design and does in general not work for every application.

Significantly more research is still required as it remains unclear what the most usable yet conservative approach is. Breakthroughs are therefore not to be expected. Instead, small improvements and adoption by the user base over time is expected to help.

#### Co-Design

In the past, vendors developed machines that could be easily deployed generically on several sites. For sustainable performance at exascale, decisions on hardware design must consider relevant scientific applications and their potential of exploiting the platforms computational power while at the same time application developers (and possibly algorithm designers) need to know about best practices but also idiosyncracies of platforms. Bringing these different groups together, i.e., scientists investigating the scientific question, software architects building the application and hardware architects building the platform, allows each group to benefit from an improved feedback-loop for their own work and test / influence the work of others, during (and not after) the construction of the machine.

This paradigm, called "co-design", fundamentally changes how machines are constructed: They are built around applications, rather than forcing applications to merely "fit in". Taking account of these benefits, IBM installed two "centers of excellence" at Lawrence Livermore National Laboratory and Oak Ridge National Laboratory that bring application and hardware developers closer together [Ead16]. This collaboration can be expected to give rise to new and more specialized hardware.

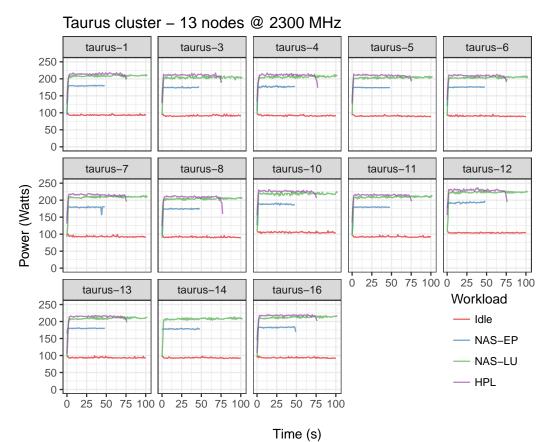

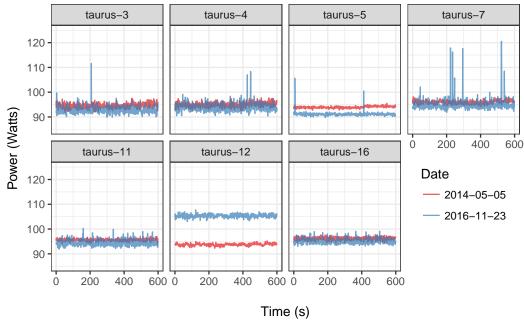

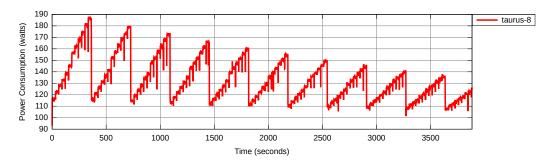

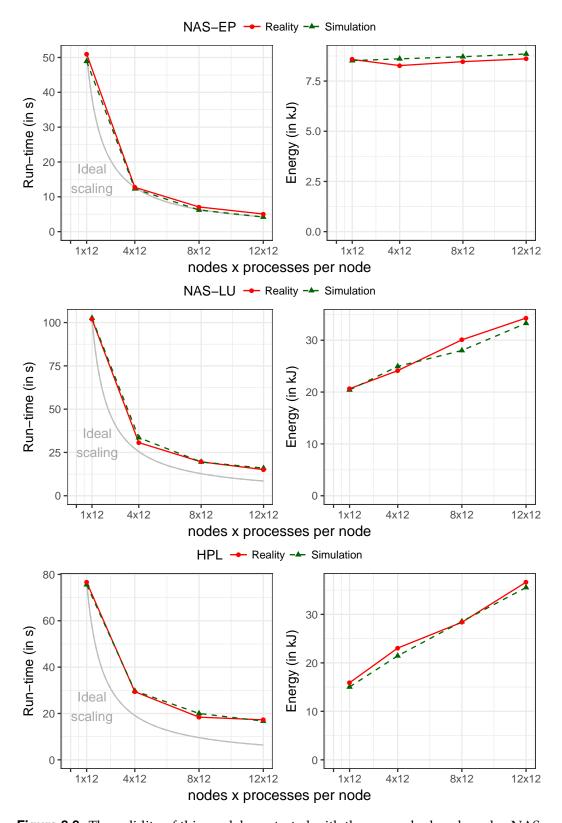

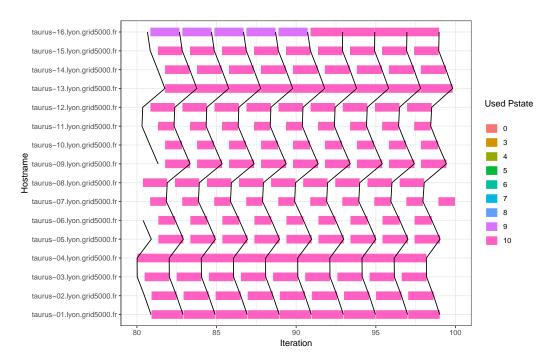

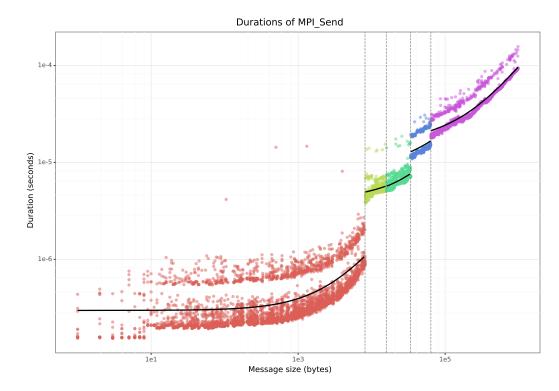

## 2.2.2 Architectures: Computation