# Design by Mathematics

Francois Rivet

#### ▶ To cite this version:

Francois Rivet. Design by Mathematics. Electronics. Université de Bordeaux, 2019. tel-02271959

# HAL Id: tel-02271959 https://theses.hal.science/tel-02271959v1

Submitted on 27 Aug 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### HABILITATION À DIRIGER DES RECHERCHES

présentée à

## L'Université Bordeaux

Ecole doctorale des Sciences Physiques et de l'Ingénieur

#### par François RIVET

SPÉCIALITÉ: ÉLECTRONIQUE

DESIGN BY MATHEMATICS

Soutenue le : 27 Juin 2019

#### Après avis de :

| Μ. | Ramesh HARJANI | Professeur | University of Minnesota                   | Rapporteur |

|----|----------------|------------|-------------------------------------------|------------|

|    | Stefan Heinen  | Professeur | RWTH Aachen University                    | Rapporteur |

|    | Ricardo Reis   | Professeur | Universidade Federal do Rio Grande do Sul | Rapporteur |

#### Devant la commission d'examen formée de :

| M. | Asad Abidi        | Professeur         | University of California Los Angeles      | Président   |

|----|-------------------|--------------------|-------------------------------------------|-------------|

|    | Yann Deval        | Professeur         | Bordeaux INP                              | Examinateur |

|    | Ramesh HARJANI    | Professeur         | University of Minnesota                   | Rapporteur  |

|    | Stefan HEINEN     | Professeur         | RWTH Aachen University                    | Rapporteur  |

|    | Eric Kerhervé     | Professeur         | Bordeaux INP                              | Examinateur |

|    | Stefano Pellerano | Principal Engineer | Intel Corporation                         | Examinateur |

|    | Ricardo Reis      | Professeur         | Universidade Federal do Rio Grande do Sul | Rapporteur  |

## Remerciements

| A ma mère qui nous a quittés trop tôt. Tu me manques chaque jour. Tu aurais été, je pense, fière de moi, |

|----------------------------------------------------------------------------------------------------------|

| à mon père, à sa compagne, à mes soeurs et à ma famille,                                                 |

| à mes amis et à ma « famille australienne ».                                                             |

A l'équipe Circuits And Systems, aux docteurs Veyrac, Bouassida et Tlili, à mes collègues du laboratoire IMS.

A l'ENSEIRB-MATMECA et Bordeaux INP, le service des Relations Internationales, à mes collègues et aux étudiants.

To the jury members, Asad, Ramesh, Stefan, Ricardo, Stefano and Eric, à Yann, pour toutes ces années de complicité scientifique et d'amitié.

# **Contents**

| Li | st of A | Abbreviations                                            | 15        |

|----|---------|----------------------------------------------------------|-----------|

| In | trodu   | ction                                                    | 17        |

| 1  | Rad     | io Frequency Transceivers                                | 19        |

|    | 1.1     | Wireless Communications Challenges                       | 21        |

|    | 1.2     | Radio-Frequency architecture                             | 25        |

|    |         | 1.2.1 State of the Art                                   | 26        |

|    |         | 1.2.2 RF Transceiver design                              | 29        |

|    | 1.3     | Conclusion                                               | 32        |

| 2  | Desi    | gn by Mathematics for Radio-Frequency IC                 | 33        |

|    | 2.1     | Design by Mathematics principles                         | 34        |

|    | 2.2     | Frequency domain                                         | 36        |

|    |         | 2.2.1 Sampled Analog Signal Processor Receiver - SASP Rx | 36        |

|    |         | 2.2.2 Walsh Transmitter - Walsh Tx                       | 42        |

|    | 2.3     | Time domain                                              | 47        |

|    |         | 2.3.1 Riemann Pump Tx                                    | 47        |

|    |         | 2.3.2 Delta Riemann - Breda Rx                           | 54        |

|    | 2.4     | Conclusion                                               | 58        |

| 3  | Desi    | gn by Mathematics for Bio-related IC                     | 59        |

|    | 3.1     | Wireless Sensor Interface - Corona Tx                    | 60        |

|    | 3.2     | ECG Converter - WiBio Rx                                 | 65        |

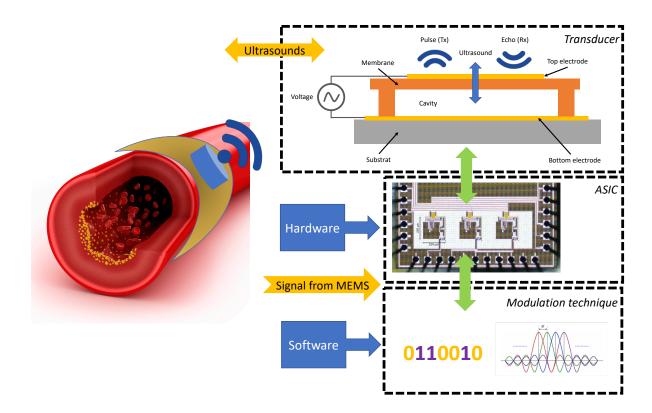

|    | 3.3     | IBC using Ultrasounds - UTRx                             | 70        |

|    | 3.4     | Conclusion                                               | 78        |

| 4  | Rese    | earch Project                                            | <b>79</b> |

|    | 4 1     | New perspectives in RF systems design                    | 80        |

| 8 | Contents |

|---|----------|

|   |          |

| Bibliogi   | Bibliography 96                                           |    |  |  |

|------------|-----------------------------------------------------------|----|--|--|

| Conclusion |                                                           | 95 |  |  |

| 4.4        | Conclusion                                                | 93 |  |  |

| 4.3        | Analog Signal Processing for Edge Computing               | 92 |  |  |

| 4.2        | An ultrasound-based network for Intra-Body Communications | 90 |  |  |

|            | 4.1.2 Access to high frequencies: Hilbert Tx              | 86 |  |  |

|            | 4.1.1 Versatile RF transceiver solution                   | 80 |  |  |

|            |                                                           |    |  |  |

| 1.1  | Exabytes per month. Cisco VNI: Global Mobile Data Traffic Forecast Update 2016-         |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | 2022. February 2017                                                                     | 21 |

| 1.2  | Mobile Traffic by Application Category - CAGR 2017-2023 - Ericsson Mobility Report,     |    |

|      | November 2017                                                                           | 22 |

| 1.3  | Technology tracks of 5G era                                                             | 23 |

| 1.4  | Spectrum allocation for sub-6GHz 5G standard                                            | 23 |

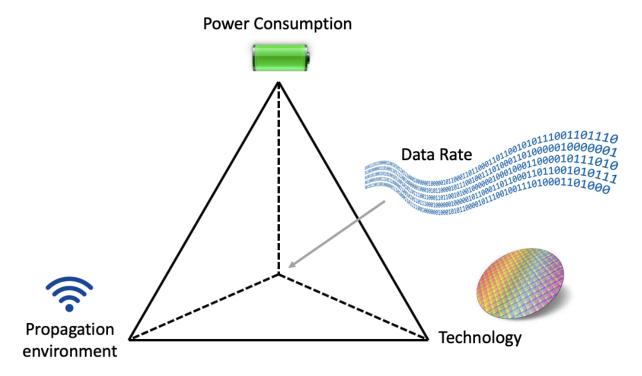

| 1.5  | Paradigm of RF Transceivers design                                                      | 24 |

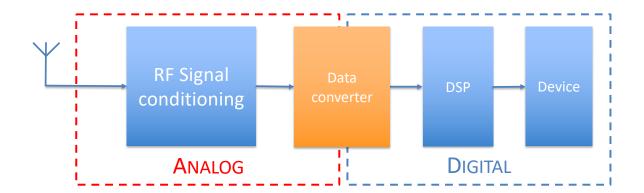

| 1.6  | Transceiver Architecture                                                                | 25 |

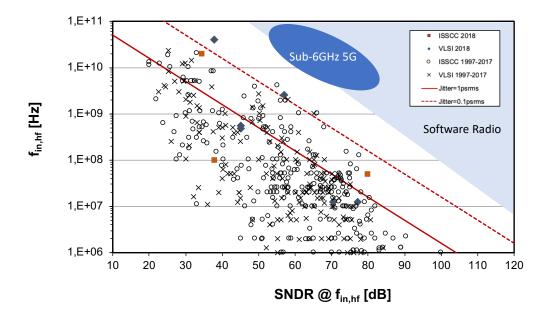

| 1.7  | Boris Murmann's ADC Performance Survey [1]                                              | 26 |

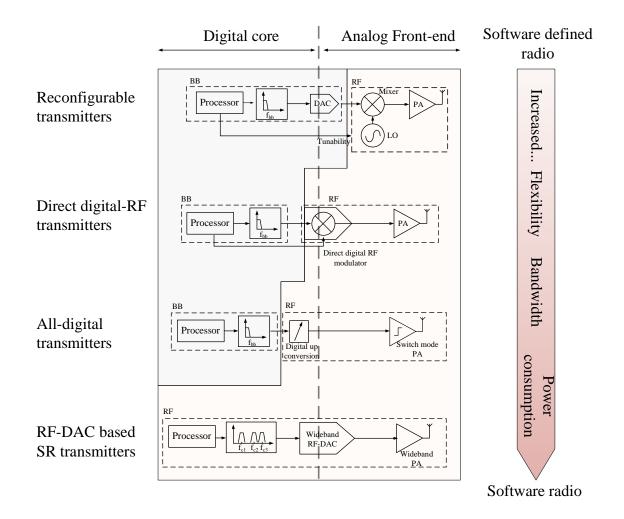

| 1.8  | Transmitter digital versus analog composition for flexible RF applications              | 28 |

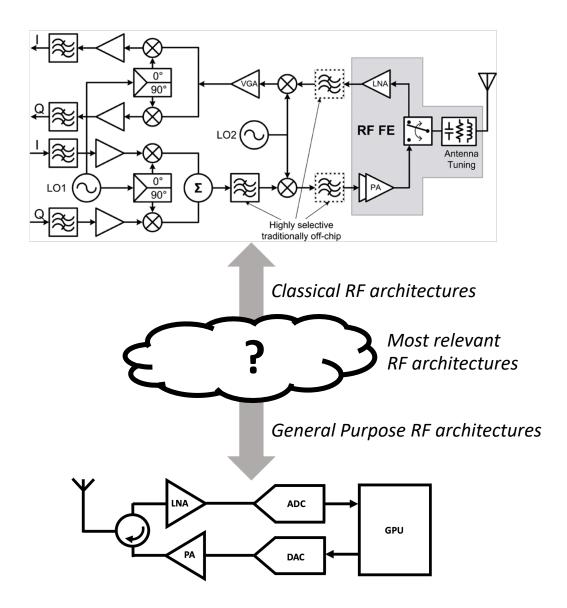

| 1.9  | Representation of trade-off between classical and general purpose RF architectures      | 30 |

| 1.10 | Transceivers architecture difference between traditional and DbM approaches             | 31 |

| 2.1  | Symbolic representation of the DbM methology                                            | 35 |

| 2.2  | SASP receiver system                                                                    | 36 |

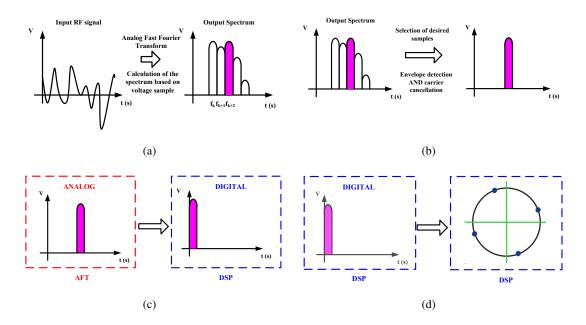

| 2.3  | Concept of the SASP, analog FFT (a), sample selection (b), A/D conversion (c), constel- |    |

|      | lation processing (d)                                                                   | 37 |

| 2.4  | SASP Architecture                                                                       | 38 |

| 2.5  | Frequency demodulation, SASPEPA-2008 (a), NIKITA-2013 (b)                               | 39 |

| 2.6  | Frequency demodulation, FM modulation (a), BPSK modulation (b), FSK modulation          |    |

|      | (c), ASK modulation (d)                                                                 | 40 |

| 2.7  | Concurrent reception, principle (a), measurements (b)                                   | 40 |

| 2.8  | Characterisation of a bin, addressing of all bins (a), frequency behavior in a bin (b)  | 41 |

| 2.9  | SASP characterization in temperature                                                    | 41 |

| 2.10 | square signal generated with 3 harmonics                                                | 42 |

| 2.11 | Harmonics recombination                                                                 | 43 |

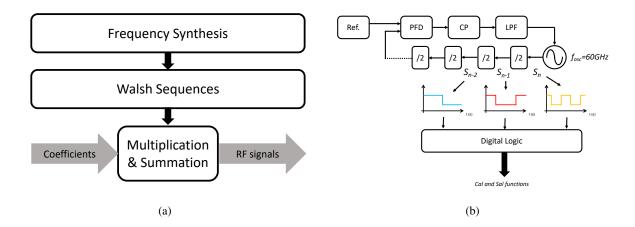

| 2.12 | Walsh system (a), and its associated sequences generation (b)                           | 44 |

| 2.13 | Percentage of coefficients used versus the Walsh order (a), number of coefficients used  |    |

|------|------------------------------------------------------------------------------------------|----|

|      | within a large frequency band based on a 64 Walsh sequence architecture (b)              | 45 |

| 2.14 | Carrier aggregation done by Walsh Tx in frequency                                        | 46 |

| 2.15 | Associated eye diagram and EVM                                                           | 46 |

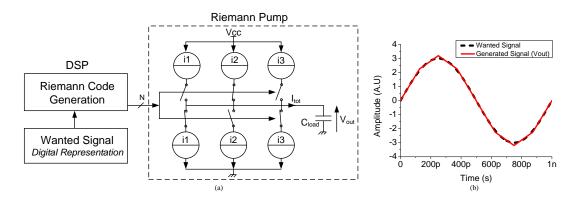

| 2.16 | Riemann Pump Architecture Principle                                                      | 48 |

| 2.17 | Riemann Pump Architecture (a) and theoretical signal generation (MATLAB) (b)             | 48 |

| 2.18 | Riemann DAC topology.                                                                    | 49 |

| 2.19 | Riemann Pump schematic                                                                   | 50 |

| 2.20 | Carrier aggregation: spectrum                                                            | 51 |

| 2.21 | Carrier aggregation: eye diagram                                                         | 51 |

| 2.22 | Device Under Test from chip to bench                                                     | 52 |

| 2.23 | Fourier Transform of a multi-carrier signal with (A) sinusoidal signal, (B) GMSK, (C)    |    |

|      | QAM4 and (D) QAM16 modulated signals                                                     | 53 |

| 2.24 | Fourier Transform of QAM4 modulated signal using different data rates                    | 53 |

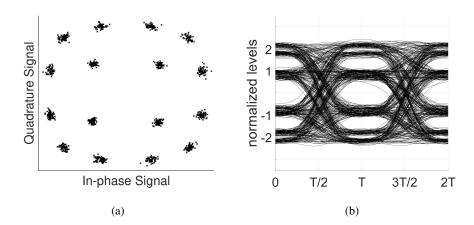

| 2.25 | Constellation associated with eye diagram of QAM16 modulated signal at 2.6GHz with       |    |

|      | a data rate of 50MS/s (a) (b)                                                            | 54 |

| 2.26 | Basic Delta-Riemann ADC                                                                  | 55 |

| 2.27 | Basic Delta-Riemann ADC                                                                  | 55 |

| 2.28 | Basic Delta-Riemann ADC                                                                  | 56 |

| 2.29 | Spectrum of Reconstructed signal - 10 aggregated channels                                | 57 |

| 2.30 | Normalized constellations after rotation and scaling                                     | 58 |

| 3.1  | Corona System View                                                                       | 61 |

| 3.2  | Proposed architecture                                                                    | 62 |

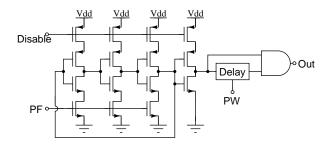

| 3.3  | Schematic of the pulse train generator                                                   | 63 |

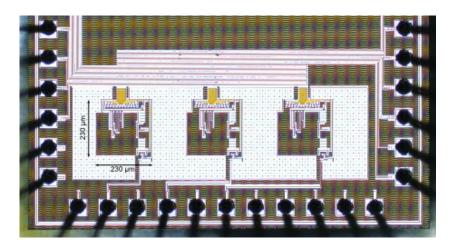

| 3.4  | Photograph of the die                                                                    | 63 |

| 3.5  | Measured voltage ramp across the sensor capacitance, (a), Measured pulse train tuned to  |    |

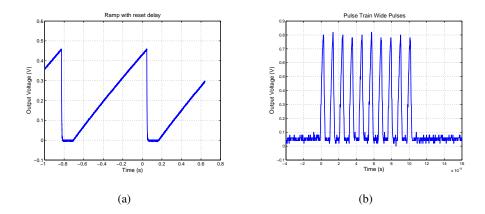

|      | have a wide spectrum, (b)                                                                | 64 |

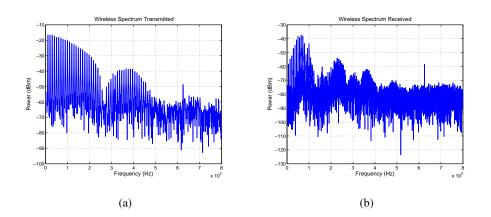

| 3.6  | Frequency spectrum at the output of the circuit, (a), Frequency spectrum of the received |    |

|      | wireless signal, (b)                                                                     | 64 |

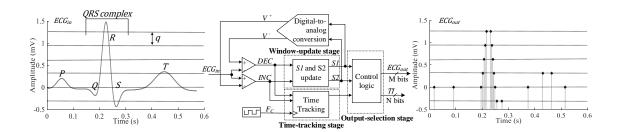

| 3.7  | LC-ADC architecture                                                                      | 66 |

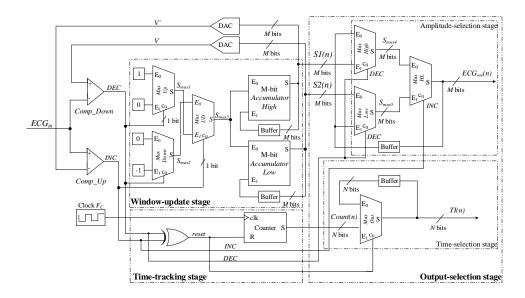

| 3.8  | Block diagram of the LC-ADC                                                              | 68 |

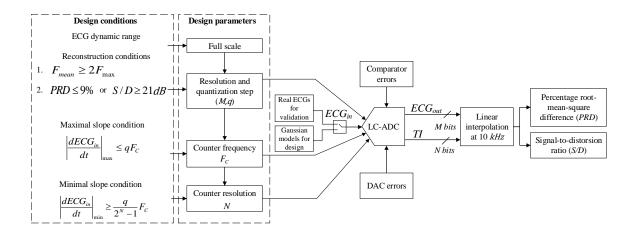

| 3.9  | LC-ADC design and evaluation methodology                                                 | 68 |

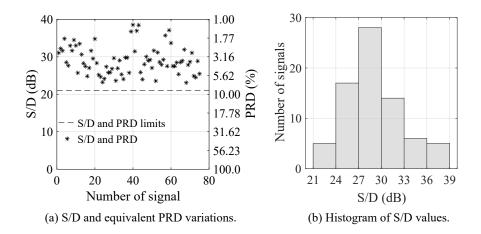

| 3.10 | LC-ADC simulation results using 75 real ECG records                                      | 69 |

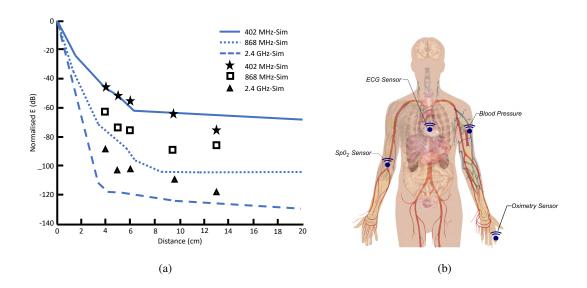

| 3.11 | Electromagnetic waves absorption within human body, (a), IBC sensor network (b)          | 71 |

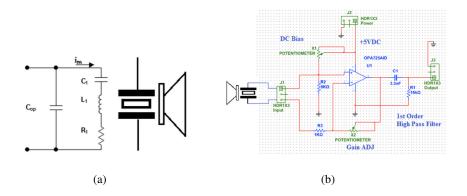

| 3.12 | Resonant circuit, (a), Ultrasonic Receiver circuit (b)                                   | 72 |

|      |                                                                                          |    |

| 3.13 | Picture of meat in the setup measurement platform for both RF and Ultrasonic propaga-                   |    |

|------|---------------------------------------------------------------------------------------------------------|----|

|      | tion analysis                                                                                           | 73 |

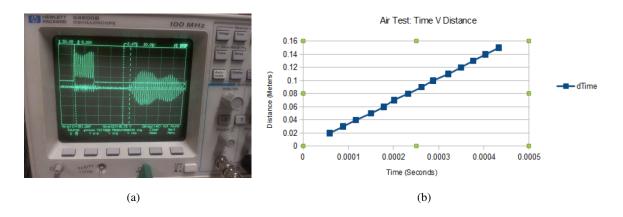

| 3.14 | Flight time measurement between Transmitter and Receiver (a), Extrapolation of Speed                    |    |

|      | of Propagation in Air (b).                                                                              | 73 |

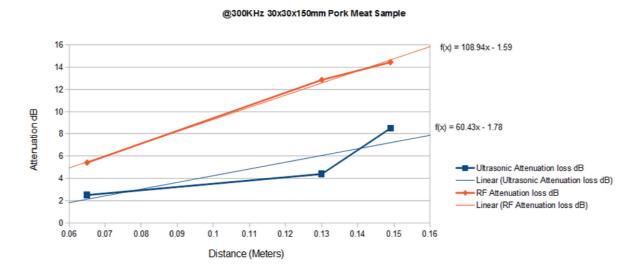

| 3.15 | RF vs Ultrasonic attenuation in human body in function of distance                                      | 74 |

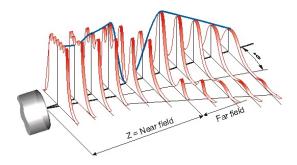

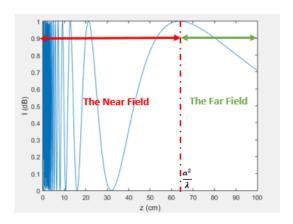

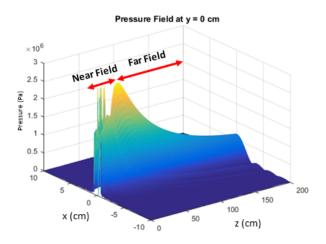

| 3.16 | Near Field and Far Field                                                                                | 75 |

| 3.17 | The axial intensity as a function of distance in the vicinity of a vibrating transmitter                | 75 |

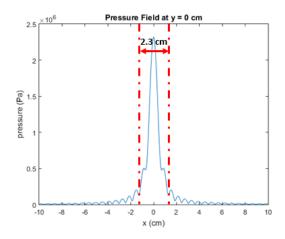

| 3.18 | Modeling of side lobes of ultrasonic wave in the far field ( $f = 10MHz$ , $\beta = 1.09$ , $a = 1cm$ , |    |

|      | $c = 1569m.s^{-1}, z = 50cm$                                                                            | 75 |

| 3.19 | Modeling of ultrasonic wave propagation in muscle ( $f = 10MHz$ , $radius = 1cm$ )                      | 76 |

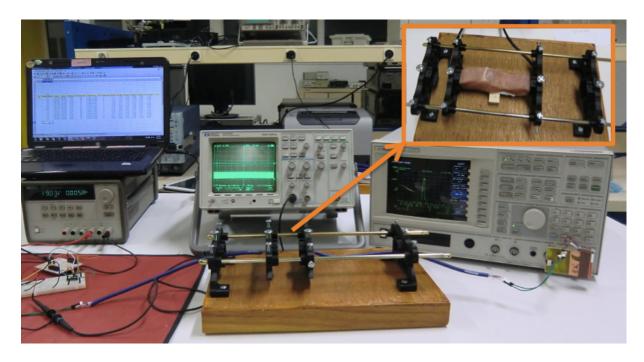

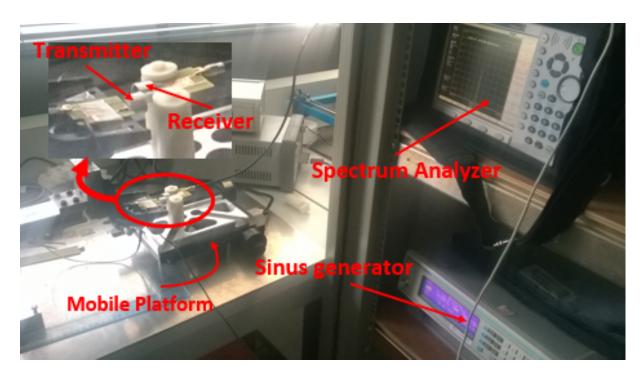

| 3.20 | Setup measurement platform for Ultrasonic propagation analysis                                          | 77 |

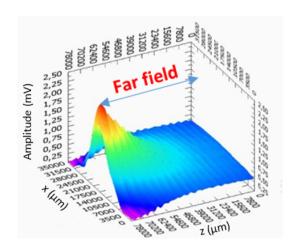

| 3.21 | Experimental measurements of an ultrasonic wave propagation in air $(f = 40kHz, radius =$               |    |

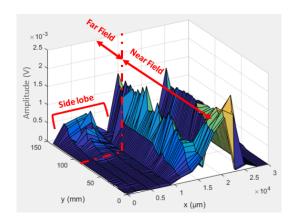

|      | 6.5 <i>mm</i> )                                                                                         | 77 |

| 3.22 | Experimental measurements of an ultrasonic wave propagation in muscle ( $f = 40kHz$ ,                   |    |

|      | radius = 6.5mm)                                                                                         | 77 |

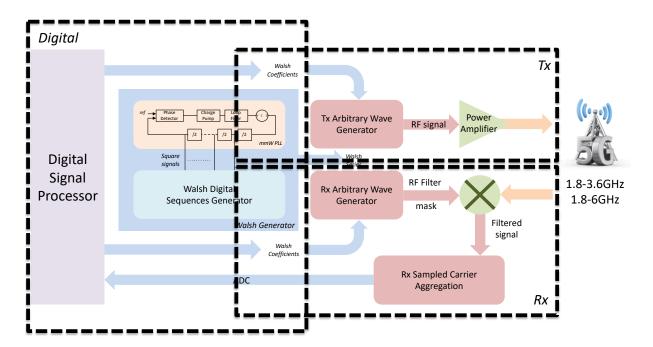

| 4.1  | 5G Transceiver using Walsh generator as a core                                                          | 81 |

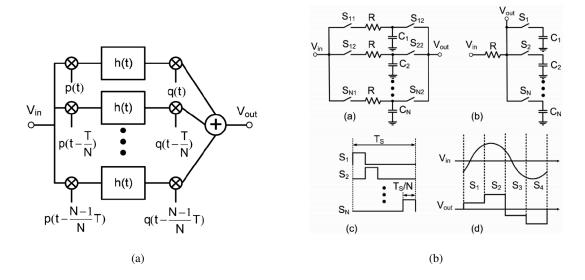

| 4.2  | (a), Architecture of an N-path filter (p and q are the mixing functions and T is the period             |    |

|      | of the mixing frequency). (b), (a) Switched-RC N-path filter. (b) Single port, single                   |    |

|      | ended N-path filter. (c) Multiphase clocking. (d) Typical (in-band) input and output                    |    |

|      | signal                                                                                                  | 82 |

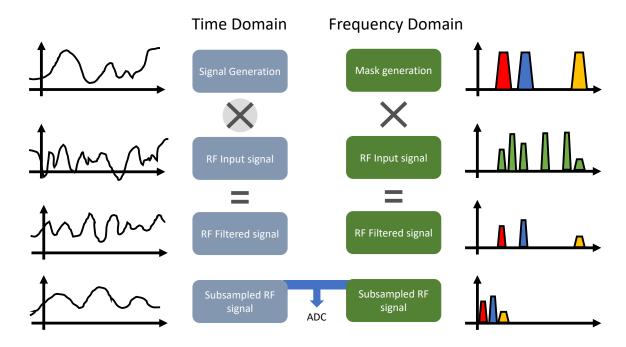

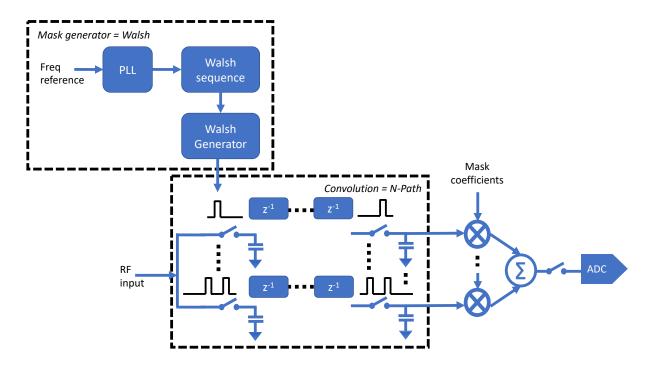

| 4.3  | Time and Frequency domain principle of on-demand filtering                                              | 83 |

| 4.4  | Principle of a Walsh N-path filter                                                                      | 84 |

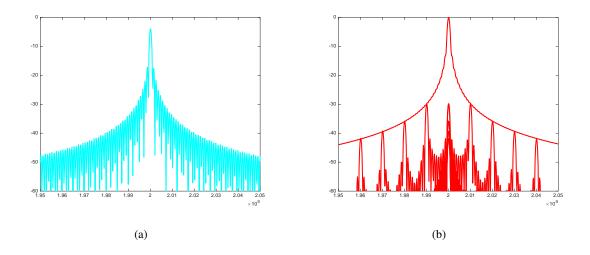

| 4.5  | (a), Mask used for a single channel at 2 GHz (b), RF filtered signal with a swept RF input              |    |

|      | signal from 1.95 GHz to 2.05 GHz with a 10 MHz-span                                                     | 84 |

| 4.6  | Walsh-enhanced Power Amplifier                                                                          | 85 |

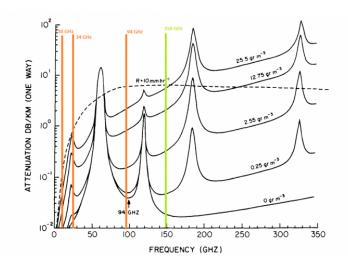

| 4.7  | Attenuation in dB/km from 0 to 350 GHz                                                                  | 86 |

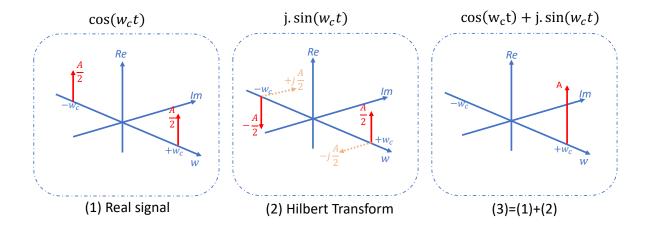

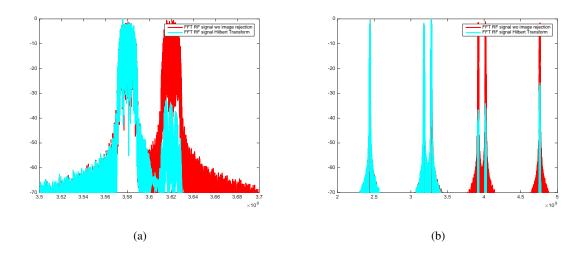

| 4.8  | Illustration of a Hilbert Transform                                                                     | 87 |

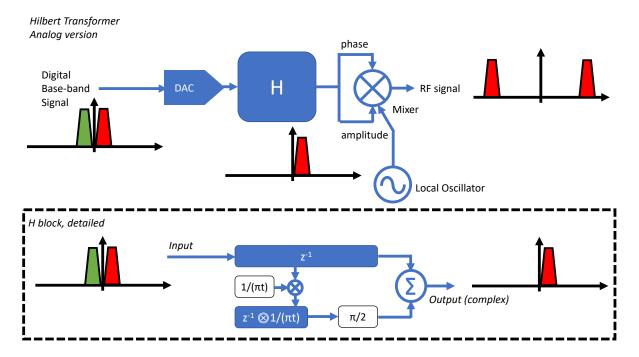

| 4.9  | Principle of the Hilbert generator (analog version)                                                     | 88 |

| 4.10 | Principle of the Hilbert generator (digital version)                                                    | 88 |

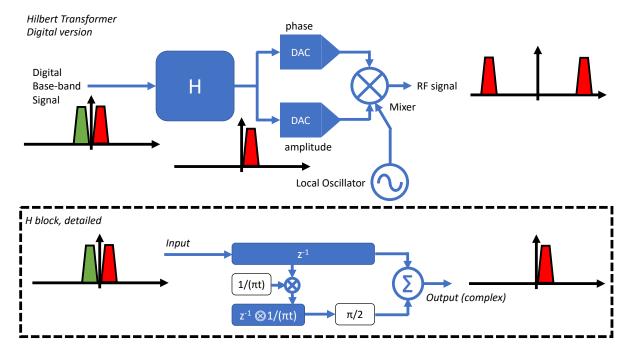

| 4.11 | (a), RF spectrum of an upconverted 5G scheme without image rejection and with Hilbert                   |    |

|      | transform (b), RF spectrum of an upconverted 5G scheme with Hilbert transform                           | 89 |

| 4.12 | Trade-off between image rejection and Hilbert transform length                                          | 89 |

| 4.13 | View of the integrated system for ultrasonic communication                                              | 91 |

# **List of Tables**

| 1.1 | RF receiver State of the Art                                                | 27 |

|-----|-----------------------------------------------------------------------------|----|

| 1.2 | RF transmitter State of the Art                                             | 28 |

| 2.1 | SASP performances                                                           | 39 |

| 3.1 | Normal ECG temporal and amplitude waves characteristics                     | 66 |

| 3.2 | LC-ADC design parameters                                                    | 67 |

| 3.3 | LC-ADC simulation results with offset voltage errors equal to 0.25 of $q$   | 69 |

| 3.4 | LC-ADC simulation results with non-linearity errors in the interval $\pm q$ | 70 |

| 3.5 | Speed of propagation in different material                                  | 72 |

| 3.6 | Characteristics of the transmitter and muscular medium                      | 76 |

14 List of Tables

# **List of Abbreviations**

**5G** 5th Generation

**A2F** Analog to Feature converter

**A2I** Analog to Information

A/D Analog-to-Digital

**AC** Alternating Current

ADC Analog-to-Digital Converter

AI Artificial IntelligenceAM Amplitude Modulation

**ASIC** Application-Specific Integrated Circuit

**BER** Bit Error Rate

**BPSK** Binary Phase Shift Keying

**CAGR** Compound Annual Growth Rate

**CDMA** Code Division Multiple Access

**CMOS** Complementary MOS

**CS** Compressed Sensing

**DAC** Digital-to-analog converter

**DbM** Design by Mathematics

**DC** Direct Current

**DFT** Discrete Fourier Transform

**DR** Dynamic Range

**DSP** Digital Signal Processor

**DUT** Device Under Test

**EDGE** Enhanced Data for GSM Evolution

**ENOB** Effective Number of Bits

EVM Error Vector Magnitude FFT Fast Fourier Transform

FM Frequency Modulation

**FSK** Frequency Shift Keying

16 List of Tables

GMSK Gaussian Minimum Shift Keying

GPRS General Packet Radio Service

GPS Global Positioning System

**GSM** Global System for Mobile Communications

**HSDPA** High-Speed Downlink Packet Access

**IBC** Intra-Body Communications

IC Integrated Circuit

**IF** Intermediate Frequency

**IFFT** Inverse FFT

**IoT** Internet of Things

**ISSCC** International Solid-State Circuits Conference

LC-ADC Level-Crossing ADCLNA Low Noise AmplifierLTE Long Term Evolution

**MEMS** Micro Electro Mechanical Systems

MOS Metal Oxide Semiconductor

NSR Noise Shaping Riemann

**OFDM** Orthogonal Frequency Division Multiplexing

OSR Over Sampling Ratio

PA Power Amplifier

PCB Printed Circuit Board

PLS Post Layout Simulation

PSK Phase Shift Keying

OPSK Ouadrature PSK

QPSK Quadrature PSK

QAM Quadrature AM

RF Radio-Frequency

SASP Sampled Analog Signal Processor

**SDR** Software-Defined Radio

**SFDR** Spurious-Free Dynamic Range

SoA State of the Art SR Software Radio

**SNR** Signal-to-Noise ratio

T/H Track-and-HoldUWB Ultra-WidebandWCDMA Wideband CDMA

# Introduction

"It's Difficult to Make Predictions, Especially About the Future" (Niels Bohr). For sure, the future will be more digital than the present as we all agree that the size of the digital universe will double every two years at least, to support an exponential data growth toward 2020 and beyond. Human-and machine-generated data is experiencing an overall 10x faster growth rate than traditional business data, and machine data is increasing even more rapidly at 50x the growth rate. We are ready to enter to the 5th generation of mobile communication with trillions of device connected.

Our lives are digital.

This development puts the pressure on research to satisfy more and more stringent requirements. The field of electronics, and more specifically the one of integrated circuit design is facing many challenges to support this fast evolution. My research activities at the IMS laboratory are in line with those challenges. They are focused on the design of radio-frequency (RF) systems to enhance the spectrum access, reduce the power consumption using mass market technologies. This paradigm has guided my thoughts during a decade by pioneering in RF architectures. This document summarizes my research work and is structured as follows.

Chapter 1 presents an overview of the RF transceivers design. We analyse the evolution of the telecommunication market with a focus on 5G standard. Then, a brief state of the art of RF architectures research work is presented. Finally, we introduce our Design by Mathematics methodology.

Chapter 2 details the research work in RF systems with 4 different architectures designed for Software Radio or arbitrary waveform generation purpose. All of them jeopardize the classical way of converting signals and revisit either the receiving or the transmitting chain by illustrating the concept of Design by Mathematics. Circuits have been designed and their performances have been evaluated in terms fo spectrum access, power consumption and integration cost.

18 List of Tables

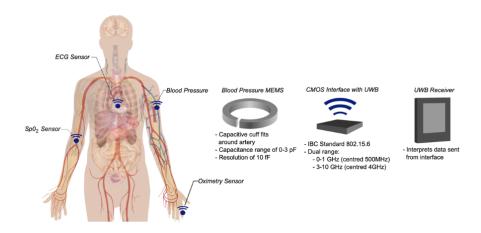

Chapter 3 is focused on architectures for health applications. We present 3 aspects of research on bio-electronics, respectively a RF interface for a blood pressure sensor, a LC-ADC for ECG conversion and a study of ultrasounds propagation within the Human body. The main goal of this work is to understand how a communication system can be customized for a given application.

Chapter 4 concludes on a research project in analog circuit design for the coming years. I propose 3 directions of research: RF systems design, ad-hoc Intra-Body Communications network and analog signal processing for edge computing. Those directions are open to discussions as it foresees more or less long term activities.

#### CHAPTER

1

# RADIO FREQUENCY TRANSCEIVERS

#### Sommaire

| omman C |                                    |  |  |  |  |  |  |

|---------|------------------------------------|--|--|--|--|--|--|

| 1.1     | Wireless Communications Challenges |  |  |  |  |  |  |

| 1.2     | Radio-Frequency architecture       |  |  |  |  |  |  |

|         | 1.2.1 State of the Art             |  |  |  |  |  |  |

|         | 1.2.2 RF Transceiver design        |  |  |  |  |  |  |

| 1.3     | Conclusion                         |  |  |  |  |  |  |

Chapter 1 presents the Radio Frequency Transceivers design facing with the evolution of standards since the last two decades. In a first part, we analyse the evolution of the telecommunication market by exhibiting figures of the exponential increase of data exchange and the need of new network to support it. A focus on 5G standard is given to provide a concrete example of our research work. In a second part, Radio-Frequency architectures research work is presented thanks to a brief state of the art to highlight directions taken by the community to tackle issues raised in the first part. Finally, we conclude on our proposed methodology to design RF transceivers based on a mathematical approach to identify the most relevant way to convert information into RF signals.

**Key words**: radio-frequency, telecommunications, 5G, conversion, software radio, integrated circuits, Design by Mathematics.

"The very small value of  $10^{-16}$  of negentropy required per bit of information plays a very important role in our modern life and it makes possible to communicate information at a negligible cost." Leon Brillouin, Science and Information theory, 1956, quoted by Dr. Yoan Veyrac in [2]

In the 50s, Leon Brillouin stated that modern life relies on the possibility to deal with large quantities of information for a minimal cost. In the same decade, the development of the transistor in Bell laboratories led to a physical media allowing to get closer to the theoretical cost of information described by Brillouin. Since then, the electronic industry followed the Moore's law by developing standalone devices that can exchange billions of bits per second for various applications that are now the backbone of our society and to some extent of our civilization. However, conventional transceiver architectures cannot support the pressure of the exponential increase of exchanged digital information while satisfying customer expectations in terms of quality of service, device cost and battery life.

RF designers are faced to technological issues such as collecting data, converting them into digital, processing them and transporting them along heterogenous network. Conversion and transport are the key of the system when hardware is concerned. Brillouin statement is challenging us on the efficiency of data exchange by lowering its cost in terms of power consumption, device price, and spectrum ressources. This chapter introduces the trade-off of wireless circuit design and proposes research directions.

#### 1.1 Wireless Communications Challenges

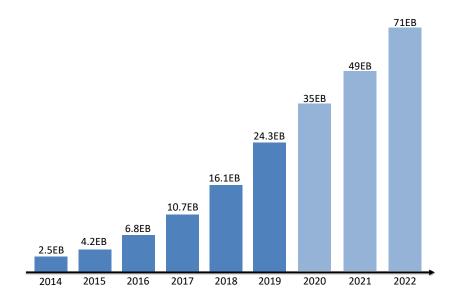

Mass market radio-frequency (RF) transceivers have emerged during the 90's with GSM as the technology driver. Since then, we can observe a continuous evolution of demand to design products wireless systems which either integrate more and more applications at the lowest price or answer specific needs such as Internet of Things (IoT). This constant growth can be seen in the mobile data traffic forecast presented in Fig. 1.1. It will be mainly supported by the 5th Generation (5G) mobile technology.

Figure 1.1 – Exabytes per month. Cisco VNI: Global Mobile Data Traffic Forecast Update 2016-2022. February 2017

What is 5G? It is said to be disruptive compared to the previous mobile networks. The change is evident but it is too soon to know what the future may hold. Analysts are projecting the expected results from 5G technology even if at this day, deployments are just beginning and commercial 5G deployment is clearly on the horizon:

- 5 Billion people forecast to be accessing the internet via mobile by 2025,

- 5G coverage will roll out rapidly to cover more than 40 percent of the global population by 2025,

- 5G will account for almost 1 in 7 connections (14 percent) by 2025,

- 9 Billion mobile connections with 5.9 Billion unique subscribers in 2025,

- 25 Billion Internet of Things devices globally in 2025,

- Global Mobile Annual Revenue of 1.1 Trillion in 2025.

The transformation to 5G will also transform everyone lives, our economy, our jobs and our industries. The early signs are beginning to show, such as wearables with self-contained mobile computing devices (Apple Watch or connected glasses), the connected car (autonomous vehicles), the healthcare system (remote monitoring and robotic surgery), drones (used for transportation and surveillance) and finally robots and Artificial Intelligence (AI) will result in a new relationship for both humans and machines.

The wireless industry has its game to play by providing new mega-networks of connecting billions of things, billions of connected people with a major shift in network operations and management. For instance by 2023, more than 30 billion connected devices are forecast with 2 main observations:

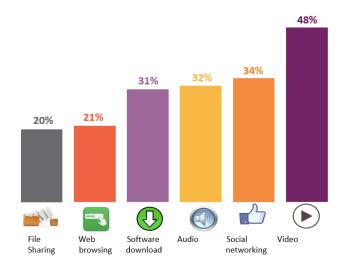

- Mobile video traffic is forecast to grow by around 50 percent annually through 2023, when it should account for nearly three-quarters of all mobile data traffic (Fig 1.2). Social networking is forecast to grow by 34 percent annually over the coming six years. The trend is accentuated by the growing use of embedded video in social media and web pages, which is considered video traffic in this context, fueled by larger device screens, higher resolution and new platforms supporting live streaming.

- 20 billion of the 30 billions of devices will be related to the IoT. Connected devices include connected cars, machines, meters, sensors, point-of-sale terminals, consumer electronics and wearables. Between 2017 and 2023, connected IoT devices are expected to increase at a Compound Annual Growth Rate (CAGR) of 19 percent, driven by new use cases and affordability.

Figure 1.2 – Mobile Traffic by Application Category - CAGR 2017-2023 - Ericsson Mobility Report, November 2017

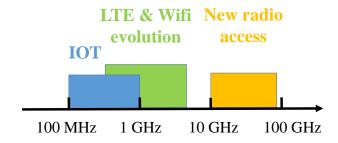

The 5G infrastructures would rely on an heterogeneous, densified network. As for frequency resources, 5G is expected to use as much spectrum as possible, divided into 3 main frequency ranges for different applications (Fig. 1.3):

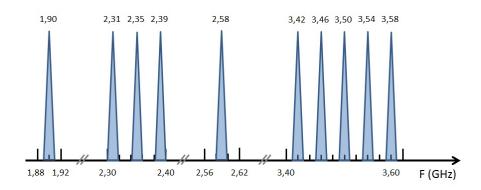

- Sub-6 GHz band: this frequency range offers less losses for a transmission in the air; a data rate higher than 1 Gbps can be achieved on this band thanks to carrier aggregation, based on an extension of the LTE standard (cf. Fig. 1.4),

- The mmW band: it has a limited range because of attenuation but gives access to wider bandwidths.

- The Internet of Things (IoT): it will be deployed in the same time, using the sub-GHz frequency band. Those devices will be equipped with low-power transceivers.

Figure 1.3 – Technology tracks of 5G era

Figure 1.4 – Spectrum allocation for sub-6GHz 5G standard

RF Transceivers are the hardware implementation of those various techniques to access the spectrum. It necessitates a high flexibility as the demand of spectrum access is large in terms of frequency ranges and number of users. For instance, sub-6GHz claim for a carrier-aggregated signal which cover frequencies from 1.8GHz up to 3.6GHz and then 6GHz.

As depicted in Fig 1.5, RF Transceivers design is thus more and more constrained by:

- **Power consumption**: mobile handsets are limited by their battery and as a matter of consequence, the power consumption has to be as low as possible with the highest efficiency

- Data rate: as data traffic is increased mainly by video applications, data rate is getting higher (from 10x to 100x from one generation mobile communication to another) and asks for higher carrier frequencies, not necessarily compatible with an efficient propagation (mmW frequencies)

- **Technology**: mass market imposes the use of a low cost technology, such as CMOS. Nevertheless, this technology is not suited for analog RF electronics.

- Propagation environment: wireless signal propagate more or less depending of the environment and their frequencies. The air is very a good medium for sub-6GHz signals in a non-dense area. New challenges are raised by mmW frequencies in dense area (such as urban) or new propagation media such as human body.

Our research work is to design radio-frequency integrated circuits to challenge this paradigm.

Figure 1.5 – Paradigm of RF Transceivers design

Figure 1.6 – Transceiver Architecture

A wireless communication system transmits and receives information at high frequencies. Fig. 1.6 summarizes the transceiver architecture with 3 main parts:

- RF signal conditioning: RF signals are amplified, filtered and up or down-converted into baseband,

- Data converter: signals are converted from analog to digital or digital to analog,

- Digital signal processing: the signal is processed digitally to recover the information contained in the data stream to be displayed by the device.

Our research aim is to adapt or invent techniques to design transceivers for new wireless communication protocols. We have to deal with CMOS technologies, high frequencies and data rate, low power consumption and system integration.

#### 1.2 Radio-Frequency architecture

RF architectures have to challenge the evolution of wireless transmission requirements as presented before. Since 20 years, a lot of researches are oriented in the direction of RF flexible solutions. Many terms are associated to those architectures, such as multi-standards, Software Defined Radio (SDR), Software Radio (SR), Cognitive Radio, adaptative radio with an updated terminology now including artificial intelligence in adaptative RF front-end design.

Fig 1.6 illustrates how a transmitter architecture can gain in flexibility. Digital conversion is brought as close as possible to the antenna to alleviate reconfigurability or adaptative RF signal processing. Nevertheless, the analog front-end is struggling with RF requirements over a wider band of operation. This depicts the technological bottleneck of the analog-to-digital conversion the scientific community is fighting against. Boris Murmann's ADC Performance Survey keeps an updated trend of ADC or DAC evolution

Figure 1.7 – Boris Murmann's ADC Performance Survey [1]

over the 2 last decades and shows clearly that a universal ADC or DAC for RF applications is not for today or tomorrow. Fig 1.7 presents how challenging could be an ADC for either SDR or sub-6GHz 5G applications. There is clearly a wall to break and recent evolution cannot fight against physics where aperture time is struggling with the jitter. That is why, research is focused on proposing solutions at the system level instead of keeping on running to the wall.

#### 1.2.1 State of the Art

Some researches provides solutions at the system level, either for the receiving or the transmitting path. The philosophy is to give flexibility at a RF system while respecting RF requirements:

- High-order modulation scheme,

- Large frequency range or wide-band,

- High resolution requirements (Signal-to-Noise Ratio (SNR)),

- Low latency.

#### **Receivers trends**

RF receiver state of the art depicts a wide range of research on new RF receivers. The following one is not exhaustive but presents a selection of circuits that highlight some interesting features. They all achieve good performance in terms of Dynamic Range (DR) or rejection, power consumption but exhibit how to challenge limited instantaneous bandwidth and concurrent reception (i.e. their potential to perform

|                         | Nauta [3] | Kinget [4]  | Pamarti [5] | Abidi [6]   | Andrews [7] | Harjani [8] |

|-------------------------|-----------|-------------|-------------|-------------|-------------|-------------|

| Tuning range            | 0.1-1GHz  | 0.2-1GHz    | 0.1-1GHz    | 0.08-2.7GHz | 0.1-2.4GHz  | 0-2.5GHz    |

| Instantaneous Bandwidth | 35MHz     | 2MHz        | 2.5-40MHz   |             |             | 312.5MHz    |

| Gain / Rejection        | NA / 70dB | 36dB / 52dB | 23dB / 45dB | 72dB/42dB   | 40-70dB/-   | 47dB        |

| Power Consumption (mA)  | 1.6 to 13 | 26          |             | 27          | 31          | 0.76        |

| Technology              | 65nm      | 65nm        | 65nm        | 40nm        | 65nm        | 65nm        |

Table 1.1 – RF receiver State of the Art

a direct carrier aggregation). Nevertheless, ideas presented by the state of the art in Tab. 1.1 pave the way to revamped approach such as N-path filters [3] [4], time-interleaved (i.e. convolution) [5], noise cancellation [6], digitally assisted systems [7] or analog signal processing [8]. We can detail 2 approaches of interest:

- Prof. Bram Nauta proposes in [3] to achieve filtering thanks to N-path filter. Despite this technique is not new, he was a pioneer to integrate it in a RF Front End. He demonstrated that we can reach very good performances such as selecting a narrow channel within a wide frequency range with a good selectivity. His work inspired many researchers and was a starting point to several improvements at the system level to enhance it as depicted by Prof. Peter Kinget in [4] and by Prof. Bram Nauta himself in [9],

- Prof. Ramesh Harjani proposes in [8] a disruptive system to select several bands in a wide range of frequency using analog signal processing thanks to a discrete Fourier Transform. This approach has demonstrated a low power and highly linear application which is well suited to RF. This work has been improved by being integrated in a receiver to sense a wide spectrum and to perform beamforming [10].

#### **Transmitters trends**

Tab. 1.2 presents a selected state of the art of transmitters that aim at achieving software radio purpose. It follows the various type of architectures in function of their flexibility as depicted in Fig. 1.8 extracted from [2]. A multi-standard transmitter detailed in [11], [12] and [13] plays on direct conversion with a carrier frequency configuration. [14] exposes a SDR transmitter supporting intra-band dual carrier aggregated signals. The trend is to generate several bands in parallel and counteract inter-modulation products by harmonics rejection techniques. Amplification itself is still a main technological bottleneck if one considers it targets wide band with high efficiency in CMOS technologies.

|                        | Craninckx [12] | Sakamoto [11] | Hashemi [13] | Wang [14] |  |

|------------------------|----------------|---------------|--------------|-----------|--|

| Tuning range           | 0.15-6GHz      | 0.7-2.7GHz    | 0.05-6GHz    | 0.1-6GHz  |  |

| Bandwidth              | 16MHz          | 20MHz         | 40MHz        | 100MHz    |  |

| Power Consumption (mW) | 100            | 200           | 900          | 103       |  |

| Technology             | 130nm          | 90nm          | 130nm        | 65nm      |  |

Table 1.2 – RF transmitter State of the Art

Figure 1.8 – Transmitter digital versus analog composition for flexible RF applications

#### 1.2.2 RF Transceiver design

Going digital at the earliest possible stage is no more the trend. Designing a RF transceiver is first to face with many circuits such as Power Amplifiers, Oscillators, Filters, Clocks, Analog-to-Digital and Digital-to-Analog Converters, Modulators (Amplitude, Phase, Frequency Modulation), Demodulators, Mixers, PLL, Multiplexers, etc... As said before, it becomes very complex to consider a complete paradigm between power, frequency, cost and bandwidth with such a diversity of standards. Software Radio is not necessarily the grail to get. We believe that RF designers have still their role to play to propose the most suited circuit for each application. The grail might not be the circuit but the methodology to design it.

When considering the RF system in its whole, we can identify a trade-off in RF circuit design. Fig. 1.9 illustrates the compromise between classical RF architectures and the general purpose one:

- Classical RF architectures: they use well-known techniques such as homodyne, heterodyne, super-heterodyne architecture. RF designers work actively to integrate the FE efficiently with the most relevant technology. The methodology is limited in terms of risks but the architecture is not necessarily optimized for power consumption, die area or over-loaded in calibration apparatus,

- General purpose RF architecture: it is the ultimate Software Radio system but we can consider that intermediate SDR systems can be included in. RF constraints are relaxed to the price of intensive digital signal processing and A/D conversion cost. The system is not optimized for power consumption and signal processing efficiency.

We envision a trade-off between classical and general purpose RF architectures. The most relevant one is a full custom RF architecture based on the wireless application. It will determine the power consumption budget, the standard (i.e. modulation), the frequency range, the bandwidth and all the inherent RF requirements. The underlying goal is to integrate Compressed Sensing (CS) as a matter to receive or transmit only the relevant information directly at the RF stage to avoid waste of power and time due to complex signal analysis.

The concept of "relevant information" is about to convert only signal information rather than its full representation. Under these conditions, Nyquist rate sampling may no longer offer the optimal digitization scheme. The trend is to reduce the sampling bandwidth as closely as possible to the signal's information rate while the new class of feature-sampling ADCs called Analog to Information (A2I) converter or Analog to Feature converter (A2F) reduce the dimensionality of the waveform through analog analytics to retain only application relevant signal features, with the intention of classifying these features instead of representing the original waveform.

Figure 1.9 – Representation of trade-off between classical and general purpose RF architectures

Our design methodology is called **Design by Mathematics** (**DbM**). It is divided into 2 parts:

- 1. A holistic consideration of the circuit:

- IEEE standard (frequency range, bandwidth, modulation scheme, etc ...),

- wireless propagation medium and its properties (attenuation, distance).

- 2. The signal is converted in the most adequate mathematical base, ideally orthonormal:

- the base is the analog Front End,

- only coefficients are converted and projected in the base.

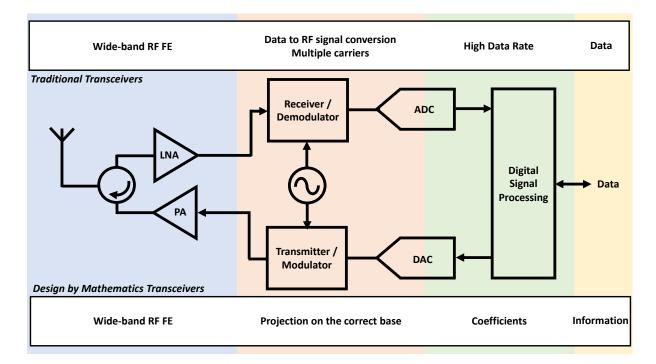

Fig. 1.10 presents the differences between a classical and the DbM approaches in the case of 5G and SDR-like transceivers:

- Wide-band RFFE are similar in both approaches,

- The conversion circuitry is no more a multiple carrier up/down converter but a base implemented in silicon in which coefficients are projected. The frequency generator can be seen as the family generator in the mathematical meaning,

- Data are no more considered as a digital signal but as information encoded or decoded in coefficients extracted from or converted in a RF signal thanks to the base.

Figure 1.10 – Transceivers architecture difference between traditional and DbM approaches

The base is the key to choose the most adequate circuitry. Mathematically: it should be orthonormal and build by a family provided by the frequency generator. Following algebra rules, we need to define Odd signals O(x) and Even signals E(x) with a scalar product to orthonormalize the base. Then, we have to demonstrate the density and verify the Dirichlet theorems to ensure that any "pseudo" periodic function can be written as the limit of a sum of O(x) and E(x). This will be the confirmation that any RF signal can be generated using this base. Thus, the base can be implemented in silicon and RF signals will be converted only thanks to their coefficients.

#### 1.3 Conclusion

Telecommunication industry claims for new RF architectures. It is faced with a huge diversity of standards and a constant evolution that impose a design of new RFIC. A decade ago, a concept called Software Radio was said to be the grail to reach by proposing a universal circuit to access to large band of the RF spectrum by moving to digital all the flexibility. This concept arrived to a dead end. The upcoming 5G standard pushes RF designers to develop wide band, low power, high resolution architectures. The boom of IoT strives RF designers to develop ultra low-power RF circuits. Last but not least, new trends such as Intra-Body Communications and up-100GHz spectrum access also push RF designers to develop new RF architectures.

In this chapter, we have discussed about the relevancy of **RF architecture design**, from its classical way to the SR one. We assume that there is a trade-off between frequency, either the carrier or the bandwidth, the power consumption, the technology and the resolution to design the most relevant architecture. A/D and D/A conversion is still the technological bottleneck to counteract because it cannot support the increasing amount of data, either on the RF or on the digital signal processing sides, or the limited power at its disposal to be performed.

This is why we propose to revisit the design methodology of RF circuits by introducing the **Design by Mathematics approach**. It consists in considering the conversion from baseband to RF in the projection of coefficients in an orthonormal base. The RF circuit is the orthonormal base and the coefficients represent the information. Each application will find the most relevant pair of bases and coefficients, which will give the most appropriate circuit displaying the **best performance at the least cost**.

CHAPTER

2

# DESIGN BY MATHEMATICS FOR RADIO-FREQUENCY IC

#### Sommaire

| ,01111116 | anc            |                                      |                                                    |  |  |  |

|-----------|----------------|--------------------------------------|----------------------------------------------------|--|--|--|

|           | 2.1            | 2.1 Design by Mathematics principles |                                                    |  |  |  |

|           | 2.2            |                                      |                                                    |  |  |  |

|           |                | 2.2.1                                | Sampled Analog Signal Processor Receiver - SASP Rx |  |  |  |

|           |                | 2.2.2                                | Walsh Transmitter - Walsh Tx                       |  |  |  |

|           | 2.3            | Time o                               | domain                                             |  |  |  |

|           |                | 2.3.1                                | Riemann Pump Tx                                    |  |  |  |

|           |                | 2.3.2                                | Delta Riemann - Breda Rx                           |  |  |  |

|           | 2.4 Conclusion |                                      | usion                                              |  |  |  |

Chapter 2 presents the research led in RF systems during the last decade. It started as an investigation focused on Software Radio receiver. Then, it was extended to arbitrary waveform generation. 4 kind of architectures were proposed and divide into 2 families: frequency domain and time domain ones. Each of it proposes a receiver and a transmitter solution. We have evaluated their efficiency in terms of spectrum access, power consumption and integration cost. The first family is about Fourier transform: the receiver implements a Discrete Fourier Transform using analog voltage samples to carry out an instantaneous image of the RF spectrum. The transmitter is based on a "digital" Fourier transform using Walsh series in order to investigate on the best trade-off between analog and digital to generate amplified wide-band signals. The second family is a time domain solution based on derivatives and integrals of a RF signal. The transmitter, called Riemann Pump, proposes to discretize the integral of a signal by encoding it thanks to a high-data rate digital stream. The receiver is about to shape the quantification noise using a feedback loop, called Delta Riemann, to display a direct RF conversion of a signal.

**Key words**: Sampled Analog Signal Processing, Walsh series, Software Radio, Arbitrary Waveform Generator, Carrier Aggregation

#### 2.1 Design by Mathematics principles

A RF signal is by nature a sine-wave that varies in amplitude, frequency and phase in time. This sine-wave is modulated to carry information. It is done by changing its amplitude, its frequency or its phase thank to slow variations compared to the sine-wave one. Assuming that, we consider that only the envelope carries information and the carrier is useless to convert information to radio-frequency.

In mathematics, an algebra over a field (simply called an algebra) is a vector space equipped with a bilinear product. Thus, an algebra is an algebraic structure, which consists of a set, together with operations of multiplication, addition, and scalar multiplication by elements of the underlying field, and satisfies the axioms implied by "vector space" and "bilinear". We consider that RF signal and signal processing is an algebra. The vector space is the RF transceiver.

A vector space is a collection of objects called vectors, which may be added together and multiplied by numbers, called scalars. An orthonormal family of vector forms a base. With given properties, this base can describe pseudo-periodic RF signals. Scalars are then called coefficients.

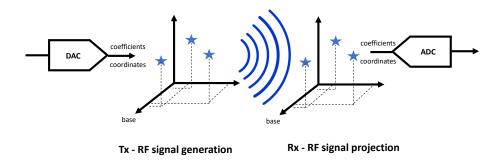

We propose a methodology to convert RF signals to base-band by representing it in the most adapted base thanks to a set of coefficients. In electronics, we consider that those coefficients carry the information and the base is the mean of conversion from RF to base-band. Fig. 2.1 depicts how Tx can generate a signal based on coefficients conversion in a base or how Rx can project RF signal in a base and recover coefficients.

Figure 2.1 – Symbolic representation of the DbM methology

We can identify some relations between the mathematical description of a RF signal and its RF properties. It can be listed as follows:

- density: it is the accuracy of the signal description based on the size of the base and its ability to represent any kind of functions. It will play on the bandwidth, i.e. the wide-band capability,

- coefficient quantification: coefficients are converted from digital to analog. Their resolution will play on properties such as SNR, SFDR, BER.

The 2 following sections present 4 kind of circuits developed during the last decade as a research prospective. They are divided in 2 categories: frequency domain and time domain, and each one presents a transmitter and a receiver. Each solution is detailed by:

- its concept,

- its architecture,

- its simulation,

- its measurements,

- its perspectives.

# 2.2 Frequency domain

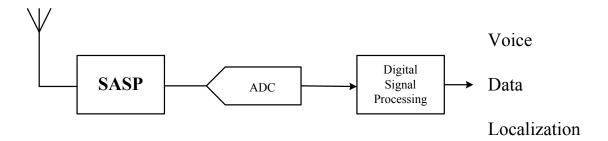

# 2.2.1 Sampled Analog Signal Processor Receiver - SASP Rx

This work was initiated in the trend of Software Radio receivers and was the subject of my PhD thesis. The objective was to design and measure a Sampled Analog Signal Processor (SASP). Its purpose is to carry out analog operations on discrete voltage samples at RF frequencies. My idea was to relax ADC constraints and coherently the DSP constraints by decreasing their working frequency as it was and it is still the main technological bottleneck as both resolution, power consumption and large bandwidth cannot be achieved at the same time.

We have proposed to interface the antenna and the A/D conversion with an analog signal processor (cf. Fig. 2.2). Its goal was to work in the frequency domain at RF frequencies to perform operations in the frequency domain instead of the time domain. Those operations are much easier and thus, less costly (filtering, mixing, carrier aggregation, ...).

Figure 2.2 – SASP receiver system

### Concept

Every sampled signal can be expressed using Fourier coefficients by Eq. 2.1.

$$x(k) = \sum_{n = -\infty}^{+\infty} c_n(f) \cdot \exp\left(jnk\frac{2\pi}{T}\right)$$

(2.1)

The SASP processes an analog Discrete Fourier Transform (DFT). Output carries out the Fourier coefficients that compose the input signal as described in Eq. 2.2.

$$X(n_{\text{sample}}) = \sum_{k=0}^{N-1} x(k) \exp\left(\frac{-j2\pi n_{\text{sample}}k}{N}\right), \qquad n_{\text{sample}} = 0, 1, \dots, N-1$$

(2.2)

The SASP works as follows (Fig. 2.3):

- RF signals are sampled,

- Voltage samples carries out analog FFT,

- Among thousands of them, only the ones representing the desired RF signal envelope are selected,

- Selected voltage samples represent the instantaneous in-band cartesian coordinates of signal envelope.

Figure 2.3 – Concept of the SASP, analog FFT (a), sample selection (b), A/D conversion (c), constellation processing (d)

The SASP emphasizes two applications:

- The frequency demodulation: as only the sample contains both phase and amplitude information, a direct demodulation of the constellation can be performed [15],

- A native carrier aggregation: the sample selection is not limited to one sample and several samples, i.e. channels, can be processed at the same time.

# **Architecture**

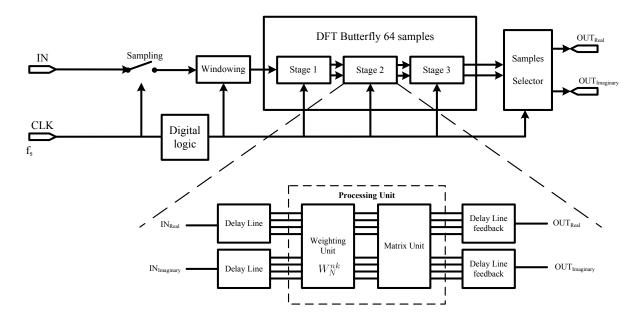

We have designed a generic architecture to implement the FFT algorithm on a given number of samples N. Sampling frequency  $f_s$  is the only parameter to scale FFT accuracy and range. We limit our study to N = 64 voltage samples, i.e. three stages of analog calculation (Fig. 2.4). This architecture was sufficient to demonstrate the feasibility, the application and the technological limitations. High level simulation results have been published in [16] [17] [18] [19] [20].

Figure 2.4 – SASP Architecture

The demonstration has exhibited main constraints in analog signal processing building blocks such as:

- The Track and Hold (T/H) sampler: it samples the signal and transfers the voltage samples to the FFT circuit. Sampling is the most important part of the system because the resolution of the calculation depends on its accuracy,

- Windowing: the range of the data processing is limited by the number of stored samples *N* and has an undesired effect on the spectrum. This effect is reduced thanks to a weighting function called *window*, here a Hamming window which was hard-wired but would be reprogrammable for more flexibility,

- Analog operations: delaying, adding and weighting operations on voltage samples bring inaccuracy such as:

- Delay suffers from leakage in storing capacitors,

- Adding and weighting suffers from distortion because of voltage-to-current conversion.

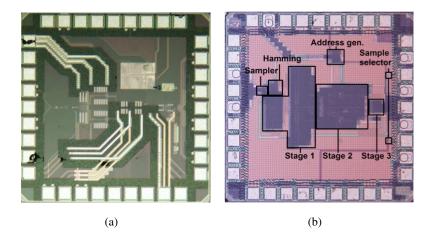

#### Measurements

Two demonstrators of the SASP were fabricated respectively in 2008 and 2013. They were using the 65nm CMOS technology from STMicroelectronics. Their die area was pad limited to  $1.44mm^2$  with an active area of  $0.13mm^2$  (Fig. 2.5). The circuits have been fully characterized and their main characteristics are given by Table 2.1.

Figure 2.5 – Frequency demodulation, SASPEPA-2008 (a), NIKITA-2013 (b)

| Characteristics     | SASPEPA       | NIKITA        |  |

|---------------------|---------------|---------------|--|

| Technology          | 65nm CMOS STM | 65nm CMOS STM |  |

| Die area            | $1.44mm^2$    | $1.44mm^2$    |  |

| Maximal $f_s$       | 1 GHz         | 2 GHz         |  |

| RF spectrum covered | 0-500 MHz     | 0-6 GHz       |  |

| Instantaneous BW    | 0-500 MHz     | 0-1 GHz       |  |

| Power consumption   | 360mW         | 97mW          |  |

Table 2.1 – SASP performances

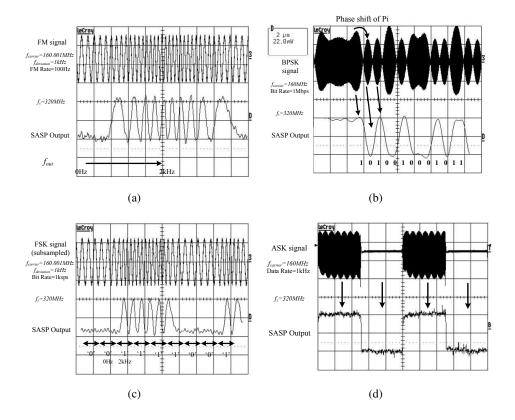

Measurements have demonstrated that frequency demodulation can performed using:

- Frequency Modulation (FM): defined by a frequency deviation of  $f_{deviation} = 1kHz$  around a central frequency of  $f_{carrier} = 160.001MHz$  (Fig. 2.6(a)).  $f_{out}$  varies a frequency range from 0 to 2kHz,

- BPSK modulation: bits are encoded through a phase shift of 180° with a bit rate of 1*Mbps*.

The output samples representing a '0' are reversed compared to a '1', thus we can read directly bits (Fig. 2.6(b)),

- 2-level Frequency Shift Keying (FSK) modulation: bits are encoded at 2 different frequencies  $f_1 = 160.002MHz$  and  $f_2 = 160MHz$  with a bit rate of 1ksps. '1' is a 2kHz-signal and '0' is a DC signal (Fig. 2.6(c))

- Amplitude Shift Keying (ASK): either the signal is the RF signal or a zero-signal to encode bits with a 1kHz-data rate ASK signal (Fig. 2.6(d)).

Figure 2.6 – Frequency demodulation, FM modulation (a), BPSK modulation (b), FSK modulation (c), ASK modulation (d)

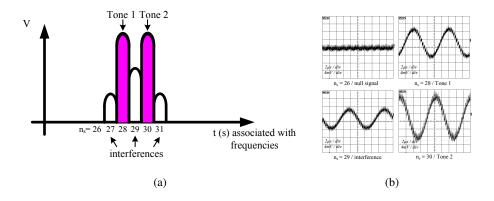

Fig. 2.7 presents the principle and the measurement of a concurrent reception which is applied to carrier aggregation. A 2-frequencies signal is carried out by samples  $n_s = 28$  and  $n_s = 30$ . We can notice interferences in samples  $n_s = 27$ ,  $n_s = 29$  and  $n_s = 31$  due to the input windowing. All the others samples are null. Measurements results have been published in [21] [22] [23] [24].

Figure 2.7 – Concurrent reception, principle (a), measurements (b)

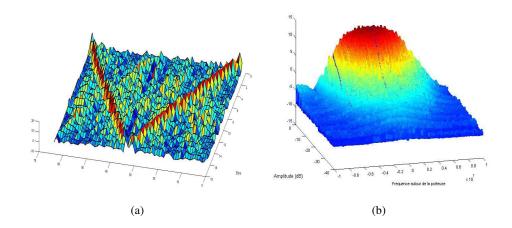

Fig. 2.8 presents the complete characterization of bins and in a bin in particular. It was measured using millions of sets thanks to an automatic bench developed for this purpose. It validates the correct addressing and behavior of every bin. It was completed with a characterization in temperature (Fig. 2.9). As one can see, SNR decreases with temperature increasing.

Figure 2.8 – Characterisation of a bin, addressing of all bins (a), frequency behavior in a bin (b)

Figure 2.9 – SASP characterization in temperature

# **Perspectives**

At this day, we can identify several research works in the line of this one such as [8] and [10] used as systems for instantaneous reception of signal within very large bands.

The work has been pursed with 2 applied scenarii:

— Civil applications: ST Microelectronics has kept financing the investigations on the SASP performances improvements. 5G is a standard that requires carrier aggregation. The SASP can receive several channel at the same time within large bandwidth [25]. Some improvement works on the design of the circuitry have been done to optimize the signal processing [26],

— Defense applications: Thales Group has financed research work on RADAR application. [27] [28] [29] [30] present the principle of a frequency detection for this purpose. The goal is to cancel any interfering signal from 0 to 20GHz+ frequencies, i.e. to localize a signal, identify its frequency, its magnitude and its modulation scheme as quickly as possible. Analog signal processing is the relevant answer to low-latency systems as no-conversion and digital signal processing are avoided to waste time.

# 2.2.2 Walsh Transmitter - Walsh Tx

This work was initiated in the trend of Software Radio transmitters and was the subject of Dr Nassim Bouassida's PhD thesis [31]. The objective was to propose a new type of RF transmitter with very wide band capabilities such as carrier aggregation purpose.

# Concept

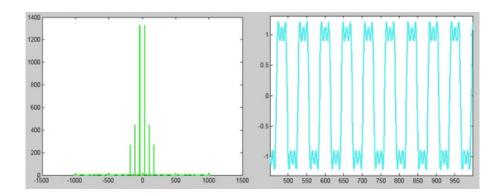

The spectral representation of a signal is a sum of harmonics. Thus, one can think that a sum of harmonics can generate arbitrary waveforms. For instance, 3 harmonics are sufficient to approximate a square wave as depicted in Fig 2.10. Nevertheless, this is hardly feasible in RFIC, such as proposed in Fig. 2.11, because it would consume a lot of power, surface and would face with various parasitic effects. However, we thought that a square signal also has a fundamental harmonic and odd harmonics. In integrated circuits, square signals are relatively straightforward to manage. We decided to investigate on how to generate a RF signal based on a square signals generation.

Joseph Walsh has proposed a base of square signals to describe any pseudo-periodic signals. This theory is described in [32]. It is based on Walsh series that are discrete trigonometric functions. It is generated following an iterative pattern given by Eq. 2.3 where  $W_0 = 1$  and n is the order of Walsh.

Figure 2.10 – square signal generated with 3 harmonics

$$W_n = \begin{pmatrix} W_{n-1} & -W_{n-1} \\ W_{n-1} & W_{n-1} \end{pmatrix}$$

(2.3)

Square signals sequences are given by each line of the matrix. We can represents those sequences in time with every line corresponding to a Walsh function. Those functions are named Wal(i), with  $i = 0 \dots 2^{Order_{Walsh}}$ . They are orthonormal and can be splitted into 2 kinds, Cal and Sal, representing the cosinus and the sinus for Walsh functions. Thus, we can describe any signal under its Walsh form based Eq. 2.4.  $a_n$  and  $b_n$  are the coefficients. Those coefficients represent the signal and are consequently refreshed no more than the envelope frequency, i.e. the data rate.

$$x(t) = Wal(0) + \sum_{n=1}^{N} a_n.Cal(n,t) + b_n.Sal(n,t)$$

(2.4)

with  $N = \frac{Order_{Walsh}}{2}$ .

# Harmonic generator

Figure 2.11 – Harmonics recombination

#### **Architecture**

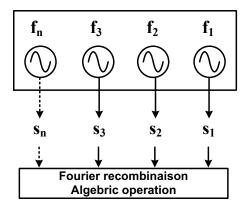

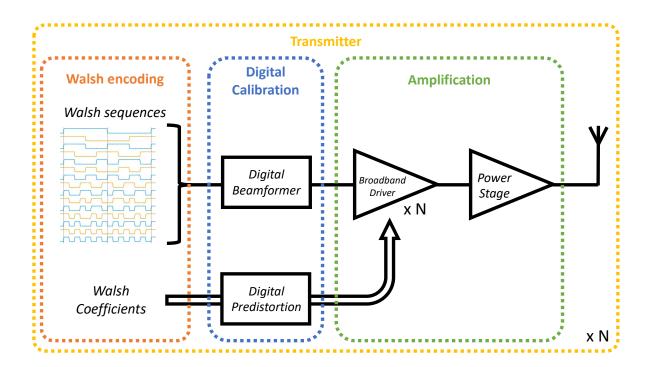

Fig. 2.12(a) presents the system as it is described in details in [33]. It is composed of 3 main parts:

- Squares signal are provided by a mmW frequency synthesis from a PLL. It is a fundamental block in RF transmission / reception and can therefore be re-used as it is. Square signals are associated together thanks to logic gates to provide every Walsh function (cf. Fig. 2.12(b)),

- Coefficients are converted from digital to analog and multiplied to Walsh functions,

- Summation of all sequences are performed by differential pairs weighted by their tail-current sources.

Figure 2.12 – Walsh system (a), and its associated sequences generation (b)

Compared to classical transmitter architectures, the signal is arbitrary generated which means that in the case of carrier aggregation, every channel is synchronized to each other. The non-dependence to a dedicated local oscillator for every channel offers first a robust architecture to asynchronicities and also a lower silicon footprint.

Our research work was to establish the trade-off between Walsh order, the number of coefficients and spectrum mask (i.e. modulated signal resolution such as SNR, EVM, etc.). We have demonstrated that the SNR is similar to the one of a regular DAC and based on the coefficients conversion one. But, the system is wide band and the coefficients refreshment is the main bottleneck as there are numerous and only a few are relevant. Thus, the tradeoff lies on identifying the "good" coefficients to convert with high resolution and the "bad" coefficients with a low impact on signal quality.

The main question is to identify how to address those coefficients. We decide to consider a limited number of parameters:

- Walsh order: it has to be as low as possible to reduce dimensions of logic glue and number of coefficients,

- Coefficient binary order: a truncature of coefficient binary code, i.e. a limited resolution for insignifiant ones.

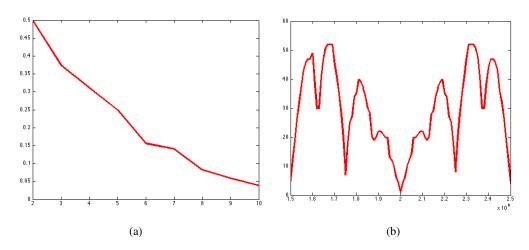

For instance, simulations have been performed to evaluate the number of coefficients to be addressed versus the Walsh order in Fig. 2.13. We can assume that:

— Walsh order: Fig. 2.13(a) depicts the percentage of coefficients used in relation with the Walsh order (here given in log<sub>2</sub>). Te higher the order is, the lower the percentage is, which means

that the number of coefficients is relatively constant whatever the order for given specification. We decide that after an order of 6, i.e. 64 Walsh sequences, resolution is sufficient for our applications,

— a non-linear behavior in terms of frequency: Fig. 2.13(b) presents the number of coefficients required among 64 to generate a CW signal at a given frequency. Within a frequency band from 1.5GHz to 2.5GHz, this number can vary from 1 to 52. Some investigations have demonstrated that all those coefficients are not necessarily relevant as some of them have small value compared to others. Quantification would determine a LSB and thus, a truncature threshold that would reduce the number of active coefficient.

Figure 2.13 – Percentage of coefficients used versus the Walsh order (a), number of coefficients used within a large frequency band based on a 64 Walsh sequence architecture (b)

#### **Simulations**

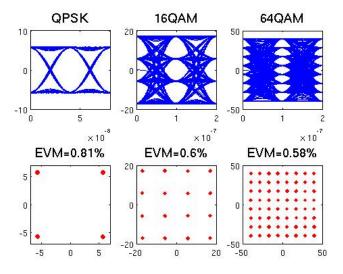

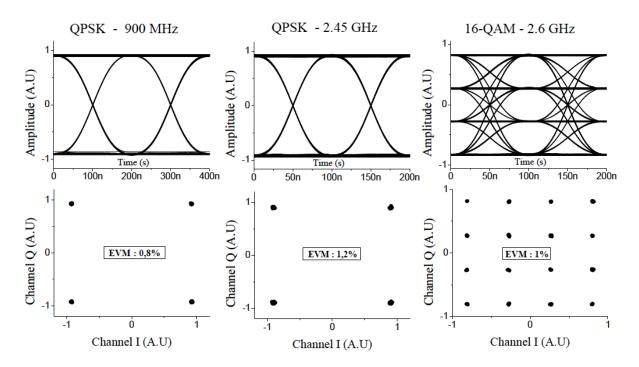

The Walsh generator circuit has been designed in the 28nm FD-SOI CMOS technology from STMicroelectronics. [31] presents the discussion about the trade-off between the Walsh order, the number of coefficients and their resolution. We have decided the most relevant number of Walsh functions is 64 with a 6-bit coefficients coding. We have simulated its behavior in a 5G scheme presenting its spectrum and associated eye diagram and EVM as depicted in Fig. 2.15).

The 3 signals are respectively:

- QAM-16 modulated signal at 2.31GHz with a bit rate of 10MS/s,

- QAM-64 modulated signal at 2.33GHz with a bit rate of 10MS/s,

- QPSK modulated signal at 3.58GHz with a bit rate of 25MS/s.

As one can see, Walsh Tx can convert very close bands while keeping very good EVM under 1% despite the limited number of coefficients.

Figure 2.14 – Carrier aggregation done by Walsh Tx in frequency

Figure 2.15 – Associated eye diagram and EVM

2.3. Time domain 47

Based on the design work, we estimate that:

- The core system would consume around 25mW and has an estimated size of  $0.35mm^2$ ,

- The Walsh DAC would consume 13.62mW under 1V and its estimated size is  $0.2mm^2$ .

# **Perspectives**

At this day, we propose to integrate the Walsh generator in a complete transceiver and investigate on the relevancy of Walsh base to undergo all the signal processing, such as RF filtering for Rx and predistortion techniques for Tx. The project is detailed in section 4.1.1.

# 2.3 Time domain

# 2.3.1 Riemann Pump Tx

An arbitrary waveform generator (AWG) architecture was the subject of Dr Yoan Veyrac's PhD thesis [2]. We proposed to generate a signal based on its piecewise linear approximation, resulting from the use of a differential digital coding associated with a suited digital-to-analog converter (DAC), named here the Riemann Pump. A first version was designed in a GaN technology [34], suited for power applications and a second version was designed in 65nm CMOS technology, suited for 5G applications [35].

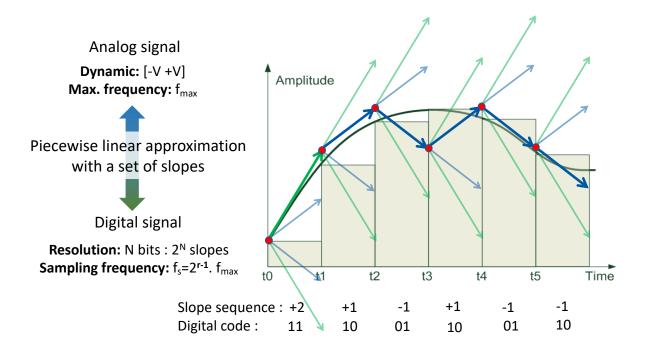

#### Concept

The purpose of the presented system is to generate arbitrary waveforms up to the GHz range with a low cost and low consumption solution. The wanted signal is available in a high resolution digital representation. It is converted in its Riemann form with a specific coding, and then converted in the analog domain thanks to a pre-determined set of slopes such as presented in Fig. 2.16.

The generation process is implemented as shown in Fig. 2.17. A Digital Signal Processor (DSP) computes the Riemann code (i.e. the slopes index sequence) from the theoretical signal we want to generate. This code controls switched current sources, in order to generate current steps that are integrated into an output capacitor, producing a piecewise linear approximation of the wanted signal.

The Riemann Pump principle is detailed in [35]. We have demonstrated that the SNR for a full scale sine wave is calculated as:

$$SNR_{dB} \approx 6.02N + 9.03r - 7.78 + 10log_{10}\left(1 - \frac{1}{2^{N-1}} + \frac{1}{2^{2N}}\right)$$

(2.5)

In the Eq. 2.5, the dependence of the SNR on the OSR has a double origin. The main effect comes from the differential coding; any doubling of the sampling frequency divides by 2 the range to be covered by

Figure 2.16 – Riemann Pump Architecture Principle.

Figure 2.17 – Riemann Pump Architecture (a) and theoretical signal generation (MATLAB) (b).

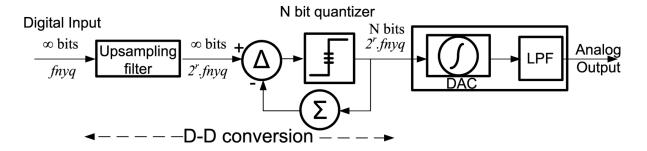

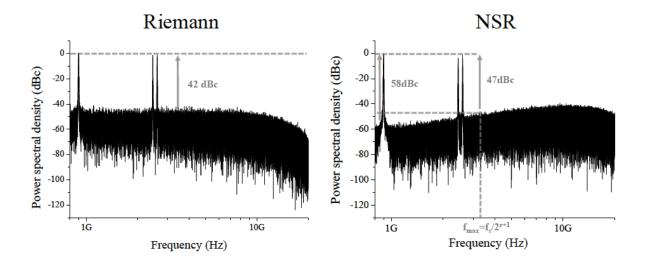

the quantizer, as well as the quantum. Thus, it generates a factor 6.02r in the SNR, corresponding to a decrease of the total quantization noise generated. The additional factor 3.01r comes from the filtering out of the noise lying on the band  $[f_{max}, \frac{f_s}{2}]$ . Considering our application, the OSR is inherently low and its effect does not mainly depend on the filtering of the out of band quantization noise. The requirements on the analog output filter are thus relaxed. This topology of digital to analog conversion is optimized for low OSR applications, in order to cover a large frequency band without a complex and resource intensive architecture. An optimized noise shaping was proposed in [36], named Noise Shaping Riemann (NSR).

2.3. Time domain 49

#### **Architecture**

The signal generation process can be formalized as shown in Fig. 2.18. A bandwidth limited analog signal of maximum frequency  $f_{max}$  can be perfectly described by an ideal digital signal sampled at the Nyquist frequency ( $f_s = f_{nyq}$ ) which is worth twice  $f_{max}$  (Nyquist-Shannon theorem). That is to say the original analog signal can be recovered without any additive noise; provided the digital signal has a perfect accuracy and the sampling images are ideally filtered. This is theoretically achievable with an infinite number of bits to code the sampled analog levels. Such a signal would exhibit an infinite signal to noise ratio (SNR). An actual DA conversion obviously involves a digital signal with a limited number of bits N to drive the DAC. The overall DA conversion can thus be split into two distinct parts:

- a digital-to-digital (DD) conversion that transforms the ideal digital signal into a resolution-limited digital signal (which produces quantization noise),

- a DAC together with an additional low pass filter.

Figure 2.18 – Riemann DAC topology.

# **Schematic**

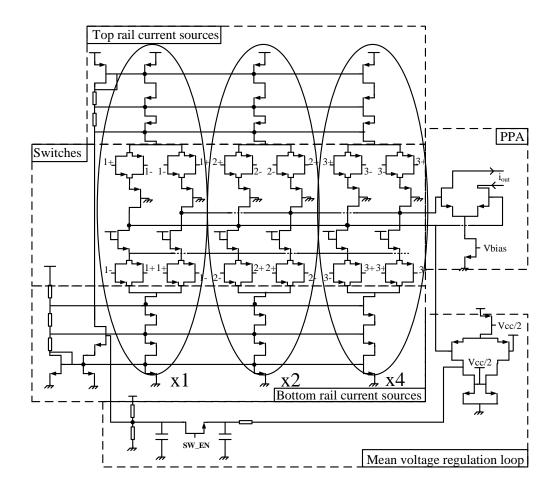

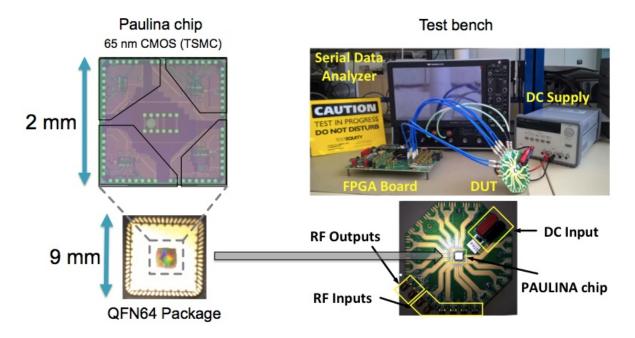

The number of bits of the prototype designed for our research work is limited to 3 bits for measurement purposes. The maximal switching frequency of this DAC core is 25 GHz, which gives a bandwidth (BW) larger than 3 GHz with an oversampling factor r of 2 ( $2.r = f_s/2.BW$ ). Provided the multi-gigahertz target bandwidth and the typical picofarad range of integrated circuit capacitances, the full scale current is limited to several hundreds of microamperes to generate output voltages of hundreds of millivolts. Considering a complete transmitter topology, the Riemann Pump can directly drive an amplifier whose input impedance is capacitive, which is most often the case in CMOS technology. It provides an inherent wide-band operation while avoiding any cumbersome matching network at the input of the amplifier. A prototype of the Riemann Pump was designed in a 65 nm CMOS technology from TSMC. A simplified version of the transistor-level schematic view of the circuit is presented in Fig. 2.19.

Figure 2.19 – Riemann Pump schematic

#### **Simulations**

The ability of the system to handle concurrent transmission is demonstrated with a combination of 3 modulated signals distributed over the [0 - 3 GHz] band corresponding to several standards with their characteristics

- QPSK modulated signal at 900MHz with a bit rate of 10Mbps.

- QPSK modulated signal at 2.45GHz with a bit rate of 20MS/s,

- QAM-16 modulated signal at 2.6GHz with a bit rate of 40MS/s,

The spectra of the composite signals corresponding to the sum of the 3 modulated signals reconstructed with respectively the Riemann and the NSR coding scheme are displayed in Fig. 2.20 [36]. One can notice that for the Riemann conversion, the noise floor is flat over the whole band. Nevertheless, the noise floor exhibits a high pass characteristic for the NSR; it is not uniformly distributed over the whole band but it turns out lower than the Riemann case in the band of interest. The 3 signals are demodulated independently for the two conversions. We only observe their respective eye diagram and EVM

2.3. Time domain 51

in Fig. 2.21. The obtained EVM values for the Riemann conversion are around 1%, which is far below the requirements for the most common standards. There is room for the command circuit and the power amplification imperfections.

Figure 2.20 – Carrier aggregation: spectrum

Figure 2.21 – Carrier aggregation: eye diagram

#### Measurements

Several campaigns of measurements have been performed such as in [37]. Our target was to demonstrate the ability to generate a multi-carrier signal over a large bandwidth. Device under test (DUT) is shown in Fig. 2.22. We present here a limited number of relevant measurements.

Figure 2.22 – Device Under Test from chip to bench

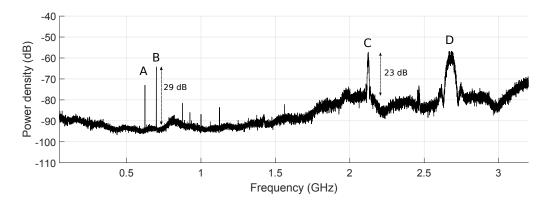

We generate various signals from 700MHz to 2.68GHz to demonstrate the feasibility of four different carriers with three modulation schemes. The Fourier Transform of this multi-carrier signal is depicted in Fig. 2.23. The 4 signals are respectively:

- A: Continuous sine-Wave (CW) at 623MHz,

- B: GMSK modulated signal at 700MHz with a bit rate of 1MS/s,

- C: QAM4 modulated signal at 2.12GHz with a bit rate of 10MS/s,

- D: QAM16 modulated signal at 2.68GHz with a bit rate of 50MS/s.

5G standard implies to reach data rate of several hundred of MS/s. QAM4 represents the kind of modulation scheme used for 5G which will be by extension QAM64 to QAM256. We decide to limit our measurements to QAM4 because of a limited size of FPGA memory which is not compatible with higher complexity of modulation scheme.

2.3. Time domain 53

Figure 2.23 – Fourier Transform of a multi-carrier signal with (A) sinusoidal signal, (B) GMSK, (C) QAM4 and (D) QAM16 modulated signals

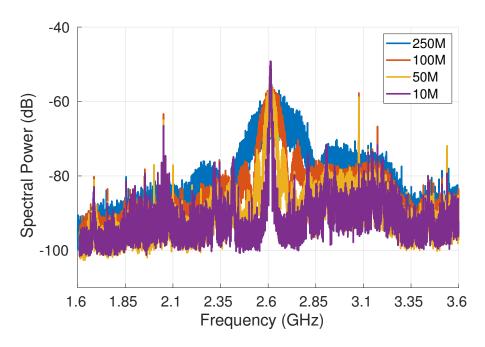

A characterization of frequency behavior of QAM4 for several data rate is depicted in Fig. 2.24 with a carrier frequency of 2.6GHz. The bandwidth increases with the data rate from several MHz to hundreds of MHz. Spurs located at 500 MHz around the carrier frequency are artefacts due to post digital signal processing and has no link with any chip imperfection.

Figure 2.24 – Fourier Transform of QAM4 modulated signal using different data rates

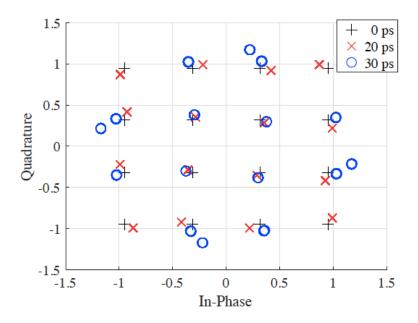

A focus is made on a QAM16 measurements at 2.6GHz in Fig. 2.25(a) and 2.25(b). As one can see, eye diagram exhibits good shape and EVM remains acceptable under 16%.

Figure 2.25 – Constellation associated with eye diagram of QAM16 modulated signal at 2.6GHz with a data rate of 50MS/s (a) (b).

# **Perspectives**

At this day, we have made the complete demonstration and characterization of this architecture. Its transfer to the industry is supported by the University of Bordeaux with a proposition to extend investigations to a complete integration of the digital and the analog part. The digital part would sustain dedicated digital-to-digital conversion and a high-data rate conversion based on multiplexing to control the Riemann Pump. Last but not least, those research opened the way for a receiver solution detailed in section 2.3.2.

# 2.3.2 Delta Riemann - Breda Rx

.

This work was proposed in the continuity of the Riemann Pump Tx. This idea was to investigate on a receiver using the same conversion scheme, which was named Delta-Riemann Rx and nicknamed Breda. There is no PhD thesis nor project associated to it but preliminary results have been published in [38].

# Concept

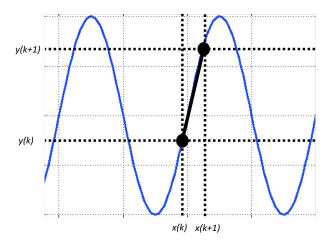

The circuit quantifies the RF signal derivative. We code the derivative by comparing a sampled input signal with a limited set of slopes like for the Riemann Pump. For instance, if we consider 2 input samples, x(k) and x(k+1), that correspond to the interval t = [x(k), x(k+1)]. The derivative is calculated as follows in Eq. 2.6:

$$D(k) = \frac{y(k+1) - y(k)}{x(k+1) - x(k)}$$

(2.6)

2.3. Time domain 55

Then, we discretize the slope by quantifying it. It leads to convert into digital the derivative as depicted in Fig. 2.26 where the slope will be approximated among a set of predetermined values representing the meaningful slopes that compose the derivative signal.

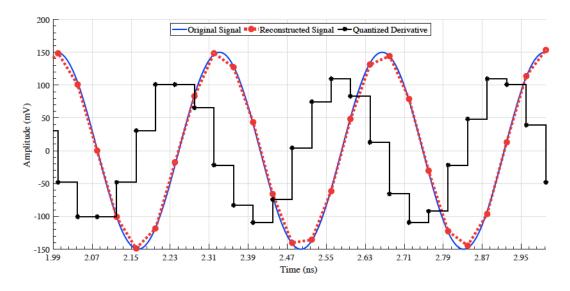

This concept is depicted in Fig. 2.27. It exhibits the original signal, the quantized derivative and the reconstructed signal. It is possible to observe that the reconstructed signal is close to the original one.

Figure 2.26 – Basic Delta-Riemann ADC

Figure 2.27 – Basic Delta-Riemann ADC

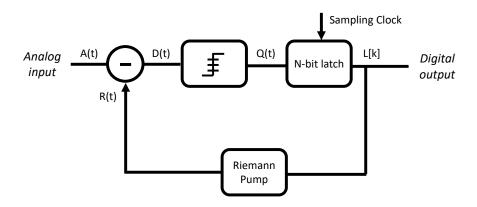

#### Architecture

Fig. 2.28 presents the architecture. First, the reference signal R(t) is subtracted from the input signal A(t) resulting in a differentiated signal D(t). Next, this differentiated signal is quantized into a N-bit code Q(t). Then, at a sampling clock transition, this signal is then latched as L[k]. The latch works as a sample and hold stage and at the sampling clock transition, its output changes switching the Riemann Pump internal current sources to the new sampled code. Finally, the Riemann Pump capacitive load will then integrate the new resulting internal current i(L[k]) for a whole sampling period (here  $T_s$ ) generating a new reference value R(t). At the new sampling clock transition, the reference value R(t+Ts) will be close to the value of input signal A(t) at the beginning of the previous sampling period. Those five septs are performed within a whole sampling period  $T_s$ : delta signal generation, quantization, latching, Riemann Pump switching and Riemann Pump integration. Due to the high GHz sampling frequencies, the sampling period is very short (for instance, 40 ps for a 25GHz sampling frequency).

Figure 2.28 – Basic Delta-Riemann ADC

As the Delta-Riemann Rx integrates a Riemann Pump, we have decided to keep the same parameters as the ones chosen in the prototype presented here below, i.e. 3-bit encoding and a sampling frequency at 25GHz.

#### **Simulations**

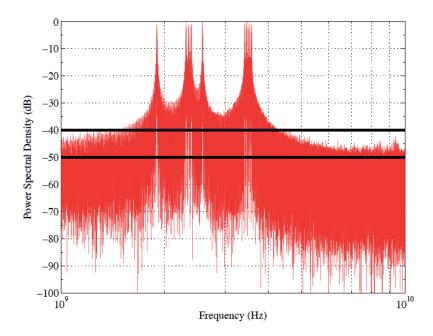

The Delta-Riemann is simulated in MATLAB using the sub-6GHz 5G standard with 10 carriers, each of it modulated with a bandwidth of 20MHz. The bit sequences of each carrier were then demodulated and the quality of signal in each channel evaluated. The resulting reconstructed signal power spectrum is shown in Fig. 2.29. Some spectral leakage is present due the non-coherent sampling resulting in a non flat noise floor. The noise floor is between -40 dB and -50 dB. Since the carrier frequencies present a power spectral density close to 0 dB, the minimal SFDR is near 40 dB.

2.3. Time domain 57

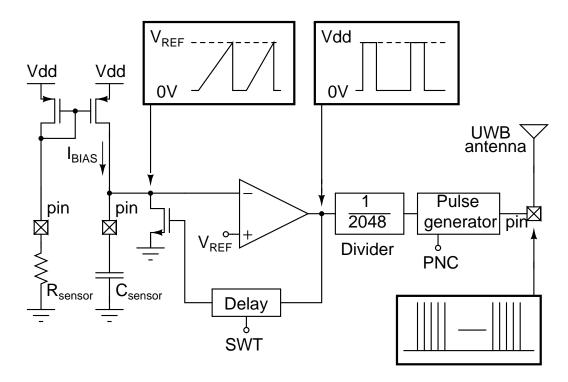

Figure 2.29 - Spectrum of Reconstructed signal - 10 aggregated channels