## Contribution to the development of UWB chipless RFID reader based on IR-UWB approach

Marco Garbati

#### ▶ To cite this version:

Marco Garbati. Contribution to the development of UWB chipless RFID reader based on IR-UWB approach. Optics [physics.optics]. Université Grenoble Alpes, 2017. English. NNT: 2017GREAT034. tel-02278206

### HAL Id: tel-02278206 https://theses.hal.science/tel-02278206

Submitted on 4 Sep 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité : OPTIQUE ET RADIOFREQUENCES

Arrêté ministériel : 25 mai 2016

Présentée par

#### Marco GARBATI

Thèse dirigée par Etienne PERRET, Maître de conférences, Univ. Grenoble Alpes, et codirigée par Romain SIRAGUSA, Maître de conférences, Univ. Grenoble Alpes

préparée au sein du Laboratoire de conception et d'intégration des systèmes dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

Contribution au développement d'un lecteur RFID sans puce basé sur l'approche ultra large bande impulsionnelle

# Contribution to the development of UWB chipless RFID reader based on IR-UWB approach

Thèse soutenue publiquement le **3 juillet 2017**, devant le jury composé de :

#### Monsieur Simone GENOVESI

Maître de conférences, Université de Pise - Italie, Rapporteur **Monsieur David GIRBAU**

Professeur, Université Rovira i Virgili - Espagne, Rapporteur

#### **Monsieur Arnaud VENA**

Maître de conférences, Université de Montpellier, Examinateur

#### Monsieur Sylvain BOURDEL

Professeur, Grenoble INP, Président

#### Monsieur Giovanni BIANCHI

R&D Engineer in the hardware/RF division Advantest Europe GmbH, Membre invité

#### Monsieur Christophe HALOPE

Directeur R&D Arjowiggins Security, Membre invité

## Contribution au développement d'un lecteur RFID sans puce basé sur l'approche ultra large bande impulsionnelle.

Mots-clés: Radio Frequency Identification (RFID), Chipless, Ulta-Wideband (UWB), Reader,

Radar

Résumé: La technologie d'identification radiofréquence (RFID) est aujourd'hui une technologie mature qui est amenée à remplacer le code à barre dans un futur proche. Au milieu de toutes les familles de RFID, la technologie RFID sans puce Ultra Large Bande (ULB) est devenue un sujet incontournable. Au cours de cette thèse, nous avons contribué au développement d'un lecteur de tag RFID sans puce ULB en nous basant sur une approche impulsionnelle.

Deux prototypes de lecteur ont été développés en suivant les limitations d'émissions de la technologie ULB imposées par les normes. Le premier lecteur a permis principalement de valider le principe de la lecture de tags RFID sans puce en utilisant le temps équivalent. Une deuxième version du lecteur plus aboutis a ensuite été développée. En effet, la précision de lecture a été optimisée grâce à la réduction du bruit d'échantillonnage. Le temps de lecture ainsi que le coût du lecteur ont aussi été des paramètres clés qui ont été drastiquement réduits. Pour cela, un générateur d'impulsion faible bruit bas coût ainsi que des antennes ULB et des cartes de front-end RF ont été conçus et optimisés. Enfin, une technique de lecture des tags basée sur la diversité en polarisation est proposée et validée en pratique. L'objectif étant de permettre la lecture de tag dépolarisant indépendamment de leur orientation. Ce point est un aspect très important pour le développement futur de la technologie RFID sans puce car cela lève des contraintes sur la conception des tags.

## Contribution to the development of UWB chipless RFID reader based on IR-UWB approach.

Keywords: Radio Frequency Identification (RFID), Chipless, Ulta-Wideband (UWB), Reader,

Radar

Abstract: The RFID technology is in full development, and is intended to compete with optical barcodes for traceability in the next future. Between all the RFID families, the UWB chipless RFID technology is a major topic nowadays. This work of thesis is focused on the development of UWB chipless RFID readers based on IR-UWB approach.

The international regulations that limit the UWB emission are taken into consideration, and two reader prototypes have been developed. The first was used as proof of concept. The second version represents a full optimized reader in all the key aspects. Between them there are the reading precision, through sampling noise reduction, the reading time, and cost effectiveness. As part of the development of the readers, a low noise and low cost UWB pulse generator prototype was realized, along with UWB antennas and RF front-end boards. As prospective, a reading technique based on polarization diversity is shown with the aim of reading cross-polarized chipless tags independently from their orientation. This approach is valuable because does not give any constraint at the tag design level.

## Index

| Int | roduct | ion                                                                  | 1  |

|-----|--------|----------------------------------------------------------------------|----|

| 1.  | Introd | uction to Chipless RFID Technology                                   | 5  |

|     | 1.     | Introduction                                                         | 5  |

|     | 2.     | Introduction to RFID                                                 | 5  |

|     |        | 2.1. Introduction                                                    | 5  |

|     |        | 2.2. Passive, semi-passive and active transponder                    | 6  |

|     |        | 2.3. RFID vs barcode                                                 | 8  |

|     | 3.     | Chipless RFID                                                        | 9  |

|     |        | 3.1. Principle of operation                                          | 9  |

|     |        | 3.2. Chipless RFID in-between RFID and barcode                       | 10 |

|     |        | 3.3. UWB chipless RFID                                               | 12 |

|     |        | 3.3.1. UWB time-coded chipless RFID tag                              | 12 |

|     |        | 3.3.1.1. Single line discontinuity UWB time-domain chipless RFID tag | 15 |

|     |        | 3.3.2. UWB frequency-coded chipless RFID tag                         | 17 |

|     |        | 3.3.2.1. Join antennas and filter                                    | 18 |

|     | 4.     | Conclusion                                                           | 22 |

|     | 5.     | References                                                           | 23 |

| 2. | UWB   | Chipless RFID Reader: State of the Art                                          | 25 |

|----|-------|---------------------------------------------------------------------------------|----|

|    | 1.    | Introduction                                                                    | 25 |

|    | 2.    | SFCW approach                                                                   | 26 |

|    | 3.    | FMCW approach                                                                   | 28 |

|    |       | 3.1. Frequency-coded tag reader                                                 | 28 |

|    |       | 3.1.1. Limitation on reading frequency-coded tag                                | 29 |

|    |       | <ol> <li>Influence of the VCO sweep time on the reading performances</li> </ol> | 30 |

|    |       | 3.1.3. Simulation result                                                        | 31 |

|    |       | 3.1.4. Conclusion                                                               | 33 |

|    |       | 3.2. Time-coded tag                                                             | 33 |

|    |       | 3.2.1. Time-coded tag as collection of steady targets                           | 33 |

|    |       | 3.2.2. Low cost solution                                                        | 34 |

|    | 4.    | SFCW-FMCW vs IR-UWB                                                             | 36 |

|    |       | 4.1. Introduction                                                               | 36 |

|    |       | 4.2. UWB regulations                                                            | 37 |

|    |       | 4.3. Link budget                                                                | 37 |

|    |       | 4.4. Conclusion                                                                 | 40 |

|    | 5.    | Conclusion                                                                      | 40 |

|    | 6.    | References                                                                      | 41 |

|    |       |                                                                                 |    |

| 3. | IR-UV | VB Chipless RFID Reader Design                                                  | 43 |

|    | 1.    | Introduction                                                                    | 43 |

|    | 2.    | IR-UWB reading system based on test equipment                                   | 44 |

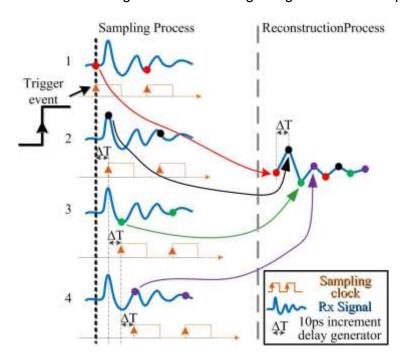

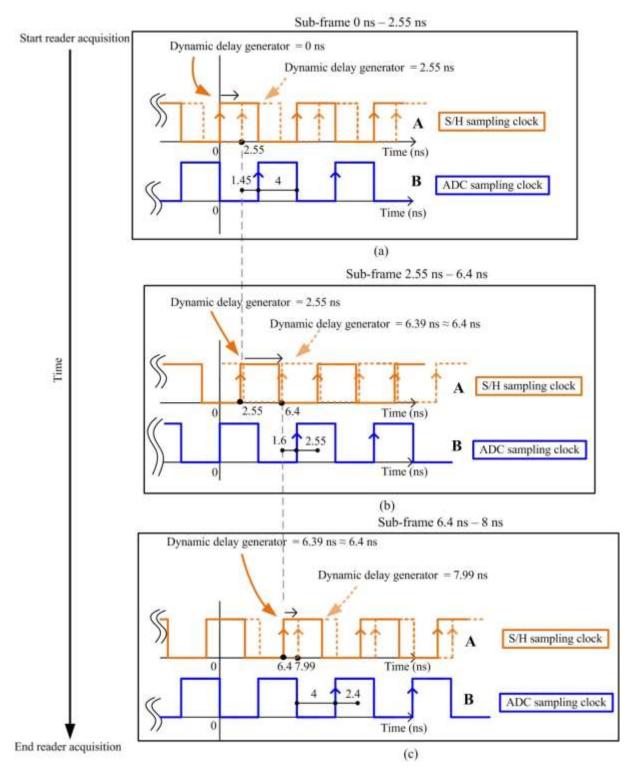

|    | 3.    | Sequential equivalent time approach                                             | 45 |

|    | 4.    | Reader developed previous the start of the thesis                               | 47 |

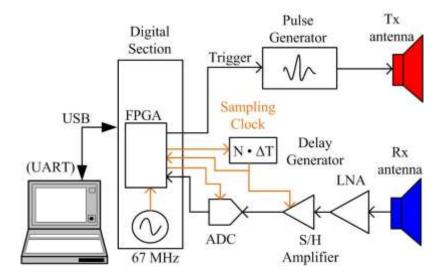

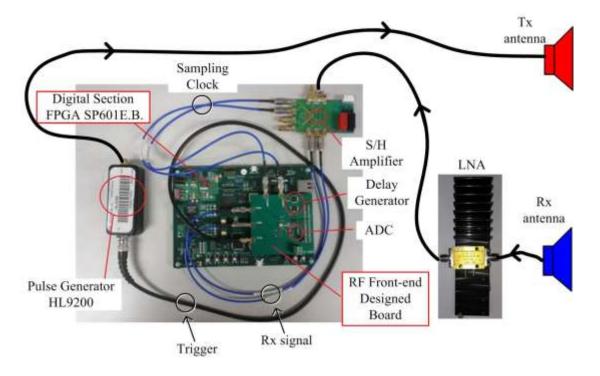

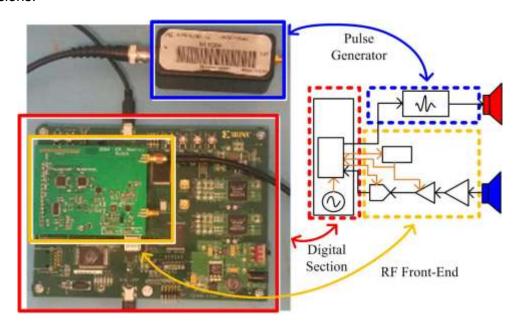

|    |       | 4.1. Schematic                                                                  | 48 |

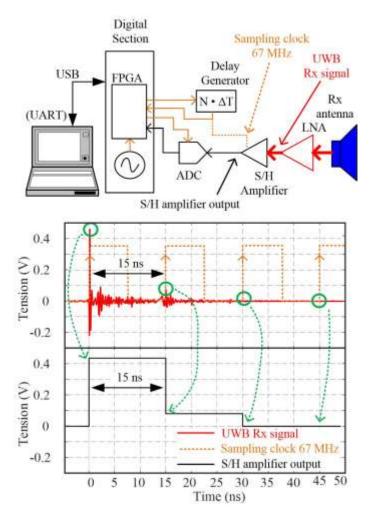

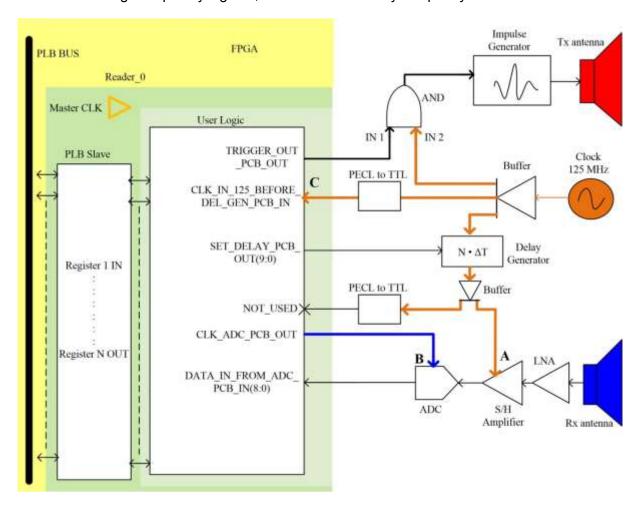

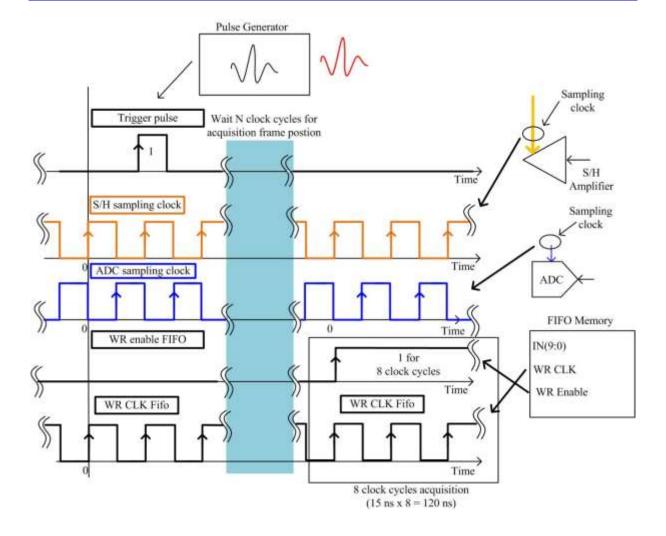

|    |       | 4.2. Implementation of the sequential equivalent time principle  | 50 |

|----|-------|------------------------------------------------------------------|----|

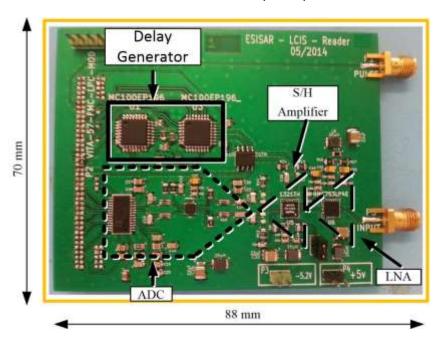

|    | 5.    | Integrated reader designed                                       | 52 |

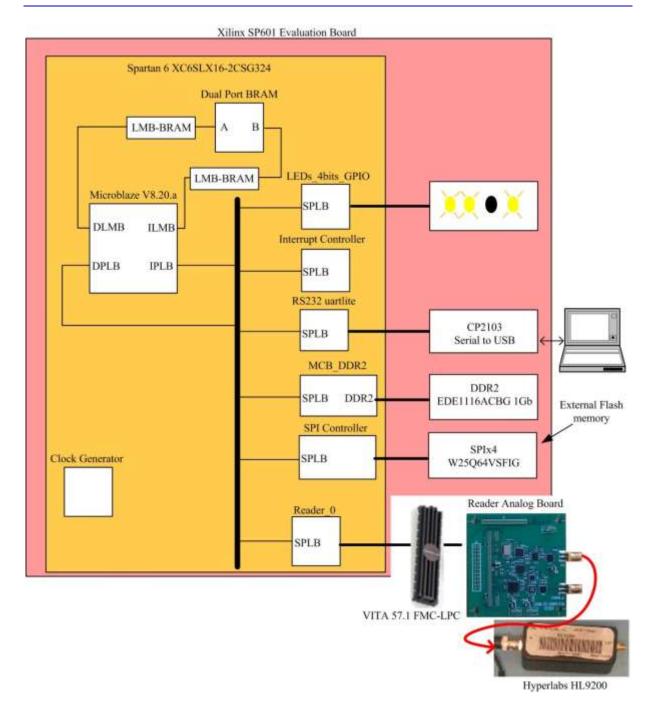

|    |       | 5.1. Hardware architecture                                       | 52 |

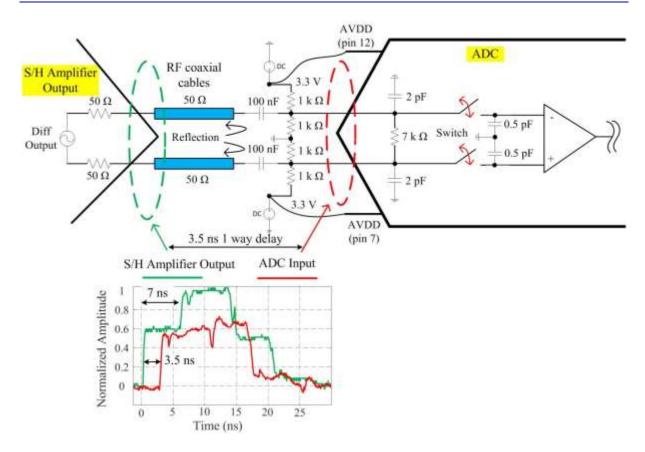

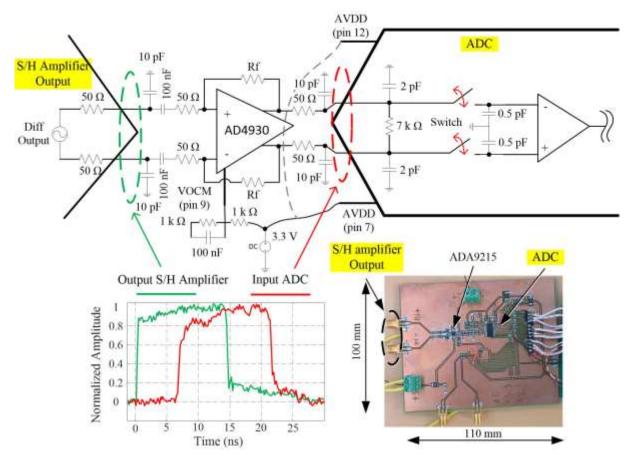

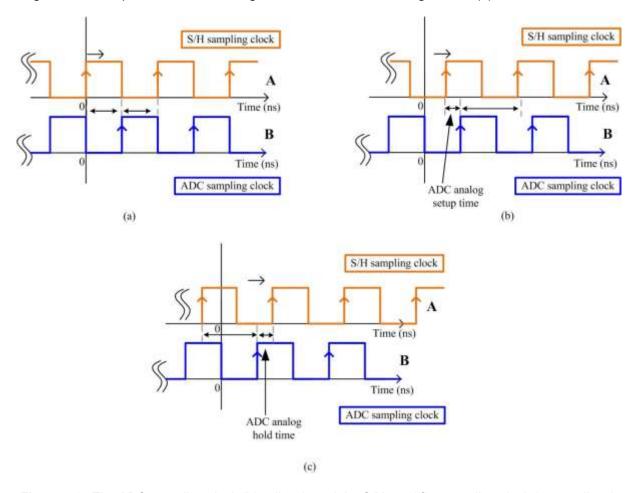

|    |       | 5.2. S/H amplifier - ADC connection improvement                  | 55 |

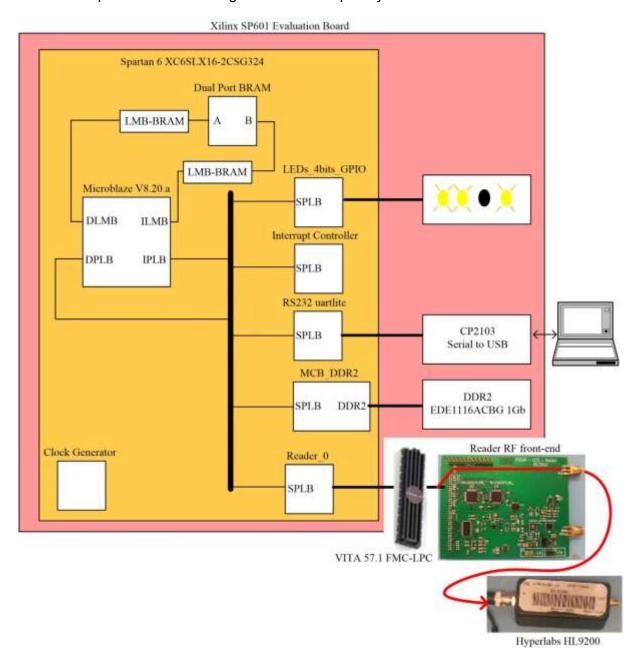

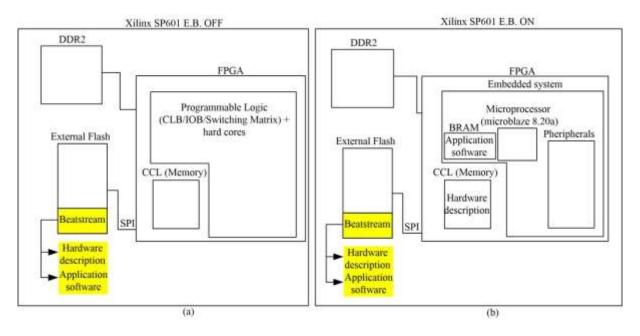

|    |       | 5.3. FPGA architecture                                           | 58 |

|    |       | 5.4. Reader specification                                        | 61 |

|    | 6.    | Tag measurement result                                           | 62 |

|    | 7.    | Conclusion                                                       | 66 |

|    | 8.    | References                                                       | 67 |

|    |       |                                                                  |    |

| 4. | Optin | nized IR-UWB Chipless RFID Reader                                | 69 |

|    | 1.    | Introduction                                                     | 69 |

|    | 2.    | ADC noise theory                                                 | 70 |

|    | 3.    | Reduced reader jitter: implemented hardware solution             | 74 |

|    |       | 3.1. Temporal characterization of reader RF front-end            | 78 |

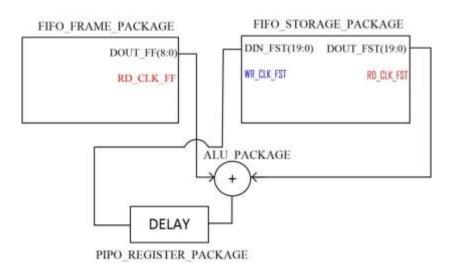

|    | 4.    | FPGA architecture                                                | 79 |

|    |       | 4.1. Reducing reading time                                       | 79 |

|    |       | 4.1.1. UART optimization                                         | 81 |

|    |       | 4.1.2. Transfer data to PC algorithm optimization                | 81 |

|    |       | 4.1.3. Hardware averaging implementation                         | 83 |

|    |       | 4.1.4. Conclusion                                                | 85 |

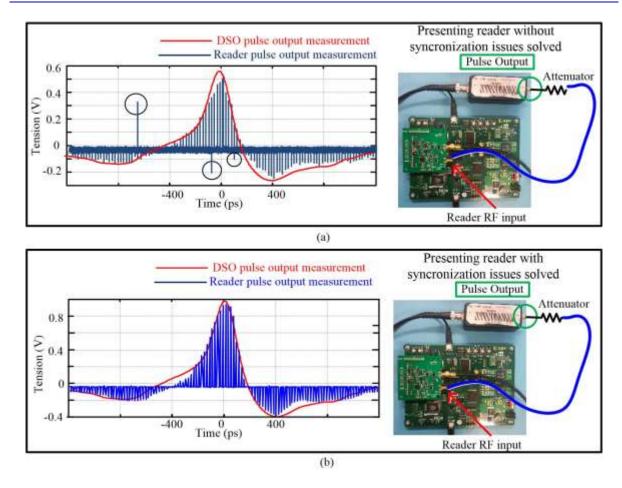

|    |       | 4.2. Solving acquisition synchronization problems                | 85 |

|    |       | 4.3. Demonstration of the resolution of synchronization problems | 89 |

|    | 5.    | Reader specification                                             | 91 |

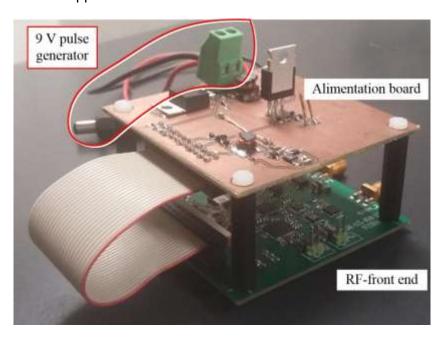

|    | 6.    | Reader power supply board                                        | 92 |

|    | 7.  | Reader tag measurement                                       | 93  |

|----|-----|--------------------------------------------------------------|-----|

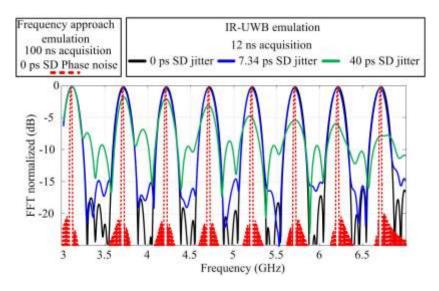

|    | 8.  | Frequency based reader vs IR-UWB with different jitter level | 96  |

|    | 9.  | Conclusion                                                   | 99  |

|    | 10  | References                                                   | 101 |

|    |     |                                                              |     |

| 5. | UWB | Pulse Generator & Antenna design                             | 103 |

|    | 1.  | Introduction                                                 | 103 |

|    | 2.  | UWB pulse generator                                          | 103 |

|    |     | 2.1. Introduction to pulse generator UWB design              | 104 |

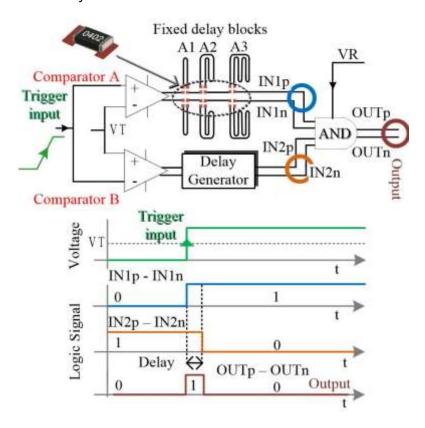

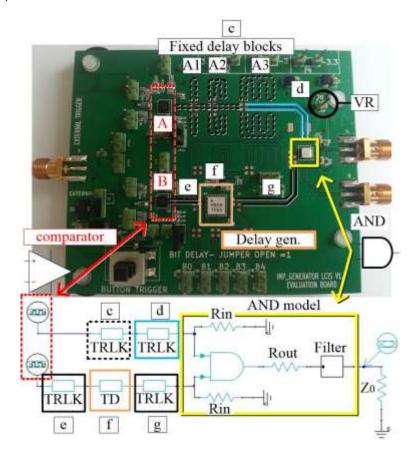

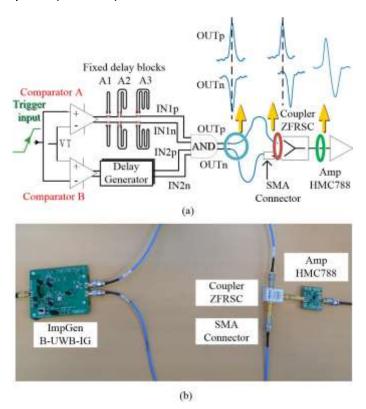

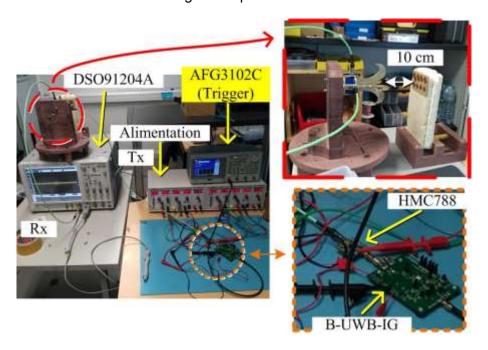

|    |     | 2.2. B-UWB-PG architecture                                   | 106 |

|    |     | 2.3. B-UWB-PG simulation model                               | 109 |

|    |     | 2.3.1. Block description                                     | 109 |

|    |     | 2.3.2. Noise rejection                                       | 111 |

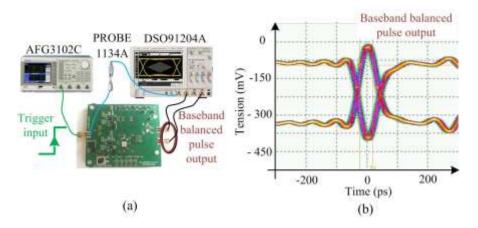

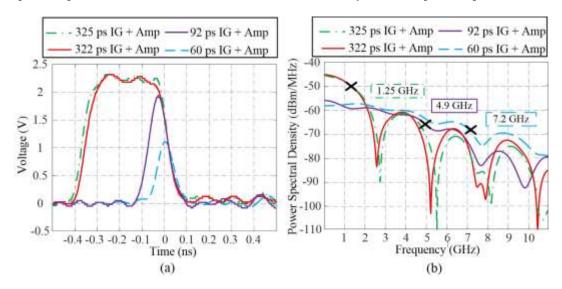

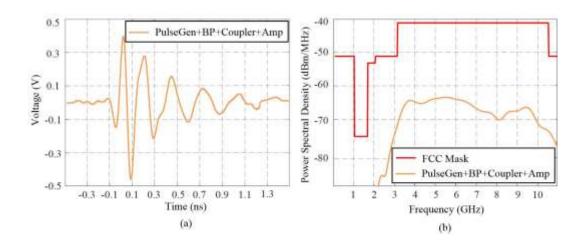

|    |     | 2.4. Measurement results                                     | 113 |

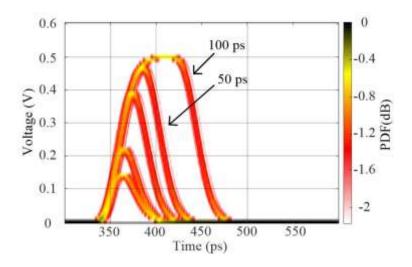

|    |     | 2.4.1. B-UWB-PG output characterization                      | 113 |

|    |     | 2.4.2. B-UWB-PG jitter characterization                      | 117 |

|    |     | 2.5. Output stage consideration                              | 118 |

|    |     | 2.5.1. Output power enhancement                              | 118 |

|    |     | 2.5.2. UWB shaping network                                   | 118 |

|    |     | 2.6. Conclusion                                              | 122 |

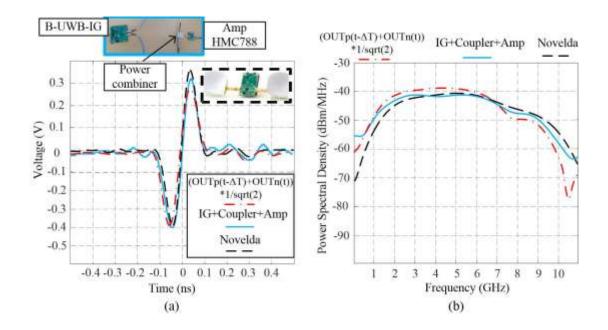

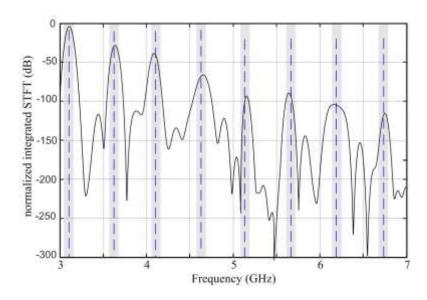

|    | 3.  | UWB pulse generator frequency-coded tag measurement          | 123 |

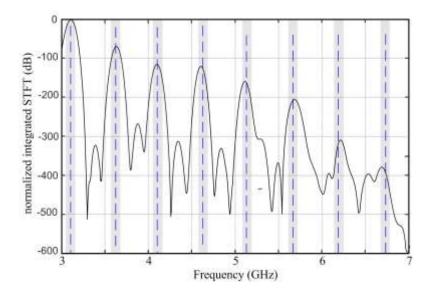

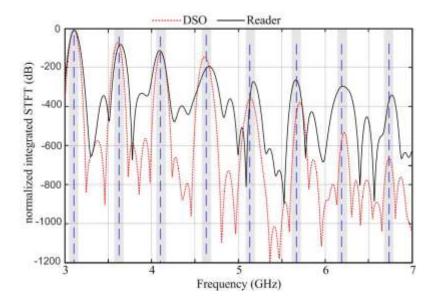

|    |     | 3.1. Pulse generator measurement result                      | 123 |

|    |     | 3.2. Conclusion                                              | 127 |

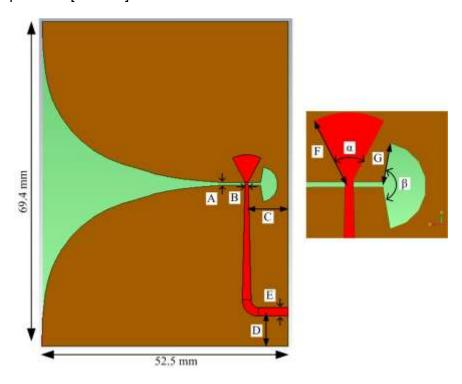

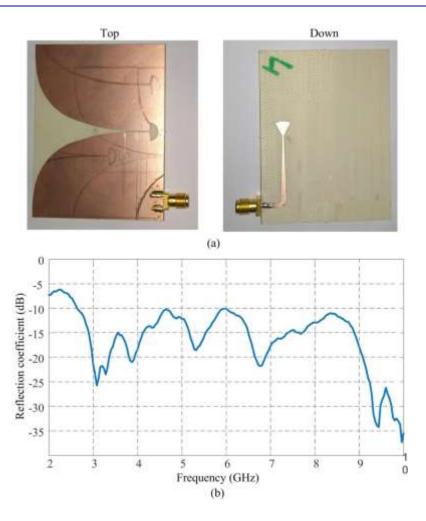

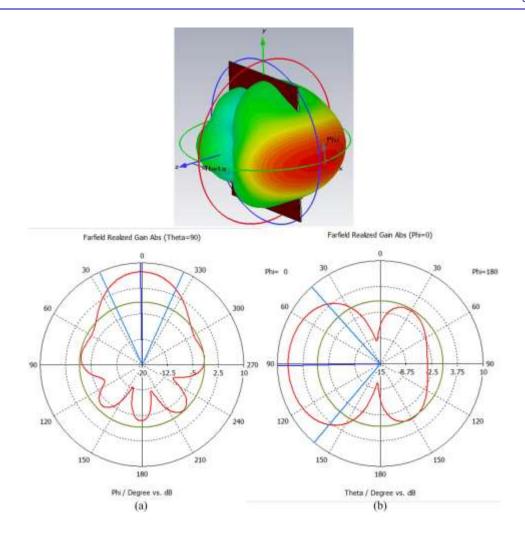

|    | 4.  | UWB antenna design                                           | 127 |

|    | 5.  | Conclusion                                                   | 131 |

|    | 6.  | References                                                   | 133 |

| ъ. | UWB Chipless RFID Reading System Independent of Tag<br>Orientation                                                                                                                                                                                    | 135                             |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|    | 1. Introduction                                                                                                                                                                                                                                       | 135                             |

|    | 2. Theory of operation                                                                                                                                                                                                                                | 136                             |

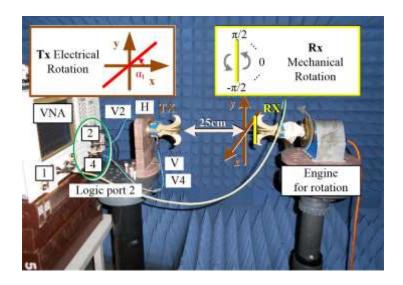

|    | 3. VNA balanced measurement                                                                                                                                                                                                                           | 140                             |

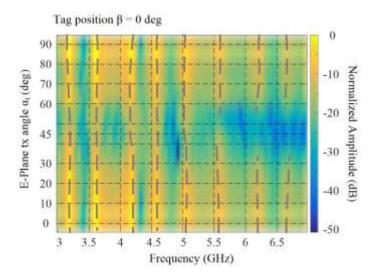

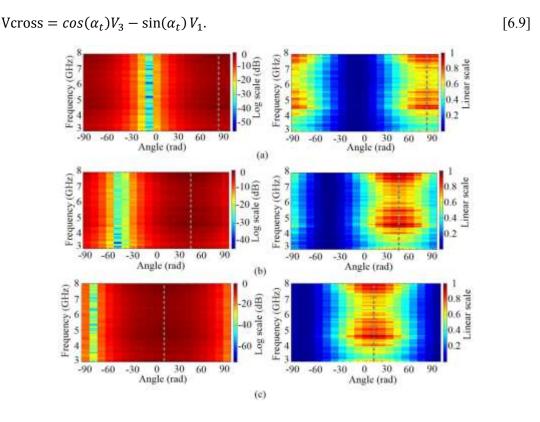

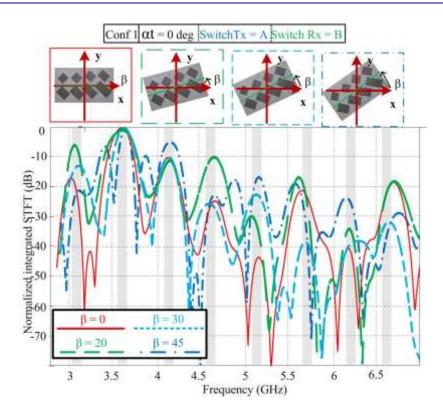

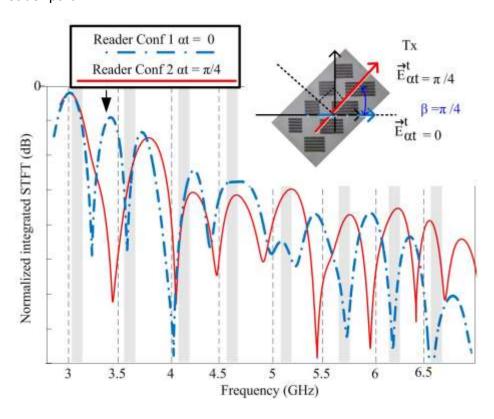

|    | 3.1. Variation of transmitting signal direction $\alpha_t$                                                                                                                                                                                            | 140                             |

|    | 3.2. Isolating the cross-polarized component in reception                                                                                                                                                                                             | 145                             |

|    | 3.3. Measure of cross-polarized tag                                                                                                                                                                                                                   | 146                             |

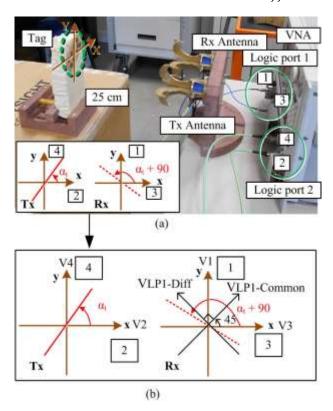

|    | 4. Tag measurements using VNA - a simplified approach                                                                                                                                                                                                 | 149                             |

|    | 4.1. Practical approach                                                                                                                                                                                                                               | 149                             |

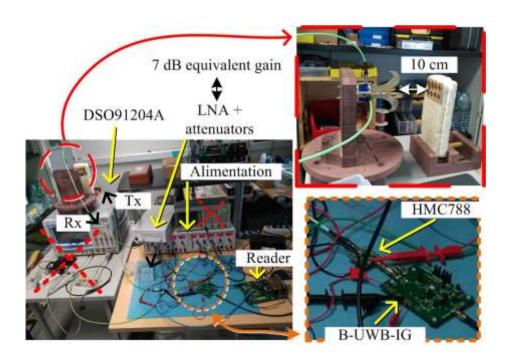

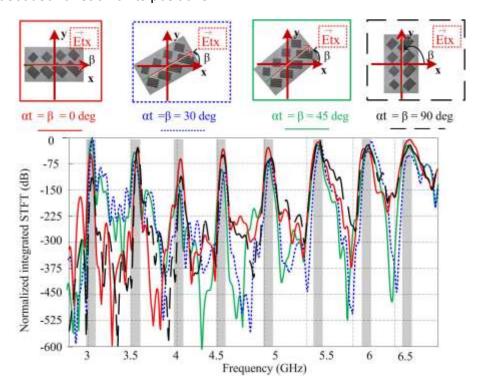

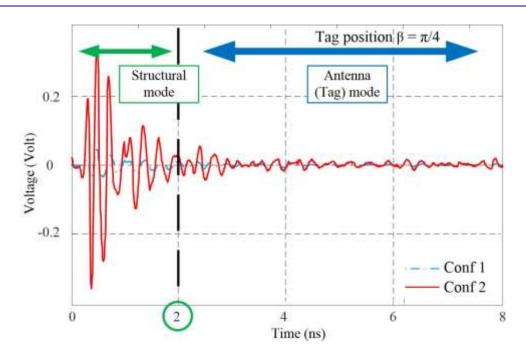

|    | 5. Optimized reader approach                                                                                                                                                                                                                          | 152                             |

|    | 6. Conclusion                                                                                                                                                                                                                                         | 157                             |

|    | 7. References                                                                                                                                                                                                                                         | 159                             |

|    |                                                                                                                                                                                                                                                       |                                 |

|    |                                                                                                                                                                                                                                                       |                                 |

| Ge | neral Conclusion and Prospective                                                                                                                                                                                                                      | 161                             |

| Ge | neral Conclusion and Prospective                                                                                                                                                                                                                      | 161                             |

|    | neral Conclusion and Prospective  Appendix                                                                                                                                                                                                            | 161<br>165                      |

|    |                                                                                                                                                                                                                                                       |                                 |

|    | Appendix                                                                                                                                                                                                                                              | 165                             |

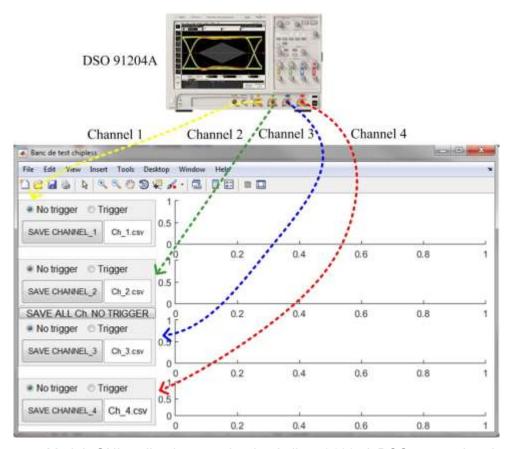

|    | Appendix  1. Matlab GUI acquisition software for Agilent DSO91204A                                                                                                                                                                                    | <b>165</b><br>167               |

|    | Appendix  1. Matlab GUI acquisition software for Agilent DSO91204A  2. PC application software for first reader version in chapter 3                                                                                                                  | <b>165</b><br>167<br>170        |

|    | Appendix  1. Matlab GUI acquisition software for Agilent DSO91204A  2. PC application software for first reader version in chapter 3  2.1.PC - reader communication                                                                                   | <b>165</b> 167 170 171          |

|    | Appendix  1. Matlab GUI acquisition software for Agilent DSO91204A  2. PC application software for first reader version in chapter 3  2.1.PC - reader communication  3. Reader chapter 3- FPGA Reader_0 block description                             | 165<br>167<br>170<br>171<br>173 |

|    | Appendix  1. Matlab GUI acquisition software for Agilent DSO91204A  2. PC application software for first reader version in chapter 3  2.1.PC - reader communication  3. Reader chapter 3- FPGA Reader_0 block description  3.1.User Logic description | 165<br>167<br>170<br>171<br>173 |

| 5. User Logic Reader chapter 4                                   |  |

|------------------------------------------------------------------|--|

| 5. Osei Logic Neader Chapter 4                                   |  |

| 5.1.ADC_CONTROLLER 183                                           |  |

| 5.2. DELAY BLOCK                                                 |  |

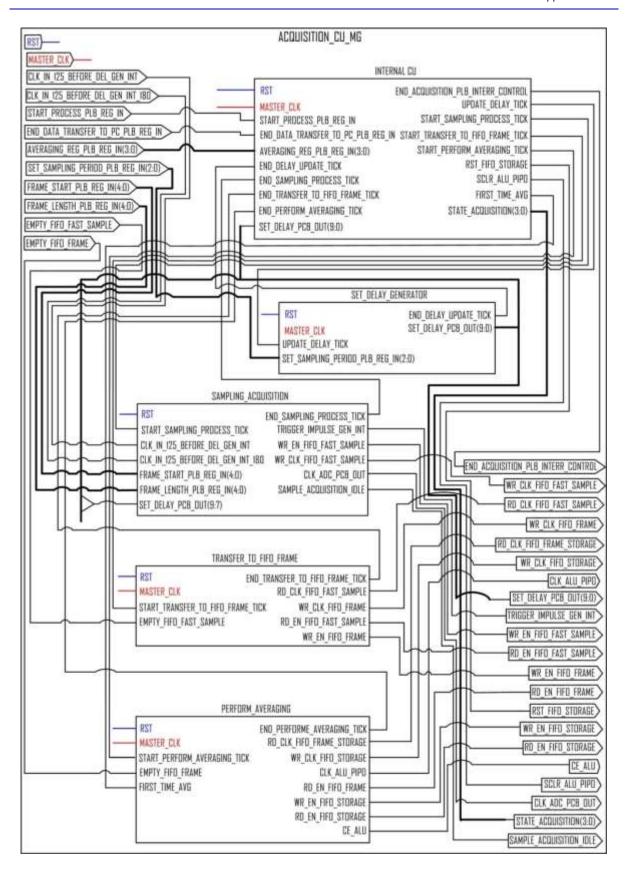

| 5.3. ACQUISITION CU MG                                           |  |

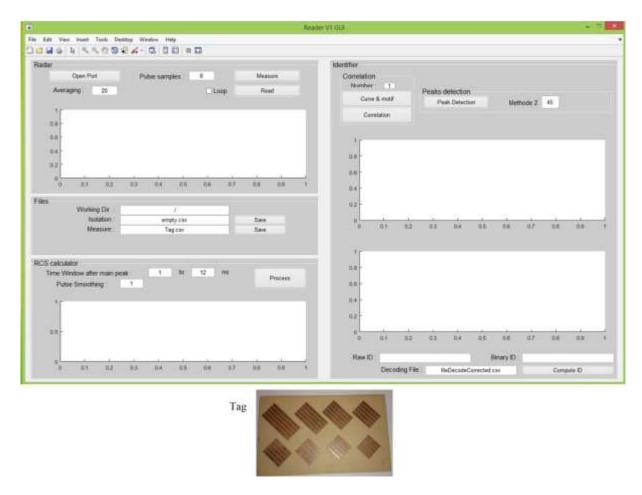

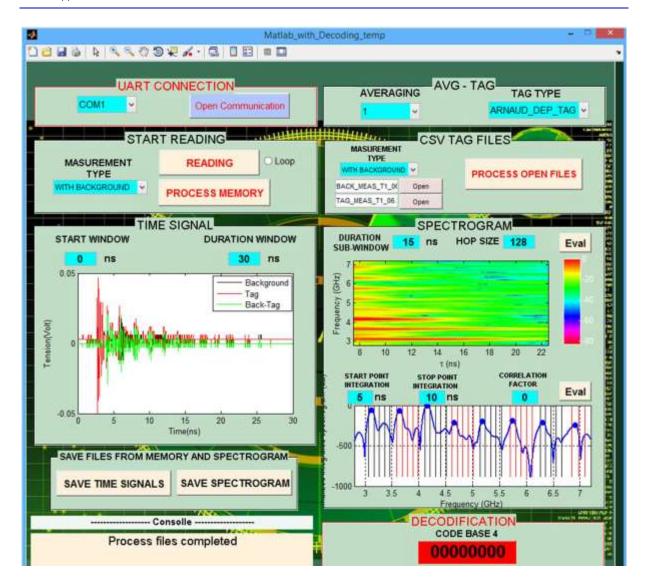

| 6. Matlab GUI reader chapter 4                                   |  |

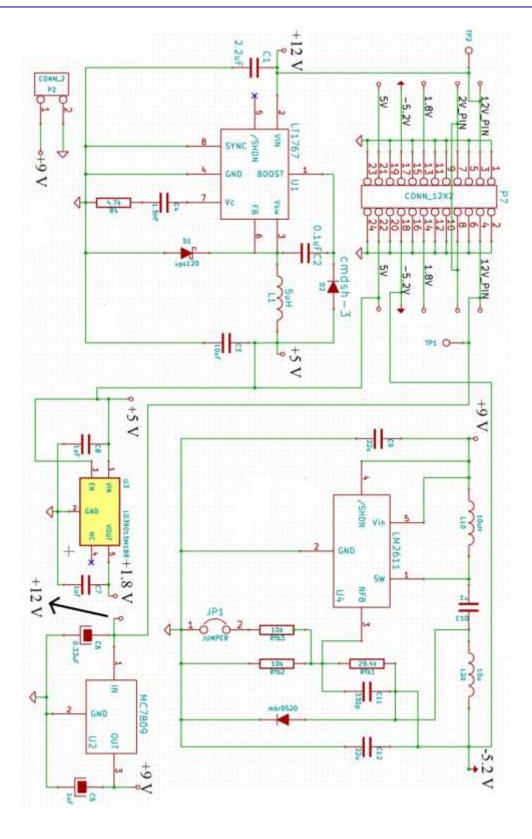

| 7. Schematic power supply board reader chapter 4                 |  |

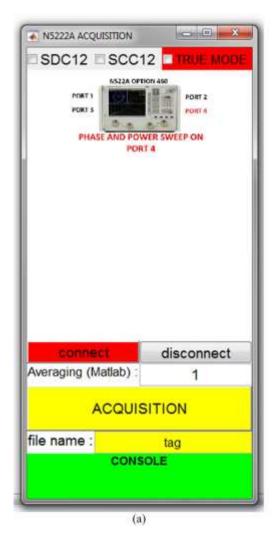

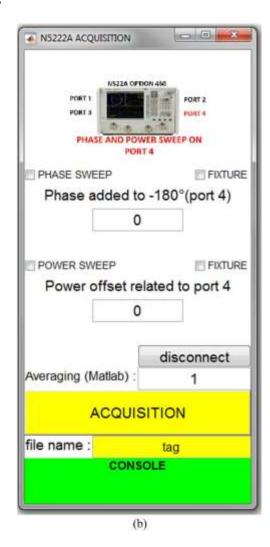

| 8. Matlab GUI acquisition software for VNA N5222A performing 195 |  |

| balanced measurement  9. References  198                         |  |

| J. INCICIOLOG                                                    |  |

| List of publications                                             |  |

## Introduction

The advent of smartphone and its diffusion have revolutionized the life of billions of people in the last decade. The smartphone combines the advantages of a Personal Computer (PC) with those of a mobile phone. A mobile phone gives you the opportunity to be connected with computers and users, exploiting the public telephone network, using a low power portable device. The PC allows for high computational capability as a result of its dedicated hardware combined with software suites. Today these devices are evolving toward a major connectivity to meet the incessant growing request of exchange of information. The increase of mobility in the era of globalization, and the continuous technologic development are changing our life at hectic pace. The home automation, the autonomy transportation, the robotic, and technology in general need a strong interchange of information where people and machines are all connected together, in a global net that is generally addressed as Internet of Things (IoT).

The IoT uses different technologies involved in Personal Area Network (PAN) wireless communications. Between them: Bluetooth, WIFI, Radio Frequency Identification (RFID), infrared, Ultra-Wideband (UWB), bar-code reading capability, and more. This thesis is focused on the RFID, which is a technique where a reader is able to catch information from a passive transceiver using the Radio Frequency (RF) spectrum. The great potentiality of this technology lies on the possibility to have a totally passive tag (transponder).

The massive use of RFID started in the nineties, and up to date, there are diverse kinds of RFID tags that are working at different RF bandwidths. All are in accordance with industrial standards, national and international regulations. The RFID tags incorporate intelligence, they are able to execute hand-shaking protocols, elaborate information, and can be interconnected with sensors. Consequently, RFID tags can be used as part of Wireless Sensor Networks (WSNs). The major use of RFID technology is in the identification of goods

with tracking and tracing ability, in smart logistic, access control, and recently have being incorporated in credit cards.

In the other hand, the most worldwide spread identification technology is still the barcode, where the labels are printed directly on objects or on paper substrate, and are read with optic technique. The barcode was conceived in 1948 from two students of the University of Drexel, Norman Joseph Woodland and Bernard Silver, and its diffusion started only in 1974 by reason of recent optical technology improvements. The barcode labels may be mono or bi-dimensional with many different symbologies. The chipless RFID is born to play an intermediate role between barcode and classical RFID. It is based on the interrogation of a label (tag) with UWB signals, and the subsequent decoding of the tag Identification (ID) based on its Radar Cross Section (RCS) signature. The tags are totally passive and do not present any electronic device attached on its surface, therefore they do not have intelligence or non-linear modulation ability. Thereby, the tags are expected to be printed on paper substrate with metallic ink.

Chipless RFID technology can be placed in-between barcode and classical RFID, where it takes in minor part the advantages of both to be used in industry. Because directly printable on paper, the chipless RFID tags may have a realization cost comparable with barcode labels, and with the use of RF they can be read in a no ling-of-sight condiction. At present there is not a real use of chipless RFID technology in industry apart from Surface Acustic Wave (SAW) devices. However the SAW tags are printed on piezoelectric substrate and they are costly compared to paper, hence they may not be seen as a potential real alternative to barcode. Apart from SAW, the chipless RFID is a young technology born at the beginning of the new century where was first published in 2002 by Richard Ribon Fletcher with its PhD dissertation, at Massachusetts Institute of Technology.

There is an increasing of interest on chipless RFID, and many researchers are redirecting their studies toward this technology. Up to date there is a prominent request in the direction of increasing chipless RFID tag coding capacity, which is hardily higher than 40 bits. Not less important ameliorations are demanded from the reader point of view. The chipless RFID technology needs a reader which is cheap, compliant with UWB regulation, small in size, and preferable integrated inside a smartphone such as for the others PAN communications techniques starting from barcode. The aim of this thesis is to improve the UWB chipless

RFID reader technology. The duration of the thesis was of three years, and all the aspects involving the design of a reader for chipless RFID are given in this manuscript.

The chapter 1 of this manuscript is an introduction of RFID technology more focusing in all the aspects concerning the chipless RFID. The different characteristics of RFID, barcode, and chipless RFID are discussed. The principle of operation of UWB chipless tags are given in detail, along with their reading techniques.

The chapter 2 presents the state of the art concerning UWB chipless RFID reader. All the proposed readers in literature are based on Frequency-Modulated Continuous-Wave Stepped-Frequency Continuous-Wave (SFCW) approaches. technologies are compared with Impulse-Radio UWB (IR-UWB) in terms of UWB regulations, and reading time.

The chapter 3 introduces the first designed IR-UWB chipless RFID reader during the thesis. It is based on equivalent time approach to reduce its realization cost, while maintaining high acquisition performance.

A second reader version was developed and is presented in chapter 4. The objective was to obtain a lower reading time and sampling noise. After a theoretical introduction to sampling noise and quantization noise, the reader hardware architecture is deeply exposed. Compared to the version in chapter 3, it also allows for flexibility in terms of equivalent sampling rate, acquisition frame length and position.

The chapter 5 discusses the design of a tunable low jitter UWB pulse generator, and of UWB planar antennas. The pulse generator could be used with the proposed readers as emission stage and radiative elements to decrease the reader realization cost. Simulation results along with characterizations are shown.

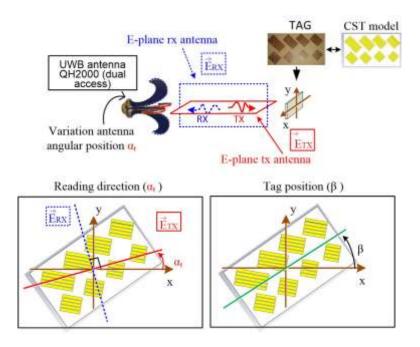

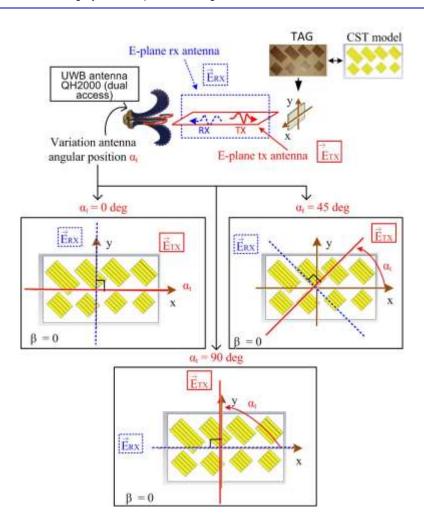

The chapter 6 presents a novel reading technique based on polarization diversity. This approach may be used to read cross-polarization based tags (i.e. chipless tags known to be robust in term of detection in real environment) independently from their orientation. After a theoretical introduction, the approach is validated first with test equipment, and after with the updated reader presented in chapter 4.

## Introduction to Chipless RFID Technology

#### 1. Introduction

In this chapter the Chipless Radio Frequency Identification (RFID) technology is introduced. After a brief discussion of classical RFID systems, the chapter is focusing on the chipless RFID. A comparison of these two technologies with barcode is given. This thesis work is focusing on the reader part of the chipless technology that interests the Ultrawideband (UWB). Thus, the principle of operation of UWB chipless tags will be given more in detail. The chapter is organized as follows:

- Section 2 does a general introduction to RFID technology, and its main features are compared with barcode.

- Section 3 presents the chipless RFID technology in UWB. The principle of work of time-coded and frequency-coded tags is given.

- Section 4 draws the conclusion of the chapter.

#### 2. Introduction to RFID

#### 2.1 Introduction

The RFID is among the most widespread technologies concerning the identification of objects and animals (humans are in this category). It is practice to date the origin of the RFID technology in 1945, with the well-known Léon Theremin espionage equipment to retrieve the conversation inside the office of the US ambassador in Moscow. The *thing* was totally passive and able to modulate its backscattered signal, once illuminated by an external electromagnetic source, according to the acoustic waves produced inside the ambassador office. Today a RFID system retains the same principle of work except for the absence of the

modulating acoustic waves, which is substituted with the smartness of an Application Specific Integrated Circuit (ASIC) that performs the modulation.

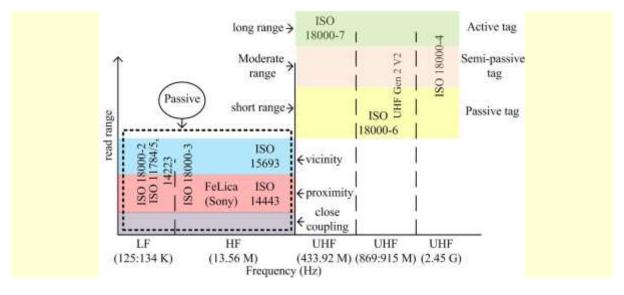

During its long evolution, RFID systems have been evolving towards numerous directions, due to the lack of standardization for many years, and the huge number of distinct application requirements. Up to date the most employed RFID systems may be classified according to their frequency band as: Low Frequency (LF), High Frequency (HF), Ultra High Frequency (UHF), and Super High Frequency (SHF). Apart from LF, the others use the unlicensed Industrial, Scientific and Medical (ISM) bands.

#### 2.2 Passive, semi-passive and active transponder

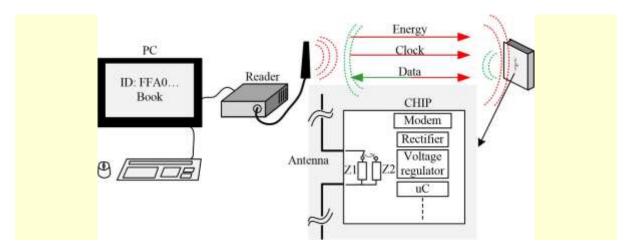

Essentially a RFID system is composed of a reader, and a bunch of transponders inside the reading volume. The transponder may be passive, semi-passive or active. A passive transponder does not have a battery. Its chip is energized by harvesting from the reader transmission Electromagnetic (EM) wave, i.e. reader interrogating signal. For the most of passive transponder the transmission of information is performed in a passive way. Once energized, the chip is able to vary the load impedance connected to its antenna, generally between two different values. It modulates the amplitude of the impinging reader signal (down-link), which is backscattered toward the reader (up-link) ensuring the communication between the two actors. This is called load modulation and is summarized in figure 1.1.

**Figure 1.1.** Schematic of a RFID system, the reader interrogates the transponder providing energy to wake up the ASIC (Chip), clock for synchronization purposes, and data as request code (down-link). After, the chip replies modulating the antenna load impedance between two values, providing a backscattering modulation to the reader (up-link).

Usually the reader adopts either an Amplitude Shift Keying (ASK) or a Frequency Shift Keying (FSK) modulation with a dual objective. First, to optimize the bandwidth available according to international regulations, and second, to retain the transponder chip well energized to accomplish the communication. Conversely the transponder can respond modulating the amplitude and the phase of the reflected carrier wave by changing the chip impedance between two states. It can adopt modulation schemes with subcarrier generation such as Binary Phase Shift Keying (PSK), Amplitude Shift Keygen (ASK), and Frequency Shift Keying (FSK). These schemes have a robust implementation at the expense of a reduced communication throughput. In a direct modulation scheme, each bit is associated with one reflecting carrier wave amplitude variation with a fixed bit period. It ensures the fastest communication at the expense of low noise immunity [MIC 02].

According to figure 1.1, the transponder chip presents an analog part involved directly in the communication, and a mixed part represented by a microcontroller. The analog part is formed of a modulator and demodulator (modem), a voltage rectifier to harvest the energy from the carrier wave, and a voltage regulator to provide the correct voltage to the chip. The digital part is a hard-core microcontroller that may embed memories, Inter-Integrated Circuit (IC2) and Serial Peripheral Interface (SPI), and analog sensor interfaces. The read-range of a passive UHF transponder is lower than 10 m (short range), and limited by the harvester efficiency that is around 20% [LE 008].

A semi-passive or active transponder is equipped with a battery to provide energy at the chip, and eventually at peripherals. The communication retains the load modulation scheme, while the part of the chip in charge of the modulation is energized directly from the battery. The transponder can be waked up, in a cooperative way, from the battery and the harvested reader interrogating signal. Thus, the transponder is read at distances up to 100 m for a UHF semi-passive transponder (moderate range). An active transponder has a Radiofrequency (RF) transmitter block used to communicate with readers, and also with other transponders. Its read-range is of several hundred of meters (long range) [DOB 12].

The RFID is a narrowband technology regulated in Europe by the European Telecommunications Standards Institute (ETSI), and by the Federal Communications Commission (FCC) in the United States of America (USA). The LF RFID applications and standards use mostly the frequencies of 125 kHz and 134 kHz, while the HF the 6.78 MHz

and 13.56 MHz. The UHF interests 433.92 MHz and 869 MHz in Europe (915 MHz in USA), and 2.45 GHz, while the SHF is for 5.8 GHz. Several standards have been proposed from the physical to the software application level, where some are international as ISO/IEC, and others are proprietary. The standardization helps the manufacturer to realize product with high level of interoperability. For instance, the ISO 18000 series is taking care of the air interface protocol (frequency, data modulation, ...) for systems, to be used to track goods in the supply chain for RFID, in all the aforementioned frequency bands [VIOL 05]. Some of the currently used standards are shown in figure 1.2 [SAT 12,DOB 05].

**Figure 1.2**. A reduced collection of RFID standard. From international organizations (ISO, GS1), to private enterprises, such as Sony.

#### 2.3 RFID vs barcode

As a result of its minimal label cost, the barcode technology is more employed than RFID in item identification. Nowadays the realization cost of a barcode label is orders of magnitude lower than a passive RFID transponder. A barcode can be printed on paper substrate with not-conductive ink because based on optic reflection. Due to the use of RF, a conductive ink is needed in RFID to generate surface currents. It is used in HF RFID to print out the antenna in label tag (transponder) for transport ticketing. It is also a subject of study for passive UHF tags for tracking item applications and for wearable electronics [BJO 16- RIZ 16]. The conductive ink is more expensive than the not-conductive ink; hence a RFID tag cannot compete with barcode label in term of cost, where the cost of the chip can be prominent. The cost of a RFID transponder is varying depending on its characteristics. It ranges from few tens of euro-cents for inlay EPC GEN2 tags, to hundreds of euros for sophisticated long life

active transponders. A barcode label may worth less than 0.5 euro-cents, even lesser if the barcode is directly printed on items.

A barcode label substrate may be composed of almost each type of solid material, and the label color has to be as much pale as possible. It is common to print the barcode motive out directly on item surface to save from substrate cost. For a printed UHF RFID transponder, the substrate can affect considerably the reading performance. Thus, it is hardly possible to print the transponder antenna directly on not-characterized tracking items. The relative permittivity of the substrate may vary the antenna operating frequency.

With the exception of cost, the RFID technology offers many advantages compared with barcode. It is smart (chip), has a higher read-range, and data bit capacity. It does not need a direct-line-of-sign to be read thanks to the use of RF, as so the transponder can be hided and made not visible. It may also work in harsh environment and be water-proof.

#### 3. Chipless RFID

#### 3.1 Principle of operation

The chipless RFID technology is born at the beginning of the new century, and is dated with the Richard Ribon Fletcher PhD dissertation published in 2002 [FLE 02]. After in 2005, Michael Pettus patented a chipless RFID system, where the tag was composed of a multitude of RF antennas, each providing different orientation and phase characteristics as so to encode the tag identification (ID). In this system the reader scans an area, and using radar imaging techniques, can retrieve the tag information [PET 05]. Since then, the chipless technology is gaining a continuous growth of interest world-wide, most from university. It is a technique of identification where the tag does not have any electronic component attached on its surface and relays on its EM property for the identification.

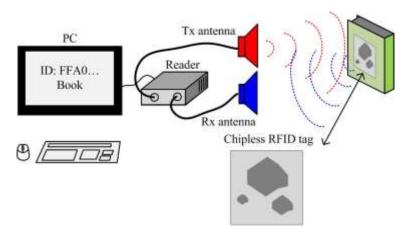

A chipless RFID reading system is shown in figure 1.3. The tag is commonly composed of a pattern (like in barcode) made of conductive material, created upon a substrate with etching or printing technique. The principle of work is similar to that of a radar application where non Radar Cross Section (RCS) modulation is expected. Contrarily to RFID, the reader transmits a wide-band signal to the environment, and the tag backscattered signal is measured and analyzed, in time and frequency domain, to retrieve the desired information.

The total absence of a chip denied the opportunity of any signal modulation therefore the chipless RFID technology is not compatible with narrow band identification utilizations such as classic RFID, and needs to be wideband.

A chipless RFID tag can be seen has a passive filter, where the information is coded based on its impulsive response: larger available bandwidth means higher coding capacity. A chipless RFID system needs to comply with (UWB) regulations in the band 3.1-10.6 GHz. The UWB at bigger frequency is reserved for different applications. The chipless technology is developing also in extremely high frequency [POP 16] and terahertz [HAM 12], where a sort of two dimensional imaging (2-D) encoding technique may be employed. Anyway, these latter two frequency bands are not subject of study in this thesis.

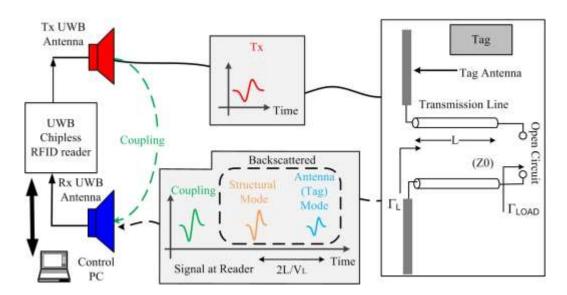

**Figure 1.3.** Schematic of a chipless RFID system. The reader interrogates the transponder with a UWB signal, then the backscattered signal from the tag is analyzed to retrieve the tag ID.

#### 3.2 Chipless RFID in-between RFID and Barcode

The chipless RFID technology may be located between the conventional RFID and the barcode. The absence of electronic devices with their package may represent a significant abatement of tag realization cost. Thus, a chipless RFID tag may be cheaper than a RFID tag, and perhaps comparable with a barcode [VEN 13a]. Up to date the cost comparison is a hard topic. Despite the absence of electronic devices the label pattern may have a total surface area larger than a passive UHF RFID tag on a costly substrate. Thus most of chipless tag prototypes have a realization cost higher than UHF RFID tag [PRE 10]. However, it is possible to find in literature miniaturized single layer chipless RFID tags for UWB compatible with ultra-low cost realization techniques. For instance, in [VEN 13a], chipless tags printed with conductive ink, using flexography, are presented. In [VEN 12], the

authors present a miniaturized chipless RFID tag of 2 cm × 2 cm, with 10 bits. The tag was realized on a rigid FR-4 substrate with etching technique, and was read with expensive laboratory equipment.

In comparison with barcode, a chipless RFID tag adds the opportunity to be read without direct line-of-sign. This is a strong advantage because the tag may be hided and read through objects. It opens to a plenty of applications for chipless RFID where barcode may not be used, such as discretion for luxury package and security. Contrarily to barcode, a chipless RFID tag may offer sensor capabilities [TED 13]. In [FEN 15] the authors present a printed chipless RFID tag on paper substrate designed as humidity sensor, with interdigital capacitor implementation. In [SCH 14] a time domain coded chipless temperature sensor was proposed. It was realized with screen-printing technology on a substrate of Allumina, with a central frequency of 7 GHz, and a -10 dB bandwidth of 2 GHz.

The chipless read-range is often considered higher than barcode, and absolutely lower than passive UHF RFID tags. This may be debatable, in fact for the chipless RFID tag the read range is also correlated with its coding capacity in terms of bits number. Some chipless RFID tags, based on time-domain reflectometry (TDR), may have a read-range over 1 m, but with a scarce number of bits, usually lower than 10. Most of the time, they are realized on high cost and RF performing substrate [RAM 11]. Higher bit capacity chipless RFID tags have a reduced read-range in order of few tens of centimiters.

The read-range depends not only on the tag characteristics but also on the reader performance, and its power emission (UWB regulations). In literature are often claimed readrange, bit capacity, and in general chipless RFID tag with high performance, but using expensive laboratory equipment as reader, in anechoic environment, and slighting taking into consideration the UWB regulations.

Multipath effects are present in chipless RFID, and they may affect the reading capability. Conversely, in barcode, the interrogating optical reader signal can be well focused on the tag, that allows for reducing multipath effects. In addition, a barcode label needs to be read with direct line-of-sign, as so the reading optic signal cannot go behind the label, and eventual reflective perturbing signals are not present. In literature is common to find tables that compare barcode, chipless RFID, and UHF RFID in terms of tag performances and realization cost [PER 14]. Almost all of them give the best place for all the parameters,

except for tag realization cost, to UHF RFID. Then chipless RFID outdo barcode in reading range, with comparable realization cost, and lower bit capacity. From our experience in the field, up to date the battle between barcode and chipless RFID for reading performances did not give a net vanquisher. For tag realization cost, the barcode is today the winner, but the match between passive UHF RFID tag and chipless RFID tag is still open.

#### 3.3. UWB chipless RFID

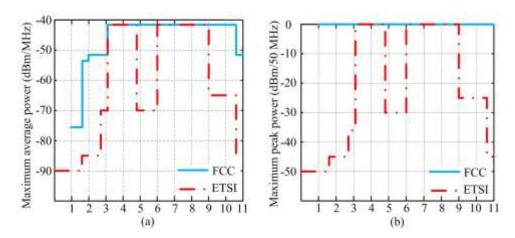

The chipless RFID technology has to comply with international regulations as all electronic communication systems. A chipless RFID system works with UWB because the tag bitcapacity increases with the frequency bandwidth. The UWB technology is referred to systems which employ large band and low power to exchange or retrieve information. The American FCC regulation concerning UWB is in Part 15 of Title 47 [FCC 17], and grants the band 3.1 - 10.6 GHz for communication systems in indoor applications such as chipless RFID. The ETSI regulation, in terms of UWB systems, is stricter compared with FCC. It allows for the same band of FCC, but with lower power between the band 6 – 8.5 GHz [ETS 04 - ETS 10]. This work of thesis is concerning the readers for UWB chipless RFID tags that may be classified in time-coded and frequency-coded based tags.

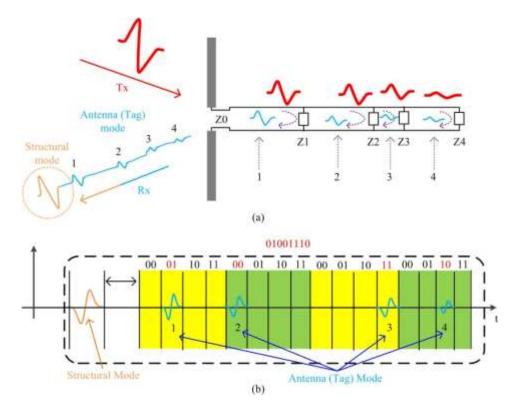

#### 3.3.1 UWB time-coded chipless RFID tag

An UWB time-coded chipless RFID tag, in its most simple representation, is composed of one UWB antenna connected to a transmission line, along which some impedance mismatchings are created. A schematic example of a 4 reflections based tag is shown in figure 1.4 (a). Once interrogated with a UWB reader, the tag reflected signal may be analyzed in time domain, and the delays between the different reflections can be estimated. The values of these delays encode the tag information. The tag response in time is composed of a tag structural mode and an antenna or tag mode. The former is due to the specular reflection of the tag assemblage. The latter is the tag behavior where the antenna is transferring energy to the transmission line, and all the reflections due to impedance mismatchings occur. The antenna (tag) mode is the essential information in chipless technology, and is exploited in copious manner with signal processing. In case of time-coded chipless tag, the structural mode is also useful. It gives information about the tag distance, and also is exploited to calculate the relative delays of the reflections to decode the tag ID. An example of encoding technique is shown in figure 1.4 (b), corresponding to the tag in (a). The time domain is divided in 4 areas, where each is referred to one reflection of the 4 that compose the tag mode. Based on the position of the reflection inside the area, a different binary code is assigned. In the figure the tag ID is  $01001110_2$  that correspond to 8 bits of information.

**Figure 1.4.** (a) Exemplification of a UWB chipless RFID tag based on a time-coded approach. The tag has 4 impedance mismatchings (Z<sub>i</sub>) that originate 4 main reflections toward the reader. (b) The tag information is encoded with the temporal distances between the structural mode, and the various reflections in the antenna (tag) mode.

The figure 1.4 is overly simplified because the impedances  $Z_n$  generate multiple-reflections. For instance, the first reflected signal by  $Z_2$ , before reaching the antenna, will be in part reflected back by the impedance  $Z_1$ , and so on. These effects will create disturbances in the reader receiving signal, and the low energy reflected signals will be decoded with more difficulty.

The major drawback of a time-coded tag is represented by the transmission line length that may be substantial. Considering a Gaussian monocycle interrogating signal with a pulse full-width of about 500 ps, then the minimum registered distance between reflections in the tag response should be of at least 500 ps. It corresponds to 250 ps transmission line delay

between two impedances (2 ways). If the tag transmission line has a relative permittivity  $\varepsilon_r$  of around 4.4 (FR-4), then the wave speed inside the line  $v_L$  is approximately,

$$\mathbf{v}_{\mathsf{L}} = \frac{\mathbf{v}_{\mathsf{0}}}{\sqrt{\varepsilon_{\mathsf{r}}}}.$$

Where  $v_0$  is the speed of light in a vacuum environment, which was estimated at about  $3\times10^8$  m/s. In such configuration,  $v_L$  is of about  $1.43\times10^8$  m/s, and multiplying it by 250 ps returns to a minimum distance between two reflectors of 3.5 cm. Hence, a UWB time-coded chipless RFID tag may have a significant dimension. It can be reduced using less number of reflective elements (lower bit-capacity), higher permittivity materials, and bending techniques.

In a chipless RFID tag, all the impedances  $Z_i$  have to be realized with layout techniques (Chipless). To reduce as much as possible the loss of the transmission line, the impedance elements  $Z_i$  should have zero resistivity. This leads to the realization of pure imaginary discontinuities. However they are known to be narrow band in its simpler realization (stub). Consequently in literature is possible to find UWB time-coded chipless RFID tags which are not really *chipless*, because the impedances are realized with discrete components [ZHA 06-SCH 09].

The use of Surface Acoustic Wave (SAW) technology is not recent, and in electronics is employed in a variety of applications, such as filters design, oscillators, and sensors. They are based on acoustic waves instead of electromagnetic waves, which have a speed in free space of about 10<sup>5</sup> times lower than the speed of light. This feature can be exploited to create much smaller RF devices. A SAW component needs two Interdigitated Transducer (IDT), and a piezoelectric substrate that can transduce between electrical and mechanical energy. Time-coded chipless RFID SAW tags are a reality nowadays, and are produced by numerous enterprises. These tags are working in the ISM band at 2.45 GHz (narrow band). The bit capacity may exceed 128 bits with a tag dimension of about 10 mm for side not considering the antenna [HAR 02]. The major drawback of a SAW tag is the realization cost caused by the need of piezoelectric substrates, and also by the use of etching techniques for metallic layer deposition. It may not represent a competitor neither for barcode, nor for UHF RFID passive technology.

In 2008 a patent about the use of cellulose substrate to propagate acoustic wave was deposited [KIM 08]. The tag was characterized by the presence of an antenna, a SAW based IDT, and a plurality of reflectors for reflecting the surface acoustic wave. All was mounted on

cellulose substrate that would help to reduce the tag substrate cost. However other challenges need to be faced, such as the printability of the tag and the immunity against environmental condition.

#### 3.3.1.1 Single line discontinuity UWB time-coded chipless RFID tag

A UWB time-coded chipless RFID tag with only one discontinuity line can be readily designed. It needs to have either a zero impedance (short circuit) or infinitive impedance (open circuit) to reflect as much energy as possible in the direction of the antenna. It is simple to realize a large band open circuit with layout technique, while for a short circuit it may depend from the transmission line technology. In microstrip a short circuit needs a via, while for coplanar it does not. This approach pays in terms of coding capacity, but gains in read-range, and dimensions. The principle schematic of a single reflector UWB time-coded chipless RFID tag, and a reading process with a bi-static reader, is shown In figure 1.5.

**Figure 1.5**. Exemplification of an UWB chipless RFID tag based on a time-coded approach using only one line discontinuity (open circuit load). A bi-static UWB chipless RFID reader is used.

In case of bi-static configuration the coupling between the two reader antennas is reduced (green dashed line on figure 1.5) compared to mono-static configuration. However it is omnipresence in short-range radar based applications such as chipless. If the coupling of the reader antennas and the tag are not influencing each other, the coupling effect can be removed from one tag identification process in post-processing. Two measurements are

necessary, one without the tag and subsequently another one with the tag (background subtraction [RAM 11]).

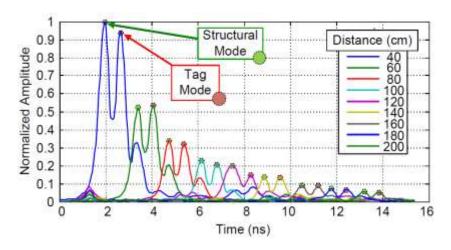

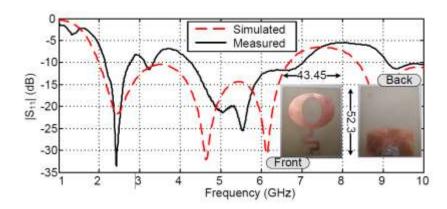

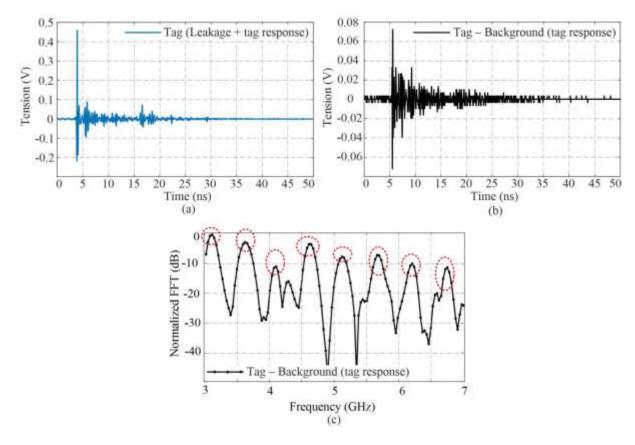

A typical bi-static co-polarization measurement results, of a time-coded chipless tag at several distances up to 2 m in practical environment [RAM 12], is shown in Figure 1.6. It uses known detection methods (background subtraction and Continuous Wavelet Transform (CWT)) [LAZ 11]. As it can be observed, both the structural and antenna (tag) modes can be detected. The tag layout along with its measured and simulated reflection coefficient is shown in Figure 1.7. The tag consists of a microstrip-fed UWB monopole [WHY 08] fabricated on Rogers RO4003C substrate.

**Figure 1.6**. Normalized result measurement after background subtraction (top) and CWT, for the monopole tag at several tag-reader distances in practical environment. Original figure in [RAM 12].

The obtained read range of 2 m is remarkable, and also the tag reduced dimension of 5.3 cm × 4.3 cm makes it smaller than a credit card size, which is of 8.560 cm × 5.398 cm according to [ISO/IEC 7810 ID-1]. The tag information capability depends also from the reader performances and post processing power. A value lower than 10 bits is reasonable, hence, this kind of UWB chipless RFID tag is more suitable for sensing and localization applications rather than identification [RAM 11, RAM 13].

**Figure 1.7**. Layout of the microstrip-fed UWB monopole tag with dimensions in millimeters, and its measured and simulated tag reflection coefficient. Original figure in [RAM 12].

#### 3.3.2 UWB frequency-coded chipless RFID tag

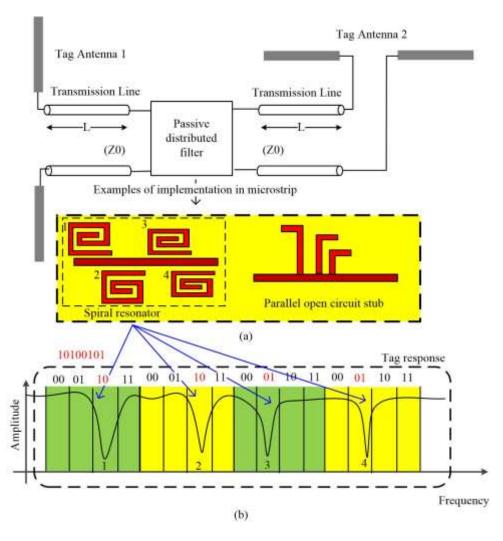

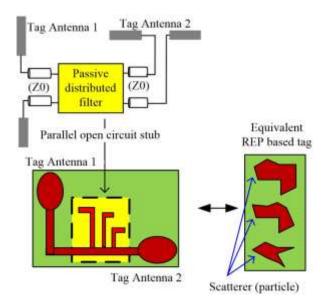

A UWB frequency-coded chipless RFID tag uses an approach based on its spectral response to encode information. The tag geometry is modified to account for specific amplitude and phase characteristics over the frequency band of interest. A well-known structure of such tag is composed of two UWB antennas (one for transmission and the other for reception), and between them a passive filter realized with distributed elements as shown in figure 1.8 (a).

If the passive distributed filter of figure 1.8 is considered lossless, part of its input signal will be reflected, and part transmitted to the other antenna. The antennas are linear polarized with a cross-polarization configuration (in perpendicular direction). If a reading approach similar to figure 1.5 (UWB bi-static) is used to read the tag, the reader antennas have to be lined up with the tag antennas, to read successfully the tag. The cross-polarization configuration allows for measuring only the part of the UWB reader interrogating signal that crosses the tag filter, and therefore the part of the signal where is encoded the tag ID.

In figure 1.8(a) are represented two examples of passive filters compatible with microstrip technology. One based on notch spiral resonators, and the other one on parallel open circuit stubs. The first solution applied to chipless technology was proposed in [PRE 09]. The spiral filters were placed along with the microstrip line, each resonator introduced a diverse band-stop resonance. It was designed in the band 3.1 - 7 GHz, and realized in Taconic TLX-0 with dimensions of 8.8 cm × 6.5 cm. The information is encoded in the amplitude part of the

spectrum reaching 35 bit of information. Varying the dimension of the spirals their first mode resonant frequency will change accordingly, as so the filter characteristics.

In [NIJ 12] the solution represented in figure 1.8 (a) using parallel open circuit stubs was proposed. The tag has a limited 8 bit capacity, and the coding is yet trusted on spectrum amplitude. The antennas are two cross-polarized monopoles, and the tag measures 5.0 cm × 3.0 cm not considering the antennas. The bandwidth of interest is between 2 - 4 GHz and the substrate is high performance from Rogers. In [NAI 16] the authors presented a UWB frequency domain chipless RFID tag where only the filter section was implemented and characterized with laboratory equipment. Instead of focusing on the amplitude of the response, they took care of the phase through the group delay. The filter was composed of cascaded commensurate C-sections which length determines the frequency with higher group delay variation. To retain a small filter dimension, a folding approach is proposed. As yet, the proposed architecture of a UWB frequency-coded chipless RFID tag presents a discrete bit capacity of around 40 bits. On the other side, it expects a reader in bi-static configuration, with two cross-polarized antennas, and the tag needs to be aligned with the reader antennas for maximum performance.

#### 3.3.2.1. Join antennas and filter

The frequency-coded chipless RFID tags proposed in [PRE 09 - NIJ 12] are based on spectrum amplitude modulation, using a set of independent notch filters, in an absence/presence encoding sort (see figure figure 1.8). In [TED 12] an exhaustive overview of UWB chipless encoding technique is given.

Using the RF Encoding Particle (REP) approach introduced in [PER 14, VEN 16], it is possible to obtain the requested spectrum amplitude modulation of the tag, in a smaller structure [VEN 11- VEN 12]. This structure is composed of several resonant scatterers (particles), in which the two antennas and the filter are enclosed. For instance the tag proposed in [NIJ 12], which is composed of parallel open circuit stubs used as Band-Stop Filter (BSF), can be translated in an equivalent tag based on REP approach. It is shown in figure 1.9 where for simplicity only three resonators of [NIJ 12] are shown.

**Figure 1.8**. Schematic of a frequency-coded UWB chipless RFID tag based on cross-polarization. Two examples of passive distributed filters are shown, one based on spiral resonator [PRE 09], and the other on parallel open circuit stubs [NIJ 12].

The REP approach is a complex subject, form a theoretical point of view, one interest is that a REP chipless tag can be seen like a radar target. The specificity here is that the tag (target) is designed to have a known number of resonant frequencies. From the Singularity Expansing Method these frequencies, which are related to the tag mode, are independent from the reading method. Thus, they can be used to encode the information [BAU 91], [REZ 13].

The study of the behavior of a loaded antenna, constructed with linear reciprocal materials, is fundamental to better understand the complexity of REP from both, analytical and physical approach. In [GRE 63] the author presents a study about the prediction of the

backscattering property of a loaded antenna with some minimal measurements. Once exited with an impinging electromagnetic field, two different scattering processes occur, one load independent and the other fully dependent. As previously explained, the first is due to the immediate reflection that occurs on the metallic part of the antenna, through the formation of surface currents (structural mode scattering). Instead the second is concerning the radiative property of the antenna connected at that specific load (antenna mode scattering). This can be seen as the property of the antenna to convey the incoming electromagnetic field towards the load, which is responsible of its dissipation. The tag of figure 1.9 with REP approach is composed of three scatterers. Each scatterer has its structural and antenna (tag) mode scattering, and then can be seen as an antenna connected to a complex load.

**Figure 1.9**. Representation of a UWB frequency coded tag based on microstrip with two UWB disc monopole antennas, and three parallel open circuit stubs similar to [NIJ 12]. The tag can be realized with three resonant scatterers using the REP approach, with similar performance than the original tag.

One of the first use of the REP approach on chipless RFID was in [JAL 05]. The authors realized a barcode type chipless tag composed of 5 scatterers. Each scatterer was considered as a short circuited dipole antenna and not yet strictly speaking as REP scatterer, the concept was introduced later [PER 4]. Each scatterer was composed of a strip with different length, in microstrip technology. It was designed in the bandwidth 5.4 - 6 GHz on Taconics TLY-5, and shown a 5 bit capacity, and a read range of tens of centimeters. The measurement was performed with a Vector Network Analyzer (VNA) in co-polarization, and shows a band rejection effect of the tag at the strip first resonance frequency ( $\lambda$ /2). This was

due to the destructive effect between the scatterer structural mode and the antenna (tag) mode.

Since [JAL 05] remarkable progresses have occurred on this approach for chipless, and many works are publishing by worldwide laboratories. The bit capacity of this kind of tag has been increased using more elaborated scattering particles, with magnitude and also phase coding information, and using mainly cross-polarization reading approach with a more elaborate post processing treatment. In [VEN 11] a tag based on C-like resonators (scatterers) is presented, it was realized on one metallic layer in a low cost FR-4 substrate with permittivity of 4.6. Using a coding based on frequency resonant position and phase characteristic of C-like resonators, the coding capacity was increased up to 22.9 bits, with a tag size of 2 cm × 4 cm, where the tag bandwidth was 2-7 GHz. The use of only one layer represents a significant reduction of the tag development cost, with the possibility to realize the tag by using printing techniques.

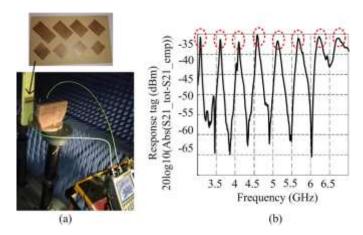

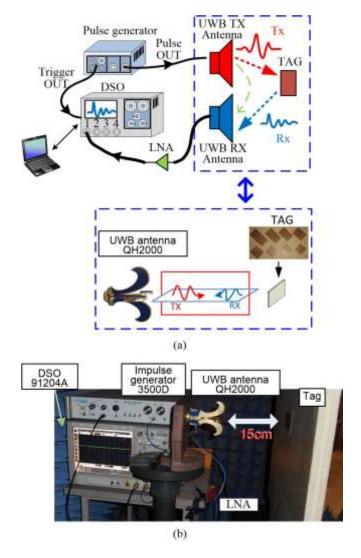

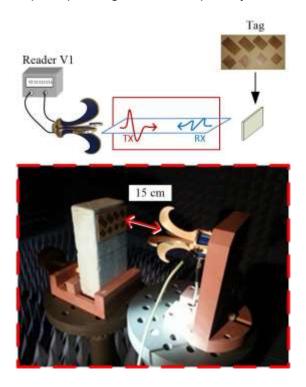

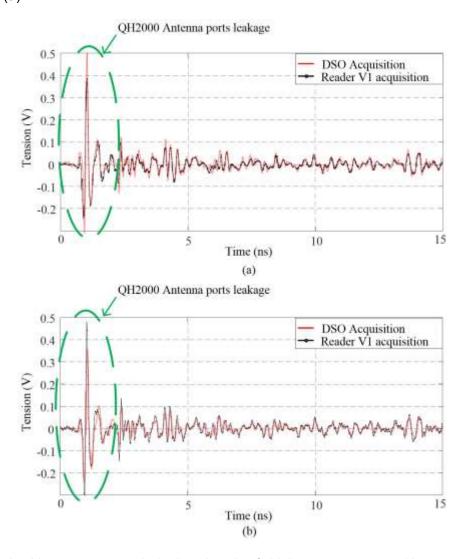

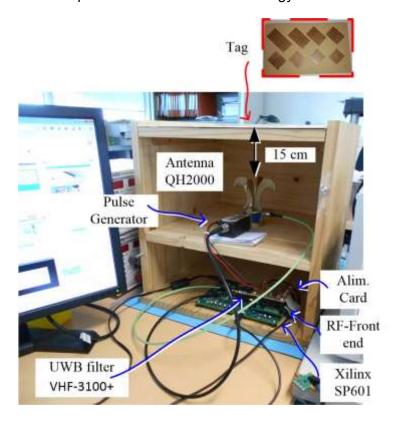

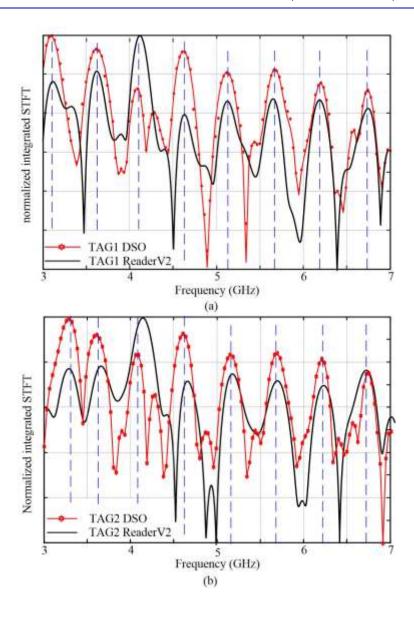

The reading process in anechoic chamber and in cross-polarization of a depolarizing REP tag introduced in [VEN 13b], is shown in figure 1.10 (a). The tag was realized in Roger R04003 with a ground plane, and was based on eight resonators composed each of five coupled dipoles in short circuit with the first resonant mode in between the band 3-7 GHz. The Agilent N9918A was used as VNA with 0 dBm of emission power. The dual access Satimo QH2000 was employed, and the tag was placed at 15 cm. The detection process used was the background subtraction. The measurement results are shown in figure 1.10 (b), where the eight resonant frequencies correspond to the visible eight peaks. The coding is based on the position of the resonances.

Figure 1.10. Measurement in cross-polarization of the frequency-coded UWB REP chipless RFID tag proposed in [VEN 13b], inside an anechoic chamber. (a) Photo of the test bench and the measured tag. The Agilent N9918A was used to measure the S-parameter (S21), with an averaging factor of 10. The tag was placed at 15 cm from the dual-access dual polarization Satimo QH2000 antenna. In (b) the tag response where the positions of the eight resonant frequencies are underlined (read circles).

#### 4. Conclusion

In this chapter the chipless RFID technology that interests the UWB was introduced. The chipless may be placed in-between the more advanced RFID and the barcode. It may represent a cheaper identification solution than RFID preserving the not direct-line-of-sign in reading process, and the possibility to embed sensor capabilities. These two characteristics represent significant advantages compared to barcode. On the other side a UWB chipless tag, in comparison with barcode, has lower bit capacity, lower multipath immunity, and higher realization cost. The latter is most due to the cost of conductive ink in case of printable tags. A UWB chipless tag may be classified in time-coded and frequency-coded, where the letter uses the REP technology to reduce its dimension.

The chipless RFID technology is based on a radar approach, where the backscattering energy from an object through its RCS, is the heart of all the radar applications. Thus, the performance of the reader has an important impact on the reading capability. Parameters such as: the read range, the impact of different tag orientations, and tag bit capacity, are strongly dependent on the reader. In the next chapter, the state of the art of chipless reading technology is reviewed.

#### **5 References**

- [BAU 91] C. E. BAUM, E. J. ROTHWELL, K. CHEN, et al. "The singularity expansion method and its application to target identification," Proceedings of the IEEE, vol. 79, no. 10, pp. 1481–1492, 1991.

- [BJO 16] BJORNIEN T., SUIKKOLA J., UKKONEN L. et al., "Testing and modeling the performance of stretchable screen printed UHF RFID tag under strain," 2016 IEEE International Symposium on Antennas and Propagation (APSURSI), Fajardo, pp. 465-466, 2016.

- [DOB 05] DOBKIN D. M., "A Radio-Oriented Introduction to RFID-Protocols, Tags and Application", *High Frequency Electronics*, Aug. 2005.

- [DOB 12] DOBKIN D.M., The RF in RFID, Second Edition: UHF RFID in Practice, Newnes Newton, MA, USA, 2012.

- [ETS 04] ETSI TR 101 994-1 V1.1.1 ("Electromagnetic compatibility and Radio spectrum Matters (ERM); Short Range Devices (SRD); Technical characteristics for SRD equipment using Ultra Wide Band technology (UWB) Part 1: Communications applications", *European Telecommunication Institute (ETSI)*, Janu. 2004.

- [ETS 10] ETSI EN 302 065 V1.2.1 "Electromagnetic compatibility and Radio spectrum Matters (ERM); Short Range Devices (SRD) using Ultra Wide Band technology (UWB) for communications purposes; Harmonized EN covering the essential requirements of article 3.2 of the RTTE Directive", *European Telecommunication Institute (ETSI)*, Oct. 2010.

- [FCC 17] Title 47 Telecommunication chapter 1 subchapter A Part 15 subpart F-Ultra-wideband operation, online available at : www.FCC.org.

- [FEN 15] FENG Y., XIE L., CHEN Q. et al., "Low-Cost Printed Chipless RFID Humidity Sensor Tag for Intelligent Packaging," in *IEEE Sensors Journal*, vol.15, no.6, pp. 3201-3208, June 2015.

- [FLE 02] FLETCHER R.R., "Low-Cost Electromagnetic Tagging: Design and Implementation," Ph.D. dissertation, Massachusetts Institute of Technology, Cambridge, MA, 2002.

- [GRE 63] GREEN R.B., "The general theory of antenna scattering", Ph.D. dissertation, Ohio State University, 1963.

- [HAM 12] HAMDI M., GARET F., DUVILLARET L. P. et al., "New approach for chipless and low cost identification tag in the THz frequency domain," 2012 IEEE International Conference on RFID-Technologies and Applications (RFID-TA), indipendentiNice, 2012, pp. 24-28.

- [HAR 02] HARTMANN C. S., "A global SAW ID tag with large data capacity," 2002 IEEE Ultrasonics Symposium, Proceedings., 2002, pp. 65-69 vol.1.

- [JAL 05] JALALY I. "RF barcodes using multiple frequency bands," *IEEE MTT-S International Microwave Symposium Digest (IMS)*, pp. 139-142, 2005.

- [KIM 08] KIM J., Saw based chipless passive RFID tag using cellulose paper as substrate and method for manufacturing the cellulose paper (2008), Patent WO/2008/056,848.

- [LAZ 11] LAZARO A., RAMOS A., GIRBAU D. et al., "Chipless UWB RFID Tag Detection Using Continuous Wavelet Transform," *IEEE Antennas Wireless Propagation Letters*, Vol. 10, 520-523, 2011.

- [LE 008] LE T., MAYARAM K., FIEZ T., "Efficient Far-Field Radio Frequency Energy Harvesting for Passively Powered Sensor Networks," in *IEEE Journal of Solid-State Circuits*, vol. 43, no. 5, pp. 1287-1302, May 2008.

- [MIC 02] MICROCHIP, microID 125 kHz RFID System Design Guide, Application Note AN680, 2004.

- [NAI 16] NAIR R. S., PERRET E., "Folded Multilayer C-Sections With Large Group Delay Swing for Passive Chipless RFID Applications," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 64, no. 12, pp. 4298-4311, Dec. 2016.

- [NIJ 12] NIJAS C. M., DINESH R., DEPPAK D., et al., "Chipless RFID Tag Using Multiple Microstrip Open Stub Resonators," in *IEEE Transactions on Antennas and Propagation*, vol. 60, no. 9, pp. 4429-4432, Sept. 2012.

- [PER 14] PERRET E., Radio Frequency Identification and Sensors from RFID to Chipless RFID, ISTE Press Elsevier, 1st Edition, 2014.

- [PET 05] PETTUS M., RFID system utilizing parametric reflective technology (2005), patent US20050280539 A1.

- [POP 16] POPPERL M., ADAMETZ J., VOSSIEK M., "Polarimetric Radar Barcode: A Novel Chipless RFID Concept With High Data Capacity and Ultimate Tag Robustness," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 64, no. 11, pp. 3686-3694, Nov. 2016.

- [PRE 09] PRERADOVIC S., BALBIN I., KARMAKAR N. C., et al., "Multiresonator-Based Chipless RFID System for Low-Cost Item Tracking," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 57, no. 5, pp. 1411-1419, May 2009.

- [PRE 10] PRERADOVIC S., KARMAKAR N. C., "Chipless RFID: Bar Code of the Future," in *IEEE Microwave Magazine*, vol. 11, no. 7, pp. 87-97, Dec. 2010.

- [RAM 11] RAMOS A., LAZARO A., GIRBAU D., et al., "Time-domain Measurement of Time-coded UWB Chipless RFID tag", *Progress in Electromagnetics*, vol 116, pp.313-331, 2011.

- [RAM 12] RAMOS A., GIRBAU D., LAZARO A., "Influence of materials in time-coded chipless RFID tags characterized using a low-cost UWB reader," *42nd European Microwave Conference*, Amsterdam, 2012, pp. 526-529.

- [RAM 13] RAMOS A., LAZARO A., GIRBAU D. et al., "Time-coded chipless RFID temperature sensor with self-calibration based on a Vivaldi antenna," *IEEE MTT-S International Microwave Symposium Digest (IMS)*, 1-4, 2013.

- [REZ 13] REZAIESARLAK R., MANTEGHI M., "Short-time matrix pencil method for chipless RFID detection applications," IEEE Transaction on Antennas and Propagation, vol. 61, no. 5, pp. 2801–2806, May 2013.

- [RIZ 16] RIZWAN M., KUTTY A.A., KGWADI M., et al., "Comparative study of inkjet and thermal printing for fabrication of passive UHF RFID tags," 2016 10th European Conference on Antennas and Propagation (EuCAP), Davos, pp. 1-5, 2016.

- [SAT 12] SATTLEGGER K., DENK U., "Navigation your way through the RFID jungle", Texas instrument white paper, Feb. 2012.

- [SCH 09] SCHÜßLER M., MANDEL C., MAASCH M., et al., "Phase modulation scheme for chipless RFID- and wireless sensor tags", *Asia Pacific Microwave Conference*, Singapore, 2009, pp. 229-232.

- [SCH 14] SCHUSSLER M., KOHLER C., WIENS A., et al., "Screen printed chipless wireless temperature sensor tag based on Barium Strontium Titanate thick film capacitor," in *SENSORS*, pp. 2223-2226, 2-5 Nov. 2014.

- [TED 12] TEDJINI S., PERRET E.., VENA A., et al., "Mastering the electromagnetic signature of chipless RFID system," in Chipless and Conventional Radio Frequency Identification: Systems for Ubiquitous Tagging, KARMAKAR N. C., IGI global, 2012, pp. 146-174.

- [TED 13] TEDJINI S., KARMAKAR N., PERRET E., et al., "Hold the Chips: Chipless Technology, an Alternative Technique for RFID," in *IEEE Microwave Magazine*, vol. 14, pp. 56-65, July 2013.

- [VEN 11] VENA A., PERRET E., TEDJINI S., "Chipless RFID Tag Using Hybrid Coding Technique," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 59, no. 12, pp. 3356-3364, Dec. 2011.

- [VEN 12] VENA A., PERRET E., TEDJINI S., "Design of Compact and Auto-Compensated Single-Layer Chipless RFID Tag," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 60, no. 9, pp. 2913-2924, Sept. 2012.

- [VEN 13a] VENA A., PERRET E., TEDJINI S. et al., "Design of Chipless RFID Tags Printed on Paper by Flexography," in *IEEE Transactions on Antennas and Propagation*, vol. 61, Issue 12, pp. 5868-5877, 2013.

- [VEN 13b] VENA A., PERRET E., TEDJINI S., "A Depolarizing Chipless RFID Tag for Robust Detection and Its FCC Compliant UWB Reading System," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 61, no. 8, pp. 2982-2994, Aug. 2013.

- [VIOL 05] VIOLINO B., "A summary of RFID standards", in RFID journal, jan. 2005.

- [ZHA 06] ZHANG L., RODRIGUEZ S., TENHUNEN H. et al., "An innovative fully printable RFID technology based on high speed time-domain reflections," *Conference on High Density Microsystem Design and Packaging and Component Failure Analysis*, Shanghai, 2006, pp. 166-170.

- [WHY 08] WHYTE G., DARBARI F., MCGREGOR I. et al., "Different Feeding Geometries for Planar Elliptical UWB Dipoles, and the Excitation of Leakage Current," 38th European Microwave Conference, 1382-1385, 2008.

- [VEN 16] VENA A., PERRET E., TEDJINI S., *Chapter 4: Design of Chipless RFID Tags*, Chipless RFID based on RF Encoding Particle, ISTE Press Elsevier, 1st Edition, pp. 98 122, 2016.

## UWB Chipless RFID Reader: State of the Art

#### 1. Introduction

In the chapter 1 the chipless RFID technology that involves the UWB was introduced. Its main peculiarities, compared with classical RFID and barcode, were underlined. The aim of this thesis is the development of a low cost reader for UWB chipless RFID tags, which is compliant with international regulations with a reduced reading time. This chapter introduces the current state of the art for chipless readers involving the UWB between 3.1 – 10.6 GHz.

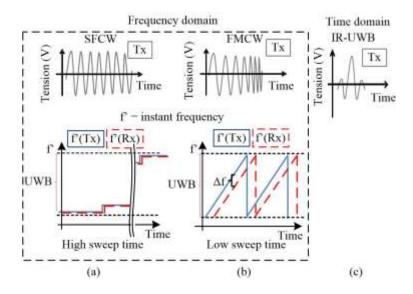

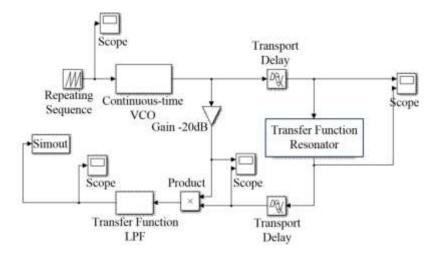

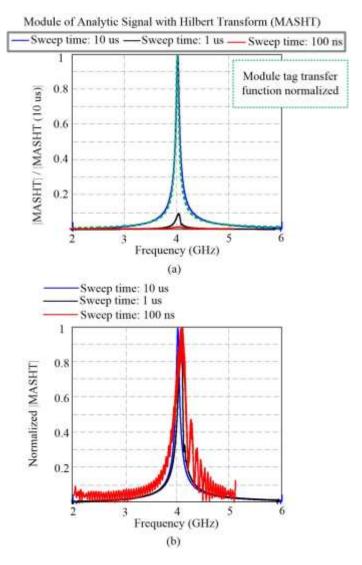

All the proposed readers in literature are based on frequency domain with either a Stepped-Frequency Continuous Wave (SFCW) or a Frequency-Modulated Continuous-Wave (FMCW) approach. Both provide a transmitting signal sweeping in between the tag bandwidth to retrieve the desired information. A SFCW reader has a higher sweep time compared with a FMCW where the transmitted CW instantaneous frequency is varying with a stair case function as shown in figure 2.1(a). The transmitting and receiving instantaneous frequency, respectively f'(Tx) and f'(Rx), have a small offset and no beat frequency is generated. This approach is also used in commercial Vector Network Analyzer (VNA) and is suitable to read both frequency-based and time-based chipless RFID tag. A FMCW approach is typically used in radar application where a beat frequency is generated due to the offset  $\Delta f$  between f'(Tx) and f'(Rx) as shown in figure 2.1(b). This approach allows for a reduced sweep time compared with SFCW and both RFID chipless tags topology can be read. However the reading of a frequency-coded tag with FMCW is low accurate and requires a complex post processing algorithm that may involve the Hilbert transform.

The chapter is organized as follows:

• Section 2 introduces two SFCW reader architectures characterized by two mixers in reception, and an IQ demodulation scheme.

- Section 3 details the readers based on FMCW architecture and their capability of reading frequency-based tags is demonstrated.

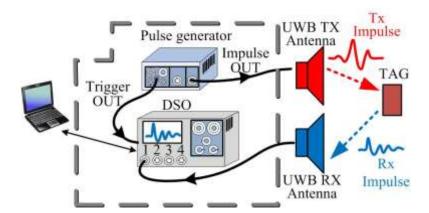

- Section 4 introduces a reading technique based on Impulse-Radio UWB (IR-UWB) as shown in figure 2.1(c). It represents a time domain approach, and up to date no IR-UWB chipless RFID readers are available in literature. A comparison between SFCW, FMCW and IR-UWB architectures, in relation with UWB regulations, is given. Finally a link-budget involving the three different approaches with a typical frequency-coded tag as target is proposed

- Section 5 draws the conclusion of the chapter.

Figure 2.1. (a) Transmitting and receiving signals of a UWB chipless RFID reader based on SFCW. It shown a high sweep time and is ideal to read frequency-coded chipless tag. (b) Transmitting and receiving signals of a UWB chipless RFID reader based on FMCW. It has a reduced sweep time and is most employed to read time-based chipless tag. (c) Transmitting signal of a UWB chipless RFID reader based on IR-UWB approach.

## 2. SFCW approach

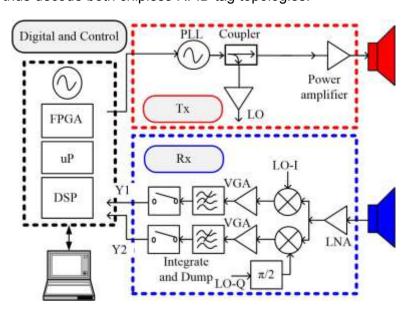

A block schematic of a bi-static SFCW reader is shown in figure 2.2. In transmission a Phase Locked Loop (PLL) is used to generate the CW interrogating signal whose instantaneous frequency f'(Tx) is controlled by the digital and control unit. In the receiving front-end is used an I/Q demodulation scheme to recover the amplitude and phase difference between the reader transmitting and receiving signal. The generation of a beat frequency is not needed with this solution, and the sweep time of the PLL can be as long as desired. In

any case the sweep time must not be excessively long to avoid unbearable reading time. With this approach is possible to characterize the impulsive response of the tag in the band of interest, and thus decode both chipless RFID tag topologies.

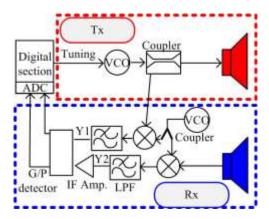

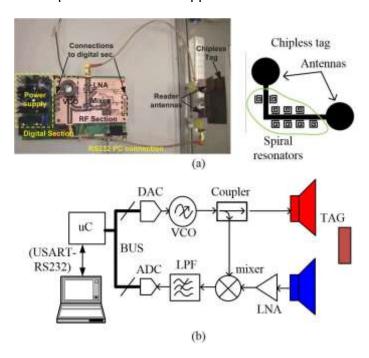

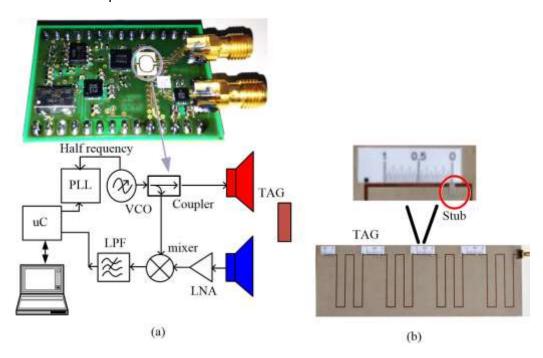

**Figure 2.2.** UWB chipless RFID reader based on FMCW approach and I/Q demodulation. Thanks to the use of two mixers, a beat frequency is not required.

A reader for UWB chipless RFID tags based on SFCW implementation was proposed in [PRE 10]. It was designed to work between 5 and 9 GHz, and a wideband Yttrium Iron Garnet sphere (YIG) Voltage Controlled Oscillator (VCO) was used in transmission. The reader schematic is based on a heterodyne configuration with the generation of an Intermediate Frequency (IF) signal to reduce the effect of flicker noise. The reader block schematic is shown in figure 2.3.

The two outputs of the low-pass filters (LPF),  $Y_1$  and  $Y_2$ , go through the AD8302 from Analog Devices. It is a gain-phase detector, which is able to measure the phase and amplitude difference between two signals. Considering that the amplitude of  $Y_2$  depends also from the amplitude of the tag response, an IF amplifier was needed after the LPF. This to compensate for the higher power present at the output of the coupler, compared with the input signal of the reader, where the tag response is present. The reader bandwidth was between 5 - 9 GHz, and its hardware cost, not including the antennas, was of 4500  $\in$  (2010). It was tested in anechoic environment with an 8 bit frequency-coded tag at few tens of centimeters. The emitted VCO output power was of 16 dBm.

**Figure 2.3.** Schematic of the UWB chipless RFID reader presented in [PRE 10]. It is based on SFCW approach with a heterodyne configuration. The use of a heterodyne configuration helps to reduce the flicker noise effects due to the active devices.

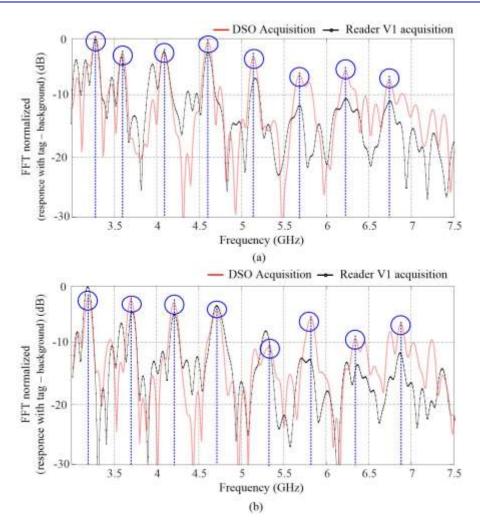

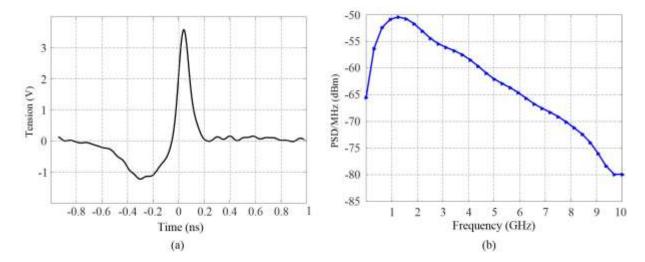

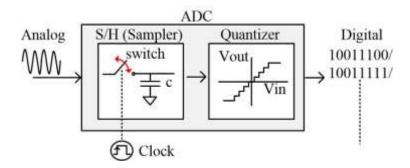

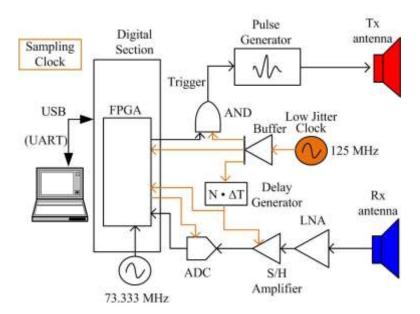

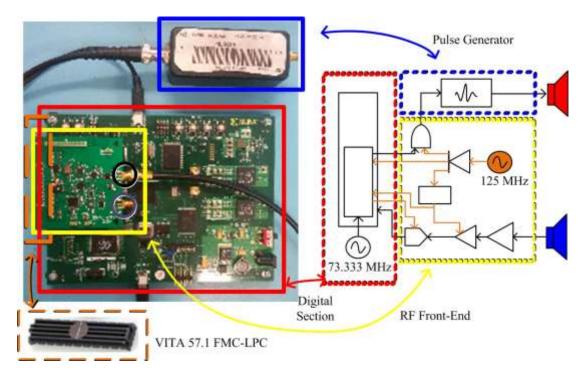

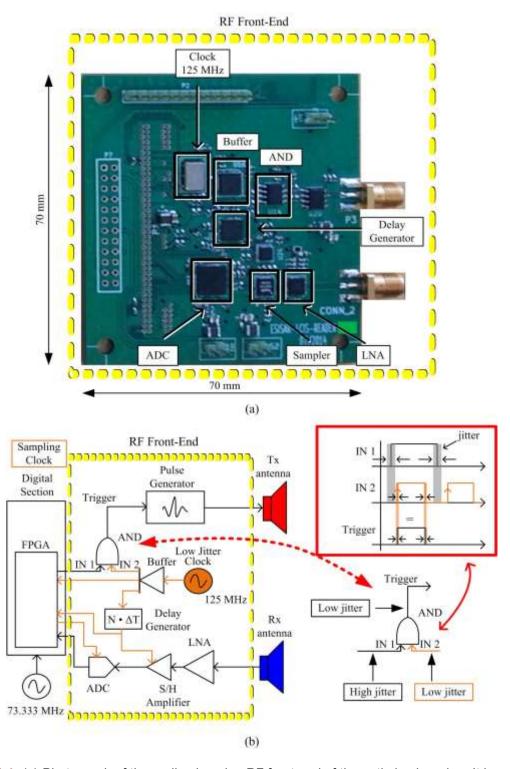

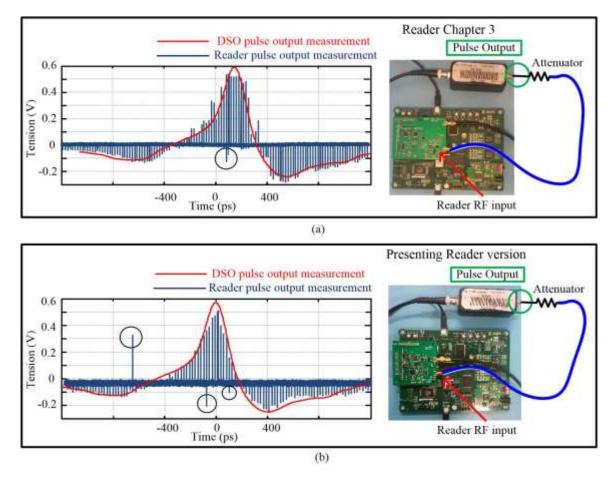

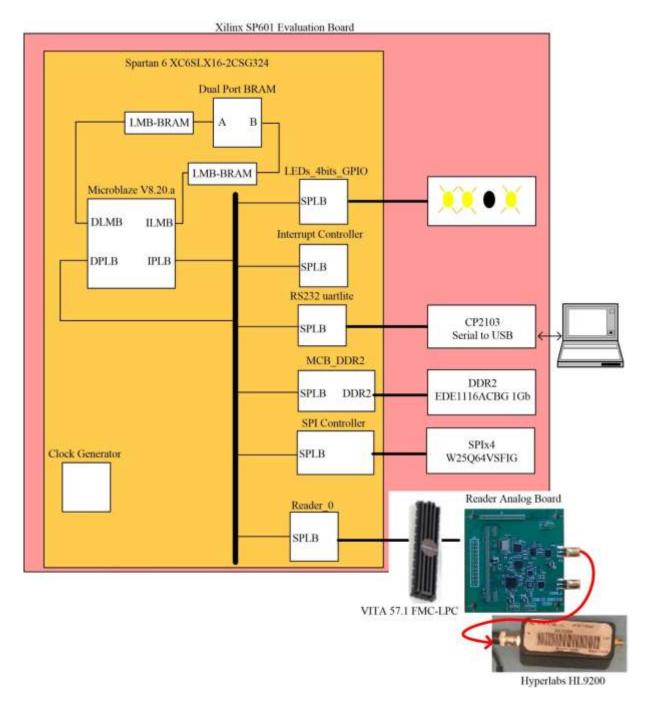

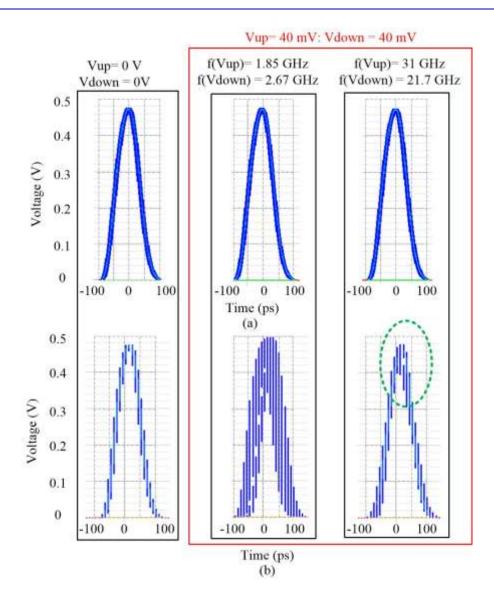

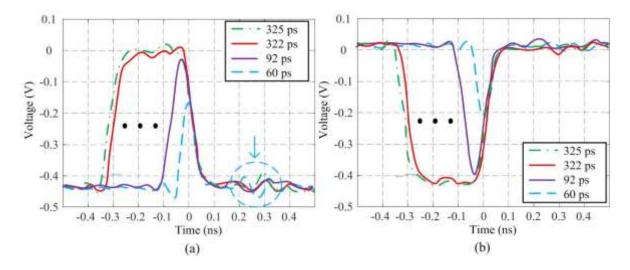

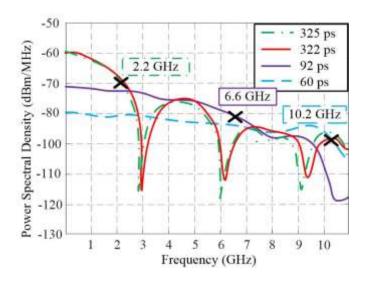

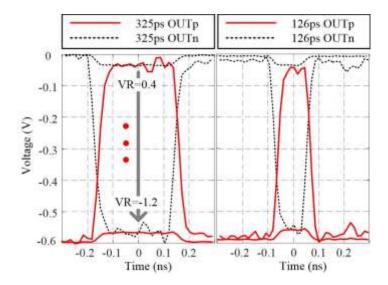

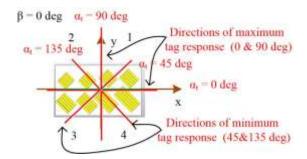

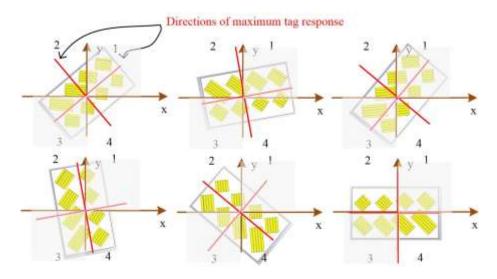

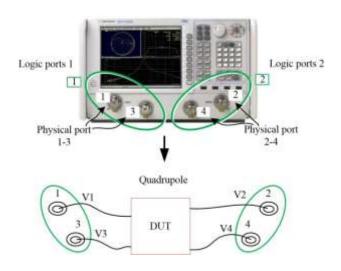

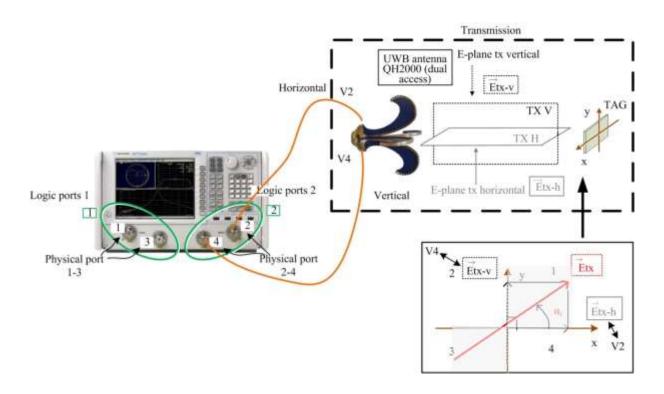

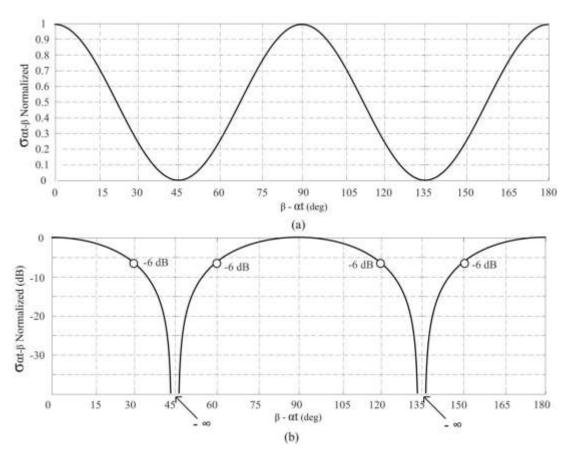

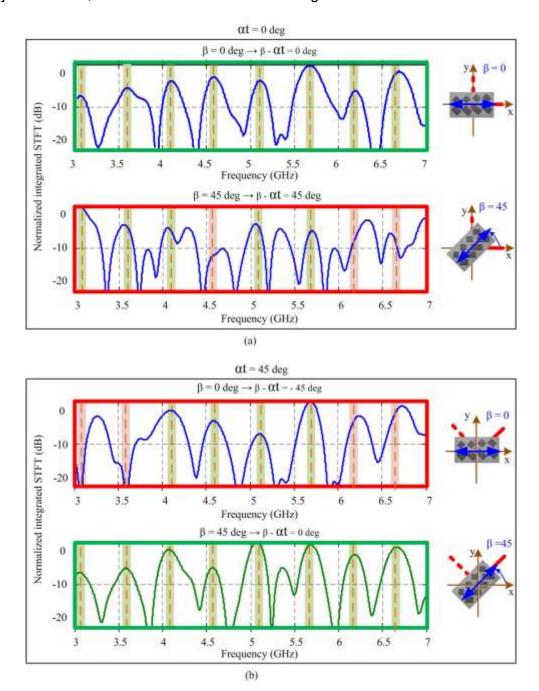

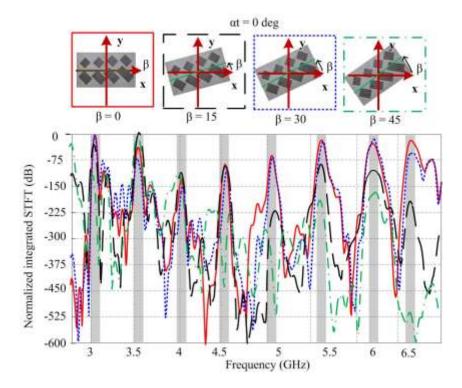

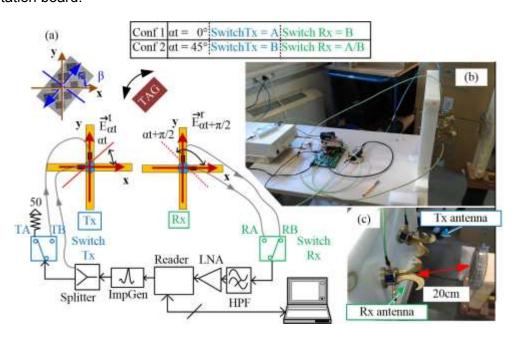

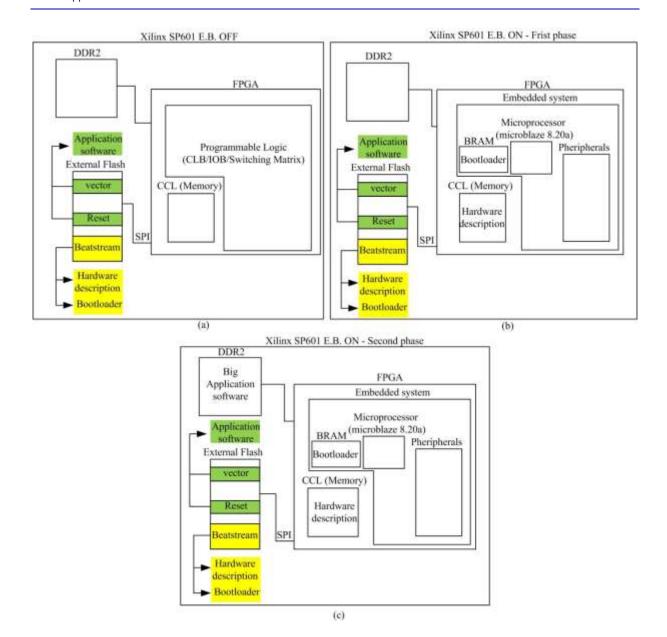

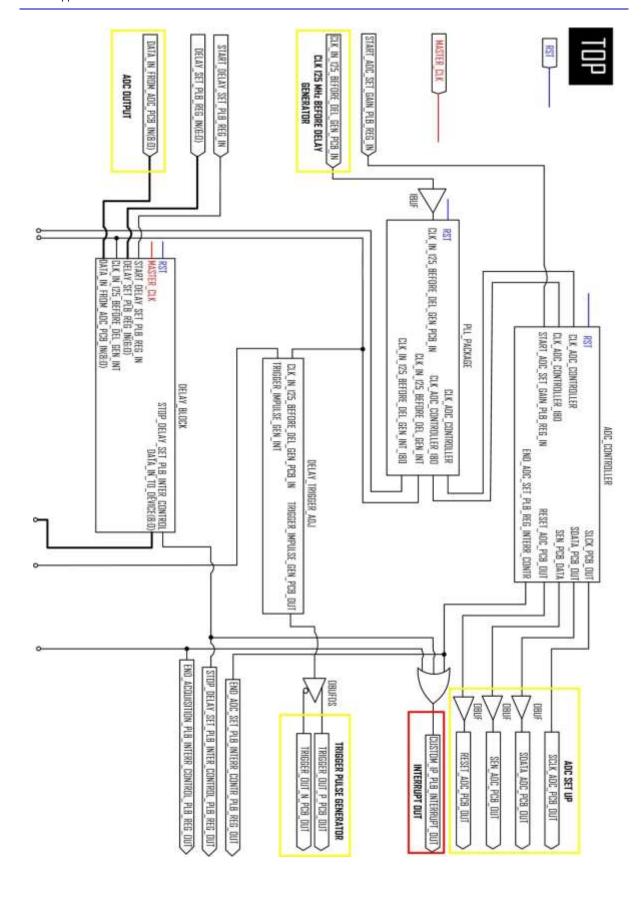

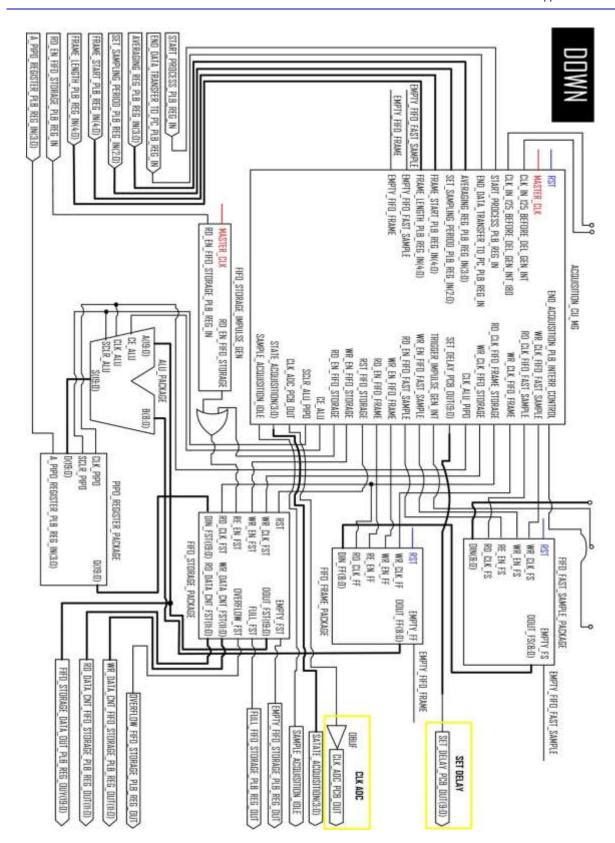

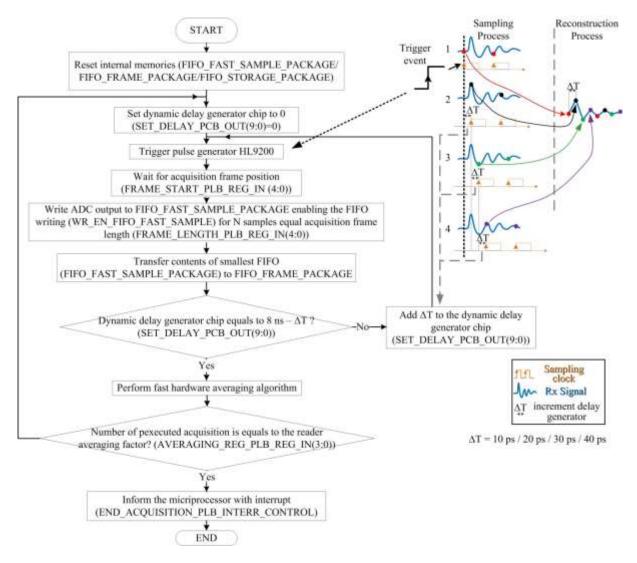

# 3. FMCW approach