## FD-SOI technology opportunities for more energy efficient asynchronous circuits

Thiago Ferreira de Paiva Leite

### ▶ To cite this version:

Thiago Ferreira de Paiva Leite. FD-SOI technology opportunities for more energy efficient asynchronous circuits. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2019. English. NNT: 2019GREAT002. tel-02295530

### HAL Id: tel-02295530 https://theses.hal.science/tel-02295530

Submitted on 24 Sep 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nano Électronique & Nano Technologies

Arrêté ministériel : 25 mai 2016

Présentée par

### Thiago FERREIRA DE PAIVA LEITE

Thèse dirigée par Laurent FESQUET et co-encadreée par Rodrigo POSSAMAI BASTOS

Préparée au sein du Laboratoire TIMA dans l'École Doctorale Electronique, Electrotechnique, Automatique & Traitement du Signal (E.E.A.T.S)

# FD-SOI technology opportunities for more energy efficient asynchronous circuits

Thèse soutenue publiquement le **21 Janvier 2019**, devant le jury composé de :

#### M. Habib MEHREZ

Professeur, Sorbonne Universités, Président

#### M. Lionel TORRES

Professeur, Université de Montpellier, Rapporteur

#### M. Gilles JACQUEMOD

Professeur, Université Nice Sophia Antipolis, Rapporteur

#### M. Robin WILSON

Technical manager, STMicroelectronics, Examinateur

#### M. Laurent FESQUET

Maître de Conférences, Université Grenoble Alpes, Directeur de thèse

#### M. Rodrigo POSSAMAI BASTOS

Maître de Conférences, Université Grenoble Alpes, Co-Directeur de thèse

### **Table of Contents**

| Ab | strac | et e e e e e e e e e e e e e e e e e e                     | XV   |

|----|-------|------------------------------------------------------------|------|

| Ré | sumé  |                                                            | xvii |

| 1  | Intro | oduction                                                   | 1    |

| 2  | The   | Fully Depleted Silicon on Insulator technology             | 5    |

|    | 2.1   | Introduction                                               | 5    |

|    | 2.2   | The problem with scaling down conventional MOS transistors | 5    |

|    | 2.3   | Alternatives to conventional bulk technology               | 6    |

|    |       | 2.3.1 Silicon on insulator                                 | 6    |

|    |       | 2.3.2 Fin field-effect transistors                         | 8    |

|    | 2.4   | The UTBB FD-SOI transistor                                 | 9    |

|    |       | 2.4.1 Advantages of a thin silicon film                    | 9    |

|    |       | 2.4.2 Advantages of an undoped channel                     | 10   |

|    |       | 2.4.3 Advantages of the isolation with a BOX               | 10   |

|    |       | 2.4.4 Advantages of an ultra thin BOX                      | 11   |

|    | 2.5   | Modulating the $V_{th}$ of UTBB FD-SOI transistors         | 12   |

|    |       | 2.5.1 Modulating $V_{th}$ through manufacturing techniques | 12   |

|    |       | 2.5.2 Modulating $V_{th}$ post manufacturing: Body Biasing | 13   |

|    | 2.6   | Overall Analysis                                           | 16   |

|    | 2.7   | Conclusion                                                 | 17   |

| 3  | The   | Asynchronous Circuits                                      | 19   |

|    | 3.1   | The limitations of synchronous circuits                    | 19   |

|    | 3.2   | The asynchronous circuits principle                        | 20   |

|    | 3.3   | Data encoding and signaling                                | 21   |

|    | 0.0   | 3.3.1 Bundled-data encoding                                | 21   |

|    |       | 3.3.2 Delay insensitive encoding                           | 21   |

|    | 3.4   | Communication protocols                                    | 22   |

|    | ٥     | 3.4.1 Two-phase protocols                                  | 22   |

|    |       | 3.4.2 Four-phase protocols                                 | 22   |

|    |       | 3.4.3 The Muller gate                                      | 24   |

|    | 3.5   | Classification of asynchronous circuits                    | 25   |

|    | 5.5   | 3.5.1 Micropipeline                                        | 26   |

|    |       | 3.5.2 Speed Independent                                    | 26   |

|    |       | 3.5.3 Delay Insensitive                                    | 26   |

|    |       | 3.5.4 Quasi Delay Insensitive                              | 27   |

|    |       | J.J.T Quasi Dolay Inscrisitive                             | 41   |

|   | 3.6  | The advantages of asynchronous circuits                                            |

|---|------|------------------------------------------------------------------------------------|

|   |      | 3.6.1 High performance                                                             |

|   |      | 3.6.2 Low power consumption                                                        |

|   |      | 3.6.3 Modularity                                                                   |

|   |      | 3.6.4 Low electromagnetic emissions                                                |

|   | 3.7  | Conclusion                                                                         |

| 4 | Con  | nparing Voltage Scaling in Synchronous and Asynchronous FD-SOI Circuits 29         |

| 7 | 4.1  | Exploiting intrinsic features of QDI asynchronous circuits for saving power 30     |

|   | 4.2  | Target Case-Study Circuits: Synchronous and Asynchronous ALU                       |

|   | 4.3  | Comparison of Synchronous and Asynchronous ALU Results                             |

|   | 4.5  | 4.3.1 Simulation Environment                                                       |

|   |      | 4.3.1 Simulation Environment                                                       |

|   | 4.4  |                                                                                    |

|   | 4.4  | Conclusions                                                                        |

| 5 | Asse | essing Adaptive Body Biasing Strategies in Asynchronous Circuits 37                |

|   | 5.1  | Body biasing strategies for asynchronous circuits                                  |

|   |      | 5.1.1 Implementing ABB schemes                                                     |

|   |      | 5.1.2 ABB schemes for QDI asynchronous circuits                                    |

|   |      | 5.1.3 BBD granularity                                                              |

|   | 5.2  | Energy efficiency of ABB strategies with asynchronous circuits                     |

|   |      | 5.2.1 Analyzing a coarse-grain strategy                                            |

|   |      | 5.2.2 Analyzing a fine-grain strategy                                              |

|   | 5.3  | Simulation Results and Analysis                                                    |

|   |      | 5.3.1 Case-Study: 8-bit QDI asynchronous ALU chain                                 |

|   |      | 5.3.2 Description of experiments                                                   |

|   |      | 5.3.3 Results and Analysis                                                         |

|   | 5.4  | Conclusions                                                                        |

| 6 | A bo | ody built-in cell for body biasing subcircuits of integrated systems and detecting |

|   |      | sient faults 51                                                                    |

|   |      | Fundamentals                                                                       |

|   |      | 6.1.1 Implementing ABB schemes                                                     |

|   |      | 6.1.2 Detecting TFs with BBICS                                                     |

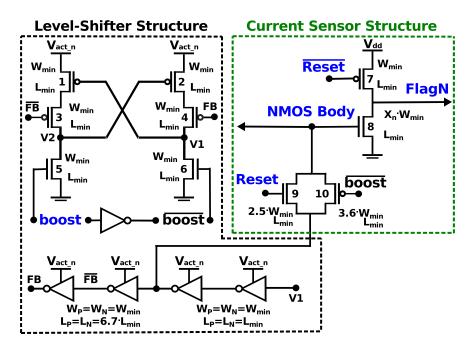

|   | 6.2  | Proposed body built-in architecture                                                |

|   | ·    | 6.2.1 Level-shifter structure                                                      |

|   |      | 6.2.2 Current sensor structure                                                     |

|   | 6.3  | Simulation Results and Analysis                                                    |

|   | 0.5  | 6.3.1 Body biasing efficiency                                                      |

|   |      | 6.3.2 Detecting TFs                                                                |

|   | 6.4  | Conclusions                                                                        |

|   |      |                                                                                    |

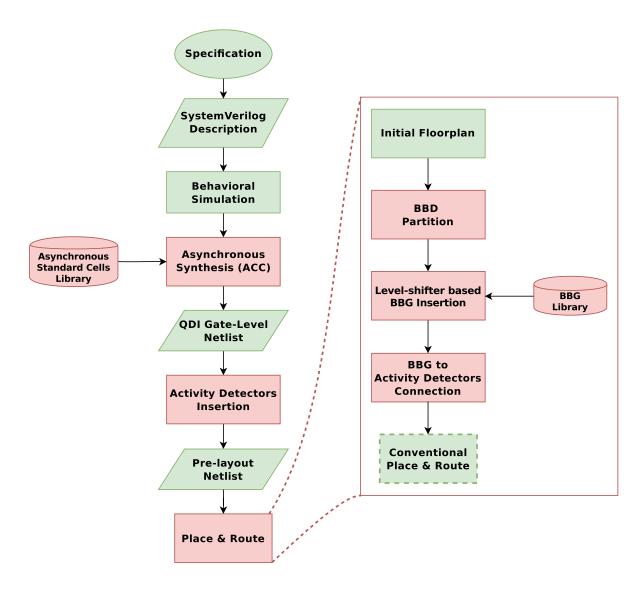

| 7 |      | ASIC Design flow adapted for asynchronous systems with multiple BBDs               |

|   | 7.1  | The proposed standard-cell based IC design flow                                    |

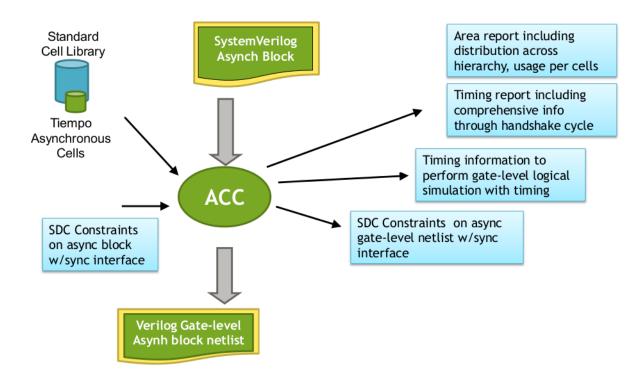

|   |      | 7.1.1 System description, simulation and asynchronous synthesis                    |

|   |      | 7.1.2 Activity detectors insertion                                                 |

|   | _    | 7.1.3 Place & Route strategies                                                     |

|   | 7.2  | Validating the proposed IC design flow                                             |

| Re  | References                            |         |                                                       |    |  |  |

|-----|---------------------------------------|---------|-------------------------------------------------------|----|--|--|

| Bil | Bibliography of Author's Publications |         |                                                       |    |  |  |

| 8   | Conclusions and Perspectives          |         |                                                       |    |  |  |

|     | 7.4                                   | Conclus | sion                                                  | 77 |  |  |

|     |                                       | 7.3.2   | Testing the TIMA ASYNC IPs: evaluating ABB strategies | 75 |  |  |

|     |                                       | 7.3.1   | Accessing the TIMA ASYNC IPs                          | 73 |  |  |

|     | 7.3                                   | Circuit | testing and preliminary results                       | 72 |  |  |

|     |                                       | 7.2.1   | The testchip                                          | 69 |  |  |

### **List of Figures**

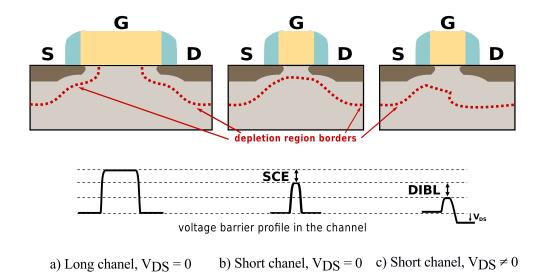

| 2.1  | Lowering of the voltage barrier caused by the reduction of transistor's gate length.              | 6  |

|------|---------------------------------------------------------------------------------------------------|----|

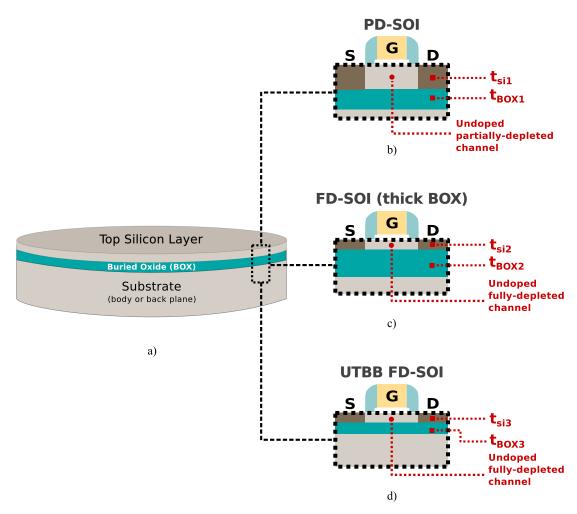

| 2.2  | Cross section of PD-SOI (b), FD-SOI (thick box) (c) and UTBB FD-SOI (d)                           |    |

|      | transistors built from silicon-on-insulator base waver (a)                                        | 7  |

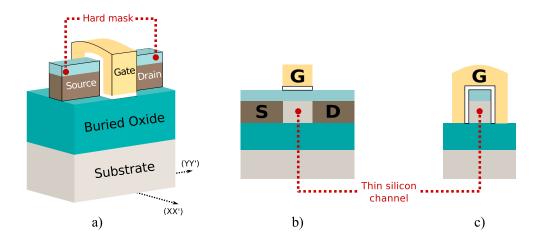

| 2.3  | 3D schematic and cross sections of a FinFET transistor                                            | 8  |

| 2.4  | Classical Bulk (a) and FD-SOI (b) NMOS transistor cross sections. The red ar-                     |    |

|      | rows represent the main leakage current components: $I_1$ is the junction leakage;                |    |

|      | $I_2$ is the gate leakage; and $I_3$ is the subthreshold leakage. In UTBB FD-SOI                  |    |

|      | technology, the path for junction leakage is eliminated, and the gate and sub-                    |    |

|      | threshold leakages are considerably reduced                                                       | 9  |

| 2.5  | Measurements of the DIBL for different gate lengths obtained for in conven-                       |    |

|      | tional bulk, FD-SOI and FinFET technologies                                                       | 10 |

| 2.6  | Measurements of the $V_{\rm th}$ variation for different gate lengths obtained for con-           |    |

|      | ventional bulk, FD-SOI and FinFET technologies                                                    | 11 |

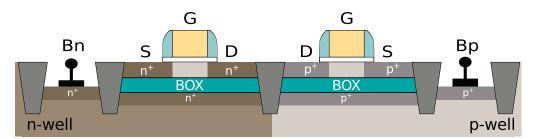

| 2.7  | Cross section of NMOS and PMOS UTBB FD-SOI transistors with conven-                               |    |

|      | tional well configuration (RVT transistors)                                                       | 12 |

| 2.8  | Cross section of NMOS and PMOS UTBB FD-SOI transistors with flip well                             |    |

|      | configuration (LVT transistors)                                                                   | 13 |

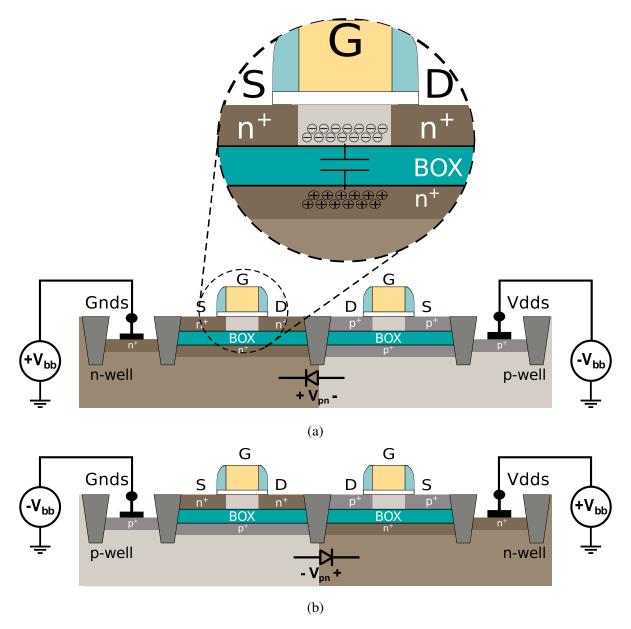

| 2.9  | Cross section view of UTBB FD-SOI NMOS and PMOS LVT (a) and RVT (b)                               |    |

|      | transistors with biasing                                                                          | 14 |

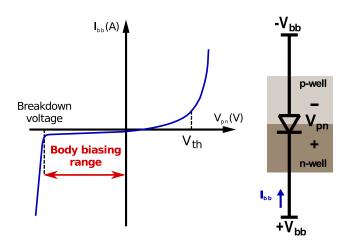

| 2.10 | Range of body biasing in FD-SOI technology. The diode formed by the p-well                        |    |

|      | and n-well junction needs to be reverse biased to limit current leakage                           | 15 |

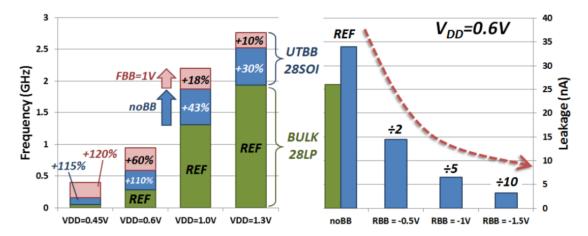

| 2.11 | Performance gains for various $V_{\rm dd}$ obtained with FBB scheme and LVT tran-                 |    |

|      | sistors (left); and leakage reduction for different $V_{\rm bb}$ values and $V_{\rm dd}$ = 0.6 V, |    |

|      | obtained with RVT transistors with RBB scheme (right) [16]                                        | 16 |

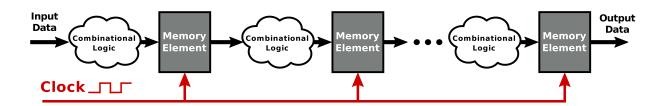

| 3.1  | Abstraction of a synchronous system                                                               | 19 |

| 3.2  | Typical representations of an asynchronous systems.                                               | 20 |

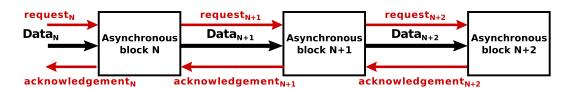

| 3.3  | Typical representations of a dual-rail encoded asynchronous systems (a). The                      | 20 |

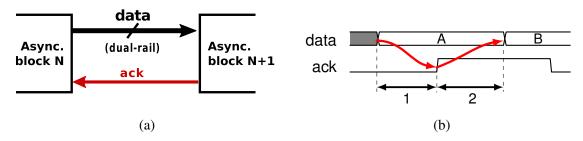

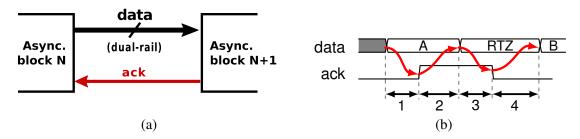

| 3.3  |                                                                                                   | 22 |

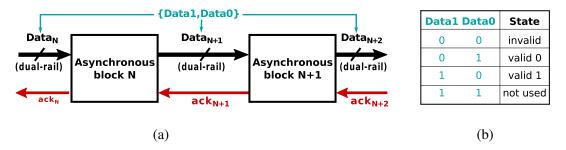

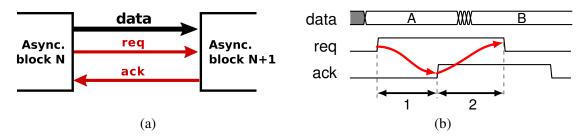

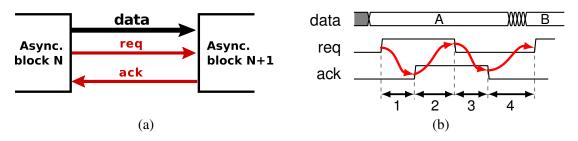

| 3.4  | Two-phase protocol implemented in a bundled-data encoded asynchronous sys-                        |    |

| 5.1  |                                                                                                   | 23 |

| 3.5  |                                                                                                   | 23 |

| 3.6  | Four-phase protocol implemented in a bundled-data encoded asynchronous sys-                       |    |

| 2.0  | tem                                                                                               | 23 |

| 3.7  | Four-phase protocol implemented in a dual-rail encoded asynchronous system.                       | 24 |

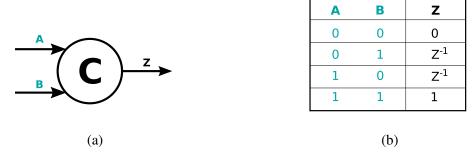

| 3.8  | 2 input symmetric C-element symbol (a) and truth table (b)                                        | 25 |

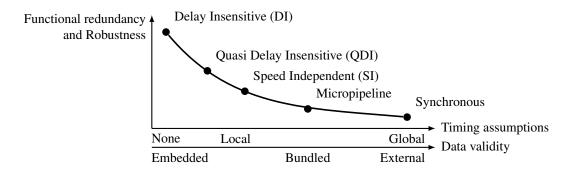

| 3.9  | Classification of asynchronous circuits in terms of functional redundancy and                     |    |

| /    |                                                                                                   | 25 |

|      |                                                                                                   | _  |

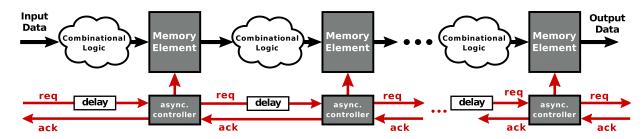

| 3.10 | Abstraction of a micropipeline asynchronous system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

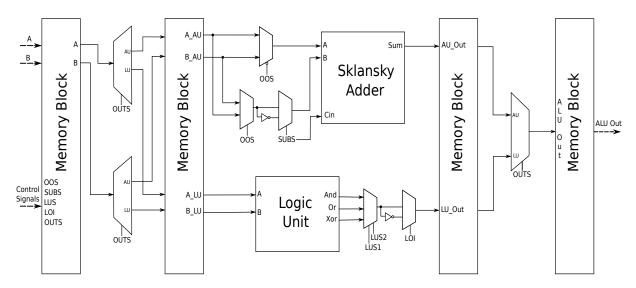

| 4.1  | ALU general architecture, designed in synchronous and asynchronous versions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3  |

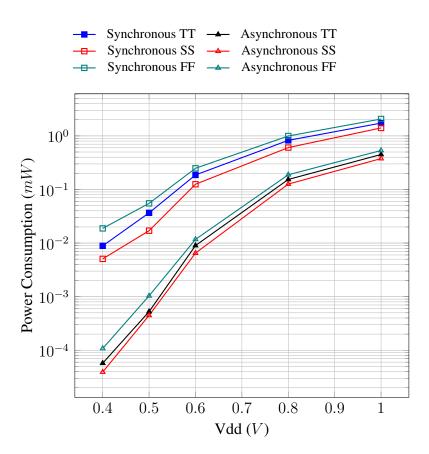

| 4.2  | Average power consumption of synchronous and asynchronous ALU in different $V_{\rm dd}$ conditions and corners typical-typical (TT), slow-slow (SS), and fast-fast (FF)                                                                                                                                                                                                                                                                                                                                                                     | 3  |

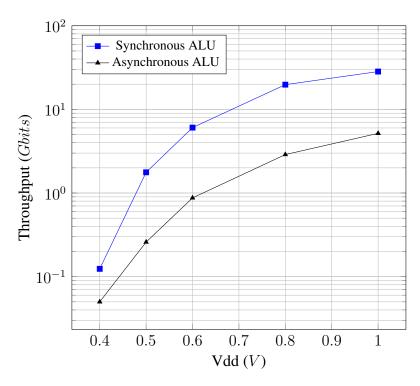

| 4.3  | Data throughput of synchronous and asynchronous ALU in different $V_{\rm dd}$ conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3  |

| 4.4  | Energy per bit of the synchronous and asynchronous ALU in different $V_{\rm dd}$ conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34 |

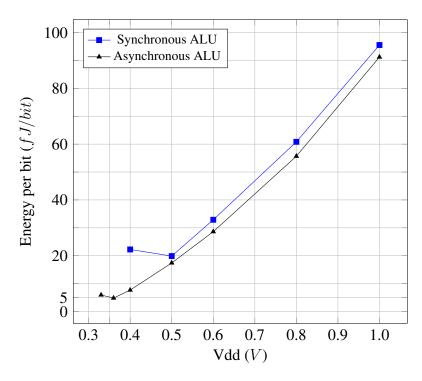

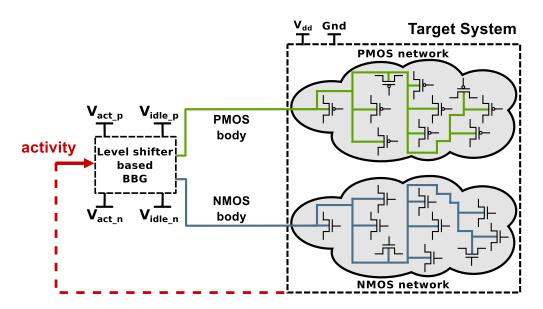

| 5.1  | Abstraction of a level-shifter based BBG controlling the $V_{\rm th}$ tuning of a generic target system. The activity signal indicates if the Target System is active or idle. The former is indicated by a logic value 1, which sets PMOS and NMOS body outputs $V_{\rm act\_p}$ and $V_{\rm act\_n}$ respectively. If the Target system is idle, the activity signal is 0, which sets PMOS and NMOS body outputs $V_{\rm idle\_p}$ and $V_{\rm idle\_n}$ respectively                                                                     | 39 |

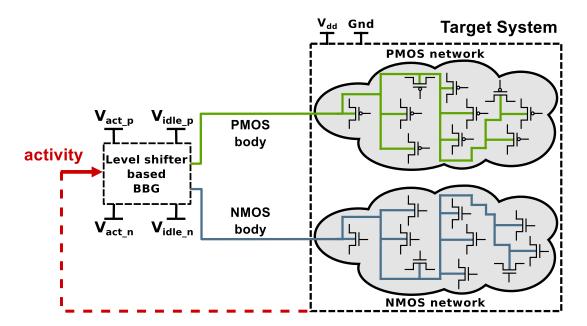

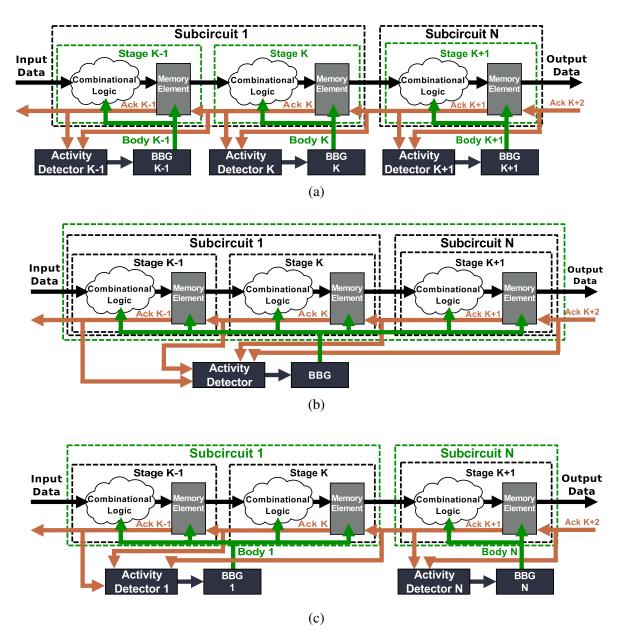

| 5.2  | Abstraction of adaptive body biasing strategies at fine (a), coarse (b), and medium (c) grain. The green dashed squares represent the BBDs of each strategy                                                                                                                                                                                                                                                                                                                                                                                 | 4  |

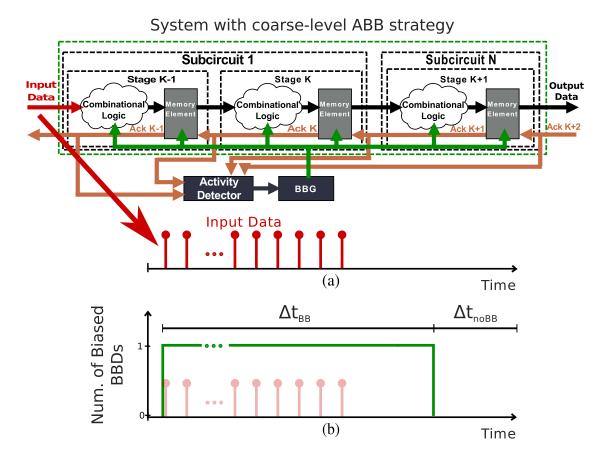

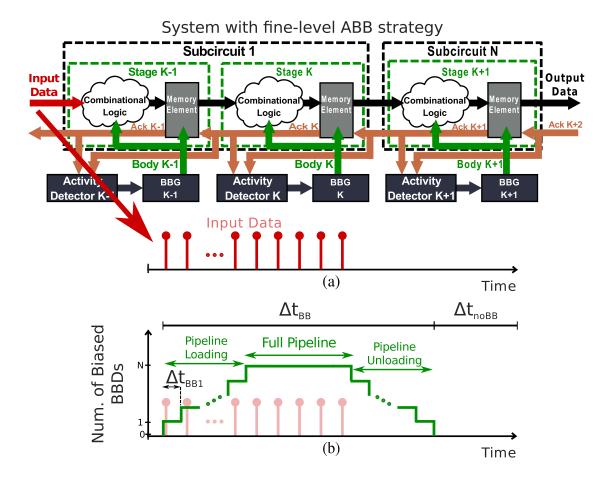

| 5.3  | Variation of the number of body biased BBDs with time (b) in a system split into a single BBD - implementation of a coarse-grain ABB strategy - as a burst of input vectors (a) is processed by the system.                                                                                                                                                                                                                                                                                                                                 | 4  |

| 5.4  | Variation of the number of body biased BBDs with time (b) in a system split into N BBDs - implementation of a fine-grain ABB strategy - as a burst of input vectors (a) is processed by the system                                                                                                                                                                                                                                                                                                                                          | 4  |

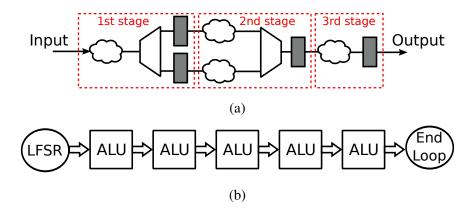

| 5.5  | Representation of the pipeline stages of the QDI asynchronous ALU used as base architecture (a), and its connection in chain (b) to serve as case-study of adaptive body biasing strategies. In (a) the clouds represent combinational logic and the grey rectangles represent memory elements. In (b), the input vectors are generated by a LFSR, connected to the first ALU of the chain. A handshake interface (End Loop) is connected to the last ALU of the chain to implement the communication protocol in the system's output stage | 40 |

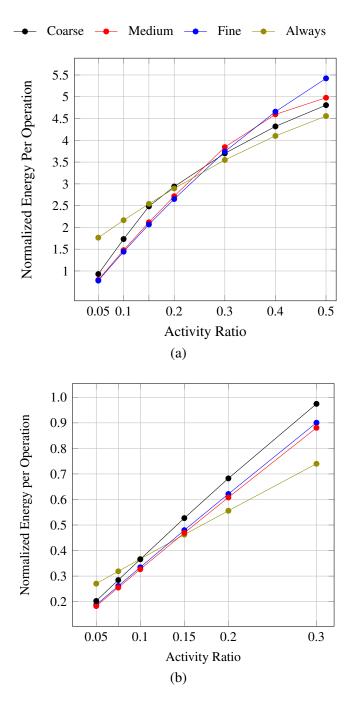

| 5.6  | Energy per operation variation with activity ratio of fine, medium, coarse and always biased strategies for a $V_{\rm dd}=1.0$ V, $V_{\rm bb}=1.5$ V in (a); and $V_{\rm dd}=0.6$ V, $V_{\rm bb}=1.0$ V in (b). The measurements in (a) and (b) were normalized to the same reference as tables 5.1 and 5.2, i.e. the energy per operation result of the always biased strategy for a a $V_{\rm dd}=1.0$ V, $V_{\rm bb}=0.0$ V and activity ratio of 0.1.                                                                                   | 4  |

| 6.1  | Abstraction of a level-shifter based BBG controlling the $V_{\text{th}}$ tuning of a generic target system.                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52 |

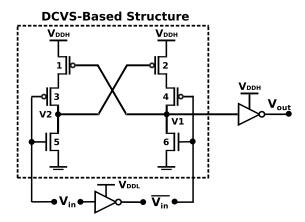

| 6.2  | State-of-the-art cross-type level shifter [149]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5. |

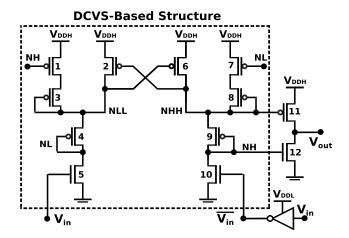

| 6.3  | State-of-the-art diode-type level shifter [78]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5  |

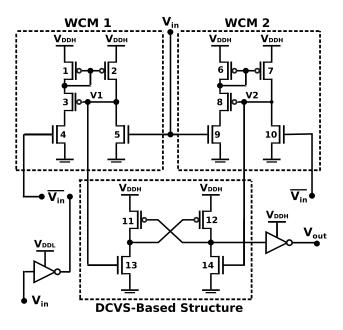

| 6.4  | State-of-the-art mirror-type level shifter [23]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5  |

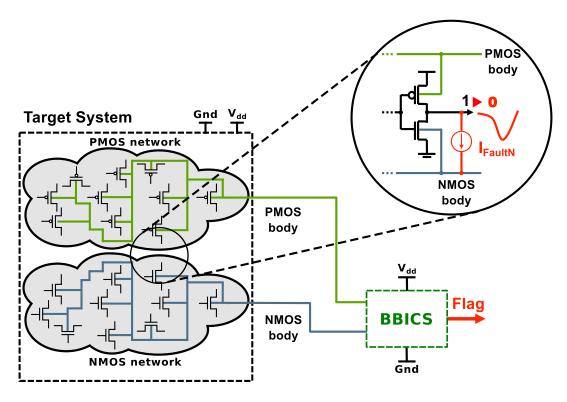

| 6.5  | Abstraction of BBICS monitoring a generic target system. A zoom in an arbitrary part of the system details the occurrence of a TF, modeled as a current source, temporarily changing the output of an inverter from 1 to 0                                                                                                                                                                                                                                                                                                                  | 5. |

| 6.6   | The proposed body built-in cell architecture. The inputs and outputs are marked in blue. $X_n$ is a design factors used for calibrating the sensitivity of the sensor                                                                                                                                                                                                                                                                                                                                                     |     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.7   | in detecting transient faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56  |

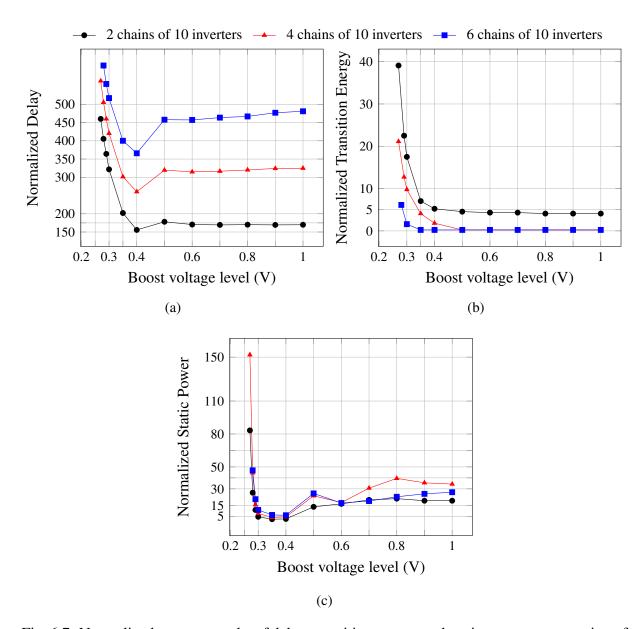

|       | respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 58  |

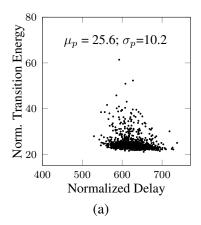

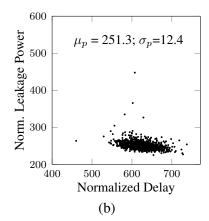

| 6.8   | Monte Carlo simulation for 1000 runs ( $V_{\text{act_n}} = 1 \text{ V}$ , $V_{\text{dd}} = 0.6 \text{ V}$ , frequency of 20 MHz and temperature of 27°C). The simulated results were normalized to the equivalent values obtained for a standard LVT inverter with minimal drive. The                                                                                                                                                                                                                                     | 60  |

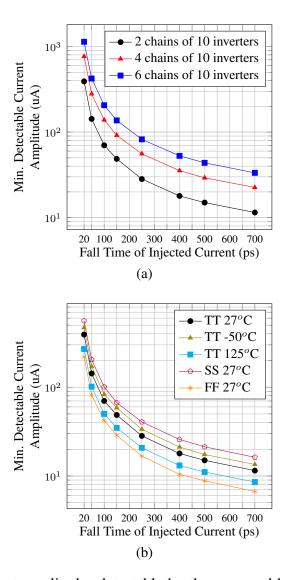

| 6.9   | reference values used in the normalization were: 4.88 ps, 0.43 fJ and 4.35 nW Minimum current amplitudes detectable by the proposed body built-in cell with the injection of a single TF with rise time of 5 ps. In a) the cell sensitivity is being compared for a varying number of monitored transistors, in a typical process and temperature of 27°C. In b), the cell is monitoring 2 chains of 10 inverters in multiple process corners: typical (TT), fast-fast (FF) and slow-slow (SS); and multiple temperatures | 60  |

| 7.1   | Proposed standard-cell based IC design flow implementing multiple BBDs in                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| , • • | QDI asynchronous circuits. The red rectangles represent the steps that have                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|       | been modified from or inserted in a standard IC design flow                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64  |

| 7.2   | Required inputs of ACC synthesis tool and generated output files. Adapted                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|       | from [166]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65  |

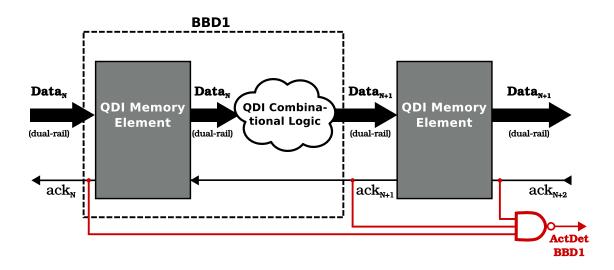

| 7.3   | Inserting an activity detector (NAND gate) for monitoring BBD1. The red gate                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|       | and nets correspond to the modifications done to the QDI gate-level netlist                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66  |

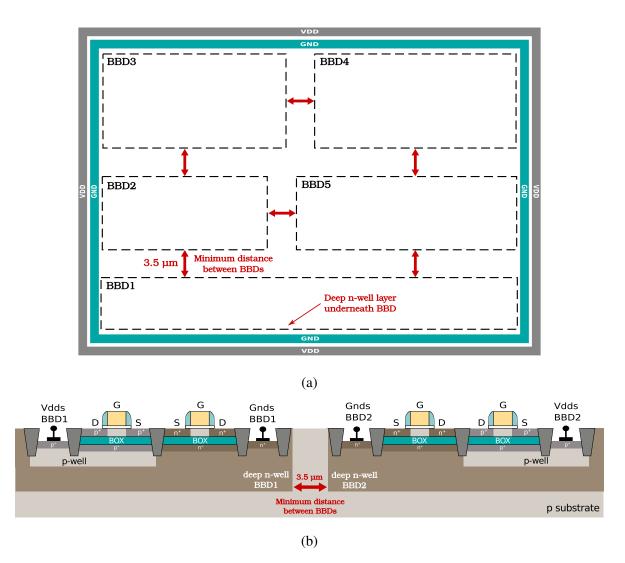

| 7.4   | Partition of the core (area surrounded by the GND and VDD rings) into BBDs                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|       | (a). The required minimum distance between adjacent BBDs is highlighted in a                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|       | cross section of transistors that belong to different BBDs (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67  |

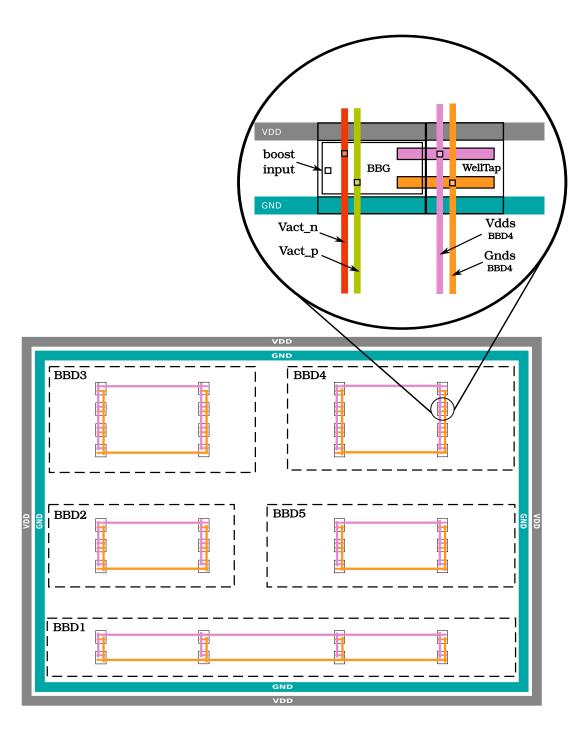

| 7.5   | Distribution of BBGs in each BBD. The <i>Vdds</i> and <i>Gnds</i> - outputs of the BBGs                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

|       | - are connected through well taps to the PMOS and NMOS body of transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|       | belonging to the same BBD respectively. $V_{\text{act_n}}$ and $V_{\text{act_p}}$ , shown in the zoom,                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|       | are input power nets common to every BBG, therefore they are the same for all                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60  |

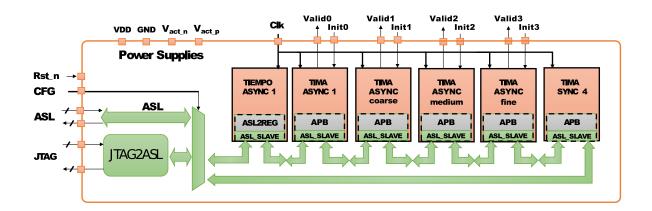

| 7.6   | BBDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68  |

| 7.0   | green belong to the Asynchronous link (ASL) and the salmon rectangles repre-                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|       | sent the IPs embedded in the testchip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69  |

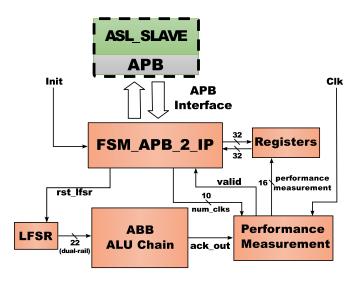

| 7.7   | Architecture of the TIMA ASYNC IPs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70  |

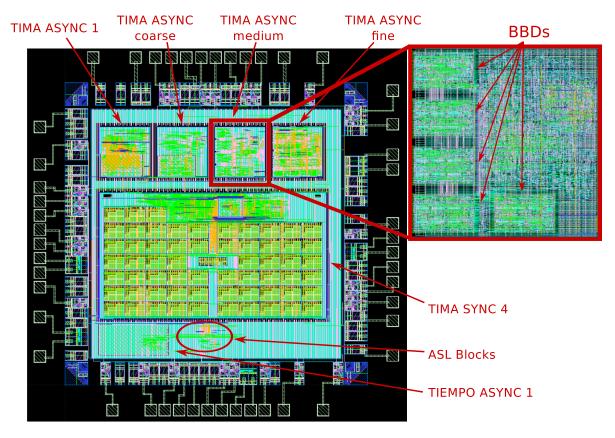

| 7.8   | Testchip top layout.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 72  |

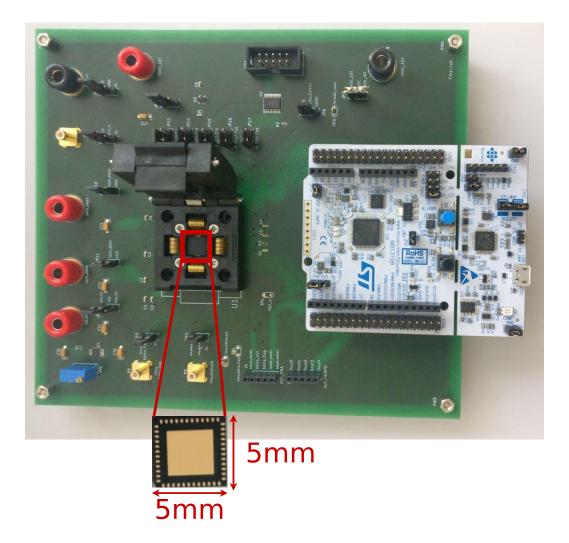

| 7.9   | Printed circuit board developed to simplify the testing of the testchip. It is                                                                                                                                                                                                                                                                                                                                                                                                                                            | , _ |

| ,     | connected to the ST32 Nucleo (white board on the left). A zoom into the socket                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|       | shows the back face of the testchip and the dimensions of the packaging                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73  |

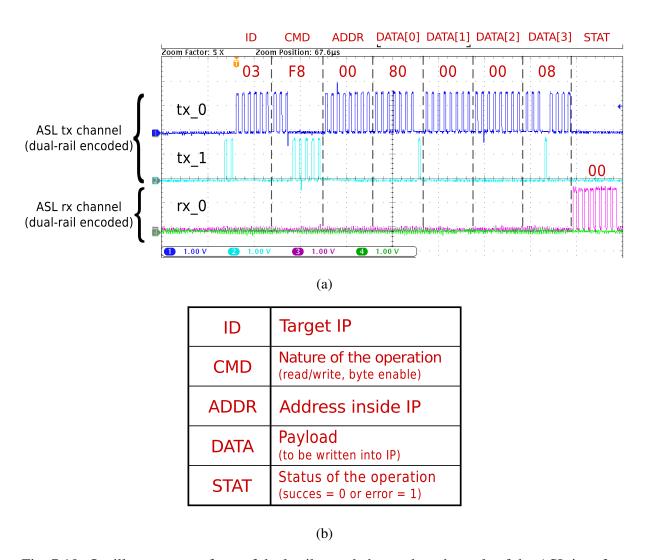

| 7.10  | Oscilloscope waveform of dual-rail encoded tx and rx channels of the ASL in-                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|       | terface (a). The meaning of each byte necessary for composing a write operation                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|       | is presented in (b). The numbers in red are the hexadecimal representation of                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|       | each dual-rail byte.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74  |

### **List of Tables**

| 2.1 | Comparison of manufacturing cost, power consumption and performance on conventional bulk, UTBB FD-SOI and FinFET technologies                                                                                                                                                                              | 16  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | Electrical simulation results for $V_{\rm dd} = 1.0$ V and activity ratio of 0.1. The values of total power, operation frequency and energy per operation were normalized to the respective values of the always biased strategy for a $V_{\rm bb} = 0.0$ V and a $V_{\rm dd} = 1.0$ V                     | 47  |

| 5.2 | Electrical simulation results for $V_{\rm dd}$ = 0.6 V and activity ratio of 0.05. The values of total power, operation frequency and energy per operation were normalized to the measurements of the always biased strategy for a $V_{\rm bb}$ = 0.0 V, a $V_{\rm dd}$ = 1.0 V and activity ratio of 0.1. | 48  |

| 7.1 | Area overhead and number of BBGs required to implement coarse, medium and fine grain ABB strategies.                                                                                                                                                                                                       | 72  |

| 7.2 | Testchip results of performance measurement compared with simulation at a                                                                                                                                                                                                                                  | , _ |

|     | $V_{\rm dd}$ = 0.6 V and activity ratio of 1                                                                                                                                                                                                                                                               | 75  |

| 7.3 | Testchip results of average power consumption compared with simulation at a                                                                                                                                                                                                                                |     |

|     | $V_{\rm dd} = 0.6 \text{ V}$ and activity ratio of 1                                                                                                                                                                                                                                                       | 76  |

### **Abstract**

Keeping the fast evolving pace of embedded systems of portable devices require ameliorations of power management techniques, without compromising the circuit performance and robustness. In this context, this thesis studies novel energy management schemes, and how to implement them, by using two main design approaches: asynchronous logic and adaptive body biasing (ABB) techniques. Four main contributions have been done, thus enabling the design of more energy efficient asynchronous circuits. 1) We contributed with the design of a Quasi-delay Insensitive (QDI) asynchronous ALU architecture, used in a comparative analysis of asynchronous versus synchronous systems. This first study has demonstrated the energy efficiency and robustness of QDI circuits, especially if operating at low power supply  $(V_{\rm dd})$ . 2) We proposed a new body built-in cell for implementing ABB schemes by tuning the circuit threshold voltage (Vth) on-the-fly; and detecting short-duration and long-duration transient faults (TF) caused by environmental radiation. The proposed cell is a key building block to fully benefit from body biasing features of the FD-SOI technology while enhancing system's reliability. 3) We assessed three different ABB strategies - based on automatic activity detection and multiple body-biasing domains (BBDs) - for QDI asynchronous circuits. Furthermore, a methodology for analyzing energy efficiency of ABB strategies in QDI asynchronous circuits is also proposed in this work. 4) We developed a standard cell-based IC design flow to apply ABB strategies with multiple BBDs by using the proposed body built-in cells. A testchip has been designed and fabricated to validate the developed design flow and the efficacy of the body built-in cell.

*Keywords:* Quasi-delay-insensitive Asynchronous Circuits, Adaptive Body Biasing, Energy Efficiency, FD-SOI.

### Résumé

Afin de suivre le rythme effréné des évolutions des systèmes embarqués et des dispositifs portables, il s'avère aujourd'hui indispensable d'optimiser la gestion de l'énergie sans pour autant compromettre la performance et la robustesse des circuits. Dans ce contexte, cette thèse étudie de nouveaux dispositifs de gestion de l'énergie ainsi que leur mise en œuvre, en combinant deux approches: la logique asynchrone et les techniques de polarisation du substrat (Adaptive Body Biasing - ABB). Cette thèse comporte quatre contributions permettant la conception de circuits asynchrones énergétiquement plus efficaces. 1) Une unité arithmétique et logique (UAL) asynchrone quasi insensible aux délais (Quasi Delay Insensitive - QDI) a été conçue et utilisée pour mener une analyse comparative entre systèmes synchrones et asynchrones. Cette étude démontre notamment la meilleure efficacité énergétique et la plus grande robustesse des circuits asynchrones QDI, surtout lorsqu'ils fonctionnent à basse tension. 2) Une cellule standard a été spécialement développée pour mettre en œuvre nos schémas d'adaptation dynamique du substrat (ABB) qui ajustent la tension de seuil ( $V_{th}$ ) des transistors. En outre, cette cellule s'est révélée très utile pour la détection de fautes transitoires causées par des radiations environnementales. Cette cellule est en outre un élément clé pour exploiter la polarisation du substrat, un des intérêts majeurs de la technologie FD-SOI, et d'améliorer la fiabilité du système. 3) Trois stratégies de polarisation de substrat ont été évaluées. Ces stratégies reposent sur la détection automatique de l'activité des circuits asynchrones QDI et de la polarisation de multiples domaines dans le substrat (Body Biasing Domains - BBD). De plus, une méthode pour analyser l'efficacité énergétique des stratégies de polarisation pour les circuits asynchrones QDI a également été proposée dans le cadre de cette thèse. 4) Enfin, un flot de conception de circuits numériques intégrés a été proposé et développé. Ce flot, basé sur des cellules standards, permet d'exploiter des stratégies de polarisation (ABB) avec plusieurs domaines (BBD) en utilisant la cellule standard spécialement développée. Un testchip a été conçu et fabriqué pour valider notre flot de conception et évaluer l'efficacité de la cellule proposée.

*Mots-clés :* Circuits Asynchrones Quasi-Insensibles aux Délais, Polarisation Adaptative du Substrat, Efficacité Énergétique, FD-SOI.

### **Chapter 1**

### Introduction

The rapid technological advances of recent years have induced a massive spread of electronic circuits to almost every apparatus that surround our environment. From smartphones to smartwatches and even personal health monitoring systems, nowadays most devices have embedded integrated circuits (ICs). We entered an era of boundlessly greater connectivity, the Internet of Things (IoT), in which these ubiquitous electronic devices exchange information between them and with the cloud. The popularity of IoT has been increasing at a incredibly fast pace. Intel Corporation has estimated that the number of connected devices was 2 billion in 2006 and reached 15 billions by 2015. Extrapolating these numbers, they projected a total of 200 billions devices to be connected to each other by 2020 [8].

This massive proliferation of connected "things" has been rapidly increasing the demand for energy. For instance, the Semiconductor Industry Association has estimated that the computer devices will require more energy than what the entire world is capable of generating by 2040 [132]. Thus, the law of the more performance the better, the predominant design theory in past years, is no longer acceptable. Instead, the systems designed for IoT applications, especially wireless sensor networks, need to prioritize energy efficiency. The result is not only batteries that last longer and increased autonomy, but also the preservation of natural resources for the sake of a greener world.

Attaining the aforementioned energy efficiency has been sought in three different research axis: technology, architectural design, and power management techniques. In the first axis, enhancing the manufacturing technology to shrink the transistors gate length has historically allowed decreasing the power consumption required for maintaining a certain performance. For instance, in [101] authors have reported that scaling the technology node of a microprocessor from 0.75  $\mu m$  to 0.35  $\mu m$  resulted in a power reduction by a factor of approximately two with an equivalent performance. Reducing the power consumption while maintaining a similar performance implies a higher energy efficiency was achieved with technology scale down. This energy gain with transistors scale down has been possible until the 100 nm node. Beyond this node, several fundamental physics limitation previously neglected, for example short channel effects, have slowed down the energy efficiency enhancement traditionally achieved with simple scale down of conventional bulk technology [128]. To overcome the 100 nm manufacturing barrier, alternative technologies, based on thin film, have been proposed. The two main alternatives proposed by the industry were: the Fully depleted Silicon on Insulator (FD-SOI) [136] and the Fin Field Effect Transistor (FinFET) [35], technologies in which the electrostatic control in the channel has been improved to enable the pursuit of power consumption and performance improvements with downscale.

Furthermore, the second axis of research towards more energy efficiency is the architectural design approach. Asynchronous circuits, systems with local synchronization instead of global synchronization, has been shown to be a promising solution for low power and high energy efficient applications [19]. In this type of circuit, a local handshake protocol controls data propagating through the system instead of a global clock signal. In the absence of the clock signal, the power consumed by the clock tree circuitry is eliminated. Additionally, the event-driven nature of the asynchronous logic automatically turns the inactive blocks to standby mode. Only blocks with data to be processed will be activated, thus the dynamic power of the system is reduced if compared to a synchronous counterpart [18, 50]. There are different methods to design asynchronous circuits that differ from each other in the number of timing assumptions used to implement sequencing. The class of Quasi-Delay Insensitive (QDI) asynchronous circuits, the design approach explored in this thesis, can operate correctly with only a few assumptions on certain forks [86]. The reduced number of timing assumptions makes QDI asynchronous circuits very robust and appropriate for low-power operation.

Another possibility for enhancing energy efficiency is implementing existing power management techniques, e.g. voltage scaling and body biasing [26, 98]. The former consists in reducing  $V_{\rm dd}$  in order to decrease the dynamic power consumption at the cost of increased gate delays, a technique imposing a permanent trade-off between power and performance. Complementarily, applying a voltage to the body of the transistors - a technique known as body biasing - artificially changes transistors threshold voltage ( $V_{\rm th}$ ) in order to decrease static power consumption or boost performance for achieving optimum energy efficiency [157]. Moreover, adaptive body biasing (ABB) allows further enhancing energy efficiency by adaptively decreasing  $V_{\rm th}$  during computation, in order to improve performance, and increase  $V_{\rm th}$  at idle periods to mitigate leakage [109, 165]. The use of ABB schemes is perfectly suitable for IoT applications, in which long periods of idleness between two calculations is a key characteristic.

In this context, we focused on merging these three research axis to design more energy efficient nano-electronic systems, as proposed by Hamon et al [56]. The extended body biasing range - achievable with the FD-SOI technology - enable the implementation of efficient ABB strategies in asynchronous circuits, systems in which the application of the aforementioned power management techniques is straightforward. The asynchronous handshake signals are directly exploited to detect the periods of activity and idleness - necessary for implementing ABB. Moreover, the local synchronization nature of asynchronous circuits allows ABB-induced on-the-fly delay variation with a minimal risk of timing violations.

This thesis brings four main contributions to enable the design of more energy efficient asynchronous circuits. The first one is the design of a QDI asynchronous ALU architecture, used in a comparative analysis of asynchronous versus synchronous systems. This first study has demonstrated the energy efficiency and robustness of QDI circuits, especially if operating at low  $V_{\rm dd}$ . The second contribution is a new level-shifter based body biasing generator (BBG) that enables applying ABB schemes by tuning the circuit Vth on-the-fly. The proposed BBG is a key building block to fully benefit from the body biasing features of the FD-SOI technology. It is also capable of detecting short-duration and long-duration transient faults (TF) caused by environmental radiation, thus enhancing system reliability.

The third contribution of this thesis is the evaluation of three different ABB strategies for QDI asynchronous circuits. The objective of this study was to determine the optimal granularity for implementing multiple body-biasing domains (BBDs) with automatic biasing activation depending on circuit activity. Furthermore, a methodology for analyzing energy efficiency of ABB strategies in QDI asynchronous circuits is also proposed.

Finally, as a final contribution of this thesis, a standard cell based IC design flow has been proposed. It uses the proposed architecture of level-shifter based BBG to implement ABB strategies with multiple BBDs in QDI asynchronous circuits. In order to validate the IC design flow, a testchip has been designed and fabricated in FD-SOI 28 nm technology, which also showed the efficacy of the developed level-shifter based BBG and gains of implementing ABB strategies in QDI asynchronous systems.

This thesis is organized as follows. Chapter 2 introduces the state of the art on the FD-SOI technology, comparing it to conventional bulk and FinFET technologies. In the sequel, the basic concepts of asynchronous circuits is presented in chapter 3, highlighting their advantages over synchronous circuits. A case study comparison of synchronous versus asynchronous circuits, the results of the first contribution, is presented in chapter 4. In chapter 5, a methodology for analyzing energy efficiency of ABB strategies in QDI asynchronous circuits is presented. It establishes the criteria for assessing three different ABB strategies based on automatic activity detection and multiple body-biasing domains (BBDs), with the goal of determining optimal use cases for each strategy. Chapter 6 presents a novel level-shifter based BBG, which is the key for implementing the strategies investigated in chapter 5. Additionally, the proposed cell enables transient fault detection, which contributes for improving the robustness of the system. Subsequently, the proposed dedicated IC design flow for implementing ABB strategies with multiple BBDs by using the proposed body built-in cells is presented and validated with the preliminary results obtained with the fabricated test-chip. Finally, chapter 8 concludes this thesis, summarizing the main contributions and presenting the conclusions and future perspectives of this work.

### **Chapter 2**

# The Fully Depleted Silicon on Insulator technology

### 2.1 Introduction

Historically, the continuous scale down of semiconductor nodes has relied on doubled integration density and significant performance gains for each new technology node, as foreseen by Moore's law [102]. Additionally, the reduction of the cost per transistor has also been seen as a key parameter that enables advances in the semiconductor industry [65]. Although the improvements with scaling have been consistent for technology nodes until 90 nm, a number of fundamental physics limitation, previously neglected, have decreased the attractiveness of conventional bulk technology scaling beyond the referred node. The main physics limitations are Short Channel Effects (SCE), reduced carrier mobility, increased gate tunneling current and increased p-n junction leakage [128]. Moreover, according to the study published in [65], for nodes below 28 nm, using conventional bulk transistor techniques will increase the cost per gate by approximately 1.6%, mainly due to process complexity and unfeasible effective gate length reduction.

In this context, alternative manufacturing technologies, based on thin film, have been proposed to overcome the issues encountered by shrinking conventional MOS transistors, thus enabling to cross the 32 nm technology node barrier. The two main alternatives proposed by the industry were: the Fully depleted Silicon on Insulator (FD-SOI) [96, 136] and the Fin Field Effect Transistor (FinFET) [35, 38]. Both technologies use an undoped thin silicon film between source and drain, which enables a much better electrostatic control of the channel by the gate. As a result, the so called short channel effect and the sub-threshold leakage are greatly reduced [35, 136]. Furthermore, the undoped silicon also substantially reduce the variation of transistor's threshold voltage ( $V_{\rm th}$ ) induced by the fabrication process, thus enabling circuit's operation at lower supply voltages ( $V_{\rm dd}$ ). The FD-SOI and FinFET technologies are presented and compared to the conventional bulk technology in the sequel of this chapter.

## 2.2 The problem with scaling down conventional MOS transistors

Many parasitic effects have appeared when shrinking conventional MOS transistors bellow 100 nm. In fact, the so called short channel effects (SCE) arise when the distance between

the source and the drain reaches the order of magnitude of the depletion region. In this case, the voltage barrier in the channel drops, as depicted in Fig. 2.1 b, causing a decrease in  $V_{\rm th}$ . In addition, biasing the drain/source terminal also influences the depth of the depletion region in a short channel transistor, as in Fig. 2.1 c. Therefore, the short channel effect is intensified by the polarization of the drain, an effect known as Drain Induced Barrier Lowering (DIBL).

Fig. 2.1: Lowering of the voltage barrier caused by the reduction of transistor's gate length.

In addition to short-channel effects, another phenomenon that also degrades electrical characteristics of short channel MOS transistors is the variation of the number of dopants in the channel, known in the literature as Random Dopant Fluctuation (RDF). In fact, RDF has become today the main source of variability of  $V_{\rm th}$  [12]. Indeed, a MOS transistor fabricated in conventional 100 nm technology has an average of approximately 100 dopant atoms in its channel [73]. Since  $V_{\rm th}$  is directly affected by variations in the channel's dopant concentration, the impact of RDF is magnified as the gate length shrinks. The result is a limited reduction of the nominal  $V_{\rm dd}$  as technology nodes scale down, which also limits the reduction of the consumed static power from node to node.

To overcome the insufficient power and performance gains caused by the arising of the aforementioned parasitic effects, many improvements in the fabrication process have been proposed [13, 14, 41]. Despite all the advances in the conventional bulk manufacturing process, the short channel effects continued to degrade the gate electrostatic control over the channel as technology nodes scaled down. Hence, the industry was forced to search alternative manufacturing technologies to continue the scale down of transistors.

### 2.3 Alternatives to conventional bulk technology

#### 2.3.1 Silicon on insulator

One of the alternatives to advance beyond the 32 nm technology node was adding a layer of oxide insulator in the substrate (buried insulator or BOX), as depicted in Fig. 2.2a. Thus, the source, drain and channel are separated from the substrate (also known as body or back plane). The addition of a BOX enabled reducing the junction parasitic capacitances, increasing the

electrostatic control of the channel, and also reducing SCE. Hence, the performance is improved while decreasing the dynamic consumption [20], what enabled the crossing of the technological barrier imposed by short channel effects.

There are several types of manufacturing technologies that use silicon on insulator [20, 34]. The basic difference between each one of them is the thickness of the silicon film on the top of the BOX ( $t_{\rm si}$ ), and the thickness of the BOX itself ( $t_{\rm BOX}$ ). One of the first proposed technologies was the Partially Depleted Silicon on Insulator (PD-SOI), illustrated in Fig. 2.2b. It contains a thick top silicon layer,  $t_{\rm si}$  is larger than the depth of the depletion region [20]. Thus, the channel is only partially occupied by the depletion region, what explains its denomination. Although PD-SOI transistors have been the focus of many scientific publications [10, 104, 129], the fluctuation of  $V_{\rm th}$  caused by the circuit switching history made PD-SOI a deprecated technology.

The problem with PD-SOI was solved by reducing  $t_{\rm si}$  to the same order of magnitude of the depletion region. In this case, the channel is fully occupied by the depletion region, which explains the reason for the name Fully Depleted Silicon on Insulator (FD-SOI). A thinner top silicon layer has shown to improve SCE, increase transconductance, improve sub-threshold

Fig. 2.2: Cross section of PD-SOI (b), FD-SOI (thick box) (c) and UTBB FD-SOI (d) transistors built from silicon-on-insulator base waver (a).  $t_{\rm si}$  represents the thickness of the top silicon layer and  $t_{\rm BOX}$  represents the thickness of BOX.  $t_{\rm si1} > t_{\rm si3}$ ;  $t_{\rm si2} = t_{\rm si3}$ ;  $t_{\rm BOX1} > t_{\rm BOX3}$ ;  $t_{\rm BOX2} > t_{\rm BOX3}$ . Figure based on information available in [139].

slope, and increase soft errors tolerance [32, 43, 140, 142].

Once  $t_{\rm si}$  is reduced to the point of generating a fully depleted channel, two technologies flavors are achievable by adjusting  $t_{\rm BOX}$ : The FD-SOI with thick BOX, depicted in Fig. 2.2c and the Ultra Thin Body and BOX FD-SOI (UTBB FD-SOI), shown in Fig. 2.2d. As illustrated Fig. 2.2, the top silicon layer of FD-SOI and UTBB FD-SOI have the same thickness:  $t_{\rm si2} = t_{\rm si3}$ ; and the BOX of the UTBB FD-SOI is thinner:  $t_{\rm BOX3} < t_{\rm BOX2}$ . As a result previous experimental and simulation work has shown that, not only the UTBB FD-SOI has been proven to have considerably reduced SCE [34,64,113,142,150,155,167], but also a thin BOX allows calibrating transistors  $V_{\rm th}$  by gate biasing [108,151].

Thanks to these advantages and the advances the technique for manufacturing SOI wafers, the UTBB FD-SOI technology prevails as the SOI alternatives to replace conventional bulk. Further details on UTBB FD-SOI will be given in the next section.

### 2.3.2 Fin field-effect transistors

The other alternative adopted by the industry to continue scaling down transistors beyond 32 nm was developing the Fin Field-Effect Transistor (FinFET) technology. This solution was largely supported by Intel corporation [87]. In this 3D manufacturing technology, the drain and the source are raised out of the substrate, forming a shape known as fin. The gate surrounds the fin in a perpendicular axis, as depicted in Fig. 2.3 a. A nitrided hard mask isolates the top part of fin. Consequently, the channel is formed in the XX' direction and the carriers move in the YY' direction. With this configuration, a better electrostatic control of the depletion region is obtained compared to regular SOI transistor. Furthermore, the influence of the drain electric field on the channel is reduced, thus reducing SCE [35].

Fig. 2.3: 3D schematic (a) and cross sections YY' (b) and XX' (c) of a FinFET transistor.

From an electrostatic point of view, FinFET transistors are better than FD-SOI transistors. The former has also shown to have better performance results [60, 168]. However, they are much more difficult to manufacture [60]. The simplified planar manufacturing process of FD-SOI transistors allow reducing the fabrication time if compared to FinFET. In addition, the structure of FD-SOI transistors is very close to that of conventional bulk. Therefore, adapting existing circuit designs from conventional bulk to FD-SOI technology is simpler than adapting it to FinFET.

### 2.4 The UTBB FD-SOI transistor

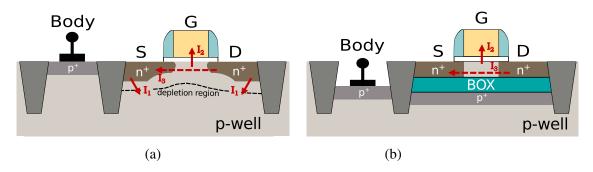

A typical cross section of an UTBB FD-SOI transistor is shown in Fig. 2.4b and compared to a cross section of a conventional bulk transistor, in Fig. 2.4a. As explained in the previous section, the main difference between these technologies is the insertion of the ultra thin BOX in the UTBB FD-SOI, separating the thin silicon film that forms source, drain and the channel from the substrate of the transistor (p-well in Fig. 2.4b).

Fig. 2.4: Classical Bulk (a) and FD-SOI (b) NMOS transistor cross sections. The red arrows represent the main leakage current components:  $I_1$  is the junction leakage;  $I_2$  is the gate leakage; and  $I_3$  is the subthreshold leakage. In UTBB FD-SOI technology, the path for junction leakage is eliminated, and the gate and subthreshold leakages are considerably reduced.

### 2.4.1 Advantages of a thin silicon film

The extremely thin top silicon layer of UTBB FD-SOI transistors provides a much better electrostatic control than conventional bulk [69]. For achieving optimal electrostatic behavior,  $t_{\rm si}$  is kept in the order of one third of the gate length value [97, 135]. For instance,  $t_{\rm si} \cong 12$  nm in UTBB FDSOI 28 nm technology [137]. As a result, two major advantages: the first one is a reduced subthreshold slope [82]. This parameter reflects the capability of the gate to effectively control the current flow through the channel. The closer the subthreshold slope is to the theoretical minimum value of 60 mV/dec, the higher is the gate control over the channel what consequently reduces the gate leakage ( $I_2$  in Fig. 2.4a) [69].

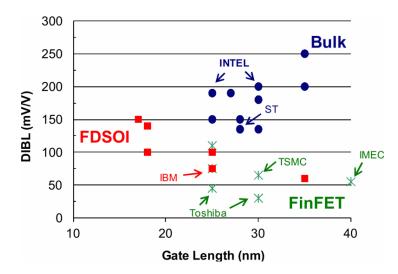

The second major advantages of a better electrostatic control is the reduction of short-channel effects, especially DIBL [69,97]. According to its theoretical equation [135], the value of the DIBL is directly proportional to the depth of the source and drain junctions. Since in UTBB FD-SOI the depth of the junctions is  $t_{\rm si}$ , which is considerably smaller than the corresponding depth in conventional bulk, the value of DIBL is considerably reduced in UTBB FD-SOI. The experimental demonstration of reduction of DIBL is depicted in Fig. 2.5, extracted from [16].

In [16], a comparison with different DIBL values obtained for the conventional bulk (circles), FD-SOI (squares) and FinFET (stars) technologies is presented, as depicted in Fig. 2.5. The presence of a thin top silicon layer make the FD-SOI and FinFET DIBL values smaller than the measurements obtain in conventional bulk technology, for every gate length shown in Fig. 2.5. Additionally, the measurements obtained with FinFET are slightly smaller than the corresponding FD-SOI measurements due to the improved electrostatic control obtained with the former, as mentioned in section 2.3.2.

Fig. 2.5: Measurements of the DIBL for different gate lengths obtained for in conventional bulk, FD-SOI and FinFET technologies [16].

Finally, the combination of reduced short-channel effects and reduced subthreshold slope achieved in the UTBB FD-SOI induces a reduction in the subthreshold leakage ( $I_3$  in Fig. 2.4a).

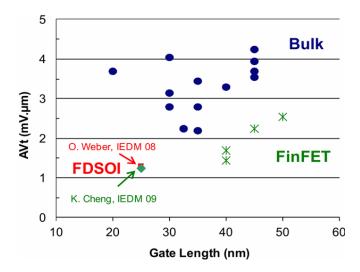

### 2.4.2 Advantages of an undoped channel

The isolation provided by the BOX free the UTBB FD-SOI technology from the obligation of doping the channel, as is the case for the conventional bulk technology. An undoped channel brings two major improvement: removing the random dopants fluctuation (RDF) of the channel and reducing the  $V_{\rm th}$  variability, which are considered as two of the most critical challenges for continuing the scale down in CMOS technology [12, 161]. Therefore, for the same gate length, an UTBB FD-SOI transistor has a coefficient of variability of threshold voltage  $(AV_t)$  approximately three times lower than an equivalent transistor in conventional bulk technology [29,116]. The values of  $AV_t$  for conventional bulk, FD-SOI, and FinFET technology are depicted in Fig. 2.6 [16]. The smaller values obtained with the FD-SOI technology demonstrates that it is less subject to local  $V_{\rm th}$  variations than conventional bulk technology.

Less variability means less power and performance differences between process corners fast-fast (FF) and slow-slow (SS). Thus, less margin needs to be added by the logical synthesis and place and route tools to guarantee timing closure. Therefore, the circuits designed in UTBB FD-SOI technology operate in a faster frequency than an equivalent circuit designed in the same technology node in conventional bulk.

Another advantage of an undoped channel is limiting the Gate induced Drain leakage (GIDL), one of the components of current leakage in MOSFET transistors. Previous studies show that the GIDL is very low in UTBB FD-SOI technology, in the order of a few  $pA/\mu m$  [22, 28, 29].

### 2.4.3 Advantages of the isolation with a BOX

The presence of the BOX, that completely isolates the source/drain from the substrate imposes certain advantages. The most straightforward one is the complete elimination of the current leakage from source/drain to the substrate, marked as I1 in Fig. 2.4a. Eliminating one of the

Fig. 2.6: Measurements of the  $V_{\rm th}$  variation for different gate lengths obtained for conventional bulk, FD-SOI and FinFET technologies [16].

sources of leakage that exists in conventional bulk technology allows reducing the static power consumption in FD-SOI technology [33].

Furthermore, the insertion of the BOX limits the depth of source and drain, which allows reducing the diffusion surface. As a consequence, a reduced parasitic junction capacitance is achieved [97]. Considering that the source/drain terminals of transistors are connected to each other to form logic gates, and considering that the output capacitance seen by a certain logic gate is the equivalent of all junction capacitances of all source/drain terminals connected to the output of that logic gate, reducing the junction capacitance directly reduces the energy required to switch a logic gate state. Therefore, the dynamic power consumption in an UTBB FD-SOI circuit is considerably lower if compared to an equivalent in conventional bulk operating at the same frequency [97].

Another positive effect of the BOX addition is the elimination of the latch-up [128]. This phenomenon occurs in conventional bulk technology, under some specific situations. A parasitic thyristor based structure forms between adjacent transistors, thus inducing a large current to flow from  $V_{\rm dd}$  to Gnd. The latch-up generally has a destructive effect to CMOS circuits and is a major problem in CMOS systems [61]. In FD-SOI, thanks to the BOX and the Shallow Trench Isolation (STI depicted in Fig. 2.4b), the adjacent transistors are electrically isolated from each other. Consequently, the parasitic bipolar transistors, formed in conventional bulk by the juxtaposition of n-wells and p-wells, are suppressed. The latch-up effect is thus eliminated in the FD-SOI technology.

### 2.4.4 Advantages of an ultra thin BOX

In UTBB FD-SOI technology, as its acronym suggests, an ultra thin BOX is used. In the 28 nm node, for instance,  $tbox \cong 25$  nm [137]. It has been demonstrated that a thinner BOX strengthens the electrostatic control over the channel by reducing the DIBL [107]. The short channel effects are also decreased with a thin BOX due to the suppression of the lateral electrostatic coupling that exists between source, drain and channel of transistors with a thick BOX [97, 150]. As a result, the reduction of tbox enhances the scalability of UTBB FDSOI transistors down to

the 11 nm node with an almost constant tsi [97].

### 2.5 Modulating the $V_{th}$ of UTBB FD-SOI transistors

In order to meet the tight power and performance constraints of nowadays complex systems, the use of transistors with different  $V_{\rm th}$  is mandatory. In high performance designs, for instance, low  $V_{\rm th}$  transistors are commonly used in critical paths to increase the performance of the overall system, whereas high  $V_{\rm th}$  transistors are preferred for non-critical paths, so that the static power consumption is reduced. Thus tuning  $V_{\rm th}$  is necessary for the establishment of any CMOS technology in the deep sub-micro era.

### 2.5.1 Modulating $V_{th}$ through manufacturing techniques

The conventional bulk technology proposes three levels of Vth, high; regular; and low [11,148]. In order to create these variants, the  $V_{th}$  is modified either by controlling the doping of the channel, or by changing the gate stack used [11]. These two options were not kept in the UTBB FD-SOI. Indeed, as described in previous sections, the channel in UTBB FD-SOI is undoped to reduced variability. Thus, doping the channel would increase the variability of the transistors. Moreover, the second method considerably raises the manufacturing cost and complexity.

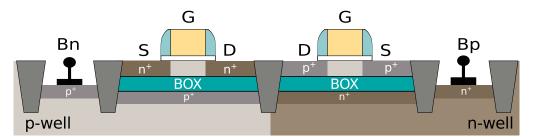

Thus, in UTBB FD-SOI technology a third method for creating a multi  $V_{\rm th}$  platform have been used. The substrate underneath the BOX is doped to a high level concentration [46, 107], illustrated by the p+ layer in Fig. 2.4b, also known as back plane. Therefore, adjusting  $V_{\rm th}$  of the transistors is done by modulating only the type and doping levels of the back plane while keeping the same gate metal type. This technique was initially used to improve the electrostatic integrity of the channel [45]. It is nowadays used to generate transistors with different  $V_{\rm th}$  levels. Depending on the type of dopants used in the back plane, two  $V_{\rm th}$  level possibilities are used in UTBB FD-SOI: a low  $V_{\rm th}$  option (LVT), and a higher  $V_{\rm th}$  option, which is known as regular  $V_{\rm th}$  (RVT).

In the RVT configuration, the back plane dopant type is the opposite of source and drain dopants, which causes an increase in transistors  $V_{\rm th}$ . A cross section schematic of a NMOS and a PMOS RVT transistors is depicted in Fig. 2.7. In this case, the p-well and n-well disposition is equal to the conventional bulk technology: the NMOS lies over a p-well and the PMOS lies over a n-well. Due to the similarity with the conventional bulk, this architecture is known as conventional well.

Fig. 2.7: Cross section of NMOS and PMOS UTBB FD-SOI transistors with conventional well configuration (RVT transistors).

Conversely, in the LVT configuration, the back plane dopant type is the same of source and drain dopants, which causes an decrease in transistors  $V_{\rm th}$ . A cross section schematic of a NMOS

and a PMOS RVT transistors is depicted in Fig. 2.8. Thus, the p-well and n-well dispositions are flipped if compared to the conventional bulk technology: the NMOS lies over a n-well and the PMOS lies over a p-well. This disposition of n-wells and p-wells are only possible since the BOX provides electrical isolation between source/drain and the back plane. It is commonly referred to as flip-well.

Fig. 2.8: Cross section of NMOS and PMOS UTBB FD-SOI transistors with flip well configuration (LVT transistors).

### 2.5.2 Modulating $V_{th}$ post manufacturing: Body Biasing