#### Etude du bruit électrique basse fréquence dans des technologies CMOS avancées

Beya Nafaa

#### ▶ To cite this version:

Beya Nafaa. Etude du bruit électrique basse fréquence dans des technologies CMOS avancées. Automatique / Robotique. Normandie Université; Université de Carthage (Tunisie), 2018. Français. NNT: 2018NORMC273. tel-02299236

#### HAL Id: tel-02299236 https://theses.hal.science/tel-02299236v1

Submitted on 27 Sep 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

## Pour obtenir le diplôme de doctorat Spécialité ELECTRONIQUE, MICROELECTRONIQUE, OPTIQUE ET LASERS, OPTOELECTRONIQUE MICROONDES

Préparée au sein de l'Université de Caen Normandie En cotutelle internationale avec Université de Carthage , TUNISIE

## Etude du bruit électrique basse fréquence dans des technologies CMOS avancées

#### Présentée et soutenue par Beya NAFAA

| Thèse soutenue publiquement le 18/12/2018<br>devant le jury composé de |                                                      |                    |  |

|------------------------------------------------------------------------|------------------------------------------------------|--------------------|--|

| Mme NATHALIE MALBERT                                                   | Professeur des universités, Université de Bordeaux   | Rapporteur du jury |  |

| M. LAURENT PICHON                                                      | Professeur des universités, Université Rennes 1      | Rapporteur du jury |  |

| M. ADANE ABDELGHANI                                                    | Professeur, Institut Natio. Sciences appliquées      | Membre du jury     |  |

| M. FRANCIS BALESTRA                                                    | Directeur de recherche, INP - ENSE3 à Grenoble       | Membre du jury     |  |

| M. REGIS CARIN                                                         | Professeur émérite, Université Caen Normandie        | Président du jury  |  |

| M. EDDY SIMOEN                                                         | Directeur de recherche, Université de Gand           | Membre du jury     |  |

| M. WALID TOUAYAR                                                       | Professeur, Institut Natio. Sciences appliquées      | Membre du jury     |  |

| M. BOGDAN MIHAIL CRETU                                                 | Maître de conférences HDR, Université Caen Normandie | Directeur de thèse |  |

Thèse dirigée par BOGDAN MIHAIL CRETU, Groupe de recherche en informatique, image, automatique et instrumentation

#### **THESE**

#### Pour obtenir le diplôme de doctorat

Spécialité Electronique, microélectronique, optique et lasers, optoélectronique micro-ondes

Préparée au sein de l'université de Caen,

En partenariat international avec « l'université de Carthage» « Tunisie»

## Etude du bruit électrique basse fréquence dans des technologies CMOS avancées

#### Présentée et soutenue par Beya Nafaa

| Thèse soutenue publiquement le 18 décembre 2018 devant le jury composé de |                                                      |                    |  |

|---------------------------------------------------------------------------|------------------------------------------------------|--------------------|--|

| Mme Nathalie Malbert                                                      | Professeur – Université de Bordeaux                  | Rapporteur         |  |

| M. Laurent Pichon                                                         | Professeur – Université de Rennes 1                  | Rapporteur         |  |

| M. Francis Balestra                                                       | Directeur de recherche, INP Grenoble                 | Examinateur        |  |

| M. Eddy Simoen                                                            | Directeur de recherche, IMEC Leuven (Belgique)       | Examinateur        |  |

| M. Adnane Abdelghani                                                      | Professeur – INSAT, Université de Carthage (Tunisie) | Examinateur        |  |

| M. Walid Touayar                                                          | Professeur – INSAT, Université de Carthage (Tunisie) | Directeur de thèse |  |

| M. Régis Carin                                                            | Professeur émérite – Université de Caen              | Examinateur        |  |

| M. Bogdan Cretu                                                           | Maître de conférences HDR – Université de Caen       | Directeur de thèse |  |

Thèse dirigée par Bogdan CRETU (GREYC) et Walid TOUAYAR (MMA)

#### Remerciements

- Je tiens tout d'abord à remercier Mr Jean Marc Routoure, Professeur à l'UNICAEN et Mr Naoufel Ismail, maître assistant à l'université de Carthage, qui m'ont donné l'opportunité de faire cette thèse.

- Je remercie mon directeur de thèse Mr Walid Touayar, Professeur à l'université de Carthage, pour avoir accepté de diriger ma thèse et pour son soutien durant mon parcours.

- J'exprime toute ma reconnaissance au Mr Régis Carin, Professeur émérite à l'UNICAEN pour son accueil, sa gentillesse et son aide tout au long de ma thèse.

- Mes vifs remerciements à mon directeur de thèse, Mr Bogdan Cretu, HDR à l'ENSICAEN, pour m'avoir accueilli au GREYC et pour avoir mis à ma disposition tous les moyens matériels sans lesquels je n'aurais pas abouti à achever mes travaux de recherche. Je le remercie aussi pour sa disponibilité, sa gentillesse, sa patience, ses critiques scientifiques, et pour tout ce que j'ai appris de lui à propos de la caractérisation, le bruit dans les dispositifs électroniques et l'instrumentation.

- Je tiens aussi à remercier tous les membres de l'équipe électronique du laboratoire GREYC qui m'ont accueillie chaleureusement parmi eux.

- Je remercie également ma famille, mes amies et mes proches qui m'avaient toujours entouré, encouragé et soutenue durant mes moments les plus difficiles.

- Enfin, je tiens à remercier les membres de jury pour m'avoir fait l'honneur d'évaluer ce travail.

## Table des matières

| Liste des figures                                                            | 8  |

|------------------------------------------------------------------------------|----|

| Liste des Tableaux                                                           | 11 |

| Introduction générale                                                        | 6  |

| Chapitre I : Rappel sur le fonctionnement du MOSFET et son                   |    |

| développement                                                                | 10 |

| Introduction                                                                 | 11 |

| I.1. Structure de base du MOSFET                                             | 11 |

| I.2. Principe de l'effet de champ                                            | 12 |

| I.3. Régimes de fonctionnement du MOSFET                                     | 12 |

| I.4. Mobilité des porteurs                                                   | 15 |

| I.4.1. Mécanismes de collisions                                              | 15 |

| I.4.2. Mobilité à faible champ et mobilité effective                         | 16 |

| I.5. Autres paramètres caractéristiques du MOSFET                            |    |

| I.5.1. Tension de seuil                                                      | 17 |

| I.5.2. Résistances d'accès                                                   | 17 |

| I.5.3. Pente sous le seuil                                                   | 17 |

| I.5.4. Les courants I <sub>ON</sub> et I <sub>OFF</sub>                      | 18 |

| I.5.5. Vitesse de saturation des porteurs, V <sub>drift</sub>                | 18 |

| I.6. La miniaturisation des MOS entre avantages et inconvénients             | 18 |

| I.6.1. Effet de confinement des porteurs                                     | 18 |

| I.6.2. Courant tunnel                                                        | 19 |

| I.6.3. Transport balistique                                                  | 19 |

| I.6.4. Impact sur la mobilité                                                | 19 |

| I.6.5. Effets de canaux courts                                               | 19 |

| I.6.6. Effets de porteurs chauds                                             |    |

| I.7. Solutions pour remédier aux inconvénients de la miniaturisation des MOS |    |

| I.7.1. Oxyde de grille                                                       |    |

| I.7.2. Grille métallique                                                     |    |

| I.7.3. Techniques de contraintes mécaniques                                  |    |

| I.8. Evolution vers des nouvelles architectures                              |    |

| I.8.1. MOSFET à multi-grilles                                                |    |

| I.8.2. Technologie FDSOI UTBOX                                               |    |

| Conclusion                                                                   | 24 |

| II.1. Architecture étudiée                                                                                            | 27 |

|-----------------------------------------------------------------------------------------------------------------------|----|

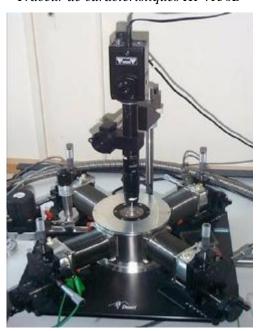

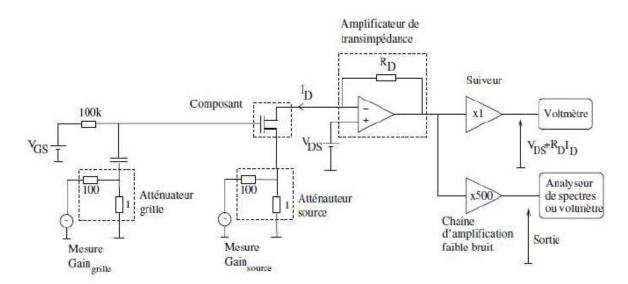

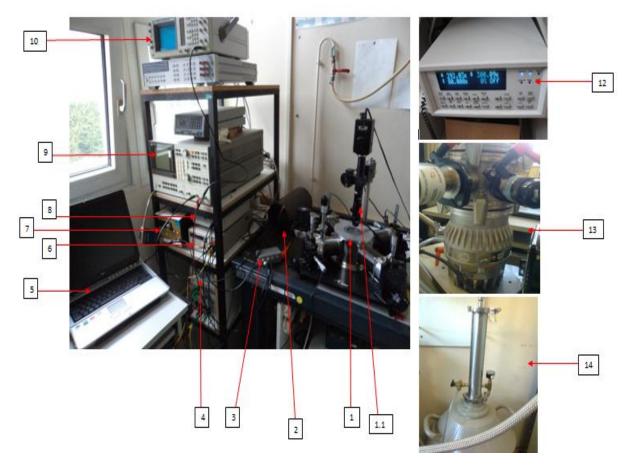

| II.2. Banc de mesure                                                                                                  | 28 |

| II.3. Extraction des paramètres électriques en régime linéaire                                                        | 28 |

| II.3.1. Méthodologie de la fonction Y                                                                                 | 29 |

| II.3.2. Méthodologie de la fonction Y à faible température (< 40 K)                                                   | 34 |

| II.4. Extraction des paramètres en régime de saturation                                                               | 36 |

| II.4.1. Extraction de V <sub>Dsat</sub> et I <sub>Dsat</sub>                                                          | 36 |

| II.4.3. Extraction du DIBL                                                                                            | 37 |

| II.5. Résultats et discussion                                                                                         | 38 |

| II.5.1. Résultats obtenus en régime linéaire                                                                          | 38 |

| II.5.2. Résultats obtenus en régime de saturation                                                                     | 45 |

| Conclusion                                                                                                            | 48 |

| Chapitre III : Bruit basse fréquence comme outil de diagnostic non                                                    |    |

| destructif                                                                                                            | 50 |

| Introduction                                                                                                          | 51 |

| III.1. Généralités                                                                                                    | 51 |

| III.1.1. Bruit blanc                                                                                                  | 52 |

| III.1.2. Bruit de génération-recombinaison                                                                            | 52 |

| III.1.3. Bruit en 1/f ou bruit excédentaire                                                                           | 54 |

| III.3. Modélisation du bruit basse fréquence dans les MOSFETs                                                         |    |

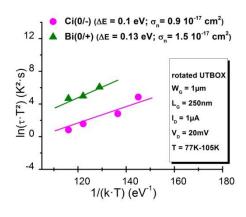

| III.4. Spectroscopie de bruit                                                                                         | 58 |

| III.4.1. Analyse du bruit de génération-recombinaison                                                                 |    |

| III.4.2. Méthodologie de la spectroscopie de bruit de génération-recombinaison                                        | 59 |

| III.4.3. Rappel sur les types de pièges                                                                               |    |

| III.5. Densité de pièges dans le film de Silicium                                                                     |    |

| III.6. Résultats et discussion                                                                                        | 64 |

| III.6.1. Bruit en 1/f                                                                                                 | 64 |

| III.6.2. Qualité du processus d'oxydation                                                                             | 69 |

| III.6.3. Qualité du film de Si                                                                                        |    |

| Conclusion                                                                                                            | 74 |

| Chapitre IV : Mise en évidence de phénomène inhabituel et des effet                                                   | S  |

| quantiques à faible température                                                                                       | 76 |

| Introduction                                                                                                          | 77 |

| IV.1. Mise en évidence à faible température d'un comportement inhabituel dans les caractéri<br>de la transconductance |    |

| IV.1.1. Phénomène observé                                                                                             |    |

| IV.1.2. Hypothèse 1 : Effet Kink Linéaire                                                                             |    |

| IV.1.3. Hypothèse 2 : Effet tunnel à travers des dopants diffusés des extensions de source et de                      |    |

| IV.1.4. Impact de la polarisation de la grille arrière                                                                | 82 |

| IV.1.5. Analyse sur l'origine du comportement inhabituel de g <sub>m</sub> par le bruit basse fréquence               | 83 |

| IV.2. Mise en évidence d'effets quantiques à température cryogénique       | 85  |

|----------------------------------------------------------------------------|-----|

| IV.2.1. Résultats en courant continu à 4.2K                                | 86  |

| IV.2.2. Bruit basse fréquence à 4.2K et liaison avec les effets quantiques | 88  |

| Conclusion                                                                 | 97  |

| Chapitre V : Synthèse                                                      | 100 |

| Conclusion générale                                                        | 107 |

| Annexe                                                                     | 110 |

| Bibliographie                                                              | 118 |

## LISTE DES FIGURES

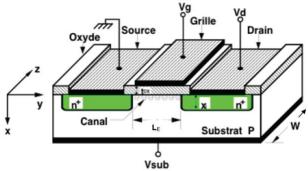

| Figure I. 1: Structure d'un MOSFET conventionnel à canal n                                                          | 12         |

|---------------------------------------------------------------------------------------------------------------------|------------|

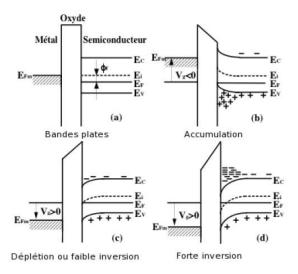

| Figure I. 2 : Diagrammes de bandes d'énergie d'un MOSFET durant ses différents régime                               |            |

| de fonctionnement [Sze'81]                                                                                          |            |

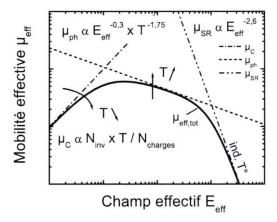

| Figure I. 3 : Dépendance en température et en champ électrique des trois mécanismes de                              |            |

| collisions impactant la mobilité effective [Takagi'94]                                                              | 16         |

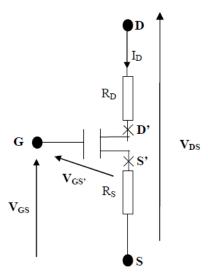

| Figure I. 4 : Modélisation des résistances d'accès de source et de drain dans un MOSFET.                            |            |

| et D' délimite les extrémités réelle de canal de conduction                                                         |            |

| Figure I. 5. Contrainte de traction suite au depot du Si sur SiGe [Esseni'2011]                                     |            |

| Figure I. 6. La technique du smart cut.                                                                             |            |

| Figure I. 7. Dépôt de couche CESL [Raymond'2009]                                                                    | 23         |

| Figure I. 8. Croissance épitaxiale sélective du SiGe dans les régions de source et drain                            |            |

| [Esseni'2011]                                                                                                       | 23         |

|                                                                                                                     |            |

|                                                                                                                     |            |

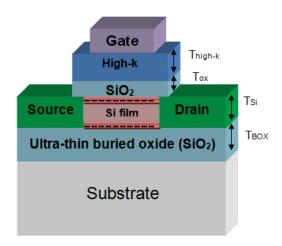

| Figure II. 1: Représentation schématique du transistor UTBOX sur SOI                                                |            |

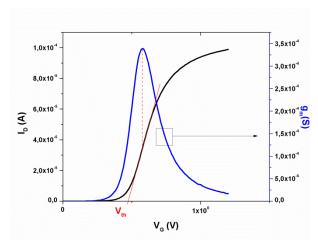

| Figure II. 2: Extraction de la tension de seuil par la méthode d'extrapolation                                      |            |

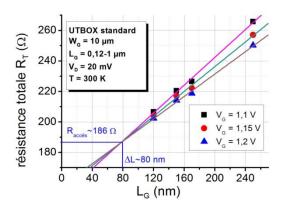

| Figure II. 3: Extraction de $R_{accès}$ et $\Delta L$ avec la méthode de la résistance totale                       |            |

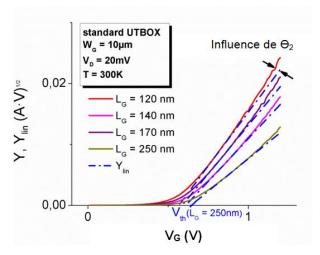

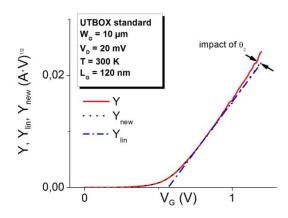

| Figure II. 4: Evolution avec $V_G$ de la fonction $Y$ et de sa linéarisation en inversion modéré                    |            |

| <i>Y<sub>lin</sub> pour différentes longueurs de grille.</i>                                                        |            |

| Figure II. 5: Evolution linéaire de la fonction $\theta_{eff}$ avec $V_G$ pour deux différentes longueurs           |            |

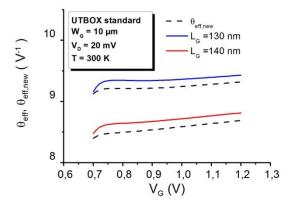

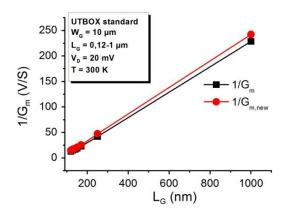

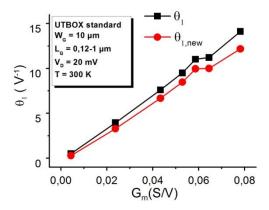

| grille                                                                                                              | 31         |

| Figure II. 6: Evolution de $1/G_m$ avec $V_G$                                                                       |            |

| Figure II. 7: Evolution de $\theta_1$ avec $G_m$                                                                    | 32         |

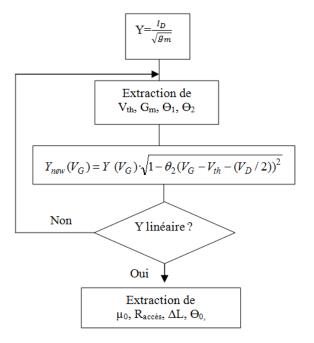

| Figure II. 8: Démarche suivie pour la construction de la fonction Y <sub>new</sub> [Lee'2011]                       | 33         |

| Figure II. 9: Convergence de la fonction Y <sub>new</sub> vers la linéarité après une seule itération               | 34         |

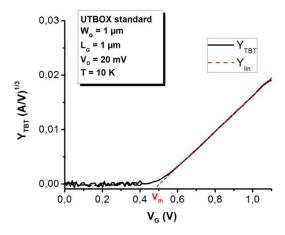

| Figure II. 10: Construction de la fonction Y à très basse température                                               | 35         |

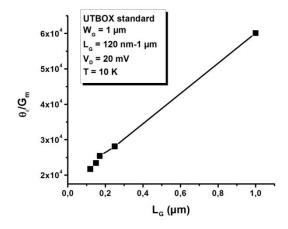

| Figure II. 11: Evolution de $\Theta_{ii}/G_m$ avec $L_G$                                                            | 35         |

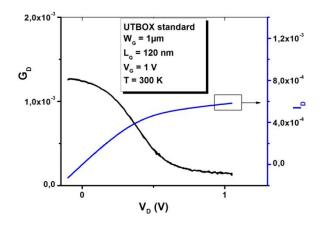

| Figure II. 12: Caractéristiques de transferts $G_D$ et $I_D$ en fonction de la tension de drain $V_D$ .             | 36         |

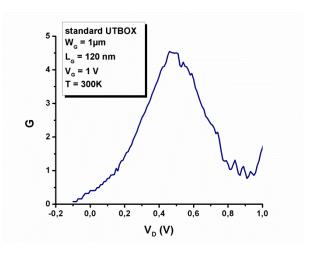

| Figure II. 13: La fonction $G(V_D)$ pour une longueur donnée à température ambiante                                 |            |

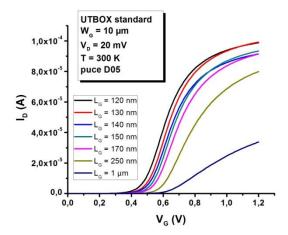

| Figure II. 14: Caractéristique de sortie $I_D(V_G)$ pour un lot de transistors UTBOX à différen                     | ntes       |

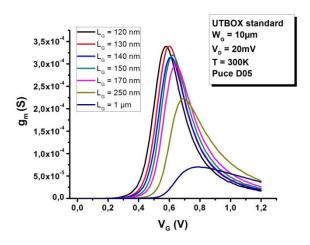

| longueurs de grille et même largeur de la puce D05                                                                  |            |

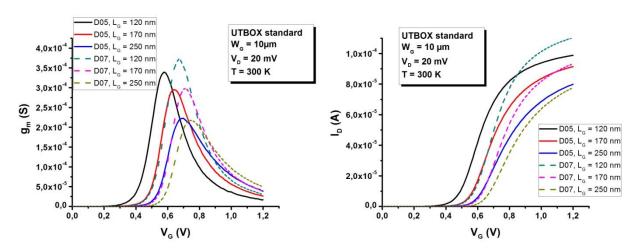

| Figure II. 15: Caractéristique de sortie $g_m(V_G)$ pour un lot de transistors UTBOX à                              |            |

| différentes longueurs de grille et même largeur de la puce D05                                                      | 39         |

| Figure II. 16: Caractéristiques de sortie $I_D(V_G)$ et $g_m(V_G)$ de trois longueurs différentes des               |            |

| puces D05 et D07                                                                                                    |            |

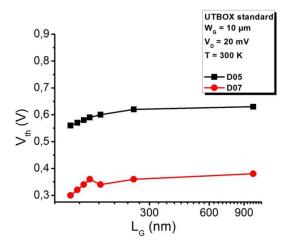

| Figure II. 17: Evolution de la tension de seuil en fonction de la longueur de grille à                              |            |

| température ambiante pour les dispositifs des puces D05 et D07                                                      | 40         |

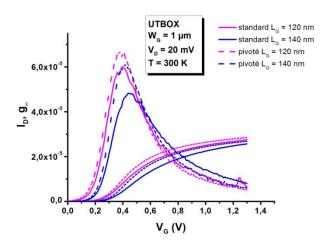

| Figure II. 18: Caractéristiques de sortie $I_D(V_G)$ et $g_m(V_G)$ comparant des dispositifs standa                 |            |

| et pivotés de même géométrie                                                                                        |            |

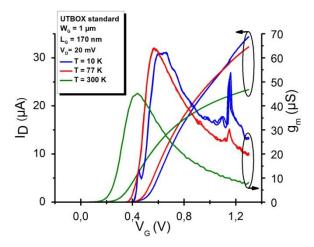

| Figure II. 19: Caractéristiques de sortie $I_D(V_G)$ et $g_m(V_G)$ à trois différentes températures                 | •• / 1     |

| pour un UTBOX donné                                                                                                 | 42         |

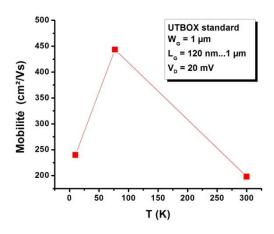

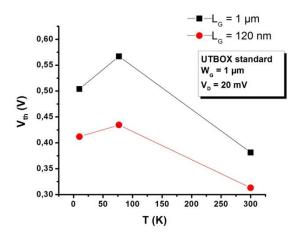

| Figure II. 21: Evolution de la tension de seuil en fonction de la température                                       |            |

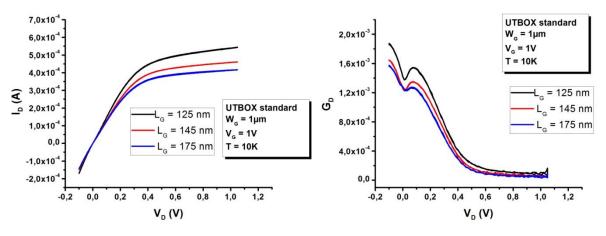

| Figure II. 22 : Caractéristiques de sortie $I_D(V_D)$ $G_D(V_D)$ pour différentes longueurs de gril.                |            |

| de la puce D07 à une température de 10 Kde la puce D07 à une température de 10 K                                    |            |

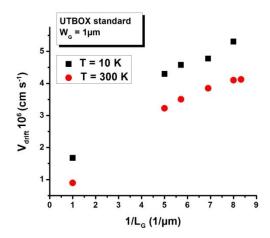

| Figure II. 23 : Evolution de la vitesse de saturation des porteurs en fonction de l'inverse de                      |            |

| Ingure II. 25. Evolution de la vitesse de saturation des porteurs en jonction de l'inverse de<br>Janqueur de grille | e 14<br>46 |

| TOTAL STREET, THE STREET                                                                                            |            |

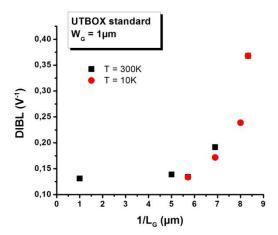

| Figure II. 24: Evolution du paramètre DIBL en fonction de l'inverse de la longueur de grille.                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure II 25: Evolution do V., on fonction do la longueur de grille.                                                                                                                         |

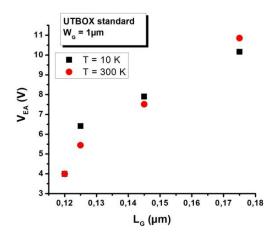

| Figure II. 25: Evolution de $V_{EA}$ en fonction de la longueur de grille                                                                                                                    |

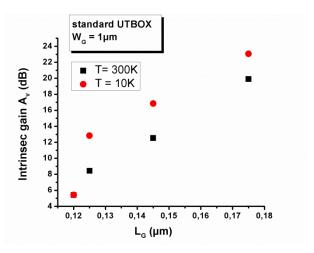

| Figure II. 20. Evolution au gain intrinseque $A_v$ en fonction de la tongueur de gritte                                                                                                      |

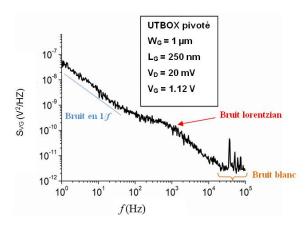

| Figure III. 1: Exemple de densité spectrale de bruit observée pour les transistors étudiés 52                                                                                                |

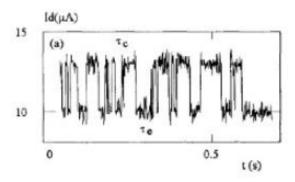

| Figure III. 2: Exemple de variations temporelles de courant de drain mettant en évidence le                                                                                                  |

| bruit RTS [Jang'2011]53                                                                                                                                                                      |

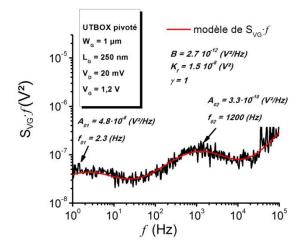

| Figure III. 3 : Exemple de modélisation d'un spectre de bruit normalisé par la fréquence et                                                                                                  |

| mesuré à température ambiante pour un transistor UTBOX à canal pivoté57                                                                                                                      |

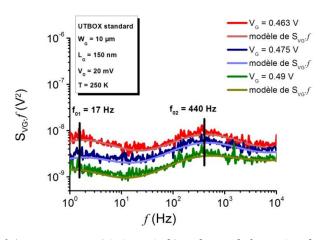

| Figure III. 4 : Exemple de fréquences caractéristiques indépendantes de la tension de grille et                                                                                              |

| correspondants ainsi à des pièges dans le film                                                                                                                                               |

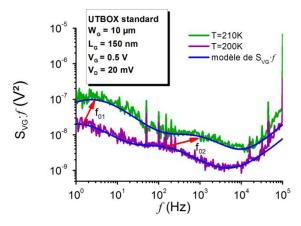

| Figure III. 5 : Exemple de fréquences caractéristiques variant avec la température et                                                                                                        |

| correspondants ainsi à des pièges dans le film                                                                                                                                               |

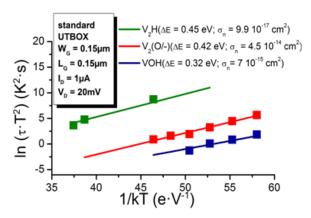

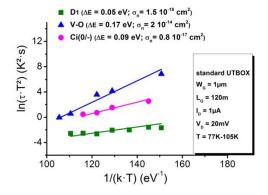

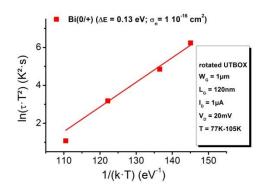

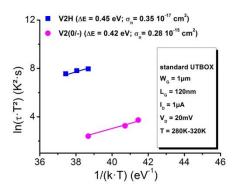

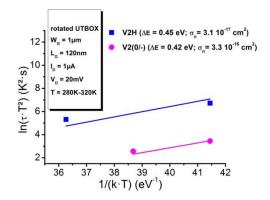

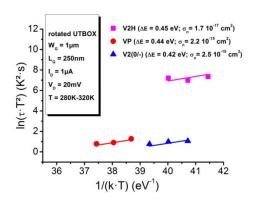

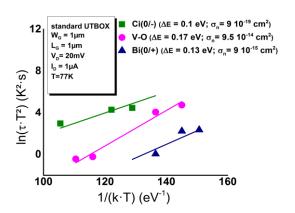

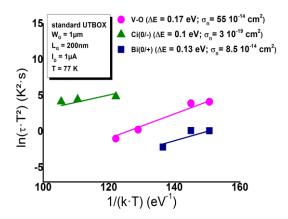

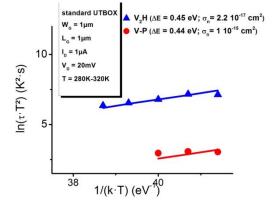

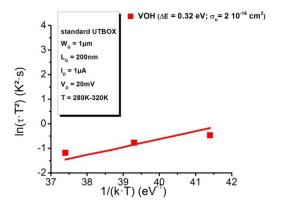

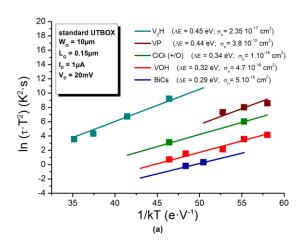

| Figure III. 6 : Diagramme d'Arrhenius obtenu pour un UTBOX standard dans une plage de                                                                                                        |

| température variant de 200 K à 330 K61                                                                                                                                                       |

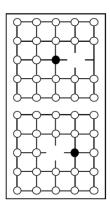

| Figure III. 7: Diffusion lacunaire [Mathiot'02]62                                                                                                                                            |

| Figure III. 8: Diffusion par auto-interstitiel [Mathiot'02]                                                                                                                                  |

| Figure III. 9: Diffusion interstitielle simple [Mathiot'02]63                                                                                                                                |

| Figure III. 10: Diffusion par mécanismes dissociatifs : (a) mécanisme de "Frank-Turnbull",                                                                                                   |

| (b) mécanisme "kick-out"                                                                                                                                                                     |

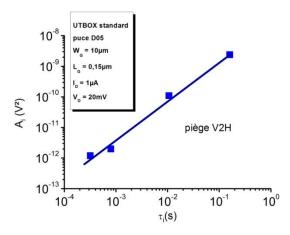

| Figure III. 11 : évolution linéaire de $A_i$ en fonction de $\tau_i$ associés au piège $V_2H$ identifiés dans                                                                                |

| une structure UTBOX standard64                                                                                                                                                               |

| Figure III. 12 : Evolution du niveau de bruit en $1/f$ en fonction de la tension $V_{GT}$ à                                                                                                  |

| température ambiante et en régime linéaire pour deux géométries de la puce $D05$ : (a) $W_G$ =                                                                                               |

| $10 \ \mu\text{m}, \ (b) \ W_G = 0.15 \ \mu\text{m}.$                                                                                                                                        |

| Figure III. 13: Evolution de la densité spectrale de courant de drain normalisée $S_{id}/I_D^2$ et de                                                                                        |

| $(g_m/I_D)^2 \cdot S_{VFB}$ en fonction du courant de drain à température ambiante et en régime linéaire                                                                                     |

| pour deux géométries de la puce D05 : (a) $W_G = 10 \mu m$ , (b) $W_G = 0.15 \mu m$                                                                                                          |

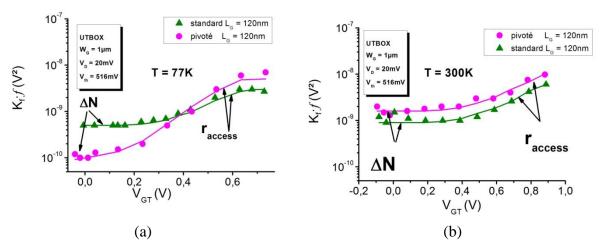

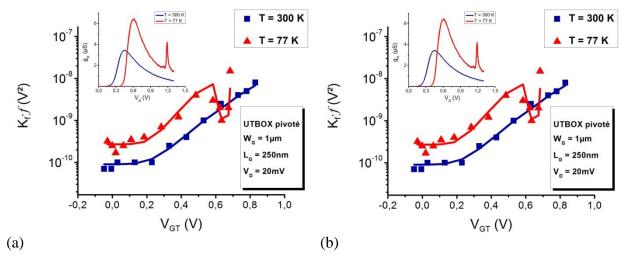

| Figure III. 14 : Evolution du niveau de bruit $1/f$ normalisé par la fréquence en fonction de $V_{GT}$                                                                                       |

| à température de l'azote liquide (a) et à température ambiante (b)67                                                                                                                         |

| Figure III. 15 : Impact du pic de transconductance apparu à basse température sur                                                                                                            |

| l'évolution du niveau de bruit 1/f pour un UTBOX (a) à canal pivoté (b) standard68                                                                                                           |

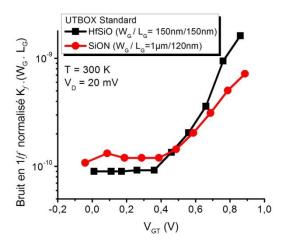

| Figure III. 16 : Evolution du niveau de bruit 1/f normalisé par la surface de grille pour deux                                                                                               |

| composant à différents diélectriques de grille69                                                                                                                                             |

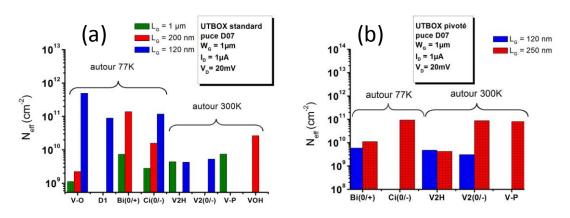

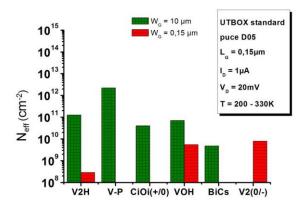

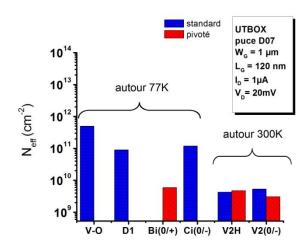

| Figure III. 17 : Densité effective de pièges pour trois longueurs de grille de composants de la                                                                                              |

| puce D07 (a) standards (b) pivoté73                                                                                                                                                          |

| Figure III. 18 : Densité effective de pièges pour deux largeurs de grille de composants                                                                                                      |

| standards de la puce D0573                                                                                                                                                                   |

| Figure III. 19 : Densité effective de pièges pour des composants standard et pivoté de la puce                                                                                               |

| D07                                                                                                                                                                                          |

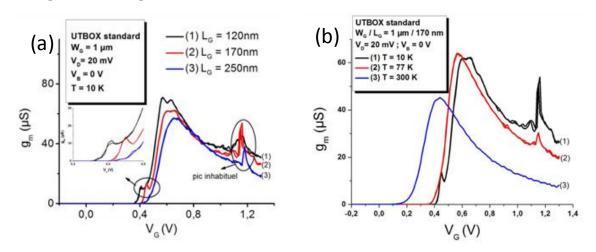

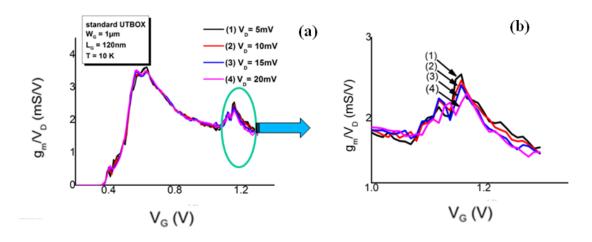

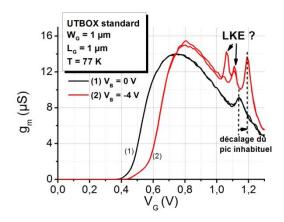

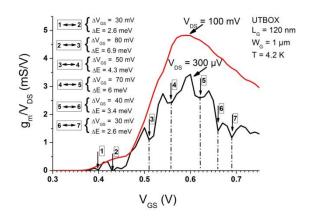

| Figure VI. 1. Canactéristiques de la transcenducture e a (V.) messurés (a) en direct de                                                                                                      |

| Figure VI. 1 : Caractéristiques de la transconductance $g_m(V_G)$ mesurée (a) en direct et en inverse à 10 K pour différentes longueurs de grille et (b) à différentes températures pour une |

| longueur de grille de 170 nm                                                                                                                                                                 |

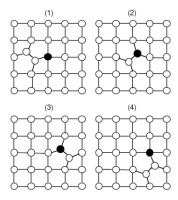

| Figure VI. 2: Schéma représentant l'effet kink linéaire dans un UTBOX à canal n                                                                                                              |

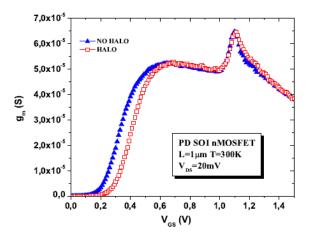

| Figure v1. 2: Schema representant t effet kink tineatre aans un 0160x a canat n<br>  Guo'2006                                                                                                |

| [Guo 2000]                                                                                                                                                                                   |

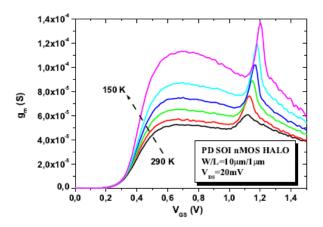

| linéaire dans un PD SOI nMOSFET [Guo'2006]79                                                                                                                                                 |

|                                                                                                                                                                                              |

| Figure VI. 4 : Evolution de l'effet du LKE avec la température pour des PD SOI nMOSFET [Guo'2006]80                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

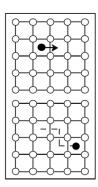

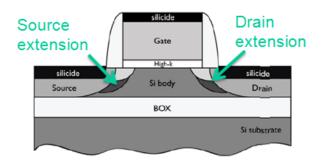

| [Guo'2006]80<br>Figure VI. 5 : Schéma représentatif d'une structure UTBOX avec les extensions de source et<br>de drain81                                                                                                                                                                                                                                                                                      |

| Figure VI. 6: Dépendance du pic inhabituel avec la tension de drain appliquée                                                                                                                                                                                                                                                                                                                                 |

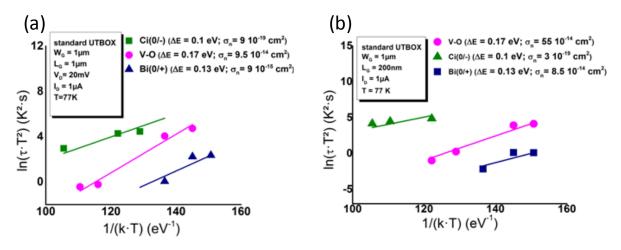

| Figure VI. 8 : Evolution de la constante de temps de lorentzienne avec la tension $V_{GT}$ à une température de (a) 10 K et (b) 77 K                                                                                                                                                                                                                                                                          |

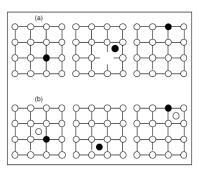

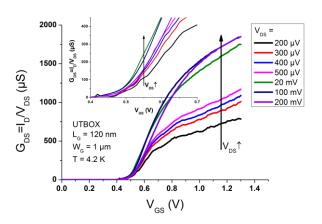

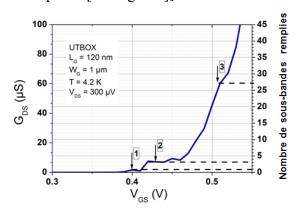

| Figure VI. 10: Caractéristiques typiques de conductance $G_{DS}$ ( $V_{GS}$ ) en régime linéaire à 4.2 $K$ pour différentes tensions de drain. Inset: un zoom du $G_{DS}$ ( $V_{GS}$ ) pour les faibles valeurs de tension de grille $V_{GS}$ montrant clairement l'allure en escalier pour des $V_{DS}$ < 500 $\mu$ V                                                                                        |

| Figure VI. 12. Le comportement en escalier de la conductance permet d'indiquer le nombre de sous-bandes d'énergie peuplées correspondant aux minima locaux de transconductance numérotés sur la Fig. VI.11                                                                                                                                                                                                    |

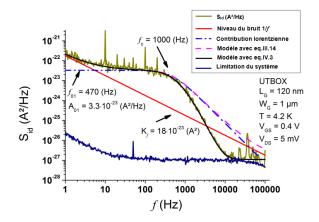

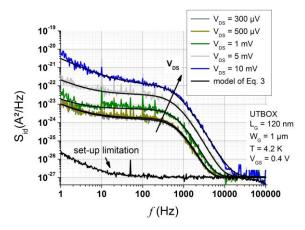

| Figure VI. 13. Comparaison entre les mesures de bruit et les modèles utilisant l'équation. III.14 et l'équation.VI.3. Un bon accord est observé entre l'expérimental et le modèle de l'équation. VI.3, dans lequel le niveau de bruit $1/f$ et une contribution lorenzienne sont pris en compte. Les spectres de bruit peuvent donner des informations une décade au-dessus de $f_c$ , jusqu'à environ 10 kHz |

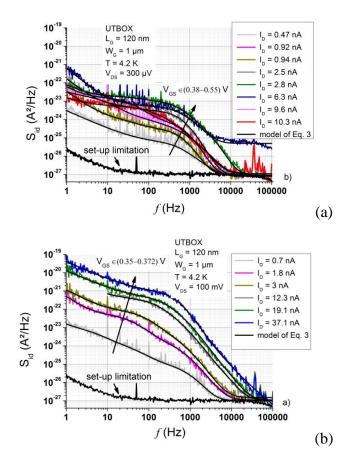

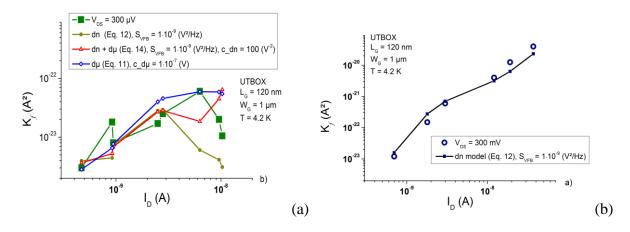

| Figure VI. 14. Densité spectrale de puissance du courant de drain normalisée par la fréquence, a) à $V_{DS}$ = 300 $\mu V$ ; b) $V_{DS}$ = 100 $m V$ . Le bruit du système ( $W_{ns}$ ) mesuré en référence par rapport à l'entrée de l'amplificateur de transimpédance est toujours quelques décades plus bas que le bruit mesuré des transistors                                                            |

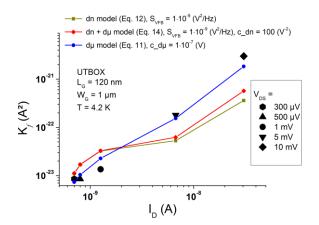

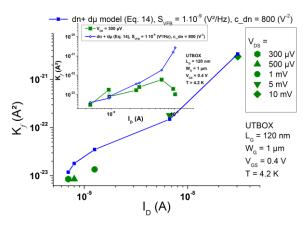

| Figure VI. 15. Évolution du niveau de bruit en $1/f(K_f)$ du courant de drain en fonction du courant de drain pour des tensions de drain fixes de a) 300 $\mu$ V et b) 100 mV                                                                                                                                                                                                                                 |

## LISTE DES TABLEAUX

| Tableau II. 1: Principales caractéristiques des transistors UTBOX étudiés                                                                                                                 | 28 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Tableau II. 2: Paramètres statiques extraits à température ambiante pour les dispositifs des                                                                                              | s  |

| puces D05 et D07                                                                                                                                                                          | 40 |

| Tableau II. 3: Principaux paramètres statiques extraits à température ambiante pour des                                                                                                   |    |

| dispositifs standards et pivotés de la puce D07.                                                                                                                                          | 41 |

| Tableau II. 4: Principaux paramètres statiques extraits à différentes températures                                                                                                        | 44 |

| Tableau II. 5: Courants I <sub>ON</sub> et I <sub>OFF</sub> extraits à différentes températures                                                                                           | 46 |

| Tableau III. 1: Evolution de SidID2 et SVG, 1/f en fonction de la tension de grille en régin de fonctionnement linéaire du MOSFET facilitant l'identification de l'origine du bruit en 1/ | f. |

| Tableau III. 2 : Valeurs estimées de la densité de pièges dans l'oxyde dans les différentes technologies étudiées                                                                         |    |

| Tableau III. 3: Pièges identifiés dans les transistors de la puces D07 et leurs paramètres                                                                                                |    |

| Tableau III. 4: Pièges identifiés dans les transistors de la puces D05 et leurs paramètres                                                                                                | 71 |

## **Symboles**

A<sub>i</sub> Niveau du plateau d'une lorentzienne

B Niveau du bruit blanc

C<sub>dep</sub> Capacité de la zone de déplétion

C<sub>i</sub> Capacité par unité de surface de la zone d'inversion

C<sub>ss</sub> /C<sub>it</sub> Capacité associée aux états d'interfaces

Cox Capacité de l'oxyde

c\_dn Paramètre lié au mécanisme fluctuation de nombre de porteurs c\_dµ Paramètre lié au mécanisme de fluctuations de la mobilité

dn Fluctuations de nombre de porteurs

du Fluctuations de mobilité

E<sub>c</sub> Energie du bas de la bande de conduction

E<sub>i</sub> Energie intrinsèque

E<sub>g</sub> Largeur de la bande interditeE<sub>T</sub> Energie d'énergie de Fermi

Ev Energie du haut de la bande de valence

E<sub>y</sub> Champ électrique longitudinalE<sub>sat</sub> Champ électrique de saturation

f Fréquence

f<sub>0i</sub> Fréquence caractéristique du bruit lorentzien

f<sub>c</sub> Fréquence de coupure

g<sub>m</sub> Transconductance d'un transistor MOSFET

G<sub>m</sub> Mobilité à faible champs

G<sub>DS</sub> Conductance

$\begin{array}{lll} h & Constante \ de \ Planck \\ I_B & Courant \ de \ substrat \\ I_D & Courant \ de \ drain \\ I_G & Courant \ de \ grille \\ I_S & Courant \ de \ source \\ \end{array}$

I<sub>DS</sub> Courant du drain-source

$\begin{array}{lll} I_{Dsat} & Courant \ de \ drain \ de \ saturation \\ I_{ON} & Courant \ de \ drain \ à \ l'état \ ON \\ I_{OFF} & Courant \ de \ drain \ à \ l'état \ OFF \\ k/k_B & Constante \ de \ Boltzmann \\ K_f & Niveau \ du \ bruit \ excédentaire \end{array}$

K<sub>r</sub> Niveau du bruit dû aux résistances d'accès

L Longueur de Masque

$\begin{array}{ll} L_G \, / L_{eff} & \quad & Longueur \, effective \, de \, la \, grille \\ m_e & \quad & Masse \, effective \, des \, \'electrons \\ m_h & \quad & Masse \, effective \, des \, trous \end{array}$

M<sub>c</sub> Nombre des minima d'énergie dans la bande de conduction

n Concentration d'électrons N<sub>eff</sub> Densité surfacique du piège

N<sub>t</sub> Densité de pièges par unité de volume et d'énergie

p Concentration des trous

q Charge électrique élémentaire absolue

Q<sub>c</sub> Charge critique

Q<sub>d</sub> Hauteur de barrière source-canal

Q<sub>inv</sub>/Q<sub>i</sub> Charge d'inversion

Qit Charge des états d'interface

Q<sub>m</sub> Charge d'inversion correspondante à la mobilité effective maximale

Q<sub>ox</sub> Charge de l'oxyde

Q<sub>sc</sub> Charge du semi-conducteur

r<sub>access</sub> résistances d'accès

r<sub>T</sub> Résistance dynamique totale R Résistance d'un matériau R<sub>accès</sub> Résistance d'accès

Raccès Resistance di acces

RD Résistance du drain

Résistance d'accès statique

S<sub>I</sub> Densité spectrale du bruit de Schottky

S<sub>ID</sub> Densité spectrale du bruit RTS

S<sub>lor</sub> Densité spectrale du bruit Lorentzien

S<sub>sortie</sub> Densité spectrale de sortie

$S_{V_{FB}}$  Densité spectrale du bruit du courant du drain  $S_{V_G}$  Densité spectrale du bruit en tension de grille

$S_{V_{\mathtt{D}}}$  Densité spectrale du bruit thermique par rapport à la tension

T Température

$\begin{array}{lll} T_{BOX} & Epaisseur de l'oxyde enterré \\ T_{hk} & Epaisseur de l'oxyde high-k \\ T_{ox} & Epaisseur de l'oxyde grille \\ T_{Si} & Epaisseur du film du silicium \\ T_{SiO2} & Epaisseur de la couche interfaciale \\ V_{drift} & Vitesse de saturation des porteurs \end{array}$

$\begin{array}{ccc} V_B & & Tension \ du \ substrat \\ V_D & & Tension \ de \ drain \\ V_G & & Tension \ de \ grille \\ V_S & & Tension \ de \ source \\ V_{DD} & & Tension \ d'alimentation \\ V_{DS} & & Tension \ drain-source \\ \end{array}$

V<sub>Dsat</sub> Tension de drain de saturation

V<sub>EA</sub> Tension Early

$V_{FB}$  Tension de bandes plates  $V_{GS}$  Tension grille-source  $V_{GT}$  Tension effective de grille

V<sub>th</sub> Tension de seuil

V<sub>Th. ext</sub> Tension de seuil extrapolée

W Largeur de masque

W<sub>G</sub>/W<sub>E</sub> Largeur effective de grille

$W_{ns}$  Bruit du système  $x_i$  Profondeur de jonction

α<sub>c</sub> Coefficient des interactions coulombiennes

α<sub>H</sub> Constante de Hooge

β Paramètre égale à  $μ_0C_{ox}W_E/L_E$

γ Exposant de l'uniformité de la densité de pièges

ΔE Différence entre l'énergie du piège et la bande de conduction

ΔI Amplitude moyenne du courant de drain

ΔL Réduction de la longueur du canal

$\Delta N$  Modèle de McWhorter  $\Delta \mu$  Modèle de Hooge

ΔW Réduction de la largeur du canal

$\epsilon_0$  Permittivité du vide  $\epsilon_{ox}$  Permittivité de l'oxyde

ε<sup>r</sup>hk Permittivité relative du diélectrique high-k

ε<sup>r</sup><sub>SiO2</sub> Permittivité relative du SiO<sub>2</sub>

$\theta_0$  Facteur d'atténuation intrinsèque de la mobilité  $\theta_1$  Premier facteur d'atténuation de la mobilité  $\theta_2$  Deuxième facteur d'atténuation de la mobilité Facteur d'atténuation effectif de la mobilité

λ Paramètre DIBLλ Paramètre tunnel

μ Mobilité

μ<sub>0</sub> Mobilité à faible champ électrique

μ<sub>c</sub> Mobilité due aux interactions des centres coulombiens

μ<sub>eff</sub> Mobilité effective

μ<sub>m</sub> Maximum de la mobilité

μ<sub>SR</sub> Mobilité due aux interactions avec la rugosité de la surface

μ<sub>ph</sub> Mobilité due aux interactions des centres avec les phonons acoustiques

$\sigma_n$  Section de capture des électrons  $\sigma_{\nu}$  Section de capture des trous  $\tau$  Constante de temps de piège  $\tau_c$  Constante de temps de capture

$\tau_i$  Constante de temps de la lorentzienne

τ<sub>e</sub> Constante de temps d'émission

Ψ<sub>s</sub> Potentiel de surface du semi-conducteur

Ψ<sub>f</sub> Potentiel de Fermi

## **Acronymes**

CESL Contact Each Stop Layer

DIBL Drain Induced Barrier Lowering

D-RAM Dynamic Random Access Memory

DSP Densité Spectrale de Puissance

EOT Equivalent Oxide Thickness

FDSOI Fully Depleted Silicon On Insulator

FinFETs Finger Field Effect Transistor

GIFBE Gate-Induced Floating Body Effects

GIDL Gate Induced Drain Leakage

HDD High Doped Drain

IRDS International Roadmap for Devices and Systems

LKE Linear Kink Effect LDD Low Doped Drain

MOSFET Metal Oxide Semiconductor Field Effect Transistor

PDMOSFET Partially Depleted Metal Oxide Semiconductor Field Effect Transistor

RTS Random Telegraph Signal SEG Selective Epitaxial Growth

SOI Silicon On Insulator SCE Short Channel Effect

sSOI Strained Silicon On Insulator

RSC Reverse Short Channel UTBOX Ultra Thin Buried OXide

## INTRODUCTION GENERALE

Le transistor MOSFET (métal oxyde semi-conducteur à effet de champ) est considéré comme l'un des composants électroniques qui ont révolutionné le monde de l'électronique moderne. En 1959, grâce à J.S. Kilby [Kilby'59], le premier circuit intégré exploitant ce transistor a été breveté. Depuis, le MOSFET est devenu à la base de plusieurs applications dans la télécommunication, l'automobile, l'automatisme, l'aérospatiale...

Ces dernières décennies, le développement des transistors MOS repose principalement sur la réduction des dimensions de ces composants. Ceci a induit l'augmentation du nombre de transistors sur une puce suivant la loi de Moore qui prévoyait que cette croissance double tous les 18 mois [Moore'65]. Ainsi, la miniaturisation des composants a permis l'augmentation de la densité d'intégration, l'amélioration de la vitesse de commutation, en plus de la réduction des coûts de fabrication et de consommation.

Toutefois, à partir d'un certain stade la miniaturisation ne pouvait se faire en respectant les règles de réduction d'échelle parce que des effets parasites ayant tendance à modifier les performances de ces transistors étaient induites. A titre d'exemple, on peut mentionner les courants de fuite vers la grille, la source et le substrat ; l'augmentation des capacités de jonctions et des résistances d'accès et la réduction de la mobilité des porteurs. Pour remédier à ces effets parasites tout en évoluant vers des géométries plus réduites, de nouvelles solutions ont été proposées, notamment : l'utilisation de nouveaux matériaux à haute permittivité diélectrique « high-k » pour l'oxyde de grille, le remplacement de la grille en polysilicium par une grille métallique, l'utilisation de nouvelles étapes technologiques durant le processus de fabrication comme les techniques de contrainte et le substrat sur isolant (SOI) et aussi le développement de nouvelles architectures remplaçant le MOSFET classique par des structures multigrilles (double grille « DGFETs », triple grille « FinFETs », gate all around « GAAFETs », etc. ..). Ces dernières permettent un meilleur contrôle électrostatique du canal de conduction autorisant une amélioration des effets de canaux courts. Ces structures sont aussi généralement caractérisées par un canal non intentionnellement dopé, ce qui aide à minimiser la variabilité. Particulièrement, les transistors complètement deplétés à film mince et sur diélectrique enterré très fin (FD UTBOX), qui sont des structures en double grilles permettant de se servir de la grille arrière pour moduler précisément la tension de seuil. Ces derniers ont vu un intérêt important pour la fabrication des mémoires volatiles à un transistor (1T-DRAM) puisqu'ils autorisent grâce à la grille arrière d'avoir un condensateur servant de stockage d'information dans une même structure que le transistor. De cette façon la densité d'intégration sur les circuits intégrés était augmentée et il n'y avait plus besoin d'une capacité externe.

Pour arriver à optimiser les performances de ces transistors MOSFETs, la compréhension du comportement physique au sein de ces structures s'avère essentielle. Pour ce faire, il y a eu recours à des techniques de caractérisation électriques permettant de déterminer les différents paramètres caractéristiques du transistor comme la tension de seuil, la mobilité.... L'étude du bruit basse fréquence est très souvent utilisée comme outil de diagnostic non destructif pour évaluer la qualité du film, de l'oxyde de grille et de l'interface film/oxyde vu que cette analyse permet d'identifier les pièges dans différentes zones du transistor et d'estimer leurs densités. Ainsi, le bruit basse fréquence peut être utilisé comme un outil de caractérisation complémentaire aidant à identifier les étapes de fabrication des transistors nécessitant une optimisation puisqu'un rapport peut être élaboré entre les pièges observés et ces étapes technologiques. En outre, l'étude du bruit basse fréquence permet d'identifier les sources de fluctuations pour avoir une meilleure vision d'analyser des mécanismes de transport des porteurs. Par ailleurs, il peut être utilisé comme facteur de mérite afin de comparer de différentes technologies.

La réduction de la température de fonctionnement des transistors était démontrée comme une alternative simple pour améliorer les performances de ceux-ci. La raison pour laquelle le refroidissement a été exploité dans certaines applications comme les amplificateurs faible bruit, les détecteurs infrarouges, le spatial... En outre, les études à basse température peuvent révéler des phénomènes inattendus dont l'analyse aide à mieux comprendre le comportement physique au sein du transistor.

C'est dans ce contexte que se situe le mémoire de cette thèse traitant des performances en statique et en bruit basse fréquence de transistors FD SOI UTBOX de la technologie 16 nm en fonction de la température. Ce travail est issu d'une thèse en cotutelle entre l'INSAT de l'université de Carthage, Tunis et le GREYC de l'université de Caen, France. Il s'inscrit dans le cadre d'un projet PHC tournesol démarré en 2012 en collaboration avec imec (Leuvain, Belgique).

Ce manuscrit de thèse est structuré en cinq chapitres. Le premier chapitre rappelle la structure d'un MOSFET, ses paramètres caractéristiques, ses régimes de fonctionnement et les étapes

de son développement technologiques durant les dernières décennies. Le second chapitre commence par décrire l'architecture étudiée avec les différentes géométries traitées pour passer ensuite à analyser les performances de ces transistors en régime linéaire et saturé tout en mettant en évidence l'influence de la réduction de température sur les performances électriques de ces composants.

Le troisième chapitre présente le bruit en basse fréquence en tant qu'outil de caractérisation non destructif des transistors MOSFET. Tout d'abord, les différents types de bruit communément trouvés dans les transistors MOSFET sont brièvement rappelés. Ensuite, une approche d'analyse du bruit est décrite mettant l'accent sur la spectroscopie de bruit comme outils d'identification de pièges dans les différentes zones du transistor. Finalement, les résultats issus de notre travail sont présentés : l'analyse du bruit en 1/f permet d'identifier l'origine de ce type de bruit d'une part et la densité de pièges dans l'oxyde de grille d'autre part. Cette étude donne des indications sur la qualité du processus d'oxydation. Ensuite, la spectroscopie du bruit permet d'identifier différents pièges dans le film de Si. Puis, une comparaison entre différentes géométries en termes de nombre et densité de pièges dans la zone de déplétion est effectuée. Une discussion est enfin établie sur l'origine de ces pièges et leur rapport avec les étapes technologiques de fabrication.

Le quatrième chapitre met en évidence un comportement inhabituel des caractéristiques de la transconductance observé à basse température. L'origine de ce comportement est discutée en exploitant les résultats d'étude du bruit en basse fréquence, en particulier la spectroscopie du bruit. Ensuite, l'analyse est focalisée sur des effets quantiques observés à température cryogénique de l'hélium liquide en discutant l'origine de ces effets et leur influence sur le bruit en basse fréquence. Dans cette partie, une nouvelle approche a été développée concernant les modèles de fluctuations mobilité et de fluctuations du nombre de porteurs corrélés aux fluctuations de mobilité. Elle mène à une formulation théorique valide en inversion modérée à très faibles températures (<40 K) de la densité spectrale de puissance du courant de drain.

Le dernier chapitre est une synthèse des résultats issus de ce travail de thèse.

# CHAPITRE I : RAPPEL SUR LE FONCTIONNEMENT DU MOSFET ET SON DEVELOPPEMENT

#### Introduction

Le fonctionnement du transistor MOS est basé sur l'effet de modulation de la densité de charges par un champ électrique perpendiculaire à leur direction. Cet effet est appelé « effet de champ » et a été mis en évidence depuis 1926 [Lilienfeld'30, Heil'35]. Mais, ce n'est qu'en 1960 que Kahng et Attalla [Kahng'60, Attala'60] ont parvenu à concevoir le premier MOSFET.

Ce premier chapitre rappelle la structure d'un MOSFET conventionnel, ses principaux paramètres électriques, les régimes de fonctionnement et les étapes de son développement technologiques durant les dernières décennies.

#### I.1. Structure de base du MOSFET

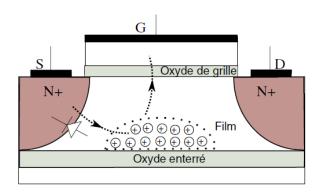

L'architecture de base d'un transistor MOSFET est composée d'un substrat en silicium dopé n ou p sur lequel sont implantées les zones de source et de drain qui sont fortement dopés. Le dopage de ces deux zones est opposé à celui du substrat (si le substrat est de type n, la source et le drain sont de type p). Entre les zones de source et de drain se trouve une couche interfaciale de SiO<sub>2</sub>, constituant le diélectrique de grille. Cette couche est couverte d'un matériau de haute conductivité (le poly-silicium ou bien un métal). Cet empilement est appelé la grille. En dessous de la grille se trouve la zone active du transistor, appelée canal.

Un MOSFET conventionnel est caractérisé par ses dimensions géométriques illustrées dans la Figure I. 1 (cas d'un transistor de type n) : la longueur et la largeur de la grille sont notées, respectivement, L et W. Il s'agit de longueur et largeur de masque. La longueur et la largeur effective sont notées  $L_E$  et  $W_E$ , respectivement. Vu la réduction d'échelle des transistors, la différence entre les dimensions de masque et les dimensions effectives n'est plus négligeable et doit être prise en compte. Ainsi, des nouveaux paramètres sont introduits, à savoir,  $\Delta L = L - L_E$  et  $\Delta W = W - W_E$ . La profondeur de diffusion des jonctions de source et drain est notée  $x_j$ , l'épaisseur de l'oxyde de grille est notée  $T_{ox}$ .

Figure I. 1 : Structure d'un MOSFET conventionnel à canal n.

#### I.2. Principe de l'effet de champ

La polarisation du MOSFET par l'application de champ électrique vertical ( $V_{GS}$ ) à travers la grille (G) permet de contrôler la densité de charges mobiles dans le canal de conduction entre la zone de source et celle de drain. Le mouvement de ces charges est entrainé par l'application d'un champ électrique horizontal entre la source et le drain ( $V_{DS}$ ). Cette modulation de la conductance du canal par un champ perpendiculaire à la direction de mouvement des charges est appelée « effet de champ » [Sze'81]. Les tensions de polarisations de grille  $V_{GS}$  et de drain  $V_{DS}$  sont référencées par rapport à la source/ substrat qui sont, généralement, reliés à la masse. La modulation de la conductance de canal est effective à partir d'une tension de grille appelée tension de seuil  $V_{th}$ . Il s'agit de la tension de grille nécessaire pour qu'un canal d'inversion soit créé.

#### I.3. Régimes de fonctionnement du MOSFET

En absence de polarisation appliquée aux électrodes du MOSFET, il y a toujours une courbure de bandes à l'interface semi-conducteur-oxyde. Cette courbure est due aux charges fixes présentes dans l'oxyde et à l'interface  $SiO_2/Si$  qui n'est pas parfaite. La valeur de tension de grille qu'il faut appliquer pour compenser cette courbure de bandes est appelée tension de bandes plates, notée  $V_{FB}$ . L'équation exprimant la relation entre cette tension et les autres paramètres du MOSFET est donnée par [Sze'81] :

$$V_{GS} = V_{FB} + \Psi_S - \frac{Q_{SC}}{C_{OX}} \tag{I.1}$$

avec  $\Psi_s$  le potentiel de surface,  $Q_{sc}$  la charge du semi-conducteur,  $C_{ox}$  la capacité de l'oxyde qui est donnée par [Sze'81] :

$$C_{ox} = \frac{\varepsilon_0 \varepsilon_{ox}}{T_{ox}} \tag{I.2}$$

$\epsilon_0$ ,  $\epsilon_{ox}$  sont les permittivités du vide et de l'oxyde, respectivement.  $T_{ox}$  est l'épaisseur de l'oxyde.

La charge du semi-conducteur est la somme de la charge d'inversion, la charge de déplétion et la charge des états d'interface :  $Q_{sc} = Q_{inv} + Q_{dep} + Q_{it}$ .

La relation entre la tension de bandes plates et la tension de seuil est donnée par [Sze'81] :

$$V_{th} = 2\Psi_s - \frac{Q_d}{c_{ox}} + V_{FB} \tag{I.3}$$

Q<sub>d</sub>/C<sub>ox</sub> étant l'hauteur de la barrière de potentiel entre la source et le canal.

En polarisant la grille du transistor, la courbure des bandes d'énergie commence à changer. Selon la valeur de la tension de grille  $V_{GS}$ , on distingue les différents régimes de fonctionnements du MOSFET (Figure I. 2) :

Figure I. 2 : Diagrammes de bandes d'énergie d'un MOSFET durant ses différents régimes de fonctionnement [Sze'81].

- Régime d'accumulation ( $V_{GS} < V_{FB}$ ): le champ électrique vertical créé par la tension de grille attire les porteurs majoritaires vers l'interface oxyde/semi-conducteur. Il y a donc une accumulation des porteurs majoritaires à l'interface oxyde/substrat.

- Régime de déplétion ou de faible inversion (V<sub>FB</sub> < V<sub>GS</sub> < V<sub>th</sub>): les porteurs majoritaires sont repoussés de l'interface donnant lieu à une zone appauvrie en porteurs majoritaires. La concentration des porteurs minoritaires attirés vers l'interface est supérieure à celle des porteurs majoritaires au même endroit conduisant à la création d'un canal de faible inversion en surface. Il est possible donc de faire circuler un courant entre les zones de source et de drain. Le courant de drain est dominé par un courant de diffusion qui évolue exponentiellement avec la tension de grille [Sze'81]:

$$I_d \propto e^{\frac{q(V_{GS} - V_{th})}{mkT}} \tag{I.4}$$

Où m est un facteur du substrat égal à  $1 + \frac{C_d + C_{it}}{C_{ox}}$  ( $C_d$  est la capacité de déplétion et  $C_{it}$  est la capacité des états d'interface).

- Régime de forte inversion (V<sub>GS</sub> > V<sub>th</sub>): la concentration des porteurs minoritaires en surface devient supérieure à la concentration des trous dans le volume. Via la couche d'inversion créée entre le drain et la source, un canal de conduction est bien formé entre ces deux zones. En augmentant la polarisation de grille, à partir d'une valeur limite de celle-ci, le potentiel de surface n'est plus influencé par la tension de grille mais plutôt par la tension de drain V<sub>DS</sub>. Dans ce cas-là, selon la valeur de cette dernière, on distingue deux modes de fonctionnement : le régime linéaire et le régime de saturation.

- Régime linéaire ou ohmique : il a lieu lorsque  $V_{DS} << V_{GS}$ . La distribution de porteurs est presque uniforme le long du canal. Pour une tension de drain donnée, le courant du canal  $I_D$  varie linéairement avec la tension de grille suivant l'équation :

$$I_{D} = \frac{W_{eff}}{L_{eff}} \mu_{eff} C_{ox} (V_{GS} - V_{th} - \frac{V_{DS}}{2}) V_{DS}$$

(I.5)

La variation de  $I_D$  en fonction de  $V_{GS}$  représente une caractéristique de transfert du transistor. Dans cette zone ohmique, la pente de la courbe linéaire présentant la variation du courant de drain par rapport à la tension de grille permet de déduire la transconductance  $g_m$ :

$$g_m = \frac{dI_D}{dV_{GS}} \tag{I.6}$$

• Régime de saturation : il a lieu lorsque  $V_{DS} > (V_{GS} = V_{Dsat})$ . Avec l'augmentation de la tension de drain, la charge d'inversion diminue en se rapprochant du drain jusqu'à une valeur limite  $(V_{Dsat})$  pour laquelle le canal est pincé du côté du drain. Dans cette région, le courant de saturation du drain est exprimé par [Mathieu'96] :

$$I_{Dsat} = \frac{1}{2} \frac{W_{eff}}{L_{eff}} \mu_{eff} C_{ox} V_{dsat}^2$$

(I.7)

avec  $\mu_{eff}$  la mobilité effective des porteurs dans le canal.

#### I.4. Mobilité des porteurs

La mobilité des porteurs caractérise l'aptitude de ceux-ci à se déplacer dans le canal. Ce paramètre est influencé par plusieurs effets : le champ longitudinal, l'orientation du réseau du canal, la température opérationnelle...

#### I.4.1. Mécanismes de collisions [Sah'72]

Au sein d'une même structure MOS, la mobilité des porteurs est fortement impactée par les mécanismes de collision, principalement, la collision sur les phonons, sur la rugosité de surface et sur les centres coulombiens:

- Collisions sur les phonons (μ<sub>ph</sub>): elles sont dues aux vibrations du réseau qui ont lieu lorsque la température opérationnelle est supérieure au zéro absolu. Lorsque cette température est inférieure à 100 K, il s'agit de phonons acoustiques qui donnent lieu à des collisions élastiques. Pour des températures plus élevées (mais inférieures à 340 K), on parle de phonons optiques. Ce type de collisions est dominant en faible inversion.

- Collisions sur les centres coulombiens (μ<sub>c</sub>): Elles se manifestent en faible inversion et à faible température lorsque les collisions sur les phonons ne sont pas dominantes. Ce type de collisions résulte des emplacements aléatoires des sites chargés prés du canal. Ces sites sont, généralement, localisés à proximité de l'interface Si/SiO<sub>2</sub>. Leurs emplacements aléatoires impactent le déplacement des porteurs dans le canal et modifient leurs mobilité.

- Collisions sur la rugosité de surface (μ<sub>SR</sub>): Les impuretés de surface, localisées à l'interface Si/SiO<sub>2</sub>, présentent une source importante de collision qui dépend de la structure de chaque composant. Ces collisions ne dépendent pas de la température et sont dominantes à fort champ électrique. Ainsi, elles sont fortement liées à la densité de charge de la zone d'inversion et de déplétion.

L'effet de ces mécanismes de collision est relié à la température et à la densité de porteurs dans le canal. Cette dépendance est décrite dans la Figure I. 3 : à basse température et en faible inversion, ce sont les collisions sur les phonons et sur les centres coulombiens qui influencent la mobilité effective. En forte inversion et indépendamment de la température, ce sont les collisions sur la rugosité de surface qui prédominent [Takagi'94].

La mobilité effective totale résultante de ces trois principaux mécanismes de collision est exprimée alors par l'équation empirique de Matthiessen qui considère que ces mécanismes de collisions sont non-corrélés :

$$\frac{1}{\mu_{eff}} = \frac{1}{\mu_{ph}} + \frac{1}{\mu_{SR}} + \frac{1}{\mu_C} \tag{I.8}$$

Figure I. 3 : Dépendance en température et en champ électrique des trois mécanismes de collisions impactant la mobilité effective [Takagi '94].

#### I.4.2. Mobilité à faible champ et mobilité effective

Lorsque le champ électrique transversal est assez faible, on parle de mobilité à faible champ électrique, notée,  $\mu_0$ . En augmentant le champ électrique vertical appliqué sur la grille, la densité de porteurs dans le canal augmente ce qui entraine une réduction de la mobilité. On parle alors d'une mobilité effective,  $\mu_{eff}$ . L'une de ses expressions simplifiées, en régime linéaire, est donnée par [Szelag'99]:

$$\mu_{eff} = \frac{\mu_0}{1 + \theta_1 (V_{GS} - V_{th}) + \theta_2 (V_{GS} - V_{th})^2}$$

(I.9)

$$\theta_1 = \theta_0 + \frac{W_G}{L_G} \mu_0 C_{ox} R_{SD} \tag{I.10}$$

$\Theta_1$ ,  $\Theta_2$  sont, respectivement, le premier et le second facteur de réduction de la mobilité :  $\Theta_1$  est lié aux collisions sur les phonons et aux résistances d'accès de source et de drain,  $\Theta_2$  est due aux collisions sur la rugosité de surface.

$\Theta_0 = C_{ox}/Q_c$  est le facteur intrinsèque de réduction de la mobilité (où  $Q_c$  ( $\approx 10^{13} q/cm^2$ ) est la charge critique caractérisant la réduction de la mobilité à forte polarisation de grille).

Il est à noter que lorsque le champ longitudinal (E<sub>y</sub>) créé par la tension de drain est suffisamment élevé, la mobilité effective est alors influencée par celui-ci et son expression est donnée par [Shin'91]:

$$\mu_{eff} = \frac{\mu_0}{\sqrt{1 + \left(\frac{E_y}{E_{sat}}\right)^2}} \tag{I.11}$$

#### I.5. Autres paramètres caractéristiques du MOSFET

#### I.5.1. Tension de seuil

Il s'agit de la tension de grille nécessaire pour qu'un canal d'inversion soit créé. Autrement, C'est la tension de grille nécessaire pour que le potentiel de surface  $\Psi_s$  soit égal à deux fois le potentiel de Fermi  $\Psi_f$ .

#### I.5.2. Résistances d'accès

Les résistances d'accès de source et de drain présentent un paramètre important impactant le courant de drain particulièrement pour les composants submicroniques. En effet, avec la miniaturisation continue des composants MOSFETs, les résistances d'accès deviennent non négligeables devant la résistance du canal. Ces résistances entrainent une chute des tensions appliquées au transistor ( $V_{GS}$  et  $V_{DS}$ ) et par la suite une chute du courant. Généralement, on considère que le transistor est symétrique par rapport à la médiane verticale de la grille. Ainsi, les résistances de source et de drain sont considérées identiques (Figure I. 4). Ces résistances d'accès sont influencées par plusieurs composantes comme la résistance du contact métal – semi-conducteur, le dopage des zones source et drain et des zones LDD...

Figure I. 4 : Modélisation des résistances d'accès de source et de drain dans un MOSFET. S' et D' délimite les extrémités réelle de canal de conduction.

#### I.5.3. Pente sous le seuil

C'est l'un des paramètres importants caractérisant le MOSFET vu qu'il renseigne sur la vitesse de passage du composant de l'état OFF à l'état ON (vitesse de commutation). Pratiquement, ce paramètre est extrait à partir de la pente du courbe  $log(I_D) = f(V_{GS})$  dans la région de sous seuil. Ce paramètre révèle la qualité de l'interface oxyde/semi-conducteur de

fait sa dépendance des diverses capacités d'interface  $(C_{it})$ , d'oxyde  $(C_{ox})$  et de la zone de déplétion  $(C_{dep})$  [Sze'81]:

$$S = \frac{kT}{q} \ln 10 \left[ 1 + \frac{C_{dep}}{C_{ox}} + \frac{C_{it}}{C_{ox}} \right]$$

(I.12)

La valeur idéale de ce paramètre est obtenue en négligeant les différentes capacités (puisque  $C_{dep} << C_{ox}$  et  $C_{it} << C_{ox}$ ). Elle est d'une valeur de 60 mV/décade à température ambiante.

#### I.5.4. Les courants I<sub>ON</sub> et I<sub>OFF</sub>

Le courant I<sub>OFF</sub> représente le courant de drain du transistor à l'état bloqué. Autrement dit, lorsqu'aucune polarisation n'est appliquée à l'électrode de drain. Idéalement, ce courant devrait être nul. En réalité il ne peut pas l'être compte tenu des courants de fuites circulant dans le canal. Le courant I<sub>OFF</sub> est responsable de la dissipation de la puissance [Andrieu'2005] qui limite la miniaturisation des composants MOSFETs.

Le courant  $I_{ON}$  est la valeur maximale que peut atteindre le courant de drain à tensions nominales ( $V_{DS} = V_{GS} = V_{DD}$ ). Il impacte directement le délai intrinsèque du transistor.

Les courants I<sub>OFF</sub> et I<sub>ON</sub> renseignent sur la performance du MOSFET.

#### I.5.5. Vitesse de saturation des porteurs, $V_{drift}$

C'est la vitesse maximale des porteurs dans le canal, notée V<sub>drift</sub>. En régime de saturation, ces porteurs de charges sont appelés des porteurs chauds vu leur énergie potentielle très élevée. Ceci entraine des phénomènes d'ionisation et dégrade la structure du transistor ce qui modifie ses performances électriques [Ghibaudo '97].

#### I.6. La miniaturisation des MOS entre avantages et inconvénients

La réduction des dimensions géométriques des composants à l'échelle nanométrique a permis d'améliorer leur qualité et d'augmenter la densité d'intégration à très grande échelle. Cette approche est connue sous le nom de « loi de Moore » [Moore'65]. Une loi qui prévoit que le nombre de transistors sur une même puce doublera presque tous les deux ans. Cependant, la miniaturisation des MOSFETs s'accompagne des effets parasites affectant la performance de ces composants [Khann'2004, Skotnicki'2000, Szelag'99].

#### I.6.1. Effet de confinement des porteurs

La réduction prononcée de l'épaisseur de la couche d'oxyde et des dimensions du transistor entraine un champ électrique très élevé à l'interface Si/SiO<sub>2</sub>. Ceci induit le confinement des porteurs dans un puits de potentiel très étroit. Ceci fait apparaître des niveaux d'énergie discrets dans ce puits. Cet effet de confinement de charge influence significativement les propriétés du transistor. Particulièrement, il augmente la dispersion de la tension de seuil [Fiori'01, Fiori'02, Fiori'03].

#### I.6.2. Courant tunnel

En diminuant l'épaisseur de l'oxyde de grille, des courants de fuite peuvent apparaitre [Yang'2004, Gehring'2004, Claeys'2002]. Pour des épaisseurs inférieures à 3 nm, la barrière de potentiel oxyde/semi-conducteur (SiO<sub>2</sub>/Si) devient tellement mince que les porteurs passent directement par effet tunnel de la grille au canal.

Aussi, avec la réduction de la longueur de grille, la distance entre la source et le drain devient de plus en plus réduite. Ceci affaiblit la barrière de potentiel source/canal/drain. Ainsi, les porteurs peuvent passer facilement par effet tunnel de la source au drain [Chang'2000, Wang'2002, Munteanu'2003, Wakabayashi'2004]. Cet effet présente une des limitations majeures de la miniaturisation des dispositifs MOS vu qu'il impacte directement le courant  $I_{OFF}$  [Yang'2004].

#### I.6.3. Transport balistique

Pour des polarisations élevées, la vitesse des porteurs atteint une limite de saturation. Cette vitesse est limitée par des mécanismes de collision et de dispersion dans le canal. Pour les nouveaux transistors nanométriques, vu la longueur réduite de la grille, ces mécanismes n'impactent plus le transport des porteurs. Ces derniers traversent alors le canal directement. Ce qu'on appelle le transport balistique. Dans ce cas- là, la vitesse des porteurs est beaucoup plus importante que la vitesse de saturation.

#### I.6.4. Impact sur la mobilité

La mobilité des porteurs est contrôlée significativement par les champs vertical et longitudinal. Avec l'augmentation du champ électrique vertical, la densité des porteurs est plus importante, induisant une réduction de leur mobilité à travers des collisions. Pour un champ longitudinal supérieur à  $10^5 \text{V/m}$ , la température des porteurs de charge accélérés vers le drain est susceptible de dépasser celle du réseau cristallin, créant ainsi des porteurs chauds.

#### I.6.5. Effets de canaux courts

En diminuant la longueur de grille, la partie de la charge contrôlée par les jonctions de source et de drain devient non négligeable devant celle effectivement contrôlée par la grille, ce qui induit une réduction de la tension de seuil. Ce phénomène est connu sous le nom d'effet de partage de charges (charge sharing). A polarisation de drain élevée, un autre phénomène devient important: c'est l'effet DIBL (pour Drain Induced Barrier Lowering). Il se traduit par une réduction de la hauteur de barrière source/substrat à fort V<sub>DS</sub> induisant également une diminution de la tension de seuil. Il en résulte une augmentation du courant de drain avec la tension de drain en régime de saturation. Un autre effet parasite apparait suite à la réduction de l'épaisseur de l'oxyde de grille, c'est le courant de fuite GIDL (« Gate Induced Drain

Leakage »). D'autres effets parasites sont créés entrainant la dégradation du fonctionnement du transistor comme le courant de perçage, le courant inverse de fuite des jonctions source/canal, canal/drain (RSC « Reverse Short Channel »)...

#### I.6.6. Effets de porteurs chauds

En régime de saturation, les porteurs de charges peuvent acquérir des énergies supérieures à la température thermique du réseau — il s'agit alors des porteurs chauds. L'injection de ces porteurs cause une génération de défauts localisés au voisinage du drain, charges piégées dans l'oxyde et/ou création d'états d'interface, ce qui entraîne une dérive des caractéristiques de ces dispositifs et par la suite une dégradation des performances électriques.

## I.7. Solutions pour remédier aux inconvénients de la miniaturisation des MOS

Pour guider les fabricants dans leur approche de miniaturisation des transistors, des lois de réduction d'échelle ont été proposées par Dennard [Dennard'74], Baccani [Baccani'84] ... Ces lois proposent des facteurs d'échelle à prendre en compte dans la réductions des dimensions du transistor. Pour des dimensions fortement submicroniques, afin de continuer la miniaturisation des transistors tout en évitant au mieux les effets néfastes, d'autres approches ont apparu, connues sous le nom de « More Moore » et « More than Moore ». De nouveaux procédés, architectures et matériaux ont vu le jour afin de poursuivre la quête du doublement de la puissance de calcul tous les deux ans utilisant des technologies silicium. Il s'agit de l'approche « More Moore ». La stratégie « More Than Moore » a pour objectifs d'améliorer les performances des MOSFET en utilisant d'autres matériaux et de créer des systèmes compacts de type Microelectromechanical system (système micro-électro-mécanique, MEMS) et System on Chip (système sur puce, SoC).

Dans ce qui suit, on présente les principales méthodes et technologies adoptées pour minimiser les effets parasites de la miniaturisation et améliorer les propriétés des transistors (More Moore).

#### I.7.1. Oxyde de grille

Avec la réduction d'échelle des transistors, l'oxyde de grille est devenu de plus en plus mince. Ceci augmente significativement les courants de fuites. Ainsi, en passant d'une épaisseur d'oxyde de 30 Å (ou 3 nm) à 10 Å (ou 1 nm), ces courants sont multipiliés par 8 [Buss'2005]. Pour palier à cet effet indésirable, le SiO<sub>2</sub> a cédé sa place à de nouveaux diélectriques caratérisés par une haute permitivité « high-k » comme le SiN<sub>4</sub>, le SiON, le TiO<sub>2</sub>... Ces

isolants permettent de garder les performances électriques de l'oxyde (capacité) avec une épaisseur plus importante. On évalue ces diélectriques en terme d'épaisseur équivalente d'oxyde EOT (« *Equivalent Oxide Thickness* »). Ceci signifie l'épaisseur réelle du SiO<sub>2</sub> qu'il faudrait pour obtenir la même valeur de capacité d'oxyde. Elle est donnée par :

$$EOT = T_{hk} \frac{\varepsilon_{SiO_2}^r}{\varepsilon_{hk}^r} \tag{I.13}$$

$\varepsilon_{hk}^r$  et  $\varepsilon_{SiO_2}^r$  sont respectivement la permittivité relative du diélectrique high-k et du SiO<sub>2</sub>.  $T_{hk}$  est l'épaisseur du matériau high-k.

Cependant, ces nouveaux matériaux ont plusieurs limites. A titre d'exemple, ils engendrent une réduction de la mobilité due aux interactions coulombiennes et avec les phonons optiques. Et une dérive de la tension de seuil à cause des pièges à l'interface et charges dans l'oxyde. Aussi, le dépôt d'un diélectrique high-k sur le silicium crée une couche de silice de mauvaise qualité qui dégrade le bon fonctionnement du transistor, d'où la nécessité d'introduire une couche interfaciale d'oxyde de silicium. Parmi les diélectriques high-k utilisés en emplilement avec une couche interfacile et une grille métalique, on trouve l'oxyde d'hafnium (HfO<sub>2</sub>) et le silicate de hafnium nitruré (HfSiON).

#### I.7.2. Grille métallique

L'utilisation de grille en polysilicium a posé plusieurs problèmes. Particulièrement, la réduction du couplage grille/canal à cause de la déplétion de la grille, et le contre dopage du canal à cause de la pénétration du bore de la grille polysilicium fortement dopée vers le canal à travers l'oxyde fin. Alors pour s'affranchir de ces problèmes, la grille en polysilicium a été remplacée par une grille métalique. Cette dernière présente une faible résistance, une meilleure integrité électrostatique et une meilleure compatibilité avec les oxydes high-k.

Les métaux les plus promoteurs sont le nitrure du titane (TiN) et le nitrure de tantale (TaN). Ils sont caractérisés par un niveau de Fermi proche du milieu de gap du silicium en régime de bandes plates, ce qu'on appelle matériau de type « midgap » [Allegret'2006].

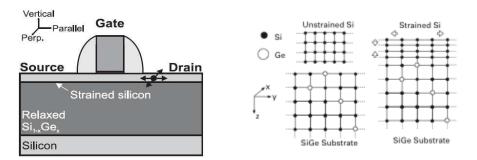

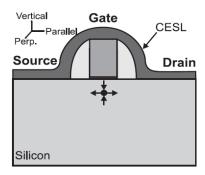

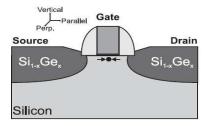

#### I.7.3. Techniques de contraintes mécaniques

C'est l'une des techniques les plus utilisées ces décennies afin d'améliorer le transport des porteurs dans le canal. L'application des contraintes mécaniques entraine des déformations au niveau du cristal. Ceci change les propriétés électroniques du transistor. Particulièrement la mobilité des porteurs qui est améliorée suite à la réduction des mécanismes de collisions. Ainsi, le courant dans le canal augmente. Le type de contrainte diffère selon le type du MOSFET. Pour les pMOS, on adopte des contraintes de compression, alors que pour les nMOS, on opte pour des contraintes de traction.

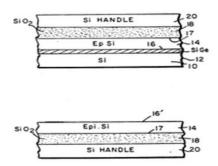

#### Silicium contraint sur isolant « sSOI »