# Caractérisations électriques et modélisation des phénomènes de piégeages affectant la fiabilité des technologies CMOS avancées (Nanofils) 10nm

Artemisia Tsiara

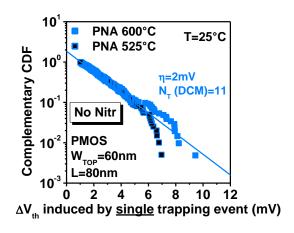

#### ▶ To cite this version:

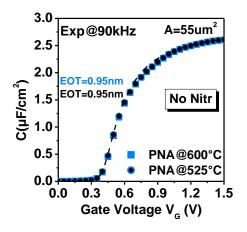

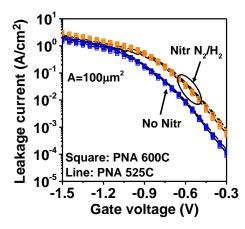

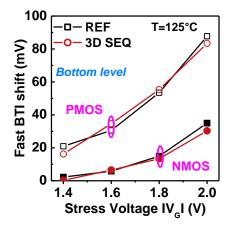

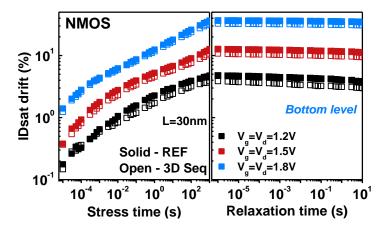

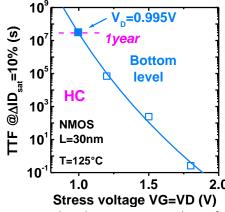

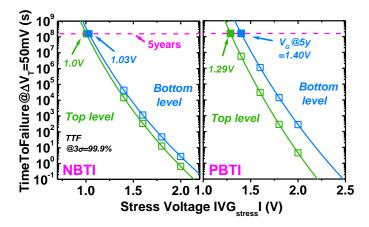

Artemisia Tsiara. Caractérisations électriques et modélisation des phénomènes de piégeages affectant la fiabilité des technologies CMOS avancées (Nanofils) 10nm. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2019. English. NNT: 2019GREAT010. tel-02328582

# HAL Id: tel-02328582

https://theses.hal.science/tel-02328582v1

Submitted on 23 Oct 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité : Nano électronique et Nano technologie

Arrêté ministériel : 25 mai 2016

Présentée par

#### Artemisia TSIARA

Thèse dirigée par **Dr. Gérard GHIBAUDO**, **IMEP-LAHC**, et codirigée par **Dr. Xavier Garros**, **CEA-LETI**

préparée au sein du CEA-LETI et de l'IMEP-LAHC dans l'École Doctorale Electronique, Electrotechnique, Automation et Traitement du Signal

# Electrical characterization & modeling of the trapping phenomena impacting the reliability of nanowire transistors for sub 10nm nodes

Thèse soutenue publiquement le 6 Mars 2019, devant le jury composé de :

#### **Monsieur Françis BALESTRA**

Directeur de recherche, CNRS, Président de jury

#### **Monsieur Olivier BONNAUD**

Professeur, Université de Rennes 1, Rapporteur

#### Madame Nathalie MALBERT

Professeur, Université Bordeaux, Rapporteur

#### **Monsieur Xavier GARROS**

Ingénieur, CEA-LETI, Co-Encadrant (Invité)

#### **Monsieur Gérard GHIBAUDO**

Directeur de recherche, IMEP-LAHC, Directeur de thèse

### Acknowledgements

Surprisingly enough, this appears to be the most difficult part of this manuscript, not really knowing what is appropriate to write about the end of an era, a.k.a. PhD, but I'll give it a go!

First of all, this work was made possible through the collaboration between CEA-Leti (LCTE laboratory) and IMEP-LaHC, under the financial support of LabEx Minos ANR-10-LABX-55-01 program that I thank very much for helping towards the realization of this project.

I would like to start my acknowledgements by thanking the reading committee, Madame Nathalie Malbert et Monsieur Olivier Bonnaud for accepting to be members of my jury and for spending time to provide their invaluable insight and comments on the manuscript, as well as to Monsieur Françis Balestra for being the president on my defense day.

My warmest thanks to my academic supervisor, Directeur de Recherche, Gérard Ghibaudo for choosing me as a student and for being there every time I needed him. His level of 'coolness' matches his immense knowledge on nanoelectronics!

A big shout out to Xavier Garros, my daily supervisor, my guide and mentor on reliability. Your patience, persistence and multitasking ability has helped me graduate from the famous X-academy (all right reserved!). Huge gratitude for everything you taught me and for constantly having time for me even when you didn't.

Many thanks to all the older and newer members of the LCTE laboratory for all the interaction we had during these last 3 years, the time we shared together and your support.

To my two exceptional French friends, Antoine Laurent and Alexandre Vernhet! Antoine, you welcomed me in B261 since day £ 2 and I cannot really choose only one thing to be grateful for. Thank you for all the laughs and very rare serious discussions we had, for all the comics you were lending me to read and for my French that never improved since we never really used it. Please be careful when you play football, you have a daughter to take care of now! To Alex, the greatest Pythonista of all time and a walking google database, I will miss you so much. I still need to find someone that insults my Greek culture and to bother when I have any kind of questions. Thank you for everything! To the Brazilian goddess, Brun(it)a, it was a real joy to meet you in Grenoble, despite the cold weather that made our stay more difficult! Thank you for all the time we spend together, for coming to France for a third time and I wish you all the best for the future! Stay in Europe girl! I'm waiting all of you in Belgium/ flat land for a degustation of all the available beers in the country (Bruna it's chocolate and waffles for you)!

Many thanks to a new colleague at imec, Emmanuel Chery for all the time he spent helping me with the dry runs of my defense and the correction of my French resume! Couldn't have been properly prepared without you!

Φυσικά και θα σου αφιέρωνα ξεχωριστή παράγραφο, ας είμαστε σοβαροί! Αν και δε συγκρατώ ονόματα το ξέρεις, Κωνσταντίνε Τριαντόπουλε! :) Καταρχάς σταμάτα να διαβάζεις τις βλακείες που γράφω παραπάνω και έλα κατά δω. Ας σοβαρευτώ για λίγο λέγοντας σου ότι ειλικρινά δε ξέρω πως τη πάλεψα τη πρώτη χρονιά του διδακτορικού στο χωρζιό και

μπ@#\$%λο που δεν ήσουν εδώ (αν κάτι μισώ είναι οι ερασιτεχνισμοί και η μιζέρια). Σ΄ευχαριστώ για όλα, που είσαι αυτός που είσαι, που είμαστε φιληνάδες, όμορφες, κοπέλες, κολλητούλες. Σταμάτα να αγοράζεις στυλό και τετράδια και προετοίμασε τον λόγο σου όταν θα κάνεις τις ανακοινώσεις για τα επόμενα επαγγελματικά σου βήματα. Εσείς εδώ τι κάνετε, με τι ασχολείστε τέλος πάντων? Λίγο έμεινε κ ετοιμάζεσαι για αποχώρηση, άντε με έχεις αφήσει σαν τη χήρα να τριγυρνάω εδώ πέρα. Εμείς σπίτι, άντρα δεν έχουμε?

Μεγάλο ευχαριστώ σε όλους τους φίλους μου, παλιότερους και νέους: Τάσα που είσαι πάντα δίπλα μου ακόμα και από μακριά (15 χρόνια είναι αυτά, ακόμα να με στεφανωθείς!), Χριστίνα συνβασανισμένη δόκτωρ πλέον επί γαλλικού εδάφους, Ιωάννα doctor to be (διάλεξες κ εσύ την επιστήμη πανάθεμα σε, δε πήγαινες για μαλλάκια-νυχάκια). Σε νομό Θεσσαλονίκης, Κοζάνης, Καστοριάς, Αιτ/νίας, οι αγαπημένες μου πόλεις, πολλά ευχαριστώ για όλα!

Και κάπου εδώ τελείωνουν οι ευχαριστιές με τους πιο σημαντικούς. Ένα μεγάλο ευχαριστώ στους γονείς μου, Βάσω και Σωκράτης, και στις μοναδικες αδερφές μου, Θάλεια και Δήμητρα, που ήταν πάντα εκεί για μένα και με στήριξαν όλα τα χρόνια που αποφάσισα να κυνηγήσω αυτό που ήθελα. Στη δεύτερη οικογένειά μου στη Θεσσαλονίκη, μόνο τεράστια ευγνωμοσύνη για όλα όσα μου έχουν δώσει και πάνω απ' όλα για την αγάπη τους. Τελευταίος και καλύτερος, Κώστα χωρίς εσένα δε θα είχα κάνει το βήμα να φύγω για το διδακτορικό. Ακόμα και όταν όλα είναι μεταβλητά, εσύ είσαι το σημείο αναφοράς μου σ'αυτή τη ζωή. Σ' ευχαριστώ για όλα..

#### Glossary

Abbreviation Description

AVGP Arbitrary VG Pattern

BL Bottom-Level

BOX Buried Oxide Layer

CCDF Complementary Cumulative Distribution Function

CDF Cumulative Distribution Function

CET Capture and Emission Time

CMOS Complementary Metal Oxide Semiconductor

CNF Carrier Number Fluctuations

CNF/CMF Carrier Number Fluctuation/ Correlated Mobility Fluctuation

CNT Carbon nanotubes

CP Charge Pumping

CV Capacitance-Voltage

DCM Defect Centric Model

DF Duty Factor

DIBL Drain-Induced Barrier Lowering

DV Dynamic Variability

EOT Equivalent Oxide Thickness

ESR Electron Spin Resonance

FDSOI Fully Depleted Silicon-On-Insulator

FEOL Front End of the Line

FFT Fast Fourier Transform

GAA Gate-All-Around

HCI Hot Carrier Injection

HK/MG High-k/Metal Gate

HMF Hooge Mobility Fluctuations

HRTEM High-Resolution Transmission Electron Microscopy

HT High Temperature

IL Interface Layer

ITRS International Technology Roadmap for Semiconductors

LFN Low Frequency Noise

LT Low Temperature

MC Monte Carlo

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MSM Measure-Stress-Measure

NBTI Negative Bias Temperature Instability

PBTI Positive Bias Temperature Instability

PDSOI Partially Depleted Silicon-On-Insulator

PNA Post Nitridation Anneal

PSD Power Spectral Density

R-D Reaction-Diffusion

RSU Remote-sense and Switch Unit

RTN Random Telegraph Noise

S/D Source/Drain

SCE Short-Channel Effects

SMS Stress-Measure-Stress

SOI Silicon-On-Insulator

SW Side Walls

TB Thermal Budget

TDDB Time Dependent Dielectric Breakdown

TDDS Time Dependent Defect Spectroscopy

TEM Transmission Electron Microscopy

TL Top-Level

TS Top Surface

TSV Through Silicon Via

TTF Time-To-Failure

WF Work Function

WGFMU Waveform Generator Fast Measuring Unit

# Contents

| <u>ACKN</u> | NOWLEDGEMENTS                                                                     | 5         |

|-------------|-----------------------------------------------------------------------------------|-----------|

|             |                                                                                   |           |

| <u>GLOS</u> | SSARY                                                                             | 7         |

|             |                                                                                   |           |

| CONT        | TENTS                                                                             | <u> 9</u> |

|             |                                                                                   |           |

| GENE        | ERAL CONTEXT                                                                      | 11        |

|             |                                                                                   |           |

| CHAP        | PTER 1. INTRODUCTION                                                              | 13        |

|             |                                                                                   |           |

| 1.1         | ISSUES ON CONVENTIONAL PLANAR TECHNOLOGIES                                        | 13        |

| 1.1.1       |                                                                                   |           |

| 1.1.2       | ·                                                                                 |           |

| 1.1.3       |                                                                                   |           |

| 1.1.4       |                                                                                   |           |

| 1.1.5       |                                                                                   | _         |

| _           | OXIDE DEFECTS OVERVIEW                                                            |           |

| 1.2.1       |                                                                                   |           |

| 1.2.2       |                                                                                   |           |

| 1.2.3       |                                                                                   |           |

| 1.2.4       |                                                                                   |           |

| 1.2.5       |                                                                                   |           |

| 1.3         | BIAS TEMPERATURE INSTABILITY                                                      |           |

| 1.3.1       | BTI DEGRADATION                                                                   | 21        |

| 1.3.2       | REACTION-DIFFUSION MODEL                                                          | 22        |

| 1.3.3       | HUARD'S MODEL                                                                     | 23        |

| 1.3.4       | GRASSER'S MODEL                                                                   | 23        |

| 1.4         | CHARACTERIZATION OF AVERAGING EFFECT                                              | 24        |

| 1.4.1       | DC stress                                                                         | 24        |

| 1.4.2       |                                                                                   |           |

| 1.5         | CHARACTERIZATION OF INDIVIDUAL DEFECTS                                            | 28        |

| 1.5.1       | . RANDOM TELEGRAPH NOISE – LOW FREQUENCY NOISE (STATIONARY METHOD)                | 29        |

| 1.5.2       | TIME DEPENDENT DEFECT SPECTROSCOPY                                                | 34        |

| 1.5.3       | CORRELATION BETWEEN STANDARD NBTI TESTS AND TDDS                                  | 38        |

| <u>CHAP</u> | PTER 2. IMPACT OF 3D ARCHITECTURES ON BTI/RTN RELIABILITY                         | 39        |

|             |                                                                                   |           |

| 2.1         | Introduction                                                                      |           |

| 2.2         | TESTED STRUCTURES                                                                 | 39        |

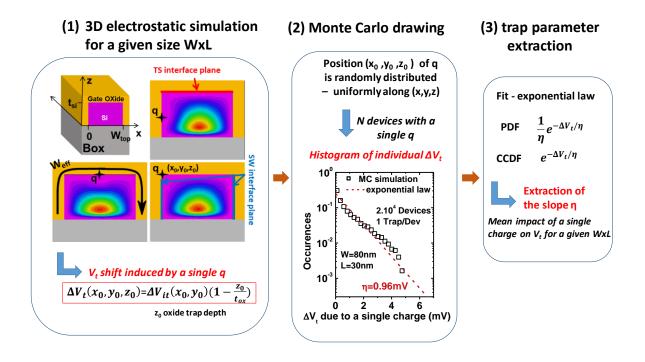

| 2.3         | <b>3D</b> ELECTROSTATIC SIMULATION OF THE IMPACT OF ONE CHARGE ON V <sub>TH</sub> | 39        |

| 2.4         | RELIABILITY OF PMOS TRANSISTORS                                                   | 40        |

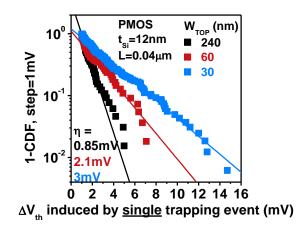

| 2.4.1       | EFFECT OF TOP WIDTH                                                               | 40        |

| 2.4.2       | EFFECT OF GATE LENGTH                                                             | 41        |

| 2.4.3       | EFFECT OF SILICON THICKNESS (HEIGHT - H)                                          | 42        |

| 2.5         | COMPARISON OF TDDS AND RTN                                        | 44         |

|-------------|-------------------------------------------------------------------|------------|

| 2.5.1       | SETUP PROCEDURE4                                                  | 45         |

| 2.5.2       | COMPARISON METHOD                                                 | 45         |

| 2.5.3       | Fresh devices4                                                    | 47         |

| 2.5.4       | "After Stress" comparison                                         | 50         |

| <u>CHAP</u> | TER 3. IMPACT OF 3D SEQUENTIAL INTEGRATION ON BTI/RTN RELIABILITY | <u>55</u>  |

| 3.1         | Introduction                                                      |            |

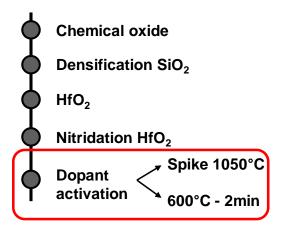

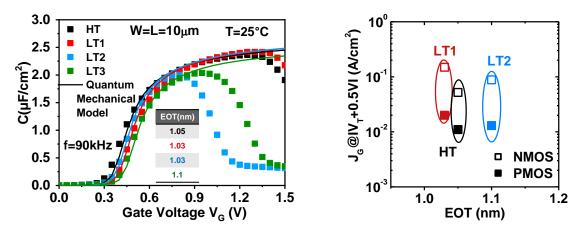

| 3.2         | IMPACT OF LOW TEMPERATURE PROCESS                                 |            |

| 3.2.1       |                                                                   |            |

| 3.2.2       |                                                                   |            |

| 3.3         | IMPACT OF DIFFERENT PROCESS STEPS                                 |            |

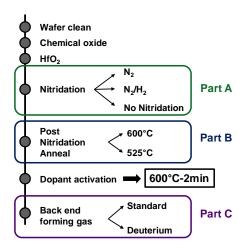

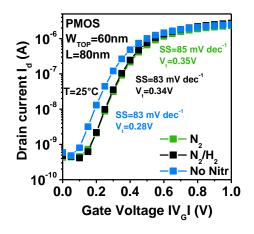

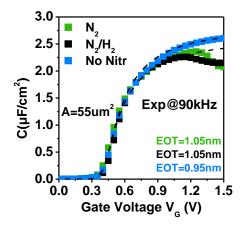

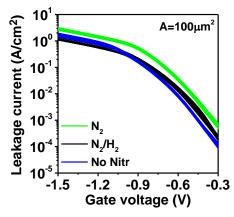

| 3.3.1       | TESTED STRUCTURES                                                 | 63         |

| 3.3.2       |                                                                   |            |

| 3.3.3       |                                                                   |            |

| 3.3.4       | FORMING GAS ANNEAL                                                | 69         |

| 3.4         | FULLY INTEGRATED 3D SEQUENTIAL TECHNOLOGY                         | 71         |

| 3.4.1       | DESCRIPTION-DEVICES                                               | 71         |

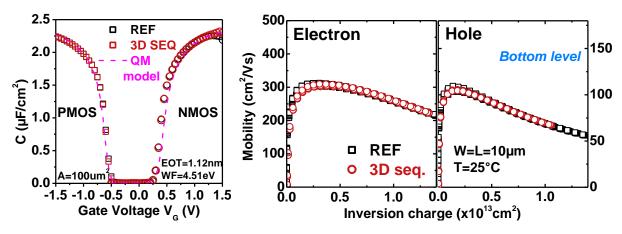

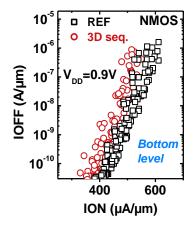

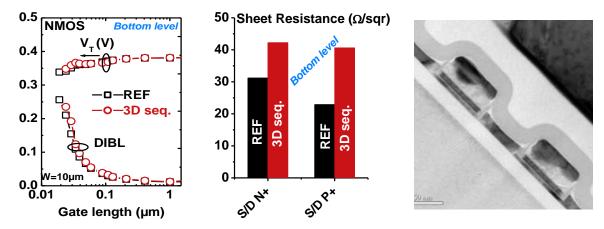

| 3.4.2       | Performance Bottom Level                                          | 72         |

| 3.4.3       | PERFORMANCE OF TOP LEVEL                                          | 75         |

| 3.4.4       | RELIABILITY BOTTOM LEVEL                                          | 76         |

| 3.4.5       | RELIABILITY TOP LEVEL                                             | 78         |

| 3.4.6       | CIRCUIT LEVEL                                                     | 79         |

| CHAP        | TER 4. IMPACT OF HIGH MOBILITY MATERIALS ON NBTI RELIABILITY      | <u>85</u>  |

| 4.1         | INTRODUCTION                                                      | 85         |

| 4.2         | TESTED STRUCTURES                                                 | 85         |

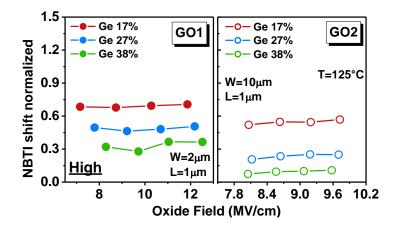

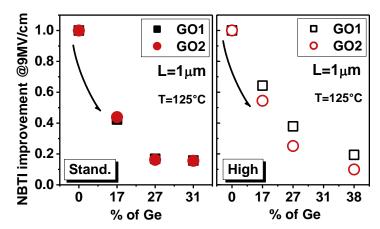

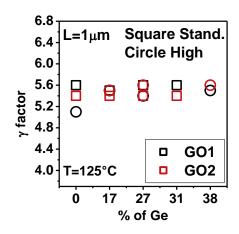

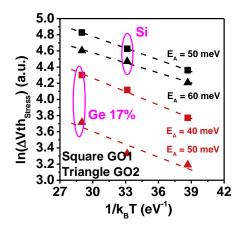

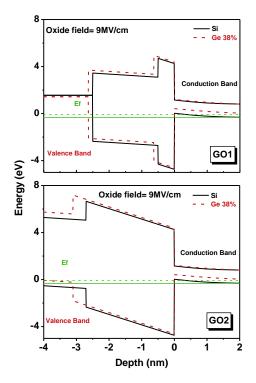

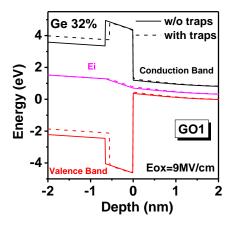

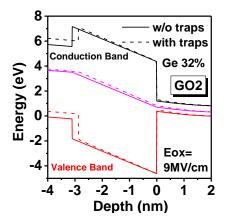

| 4.3         | STUDY ON GO1 AND GO2 SHORT CHANNEL DEVICES                        |            |

| 4.3.1       |                                                                   |            |

| 4.3.2       |                                                                   |            |

| 4.4         | STUDY ON GO1 AND GO2 LONG CHANNEL DEVICES                         |            |

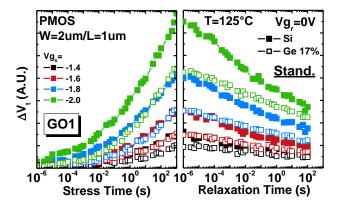

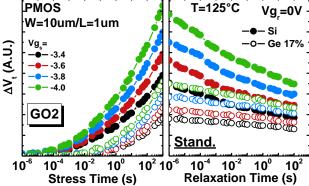

| 4.4.1       | STANDARD NITRIDATION                                              | 91         |

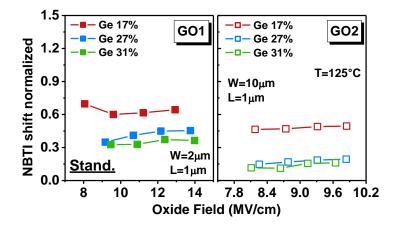

| 4.4.2       |                                                                   |            |

| <u>GENE</u> | RAL CONCLUSIONS                                                   | <u>97</u>  |

| REFE        | RENCES10                                                          | <u>01</u>  |

| <u>PUBL</u> | ICATIONS1                                                         | <u>13</u>  |

| <u>RESU</u> | ME EN FRANÇAIS1                                                   | <u> 17</u> |

#### General context

Around 70 years ago, at the end of 1947, three colleagues - W. Shockley, J. Bardeen and W. Brattain - made an invention that was about to change the world of solid-state electronics. It was the first working bipolar point junction transistor in Bell laboratories. A few years later, the most commonly used transistor up to this date was fabricated, the Metal Oxide Semiconductor Field Effect Transistor (MOSFET) with Gordon Moore making the prediction that the number of transistors per chip would double every two years [1] and the integrated circuits (ICs) would become smaller, faster and cheaper. In order to continue the frantic chase of these three characteristics, we kept on scaling our devices. It is possible to divide the different ages of scaling in three categories [2]:

- Geometrical scaling (1975-2003): During this period, we experienced the reduction of the physical dimensions which, in turn, improved the transistors' performance.

- Equivalent scaling (2003~2024): Here we not only have the geometrical scaling, but also the introduction of new materials either in the gate stack or incorporated in the channel, even though the silicon remains the top candidate in terms of performance and cost. In addition to that, new architecture designs, like Fully Depleted Silicon-On-Insulator (FDSOI), FinFETs and Trigate Nanowires, have been proposed to replace the standard planar MOSFETs.

- 3D power scaling (2024~203X): Alternatively known as "More than Moore", in which we will have heterogeneous integration (MEMS, Photonics, Biochips, etc.) and reduced power consumption with the help of vertical structures.

However, along with the advancements in the semiconductor industry targeting an improved performance, additional reliability issues have emerged. Reliability, which is defined as "The probability that an item will perform a required function under stated conditions for a specific period of time" is impacted by the microscopic defects that are induced by the fabrication process or the ageing of the device under electrical stress. It is essential to be confident that the designed everyday used products will not fail after a short time, like the processor of our computer or the battery in our mobile. Since this aspect of CMOS technology becomes more and more important nowadays, it is necessary to study the degradation mechanisms that take place in the above scaling categories which is the purpose of this thesis.

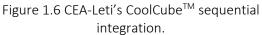

In the first chapter, we will see an introduction on new generation devices, having novel architectures or newly introduced materials, as well as an introduction to a cutting-edge integration process; the 3D sequential integration (CoolCube<sup>TM</sup>). In addition to that, we will describe the meaning of reliability and the trapping phenomena that occur on CMOS transistors along with a review of the existing models that help us describe the physical mechanisms behind them. Finally, we will have an analytical report of the measurement methods that were used during this thesis.

In the second chapter, we will focus on the 3D architectures that have been studied (Trigate nanowires) and their channel size dependence on  $t_0$  reliability, due to pre-existing defects, compared to previously reported works w.r.t. the results from Monte Carlo simulations. After

that we will see how the already known methods for trap extraction can be applied in 3D architectures and compare the two most popularly used at this time.

The third chapter will show a study concerning the impact of 3D sequential integration on reliability. At first, "simulating" the behavior of a Top-Level transistor and providing a set of guidelines with all the important process steps that can be improved. And at the end of the chapter, we will present, for the first time, a complete study of a fully integrated 3D sequential technology concerning performance reliability of both levels.

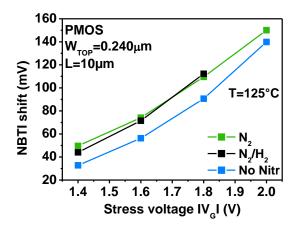

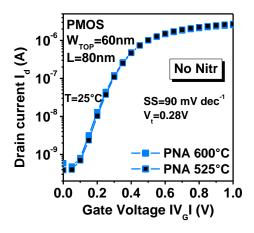

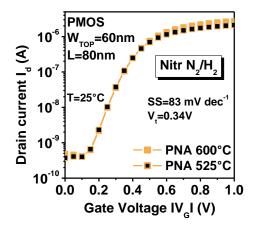

For the fourth, and final, chapter, we will see how new high mobility materials incorporated in the channel (Germanium in particular) are affecting NBTI reliability and we will provide a new insight regarding the physical mechanisms that are repeatedly reported to be improving the degradation in SiGe channel planar PMOSFETs. To do so, we will present an extensive set of reliability measurements on large and smaller transistors, having a thin or thick gate oxide and conclude on which are the defects that are responsible for this improvement or not.

#### Chapter 1. Introduction

#### 1.1 Issues on conventional planar technologies

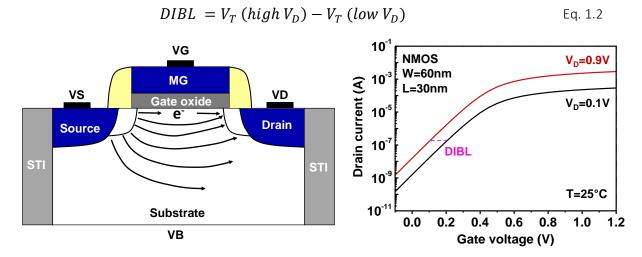

We already live in the era of technological breakthroughs, where we can fit in the palm of our hand the power, the speed and the performance of a supercomputer that a few years ago would fit in a room. Surely, none of the transistor's inventors would imagine that the impact of their research, 70 years later, still plays the most important role in the digital revolution. The building block of every electronic device that we use is the MOSFET, but as we try to make it smaller and reduce the cost of fabrication at the same time, we face different challenges. Standard bulk planar MOSFETs are particularly susceptible to two phenomena: the so-called Short-Channel Effects (SCE) (Figure 1.1) and Drain-Induced Barrier Lowering (DIBL) (Figure 1.2). During the first one, the gate loses the electrostatic control of the channel as the electric field lines propagate through the depletion regions of the source and drain, as they move closer to one another on shorter gate lengths. The second one is due to the lowering of the potential barrier between the drain and the source caused by the drain polarization. The lowering of the source barrier causes an injection of extra carriers which, in turn, increases the current substantially. This increase of current shows up in both, above-threshold and subthreshold regimes. As a result from SCEs we have a decrease of the threshold voltage which, finally, is calculated as [3]:

$$V_{T,Short} = V_{T,long} - SCE - DIBL$$

Eq. 1.1

with DIBL to be defined as:

Figure 1.1 Schematic of a Bulk transistor suffering from Short-Channel Effects (SCE), reproduced from [4].

Figure 1.2 Increase of drain current and shift of threshold voltage due to Drain-Induced Barrier Lowering (DIBL).

#### 1.1.1 Equivalent scaling opportunities

As was presented before, two decades ago it became quite obvious that the requested performance improvement could not be easily reached and the technology optimization for

very short gate lengths (<30nm) had to be done in a different way in order to avoid parasitic effects and for the gate to maintain the control of the channel. At this very moment we are living the "Equivalent scaling era", so in the next part, we will present the major technological advancements over the past few years to meet the expectations of ITRS concerning the aggressive gate dimensions.

#### 1.1.2 SOI process

In order to avoid the aforementioned issues with planar transistors, the industry turned to a new type of process technology, called SOI (Silicon-On-Insulator). The difference from the standard MOS is that now we have a Buried Oxide Layer (BOX), constituting of Silicon Dioxide (SiO<sub>2</sub>) providing an extra isolation to the body from the substrate with the silicon film that is used to form the channel to be a single crystal, very thin and undoped (typical doping value  $N_A=10^{15}~\rm cm^{-3}$ ).

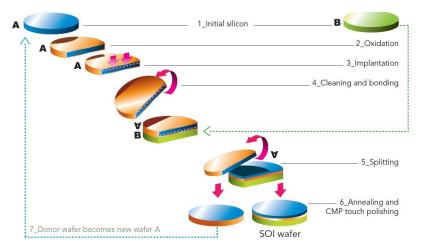

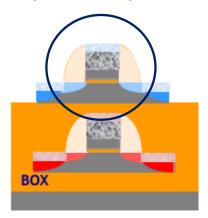

The fabrication process that has changed the SOI production is called SmartCut<sup>TM</sup> [5] and was developed by Soitec in collaboration with CEA-Leti. In Figure 1.3, we can see a simplified description of the followed procedure. The whole process starts with wafer A acting as a donor that becomes thermally oxidized to develop the  $SiO_2$  layer that will be used as BOX of the final wafer. Hydrogen implantation through cleavage layer creation is applied to settle the transferred Si thickness. After that, the surface is cleaned and the two wafers are bonded, while the cleavage layer is split. As a result, we have structures with a thin silicon film on BOX with two additional parameters to consider: the silicon thickness,  $t_{Si}$ , and the thickness of the BOX,  $t_{BOX}$ . According to them, the SOI devices can be separated in two categories:

- ullet Partially Depleted SOI (PDSOI): If  $t_{Si} > W_D$  (thickness of the depletion zone), the silicon film has a non-depleted neutral zone and avalanche ionization at the drain can lead to accumulation of charges in the partially depleted zone, what we call floating body effect

- Fully Depleted SOI (FDSOI): when the t<sub>Si</sub> is smaller than the depletion zone and there is no floating body effect.

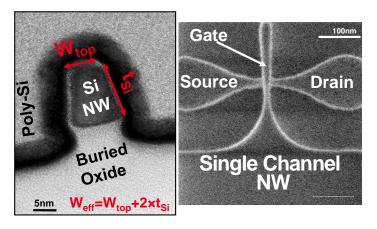

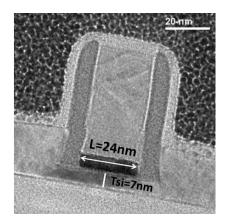

In the thesis, only the second category, the FDSOI structures, has been studied with the silicon thickness to vary from 7nm for planar transistors to 24nm for Trigate MOSFETs.

Figure 1.3 SmartCut<sup>™</sup> fabrication process [5] for the manufacturing of SOI wafers.

#### 1.1.3 3D architectures

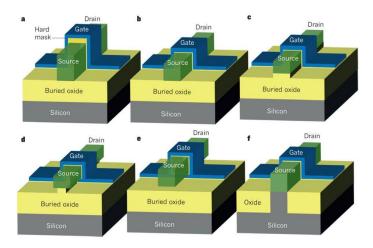

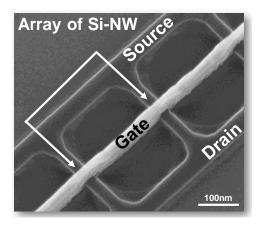

Along with FDSOI, there have been other technologies that have pushed the equivalent scaling area into new limits giving, also, solutions for decreasing SCEs. By introducing 3D architectures [6]–[8] as alternative candidates to the conventional planar ones, it is possible to increase the gate area without increasing the total surface of the transistor and continue obey the scaling law. In that way, we can achieve the requested electrostatic control [9], [10], shielding of the channel from parasitic electric fields, lower gate leakage current, higher gate-drive current and lower DIBL.

These architectures, shown in Figure 1.4 [7], are characterized by the number of gates that they have, like double, triple or even all around. The first multi-gate device (double-gate), in Figure 1.4 (a), was introduced in the late '90s [6], [11], having a thick dielectric, called 'hardmask' that prevented the formation of the inversion channel on the top surface, so only the two sides were used for conduction. Regarding Trigate structures, we can find them in the literature implemented either on an SOI or a Bulk wafer ((b) and (f) in Figure 1.4) and the three conduction surfaces help us towards the advantages that we reported before. Two other possible design are  $\Pi$ -gate and  $\Omega$ -gate FETs ((c) and (d) in Figure 1.4), which improve the gate control compared to Trigate due to the lateral electric field at the bottom and, of course, the increased channel surface. For the second one the use of  $H_2$  anneal helps us smooth the fin surfaces and round the corners, improving the mobility and reducing even more the gate leakage. The same procedure is followed for processing a Gate-All-Around (GAA) FETs (Figure 1.4 (e)), devices in which the gate is completely wrapped around the channel and that they have shown to be able to maintain the electrostatic control for dimensions down to 3nm [12].

Figure 1.4 Overview of the existing 3D MOSFET architectures (a) SOI FinFET, (b) SOI Trigate, (c) SOI  $\Pi$ -gate, (d) SOI  $\Omega$ -gate, (e) SOI GAA, (f) Bulk Trigate [7].

#### 1.1.4 New materials

Along with the width, length and height, W, L and  $t_{Si}$  respectively, there is another dimension that has to decrease on this scaling "game": the thickness of the oxide, according to Eq. 1.3,

$$C_{OX} = rac{arepsilon_{OX}}{T_{OX}}$$

Eq. 1.3

where  $C_{OX}$  is the gate oxide capacitance,  $\epsilon_{OX}$  the dielectric constant and  $T_{OX}$  the oxide thickness. Having a small oxide thickness leads to an increased gate capacitance and as consequence to reduce SCEs. For some years,  $SiO_2$  was scaling proportionally to the gate length, down to an Equivalent Oxide Thickness (EOT) equal to 1.1nm in 2006 when it reached its lowest limit. After that, the known problem of leakage current emerged again due to the direct tunneling of carrier phenomena and lifetime prediction as well as power consumption became an issue. Everyone wanted to avoid these phenomena, so the research community started looking for other materials that could replace  $SiO_2$  and since,

$$EOT = rac{arepsilon_{SiO_2}}{arepsilon_{OX}} * T_{OX}$$

Eq. 1.4

with  $\epsilon_{SiO2}$  the relative permittivity of  $SiO_2$  equal to 3.9 and  $\epsilon_{OX}$  the permittivity of the new dielectric, it was clear that we needed something with a high dielectric constant to do so.

In Figure 1.5, we can see a list of studied high-k materials towards this goal which had to be evaluated according to four criteria [13]:

- 1) to be able to scale to lower EOTs

- 2) to limit the loss of carrier mobility in the Si channel

- 3) to stop the gate threshold instabilities caused by the high defect densities of the poor-quality interface between the channel and the high-k

- 4) and to control the gate threshold voltage, which led to the need of metal gates.

| Material         | Dielectric constant $(\kappa)$ | Band gap $E_G$ (eV) | $\Delta E_C$ (eV) to Si |

|------------------|--------------------------------|---------------------|-------------------------|

| SiO <sub>2</sub> | 3.9                            | 8.9                 | 3.2                     |

| $Si_3N_4$        | 7                              | 5.1                 | 2                       |

| $Al_2O_3$        | 9                              | 8.7                 | $2.8^{a}$               |

| $Y_2O_3$         | 15                             | 5.6                 | 2.3 <sup>a</sup>        |

| $La_2O_3$        | 30                             | 4.3                 | 2.3 <sup>a</sup>        |

| $Ta_2O_5$        | 26                             | 4.5                 | 1 - 1.5                 |

| $TiO_2$          | 80                             | 3.5                 | 1.2                     |

| $HfO_2$          | 25                             | 5.7                 | 1.5 <sup>a</sup>        |

| $ZrO_2$          | 25                             | 7.8                 | 1.4 <sup>a</sup>        |

Figure 1.5 Electrical properties of the most researched high-k materials [13].

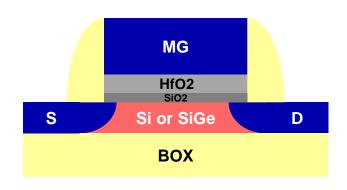

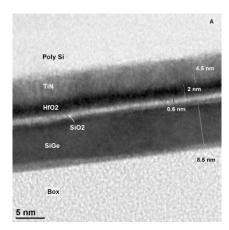

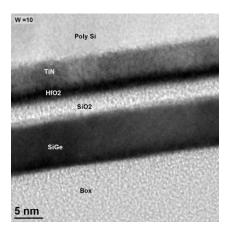

Nowadays, most of the HK/MG stacks consist of  $HfO_2$  or middle solutions, like Hafnium-based oxides (HfSiON) to lower the defect density. An alternative way that is widely used is a combination of  $HfO_2$ , on top, and  $SiO_2$ , next to the silicon, to improve the interface quality. In both cases, we need to be compatible with the applied metal gate, for example TiN, whose workfunction can be adjusted using different deposition process or thickness.

Besides the gate stack material, we have been looking for different channel materials as well. Germanium incorporation [14] in the channel of PMOSFETs has improved, not only the mobility [15]- aka performance of transistors, but has also given an improved reliability [16], [17]. This part will be presented extensively in the last chapter of the thesis. Alternative materials, such as III-V semiconductors (GaAs, InGaAs, InAs, InP) [18] which are the number one choice for NMOSFETs' advancement, are investigated for the next generation CMOS technology as well as 2D materials (Graphene, MoS<sub>2</sub>, etc.) [19]–[21] or Carbon nanotubes (CNT) [22]. Even though, the most important part is to find ways to obtain high interface quality, low access resistance and, of course, low cost CMOS integration methods, they appear as very promising candidates for future flexible and transparent devices.

#### 1.1.5 3D sequential integration

The last, and apparently final, report of ITRS [23], [24] was published in 2015 reporting that Moore's law will not continue in the traditional dimensional scaling way that we know so far and will reach its final limit at 2021. So the electrical performance and current limit will no longer be the primary target, but the focus will now be on how we can take advantage of the existing technology and adapt it to the needs of the market [25], [26] and the world, like the use of GPS, clinical wearables and biosensors. Even from the economical aspect of view [27], the fabrication of a new scaled node becomes more and more expensive due to the necessity of high-precision equipment and design tools. So, it is quite obvious that we march, or better run, towards the 3D power scaling era, with the 3D integration to be one of the frontrunners in "More than Moore" (r)evolution.

The whole concept of this integration is to fabricate one transistor on top of another to achieve a high density of components which results in high performance and reduced scaling for lower cost [27], using its unique 3D contact characteristics towards the new age [28], [29]. Depending on the requested application, it can feature the different technologies described before, like FDSOI on FDSOI structures [30] or FinFET on FinFET [31] in order to achieve the best possible outcome each time. Towards this road, we can distinguish two types of 3D integration: the parallel and the sequential.

In the parallel one, the wafers are processed separately and the two levels are connected at the end using Through Silicon Vias (TSVs) which limit substantially the alignment precision. Another drawback is that the TSVs are quite large and as a result we have higher parasitic impedances.

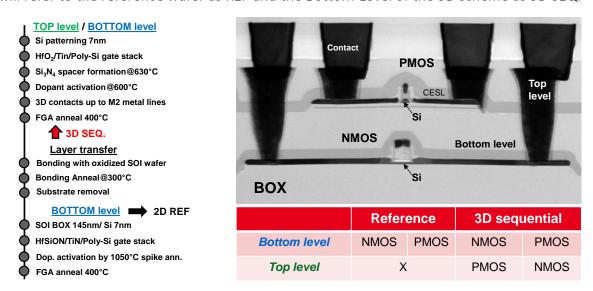

In the sequential integration (Figure 1.6 & Figure 1.7), the process is done continuously, with the Top-Level using the previous alignment marks from the bottom one. In that way, the two transistors are fully aligned which in turn, favors the increase of 3D contacts density. But the Top-Level device has to be processed in a certain way, so that the bottom transistor remains unaffected, which means that the thermal budget must be decreased [32], [33]. Additionally to the temperature limitation, the integration itself is particularly complex and all the processing steps have to be evaluated at the same time [34], [35].

Figure 1.7 3D sequential stacked transistors with process secured alignment [36].

The pioneer towards this concept is CEA-Leti with several groups around the globe becoming attracted by the idea and working towards this kind of integration (like IMEC [37], NDL [38] and Stanford [39]). Even though, there is a lot of research regarding the processing procedure that has to be followed to reach a high Top-Level performance, there are limited results regarding the reliability of the integration [40], an issue that we will try to address fully in Chapter 3.

#### 1.2 Oxide defects overview

Until now, we have only talked about the advancements on CMOS technology from the performance point of view. Of course, it's great to have a fast computer or a high-resolution camera on your smartphone, but you have to be sure that it will continue doing its job for a long time. This is where reliability comes and since MOSFET is the building block of all electronic devices, it is important to know and understand the degradation mechanisms that take place due to an increased gate voltage application, a transistor's operation under an elevated temperature (Reliability) or even the ones that are due to the manufacturing process (Yield).

Whether a device is reliable or not, there is one thing to blame: the defects that exist in the gate oxide of the transistor [41], [42]. For many years, the CMOS technology has been successful due to the advantageous properties of  $SiO_2$  [43]: high energy band, low defect density, easy to become process integrated etc. But the introduction of the high-k materials that we saw before, introduced also additional problems. In this part, we will present an overview of the different oxide defect categories and try to see how each one is affecting both Yield and Reliability.

#### 1.2.1 Fixed oxide charge

Fixed oxide charges were one of the first observed defects since the beginning of CMOS production. They are located near the  $Si/SiO_2$  interface and are directly related to the fabrication process, specifically from the Si oxidation step and the used temperature. The good news is that there is no electrical communication with the silicon channel, therefore it belongs to the pre-existing defects category and only affects the initial MOSFET parameters, like a static shift on the flatband voltage.

#### 1.2.2 Mobile oxide charge

The mobile oxide charge is mainly caused by the ionic impurities of sodium (Na+), lithium (Li+) and potassium (K+). They are also related to the processing techniques, so the yield part, and are causing threshold voltage instabilities when positive gate bias is applied, with sodium being the first impurity to be related to this gate bias instability [44]. In order for them not to become an oxide reliability problem, the density should be kept low, around 10<sup>9</sup>cm<sup>-2</sup>.

#### 1.2.3 Oxide trapped charge

Moving now to a more serious category of oxide defects, the oxide trapped charge. This charge can be either positive or negative, in the bulk of the oxide, and is due to the filling of the defects by holes or electrons, with the electron traps being distributed through the oxide and the hole traps located near the  $Si/SiO_2$  interface. This too, can originate from the processing after the oxide growth but also from the defects that are generated when the transistor is under operation, like during electrical stress in a high field. As we will see later, this type of defects plays an important role during Positive Bias Temperature Instability (PBTI), on NMOS, during which the traps in the high-k prevail.

#### 1.2.4 Interface trapped charge

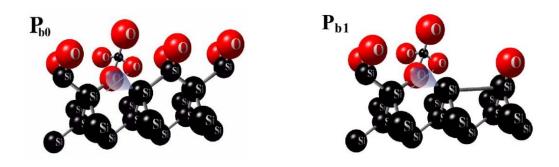

The number one danger for the gradual, or even without return, degradation is the interface trapped charge. They are next to the silicon channel and can be either acceptors or donors, depending on their position w.r.t. the bandgap, upper or lower half respectively. The number of caused effects are numerous: impact on capacitance, leakage current, noise level and, of course, on the Negative Bias Temperature Instability (NBTI) that we will see later on. They are originally created by the dangling bonds at  $Si/SiO_2$  interface, with their density ( $D_{IT}$ ) to be depending on the surface orientation. When they were first identified by Electron Spin Resonance (ESR) [45], they were called  $P_b$  centers and were divided into two types (Figure 1.8):

- P<sub>b0</sub>, for •Si ≡ Si<sub>3</sub> bonds and

- $P_{b1}$ , for the  $Si_2 = Si \cdot -Si \equiv Si_2O$  ones,

with the latter having a minor impact compared to the first one [46].

Figure 1.8 The two types of interface charge [47].

Regarding the occupying states at flatband, each time, they can be distinguished in three categories:

- Neutral: states at the lower half of the bandgap when the electron occupied states are below the Fermi level (occupied donors) or above the Fermi level (unoccupied acceptors)

- Negative: states between the midgap and the Fermi level (occupied acceptors)

- Positive: when a PMOSFET is inverted, the interface traps between midgap and Fermi level are unoccupied donors and as a result we have positively charged interface traps which lead to negative threshold voltage shifts (NBTI mentioned before).

A way to decrease the density of interface traps and avoid, at some part, the detrimental impact of these defects is the use of  $H_2$  anneal [48]. The hydrogen atom will fill the dangling bond and neutralize it, the so-called passivation. However, the hydrogen chemistry is very important since it can go sideways and depassivate again the bond, especially under the application of electrical stress.

#### 1.2.5 Border traps

Around 24 years ago, D. Fleetwood [49] suggested an extension of the, already long, list of gate oxide defects by introducing the border traps, positively charged oxide traps passivated with hydrogen. The most common border traps are oxygen (O) vacancies and/or defects that contain hydrogen (Hydrogen bridge & Hydroxyl E' center). They are characterized as near-interfacial oxide traps and can communicate by tunneling from the semiconductor to the traps and back having larger emission and capture time constants than the interface or oxide traps. Recent studies have shown that this "communication", in PMOSFETs, can happen not only through tunneling but also through trap-assisted tunneling or even thermal activation [50], [51]. All these sound familiar since they are similar processes occurring during the recovery part of a fast NBTI measurement [52], whose modeling we'll see in the next section.

For quite some time, it was difficult to distinguish the impact of border and interface traps with the key point being the measurement speed. In the chase of border traps' identification, we have some measurement methods as allies, like Charge Pumping, Low Frequency Noise and Time Dependent Defect Spectroscopy. Details for all of them will be presented in the next sections.

#### 1.3 Bias Temperature Instability

Now that we have a general idea regarding the defects in the gate oxide, let's discuss about how they affect the electrical parameters of MOSFETs, unfortunately always in a negative way: the widely known reliability.

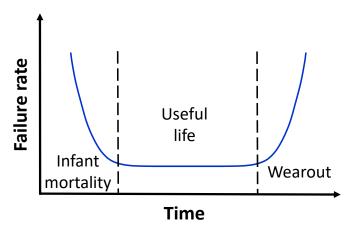

Maybe the most recognized illustration among reliability engineers is the one in Figure 1.9, the bathtub curve. It indicates the lifecycle of an electronic component, or a transistor in our case, and is composed of three parts: the infant mortality, the useful life and the wearout. We all want to avoid the first one and stay as much as possible in the second one. Regarding the third part, we would all wish to never go there, but that's not how it works! The infant mortality

is related to pre-existing defects and is correlated to the yield that we mentioned before. During the useful life, there are only some random defects in the transistor, now necessarily affecting it. Eventually, we arrive in the wearout part, caused usually by accelerated testing and characterization in extreme conditions of voltage, current or temperature. The questions that emerge in this part are: why, when and how this failure has occurred. In the case of the CMOS technology, specifically the Front End of the Line (FEOL) reliability, there are three degradation mechanisms: one that describes the sudden failure of transistors, called Time Dependent Dielectric Breakdown (TDDB) or the gradual one, as it is the case with the Bias Temperature Instability (BTI) and the Hot Carrier Injection (HCI).

In this section and, in general in this thesis, we will focus only on the second type of failure and specifically the BTI.

Figure 1.9 Bathtub curve showing the lifecycle of a product.

#### 1.3.1 BTI degradation

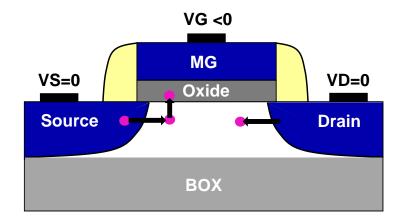

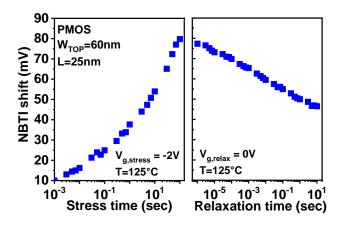

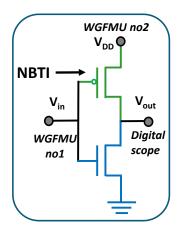

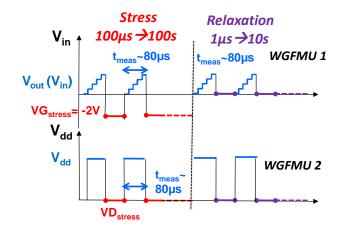

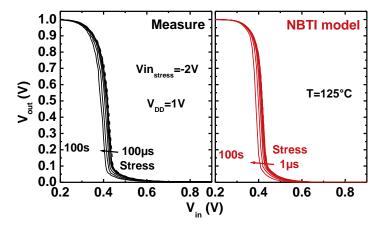

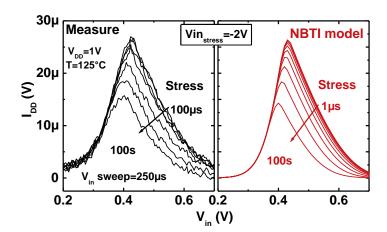

The principle of BTI is to force a stress voltage on the gate by keeping, at the same time, the drain and the source at 0V as it appears in Figure 1.10. In that way, there is no drain current flowing in the channel and makes it possible to record the threshold voltage drift that occurs with time. Since it is an acceleration test, part of the wearout period, it is typically performed at a high temperature of 125°C. When this method is implemented on NMOSFETs the  $V_G$  stress is positive (PBTI) which causes a negative oxide charge that leads to a positive  $V_{TH}$  shift. The opposite applies on PMOSFETs (NBTI): the  $V_{G, \, stress}$  is negative which induces a positive oxide trapping that results to a negative  $V_{TH}$  shift (Figure 1.11). But this time, there is an additional impact: the creation of interface states, as well, impacting the mobility, transconductance and subthreshold slope degradation. Historically, it's the NBTI that constitutes the major reliability problem, since PMOSFETs are subjected to a degradation almost four times higher than the corresponding NMOS. For that reason, the research for a model suitable for NBTI prediction and description is of an imperative need.

Figure 1.10 FDSOI MOSFET under BTI stress.

Even though NBTI is a problem that is bothering the reliability community for more than 50 years, there are still some blank spots regarding its origin which, consequently, has emerged disputes for its modeling [53], [54]. Especially, with the CMOS advancement on oxides (high-k), process (i.e. nitridation) or structures (Trigate), it has become an important concern will trying to ensure the lifetime of a transistor. We'll see now an overview of the existing models, separated in two different approaches, and the recent progress regarding the physical explanation of this reliability concern.

Figure 1.11 Typical  $V_{TH}$  shift of stress and recovery in FDSOI MOSFET.

#### 1.3.2 Reaction-Diffusion model

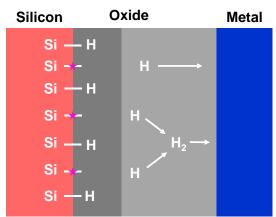

The first attempted try, to describe the creation of interface traps during a NBTI stress was called Reaction-Diffusion (R-D) model [55], [56]. This model is based on the breaking of the Si-H bonds at the Si/SiO<sub>2</sub>, forming dangling bonds, and the diffusion of the charged hydrogen atoms into the gate oxide. The free hydrogen can then recombine with other available atoms forming molecular  $H_2$  that can also diffuse into the gate oxide (Figure 1.12). Nonetheless, several process knobs tend to improve this situation, like with the use of forming gas ( $H_2$ ) or high-pressure deuterium anneal that seems to "cure" the dangling bonds which means that the NBTI degradation is mainly related to the interface states. This worked really well during that time, since everyone was mostly concerned about the kinetics of interface traps to explain the degradation.

Figure 1.12 Reaction-Diffusion model principle.

But, the development of fast measuring techniques, over the past decade, has revealed the limitations of the model. Specifically, it has proven difficult for the R-D to fully describe experimental results [57], especially in the relaxation part [58], [59], [60]. The recovery part starts as soon as the stress is removed and it is globally uniform over the entire relaxation period. The R-D model could only predict a relaxation during 4 decades of time while the recovery should be relatively slow. In addition, the relaxation predicted by the R-D model is due to the back scattering of the neutral  $H_2$  species to the substrate. Since they are neutral, they should not be influenced by the gate bias during relaxation, but experiments have shown that the relaxation is highly dependent on the applied  $V_{G, relax}$  [60]. Finally, while the R-D model predicts that the relaxation depends on the initial hydrogen concentration, it has been shown that is independent of the Si/SiO<sub>2</sub> interface passivation [58], [61].

#### 1.3.3 Huard's model

It was not until 2006 that a new interpretation of the NBTI physical mechanisms appeared [61]–[63]. Huard this time considered two different components of NBTI degradation, independent from one another, the permanent and the recoverable. The recoverable part that is due to the hole trapping occurring mostly in pre-existing defects with long capture and emission time constants, which can be reversible since the holes can be re-emitted into the channel or the gate. This means that this part of degradation is exclusively related to the fabrication process of the device. On the other hand, the permanent part, attributed to the aforementioned dangling bonds created by stress. This time, we are talking about very fast defects with short time constants which are very difficult to be repassivated with the process steps that we saw before.

#### 1.3.4 Grasser's model

A few years later, in 2009 [64], Grasser proposed a different version of Huard's model where the permanent and recoverable phenomena are related. The creation of interface states may be justified from the R-D model but not only, while it predicts the hole trapping taking place in stress-driven gaps. It is now called a quasi-permanent phenomenon since it can have long recovery times, longer than the experimental timescale. The recoverable part, at the same time, is considered to be explained by the capture of holes in oxygen deficiencies through Multi Phonon Field Assisted Tunneling. Even though this model, can reproduce experimental data of stress and relaxation, it faces some difficulties when it comes to other gate oxides or processing steps, since it cannot consider deficiencies other than the oxygen ones. This led to an update

of the existing model in 2014 [65], indicating that the recovery is more reaction-limited than diffusion-limited.

Right now, we are still considering two different components of the NBTI degradation, but there are some updates regarding the microscopic defects that are responsible for each one [66], [67]. For the hole trapping and the recoverable part, it is assumed that it is due to hydroxyl E' center created by the attachment of the released atomic hydrogen to strained bridging oxygen centers. In the meantime, the quasi-permanent kinetics, of the interface states, are still following a power law dependence, but there is an extra consideration. Apart from the dangling bonds in Si/SiO<sub>2</sub> we may have hydrogen diffusing from the gate that could create additional border traps. In both cases, the repassivation or redistribution of H is possible, but has very long recovery times.

In general, there are some parts of common agreement among the researchers, like the role of hole trapping/detrapping and the creation of defects during stress, but there is still no consensus and, most importantly, no predictive physical model that allows simulation under different circuit conditions [53].

#### 1.4 Characterization of averaging effect

To identify and characterize the defects that cause the CMOS devices to degrade over time, we need some techniques to help us do that. In the next sections, we'll see an overview of the used characterization methods in this thesis, starting with the ones that show the averaging effect of traps.

The first reliability characterization technique that has been used in this thesis, is the Bias Temperature Instability: a method to stress both N&PMOSFETs, called Positive (PBTI) and Negative (NBTI) respectively. The main ageing feature, as we saw before, is the shift of the threshold voltage with time while the transistor is on standby mode, there is no drain current flowing in the channel ( $V_D=0V$ ). It is an indicator of the gate oxide quality and helps towards the optimization of the gate oxide or the channel material depending on the results each time. It can be applied in two forms: the DC and the AC that we'll describe separately.

#### 1.4.1 DC stress

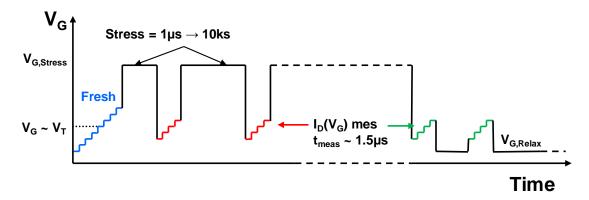

The BTI application has two different stages, the stress and the relaxation. BTI is strongly activated by temperature and so it's globally measured at  $125^{\circ}$ C. At the beginning of the technique, we perform an initial  $I_D$ - $V_G$  to characterize the device and evaluate its  $V_{TH}$ . During stress, a high gate voltage is applied for a specific time period, followed by the measurement itself during which we observe the degradation of the transistor's parameters. The whole sequence is repeated several times over the total stress period, that's why it is often referred to Stress-Measure-Stress (SMS) or Measure-Stress-Measure (MSM) in the literature (Figure 1.13). The only difference between NBTI/PBTI is the application of negative/positive  $V_{G, \, stress}$ . However, once the stress stops the degraded electrical characteristics tend to return in their original state, called relaxation.

Figure 1.13 Time chart of the applied gate voltage during an DC BTI stress.

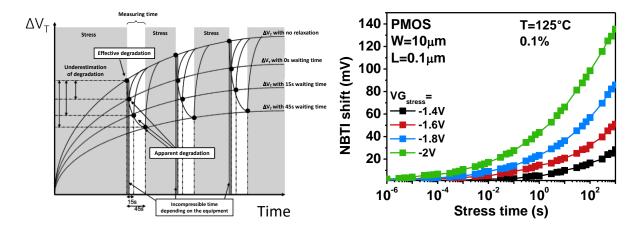

Depending on the stress time, the degradation is not the same each time and since the recovery is quite strong, it is possible to overestimate/underestimate the reliability/degradation as it is evident in Figure 1.14. Due to that, it is suggested, if not imposed, to use a fast measurement methodology to limit the relaxation and along with a shorter measuring time after stress (fewer  $I_D$ - $V_G$  points for example) we can have a clear aspect of the actual degradation.

Figure 1.14 Impact of BTI relaxation in the final degradation level, reproduced from [68].

Figure 1.15 Threshold voltage drifts with time for different  $V_{G,\,stress}$  during a fast range NBTI.

The difference between conventional and fast range methodology lies in the measuring tools. Typically, the  $V_{G, \ stress}$  is applied through a System Measuring Unit (SMU) which, unfortunately, has settling time in a millisecond range. So, in our case, it has been replaced by a Waveform Generator Fast Measuring Unit (WGFMU) connected to a Remote-sense and Switch Unit (RSU), placed in a B1530A Keysight module. An extra advantage is that we are able to watch the degradation for over 9 decades of time, from 1 $\mu$ s to 1ks (Figure 1.15). However, there is a trade-off between accuracy and speed. For a device with a large width (common in BTI measurements) we reach a current range of 100 $\mu$ A which means we can have an accuracy/speed of 1 $\mu$ s in our results. On the contrary, if we move to smaller gate width, like in the case of nanowires (used in TDDS measurements in next section), we acquire an  $I_D \sim 10 \mu$ A which forces us to measure with a speed of 100 $\mu$ s.

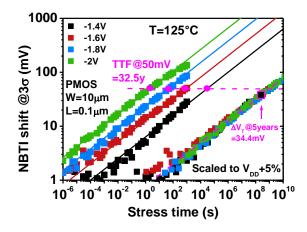

As a result of the two aforementioned advantages, we are able to extract the real lifetime for our devices using this fast range methodology. The reliability criterion, in CMOS technology, is to establish a  $V_{TH}$  shift of 50mV after a 5-year operation at the circuit operating voltage, so for a  $V_{DD}$ =0.945V in our technology (Figure 1.16). An extra consideration has to be the variability, which is enhanced in advanced MOSFETs. Just like one transistor is not identical with another one, so is their reliability. NBTI shifts differ from one device to another due to the fluctuation of the number of traps per device. Consequently, the level of degradation is not the same, so the extrapolation is better to be made within a 3-sigma deviation (3 $\sigma$ ) in order to include the variability and have rock evidence about the reliability each time. By measuring the  $\Delta V_{TH}$  through a range of  $V_{G, stress}$  and scaling it to the supply voltage, it is possible to extract the shift at 5 years lifetime and also the Time-To-Failure for the 50mV criterion (Figure 1.16 & Figure 1.17).

PASS if VG>0.9V

10<sup>9</sup>

10<sup>8</sup>

10<sup>7</sup>

10<sup>6</sup>

V<sub>a</sub>@5y

=1.01V

10<sup>1</sup>

10<sup>3</sup>

10<sup>2</sup>

PMOS

W=10μm

L=0.1μm

10<sup>0</sup>

10<sup>6</sup>

10<sup>1</sup>

10<sup>8</sup>

10<sup>8</sup>

10<sup>8</sup>

10<sup>8</sup>

10<sup>8</sup>

10<sup>9</sup>

10<sup>1</sup>

10<sup>2</sup>

10<sup>1</sup>

10<sup>1</sup>

10<sup>1</sup>

10<sup>2</sup>

10<sup>2</sup>

10<sup>3</sup>

Figure 1.16 Log-log plot of Figure 1.15 scaled at  $V_{DD}$  to extract the  $V_{TH}$  shift after a 5-year operation.

Figure 1.17 Demostration of successful technology validation, reaching and exceeding the reliability criterion for a  $V_6>0.9V$ .

Using the following power law model (Eq. 1.5), we can estimate the maximum applied voltage, in order not to pass the  $\Delta V_{TH}$ =50mV, and which has to be higher than the supply voltage in order to validate each technology.

$$\Delta V_{TH}(t, V_G, T) = C \cdot V_G^{\gamma} \cdot e^{-\frac{E_a}{kT}} \cdot t^n$$

Eq. 1.5

where:

- C: a constant depending on the technology, specifically on the gate stack

- T: the used temperature (125°C at BTI setups)

- V<sub>G</sub>: the stress voltage applied at the gate

- γ: the voltage acceleration factor

- E<sub>a</sub>: the activation energy of the generated traps

- k: Boltzmann's constant

- n: a time acceleration constant

- t: the total stress time

As a result, and as we continue scaling and reducing the supply voltage even more, it is essential to measure the degradation as fast as possible, in order to correctly evaluate the lifetime duration of the transistors and, eventually, of the circuits. In addition to the proper equipment, it is important to understand the physical mechanisms lying behind the measured degradation and build correctly calibrated models to help us predict the behavior of our devices during long operating times.

#### 1.4.2 AC stress

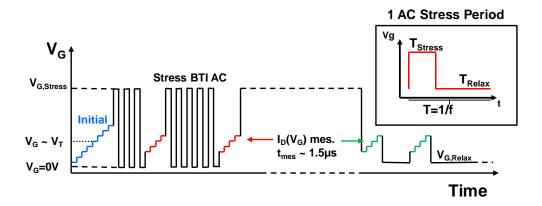

Like the name indicates, there is an alternative way to apply BTI stress in a transistor, this time using the AC method. In that case, we better reproduce the circuit operation for which the stress voltage is not applied constantly. Like a circuit oscillates between 0V and the supply voltage  $V_{DD}$ , the applied stress switches from 0V to  $V_{G,\,stress}$ . Again, there is a series of stress and relax events, called cycle, and the measuring principle is the same, a Measure-Stress-Measure sequence, recording the  $I_D$ - $V_G$  characteristic to extract the  $V_{TH}$  shift, similar to the DC BTI (Figure 1.18).

Figure 1.18 Time chart of the applied gate voltage during an AC BTI stress with the inset showing a single period of it, taken from [69].

Using the AC technique, we have to identify two parameters: the frequency and the Duty Factor (DF), described by:

$$f = \frac{1}{T}$$

Eq. 1.6

$$DF = \frac{T_{stress}}{T_{stress} + T_{relax}} \cdot 100\%$$

Eq. 1.7

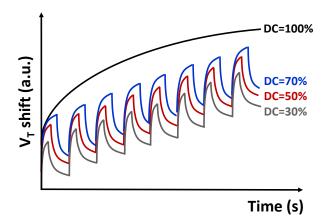

The frequency is describing the operation speed of the circuit while the duty factor reveals the percentage of the period that the circuit is "on". For example, during a 10% AC BTI application, the transistor is stress during 10% of the defined period and the rest 90% is under relaxation. We can perform tests from a duty cycle of 1% up to 100% (Figure 1.19), with the maximum percentage being the DC BTI that we saw before, and over a wide range of frequencies from 100Hz up to 1MHz. Each time the AC degradation will be lower than the DC one. This is due to the fact that the end of AC signal has a 0V state which means relaxation. So again in this type of measurement, it is necessary to have a fast range setup to avoid any

relaxation phenomena. In our case, we have used a previously developed fast methodology, operating under the "Arbitrary VG Pattern" (AVGP) method, described in details in [70].

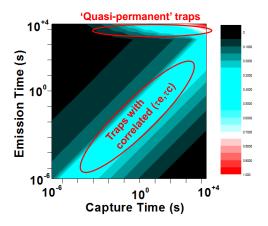

The best way to exploit AC BTI data, is to build the Capture and Emission Time (CET) maps [71] (Figure 1.20). Using this method, we can identify two trap populations, the permanent and the recoverable. The first one has a very high emission time compared to the capture ones and is related to the interface traps while the latter experiences a strong correlation between capture and emission and is mostly due to the traps deeper in the oxide.

Figure 1.19 . Illustration of a PMOSFET  $\ensuremath{V_{\text{TH}}}$  degradation under DC and AC stress conditions.

Figure 1.20 CET map revealing the two populations according to their time constants [70].

Of course, the next step is to have a model that is able to describe the experimental results and predict the degradation for AC and AVGP stress. The model that has been used to reproduce the  $V_{TH}$  shift in combination with the CET maps, is the RC model [70], [72] (Eq. 1.8).

$$\Delta V_{TH}(t) = K \cdot \sum_{i=1}^{N} g(\tau_c^i, \tau_e^i) \cdot U^i(t)$$

Eq. 1.8

where K is a technological constant,  $g(\tau_c, \tau_e)$  the local density of capture and emission time constants and U the voltage after n stress cycles: all of them individual parameters for each "i" trap. In this model, each trap can be seen as a lumped RC element with given resistance and capacitance. Taking the local trap density extracted from Figure 1.20, we are able to successfully fit our data, like the  $\Delta V_{TH}$  recovery for different AC stress periods, the normalized stress and recovery for different frequencies or w.r.t. the duty factor.

#### 1.5 Characterization of individual defects

Besides the characterization methods used for large devices to record the averaging effect of traps, as we move on to deeply scaled devices, we are witnessing the impact of only a handful of random defects. For that, it becomes imperative to have reliable techniques to characterize the individual traps.

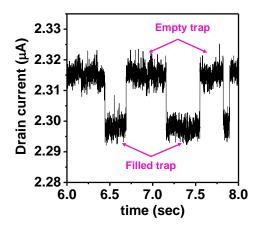

#### 1.5.1 Random Telegraph Noise – Low Frequency Noise (stationary method)

One of the first applied techniques for trap detection method is the Random Telegraph Noise (RTN), a method suitable for small gate areas. When a trap inside the oxide randomly captures and emits a carrier from the conduction channel, it causes a fluctuation of the electrical parameters of the transistor, especially in the drain current. This appears like discrete switching between two current levels in the time domain. Two current levels correspond to one trap, four levels to two traps etc. Each trap has three specific characteristics that make it unique: the capture time constant  $\tau_c$ , the emission time constant  $\tau_e$  and the drain current variation  $\Delta I_D$  that eventually has an impact on the threshold voltage. These type of fluctuations have been observed for quite some time and are evident in devices with surface smaller than  $0.1\mu m^2$  [73], [43], where it is easier to be detected due to the smaller existing number of traps.

Figure 1.21 RTN of a FDSOI PMOSFET transistor during a  $V_{G,\, bias}$  of -0.5V.

Figure 1.22 Impact of a single trap in the drain current

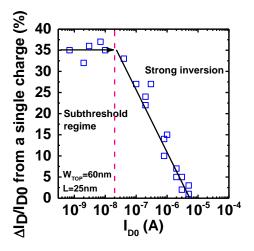

The usually applied gate voltage is part of the subthreshold region. Figure 1.22 shows the reason for this choice. Applying different gate bias on a MOSFET, we can identify two different zones of the trap. The left part in which the impact on the drain current reaches a maximum and constant value and the right part during which this effect decreases with the increasing operating drain current. The decrease in the strong inversion regime results from the screening of the oxide layer by mobile carriers of the inversion layer [43]. It is therefore related to the current flowing across the transistors through the equation [74]:

$$\frac{\Delta I_D}{I_D} = \frac{G_m}{I_D} \cdot \frac{q}{W \cdot L \cdot C_{OX}}$$

Eq. 1.9

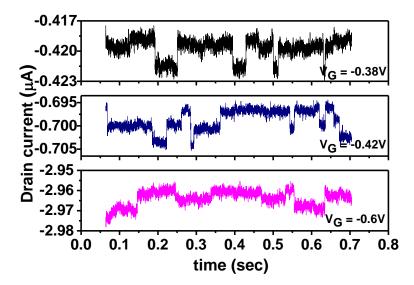

During the bias application, we keep the device in quasi-thermal equilibrium and we see the multiple captures and emission of the same defect. This means that we can see and detect only a small portion of the existing oxide traps, depending on the setup each time, like the bias conditions and the experimental measuring window. Figure 1.23 shows the current transients of the same PMOSFET, having a constant sampling time, but a different applied gate voltage. It

is obvious that the number of detected traps is directly related to the applied  $V_G$  and such, we can see from zero up to two current fluctuations.

Figure 1.23 Current fluctuations of one transistor under different bias application.

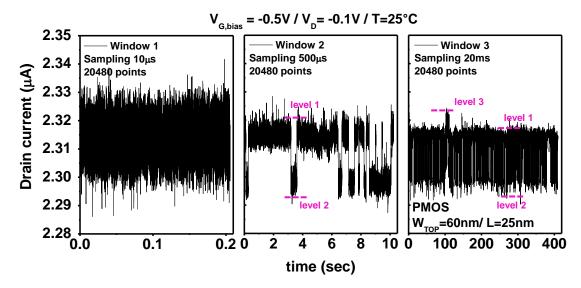

Besides the voltage, it is also the experimental window that affects our results. In Figure 1.24, it is evident that the sampling rate plays an important role in the measurements. We can see that, under a fixed pair of  $(V_G, V_D)$  there are some differences: in the first "window", there is no discrete switching visible while one the second and the third one, there are two and even four witnessed current levels, meaning that we have slower traps. In addition to that, the need of a large number of points [75], like here the selected 20.480, makes it more complicated to analyze the data after, especially when it comes to the determination of their characteristic capture and emission times.

Figure 1.24 Three experimental measuring windows with different sampling rates showing the complexity of RTN method for trap detection.

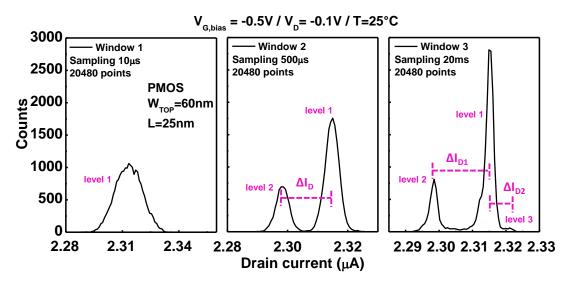

A relatively easier way to exploit the RTN data is to construct the drain current histograms (Figure 1.25) [76]. Even with a first glance, we can be more confident on the current fluctuations that have been measured and the existence (or not) of a defect. If we observe window 1, we see that the current is drifting around a specific level; one that is directly illustrated on the left histogram ( $\sim$ 2.31 $\mu$ A). On the contrary, in the two other windows/histograms, there are two or even three different ID levels, showing a series of capture/emission events that correspond to one or two traps respectively.

Figure 1.25 Respective drain current histograms of Figure 1.24.

Now, we also have the option to switch from the time domain to the frequency domain and use the Low Frequency Noise as a diagnostic approach for the detection of defects. To do so, we take the raw data of  $I_D$ -t and use Welch's method [77] to make this transformation resulting to use the Power Spectral Density (PSD  $[A^2/Hz]$ ) as a tool.

The method is based on the following concept: The original time signal is split in 1024 overlapping subparts, in our case, defining like this the averaging in the calculating periodograms, an important factor that reduces the variance of the individual power spectral results. Then, these overlapping segments have a window applied to them, in the time domain: we selected the Hanning window which is most commonly used in noise analysis due to its good frequency resolution.

After, we take the difference between the timestamps:

$$\Delta T = t_2 - t_1$$

Eq. 1.10

and calculate the minimum and the maximum frequency of our segment using the previously mentioned number of points per window (here 1024):

$$f_{min} = \frac{1}{\Delta T \cdot 1024}$$

Eq. 1.11

$$f_{max} = \frac{1}{\Delta T}$$

Eq. 1.12

continuing with their difference, which will serve as our sampling frequency in the PSD:

$$\Delta f = \frac{f_{max} - f_{min}}{1024}$$

Eq. 1.13

The corresponding periodogram (PSD) is calculated for each window using Fast Fourier Transform (FFT) and finally, we average the calculated periodograms, with the previous value.

$$PSD = \frac{FFT^2}{\Delta f}$$

Eq. 1.14

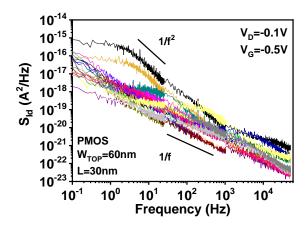

The PSD shape of RTN has a  $1/f^2$  dependence, called Lorentzian and as we scale down we experience a strong noise dispersion (Figure 1.26). The PSD is described by [78]:

$$S_{ID} = 4 \cdot A \cdot \Delta I_D^2 \cdot \frac{\tau}{1 + (2\pi f)^2 \tau^2}$$

Eq. 1.15

where  $\Delta I_D$  is the average RTN amplitude (Eq. 1.9),  $\tau$  is the time constant of transitions given by:

$$\tau = \left(\frac{1}{\tau_c} + \frac{1}{\tau_c}\right)^{-1}$$

Eq. 1.16

with  $\tau_c$  and  $\tau_e$ , the capture and emission time, respectively and A the space mark ratio described by:

$$A = \left(\frac{\tau}{\tau_c + \tau_e}\right)$$

Eq. 1.17

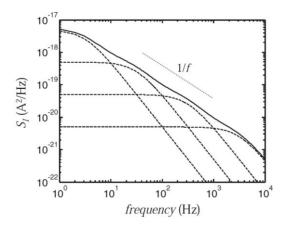

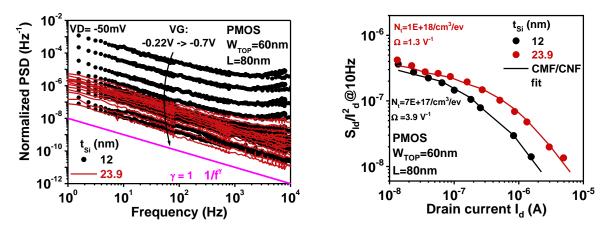

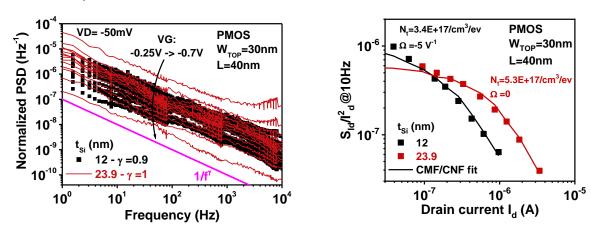

This method can be applied on both large and small area devices with the difference lying on the shape of PSD. On larger transistors, there is an increased number of traps, each one with a distinguished Lorentzian spectrum. As they are averaging, the new spectrum will fit the  $1/f^{\gamma}$  form, the so-called flicker noise (Figure 1.27). Depending on the  $\gamma$  value, we can identify the position of the traps in the oxide (0.7<  $\gamma$  <1.3) [79]. For a value lower than 1 the traps are located near the interface while when the value is higher than 1 the traps are positioned deeper in the oxide. If  $\gamma$ =1, then we have a uniform trap distribution near the interface.

Figure 1.26 Strong PSD dispersion in deeply scaled transistors, here showing Trigate PMOSFETs.

Figure 1.27 Superposition of Lorentzian spectra creating a 1/f dependence on a large device [80].

Even after all the years of LFN studies, there is still a debate regarding the physical mechanisms that are responsible for the origin of flicker noise in semiconductors, especially in MOSFETs where the PSD spectrum is a combination of Lorentzian and flicker. There are two major "schools": the Carrier Number Fluctuations (CNF) and the Hooge Mobility Fluctuations (HMF) [81]. But, it seems that a combination of both (Carrier Number Fluctuation/ Correlated Mobility Fluctuation-CNF/CMF) is more suitable to describe this more complex PSD (Eq. 1.18 [82], [83]).

$$S_{Id} = g_m^2 \cdot S_{Vfb} \left( 1 \pm \alpha_{sc} \mu_{eff} C_{ox} \frac{I_d}{g_m} \right)^2$$

Eq. 1.18

where  $\mu_{eff}$  is the effective mobility,  $\alpha_{sc}$  the Coulomb scattering coefficient and  $S_{Vfb}$  the flatband voltage that is described by (Eq. 1.19) if the carrier trapping-detrapping takes place through a tunneling process:

$$S_{Vfb} = rac{q^2 \lambda k T N_t}{f^\gamma W L C_{ox}^2}$$

Eq. 1.19

with N<sub>t</sub> being the oxide trap surface state density.

To have a complete study, it is necessary to perform the noise measurements in a large range of  $V_{G,\,bias}$ , always at a small  $V_D$  and, at least, one decade above the equipment noise level. In that way, we can extract some useful information regarding the oxide/channel interface properties. Plotting the normalized PSD w.r.t. the drain current for a specific frequency, usually at 10Hz, and fitting the data with the CNF/CMF model, we are able to extract the two major parameters:  $N_t$  and the correlated mobility fluctuations factor,  $\Omega = \alpha_{sc}\mu_{eff}C_{ox}$  [84]. The first one indicating the quality of the oxide depending on different technological aspects, like the various processing steps [85], or the impact of electrical stress and the second one to characterize the scattering rate induced by the interface charge fluctuations.

#### 1.5.2 Time Dependent Defect Spectroscopy

Another technique, very similar to RTN and also qualified for small area transistors, like the Trigate nanowires in this thesis, is the Time Dependent Defect Spectroscopy (TDDS) [86], [87]. Several studies have shown that the recoverable component of BTI degradation and the Random Telegraph Noise (RTN) are caused by the same oxide defects having a match between their extracted characteristics, like the carrier-emission constants or the characteristic step height. Even though TDDS and RTN study the same phenomenon [87]–[89], there are still some differences between them. Just like BTI, the TDDs technique is also divided in two parts, the filling (called stress in BTI) and the recoverable.

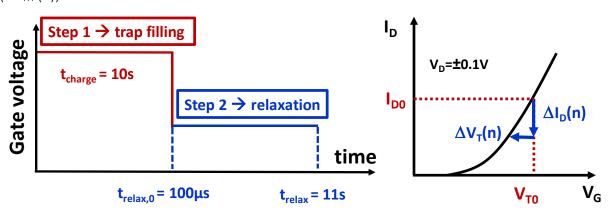

To begin with, the basic difference with RTN is that the TDDS method is identified as a transient effect (Figure 1.28). We apply a high enough charging gate voltage ( $V_{G,\,charge}$ ) in order to fill the traps and have an almost 100% occupancy of them, but without stressing our device. So, for a single-channel transistor the usual value for N/PMOSFETS is  $\pm 1.2V$ , respectively, in order to charge in strong inversion and characterize the pre-existing defects without creating new ones. The filling time is set to 10s in all our tests during which we do not make any drain current measurements. After that we switch to a lower discharging voltage ( $V_{G,\,relax}$ ), choosing a value close to the threshold voltage and recording directly the relaxation drain current transient for a period of 11sec using 3.000 timestamp points. During that time, the filled traps are emptying and we can measure the carrier emissions from single defects that appear as steps. Considering that we are in linear operation and the current degradation is due to the  $V_{TH}$  degradation [90], we transform the  $\Delta I_D$  into  $\Delta V_{TH}$  as shown in Figure 1.29. We perform an initial  $I_D$ - $V_G$  measurement, before the filling of the traps and compare it with the recorded jumps after the relaxation part ( $\Delta I_D$  (n)). Like that, we can obtain the equivalent  $V_{TH}$  shift of a single defect ( $\Delta V_{TH}$  (n)).

Figure 1.28 Experimental setup of Time Dependent Defect Spectroscopy.

Figure 1.29 Transformation of individual  $\Delta I_D$  jumps to a  $V_{\text{TH}}$  shift.

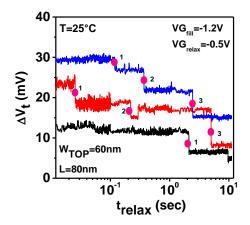

There are two attention points in this method: Firstly, in order to be sure that we are measuring above the equipment noise level, the minimum step height limit is set to 1mV. After that, depending on the measurement conditions, we can set it to 2 or 2.5mV, but always keeping in mind the 1mV minimum limitation. Secondly, when there is a comparison between different geometries, it is advisable to choose the  $V_{G, \, sense}$  correctly so that the same current level is reached each time, hence the same oxide field. The fact that TDDS is applied in deeply

scaled devices, makes it understandable that the variability, even between the same geometry transistors, is increased (Figure 1.30). For this reason, it is an imperative need to acquire a statistical interpretation of the results, using a minimum of 60 tested devices each time.

Figure 1.30 Typical TDDS relaxation transients of different devices having the same geometry.

Figure 1.31 Histogram of the recorded jumps after applying the TDDS method on 60 devices.

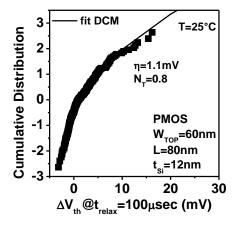

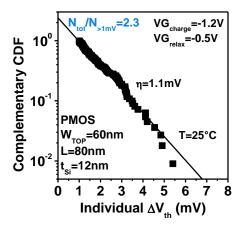

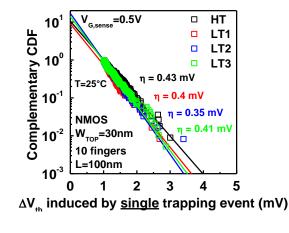

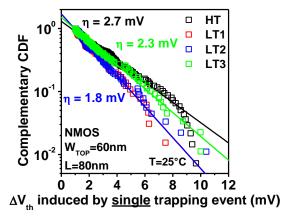

So, now the question is how we can obtain some useful information from this procedure. The first "easy" statistical representation of these steps is to plot their histogram (Figure 1.31) from which itis clear that they follow an exponential law and we'll see now what kind of parameters can help us characterize their impact on a decananometer device. In this direction, we use the above results and plot two different figures, the Cumulative Distribution Function (CDF) of the total  $V_{TH}$  shift per device measured just after the filling step and the Complementary Cumulative Distribution Function (CCDF) of the individual steps (Figure 1.32). We'll look at both separately regarding the qualitative information that we can extract from them and then make a comparison of the parameters.

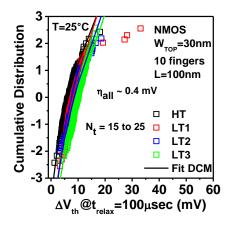

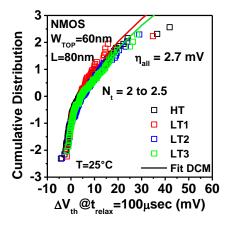

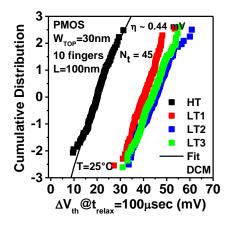

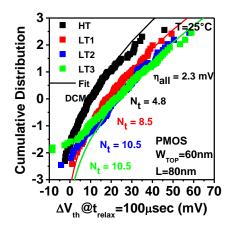

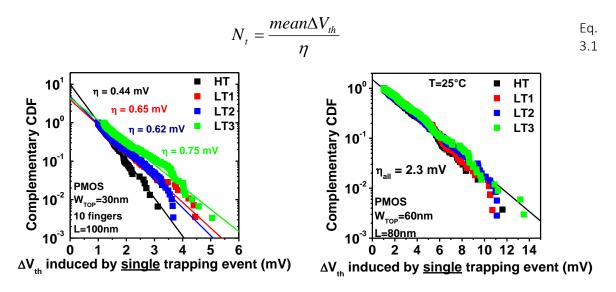

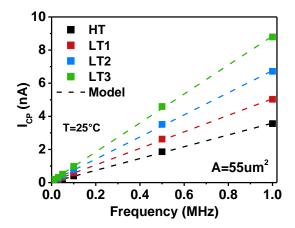

Starting from the Cumulative Distribution of the total  $\Delta V_{TH}$ , measured at the first relaxation point, fitting the raw data with the Defect Centric Model (DCM). The DCM was, firstly, introduced by in 2010 [91] in order to obtain the needed statistics for deeply scaled devices and it is based on two assumptions. Firstly, that the  $\Delta V_{TH}$  distribution of individual devices is exponentially distributed. And secondly, that the mean number of defects that are present in the gate oxide is Poisson distributed (Eq. 1.20 - Eq. 1.22).

Combining both distributions, the number of traps and the impact of each one of them, we conclude to these forms allowing us to express the two parameters in terms of mean value and variance and have a technological or geometrical independent calculation of them.

$$F_n(\Delta V_{th}, \eta) = \sum_{n=1}^{\infty} \frac{e^{-N} * N_{trap}^n}{n!} * \left[ 1 - \frac{\Gamma(n, \frac{\Delta V_{th}}{\eta})}{(n-1)!} \right]$$

Eq. 1.20

with  $\eta$  being the average  $V_{TH}$  shift from a single defect, equal to:

$$\eta = rac{\sigma \Delta V_{th}^2}{2*mean\Delta V_{th}}$$

Eq. 1.21

and N<sub>T</sub>, the average number of charged defects calculated from:

$$N_{Trap} = 2 * \left(\frac{mean\Delta V_{th}}{\sigma \Delta V_{th}}\right)^2$$

Eq. 1.22

Figure 1.32 (left) CDF of the total  $V_{TH}$  shift per device at the first relaxation point and (right) CCDF of all the recorded individual steps.

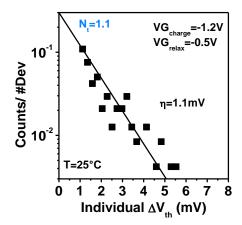

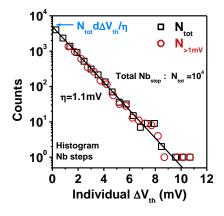

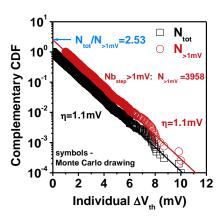

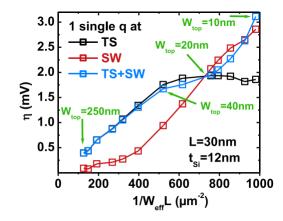

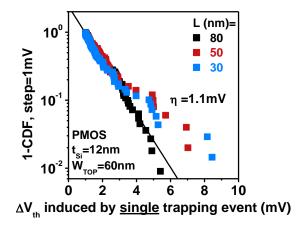

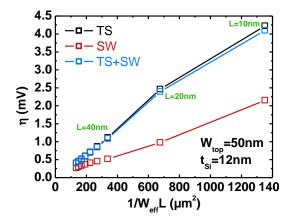

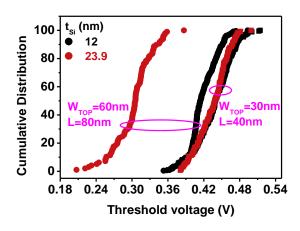

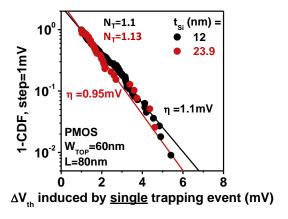

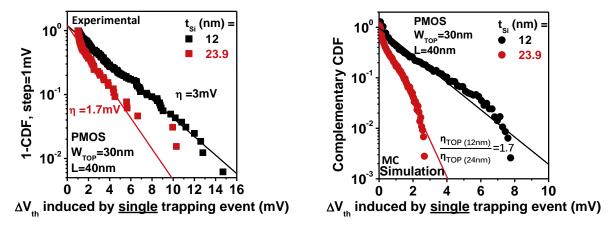

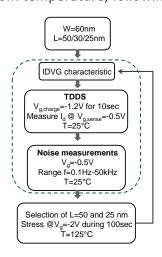

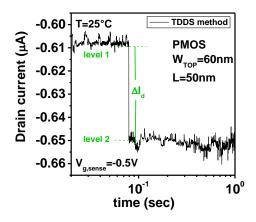

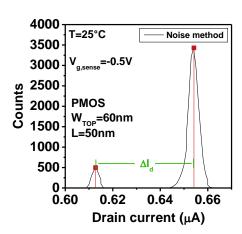

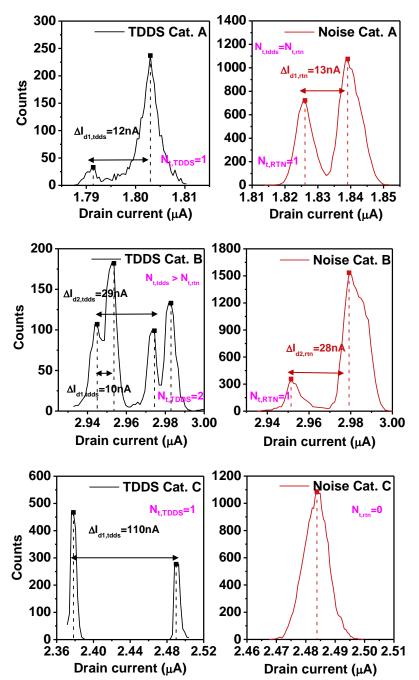

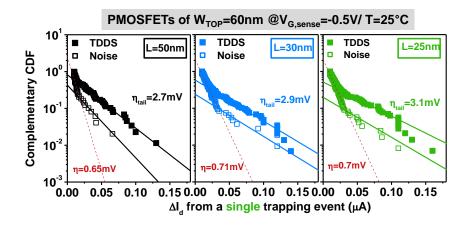

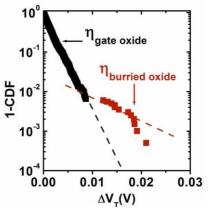

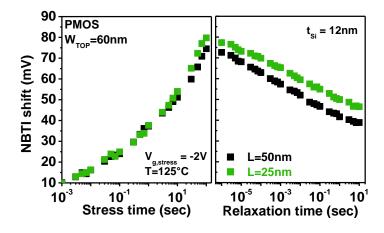

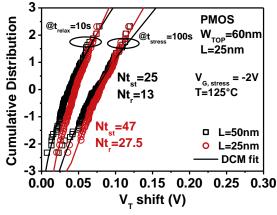

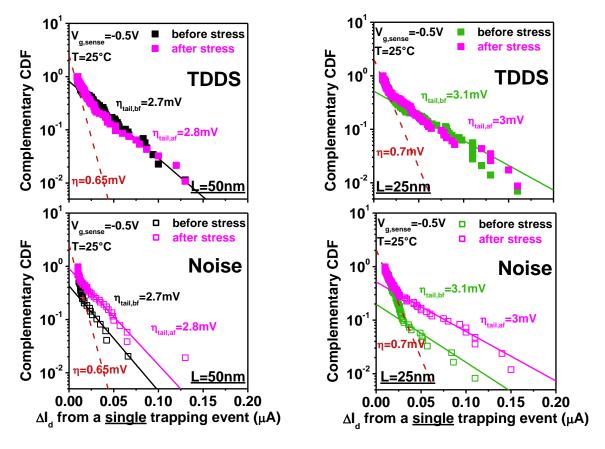

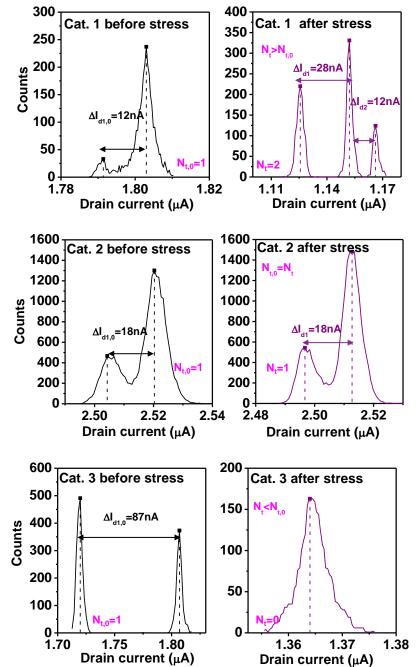

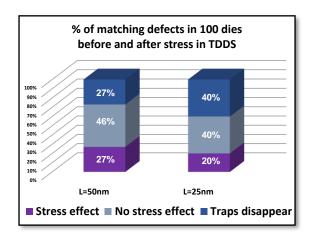

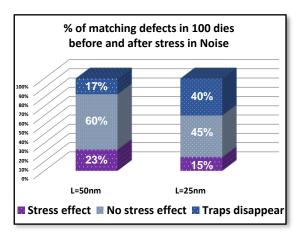

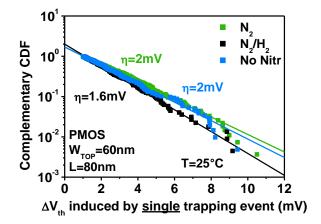

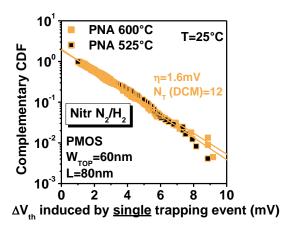

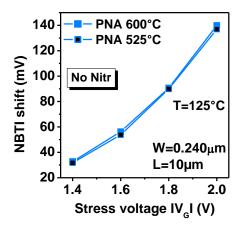

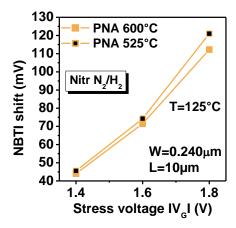

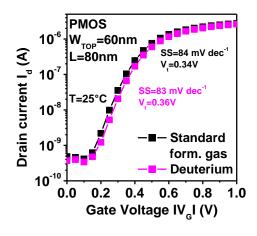

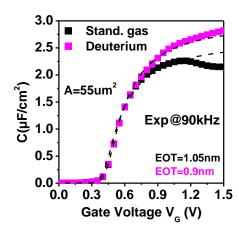

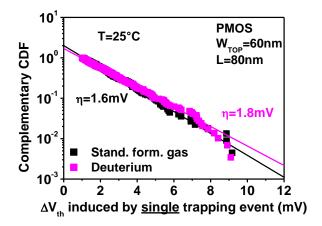

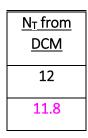

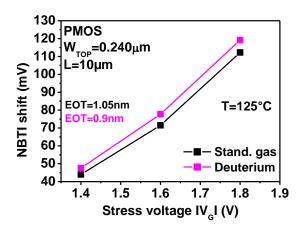

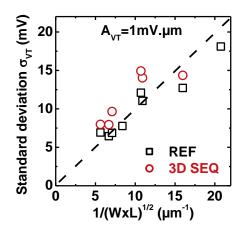

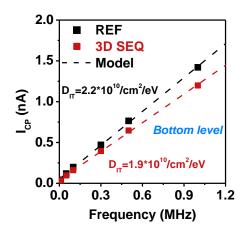

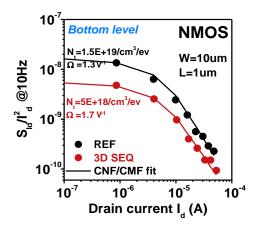

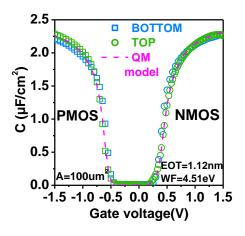

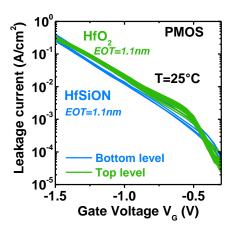

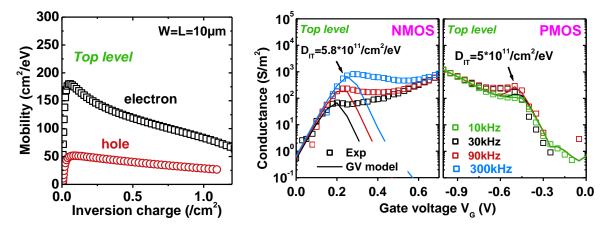

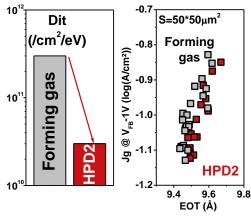

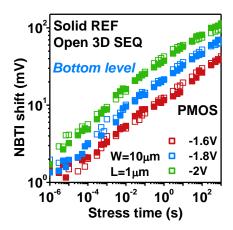

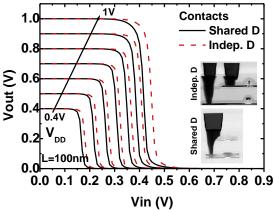

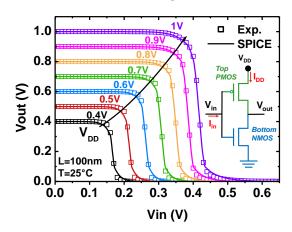

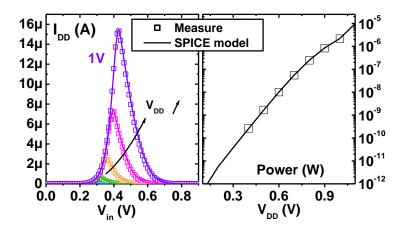

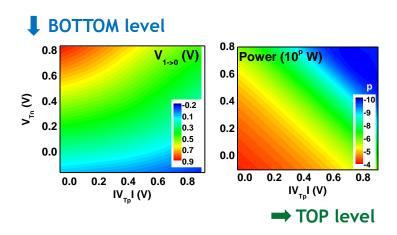

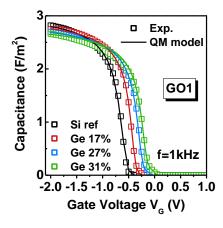

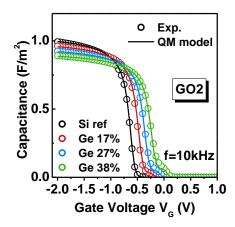

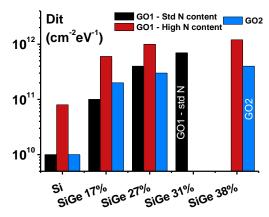

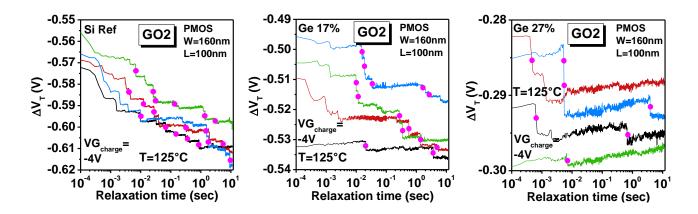

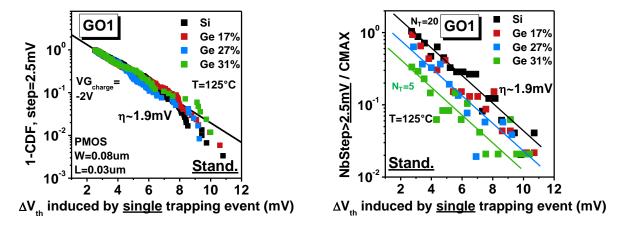

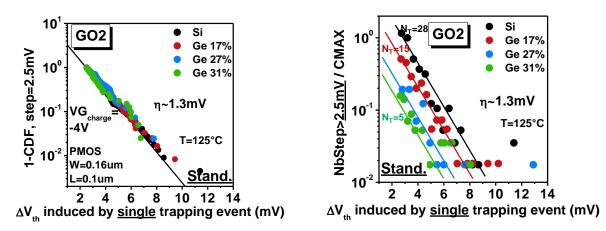

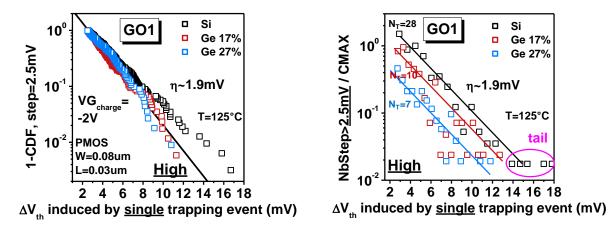

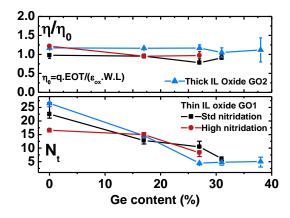

At the same time, there is the CCDF plot, constructed using the carrier emissions from single microscopic defects and as the histogram before, it appears exponentially distributed. It originates from the random position of the trapped charged in the gate oxide, an observation already made on FDSOI devices [92]–[94]. Fitting the data helps us extract two parameters: the reverse of the slope gives us the  $\eta$  parameter and as presented by many works, the  $N_T$  is considered to be the intercept with y-axis. Experimentally, it is also necessary to fix a threshold on  $\Delta V_{TH}{}^{ind}$  to distinguish a true emission event from the system noise level. It is fixed to 1mV in all our experiments. Such a threshold implies that the defects with  $\Delta V_{TH}{}^{ind}$  below 1mV cannot be detected properly by the technique. In order to know how this limitation can affect the extraction of the trap parameters, we simulate the  $\Delta V_{TH}{}^{ind}$ s of 10.000 defects exponentially distributed through a Monte Carlo drawing. Amongst the  $10^4$  traps, only the  $N_{>1mV}$  defects, which exhibit a  $V_{TH}$  shift above 1mV, can be detected experimentally. The histogram and CCDF of the total number of defects  $N_{tot}$  are then compared to the ones of detectable traps  $N_{>1mV}$  in Figure 1.33. For the simulation,  $\eta$  is fixed to 1.1mV. We first notice that both histograms are very similar and lead to the same  $\eta$  extraction. This proves that the method is effective to