### Millimeter-wave and terahertz frequency synthesis on advanced silicon technology

Raphael Guillaume

### ▶ To cite this version:

Raphael Guillaume. Millimeter-wave and terahertz frequency synthesis on advanced silicon technology. Electromagnetism. Université de Bordeaux, 2018. English. NNT: 2018BORD0412. tel-02329132

### HAL Id: tel-02329132 https://theses.hal.science/tel-02329132

Submitted on 23 Oct 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE PRÉSENTÉE POUR OBTENIR LE GRADE DE

### DOCTEUR DE L'UNIVERSITÉ DE BORDEAUX

École Doctorale des Sciences de l'Ingénieur SPÉCIALITÉ : ÉLECTRONIQUE

par Raphaël GUILLAUME

# Millimeter-Wave and Terahertz Frequency Synthesis on Advanced Silicon Technology

Directeurs de thèse : Andreia CATHELIN Yann DEVAL

> Préparée à STMicroelectronics et au Laboratoire IMS

Soutenue le : 18 décembre 2018

Devant la commission d'examen formée de :

Sylvain BOURDEL Franck BADETS Andreas KAISER Cristell MANEUX François RIVET Nathalie DELTIMPLE Andreia CATHELIN Yann DEVAL

Professeur des Universités Docteur Ingénieur – HDR Directeur de recherche CNRS Professeur des Universités Maître de Conférence Maître de Conférence – HDR Docteur Ingénieur – HDR Professeur des Universités Grenoble INP **CEA LETI Grenoble** ISEN Lille Université de Bordeaux Bordeaux INP Bordeaux INP **STMicroelectronics** Bordeaux INP

Rapporteur Rapporteur Président Examinateur Examinateur Examinateur *Co-directrice* Directeur

Thèse réalisée au Laboratoire de l'INTÉGRATION DU MATÉRIAU AU SYSTÈME (IMS) de Bordeaux, au sein de l'équipe CAS du groupe CONCEPTION.

Laboratoire IMS – Bâtiment A31 351 Cours de la Libération 33405 Talence Cedex

Thèse CIFRE réalisée dans l'entreprise STMICROELECTRONICS, au sein de l'équipe PROCESS R&D.

STMicroelectronics 850 Rue Jean Monnet 38926 Crolles Cedex "La science est une lanterne sur les faits. Elle éclaire les choix, qui eux sont politiques." Anonyme

### Résumé

Ces dernières années les bandes de fréquence millimétriques et térahertz (THz) ont montrées un fort potentiel pour de nombreuses applications telles que l'imagerie médicale et biologique, le contrôle de qualité ou les communications à très haut débit. Les principales raisons de cet intérêt sont les nombreuses propriétés intéressantes des ondes THz et millimétriques, telles que leur capacité traverser la matière et ceci de manière inoffensive ou le large spectre disponible à ces fréquences. Les applications visées nécessitent des sources de signaux énergétiquement efficaces, à forte puissance de sortie et, pour certaines applications, à faible bruit de phase. De plus, la demande croissante pour des applications dans ces bandes de fréquence imposent l'utilisation de technologie de hautes performances à coût métrisé et permettant une intégration à très grande échelle, telle que la technologie 28nm CMOS FD-SOI.

Dans ce contexte, cette thèse propose une solution innovante pour la génération de fréquence millimétrique et THz en technologie CMOS : l'oscillateur distribué verrouillé par injection. Les travaux présentés dans ce manuscrit englobent l'analyse détaillé de l'état de l'art et de ses limites, l'étude théorique approfondie de la solution proposée pour une intégration en ondes millimétriques, le développement d'une méthodologie de conception spécifique en technologie CMOS ainsi que la conception de démonstrateurs technologique. Les différents oscillateurs intégrés en technologie 28nm FDSOI et opérant à des fréquences respectivement de 134 GHz et 200 GHz ont permis de démontrer la faisabilité de sources de signaux millimétrique et THz, à forte efficacité énergétique, forte puissance de sortie et faible bruit de phase en technologie CMOS à très grande échelle d'intégration. Enfin, la capacité de verrouillage par injection de tels oscillateurs distribués a été démontrée expérimentalement ouvrant la voie à de futurs systèmes THz totalement intégrés sur silicium. Les solutions intégrées démontrées dans cette thèse ont, à l'heure actuelle, la plus grande fréquence d'oscillation dans un nœud Silicium 28nm CMOS.

### Abstract

In recent years, millimeter-wave (mm-wave) and terahertz (THz) frequency bands have revealed a great potential for many applications such as medical and biological imaging, quality control, and very-high-speed communications. The main reasons for this interest are the many interesting properties of THz and millimeter waves, such as their ability to harmlessly penetrate through matter or the broad spectrum available at these frequencies. Targeted applications require energy efficient signal sources with high power output and, for some applications, low phase noise. In addition, the increasing demand in mmwave/THz applications requires the use of a cost-optimized, high-performance, and very large scale integration (VLSI) technologies, such as the 28nm CMOS FD-SOI technology.

In this context, this thesis proposes an innovative solution for mm-wave and THz frequency generation in CMOS technology: the injection locked distributed oscillator (ILDO). The work presented in this manuscript includes the detailed analysis of the state-of-the-art and its limitations, the detailed theoretical study of the proposed millimeter-waves band solution, the development of a specific design methodology in CMOS technology as well as the design of technological demonstrators. The several 28nm FDSOI integrated distributed oscillators at 134 GHz and respectively 200 GHz have demonstrated the feasibility of mm-wave and THz signal sources with high-energy efficiency, high output power, and low phase noise in a VLSI CMOS technology. Finally, the injection locking capability of such distributed oscillators has been demonstrated experimentally paving the way for a future silicon-based fully integrated THz systems. The proposed circuits are as of today the highest oscillation frequency solutions demonstrated in a 28nm CMOS Silicon technology.

### Remerciements

Cette section a sans doute été pour moi la plus difficile à rédiger. Il y a tant de personnes qui ont participé à la réussite de ces travaux et tous les mots que j'écris aujourd'hui me semblent trop faibles pour refléter la profonde gratitude que je ressens.

En premier lieu, je tiens à remercier les membres du jury pour l'intérêt qu'ils ont porté à ces travaux et pour les échanges scientifiques très enrichissant qui ont suivi.

Je souhaite sincèrement remercier mes directeurs de thèse pour l'honneur qu'ils m'ont fait d'encadrer ces travaux. Merci Yann, ces trois années à travailler à tes côtés resteront inoubliables. Merci Andreia d'avoir su me guider pour hisser ces travaux au plus haut niveau.

Merci à tous mes collègues du laboratoire IMS et de STMicroelectronics d'avoir contribué à l'excellente ambiance de travail. Ainsi, merci Yoan, David P., Manuel, Jérémie, Boris, Florent, Florian, David G., Thibaut D., Dwight, Julian, Nassim, Khoa, Samuel, Romane, Magali, Hervé, Dominique, Camille, Arnaud, Eric. Merci également à Thomas, Louise, Mohammed, Ronan, Angel, Philippe et Robin.

Je tiens tout particulièrement à adresser un énorme merci à Thibaud et Fanny sans qui ces années de thèse auraient été radicalement différentes.

Merci à François, tu as été un chef d'équipe exemplaire et c'était un honneur de faire vivre l'équipe CAS à tes côtés. Mais tu as surtout été un ami sans faille dans les moments difficiles.

Je tiens également à remercier tout particulièrement Nathalie pour m'avoir fait découvrir le monde de la recherche et sans qui il ne me serait pas venu l'envie de réaliser une thèse.

Un grand merci à tous mes amis et à mes parents pour m'avoir supporté dans mes choix, mes réussites et mes échecs. Merci Niels et Sarah, les meilleurs frère et soeur du monde.

Infine, ringrazio amorevolmente Elisa per avermi aiutato a realizzare questa avventura.

# Contents

| Abstract i    |                                                                              |                                                                                           |                                                                                                       |                                                                                |  |  |

|---------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|

| A             | Acknowledgements v                                                           |                                                                                           |                                                                                                       |                                                                                |  |  |

| Co            | onter                                                                        | nts                                                                                       |                                                                                                       | vii                                                                            |  |  |

| $\mathbf{Li}$ | st of                                                                        | Figures                                                                                   | S                                                                                                     | xi                                                                             |  |  |

| Li            | st of                                                                        | Tables                                                                                    |                                                                                                       | xvii                                                                           |  |  |

| In            | trod                                                                         | uction                                                                                    |                                                                                                       | 1                                                                              |  |  |

| 1             | <ul> <li>Mill</li> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>1.4</li> </ul> | Mm-wa<br>1.1.1<br>1.1.2<br>Mm-wa<br>1.2.1<br>1.2.2<br>State-of<br>1.3.1<br>1.3.2<br>1.3.3 | •wave and Terahertz Technologies.ve and THz applicationsNon-ionizing imagingHigh-speed communications | $ \begin{array}{c} 4 \\ 6 \\ 7 \\ 8 \\ 9 \\ 12 \\ 12 \\ 15 \\ 17 \end{array} $ |  |  |

| 2             | <b>An</b> 2.1 2.2                                                            | The inje<br>2.1.1<br>2.1.2<br>2.1.3<br>Theoret                                            | ative: The Injection Locked Distributed Oscillator         ection locked oscillator                   | 22<br>23<br>26<br>33                                                           |  |  |

|   |     | 2.2.2<br>2.2.3<br>2.2.4 | Parallel injection – example of Colpitts oscillator34Series injection – example of Colpitts oscillator37Generalization38            |

|---|-----|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 2.2.5                   | Simulation results                                                                                                                  |

|   | 2.3 | The in                  | jection locked distributed oscillator                                                                                               |

|   |     | 2.3.1                   | Overview of the distributed oscillator and its properties 43                                                                        |

|   |     | 2.3.2                   | Distributed oscillator for operation frequencies close to $f_{max}$ 44                                                              |

|   |     | 2.3.3                   | Theory of injection locked distributed oscillator                                                                                   |

|   |     | 2.3.4                   | Simulation results 51                                                                                                               |

|   | 2.4 | Chapte                  | er Conclusion                                                                                                                       |

| 3 | Mn  | n-wave                  | and THz Sources Design in 28nm FD-SOI Technology 55                                                                                 |

|   | 3.1 | Overvi                  | ew of the 28nm FD-SOI technology for mm-wave THz applications 56                                                                    |

|   |     | 3.1.1                   | Active devices                                                                                                                      |

|   |     | 3.1.2                   | Body-Biasing 58                                                                                                                     |

|   |     | 3.1.3                   | Back-end-of-line                                                                                                                    |

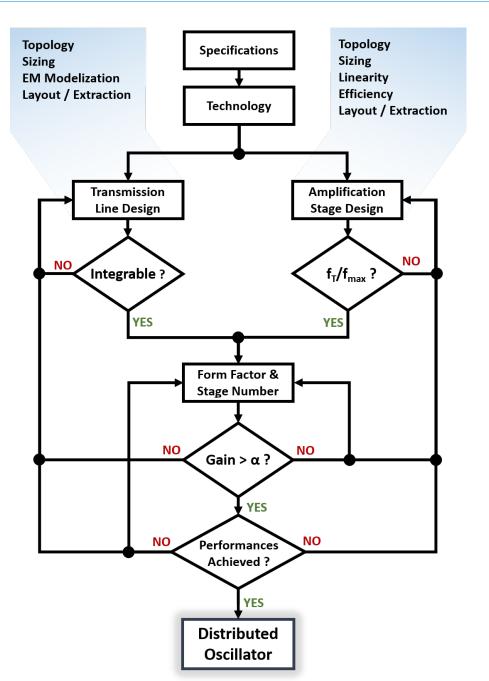

|   | 3.2 | Distrib                 | buted oscillator design methodology $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 62$                                    |

|   |     | 3.2.1                   | Amplification stage    62                                                                                                           |

|   |     | 3.2.2                   | Transmission line                                                                                                                   |

|   |     | 3.2.3                   | Form factor and stage number                                                                                                        |

|   | 3.3 | Energy                  | v efficient 135 and 200 GHz distributed oscillators design $\ldots \ldots 70$                                                       |

|   |     | 3.3.1                   | Amplification Stage Design    70                                                                                                    |

|   |     | 3.3.2                   | Transmission Line Design                                                                                                            |

|   |     | 3.3.3                   | Other passives design                                                                                                               |

|   |     | 3.3.4                   | Final layout                                                                                                                        |

|   | 3.4 | Chapte                  | er conclusion                                                                                                                       |

| 4 | Exp | oerimer                 | ntal results 87                                                                                                                     |

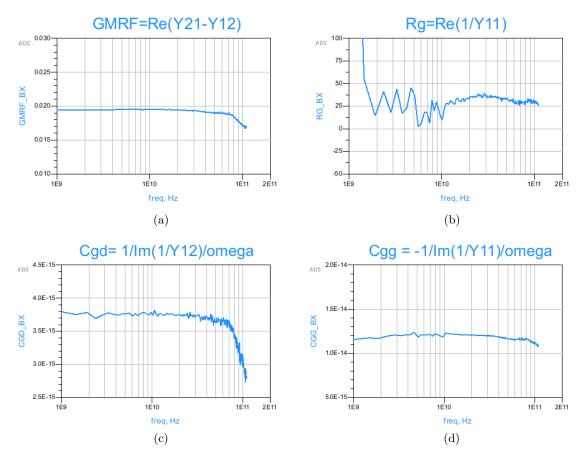

|   | 4.1 | Standa                  | $lone transistor \dots \dots$ |

|   |     | 4.1.1                   | De-embedding                                                                                                                        |

|   |     | 4.1.2                   | Measurement setup                                                                                                                   |

|   |     | 4.1.3                   | Measurement results                                                                                                                 |

|   | 4.2 | Distrik                 | puted oscillators                                                                                                                   |

|   |     | 4.2.1                   | Measurement setup                                                                                                                   |

|   |     | 4.2.2                   | Measurement results                                                                                                                 |

|   |     | 4.2.3                   | On-wafer mapping measurement for variability study 98                                                                               |

|   |     | 4.2.4                   | Phase noise optimization through body-bias control 100                                                                              |

|   |     | 4.2.5                   | State-of-the-art comparison                                                                                                         |

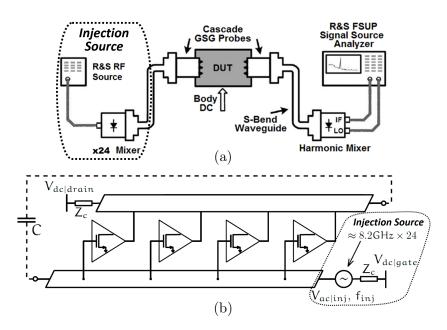

|   | 4.3 | Injecti                 | on locked distributed oscillator $\ldots \ldots 104$                 |

|   |     | 4.3.1                   | Measurement setup                                                                                                                   |

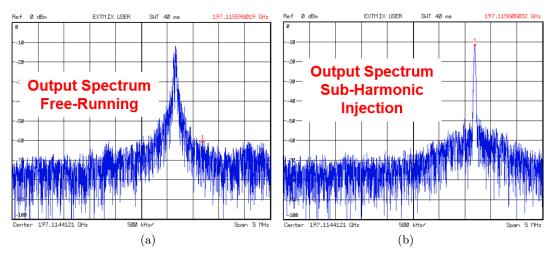

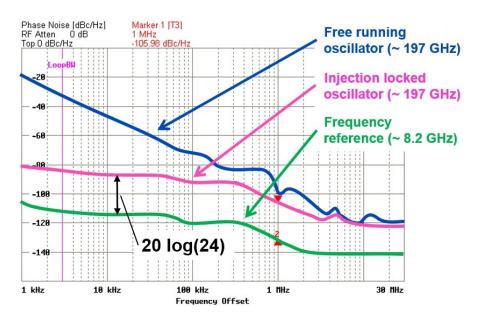

| 44           | 4.3.3 | 200 GHz ILDO measurement results | 107 |

|--------------|-------|----------------------------------|-----|

|              | -     | nd perspectives                  | 109 |

| Bibliography |       |                                  | 115 |

# List of Figures

| 1.1  | Electromagnetic spectrum (From the Southeastern Universities Research        |    |

|------|------------------------------------------------------------------------------|----|

|      | Association).                                                                | 4  |

| 1.2  | Terahertz image examples. (a) Hidden knife in mattress from [4] and (b)      | _  |

|      | structure of leaves from [5]                                                 | 5  |

| 1.3  | (a) THz image of colon tissue showing healthy tissue in green and cancerous  |    |

|      | tissue in dark red (fake colors). (b) Imaging performed by THz system        | ~  |

|      | from Teraview [6]. $\ldots$                                                  | 5  |

| 1.4  | Simple oscillator behavior model.                                            | 7  |

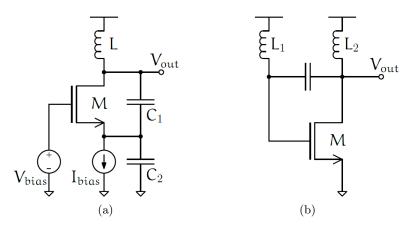

| 1.5  | Schematic examples of (a) Single mode Colpitts oscillator and (b) single     | 0  |

|      | mode Hartley oscillator                                                      | 8  |

| 1.6  | Schematic differential cross-coupled oscillator.                             | 9  |

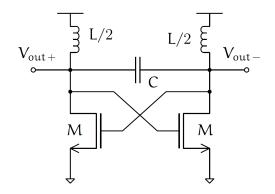

| 1.7  | Push-push oscillator architecture based on crossed-coupled oscillator        | 10 |

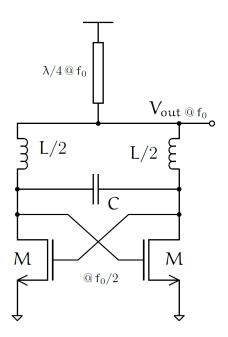

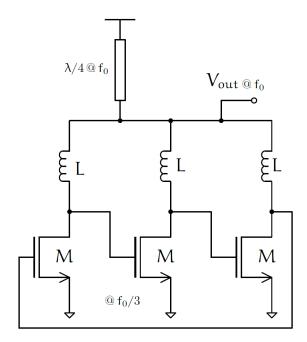

| 1.8  | Triple-push oscillator architecture.                                         | 11 |

| 1.9  | (a) Oscillator seems as a looped back power amplifier. (b) Maximally         |    |

|      | Efficient Power Gain optimization. [29]                                      | 12 |

| 1.10 | Simulated and measured (a) output power and (b) DC-to-RF efficiency          |    |

|      | under different bias condition. (c) Die photomicrograph. [29]                | 13 |

| 1.11 | (a) Schematic of the presented push-push oscillator. (b) Bipolar base-       |    |

|      | emitter parasitic capacitance $C_{\pi}$ at different bias points. [20]       | 14 |

| 1.12 | Measured (a) frequency and (b) output power under different bias point.      |    |

|      | (c) Die photomicrograph. $[20]$                                              | 14 |

| 1.13 | (a) Push-push ILO based design proposed in [30]. (b) Triple-push ILO         |    |

|      | based design presented in [31] and (c) layout of the cascaded ILO introduced |    |

|      | in [32]                                                                      | 15 |

| 1.14 | Architecture of the 300 GHz frequency synthesis proposed in [33]             | 16 |

| 1.15 | Architecture of the 320 GHz frequency synthesis proposed in [34]             | 17 |

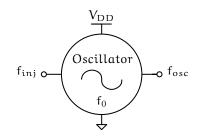

| 2.1  | Oscillator with a synchronization input.                                     | 22 |

| 2.2  | Oscillator pulling in (a) broadband transceiver and (b) RF transceiver       | 23 |

| 2.3  | Beamforming transmitter using injection locked COA.                          | 24 |

|      |                                                                              |    |

| 2.4  | Frequency synthesis using an ILO as divider by 4                                                 | 25 |

|------|--------------------------------------------------------------------------------------------------|----|

| 2.5  | Frequency synthesis using a SHILO.                                                               | 26 |

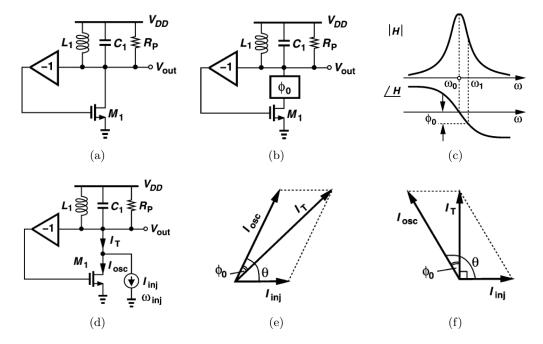

| 2.6  | (a) Conceptual oscillator. (b) Frequency shift due to additional phase-shift.                    |    |

|      | (c) Open-loop characteristics. (d) Frequency shift by injection. (e) and (f)                     |    |

|      | Phase difference between input and output for two values of $ \omega_{inj} - \omega_0 $ .        |    |

|      | (Figures from [66])                                                                              | 28 |

| 2.7  | Representation of oscillator for Huntoon-Weiss theory                                            | 29 |

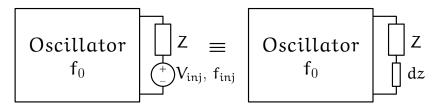

| 2.8  | Representation of oscillator for (a) proposed series injection, (b) proposed parallel injection. | 33 |

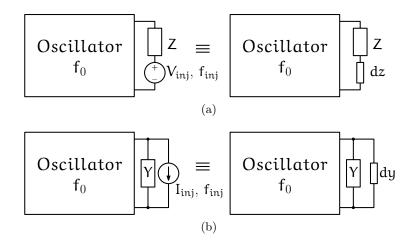

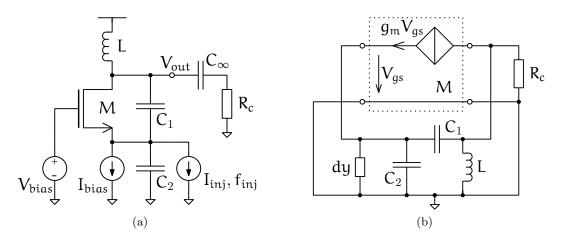

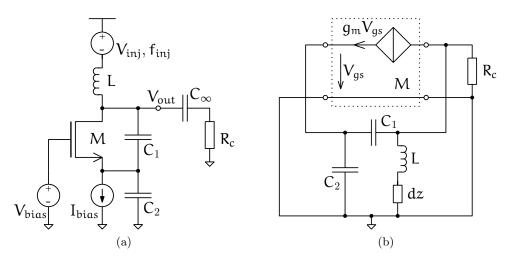

| 2.9  | Colpitts oscillator loaded with resistance $R_c$ (a) schematic with parallel-                    |    |

|      | injection source, (b) small-signal equivalent circuit.                                           | 35 |

| 2.10 | Colpitts oscillator loaded with resistance $R_c$ (a) schematic with series-                      |    |

|      | injection source, (b) small-signal equivalent circuit.                                           | 37 |

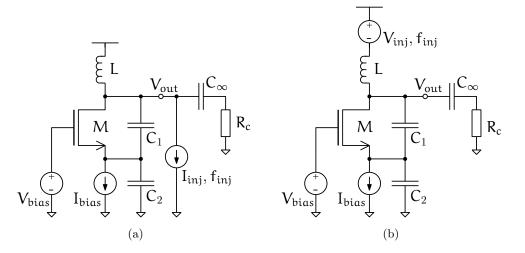

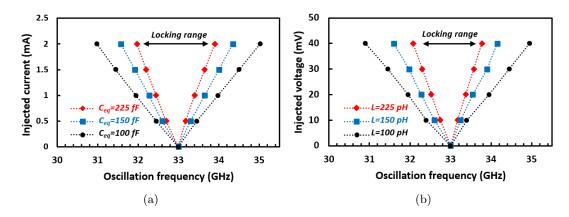

| 2.11 | Simulated schematics of (a) parallel synchronized and (b) series synchro-                        |    |

|      | nized Colpitts oscillators.                                                                      | 39 |

| 2.12 | Simulated oscillation frequency and locking range for the (a) parallel                           |    |

|      | synchronized and (b) series synchronized Colpitts oscillators.                                   | 40 |

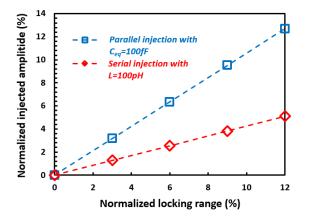

| 2.13 | Colpitts ILO normalized injected signal amplitude as a function of the                           |    |

|      | normalized locking range.                                                                        | 41 |

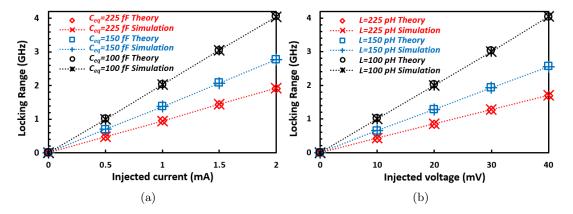

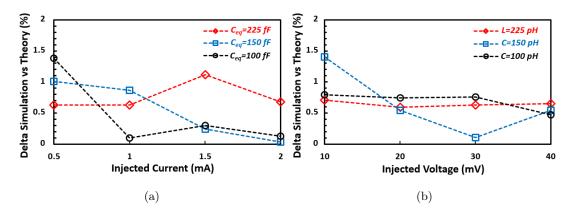

| 2.14 | Simulation versus theory of the locking range for the (a) parallel synchro-                      |    |

|      | nized and (b) series synchronized Colpitts oscillator. $\ldots$ $\ldots$ $\ldots$                | 41 |

| 2.15 | Normalized error between theory and simulation for the (a) parallel syn-                         |    |

|      | chronized and (b) series synchronized Colpitts oscillator                                        | 42 |

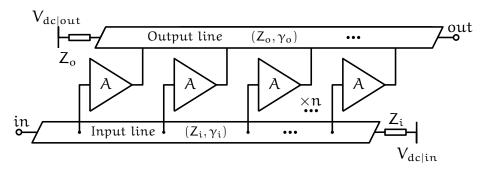

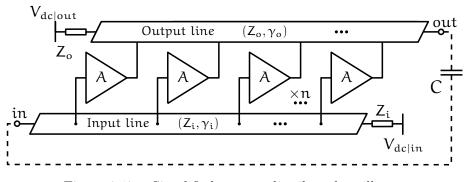

| 2.16 | Simplified n-stage distributed amplifier.                                                        | 43 |

| 2.17 | Simplified n-stage distributed oscillator.                                                       | 43 |

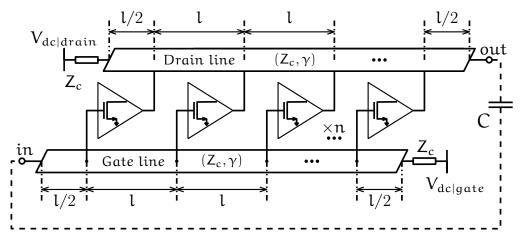

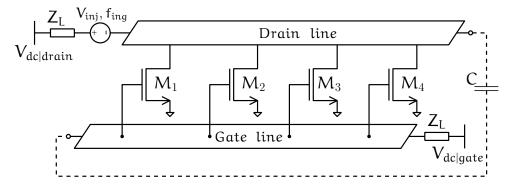

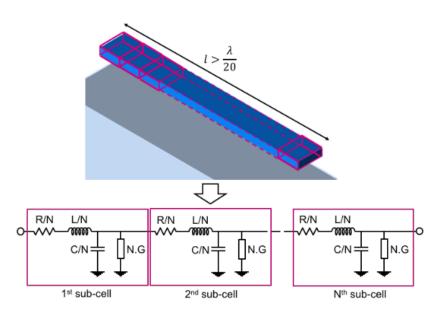

|      | Distributed oscillator architecture used in the theory                                           | 45 |

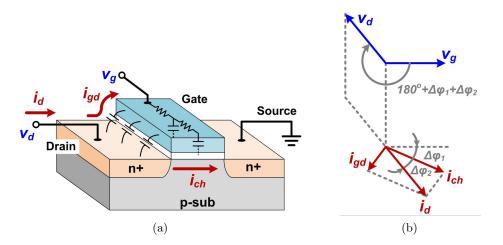

| 2.19 | (a) Standrad CMOS transistor and (b) its gate/drain phase relationship.                          |    |

|      | (Figures from $[80]$ )                                                                           | 46 |

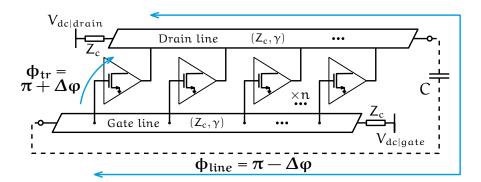

|      | Distributed oscillator for operation frequency close to $f_{\max}$                               | 47 |

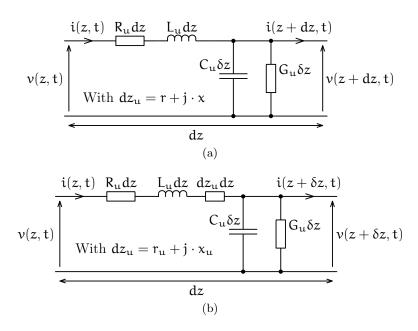

| 2.21 | Unit length element equivalent circuit of (a) classic TL and (b) TL under                        |    |

|      | series injection.                                                                                | 48 |

|      | Simulated schematics of the series synchronized distributed oscillators                          | 51 |

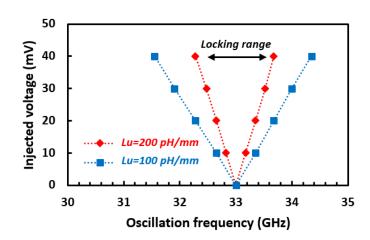

|      | Simulated ILDO oscillation frequency and locking range.                                          | 52 |

| 2.24 | (a) Simulation versus theory of the ILDO locking range and (b) Normalized                        | -  |

|      | error between theory and simulation                                                              | 53 |

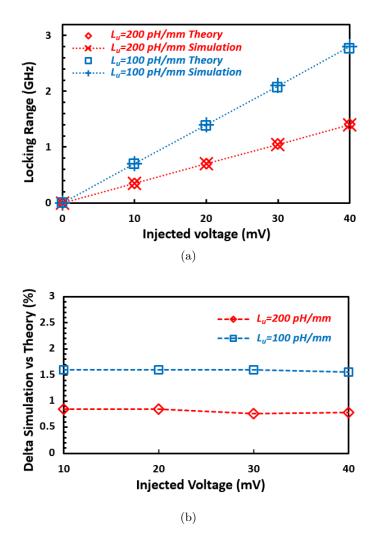

| 3.1  | Cross-section of (a) regular Bulk CMOS technology and (b) 28nm FD-SOI                            |    |

|      | CMOS technology transistors [81]                                                                 | 56 |

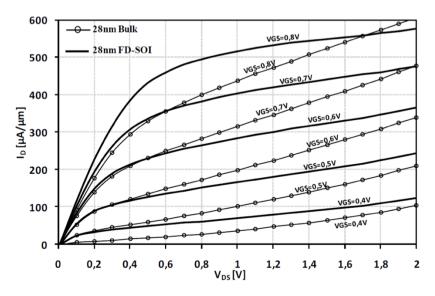

| 3.2  | I-V characteristic measurement comparison between 28nm Bulk and FD-                              |    |

|      | SOI technology. [82]                                                                             | 57 |

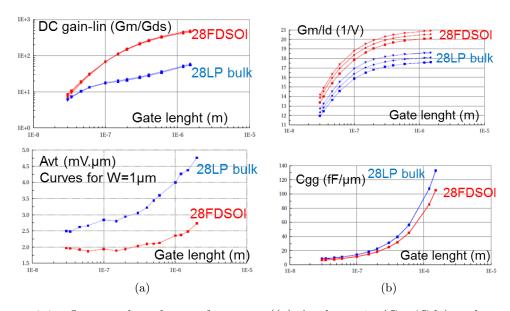

| 3.3  | Improved analog performance ((a) Analog gain (Gm/Gds) and matching (AVT) and (b) Gm/Id and total gate capacitance Cgg) for NMOS LVT devices in 28nm FDSOI technology (red) and comparison with 28nm LP |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | bulk (blue) [81]                                                                                                                                                                                       | 58 |

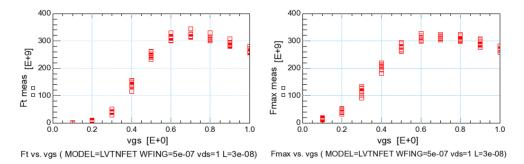

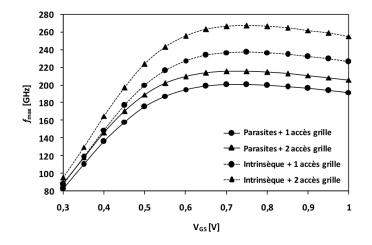

| 3.4  | High frequency behavior $(f_T \text{ and } f_{max})$ of LVT NMOS with $0.5 \mu m/30 nm$ finger size in 28nm FDSOI CMOS [81].                                                                           | 58 |

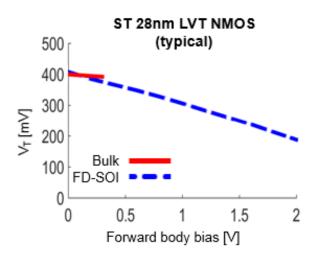

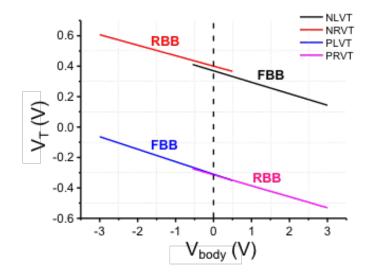

| 3.5  | 28nm FD-SOI CMOS technology transistors body biasing mode, limits                                                                                                                                      | 00 |

| 0.0  | and nominal voltage                                                                                                                                                                                    | 59 |

| 3.6  | $V_{\rm T}$ variation comparison between regular Bulk NMOS (in red) and FD-SOI                                                                                                                         | 00 |

| 0.0  | LVT NMOS (in blue).                                                                                                                                                                                    | 60 |

| 3.7  | $V_{T}$ variation range with respect to body-biasing voltage for RVT and LVT                                                                                                                           |    |

|      | devices in 28nm FD-SOI technology [81]                                                                                                                                                                 | 60 |

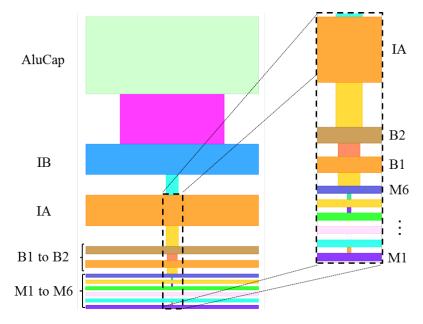

| 3.8  | 10 metal layers back-end-of-line of 28nm FD-SOI CMOS technology from                                                                                                                                   |    |

|      | ST Microelectronics                                                                                                                                                                                    | 61 |

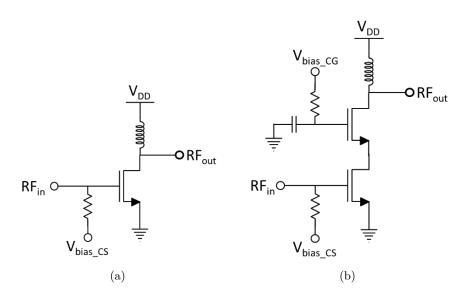

| 3.9  | (a) Common source topology and (b) cascode topology scheme                                                                                                                                             | 62 |

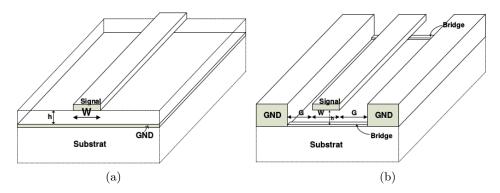

| 3.10 | (a) Microstrip topology and (b) coplanar topology scheme                                                                                                                                               | 64 |

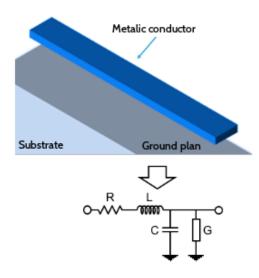

| 3.11 | Equivalent RLCG model of a transmission line.                                                                                                                                                          | 66 |

| 3.12 | Equivalent RLCG model of a transmission line with length over $\lambda/20$                                                                                                                             | 66 |

| 3.13 | Distributed oscillator form factor examples with (a) 4 stages in square                                                                                                                                |    |

|      | shape and (b) 10 stages in boustrophedon shape.                                                                                                                                                        | 67 |

| 3.14 | Distributed oscillator design methodology diagram.                                                                                                                                                     | 69 |

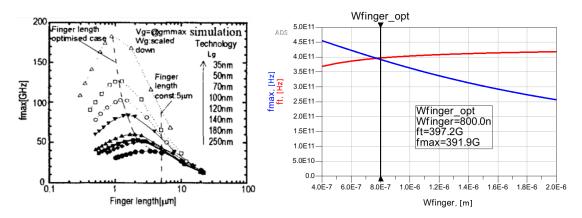

| 3.15 | Finger width determination: (a) charts proposed in [84] and (b) 28nm ED SOL NMOS $f_{\rm c}/f_{\rm c}$ simulations as a function of finger length at a                                                 |    |

|      | FD-SOI NMOS $f_T/f_{max}$ simulations as a function of finger length at a constant current density.                                                                                                    | 71 |

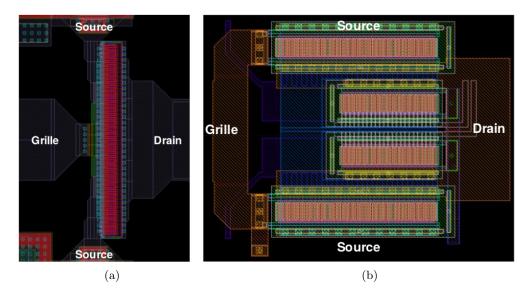

| 3 16 | Example of transistor layout from [82]: (a) single cell transistor and (b)                                                                                                                             | 11 |

| 5.10 | multiple cells transistors (The topology on the right contains two different                                                                                                                           |    |

|      | sizes transistors split each into two other ones).                                                                                                                                                     | 71 |

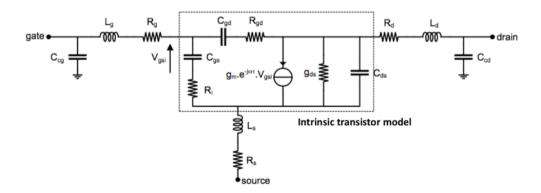

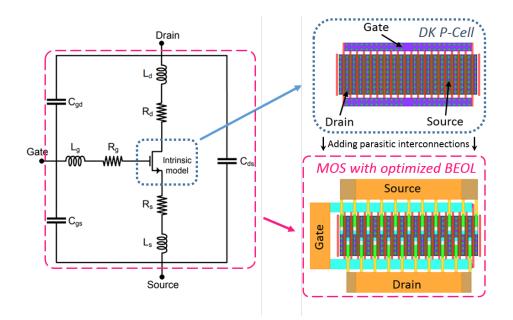

| 3.17 | Small-signal model of MOS transistor with its interconnections [86]                                                                                                                                    | 72 |

|      | Example of layout with thin staircase accesses for drain and source [82].                                                                                                                              | 73 |

|      | Impact of dual gate access on $f_{max}$ [82]                                                                                                                                                           | 73 |

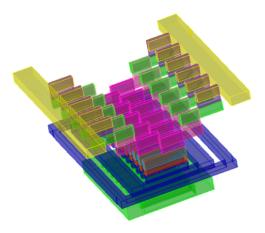

|      | BEOL layout optimization of the amplification stage transistor                                                                                                                                         | 74 |

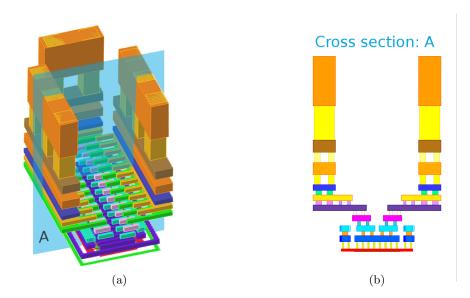

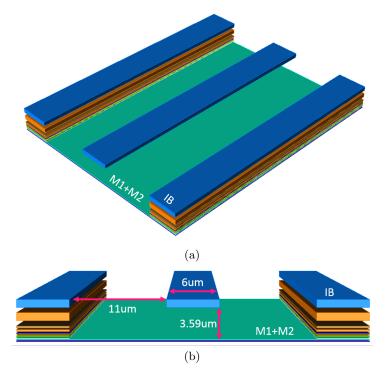

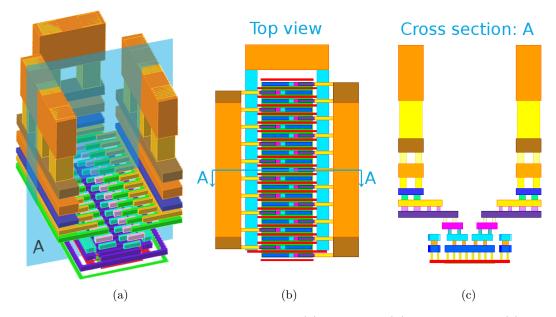

|      | Transistor layout with optimized BEOL (a) 3D view and (b) cross section                                                                                                                                |    |

|      | on the plane A                                                                                                                                                                                         | 74 |

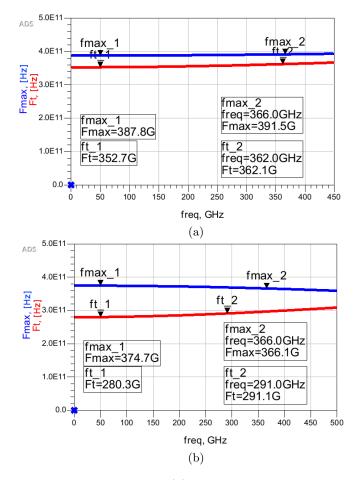

| 3.22 | $f_T/f_{max}$ performances of (a) the Design kit PCell up to M1 and (b) PCell                                                                                                                          |    |

|      | with full BEOL.                                                                                                                                                                                        | 75 |

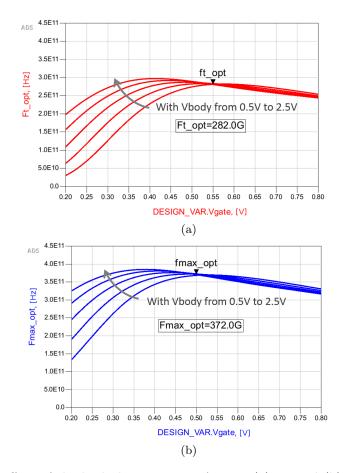

| 3.23 | Effect of the body-biasing on $f_T/f_{max}.$ (a) $f_T$ and (b) $f_{max}$ as a function                                                                                                                 |    |

|      | of Vgate for sevegal Vbody.                                                                                                                                                                            | 76 |

| 3.24 | Proposed transmission line topology.                                                                                                                                                                   | 77 |

xiii

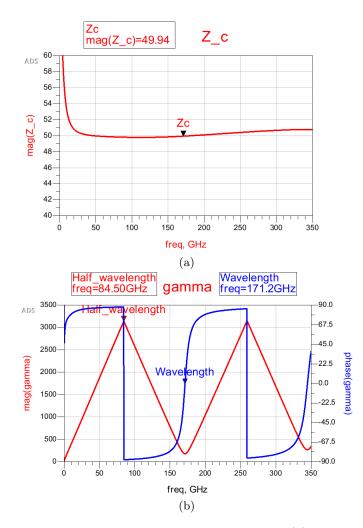

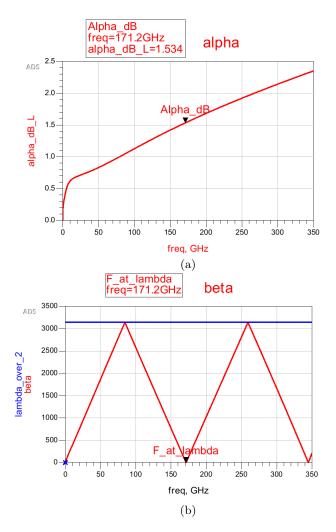

| 3.25 | Electromagnetic extraction of transmission line (a) characteristic impedance                                                                                       |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $Z_c$ and (b) complex propagation constant $\gamma$ over 1mm                                                                                                       | 78 |

| 3.26 | Electromagnetic extraction of transmission line (a) attenuation constant $\alpha$ and (b) phase constant $\beta$ over 1mm.                                         | 79 |

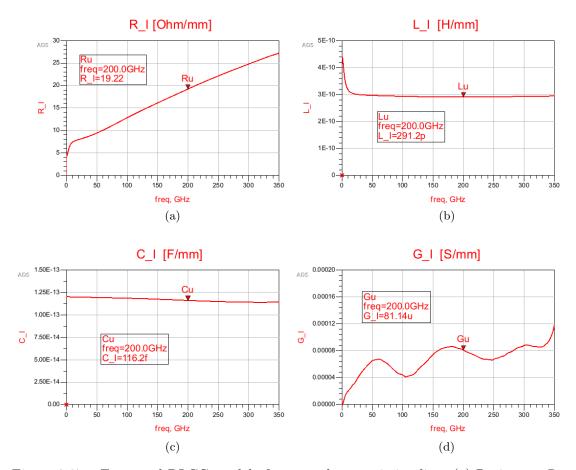

| 3.27 | Extracted RLCG model of proposed transmission line. (a) Resistance $R_u$ , (b) inductance $L_u$ , (c) capacitance $C_u$ and (d) conductance $G_u$ per unit length. | 80 |

| 3.28 | Transmission line totel length as a function of targeted oscillation frequency.                                                                                    | 81 |

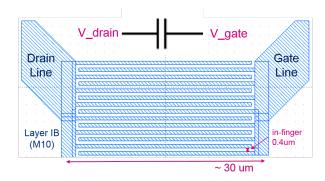

| 3.29 | DC isolation $ad$ -hoc MoM capacitance drawn on IB layer (metal 10)                                                                                                | 82 |

| 3.30 | Designed RF pad with 100 $\mu m$ and 50 $\mu m$ pitch probes compatibility                                                                                         | 82 |

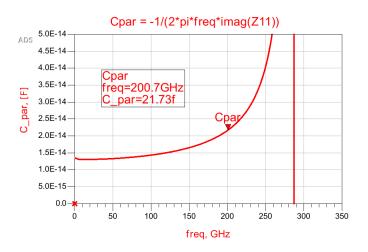

| 3.31 | Extracted parasitic capacitance of designed RF pad                                                                                                                 | 83 |

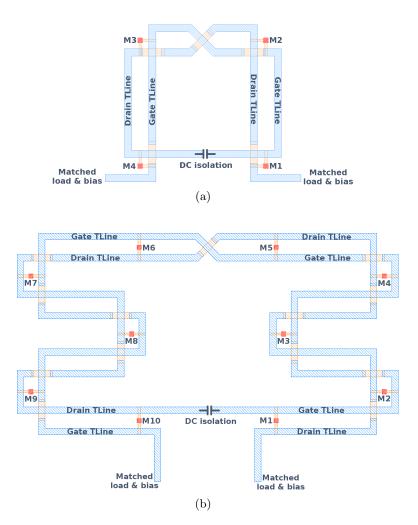

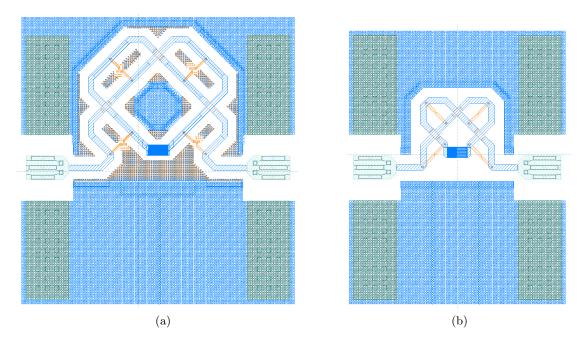

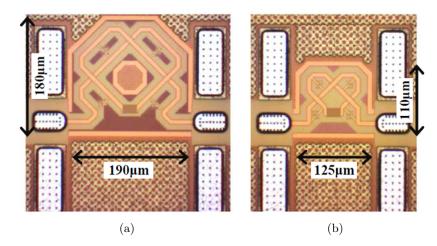

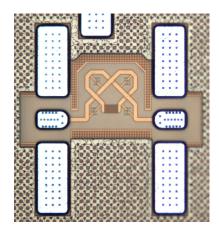

| 3.32 | Layout views of the (a) 135GHz and (b) 200GHz distributed oscillators. $\ .$                                                                                       | 83 |

| 4.1  | Standalone transistor under test (a) 3D view, (b) top view and (c) cross section on the plane A                                                                    | 88 |

| 4.2  | On-wafer test structures: (a) standalone transistor, (b) open and (c) short.                                                                                       | 89 |

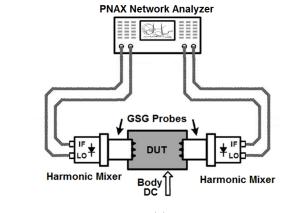

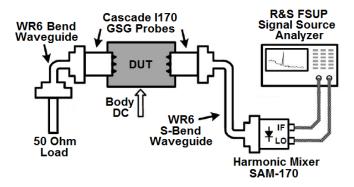

| 4.3  | (a) Measurement setups schematic, (b) first bench from DC to 110 GHz                                                                                               |    |

|      | picture and (c) second bench from 220 to 330 GHz picture                                                                                                           | 90 |

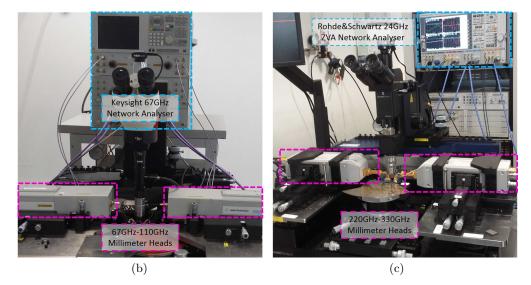

| 4.4  | Standalone transistor measurement up to 110GHz: (a) RF transimpedance,                                                                                             |    |

|      | (b) gate parasitic resistance, (c) gate to drain parasitic capacitance and (d)                                                                                     | 01 |

| 4.5  | gate to substrate parasitic capacitance                                                                                                                            | 91 |

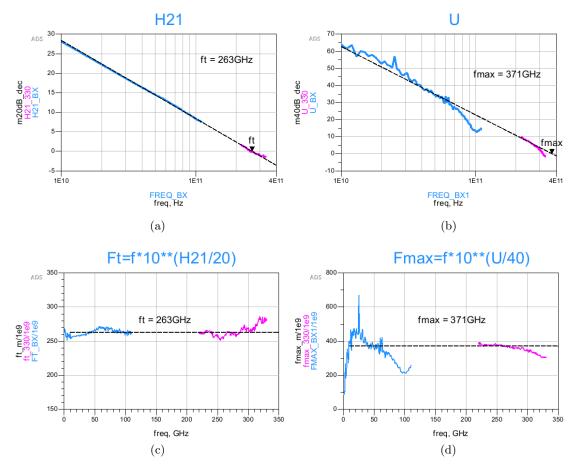

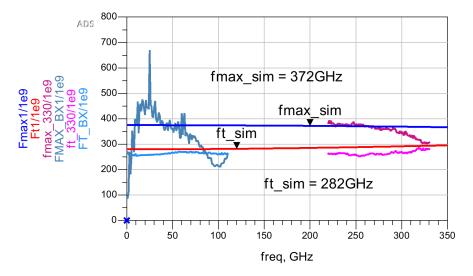

|      | U, (c) cutoff frequency $f_{T}$ and (d) maximum oscillation frequency $f_{max}.$ .                                                                                 | 92 |

| 4.6  | Standalone transistor measurement versus simulation results for cutoff                                                                                             |    |

|      | frequency $f_{T}$ and maximum oscillation frequency $f_{\texttt{max}}.$                                                                                            | 93 |

| 4.7  | Microphotograph of the (a) first (134GHz) and (b) second (202GHz) dis-                                                                                             |    |

|      | tributed oscillator. (same metric scale).                                                                                                                          | 94 |

| 4.8  | Measurement setup.                                                                                                                                                 | 94 |

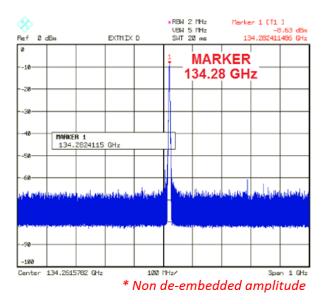

| 4.9  | Measured output spectrum of the first $(134 \text{GHz})$ distributed oscillator                                                                                    | 95 |

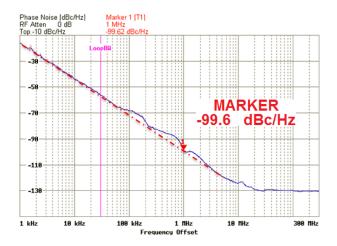

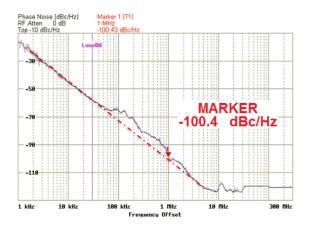

|      | Measured phase noise of the first (134GHz) distributed oscillator                                                                                                  | 95 |

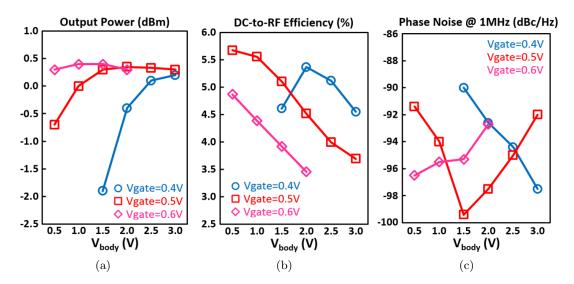

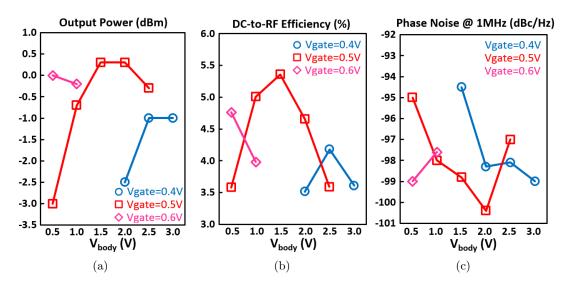

| 4.11 | Measured (a) output power, (b) DC-to-RF efficiency and (c) phase noise at                                                                                          |    |

|      | 1MHz offset for different Vbody and Vgate, for the first (134GHz) oscillator.                                                                                      | 96 |

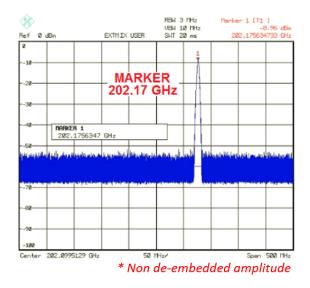

|      | Measured output spectrum of the second (202GHz) distributed oscillator.                                                                                            | 97 |

|      | Measured phase noise of the second (202GHz) distributed oscillator                                                                                                 | 97 |

| 4.14 | Measured (a) output power, (b) DC-to-RF efficiency and (c) phase noise                                                                                             |    |

|      | at 1MHz offset for different Vbody and Vgate, for the second (202GHz)                                                                                              | 00 |

|      | oscillator.                                                                                                                                                        | 98 |

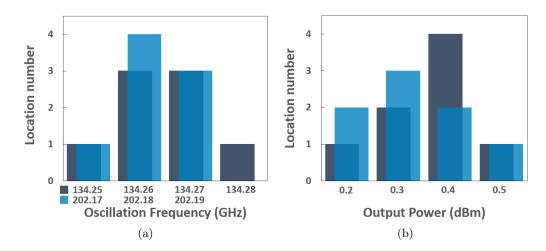

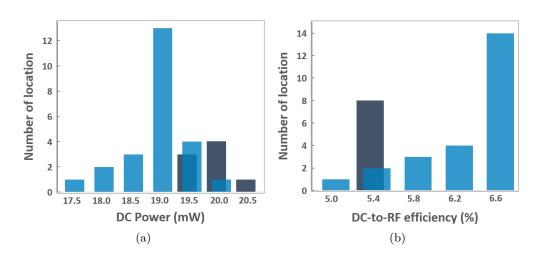

| 4 15  | Distribution histograms for the (a) oscillation frequency and (b) output                                                    |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 1.10  | power as a function of on-wafer location. (8 different locations measured                                                   |

|       | on a same wafer for each topology. Dark bar for the first (134GHz) and                                                      |

|       | blue bar for the second (202GHz) oscillator)                                                                                |

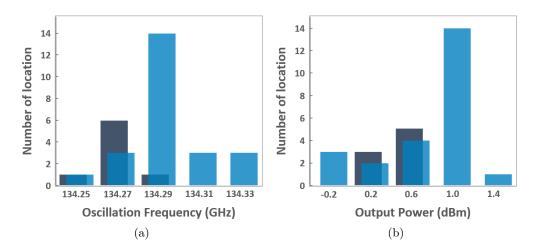

| 1 16  | Distribution histograms for the (a) oscillation frequency and (b) output                                                    |

| 4.10  | power as a function of on-wafer location. 32 different locations on two                                                     |

|       | A                                                                                                                           |

|       | different wafers. (Dark bar for the first wafer and blue bar for the second                                                 |

| 4 1 7 | wafer). $\dots \dots \dots$ |

| 4.17  | Distribution histograms for the (a) DC power consumption and (b) DC-                                                        |

|       | to-RF efficiency as a function of on-wafer location. (32 different locations                                                |

|       | on two different wafers. (Dark bar for the first wafer and blue bar for the $100$                                           |

| 4.10  | second wafer)                                                                                                               |

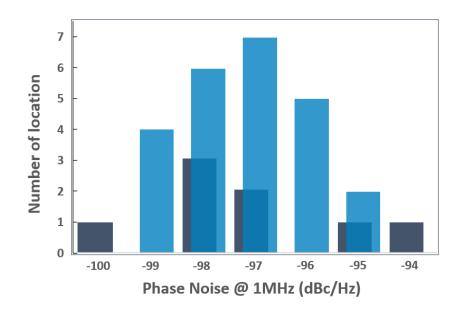

| 4.18  | Distribution histograms for the phase noise at 1MHz offset as a function of                                                 |

|       | on-wafer location. (32 different locations on two different wafers. (Dark                                                   |

|       | bar for the first wafer and blue bar for the second wafer)                                                                  |

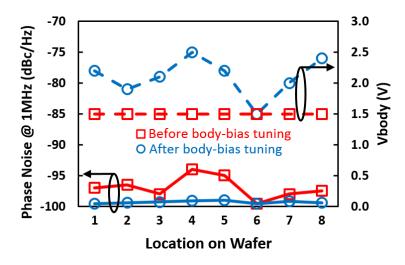

| 4.19  | Phase Noise optimization by body-biasing; measurement over 8 locations                                                      |

|       | on wafer, for the first (134GHz) oscillator                                                                                 |

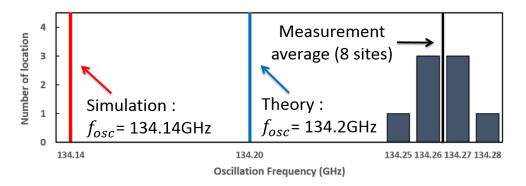

| 4.20  | Oscillation frequency comparison between measurements over the 8 lo-                                                        |

|       | cations of the first wafer, post-layout simulation and theoretical value.                                                   |

|       | (precision less than $0.1\%$ )                                                                                              |

| 4.21  | Microphotograph of the tested distributed oscillator                                                                        |

| 4.22  | (a) Measurement setup and (b) equivalent schematic under injection 105                                                      |

| 4.23  | Output spectrum of (a) free-running DO and (b) locked SHILDO 105                                                            |

| 4.24  | Measured phase-noise of the free-running oscillator, the low frequency                                                      |

|       | reference and the injection locked oscillator                                                                               |

| 4.25  | ILDO locking range (a) measurement (crosses) versus Adler theory (solid                                                     |

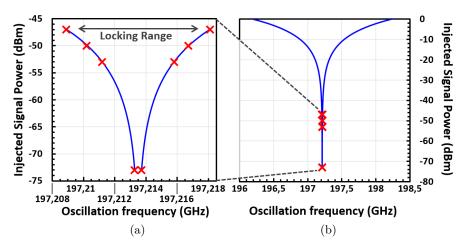

|       | line) and (b) extrapolation as a function of injected amplitude. $\ldots$ 107                                               |

| 4.26  | Proposed architecture of a DO with boosted gain amplification stages and                                                    |

|       | example of gain boost achieved with this technique in [93] 111                                                              |

| 4.27  | Proposed injection technique using a TLine coupled all along the DO line. $112$                                             |

| 4.28  | Proposed architecture for fully integrated THz locked-source in a VLSI                                                      |

|       | CMOS technology                                                                                                             |

# List of Tables

| 1.1 | State-of-the-art of silicon based mm-wave and THz oscillators per type of                        |     |

|-----|--------------------------------------------------------------------------------------------------|-----|

|     | oscillator, the references are reported upon their publication year                              | 18  |

| 1.2 | State-of-the-art of silicon based mm-wave and THz frequency synthesis                            |     |

|     | solutions                                                                                        | 18  |

| 3.1 | Distributed oscillators design specifications.                                                   | 70  |

| 3.2 | $f_{T}$ and $f_{{\mathfrak{max}}}$ simulations with and without BEOL parasitic interconnections. | 76  |

| 3.3 | Determination of the transmission line total length as a function of targeted                    |     |

|     | oscillation frequency.                                                                           | 81  |

| 4.1 | $f_{T}$ and $f_{\mathfrak{max}}$ simulations with and without BEOL parasitic interconnections    |     |

|     | versus measurement.                                                                              | 93  |

| 4.2 | Comparison with Previous State-of-the-Art.                                                       | 102 |

| 4.3 | Comparison with Previous State-of-the-Art.                                                       | 107 |

### Introduction

Millimeter-wave (mm-wave) and terahertz (THz) frequency bands have many attractive properties, such as the ability to penetrate through matter, non-ionizing radiation, and large bandwidth availability. These features make mm-waves and THz systems suitable for many applications such as non-ionizing biomedical imaging, non-destructive quality control, and very high data rate communication.

Because of the recent increasing demand on mm-wave/THz applications, many researchers have been interested in integrating signal sources in this frequency range, especially in cost-optimized silicon technology as SiGe and CMOS.

Several silicon-based mm-wave and THz oscillators have been recently reported. Nevertheless, most of them are integrated in SiGe technology and the targeted applications drive the need for high performances and very large scale integration that FD-SOI CMOS can offer. Moreover, all these mm-wave/THz systems require an efficient signal source with a maximized output power and, for some applications, the phase noise performances are critical. For these reasons, this thesis, realized in the frame of the ST-IMS common laboratory, is focusing on the following goals:

- Highlight the intrinsic limitations of classic oscillator topologies for efficient silicon integration of mm-wave and THz sources.

- Propose and demonstrate an alternative design solution to overcome these limitations and meet the challenging performances in terms of output power, energy efficiency, and phase-noise.

- Explore the 28nm FD-SOI CMOS technology for mm-wave/THz applications and demonstrate its capabilities for mmW design with industrial margin, through a well defined design methodology.

This manuscript is composed of four chapters. The first chapter is defining the context

#### List of Tables

of this work and presents the state-of-the-art of silicon-based mm-wave and THz signal source. The main limitations of classic oscillator topologies are highlighted and recent design techniques are introduced. The challenges for future THz applications are then discussed and key mm-wave source parameters are exposed.

The second chapter is proposing an alternative for mm-wave and THz frequency generation in CMOS technology: the injection locked distributed oscillator (ILDO). In this chapter, injection locked oscillator (ILO) theory is introduced and extended to the study of ILDO for operation close to transistors'  $f_{max}$ .

The third chapter presents first the 28nm FD-SOI CMOS technology for mm-wave and THz applications. A distributed oscillator design methodology is then presented and this methodology is used to realize two distributed oscillators at mm-wave/THz frequencies taking advantage of the high performances of the 28nm FD-SOI technology.

The fourth chapter describes the experimental results of this thesis work. First standalone transistor measurements are presented, highlighting the excellent high-frequency performances of the 28nm FD-SOI NMOS transistors. Then, the two designed distributed oscillators results are described. Excellent performances in terms of output power and DC-to-RF efficiency are reported, despite the limited back-end performances of such very dense technology nodes. The presented oscillators exhibit the measured highest oscillation frequency for an integrated CMOS oscillator in a 28nm node, upon the state-of-the-art at the date this manuscript is proposed. On-wafer probing measurements have been conducted exhibiting the low variability feature of such distributed oscillator architectures. Moreover, phase-noise optimization feature is introduced taking advantage of FD-SOI uniquely large body-bias tuning range. Finally, the injection locked capability of such distributed oscillators is demonstrated by experimental injection trials.

The final part of this thesis manuscript is dedicated to the general conclusion and presents research perspectives for future mm-wave and THz integration in CMOS VLSI technology.

# **1** Millimeter-wave and Terahertz Technologies

In recent years, millimeter-wave (mm-wave) and terahertz (THz) systems have attracted many researchers due to the promising applications in these frequency bands, from imaging to high data rate applications. The most important block of such systems is the signal source which needs to reach the highest possible output power, high efficiency, and low phase noise.

In this chapter, we will first introduce the context of silicon-based mm-wave and THz applications. Then, mm-wave and THz oscillator topologies will be described to highlight their intrinsic limitations. Finally, a state-of-the-art analysis of mm-wave and THz sources will be performed in order to identify the most relevant research axes for future silicon-based mm-wave and THz systems.

| 1.1 | Mm-w   | vave and THz applications                                            | 4  |

|-----|--------|----------------------------------------------------------------------|----|

|     | 1.1.1  | Non-ionizing imaging                                                 | 4  |

|     | 1.1.2  | High-speed communications                                            | 6  |

| 1.2 | Mm-w   | vave and THz silicon oscillators                                     | 7  |

|     | 1.2.1  | Mm-wave and THz fundamental frequency generation $\ . \ . \ .$       | 8  |

|     | 1.2.2  | Mm-wave and THz indirect frequency generation $\ldots \ldots \ldots$ | 9  |

| 1.3 | State- | of-the-art in mm-wave and THz sources                                | 12 |

|     | 1.3.1  | State-of-the-art in mm-wave and THz oscillators $\hdots$             | 12 |

|     | 1.3.2  | State-of-the-art in mm-wave and THz synthesis                        | 15 |

|     | 1.3.3  | Challenges for future THz applications                               | 17 |

| 1.4 | Chapt  | er conclusion                                                        | 20 |

### 1.1 Mm-wave and THz applications

Since the beginning of 21<sup>th</sup> century, millimeter-wave (mm-wave) and terahertz (THz) frequency ranges become increasingly attractive for many applications [1–3]. The main reasons for this interest are linked to the interactions between THz rays and matter. Indeed, THz radiations are able to penetrate through dielectric matter like plastics, clothes, ceramic, etc...

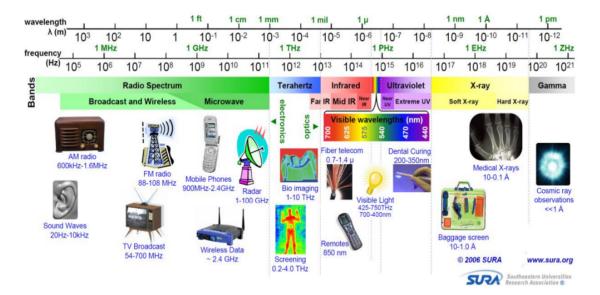

Nevertheless, the THz frequency band suffers from its position in the electromagnetic spectrum. Indeed, as depicted in figure 1.1, this band is located at the frontier between optics and electronics. Also named the *THz Gap*, this band cannot be approached using classic optic principles because of the larger wavelengths of the THz radiations. From an electronic point of view, this band is also extremely hard to reach due to the limited  $f_T/f_{max}$  of silicon technologies.

Figure 1.1 – Electromagnetic spectrum (From the Southeastern Universities Research Association).

#### 1.1.1 Non-ionizing imaging

THz radiations have low photon energy:  $\sim 4$  meV at 1 THz compared to several MeV for X-ray. Consequently, this kind of technology does not cause harmful photon ionization in biological tissues. This characteristic enables the use of this technology in safety and security areas.

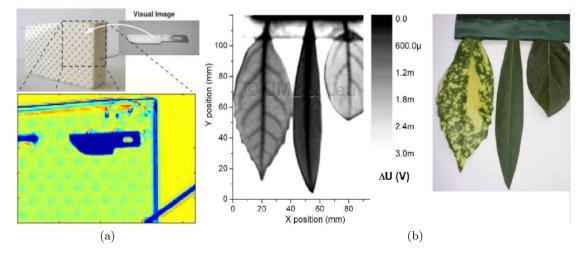

As a matter of example, THz imaging can detect objects such as guns or blades hidden inside packages, clothing, or foams [4]. (see figure 1.2(a)) This allows them to be used at airport or post offices for example. The fact that dielectrics are transparent for THz rays also allows the use of THz imaging in the field of non-destructive quality control. Biomedical THz imaging can also, for example, see the humidity level and structure of different living cells thanks to a THz image [5]. (see figure 1.2(b))

Figure 1.2 – Terahertz image examples. (a) Hidden knife in mattress from [4] and (b) structure of leaves from [5].

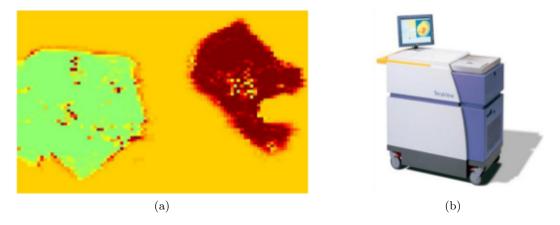

Finally, medical imaging is also a promising field for THz applications. The major benefit comes from the safe energy levels of THz rays. Indeed, THz radiation was recently used in several works to detect various cancerous tissues as for example the one presented in figure 1.3 [6].

Figure 1.3 - (a) THz image of colon tissue showing healthy tissue in green and cancerous tissue in dark red (fake colors). (b) Imaging performed by THz system from Teraview [6].

### 1.1.2 High-speed communications

THz and mm-wave have attractive bandwidth to realize high-speed communications with data rates above 10Gbit/s. Indeed, the demand for high data rate is increasing with new technologies and the congestion of traditional communication spectrum drives researchers to exploit the unlicensed THz bands between 100 GHz and 300 GHz [7–9].

Actual studies are mainly focused on exotic technologies. The main reason for this is the lack of output power of classic silicon technologies due to the proximity between operating frequency and cut-off frequency.

Nevertheless, some works present promising results in advanced silicon technologies [10-12]. As a matter of example, Yu *et al.* have presented in [12] a 165 GHz ON-OFF keying transmitter in a 65 nm CMOS technology.

### 1.2 Mm-wave and THz silicon oscillators

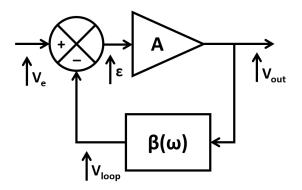

An oscillator is a circuit which produces a stable periodic signal without any input signal. The oscillator behavior can be explained using the simple model depicted in figure 1.4.

Figure 1.4 – Simple oscillator behavior model.

The closed loop transfer function of this model can be expressed as:

$$H(j\omega) = \frac{V_{out}}{V_e} = \frac{A}{1 + A\beta(j\omega)}$$

(1.1)

Thus, if it exists a specific frequency at which  $A \beta(j\omega) = -1$ , the closed loop gain is theoretically infinite and hence an output signal  $V_{out}$  can appear in the absence of input signal  $V_e$ . This condition is usually named the *Barkhausen criterion*.

Barkhausen criterion can be decomposed in two criteria. The phase Barkhausen criterion describes the phase condition to ensure the oscillation starting at a giving frequency. The gain Barkhausen criterion describes the minimum loop gain to maintain oscillations. These two criteria are represented by the following expressions:

$$|\mathsf{A}| \ge \frac{\mathsf{A}}{|\mathsf{\beta}(\mathsf{j}\omega)|} \tag{1.2}$$

$$\arg\left(A\,\beta(j\omega)\right) = \pi \tag{1.3}$$

There are two main classes of integrated oscillators at mm-wave and THz frequencies. The first one generates directly the output frequency at fundamental while the second performs an indirect frequency generation by oscillating at a lower frequency and using harmonic recombination to generate an output signal at a high frequency.

#### 1.2.1 Mm-wave and THz fundamental frequency generation

At mm-wave and THz frequency bands, the main used fundamental generation oscillator topologies are based on LC oscillators. These oscillators use passive resonators, such as LC tank, to create a band-pass filter and hence set the oscillation frequency.

There are different kinds of LC oscillator. In single mode, the two main used are the Colpitts and the Hartley oscillators, introduced in figure 1.5.

Figure 1.5 – Schematic examples of (a) Single mode Colpitts oscillator and (b) single mode Hartley oscillator.

The oscillation frequency of the Colpitts and Hartley oscillators can be expressed respectively as:

$$f_{osc|colpitts} = \frac{1}{2\pi\sqrt{\frac{C_1C_2}{C_1+C_2} \cdot L}}$$

(1.4)

$$f_{osc|hartley} = \frac{1}{2\pi\sqrt{(L_1 + L_2) \cdot C}}$$

(1.5)

These two single-mode oscillators can be adjusted to work in differential mode. The figure 1.6 presents the differential version of the Hartley oscillators.

This structure, also known as the cross-coupled oscillator, is the most used topology for fundamental THz and mm-wave oscillator [13, 14].

Figure 1.6 – Schematic differential cross-coupled oscillator.

#### 1.2.2 Mm-wave and THz indirect frequency generation

Fundamental generation oscillators are limited by the transistors cut-off frequency. To overcome this limitation, indirect frequency generation oscillators have been proposed in literature. These oscillators use a technique named *harmonic recombination* to generate an output signal at a frequency beyond the transistor  $f_T/f_{max}$ .

The harmonic recombination techniques are based on the current recombination of multistage oscillators. This technique allows the  $N^{th}$  harmonic extraction of an N-stages oscillator.

Thus, to extract a signal at a frequency  $f_{osc}$ , one can use an N-stages oscillator with a fundamental frequency of  $f_{osc}/N$ . Nevertheless, the output level of the extracted signal is decreasing with the number of stages. For an N-stages oscillator, the extracted signal amplitude is theoretically reduced by a factor  $1/2^{(N-1)}$ . For this reason, the stage number of this kind of oscillator is usually limited at two or three (even if it exists some examples with four or five stages in literature [2, 15]).

#### Push-push oscillators

The two stages harmonic recombination oscillator is named *push-push* oscillator. This is probably the most used architecture in mm-wave and THz design due to its relatively high output power compared to architectures with a higher number of stages.

The push-push oscillator is usually based on a crossed-coupled architecture, as depicted in figure 1.7. However, instead of taking the output signal in differential mode on the two MOS drains, the output signal is probed at the common node beyond the two inductances. A  $\lambda/4$  (@ f<sub>out</sub>) TL performs an AC isolation between the supply and the output node.

Figure 1.7 – Push-push oscillator architecture based on crossed-coupled oscillator.

This kind of architecture has been widely used in literature [16-21]. Indeed, its relatively high output power makes the push-push oscillator a good compromise between output power and oscillation frequency. However, with this kind of architecture, the oscillation frequency is limited to twice the cut-off frequency of the active device. To reach higher frequency, topologies with a higher number of stages are required.

### Triple-push oscillators

The three stages harmonic recombination oscillator is named *triple-push* oscillator. After the push-push oscillator, it is the second most used architecture for mm-wave and THz frequency generation. This topology allows to reached frequencies up to three time the active device cut-off frequency. Nevertheless, this high output frequency is provided at the expense of output power which is reduced by a factor of 1/4.

A triple-push oscillator architecture is presented in figure 1.8. As for the push-push version, the triple-push oscillator output is located at the common node beyond the three inductances. Here again, a  $\lambda/4$  (@ f<sub>out</sub>) transmission line performs an AC isolation between the supply node and the output node. The three transistors are connected in an inductive-load ring oscillator. Thus, the ring loop oscillates at a frequency of f<sub>0</sub>/3 and each drain voltages are phase-shifted by 120 degrees one respective to the others.

Figure 1.8 – Triple-push oscillator architecture.

Triple-push oscillators have been used in a lot of recent works [22–26]. Indeed, even if the output signal level is relatively low, the very high frequency reachable by this kind of architecture makes the triple-push a very attractive topology for mm-wave and THz frequency generation.

### 1.3 State-of-the-art in mm-wave and THz sources

To well understand the technological issues to tackle in mm-wave and THz frequency generation, a state-of-the-art study is necessary. This study will begin by focusing on oscillators state-of-the-art. Then, we will discuss locked frequency synthesizers.

#### 1.3.1 State-of-the-art in mm-wave and THz oscillators

#### Fundamental mode oscillators

Silicon based fundamental oscillators with output frequency above 100 GHz started being published by 2006-2007 [13,27]. When operating very close to active component cut-off frequency, the challenge is to maximize output power and DC-to-RF efficiency. At the beginning of this thesis work, mm-wave and THz fundamental generation were very rare because transistor performances of theses frequency were very limited.

Nevertheless, very recent works have demonstrated excellent performances near the transistors  $f_T/f_{max}$  [28,29].

Let us focus on the one which presents, today, the best performances: [29] published in 2017 by Khatibi *et al.*.

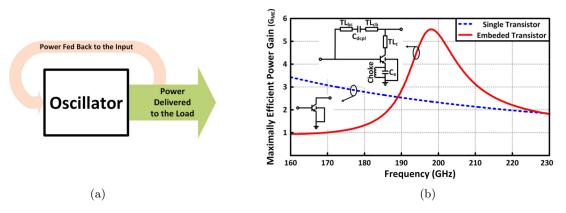

As presented in figure 1.9(a), in this work the oscillator is seen as a power amplifier which feeds part of its output power back to its own input and which delivers the excess power to the load. From this point of view, to design a high output power and high-efficiency oscillator the authors choose to maximize the *Maximally Efficient Power Gain* (see figure 1.9(b)).

Figure 1.9 – (a) Oscillator seems as a looped back power amplifier. (b) Maximally Efficient Power Gain optimization. [29]

Using this new approach, [29] presents a 195 GHz fundamental oscillator with 6.5 dBm output power and a very high DC-to-RF efficiency of 15.3%, as depicted in figure 1.10. This work was designed in a 55 nm SiGe BiCMOS technology from ST Microelectronics which exhibit a  $f_{max}$  of  $\approx 340$  GHz. It is important to note that in this technology the active component has excellent performances at high frequencies. Such performances are not comparable to CMOS transistor performances at these frequencies.

Figure 1.10 – Simulated and measured (a) output power and (b) DC-to-RF efficiency under different bias condition. (c) Die photomicrograph. [29]

#### Push-push oscillators

As explained in the previous section, push-push architectures have been widely used to overcome cut-off frequency limitation. This kind of architecture has allowed output frequency of almost 200 GHz since 2005 in both BiCMOS and CMOS technologies [16, 19]. Later, in 2008, Seok *et al.* have proposed the very first oscillator beyond 300 GHz in a CMOS technology [18].

The main limitation of the push-push oscillator is its low DC-to-RF efficiency and its medium output power level coming from the second harmonic extraction. Since the beginning of this thesis work, mm-wave and THz push-push oscillators with good performance have been proposed [20,21].

Let us focus on one of them which proposed an innovative architecture: [20] which was published in 2017 by Jiang *et al.*.

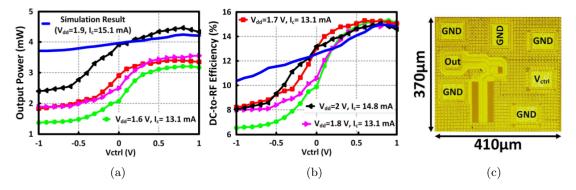

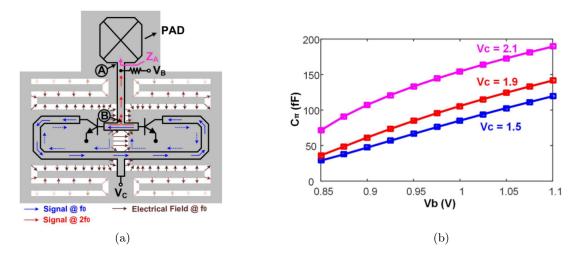

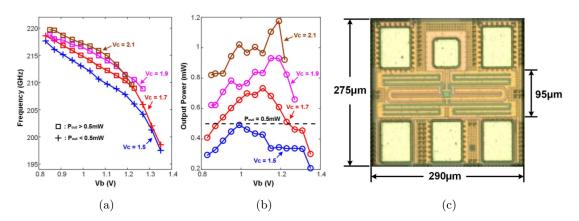

This oscillator is based on two self-feeding oscillator structures which are looped through a Return-Path Gap (RPG) in order to perform both DC isolation and second harmonic isolation, as shown in figure 1.11(a). The authors also used the bipolar base-emitter parasitic capacitance  $C_{\pi}$  (which is highly sensitive to bias point, as depicted in figure 1.11(b)) as a varactor to allow large frequency tuning range.

Figure 1.11 – (a) Schematic of the presented push-push oscillator. (b) Bipolar base-emitter parasitic capacitance  $C_{\pi}$  at different bias points. [20]

Using this technique, [20] presents a 10.6% tuning range 210 GHz push-push oscillator with 1.4 dBm maximum output power and 2.4% maximum DC-to-RF efficiency, as shown in figure 1.12(a-b). This work was designed in a 130 nm SiGe BiCMOS technology from ST Microelectronics with a chip area of  $290 \times 275 \mu m^2$ , as presented in figure 1.12(c).

Figure 1.12 – Measured (a) frequency and (b) output power under different bias point. (c) Die photomicrograph. [20]

## **Triple-push** oscillators

Triple push oscillators have been also widely used in literature [24,26]. In 2011, Momeni and Afshari have proposed a systematic approach to design optimized triple-push oscillator [26]. Since this date, numerous works have proposed techniques to increase the output signal

power which is the main drawback of this kind of architecture.

As a matter of example, [23–25] proposed to couple several triple-push oscillators to extract a recombination of them and thus increase the output power. Nevertheless, these architectures still suffer from low DC-to-RF efficiency since DC consumption still increases with output power.

Triple-push oscillators have been also used in several locked frequency synthesis architectures, as presented in the next section.

## 1.3.2 State-of-the-art in mm-wave and THz synthesis

Two main approaches are privileged for silicon-based integration of mm-wave and THz sources.

## Frequency synthesis based on injection locked oscillators

The first one is based on sub-harmonic injection locked oscillator (ILO). As a matter of example:

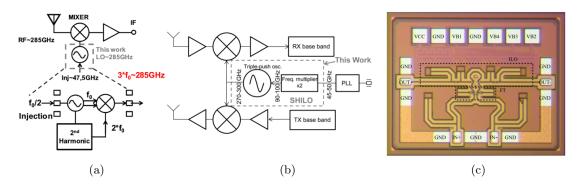

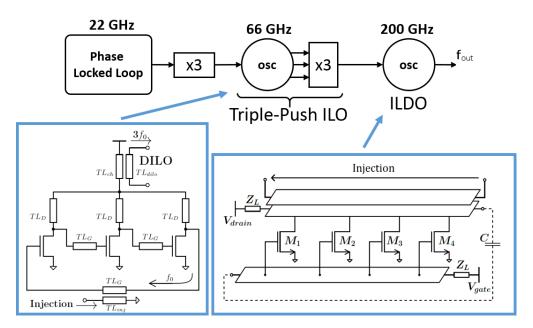

- In [30] Guerra *et al.* present a push-push ILO follows by a mixer which takes the extracted second harmonic and multiplies it with the ILO fundamental. It results in a frequency multiplication by 6, as presented in figure 1.13(a). Nevertheless, output power (-19 dBm) and DC-to-RF efficiency (0.018%) are here very low.

- In [31], authors present an injection locked triple-push oscillator following a selfmixer to perform a frequency multiplication by 6, as shown in figure 1.13(b). But,

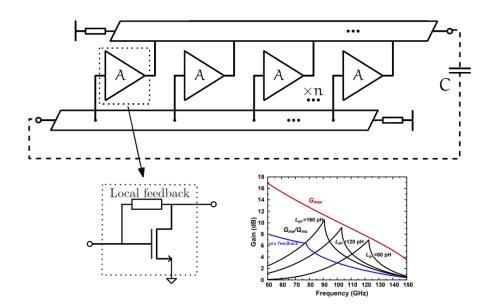

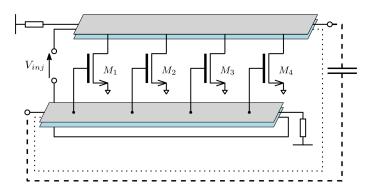

Figure 1.13 - (a) Push-push ILO based design proposed in [30]. (b) Triple-push ILO based design presented in [31] and (c) layout of the cascaded ILO introduced in [32].

the output power of -9 dBm and DC-to-RF efficiency of 0.25% are still low.

• In [32], more recently (in 2018), Li *et al.* presents a 200 GHz ILO based on differential Colpitts oscillator cascaded with a frequency tripler, performing a frequency multiplication by 3 as depicted on figure 1.13(c). This solution presents a good output power of 0 dBm for an Efficiency of 3.5%.

## Frequency synthesis based on phase locked loops

The second approach performing silicon-based frequency synthesis at mm-wave and THz frequency ranges is based on a full phase locked loop (PLL). There are only two examples of silicon integrated PLL above 200 GHz in literature:

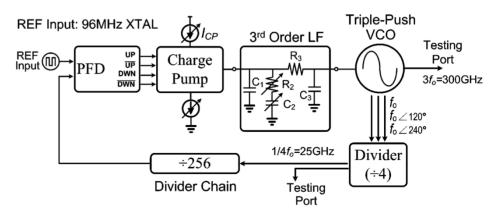

• The first one, introduced in 2014 by Chiang *et al.* in [33] proposed a classical PLL architecture using a 100 GHz voltage controlled oscillator (VCO). The VCO architecture is a three-stages inductively loaded ring oscillator. Thus, using a triple-push technique, the 300 GHz output frequency is probed at the common node of the ring stages which is isolated from supply thanks to a  $\lambda/4$  TL. The figure 1.14 presents the architecture proposed in this work.

Figure 1.14 – Architecture of the 300 GHz frequency synthesis proposed in [33].

This work was the first silicon-based frequency synthesis published above 200 GHz with a center frequency of 290 GHz and a 7.9% locking range. The output power is -14 dBm for a 376 mW DC consumption resulting in a DC-to-RF efficiency of 0.01%. Finally, the phase noise was measured at -77.8 dBc/Hz at 100kHz offset and -82.5 dBc/Hz at 1MHz offset.

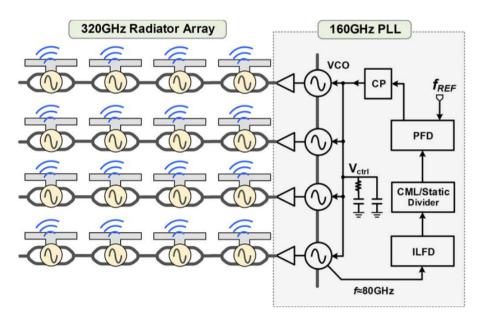

• The second example of silicon integrated PLL above 200 GHz was published in 2015 by Han *et al.* in [34] (and reused in 2016 by Jiang *et al.* in [35]). In this work,

the authors proposed a PLL architecture using four coupled 80 GHz VCOs. The VCOs architecture is based on a push-push oscillator to extract its second harmonic at 160 GHz. The locked signal at 160 GHz is then used to synchronize (locked by injection) four rows of four coupled 320 GHz oscillators (*i.e.* a  $4 \times 4$  oscillator array). The 320 GHz oscillators are based on a push-push architecture similar to the one presented in [20] (see figure 1.11 in previous section). The architecture of the 320 GHz frequency synthesis is presented in figure 1.15.

Figure 1.15 – Architecture of the 320 GHz frequency synthesis proposed in [34].

This work exhibits the best performances above 320 GHz in terms of output power (5.2 dBm) for a 610 mW DC consumption resulting in a DC-to-RF efficiency of 0.54%. The output signal center frequency is 317 GHz and its phase noise was measured at -79 dBc/Hz at 1MHz offset. The only limitation of this work is its tuning range which is limited to 200 MHz at 320 GHz (corresponding to 0.06%).

# 1.3.3 Challenges for future THz applications

The tables 1.1 and 1.2 summarize the state-of-the-art of silicon based mm-wave and THz frequency sources. It is notable that the main challenge in mm-wave frequency generation is to reach high DC-to-RF efficiency and high output power near or beyond the cut-off frequency.

Structures like triple-push (or more quad.) allow oscillating at very high frequency but

| Ref. | Freq. | Pout  | P <sub>DC</sub> | DC-to-RF   | PN <sub>@1MHz</sub> | Tuning | Technology | Year | Type   | Phase   |

|------|-------|-------|-----------------|------------|---------------------|--------|------------|------|--------|---------|

|      | (GHz) | (dBm) | $(\mathrm{mW})$ | Efficiency | (dBc/Hz)            | Range  |            |      |        | Locked? |

| [13] | 140   | -19   | 9.6             | 0.13~%     | -93**               | 0.86 % | 90nm CMOS  | 2006 |        |         |

| [26] | 104   | -2.7  | 28              | 1.92~%     | -93.3               | N/A    | 130nm CMOS | 2011 |        |         |

| [26] | 121   | -3.5  | 21              | 2.13~%     | -88                 | N/A    | 130nm CMOS | 2011 | Fund.  |         |

| [14] | 219   | -3.0  | 24              | 2.08 %     | -77.4               | N/A    | 65nm CMOS  | 2016 | runa.  |         |

| [28] | 176   | 4.8   | 25.8            | 11.7 %     | -101.7              | 0.34 % | 130nm SiGe | 2017 |        |         |

| [29] | 195   | 6.5   | 29.2*           | 15.3~%     | -98.6               | 1.1 %  | 55nm SiGe  | 2017 |        |         |

| [19] | 190   | -4.5  | 215             | 0.16 %     | -73                 | 3.8 %  | 140nm SiGe | 2005 |        |         |

| [16] | 192   | -20   | 16.5            | 0.06 %     | -100**              | 0.68 % | 130nm CMOS | 2006 |        |         |

| [17] | 202   | -7.2  | 30              | 0.64~%     | -87                 | 3.5 %  | 130nm SiGe | 2013 | Push   |         |

| [17] | 212   | -7.1  | 30              | 0.65~%     | -92                 | 2.8 %  | 130nm SiGe | 2013 | push   |         |

| [20] | 210   | 1.4   | 56.5*           | 2.40 %     | -87.5               | 10.6 % | 130nm SiGe | 2016 |        | No      |

| [21] | 215   | 5.6   | 79              | 4.60~%     | -94.6               | 0.65~% | 65nm CMOS  | 2017 |        |         |

| [26] | 256   | -17   | 71              | 0.03~%     | -88                 | N/A    | 130nm CMOS | 2011 |        |         |

| [26] | 482   | -7.9  | 61              | 0.27~%     | -76                 | N/A    | 65nm CMOS  | 2011 |        |         |

| [26] | 482   | -9.0  | 27.5            | 0.46~%     | -76                 | N/A    | 65nm CMOS  | 2011 | Triple |         |

| [24] | 288   | -1.5  | 275             | 0.26~%     | -87                 | 1.4 %  | 65nm CMOS  | 2013 | push   |         |

| [22] | 200   | -8.8  | 28.8            | 0.46~%     | N/A                 | N/A    | 65nm CMOS  | 2016 |        |         |

| [25] | 298   | 0.9   | 235             | 0.51~%     | -79                 | 1.7 %  | 65nm CMOS  | 2016 |        |         |

| [23] | 210   | -6.0  | 28.6            | 0.88~%     | -88                 | 5.1 %  | 90nm CMOS  | 2018 |        |         |

| [15] | 290   | -1.2  | 325             | 0.23~%     | -78                 | 4.5 %  | 65nm CMOS  | 2012 | Quad.  |         |

| [15] | 320   | -3.3  | 339             | 0.13~%     | -77                 | 2.6~%  | 65nm CMOS  | 2012 | Quad.  |         |

Chapter 1. Millimeter-wave and Terahertz Technologies

$\ast$  Estimated from provided data,  $\ast\ast$  @10MHz offset.

Table 1.1 – State-of-the-art of silicon based mm-wave and THz oscillators per type of oscillator, the references are reported upon their publication year.

| Ref. | Freq. | Pout  | PDC  | DC-to-RF   | PN <sub>@1MHz</sub> | Tuning | Technology | Year | Type | Phase   |

|------|-------|-------|------|------------|---------------------|--------|------------|------|------|---------|

|      | (GHz) | (dBm) | (mW) | Efficiency | (dBc/Hz)            | Range  |            | rear | lype | Locked? |

| [30] | 285   | -19   | 71   | 0.02 %     | -80.5 †             | 1.7 %  | 65nm CMOS  | 2013 |      |         |

| [31] | 285   | -9.0  | 52   | 0.24~%     | -105 †              | 10.8~% | 55nm SiGe  | 2015 | ILO  |         |

| [32] | 195   | 0.0   | 28.8 | 3.50~%     | -117.5*†            | 5.4~%  | 130nm SiGe | 2018 |      | Yes     |

| [32] | 195   | -3.7  | 21.6 | 2.00~%     | -117.5*†            | 12.3~% | 130nm SiGe | 2018 |      | 105     |

| [33] | 290   | -14   | 376  | 0.01~%     | -82.5               | 7.9~%  | 90nm SiGe  | 2014 | PLL  |         |

| [34] | 317   | 5.2   | 610  | 0.54~%     | -79                 | 0.06 % | 130nm SiGe | 2015 | TDD  |         |

\* Estimated from provided data, <sup>†</sup> Depends on reference phase noise.

Table 1.2 - State-of-the-art of silicon based mm-wave and THz frequency synthesis solutions.

always at the expense of a huge DC consumption and thus a very low DC-to-RF efficiency. Moreover, phase noise performances of this kind of structures are not very good.

Push-push structures have suffered from the same problems during a long time. Nevertheless, very recent works exhibit several alternatives with improved performances. Indeed, today's best CMOS push-push oscillator ([21], published in 2017) exhibits a very high output power of 5.6dBm for a 4.6% efficiency. This with the measured -95 dBc/Hz at 1MHz from the carrier makes this topology still very interesting for frequency generation above 200 GHz. These results were obtained thanks to optimizations of large-signal transistor behavior to boost harmonic extraction.

Finally, fundamental oscillators helped by recent sub-micron silicon technology improvements, present the best today's output power and efficiency. Indeed, [29] proposed in 2017 a single transistor oscillator achieving 6.5 dBm output power for a 15.3% DC-to-RF efficiency and a phase noise of -98.6 dBc/Hz at 1MHz offset. These excellent results were obtained thanks to an innovative approach. Indeed, by considering the oscillator as a looped back unstable power amplifier, authors choose to maximize an old figure of merit: the Maximally Efficient Power Gain ( $G_{ME}$ ). Unlike the maximum available gain ( $G_{MA}$ ), which is defined only for stable network,  $G_{ME}$  is defined in order to have a power gain which remains finite and well-behaved for both stable and unstable network.

Regarding these results, it appears clear that to design high efficiency and high output power oscillators at mm-wave and THz frequencies the most efficient way is to optimize the active part as a looped back power amplifier as in [20, 28, 29]. Moreover, large-signal transistor behavior must be fully understood to allow an optimized power extraction and hence maximized the output power and the efficiency [21]. These design techniques helped by recent sub-micron technologies improvements should allow reaching excellent performances at mm-wave and THz operation frequencies.

Concerning the phase locked systems, the same limitations appear. Injection-locked oscillators have presented very interesting behavior for this kind of systems and must be investigated. But to guarantee good locked system performances (especially in terms of output power and efficiency) it appears evident that research must first focus on good oscillator performances.

It is important to note that, depending on the targeted application, different parameters must be optimized. Indeed, in some mm-wave/THz applications, especially for sensing, sources do not need to be locked as the phase noise is not critical. For this kind of systems, only the output power and the efficiency have to be maximized. On the other hand, for very high data rate communications with complex modulations, the phase noise is critical and locked sources are mandatory.

# 1.4 Chapter conclusion

This chapter has introduced the context of silicon-based mm-wave and THz applications, from imaging to high data rate application. Several mm-wave and THz oscillator topologies have been introduced and intrinsic limitations have been highlighted.

Following the state-of-the-art analysis, it appears that to guarantee good system performances at mm-wave and THz operation frequencies (especially in terms of output power and efficiency) research must first focus on oscillator performances.

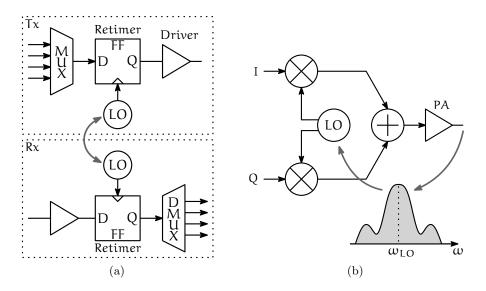

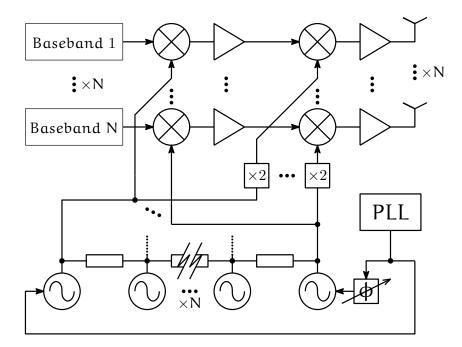

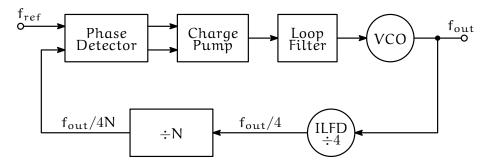

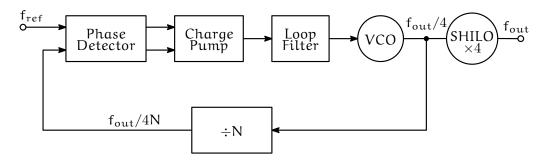

Recent techniques based on the large-signal optimization of the oscillator active part (seen as a loop power amplifier) provide good results at mm-wave and THz operation frequencies. These new design techniques must be investigated to take full advantage of sub-micron technologies possibilities.