### Pre-Design by Optimization Methodology in Power Electronics

Mylène Delhommais

### ▶ To cite this version:

Mylène Delhommais. Pre-Design by Optimization Methodology in Power Electronics. Electric power. Université Grenoble Alpes, 2019. English. NNT: 2019GREAT017. tel-02360918

### HAL Id: tel-02360918 https://theses.hal.science/tel-02360918

Submitted on 13 Nov 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité : **Génie Electrique**Arrêté ministériel : 25 mai 2016

Présentée par

### Mylène Delhommais

Thèse dirigée par Jean-Luc Schanen, Professeur des universités, Grenoble INP, et codirigée par Frédéric Wurtz, Directeur de recherche, CNRS

préparée au sein du Laboratoire G2ELab dans l'École Doctorale EEATS

### Méthode de Pré-design par Optimisation en Electronique de Puissance

Preliminary Design Method in Power Electronics

Thèse soutenue publiquement le **28 Mars 2019**, devant le jury composé de :

### **Monsieur Thierry MEYNARD**

Directeur de Recherche au CNRS au LAPLACE, Président

#### Monsieur Johann Walter KOLAR

Professeur des Universités à l'ETH Zürick, Rapporteur

#### **Monsieur Bruno SARENI**

Professeur des Universités à l'INP de Toulouse, Rapporteur

#### Monsieur Jean-Luc SCHANEN

Professeur des Universités à l'INP de Grenoble, Directeur de thèse

### Monsieur Frédéric WURTZ

Directeur de Recherche au CNRS au G2ELab, Co-Directeur de thèse

### Madame Cécile RIGAUD

Ingénieure d'étude à Bio-logic, Examinatrice

#### Monsieur Jonathan GILBERT

Ingénieur à Tronico, Invité

Abstract

When a designer of power electronics systems is involved in a pre-design process, i.e. the definition of the system

specifications, he/she has to overcome several difficulties. The first is to find, based on its experience and literature,

all the architectures, conversion topologies and component technologies that can meet the needs of the system.

From this list of possibilities, the designer must eliminate a certain number of them via qualitative or quantitative

arguments until only a small number remains. It is essential for the designer that he/she knows the design limits of

each remaining choices to define with certainty the product development plan and the future design issues to be

solved. In other words, it must define the correct problem formulation.

Having a method to achieve this objective with confidence and on schedule is highly desirable. This is the

purpose of this thesis.

We therefore propose a new approach based on preliminary design by optimization in the continuous (imaginary)

world of power electronics systems. The proposed method uses an optimization algorithm based on the calculation of

the gradient of the system model. This algorithm allows to manage a very large number of design parameters, in

other words to explore a wide range of solutions in the imaginary world. It therefore requires continuous and

differentiable models of power electronics systems with continuous (imaginary) optimization variables despite the

discrete nature of the components used in electronics.

The present thesis work has thus consisted in proposing continuous and derivable optimization models of an

interleaved Buck converter used in an aircraft called "Stratobus" and validating these optimization models by an

experimental approach on a complete prototype. These models have then been used for the pre-dimensioning of this

converter as part of the Stratobus project. Firstly a study on the conduction mode and magnetic materials minimizing

the mass of the converter has been performed. And then the impact of variation of the specifications on the mass of

the converter has been analyzed. Finally, since the converters are built from electronic components chosen off the

shelf, a discretization procedure has been set up to return to the real world.

**Key word:** Optimization – Power Electronics – Pre-design – Aeronautical

### Résumé

Lorsqu'un concepteur de systèmes d'électronique de puissance est engagé dans un processus de pré-design, c'està-dire la définition du cahier des charges du système, il doit surmonter plusieurs difficultés. La première étant de trouver grâce à son expérience et à la littérature, toutes les architectures, topologies de conversion et technologies de composants susceptibles de répondre aux besoins du système.

A partir de cette éventail, le concepteur doit en éliminer un certain nombre via des arguments qualitatifs ou quantitatifs jusqu'à ce qu'il n'en reste plus qu'un nombre très restreint. Il est primordial pour le concepteur que parmi les choix restant, celui-ci en connaisse les limites de design pour définir avec certitude le plan de développement du produit et les problématiques futures à résoudre. En d'autres termes, il lui faut définir la juste formulation du problème qui lui est posée.

Posséder une méthode lui permettant d'atteindre cet objectif en toute confiance et dans les délais impartis est fortement désirable. Ceci est l'objet de cette thèse.

Nous proposons donc une nouvelle approche basée sur le pré-dimensionnement par optimisation dans le monde continu (imaginaire) de systèmes d'électronique de puissance. La méthode proposée utilise en effet un algorithme d'optimisation basé sur le calcul du gradient du modèle du système. Cet algorithme permet de gérer un très grand nombre de paramètres de design, autrement dit permet d'explorer un large éventail de solutions dans le monde imaginaire. Il nécessite donc des modèles de systèmes d'électronique de puissance continus et dérivables avec des variables d'optimisation continues (imaginaires) malgré le caractère discret des composants utilisés en électronique.

Les présents travaux de thèse ont donc consistés à proposer des modèles d'optimisation continus et dérivables d'un convertisseur Buck entrelacé utilisé dans un aéronef appelé « Stratobus » et à valider ces modèles d'optimisation par une démarche expérimentale sur un prototype complet. Ces modèles ont ensuite été utilisés pour le pré-dimensionnement de ce convertisseur dans le cadre du projet Stratobus permettant dans un premier temps une étude sur le mode de conduction et les matériaux magnétique minimisant la masse du convertisseur, puis une analyse de l'impact de variation de cahier des charges sur la masse du convertisseur. Enfin, les convertisseurs étant construits à partir de composants électroniques choisis sur étagère, une procédure de discrétisation a été mise en place pour revenir au monde réel.

Mots clés: Optimisation – Electronique de puissance – Pré-design – Aéronautique

### Acknowledgments ~ Remerciements

I would like to first thank all my jury members for attending to my defense in Grenoble and for asking me incisive questions;-)! A particular thank to my reviewers professor Sareni and professor Kolar for their wise remarks and the discussions that followed the defense. I hope we will have further in the future!

I would like to underline the deep investment of my thesis directors Jean-Luc and Fred and Tronico's supervisors Cécile and Sylvain. I particularly enjoyed all the discussions we had for making a meaningful and coherent thesis according to academic and industrial needs. It was a real pleasure to work with all of you. I even more enjoyed the time we spent outside of work!

Thanks to Tronico's management for trusting its engineers and letting them be innovative.

This work could not have been possible without my colleagues. Especially the Gronicois that supported me these last 3 years, the technicians that helped me (Jennifer and Loïc for the prototype layout, Edyta for the BOM, Cyrille for the inductor samples), Maryline for the daily help and to the engineers such as Jonathan and Valentin that were openmind to new design methods.

I would also like to thank the other PhD students of G2ELab and the administration and technical services for the positive ambiance inside the lab, particularly during my first year thesis. I would also like to express my gratitude to my master professors (IEE teachers and especially Elisabeth and Laurent) who have shared their passion for electrical engineering and research.

Merci maman pour m'avoir toujours encouragé dans mes études depuis la maternelle (sans t'imaginais que j'aille jusqu'à BAC+8!).

Cảm on bạn Anh Dao et merci aux ladies 2000 (#Lucie#Pauline#Ambre) pour être des soutiens indéfectibles.

Merci aussi à mon Doudou d'amour pour tes encouragements sur cette fin de thèse et d'être à mes côtés chaque jour, chose qui me remplit de bonheur !

## Glossary of abbreviations

| Abbreviation                                        | Signification                                                                                                         |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| μ                                                   | Fluid dynamic viscosity                                                                                               |  |  |

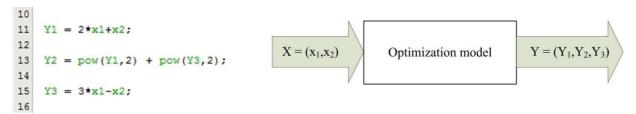

| CADES                                               | Component Architecture for Design of Engineering Systems (optimization framework)                                     |  |  |

| Cal_Idiode                                          | SiC 1200 V Schottky diode current rating                                                                              |  |  |

| Cal_Imos                                            | SiC 1200 V MOSFET current rating                                                                                      |  |  |

| CCM                                                 | Continuous Conduction Mode: conduction mode of a converter                                                            |  |  |

| CD                                                  | Conduction mode                                                                                                       |  |  |

| $C_D$                                               | Diode junction capacitance                                                                                            |  |  |

| C <sub>GD</sub> , C <sub>GS</sub> & C <sub>DS</sub> | MOSFET junction capacitances                                                                                          |  |  |

| Chigh                                               | Input single capacitor value                                                                                          |  |  |

| C <sub>L</sub> or CL                                | Phase inductor capacitance                                                                                            |  |  |

| Clow                                                | Output single capacitor value                                                                                         |  |  |

| COTS                                                | Commercial Off-The-Shelf: components taken in manufacturer catalogs                                                   |  |  |

| d                                                   | Command delay between the MOSFETs of each phase                                                                       |  |  |

| DC                                                  | Optimization variable that indicates the conduction mode of the converter (=1 if DCM, =0 if CCM)                      |  |  |

| DCD                                                 | Diode conduction duration                                                                                             |  |  |

| DCM                                                 | Depends on the context: either Discontinuous Conduction Mode of the converter, either Duty-Cycle of the MOSFET        |  |  |

| Dh                                                  | Hydraulic diameter                                                                                                    |  |  |

| DIL                                                 | Current ripple in the phase inductor                                                                                  |  |  |

| Din                                                 | Inductor core internal diameter                                                                                       |  |  |

| Dlitz <sub>ext</sub> or<br>Dlitz_ext                | External diameter of the Litz wire                                                                                    |  |  |

| DlitzLphase                                         | Litz strand diameter of the phase inductor                                                                            |  |  |

| Dout                                                | Inductor core external diameter                                                                                       |  |  |

| EMC                                                 | ElectroMagnetic Compatibility                                                                                         |  |  |

| EMI                                                 | ElectroMagnetic Interferences                                                                                         |  |  |

| Fs                                                  | Switching frequency                                                                                                   |  |  |

| Н                                                   | Inductor core height                                                                                                  |  |  |

| HVPCU                                               | High Voltage Power Conditioning Unit (set of the DC-DC converters of Stratobus between solar panels and DC power bus) |  |  |

| IBC                                                 | Interleaved Buck Converter                                                                                            |  |  |

| ID or I <sub>D</sub>                                | Diode current                                                                                                         |  |  |

| IDmoy                                               | Average current in the diode                                                                                          |  |  |

| Abbreviation                                   | Signification                                                                                              |  |  |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|

| IDrms                                          | Diode RMS current                                                                                          |  |  |

| Ihigh                                          | Input current of the IBC                                                                                   |  |  |

| IL or I <sub>L</sub>                           | Phase inductor current                                                                                     |  |  |

| Ilow                                           | Output current of the IBC                                                                                  |  |  |

| IQ or I <sub>Q</sub> or I <sub>DS</sub> or Ids | MOSFET drain current                                                                                       |  |  |

| IQrms                                          | MOSFET RMS current                                                                                         |  |  |

| Lcrit                                          | Critical value of the phase inductor to be on the limit of the continuous or discontinuous conduction mode |  |  |

| Ld or L <sub>D</sub>                           | MOSFET drain inductance of the switching cell                                                              |  |  |

| Lhigh_max                                      | Input single filtering inductor value @ 0A                                                                 |  |  |

| Llow_max                                       | Output single filtering inductor value @ 0A                                                                |  |  |

| Ls or Ls                                       | MOSFET source inductance of the switching cell                                                             |  |  |

| material                                       | Inductor core material                                                                                     |  |  |

| N_Chigh                                        | Number of input capacitors in parallel                                                                     |  |  |

| N_Clow                                         | Number of output capacitors in parallel                                                                    |  |  |

| NA                                             | Not Applicable                                                                                             |  |  |

| NBphase or<br>Nb_phase or<br>Nphase            | Number of phase of the IBC                                                                                 |  |  |

| Nbunching                                      | Number of bunching operations for the Litz wire                                                            |  |  |

| Neabling                                       | Number of cabling operations for the Litz wire                                                             |  |  |

| Np_Lhigh                                       | Number of input inductors in parallel                                                                      |  |  |

| Np_Llow                                        | Number of output inductors in parallel                                                                     |  |  |

| Ns_Lhigh                                       | Number of input inductors in series                                                                        |  |  |

| Ns_Llow                                        | Number of output inductors in series                                                                       |  |  |

| nstrandLphase                                  | Litz number of strands                                                                                     |  |  |

| NturnsLphase                                   | Phase inductor number of turns                                                                             |  |  |

| Nu <sub>exp</sub>                              | Experimental Nusselt numer                                                                                 |  |  |

| Nu <sub>predict</sub>                          | Predicted Nusselt numer                                                                                    |  |  |

| OP                                             | Operating point                                                                                            |  |  |

| PCB                                            | Printed circuit board                                                                                      |  |  |

| Pcond <sup>diode</sup>                         | Diode on-state losses                                                                                      |  |  |

| Pcond <sup>MOSFET</sup>                        | MOSFET on-state losses                                                                                     |  |  |

| PDR                                            | Preliminary Design Review (design phase milestone)                                                         |  |  |

| Phigh                                          | Input power of the IBC converter                                                                           |  |  |

| Pr                                             | Prandt number                                                                                              |  |  |

| PWM                                            | Pulse Width Modulation                                                                                     |  |  |

| Q                                              | Fluid flow rate                                                                                            |  |  |

| Abbreviation                                   | Signification                                                                                             |  |  |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| RacLitz                                        | AC resistance of the Litz wire                                                                            |  |  |

| RdcLitz                                        | DC resistance of the Litz wire                                                                            |  |  |

| Rdson                                          | On-state resistance of the MOSFET                                                                         |  |  |

| Re                                             | Reynolds number                                                                                           |  |  |

| $R_G$                                          | Gate resistance of a MOSFET                                                                               |  |  |

| RMS                                            | Root Mean Square                                                                                          |  |  |

| Rs                                             | Linear resistance of a strand                                                                             |  |  |

| Rt                                             | Diode on-state resistance                                                                                 |  |  |

| Rth                                            | Thermal resistance of a device/material                                                                   |  |  |

| S                                              | Thermal exchange surface of a device/material                                                             |  |  |

| SiC                                            | Silicon Carbide                                                                                           |  |  |

| SML                                            | System Modeling Language (CADES specific)                                                                 |  |  |

| SQP                                            | Sequential Quadratic Programming (gradient based optimization algorithm)                                  |  |  |

| SRR                                            | System Readiness Review (design phase milestone)                                                          |  |  |

| TBD                                            | To Be Defined                                                                                             |  |  |

| THD                                            | Total Harmonics Distortion                                                                                |  |  |

| Tj                                             | Junction temperature of a semiconductor                                                                   |  |  |

| T <sub>Oscill</sub>                            | Period of the oscillations that appear on diode, MOSFET and phase inductor voltages in DCM                |  |  |

| Ts                                             | Switching period                                                                                          |  |  |

| VD or V <sub>D</sub>                           | Diode voltage                                                                                             |  |  |

| Vhigh                                          | Input voltage of the IBC                                                                                  |  |  |

| VL or V <sub>L</sub>                           | Phase inductor voltage                                                                                    |  |  |

| Vlow                                           | Output voltage of the IBC                                                                                 |  |  |

| VQ or V <sub>Q</sub> or V <sub>DS</sub> or Vds | MOSFET drain-source voltage                                                                               |  |  |

| Vt                                             | Diode threshold voltage                                                                                   |  |  |

| α                                              | Fluid coefficient (0.33 for water) for Nu <sub>predict</sub>                                              |  |  |

| $\Delta T_{exp}$                               | measured temperature difference between the heated wall and the bulk fluid                                |  |  |

| η <sub>computed</sub>                          | Computed converter efficiency (optimization output variable)                                              |  |  |

| $\eta_{des}$                                   | Desired converter efficiency (optimization input variable)                                                |  |  |

| λork                                           | Material thermal conductivity                                                                             |  |  |

| ρ                                              | Fluid volume density                                                                                      |  |  |

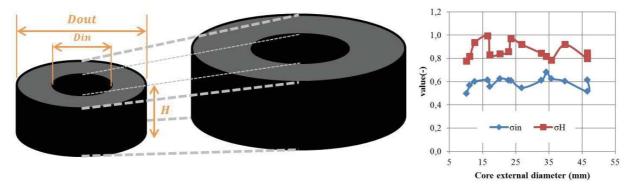

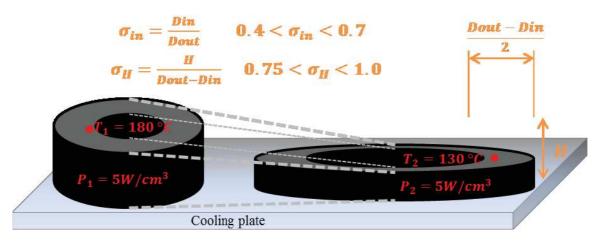

| σн                                             | Coefficient about the proportions of the inductor core geometries (on height)                             |  |  |

| $\sigma_{\text{in}}$                           | Coefficient about the proportions of the inductor core geometries (on internal diameter)                  |  |  |

| σturns                                         | Coefficient about the proportions between the inductor actual number of turns and maximum number of turns |  |  |

| Фехр                                           | Heat flux                                                                                                 |  |  |

### Résumé en Français

# Partie A : Enjeux et solution proposée pour relever le défi de la phase de conception préliminaire des systèmes électroniques de puissance

### Chapitre 1: Processus de conception actuel en électronique de puissance

L'électricité est le vecteur énergétique préconisée par les scientifiques pour faire face à l'un des plus grands défis de l'humanité qu'est le réchauffement climatique et donc la réduction d'émission de CO<sub>2</sub> dans l'atmosphère. Cela signifie que les besoins de système d'électronique de puissance pour contrôler et convertir l'énergie électrique continueront de grandir dans les prochaines décennies.

Mais un convertisseur statique n'assurant pas une fonction finale mais seulement une fonction partiel d'un système, les contraintes de design sont souvent très fortes. Par exemple, son rendement doit s'approcher de 100% pour être transparent dans les calculs d'efficacité énergétique des systèmes, et ce dans un volume et un poids minimaux.

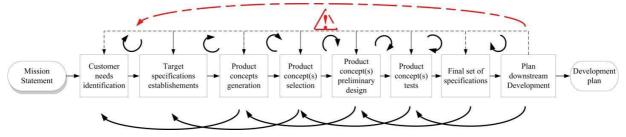

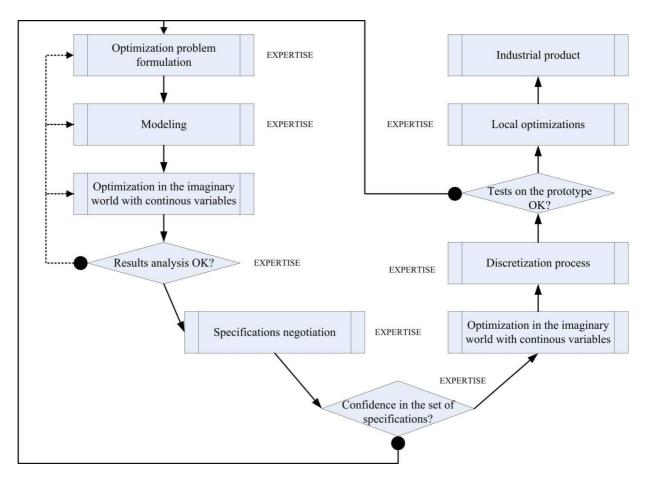

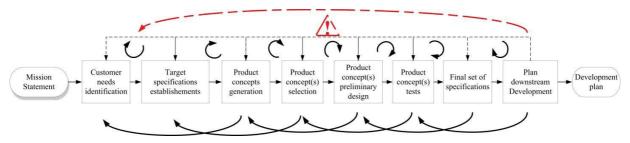

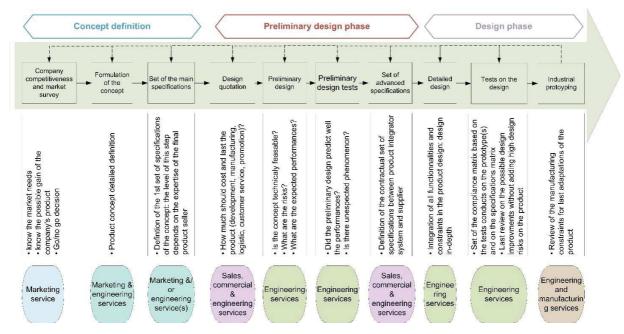

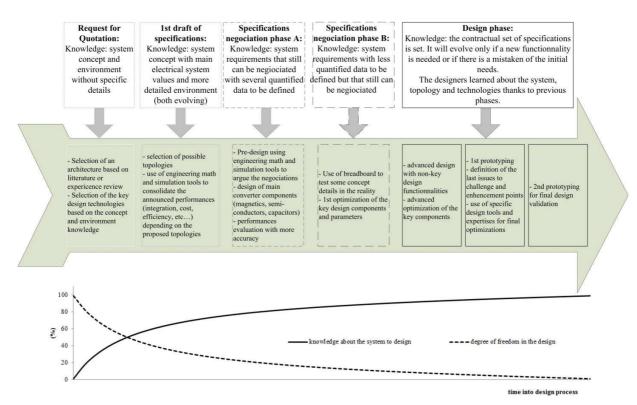

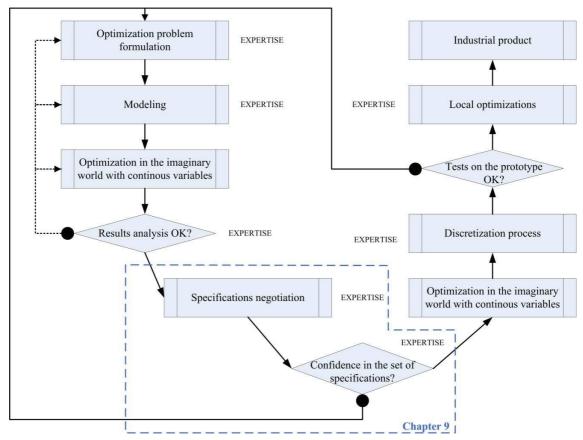

Pour définir un cahier des charges réalisable d'après les exigences des intégrateurs systèmes, les concepteurs d'électronique de puissance suivent un processus de pré-design comme présenté par la Figure 1.

Figure 1: Processus de pré-design selon Ulrich and Eppinger

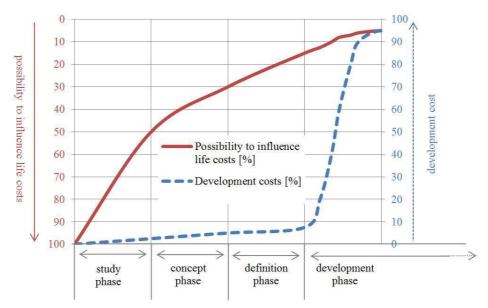

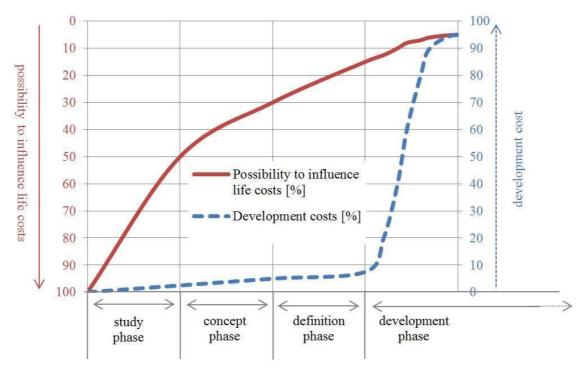

Cette phase de pré-design est très importante puisqu'elle influence 90% du coût du développement du convertisseur dans la phase de conception détaillée Figure 2. Cette phase de préconception ne doit pas être négligée.

Résumé en Français

Figure 2: Effet de levier sur le coût du développement du produit selon Zablit et Zimmer

Selon Kline et Schindel, les conceptions qui aboutissent à un produit coûteux sont parfois dues à des raccourcis pris par concepteurs : ils ne recueillent pas assez d'information ou la bonne information avant de commencer à concevoir, ils ne se concentrent que sur une ou quelques idées ou ils suivent un chemin linéaire simple ou d'autres processus infructueux lors de la conception.

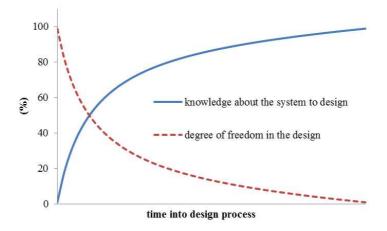

Ce constat fait échos avec le paradoxe du processus de design qui est que le nombre de degrés de liberté du concepteur diminue avec l'accroissement des connaissances du systeme lors de l'avancement dans le design.

Le domaine de l'électronique de puissance a, qui plus est, la particularité d'être intrinsèquement très discrétisé puisque les convertisseurs statiques sont principalement constitués de composants électroniques choisis sur catalogue. Mais il existe peu de méthodes et d'outils pour cette phase de pré-design dans ce domaine (contrairement aux méthodes de design sur un cahier des charges fixé largement étudiées dans la littérature).

Résumé en Français II

## Chapitre 2: Une nouvelle approche pour la conception préliminaire de l'électronique de puissance

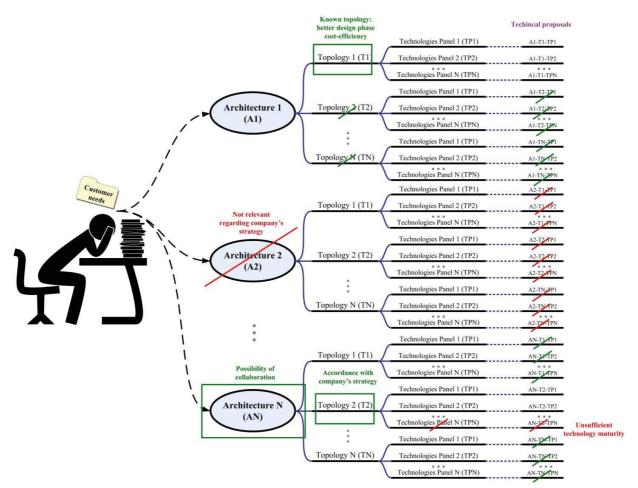

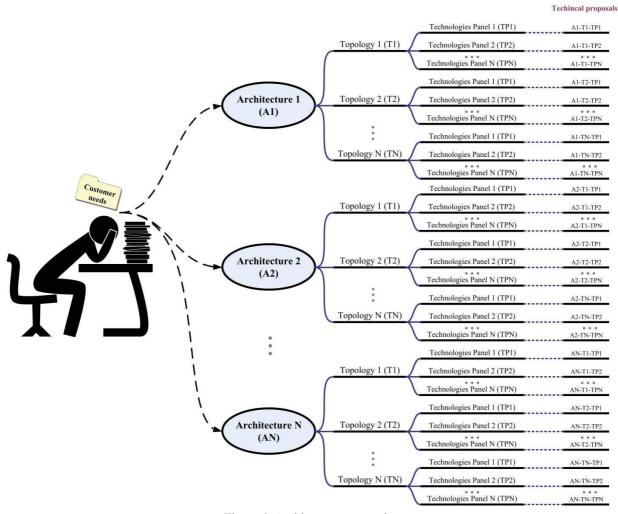

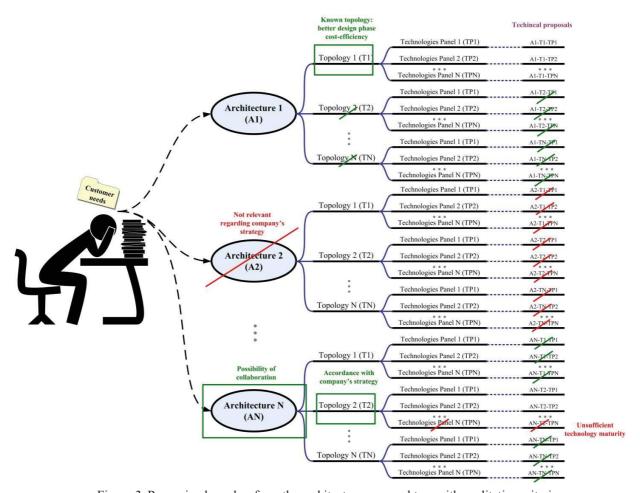

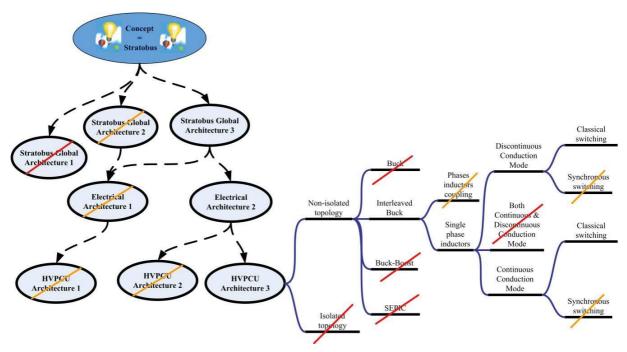

En électronique de puissance le concepteur doit sélectionner l'architecture puis la topologie puis les technologies à utiliser dans son système. Parce que le choix est grand, le nombre de branches de l'arbre des propositions techniques possibles peut très vite exploser (Figure 3). Le nombre de choix possible peut diminuer à l'aide d'arguments qualitatifs mais parmi les choix restants, les données quantitatives sont indispensables.

Figure 3: Arbre de propositions techniques possibles pour un cahier des charges donné

Afin de fournir ces données, une nouvelle méthode de pré-design qui a la capacité d'explorer rapidement un large éventail de solutions pour chaque proposition et de les comparer objectivement (c'est-à-dire optimisées selon les mêmes critères) permettrait d'aider les designers dans cette phase.

C'est pourquoi, afin de répondre à la problématique de conception préliminaire de systèmes d'électronique de

Résumé en Français III

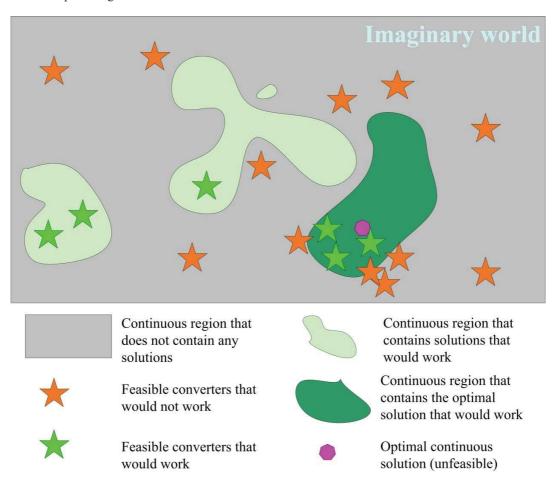

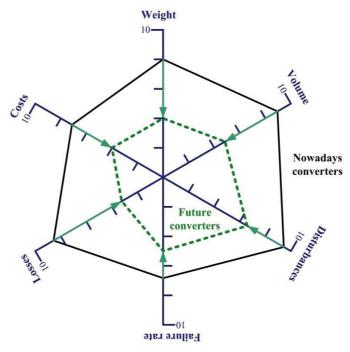

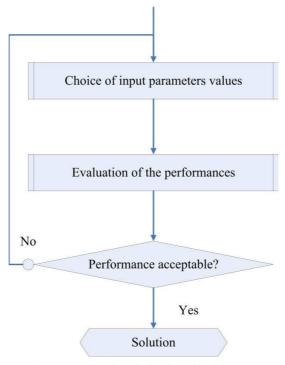

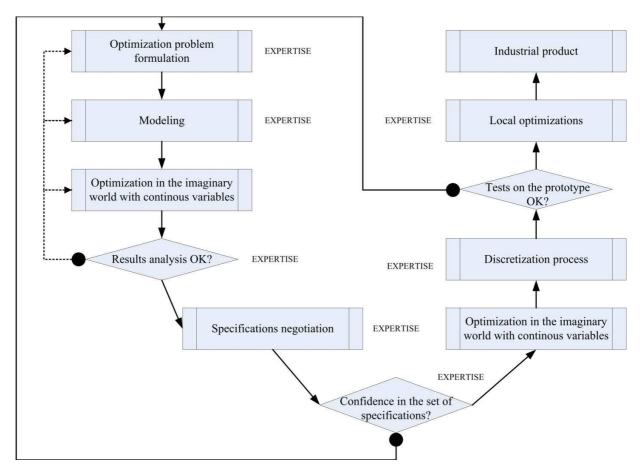

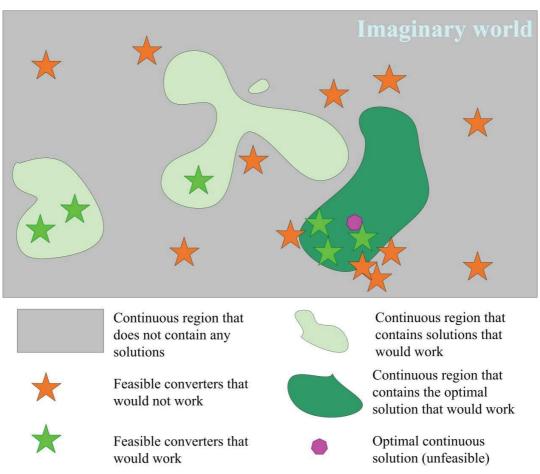

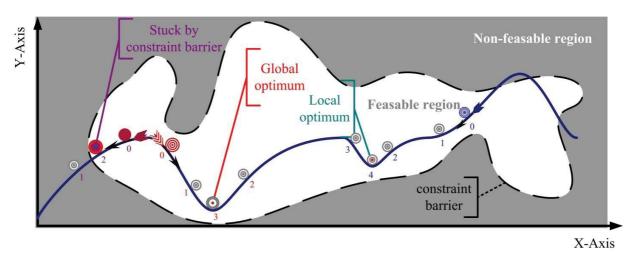

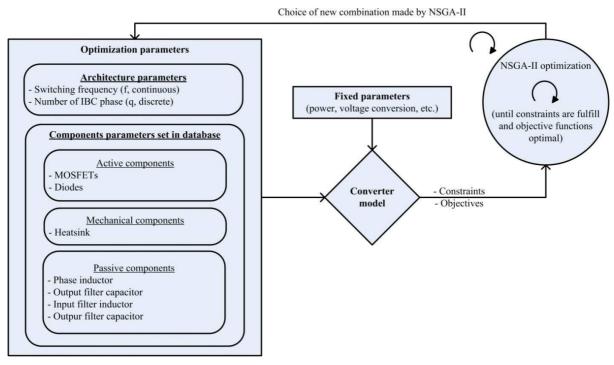

puissance, nous proposons une nouvelle approche basée sur l'algorithme d'optimisation par gradient SQP qui est capable de gérer jusqu'à quelques centaines de paramètres de conception et correspond donc plus ou moins à la taille du problème de pré-dimensionnement d'une alimentation à découpage. Elle a l'inconvénient de ne pas pouvoir traiter des paramètres discrets : toutes les variables de conception doivent être continues et les modèles dérivables. Malheureusement pour les concepteurs d'électronique de puissance qui travaillent avec des composants discrets, tout algorithme (heuristique ou énumération) ou technique (branche & bound) capable d'utiliser des variables discrètes est nécessairement moins efficace pour des problèmes d'optimisation importants et fortement contraints. Cette approche consiste donc à optimiser chaque proposition technique avec des variables continues et non discrètes dans le monde imaginaire décrit par la Figure 4.

Figure 4: Illustration du monde imaginaire des convertisseurs statiques

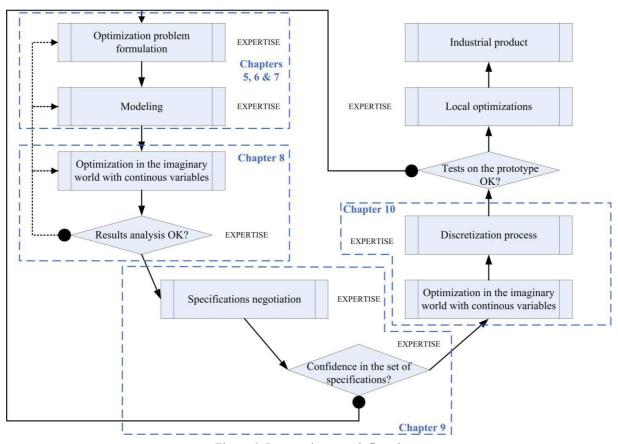

Elle est résumée par la *Figure 5* : le processus commence par la formulation du problème d'optimisation et la modélisation du système. L'analyse des résultats de l'optimisation dans le monde imaginaire permet de modifier et

Résumé en Français IV

corriger la formulation du problème. Lorsque celle-ci est figée, des optimisations paramétrées en fonction des paramètres du cahier des charges et des fronts de Pareto permettent aux designers de dialoguer et négocier le cahier des charges rapidement, i.e. lorsque le degré de liberté dans la conception est encore important. Lorsque le systémier et l'intégrateur système se sont mis d'accord sur un cahier des charges, les concepteurs peuvent utiliser un processus de discrétisation de la solution imaginaire du cahier des charges. Cette discrétisation permet notamment de définir rapidement les propriétés du convertisseur réel (fabricable) et de définir les axes de travail lors de la phase de design.

Figure 5: Organigramme de l'approche de pré-dimensionnement dans le monde imaginaire

Résumé en Français V

### Chapitre 3: Un défi de conception pour l'exemple

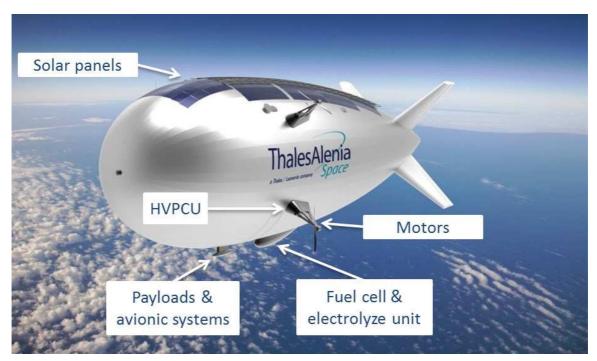

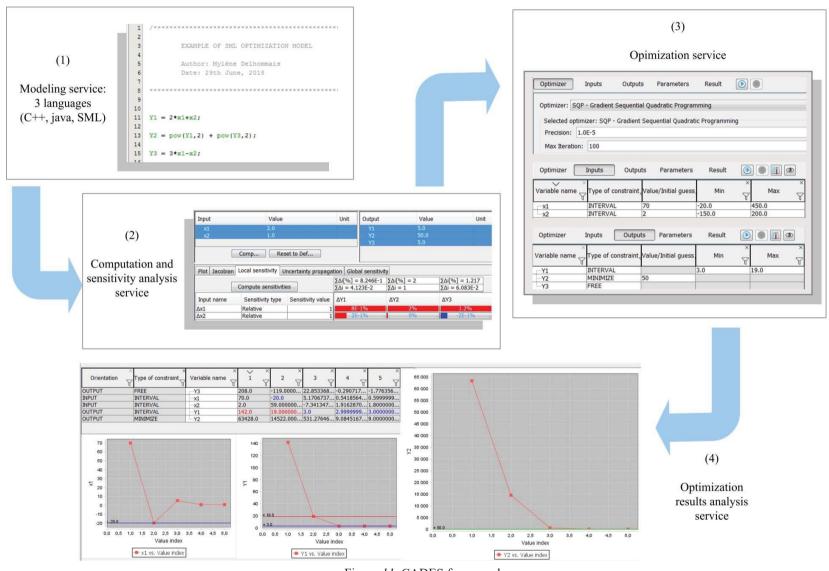

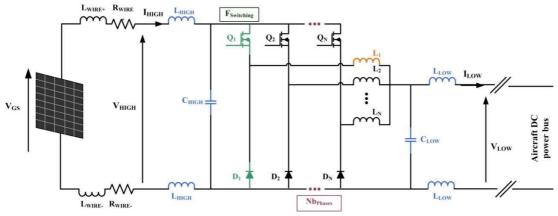

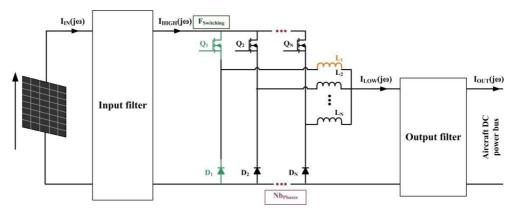

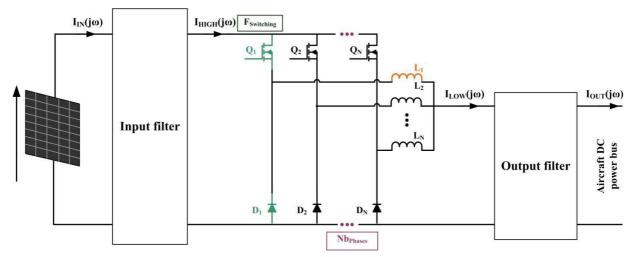

Le pré-design du convertisseur DC-DC situé entre les panneaux photovoltaïques et le bus de distribution d'énergie de l'aéronef Stratobus (Figure 6) est un parfait exemple pour illustrer cette thèse.

Figure 6: Illustration 3D du Stratobus (projet mené par Thalès Alenia Space)

Dans ce projet où le nombre d'innovations technologiques est très important, la phase plateau sert à la définition du cahier des charges de chaque sous-système permettant le meilleur compromis d'un point de vue système. C'est lors de cette phase plateau que l'approche proposée dans cette thèse a une vraie valeur ajouté pour la formulation de la problématique de design du convertisseur DC-DC. En effet, les caractéristiques du convertisseur ne sont pas figées mais l'intégrateur système a besoin de données quantitatives pour déterminer la faisabilité du système complet.

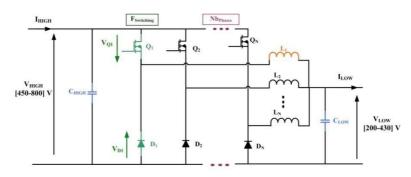

Néanmoins, les ordres de grandeurs de la plage de fonctionnement du convertisseur sont connus : large plage de tension d'entrée ([450 - 800] V) et de sortie ([200 - 430] V) avec une puissance variant de 0 à 5 kW<sup>1</sup>. Il est aussi certain que le critère le plus important du convertisseur est sa masse à minimiser.

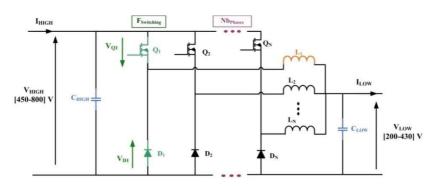

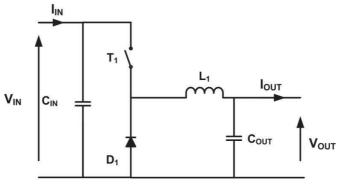

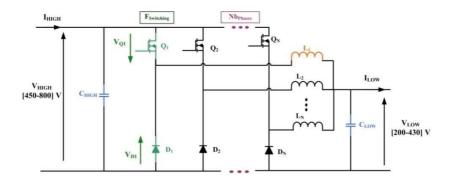

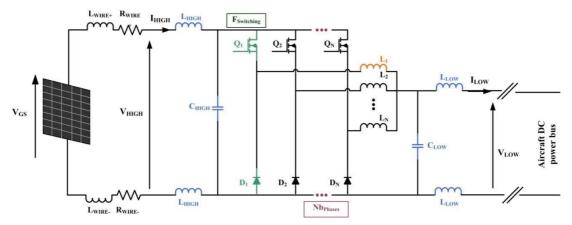

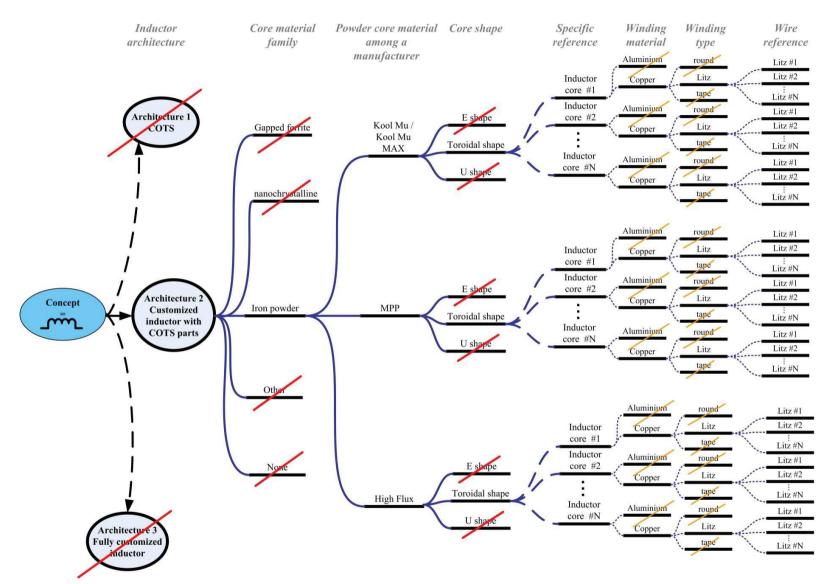

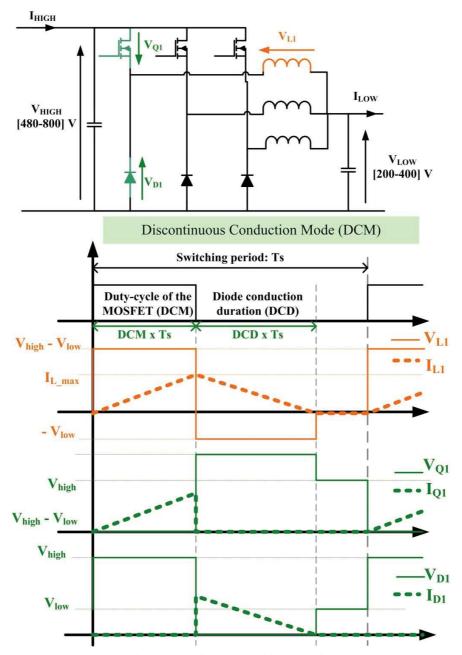

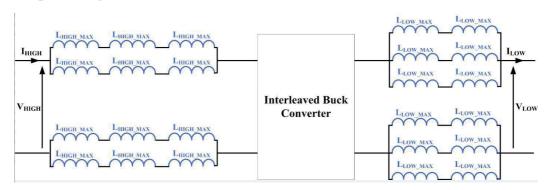

Les arguments qualitatifs ont permis de définir une architecture et une topologie de ce convertisseur : le Buck entrelacé à inductances non couplées (Figure 7). Cependant, de nombreux paramètres restent à déterminer : le mode

Résumé en Français VI

<sup>&</sup>lt;sup>1</sup> Toutes ces données sont purement fictives (mais du même ordre de grandeur) pour des raisons de confidentialité

de conduction, le nombre de bras et les composants.

Figure 7: Schéma du Buck entrelacé et ses formes d'ondes idéales associées

Les technologies de chaque composant du hacheur série entrelacé ont aussi été présélectionnées. La cellule de commutation sera en Carbure de Silicium. L'inductance de bras sera constituée d'un noyau magnétique à poudre de fer et de fil de Litz entourés d'une résine.

Résumé en Français VII

### Partie B : Formulation du problème d'optimisation pour le prédimensionnement dans le monde imaginaire

## Chapitre 4 : Formulation du problème d'optimisation des systèmes électroniques de puissance pour l'utilisation de l'algorithme d'optimisation par gradient

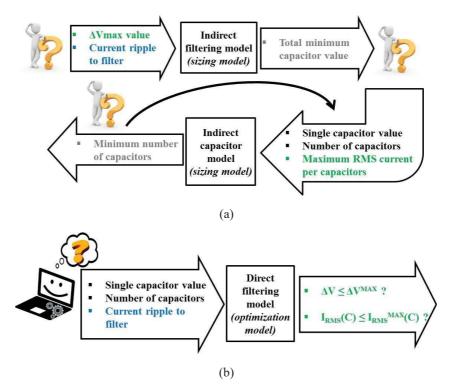

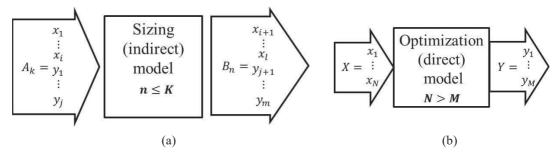

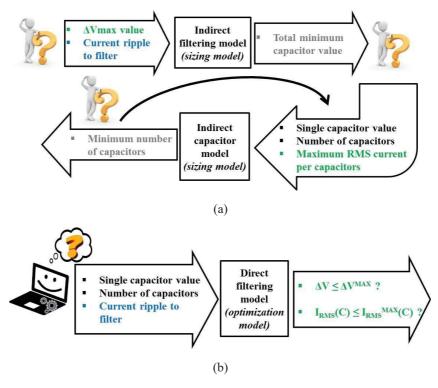

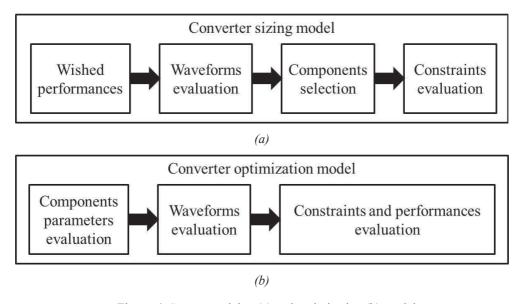

Alors qu'un dimensionnement manuel requière un modèle « indirecte », il est préférable d'appliquer les algorithmes d'optimisation sur des modèles dits « directes ». La différence entre ces deux types de modèles pour un même système est illustrée avec la Figure 8 sur le dimensionnement d'un condensateur de filtrage. Il est à noter que le degré de liberté sera plus important avec un modèle directe.

Figure 8: Illustration des modèles (a) de dimensionnement « indirects » et (b) d'optimisation « directs »

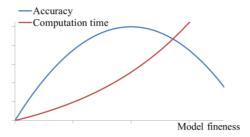

Un modèle doit être construit suivant le contexte dans lequel il est utilisé. Dans le cadre de cette thèse, les modèles d'optimisations se doivent d'être directs, continus, dérivables et avoir un coût de calcul faible. Les modèles analytiques sont alors préférentiels.

Afin de réaliser un modèle direc de convertisseur statique, il est conseillé de construire ce modèle suivant la Figure 9. C'est-à-dire partir de la description physique du convertisseur : les performances du convertisseur

Résumé en Français VIII

dépendent de ses formes d'ondes qui dépendent elles-mêmes des propriétés des composants sélectionnés.

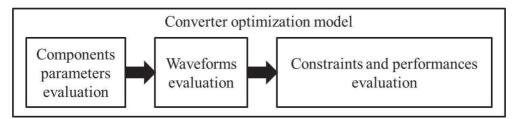

Figure 9: Modèle d'optimisation directe d'un convertisseur statique

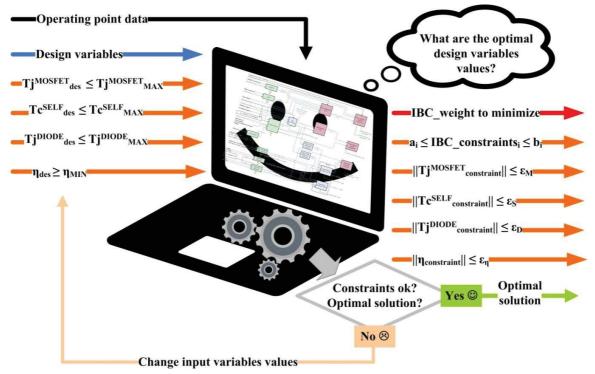

En électronique de puissance, les performances du système influent sur les propriétés de ses composants qui influent sur les performances du dit système... C'est par exemple le cas avec la température de jonction du transistor qui dépend des pertes qui sont liées à sa température. Afin de gérer cette boucle, appelée implicite car non résoluble directement, des contraintes d'optimisation sont ajoutées et résolues par l'algorithme d'optimisation comme indiqué par la Figure 10.

Figure 10: Illustration de la résolution des boucles implicites par l'algorithme d'optimisation

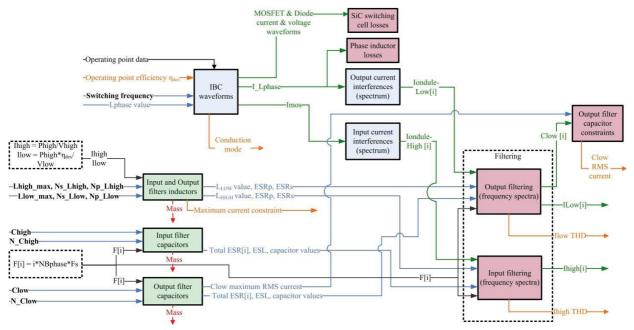

Les chapitres suivants présentent la modélisation du convertisseur Buck entrelacé pour l'application Stratobus.

Résumé en Français IX

## Chapitre 5 : Modèles d'évaluations des paramètres des composants et des formes d'ondes du convertisseur Buck entrelacé

Comme dit précédemment, les modèles d'optimisation se doivent d'être continus et dérivables.

Parmi les composants électroniques dont nous désirons déterminer les paramètres, nous identifions trois types de discontinuités :

- Une simple discrétisation du paramètre continu, pour des raisons industrielles et économiques. Par exemple, les valeurs des condensateurs dépendent de la surface diélectrique et sont intrinsèquement continues, mais sont discrétisées en séries industrielles.

- Variables numériques intrinsèquement discrètes comme le nombre de tours d'une inductance ou le nombre de bras d'un convertisseur Buck entrelacé. Le monde imaginaire avec des valeurs non entières de phases nécessitera des développements spécifiques pour proposer des modèles continus et dérivables.

- Choix intrinsèquement discret d'une technologie, comme par exemple SiC vs Si, ou de matériaux magnétiques spécifiques.

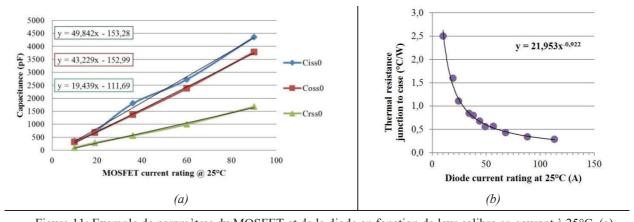

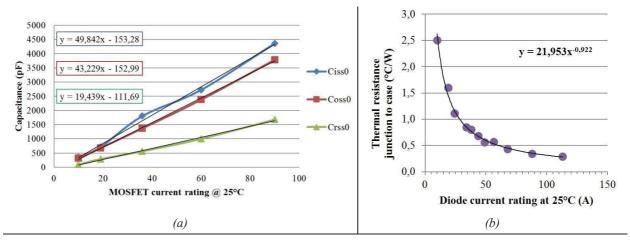

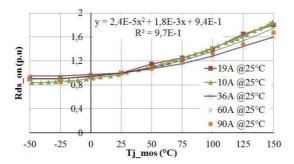

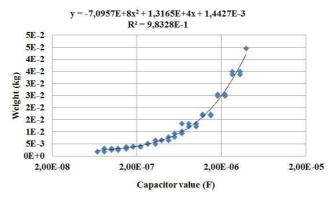

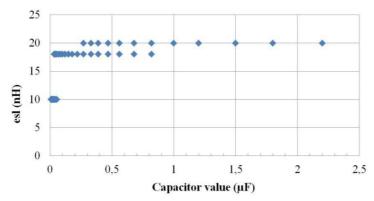

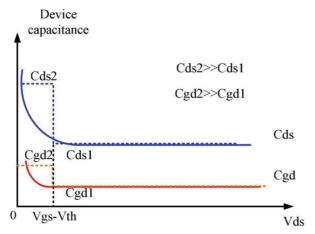

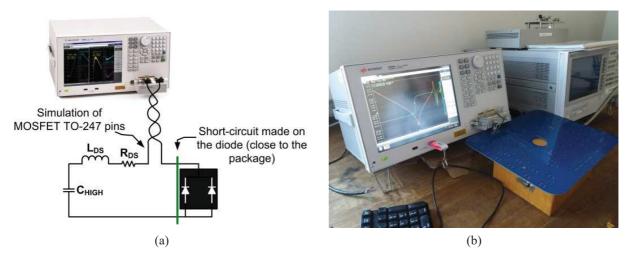

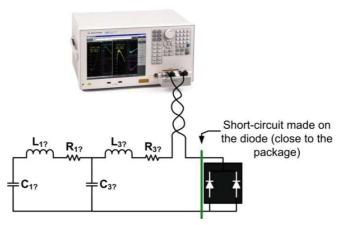

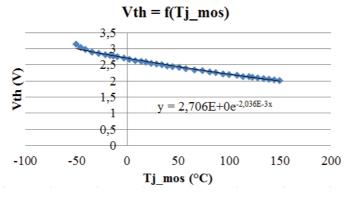

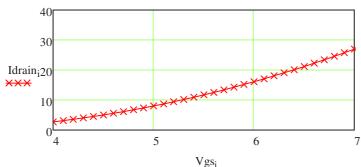

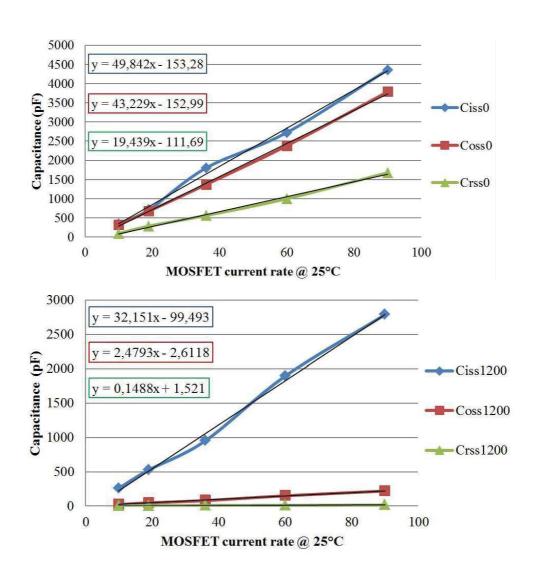

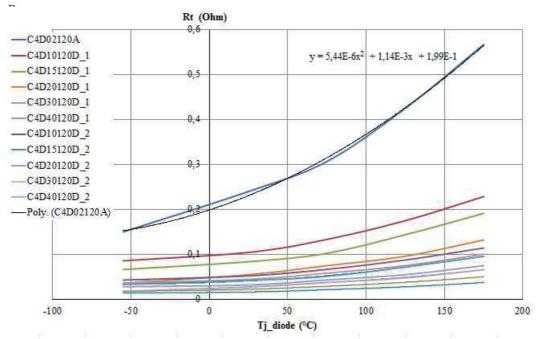

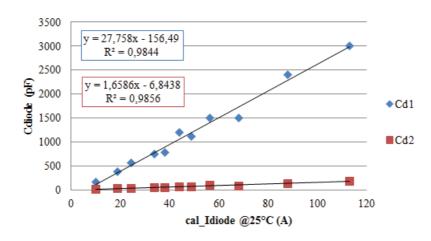

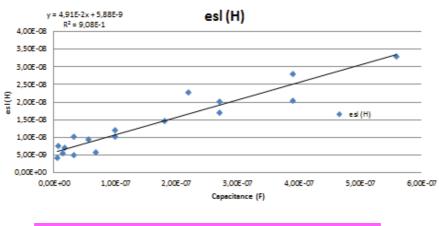

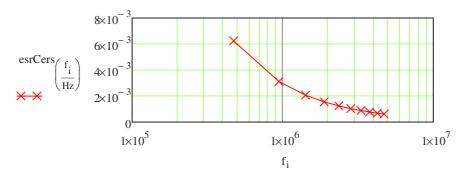

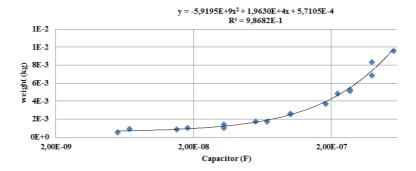

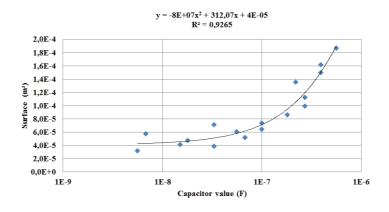

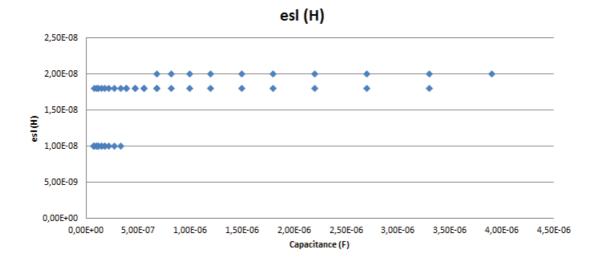

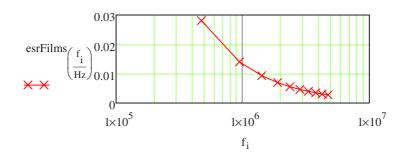

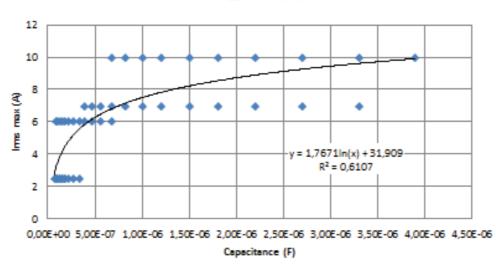

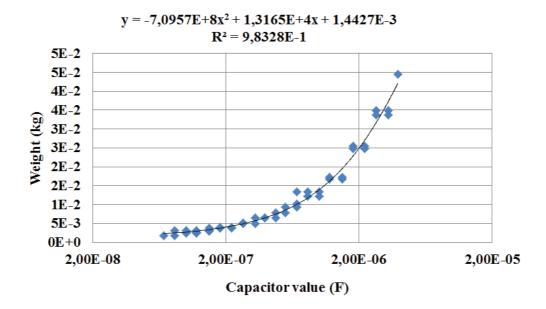

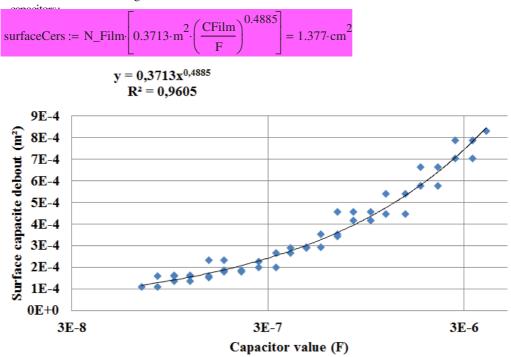

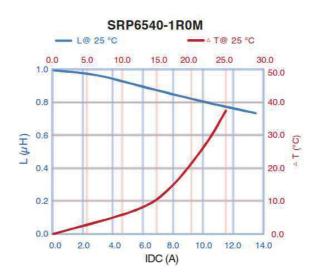

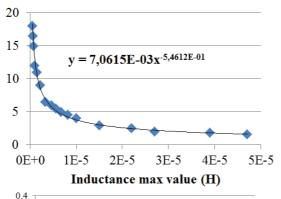

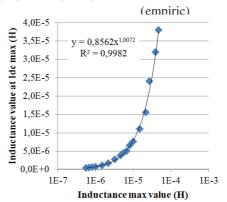

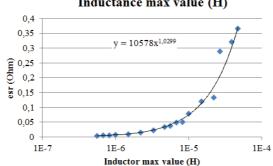

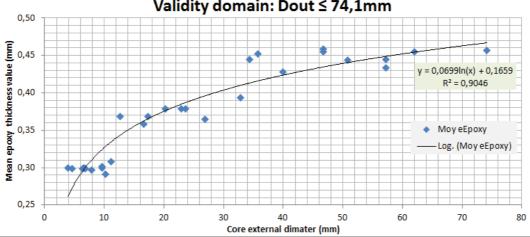

Parmi les composants du convertisseur, les semi-conducteurs font partie des variables de dimensionnement discrétisées pour des raisons industrielles. En effet, pour une technologie et un processus de fabrication donnée, leurs propriétés sont liées à la hauteur et surface de la puce semi-conductrice. Dans le cas étudié le choix du calibre en tension ne se pose pas. Les paramètres du MOSFET et de la diode comme leur résistance à l'état passant ou leurs capacités de jonction ont donc été interpolés en fonction de leur calibre en courant d'après les données du fabricant (Figure 11).

Figure 11: Exemple de paramètres du MOSFET et de la diode en fonction de leur calibre en courant à 25°C, (a) capacités du MOSFET, (b) résistance thermique de la diode

Résumé en Français X

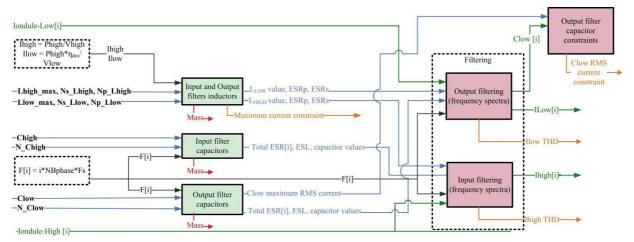

La même méthodologie de modélisation fut appliquée pour les composants de filtrage.

Quant à l'inductance de bras qui est constituée d'un noyau magnétique en poudre de fer, de fil de Litz et de résine, une description géométrique et matérielle avec des équations analytiques permet de déterminer sa valeur. La densité de courant dans le fil de Litz étant limitée à une valeur faible pour des raisons techniques, le modèle de résistance parasite du fil de Litz n'a pas besoin d'être d'une grande précision et résulte d'une simple équation analytique fournie par le fabricant.

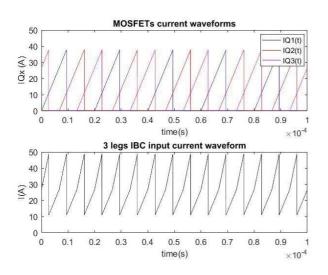

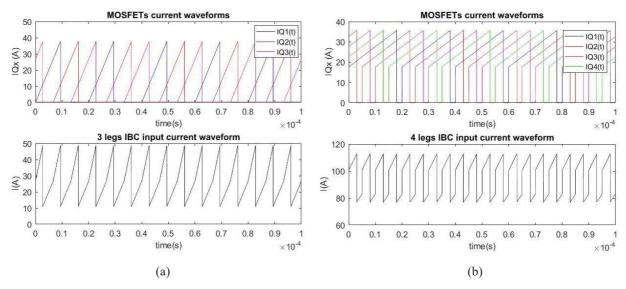

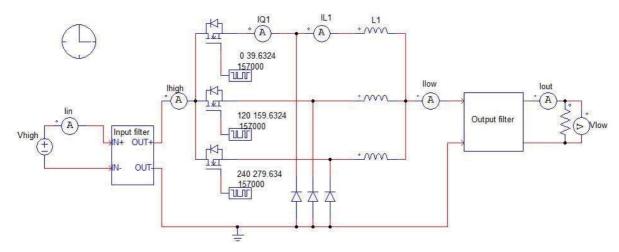

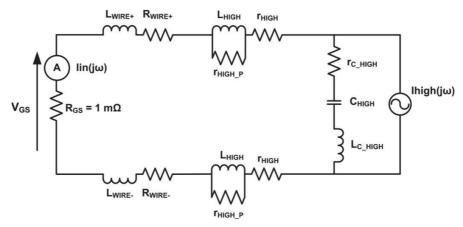

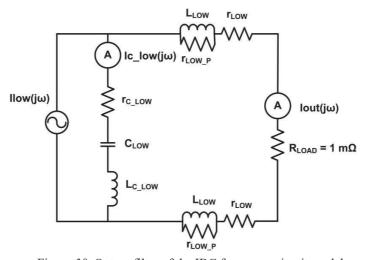

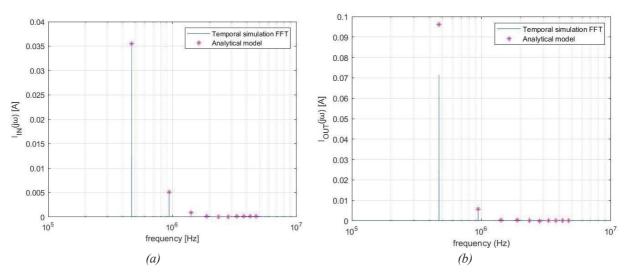

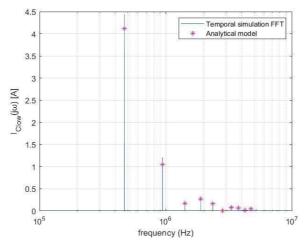

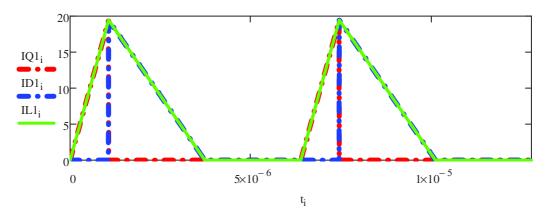

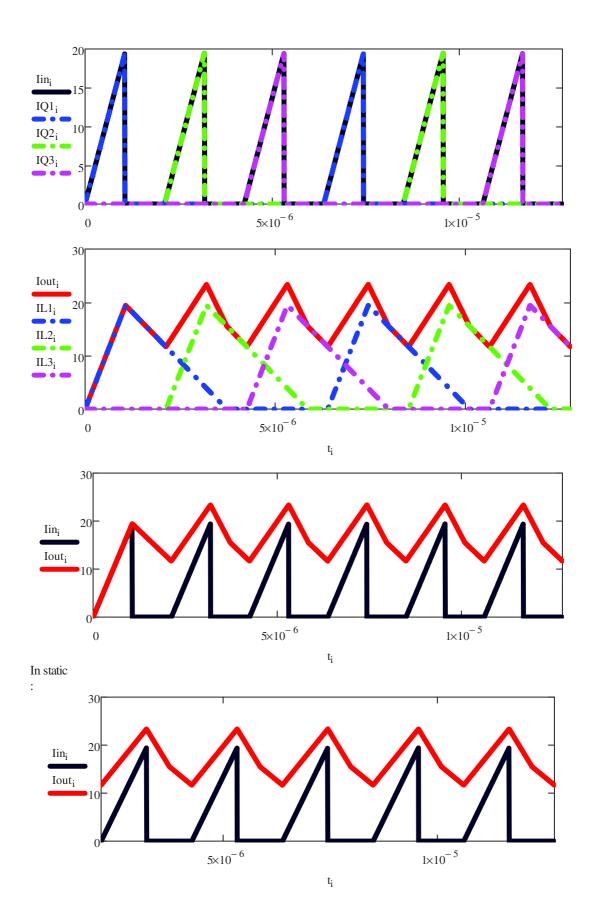

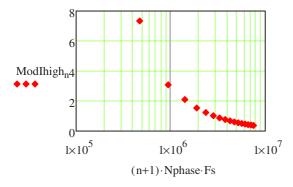

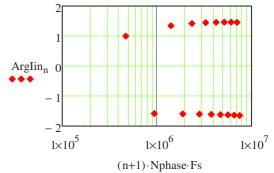

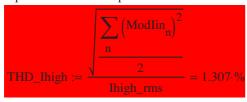

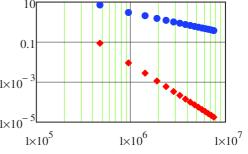

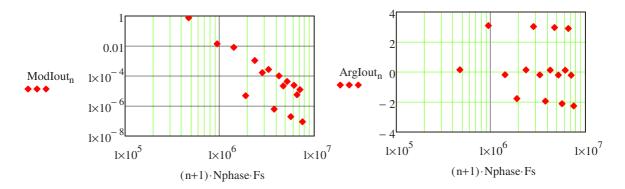

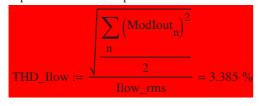

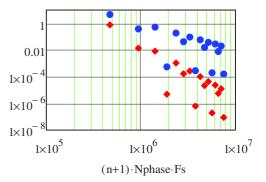

L'évaluation dans le domaine temporel des oscillations et du taux de distorsion harmonique en courant en entrée et sortie du convertisseur n'est pas aisée pour les convertisseurs entrelacés avec des modèles analytiques continus et dérivables (Figure 12). Cependant, transposer ce problème dans le domaine fréquentiel est tâche facile (Figure 13).

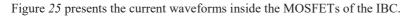

Figure 12: Formes d'ondes temporelles du courant dans les MOSFET et en entrée d'un Buck entrelacé 3-bras en conduction discontinue

Figure 13: Spectre fréquentiel du courant en entrée du convertisseur Buck entrelacé 3-bras

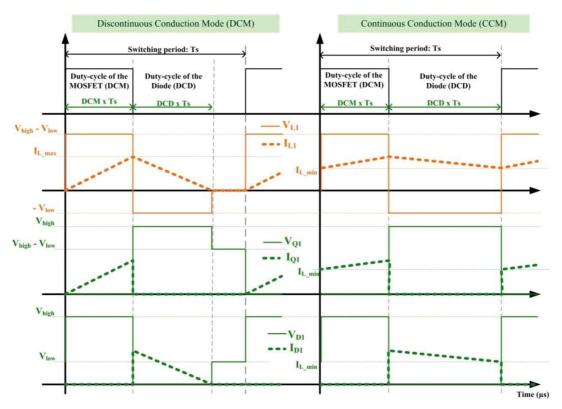

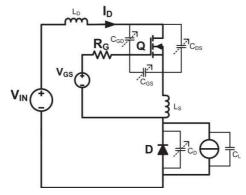

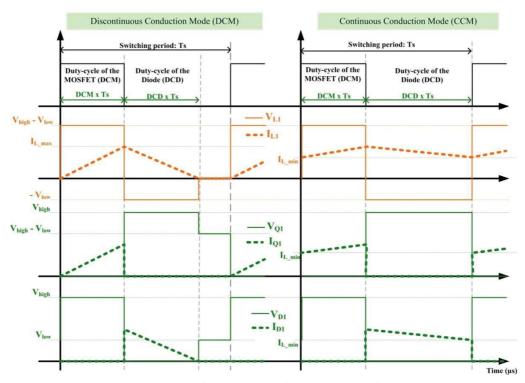

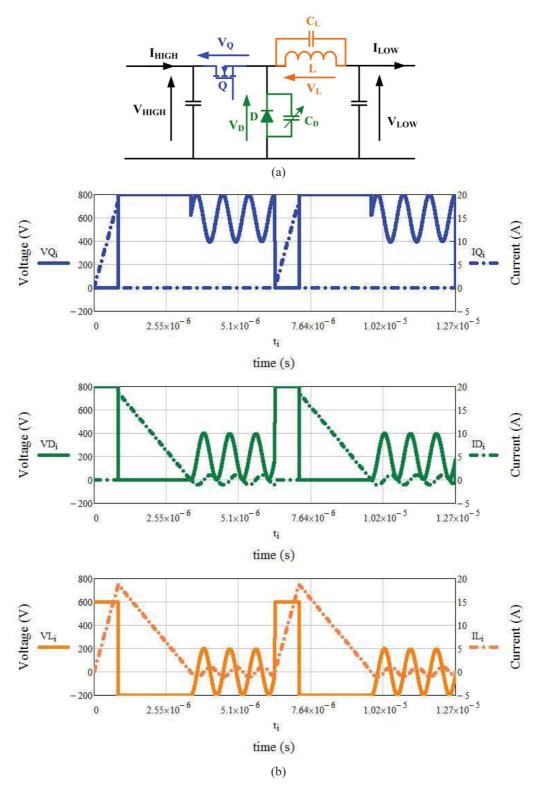

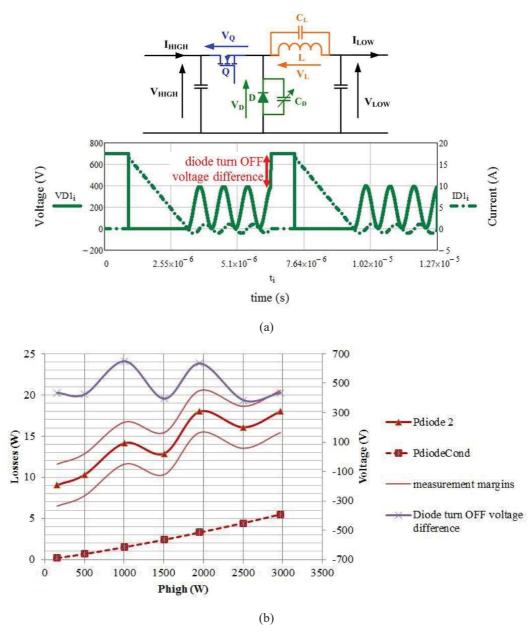

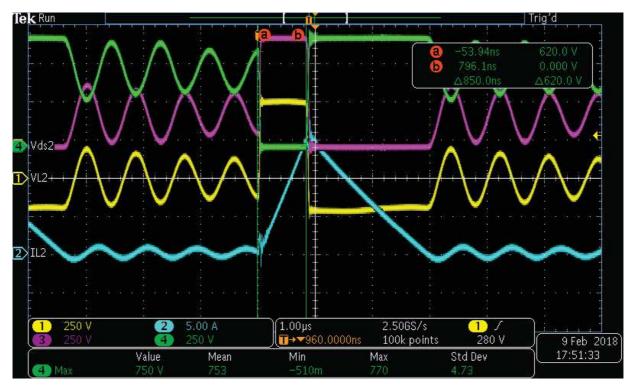

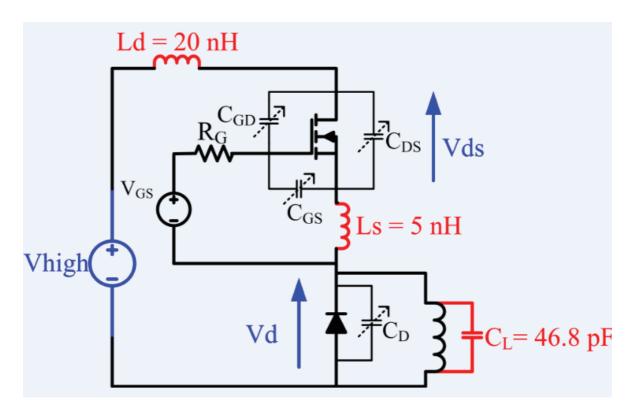

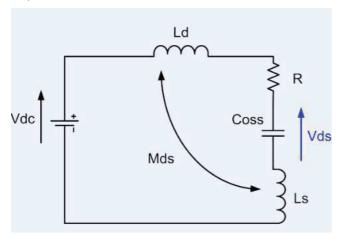

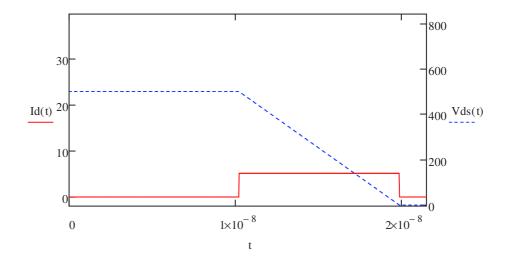

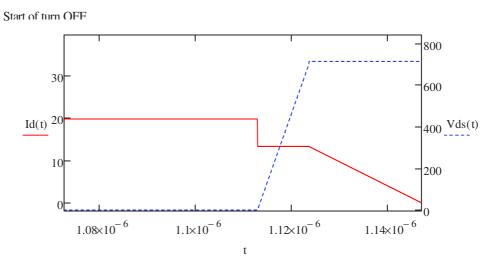

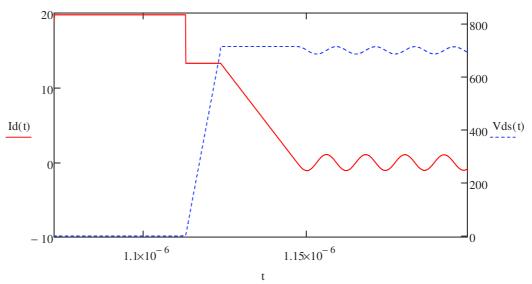

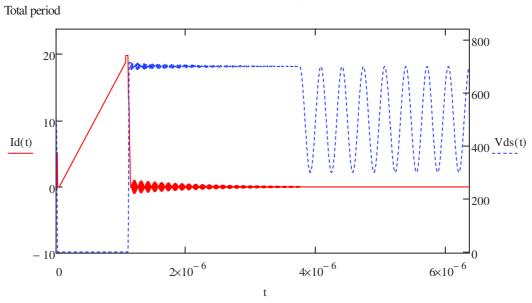

Pour les formes d'ondes des composants dans un bras du hacheur entrelacé, les équations sont très connues si l'on reste dans le cas idéal. Cependant, lorsque les éléments parasites entre en jeu, notamment pour la conduction discontinue (Figure 14), il faut choisir le juste équilibre dans la précision du modèle.

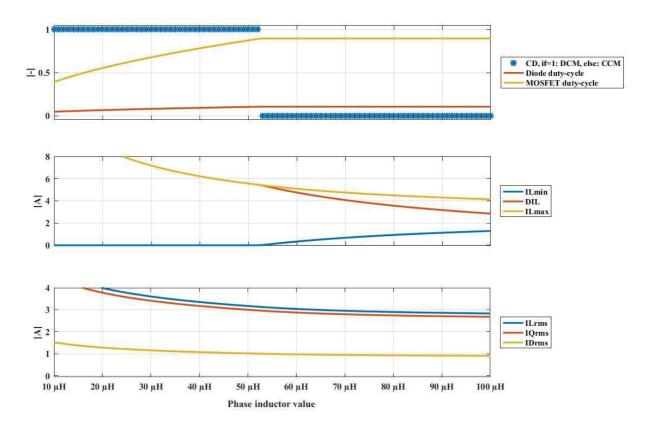

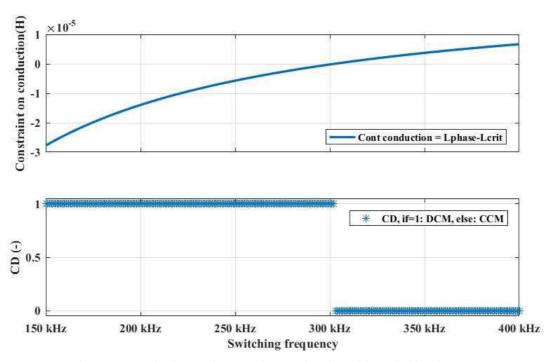

Par ailleurs, le passage entre conduction continue et discontinue durant l'optimisation et la contrainte associée doit se faire de manière intelligente. Évaluer la différence entre la valeur de l'inductance de bras et la valeur critique pour être en limite de conduction continue et discontinue permet une formulation continue de la contrainte.

Résumé en Français XI

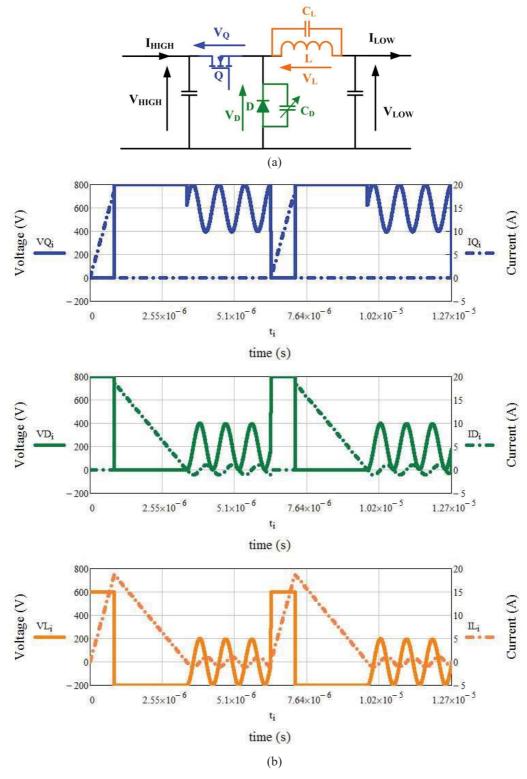

Figure 14: Formes d'ondes du convertisseur Buck en conduction discontinue avec la résonance due aux éléments parasites, (a) schéma de Buck avec les éléments parasites, (b) formes d'onde des composants de puissance

Résumé en Français XII

## Chapitre 6 : Modèles de pertes et thermiques des composants de puissance du convertisseur Buck entrelacé

#### Modèles de pertes et thermiques de la cellule de commutation

Les pertes en conduction des semi-conducteurs sont évaluées à l'aide des classiques équations Eq. 1et Eq. 2.

$$Pcond^{MOSFET} = Rds_{on} * IQrms^2$$

Eq. 1

Avec Rds<sub>on</sub> la résistance à l'état passant du MOSFET et IQrms le courant efficace de ce dernier (obtenu à l'aide des modèles de formes d'ondes).

$$Pcond^{diode} = Vt * IDmoy + Rt * IDrms^2$$

Eq. 2

Avec Vt la tension de seuil, IDmoy le courant moyen dans la diode, Rt sa résistance à l'état passant et IDrms son courant efficace

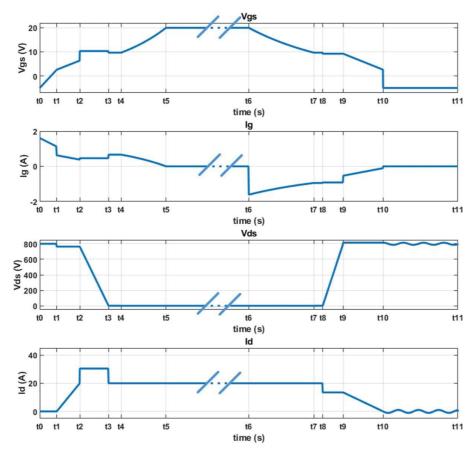

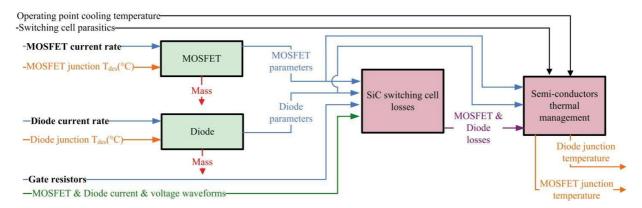

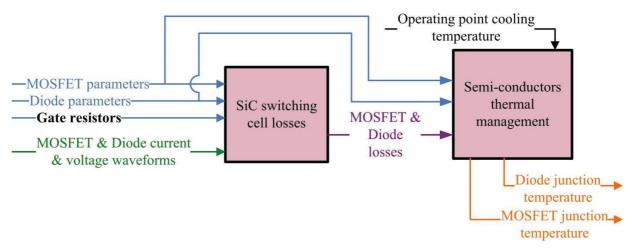

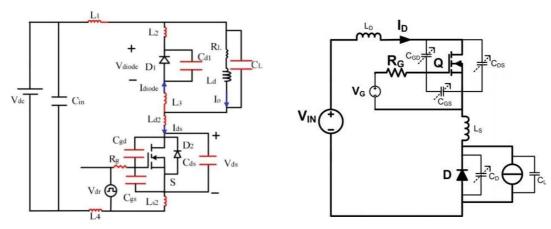

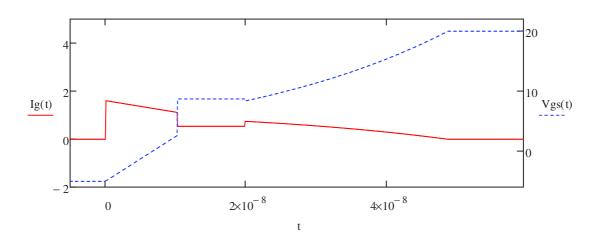

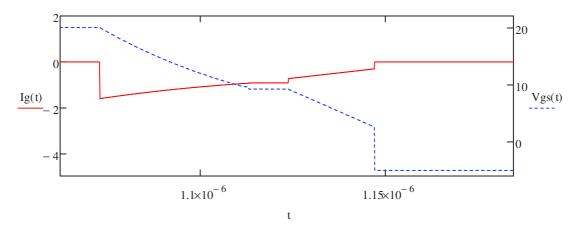

Le modèle de pertes en commutation de la cellule en Carbure de Silicium est basé sur le découpage en plusieurs phases de la commutation (Figure 15). Pour chaque phase, les équations du circuit sont résolues de manière analytique.

Figure 15: Formes d'ondes de la commutation utilisées pour évaluer les pertes

Résumé en Français XIII

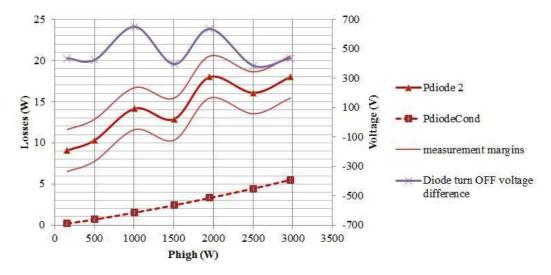

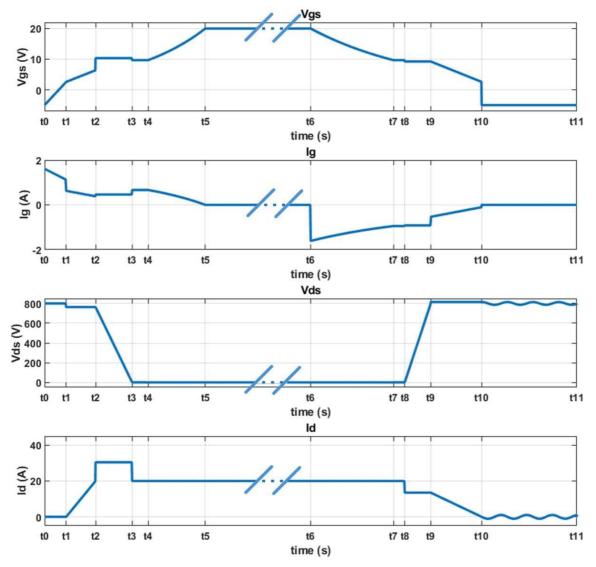

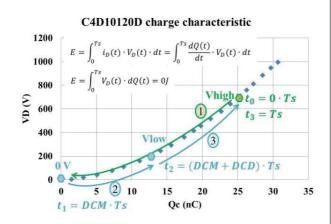

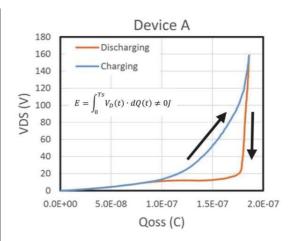

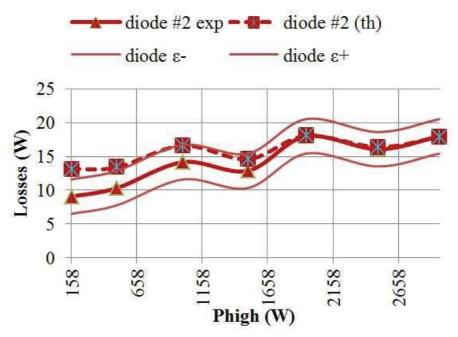

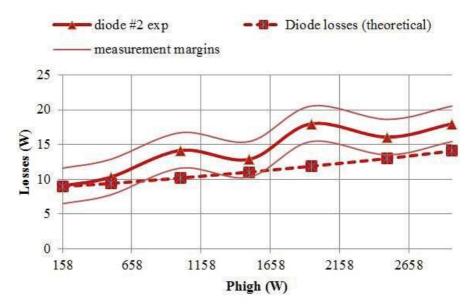

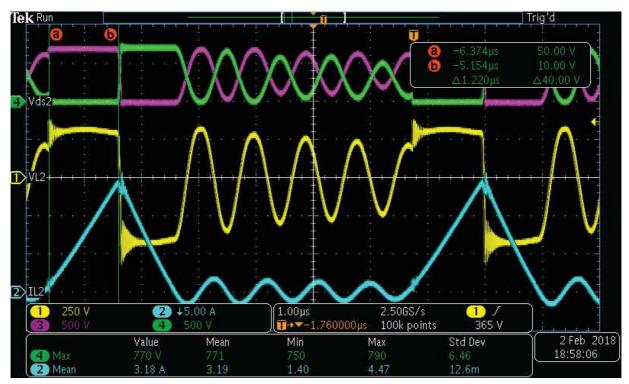

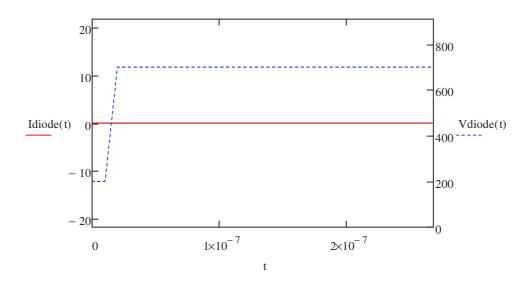

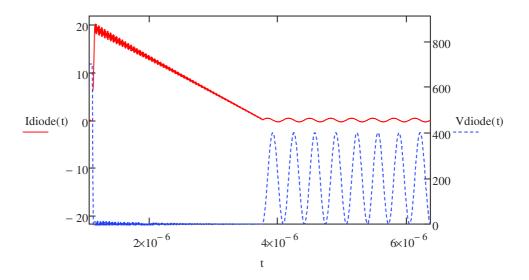

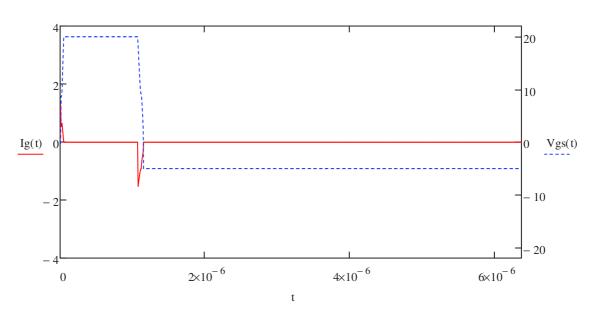

Pour obtenir des modèles continus et dérivables, il fut nécessaire de faire quelques hypothèses comme négliger l'influence de l'inductance de grille du MOSFET pour le calcul des pertes en commutation. Comme expliqué dans le chapitre 2, la formulation du problème d'optimisation et la modélisation associée est un processus itératif. Or, les expérimentations conduites sur un prototype ont révélé un phénomène physique inattendu sur la diode SiC Schottky. En effet, celle-ci chauffait plus qu'elle ne l'aurait due démontrant l'existence de pertes non quantifiées mais reliées à la différence de tension entre la phase oscillatoire et la phase de conduction du MOSFET (Figure 16).

Figure 16: Diode Schottky SiC dans un IBC à 3 bras (a) formes d'onde théoriques à Pin = 2,5 kW, Vin = 700 V et Vout = 200 V, (b) mesure des pertes (Pdiode2) avec ses marges d'erreur, ses pertes théoriques par conduction et la différence de tension de la diode entre la phase oscillatoire et la phase de conduction du MOSFET

Ces pertes supplémentaires proviennent très probablement du comportement hystérétique de la charge de la capacité de jonction de la diode (phénomène découvert en 2018 par l'équipe de recherche de Juan Rivas-Davila à l'université de Standford). Après avoir observé et partiellement compris ce phénomène, une équation analytique a été proposée puis simplifiée (pour le modèle d'optimisation) pour évaluer quantitativement ces pertes.

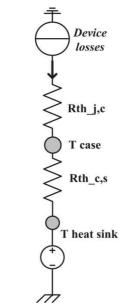

Le modèle thermique des composants semi-conducteurs est un modèle 1D classique.

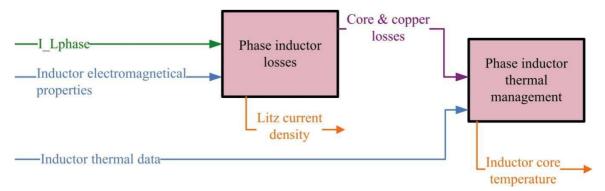

### Modèles de pertes et thermique l'inductance de bras

Les pertes dans le noyau magnétique de l'inductance de bras du Buck sont évaluées à l'aide du modèle IGSE (Improved Generalized Steinmetz Equation). Les pertes dans le bobinage sont la résultante de l'évaluation de la résistance continue et alternative du fil de Litz avec le courant moyen et efficace de l'inductance.

Résumé en Français XIV

La littérature propose de nombreux modèles analytiques de pertes, mais est encore relativement peu fournie quant aux modèles thermiques analytiques d'inductances. Cela est d'autant plus regrettable pour le Buck entrelacé dont le composant le plus lourd est d'inductance de bras et que l'on cherche à définir le meilleur cahier des charges minimisant la masse du système Stratobus.

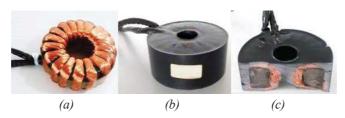

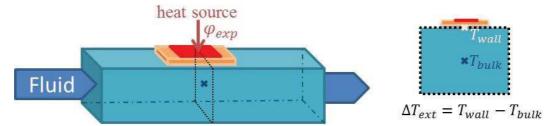

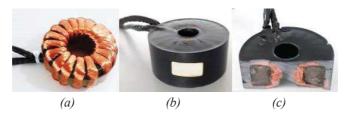

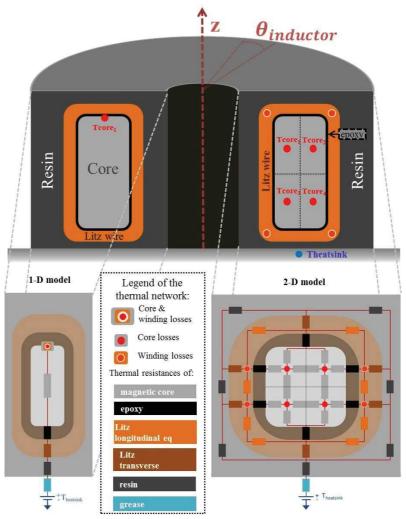

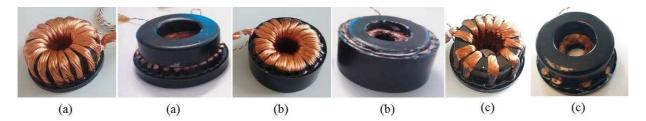

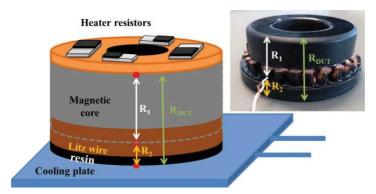

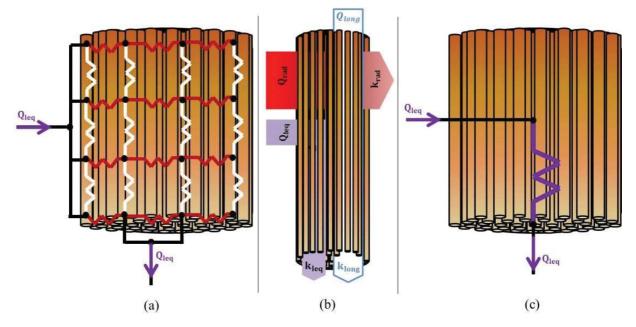

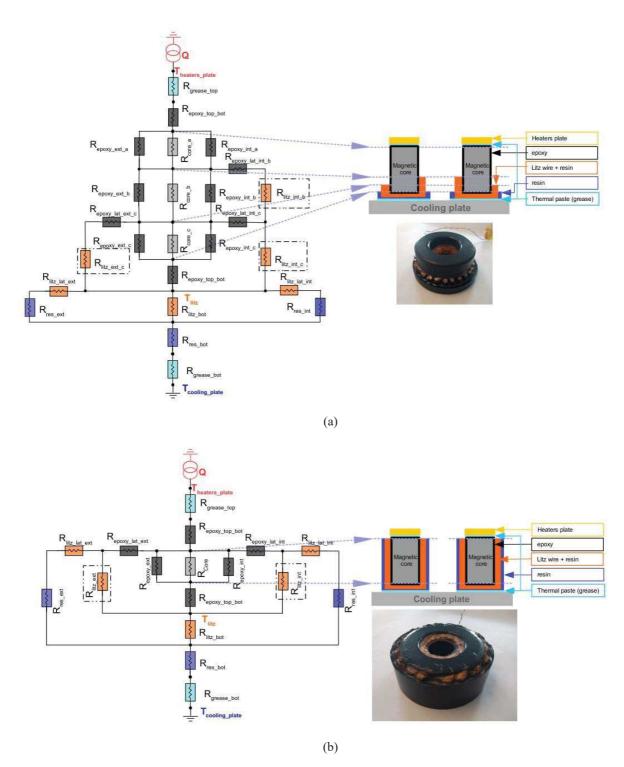

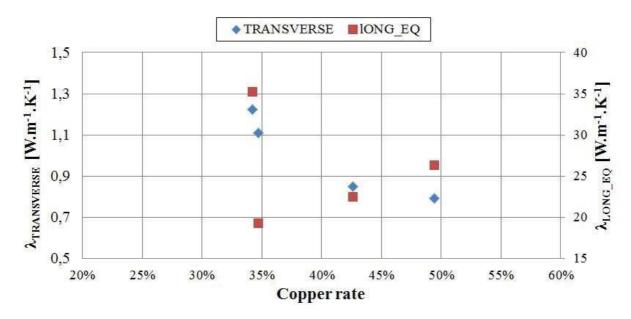

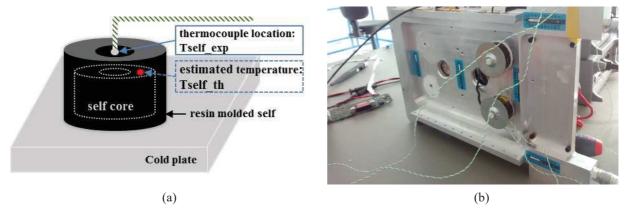

Les conductivités thermiques des matériaux constituants l'inductance étaient notamment inconnues, particulièrement en ce qui concerne le fil de Litz. Celui-ci étant constitué d'isolant électrique, de cuivre et de résine entre chacun de ses brins (Figure 17), il est aussi anisotrope.

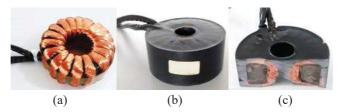

Figure 17: Inductance de puissance du Buck entrelacé (a) sans la résine, (b) moulée dans la résine, et (c) coupe transversale montrant la répartition de la résine

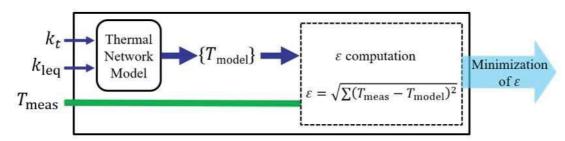

Figure 18: Modèles thermiques 1D ou 2D de l'inductance de bras du hacheur série entrelacé

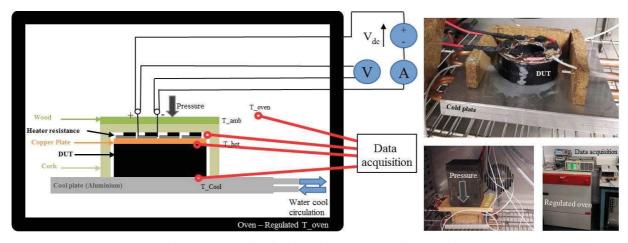

Des mesures expérimentales (Figure 19) nous ont permis d'identifier les conductivités thermiques du noyau magnétique ainsi que celles du fil de Litz. Cette étude expérimentale a aussi démontré l'importance de modéliser le comportement thermique de l'inductance en 2 dimensions malgré une plus grande complexité du modèle d'optimisation que pour le modèle 1-D (Figure 18).

Figure 19: photos du banc de test

Résumé en Français XV

## Chapitre 7 : Comparaisons des modèles de pertes des composants de puissance du convertisseur Buck entrelacé avec des données expérimentales

#### **Démarche**

L'objectif principal des expérimentations est de définir le domaine de validité des modèles d'optimisation du convertisseur Buck entrelacé dans le but global de définir les limites propres de l'optimisation et de vérifier qu'aucun phénomène physique n'a été oublié.

La validité des modèles sera remise en question en deux étapes :

- d'abord en utilisant toutes les données disponibles (circuit de cellule de commutation, données de caractérisation de l'inductance et mesure de la tension du MOSFET à sa fermeture) afin de confirmer la compréhension de la physique du système (c'est-à-dire sans les simplifications et hypothèses nécessaires faites sur certains paramètres pour les modèles d'optimisation),

- deuxièmement, en comparant les mesures expérimentales au modèle d'optimisation avec les paramètres estimés du système.

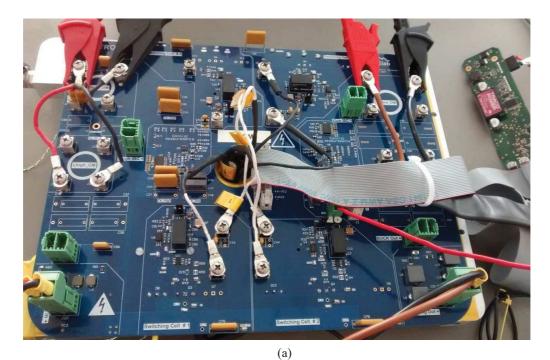

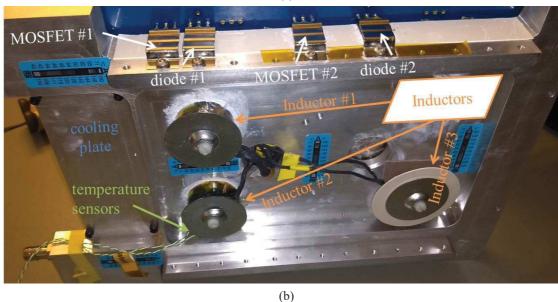

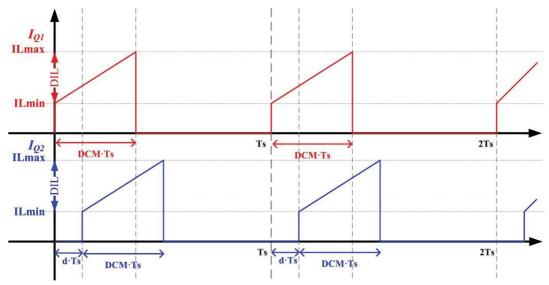

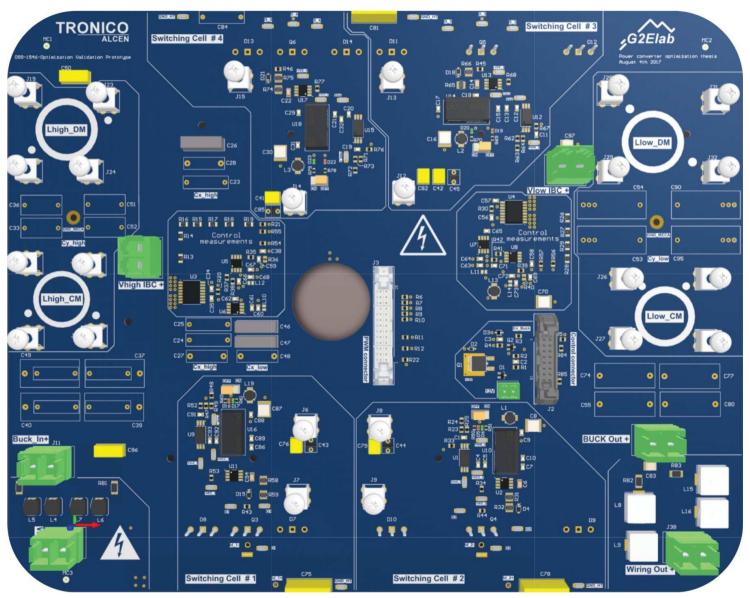

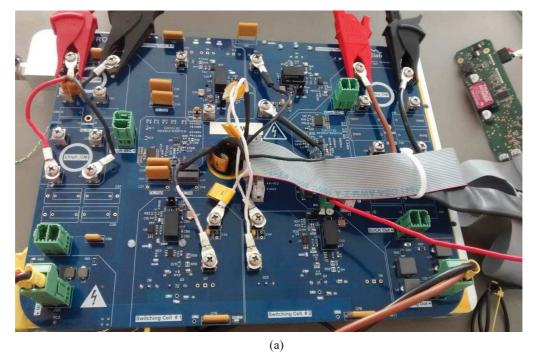

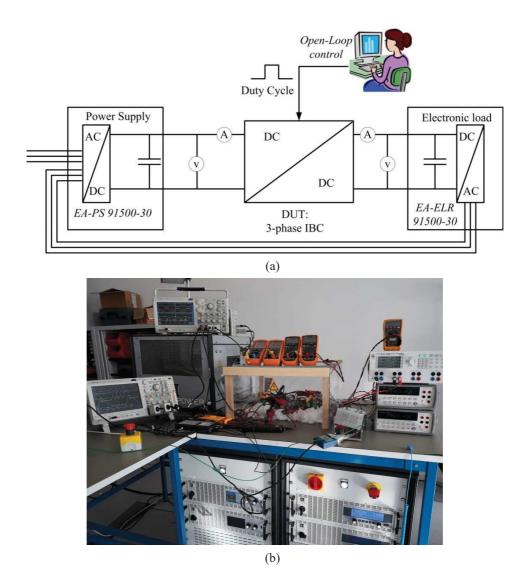

Un convertisseur Buck entrelacé à 3 bras (Table 1) fonctionnant en conduction discontinue a été réalisé (Figure 20) à des fins de mesures expérimentales. Celui-ci est donc instrumenté et tout l'espace nécessaire fut occupé (il n'y a pas eu de recherche d'optimisation de l'intégration volumique).

Table 1: Caractéristiques principales du prototype

| Puissance d'entrée    | [0-3] kW      | Fréquence de découpage | 157 kHz                               |

|-----------------------|---------------|------------------------|---------------------------------------|

| Tension d'entrée      | [480 – 800] V | référence MOSFET       | C2M0040120D                           |

| Tension de sortie     | [200 – 400] V | référence Diode        | C4D10120D                             |

| Refroidissement à eau | [35 – 65] °C  | Résistance de grille   | 13.8 Ω                                |

| Mode de conduction    | DCM           | Inductance de phase    | matériau: KoolMu 26 ; valeur: 28.5 μH |

| Nombre de bras        | 3             | fil de Litz            | 143 brins de 100 μm                   |

Résumé en Français XVI

Figure 20: Photos du prototype, (a) vue du dessus, (b) vue du dessous

Avant de réaliser les tests fonctionnels, les composants du convertisseur ont été caractérisés. Ainsi les paramètres électriques des 3 inductances de phases ont été mesurés à l'analyseur d'impédance ainsi que les inductances parasites du circuit imprimé. Il a été confirmé les que la fréquence des oscillations apparaissant en conduction discontinue ne sont pas prévisibles. De plus, les valeurs des éléments parasites du circuit imprimé sont du même ordre de grandeur

Résumé en Français XVII

que ceux estimés dans le chapitre 5.

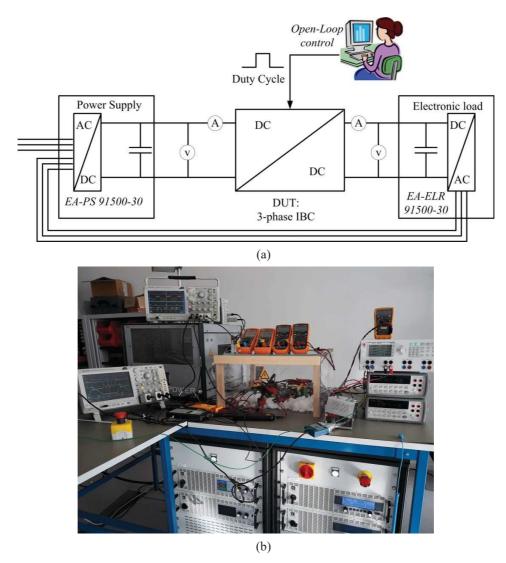

Pour caractériser le convertisseur en fonctionnement, le banc de test expérimental illustré par la Figure 21 a été mis en œuvre.

Figure 21: Banc de test électrique: (a) schéma, (b) photo

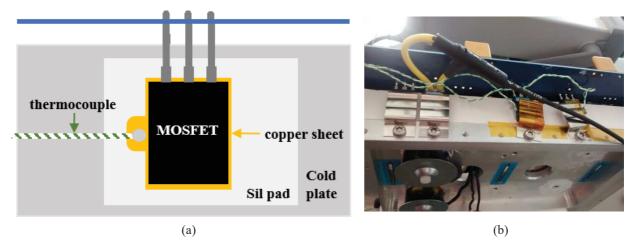

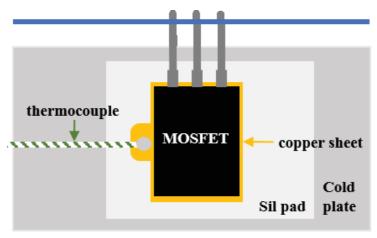

Puisque l'objectif des expérimentations est de valider les modèles de pertes des composants de puissance sans en modifier le comportement, les pertes globales des semi-conducteurs ont été mesurées thermiquement (Figure 22) et les pertes de l'inductance de bras électriquement.

Résumé en Français XVIII

Figure 22: (a) Schéma, (b) photo de la mesure de la température du boîtier du MOSFET côté semelle

#### Validation des modèles analytiques

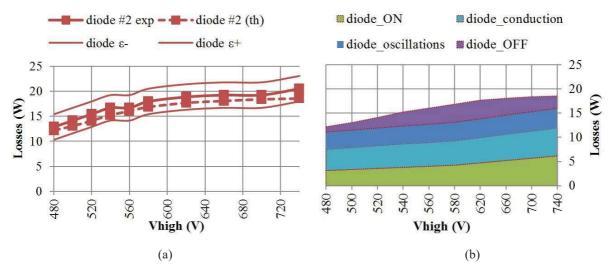

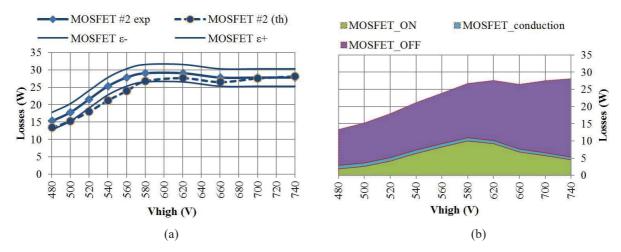

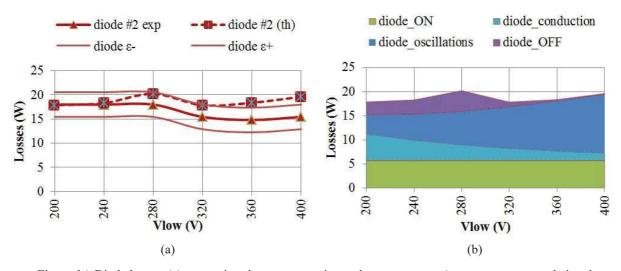

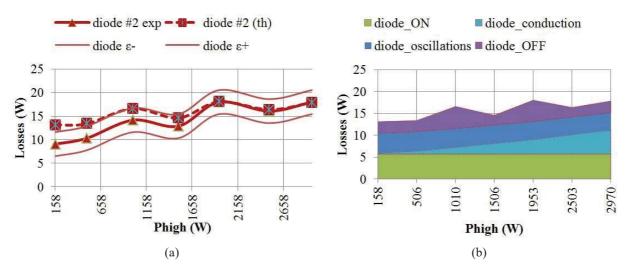

Figure 23 est un exemple de comparaison entre le modèle analytique et les mesures expérimentales où la tension d'entrée du convertisseur fut variée de 480 à 740 V pour une tension de sortie de 200 V et une puissance de 3kW.

Figure 23: pertes dans la diode du bras #2 : (a) comparaison entre les mesures expérimentales (les erreurs de mesure étant représentés par les petites lignes) et le modèle analytique, (b) pertes de la diode #2 dans chaque de phase de la commutation

### Validation des modèles d'optimisations créés à partir d'hypothèses faites sur les modèles analytiques

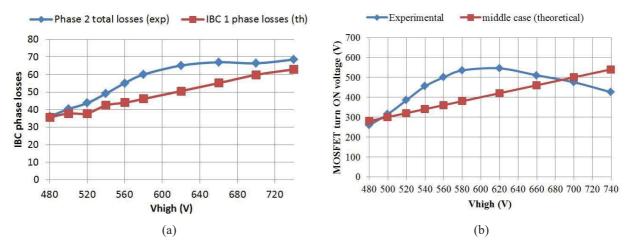

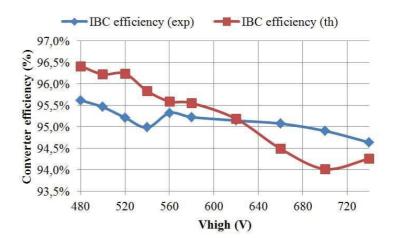

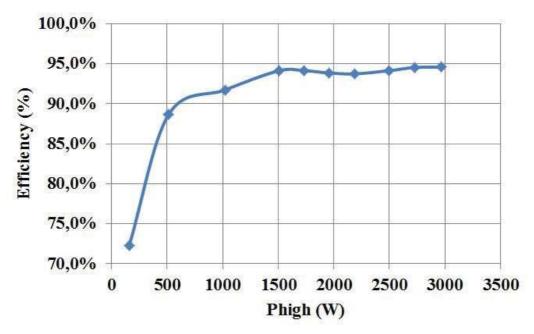

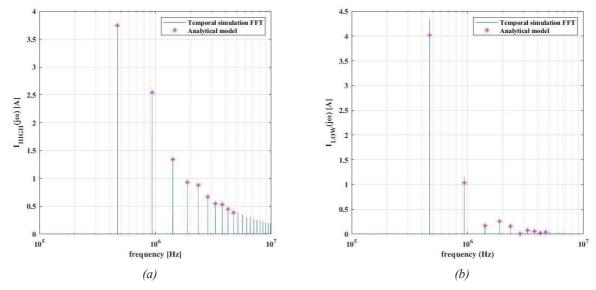

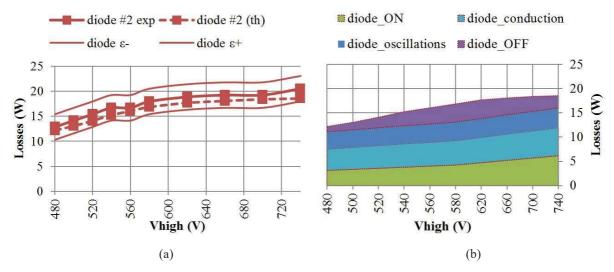

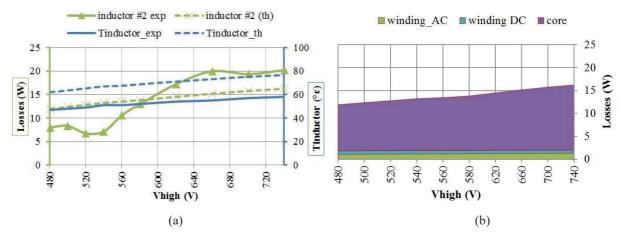

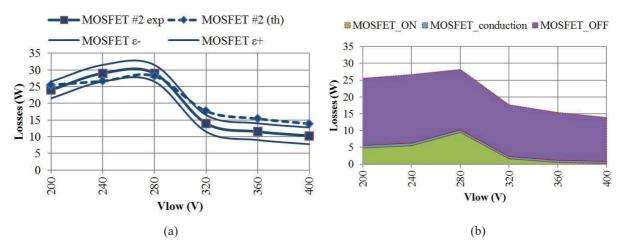

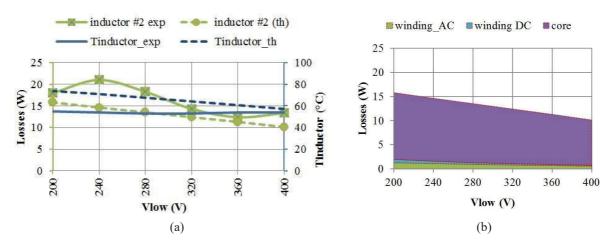

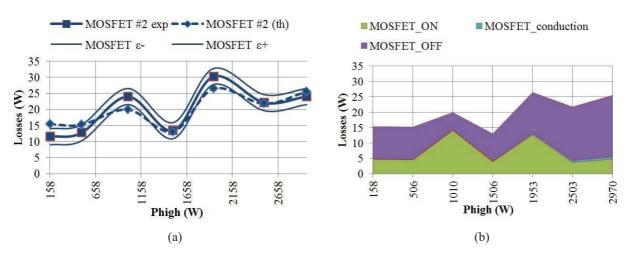

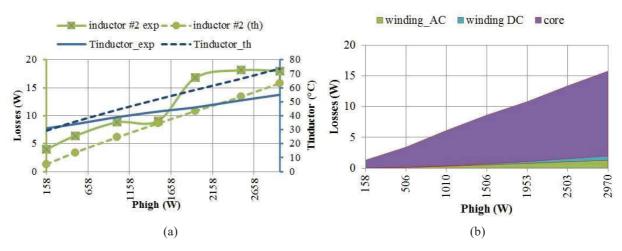

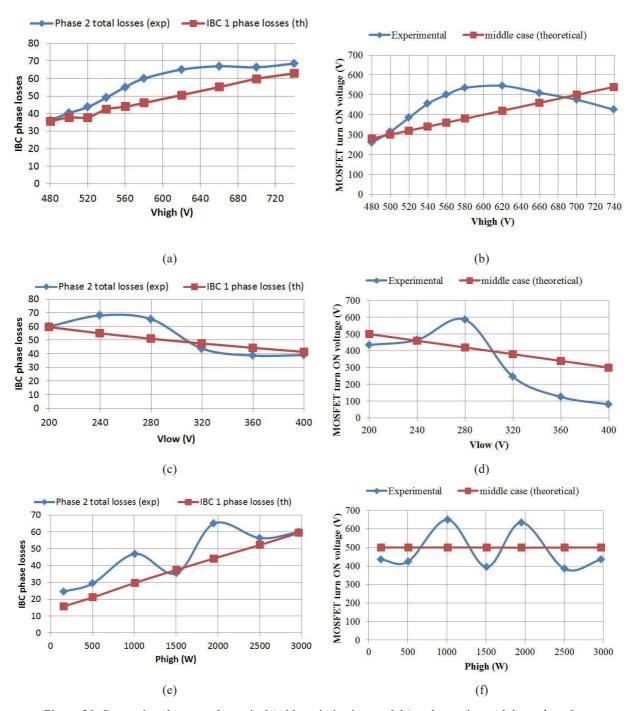

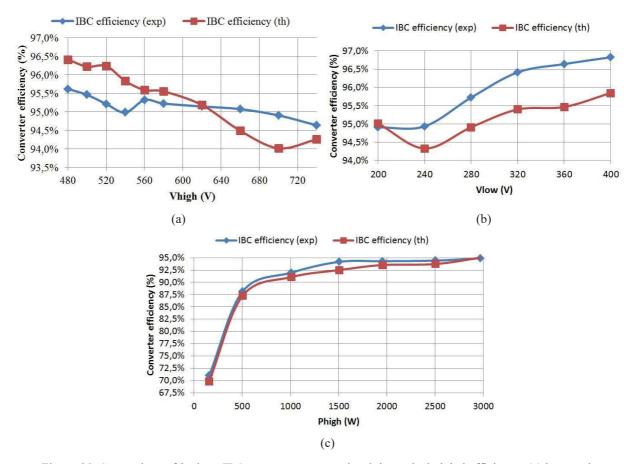

Enfin, les modèles d'optimisation de pertes du convertisseur sont validés en comparant les résultats théoriques et expérimentaux sur les pertes du bras #2 (Figure 24) et sur le rendement global du convertisseur (Figure 25).

Résumé en Français XIX

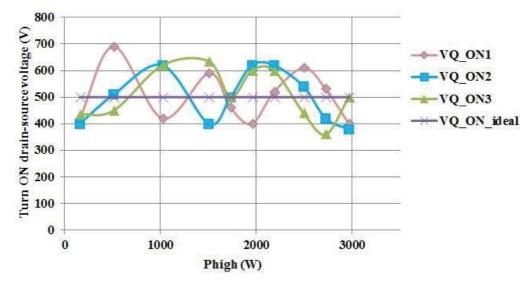

Figure 24: comparaison entre données théoriques (avec modèles d'optimisation) et données expérimentales : (a) pertes de phase (b) tension du MOSFET #2 lors de sa fermeture

L'erreur sur le calcul des pertes globales des convertisseurs est inférieure à celle des modèles d'optimisation dont les pertes sont mesurées sur la phase #2. Ceci est normal puisque les modèles d'optimisation sont basés sur le pari qu'en faisant la moyenne des N phases du convertisseur, l'erreur sur le rendement global sera faible et que le convertisseur ne sera donc pas surdimensionné.

Figure 25: Comparaison du rendement global théorique avec le rendement global mesuré en fonction de la tension d'entrée du convertisseur

Ainsi la formulation du problème d'optimisation et les modèles associés sont jugés suffisamment bons pour être utilisés dans des routines d'optimisation pour la négociation du cahier des charges.

Résumé en Français XX

### Partie C :

# Illustration de la force du pré-dimensionnement dans le monde imaginaire de systèmes d'électronique de puissance

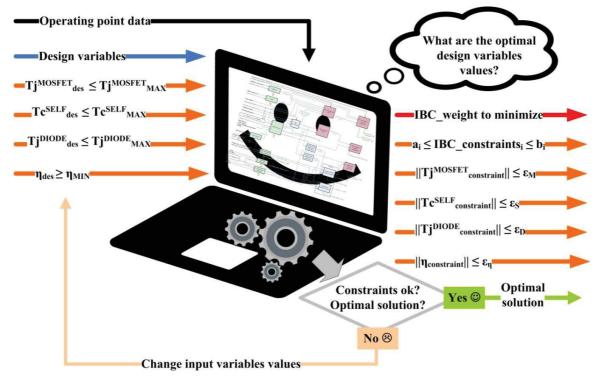

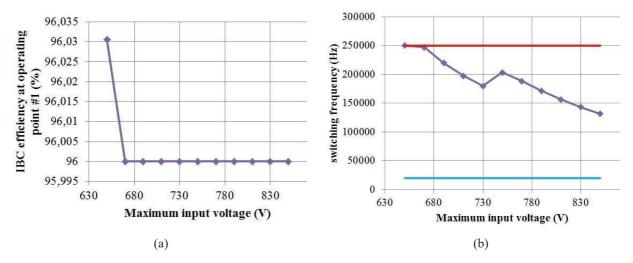

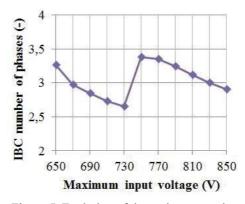

## Chapitre 8 : Pré-dimensionnement par optimisation du hacheur série entrelacé sur un cahier des charges initial

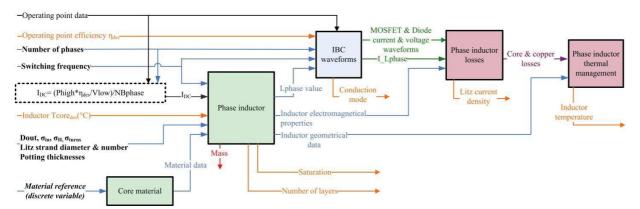

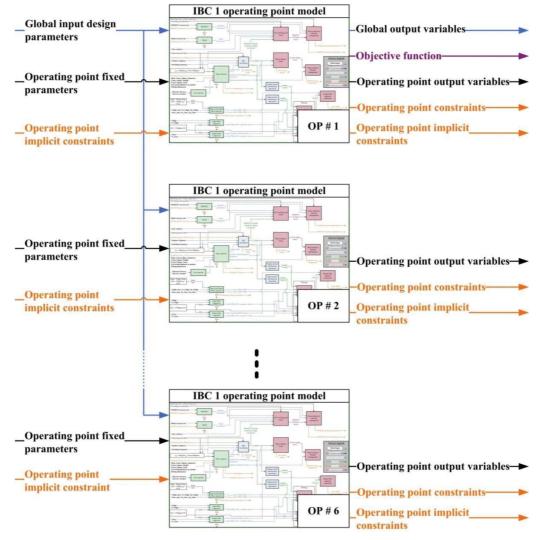

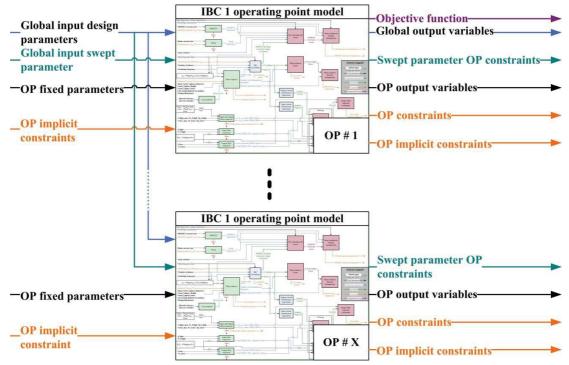

Le convertisseur de l'étude de cas (Stratobus) ayant de larges plages de fonctionnement, il est nécessaire de définir les points de fonctionnement dimensionnant. Pour cela, d'une part l'expertise du designer est nécessaire. Ensuite, il est démontré comment un algorithme basé sur le calcul du gradient peut aisément supporter des points de fonctionnements supplémentaires (i.e. voir la taille du problème d'optimisation augmenter) en cas de doutes du designer. L'analyse des résultats d'optimisation aide les concepteurs à finaliser le choix des points de fonctionnements à optimiser simultanément, autrement dit à formuler le problème correctement.

Table 2: Cahier des charge initial<sup>2</sup>

| Criteria                           | Minimum Value           | Maximum Value          | Conditions/Remarks                                                                |

|------------------------------------|-------------------------|------------------------|-----------------------------------------------------------------------------------|

| Power density (objective)          | 7 kW/kg is<br>mandatory | 10 kW/ kg nice to have | Depends on the following specifications complexity                                |

| Input power                        | 0 W                     | 5 kW                   | For the entire of input/output voltage ranges (at this point of project starting) |

| Input voltage                      | 450 V                   | 800 V                  | For a power range [0; 5] kW                                                       |

| Output voltage                     | 200 V                   | 400 V                  | For a power range [0; 5] kW                                                       |

| Efficiency                         | 96 %                    | NA                     | at 5 kW                                                                           |

| Efficiency at a third of full load | 90 %                    |                        | at 1.7 kW                                                                         |

| Input/Output current THD           | NA                      | 5 %                    | For a power range [1.7; 5] kW                                                     |

| Cooling temperature                | -40 °C                  | 65 °C                  | For a power range [0; 5] kW                                                       |

| Conduction mode                    | NA                      | NA                     | Must be the same for a power range [1.7; 5] kW                                    |

Ainsi, sur le cahier des charges initial (Table 2) <sup>2</sup> du convertisseur, les points de fonctionnement dimensionnant en conduction discontinue sont les #1, #3 et #4 lorsque le critère de l'optimisation est la masse des composants électronique du convertisseur.

Résumé en Français XXI

-

<sup>&</sup>lt;sup>2</sup> Fictif pour des raisons de confidentialités

Table 3: Points de fonctionnement dimensionnant

| Operating point number | Input voltage<br>(Vhigh) [V] | Output voltage (Vlow) [V] | Input power<br>(Phigh) [W] | Cooling plate temperature (Tcooling)   PC | Concerned<br>conduction mode | Possible limiting constraints                                                                                       |

|------------------------|------------------------------|---------------------------|----------------------------|-------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------|

| # 1                    | 800                          | 200                       | 5000                       | 65                                        | Both                         | IBC efficiency, power components temperature, current density in the phase inductor and output filtering components |

| # 2                    | 800                          | 200                       | 5000                       | -40                                       | Both                         | IBC efficiency due to diode on state resistance?                                                                    |

| # 3                    | 800                          | 200                       | 1700                       | 65                                        | Both                         | input and output current THD, efficiency                                                                            |

| # 4                    | 450                          | 400                       | 5000                       | 65                                        | DCM                          | conduction mode, maximum input DC current in filtering inductors                                                    |

| #5                     | 450                          | 200                       | 1700                       | 65                                        | CCM                          | conduction mode, maximum input DC current in filtering inductors                                                    |

| # 6                    | 800                          | 400                       | 5000                       | 65                                        | CCM                          | phase inductor temperature                                                                                          |

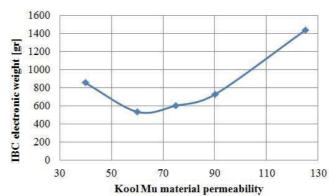

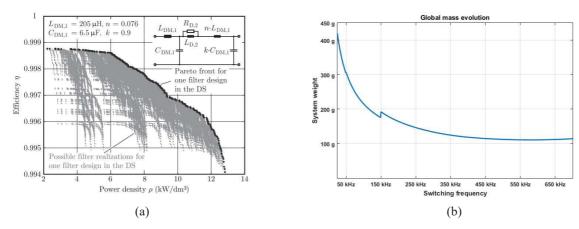

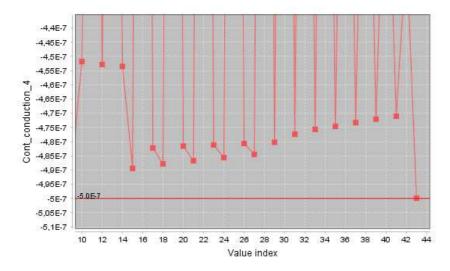

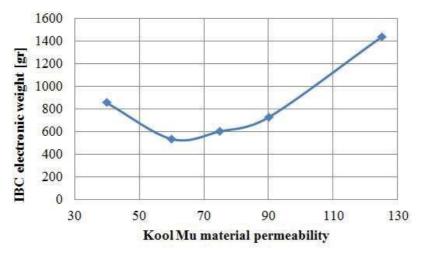

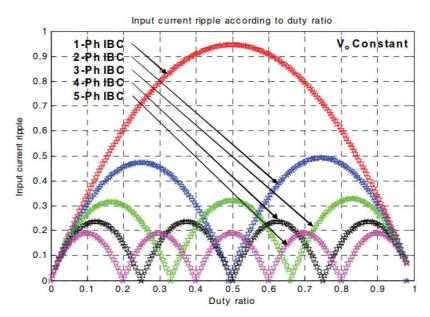

Par la suite, il est démontré que la rapidité des optimisations dans le monde imaginaire (à peine quelques secondes pour un convertisseur optimisé sur 3 ou 4 points de fonctionnement simultanément) permet d'explorer différentes solutions technologiques de manière séquentielle. Cette exploration s'est fait dans le cas présent sur le matériau magnétique de l'inductance de bras du hacheur série entrelacé ainsi que sur le mode de conduction du convertisseur.

Par exemple, la Figure 26 démontre que sur ce cahier des charges, la perméabilité 60μ du matériau KoolMu 60 donne un résultat optimal en conduction continue.

Finalement, sur ce cahier des charges fictif, la meilleure densité de puissance massique fut obtenue avec un mode de conduction discontinue et du MPP  $60\mu$  comme matériau magnétique d'inductance de bras.

Figure 26: Poids du convertisseur en conduction continue pour différentes perméabilités du noyau Kool Mu (résultats d'optimisation)

Résumé en Français XXII

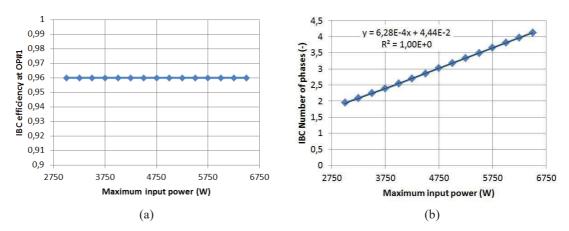

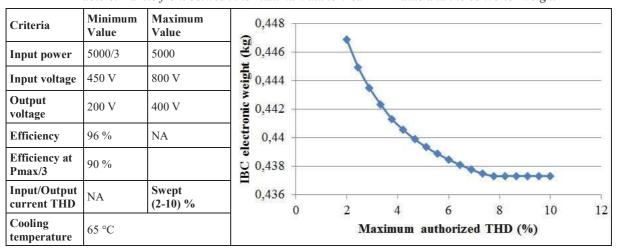

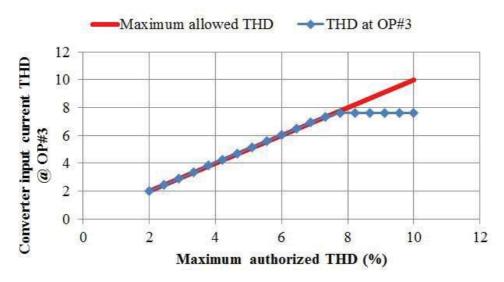

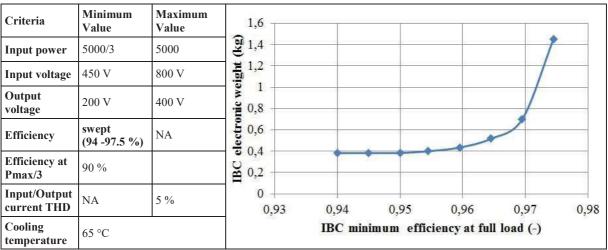

### Chapitre 9 : Négociation des exigences

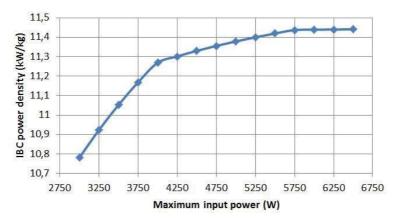

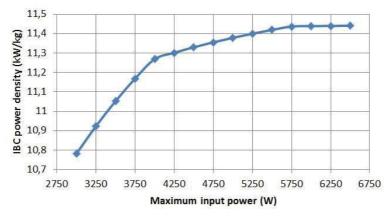

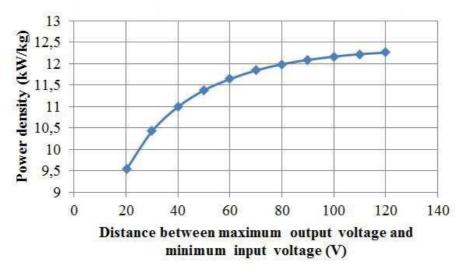

La négociation du cahier des charges peut désormais se faire à partir de la solution optimale déterminée à partir du cahier des charges initial. Dans un premier temps, des optimisations paramétrées imaginaires permettent de négocier les plages de fonctionnement du convertisseur. Il est en effet évident qu'un convertisseur 5 kW sera plus lourd qu'un convertisseur de 3 kW. Mais quand est-il de la densité de puissance ? La Figure 27 obtenue en moins de 5 minutes permet au concepteur de répondre à cette question.

Figure 27: Evolution de la densité de puissance du convertisseur en fonction de sa puissance nominale

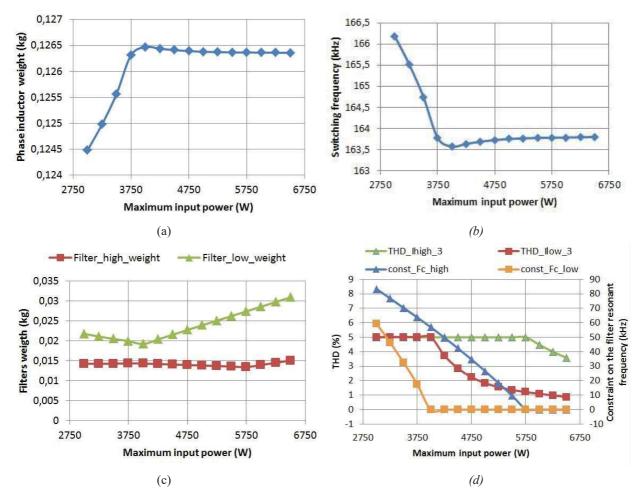

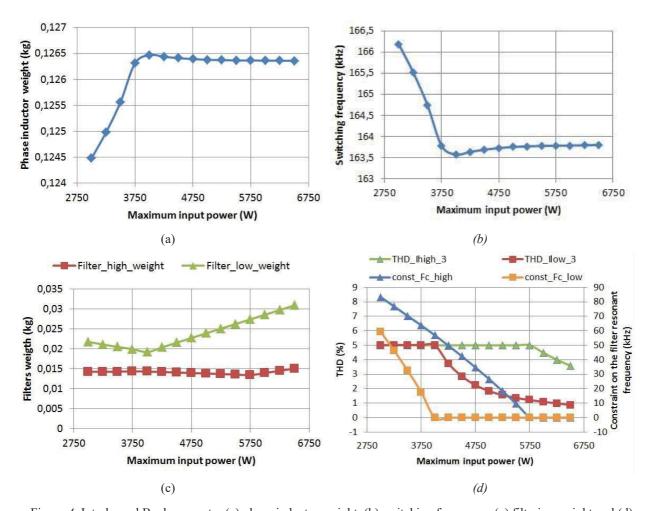

Cela est l'objectif premier des optimisations paramétrées : renseigner quantitativement les concepteurs sur un l'impact d'un changement de cahier des charges. De plus, l'utilisation d'un algorithme d'optimisation basé sur le calcul du gradient et utilisé dans le monde imaginaire permet d'analyser très facilement les résultats : ainsi le concepteur connaît quelle est la contrainte limitante déterminant la forme de la courbe paramétrée. Sur la Figure 27, les 3 morceaux de courbes différentes sont liées aux contraintes sur le filtrage du convertisseur qui impactent la fréquence de découpage et la masse de l'inductance de bras (Figure 28).

Résumé en Français XXIII

Figure 28: (a) Masse de l'inductance de bras, (b) fréquence de découpage, (c) masse des filtres et (d) contraintes sur les filtres via le THD du point de fonctionnement #3 (doit être < 5 %) et la fréquence de coupure du filtre (doit être > 0 kHz), en fonction de la puissance nominale du convertisseur

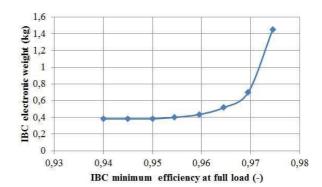

Enfin, pour les même raisons que précédemment, les Fronts de Pareto imaginaires (comme sur la Figure 29) permettent de comprendre le système et de trouver le meilleur compromis entre équipementiers de l'aéronef.

Une fois déterminé ce meilleur compromis et formalisé dans un nouveau cahier de charges, une dernière optimisation du convertisseur est réalisé dans le monde imaginaire.

Figure 29: Front de Pareto entre le rendement et la masse du convertisseur

Résumé en Français XXIV

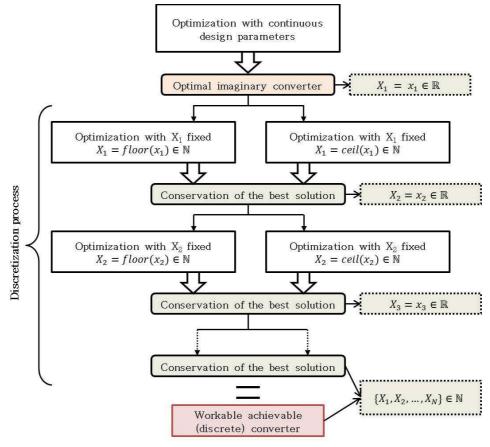

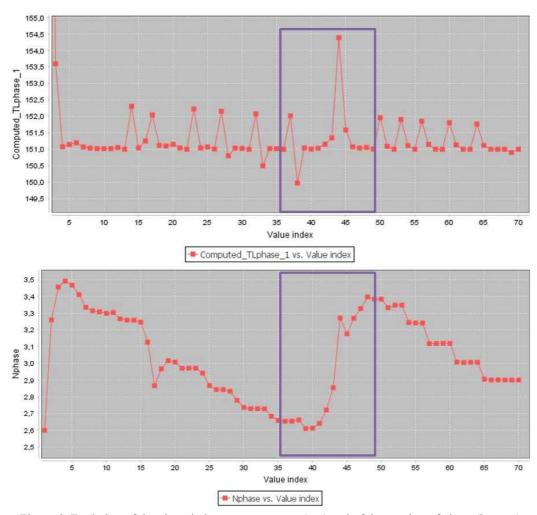

### Chapitre 10 : Procédure de discrétisation pour revenir dans le monde réel

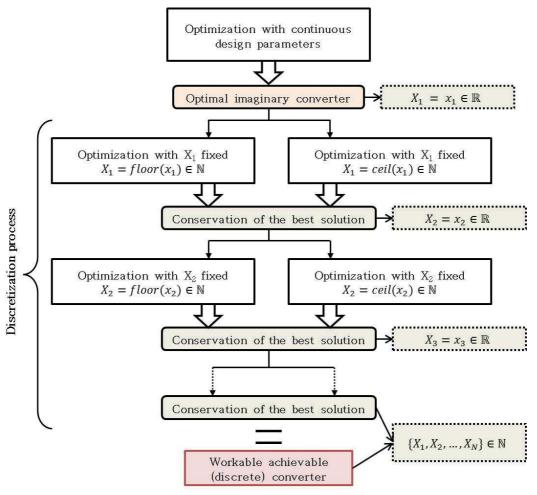

A partir de la solution imaginaire optimale sur le cahier des charges négocié, il est essentiel de revenir dans le monde réel en discrétisant la solution imaginaire pour deux raisons majeures :

- Déterminer de combien la solution sera dégradée lors du processus de discrétisation

- Rapidement prototyper cette dernière, valider qu'aucun phénomène n'a été oublié et définir les prochains axes de travail lors de la phase de design

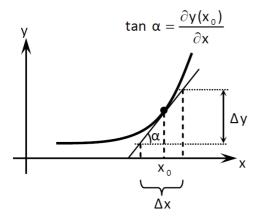

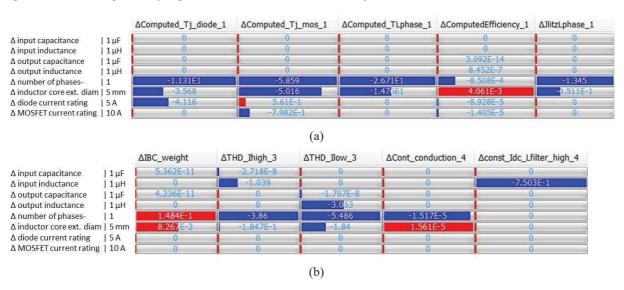

La procédure de discrétisation proposée dans la thèse permet de profiter des efforts mis dans la formulation du problème d'optimisation. En effet, celle-ci se base sur de l'analyse de sensibilité locale rendue possible grâce aux modèles d'optimisation continus et dérivables, ainsi que sur l'expertise des concepteurs, d'où une procédure dite heuristique.

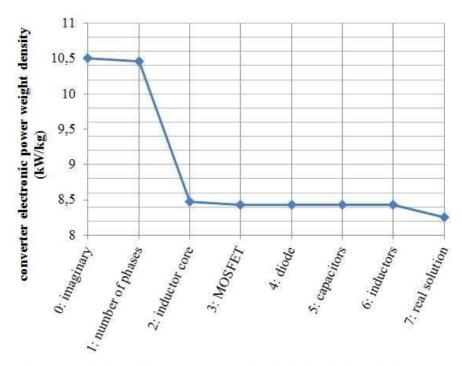

Cette procédure est décrite par la Figure 30.

Figure 30: Processus de discrétisation heuristique avec  $X_n$  la  $n^{\hat{e}me}$  variable discrète, et la function objectif plus sensible à la variable  $X_1$  que  $X_2$ , etc.

Résumé en Français XXV

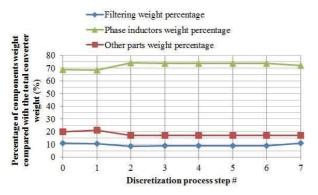

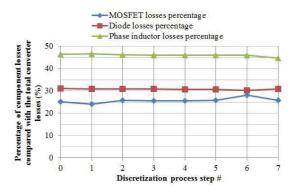

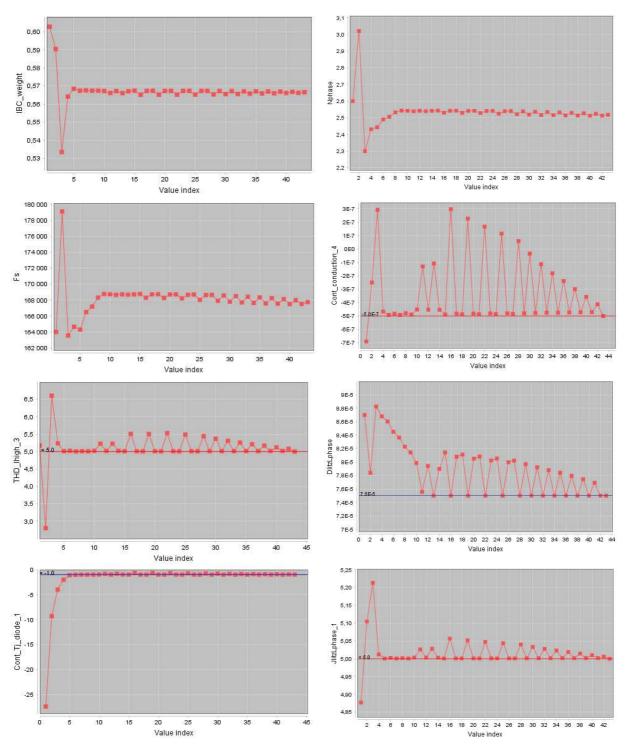

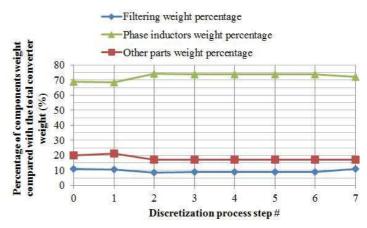

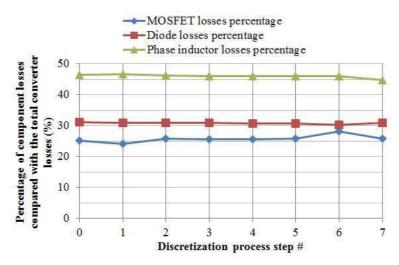

Cette procédure est une recherche de solution discrète locale et est par conséquent proche de la solution imaginaire. Cette particularité est visible sur les Figure 31 et Figure 32 puisque les ratios de masse et pertes sont conservatifs durant le processus de discrétisation.

Figure 31: Evolution du ratio de la masse des composants durant le processus de discrétisation

Figure 32: Evolution du ratio des pertes des composants durant le processus de discrétisation

Résumé en Français XXVI

### Conclusion et perspectives

Le nombre de systèmes électroniques de puissance va continuer à augmenter dans les décennies à venir car l'électricité est l'énergie la plus appropriée pour relever le défi de la réduction des émissions de CO2. Au cours des dernières décennies, plusieurs méthodes et outils de conception ont été développés pour aider les concepteurs d'électronique de puissance pendant la phase de conception d'un produit. Cependant, il n'existait jusqu'à présent aucun outil ou méthode pour une phase de conception préliminaire d'un système électronique de puissance. Pour rappel, une phase de conception préliminaire doit déboucher sur des exigences fixes (et réalisables) du système à concevoir et sur un plan de développement consolidé du produit. Les exigences doivent donc être négociées entre les différents partenaires avec des données quantitatives. Il est également préférable de disposer d'un large champ de recherche pour proposer des solutions innovantes.

Cette thèse s'appuie sur cette observation et propose une nouvelle approche de conception préliminaire pour les systèmes électroniques de puissance capable d'explorer rapidement un large éventail de solutions tout en offrant une facilitation d'analyse. Ces particularités de l'approche proposée sont garanties par l'utilisation d'un algorithme d'optimisation de 1<sup>er</sup> ordre (basé sur le calcul du gradient) appliqué au monde imaginaire (continu) des systèmes électroniques de puissance.

Cette nouvelle approche suit la philosophie de la célèbre phrase d'Albert Einstein : "Si je n'avais qu'une heure pour résoudre un problème, je prendrais 55 minutes à définir le problème et seulement 5 minutes à trouver la solution". Sur l'organigramme de l'approche (illustré par la *Figure 5*), les premières étapes consistent à formuler le problème d'optimisation et à créer le modèle associé. Ces étapes sont détaillées dans les chapitres 5 à 7 de cette thèse et ont pris une douzaine de mois de travail. A l'inverse, les optimisations appliquées sur un ensemble d'exigences fixées afin d'identifier les propriétés critiques et le matériau de noyau magnétique le plus approprié d'un hacheur série entrelacées n'ont nécessité qu'une journée de travail (chapitre 8). Le même temps a été nécessaire pour tracer les optimisations paramétrées imaginaires et les fronts de Pareto du chapitre 9. Une autre journée de travail a été nécessaire pour revenir dans le monde réel avec une solution discrétisée basée sur la solution optimale imaginaire (chapitre 10).

Résumé en Français XXVII

#### Perspectives de la thèse

Les perspectives de cette thèse sont nombreuses, tant dans le domaine de l'électronique de puissance que dans le domaine du pré-dimensionnement par optimisation de systèmes d'électronique de puissance.

Tout d'abord, les optimisations appliquées à un convertisseur entrelacé utilisant des semi-conducteurs grand-gap (SiC) démontrent que le prochain axe de travail pour l'amélioration de la densité de puissance des systèmes d'électronique de puissance est la recherche de matériaux magnétiques performants à des fréquences de découpage élevées. Cependant, le travail sur les semi-conducteurs, bien que très avancé n'est pas encore terminé : il serait intéressant de comprendre en détails le phénomène hystérétique de la capacité de jonction de la diode Schottky puisque gênante pour les topologies à résonnance sensées minimiser les pertes en commutations des semi-conducteurs.

Concernant le pré-dimensionnement par optimisation pour des systèmes d'électronique de puissance, il serait intéressant de posséder un outil de capitalisation ergonomique utilisé par une large communauté de designers pour diminuer le temps passé à créer des modèles d'optimisation continus et dérivables. Cet outil devra cependant intégrer le contexte de chaque modèle créé afin que les concepteurs puissent le reprendre et modifier en toute confiance.

Une étude sur l'impact du niveau de précision des modèles sur les résultats d'optimisation, optimisation paramétrée et Front de Pareto pourrait aussi définir si l'une des pistes pour la diminution du temps de formulation du problème réside dans cette voie. L'étude de la prise en compte ou non des tolérances des composants électronique pourrait y être adjointe.

Enfin, il est nécessaire de définir à l'avenir la meilleure articulation entre les différentes méthodologies de prédesign et de design lors de la conception d'un produit suivant les acteurs (systémiers ou équipementiers) concernés.

Résumé en Français XXVIII

Résumé en Français XXIX

# **Outline**

| Introdu                                                                                                                      | Introduction                                                                |    |  |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----|--|

| Part A: Issues and a Proposed Solution to Address the Challenge of the Preliminary Design Phase of Power Electronics Systems |                                                                             |    |  |

| Chapter                                                                                                                      | l: Present Design Processes in Power Electronics                            | 5  |  |

| I.                                                                                                                           | WHY DESIGNING STATIC CONVERTERS?                                            | 6  |  |

| II.                                                                                                                          | GENERAL DESIGN PROCESS DESCRIPTION                                          | 7  |  |

| III.                                                                                                                         | TYPICAL POWER ELECTRONICS DESIGN PROCESS                                    | 9  |  |

| A. Deta                                                                                                                      | ail of the various design phases involved in power electronics development  |    |  |

| B. An e                                                                                                                      | example of specific difficulties in power electronics preliminary design    | 12 |  |

| C. Met                                                                                                                       | hods and tools used in power electronics design                             | 12 |  |

| IV.                                                                                                                          | CONCLUSION                                                                  | 13 |  |

| V.                                                                                                                           | REFERENCES                                                                  | 14 |  |

| Chapter .                                                                                                                    | 2: Present Design Processes in Power Electronics                            | 18 |  |

| I.                                                                                                                           | REASONS FOR USING OPTIMIZATION DURING A PRELIMINARY DESIGN                  | 20 |  |

| II.                                                                                                                          | INTRODUCTION TO OPTIMIZATION CONCEPTS AND VOCABULARY                        | 22 |  |

| A. Opi                                                                                                                       | imization problem definition                                                | 22 |  |

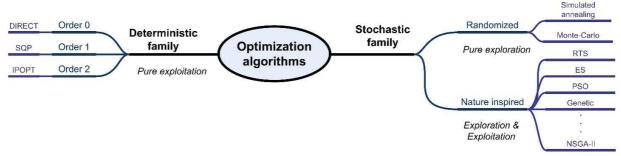

| B. An                                                                                                                        | overview of the different optimization algorithms                           | 23 |  |

| C. Usi                                                                                                                       | ng a gradient-based optimization algorithm to design in the imaginary world | 24 |  |

| III.                                                                                                                         | DETAILED DESCRIPTION AND IMPLEMENTATION OF THE GRADIENT BASED               |    |  |

|                                                                                                                              | OPTIMIZATION ALCODITUM SOD                                                  | 20 |  |

| A. Gr     | adient-based optimization algorithm SQP                                                             | 29   |

|-----------|-----------------------------------------------------------------------------------------------------|------|

| B. SQ     | P algorithm implementation                                                                          | 31   |

| IV.       | Conclusions                                                                                         | 35   |

| V.        | References                                                                                          | 36   |

| Chapter 3 | 3: A Design Challenge for Illustration                                                              | 30   |

| I.        | STRATOBUS PROJECT DESCRIPTION                                                                       | 39   |

| A. A v    | very complex and ever evolving system                                                               | 39   |

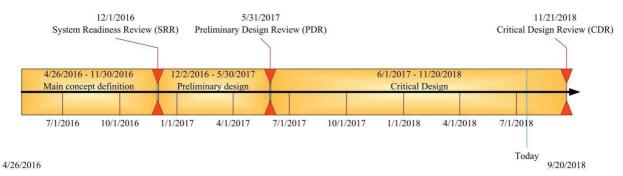

| B. A t    | ight timeline                                                                                       | 40   |

| II.       | GLOBAL ARCHITECTURE CHOICES OF STRATOBUS HIGH VOLTAGE PO                                            | OWER |

|           | CONDITIONING UNIT (HVPCU)                                                                           | 41   |

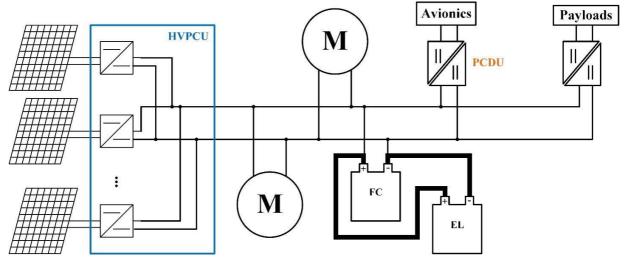

| A. Str    | atobus energy supply: HVPCU environment                                                             | 41   |

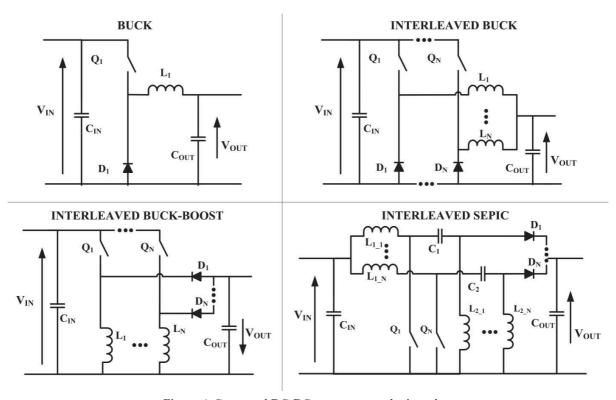

| B. HV     | PCU DC-DC topology selection through the architecture proposals tree                                | 42   |

| III.      | DETAILED DESIGN CHOICES OF HVPCU                                                                    | 47   |

| A. Co     | onverter main specifications at the beginning of the project                                        | 47   |

| B. IBO    | C technological choices through the architecture proposals tree                                     | 48   |

| IV.       | CONCLUSION                                                                                          | 52   |

| V.        | REFERENCES                                                                                          | 53   |

| world     | Optimization problem formulation for the predesign in the                                           | 54   |

| _         | A: Formulation of the Optimization Problem of Power Electronics adient-based Optimization Algorithm | •    |

| I.        | Introduction                                                                                        | 57   |

| II.       | DEFINITION OF A MODEL                                                                               | 57   |

| A. Ma     | ain but not exhaustive characteristics of a model                                                   | 57   |

| B. Co     | ncrete example of the differences between a sizing and an optimization model                        | 58   |

| C. Gu                                  | idelines and recommendations toward models for gradient-based optimization algorithms                                                                                                                                                             |                |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| III.                                   | MODELING STRATEGIES FOR 1ST ORDER OPTIMIZATION ON P                                                                                                                                                                                               | OWER           |

|                                        | ELECTRONICS SYSTEMS                                                                                                                                                                                                                               | 61             |

| A. M                                   | odel requirements regarding SQP algorithm                                                                                                                                                                                                         | 61             |

| B. M                                   | odeling power electronics parts in the continuous world                                                                                                                                                                                           | 61             |

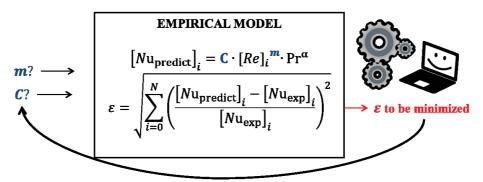

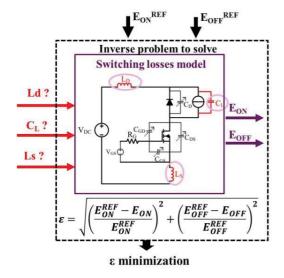

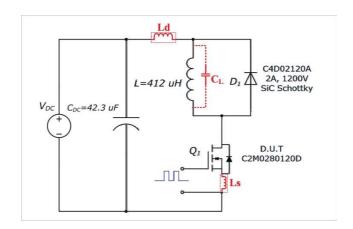

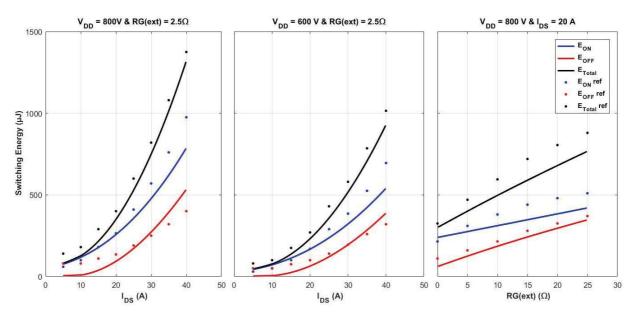

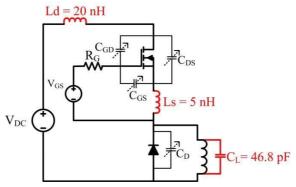

| IV.                                    | IDENTIFICATION BY OPTIMIZATION OF SOME MODEL PARAMETERS                                                                                                                                                                                           | 62             |

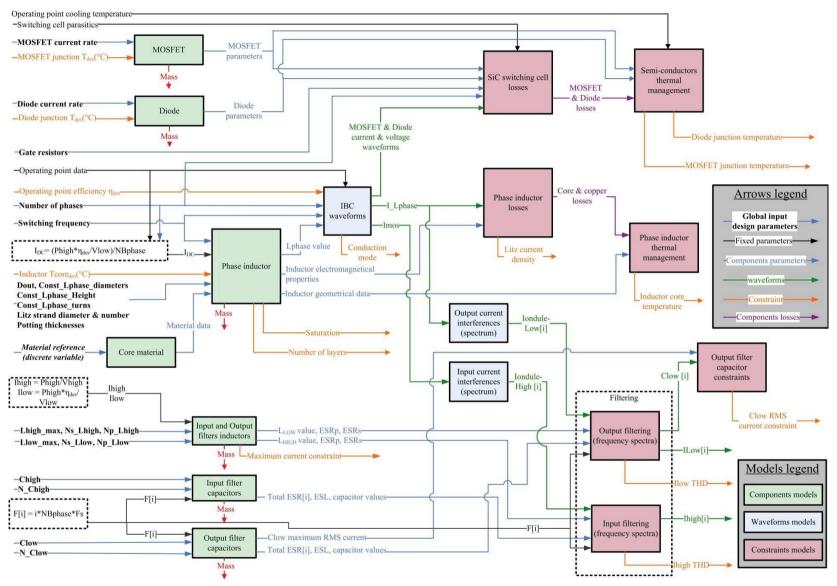

| V.                                     | SETTING OF THE INTERLEAVED BUCK CONVERTER MODEL                                                                                                                                                                                                   | 64             |

| A. P                                   | roposed problem formulation for the optimization of a converter                                                                                                                                                                                   | 64             |

| В. Р                                   | roposed problem formulation for the IBC of Stratobus project for one operating point                                                                                                                                                              | 65             |

| VI.                                    | CONCLUSION                                                                                                                                                                                                                                        | 68             |

| VII.                                   | References                                                                                                                                                                                                                                        | 68             |

| -                                      | 5: Evaluation Models of the Components Parameters and Converter Wave<br>terleaved Buck Converter                                                                                                                                                  | •              |

| -                                      | · -                                                                                                                                                                                                                                               | 70             |

| he Int                                 | terleaved Buck Converter                                                                                                                                                                                                                          | 70<br>72       |

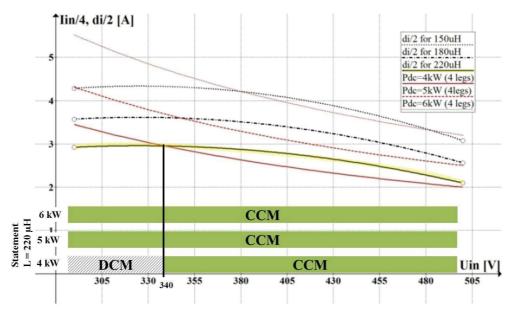

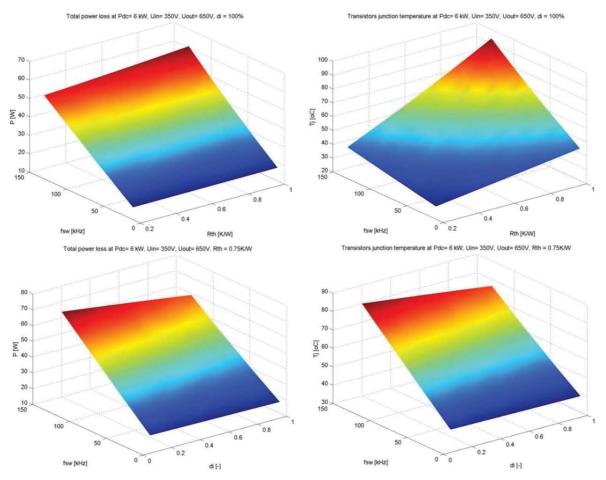

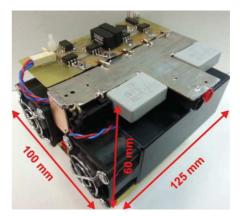

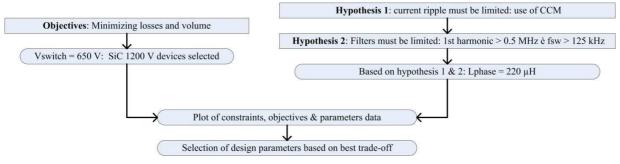

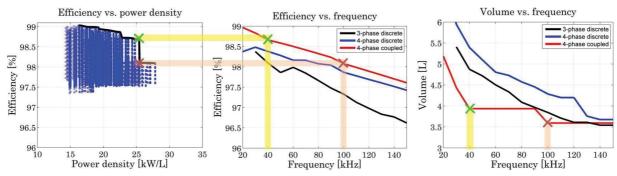

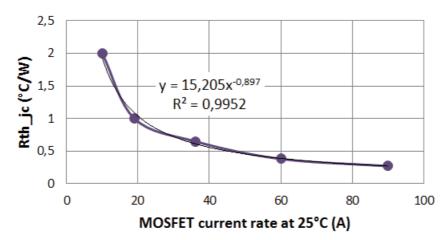

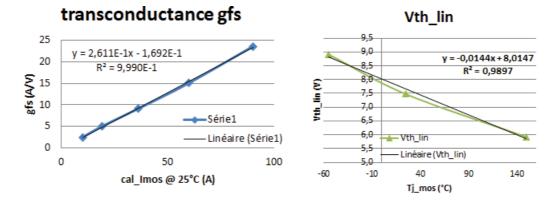

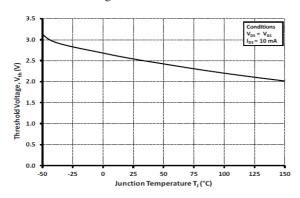

| The Int                                | Introduction                                                                                                                                                                                                                                      | 70<br>72       |