# Model based testing techniques for software defined networks

Asma Berriri

### ▶ To cite this version:

Asma Berriri. Model based testing techniques for software defined networks. Networking and Internet Architecture [cs.NI]. Université Paris Saclay (COmUE), 2019. English. NNT: 2019SACLL017. tel-02374706v3

### HAL Id: tel-02374706 https://theses.hal.science/tel-02374706v3

Submitted on 22 Nov 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Model Based Testing Techniques for Software Defined Networks

Thèse de doctorat de l'Université Paris-Saclay préparée à Télécom SudParis

École doctorale n°580 Sciences et technologies de l'information et de la communication (STIC)

Spécialité de doctorat: Réseaux, Information et Communications

Thèse présentée et soutenue à Evry, le 22 Octobre 2019, par

### **ASMA BERRIRI**

### Composition du Jury :

Pierre SENS

Professeur, Université Paris 6 Président

Yacine GHAMRI-DOUDANE

Professeur, La Rochelle Université Rapporteur

Antoine ROLLET

Maître de Conférences, HDR, Université de Bordeaux Rapporteur

Nikolai KOSMATOV

Chercheur, HDR, CEA LIST Saclay Examinateur

Djamal ZEGHLACHE

Professeur, Télécom SudParis Directeur de thèse

Natalia KUSHIK

Maitre de Conférence, Télécom SudPAris Co-encadrante

### **Abstract**

Having gained momentum from its concept of decoupling the traffic control from the underlying traffic transmission, Software Defined Networking (SDN) is a new networking paradigm that is progressing rapidly addressing some of the long-standing challenges in computer networks. Since they are valuable and crucial for networking, SDN architectures are subject to be widely deployed and are expected to have the greatest impact in the near future. The emergence of SDN architectures raises a set of fundamental questions about how to guarantee their correctness. Although their goal is to simplify the management of networks, the challenge is that the SDN software architecture itself is a complex and multi-component system which is failure-prone. Therefore, assuring the correct functional behaviour of such architectures and related SDN components is a task of paramount importance, yet, decidedly challenging.

How to achieve this task, however, has only been intensively investigated using formal verification, with little attention paid to model based testing methods. Furthermore, the relevance of models and the efficiency of model based testing have been demonstrated for software engineering and particularly for network protocols. Thus, the creation of efficient and reusable model based testing approaches becomes an important stage before the deployment of virtual networks and related components. The problem addressed in this thesis relates to the use of *formal models* for guaranteeing the correct functional behaviour of SDN architectures and their corresponding components. Formal and effective test generation approaches are in the primary focus of the thesis. In addition, automation of the test process is targeted as it can considerably cut the efforts and cost of testing.

The main contributions of the thesis relates to model based techniques for deriving high quality *test suites*. Firstly, a method relying on *graph enumeration* is proposed for the functional testing of SDN architectures. Secondly, a method based on *logic circuit* is developed for testing the forwarding functionality of an SDN switch. Further on, the latter method is extended to test an application of an SDN controller. Additionally, a technique based on an *extended finite state machine* is introduced for testing the switch-to-controller communication. As the quality of a test suite is usually measured by its *fault coverage*, the proposed testing methods introduce different *fault models* and seek for test suites with *guaranteed fault coverage* that can be stated as sufficient conditions for a test suite *completeness / exhaustiveness*.

## Résumé en français

Les réseaux logiciels (connus sous l'appellation : Software Defined Networking, SDN), qui s'appuient sur le paradigme de séparation du plan de contrôle et du plan d'acheminement, ont fortement progressé ces dernières années pour permettre la programmabilité des réseaux et faciliter leur gestion. Reconnu aujourd'hui comme des architectures logicielles pilotées par des applications, offrant plus de programmabilité, de flexibilité et de simplification des infrastructures, les réseaux logiciels sont de plus en plus largement adoptés et graduellement déployés par l'ensemble des fournisseurs. Néanmoins, l'émergence de ce type d'architectures pose un ensemble de questions fondamentales sur la manière de garantir leur correct fonctionnement. L'architecture logicielle SDN est elle-même un système complexe à plusieurs composants vulnérables aux erreurs. Il est essentiel d'en assurer le bon fonctionnement avant déploiement et intégration dans les infrastructures.

Dans la littérature, la manière de réaliser cette tâche n'a été étudiée de manière approfondie qu'à l'aide de vérification formelle. Les méthodes de tests s'appuyant sur des modèles n'ont guère retenu l'attention de la communauté scientifique bien que leur pertinence et l'efficacité des tests associés ont été largement démontrés dans le domaine du développement logiciel. La création d'approches de test efficaces et réutilisables basées sur des modèles nous semble une appropriée avant tout déploiement de réseaux virtuels et de leurs composants. Le problème abordé dans cette thèse concerne l'utilisation de modèles formels pour garantir un comportement fonctionnel correct des architectures SDN ainsi que de leurs composants. Des approches formelles, structurées et efficaces de génération de tests sont les principales contributions de la thèse. En outre, l'automatisation du processus de test est mise en relief car elle peut en réduire considérablement les efforts et le coût.

La première contribution consiste en une méthode reposant sur l'énumération de graphes et qui vise le test fonctionnel des architectures SDN. En second lieu, une méthode basée sur un circuit logique est développée pour tester la fonctionnalité de transmission d'un commutateur SDN. Plus loin, cette dernière méthode est étendue pour tester une application d'un contrôleur SDN. De plus, une technique basée sur une machine à états finis étendus est introduite pour tester la communication commutateur-contrôleur.

Comme la qualité d'une suite de tests est généralement mesurée par sa couverture de fautes, les méthodes de test proposées introduisent différents modèles de fautes et génèrent des suites de tests avec une couverture de fautes guarantie.

### **Acknowledgments**

This thesis would not have been possible without the guidance of Professor Djamal ZEGH-LACHE, whose broad vision and farsightedness have helped me sail my way through this research work. The thing I find most amazing about Djamal is his foresight. Providing me scientific support and professional advice, he has been a person who embodies characteristics that I can only aim to model myself after. I offer my sincerest gratitude for making me aware of the new perspectives that have found their way into this work, as well as enlightened my mind.

I would like to offer my deepest thanks to Doctor Natalia KUSHIK. She has made this endeavor academically possible, shaped research, and instilled in me the quality to cultivate my own potential. Her knowledge and suggestions have proven to be invaluable and have contributed profoundly to the results presented in this thesis. It has been an exceptional privilege to work with her. I dearly appreciate her personality, her work ethics, and the positive energy that she always emits, as well as how it affects and impacts those around her. These all are rare virtues. I would like to express my sincerest gratitude towards her. Thank you so much, Natalia!

I am sincerely grateful to Professor Yacine GHAMRI-DOUDANE, Doctor Antoine ROLLET, Professor Pierre SENS and Doctor Nikolai KOSMATOV for sparing the time to read and examine this thesis.

My sincere thanks go to Fondation Mines Télécom and Carnot Télécom & Société Numérique for the financial grant within the Futur & Ruptures (Future and Disruptive Innovation) programme.

My genuine appreciation goes out to my co-authors, Professor Nina YEVTUSHENKO and Doctor Jorge LOPEZ for their invaluable, precise, and diligent contribution to improve this work.

In addition, I had the honor of discussing the topics related to this thesis with researchers Igor BURDONOV and Alexander KOSSATCHEV. It is my privilege to extend my thanks to them for inspiring me with their interest in my research.

Deep respect I express to my work colleagues at Télécom SudParis.

To my parents, Mustapha and Mennana, for accepting nothing less than excellence from me. To my beloved brothers, Ghassen and Houssem, for always believing in me and encouraging me to follow my dreams.

# **Contents**

| Al | ostract                                                                                               | iii                                          |

|----|-------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Re | ésumé en français                                                                                     | V                                            |

| A  | cknowledgments                                                                                        | vii                                          |

| 1  | Introduction  1.1 Motivation                                                                          | 3<br>5<br>7                                  |

| 2  | Background  2.1 Software Defined Networking  2.2 Verification and Testing                             | 16<br>17<br>23<br>24                         |

| 3  | State Of The Art  3.1 Introduction                                                                    | 28<br>42                                     |

| 4  | Model Based Testing for SDN Architectures: A Graph / Path Enumeration based Approach 4.1 Introduction | 51<br>52<br>52<br>53<br>55<br>56<br>57<br>60 |

| 5  | Test Derivation for SDN-enabled Switches: A Logic Circuit based Approach 5.1 Introduction             |                                              |

|   | 5.3 | Formal Representation of an SDN Switch and Notations                         | 67  |

|---|-----|------------------------------------------------------------------------------|-----|

|   | 5.4 | Introducing a Fault Model                                                    | 69  |

|   | 5.5 | Fault models for Logic Circuits                                              | 70  |

|   | 5.6 | Deriving a Logic Circuit for a Switch Specification                          | 71  |

|   | 5.7 | Active and Passive Testing Approaches                                        | 73  |

|   | 5.8 | Experimental Evaluation for Testing an SDN-enabled Switch                    | 77  |

|   | 5.9 | Chapter Conclusions                                                          | 81  |

| 6 | Tes | t Generation for OpenFlow Switches: An Extended Finite State Machine base    | d   |

|   | App | roach                                                                        | 83  |

|   | 6.1 | Introduction                                                                 | 84  |

|   | 6.2 | Problem Statement                                                            | 85  |

|   | 6.3 | Extended Finite State Machine Model for an OF Switch                         | 86  |

|   | 6.4 | Introducing User-Defined Mutations and a Fault Model                         | 88  |

|   | 6.5 | EFSM based Technique for Test Generation                                     | 89  |

|   | 6.6 | Experimental Evaluation for Testing an OF Switch                             | 93  |

|   | 6.7 | Chapter Conclusions                                                          | 97  |

| 7 | Tes | t Derivation for a Controller Application: An Adaptation of the Logic Circui | t   |

|   | bas | ed Approach                                                                  | 99  |

|   | 7.1 | Introduction                                                                 | 100 |

|   | 7.2 | Problem Statement                                                            | 101 |

|   | 7.3 | Formal Representation of a Controller Application and Notations              | 103 |

|   | 7.4 | Deriving a Logic Circuit for a Controller Application Specification          |     |

|   | 7.5 | Test Suite Generation                                                        | 107 |

|   | 7.6 | Test Suite Execution                                                         | 107 |

|   | 7.7 | Chapter Conclusions                                                          | 109 |

| 8 | Con | clusion and Future Work                                                      | 111 |

|   | 8.1 | Contributions: Summary                                                       | 111 |

|   | 8.2 | Perspectives and Future Directions                                           | 113 |

# **List of Figures**

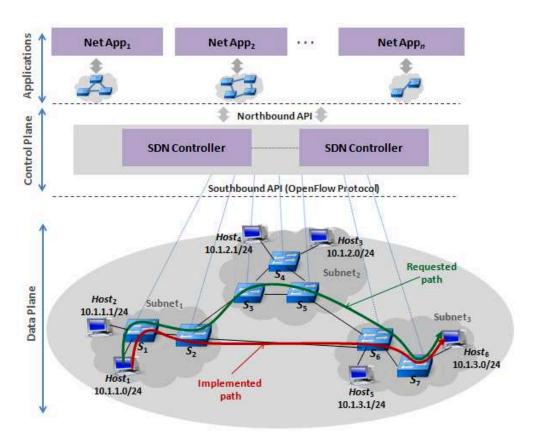

| 2.1 | SDN layered architecture.                                                                | 13  |

|-----|------------------------------------------------------------------------------------------|-----|

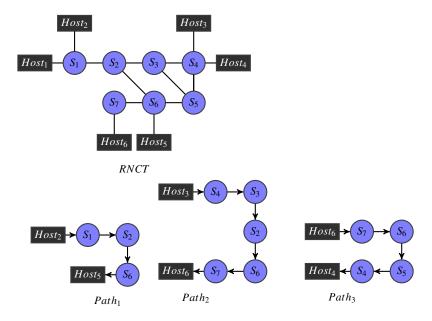

| 2.2 | RNCT of the network topology in Figure 2.1 and examples of its paths                     | 18  |

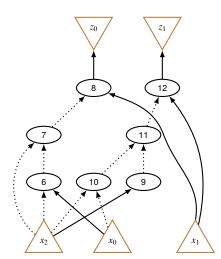

| 2.3 | An example of a partial logic circuit specification designed as an AIG $(c_{\it ex})$    | 20  |

| 2.4 | A BLIF description of $C_{ex}$ shown in Figure 2.3                                       | 20  |

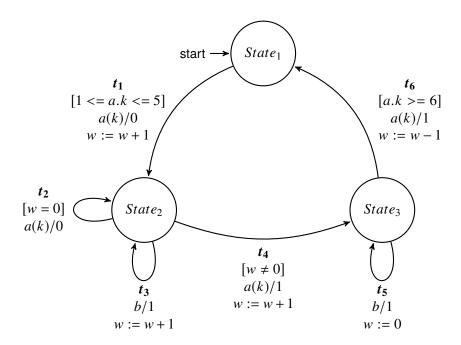

| 2.5 | Example of an EFSM                                                                       | 22  |

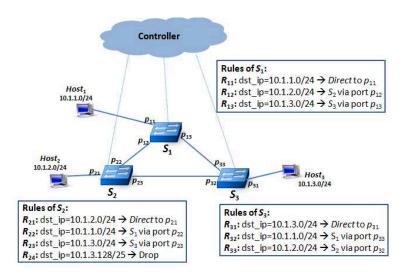

| 3.1 | An example of an SDN network topology                                                    | 29  |

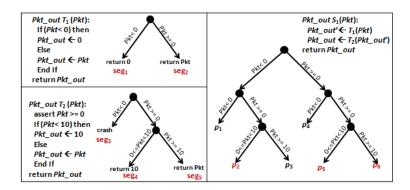

| 3.2 | A symbolic execution encoding of the switch $\mathit{S}_1$ of the topology in Figure 3.1 | 33  |

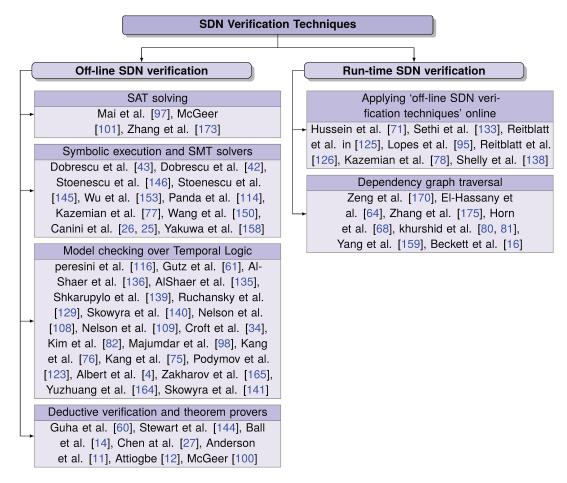

| 3.3 | SDN verification techniques taxonomy                                                     | 41  |

| 3.4 | Example showing a log analysis for test generation technique                             | 43  |

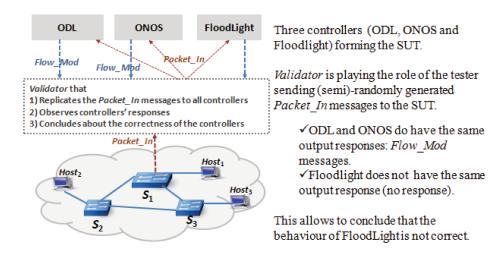

| 3.5 | Example illustrating the test execution of tests (semi)-randomly generated               | 45  |

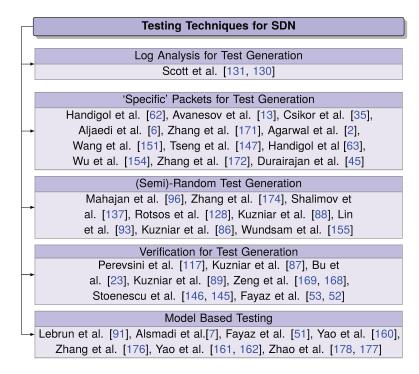

| 3.6 | SDN testing techniques taxonomy                                                          | 48  |

| 4.1 | Topology showing an SDN architecture as the SUT                                          | 53  |

| 4.2 | Traffic generation and flow observation w.r.t. the <i>RNCT</i> of Figure 4.1             | 56  |

| 4.3 | RNCT of the network topology in Figure 4.1 and examples of two equivalent                |     |

|     | paths                                                                                    | 58  |

| 4.4 | Testbed framework for an SDN architecture analysis                                       | 61  |

| 5.1 | Topology showing an SDN-enabled switch as the SUT                                        | 68  |

| 5.2 | Examples of SSF, SBF, and HDF mutants of $C_{ex}$ shown in Figure 2.4                    | 71  |

| 5.3 | Experimental set up topology for testing an SDN-enabled switch                           | 77  |

| 6.1 | Topology showing a switch-to-controller communication as the SUT                         | 85  |

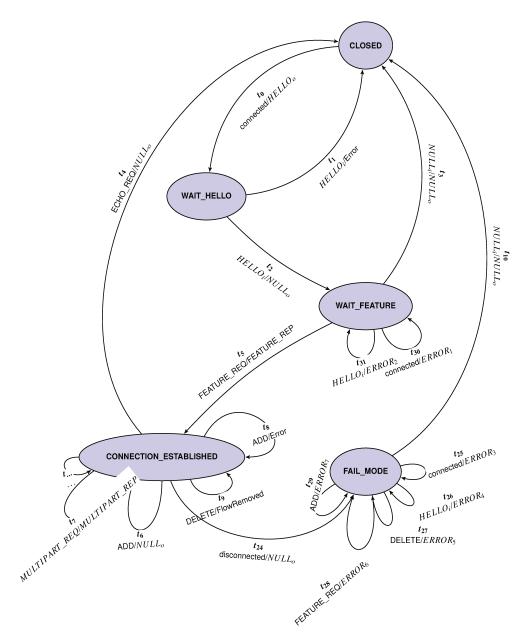

| 6.2 | Part of the specification EFSM of the switch                                             | 88  |

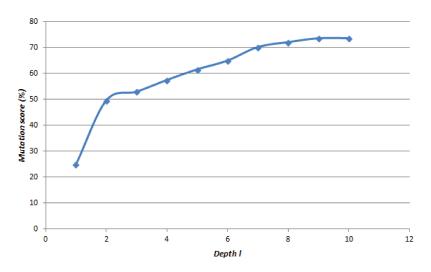

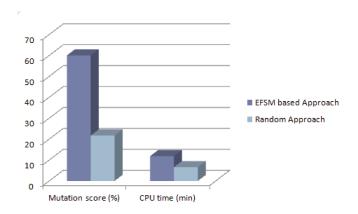

| 6.3 | Mutation score as the depth increases                                                    | 94  |

| 6.4 | Average mutation score and execution time for $TS$ s derived by the proposed             |     |

|     | approach Vs $\mathit{TS}$ s randomly generated                                           | 94  |

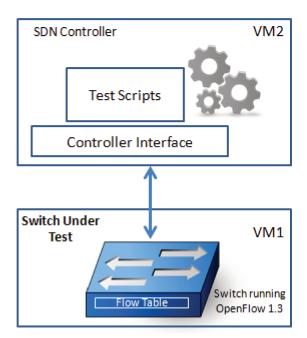

| 6.5 | Testbed framework for an OF switch analysis                                              | 96  |

| 7.1 | Topology showing a controller application as the SUT                                     | 102 |

| 72  | Illustration of the execution of a test case of the running example                      | 110 |

# **List of Tables**

| 2.1 | Example of rules installed in a switch                                                    | 15  |

|-----|-------------------------------------------------------------------------------------------|-----|

| 2.2 | The look-up table $(LUT)$ of the specification $c_{ex}$ illustrated in Figure 2.3 $\dots$ | 20  |

| 3.1 | Comparison of SDN verification techniques w.r.t. checked properties                       | 42  |

| 3.2 | Comparison of verification techniques applied to various SDN components                   | 42  |

| 3.3 | Comparison of testing techniques applied to various SDN components                        | 48  |

| 5.1 | Look-up table for the switch running example                                              | 73  |

| 5.2 | Experimental platform for an SDN switch                                                   | 78  |

| 5.3 | Example of a look-up table entry for the rule in Equation 5.11                            | 78  |

| 5.4 | Number of generated mutants                                                               | 79  |

| 5.5 | Fault Coverage for traditional digital circuit fault models                               | 79  |

| 6.1 | The characteristics of the EFSM switch model                                              | 87  |

| 7.1 | MAC addresses of the nodes of the topology illustrated in Figure 7.1                      | 107 |

| 7.2 | Look-up table for the controller application (Link_Translator) running example 1          | 107 |

# **List of Algorithms**

| 1 | White Box Test Suite Generation for an SDN Architecture                                              |

|---|------------------------------------------------------------------------------------------------------|

| 2 | Logic Circuit Derivation from a Set of Switch Rules                                                  |

| 3 | Equivalence Check for a Switch Mutant                                                                |

| 4 | SDN-enabled Switch Monitoring                                                                        |

| 5 | EFSM based Approach: Algorithm that derives a test suite $TS$ and a set $\mathcal{FD}\prime$ of      |

|   | distinguishable mutants                                                                              |

| 6 | DistinguishingSequenceAppend( $\mathcal{S}$ , $\mathcal{M}$ , ( $s_i$ , $\mathbf{v_i}$ ), $length$ ) |

| 7 | Logic Circuit Derivation from a Controller Application (Link_Translator) 106                         |

| 8 | Test Translation for the Controller Application Under Test                                           |

# Introduction

### **Contents**

| olem Statement / Restributions and Struc | _           |        | <b>S</b> . |   |   |   |   |   |   |   |     |                  |

|------------------------------------------|-------------|--------|------------|---|---|---|---|---|---|---|-----|------------------|

| tributions and Struc                     | . 4 C 41-   |        |            |   |   |   |   |   |   |   |     |                  |

| n ibunons and Su uc                      | cture of th | e Thes | is .       |   |   |   |   |   |   |   | • ( |                  |

| ertation Roadmap .                       |             |        |            |   |   |   |   |   |   |   |     |                  |

|                                          | •           | •      | •          | • | • | • | • | • | • | • | •   | ertation Roadmap |

### 1.1 Motivation

Computer networks and Internet structure usually consist of different network devices such as routers, switches and different types of middle-boxes. For managing and configuring such network devices, a set of specific and predefined command lines based on embedded operating system is usually used. Thus, traditional networks are essentially hardware-based and suffer from significant shortcomings regarding research and innovations, reliability, flexibility and manageability. For example, it can be argued that managing a large number of network devices is a big challenge and is prone to many errors. The emergence of new technologies, such as cloud and virtualization, generated the need for networks with higher accessibility and dynamic management. For solving the problems and limitations of traditional networks, the concept of Software Defined Networking (SDN), that separates control and data planes, was introduced along with an associated interaction protocol between the two planes known as OpenFlow (OF) [102]. OF is an emerging standard for SDN that ensures a clear separation of the data and control planes and provides central programmable control and management of the network using an SDN controller. Although SDN and OpenFlow started as academic experiments [102], they gradually gained the approval of the IT and telecommunications industries that have since adopted and started using and integrating the SDN paradigm into their cloud and network infrastructures.

The emerging field of SDN has enabled network deployment and service upgrade on software time scales which has huge benefits in the network domain. This is because in the future,

2 1. Introduction

the network operators will not compete on the basis of network coverage alone but on the basis of features and services. The initial impact of SDN was seen in the datacenters. As early as 2012, Google had their full scaled datacenter running as an SDN based architecture. SDN is now all set to integrate the wireless domain too. With SDN, network administrators can adopt many new technologies and applications rapidly on hardware-independent network architectures regardless of multiple vendor-dependent protocols. The architecture involves SDN controller(s) residing in the control plane while the forwarding element(s) (switches) and hosts make the data plane. The SDN architecture allows end-users (e.g., network administrators, operators, etc.) to specify *requested paths* (e.g., network policies, services) that should be implemented as routes or simply *implemented paths* followed by traffic in the data plane.

Consequently, the impact of SDN on the networking domain will be enormous. Kreutz et al. [84] conclude that SDN is established as a key technology in the future of networking systems.

Although SDN goal is to simplify the management of networks, several challenges arise. Firstly, the software SDN architecture itself is a complex multi-component system, operating in heterogeneous and failure-prone environments. Additionally, the requirements defining these architectures and their related components are also complex and evolving. Therefore, it becomes of the highest priority to further raise the quality of such architectures and components before their wide deployment.

SDN architectures and their components are built on software and as a result, unlike traditional networking systems, they have become increasingly sophisticated. Such large and complex software more likely contain bugs that may disrupt the network functioning and corrupt its operation. A recent study on the hazards in SDN-based Google network architectures [57] reported that software bugs contributed to more than 33% of the high impact failures documented in postmortem reports, which they attribute mainly to a high speed of network evolution, and the need to keep up with the growing user traffic and demand for new features and services. Another large-scale study by Microsoft [94] on root causes of end-users impacting incidents in their production networks reports similar results. It shows that software bugs contributed to 36% of critical outages, being major problem, way ahead of hardware failures and human errors. To summarize, in terms of virtualized networking systems, increased complexity and higher customer expectations of quality impose thorough testing before any deployment. Indeed, the software nature of such complex networks makes them error prone, so the process of defect detection plays a crucial role. The typical testing process applied to SDN is nonetheless human-intensive and is as such usually unproductive and often inadequately realized. More importantly, this testing process does not provide any assurance about the quality of the tests. Research on test techniques that guarantee the fault coverage is therefore essential and required to foster the adoption and deployment of SDN based solutions and systems.

The requirements that must be fulfilled by the SDN architectures and their components are extremely complex and evolving very fast with the support of open source developments and communities. For example, in the OF protocol requirements [113], just the flow entries installation command  $(Flow\_Mod)$  is more than two pages long [113]. Thus, these requirements can be subject to ambiguities. Further on, these requirements are expressed in informal languages which can cause different interpretations by developers. Therefore, all of these factors would contribute to increasingly higher likelihood of implementations exhibiting diverging behaviours from their requirements. Consequently, informal reasoning does not lead to proving the correctness of such architectures/components. Under these circumstances, the introduction of formal testing techniques in SDN domain becomes necessary and obvious and is the focus of this thesis work.

Although, a number of valuable efforts in the context of formal verification and testing SDN

architectures and their components already exist (see Chapter 3), there is still a lot of space to improve the situation. In fact, prior research focusing on assuring the correctness/consistency of SDN architectures/components has resulted in techniques that belong either to verification or testing. The techniques of the former can ensure the respect of a given policy in the data plane and can help checking configuration errors and problematic controller programs in the control plane. Yet, as they check whether a model of the SDN architecture/component satisfies a given set of properties, they can only guarantee that the properties hold for the model and hence some implementation faults can still escape this check as no test cases are applied to the implementations. The techniques of the latter alleviate this challenge by targeting the implementation under test (IUT). However, they are either performed for checking the paths / networks implemented in the data plane rather than checking the functionality of a given critical SDN component, or they do not provide any guarantee about the test effectiveness. This brings to the picture *model based testing* methods where test generation is based on the model of a system under test (SUT). This line of work in the context of SDN in particular has not matured yet. Not only the proposed approaches are rare but also they mostly focus on testing the correct packets pipeline processing when it comes to testing the data plane for example rather than assuring the correct functioning of the switch as an integral component of the SDN architecture.

In summary, we feel or contend that model based testing is one of the most convenient testing method which helps in detecting errors and bugs and can assure the proper functioning of SDN architectures and their components. Indeed, model based testing allows the creation of consistent, reusable, and well-documented models on the one hand and the derivation of test cases with guaranteed fault coverage on the other hand. This is an important stage in the testing process of SDN.

### 1.2 Problem Statement / Research Questions

The goal of this thesis is to check that the implementations of an SDN architecture and corresponding components conform to their requirements. Due to their phenomenal success, SDN implementations are becoming increasingly complex, with such features as accepting complex inputs (end-user requests), packets processing and interaction with a logically centralized controller. In the quest for conformance, the task of guaranteeing their correctness is becoming ever more challenging. Further on, it is not unusual that an entire SDN architecture might exhibit a behaviour such that the requests are correctly implemented in the underlying data plane while the SDN components of such architecture (e.g., switch, controller) are not implemented and/or operating correctly (hidden bugs).

The main research issue this thesis is concerned with, relates to assuring the compliance of Software Defined Networking architectures and their components with respect to their specifications by means of model based testing.

The first critical *challenge* is to guarantee the consistency between the high level requested paths and the configurations' implementations of these requests in the data plane. In other words, given an SDN architecture as the system under test, i.e., the SDN controller translating end-user requested paths into flow rules and the SDN switches implementing these flow rules in the data plane to correctly forward traffic to hosts, what inputs should be applied to the controller and what outputs should be observed at the data plane level such that conclusions about the correctness of the whole architecture can be drawn, i.e., whether the SDN architecture is functioning as expected/desired.

Resolving this first challenge will increase the confidence in reliable SDN architectures

4 1. Introduction

deployment without which trust in their implementations and operation can not be established or built.

However, resolving the first challenge does not guarantee the correctness of the SDN components forming the architecture. Moreover, should a bug be discovered by testing the entire architecture, it certainly becomes of interest to localize its cause (possible root cause) or responsible SDN components. Indeed, the functional correct behaviour of SDN components should not be taken for granted. Therefore, a second critical *challenge* that needs to be addressed concerns guaranteeing the correct behaviour of crucial SDN components, particularly the switch and the controller.

The switch exposes two interfaces, one to perform packet processing in the data plane and the second to communicate with a controller that instructs it how to process these packets. Therefore, two major *challenges* arise. Firstly, given the switch specified as a set of configurations to forward packets in the data plane, how the correctness of its forwarding functionality can be guaranteed. Secondly, given the switch in its communication with the controller as the system under test. The SUT takes as input OF messages from the controller and outputs replies to the controller as specified by the OF requirements. The correctness of such interaction needs to be assured.

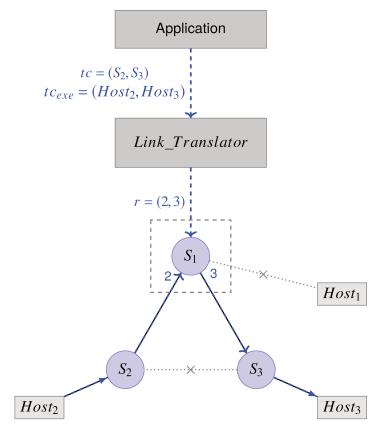

The controller in an SDN architecture is also a core SDN component responsible for making decisions on managing switches in the underlying data plane. Therefore, ascertain the correct implementation of the controller is crucial. To this end, it is important to guarantee the correct behaviour of its modules / applications. One critical module considered in this work is the one responsible for translating end-users requests, specifying two devices between which a link should be implemented, to corresponding configurations. The SUT in this case has a one-direction communication with a given application from which it receives a request. It has also a one-direction communication with a given switch in the data plane. The *challenge* is to guarantee that the controller module under investigation assigns correctly the ports of the network devices as specified by the request.

Based on the previous analysis, we focus on the following arising research questions:

- 1. **RQ1** How to assure the correct behaviour of SDN architectures?

- 2. **RQ2** How to assure the correct *forwarding behaviour* of an SDN-enabled switch in the data plane?

- 3. **RQ3** How to assure the correct behaviour of an SDN switch in its *interaction and interfacing with a controller*?

- 4. **RQ4** How to assure the correct behaviour of the *module/application of an SDN controller* responsible for translating, for a given switch in the data plane, requests into corresponding ports of the switch of interest?

To tackle these questions and challenges, in the upcoming section, the structure of this work will be related to the solutions proposed by this thesis for addressing each key question.

This thesis develops novel testing techniques for guaranteeing the correct behaviour of SDN architectures and their components. The techniques combine model based testing and mutation analysis. The proposed approaches allow testing the actual implementations rather than checking some network properties by means of formal verification as done by most of the state of the art.

### 1.3 Contributions and Structure of the Thesis

To address the aforestated research questions, we opt for *model based testing* because it systematically generates from the model a collection of tests (test suites) that, when run against the SUT, will provide sufficient confidence that it behaves as the model predicted it would. The difference between model based testing methods and verification methods (massively used in the state of the art; Chapter 3) is basically about the stimulation of the system under test vs. the checking of the model. Now, the complexity of SDN architectures and related components is not low, which results in verification methods being hard to apply to such systems. Model based testing on the other hand scales much better and has been used to test large systems.

Although model based testing requires more up-front effort in building the model, it offers substantial advantages over traditional software testing methods. Firstly, once a model is built, it is easier to generate and re-generate test cases than it is with hand-generated test cases. Besides, the quality of the generated test cases is high in comparison to other testing techniques. This helps in detecting subtle errors. Indeed, model based testing techniques strive to automatically generate test cases that are able to reveal whether any modelled fault has been implemented. As a result, these techniques guarantee a fault coverage of the model and are able, and have shown, to produce high quality test suites.

The result of this thesis can be divided into four main facets and contributions:

- 1. Model based approach for testing the functional behaviour of entire SDN architectures;

- 2. Model based approach for testing the forwarding functionality of the switch as a critical SDN component;

- 3. Model based approach for testing the switch in its interaction with the controller;

- 4. Model based approach for testing a module/application of the controller. Specifically, the controller application responsible for translating requested paths into pairs of ports of a given switch.

The thesis is organized as follows. This chapter gives an overview and motivation of the research topics of this thesis. It introduces the problems that the work is dealing with, its objectives, contributions and structure.

Next, Chapter 2 has a foundation nature and includes the background on Software Defined Networking architectures and their components and interfaces, verification and testing concepts, model based testing, mutation analysis and black and white box testing approaches. Additionally, while introducing these foundations and concepts, we point out which chapter(s) they are used in and how they relate to the thesis work.

Chapter 3 examines the related work on verification and testing techniques with respect to SDN architectures and their components. For that purpose, a taxonomy is provided. Herewith, a link to the current chapter is done. The literature investigation has elicited a set of limitations and concerns and a set of research directions that the work of this thesis follows. The observed lack of model based testing techniques applied to SDN in the current literature and ensuing analysis, has led to the model oriented testing methodologies adopted and proposed in this thesis.

The four following chapters relate to these proposed testing approaches.

Chapter 4 characterizes a novel model based technique for testing entire SDN architectures taking into account potential interoperability issues in the controller-to-switch communication. The technique aims to ensure that requests expressed by end-users are correctly

6 1. Introduction

implemented in the data plane. The approach relies on *graph/path enumeration*. The chapter relates to the first *challenge* of answering the question of how to guarantee the correct functioning of such architectures. In particular, a *fault model* is introduced where the *fault domain* contains potential implementations of *virtual paths* requested by an end-user. Afterwards, approaches for test generation under *black box* and *white box* testing assumptions are proposed. To guarantee the *fault coverage*, the conditions are proven such that when under both testing assumptions, a *complete* test suite with respect to such fault model can be derived. Additionally, Chapter 4 provides an experimental evaluation of the proposed approach. A discussion on the obtained results is then given so as to support the effectiveness of the presented testing method. Results show that the derived test suites were able to detect a number of functional inconsistencies in the considered SDN architectures.

Now that we have provided a novel testing technique guaranteeing to check for the correctness of the entire SDN architecture, the question that automatically arises is how about the correctness of its components. Further ahead, one might want to identify which exact component is not working as expected. This is addressed in detail in Chapters 5, 6, and 7.

In particular, the second part of the thesis proposes novel model based techniques for testing critical SDN components. At first, the thesis looks at testing the switch as a crucial component of SDN architectures in two aspects, then a module of the controller is considered.

The forwarding functionality of the switch modelled and analyzed as a 'stateless' system without considering its interaction with the controller is investigated in Chapter 5. For this purpose, the chapter proposes a logic circuit based testing approach. An appropriate fault model is introduced and a logic synthesis algorithm is presented. Some mutation operators over the derived switch specification are introduced, then logic circuit based approach and related SAT solving are utilized for detecting equivalent mutants. Further on, both active and passive testing strategies are explored. Finally, the chapter demonstrates the effectiveness of the approach using experimental evaluation. The results show for example that test suites derived based on traditional logic circuit fault models have a high fault coverage for SDN-enabled switch faults. This piece of work relates to the second challenge.

Despite the effectiveness potential of the solution presented in Chapter 5 in detecting implementation forwarding errors, it does not cover the behaviour of the switch in its interaction with the controller. This is tackled in Chapter 6. The chapter proposes an *extended finite state machine* based test generation strategy for testing the functional behaviour of a switch in its communication with an SDN controller with respect to requirements described in the Open-Flow specification. A part of the requirements is formalized, then based on the derived model, an appropriate *fault model* is introduced and a test generation method for deriving exhaustive test suites with respect to such fault model is presented. To demonstrate the effectiveness of the proposed approach, an experimental evaluation is performed which aims at the assessment of the derived test suites *fault coverage* on one hand and at the execution of the derived tests against an OF implementation under test, on the other hand. The conducted evaluation shows the effectiveness of the approach; besides, experiments reveal several implementation faults and specification ambiguities when a switch implementation is tested. By that, the *third challenge* is covered.

Chapter 7 utilizes the results of Chapter 5 and addresses the further question of the outlined challenges. The model based approach presented and discussed in Chapter 5 is adapted and adjusted to tackle one module of the controller, particularly the one responsible for translating end-user requests into corresponding pairs of ports of a switch of interest. First, the problem is described. Then, the formalization of the specification, the test generation approach, and the test execution strategy follow subsequently. This relates to the *fourth challenge*.

Chapter 8 completes this work with a summary and outlook. The proposed testing ap-

proaches' capabilities and limitations are reviewed, the general trends of the quality assurance for SDN architectures and their components are recalled and influences of the contributions of this thesis are outlined.

### 1.4 Dissertation Roadmap

In this section, the dependencies between chapters throughout this thesis are outlined.

The detailed discussion on SDN, verification and testing in Chapter 2 serves mostly as a foundation for the considered topics.

Chapter 3 includes a review of the state of the art work on verification and testing techniques for SDN architectures and SDN components yielding to the position of our contributions in the field.

Chapters 4, 5, 6 and 7 contain the central achievements of the presented work. Additionally, the reader can refer to the summaries given at the end of each chapter, which provide the essential overview of the subjects and results on their contents.

The concept of the *Logic Circuit* based approach which is presented in Chapter 5 is used as the basis for Chapter 7.

8 1. Introduction

### **Author's Publications & Talks**

The work presented in this thesis is original work undertaken between October 2016 and September 2019 at SAMOVAR/CNRS, Télécom SudParis / Université Paris Saclay. It has been financed by the "Futur & Ruptures" (Future and Disruptive Innovation) programme grant awarded to the author by "Fondation Mines-Télécom" and "le Carnot Télécom & Société Numérique". The work resulted in the following publications.

### **Conferences**

- [1] Asma Berriri, Jorge López, Natalia Kushik, Nina Yevtushenko, and Djamal Zeghlache. "Towards Model based Testing for Software Defined Networks." In: *Proceedings of the 13th International Conference on Evaluation of Novel Approaches to Software Engineering, ENASE, Funchal, Madeira, Portugal, March 23-24*. 2018, Pages 440–446.

- [2] Jorge López, Natalia Kushik, Asma Berriri, Nina Yevtushenko, and Djamal Zeghlache. "Test Derivation for SDN-Enabled Switches: A Logic Circuit Based Approach." In: *Proceedings of the* IFIP International Conference on Testing Software and Systems. Springer. 2018, Pages 69–84.

### **Archives**

[1] Asma Berriri, Natalia Kushik, and Zeghlache Djamal. "Extended Finite State Machine based Test Generation for an OpenFlow Switch." working paper or preprint. 2019. URL: https://hal.archives-ouvertes.fr/hal-02262841.

Some of the research leading to this thesis has appeared previously in the following.

### **Journals**

[1] Asma Berriri, Natalia Kushik, and Djamal Zeghlache. "On using finite state models for optimizing and testing SDN controller components." *Russian Physics Journal* 59.8/2 (2016), Pages 5–7.

Portions of this work have been already presented in the following.

### **Participation in Seminars and Conferences**

- [1] Asma Berriri. Formal Approaches for Testing in Software Defined Networks. Poster and presentation. Journée doctorants Samovar 2018, Paris, France. 2018. URL: http://samovar.telecom-sudparis.eu/spip.php?article1177.

- [2] Asma Berriri. Formal Approaches for Testing in Software Defined Networks. Poster presentation. Visite HCERES évaluation laboratoire Samovar les 4 et 5 décembre 2018, Paris, France. 2018. URL: http://samovar.telecom-sudparis.eu/spip.php?article1158.

- [3] Asma Berriri. Formal Approaches for Verification and Testing in Software Defined Networks. Presentation. The 4th GDR RSD and ASF Winter School on Distributed Systems and Networks 2019, Pleynet, Sept Laux, France. 2019. URL: https://sites.google.com/site/rsdwinterschool/program-2019.

- [4] Asma Berriri. Formal Approaches for Verification and Testing in Virtual Networks. Presentation. Méthodes de Test pour la Vérification et la Validation (MTV2) du GdR GPL du CNRS, ENSIIE, Paris, France. 2018. URL: http://logimas.mics.centralesupelec.fr/wp-content/uploads/2018/12/MTV2-A.Berriri-final-extended.pdf.

- [5] Asma Berriri. *Testing and Verification for Software Defined Networks. Presentation.* The 7th Halmstad Summer School on Testing, HSST 2017 in cooperation with TOCSYC Network, Halmstad University, Sweden, June 12-15th. 2017. URL: http://ceres.hh.se/mediawiki/HSST\_2017.

- [6] Asma Berriri. Towards Testing and Verification in SDN. Poster presentation. Journée Futur & Ruptures, février 2017, IMT, Télécom ParisTech, Paris, France. 2017. URL: https://www.imt.fr/journee-futur-ruptures-jeudi-2-fevrier-2017-a-limt/.

- [7] Asma Berriri. Towards Testing and Verification in Software Defined Networks. Poster and presentation. Journée doctorants Samovar 2017, Paris, France. 2017. URL: http://samovar.telecom-sudparis.eu/spip.php?article1063.

- [8] DigiCosme Spring School on Formal Methods and Machine Learning. *ForMaL*. 2019. URL: https://formal-paris-saclay.fr.

- [9] GT LTP Langages Types et Preuves du GdR GPL du CNRS. *ENSIIE*, *Paris*, *France*. 2018. URL: http://web4.ensiie.fr/~guillaume.burel/ltp/journee\_2018.html.

1. Introduction

# 2 Background

### **Contents**

| 2.1 | Softwa  | are Defined Networking                              | 12 |

|-----|---------|-----------------------------------------------------|----|

|     | 2.1.1   | Overview of the SDN Architecture and SDN Interfaces | 12 |

|     | 2.1.2   | Application Layer                                   | 13 |

|     | 2.1.3   | Control Plane                                       | 14 |

|     | 2.1.4   | Data Plane                                          | 14 |

| 2.2 | Verific | cation and Testing                                  | 16 |

|     | 2.2.1   | Verification                                        | 16 |

|     | 2.2.2   | Testing                                             | 17 |

| 2.3 | Model   | Based Testing                                       | 17 |

|     | 2.3.1   | Formal Representation of an SDN Architecture        | 18 |

|     | 2.3.2   | Logic Circuit                                       | 19 |

|     | 2.3.3   | Extended Finite State Machine                       | 19 |

|     | 2.3.4   | Fault Models                                        | 23 |

| 2.4 | Mutat   | tion Analysis                                       | 23 |

| 2.5 | Black   | Box and White Box Testing                           | 24 |

| 2.6 | Chapt   | ter Conclusions                                     | 25 |

In this chapter, the fundamentals and basic background information, on which we base our work of testing SDN architectures/components, are provided. Firstly, in Section 2.1, the SDN paradigm concepts, architecture, and components are presented. The necessary theoretical background on the terminology and semantic of verification and testing used in the thesis is covered in Section 2.2. Armed with these basics, we dig deeper into notions related to model based testing in Section 2.3 with a brief insight into how these concepts will be used in our contributions. Further on, in Section 2.4, the concepts of mutation analysis are introduced. An overview of the black and white box testing approaches in Section 2.5 completes the theoretical basics.

12 2. Background

### 2.1 Software Defined Networking

In this section, we provide a general description of SDN and give an overview of the components and interfaces.

SDN is an emerging networking paradigm that is now growing in usage and popularity, progressing rapidly and addressing some of the long-standing challenges in computer networking. SDN platforms are subject to be widely used and deployed. Recently, they are deployed into several core and data center networks. This paradigm brings a major concept, namely it decouples the data control of the network from the data transmission. It moves the control logic into a logically centralized component called controller. In contrast to the traditional network architectures, the separation of roles in an SDN architecture is the key to achieving flexibility and to making it easier to introduce new concepts in networking. One can certainly observe that the abstraction offered by the SDN architecture provides wider flexibility on developing and implementing new network functionalities and simplifies the configuration and management of modern networks suggesting the opportunity for more innovations.

### 2.1.1 Overview of the SDN Architecture and SDN Interfaces

The foundation of SDN is proposed by the standardization organization called Open Network Foundation (ONF) [142]. In an SDN architecture, a logically centralized control function (the *controller*) translates the applications' requirements and applies control instructions over the *forwarding devices* (the *switches*) in the data plane, while providing relevant information up to the SDN *applications* [102]. The forwarding devices in the data plane then reroute data packets to other forwarding devices and to *hosts* according to these control instructions [132], [54], more specifically, forwarding and filtering *rules* [134].

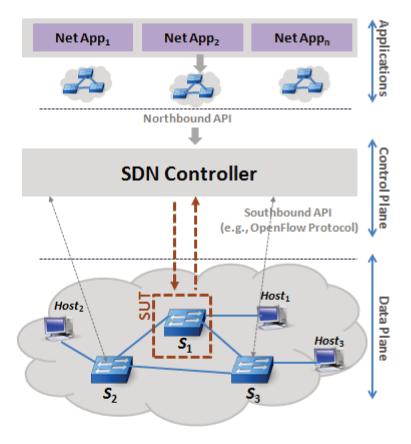

An SDN architecture is composed of three layers, i.e., (i) the network applications, (ii) the control plane composed of one or multiple controllers, and (iii) the data plane composed of the forwarding devices and hosts [142]. The interaction between these layers is performed through Application Programming Interfaces (APIs). The SDN controller has mainly two APIs. The southbound API responsible for collecting network status and updating forwarding rules in the forwarding devices. The northbound API such as the 'Representational State Transfer' (REST) API handles interaction with the application layer, i.e., receiving requests/policies described in high level languages from SDN applications and providing a synchronized global view. It enables direct expression of network behaviour and requirements. Northbound API presents a programmable API to network control and management applications. The southbound API allows the exchange of control messages between the controller and the SDN forwarding devices. This interface dictates the format of the exchanged control messages. Multiple southbound interfaces exist such as OpenFlow (OF) [102], ForCES [44], and POF [143]. The OpenFlow protocol is the most deployed SDN protocol as the southbound interface [152]. Multiple OpenFlow protocol versions exist including versions 1.0, 1.3, 1.5. During the thesis, we used the stable releases of OpenFlow at the time (versions 1.0 and 1.3). All OF versions use the same structure of SDN rules, with some action and match field additions in each version.

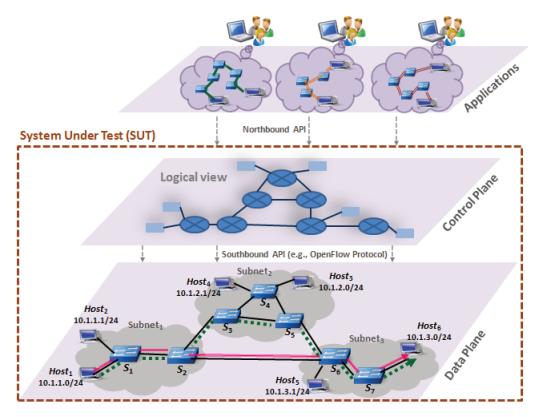

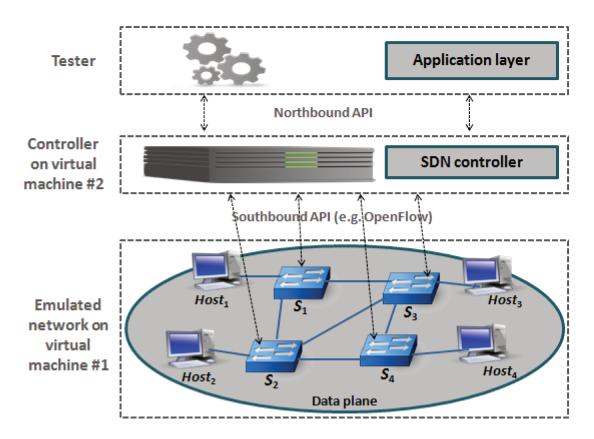

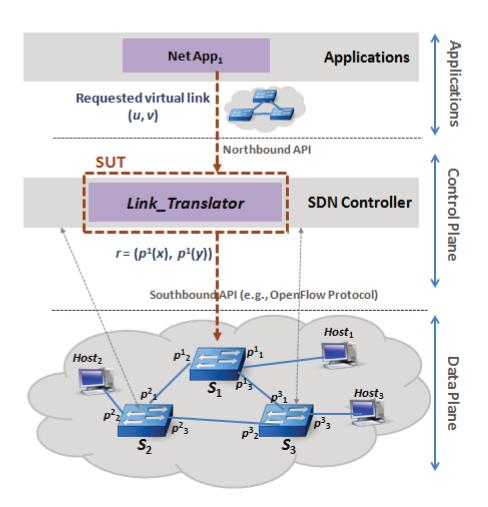

An example of an SDN architecture is depicted in Figure 2.1.

SDN network architectures allow end-user (e.g., a network administrator) requests/requirements representing network policies to be specified and implemented in the data plane. Network applications can issue the requests on the shape of data paths that have to be implemented between pairs of sources and destinations through the network architecture. The controller then computes the appropriate flow rules and pushes them to the switches. A switch acts as a forwarding device receiving and sending network packets in accordance with the configured rules. It also sends events such as traffic statistics, network changes and acknowledgments to the controller. An end-user request might impose for example the traversal of a given sequence of switches. An example of a request is 'traffic from hosts in local area network  $Subnet_1$  to the internet must traverse the switch  $S_1$  and one of the switches  $S_6$  and  $S_7$  (Figure 2.1).

In this thesis, we assume that the network architecture is *functioning correctly* if the network policies (requests) defined by the network applications and translated by the controller are correctly implemented by network devices in the data plane. In Chapter 4, we propose a *model based testing technique* to guarantee such correctness.

In the following, we detail the layers of the SDN architecture.

Figure 2.1 – SDN layered architecture.

### 2.1.2 Application Layer

As illustrated in Figure 2.1, the application layer resides above the control layer. Through the northbound API, SDN applications can conveniently access a global network view and can implement different strategies to configure the underlying physical infrastructure (data plane) using a high level language. The application layer mainly consists of the end-user network applications or functions that consume the SDN network services. Examples of such applications include network visualization, load balancing and firewalls applications. Based on the network configuration requirements and specific needs, a network administrator can program new network applications (new network functionalities) in standard programming languages.

14 2. Background

### 2.1.3 Control Plane

The control layer bridges the application layer and the data plane. It consists of a set of software based SDN controllers providing a consolidated control functionality through open APIs [59]. This layer supervises the network forwarding behaviour.

The controller sets up all forwarding devices in the data plane, maintains topology information, and monitors the overall status of the entire architecture [102]. It updates the flow table by adding and removing rules using protocols such as OpenFlow [102]. Each forwarding device has a set of flow tables with rules. A rule has three parts: the matching condition to a specific flow; the action to be applied to this flow, and counter to track the rule occurrence for management purposes.

The Controller presents two behaviours, namely reactive and proactive. In the reactive mode, the first packet of flow received by a forwarding element triggers the controller to insert rules in each forwarding element of the data plane. In fact, the controller listens to switches passively and configures routes on-demand (by installing the corresponding rules). It receives messages of connected hosts from the switches. Upon receiving a  $Packet\_In$  message from the switch, the controller looks for the destination host location and sets the path by sending  $Flow\_Mod$  messages to affected switches in the path. In the proactive mode, the controller pre-populates the flow tables in each forwarding element.

All functions of the control plane are performed by the controller. It has full network topology information and the location of hosts. When a forwarding element receives a packet for which there is no matching rule in its flow tables, it forwards it (using  $Packet\_In$ ) to the controller asking for the action to take upon this new flow. The controller can define the port that the flow must be forwarded to or take other actions, such as dropping the packet. The controller must set the entire path by sending  $Flow\_Mod$  messages to all switches from the source to the destination.

The SDN controller allows the applications to communicate with the SDN forwarding devices, and creates the global view of the network. The controller is also able to monitor all the network forwarding elements regularly. It then informs the network applications of the network changes using the northbound interface. Then, the network applications manage and implement policies in the network devices using the northbound interface.

Throughout the thesis, we consider architectures with controllers' deployments logically representing a single controller. However, the proposed approaches can easily be extended with an architecture with multiple controllers.

### 2.1.4 Data Plane

The data plane consists of forwarding devices and hosts. The forwarding devices include physical and virtual switches which are interconnected between each other and with hosts. An example of an SDN switch is the software OpenvSwitch (OVS) [121].

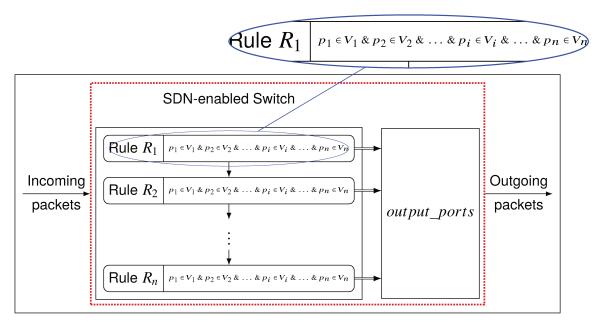

### The Switch

A switch exposes two interfaces allowing its interaction with packets in the data plane on one hand (forwarding functionality) and its interaction with the controller on the other hand. A switch does not have any built intelligence and relies on the controller to give it a set of rules to know how to treat/forward incoming packets. These rules are then saved in the switch flow tables [113]. When a packet arrives to the forwarding device, it is matched against rules in the flow tables. The action is triggered if the matching is satisfied and then, the counter is updated. If the packet does not match any entry in the flow tables, it is sent to the controller

over a secure channel to ask for an action. Packets are matched against all rules based on some prioritization scheme. The flow table could have a priority field associated with each rule. Higher number indicates that the rule should be processed before.

An SDN forwarding rule (also called a flow entry) is composed of three parts [113]

- Matching fields: packet header values to match the incoming packets in addition to the input port. We refer to the matching fields as *matching parameters*.

- Actions: set of instructions to apply to the matching packet such as forward to specific output port, flood, drop, send to controller or modify packet headers.

- Locations / priorities: to control the rule hierarchy.

The Switch in its Data Plane Interface (Forwarding Functionality) The forwarding rules are grouped in different flow tables and are considered to be the *configurations* of switches with respect to packets and application flow management.

As an example of rules installed in a switch, consider the set of rules defined in Table 2.1. The table includes the following *matching parameters*:

- Flow Table, a virtual partition for the installed rules;

- *Priority*, the order attributed to the rule to be applied with respect to other rules in the flow table;

- *Input Port* (*In\_port*), the ingress port of the incoming packets;

- Ethernet Type (Eth\_type), the type of traffic carried by the Ethernet datagram;

- Source and Destination IP Addresses respectively (IP\_source, IP\_dest), define the IP protocol source and destination addresses;

- Output ports (Output) defines the set of ports to which a matching packet should be forwarded.

| Flow Table          | Flow Table   Priority   In_port |   |             | IP_source   | IP_dest     | Output |  |  |

|---------------------|---------------------------------|---|-------------|-------------|-------------|--------|--|--|

| 0 500 * ARP (0x806) |                                 |   | *           | *           | Port 1      |        |  |  |

| 0                   | 0 500 1 ARP (0x806              |   | ARP (0x806) | *           | *           | "All"  |  |  |

| 1                   | 501                             | 1 | IP (0x800)  | 10.0.0.1/32 | 10.0.0.2/32 | Port 2 |  |  |

| 1                   | 501                             | 2 | IP (0x800)  | 10.0.0.2/32 | 10.0.0.1/32 | Port 1 |  |  |

Table 2.1 – Example of rules installed in a switch

For example, the third rule in Table 2.1 is specified in the flow table 1 with the priority 501. When the packets having the source IP address 10.0.0.1 and destination IP address 10.0.0.2 arrive to Port 1 of the switch, these packets have to be forwarded through the (output) Port 2 of the switch.

Chapter 5 answers the question of how to guarantee the forwarding functionality of a switch specified as a set of configurations in the data plane.

### The Switch in its Southbound Interface

The OF specification [113] describes the behaviour of the switch and its communication with the controller. It specifies OF messages handling via the southbound API. Examples of messages received/sent by the switch include OFPT\_HELLO message for connection establishment; OFPT\_FEATURE for advertising the supported capabilities; FLOW\_MOD for handling modification of rules in the switch; OFPT\_BARRIER to get the information about when a given

16 2. Background

command is applied; OFPT\_MULTIPART for reporting statistics and OFPT\_ECHO for sensing the liveness.

Before any messages can be exchanged, the connection establishment process takes place implying OF version and capability negotiation. Both ends of the connection exchange HELLO messages immediately after the lower layer (TCP/TLS) connection establishment. Afterwards, to be aware of the capabilities of the switch, FEATURE is exchanged. In case this message is not received by the controller and after a timeout, the latter disconnects the switch. Once the connection is successfully established, different messages can be exchanged, e.g., ECHO, FLOW\_MOD, BARRIER and MULTIPART. The actions of rules installed by the FLOW\_MOD messages are defined by the OF requirements and include for example modification of IP and VLAN values.

If an OF implementation complies with the requirements, the exchange of these messages should be performed correctly with the specified parameters. In Chapter 6, a *model based* approach is proposed to test the switch in its communication with the controller.

### 2.2 Verification and Testing

It is necessary to evaluate or judge the 'correctness' of an SDN architecture and its related SDN components, i.e., whether the SDN architecture/component meets its requirements and specifications and whether it fulfills its intended purpose.

In the following subsections, basic concepts related to verification and testing employed throughout the thesis are briefly introduced.

### 2.2.1 Verification

*Verification* is a process that involves mathematical proof showing that a system satisfies a set of desired properties. Formally, given a system M, verification aims at the creation of a set of properties P that are iteratively checked during phases of development of M to determine whether or not the behaviour of M meets the set of properties P [32, 46].

In the context of SDN, the network verification problem can be formulated as follows. Given an abstract model of an SDN component(s) (or a composition of those) Model(N) and a set of network properties P expressed in a given logic formulae, determine whether Model(N) satisfies P.

We distinguish the different verification methods applied to SDN based on the mathematical formalism used in the reasoning process during the verification. In this work, under verification we understand a process that does not require any stimulation of the system under verification.

Examples of network properties (referred to as invariants as well) to be verified include:

- Reachability [43] is concerned with whether the network always successfully delivers

packets to the intended end hosts. A definition of reachability property can be for example that a packet pkt can get from the source host Host1 to the end host Host6 in

Figure 2.1.

- Forwarding Loop [97] occurs if the same packet returns to a location that it has visited before. There are several possible definitions of this property, e.g., returning to the same location with exactly the same header, or returning to the same location with a possibly different header. The former case indicates the presence of an infinite loop, since this packet will repeatedly return to this location. The latter case may also be undesirable since there is usually no reason for a packet to return to the same location.

Black-holes [141] means that packets are dropped because there is no destination configured on one of the forwarding devices they traverse.

### 2.2.2 Testing

In software development methods, *testing* occupies a central position of ensuring software quality. In order to judge the correctness of a system under test, one should observe or monitor for each test execution what the system does, how it does it, and perhaps when it does it. *Active testing* is defined when a system under test (SUT) is stimulated by appropriate inputs, i.e., test sequences / cases, and the conclusion about its correctness is made based on the observations of its output responses. Testing techniques applied to SDN architectures/component (s) are based on stimulating the architecture/component(s) (or composition of those) under test by test cases and observing their reactions with the intent of finding errors. *Passive testing* is defined when one just monitors the SUT and observes that the behaviour is correct or incorrect without stimulating the SUT. Debugging / troubleshooting is defined as stimulating the SUT by appropriate inputs and observing its reactions in the objective of localizing errors [10], [107].

Random testing [10] generates test cases in a (uniformly) random way with negligible effort. A more evolved form, referred to herewith as 'semi-random' consists of 'controlling' the way random test cases are generated. For example, starting with randomly generated inputs and repeatedly modifying them, more or less at random, to produce new inputs. This increases the probability of inputs found in this way being 'interesting'.

### 2.3 Model Based Testing

Model based testing has received increasing attention due to its ability to improve productivity, by automating test planning, generation, and execution. In model based testing, test cases/sequences forming a *test suite* are generated from an abstract model, which captures the desired behaviour of the system. Then, the test cases/sequences are executed against a real implementation of the system and the conformance of the implementation to the specification is checked by comparing the observed outputs with the ones specified by the model, for some suitable definition of conformance. The specification can be a formal model of the system and might also be defined by a set of (end-user) requirements that should be correctly implemented.

The central artifact of model based testing is the *model*. It serves as an abstraction of the system under test (SUT), manageable by the test engineers. In this context, the primary idea behind a model based method is the benefit of deriving a specification for a system that might cover its functional behaviour. The model/specification may be utilized as the basis for automating parts of the testing process and can lead to the generation of more efficient and effective test cases/sequences.

A large number of possibilities is present with respect to how to model the SUT. For example *logic circuits* or state based models such as Finite State Machines, *Extended Finite State Machines*, Input/Output Transition Systems, etc., might be considered. For state based models, most notations for test modeling are based on *states* and their identification.

In the following subsections, we provide a glance insight into preparatory ingredients for the author contributions. In subsection 2.3.1, we give an introductory overview of a formal representation of an SDN architecture that supports our first contribution in Chapter 4. In subsections 2.3.2 and 2.3.3, we introduce logic circuit and extended finite state machine as

18 2. Background

models that we use in Chapter 5 and 6 respectively to support the proposed test generation techniques. In subsection 2.3.4, definitions related to the notion of fault models are provided.

### 2.3.1 Formal Representation of an SDN Architecture

SDN architectures satisfy end-user requests/requirements by forwarding data in a given data plane. At the level of a switch in the data plane, forwarding decisions are defined by rules. To implement desired requirements during forwarding, network administrators/operators define requests to be implemented in the data plane. For instance, they impose some policies to be applied to the flows. The 'specification' in this case is defined by a set of (end-user) requirements that should be correctly implemented.

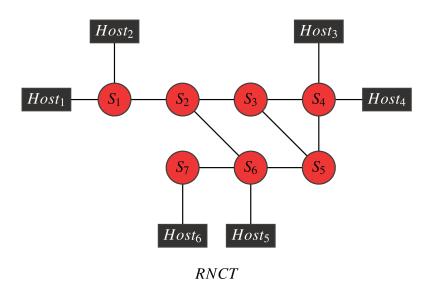

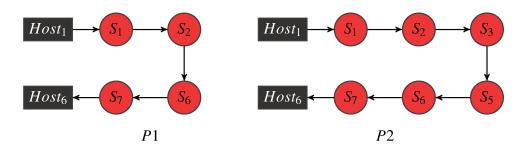

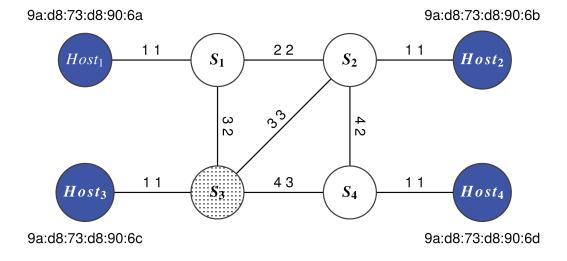

In the thesis, unless the context is explicitly indicated, we refer to the data plane as the Resource Network Connectivity Topology  $(RNCT^1)$  for which a formal definition is given in Chapter 4. An RNCT depicts the SDN components in the resource connectivity network. An informal description of a path in an RNCT is depicted in Definition 2.1. A more formal definition is provided in Chapter 4.

Figure 2.1 presents an example of a network topology consisting of one controller, seven switches and six hosts. Each switch is connected to the SDN controller.  $S_1$  is connected to hosts  $Host_1$  and  $Host_2$ ,  $S_4$  is connected to  $Host_3$  and  $Host_4$ ,  $S_6$  is connected to  $Host_5$  and  $S_7$  is connected to  $Host_6$ .

#### **DEFINITION 2.1.**

A *path* in an *RNCT* between two given hosts is a sequence of network devices that starts and ends with hosts and all other intermediary devices are switches.

Based on the topology of Figure. 2.1, the corresponding RNCT and some examples of its paths are illustrated in Figure. 2.2. In this example, the RNCT is a network with seven switches and six hosts.

Figure 2.2 - RNCT of the network topology in Figure 2.1 and examples of its paths

The presence of potential errors/bugs in the SDN architecture certainly breaks the intended

<sup>&</sup>lt;sup>1</sup>Hosting infrastructures can be physical or virtualized.

network functions. The errors might be due to the inconsistencies between end-users' (e.g., network administrators) logical requests and the actual flow-level implementations. Figure 2.1 shows a misbehaviour of an SDN architecture consisting in implementing a different request (marked in red in the data plane) than the desired/specified one (marked in green). Chapter 4 tackles this problematic and proposes a model based testing approach aiming to the detection of such misbehaviours.

### 2.3.2 Logic Circuit

The specification of a system can be represented by a *logic circuit* as the underlying model in model based testing. We propose this model for the testing approach developed in Chapter 5.

A sequential logic circuit consists of combinational logic and memory elements, namely latches. A *combinational circuit* is composed of logic gates (AND, OR, etc.); each logic gate implements a Boolean function. Unlike sequential logic circuits whose outputs are dependent on both their present inputs and their previous output, which gives them memory, i.e., state, the outputs of combinational logic circuits are only determined by the logic function of their current input, logic vectors of '0' or '1', at any given instant in time. Thus a combinational circuit is memoryless.

### **DEFINITION 2.2.**

A logic circuit, representing the system specification, is said to be *Complete* (or completely specified) if the output is defined for every possible input vector, otherwise, it is said to be *Partial*.

There are different formats of logic circuit representation. In this work, we consider the Berkley Logic Interchange Format (BLIF) [18]. In this format, a combinational circuit is described by the corresponding look-up table (LUT). An LUT contains a set of input/output Boolean vectors describing the circuit's behaviour. The LUT table of the partial specification, portrayed in Figure 2.3, is shown in Table 2.2.

Figure 2.4 shows an example of the BLIF file for the logic circuit of Figure 2.3. The names of external inputs and outputs are listed in the file. Then, following those declarations, the truth tables for each of the gates with their inputs and outputs are listed. For example, element n6 is a function of two arguments x0 and x2.

A logic circuit can be modelled as an AND-INVERTER Graph (AIG). In fact, a Boolean network is a directed acyclic graph with nodes representing logic gates and directed edges representing wires connecting the gates. AIG is a combinational Boolean network composed of two-input AND-gates and inverters [106]. In an AIG, each node has at most two incoming edges. A node with no incoming edges is a primary input. Primary outputs are represented using special output nodes. Each internal node in the AIG represents a two-input AND function.

### **Example**

Figure 2.3 illustrates an example of a partial specification (logic circuit) designed as an AIG.

### 2.3.3 Extended Finite State Machine

A state based model is one of the most powerful ways to represent a system Sys where a number of stimuli (inputs) is received by Sys and actions (outputs) are produced by Sys. For example, the specification of a system can be represented by a state based model such as

20 2. Background

Figure 2.3 – An example of a partial logic circuit specification  $c_{ex}$  illustrated designed as an AIG  $(c_{ex})$

| <i>x</i> 0, <i>x</i> 1, <i>x</i> 2 | z0, z1 |

|------------------------------------|--------|

| 010                                | 0 1    |

| 011                                | 10     |

| 111                                | 11     |

| 110                                | 10     |

Table 2.2 – The look-up table (LUT) of the in Figure 2.3

- . model cirex

- . inputs x0 x1 x2

- . outputs z0 z1

- . names x0 x2 n6 10 1

- . names x2 n6 n7 00 1

- . names x1 n7 z0 101

- . names x0 x2 n9

- 11 1

- . names x0 x2 n10 00 1

- . names n9 n10 n11 00.1

- . names x1 n11 z1

- 101

- . end

Figure 2.4 – A BLIF description of  $C_{ex}$ shown in Figure 2.3

Finite State Machine (FSM) or Extended Finite State Machine (EFSM) as the underlying model while testing.

These models are used to describe behaviours of sequential systems where outputs depend on inputs and the current state. This is to be opposed to combinational behaviours where the output is only dependent on the set of inputs as described earlier with combinational logic circuits in Subsection 2.3.2.

In this context, classical FSM for example can be used. An FSM is a transition system with a finite number of inputs, outputs, states and transitions each labeled by an input/output pair [48]. FSMs are widely used in various application domains, such as modeling and testing communication protocols, and other reactive systems.

States, transitions, inputs, and outputs are the building blocks of an FSM. The collection of states represents all the possible situations in which the FSM may be. The model goes through a sequence of transitions to reach a certain state. A state is some kind of a memory that represents the current state of the model. From a software point of view, a state can be a set of specific values for a collection of variables. A transition is an allowable two-state sequence that results in an output and must specify a starting state and a final state (of the transition). A transition usually means a change in the value for state variables. An input triggers a transition.

### **DEFINITION 2.3.**

Formally, an *FSM* [48] is a quintuple  $(S, I, O, h_S, S_{in})$ , where

- *S* is a finite set of states with the set  $S_{in} \subseteq S$  of initial states;

- *I* is a finite non-empty set of inputs;

- O is a finite non-empty set of outputs;

- $h_S \subseteq S \times I \times O \times S$  is a transition or behaviour relation, where a 4-tuple  $(s, i, o, s') \in h_S$  is

a transition.

If  $|S_{in}| = 1$ , then the machine is *initialized*, otherwise it is *non-initialized*. In this work, we consider initialized machines.

In spite of their good expressiveness, FSMs are not powerful enough to model in a succinct way practical systems. For example, systems which contain variables and where their operations depend on the variable values. The EFSM model extends the classical FSM model with input and output parameters, context variables, update functions and predicates defined over context variables and input parameters. It is more adequate to model complex reactive systems.

The contribution of Chapter 6 proposes an EFSM to model the switch-to-controller communication and investigates the problem of deriving input test sequences based on such model.

In the remaining of this subsection, we give formal definitions related to EFSM and a simple illustrative example.