# A DC-DC power converter study for High Voltage Direct Current (HVDC) grid: Model and control of the DC-DC Modular Multilevel Converter (M2DC)

Yafang Li

### ► To cite this version:

Yafang Li. A DC-DC power converter study for High Voltage Direct Current (HVDC) grid: Model and control of the DC-DC Modular Multilevel Converter (M2DC). Other. Ecole Centrale de Lille, 2019. English. NNT: 2019ECLI0006. tel-02384233

# HAL Id: tel-02384233 https://theses.hal.science/tel-02384233

Submitted on 28 Nov 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **CENTRALE LILLE**

### THESE

Présentée en vue d'obtenir le grade de

### DOCTEUR

En

### Spécialité : Génie électrique

Par

# Yafang LI

### DOCTORAT DELIVRE PAR CENTRALE LILLE

Titre de la thèse :

Etude d'un convertisseur DC-DC pour les réseaux haute tension à courant continu (HVDC) : modélisation et contrôle du convertisseur DC-DC modulaire multiniveaux (M2DC)

### A DC-DC power converter study for High Voltage Direct Current (HVDC) grid: Model and control of the DC-DC Modular Multilevel Converter (M2DC)

Soutenue le 11 Juillet 2019 devant le jury d'examen :

| Président          | LADOUX Philippe            | Professeur, Institut National Polytechnique de<br>Toulouse, LAPLACE             |

|--------------------|----------------------------|---------------------------------------------------------------------------------|

| Rapporteur         | BACHA Seddik               | Professeur, Université Joseph Fourier de Grenoble,<br>G2Elab                    |

| Rapporteur         | CARPITA Mauro              | Professeur, Haute Ecole d'Ingénierie et de Gestion du<br>Canton de Vaud, Suisse |

| Examinatrice       | CHAPALAIN Nadine           | Docteur, Ingénieur R&D, Mitsubishi Electric R&D<br>Centre Europe, Rennes        |

| Examinateur        | MERLIN Michaël Marc Claude | Lecturer, University of Edinburgh                                               |

| Directeur de thèse | LE MOIGNE Philippe         | Professeur, Centrale Lille, L2EP                                                |

| Invité             | DELARUE Philippe           | Maître de conférences, Université de Lille, L2EP                                |

| Invité             | GRUSON François            | Maître de conférences, Arts et Métier ParisTech,<br>Campus de Lille, L2EP       |

Thèse préparée dans le Laboratoire L2EP

Ecole Doctorale SPI 072 (Université de Lille, Artois, ULCO, UVHC, Centrale Lille)

To the future

# Remerciements

Je tiens à envoyer mes gratitudes envers les membres de jury et mes encadrants et collègues durant ces quatre ans de travail dans la langue de Molière pour exprimer mes respects et admirations à leur culture.

Tout d'abord, je tiens à remercier à M. Seddik BACHA, Professeur à l'Université Joesph Fourier de Grenoble et M. Mauro CARPITA, Professeur à Haute Ecole d'Ingénierie et de Gestion du Canton de Vaud, Suisse pour avoir accepté de rapporter sur cette thèse, et pour leur précieux temps accorder à la lecture du rapport et leurs remarques pertinentes. Je suis honorée d'avoir reçu les idées présentées lors de la soutenance de la part de M. Michäel Marc Claude MERLIN, lecturer à University of Edinburgh qui pourraient potentiellement améliorer le fonctionnement du convertisseur au travers de ses lectures rigoureuses. Mes remerciements vont également à M. Philippe LADOUX, Professeur à l'Institut National Polytechnique de Toulouse et Mme. Nadine CHAPALAIN, Ingénieur R&D à Mitsubishi Electric Rennes pour leurs remarques pertinentes qui complètent mes connaissances.

Ensuite, j'adresse mes profondes gratitudes à mes encadrants, M. Philippe LE MOIGNE, M. Philippe DELARUE et M. François GRUSON, avec lesquels j'ai eu honneur de passer ces quatre ans, sans qui je n'aurais pas eu cette chance de travailler sur le sujet et sans qui rien n'aurait abouti. Je remercie le temps qu'ils ont consacré, leur écoute, encouragements et leurs commentaires qui font la base de ce travail. Malheureusement, sur une si petite place, je ne peux pas citer tous leurs conseils enrichissant, que ce soit sur la thèse ou la vie quotidienne. Mais tous mes remerciements se résument à ces simples mots « Merci beaucoup ».

Enfin, je souhaite remercier à tous mes collègues, avec qui j'ai eu l'occasion d'échanger les idées (Le nombre de noms est indénombrable). Je crois que « chaque rencontre est un apprentissage ». L'apparition de chaque personne m'a permis de devenir cette personne actuelle. Merci d'avoir été là.

# Résumé étendu

#### Contexte

Lors du siècle précédent, les développements technico-économique de l'énergie électrique se sont basés sur les énergies fossiles (charbon, gaz naturel, pétrole et nucléaire). L'exploitation de ces énergies a provoqué une augmentation des émissions de gaz à effet de serre avec les conséquences que nous connaissons actuellement. Suite à une prise de conscience mondiale, des protocoles ont été signés et des démarches ont été mises en œuvre pour limiter les dégâts. L'une des principales actions consiste à limiter progressivement les sources d'énergies fossiles en les remplaçant par des sources d'énergies plus propres, (solaire et/ou éolien). Le potentiel du gisement éolien en Europe est très fort et un grand nombre de projet sont en développement.

En Europe, ces sources d'énergies renouvelables à haut gisement sont plutôt disponibles sur des sites en mer, en général au large. La localisation de ces sites, nécessite des câbles sous-marins (et/ou sous terrain). L'utilisation de la transmission en régime alternatif (sous acronyme anglophone : AC) est non faisable d'un point de vue technique. De plus, pour des raisons environnementales, d'acceptabilité de la société, des décisions politiques ont limité le développement de nouvelles lignes aériennes. Les investissements se sont donc orientés vers de liaisons enterrées, engendrant les mêmes contraintes que précédemment. De ce fait, la migration vers des liaisons en courant continu (sous acronyme anglophone : DC) pour les réseaux électriques en haute tension devient une nécessité face aux défis actuels.

Un défi majeur de ces dernières décennies était de proposer un système d'interfaçage entre les réseaux AC existant et les réseaux DC proposés. Cette interface a été dans un premier temps réalisée par des convertisseurs de puissance à base de thyristors appelés LCC (convertisseurs commutés par la ligne or Line Commutated Converter). Cette technologie permet de transiter une grande quantité de puissance (plusieurs GW) mais nécessite un gros dispositif de filtrage et de compensation de la puissance réactive. De plus, elle possède une dynamique relativement lente nécessitant l'inversion de polarité du câble.

L'émergence des convertisseurs de type source de tension (Voltage Source Converter, VSC) s'est faite suite aux développements technologiques et pour répondre aux exigences des cahiers des charges. Le recours à cette technologie se justifie en partie par le fait que les flux de puissance peuvent être commandés dans les deux sens sans changer la polarité de la tension continue et facilite l'intégration de sources d'énergies renouvelables tout en équilibrant les puissances sur des grandes étendues. Dans la littérature, il existe de nombreuses topologies de convertisseurs de type VSC, néanmoins une topologie sort du lot pour l'application des réseaux électriques continus en haute tension. Connue dans le domaine, sous la dénomination de Convertisseur Modulaire Multi-niveaux (Modular Multilevel Converter, MMC), cette topologie a été largement présentée dans la littérature, avec beaucoup de succès, par Dr. Lesnicar et Prof. Marquardt. Les avantages majeurs de cette topologie sont d'être modulaire (en terme de tension, puissance, etc.) tout en apportant la possibilité de travailler avec des fréquences de commutation assez faibles (limitant les pertes) et garantissant une meilleure performance harmonique suffisamment élevée pour limiter les filtres.

Cette technologie est, depuis sa 1<sup>ère</sup> publication, devenue mature et industriellement utilisée dans les liaisons HVDC (mentionnées précédemment comme les réseaux continus en haute tension) comme TRANSBAY, INELFE, Zhoushan Multi-terminal DC Interconnection et Nan'ao.

L'augmentation de la fiabilité du réseau DC se fera comme pour le réseau AC au travers du maillage du réseau. Basé sur ce constat, le concept de réseau Continu Multi-Terminaux (MTDC) émerge depuis une dizaine d'années permet aussi d'assurer une meilleure continuité de service, de renforcer les interconnexions entre différentes zones de l'Europe voire de plusieurs continents avec le concept de SuperGrid dans la mer du nord.

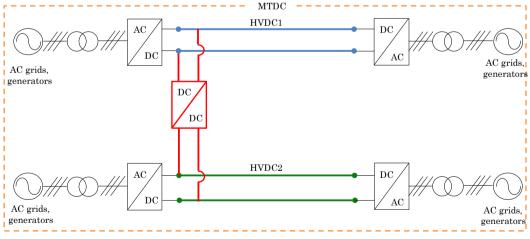

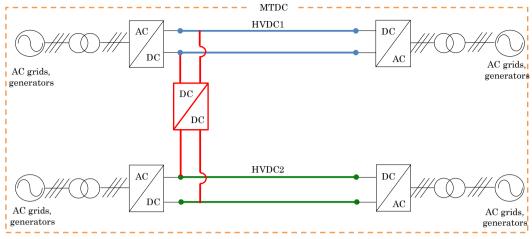

La multitude de projets de liaison HVDC indique que les premiers réseaux MTDC se feront par l'interconnexion de plusieurs liaisons. L'interconnexion directe de plusieurs liaisons HVDC ne sera assurément pas possible dans une grande partie des cas. En effet, il n'est pas certain que les niveaux de tension, le système de mise à la terre de ces réseaux et/ou que le propriétaire/constructeur de ces liaisons soient identiques. Il s'avère donc nécessaire d'introduire des convertisseurs statiques DC/DC pour assurer l'interfaçage de ces différents réseaux comme le montre la figure ci-dessous (fig. i).

fig. i. Réseau DC Multi-Terminaux

La technologie de convertisseur DC/DC haute tension et haute puissance pour le réseau HVDC n'est pas encore suffisamment développée pour être proche de l'industrialisation dont les principaux défis liés au convertisseur DC/DC sont la difficulté de monter en tension et la protection du défaut. Cette thèse se focalise sur l'étude et le contrôle de ces convertisseurs existants de la littérature et plus particulièrement sur la topologie du convertisseur DC-DC Modulaire Multiniveau (M2DC).

#### Plan de la thèse

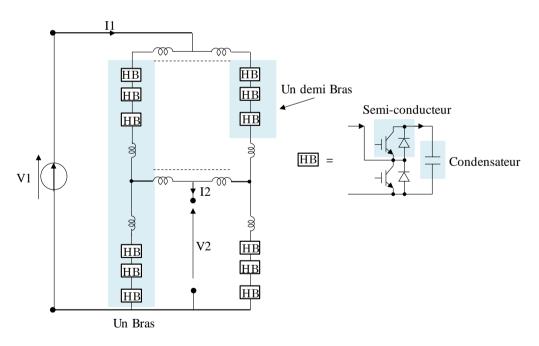

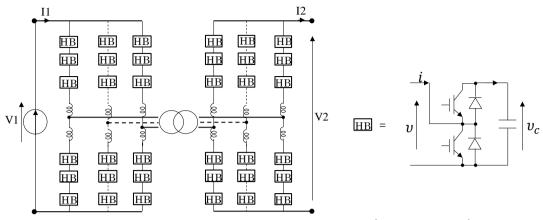

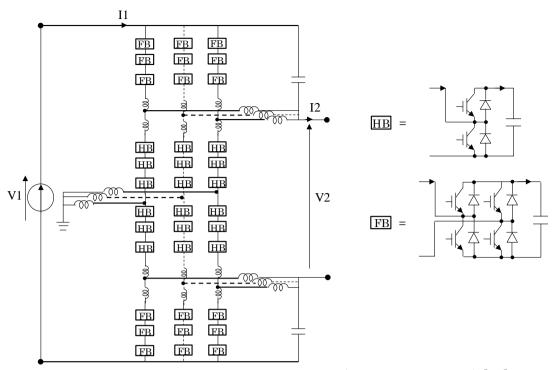

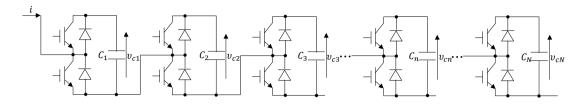

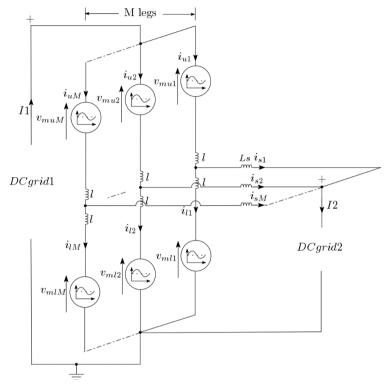

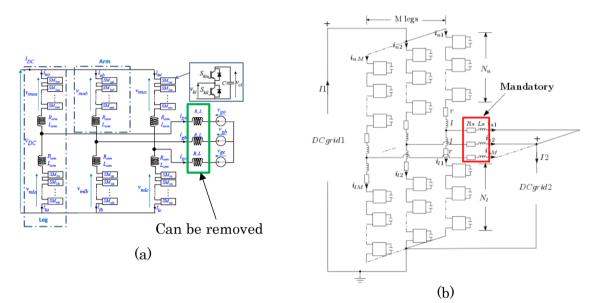

Le Chapitre 1 de cette thèse introduit dans un premier temps le contexte de cette l'étude et confirme la nécessité de développer des topologies de convertisseur DC/DC pour les réseaux HVDC. Dans un second temps, un état de l'art des convertisseurs DC/DC passera en revue les topologies existantes de la littérature. Deux familles de convertisseurs peuvent être définies, les convertisseurs classiques et modulaires. Cette deuxième partie est constituée de deux types de conversion, direct ou indirect. Le direct a un seul étage tandis que l'indirect en a au moins deux, car ce dernier se réalise par au moins un DC/AC et un AC/DC. Parmi les propositions, le convertisseur DC-DC modulaire multiniveau (M2DC) est sélectionné pour sa structure potentiellement intéressante. Ce convertisseur est présenté dans fig. ii.

fig. ii. Convertisseur DC-DC modulaire multiniveaux

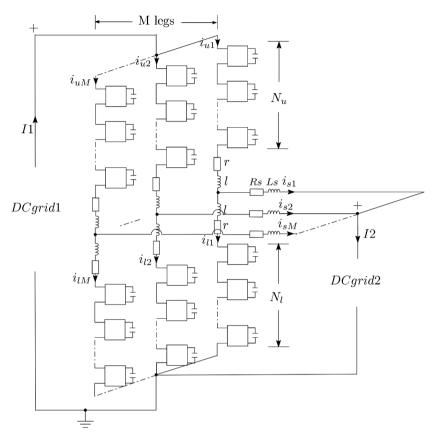

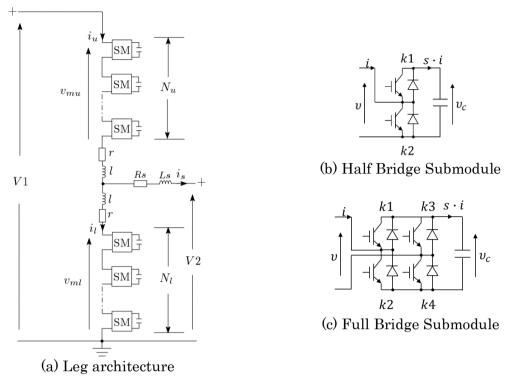

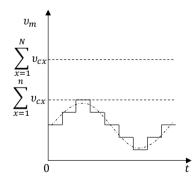

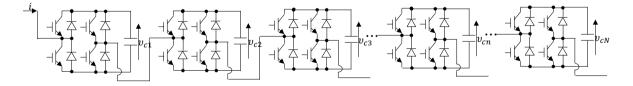

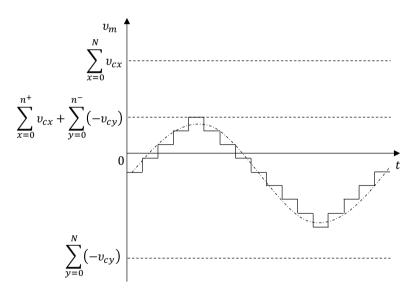

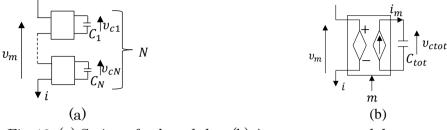

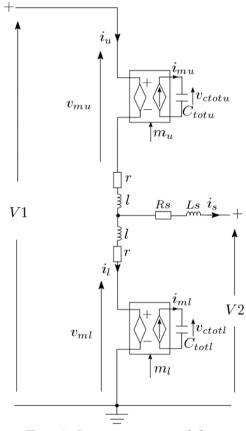

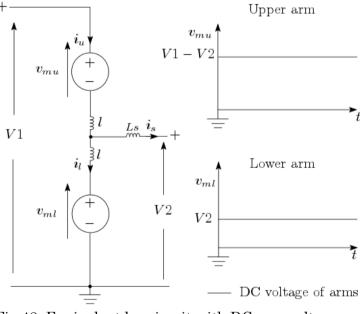

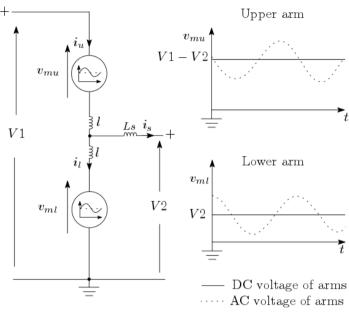

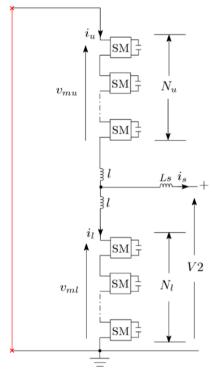

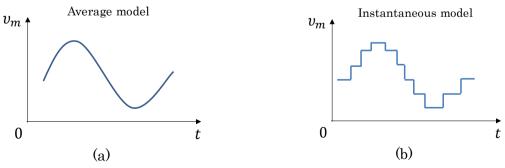

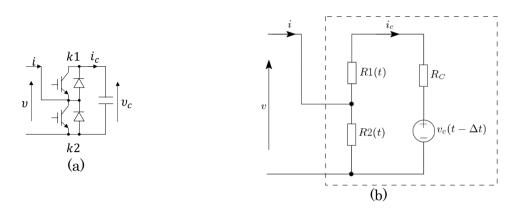

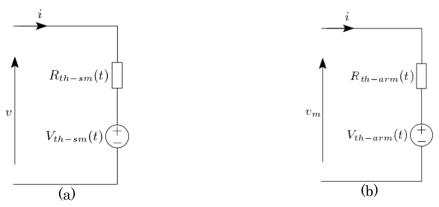

Le Chapitre 2 présente la topologie du convertisseur M2DC et son principe de fonctionnement. Ce chapitre commence par une analyse générale de l'architecture du convertisseur. La topologie est composée de sous-modules (demi-pont ou pont complet) identiques à ceux nécessaires aux MMCs. Comme ce dernier, le M2DC bénéficie donc des pertes par commutation assez faibles, d'une modularité d'une évolutivité forte. De plus, le M2DC hérite directement d'une maturité relative, provenant de l'industrialisation du MMC, plus importante que d'autre topologie. Le principe de fonctionnement du convertisseur M2DC et sa conception sont centrés sur la topologie de sous-modules en demi-pont. La première partie établit le modèle moyen équivalent des bras du M2DC. Le modèle de bras permet d'identifier le comportement global du convertisseur en régime établi en négligeant la commutation des semi-conducteurs.

L'étude du comportement global se poursuit par la présentation du moyen d'équilibrer l'énergie stockée dans les condensateurs des sous-modules. Le modèle moyen du convertisseur permet d'étudier et d'illustrer le principe de fonctionnement, les caractéristiques et les contraintes électriques du convertisseur.

Dans le Chapitre 3, une stratégie de contrôle du convertisseur est passée en revue. Le premier objectif est de confirmer les comportements statiques analysés dans le chapitre précédent. Le second est d'étudier les comportements dynamiques du M2DC au travers des énergies stockées internes. Le contrôle de l'énergie comprend deux boucles en cascade, une boucle de courant qui est la boucle interne et une boucle d'énergie (ou boucle de tension) qui est la boucle externe. Étant donné que chaque branche du convertisseur doit fonctionner de la même manière (avec les courants/tensions déphasés pour ne pas avoir de composante AC dans les réseaux DC), le contrôle présenté dans ce chapitre s'applique à n'importe quel nombre de branches. Une opération de découplage du modèle est nécessaire pour fiabiliser la commande. Le chapitre commence par la proposition d'un modèle découplé obtenu par un changement de variables. Ce découplage modifie également le cadre de référence sur lequel le modèle de convertisseur a été construit dans le chapitre. Sur la base du modèle découplé, des boucles de contrôle sont développées pour valider l'analyse en régime permanent du chapitre précédent et permettre une meilleure compréhension du comportement dynamique du convertisseur. Une étude des performances dynamiques du convertisseur permet de comprendre les avantages et les limitations du contrôle proposé.

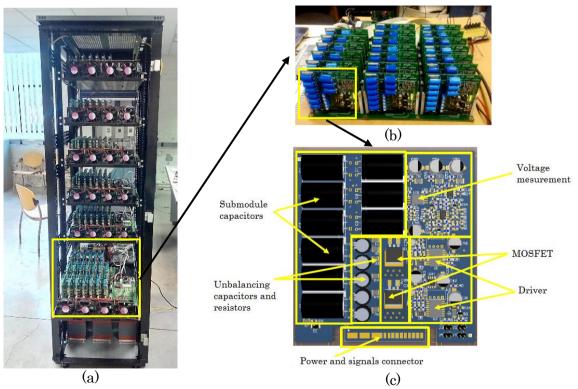

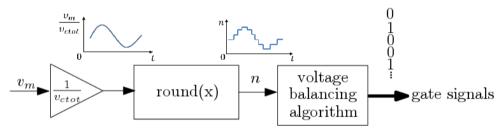

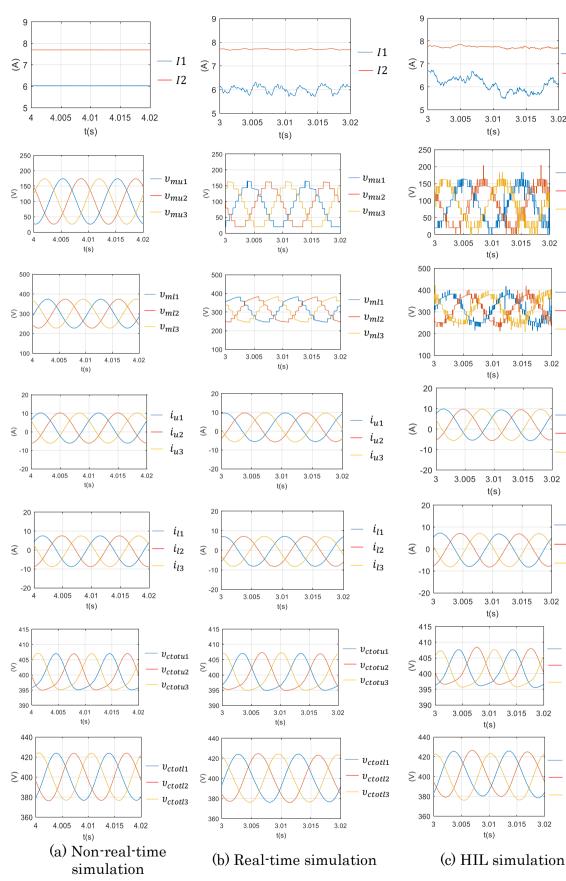

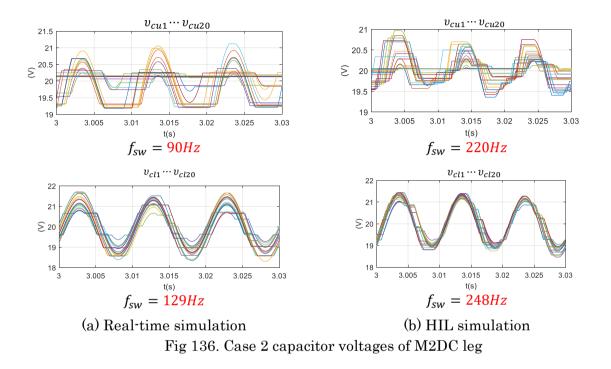

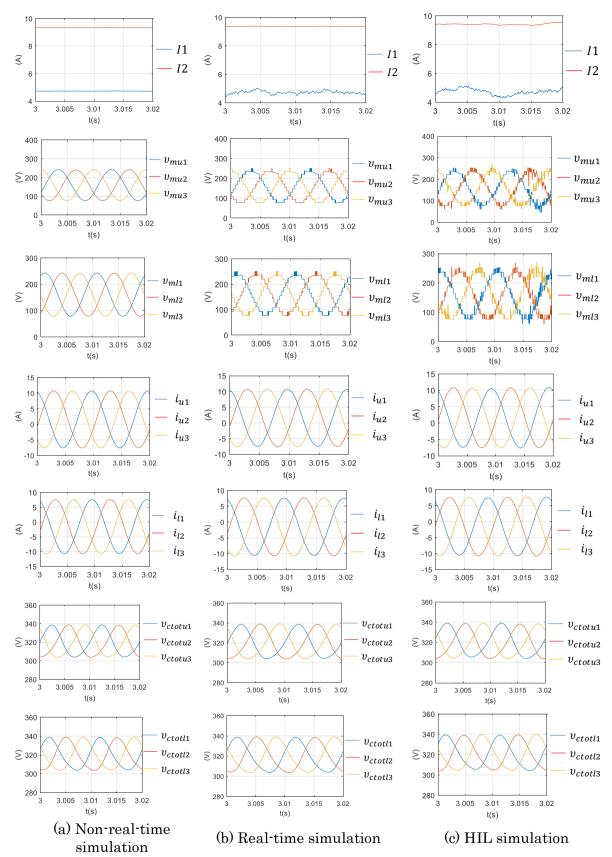

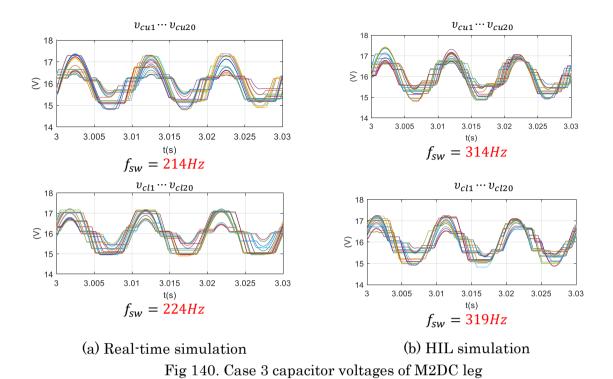

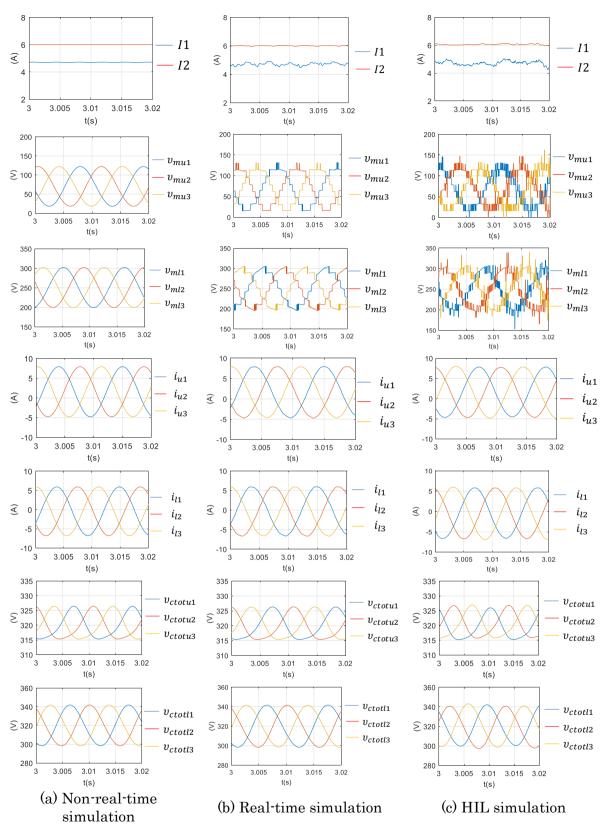

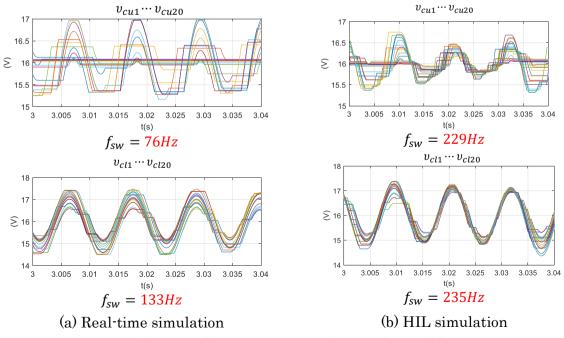

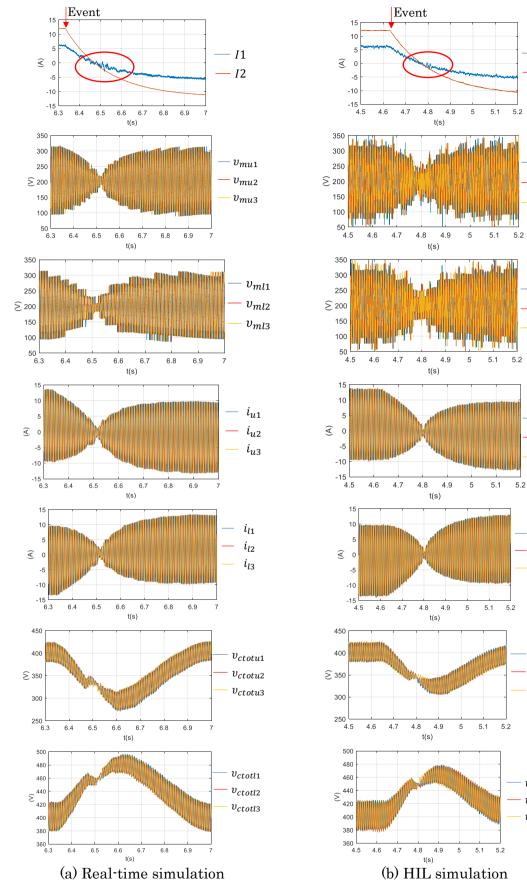

Le quatrième chapitre se focalise sur la validation de l'implantation du contrôle développé précédemment sur un DSP cible de type Texas Instrument TMS320F28377D. La validation de ce contrôle est réalisée à l'aide des outils de simulation temps réel et avec un environnement de test HIL (Hardware in the Loop). Cette validation se base sur les paramètres non modifiables du convertisseur MMC présent au laboratoire L2EP (Laboratoire d'électrotechnique et de puissance de Lille) mis au point lors de précédents projets (nombre de sous modules, sous-modules en demi-pont, valeur des condensateurs). Ce chapitre commence par une description des cas d'étude se basant sur le prototype MMC associé au cas test du groupement CIGRE B4.76 travaillant sur ce type de convertisseur. La méthodologie de développement du contrôle est ensuite présentée en commençant par la partie simulation temps réel du convertisseur M2DC se basant sur un système de technologie OPAL-RT puis sur la partie simulation HIL. Le modèle instantané du convertisseur et du contrôle rapproché des sous-modules est présenté. Ce dernier a pour vocation de maintenir l'équilibrage des tensions flottantes des condensateurs des sous-modules dans un bras tout en générant la tension de référence que lui demande le contrôle éloigné. Ce chapitre se termine par la comparaison sur les résultats entre la simulation Matlab (dite hors ligne), la simulation temps réel et le test HIL aussi bien sur le régime statique que dynamique. Ces conclusions montrent que le prototype actuel du MMC ne peut pas être utilisé dans certains cas test car la capacité interne des sous-module est trop faible pour l'application M2DC. La partie HIL montre aussi qu'il est nécessaire d'améliorer la stratégie de contrôle à puissance nulle pour des raisons de stabilité numérique qui n'ont jamais été mise en évidence en simulation hors ligne ou temps réel.

#### Les conclusions de la thèse

Les réseaux à Courant Continu (HVDC) représentent une solution fiable et moins chère pour transmettre l'électricité haute tension et forte puissance sur de longues distances. Pour augmenter la flexibilité de ces réseaux, les réseaux Continus Multi-Terminaux (MTDC) sont proposés pour interconnecter différentes liaisons DC. Dans les interconnections, des convertisseurs DC/DC de puissance sont nécessaires au cas où les liaisons DC ne sont pas identiques. Donc, l'objective de cette thèse est d'étudier un convertisseur DC/DC haute tension et forte puissance.

En réponse à la problématique liée au convertisseur DC/DC « haute tension forte puissance », le premier chapitre révise les structures proposées dans la littérature. En comparant leur volumes et rendements, le convertisseur « DC-DC modulaire multiniveaux » (M2DC) a été choisi pour les applications HVDC.

Le chapitre 2 propose le modèle moyen et explique le fonctionnement du convertisseur M2DC. Pendant les analyses, il observe que le M2DC a besoin des composants alternatif qui sont limités par la structure du convertisseur. La fin de ce chapitre propose les dimensionnements des inductances des demi-bras et des condensateurs des sous-modules.

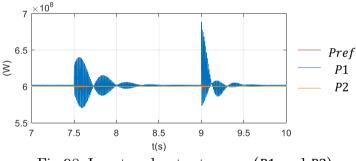

Les analyses théoriques du chapitre 2 sont validées dans le troisième chapitre. Ces validations sont réalisées par un simple contrôle du convertisseur en inversant le modèle moyen. Les simulations sous Matlab ont également validé la capacité de la haute tension et forte puissance du convertisseur par le cahier des charges du CIGRE.

Dans le chapitre 4, un dimensionnement du M2DC en utilisant le MMC existant du L2EP est proposé, tout d'abord, basé sur les analyses théoriques du deuxième chapitre. Le chapitre propose ensuite une méthodologie d'implémentation de contrôle sous HIL. La fin du chapitre valide le dimensionnement et le contrôle du convertisseur par des

comparaisons de trois types de simulation : simulation hors ligne, simulation en temps réel et simulation HIL.

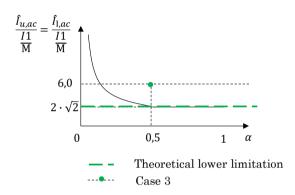

Sur le M2DC, il est aussi possible d'en conclure que ce convertisseur est plus adapté pour un ratio  $\alpha > 0.5$  du aux moindres courants alternatives internes, donc moins de pertes.

Toutefois, pour avoir une vision plus complète sur les structures proposées dans la littérature, il est nécessaire de comparer le M2DC avec les autres structures qui ne sont pas étudiées dans la thèse.

En plus, certaines perspectives concernant le M2DC sont proposées pour améliorer sa performance. Ces perspectives concernent le dimensionnement, le contrôle éloigné, le contrôle rapproché et l'intégration du M2DC dans le MTDC.

### Mots-clés :

MTDC, DC/DC, M2DC, modélisation, analyse en régime établi, contrôle, Simulation en Temps Réel, Hardware-In-the-Loop (HIL)

# Contents

| Nomenclature |        | V             |                                                       |    |

|--------------|--------|---------------|-------------------------------------------------------|----|

| Int          | troduc | ion           |                                                       | 1  |

| I            | Cont   | ext and state | e of the arts for HVDC DC/DC converters               | 3  |

|              | I.1    | Backgroun     | d                                                     | 3  |

|              |        | I.1.1 AC a    | ransmission versus DC transmission                    | 3  |

|              |        | I.1.2 Exis    | ting and future installation equipment for HVDC grids | 6  |

|              |        | I.1.3 Mul     | ti-Terminal DC transmission                           | 9  |

|              |        | I.1.4 CIG     | RE test case analysis                                 | 11 |

|              |        | I.1.5 Prob    | lem statement                                         | 13 |

|              | I.2    | State of the  | e arts for DC/DC converters                           | 13 |

|              |        | I.2.1 Clas    | sical DC converters                                   | 14 |

|              |        | I.2.2 Mod     | ular DC converters                                    | 18 |

|              | I.3    | Conclusion    |                                                       | 28 |

|              | I.4    | References    |                                                       | 30 |

| II           | DC-I   | C Modular     | Multilevel Converter (M2DC)                           | 35 |

|              | II.1   | Introductio   | n                                                     | 35 |

|              | II.2   | Topology of   | the DC-DC Modular Multilevel Converter                | 35 |

|              | II.3   | Submodule     | topologies                                            | 38 |

|              |        | II.3.1 Hali   | <sup>e</sup> Bridge Submodule                         | 38 |

|              |        | II.3.2 Full   | -Bridge Submodule                                     | 40 |

|              | II.4   | Average m     | odel of a string of submodules                        | 41 |

|              |        | II.4.1 Volt   | age relations for a string of submodules              | 42 |

|              |        | II.4.2 Curr   | rent relations of a submodule string                  | 43 |

|              |        | II.4.3 Ene    | rgy relations of a string of submodules               | 44 |

|              | II.5   | Steady stat   | e analysis                                            | 45 |

|              |        | II.5.1 Stat   | ic analysis of an M2DC leg                            | 46 |

|              |        | II.5.2 DC     | buses currents                                        | 48 |

|              |        | II.5.3 Ope.   | rating principle                                      | 50 |

|              | II.6   | Model of M    | 2DC Converter and parameters design                   | 52 |

|              |        | II.6.1 DC a   | and AC behavior modeling                              | 53 |

|              |        |               |                                                       |    |

|          | II.6.2 Degrees of freedom                                        | 55  |

|----------|------------------------------------------------------------------|-----|

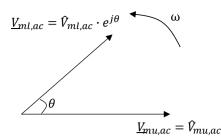

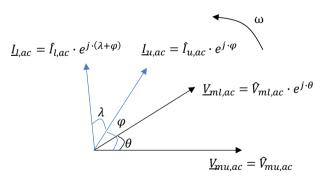

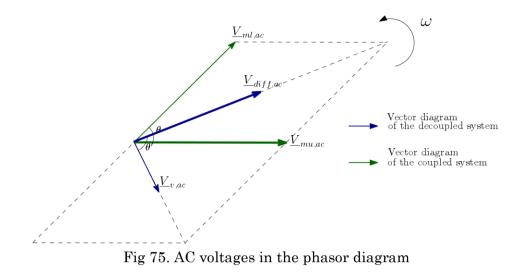

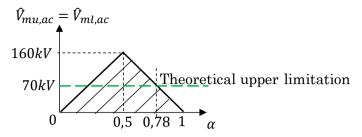

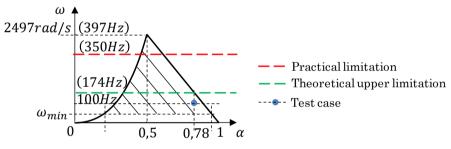

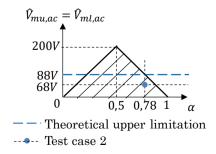

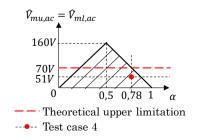

| II.7     | AC voltage components analysis                                   | 56  |

|          | II.7.1 Choices of angle $\theta$ and amplitudes of AC voltages   | 56  |

|          | II.7.2 Limits of operation                                       | 58  |

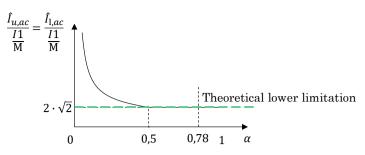

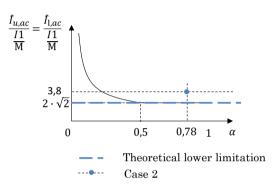

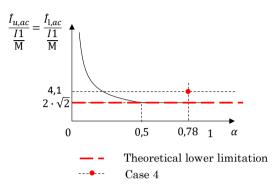

| II.8     | AC currents analysis with $Ls \gg l$                             | 64  |

|          | II.8.1 Minimized AC currents                                     | 64  |

|          | II.8.2 Analysis of arm currents                                  | 66  |

| II.9     | Arm inductance design and Capacitance design                     | 70  |

|          | II.9.1 Arm inductance design                                     | 70  |

|          | II.9.2 Capacitance design                                        | 71  |

| II.10    | Conclusion                                                       | 75  |

| II.11    | References                                                       | 76  |

|          |                                                                  |     |

| III Conv | erter control strategy and dynamics                              | 79  |

| III.1    | Introduction                                                     | 79  |

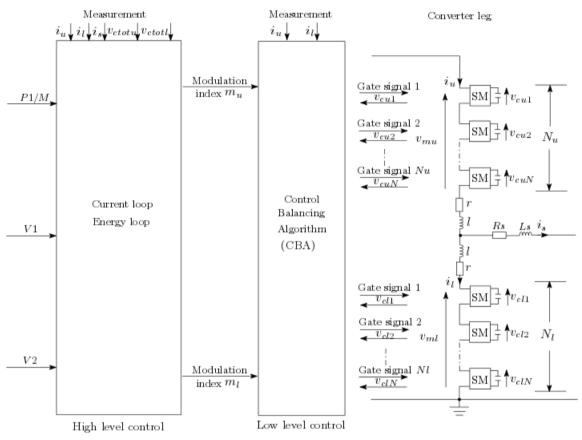

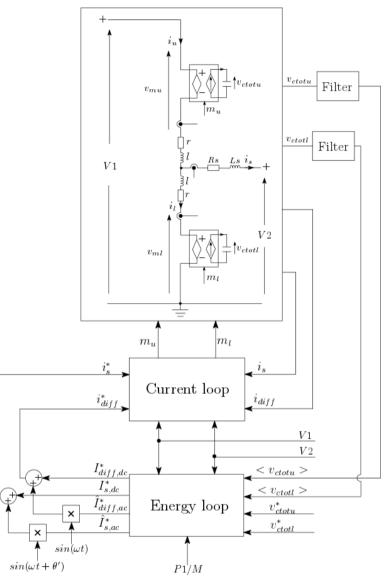

| III.2    | Control architecture                                             | 79  |

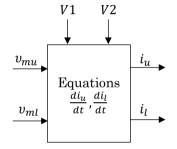

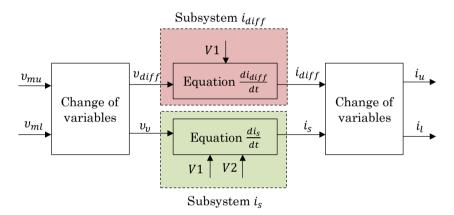

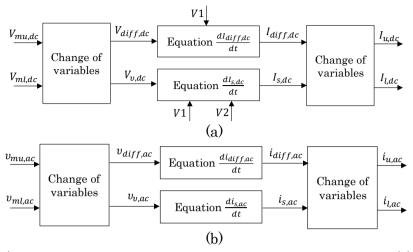

| III.3    | Decoupling average current model                                 | 81  |

|          | III.3.1 Decoupled average model                                  | 82  |

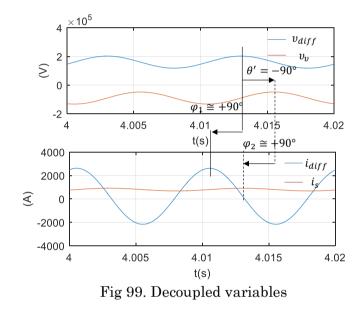

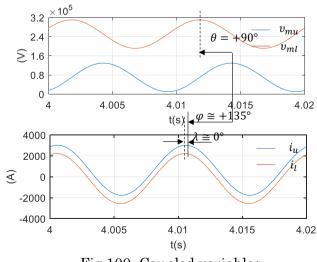

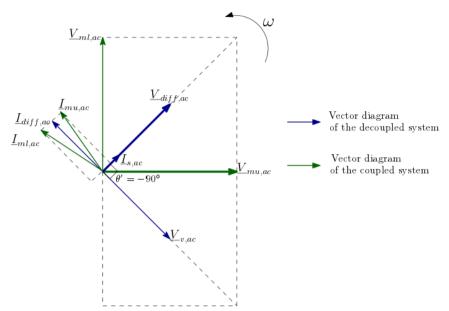

|          | III.3.2 Steady state analysis of variables                       | 84  |

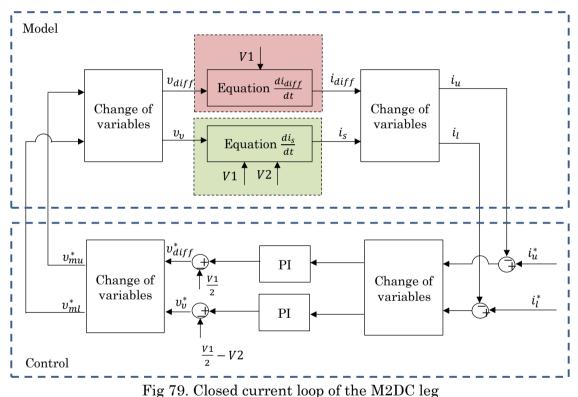

| III.4    | Current loop design                                              | 87  |

|          | III.4.1 Continuous time transfer functions                       | 87  |

|          | III.4.2 PI controller and closed current loop                    | 88  |

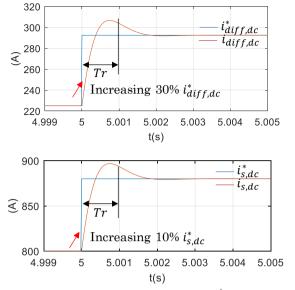

|          | III.4.3 Static and dynamic analysis of the closed current loop   | 90  |

| III.5    | Energy model                                                     | 96  |

|          | III.5.1 Energy definition                                        | 96  |

|          | III.5.2 Energy model                                             | 97  |

|          | III.5.3 Steady state analysis of energy stability                | 99  |

| III.6    | Energy loop design                                               | 100 |

|          | III.6.1 Equivalent Low pass filter                               | 100 |

|          | III.6.2 Continuous time transfer function and closed energy loop | 101 |

|          | III.6.3 Static and dynamic analysis of the energy loop           | 103 |

| III.7    | Validation of AC components using average model                  | 107 |

|          | III.7.1 Validation of frames of reference                        | 108 |

|          | III.7.2 Validation of limitations of AC components               | 109 |

|          | III.7.3 M2DC global simulation results of CIGRE test case        | 110 |

| III.8    | Conclusion                                                       | 114 |

| III.9    | References                                                       | 115 |

| IV Impl     | ementation: Laboratory-based Real-Time simulation and Contro    | l Hardware- |

|-------------|-----------------------------------------------------------------|-------------|

| In-the-Loop | (HIL) simulation                                                | 117         |

| IV.1        | Introduction                                                    | 117         |

| IV.2        | Description of test scenarios                                   | 119         |

|             | IV.2.1 Selection of secondary inductor and DC voltages          | 119         |

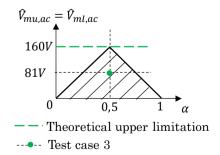

|             | IV.2.2 AC voltage limitation                                    | 120         |

|             | IV.2.3 DC current leg limitation                                | 121         |

|             | IV.2.4 AC frequency selection                                   | 121         |

|             | IV.2.5 Selection of transmission power                          | 122         |

| IV.3        | Control development methodology: definitions and simulation 124 | development |

|             | IV.3.1 Real-time simulation definition                          | 124         |

|             | IV.3.2 HIL simulation definition                                | 125         |

|             | IV.3.3 Simulations development methodology                      | 127         |

| IV.4        | Instantaneous model of an arm                                   | 128         |

| IV.5        | Low-level control                                               | 130         |

| IV.6        | Description of simulation devices                               | 131         |

|             | IV.6.1 Description of real-time simulation devices              | 131         |

|             | IV.6.2 Presentation of HIL setup                                | 132         |

| IV.7        | Comparison and validation                                       | 134         |

|             | IV.7.1 Simulation results in the steady state                   | 134         |

|             | IV.7.2 Dynamic state: case 1                                    | 151         |

| IV.8        | Conclusion                                                      | 153         |

| IV.9        | References                                                      | 155         |

| V Gene      | ral conclusion and perspectives                                 | 157         |

# V General conclusion and perspectives

# Nomenclature

Lists of symbols used in this work are found in the following descriptions.

| Acronyms          |                                                               |

|-------------------|---------------------------------------------------------------|

| AC                | Alternative Current                                           |

| ADC               | Analog-to-Digital Converter                                   |

| CBA               | Control Balancing Algorithm                                   |

| CIGRE             | Conseil International des Grands Réseaux Electriques          |

| CPU               | Central Processing Unit                                       |

| $\mathbf{CSC}$    | Current Source Converter                                      |

| DAB               | Dual Active Bridge converter                                  |

| DC                | Direct Current                                                |

| DQ transformation | Direct-Quadrature transformation                              |

| DSP               | Digital Signal Processor                                      |

| $\mathbf{FB}$     | Full Bridge                                                   |

| $\mathbf{FC}$     | Flying Capacitors converter                                   |

| FPGA              | Field-Programmable Gate Array                                 |

| FTBO              | Fonction Transfer en Boucle Ouverte (open loop transfer       |

|                   | function)                                                     |

| FTBF              | Fonction Transfer en Boucle Fermée (closed loop transfer      |

|                   | function)                                                     |

| HB                | Half Bridge                                                   |

| HIL               | Hardware In-the-Loop                                          |

| HuT               | Hardware under Test                                           |

| HVDC              | High-Voltage Direct Current                                   |

| IEA               | International Energy Agency                                   |

| IGBT              | Insulated Gate Bipolar Transistor                             |

| L2EP              | Laboratoire d'Electrotechnique et d'Electronique de Puissance |

|                   | de Lille                                                      |

| LCC               | Line Commutated Converter                                     |

| NLC               | Nearest Level Control                                         |

| NPC               | Neutral-Point-Clamped converter                               |

| NVC               | Nearest Vector Control                                        |

| M2DC              | DC-DC Modular Multilevel Converter                            |

| MMC               | Modular Multilevel Converter                                  |

| MOSFET            | Metal Oxide Semiconductor Field Effect Transistor             |

| MTDC              | Multi-Terminal Direct Current                                 |

| Mtoe              | Million tons of oil equivalent energy                         |

| PI                | Proportional Integral                                         |

| PID               | Proportional Integral Differential                            |

|                   |                                                               |

| PR       | Proportional Resonance                                      |  |

|----------|-------------------------------------------------------------|--|

| PLL      | Phase-Locked Loop controller                                |  |

| PWM      | Pulse Width Modulator                                       |  |

| RoS      | Rest of System                                              |  |

| RT       | Real-Time                                                   |  |

| SACOI    | Sardinia-Corsica-Italy                                      |  |

| SM       | Submodule                                                   |  |

| SHE      | Selective Harmonic Elimination                              |  |

| SVM      | Space-Vector Modulation                                     |  |

| TWENTIES | Transmission system operation with a large penetration of   |  |

|          | wind and other renewable electricity sources in electricity |  |

|          | networks using innovative tools and integrated energy       |  |

|          | solutions                                                   |  |

| VSC      | Voltage Source Converter                                    |  |

| XLPE     | cross-linked polyethene insulation                          |  |

## Subscripts, circumflexes and prefixes

| Complex conjugate |

|-------------------|

| Sum               |

| Difference        |

| Peak value        |

| Vector            |

| Average value     |

| Opposite          |

| Upper/lower arm   |

| Reference         |

| DC components     |

| AC components     |

|                   |

### Converter and grid parameters

| ų i        |                                                   |

|------------|---------------------------------------------------|

| <i>V</i> 1 | High pole-to-ground DC voltage side               |

| V2         | Low pole-to-ground DC voltage side                |

| <i>I</i> 1 | DC current of high DC voltage side                |

| <i>I</i> 2 | DC current of low DC voltage side                 |

| <i>P</i> 1 | Transmission power seen from high DC voltage side |

| P2         | Transmission power seen from low DC voltage side  |

| Pref       | Transmission power reference                      |

| P1ref      | Power reference of high DC voltage side           |

| P2ref      | Power reference of low DC voltage side            |

| α          | DC voltage ratio                                  |

| Μ          | Number of legs                                    |

| Ν          | Number of submodules per arm                      |

| С          | Submodule capacitance                             |

|            |                                                   |

| C <sub>tot</sub> | Capacitance of equivalent arm model |

|------------------|-------------------------------------|

| l                | Arm inductance                      |

| r                | Parasitic arm resistance            |

| Ls               | Secondary inductance                |

| Rs               | Parasitic secondary resistance      |

Variables

| m                 | Modulation index                                    |

|-------------------|-----------------------------------------------------|

| n                 | Inserted number of submodules                       |

| t                 | Time                                                |

| i <sub>u,l</sub>  | Current of upper and lower arms                     |

| i <sub>s</sub>    | Secondary current                                   |

| $v_{mu,l}$        | Voltages of upper and lower arms                    |

| i <sub>diff</sub> | Average current of two arm currents                 |

| $v_{diff}$        | Average voltage of two arm voltages                 |

| $v_v$             | Half of difference of two arm voltages              |

| v <sub>c</sub>    | Submodule capacitor voltage                         |

| $v_{ctot}$        | Capacitor voltage of equivalent arm model           |

| i <sub>m</sub>    | Current of capacitor of equivalent arm model        |

| W <sub>C</sub>    | Stored energy of equivalent arm model               |

| $W_{u,l}$         | Stored energy in upper and lower arms               |

| $W_c^{\Sigma}$    | Stored capacitor energy per leg                     |

| $W_c^{\Delta}$    | Imbalanced capacitor energy                         |

| $P_{DC}$          | Average value of power of DC component              |

| $p_{DC}$          | Instantaneous power of DC component                 |

| P <sub>AC</sub>   | Active power of AC component                        |

| $p_{u,l}$         | Arm instantaneous power                             |

| $P_{u,l}$         | Arm average power                                   |

| λ                 | Phase angle between $i_u$ and $i_l$                 |

| arphi             | Phase angle between $i_u$ and $v_{mu}$              |

| $\varphi_1$       | Phase angle between $i_{diff,ac}$ and $v_{diff,ac}$ |

| $\varphi_2$       | Phase angle between $i_{s,ac}$ and $v_{v,ac}$       |

| θ                 | Phase angle between $v_{mu}$ and $v_{ml}$           |

| heta'             | Phase angle between $v_{diff}$ and $v_v$            |

| f                 | Fundamental AC frequency                            |

| ω                 | Fundamental angular frequency / pulsation           |

|                   |                                                     |

### Controller parameters and transfer functions

| Кр         | Proportional Gain                     |

|------------|---------------------------------------|

| Ki         | Integral Gain                         |

| G(s)       | Canonical form of second order system |

| Tr         | Response time                         |

| $\omega_n$ | Natural Frequency                     |

| ξ               | Damping ratio                                  |

|-----------------|------------------------------------------------|

| $H_{diff}(s)$   | Transfer function of the subsystem $i_{diff}$  |

| $H_s(s)$        | Transfer function of the subsystem $i_s$       |

| $H^{\Sigma}(s)$ | Transfer function of the energy $W_c^{\Sigma}$ |

| $H^{\Delta}(s)$ | Transfer function of the energy $W_c^{\Delta}$ |

# Introduction

More and more energy is required to satisfy our daily electricity demand. Facing climate change and preserving at the most environment, modern electricity production is changing from burning fossil fuels to clean renewable energy (solar/hydro/biomass/wind/ocean/geothermal energy, etc.).

Electrical energy can be transmitted in two ways: AC transmission or DC transmission. Historically, AC transmission is the most used electricity transportation thanks to its low losses and low costs, but limited by the line capacitance in long distance transportation. Nowadays, DC transmission used for dozens of years has been proved more suitable and reliable for long distance transmission thanks to its no reactive power and no need of compensation. Thereby, as renewable energy generators are usually far from consumers, DC transmission is deemed more suitable than AC transmission.

So far, most DC links are "Point to Point" with electricity transmitted from one converter station to another. To improve the power flow control and connect different existing DC links, MTDC grids are necessary with three or more converter stations. The first industrially realized MTDC grids has parallel connections using thyristor technology DC links with the same DC voltage on each converter stations. With the escalated number of DC links, DC voltage of each link can be different, as well as the converter technology. HVDC DC/DC converters are mandatory to connect these different DC voltage links together.

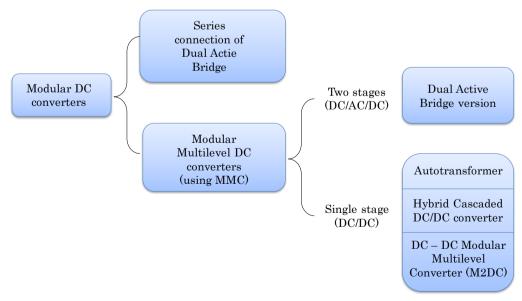

An example of these requirements is illustrated in the CIGRE test case, where each DC/DC converter should have more than 100kV of voltage capability, more than 100MW of power capability and bi-directional power transmission. The converter satisfying these requirements is still unknown due to voltage and power level regarding the semiconductor technology. Thereby, with high voltage and high power issue, Chapter 1 reviews existing potential DC/DC topologies. These existing topologies are presented in two categories: classical DC/DC converters and modular DC/DC converters. The classical DC/DC converters are conventional non modular topologies, such as buck, double buck and flying capacitors DC converters. In modular DC/DC converters, a series connection of Dual Active Bridges and Modular Multilevel DC Converters using Modular Multilevel Converter (M2DC) has been selected as an investigation subject.

Focusing on M2DC, Chapter 2 proposes a mathematical model and investigates its operation principle in steady state to understand the converter limitations. This analysis will be helpful for the converter design and is the central part of the thesis.

Based on the converter model, a basic control algorithm is proposed in Chapter 3 to validate the analysis presented in Chapter 2. The principle is to maintain energy of each capacitor of the converter. Using the proposed control, the converter theoretical analysis is confirmed with Matlab simulations.

Once the converter is analyzed theoretically (Chapter 2) and confirmed with simulations (Chapter 3), its implementation in an existing smaller scaled laboratory MMC mock-up is investigated in Chapter 4. Firstly, a design method of an M2DC based on MMC is proposed. Then, this chapter develops a methodology of control implementation in Hardware-In-the-Loop (HIL) simulation, which is a preparation for a safe and secure M2DC practical test.

Finally, a conclusion for the realized work is presented and perspectives are discussed, which includes a necessary performance comparison between other topologies and M2DC, and also propositions to improve M2DC performances.

# I Context and state of the arts for HVDC DC/DC

### converters

### I.1 Background

According to the International Energy Agency (IEA) statement, global energy demand grew by 2.1% in 2017, which is more than twice the growth rate in 2016. It reached an estimated 14 gigatonnes of oil equivalent energy (Mtoe), in which fossil fuels are the principal growth (70%) [1], [2]. At the same time, IEA states also that global energy related CO2 emission grew by 1.4% in 2017 than 2016, reaching a historical high of 32.5 gigatonnes, which contrasts with the demand of Paris Agreement established in December 2015.

However, it is hopeful to see that emissions dropped in some countries in 2017, such as United States, United Kingdom, Mexico and Japan, thanks to coal-to-gas switching, higher renewable based electricity generation and nuclear generation [1]. Moreover, China, which is the "first" country for carbon emissions, has increased its emission increased just by 1% in 2017 than their 2014 level, thanks to a continued renewable deployment and a coal-to-gas switching [1].

These reports confirm positively that renewable energy generation is possible and efficient to reduce carbon emissions. But there are still a lot of works and efforts to do to cope with climate change and meet the Paris Agreement.

The renewable energy mentioned above includes solar/hydro/biomass/wind/ocean/ geothermal energy [2]. The thesis focuses on High Voltage Direct Current (HVDC) transmission, which is the technology trend to integrate renewable energy in power systems.

#### I.1.1 AC transmission versus DC transmission

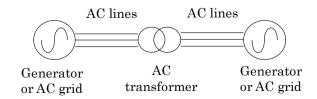

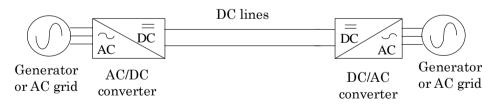

Alternative Current (AC) transmission (Fig 1) is the most used transmission technique. The three-phase alternative current allows the direct use of electrical machine as power generator and transformers ensuring voltage adaptation in a low losses and low cost way.

Fig 1. AC grid or transmission

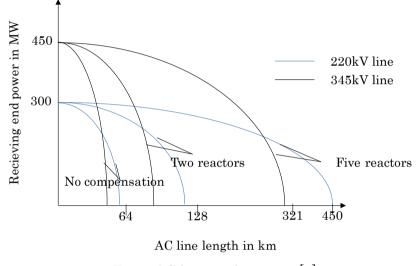

However, the limitation of AC transmission is linked to the capacitance value of long cable in great power transmissions [3] creating reactive power, which greatly increases cable currents and definitely limits power transmission. It can be solved by two methods explained in [3]: using shunt inductive reactors along the cable line to compensate reactive power or using DC transmission instead of AC transmission.

Fig 2 shows AC line performance with and without compensation. Transmission distance decreases when delivered power and line voltage increase. To transmit more power in high voltage, inductive compensation is mandatory to extend the transmission distance. However with reactors, a higher cost is necessary. This solution is also ineffective for undersea transmissions where numerous offshore substations are needed.

Fig 2. AC line performance [3]

Thereby, DC transmission (Fig 3) is a solution to deliver the high power from remote generator plants without reactive power compensators.

Fig 3. DC grid or transmission

Some advantages of DC transmission over AC are described as follows:

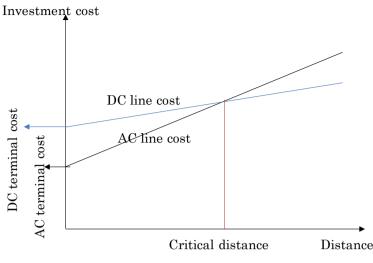

• Low costs for long distance:

DC transmission shows lower costs over the critical distances (Fig 4), according to power and voltage (approx underground: 600-800km, undersea: 50km), than AC even though DC terminal stations are more expensive [5]. It is linked to the huge cost of compensators increasing according to the line distance.

Fig 4. Comparison of AC and DC investment costs [5]

• Interconnection of asynchronous grids:

If two AC grids need to be connected, their frequency, voltage and phase must be identical. However, the interconnection can be realized by DC transmission thanks to AC/DC and DC/AC converters [6].

• No skin effect:

Skin effect exists in AC conductors where current frequency is high. DC transmission avoid the skin effect using direct current which reduces conductor losses compared to AC transmission.

These advantages make DC transmission the preferred solution for long distance, high voltage and great power transmission. However, several disadvantages should be also taken into account to minimize costs and losses:

• Expensive:

Fig 4 shows DC transmission economic benefits for long distance. However, it is also true that DC/AC and AC/DC converter stations are more expensive than AC substations. Therefore, converter design criteria has small footprint and low cost.

• Harmonics:

Power converters are sources of harmonics [7]. These harmonics spread to DC and AC grids, impacting power quality. To reduce high-frequency harmonics, filters are needed to improve power quality which increases costs and weight, especially for high voltage and high power applications. Therefore, efficient high power converters are necessary.

• DC short circuit protection:

Unlike AC grids, DC grids are more vulnerable for short circuit at DC sides. Then, most of DC grids are protected actually from the AC side by AC breaker or protected by control algorithms. A research trend is now to develop DC circuit breakers demonstrators to protect directly DC grid at DC side.

Despite the disadvantages described above, a hundred of DC lines ( around 139 projects reported by ABB and Siemens in 2019 [8]-[11] ) have been commissioned.

### I.1.2 Existing and future installation equipment for HVDC grids

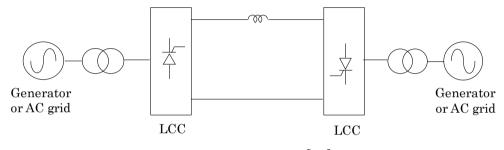

#### I.1.2.1 Existing installation equipment

A DC link is created by the connection of two AC/DC converter stations to AC generators transmitting power in DC cables (Fig 5). Regarding the converter stations, two main types of stations exist: Line Commutated Current Source Converter (LCC or CSC) and Voltage Source Converter (VSC).

The LCC is the converter topology after mercury-arc valve industrially confirmed to be suitable for high voltage and power application thanks to high blocking voltage of Thyristor [12].

Fig 6. LCC DC link [12]

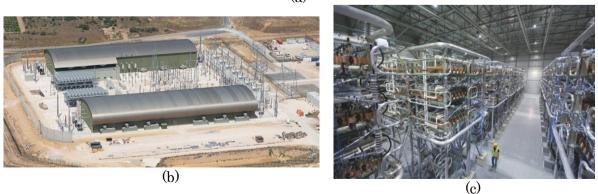

This converter technology is spread all over the world. Fig 7 shows the example of LCC converter installation at Sellindge side built in 1985 [13] used in the cross-Chanel DC link Britain-France from Sellindge to Les Mandarins (in Bonnigues-Les-Calais).

Fig 7. Sellindge LCC converter station [13]

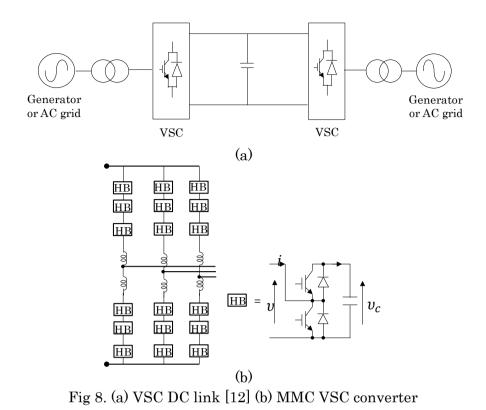

But due to the LCC technology based on thyristor control, harmonics in AC currents are important. To increase converter performances, VSC DC link is used instead of LCC DC link Fig 8. (a). The VSC DC link uses new VSC multilevel (2 or 3 level) converter technology, Modular Multilevel Converter (MMC) Fig 8. (b). The MMC solution, with its multilevel output voltage, ensures current quality, high efficiency (low frequency switching) and interresting electric performances.

A VSC DC link is used in Baixas-Santa Llogaia Fig 9. (a), where MMC converter station

Fig 9. (b) and (c) was built in 2015.

Fig 9. (a) Baixas-Santa Llogaia VSC DC link (b) MMC converter station outside view [15] (c) inside view [18]

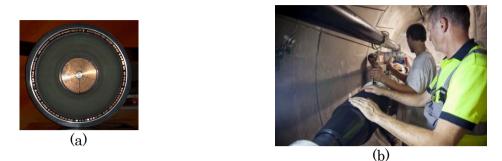

Regarding DC transmission cable, Fig 10. (a) and (b) show the extruded dielectric cable with cross-linked polyethene insulation (XLPE) used in Baixas-Santa Llogaia to ensure electrical and mechanical properties.

Fig 10. (a) DC cable [16] (b) cable installing in Baixas – Santa Llogaia [15]

### I.1.2.2 Future equipment

New technologies are proposed for future project installation, for example DC breakers. The potential solution (Fig 11) is able to achieve a DC current breaking in a 320kV/2kA DC grid. It is currently the first high voltage and high current DC breaker. The tested DC breaker is shown in Fig 12.

Fig 11. DC breaker [19]

Fig 12. Installation [21]

Besides, robots (Fig 13) are also proposed for monitoring the installed equipment, such as for converter stations.

Fig 13. Monitoring robots (a) Rope robotics [22] (b) ANYmal [23]

These equipment aim to prove the future development of HVDC grids. Along with this development, it is expected to connect different DC links, as it has been done in the past for AC grids in order to assure a high power flexibility.

### I.1.3 Multi-Terminal DC transmission

Similarly to massively interconnected AC grid, existing point to point DC links are expected to be interconnected to realize the power control. The pre-mentioned DC links with two converter stations are "point to point" DC links. Energy is transmitted from one station to another. To increase power flexibility, future DC grid should be Multi-Terminal DC grid with power exchanged between three or more converter stations.

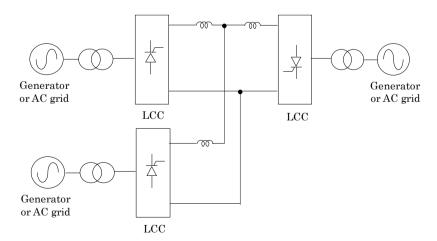

The Multi-Terminal DC (MTDC) grid is a basic concept proposed in 1956 [24]. The realized MTDC configuration was a parallel connection with the same DC voltage using LCC converter technology (Fig 14).

Fig 14. Three terminal LCC DC grid principle

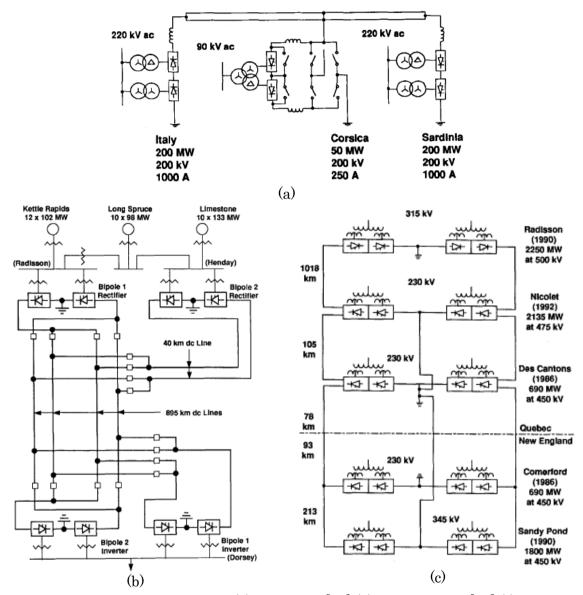

Fig 15. (a), (b), (c) show respectively the commissioned MTDC project Sardinia-Corsica-Italy (SACOI) in 1967, Nelson River project in 1972 and Hydro-Quebec – New England project in 1983.

Fig 15. Basic parallel connection (a) in SACOI [25] (b) Nelson River [25] (c) Hydro-Quebec – New England [25]

Due to their parallel configuration, the essential role of those MTDCs was the control of power flow between each station [25]. However, with the escalated number of DC lines, voltage levels or converter technologies can be different in each DC links. Thereby, the parallel configuration is no longer suitable in the general MTDC concept.

To overcome voltage differences, DC/DC converters could be a potential solution to manage the voltage adaptation. The MTDC concept is illustrated in Fig 16.

Fig 16. Multi-Terminal DC grid basic principle

DC/DC converters are usually used in Switch Mode Power Supplies with low voltage, but rarely in HVDC applications due to high voltage and high power value. Thereby, five main requirements are expected for the future DC/DC converters:

- High voltage and power: The converter should be able to stand for hundreds kilo volts and hundreds kilo watts.

- Voltage regulation: The converter should be able to step down or up a DC voltage to avoid voltage conflicts between different links.

- Power regulation: The converter should be able to easily control and change the power flow in both directions.

- DC current fault blocking capability: It is better to have self DC current fault protection, as the new DC circuit breaker is not mature.

### I.1.4 CIGRE test case analysis

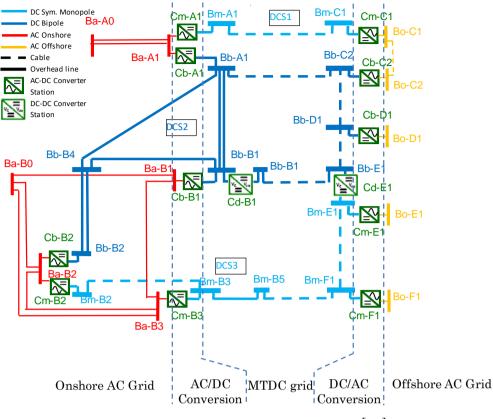

To illustrate the previous requirements, the test case proposed by CIGRE Group B4.76 (Conseil International des Grand Réseaux Electriques) is presented and used in our future simulations. A Multi-Terminal DC grid test case provided by CIGRE B4 group in [26] in 2013 is shown in Fig 17.

From right to left, the test case consists of offshore AC grids, AC/DC conversion, MTDC grid, DC/AC conversion, onshore AC grids and, from up to low, three transmission systems, DCS1, DCS2 and DCS3 with different voltage levels and power ratings.

DCS1 is a point to point DC link with rated voltage +/-200kV and power 800MVA. It connects directly an offshore generator to an onshore consumer via submarine DC cables.

DSC2 is a five sources MTDC system with rated voltage +/-400kV. Connections of the five sources are planned by six headlines (solid line) and four submarine cables (dashed line). Five DC/AC converter stations are designed with power rating 1200MVA for Cb-A1, 1200MVA for Cb-B1, 1200MVA for Cb-B2, 400MVA for Cb-C2 and 800MVA for Cb-D1.

Fig 17. CIGRE B4 DC Grid Test System [26]

DSC3 is a four sources MTDC system. Its rated voltage is +/-200kV. It needs three submarine cables (dashed line) and one headline (solid line). Its four converter stations have a rated power of 800MVA for Cm-B2, 1200MVA for Cm-B3, 200MVA for Cm-E1 and 800MVA for Cm-F1.

To connect DC grids DSC2 and DSC3, the DC/DC converter station Cd-E1 is mandatory to adapt to DC voltages between +/-400kV and +/-200kV. This converter participates in the power control with a rating power of 1000MW.

Moreover, in the DSC2 DC grid, a DC/DC converter Cd-B1 is shown in the plan. Depending on CIGRE, Cd-B1 needs a power rating of 2000MW between two similar sides voltage +/-400kV. Its principal role is to control the power flow.

Regarding the positions of two DC converters, Cd-B1 can be an onshore station or an offshore station. But Cd-E1 can only be an offshore station, which is connected with two submarine cables (dashed line).

To conclude, the requirements of MTDC DC/DC converter are described in Table 1. It confirms the demand for DC/DC converters in MTDC grids.

| Stations      | Cd-B1                   | Cd-E1                     |

|---------------|-------------------------|---------------------------|

| Rated voltage | $\pm 400 kV/\pm 400 kV$ | $\pm 400 kV / \pm 200 kV$ |

| Power rating  | 2000MW                  | 1000MW                    |

| Position      | Onshore or offshore     | Offshore                  |

Table 1 DC/DC converter stations Cd-B1, Cd-E1 requirement [26]

Following parts of the thesis will take the requirements described in Table 1 as criteria for DC/DC converter selection, design reference and simulations.

### I.1.5 Problem statement

As shown previously, several DC links have been developed to deliver great power in high voltage range. Most existing links are point to point DC links with power exchanged between two converter stations. To increase system flexibility, it is envisaged to build MTDC grids, where the power is exchanged between three or more converter stations. The existing MTDC grids are parallel connections of DC links where each link has the same voltage and converter technology. To adapt to the differences between different DC links, DC/DC converters are mandatory for several hundreds of kilovolts and several hundreds of megawatts. The high voltage and power range are actually the difficulties of DC/DC converter topology.

To deal with the difficulties and answer CIGRE requirements, the main existing DC/DC converter topologies are reviewed in order to extract or propose innovative solutions for MTDC grid connections.

### I.2 State of the arts for DC/DC converters

Topologies presented in this section are principally selected with two imposed criteria:

- DC voltage regulation

- and bidirectional power flow

However, the most encountered issues of these topologies are their low voltage and current range. Thereby, this section intends to increase their range to HVDC applications, regarding to CIGRE requirements. Then, the possibility and difficulties of extending voltage and current range are discussed.

The topologies are classified according to their potential modularity. In each class, topologies are also distinguished with their "multilevel" and eventually with their "galvanic isolation" possibilities.

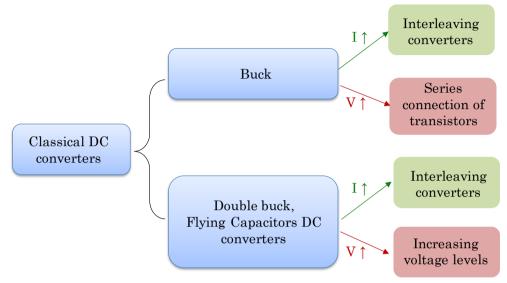

### I.2.1 Classical DC converters

The classical DC converters are non-modular DC converters. They are principally Buck (or boost), Double buck and Flying Capacitors converters (Fig 18). Due to the low voltage and power applications, this part reviews the possibility of extending their voltage and current range.

Fig 18. Classical DC converters

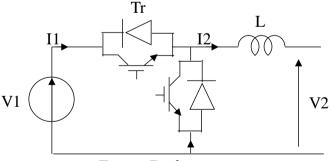

#### I.2.1.1 Buck

The Buck converter (shown in Fig 19) is widely used in the low voltage industry such as Switched-Mode Power Supply (SMPS) with two alternative power semiconductors (Transistor/diode). DC power and voltage are stood by only one semiconductor at each time, thereby power and voltage range of the converter are determined by the semiconductor technology.

Fig 19. Buck converter

So far available commercial semiconductors can barely support a few kilo volts and a few kilo amperes, which is far from the CIGRE requirements. Thereby, one semiconductor is not sufficient to operate buck converter in MTDC grid.

To raise the voltage and current range, two solutions are:

- using parallel connection and interleaved control to increase the power range

- series connection of transistors to increase the voltage range.

#### I.2.1.2 Interleaved converters

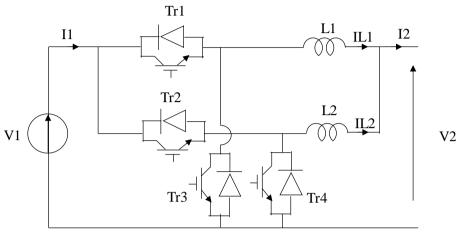

Interleaved converters use a parallel connection of converters to increase current range and are modulated with an interleaved control. Fig 20 shows interleaving technique used in two buck converters. The number of buck converters (N) can be still increased until satisfying MTDC grids current requirement.

Fig 20. Interleaved buck converter

The interleaving technique is an operation of transistors with phase shift  $2 \cdot \pi/N$  to product phase shifted current in the inductors. As shown in Fig 21, IL1 and IL2 are phase shifted by  $\pi$  radian during Tr1 and Tr2 alternatively turning-on and off.

Fig 21. Current waveforms of the converter control

In the case of N = 2, the frequency  $(f_{out})$  of output current ripple (I2) is twice the switching frequency  $(f_{sw})$ . The increased frequency in the output implies the possibility of reduction of inductance footprint using coupled inductance and a reduction of current ripple  $\Delta$ I2. Thereby the interleaved converters are proved to be suitable for low voltages and high currents applications, e.g. voltage regulator modules (VRMs) [28].

#### I.2.1.3 Series connection of transistors

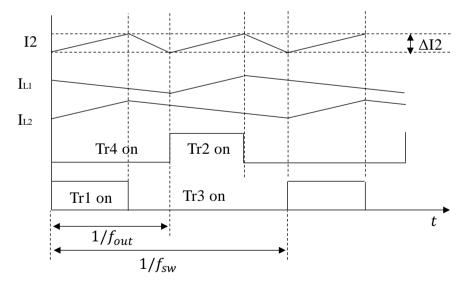

To increase the voltage range, a series connection of transistors has been used and investigated in the literature. Fig 22 shows an example of the series connection of transistors applied in a Buck converter.

Fig 22. Series connection of transistors applied to Buck converter [29]

The direct series connection of transistors is not as easy as it looks like. According to [30], several issues prevent the spread of the technique as:

- Unequal voltage sharing across transistors due to different delay times of driving circuits.

- Unequal voltage sharing across transistors due to small parameter deviation amongst different devices.

- Unequal voltage sharing across the freewheeling diodes due to different reverse recovery behavior.

- Increase of dv/dt with the number of series connected devices at the terminals of the converter.

[29], [30] have had also solutions to overcome these pre-mentioned issues using complex controls to keep the same collector-emitter-voltage of each transistor, same transient voltage (dv/dt) and current (di/dt) of each transistor and the same gate voltage of each transistor at each moment to avoid destructing transistors. Due to the high accuracy demand, extreme complex control and lack of component failure management, the series connection of semiconductors are finally deemed as difficult to be realized for HVDC applications.

#### I.2.1.4 Double Buck and Flying Capacitor DC converter

A second potential solution are the multilevel converter topologies, as shown in Fig 23. (a) Double buck converter [32] (b) flying capacitor DC converter [33].

Fig 23. (a) Double bucks (b) Flying capacitor DC converter

Those topologies reduce the voltage of each switch to V1/2 instead of V1 in buck. The output frequency is also increased to twice the fundamental switching frequency, thereby the output inductor footprint can be reduced thanks to the reduced voltage and increased frequency. With these advantages, these converters are widely used for applications in electric vehicle (EV) [31], [32].

Fig 24. 5 levels Flying Capacitor DC converter

However, it is difficult to apply those topologies in HVDC grids due to the difficulty of balancing capacitors voltage in extending their voltage levels, even though the prementioned interleaving technique can be used to raise the current range. So far as shown in the literature, five levels are the most level numbers for the topologies, e.g. Fig 24 is the extension of FC to five levels.

The increased number of levels is helpful to decrease the voltage of each switches and increase the output switching frequency, thereby reducing inductor filter footprint. In response to the CIGRE requirements (V > 100kV and 1kA < I < 10kA), the maximum five voltage levels are far from the almost hundreds of levels needed according to the semiconductor technology. Moreover, the topologies have capacitors concentrate connection in which energy is stored. The great energy stock could involve a danger if a short circuit occurs in the circuit.

In conclusion, multilevel converters are not suitable for HVDC applications due to the issue of raising voltage range of converters. To overcome this obstacle, a last solution is using topologies with high modularity, called hereby "modular converters".

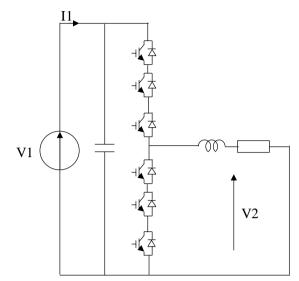

#### I.2.2 Modular DC converters

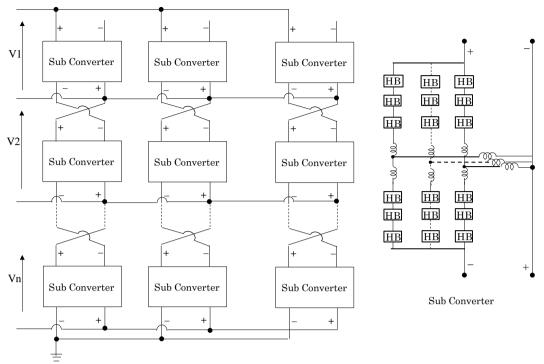

DC converters with high modularity (Fig 25) are the series connection of Dual Active Bridge (DAB) and Modular Multilevel DC converters based on the Modular Multilevel Converter (MMC). The Modular Multilevel DC converter topologies are also classified by their converting methods: two stage conversion and single stage conversion.

Fig 25. Modular DC converters

#### I.2.2.1 Series connection of Dual Active Bridge

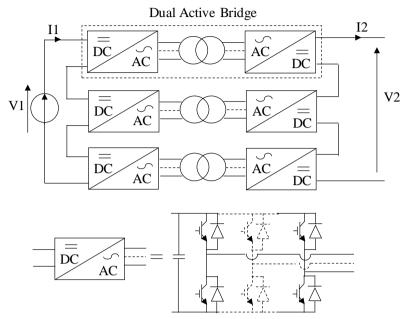

The series connection of Dual Active Bridge (DAB) converter is shown in Fig 26, which consists of several DAB converters interconnected (output and input).

Fig 26. Series connection of Dual Active Bridge

A single Dual Active Bridge (DAB) is a DC/DC bidirectional power converter containing two DC/AC converters interconnected through an AC transformer. The DAB can be three phases or single phase depending on the current range. More phases are, higher DC current is. The transformer is mandatory to isolate current from the primary to secondary. Its volume can be reduced by a higher frequency, which involves potentially more semiconductors losses.

DABs are connected in series to raise the voltage range (Fig 27). The modular topology prevents the issues existed in the pre-mentioned topologies. However, in HVDC applications, the number of modules could be in the hundreds, thereby hundreds of transformers. This great number increases physically the converter volume and technically difficulties of control, e.g. synchronization of different DABs.

As a result, the series connection of DABs succeeds in overcoming the voltage level raising obstacle with the modular topology, but is still deemed unsuitable in HVDC applications due to the great number of transformers.

#### I.2.2.2 Modular Multilevel DC Converter (DC-DC MMC)

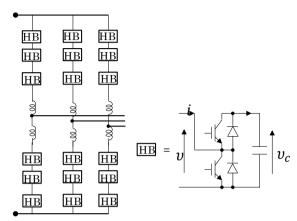

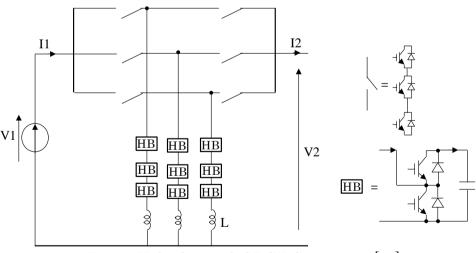

To reduce the number of transformers, thereby prevent synchronization issues and losses from transformers, a fourth potential solution is Modular Multilevel Converter (MMC) topology based DC/DC converters.

The MMC (Fig 28) has modular topology with basically Half Bridge (HB) submodule which allows raising easily voltage levels. Numerous of Half Bridge submodules are connected in series that the number depends on the semiconductor technology. Meanwhile, the power range is determined by the number of legs same as the prementioned interleaving technique. With the two characteristics, MMC has been confirmed suitable for HVDC applications and already installed in several links, for example, interconnection Baixas - Santa Llogaia.

Fig 28. Modular Multilevel Converter

Recently, different submodule topologies are emerged, e.g. Full Bridge (FB) submodule used in Alternative Arm Converter (AAC) (Fig 29).

Fig 29. Alternative Arm Converter

Thanks to the reliability and efficiency of the MMC confirmed by numerous projects, DC/DC topologies proposed in the literature are mostly based on the MMC toward the same advantages, e.g. the DC-DC MMC. It is a DC/DC converter which associates directly two MMCs with a transformer in their AC sides as shown in Fig 30.

Fig 30. Modular Multilevel DC Converter (DC-DC MMC)

For a DC/DC converter application, two DC sides connect directly to different DC grids and the transformer can isolate current from primary to secondary and help voltage regulation. However, the general hypothesis toward the MMC and transformer is no power dissipation, which implies the two MMCs and the transformer have approximately same power. Regarding the power range of an HVDC grid and the installed MMC volume, the DC-DC MMC could have twice the MMC volume.

In another side, this topology reduces the number of transformers comparing the previous topology with Series connection of DABs. The transformer is an intermediate stage without connections to grid. Thereby, a higher frequency than the grid frequency is possible to reduce the transformer volume. However, losses due to high frequency and volume are always a compromise during the converter design.

Some studies have already been realized on this topology until 2019. For example, [38] studied DC current fault on the converter. [39] proposes a control strategy involving different phase numbers. An overview of the converter losses is shown in [40] and [41]. Then, [42] presents an integration of the converter in MTDC grid to test its dynamic behavior.

The DC-DC MMC is a DC/DC converter with galvanic isolation thanks to the intermediate transformer. However, the transformer is only an option that two MMCs can also be directly connected, as shown in Fig 31. L represents a small value line inductors. In this case, the DC-DC MMC converter has no galvanic isolation, but benefits of a smaller volume.

Fig 31. Modular Multilevel DC Converter without transformer (DC-DC MMC)

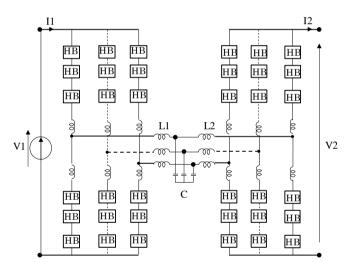

Otherwise, the AC side of two MMCs can also be replaced by an LCL circuit (Fig 32) to reduce the volume. According to [43], the circuit allows also blocking DC current fault, but eliminates galvanic isolation.

Fig 32. Modular Multilevel DC Converter without transformer (DC-DC MMC)

In any case, these topologies use directly MMC which are currently developed for HVDC DC/AC conversions.

## I.2.2.3 Modular Multilevel DC converter (Autotransformers)

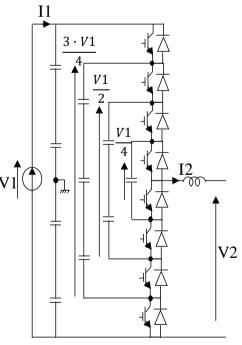

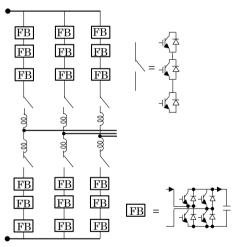

The second possibility to convert an MMC to a DC/DC is based on autotransformers (MMC-AT or HVDC/DC AT) and shown in Fig 33 [45], which is a DC/DC direct conversion converter inspired from autotransformers.

Fig 33. Modular Multilevel DC Converter (Autotransformer 1) [45]

The topology has a series connection of two MMCs, one on the top and another on the bottom. The AC sides of MMCs are always connected by a transformer, but alters to participate in energy balancing instead of galvanic isolation. Compared to the DC-DC MMC, MMC-AT aims to reduce the transformer volume and the number of submodules in MMCs according to [45].

Since the power in the transformer is lower than the grid power (I.2.1) [45], transformer footprint of the MMC-AT is smaller than isolated DC-DC MMC.

$$P_{transformer} = P_{DC} \cdot (1 - \alpha) \tag{I.2.1}$$

where  $P_{transformer}$  indicates power of the transformer.  $P_{DC}$  is the power in DC grid.  $\alpha = V2/V1$  is the DC voltage ratio. V1 and V2 are the two HVDC voltages.

Moreover, the top and bottom MMCs can have different numbers of submodules in terms of different voltage ratios. As a result, these two MMCs will have less submodules than the DC-DC MMC, thereby lower volume.

Another MMC-AT topology proposed in the literature is Fig 34 with monopole symmetrical configuration, which is different from monopole asymmetrical configuration in Fig 33.

Fig 34. Modular Multilevel DC Converter (Autotransformer 2) [46]

Submodules in the topology are Full Bridge and Half Bridge. The DC voltage is obtained from AC side, thereby output LC filters are mandatory. Thanks to half of Full Bridges utilization, Fig 34 can step down and up a DC voltage without flipping two DC sides that only half bridge cannot afford.

In conclusion, the two topologies of MMC-AT have smaller footprint thanks to their reduced number of submodules and smaller transformer. The transformer is used as power transmission and current filter, thereby lack of galvanic isolation.

Moreover, both converters have DC current fault blocking function from either the internal AC sides or utilization of Full Bridge submodules. With different submodule topologies, MMC-AT could have monopole asymmetrical configuration or monopole symmetrical configuration.

Finally, the phase leg numbers are always an option to raise current range, according to the interleaving technique principle.

Some recent work in 2018 and 2019 about these two topologies [47], [48] analyzed respectively a multi-frequency operation and DC current fault blocking. In [49], authors proposed a new multiport DC/DC converter (Fig 35).

Fig 35. Multiport DC/DC converter [49]

## I.2.2.4 Modular Multilevel DC Converter (Hybrid cascaded DC/DC converter)

A third DC/DC topology based on MMC is the Hybrid cascaded DC/DC converter shown in Fig 36 [50].

Fig 36. Hybrid cascaded DC/DC converter [50]

This solution is similar to the "Direct series connection of transistors applied in Buck Boost converter". The principle operation is using inductors to stock energy. However, instead of using single inductors, MMC submodules with capacitors are connected in series with the inductors to provide a zero current and zero voltage switching.

Due to the submodule capacitors, the energy discharge of capacitors could take time to get the desired DC voltage. Thereby, this proposition is considered as a low voltage ratio

DC/DC converter, that two DC sides have similar voltages. Finally, the direct series connection of transistors could make the control complicated to maintain voltage of each transistor.

#### I.2.2.5 Modular Multilevel DC Converter (M2DC)

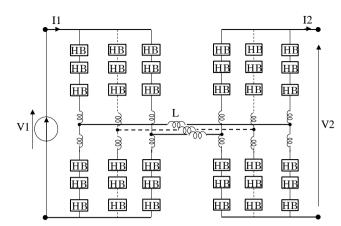

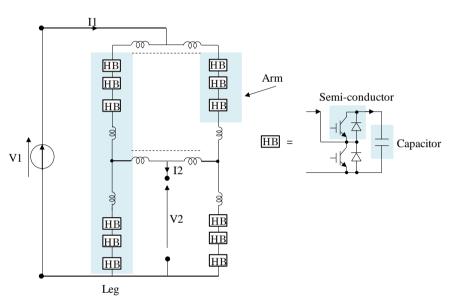

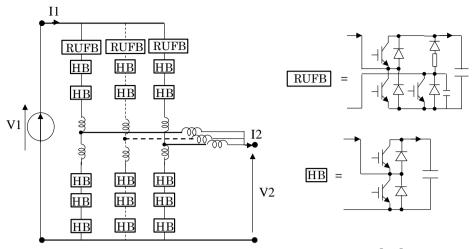

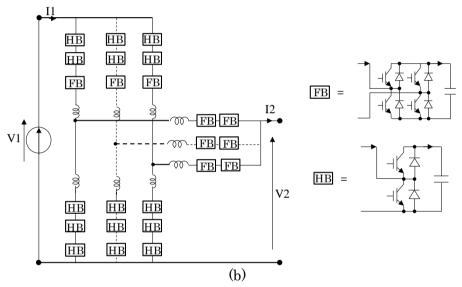

The last DC/DC topology is Modular Multilevel DC converter (M2DC), which is a direct conversion topology without transformer shown in Fig 37, more compact than the DC-DC MMC constituted of two MMC connected through their AC side.

Fig 37. M2DC topology [51]

The topology has four arms, two upper arms and two lower arms. Each arm composed by Half Bridge submodules has the same function as an arm in MMCs, thereby to stock energy in the submodule capacitors. Energy balancing is crucial.

Compared to the MMC-ATs, M2DC eliminates the transformer, then no transformer volume during the converter design. The number of submodules can also be regulated in terms of different voltage ratios. Thereby, the M2DC seems to be the simplest DC/DC topology with most benefits of converter volume.

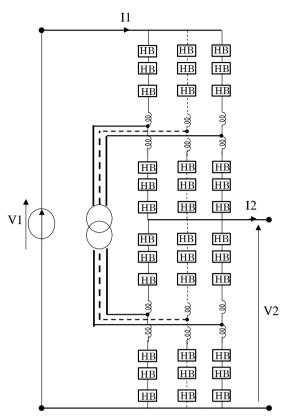

Some recent work on M2DC are [52], [53] and [56]. In their analysis, methods for converter modelling, design and control are presented. [54], [55] proposed also different methods for DC current fault blocking (Fig 38 and Fig 39) in 2018 and 2019, respectively.

Fig 38. DC fault current blocking structure [54]

Fig 39. DC fault current blocking structure [55]

## I.3 Conclusion

This chapter reviews four types of HVDC DC/DC converters. Each topology is able to realize a voltage regulation and bi-directional power flow control. Table 2 synthetizes their advantages and disadvantages.

| Table 2 Review of existing DC/DC converters |                                                      |                                                             |                                               |           |  |  |

|---------------------------------------------|------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------|-----------|--|--|

| Topologies                                  | Classical DC converters                              |                                                             | Modular DC converters                         |           |  |  |

|                                             | Buck/boost                                           | Double buck, three or five levels FC                        | Series connection of<br>DABs                  | MMC based |  |  |

| High voltage<br>(>100kV)                    | No,<br>(Need series<br>connection of<br>transistors) | No,<br>(Need voltage<br>levels extension<br>more than five) | Yes,<br>(Important number<br>of transformers) | Yes       |  |  |

| High current<br>(>1kA)                      | No,<br>(Need<br>interleaving<br>converters)          | Yes,<br>(with more than<br>one leg)                         | Yes                                           | Yes       |  |  |

| Modularity                                  | Low                                                  | Low                                                         | High                                          | High      |  |  |

Table 2 Review of existing DC/DC converters

The first topologies are based on Buck topology. Due to the semiconductor technology, it is mandatory to interleave several Buck converters to raise the current range and connect transistors in series to increase the voltage range. But series connection of transistors has met the difficulty of control and protection of each semiconductor and lack failure management. Thereby, Buck converters are deemed unsuitable in HVDC applications due to their low stand-by voltage.

The second topologies are multilevel converters, increased in voltage range thanks to their multilevel topologies. However, the increased voltage range is still insufficient in HVDC applications due to their low modularity and difficulty of energy balance, thereby these topologies are usually applied in electrical vehicle applications.

The high voltage range obstacle is overcome by series connection of DABs and topologies based on MMC using a high modularity. The series connection of DABs is able to raise the voltage range increasing the number of DAB. Each DAB can have single or three phases in AC side adapting different current range. But transformers are mandatory for each DAB to avoid short circuit, thereby transformer numbers become important in high voltage applications.

To decrease the number of transformers, four DC/DC topologies based on MMC are presented, DC-DC MMC, MMC-ATs, Hybrid cascaded DC/DC converter and M2DC. They are deemed more suitable for HVDC applications thanks to high modularity and reduced transformer number. Based on the MMC topology, Table 3 shows a qualitative comparison of potential active and passive components necessary in different presented topologies. These table has to be deepened in the future, but gives the trend of our research work.

|                       | Two stage<br>conversion<br>(DC/AC/DC)                              | Single stage<br>(DC/DC) |                                          |                       |

|-----------------------|--------------------------------------------------------------------|-------------------------|------------------------------------------|-----------------------|

| Topology              | DC-DC MMC                                                          | MMC-ATs                 | Hybrid<br>Cascaded<br>DC/DC<br>converter | M2DC                  |

| Active<br>components  | $2 \times \text{MMC}$                                              | $2 \times \text{MMC}$   | N × Half bridge<br>+<br>N × transistors  | $1 \times \text{MMC}$ |

| Passive<br>components | 1 × transformer<br>or<br>1 × LCL<br>or<br>No passive<br>components | 1 × transformer         | -                                        | $1 \times L$          |

| Table 3 Comparative potential components used in different MMC based $DC/DC$ |

|------------------------------------------------------------------------------|

| converters                                                                   |

As it can be seen, hybrid cascaded DC/DC converter and M2DC seems to need less active components, thereby fewer transistors and lower losses than Dual Active Bridge MMC and MMC-ATs, that both need two MMCs involving more submodules and losses. However, due to the series connection of transistors, Hybrid cascaded DC/DC converter is less feasible and lower modularity than the M2DC. As the results, the M2DC has been selected as the central research in order to confirm the trend given in Table 3.

Some studies on the M2DC have already been realized. However, this report aims to clarify basic operation principles and limitations of the M2DC converter. The analysis will show the differences between MMC and M2DC control. Its control principle will be presented and validated in the following chapters. Firstly, the second chapter will theoretically explain the principle operation and limitation of the topology. Then, the third chapter will show a basic control to validate the theory explored in the second chapter.

The HIL validation will be shown in the fourth chapter, which will involve the validation methodology and a MMC based design.

## I.4 References

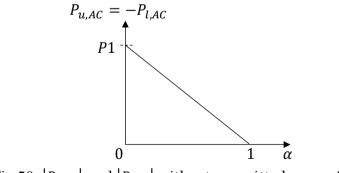

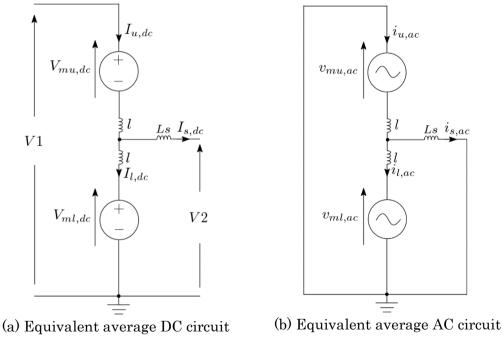

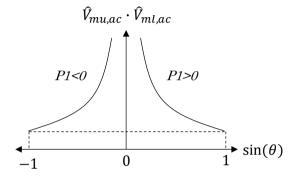

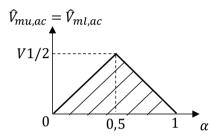

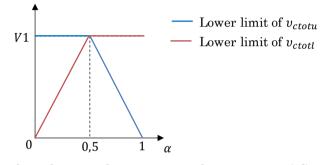

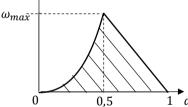

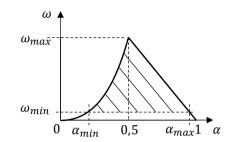

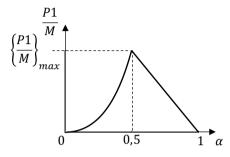

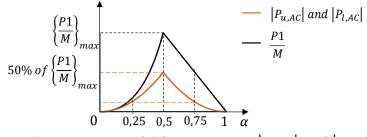

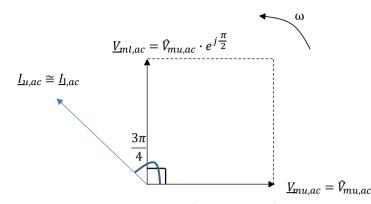

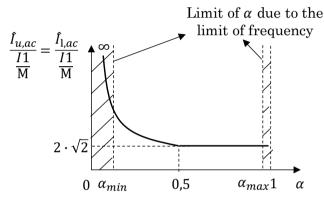

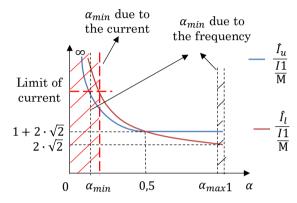

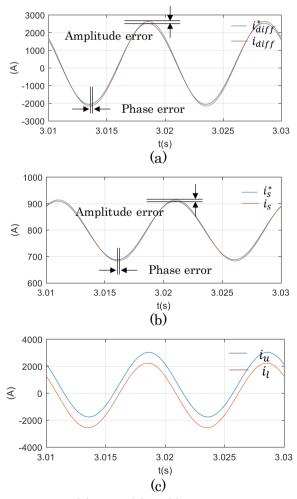

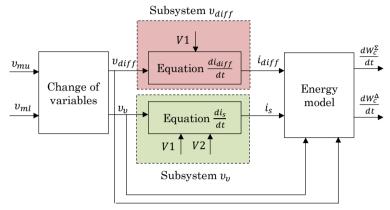

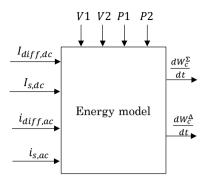

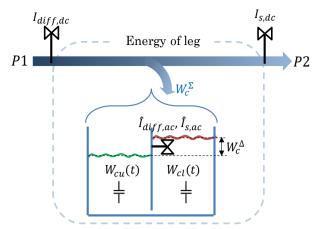

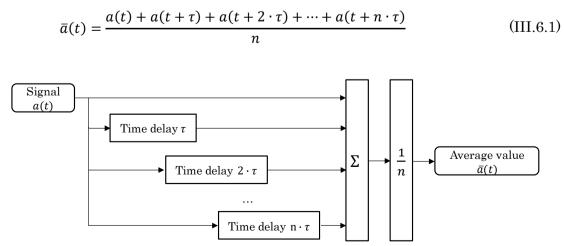

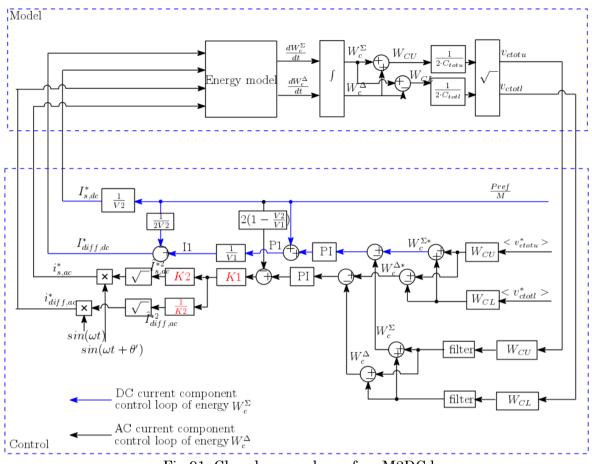

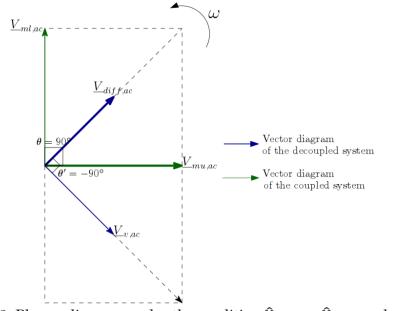

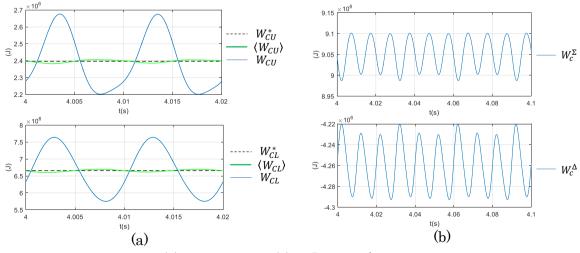

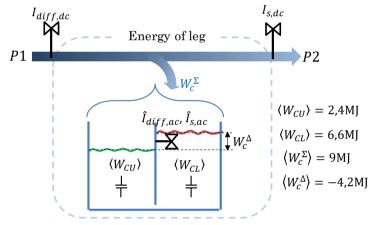

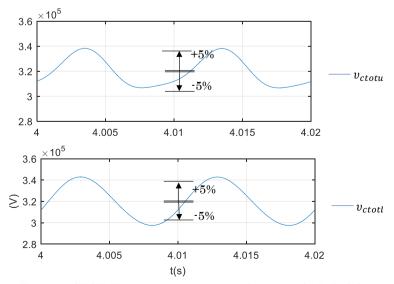

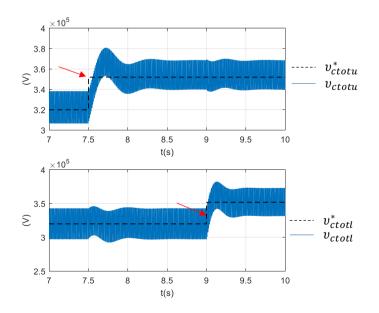

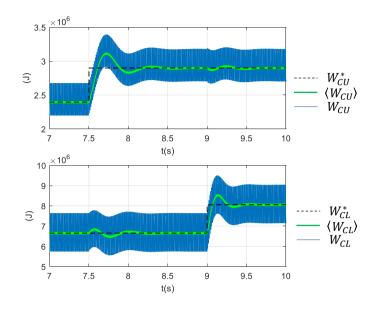

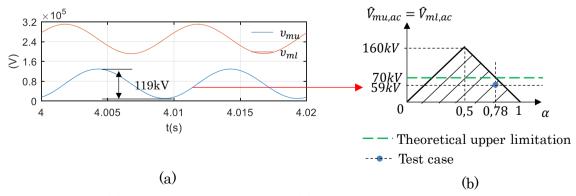

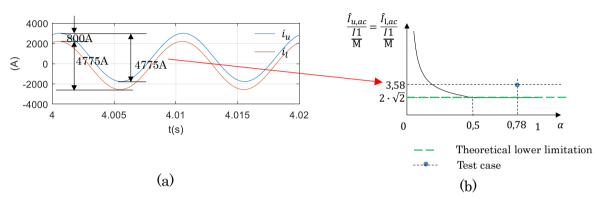

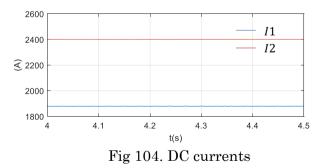

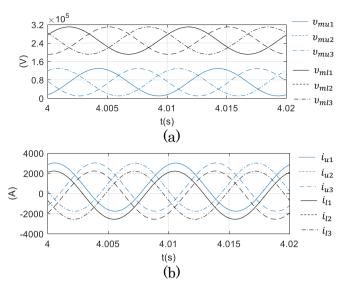

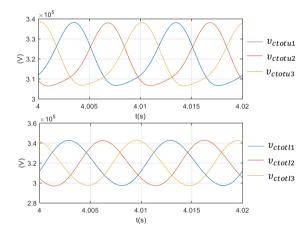

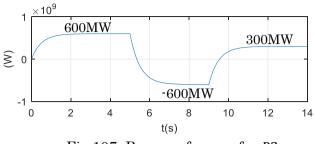

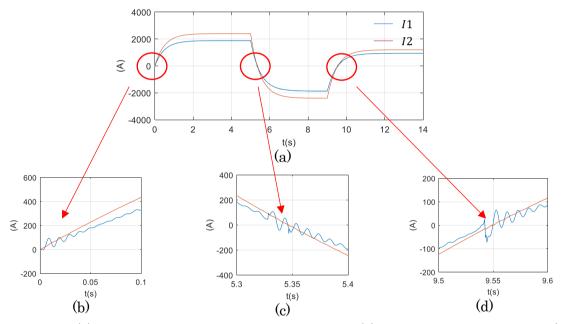

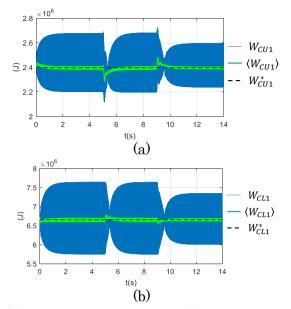

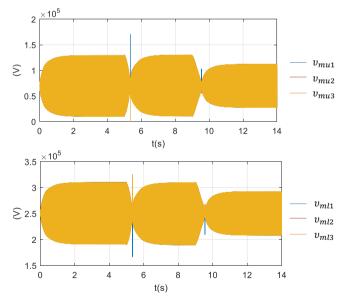

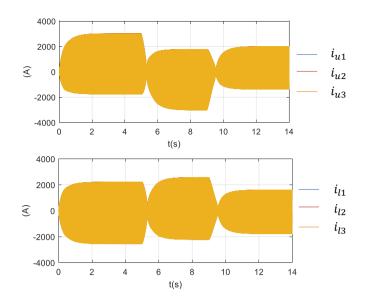

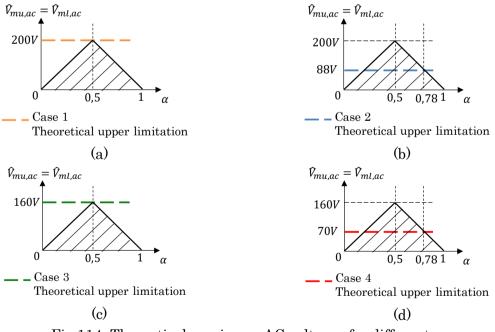

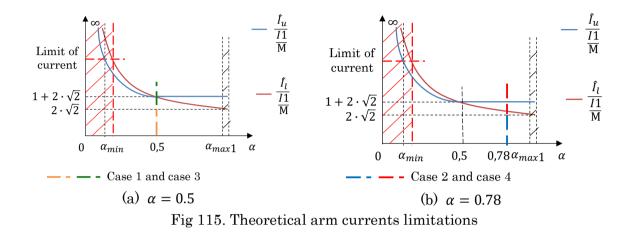

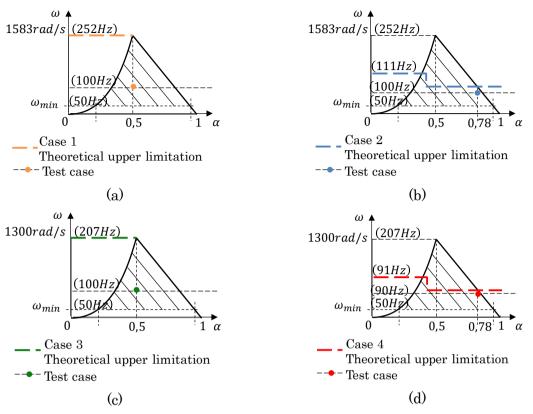

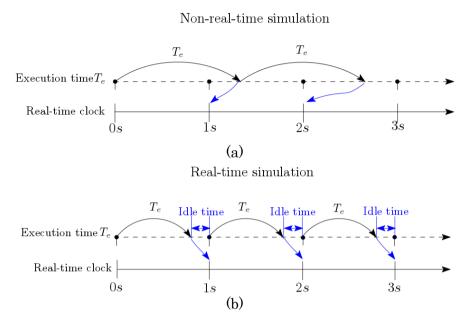

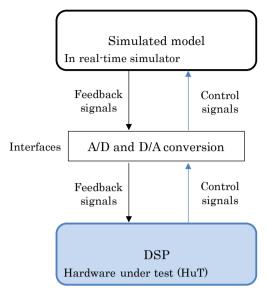

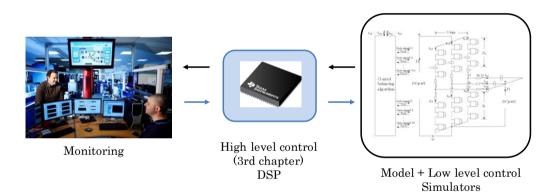

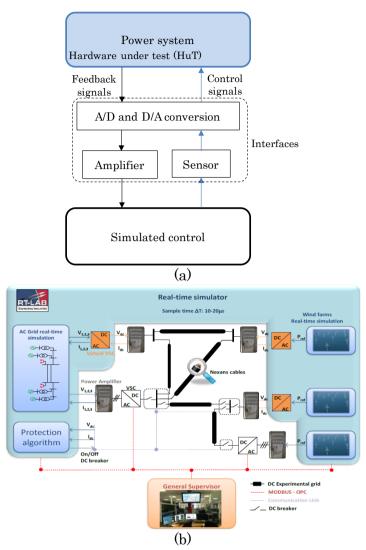

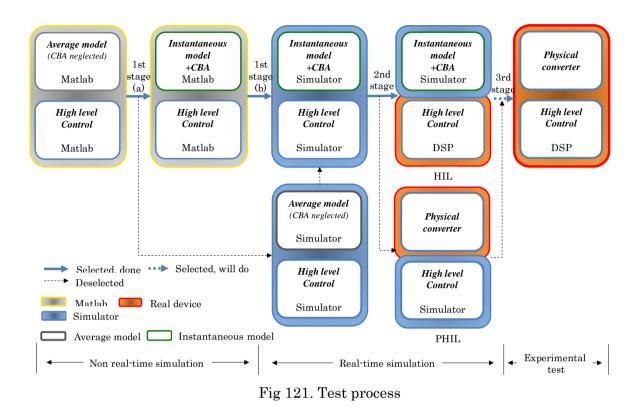

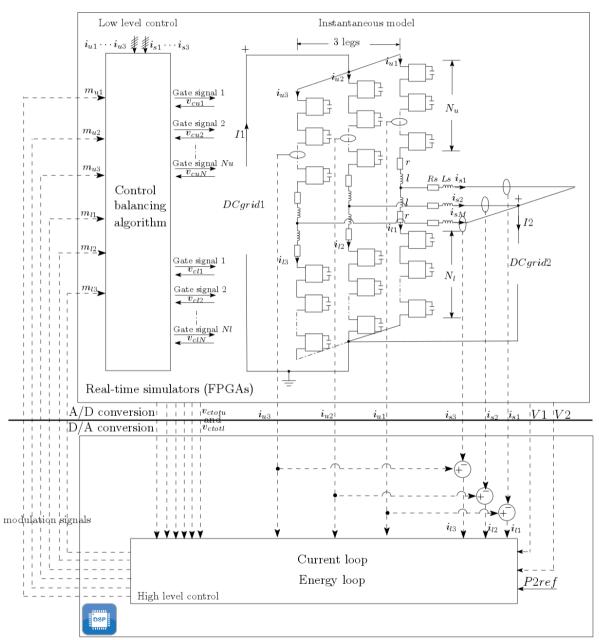

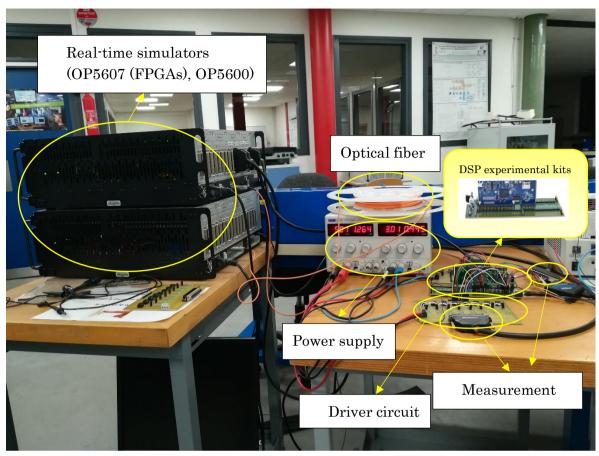

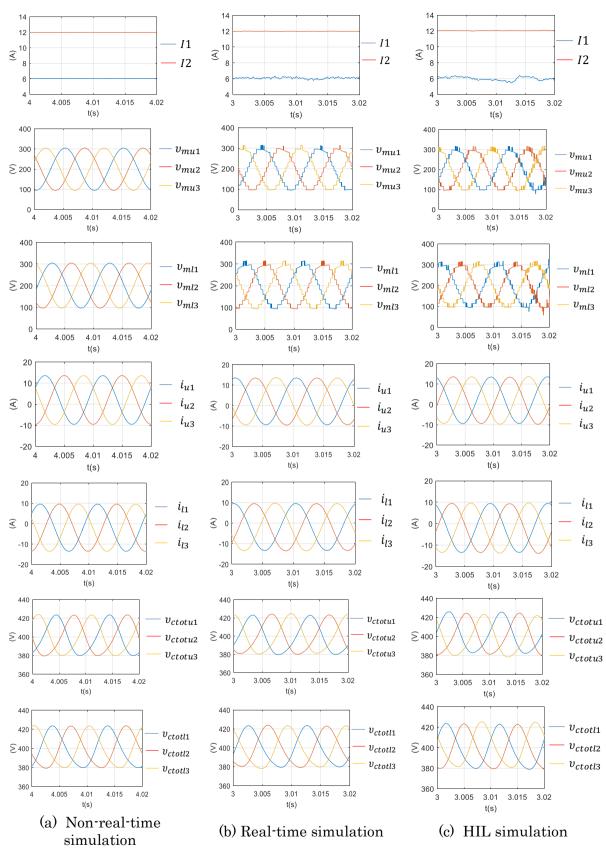

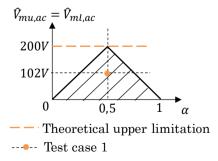

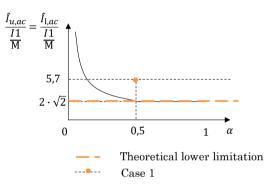

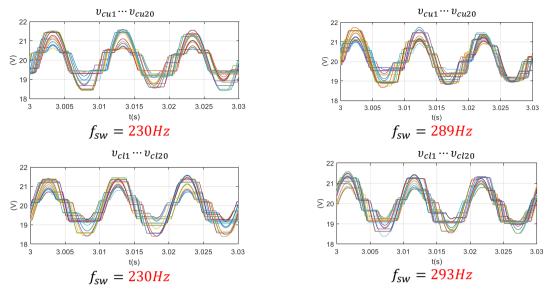

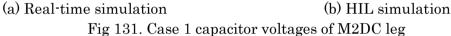

- [1]. The IEA's global energy and co2 status report, https://www.iea.org/publications/freepublications/publication/GECO2017.pdf