# Formal fault injection vulnerability detection in binaries: a software process and hardware validation

Nisrine Jafri

#### ▶ To cite this version:

Nisrine Jafri. Formal fault injection vulnerability detection in binaries: a software process and hardware validation. Cryptography and Security [cs.CR]. Université de Rennes, 2019. English. NNT: 2019REN1S014. tel-02385208

### HAL Id: tel-02385208 https://theses.hal.science/tel-02385208

Submitted on 28 Nov 2019

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE DE DOCTORAT DE

L'UNIVERSITE DE RENNES 1 COMUE UNIVERSITE BRETAGNE LOIRE

Ecole Doctorale N°601 Mathèmatique et Sciences et Technologies de l'Information et de la Communication Spécialité: Informatique Par

### « Nisrine JAFRI »

« Formal Fault Injection Vulnerability Detection in Binaries »

«A Software Process and Hardware Validation»

Thèse présentée et soutenue à RENNES, le 25 mars 2019

Unité de recherche : Inria, TAMIS team

Thèse N°:

#### Rapporteurs avant soutenance:

Marie-Laure POTET, Professeur des Universités, ENSIMAG Jean-Yves MARION, Professeur des Universités, Université de Lorraine Composition du jury :

Président : Pierre-Alain FOUQUE, Professeur des Universités, Université Rennes 1

Examinateurs:

Leijla BATINA, Professeur des Université s, Université Radboud de Nimegue

Shivam BHASIN, Chercheur, Université technologique de Singapour Sylvain GUILLEY, Professeur des Universités, Télécom ParisTech

Annelie HEUSER, Chercheur, CNRS

Dir. de thèse: Jean-Louis LANET, Chercheur, Inria

Co-dir. de thèse : Axel LEGAY, Professeur des Universités, Université catholique de Louvain

Invité(s)

"The summit of happiness is reached when a person is ready to be what he is."

Desiderius Erasmus

إلى من بالحب غمروني وبجميل السجايا أدبوني إلى أسي و أبي

#### **UNIVERSITY RENNES 1**

### **Abstract**

### Inria

#### Doctoral School MATHSTIC

Doctor of Philosophy

## Formal Fault Injection Vulnerability Detection in Binaries - A Software Process and Hardware Validation

by Nisrine JAFRI

Fault injection is a well known method to test the robustness and security vulner-abilities of systems. Detecting fault injection vulnerabilities has been approached with a variety of different but limited methods. Software-based and hardware-based approaches have both been used to detect fault injection vulnerabilities. Software-based approaches can provide broad and rapid coverage, but may not correlate with genuine hardware vulnerabilities. Hardware-based approaches are indisputable in their results, but rely upon expensive expert knowledge, manual testing, and can not confirm what fault model represent the created effect.

First, this thesis focuses on the software-based approach and proposes a general process that uses model checking to detect fault injection vulnerabilities in binaries. The efficacy and scalability of this process is demonstrated by detecting vulnerabilities in different cryptographic real-world implementations.

Then, this thesis bridges software-based and hardware-based fault injection vulnerability detection by contrasting results of the two approaches. This demonstrates that: not all software-based vulnerabilities can be reproduced in hardware; prior conjectures on the fault model for electromagnetic pulse attacks may not be accurate; and that there is a relationship between software-based and hardware-based approaches. Further, combining both software-based and hardware-based approaches can yield a vastly more accurate and efficient approach to detect genuine fault injection vulnerabilities.

**Keywords:** Fault Injection, Vulnerability Detection, Model Checking, Formal Methods

## Acknowledgements

I would start by expressing my gratitude to my thesis directors Jean-Louis Lanet and Axel Legay. Thank you for giving me the opportunity to experience the PhD journey. Thanks for your directions through the path, your advices and comments.

My sincere thanks to Marie-Laure Potet and Jean-Yves Marion for accepting to review my work. Marie-Laure Potet, thank you for your advices and goodwill. Jean-Yves Marion, thank you for your availability and pertinent remarque.

Thanks for the jury members, Leijla Batina, Shivam Bhasin, Pierre-Alain Fouque, Sylvain Guilley for accepting to be part of my jury.

Special thanks to my supervisor Thomas Given-Wilson. My research would have been impossible without your aid, support, and encouragement. Thanks for all the shared techniques and tips that I will carry on with me, and share as well.

I owe a very important debt to Annelie Heuser, thanks for helping me finalise this manuscript, but also for all your support and encouragement, it was a real pleasure working with you.

Thanks to Clementine Maurice my monitor, your advices, suggestion and encouragement were a great help to me.

I would also like to thank Ronan Lashermes and Sebanjila Kevin Bukasa from the LHS lab for their help in conducting the hardware experiments.

Heartfelt thanks go to all the tamis team members. A special thank to Olivier Zendra the team leader for his support and help in order to defend my thesis. A unique thanks to Cecile Bouton. Thank you for your goodwill and support, you have been a second mother to me. thanks to the members who become true friends to me. Alex and Kevin we will remain the Trio of Porto. Tania, thanks for everything but especially for the free hugs. Cassius, thanks for your positive energy, and all the shared information about the music bands. Delphine, it was a pleasure to have you as an officemate. Thanks to all the team members with whom I shared a great moment: Stefano, Ioana, Lamine, Céline, Yoann, Christophe, Laurent, Leo, Ludo, Jean, Hélène, Florian, Fabrizio ...

I am profoundly grateful to all my friends for their emotional support through the way, thanks Meriem, Fati, Mouad, Routa, Rahaf, Farah. A special thanks to Pierre-Yves who become more than a friend. Thanks for your support, through the last miles of this journey you had the right words to boost my motivation.

Thanks to all my Spanish, Sewing, Swimming, and Salsa teachers, spending time in your courses helped me having a balanced life.

Thanks to my second family in Rennes, Gabrielle and Claire. You've been a true family to me, you embraced me with your love and care, and made me feel at home.

And lastly, all the thank goes to my beloved family for their unlimited love and support. Thanks to my parents and brothers Youssef and Youness. My grandparents and to all members of JAFRI and Chouka families, for providing me with unfailing support and continuous encouragement throughout my years of study and through the process of researching and writing this thesis. This accomplishment would not have been possible without them. Thank you.

# **Contents**

| Al      | ostra | et                                                                          | v   |

|---------|-------|-----------------------------------------------------------------------------|-----|

| A       | cknov | wledgements                                                                 | vii |

| Ré      | ésum  | é en français                                                               | 1   |

| In      | trod  | uction and Background                                                       | 5   |

| 1       | Intr  | oduction                                                                    | 5   |

|         | 1.1   | Context and Motivation                                                      | 5   |

|         | 1.2   | Motivating Example: Verify PIN Example                                      | 7   |

|         | 1.3   | Contributions                                                               | 8   |

|         | 1.4   | Publications                                                                | 10  |

|         | 1.5   | Organisation of the Thesis                                                  | 12  |

| 2       | Bac   | kground                                                                     | 15  |

|         | 2.1   | Fault Injection                                                             | 15  |

|         |       | 2.1.1 Software-Based Fault Injection Approaches                             | 18  |

|         |       | 2.1.2 Hardware-Based Fault Injection Approaches                             |     |

|         |       | 2.1.3 Fault Model                                                           |     |

|         | 2.2   | Formal Verification                                                         |     |

|         |       | 2.2.1 Model Checking                                                        |     |

|         |       | 2.2.2 Properties                                                            |     |

|         | 2.3   | Working on Binaries                                                         |     |

|         |       | <ul><li>2.3.1 Binary Model Checking</li></ul>                               |     |

| I<br>ab |       | Automated Formal Process For Detecting Fault injection Vulneres in Binaries | 31  |

| 3       | Ove   | erview of Part I                                                            | 33  |

|         | 3.1   | Introduction                                                                | 33  |

|         | 3.2   | State of the Art                                                            |     |

|         | 3.3   | Case Studies: Cryptographic Algorithms                                      | 36  |

| 4       | Pro   | cess, Implementation and Methodology                                        | 41  |

|         | 4.1   | Fault Injection Vulnerability Detection FIVD Process                        |     |

|         | 4.2   | FIVD Process Implementation                                                 |     |

|         | 4.3   | FIVD Process Methodology                                                    | 46  |

| 5       | Exp   | erimental Results                                                           | 49  |

|         | 5.1   | Motivating example                                                          |     |

|         | 5.2   | Cryptographic Algorithm                                                     | 54  |

| 6  | Details on the Experimental Results and Implementation for the PRESENT Algorithm                                                                                     | 59  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7  | Discusion and Limitations 7.1 Discusion                                                                                                                              |     |

|    | Bridging Software-Based and Hardware-Based Fault injection Atcks                                                                                                     | 71  |

| 8  | Overview of Part II  8.1 Introduction                                                                                                                                | 75  |

| 9  | Process, Implementation and Methodology9.1Software and Hardware based Process9.2Software and Hardware based Implementation9.3Software and Hardware based Methodology | 83  |

| 10 | Experimental Results 10.1 Control Flow Hijacking                                                                                                                     |     |

| 11 | Details on the Experimental Results and Implementation for the CFH Case Study                                                                                        | 99  |

| 12 | Discussion and Limitations 12.1 Discussion                                                                                                                           |     |

| Co | onclusions and Future Work                                                                                                                                           | 109 |

| 13 | Conclusions                                                                                                                                                          | 109 |

| 14 | Future Work                                                                                                                                                          | 113 |

| A  | FIVD Process Implementation Details                                                                                                                                  | 117 |

| В  | PRESENT Experimental Results                                                                                                                                         | 121 |

| Bi | bliography                                                                                                                                                           | 125 |

# **List of Figures**

| 1 2                                           | Première Contribution : Le processus FIVD                                                                                                              |                                      |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|                                               | sique                                                                                                                                                  | . 2                                  |

| 1.1<br>1.2<br>1.3                             | Motivating Example: VerifyPIN Source Code                                                                                                              | . 10                                 |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | Fault Types Fault Causes Fault Injection Approaches Fault Model Types Model checking diagram Manual Binary Translation Automatic Binary Translation    | . 17<br>. 19<br>. 23<br>. 24<br>. 28 |

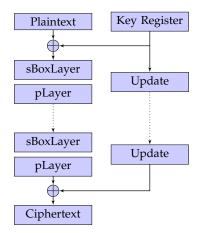

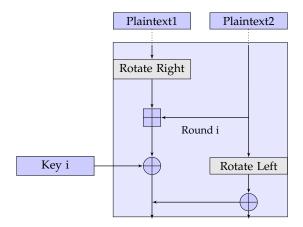

| 3.1<br>3.2                                    | PRESENT Algorithm Figure                                                                                                                               |                                      |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5               | FIVD Process Diagram Process Diagram with Pre-Analyse Step Motivating Example Code Implementation Diagram Implementation Diagram with Pre-Analyse Step | 43<br>44<br>45                       |

| 5.1<br>5.2<br>5.3                             | Experimental Results for the Motivating Example                                                                                                        | . 56                                 |

| 9.1<br>9.2<br>9.3                             | Software Process Diagram                                                                                                                               | . 84                                 |

| 10.2                                          | Software-Based Control Flow Hijacking Results                                                                                                          | . 92                                 |

|                                               | struction Results                                                                                                                                      | . 95                                 |

| A.1<br>A.2<br>A.3                             | Motivating Example Code                                                                                                                                | 120                                  |

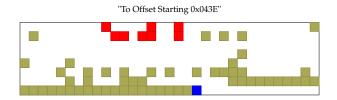

| B.1<br>B.2                                    | Unconditional Jumps from Jump at 0x014B                                                                                                                |                                      |

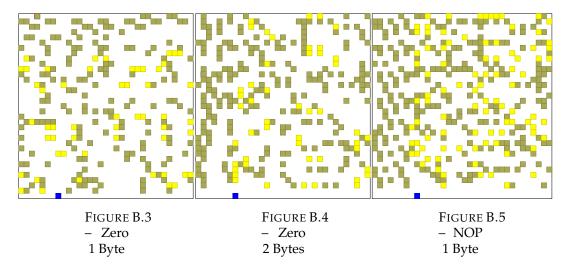

| B.3        | Zero 1 Byte  | 123 |

|------------|--------------|-----|

| <b>B.4</b> | Zero 2 Bytes | 123 |

| B.5        | NOP 1 Byte   | 123 |

# **List of Tables**

| 2.1 | List of Some Existing Binary Model Checkers     | 26  |

|-----|-------------------------------------------------|-----|

|     | Overview of Fault Injection Pre-Analyse Results |     |

|     | Clock Cycle Duration Per Instruction            |     |

| B.1 | Overview of Fault Injection Results             | 122 |

## Résumé en français

L'injection de faute est une technique utilisée pour attaquer les systèmes mais aussi pour évaluer leur robustesse. Le but d'une injection de faute est d'induire un effet spécifique au niveau du matériel créant une erreur exploitable au niveau du logiciel.

Actuellement de plus en plus de systèmes opèrent dans des milieux hostiles ce qui les rend vulnérables à toutes sortes d'attaques, d'où la nécessité d'évaluer leur robustesse face aux attaques par injection de fautes.

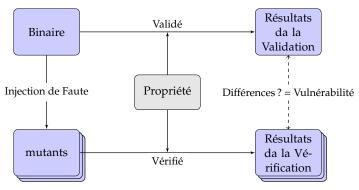

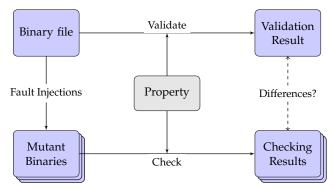

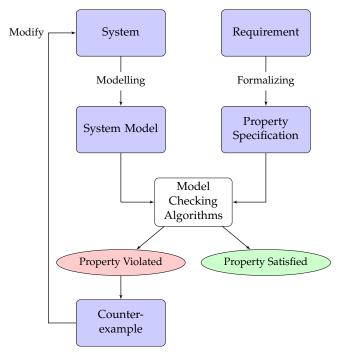

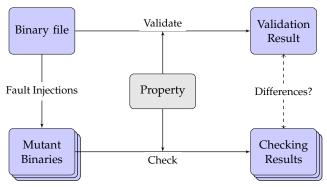

L'objectif de cette thèse est d'étudier l'effet d'une telle faute matérielle sur le logiciel, et voir si un tel effet peut créer une vulnérabilité au niveau logiciel. En premier lieu nos recherches visaient à explorer les différentes approches logicielles existantes qui étaient limitées à certains types de vulnérabilités et de modèles de faute. La première contribution de cette thèse est donc une approche automatisée qui utilise des techniques de vérification formelle pour la détection de vulnérabilité intitulé FIVD (Fault Injection Vulnerability Detection process). En outre la vérification est faite au niveau binaire ce qui représente le mieux la majorité des attaques et qui ne limite pas le type de modèle de faute utilisé pour la simulation.

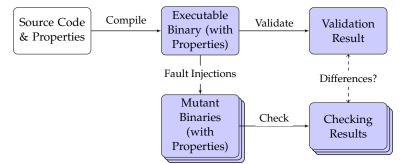

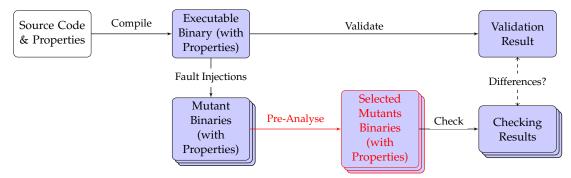

FIGURE 1 – Première Contribution : Le processus FIVD

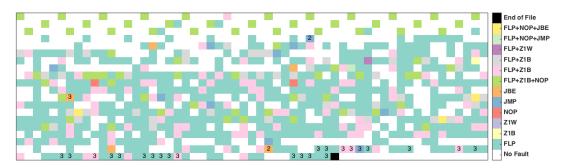

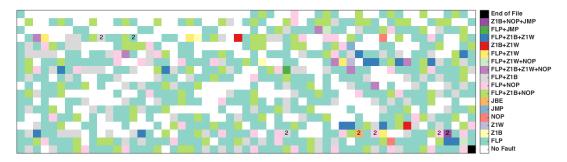

L'efficacité de cette approche a été montrée en l'appliquant à des algorithmes de cryptographie (PRESENT, SPECK) implémentés dans les systèmes embarqués. Les résultats des expériences ont montré qu'en utilisant l'approche logicielle, il était possible de détecter différents types de vulnérabilités, des vulnérabilités déjà connues dans la littérature mais aussi des vulnérabilités nouvelles.

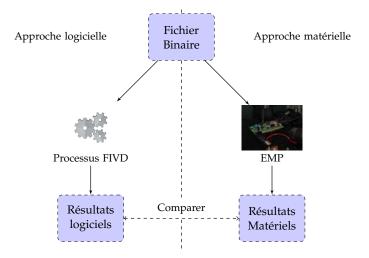

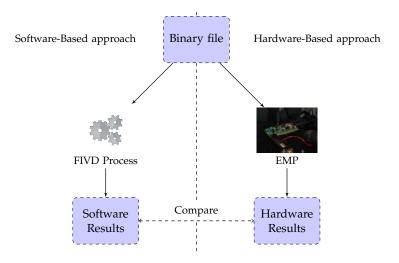

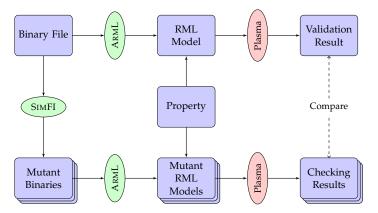

En deuxième lieu, et vu que l'approche logicielle n'est pas suffisante pour confirmer que la vulnérabilité détectée correspond à une vulnérabilité réelle qui peut être créée physiquement, il a été nécessaire d'explorer aussi l'approche physique. La deuxième contribution de cette thèse est donc la combinaison des deux approches (logicielles et physiques) afin d'explorer de nouvelles méthodes de détection de vulnérabilité par injection de fautes.

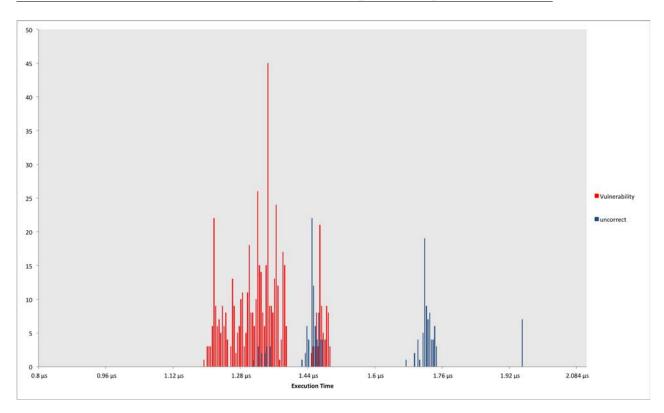

Les expériences réalisées ont montré que les résultats des deux approches coïncident mais ne sont pas totalement identiques. L'approche physique permet la détection de vulnérabilités réelles mais c'est une approche très couteuse qui nécessite beaucoup

2 List of Tables

FIGURE 2 – Seconde Contribution : la combinaison de l'approche logicielle et physique

d'expertise et de temps. L'approche logicielle est moins couteuse et nécessite moins d'efforts et de temps mais les résultats de l'approche logicielle n'étaient pas tous validés par les expériences physiques. Afin de limiter le coût, le temps, et l'effort nous proposons la combinaison des deux approches de la manière suivante. Utiliser l'approche logicielle pour détecter les endroits les plus susceptibles d'être vulnérables dans le système à vérifier, et après utiliser l'approche physique pour tester directement ces endroits vulnérables sans avoir à analyser tout le système.

# Introduction and Background

### Chapter 1

### Introduction

This chapter gives an introduction to this thesis. It first presents the context and motivation behind the subject of this thesis. Next, it shows the contributions of this thesis. Then, it lists the papers published during this thesis. Finally, it describes how the rest of this thesis is organised.

#### Sommaire

| 1.1 | Context and Motivation                 | 5  |

|-----|----------------------------------------|----|

| 1.2 | Motivating Example: Verify PIN Example | 7  |

| 1.3 | Contributions                          | 8  |

| 1.4 | Publications                           | 10 |

| 1.5 | Organisation of the Thesis             | 12 |

#### 1.1 Context and Motivation

Embedded systems are becoming "unavoidable" in many domains, e.g., health care, aerospace, transportation, and energy, where they manipulate private and sensitive data, and perform mission critical tasks. In the health care domain, the manipulated data is vital to a patient's life, any flaw in the system may cause death. In the aerospace domain, the systems must be designed to operate in space, where the temperature and environment can be fatal to system hardware. In the transportation domain, a flaw in a flight system can cause the death of hundreds of people.

The majority of embedded systems operate in hostile environments, where an embedded system's hardware may be disrupted. Embedded system disturbance can be unintentional (e.g. background radiation, power interruption [12, 90]) or intentional (e.g. induced electromagnetic pulse (EMP) [41, 96], rowhammer [113, 127, 150]).

Unintentional disturbance is generally attributed to the environment [49, 90]. An example of this is one of the first observed fault injections where radioactive elements present in packing materials caused bits to flip in chips [12].

Intentional disturbance occurs when the injection is done by an *attacker* with the intention of changing program execution [96, 113, 127, 150]. For example fault injection attacks performed on cryptographic algorithms (e.g. RSA [35], AES [123], PRESENT [144]) where the fault is introduced to reveal information that helps in computing the secret key.

Disturbing the hardware component of an embedded system can have an effect on the embedded software functionalities. This may impact the integrity and confidentiality of the system which will have consequences on the security, safety and privacy of the users behind.

Hardware disturbance is seen as a fault that is injected into the hardware which may lead to a modification of the program execution. Since the software is implemented in the hardware, any modification (fault) at the hardware level can lead to an exploitable error at the software level. In this thesis, fault injection is considered to be any perturbation at the hardware level which may modify normal execution of the embedded software.

Since embedded systems are essential and irreplaceable in many domains, it is important to ensure their dependability under fault injection. The concept of **dependable computing** [7] was used during the 1950's in the first generation of electronic computers. After discovering the first fault injections on hardware in 1954 [62], research was directed to have dependable computing and fault tolerance systems.

Later, laser was used as one of the first techniques to simulate the injection of faults and study the effect that fault injection may have at the software behaviour [61]. After fault injection was considered to be used as a technique to assess the robustness of systems. Since then new software and hardware fault injection approaches were proposed [47, 80, 81, 107, 108, 152]. The usage of fault injection techniques became an important step in the validation process of developed systems [5].

Fault injection is used as a technique to simulate the effect of hardware fault that can be induced due to the environment or by a malicious attacker. But at the same time fault injection is an approach to detect vulnerabilities created by injected faults in the hardware. Fault injection vulnerabilities are any vulnerability at the software level which is triggered by the hardware level fault injection. Detecting fault injection vulnerabilities is done using fault injection approach combined with other techniques, such as test or verification.

There are two main approaches to the detection of fault injection vulnerabilities: software-based and hardware-based approaches. Software-based approaches simulate fault injection on some aspect of the program and test/verify whether or not the injected fault yields a vulnerability in the program [31, 55, 107, 110]. Hardware-based approaches use direct experimentation on the hardware and program being executed inside, using hardware-based approaches vulnerabilities are observed by direct experimentation [10, 14, 114, 130].

Both approaches have advantages and disadvantages.

The advantages of software-based approaches are in cost, automation, and breadth. Software-based simulations do not require expensive or dedicated hardware and can be run on most computing devices easily [108]. Also with various software tools being developed and matured, compared to hardware experiments, it is easier to plug together a toolchain to do fault injection vulnerability detection [54, 55]. Such a toolchain can then be automated to detect fault injection vulnerabilities without direct oversight or intervention. Furthermore, simulations can cover a wide variety of fault models that represent different kinds of attacks and can therefore test a broad range of attacks with a single system. Combining all of the above allows for an easy automated process that can test a program for fault injection vulnerabilities against a wide variety of attack models, and with excellent coverage of potential attacks.

The disadvantages of software-based approaches are largely in their implementations or in the confidence in the feasibility of their results. Many software-based approaches have shown positive results, but are often limited by the tools and implementation details, with limitations in architecture, scope, etc. However, the biggest weakness is the lack of confidence in the feasibility of their results: software-based approaches have not been proven to map to genuine vulnerabilities in practice.

The advantages of hardware-based approaches are in the quality of the results. A fault injection that has been demonstrated in practice with hardware cannot be denied to be genuine.

The disadvantages of hardware-based approaches are the cost, automation, and breadth. To do hardware-based fault injection vulnerability detection requires specialised hardware and expertise to conduct the experiments. This is compounded when multiple kinds of attacks are to be considered; since different equipment is needed to perform different kinds of fault injection (e.g. EMP, laser, power interrupt). Further, hardware-based approaches tend to be difficult to automate, since the experiments must be done with care and supervision, and also the result can damage or interrupt the hardware in a manner that breaks the automation. Lastly, hardware-based approaches tend to have limited breadth of application; this is due to requiring many different pieces of hardware to test different architectures, attacks, etc. and also due to the time and cost to test large numbers of locations for fault injection vulnerability.

#### 1.2 Motivating Example: Verify PIN Example

This section presents a motivating example that is used to illustrate how a single bit flip can change a normal behaviour of a program and create a vulnerability. The example is of a program that checks a PIN supplied by a user when authenticating to use a credit card. This example has been widely used in the literature [45, 117].

Consider the code in Figure 1.1 that checks the value of a candidate PIN entered by a user when authenticating to use a credit card. Prior to this code fragment the true PIN is assumed to be defined and initialised with the true PIN value. Similarly the candidate PIN PINCandidate is defined and initialised with a value input by the user. Further, both PINs are checked to be the same length and this length is defined to be their size PINSize (in the program the size of the PIN is set to 4, PINSize = 4).

The code fragment in Figure 1.1 starts by setting the variables grantAccess and badValue to false, and initialising the variable i to 0. Which means that initially the access to the credit card functionalities is not given (grantAccess = false), and it is assumed that the two PINS values are equal (badValue = false).

Then, to check if the values of the two PINS are equal a while loop is used (line 4 in Figure 1.1). The loop iterate through the values of PINCandidate and PINSize, checks for each i iteration if the two values are equal (line 5 in Figure 1.1). If the iteration values of the two PINS are equal the code loops to the following one, if not badValue is set to true (line 6 in Figure 1.1). When all the values of the two PINS are compared, the code checks the value of the variable badValue. If badValue == false this means that the PINCandidate and PINTrue are the same, so the access can be granted (grantAccess = true), if not the access will remain denied (grantAccess = false).

```

1

bool grantAccess = false;

2

bool badValue = false;

3

int i = 0;

while (i < PINSize) {

4

if (PINCandidate[i] != PINTrue[i]) {

5

badValue = true;

6

}

7

8

i++;

}

9

10

if (badValue == false) {

11

grantAccess = true;

12

}

```

FIGURE 1.1 – Motivating Example: VerifyPIN Source Code

Notice, that in line three in Figure 1.1, by changing a single bit, an attacker could change the value of i from 0 to 4. (This succeeds since 0 = 0...0000 in binary, and changing the sixth bit from 0 to 1 yields 4 = 0...0100.) Observe that this would bypass the loop since i < PINSize (i.e. 4 < 4) would not hold, and therefore the checking of any digits of the candidate PIN. Thus, the example is vulnerable to this kind of 1-bit fault injection attack (as well as several other attacks that will be introduced later, see section 5.1).

The above paragraph describes a fault that can be injected into the executable binary that would allow the attacker to gain access even without the correct PIN. This research proposes and explains a process that can be used to detect such fault injection vulnerability.

#### 1.3 Contributions

To detect fault injection vulnerabilities, this thesis combined three different domains: fault injection, formal methods, and binary lifting. This section presents the key contributions of this thesis. The first contribution is a general automated formal process that allows the detection of fault injection vulnerabilities in binaries. The second contribution is the exploration of correspondence between software and hardware approach in detecting fault injection vulnerabilities.

The rest of this section details the two contributions.

# Automated Formal Process For Fault Injection Vulnerability detection in binaries

Software-based approach is cheaper, faster, and offers higher controllability over the injected fault. Despite software-based approach disadvantages, a lot of researchers are interested in exploring the simulation result using software-based approach [139, 141]. This explains the existence of a large number of software-based simulation tools [31, 46, 47, 65, 107, 118, 119, 128].

Similarly, formal methods and in particular model checking, are becoming increasingly popular for verifying the correct behaviour of systems. The majority of existing simulation tools use test oracles to check wether or not the fault injection created

1.3. Contributions 9

vulnerability. Few combine formal methods with fault injection to detect fault injection vulnerabilities. Associating formal methods to fault injection technique will allow formal proofs of the detected vulnerabilities.

Despite all the existing software-based approaches to detect fault injection vulner-abilities in the literature [31, 46, 47, 65, 107, 118, 119, 128], there still no general approach developed for a broad use. The majority of existing works were realised in the scope of specific projects. No existing approach was proposed to be architecture independent. No existing approach uses model checking to detect vulnerabilities, related to the behaviour of the system, after simulating the fault injection.

The first contribution of this thesis is to improve the existing state of the art by proposing a general process that allows automated formal detection of fault injection vulnerabilities in binaries.

The motivation for an automated process is to facilitate the detection of fault injection vulnerabilities. An automated process will allow the evaluating of the robustness of codes during the whole development process. This will produce robust program (systems) against fault injection, with low cost. The correctness or robustness of systems at the last stages of development has a higher cost, being able to detect vulnerabilities at earlier stages saves a lot of money and time [7, 44].

Combining formal methods with fault injection detection ensures the rigour of the analysis and gives a guarantee to the detected vulnerabilities. Formally proving the presence of vulnerability is sufficient to claim the existence of software vulnerability.

Simulating fault injection at the binary level allows the simulation of faults which are representative of fault that can occur in physical fault injection. Contrary to simulating fault injection at the source code for example, simulation at the binary level allows the simulation of bit flips, this allows a fine granularity to the possible faults that can be injected. Working at the binary level gives a more realistic aspect to the detected vulnerabilities.

In addition to the proposed process, an implementation of this one that allows easy automation is given using existing open source tools and tools developed during this thesis.

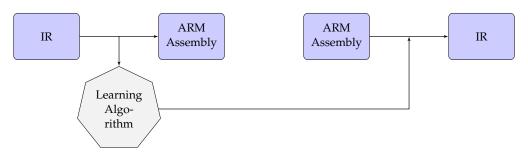

Two tools were developed during this thesis. The SIMFI tool, a fault injection simulator tool, that allows the simulation of faults at the binary level based on a chosen fault model and generates the corresponding mutants. The ARML tool, an ARM to RML translator, that allows the translation of ARM assembly to Reactive Modelling Language (RML) which allows the formal verification of binary files. The two developed tools contributed in advancing the state of the art of available tools and pushing the bounds of some existing limitations.

A case study demonstrates the efficacy of using the process on cryptographic algorithms (PRESENT and SPECK), used widely in embedded systems. The conducted experiments detected known vulnerabilities on the two cryptographic algorithms, but also pointed out new ones that can be severe to the security of the system.

#### Combining Software-based and Hardware-based fault injection approaches

Combining fault injection and formal methods using software-based approach is not sufficient to claim that the vulnerability is real. Hardware experiments are needed to validate the existence of vulnerability in reality. Hardware experiments compared

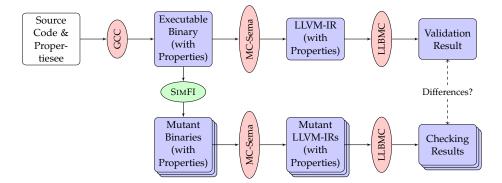

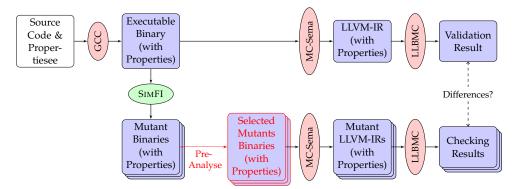

FIGURE 1.2 – FIVD process Figure

to simulation experiments are expensive, time consuming and requires a lot of expertise.

The second contribution of this thesis is proposing an approach that combines the software and hardware based approach to detect fault injection vulnerabilities in an efficient way. To our knowledge, no research has been done trying to bridge the software and hardware based approach to detect fault injection vulnerabilities the way it is done in this thesis.

Using both the software and hardware based approaches showed that:

- Software-based approaches detect genuine fault injection vulnerabilities.

- Software-based approaches yield false-positive results.

- Software-based approaches did *not* yield false-negative results.

- Hardware-based EMP approaches do *not* have a simple fault model.

- Combining software and hardware based approaches yields a vastly more efficient method to detect genuine fault injection vulnerabilities.

FIGURE 1.3 – Bridging Software and Hardware based approches

#### 1.4 Publications

This section presents the list of papers published during this thesis. For each paper an abstract is given. The list of papers is classified in two categories: papers that presents the same results as in this thesis and thus related to the work presented

1.4. Publications 11

here, and a paper that represents collaboration that makes use of some contribution of this thesis but which are not related to the work present in this thesis. Note that the papers are not presented in the order of publication.

#### Papers related to this thesis

In [69] a formal approach that detects fault injection vulnerability was presented. The result presented in this paper was a proof of concept. It explores a first try to combine existing tools to implement the automated formal Fault Injection Vulnerability Detection (FIVD) process. The proposed implementation of the FIVD process was tested on a small example (the verify PIN example).

[55] presents the automated formal process for fault injection vulnerability detection. An implementation of the process is presented using existing tools. The feasibility of the process and its implementation is demonstrated by detecting vulnerabilities in the PRESENT cryptographic algorithm binary. The content of this paper is presented in Chapter 4 in this thesis.

[54] presents an extension of the automated formal process for fault injection vulnerability detection presented in [55]. In [54] the FIVD process was improved to make it scalable to real-world implementation. The scalability is demonstrated by detecting vulnerabilities in different cryptographic implementations (PRESENT and SPECK). Chapter 5 presents in more details the content of this paper.

[53] presents a new methodology of bridging the software-based and hardware-based approach for fault injection simulation. This paper presents an extension to the software-based process presented in [54, 55]. The implementation of the process in this paper proves that the process is architecture independent. The bridging methodology is applied of two different case studies. The experiment results shows that bridging the software-based and hardware-based approaches can save time, effort, and money, and get more accurate results. In this thesis Part II presents in details the combination of software-based and hardware-based approaches.

[69] gives an overview of the fault injection vulnerability detection techniques and tools. This paper can be considered as a survey that present the existing work and highlight the contributions of this thesis.

#### Paper not related to this thesis

An additional publication not completely related to the subject of this thesis were also published. This paper was a collaboration with another PhD student.

In [6] The objective was to verify the Dynamic Software Updating (DSU) system. DSU system consists in updating running programs without any downtime. This is needed specifically for critical applications that must run continuously. In this work model checking was used as a technique to verify if the system satisfies a list of properties (Deadlock, Safety, Liveness properties).

#### 1.5 Organisation of the Thesis

This thesis is organised in two parts. Part I focuses on the software-based fault injection approach. Part II explores the potential of bridging the software-based and hardware-based fault injection approaches.

Prior to these areas (parts) is the background in Chapter 2. Chapter 2 introduces mains concepts needed to the understanding of this thesis, concept like fault injection, model checking, and binary translation.

Part I consists of 4 chapters. Chapter 3 introduces Part I of this thesis. Related works are presented to give an overview of existing works and how it is compared to the work presented in Part I. Cryptographic algorithms (PRESENT and SPECK) are presented in details in this chapter.

Chapter 4 presents the automated formal process for fault injection vulnerability detection FIVD and its extension adapted for larger programs. This chapter presents an implementation of the FIVD process and its extension using existing and developed tools.

Chapter 5 presents the experimental results of the FIVD process. First this chapter shows the feasibility of the FIVD process and its implementation on the Verify Pin motivating example. Then the scalability of the process and its implementation is demonstrated on the two cryptographic algorithms presented in chapter 3.

Chapter 6 gives details on the experimental results and implementation for the PRESENT Algorithm, it is complementary to Chapter 5.

Chapter 7 concludes Part I of this thesis and discusses some of the limitations of the FIVD process and the tools used in the implementation.

Part II consists of 4 chapters. Chapter 8 introduces Part I of this thesis. Related works that explore the combination of the software-based and hardware-based approaches are presented, to give an overview of existing works and how they compare to the work presented in Part II. Two case studies (Control Flow Hijacking and Backdoor) used in the experiments are shown as well.

Chapter 9 details the software-based and hardware-based processes used to conduct the experiments, and their implementation respectively. The software-based process used here is the FIVD process presented in the previous part with some improvement. The software-based process implementation uses ARML tool that was developed during this thesis. The hardware-based process is based on general process. The hardware-based process implementation uses the electromagnetic pulse to inject physical faults.

Chapter 10 presents the experimental results of applying the software-based and hardware-based approaches on the case studies. For each case study the results of the two approaches are shown separately and a comparaison of the two is made after.

Chapter 11 gives details on the experimental results and implementation for the control flow hijacking case study, it is complementary to Chapter 10.

Chapter 12 concludes Part II of this thesis and discusses some of the limitations of combining the two approaches (the software-based and hardware-based).

13

Chapter 13 provides a conclusion for both parts and a conclusion for a thesis as whole. It also presents a list of potential future work.

### **Chapter 2**

# Background

This chapter recalls three main key concepts needed in the understanding of this thesis. First, fault injection is presented in detail from the different type of faults to the existing fault injection approaches used to inject faults. Next, formal verification is introduced through different existing techniques, the focus is then on model checking techniques, since it is used in this thesis. Finally, working on binaries is presented through two perspectives, model checking binary and translating binary to an intermediate representation.

#### Sommaire

| 2.1 | Fault Injection     |                                           |    |  |  |

|-----|---------------------|-------------------------------------------|----|--|--|

|     | 2.1.1               | Software-Based Fault Injection Approaches | 18 |  |  |

|     | 2.1.2               | Hardware-Based Fault Injection Approaches | 20 |  |  |

|     | 2.1.3               | Fault Model                               | 22 |  |  |

| 2.2 | Formal Verification |                                           |    |  |  |

|     | 2.2.1               | Model Checking                            | 23 |  |  |

|     | 2.2.2               | Properties                                | 25 |  |  |

| 2.3 | Work                | ing on Binaries                           | 25 |  |  |

|     | 2.3.1               | Binary Model Checking                     | 26 |  |  |

|     | 2.3.2               | Binary Translation                        | 28 |  |  |

|     |                     |                                           |    |  |  |

### 2.1 Fault Injection

#### **Fault Types**

**Fault** is defined in the ISO 10303-226 document [111] as: "an abnormal condition or defect at the component, equipment, or sub-system level which may lead to a failure".

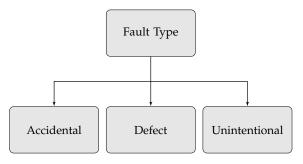

A fault can be e.g., an accidental condition, a defect, or an unintentional short-circuit.

Accidental condition that occurs in the hardware can lead to a failure in performing a required function. An example is a fault that occurs due to deterioration or wear of hardware materials. This may concerns all products, it was shown that at a stage in its lifetime the failure rate of a product increases (bathtub curve) [147].

A defect in the construction process can cause a reproducible malfunction, which will occur consistently under the same conditions. This is usually a result of an error in the specification of the equipment and therefore affects all examples of that type. An example is the recent fundamental design flaw in Intel's processor chips [34],

that forced the redesign of the Linux and Windows kernels to bypass the chip-level security bug.

In power systems, fault can be an unintentional short-circuit between two adjacent interconnects or between energised conductor and ground. This kind of fault concerns all powered devices with an electronic circuit.

The focus in this thesis is not to a specific fault. The objective is to detect all kinds of faults.

FIGURE 2.1 – Fault Types

#### **Fault Causes**

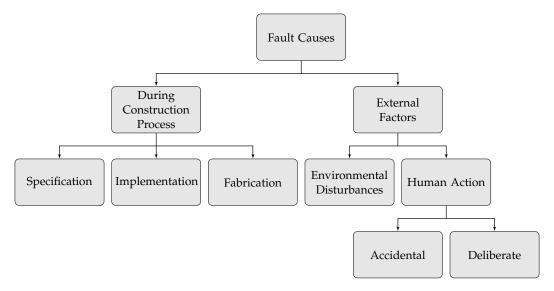

Fault can be caused due to problems occurring during the construction process of the hardware, or due to external factors [44, 72].

First, fault that occurs during the construction process. During the construction process numerous problems can occur either at the specification, implementation, or fabrication stages, which may lead to a fault.

Faults due to incorrect specification are called *specification faults*, this happen when the specification requirements ignore aspects of the environment where the system operates. It is possible that the systems with specification faults operates correctly most of the time, but they could be instances of incorrect performance. System-on-Chip (SoC) [115] are the common example for the specification faults, since the specification considered by the SoC vendors do not always contain all the details that SoC users need [124].

Faults due to incorrect implementation are called *design fault*, this happen when the system implementation does not appropriately implement the specification. These include poor component selection, logical mistakes, poor synchronisation, or bugs in the software. An example of design fault is the Ariane 5 rocket accident [87]. Ariane 5 is a European heavy-lift launch vehicle that exploded 37 seconds after lift-off on June 4,1996. The explosion was due to a software fault that resulted from converting a 64-bit floating point number to a 16-bit integer.

Faults due to fabrication defects or *component defects* were the primary reason for applying fault tolerance technique to early computing systems [44]. Fabrication defects are generally due to the chemical and physical reactions that the used material can have during the processing operation of fabrication [146]. But nowadays the development of hardware components has become more reliable and the percentage of fabrication defects faults was reduced [44].

Then faults that can be caused by external factors, such as environmental disturbances or human action, either accidental or deliberate.

Environmental disturbances arise from outside the physical system boundary. Such environments include aviation, military, space, etc. where atmospheric radiation, EMP, cosmic rays etc. may induce faults. An example is the Mars Pathfinder spacecraft where the mission was jeopardised by a concurrent software bug in the lander, the software bug being caused by a hardware glitch [48].

When the fault is due to an action that a person did, it can be accidental or deliberate. Accidental, when exposing your credit card to high temperature by accident, which may cause a disfunction in the card functionalities. Deliberate, when a person will expose the target system to electromagnetic radiation with the objective to bypass a security check for example.

In this thesis the focus is to detect the change of behaviour at the software level after a fault occurs. Note that this thesis does not focus on a specific fault cause.

FIGURE 2.2 - Fault Causes

#### **Academic Use**

This section investigates fault and their use in academic research. The effect of faults on electronic systems was discovered accidentally in 1954, when radioactive elements present in packing materials caused bits to flip in chips [12]. In 1979 researchers were interested in studying the effect of cosmic rays on computer memory and see what impact they can have on the correct functionalities of chips [154]. Research showed that fault can have an impact on the correct behaviour of systems [5, 43, 72, 75, 154]. Fault injection was developed as a technique to test the fault tolerance of systems using faults. <sup>1</sup>

Injecting faults in systems has two main objectives: system validation and system evaluation [32]. In the first case, the objective is to test the fault tolerance mechanism designed to protect a system in presence of faults, and see if the implemented solutions are handling the faults they were designed to handle. In the second case, the goal is to evaluate system performance under fault, and see how it will behave after a fault injection.

<sup>1.</sup> In the literature four different terminologies exist for fault injection: fault insertion, fault injection, fault attack, fault injection attack. For the rest of this thesis the wording choice is fault injection.

Fault injection is a technique used to test and evaluate systems under fault [139]. In order to have reliable systems it is important to test them under fault and see their reaction. Fault injection was used first in the validation procedure of systems. Injecting faults physically in the hardware or simulating faults on the systems under tests yields three main benefits [32].

First, understanding the effects of real faults. Fault injection allows the reproduction of what may happen to the system in its real environment [61, 81]. Experiments are usually done in a controllable experimental environment, which allows an easiness of understanding the effect a real fault can produce.

Second, feedback for system correction or enhancement. Fault injection was first used to test the system dependability, and it showed its efficiency in evaluating systems and prove their correctness and dependability [5, 19, 32].

Third, forecast of expected system behaviour. Fault injection can also be used to predict the effect that faults will have on the system's behaviour. This can reveal the weaknesses in systems and help improving the system security [19, 59, 71, 117].

Faults lead a system to error and error can lead to system failure. "Failure is deviation of the component or system from its expected delivery, service or result that is due or expected" [139]. System failure can be classified to failure that will lead system to crash or disfunction, or failure that will lead system to perform unsecured operation and disclose secured informations. Failure can lead to system vulnerability.

A vulnerability is defined in the National Institute of Standards and Technology (NIST) Special Publication 800-30 [133] as a flaw or weakness in system security procedures, design, implementation, or internal controls that could be exercised (accidentally triggered or intentionally exploited) and result in a security breach or a violation of the system's security policy.

In this thesis, fault injection *vulnerability* is a fault injection that yields a change to the program execution that is useful from the perspective of an attacker. This is in contrast to other effects of fault injection that are not useful, such as simply crashing a program, causing an infinite loop, or changing a value that is subsequently overwritten. Observe that the definition of a vulnerability is not necessarily trivial or stable, the above example of a program crash may be a vulnerability if the attacker desires to achieve a denial of service attack.

To test/verify systems using fault injection, faults are injected either at the hardware level (logical or electrical faults) or at the software level (code or data corruption) [67]. Fault injection techniques can be divided into two approaches: software-based fault injection approach, and hardware-based fault injection approach.

#### 2.1.1 Software-Based Fault Injection Approaches

This section presents the different classification of the software-based approaches, and investigates their advantages and disadvantages.

Software-based approaches consist of reproducing at software level the effect that would have been produced by injecting a fault at the hardware level.

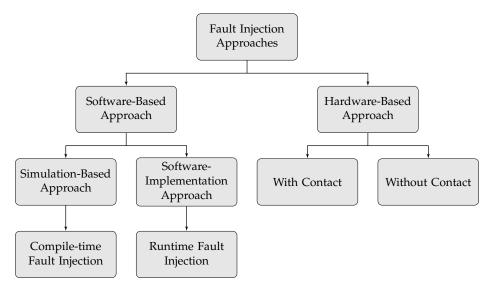

From a first perspective, the software-based approach can be classified in two sub approaches: the software-implemented approach and the simulation-based approach.

FIGURE 2.3 - Fault Injection Approaches

# In this thesis, the simulation-based approach is used for the software-based approach.

The software-implemented approach consists in simulating the fault injection at software level while it is running on the target hardware. It consists of influencing the software application by altering its data or timing using an embedded fault injection simulator software while the target application is running on the target hardware. The software-implemented fault injection approach provides a cheap means to modify the software/hardware state of the target application while it is running on the target hardware without using any physical material. One major drawback of the software-implemented approach is the inability to inject faults to locations not accessible to software. Since only software is used to simulate the fault at the target application, the simulated faults are limited to locations where software can access.

In **the simulation-based** approach, the whole system behaviour is modelled and imitated using simulation. The simulation-based approach consists in taking the program and using software to build a model of its behaviour [80]. The faults may be injected into the program before or after the model is constructed, but the model is then tested for specific behaviours or properties and the results used to reason about the behaviour of the program. Simulation-based approach offers perfect controllability over the target system, and is becoming more popular as formal methods can be used on the model that allow for reasoning about all possible outcomes, and verifying when properties of the model may hold. Note that during the conceptual and design phase the simulation-based approach is useful for evaluating system's dependability [67].

From another perspective software fault injection attacks can also be classified into two kinds of fault injection attacks [67], run time and compile time.

Run time fault injection attacks are those that occur only while the code being attacked is being executed. Run time fault injection attack consists in injecting the fault while the program is executed. Compared to the classification presented before, run time fault injection will be possible only at the software-implemented approach. Compile time fault injection attacks are those that occur at any time starting form compilation of the code, and up until just prior to execution.

Compile time fault injection attack consists in injecting the fault before the program image is loaded and executed. Compared to the classification presented before, compile time fault injection corresponds to the simulation-based approach.

The advantages of software-based approaches are in cost, automation, and breadth. Software-based simulations do not require expensive or dedicated hardware and can be run on most computing devices easily [108]. Also with various software tools being developed and matured, limited expertise is needed to plug together a toolchain to do fault injection vulnerability detection. Such a toolchain can then be automated to detect fault injection vulnerabilities without direct oversight or intervention. Further, simulations can cover a wide variety of fault models that represent different kinds of attacks and can therefore test a broad range of attacks with a single system. Combining all of the above allows for an easy automated process that can test a program for fault injection vulnerabilities against a wide variety of attack models, and with excellent coverage of potential attacks.

The disadvantages of software-based approaches are largely in their implementations or in the veracity of their results. Many software-based approaches have shown positive results, but are often limited by the tools and implementation details, with limitations in architecture, scope, etc. However, the biggest weakness is the lack of veracity of the results: software-based approaches have not been proven to map to actual vulnerabilities in practice.

#### 2.1.2 Hardware-Based Fault Injection Approaches

This section presents the different types in the literature of hardware-based fault injection, and investigates the advantages and disadvantages of the hardware-based approach.

Hardware-based approaches consists of disturbing the hardware at physical level, using hardware materiel (e.g EMP, Laser, Temperature, etc.). Hardware-based approaches are usually achieved by configuring the specific hardware to be experimented on and loading the program to be tested for vulnerabilities. A special device is then used to perform fault injection on the hardware during execution, e.g. EMP a chip, laser a transistor, overheat a chip. The result of the execution of the program is observed under this fault injection, with some particular outcomes considered to be "vulnerable" and thus a vulnerability is considered to have been achieved. One typical requirement for this approach is to have an idea of how a vulnerability is observable from program execution, since otherwise it is unclear whether the outcome of execution is a vulnerability or merely some normal or faulty behaviour.

Depending on the fault, hardware-based approaches fall into two categories[67]: hardware fault injection with contact and without contact.

In hardware fault injection with contact, the injector has direct physical contact with the target system. Examples are methods that use pin-level probes and sockets.

In hardware fault injection without contact, the injector has no direct physical contact with the target system. Examples are methods such as heavy-ion radiation and electromagnetic interference.

Various techniques exist to perform hardware fault injection either with contact or without contact [51, 67, 108, 152]. In this thesis, the hardware-based approach used is the electromagnetic pulse for the hardware experiments conducted in the later

chapters. Other technique are also presented in this section to give the reader other examples, and compare the chosen technique with the other existing ones.

Pin-level fault injection is believed to be the first technique used to inject fault [32]. Pin-level fault injection consists in changing the electrical signals at selected target device pins.

An other hardware fault injection attack, is when a fault in injected by tampering with the external clock signal of the target device. Two known ways of exploiting the clock signal for fault injection are: overclocking [60] and clock glitching [81]. Overclocking attacks consist in applying persistently a higher frequency clock signal then the normal clock frequency of the device. Clock glitching and contrary to overclocking consists in shortening the length of a single clock cycle. Both attacks causes the violation of the setup time constraints of the device and creates erroneous behaviour.

Fault injection through power supply is considered to be an inexpensive and sometime a natural way to introduce faults. This attack consists in altering the external power supply on the device, which can be done in two ways [108]: underfeeding or voltage glitch. This kind of attack can be used to skip the execution of an instruction.

One of the recent hardware fault injection method is the use of laser beams. Laser usage in fault injection attacks was first used to simulate radiation induced faults [61]. It was shown [94] that there is correlation between the results obtained from cosmic radiations and laser. Laser is able to inject faults in a very accurate and precise way.

An other hardware fault injection attack is fault injection trough electromagnetic fields. In electromagnetic fault injection, the faults are induced on the target through a fault injection probe which is placed above the target. The fault injection probe is designed as an electromagnetic coil, which induces eddy currents inside the target after receiving a voltage pulse. The electromagnetic pulse fault injection attacks is known to be less precise compared to the laser, although precise attacks can be conducted (up to a level of a single bit) but detailed knowledge of the target chip (device) in order to identify the precise point of attack with the precise parameters to set on the electromagnetic pulse hardware.

Other hardware approaches exist in the literature but will not be presented in this section such as: fault injection through temperature, fault injection through focused Ion Beams, fault injection through light.

The advantages of hardware-based approaches are in the quality of the results. A fault injection that has been demonstrated in practice with hardware cannot be denied to be genuine.

The disadvantages of hardware-based approaches are the cost, automation, and breadth. To do hardware-based fault injection vulnerability detection requires specialised hardware and expertise to conduct the experiments. This is compounded when multiple kinds of attacks are to be considered; since different equipment is needed to perform different kinds of fault injection (e.g. EMP, laser, power interrupt). Further, hardware-based approaches tend to be difficult to automate, since the experiments must be done with care and oversight, and also the result can damage or interrupt the hardware in a manner that breaks the automation. Lastly, hardware-based approaches tend to have limited breadth of application; this is due to requiring many different pieces of hardware to test different architectures, attacks, etc. and also due to the time and cost to test large numbers of locations for fault injection vulnerability.

#### 2.1.3 Fault Model

This section gives an overview of different types of fault models. Each fault model describes an attack that can be conducted through a hardware or software fault injection.

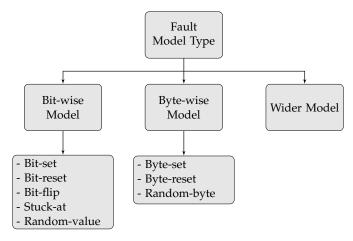

In fault detection process, faults are simulated based on a fault model. Fault models are used to specify the nature and scope of the induced modification. A fault model has two important parameters, location and impact. The location includes the spatial and temporal location of fault injection relating to the execution of the target program. The impact depends on the type and granularity of the technique used to inject the fault, the granularity can be at the level of bit, byte, or multiple bytes.

According to their granularity fault models can be classified into the following kinds [118].

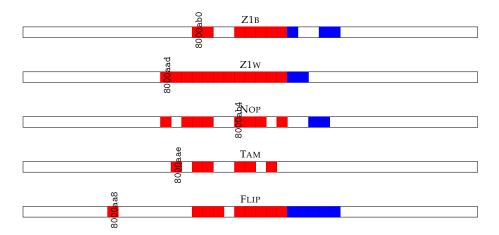

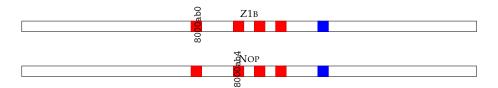

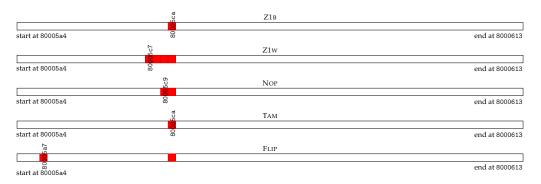

**Bit-wise models**: in these fault models the fault injection will manipulate a single bit. One can distinguish five types of bit-wise fault model [118]: bit-set, bit-flip, bit-reset, stuck-at and random-value. In the scope of this thesis the fault model that represents the bit-wise models is the *bit flip* (FLP) fault model that flips the value of a single bit, either from 0 to 1 or from 1 to 0, this fault model is an example of a Bit-wise model.

Byte-wise models: in these fault models the fault injection will modify eight contiguous bits at a time (usually in the same byte from the program or hardware perspective, *not* spread across multiple bytes). One can distinguish three types of byte-wise fault model: byte-set, byte-reset or random-byte. In the scope of this thesis three fault models represents the byte-wise models: the *zero one byte*, the *non-operation*, and the *unconditional/conditional jump*. The *zero one byte* (Z1B) fault model that sets a single byte to zero (regardless of initial value), this fault model is an example of a Byte-wise model. The *non-operation* (NOP) fault model that sets a byte to a non-operation code for the chosen architecture, this is an example of a Byte-wise fault model (but can also be implemented as a Wider model by changing the value of the whole instruction word). The *unconditional jump* (JMP) and *conditional jump* (JBE) fault models that change the value of a single byte in the target of an unconditional or conditional jump instruction (respectively), these are examples of Byte-wise fault models.

**Wider models**: in these fault models the fault injection will manipulate an entire word (defined for the given architecture). For this fault model a sequence of 8 to 64 bits will be modified depending on the architecture, e.g. changing the value of an entire word at once. This will typically target the modification of an entire instruction or single word value. In the scope of this thesis the fault model that represents the wider models is the *zero one word* (Z1w) fault model that sets a whole word to have the value zero (regardless of prior value).

## 2.2 Formal Verification

Formal verification in the context of both software and hardware systems is the act of proving or disproving the correctness of a system with respect to certain formal specification or property.

Formal verification techniques can be classified in three different techniques: manual, semi-manual, and automatic techniques.

FIGURE 2.4 – Fault Model Types

Manual techniques are human directed proof. They are in general handwritten proofs in the style of mathematical proofs using natural languages.

Semi-manual techniques are when theorem proving is used to prove or disprove the correctness of a system. This technique is mainly based on deductive inference.

Automatic techniques are based on algorithm which are implemented in tools that take as input the model of the system and the property to verify, and decide if the model satisfies the property or not in return. In this thesis the focus is on automatic techniques, specially model checking

Formal verification techniques were applied in the last 20 years in variety of industriel domains [33, 148], particularly to verify the correctness of safety-critical systems [58], systems that can cause death, injury, or big financial loses (e.g., medical, automotive, and aerospace).

## 2.2.1 Model Checking

Model checking (MC) [9] is a formal verification technique used to verify if a given model satisfies specified properties. MC has the advantage that all possible states of the model are considered, and so is guaranteed to be able to answer whether or not a given property holds for a given model. Hence MC is an interesting technique for detecting the change of behaviour.

MC has become a standard method of analysing complex systems in many application domains. MC has demonstrated its efficiency in verifying systems [50, 149], although MC still has some limitations. Large or complex programs can have extremely large models that MC may fail to check in reasonable time [9], since MC is exploring every possible state of the model.

MC can fall into four classes: explicit state MC; Symbolic MC; Bounded MC; Constraint satisfaction MC.

Software model checking is the algorithmic analysis of programs to prove properties of their executions. Two approaches exist for software model checking [92]. The first approach model checks the actual software implementation by instrumenting either a simulator or the virtual machine for target architecture. The second approach directly instruments the machine code of the program and runs an analysis on the native hardware.

FIGURE 2.5 – Model checking diagram

## **Bounded Model Checking**

Bounded model checking (BMC) is a refinement of model checking that alleviates some of the issues with possibly infinite complexity by bounding the checking [22]. The key idea in bounded model checking is to put a bound on parts of the model that could be infinite (or at least extremely large). For example, checking a program with a loop, going through hundreds or millions of iterations could be very costly for model checking. However, bounded model checking of such an example could limit the number of times to iterate through a loop. Thus, bounded model checking allows limits to be placed upon such potentially unbounded aspects of model checking.

## Statistical Model Checking

Due to the limitations of using MC and BMC on large and complex programs, *Statistical Model Checking* (SMC) is an alternative approach that can rapidly find approximate results [85].

SMC is seen as a trade-off between testing and formal verification. The core idea of SMC is to conduct some simulations of the system and verify whether they satisfy a given property. The results are then used together with algorithms from the statistical area in order to decide whether the system satisfies the property with some probability. Of course, in contrast with an exhaustive approach, a simulation-based solution does not guarantee a result with 100 confidence. However, it is possible to bound the probability of making an error. Simulation-based methods are known to be far less memory and time intensive than exhaustive ones, and are sometimes the only option. Over past years SMC has been used to 1. Assess the absence of errors in various areas from aeronautic to systems biology, 2. To measure cost average and energy consumption for complex applications such as nanosatellite and 3. Detect rare bugs in concurrent systems. The approach is now widely studied in academia, It is also used in research projects and endorsed by industry (IBM, THALES, EADS ...).

## 2.2.2 Properties

In MC, BMC, and SMC properties are used to define the correct or incorrect behaviour of the model. Here properties are used to define specific vulnerabilities that may be introduced by fault injection.

To perform model checking, the *properties* to be checked upon the model need to be specified. There are two main kinds of properties that can be checked: *safety*, and *liveness* [9]. Safety properties are used to express that certain propositions hold when they are encountered. Liveness properties express that propositions hold over some temporal dimension. This thesis only considers safety properties since these are clearer, more intuitive to represent, and sufficient to illustrate the feasibility of the process. Liveness properties can also be checked in a similar manner, although this is not presented in this thesis.

Safety properties can be expressed by simple propositions that can be annotated into the code of the program being considered. Recalling the motivating example (in Figure 1.1 on page 8), a naive safety property could be expressed by an assert statement such as

```

__llbmc_assert(i == 4);

```

that is inserted between lines 9 and 10 in Figure 1.1 on page 8. This property would be checked by the model checker to ensure that the variable i has the value 4 at this point in the model.

More generally such asserts support properties defined with boolean propositions. Here we exploit properties supporting: negation denoted !, equality denoted ==, inequality denoted !=, conjunction denoted &&, and disjunction denoted ||. For example, the following property

```

__llbmc_assert( !(PINCandidate != PINTrue) || grantAccess == false);

```

combines negation with inequality, disjunction, and equality. The semantics are that when the two PINs are not equal, then access is not granted.

In the second part of this thesis, the properties are specified using *Bounded Linear Temporal Logic* (B-LTL). B-LTL is chosen here for being able to represent the key concepts required and as it is used in the first part that uses the same foundations as exploited in the paragraph above. The properties in the second part of this thesis are mostly specified using simple (in)equality relations, however the temporal and bounding operations can be exploited to account for infinite loops induced by fault injection.

## 2.3 Working on Binaries

Working at the binary level is considered to be an efficient way to test, analyse, and verify the correctness and/or robustness of the developed systems in a variety of domains.

Binary code represent the last form of the program at the development cycle. Hence, all the errors (that affect the correctness of the system) and flaws (that represent a threat to the robustness of the system) which were introduced during the development process can be found.

| Tool Name | Ref   | Input           | Architecture                | Properties |

|-----------|-------|-----------------|-----------------------------|------------|

| JPF       | [143] | Java bytcode    | JVM                         | safety     |

| StEAM     | [91]  | C++             | -                           | safety     |

| Arcade    | [21]  | compiled binary | ATmega16, ATmega128, R8C/23 | safety     |

| mc-square | [126] | С               | ATmega16                    | safety     |

TABLE 2.1 – List of Some Existing Binary Model Checkers

The ideal solution is to detect vulnerability at the binary, since it is the most representative at the hardware level. Applying the fault injection vulnerability detection process at the binary will allow the detection of vulnerabilities which could not be found at the source code level for example.

In the scope of this thesis, one of the main objective is to be able to use formal methods (model checking) directly at the binary level to detect fault injection vulnerabilities. This introduced many constrains. The rest of this section presents a literature review of model checking binary. A list of advantages, disadvantages, and limitations is given. An explanation of why it is needed to go through an intermediate representation of the binary is given.

## 2.3.1 Binary Model Checking

Model checking is recognised as promising technique for the verification of systems in a variety of domains [9, 50, 78, 116]. The majority of existing model checker tools operates at a specific modelling language [66, 86], or on source code [13, 93]. But recently researchers were also interested in applying model checking to the binary level for various reason: first, when the source code is not available. Second, to be able to detect errors that might be introduced in the compiling process. Third, to detect malicious code inside executables. Finally, related to this thesis, to be close to the hardware representation.

Model checking binaries comes with many constrains. Model checking low level language adds hardware specification, which means that it needs to be adapted for every new hardware architecture. Beside the state space tends to be bigger than when model checking higher level language as more details are involved.

An example of model checking assembly is in [149], here the authors proposed the following method: Generating models including block cycles; Abstract and refinement method of bit level; Generating exact models by dynamic program analysis; Verifying model by model checking while generating the model by dynamic program analysis.

In the following paragraph a list of model checkers that handle binaries will be given (see Figure 2.1), highlighting their main limitations. In the scope of this thesis, an ideal model checking tool is a tool that takes binary file as input, that supports multiple architecture instruction sets (specially ARM or X86), that allows the verification of liveness and safety properties.

Java PathFinder (JPF)[143] is a verification framework dedicated for Java programs, it takes as input executable Java bytecode programs. It allows the verification of general software safety properties such as exceptions, deadlock, and user defined assertions which are specified in the source code directly. The main limitation of JPF is that it's limited to the executable Java bytecode programs it does not check executable ARM or x86 binaries, and it does not support liveness properties.

State Exploring Assembly Model checker (StEAM)[91], takes the C++ source code as an input. StEAM performs model checking on the assembly level compiled from C++ source code. In case the user had only the assembly code it will not be possible to verify it, since it needs the source code as input.

Aachen Rigorous Code Analysis and Debugging Environment (Arcade)[21], is a framework for the verification and analysis of embedded software. It verifies binary code for microcontroller. As input, it takes compiled binary code. Arcade is limited to a restricted list of supported architecture (X86 and ARM architecture are not supported), it only verifies safety properties.