#### Design of ULP circuits for Harvesting applications

Nicola Verrascina

#### ▶ To cite this version:

Nicola Verrascina. Design of ULP circuits for Harvesting applications. Electronics. Université de Bordeaux, 2019. English. NNT: 2019BORD0115 . tel-02408334

## HAL Id: tel-02408334 https://theses.hal.science/tel-02408334

Submitted on 13 Dec 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE PRÉSENTÉE POUR OBTENIR LE GRADE DE

# DOCTEUR DE L'UNIVERSITÉ DE BORDEAUX

SPI

Electronique

#### Par Verrascina Nicola

### Design of ULP circuits for harvesting applications

Sous la direction de : Jean-Baptiste Begueret (co-directeur : Mattia Borgarino)

Soutenue le 05/07/2019

#### Membres du jury:

M. Thierry Tarris PB Président

M. Hervé Barthelémy Université Toulon-Var Rapporteur

M. Patrice Gamand XLIM Examinateur

M. Nicola Regimbal Invyssis Examinateur

**Titre:** Conception des circuits à très faible consommation pour des applications Harvesting

**Résumé**: La très faible consommation dans les appareilles modernes est le facteur-clé pour les capteurs alimentée par une source d'énergie récupérée. La réduction du budget de puissance peut être atteinte grâce à différents techniques lié à trois niveaux d'abstraction : transistor, circuit et système. L'objet de cette thèse est l'analyse et la conception des circuits à très faible consommation pour des réseaux des capteurs sans fils. A' régulateur de tension et an émetteur RF ont été examiné. Le premier est le circuit principal pour la gestion de puissance ; il agit comme interface entre le transducteur et les autres circuits du capteur. L'metteur est le circuit que exiges le plus de puissance pour fonctionner, donc une réduction de sa puissance il permet une augmentation de la vie opérationnelle du capteur.

Mots clés: WSN, régulateur de tension, émetteur courte portée

**Title:** Design of Ultra Low-Power Circuits for Harvesting Applications

**Abstract:** In the modern devices Ultra-low power consumption is the survival key for the energy-harvested sensor node. The reduction of the power budget can be achieved by mixing different low—power techniques at three levels of abstraction: transistor level, circuit level and system level. This thesis deals with the analysis and the design of Ultra-Low Power (ULP) circuits suitable for Energy-Harvesting Wireless Sensor Networks (EHWSN). In particular, voltage regulator and RF transmission circuits are examined. The former is the main block in power management unit; it interfaces the transducer circuit with the rest of the sensor node. The latter is the most energy hungry block and thus decreasing its power consumption can drastically increases the sensor on-time.

**Keywords:** WSN, LDO, Short-range transmitter, Data-rate

#### Abstract

The increasing diffusion of Wireless Sensor Node (WSNs) and Body-Area sensor Network (BAN) is mainly due to the demand of smart environment in order to increase the quality of life. Several are the application domains:from domotic to industry, from medicine to rural applications. Normally a sensor network counts huge number of sensors that may be placed in hostile environment. Many time the batteries replacement is hard and expensive. Therefore the need to find another type of energy source, replacing the batteries, has created an increasing interest in the scientific academy.

The development of new material and the technological progress have supported the possibility to extract the energy from non-conventional sources for small scale applications. However the amount of energy density is not high as it spans from the highest value of  $500~\mu\mathrm{W}/\mathrm{cm}^2$  for solar source to the lowest one of  $1~\mu~\mathrm{W}/\mathrm{cm}^2$  for radio-frequency source. The energy constraint poses a several challenge for the designers to extend the lifetime devices. Ultra-low power consumption is the survival key for the energy-harvested sensor node. The reduction of the power budget can be achieved by mixing different low -power techniques at three levels of abstraction: transistor level, circuit level and system level. This thesis deals with the analysis and the design of Ultra-Low Power (ULP) circuits suitable for Energy-Harvesting Wireless Sensor Networks (EHWSN). In particular, voltage regulator and RF transmission circuits are examined. The former is the main block in power management unit; it interfaces the transducer circuit with the rest of the sensor node. The latter is the most energy hungry block and thus decreasing its power consumption can drastically increases the sensor on-time.

The thesis is structured as follows:

Chapter 1 describes the harvesting sources available in the environment, highlighting for each of them the main advantages and drawbacks when they are applied in small scale devices. The second part of this chapter is dedicated to the low-power techniques. Three levels of abstraction are introduced (CMOS technology, Circuit and System) with their advantages and drawbacks.

Chapter 2 is dedicated to the study of wireless sensor networks. A general framework is given on the sensor architecture with highlights on the fundamental blocks. The expression for the required radiated power is obtained for a given distance. The duty-cycled equation is also obtained to get the best trade-off in terms of required energy, communication channel quality and amount of data transfer.

Chapter 3 focuses on the design of very efficient Low-DropOut voltage (LDO) regulator. Many are the efforts to achieve a good regulation accuracy by addressing ultra low power consumption. Especially for transient response the closed loop frequency response and the slew-rate of the error amplifier requires high quiescent current to achieve good performances. In this work an adaptively bias current and a class-AB error amplifier are implemented in such way the increase in quiescent current is proportional to the very large load current. With these techniques the impact on the global power consumption of LDO is reduced. Moreover high current efficiency for all load conditions is also achieved. The stability of closed loop is ensured by a current buffer and a Miller's capacitor for the whole range of operational load current. The stability is guaranteed also for very low stand-by current.

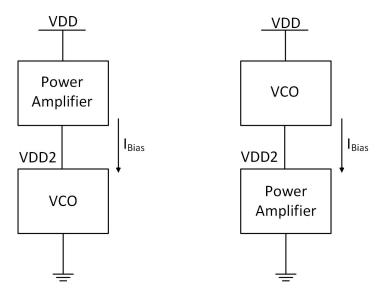

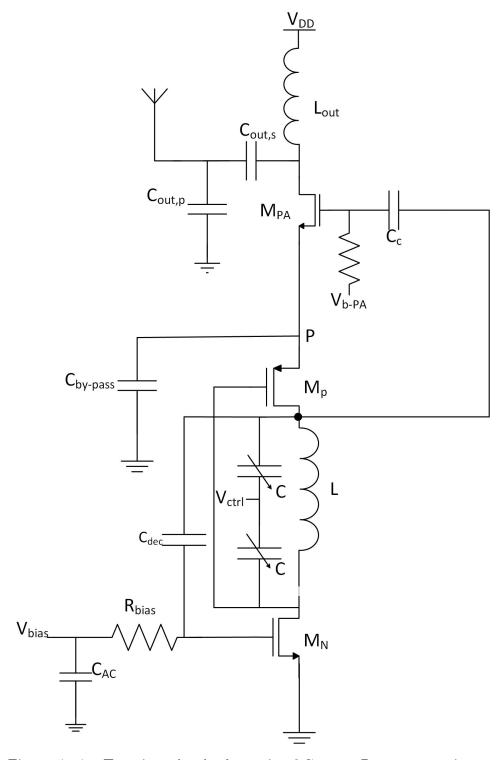

In chapter 4 the design flow of OOK modulation transmitter is addressed. The low targeted radiated power of -15 dBm poses a severe limitation for the global transmitter efficiency. The first part of the chapter is dedicated to the study of classical cascaded architectures where the oscillator (VCO) is directly connected to the input of the power driver. The trade-off between the supply voltage and the matching network is described highlighting the difficulty to integrate the passive elements of matching network when the supply voltage for the power amplifier is about 1 V and the peak to peak output voltage required over a 50  $\Omega$  is in the order of tens millivolts. To circumnavigate this problem a current reuse transmitter is proposed where the power driver and the VCO are stacked and the same bias current is used. With this architecture the supply voltage can be tuned between the two circuits to achieve the best trade-off between the power consumption and the performances of each circuit.

#### Résumé

La demande toujours croissante d'amélioration de la qualité de vie avec la création des environnements intelligents, a permis la diffusion des reseaux des capteurs sans fil. Les applications envisagées peuvent aller de la domotique à l'industrie, de la medicine à l'agriculture. Le probléme principal pour ces types des capteurs est le remplacement des batteries, étant donné que l'installation pourrait avoir lieu dans des environnement hostiles. Donc la recherche d'autres types des sources d'énergie qui peuvent remplacer les batteries a attiré l'attention de la Communauté scientifique internationale.

Nombreux sont les sources à partir des quelles il est possible obtenir de l'énergie électrique pour des systèmes miniaturisés. Néanmoins la faible énergie mise à disposition par des sources non-conventionnelles, pose un vrai défi pour les concepteurs s'ils veulent augmenter la durée de vie des systèmes. C'est seulement par l'utilisation des circuits à trés faible consommation que les capteures autonomes peuvent représenter un choix valable pour le marché. La réduction du besoin d'énergie peut être atteinte en mélegeant différentes tecniques à trois différent niveaux d'abstraction : transistor, circuit et système.

L'objectif de la thése est la conception et l'analyse des circuits à trés faible consommation appropriés pour des applications d' Energy-Harvesting Wireless Sensor Networks (EHWSN). La première partie détaille le régulateur de tension, qui est le circuit fondamental du bloc dédiée à la gestion de la puissance. La deuxième partie est dédié à l'analyse et à la conception d'un emetteur RF, qui représente le circuit avec la consommation de puissance la plus haute présent dans le capteur. Par conséquent une reduction de la consommation de ce dernier circuit, baisse considérablement la démande d'énergie du systeme dans sa totalité.

La thése est ainsi organisée : Le chapitre 1 décrit les sources de récupération d'énergie disponibles dans l'environnement, soulignant les avantages et les inconvénients quand elle sont appliquées à des circuits miniaturisés. La deuxième partie est dédiée à l'étude des techniques permettant la réduction de la consommation de puissance.

Le chapitre 2 est dédié à l'étude des réseaux de capteurs sans fil. Un cadre genéral de leur architecure est donné. L'équation pour calculer la puissance radiative nécessaire pour couvrir une certaine distance est donnée. En dernier lieu le rapport cyclic optimale est derivée à partir de l'énergie nécessaire, de la qualité du canal de communication et de la quantité des données à transmettre.

Le chapitre 3 décrit la conception d'un régulateur Low-DropOut (LDO) à haute efficacité. L'attention est centrée pour obtenir une trés faible consommation de puissance sans sous-estimer la précision du réglage de tension. Pour obtenir un bonne réglage de tension, l'amplificateur d'erreurs doit avoir un slew-rate élevé, et la réponse en fréquence de la boucle, donc la vitesse de réglage du circuit, doit etre rapide. Les solutions adoptées pour surmonter le problème sont un amplificateur d'erreur de classe-AB, avec un courant de polarisation qui s'adapte au courant de sortie du régulateur. L'efficacité est élevée pour toutes les conditions du courant de sortie avec moins d'impact sur la consommation de puissance globale du circuit. La stabilité de la boucle est assurée dans toutes les conditions par un buffer de courant et une capacité Miller, meme pour un courant trés faible de stand-by en sortie. Le chapitre 4 décrit la conception d'un émetteur avec une modulation OOK. La faible puissance émise de -15 dBm limite l'efficacité globale du systém.

La première partie du chapitre est dédiée à l'étude d une structure classique en cascade, où la sortie du synthétiseur de fréquence (VCO) est directement connectée à l'entrée de l'amplificateur de puissance. Le chapitre continue présentant les compromis de conception pour le réseau d'adaptation quand la tension d'alimentation est élevée alors que la tension aux bor de la charge de  $50~\Omega$  est de quelques mV. Une architecture empilée est finalement proposée, où le VCO et le driver de puissance partagent le meme courant de polarisation, afin de répartir la tension d'alimentation entre les deux circuits.

# Contents

| 1 | Low                                | Power   | r techniques for energy harvesting system                | 1  |

|---|------------------------------------|---------|----------------------------------------------------------|----|

|   | 1.1                                | Energy  | Harvesting                                               | 1  |

|   |                                    | 1.1.1   | Solar Energy                                             | 1  |

|   |                                    | 1.1.2   | Thermal Energy                                           | 3  |

|   |                                    | 1.1.3   | Kinetic Energy                                           | 4  |

|   |                                    | 1.1.4   | Radio-Frequency Energy                                   | 4  |

|   | 1.2                                | Design  | techniques for ULP circuits                              | 5  |

|   |                                    | 1.2.1   | CMOS level                                               | 5  |

|   |                                    | 1.2.2   | Circuit Level                                            | 7  |

|   |                                    | 1.2.3   | System level                                             | 11 |

|   |                                    | 1.2.4   | Conclusion                                               | 13 |

| 2 | $\mathbf{S}\mathbf{v}\mathbf{s}$ 1 | tem Ar  | oproach                                                  | 14 |

|   | 2.1                                | _       | Management                                               | 19 |

|   | 2.2                                |         | udget, data rate and duty cycle                          | 22 |

|   |                                    | 2.2.1   | Required link Budget                                     | 22 |

|   |                                    | 2.2.2   | Data Rate and Duty Cycle Trade-off                       | 26 |

|   |                                    | 2.2.3   | Conclusions                                              | 28 |

| 3 | Volt                               | tage Re | egulator                                                 | 29 |

|   | 3.1                                |         | cound                                                    | 29 |

|   | 3.2                                | _       | e Regulator                                              | 30 |

|   |                                    | 3.2.1   | Static Characteristics                                   | 31 |

|   |                                    | 3.2.2   | Dynamic Characteristics                                  | 32 |

|   | 3.3                                | Switch  | ing versus Linear                                        | 33 |

|   | 3.4                                |         | rop-Out Regulator                                        | 37 |

|   | 3.5                                |         | Implementation                                           | 45 |

|   |                                    | 3.5.1   | Output Target                                            | 45 |

|   |                                    | 3.5.2   | Overcome current efficiency-transient response trade-off | 47 |

|   |                                    | 3.5.3   | Slew-rate enhancement                                    | 49 |

|   |                                    | 3.5.4   | Extended closed loop Bandwidth                           | 54 |

|   |                                    | 3.5.5   | Compensation Strategy                                    | 55 |

|   |                                    | 3.5.6   | Transistor Level Design                                  | 61 |

|   | 3.6                                | Voltage | e Reference                                              | 67 |

|   | 3.7                                | 0       | t Design                                                 | 71 |

|   | 3.8                                |         | e Regulator Simulation Results                           | 74 |

|   | 3.0                                | _       | ısion                                                    | 82 |

#### CONTENTS

| 4       | Ultı | a-Low   | power transmitter                                                | 83    |

|---------|------|---------|------------------------------------------------------------------|-------|

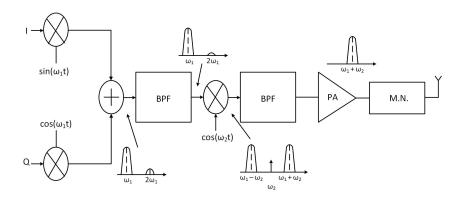

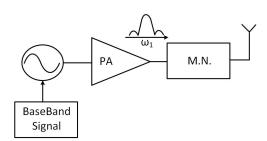

|         | 4.1  | Transr  | nitter architecture                                              | . 84  |

|         | 4.2  | ULP I   | Direct Modulation Transmitters                                   | . 88  |

|         |      | 4.2.1   | Local Oscillator                                                 | . 88  |

|         |      | 4.2.2   | Ring versus LC Oscillator                                        | . 90  |

|         |      | 4.2.3   | Designing Low Power LC Oscillator                                | . 91  |

|         |      | 4.2.4   | Power Amplifier                                                  | . 93  |

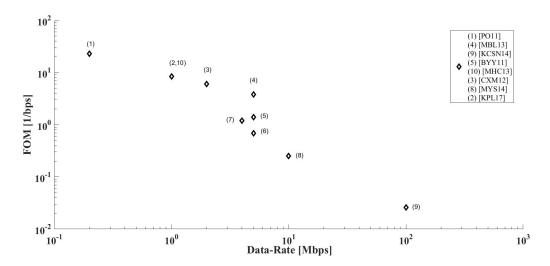

|         |      | 4.2.5   | Comparison of different low power direct modulation transmitters | . 96  |

|         |      | 4.2.6   | Transmitter Design Steps                                         | . 96  |

|         |      | 4.2.7   | Transmitter Simulation Results                                   | . 106 |

|         | 4.3  | Currer  | nt Reuse Transmitter                                             | . 109 |

|         |      | 4.3.1   | Current Reuse VCO                                                |       |

|         |      | 4.3.2   | Designed current Reuse transmitter                               | . 114 |

|         | 4.4  | Conclu  | ısion                                                            |       |

| 5       | Con  | clusion | ıs                                                               | 120   |

| ${f A}$ | Dra  | in curi | rent calculation in class AB Error Amplifier                     | 122   |

# List of Figures

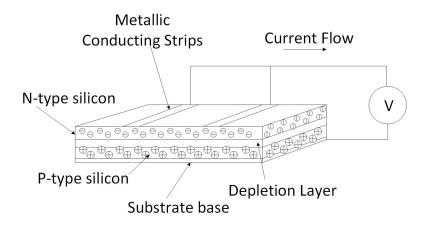

| 1.1  | Section of Photovoltaic Cell                                                   | 2  |

|------|--------------------------------------------------------------------------------|----|

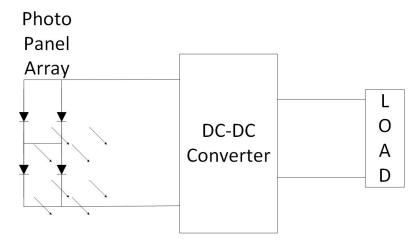

| 1.2  | Typical implementation of PV harvesting maximum power point tracking.          | 2  |

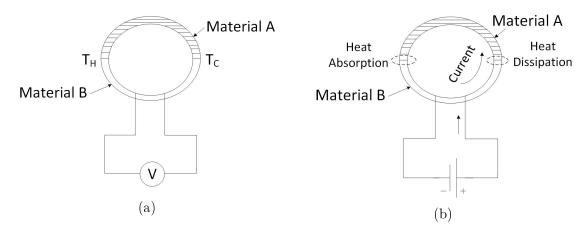

| 1.3  | (a) Seedback effect, the generated voltage is proportional to the tempera-     |    |

|      | ture gradient between the hot point $T_H$ and the cold point $T_C$ (b) Peltier |    |

|      | effect the current generated by the applied voltage causes a thermal diffu-    |    |

|      | sion from the heat dissipation to the heat absorption                          | 3  |

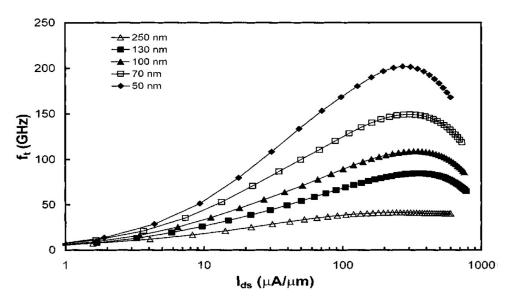

| 1.4  | Cut-off Frequency trend in function of current density for different node      |    |

|      | technology [WKvL $^+$ 01]                                                      | 6  |

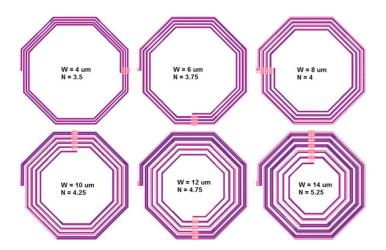

| 1.5  | Combinations to achieve 8 nH inductance [Van15] where W is the metal           |    |

|      | width and N is the numbers of turns                                            | 7  |

| 1.6  | Inversion coefficient line number with voltage and shape factor MOSFET         |    |

|      | properties [Bin07]                                                             | 9  |

| 1.7  | Minimum supply voltage required in classical cascode OTA when the tran-        |    |

|      | sistors are biased in strong and in moderate inversion                         | 10 |

| 1.8  | Cascaded circuit block with two separate supply voltage and independent        |    |

|      | bias currents                                                                  | 11 |

| 1.9  | Multi-threshold application in logic circuit.                                  | 11 |

| 1.10 | Wake-up scheme timeline                                                        | 12 |

| 2.1  | Plot obtained from the measurement results for $I = 2.3$ mA and $k = 1.25$ .   | 15 |

| 2.2  | Market forecast for EH devices used in WSN applications                        | 16 |

| 2.3  | Energy Harvesting WSN market in 2012 (a) and prevision of market in            |    |

|      | 2017 (b)                                                                       | 17 |

| 2.4  | Power comparison between WSN and Energy Harvested circuit                      | 18 |

| 2.5  | Architecure of energy harvesting sensor node                                   | 19 |

| 2.6  | Power management transistor level schematic implemented in [PCFP14] .          | 20 |

| 2.7  | The top graph depicts an example of energy profile in harvesting system.       |    |

|      | In the bottom graph the trend of voltage stored into the capacitor (red        |    |

|      | line) and the regulated voltage at the output of the PMU                       | 21 |

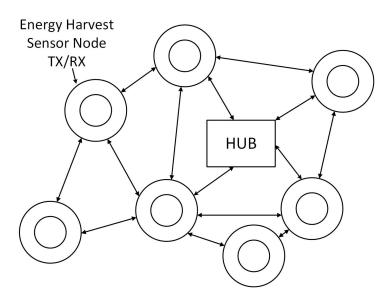

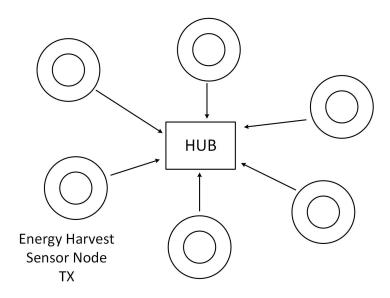

| 2.8  | Wireless sensor network mesh architecture                                      | 24 |

| 2.9  | Wireless sensor network star architecture                                      | 25 |

| 2.10 | RICER                                                                          | 25 |

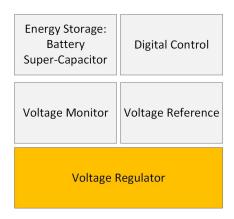

| 3.1  | Power Management Unit                                                          | 29 |

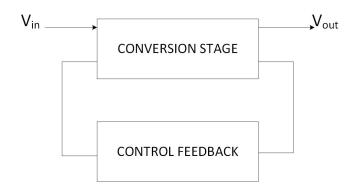

| 3.2  | General block diagram of voltage regulator                                     | 30 |

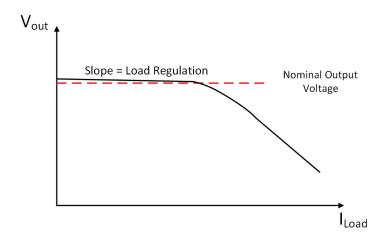

| 3.3  | Load Regulation                                                                | 31 |

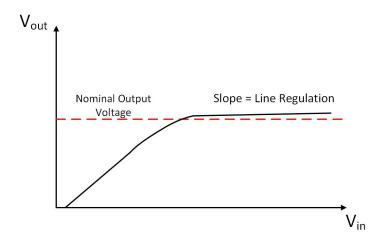

| 3.4  | Line Regulation                                                                | 32 |

#### LIST OF FIGURES

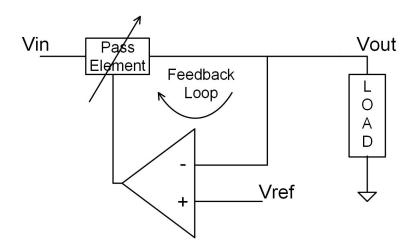

| 3.5  | Linear Regulator                                                                                                            | 34 |

|------|-----------------------------------------------------------------------------------------------------------------------------|----|

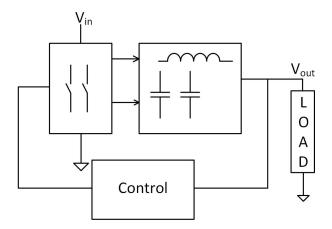

| 3.6  | Switching Regulator                                                                                                         | 35 |

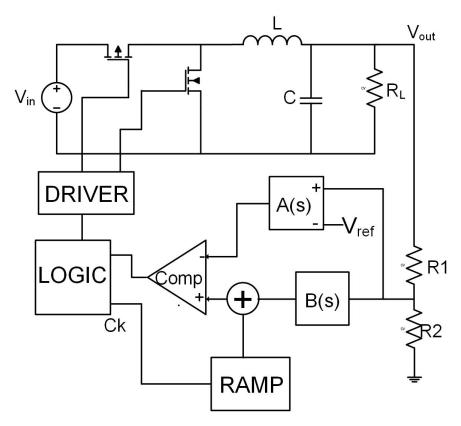

| 3.7  | Block Diagram of Buck Converter [WTM10]                                                                                     | 36 |

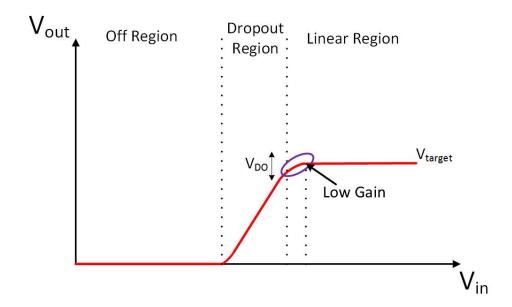

| 3.8  | Regulated output voltage versus input voltage                                                                               | 38 |

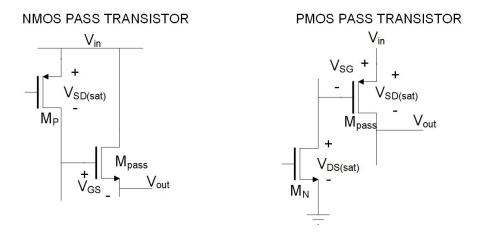

| 3.9  | N-type and P-type pass element                                                                                              | 38 |

| 3.10 |                                                                                                                             | 39 |

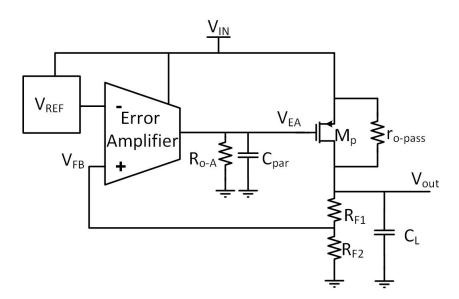

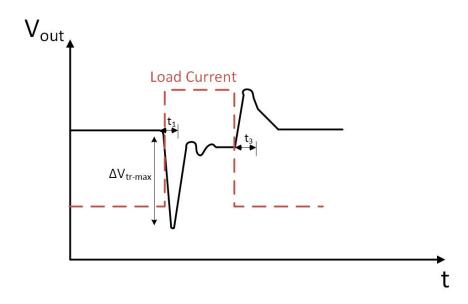

| 3.11 | Typical transient Response of LDO regulator                                                                                 | 40 |

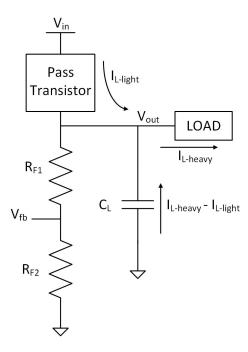

|      | Energy balancing from light to heavy step                                                                                   | 41 |

|      | Energy balancing from heavy to light step                                                                                   | 41 |

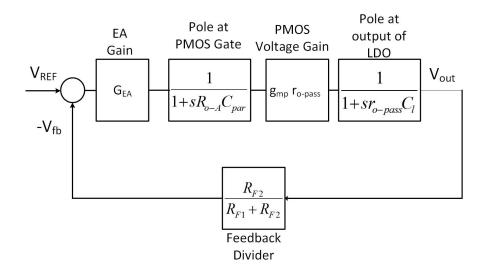

|      | LDO negative feedback diagram                                                                                               | 42 |

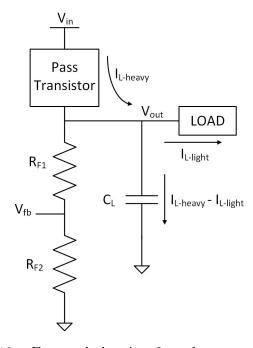

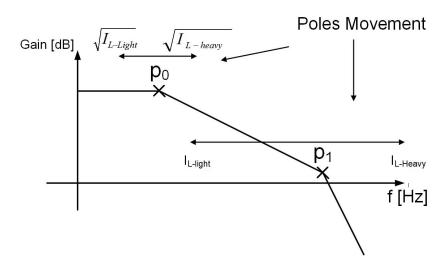

|      | Poles movement with load current                                                                                            | 43 |

|      | Parasitic gate capacitance $C_g$ (a) and saturation drain-source volatage                                                   |    |

|      | $V_{sd-sat}$ (b) of the pass transistor for different width W                                                               | 47 |

| 3.17 | Class-A bias topology                                                                                                       | 49 |

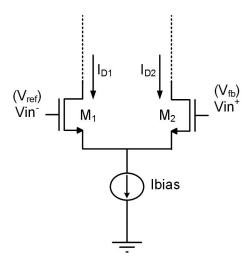

|      | Class-AB bias topology                                                                                                      | 50 |

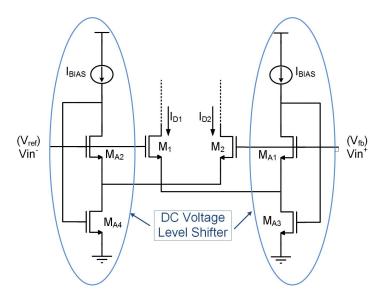

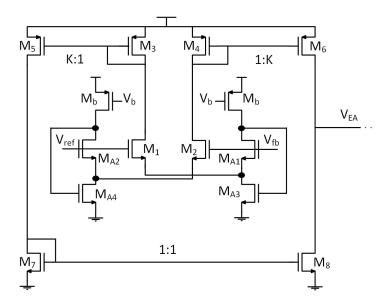

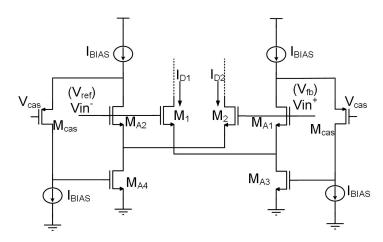

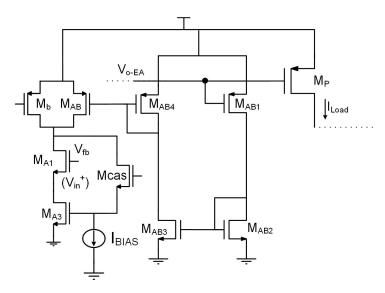

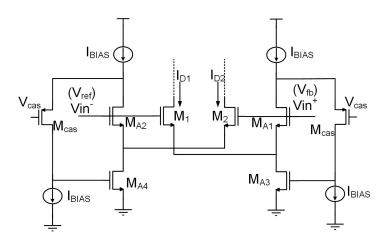

|      | Class AB error amplifier                                                                                                    | 51 |

|      | FVF cell with cascode Pmos transistor                                                                                       | 52 |

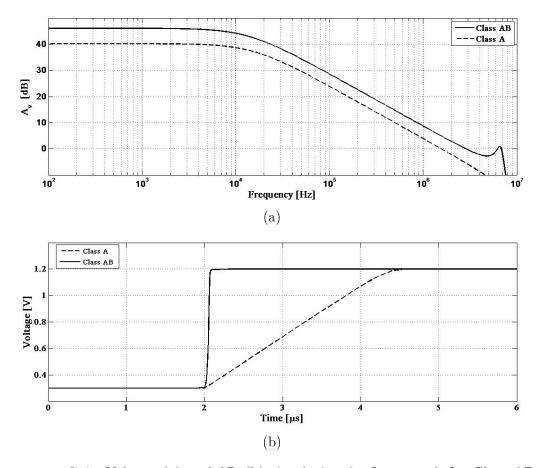

|      | Gain Voltage (a) and SR (b) simulation for $I_b = 60$ nA for Class-AB error                                                 |    |

|      | amplifier in solid line and class-A dot line. The simulations are performed                                                 |    |

|      | with $C_L=350$ fF                                                                                                           | 53 |

| 3.22 |                                                                                                                             |    |

|      | purposes                                                                                                                    | 54 |

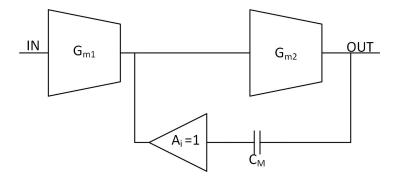

| 3.23 | Block Diagram of two stages amplifier with current buffer compensation                                                      |    |

|      | technique                                                                                                                   | 55 |

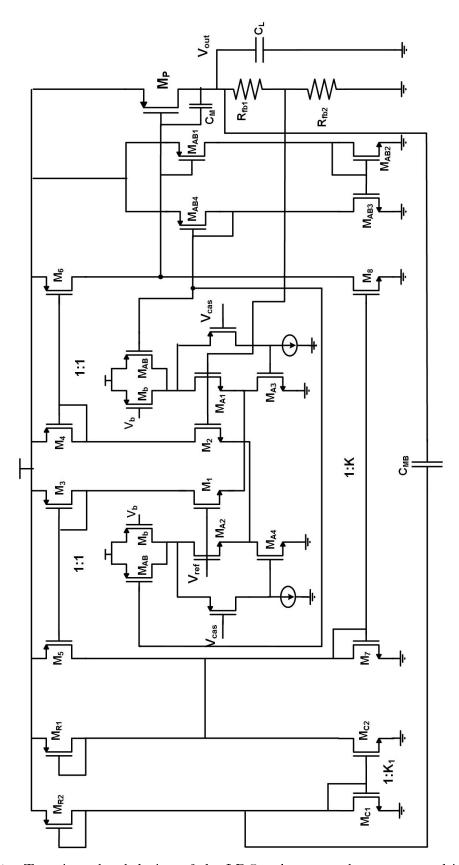

| 3.24 | Transistor level design of the LDO voltage regulator proposed in this work                                                  | 56 |

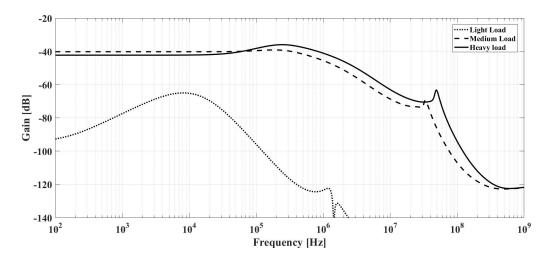

| 3.25 | AB loop gain for different load current                                                                                     | 57 |

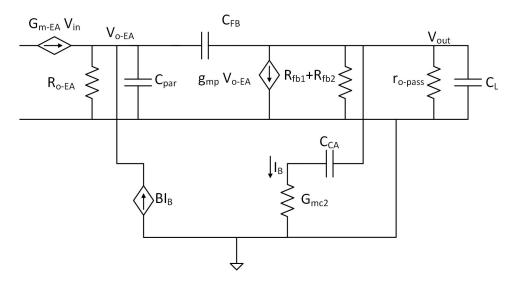

| 3.26 | LDO small-signal feedback representation                                                                                    | 58 |

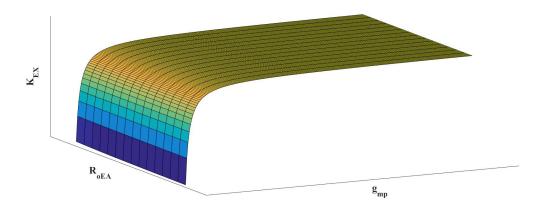

| 3.27 | $K_{EX}$ for different values of $R_{o-EA}$ and $g_{mp}$ . The minimum value of separa-                                     |    |

|      | tion factor is for light load condition. $R_{o-EA}$ has negligible impact                                                   | 60 |

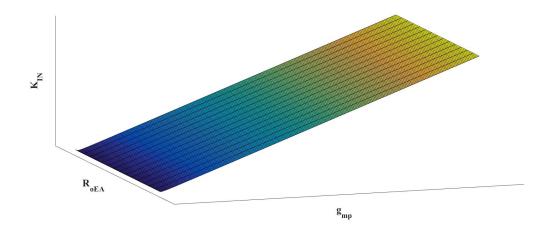

| 3.28 | $K_{IN}$ for different values of $R_{o-EA}$ and $g_{mp}$ . The minimum value of separa-                                     |    |

|      | tion factor is for light load condition. Also in this case $R_{o-EA}$ has negligible                                        |    |

|      | $impact. \dots \dots$ | 61 |

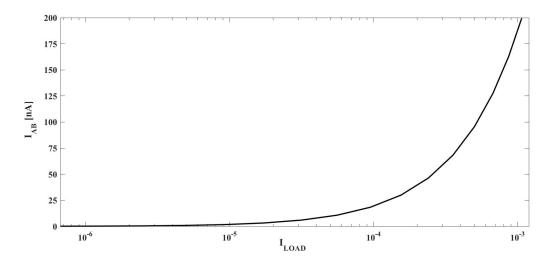

| 3.29 | The trend of the bias current adaptability versus the load current                                                          | 62 |

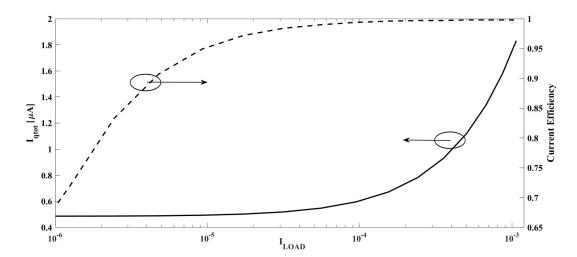

| 3.30 | LDO quiescent current and current efficiency versus load current. In this                                                   |    |

|      | case the trend is shown only for operation mode ( $I_{Load}$ = 1 $\mu$ A-1 mA).                                             |    |

|      | For stand-by mode the current efficiency is worsen by the minimum drain                                                     |    |

|      | current needed to keep ON the pass transistor                                                                               | 62 |

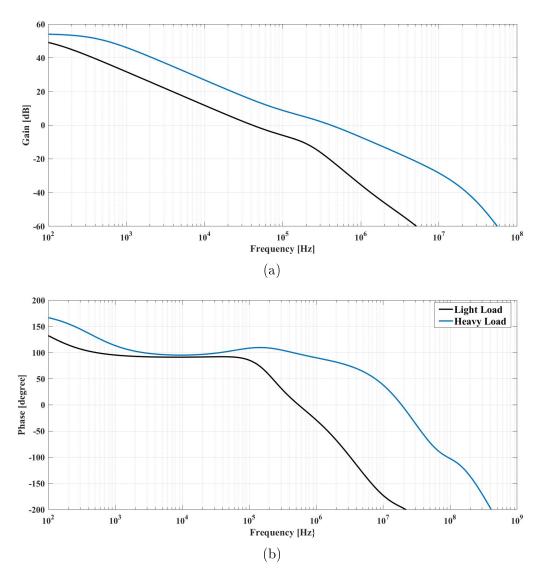

| 3.31 | (a) Open loop gain for $I_{Load}=1~\mu\mathrm{A}$ (black line) and for $I_{Load}=1~\mathrm{mA}$ (blue                       |    |

|      | line). It is evident the GBW product is increased at heavy load condition                                                   |    |

|      | due to higher $G_{mEA}$ . GBW extends from 40 kHz to 360 kHz (b) Phase for                                                  |    |

|      | the two load conditions                                                                                                     | 63 |

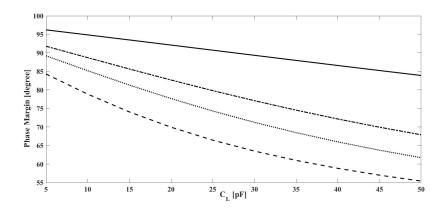

| 3.32 | Phase margin versus output capacitor value, for different stand-by output                                                   |    |

|      | current values. From $I_L^{stand-by}=205$ nA (dash line) to $I_L^{operation-mode}=1$                                        |    |

|      | $\mu$ A (solid line)                                                                                                        | 64 |

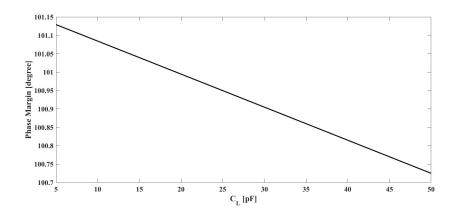

|      | Phase margin versus output capacitor value at heavy load condition                                                          | 64 |

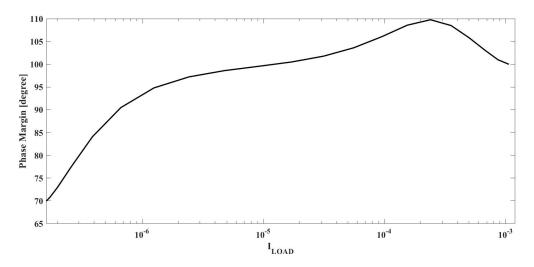

|      | Phase margin versus output current for all operating regions                                                                | 65 |

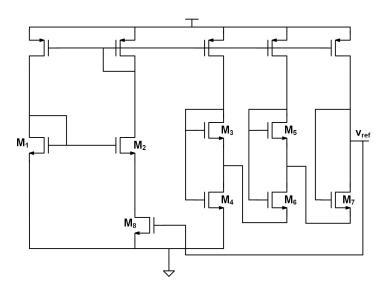

| 3.35 | Ueno voltage reference                                                                                                      | 68 |

#### LIST OF FIGURES

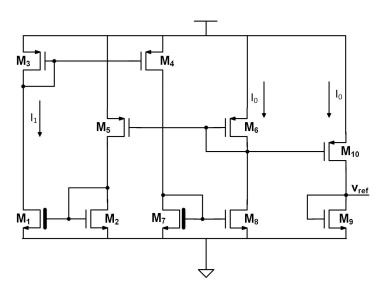

| 3.36 | De Vita voltage reference                                                                                                                                 | 69  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.37 | Bandgap Voltage reference proposed in [HUKN10]                                                                                                            | 69  |

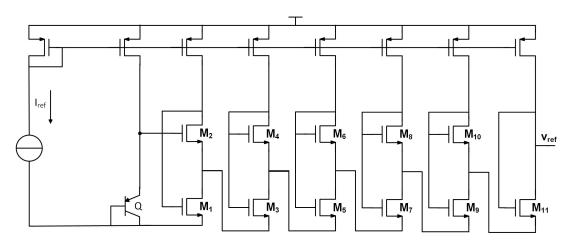

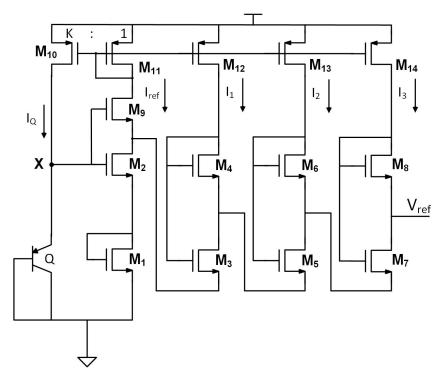

|      | Sub-bandgap voltage reference used in this work                                                                                                           | 71  |

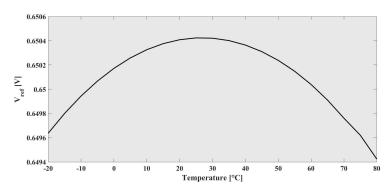

|      | Output voltage reference versus the temperature                                                                                                           | 73  |

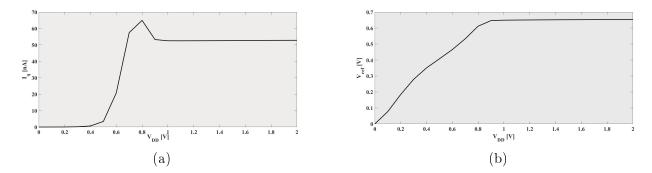

| 3.40 | The quiescent current (a) and the voltage reference (b) versus supply voltage                                                                             | 73  |

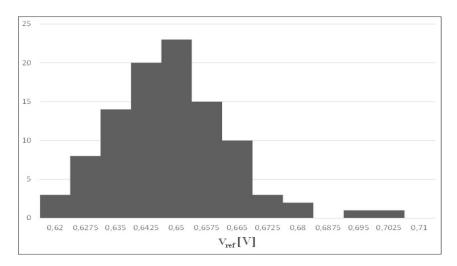

|      | Monte Carlo simulations on the output voltage reference with 100 runs                                                                                     | 74  |

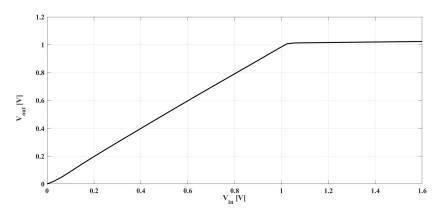

|      | Line regulation (orange line) of LDO when $V_{IN}$ moves from 0 V to 1.6 V.                                                                               |     |

|      | The simulation is performed at heavy load condition                                                                                                       | 74  |

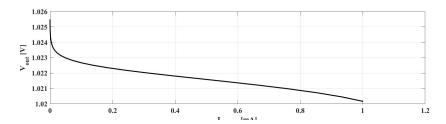

| 3.43 | Output Voltage versus output current                                                                                                                      | 75  |

|      | Transient response for a load current step in operation mode. From 1 $\mu$ A                                                                              |     |

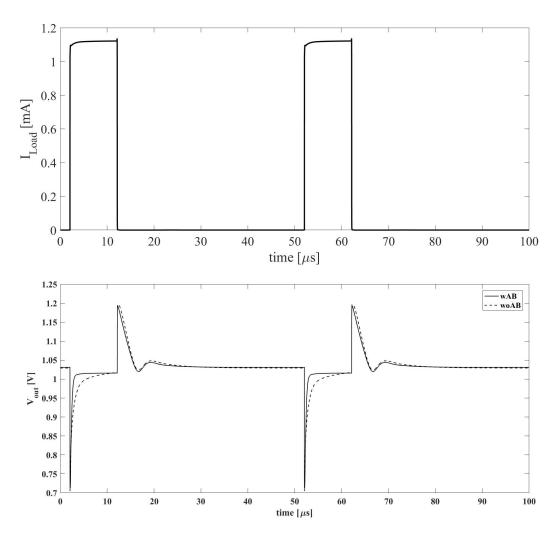

|      | to 1 mA                                                                                                                                                   | 76  |

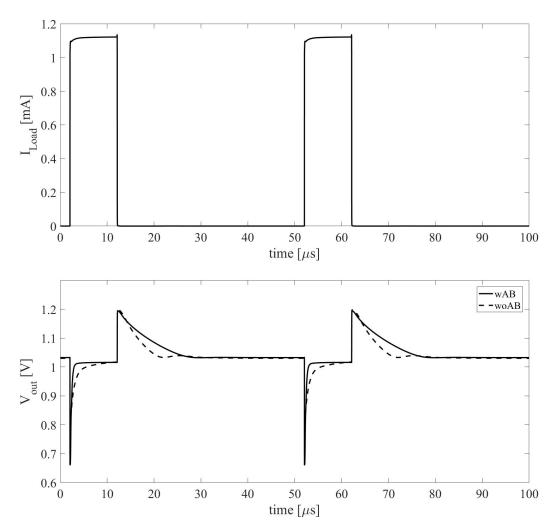

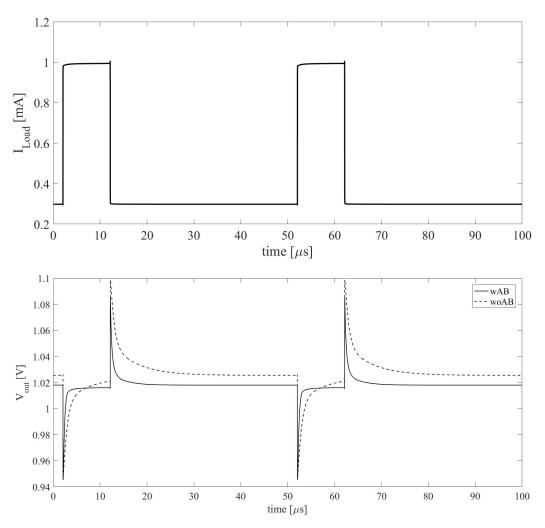

| 3.45 | Transient response for a full load current step. From 300 nA to 1 mA                                                                                      | 77  |

|      | Transient response for a load current step in moderate condition. From 300                                                                                |     |

|      | $\mu A$ to 1 mA                                                                                                                                           | 78  |

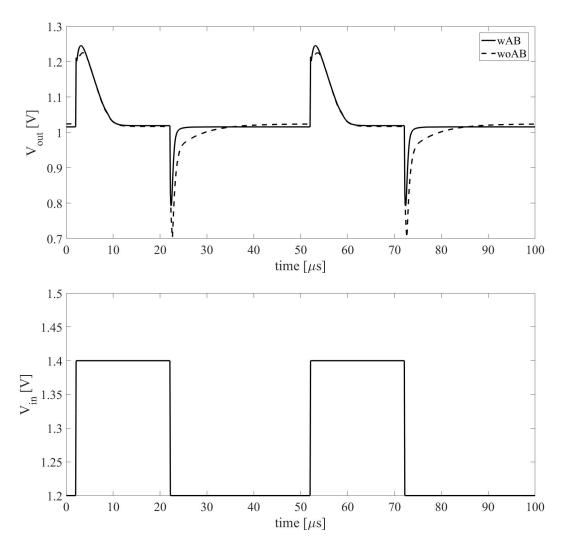

| 3.47 | Line transient at heavy load condition                                                                                                                    | 79  |

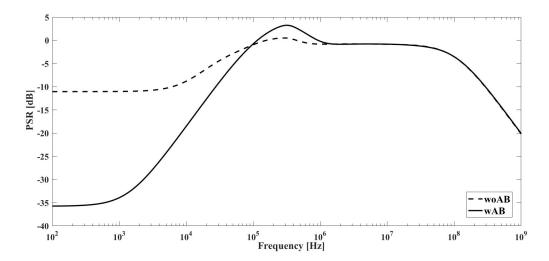

| 3.48 | PSR at heavy load condition                                                                                                                               | 79  |

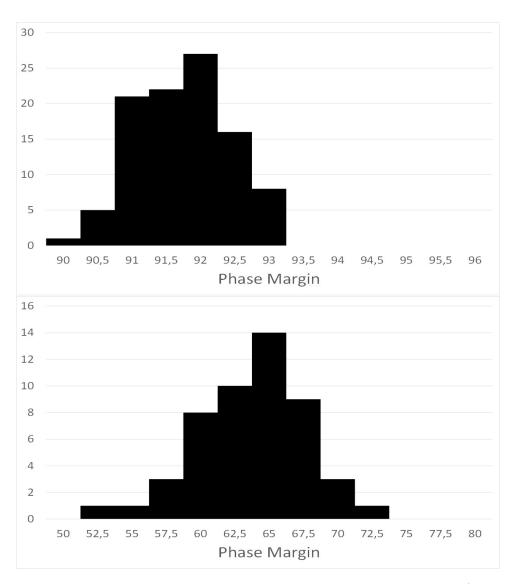

| 3.49 | Monte Carlo simulations on the phase margin with 100 runs.a) for stand-by                                                                                 |     |

|      | condition b) for minimum operating load condition                                                                                                         | 80  |

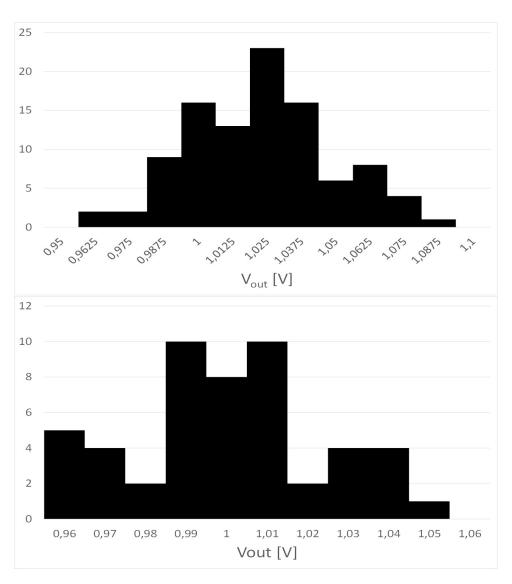

| 3.50 | Monte Carlo simulations on the regulator output voltage with 100 runs.                                                                                    |     |

|      | a) for minimum operating load condition b) for maximum operating load                                                                                     |     |

|      | condition                                                                                                                                                 | 81  |

|      |                                                                                                                                                           | 0.4 |

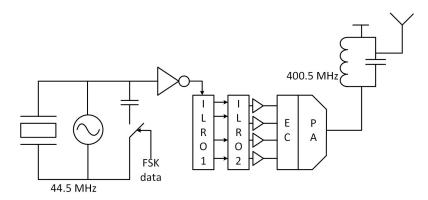

| 4.1  | Block diagram of two-step conversion transmitter                                                                                                          | 84  |

| 4.2  | Block diagram of direct modulation transmitter                                                                                                            | 84  |

| 4.3  | FOM versus data-rate for recent ULP transmitter. [KPL17]                                                                                                  | 86  |

| 4.4  | Block diagram of sub-harmonic injection locking transmitter [PO11]                                                                                        | 86  |

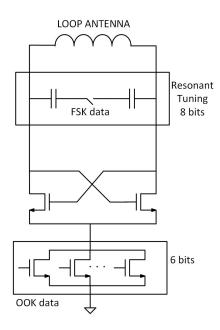

| 4.5  | Power VCO transmitter presented in [MBL+13]                                                                                                               | 87  |

| 4.6  | Current starved VCO                                                                                                                                       | 88  |

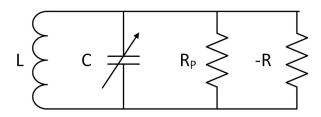

| 4.7  | LC resonator with negative resistor to compensate the losses due to para-                                                                                 | 00  |

| 1.0  | sitic resistor $R_P$                                                                                                                                      | 89  |

| 4.8  | Output voltage variation in presence of noisy source. At the left side the noise is injected at the peak voltage, at the right side the noise is injected |     |

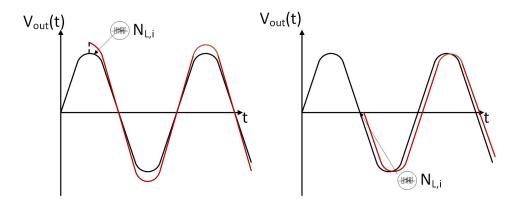

|      | at zero transition                                                                                                                                        | 90  |

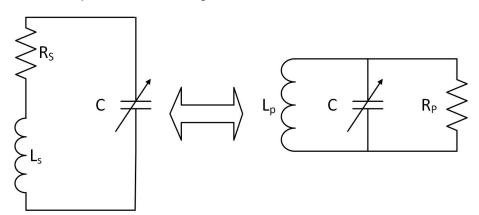

| 4.9  | Transformation of series LC tank to parallel one                                                                                                          | 91  |

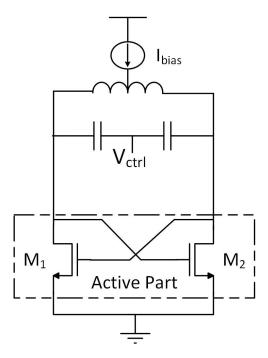

|      | NMOS cross coupled LC oscillator                                                                                                                          | 92  |

|      | CMOS LC oscillator                                                                                                                                        | 93  |

|      | General representation of power amplifier.                                                                                                                | 93  |

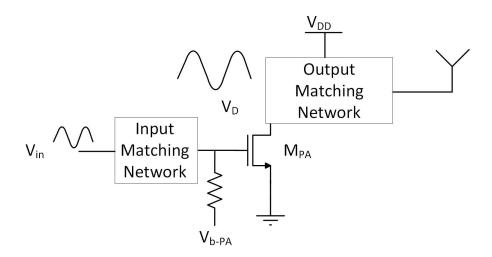

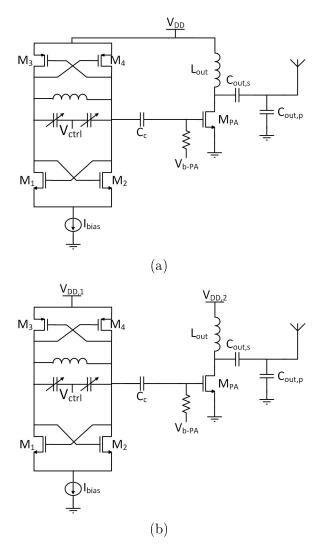

|      | Transistor level schematic of direct modulation transmitters. Single voltage                                                                              | 94  |

| 1.10 | supply for both VCO and PA (a), double voltage supply to optimize the                                                                                     |     |

|      | PA efficiency (b)                                                                                                                                         | 97  |

| 4 14 | Bias point to perform class-C operation mode(a) typical voltage and cur-                                                                                  | 91  |

| 7.17 | rent waveforms at the transistor drain(b) Biasing the transistor at voltage                                                                               |     |

|      | lower than the threshold voltage permits to reduce the voltage and current                                                                                |     |

|      | overlapping period                                                                                                                                        | 98  |

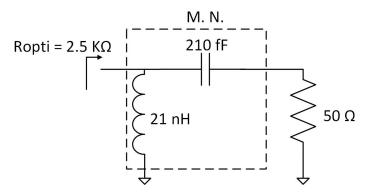

| 4.15 | Implementation of L-matching network to transform 50 $\Omega$ to the optimum                                                                              | 00  |

|      | load resistance of 2.5 k $\Omega$ . The large value of inductor makes difficult the                                                                       |     |

|      | <del>_</del>                                                                                                                                              | 100 |

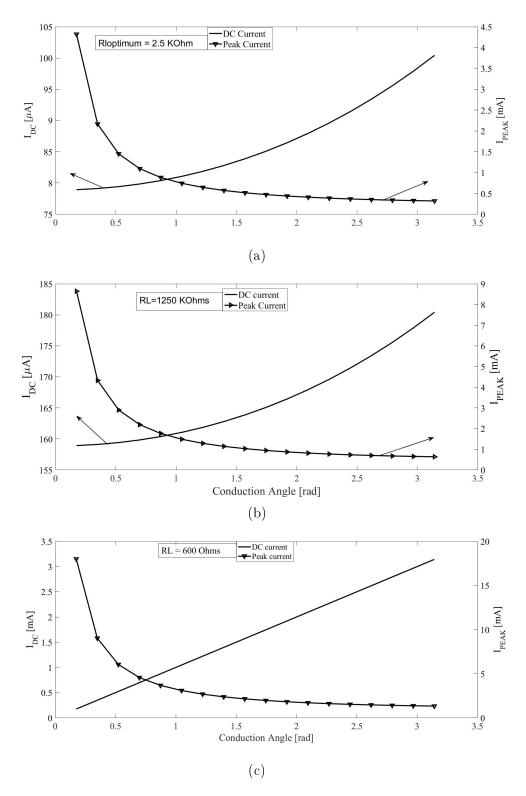

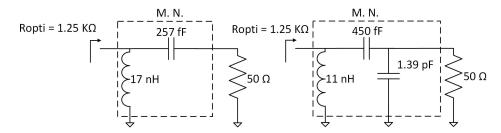

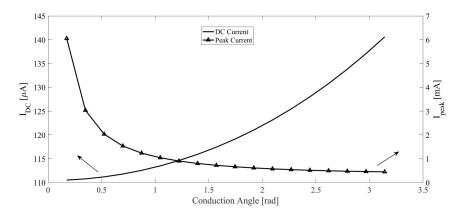

| 4.16 | DC RF current and Peak RF current depending on the conduction angle                         |       |

|------|---------------------------------------------------------------------------------------------|-------|

|      | for three different output resistances and for a $V_{o,max} = 0.4$ V. The period            |       |

|      | of conduction refers only to class-C operating mode for $10^{\circ} < \alpha < 180^{\circ}$ | . 101 |

| 4.17 | Implementation of L-matching and $\pi$ -matching networks to transform 50                   |       |

|      | $\Omega$ to the load resistance of 1.25 k $\Omega$ . A lower value of inductor is possible  |       |

|      | when a shunt capacitor is added to the network                                              | . 102 |

| 4.18 | DC RF load current and peak RF load current for $R_L=1.25k\Omega$ and                       |       |

|      | $V_{o,max} = 0.282V$ depending on conduction angle                                          | . 102 |

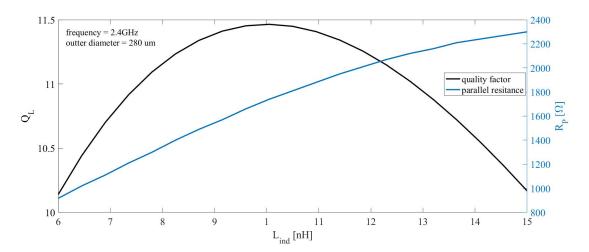

| 4.19 | Simulated quality factor $Q_L$ and relative parallel resistance for different               |       |

|      | inductance values                                                                           | . 104 |

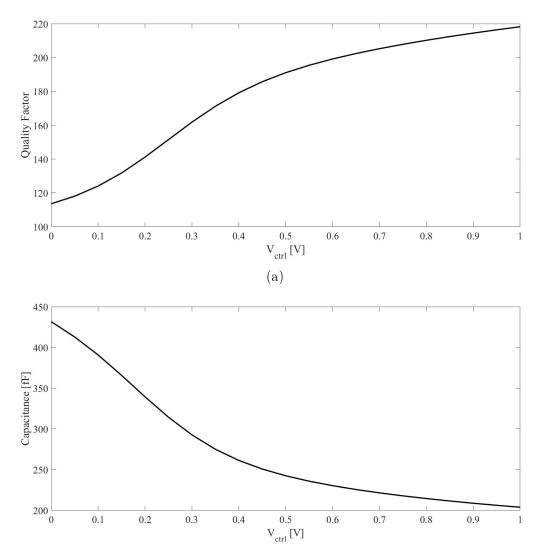

| 4.20 | Varactor quality factor (a) and capacitance versus tuning voltage (b)                       | . 105 |

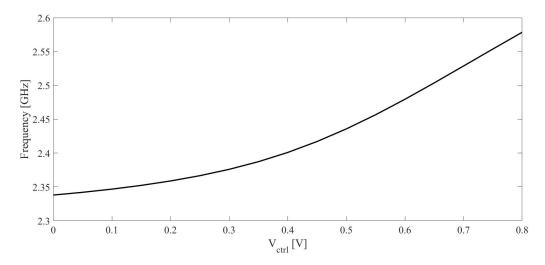

| 4.21 | Frequency range versus tunning voltage                                                      | . 106 |

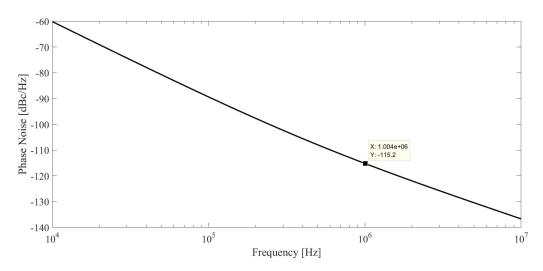

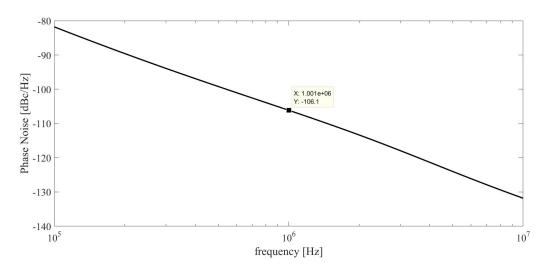

| 4.22 | Phase noise performance measured at 1 MHz from the carrier frequency.                       | . 106 |

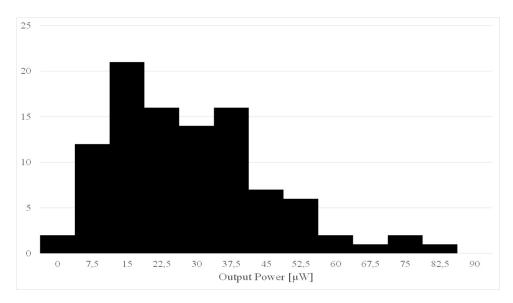

| 4.23 | Monte Carlo simulation on the single supply voltage transmitter output                      |       |

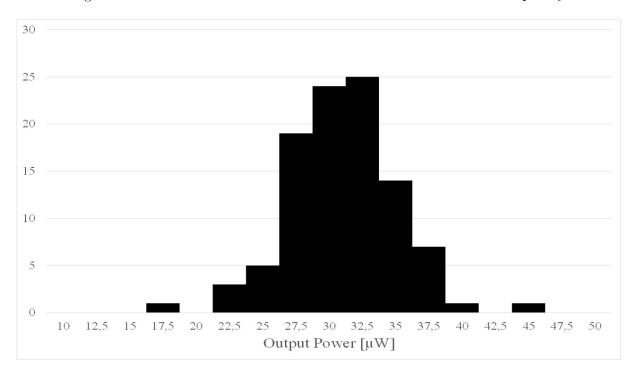

|      | power with 100 runs                                                                         | . 108 |

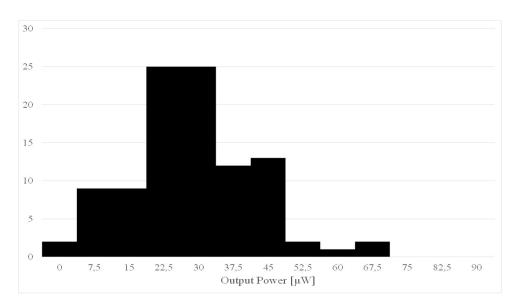

| 4.24 | Monte Carlo simulation on the double supply voltage transmitter output                      |       |

|      | power with 100 runs                                                                         | . 108 |

| 4.25 | Block diagrams of current reuse transmitter. The two possible solutions are                 |       |

|      | reported depending on the position of the VCO and the PA                                    | . 109 |

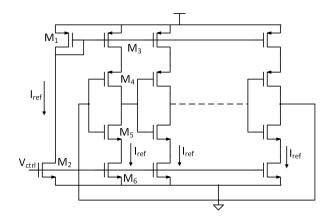

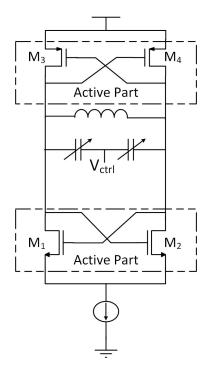

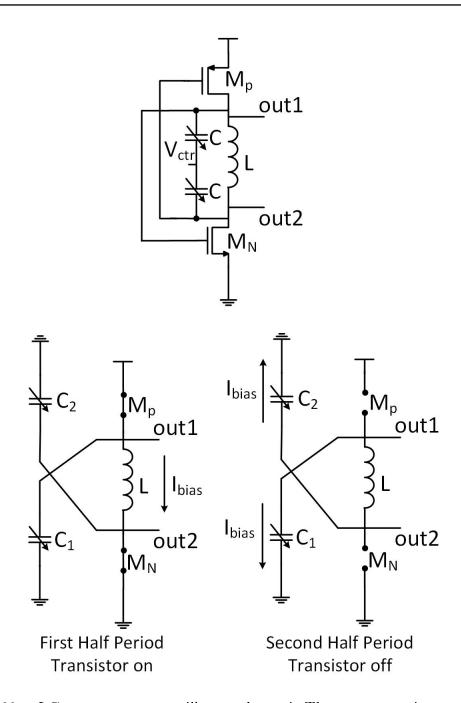

| 4.26 | LC current reuse oscillator schematic. The two operating states are also                    |       |

|      | illustrated for the two different oscillation periods                                       | . 111 |

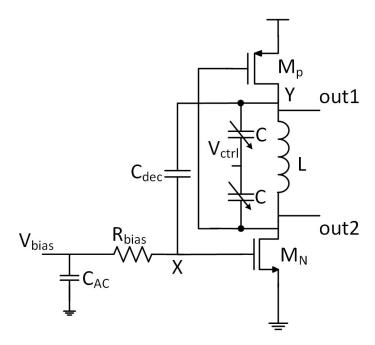

| 4.27 | Modified current reuse VCO for low supply voltage                                           |       |

| 4.28 | Voltage divider ratio versus the decoupling capacitor $C_{dec}$                             | . 113 |

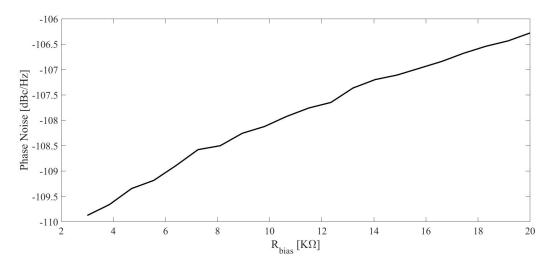

|      | Phase noise performance measured at 1 MHz offset from the carrier fre-                      |       |

|      | quency versus the bias resistance                                                           | . 113 |

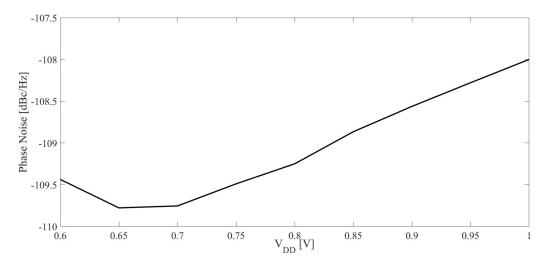

| 4.30 | Phase noise simulation at 1 MHz offset from the carrier frequency versus                    |       |

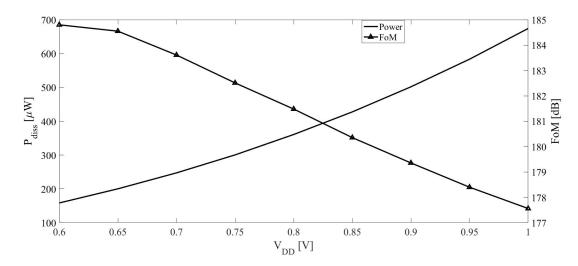

|      | the supply voltage                                                                          | . 114 |

| 4.31 | FoM and power consumption for different supply voltage                                      | . 114 |

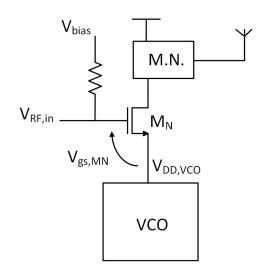

| 4.32 | Supply voltage trend                                                                        | . 115 |

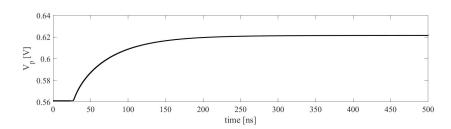

| 4.33 | Trend of the voltage at the common node P                                                   | . 115 |

|      | Transistor level schematic of Current Reuse transmitter                                     |       |

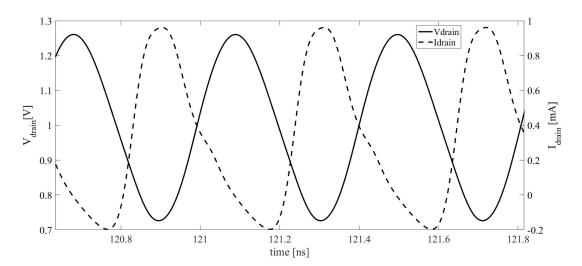

|      | Voltage and Current transient at the $M_{PA}$ drain                                         |       |

|      | Phase noise simulated at 1 Mhz from the carrier frequency                                   |       |

|      | MonteCarlo simulation performed over output power                                           |       |

|      |                                                                                             |       |

| A.1  | FVF cell with cascode Pmos transistor                                                       | . 122 |

# List of Tables

| 1.1 | Comparative energy sources                                            |

|-----|-----------------------------------------------------------------------|

| 2.1 | Comparative ULP receiver                                              |

| 3.1 | Comparative switching regulator                                       |

| 3.2 | Current consumption of designed examples                              |

| 3.3 | Transistors Size                                                      |

| 3.4 | Comparative switching regulator                                       |

| 4.1 | Drain current terms of PA MOSFET for different channel width, for the |

|     | same conduction angle and output power                                |

| 4.2 | Devices size for the designed transmitter                             |

# Chapter 1

# Low Power techniques for energy harvesting system

#### 1.1 Energy Harvesting

The concept of making electronic devices electrically independent of expensive, not always available, and exhaustible sources is not new and it has wider applications that are very common. Nowadays it is easy to find large surface solar panels or wind turbines especially in rural environment. In nature many are the sources from which it is possible to obtain electrical energy and several are the environments where harvesting process can find use whether internal or external.

Solar energy, thermal energy, vibrational energy and radio-frequency (RF) energy are the main sources exploited to replace the batteries in micro-scale or nano-scale electronic devices. Excluding solar and thermal energy, kinetic and RF source are not suitable for large-scale applications due to their low energy density.

In the next section these energy sources will be briefly introduced by describing the advantages and the drawbacks.

#### 1.1.1 Solar Energy

The solar harvesting is based on the Photo-Voltaic (PV) effect where photon energy is used to excite an electron from its ground state to an excited state. Most of solar panels are made of by a semiconductor material; when the photon strikes the photo-cell an electron-hole pair is formed, therefore the semiconductor conductivity increases. To avoid the recombination of the two particles a PN junction is needed (N-type and P-type semiconductor overlapping). Basically a solar cell is an unbiased diode that is exposed to the light. If the N and P regions are connected by a load (see Fig. 1.1), power can be extracted from the device. To extract the maximum power from the PV cell the system has to be able to change the PV cell load, because an optimum value is needed for different illumination conditions. A DC-DC converter should be placed between the PV array and the load (see fig. 1.2) for the Maximum Power Point Tracking (MPPT).

One of the main problem with this type of source is the power density variability due to the incident solar luminosity. In outdoor condition high power density is achieved with 100  $mW/cm^2$  while in indoor environment the irradiated power decreases drastically to 0.5  $mW/cm^2$  [TTKS14] [WTY11]. Currently, the main efforts in PV harvesting sensor node

Figure 1.1 – Section of Photovoltaic Cell

Figure 1.2 – Typical implementation of PV harvesting maximum power point tracking.

are devoted to the system design and the circuit implementation to extract the maximum power from panels which become smaller and smaller [WTY11] [LSS15]and suitable for highly integrated devices.

Figure 1.3 – (a) Seedback effect, the generated voltage is proportional to the temperature gradient between the hot point  $T_H$  and the cold point  $T_C$  (b) Peltier effect the current generated by the applied voltage causes a thermal diffusion from the heat dissipation to the heat absorption.

#### 1.1.2 Thermal Energy

Thermo-electrical basics are used in modern devices to generate electrical or thermal energy depending if Seedback or Peltier effect are exploited as depicted in fig. 1.3. The Seedback effect describes a phenomena that produces a voltage from a temperature

The Seedback effect describes a phenomena that produces a voltage from a temperature gradient. Applying a temperature difference  $\Delta T = T_C - T_H$  across two metal or semiconductor junctions a voltage V is generated into the circuit

$$V = \alpha_{SB} \Delta T \tag{1.1}$$

where  $\alpha_{SB}$  is the Seedback coefficient associated to the material properties.

The Peltier effect produces the opposite phenomenon. The current generated by a voltage applied across two metal junctions causes the electron movement from one side to the other side. Consequently a heat absorption occurs at one junction and a heat dissipation at the other one. The amount of heat removed per time unit from one junction to the another one is given by

$$Q = I\pi_{Pel} \tag{1.2}$$

where I is the circuit current,  $\pi_{Pel}$  is the Peltier coefficient that has to be measured in isothermal condition for the two metals.

It is clear that the material composition, the surface and geometry of contact between the two elements are the main parameters to achieve high conversion efficiency. In [RM17] a thermoelectric energy harvester demonstrates to be able to generate 0.78 mW/ $cm^2$  with 3.5 K of gradient temperature. With such of power it is possible to accomplish sensing task in 32x32 mm for body area network with comfort wearability. One of main drawbacks of thermal source is its power density variability due to a not constant temperature gradient. Moreover the small output voltage ( $\approx 40$  mV) requires step-up circuit to get a usable voltage.

#### 1.1.3 Kinetic Energy

Kinetic harvesting sensor exploits the energy generated from movement, displacement or mechanical strain to produce electrical energy through electromagnetic, piezoelectric or electrostatic mechanisms.

#### — Piezoelectric mechanism

Piezoelectric materials exhibit the capacity to generate electrical energy when subjected to a mechanical strain. The dipoles present inside a piezoelectric material becomes polarized when an external force is applied, and the polarization degree is proportional to the strain.

#### — Electromagnetic mechanism

The conductor movement or the coil rotary in electromagnetic field is used to generate a potential difference which follow the Faraday's law. When an electric conductor is moved through a magnetic field, an electromotive force is induced between the ends of the conductor. This voltage is proportional to the electromagnetic field variations in the time.

#### — Electrostatic mechanism

A variable capacitor is used to generate an electrical energy when a external vibration is applied. For a charge-constrained device, the plates movement causes an increasing or decreasing voltage across the capacitor, since the charge has to remain the same.

In [MPW<sup>+</sup>17] the breath movement is used to monitor the patient respiration. The frontend transducer is a piezoelectric material-based sensor. The harvested source is able to sustain a power consumption about 800  $\mu$ W when the impulse radio ultra-wideband transmitter is active.

#### 1.1.4 Radio-Frequency Energy

Probably nowadays the Radio-Frequency (RF) energy is the most easily available source: the mobile phone, Wi-Fi and Bluetooth connections. The RF harvesting devices are equipped with a antenna, picking-up the RF wave. The corresponding AC voltage is then transformed in a more suitable DC voltage for the electronic blocks by a rectifier circuit.

The conversion efficiency and the voltage available at rectifier output depend mainly on the channel communication qualities, on the antenna performances and on the rectifier losses. As the energy available is small a storage element is mandatory to achieve sensing and transmission operations. The device dimensions are mainly tied to the antenna design, and the conversion efficiency relates on the antenna gain and on power level of the incoming signal. The average energy density of RF source is about 1  $\mu$  W/cm<sup>2</sup>, but the RF-DC conversion circuit is able to generate voltage in the order of fews volts (1.4 V - 3 V) with an output power of hundreds of micro-watts.

The low energy available from the environment sources (Tab. 1.1) poses an hard challenge for the designers, to guarantee the required performances. Designing nano-watt or microwatt circuits surely can ensure long lifetime devices but at cost of poor performances.

However there are several approaches to reduce the power consumption in radio and system circuits, which extend at different design level. In the next section the main techniques to design ultra-low power (ULP) system are introduced.

|                | Energy Density            | Advantages            | Drawbacks             |  |

|----------------|---------------------------|-----------------------|-----------------------|--|

| Solar Energy   | $500~\mu\mathrm{W}/~cm^2$ | - High energy density | -Large occupied area  |  |

|                |                           | -Well developed       | -Indoor degradation   |  |

|                |                           | technology.           |                       |  |

| Thermal Energy | $60~\mu\mathrm{W}/~cm^2$  | - Always Available    | -Difficult to control |  |

| Thermal Energy |                           |                       | - Low output volt-    |  |

|                |                           |                       | age                   |  |

| Kinetic Energy | $200~\mu\mathrm{W}/~cm^3$ | -Several applica-     | -Low conversion ef-   |  |

| Kinetic Energy | 200 $\mu$ W / Cm          | tions                 | ficiency.             |  |

|                |                           | -Light weight         |                       |  |

| RF Energy      | $1~\mu\mathrm{W}/~cm^3$   | -Available every-     | -Low energy density   |  |

| Ar Energy      | $1 \mu \text{ w} / cm$    | where                 |                       |  |

|                |                           | -Small surface        | -Distance depen-      |  |

|                |                           |                       | $\operatorname{dent}$ |  |

Table 1.1 – Comparative energy sources

#### 1.2 Design techniques for ULP circuits

The technology progress in CMOS fabrication has allowed the designers to develop several techniques in order to reduce power consumption in modern devices; not only at the transistor level but there are three different abstraction levels to address, in order to achieve low power consumption for the sensor node:

- CMOS level: Scaling down, thick metal layer, ultra-low leakage MOSFET

- Circuit level: weak inversion, current reuse, multi-threshold CMOS (MTCMOS)

- System approach: wake-up protocol.

#### 1.2.1 CMOS level

It is well-known that the transistor size scaling is described by the Moore's law: the number of transistors into an integrated-circuit chip is doubling approximately every two years without correspondingly increasing the chip costs. The reduced channel length  $(L_{channel})$  in metal-oxide-semiconductor FET increases the cut-off frequency as the parasitic capacitances decrease proportionally to the  $L_{channel}$

$$C_{gate} = \frac{\epsilon_{ox}\epsilon_o}{t_{ox}} L_{channel} \tag{1.3}$$

where  $C_{gate}$  is the MOSFET gate capacitance,  $\epsilon_{ox}$  is the dielectric constant of silicon oxide,  $\epsilon_{o}$  is the permittivity of free space and  $t_{ox}$  is the oxide thickness. Considering  $C_{gate}$  as the most important parasitic capacitance inside the MOSFET the cut-off frequency  $f_t$  can be written as:

$$f_t = \frac{g_m}{2\pi C_{oute}} \tag{1.4}$$

where  $g_m$  is the MOSFET transconductance. The  $f_t$  is the frequency at which the short circuit small-signal current gain is unitary; fig. 1.4 plots  $f_t$  versus the normalized drain

Figure 1.4 – Cut-off Frequency trend in function of current density for different node technology [WKvL<sup>+</sup>01]

source current density for five technology nodes. RF circuits (Power amplifier, Oscillator, Mixer,etc) take advantages from the MOSFET scaling because the transistor exhibits higher current gain for the same operation frequency. Therefore same performances can be achieved with less current and lower power consumption consequently.

Also the threshold voltage decreases with the size downscaling, because the reduction in oxide thickness allows lower differential potential needed to the MOSFET gate, in order to create the conduction channel. As consequence, it is possible to decreases the supply voltage needed to put the transistors in saturated region. The main benefit when the circuit operates at lower power supply voltage is the reduction in active power dissipation  $P_{act}$  for switched topology circuits.  $P_{act}$  is proportional to the square of supply voltage  $V_{DD}$ , to the capacitors involved in charge and discharge operations and to the switching frequency  $f_{switch}$ :

$$P_{act} = C_{switch} V_{DD}^2 f_{switch} (1.5)$$

It seems clear from eq. 1.5, that with the possibility to operate at lower  $V_{DD}$  the power consumption decreases. However as the distance between drain-source is reduced and the oxide is thinner, the probability that an electron moves in transistor off-state is higher and thus the leakage current increases degrading the power consumption performance in sleep mode; especially in ultra low duty-cycled system, where the circuit is off most of the time, the leakage current impacts the power budget; ultra-low leakage MOSFET can help with reducing the off-state current.

Moreover the higher chip cost in deeply scaling technology has to be considered especially when low cost system is targeted.

#### Thick metal layer

Generally speaking the reduction of parasitic resistance allows to reduce the static power dissipation. This is the case for the drain source MOSFET resistance  $R_{DS}$  in switching circuit and also for the inductor and capacitor parasitic resistance. In energetic circuit

Figure 1.5 – Combinations to achieve 8 nH inductance [Van15] where W is the metal width and N is the numbers of turns.

(LC oscillator, tuned amplifier, buck/bust voltage converter) the impact of lossy elements can be traduced through the quality factor Q [Raz]

$$Q = 2\pi \frac{EnergyStored}{EnergydissipatedperCycle}$$

(1.6)

High quality factor is preferable because the energy dissipated in lossy elements is low. A reduction in power consumption can be achieved by using high-Q elements and LC oscillator is a perfect example. In LC oscillator the oscillation is assured if the losses (the parasitic series resistances  $R_s$  of Inductor and Capacitor) are counterbalanced by an active element as the MOSFET transconductance  $g_m$ .

$$g_m \ge \frac{1}{R_s} \tag{1.7}$$

In first approximation the  $g_m$  is proportional to the drain-source current. Therefore for small value of parasitic resistance (high-Q) the  $g_m$  needed is lower and the drain-source current decreases proportionally. At low to medium frequency oscillation (from 400 MHz to 15 GHz) a customized inductor can helps in power consumption reduction with higher Q. In [Van15] thick metal and dense tapered spiral inductor shows quality factor improvements for 10 GHz frequency oscillation. Fig. 1.5 depicts different geometries to get 8 nH inductance with the highest Q at the same generated frequency.

#### 1.2.2 Circuit Level

#### MOSFET operating region

Traditionally, the MOSFET is mostly used in strong inversion (SI) region with a drain-source current in the milli-Ampere range where the gate-source voltage  $V_{gs}$  has to be greater than the threshold voltage  $V_{th}$

$$V_{qs} >> V_{th} \tag{1.8}$$

In SI, for N-type Mosfet,  $I_{DS}$  is proportional to the square of the effective gate-source voltage

$I_{DS} = \frac{1}{2} \frac{\mu_n C_{ox}}{n} \frac{W}{L} (V_{gs} - V_{th})^2$ (1.9)

Where  $\mu$  is the carrier velocity,  $C_{ox}$  is the oxide capacitance, n is a slope factor, W and L are the width and the length of conduction channel. Only from the second half of 90s [EV96], with the diffusion of portable devices the weak inversion (WI) has been taken in consideration to address low power consumption in integrated circuit. In fact when  $V_{gs}$  is lower than  $V_{th}$

$$V_{qs} << V_{th} \tag{1.10}$$

the transistor operates in WI with an  $I_{DS}$  in the range of micro-Ampere to the nano-Ampere. In this case the current is not more governed by a square law, but it follows an exponential behavior

$$I_{DS} = 2n\mu C_{ox}V_t^2 \left(\frac{W}{L}\right) \exp\left(\frac{V_{gs} - V_{th}}{nV_t}\right)$$

(1.11)

where  $V_t$  is the thermal voltage. However the passage from SI to WI is not abrupt and the two regions are separated by the moderate inversion (MI), where  $V_{gs}$  differs above or below  $V_{TH}$  to a few tens of mV. Therefore the three regions represent three different degrees of MOS channel inversion. To give a coherent circuit design with the three level of channel inversion the Inversion Coefficient (IC) has been introduced, which allows a continuous design flow from the WI to the SI. The IC [Bin07] can be found by the drain-source current, divided by the product of the shape factor  $S = \frac{W}{L}$  and the technology current  $I_o = 2n\mu C_{ox}V_t^2$

$$IC = \frac{I_{DS}}{I_o S} \tag{1.12}$$

The IC ranges from 0.01 in WI to 100 in SI and the center value is 1 at the middle of MI. Therefore every value of IC corresponds to a precise level of inversion with a well defined bias point. The transistor width is calculated from the choice of the channel length L, the drain-source current and the inversion coefficient. Depending on the circuit performances, every operating region can accomplish a specific trade-off as shown in fig. 1.6. Many works [EC15] [TSM15] [SH06] demonstrate that designing analog or radio-frequency circuits in MI ensures the best trade-off between power consumption,  $\frac{g_m}{I_{ds}}$  efficiency, low voltage design and AC response.

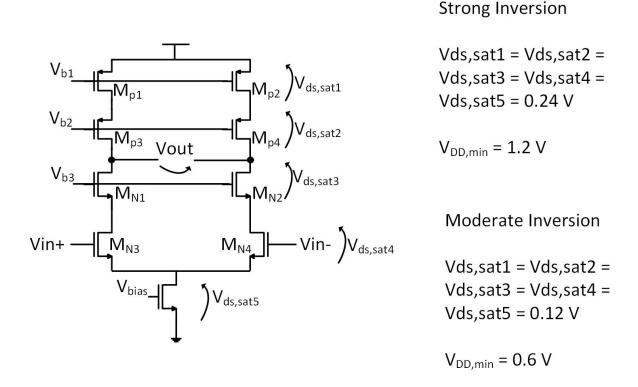

Fig. 1.7 shows a cascoded single stage Operational Transconductance Amplifier OTA where the transistors operate in saturation region. When the MOSFET are biased at the low side of SI (IC = 10) a  $V_{ds,sat} = 0.24$  V for each transistor can be assumed, while when the low side of MI (IC = 0.1) is considered the  $V_{ds,sat} = 0.12$  V. The only parameter analyzed is the minimum supply voltage needed to bias each transistor in saturation, and the reduction of  $V_{DD,min}$  is quite evident. The main drawback when MOSFET operates in WI is the poor frequency response due to a large parasitic capacitance forced by the large MOSFET size. Moreover WI introduces a pronounce dependence en process and temperature variations.

| _ | 0.01                  | 0.1   | 1                     | 10     | 100                 | IC                                 |

|---|-----------------------|-------|-----------------------|--------|---------------------|------------------------------------|

|   | Weak Inversio<br>(WI) | n     | Moderate Invo<br>(MI) | ersion | Strong Inve<br>(SI) | ersion                             |

| _ | 104 mV                | 108 m | V 135 mV              | 245 (  | mV 245 m            | V V <sub>DS,sat</sub>              |

|   | -163 mV               | -72 m | V 40 mV               | 225 r  | mV 700 m            | V V <sub>GS</sub> -V <sub>TH</sub> |

| _ | 100                   | 10    | 1                     | 0.1    | 0.01                |                                    |

| _ | 100                   | 10    | 1                     | 0.1    | 0.01                | W/L                                |

Figure 1.6 – Inversion coefficient line number with voltage and shape factor MOSFET properties [Bin07].

#### **Current Reuse**

The static power consumption in electronic circuit is given by the supply voltage  $V_{DD}$  and the bias current  $I_{bias}$  flowing from the supply voltage to the ground

$$P_{stat} = V_{DD}I_{bias} (1.13)$$

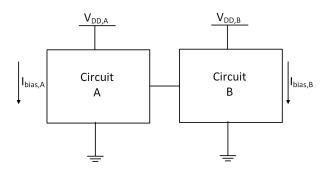

If two cascaded circuits (A and B) are considered (Fig. 1.8) the total power consumption is equal to the sum of the single consumption:

$$P_{stat,tot} = P_{stat,A} + P_{stat,B} = V_{DD,A}I_{bias,A} + V_{DD,B}I_{bias,B}$$

$$(1.14)$$

The  $P_{stat,tot}$  is reduced if the four variables are optimized. The main disadvantage is that the generation of two separate supply voltages increases the system complexity and power budget. In many case the chip size constraint and/or the energy available reduce space freedom degree in the design. Typically a single supply voltage is available for all circuit blocks. Therefore the optimization, from the supply voltage point of view, cannot be achieved completely and a lot of power is wasted. To overcome this problem and if an adequate supply voltage is available, stacked structure can allow power consumption reduction. In this case the bias current is recycled (reused) from the top circuit to the bottom one and the total power consumption is

$$P_{stat,stack} = V_{DD,stack}I_{bias,stack} (1.15)$$

The condition to achieve lower power consumption in stacked topology is  $V_{DD,stack} = V_{DD,A} = V_{DD,B}$  and  $I_{bias,stack} = I_{bias,A} = I_{bias,B}$ . Moreover some precautions have to be taken against cross-talk phenomena, noise and high frequency loop. In [TSM15] a stacked LNA-VCO is presented, where each block achieves comparable performances with the state of the art of stand alone circuit; a LC filter is inserted between the two circuits to present high impedance at the frequency of interest avoiding cross-talk degradation.

The reuse concept can be readapt to circuit level as in [?]. The RC relaxation oscillator used to generate the time reference to the system is reused to implement reading-out circuit for the measurement of the Relative Humidity. Therefore the oscillator accomplishes two tasks saving power consumption and area occupied.

Figure 1.7 – Minimum supply voltage required in classical cascode OTA when the transistors are biased in strong and in moderate inversion.

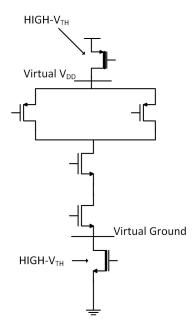

#### Multi-threshold CMOS

The leakage power consumption has become a serious problem in below 100 nm technologies. In multi-threshold CMOS (MTCMOS) circuit, high- $V_{TH}$  transistors are used to block the leakage path because of their low leakage current [SGMK15]. Basically it shutsdown a part of the circuit, disconnecting the main blocks from the power supply. Fig. 1.9 illustrates a typical application where high threshold transistors cut-off the NAND logic circuit. However this technique implies an increase in cost process due to an extra mask for the two different threshold voltages. Moreover there is a trade-off between the size of high- $V_{TH}$  transistor and the performances degradation of the main circuit.

Figure 1.8 – Cascaded circuit block with two separate supply voltage and independent bias currents.

Figure 1.9 – Multi-threshold application in logic circuit.

#### 1.2.3 System level

#### Wake-up scheme and duty-cycled radio

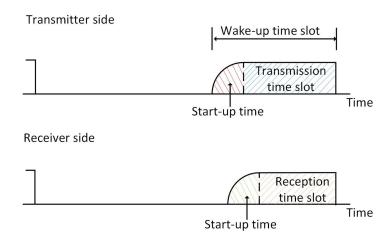

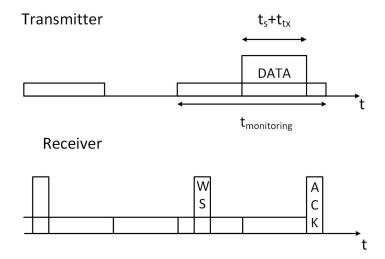

As it will be described in the next chapters the most hungry part in wireless sensor node is the transceiver circuit. A large number of papers suggest to keep the nodes transmitter part in low-power sleep mode for most of the time, allowing the node to operate at highest power consumption level only for a very short time. Wake-up scheme is a largely adopted technique to reduce the energy consumption extending the sensor node lifetime. Fig. 1.10 depicts the time-slot division for waked-up sensor node. The active time-slot includes:

- start-up time where auxiliary circuits generate the wake-up signal for the transmission/reception part. After the radio-frequency circuits need a settling time to achieve proper operation (especially for the frequency synthesizer).

- transmission/reception time where the communication between the sensor node effectively takes place.

To reduce the required overall energy both start-up and transmission slots have to be as short as possible for a lower power consumption. In [JLBS15] a 5.8 nW wake-up timer

Figure 1.10 – Wake-up scheme timeline.

is presented and it is suitable for EHWSN, whereas in [TRE15a] the long start-up time phase-locked loop (PLL) frequency synthesizer is avoided using a fast film-buck acoustic wave resonator with a time reduction of  $\approx 1000$ X.

However the system can be further optimized adopting duty-cycled operations during the transmission time. In this case the radio block is turned on/off with a rating that depends on the duty-cycle value:

$$DC = \frac{T_{on}}{T_{on} + T_{off}} \tag{1.16}$$

Aggressive DC in the range of (1-5)% can be adopted in burst communication mode, where a large amount of data is transmitted in short time with high data-rate.

#### 1.2.4 Conclusion

In this chapter a description of the different energy harvesting sources usable for small scale applications has been presented. The low energy density available and the high variability pose a big challenge for the designers. Low-power design techniques are mandatory to extend the devices lifetime. The second part of chapter has described these techniques highlighting the advantages and the drawbacks.

The three level of optimization, transistor, circuit and system, can be combined to achieve the best trade-off between the performances and the power consumption. In the next chapters a system overview and a design flow for very efficient voltage regulator and ultra-low power transmitter are presented.

## Chapter 2

## System Approach

The technology progress occurred in the last ten years in highly integrated microelectronic circuits, sensors, actuators, and wireless communications technology allowed the dissemination of wireless sensor network (WSN) in several domains:

#### — Environmental Monitoring

WSN can be used for forest surveillance, weather forecasting. It is a natural candidate, because the variables to be monitored are usually distributed over a large area. In addition WSN can facilitate the measurement of a large variety of environmental data for a huge number of applications such as agriculture, meteorology, geology, zoology, etc.

#### — Health monitoring

WSN could potentially provide better health-care delivery. They could improve the interaction between the patient and the medical staff. Several physiological parameters can be monitored, as (hearth condition, blood pressure, blood glucose, organ monitor, cancer detector). When the sensors are implanted for healthcare purpose, they are called Body Sensor Network (BSN).

#### — Industrial Sensing

The industrial sector is one of the most involved player for the development of WSN. With the possibility to acquire information in real-time, unexpected failures can be avoided improving production quality and reducing costs. One of the main use is in the food industry to monitor the food supply chain.

#### — Home Security

Domestic represents another potential area for WSN. The "smart home" can regulate the room temperature, control air quality, adjusting lighting. Sensor networks can also improve the security of the house by sending an alarm message to the resident when it detects intruders, gas leakage, fire occurrence or other safety risks.

WSN can generally be described as a network of nodes that cooperatively sense and may control the environment enabling interaction between persons or computers and the surrounding environment. In spite of their versatility, the main constraint is the energy needed for the operation, specially when WSN are deployed in hostile environment or over a large area making the battery replacement very difficult, expensive or even impossible. For example, the study carried-out in [KBA16] shows the battery duration for WSNs with ZigBee/IEEE 802.15.4 protocol. This standard has been developed by the Institute of Electronic and Electrical Engineer (IEEE) for low-power, low data-rate wireless personal sensor networks (WPSNs). The most adopted transmission frequency is 2.4 GHz with

Figure 2.1 – Plot obtained from the measurement results for I = 2.3 mA and k = 1.25.

max data-rate of  $250~\rm kits/s$  and QPSK as transmission modulation. The IEEE  $802.15.4~\rm standard$  is used as a base for developing ad-hoc standard as in the case of ZigBee.

ZigBee protocol adds different enhancements as authentication valid nodes, encryption for security and data routing. Moreover ZigBee supports energy harvesting technology for no battery supply.

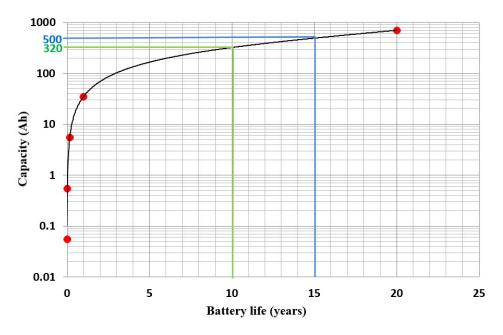

Therefore one of the main problem of this standard, even if the low power consumption is one of the key point, remains the battery duration. In [KBA16] the study is based on the Peukert's law where the battery life is calculated as

$$L = \frac{C^{k}}{IH} \tag{2.1}$$

where L is the time in hours for a given rate of discharge, H is the discharge time in hours, C the battery capacity in Amp.hours, I current in Amp and k Peukert exponent parameter which is a unique number for each battery. The experiment is conducted for three different batteries with different capacities. The communication distance is about 9 m and the data transmission is continuous. The results are summarized in Fig. 2.1 for I = 2.3 mA and k = 1.25.

Fig. 2.1 shows that, for 10 years of operation a battery with 320 Ah capacity is needed. However such type of battery exhibits large sizes; it is therefore not suitable for high integrated applications.

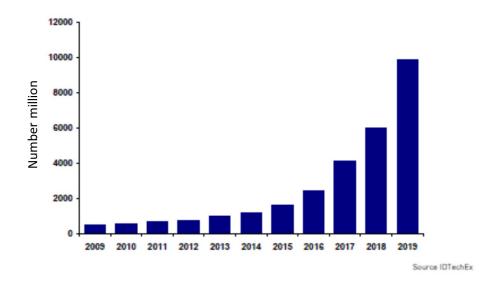

After a first wave, WSNs have meet a stop in the popularity due to the size limitation. WSN have found a second youth with the technology progress in energy harvesting (EH) domain, where the circuits responsible of energy conversion have assumed sizes more and more tiny easily fitting the request of smaller devices. Therefore, the possibility to have independent small sensor has open the future for new opportunities. The markets for WSNs invoices \$ 552.4 millions in 2012 with a forecast of \$ 14.6 billions in 2019. The Fig. 2.2 shows the trend of devices powered by EH system used in WSN.

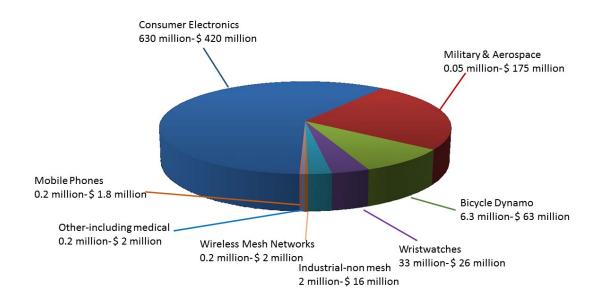

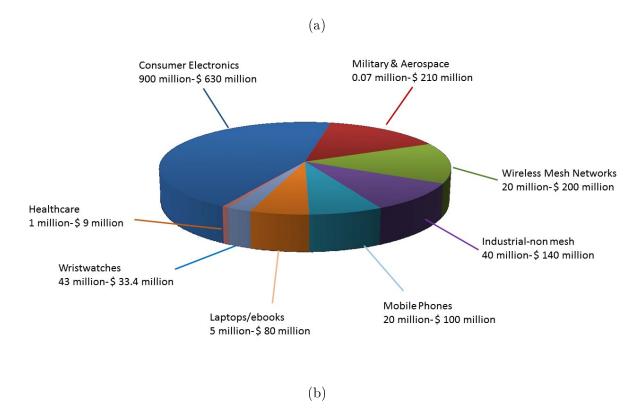

Fig. 2.3 shows the market movement of EHWSN applications from 2012 to 2017. All

Figure 2.2 – Market forecast for EH devices used in WSN applications.

sectors exhibit an growth in the number of employed devices.

To make a sensor networks adaptable for a wide range of applications, the following requirements should be addressed:

- Low Cost: The utility and scalability of a WSN highly depend on its density, which means large number of sensor nodes in the assignment area. To make the installation cost effective, the cost of individual sensor node should be extremely low.

- Low Power: Nodes must be able to ensure a permanent connectivity and coverage for long periods, up to 10-20 years, without service interruption. Low power consumption represents one of the main challenge in modern devices, and it is of great importance when the sensor is supplied by low density energy source.

- Small Size: WSNs are desired to replace cables that are often impracticable. Therefore, the size of the sensor node must be small enough in order to allow the WSNs to monitor the environment in a discreet and transparent manner.

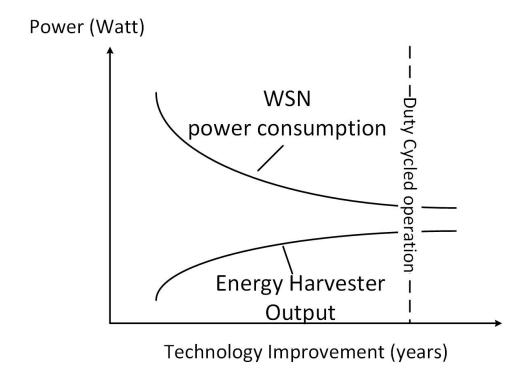

However nowadays as introduced in the Chapter 1, the energy available from the harvesting transformation is not sufficient to power the sensor node in continuous mode operation. For example the harvested power from vibration in industrial application can easily achieve  $100~\mu\mathrm{W}/\mathrm{cm}^2$  [RM10], but modern sensor node in transmission mode requires about 5 to 10 mW depending on the application. Fig. 2.4 shows that if one hand WSN requires less power thanks to development technological, on the other hand high efficient harvesting circuits allow to maximize the low energy available from the environmental sources.

However until now, technologies limitation (for example leakage current, process deviations) and performance constrains (noise, PVT variations) prevent the two curves to reach a intersection point. Actually a continuous autonomous operations can not be therefore assured. The sensing and data communication reliability can be assured only if sensor node operates for a fraction of total time. Therefore the two curves can approach, because micro-watt power availability is able to sustain operations in the range of mW. The building block diagram of an EH sensor node is shown in the Fig. 2.5

Figure 2.3 – Energy Harvesting WSN market in 2012 (a) and prevision of market in 2017 (b)

Figure 2.4 – Power comparison between WSN and Energy Harvested circuit.

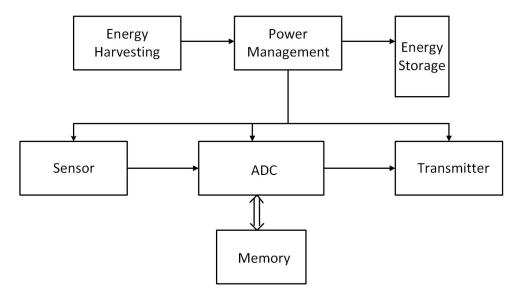

The electrical energy coming from the harvest transformation can be used to directly supply the sensor node or stored into a supercapacitor or a rechargeable battery. Although in some applications it is possible to bypass the energy storage, in most of the case the storage component acts as an energy buffer for the system, with the main purpose of accumulating and preserving the energy.

In order to manage the energy available from the storage element, the power management unit (PMU) has to be designed to extend the sensor lifetime. It controls the level of stored energy and at the demand of power depending on the adopted protocol, it supplies the sensor and/or the other circuits. The environmental information sensed is then transformed into digital information by the ADC and stored in the memory. In general the sensing and the data transmission are not accomplished at the same time, because the transmitter is the main power hungry block and the energy available is not enough to guarantee the two operations at the same time.

Finally the data transmission can be validated internally by the PMU or externally on demand by the users.

Figure 2.5 – Architecure of energy harvesting sensor node.

#### 2.1 Energy Management

The purpose of this work is to design low-power circuits for RF-energy harvesting WSN. In particular low drop-out voltage regulator and transmitter block have been designed. A framework at the system level can facilitate the circuit design.

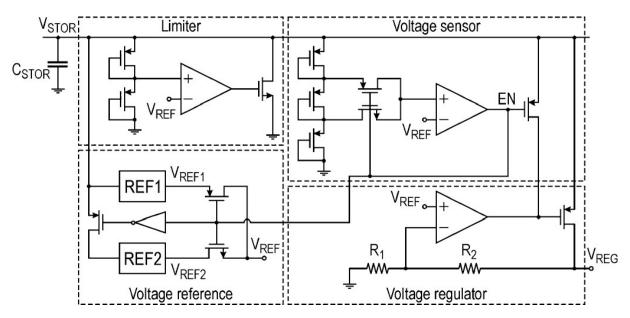

As briefly introduced an energy buffer (rechargeable battery or super-capacitor) is mandatory for duty-cycled power manager to stock the energy when the system is in idle mode and then make it available when requested. A simple PMU introduced in [PCFP14] is depicted in Fig.2.6. To supply the regulated voltage to the RF front-end blocks, PMU uses different circuits to manage the stored energy.

Voltage limiter is used to limit the maximum voltage with a safe margin.

The voltage sensor verifies that the voltage across the capacitor is between two defined bends  $V_{low}$  and  $V_{high}$ .

When the voltage stored into the capacitor reaches  $V_{low}$ , the PMU turns-off the voltage regulator and the system is in idle mode. During the idle mode the PMU draws a little bias current due to the monitoring circuits that are continuously on to ensure proper operation. When the voltage capacitor reaches  $V_{high}$ , the PMU turns on the voltage regulator, the current flows from the capacitor to the voltage regulator output and the sensing operation and data transmission can take place.

It seems clear that in the case of linear voltage regulator, where the regulated output voltage is obtained "loosing" a part of input voltage over a variable resistor, the stable PMU output voltage  $V_{reg}$  has to respect the following condition

$$V_{reg} < V_{low} < V_{high} \tag{2.2}$$

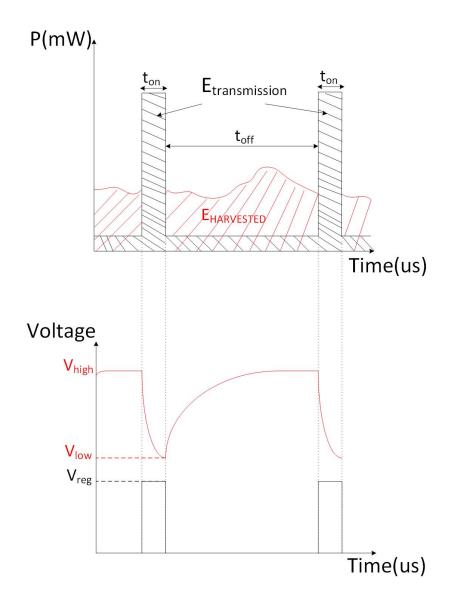

where  $V_{reg}$  depends on the application specifications (transmission distance, quality and speed of transmission) and on the circuit architecture (stacked topologies, technology reliability),  $V_{low}$  depends on the voltage regulator performances and on the minimum input voltage for which the regulation is ensured,  $V_{high}$  can be obtained by the system energy analysis. Fig. 2.7 shows the energy profile (top figure) of harvesting sensor node where the

Figure 2.6 – Power management transistor level schematic implemented in [PCFP14]

transmission time  $t_{on}$  is less than the idle time  $t_{off}$ . In this case high power hungry circuits as frequency synthesizer and power amplifier can be sustained by low power source as RF energy harvesting. The bottom graph in Fig. 2.7 shows the transient of voltage stored in the capacitor and the voltage at the regulator output. During  $t_{off}$  the sensor node is in harvesting mode and the capacitor is charging. The charging time depends on source signal quality. During this time interval the energy cost of monitor circuits has to be very low in such way to preserve the capacitor charge.

Figure 2.7 – The top graph depicts an example of energy profile in harvesting system. In the bottom graph the trend of voltage stored into the capacitor (red line) and the regulated voltage at the output of the PMU.

The energy stored in the capacitor C is given by

$$E_C = \int_{Q_i}^{Q_f} \frac{Q}{C} dq = \frac{1}{2C} (Q_f^2 - Q_i^2)$$

(2.3)

where  $Q_f$  is the charge stored at  $V_{high}$  and  $Q_i$  is the charge stored at  $V_{low}$ . The energy stored in the capacitor can be rearranged as