## Harmonic feedback multi-oscillator for 5G application $${\rm Ali\ Mohsen}$$

#### ▶ To cite this version:

Ali Mohsen. Harmonic feedback multi-oscillator for 5G application. Electronics. Université de Bordeaux, 2018. English. NNT: 2018BORD0335 . tel-02410778

### HAL Id: tel-02410778 https://theses.hal.science/tel-02410778

Submitted on 14 Dec 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### THÈSE PRÉSENTÉE

#### POUR OBTENIR LE GRADE DE

### **DOCTEUR DE**

## L'UNIVERSITÉ DE BORDEAUX

#### ÉCOLE DOCTORALE DES SCIENCES PHYSIQUES ET DE L'INGENIEUR

SPÉCIALITÉ: ELECTRONIQUE

Par Ali Mohsen

### Harmonic Feedback Multi-Oscillator for 5G Application

Sous la direction de: Nathalie DELTIMPLE (Co-supervisor: Adnan Harb)

Soutenue le 13 décembre 2018

Membres du jury:

| M.   | Gilles Jacquemod   | Professeur  | Nice Sophia Antopolis             | Rapporteur         |

|------|--------------------|-------------|-----------------------------------|--------------------|

| М.   | Hervé Barthélémy   | Professeur  | Sud Toulon                        | Rapporteur         |

| М.   | Mohamad Sawan      | Professeur  | École Polytechnique               | Examinateur        |

| М.   | Eric Kerhervé      | Professeur  | Bordeaux INP                      | Président du jury  |

| М.   | Adnan Harb         | Professeur  | Lebanese International University | Co-supervisor      |

| Mme. | Nathalie Deltimple | Maitre de   | Bordeaux INP                      | Directeur de thèse |

|      |                    | Conférences |                                   |                    |

|      |                    | HDR         |                                   |                    |

### Table of Contents

| Chapter 1 : Background from 5G towards Oscillators |    |

|----------------------------------------------------|----|

| 1.1 Mobile Technology: an overview                 |    |

| 1.2 Fifth generation 5G                            |    |

| 1.2.1 5G applications and specifications           |    |

| 1.2.2 5G Bands                                     |    |

| 1.3 Millimeter Transmitter                         |    |

| 1.3.1 Heterodyne architecture                      |    |

| 1.3.2 Homodyne architecture                        |    |

| 1.4 Millimeter Wave Oscillators                    |    |

| 1.4.1 Oscillator Model                             |    |

| 1.5 Phase noise                                    |    |

| 1.5.1 Principle of noise generation in oscillators |    |

| 1,5.2 Phase noise in oscillators                   |    |

| 1.6 Oscillator Types                               |    |

| 1.6.1 LC Oscillators                               |    |

| 1.6.2 LC Oscillator State of Arts                  |    |

| 1.7 Objective and Methodology                      |    |

| 1.8 Chapter Conclusion                             |    |

| 1.9 References                                     |    |

| Chapter 2 Technology and Design Building Issues    |    |

| 2.1 CMOS Transistors toward Fully Depleted         |    |

| 2.1.1 . Alternative Transistors                    |    |

| 2.1.2 28-nm UTBB FD-SOI                            |    |

| 2.1.3 Body Bias                                    |    |

| 2.1.4 22-nm Intel's 3D Tri-Gate Transistor         |    |

| 2.1.5 28-nm UTBB FD-SOI VS 22-nm Tri-Gate FinFET   |    |

| 2.2 Power amplifier                                |    |

| 2.2.1 Gain                                         | 61 |

| 2.2.2 Efficiency:                                  |    |

| 2.2.3 Linearity:                                   |    |

| 2.2.4 PAs Architectures                    |    |

|--------------------------------------------|----|

| 2.2.5 PA Classes                           |    |

| 2.2.6 Transistor Size                      |    |

| 2.2.7 Class J Power Amplifier              | 75 |

| 2.2.8 Stability                            |    |

| 2.2.9 Optimum Load Impedance               |    |

| 2.2.10 State of Arts                       |    |

| 2.3 Noises                                 |    |

| 2.3.1 Noise Figure                         |    |

| 2.3.2 Noise of a System                    |    |

| 2.4 Proposed System                        |    |

| 2.5 Conclusion                             |    |

| 2.6 References                             |    |

| Chapter 3 Design of Power Oscillator       |    |

| 3.1 FD-SOI BEOL                            |    |

| 3.1.1 RF PADs                              |    |

| 3.1.2 Passive Elements                     |    |

| 3.2 LNPA                                   |    |

| 3.2.1 LNPA circuit                         |    |

| 3.2.2 LNPA Results                         |    |

| 3.3 PA                                     |    |

| 3.3.1 Proposed Transistor                  |    |

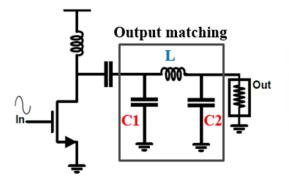

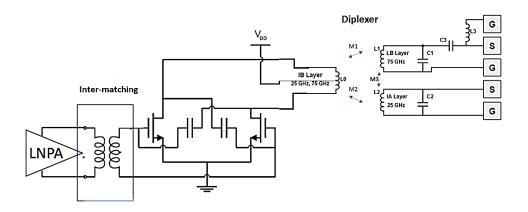

| 3.3.2 Output Matching-Diplexer             |    |

| 3.3.3 Inter-matching                       |    |

| 3.3.4 PA Results                           |    |

| 3.4 Coupler                                |    |

| 3.5 Phase shifter                          |    |

| 3.6 Overall Architecture Simulated Results |    |

| 3.7 References                             |    |

| Chapter 4 Conclusion                       |    |

### **Table of Figures**

| Figure 1-1.Evolution of the number of devices connected to an IP network [1]              | 12       |

|-------------------------------------------------------------------------------------------|----------|

| Figure 1-2. Evolution of the number of devices connected to a mobile network              | 13       |

| Figure 1-3. The three main categories of 5G [4]                                           | 14       |

| Figure 1-4. Enhancement of key capabilities from IMT-Advanced to IMT-2020 [4]             | 15       |

| Figure 1-5. The spectra availability and possible usage for 5G deployment                 | 17       |

| Figure 1-6. Millimeter band Sea level atmospheric attenuation                             | 18       |

| Figure 1-7. The vision of 5G services                                                     | 19       |

| Figure 1-8. Heterodyne Transmitter Schematic                                              | 20       |

| Figure 1-9. Heterodyne Transceiver [8]                                                    | 21       |

| Figure 1-10. Homodyne Transmitter Schematic                                               | 21       |

| Figure 1-11. Homodyne Transceiver [10]                                                    | 22       |

| Figure 1-12. a) Oscillator Closed Loop Model b) Oscillator Open Loop Model                | 23       |

| Figure 1-13. Phase Noise Power Spectrum                                                   | 25       |

| Figure 1-14. a) Transistor Noise b) Phase Noise of an Oscillator                          | 25       |

| Figure 1-15. a) VCO proposed by [16] b) Circular Inductor [16]                            | 27       |

| Figure 1-16. a) VCO schematic [17] b) Admittance Transformation [17]                      | 28       |

| Figure 1-17. a) VCO schematic [18] b) switched Triple Transformer [18]                    | 28       |

| Figure 1-18. VCO proposed by [19]                                                         | 29       |

| Figure 1-19. a) VCO proposed by [20] [21] b) Multilayer Coplanar Waveguide [20] [21]      | 29       |

| Figure 1-20. a) DiCAD differential transmission line layout b) DiCAD strips schematic     | c)       |

| Digital Control Oscillator [22] 30                                                        |          |

| Figure 1-21. a) VCO proposed by [23] b) Inductor Tank Layout [23]                         | 30       |

| Figure 1-22. a) VCO proposed by [24] b) Transformer Tuned layout [24]                     | 31       |

| Figure 1-23. Fundamental Feedback Oscillator Topology                                     | 32       |

| Figure 1-24. Fundamental Feedback Oscillator proposed by [25]                             | 32       |

| Figure 1-25. a) Class E PA [26] b) Output matching in [26]                                | 33       |

| Figure 1-26. a) Oscillator Schematic b) Drain voltage and current c) Output Spectrum [27] | 33       |

| Figure 1-27. Pulling Effect between LO and PA in TX [29]                                  | 34       |

| Figure 1-28. a) Obstacles Effect in Antenna Environment b) Pulling Effect in FFO          | 35       |

| Figure 1-29. a) HFO schematic b) Diplexer S-parameter                                     | 36       |

| Figure 1-30. HFO vs. FFO vs. FFO+3dB attenuator a) Phase Noise b) Frequency Pulling       | 36       |

| Figure 1-31. Harmonic Feedback Multi-Oscillator Plan                                      | 38       |

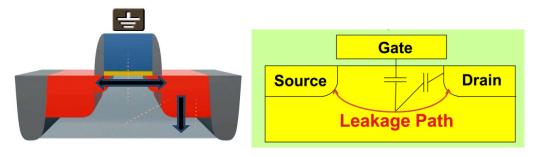

| Figure 2-1. a) Bulk CMOS leakage currents at OFF state b) Leakage path [5]                | 44       |

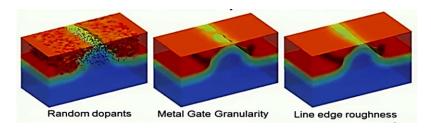

| Figure 2-2. Statistical variability in 20 nm CMOS [7]                                     |          |

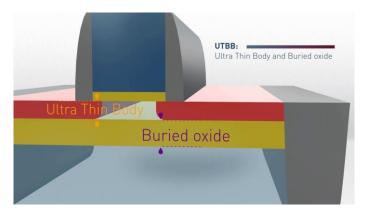

| Figure 2-3. UTBB FD-SOI Geometry                                                          |          |

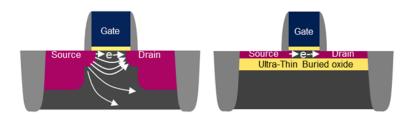

| Figure 2-4. Electron Flow                                                                 | 45       |

|                                                                                           |          |

| Figure 2-5. Field lines in partially depleted and fully depleted [9]                      | 45       |

|                                                                                           | 45<br>46 |

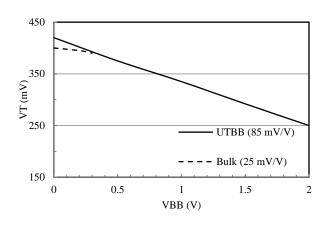

| Figure 2-8. Threshold voltage w.r.t. UTBB FD-SOI& Bulk body bias voltage                           | 49      |

|----------------------------------------------------------------------------------------------------|---------|

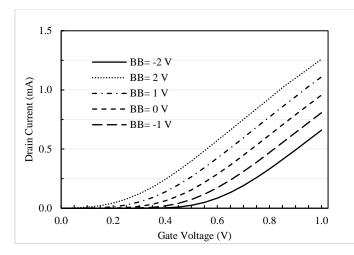

| Figure 2-9. Simulation of the shifting effects on the VT introduced by the back-gate bias          | sing n- |

| channel UTTB FDSOI.                                                                                | 50      |

| Figure 2-10. Combining DVFS with body Bias [19]                                                    | 50      |

| Figure 2-11. RBB Impacts on leakage current [18]                                                   | 51      |

| Figure 2-12. Temperature of UTBB vs Bulk [20]                                                      | 51      |

| Figure 2-13. Types of UTBB-FD-SOI Transistors                                                      | 52      |

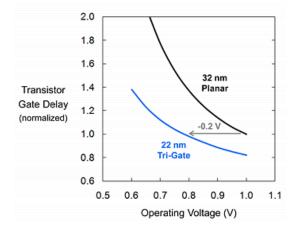

| Figure 2-14. Planar (to the left) and Tri-Gate FinFETs [23]                                        |         |

| Figure 2-15. Tri-Gate FinFET Drain current w.r.t. gate voltage [23]                                |         |

| Figure 2-16. Tri-Gate FinFET Performance Improvement [23]                                          |         |

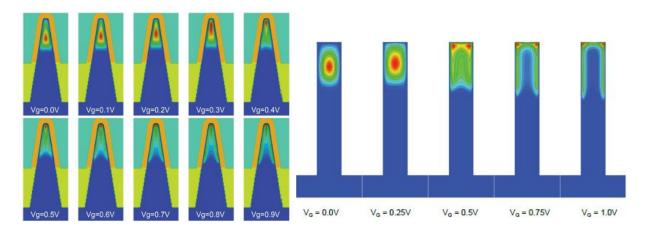

| Figure 2-17. Charge distribution in the taper and rectangular Fin respectively [7]                 | 54      |

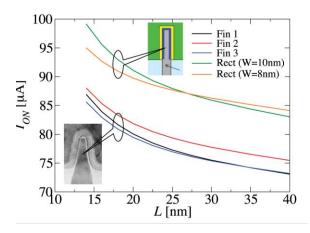

| Figure 2-18. Comparison of ION between rectangular and taper Fins for equivalent wide              |         |

| heights [7]                                                                                        | 55      |

| Figure 2-19. Tri-Gate FinFET additional parasitic capacitors [26]                                  | 55      |

| Figure 2-20. Different fins shape due fabrication [7]                                              | 56      |

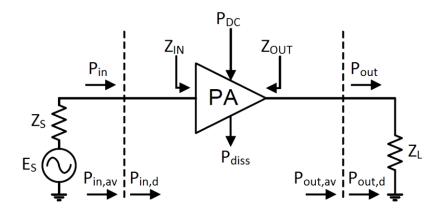

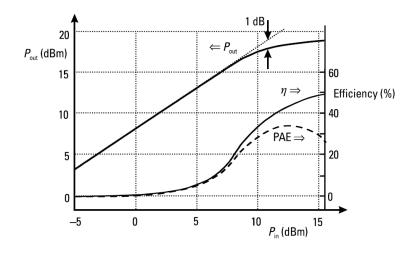

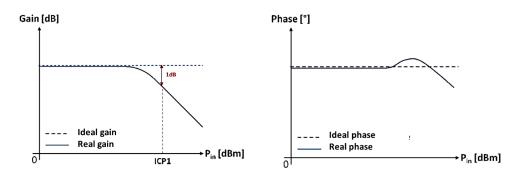

| Figure 2-21. PA Parameters                                                                         | 61      |

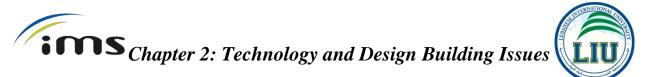

| Figure 2-22. PA Linearity Behavior                                                                 | 63      |

| Figure 2-23. Gain and power-added efficiency versus input power                                    | 64      |

| Figure 2-24. Amplitude and Phase non-linearity                                                     | 64      |

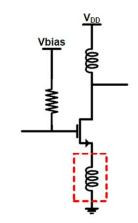

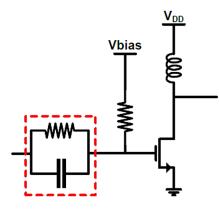

| Figure 2-25. a) Single-ended topology schematic b) Implementation example [49]                     | 65      |

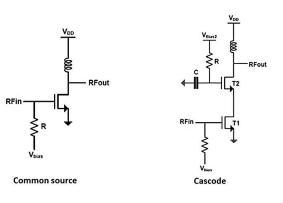

| Figure 2-26. Common Source and Cascode Schematic                                                   | 66      |

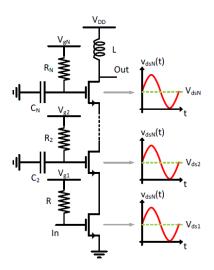

| Figure 2-27. Stacked Topology Schematic                                                            | 66      |

| Figure 2-28. a) Differential topology schematic and b) implementation example [51]                 | 67      |

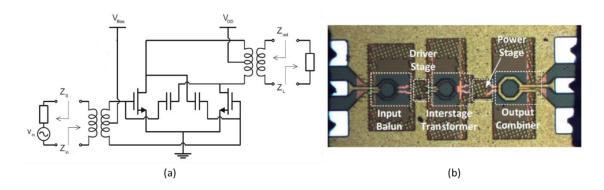

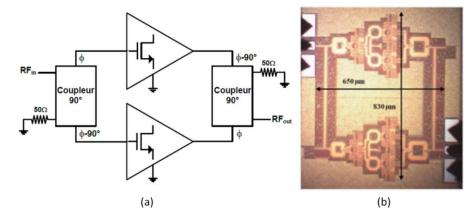

| Figure 2-29. a) Balanced Architecture Schematic and b) Implementation example [52]                 | 68      |

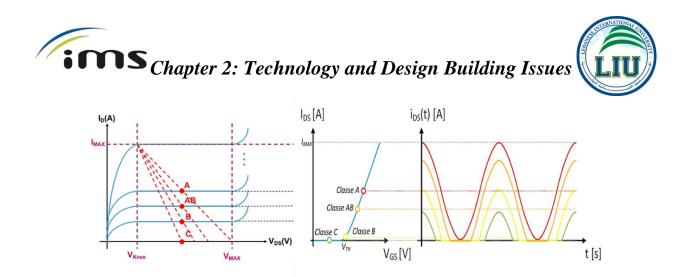

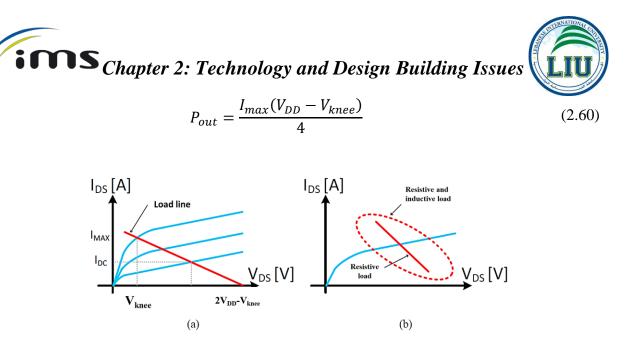

| Figure 2-30. Drain Current characteristics w.r.t. Drain and Gate Voltages of Sinusoidal C          | lasses  |

|                                                                                                    | 69      |

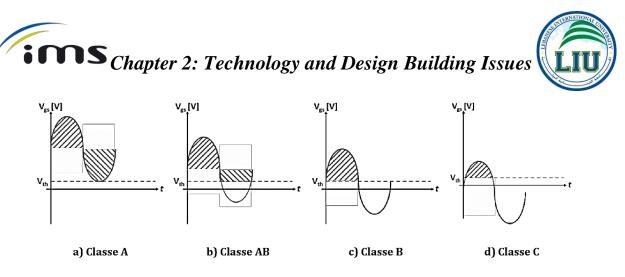

| Figure 2-31. Gate Bias Voltages for Sinusoidal Classes                                             | 70      |

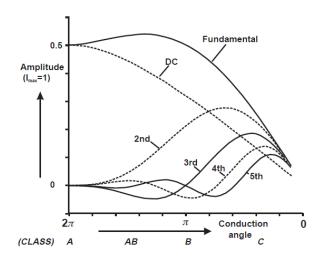

| Figure 2-32. Current. Harmonics according to the angle of conduction                               | 70      |

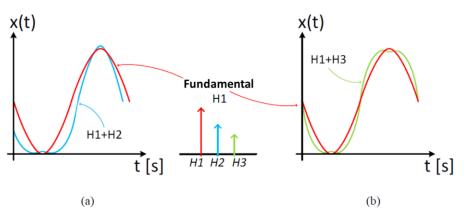

| Figure 2-33. Impact of harmonics (a) 2 and (b) 3 on the waveform of a signal X(t)                  | 71      |

| Figure 2-34. a) Circuit diagram of the class D amplifier. b) Voltage and current waveforms         | 71      |

| Figure 2-35. a) Circuit diagram of the class E amplifier. b) Voltage and current waveforms         | 72      |

| Figure 2-36. a) Voltage and current waveforms. b) Circuit diagram of the class F amplifier.        | 72      |

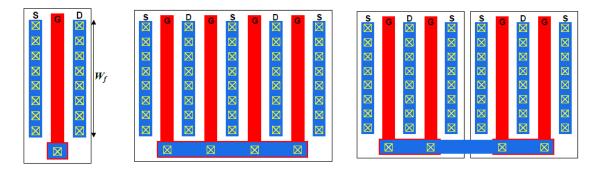

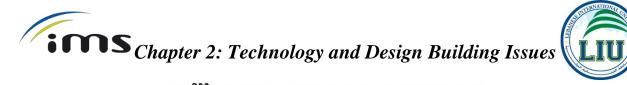

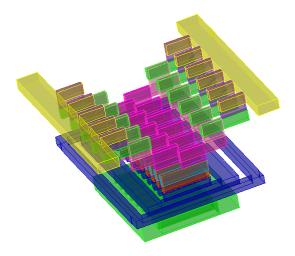

| Figure 2-37. a) Elementary Transistor. b) Transistor of Nf=4 Fingers. c) Transistor of Nf=2,       |         |

| Figure 2-38. fmax according to the gate width Wf [53]                                              |         |

| Figure 2-39. Staircase structure of drain and source connections                                   |         |

| Figure 2-40. Layout Optimization                                                                   |         |

| Figure 2-40. Layout Optimization<br>Figure 2-41. Pi- Section Network Operation                     |         |

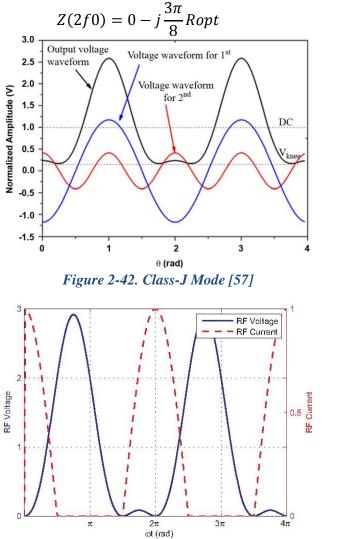

| Figure 2-42. Class-J Mode [57]                                                                     |         |

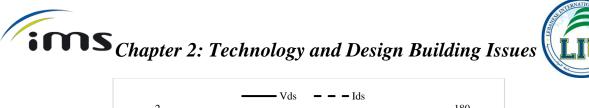

| Figure 2-42. Class-J Mode [57]<br>Figure 2-43. Class-J Drain-Source Voltage/Current Waveforms [58] |         |

| rigure 2 +5. Class-5 Dram-Source voltage current waveforms [50]                                    | / /     |

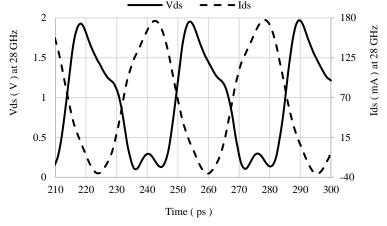

| Figure 2-44. Drain  | n-Source IV Curves of Class-J at 28 GHz                 | 78 |

|---------------------|---------------------------------------------------------|----|

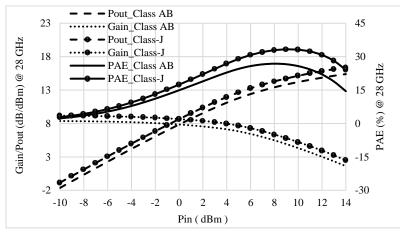

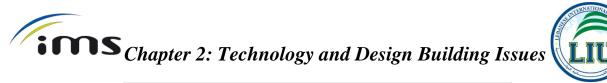

| Figure 2-45. PAE,   | $P_{out},$ and Gain Comparison for W= 250 $\mu m$       | 78 |

| Figure 2-46. PAE,   | $P_{out},$ and Gain Comparison for W= 350 $\mu m$       | 79 |

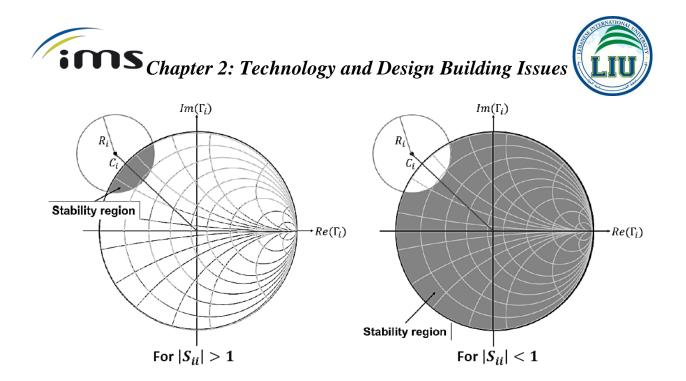

| Figure 2-47. Stabi  | lity Circle                                             | 82 |

| Figure 2-48. Induc  | ctive source degeneration CS                            | 83 |

|                     | hunt Feedback CS                                        |    |

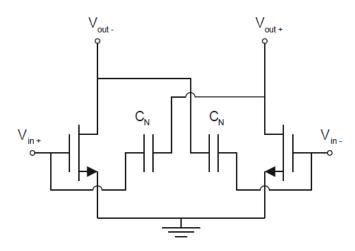

| Figure 2-50. Neutr  | ralization capacitors in Differential topology          | 85 |

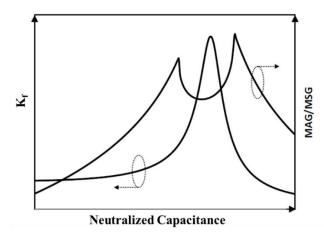

| Figure 2-51. Kf an  | nd MAG/MSG w.r.t. Cn                                    | 85 |

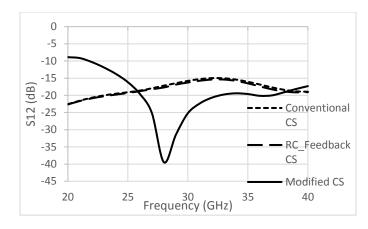

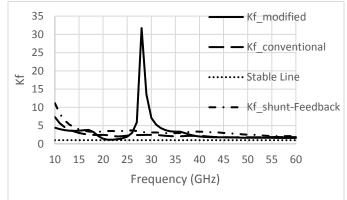

| Figure 2-52. Reve   | rse Isolation S12 Comparison                            | 86 |

|                     | Conventional vs Shunt Feedback vs Modified CS           |    |

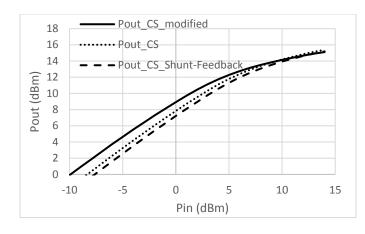

| Figure 2-54. Pout   | of Different CS Techniques                              | 87 |

| Figure 2-55. PAE    | of Different CS Techniques                              | 87 |

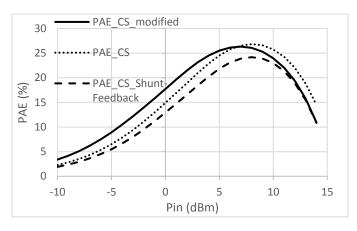

| Figure 2-56. Conju  | ugate match and load line match [56]                    | 88 |

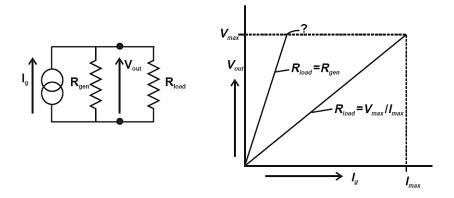

| Figure 2-57. (a) R  | esistive load line and (b) Both resistive and inductive | 89 |

| Figure 2-58. Pout   | and PAE Contours of Load-Pull Analysis                  | 90 |

| Figure 2-59. Harm   | nonic Injection PA Structure in [64] and [65]           | 90 |

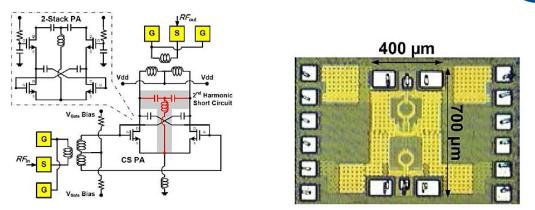

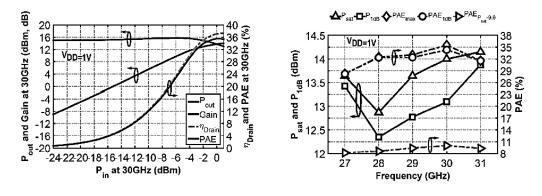

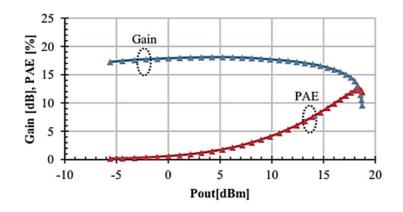

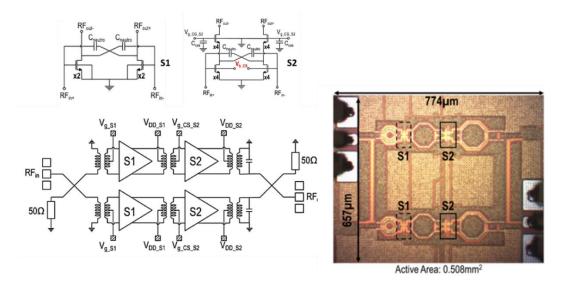

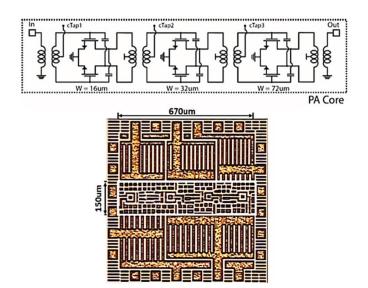

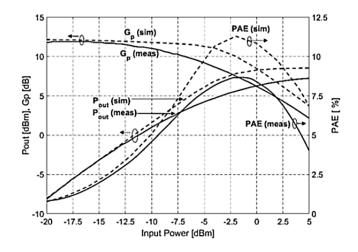

| Figure 2-60. The s  | schematic view and the photograph of PA [66]            | 91 |

| Figure 2-61. PA P   | erformances [66]                                        | 91 |

| Figure 2-62. The s  | schematic view and the photograph of PA [67]            | 92 |

| Figure 2-63. PA P   | erformance [67]                                         | 92 |

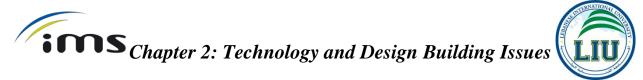

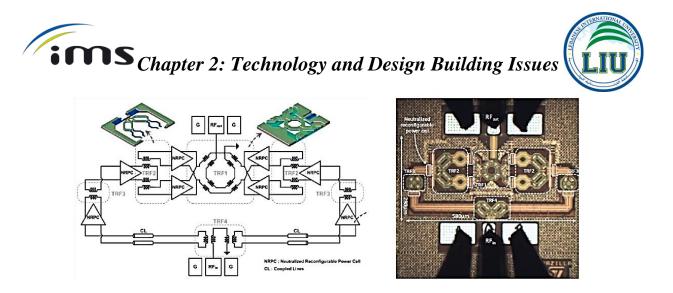

| Figure 2-64. The s  | schematic view and the photograph of PA [54]            | 93 |

| Figure 2-65. PA P   | erformance [54]                                         | 93 |

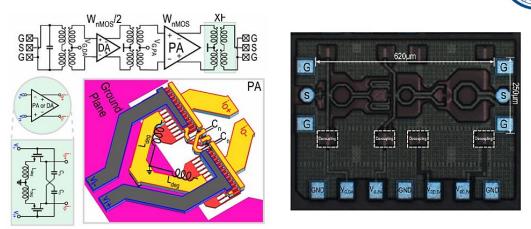

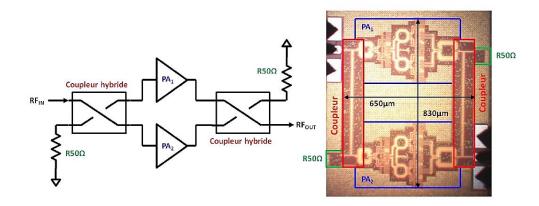

| Figure 2-66. The s  | schematic view and the photograph of PA [52]            | 94 |

| Figure 2-67. Scher  | matic view of individual PA [52]                        | 94 |

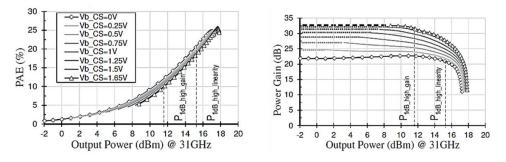

| Figure 2-68. PA P   | erformance [52]                                         | 95 |

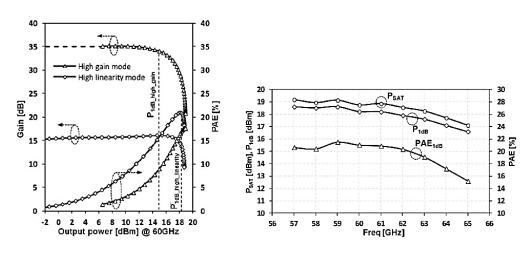

| Figure 2-69. Scher  | matic view of individual PA [68]                        | 95 |

| Figure 2-70. PA P   | erformance [68]                                         | 96 |

| Figure 2-71. The s  | schematic view and the photograph of PA [69]            | 96 |

| Figure 2-72. PA P   | erformance [69]                                         | 97 |

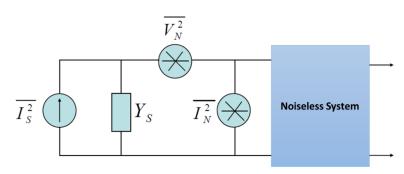

| Figure 2-73. Noise  | e modeling of a two-port system                         | 98 |

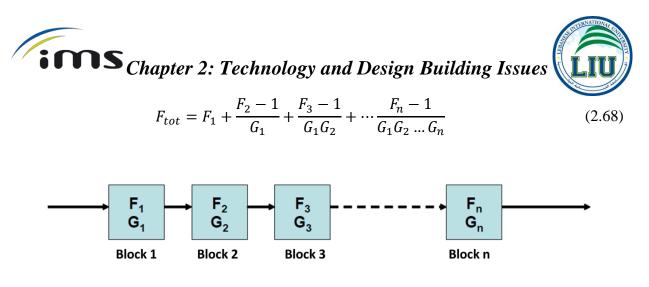

| Figure 2-74. Noise  | e factor of n-stage cascade system                      | 99 |

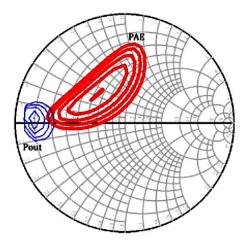

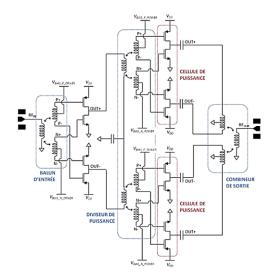

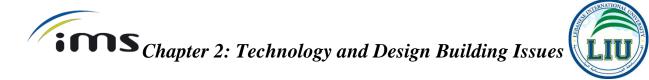

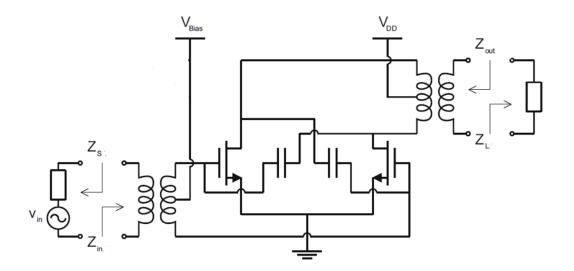

| Figure 2-75. HFM    | O Schematic Diagram                                     | 00 |

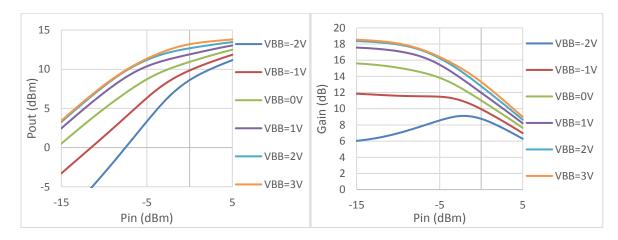

| Figure 2-76. HFM    | O Power Performance                                     | 02 |

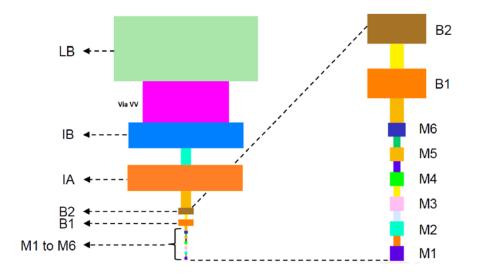

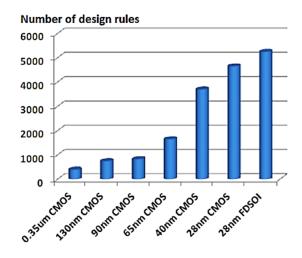

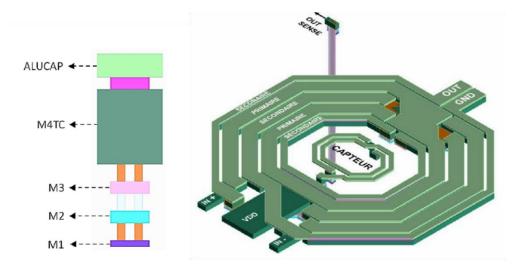

| Figure 3-1. 28nm    | FD-SOI BEOL 1                                           | 11 |

| Figure 3-2. CMOS    | S Technology DRC numbers 1                              |    |

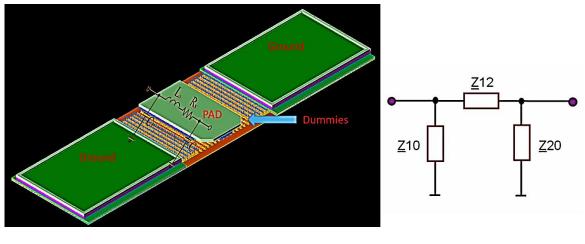

| Figure 3-3. a) RF   | PAD b) PI model                                         | 13 |

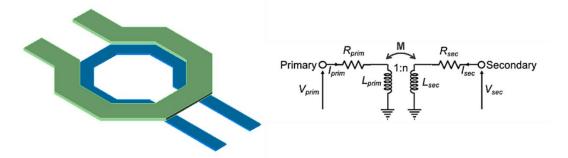

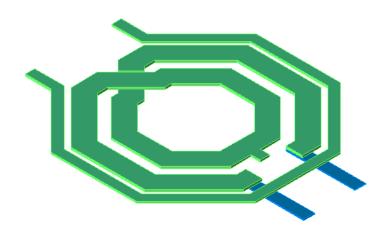

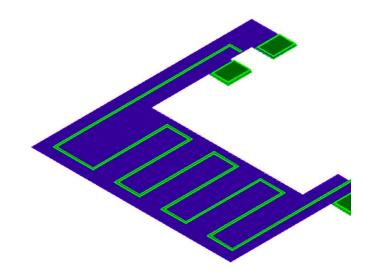

| Figure 3-4. Transf  | former a) 3D view b) model1                             | 14 |

| 0                   | Schematic1                                              |    |

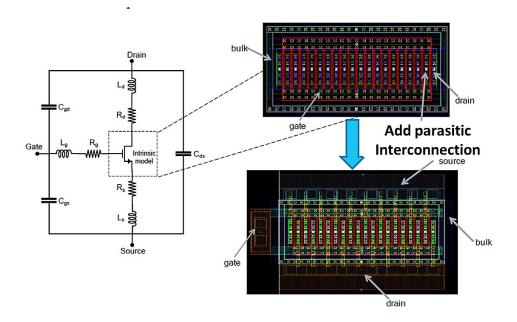

|                     | stor unit cell of W=50 µm1                              |    |

| Figure 3-7. Input M | Matching Transformer                                    | 18 |

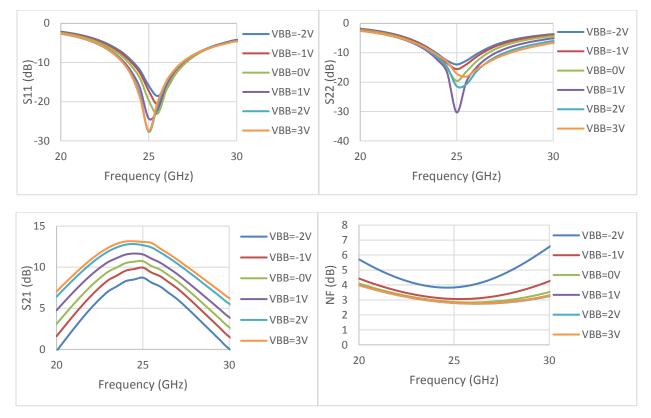

| Figure 3-8. LNPA SP and NF at different VBB                                          |

|--------------------------------------------------------------------------------------|

| Figure 3-9. Output Power and Gain at different VBB 120                               |

| Figure 3-10. PAE at different VBB                                                    |

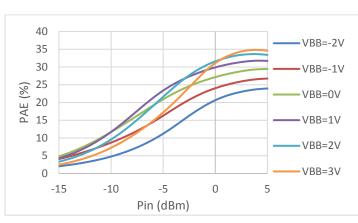

| Figure 3-11. PA Design Flowchart                                                     |

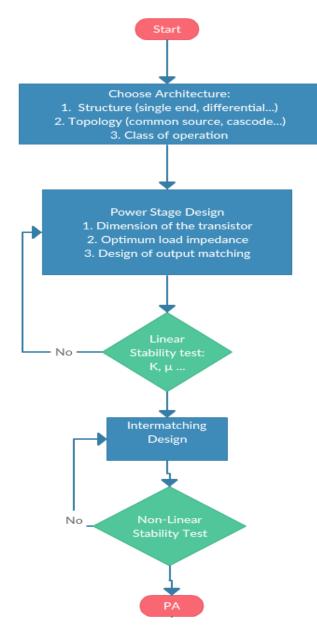

| Figure 3-12. PA Transistor Unit Cell                                                 |

| Figure 3-13. Differential Transistors View                                           |

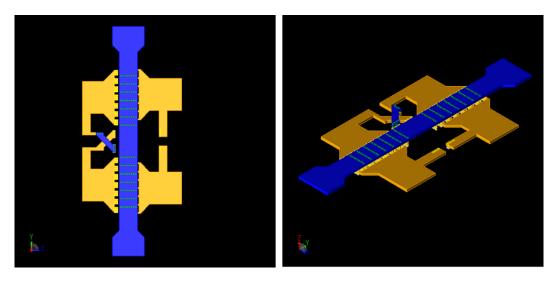

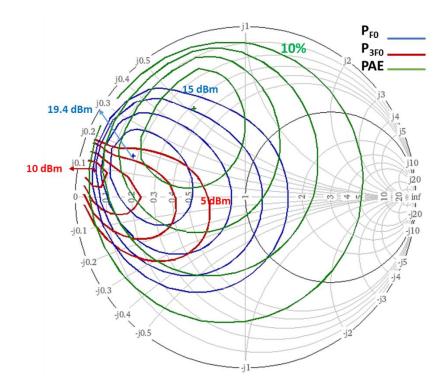

| Figure 3-14. PA Load-pull Analysis                                                   |

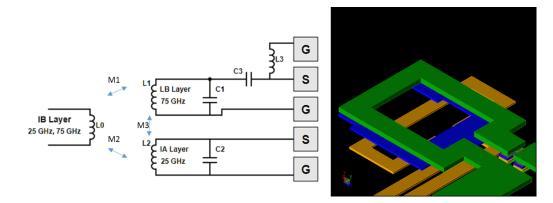

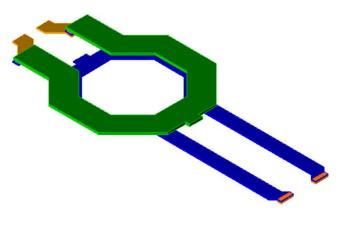

| Figure 3-15. Diplexer Schematic and Layout View                                      |

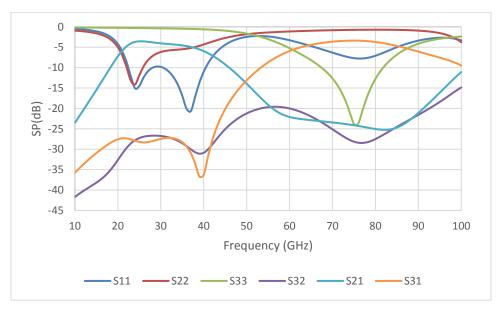

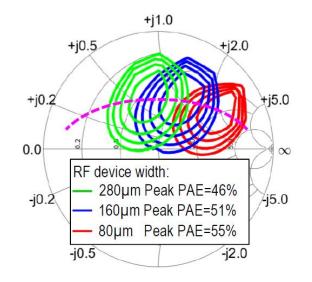

| Figure 3-16. Diplexer SP analysis                                                    |

| Figure 3-17. Typical Optimum Load Impedance and Peak PAE vs. Device Sizes @28GHz 128 |

| Figure 3-18. Inter-matching Transformer                                              |

| Figure 3-19. PA Schematic                                                            |

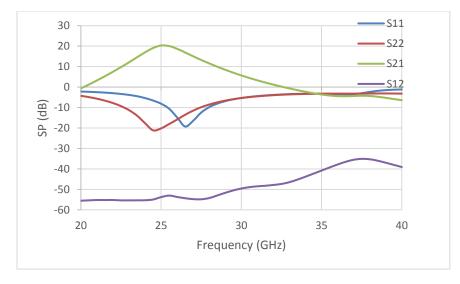

| Figure 3-20. PA S-Parameters                                                         |

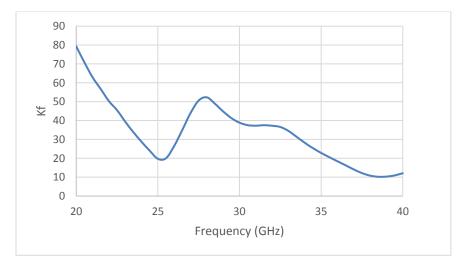

| Figure 3-21. Stability Factor Kf                                                     |

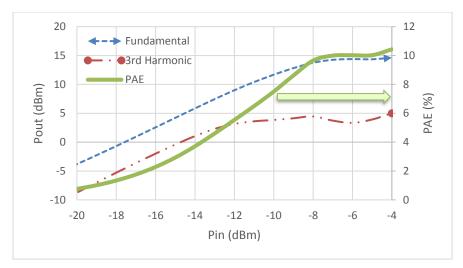

| Figure 3-22. PA Large Signal Analysis                                                |

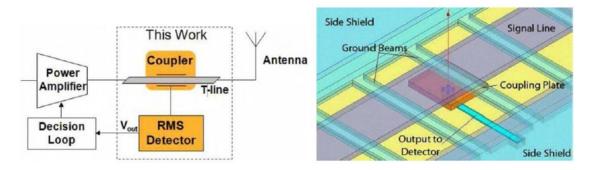

| Figure 3-23. Integrated Coupler in H9SOI [11]                                        |

| Figure 3-24. Proposed Coupler in [12]                                                |

| Figure 3-25. Capacitive Coupler Layout                                               |

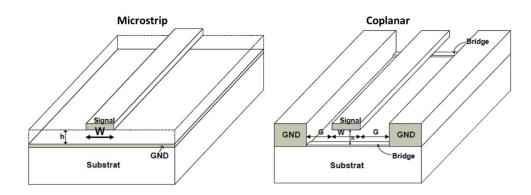

| Figure 3-26. Microstrip vs Coplanar TL                                               |

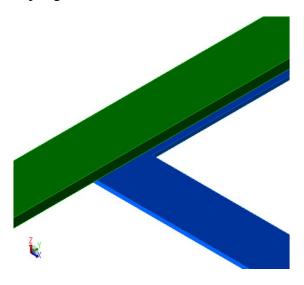

| Figure 3-27. Phase Shifter TL                                                        |

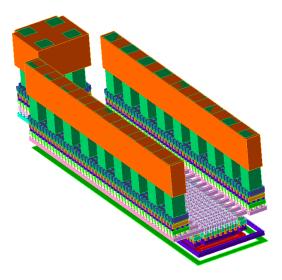

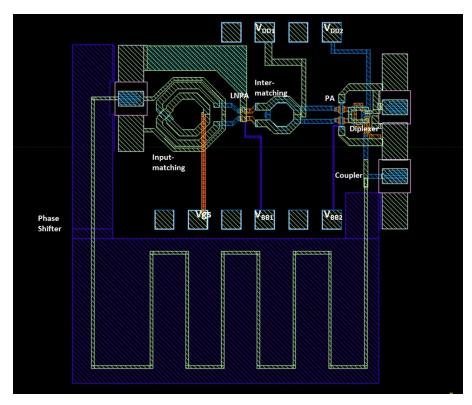

| Figure 3-28. HFMO Layout                                                             |

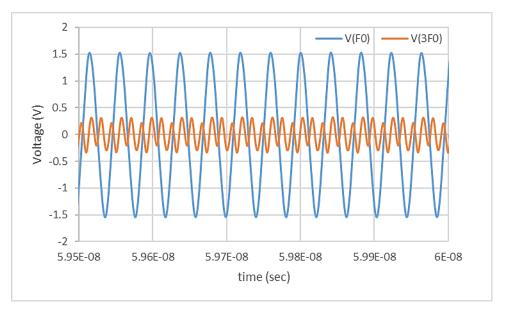

| Figure 3-29. HFMO Voltages Waveform                                                  |

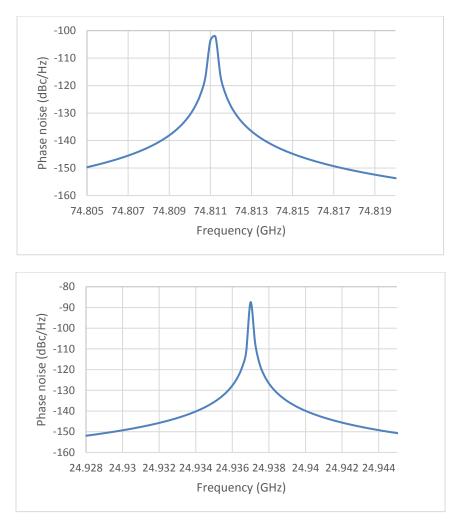

| Figure 3-30. HFMO Phase Noise                                                        |

| List of Tables                                                                       |

| Table 1. Comparisons between the performances of 4G and 5G                      | 16            |

|---------------------------------------------------------------------------------|---------------|

| Table 2. LC Oscillators State of Arts                                           |               |

| Table 2-1. DIBL, SS, ION, and IOFF comparison between Tri-Gate FinFET and 28-   | nm UTBB57     |

| Table 2-2. Smart watch performance over transistors [19]                        | 59            |

| Table 2-3. Performance of CS vs Cascode                                         | 66            |

| Table 2-4. Bandwidth Comparison                                                 | 79            |

| Table 2-5. Conditions of Stability Factors                                      | 80            |

| Table 2-6. Power Performance and PAE Comparison                                 | 87            |

| Table 2-7. Power Oscillator Targeted Specification                              | 100           |

| Table 3-1. RLC extraction of RF PAD                                             | 114           |

| Table 3-2. Amplifiers State of Arts                                             |               |

| Table 3-3. Comparison between the different technologies used to design mm-wave | diplexers [8] |

|                                                                                 | 126           |

| Table 3-4. PA State of Arts                                                     | 131           |

| Table 3-5. Load Impedance Variation Test                                        |               |

| Table 3-6. Oscillators State of Arts                                            |               |

#### **Glossary:**

- 1G First Generation of Wireless Cellular Technology

- 2G Second Generation of Wireless Cellular Technology

- 3G Third Generation of Wireless Cellular Technology

- 4G Fourth Generation of Wireless Cellular Technology

- 5G Fifth Generation of Wireless Cellular Technology

- BEOL Back-End of Line

- CAD Computer Aided Design

- CMOS Complementary Metal-Oxide-Semiconductor

- CP1 1 dB Compression Point

- CPW Coplanar Wave Guide

- CS Common Source

- DIBL Drain Induced Barrier Lowering

- DRC Design Rules Check

- ESR Equivalent Series Resistance

- FBB Forward Body Bias

- FD-SOI Fully Depleted Silicon on Insulator

- FET Field-Effect Transistor

- FFO Fundamental Feedback Oscillator

- fmax Maximum Oscillation Frequency

- ft Transit Frequency

- gds Source-Drain Conductance

- gm Trans-conductance

- HFO Harmonic Feedback Oscillator

- HFMO Harmonic Feedback Multi-Oscillator

- IC Integrated Circuit

- ICP1 Input 1 dB Compression Point

- IoT Internet of Things

- ITRS International Technology Roadmap for Semiconductors

- ITU International Telecommunication Union

- LNA Low Noise Amplifier

- LNPA Low Noise Power Amplifier

- LVT Low Voltage Threshold

- M2M Machine-to-Machine

- MAG Maximum Available Gain

- MIMO Multiple-Input Multiple-Output

- mm-wave Millimeter wave

- MOM Metal Oxide Metal

- MSG Maximum Stable Gain

- NF Noise Figure

- OCP1 Output 1 dB Compression Point

- PA Power Amplifier

- PAE Power Added Efficiency

- PCB Printed-Circuit Board

- PDC Consumed DC Power

- Pin Input Power

- PLS Post-Layout Simulation

- Pout Output Power

- Psat Saturated Output Power

- RBB Reverse Body Bias

- RF Radio-frequency

- RVT Regular Voltage Threshold

- SoC System on Chip

- SOI Silicon on Insulator

- SS Sub-threshold Slope

- TL Transmission Line

- URLLC Ultra-Reliable Low Latency

- UTBB Ultra-Thin Body and Buried oxide

- VCO Voltage Control Oscillator

- Vth Threshold Voltage

#### **General Introduction**

The 5G rising is on the horizon. As we embark on the road to 5G, the next-generation wireless communications system, there are countless challenges and opportunities emerging for the engineering community. 5G represents both an evolution and a revolution of mobile technologies that reaches the various high level goals. It is widely seen as the generation of wireless that will enable cellular to expand into a completely new set of use and connectivity for a wide range of new applications as smart home, autonomous cars, smart city, and internet of things... These demands motivates the work on mm-wave frequencies, which imposes increasing the specifications and standards of each block. One of the most important blocks in wireless technology is the oscillator. The performance of the oscillator, which is characterized by the phase noise parameter, can dictates the whole communication system performance. This work will present a new architecture of oscillator for the 5G application using the 28 nm UTBB FD-SOI technology from STMicroelectronics. It composed of four chapters.

Chapter 1 will cover the topics of 5G applications, specifications, and bands to be considered. Then it passes to the mm wave transmitter to go deeply inside to the oscillator block then define the phase noise parameter. It discusses the types of LC oscillator used in mm-wave bands. Each type is provided with real examples, and measurement values, in order study the performances of each technique used. A state of arts will be labeled for each type. Then the idea of fundamental feedback oscillators will be presented showing its drawbacks and compare it with the enhanced edition of that which is the harmonic feedback oscillator, showing its improvements on phase noise, frequency-pulling effects, and on behavior with load impedance variation. Then the new architecture will be introduced, which is the harmonic feedback multi-oscillator, showing its improvements over the FFO and the HFO.

Chapter 2 will discuss the technology and the building blocks issues used in the HFMO. First, it covers the bulk CMOS limitation in 28 nm transistor scale and the alternative transistors showing the performances and enhancement of the 28 nm FD-SOI technology in mm-wave applications. The second part is about the power amplifier design parameters, architectures, and classes, which the HFMO is based on. The last part of this chapter is showing the architecture and specifications of the proposed power oscillator HFMO.

Chapter 3 will shows the design steps of each part in the power oscillator system. The overall results of the oscillator is then compared with other oscillators working on the same mm-wave band. Finally, in chapter 4, the work ends with a general conclusion, which provides an overview of the thesis and perspectives for future works.

# Chapter 1: Background from 5G towards Oscillators

### **Chapter 1 : Background from 5G towards Oscillators**

#### 1.1 Mobile Technology: an overview

In just 20 years, mobile phone networks have experienced a profound transformation from the second generation 2G (speech communication), the third generation 3G (voice communication and data transfer), to the fourth generation 4G (communication and broadband data transfer). Indeed, a phone designed originally to perform a voice conversation between two users without providing any other service that is to send/receive text message, the modern smartphone has become today a center of data access to a big number of services and applications as games, cameras, economic transactions, internet browser... This generalization of the internet access, via the smartphone and the arrival of video calls grow and keep straight ahead.

The flow of communication started with the invention and development of scientist theories. It started with the theory of "On a Dynamical Theory of the Electromagnetic Field" in 1865 and "A Treatise on Electricity and Magnetism" in 1873 for the Scottish scientist James Clerk Maxwell that named now a day as Maxwell equations. Maxwell equations explain the movement of the electromagnetic waves in a free space, but they were mathematically complex until Oliver Heaviside simplify them by introducing the vector notation and apply them on practical applications as guided waves and transmission lines in 1887. Then, the German physicist Heinrich Hertz prove and validate the theories of electromagnetic waves introduced by Maxwell by a set of experiments in 1891.

Nikola Tesla, a Serbian scientist and inventor, is one of the few individuals that is rarely discussed accredited with major technological advancements. He is the first one who think and apply a wireless transfer of energy without data (power transfer), then he invented the radio wireless communication, which is falsely attributed to an Italian engineer Guglielmo Marconi in 1895 since Nikola Tesla was not submitting his patents to be under his name. Then the microwave enter a freezing stage until the start of World War II that make the wireless communication under field of interest. Most of the nations who participate in the World War II developed the radar system independently which launch the analog communication technique.

The first generation of mobile communication, which was mostly analog wireless system, introduced in 1979. The second-generation 2G mobile networks and the digital switchover with the creation of the GSM standard has introduced new services of transfer of data such as SMS (Short Message Service). Nevertheless, the 2G could not yet respond to the request for access to the internet from mobile phones. This has motivated the development of 3G, which came on the market in 2001 with the first smartphones. Then in 2009, data transfer rates much greater than those of 3G was achieved with the definition of 4G video calls and much larger file transfer.

However, the 4G network cannot meet the growing demand of the number of connected objects. That is why the mobile phone industry chose to develop the network of fifth generation 5G to provide a technical solution to the problem faced by the 4G today.

The 5G will not be an evolution of 4G, rather it will be a full new mobile system; it will be faster, reactive for real time services, connecting people, objects, cars...going toward digitizing the society.

#### **1.2 Fifth generation 5G**

#### 1.2.1 5G applications and specifications

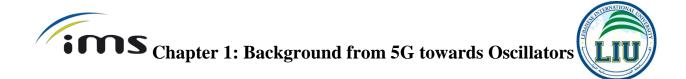

Before talking about the specifications of this network, it is necessary to be interested in the evolutions in the world market communications between today and 2020. In their annual report, the Cisco analysts detail their projections for the period 2015-2020. Several predictions are particularly interesting. The first concern is the number of objects connected to an IP network [1] [2]. In 2014 we had 14 billion objects connected to an IP network, in 2019 this number will exceed 24 billion, increase of 10 billion in 5 years as shown in Figure 1-1.

Figure 1-1. Evolution of the number of devices connected to an IP network [1]

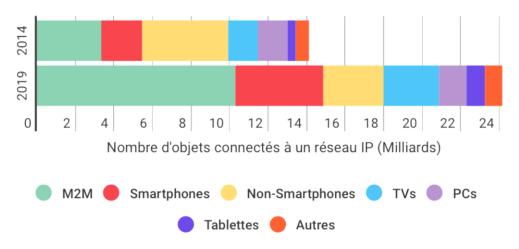

The second concern is the number of the wireless connected objects to the mobile network [3]. This number will increase from 7.9 billion in 2015 to 11.6 billion in 2020, an increase of 4 billion in 5 years. In Figure 1-2, it can notice that the share of smartphones objects will exceed 40% by 2020; an increase of 12% compared to 2015.

Figure 1-2. Evolution of the number of devices connected to a mobile network

The 5G will provide connectivity for a wide range of new applications as home automation, autonomous car, E-Health, smart City, virtual realities with high definition, industrial process control, entertainment, gaming, and internet of things (IoT). These applications have very different connectivity needs: whereas virtual reality requires a lot of bandwidth to provide a good user experience, autonomous vehicle communications must be reliable and almost instantaneous to be able to mitigate the risks of traffic accidents. IoT (Internet of Things) requires a network capable of communicating simultaneously with a large number of objects, while consuming very little energy to ensure a long battery life.

To meet these heterogeneous needs, International Telecommunication Union ITU [4] has defined three main categories of performance for 5G to be achieve:

- **eMBB:** enhanced Mobile Broadband, meeting very high speed needs

- URLLC: Ultra Reliable Low Latency Communications, Addressing Ultra-Fast and Reliable Connection Requirements

- **mMTC:** Massive Machine Type Communications, which concerns communications related to connected objects.

Figure 1-3. The three main categories of 5G [4]

The eMBB is for all applications and services that require connection always faster, for example to allow watching videos in ultra-high definition (8K) or wireless "streamer" virtual reality or augmented reality applications. The Ultra-low latency communications (uRLLC) are all applications requiring extremely high reactivity and a very strong transmission guarantee of the message. These needs are mainly found in transport (reaction time in case of accident risk), in medicine (tele surgery) and, in general, for digitization of the industry. The mMTC mainly encompasses all uses related to the Internet of Things. These services require extensive coverage, low energy consumption and relatively small. The announced contribution of 5G compared to current technologies lies in its ability to connect objects distributed very densely over the territory.

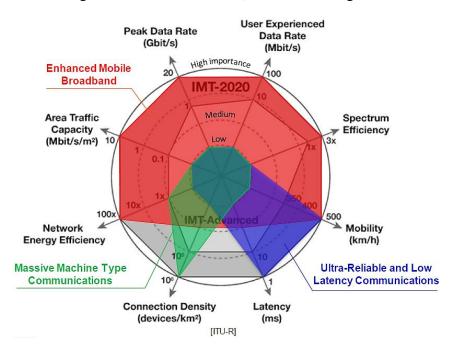

In order to implement these three types of use, eight performances indicators Key performance indicators KPI have established by the International Mobile Telecommunications ITU to specify, quantify and measure features of IMT-2020 (5G) systems:

- Peak data rate (Gbit/s);

- User experienced data rate (Mbit/s);

- Spectrum efficiency (bit/Hz);

- Maximum speed of the terminals or mobility (km/h);

- Latency (ms);

- Connection density or number of objects connected to a zone (devices/km<sup>2</sup>);

- Network energy efficiency;

- Area traffic capacity (Mbit/s/m<sup>2</sup>);

According to 5G plan, it should be able to offer a user data rate and a peak data rate respectively 10 and 20 times higher than what is currently available. The maximum density of connections will be multiplied by 10 and the latency divided by at least 10 (the target point-to-point latency is 1 ms, as against 30 to 40 ms to date) as shown in Figure 1-4.

Figure 1-4. Enhancement of key capabilities from IMT-Advanced to IMT-2020 [4]

The goal of 5G, as a successor to 4G, will also be to provide:

- An extremely reliable network, with more homogeneous performances, whatever the position of the user compared to the base station;

- A stable connection even in mobility (with speeds of the order of 500 km/h);

- An increase in energy efficiency (batteries up to 100 times less energy intensive).

The table below summarizes the expected performance of 5G and those currently available with 4G:

|                              | <b>4</b> G | 5G [4] |

|------------------------------|------------|--------|

| Peak data rate (Gbit/s);     | 1          | 20     |

| User experienced data rate   | 10         | 100    |

| (Mbit/s)                     |            |        |

| Spectrum efficiency (bit/Hz) | x1         | x3     |

| mobility (km/h)              | 350        | 500    |

| Connection density           | 105        | 106    |

| (devices/km <sup>2</sup> )   |            |        |

| Latency (ms)                 | 10         | 1      |

| Network energy efficiency    | 1x         | 100x   |

| Area traffic capacity        | 0.1        | 10     |

| (Mbit/s/m <sup>2</sup> )     |            |        |

#### Table 1. Comparisons between the performances of 4G and 5G

#### **1.2.2 5G Bands**

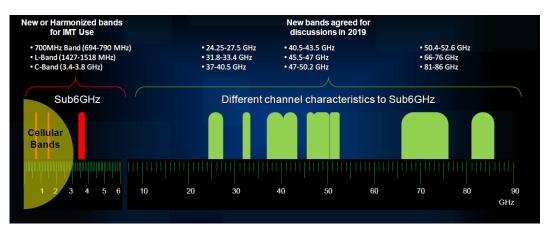

The millimeter band corresponds to frequencies higher than 6 GHz, which mostly not taken into account for the deployment of mobile networks (fronthaul) for reasons of technological maturity and quality of propagation noting that the fronthual is the connection between the cell tower radio itself and the mobile network control backbone (Baseband Unit). To respond to the incessant increase in data rates and volumes exchanged, it is necessary to use new bands with very large pipelines (more than 100 MHz per user): the millimeter bands could offers such spectrum reserves and their use would in some cases achieves the rates shown in Table 1. In return, their use requires the development of all necessary technologies, miniaturized, low cost and with an energy consumption compatible with portable terminals (oscillators, amplifiers, signal processing, antennas ...). In particular, because of the low propagation quality of the millimeter waves, each cell will have a reduced coverage, which will require the implementation of beamforming techniques, to focus the energy transmitted by the antennas.

5G presents itself as a technology that will use both low frequencies (f < 1 GHz), medium frequencies (1 GHz < f < 6 GHz) and, for the first time in consumer networks, high frequencies (f > 6 GHz) towards mm-wave bands. This spectral diversity is link to the promises of 5G: extended coverage (low frequencies), ultra-high speed (very wide channels in very high bands), low energy consumption. In addition, satellite services will also be able to participate in the development of this new technology, particularly in the most difficultly covered areas or to provide additional backhaul (the link between a base station and the core wired network that is even fiber, coax, or wireless). In this respect, the satellite world is interested in 5G and wishes to be involved in the definition of this generation.

# Chapter 1: Background from 5G towards Oscillators

#### 1.2.2.1 Above 6 GHz

At the World Radio communication Conference (WRC-15) in Geneva, under the aegis of the ITU whose objective is to change the distribution of frequencies between users, various discussions on the definition of future mobile bands have enabled the 5G studies to focus on millimeter frequencies over a number of bands between 24 GHz and 86 GHz. The candidates are 24.25 - 27.5 GHz, 31.8 - 33.4 GHz, 37 - 43.5 GHz, 45.5 - 50.2 GHz, 50.4 - 52.6 GHz, 66 - 76 GHz, and 81 - 86 GHz as shown in Figure 1-5. It is important to note that while the above-mentioned bands have identified as 5G bands, there is still no indication at this stage whether they can really inserted for the deployment of this latest generation. Only the results of the technical studies will make it possible to establish the constraints and the rules.

Figure 1-5. The spectra availability and possible usage for 5G deployment

Contrary to the conclusions of the Conference, which reflect the European recommendations, the United States and other Asian countries (Korea, Japan) have decided to launch 5G experiments in the 28 GHz band and equipment manufacturers, such as for example Qualcomm or Samsung, began manufacturing products in the 28 GHz band.

Europe, for its part, decided, following the publication of an opinion of the RSPG (Radio Spectrum Policy Group, a European group of spectral policy in which France is represented by the ANFR) [5], to carry out, as a priority, studies on the 26 GHz band (pioneer band), then on the 32 GHz and 42 GHz bands. In a second step, studies for the introduction of 5G in all other bands identified by WRC-15 will be continue.

The rapid selection of the 26 GHz band as a pioneer band is to allow economies of scale in the production of equipment, since it is very likely that dual-mode equipment, operating in both the 26 GHz band and 28 GHz will be available from the first deployments.

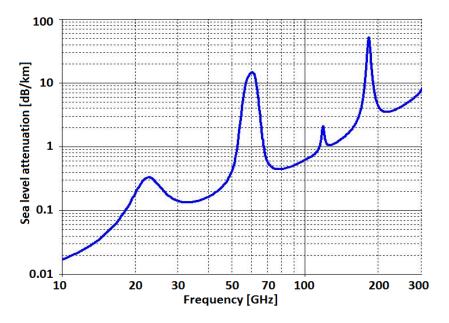

Figure 1-6 shows the sea level atmospheric attenuation for the millimeter band. It shows a small peak at 23 GHz and large peak at 60 GHz of 13dB/km. Indeed, low attenuation level between 10 GHz and 50 GHz of 0.3 dB/km or less occur. A clear atmospheric window can be seen from 70 GHz to 110 GHz with low atmospheric attenuation around 0.5 dB/km. This shows the advantage of the 5G frequency candidates that choose by the ITU.

Figure 1-6. Millimeter band Sea level atmospheric attenuation

#### 1.2.2.2 Bands below 6 GHz

#### • The band 3.4-3.8 GHz

The 5G cannot completely conveyed by the millimeter bands: the propagation qualities of these bands make delicate an extended coverage, especially in the less densely populated areas of the territory. In addition, the technological maturity of the use of these tapes for consumer communications is still very low. It is therefore necessary to identify a "core" band, which is less than 6 GHz and proposes network large enough for future 5G operators to be able to provide innovative services and improved quality of service compared to 4G

The 3400 - 3800 MHz band seems to be a good candidate to meet this need. At first, the band 3400 - 3600 MHz then the band 3600 - 3800 MHz have been identified as IMT bands for mobile broadband. In addition, it has a large amount of available spectrum (up to 400 MHz). Finally, technological advances (antenna and signal processing) make it possible to consider the use of these frequencies for the establishment of macro cells, and not just microcells.

This analysis has been confirmed by the European Commission (in its 5G mandate at RSCOM [6]) and the RSPG [7], which consider the 3.4 - 3.8 GHz band as the only credible 5G band for deployment by the end of 2020.

#### • Other bands below 6 GHz

The bands currently used for 2G, 3G and 4G can also be use in the future for 5G deployments. However, the reforming of the 2G, 3G and 4G bands could be tricky, because of the mode of duplexing used by them. Indeed, most mobile communications in Europe use the FDD - Frequency Division Duplexing mode to exchange information. The technical discussions around the 5G however announce the TDD - Time Division Duplexing mode as privileged (if not unique) duplexing mode for this new generation, in particular because it makes it possible to adapt the bandwidth used to the debit and because it is particularly effective when beamforming is used. The use of already harmonized mobile bands for 5G networks will therefore require in-depth technical studies to define the conditions of use and sharing with the services in place. In this respect, the ECC - Electronic Communications Committee has decided to evaluate the potential of some already harmonized bands, in particular the 700 MHz band and the L-band (1427-1492 MHz).

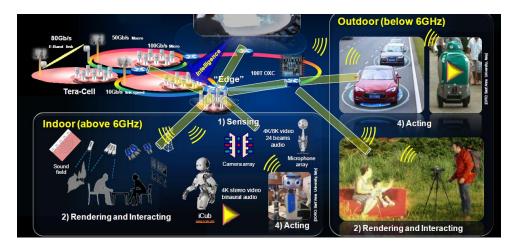

The Bands details can give a vision of networks and services at the horizon 2020 and beyond as shown in Figure 1-7. The 5G service delivery will not be limited to any specific frequency band; rather, it will follow the optimal delivery over the best available spectra. The assumption of the wireless network capabilities:

- 1) 50-Gb/s macro coverage

- 2) 100-Gb/s micro local coverage

- 3) 80-Gb/s E-band back/front-hauling links.

Figure 1-7. The vision of 5G services

## Chapter 1: Background from 5G towards Oscillators

#### **1.3 Millimeter Transmitter**

The millimeter transmitter and transceiver based on two structures: heterodynes and homodynes. The digital I and Q data, which generated by the Digital Signal Processor (DSP), are converted to continuous signals through digital to analog converters (DACs). These signals are then modulated on a carrier frequency before be amplified by the power amplifier and transmitted by the antenna. The analog part contains local oscillator with phased locked loop (PLL), mixers, and power amplifier.

#### 1.3.1 Heterodyne architecture

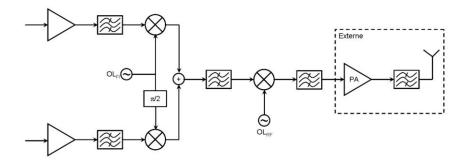

The most common structure of issuer architectures is undoubtedly the heterodyne structure. This structure, illustrated in Figure 1-8, is composed as following; the baseband signals Q and I, after being filtered and amplified, are transposed at an intermediate frequency  $f_{Fi}$  thanks to twoquadrature mixers phase. The signal is then filtered to remove the  $f_{Fi}$  harmonics. Then the signal is transposed again to the frequency  $f_{Fi} + f_{HF}$  with a last mixer. This mixture results not only the frequency  $f_{Fi} + f_{HF}$  but also the frequency  $f_{Fi} - f_{HF}$ . The latter is eliminate by a band pass filter. Finally, the signal is then amplified and filtered before being transmitted to the antenna. The useful signal and the image signal have the same power, which mean that the band pass filter of the second conversion stage must be enough to reject the image signal. For a good suppression of harmonics, the integrated band pass filter must have a high order. This architecture also imposes the use of two PLLs with low phase noise. A super heterodyne architecture uses one oscillator with one PLL in which  $f_{HF}=n.f_{Fi}$

Figure 1-8. Heterodyne Transmitter Schematic

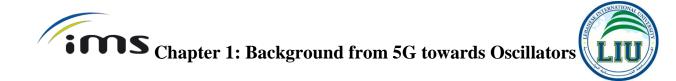

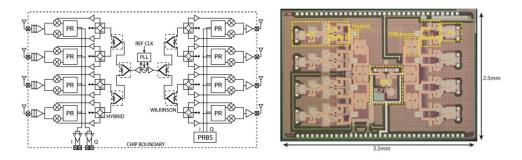

An example of super heterodyne fully integrated 60 GHz transceiver module in a 65nm CMOS technology for wireless high-definition video streaming is illustrated on Figure 1-9. It covers the room 57 to 66 GHz frequency band. It delivers 16 dBm saturated output power with maximum gain of 17.5 dB [8].

Figure 1-9. Heterodyne Transceiver [8]

#### **1.3.2 Homodyne architecture**

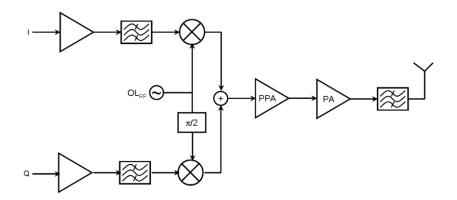

To remove the problem of image frequencies, transmitters' studies led to homodyne architecture, also called direct conversion or Zero - Intermediate Frequency (Zero-IF). The signal is directly converted to the frequency at which the signal will be transmitted. This architecture is illustrated in Figure 1-10. This architecture allows a reduction of the cost and the general consumption by grouping I Q modulators and frequency synthesis. This leads to a greater level of integration and better treatment of digital data. Thus, the baseband signal is directly modulated at the RF frequency with two quadrature mixers, a PLL and a local oscillator operating at the RF frequency.

Figure 1-10. Homodyne Transmitter Schematic

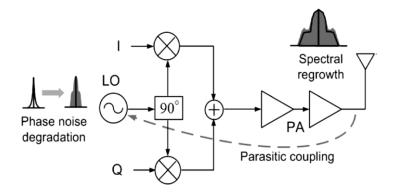

This architecture is more compact than heterodyne transmitter because it uses fewer components. Indeed, the image rejection of the channel is performed dynamically by summing the output of the mixers. We thus remove a band pass filter, a second conversion stage in frequency and an external filter of the image frequency. However, it is necessary for the I and Q channels to be well tuned in terms of amplitude and phase. Indeed, it is important to realize a precise phase

quadrature operating at the RF frequency. Inaccurate quadrature leads to bad rejection of the image of the mixture. One of the recurring problems with this architecture is that the elements, much closer to each other, can bring a pulling phenomenon [9]. Indeed, when two oscillating systems are too close, they tend to match by coupling. In a direct conversion transmitter, the local oscillator and the output of the Power Preamplifier (PPA) operate at frequencies, which are close to each other and can be coupled by the substrate. The output signal of the PPA having an output power far superior to that of the local oscillator, the latter can be shifted in frequency. Therefore, it must be ensured that these elements not too close.

An example of homodyne transceiver manufactured in 65nm CMOS technology at 60 GHz is illustrated in Figure 1-11. It is composed of four cells in transmitter and receiver. Each power amplifier can delivers -1,5dBm saturated power with a gain of 24 dB over 8 GHz bandwidth [10].

Figure 1-11. Homodyne Transceiver [10]

#### **1.4 Millimeter Wave Oscillators**

An oscillator is a circuit generating a periodic signal at a constant or variable frequency. In the latter case, we often talk about voltage-controlled oscillator. Indeed, they are used to generate the signals timing (clocks), to modulate and demodulate signals.

In 5G, there is a clear trend towards the use of high-speed links between mm wave transceivers and digital signal processing in baseband, which requires generation of a frequency clock in the same band with increasing performance in terms of jitter and phase noise. These performances seem to be less compatible with classical architectures of ring oscillators. Moreover, the use of a LC oscillator has many disadvantages for these applications (area, sensitivity, radiation, pulling...).

# Chapter 1: Background from 5G towards Oscillators

#### **1.4.1 Oscillator Model**

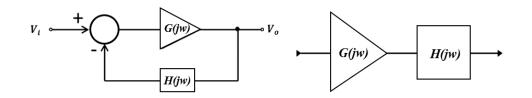

An oscillator is often modeled by the looped system shown in Figure 1-12. It consists of an active part (the gain element) and a passive element (the resonator) buckled by a positive feedback that reinjects part of the signal of the exit at the entrance.

Figure 1-12. a) Oscillator Closed Loop Model

#### b) Oscillator Open Loop Model

where A (jw) is the closed loop gain, G (jw) is the gain of the amplifier, and H (jw) is the feedback transfer function.

$$A(jw) = \frac{V_o(jw)}{V_i(jw)} = \frac{G(jw)}{1 - G(jw) \cdot H(jw)}$$

(1.1)

To determine the oscillation conditions. The open loop should be studied. The open loop transfer function is:

$$A_{OL} = \frac{V_o(jw)}{V_i(jw)} = G(jw).H(jw)$$

(1.2)

For the system to oscillate in steady state, it is necessary that  $V_o(jw) = V_i(jw)$  so that G(jw). H(jw) = 1. This amounts to satisfy the conditions of Barkhausen criteria, which are:

$$|G(jw).H(jw)| = 1$$

,  $Arg\{G(jw).H(jw)\} = 0[2k\pi]; k \in N$

Generally, an oscillation starts with the amplification of the noise of the elements of the loop [11]. Indeed, in equilibrium, there is, in principle, no energy transfer between the different elements of the circuit. That's, in fact, the intrinsic noise of the components (the thermal agitation of electrons), which is a random phenomenon that imbalance the device. This imbalance is then amplified by the gain of the loop and the oscillation can then start. To set up the oscillation, the gain of the active part G (jw) is greater to the gain of the transfer function of the resonator H (jw) Once the oscillation of the device ensured, the main performances of an oscillator are defined as: the oscillation frequency, the power delivered at this frequency, and the phase noise level.

# Chapter 1: Background from 5G towards Oscillators

#### **1.5 Phase noise**

The noise in the oscillators and, more specifically, the phase noise is the most important parameter to consider in the design of oscillators. In order to understand how important the noise performance can be in oscillator, it is necessary to take an example of some points in RF communication. The space of the frequency bands is divided to several standards of communication. Many standards subdivide their own space into two bands: one for the transmission (Tx), the other for the reception (Rx). Each band is subdivided into channels that are assigned to one or more users. As an example, in the GSM, the Tx transmit band is in the [880 MHz - 915 MHz] range and the Rx receive band is in the [925 MHz - 960 MHz] range and the channels are wide 200 kHz. A high phase noise level in a band can disturb the communications located on an adjacent band. In our example, the phase noise at 11 MHz offset of the carrier of the transmitted signal in the last channel of the band Tx transmission (915 MHz), will end up in the reception band Rx (915 + 11 = 926 MHz). It will therefore scramble the reception signal, which is generally weaker than the broadcast level from the phone.

#### **1.5.1 Principle of noise generation in oscillators**

The noise of the oscillators arises from the electronic noise of the constituent components. The phase noise is a phenomenon due to the conversion of different sources of noise into semiconductors around the carrier frequency thereby generating phase modulation. The consequence is the random variation of the frequency of the output signal of the oscillator.

#### **1.5.2 Phase noise in oscillators**

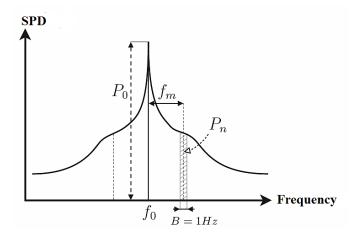

Phase noise is manifested by random fluctuations in the period of the output signal of the oscillator. These fluctuations are due to different sources of spreading noise in the spectral power density around the carrier frequency. The phase noise is expressed as a single sideband brought back into a measuring band of 1 Hz. This magnitude noted L is expressed by the ratio between the power in a sideband of the phase noise and the power of the carrier:

$$L(f_m, B) = 10 \log\left\{\frac{P_n}{P_0}\right\}$$

(1.3)

$$P_n = \int_{f_0 + f_m - \frac{B}{2}}^{J_0 + J_m + \frac{1}{2}} SPD(f) df$$

(1.4)

The power of the noise is in a frequency band B at the distance fm of the carrier.  $P_0$  denotes the power of the carrier. Since L (fm) expresses itself in power by relative to the carrier per frequency band, its unit is in dBc / Hz Figure 1-13. The single sideband phase noise L is defined in dBc / Hz when the power Pn is determined on a bandwidth of 1 Hz [12].

Figure 1-13. Phase Noise Power Spectrum

Many authors have established phase noise estimation techniques that have the advantage of highlighting the influence of certain parameters of the oscillator. The most important one is for Leeson. Leeson's model is a linear model prediction of phase noise defined by the following equation [13]:

$$L(f_{off}) = 10 \log\left(\frac{1}{2} \left[ \left(1 + \left(\frac{f_0}{2.Q.f_{off}}\right)^2\right) \left(1 + \frac{f_c}{f_{off}}\right) \left(\frac{F.K.T_0}{P_{diss}}\right) \right] \right)$$

(1.5)

Where Q is quality factor in charge. F is noise factor.  $f_0$  is the oscillation frequency. K is Boltzmann constant.  $f_{off}$  is frequency of the offset.  $T_0$  is temperature (290K). fc is cutoff frequency.  $P_{diss}$  is Power consumed.

According to Leeson, the frequency fluctuations of the oscillator are directly related to the inherent noise of the amplifier of the oscillation loop. The voltage or current fluctuations at the origin of the low frequency noise of the amplifier, and therefore of the transistor in most cases, are converted into frequency fluctuations by the oscillation loop.

b) Phase Noise of an Oscillator

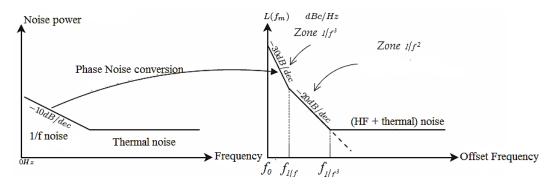

The phenomenon of converting the amplitude of power noise into phase noise is complex and has different origins as shown in Figure 1-14. The zone  $1/f^3$  translates the noise conversion of 1/f noise of the transistor. The zone in  $1/f^2$  denotes the conversion of white noise by the oscillator. In the noise floor zone (or thermal noise), it is considered that does interfere in the conversion process [14], where:

$$f_{\frac{1}{f^3}} = \frac{f_0}{2Q_{ch}}$$

(1.6)

The quality factor has several definitions. The most general definition is  $2\pi$  times the ratio of stored energy by dissipated energy per cycle [15].

$$Q = 2\pi \frac{Stored \, Energy}{Dissipated \, Energy \, per \, cycle}$$

(1.7)

And

$$Q = \frac{w_0}{2} \frac{d\varphi}{dw} \tag{1.8}$$

From the approximation of the linear system made by B.RAZAVI in [15], the calculation of the quality factor in open loop by the following formula:

$$Q = \frac{w_0}{2} \sqrt{\left(\frac{dA}{dw}\right)^2 + \left(\frac{d\varphi}{dw}\right)^2}$$

(1.9)

With

$$H(jw) = A(w)\exp(j\varphi(w))$$

(1.10)

Where A,  $\varphi$  and  $\omega_0$  are the amplitude, the phase and the angular velocity of the signal.

#### **1.6 Oscillator Types**

#### **1.6.1 LC Oscillators**

The LC oscillator can be seen as a set composed of an LC resonator and a negative resistance. The LC circuit is configured to have a resonance frequency close to the desired operating frequency for the oscillator. While the negative resistance realized via the active circuit, allows compensating the resistive portion of the LC block. The advantages of LC oscillators are good phase noise and low jitter noise at high frequency. On the other hand, their surface is very large because they contain an inductance. Moreover, these oscillators consume a lot of energy and have a range of relatively small use. Despite these disadvantages, the LC oscillators remain the oscillators most used in radio communication applications.

## Chapter 1: Background from 5G towards Oscillators

#### 1.6.2 LC Oscillator State of Arts

The LC oscillator uses and inductor and a variable capacitor (varactor). The quality factor is usually low at mm wave band that dominates the quality factor of the inductor, which leads to degrade the phase noise. Another limitation is that the transistor cannot be increased in size since the parasitic capacitance will let the designer decrease the size of the varactor, which degrade the frequency tuning range (FTR). Many topologies were proposed to improve the quality factor of the LC resonator in the mm wave band. The topologies can be divided into three categories; the conventional one that uses lumped element (inductor, varactor), hybrid resonator, which uses lumped elements and transmission lines, and finally the distributed resonator which uses only transmission lines.

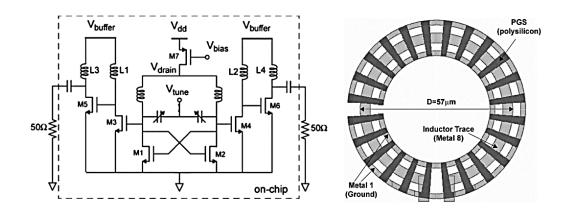

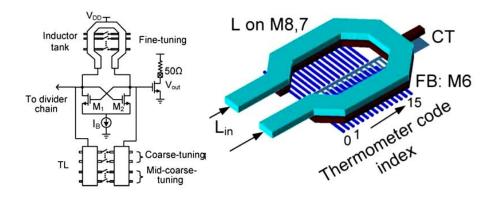

The work in [16] shows an optimization of the layout level; he made a circular inductor as shown in Figure 1-15 and decreased the parasitic capacitance of the transistor by minimizing the interconnection between the two transistors. The phase noise enhanced to -89 dBc/Hz at 1 MHz offset, 59 GHz center frequency, and 5.8 GHz tuning range.

#### Figure 1-15. a) VCO proposed by [16]

b) Circular Inductor [16]

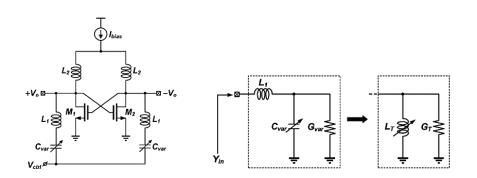

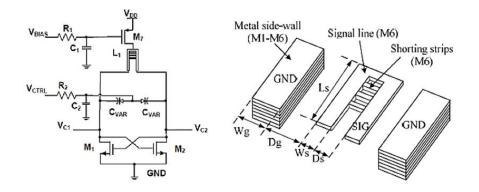

The authors [17] introduce a new technique; it is based on adding a series inductor with the varactor, then the equivalent shunt conductance of the whole resonator will effectively decreased as higher frequencies, which make the frequency of the oscillator close to the maximum frequency of the transistor. The circuit is shown in Figure 1-16. The varactor losses will be reduced with respect to high frequencies and it will be treated as a variable inductor at a frequency greater than the resonance frequency of  $L_1$  and  $C_{var}$ . An attention should be taken in selecting the values of the components. It is designed in 180 nm CMOS technology at 49 GHz with -101 dBc/Hz and 0.8 GHz frequency tuning range (FTR).

Figure 1-16. a) VCO schematic [17] b) Admittance Transformation [17]

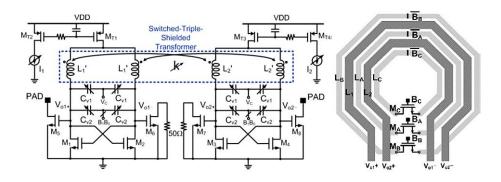

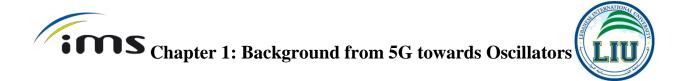

A novel technique was proposed by the authors in [18] to increase the FTR. As shown in Figure 1-17, a switched triple transformer is designed instead of increasing the size of the varactor; it had three states with different values of magnetic coupling. It is designed in 65 nm CMOS technology with 32 GHz FTR and 73.8 GHz center frequency with -112 dBc/Hz at 10 MHz offset. The proposed topology by [15] suffers from complexity in design and from big step size during frequency tuning (1GHz/bit).

b) switched Triple Transformer [18]

The authors in [19] also worked in increasing the tuning range, but unlike the work in [18], he utilized a single turn inductor with switched capacitor bank that are digitally controlled, then the effective value of the total capacitance will be varied allowing the oscillation frequency to be varied too. The schematic is shown in Figure 1-18. It is designed in 65 nm CMOS technology with 9.3 GHz FTR and 56 GHz center frequency with -99.4 dBc/Hz at 1 MHz offset.

Figure 1-18. VCO proposed by [19]

The works in [20] and [21] are divided into two steps. First, in [20], a high quality factor inductor was designed using multilayer coplanar waveguide with constant length as shown in Figure 1-19. While in [21], the length of the same inductor is varied and tuned after fabrication by the focused ion beam (FIB) technique that trim the shorting pins shown in Figure 1-19 instead of using switches, then as a result, a variable inductor will be utilized by adjusting the length of the transmission line which vary the frequency of oscillation.

A phase noise of -109 dBc/Hz at 10 MHz offset with tuning range of 4.8 GHz in [20] while -108.4 dBc/Hz at 10 MHz offset with tuning range of 10.6 GHz in [21] at 76.5 GHz oscillating frequency in 65 nm CMOS technology.

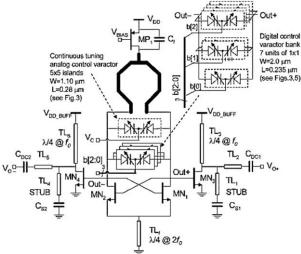

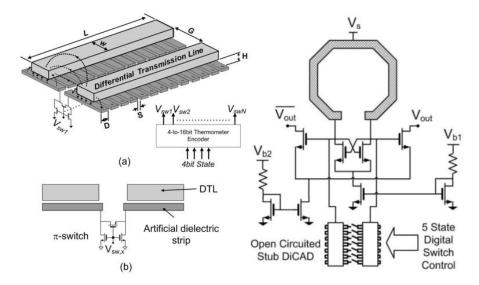

In the work in [22], the tuning element was an open circuit dielectric artificial drawing (DiCAD), it is digitally controlled. A slow wave differential transmission line is controlled by

varying the effective permittivity, which is controlled by NMOS Pi-switches as shown in Figure 1-20. It achieves -90 dBc/Hz phase noise at 1 MHz offset, 6 GHz tuning range, and 61 GHz oscillating frequency.

Figure 1-20. a) DiCAD differential transmission line layout b) DiCAD strips schematic c) Digital Control Oscillator [22]

The same tuning method in [22] is applied on an inductor in [23] as shown in Figure 1-21, and on transformer in [24] as shown in Figure 1-22, to form a digital control oscillator. The work in [23] has a resolution or step size of 160 KHz, while [24] has step size of 2.5 MHz, which are better than that of [22] with 1.16 GHz. Both are also designed in 90 nm CMOS technology with 59 GHz oscillating frequency, 6 GHz tuning range, and -93 dBc/Hz phase noise.

Figure 1-21. a) VCO proposed by [23]

b) Inductor Tank Layout [23]

Figure 1-22. a) VCO proposed by [24]

b) Transformer Tuned layout [24]

| Reference | CMOS<br>Technology<br>(nm) | F <sub>osc</sub> (GHz) | Tuning<br>Range<br>(GHz) | Phase Noise<br>(dBc/Hz) | P <sub>out</sub><br>(dBm) | P <sub>DC</sub> (mW) |

|-----------|----------------------------|------------------------|--------------------------|-------------------------|---------------------------|----------------------|

| [16]      | 130                        | 59                     | 5.8                      | -89@1MHz                | -18                       | 9.8                  |

| [17]      | 180                        | 49                     | 0.8-1.1                  | -101@1MHz               | -11                       | 45                   |

| [18]      | 65                         | 73.8                   | 32                       | -105@10MHz              | -20                       | 10.8                 |

| [19]      | 65                         | 56                     | 9.3                      | -99.4@1MHz              | -9.8                      | 15                   |

| [20]      | 65                         | 76.5                   | 4.8                      | -109@10MHz              |                           | 14.3                 |

| [21]      | 65                         | 76.5                   | 10.6                     | -108@10MHz              |                           | 14.3                 |

| [22]      | 90                         | 61                     | 10                       | -90@1MHz                | -5                        | 8.52                 |

| [23]      | 90                         | 59.2                   | 10                       | -93@1MHz                | -3.4                      | 12                   |

| [24]      | 90                         | 58.7                   | 9.75                     | -94@1MHz                |                           | 14                   |

Table 2. LC Oscillators State of Arts

Each topology is designed with different Back End of Line (BEOL), which make the comparison of the performances more complex. It is clearly that to improve the quality factor of the LC resonator, a switchable or variable inductor is better from utilizing varactor. In addition, the best phase noise achieved is -101 dBc/Hz, and the highest output power is -3.4 dBm that make the presence of the power amplifier obligatory in the transmitter chain.

#### **1.7 Objective and Methodology**

Most of the VCOs are implemented in a phased locked loop (PLL); a control system consist of phase detector, low pass filter, and VCO. It is a closed loop to ensure the oscillation at the desired frequency. In [25], he proposed a new topology of microwave and mm wave oscillator. It

is based on an amplifier and a substrate-integrated waveguide (SIW) that has a high quality factor. The fundamental signal, which is amplified, divided into two path: the transmission path, which fed the output with the oscillation signal at the same fundamental frequency, and the coupling path, which fed the input of the amplifier as a feedback system to ensure the oscillation according to Barkhausen law conditions as shown in Figure 1-23 and Figure 1-24.

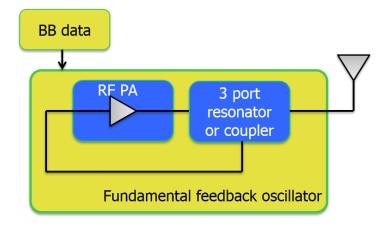

Figure 1-23. Fundamental Feedback Oscillator Topology

Figure 1-24. Fundamental Feedback Oscillator proposed by [25]

In [25], the output frequency is 12.02 GHz with phase noise -73 dBc/Hz at 100 KHz offset. This topology open a flow that it can be get rid of the power amplifier in the transmitter chain because the power amplifier in the fundamental feedback oscillator that is not found in VCOs (based mainly on PLL), already amplify the signal to fed the antenna directly, which decrease the complexity of the transmitter.

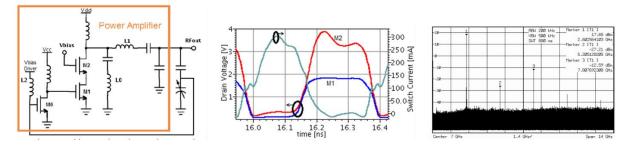

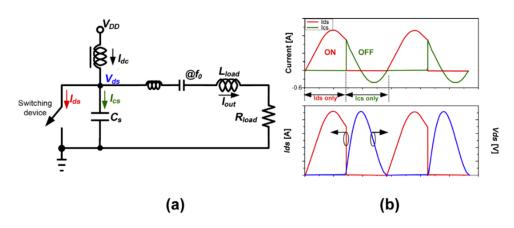

Our team in the IMS Lab worked on the power oscillator as fundamental feedback oscillator. The author in [26] show a TX architecture based on power oscillator using 65nm CMOS

technology from STMicroelectronics. The PA has a class E to achieve high efficiency as shown in Figure 1-25. The output of the PA is connected to a capacitive divider with a filter to form a loop. The power oscillator achieves a high output power of 23.3 dBm at 2.5 V supply voltage, PAE of 60.3%, and oscillating frequency of 1.95 GHz.

Figure 1-25. a) Class E PA [26] b) Output matching in [26]

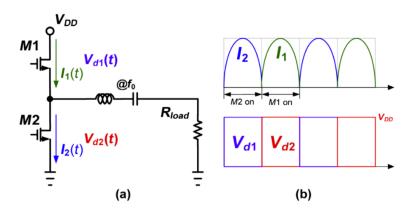

Another work is done by the IMS team in [27], it proposed class EF2 power amplifier path using 130 nm CMOS technology at 2.5 GHz operating frequency, and a feedback consist of MOS varactor to form a power oscillator as shown in figure. The use of class EF2 is to reduce the stress voltage across the transistor that has low breakdown voltage, enabling higher output power.

Figure 1-26. a) Oscillator Schematic b) Drain voltage and current c) Output Spectrum [27]

The work in [27] achieves output power of 17.65 dBm at 2.5 V supply voltage, efficiency of 27.1%, and phase noise of -101.6 dBc/Hz at 1 MHz offset

The power oscillator based on fundamental feedback oscillator decreases the pulling effects that occurred between the power amplifier and the local oscillator due to limited on-chip isolation (coupling through substrate) in the conventional transmitter, which degrade the phase noise [9]. While it has a pulling effect between the PA and the antenna

In 17th century, Christiaan Huygens, a Dutch scientist, was confined to bed because of sickness, noticed that the pendulums of two clocks on the wall moved in unison if the clocks were hung close to each other [28]. He assumed that the coupling of the mechanical vibrations through the wall drove the clocks into synchronization. Bahzad Rasavi in [9] ensure that the oscillators are prone to injection locking or pulling. The idea of pulling effect in transmitter chain is that the modulated output signal of the power amplifier has the same frequency of the oscillator. This make

the lattice susceptible to interface the PA output through the substrate causing frequency pulling and phase noise degradation, especially that the output signal of the PA is mainly higher than the output of the oscillator as shown in Figure 1-27.

Figure 1-27. Pulling Effect between LO and PA in TX [29]

Various digital processing and shielding techniques are done to increase the isolation between the VCO and PA, but no general solution eliminates the pulling effects [29]. This problem keeps the door open to search for a topology other than PLL in addition to its low efficiency.

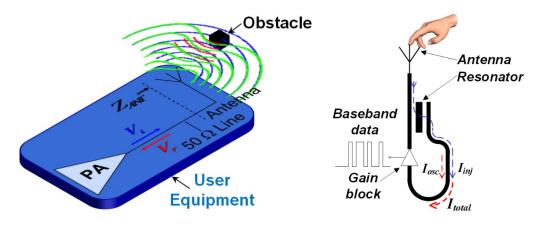

In addition, the fundamental feedback oscillator in transmitter chain has two main problems, which are the variation of the load impedance (antenna) and the pulling/locking effect. The antenna has a function to transform the electric energy to electro-magnetic energy where its impedance should be constant at 50 $\Omega$ . The incident signal is fed from the PA to the antenna through a transmission line of 50 $\Omega$  too. Adding some parasitic elements as metal obstacles in the environment of the antenna will increase the voltage standing wave ratio. First, the VSWR in the circuit is defined by

$$VSWR = \frac{max(V(x,t))}{min(V(x,t))} = \frac{1 + |\Gamma_L|}{1 - |\Gamma_L|}$$

(1.11)

Where  $\Gamma_L$  is the ratio of the reflected signal over the incident signal in the transmitter chain, if  $\Gamma_L = 0$ , it means that there is no reflection and the incident wave is totally radiated from the antenna, and if  $\Gamma_L = 1$ , it means that all the power of the signal is reflected backward to the PA. The VSWR refers to the minimum and maximum voltage signal that is formed under the effects of reflections. The Figure 1-28 show the phenomena that produce a variation of the antenna impedance. The blue wave in the incident wave, which is radiated by the antenna, the red wave is the reflected signal due to the presence of the obstacle, and the green wave is the sum of both signals. The same phenomena will occurs in the transmission line between the PA and the antenna, which results a variation of the antenna impedance. No such publications for the effects of human body on the antenna in the mm wave band, the only publication is [30], which shows the effects of human body on a horn antenna at the GSM applications band (400 MHz – 900 MHz). It shown a VSWR of 7:1

at 450 MHz and 4:1 at 900 MHz when a human body touches the antenna. A VSWR of 7:1 means that the real impedance change between  $7\Omega$  and  $30\Omega$  while it should be constant at  $50\Omega$ . In mm wave band, the results will be very different but no further studies at this band.

Figure 1-28. a) Obstacles Effect in Antenna Environment b) Pulling Effect in FFO

The second problem is the puling effect. Because of the reciprocity of the resonator, the reflections of the output signal results in a current injection in the feedback loop as shown in Figure 1-28. Therefore, the conditions of oscillations are modified, and the working frequency with the amplitude of the output signal are altered.

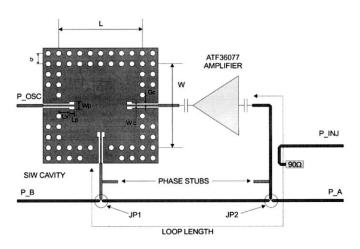

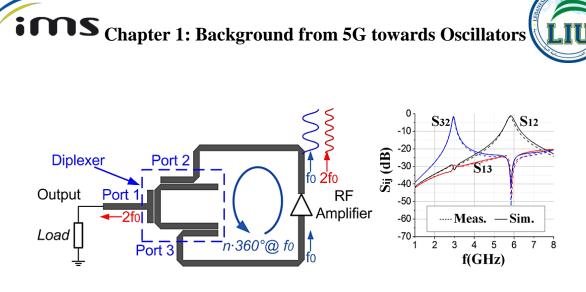

A new novel architecture is proposed in [31]. The idea is to replace the resonator structure by a diplexer port (not duplexer) that will allow the feedback loop to ensure oscillation at the fundamental frequency and being isolated from the output, which supply the signal to be transmitted through the second harmonic. This greatly reduces the impact of the load impedance variation on the nonlinear dynamics of the feedback loop. To show the improvement provided by the choice of using the second harmonic frequency as the transmission signal, two circuits on PCBs were designed in [31] : Fundamental feedback oscillator (FFO) and Harmonic feedback oscillator (HFO). Thus, the proposed new transmitter structure operates at 5.8 GHz with fundamental frequency at 2.9GHz for on-off keying (OOK) transmitters for active RFID tags.

Figure 1-29 shows the harmonic feedback oscillator schematic and the s-parameters of the diplexer. The diplexer has a "U" structure formed from a microstrip line in  $\lambda/4$  folded and integrated on a substrate Rogers RT/duroid. The s-parameters of the diplexer show two operating modes with a band-pass effect on the fundamental signal and the other on the second harmonic signal. A loadpull is applied on both circuits to vary the impedance of the load on the oscillator output port in order to have the necessary information on the frequency shift induced by the variation of impedance as well as the phase noise and power on the output port.

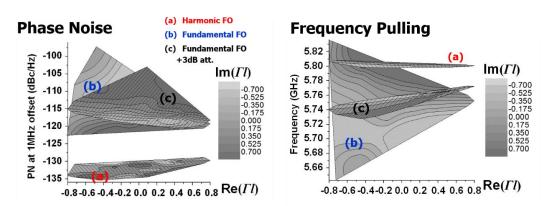

The frequency pulling varies from -0.74 to 1.05 % for HFO and from -19 to 15 % for FFO. The phase noise varies from -129 to -135 dBc/Hz for HFO and from -99 to -123 dBc/Hz for FFO. The output power varies from 1.86 to 7.56 dBm for HFO and from -1.5 to 9.5 dBm for FFO. The results show a big enhancement in decreasing the pulling effects and improving the phase noise.

In order to have a comprehensive comparison against the possible mitigations techniques about the effect of "pulling" on the frequency, a third version is added to the comparative study. This version uses the structure based on the fundamental frequency but adds the output port 3dB attenuator. The attenuator is non-reciprocal and can introduce 6 dB attenuation on the injected current. The measurements made on the three structures are grouped in Figure 1-30.

# Chapter 1: Background from 5G towards Oscillators

The topology based on the second harmonic has the best compromise and the best performance with a pulling effect of frequency 1.8 ‰ against 7.8 ‰ for the structure with the 3 dB attenuator. Totally, the phase noise is improved by 15 dB to be -133 dBc/Hz in HFO while the output power of the oscillating signal (7.34 dBm) is degraded by 1.4 dB compared to that in FFO (8.75 dBm).

The HFO has a disadvantage that the generation of second harmonic power in the amplifier is at the expense of the fundamental one. Choosing the load impedance seen by the amplifier to generate maximum second harmonic conflicts with optimum load impedance to generate the fundamental power, so that a compromise should be taken to have a sufficient power of fundamental power to ensure the oscillation at the feedback including the loss of the diplexer. In addition, the diplexer is a distributed element that occupy a large area with respect to the integrated circuits.

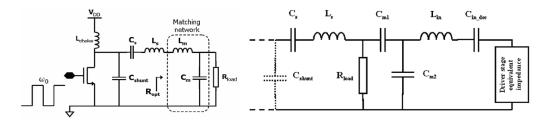

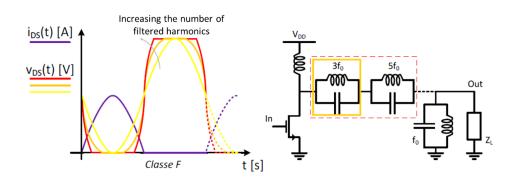

The 5G in mm wave bands are facing challenges in terms of requirements, energy consumption, and high degree of integration. In the domain of oscillators, the HFO shows good performances that well worth the attention to study the design of harmonic oscillator in the mm wave band especially in the 5G frequency candidates found in section 1.2.2. The whole oscillator should be integrated on-chip to increase the efficiency and decrease the whole size. The study will be applied and designed in CMOS technology using 28 nm Ultra-Thin Buried Oxide Fully Depleted Silicon on Insulator UTBB FD-SOI from STMicroelectronics, which will be discussed later about its advantages and specifications. First, the plan begins with choosing the second harmonic and study the performance in addition to the capability of generating output power in the PA in different topologies as common source, cascade, and with different classes as class AB, class B, class C... The idea is then developed after the differential topology is studied; in differential amplifier, the output voltage Volterra series is:

$$V_o = V_{in}^+ - V_{in}^- \tag{1.12}$$

Where

$$V_{in}^{+} = V_{noise} + a_0 + a_1 V_i^{1} + a_2 V_i^{2} + a_3 V_i^{3} + a_4 V_i^{4} + a_5 V_i^{5} \dots$$

(1.13)

$$V_{in}^{-} = V_{noise} + a_0 - a_1 V_i^1 + a_2 V_i^2 - a_3 V_i^3 + a_4 V_i^4 - a_5 V_i^5 \dots$$

(1.14)

Then

$$V_0 = 2a_1V_i^1 + 2a_3V_i^3 + 2a_5V_i^5 \dots$$

(1.15)

Several issues can be noticed from the previous equation. First, the noise voltage will be canceled, which decrease the noise floor of the amplifier, which enhance the phase noise as

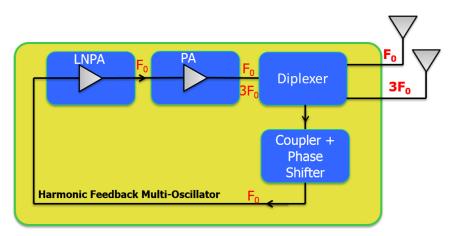

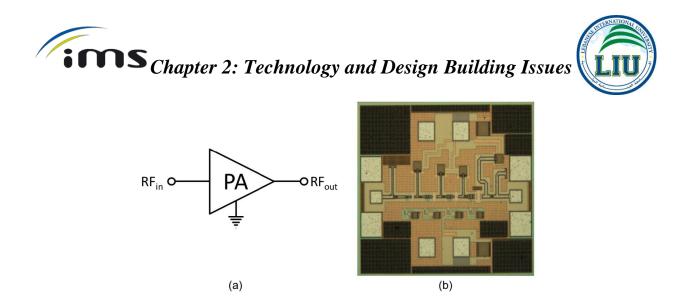

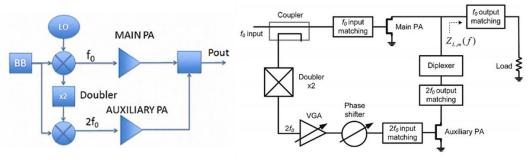

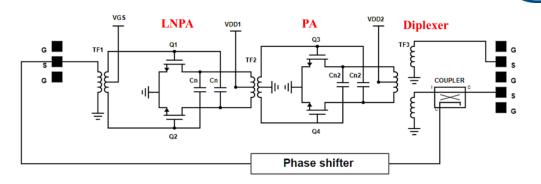

detailed in section. Second, the even harmonics are also canceled that mean this topology cannot generate a second harmonic signal in the ideal case. However, the third harmonic voltage is doubled which increase the level of the project to work in generating the oscillation signal at the third harmonic. In addition, the fundamental signal voltage is doubled too, which gives the opportunity to have an excess power rather than that need it in the feedback branch, so that the system will be a multi-oscillator which gives two oscillating frequency: at fundamental and at the third harmonic. Figure 1-31 shows the diagram of the proposed harmonic feedback multi-oscillator system. The LNPA block is a low noise power amplifier. It has the function of both: low noise amplifier and power amplifier. Then it is an amplifier, which generates low noise figure (NF) to decreases the noise floor of the oscillator, and outputs a large signal in order to drive the second stage PA. The function of the PA is to generate both power signal at F0 and 3F0. The diplexer will separate the two frequencies with high isolation between the ports. The coupler and the phase shifter are to take a quantity from the fundamental power signal with the appropriate phase shift to ensure the oscillation conditions of Barkhausen.

Figure 1-31. Harmonic Feedback Multi-Oscillator Plan

In the third harmonic branch, the diplexer will greatly reduce the impact of the load impedance variation and frequency pulling on the feedback loop. While in the fundamental branch, the coupler will have a power-coupling ratio around -15 dB that means the injected current on the feedback loop will be attenuated by 30 dB. This technique will reduce the impact of the load impedance variation and frequency pulling on the feedback loop, and enhance the performances of the fundamental feedback oscillator topology.

#### **1.8 Chapter Conclusion**

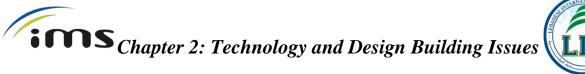

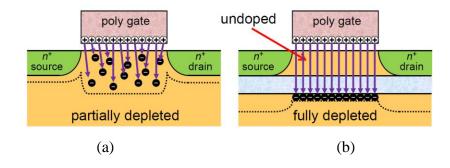

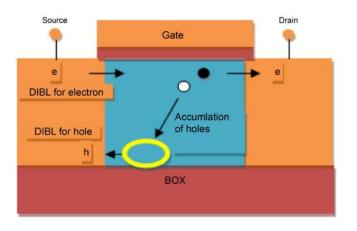

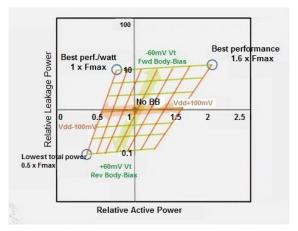

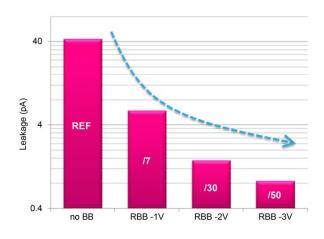

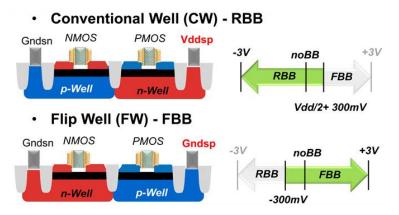

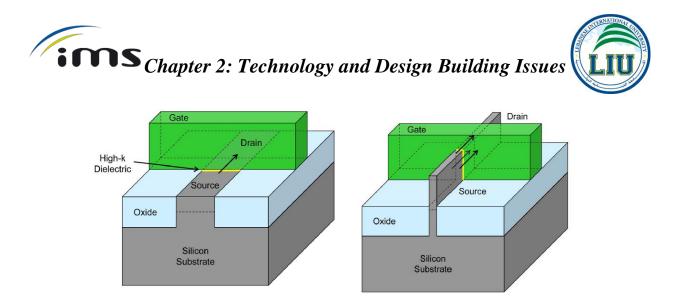

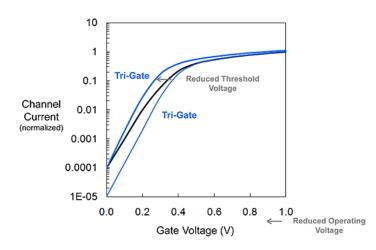

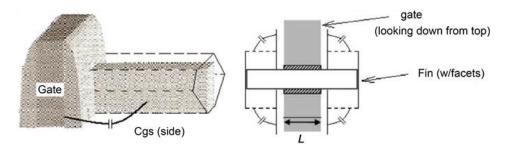

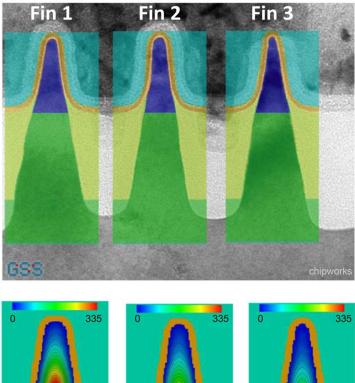

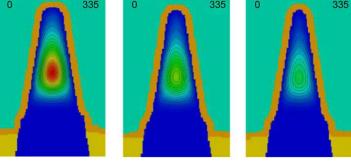

In this chapter, an overview of mobile technology is introduced, beginning from the theory ideas of wireless communication until the fourth generation used in our days. Then, a brief explanation of the fifth generation is introduced showing its goals, services, capabilities, and