### Contributions to the Design of Reconfigurable Embedded Systems: from Modelling to Implementation

Jean-Christophe Prévotet

### ▶ To cite this version:

Jean-Christophe Prévotet. Contributions to the Design of Reconfigurable Embedded Systems: from Modelling to Implementation. Hardware Architecture [cs.AR]. Université de Rennes1, 2019. tel-02415974

### HAL Id: tel-02415974 https://theses.hal.science/tel-02415974

Submitted on 17 Dec 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Mémoire

# Habilitation à Diriger des Recherches

# Contributions to the Design of Reconfigurable Embedded Systems: from Modelling to Implementation

### Jean-Christophe Prévotet

Maître de Conférences à l'INSA de Rennes Laboratoire IETR / Équipe de recherche SYSCOM

A soutenir le 07/06/2019 devant le jury composé de

### Rapporteurs

Diana GöhringerProfesseure au TU, DresdenChristophe JégoProfesseur à ENSEIRB-MATMECA, IMS, BordeauxGilles SassatelliDirecteur de recherche CNRS, LIRMM, Montpellier

### **Examinateurs**

Guy Gogniat Professeur à l'université de Bretagne-Sud, Lab-STICC Christophe Moy Professeur à l'université de Rennes 1, IETR Frédéric Pétrot Professeur à l'université de Grenoble, TIMA Fabienne Nouvel Maître de conférences HDR, INSA de Rennes, IETR

| Part. | 1   | Synthesis of Research Works                              | 1  |

|-------|-----|----------------------------------------------------------|----|

|       | Pre | liminaries                                               | 3  |

| Chap. | 1   | Introduction                                             | 4  |

| O     | 1   | Summary of studies                                       |    |

|       | 1.1 | OS Modelling                                             | 4  |

|       | 1.2 | Reconfiguration Management                               | 5  |

|       | 1.3 | Power Modelling                                          |    |

|       | 2   | Historical Research Background                           |    |

|       | 2.1 | PhD Studies                                              | 7  |

|       | 2.2 | ETIS 2002-2007                                           | 7  |

|       | 2.3 | IETR 2007- Today                                         | 7  |

|       | 2.0 | TETH 2007- Today                                         | -  |

| Chap. | 2   | From OS Modelling to Implementation                      | 9  |

|       | 1   | Context and Related Works                                | 9  |

|       | 2   | A new Design Methodology for Operating Systems           | 11 |

|       | 2.1 | System Specifications                                    | 12 |

|       | 2.2 | The Dogme Tool                                           | 14 |

|       | 3   | OS Model Description                                     | 14 |

|       | 3.1 | Task Manager Service                                     |    |

|       | 3.2 | Scheduling Service                                       | 16 |

|       | 3.3 | The IRQ Manager Service                                  |    |

|       | 3.4 | The Communication Service                                |    |

|       | 3.5 | The Intercommunication Service                           |    |

|       | 3.6 | The Reconfiguration Management Model                     |    |

|       |     | 3.6.1 The HW Task Concept                                |    |

|       |     | 3.6.2 The Dispatcher                                     |    |

|       |     | 3.6.3 The placer                                         |    |

|       |     | 3.6.4 The Offloader                                      |    |

|       | 4   | Modelling Evaluation                                     |    |

|       | 4.1 | Description                                              |    |

|       | 4.2 | System Model                                             |    |

|       |     | 4.2.1 Application Model                                  |    |

|       |     | 4.2.2 Architecture Model                                 |    |

|       |     | 4.2.3 Kernel Model                                       |    |

|       | 4.3 | Simulation and results                                   |    |

|       | 5   | OS Code Generation                                       |    |

|       | 5.1 | OS Meta-model                                            |    |

|       | 5.2 | Model to Model Transformation                            |    |

|       | 6   | From the OS to the Hypervisor                            |    |

|       | 6.1 | Is virtualization compatible with real time constraints? |    |

|       | 6.2 | Virtualization Overhead                                  |    |

|       | 6.3 | Overhead aware schedulability analysis                   |    |

|       | 6.4 |                                                          | 33 |

|            |     | 6.4.1 Overview                                              | 33        |

|------------|-----|-------------------------------------------------------------|-----------|

|            |     | 6.4.2 Resource Virtualization                               | 34        |

|            |     | 6.4.3 Event Management                                      | 35        |

|            | 6.5 | Performance Evaluation                                      |           |

|            |     | 6.5.1 Basic Virtualization Functions Overhead               | 35        |

|            |     | 6.5.2 RTOS Virtualization Evaluation                        | 38        |

|            | 7   | Summary                                                     | 39        |

| <u>i</u>   | 0   |                                                             |           |

|            | 3   | Reconfiguration Management                                  |           |

|            | 1   | Context and Related Works                                   |           |

|            | 2   | General Framework                                           |           |

|            | 3   | HW Level                                                    |           |

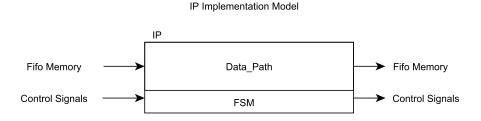

|            | 3.1 | HW Task Model                                               |           |

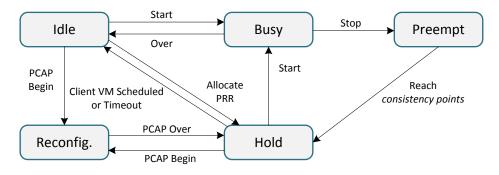

|            | 3.2 | PRR HW Management                                           |           |

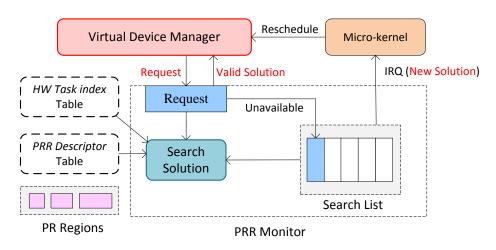

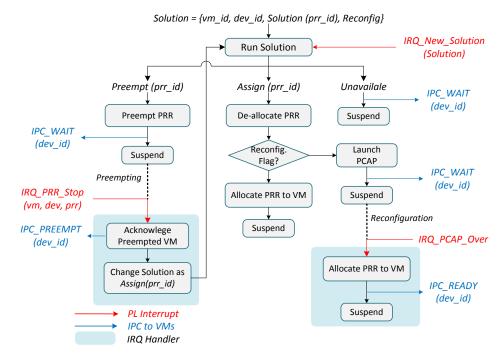

|            | 3.3 | The PRR Monitor                                             |           |

|            | 4   | OS Level                                                    |           |

|            | 4.1 | The Configuration Controller (Virtual Device Manager)       |           |

|            | 4.2 | Other OS services to handle reconfiguration                 |           |

|            |     | 4.2.1 The Parameters Provider                               | 50        |

|            |     | 4.2.2 The HW Updater                                        | 50        |

|            | 4.3 | The particular case of Virtualization : Security Mechanisms | 50        |

|            | 5   | Application level                                           | 51        |

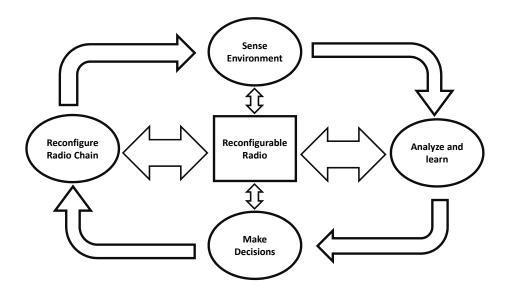

|            | 5.1 | Context                                                     | 51        |

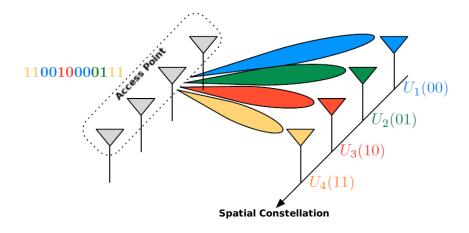

|            | 5.2 | Case study: VHA for WI-FI and WiMax heterogeneous networks  | <b>52</b> |

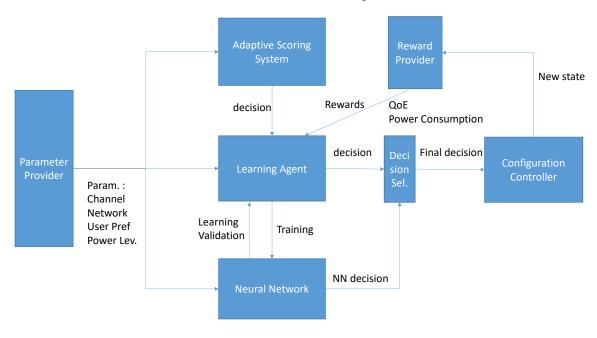

|            | 5.3 | The Adaptive Scoring System                                 | <b>52</b> |

|            | 5.4 | Towards a Smart Reconfiguration Management                  | 54        |

|            |     | 5.4.1 Overview                                              | 54        |

|            |     | 5.4.2 Modules Description                                   | 54        |

|            | 5.5 | Results                                                     | 56        |

|            | 6   | Performances Evaluation                                     | 57        |

|            | 6.1 | Overhead Analysis                                           | 59        |

|            | 6.2 | Experiments and Results                                     | <b>30</b> |

|            |     | 6.2.1 Description                                           | 60        |

|            |     | 6.2.2 Results                                               | 31        |

|            | 7   | Summary                                                     | 32        |

| <u>i</u> = |     |                                                             |           |

| Clap       | 4   | From Power Modeling to highly Energy-Efficient Devices      |           |

|            | 1   | Context and Related Works                                   |           |

|            | 2   | The Classic Implementation Approach                         |           |

|            | 2.1 | <b>, , , , , , , , , ,</b>                                  | 86        |

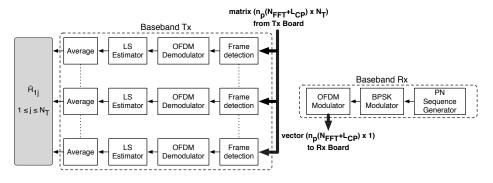

|            | 2.2 | Proposed Offline Hardware Platform                          |           |

|            |     | 2.2.1 System Description                                    |           |

|            |     | 2.2.2 Studied configurations                                |           |

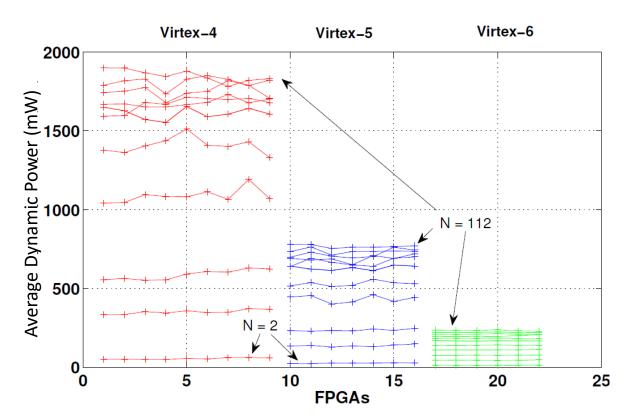

|            |     | 2.2.3 Results                                               |           |

|            | 2.3 | Studying the SW limitations                                 |           |

|            | 2.4 | The Receive Spatial Modulation scheme                       |           |

|            |     |                                                             | 77        |

|            |     | 2.4.2 Results                                               |           |

|            | 3   | Evaluation of FPGA-Based Wireless Communications Systems    |           |

|            | 3.1 | Proposed approach                                           |           |

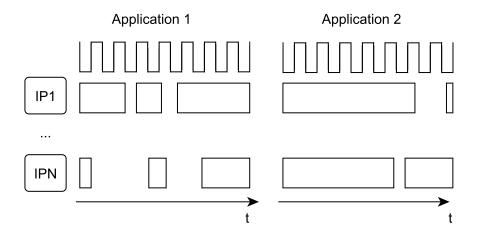

|            |     | 3.1.1 Scenario Definition                                   |           |

|            |     | 3.1.2 IP Characterization                                   |           |

|            |     | 3.1.3 Modeling and High Level Simulation                    | 32        |

|       | 3.2 | Use Case                                       | 34         |

|-------|-----|------------------------------------------------|------------|

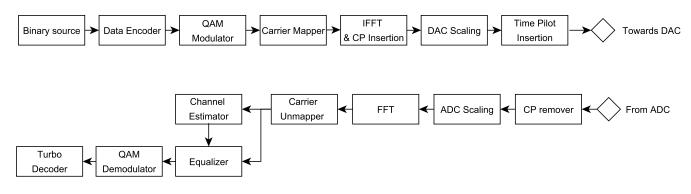

|       |     | 3.2.1 System Description                       | 34         |

|       |     | 3.2.2 Power Estimation                         | 35         |

|       |     | 3.2.3 Power Estimation Speed-Up                | 36         |

|       | 4   | Towards Fine grain Modeling                    | 36         |

|       | 4.1 | Analytical Modeling                            | 36         |

|       | 4.2 | Extension to other FPGA Devices                | 37         |

|       | 4.3 | Neural Networks based Modeling                 | 37         |

|       |     | 4.3.1 Model Definition                         | 39         |

|       |     | 4.3.2 Results                                  | 90         |

|       | 5   | Summary                                        | <b>)</b> 2 |

| Chap. | 5   | Research Perspectives                          | )3         |

|       | 1   | Embedded Systems Virtualization                |            |

|       | 1.1 | Hypervisor structure                           |            |

|       | 1.2 | Reconfigurable Hardware Resources Sharing      |            |

|       | 1.3 | VM Scheduling and Off-Loading Service          |            |

|       | 2   | End to End Reconfiguration Management          |            |

|       | 2.1 | Multi-standards Reconfiguration                |            |

|       | 2.2 | Machine Learning                               |            |

|       | 3   | Towards Energy-Efficient Communicating Devices |            |

|       | 3.1 | New Waveforms                                  |            |

|       | 3.2 | Hardware Power Models                          |            |

|       | 3.3 | From Device to Protocol                        |            |

|       |     |                                                |            |

|       | Bib | liography                                      | 19         |

# Partie I

# **Synthesis of Research Works**

# **Preliminaries**

The second part of this document describes my research activities in details. Chapter 1 describes the context of the different studies and the research tracks that have been followed. The subsequent chapters describe the different topics that have been studied and provide the main contributions for each of them.

### Outline

| Chapter 1 : Introduction                                          | p.4               |

|-------------------------------------------------------------------|-------------------|

| Chapter 2 : OS Modelling                                          | p. <mark>9</mark> |

| Chapter 3: Reconfiguration Management                             | p.40              |

| Chapter 4: From Power Modeling to highly Energy-Efficient Devices | p.64              |

| Chapter 5: Research perspectives                                  | p.93              |

# Introduction

# Chap. 1

# 1

### SUMMARY OF STUDIES

Nowadays, algorithmic complexity keeps on increasing in many domains such as signal, image processing, communications or control. Applications that implement these algorithms are often executed on embedded systems that generally require a significant power of computation. As a response to this issue, hardware architectures are now composed of numerous heterogeneous and optimized computation units that operate in parallel. For example, devices such as SoC (System on Chip) may exhibit programmable computation units, reconfigurable units, or even dedicated data-paths to reach the highest level of performance.

Such devices are extremely complex to design and manage and require a lot of expertise to be handled. In this context, the use of an operating system (OS) is often considered since it allows users to obtain an abstraction of the underlying hardware. Services such as communications, memory management, tasks' scheduling, resources management are directly handled by the operating system, which considerably relieve the systems' management.

The first research subject that I have been focusing on has been to propose new methods that would help designers in building their custom embedded Operating System(s) to manage heterogeneous platforms. This work is presented in Section 1.1.

A second research axis deals with the specificity of the platform itself and particularly focuses on reconfigurable architectures. The issues related to reconfiguration management have been studied thoroughly in my career and the challenges that I tried to tackle are summarized in Section 1.2.

Finally, for several years, I have also investigated the energy efficiency of reconfigurable embedded systems from a design perspective. The privileged domain of study was wireless communications but it can, of course, be extended to other domains. In this axis, I have proposed new exploration methods and tools to help designers in choosing the right algorithms for a given platform. The research issues as well as the proposed solutions are described in Section 1.3.

# 1.1

### **OS MODELLING**

Today embedded systems have become so complex that they are able to process applications with various types of constraints. This diversity of constraints has a direct impact on the underlying management of these applications and on operating systems specifically. For example, some applications may be real-time constrained imposing a Real-Time Operating System (RTOS), with specific features, scheduling properties, inter-blocking resolution, etc. Some other applications may be more general-purpose and have other types of constraints (like in multimedia, consumer electronics, etc.). For the latter, General-Purpose Operating Systems (GPOS) are more appropriate.

In modern embedded systems, it is not rare to find several operating systems with different purposes. This is the case, for example, in mobile phones, where an OS is dedicated to the user-machine interface and another one is hidden, which is responsible for managing communicating parts implemented in hardware. In order to get an optimal use of resources, hardware virtualization can help, by enabling the concurrent execution of an application OS (Linux, Windows, etc.) and of a real-time OS on the same processor.

Virtualization has a lot of interests. It makes the support of architectural abstraction possible since a given application may migrate from several physical cores to a single virtual one. It also enables to execute legacy applications without any modification since the underlying operating system may be easily

### 1. Summary of studies

ported as a guest within a virtual machine. Another major aspect of virtualization is security since virtual machines are fully isolated and each of them has its own encapsulated application code that cannot access the rest of the system. Only the Virtual Machine Monitor (VMM) or hypervisor, that is significantly more secure, may have specific rights to access resources.

Today, such systems have become so cumbersome that their design process is very elaborate and require huge skills and expertise. In order to help designers in their task and increase their productivity, it seems very important to first raise the design abstraction level. Second it also seems important to provide designers with dedicated tools that automate design tasks from a high-level model.

In this work, the privileged target has been Reconfigurable Systems-on-Chip (RSoC) or any device that is composed of a processing core that is associated with a reconfigurable region. This, of course, includes current System on Programmable Chip (SoPC) devices based on FPGA circuits. Here are some questions we have tried to tackle:

- How to design the software architecture of an embedded OS that takes hardware specificity (e.g the reconfigurable parts) into account?

- How can designers simulate the OS behaviour, which are the obtained metrics, and what is the degree of confidence that we can get from the results?

- Is it possible to generate pieces of code corresponding to the software architecture from high-level models?

These questions have been first treated in a single-OS environment. With the advent of virtualization in embedded systems, we have tried to adapt our research to take into account multi-OS environment. This has, of course, raised specific issues:

- Is the methodology proposed for single-OS architectures compatible with more complex systems?

- Is it possible to evaluate the feasibility and performance of virtualization in the early stages of the design flow?

- What is the overhead that is due to the hypervisor on the application performance?

- How must the hypervisor be designed to abstract all hardware resources?

### 1.2

### RECONFIGURATION MANAGEMENT

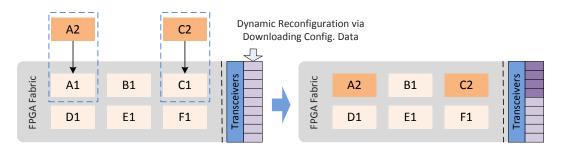

The second main axis of my research has always been devoted to reconfigurable systems and particularly the management of such systems. Reconfiguration has always been a concept guaranteeing a system to adapt to environmental changes in many technical or biological systems. In the domain of hardware architectures, reconfiguration allows an architecture to adapt to a specific task by modifying its own functionality. This is exactly the opposite of classical computing schemes in which variable tasks require to be modified to adapt to a fixed architecture.

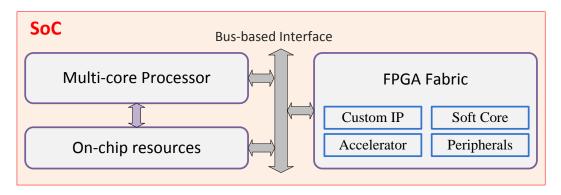

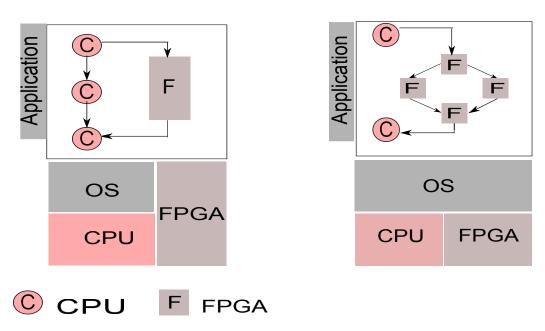

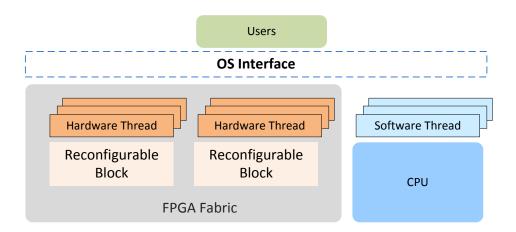

In this research axis, I have mostly focused on specific types of reconfigurable architectures. These architectures are composed of one or several cores that are implemented in hardware as part of a SoC fabric. Besides these cores, a reconfigurable fabric is available that makes it possible to implement reconfigurable architectures with different granularity of configuration. These architectures may be seen as hardware accelerators that aim to alleviate the processors' tasks. In our studies, we have proposed several levels of reconfiguration management: at physical level, at operating system level and at application level. For each of these levels, specific issues have been met and my PhD students and myself have tried to tackle them independently.

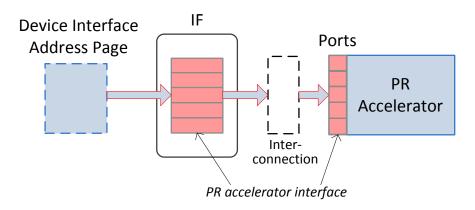

First, at physical level, we have mainly focused on all problems that are related to the hardware reconfiguration mechanisms and on the placement aspects of an abstract object that is a hardware task. The main issues deal with the structure of a hardware task:

- How can it interact with the software environment?

- How may tasks communicate with each other to exchange data?

Other issues are related to the spatial dimension of these tasks:

- how can a task be configured and dynamically placed within the reconfigurable area?

- Which type of management is required to handle the task processing in this area?

Second, at OS level, we also identified several issues that need to be taken into consideration. For example,

- what type of abstraction must have a given hardware task to make it easily manageable by an operating system?

- How is it possible to keep the management of these tasks as transparent as possible, from the application point of view?

Some other issues are directly related to the structure of the OS and deal with the additional mechanisms or services that are required to handle reconfiguration without too much overhead.

Finally, at application level, other issues may occur. These deal with the way an application may adapt to the environment. Which are the mechanisms that are necessary to allow an application to take a good decision regarding reconfiguration? Can we imagine a common framework that make this decision transparent? What would be the overhead due to this framework in this case? Finally, is it possible to imagine smart reconfiguration mechanisms that are based on machine learning processes to allow a platform to reconfigure itself automatically?

All these questions have been treated in our works and some answers have been proposed and explained in Chapter 3.

# 1.3 Por

### **POWER MODELLING**

Another significant aspect of my research studies has started dealing with energy efficiency of reconfigurable systems. The fact is that energy consumption has a huge role in such systems since they are often operated with limited energy resources like simple batteries. This is particularly the case of wireless communications systems that constitute the main elements of the future IoT. These systems have been our main target since they may represent a significant part of future devices that will have a real impact on worldwide energy consumption [BBFH+08].

In our works, we have decided to deal with the design aspects of these devices. More specifically, we have focused on the System Level, since most of the power optimization solutions intervene in the early stages of the design flow. When designing an embedded communicating device, one of the first questions designers have to answer deals with the functions to implement to perform processing and communication tasks. This first study generally results in a trade-off between the performance or Quality of Service (QoS) to achieve and the energy cost.

In this research axis, we have first concentrated on proposing efficient energy-aware communication schemes that might be implemented in very small devices, while guaranteeing a high level of performance. These types of solutions are classically studied by communication researchers or engineers using dedicated tools such as Matlab. Today, designers may even have the possibility to implement their algorithms on prototypes to get a first overview of their performance. Although very interesting in practice, this approach remains limited since solutions are often implemented in software, which does not give sufficient indications on the hardware complexity. This raises important questions:

- How can we exhibit the specificity of hardware in this case?

- How is it possible to evaluate the hardware resources that will be necessary as well as the energetic cost?

- How can we efficiently and rapidly compare different solutions to find the best?

These questions have led to us to propose new methodologies and power models that would help designers in exploring design choices at System Level. The main issues are related to the models themselves:

- What is the nature of these models?

- What is the expected accuracy?

- How can we generalize the approach to other types of devices?

### 2. Historical Research Background

All these questions have been addressed and some solutions are presented in this manuscript and specifically in Chapter 4.

### HISTORICAL RESEARCH BACKGROUND

The purpose of this section is to provide an overview of my research work chronologically. It also intends to explain the context and the strategic directions that have been followed according to the work environment in which my work was led.

# 2.1

### **PhD Studies**

After a "Diplôme d'Etudes Approfondies" (DEA) obtained at the Pierre et Marie Curie University (UMPC), my first contact with research was during my PhD studies. My PhD started back in 1999 and was led in the "Laboratoire des Instruments et Systèmes d'Île de France" under the supervision of P. Garda, B. Denby and B. Granado. The subject mainly dealt with the study of hardware architectures to implement Neural Networks in real time. The application domain of my studies was physics in general, and particle physics in particular.

During my first year of PhD, I had the opportunity to work in Munich, Germany in the "Max Planck Institut Fuer Physik" to get familiar with the context study of my work. The study aimed at designing a neural pre-processing circuit for on-line event triggering in a particle physics experiment. This experiment, H1, in which many European researchers were involved, was located in Hamburg on the DESY website. A second part of my thesis was dedicated to the hardware design of a very fast architecture destined to process neural networks within very tight timing constraints i.e. 500 ns. The targeted application was again a high-performance particle recognition system as part of the ATLAS experiment, located on the site of the LHC (Large Hadron Collider) at CERN.

# 2.2

### ETIS 2002-2007

After my PhD studies, in 2002, I obtained an "Attaché Temporaire d'Enseignement et Recherche" (ATER) and then an associate professor position at the university of Cergy-Pontoise. I joined the AR-CHITECTURE team of the ETIS laboratory where my research interests have evolved towards the study of reconfigurable architectures for images or signal processing applications. This research team was led by Didier Demigny at that time and was composed of 5 people deeply involved in reconfiguration. It is in this context that I had the opportunity to work with L. Kessal on the supervision of Sonia Khatchadourian's thesis.

Other works that have been initiated in the ETIS lab have demonstrated the interest of managing dynamic reconfiguration efficiently. That is in this context that first research works started on operating systems for reconfigurable devices. At this time, the OveRSoC project, in which I was involved as the main leader has started.

# 2.3

### **IETR 2007- TODAY**

The third part of my research career has started in 2007, time at which I joined the "INSA de Rennes" and the IETR lab. I was integrated in the Communication System team that was composed of 7 researchers mainly involved in the design of communications systems at the algorithmic level, which was quite far from my first expertise domain. Only one colleague of mine (F. Nouvel) was more interested in hardware architectures and communications prototyping.

When I first joined the SysCom team, I brought new skills related to operating systems, reconfiguration and modeling. With the help of my colleagues, I continued leading the OveRSoC project and was able to supervise PhD students as well as master students in this research area. Later, I developed the virtualization research axis, which can be seen as an extension of the studies that have been led on operating systems. Finally, M. Hélard and myself proposed a new research axis dealing with the study of energy consumption in reconfigurable systems, which gave me the chance to supervise 3 PhD students on this topic.

# From OS Modelling to Implementation

Chap. 2

# 1

### **CONTEXT AND RELATED WORKS**

Since the beginning of computing, it has always been envisaged to design efficient architectures capable of executing more and more complex applications. In parallel, new constraints have progressively appeared such as the devices' size, that led to the concept of embedded systems. Regarding the design of such systems, one of the first issues has consisted in providing more computing power in smaller and smaller devices. Other issues have also progressively appeared due to a new usage of these systems, such as the the possibility to execute many applications at the same time, in a transparent manner.

For several decades, hardware devices such as SoCs have been an efficient solution to tackle these issues. These circuits often feature processing cores as well as dedicated hardware, which makes it possible to benefit from both software and hardware assets. Flexibility is guaranteed by the presence of software, whereas performance is ensured by hardware parts. Some of these devices feature a reconfigurable area that allows an hardware architecture to dynamically adapt during the execution of applications. These circuits constitute the targeted architecture in the works that I led since my PhD studies.

The will to efficiently use embedded systems raises a lot of questions. One of the most interesting relates to the capability of managing these systems in real-time. Today, most of them feature an Operating System (OS) that aims at virtualizing all hardware parts. This OS must, at least, manage memory, schedule different tasks under specific constraints and ensure resource sharing. Furthermore, it must be capable of offering new programming models that are completely independent of the underlying hardware architecture. When an OS has to response to real-time constraints, it is denoted as a Real-Time OS (RTOS).

Building a full embedded system based on an RTOS or several RTOSs is a delicate design process. Designers basically have to make sure that tasks operate correctly during the execution of the application while meeting the imposed constraints. Usually, the design of embedded systems is performed at high level of abstraction in order to allow designers to explore various choices and finally retain the most efficient one [JW05].

In the past, numerous methodologies and associated tools have been proposed to design complex embedded systems at high level of abstraction. Languages or libraries such as SpeC [spe] or SystemC [Sysc] have been used for years to build models. Unfortunately, a limited amount of studies only take into account RTOS modeling in their intrinsic design flow. A very complete survey in the area of RTOS modelling is presented in [Yu10]. The author introduces three criteria to classify RTOS models: application scope, software simulation method and functional accuracy. He also divides the different studies into two distinct categories according to the modeling granularity.

Regarding coarse grain models, the modeling process has several objectives. First, the full system is specified. It is then analyzed to perform hardware/software partitioning. This step intervenes very soon in the design process and since the hardware platform is not known at this stage, it is very difficult to obtain accurate results. At this level, an application is seen as a set of tasks with simple parameters such as the execution time, period and deadline [HKH04]. Furthermore, resource sharing and synchronization between tasks or with hardware parts are generally not taken into account in these models. The main interest to work at this level of abstraction is the simulation time that is greatly reduced. On the other hand, the main drawback is the lack of accuracy in the timing evaluation.

Authors in [GYG08] have presented an abstract RTOS model that is described in SpecC. Unfortunately, interrupts are not modelled in this work and interactions with hardware modules are not accurately defined. In other works, Zabel [ZMG09] uses a SystemC model that is based on [GYG08]. The SW/HW

synchronization is resolved by using the wait-for-event() method that is available in SystemC. An early work by [MVG] presents a SystemC-based abstract RTOS model. This model is a good basis for system exploration but has also some limitations. Service overhead is not included in the model and the task model is very simple and cannot really mimic a real system. This limitation is also met in another work by Hessel et al. [HRR+04]. In [LPC04], Le Moigne et al. describe a SystemC model of a multitask RTOS. This model is a part of the Cofluent tool which allows timing parametrization and validation of the RTOS model by configuring context load, context save, and scheduling duration. [HKRN08] present an abstract RTOS simulation model that is included in their SystemC-based design flow. They model pieces of software on a generic run-time system rather than directly modelling existing RTOS services.

After modelling and simulating high-level RTOS representation, another problem addressed by Gauthier et al. is the automatic generation of RTOS code. In [GYJ01], authors present a method of automatic generation of operating systems for a target processor. This method determines the OS services that are required in the code of the application and generates the corresponding code deduced from dependencies between services in an OS service library.

A first observation that we have made when starting to work on the subject was that none of the current works around RTOS modeling actually managed the dynamic creation of tasks. However, this particular point seemed very important to us and that is the reason why we decided to tackle this problem in the OveRSoC ANR project that is described in section 2 of the current chapter.

### ► From RTOS models to systems of OS

Another part of our studies has consisted in extending our RTOS modelling approach on more complex systems. The systems that we were interested in are capable of running several operating systems on the same platform. One very interesting configuration occurs when a RTOS executes concurrently with other general-purpose OS (GPOS). Today, this configuration is not rare and is met in a lot of domains. For example, in automotive, an AUTOSAR compliant RTOS and a Linux Genivi OS that supports in-vehicle infotainment application, could be co-located on the same Electronic Control Unit (ECU) [Hei].

A Virtual Machine (VM) system is a concept intended to simultaneously host multiple operating systems on a single hardware platform. Each guest operating system is executed in a separate and secure virtual machine. A virtual machine can be seen as an abstraction of the hardware resources provided to the guest operating systems. It is managed by a low-complexity kernel referred to as a Virtual Machine Monitor (VMM). This virtual machine monitor must ensure that a temporal or local fault in one virtual machine (e.g., an infinite loop, out-of-bounds array access, exhaustion of assigned resources) does not affect the operation of the other virtual machines. This feature is referred to as logical and temporal isolation in the real-time community, and as space and time partitioning in the RTOS industry.

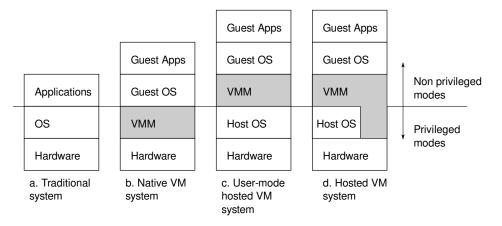

Virtualization can be implemented in different ways. The classic approach to design a virtual machine system is to place the VMM on bare metal hardware whereas the virtual machine fits on top. The VMM runs in the most highly privileged level 1, while all guest operating systems run with lower privileges, as shown in Figure 2.1. Then, in a completely transparent way, the VMM can intercept and implement all the guest OS's actions that interact with the hardware resources. In this configuration, the VMM may also be called hypervisor.

An alternative implementation builds the VMM on top of an existing host operating system, resulting in what is called a hosted VM as shown in Figure 2.1c and Figure 2.1d. In this configuration, the installation process is similar to installing a typical application program on the host OS.

### **▶** Virtualization Implementation

Researches on embedded virtualization have been focusing on several features or challenges including security issue, virtualization overhead, software complexity, high-bandwidth VM inter-communication, and real-time task capability.

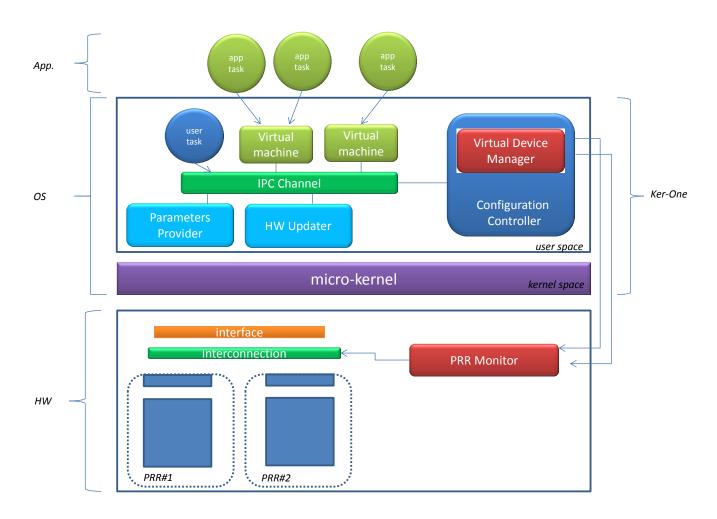

In conventional para-virtualization approaches, a guest OS is normally equipped with a virtualization patch to interact with the VMM, which requires the OS source code to be modified and must then be available [PKR+13]. One possible para-virtualization solution is to use a micro-kernel, which is a small Trust Computing Based (TCB) set of features defined as address space, threads and inter-process communication (see [Lie95]). Additional functionality is normally implemented at user level.

### 2. A new Design Methodology for Operating Systems

FIGURE 2.1 – Native and hosted VM Systems.

Examples of such kernels are the L4 micro-kernels usually relying on Linux to support user-level virtual machines. For example, in [GBL+09] and [XBG+10], EMUCO and Fiasco L4 were respectively used in communication and mobile phone systems by leveraging L4Linux as a client server. Some successful solutions are the OKL4 microvisor from Open Kernel Labs [HL10], or ARMvisor [DLC+12], based on KVM for the ARM architecture.

# 2

### A NEW DESIGN METHODOLOGY FOR OPERATING SYSTEMS

The works that are presented in this section have been initiated as soon as I obtained my position of associate professor at the IUT of Cergy Pontoise in 2003. They led to the elaboration of a national ANR project named OveRSoC, in which I was the main leader. This project started in 2005 and ended in 2008. The teams that were involved in the project were:

- the Architecture team of the ETIS laboratory (UMR CNRS 8051, Cergy-Pontoise)

- the R2D2 team of the IRISA laboratory (University of Rennes1, Lannion)

- the SYEL team of the LISIF laboratory (now LIP6) (University Pierre and Marie Curie, Paris)

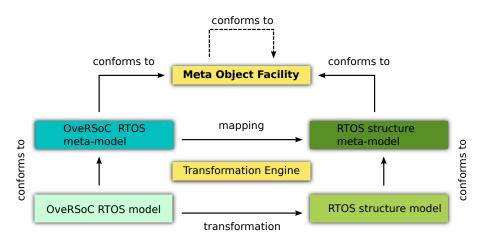

The OveRSoC project has been proposed to not only take into account RTOS design but also define the underlying hardware platform. Its purpose was to propose an efficient design space exploration methodology and an associated simulation tool as well. Today, the OverSoC methodology is based on 4 important design concepts: exploration, separation of concerns, incremental refinement and re- usability.

We advocate the use of a high-level model of Reconfigurable SoCs (RSoC) in order to explore different critical design choices. Among these important choices, two exploration issues have been distinguished:

- the exploration of the application partitioning onto the processing resources

- the exploration of the RTOS services distribution and their algorithms.

Each design strategy belonging to these exploration levels is manually performed by designers. However, the proposed method intends to help in easily and quickly building the executable specification of the corresponding system. The underlying tools are used to evaluate performance in order to analyze and compare design strategies. The design choices corresponding to the second exploration issue (RTOS) are the architecture of the embedded RTOS (centralized or distributed, OS services organization, software, or hardware implementation, etc.), the services algorithms (scheduling policies, etc.), the interactions between OS service functions and underlying resources (reconfigurable areas, memories, interconnect type) and the software programming model.

Second, once validated the candidate design solutions are incrementally refined towards lower levels of abstraction down to the final implementation. The OveRSoC methodology permits the separation of concerns during the modeling and refinement process. It also defines modeling rules that facilitate independence and re-usability between components. For each design concern, specific and related refinement steps are proposed.

### **Chapitre 2. From OS Modelling to Implementation**

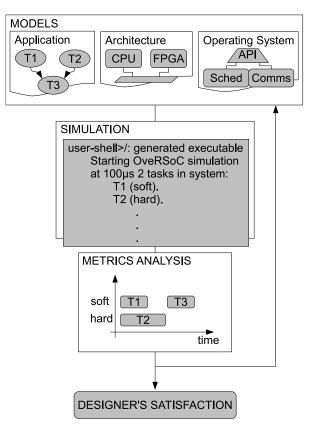

Finally, the method imposes a functional approach at each level of abstraction, which validates the application functionality and makes it possible to evaluate the performance. As depicted in Figure 2.2, the main aspect of the framework consists of an iterative process of exploration. It means that this process is repeated as many times as required, until the system constraints are met.

The exploration flow starts with the description of three different models: the application model, the architecture model and the operating system model. In a second step, all these descriptions are combined to create a global model representing the entire system. This model is generated in SystemC in order to exploit the advantages offered by this library, namely the high-level description allowing high-speed simulations. The global model is then simulated with the SystemC kernel. After this simulation step, metrics are evaluated and designers have the possibility to analyze the generated results. If the obtained results are not satisfactory, designers may restart a new iteration by modifying the corresponding attributes. Finally, the simulation normally ends up by showing no incoherence between the initial specifications and the timing behaviour of the application.

FIGURE 2.2 – OveRSoC design methodology.

2.1 System Specifications

This first stage of the methodology consists in setting the specifications of the system. The functional specifications define the algorithmic behaviour, i.e. the application, whereas the architecture specifications define the characteristics of the targeted hardware. Specifications also include the constraints which must be respected by the system. For instance, it may refer to timing latency for an application, or to memory size limitations for hardware elements. Moreover, it includes the operating system structure which defines the required services and their localization.

### ► Application Model

The application model is one of the components of the system framework. It is composed of a directed graph representing the set of tasks in which the application is split, and the precedence order among the tasks. The graph is introduced to the system as an XML file as depicted in Figure 2.3.

### 2. A new Design Methodology for Operating Systems

**FIGURE** 2.3 – XML description and the corresponding graph.

In addition, each task is related to a set of indispensable characteristics, e.g. the task's functionality. In our platform, such characteristics are called "attributes". These attributes are summarized in Table 2.1.

| Attribute | Description                                                                   |

|-----------|-------------------------------------------------------------------------------|

| Function  | Functional code written in C or C++.                                          |

| Priority  | Order of execution for a fixed priority scheduling policy.                    |

| Deadline  | Maximum length of time to execute the task. It is related to the task's start |

|           | time.                                                                         |

| NbCycles  | Execution time on the target processor.                                       |

**TABLE** 2.1 – Attributes for each node of the application graph.

The *Function* attribute designates the set of instructions that will be executed by the task. The task function may contain either a behavioural description written in C or C++, or just quantitative information about the time overhead. In the latter case, the platform only provides system latencies, which constitutes the primary objective. In any case, *Function* contains the Application Program Interface (API) primitives that gives access to the operating system's services.

### ► Architecture Model

The architectural specifications define the main components of the system's hardware structure (e.g. processors, buses etc.). Specifications include basic characteristics of such components, e.g. the processor's frequency and bandwidth. With the help of the platform's library, the architectural specifications can be built from predefined blocks. Currently, the components are available in two categories: Processing Elements (PE) and Communication Elements (CE). In Processing Elements, different types of microprocessors (e.g. GPP and DSP) can be found. The Communication Elements (CE) category is composed of components that ensure communication between PEs (e.g. Bus, Crossbar, Network). Memories and Timer peripherals can be also found. Table 2.2 lists example of elements that are currently implemented and their corresponding attributes.

| Component  | Attribute       | Description                               |

|------------|-----------------|-------------------------------------------|

| Processors | Clock frequency | Processing speed in cycles per second.    |

| Memory     | Size            | Capacity in number of bytes.              |

| Timer      | Period          | Regulates the execution of the scheduler. |

**TABLE** 2.2 – Attributes for the architecture components.

### **▶ RTOS Model**

The RTOS model describes the characteristics that an operating system should implement for the targeted system. For example, these characteristics ensure the right progress of the application tasks and the

handling of communication with other peripherals. In the proposed platform, designers also determine the structure of the operating system that better fits their system. Like in the other models, the RTOS model is also built from elements that are available in a library. Such elements are also characterized by predefined attributes. The RTOS model is detailed in section 3 of this chapter.

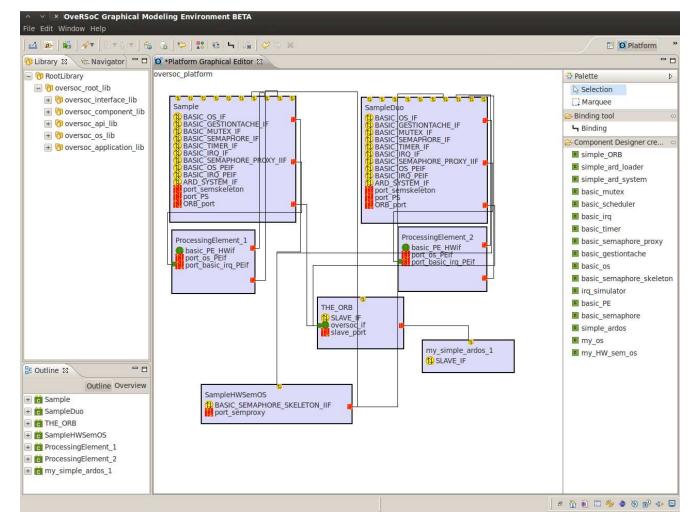

# 2.2 THE DOGME TOOL

Due to the complexity of the exploration process, it has clearly appeared that HW/SW designers should rely on tools to apply the OveRSoC methodology. The DOGME (Distributed Operating system Graphical Modeling Environment) software provides an integrated graphical environment to model, simulate, and validate the distribution of OS services on an RSoC. The goal of this tool is to ease the use of the exploration methodology and to generate a complete executable model of the RSoC platform (hardware and software), automatically. The automation is based on a flexible SystemC model of the RTOS that consists of a package of modular services. To develop each service, an Object Oriented Approach has been adopted and implemented using the SystemC 2.2 library. This tool allows an application-specific RTOS to be built by assembling generic and custom OS basic blocks using a graphical editor. The application is linked to the resulting OS thanks to a standard POSIX API. Finally, the entire platform is simulated using the SystemC kernel.

Using the DOGME tool implies to follow several design stages, which are summarized as follows:

Platform Design: the design phase consists in choosing and instantiating toolbox components into the graphical workspace editor in order to assemble the OS services and distribute them onto the RSoC processing elements. At this step, designers successively, (and according to the separation of concerns paradigm), take decisions about functions mapping into threads, perform hardware/software partitioning, instantiate the required services and distribute the services onto the PEs.

**SystemC source code generation:** after interconnecting all components and verifying the bindings between services, the structural source code of all objects being instantiated into the platform is automatically generated.

**Compilation and simulation of the platform:** to complete the design of the platform, the parametrized structural SystemC description is combined with the behavioral source code of the components provided by the user. The global SystemC description is compiled and simulated.

**Analysis of the simulation results:** graphical diagrams are produced to visualize the evolution of the system metrics during the simulated time. This step helps designers to evaluate the current design quality. It acts as a decision guide for the exploration of the design solution space.

The DOGME tool has been designed during the OveRSoC project by Mehdi Aichouch in the ETIS laboratory. A screen capture of the tool is illustrated in Figure 2.4.

### OS Model Description

The works presented in this section have been led in the PhD studies of Yaset Oliva who joined the OveRSoC project in 2008. In his thesis, he proposed a modular description of OS services as well as the corresponding models.

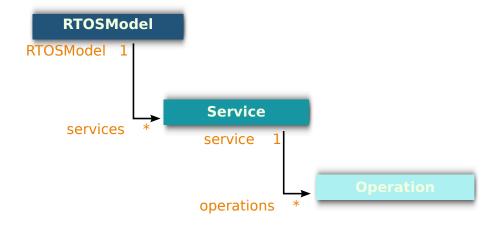

A modular organization is one of the main assets of our RTOS model. The functions that implement the RTOS mechanisms (e.g. multitasking, interrupt management) have been gathered into independent services. A service is composed of functions sharing a common concern. For example, properties that are related to a task, such as the creation or deletion are contained within the same service. This modularity is very interesting as it favours the scalability of the model. In this context, new services can be incorporated without requiring any modification of the entire system.

The Application Program Interface (API) ensures the communication between the application and the operating system services. It contains a list of definitions representing the features that services may provide to an application. Such definitions are known as "primitives" and constitute the only means by

### 3. OS Model Description

**FIGURE** 2.4 – The OveRSoC DOGME tool.

which a program can communicate with the operating system. In the following, the services defined in the OS model are described.

# 3.1 TASK MANAGER SERVICE

This service aims at managing the tasks' structure (i.e TCB) within the OS. TABLE 2.3 describes the primitives that are associated with this service.

| Primitive     | Function                                                                 |

|---------------|--------------------------------------------------------------------------|

| OSTaskCreate  | Creates an RTOS task object taking the task function as input parameter. |

| OSTaskDel     | Deletes a task so that it is no longer considered by the scheduler.      |

| OSTaskSuspend | Suspends a task for a given time or until it is implicitly resumed.      |

| OSTaskResume  | Resumes a task that was previously suspended.                            |

| OSTaskExec    | Simulates execution times.                                               |

**TABLE** 2.3 – Primitives exported by the Task Manager.

# 3.2 SCHEDULING SERVICE

The scheduling service is responsible for implementing the most important function of an operating system, that is the schedule function. The goal of the scheduler is to establish the order in which tasks are going to be implemented into the processing element.

Two types of scheduling processes are foreseen in the model. The first may be performed "off-line", which corresponds to a static table in which the tasks' order of execution has been previously stored. The second is performed "on-line".

In general, the new task selection process is straightforward. It consists in assigning a priority to each task, and then loading the context of the highest priority task that is in the ready state. How priorities are assigned to tasks is designated by the scheduling policy. In the proposed scheduling model, the selection process follows the same principle. First, the ready tasks are selected from a list of available tasks. Then, the list of ready tasks is ordered according to a predefined criterion. The criterion that is used to order the list may change from one design to another. Currently, Rate Monotonic (RM) and Earliest Deadline First (EDF) have been implemented. The type of scheduling strategy constitutes an attribute of the Scheduling service.

# 3.3 THE IRQ MANAGER SERVICE

The handling of interrupts is an indispensable mechanism for any operating system. Interrupts are a means by which the peripherals communicate with the main processor, for example I/O controllers, timers or other processing elements. If an interrupt can be serviced by the processor, a default action may be performed. The action executed after an interrupt is called an interrupt routine, and the process of reorienting the processor to the corresponding routine is called interrupt handling. Basically, when an interrupt occurs, the interrupt handler is responsible for determining the source of this interrupt. As mentioned before, several causes may interrupt a system, e.g. an event on an input port or a timer at the end of a period. In our model, the interrupt handler has been defined as a separate service named IRQManager service.

# 3.4 The Communication Service

Inter-tasks communication or synchronization mechanisms must also be ensured by the OS model. In order to implement this functionality, the Communication Service implements three types of mechanisms: the mailbox, the mutex and the semaphore. Mailbox objects define memory locations where to/from tasks can write/read data. Both the mutex and the semaphore provide exclusive access to a shared resource. The difference between them is that the semaphore also allows multiple concurrent accesses. Table 2.4 lists the primitives giving access to these objects.

# 3.5 The Intercommunication Service

It has been seen that services may need to communicate between them. For example the IRQManager calls the scheduling function from the interrupt routine. A similar situation occurs for the Task Managerservice after a new task is created. Therefore, to facilitate the addition of new services and their interconnections, a TLM based mechanism has been used. To that purpose, a special class named *oversoc\_if* has been defined. This class inherits from the *sc\_interface* SystemC class and thus can be used as a class template for the creation of ports. Every service inherits from this class and implements the *transport* method.

The transport method is responsible for translating incoming transactions into calls to the correspon-

### 3. OS Model Description

| Primitive     | Function                                                              |

|---------------|-----------------------------------------------------------------------|

| OSMBoxCreate  | Creates a mailbox object with a maximum number of N-size messages.    |

| OSMBoxPostMsg | Writes a message into a mailbox. Blocks if the mailbox is full.       |

| OSMBoxPendMsg | Retrieves a message from the mailbox. Blocks if the mailbox is empty. |

| OSMutexCreate | Creates a mutex.                                                      |

| OSMutexLock   | Locks a mutex.                                                        |

| OSMutexUnlock | Unlocks a mutex.                                                      |

| OSSemCreate   | Creates a semaphore object with an initial value.                     |

| OSSemPost     | Increases the value of the semaphore.                                 |

| OSSemPend     | Decreases the value of a semaphore. Blocks if the value is zero.      |

**TABLE** 2.4 – Primitives exported by the Communications service.

ding functions. In such a way, it is possible to have access to service functions by just defining a port of the targeted service type and calling its *transport* method.

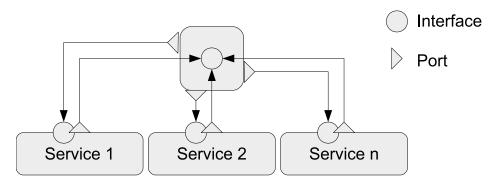

Additionally, since one port may be connected to only one interface, several ports would be required to connect one service to several ones. Instead, we have defined another element that interconnects all services between them. This element contains an array of n ports that are connected to the n services of the system. It also inherits and implements the  $oversoc_if$  so that each service port can be connected to it.

The *transport* method implementation of this element differs from the implementation inside each service. In this case, whenever a request arrives, the array of ports is examined looking for a service that is able to process the request. To do this, each request was enlarged with an identifier and a *compatible* method has been included to the *oversoc\_if* class. With these two modifications, it is possible to determine to which service the request must be redirected.

**FIGURE** 2.5 – Interconnection of several services.

Note that it is also possible to build a hierarchical structure which interconnects several groups of services like those depicted in Figure 2.5. This can be useful for systems in which the operating system is distributed between several processing elements. This is an aspect of the platform which has been studied in another work [Huc11].

# 3.6 The Reconfiguration Management Model

Yaset Oliva's proposed in its thesis an offloading mechanism that may be used to migrate computations at runtime in order to relieve the load of processors. It has naturally been applied to reconfigurable architectures but more generally to multiprocessors systems. In order to implement this mechanism, the concept of hardware tasks has first been introduced.

# 3.6.1 THE HW TASK CONCEPT

A HwTask is a structure representing an off-loadable section. It contains the information that is required by the OS offloading mechanism. At present, it is assumed that a task can contain only one off-loadable section. The structure is allocated at the creation of a task, and its reference is included into the corresponding TCB (Task Control Block). Table 2.5 summarizes the most important members of the HwTask structure.

| Member   | Description                                 |

|----------|---------------------------------------------|

| State    | Current state                               |

| OSTask   | A reference to the container TCB            |

| NbCycles | Duration in number of cycles                |

| BinSize  | Size of the binary file in bytes            |

| HwWidth  | Width in terms of reconfigurable resources  |

| HwHeight | Height in terms of reconfigurable resources |

| HwPosX   | Horizontal coordinate on the RH             |

| HwPosY   | Vertical coordinate on the RH               |

**TABLE** 2.5 – Members of the HwTask structure.

We argue that the proposed offloading mechanisms can considerably improve the performances of embedded systems. This statement lies on the premise that the application's main computations can be offloaded onto slave processors (including RH), while the master is dedicated to the execution of the OS and other less demanding tasks (e.g. I/O operations).

In this work, an off-loadable section is defined as a part of the application code which does not contain any primitive call, and that can be executed by any slave processor. Off-loadable sections can be seen as HWTasks whose hardware and/or software implementations are stored in the system. The offloading mechanism involves several actions from the arrival of the offloading request until the end of the slave execution (in the successful case). These actions are listed below:

- 1. Acceptance of the offloading request.

- 2. Search for an available slave processor.

- 3. Transfer of the section's code (optional).

- 4. Restitution of the original task.

The offloading algorithm has been decomposed into multiple SW modules, i.e. the Dispatcher and at least the Offloader and Placer modules.

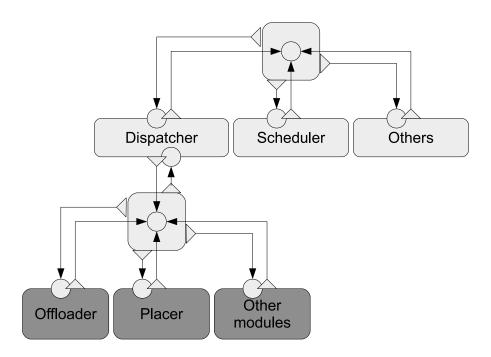

The Dispatcher module implements the OS primitive that is exported to the API. The Offloader is the most important module. It implements the decision algorithm (which is described later), and is responsible for transferring the section's code to the slave(s). The Placer module aims at finding the slave processors that are able to implement the off-loadable section. A more representative scheme of the offloading mechanism is shown in Figure 2.6.

### 3.6.2

### THE DISPATCHER

The Dispatcher module implements the primitive which allows the application to designate an off-loadable section. Note the interest of changing the task's state to *offloading*. This is especially profitable in case where the Offloader module is configured as a separate hardware module. Since the processor continues executing and calls the scheduler, a new task is going to be selected as the current task. By modifying the old task's state, it is ensured that the same task is not going to be selected by the scheduler. Undetermined behaviour would result if this precaution is not taken into account.

### 3. OS Model Description

**FIGURE** 2.6 – Offloading mechanism blocks.

3.6.3 THE PLACER

The placer is the module that is the closest to the hardware structure. In order to place a HwTask, the Offloader must determine available processing elements from the Placer. To that purpose, the latter must keep control of the slave processors' status. The behaviour of this module partially depends on the type of the slave processing elements contained in the architecture.

The Placer module's model implements the *PlaceHwTask()* function. In this proposed service, two types of algorithms are considered, one for reconfigurable hardware and one for a processor set. Moreover, in the case of reconfigurable hardware, the algorithm can use two different strategies: BestFit and FirstFit. Note that a mixed architecture comprising both types of slave elements is also possible. Since each algorithm executes its own placement strategy, it incurs a different timing overhead which is accumulated and simulated.

3.6.4 THE OFFLOADER

The Offloader module manages tasks' off-loadable sections. To this purpose, it implements the OffloadingAlgorithm function whose principle is simple. It basically consists in sending a request to the Placer, and then updates the OS task and HwTask states according to the Placer's response.

Currently, three levels of complexity have been proposed. The first level implements a direct response, the HwTask is executed by the master processor itself. At the second level, the slaves' status are analyzed. If any slave has implemented a Hwtask that is finished, it is replaced by a new HwTask. Finally, at the third level, if the previous solutions have failed, it means that all slaves are busy. In this case, a computation is performed to approximate the time delay that is required to handle the task by the processor.

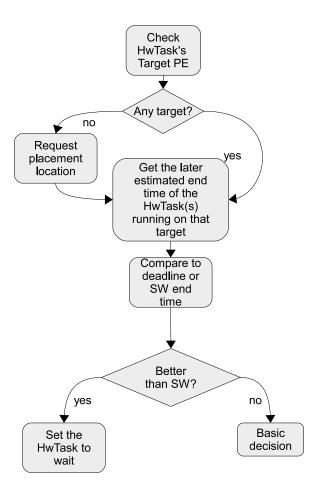

In order to give an example of a reconfiguration management model, we focus here on the mechanisms that are implemented at level 3. The following algorithm computes an estimate of the time that is required before resources are available. Then it determines whether it is worth delaying the HwTask. The decision can be based on the HwTask's deadline attribute. In short, if the computed delay does not cause the HwTask to miss its deadline, it continues waiting for the required resources. Another alternative is to compare estimates of the execution end time: if the estimation of the execution end time on the slave is closer than the execution end time on the master, the task waiting for the slave is freed. In order to

### Chapitre 2. From OS Modelling to Implementation

compute the waiting time, estimates of the end times of each HwTask in running state are computed in a specific function.

Therefore, if the HwTask to be transferred targets a given processor, then the waiting delay simply corresponds to the estimated end time of the HwTask currently running in that processor. In the case where the target processor is reconfigurable hardware, since several HwTasks may occupy the required resources, the waiting time corresponds to the maximum end time of the HwTasks.

However, if a HwTask can be placed anywhere, the computation of the waiting time is a bit more complex. In the set of processors' case, it is required to find the earliest estimated end-time among all running HwTasks. In case of reconfigurable hardware, the placement algorithm furnishes a list of areas in which the new HwTask can be placed. Each area comprises a group of running HwTasks with their corresponding estimated end times. The estimated end-time of a group, and thus of an area, is the latest estimated end-time among all the contained HwTasks. Then the candidate area in which the new HwTask will be placed, is the area (or group) with the earliest estimated end-time among all the areas. The behaviour of the algorithm is represented in Figure 2.7.

**FIGURE** 2.7 – Scheme of the *EstimateEndTimes* algorithm.

# 4 Modelling Evaluation

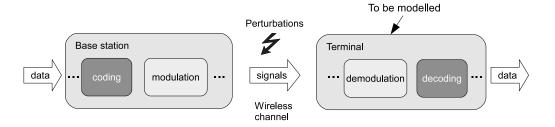

The role of this section is to demonstrate the use of the OveRSoC methodology on a real use case. The proposed system consists of a terminal whose mission is to decode the signals it receives through a wireless channel (see Figure 2.8). This type of system is typical in the wireless communications domain. This use-case has been studied in the context of the GDR-ISIS, young researcher project in collaboration with Laura Conde-Canencia of the Lab-STICC Laboratory.

### 4. Modelling Evaluation

FIGURE 2.8 – Target system.

In this application, high-order modulation schemes and error-correcting codes are jointly used to transmit more bits per Hz bandwidth and maximize performance. However, as the radio signal often propagates in a varying environment, the transmission scheme should be able to adapt itself to the state of the channel in real-time. A promising scheme is the Adaptive Coded Modulation (ACM) [CCEPO12], where the transmitter switches between signal constellations (of varying size) and code rates at discrete time instants. In other words, at a given time, the transmitter chooses symbols from the biggest constellation meeting the Bit Error Rate (BER) requirements and thus ensures maximum spectral efficiency for a given acceptable BER.

The ACM technique consists in choosing the Modulation and Coding Scheme (MCS) pattern that maximizes the system throughput, while guaranteeing an acceptable BER. Each MCS is characterized by a modulation (of order M) and a coding rate (R). Besides, M and R are used to calculate the spectral efficiency  $(\eta)$  of a communication, according to the equation :

$$\eta = R*log_2\,M$$

where  $\eta$  is defined as the maximum throughput (in bits/s/Hz).

In this case study, we consider an application which is compatible with the WiMAX 802.16m standard [CCEPO12]. In this standard, 12 MCSs are supported. These MCSs are detailed in Table 2.6, which is to be read as:  $MCS_1$  corresponds to a QPSK modulation (M = 4) and (R = 1/2) or MCS<sub>7</sub> corresponds to a 16-QAM (M = 16) and (R = 3/4).

| MCS           | Modulation | Code rate          |

|---------------|------------|--------------------|

| 1, 2, 3, 4    | QPSK       | 1/2, 2/3, 3/4, 5/6 |

| 5, 6, 7, 8    | 16-QAM     | 1/2, 2/3, 3/4, 5/6 |

| 9, 10, 11, 12 | 64-QAM     | 1/2, 2/3, 3/4, 5/6 |

**TABLE** 2.6 – MCSs in the WiMAX 802.16m standard. Source [CCEPO12]

Regarding the channel (or error-correcting) coding, this work has considered COD codes [DM98]. A Non Binary Low Density Parity Check (NB-LDPC) code is defined by an ultra-sparse matrix, characterized by specific parameters such as the frame length (N) and the code rate (R). In the ACM context, the system switches from one code rate to another depending on the channel state. Also, an NB-LDPC over GF(64) coding has been considered, thus each symbol corresponds to 6 bits and a frame contains 192 symbols.

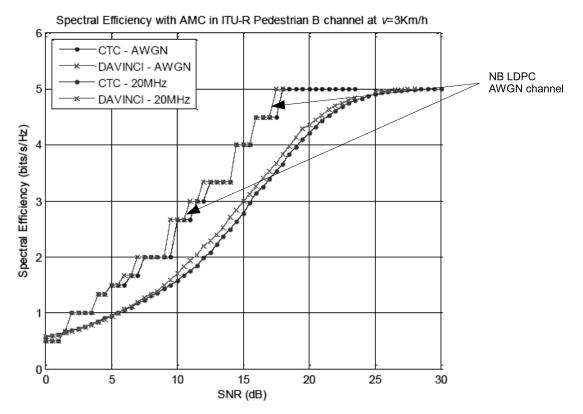

Figure 2.9 shows  $\eta$  as a function of SNR for two decoders and two types of channels using the ACM technique. The decoders are the Convolutional Turbo Decoder (CTC) and NB-LDPC while the channels are, the Additive White Gaussian Noise (AWGN) channel and the ITU Pedestrian B (at 3 km/h) using a bandwidth of 20 MHz. The curve marked with the arrow indicates the behaviour considered in our case: COD coding and AWGN channel.

For our case study, we defined a scenario where signals are constantly sent to the receiver. Also, at given intervals, channel conditions are analyzed. As soon as the channel changes, the system must be reconfigured without interrupting the transmission. Moreover, each signal is equivalent to a frame and a

FIGURE 2.9 – Spectral efficiency as a function of the SNR with ACM. Source [CCEPO12]

pause is required between the transmission of two frames. This is due to side effects of the channel, e.g. multiple paths. In our case, this pause lasts  $10 \,\mu s$ , which corresponds approximately to 10% of the frame's duration.

The tasks that constitute the system are the following:

The sensor task is responsible for inspecting the transmission channel and estimating the SNR. Whenever the channel conditions change, sensor configures the MCS that is the most suitable for the next transmission. Afterwards, sensor locks on a MUTEX until the next transmission is started.

The MCS<sub>c</sub> task represents the MCS scheme that is being used for the current transmission. At the end of each frame, the task is suspended for the inter-frame time. After the pause, MCS<sub>c</sub> unlocks the MUTEX that is required by **sensor**, to indicate that a new transmission is going to be started. Every time a channel change has been indicated by **sensor**, the MCS<sub>c</sub> activates the next MCS scheme and deletes itself.

The  $MCS_n$  task represents the MCS scheme that has been configured by the **sensor** for a future transmission. Whenever a change on the channel's conditions is detected, this task becomes the current MCS.

4.2 System Model

4.2.1 Application Model

Table 2.7 lists the attributes of each system task. The execution time of the sensor task has been estimated according to the results of previous implementations of communication systems. Assuming a basic channel estimation, the time of this task is negligible with respect to the frame processing time. Regarding the MCS tasks, their execution times as well as their bitstream's sizes have been extracted from an implementation on a Virtex5 FPGA [CCLJ12]. Note that the Columns and Rows of the MCS tasks

### 4. Modelling Evaluation

correspond to the number of columns and rows of the FPGA in terms of reconfigurable resources.

| Task                                  | Туре | Mean cycles   | Columns     | Rows        | Bitstream |

|---------------------------------------|------|---------------|-------------|-------------|-----------|

|                                       |      | •             | (resources) | (resources) | size (Mb) |

| SENSOR                                | SW   | 1000          | -           | -           | -         |

| MCS <sub>1</sub> to MCS <sub>12</sub> | HW   | 8750 to 18350 | 20          | 10          | 2.25      |

**TABLE** 2.7 – Task models and their attributes.

4.2.2

### ARCHITECTURE MODEL

The dynamic behaviour of the ACM-based terminal requires a flexible architecture, which is able to adapt to new channel conditions. In addition, MCS operations require considerable computing power and should ideally be implemented as dedicated hardware elements. Given these characteristics, an architecture containing a reconfigurable part has been selected. Moreover, we have considered the use of two processors, one master and one slave. The master is responsible for executing the kernel functions. The slave processor executes the application tasks. The attributes of the architecture model are summarized in Table 2.8.

| Element   | Attribute | Value       |  |

|-----------|-----------|-------------|--|

| Timer     | Frequency | 50 MHz      |  |

| Processor | Frequency | 50 MHz      |  |

| RH        | Width     | 200 columns |  |

|           | Height    | 200 rows    |  |

|           | Frequency | 50MHz       |  |

**TABLE** 2.8 – Architecture model attributes.

4.2.3

### KERNEL MODEL

Considering the target system, the model of the kernel is composed of the services that are listed in Table 2.9. In this model, the Task Manager service has been parametrized to handle 13 tasks at most. In a first model, since the target architecture contains two processors, the scheduler type has been chosen to be Symmetric Multiprocessing (SMP) and the scheduling policy is classical rate-monotonic.

| Service        | Attribute            | Value         |

|----------------|----------------------|---------------|

| Task Manager   | MAX_NB_TASKS         | 13            |

| Scheduler      | Scheduling type      | SMP           |

| IRQ Manager    | Sources              | IRQ_END_TASK  |

|                |                      | IRQ_TICK      |

| Communications | Mechanisms           | MUTEX         |

| Offloading     | ALLOW_IRQ            | yes           |

|                | OFF_LEVEL            | 1             |

|                | PLACEMENT_POLICY     | BEST_FIT_ALGO |

|                | PROCESSORS_SET_SLAVE | no            |

|                | REMOTE_BLOCK         | no            |

|                | RH_SLAVE             | yes           |

|                | IRQ_TRANSFER         | no            |

**TABLE** 2.9 – Kernel model.

### Chapitre 2. From OS Modelling to Implementation

Moreover, since HW tasks are considered in this architecture, an IRQManager is required. This manager must handle interrupts coming from hardware elements. Additionally, a tick interrupt is also provided to manage the tasks' delay. According to the synchronization requirements, it has been decided to only implement mutexes since they are simple and sufficient for this application. An offloading algorithm has also been included since reconfigurable hardware must be managed. Initially, the algorithm has been parametrized with the first level of complexity. In this configuration, the offloading algorithm will be executed only in software. Moreover, the configuration data transfer (IRQ\_TRANSFER) is not preemptible. Finally, the placement policy has been chosen to be a best-fit algorithm.

# 4.3 SIMULATION AND RESULTS

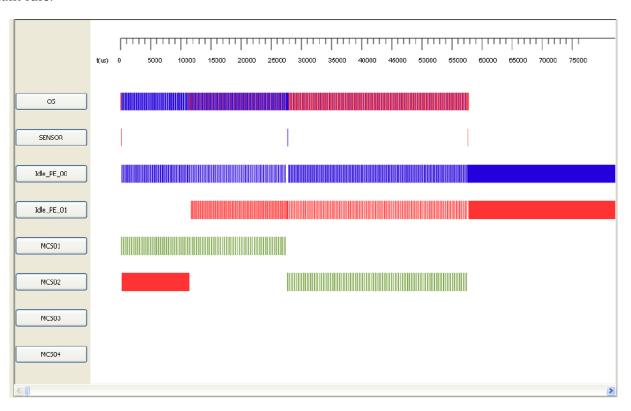

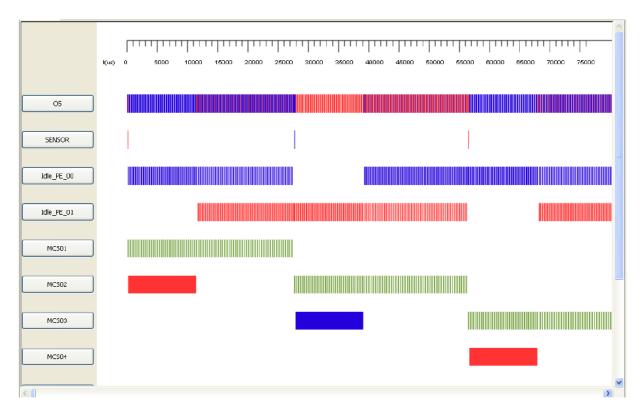

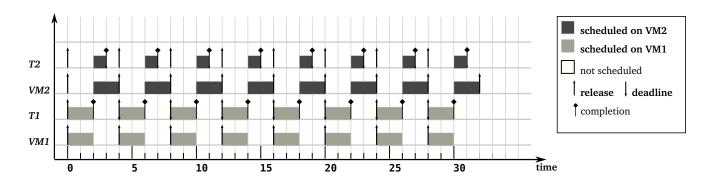

After the SystemC code generation step, the initial model has been simulated. The Gantt diagram displaying the tasks' executions is shown in Figure 2.10. As can be seen in this figure, the system is unable to run continuously since no more frames are decoded after the second configuration. Only  $MCS_{01}$  and  $MCS_{02}$  can be executed. Note that no other MCSs are configured and executed and that the two processors remain idle.

**FIGURE** 2.10 – Gantt diagram for 2 processors and the Level1-Offloader.

In this situation, it is then necessary to modify the initial model by considering different values of attributes in the kernel, application and architecture models. In this scenario, among all available attributes, it has been decided to modify the offloading algorithm complexity.

After the modification of the kernel model, the simulation has produced the results shown in Figure 2.11. Now, the system is working properly because the frames are decoded without interruption, despite the changes in MCS. All MCS are periodically executed. Since the offloading is now parametrized at level 2, the system behaves in such a way that, each time a new MCS cannot be configured, the offloader checks whether there are other idle MCs whose resources can be taken. In this case, the old MCS is replaced by the new one. For example,  $MCS_{03}$  uses the resources of the  $MCS_{01}$  which is not currently being used.

However, taking a look at the processors' usage (in Table 2.10), it can be seen that the processors are not used efficiently. Therefore, it would be interesting to consider a single processor architecture in

FIGURE 2.11 – Gantt diagram for 2 processors and the Level2-Offloader.

order to optimize the system. It has then been decided to modify the architecture model. In the new configuration, only one processor and reconfigurable hardware have been considered. Figure 2.12 shows the simulation of such model.

| Processor               | Idle time | Percentage of use |

|-------------------------|-----------|-------------------|

| P <sub>0</sub> (master) | 97.121    | 51.44%            |

| P <sub>1</sub>          | 56.619    | 71.7 %            |

**TABLE** 2.10 – Processor usage.

As shown in Figure 2.12, the system also works properly with one processor. However, it may be noted that the overall latency has increased. In this new configuration, processing 80 frames is performed in 37ms whereas in the previous configuration (in Figure 2.11), the same processing was executed in 28ms.

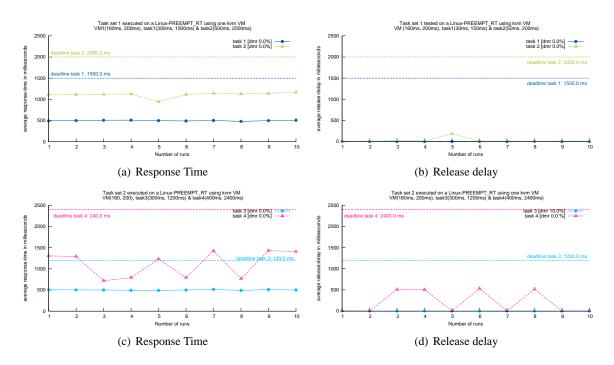

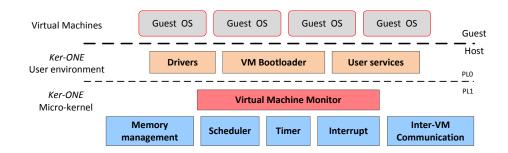

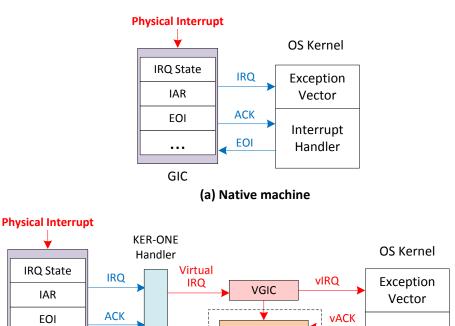

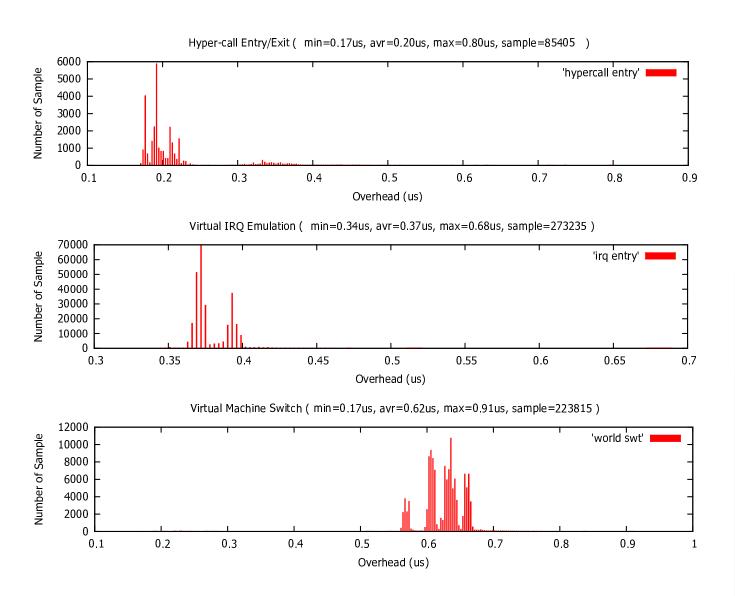

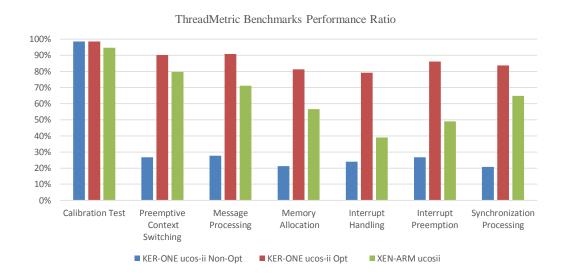

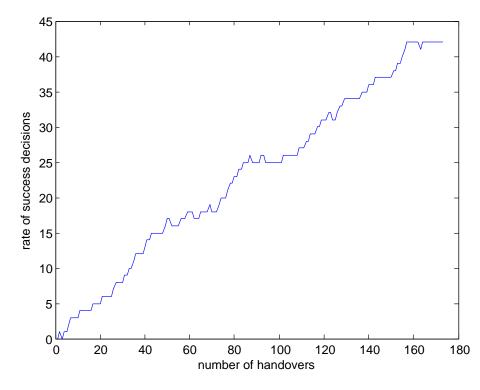

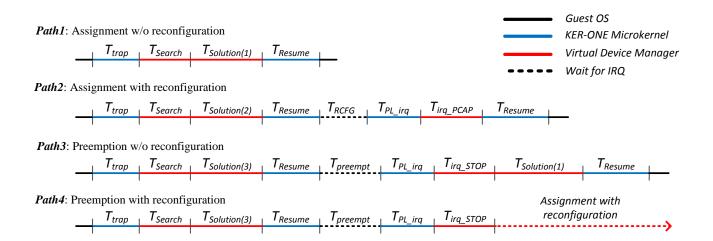

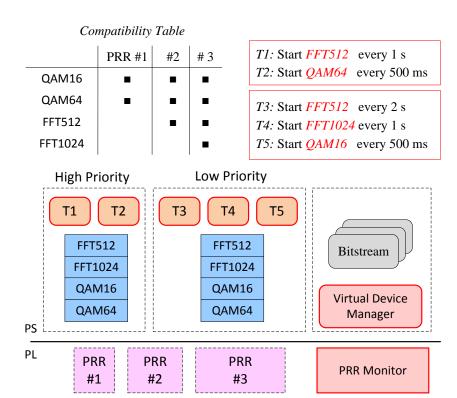

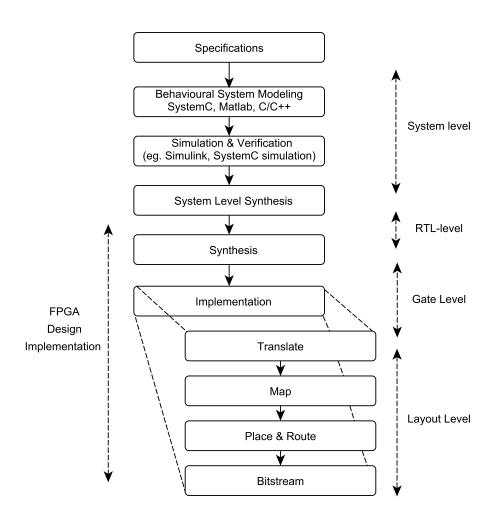

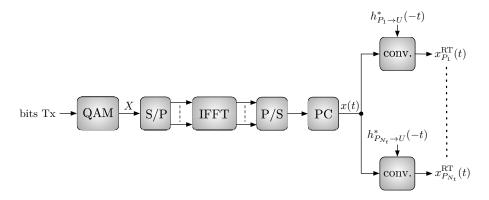

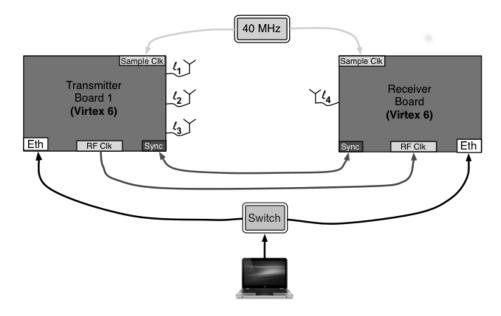

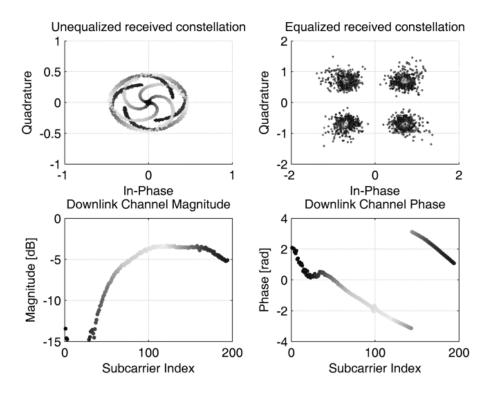

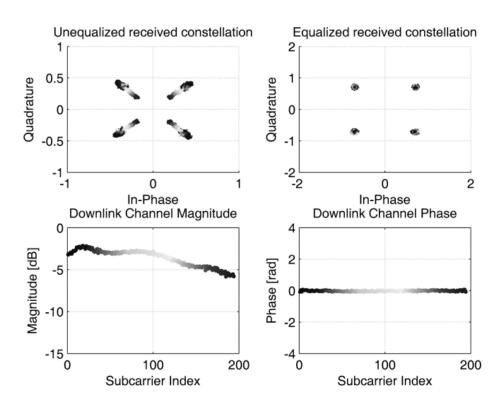

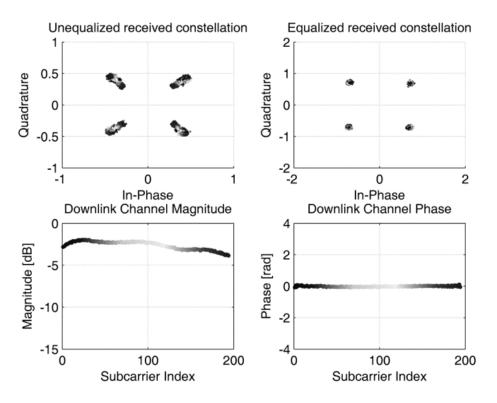

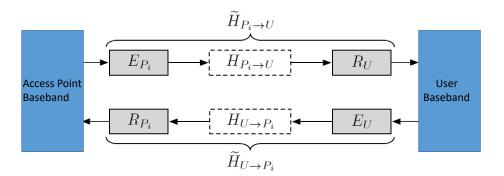

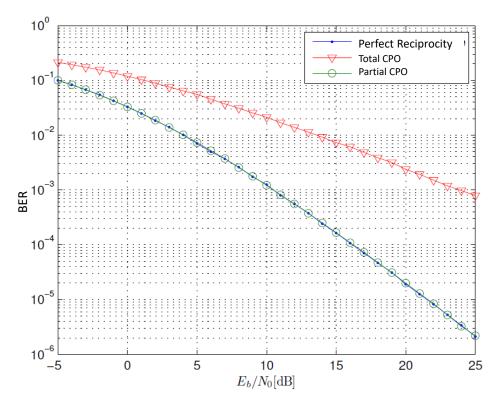

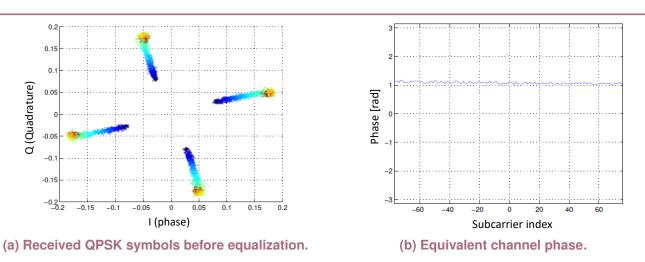

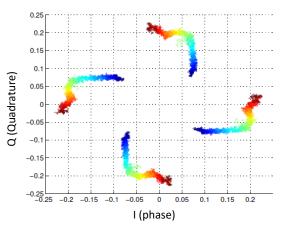

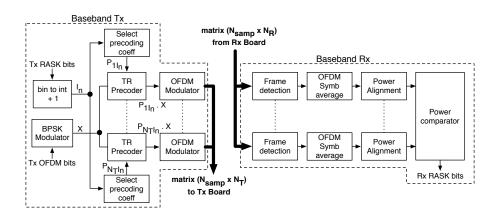

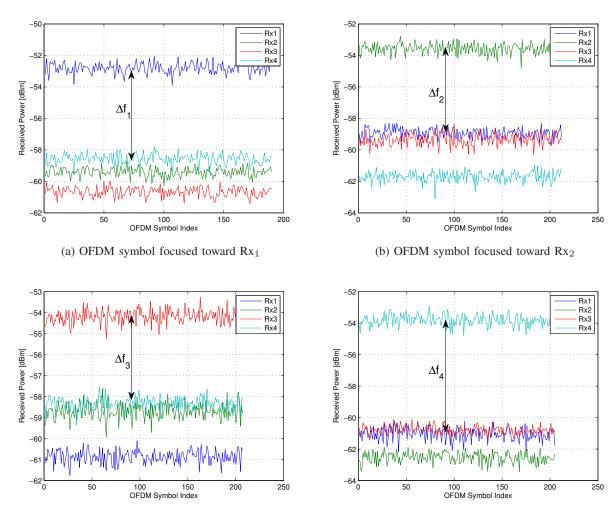

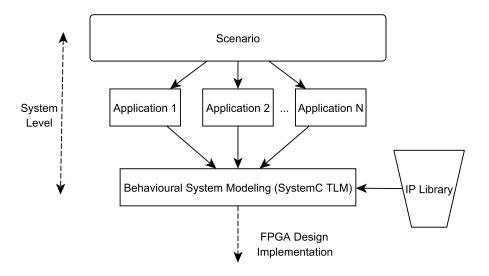

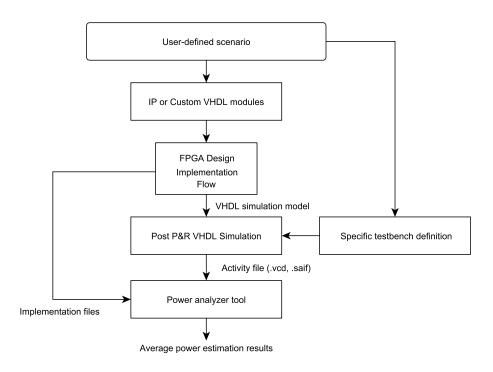

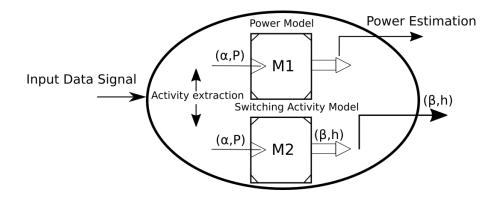

### **OS CODE GENERATION**