# Mastering the O-diamond/Al2O3 interface for unipolar boron doped diamond field effect transistor

Thanh-Toan Pham

## ▶ To cite this version:

Thanh-Toan Pham. Mastering the O-diamond/Al2O3 interface for unipolar boron doped diamond field effect transistor. Electronics. Université Grenoble Alpes, 2017. English. NNT: 2017GREAT051. tel-02417437

## HAL Id: tel-02417437 https://theses.hal.science/tel-02417437

Submitted on 18 Dec 2019

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ DE GRENOBLE

Spécialité : Nano Electronique et Nano Technologies (NENT)

Arrêté ministériel : 7 août 2006

Présentée par Thanh-Toan PHAM

Thèse dirigée par **Julien PERNOT** et codirigée par **Nicolas ROUGER**

préparée au sein de l' Institut Néel - CNRS Grenoble and Grenoble Electrical Engineering Lab (G2ELab)- CNRS Grenoble et de l'école doctorale : Electronique, Electrotechnique, Automatique & Traitement du Signal (EEATS)

# Mastering the O-diamond/Al2O3 interface for unipolar boron doped diamond field effect transistor

Thèse soutenue publiquement le **12 April 2017**, devant le jury composé de :

M. Yvon CORDIER Directeur de recherche, CRHEA-CNRS (France), Examinateur **M. Florin UDREA** Professeur, University of Cambridge (ROYAUME-UNI), Examinateur M. Philippe BERGONZO Directeur de recherche, CEA-LIST (France), Rapporteur M. Philippe GODIGNON Professeur, Centro Nacional de Microelectrónica (Espagne), Rapporteur M. Daniel ARAUJO Professeur, Universidad de Cádiz (Espagne), Président M. Hitoshi UMEZAWA Chargé de recherche, AIST (JAPON), Examinateur **M. Julien PERNOT** Professeur, Université Grenoble Alpes (France), Directeur de thèse M. Nicolas ROUGER Chargé de recherche, ENSEEIHT-CNRS (France), Co-Directeur de thèse

# Contents

| Int      | trod | uction                                                                                           | 1  |

|----------|------|--------------------------------------------------------------------------------------------------|----|

| 1        | Bor  | on doped diamond semiconductor for unipolar power devices                                        | 2  |

|          | 1.1  | Unipolar device's Figure-of-Merit(FOM)                                                           | Ę  |

|          | 1.2  | Diamond semiconductor for power devices                                                          | 10 |

|          |      | 1.2.1 Doping                                                                                     | 10 |

|          |      | 1.2.2 Carrier mobility and density                                                               | 13 |

|          |      | 1.2.3 Dielectric breakdown field                                                                 | 15 |

|          | 1.3  | States-of-the-art of diamond unipolar power devices                                              | 17 |

|          |      | 1.3.1 Diamond Schottky diode                                                                     | 17 |

|          |      | 1.3.2 Diamond unipolar transistor                                                                | 17 |

|          | 1.4  | Metal Oxide Semiconductor Field Effect Transistors (MOSFET)                                      | 23 |

|          |      | 1.4.1 MOS capacitor working principle                                                            | 23 |

|          |      | 1.4.2 O-diamond MOS capacitor                                                                    | 25 |

|          | 1.5  | Conclusion                                                                                       | 28 |

| <b>2</b> | Oxy  | gen terminated boron doped diamond metal oxide semiconductor                                     | •  |

|          |      | acitor                                                                                           | 31 |

|          | Ĩ    |                                                                                                  |    |

| Ι        | Ele  | ectrostatics                                                                                     | 33 |

|          | 2.1  | Methodology                                                                                      | 35 |

|          |      | 2.1.1 MOS Capacitor test device structure                                                        | 35 |

|          |      | 2.1.2 Substrates and cleaning substrates                                                         | 36 |

|          |      | 2.1.3 Diamond growth                                                                             | 37 |

|          |      | 2.1.4 Test devices fabrication                                                                   | 39 |

|          |      | 2.1.5 Electrical measurement                                                                     | 42 |

|          |      | 2.1.6 Electrostatics simulation                                                                  | 46 |

|          |      | 2.1.7 C-V characteristic of an ideal MOS capacitor                                               | 47 |

|          | 2.2  | Electrostatics of O-diamond MOS capacitor                                                        | 48 |

|          |      | 2.2.1 I-V and C-V characteristics                                                                | 48 |

|          |      | 2.2.2 Capacitance-frequency characteristics                                                      | 52 |

|          |      | 2.2.3 Charges in the MOS capacitor system                                                        | 56 |

|          |      | 2.2.4 Gate controlled diamond semiconductor                                                      | 58 |

|          |      | 2.2.5 Electrostatics simulation                                                                  | 62 |

|          |      | 2.2.6 Conclusion                                                                                 | 64 |

|          |      |                                                                                                  | 01 |

| тт       | 0    | Dismond MOS consister under repeties bies, comment                                               |    |

| II<br>m  |      | -Diamond MOS capacitor under negative bias: current<br>anism and capacitance-frequency dependent | 65 |

| 111      | 2.3  | Introduction                                                                                     | 67 |

|          |      | Results and Discussion                                                                           | 68 |

4 Results and Discussion

68

2.4.1 Typical electrical characteristics

68

|    |            | 2.4.2                                                                                                       | Forward current mechanism                                                                                                                    | . 68                                                                                                                                                                                                                                                                                    |

|----|------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |            | 2.4.3                                                                                                       | Equivalent circuit and conductance method                                                                                                    | . 76                                                                                                                                                                                                                                                                                    |

|    |            | 2.4.4                                                                                                       | Capacitance-frequency dependence                                                                                                             | . 84                                                                                                                                                                                                                                                                                    |

|    |            | 2.4.5                                                                                                       | Electrostatics simulation                                                                                                                    | . 85                                                                                                                                                                                                                                                                                    |

|    | 2.5        | Conclu                                                                                                      | usion                                                                                                                                        | . 86                                                                                                                                                                                                                                                                                    |

|    |            |                                                                                                             |                                                                                                                                              |                                                                                                                                                                                                                                                                                         |

| ΤT | Τ          | D-Dia                                                                                                       | mond MOS capacitor under positive bias: curr                                                                                                 | ent                                                                                                                                                                                                                                                                                     |

| m  |            |                                                                                                             | and capacitance-frequency dependent                                                                                                          | 89                                                                                                                                                                                                                                                                                      |

|    | 2.6        |                                                                                                             | $ation \ldots \ldots$ | . 91                                                                                                                                                                                                                                                                                    |

|    | 2.7        |                                                                                                             | s and Discussion                                                                                                                             |                                                                                                                                                                                                                                                                                         |

|    |            | 2.7.1                                                                                                       | Device characteristics-substrate profile correlation                                                                                         | . 94                                                                                                                                                                                                                                                                                    |

|    |            | 2.7.2                                                                                                       | Reverse current mechanism                                                                                                                    | 99                                                                                                                                                                                                                                                                                      |

|    |            | 2.7.3                                                                                                       | Capacitance-frequency dependence                                                                                                             | . 100                                                                                                                                                                                                                                                                                   |

|    | 2.8        | Conclu                                                                                                      | usion                                                                                                                                        | . 104                                                                                                                                                                                                                                                                                   |

|    | 2.9        | Conclu                                                                                                      | usion of Chapter 2                                                                                                                           | . 105                                                                                                                                                                                                                                                                                   |

| 3  | Dor        | lation                                                                                                      | -mode Metal Oxide Semiconductor Field Effect Transi                                                                                          | stor                                                                                                                                                                                                                                                                                    |

| Э  | -          |                                                                                                             | () on Oxygen Terminated boron doped Diamond                                                                                                  | 125                                                                                                                                                                                                                                                                                     |

|    | 3.1        |                                                                                                             | uction                                                                                                                                       |                                                                                                                                                                                                                                                                                         |

|    | 0.1        | 3.1.1                                                                                                       | Transistor electrical characteristics                                                                                                        |                                                                                                                                                                                                                                                                                         |

|    |            | 3.1.2                                                                                                       | Diamond FET devices                                                                                                                          |                                                                                                                                                                                                                                                                                         |

|    | 3.2        | -                                                                                                           |                                                                                                                                              |                                                                                                                                                                                                                                                                                         |

|    |            | metho                                                                                                       | odology                                                                                                                                      |                                                                                                                                                                                                                                                                                         |

|    |            | 3.2.1                                                                                                       | odology                                                                                                                                      | . 129                                                                                                                                                                                                                                                                                   |

|    |            |                                                                                                             | odology                                                                                                                                      | . 129<br>. 129                                                                                                                                                                                                                                                                          |

|    |            | 3.2.1                                                                                                       | Transistor design                                                                                                                            | . 129<br>. 129<br>. 133                                                                                                                                                                                                                                                                 |

|    |            | $3.2.1 \\ 3.2.2$                                                                                            | Transistor design    Fabrication                                                                                                             | 129<br>129<br>133<br>133                                                                                                                                                                                                                                                                |

|    | 3.3        | $\begin{array}{c} 3.2.1 \\ 3.2.2 \\ 3.2.3 \\ 3.2.4 \end{array}$                                             | Transistor design          Fabrication          Measurements          Simulation          s and Discussion                                   | 129<br>129<br>133<br>135<br>135<br>135<br>135<br>136                                                                                                                                                                                                                                    |

|    | 3.3        | $\begin{array}{c} 3.2.1 \\ 3.2.2 \\ 3.2.3 \\ 3.2.4 \end{array}$                                             | Transistor design          Fabrication          Measurements          Simulation          s and Discussion          Test devices             | 129         129         133         135         135         135         135         135         135         136         136                                                                                                                                                             |

|    | 3.3        | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Result                                                                  | Transistor design                                                                                                                            | 129         129         133         135         135         135         136         136         144                                                                                                                                                                                     |

|    | 3.3        | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Result<br>3.3.1<br>3.3.2<br>3.3.3                                       | Transistor design                                                                                                                            | 129         129         133         135         135         135         135         135         136         136         136         136         136         136         136         136         136         136         136         136         136         136         136         153 |

|    |            | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Result<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4                              | Transistor design                                                                                                                            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                    |

|    | 3.4        | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Result<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>Bench                     | Transistor design                                                                                                                            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                    |

|    | 3.4<br>3.5 | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Result<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>Bench<br>Conclu           | Transistor design                                                                                                                            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                    |

|    | 3.4        | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Result<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>Bench<br>Conclu<br>Genera | Transistor design                                                                                                                            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                    |

|    | 3.4<br>3.5 | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>Result<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>Bench<br>Conclu           | Transistor design                                                                                                                            | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                    |

## Bibliography

# List of Figures

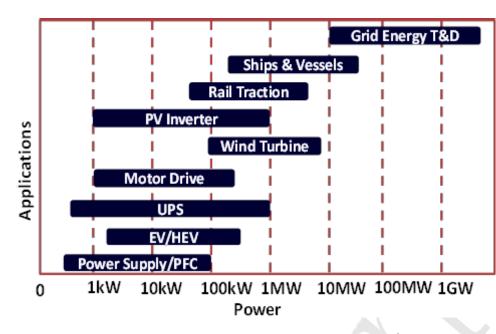

| 1.1  | Power range requirements of various applications (chart is based on Yole                                                                    |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Development report).                                                                                                                        | -4 |

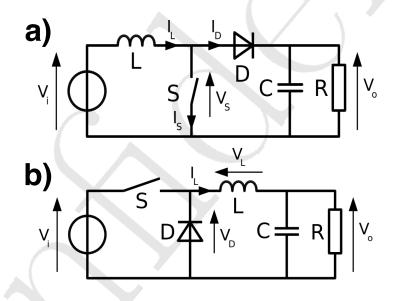

| 1.2  | Electrical circuit of the power converter a) DC-DC boost converter; b)                                                                      |    |

|      | DC-DC buck converter.                                                                                                                       | 4  |

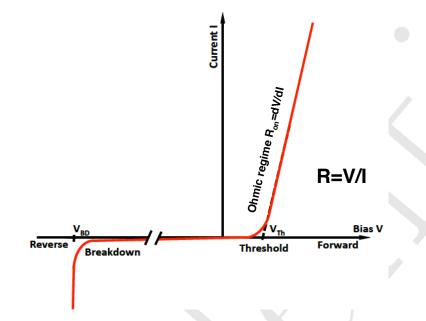

| 1.3  | Typical electrical characteristic of simple power device (diode) where the                                                                  |    |

|      | loss in the ON-state and breakdown in the OFF-state are unavoidable. $% \mathcal{A}$ .                                                      | 5  |

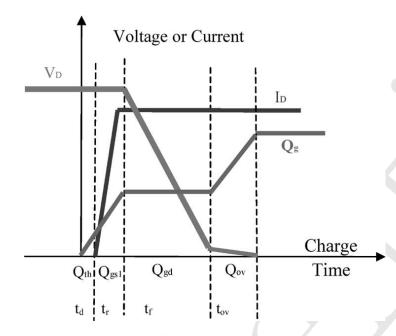

| 1.4  | Switching waveforms of a generic unipolar power device. Courtesy of                                                                         |    |

|      | Huang et al. $[1]$                                                                                                                          | 6  |

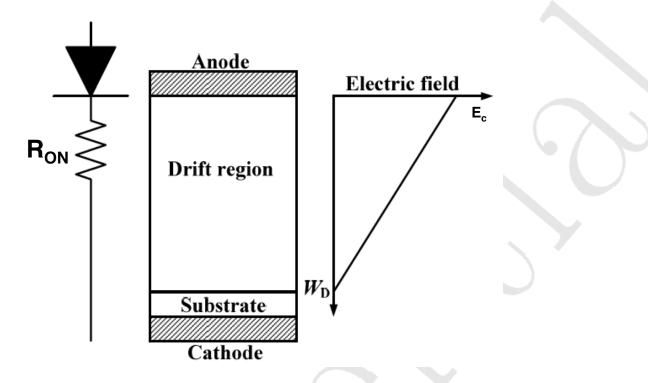

| 1.5  | Ideal drift region in Non-Punch-Through (NPT) design that considering                                                                       |    |

|      | the compromise between ON-state loss and OFF-state breakdown, consid-                                                                       |    |

|      | ering breakdown is due to avalanche effect when maximum electric field in                                                                   |    |

|      | the structure reached material critical electric field.                                                                                     | 7  |

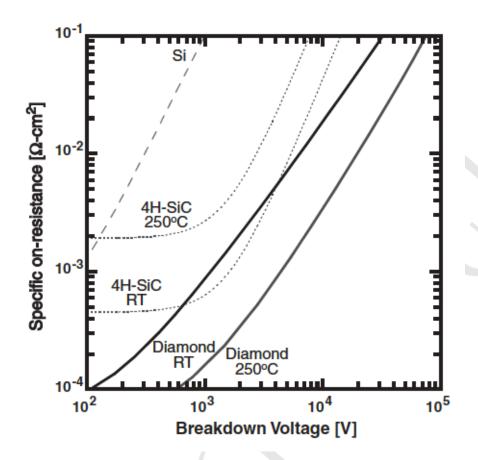

| 1.6  | ON-resistance and breakdown voltage of different semiconductor at RT                                                                        |    |

|      | and at 250 °C, courtesy of Umezawa et al.[2]. $\ldots$ $\ldots$ $\ldots$                                                                    | 10 |

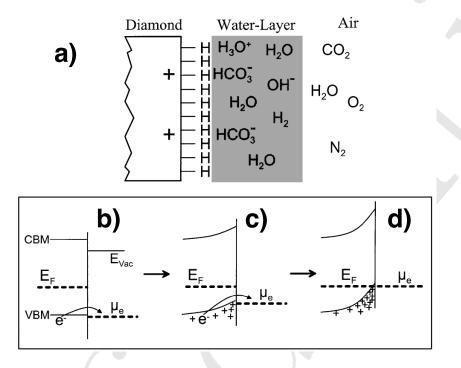

| 1.7  | Schematic description of surface doping model in H-diamond. Courtesy of                                                                     |    |

|      | Maier et al. [3]                                                                                                                            | 11 |

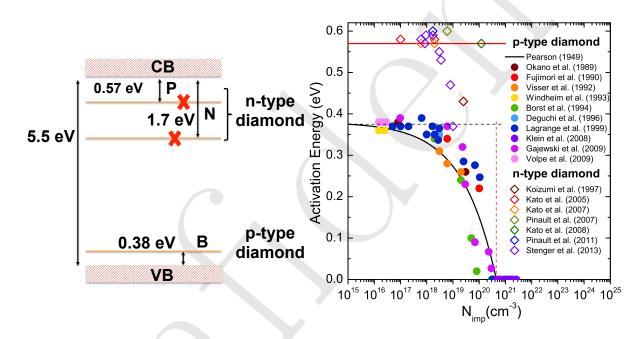

| 1.8  | Ionization energy of dopants as a function of the impurity concentration in                                                                 |    |

|      | diamond. The experimental boron ionization energies are taken from the                                                                      |    |

|      | literature [Okano 1989, Fujimori 1990, Visser 1992, Windheim 1993, Borst                                                                    |    |

|      | 1995, Deguchi 1996, Lagrange 1999, Klein 2007, Gajewski 2009, Volpe 2009] and the solid curve is drawn after Pearson and Bardeen law [Pear- |    |

|      | son 1949]. Phosphorus ionization energies are taken from the literature                                                                     |    |

|      | [Koizumi 1997, Kato 2005, Kato 2007, Pinault 2007, Kato 2008, Pinault-                                                                      |    |

|      | Thaury 2011, Stenger 2013]. Its value is assumed to be constant over the                                                                    |    |

|      | entire doping range. Courtesy of Fiori's PhD thesis [4]                                                                                     | 12 |

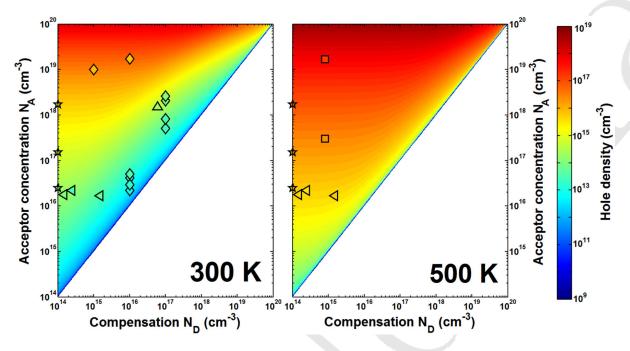

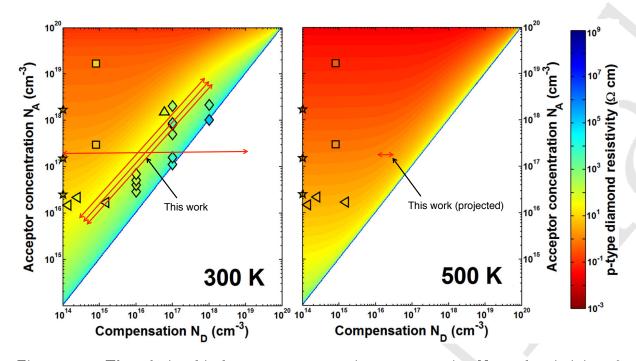

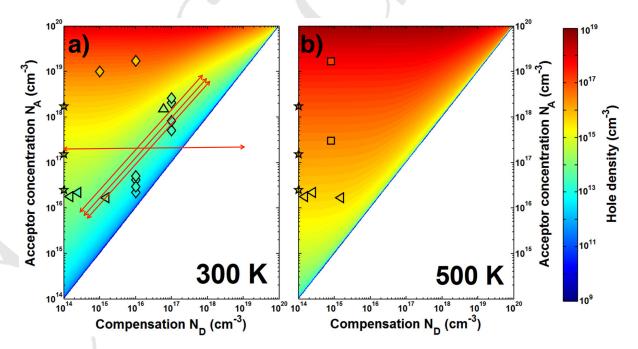

| 1.9  | Theoretical hole density as function of acceptor concentration and com-                                                                     |    |

|      | pensation at 300 and 500 K. The symbols are experimental data reported                                                                      |    |

|      | by: Barjon et al. [5], Volpe et al. [6], Gabrysch et al. [7], Werner et al.                                                                 |    |

|      | [8], and Tsukioka et al. [9]. Courtesy of Traore et al. [10]                                                                                | 13 |

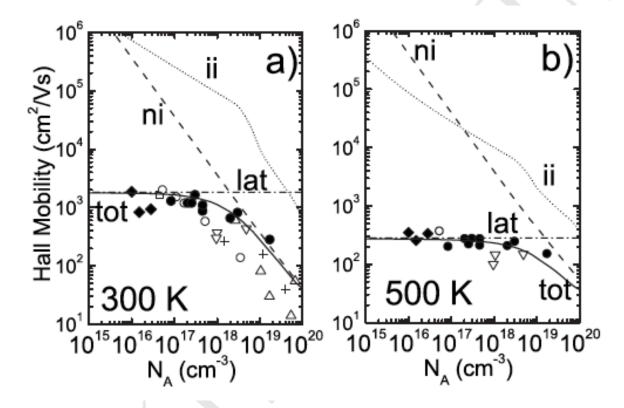

| 1.10 | The dependence of hole mobility to boron concentration at a) 300 K; b)                                                                      |    |

|      | 500 K. Courtesy of Pernot et al. [11]                                                                                                       | 14 |

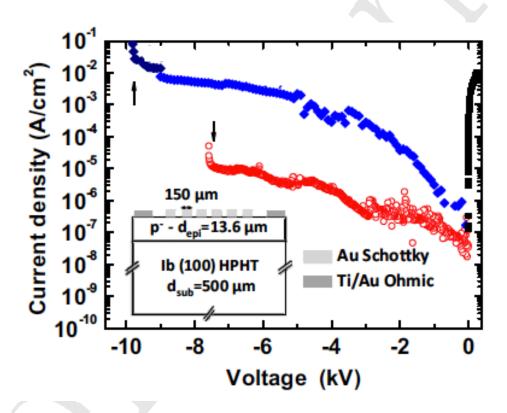

| 1.1  | 1 O-diamond Schottky diode on homoepitaxial boron doped diamond with a                                                                      |    |

|      | breakdown voltage of 10 kV and a breakdown electric field of 7.7 $\rm MV/cm.$                                                               |    |

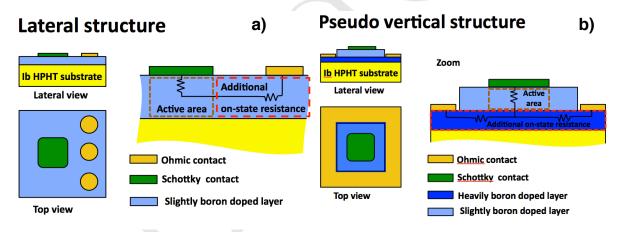

|      | Courtesy of Volpe et al. [12].                                                                                                              | 16 |

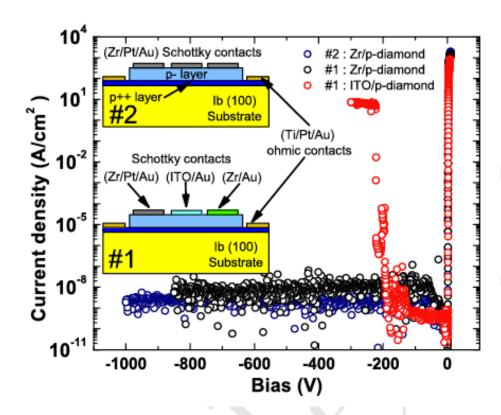

| 1.12 | 2 Pseudo-vertical diamond Schottky diode and its electrical characteristics,                                                                |    |

|      | Courtesy of Traore et al. [13]                                                                                                              | 18 |

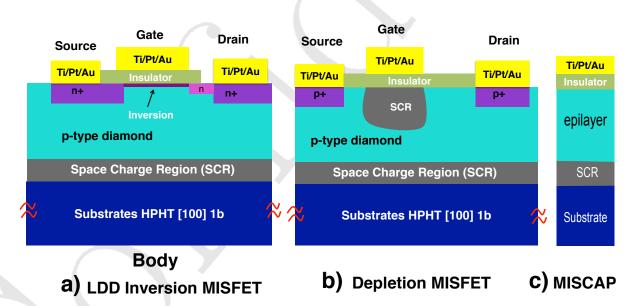

| 1.13 | 3 Cross-section structure of a) Lightly doped drain inversion MISFET; b)                                                                    |    |

|      | depletion MISFET; c) building block MISCAP.                                                                                                 | 18 |

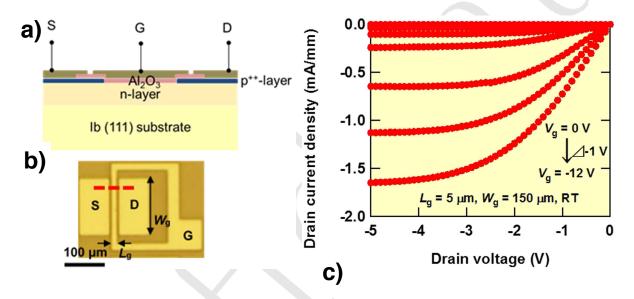

| 1.14 | 4 Inversion mode of pMOS phosphorous doped oxygen terminated diamond                                                                        |    |

|      | MOSFET: a) cross-section structure; b) top view structure; c) electrical                                                                    |    |

|      | characteristics. Courtesy of Matsumoto et al. [14]                                                                                          | 19 |

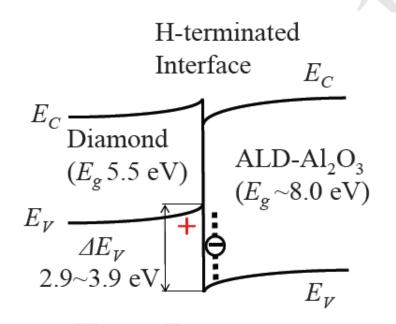

| 1.15 | The proposed model for the 2DHG at H-diamond/oxide interface. Courtesy of Kawarada et al. [15].                                                                                                                                                                                                                                                             | 20       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

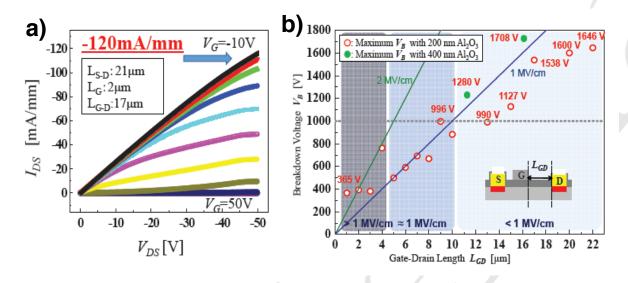

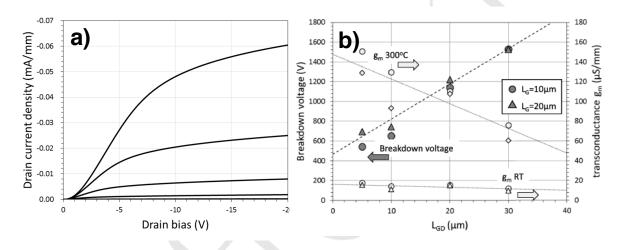

| 1.16 | Electrical characteristics and breakdown voltage at different gate to drain distances of H-diamond MOSFET. Courtesy of Kawarada et al. [15].                                                                                                                                                                                                                | 21       |

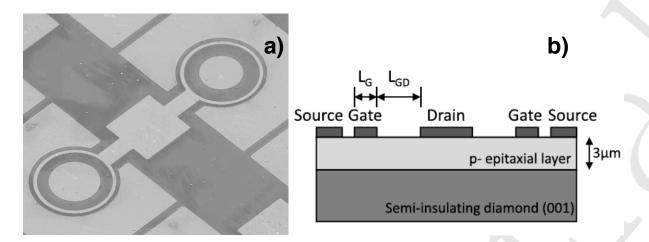

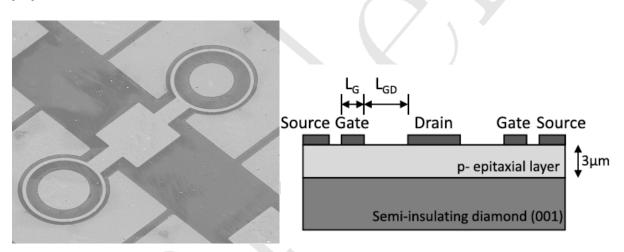

| 1.17 | Top view structure and cross-section structure of the oxygen terminated boron doped diamond MESFET. Courtesy of Umezawa et al. [16].                                                                                                                                                                                                                        | 22       |

| 1.18 | MESFET electrical characteristics and breakdown voltage at different gate to length distance. Courtesy of Umezawa et al. [16]                                                                                                                                                                                                                               | 22       |

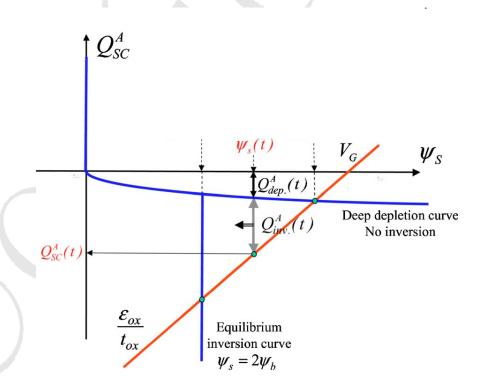

| 1.19 | Relationship between semiconductor charge $Q_{SC}$ and semiconductor surface potential $\Psi_S$ . Courtesy of Vincent et al. [17].                                                                                                                                                                                                                          | 23       |

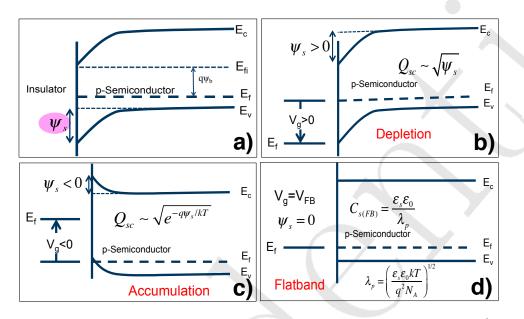

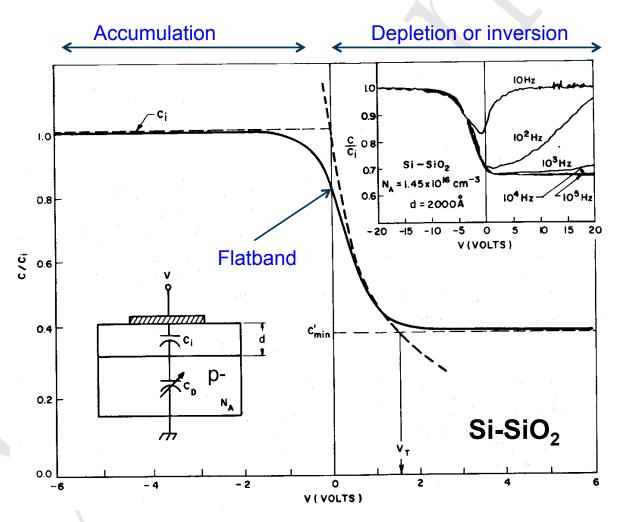

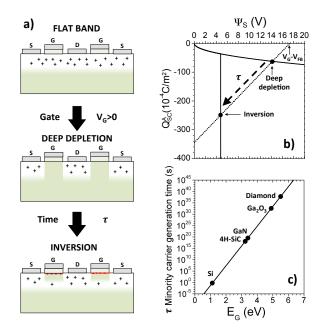

| 1.20 | Schematics description of different regimes of a MOS capacitor: a) defini-<br>tion of semiconductor surface potential $\Psi_S$ ; b) accumulation regime under<br>negative bias; c) depletion and deep depletion regime under positive bias;<br>d) Flatband regime where there are no energy different between surface<br>and neutral part of semiconductor. | 24       |

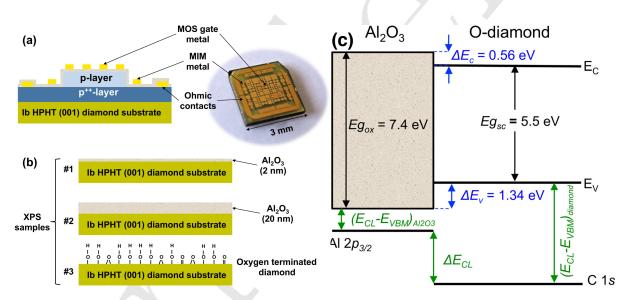

| 1.21 | First propositional structure of a O-diamond MOS capacitor. Courtesy of Chicot et al. [18]                                                                                                                                                                                                                                                                  | 24<br>26 |

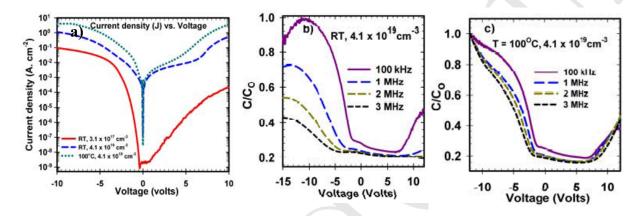

| 1.22 | Typical J-V and C-V characteristics of some first O-diamond MOS capac-<br>itor. Leakage current in both forward bias and reverse bias is observed.<br>Capacitance are strongly frequency dependent. Courtesy of Chicot et al.<br>[18]                                                                                                                       | 27       |

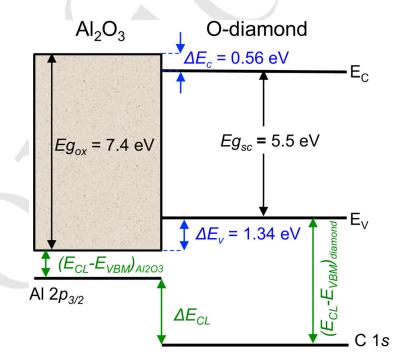

| 1.23 | a) Pseudo-vertical structure O-diamond MOS capacitor; b) Band alignment between O-diamond and $Al_2O_3$ deposited at 250 °C. Courtesy of Marechal et al. [19]                                                                                                                                                                                               | 27       |

| 1.24 | Electrical characteristics of the pseudo-vertical O-diamond MOS capacitor,<br>a) C-V characteristic; b) J-V characteristic. Courtesy of Marechal et al. [19]                                                                                                                                                                                                | 28       |

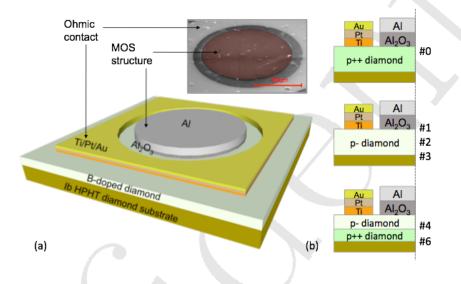

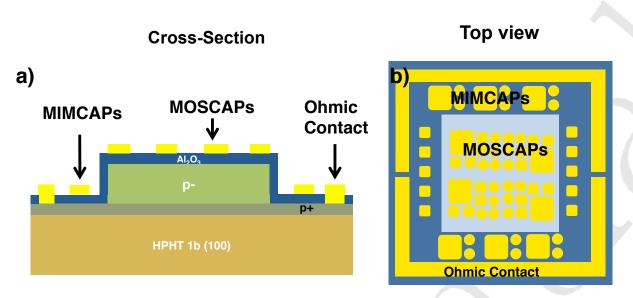

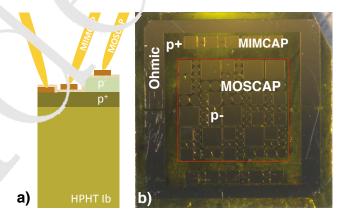

| 2.1  | Illustration of the conduction path in MOS structures; a) without a buried $p++$ layer; b) with a buried $p++$ layer                                                                                                                                                                                                                                        | 35       |

| 2.2  | a) Conceptual cross-section structure of test devices included Ohmic con-<br>tact, MIM Capacitors and MOS Capacitors; b) Corresponding plan view<br>of test device structure where MIM capacitors and MOS capacitors are                                                                                                                                    |          |

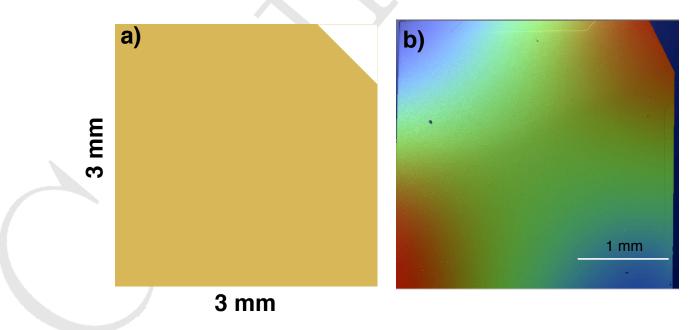

| 2.3  | fabricated with different shapes and sizes                                                                                                                                                                                                                                                                                                                  | 36       |

|      | meter photograph of the substrate.                                                                                                                                                                                                                                                                                                                          | 36       |

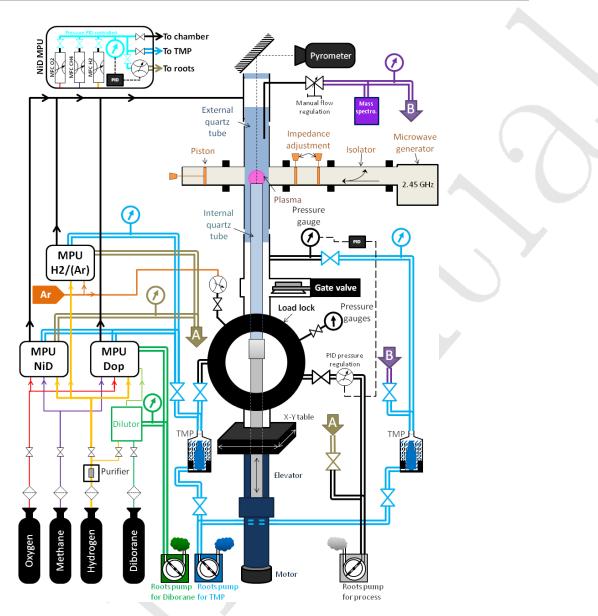

| 2.4  | MPCVD reactor at Institut NEEL.                                                                                                                                                                                                                                                                                                                             | 37       |

| 2.5  | Schematics representing the structure and the working principle of the reactor. Courtesy to Fiori's PhD thesis [4]                                                                                                                                                                                                                                          | 38       |

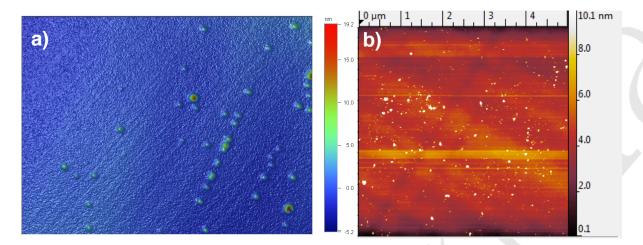

| 2.6  | Diamond surface topography after growth measured by a) Optical profile-<br>meter; b) AFM                                                                                                                                                                                                                                                                    | 39       |

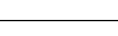

| 2.7  | Schematics describing the process for diamond etching and ohmic contact fabrication.                                                                                                                                                                                                                                                                        | 40       |

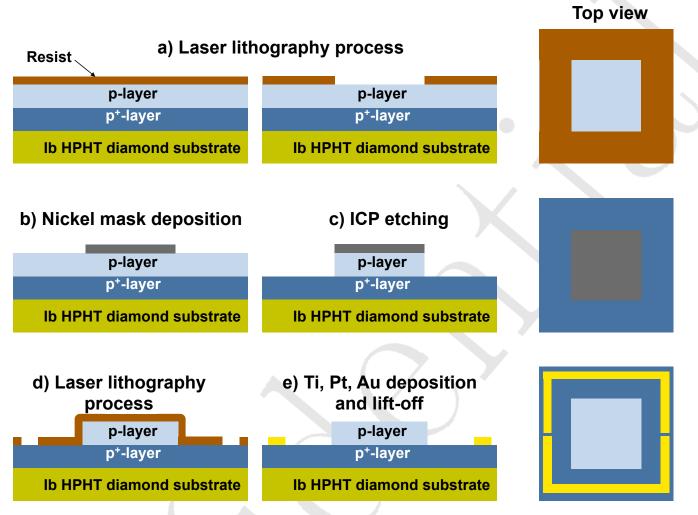

| 2.8  | a) Optical profile-meter of the etched mesa structure                                                                                                                                                                                                                                                                                                       | 40<br>40 |

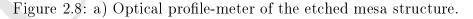

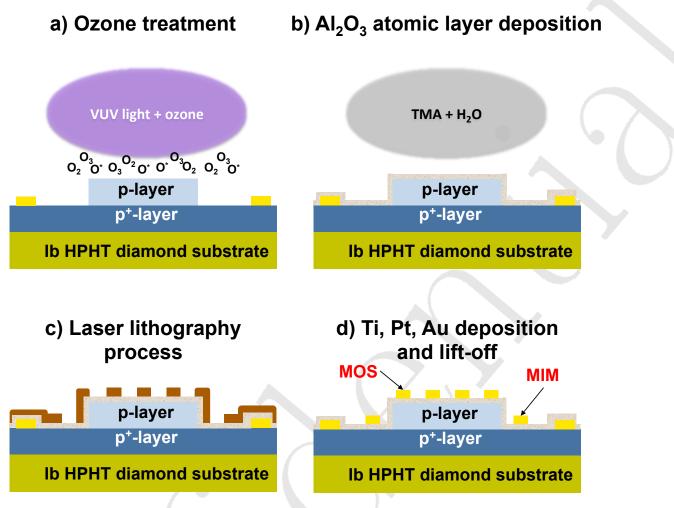

| 2.9  | Schematic describing MOS capacitors and MIM capacitors fabrication steps.                                                                                                                                                                                                                                                                                   |          |

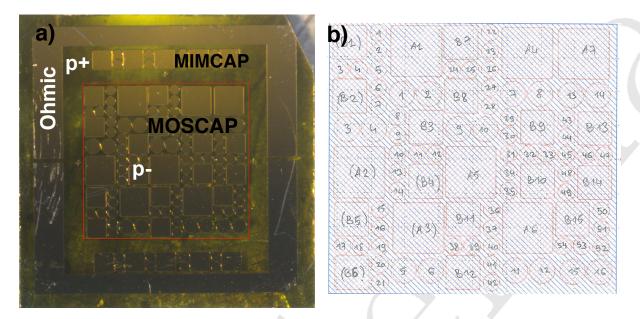

| 2.10  | a) Optical photograph of the fabricated test devices included Ohmic con-                                                                |     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | tact, MIM capacitors and MOS capacitor. b) the mask of MOS capacitor                                                                    | 10  |

| 0.4.4 | after numbering.                                                                                                                        | 42  |

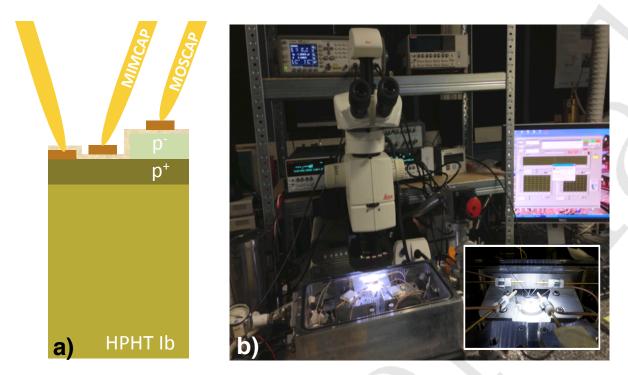

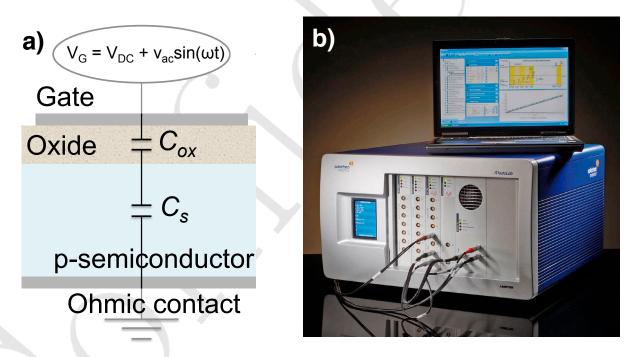

| 2.11  | a) General electrical measurement configuration; b) Electrical measure-                                                                 |     |

|       | ment platform at Wide bandgap Semiconductor Group (SC2G)- Institut                                                                      |     |

|       | NEEL                                                                                                                                    | 43  |

| 2.12  | a) Impedance measurement configuration; b) Solartron modulab and the                                                                    |     |

|       | accessories                                                                                                                             | 43  |

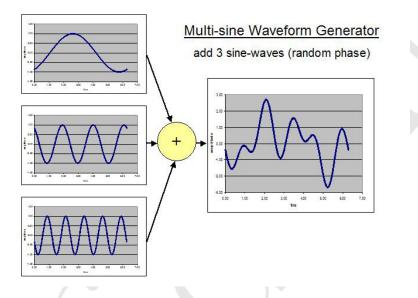

| 2.13  | Multisine waveforms concept of Solartron Modulab                                                                                        | 44  |

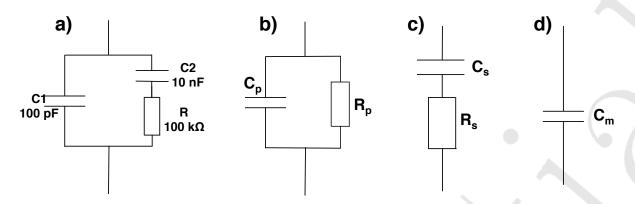

| 2.14  | a) The calibrated test circuit provided by Ametek Scientific Instruments;                                                               |     |

|       | b) $C_p - R_p$ circuit; c) $C_s - R_s$ circuit; d) $C_m$ circuit.                                                                       | 45  |

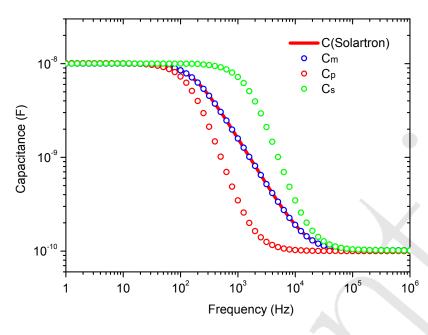

| 2.15  | Capacitance-frequency characteristic of the calibrated test circuit by using                                                            |     |

|       | different measurement configurations                                                                                                    | 46  |

| 2.16  | Band alignment input configuration for nextnano electrostatics simulation                                                               |     |

|       | [19]                                                                                                                                    | 46  |

| 2.17  | Typical Capacitance-Voltage characteristics of an ideal MOS capacitor .                                                                 | 47  |

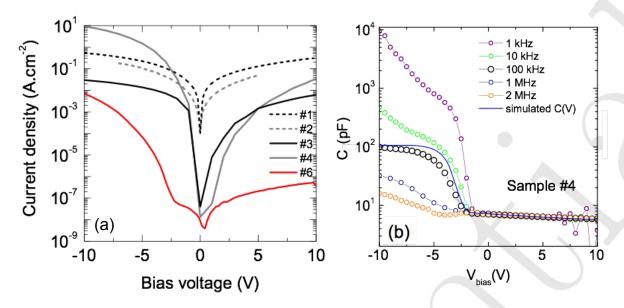

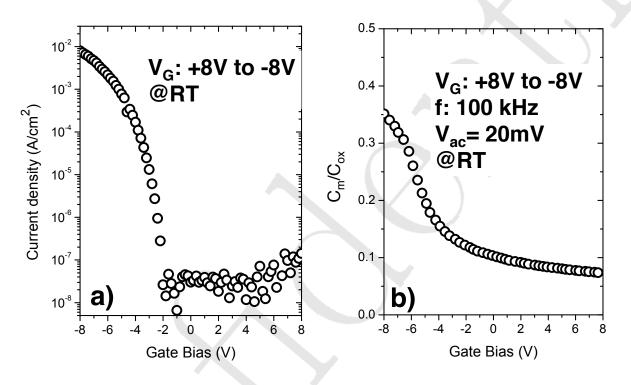

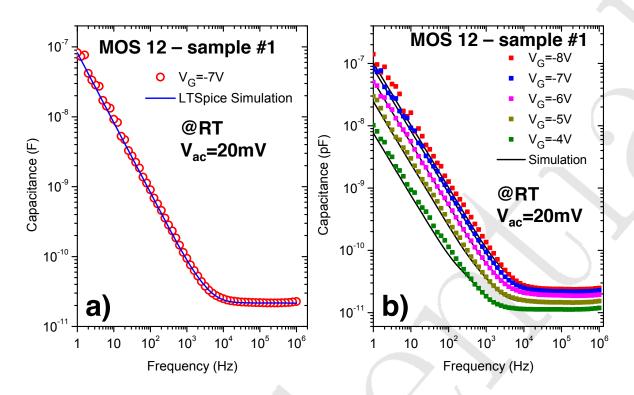

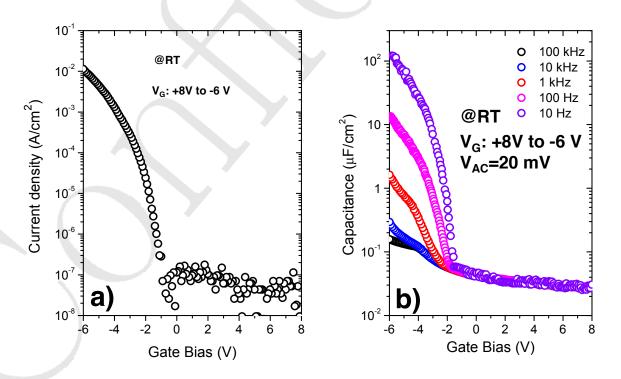

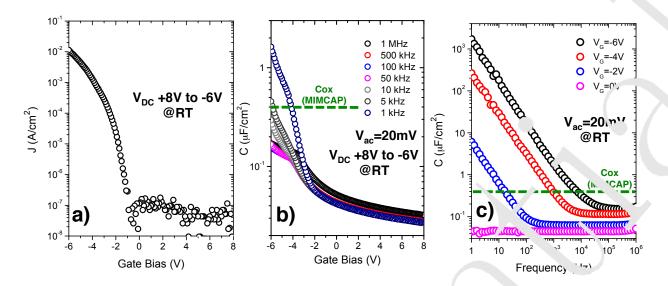

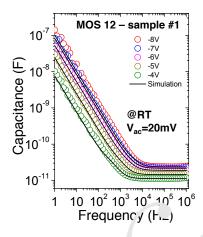

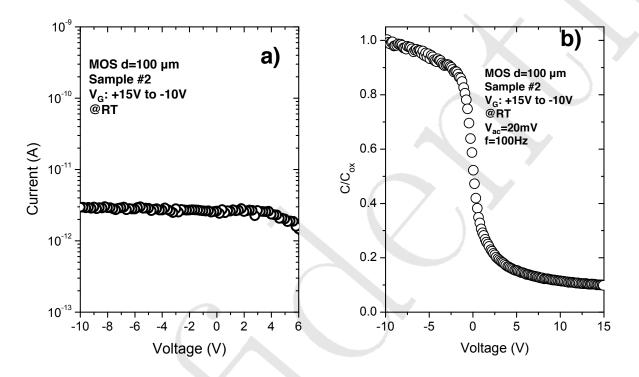

|       | a) Typical I-V characteristics of O-diamond MOS capacitors for $-8V \le$                                                                |     |

| 2.10  | $V_G \leq +8V$ ; b) C-V characteristics of O-diamond MOS capacitor measured                                                             |     |

|       | by biasing $V_G$ : +8V to -8V at $f=100$ kHz and $V_{ac}=20$ mV (MOS12 -                                                                |     |

|       | Sample #1)                                                                                                                              | 49  |

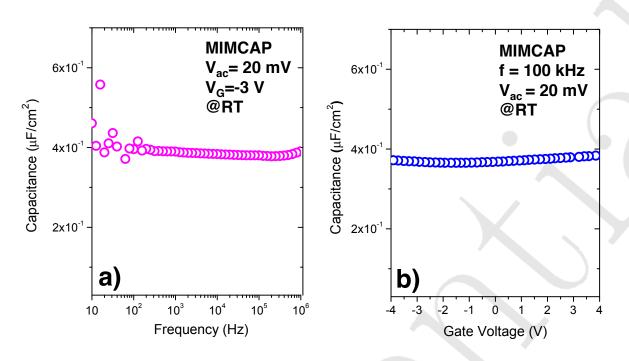

| 9.10  |                                                                                                                                         | 49  |

| 2.19  | Measured capacitance of MIM capacitor by a) Capacitance-Frequency at $V_{\rm exp} = 2V_{\rm e}$ b) Capacitance Valtage at $f = 100$ kHz | FO  |

| 0.00  | $V_G = -3V$ ; b) Capacitance-Voltage at $f=100$ kHz                                                                                     | 50  |

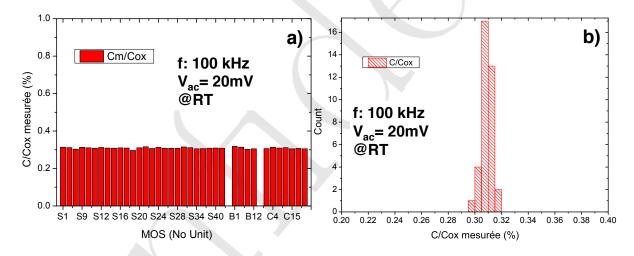

| 2.20  | Systematic measurements demonstrate the general and reproducible of the $C_{1}V_{2}$                                                    | 50  |

| 0.01  | C-V characteristics (Sample $\#3$ )                                                                                                     | 50  |

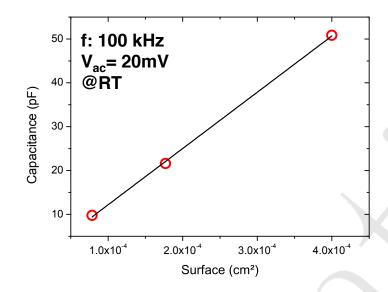

| 2.21  | Scaling of maximum measured capacitance versus the MOS capacitor sur-                                                                   | ~ . |

|       | face area (Sample $\#3$ )                                                                                                               | 51  |

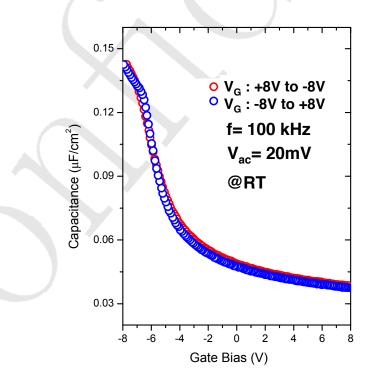

| 2.22  | The hysteresis C-V characteristics of sample 1 measured by switching the                                                                |     |

|       | bias direction, from $(+8V \text{ to } -8V)$ to $(-8V \text{ to } +8V)$ to estimate the mobile                                          |     |

|       | oxide charge (MOS45-Sample $\#1$ ).                                                                                                     | 51  |

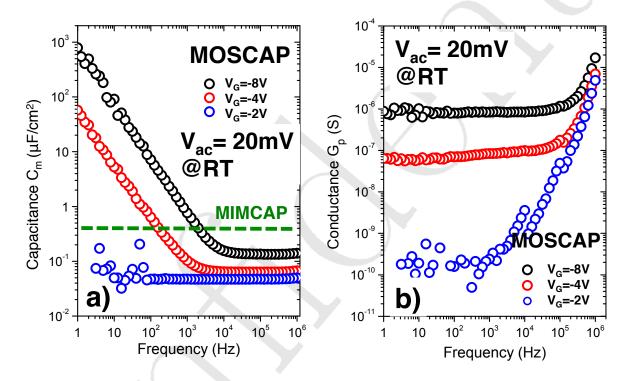

| 2.23  | a) Capacitance-frequency characteristics at $V_G$ =-8V, -4V, -2V; b) Conductan                                                          | ce- |

|       | frequency $(G_p - f)$ characteristics obtained from the same measurement                                                                |     |

|       | (MOS12-sample $\#1$ ).                                                                                                                  | 52  |

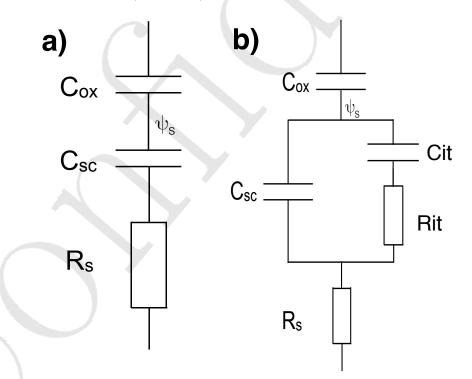

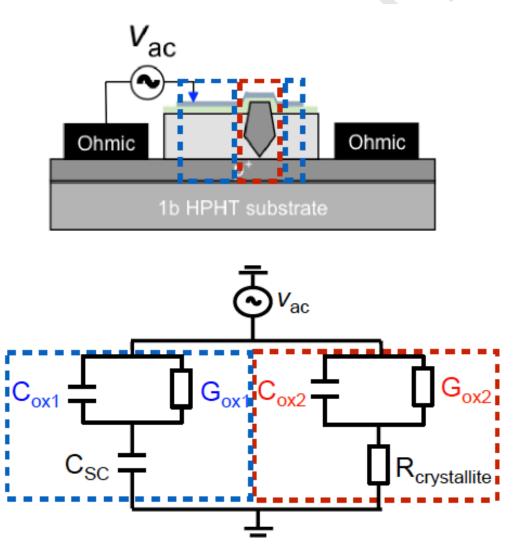

| 2.24  | Equivalent circuit of a MOS capacitor system in case of a) high frequency                                                               |     |

|       | regime; b) taking into account the contribution from interface states                                                                   | 53  |

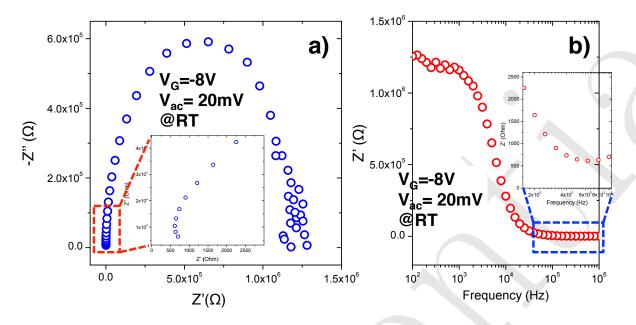

| 2.25  | a) Nyquist plot $(Re(Z) \text{ versus } Im(Z))$ of impedance measurements; b) Real                                                      |     |

|       | part impedance $Re(Z)$ versus frequency (MOS12-sample #1)                                                                               | 54  |

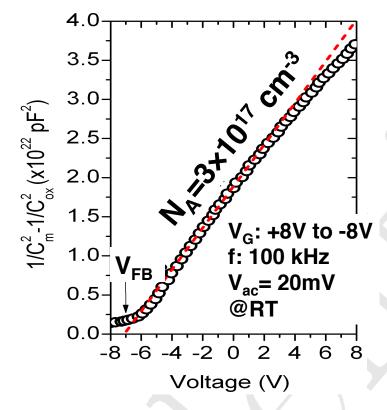

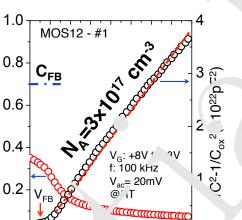

| 2.26  | Inverse square capacitance-voltage characteristics of O-diamond MOSCAP                                                                  |     |

|       | for extracting doping concentration (MOS12 - sample $\#1$ )                                                                             | 57  |

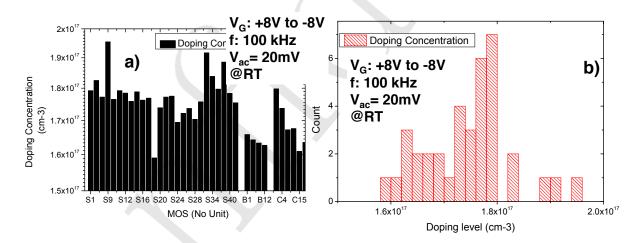

| 2.27  | Systematic measurement of the doping concentration by using the Schottky-                                                               |     |

|       | Mott plot (sample $\#3$ )                                                                                                               | 57  |

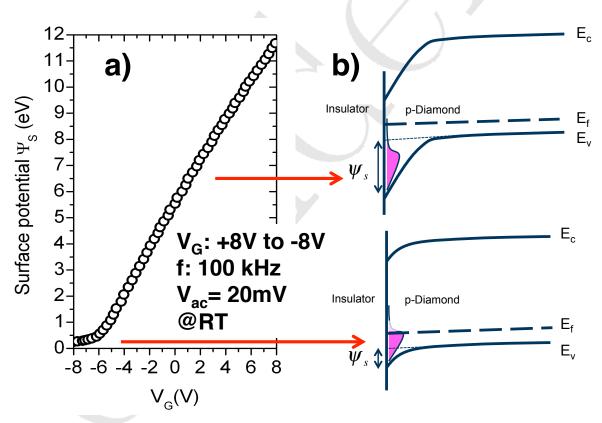

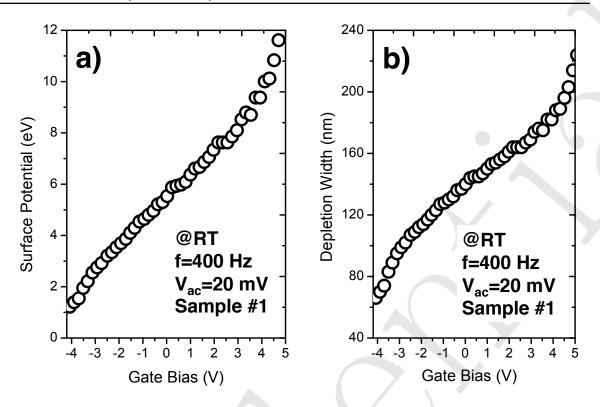

| 2.28  | a) Diamond surface potential variation with gate bias (MOS12 - sample                                                                   |     |

|       | #1); b) description corresponding to diamond Fermi level moving against                                                                 |     |

|       | gate bias in Figure 2.7a. Fermi level pinning effect is suggested due to                                                                |     |

|       | interface states (Magenta part in Fig. 2.7 b is the descriptive interface                                                               |     |

|       | states density)                                                                                                                         | 59  |

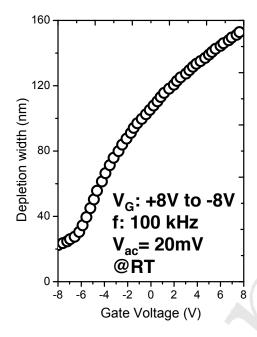

| 2.29  | Depletion region variation with gate bias (MOS12 - sample $\#1$ ).                                                                      | 61  |

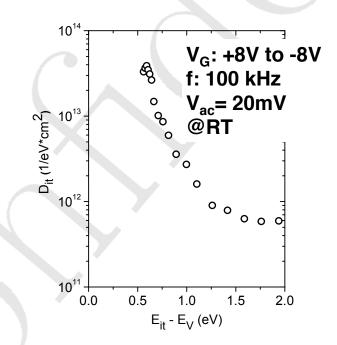

|       |                                                                                                                                         |     |

$\mathbf{v}$

| 2.30 | Interface density extracted from high frequency method (MOS 12- sample $(11)$                                                                                         | 61 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 0.01 | $\#1) \qquad \dots \qquad $                                   | 61 |

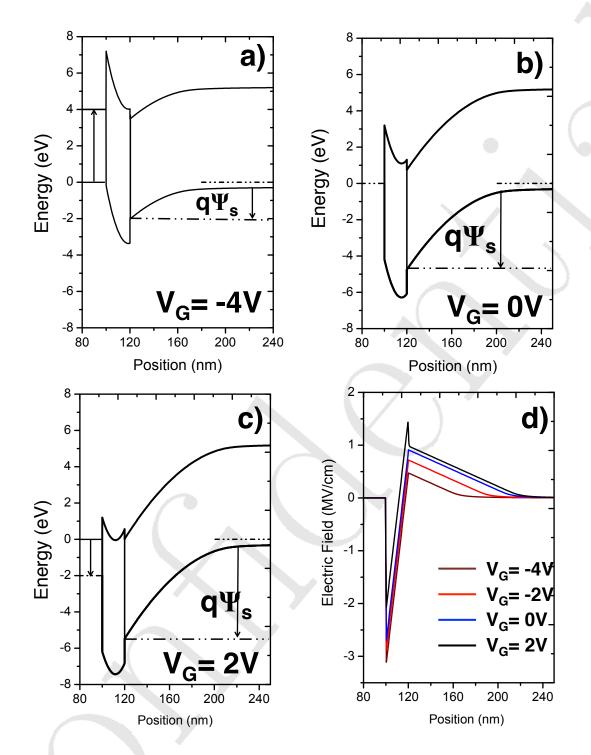

| 2.31 | Electrostatics band diagram of O-diamond MOS capacitor calculated by                                                                                                  |    |

|      | Nextnano <sup>3</sup> at different metal gate potentials a) When device is biased pos-<br>itivaly toward doep depletion; b) When device is under zero bias condition: |    |

|      | itively toward deep depletion; b) When device is under zero bias condition;<br>c) When device is negatively biased toward accumulation; d) Electric field             |    |

|      | distribution at different bias condition.                                                                                                                             | 63 |

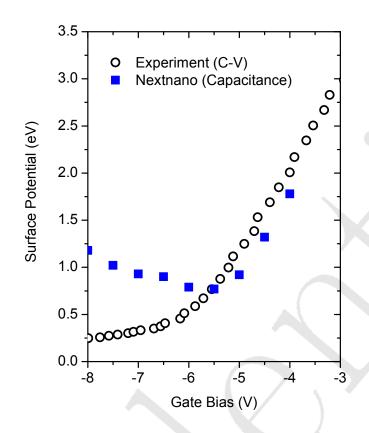

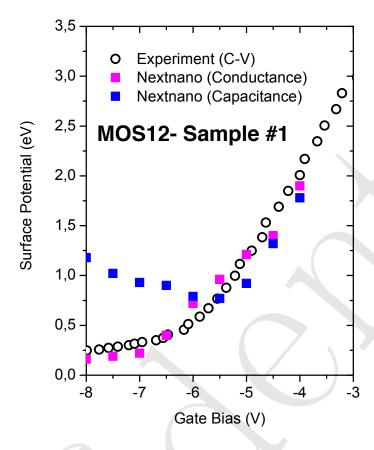

| 0.20 | Nextnano simulation result compared with experiment by mean of surface                                                                                                | 00 |

| 2.32 | potential (MOS12-sample $\#1$ )                                                                                                                                       | 64 |

| 0.00 |                                                                                                                                                                       | 04 |

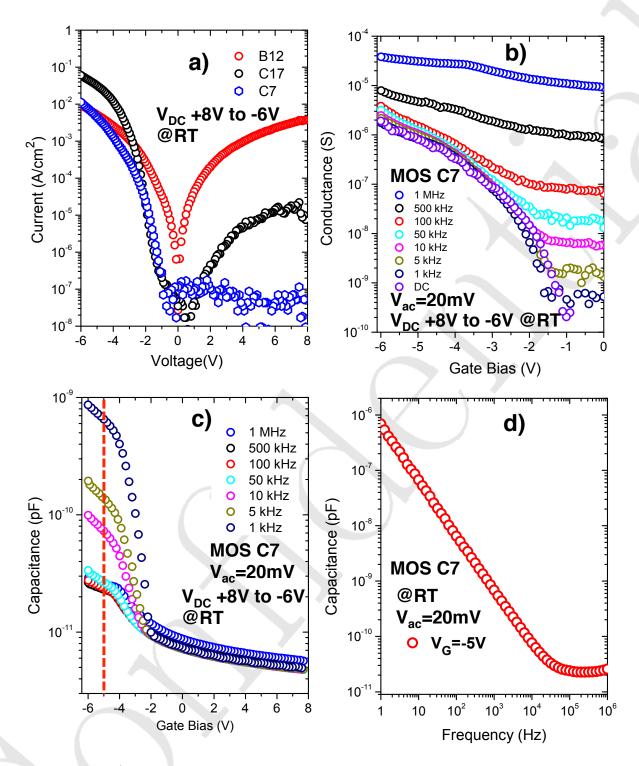

| 2.33 | a) Current-Voltage characteristics of three MOSCAP: B12, C7 and C17 of sample #3; b) Conductance-Voltage characteristics of MOS C7 measured                           |    |

|      | at different frequencies; b) Capacitance-Voltage characteristics of MOS C7 measured $(1, 2, 3, 5)$                                                                    |    |

|      | measured at different frequencies; d) Capacitance-frequency of MOS C7                                                                                                 |    |

|      | measured at $V_G = -5V$ .                                                                                                                                             | 69 |

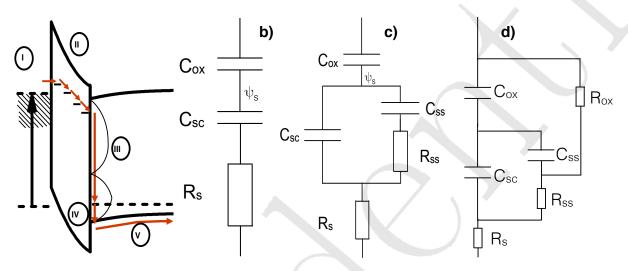

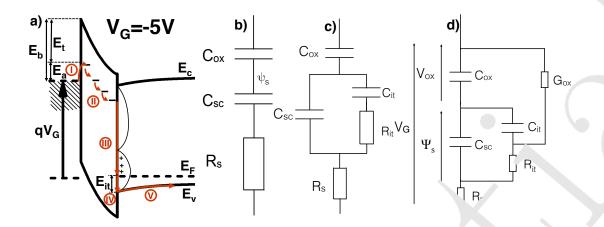

| 2.34 |                                                                                                                                                                       | 00 |

| 2.04 | neling from metal gate electrode to oxide gate, II. Hopping from traps to                                                                                             |    |

|      | traps in the oxide, III. Recombination to surface traps state, IV. Electron                                                                                           |    |

|      | from surface states emit to valence band or hole from valence band cap-                                                                                               |    |

|      | tured to interface states, V. Carriers drift in diamond epilayer to the back                                                                                          |    |

|      | gate contact. (b) Equivalent circuit of a MOS capacitor without interface                                                                                             |    |

|      | states and leakage current; (c) Equivalent circuit including interface states                                                                                         |    |

|      | and an ideal gate oxide without leakage current (d) Equivalent circuit                                                                                                |    |

|      | where the injected carriers from metal to interface states and the charges                                                                                            |    |

|      | transfer between interface states and valence band are taken into account.                                                                                            | 70 |

| 2.35 | Proposed current mechanism of different processes and its corresponding                                                                                               |    |

|      | energy level.                                                                                                                                                         | 72 |

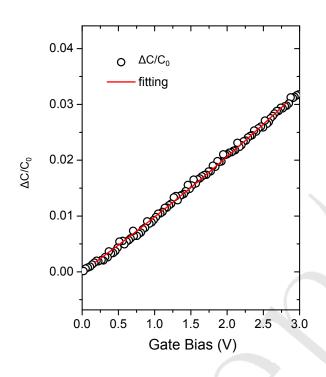

| 2.36 | DC Capacitance-Voltage non-linearity of MIM capacitors and the fitting                                                                                                |    |

|      | to extract hopping distance.                                                                                                                                          | 73 |

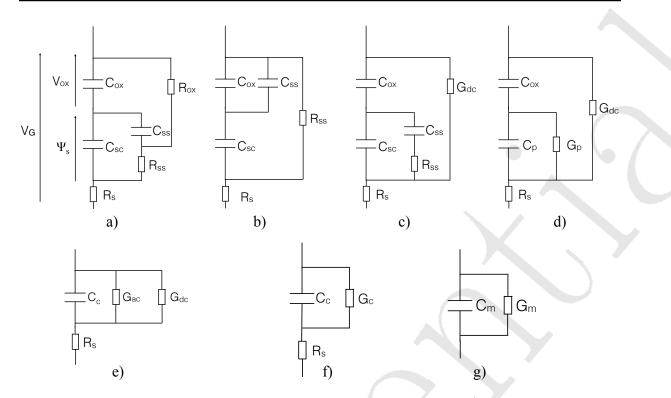

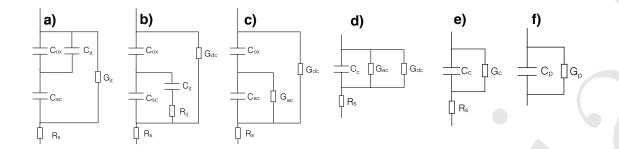

| 2.37 | Equivalent circuit for O-diamond MOS capacitor: a) general circuit with                                                                                               |    |

|      | gate carriers injected to single level interface states; b) approximated equiv-                                                                                       |    |

|      | alent circuit for interface states recombination limited; c) approximated                                                                                             |    |

|      | equivalent circuit for oxide tunneling limited; d)-g) step by step circuit                                                                                            |    |

|      | transform to achieve measurement circuit; d) Circuit transformed from circuit c); e) circuit transformed from circuit d); f) Circuit transformed                      |    |

|      | from circuit e); g) the parallel circuit for measured capacitance and mea-                                                                                            |    |

|      | sured conductance.                                                                                                                                                    | 78 |

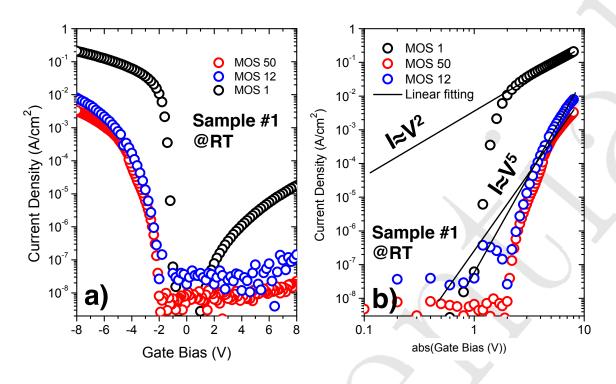

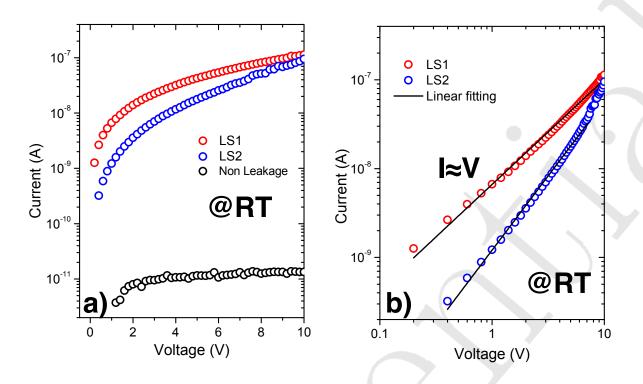

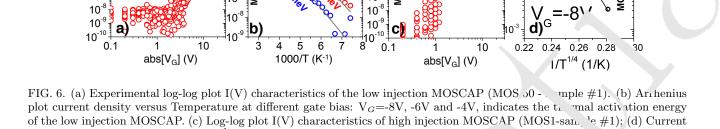

| 2.38 | a) Semi-log plot Current-Voltage characteristics of high injection MOS                                                                                                | 10 |

| 2.00 | capacitor and low injection MOS capacitor; b) the log-log plot to identify                                                                                            |    |

|      | the current-voltage power law from linear fitting (MOS 1 and MOS 50 -                                                                                                 |    |

|      | Sample $\#1$ ) @RT.                                                                                                                                                   | 79 |

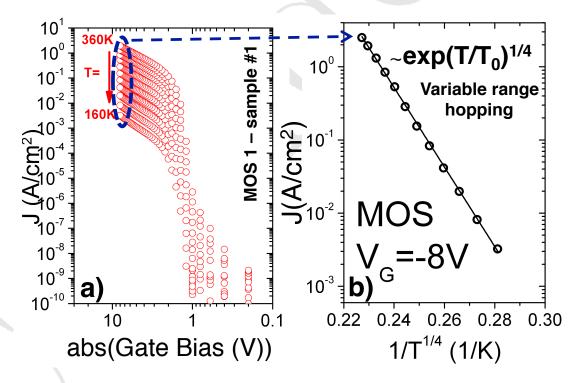

| 2.39 |                                                                                                                                                                       | -  |

|      | ferent temperatures ; b) Temperature dependence of gate leakage current                                                                                               |    |

|      | versus $\frac{1}{T^4}$ measured at $V_G = -8V$ in MOS 1-sample #1. The logJ versus                                                                                    |    |

|      | $\frac{1}{T^4}$ dependence well fitted by the straight line indicates a variable range                                                                                |    |

|      | hopping in the oxide.                                                                                                                                                 | 79 |

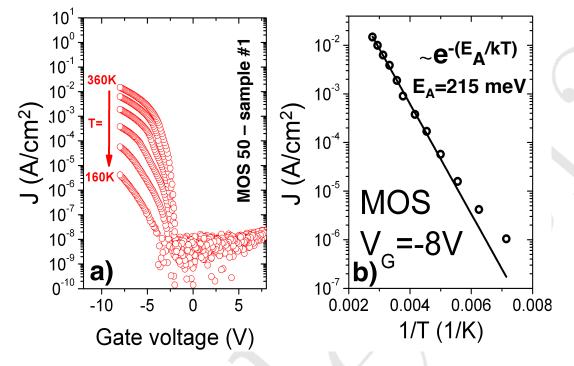

| 2.40 | a) I-V characteristics of low injection diode measured at different temperatures; b) Arrhenius plot of current density at different temperatures when $V_G$ =-8V indicates a thermal activation energy of 215 meV (MOS 50             |          |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | - sample #1)                                                                                                                                                                                                                          | 80       |

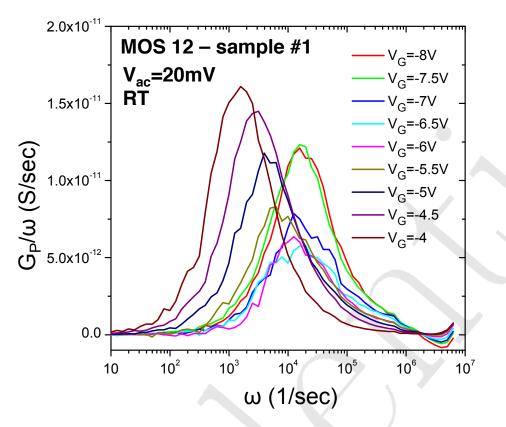

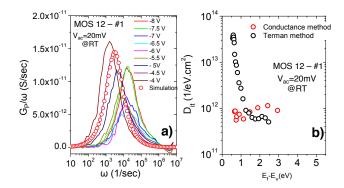

| 2.41 | Equivalent conductance $G_p/\omega$ at different gate bias measured at RT (MOS 12 - Sample #1).                                                                                                                                       | 81       |

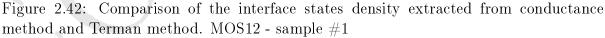

| 2.42 | Comparison of the interface states density extracted from conductance method and Terman method. MOS12 - sample $\#1$                                                                                                                  | 82       |

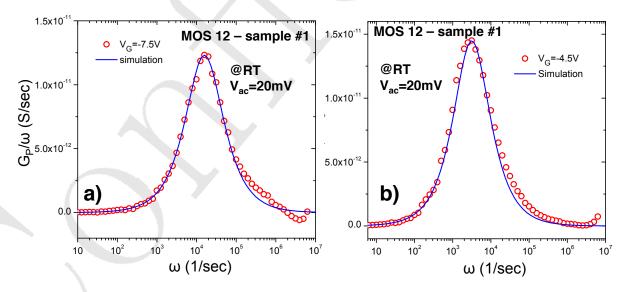

| 2.43 | Representative equivalent conductance $G_P/\omega$ and the simulation by using single level interface state model at $V_G = -7.5V$ and $V_G = -4.5V$ . (MOS                                                                           | 0.0      |

| 2.44 | 12 - Sample #1)                                                                                                                                                                                                                       | 83<br>85 |

| 2.45 | Semiconductor surface potential variation with gate bias determined from<br>experiment and from nextnano simulation by using interface states den-<br>sity extracted from Terman method (blue curve) and conductance method           | 00       |

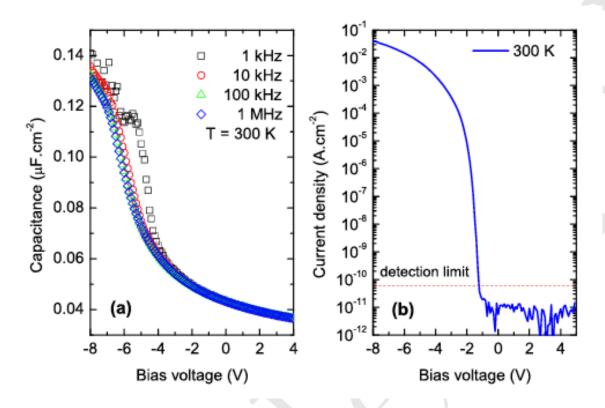

| 2.46 | (magenta curve)                                                                                                                                                                                                                       | 86       |

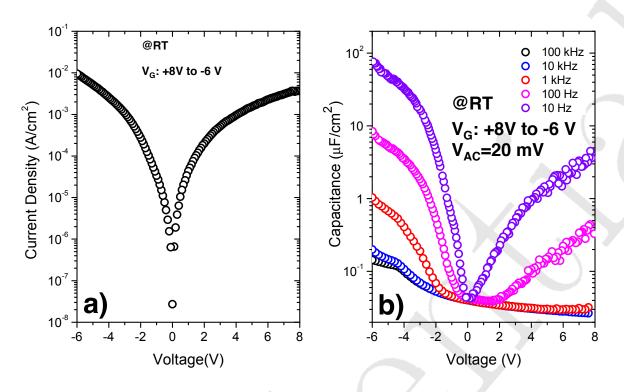

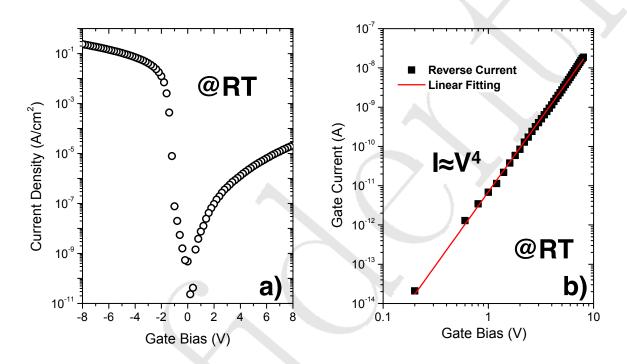

| 2.47 | quencies of O-diamond MOS capacitor presented by Kovi et al. [20] a) Current-Voltage and b) Capacitance-Voltage characteristics at different fraguencies of the MOS P12 (sample -#2)                                                  | 91<br>02 |

| 2.48 | frequencies of the MOS B12 (sample #3)                                                                                                                                                                                                | 92<br>92 |

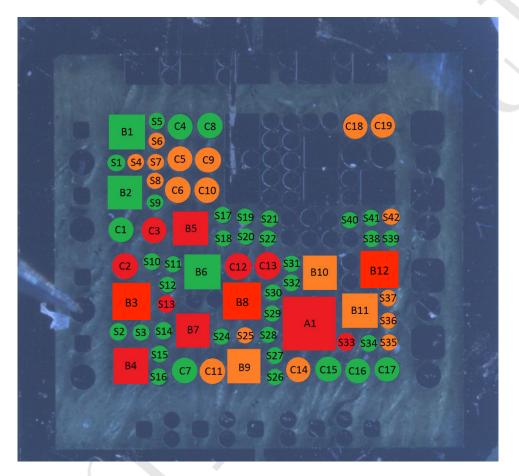

| 2.49 | Reverse current distribution of different MOS capacitors of sample #3. Green color indicates the MOS capacitors without reverse current (below $10^{-7}$ A/cm <sup>-2</sup> at positive bias). Red color indicates the MOS capacitors |          |

| 2.50 | with reverse current                                                                                                                                                                                                                  | 93<br>94 |

| 2.51 | a) Current-voltage characteristics of the MOS A1 - sample #1 (Figure 2.50) in semilog plot; b) Reverse current-voltage characteristic (gate under positive bias) in log-log plot (Sample #1).                                         | 94<br>95 |

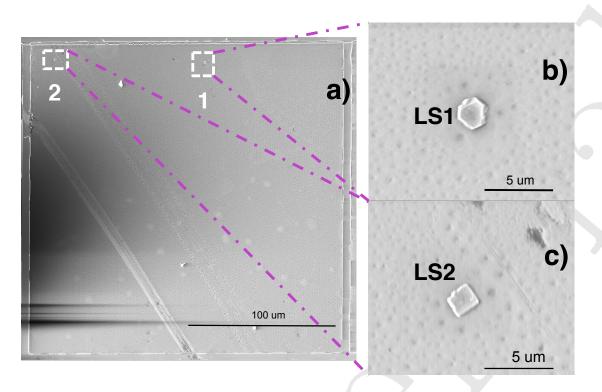

| 2.52 | a) FESEM image of the grid region corresponding to the A1 MOS capaci-<br>tor. b) the hexagonal defective leakage spot and c) the rectangle defective<br>leakage spot in the grid region (Sample $\#1$ ).                              | 96       |

| 2.53 | a) Current-Voltage characteristics of defective spots under positive bias in semilog plot; b) Current-Voltage characteristics of defective spots under positive bias in log-log plot (Sample $\#1$ ).                                 | 97       |

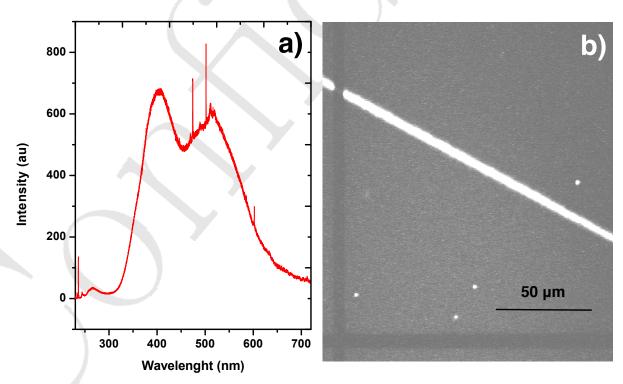

| 2.54 | a) CL spectrum of diamond substrate; b) CL mapping of diamond sub-<br>strate recorded at A-band luminescence (sample $\#1$ )                                                                                                          | 97       |

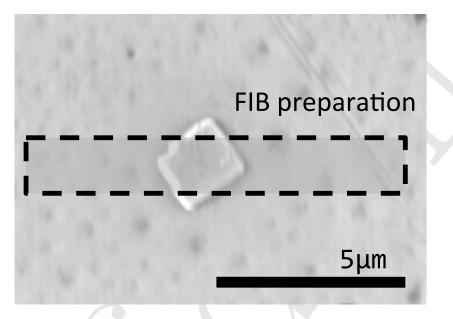

| 2.55 | FIB preparation for TEM measurement (Sample $\#1$ )                                                                                                                                                                                   | 98       |

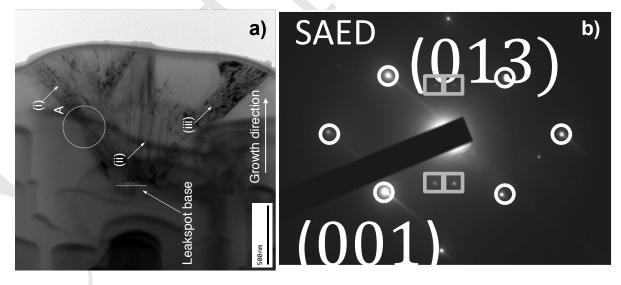

| 2.56  | a) TEM image of the defective leakage spot; b) Selected Area Electron                                    |      |

|-------|----------------------------------------------------------------------------------------------------------|------|

|       | Diffraction SEAD pattern obtained at position A of Figure 2.56a (sample                                  |      |

|       | #1).                                                                                                     | 98   |

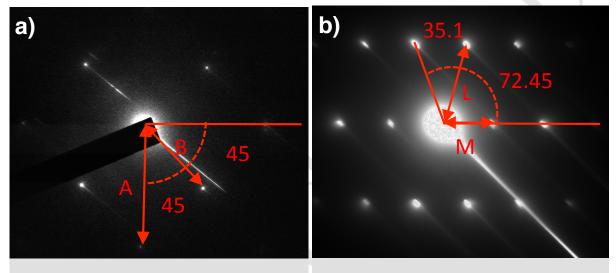

| 2.57  | Selected Area Electron Diffraction pattern obtained at a) Substrate; b)                                  |      |

|       | center of defective leakage spot (sample $\#1$ )                                                         | 99   |

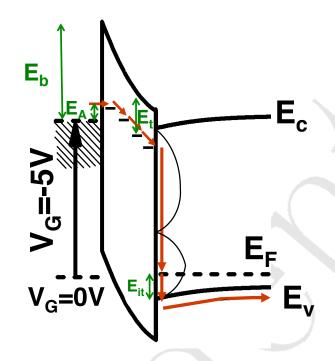

| 2.58  | Proposed current mechanism and its corresponding electrostatic band di-                                  | 00   |

| 2.00  |                                                                                                          | 100  |

| 2 50  | 0                                                                                                        | 100  |

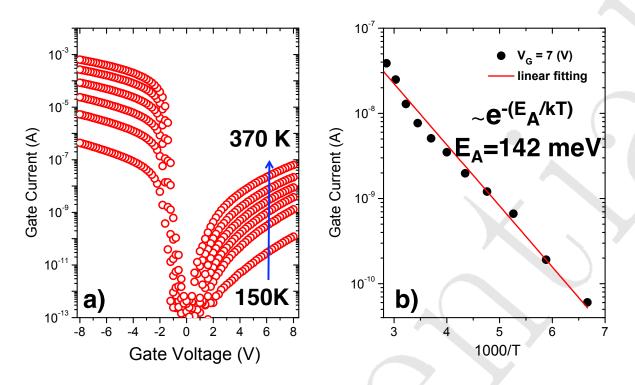

| 2.09  | a) Current-Voltage of MOS capacitor measured at different temperatures,                                  |      |

|       | ranging from 150K to 370K; b) Arrhenius plot of current measured at                                      |      |

|       | different temperatures when gate are biased at $V_G = 7V$ (MOS A1 - sample                               | 101  |

| 2.00  | #1).                                                                                                     | 101  |

| 2.60  | Proposed equivalent circuit which is corresponding to the current mecha-                                 |      |

|       | nism for simulating the a.c measurement.                                                                 | 102  |

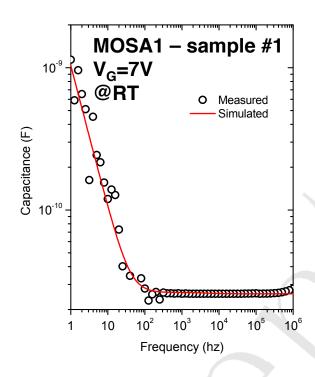

| 2.61  | Capacitance-frequency dependent in the reverse regime from a.c measure-                                  |      |

|       | ment (closed black circular) and simulation (red line)                                                   | 104  |

| 0.1   |                                                                                                          |      |

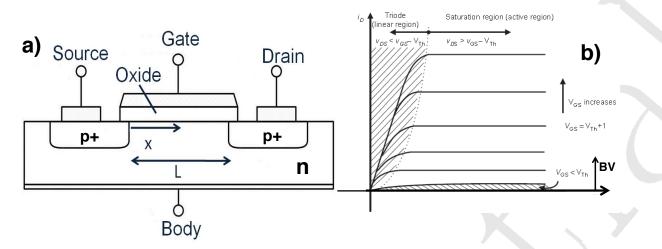

| 3.1   | a) Typical structure of an enhancement transistor; b) Typical electrical                                 | 107  |

|       | characteristics of a Transistor                                                                          | 127  |

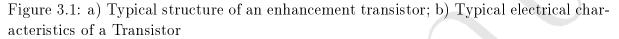

| 3.2   | Structure of a transistor on H-diamond. a) Cross-section structure; b)                                   | 105  |

|       | Plan view structure. Courtesy of Kawarada et al. [21]                                                    | 127  |

| 3.3   | Structure of the p-type diamond MESFET a) top view; b) cross-section.                                    |      |

|       | Courtesy of Umezawa et al. [16].                                                                         | 128  |

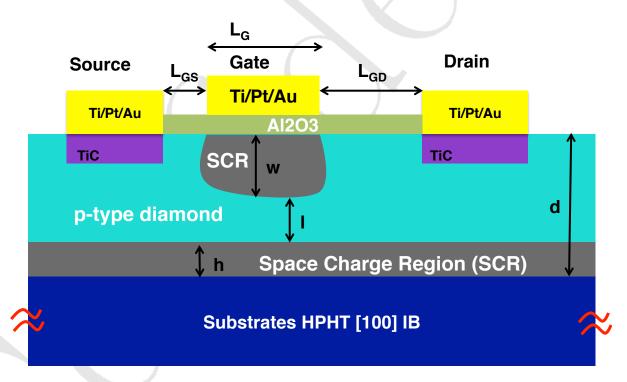

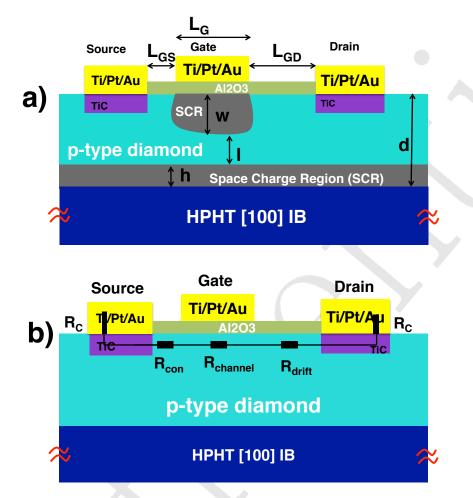

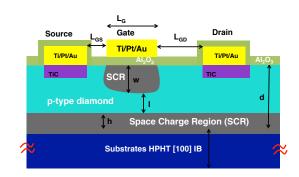

| 3.4   | Cross-section structural concept of depletion mode oxygen-terminated boron                               |      |

|       | doped diamond MOSFET                                                                                     | 129  |

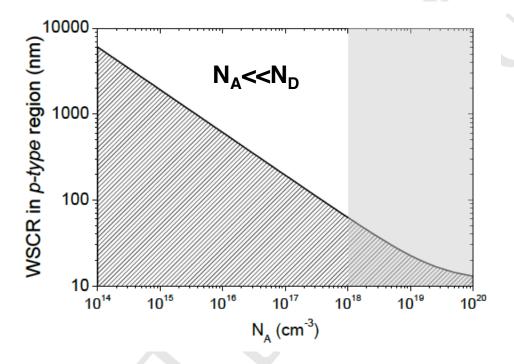

| 3.5   | Expected depletion region width between substrate and epilayer with dif-                                 |      |

|       | ferent doping concentration. Considering the 1b substrate is highly nitro-                               |      |

|       | gen doped (N <sub>D</sub> = $3 \times 10^{19}$ cm <sup>-3</sup> ). Courtesy of Chicot's PhD thesis [22]. |      |

|       |                                                                                                          | 130  |

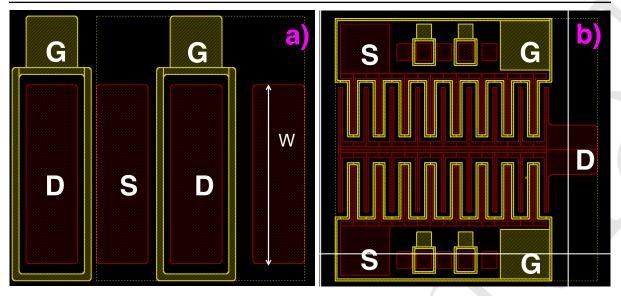

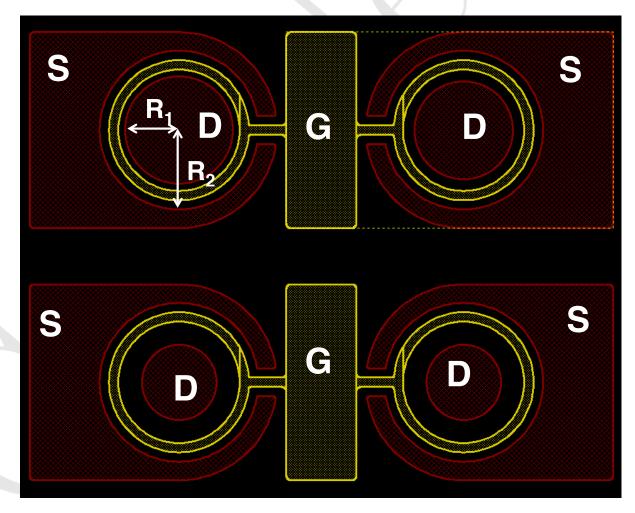

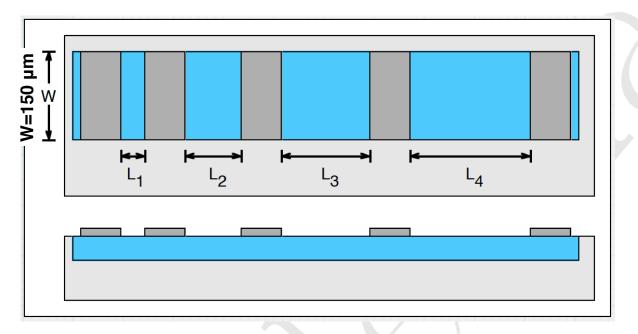

| 3.6   | Transistor structure target high ON-states current a) Stripe structure; b)                               |      |

|       | Fingers structure.                                                                                       | 132  |

| 3.7   | Circular structure transistor target high OFF-state breakdown voltage.                                   | 132  |

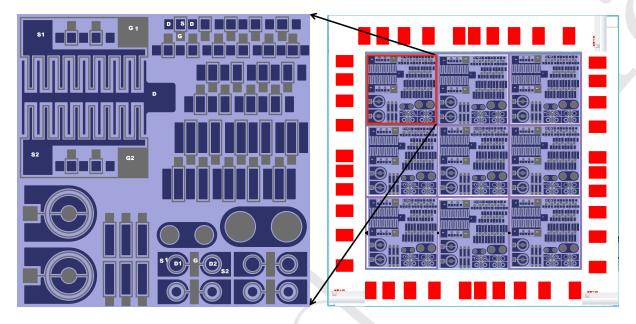

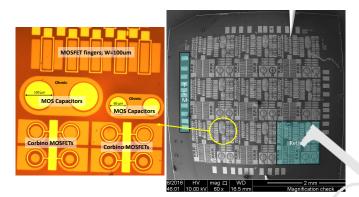

| 3.8   | a) A complete structure of a reticule included different device structures                               |      |

|       | and test device; b) The full mask structure includes $3 \times 3$ reticules and the                      |      |

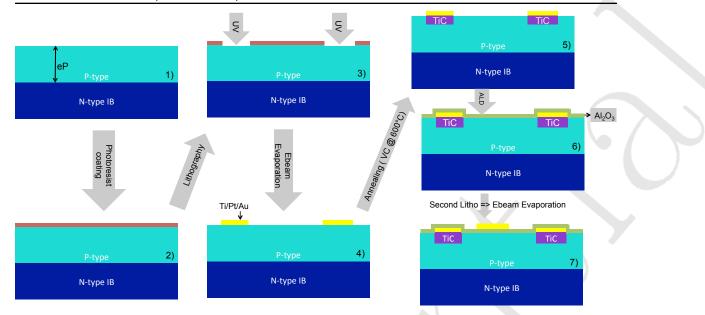

|       | TLM                                                                                                      | 133  |

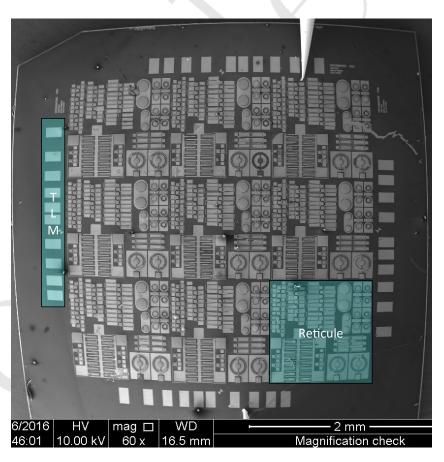

| 3.9   | The flow chart fabrication process of depletion mode O-diamond MOSFET.                                   | .134 |

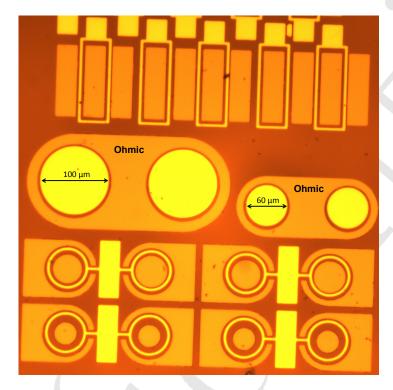

|       | Top view FESEM photograph of the completed boron doped diamond                                           |      |

| 0.10  | MOSFET and test devices (sample $\#1$ )                                                                  | 134  |

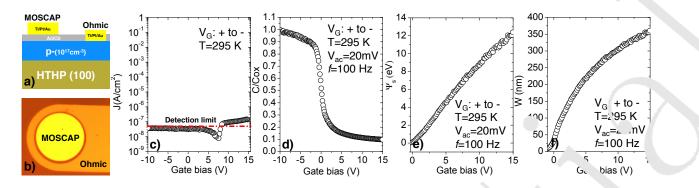

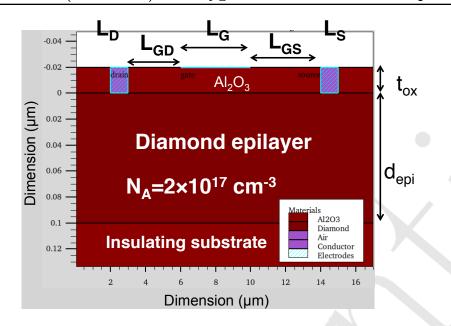

| 3 11  | Silvaco simulation configuration with diamond epilayer thickness of $100$                                | 101  |

| 0.11  | nm and doping concentration of $2 \times 10^{17} cm^{-3}$ , oxide thickness of 20 nm,                    |      |

|       | $L_{GS} = 4\mu m$ , $L_G = 4\mu m$ , $L_{GD} = 3\mu m$ , $L_D = 1\mu m$ , $L_S = 1\mu m$ . Substrate     |      |

|       | were considered as an insulator to minimize the simulation time constant.                                | 136  |

| 2 1 9 |                                                                                                          |      |

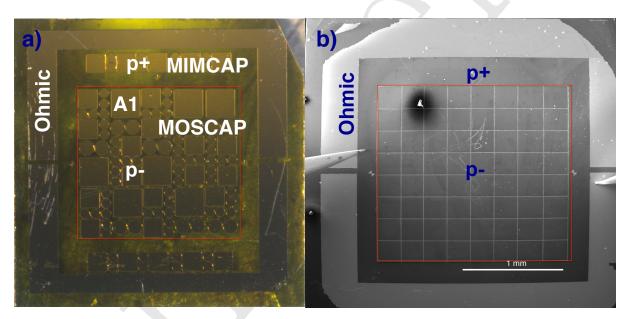

|       | Top view of MOS capacitor structures captured by optical microscope.                                     | 137  |

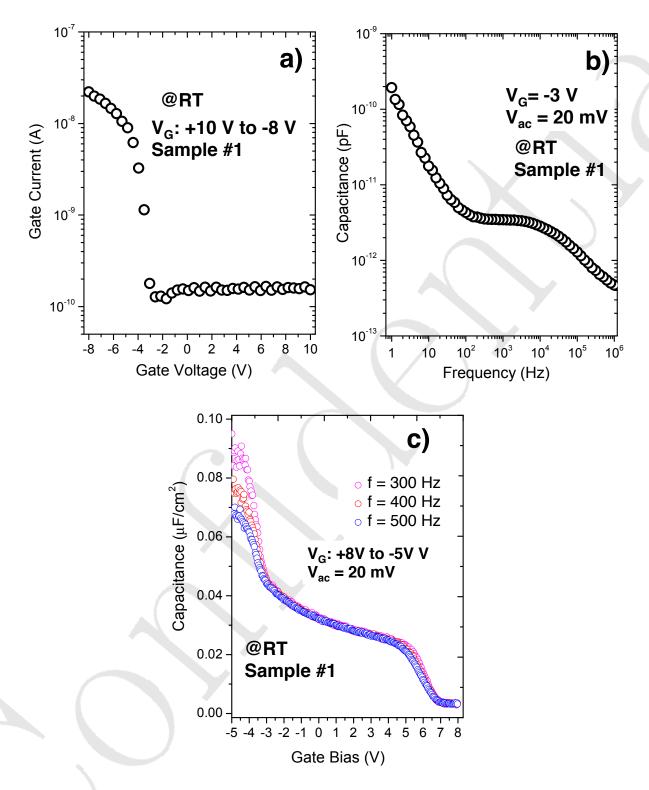

| ა.13  | Electrical characteristics of MOS capacitor test devices on the diamond                                  |      |

|       | transistor sample: a) Current-Voltage characteristic; b) Capacitance-frequence                           | зy   |

|       | characteristic at $V_G = -3 V$ ; Capacitance-Voltage characteristics mea-                                | 190  |

|       | sured at different frequency. (Sample $\#1$ - @RT)                                                       | 138  |

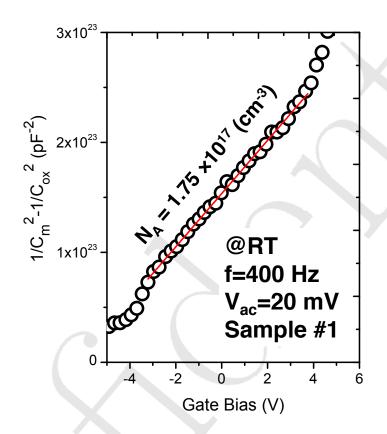

| 3.14 | Reciprocal square capacitance plotted with gate bias to extract effective doping concentration (sample $\#1$ at RT)                                                               | 139   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 3.15 | a) Surface potential variation with metal gate bias; b) Corresponding de-                                                                                                         |       |

|      | pletion width variation with gate bias.                                                                                                                                           | 140   |

|      | · ·                                                                                                                                                                               | 141   |

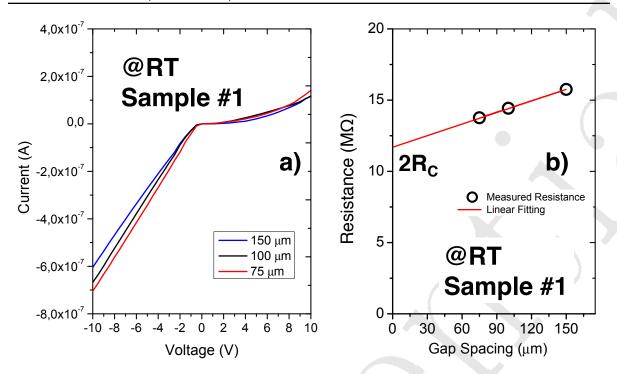

| 3.17 | a) Typical IV characteristics of the Ohmic contact after annealing at 600°C;                                                                                                      |       |

|      | b) Measured resistance as function of electrode spacing with linear fitting                                                                                                       | 140   |

| 0.10 | to extract sheet resistance and contact resistance                                                                                                                                | 142   |

| 3.18 | The relationship between compensation concentration $N_D$ and resistivity<br>of boron doped diamond at different dopant concentration $N_A$ . Courtesy                            |       |

|      | to Traore et al. $[10]$                                                                                                                                                           | 143   |

| 3 10 | The relationship between compensation concentration $N_D$ and hole con-                                                                                                           | 140   |

| 0.15 | centration of boron doped diamond at different dopant concentration $N_A$ .                                                                                                       |       |

|      | Courtesy to Traore et al. $[10]$                                                                                                                                                  | 143   |

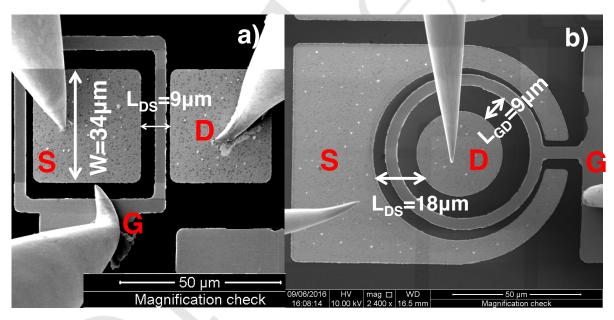

| 3.20 | FESEM image of the boron doped diamond MOSFET. a) Stripe struc-                                                                                                                   |       |

|      | ture MOSFET target high ON-state current; b) Circular structure target                                                                                                            |       |

|      | high OFF-state breakdown voltage. Device dimension parameters were                                                                                                                |       |

|      | taken from mask design. Measurements have been performed at RT in the                                                                                                             |       |

|      | vacuum chamber of FESEM system.                                                                                                                                                   | 144   |

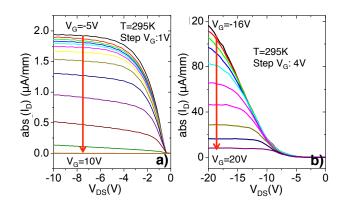

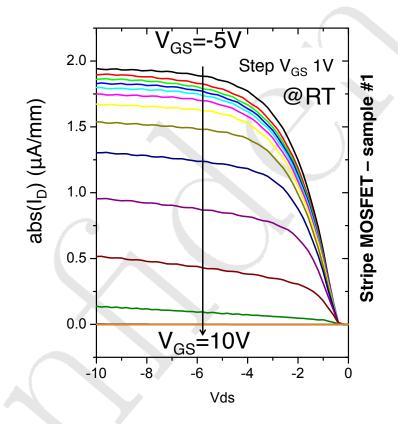

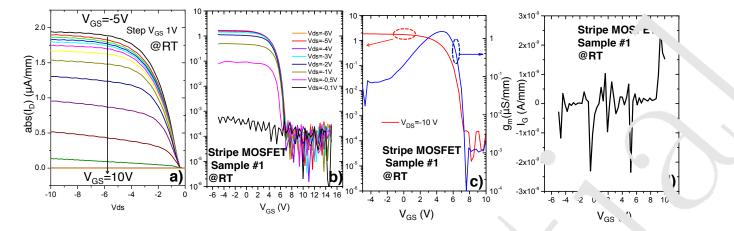

| 3.21 | Transfer characteristics of the stripe transistor -sample $\#1$ measured by                                                                                                       |       |

|      | sweeping $V_{DS}$ from 0V to -10V at different fixed gate bias $V_{GS}$ ( $V_{DS}$ : -5V                                                                                          |       |

|      | to 10 V, step $V_{GS}$ : 1V). The measurements have been performed at RT in the measurement of FESEM system.                                                                      | 145   |

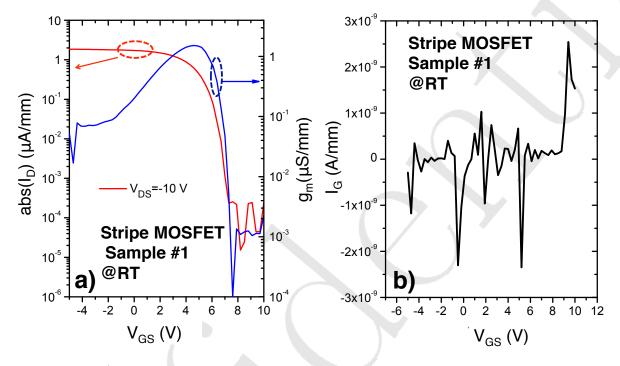

| ว คค | in the vacuum chamber of FESEM system                                                                                                                                             | 145   |

| 3.22 | sweeping $V_{GS}$ from +10V to -5V at a fixed $V_{DS}$ ( $V_{DS}$ =-10V); b) Gate                                                                                                 |       |

|      | leakage current $I_{GS}$ measured instantaneously with transfer $I_D$ . The mea-                                                                                                  |       |

|      | surement have been performed at RT in the vacuum chamber of FESEM                                                                                                                 |       |

|      | system.                                                                                                                                                                           | 146   |

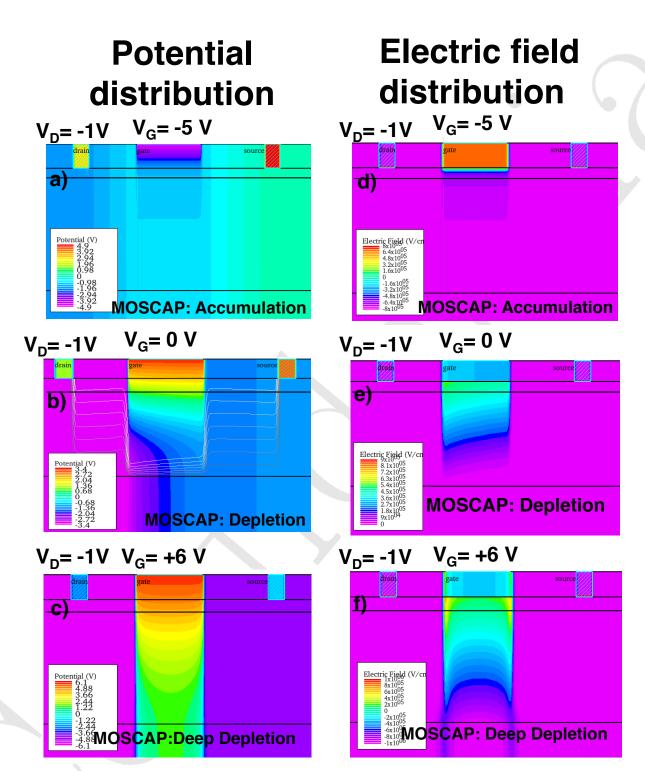

| 3.23 | Silvaco Atlas simulation the potential distribution at different gate bias                                                                                                        |       |

|      | a) $V_{GS}=-5 V$ ; b) $V_{GS}=0 V$ ; c) $V_{GS}=6 V$ ; and electric field distribution                                                                                            |       |

|      | at three different gate bias: a) $V_{GS}=-5$ V ; b) $V_{GS}=0$ V; c) $V_{GS}=6$ V.                                                                                                |       |

|      | Simulation configuration were presented in Fig. 3.11 and temperature is                                                                                                           | 1 4 7 |

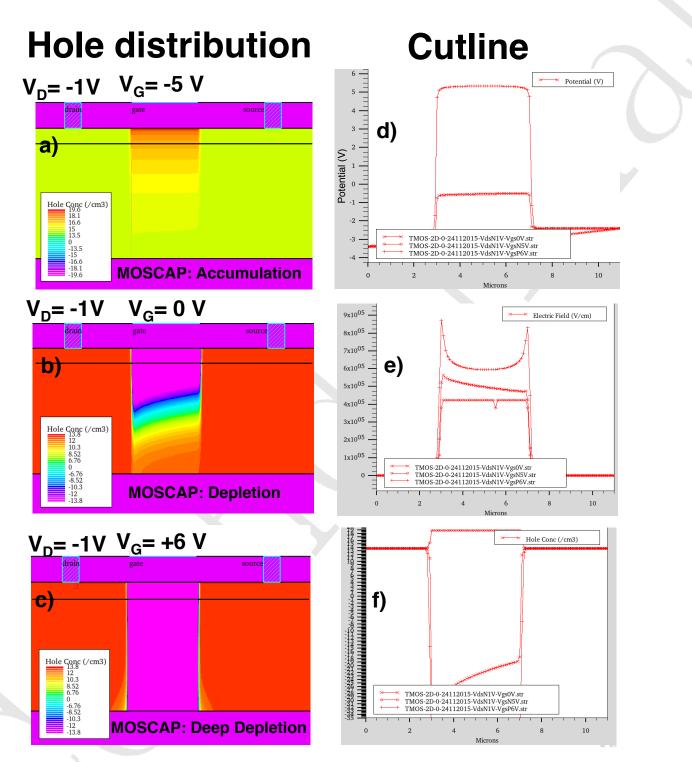

| 9.94 | assumed at RT.                                                                                                                                                                    | 147   |

| 3.24 | Silvaco Atlas simulation of the hole distribution at different gate bias a)<br>$V_{i} = 5 V_{i}$ ; b) $V_{i} = 0 V_{i}$ ; c) $V_{i} = -6 V_{i}$ ; Cutling of the d) potential dia |       |

|      | $V_{GS}=-5$ V ; b) $V_{GS}=0$ V; c) $V_{GS}=6$ V; Cutline of the d) potential dis-<br>tribution; e) electric field distribution; f) hole distribution. Simulation                 |       |

|      | configuration were presented in Fig. 3.11 and temperature is assumed at                                                                                                           |       |

|      | RT                                                                                                                                                                                | 148   |

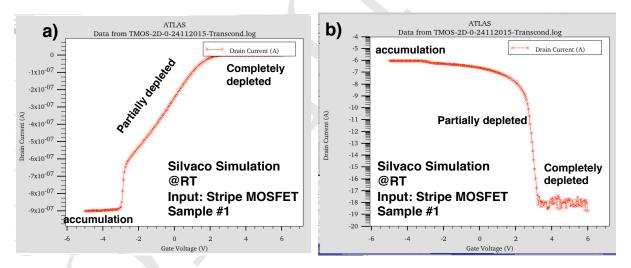

| 3.25 | Silvaco simulation of drain current $(I_D)$ for $V_{DS} = -1V$ at different gate                                                                                                  |       |

|      | bias $(V_{GS} : -5V \text{ to } +6V)$ in a) linear scale; b) semilog scale. Simulation                                                                                            |       |

|      | configuration is identical with the Fig. 3.11 and temperature is kept at RT.                                                                                                      | 149   |

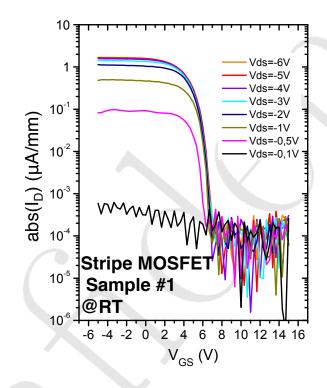

| 3.26 | a) Transfer characteristics of the stripe transistor -sample $\#1$ measured by                                                                                                    |       |

|      | sweeping $V_{GS}$ from +14V to -5V at different fixed $V_{DS}$ ( $V_{DS}$ : -0.1V to -                                                                                            |       |

|      | 6V). The measurement have been performed at RT in the vacuum chamber                                                                                                              | 150   |

|      | of FESEM system.                                                                                                                                                                  | 150   |

| 3.27 | a) Descriptive cross-section of the depletion mode diamond MOSFET; b)                    |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | Equivalent Source to Drain resistance of the MOSFET corresponding to                     |     |

|      | the cross-section and non-negligible contact resistance.                                 | 151 |

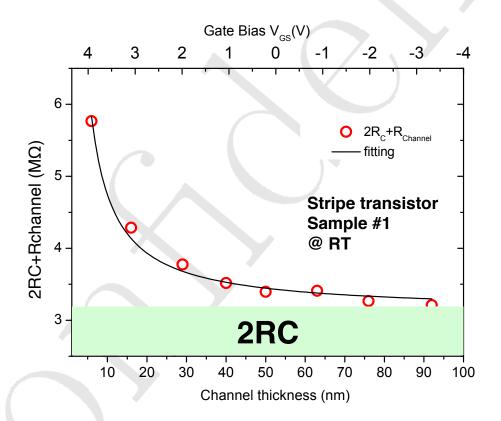

| 3.28 | $2\mathrm{RC+R}$ channel versus channel thickness (the width of neutral region under     |     |

|      | gate) at different $V_{GS}$ (top x-axis)                                                 | 152 |

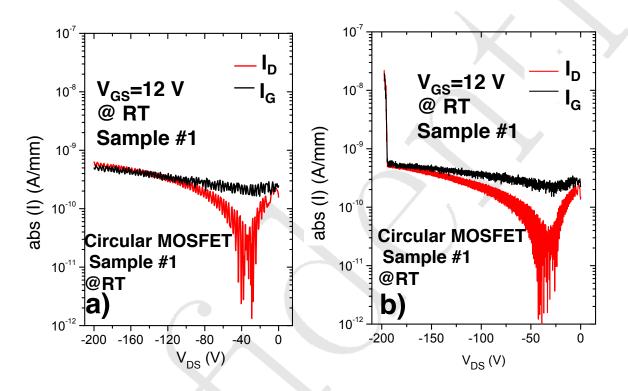

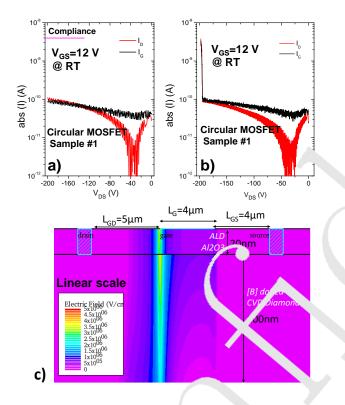

| 3.29 | Breakdown voltage measured with $V_{GS}$ =-12 V and drain voltage sweeping               |     |

|      | in negative bias voltage to $V_{DS} = -200 \text{ V}$ (limit of the apparatus): a) first |     |

|      | cycle breakdown measurement; b) 5th cycle breakdown measurement.                         | 154 |

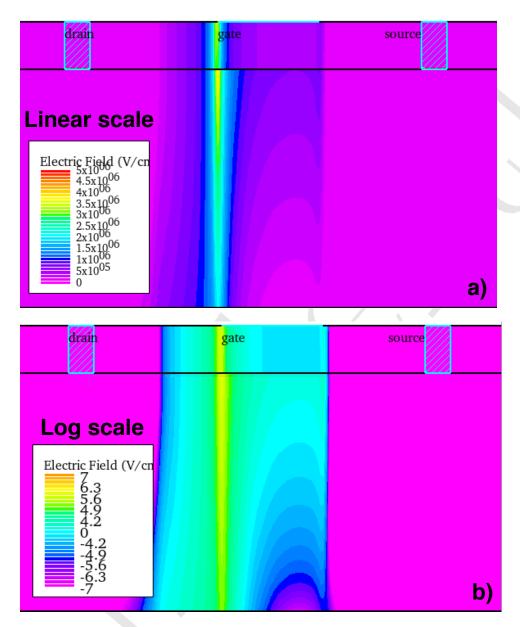

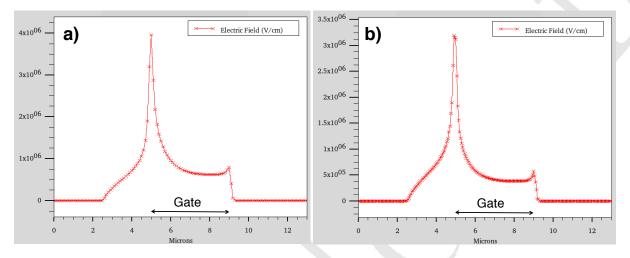

| 3.30 | Silvaco Atlas simulation critical electric field for $V_{DS}$ =-200 V without im-        |     |

|      | pact ionization a) in linear scale; b) logarithm scale                                   | 155 |

| 3.31 | Cut line of Silvaco Atlas simulation critical electric field for $V_{DS}$ =-200V         |     |

|      | without impact ionization a) In diamond epilayer; b) In oxide layer $\ldots$             | 156 |

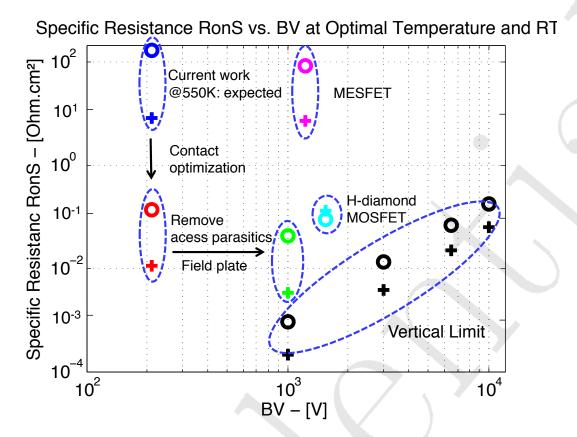

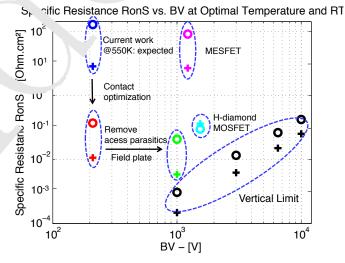

| 3.32 | Specific ON-resistance versus breakdown voltage of different diamond tran-               |     |

|      | sistors                                                                                  | 157 |

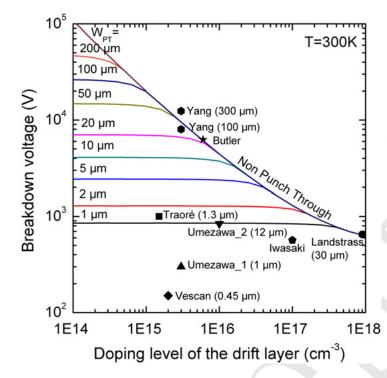

| 3.33 | Specific ON-resistance vs. different breakdown voltage of NPT boron                      |     |

|      | doped diamond devices. Courtesy to Chicot et al. [23]                                    | 159 |

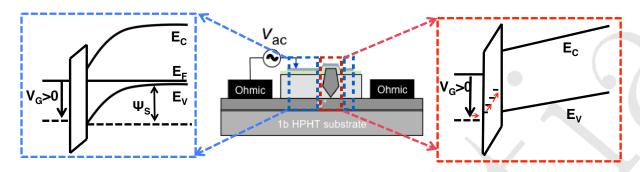

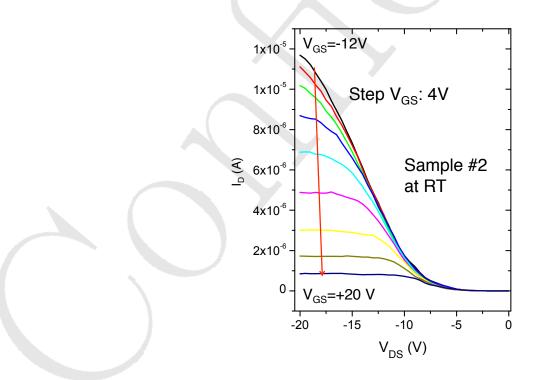

| 3.34 | Electrostatics gate controlled the current between Source and Drain at                   |     |

|      | different gate bias. Transistor sample $#2$                                              | 161 |

| 3.35 | a) DC leakage current and b) Capacitance-voltage characteristic measured                 |     |