# Design of mechanisms for filtering and isolations of industrial protocols

Peter Rouget

# ▶ To cite this version:

Peter Rouget. Design of mechanisms for filtering and isolations of industrial protocols. Micro and nanotechnologies/Microelectronics. Université Montpellier, 2019. English. NNT: 2019MONTS027 . tel-02446150v1

# HAL Id: tel-02446150 https://theses.hal.science/tel-02446150v1

Submitted on 20 Jan 2020 (v1), last revised 20 Jan 2020 (v2)

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE MONTPELLIER

En : Génie Informatique, Automatique et Traitement du signal

École doctorale : Information, Structures, Systèmes

Unité de recherche : Systèmes Automatiques et Microélectroniques

# Étude et conception de mécanismes de rupture et de filtrage de protocoles industriels

# Présentée par Peter ROUGET Le 29 août 2019

# Sous la direction de Lionel TORRES et Pascal BENOIT

Devant le jury présidé par

Sébastien PILLEMENT, Professeur, Université de Nantes

Et composé de

David HELY, Maître de Conférence HDR, Grenoble INP

Guy GOGNIAT, Professeur, Université Bretagne Sud

Lionel TORRES, Professeur, Université de Montpellier

Pascal BENOIT, Maître de Conférence HDR, Université de Montpellier

Directeur de Thèse

Benoît BADRIGNANS, Directeur Technique, Seclab

Examinateur

Examinateur

# **Abstract**

With the rise of Industry 4.0, many infrastructures were forced to open their networks to the Internet, mainly to meet the growing need for supervision and remote control. But where these infrastructures were previously isolated, spared from external threats, their opening has caused the emergence of new threats, particularly network ones, which were not addressed and present serious risks.

Network cybersecurity solutions, like Firewalls, Intrusion Detection Systems or Intrusion Protection Systems are commonly used to address the concern of industrial infrastructures cybersecurity. However the trend of relying on software-based systems to ensure network protection brought to light the vulnerabilities of these systems, due to their inherent software implementation. Furthermore, the industry is tied to its own specificities (low-latency, support of specific network protocols), which are rarely covered by common IT solutions.

The main goal of this thesis is to study the use of FPGA-based devices applied to cybersecurity for industrial networks. Either as support for software-based security applications, or to perform critical network analysis operations. First it presents the industrial context, with control systems, their architectures, needs, implementation rules, specific protocols and also gives two examples of control systems as they can be found in the industry. Then it highlights the security problematic, with a description of the most common threats, case studies about their applications and impact in a control system, and discussions on the state of the art counter-measures available on the market. Through the establishment of a security target, it points the vulnerability of software elements and operating systems as well as the lack of process state aware security analysis.

To address these issues, we propose, through a first contribution, to enforce the security of the software system by taking advantage of existing FPGA's protection mechanisms. Finally, to answer specific application threats, we introduce an implementation of a patterns matching architecture with time and operational-process awareness, on FPGA. This thesis was conducted in collaboration between the Montpellier computer science, robotic and microelectronic laboratory (LIRMM) and the SECLAB company.

# Résumé

Avec l'essor de l'Industrie 4.0, de nombreuses infrastructures ont été contraintes d'ouvrir leurs réseaux à Internet, principalement pour répondre au besoin croissant de supervision et de contrôle à distance. Mais là où ces infrastructures étaient auparavant isolées, épargnées par les menaces extérieures, leur ouverture a provoqué l'émergence de nouveaux risques, en particulier à travers le réseau, potentiellement sérieux et qui ne sont pas couverts.

Les solutions de cybersécurité, comme les pare-feux, les systèmes de détection d'intrusion ou les systèmes de protection contre les intrusions, sont couramment utilisés pour répondre aux préoccupations liées à la cybersécurité des infrastructures industrielles. Cependant, la tendance à se fier aux systèmes logiciels pour assurer la protection du réseau a mis en lumière les vulnérabilités de ces systèmes, en raison de leurs implémentations logicielles inhérentes. En outre, l'industrie est liée à ses propres spécificités (faible latence, support de protocoles réseaux spécifiques), qui sont rarement couvertes par les solutions informatiques communes.

L'objectif principal de cette thèse est d'étudier l'utilisation de dispositifs FPGA appliqués à la cybersécurité pour les réseaux industriels, soit comme support pour des applications de sécurité logicielle, soit pour effectuer des opérations critiques d'analyse réseau. Ce travail présente d'abord le contexte industriel, avec les systèmes de contrôle, leurs architectures, leurs besoins, les règles de mise en œuvre, les protocoles spécifiques et donne également deux exemples de systèmes de contrôle comme on peut en trouver dans l'industrie. Il met ensuite en lumière les problèmes de sécurité, avec une description des menaces les plus courantes, des études de cas sur leurs applications et leurs impacts dans un système de contrôle, et des discussions sur les contre-mesures de pointe disponibles sur le marché. Suite à l'établissement d'une cible de sécurité, nous mettrons en évidence la vulnérabilité des éléments logiciels et des systèmes d'exploitation. Nous verrons aussi comment l'absence d'analyse de sécurité tenant compte de l'état des processus peut mener à certaines vulnérabilités.

Pour pallier à ces problèmes, nous proposons, par une première contribution, de renforcer la sécurité des systèmes logiciels en tirant parti des mécanismes de protection existants du FPGA. Enfin, pour répondre à des menaces applicatives spécifiques, nous proposons la mise en œuvre d'une architecture de reconnaissance de motifs, sur FPGA, prenant en considération le cadre temporel et l'état du procédé industriel. Cette thèse a été réalisée en collaboration avec le Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier (LIRMM) et la société SECLAB.

# Acknowledgements

First of all, I would like to thanks my advisors, Pascal Benoit and Lionel Torres for their support and guidance throughout this Ph.D. I have learned a lot from conducting researches as from giving presentations. Thanks to Benoît Badrignans for his accompaniment during this research work and his help on many technical problems.

I thank all my coworkers who believed in me and all those who did not believe it, thank you for this warm atmosphere that allowed me to stay motivated.

Finally, I thank my family: my beloved wife Melody, my parents Christine and Daniel, my step mother Lina for their unfailing love and encouragements, and my friends: Loic, Guillaume, Yohan, Geoffroy and Mathieu for all these good moments of laughter.

This thesis was brought and supported by SECLAB whom I thank for this opportunity and for the resources they put at my disposal.

# **Contents**

| 1 | Intr                  | oduction                                                             | 1  |  |  |

|---|-----------------------|----------------------------------------------------------------------|----|--|--|

| 2 | 2 Industrial Networks |                                                                      |    |  |  |

|   | 2.1                   | Definitions                                                          | 5  |  |  |

|   |                       | 2.1.1 Information Technology (IT) versus Operational Technology (OT) | 5  |  |  |

|   |                       | 2.1.2 Critical Network                                               | 12 |  |  |

|   | 2.2                   | Industrial Communication Protocols                                   | 14 |  |  |

|   |                       | 2.2.1 ModBus                                                         | 15 |  |  |

|   |                       | 2.2.2 S7                                                             | 17 |  |  |

|   |                       | 2.2.3 BacNet                                                         | 19 |  |  |

|   |                       | 2.2.4 OPC-UA                                                         | 21 |  |  |

|   |                       | 2.2.5 Profinet                                                       | 21 |  |  |

|   |                       | 2.2.6 Synthesis                                                      | 22 |  |  |

|   | 2.3                   | Threats                                                              | 23 |  |  |

|   |                       | 2.3.1 Incident Scenarios                                             | 26 |  |  |

|   | 2.4                   | Case Study                                                           | 28 |  |  |

|   |                       | 2.4.1 Electric Post                                                  | 28 |  |  |

|   |                       | 2.4.2 Bottle filling line                                            | 32 |  |  |

|   | 2.5                   | Protections                                                          | 35 |  |  |

|   |                       | 2.5.1 Isolation                                                      | 35 |  |  |

|   |                       | 2.5.2 Firewall                                                       | 36 |  |  |

|   |                       | 2.5.3 IPS / IDS                                                      | 37 |  |  |

|   | 2.6                   | Threat Model and Security Target                                     | 38 |  |  |

|   |                       | 2.6.1 Denelis                                                        | 41 |  |  |

|   | 2.7                   | Problematic                                                          | 46 |  |  |

|   |                       | 2.7.1 Secure Boot                                                    | 17 |  |  |

|   |                       | 2.7.2 Application Filtering                                          | 18 |  |  |

| 3 | Secu                  | ure Boot                                                             | 19 |  |  |

|   | 3.1                   | Operating system boot on FPGA                                        | 50 |  |  |

|   | 3.2                   | Threat Model                                                         | 52 |  |  |

|   | 3.3                   | Related Works                                                        | 53 |  |  |

|   |                       | 3.3.1 Operating System Security                                      | 53 |  |  |

|   |                       | J                                                                    | 54 |  |  |

|   | 3.4                   | SecBoot - Secure boot using embedded boot parts                      | 54 |  |  |

|   |      | 3.4.1 Concept                                         | 54 |

|---|------|-------------------------------------------------------|----|

|   |      | 3.4.2 Architecture                                    | 55 |

|   |      | 3.4.3 Results                                         | 56 |

|   | 3.5  | Discussion                                            | 58 |

| 4 | Vers | tile patterns matching for application analysis       | 60 |

|   | 4.1  | ndustrial Protocol Common Model and Protocol Breakage | 61 |

|   | 4.2  | Operational-Process Aware Filtering                   | 64 |

|   |      |                                                       | 66 |

|   | 4.3  |                                                       | 66 |

|   |      | -                                                     | 67 |

|   |      |                                                       | 70 |

|   |      | 4.3.3 State Automaton                                 | 72 |

|   |      | 4.3.4 Synthesis                                       | 74 |

|   | 4.4  | Versatile Operational-Process Aware pattern matching  | 74 |

|   |      | 4.4.1 Concept                                         | 75 |

|   |      | 4.4.2 Architecture                                    | 82 |

|   |      | 4.4.3 Experimentation                                 | 89 |

|   |      | 4.4.4 Results                                         | 96 |

|   |      | 1.4.5 Discussion                                      | 99 |

| 5 | Con  | usion 1                                               | 01 |

| 6 | Pub  | cations relative to the study                         | 06 |

|   | 6.1  | nternational Conferences                              | 06 |

# **List of Figures**

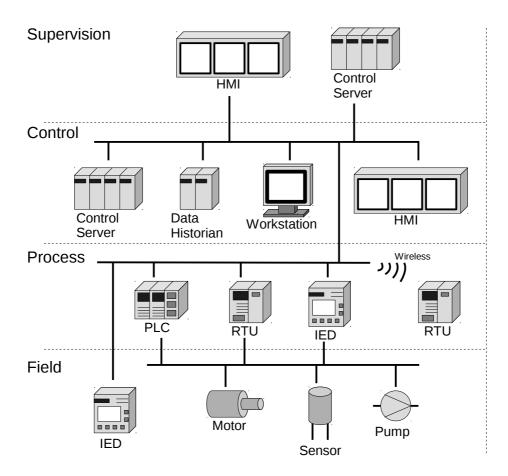

| 2.1  | Industrial Network Architecture                                         | 8  |

|------|-------------------------------------------------------------------------|----|

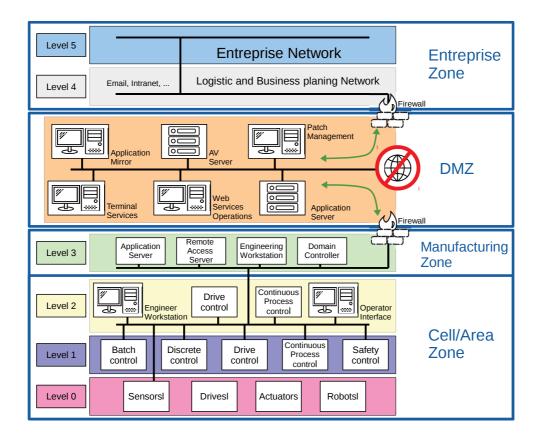

| 2.2  | Purdue Model                                                            | 10 |

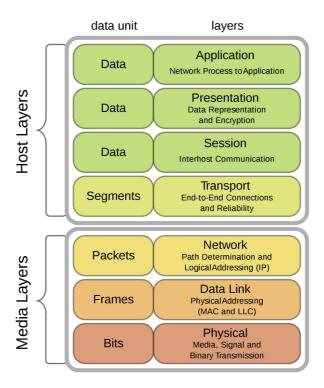

| 2.3  | OSI Model                                                               | 15 |

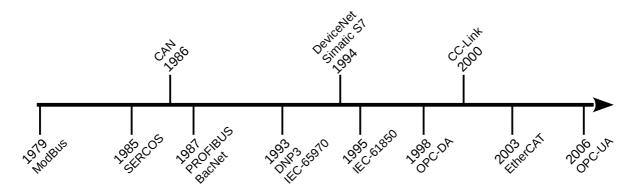

| 2.4  | Chronology of major Industrial Protocols release                        | 16 |

| 2.5  | ModBus TCP Application Data Unit                                        | 17 |

| 2.6  | S7 TCP Application Data Unit                                            | 19 |

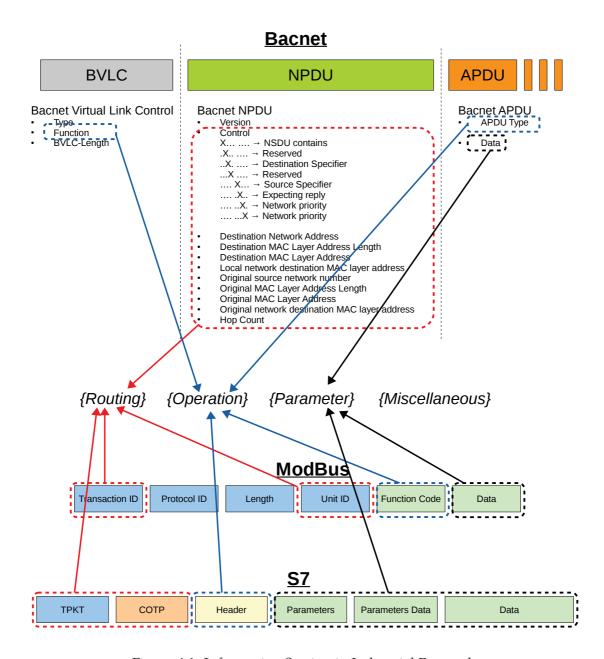

| 2.7  | Bacnet IP packet structure                                              | 21 |

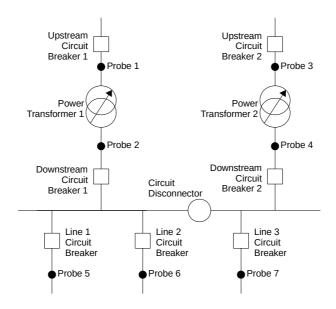

| 2.8  | Example of an electrical Post                                           | 29 |

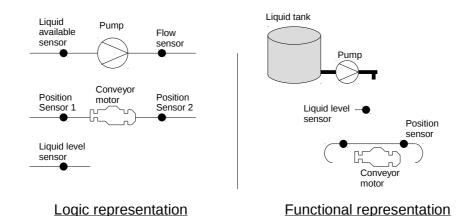

| 2.9  | Example of Bottle Filling Line                                          | 33 |

| 2.10 |                                                                         | 42 |

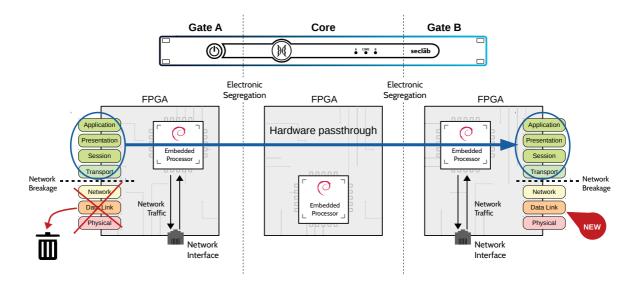

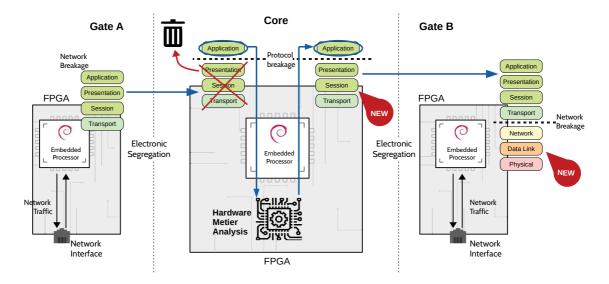

| 2.11 | DENELIS high level Architecture                                         | 42 |

|      | Research Platform high level Architecture                               | 45 |

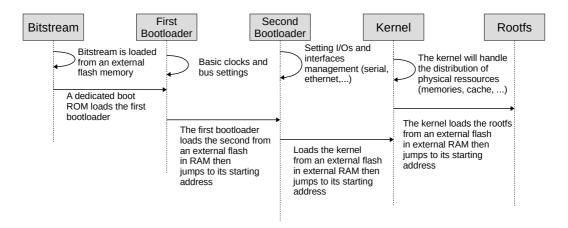

| 3.1  | Boot chain of a FPGA based System on Chip                               | 51 |

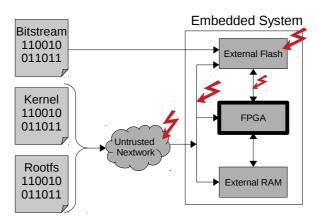

| 3.2  | Threat Model                                                            | 53 |

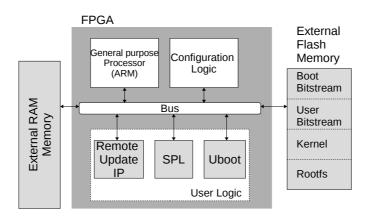

| 3.3  | FPGA boot elements locations                                            | 55 |

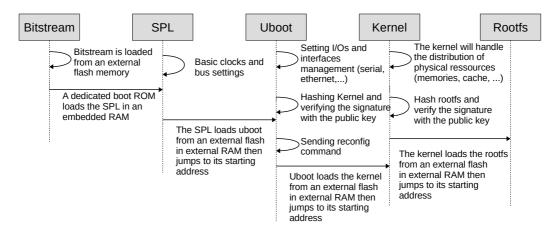

| 3.4  | Secure Boot Chain with FPGA reconfiguration and kernel verification     | 57 |

| 4.1  | Information Sorting in Industrial Protocols                             | 64 |

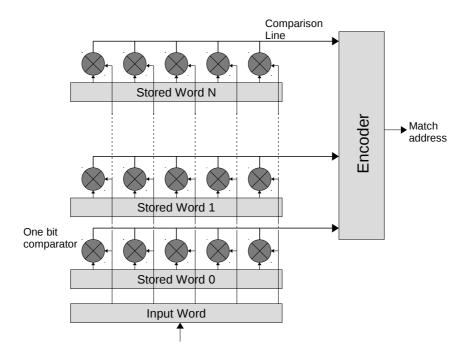

| 4.2  | Typical Architecture of a Content Addressable Memory                    | 68 |

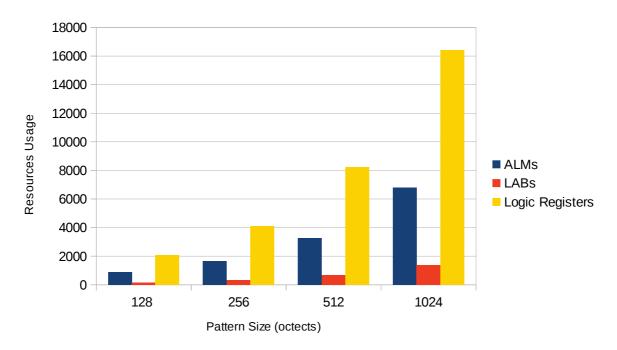

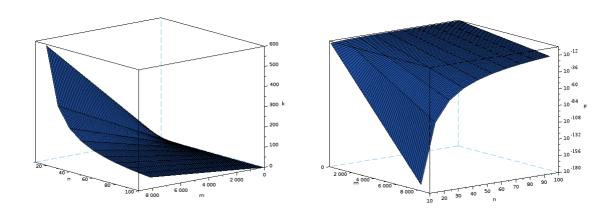

| 4.3  | Logic Resources Usage for one pattern in accord to the CAM words size . | 69 |

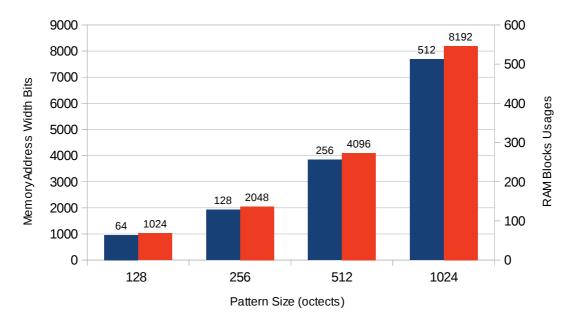

| 4.4  | Memory Resources Usage according to the CAM words size                  | 70 |

| 4.5  | k and p function of m and n                                             | 71 |

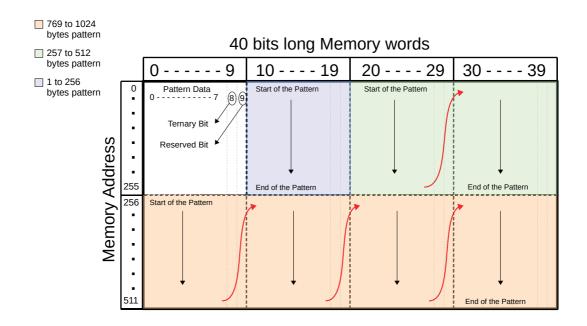

| 4.6  | Patterns storage and representation in RAM                              | 77 |

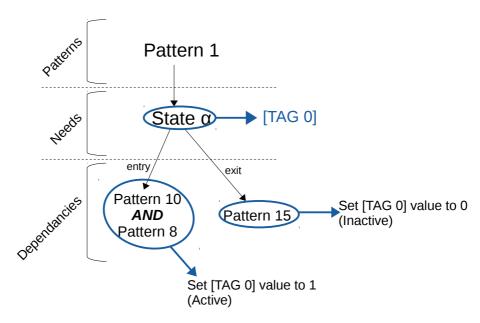

| 4.7  | TAGs definition and usage                                               | 79 |

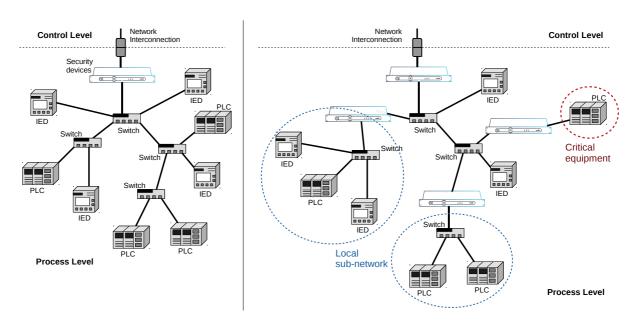

| 4.8  | Network Architecture with distributed security devices                  | 82 |

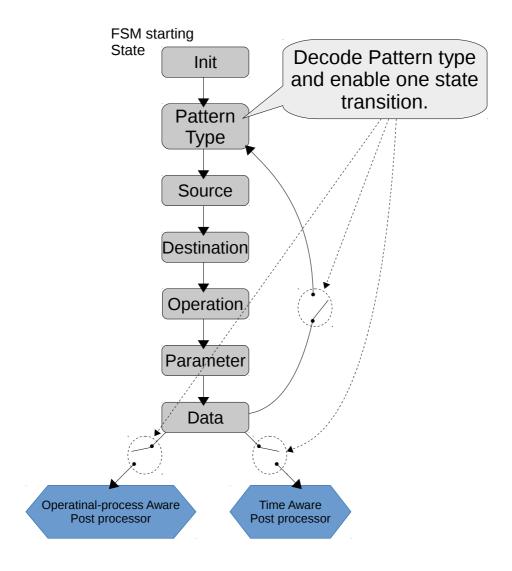

| 4.9  | Post processor set-up in accord with pattern type                       | 83 |

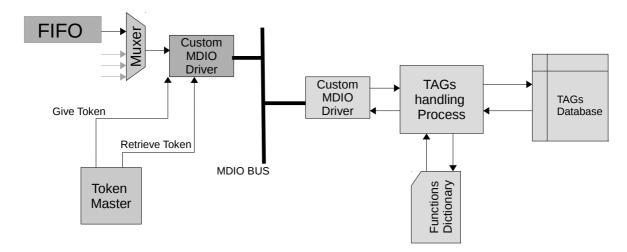

| 4.10 |                                                                         | 84 |

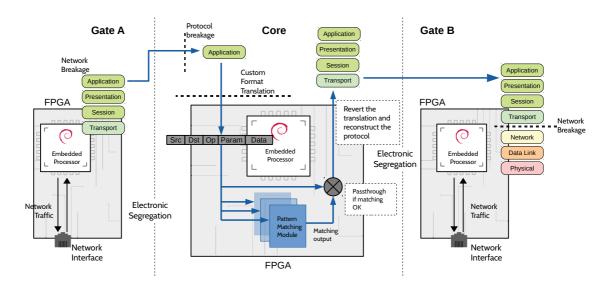

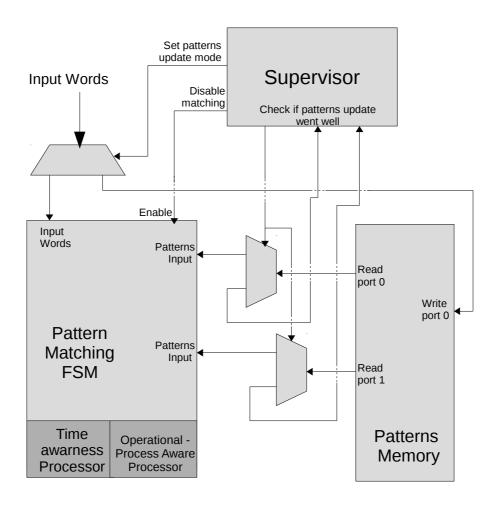

|      | Operational-Process Aware Pattern Matching System                       | 85 |

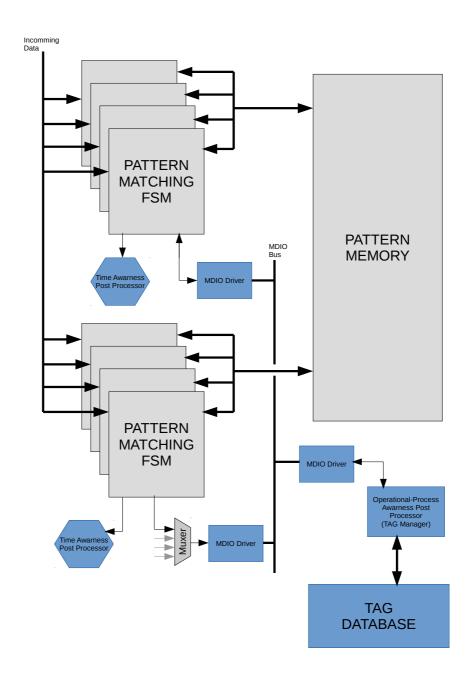

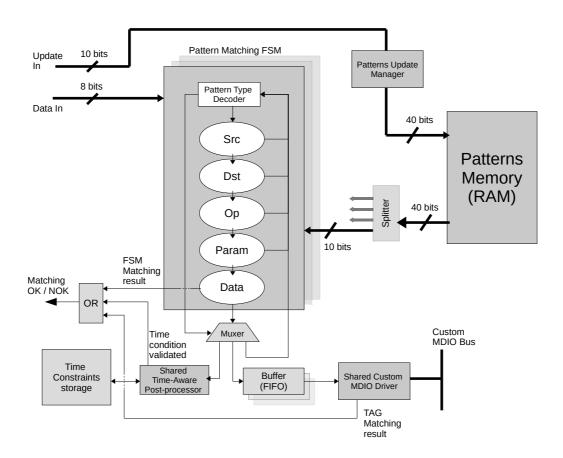

|      | Architecture of a Operational-Process Aware Pattern Matching Module     | 86 |

| 4.13 | Comparison between the standard MDIO packet and the custom payload used | 87 |

| 4.14 | Architecture of the TAGs handling Process                               | 88 |

|      | Patterns Update mechanism                                               | 89 |

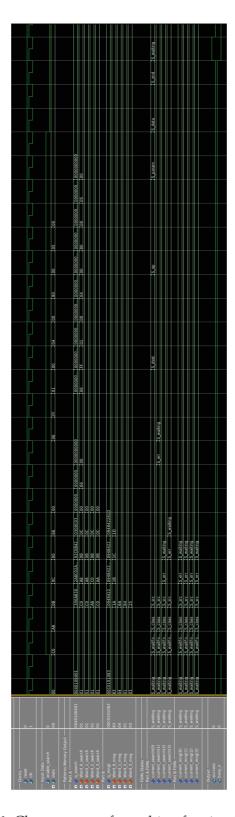

|      | Chronogram of matching for simple patterns                              | 93 |

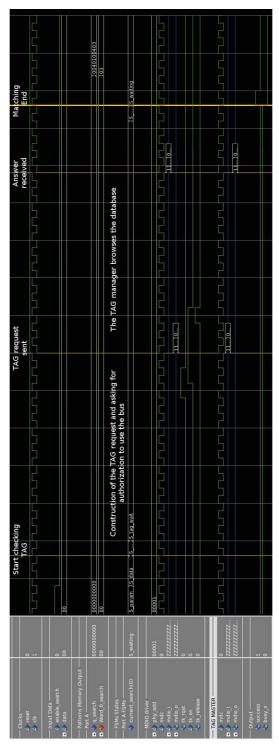

|      | TAG request chronogram                                                  | 95 |

| 4.18 | FPGA requirement of the distributed security analysis in accord with the |    |

|------|--------------------------------------------------------------------------|----|

| ]    | patterns distribution                                                    | 99 |

# **List of Tables**

| 2.1 | ModBus TCP Function Codes                                                 | 18 |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | Industrial protocols specifications synthesis                             | 23 |

| 2.3 | Table of Threats and Vulnerabilities                                      | 24 |

| 2.4 | ModBus Control Table of the Electric Post                                 | 31 |

| 2.5 | ModBus Control Table of the Bottle filling line                           | 34 |

| 2.6 | Sensitive assets synthesis                                                | 39 |

| 2.7 | Security features coverage over identified threats                        | 44 |

| 3.1 | Resource Usage Summarize                                                  | 57 |

| 3.2 | Related Works Comparison                                                  | 59 |

| 4.1 | Resource cost of FSM implementations for one 1024 bytes pattern           | 76 |

| 4.2 | Resource cost of a versatile pattern matching module                      | 90 |

| 4.3 | Resource cost of the TAGs handling database and the custom MDIO bus       |    |

|     | arbitrator                                                                | 91 |

| 4.4 | Total cost of the pattern matching engine with only one versatile pattern |    |

|     | matching module                                                           | 92 |

| 4.5 | Latencies summary                                                         | 96 |

| 4.6 | Patterns scaling in function of the FPGA size and available resources     | 97 |

| 4.7 | Realistic Patterns scaling in the research architecture                   | 98 |

|     |                                                                           |    |

# Chapter 1

# Introduction

Nowadays, industry needs a high level of automation and control, whether in production environments but also in transport, energy, all require fast and reliable exchanges to perform their duties. Dedicated networks which achieve these needs are referred as industrial networks and even if they share common features with IT networks, their needs and goals are very different. The main problematic of industrial networks is *availability above all*, the worst nightmare of an industrial is losing control of its own process or being unable to access a specific equipment. In consequence those networks generally focus on availability, with low latency exchanges and a strong deterministic requirement. All these constraints make industrial networks a delicate environment where safety is the key word in order to allow a smooth operating.

With the increased connectivity of industrial control systems, numerous threats and vulnerabilities which were unknown to these systems appeared. Their criticality but also the potential consequences made them targets of choice for a wide variety of criminal organizations. Threats are generally addressed using common IT counter-measures which, although effective, lack the application or operational intelligence. In 2015 the Trojan BlackEnergy [38] plunged hundreds of thousands of Ukrainians into the dark for several hours. The attackers used spearfishing to introduce the trojan into the company network and then spread it until getting a remote control access to the industrial process and cutting the power. In addition to highlighting a lack of staff's awareness about common network threats, this attack showed that the industrial process was not ready to face application threat. The fact that a remote order asking to shut down circuit breakers, potentially leading to power failure, was not detected nor considered suspicious shows a vital need for operational oriented security devices. In this context, dedicated solutions came on the market to address this concern, but even so it is still badly addressed. Furthermore, most of the solutions are pure software applications which present flaws and vulnerabilities inherited from the software components. The aim of my work, during this thesis, was to enforce the security of industrial control system against operational threats, through extensive usage of hardware resources. We plan to increase the security of existing network devices through boot chain protection and suggest the appeal of a dedicated hardware patterns matching to harden the security process.

This work is structured around two major contributions:

- First, it addresses protection against persistent threats for network security software application. Through usage of FPGAs, a chain of verification of each boot element by the previous one ensures that the running software application is authentic and not compromised.

- Secondly, a hardware process-oriented patterns matching engine on FPGA is proposed, instead of securing software security application, we replace it by a hardware one. It allows to perform security operations on the application level, similar to dedicated solutions of the market, but with enforced security offered by pure hardware.

Chapter 2 introduces the industrial context by describing the industrial network, its components, architecture and problematic followed by case studies. Then, this chapter addresses the security problematic with vulnerabilities, threats and attacks as well as the possible consequences through examples. We then speak of the existing countermeasures, with their advantages and disadvantages, before building the security target that we intend to address. Chapter 3 is about the first contribution, we discuss the boot process of an Linux operating system on a System on Chip FPGA's platform, with security issues and existing counter-measures. And then we introduce the contribution in two steps, with its basic concept, architecture and with a second optimized proposition as well as the results of experiments. Chapter 4 addresses the second contribution, about hardware patterns matching, firstly by discussing on industrial protocols breakage then on hardware patterns matching implementation recommendations. Then a versatile patterns matching solution is suggested, in both concept and architecture, before implementation experiments and results. Finally, we conclude this thesis through discussions about further works.

# Chapter 2

# **Industrial Networks**

| 2.1 | Defin  | itions                                                         | 5  |

|-----|--------|----------------------------------------------------------------|----|

|     | 2.1.1  | Information Technology (IT) versus Operational Technology (OT) | 5  |

|     | 2.1.2  | Critical Network                                               | 2  |

| 2.2 | Indus  | strial Communication Protocols                                 | 4  |

|     | 2.2.1  | ModBus                                                         | 5  |

|     | 2.2.2  | S7                                                             | 7  |

|     | 2.2.3  | BacNet                                                         | 9  |

|     | 2.2.4  | OPC-UA                                                         | .1 |

|     | 2.2.5  | Profinet                                                       | 1  |

|     | 2.2.6  | Synthesis                                                      | 2  |

| 2.3 | Threa  | ats                                                            | 3  |

|     | 2.3.1  | Incident Scenarios                                             | .6 |

| 2.4 | Case S | Study                                                          | .8 |

|     | 2.4.1  | Electric Post                                                  | .8 |

|     | 2.4.2  | Bottle filling line                                            | 2  |

| 2.5 | Protec | ctions                                                         | 5  |

|     | 2.5.1  | Isolation                                                      | 5  |

|     | 2.5.2  | Firewall                                                       | 6  |

|     | 2.5.3  | IPS / IDS                                                      | 7  |

| 2.6 | Threa  | nt Model and Security Target                                   | 8  |

|     | 2.6.1  | Denelis                                                        | 1  |

| 2.7 | Probl  | ematic                                                         | 6  |

|     | 2.7.1  | Secure Boot                                                    | 7  |

|     | 2.7.2  | Application Filtering                                          | .8 |

Chapter 2 2.1. Definitions

Historically Industry has always attracted malicious intents as it presents important economic and human stakes. Where industrial infrastructures were isolated, separated from others, and so hard to access and attack, today needs for remote control and supervision [24] have required the opening of their networks to the Internet along with the appearance of new problematic and threats. The emergence of connected objects is one of many reasons these infrastructures "open their network access". But as these networks have specific needs and peculiarities which differ from Information Technology's standard, network cybersecurity solutions are rarely sufficient to answer to these emerging threats. In order to understand these needs and to propose adequate solutions, it is necessary to understand what is an Industrial network.

# 2.1 Definitions

Industrial Network is a common term used to qualify a network whose usage is dedicated toward industrial purposes [2]. It is generally architected in 3 levels, the SCADA ensures supervision and remote control over automatons which control the operating field level. The manufacturing process is automated, then controlled and supervised through Control Systems, which may be potentially geographically distant. The following sections highlight and discuss the peculiarities of this type of network, whether in terms of equipments, traffic, architecture and implementation or in terms of vulnerabilities and protection.

# 2.1.1 Information Technology (IT) versus Operational Technology (OT)

It exists a wide variety of industrial contexts for use of industrial networks, but they are generally used when machinery needs monitoring, remote control or automation. Despite this diversity and different sets of requirements, great implementation principles stay unchanged. Resources and devices must stay available, industrial environment imposes a strict control to ensure no failures or accidents because their severity is far more serious. Furthermore, industrial networks are real time, so communications must respect fixed delays, with deterministic answer times. These needs are reflected by a network architecture different of common IT one. The following work describes in more details these specificities, from the network architecture, traffic and its components, to implementation problematic and failures severity.

### **Components and Devices**

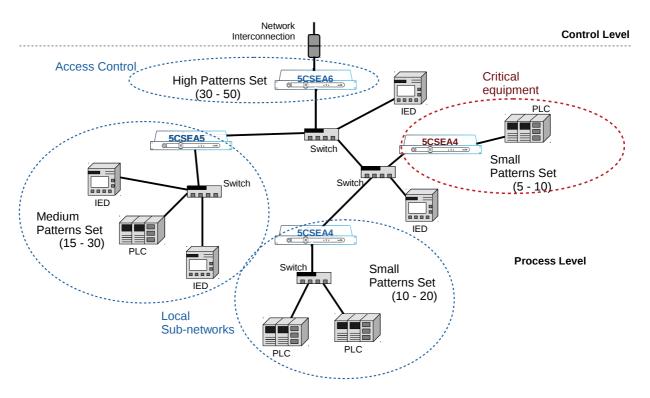

Industrial networks are made of specific devices whose functions are centered around the application needs and the manufacturing process. It is to ensure the communication between and toward these equipments that is built the industrial network. Following is a list of the primary devices which constitutes these networks, with their functions, while Figure 2.1 locates them according to the levels of the control system.

Human-Machine Interface (HMI) is a hardware and software element allowing human operators to visualize and control a process through modifying settings, objectives, sending requests, override automatic controls, emergency stops. It is the primary communication interface between a human and the automated process. The control engineer can access process information, status and historic as well as directly querying controllers. HMIs are generally set up on the application or supervision layer of the network, on various platforms, like laptops, dedicated desktops, browsers and even through Internet. Exchanges between equipments, part of the industrial system, are not made to be understandable by humans. On the fieldbus level, they are logical values (1 or 0) and electrical levels, and the more it goes up in the architecture, the more they become addresses and values. It would require tremendous knowledge about the network architecture, devices configurations and characteristics to be able to understand these exchanges. The HMI gives the necessary amount of information to the user with graphical representations and allows him to simply act on the process.

**Data Historian** stores process information, operations and logs of the control network. It is a database which collects and stores information through the network. These data can be used for statistical analysis about the control process as well as production planning. In case of attacks or failures, stored logs are precious for diagnostics and upgrades.

**Programmable Logic Controllers** (PLCs) are small industrial computers running custom and dedicated Operation Systems. It is one of the primary controller resources of industrial networks with the ability to control complex and automated processes. It is very versatile as it offers numeric and analog I/Os, time control, digital interfaces. It controls actuators, sensors and the field process. PLCs are configurable devices, programmable through a dedicated interface, located on engineering workstations of the Local Area Network (LAN). Users will implement specific functions, stored in the user-space memory of the devices, while backed up on Data Historians.

**Remote Terminal Unit** (RTU) is a data acquisition and control field device whose purpose is to support SCADA remote stations. It is basically a PLC designed for specific control applications. It is generally deployed in low connectivity environments, with wireless or radio communications, both being features rarely present on industrial equipments unless specific cases.

**Intelligent Electronic Devices** (IEDs) are "smart" field devices able to perform data acquisition, network communications and local processing. It is intended to be relatively autonomous, to perform simple processing based on acquired data, without the need of

Chapter 2 2.1. Definitions

a PLC, and to refer directly to Control Servers. These devices are generally close to the field process if not in it.

Supervisory control and data acquisition (SCADA) is a control system, used by industrial processes, which uses network data and HMI for high level supervision, as well as PLC, RTU and IED to interface with the process. It is a privileged solution to interface devices from different manufacturers allowing access through standard automation protocols. It is one of the most commonly-used type of industrial control system, used in power plants, railways, water distribution, gas and oil as well as in variety of factories. SCADAs are designed to abstract communications and data collect, from the fieldbus and other controllable devices, and to display it understandably (graphically or textually) to the operators. It allows, as well, actions, operations, modifications of the process through its interface. It is a mixed solution made of software applications and hardware components. Generally speaking, a Master Terminal Unit collects and stores information from Control Centers, while PLCs and RTUs control and monitor devices on the field bus. IEDs directly converse with the SCADA master unit. The combination of software and hardware allows data exchanges back and forth between the SCADA, PLCs and RTUs with a control over the permitted actions (allowed operations, data ranges, values). The SCADA acts as a high level understandable representation of a whole system, potentially geographically extensive, for supervision and punctual actions, while the regular industrial process is automated by PLCs, RTUs and IEDs.

**Distributed Control System** (DCS) is a control system for industrial process, with autonomous controllers distributed along the system and a central operator supervisory control. It is very similar to SCADA but more focused on continuous process control with local control instances. DCSs are made for control systems within the same geographical location, they are made for continuous control and supervision, through usage of similar devices to the SCADA (PLC,RTU,IED) but with lesser automation.

**Control Server** hosts SCADA and DCS applications. It is basically a medium to access low level fieldbus devices as well as subordinates control modules and other devices inside the control system.

Furthermore common network devices are present into the industrial environment, such as routers and modems for interconnection and routing in the network, firewalls for security purpose, access points for wireless data exchanges and servers for data storage and calculation.

Industrial networks rely on specific devices on each level for its control system, while the key cores of the automated process are PLC, RTU and IED. The environment made of server, data historian, HMI and DCS allows to make a complete remote controlled and supervised process. But this is the specificities of all these equipments and their needs, in

Figure 2.1: Industrial Network Architecture

terms of control and proximity to the field, that will influence the network architecture and explain the differences compared to common IT architectures. And as this architecture differ, the attacks methods and associated vulnerabilities evolve accordingly.

# **Network Architecture**

Industrial control network architectures are much more hierarchical that common Commercial networks. Organized in layers, generally 3 or 4, each corresponding to one process level, they are interconnected through gateways, routers and modems. The connection between instruments, actuators and controllers is made on the lower layer, then controllers interconnections, followed by HMIs and control commands and finally the upper layer for Supervision and remote control. Unlike Commercial Networks which are more flattened and made of interconnected LANs. This difference is explained by the multiple

Chapter 2 2.1. Definitions

connections and communication mediums of devices in the industrial control system. Field devices generally discuss through serial protocols or raw analog data exchanges, they are rarely directly connected to the network (except for IEDs). Instead, they are connected to PLCs and RTUs which are able to use common network protocols (TCP/UDP over Ethernet for example). Furthermore Control systems and supervision are commonly geographically distant and it is not uncommon that they are connected through the internet.

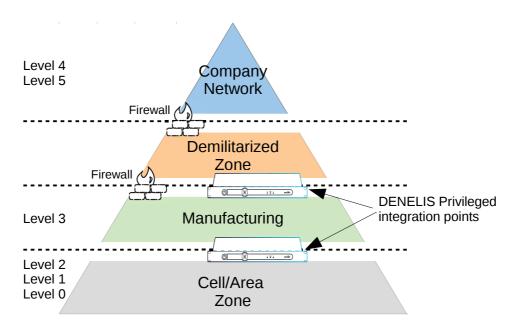

To give a representation of the complete company network, with interconnections between Industrial and IT networks, the most common standard is the Purdue Enterprise Reference Architecture or Purdue Model [81]. This is a reference architecture which gives a model of the network through multiple layers and stages. In Figure 2.2 we give an example of a classical Purdue Model for a company which owns an administrative network and an industrial control network.

The levels 5 and 4 are dedicated to the Enterprise zone with Intranet, emails and Internet connection while the lower levels are for Industrial purposes.

We find in layer 0 the field level, the level 1 is dedicated to automated control, with PLCs and RTUs, while the level 2 is the first layer of process control, with control command and HMIs.

The layer 3 is for supervision, it hosts the manufacturing process of the company. Both networks (industrial and IT) are generally connected, through firewalls, to a Demilitarized Zone (DMZ) which allows communication and embedded most application servers and services of the company.

But beyond a dedicated network architecture, Industrial networks are characterized by specific implementation problematic which prioritizes the **Quality of Service over the security**. Security devices will need to take account these constraints, as they will face network architectures which were purposely not made taking the security into account.

### **Implementation**

Industrial process requires good reactivity due to being in direct contact with physical equipments, as well as it needs to take decisions and send control in real time. These requirements resulted in changing the primary needs of the network while the Quality of Service (QoS) became dedicated on availability. [50] presents several requirements of industrial networks in comparison with IT networks, but following are what we consider as the two major implementation rules of these networks.

Availability is one, if not the first, implementation rule of industrial networks, the concept of security is predominantly associated to safety operating. It means that resources

Figure 2.2: Purdue Model

must stay available, remain controllable and observable. Being unable to access a device or to properly monitor the process, may lead to failures. Due to the fact that industrial control networks are directly interfaced with physical devices, the failures severity is far more greater. Availability in an industrial control system means devices availability, equipments must be robust and keep working in any cases. If a hardware or software failure occurs, the device is not available for configuration, maintenance as well as for the process. That is why, Industrials often store spare equipments to be able to quickly restore availability.

The network, its architecture and state, may also impact and degrade the availability. A ill-conceived network architecture or overloader network will cause increasing latencies and congestion, while dedicated attacks, such as denial of services ([82]), can completely sever accesses to devices. But resorting to high availability architectures with redundancy, loadbalancing methods and adequate security allow to reduce the impact of these problematics on the network availability.

• For the process to be deterministic means that devices state must be predictable

Chapter 2 2.1. Definitions

based on their Inputs and Outputs, operations and behaviors must be consistent under the same conditions. It is a criteria of good construction and operation of the industrial control system, the typical working flow should stay predictable and must not present inconsistencies.

Regarding the network, Industrial control systems are real time, so it must have bounded latencies and low variances. The time between a transmission and its reply should be low and predictable. Furthermore, where IT networks accept high data loss and retransmissions, it must not occur inside industrial networks as it will greatly degrade the determinism.

As QoS principles fundamentally differ from IT networks, network exchanges need to be adapted for this purpose with priority to short messages with high efficiency.

#### **Network Traffic**

In order to satisfy availability and determinism needs, data exchanges inside an industrial network prevail efficiency and low latencies. The physical medium is, in many case, common Ethernet, in accordance with widely used transport protocols such as TCP and UDP, but serial line as well as industrial Ethernet, and in some uncommon cases wireless, are also in used. Beyond those layers, and focusing more particularly over TCP/UDP over Ethernet, data are expressed through specific communication protocols which consist of small messages, only a few bytes long. Such transmissions are often single binary value, up to one or to bytes registers, the lower in the network architecture, the smaller packets are. It is in complete opposition with network exchanges within IT networks which are far bigger with regularly kilobytes of data sent.

The common network traffic of an Industrial System is deterministic, it consists of commands or periodically sampled data. But one particularity of these networks is the existence of aperiodic events such as alerts, failures or production rushes which cause sudden changes in the network traffic. It is called an "avalanche" and is characterized by a sudden and very intensive network traffic with maximum priority. When it happens, the availability of the network and the devices is more than ever critical. Even if unusual, these events are to be taken in account when dimensioning the industrial process and control system as it is fundamental for network equipments to support it, even with aging technologies.

#### **Failure**

In common IT networks, failures (criminal or accidental) can induce various consequences, from network or resources unavailability, devices compromise, data leakages. It usually

results on financial losses but rarely material or human. For industrial control systems, this remains true, but, as the network is closely linked to the industrial process, any failure directly impacts devices underneath. It is translated by heavy material and potential human losses, and in some uncommon cases industrial disaster.

Taking as example a power plant, a failure can mean malfunction of a relay or a power coupling device, locally speaking it causes material losses. But when taking into account the power shortage ensuing, it implies tremendous financial consequences, potential human losses, operating losses for surrounding companies, traffic accidents and more.

#### **Environment**

Industrials devices and machineries working conditions are very harsh as it can include high temperatures, high humidity, vibrations, dust or electromagnetic waves. Networks devices integrated in these environments need to match drastic working constraints. Whether in the design (welding, components choice) or in integration (protection against fluids, dust), it contrasts strongly to commercial networks which are located in clean, temperature controlled environments.

In fact industrial and IT networks are fundamentally different, as devices and QoS priorities differ the whole network communications are mend to adapt to these needs. Furthermore industry imposes very uncommon and harsh conditions, on the contrary to the well known air-conditioned network rooms. Among the multiplicity of domains and industrial applications which require the use of industrial control systems, a small number of infrastructures presents a critical risk for the security of a country. These infrastructures are referred as "Critical infrastructures" and their control systems are referred as "Critical networks".

### 2.1.2 Critical Network

The term "Critical infrastructure" is evolving but it was used for the first time in terms of National Security (President of the US 1996). One of the definition given by the Commission of the European Communities (European Union 2008) is: " An asset, system of part thereof located in Member States which are essential for the maintenance of vital societal functions, health, safety, security, economic or social well-being of people, and the disruption or destruction of which would have a significant impact in a Member State as a result of the failure to maintain those functions". Among existing networks, European critical infrastructures classification includes (Commission of the European Communities 2004):

• Energy: It addresses all the infrastructures that produce energy, whether it is electricity, oil or natural gas. This category includes for example coal centrals, nuclear

Chapter 2 2.1. Definitions

plants, dams, as well as drilling wells and oil platforms. But in addition to primary production sites it also covers processing and distribution infrastructures. All the other sectors depend on the energy one, as they virtually all need electricity, thus making the energy a key point of all critical infrastructures.

- Communications and information: This sector is central to the economy, academia, security, health and many others. In the era of the "All Connected" where more and more services rely on communication infrastructures this sector criticality never ceased to increase.

- **Finance**: The challenges of this sector are easily judged as it covers all economic assets, publics and privates.

- Health care: It covers a nation's healthcare and public health infrastructures such

as public and private clinics, pharmaceutical companies, and distribution circuits.

This sector protects all others from hazards but as most of its assets are owned by

private parties it requires great collaboration and information sharing.

- **Food**: Food distribution and production is a vital asset for the well being and health of a population. Associated infrastructures come from agricultural sector but also transformation and distribution assets such as factories, shops and group catering companies.

- Water: Drinkable water is one of the first necessity goods, if not more important than food, but this sector addresses as well wastewater storage and treatment as it is vital for diseases prevention.

- **Transport**: The transportation sector includes aviation, freight and passenger rails, maritime transport, postal and road infrastructures. It presents an huge economic stake as well as a convenience of use for the population.

- **Production, storage and transport of dangerous goods**: Many sectors such a Energy and Health care reject dangerous wastes that need to be handle with caution to avoid potential dangers to the population and the environment. This sector covers mostly infrastructures needed for the transportation and storage of these wastes.

- Government: And finally one of the most obvious critical sector addresses governmental assets, whether it is military infrastructures, administrative buildings and schools.

Despite multiple other definitions, Critical infrastructures play an essential role in all main functions of modern society, [3] provides further information and researches on

these infrastructures. Most of it relies on an automated control process which inherited the criticality of the infrastructure, in this case we speak of Critical networks. These networks answer to the same problematic and specificities as defined previously but with a criticality level way higher which justifies a greater interest in safety. This work focuses mainly on these particular networks as they require stronger security measures.

As industrial networks fundamental principles target availability and determinism, communications and data exchanges between network devices are designed to promote these needs, hence the use of dedicated network communication protocols. But like in IT's context, the communication protocol is another risk factor in a network and to measure this risk it is necessary to understand how these protocols are constructed and how do they work.

# 2.2 Industrial Communication Protocols

Communication protocols are sets of rules and syntax used by interlocutors to standardize information exchanges. Today communication systems use well-defined protocols, in network communications based on Ethernet, which is the physical medium, we found the physical layer (MAC) then in most cases IP and TCP (or UDP) both being well known communication standards. In the industrial context, networks rely on dedicated communication protocols, either above the TCP layer or using completely different standards and medium.

To communicate, equipments of the industrial network use industrial protocols. They are communication protocols which were created and specified to address industrial needs. It exists industrial protocols over serial line, Ethernet, TCP, UDP or virtually over any layer of the OSI model (Figure 2.3), but in the field of this work we will center the study over TCP/UDP protocols. Figure 2.4 shows a timeline of release of the main industrial protocols still used in the industry. Looking at the OSI Model Figure 2.3, industrial protocols to which we will be interested take place on the upper layers (Session, Presentation, Application), among these some are proprietary (generally made by PLC vendors) and other are open source. As years go by, numerous industrial protocols were introduced, but in the field of this work we will present four of them, presented below, ModBus, S7, BacNet and OPC-UA, with a major focus of the first two.

We chose those Modbus and S7 because they are both very common in the industry and have no concern about security. Even so they are old and tend to be replaced by more recent ones, in newly made industrial networks, existing networks which use those protocols are mend to last for many years before being updated. One major point of industrial networks, and more particularly for critical one, is "if it still works there is no reasons to

Figure 2.3: OSI Model

change it", which means equipments will not be changed as they are still working and even so there is always some identical spare equipments for quick replacement. For an industrial replacing its equipments by different or newer models is a complex and expensive operation. It would require, in prior, months of test on a simulation network which emulates the real one. Then it would be necessary to stop a part or the totality of the industrial process to perform the change. Those problems are even more true on critical industrial processes. For these reasons it is important to address the security of existing industrial protocols without systematically resorting to changes for newer and more secure ones.

### 2.2.1 ModBus

ModBus [39] is a communication protocol created in 1979 by Modicon, to address communication between industrial equipments, such as PLC and DCS, over serial lines. Due to its simplicity yet efficiency it became the de-facto standard for automated industry, but at the time it was designed, security and networks interconnection were not existing problematics. It allows a master to communicate with many slaves (up to 240 devices in the ModBus system), the master initiates the connection then performs a request and the targeted slave answers. ModBus allows variety of medium such as serial line, wireless but the most common types are :

Figure 2.4: Chronology of major Industrial Protocols release

- ModBus ASCII, messages are coded in hexadecimal, using 4-bit ASCII characters.

It is the slowest of the modBus protocols, each byte of information needing two communication bytes. Therefore it is privileged for wireless communication, such as Radio (RF) or telephone modems, because it allows rather long time intervals between characters without causing errors.

- *ModBus RTU* is the ModBus standard for serial line, twisted pair links, and the more popular of the ModBus protocols. The most common speeds are 9,600 and 19,200 baud.

- ModBus TCP is simply ModBus over Ethernet using TCP/IP standard, the data is

encapsulated inside a TCP/IP packet. Any Ethernet network is able to support this

ModBus standard making it very popular among more recent industrial control systems where the Ethernet norm became standard. For these reasons the following

work is focused over ModBus TCP but remains true in some part for all modBus

standard as the Memory model and principle are shared by all.

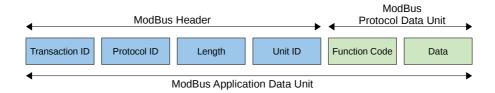

Over TCP the addressing between equipment is done using the Ethernet and TCP/IP, through MAC Address and IP address, the default communication port should always be the 502. The Unit identifier present in the ModBus packet is not always used, as it was necessary for serial communication, depending of the device some use it as supplementary check for addressing. The modBus Application Data Unit (ADU) is maximum 260 Bytes long, it consists of 253 bytes of Modbus protocol data and 7 bytes specific for Modbus TCP addressing. Figure 2.5 shows the complete ModBus ADU which contains the following fields:

• *Transaction Identifier* serves for synchronization purpose, the request and the answer share the same transaction identifier allowing the master to match both.

Figure 2.5: ModBus TCP Application Data Unit

- Protocol Identifier is a field set to 0, unused in ModBus TCP.

- Length indicates the number of remaining bytes in the modBus message. It is a common type of field in network protocols, allowing devices to know how many bytes they must expect in the frame.

- *Unit Identifier*, natively ModBus TCP devices ignore this field, setting it to 255. But in some cases of composite equipments (ModBus TCP to ModBus RTU gateway) it is used to give the slave address of the targeted device.

- Function Code is a one byte hexadecimal value from 0x01 to 0x02B which codes the operation related to the modBus message. The basic operations, read and write, are performed over single or multiple elements, and followed by the address, and eventually a data in case of writing. The corresponding answer, from the slave, uses the same function code with the requested information or acknowledgement. ModBus allows exception code for return, differentiated by an offset of 0x80, supplementary to the function code, used to indicate a processing error or a unknown request. Further functions are available (Figure 2.1) mainly for management, control, update, and unused function codes are reserved to the user for specific needs.

The ModBus memory model consists on 4 basic types of data which are: Coil (single bit, read-write), Holding Register (16-bit word, read-write), Input Register (16-bit word, read-only) and Discret Input (single bit, read-only). Generally a device has 4 memory spaces known as Blocks which work as memory pages, each one managing one type of data. Internal data (coil, register, input) accessible by their address, are either directly mapped to the PLC I/O or used to perform combinatorial operations as expected in the automaton program.

### 2.2.2 S7

S7 is a proprietary protocol, over TCP, belonging to Siemens. Similar to Modbus, it is a request/reply protocol with one master and multiple slaves. One of its specificity is that

| Function Code (hex)     | Operation                     |

|-------------------------|-------------------------------|

| 01                      | Read Coils                    |

| 02                      | Read Discrete Inputs          |

| 03                      | Read Holding Registers        |

| 04                      | Read Input Register           |

| 05                      | Write Single Coil             |

| 06                      | Write Single Register         |

| 07                      | Read Exception Status         |

| 08                      | Diagnostic                    |

| 0B                      | Get Com Event Counter         |

| 0C                      | Get Com Event Log             |

| 0F Write Multiple Coils |                               |

| 10                      | Write Multiple Registers      |

| 11                      | Report Server ID              |

| 14                      | Read File Record              |

| 15                      | Write File Record             |

| 16                      | Mask Write Register           |

| 17                      | Read/Write Multiple Registers |

| 18                      | Read FIFO Queue               |

| 2B                      | Read Device Identification    |

Table 2.1: ModBus TCP Function Codes

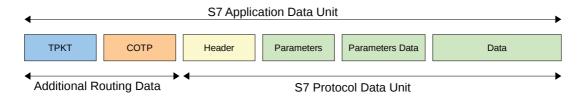

multiple motherboards can be installed in the same device (PLC). It requires supplementary routing information, in the form of rack and slot numbers, to address the correct target. Considering that it is the standard protocol for Siemens PLCs, it is widely used. More recent PLCs now use S7+ which is an upgraded version of S7 including security features. S7 ADU consists in a S7 PDU wrapped in TPKT [46] and ISO-COTP protocol which is define in RFC1006 [44], based on the ISO8073 protocol [45]. The S7 PDU 2.6 is made of:

- *Header* which contains protocol constants and references as well a length information

- *Parameters* are supplementary data necessary for the correct application of the operation, such as addresses.

- *Data* carries the data relative to the operation and parameters, typically memory values, firmware, memory blocks.

The Header is 10 to 12 bytes long and embeds:

• *Protocol Identifier*, constant always set to 0x32.

Figure 2.6: S7 TCP Application Data Unit

- *Message Type* is a first indication of the requested operation, combined with the Parameters it forms the complete operation identifier.

- *Reserved*, data always set to 0 and probably ignored or reserved for future use.

- *PDU Reference* works as a tracking number used by the master to link the request and the answer.

- *Parameter Length* is the length of the Parameter field.

- *Data Length* is the length of the Data field.

Additionally, the header may contain Error Code and Class in case of failure, this field is not mandatory. The rest of the S7 message, Data and Parameters, content depend on the Message Type. The S7 memory model works using Db (for database), those are memory pages which data are addressed inside either individually (through address) or multiple, up to the whole page. This protocol shares many common points with ModBus, in the header many fields have similar functions or meaning, and in the way of addressing data.

### 2.2.3 BacNet

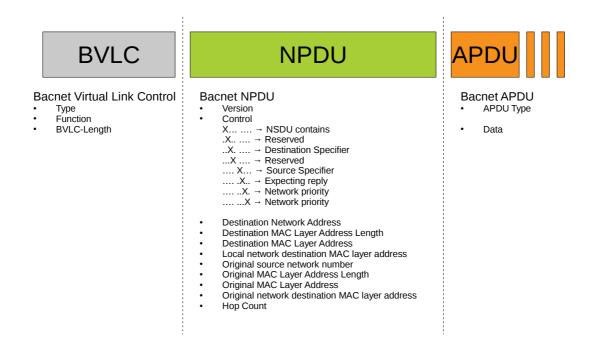

BacNet [41] is a communication protocol for Building Automation and Control, supported and maintained by the American Society of Heating, Refrigerating and Air-Conditioning Engineers (ASHRAE). It is a very popular ISO standard, especially in America and Europe. BacNet was designed to allow communication of building automation and control systems for applications such as heating, ventilating, and air-conditioning, lighting control, access control and fire detection systems and their associated equipments. A BacNet equipment is defined by an Object identifier composed of an object type and an instance number. In the same way, a bacnet equipment possesses a number of object defined by object name and identifier, while those objects possess parameters. The ANSI/ASHRAE 135-2016 defines 60 standard object types among which are Calendar, Lift and many others, but it also allows the user to define its own. In short, a bacnet equipment is like a

meta-structure embedding a number a lower structures, each one made of multiple fields. One of the consequences of this construction is that the protocol is very verbose and requires lots of text strings to ask for an operation. Due to its use, often confined to building automation, Bacnet has very low concern toward security.

The BacNet network has its own representation made of interconnected devices, it leans on the following concepts:

- The *segment* is made of devices connected, eventually through repeaters, under the same physical layer.

- The *network* is made of connected segments, homogeneous of the bonding layer.

- The *internetwork* is made of connected BacNet network, through routers, with no constraints over physical and bonding layers.

The addressing in the BacNet protocol appeals a number of mechanisms:

- On the physical layer, it depends of the specified technology.

- On the network layer, it uses a combination of MAC address and network identifier.

Multiple devices inside the same BacNet network must share the address domain, else they must be divided between multiple networks with different network identifiers.

- On the application layer, the addressing uses the common addressing mechanism of the BacNet protocol, the Object Identifier.

Bacnet is a more recent protocol and, unlike Modbus and S7, its data model departs from a proximity to the material to a more abstract representation with complex objects having multiple properties. This difference is also felt in the message construction, data is intended to cross multiple bacnet *networks* or *internetworks* with a wider variety of functions, which explains a more complex protocol structure. Figure 2.7 shows the representation of a typical bacnet packet, it does not cover all possible cases but gives a solid example of how are organized the fields in the bacnet message. The Bacnet Virtual Link Control helps to identify the type of Bacnet protocol we are using (Bacnet IP for example) and gives a first indication on the message type. It is in the NPDU that are found most of the routing data, with the Control field that indicated which data will appear in the remaining NPDU. And in the APDU we find the remaining message type indicator while the rest of the follow-up differs in function of this type.

Figure 2.7: Bacnet IP packet structure

### 2.2.4 OPC-UA

OPC-UA [42] is a machine to machine communication protocol for industrial automation developed by the OPC Foundation and released in 2006. It was designed to be the new generation of industrial protocols, including multi platforms support, security features, flexibility and scalability toward the network architecture and devices. OPC-UA uses concepts from recent object oriented programming, it works with a so-called Full Mesh Network using nodes: a node is an entity embedding any kind of data or metadata, it can be data, attributes (Read access), as well as complex commands or events. It allows OPC-UA devices to manipulate abstract objects but it also allows more complex operations than in most of the common industrial protocols. Devices can perform basic operations as well as Subscription to an object, discovery, heartbeats. Its versatility makes it a privileged choice for new industrial standards, it is usable in nearly all industrial contexts (energy, transport, manufacturing) as it addresses needs from the managing level to the lower level of the operational process.

### 2.2.5 Profinet

Even if it will not be discussed in this work, it is interesting to mention Profinet [40] as it is one of the most popular protocol, the most used in the automotive sector. It is an open

communication standard for industrial automaton, created by PROFIBUS and PROFINET in 2001, and designed to address tight time constraints in data delivery. It is optimal over industrial Ethernet with support of TCP/IP, while its versatility allows integration of variety of devices from operating to management layer. Profinet leans on three protocol levels:

- TCP/IP for non-critical data with moderate time constraints.

- Real Time with Profinet IO for short time constraints.

- Isochronous Real Time with Profinet IO is the fastest protocol level for very tight time constraints.

Profinet relies on a combination of MAC address, IP address and device station name for addressing while the connection establishment is made using UDP.

# 2.2.6 Synthesis

According to [48], among existing industrial protocols, ModBus is one of the most popular, 42% of usage, it is well known and easy to use, making it a standard adopted by most industrial controllers. Profinet follows with 29% of usage and Bacnet is a bit less popular with 9% of usage, because it is mainly used for building automating and not much else. S7 is not represented in the study, this proprietary protocol is fairly discrete in its information disclosure, but because it is a standard for most of the Siemens PLCs, we can assume that it is quite common. Today with the emergence of new protocols, more versatile and secure, the old ones are destined to be replaced but it will take time.

In terms of security it appears unsurprisingly that older protocols, such as ModBus and BacNet, do very little or no state of security. In fact these protocols were designed at a time when the cybersecurity context was almost nonexistent and as a result they are particularly exposed to cyber attacks. Today most recent industrial protocols make good progress in order to integrate many security features such as encryption and authentication mechanisms. Among them we can find OPC-UA which is the most famous and others like S7+ which is a newly and more secured version of the Siemens's protocol. These protocols, although still not widespread, are much more resistant to attacks. Table 2.2 summarize the specificities of each industrial protocol previously addressed.

Industrial protocols listed before are examples of what can be find in today industrial networks, it is not exhaustive, as it exists numerous other ones. In the field of this work we will focus on S7, Modbus and will keep in mind Bacnet and OPC-UA for extensible parts of the study.

Chapter 2 2.3. Threats

| Industrial<br>Protocols | Security                                                                         | Flexibility                                                                                                                                              | Interoperability                                                                                                           |

|-------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| ModBus                  | Null, modbus integrates no concepts toward Authentication and Confidentiality.   | The protocol is closely linked to the memory model and information must match one of the basic data types.                                               | It does not handle interoperability with other protocols or network types.                                                 |

| S7                      | Null, as modbus, S7 takes no account of Authentication and Confidentiality.      | The protocol is closely linked to the memory model and information must match one of the basic data types.                                               | It does not handle interoperability with other protocols or network types.                                                 |

| BacNet                  | This protocol takes not care toward Authentication and Confidentiality.          | It offers possibility<br>for the user to de-<br>fine its own object<br>types and labels,<br>through string,<br>even beyond exist-<br>ing specifications. | It does not handle interoperability with other protocols or network types.                                                 |

| OPC-UA                  | It offers many features toward security with encryption and challenge responses. | OPC-UA's data model is fully customizable by the user, allowing to declare its own data types.                                                           | This protocol was design to be compatible with administrative networks and many data representation standards (XML,JYSON). |

Table 2.2: Industrial protocols specifications synthesis

# 2.3 Threats

The target of this thesis is to study the threats and risks which can affect an industrial control system and then to work on counter-measures in accordance with the state of the art. To do so it is essential to classify and understand the vulnerabilities and associated attacks these systems are exposed to. The vulnerability of common network infrastructures is not to be proven yet, and [4] shows that industrial networks are not spared. The definition of the various threats which endangered these networks is orchestrated on multiple layers.

Firstly, considering the hardware platform, it concerns the physical integrity of the

|             | Vulnerability                          | Impact                                       |  |  |

|-------------|----------------------------------------|----------------------------------------------|--|--|

|             | Inadequate log mechanisms              | Poor detection of                            |  |  |

|             | madequate log mechanisms               | failures and attacks.                        |  |  |

| Network     | Missing security devices               | Open security breaches and                   |  |  |

| K           | whissing security devices              | access points for attackers.                 |  |  |

| Z           |                                        | Allows transmission of unnecessary           |  |  |

|             | Misconfigured security devices         | or dangerous data, leading to data           |  |  |

|             |                                        | leakage or malwares spreading.               |  |  |

|             | Inadequate network architecture        | Increase the possibility of                  |  |  |

|             | madequate network architecture         | security flaws.                              |  |  |

|             | Inadequate Security Perimeter          | Unknow security flaws and missconfiguration  |  |  |

|             | 1 ,                                    | of security devices.                         |  |  |

|             | Unpatched security Vulnerabilities     | Vulnerability to known threats and exploits. |  |  |

| п           | Communication protocols Integrity      | Protocol Messages compromise                 |  |  |

| tio         | Communication protocols integrity      | and malicious modifications.                 |  |  |

| ica         | Communication protocols Authentication | Facilitate messages interception and         |  |  |

| Application | -                                      | impersonification of interlocutors.          |  |  |

| A           | Unpatched security Vulnerabilities     | Vulnerability to known threats and exploits. |  |  |

|             | Lack of dedicated security solutions   | Not adapted and unsufficient security.       |  |  |

Table 2.3: Table of Threats and Vulnerabilities

devices as well as the control of the peoples inside the infrastructure and the security policies, excluding network related ones. The access control as well as the physical protection of the devices is one of the crucial points if not the first which may concern an infrastructure. It includes protecting the power supply and protection against Radio and Electro-magnetic interferences. Physical access to equipments is a grave problem, USB ports are often left accessible, and a malicious USB device can easily cause damages. The lack of backup or redundant equipments as well as non-existing test facilities are aggravating factors. Security policies play a critical role in the vulnerability to the threats of the devices. Password policy, remote access protection, configuration's backup and unHardened OS or applications are representative weaknesses of wrong security policies. And obviously, unpatched security vulnerabilities are the most evident threats. Event if critical these threats will not be discussed further as they concern problematic not addressed in this work.

Table 2.3 summarizes the threats which concern either the network or the applications. These are addressed in more details, with their consequences, below, starting with the network ones:

• *Inadequate log mechanisms*: the use of logs from network equipments (security equipments as well as process devices) is one of the most efficient way to detect network

Chapter 2 2.3. Threats

failures or attacks. Furthermore, after the occurrence, they are useful to track causes and consequences. The non emission of logs from a device generally results of a bad configuration, but missing storages and non monitoring of these logs are also problematical.

- Missing or misconfigured security devices: The lack of security equipments, or their

misconfigurations, allows transmission of unnecessary or dangerous data. It opens

security vulnerabilities which may lead to malware spreading, data leakage and any

other potentials attacks. It is the most obvious and common security threat as it is

based on the lack of security.

- *Inadequate Network architecture*: Inadequate or poorly built network architecture offers more security flaws, makes more difficult to define proper security perimeter and policy. Furthermore it can impact the operational process as it may induce loopholes and delays.

- *Inadequate Security perimeter*: The security perimeter, or Information Systems Security Policy (ISSP), is used to validate that necessary security controls are deployed, it defines which are the assets and devices needing protection, against what and how they need to be protected. Without a proper one it may lead to unknown security flaws. Furthermore, it increases the difficulty to properly configure security devices.

- *Unpatched security vulnerabilities*: One of the scourge of the industrial network cybersecurity are the existing, known but unpatched vulnerabilities. Industrial infrastructures have a big inertia toward security updates as the standard delay between the publication of a security patch and its implementation on the network is between 3 to 6 months, when the patch is accepted, which is not always the case. It is common for those patches to be voluntary ignored as long as their effects on the whole network is not fully known. Furthermore, some vulnerabilities require scientific monitoring to be aware of and patched, this work is not always done as it needs specific skills and time. The problem of updates is also related to how they can be applied. Not all assets are necessarily connected to a network. Some updates can only be deployed through USB, with the security problems inherent to this protocol.

- Denial of Services: Denial Of Services or Distributed Denial Of Services are very common attacks where a targeted device or network is flooded by network traffic to render it unavailable. It is a security threat that targets specifically one of the major problematic of the industrial network, the availability of the resources.

These threats are a sample of the most common threats targeting a network, as new

ones emerge every day, they are not specific to industrial networks and affect all types of network.

Furthermore the communication protocol used from the presentation of the application layer of the OSI model brings its own vulnerabilities.

- Industrial protocols address availability and determinism of data exchanges in the

industrial network, they rarely integrate security features such a encryption or authentication. It facilitates greatly the work of attackers as message exchanges are

easy to intercept (often in clear text mode), understand, and it becomes easy to impersonate one of the interlocutors.

- Some Industrial protocols have their own integrity checking, through hash and Cyclic Redundancy Check (Modbus), but most of them rest on the transport layer integrity checking. It facilitates the compromise of a protocol's message.

- As well as for network devices, RTUs and PLCs are rarely updated, even for security updates. As they directly handle the industrial process, any patch or update that may change their functions or behaviors is regarded more dangerous that the security breach itself.

- The network security of industrial control systems is generally handled by common

IT solutions (firewalls). But even if these devices are able to analyse the network

traffic, it rarely goes up to the application layer. Understanding and analysing the

application layer of the network packet is fundamental to assess the incoming threat.

The commercial state of the art lacks of dedicated industrial network supervision

devices (there are still companies that offer these kinds of solutions, but they are

rare).

These threats are common to most of the industrial networks, but each industrial protocol brings its own sets of exploits [6], depending of its specifications and implementations. Simple protocols, such as Modbus and S7 are particularly vulnerable to fuzzing, as they are relatively compact and made of small sized fields, this basic brute force techniques brings results with relatively low implementation complexity. [5] illustrates this example and gives a complete taxonomy of Modbus flaws and attacks. The more complex is the protocol, the more the attacks complexity increases [7].

### 2.3.1 Incident Scenarios

From the vulnerable machine, left inadvertently accessible (open session), to complex attacks involving propagation through other networks and remote control, passing through

Chapter 2 2.3. Threats

the insertion of a malicious program, it exists numerous scenarios with increasing degrees of difficulty. Following are chosen failures, or incident scenarios, for Industrial Control Systems, based on the previously listed vulnerabilities and the threats we intend to address:

- Man in the middle: A malicious entity manages to access the network between the Control System and the PLCs/RTUs. Using simple network manipulation techniques (ARP spoofing), it is able to usurp both the identity of the Control and one or more PLC. So data and commands sent by the control system to destination of the PLC will be intercepted by the attacker and the same goes for answers from the PLC to the control. From this point multiple possibilities are open: