## Design and characterization of a three-phase current source inverter using 1.7kV SiC power devices for photovoltaic applications

Luis Gabriel Alves Rodrigues

### ▶ To cite this version:

Luis Gabriel Alves Rodrigues. Design and characterization of a three-phase current source inverter using 1.7kV SiC power devices for photovoltaic applications. Electric power. Université Grenoble Alpes, 2019. English. NNT: 2019GREAT030 . tel-02476261

### HAL Id: tel-02476261 https://theses.hal.science/tel-02476261

Submitted on 12 Feb 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### **THÈSE**

Pour obtenir le grade de

### DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité : Génie Electrique

Arrêté ministériel : 25 mai 2016

Présentée par

### Luís Gabriel ALVES RODRIGUES

Thèse dirigée par **Jean-Paul FERRIEUX**, Professeur, Université Grenoble Alpes et co-encadrée par **Jérémy MARTIN**, CEA-INES

préparée au sein du Laboratoire des Systèmes Photovoltaïques (LSPV/CEA-INES) / Laboratoire de Génie Electrique de Grenoble (G2Elab)

dans l'École Doctorale Electronique, Electrotechnique, Automatique et Traitement du Signal

# Design and Characterization of a Three-phase Current Source Inverter using 1.7kV SiC Power Devices for Photovoltaic Applications

Thèse soutenue publiquement le **28 mai 2019**, devant le jury composé de :

### M. François FOREST

Professeur, Laboratoire IES, Montpellier, Rapporteur

### M. Philippe LADOUX

Professeur, Laboratoire LAPLACE, Toulouse, Rapporteur

#### M. Serge BONTEMPS

Ingénieur, Microsemi Corporation, Bruges, Examinateur

#### M. Stéphane LEFEBVRE

Professeur, Laboratoire SATIE, Cachan, Président du jury

#### M. Jean-Paul FERRIEUX

Professeur, Laboratoire G2Elab, Grenoble, Directeur de thèse

### M. Jérémy MARTIN

Ingénieur, CEA-INES, Le Bourget-du-Lac, Co-encadrant

### Abstract

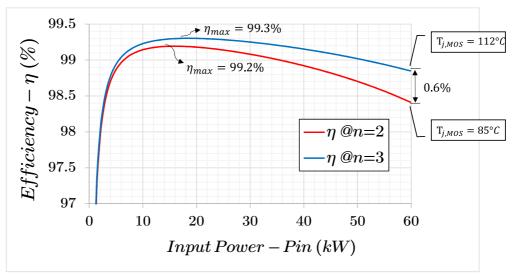

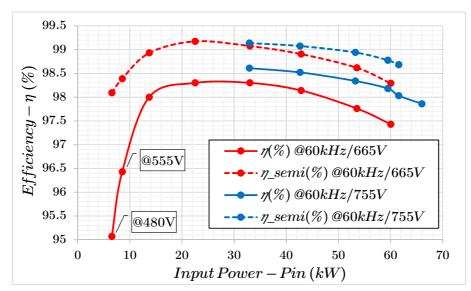

Classically, the energy conversion architecture found in photovoltaic (PV) power plants includes solar arrays delivering a maximum voltage of 1kV followed by a step-up chopper connected to a three-phase Voltage Source Inverter. This multistage conversion system (DC/DC + DC/AC) is then connected to the medium-voltage grid through a low-voltage/medium-voltage transformer. In order to simplify the PV systems, this research work focuses on the study and implementation of a DC/AC topology employing a single power processing stage: the three-phase Current Source Inverter (CSI). To deal with the inconvenient of high conduction losses when implementing this topology, wide-bandgap Silicon Carbide (SiC) semiconductors are used, allowing to efficiently convert energy while keeping a relatively high switching frequency. Nonetheless, since the available power semiconductor modules on the market are not compatible with the CSI, a novel 1.7kV SiC-based voltage bidirectional module is developed in the context of this thesis. Hence, the dynamic characterization of the new SiC device is carried out and serves as the basis for the design of a 60kW CSI prototype. Finally, the inverter efficiency is evaluated at nominal operating conditions, employing both a calorimetric and electrical methods. The obtained results confirm the CSI ability to operate efficiently at high switching frequencies  $(\eta > 98.5\%)$  @60kHz). The originality of this work lies mainly in the design, characterization and implementation of the new 1.7kV full-SiC power module adapted to the CSI topology.

**Keywords**: Power electronics, DC/AC converters, Current Source Inverter (CSI), Silicon Carbide (SiC), Photovoltaics, Power module.

### Résumé

Classiquement, la chaîne de conversion d'énergie électrique des centrales photovoltaïques comporte un champ photovoltaïque (PV) délivrant une tension maximale de 1kV suivi d'un hacheur élévateur connecté à un onduleur de tension triphasé. Cette chaîne de conversion à deux étages (DC/DC + DC/AC) est ensuite raccordée sur le réseau moyenne tension à l'aide d'un transformateur élévateur. Dans l'objectif de simplifier les systèmes de conversion PV, ce travail de recherche s'intéresse à l'étude et la mise en œuvre d'une topologie DC/AC n'employant qu'un seul étage de conversion : l'onduleur de courant triphasé. Bien que relativement simple, l'onduleur de courant présente comme inconvénient majeur ses pertes par conduction. Pour pallier à ce problème, des interrupteurs grand-gap au Carbure de Silicium (SiC) sont employés, ce qui permet de convertir l'énergie à haut rendement ( $\eta > 98.5\%$ ) tout en gardant une fréquence de découpage élevée (plusieurs dizaines de kHz). Les modules à semi-conducteurs de puissance disponibles sur le marché n'étant pas compatibles avec ce type de convertisseur, des modules dédiés intégrant du SiC ont été développés dans le cadre de cette thèse. La caractérisation dynamique de ces nouveaux modules a été réalisée dans le but de servir de point d'appui à la conception d'un démonstrateur d'onduleur de courant d'une puissance nominale de 60kW. Enfin, le rendement de la partie semi-conducteur de puissance est évalué à l'aide d'une méthode calorimétrique confirmant la capacité de cette topologie à fonctionner à des fréquences de découpage plus élevées. L'originalité de ces travaux réside principalement dans la conception, la caractérisation ainsi que la mise en œuvre d'un nouveau module de puissance dédié à cette topologie. Cette dernière étant connue mais peu étudiée à l'heure actuelle avec des interrupteurs au SiC.

Mots-clés: Electronique de puissance, Conversion DC/AC, Onduleur de courant, Carbure de Silicium (SiC), Photovoltaïque, Modules de puissance.

## Acronyms and Abbreviations

4qCSI CSI with four-quadrant switches

AC Alternating current

AMB Active metal brazing

BOS Balance of system

BW Bandwidth

CAPEX Capital expense

CCM Continuous conduction mode

CM Common mode

CSC Current source converter

CSI Current source inverter

CSI7<sub>op.1,2</sub> CSI with 7 switches employing modulation strategy 1 and 2

CT Current transformer

CTE Coefficient of thermal expansion

D<sup>2</sup>PAK Semiconductor package also kwon as TO-263

DC Direct current

DCM Discontinuous conduction mode

DMOSFET Double-diffused MOSFET

DPF Displacement power factor

DPT Double-pulse test

DSCT Double-stage current transformer

DUT Device under test

EMC Electromagnetic compatibility

EMI Electromagnetic interference

EPBT Energy payback time

ESL Equivalent series inductance

ESR Equivalent series resistance

FEA Finite element analysis

FOM Figure of merit FR4 Flame resistant 4

HS High-side

HVDC High-voltage direct currentHVRT High voltage ride-throughiBoost Interleaved boost converter

IGBT Insulated gate bipolar transistor

LCOE Levelized cost of energy

LS Low-side

LV/MV Low-voltage/medium-voltage

LVRT Low voltage ride-through

MOSFET Metal-oxide-semiconductor field-effect transistor

MOV Metal oxide varistor

MPPT Maximum power point

MPP Maximum power point tracking

MPS Merged pin-Schottky

NPC Neutral point clamped

OPEX Operating expense

PBT Polybutylene terephthalate

PCB Printed circuit board

PTC Positive temperature coefficient

PV Photovoltaic

PWM Pulse width modulation

RMS Root-mean-square

SBD Schottky barrier diode SMD Surface-mount device SOA Safe operating area

SVM Space vector modulation

TCC 3-level camping cell

THD Total harmonic distortion

TIM Thermal interface material

VSC Voltage source converter

VSI Voltage source inverter

WBG Wide-bandgap

ZCS Zero-current switching ZVS Zero-voltage switching Ag Silver

Al Aluminum

Al<sub>2</sub>O<sub>3</sub> Aluminium oxide or alumina

AlN Aluminium nitride

AlSiC Aluminum/Silicon carbide

Cu Copper

$\begin{array}{ll} {\rm GaN} & {\rm Gallium\ nitride} \\ {\rm MnZn} & {\rm Manganese/Zinc} \end{array}$

NiZn Nickel/Zinc

Pb Lead Si Silicon

$Si_3N_4$  Silicon nitride SiC Silicon carbide SiO<sub>2</sub> Silicon dioxide

Sn Tin

### Remerciements

Après un long chemin parcouru, j'arrive enfin à l'aboutissement de mes travaux de thèse. Il est donc temps de remercier tous ceux et celles qui ont contribué à la réalisation de ce projet qui m'a tenu à cœur pendant plus de trois ans.

En premier lieu, mes remerciements sont pour mes encadrants de thèse. Jean-Paul FERRIEUX, Professeur et chercheur au laboratoire G2Elab, pour m'avoir encadré et supporté pendant toute cette période de thèse. En dehors de vos compétences techniques en Electronique de Puissance (plus que connues et reconnues!), j'ai toujours estimé vos qualités personnelles, votre sérieux et votre manière de travailler. Je tiens à vous remercier pour m'avoir aidé à comprendre le sens et le fonctionnement de la recherche scientifique. C'est grâce à vos humbles conseils, comme « personne n'est à l'abri d'une erreur » ou « ce n'est pas grave, tu avais deux ans d'expérience en moins », que j'ai pu comprendre la notion de construction du savoir scientifique, pour ensuite essayer d'y apporter ma brique. Et Jérémy MARTIN, ingénieur-chercheur au CEA/INES, pour m'avoir accepté en thèse. Je tiens à te remercier aussi pour m'avoir toujours fait confiance, même aux moments les plus incertains, quand la date de démarrage de la thèse avait été décalée. Merci pour tous les très bons moments partagés lors de nos repas (principalement ceux au buffet asiatique et au Grillon!) et ta bonne humeur habituelle. Je te remercie d'avoir co-encadré ce travail de thèse et d'avoir proposé un sujet de recherche aussi riche, fructueux et ambitieux comme celui-là.

Je voudrais également remercier François FOREST et Philippe LADOUX, les rapporteurs de ce mémoire de thèse, de l'intérêt manifesté pour mon travail et de l'ensemble de vos retours lors de nos discussions. Je tiens naturellement à exprimer ma gratitude aux membres du jury, Stéphane LEFEBVRE pour m'avoir fait l'honneur de présider ce jury et Serge BOMTEMPS pour le support pendant les phases de réalisation et instrumentation des modules de puissance développés.

Je souhaite remercier également mes collègues (et camarades !) du LSPV. En commençant par le Général Electrique – Stéphane CATELLANI, pour toute son

aide, support et encouragement pendant les hauts et les bas de la thèse. Merci pour tous les conseils que tu as pu me donner (y inclus toutes les Zeners et ferrites qui ont d'ailleurs sauvé mes essais à chaque fois!) – merci beaucoup Steph'! Un très grand merci à Guillaume LEFEVRE pour tous les conseils et discussions toujours intéressantes, celles-ci sur une multitude de sujets en Electronique de Puissance; tes vastes connaissances techniques et ton regard scientifique minutieux m'ont beaucoup aidé à progresser pendant la thèse – merci Guillaume! Je remercie également Anthony BIER (le plus grand chasseur de sanglier de Savoie) pour son support et disponibilité tout au long de ce projet, principalement autour de la commande du CSI. Un merci aussi à notre mathématicien préféré, Sylvain LESPINATS, pour tous les très bons moments et connaissances partagés ensemble (principalement quand cela concerne les questions du mutualisme entre les biches et les singes au Japon). Un merci spécial à Van Charles NGUYEN pour m'avoir aidé pendant la période où j'avais eu une lésion du ménisque. Merci Guillaume PIQUET-BOISSSON pour les bons moments partagés (et aussi pour les bières qu'on a bu ensemble!). Merci également à Franck ALSHAKARCHI pour le support en tant que chef de service du S3E (merci Kaïs).

Je tiens à remercier mes amis de Chambéry (et d'ailleurs) pour le support dans la vie de tous les jours, les très bons week-ends passés ensemble et aussi les galères partagées (parce qu'il en faut). La liste commence par lui, o Carcará do Nordeste, o Professor, o Majó, meu amigo Felipe E. SILVA CASTRO! O reizinho da simulação por elemento finito! Muito obrigado por tudo! Sou muito grato por todos esses anos de amizade, no perrengue ou na fartura, como já vivenciamos. Je continue cette liste avec la personne la plus cosmopolite de la planète : mon pote Juan David A. GARZON (connu en Colombie comme Gordito, à ce qu'il paraît). Merci pour ton support Juanito, ceci depuis les temps que l'on se partageait le bureau des stagiaires! Je te souhaite bonne chance pour tes prochaines aventures à Orléans (j'attends ton invitation pour la crémaillère). Ensuite je tiens à remercier le libanais le plus parisien que je ... ou serait-il le parisien le plus libanais que je connais? Merci pour tout Maroun HARRAN (a.k.a. Mahumus) – je te souhaite que du bonheur pour tes prochaines aventures à Paris et ailleurs! Merci aussi au papa du groupe, Arnaud AWAMBY, pour les fous rires (principalement après deux ou trois cachaças!!). A Mouhannad DBEISS, un grand merci à toi Zereeeeba!!! Et merci encore à tous ceux ou celles qui ne sont pas cités dans ce paragraphe, mais qui ont fait partie de ma vie ces dernières années en Savoie.

Deixemos agora a "langue de Voltaire" de lado para os agradecimentos aqueles que estão no Brasil. Eu acredito que a realização de um trabalho de doutorado se constrói gradativamente através da Educação. Assim, eu gostaria de agradecer imensamente a todos os meus professores. Graças a vocês eu pude chegar até aqui.

Eu agradeço também a todos os meus amigos brasileiros que me ajudaram a enfrentar esta longa jornada acadêmica, seja na França ou no Brasil: Ana Paula W. B. (Aninha), Gustavo "Guga" Saran, Luis Cardassi (Tio Barna), Ricardo Rangel (Carioca), Caio F. Batista (Zina), Wellington Machado, Vitor E. (Vitão), Filipe A. Caniatti (Tesouro), Mario N. A. Junior (Fiapo), dentre tantos outros. Gostaria também de expressar minha gratidão a Chayenne K. F. GOMES por todo o incentivo e suporte na continuidade dos meus estudos do doutorado na França. Um agradecimento especial vai para o meu amigo marinheiro Rafael A. de ARAUJO pela boa e velha amizade que cultivamos desde o primeiro dia em Toulouse (valeu, Chitão !!!). Ao meu amigo Danteh C. J. (o Lerdão), deixo meus agradecimentos (e também a pergunta de quando vamos finalmente correr a São Silvestre). E com todo carinho, agradeço àquela que me faz tão bem, Larissa dos S. S. ARAUJO. Obrigado pelo apoio na fase final do meu doutorado e pelos incentivos nesta minha nova jornada.

Por fim, eu gostaria de agradecer a toda minha família pelo apoio incondicional que me deram até aqui. Graças aos meus familiares, eu pude trilhar o meu caminho em busca de um sonho. Obrigado aos meus pais, irmãos, avós, primos, tios e tias. Nenhuma palavra seria capaz de retribuir todo o carinho e amor que a mim foram dados. Este doutorado é de todos vocês.

Luís Gabriel ALVES RODRIGUES

Corre um boato aqui donde eu moro

Que as mágoas que eu choro são mal ponteadas

Que no capim mascado do meu boi

A baba sempre foi santa e purificada

Diz que eu rumino desde menininho

Fraco e mirradinho a ração da estrada

Vou mastigando o mundo e ruminando

E assim vou tocando essa vida marvada

É que a viola fala alto no meu peito humano

E toda moda é um remédio pros meus desenganos

É que a viola fala alto no meu peito, humano

E toda mágoa é um mistério fora deste plano

Pra todo aquele que só fala que eu não sei viver

Chega lá em casa pruma visitinha

Que no verso ou no reverso da vida inteirinha

Há de encontrar-me num cateretê

Vide vida marvada Rolando Boldrin, o Sr. Brasil

A toda minha família, especialmente a minha mãe, Nilza, e aos meus avós, vó Maria, vó Ana e vô Luiz.

# **Table of Contents**

| Chapter 1                                                                                                                                                 | 23 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Introduction                                                                                                                                              | 23 |

| 1.1 Photovoltaic Scenario Overview                                                                                                                        | 24 |

| 1.2 Power Electronics for Photovoltaics                                                                                                                   | 25 |

| 1.3 Research Motivations and Objectives                                                                                                                   | 27 |

| 1.4 Dissertation Outline                                                                                                                                  | 29 |

| 1.5 References                                                                                                                                            | 30 |

| Chapter 2                                                                                                                                                 | 33 |

| State of the Art Review                                                                                                                                   | 33 |

| 2.1 Review of Three-phase Photovoltaic Inverter Topologies                                                                                                | 34 |

| 2.2 SiC vs. Si – Potentials of Wide-bandgap Devices for Performance<br>Improvement in Energy Conversion Systems                                           | 36 |

| 2.2.1 Brief Overview of WBG Materials and Properties                                                                                                      | 36 |

| 2.2.2 SiC-based Semiconductor Devices                                                                                                                     | 37 |

| 2.2.3 SiC Devices for Inverter Performance Improvement                                                                                                    | 39 |

| 2.3 Three-phase Current Source Inverter for Photovoltaic Applications Single-stage Topology as an Alternative Solution to Voltage Source-based Converters | d  |

| 2.4 Research Challenges and Opportunities                                                                                                                 |    |

| 2.5 References                                                                                                                                            |    |

| Chapter 3                                                                                                                                                 |    |

| Three-phase Current Source Inverter Topology                                                                                                              |    |

| 3.1 Introduction                                                                                                                                          |    |

| 3.2 Principle of Operation                                                                                                                                |    |

| 3.2.1 Space Vector Transformation                                                                                                                         |    |

| 3.2.2    | CSI Operation in Combination with a PV String – Steady-state              |

|----------|---------------------------------------------------------------------------|

| Analy    | vsis55                                                                    |

| 3.2.3    | Analysis of the Switching Cell Disposition57                              |

| 3.2.4    | Current and Voltage Stresses of Power Semiconductors                      |

| 3.2.5    | Typical waveforms                                                         |

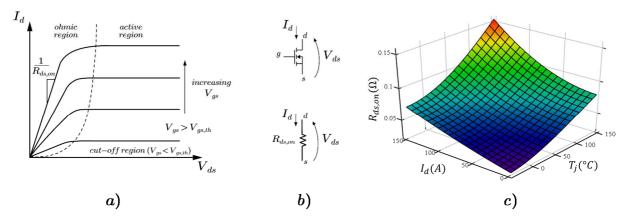

| 3.3 S    | emiconductor Conduction Losses                                            |

| 3.3.1    | Static modeling of semiconductor devices                                  |

| 3.3.2    | Conduction losses estimation                                              |

| 3.3.3    | Comparison of different CSI switch configurations in terms of             |

| condu    | action losses                                                             |

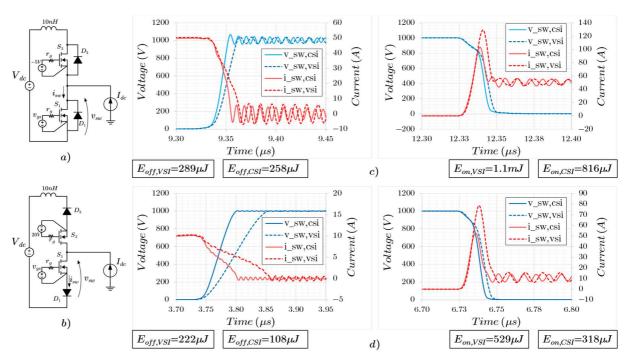

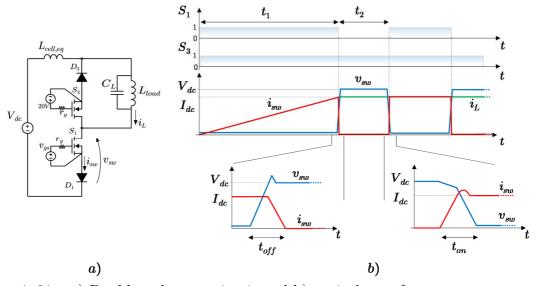

| 3.4 S    | witching Event in the CSI Topology71                                      |

| 3.4.1    | Simulation-based comparison of switching event in the CSI and VSI         |

| topol    | ogies                                                                     |

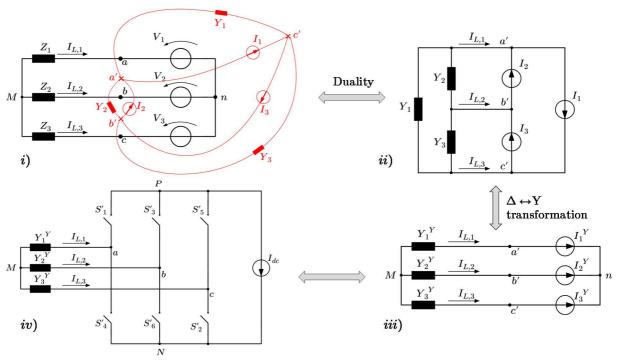

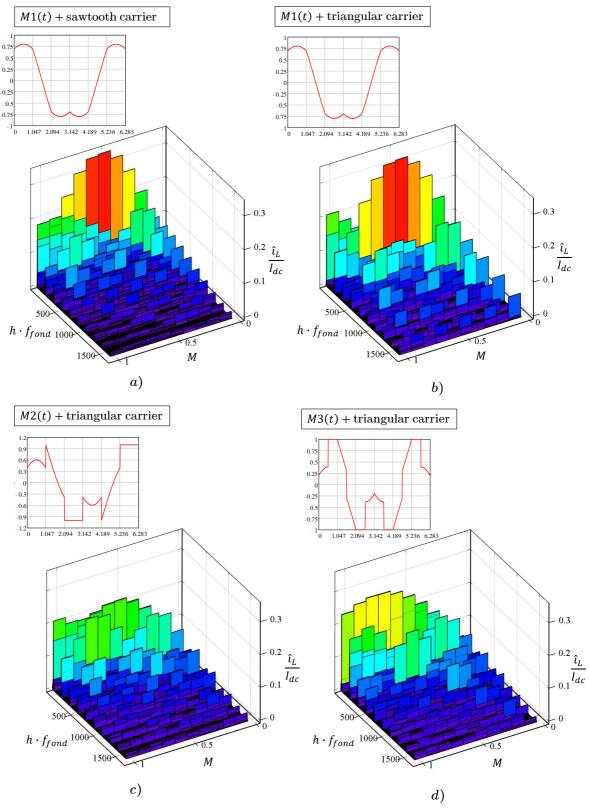

| 3.5 S    | pace Vector Modulation Strategies                                         |

| 3.5.1    | Methodology for Current Spectrum Determination                            |

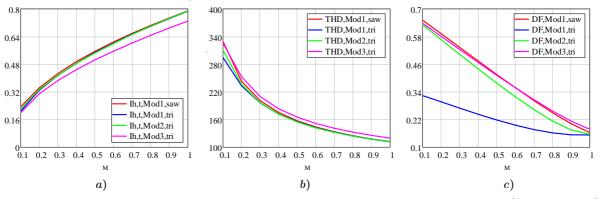

| 3.5.2    | Calculation Results                                                       |

| 3.6 S    | ummary and Conclusion84                                                   |

| 3.7 R    | eferences84                                                               |

| Chapter  | 489                                                                       |

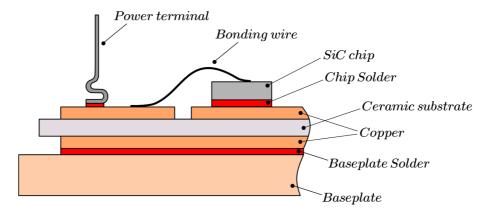

| Design a | and Characterization of a Novel 1.7kV Full-SiC Power Module               |

|          | 89                                                                        |

| 4.1 In   | ntroduction90                                                             |

| 4.2 P    | ower Integration for Current Source-based Topologies91                    |

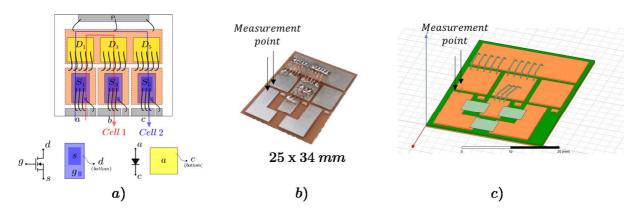

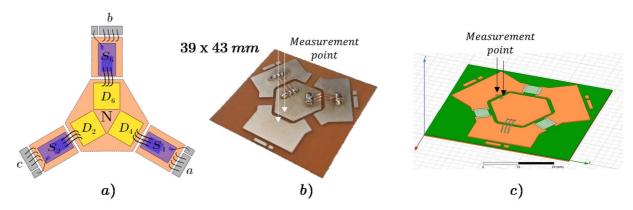

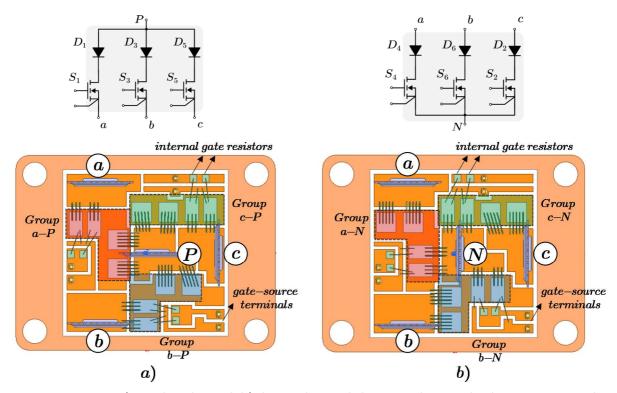

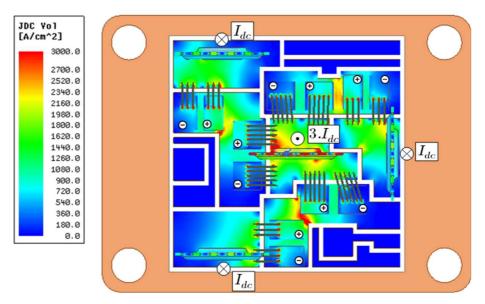

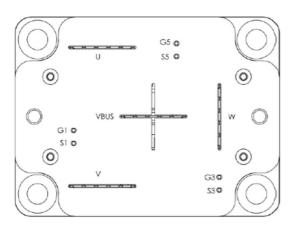

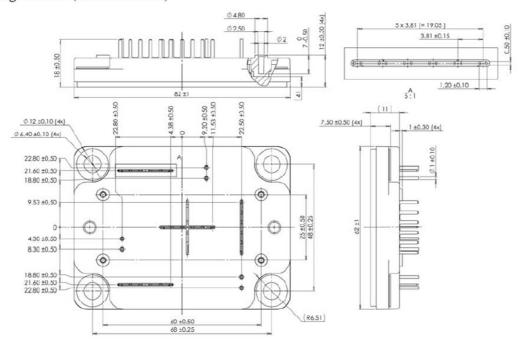

| 4.2.1    | Module Substrate Design                                                   |

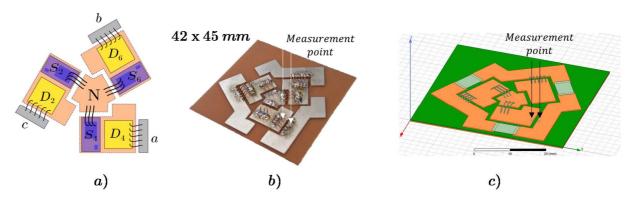

| 4.2.2    | Electrical Performance Evaluation                                         |

| 4.2.3    | Qualitative Modeling of a Coupled Microstrip – a Generic Case $\dots. 98$ |

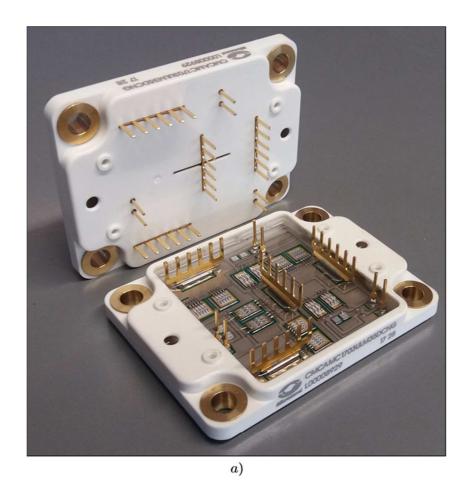

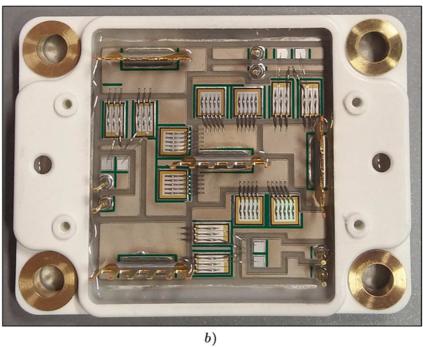

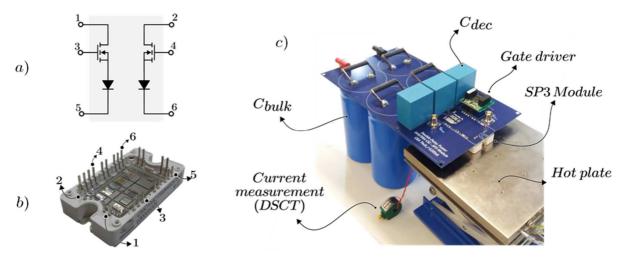

| 4.3 In   | ndustrial Realization of the Full-SiC CSI Module                          |

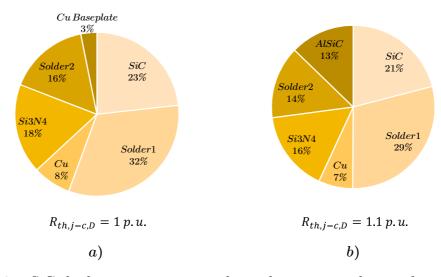

| 4.3.1    | Material Selection                                                        |

| 4.3.2    | Definition of Module Voltage and Current Ratings104                       |

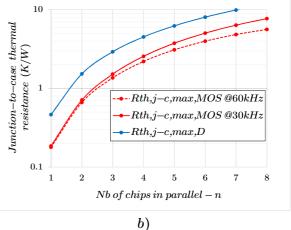

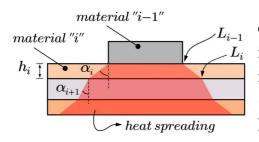

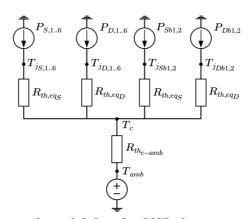

| 4.3.3    | Analysis of the Packaging Thermal Resistance Sharing                      |

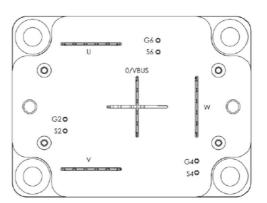

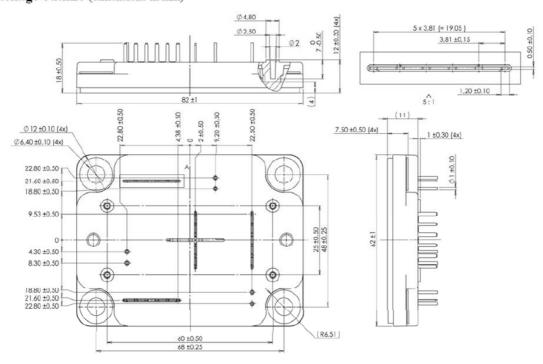

| 4.3.4    | Module Design                                                                         | 107 |

|----------|---------------------------------------------------------------------------------------|-----|

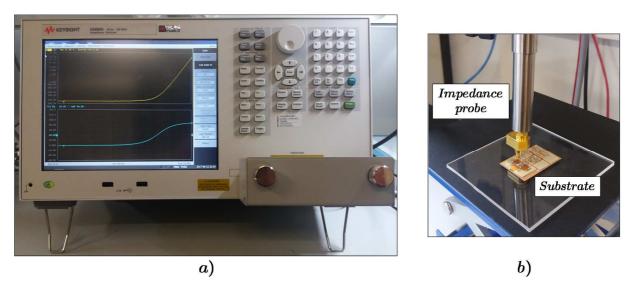

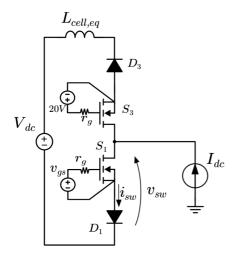

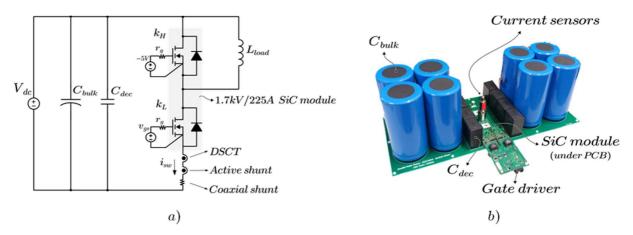

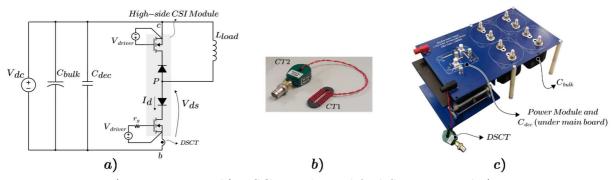

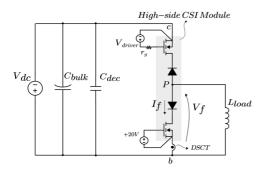

|          | nplementation of the Double-Pulse Test Characterization Method for vices Benchmarking |     |

| 4.4.1    | Switching Losses Measurement Methods                                                  | 112 |

| 4.4.2    | Double-Pulse Test Method.                                                             | 113 |

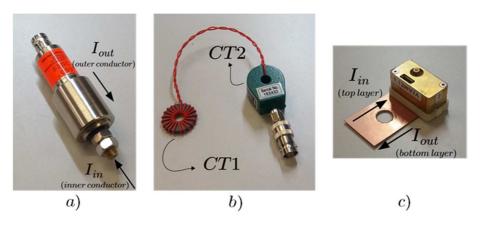

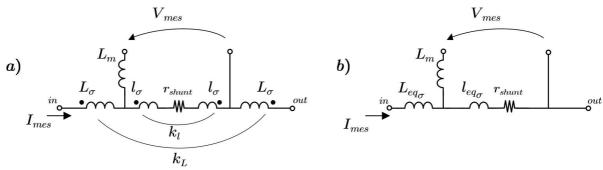

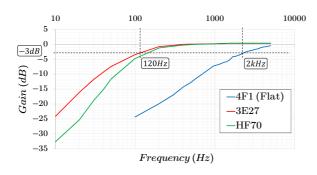

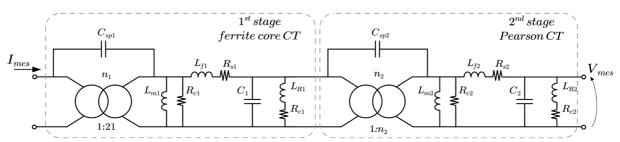

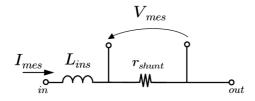

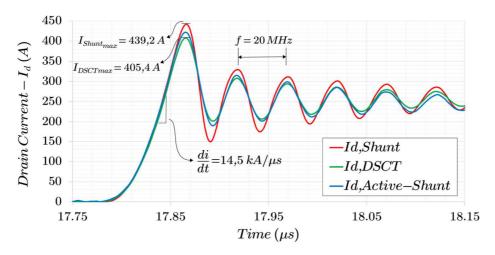

| 4.4.3    | Current Measurement Techniques                                                        | 115 |

| 4.4.4    | Selection of SiC Devices                                                              | 120 |

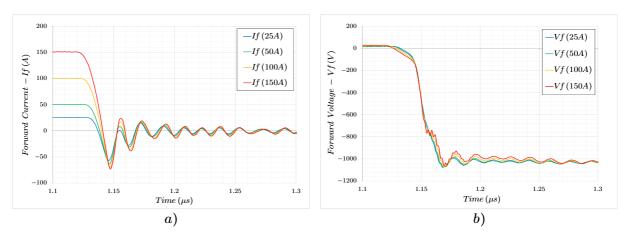

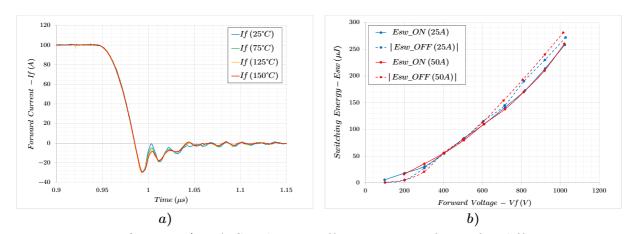

| 4.5 D    | ynamic Characterization of the Developed CSI Module                                   | 122 |

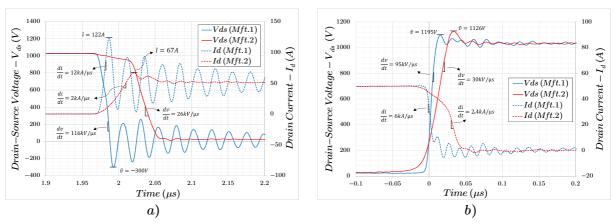

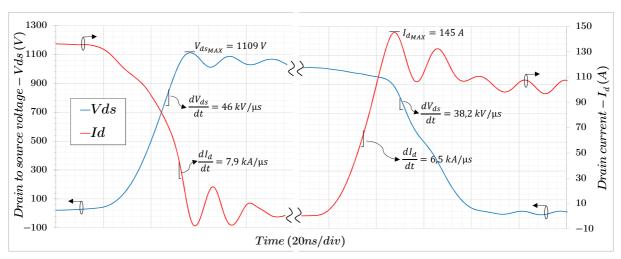

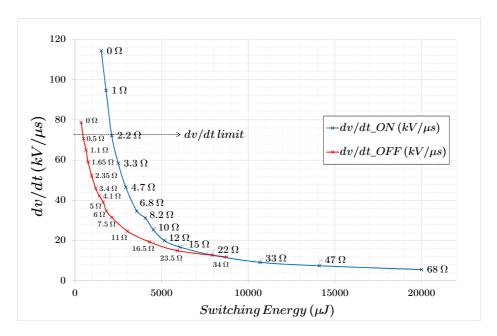

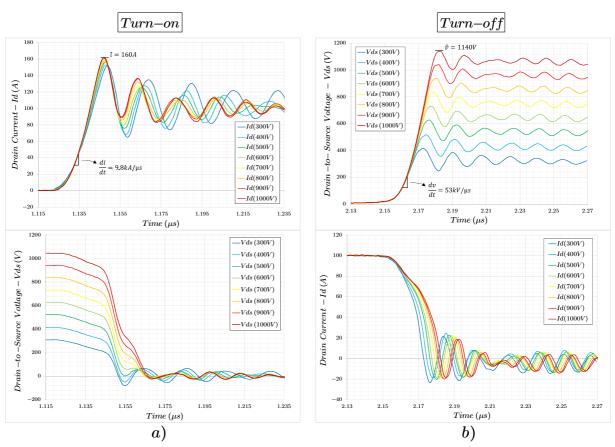

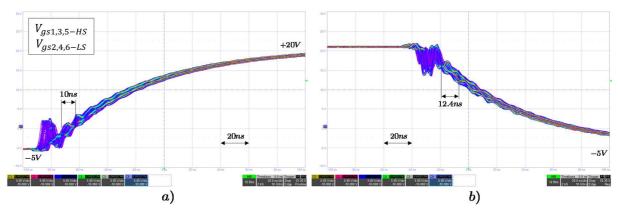

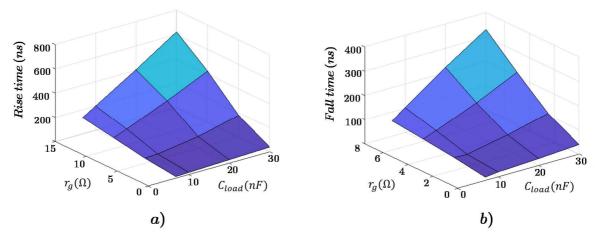

| 4.5.1    | Switching Speed Characterization                                                      | 124 |

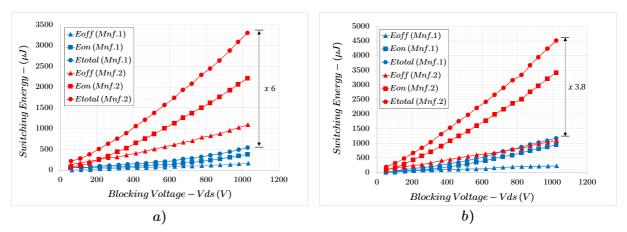

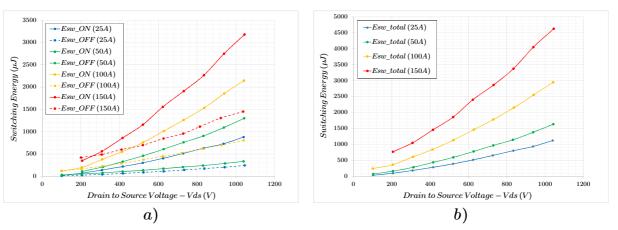

| 4.5.2    | Switching Losses Characterization                                                     | 125 |

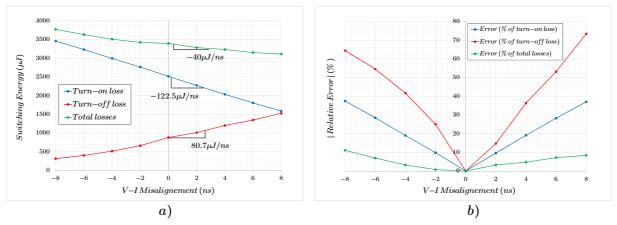

| 4.5.3    | Influence of Probes' Relative Delay on Switching Losses                               | 126 |

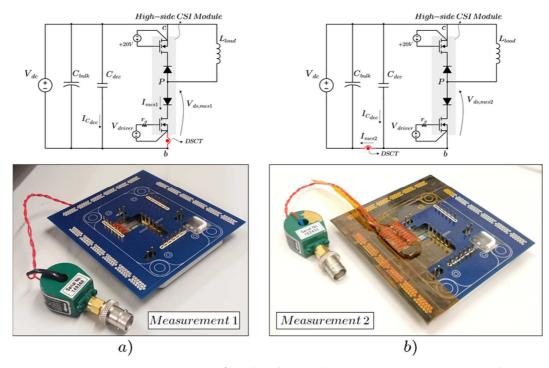

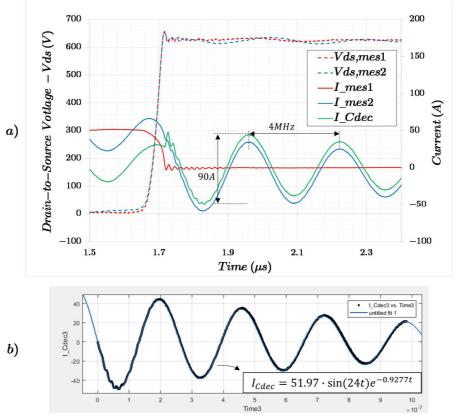

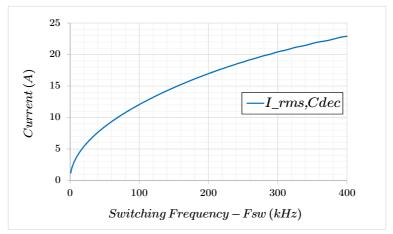

| 4.5.5    | Decoupling Capacitor Current Measurement and Sizing                                   | 129 |

| 4.6 St   | ummary and Conclusion                                                                 | 132 |

| 4.7 R    | eferences                                                                             | 133 |

| Chapter  | 5                                                                                     | 139 |

| Design a | and Experimental Evaluation of the 60kW CSI Prototype                                 | 139 |

| 5.1 In   | ntroduction1                                                                          | 140 |

| 5.2 Si   | izing of Passive Components                                                           | 141 |

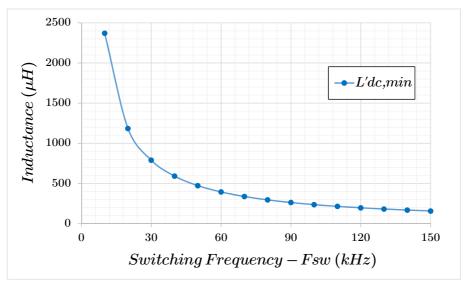

| 5.2.1    | DC Inductor                                                                           | 141 |

| 5.2.2    | DC Capacitor                                                                          | 142 |

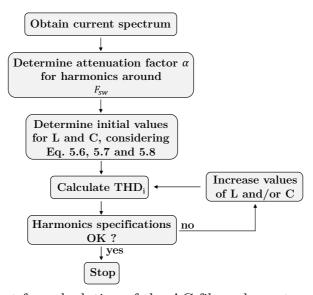

| 5.2.3    | AC Filter                                                                             | 143 |

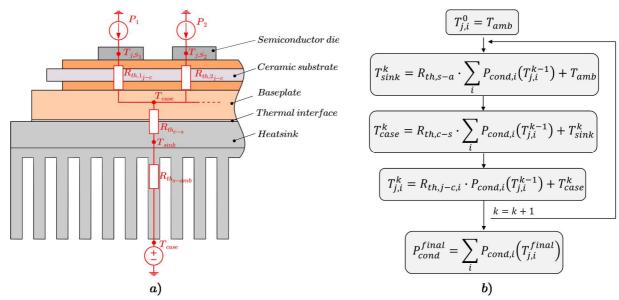

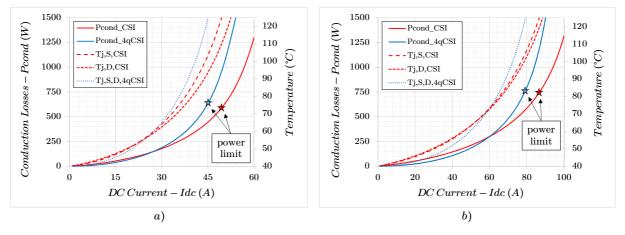

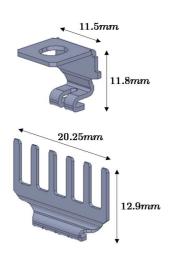

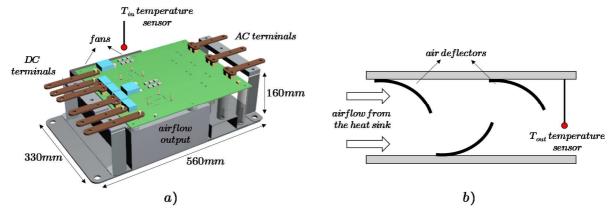

| 5.3 T    | hermal Management                                                                     | 145 |

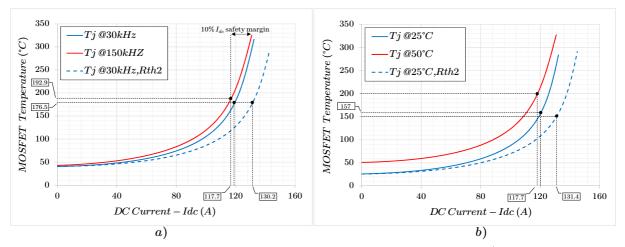

| 5.3.1    | Heat Sink Sizing                                                                      | 145 |

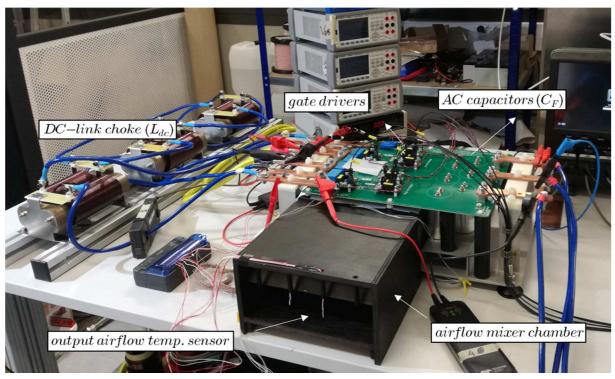

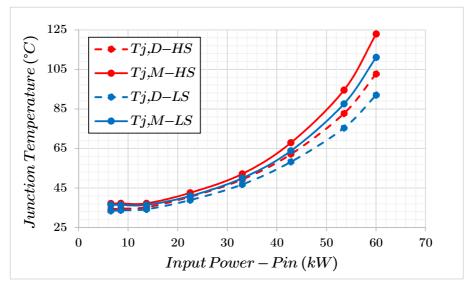

| 5.3.2    | SiC Module Thermal Runaway                                                            | 146 |

| 5.3.3    | Experimental Evaluation of the Module Thermal Behavior                                | 148 |

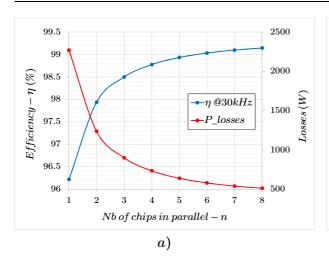

| 5.4 E    | fficiency Estimation                                                                  | 153 |

| 5.4.1    | CSI Operation on a Three-phase 800V Grid                                              | 155 |

| 5.5 C    | omparison with a Standard Solution: DC-DC Boost Converter in                          |     |

| combina  | ation with a Three-phase Two-level Voltage Source Inverter                            | 156 |

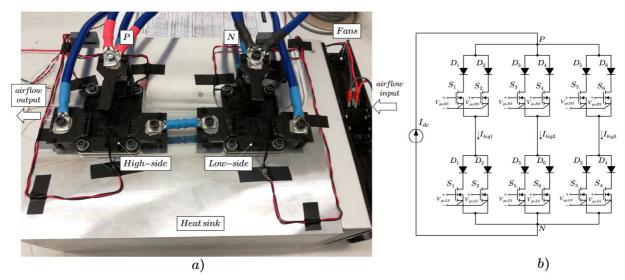

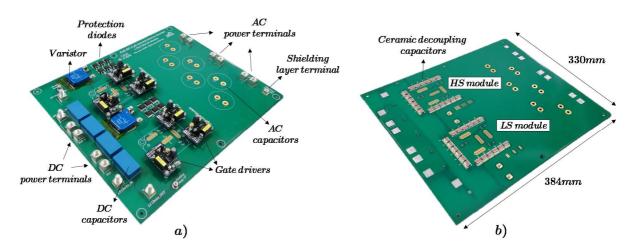

| 5.6 H    | ardware Description                                                                   | 159 |

|    | 5.6.1    | Protection Circuit                                                                                                       | 160 |

|----|----------|--------------------------------------------------------------------------------------------------------------------------|-----|

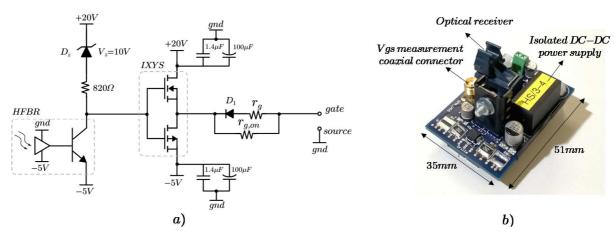

|    | 5.6.2    | Gate Driver                                                                                                              | 163 |

|    | 5.6.3    | Busbar                                                                                                                   | 165 |

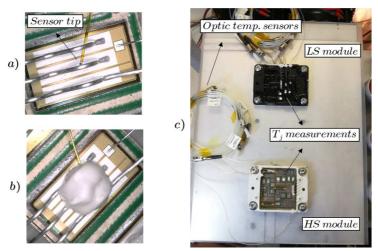

|    | 5.6.4    | Setup for Direct Measurement of Junction Temperatures                                                                    | 166 |

| 5  | .7 CS    | [ Characterization                                                                                                       | 167 |

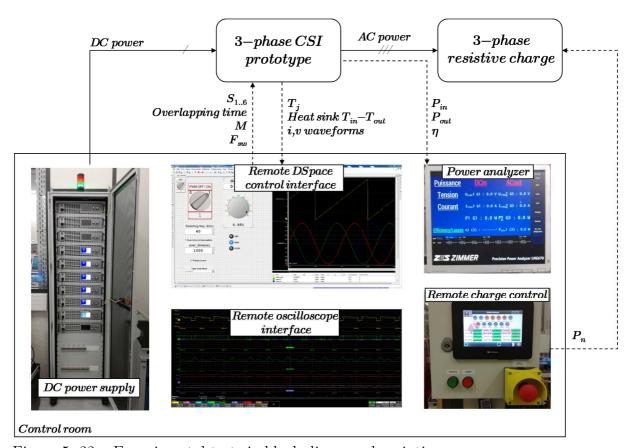

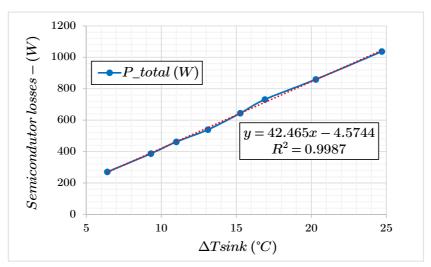

|    | 5.7.1    | Heat Sink Characterization for Calorimetric Semiconductor Losses                                                         | S   |

|    | Determ   | ination                                                                                                                  | 169 |

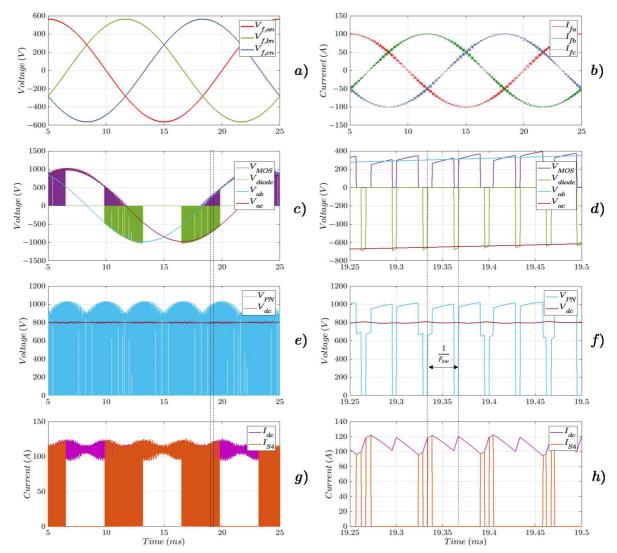

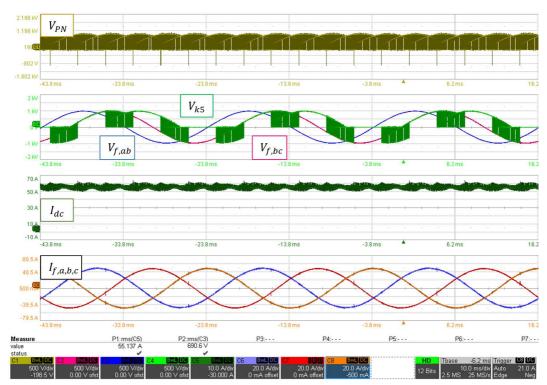

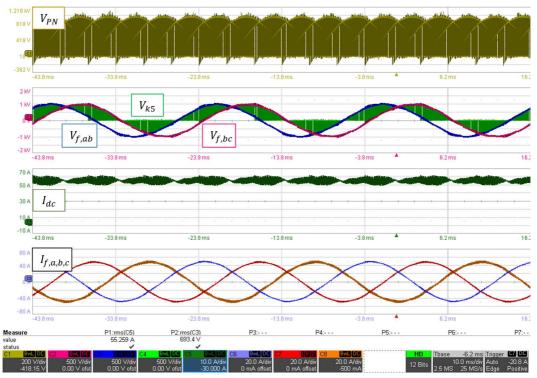

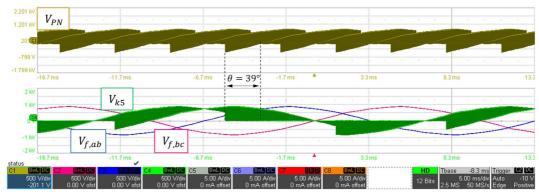

|    | 5.7.2    | Waveforms at Nominal Switching Operation                                                                                 | 170 |

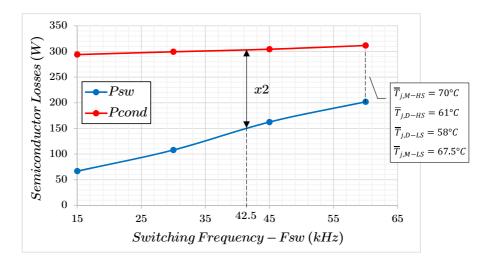

|    | 5.7.3    | Influence of Switching Frequency on Semiconductor Losses                                                                 | 172 |

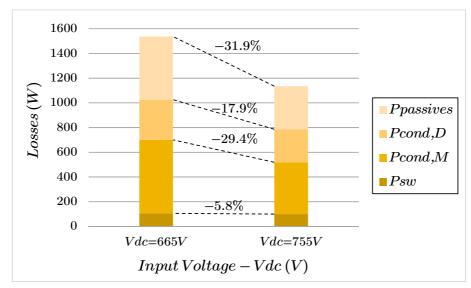

|    | 5.7.4    | Efficiency Measurements                                                                                                  | 173 |

| 5  | .8 Sur   | nmary and Conclusion                                                                                                     | 175 |

| 5  | .9 Ref   | erences                                                                                                                  | 177 |

| Ch | apter 6  | <b>5</b>                                                                                                                 | 181 |

| Co | nclusio  | ns and Future Work                                                                                                       | 181 |

| 6  | .1 Pov   | ver Integration for CSI Applications                                                                                     | 182 |

| 6  | .2 Dyn   | namic Characterization of 1.7kV SiC Devices                                                                              | 183 |

| 6  | .3 Inv   | erter Level                                                                                                              | 184 |

| 6  | .4 Ref   | erences                                                                                                                  | 186 |

| Αp | pendic   | es                                                                                                                       | 187 |

| A  | Append   | $\mathbf{i}\mathbf{x}$ I – On-state Characteristic Fitting Constants for the employed                                    |     |

| S  | iC devic | es                                                                                                                       | 188 |

| A  | Append   | ix II – Datasheet of the 1.7kV Full-SiC CSI Modules                                                                      | 191 |

|    |          | ix III – Design Considerations for the DC-DC Boost Converter in ion with a Three-phase Two-level Voltage Source Inverter | 195 |

Chapter 1

Introduction

#### 1.1 Photovoltaic Scenario Overview

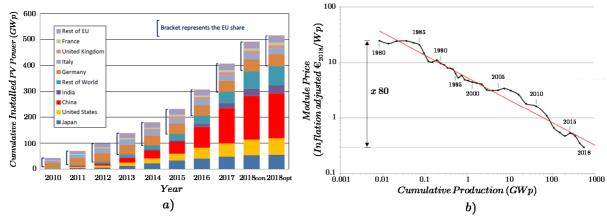

The most important challenges faced by society in recent years are related to sustainable development and climate change. Due to the limited resources of fossil fuels together with efforts to reduce global warming, governments have been leading the change to low-carbon energy systems. In this energy transition context, in both academia and industry, great research effort is focused today to increase efficiency and limit costs of renewable energy sources as hydropower, wind, solar, and biomass. Among all alternative energy sources, solar photovoltaic (PV) technologies have been drawn particular attention, attracting in 2017, 58% of all new renewable energy investments worldwide, i.e., €140 billion [1]. As pointed out in [2], [3], the levelized cost of energy (LCOE) in utility-scale PV power plants has reached, in some cases, that of fossil fuel-fired electricity. Also, the benchmark PV system LCOE has decreased by over 75% during the period 2009 – 2018 [1]. The main contributor to that is the decrease of PV solar panel prices (85% for the same period). In Figure 1.1 are depicted the cumulative installed PV power worldwide and the learning curve of PV module prices, where all commercially available technologies are included.

Figure 1. 1 – a) Cumulative installed PV power worldwide from 2010 to 2018. Source: modified from [1] and b) PV module price learning curve – all commercially available technologies included. Source: modified from [4].

Thanks to the attained maturity level of PV technology, the energy payback time<sup>2</sup> (EPBT) of PV systems in high solar irradiance regions in Europe might be

<sup>&</sup>lt;sup>1</sup> The LCOE is an average cost indicator that takes into account the amount of energy produced by a power plant during its entire lifetime with regard to its total cost of manufacturing, installation and operation.

<sup>&</sup>lt;sup>2</sup> The EPBT of a power generating system is defined as the time required to generate as much energy as is consumed during production and lifetime operation of the system. The energy required to recycle the PV system when it reaches the end-of-life is not taken into account here.

as low as one year [4]. Hence, considering a typical PV power plant lifespan of 20 years, such a PV system is capable of producing twenty times the amount of energy that was needed for its manufacturing, installation and lifetime operation.

For the reasons mentioned above, the PV technology has known an exponential growth in terms of installed power in the last decade, reaching more than 0.5TW<sub>p</sub> worldwide in 2018 (see Figure 1.1 (a)). Nevertheless, to keep making this technology more competitive, several challenges must be addressed with the aim of capping costs and increasing energy yield. With this in mind, all elements in the balance of system<sup>3</sup> (BOS) (e.g., inverter, junction boxes, installation equipment and etc.) are equally concerned.

### 1.2 Power Electronics for Photovoltaics

Although being the most known element in photovoltaics, the PV generator (or PV cell) is not the only fundamental component of a PV system. In reality, the voltage and current produced by a PV generator are DC quantities. Thus, to be able to inject power into the grid or feed an AC load, a DC-AC converter (or inverter) is often employed. Furthermore, due to its non-linear i-v characteristic<sup>4</sup>, the PV cell presents a single maximum power point (MPP), which must be constantly tracked by the inverter to maximize energy yield during operation. In the literature, numerous maximum power point tracking (MPPT) techniques can be found [5], [6]. Since the PV voltage varies during the day according to the weather and cell's temperature conditions, the inverter is also responsible to dynamically ensure a constant RMS AC output voltage. PV inverters can be designed in single- and three-phase configurations. Due to the presence of a lowfrequency (100Hz) fluctuating power component in single-phase systems, this inverter category is usually limited to a few kW and plays a minor role in the overall PV inverter market share [4] (mainly due to cost reasons). On the other hand, three-phase inverters account for more than 95% of the market share [4] and are the preferred solution in commercial and utility sectors [3].

When operating in grid-tied mode, the inverter must be able to: i) insure the DC-AC conversion with minimum power quality requirements [7]; ii) offer grid support injecting or absorbing reactive power, complying with grid codes and regulations [8]; iii) disconnect itself from the grid, when necessary (anti-islanding)

<sup>&</sup>lt;sup>3</sup> All PV power plant components and costs other than PV modules.

<sup>&</sup>lt;sup>4</sup> The *i-v* characteristic of a PV cell depends mainly on the cell's temperature and weather conditions [5]. In its simplest electrical model, a DC current source in anti-parallel with a diode is often employed [5], [6].

[9] and *iv*) have the capability to ride-through low and high voltage grid fault events, complying with LVRT and HVRT requirements, respectively [10].

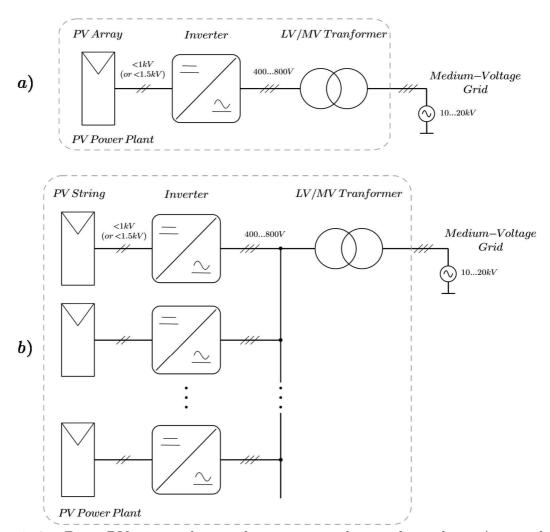

Figure 1.2 shows the basic architectures found in utility-scale PV power plants employing three-phase central and string inverter concepts.

Figure 1. 2 – Basic PV power plant architectures employing three-phase a) central and b) string inverter concepts.

Considering the case of multi-MW central inverter, the PV strings are paralleled to obtain a single electricity-producing unit called PV array<sup>5</sup>. Diversely, with the string inverter concept, smaller generating units are employed and, not rarely, string inverters of up to 150kW presenting multi-MPPT inputs are used.

<sup>&</sup>lt;sup>5</sup> In the literature, some confusion exists between the terms array and string. As pointed out in [11] and employed in this work, string consists of a number of PV modules interconnected electrically in series to produce a given maximum operating voltage  $(V_{oc})$  and array is an interconnected system of PV modules that function as a single electricity-producing unit. The modules are assembled as a discrete structure, with common support or mounting.

In both architectures, a low-voltage/medium-voltage (LV/MV) step-up transformer allows the PV power plant to be connected to the local MV grid.

Concerning the lifetime aspect of PV systems, there is a considerable gap between the typical lifespan of inverters (5 to 15 years [3], [12]) and that of PV panels (around 25 years [13]). From an operation and maintenance point of view, inverters are considered to be the weakest components in PV systems. In [14], it is reported that inverters were responsible for 37% of unscheduled maintenance events in a 50MW<sub>p</sub> PV plant, accounting for 59% of the associated overall repair costs. In [15], similar results are presented about the high cost of inverter failures, which comprises not only the service cost itself, but also the energy losses due to the PV power plant downtime. When identifying the root causes of inverter reliability issues, power semiconductors and DC-link capacitors (often electrolytic type) represent the most common failure sources [16]. Taking all this into consideration, the improvement of PV inverter reliability remains a topic to be addressed in order to reduce operation and maintenance costs, as well as energy losses due to inverter downtime.

### 1.3 Research Motivations and Objectives

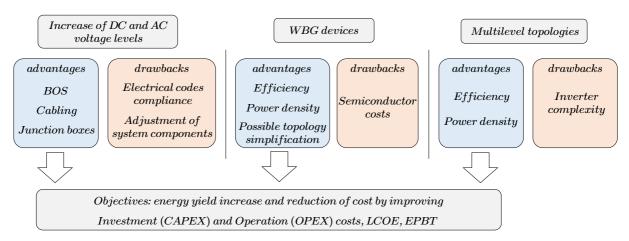

In Figure 1.3 is depicted a chart with three possible actions to be taken at the inverter design level to increase the energy yield and reduce costs of utility-scale PV power plants.

Figure 1. 3 – Possible actions to be taken at the inverter design level to increase the energy yield and reduce costs in large-scale PV systems.

A historical trend in PV systems is the progressive rise of the string voltage levels. In recent years, the first 1.5kV PV power plants have started operating [17]. When shifting from 1kV to 1.5kV strings, savings related to the initial PV plant investment costs (CAPEX) are possible (up to 4.5%) [17]. This cost

reduction is mainly related to the BOS, thanks to the reduction of cabling crosssection and number of system components. On the other hand, the main drawbacks of higher string voltages (consequently grid voltages as well) relate to electrical codes compliance (not yet well stablished in some countries) and adjustment of existent materials and system components to higher DC voltages [17].

Another possible action to facilitate capping costs in PV domain is the implementation of wide-bandgap (WBG) semiconductors, especially Silicon Carbide (SiC) and Gallium Nitride (GaN) devices. Due to their superior physical and electrical properties, the efficiency of energy conversion systems can be sensibly improved, lowering PV LCOE. Thanks to their aptitude to operate at superior switching frequencies, the inverter power density can be increased, helping to reduce the PV plant mounting and shipment costs, for example. Furthermore, WBG devices present outstanding on-state characteristics, allowing the power electronic engineer to redesign and simplify standard converter topologies. For example, by reducing the number of active switches and the associated complexity, while improving reliability and possibly lifetime. However, the major drawbacks of such semiconductors are related to their early stage of technological maturity, leading to: i) relatively high cost, which might be overcome to some extent by massive-scale production and ii) reliability issues. Concerning SiC devices, the reliability-critical aspects have been reported to involve gate-oxide long-term reliability and stability [18], [19], operation under short-circuit and avalanche conditions [20] and power cycling capability [21], [22]. Countermeasures to some of these problems can already be found in the literature and involve improved semiconductor manufacturing processes and advanced packaging technologies.

A final possibility considered here to improve PV yield is the use of multilevel inverters. The associated advantages are similar to that of WBG devices, with exception to the possibility of simplifying the inverter system. In reality, the implementation of multilevel inverters often comes with the price of increasing semiconductor switch part count and complexity.

Having the chart of Figure 1.3 in mind, this Ph.D. project aims to redesign, based on WBG semiconductors, the standard DC-AC converter architecture in PV applications. With the purpose of suppressing the DC-link capacitors and simplifying the inverter topology, the single-stage three-phase Current Source Inverter (CSI) is proposed. Thanks to their compatible voltage rating levels together with exceptional on-state characteristics, Silicon Carbide (SiC) devices

are employed in this work. Thereby, implementing the CSI topology with SiC devices brings the possibility to increase the grid voltage level, suppress the DClink capacitors, reduce the switches part count and simplify the power stage topology. Each of these advantages and potentials limitations will be discussed in detail in the following chapters.

#### 1.4 Dissertation Outline

Chapter 2 aims to present and analyze the most recent research advances in both academia and industry areas concerning the following aspects: i) state-ofthe-art commercially available PV inverter topologies, ii) WBG devices in power electronic systems for performance improvement and iii) implementation of the CSI topology in PV applications. Thereby, the main research opportunities are identified.

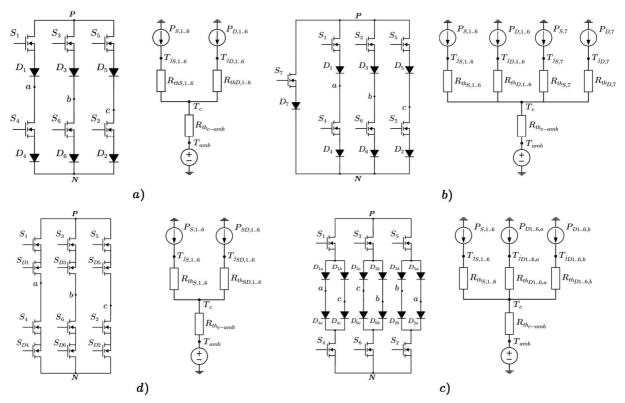

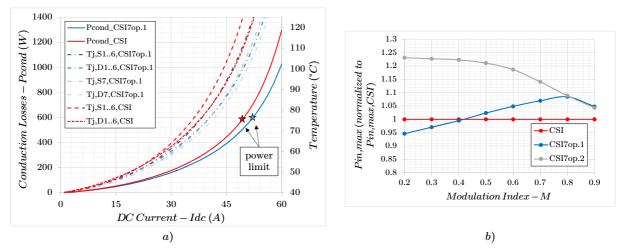

In Chapter 3, the CSI principle of operation is discussed. This serves as the basis for the inverter semiconductor losses analyses. Particular attention is given to semiconductor conduction losses, since they represent one of the major CSI drawbacks. Besides the standard CSI switch configuration, other three variants found in the literature claiming to reduce conduction losses are compared, taking into account their advantages and limitations to operate with a PV generator. From this comparative study, a final CSI switching configuration is chosen, in order to be implemented in a new full-SiC power module in Chapter 4.

Chapter 4 covers the semiconductor power integration for CSIs. Initially, based on the topology specificities and the target PV application, attention is given to the design of a novel 1.7kV full-SiC power module. Then, all steps to an industrial realization of this new device are discussed – from the packaging material selection, passing by the substrate and housing layout designs to the choice of semiconductor bare dies. The second part of Chapter 4 is dedicated to the dynamic characterization of the developed SiC module. In this context, switching losses are obtained, providing the basis for the CSI design in the subsequent chapter.

In Chapter 5, the CSI validation is carried out through experiments at nominal power. For this purpose, a 60kW prototype employing the developed 1.7kV SiC modules is fully presented, together with the main design guidelines for passive elements and cooling system. Focus is given to the module's thermal aspects and efficiency at switching operation conditions. Thus, the developed

60kW CSI prototype is characterized using both electrical and calorimetric methods.

Finally, **Chapter 6** summarizes the main research achievements and conclusions presented in this dissertation. Also, future research areas are identified and discussed accordingly.

### 1.5 References

- [1] A. JAEGER-WALDAU, "PV Status Report 2018," EUR Scientific and Technical Research Reports, Nov. 2018.

- [2] "International Renewable Energy Agency Solar energy." [Online]. Available: https://www.irena.org/en/solar. [Accessed: 31-Mar-2019].

- [3] M. Woodhouse *et al.*, "On the Path to SunShot. The Role of Advancements in Solar Photovoltaic Efficiency, Reliability, and Costs," National Renewable Energy Lab.(NREL), Golden, CO (United States), 2016.

- [4] "Photovoltaics Report Fraunhofer ISE," Mar. 2019.

- [5] M. A. G. De Brito, L. Galotto, L. P. Sampaio, G. de A. e Melo, and C. A. Canesin, "Evaluation of the main MPPT techniques for photovoltaic applications," *IEEE Trans. Ind. Electron.*, vol. 60, no. 3, pp. 1156–1167, 2013.

- [6] C. Photong, "A current source inverter with series AC capacitors for transformerless grid-tied photovoltaic applications," PhD Thesis, University of Nottingham, 2013.

- [7] I. E. C. Standard, "61727,'Characteristic of the utility interface for photovoltaic (PV) systems," IEC, Tech. Rep, 2002.

- [8] B. I. Crăciun, T. Kerekes, D. Séra, and R. Teodorescu, "Overview of recent Grid Codes for PV power integration," in 2012 13th International Conference on Optimization of Electrical and Electronic Equipment (OPTIM), 2012, pp. 959–965.

- [9] I. S. Board, IEEE Standard for Interconnecting Distributed Resources with Electric Power Systems: 1547-2003. IEEE, 2003.

- [10] S. Fan, P. Chao, and F. Zhang, "Modelling and simulation of the photovoltaic power station considering the LVRT and HVRT," *J. Eng.*, vol. 2017, no. 13, pp. 1206–1209, 2017.

- [11] "Solar Energy Glossary," *Energy.gov*. [Online]. Available: https://www.energy.gov/eere/solar/solar-energy-glossary. [Accessed: 31-Mar-2019].

- [12] C. Sintamarean, H. Wang, F. Blaabjerg, and F. Iannuzzo, "The impact of gate-driver parameters variation and device degradation in the PV-inverter

- lifetime," in 2014 IEEE Energy Conversion Congress and Exposition (ECCE), 2014, pp. 2257-2264.

- A. Meisel et al., SolarCity photovoltaic modules with 35 year useful life. SolarCity, 2016.

- L. M. Moore and H. N. Post, "Five years of operating experience at a large, utility-scale photovoltaic generating plant," Prog. Photovolt. Res. Appl., vol. 16, no. 3, pp. 249–259, May 2008.

- P. Hacke et al., "A status review of photovoltaic power conversion equipment reliability, safety, and quality assurance protocols," Renew. Sustain. Energy Rev., vol. 82, pp. 1097–1112, Feb. 2018.

- Sangwongwanich, "Grid-Friendly High-Reliability Photovoltaic Systems," PhD Thesis, Aalborg Universitetsforlag, 2018.

- A. N. Jiméneza and R. Bkayratb, "Utility scale 1,500 VDC PV power plant architecture evolution: advantages and challenges."

- M. Beier-Moebius and J. Lutz, "Breakdown of Gate Oxide of SiC-|18|MOSFETs and Si-IGBTs under High Temperature and High Gate Voltage," in PCIM Europe 2017; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2017, pp. 1–8.

- T. Aichinger, G. Rescher, and G. Pobegen, "Threshold voltage peculiarities and bias temperature instabilities of SiC MOSFETs," Microelectron. Reliab., vol. 80, pp. 68–78, Jan. 2018.

- [20]T. A. Nguyen, N. Boucenna, D. Labrousse, G. Chaplier, S. Lefebvre, and S. Azzopardi, "Investigation on Reliability of SiC MOSFET Under Long-Term Extreme Operating Conditions," in PCIM Europe 2018; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2018, pp. 1–8.

- [21]T. Poller and J. Lutz, "Comparison of the mechanical load in solder joints using SiC and Si chips," in 10th International Seminar on Power Semiconductors ISPS, 2010.

- C. Herold, M. Schaefer, F. Sauerland, T. Poller, J. Lutz, and O. Schilling, "Power cycling capability of Modules with SiC-Diodes," in CIPS 2014; 8th International Conference on Integrated Power Electronics Systems, 2014, pp. 1-6.

## Chapter 2

## State of the Art Review

With the purpose of placing the Ph.D. project objectives with regard to the cutting edge research advances in power electronics, a literature review is carried out in this chapter. Starting from common PV inverter topologies and their associated drawbacks, the implementation of wide-bandgap (WBG) devices in combination with the single-stage three-phase Current Source Inverter (CSI) is proposed. With such a solution, PV inverter's complexity could be reduced while increasing performances. Due to their higher blocking voltage rates, focus is given to SiC devices in this work. Then, a review of CSI for PV applications is presented and a more detailed analysis on the potentials of the proposed SiC-based CSI for performance improvement is carried out. Finally, the chapter summarizes the main research challenges and opportunities.

### 2.1 Review of Three-phase Photovoltaic Inverter Topologies

PV inverters are normally voltage source-based converters [1], [2] and can be classified with regard to their number of power processing stages. Thereby, two main categories arise, namely single-stage and multistage inverters [2]. In Figure 2.1 (a) and (b) are depicted, respectively, the block diagram of a three-phase single- and two-stage inverter topologies.

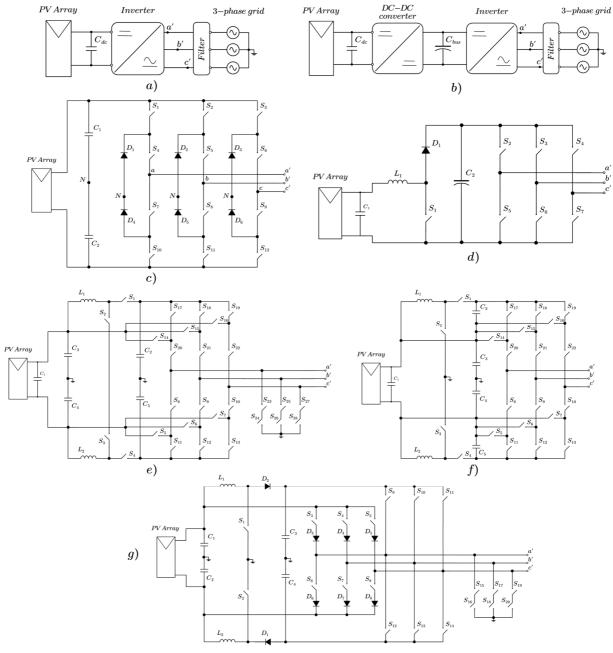

Figure 2. 1 – Three-phase inverter block diagram for a) single-stage and b) two-stage architectures. c) Single-stage three-phase NPC inverter. Two-stage three-phase architectures: d) boost + VSI, e) symmetric boost + 5-level VSI, f) symmetric boost + 4-level VSI and g) symmetric boost + 5-level TCC VSI.

As can be seen, in the two-stage inverter topology, a DC-link capacitor bus  $(\mathcal{C}_{bus})$  is implemented in order to respect the interconnection rule of sources and limit the DC voltage ripple [3]. For these purposes, electrolytic capacitors are often employed, thanks to their good compromise between energy density and costs [4]. Nevertheless, as mentioned in § 1.2, these components are often associated to high failure rates in field operation [5], [6]. On the other hand, the DC filter capacitor  $(\mathcal{C}_{dc})$  – present in both inverter categories – serves to stabilize the PV voltage, helping to perform the MPPT.  $C_{dc}$  represents minor reliability issues, since it is often of small value and then realized through metallized polypropylene film capacitors (known to have superior reliability performances [4]). The choice for a supplementary power processing stage is justified, in many cases, by the wider input DC voltage range (i.e., MPP voltage range) [2], which facilitates the PV power plant design [7] and increases energy yield.

With the rapid growth of photovoltaics in recent years, several companies have joined the market, making available a vast range of PV inverter systems, featuring different topologies and characteristics [8]. In Figure 2.1 are depicted some of these commercial three-phase PV inverters. In greater detail, Figure 2.1 (c) shows an example of a single-stage topology, the Neutral Point Clamped (NPC) inverter [1]. Figures 2.1 (d), (e), (f) and (g) present multistage converters, respectively, boost + 2-level Voltage Source Inverter (VSI) [8], e) symmetric boost + 5-level VSI [9], f) symmetric boost + 4-level VSI [10] and g) symmetric boost + 5-level VSI with 3-level camping cell (TCC) [11]. These topologies are found in a large power range (from a few tens of kW to more than 1MW), featuring single or multi MPPT inputs. Although not extensive, from Figure 2.1, the common aspects usually shared by PV inverters become clear: they all implement multilevel and/or multistage topologies. Thereby, an increase of the device's part count (i.e., number of semiconductor switches, gate driver units, voltage/current sensors and etc.) as well as the converter complexity is inevitable.

In the light of this, next section discusses the implementation of WBG devices (especially SiC devices) in power electronic systems for performance improvement, i.e., reduction of the converter's complexity and increase of power density and efficiency.

# 2.2 SiC vs. Si – Potentials of Wide-bandgap Devices for Performance Improvement in Energy Conversion Systems

#### 2.2.1 Brief Overview of WBG Materials and Properties

Since the development of solid-state electronics in the 1950s, Silicon (Si) has been the most commonly used semiconductor material in energy conversion systems. Today, thanks to its advanced maturity level, innovative breakthroughs are rarely achieved with this technology [12]. Thus, in order to keep improving the performance of power electronic converters, alternative semiconductor materials are of interest, especially those presenting wider bandgaps. Among the most developed WBG materials are Silicon Carbide (SiC) and Gallium Nitride (GaN). Table 2.1 presents the main physical properties of these WBG semiconductors. For comparison, Si properties are presented as well. Due to their blocking voltage rating limitation (typically <650V), GaN devices are not the focus of this work.

| Property                                                    | Symbol (unit)                                 | Si   | 4H-SiC <sup>1</sup> | GaN <sup>2</sup> |

|-------------------------------------------------------------|-----------------------------------------------|------|---------------------|------------------|

| Bandgap                                                     | $E_G(eV)$                                     | 1.1  | 3.26                | 3.45             |

| Relative dielectric const.                                  | Relative dielectric const. $\varepsilon_r(-)$ |      |                     | 9.0              |

| Breakdown electric field                                    | $E_{crit}$ (MV/cm)                            | 0.3  | 3.0                 | 5.0              |

| Thermal conductivity                                        | $\lambda (W/K.cm)$                            | 1.5  | 4.9                 | 1.3              |

| Melting temperature                                         | $T_m$ (°C)                                    | 1420 | 2830                | -                |

| Electron mobility                                           | $\mu_n (cm^2/V.s)$                            | 1500 | 1140                | 1250             |

| Hole mobility                                               | nobility $\mu_p (cm^2/V.s)$                   |      | 50                  | 850              |

| Baliga's FOM <sup>3</sup> FOM <sub>B</sub> (relative to Si) |                                               | 1.0  | 554                 | 188              |

Table 2. 1 – Main physical properties of semiconductor materials [13], [14].

When designing high-voltage power semiconductors, one of the major material properties to consider is the critical electric field strength  $(E_{crit})$ . The  $E_{crit}$  for SiC is ten times higher than that for Si. The higher breakdown level is the main parameter which allows SiC-based devices to drastically reduce specific on-state resistance  $(R_{on,sp})$ . Taking the case of unipolar devices, by simply shifting from Si to SiC, a drift-layer resistance reduction of two to three orders of magnitude is possible at any blocking voltage level [12]. Otherwise, for a given

<sup>1)</sup> Only 4H-SiC polytype is considered here, since it is the most common choice for power devices due to its relatively good manufacturability and superior physical properties [15]. 2) Properties of GaN material and not that of HEMT GaN [14]. 3)  $FOM_B$  defines the material efficiency to minimize conduction losses for unipolar devices.

current rating, SiC devices tend to present much smaller active chip area than their Si counterparts. This analysis is supported by the Baliga's figure of merit  $(FOM_B \text{ in Table 2.1})$ , which defines the material efficiency to minimize conduction losses for unipolar devices.

Concerning the comparison of switching behaviors for Si- and SiC-based devices, this should be done carefully. When compared to Si-based bipolar switches (e.g., insulated gate bipolar transistor – IGBT), the faster switching behavior of SiC unipolar devices (e.g., metal-oxide-semiconductor field-effect transistor – MOSFET) must not be only attributed to the SiC material itself. In reality, due to the absence of minority carrier storage of unipolar structures, their switching transition is only dependent of the device's parasitic capacitances. This is typically not the case for IGBTs, no matter the employed material (Si or SiC). Nevertheless, if comparing, for example, a given bipolar device based on Si and SiC, the later will present faster switching transient [12]. Thanks to the high SiC  $E_{crit}$ , a thinner blocking-voltage layer can be implemented, leading to less overall stored charges during operation.

Another key factor for performance improvement often related to SiC utilization is the material aptitude for operating at elevated temperatures (>500°C). Indeed, the SiC material properties are well suitable for this purpose, since its thermal conductivity, melting point and chemical stability are sensibly better than those of Si [12]. However, when taking into account realistic power application conditions, thermal runaway is likely to occur if junction temperatures exceed a certain threshold – due to carrier mobility degradation with temperature [16]. From the integration perspective, packaging reliability represents another bottleneck for high-temperature operation [17].

For deeper discussion on SiC technology and properties, the reader is invited to consult the following references: [15], [18], [19].

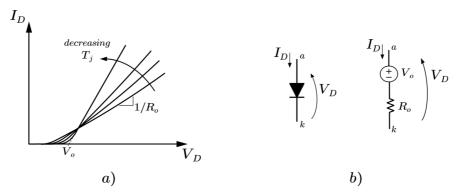

#### SiC-based Semiconductor Devices 2.2.2

Since 2001, when the first SiC device (the Schottky barrier diode – SBD) was introduced in the market by Infineon, much progress has been done in terms of device's structure and process optimization. Nowadays, most of SiC diodes present a merged pin-Schottky (MPS) structure and SiC trench MOSFET structures are not rarely employed. Figure 2.2 presents the basic structures found in state-ofthe-art SiC diodes and MOSFETs.

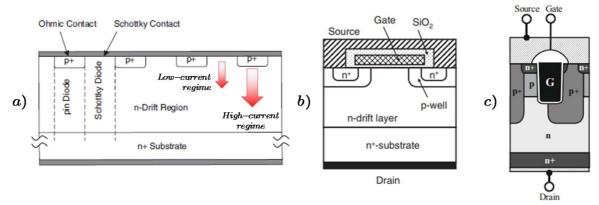

Figure 2. 2 – a) Structure of MPS diode (source: modified from [15]), b) DMOSFET (source: modified from [12]) and c) trench MOSFET with asymmetrical channel (source: modified from [20]).

The MPS diode, presented in Figure 2.2 (a), is a structure that combines the advantages of both pin and Schottky diodes, featuring no reverse recovery characteristic under nominal operation, improved surge current capability and low reverse-bias leakage-current [15], [18]. Thanks to the interdigitated Schottky and highly-doped p-type regions, the device presents two distinct operating behaviors. At nominal forward current condition, the p<sup>+</sup> regions are not triggered and the device acts as a standard unipolar SBD. On the other hand, at high-current events (e.g., surge current), the p<sup>+</sup> regions start to inject carriers acting then as a bipolar device, reducing the on-state losses and giving a supplementary surge capability margin. Figure 2.2 (b) and (c) presents the common MOSFETs structures employed by manufacturers Wolfspeed and Infineon, respectively. Due to the smaller cell pitch featured by SiC MOSFETs (thanks to the higher  $E_{crit}$ ), their gate-oxide (SiO<sub>2</sub>) structure is more prone to suffer from high electric field gradients, possibly degrading long-term reliability. Furthermore, the low electron mobility at the SiC/SiO<sub>2</sub> interface (due to interface defects) represents a challenge to threshold voltage  $(V_{as,th})$  stability [20]. Having in mind the object of improving the channel mobility (to reduce  $R_{on,sp}$ , increasing then wafer yield) while not degrading long-term reliability aspects, manufacturers have been improving their processes and developing their own specific device structures.

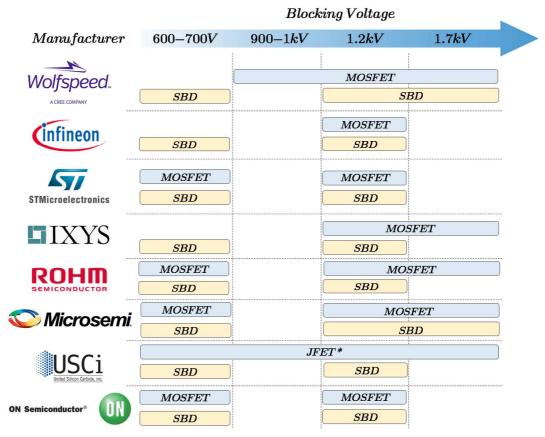

Figure 2.3 presents the major SiC device manufacturers and their commercially available components at the time of the present work. Manufactures which do not commercialize their SiC devices, such as GE, are not considered in this chart. As can be seen, all manufacturers, except for United Silicon Carbide, concentrate their efforts on the development of SiC MOSFETs and SBDs, especially for low-voltage applications (600-700V) and 1.2kV. The progressive migration to higher blocking voltages, i.e., 1.7kV, can also be seen.

Figure 2. 3 – Major SiC device manufacturers and their commercially available components. \*normally-on and -off devices are included. Source: modified and updated from [17].

#### 2.2.3 SiC Devices for Inverter Performance Improvement

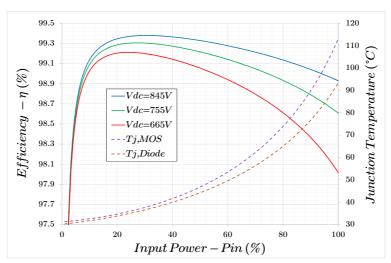

Given the superior SiC properties discussed in the previous sections, a typical example is presented here concerning the performance improvement of inverters through SiC implementation. Figure 2.4 depicts the performance of a 2.5MW SiC-based PV central inverter [21]. Originally, such PV application employed 1.7kV Si-based IGBTs operating at 2.6kHz in a VSI configuration (number of levels not specified in [21]). Due to the relatively high semiconductor losses, water-cooling system was implemented.

Figure 2. 4 - a) Output current derating as a function of the switching frequency when employing Si IGBTs and SiC MOSFETs modules and b) inverter efficiency at different input voltages and three-phase bridge mounted on air-cooled heatsink. Source: modified from [21].

From Figure 2.4 (a), one concludes that, in its SiC version, the PV inverter is capable of operating at much higher switching frequencies without strongly penalizing the output power (due to devices' junction temperature limit), which is notably not the case when employing Si IGBTs. Also, a 25°C additional junction temperature margin is obtained with the SiC modules. Concerning the new selected switching frequency ( $F_{sw,SiC}$ ), it is set to be 8kHz, i.e.,  $F_{sw,SiC} = 3 \cdot F_{sw,Si}$ . However, at the highest possible switching frequency operating point  $F_{sw,SiC} = 10 \cdot F_{sw,Si}$ . Thanks to semiconductor losses reduction (up to 50%), the SiC-based inverter is now air-cooled, allowing to reduce thermal cooling system complexity and increase power density. With regard to the new achieved efficiency, the SiC inverter has shown to be capable of operating with 99% efficiency at lower input voltage levels (900V). To summarize, when replacing the Si-based semiconductors by their SiC counterparts, increased switching frequency, efficiency and power density were achieved together with important cooling system simplification.

# 2.3 Three-phase Current Source Inverter for Photovoltaic Applications: a Single-stage Topology as an Alternative Solution to Voltage Source-based Converters

Historically, Current Source Converters (CSCs) have been employed in energy conversion systems since the early 1960s and 1970s, for HVDC and motor drive applications, respectively [22]. Nonetheless, in recent years, a growing number of scientific papers have proposed the use of CSCs in a large variety of systems, ranging from power factor correction rectifiers [23], [24] to renewable

energy source integration to the grid [25]–[29]. Due to the high level of conduction losses in the CSC [23], this topology is not rarely out of consideration, as long as semiconductors presenting good on-state characteristics are employed (e.g., in higher voltage applications, by using bipolar devices as IGBTs). However, as discussed in § 2.2.1, their intrinsic charge storage characteristic make their switching behavior slower and the presence of tail current and turn-off recovery (e.g., for pin diodes) is inevitable. Consequently, to cap switching losses within reasonable boundaries, the designer has no choice but to limit the switching frequency, resulting in a bulky and expensive DC-link inductor. In view of these facts, Voltage Source Converters (VSCs) have historically been preferred over CSCs in most cases. Nevertheless, the recent advances in power electronic semiconductors (especially concerning WGB devices) have made possible to improve the performances of CSCs by reducing conduction losses and increasing switching frequency at the same time. Thereby, making the CSC a compelling solution to standard VSCs. That represents one of the main reasons behind the emerging research interest on CSC-related topics.

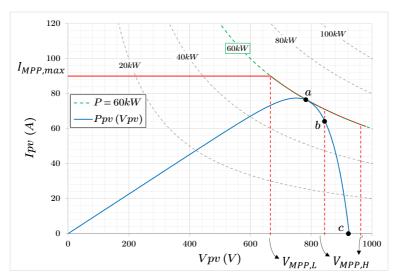

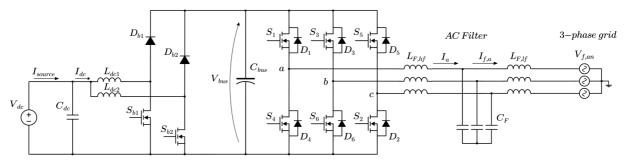

Having in mind the research motivations and objectives discussed in § 1.3, this Ph.D. project aims to evaluate the potentials of the single-stage three-phase SiC-based Current Source Inverter in photovoltaic applications. The adopted CSI power range is that of a typical string inverter (around 60kW). Figure 2.5 illustrates the three-phase PV CSI operating with the grid.

Figure 2. 5 – Grid-connected single-stage three-phase Current Source Inverter operating with a PV array.

In the literature, the CSI utilization as grid interface for photovoltaics has been investigated in a few research works, especially for low power PV applications, i.e., limited to a few kW. In the following, the most relevant works are summarized and discussed.

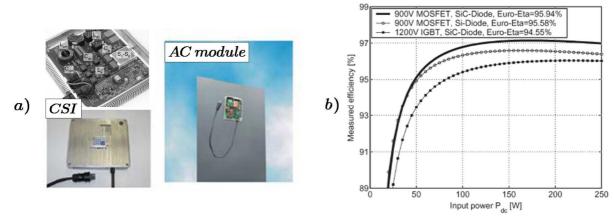

In [29], [30], a 250W three-phase CSI is proposed to operate as grid interface for PV modules. By directly integrating the microinverter on the PV module's backside, an "AC module" results, being capable of directly injecting power into the 400V grid. Figure 2.6 (a) depicts the final CSI inverter and the AC module. Due to absence of galvanic insulation, a special modulation strategy has been developed, in order to minimize common mode earth leakage currents at the PV module level. Note that this issue is not found in utility-scale PV plants, thanks to the LV/MV transformer (see Figure 1.2). In terms of efficiency, three different semiconductor configurations are analyzed under 25kHz switching operation, leading to a maximum European Efficiency  $(\eta_{euro})$  of 95.8% when employing 900V MOSFETs and SiC series diodes. As claimed by the authors, the CSI implementation approach might increase the PV reliability, thanks to its single-stage approach and elimination of electrolytic capacitors.

Figure 2. 6 – a) CSI prototype and "AC PV module" with integrated inverter on the backside and b) efficiency results. Source: modified from [30] and [29].

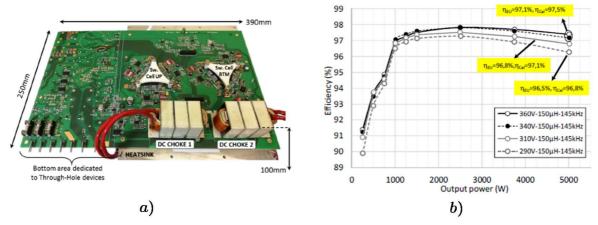

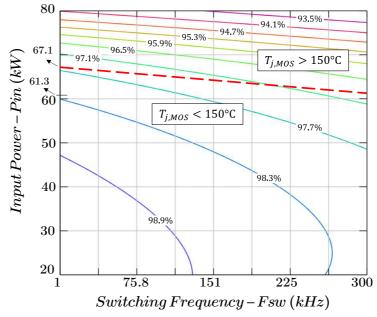

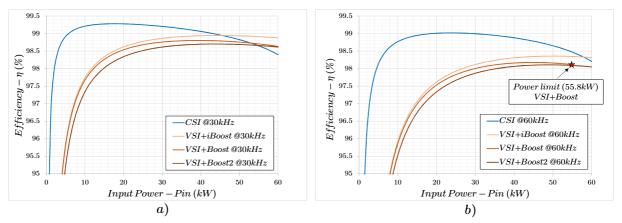

Another interesting CSI implementation is presented in [25], where the switch configuration is chosen to be based on SiC MOSFETs in synchronous rectification mode. Thus, a 5kW three-phase PV CSI is developed to operate with the 400V grid. Figure 2.7 presents the CSI prototype and its efficiency. In the referred work, the switching frequency is 145kHz, in order to fulfill conducted emissions requirements with reasonable filtering efforts. Then, the intrinsic low level of the full-SiC CSI switching losses is put in evidence in the paper. As demonstrated through losses calculations, the operation at 300kHz with relatively high  $\eta_{euro}$  (>97.5%) is also possible, especially with devices integrated in D<sup>2</sup>PAK

<sup>&</sup>lt;sup>6</sup> The European Efficiency is calculated from the efficiency average over a given power distribution (power range) corresponding to the operating climatic conditions of a central European location, where:  $\eta_{euro} = 0.03 \cdot \eta_{5\%} + 0.06 \cdot \eta_{10\%} + 0.13 \cdot \eta_{20\%} + 0.1 \cdot \eta_{30\%} + 0.48 \cdot \eta_{50\%} + 0.2 \cdot \eta_{100\%}$ .

packaging (thanks to the reduced parasitics). As pointed out by the authors, the CSI equipped with latest generation SiC devices represents a compelling alternative to standard VSIs. Furthermore, thanks to its low switching losses, the CSI topology represents a good candidate for high-power density applications.

Figure 2. 7 - a) CSI prototype and b) efficiency results. Images courtesy of [25].

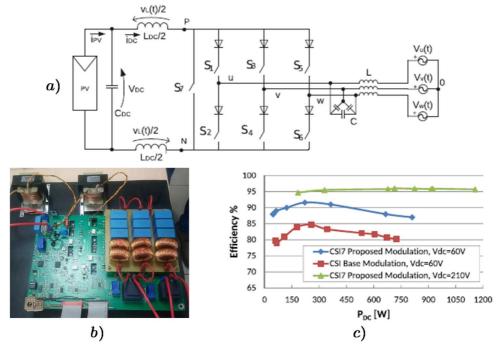

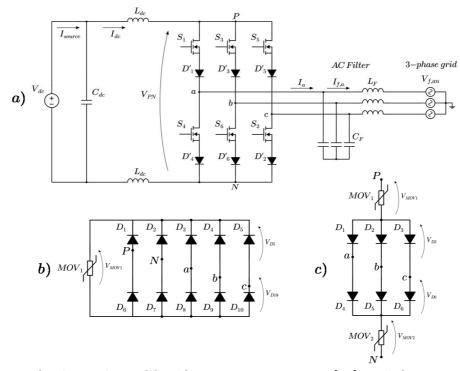

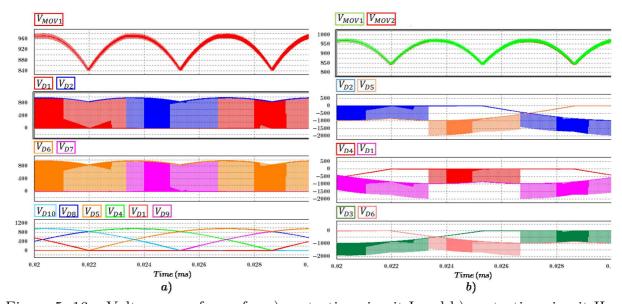

In [26], a modified CSI topology, named CSI7, is proposed for PV applications (cf. Figure 2.8 (a)). With the aim of reducing conduction losses, an additional switch (S<sub>7</sub>) is added to the traditional CSI bridge. Thus, during the freewheeling phases (or zero vector application times), the DC current flows uniquely through S<sub>7</sub>. In general terms, the CSI7 is particularly interesting when a high voltage stepup ratio  $(G_{\nu})$  between the PV array and the grid is required, since greater  $G_{\nu}$ ratios lead to longer freewheeling phases.

Figure 2. 8 – a) CSI7 topology, b) developed prototype and c) efficiency results. Source: modified from [26].

Figure 2.8 presents the CSI prototype employing 1.2kV Si IGBTs and the obtained efficiency curves. Another important CSI7 advantage is related to common mode earth leakage currents, which can be reduced when implementing specific modulation techniques.

Taking into consideration all the elements presented in this chapter, if compared to multistage and/or multilevel voltage source-based structures, the SiC-based Current Source Inverter for PV applications might bring the following benefits:

- Reduced device's part count (number of switches, associated gate driver units, current/voltage sensors);

- Reduced complexity, thanks to the single power processing stage;

- Potentially improved reliability, thanks to the elimination of DC-link capacitors and reduced complexity; and

- Potentially higher efficiency, thanks to the single power processing stage;

- Potentially higher power density, thanks to the fast switching behavior of unipolar SiC devices in combination with the inherent CSI low level of switching losses.

## 2.4 Research Challenges and Opportunities

The main research challenges and opportunities are listed as follows:

- Very few research on power integration/packaging for WBG-based CSC applications has been reported in the literature. As far as the author is aware, only one work deals with the realization of a SiC-based power module laboratory prototype intended for CSC applications [31];

- Since VSCs are the predominant topology in most applications today, there is a lack of CSC adapted components, as gate drivers and related protections;

- Implementation of SiC devices with minimum parasitics, in order to take full advantage of their properties;

- Characterization of SiC devices presenting fast switching transients;

- Investigation and minimization of CSI losses, mainly conduction losses, for efficiency improvement considering PV operating conditions; and

- Challenges related to the practical implementation and characterization of a medium-power (60kW) SiC-based CSI.

#### 2.5 References

- [1] S. Kouro, J. I. Leon, D. Vinnikov, and L. G. Franquelo, "Grid-Connected Photovoltaic Systems: An Overview of Recent Research and Emerging PV Converter Technology," IEEE Ind. Electron. Mag., vol. 9, no. 1, pp. 47–61, Mar. 2015.

- [2] K. Zeb et al., "A comprehensive review on inverter topologies and control strategies for grid connected photovoltaic system," Renew. Sustain. Energy Rev., vol. 94, pp. 1120–1141, Oct. 2018.

- [3] H. Foch, P. Ladoux, and H. Piquet, "Association de convertisseurs assurant une liaison énergétique," Tech. Ing., p. d3178, 2010.

- [4] H. Wang and F. Blaabjerg, "Reliability of Capacitors for DC-Link Applications in Power Electronic Converters—An Overview," IEEE Trans. Ind. Appl., vol. 50, no. 5, pp. 3569–3578, Sep. 2014.

- [5] H. Wang, M. Liserre, and F. Blaabjerg, "Toward Reliable Power Electronics: Challenges, Design Tools, and Opportunities," IEEE Ind. Electron. Maq., vol. 7, no. 2, pp. 17–26, Jun. 2013.

- [6] S. Yang, A. Bryant, P. Mawby, D. Xiang, L. Ran, and P. Tavner, "An Industry-Based Survey of Reliability in Power Electronic Converters," *IEEE* Trans. Ind. Appl., vol. 47, no. 3, pp. 1441–1451, May 2011.

- [7] B. Lumby, "Utility-Scale Solar Photovoltaic Power Plants: A Project Developer's Guide," 99396, 2015.

- [8] B. Burger, "Power Electronics for Photovoltaics," in OTTI Renewable Energy Seminars, 2014, pp. 753–798.

- [9] D. Fu, B. He, and Q. Li, "Multilevel inverter device and method," US9413268B2, 09-Aug-2016.

- D. Martini, M. Valiani, and S. Soldani, "Multi-level dc/ac converter," EP2561606B1, 05-Dec-2018.

- [11]J. Hantschel, "Wechselrichterschaltung für erweiterten Eingangsspannungsbereich," DE102006010694B4, 07-Jan-2010.

- T. Kimoto, "Material science and device physics in SiC technology for high-|12|voltage power devices," 2015.

- A. Traoré, "High power diamond Schottky diode," PhD Thesis, Université de Grenoble, 2014.

- G. Perez, "Caractérisation de diodes Schottky en diamant de structure pseudo-verticale," PhD Thesis, Université Grenoble Alpes, 2018.

- T. Kimoto and J. A. Cooper, Fundamentals of silicon carbide technology: growth, characterization, devices and applications. John Wiley & Sons, 2014.

- [16] C. Buttay, C. Raynaud, H. Morel, G. Civrac, M. Locatelli, and F. Morel, "Thermal Stability of Silicon Carbide Power Diodes," *IEEE Trans. Electron Devices*, vol. 59, no. 3, pp. 761–769, Mar. 2012.

- [17] Z. Chen, "Electrical integration of SiC power devices for High-Power-Density applications," PhD Thesis, Virginia Polytechnic Institute and State University, 2013.

- [18] J. Lutz, Ed., Semiconductor power devices: physics, characteristics, reliability. Berlin: Springer-Verlag, 2011.

- [19] B. B. Jayant, Silicon carbide power devices. World scientific, 2006.

- [20] R. Siemieniec et al., "A SiC Trench MOSFET concept offering improved channel mobility and high reliability," in 2017 19th European Conference on Power Electronics and Applications (EPE'17 ECCE Europe), 2017, p. P.1-P.13.

- [21] L. Stevanovic, "From SiC MOSFET Devices to MW-scale Power Converters APEC 2017/Plenary Sessions," 2017.

- [22] O. Anaya-Lara, D. Campos-Gaona, E. Moreno-Goytia, and G. Adam, Offshore wind energy generation: control, protection, and integration to electrical systems. John Wiley & Sons, 2014.

- [23] A. Stupar, T. Friedli, J. Minibock, and J. W. Kolar, "Towards a 99% Efficient Three-Phase Buck-Type PFC Rectifier for 400-V DC Distribution Systems," *IEEE Trans. Power Electron.*, vol. 27, no. 4, pp. 1732–1744, Apr. 2012.

- [24] B. Guo, F. F. Wang, and E. Aeloiza, "A novel three-phase current source rectifier with delta-type input connection to reduce the device conduction loss," *IEEE Trans. Power Electron.*, vol. 31, no. 2, pp. 1074–1084, 2016.

- [25] L. Guillaume, B. Anthony, and C. Stéphane, "A cost-controlled, highly efficient SiC-based Current Source Inverter dedicated to Photovoltaic applications," in 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), 2018, p. P.1-P.10.

- [26] E. Lorenzani, F. Immovilli, G. Migliazza, M. Frigieri, C. Bianchini, and M. Davoli, "CSI7: A Modified Three-Phase Current-Source Inverter for Modular Photovoltaic Applications," *IEEE Trans. Ind. Electron.*, vol. 64, no. 7, pp. 5449–5459, Jul. 2017.

- [27] L. Gabriel, A. Rodrigues, J.-P. Ferrieux, J. Martin, S. Catellani, and A. Bier, "Design of a three-phase 70 kW Current Source Inverter for Photovoltaic Applications Using a New 1.7 kV Full-SiC Voltage Bidirectional Power Module," in *PCIM Europe 2018; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management*, 2018, pp. 1–8.

- J. Martin, A. Bier, S. Catellani, L. G. Alves-Rodrigues, and F. Barruel, "A [28]high efficiency 5.3kW Current Source Inverter (CSI) prototype using 1.2kV Silicon Carbide (SiC) bi-directional voltage switches in hard switching," in PCIM Europe 2016; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2016, pp. 1-8.

- B. Sahan, A. N. Vergara, N. Henze, A. Engler, and P. Zacharias, "A Single-Stage PV Module Integrated Converter Based on a Low-Power Current-Source Inverter," IEEE Trans. Ind. Electron., vol. 55, no. 7, pp. 2602–2609, Jul. 2008.

- N. Henze, B. Sahan, R. Burger, and W. Belschner, "A novel AC module with high-voltage panels in CIS technology," in 23rd European PV Solar Energy Conference and Exhibition, Valencia, Spain, 2008.

- B. Guo, "High-Efficiency Three-Phase Current Source Rectifier Using SiC Devices and Delta-Type Topology," PhD Thesis, University of Tennessee, 2014.

# Chapter 3

# Three-phase Current Source Inverter Topology

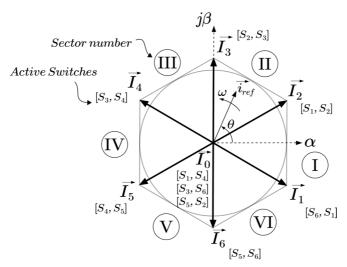

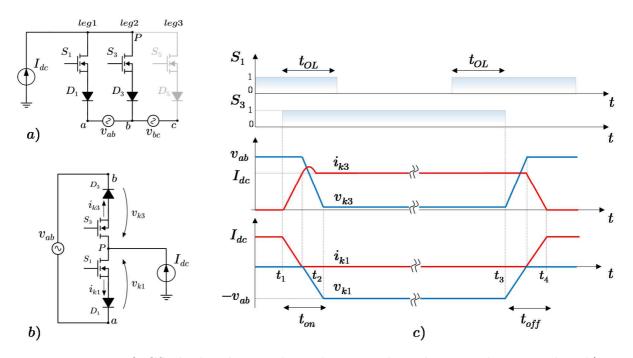

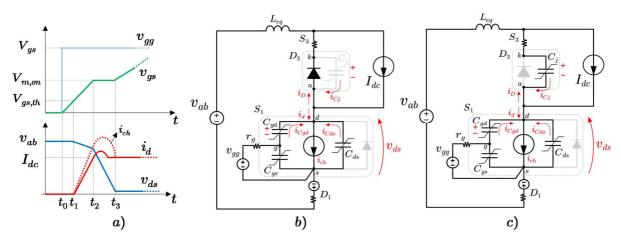

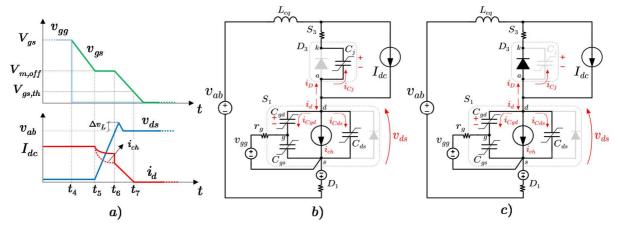

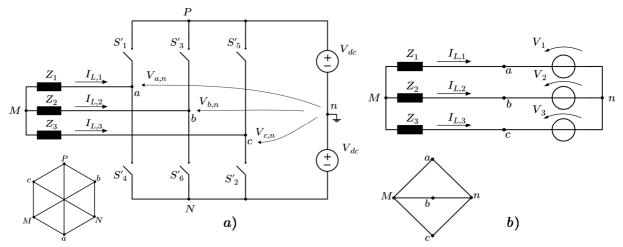

In this chapter, the Current Source Inverter (CSI) topology is introduced. Firstly, its principle of operation is presented implementing space vector transformation. From that, the CSI switching cells arrangement is analyzed together with their main switching losses mechanisms. Since conduction losses represent one of the major CSI drawbacks, particular attention is given to this topic. Therefore, the mechanisms of on-state losses for SiC MOSFETs and diodes are studied in detail. Besides the standard CSI switch configuration, other three variations found in the literature claiming to reduce conduction losses are compared, taking into account their advantages and limitations to operate with a photovoltaic string. Finally, the topological duality between Voltage Source and Current Source Converters is explored in order to implement an analytical method for the AC line current spectrum determination.

#### 3.1 Introduction

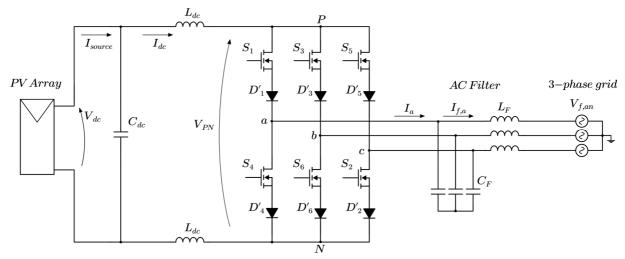

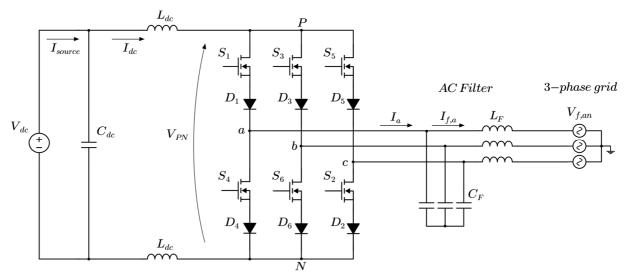

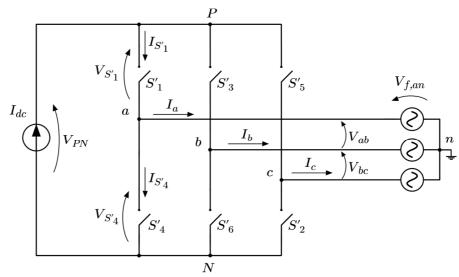

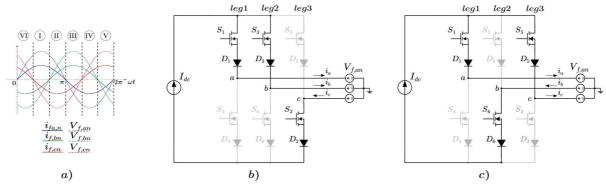

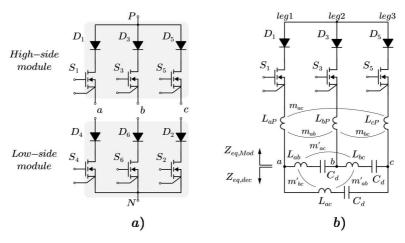

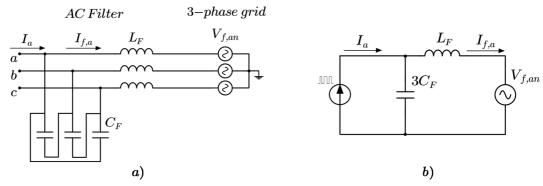

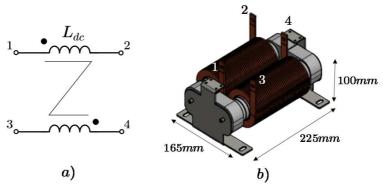

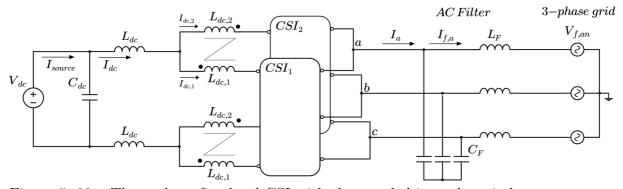

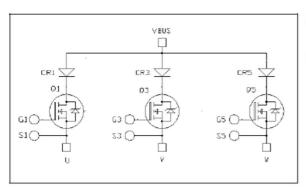

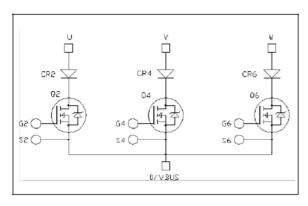

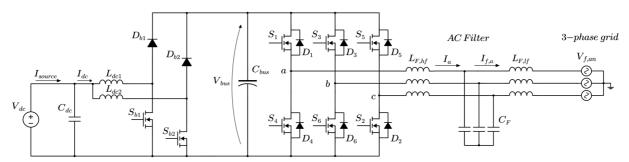

The three-phase Current Source Inverter (CSI) topology is depicted in Figure 3.1. The inverter bridge is composed of six current-unidirectional switches with reverse voltage blocking capability  $(S_{1..6}, D_{1..6})$ . On the DC side, a DC-link choke  $(L_{dc})$  ensures the converter's current-source based characteristic and a filtering capacitor  $(C_{dc})$  is normally added in order to attenuate the current ripple in the DC source  $(I_{source})$  and to stabilize its voltage  $(V_{dc})$ . On the other hand, the CSI bridge is connected to the mains through a three-phase C-L filter  $(C_F, L_F)$ . The presence of  $C_F$  guarantees the mains instantaneous voltage source behavior allowing the interconnection of DC and AC sources - and is responsible for filtering the AC line current  $(I_a)$ , together with the line inductor  $(L_F)$ . With an appropriate control, the CSI is capable of injecting sinusoidal current waveforms  $(I_{f,a})$  into the grid.

Figure 3. 1 – Three-phase Current Source Inverter topology.

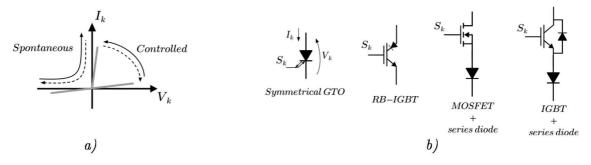

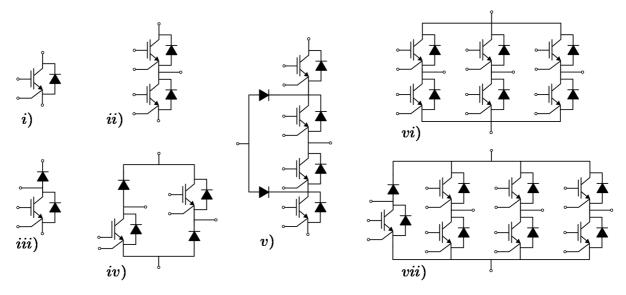

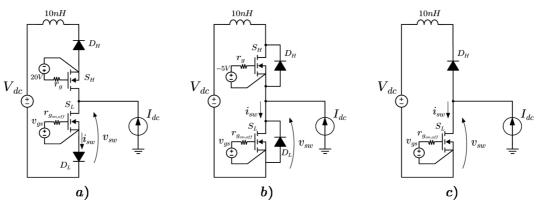

In this work, Pulse Width Modulation (PWM) technique is employed. For that reason, the use of fully controlled turn-on and turn-off switches is required [1]. Figure 3.2 shows the idealized i-v characteristic for the CSI power devices, as well as four possible switch realizations. Considering the case where the voltage bidirectional device is made out of a serial connection of an IGBT and a diode, the need for an IGBT anti-parallel diode should be pointed out. Although it does not conduct any current, this additional diode is necessary since IGBTs are not designed to withstand reverse voltages [2]. Diversely, if MOSFETs are employed, any anti-parallel device is needed, thanks to the intrinsic body-diode presence within the MOSFET structure.

Figure 3. 2 – a) Idealized i - v characteristic for CSI power devices and b) possible switch realizations.

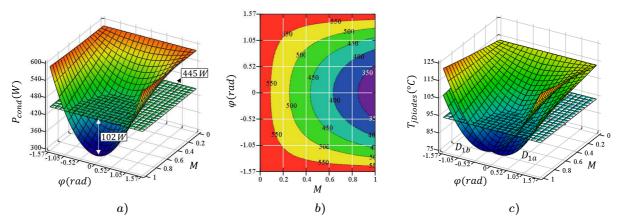

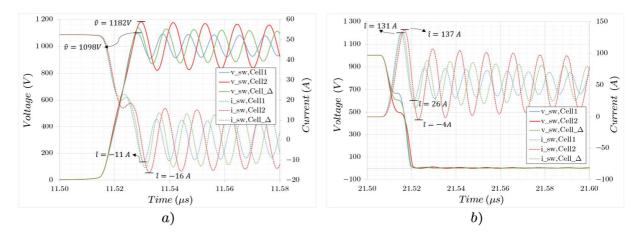

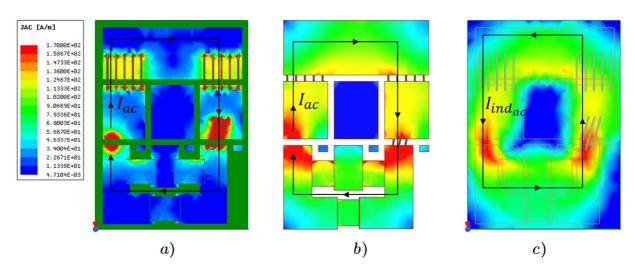

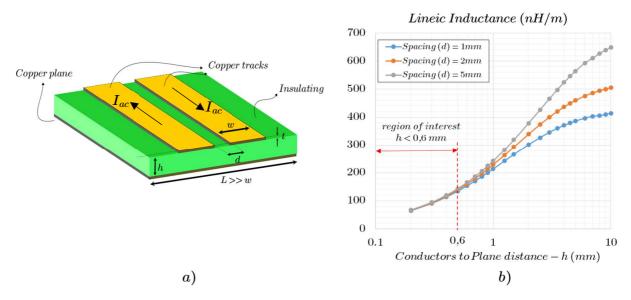

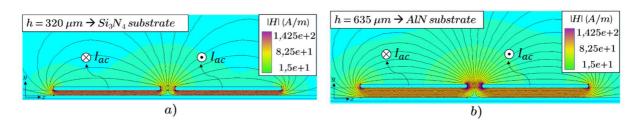

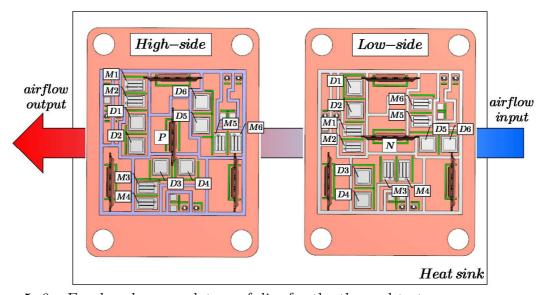

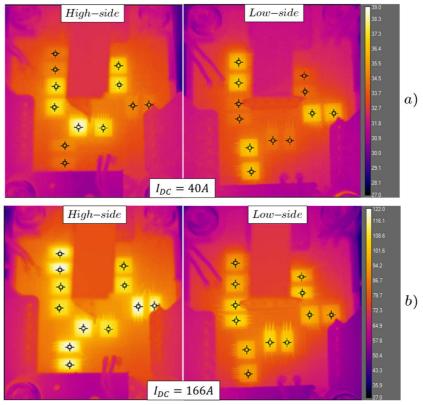

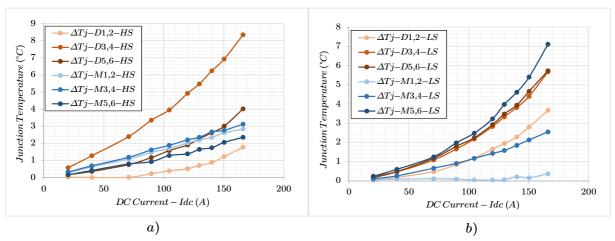

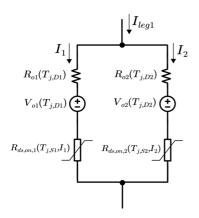

### 3.2 Principle of Operation