## Infrared Imaging for Integrated Circuit Trust and Hardware Security

Maxime Cozzi

## ► To cite this version:

Maxime Cozzi. Infrared Imaging for Integrated Circuit Trust and Hardware Security. Micro and nanotechnologies/Microelectronics. Université Montpellier, 2019. English. NNT: 2019MONTS046. tel-02478875

## HAL Id: tel-02478875 https://theses.hal.science/tel-02478875v1

Submitted on 14 Feb 2020  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE MONTPELLIER

En microélectronique

École doctorale I2S

Unité de recherche LIRMM

# Imagerie Infrarouge, Intégrité des Circuits Intégrés et Sécurité Matérielle

## Présentée par Maxime COZZI Le 18 novembre 2019

## Sous la direction de Philippe MAURINE et Jean-Marc GALLIERE

### Devant le jury composé de

Jean Michel PORTAL Vincent BEROULLE Séverine GOMES Pascal NOUET Laurent SAUVAGE Philippe MAURINE Jean Marc GALLIERE

| - | Professeur            |

|---|-----------------------|

|   | Professeur            |

|   | Directrice de Recherc |

|   | Professeur            |

|   | MCF                   |

|   | MCF                   |

| Ξ | MCF                   |

|   |                       |

Université de Aix – Marseille Université Grenoble – Alpes che CETHIL – Université de Lyon LIRMM – Université de Montpellier Télécom Paris LIRMM – Université de Montpellier LIRMM – Université de Montpellier Rapporteur Rapporteur Examinatrice Président du jury Invité Directeur de Thèse Co-encadrant de Thèse

## Acknowledgements

Mes premiers remerciements s'adressent à mes encadrants de thèse, Philippe MAURINE et Jean-Marc GALLIERE pour leur confiance, leur soutien ainsi que pour m'avoir challengé tout au long de ces trois années de doctorat. Je les remercie également fortement pour la bonne humeur qu'ils ont su instaurer au sein de l'équipe et pour leur encadrement de qualité qui m'a permis de mener ce projet à bien. J'ajoute une mention spéciale pour les barbecues chez Philippe qui m'ont permis de découvrir le HB, boisson aux moult propriétés bénéfiques et inspirantes. Je remercie aussi Marc LACRUCHE pour son aide, nos montages bricolos et pour sa passion (grandement partagée) pour les boissons houblonnées.

J'aimerais également remercier fortement mes parents, Laura CAZAUX, et plus généralement toute ma famille pour leur soutien et leurs conseils durant cette thèse. J'adresse une pensée toute particulière à mes parents qui ont su me transmettre leur esprit curieux ainsi que leur intérêt pour la science. Je souhaite également mentionner mon grand-père Ennio COZZI pour l'intérêt ainsi que le soutien apporté durant mes études, et en particulier pendant mon doctorat.

Je suis particulièrement reconnaissant envers Victor LOMNE et Thomas ROCHE de la société NinjaLab pour leur soutien ainsi que pour m'avoir guidé et conseillé pendant mon doctorat. Je les remercie également pour toutes les pauses café et les échanges que nous avons eus et qui m'ont permis d'enrichir mes connaissances sur le milieu de la sécurité matérielle.

Je remercie très sincèrement Caroline LEBRUN pour sa bonne humeur, son aide et sa franche camaraderie qui ont été essentiels au maintien de ma santé mentale. En particulier, je tiens à mentionner ses actions héroïques au cours de la défense des doctorants contre les forces du mal. Je la remercie également d'avoir assuré mon index glycémique grâce aux "Napolitain" et autres pâtisseries.

Finalement, j'aimerais remercier toutes les personnes avec qui j'ai tissé de forts liens d'amitié pendant ce doctorat. En particulier, je remercie Nicolas JEANNIOT pour ses nombreux traquenards et son soutien, Guillaume AICHE co-fondateur des apéros MICROB, pour son assistance à l'impression 3D ainsi que pour les plans du V2, Mégane MIQUEL pour son "popolopopopo" et ses talents d'organisatrice, João SANTOS pour son amour des canapés, Vinayak KALAS pour sa passion lunaire, JR REALPE pour ses pintes de tequila, Julien TOULEMONT pour nos séances de râlerie et nos délires vidéo-ludiques, Gwenaël CHAILLOU alias "Msieur CHAILLOU" pour les pauses café et ses folles anecdotes de soirées, Geoffrey ENJOLRAS pour son humour poilant et pour m'avoir permis d'économiser sur tout les produits iodés.

# Contents

| Ac | cknov   | wledgements                                |       | iii  |

|----|---------|--------------------------------------------|-------|------|

| Li | st of ] | Figures                                    |       | ix   |

| Li | st of ' | Tables                                     | )     | ciii |

| Li | st of . | Abbreviations                              |       | xv   |

| Li | st of ] | Publications                               | x     | vii  |

| Fr | ench    | Summary                                    |       | 1    |

| 1  | Gen     | neral Introduction                         |       | 27   |

|    | 1.1     | Security and Trust for IC                  |       | 27   |

|    | 1.2     | Perspective of the Thesis                  |       | 29   |

|    |         | 1.2.1 IC imaging                           |       | 29   |

|    |         | 1.2.2 Comparison of IC Thermal Images      |       | 30   |

|    |         | 1.2.3 Contribution of the Thesis           |       | 31   |

|    | 1.3     | Structure of the Thesis                    | <br>• | 31   |

| 2  | The     | ermal Investigation Of Integrated Circuits |       | 33   |

|    | 2.1     | Chapter Introduction                       |       | 33   |

|    | 2.2     | Investigation of Integrated Circuits       |       | 34   |

|    |         | 2.2.1 Electromagnetic Emission Imaging     |       | 34   |

|   |      | 2.2.2  | Body Bias Injection Imaging                 | 35 |

|---|------|--------|---------------------------------------------|----|

|   |      | 2.2.3  | Photo-Emission Imaging                      | 36 |

|   |      | 2.2.4  | Laser Voltage Imaging and Probing           | 38 |

|   |      | 2.2.5  | Thermal Imaging                             | 40 |

|   | 2.3  | Therm  | nal Infrared Emissions of Materials         | 42 |

|   |      | 2.3.1  | Black Bodies                                | 42 |

|   |      |        | Planck's Law                                | 42 |

|   |      | 2.3.2  | Real Bodies                                 | 43 |

|   |      |        | Emissivity vs Absorptivity                  | 44 |

|   |      |        | Reflection $\rho$                           | 44 |

|   |      |        | Transmission $\tau$                         | 45 |

|   |      |        | Radiation Balance                           | 45 |

|   |      |        | Infrared and silicon investigation          | 45 |

|   | 2.4  | Heat S | Source Detection in Integrated Circuits     | 46 |

|   |      | 2.4.1  | Thermal Measurement Acquisition             | 46 |

|   |      |        | Terminology                                 | 46 |

|   |      |        | Types of IR sensors                         | 47 |

|   |      | 2.4.2  | Passive thermal acquisition strategies      | 53 |

|   |      |        | Steady State Thermography                   | 53 |

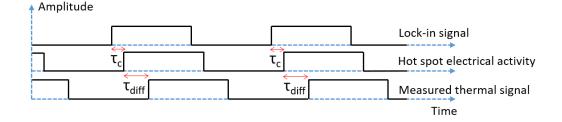

|   |      |        | Lock-in Thermography                        | 56 |

|   | 2.5  | Chapt  | er conclusion                               | 61 |

| 3 | IR N | Aeasur | ement Platform and Thermal Scan Methodology | 63 |

| - | 3.1  |        | er Introduction                             |    |

|   |      | -      |                                             |    |

|   | 3.2  | Acqui  | sition chain                                | 65 |

|   |      | 3.2.1  | Sensor                                      | 65 |

|     | 3.2.2                           | Signal Conditioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 3.2.3                           | Acquisition and post-treatment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

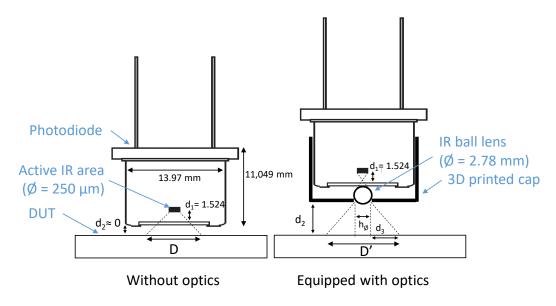

|     | 3.2.4                           | Optics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.3 | Thern                           | nal Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 3.3.1                           | Thermal Modulation Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

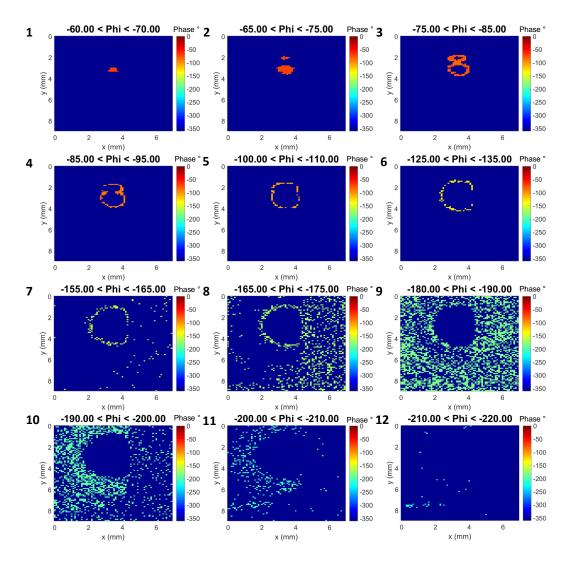

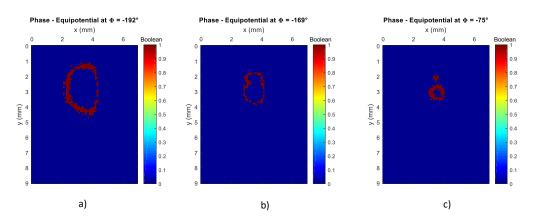

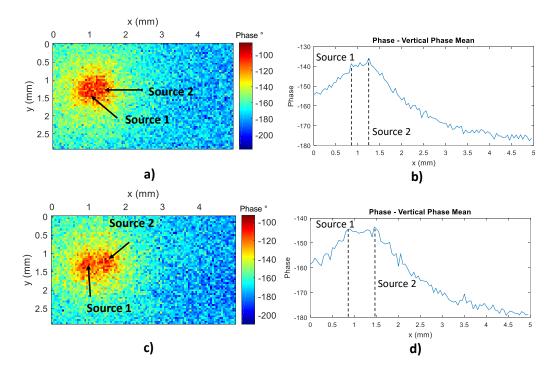

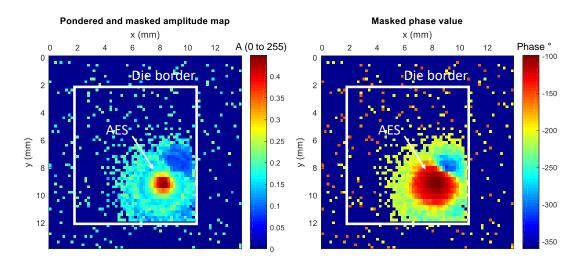

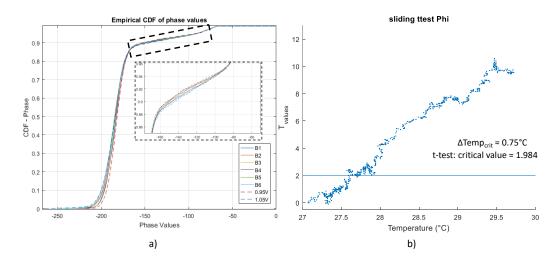

|     | 3.3.2                           | Phase Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

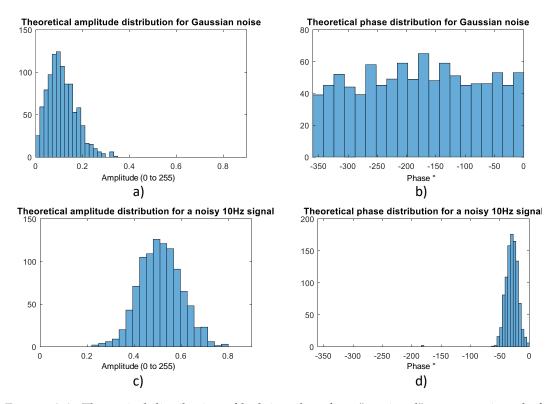

|     | 3.3.3                           | Signal Detection Criteria                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

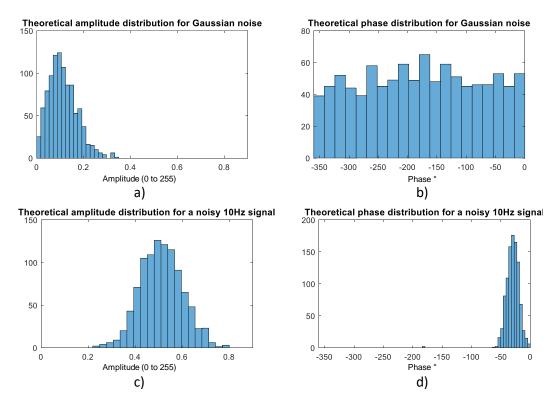

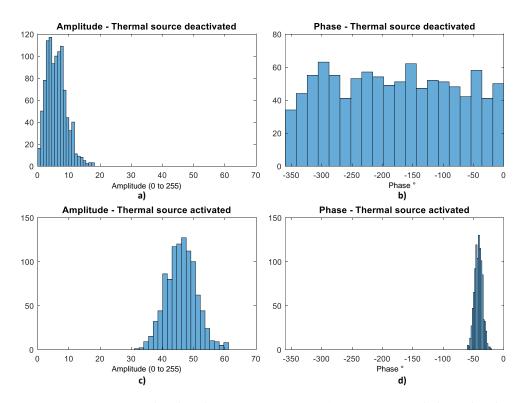

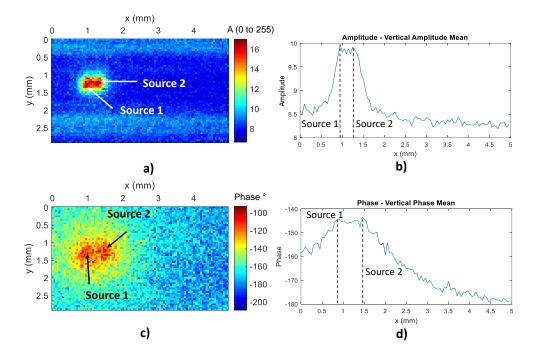

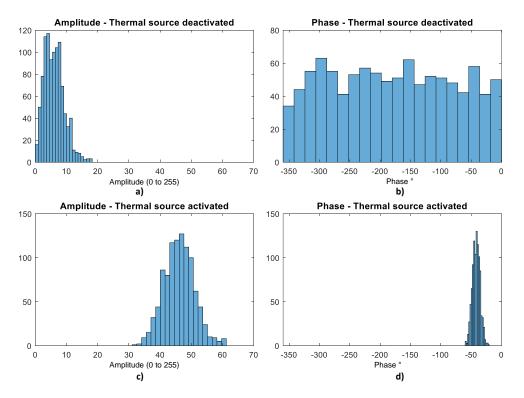

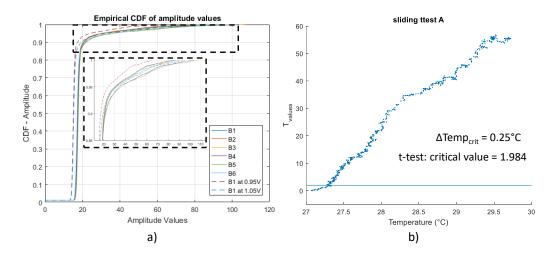

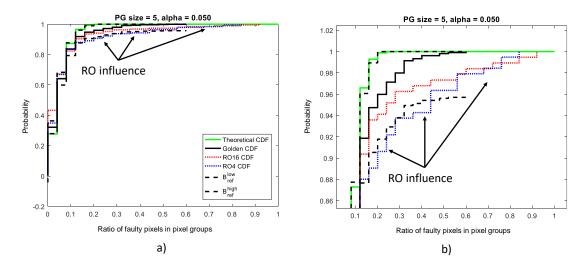

|     |                                 | Statistical Distributions of Lock-in Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

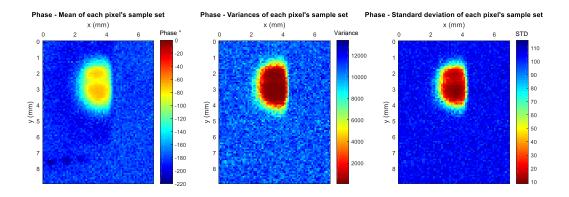

|     |                                 | Variance Criterion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

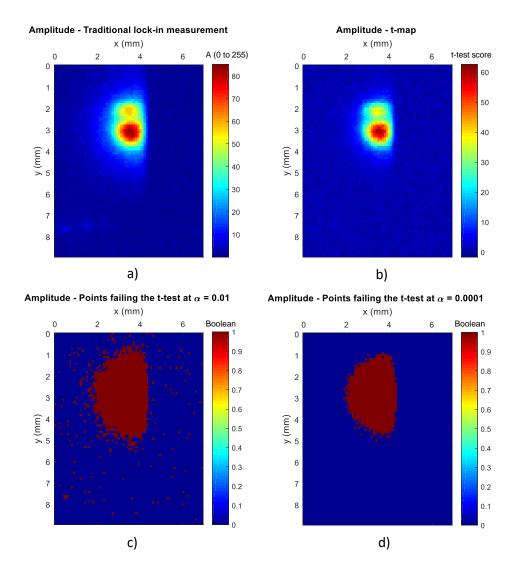

|     |                                 | Reference Point Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

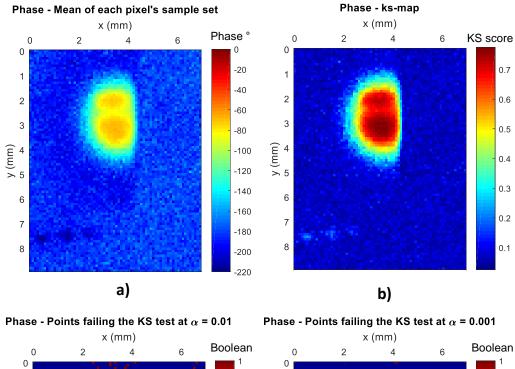

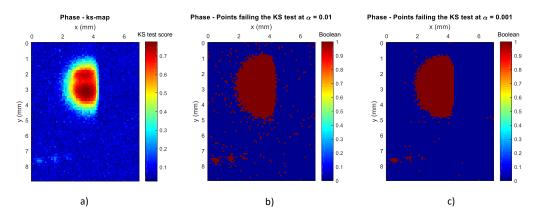

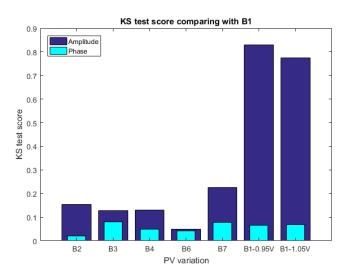

|     |                                 | Goodness of Fit Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

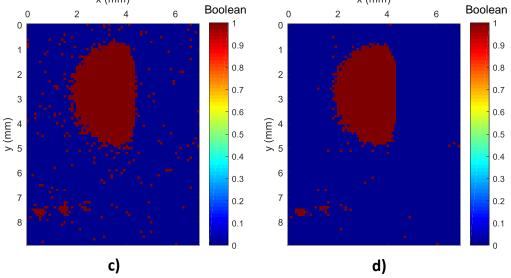

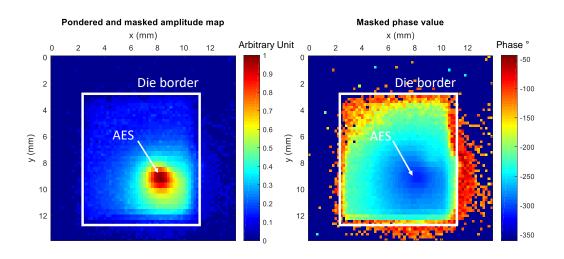

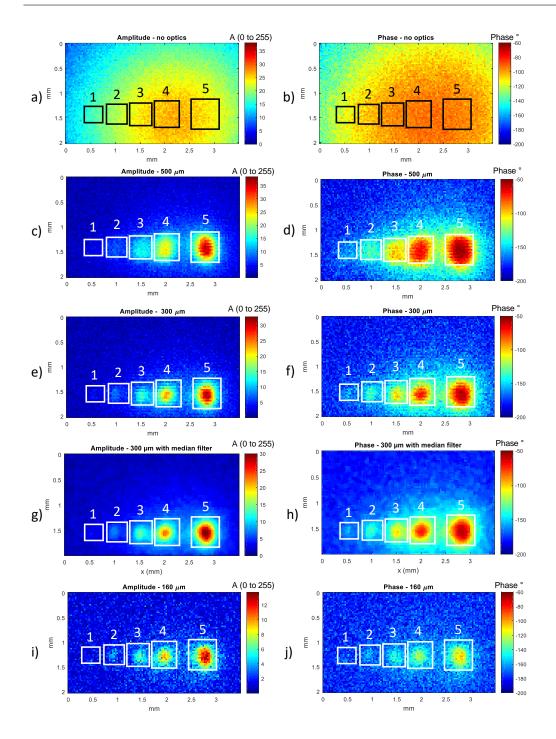

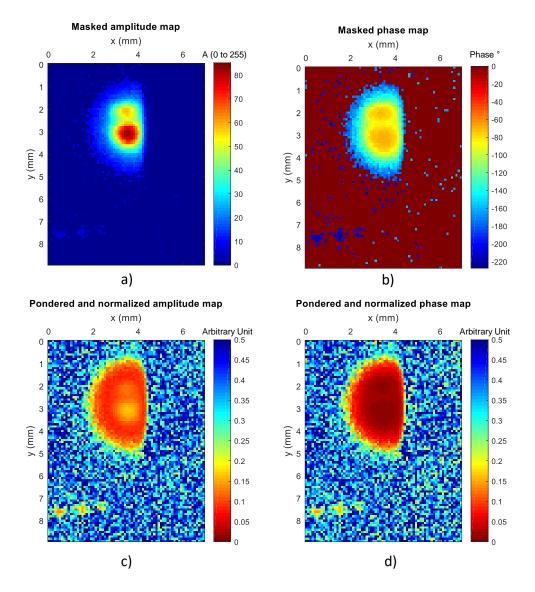

|     |                                 | Enhanced lock-in images                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

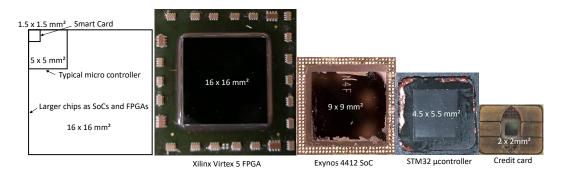

| 3.4 | Platfo                          | rm Characterization and Test Cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 3.4.1                           | FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |                                 | Circuit Preparation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

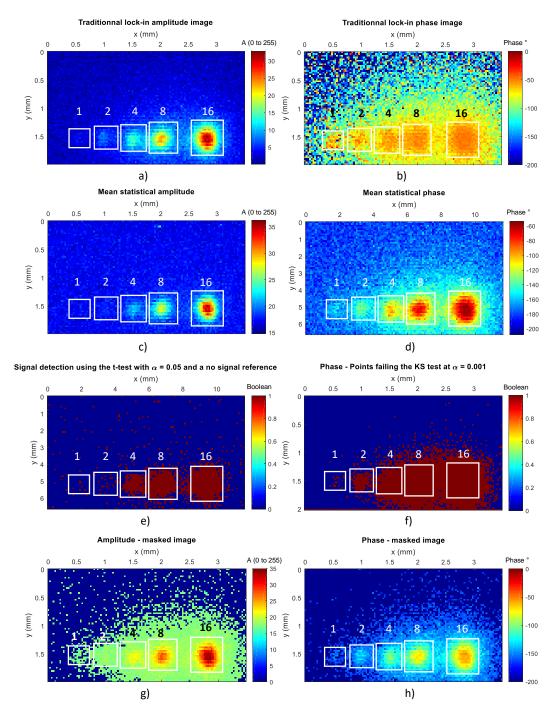

|     |                                 | Thermal Detection Limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

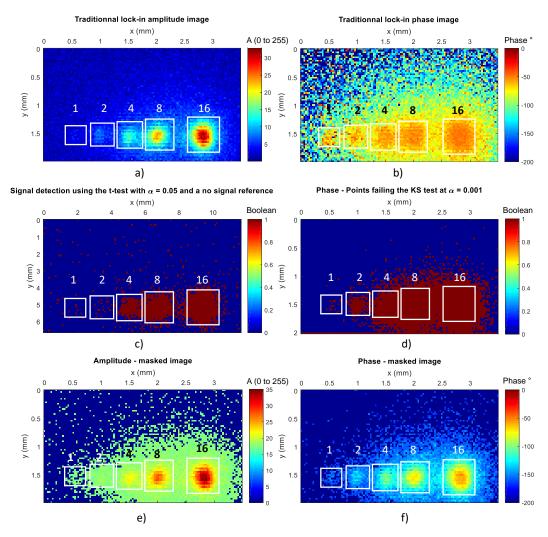

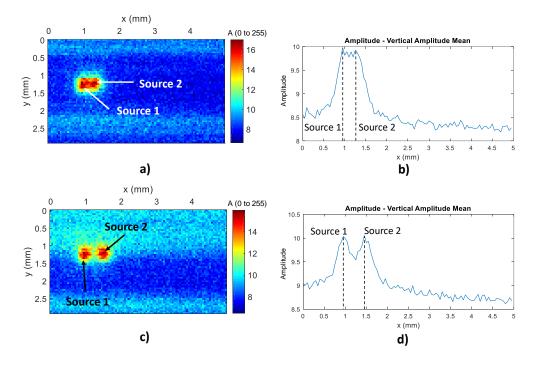

|     |                                 | Spatial Resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

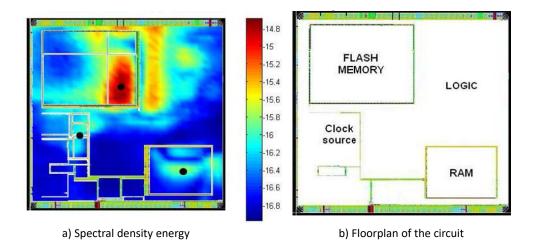

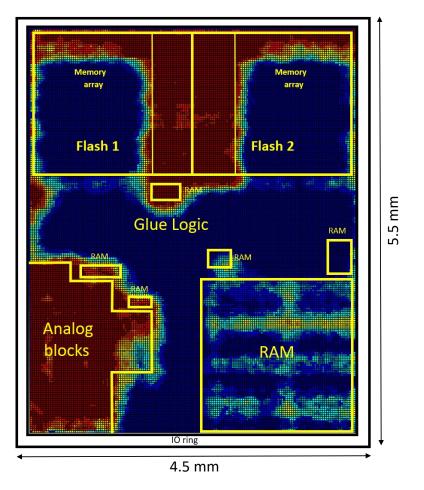

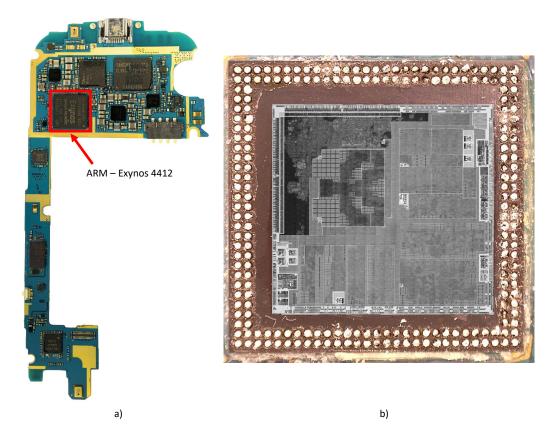

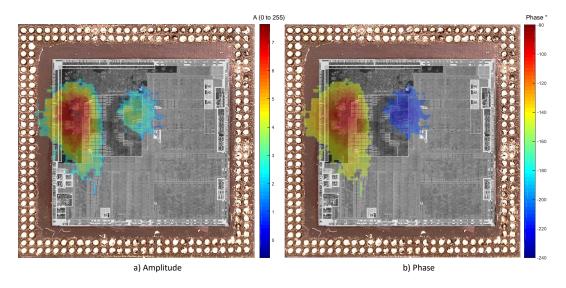

|     | 3.4.2                           | Modern SoC Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

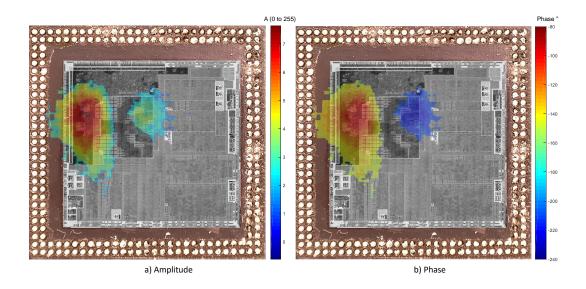

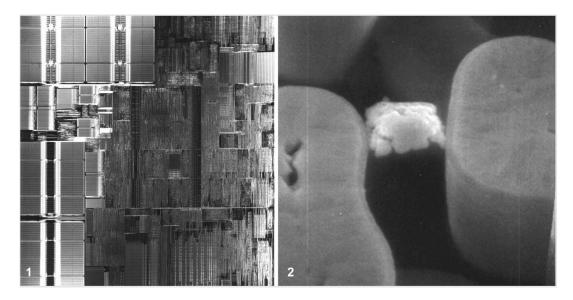

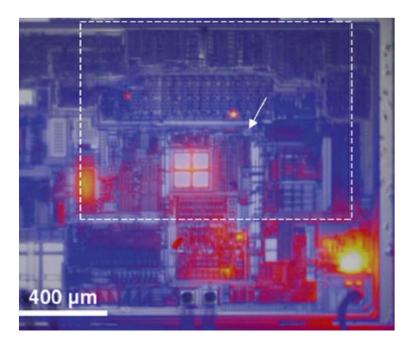

|     |                                 | Decapsulated SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

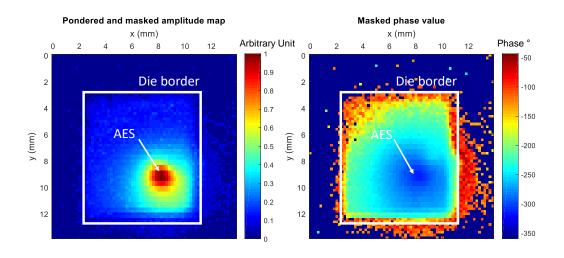

|     |                                 | Packaged Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.5 | Chapt                           | ter Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Nev | v Statis                        | tical Methodology for Thermal Map Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.1 |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

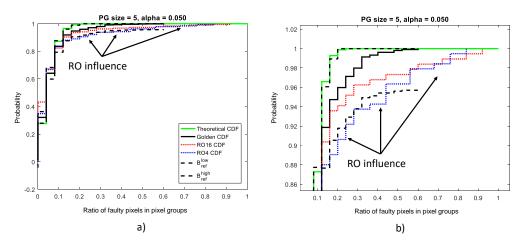

| 4.2 | PVT i                           | nfluence on Lock-in Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 4.2.1                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     | 3.4<br>3.5<br><b>Nev</b><br>4.1 | 3.2.3<br>3.2.4<br>3.3<br>Therm<br>3.3.1<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.2<br>3.3.3<br>3.3.3<br>3.3.2<br>3.3.3<br>3.3.3<br>3.3.4<br>2.4<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.3<br>3.3.4<br>3.4.1<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.1<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.4.2<br>3.5<br>3.5<br>3.5<br>3.5<br>3.5<br>3.5<br>3.5<br>3.5 | 32.3       Acquisition and post-treatment         32.4       Optics         3.3       Thermal Measurements         3.3.1       Thermal Modulation Techniques         3.3.2       Phase Values         3.3.3       Signal Detection Criteria         3.3.3       Signal Detection Criteria         3.3.3       Signal Detection Criteria         Statistical Distributions of Lock-in Values       Variance Criterion         Reference Point Comparison       Goodness of Fit Tests         Enhanced lock-in images       Statistical Distribution and Test Cases         3.4.1       FPGA         Circuit Preparation       Thermal Detection Limits         Spatial Resolution       Spatial Resolution         3.4.2       Modern SoC Analysis         Decapsulated SoC       Packaged Circuit         3.5       Chapter Conclusion         A:1       Introduction         4.1       Introduction |

| Ré | ésumo  | é       |                                                     | 142   |

|----|--------|---------|-----------------------------------------------------|-------|

| Al | ostrac | ct      |                                                     | 142   |

| 5  | Gen    | eral Co | onclusion                                           | 129   |

|    | 4.5    | Chapt   | er Conclusion                                       | . 127 |

|    |        | 4.4.3   | Result Discussion                                   | . 126 |

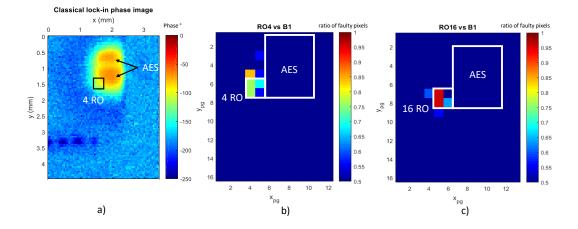

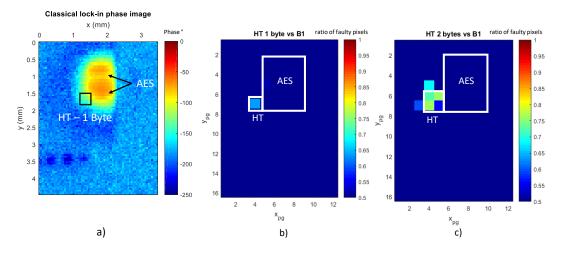

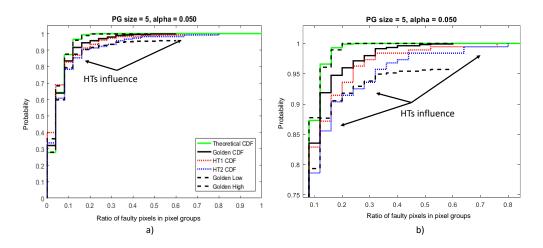

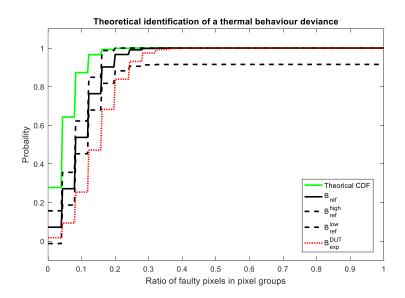

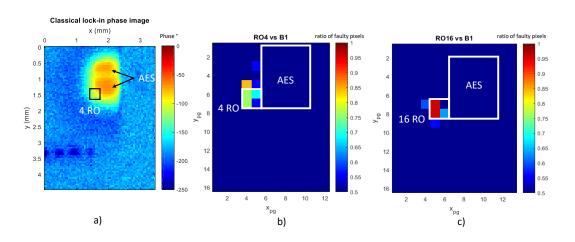

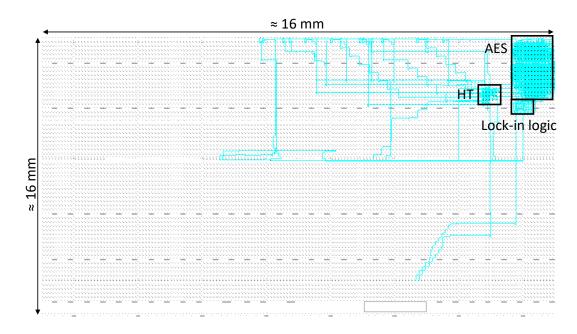

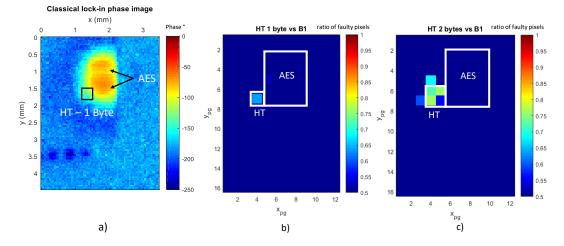

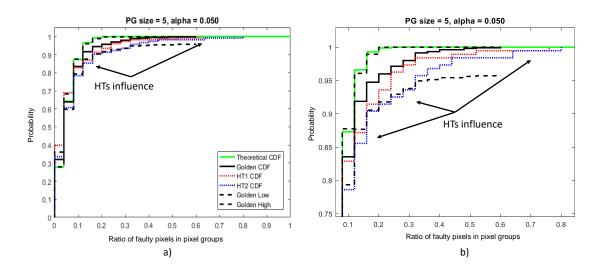

|    |        |         | HT Detection Using Statistical Lock-in Thermography | . 124 |

|    |        |         | Post-Silicon HT Detection                           | . 122 |

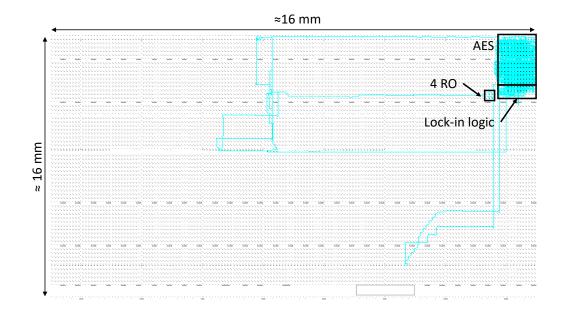

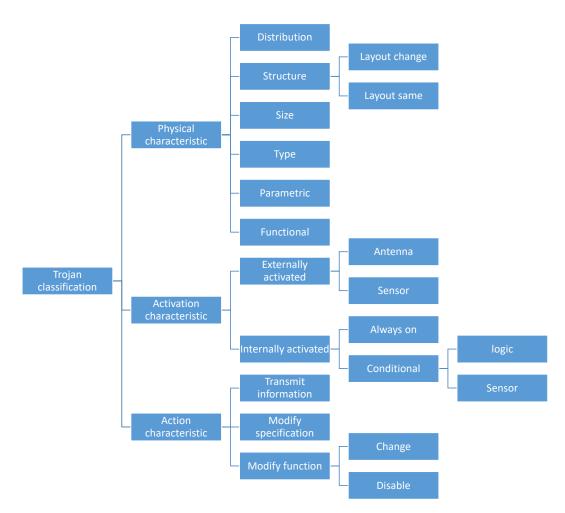

|    |        |         | Threat model                                        | . 122 |

|    |        |         | Context                                             | . 120 |

|    |        | 4.4.2   | Hardware Trojan Insertion                           |       |

|    |        |         | FA Using Statistical Lock-in Thermography           |       |

|    |        |         | Existing FA Methodologies                           | . 115 |

|    |        |         | Context                                             | . 113 |

|    |        | 4.4.1   | Failure Analysis                                    | . 113 |

|    | 4.4    | Applie  | cations                                             | . 112 |

|    | 4.3    | Metho   | odology                                             | . 109 |

|    |        | 4.2.2   | Process voltage and temperature robustness of phase | . 105 |

# **List of Figures**

| 2.1  | EM cartography of a microcontroller by analysis of the spectral den-<br>sity for $f \in [1\ 1000]\ MHz\ [OLS^+09]$ .                                                                                                                                                                                                  | 35 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Analysis of VDD and GND currents when performing body bias injection at different locations of a micro-controller [MTOL12]                                                                                                                                                                                            | 36 |

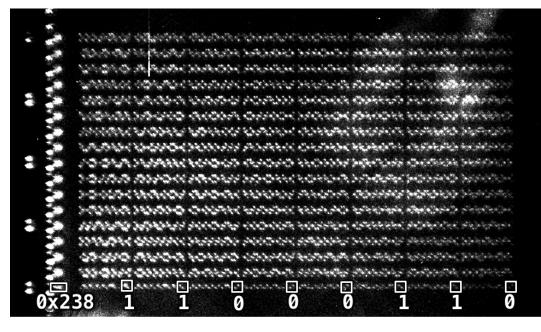

| 2.3  | SRAM content from an AES S-box of an ATmega328p using photonic microscopy [SNK <sup>+</sup> 12].                                                                                                                                                                                                                      | 37 |

| 2.4  | Detection of active transistors using LVI technique [SNL+10]                                                                                                                                                                                                                                                          | 38 |

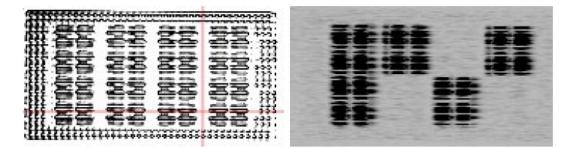

| 2.5  | <b>a)</b> Critical register overview using LVI <b>b)</b> Detailed image of the critical registers and their values [TLSB16]                                                                                                                                                                                           | 39 |

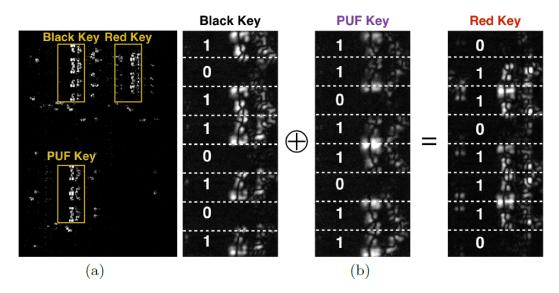

| 2.6  | Thermoreflectance image of a gold resistor through a $500 \mu m$ silicon substrate [TBB <sup>+</sup> 07]                                                                                                                                                                                                              | 41 |

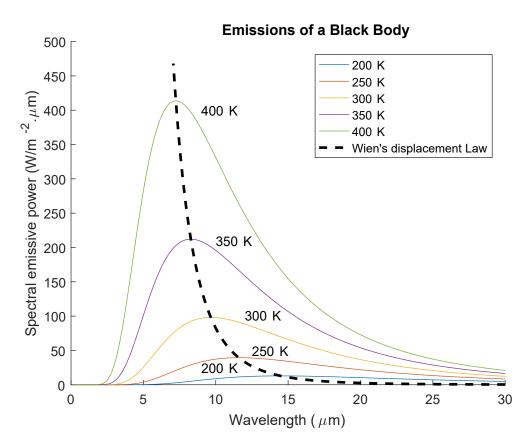

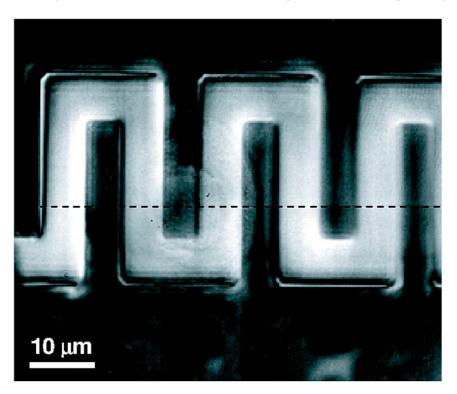

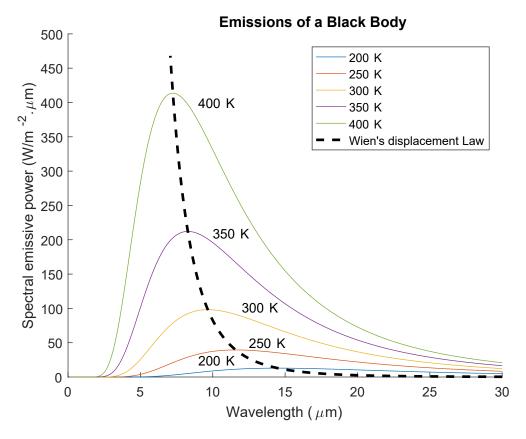

| 2.7  | Relation of the spectral emission of a BB to temperature and wavelength.                                                                                                                                                                                                                                              | 43 |

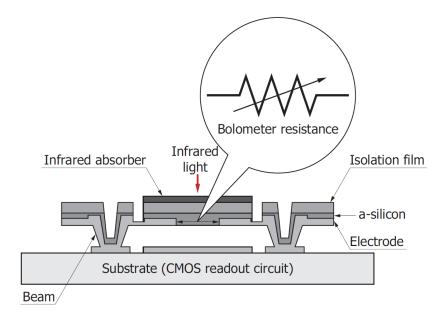

| 2.8  | Cross-sectional view of a bolometer's pixel [HP11b]                                                                                                                                                                                                                                                                   | 48 |

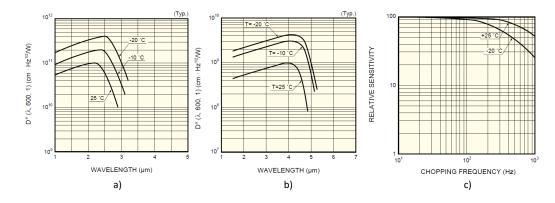

| 2.9  | Example of characteristics of Hamamatsu PbS and PbSe photocon-<br>ductive detectors. <b>a</b> ) Spectral detectivity of PbS sensors for three dif-<br>ferent temperatures <b>b</b> ) Spectral detectivity of PbSe sensors for three<br>different temperatures <b>c</b> ) Bandwidth of PbS and PbSe detectors [HP11a]. | 50 |

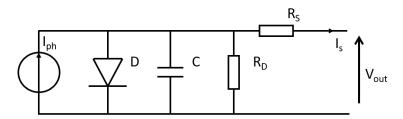

| 2.10 | Equivalent electronic circuit of an InAs photovoltaic detector.                                                                                                                                                                                                                                                       | 51 |

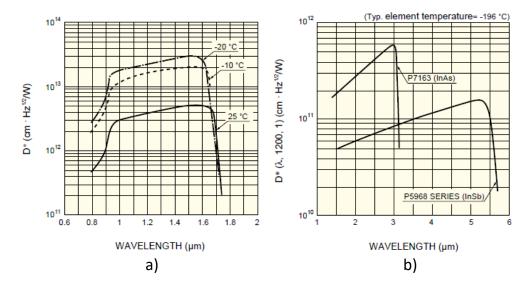

| 2.11 | Example of characteristics of Hamamatsu InGaAs, InAs and InSb photovoltaic detectors. <b>a)</b> Spectral detectivity of InGaAs sensors for three different temperatures <b>b)</b> Spectral detectivity of InAs and InSb sensors at $-196^{\circ}C$ [HP11a].                                                           | 52 |

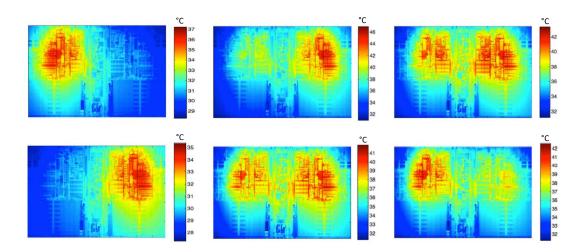

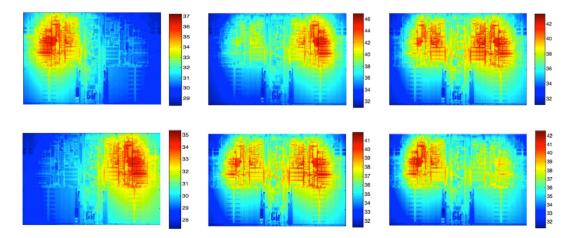

| 2.12 | Tracking electronic activity using steady state thermography on an AMD Athlon II 240. Each image corresponds to a different workload, therefore highlighting different power consumption locations on the die [RCN11].                                                                                                | 54 |

|      |                                                                                                                                                                                                                                                                                                                       | 34 |

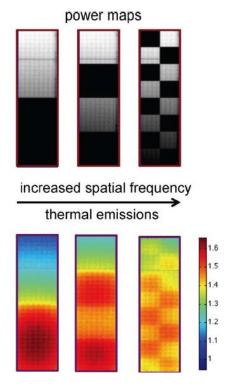

| 2.13 | Illustration of the spatial low pass filter effect affecting thermal signals[Red11]                                                                                                                                                                                                                              | 55 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

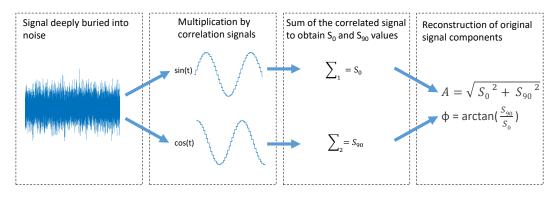

| 2.14 | Discrete lock-in process.                                                                                                                                                                                                                                                                                        | 58 |

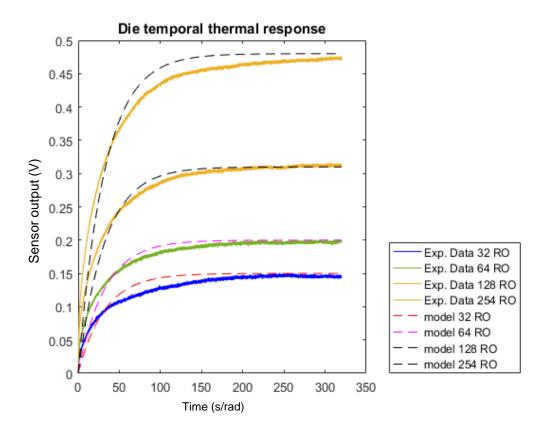

| 2.15 | Experimental and calculated first order thermal responses of the DUT to several thermal step inputs.                                                                                                                                                                                                             | 59 |

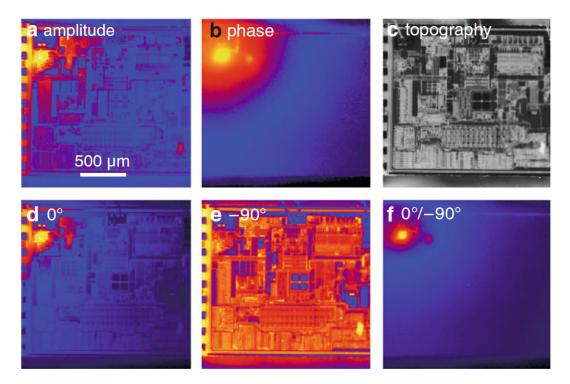

| 2.16 | Example of lock-in thermal maps [ <b>BWL10a</b> ]. <b>a</b> ) Amplitude image <b>b</b> )<br>Phase image <b>c</b> ) Topography image <b>d</b> ) $S_0$ image <b>e</b> ) $S_{-90}$ image <b>f</b> ) $\frac{S_0}{S_{-90}}$ image.                                                                                    | 60 |

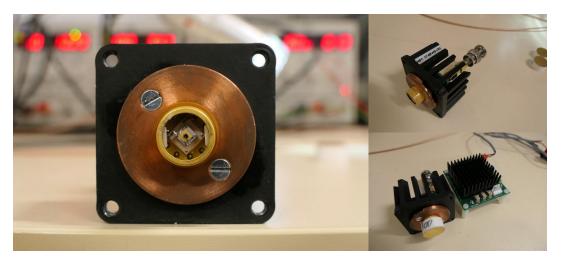

| 3.1  | J12TE3 detector and its thermo-regulation module                                                                                                                                                                                                                                                                 | 65 |

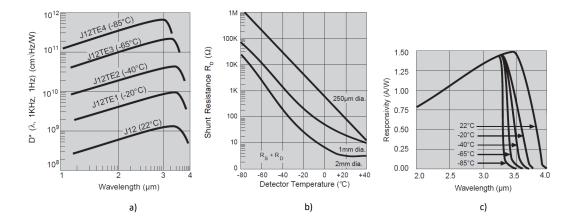

| 3.2  | Teledyne J12 photodiode characterization <b>a</b> ) Detectivity over wave-<br>length for different cooling temperatures <b>b</b> ) Shunt resistor value over<br>temperature for different sensor sizes <b>c</b> ) Responsivity of the detector<br>over light spectrum for different cooling temperatures [TEL00] | 66 |

| 3.3  | Femto current amplifier (left) and voltage amplifier (right) used on the platform.                                                                                                                                                                                                                               | 67 |

| 3.4  | IR acquisition platform in its isolation container.                                                                                                                                                                                                                                                              | 69 |

| 3.5  | Optical system designed to improve spatial resolution.                                                                                                                                                                                                                                                           | 70 |