# TEST TECHNIQUES FOR APPROXIMATE DIGITAL CIRCUITS

Marcello Traiola

#### ▶ To cite this version:

Marcello Traiola. TEST TECHNIQUES FOR APPROXIMATE DIGITAL CIRCUITS. Micro and nanotechnologies/Microelectronics. Université Montpellier, 2019. English. NNT: 2019MONTS060. tel-02485781

## HAL Id: tel-02485781 https://theses.hal.science/tel-02485781v1

Submitted on 20 Feb 2020

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE POUR OBTENIR LE GRADE DE DOCTEUR DE L'UNIVERSITÉ DE MONTPELLIER

En SYAM - Systèmes Automatiques et Micro-Electroniques

École doctorale : I2S – Information, Structures et Systèmes

Unité de recherche : LIRMM - Laboratoire d'Informatique, de Robotique et de Micro-électronique de Montpellier

## TECHNIQUES DE TEST POUR CIRCUITS DIGITAUX BASÉS SUR LE CALCUL APPROXIMATIF

### TEST TECHNIQUES FOR APPROXIMATE DIGITAL CIRCUITS

## Présentée par Marcello TRAIOLA Le 25 septembre 2019

#### Devant le jury composé de

| Alberto BOSIO                  | Professeur à l'École Centrale de Lyon, INL, Lyon                       | Directeur de thèse    |

|--------------------------------|------------------------------------------------------------------------|-----------------------|

| Patrick GIRARD                 | Directeur de recherche au CNRS, LIRMM, Montpellier                     | Co-Directeur de thèse |

| Arnaud VIRAZEL                 | Maître de conférence à l'Université de Montpellier, LIRMM, Montpellier | Co-encadrant          |

| Olivier SENTIEYS               | Directeur de recherche a l'INRIA, IRISA, Rennes                        | Rapporteur            |

| Matteo SONZA REORDA            | Professeur au Politecnico di Torino, Italie                            | Rapporteur            |

| Lirida Alves de Barros NAVINER | Professeur à Telecom ParisTech, Paris                                  | Présidente            |

"No man ever steps in the same river twice, for it's not the same river and he's not the same man."

Heraclitus

#### UNIVERSITY OF MONTPELLIER

### **Abstract**

Graduate School for Information, Structures and Systems (I2S)

Laboratory of Computer Science, Robotics, and Microelectronics of Montpellier

(LIRMM)

Doctor of Philosophy

#### **Test Techniques for Approximate Digital Circuits**

by Marcello TRAIOLA

Approximate Computing (AxC) is increasingly emerging as a new design paradigm to produce more efficient computation systems by meticulously reducing the computation quality. In particular, AxC has been successfully applied to Integrated Circuits (ICs), in the last years. Hence, concerning the test of such new class of ICs, namely Approximate Integrated Circuits (AxICs), new challenges – as well as new opportunities – have emerged. In this thesis, we provide a thorough analysis of issues related to testing procedures for AxICs and present innovative techniques to deal with them. We resort to an illustrative example having the twofold aim of: (i) guiding the reader through the AxIC testing challenges and (ii) illustrating the proposed solutions to correctly overcome them, while suitably taking advantage of opportunities coming from approximation. We analyze experimentally all the proposed test techniques for AxICs. Experimental outcomes show that the synergy of the proposed techniques leads to achieve important results.

## Resumé (FR)

Au cours des dernières décennies, la demande d'efficacité informatique n'a cessé de croître. L'avènement d'applications de nouvelle génération consommatrices d'énergie d'un côté, et d'appareils portables basse consommation de l'autre, exige un nouveau paradigme informatique capable de faire face aux exigences concurrentes des défis technologiques actuels [1]. Ces dernières années, plusieurs études sur les applications dites (en anglais) de *Recognition, Mining and Synthesis (RMS)* ont été menées [1]–[4]. Une particularité très intéressante a été identifiée : la *résilience intrinsèque* de ces applications. Une telle propriété permet aux applications RMS d'être très tolérantes aux erreurs. Ceci est dû à différents facteurs, tels que les données bruyantes traitées par ces applications, les algorithmes non déterministes utilisés et les réponses non uniques possibles [1]. Ces propriétés ont été exploitées par un nouveau paradigme informatique de plus en plus établi : le *calcul approximé* (AxC) [1], [2].

L'AxC profite intelligemment de la résilience intrinsèque des applications RMS pour réaliser des gains en termes de consommation électrique, de temps de fonctionnement et/ou de surface de puce. En effet, en introduisant des assouplissements sélectifs des spécifications non critiques, certaines parties du système informatique cible peuvent être simplifiées, pour finalement atteindre l'objectif de l'AxC. De plus, l'AxC est capable de cibler différentes couches des systèmes informatiques, du matériel au logiciel [2].

Dans cette thèse, nous nous concentrons sur les circuits intégrés approximés (AxICs), qui sont le résultat de l'application AxC au niveau matériel. En particulier, nous nous concentrons sur l'approximation fonctionnelle des circuits intégrés, utilisée au cours des dernières années afin de concevoir efficacement les AxICs [5]–[25]. En raison de la pertinence croissante des AxICs, il devient important de relever les nouveaux défis pour tester de tels circuits. À cet égard, certains travaux [26]–[29] ont attiré l'attention sur les défis que représente l'approximation fonctionnelle pour les procédures de test. En même temps, l'approximation fonctionnelle des circuits intégrés offre également des possibilités. Plus en détails - d'une part - le concept de *circuit acceptable* change : alors qu'un circuit est conventionnellement *bon* si ses réponses ne sont jamais différentes de celles attendues, dans le contexte AxIC certaines réponses inattendues peuvent encore être acceptables. Pour la même raison -

d'autre part - certains *fautes acceptables* peuvent ne pas être détectées, ce qui mène à un gain de rendement de production (c.-à-d., augmentation du pourcentage de circuits acceptables, parmi tous les circuits fabriqués). Pour mesurer l'erreur produite par un AxIC, plusieurs métriques d'erreur ont été proposées dans la littérature [30].

Dans cette thèse, nous présentons un ensemble de techniques de test pour les circuits approximés. En particulier, nous nous concentrons sur trois phases fondamentales du déroulement du test. Premièrement, la classification des fautes AxIC en *nonredundant* et *ax-redundant*. (c.-à-d. catastrophique et acceptable, respectivement) en fonction d'un seuil d'erreur (c.-à-d. la quantité maximale tolérable d'erreur). Cette classification permet d'obtenir deux listes de fautes (c.-à-d. non-redundant et ax-redundant). Ensuite, nous proposons une génération automatique de séquences de test (en anglais Automatic Test Pattern Generation ou ATPG) qui soit "consciente de l'approximation". Les tests obtenus préviennent les défaillances catastrophiques en détectant les fautes non-redundant. En même temps, ils minimisent la détection sur les ax-redundant. Enfin – puisque dans certains cas le gain de rendement obtenu ne correspond toujours pas à celui attendu, à cause de la structure propre des AxICs – nous proposons une technique pour classer correctement les AxICs dans les catégories "catastrophiquement défectueux" et "acceptablement défectueux", après l'application du test.

### 1. Contexte et informations générales

Dans ce chapitre, nous rassemblons quelques informations de base, qui seront utiles pour bien comprendre cette thèse et en tirer profit.

Tout d'abord, nous décrivons brièvement le test conventionnel de circuits intégrés. Nous rappelons les principes de base du test conventionnel pour les circuits numériques intégrés. Après une brève classification des différents objectifs du test, nous passons en revue la modélisation des fautes, les concepts de simulation des fautes, la procédure de génération de test et quelques concepts de base de la *conception en vue du test*, tels que la conception du *boundary scan* et le test automatique intégré (BIST).

Deuxièmement, nous passons en revue différents aspects du calcul approximé (AxC). En particulier, nous décrivons le problème abordé par l'AxC et les différents contextes dans lesquels il a été appliqué. En effet, plusieurs travaux ont abordé le problème de l'identification des parties appropriées d'un système informatique pour l'application de l'AxC. Ensuite, nous avons montré que l'AxC a une très large gamme d'applications. En effet, des études sur l'AxC au niveau logiciel, l'AxC au niveau architectural et l'AxC au niveau circuit ont été menées au cours des deux

dernières décennies. En particulier, nous décrivons les circuits intégrés approximés (AxICs).

Enfin, nous regroupons ces deux thèmes, dont l'union fait l'objet de cette thèse. Nous montrons comment les propriétés inhérentes aux AxICs nous ont conduit à reconsidérer les procédures de test et à proposer de nouvelles solutions. En d'autres termes, dans cette thèse, nous présentons des études sur les techniques de test matériel pour les circuits intégrés approximés.

#### 2. Test des circuits approximés

L'un des problèmes majeurs qui affectent aujourd'hui la technologie CMOS à l'échelle nanométrique est ce qu'on appelle en anglais *process variability* ou *variabilité*. La variabilité est le résultat de la nature aléatoire des processus physiques qui ont lieu pendant la fabrication des circuits intégrés. Les circuits CMOS à l'échelle du nanomètre subissent l'effet de la variabilité et des mécanismes de dégradation, qui mènent à une baisse de rendement du procédé de fabrication [31].

L'AxC vise à transformer ce problème en opportunité. L'idée de base est d'accepter les erreurs en tant que propriété intrinsèque des circuits intégrés et de concevoir des circuits approximés optimisés fonctionnant indépendamment des erreurs. À cet égard, l'objectif ultime est d'augmenter le rendement du procédé de fabrication (c.-à-d. le pourcentage de circuits acceptables, parmi tous les circuits fabriqués), en acceptant les circuits dégradés qui fonctionnent de façon acceptable. Pour atteindre un tel objectif, les procédures de test doivent être repensées pour tenir compte de l'approximation introduite.

Par conséquent, nous devons examiner l'impact d'AxC sur le rôle des tests au niveau matériel. Dans le contexte des AxICs, le concept de *circuit défectueux* change et nécessite une enquête approfondie. Comme décrit dans la section précédente, l'approximation fonctionnelle vise à réaliser des gains d'efficacité (temps/surface/énergie) en assouplissant certaines exigences de précision. Afin d'obtenir des résultats satisfaisants, les concepteurs modifient attentivement la structure du circuit pour introduire une erreur *acceptable*. Pour définir la signification de *acceptable*, les concepteurs utilisent des métriques d'erreur. Ensuite, ils définissent des seuils d'erreur pour fixer l'erreur maximale autorisée (c.-à-d. acceptable).

Dans le contexte des tests, l'impact des fautes qui peuvent apparaître dans un circuit peut être mesuré et exprimé en erreur en utilisant de telles métriques. Si la mesure obtenue s'avère supérieure au seuil acceptable, le circuit doit être rejeté. Cependant, il peut arriver que l'erreur mesurée reste en dessous du seuil acceptable,

alors l'AxIC ne doit pas être rejeté. Par conséquent, dans ce contexte, les procédures de test ont un double rôle :

- rejeter les circuits dont l'erreur observée est supérieure au seuil, et

- éviter de détecter les fautes acceptables.

Il en résulte une augmentation du rendement et possiblement une réduction des coûts de test (c.-à-d. pour vérifier moins de défaillances, il faut moins de vecteurs de test).

De plus, en fonction de la métrique d'erreur, l'impact de la faute change. En effet, en stimulant un AxIC défectueux avec un vecteur d'entrée i, on peut mesurer l'erreur  $e_{s_i}$  - causée par la faute  $f_s$  - en utilisant une mesure M. En considérant le même vecteur d'entrée i mais une autre métrique  $\widehat{M}$ , l'erreur due à la même faute  $f_s$  est mesurée comme  $\widehat{e_{s_i}}$ . Généralement,  $e_{s_i}$  et  $\widehat{e_{s_i}}$  ont des valeurs différentes. De plus, en stimulant le circuit défectueux avec deux vecteurs d'entrée différents i et j, les erreurs mesurées seront  $e_{s_i}$  et  $e_{s_j}$ , pour la métrique M, et  $\widehat{e_{s_i}}$  et  $\widehat{e_{s_j}}$ , pour la métrique  $\widehat{M}$ . Là encore, les quatre erreurs ont généralement des valeurs différentes. Par conséquent, la faute  $f_s$  peut être considérée comme acceptable ou comme catastrophique selon la (ou les) métrique(s) considérée(s) pour l'application finale. En conséquence, les procédures de test doivent être attentivement repensées afin de relever les défis posés par l'approximation et de tirer profit des possibilités qui s'offrent. C'est pourquoi les tests conscients de l'approximation entrent en jeu. Nous identifions trois phases principales de tests conscients de l'approximation – ou Approximation-Aware (AxA) testing :

- **AxA fault classification** Dans cette phase, les fautes sont classées en *catastrophique* (à tester) et *acceptable* (à ne pas tester), selon certains paramètres.

- **AxA test pattern generation** Cette phase concerne la génération de vecteurs de test capables de couvrir tous les fautes catastrophiques et de laisser autant que possible les fautes acceptables non détectées.

- **AxA test set application** Après l'application des séquences de test, une classification supplémentaire doit être effectuée. L'AxIC testé est classé comme *catastrophiquement défectueux*, ou *acceptablement défectueux*, ou *sans fautes*.

Par conséquent, seuls les AxICs classifiés en tant que *catastrophiquement défectueux* seront rejetés. Il en résulte une augmentation du rendement, puisque certains circuits défectueux - mais encore acceptables - ne seront pas rejetés.

xi

Dans cette thèse, nous analysons en détail les phases du test conscient de l'approximation. De plus, nous présentons différentes techniques de mise en œuvre des tests conscients de l'approximation et d'optimisation de la qualité et de l'efficacité des tests. Nous effectuons des expériences approfondies pour évaluer leur efficacité.

#### 3. Classification des fautes consciente de l'approximation

La complexité de la classification des fautes est influencée par le choix de la métrique d'erreur. En effet, l'erreur causée par une faute – ainsi que l'effort pour la mesurer – peut changer de manière significative en fonction de la métrique considérée. Comme nous l'avons souligné dans les sections précédentes, des métriques d'erreur sont nécessaires pour déterminer l'approximation des systèmes informatiques. En effet, il est obligatoire de mesurer l'erreur introduite par les approximations pour pouvoir produire des systèmes donnant de bons résultats. À différents niveaux d'abstraction, nous pouvons définir des métriques d'erreur appropriées. Pour les techniques d'approximation appliquées au niveau matériel, certaines mesures d'erreur bien acceptées existent. Par exemple, parmi ces métriques, on peut compter l'erreur absolue maximale, la probabilité d'erreur, l'erreur absolue moyenne. Pour classer une faute comme non-redundant selon la métrique d'erreur absolue maximale, il suffit de prouver une seule condition : l'existence d'une séquence de test conduisant le circuit défectueux à présenter une erreur supérieure au seuil d'erreur. Au contraire, pour classer une faute comme non-redundant selon la métrique de probabilité d'erreur et d'erreur absolue moyenne, il faut prouver que la probabilité et la moyenne de l'erreur ne dépassent pas les seuils d'erreur. Pour y parvenir, la contribution de l'ensemble exhaustif de vecteurs d'entrée doit être évaluée. En conséquence, il s'avère peu complexe d'évaluer l'impact d'une faute lorsqu'on considère des métriques pour lesquelles une seule condition doit être vérifiée, comme l'erreur absolue maximale. Inversement, classer les fautes selon des métriques qui impliquent le calcul d'une moyenne est un problème de complexité  $O(2^n)$ , où n est le nombre de bits en entrée.

Dans ce chapitre, nous présentons deux techniques pour traiter de la classification des fautes, en considérant les deux types de mesures. Les deux techniques sont basées sur une architecture spécifique capable de classer les fautes en non-redundant et ax-redundant en mesurant leur impact sur les sorties de l'AxIC. L'idée fondamentale est de "cacher" les fautes ax-redundant au moyen d'une *boîte de filtrage*. Ainsi, pour une faute donnée, une condition d'anomalie n'est générée que si la faute entraîne des erreurs catastrophiques. Une telle architecture de classification n'est jamais fabriquée, mais seulement utilisée au moment de la conception pour classer les

fautes.

#### 4. Génération de vecteurs de test consciente de l'approximation

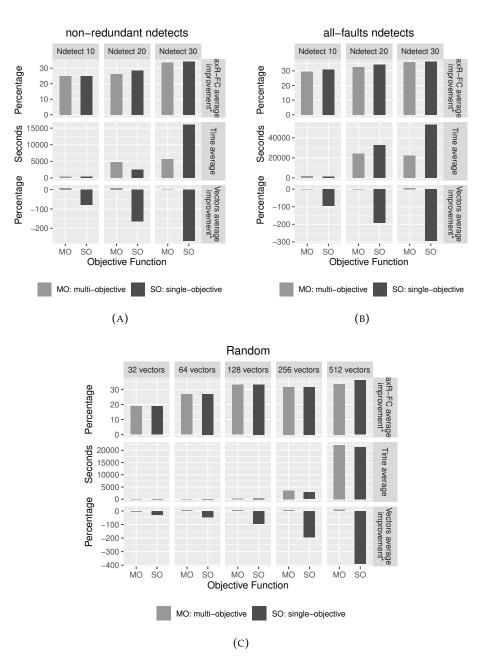

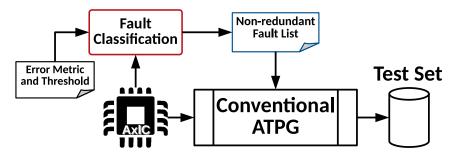

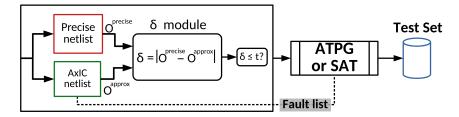

Dans ce chapitre, nous discutons du problème de génération des séquences de test consciente de l'approximation et présentons nos propositions pour y remédier. Comme précédemment indiqué, le rôle de la génération des séquences de test conscients de l'approximation est double : (i) les vecteurs de test doivent détecter tous les fautes non-redundant, afin d'éviter des erreurs catastrophiques aux sorties du circuit ; (ii) les séquences de test devraient détecter le moins de fautes ax-redundant possible, afin de ne pas considérer l'AxIC comme défectueux lorsqu'il est encore acceptable. En d'autres termes, un ensemble de tests qualitativement bon devrait atteindre 100% non-redundant FC (nR FC) et 0% ax-redundant FC (axR FC). Cependant, deux problèmes peuvent affecter la procédure de génération des séquences de test, en ce qui concerne les AxICs :

- 1. Afin d'atteindre 100% nR FC, il n'est pas toujours possible d'éviter de tester certains fautes ax-redundant (i.e., axR FC > 0%);

- 2. Les procédures conventionnelles de génération de tests pourraient ne pas être capable d'obtenir un ensemble de tests de bonne qualité.

Le premier problème est intrinsèque à la structure de l'AxIC testé, le second est relatif aux algorithmes conventionnels de génération de test. Par conséquent, un AxIC encore fonctionnel affecté par une faute ax-redundant serait rejetée en phase de test. Le phénomène en raison duquel un bon produit est considéré comme défectueux par le processus de test est communément appelé en anglais *over-testing*. Ce phénomène, si mal géré, finira par entraîner une importante diminution du rendement.

Ensuite dans ce chapitre, nous montrons comment la technique de classification des fautes présentée dans le chapitre précédent traite avec succès aussi la *génération des séquences de test consciente de l'approximation*, en détectant tous les fautes non-redundant. Néanmoins, la technique est limitée par certaines conditions particulières (c.-à-d. que la métrique utilisée dans la classification est l'erreur absolue maximale). De plus, nous montrons que en considérant différents ensembles de tests obtenant une non-Redundant Fault Coverage (nR FC) de 100%, différentes valeurs de ax-Redundant Fault Coverage (axRedundant Fault Coverage - axR FC) sont obtenues. Les techniques existantes ne permettent pas de résoudre le problème de trouver le meilleur ensemble de tests, c.-à-d. celui qui atteint une nR FC de 100% et qui minimise l'axR FC. C'est pourquoi nous proposons une technique plus

générale - basée sur une sélection minutieuse des séquences de test - conçue spécifiquement pour la génération des séquences de test consciente de l'approximation. Enfin, nous comparons les résultats des différentes techniques de génération des séquences de test, c.-à-d. la génération conventionnelle (ATPG ne prenant en compte que les fautes non-redundant), la génération consciente de l'approximation (c.-à-d. les séquences générées au même moment de la classification) et la génération consciente de l'approximation avec sélection de séquences.

Bien que les résultats obtenus soient assez bons, ils sont encore loin des résultats idéaux. Par conséquent, nous devons recourir à AxA test set application pour améliorer encore la qualité des tests.

#### 5. Application de vecteurs de test consciente de l'approximation

Pour améliorer la qualité finale du processus de test, l'application des tests consciente de l'approximation joue un rôle important. Dans cette phase, nous avons besoin de techniques capables - en observant les réponses du circuit - de distinguer entre la détection d'une faute ax-redundant (le test passe) et celle d'une faute non-redundant (l'AxIC est rejeté). Dans ce chapitre, nous présentons l'application de vecteurs de test conscients de l'approximation. Tout d'abord, nous montrons et discutons les problèmes liés à l'application des tests dans le contexte des AxICs. Nous montrons qu'il n'est pas toujours possible d'éviter la détection de certains fautes ax-redundant, à cause de la structure des AxICs.

Pour éviter le phénomène d'over-testing qui en résulte, nous devons reconsidérer la phase d'application du test. En détail, après l'application des séquences de test à l'AxIC sous test, nous devons vérifier que la sortie de l'AxIC remplit certaines conditions et pas seulement si elle diffère de la sortie attendue.

Dans la littérature, aucune technique n'a été présentée jusqu'à présent pour traiter de cet aspect. Néanmoins, une technique présentée dans [32] pour les circuits conventionnels, le *threshold testing*, peut être adapté aux AxICs. C'est pourquoi nous essayons d'adapter cette technique aux AxICs. Malheureusement, des conditions restrictives spécifiques doivent être remplies pour que la technique soit appliquée avec succès.

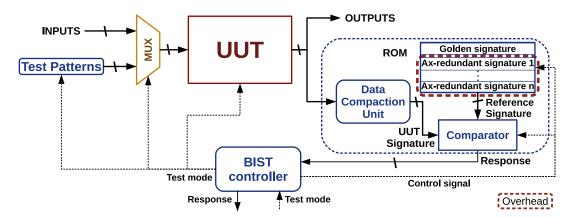

Donc, nous proposons une nouvelle technique d'application des tests consciente de l'approximation pour faire face aux limitations rencontrées. La technique est basée sur le concept bien connu d'analyse de signature, appliqué aux architectures de test automatique intégrées (BIST) dans les années 70 [33]. Le résultat obtenu avec la technique proposée est vraiment bon. Nous décrivons également le phénomène de

*l'aliasing* dans le contexte des AxICs et évaluons quelques méthodes correctives pour y faire face.

#### 6. Conclusions

L'introduction du paradigme du calcul approximé dans le panorama des technologies de l'information a apporté de multiples possibilités à des degrés divers. L'objectif fondamental du calcul approximé est d'améliorer l'efficacité du système (temps/surface/énergie) en assouplissant les exigences de précision des résultats. Le calcul approximé a été appliquée à différents niveaux des systèmes informatiques, du matériel au logiciel, en passant par les architectures. Parmi tous les travaux des deux dernières décennies, le calcul approximé a également été utilisé pour réaliser une nouvelle classe de circuits intégrés, c.-à-d. des circuits intégrés approximés ou AxIC. L'introduction d'une nouvelle classe de circuits a apporté de nouveaux défis, ainsi que de nouvelles opportunités, concernant le test et la vérification des puces. En particulier, les concepteurs de puces approximées modifient attentivement la structure du circuit pour introduire une erreur acceptable, afin d'obtenir des résultats satisfaisants. Pour définir correctement le concept d'erreur acceptable, les concepteurs utilisent métriques d'erreur. Ensuite, ils définissent des seuils d'erreur pour fixer l'erreur maximale autorisée (c.-à-d., acceptable). Par conséquent, le concept de circuit défectueux change. En effet, deux nouvelles catégories de défaillances sont introduites : les fautes axredundant (c.-à-d. causant des erreurs acceptables) et les fautes non-redundant (c.-à-d. causant des erreurs catastrophiques). Dans le contexte du test, la classe d'une faute détectable peut être déterminée en mesurant l'erreur causée à la sortie de l'AxIC. Si l'erreur mesurée est supérieure au seuil acceptable, le circuit doit être rejeté. Cependant, il peut arriver que l'erreur mesurée reste en dessous du seuil acceptable, alors l'AxIC ne doit pas être rejeté. Par conséquent, dans ce contexte, le rôle test change comme suit :

- les AxICs dont l'erreur observée est supérieure au seuil doivent être rejetés ;

- les AxICs affecté par des fautes acceptables ne doit pas être rejeté.

En conséquence, cela conduit à une augmentation du rendement de production.

En conséquence de ces considérations, nous introduisons les tests AxA, composés essentiellement de trois phases : (i) Classification des fautes consciente de l'approximation, (ii) Génération de séquences de test consciente de l'approximation, et (iii) Application des tests consciente de l'approximation. Toutes les phases de test conscientes de l'approximation apportent des contributions importantes à l'objectif final du test, dans le contexte des AxICs. Tout au long de la thèse, nous discutons en

détail de toutes les phases de test conscientes de l'approximation et nous présentons plusieurs techniques pour traiter de chaque aspect. Nous montrons que la synergie des techniques proposées permet d'obtenir des résultats optimaux.

## Acknowledgements

I would like to thank some people for supporting me in the last three years. This thesis would not have been possible without them.

Thanks to my thesis supervisors, Alberto Bosio, Patrick Girard and Arnaud Virazel, for their precious guidance through this exciting and challenging path.

Thanks to the precursor of all this, Mario Barbareschi, for his valuable advice.

Thanks to Matteo Sonza Reorda and Olivier Sentieys for agreeing to review my work and to join the thesis committee. Thanks to Lirida Naviner, for agreeing to join the thesis committee.

Thanks to my family, my brother, my mother, my father, for being there for me, always, no matter what. Thanks to my new family, the love of my life Ada, for strongly supporting and lovingly encouraging me, every day more.

Thanks to my colleagues and friends, Bastien, Clement, Emanuele, Ilaria, Linh, Mathieu, Safa, and all the others at LIRMM: they made this "journey" easier and cheerful. Thanks to Caroline Lebrun, without whom all the administrative procedures would have been impossible. Thanks to the LIRMM, where I learned a lot. Thanks to Montpellier, where I spent three wonderful years,

Thanks to all the people who have shared with me a piece of their life.

# **Contents**

| A  | bstra  | ct       |                                         | v    |

|----|--------|----------|-----------------------------------------|------|

| R  | esum   | é (FR)   |                                         | vii  |

| A  | cknov  | wledge   | ments                                   | xvii |

| In | itrodu | ıction   |                                         | xxix |

| 1  | Con    | ıtext an | d background concepts                   | 1    |

|    | 1.1    | Conve    | entional IC testing                     | . 2  |

|    |        | 1.1.1    | Defect modeling                         | . 4  |

|    |        | 1.1.2    | Fault simulation                        | . 6  |

|    |        | 1.1.3    | Test generation                         | . 7  |

|    |        | 1.1.4    | Built-In Self-Test                      | . 9  |

|    | 1.2    | Appro    | oximate computing (AxC)                 | . 10 |

|    |        | 1.2.1    | How to determine where to apply AxC?    | . 11 |

|    |        | 1.2.2    | Software-level AxC                      | . 12 |

|    |        | 1.2.3    | Architectural-level AxC                 | . 13 |

|    |        | 1.2.4    | Circuit-level AxC                       | . 14 |

|    |        | 1.2.5    | Error Metrics for Approximate Computing | . 15 |

|    | 1.3    | Testin   | g circuits in approximate context       | . 16 |

|    | 1.4    | Chapt    | ter summary                             | . 18 |

| 2  | App    | oroxima  | ation-Aware (AxA) testing               | 21   |

|    | 2.1    | AxA t    | resting phases                          | . 22 |

|    |        | 2.1.1    | AxA Fault Classification                | . 22 |

|    |        | 2.1.2    | AxA Test Pattern Generation             | . 23 |

|    |        | 2.1.3    | AxA Test Set Application                | . 23 |

|    |        | 2.1.4    | Relationships between AxA test phases   | . 24 |

|    | 2.2    | Relate   | ed work                                 | . 24 |

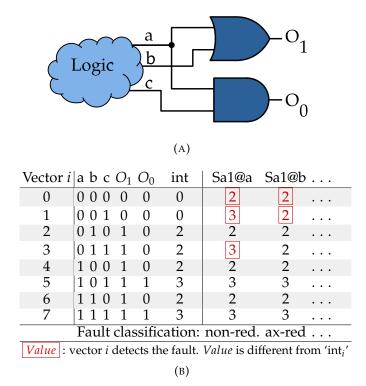

|    | 2.3    | Illustr  | rative example                          | . 25 |

|    | 2 4    | Chant    | ter summary                             | 26   |

| 3 | AxA  | A fault classification                        | 29 |

|---|------|-----------------------------------------------|----|

|   | 3.1  | Problem statement                             | 30 |

|   | 3.2  | SCT-metric-aware fault classification         | 32 |

|   |      | 3.2.1 Proposed technique                      | 33 |

|   |      | 3.2.2 Experimental results                    | 34 |

|   |      | 3.2.3 Related works                           | 35 |

|   |      | 3.2.4 Comparison                              | 36 |

|   | 3.3  | ME-metric-aware fault classification          | 37 |

|   |      | 3.3.1 Proposed technique                      | 37 |

|   |      | 3.3.2 Experimental Results                    | 39 |

|   | 3.4  | Chapter summary                               | 41 |

| 4 | AxA  | A test pattern generation                     | 43 |

|   | 4.1  | Problem statement                             | 44 |

|   | 4.2  | An Ax-aware technique                         | 47 |

|   | 4.3  | An ILP-formulated Pattern Selection Procedure | 47 |

|   |      | 4.3.1 Optimization problem                    | 49 |

|   |      | 4.3.2 Ax-aware ATPG as an ILP problem         | 50 |

|   |      | 4.3.3 Experimental results                    | 55 |

|   | 4.4  | Evaluation                                    | 59 |

|   | 4.5  | Chapter summary                               | 62 |

| 5 | AxA  | A test set application                        | 65 |

|   | 5.1  | Problem statement                             | 66 |

|   | 5.2  | A state-of-the-art solution                   | 67 |

|   |      | 5.2.1 Suitability investigation               | 68 |

|   |      | 5.2.2 Experimental results                    | 69 |

|   | 5.3  | A new AxA test set application technique      | 70 |

|   |      | 5.3.1 Proposed technique                      | 71 |

|   |      | 5.3.2 Signature aliasing problem              | 72 |

|   |      | 5.3.3 Experimental results                    | 73 |

|   | 5.4  | Evaluation                                    | 75 |

|   | 5.5  | Chapter summary                               | 77 |

| 6 | Disc | cussion and conclusions                       | 79 |

|   | 6.1  | Summary and considerations                    | 80 |

|   |      | 6.1.1 Contributions                           | 81 |

|   |      | 6.1.2 Considerations                          | 82 |

|   | 6.2  | Future perspectives                           | 83 |

|    |              |                         | xxi |

|----|--------------|-------------------------|-----|

|    |              | Contexts of application |     |

| 7  | Scientific C | Contributions           | 87  |

| Bi | bliography   |                         | 91  |

# **List of Figures**

| 1   | Inherent resiliency property [4]                                                   | xxix |

|-----|------------------------------------------------------------------------------------|------|

| 1.1 | Digital testing [34]                                                               | 2    |

| 1.2 | Scan design                                                                        | 8    |

| 1.3 | Generic BIST process [34]                                                          | 10   |

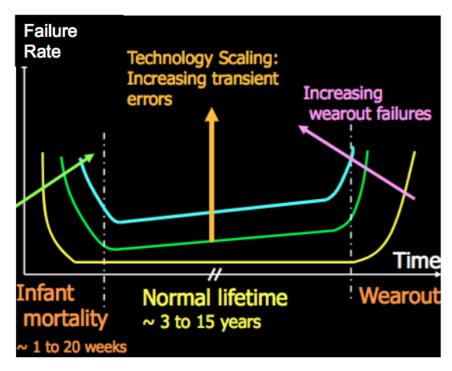

| 1.4 | Reliability decrease with technology scaling [85]                                  | 17   |

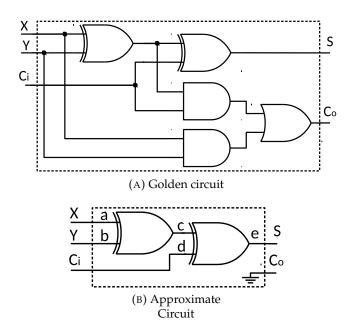

| 2.1 | Schematics of the Full adder (a) and of its approximation (b) obtained             |      |

|     | by re-synthesizing the circuit with $C_{\sigma}=0$ ; (c): truth tables of both go- |      |

|     | den (i.e., non-approximate) and approximate versions. Output's in-                 |      |

|     | teger representation for both circuits are also reported ("Int" column);           |      |

|     | (d): approximate circuit's error metric values                                     | 26   |

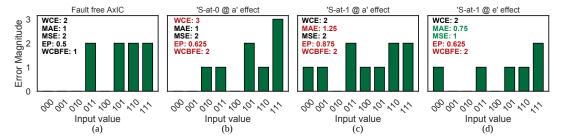

| 3.1 | (a) Error profile of the fault-free approximate circuit; (b) approximate           |      |

|     | circuit error profile in presence of the S-at-0 fault at the <i>a</i> net; (c) ap- |      |

|     | proximate circuit error profile in presence of the S-at-1 fault at the <i>a</i>    |      |

|     | net; (d) approximate circuit error profile in presence of the S-at-1 fault         |      |

|     | at the <i>e</i> net                                                                | 31   |

| 3.2 | SCT-metric-aware classification scheme                                             | 32   |

| 3.3 | A schematic view of the proposed flow                                              | 33   |

| 3.4 | Fault Filtering Architecture (FFA)                                                 | 37   |

| 3.5 | Overall flow                                                                       | 39   |

| 4.1 | Proposed Approximation-Aware ATPG                                                  | 48   |

| 4.2 | Average results for "non-redundant ndetects" (a), "all-faults ndetects"            |      |

|     | (b), and "random" (c) vector generation methods                                    | 58   |

| 4.3 | Conventional test pattern generation schema                                        | 60   |

| 4.4 | Ax-aware test pattern generation schema                                            | 60   |

| 5.1 | Proposed test application technique                                                | 71   |

| 5.2 | Aliasing effect                                                                    | 73   |

| 6.1 | ax-aware BIST hypothetical architecture                                            | 82   |

# **List of Tables**

| 3.1 | Approximate full adder error metric values for all possible Stuck-at     |    |

|-----|--------------------------------------------------------------------------|----|

|     | faults, under single-fault assumption.                                   | 30 |

| 3.2 | EvoApprox8b Circuits' WCE range                                          | 34 |

| 3.3 | ATPG-based fault classification results [88], in terms of expected Yield |    |

|     | Increase (eYI)                                                           | 34 |

| 3.4 | SAT-based fault classification results [86] in terms of expected Yield   |    |

|     | Increase (eYI)                                                           | 35 |

| 3.5 | SAT-based fault classification results [94] in terms of expected Yield   |    |

|     | Increase (eYI)                                                           | 36 |

| 3.6 | EvoApprox8b Circuits' EP, MAE and MSE ranges                             | 39 |

| 3.7 | ME-metric-aware fault classification results of [95], in terms of ex-    |    |

|     | pected Yield Increase (eYI)                                              | 39 |

| 3.8 | ME-metric-aware fault classification results for random workload ex-     |    |

|     | periments, in terms of expected Yield Increase (eYI)                     | 40 |

| 4.1 | Approximate full adder test vectors for all possible Stuck-at faults,    |    |

|     | under single-fault assumption                                            | 45 |

| 4.2 | Test vector generation results when using an ideal ax-aware test vec-    |    |

|     | tor generation and a conventional ATPG tool [87] on the example cir-     |    |

|     | cuit in Figure 2.1                                                       | 46 |

| 4.3 | Fault coverage (FC) report conceptual model                              | 50 |

| 4.4 | Fault coverage report, for the example circuit (see Figure 2.1). Faults  |    |

|     | are classified according to MAE metric (threshold=1)                     | 53 |

| 4.5 | ILP problem solution                                                     | 54 |

| 4.6 | Ax-unaware and ax-aware generated test vectors comparison                | 55 |

| 4.7 | AxICs attributes and conventional ATPG ineffectiveness evidences         | 56 |

| 4.8 | Ax-redundant FC (axR FC) and Yield Increase Loss (YIL) results. YIL      |    |

|     | and axR FC indicate the absolute and the relative loss of yield in-      |    |

|     | crease, respectively (see Section 2.1)                                   | 61 |

| 4.9 | Improvements obtained by using ax-aware generation and pattern se-          |    |

|-----|-----------------------------------------------------------------------------|----|

|     | lection generation techniques, compared to conventional generation          |    |

|     | technique. Higher is better                                                 | 62 |

| 5.1 | Output (in integer format) of the example circuit (see Figure 2.1) for      |    |

|     | different cases: precise (Fig 2.1a), fault-free approximate (see Fig 2.1b), |    |

|     | and faulty approximate with different Stuck-at faults                       | 66 |

| 5.2 | Test set generated using an ideal ax-aware test vector generation and       |    |

|     | a conventional ATPG tool [87] on the example circuit in Figure 2.1.         |    |

|     | (see Section 4.1)                                                           | 68 |

| 5.3 | Example of test set application technique by [32] used on the FA ex-        |    |

|     | ample (Figure 2.1)                                                          | 69 |

| 5.4 | Non-redundant FC results when using the test set application tech-          |    |

|     | nique by [32]                                                               | 69 |

| 5.5 | Ax-redundant FC (axR FC) and Yield Increase Loss (YIL) results when         |    |

|     | using the test set application technique by [32]                            | 70 |

| 5.6 | Ax-R faults detected with proposed technique compared to conven-            |    |

|     | tional test                                                                 | 75 |

| 5.7 | Ax-redundant FC (axR FC) and Yield Increase Loss (YIL) results when         |    |

|     | using the proposed test set application technique                           | 76 |

|     | · · · · · · · · · · · · · · · · ·                                           |    |

xxvii

## List of Abbreviations

ATE Automatic Test Equipment

ATPG Automatic Test Pattern Generation

AxA Approximation Aware

AxC Approximate Computing

AxIC Approximate Integrated Circuit

axR approximation-Redundant

AxRFM Ax-Redundant Fault Masking

BFE Bit-Flip Error

BIST Built-In Self-Test

DfT Design for Testability

DUT Device Under Test

EM Error Magnitude

EP Error Probability

eYI expected Yield Icrease

FA Full AdderFC Fault Coverage

FFA Fault Filtering Architecture

IC Integrated Circuit

ILP Integer Linear Programming

IoT Internet of ThingsMAE Mean Absolute Error

ME Mean Error

MSE Mean Squared Error nR non-Redundant

RMS Recognition, Mining and Synthesis

RYG Relative Yield Gain SaF Stuck-at-Fault

SAT Boolean SATisfiabilitySCT Single-Condition-Test

TF Transition Fault UUT Unit Under Test

WCBFE Worst Case Bit-Flip Error

WCE Worst Case Error YIL Yield Increase Loss

## Introduction

Despite significant energy efficiency improvements in the semiconductor industry, computer systems keep consuming more and more energy [1]. Many widely used applications – such as Recognition, Mining and Synthesis (RMS) applications – are increasingly deployed as mobile applications and on Internet of Things (IoT) structures. Therefore, it is necessary to improve the next-generation silicon devices and architectures on which these applications will run. The *inherent resiliency property* of RMS applications has been thoroughly investigated over the last few years [1]–[4]. This interesting property leads applications to be tolerant to errors – as long as their

Vinay K. Chippa, Srimat T. Chakradhar, Kaushik Roy, Anand Raghunathan, "Analysis and characterization of inherent application resilience for approximate computing," DAC 2013.

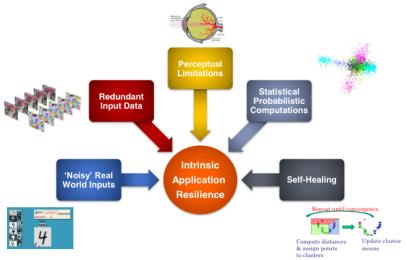

FIGURE 1: Inherent resiliency property [4]

results remain close enough to the expected ones. As shown in Figure 1, the main sources of error tolerance for these applications are:

- noisy real-world inputs,

- redundant data,

- perceptual limitations of individuals who will use the computation output,

- non-deterministic algorithms which lead to non-unique outcomes, and

- self-healing capable systems.

Approximate Computing (AxC) [1], [2] is an emerging computing paradigm which takes advantage of the inherent resiliency property. AxC has garnered increasing interest in the scientific community in the last years. It is based on the intuitive observation that selectively relaxing non-critical specifications may lead to improvements in power consumption, run time, and/or chip area. AxC has been applied to the whole digital system stack, from hardware to applications.

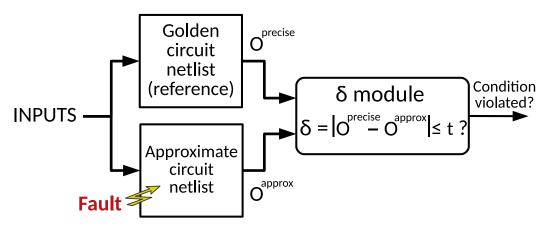

This work focuses on Approximate Integrated Circuits (AxICs). AxICs stem from the application of AxC at hardware level. A widely used method to design those circuits is functional approximation of conventional integrated circuits (ICs) [5]–[25]. We focus more specifically on the testing aspects of functionally approximate ICs. Indeed, since approximation changes the functional behavior of ICs, we have to revisit techniques to test them. In fact, previous studies [26]-[29] have shown that circuit approximation brings along challenges for testing procedures, but also opportunities. In particular, approximation procedures intrinsically lead the circuit to produce errors, which have to be taken into account in test procedures. Error can be measured according to different error metrics [30]. On the one hand, the occurrence of a defect in the circuit can lead it to produce unexpected catastrophic errors. On the other hand, some defects can be tolerated, when they do not induce errors over a certain threshold. This phenomenon could lead to a yield increase, if properly investigated and managed. To deal with such aspects, conventional test flow should be revisited. Therefore, we introduce *Approximation-Aware testing (AxA test*ing). We identify three main AxA testing phases: (i) AxA fault classification, (ii) AxA test pattern generation and (iii) AxA test set application. Briefly, the first phase has to classify faults into catastrophic (to test) and acceptable (not to test); the test pattern generation has to produce test vectors able to cover all the catastrophic faults and, at the same time, to leave acceptable faults undetected; finally, the test set application needs to correctly classify AxICs under test into catastrophically faulty, acceptably faulty, fault-free. Only AxICs falling into the first group will be rejected.

In this thesis, we thoroughly discuss the three phases of AxA testing, and we present a set of AxA test techniques for approximate circuits.

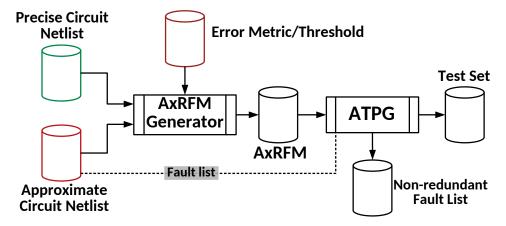

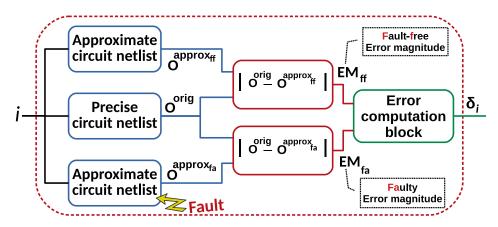

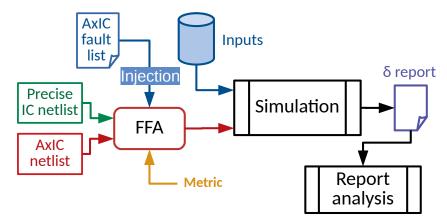

- Firstly, we work on the classification of AxIC faults into *catastrophic* and *acceptable* according to an error threshold (i.e. the maximum tolerable amount of error). This classification provides two lists of faults (i.e. catastrophic and acceptable).

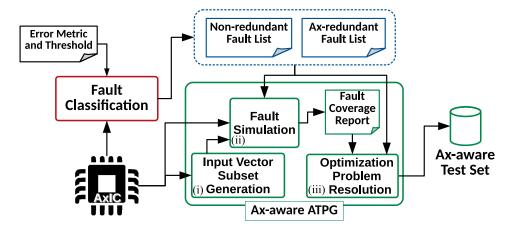

- Then, we propose an approximation-aware (ax-aware) Automatic Test Pattern Generation (ATPG). Obtained test patterns prevent catastrophic failures by detecting catastrophic defects. At the same time, they minimize the detection of

acceptable ones.

• Finally – since the AxIC structure often leads to a yield gain lower than expected – we propose a technique to correctly classify AxICs into "catastrophically faulty", "acceptably faulty", "and fault-free", after the test application.

To evaluate the proposed techniques, we perform extensive experiments on state-of-the-art AxICs.

## Chapter 1

# Context and background concepts

| Contents |                             |                                         |    |  |  |

|----------|-----------------------------|-----------------------------------------|----|--|--|

| 1.1      | Conventional IC testing     |                                         |    |  |  |

|          | 1.1.1                       | Defect modeling                         | 4  |  |  |

|          | 1.1.2                       | Fault simulation                        | 6  |  |  |

|          | 1.1.3                       | Test generation                         | 7  |  |  |

|          | 1.1.4                       | Built-In Self-Test                      | 9  |  |  |

| 1.2      | Approximate computing (AxC) |                                         |    |  |  |

|          | 1.2.1                       | How to determine where to apply AxC?    | 11 |  |  |

|          | 1.2.2                       | Software-level AxC                      | 12 |  |  |

|          | 1.2.3                       | Architectural-level AxC                 | 13 |  |  |

|          | 1.2.4                       | Circuit-level AxC                       | 14 |  |  |

|          | 1.2.5                       | Error Metrics for Approximate Computing | 15 |  |  |

| 1.3      | Testin                      | g circuits in approximate context       | 16 |  |  |

| 1.4      | Chapt                       | ter summary                             | 18 |  |  |

In this chapter, we put together some background information, which will be useful for fully understand and profit from this thesis. Firstly, we briefly describe conventional Integrated Circuit (IC) testing. IC testing represents the *technical focus* of this thesis. Secondly, we review different aspects of Approximate Computing (AxC). In particular, we describe approximate integrated circuits (AxICs), that constitute the *context* of this work. Finally, we put together the two aforementioned topics, the union of which forms the subject of this thesis. We show how inherent properties of AxICs led us to reconsider the test procedures and to propose new solutions. In other words, in this thesis we present studies on *hardware test techniques for approximate integrated circuits*.

#### 1.1 Conventional IC testing

In this section we recall some basic principles of conventional IC testing, which will be useful in different parts of this thesis. The concepts reported are not intended to be exhaustive. Extensive disquisitions on the concepts reported below can be found in [34].

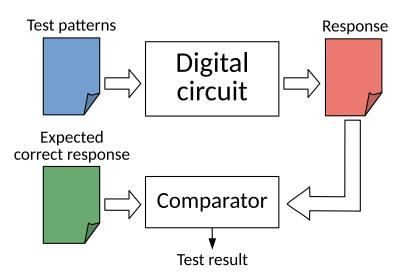

As sketched in Figure 1.1, in digital testing, binary patterns (or *test patterns*) are applied to circuit's inputs. Responses are compared with the expected ones (*golden* responses). If they match, the circuit is considered good, otherwise it is marked as

FIGURE 1.1: Digital testing [34]

faulty. VLSI testing can be classified depending on the goal it is intended to serve:

**Verification testing** Before sending a new design to production, its correctness and adherence to specifications must be verified. In this phase, functional and parametric tests are applied to ICs. Physical quantities (AC, DC) are measured

under different operative conditions. As a result, the operating limits of the chips are determined. Thus, correction on the design are performed and the final specifications are set. Verification testing can be employed also during the product lifetime to possibly improve the design and the process yield. Usually, this is done on chips rejected by production test or in the field.

**Production testing** After chip manufacturing, production testing must determine whether the actual fabricated devices meet specifications or not under normal operating conditions. Test vectors must have a high coverage of modeled faults and – since every device must be tested – test time (thus the cost) must be kept short. Test is performed either at the speed required by the application of the device or at the speed guaranteed by the supplier.

Burn-in testing Burn-in puts chips in high temperature environments, while applying production tests and over-voltage power supply. By doing this over a certain period, the reliability of the tested devices is ensured. Indeed, some chips that passed production tests can still fail after a very short time. Failures of this kind are usually called *infant mortality* failures. Defects causing this kind of failures must be detected early. In order to accelerate the occurrence of such failures, high temperatures turn out to be effective. Depending on the desired trade-off between reliability and cost, the burn-in time changes. Long burn-in time is expensive but usually leads to have a more reliable device.

**Incoming Inspection** Before system integration, customer may want to inspect devices. Indeed, discovering defective devices before the integration is by far less expensive than perform a system diagnosis. Depending on the customer needs, test procedures may be similar to production testing, more thorough or dependent on the specific system application.

More in general, two types of tests are performed on VLSI chips:

**Parametric Tests** Necessary to decide whether the chip pins meet various non-functional specifications, such as rise and fall times, setup and hold times, low and high voltage thresholds, and low and high current.

Functional tests Necessary to determine whether the chip internal digital logic behaves as designed. Tests consist in driving input vectors to the Device Under Test (DUT) and verifying that the corresponding responses match the expected ones. The goal is testing the proper operation of internal chip nodes.

In this latter category, the *manufacturing test* (or *hardware test*) aims at discovering any manufacturing defect. In 1959, Eldred proposed tests capable of observing the

internal state of signals in large digital system, by propagating their effect at primary outputs [35]. This type of tests are commonly referred to as *structural test*, because they depend on the internal structure of the circuit. As a consequence, algorithms based on IC's internal structure can be developed. Fault models – briefly discussed in next section – are the core of structural test algorithms. In this thesis, we focus on structural tests.

Finally, functional and physical characteristics, type of device, technology, desired reliability, and environment specification determine the type of test equipment to use. Testers – popularly known as Automatic Test Equipment (ATE) – drive the inputs and monitor the outputs of a DUT. Test data obtained from the ATE helps to accept or reject the DUT. Moreover, information about the fabrication process and about design problems can be extracted.

#### 1.1.1 Defect modeling

To correctly describe an *incorrect* electronic system, different terms have to be defined. Below, we report common definitions of Defect, Error and Fault.

**Defect** Unintended difference between the implemented hardware and its design. Defects can occur during manufacture, as well as during the device lifetime.

**Error** A wrong output signal produced by a defective system. An error is caused by some defect in the hardware.

Fault An abstraction model of a defect.

Even if a defect is present within an IC, its manifestation might never happen. In general, given the list of all possible defects (modeled as faults) that can occur within an IC, a subset of them is referred to as *detectable faults*. A fault is defined as detectable if it exists an input pattern sensitizing and propagating the fault effect to outputs. From now on in the text, we will refer to defect and to its model – the fault – interchangeably.

Fault modeling is performed at different levels of abstraction:

**Behavioral level** Sometimes referred to as *high level*, behavioral level fault models may not have correspondence in manufacturing defects. Mostly, they are used in design verification rather than testing.

**Logic level or Register-transfer level (RTL)** At this level, we find fault models usually built by considering the *netlist*, i.e., the circuit component list and their inter-connections. Stuck-at fault model is the most popular and used one in

5

digital testing. Among others, we find delay fault model and bridging fault model.

**Component level** At this level we find lower abstraction level, such as the transistor level. Stuck-open fault model, which is a technology-dependent model, is mainly used at this level. Mostly, analog circuit testing resorts to component level fault models.

In this thesis, we focus on logic level fault models, since we address digital integrated circuit testing.

In the following, we report some definitions concerning faults, in order to provide possible inexperienced readers with some useful terms for the rest of the thesis.

- Stuck-at fault model In this abstraction, a circuit net is considered to be permanently set at a constant value. By assigning a fixed (0 or 1) value to an input or an output of a logic gate or to a flip-flop in the circuit, the SaF model represents this condition. The SaF model is the most popular fault model used in practice for digital IC testing. The most popular forms are the *single stuck-at faults*. In this abstraction, a single fault line is assumed to be present in the IC, either stuck-at-1 (sa1) or stuck-at-0 (sa0).

- **Delay fault model** Defects modeled by delay fault model prevent the correct data from reaching outputs at the right time. Among different types of delay faults models we find transition faults, gate-delay faults, path-delay faults.

- **Redundant fault** In a combinational circuit, a redundant fault does not modify the circuit's output for any input combination. Thus, a test detecting a redundant fault cannot exist. Redundant faults are a subset of the more general *untestable faults*. In sequential circuits, faults for which no test pattern can be found fall into the untestable fault category.

- **Multiple fault** The condition that simultaneous single faults affect the same circuit is referred to as multiple fault. Multiple Stuck-at faults model is usually not considered, due to the tremendous complexity. Moreover, a very high percentage of these faults are covered by single stuck-at faults tests.

- **Equivalent faults** If two faults  $f_1$  and  $f_2$  lead a circuit to have the exact same function, they are defined as *equivalent*. A test detecting  $f_1$  detects also  $f_2$  and viceversa. This leads to *fault collapsing*: partitioning all the faults of a circuit into disjoint equivalence sets and selecting one fault from each equivalence set to test. For a circuit having n lines (thus 2n single stuck-at faults) the equivalence

between  $2(n^2 - n)$  pairs of faults should be determined, which is complex. Therefore, for stuck-at fault model, the fault equivalence is usually determined between faults affecting each Boolean gate.

#### 1.1.2 Fault simulation

In the design of VLSI circuits, the concept of *simulation* is of great importance. Firstly, it serves the purpose of verifying the circuit correctness. Secondly, it verifies whether and how efficiently a test set fulfill its purpose.

The circuit correctness verification is a fundamental step of the design activity. After the synthesis process, the produced netlist is verified by a *true-value simulator*, i.e., it produces the responses of the defect-free circuit. Since the goal is to verify the circuit functionality according to the specification, the input stimuli applied by the simulator to the circuit are based on the specification. Any errors lead to change the design to make responses to all stimuli match the specification.

Simulation is also used for the development of manufacturing tests. A so-called *fault simulator* acts like a true-value simulator with the capability to simulate a faulty-circuit. Once the verified circuit netlist is available, the fault simulator can verify the coverage of a given set of input stimuli (usually, the verification ones) for a given fault list. Faults covered by the given set are marked as *detected* and the *Fault Coverage* is measured.

**Fault Coverage (FC)** The ratio of the number of faults detected by a set of test patterns to the total number of faults in the fault list.

An adequate FC (98% - 100%) is usually required in order to ship high quality devices to the customers. A good-quality test is a test that can minimize the number of faulty circuits sold, while keeping the test cost acceptable.

**Test quality** The test quality is expressed as *defect level* (or *field reject rate*): the fraction of chips that, despite having passed the test, are actually faulty. Defect level is expressed as *parts per million* (*ppm*). High quality tests are considered as providing chips with a defect level of 100 ppm or lower.

Process variations, such as impurities in materials, dust particles, etc., can produce defects during the manufacture. In turns, defects can cause circuits to fail. Process variation effects reflect on the *process yield*:

**Process yield** The fraction (or percentage) of acceptable parts (thus, sold) among all fabricated parts is commonly referred to as process yield, or simply as *yield*.

In a typical case, a newly designed chip has a low yield, at its early manufacturing period. Thanks to process diagnosis and correction, higher process maturity is achieved and, thus, significantly higher yield.

While the role of conventional testing is rejecting defective circuits, yet it cannot improve the process yield. All along this thesis, we will discuss the role of IC testing when approximate computing comes into play. It turns out that – in this particular context – test procedures have a different role which includes the opportunity to increase the process yield.

Verification stimuli may not produce an adequate FC. As shown in the next subsection, test generator programs can produce new test vectors to increase the FC.

#### 1.1.3 Test generation

In late-fifties, Eldred highlighted the necessity for the structural testing of logic circuits to prevail over the classic functional test [35]. He argued that formulating test conditions at the level of the components is "the only way in which all conditions of operation of each logical function can be uniquely [...] defined and all logical components within each logical function can be made to perform the task to which they are assigned [...] thereby producing a minimum program which tests and detects failure". The goal of structural test is to verify the presence of the minimal set of faults in the circuit. Therefore, the application of fault equivalence is important to reduce the final set of faults to test.

Automatic Test Pattern Generation (ATPG) serves the purpose of producing patterns to test the internal structure of a digital circuit, starting from its netlist description. The commonly used method in ATPG, namely path sensitization is based on three steps:

- 1. fault *injection* in the circuit netlist;

- 2. fault activation;

- 3. fault effect *propagation* toward circuit outputs.

To briefly describe path sensitization, let us resort to the stuck-at fault model (see Subsection 1.1.1). Let us assume that we want to test if a line l is stuck to a constant value (say 1). The test vector v detecting that fault is composed of input values such that:

• the line *l* is set to the opposite value of the fault (say 0). This is commonly referred to as fault *sensitization* or *activation* or *excitation*;

• the effect of the previous action is propagated to circuit outputs. This is commonly referred to as fault *propagation* or *path sensitization*.

By simulating the pattern with the fault-free circuit, we obtain the fault-free output value (expected output). Now, let us assume that an actual stuck-at fault (say Sa1) occurs at line l. In presence of the fault, circuit outputs will be different from expected. Therefore, by applying the test vector v to the circuit and knowing the expected output, we are able to detect the fault by observing a difference between actual and expected outputs.

In the context of conventional IC test, even a little difference between the nominal behavior and the manufactured IC's leads to reject the circuit. Later in this thesis, we will discuss this aspect when approximate computing is considered. In this particular context, the value of the difference between the nominal behavior and the manufactured IC's is important. In fact – under specific conditions – the manufactured circuit may be still accepted even if some defects occur.

Unfortunately, the described ATPG method works correctly only for combinational circuits, i.e. without cycles. In fact, any circuit with cycles will lead the aforementioned method to fall into an infinite loop. ATPG methods for sequential circuits exist but are usually very resource-consuming and sometimes inefficient. The main difficulty for *sequential ATPG* is to control and to observe the internal state of the circuit.

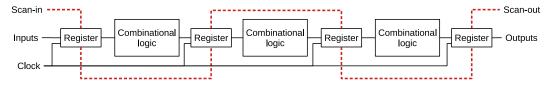

Therefore, *design-for-testability* (*DfT*) comes into play. As stated by Agrawal and Seth [36], "*testability is the property of a circuit that makes it easy* (*and sometimes possible!*) *to test*". DfT refers to the set of design techniques for ICs aiming at improving the testability of the target design. The most popular DfT technique is the scan

FIGURE 1.2: Scan design

design. Figure 1.2 depicts the scan design basic concept. This technique aims at increasing controllability and observability of flip-flops in a sequential design. This is done by connecting all the flip-flops together, to form a long shift register when a *test-mode* is activated. By shifting logic values in and out, it is possible to control and observe the internal state of the circuit. As a result, this approach converts the ATPG problem for sequential circuits into a well-known and more tractable ATPG

for combinational circuits. Of course, this comes at the cost of extra hardware, delay, and test time. Such cost may be justified by time-to-market-driven decisions. In fact, existing ATPG for sequential circuits often introduce design delay, while ATPG for combinational logic has a predictable test development time.

#### 1.1.4 Built-In Self-Test

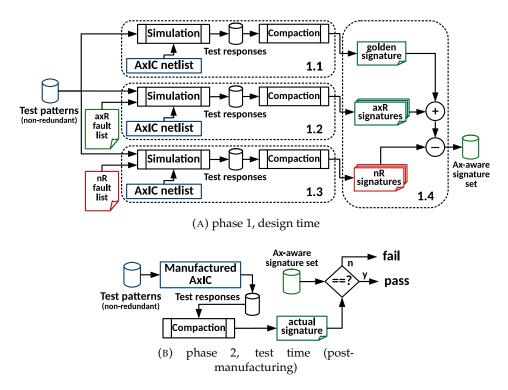

As the VLSI matured, the complexity of microelectronic systems grew considerably. As a consequence, performing IC testing became more and more difficult. As mentioned in the previous subsection, design-for-testability techniques contributed to simplify the testing of circuits at the cost of some additional resources. In 1977, the concept of *signature* was introduced by Frohwerk as a new method to determine IC correctness [33].

**Test signature** The *word* resulting from the compaction of IC test responses is defined test *signature*

This reduced the IC test to a comparison of two signatures. In details, after the design of the patterns to test the IC, the responses of the fault-free IC are compacted in a test signature (golden signature). When the manufactured IC is tested by applying the same patterns, the signature obtained by compacting the responses is compared with the golden one. If they match, the circuit is considered fault-free. Otherwise, it is marked as faulty. Sometimes, it can happen that the signature of a faulty circuit matches the golden one. This is referred to as *aliasing* phenomenon.

**Aliasing** During the compaction of the circuit's response, a signature of a bad device may match the golden signature. This is due to the information loss during the compaction. When aliasing occurs, a failing circuit might pass the test and be shipped to the customer.

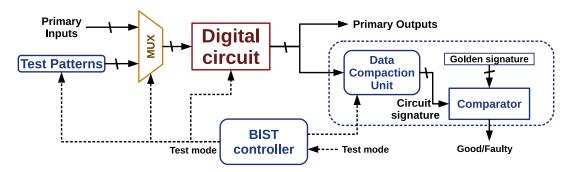

As a matter of fact, the real breakthrough was the application of signature analysis to the so-called Built-In Self-Test (BIST).

**Built-In Self-Test (BIST)** A circuit which is capable to autonomously determine whether it is fault-free or not has BIST capabilities.

In Figure 1.3 we report the generic BIST architecture as presented in [34]. In detail – when the test mode is activated – test patterns are applied to the circuit and a signature is generated. Then, the latter is compared with the golden signature, which was generated by the fault-free circuit and stored within the BIST architecture. If the two signatures are identical, the circuit is considered fault-free. Otherwise, a malfunction

FIGURE 1.3: Generic BIST process [34]

is detected. Different pattern generation and signature compaction methods exist in the literature. An extensive review of those methods can be found in [34].

With the BIST introduction, test became part of the system functionalities rather than a procedure performed only occasionally. Indeed, during its lifetime, a modern digital system is tested very often. As a consequence, test must be performed in the most rapid and efficient way possible. BIST serves this purpose very efficiently and, when properly designed, the extra hardware cost is more than balanced by the benefits in terms of reliability and reduced maintenance cost.

## 1.2 Approximate computing (AxC)

Let us now introduce the context of this thesis, the *Approximate Computing (AxC)*. Some definition of Approximate Computing have been provided in last years:

"Approximate computing [...] is based on the intuitive observation that while performing exact computation or maintaining peak-level service demand require high amount of resources, allowing selective approximation or occasional violation of the specification can provide disproportionate gains in efficiency." — Mittal, 2016 [2]

"By relaxing the numerical equivalence between the specification and implementation of error-tolerant applications, approximate computing deliberately introduces 'acceptable errors' into the computing process and promises significant energy-efficiency gains." — Xu, Mytkowicz, Kim, 2016 [1]

"A new design paradigm, Approximate Computing (AxC), has been established to investigate how computing systems can be more energy efficient, faster, and less complex. Intuitively, instead of performing exact computation and, consequently, requiring a high amount of resources, AxC aims to selectively relax the specifications, trading accuracy off for efficiency." — Bosio, Menard, Sentieys, 2019 [37]

The three definitions above respectively highlight *the problem, the context,* and *the purpose* of AxC.

**The problem** As energy-demanding applications more and more establish in the information technology scene, it is expected that in the next decades the amount of information will grow so much that it will exceed available resources [2].

**The context** The so-called Recognition, Mining and Synthesis (RMS) applications have a very interesting peculiarity, i.e., *error resiliency* [4]. Indeed, RMS applications turn out to be intrinsically tolerant to errors thanks to different factors, such as noisy data processed, non-deterministic algorithms used, and possible non-unique outcomes.

**The purpose** In the last decades, several works have been inspired by the opportunity that aforementioned resilient applications brought along for energy-efficiency. The purpose of AxC is to represent a new paradigm that drives the investigation of new energy-efficient computing solutions.

AxC has drawn the attention of both academia and industry, and a lot of works have focused on different aspects of AxC [1], [2].

#### 1.2.1 How to determine where to apply AxC?

Approximation can be applied at different levels. Specifically – according to the classification in [1] – there are three main categories of so-called *approximate kernels*: Software-level, Architectural-level, and Circuit-level. All the three categories have in common the need of *identify* and *characterize* the resilient parts of the target system. Generally, when the *approximable* regions are somehow known, the target applications/systems are "annotated" to express the opportunity to approximate [38], [39]. Alternatively, the resiliency of the different parts of the system can be explored by means of sensitivity analysis [4], [40]. Other techniques resort to dynamic output monitoring to adapt the accuracy of the computation at run-time [41]–[44]. To suitably identify the approximation opportunities, the above methods resort to *metrics* to measure the accuracy loss as the approximation is introduced. As reported in [2], several error metrics have been used in the literature, such as:

Peak Signal-to-Noise Ratio (PSNR), Structural SIMilarity (SSIM), pixel difference for image/video processing algorithms (e.g., JPEG, MPEG);

- classification/clustering accuracy for the classification/clustering algorithms (e.g., k-means);

- ranking accuracy for document search algorithms (e.g., Supervised Semantic Indexing).

Furthermore, more generic metrics can be used to evaluate approximate systems' accuracy. For instance, the Error Probability (EP) measures the percentage of erroneous outputs produced by an approximate system/application compared to its precise version.

#### 1.2.2 Software-level AxC

At software level, AxC has been employed to provide programmers with the possibility to realize complex yet energy-efficient programs. This task is possible thanks to the abstraction of the *approximation concept* by means of *approximation-aware* (axaware) programming languages, ax-aware correctness analysis engines, and ax-aware compilers.

**Ax-aware programming languages** The main goal of programming languages is to allow programmers to express *what to do* instead of *how to do* it, by using resource abstraction. Likewise, approximation-aware programming languages help programmers expressing *randomness* [1]. Examples of such languages are in [38], [39], [45], which provide the programmers with approximation-related syntax.

Ax-aware correctness analysis The goal of analyzing an "ax-aware source code" is to build a model of it. The goals are (i) to state whether the code is correct or not and (ii) verifying if the code respects some properties about the produced output error. To do so, *probabilistic modeling* is suitable [1]. Some probabilistic model checking works have been proposed, such as [46], [47]. Other propositions focus on adapting conventional static and dynamic program analysis to compute the probability of critical output deviations in the final program [48]–[51].

Ax-aware compilers In general, the goal of compilers is to translate the source code into a sequence of tasks that the underlying hardware system has to perform. In addition, ax-aware compilers can exploit the information gathered from the ax-aware source code and the ax-aware analysis to transform the program semantics. The final goal is to sacrifice some accuracy (within some boundaries) to improve energy consumption or performance. Examples are the use of loop

perforation (execute fewer iterations than usual) [52], and of operand bit-width reduction [53].

#### 1.2.3 Architectural-level AxC

At architectural level, the fundamental components are *computing units, memories* and *storage devices*. When building a computer system, the ideal goal is to obtain high-performance processing units at a low energy cost, and to obtain a good trade off between performance and density, for memories and storage units [1]. AxC has put into play a new parameter to push farther next generation hardware components, i.e., the quality. Indeed, by sacrificing some quality, one can further improve performance, density and energy efficiency.

**Approximate computing units** Classic computing units are usually grouped into two broad categories: *general purpose* computing units and *special purpose* computing units. General purpose units combine high-level instructions to realize generic tasks. On the contrary, special purpose units are built to fast execute a set of predefined actions. Along this same lines, AxC has been applied (i) to enhance general purpose computing units that execute selected instruction (or code segments) in an energy-efficient fashion [54], [55] and (ii) to transform whole approximable algorithms into neural accelerators [56].

Approximate memories Some problems limit the energy efficiency of conventional SRAMs and DRAMs, in the precise domain. SRAMs start producing errors when the operating voltage decreases under a threshold, and they are also vulnerable to particle strikes if not properly protected by using big memory cells. AxC profits from data resiliency by systematically storing the least significant bits in energy-efficient small SRAM cells [57]–[59]. Conventional DRAMs need to be refreshed periodically, which entails a big energy consumption. To take advantage of error-resilient data, AxC techniques apply longer refresh periods to memory rows storing those data to improve energy-efficiency [60]–[62]. In [63], also multi-level approximate memory architecture based on data significance analysis was proposed. Furthermore, the applicability for approximate computing of emerging non-volatile memories, such as the Spin Transfer Torque Magnetic RAM (STTMRAM), has been evaluated in [64].

**Approximate storage** In solid-state storage units, a lot of effort in terms of energy/latency is required to precisely store and retrieve multiple data. AxC comes into play

when data precision can be relaxed, thus storage and retrieval can be performed with less effort. Moreover, storing resilient data into overused storage blocks increases the lifetime of the storage unit [65].

#### 1.2.4 Circuit-level AxC

Finally, we come to circuit-level, where AxC has basically been applied in two ways: (i) *over-scaling* and (ii) *functional approximation*. Over-scaling consists in lowering the circuit supply voltage to reduce its energy consumption. If the circuit is systematically designed to profit from over-scaling [66], [67], the timing errors are negligible compared to the energy gain. Nevertheless, the energy gain for over-scaling techniques turns out to be still small [1]. Therefore, a considerable amount of works has been presented on circuit *functional approximation*: the circuit functionality is systematically changed – thus, some controlled errors are introduced – to achieve energy-efficient circuits. So far, three main approaches have been used to design approximate integrated circuits (AxICs):

Ad-hoc approximate circuits RMS applications mostly rely on simple arithmetic operations, such as addition and multiplication. A lot of work have been done to realize energy-efficient and performance-enhanced approximate adders [10], [11], [22], [23], [25], [68]–[71]. A comprehensive review and comparison can be found in [6]. Moreover, non-volatile logic-in-memory approximate adders were proposed in [72]. Specifically, Spin Torque Transfer Magnetic Tunnel Junction (STT-MTJ) was used to implement a magnetic full adder. Furthermore, also a lot of effort has been put in the design of approximate multipliers [5], [7], [8], [13], [25].

Approximate circuit synthesis Unlike above discussed arithmetic circuits, for general logic circuits we cannot use ad-hoc techniques, due to the exponential complexity that VLSI circuits bring along. In the eighties, logic minimization techniques were proposed to cope with this complexity and drive the cutting-edge automated logic synthesis techniques [73]. First attempts of AxCoriented methodologies have been proposed in [14] and [74] to implement the automated synthesis of AxICs. The main challenge was the absence of a well-accepted error model for general circuits. In fact, only simple error models were used. Therefore, some frameworks to flexibly represent the error were proposed in [15], [20], [75]. Finally, also RTL-level [76] and HLS-level [77], [78] languages were proposed to guide the approximation-oriented logic synthesis.

Hardware neural accelerators The intrinsic approximate nature of neural accelerators are particularly suitable to implement approximate functions. Different works have been proposed on hardware neural network implementations both with digital logic circuits [56] (precise and reliable) and analog circuits [79] (compact and energy-efficient). Furthermore, also ReRAM crossbar arrays were used to implement really energy-efficient solutions [80]. However, challenges related to the interfacing energy overhead and to the premature technology still have to be faced.

#### 1.2.5 Error Metrics for Approximate Computing