# Innovative devices in FD-SOI technology

Hyungjin Park

### ▶ To cite this version:

Hyungjin Park. Innovative devices in FD-SOI technology. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2019. English. NNT: 2019GREAT039. tel-02506292

# HAL Id: tel-02506292 https://theses.hal.science/tel-02506292

Submitted on 12 Mar 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# **THÈSE**

Pour obtenir le grade de

# DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité: NANO ELECTRONIQUE ET NANO TECHNOLOGIES

Arrêté ministériel : 25 mai 2016

Présentée par

# Hyungjin PARK

Thèse dirigée par **Jean-Pierre COLINGE**, CEA LETI et codirigée par **Maryline BAWEDIN**, Universite Grenoble Alpes et par **Sorin CRISTOLOVEANU**, Directeur de Recherche, CNRS

préparée au sein du Laboratoire Institut de Microélectronique, Electromagnétisme et Photonique - Laboratoire d'hyperfréquences et de caractérisation dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

# Dispositifs innovants de la technologie FDSOI

# Innovative devices in FD-SOI technology

Thèse soutenue publiquement le **10 juillet 2019**, devant le jury composé de :

#### M. Gerard GHIBAUDO

Directeur de Recherche, CNRS, Président

#### M. Carlos SAMPEDRO

Professeur, University of Granada, Rapporteur

### M. Bogdan CRETU

Maître de Conférences, ENSICAEN, Rapporteur

#### M. Olivier BONNAUD

Professeur Emérite, University of Rennes 1, Examinateur

### M. Jean-Pierre COLINGE

Professeur, Universite Grenoble Alpes, CEA LETI, Directeur de thèse

### **Mme. Maryline BAWEDIN**

Maître de Conférences, Grenoble INP, Co-encadrante de thèse

#### M. Sorin CRISTOLOVEANU

Directeur de Recherche, CNRS, Co-encadrant de thèse

To my lovely wife Jihye and two sons Seungmin, Seunghyun

For my father-in-law Eunhyun and mother-in-law Boktae

For my parents, Younghong and Juemyung

# Acknowledgement

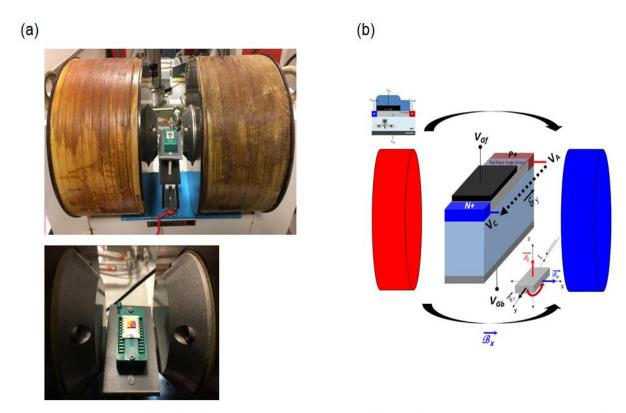

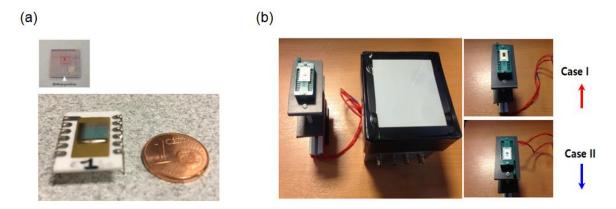

While I have worked on the PhD dissertation in Grenoble, my lovely wife, Jihye CHOI has been supported me and the family with her unlimited devotion. Her sacrificial contribution made me stand more energetic and creative. My two sons, Seungmin PARK and Seunghyun PARK, have been done very well in a French public school and played well closely with their friends. They have been growing up excellent as awesome adolescent men although the boys had experienced many difficulties such as language barrier in class, exotic food, and different educational system. My parents, Younghong PARK and Juemyung JI, always believed me whatever I did. There are four very important persons who lead me to reach here as a PhD: official directors, Dr. Philippe Ferrari (2015-2018), Dr. Jean-Pierre Colinge (2018-2019) and co-directors: Dr. Sorin Cristoloveanu, Dr. Maryline Bawedin. I would like to give props to them with special many thanks. They led me a lot during my thesis and encouraged me to be a real member of SOI mafia during the 4-years long trip. When I first arrived at Grenoble in August 16th 2015, especially, Sorin helped me and my family to settle down safely and quickly. He was willing to give me various useful tips for Grenoble's life. He has also guided and inspired me for doctoral works: an investigation of floating body effects in FDSOI device, advanced devices based on SOI technology. I felt like fun and interesting after reaching a threshold point of my patience. Maryline usually has made me triggering deep thinking about dynamic body potential variation in FDSOI MOSFET. Indeed, I did approach many-sides experiments and TCAD simulation in order to understand the gist of body potential variation in ultrathin FDSOI MOSFETs. After all, we have found an original finding about gate-coupling and explaining super coupling effect in ultrathin devices. I really appreciate to her detailed observation and valuable comments. Many thanks are due to Xavier Mescot (an awesome manual fixture for measuring a magnetodiode under magnetic field) and Martine Gri (many special package samples for optical sensor and magnetodiode). I am glad to work with all their valuable devotion and outstanding availability in IMEP-LAHC. Furthermore, I kindly thank for the help that I received from all the HR team members: Isabelle, Dalhila, Valérie, and Annaïck. I also thank everyone else in IMEP-LAHC providing all sorts of tangible and intangible support. I am lucky to spend lots of time with many office mate and colleagues: Dr. Luca Pirro, Dr. Elodie Jordan, Dr. Walid Aouimeur, Dr. Mukta Singh Parihar, Dr. Dimitris Damianos, (Dr.) Licinus Benea, Dr. Kyungwha Lee, (Dr.) Miltiadis Alepidis, and (Dr.) Namanu Panaymthatta. It was delightful and alluring thanks to my office family. I will never forget the good memories and moments with them.

Finally, to all members of Association des Scientifiques Coréens en France (ASCoF) in Grenoble region: Dr. Soongeun Je, Prof. Daeseok Lee, Prof. Youngjun Choi, Prof. Woojin Jeon, Dr. Jinhwa Shin, Dr. Yunghee Kim, Dr. Youngjin Kim, Dr. Youngsoo Kim, Dr. Youngpil Kim, Dr. Jungbin Song, Dr Jongmin Lee, Mr. Woncheol Kwak, Dr. Sanghoon Kwak, Dr. Yunji Shin, Mme. Rhye-ja Chu and Prof. Guy Vitrant. I am truly happy to be known you all. We all together did many activities under the name of ASCoF Grenoble. Thank you for being there for me so far, for amusing times as well as the beautiful moments that you and I created. I am now standing a new stage as an expert for developing new DRAM memory based on FDSOI and nano-wire like device and its technology. I am definitely willing to contribute for SKhynix in order to be the world best memory solution supplier. FDSOI technology will probably be a promising technology for new DRAMs (4F²).

# Abstract/Résumé

# **Investigation of Innovative FDSOI Devices and Applications**

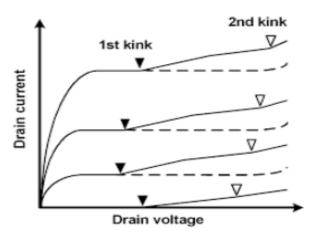

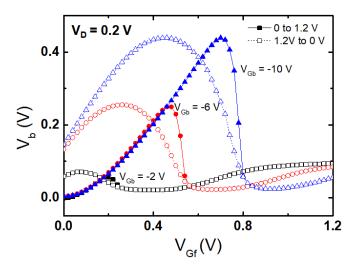

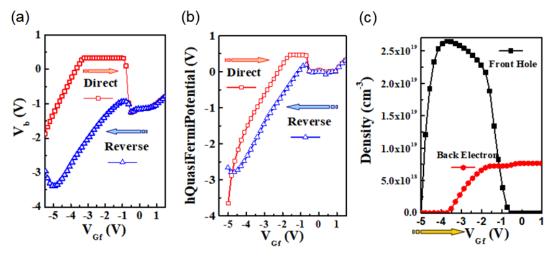

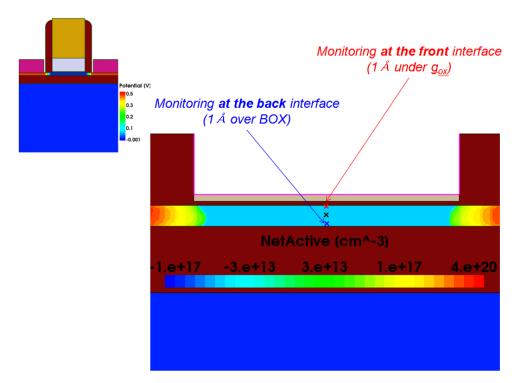

The main purpose of this PhD work is to investigate the fundamentals of floating body effects (FBEs) in recent generations of ultrathin FDSOI devices. Several FBEs, (i) kink effect, (ii) gate-induced FBE, (iii) parasitic bipolar transistor, (iv) sharp switching, (v) current hysteresis, and (vi) transient and history effect (MSD), are scrutinized in terms of interaction between holes and electrons in ultrathin transistor body. The key point is that in an n-channel SOI MOSFET the FBEs are originated from the interplay of the excess holes which are either being stored or eliminated. For better understanding of FBEs, the body potential  $V_b$  has measured directly in H-gate body contact n-MOSFETs. The dynamic  $V_b$  variation has also been monitored successfully thanks to lateral  $P^+$  body contacts extended into the undoped-silicon film underneath the front-gate.

Through the measurements of  $V_b$ , there are three major findings highlighted for the first time: (i) correlation between the onset of the FBEs and the  $V_b$  variation, (ii) new experimental evidence of super-coupling effect observed while the surface potential is changed from depletion to volume inversion, (iii) establishment of a new technique for extracting threshold voltage  $V_T$  compared with the typical methods based on the current-voltage characteristics.

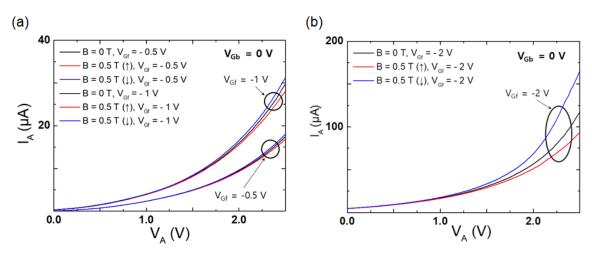

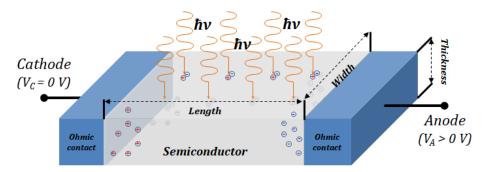

Finally, innovative FDSOI devices such as back-gated InGaAs lateral N<sup>+</sup>NN<sup>+</sup> MOSFET, and  $Z^2$ -FET sensors, are characterized. We demonstrate the basic performance of the InGaAs-on-Insulator substrate by using  $\Psi$ -MOSFET technique. Sensing features of the  $Z^2$ -FET are investigated under magnetic field or illumination.

# Etude de dispositifs et applications FDSOI innovants

L'objectif principal de ce travail de doctorat est d'étudier les principes fondamentaux des effets de corps flottants (FBE) dans les dispositifs FDSOI ultraminces de dernières générations. Plusieurs FBE, (i) kink, (ii) FBE induit par la grille, (iii) transistor bipolaire parasite, (iv) commutation brusque, (v) hystérésis de courant, et (vi) effet transitoire (MSD), sont examinés en termes d'interaction entre des trous et des électrons dans le corps ultramince. La clé de voûte est que les FBE proviennent de l'interaction des trous en excès qui sont stockés ou éliminés. Pour une meilleure compréhension des FBE, la variation du potentiel interne  $V_b$  a été mesurée directement sur les n-MOSFET a contact en H. La variation dynamique de  $V_b$  a également été étudiée grâce aux contacts latéraux  $P^+$  prolongés dans le silicium non dopé situé sous la grille avant.

Grâce à la mesure de  $V_b$ , trois résultats principaux ont été mis en évidence pour la première fois: (i) la corrélation entre l'apparition des FBE et la variation de  $V_b$ , (ii) de nouvelles preuves expérimentales de l'effet de super-couplage observé alors que le potentiel de surface voire entre déplétion et inversion, (iii) une nouvelle méthode d'extraction de la tension de seuil, comparée à la méthode typique basée sur la caractéristique courant-tension.

Enfin, des dispositifs FDSOI innovants, comme le MOSFET latéral N<sup>+</sup>NN<sup>+</sup> sur InGaAs à grille arrière, et le Z<sup>2</sup>-FET en tant que magnétodiode et capteur optique, sont caractérisés. Nous démontrons les performances de base du substrat InGaAs sur isolant en utilisant la technique du pseudo-MOSFET. Les caractéristiques de détection du Z<sup>2</sup>-FET sont vérifiées sous champ magnétique et sous éclairage.

# **Table of Acronyms**

| Acronym Nomination | Nomination                                             |

|--------------------|--------------------------------------------------------|

| BCN                | Body contact n-MOSFET                                  |

| BJT                | Bipolar junction transistor                            |

| BTBT               | Band-to-band tunneling                                 |

| BOX                | Buried oxide                                           |

| CMOS               | Complementary metal oxide semiconductor                |

| CMP                | Chemical mechanical polishing                          |

| DRAM               | Dynamic random access memory                           |

| DIBL               | Drain induced barrier lowering                         |

| DSPT               | Double spacer patterning technique                     |

| EUV                | Extreme ultraviolet                                    |

| FDSOI              | Fully depleted silicon-on-insulator                    |

| FBEs               | Floating body effects                                  |

| FET                | Field effect transistor                                |

| GIFBE              | Gate induced floating body effect                      |

| GIDL               | Gate induced drain leakage                             |

| hQFP               | Hole quasi Fermi potential                             |

| ITRS               | International technology roadmap for semiconductors    |

| IC                 | Integration circuit                                    |

| MOSFET             | Metal oxide silicon field effect transistor            |

| MSD                | Meta stable dip                                        |

| PDSOI              | Partially depleted silicon-on-insulator                |

| PBT                | Parasitic bipolar transistor                           |

| PW                 | Pulse width                                            |

| RSD                | Raised source and drain                                |

| SOI                | Silicon-on-insulator                                   |

| SCEs               | Short channel effects                                  |

| SS                 | Subthreshold swing                                     |

| SRH                | Shockley-Read-Hall                                     |

| SOS                | Silicon-on-sapphire                                    |

| SPT                | Spacer pattern technique                               |

| SEU                | Single event upset                                     |

| SIMOX              | Separation by implanted oxygen                         |

| TFET               | Tunneling field effect transistor                      |

| UTBB               | Ultrathin body and BOX                                 |

| $Z^2$ -FET         | Zero impact ionization and zero subthreshold swing FET |

# **Table of Symbols**

| Symbol                                  | Unit              | Description                                            |

|-----------------------------------------|-------------------|--------------------------------------------------------|

| С                                       | F                 | Capacitance                                            |

| $C_{ox}$                                | F/cm <sup>2</sup> | Oxide capacitance per unit area                        |

| $C_{Si}$                                | F/cm <sup>2</sup> | Silicon capacitance per unit area                      |

| $C_{it}$                                | F/cm <sup>2</sup> | Interface trap capacitance per unit area               |

| $C_G$                                   | F                 | Total gate capacitance                                 |

| $C_{BOX}$                               | F                 | Buried oxide capacitance                               |

| $\Delta V_{FB}$                         | V                 | Shift in flat band voltage                             |

| $\Delta V_T$                            | V                 | Threshold voltage roll-off due to short channel effect |

| $E_{C}$                                 | J                 | Conduction band edge                                   |

| $E_{V}$                                 | J                 | Valance band edge                                      |

| $\mathrm{E_{f}}$                        | J                 | Fermi energy level                                     |

| $E_{\mathrm{g}}$                        | J                 | Energy gap of silicon (= 1.12 eV)                      |

| $E_{i}$                                 | J                 | Intrinsic Fermi level                                  |

| $E_{fn, fp}$                            | J                 | Fermi energy level on the n-side, p-side of a PN diode |

| $\epsilon_0$                            | F/cm              | Vacuum permittivity (= $8.854 \times 10^{-14}$ )       |

| $\epsilon_{\mathrm{Si}}$                | F/cm              | Silicon permittivity (= $1.04 \times 10^{-12}$ )       |

| $\epsilon_{ m ox}$                      | F/cm              | Oxide permittivity (= $3.45 \times 10^{-14}$ )         |

| $\phi_{ms}$                             | V                 | Work-function difference between metal and silicon     |

| $\phi_n$                                | V                 | Electron quasi-Fermi potential                         |

| $\phi_{\mathrm{p}}$                     | V                 | Hole quasi-Fermi potential                             |

| $\Psi_{	extsf{S}}$                      | V                 | Surface potential                                      |

| $\Psi_{\mathrm{B}}$                     | V                 | Bulk potential                                         |

| $\Psi_{bi}$                             | V                 | Built-in potential                                     |

| $\Psi_{	extsf{F}}$                      | V                 | Fermi potential                                        |

| $I_{D,}I_{S}$                           | A                 | Drain and source current                               |

| ${ m I}_{{ m G}\!f\!,}{ m I}_{{ m G}b}$ | A                 | Front-gate and back-gate current                       |

| $I_b$                                   | A                 | Body current                                           |

| $K_{\mathrm{B}}$                        | J/K               | Boltzmann constant (= 1.38 x 10 <sup>-23</sup> )       |

| L, W                                    | cm                | Source and drain diffusion lengths                     |

| $L_G, L_{eff}$                          | cm                | Gate length in layout, effective gate channel length   |

| $N_A, N_D$                              | cm <sup>-3</sup>  | Acceptor, donor impurity density                       |

| $n_i$                                   | cm <sup>-3</sup>  | Intrinsic carrier density                              |

| T                                       | K                 | Absolute temperature (e.g. room temperature = 300 K)   |

| $V_{D,}V_{S}$                           | V                 | Drain and source voltage                               |

| $V_{Gf}$ , $V_{Gb}$                     | V                 | Front-gate and back-gate voltage                       |

| $V_b$                                   | V                 | Body voltage (at body contact terminal)                |

| $V_{Tf}, V_{Tb}$                        | V                 | Front-gate and back-gate threshold voltage             |

| $W_{d,}W_{dmax}$                        | cm                | Depletion-layer width, maximum depletion-layer width   |

| $X_{j}$                                 | cm                | Junction depth                                         |

# **Table of Contents**

| Chapter 1:Introduction                                                   | ····1 |

|--------------------------------------------------------------------------|-------|

| 1.1 General Introduction                                                 | 3     |

| 1.2 Silicon-on-Insulator (SOI) Technology                                | 3     |

| 1.2.1 Scaling Limit of Bulk Silicon MOSFETs                              |       |

| 1.2.2 State-of-the-art of SOI Technology                                 |       |

| 1.2.3 SOI Wafer Fabrication: Smart-Cut <sup>TM</sup> Process······       |       |

| 1.2.4 Summary ·····                                                      | ···10 |

| 1.3 Ultimate Scalability and Flexibility of SOI Devices                  |       |

| 1.3.1 Planar Partially Depleted and Fully-Depleted SOI Devices           |       |

| 1.3.2 Multi-Gate FDSOI Devices                                           |       |

| 1.3.3 Ultrathin Body and BOX (UTBB) MOSFETs                              | …16   |

| 1.3.3.1 Inter-Gate Coupling Effect: Typical Coupling Mechanism·········· |       |

| 1.3.3.2 Super-Coupling Effect·····                                       | ···18 |

| 1.3.3.3 Short Channel Effects in FDSOI                                   | 23    |

| 1.3.4 Compound Semiconductor on Insulator Devices·····                   | 25    |

| 1.4 Conclusion                                                           | ···26 |

| 1.5 References·····                                                      | ···27 |

| Chapter 2: Floating Body Effects in Ultrathin FDSOI MOSFETs              |       |

| 2.1 Introduction                                                         | 33    |

| 2.2 Kink Effect in Ultrathin Fully-Depleted SOI MOSFETs                  |       |

| 2.2.1 Experimental Details·····                                          |       |

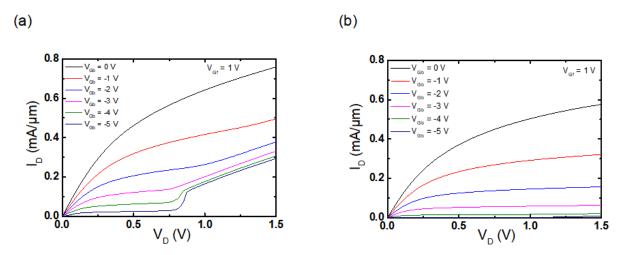

| 2.2.2 DC Measurement·····                                                |       |

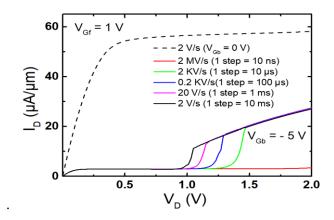

| 2.2.3 Pulsed-Mode Measurement                                            |       |

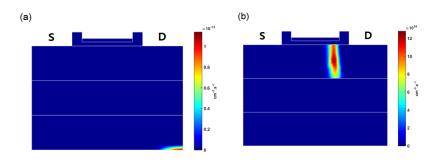

| 2.2.4 TCAD Device Simulation                                             | ···46 |

| 2.2.5 Summary                                                            | 50    |

| 2.3   | Gate-Induced FBE (GIFBE) in Ultrathin MOSFETs                       | ·····51   |

|-------|---------------------------------------------------------------------|-----------|

|       | 2.3.1 Experimental Details·····                                     | 51        |

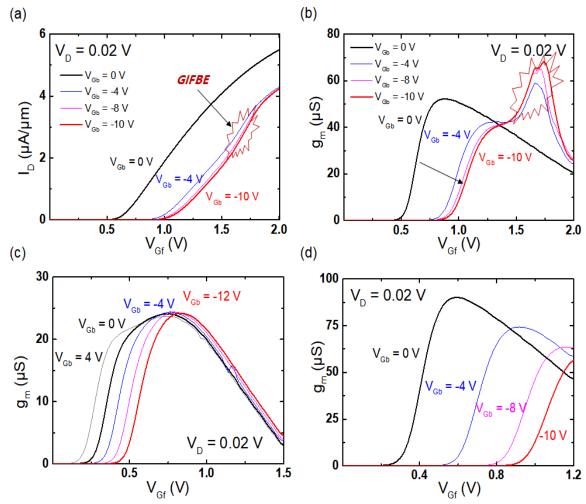

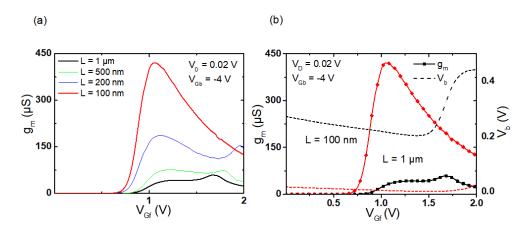

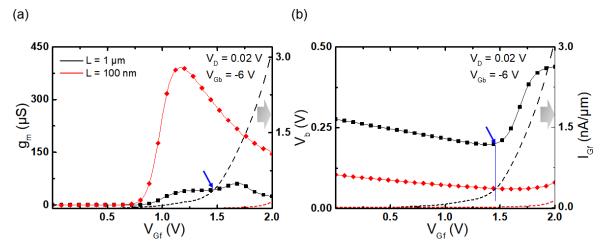

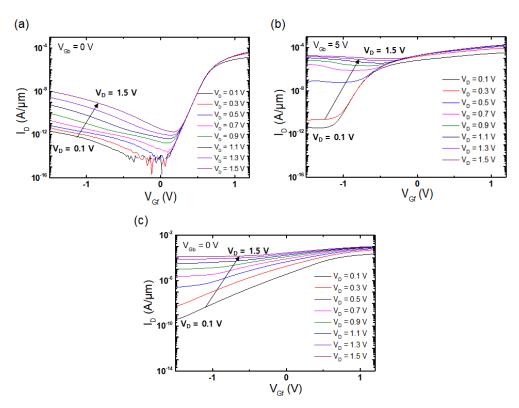

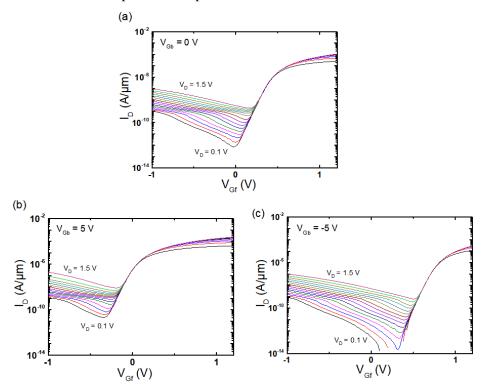

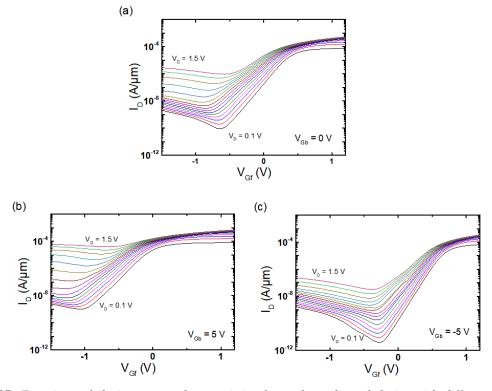

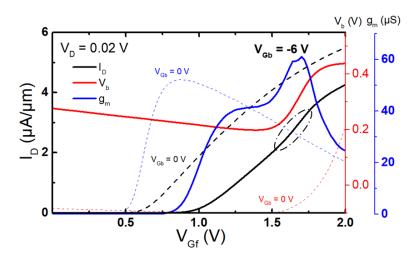

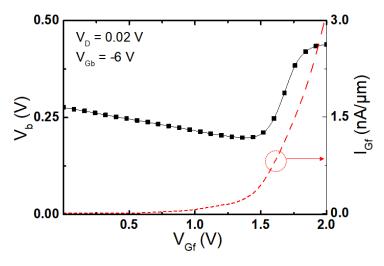

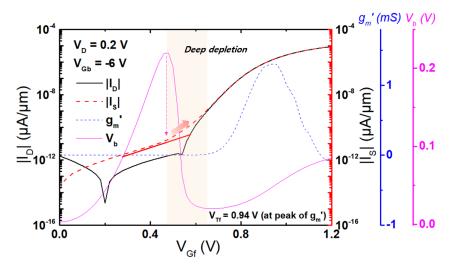

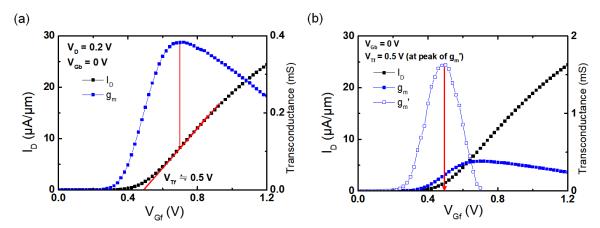

|       | 2.3.2 Current and Transconductance Characteristics                  | 52        |

|       | 2.3.3 Summary                                                       | 58        |

| 2.4 P | Parasitic Bipolar Transistor (PBT) Effect                           | 58        |

|       | 2.4.1 Experimental Details                                          |           |

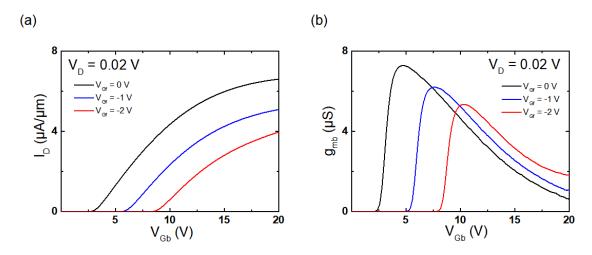

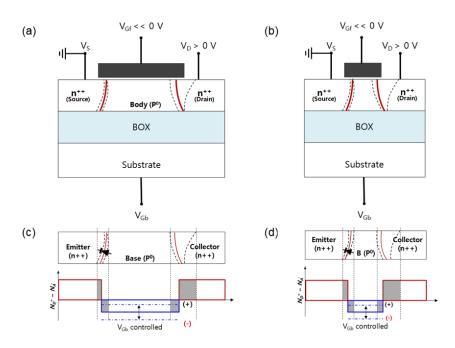

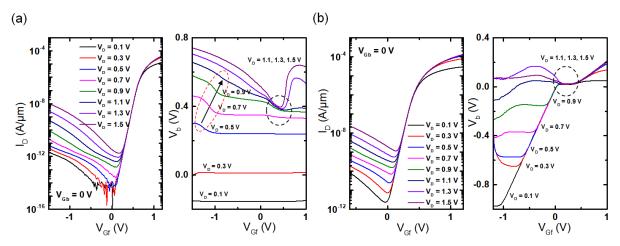

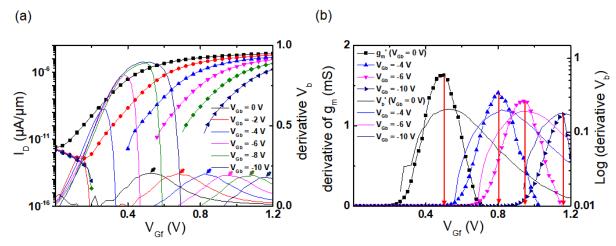

|       | 2.4.2 Transfer Characteristics                                      |           |

|       | 2.4.3 Summary                                                       | 63        |

| 2.5 S | Sharp-Switching and Hysteresis Characteristics                      | 63        |

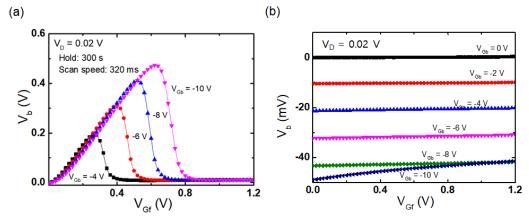

|       | 2.5.1 Steady-State Characteristics·····                             | 65        |

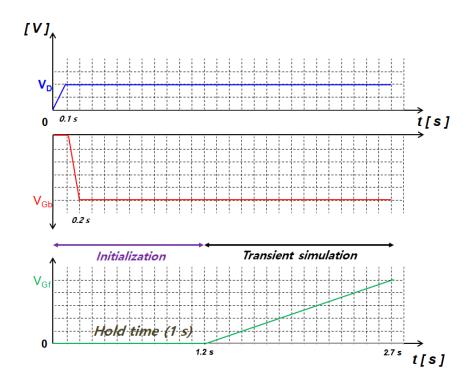

| 2.6 T | Transient and History Effect: Meta-Stable-Dip (MSD) Effect          | 66        |

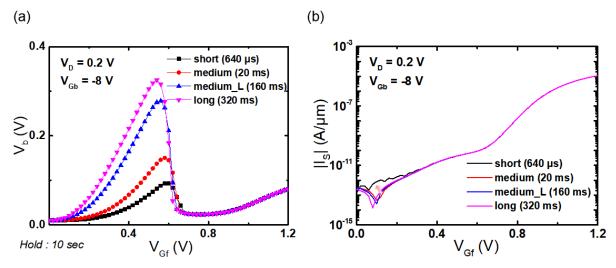

|       | 2.6.1 Generic MSD Feature and New Memory Effect·····                |           |

|       | 2.6.2 Transient Current Evaluation                                  | 68        |

|       | apter 3: Dynamic Body Potential Variation in Ultrathin I            |           |

| 3.1   | Introduction                                                        | 77        |

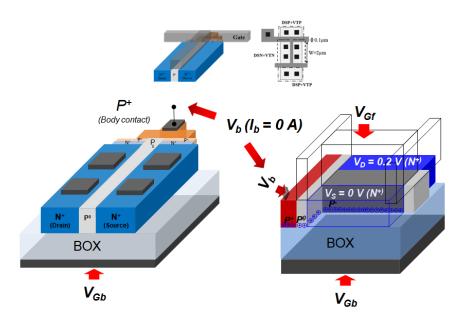

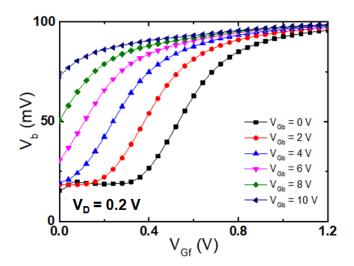

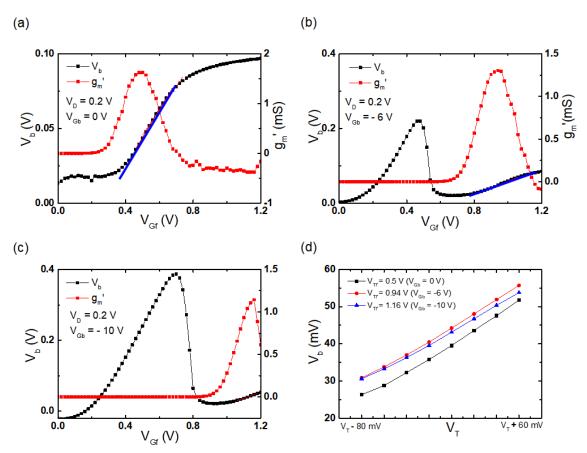

| 3.2   | Body Potential Measurement in Non-Equilibrium                       | 78        |

|       | 3.2.1 Experimental Details                                          |           |

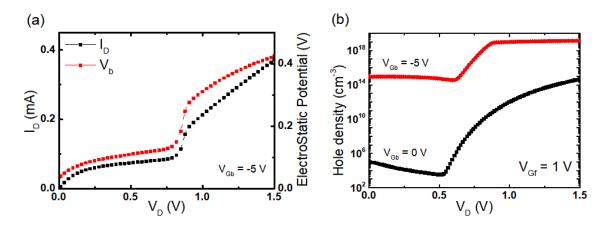

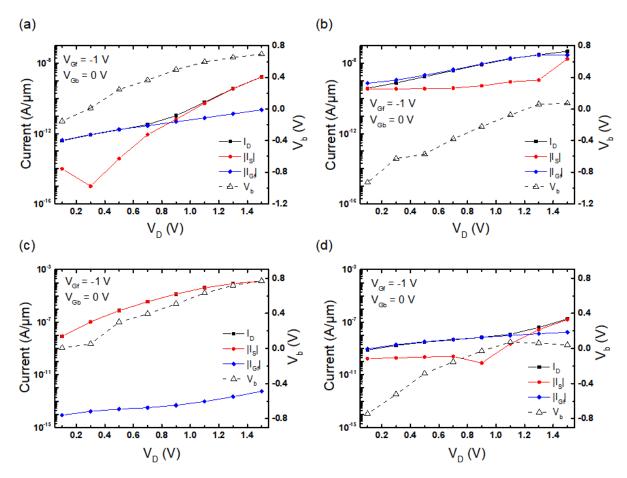

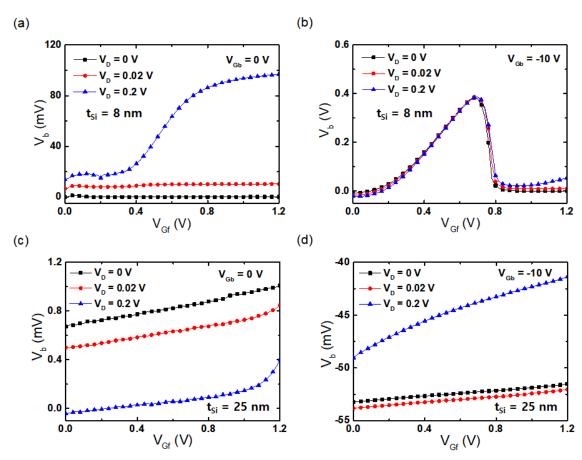

|       | 3.2.2 DC Characteristics of Body Contacted n-MOSFET                 | 80        |

|       | 3.2.3 Correlation with FBEs·····                                    |           |

| 3.3 ( | Gate Coupling Characterization in Ultra-thin Film Revisited by Body | Potential |

| Mea   | surements·····                                                      |           |

|       | 3.3.1 Introduction·····                                             |           |

|       | 3.3.2 Measurement Setup·····                                        | 89        |

|       | 3.3.3 Experiments·····                                              |           |

|       |                                                                     | 89        |

|       | 3.3.4 TCAD Device Simulation                                        |           |

| Chapter 4: Investigation of Advanced SOI                                           | applications109          |

|------------------------------------------------------------------------------------|--------------------------|

| 4.1 Introduction                                                                   | 111                      |

| 4.2 Back-Gated InGaAs-on-Insulator Lateral N <sup>+</sup> NN<br>4.2.1 Introduction | T <sup>+</sup> MOSFET111 |

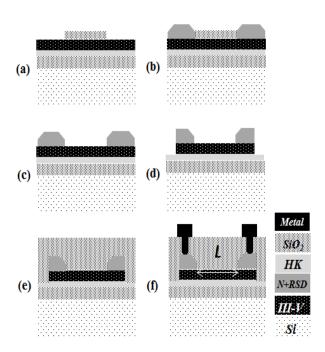

| 4.2.2 Device Fabrication                                                           | 112                      |

| 4.2.3 Measurement Setup: Pseudo Ψ-MOSFET                                           | ······114                |

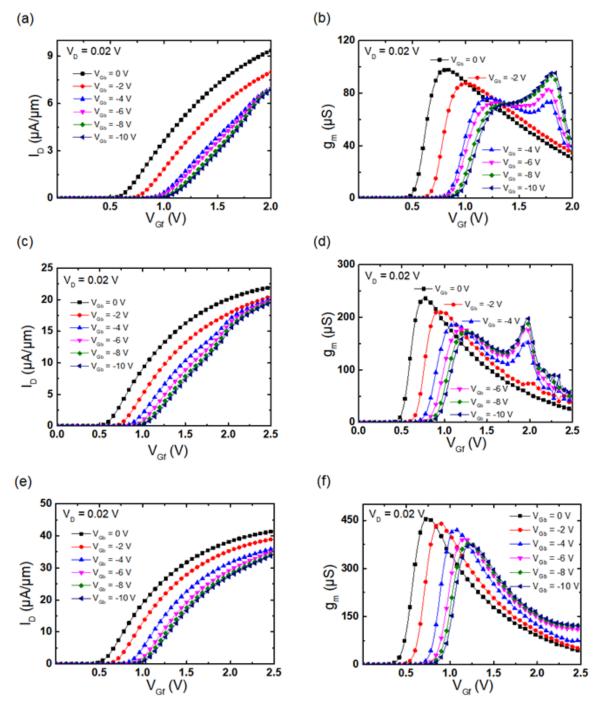

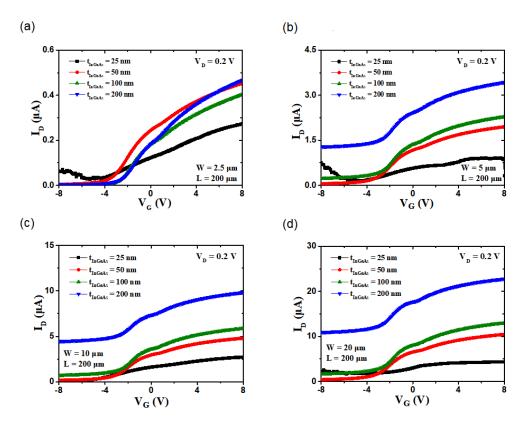

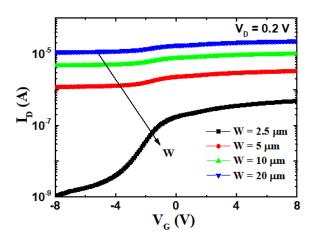

| 4.2.4 Current and Transconductance Characteris                                     | stics115                 |

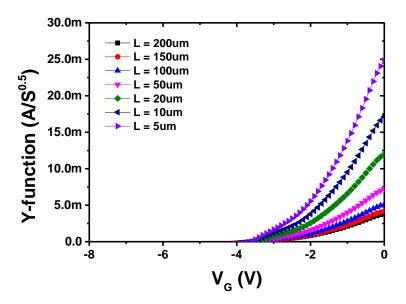

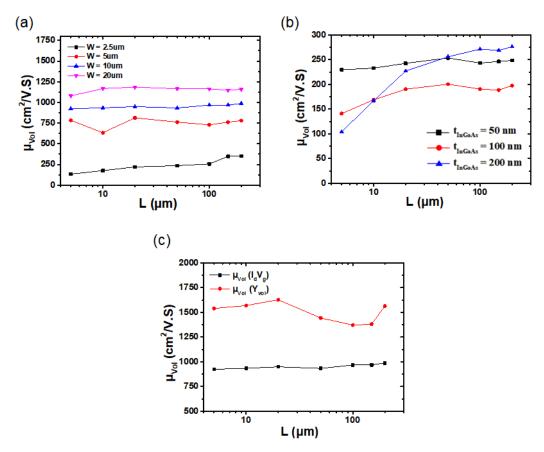

| 4.2.5 Mobility Evaluation                                                          |                          |

| 4.2.6 Summary·····                                                                 | 126                      |

| 4.3 Transducers using Z <sup>2</sup> -FET                                          |                          |

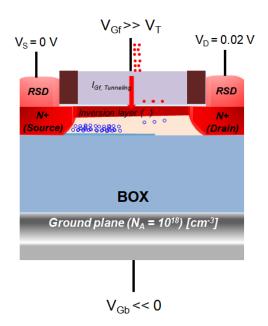

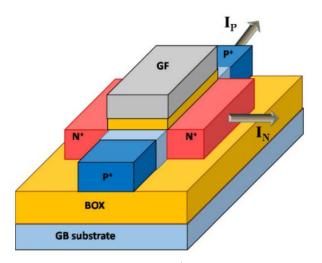

| 4.3.2 Z <sup>2</sup> -FET Device Operation                                         | 127                      |

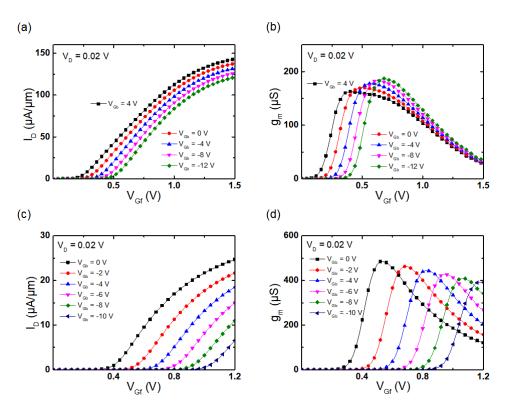

| 4.3.3 Magnetic Sensor                                                              | 130                      |

| 4.3.3.1 Measurement Setup·····                                                     | 132                      |

| 4.3.3.2 DC Characteristic under Magne                                              | etic Field·····133       |

| 4.3.3.3 Summary                                                                    | 133                      |

| 4.3.4 Optical Sensor·····                                                          | 134                      |

| 4.3.4.1 Measurement Setup                                                          | 134                      |

| 4.3.4.2 DC Characteristic                                                          | 135                      |

| 4.4 Conclusion                                                                     | 137                      |

| 4.5 References·····                                                                | 138                      |

|                                                                                    |                          |

| 5. General Conclusion                                                              | 143                      |

| 6 Contributions and Dublications                                                   | 145                      |

| 6. Contributions and Publications                                                  |                          |

| 7. Résumé de la Thèse·······                                                       | 147                      |

# **Chapter 1**

Introduction

# **Contents of Chapter 1**

| Chapter 1:Introduction                                                                 |    |  |

|----------------------------------------------------------------------------------------|----|--|

| 1.1 General Introduction                                                               | 3  |  |

| 1.2 Silicon-on-Insulator (SOI) Technology  1.2.1 Scaling Limit of Bulk Silicon MOSFETs | 3  |  |

| 1.2.2 State-of-the-art of SOI Technology                                               |    |  |

| 1.2.3 SOI Wafer Fabrication: Smart-Cut <sup>TM</sup> Process······                     |    |  |

| 1.2.4 Summary ·····                                                                    | 10 |  |

| 1.3 Ultimate Scalability and Flexibility of SOI Devices                                | 10 |  |

| 1.3.1 Planar Partially Depleted and Fully-Depleted SOI Devices                         | 12 |  |

| 1.3.2 Multi-Gate FDSOI Devices·····                                                    | 14 |  |

| 1.3.3 Ultrathin Body and BOX (UTBB) MOSFETs·····                                       | 16 |  |

| 1.3.3.1 Inter-Gate Coupling Effect: Typical Coupling Mechanism······                   | 16 |  |

| 1.3.3.2 Super-Coupling Effect·····                                                     | 18 |  |

| 1.3.3.3 Short Channel Effects in FDSOI                                                 | 23 |  |

| 1.3.4 Compound Semiconductor on Insulator Devices·····                                 | 25 |  |

| 1.4 Conclusion                                                                         | 26 |  |

| 1.5 References                                                                         | 27 |  |

## 1.1 General Introduction

This first chapter represents a general introduction of silicon-on-insulator (*SOI*) technology. We briefly touch upon scaling limit issues which are well documented in the complementary metal–oxide–semiconductor (*CMOS*) industry. Recently, the scaling trend has begun to saturate and short-channel effects have forced semiconductor manufacturer to abandon the traditional planar bulk MOSFET for novel types of devices such as the Fin-FET or fully depleted SOI devices. In the following section, the state-of-the-art SOI technology is introduced as a realistic option in terms of overcoming the fabrication complexity for the CMOS industry and expanding the scaling limits. In particular, the innovative wafer fabrication process called Smart-Cut<sup>TM</sup> has been invented and commercialized for high-end and reliable CMOS products. This technology leads to a new business model for those who want to make creative and high performance products. The fundamental features of SOI devices are presented in the following section as well.

# 1.2 Silicon-On-Insulator (SOI) Technology

SOI technology has emerged about 40 years ago for eliminating the parasitic elements in the bulk CMOS technology. One of the motivations was to decrease the parasitic capacitance of source and drain due to the presence of a buried oxide (*BOX*) underneath the devices [1], [2]. Another motivation for developing SOI technology was the anticipated better robustness of SOI transistors to ionizing radiations, making it attractive for military and aerospace applications [3]–[5]. SOI technology, due to the presence of a BOX layer between the device and the substrate, enables one to achieve a smart solution against the previously issued problems and to enhance device performance. The BOX can prevent the interference for a device active layer from electron-hole pairs generated by a radiation event. Lastly and most importantly, the SOI technology would definitely be a promising alternative to bulk silicon MOSFETs in nanoscale device technology. Since the beginning of the 21<sup>st</sup> century, SOI technology has steadily increased its market share for specific applications such as a radio frequency (RF) device, advanced satellite components, photonics based on SOI, and solar-cell application. The high manufacturing cost of SOI wafers, however, is an obstacle to its adoption for mainstream CMOS products. Today's CMOS devices have reached the 10 nm node, and bulk MOSFET technology has run out of steam because of insurmountable short-channel effects. In this

respect, the advanced SOI technology enables one to surmount almost all of the technical issues experienced in the bulk CMOS process.

Some of the remarkable features of advanced SOI technology are:

- (i) The use of an SOI substrate can inherently eliminate the detrimental parasitic effects such as the source/drain junction capacitance, latch-up, single event upset (*SEU*), and reduce body effect.

- (ii) Shallow junctions are easily formed to diminish the SCE by adjusting the thickness of the top silicon.

- (iii) Back-channel contribution can be controllable via the competition between the two gates (inter-gate coupling or double gate action).

Furthermore, using the back-gate action, the threshold voltage can be tune, even dynamically, in FDSOI MOSFETs [6].

# 1.2.1 Scaling Limit of Bulk Silicon MOSFETs

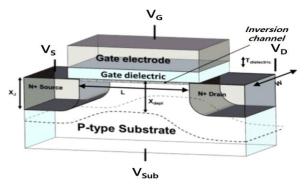

The miniaturization of MOSFETs has been driven by reducing the geometrical parameters of transistor as illustrated to Figure 1.1. It has been enabled the increase of the density of transistors and enhanced the performances of integrated circuits. Hence, semiconductor manufacturers could gain high revenue and got low-cost competitiveness thanks to device scaling.

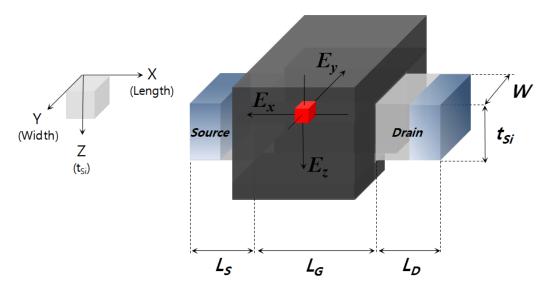

Figure 1.1: A simple schematic view of the bulk MOSFET [7].

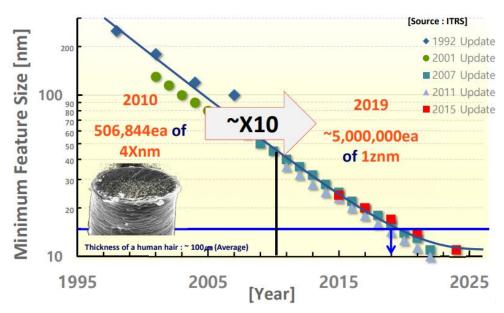

However, classical scaling has now reached some fundamental limits and device shrinking is near saturation. For conventional DRAMs, for example, the scaling trend has been tracked well on the market prediction until approximately 29 nm technology node in 2013. In the same generation, by the way, two more nodes (*i.e.* around 25 and 21 nm) were added in order to overcome the patterning complexity and extend the life span of the lithography technique. Since then, the prediction trend of

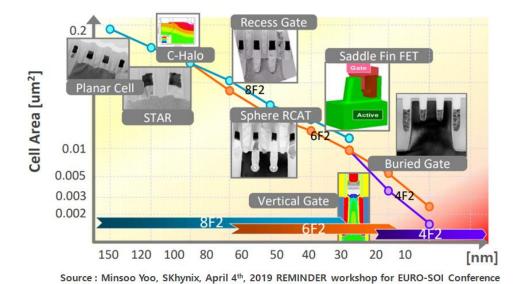

ITRS began slowing down and even lagging behind the market requirements. The scaling trend was updated in the ITRS 2015, showing three or more than three nodes (i.e. 2x, 2y, 2z and 1x, 1y, 1z, 1a) in the same generation (Fig. 1.2). Major DRAM companies constantly search a breakthrough to meet the market requirements such as lowering operating voltage, reducing power consumption, and increasing high density or bandwidth. Figure 1.3 shows the revolutionary history of scaling the DRAM cell transistor for 25 years. Nowadays, all chip makers have been developing for DRAM products based on a 6F2 layout and a Fin-FET with buried word-line scheme. Furthermore, the development period near the 10 nm technology node becomes almost 2 years long whereas 20 nm nodes had been developed for more or less 1.5 years each.

Figure 1.2: Evolution of the DRAM scaling trend with minimum feature size.

Figure 1.3: History of evolution for DRAM cell transistor and scaling roadmap.

The semiconductor industry is trying its hardest to push scaling to the limits. This requires investments in new equipments, such as extreme-ultraviolet (*EUV*) photolithography. Changing a device structure or material is the other way for pushing scaling to the limit. Among the two transistor architectures adopted by industry, namely the Fin-FET and the FDSOI transistor, we have chosen to study the latter. The family of Silicon-on-Insulator MOSFETs brings versatile benefits in terms of structural point of views such as reduction of junction capacitance, thin silicon body for shallow source/drain junctions, device isolation by buried oxide (*BOX*), and back-gate biasing for threshold voltage tunability.

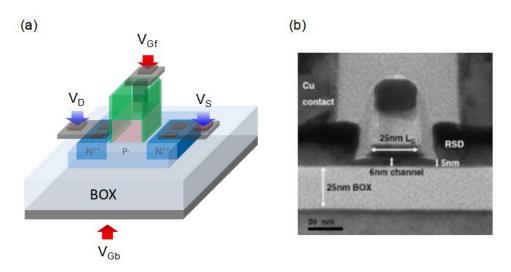

Figure 1.4: (a) 3D-view of a classical Silicon-on-Insulator (SOI) n-MOSFET, (b) a cross-section TEM view of SOI MOSFET fabricated by STMicroelectronics [8].

# 1.2.2 State-of-the-art of SOI Technology

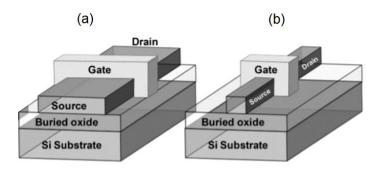

The SOI technology has unique fundamentals which enhance CMOS device characteristics. It has the following inherent basic features: (i) Dielectric isolation (BOX), (ii) Shallow junction via a thin body (or ultrathin body; UTB), (iii) use of high-quality, ultrathin advanced Smart-Cut<sup>TM</sup> material. A classical planar fully-depleted (FD) SOI MOSFET can be integrated with a second gate underneath the BOX (back gate) which can be used to modulate the threshold voltage (Fig. 1.4). Double-gate or triple-gate devices, using a multi-gate architecture, care expected to replace single-gate devices at some point in the future. (Fig. 1.5a, b) [7], [9]. Better short channel effect (*SCE*) reduction is the reason why the multi-gate architecture is attractive for making very short transistors. The SCE in the bulk silicon device is inevitably uncontrolled when the gate channel length becomes shorter than about 15 -20 nm. In sub-section 1.2.2, we introduce the multi-gate FDSOI MOSFETs and the way to mitigate the SCE due to improvements in electrostatic control of the channel by the gate.

Figure 1.5: (a) Single-gate SOI MOSFET, (b) Double-gate (or trigate) SOI MOSFET [2].

The BOX layer in SOI MOSFETs can basically eliminate the parasitic elements which were experienced in the bulk-silicon MOSFETs. For example, in a bulk CMOS design aiming at low power consumption, the leakage current and S/D capacitance elements can degrade the device performance. But, in SOI technology, the active layer is naturally separated from the bulk substrate by the BOX. Consequently, the junction leakage and capacitance are minimized thanks to the basic SOI structure.

A shallow junction is naturally obtained in the SOI structure by adjusting the thickness of the top silicon film. This is also helpful in reducing SCEs. The absence of vertical S/D junctions yields a substantial reduction of the parasitic elements between the substrate and the source and drain. This can lower RC-delay time and power consumption. Thus, these fundamental benefits can contribute that SOI devices operate much faster and with lower leakage current than bulk CMOS devices.

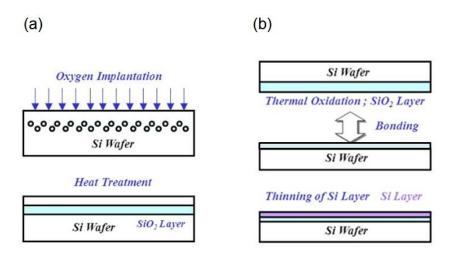

In the past, several methods for manufacturing SOI wafers were investigated, such as epitaxial lateral overgrowth [10]–[12], zone-melting recrystallization [13]–[15], ion implantation [16]–[18], and wafer bonding [19]–[21]. Among those, we will only mention two types of SOI structure fabrication: Separation by Implanted Oxygen (*SIMOX*) [16], [22]–[25], and the wafer bonding technique [26], [27].

Figure 1.6: Two different techniques to produce SOI wafer: (a) separation by ion implantation of oxygen (SIMOX), (b) direct wafer bonding and etch-back technique.

The essential principle of SIMOX is to use ion implantation technique in order to create a buried  $SiO_2$  layer in the silicon wafer (Figure 1.6a). The deeply implanted oxygen atoms in the silicon wafer oxidize and form the BOX during high temperature annealing process. The wafer bonding and etch-back technique is simpler than other SOI fabrication methods. Two oxidized wafers are naturally bonded, then etched (or polished) down to a target thickness for SOI application. The bonding mechanism is related to hydrophilic surfaces of two oxidized wafers even in room temperature. Since the wafers are bonded at room temperature, thermal annealing is followed in order to strengthen the bonding energy in between the wafers. In the following section, another technique for SOI wafer fabrication method is introduced. This technique turns out to be the most successful at the present time.

# **1.2.3 SOI Wafer Fabrication: Smart-Cut**<sup>TM</sup> **Process**

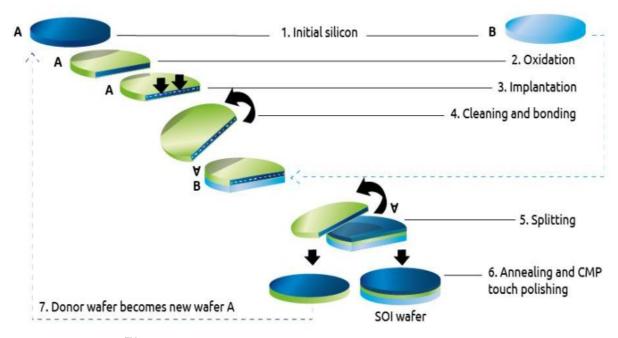

UNIBOND SOI wafers are produced using the Smart-Cut<sup>TM</sup> process [28]. The key to this process is the combination of ion implantation process and wafer bonding techniques in order to transfer a thin sheet of the semiconductor material onto a dielectric, which becomes the BOX layer. This widely-used technology was invented at the *CEA-LETI* and is now used to produce SOI wafers at the industrial scale. The Smart-Cut<sup>TM</sup> process has been gradually expanded gradually and is used to produce various types of SOI wafers. The process has been transferred to *SOITEC*, the market leader for SOI wafers.

Figure 1.7: Smart-Cut<sup>TM</sup>, an advanced SOI wafer fabrication technique by SOITEC Inc.

The Smart-Cut<sup>TM</sup> process is illustrated in Figure 1.7 and can be explained as follows:

- (i) Two wafers are needed for the Smart-Cut. One wafer 'A' (in Figure 1.6), 'donor' wafer, has been oxidized prior to the hydrogen implantation process. This oxide layer at the top surface will become the BOX. Hydrogen atoms are implanted into the donor wafer at a specific depth for splitting the two wafers later.

- (ii) Wafer 'B', called 'handling' wafer, can be either in bare condition or oxidized. The handle wafer plays the important role as a mechanical support for the SOI structure.

- (iii) The wafer 'A' is placed onto wafer 'B' in a face-down direction for direct wafer bonding. Two-phase heat treatment is performed. During the first phase, at a temperature of about 500 °C, the donor wafer 'A' splits along a plane defined by the hydrogen implantation range, and the thickest part of wafer 'A' is separated from the bonded wafer structure. As a result, there are two parts left behind this process: a thin layer of mono-crystalline silicon on oxide on top of the handle wafer 'B' and a remainder of the donor wafer 'A' which can be recycled and be used again as a donor wafer. The second phase of the heat treatment is conducted at a higher temperature for strengthening the bond between the Si/BOX layers and the handling wafer 'B'.

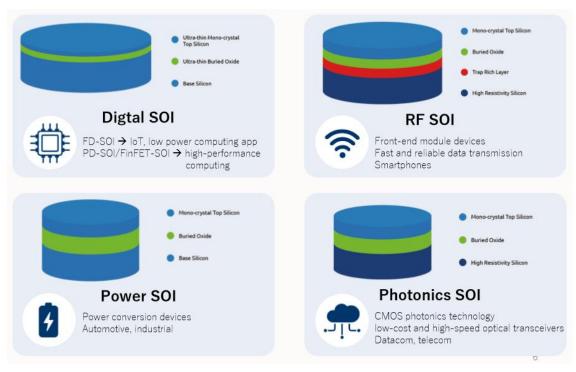

- (iv) Finally, a touch-CMP process is carried out to achieve good uniformity of the silicon films. The process can be engineered differently to yield SOI wafers required for specific applications such as RF switches or photonics (Fig. 1.8).

Figure 1.8: Different types of engineered SOI wafer for specified commercialized products: generic CMOS devices, RF circuit and components, power chips, and photonics applications.

# **1.2.4 Summary**

The SOI technology shows substantial potential to overcome the CMOS scaling limit via its unique features. In particular, parasitic elements can be minimized or eliminated. Many parasitic effects found in the bulk silicon devices originate from the interaction between the device and the substrate. In this respect, it is easy to understand that SOI devices are free from the interactions with the supporting substrate thanks to the BOX layer. The SOI substrate allows being robust against the latch-up phenomenon, which is caused in bulk devices by the feedback of the two inherent bipolar transistors.

The *Smart-Cut*<sup>TM</sup> technique has been established as the mainstream procedure to produce standard and creative SOI wafers. This technology expands progressively into the CMOS industry. It enables to design and fabricate novel multi-gate architectures in order to improve device performance and electrical properties.

# 1.3 Ultimate Scalability and Flexibility of SOI Devices

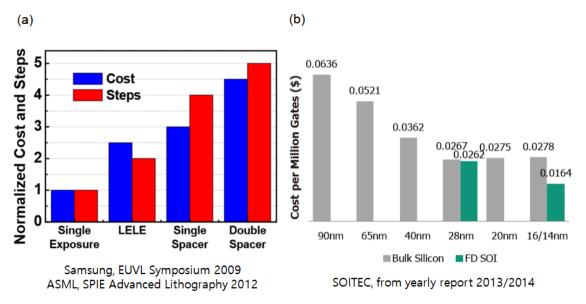

Regarding the limitation of photolithography technology, a common issue in the CMOS industry was to obtain a fine pattern from a single exposure step. However, the single exposure was faced the critical problem to shrink device dimension under the 20 nm generation node because of a lack of photolithography process margin: pattern collapse and distortion. In order to solve this issue, multiple-patterning techniques have been proposed and set up. These spacer pattern technique (SPT) or double spacer pattern technique (DSPT or DPT) make the production cost and process complexities inevitably rise (in Fig. 1.9a), albeit IC chip makers can extend their technology road-map. That rising cost is a tremendous obstacle for the growth rates of IC industries. Meanwhile, the cost competitiveness of a FDSOI technology is expected be lower than the bulk silicon process as we approach the 10 nm generations (Fig. 1.9b). Despite the higher cost of SOI wafers, the FDSOI CMOS technology already begins to compete with the bulk silicon and FinFETs in the total fabrication cost.

Figure 1.9: (a) Comparison of production cost, depending on different lithography methods. (b) Possible competitiveness of production cost optimization using FDSOI technology.

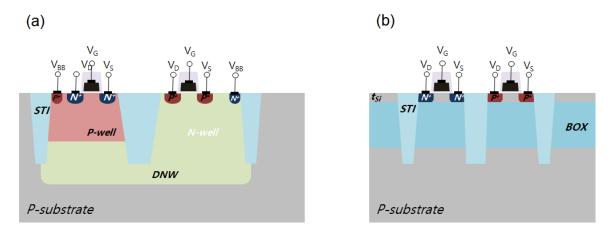

One should note here that the process flow in FDSOI is much simpler than the bulk silicon process. For designing a simple inverter using the bulk silicon process, twin-well must be defined and kept within the minimum design rules between each well, i.e. N-well and P-well (Fig.1.10a). In contrast, for the FDSOI CMOS inverter, there is no need to form the well to place each type of transistors (Fig. 1.10b).

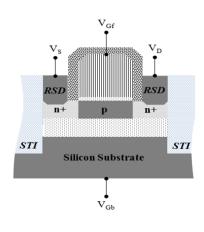

Figure 1.10: Cross-section views of CMOS inverter (a) in the bulk process, and (b) in the FDSOI technology.

In FDSOI devices, the ultrathin active layer for transistors is explicitly determined by oxidation and etching. The source and drain terminals can be made thicker using the selective epitaxial growth, i.e. raised source-drain (*RSD*) technique. To put it differently, SOI devices density is increased over bulk because there are no restricting design rules associated with well formation.. The absence of wells offers area flexibility. This means that FDSOI devices are more efficient than bulk silicon

transistors in terms of integration density.

In the following sub-sections, we describe two different types of SOI devices: the typical planar PD or FDSOI MOSFET with one gate and advanced FDSOI with multi-gate shapes. Afterward, the electrical mechanisms in ultrathin SOI MOSFETs will be discussed: inter-gate coupling, supercoupling effect, and short channel effects.

# 1.3.1 Planar Partially-Depleted and Fully-Depleted SOI Devices

Thus far, CMOS devices have been designed and fabricated by the bulk silicon technology. The devices are just placed at the top surface of the wafer, reaching a depth of less than approximately 200 nm (0.01% of the wafer thickness). This means that almost all (99.99%) of the remainder silicon serves as a mechanical support and can cause parasitic effects to occur.

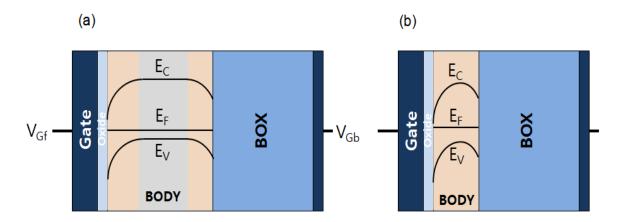

In contrast, SOI technology can precisely adjust the necessary thickness of the active areas by Smart-Cut<sup>TM</sup> process. Basically, the SOI devices can be categorized by the top thickness ( $t_{Si}$ ) of the silicon film: partially depleted (PD) SOI and fully depleted (FD) SOI. The difference is that whether or not the space-charge region (or depletion-region) induced by the gate covers the whole silicon body. The formation of the depletion region and its depth are crucial factors to eliminate the floating body effects (FBEs) and improve the electrical properties in SOI MOSFETs. For simplicity, there are two types of SOI devices described by the energy band diagram shown in Figure 1.11.

Figure 1.11: Energy band diagrams for (a) partially- (b) fully-depleted n-MOSFET devices, operated in strong inversion condition beyond the threshold voltage. The highlighted regions in the body show the depleted regions induced by the front- and back-gate biases, which inhibit the presence of majority carriers. In this diagram, the back interfaces is about to reach the condition of weak inversion.

The band bending commands the majority carrier (holes) to stay away from the interface between the silicon film and the gate oxide or BOX. The depletion region is proportional to the positive gate bias, thereby reflecting the surface potential ( $\varphi_s$ ) variation. The depth of the depletion region is given by a simple formula derived from the Poisson's equation:

$$W_{depletion} = \sqrt{\frac{2\varepsilon_{Si}\varphi_{S}}{qN_{A,D}}}$$

(1.1)

where  $\varphi_s$  indicates the surface potential at the front interface and the doping levels for n- or p-MOSFET is  $N_A$  or  $N_D$ , respectively. The maximum depletion width,  $W_{d max}$ , is reached at threshold voltage; where  $\varphi_{S} = 2 \varphi_{F}$ :

$$W_{d max} = \sqrt{\frac{4\varepsilon_{Si}\varphi_F}{qN_{A, D}}}$$

(1.2)

where the bulk Fermi potential is  $\varphi_F = \frac{kT}{q} ln \left( \frac{N_{A,D}}{n_i} \right)$ .

If the silicon body is much thicker than the maximum depletion width ( $W_{d max}$ ), a neutral region subsists underneath the front depletion region. The name of partially depleted (PD) MOSFET is originated from this neutral region (Fig.1.10a). The neutral region can be connected to an external terminal via a  $P^+$  body contact (assuming an n-channel transistor). Through this connection, the body potential variation can be monitored and correlated with the onset of the floating body effects. This measurement is utilized in chapter 2 and elaborated in detail in chapter 3.

For a thin-film SOI device (Fig. 1.10b), however, the silicon film is thinner than the maximum depletion width ( $W_{d max}$ ). This means that the depletion width covers the entire volume of the silicon body, thereby expelling out all majority carrier (holes). These devices, called FDSOI MOSFETs, are considered to be free of floating body effects because there is no longer a neutral region where the holes can accumulate in. In order to verify this postulate, we experimentally scrutinize the floating body effects such as kink effect, PBT, Gate-induced FBE, sharp-switching characteristics, transient effect, Meta-Stable-Dip (MSD) effect, and super-coupling effect in chapter 2 and chapter 4.

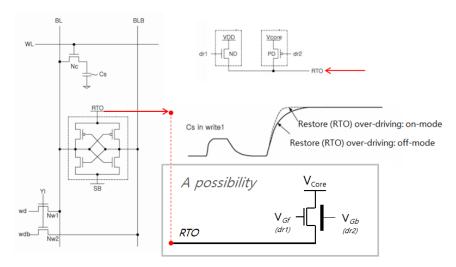

Figure 1.12: A possibility: an FDSOI over-drive for current boosting during writing mode in DRAM.

From a pragmatic point of view, the FDSOI MOSFETs with depleted back interface have attractive features such as superior short-channel behavior, boosted current characteristics, and low subthreshold slope. These unique electrical properties can be taken into account for the analog circuit design. In current over-driving mode, for example, one FDSOI driver can be used instead of two transistors as depicted in the grey box (Fig. 1.12). In this case, a RTO driver needs to boost the current gain quickly while a selected cell capacitor is written for high state '1'. Generally, a conventional DRAM consists of two pull-up drivers to control the over-driving mod. They operate one by one via synchronized signals. For the FDSOI driver, the current can be controlled by the interaction of two gates independently.

### 1.3.2 Multi Gate FDSOI Devices

Typical SOI MOSFETs consist of two gate electrodes: one is the top gate with the thin gate oxide and the other is the bottom gate underneath the BOX layer. The top gate is used to manage the current conduction and the bottom gate to control the threshold voltage. The back channel conduction is unsuitable for normal operation. It is necessary to maintain a certain condition of depletion or accumulation at the back interface in order to benefit from the coupling effect. This inter-gate coupling allows enhancing the device characteristics. The body factor 'n' is derived from the subthreshold swing as expressed below:

$$SS = n \cdot \frac{K_B \cdot T}{|q|} \ln(10) = \boldsymbol{n} \cdot 59.6 \cdot \frac{T}{300 \text{ K}} \text{ mV/dec,}$$

(1.3)

where  $K_B$  is Boltzmann's constant, T is the temperature, and q is the charge of an electron. The body factor indicates how efficiently the gate controls the channel region in terms of electrostatics and is associated with the electrostatic coupling effect between the gate and the channel. The body factor is generally  $n = 1.2 \sim 1.5$  in bulk silicon devices and  $n = 1.05 \sim 1.11$  in FDSOI devices [29]. The theoretical lowest value n=1 corresponds to ideal characteristics of devices. This low value is not always attained in FDSOI because of the capacitance mismatch between the front gate oxide and the BOX. The concept of the symmetric double-gate SOI MOSFET was proposed to solve this issue: the two gate electrodes have the same thickness of gate oxide as depicted in Figure 1.13a. The left- (or front) and right-gate (or back) are tied together physically, and therefore induce the same electric field, but in opposite directions, into the silicon body via the gate oxide. The total electric field is lower which enables higher mobility and volume inversion (or bulk inversion) effect [30].

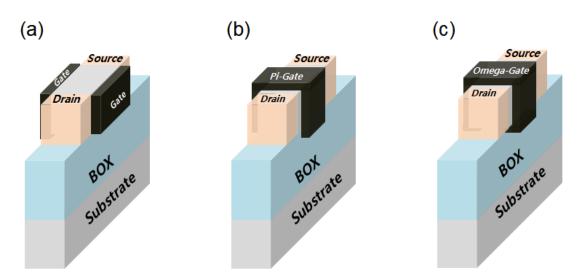

Figure 1.13: Different types of the multi-gate SOI MOSFET distinguished by the gate configuration: (a) double gate, (b)  $Pi(\Pi)$  gate (likewise the tri-gate Fin-FET), and (c)  $Omega(\Omega)$ -gate.

Among many cases, there are two best-suited multi-gate architectures: the channel region is partially covered with the gate material (Fig. 1.13b; *tri-gate or II-gate*) or almost surrounded by the gate electrode (Fig. 1.13c; Omega-gate). The capacitive coupling between the gate electrode and the channel region governs the electrostatic behavior. To put it differently, a better electrostatic controllability of the channel region can be achieved by increasing the influence from the gate. The simplest way is to enlarge the area of the gate region (wrapped sides). It can also be accomplished by reducing the cross section of the channel region, i.e. film height and width. Accordingly, an improved multi-gate SOI MOSFET would look like a nanowire device.

That is why chip makers have considered switching from the bulk silicon technology to more advanced CMOS architecture: FinFET or FDSOI. The FDSOI and the family of multi-gate MOSFETs are unavoidable for low power and RF applications in the CMOS industry.

# 1.3.3 Ultrathin Body and BOX (UTBB) MOSFETs

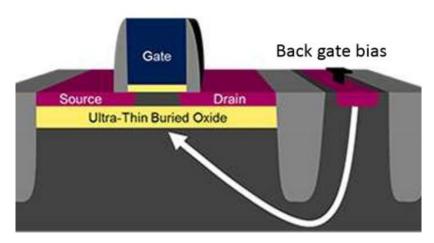

The presence of an ultrathin body and BOX (*UTBB*) is used to control the SCE more effectively in nanoscale FDSOI MOSFETs. For a thinner BOX layer formed under the silicon body, a more precise channel controllability can be achieved as illustrated in Figure 1.14. The channel control depends on the electrostatic influence from the front- and back-gate in FDSOI MOSFETs. A thinner BOX enhances the action of the back gate. The two gates compete and interfere with each other in order to govern the channel region: the inter-gate coupling effect. The fundamental inter-gate coupling effect in a floating body FDSOI MOSFET was first modeled by *Lim and Fossum* [6].

In the following sections, the typical implications of the coupling effect are summarized. In addition, the extreme case of the inter-gate coupling named super-coupling effect is explained in ultrathin FDSOI MOSFETs.

Figure 1.14: UTBB FDSOI MOSFET with back-bias applied via a P+ contact.

# 1.3.3.1 Inter-Gate Coupling Effect: Typical Coupling Mechanism

One of the innate features in SOI MOSFETs is that electrical properties of the channel region are influenced by the completion between the front gate and the back gate bias. In a relatively thick silicon body, *i.e.*, PDSOI MOSFETs, the front- and back-interface can be triggered independently and contribute simultaneously to the channel conduction. This means that each channel is mutually exclusive and does not affect the opposite channel. Conversely, for FDSOI MOSFETs, the inter-gate coupling mixes the contributions of each interface. Note that since the front interface is prevailing due to a relatively thin gate oxide, the back interface acts as a virtually linked component. This can be possibly analyzed via the body potential variation. This practical approach is dealt with in the following chapter 3. The general main consequences of the inter-gate coupling are described below:

- Tuning threshold voltage via the opposite interface contribution.

- Boosting current conduction with trimming the interaction of the two gate biases.

- Adjusting transconductance and field-effect mobility (in chapter 2).

- Designing innovative devices featuring steep switching characteristics (in chapter 4).

- Mitigating SCE in UTBB MOSFETs.

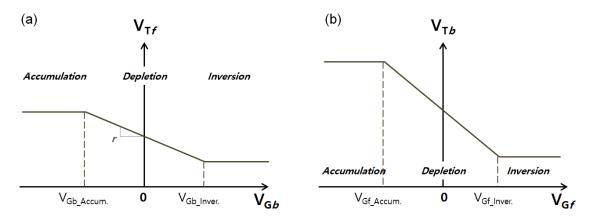

To begin with, we remind how one interface can change the threshold voltage of the other side base on the model established by Lim and Fossum [6]. The model explains the variation of the front-channel threshold voltage versus back-gate bias, represented in Figure 1.15. There are three obvious domains. For depletion of the back interface, there is a linear change of the threshold voltage. This case is extremely important for the design of low-power circuits. Although this model assumes several conditions (long channel, low drain bias, constant doping profile, no quantum effect), it has been proven by exhaustive measurement to be valid and useful.

Figure 1.15: The classical inter-gate coupling model proposed by Lim and Fossum for (a) front- and (b) back-interface threshold voltage. Three distinct domains can be indicated, depending on the opposite interface conditions: accumulation, depletion, and inversion, respectively.

The standard definition of front-channel threshold voltage,  $V_{Tf}$ , implies that  $\phi_{sf} = 2 \phi_F$  (Lim and Fossum used the Fermi level as the potential reference [6], [9]). The relationship between gate voltage and surface potentials are given by Equation (1.4):

$$V_{Tf, b} = \phi_{Sf, b} + \phi_{oxf, b} + \phi_{msf, b}$$

$$\tag{1.4}$$

where  $\phi_{msf,b}$  are metal-semiconductor work functions. The front-gate voltage is given by Equation 1.5:

$$V_{Gf,b} = \phi_{FBf,b} + \phi_{Sf,b} \left(1 + \frac{C_{Si_{-}} + C_{itf,b}}{C_{oxf,b}}\right) - \phi_{Sb,f} \frac{C_{Si}}{C_{oxf,b}} - \frac{2Q_{cf,b} + Q_{Si}}{2C_{oxf,b}}.$$

(1.5)

Equation 1.5 is obtained for the front-gate voltage.

### **Case 1: Back-interface accumulated** ( $\phi_{sb} = 0$ )

Since the back surface potential is pinned to zero, i.e.  $\phi_{sb} = 0$ , the front-gate threshold voltage  $V_{Tf}$  becomes independent as depicted in Figure 1.15. The value is given by Equation 1.6.

$$V_{Tf\_acc} = \phi_{FBf} + (1 + \frac{C_{Si} + C_{it\_f}}{C_{oxf}}) \cdot 2\phi_F - \frac{Q_{Si}}{2 C_{oxf}}$$

(1.6) [31].

# Case 2: Back-interface depleted (and $0 \le \varphi_{sb} \le 2\varphi_F$ )

As soon as the back interface is depleted, the  $V_{Tf}$  begins to decrease more for positive  $V_{Gb}$  as described by Equation 1.7:

$$V_{Tf\_dep} = V_{Tf\_acc} - \frac{C_{Si} \cdot C_{BOX}}{C_{oxf} \cdot (C_{BOX} + C_{Si} + C_{it\_BOX})} (V_{Gb} - V_{Gb\_acc})$$

(1.7) [31].

$V_{Gb\_acc}$  represents the limiting voltage below which the back interface is accumulated whatever  $V_{Gf}$  values are.  $V_{Gb\_acc}$  is given by Equation 1.8:

$$V_{Gb\_acc} = \phi_{FBb} - \frac{C_{Si}}{C_{BOX}} \cdot 2\phi_F - \frac{Q_{Si}}{2 C_{BOX}}$$

(1.8) [31].

### **Case 3: Back-interface inverted** $(\phi_{sb} = 2\phi_F)$

In the end, the back interface is completely inverted and then the  $V_{Tf}$  again reach a saturation region independent on the back gate bias. The  $V_{Tf}$  is given by Equation 1.9:

$$V_{Tf_{\_inv}} = \phi_{FBf} + (1 + \frac{C_{it\_f}}{C_{oxf}}) \cdot 2\phi_F - \frac{Q_{Si}}{2C_{oxf}}$$

(1.9) [31].

### 1.3.3.2 Super-Coupling Effect

The critical case of inter-gate coupling is called "super-coupling" effect [32]. The super-

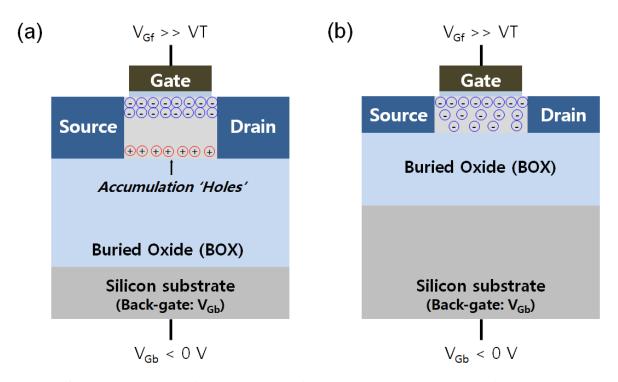

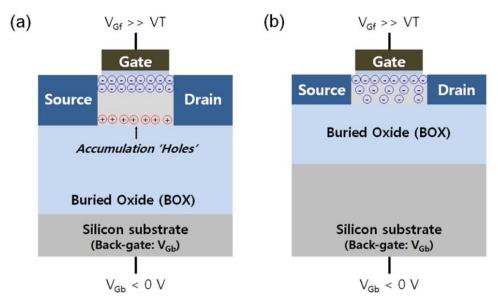

coupling effect dictates that only one type of mobile carriers can be accommodated in an ultrathin silicon body. The limit for the silicon thickness where the supercoupling is revealed or not is known as critical thickness,  $t_{Si}$ \* [6], [30], [33]. If the silicon film thickness ( $t_{Si}$ ) is thinner than the critical thickness, *i.e.*  $t_{Si}$ \*, the potential drop across the body is insufficient to sustain both carriers simultaneously. Namely, the body acts like a quasi-rigid potential well where one of the gates prevails. Figure 1.16 shows thick-body and ultrathin body SOI transistors. For the thick-body device (Fig. 1.16a), electrons and holes can co-exist in the body. However, for ultrathin device, the supercoupling inhibits the presence of both carriers.

Figure 1.16: Cross-section views showing (a) thick and (b) ultrathin FDSOI MOSFETs with negative V<sub>Gb</sub>

This implies that the dominant gate governs the whole silicon body (volume inversion as accumulation): Not only the front channel but also the back channel tend to follow the regime of operation imposed by the front gate, instead of being independent (Fig. 1.16b). The hole accumulation layer disappears in ultrathin body due to super-coupling effect.

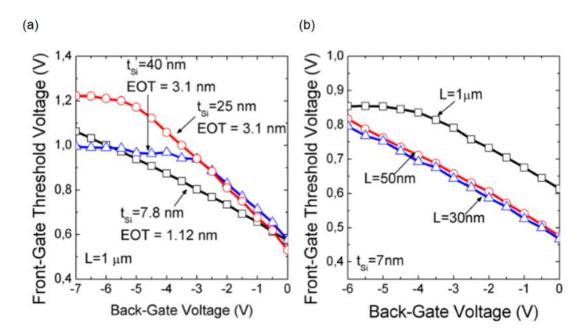

The supercoupling is an intrinsic size effect, occurring typically for body thickness in the sub-10nm range. Technology parameters (gate stack, BOX thickness) and biases can only modify the critical thickness  $t_{Si}^*$  without questioning the fundamental nature of supercoupling [33]. Figure 1.17a shows three curves, showing experimental evidence of 1D supercoupling as a function of silicon film thickness. For thicker devices ( $t_{Si} > 25$  nm), there are plateau regions where the front-gate threshold voltage is independent at the negative back-gate voltage. This saturated region can be attributed to the

holes populations at the back-channel. The accumulated holes layer screens the impact of the back-gate bias into the front-channel.

However, for the ultrathin body ( $t_{Si} = 7.8 \text{ nm}$ ), the plateau is no longer visible ( $t_{Si}^* = 9.6 \text{ nm} > t_{Si}$  at  $V_{Gb} = -7 \text{ V}$ ) [33].

Figure 1.17b presents the role of gate length. For long channel device (1  $\mu$ m), the flat region in accumulation is observed around  $V_{Gb} = -5$  V. This region disappears in shorter channels where the super-coupling effect becomes stronger and 2-dimensional. The practical consequence is that the range of  $V_{Tf}$  tuning is extended.

Figure 1.17: Experimental variation of front-gate threshold voltage versus back-gate bias, showing impact of (a) silicon thicknesses and (b) gate lengths.  $L = 1 \mu m$ ,  $t_{BOX} = 25 nm$ ,  $N_A = 10^{15} cm4 V_D = 0.02 V$  [33].

#### A. Critical Si-Film Thickness (tsi\*)

The  $t_{Si}^*$  is the minimum body thickness where both a front-inversion channel and a back-accumulation simultaneously co-exist. Eminente et al. showed the analytical 1-D expression for the critical thickness is given by Equation 1.11 [30]:

$$t_{Si}^* = \frac{k_B \cdot T \varepsilon_{Si}}{q \cdot C_{BOX} (V_{FB_{Gb}} - V_{Gb})} \ln \left[ \frac{N_A \cdot C_{OX} \cdot C_{BOX} (V_{FB_{Gb}} - V_{Gb})}{q \cdot \varepsilon_{Si} \cdot n_i^2} \right]. \tag{1.11}$$

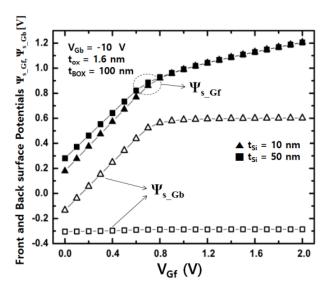

Figure 1.18: Surface potential as a function of the front-gate bias for thick- and thin-silicon body [30]. For the ultrathin device (triangle shape), the back-surface potential follows the front-surface potential because of the supercoupling effect.  $V_{Gb} = -10 \text{ V}$ ,  $t_{OX} = 1.6 \text{ nm}$ ,  $t_{BOX} = 100 \text{ nm}$ .

In FDSOI MOSFETs with sub-critical thickness, the potential variation across the silicon body is not strong enough to induce large concentrations of electrons and holes at opposite interfaces. Figure 1.18 shows surface potential variation at the front- and back-interface versus the front-gate bias. For the thick film ( $t_{Si} = 50$  nm), the front-surface potential ( $\Psi_{s\_Gf}$ ) is varied with the front-gate bias but the back-surface potential ( $\Psi_{s\_Gb}$ ) is unchanged. In contrast, for thin film ( $t_{Si} = 10$  nm), while the front-surface potential is increased, the back-surface potential follows due to the inter-gate coupling. This indicates that the back-channel is strongly associated with the front-gate bias, leading to 'volume' inversion. In this respect, we scrutinize the body potential variation in FDSOI MOSFETs. It was measured directly in quasi-steady-state condition using the P+ body contact of n-MOSFETs. The body potential variation, which is the main topic of Chapter 3, provides new experimental evidence of the super-coupling effect in ultrathin FDSOI MOSFETs.

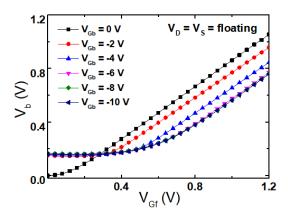

### **B.** Threshold Voltage Coupling

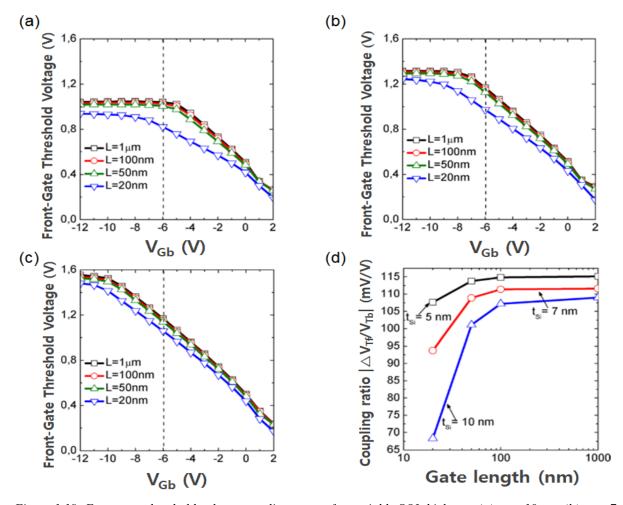

The supercoupling effect is examined by evaluation the threshold voltage variation with the back-gate bias. Figure 1.19 shows the simulated results, depending on several film thicknesses from 10 nm to 5 nm. For  $t_{Si} = 10$  nm film (Fig. 1.19a), the front threshold voltage ( $V_{Tf}$ ) varies from 2 V to -5 V and then it saturates beyond the  $V_{Gb} = -5$  V. A plateau region is observed because of the presence of an accumulation holes layer at the back-interface; i.e. inter-gate coupling stops.

Figure 1.19: Front-gate threshold voltage coupling curves for variable SOI thickness, (a)  $t_{Si} = 10$  nm, (b)  $t_{Si} = 7$  nm, and (c)  $t_{Si} = 5$  nm. (d) The coupling coefficient extracted from the maximum slope in the decreasing threshold voltage region.  $t_{OX} = 1$  nm,  $t_{BOX} = 10$  nm,  $V_D = 0.02$  V, and  $V_{Gf} = 1$  V [33].

The plateau appears for  $V_{Gb}$  more negative in thinner silicon films as demonstrated in Figure 1.19b, c. The enhancement of electrostatic control is accomplished by thinning the silicon thickness. For a short channel device ( $L_G = 20$  nm) on  $t_{Si} = 10$  nm (Fig. 1.19a), this curve deviates from the long channel coupling curves, due to the SCE. In an ultrathin body ( $t_{Si} = 5$  nm), however, the lateral encroachment from drain is well controlled. The saturation region tends to disappear, therefore reducing the SCE [7]. In a practical point of view, the back-gate control can be applicable even for voltages lower than -6 V in the ultrathin body (< 10 nm) and BOX (> 10 nm).

Figure 1.19d shows the front body factor (or front-to-back gate coupling ratio) versus the gate length. When the body thickness is much thinner than the gate length ( $L_G$ ), the gate coupling ratio is very high and shows little variation with  $L_G$ . This implies that the front-gate bias is stronger thanks to the thinner body. In thicker films, the SCEs make the coupling coefficient to decrease dramatically.

### 1.3.3.3 Short channel Effects in FDSOI

In modern electronic industries based on VLSI circuits, the device scaling is the most substantial factor to enhance device performances such as high-speed operation, low-power consumption, and increasing integration density. To achieve all of that, the critical dimensions of MOSFETs have to be shrunk physically. Reducing the channel length is a simple way to meet the requirement but the short-channel effects (*SCE*) must be considered completely. The performances of MOSFET devices are related to the electrostatic control of the channel by the gate.

In general, for the nanoscale VLSI circuit design, the effective channel length influences the device characteristics related to the SCEs such as subthreshold slope degradation and drain-induced barrier lowering (DIBL). It is obvious that the SCEs are originated by the encroachment of the electric field from the terminals, i.e. source and drain, into the effective channel region underneath the gate. This encroachment leads to competition for the control of the available depletion area underneath the gate, thereby decreasing the threshold voltage. When the drain voltage is high enough, the surface potential in the channel and inversion electrons are no longer controlled by the gate bias. The lateral depletion width ( $W_d$ ) of source and drain is given by Equation 1.12 [2] with source bias ( $V_s$ ), drain bias ( $V_D$ ), and built-in potential barrier ( $V_{bi}$ ):

$$W_{d_{S,D}} = \sqrt{\frac{2 \cdot \varepsilon_{Si} N_{D}(V_{bi} + V_{S,D})}{q \cdot N_{A}(N_{D} + N_{A})}}.$$

(1.12)

No matter what novel technologies are used for device integration, this depletion width has to be minimized. Less influence from the lateral encroachment yields good immunity against the main SCE: threshold voltage roll-off (due to shared depletion charges) and drain induced barrier lowering (*DIBL*).

In FDSOI MOSFETs, especially, the SCE is inherently mitigated by the shallow silicon thickness but it is not perfectly diminished due to the source and drain electric field, *i.e.* 2-D effects [1], [7], [30], [33]. The latter matter thus has to be considered and solved even for ultrathin FDSOI MOSFETs. Regarding the reduction of the SCE, a viable approach is used to the multi-gate architectures discussed in section 1.2.2.

Figure 1.20: (a) Pi ( $\Pi$ ) gate or (b) Omega ( $\Omega$ )-gate shape can reduce the SCEs because the surrounding gate dominates, attenuating the contribution of the electric field from the source and drain into the channel region.

In case of FDSOI MOSFETs, very thin body and BOX are helpful to attenuate the SCE by increasing the electrostatic control. In order to be immune from the SCE, the depletion width (Equation 1.12) and natural length (Equation 1.13) should be at least six-times [7] to one order [34] of magnitude smaller than the gate length. The natural length is defined by the extension of the electric field lines from the source and drain into the channel region. It is given by the general expression:

$$\lambda_{\rm n} = \sqrt{\frac{\varepsilon_{\rm Si}}{n \cdot \varepsilon_{\rm ox}} \left(1 + \frac{\varepsilon_{\rm ox}}{4\varepsilon_{\rm Si}} \frac{t_{\rm Si}}{t_{\rm ox}}\right) t_{\rm Si} \cdot t_{\rm ox}}.$$

(1.13)

The effective number of gates, denoted 'n', corresponds to 1, 2, 3, or 4 for a single- [35], double- [36], triple- [37], and quadruple-gate devices [29]. In particular, the 'n' can be extended to  $\Pi$ -gate and  $\Omega$ -gate devices albeit a non-integer value of n ranging between 3 and 4 [38], [39].

In multi-gate MOSFETs (Fig. 1.21), the silicon body is more or less surrounded by the gate material. This means that the electric field on the many-sides of the gate can control the channel conduction until forming the inversion layer, electrons in a case of n-MOSFET, at the surface.

Figure 1.21: Electric field elements depicted in rectangular coordinate system.

Within the spatial potential distribution in the channel region, the x-direction electric field  $(E_x)$  term is reduced by the other components  $(E_y, E_z)$  in Figure 1.21. The ultimate target is to eliminate the influence of the x-direction that causes short channel effects. Increasing the other components of the electric field countervails the encroachment of the drain bias, therefore enabling shorter transistors to operate correctly.

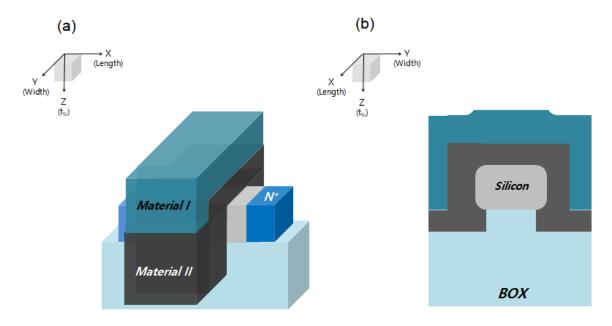

#### 1.3.4 Compound Semiconductor on Insulator Devices

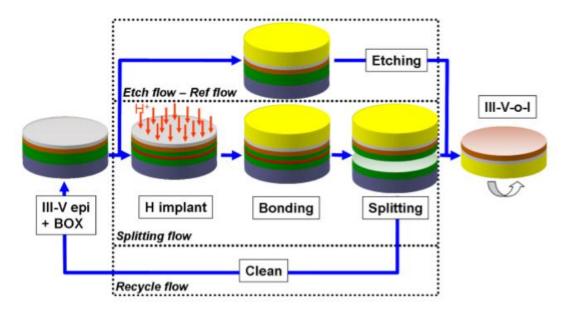

Semiconductor on Insulator (*SOI*) is a generic term describing the various CMOS applications. Among those, boosting the carrier mobility is a valuable approach to enhance device performance without side effects. This is because current density is proportional to the carrier mobility. There are many possible solutions to get high-mobility channels such as Ge, strained silicon (*SiGe*), and all III-V compounds materials for advanced high-speed devices [40], [41]. Figure 1.22 shows the process flow for III-V-on-Insulator wafers fabricated by *IBM Zurich Research Laboratory*. Direct wafer bonding (*DWB*) is used to prepare large-scale wafers before processing the ultrathin III-V-OI devices.

The III-V compound semiconductors are now taken into account for mainstream research in order to extend the CMOS technology roadmap beyond the 14 nm node. In particular, it is envisioned that  $In_{(x)}Ga_{(1-x)}As_{(x \ge 0.53)}$  n-MOSFETs will be coupled to (Si)Ge p-MOSFETs to deliver an optimum electron/hole performance while leveraging the wide industry experience with SiGe. The potential benefits of InGaAs-based nMOSFETs have already been demonstrated [42]–[45].

Figure 1.22: Process flow of III-V-on-Insulator wafer fabrication fully compatible with VLSI standards using Direct wafer bonding (DWB), hydrogen implantation, thermal splitting, selective etching, and reusing the InP donor wafer [46].

In chapter 4, InGaAs-On-Insulator MOSFETs are demonstrated in terms of device fabrication, and typical characterizations.

#### 1.3. Conclusion

Thus far, the bulk silicon technology has been flourishing by the down-sizing strategy, i.e. device scaling. However, the "happy scaling" period is now terminated because of the poor electrostatic control of the channel by the gate in ultra-short devices and complexity of the device fabrication. Device scaling becomes the most critical concern of the CMOS industry in terms of reducing production cost and achieving high device performance. With its superior short-channel effect control, the FDSOI technology stands as an attractive and realistic option instead of the silicon process for the semiconductor industry. In particular, several types of SOI wafer and SOI devices enable easily implemented commercial products: RF IoT and low-voltage devices, aerospace components, solar application. Thinning the transistor body is crucial for dealing with the short channel effects. In such ultrathin transistors, the coupling and super-coupling mechanisms are emphasized opening new sources for circuit design. Newly suggested architectures, i.e. multi-gate FDSOI devices, are also taken into account to enhance the electrostatic dominance of the gate on the

channel region.

Chapter 2 will demonstrate several floating body effects (FBEs) in FDSOI MOSFETs, showing experimental results via multi-angled approaches. The main implication is whether or not the FBEs are still alive in FDSOI MOSFETs.

Chapter 3 will investigate the dynamic body potential variation in non-equilibrium conditions. This enables to inspect the change of the body state during the onset of the FBEs. The results are useful for explaining the steady-state FBEs and for developing several applications.

Chapter 4 will show advanced SOI devices: A lateral junctionless MOSFET based on a InGaAson-Insulator structure. In addition, sensor applications are demonstrated using  $Z^2$ -FET device.

#### 1.4. Reference

- [1] S. Cristoloveanu and S. S. Li, *Electrical Characterization of Silicon-On-Insulator Materials* and Devices. 1995.

- [2] J. P. Colinge, Silicon-On-Insulator technology: Materials to VLSI. 1997.

- [3] G. C. Messenger and M. S. Ash, The Effects of Radiation on Electronics Systems. 1986.

- [4] J. R. Schwank, "Short course on Silicon-on-Insulator circuits," in *IEEE International SOI Conference*, 1996, p. 5.1.

- [5] A. M. Ionescu *et al.*, "A systematic investigation of radiation effects in MOS/SIMOX structures."

- [6] H-K Lim and J. G. Fossum, "Threshold voltage of thin-film Silicon-on-insulator (SOI) MOSFET's," *IEEE Trans. Electron Devices*, vol. 30, no. 10, pp. 1244–1251, 1983.

- [7] J. P. Colinge and J. C. Greer, *Nanowire Transistors*. 2016.

- [8] N. Planes *et al.*, "28nm FDSOI technology platform for high-speed low-voltage digital applications," in *Symposium on VLSI Technology (VLSIT)*, 2012, p. 12879783.

- [9] J. G. Fossum and V. P. Trivedi, Fundamentals of ultra-thin-body MOSFETs and FinFETs. 2013.

- [10] Y. Fujimoto and A. Ogura, "Novel technique for Si lateral epitaxial overgrowth: tunnel epitaxy," *Appl. Physics. Lett.*, vol. 55, p. 2205, 1989.

- [11] C. I. Drowley and M. Hammond, "Conditions for uniform selective epitaxial growth," Solid

- State Technol., p. 135, 1990.

- [12] G. W. Neudeck and P. J. Schubert, "Confined lateral selective epitaxial growth of silicon for device fabrication," *IEEE Electron Device Lett.*, vol. 11, p. 181, 1990.

- [13] J. A. Knapp, "Silicon-on-insulator structures formed by aline-source electron beam: experiment and theory," *J. Appl. Phys.*, vol. 58, p. 2584, 1985.

- [14] B. Y. Tsaur, "Zone-melting-recrystallization silicon-on-insulator technology," *IEEE Circuits Devices*, vol. 3, p. 13, 1987.

- [15] M. Haond, D. P. Vu, A. M. Aguirre, and S. Perret, "Electrical performances of devices made on SOI films obtained by lamp ZMR," *IEEE Circuits Devices*, vol. 3, p. 27, 1987.

- [16] M. Watanabe and A. Tooi, "Formation of SiO2 films by oxygen-ion bombardment," *Jpn. J. Appl. Physics*, vol. 5, p. 737, 1966.

- [17] K. Izumi, M. Doken, and H. Ariyoshi, "CMOS devices fabricated on buried SiO2 layers formed by oxygen implatation into silicon," *Electron. Lett.*, vol. 14, p. 593, 1978.

- [18] C. G. Tuppen, M. R. Taylor, P. L. F. Hemment, and R. P. Arrowsmith, "The effects of implantation temperature on the properties of buried oxide layers in silicon formed by oxygen ion implantation," *Thin Solid Films*, vol. 131, p. 233, 1985.

- [19] T. Abe, A. Uchiyama, K. Yoshizawa, Y. Nakazato, M. Miyawaki, and T. Ohmi, "Surface impurities encapsulated by silicon wafer bonding," *Jpn. J. Appl. Physics*, vol. 29, p. L2311, 1990.

- [20] K. Mitani and U. M. Gosele, "Wafer bonding technology for silicon-on-insulator applications: a review," *J. Electron Mater.*, vol. 21, p. 669, 1992.

- [21] P. B. Mumola, G. J. Gardopee, P. J. Clapis, C. B. Zarowin, L. D. Bollinger, and A. M. Ledger, "Plasma thinned SOI bonded wafers," in *IEEE International SOI Conference*, 1992, p. 152.

- [22] G. K. Celler, P. L. F. Hemment, K. W. West, and J. M. Gibson, "High quality Si-on-SiO2 films by large dose oxygen implantation and lamp annealing," *Appl. Physics. Lett.*, vol. 48, p. 532, 1985.

- [23] J. Stoemenos, "Microstructure of SIMOX buried oxide, mechanisms of defect formation and related reliability issues," *Microelectron. Eng.*, vol. 22, p. 307, 1993.

- [24] J. R. Davis, A. Robinson, K. Reeson, and P. L. F. Hemment, "Fully isolated SOI islands by masked oxygen implantation," in *IEEE SOS/SOI Technology Conference*, 1987, p. 71.

- [25] S. Cristoloveanu, "A review of the electrical properties of SIMOX substrate and their impact on device performance," *J. Electrochem. Soc.*, vol. 138, p. 3131, 1991.

- [26] J. B. Lasky, "Wafer bonding for silicon-on-insulator technology," *Appl. Physics. Lett.*, vol. 48, p. 78, 1986.

- [27] J. Haisma, E. M. . Alexander, T. M. Michielsen, J. A. Pals, G. A. Spierings, and J. W. A. Van der Velden, "Novel trends in SOI technology: wafer bonding and thinning," in *Euro SOI*

- Conference, 1988, p. E2.

- [28] M. Bruel, "Process for the production of thin semiconductor material films," 1991.

- [29] J. P. Colinge, "Multiple-gate SOI MOSFETs," *Solid State Electron.*, vol. 48, no. 6, pp. 897–905, 2004.

- [30] S. Eminente, S. Cristoloveanu, R. Clerc, A. Ohata, and G. Ghibaudo, "Ultra-thin fully-depleted SOI MOSFETs: Special charge properties and coupling effects," *Solid. State. Electron.*, vol. 51, no. 2, pp. 239–244, 2007.

- [31] S. Cristoloveanu and L. S.S., *Electrical Characterization of Silicon-On-Insulator Materials* and Devices. 1995.

- [32] S. Eminente, S. Cristoloveanu, R. Clerc, A. Ohata, and G. Ghibaudo, "Ultra-thin fully-depleted SOI MOSFETs: Special charge properties and coupling effects," *Solid. State. Electron.*, vol. 51, no. 2, pp. 239–244, 2007.

- [33] S. Cristoloveanu, F. Martinez, B. Sagnes, M. Bawedin, F. Andrieu, and C. Navarro, "Supercoupling effect in short-channel ultrathin fully depleted silicon-on-insulator transistors," *J. Appl. Phys.*, vol. 118, no. 18, p. 184504, 2015.

- [34] S. Veeraraghavan and J. G. Fossum, "Short-channel effects in SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 36, no. 3, pp. 522–528, 1989.

- [35] R. H. Yan, A. Ourmazd, and K. F. Lee, "Scaling the Si MOSFET: from bulk to SOI to bulk," *IEEE Trans. Electron Devices*, vol. 39, no. 7, pp. 1704–1710, 1992.

- [36] K. Suzuki, "Scaling theory for double-gate SOI MOSFETs," *IEEE Trans. Electron Devices*, vol. 40, no. 12, pp. 2326–2329, 1993.

- [37] C.-W. Lee, "Device design guidelines for nano-scale MuGFETs," *Solid State Electron.*, vol. 51, pp. 505–510, 2007.

- [38] C. P. Auth and J. D. Plummer, "Scaling theory for cylindrical, fully depleted surrounding-gate MOSFETs," *IEEE Electron Device Lett.*, vol. 18, no. 2, pp. 74–76, 1997.

- [39] T.-Y. Chian, "A novel scaling theory for fully depleted, multiple-gate MOSFET, including effective number of gates (ENGs)," *IEEE Trans. Electron Devices*, vol. 61, no. 2, pp. 631–632, 2014.

- [40] M. Edgard, "High Transconductance Self-Aligned Gate-Last Surface Channel InGaAs MOSFET," in *IEDM Tech. Dig.*, 2011.

- [41] J. Lin, D. A. Antoniadis, and J. A. Del Alamo, "Sub-30nm InAs Quantum-Well MOSFETs with Self-aligned Metal Contacts and Sub-1 nm EOT HfO2 Insulator," in *IEDM Tech. Dig.*, 2012.

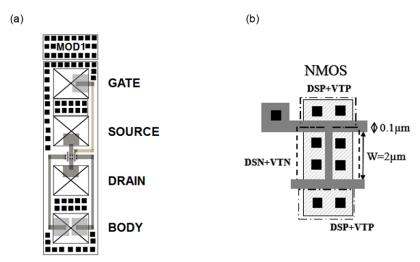

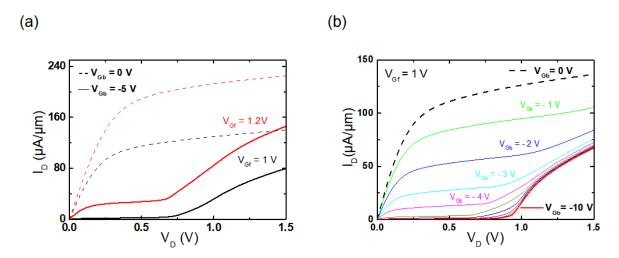

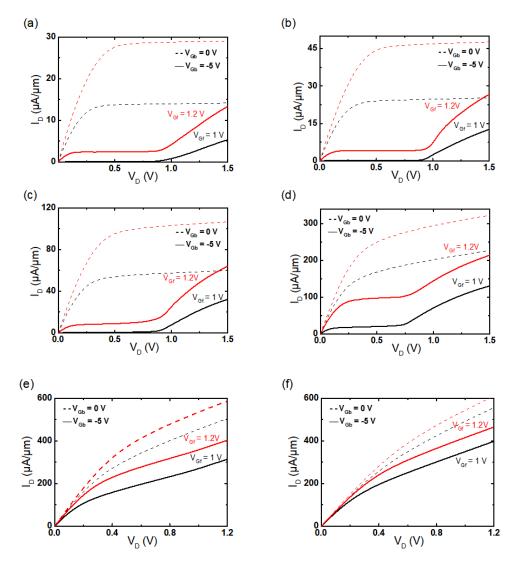

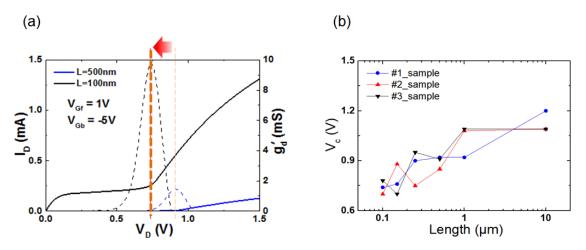

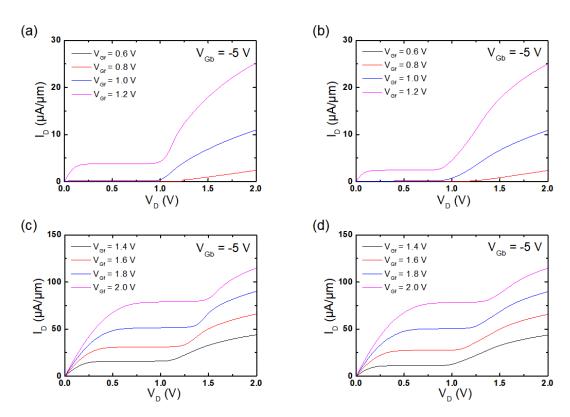

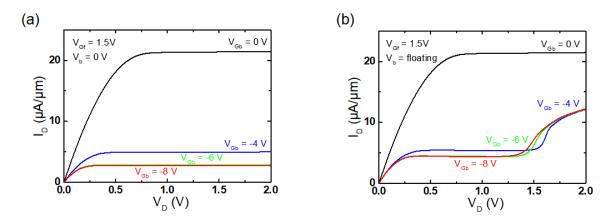

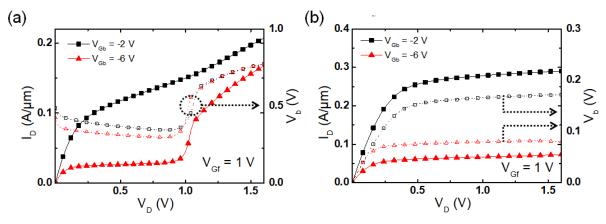

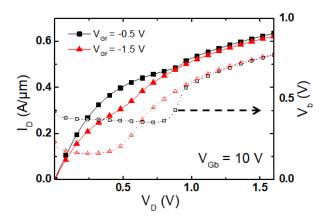

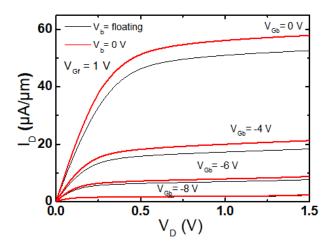

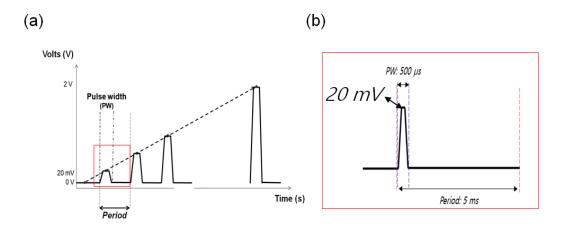

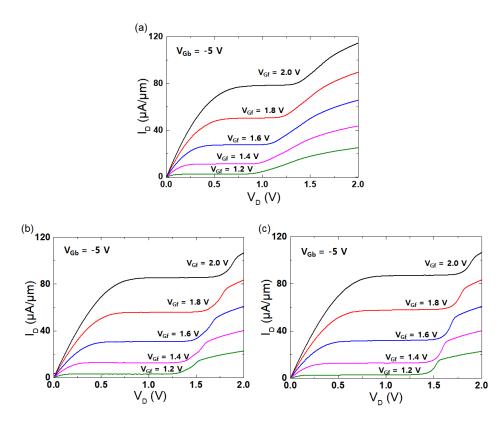

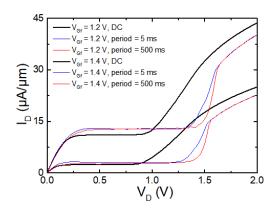

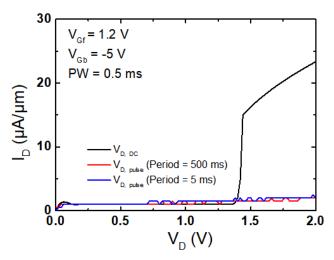

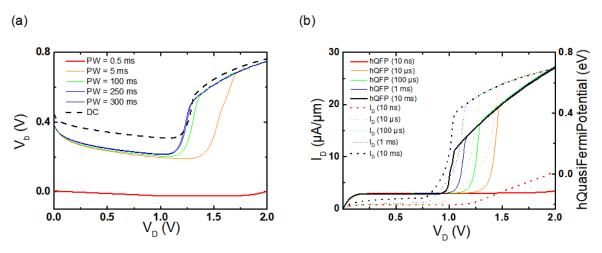

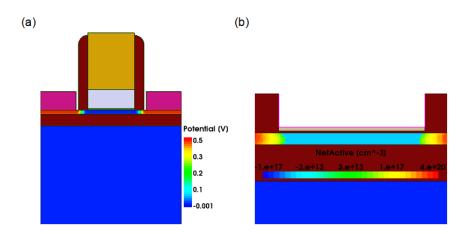

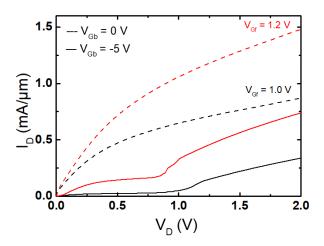

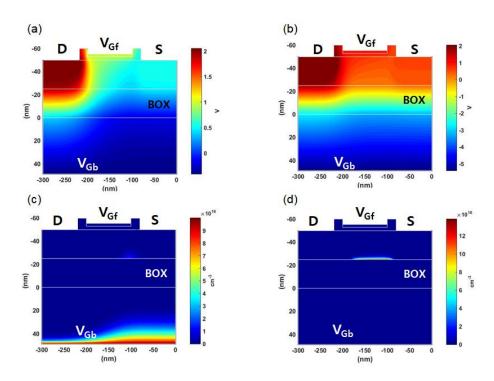

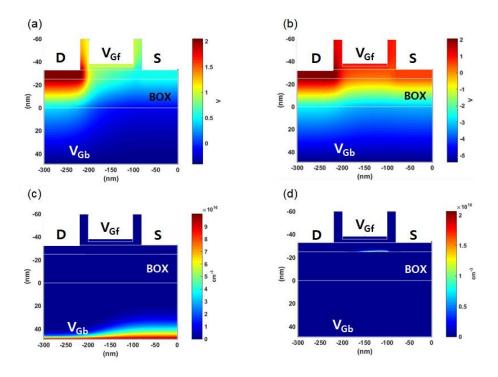

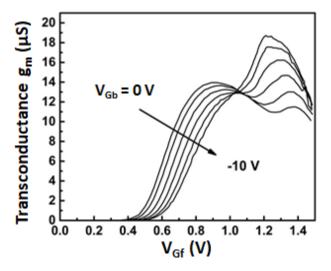

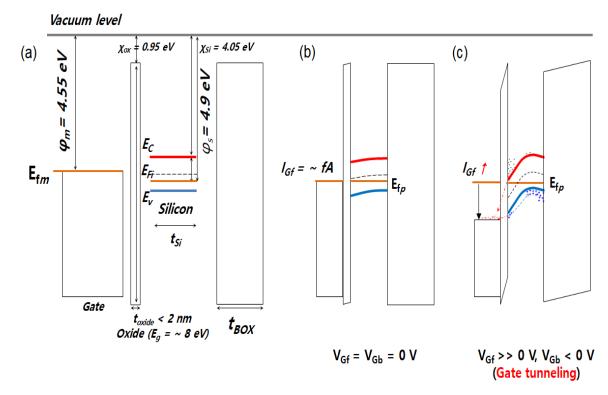

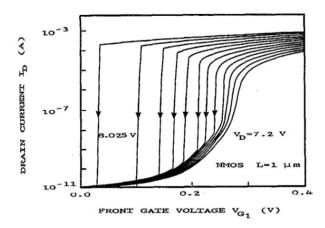

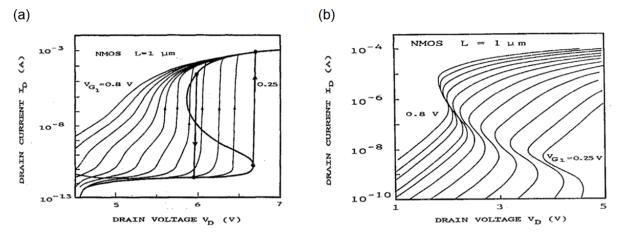

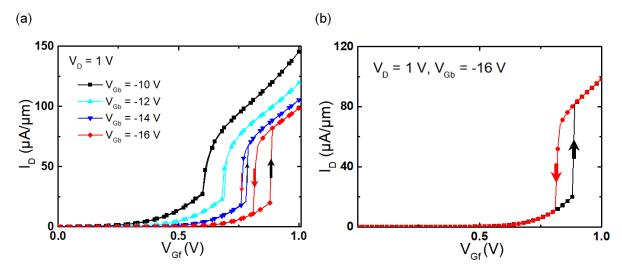

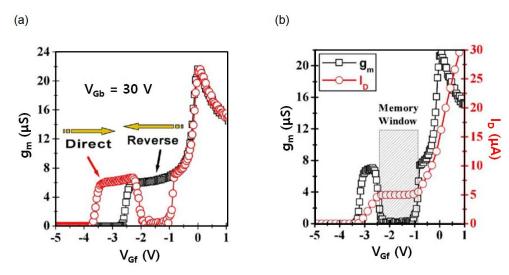

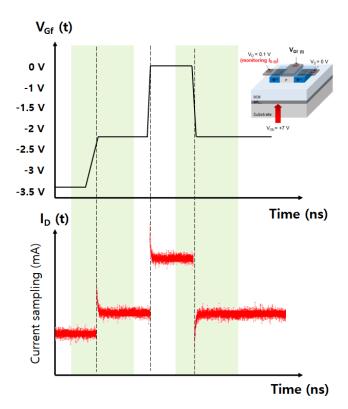

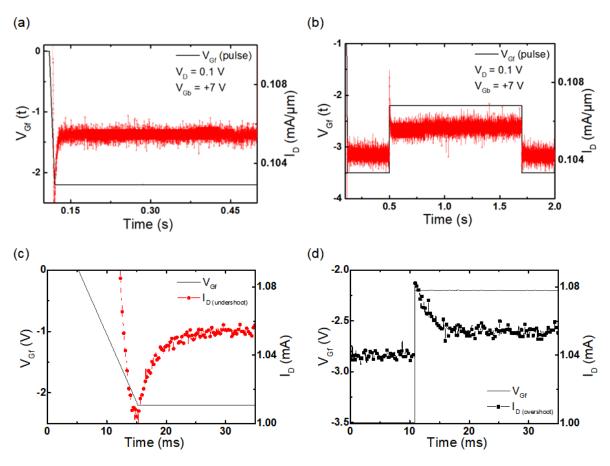

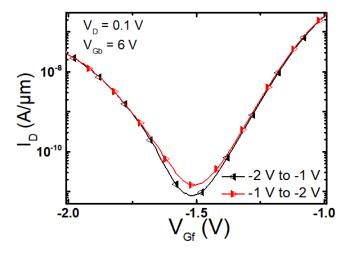

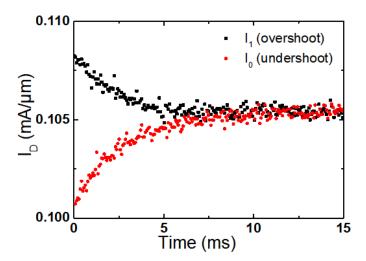

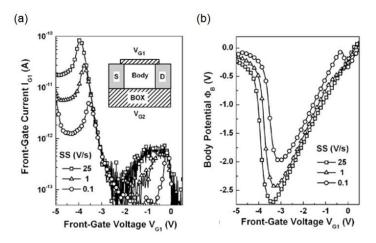

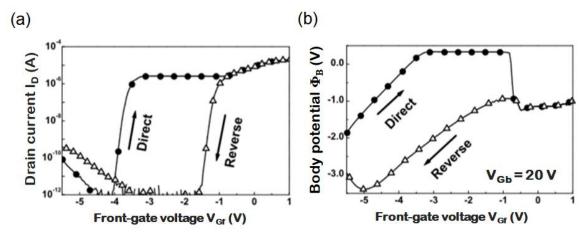

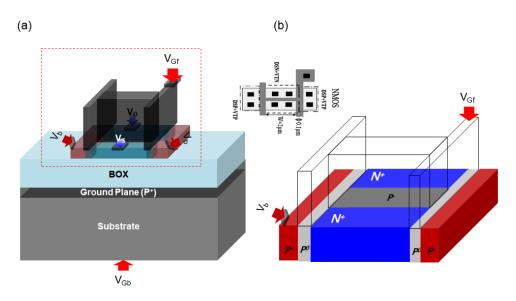

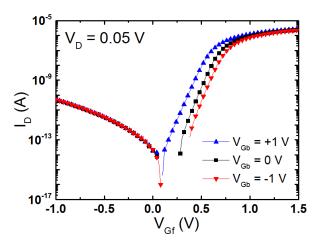

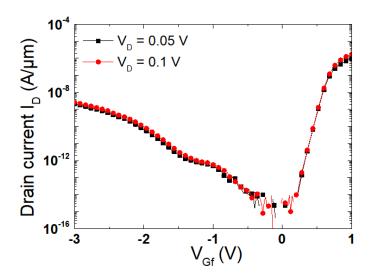

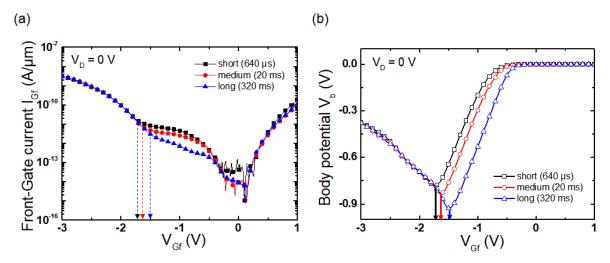

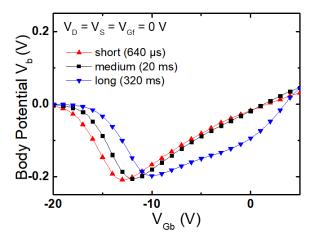

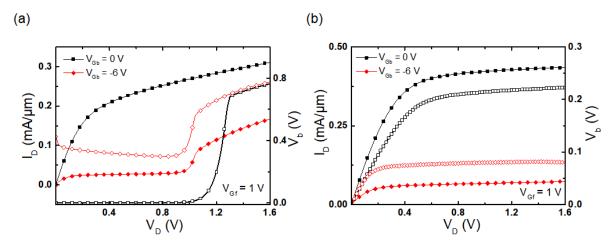

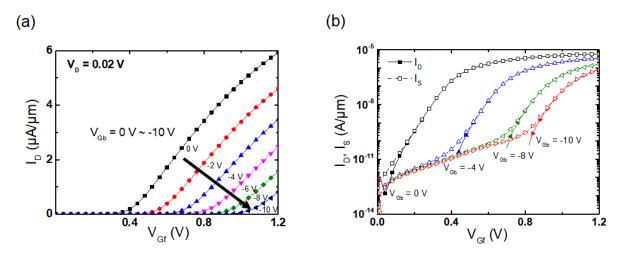

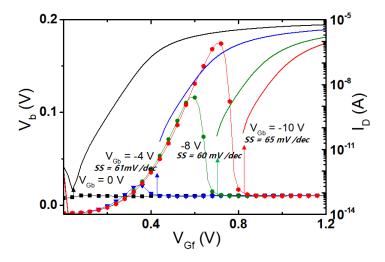

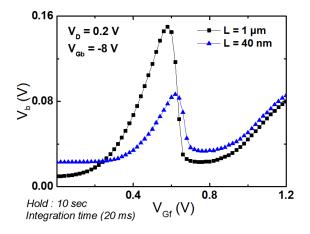

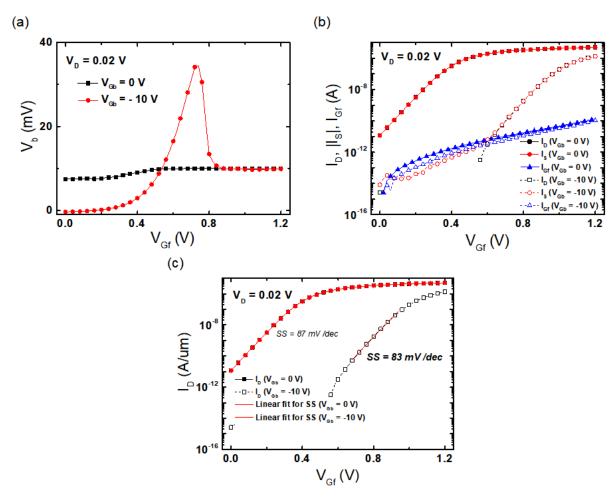

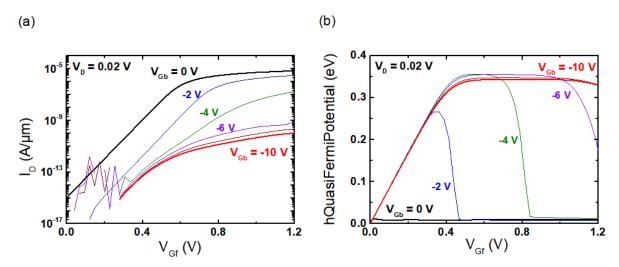

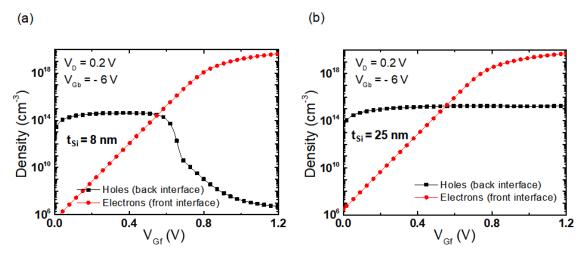

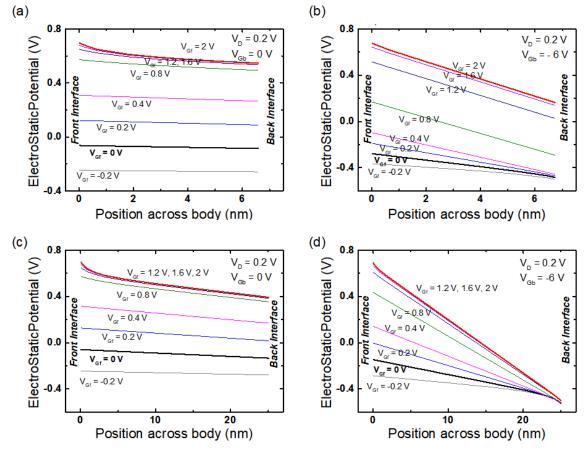

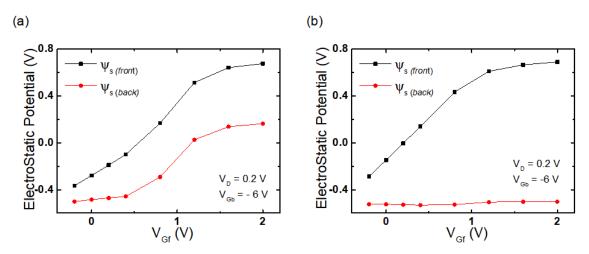

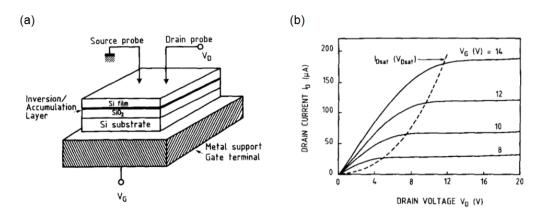

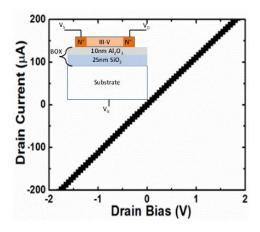

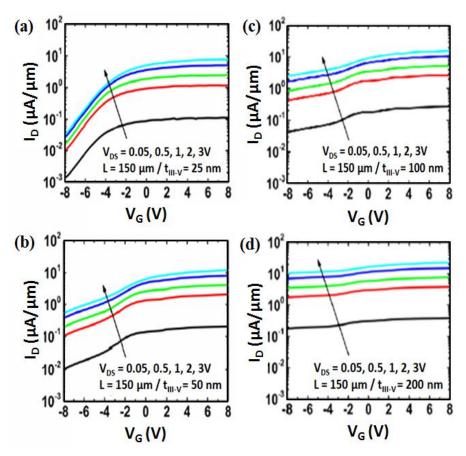

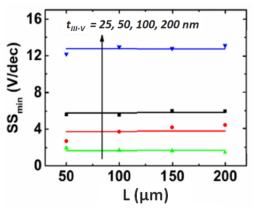

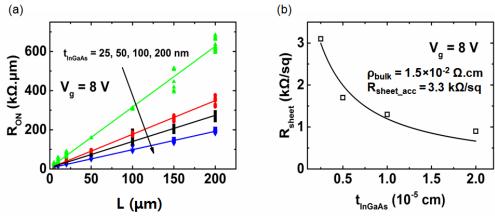

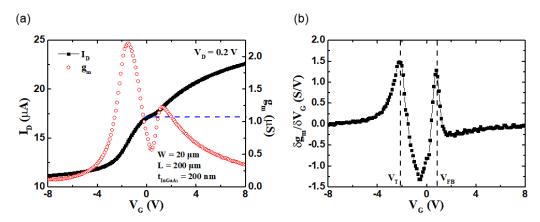

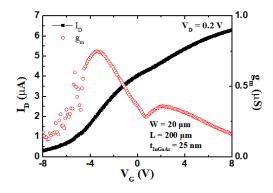

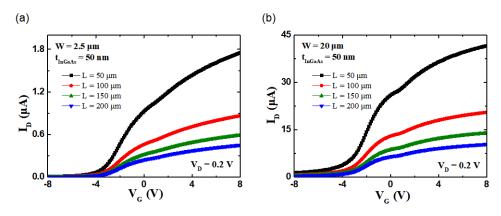

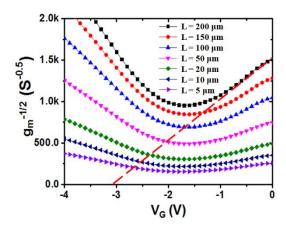

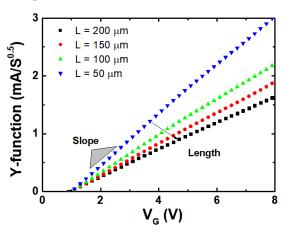

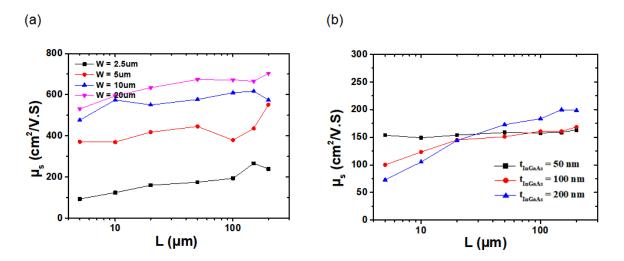

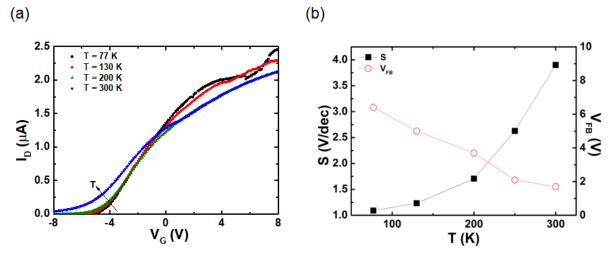

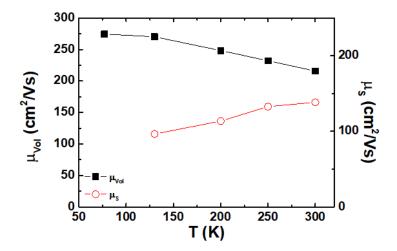

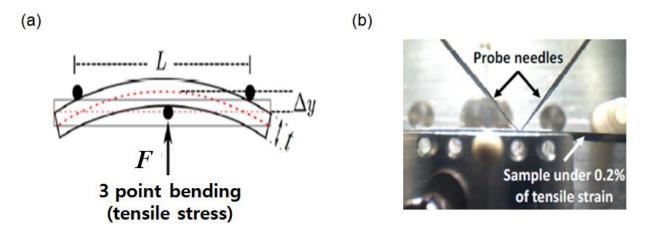

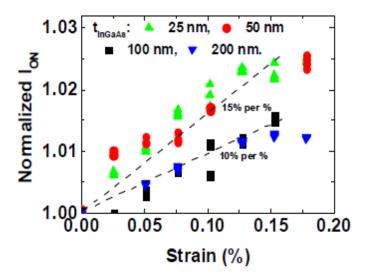

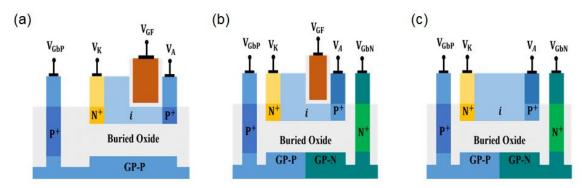

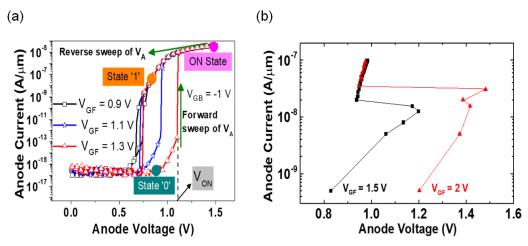

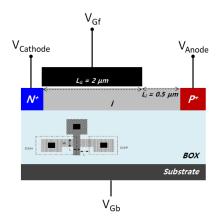

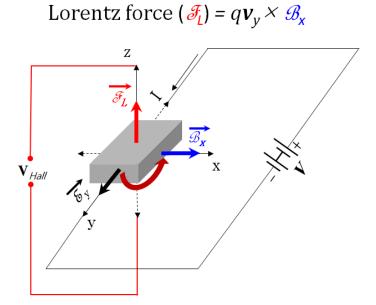

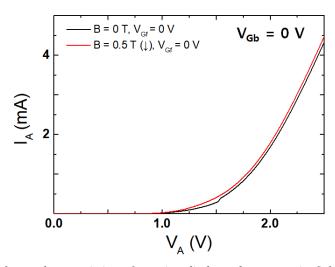

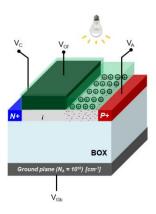

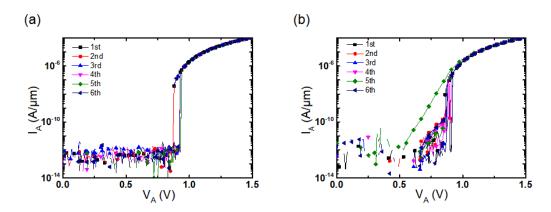

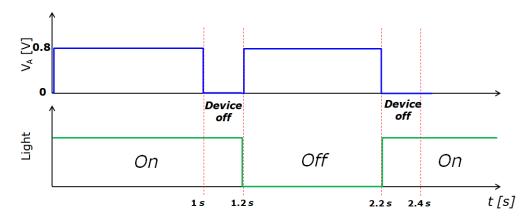

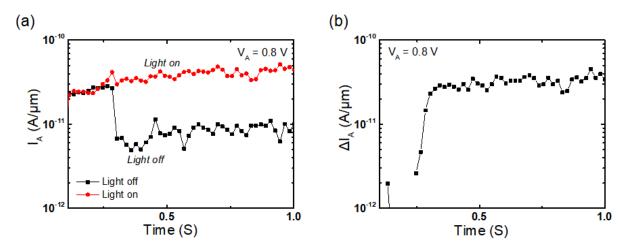

- [42] L. Czornomaz *et al.*, "Co-integration of InGaAs n- and SiGe p-MOSFETs into digital CMOS circuits using hybrid dual-channel ETXOI substrates," *Tech. Dig. Int. Electron Devices Meet. IEDM*, pp. 52–55, 2013.