## Verifying Software Fault Isolation

Julien Lepiller

### ▶ To cite this version:

Julien Lepiller. Verifying Software Fault Isolation. Performance [cs.PF]. Université de Rennes, 2019. English. NNT: 2019REN1S067. tel-02513105

## HAL Id: tel-02513105 https://theses.hal.science/tel-02513105v1

Submitted on 20 Mar 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE DE DOCTORAT DE

## L'UNIVERSITÉ DE RENNES 1

COMUE UNIVERSITÉ BRETAGNE LOIRE

ÉCOLE DOCTORALE Nº 601

Mathématiques et Sciences et Technologies de l'Information et de la Communication Spécialité : Informatique

Par

## « Julien LEPILLER »

- « Vérification d'isolation de fautes logicielle »

- « Verifying Software Fault Isolation »

Thèse présentée et soutenue à « Rennes », le « 11/12/2019 »

Unité de recherche : IRISA

### Rapporteurs avant soutenance:

Antoine Miné Professeur à l'Université Sorbonne Marie-Laure Potet Professeure à l'INP Grenoble

#### **Composition du Jury:**

Dir. de thèse :

Attention, en cas d'absence d'un des membres du Jury le jour de la soutenance, la composition du Jury ne comprend que les membres présents

Président : Sandrine Blazy Professeure à l'Université de Rennes 1

Examinateurs : Frédéric Besson Chargé de recherche Inria

Antoine Miné Professeur à l'Université Sorbonne

Gustavo Petri Chercheur chez ARM Ltd

Marie-Laure Potet Professeure à l'INP Grenoble

Thomas Jensen Directeur de recherche Inria

## REMERCIEMENTS

Je tiens à remercier Thomas Jensen et Frédéric Besson pour avoir encadré cette thèse. Ils ont su être présents aux moments cruciaux pour m'aiguiller dans mes réflexions et mon travail. Plus généralement, je voudrais remercier toute l'équipe Celtique qui m'a accueillie pendant ces trois dernières années et avec qui j'ai eu plaisir à travailler.

J'aimerais remercier mes rapporteurs, Marie-Laure Potet et Antoine Miné pour avoir accepté de relire le présent manuscrit. Je veux aussi remercier mon jury, composé de Sandrine Blazy et de Gustavo Petri.

J'adresse également toute ma reconnaissance à Lydie Mabil et à Stéphanie Lemaile, nos deux merveilleuses assistantes d'équipe qui m'ont aidé et aiguillé dans mes différentes démarches administratives.

Je voudrais aussi remercier toutes les personnes qui m'ont écouté et soutenu durant cette thèse, mes parents, Sylvie et Guillaume, et mes sœurs, Oriane et Éloïse (ils n'ont pas eu le choix). Enfin, je remercie Amaury Jacques, les hackers de GNU Guix et les libristes croisés pendant ma thèse, qui ont eu la gentillesse de m'écouter et de m'aider à mieux présenter mes idées.

## **TABLE OF CONTENTS**

| V  | érific | cation  | d'isolation de fautes logicielle         | 9  |

|----|--------|---------|------------------------------------------|----|

| In | trod   | uctio   | n                                        | 15 |

| I  | Coi    | ntext   |                                          | 19 |

| 1  | SFI:   | A Sec   | eure Extension Mechanism                 | 21 |

|    | 1.1    | Secur   | e Extension by Untrusted Modules         | 21 |

|    | 1.2    | Princi  | ples of SFI                              | 23 |

|    |        | 1.2.1   | Foundations of SFI                       | 24 |

|    |        | 1.2.2   | Code Generation                          | 25 |

|    |        | 1.2.3   | Verification                             | 28 |

|    | 1.3    | Implei  | mentations                               | 31 |

|    |        | 1.3.1   | Splitting the Code into Constant Bundles | 31 |

|    |        | 1.3.2   | Protecting the Return Address            | 33 |

|    |        | 1.3.3   | Interfacing with Trusted Libraries       | 35 |

|    |        | 1.3.4   | Transformation Point                     | 36 |

|    |        | 1.3.5   | Self-modifying Code                      | 37 |

|    | 1.4    | Optim   | iizations                                | 38 |

|    |        | 1.4.1   | Using Hardware Security for Isolation    | 38 |

|    |        | 1.4.2   | The Art of Choosing the Mask             | 39 |

|    |        | 1.4.3   | Register Management                      | 40 |

|    |        | 1.4.4   | Guard Zones                              | 42 |

|    |        | 1.4.5   | Protecting the Control Flow Graph        | 43 |

|    |        | 1.4.6   | Range Analysis                           | 43 |

|    | 1.5    | Verific | cation Techniques                        | 45 |

|    |        | 1.5.1   | Linear Disassembly                       | 46 |

|    |        | 1.5.2   | Certified Verification                   | 46 |

### TABLE OF CONTENTS

|    |      | 1.5.3    | Certified Sandboxing                                | 47  |

|----|------|----------|-----------------------------------------------------|-----|

|    |      | 1.5.4    | Static Analysis                                     | 48  |

| 2  | Abs  | tract Ir | nterpretation as a Tool for Analysis                | 49  |

|    | 2.1  | A Mini   | imal Theory of Abstract Interpretation              | 50  |

|    |      | 2.1.1    | Abstract Domains                                    | 50  |

|    |      | 2.1.2    | Abstract State                                      | 52  |

|    | 2.2  | A Met    | hodology for Showing Property Preservation          | 56  |

| II | Мс   | odular   | Software Fault Isolation as Abstract Interpretation | 59  |

| 3  | An I | nterme   | ediate Language to Represent Assembly               | 61  |

|    | 3.1  | A Sen    | nantics for Running SFI Modules                     | 61  |

|    | 3.2  | Execu    | ition Model                                         | 64  |

| 4  | Ana  | lyzing   | a Single-threaded Module                            | 67  |

|    | 4.1  | Secur    | ity Property as a Defensive Semantics               | 67  |

|    |      | 4.1.1    | Defensive Semantics                                 | 70  |

|    |      | 4.1.2    | The Sandbox Property                                | 74  |

|    | 4.2  | Datale   | ess Semantics                                       | 75  |

|    | 4.3  | Intra-p  | procedural Semantics                                | 80  |

|    |      | 4.3.1    | Formal Proof of Security                            | 81  |

|    | 4.4  | Abstra   | act Semantics                                       | 88  |

|    |      | 4.4.1    | Abstract Domains                                    | 88  |

|    |      | 4.4.2    | Abstract State                                      | 89  |

|    |      | 4.4.3    | Abstract Semantics                                  | 90  |

| 5  | Ехр  | erimen   | ting with an Analyzer Implementation                | 95  |

|    | 5.1  | REIL 8   | and Lifting                                         | 95  |

|    |      | 5.1.1    | Intermediate Representations                        | 95  |

|    |      | 5.1.2    | Comparison                                          | 99  |

|    | 5.2  | Impler   | mentation                                           | 99  |

|    |      | 5.2.1    | Relation between semantics and REIL                 | 100 |

|    |      | 5.2.2    | Implementation Details                              | 100 |

|    |      | 5.2.3    | Tests                                               | 101 |

|    |      | 5.2.4    | Verifying Incorrect Programs                  | . 102 |

|----|------|----------|-----------------------------------------------|-------|

|    |      | 5.2.5    | Verifying Redundant Sandboxing Elimination    | . 102 |

| Ш  | Ex   | (tendi   | ng SFI to Thread-level Isolation              | 107   |

| 6  | Wea  | ık Mem   | ory Models                                    | 109   |

|    | 6.1  | An Intr  | roduction to Concurrency                      | . 109 |

|    |      | 6.1.1    | Interleaving Semantics                        | . 109 |

|    |      | 6.1.2    | Weak Memory Models                            | . 112 |

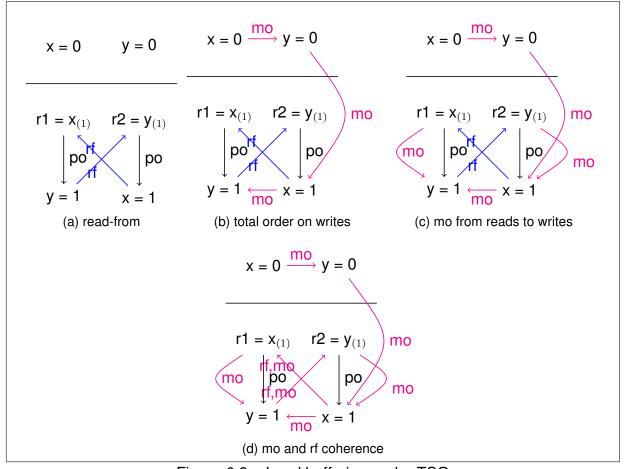

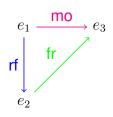

|    |      | 6.1.3    | Axiomatic Weak Memory Models                  | . 116 |

|    | 6.2  | REIL i   | n a Weak Memory Model                         | . 120 |

|    |      | 6.2.1    | Event                                         | . 120 |

|    |      | 6.2.2    | State                                         | . 122 |

|    |      | 6.2.3    | Execution Traces                              | . 122 |

|    |      | 6.2.4    | Well-formedness Conditions                    | . 123 |

|    |      | 6.2.5    | Memory Model                                  | . 125 |

| 7  | Ana  | lyzing l | Multithreaded Modules                         | 127   |

|    | 7.1  | Securi   | ity Property                                  | . 128 |

|    | 7.2  | Anarch   | hic Semantics                                 | . 129 |

|    | 7.3  | Seque    | ential Semantics                              | . 133 |

|    |      | 7.3.1    | Intuition                                     | . 133 |

|    |      | 7.3.2    | Proofs                                        | . 134 |

|    | 7.4  | Bridgir  | ng the gap with the Single-threaded Semantics | . 140 |

|    |      | 7.4.1    | Small Step Dataless Semantics                 | . 140 |

|    |      | 7.4.2    | Small-Step Security                           | . 142 |

|    |      | 7.4.3    | Sequential Security                           | . 145 |

|    |      | 7.4.4    | Final Theorem                                 | . 149 |

| Co | oncl | usion    |                                               | 151   |

| Bi | blio | graph    | ı <b>v</b>                                    | 155   |

# VÉRIFICATION D'ISOLATION DE FAUTES LOGICIELLE

Les gros systèmes logiciels sont complexes à maintenir et à personnaliser. De nombreux projets populaires s'appuient alors sur des modules développés par des programmeurs tiers. C'est le cas des modules du noyau Linux, des extensions des navigateurs, des bibliothèques natives de certains langages de programmation ou de toutes sortes de greffons dans toutes sortes de logiciels. Bien que le logiciel hôte soit de bonne qualité, régulièrement entretenu et testé, ses modules n'ont aucune garantie de ce genre et peuvent même être malicieux.

Si l'on veut garantir la sécurité de l'hôte face à ses modules, une solution est d'isoler ces modules. Seulement, s'ils sont complètement isolés, ils sont inutiles. On leur donne donc une interface de programmation qui leur permet d'interagir avec l'hôte. Cette interface devra être indépendante du module et correctement sécurisée. La sureté d'un module peut alors se résumer au fait que ce module n'utilise que cette interface pour interagir avec l'hôte ou d'autres modules.

La sureté doit être assurée dans le cas de certains scénarii d'attaque. Nous définissons deux scénarii : soit l'attaquant est capable de proposer un module arbitraire, soit l'attaquant est capable d'exploiter une faille dans un module.

Software fault isolation (isolation de fautes logicielle, ou SFI) est une excellente technique pour garantir la sécurité des module. Elle se base sur un vérifieur qui s'assure, avant de lancer un module, qu'il est sûr. Le vérifieur peut rejeter le module si celui-ci n'est pas sûr, ou si le vérifieur ne sait pas conclure. Le module n'est alors pas exécuté.

La technique se base sur un système de bac à sable : une zone mémoire est dédiée au module, une autre à son code. L'emplacement de ces zones est déterminé par le programme hôte et passées au module via quelques registres. Si les zones mémoire en question sont correctement alignées, il est certain qu'en réécrivant les bits de poids fort de chaque adresse mémoire auxquelles le module souhaite accéder, celui-ci ne pourra pas accéder à de la mémoire en dehors de ses zones dédiées, et donc interagir

avec le module autrement qu'en appelant son code.

La réécriture est introduite par le compilateur, mais il n'est pas nécessaire de faire confiance au compilateur utilisé : un attaquant qui n'utiliserait pas le compilateur pourrait fournir un binaire sans réécriture. C'est le rôle du vérifieur que de s'assurer que le module réécrit correctement ses adresses. Pour cela, il vérifie aussi d'autres propriétés sur le binaire. Par exemple, l'alignement de blocs de codes, la cible des sauts et l'emplacement des réécritures par rapport à l'utilisation des adresses.

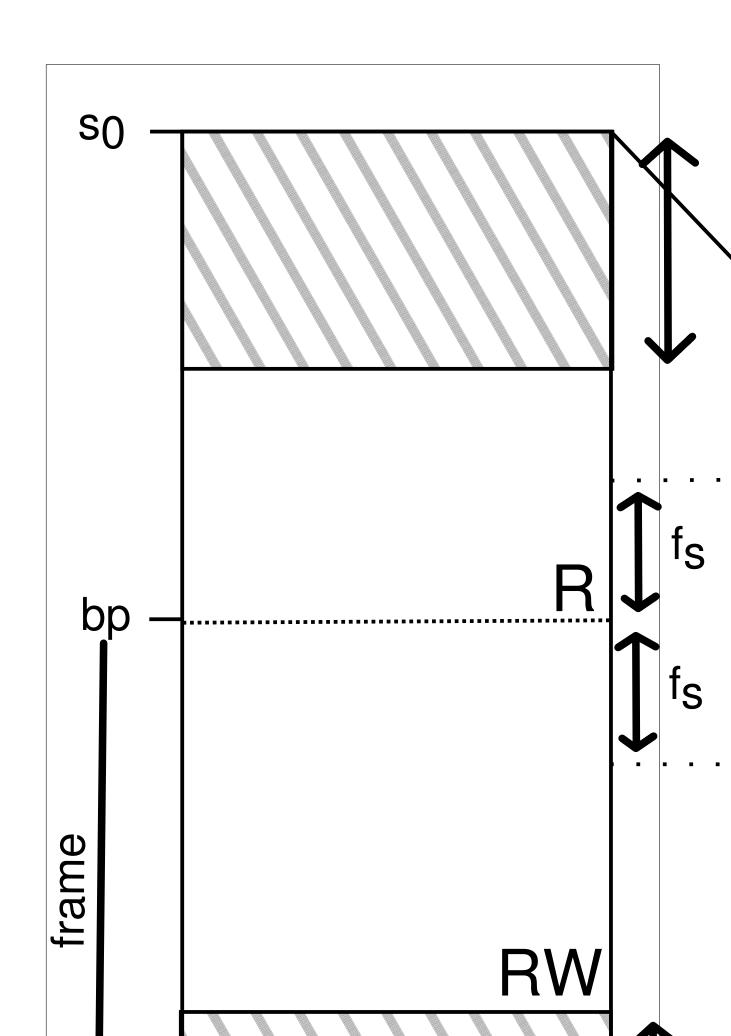

Dans cette thèse, nous proposons une nouvelle définition de SFI, basée non pas sur un critère purement syntaxique, mais sur une propriété sémantique. Il s'agit de définir la propriété le plus largement possible pour en extraire précisément les points qui définissent la sécurité, et non pas seulement des critères suffisants. Ainsi, nous continuons d'allouer une zone mémoire dédiée au bac à sable, mais le code n'est plus séparé de celui de l'hôte. La pile est partagée entre l'hôte et le module. Le module a alors accès en lecture et en écriture au bac à sable, à ses trames de pile et en exécution à son code et aux fonctions de l'interface de programmation, que nous appelons la bibliothèque de confiance, dans la tradition de SFI. La pile en particulier est un problème, car l'appartenance d'une trame à tel ou tel « domaine » (hôte ou module) n'est pas une donnée statique, mais dynamique, et est susceptible de changer au cours du temps.

Nous proposons de définir la sécurité d'un module au moyen d'une *sémantique défensive*, c'est-à-dire une sémantique qui ressemble à la sémantique standard du langage, mais qui effectue des vérifications supplémentaires à l'exécution. Un module est alors dit sûr si sa sémantique défensive n'est pas bloquée.

Nous définissons une théorie simplifiée de l'interprétation abstraite, qui permet d'obtenir un analyseur statique à partir d'une sémantique abstraite. Cette sémantique abstraite définie une abstraction de l'exécution d'un programme, examiné par l'analyseur statique. Avec la sémantique abstraite, nous devons définir une concrétisation, qui à partir d'un état abstrait renvoie un ensemble d'états concrets. En analysant le programme, on associe à chaque point de programme un état abstrait. Si l'abstraction est correcte, la concrétisation de ces états donne un sur-ensemble des états qui sont effectivement atteints à ces points de programme durant l'exécution du module. Nous suivons ensuite une méthodologie qui nous permet de découper la preuve de correction de l'abstraction en plusieurs preuves de correction plus petites, en passant par des sémantiques intermédiaires qui présentent chacune un aspect important de

l'abstraction.

Suite à cela, nous avons implémenté un prototype d'analyseur en se basant sur bincat, un outil d'analyse binaire existant, basé lui aussi sur l'interprétation abstraite. Nous y avons apporté nos propres domaines abstraits et modifié la fonction principale et le domaine concret pour correspondre à nos besoins d'analyse. Nous avons effectué des expérimentations pour valider nos attentes : avec des programmes spécifiquement non sûrs, des programmes sûrs et des programmes plus gros, qui utilisent un compilateur qui produit des modules sûrs. Nous avons aussi mesuré le temps d'exécution de l'analyseur, qui varie essentiellement en fonction de la quantité de boucles imbriquées dans les fonctions.

La dernière partie de cette thèse s'articule autour de l'extension du travail déjà effectué au cas d'une exécution parallèle du programme hôte et du module. Dans ce nouveau contexte, le programme exécute plusieurs fils d'exécution qui commencent tous dans le programme hôte. Chacun de ces fils d'exécution peut alors exécuter du code de l'hôte ou du module. Il convient de redéfinir la propriété de sécurité qui ne convient plus : le blocage d'un fil d'exécution n'entraine pas le blocage des autres fils. Pire encore : si notre langage proposait des fonctionnalités de synchronisation, il pourrait y avoir des interblocages, mais ce ne sont pas des problèmes de sécurité. Si le programme ne s'exécute plus, il n'y a pas de vulnérabilité.

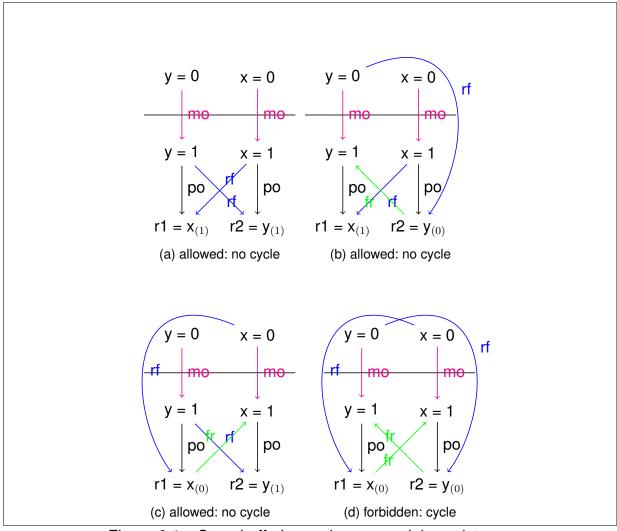

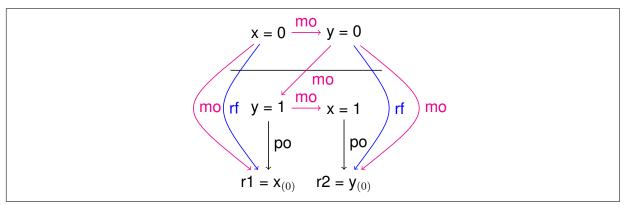

On pourrait penser qu'une sémantique d'entrelacement suffirait à représenter tous les aspects de l'exécution parallèle d'un programme. Une sémantique d'entrelacement est une sémantique où à chaque pas, c'est un fil d'exécution choisi arbitrairement qui fait un pas d'exécution de son côté, et où la mémoire est partagée entre tous les fils. Malheureusement, l'exécution de programmes sur du vrai matériel ne fonctionne pas de cette manière : chaque cœur du processeur a son propre cache, peut éventuellement réordonner des instructions, etc. En utilisant un modèle mémoire faible, il est possible de représenter, de manière abstraite, ces comportements du matériel en représentant plus de comportements possibles du programme. Plus un modèle mémoire permet de comportements, plus on dit qu'il est faible. On peut les comparer en comparant les comportements autorisés ou non par ces modèles.

Nous avons proposé un modèle mémoire faible suffisamment faible pour représenter plus de comportements que ceux observables sur un multi-processeur x86 ou arm par exemple. Ce modèle est utilisé avec une sémantique axiomatique (ce qui est habituel pour les sémantiques de programmes dans des modèles mémoire faibles) et la

propriété de sécurité est définie en fonction des événements qui ont lieu dans cette sémantique. Chaque événement est soit un calcul local, une lecture en mémoire, une écriture en mémoire, un saut ou l'exécution de code de l'hôte. La propriété de sécurité définit ce qu'est un événement sûr : par exemple, une écriture doit avoir lieu soit dans le bac à sable, soit dans la trame de pile actuelle, de même pour l'écriture en mémoire.

Comme précédemment, nous abstrayons cette sémantique concrète pas à pas, en plusieurs sémantiques intermédiaires. À chaque étape, nous montrons que la sécurité du module dans la nouvelle sémantique, plus abstraite, entraine la sécurité du module dans l'ancienne, plus concrète. Ainsi, nous abstrayons d'abord le bac à sable, en permettant la lecture d'une valeur arbitraire, puis nous abstrayons le modèle mémoire par un modèle d'entrelacement, puis nous abstrayons le tout en une sémantique non parallèle.

Enfin, cette thèse se termine là où elle a commencé : en montrant que la sécurité de cette dernière sémantique se réduit à la sécurité d'une sémantique défensive. Précisément, la première sémantique intermédiaire après la sémantique défensive qui définit la sécurité d'un module dans une exécution non parallèle. Cela signifie alors que le même analyseur est capable de déterminer la sureté d'un module, indépendamment du modèle mémoire considéré.

Ce travail pourra être étendu ensuite à plusieurs modules. Les preuves actuelles se font sous l'hypothèse qu'un seul module sera exécuté. S'il y a plusieurs modules, cela changerait un peu la sémantique défensive, et donc le contenu des preuves. Il est cependant probable que la sémantique abstraite et l'analyseur n'auront pas besoin de changements pour pouvoir vérifier un nombre arbitraire de modules. Il pourrait être intéressant d'implémenter cet analyseur et les preuves de correction dans un assistant à la preuve comme Cog, pour assurer la fiabilité des résultats. L'implémentation pourrait aussi être améliorée, entre autres pour raffiner les conditions sur les gardes, et pour exécuter une version plus grossière mais plus rapide et toujours correcte avant de lancer une version plus subtile si la première n'a pas fonctionné. Enfin, il serait intéressant d'étudier le lien entre ces deux définitions sémantiques de SFI et la définition syntaxique d'autres implémentation, comme NaCl. Nous pouvons nous demander si, et dans quelle mesure, l'analyseur que nous avons développé serait capable de vérifier ces modules. Enfin, on pourrait s'intéresser au contenu du bac à sable, qui permettrait d'avoir une analyse plus fine et plus précise, qui tient compte par exemple du comportement de certains modules standards, qui créent leur pile dans le bac à sable. Cela représenterait un défi important, puisque l'abstraction complète du bac à sable est un élément central du raisonnement dans le cas parallèle.

## INTRODUCTION

We are now used to have computers with multiple software installed, from different software vendors. Some of the software comes from the same company or group who published the operating system you are running, and some of it comes from other groups. Although some operating systems used to rely on software cooperation for them to run together, modern operating systems and hardware architectures are able to manage uncooperative software. In fact, software are now mostly designed to be uncooperative and act as if they were the only software running on the machine.

One of the techniques to force uncooperative software to cooperate and not step on one another is the use of virtual memory spaces. The memory of a computer is a memory space that maps addresses to values. When two programs run at the same time, and they are not cooperating, it is not guaranteed that they will not try to access the same memory location for different purposes. Modern hardware have an *MMU* (Memory Management Unit) that allows an operating system to set up virtual memory for processes. An MMU is tasked with the mapping of virtual memory addresses of a process to actual memory addresses. The operating system selects a free memory zone for each new process, and creates a memory map for each process, where actual addresses are in this free memory zone. With the help of the MMU, the software can now access the same address as others, while clashes are prevented by the mapping of this address for each program to completely different addresses in the real memory.

Failing to do so can have damaging consequences. In 11th grade, we had to have and use an advanced calculator during some math and science classes. There were different brands and models, but they were all effectively a small computer with a calculator keyboard and a simple operating system. The calculator was even able to load programs from a computer, and exchange files and programs with other calculators of the same model. I was intrigued and quickly found how to create programs for the calculator. It was possible to use a computer to program in C and compile for the calculator's processor. One of my first achievements was a snake game, where a snake has to eat dots that appear at random on the screen and grows with each dot eaten, but must not cross itself.

I showed the game to comrades and immediately became very popular. Some of them had the same model of calculator and we copied the executable to their calculator. I'm very bad at games, so I could not score more than 20 or maybe 30 points. Some of my friends though managed to be way better than me and get more than 100 points! All went well for a time, until the game ended. Friends who made more than 100 points quickly found that, when quitting the game, the operating system had crashed. Thankfully, a hard reset (which made all files and custom programs disappear) was able to fix it.

The reason for the crash was simple, although it took me some time to understand it. My snake game registered the positions of the snake with an array: at each tick, it would update every position in the array with the position of the element after it, or if it was the head, with the new position of the head. Unfortunately, if you were too good at the game and your snake managed to grow beyond 100, the array overflowed... into a memory region that was part of the operating system's memory.

This example shows the importance of using virtual memory, or at least some sort of memory segmentation or isolation. It was a genuine mistake that had almost no bad long-term consequences. But what if the program came from a malevolent programmer? It could have made much more harm, taking over the entire operating system.

Even more recently, we are seeing more and more programs allowing third-party programmers to add features through a module system. These modules are loaded inside the program that hosts them. We can draw a parallel between the operating system and the host program, and between the snake game and the module. At this level, there is no support from the operating system for memory isolation, nor does the hardware help. If the module is not carefully written or the host program does not take specific actions to prevent a disaster, the same kind of outcome may happen.

When the hardware cannot help with isolation of processes or modules (either because there is no MMU or because no hardware really supports isolation of modules in the same address space), we can only rely on software techniques. Chapter 1 introduces such a technique, called *Software Fault Isolation*.

Although we will see there are multiple variants of the technique, it is mostly a syntactic technique. In order to better understand how Software Fault Isolation works, this thesis started by working on a semantic definition of it. We tried to really understand what it meant for a module to be isolated from its host program. We started by designing a small language that acted like an assembly language. This language is presented in

Chapter 3. We came up with a *defensive semantics*, which means a semantics that acts as a normal semantics with additional checks, to model isolated modules. We refined it multiple times to arrive at the current form that we will present in this thesis.

Once we had grasped what it meant for a module to be isolated, we ended up with a semantics property that allowed for more behaviors than other implementations. In order to check whether a particular module respects the property, a single pass to verify syntactic properties was not enough any more. Based on abstract interpretation and a methodology for decomposing a proof of correctness in smaller steps, with intermediate semantics, that we present in Chapter 2, we developed a static analyzer. We present in Chapter 5 the implementation we wrote and experiments we ran on it. Chapter 4 presents the defensive semantics, the intermediate semantics and the abstract semantics the analyzer is based on.

This work has a fundamental flaw: it assumes a single-threaded application. Modern software however often take advantage of the multithreaded hardware we have now. In order to solve this flaw, we studied multithreading models. We wanted to stay as close as possible to actual hardware behaviors, so we decided to study SFI under a weak-memory model, which had never been done before.

A weak-memory model is a memory model where some assumptions about memory in a multithreading context are not held anymore. The reason is that these assumptions are not guaranteed by actual hardware. We will see in Chapter 6 what these assumptions are, and how to define a weak-memory model. Chapter 7 will later define the semantics of our language under this weak-memory model and present a proof that the analyzer we defined before is correct even under this new model, using multiple intermediate semantics.

### Part I

## Context

# SFI: A SECURE EXTENSION MECHANISM

This chapter is derived from a survey written in collaboration with Alexandre Dang.

## 1.1 Secure Extension by Untrusted Modules

Because big software systems are complex to maintain and customize, many popular projects can be extended by third-party modules. They can be operating system kernel's modules such as Linux's .ko modules, web-browser extensions, native libraries in an interpreted language, or any kind of plugin or module in any software. They extend the possibilities of their host software.

Although the host software is usually of good quality, carefully developed and extensively tested, its modules can lack such quality or be downright malicious.

This thesis starts with the question of securing such modules, even if we do not trust them. Expressing a security property for such a system is difficult: sending a user file to a webmail server is expected when the user clicks on the attachment icon. This behavior is normal, and certainly not considered malicious. The same behavior from a disk device driver however, is not expected and can be considered malicious.

So, we can intuitively express the security of an extension in terms of "user expectation": a secure module cannot do something the user does not expect. This definition however is too broad and not formal enough for our purposes. Let's first examine an example of extension usage and then come back to the security property, with a better definition.

Some video games allow their players to add content to the game through "mods". Content added this way are typically assets (game data) and code in a simple extension language, such as lua or python for instance. The code itself can interact with the rest

of the virtual environment through predefined functions.

This example shows a very interesting technique: since the language is interpreted, the extension can only interact with specific parts of the host's code, that is especially designed to interact with extensions. This interface between the host code and the extension code is key to the definition of the security property.

**Definition 1** (Extension Security). Given a programming interface between the host program and its modules, defined by the host, a secure module is a module that only uses this interface to interact with the rest of the host program and system.

Additionally, we need to define a threat model that motivates us to create a security mechanism in the first place. Intuitively, we want an attacker to be able to do anything, except directly compromising the host program:

**Definition 2** (Threat Model). Attackers might distribute malicious extensions to users (the code might not follow our security property), or compromise a vulnerable extension running on a user's computer by controlling any data read by the extension.

To illustrate this threat model, a first attack scenario could be that the attacker crafts a malicious extension that is installed by a user. That extension does not comply with the security property and interacts directly with the system or parts of the host software that is not in the programming interface. A second scenario is a vulnerable extension, asking for data coming from an untrusted source, such as a website content. A maliciously crafted data (which is allowed by our threat model since attackers control data read by the extension) triggers a buffer overflow that ultimately overrides a return address. Later on, on return of the function, the module jumps to an unexpected address, breaking the security property.

In addition to security, we are also interested in performance. With two secure implementations of an extension mechanism, we would prefer to use the fastest one. However, naive implementations of faster extension mechanisms are also more vulnerable. The challenge is to combine extensibility, security and speed.

In the video game example, extensions are written in a high-level programming language, which gives some guarantees on what it can do or not. This solution however is rather slow, and requires us to believe the interpreter is bug-free, or at least not exploitable. <sup>1</sup> In short, we have an extension mechanism, but not at full speed and with

<sup>1.</sup> and that is not always the case. For instance, see a recent vulnerability in Firefox's JavaScript engine that was used to distribute malware: https://www.mozilla.org/en-US/security/advisories/mfsa2019-18/

security that is difficult to prove. In software where speed is more important such as in kernels, it would be very inconvenient to use a slow interpreted extension language. Therefore, these programs are extended with binary modules.

For the Linux kernel, these are the .ko modules that can be loaded using the modprobe command. For a web browser, these are native plugins such as Adobe's flash player. For interpreters, these are the native libraries of the system that can be loaded and used from the interpreted language. In Java, this is a native method.

To further increase the speed of the module, software designers may want to load the module directly in the address space of their software, especially when the software and modules communicate frequently. When two separate software want to communicate, they have to use costly context switching. Kernel modules reside in kernel space while other software would use the <code>dlopen()</code> function to load a binary extension.

However, when we gain the speed of native code, we lose the guarantees of an interpreted language, where it's not possible to express code that interacts with parts of the system that were not designed for that purpose. Since every native code is not secure, the challenge is to find a procedure to decide whether a specific extension can be run safely or not.

Software Fault Isolation (SFI) is an excellent candidate to solve that issue of having extensions, speed and security. It was originally presented in the work of Wahbe et al. [41] It supports the idea that third-party programmers are not trusted and provides a verifier, that decides whether an extension can be run safely. We will see in the next section why it is a good candidate and how it works.

This chapter is an overview of different techniques used in different implementations. We will first see in section 1.2 the principles of SFI as defined in [41], with naive implementation details to get a first intuition of the way it works. In section 1.3, we will see and compare implementation choices of different papers, in terms of security, efficiency and practicality when applied to extensions. In section 1.4, we will see and compare different optimizations that can be used to improve the speed of an implementation. Finally, in section 1.5, we will see how to write a verifier for SFI.

## 1.2 Principles of SFI

We introduce here the main ideas of *Software Fault Isolation*. All recent implementations are derived from these principles. The goal of SFI is to allow a host program to

safely execute potentially dangerous modules in its own address space. To accomplish that, these modules are isolated in specific memory areas called *sandboxes*. In fact, each module has two sandboxes: one for its code, and the other for its data.

The SFI approach has two main components: the first one is the rewriting of the untrusted module to prevent it from accessing any memory out of its sandbox. The second component is the verification of the module's code before loading it into memory. This step checks whether the rewriting done in the previous part is still present and valid in the code.

### 1.2.1 Foundations of SFI

The main principle behind SFI was first presented in the work of Wahbe et al. [41]. The implementation described in their paper was made for a RISC architecture like MIPS or Alpha.

We consider that an untrusted code is effectively contained in the sandbox if the following three security properties are true:

- Verified code: only instructions that have been checked by the verifier will be executed

- Memory safety: untrusted modules will not do any write operation out of the sandbox

- Control flow: every control flow transfer from the untrusted module to the host program is identified and verified

The first property protects the host against self-modifying code which can bypass the SFI measures. *Memory safety* prevents any illegal access to the memory of the host program. The last property allows only licit interactions between the host and its modules. SFI forbids any call from untrusted modules that could modify the control flow of the program. If the control flow is compromised, it can lead to an unexpected behavior of the program which we want to avoid.

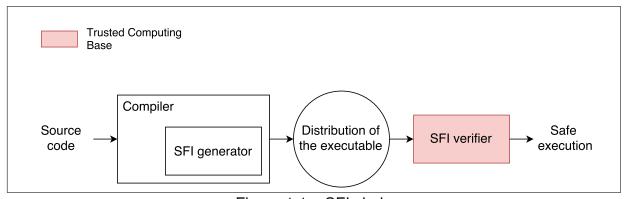

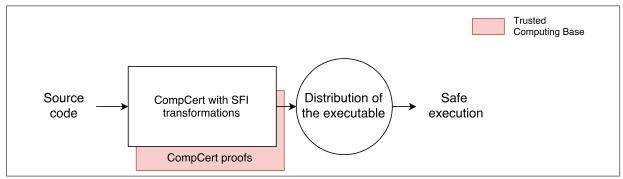

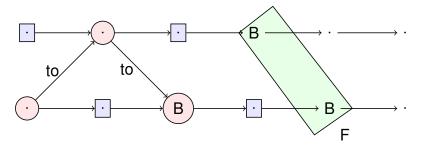

The whole SFI chain of execution is presented in Figure 1.1: a module code is written and compiled by a third-party developer. The developer may comply with the requirements of SFI and use a specific generator, that generates an effectively contained binary module. As we have seen before, the threat model allows an attacker to be a third-party developer, so we cannot assume all extensions are generated with the

generator. Then, the extension is distributed in some way to end-users. For instance, through an app store or by a direct download link from the developer's website. Here, an attacker could potentially act and replace the downloaded code with its own. Finally, once the user downloaded an extension, they run a verifier on their computer to check that the code they downloaded is effectively sandboxed.

If the verification fails the module is rejected and is not executed. With this model, we only have to trust the verifier in order to trust that accepted modules are effectively contained. This is one advantage of SFI: only the verifier needs to be in the *Trusted Computing Base* (TCB). The TCB is the set of computer hardware and software whose bugs may lead to a security issue. If we trust that the TCB does not have bugs, then the rest of the system is secure. In particular, the TCB ensures that the rest of the system does not have bugs, or cannot exploit them to gain privileges, etc.

Figure 1.1 – SFI chain

### 1.2.2 Code Generation

To protect a program from its modules, the generator will restrict every write and jump instructions of the modules to addresses of their sandbox.

The generator has to face three issues to do so. The first one is to introduce protection mechanisms before every potentially dangerous instruction. For example it prevents any destination address of jump instructions to be located out of the sandbox.

Secondly, we have to make sure that these protection mechanisms cannot be avoided.

Finally, the transformations injected have to authorize only legal calls from the sandbox to the host program by using entry points specified by the latter. This is the interface we talked about in the introduction of this chapter.

Confining memory accesses. The sandbox is a contiguous memory area reserved for a module's use. The confinement to the sandbox is done by a rewriting process: any address used in the module as a target to a read, a write or a control flow jump is rewritten at run-time to an address that is guaranteed to be inside the sandbox. The sandbox size is chosen to be a power of two. This requirement eases the confinement of the modules in their sandbox by allowing the use of bit arithmetic which accelerates the rewriting process. In fact, we only need to rewrite the most significant bits of addresses to ones that match the sandbox area.

In future examples, we will limit ourselves to the addresses whose most significant bits are 0xda. This sequence of bits is also called a *tag*. Each tag is specific to a unique sandbox and this designation will be used repeatedly in this thesis.

The transformation is simple in theory: the targeted addresses simply have their most significant bits replaced by the tag of the sandbox. In the case of direct addressing, compilers can easily rewrite the address, or fail to compile an explicitly incorrect program. In the case of indirect addressing, things are more complicated. The destination address is stored in a register and its value cannot always be known at compile time.

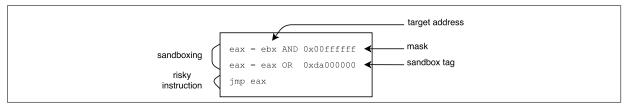

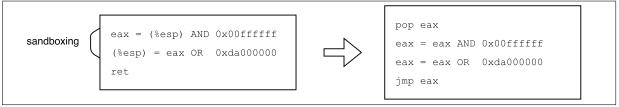

To address these situations, SFI injects runtime modifications in the code of the untrusted module. These modifications consist in the rewriting of the address before the jump or store, and are called *sandboxing*.

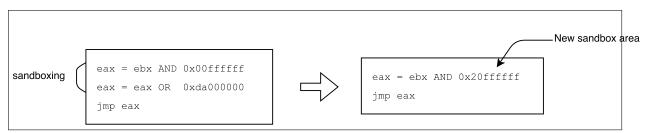

Figure 1.2 – Pseudo code of the sandboxing operation

Figure 1.2 represents an example of the sandboxing operation. The sandboxing starts with a masking operation which sets the most significant bits of the address stored in the register ebx to zero. Afterwards the second instruction writes the tag of the sandbox on the bits it just reinitialized before. Hence we are sure that the jmp instruction will target a location in the sandbox of the untrusted module. Note that the sandboxing does not change the behavior of the module if the targeted address was

already in the sandbox. For the write instructions the principle is the same. Sandboxing instructions are injected before every write that can endanger the program.

Protection of the sandboxing mechanism. We made sure in the previous section that any untrusted module cannot either jump or write on a location out of its sandbox. But this first implementation was very naive: we also need to protect the sandboxing operations, to prevent any malicious code to bypass the runtime checks inserted by SFI. Using the example in Figure 1.2, we could imagine code which directly jumps on the jmp eax instruction. To protect the sandboxing, the solution found by SFI is to reserve dedicated registers exclusively used for sandboxing. These registers will not be available anymore for the rest of the code. Naive sandboxing requires three dedicated registers for each sandbox. A first register is used to keep the mask value (we used the immediate value 0x00fffffff in Figure 1.2). A second register is reserved to store the tag of the corresponding sandbox (we used the immediate value 0xda000000 in Figure 1.2). The third dedicated register is used to manage the operations contained in the sandboxing, in our example in Figure 1.2 it is the eax register. The first two registers are necessary in implementations where the tag and sandbox size is not known at compile time, because there might be more than one module for instance. The third register (eax in our example) is ensured to only store addresses that are inside the sandbox during the whole execution. Then even if malicious code can jump directly to the instruction jmp eax, we will still be sure that the next instruction stays in the sandbox.

The worst case scenario would be that the value stored in eax was wrong and the untrusted module crash or has unexpected behavior, but always contained in the sand-box. Note that since the security property is that the untrusted module stays contained in its sandbox, crashes and unexpected behaviors are considered safe.

These dedicated registers are never used by the rest of the code and their values cannot change except during sandboxing operations. Since we have two sandboxes, one for the data and one for the code we then have a total of six dedicated registers. SFI manages to reduce the number of dedicated registers to five by sharing the same mask for both sandboxes, and we could reduce the number to four by using a statically-defined mask.

Allocating five registers for the sandboxing means that they cannot be used by the program. This is not a problem on RISC architectures like MIPS, Alpha or RISC-V

that have 32 general-purpose registers. Indeed, experiments in the original paper [41] shows that removing five registers from GCC's register allocation phase did not significantly impact performance of test programs. For other architectures, we will see that there are different mechanisms to work around this limitation, without sacrificing security.

**Controlled interactions with the protected program.** It is necessary for SFI to also control the different interactions that modules have with the main program. Without restrictions, malicious modules could, for example, make function calls with wrong parameters which could compromise the state of the main program.

To avoid such a situation, SFI needs the host program to define an interface which describes all the authorized entry points available to external modules. This interface is assumed to be composed of *stubs*, i.e. small functions that execute checks on their parameters, before calling the actual function from the host program. It is assumed that these checks are enough to ensure that the module cannot corrupt its host program by calling stubs of the interface.

Any other means of interacting with the host module or the rest of the system is forbidden. In particular, system calls are forbidden in modules: instead, the module must use a stub that then calls a function from the main program that implements the system call. An implementation could for instance add a stub for a system call. The module would call that stub to perform the system call. Another implementation could refuse to add stubs for system calls, but allow some high-level functions that will, in its expected behavior, make some system calls.

As a nice side effect, such modules are perfectly portable across operating systems on which the host program can run, although they still of course depend on the processor architecture.

### 1.2.3 Verification

As we have seen before, an attacker could provide a malicious module to a user either as being a developer of that module or by substituting a legitimate module with its own. Because of this attacker model, the user needs a protection mechanism. We could think of a central authority delivering certificates, but our experience in, for instance, mobile application stores, show that it does not work well in practice. Instead, the user

is provided with a verifier, a trusted piece of software that checks that all the necessary sandboxing is indeed present in the untrusted module.

The verifier is part of the Trusted Computing Base. This means that it must not have bugs. Indeed, if it works well, it is able to reject incorrectly sandboxed untrusted modules, which could result from a faulty implementation of the generator, or from attacker provided modules. The verifier still relies on the generator, but not critically. The generator produces a binary with a certain format that should be easy to analyze and the verifier simply checks that this format is respected (e.g. that all writes and jumps are sandboxed).

We will see in section 1.5 some verifier designs. They mostly work the same way though: a first pass disassembles the binary. A second pass checks that the SFI properties are respected and that no code that was not disassembled is reachable from the untrusted module, except for a trusted library outside of the sandbox.

|                |                     | nacl          | misfit   | pittsfield     | ARMor    | xfi      | psfi     | fbgi           | bakersfield    |

|----------------|---------------------|---------------|----------|----------------|----------|----------|----------|----------------|----------------|

| References     |                     | [42][33]      | [38]     | [27]           | [45]     | [19]     | [25]     | [12]           | [22]           |

| security model | malicious           | <b>√</b>      | ×        | <b>√</b>       | ×        | ×        | ✓        | ×              | ✓              |

|                | module <sup>2</sup> |               |          |                |          |          |          |                |                |

|                | ARM                 | <b>√</b>      | ×        | ×              | <b>√</b> | ×        | <b>√</b> | ×              | ×              |

| architecture   | x86                 | <b>√</b>      | <b>√</b> | <b>√</b>       | ×        | <b>√</b> | ✓        | <b>√</b>       | ×              |

|                | x86_64              | <b>√</b>      | ×        | ×              | ×        | ×        | ×        | ×              | ✓              |

|                | IR                  | ×             | ×        | ×              | ×        | ×        | <b>√</b> | <b>√</b>       | ×              |

| transformation | assembly            | ✓             | <b>√</b> | <b>√</b>       | ×        | <b>√</b> | ×        | ×              | ✓              |

|                | binary              | ×             | ×        | ×              | ✓        | ×        | ×        | <b>√</b>       |                |

|                | Bundles             | ✓             | × 3      | <b>√</b>       | ×        | × 3      | ×        | × <sup>4</sup> | ✓              |

| Techniques     | Return              | pop+jmp       | outside  | × <sup>5</sup> | shadow   | scoped   | shadow   | no write       | × <sup>5</sup> |

|                | Self modi-          | <b>√</b>      | ×        | ×              | ×        | ×        | ×        | ×              | ×              |

|                | fying code          |               |          |                |          |          |          |                |                |

|                | kernel              | ×             | ×        | ×              | ×        | ✓        | ×        | <b>√</b>       | ×              |

| application    | web                 | <b>√</b>      | ×        | ×              | ×        | ×        | ×        | ×              | ×              |

|                | browser             |               |          |                |          |          |          |                |                |

|                | language            | √ [37][39]    | ×        | ×              | ×        | ×        | ×        | ×              | ×              |

|                | extension           |               |          |                |          |          |          |                |                |

|                | general             | ×             | ✓        | ✓              | ✓        | ×        | ✓        | ×              | ✓              |

|                | purpose             |               |          |                |          |          |          |                |                |

| Certifi        | ed                  | <b>√</b> [30] | ×        | ×              | ✓        | ×        | ✓        | ×              | ×              |

Table 1.1 – Summary of techniques

<sup>2.</sup> if x, the module is still protected against an external attacker that interacts with it

<sup>3.</sup> Indirect calls are checked dynamically

<sup>4.</sup> This technique does not reserve memory blocks, but uses access checks on every byte read, written or executed. The return address is not allowed to be modified.

<sup>5.</sup> Secure on single-threaded applications

## 1.3 Implementations

In this section, we will show the major implementation techniques used in different papers. Instead of showing each individual paper and explaining the techniques they used, this section is organized around the techniques themselves, while citing and explaining differences and common points between implementations that use the technique. You can refer to table 1.1 to get a summary of techniques and applications used in different implementations.

### 1.3.1 Splitting the Code into Constant Bundles

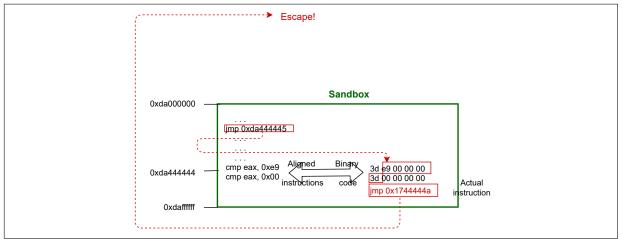

Figure 1.3 – Jumping on an unaligned instruction to bypass SFI

In CISC architectures, instructions are not of a constant size, and the huge number of different possible instructions makes it very likely that reading an instruction starting at the middle of another will execute something meaningful for the processor. In these architectures, it is perfectly possible to hide an arbitrary jump inside a seemingly innocent instruction, as shown in Figure 1.3: by decoding the instructions one by one, an analyzer would be lead to decode the instruction at 0xda444444, which is a simple comparison instruction, just as the next instruction. However, in reality, this instruction is machine code, shown on the right of the figure. The jump before them is misaligned:

it does not target 0xda444444, but one byte later, which happens to be decoded by the processor as another jump instruction, which exits the sandbox.

Figure 1.4 – Vulnerability of basic SFI

Additionally, it is easy to imagine how a malicious module could present sandboxing instructions before every jump, and yet be able to jump to arbitrary addresses. As shown in Figure 1.4, one could write the target address to a register and jump directly to the jump instruction after the sandboxing, bypassing it entirely. The malicious jmp allows the attacker to bypass the masking operation put by the techniques of SFI and then, reach illegal code.

To avoid this, Pittsfield [27] suggests to divide the code into chunks whose size and location are a power of two. These chunks behave like atomic operations. Hence it is not possible to execute the second instruction of a chunk without executing the first one. Thanks to these properties the sandboxing mechanism can be protected so an attacker cannot avoid the masking present before every dangerous instruction. Therefore to obtain such properties on these chunks, the following conditions need to be fulfilled:

- 1. Chunks have a fixed size equal to a power of two;

- 2. Chunks locations are aligned on their size;

- 3. Instructions that are targets of jumps are put at the beginning of a chunk;

- 4. Jump and call instructions are checked so they have their target address always aligned with the chunks size;

- 5. Call instructions are placed at the end of a chunk to have the return at the beginning of the next chunk;

- 6. A protected instruction and its sandboxing are gathered in the same chunk;

- 7. It is forbidden to have an instruction overlap on two different chunks;

- 8. Chunks are padded with no-op instructions.

Drawbacks of this approach are the increased size of the code but also the overhead due to added nop instruction. Indeed the Pittsfield paper <sup>6</sup> judged that between 25 and 50 percent of the slowdows encountered was due to the additional nops used to pad instruction chunks.

### 1.3.2 Protecting the Return Address

The return address is a difficult case for SFI. Indeed since the target address is not stored in a register, it is possible to have race conditions with the classic masking mechanism. For example if a malicious thread modifies the return address in the stack after the masking operation, this could disrupt the flow of the host program.

Since this issue only appears in the context of a multithreaded program, some implementations have choosen not to implement counter-measure, which is insecure in the general case, but is still secure in the case of a mono-threaded execution. In this thesis, we are interested in multithreaded programs, so we now examine different ways to prevent this time-of-check to time-of-use race.

### **Changing the Return Instruction**

A common technique to tackle this issue is to replace the ret instruction with a pop+jmp combination presented in Figure 1.5. The pseudo-code on the left masks the return address directly on the stack. Since stack memory is reachable from other threads of the module, it is possible that the value pointed to by esp has been modified by another thread between the sandboxing operation and the ret instruction. Therefore instead of masking the value stored at the location pointed to by esp we use traditional masking on register eax and we replace ret by pop+jmp.

McCamant and Morrisett [27] have done exactly that in their initial implementation, but decided to go back to a simple ret because of performance issues. Indeed, this technique does not make any use of jump target caches. The technique is also used in

<sup>6.</sup> See [27], page 8

Zeng et al [43], although they also insert an additional check to ensure they return to the caller, and not only to a module's instruction.

Figure 1.5 – Transforming ret into pop+jmp

### **Scoped Stack**

A scoped stack [19] is a slightly more restrictive stack than the usual one. A module can access data on this stack only statically. That means that the only way to read and write to the stack, is via a constant positive offset of the stack pointer, at each program point. A different stack called an access stack can be used when it is necessary to have a stack that can be accessed via computed addresses.

At each point in the program, the depth of the scoped stack is known statically, because only push, pop, call and ret can modify it. Direct modification of the stack pointer is forbidden. Combined with the fact that a write is done at a statically known offset from the stack pointer, it is easy to see when a write occurs outside the stack or on the return address, and reject such modules.

#### **Control Stack**

A control stack (or shadow stack) is a special stack that records return addresses of functions. In ARMor [45], a routine copies and restores return addresses from and to the normal stack upon function call and return. The shadow stack is protected against access by the sandbox, and thus guaranteed to only contain legal addresses. Even if the return address is changed on the stack by the module on the normal stack, its normal value is restored upon return, and thus the return instruction is safe. This technique requires a dedicated register to point to the shadow stack.

MiSFIT [38] uses a per-thread global state outside of the sandbox to record the return addresses of module functions that were called, and a special procedure is used to read it and jump to it on function return. This is not exactly a scoped stack, since this data is not necessarily stored in a stack, but the technique and usage is very similar. Having the return address outside of the sandbox ensures that the module cannot modify it. Compared to the shadow stack technique, this looses processor optimizations and caches for the return address, but it does not require an additional dedicated register.

### 1.3.3 Interfacing with Trusted Libraries

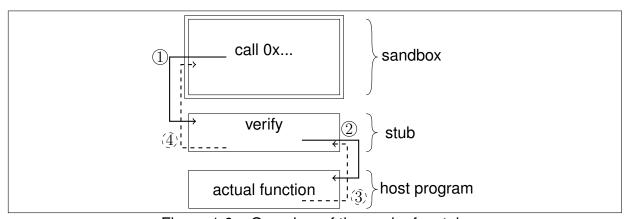

Figure 1.6 – Overview of the work of a stub.

Wahbe et al. [41] introduce the concept of stubs in the context of SFI. Stubs are small, trusted pieces of code, available in a statically known location outside the sand-box. Module code is allowed to call them directly, and their role is to dynamically check the arguments passed to the host function or system call they protect. Figure 1.6 summarizes the role of the stub:

- 1: Direct call to the stub;

- 2: After verifying the arguments, the stub calls the library function;

- **3**, **4**: Return to the sandbox.

The multiple implementations seen are quite similar to these stubs but hold different names. Nacl [42] uses the concept of trampoline and springboard which are also part of the sandbox. On x86, trampolines are also used to execute a far call to a library function that is in another segment, while springboards restore the sandbox environment before returning to the isolated module.

PSFI [25] and MiSFIT [38] both allow function pointers to be used to call the trusted library. To quickly check that the module is correctly sandboxed, SFI uses a sandboxing operation. Similarly, instead of statically verifying the possible value of a function pointer, these implementations verify the content of the function pointer at runtime. They have a hash table containing the set of authorized function pointers outside of the sandbox and allow only a static call to a procedure that checks whether a function pointer is in the hash table. If not, the pointer is rejected and the function is not called.

#### 1.3.4 Transformation Point

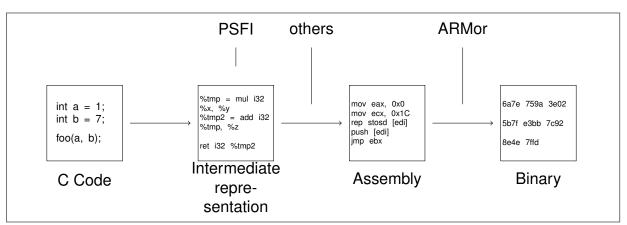

In order to ensure safety of a module, SFI implementations need to apply transformations (mainly adding sandboxing) to the code. Different implementations choose a different place in the build toolchain to apply its transformations, with different benefits and drawbacks. The vast majority of implementations choose to modify the compiler to output sandboxed assembly code. Here, we highlight two outliers.

Figure 1.7 – Transformation point in different implementations

#### **Binary Rewriting**

This method consists in rewriting the module at link-time, between the assembly and the binary representation. Link-Time Optimization can be used to decrease the overhead. ARMor [45] uses Diablo, a link-time binary rewriting framework to rewrite the binary output by GCC.

## **High-level Transformation**

Psfi [25] is the only implementation which rewrites the code at a higher level than assembly. They are taking advantage of the main theorem of CompCert [26] to produce isolated modules. CompCert is a formally verified C compiler. It is provided with a main theorem which says that, if it produces a result, the behavior of the resulting binary is a behavior of the initial sources, if it does not have undefined behaviors. CompCert is written and proved with the Coq [40] proof assistant. Coq is a programming environment in which one can express programs, mathematical properties and proofs. The assistant is able to follow a proof development and validate every step of reasoning, which gives a high assurance that a mathematical property proved in Coq is actually true.

In PSFI, the transformations are done at the CMinor level, an intermediate language that can be targeted by many languages, but that is still high-level enough to then be compiled to assembly for different architectures.

At this level, they isolate modules by targeting all pointer dereferences for writes and calls and add the sandboxing mechanism with simple if..then conditionals. Additionally, since CMinor is the language for optimizations, they benefit from it: runtime checks can be optimized away by the compiler.

The benefits are that they take advantage of the optimizations of the compiler which can reduce the sandboxing overhead and also that the code transformations introduced by SFI are easily portable. A drawback is that the security property is not easily provable by a verifier after the compilation phase since the compiler may modify the sandboxing instructions during the code optimizations. More details are given on the verification of a high-level code generation in Section 1.5.3.

## 1.3.5 Self-modifying Code

One of the fundamental requirements of SFI is that the verifier checked every instruction that is going to be executed by the module. Self-modifying code can therefore not be allowed, since the generated instructions have not been verified statically before the module's execution.

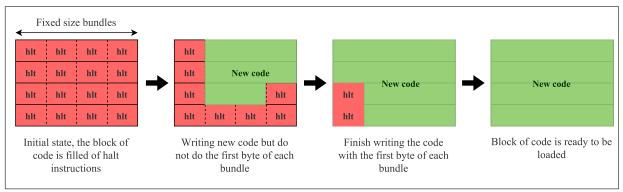

However, some applications, such as JIT compilers, need to modify the code they execute for better efficiency. In NaCl [4], the authors suggest an extension of NaCl that allows code to modify itself. It introduces new library functions available to the code

to load, modify and unload dynamically generated code. Unallocated space is filled with hlt instructions. This feature makes use of the fixed size bundles memory layout described in Section 1.3.1.

- To load a code, the implementation verifies that it respects the sandbox policy. If it does, it loads it at an unallocated space in the sandbox space. The loading phase is presented in Figure 1.8 with four bundles of memory. It needs to load the first byte of each bundle last, so that a thread that would execute during the loading of the bundle will immediately execute a hlt. Otherwise, the thread would be able to execute statically unknown instruction because when the writing process is in the middle of an instruction, the semantic of that instruction is unknown.

- To unload a code, the implementation writes back the hlt instructions, starting with the first byte of each affected bundle. In this way, any execution in this invalidated region will crash the module. Then, marking the region free can happen only when the implementation knows no thread is currently executing in the affected bundle. For that purpose, it waits for each thread to enter a trampoline (Section 1.3.3), because at that time they are not inside a freed bundle, and they would execute a hlt instruction, at the beginning of a freed bundle afterwards. That is especially important for threads sleeping in the middle of a bundle: they should not wake up in the middle of an instruction later affected to the same location.

- To modify a code, the implementation needs to ensure the modified code is laid out exactly as the old one. First, the first byte of each bundle is rewritten to hlt. Each instruction is then rewritten in order using an eight-byte atomic write (because of a hardware limitation). If an instruction is longer than that, it is first replaced by a hlt instruction, rewritten entirely except for the first byte, and then only the first byte is rewritten to the correct value.

## 1.4 Optimizations

## 1.4.1 Using Hardware Security for Isolation

Some architectures may provide specific hardware protection mechanisms. Some implementations use these protections to implement the security and speed of the

Figure 1.8 – Loading code during runtime with SFI

### transformed binary.

Most architectures have a mechanism to give read, write and execution privileges to memory areas. For instance on x86, segments can have a NX flag, forbidding execution, and memory pages can be read-only or read-write. On x86\_64, memory pages can handle execution as well as write privileges. This mechanism is exploited in most operating systems to disable execution on the stack, and the heap, and writes to the code of a program <sup>7</sup>. This is especially useful to prevent writes to the code section from self-modifying code, and execution of arbitrary code from the data section.

Moreover x86-32's segment mechanism can prevent jumping, reading or writing outside designated areas. For instance, NaCl [42] and Pittsfield [27] use those to constrain the module to its sandbox. Since a hardware check is used instead of a software check, this technique implies no overhead. To use it safely, implementations must forbid any modification of the segment registers from untrusted code.

## 1.4.2 The Art of Choosing the Mask

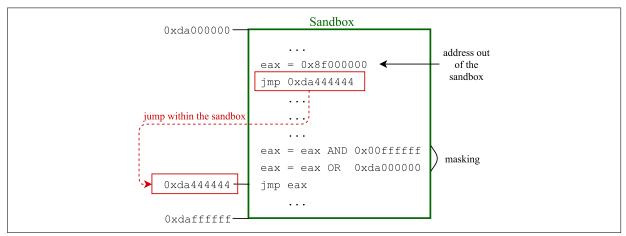

The sandboxing operation usually uses two instructions as shown on the left side of Figure 1.9. A first AND instruction to turn off the bits matching the tag of the SFI memory region, then an OR instruction to set these bits to the sandbox tag.

Pittsfield [27] suggests using tags with only one bit set for the sandboxed code and sandboxed data. The reason is that with a one-bit tag, we can replace the sandboxing

<sup>7.</sup> As long as the binary has metadata to request this protection mechanism, see the Executable and Linking Format specification [13], at page 2-3. The program header (used to specify a list of memory regions that must be loaded to prepare the program for execution) contains a flag to specify read, write and execution privileges.

operation with a simple and: by setting every tag bit to zero, except the bit that makes up the tag, the resulting address has either the correct tag (with one bit set), or the zero-tag (with no bit set). If the tag is correct, execution continues safely, and if it is incorrect, execution stops, since data is read/written or code is executed from a memory that does not have the corresponding priviledges.

For example [0x00000000 - 0x0ffffffff] is the zero-tagged region, [0x100000000 - 0x1ffffffff] is the sandboxed data and [0x20000000-0x2ffffffff] is the sandboxed code. Pointers are rewritten either to the sandbox' tag, or to the zero tag which was reserved for this situation. We see in Figure 1.9 that by placing the sandbox areas cleverly, the AND and OR operations reduce to a single AND operation for the sandboxing.

Figure 1.9 – Reducing the sandboxing to a single instruction

This optimisation has also been reused in NaCl [42] and BakerSFleld [22].

## 1.4.3 Register Management

#### **Naive Implementation**

During the code transformation by the SFI techniques the program is already in the form of assembly code. Eventually, for the sandboxing instructions, SFI techniques need to use some registers, which have already been assigned values by the program. Therefore, before executing the sandboxing mechanisms, the program should save the register values and restore them after the sandboxing. An implementation of this sequence can be seen in Figure 1.10(a). Before starting the sandboxing instructions, the value of the register eax is stored on the stack with the instruction push eax. At the end of the sandboxing operation the register eax is restored with pop eax.

```

push eax

eax = ebx AND 0x00ffffff

eax = eax OR 0xda000000

jmp eax

pop eax

(a) Classic sandboxing

(b) SFI with dedicated registers

```

Figure 1.10 – Register management for sandboxing

## **Dedicated Registers**

The naive implementation main issue is obvious: the sandboxing operation needs at least four instructions! The cost of sandboxing becomes quite high.

An idea already used in the work of Wahbe et al. [41] is to use dedicated registers for the sandboxing operations. In the previous example in Figure 1.10(a), the register eax would be specifically used for the masking operations. Hence the instructions used to save and restore register values would not be necessary anymore and our sandboxing would become as in Figure 1.10(b), reduced to two sandboxing instructions. Additionally, using a dedicated register means that, the register will always contain an address in the sandbox, reducing the number of sandboxing instructions when the same address is used multiple times.

Keeping some registers solely for the sandboxing operations also means that the program cannot access these registers for its execution. With a reduced number of available registers, overheads are also more likely to happen due to register pressure. This downside is especially true on some architectures with few general purpose registers like x86-32 which only has eight.

#### Register Management with Liveness Analysis

Another possibility for register management is possible thanks to the use of static analysis and especially liveness analysis [43]. Liveness analysis allows the system to know whenever a register is considered dead which means that the value stored in the register will not be used in the future instructions. In our case knowing the dead registers allows the SFI techniques to use these registers for the sandboxing since these registers' values can be modified without hindering the program. Thus, when there are

enough dead registers, the sandboxing operations will be similar to the one with dedicated registers as in Figure 1.10(b). But when available registers are not enough, the classic implementation will take place as in Figure 1.10(a). This implementation can be considered a compromise between the two previous solutions: it both optimizes the use of registers and avoids the overhead due to register pressure in the dedicated registers proposition, at the cost of not being able to skip a sandboxing safely.

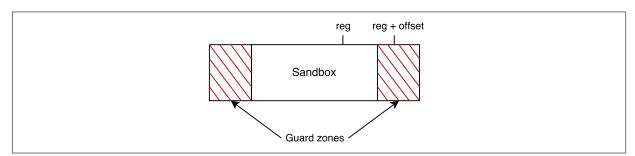

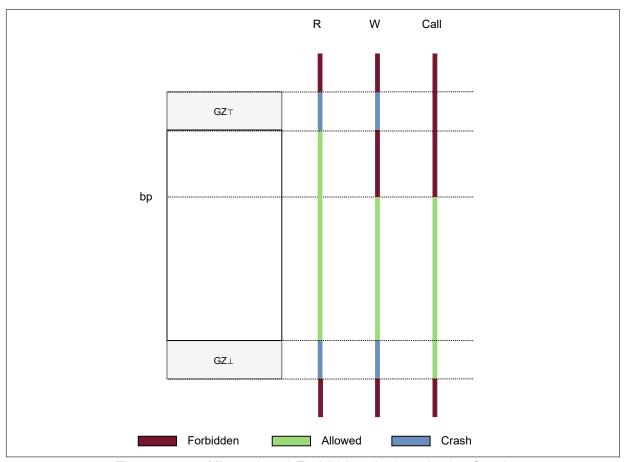

#### 1.4.4 Guard Zones

Some registers like ebp or esp are often used with offsets to deal with local variables or return addresses. Another example is the use of arrays. When accessing a value, an array dereferences its base pointer with some offset. Since these registers are repeatedly used after being set, it might be ineffective to check their value before each use. To optimize this case, similarly to loop optimization in Section 1.4.6, these registers are checked only once, when their value is modified. Afterwards they do not need to be checked when used with a small offset.

This optimization is implemented with so-called guard zones around the sandboxes (Figure 1.11). A guard zone is an unallocated memory region: a read, write or jump to that memory region will lead to a crash of the program. By checking that a register is inside the sandbox and that the offset is smaller than the size of the guard zone, the verifier can check that the actual value (value of register + offset) is either inside the sandbox, or inside the guard zone. Execution therefore either continues as expected, or aborts immediately. If the offset is bigger than the guard zone however, the address could be outside of the sandbox and guard zones, so the generator should reapply a sandboxing operation, or the verifier will reject the program as potentially unsafe.

Figure 1.11 – Guard zones

## 1.4.5 Protecting the Control Flow Graph

In SFI, indirect jumps are required to point to aligned addresses in the sandbox. A more fine-grained technique is called Control Flow Integrity [1]. This technique inserts run-time checks that the computed jump follows a certain policy. In particular, this technique is able to discriminate between function start and the middle of a function. It is then able to block jumps that do not target the beginning of a function. With this technique, bundles are not required anymore, and their overhead can be spared. However, the threat model is different, as the control flow is given by the programmer. CFI requires trust on the programmer to provide adequate control flow information.

CFI works by indicating the beginning of functions by a four-byte constant, that cannot be found anywhere else in the code, except for the start of a function. Indirect jumps and calls are rewritten to execute a small routine that checks the presence of the constant. The routine itself must recompute the constant to prevent embedding it, outside the beginning of a function. Otherwise, somewhere inside the routing would be considered a safe place to call. If the routine finds the constant just before the jump target, it executes the jump, otherwise it prevents it.

XFI [19] uses CFI to create a sandbox similar to SFI. In this implementation, data access is sandboxed exactly like in [41], while code is sandboxed using CFI. It assumes the code producer is not malicious and provides correct control flow information too. In general, this technique is more precise on what is allowed, but provides different guarantees than SFI.

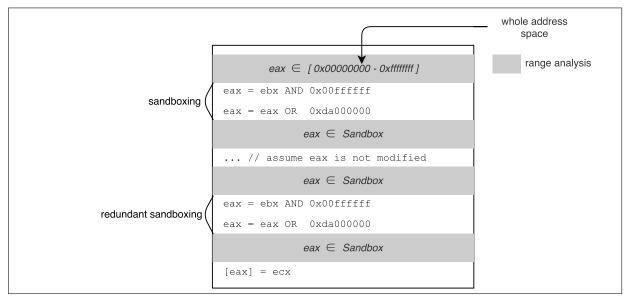

## 1.4.6 Range Analysis

Range analysis is a static analysis, which evaluates the range of the possible values of the registers. For example a freshly modified register will have its range equal to the whole virtual memory, whereas a register which has just been sandboxed will have its range equal to the sandbox memory area. These information allow two new optimizations presented in this section. These techinques are presented in Zeng et al [43].

#### **Redundant Checks**

This optimization takes place after the transformation of the code by the SFI techniques. It aims at removing sandboxing operations which are redundant and slow the untrusted module down. To detect such occurrences, a range analysis is performed for every register. An example can be seen in Figure 1.12, where the register eax starts with an unknown range value. Afterwards eax is sandboxed with a value matching an address in the sandbox. Later we see that eax without its value having been modified is subject to another sandboxing operation. Hence this second sandboxing is redundant and can be removed from the isolated module for better speed.

Figure 1.12 – Redundant check

#### **Loop Check Hoisting**

This optimization allows the isolated module to reduce the number of sandboxing during loops by hoisting the sandboxing before the loop. This speedup can only be applied in certain loops where the range analysis deems that in the loop, no write or jump instruction can exit the sandbox.

A simple example is presented Figure 1.13 where the fields of an array are being incremented. array is a pointer to an array of integers. On every occurrence of the loop, a field of the array is incremented. Therefore the SFI techniques make sure that

the pointers used to access these fields (array+i) cannot point to a location outside of the sandbox and do the pseudo-operation sandbox(array+i).

However thanks to range analysis on this case, one can know that if the pointer array is within the sandbox then the pointers array+i always point to the area covered by the sandbox plus its guard zones described in Section 1.4.4. Thus the sandboxing in the loop is unnecessary and can be hoisted at the beginning of the loop as shown on the right side of Figure 1.13.

```

int i = 0;

while (i < array_len) {

sandbox(array + i);

array[i] = array[i] + 1;

}

int i = 0;

sandbox(array);

while (i < array_len) {

array[i] = array[i] + 1;

}</pre>

```

Figure 1.13 – Loop check hoisting

## 1.5 Verification Techniques

Verification is usually the last step of SFI. This code is the major part of the Trusted Computing Base in SFI techniques (the interface between the host and untrusted modules are in the TCB too). This means that the amount of trust one can put in the SFI implementation is more or less equal to the trust put in their verification.

Since the verification step needs to be sound, all the verifiers seen in the literature have a conservative policy. Indeed the verifier checks if the code transformation done previously are enough to guarantee the security property of SFI. Hence all executables accepted by the verifier are safe. However that also means that a safe program, which does not fulfill the criteria of the verifier will not be accepted either.

In SFI, most of the time, the verification consists in checking that every dangerous instruction is preceded by a sandboxing operation. To execute this step multiple solutions are available, RockSalt [30] for example directly uses regular expressions on binary files. But most implementations of verifiers start by disassembling the executables then check that the program follows the procedures of SFI. Unfortunately disassembling is a non computable problem for generic programs and is still widely searched, which is problematic for this verification step. Most of the time the verification of assembly code is much simpler than the disassembly phase so the amount of trusted code can generally be reduced to the disassembler.

Therefore this section will address the different ways found in the literature of SFI to have reliable verification like having compilation constraints for better disassembly or using formal methods for the verification.

## 1.5.1 Linear Disassembly