## Numerical and Experimental Investigations on Mechanical Stress in 3D Stacked Integrated Circuits for Imaging Applications

Clément Sart

### ► To cite this version:

Clément Sart. Numerical and Experimental Investigations on Mechanical Stress in 3D Stacked Integrated Circuits for Imaging Applications. Chemical and Process Engineering. Université Grenoble Alpes, 2019. English. NNT: 2019GREAI084. tel-02517015v1

## HAL Id: tel-02517015 https://theses.hal.science/tel-02517015v1

Submitted on 24 Mar 2020 (v1), last revised 26 Mar 2020 (v2)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Communauté UNIVERSITÉ Grenoble Alpes

## THÈSE

Pour obtenir le grade de

## DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Matériaux, Mécanique, Génie Civil, Électrochimie

Arrêté ministériel : 25 mai 2016

Présentée par

## **Clement SART**

Thèse dirigée par **Rafael ESTEVEZ**, **Professeur, Université** Grenoble Alpes sous l'encadrement de Vincent FIORI, Sébastien GALLOIS-GARREIGNOT et Sandrine LHOSTIS

préparée au sein du Laboratoire de Science et Ingénierie des Matériaux et Procédés (SIMaP) dans l'École Doctorale d'Ingénierie - Matériaux, Mécanique, Environnement, Énergétique, Procédés, Production (I-MEP2)

## Numerical and Experimental Investigations on Mechanical Stress in 3D Stacked Integrated Circuits for Imaging Applications

Thèse soutenue publiquement le **13 décembre 2019**, devant le jury composé de :

M. Olivier THOMAS

Professeur, Aix Marseille Université, Président, Rapporteur

M. Philippe DJEMIA

Professeur, Université Paris 13, Rapporteur

Mme Hélène FRÉMONT

Maître de Conférences HDR, IMS Bordeaux, Examinatrice

M. Rafael ESTEVEZ

Professeur, Université Grenoble Alpes, Examinateur, Directeur de thèse

Mme Sandrine LHOSTIS

Docteur-Ingénieur, STMicroelectronics Crolles, Invitée, Co-encadrante

**M. Sébastien GALLOIS-GARREIGNOT** Docteur-Ingénieur, STMicroelectronics Crolles, Invité, Co-encadrant

# Contents

| Re | merci                                                                             | iements                                                                                                                                           | ix                                      |  |  |  |  |  |  |

|----|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|--|

| Ge | neral                                                                             | Introduction                                                                                                                                      | 1                                       |  |  |  |  |  |  |

| Ι  | 3D S<br>I.1<br>I.2                                                                | Stacking of Integrated Circuits for Imaging Applications         Context       Stacking steps         Basic processing steps       Stacking steps | $5\\5\\7$                               |  |  |  |  |  |  |

|    |                                                                                   | I.2.1       Film deposition          I.2.2       Lithography                                                                                      | $\begin{array}{c} 7 \\ 10 \end{array}$  |  |  |  |  |  |  |

|    |                                                                                   | I.2.3         Etching                                                                                                                             | $\frac{11}{12}$                         |  |  |  |  |  |  |

|    | I.3                                                                               | I.2.5 Planarization                                                                                                                               | $\frac{13}{14}$                         |  |  |  |  |  |  |

|    |                                                                                   | I.3.1Semiconductor devices (front-end-of-line)                                                                                                    | $\begin{array}{c} 14 \\ 17 \end{array}$ |  |  |  |  |  |  |

|    |                                                                                   | I.3.3Metal interconnections (back-end-of-line)                                                                                                    | $\frac{18}{20}$                         |  |  |  |  |  |  |

|    | I.4                                                                               | I.3.5 Pixel array Back-end processing: from IC to packaged chip                                                                                   | $\frac{21}{23}$                         |  |  |  |  |  |  |

|    |                                                                                   | I.4.1         Thinning                                                                                                                            | $\frac{23}{24}$                         |  |  |  |  |  |  |

|    |                                                                                   | I.4.3         Assembly                                                                                                                            | $\frac{24}{28}$                         |  |  |  |  |  |  |

|    | I.5                                                                               | Current challenges in integrated circuit manufacturing                                                                                            | 29<br>30<br>32                          |  |  |  |  |  |  |

|    | I.6                                                                               | I.5.2 3D packaging                                                                                                                                | 33<br>37                                |  |  |  |  |  |  |

|    |                                                                                   |                                                                                                                                                   | 40                                      |  |  |  |  |  |  |

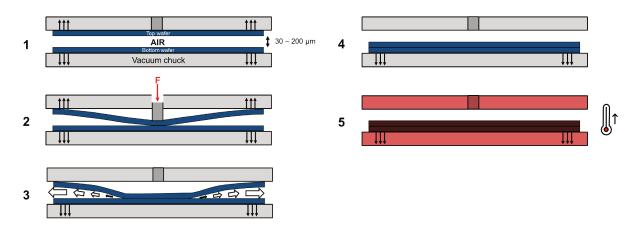

| Π  | Cu/SiO <sub>2</sub> hybrid bonding process for chip stacking<br>II.1 Introduction |                                                                                                                                                   |                                         |  |  |  |  |  |  |

|    |                                                                                   |                                                                                                                                                   | 53<br>54<br>54                          |  |  |  |  |  |  |

|    |                                                                                   | II.2.1       Flocess variants         II.2.2       Surface preparation         II.2.3       Bonding sequence                                      | 55<br>57                                |  |  |  |  |  |  |

|    |                                                                                   | II.2.6       Donting bequence :                                                                                                                   | 58<br>64                                |  |  |  |  |  |  |

|    | II.3                                                                              | II.2.6 Current challenges                                                                                                                         | 65<br>66                                |  |  |  |  |  |  |

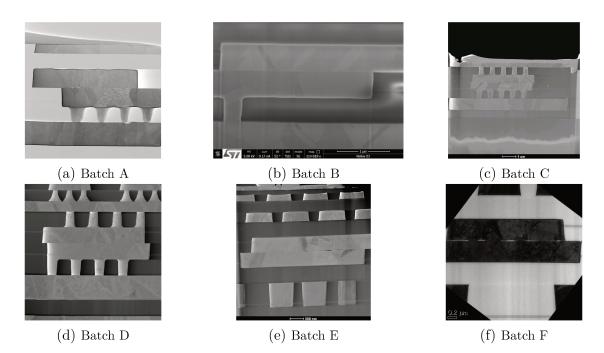

|     |       | II.3.1    | Samples description                                                                                                           | 66  |

|-----|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------|-----|

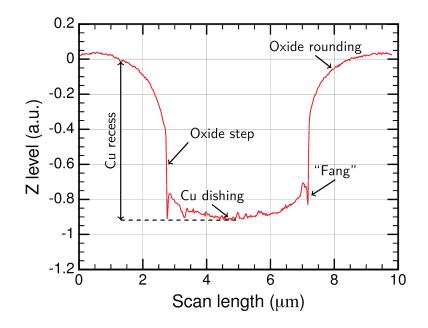

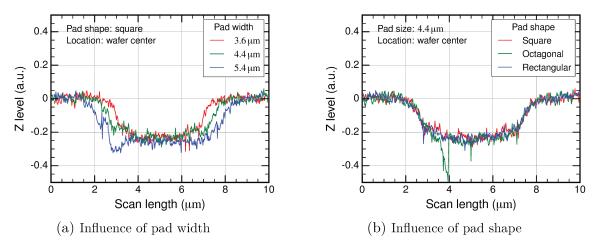

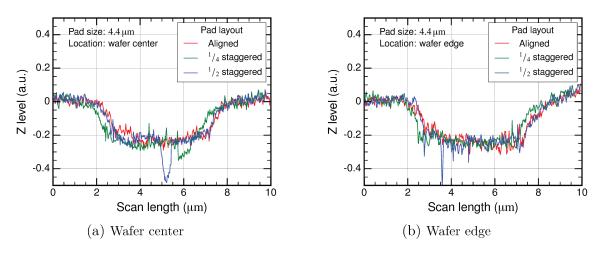

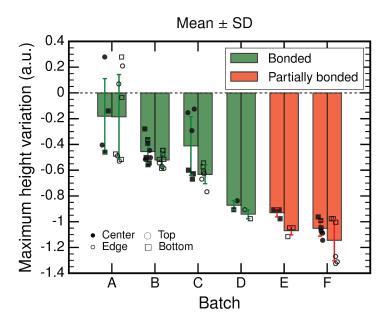

|     |       | II.3.2    | $Cu/SiO_2$ surface topography characterization before bonding                                                                 | 67  |

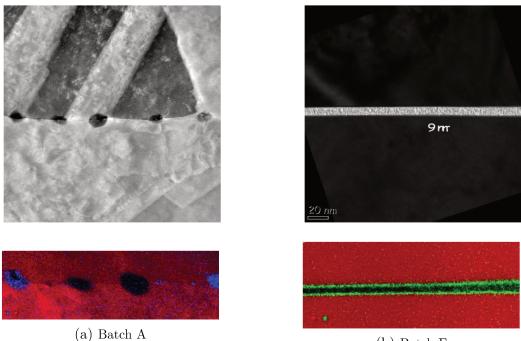

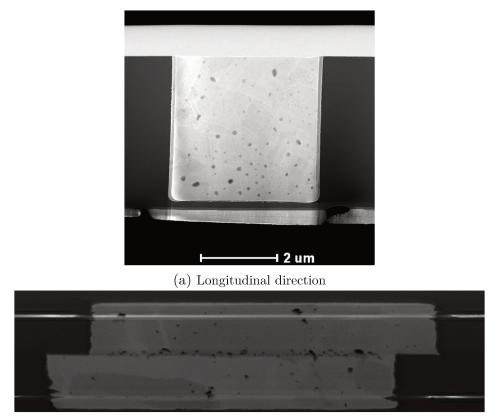

|     |       | II.3.3    | Cu-Cu interface morphological characterization after annealing                                                                | 70  |

|     |       | II.3.4    | Discussion                                                                                                                    | 75  |

|     | II.4  | Numer     | rical study                                                                                                                   | 76  |

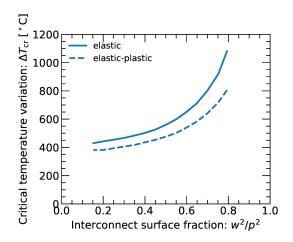

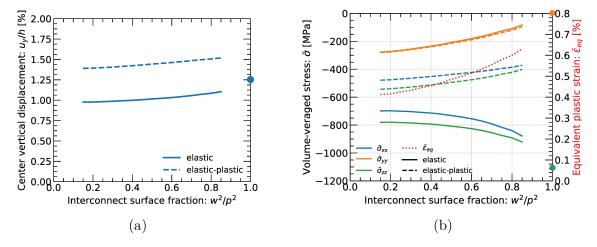

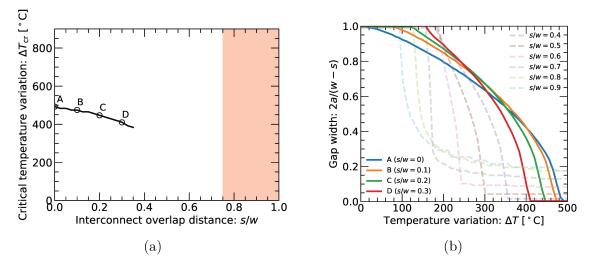

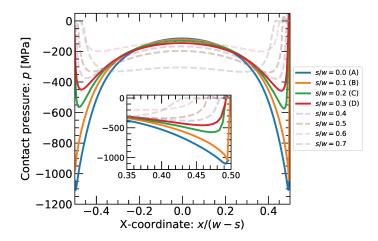

|     |       | II.4.1    | •                                                                                                                             | 77  |

|     |       | II.4.2    |                                                                                                                               | 79  |

|     |       | II.4.3    |                                                                                                                               | 95  |

|     | II.5  |           |                                                                                                                               | 97  |

|     |       |           |                                                                                                                               | 98  |

|     |       |           |                                                                                                                               |     |

| III | Inves | stigation | n of mechanical failures in interconnect layers induced by wire bonding on                                                    |     |

|     |       | side pa   |                                                                                                                               | .09 |

|     | III.1 | Introdu   | $\mathrm{uction}$                                                                                                             | .09 |

|     | III.2 | Literat   | ture review                                                                                                                   | .11 |

|     |       | III.2.1   | Methodology                                                                                                                   | .11 |

|     |       | III.2.2   | Robustness index                                                                                                              | .13 |

|     |       | III.2.3   | Influence of interconnection layout                                                                                           | .16 |

|     | III.3 | Strateg   | gy                                                                                                                            | .18 |

|     | III.4 | Experi    | mental procedure                                                                                                              | 19  |

|     |       | III.4.1   | Cratering test                                                                                                                | .19 |

|     |       | III.4.2   | Test chip                                                                                                                     | .19 |

|     |       | III.4.3   | Test structures                                                                                                               | .20 |

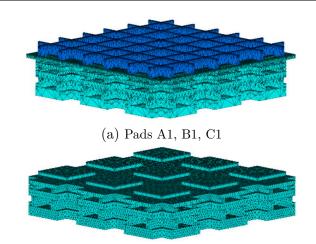

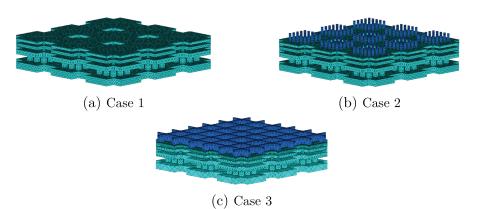

|     | III.5 |           | ing methodology                                                                                                               |     |

|     |       |           | Global model                                                                                                                  |     |

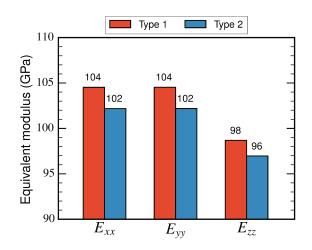

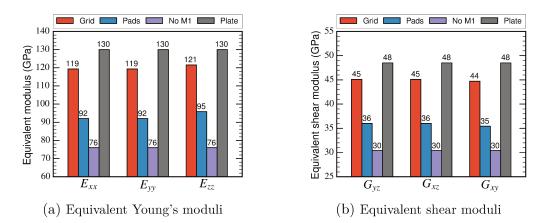

|     |       |           | Homogenization procedure                                                                                                      |     |

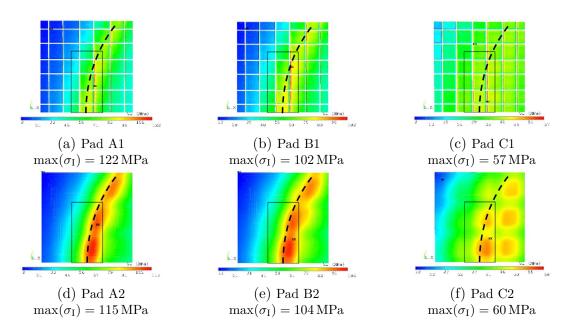

|     |       |           | Submodel                                                                                                                      |     |

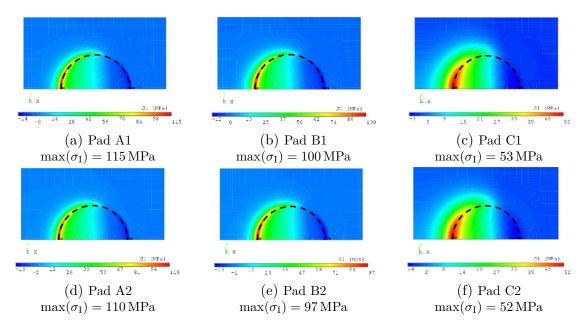

|     |       |           | Robustness criterion                                                                                                          |     |

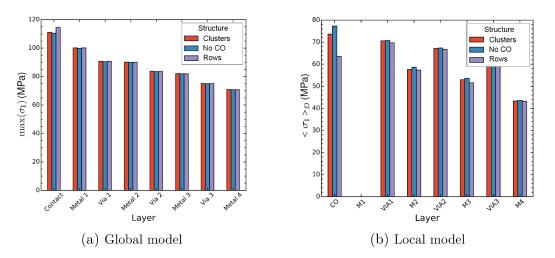

|     | III.6 |           | ${f s}$                                                                                                                       |     |

|     |       |           | Cratering test                                                                                                                |     |

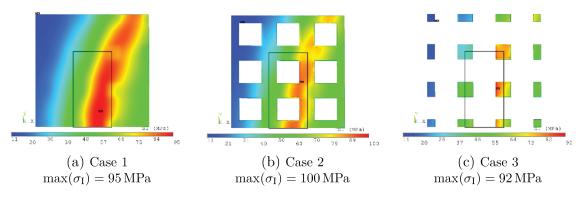

|     |       |           | Numerical comparison                                                                                                          |     |

|     |       |           | Parametric study                                                                                                              |     |

|     | III.7 |           | sion                                                                                                                          |     |

|     |       |           | Influence of bondpad capping                                                                                                  |     |

|     |       |           | Influence of interconnect layout                                                                                              |     |

|     |       |           | Methodology                                                                                                                   |     |

|     | 111.8 |           | $1$ sions $\dots \dots \dots$ |     |

|     |       |           |                                                                                                                               |     |

|     | 10010 |           |                                                                                                                               | 0   |

| IV  | Proc  | ess-indu  | uced Thermomechanical Stresses in a 3D BSI Image Sensor Stacked by Hybrid                                                     |     |

|     | Bond  | ding      | 1                                                                                                                             | .57 |

|     | IV.1  | Introdu   | uction                                                                                                                        | .57 |

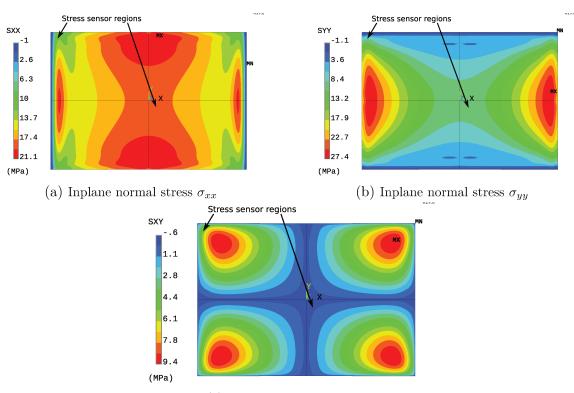

|     | IV.2  | In situ   | stress evaluation using Si piezoresistive stress sensors                                                                      | .58 |

|     |       |           | Overview of stress sensors technologies for integrated circuits 1                                                             |     |

|     |       |           |                                                                                                                               | .60 |

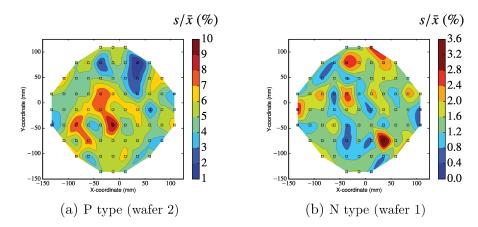

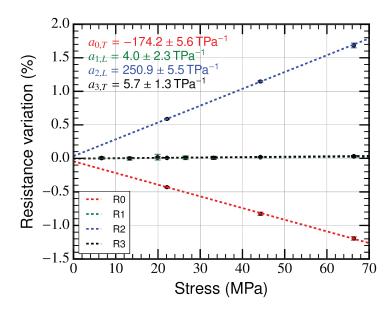

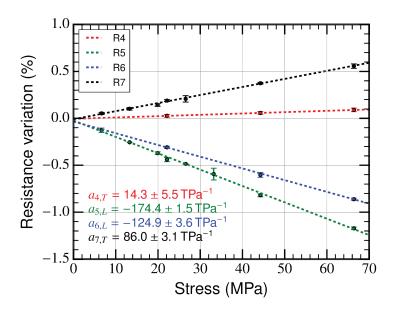

|     |       |           |                                                                                                                               | .68 |

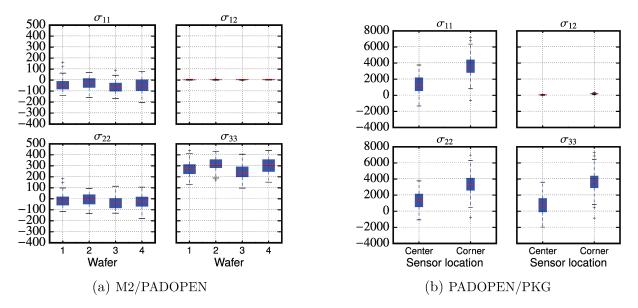

|     |       |           |                                                                                                                               | 73  |

|     |       |           |                                                                                                                               |     |

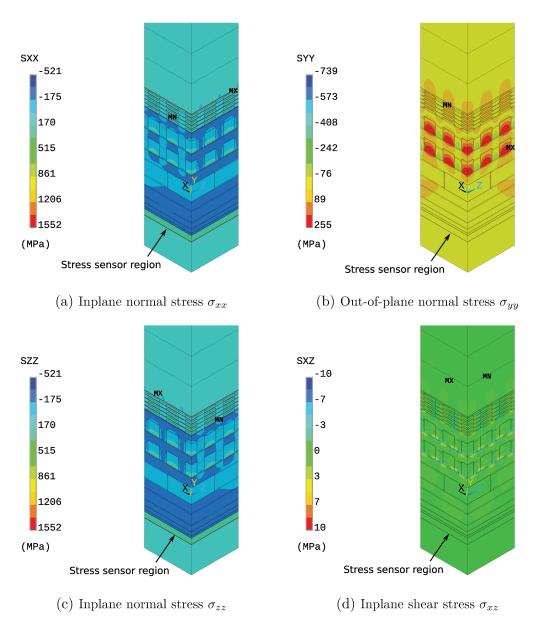

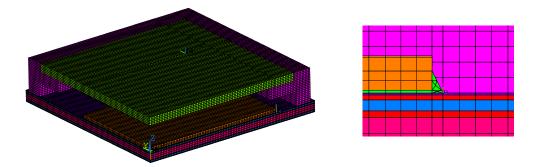

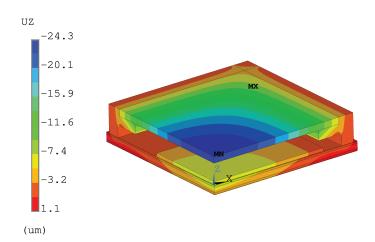

|     | IV.3  | Finite    | element modeling of process-induced stress build-up                                                                           | .91 |

|     | IV.3  |           | element modeling of process-induced stress build-up                                                                           |     |

|    | IV.4 Discussion       IV.4.1 Influence of temperature         IV.4.1 Influence of temperature       IV.4.2 Stress sensor sensitivity         IV.4.2 Stress sensor sensitivity       IV.4.3 Measurement procedure         IV.4.3 Measurement procedure       IV.4.3 Measurement procedure | 204<br>207<br>209 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|    | IV.5 Conclusions                                                                                                                                                                                                                                                                         |                   |

| A  | Semiconductor devices: P-N diode, MOS capacitor and MOSFET transistor                                                                                                                                                                                                                    | 227               |

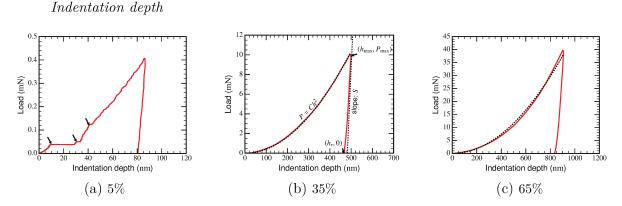

| В  | Estimation of the elastoplastic properties of an electroplated Cu thin film by nanoinden-<br>tation                                                                                                                                                                                      | 233               |

| С  | General equations for the various piezoresistive stress sensor configurations on $(100)$ Si wafers                                                                                                                                                                                       | 243               |

| Ré | sumé                                                                                                                                                                                                                                                                                     | 251               |

# Acronyms

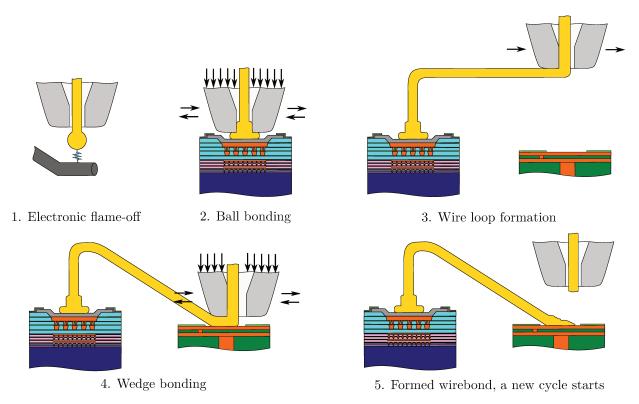

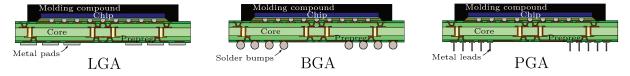

3D three-dimensional ADAS automated driver-assistance systems ADC analog/digital converter AFM atomic force microscope APS active pixel sensor ARE area release energy ASIC application-specific integrated circuit BCB benzocyclobutene BE back-end BEoL back-end-of-line BGA ball-grid-array BOA bond-over-active BSI backside-illuminated C4 controlled-collapse chip connection CIS CMOS image sensor CMOS complementary MOS CMP chemical-mechanical polishing CO contact CSP chip-scale packaging CTE coefficient of thermal expansion CUP circuit-under-pad CV constant velocity CVD chemical vapor deposition DC direct current DIB device interface board DRAM dynamic random-access memory DRIE deep reactive-ion etching EBSD electronic backscattering diffraction ECD electrochemical deposition EDX energy-dispersive X-ray spectroscopy EFO electronic flame-off

F2B face-to-back F2F face-to-face FAB free air ball fBEoL far-back-end-of-line FC flip-chip FE front-end FEoL front-end-of-line FIB focused ion beam FSG fluorosilicate glass FSI frontside-illuminated GPS generalized plane strain GS global shutter HAST highly accelerated stress test HB hybrid bonding HBM hybrid bonding metal HBV hybrid bonding via HDPCVD high-density plasma CVD HDR high-dynamic-range HTS high-temperature storage IC integrated circuit ILD interlayer dielectric IMC intermetallic compound IMD intermetal dielectric IO input/output IRDS International Roadmap for Devices and Semiconductors ISP image signal processing ITRS International Roadmap for Semiconductors KOZ keep-out zone LGA land-grid-array

LPCVD low-pressure CVD MC molding compound ML metallization level MOL middle-of-line MOS metal-oxide-semiconductor MOSFET MOS field-effect transistor MPU microprocessing unit NRE nodal release energy NTRS National Roadmap for Semiconductors PECVD plasma-enhanced CVD PGA pin-grid-array PMD pre-metal dielectric PSG phosphosilicate glass PTFE polytetrafluoroethylene PVD physical vapor deposition **RF** radiofrequency RS rolling shutter RS row select RST reset RT room temperature RUC representative unit cell SACVD sub-atmospheric CVD

SEM scanning electron microscopy SF source follower SiP system-in-package SLID solid-liquid interdiffusion SN sensing node SOI silicon-on-insulator SPAD single-photon avalanche diode STI shallow trench isolation TC thermal cycling TCR temperature coefficient of resistance TEM transmission electron microscopy TEOS tetraethyl orthosilicate THB thermal-humidity bias TSV through-silicon via ULK ultra-low-k USG undoped silicate glass UV ultraviolet VCCT virtual crack closure technique via vertical interconnect access WB wire bonding WLCSP wafer-level chip-scale-packaging

## Remerciements

Ces travaux de thèse ont été menés dans le cadre d'un contrat CIFRE à STMicroelectronics Crolles, en collaboration avec le laboratoire SIMaP de l'Université Grenoble-Alpes.

Je tiens d'abord à remercier Rafael Estevez d'avoir accepté de diriger cette thèse, pour son suivi régulier et ses conseils, ses encouragements et sa bonne humeur ! Je remercie également vivement Vincent Fiori, Sandrine Lhostis et Sébastien Gallois-Garreignot pour leur encadrement. Merci de m'avoir fait confiance pour mener à bien ce projet, puis donné tous les moyens pour réussir. J'ai beaucoup apprécié travailler à vos côtés. Merci pour votre soutien, votre rigueur, votre enthousiasme, votre patience aussi...

À MM. Olivier Thomas et Philippe Djémia, j'adresse mes plus sincères remerciements pour leur retour critique et attentif sur ce manuscrit, malgré sa longueur, et d'avoir accepté de participer à mon jury de thèse. Je suis également très reconnaissant envers Mme Hélène Frémont d'avoir examiné ce travail, pour ses remarques constructives et ses encouragements.

Merci à Clément Tavernier et Roberto Gonella de m'avoir accueilli dans leurs services respectifs à STMicroelectronics Crolles, et tout particulièrement à Eric Sabouret, Emmanuel Vincent et Olivier Noblanc pour l'après-thèse.

Une partie de ce travail a été rendue possible grâce au soutien d'une multitude d'experts, notamment dans les équipes R&D Crolles 300 à STMicroelectronics. Merci à Frédéric Lorut pour les observations FIB/SEM, à Vincent Coutellier pour les essais de nanoindentation, à Sébastien Pelissier pour les mesures AFM, à Bart Van Haaren pour le design des structures de test, à Frédéric Ibars et Yann Henrion pour les mesures électriques. Merci également à Grégory Imbert, à l'initiative de la campagne de cratering test.

Je dois beaucoup à Alexis Farcy et Sandrine Lhostis pour leur soutien dans les derniers jours avant la soutenance. Comme des générations de thésards avant moi Alexis, j'ai pu bénéficier de ton coaching en présentation de transparents (en plus de ton expertise sur l'intégration 3D). Tu mérites vraiment ton titre de "gourou" des slides... Quel chemin parcouru entre la première répétition et la soutenance !

Merci à vous avec qui j'ai eu la chance de partager ce moment, de près ou de loin, temporairement ou depuis le tout début. Aux collègues de MTM, Idir, Komi, Axel, Sarah et Marie-Clotilde. Aux collègues de CPI, Chantal, Christophe, Flore, Greg, Lucile, Olivier, Vivien, Yves. Aux collègues de TCAD, Antonin, Benjamin, Chrystel, Denis, Edgar, Edouard, Fabio, Floria, Fred, Gaby, Gaëlle, Guillaume, Jérémy, Marianne, Nico, Pascal, Pierre-Louis, Olivier(s), Romain, Sébastien, Thomas, Yassine, Yvan...

A mes amis et ma famille, pour leurs encouragements tout au long de la thèse (*"Alors cette thèse, ça avance ??"*).

A Xiaoxiao... Pour ton soutien sans faille, tes sacrifices dans les moments difficiles, et ton infinie patience pendant ces "trois ans". Il ne nous reste plus qu'à profiter maintenant !

To Xiaoxiao To my family

# **General Introduction**

Pursuing the trend towards miniaturization and increased performance of integrated circuits, new processes and architectures are constantly developed. For decades, integrated circuit manufacturing has been driven by a continuous increase of the number of semiconductor devices (typically, transistors) integrated per unit surface. In recent years however, many challenges have arisen in that regard. Indeed, as transistor dimensions reach the ten-nanometer range quantum effects become no longer negligible, leading to increased power consumption and heat generation due to leakage currents. In addition, the need for ever-increasing wiring density between semiconductor devices also results in larger delays in the signal propagation due to the generation of parasitic capacitances.

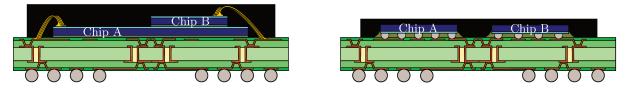

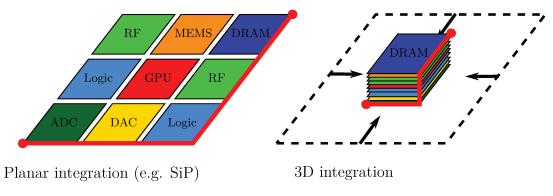

As an alternative to further device downscaling, a progressive shift towards *3D integration* is currently observed in the semiconductor industry. The aim of this innovative approach is to combine chips of different technologies or different functionalities into a single module. This is typically achieved by vertically stacking integrated circuits instead of tiling them on a plane, enabling considerable gain in several aspects: (i) increased compactness, by leveraging the vertical direction to integrate a larger number of devices at constant chip footprint, (ii) decreased complexity, as all of the different functionalities need not be integrated within a single circuit, (iii) improved versatility, since already developed chips can be combined to form a more complex system, for which the different building blocks can be developed independently.

In particular, 3D integration opens up a host of new possibilities for imaging applications. Indeed, vertical stacking enables to move existing peripheral circuitry around the pixel matrix to a separate chip directly below the image sensor, allowing increased performances through shorter wiring, but also the incorporation of additional functionalities such as advanced image signal processing.

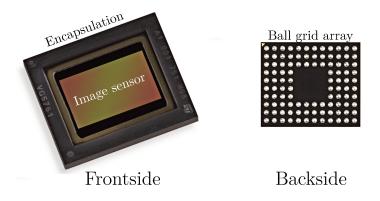

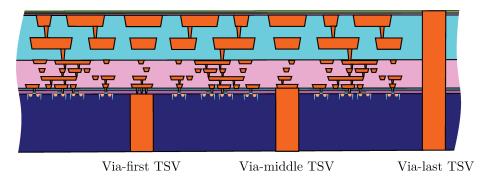

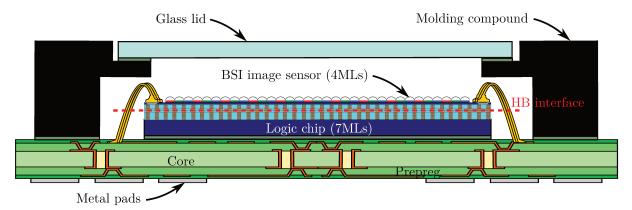

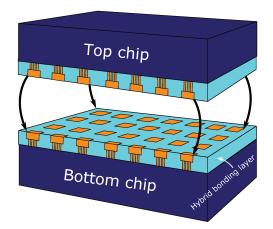

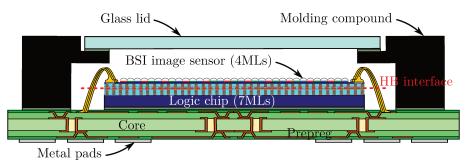

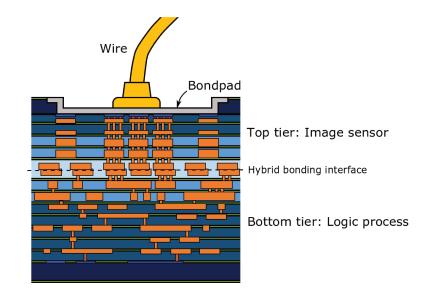

Among various possible strategies to process direct vertical interconnections between the image sensor and its carrier chip (e.g. through-silicon vias, metal pillars), a promising method is  $Cu/SiO_2$  hybrid bonding. This technique consists in the simultaneous direct bonding of metal interconnection pads and their surrounding dielectric surfaces on both sides of the assembly, thereby providing mechanical and electrical connection between the stacked chips, with an interconnection pitch only limited mostly by photolithography resolution and alignment accuracy (i.e. below 1  $\mu$ m). In earlier work at STMicroelectronics and CEA-Leti, a  $Cu/SiO_2$  hybrid bonding process has been developed on several test chips, for which the electrical performance, environmental reliability and bonding interface morphology has been extensively studied<sup>1</sup>, allowing the transfer from the development stage to the manufacturing stage. In the present work, the integration of a more complex stack, namely a backside-illuminated image sensor on a logic integrated circuit, is considered. Compared to previous studies, a broader scope of process steps is therefore investigated, encompassing image sensor chip fabrication and its encapsulation into a supporting case for interfacing with external devices<sup>2</sup>, in addition to the Cu/SiO<sub>2</sub> hybrid bonding process for chip stacking.

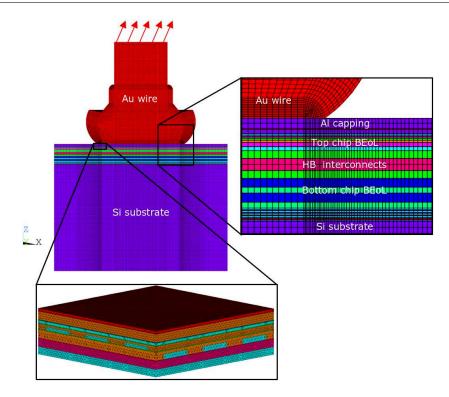

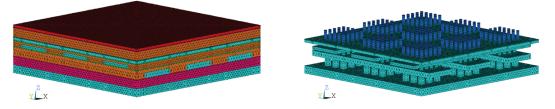

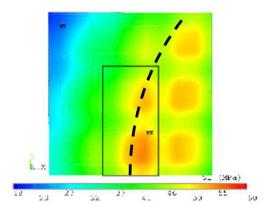

The focus of this thesis is on the mechanical robustness of such a 3D integrated imager-on-logic device during its fabrication, aiming to address a number of possible issues for this relatively new technology in semiconductor manufacturing and secure product integration from a thermomechanical perspective. Mechanical stresses building up in the image sensor during chip processing and assembly onto a package are investigated, and the interactions between the different system components analyzed. The mechanical integrity of several key structures is studied, namely (i) interconnection pads at the hybrid bonding interface between the imager/logic chips, (ii) bondpad structures below the wires connecting the imager to the package substrate, and (iii) semiconductor devices in the image sensor, through the evaluation of process-induced mechanical stresses using Si piezoresistive stress sensors. For each item, combined numerical and experimental investigations are carried out, relying on finite element analysis and morphological, mechanical or electrical experimental characterization.

Firstly, we will provide in Chapter I an overview of the fabrication of 3D integrated image sensors, and discuss the main benefits and new perspectives brought by chip stacking. The specific risks and challenges in terms of thermomechanical robustness for this kind of architecture will also be highlighted, and the main objectives of the thesis outlined.

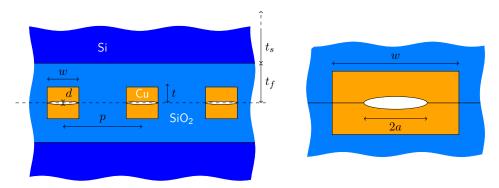

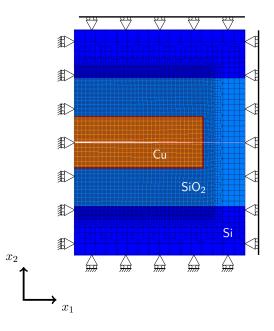

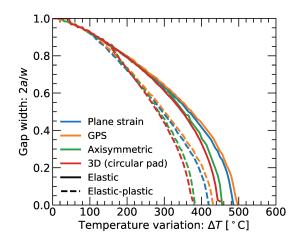

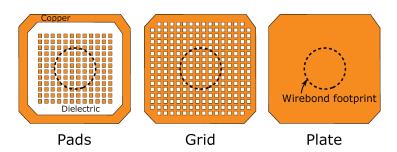

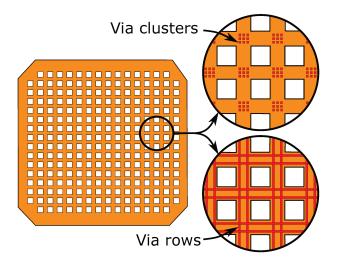

In Chapter II, we will focus on the  $Cu/SiO_2$  hybrid bonding interface between the image sensor and its carrier chip. In a first part, we will evaluate experimentally the influence of various geometries and layouts for the Cu interconnection pads on the bonding surface topography after planarization by chemical-mechanical polishing. In turn, the influence of this initial surface topography on the Cu-Cu bonding interface morphology will be examined. Then, thermomechanical finite element modeling of the hybrid bonding process at the interconnect scale will be carried out, aiming to assess the influence of additional process and design parameters identified as critical for future applications, e.g. interconnect pitch distance or alignment accuracy.

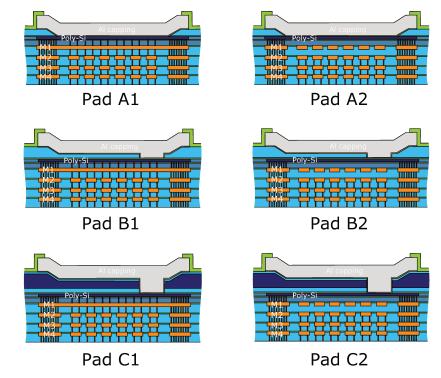

In Chapter III, we are interested in the mechanical robustness of wirebond pads at the backside of the 3D stacked image sensor. An experimental comparison between several pad architectures will be carried out, by failure inspection after the wire bonding process to detect possible cracks or delaminations in the multi-layer interconnection stack. The focus is on the influence of

<sup>&</sup>lt;sup>1</sup>Taibi (2012) and Beilliard (2015)

<sup>&</sup>lt;sup>2</sup>Referred to in the semiconductor industry as an "integrated circuit package".

interconnection layout below the pad, as well as the introduction of a capping layer between the bonding surface and the interconnection stack. Aiming to provide a better understanding of the experimental trends, a multi-scale finite element analysis of a standardized wirebond qualification test, namely the wire pull test, is carried out. This model is then used to investigate the influence of various pad configurations on the mechanical robustness, and thereby propose guidelines to decrease the occurrence of pad mechanical failure.

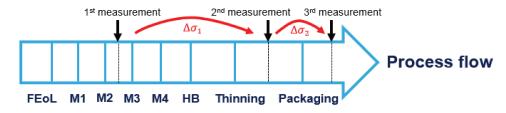

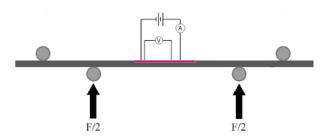

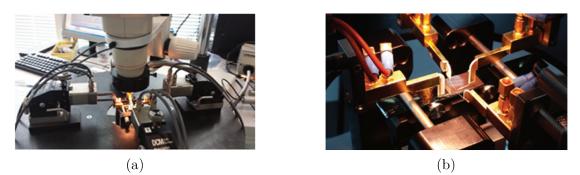

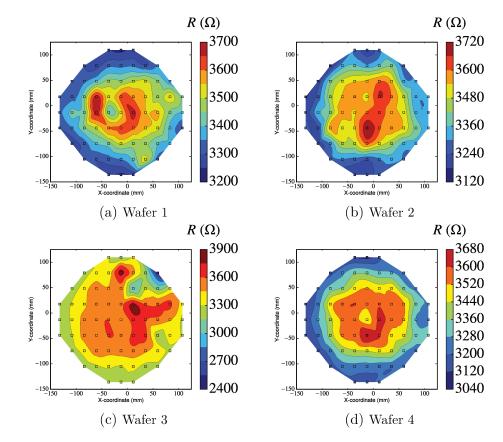

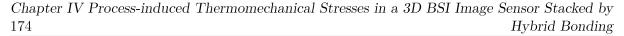

In Chapter IV, a methodology based on Si piezoresistive stress sensors is proposed for *in situ* monitoring of the stress distribution in the active semiconductor region during the image sensor fabrication sequence, including encapsulation in a package. First, sensor calibration is carried out using a previously developed in-house instrumented four-point bending fixture to determine the piezoresistive coefficients<sup>1</sup>. Inline stress measurements are then carried out both at the wafer-level and the package-level, and compared with thermomechanical finite element modeling of the process sequence. The limitations of this method will be discussed and directions for further work proposed.

In a last part, the main achievements of this work are presented and propositions for further developments outlined.

$<sup>^{1}</sup>$ Ewuame (2016)

## Chapter I

# **3D** Stacking of Integrated Circuits for Imaging Applications

The aim of this chapter is to provide an overview of the fabrication processes of integrated circuits for imaging applications (i.e. image sensors), more specifically within the context of 3D stacking, a new integration strategy enabling improved compactness and performance. After an overview of integrated circuit fabrication processes, some of the key challenges currently facing the semiconductor industry are presented. In this context, the main benefits and new perspectives brought by the 3D stacking approach are discussed. For imaging applications, the shift towards 3D architectures gives rise to specific risks and challenges in terms of thermomechanical robustness, that will be highlighted. Finally, the main objectives of the thesis will be outlined.

### I.1 Context

During the first half of the 20<sup>th</sup> century, electronic devices consisted of individual components interconnected by pieces of wire to form discrete circuits. However, shortly after World War II, two major inventions enabled tremendous miniaturization of electronic circuits:

- the discovery of the transistor effect and the realization of the first transistor in 1947 by Bardeen, Brattain and Shockley [1], which provided a more compact replacement for the large and fragile vacuum tubes used at the time;

- the invention of the integrated circuit by Kilby and Noyce [2] in 1958, which enabled further miniaturization by embedding several electronic components together at the surface of the same substrate.

An integrated circuit (IC) can be defined as a collection of electronic devices (mostly transistors, but also diodes, capacitors and resistors) processed and electrically interconnected together onto a flat circular slice of semiconductor material (typically high-purity single-crystal silicon), called

*wafer.* Among the different types of electronic components present on an IC, transistors are the fundamental building blocks for circuit design. A transistor acts as a voltage-controlled switch and is used to build the logic gates that confer ICs their functionalities.

The first ICs in the beginning of the 1960s comprised only a few dozens of transistors, mostly for aerospace and military applications: a level of integration nowadays referred to as smallscale integration. After the commercialization of the first microprocessors in the early 1970s, IC manufacturing shifted to mass production, with circuits of several thousands of transistors (large-scale integration). It was around that time that Gordon Moore, co-founder of Intel, made his famous observation that the density of components at minimum cost roughly doubles every year<sup>1</sup> [4]. This prediction has verified quite well since then, with ICs comprising hundreds of thousands of transistors in the early 1980s (very-large-scale integration), and the milliontransistor milestone<sup>2</sup> crossed in the second half of the 1980s (ultra-large-scale integration).

Nevertheless, in the early 1990s several major difficulties began to arise for keeping the pace of IC miniaturization and performance, requiring the introduction of new fabrication processes and new materials<sup>3</sup>. Since then, IC scaling has therefore been driven by technology roadmaps<sup>4</sup> produced by a group of semiconductor industry experts [5]. These documents assess the current challenges for IC performance improvement, determine directions for research, and set the milestones to be reached by the industry for each IC technology or processing area in the upcoming years (Table I.1).

|                | 1995            | 1997            | 1999             | 2001             | 2004            | 2007            | 2010            | 2013            | 2016            | 2019            | 2022            |

|----------------|-----------------|-----------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Node           | $0.35\mu{ m m}$ | $0.25\mu{ m m}$ | $180\mathrm{nm}$ | $130\mathrm{nm}$ | $90\mathrm{nm}$ | $65\mathrm{nm}$ | $45\mathrm{nm}$ | $28\mathrm{nm}$ | $22\mathrm{nm}$ | $17\mathrm{nm}$ | $13\mathrm{nm}$ |

| $\mathbf{MLs}$ | 5               | 6               | 7                | 7                | 10              | 11              | 12              | 13              | 13              | 14              | 15              |

TABLE I.1: Summary of semiconductor technology roadmaps: process nodes for DRAM applications and number of metallization levels (MLs) for MPU applications

[6-10].

During the short history of ICs, continuous improvement of circuit performances was made possible through device miniaturization. Many technological advances in terms of the processes and materials used were necessary to sustain this trend. In the next section, the main fabrication processes involved in the manufacturing of image sensors (but also for virtually any other kind of IC) are presented.

<sup>&</sup>lt;sup>1</sup>A decade later, Moore adjusted this projection to a twofold increase every two years [3].

$<sup>^{2}</sup>$ It can be noted that, rather than transistor count, the commonly used metric to designate IC generations is the *process node* or *technology node*. This terminology refers to the set of fabrication processes and design rules required to reach a given level of miniaturization.

$<sup>^{3}</sup>$ Notable examples include (i) the introduction of chemical-mechanical polishing for planarity improvement in 1990, (ii) the use of copper to replace aluminum interconnections in 1997, (iii) the move to low- and ultra-low-permittivity dielectrics to insulate fine interconnects, respectively for the 90 and 45 nm nodes. These processes and materials will be described in the next section.

<sup>&</sup>lt;sup>4</sup>First from 1991 with the National Roadmap for Semiconductors (NTRS) in the USA, then from 1998 the International Roadmap for Semiconductors (ITRS), and since 2017 the International Roadmap for Devices and Semiconductors (IRDS).

### I.2 Basic processing steps

Many different processes are involved in IC fabrication, each resulting from technological and scientific advances in various research fields. During the fabrication sequence, the *wafers* on which the circuits are processed go back and forth between many processing tools, each devoted to one of the following fundamental operations: film deposition, lithography, etching, oxidation, doping and surface planarization. In the following, these processes are described as they can have an influence on the morphological features, material behavior, or electrical operation of several structures present in the studied image sensor chip, e.g. hybrid bonding interconnects (Chapter II) or piezoresistive stress sensors (Chapter IV).

#### I.2.1 Film deposition

To form electronic components at the surface of the wafer, to create the metal contacts needed to access them electrically, or simply to provide electrical insulation, thin films of conducting and dielectric materials are deposited successively, layer-upon-layer, onto the substrate. To achieve this, many film deposition techniques have been developed throughout the last decades, each with specific features tailored to adapt to different constraints for IC fabrication. Depending on the mechanism underlying film growth, these deposition processes fall into three broad categories, namely physical vapor deposition (PVD), electrochemical deposition (ECD) and chemical vapor deposition (CVD).

#### I.2.1.1 Physical vapor deposition

In the semiconductor industry, physical vapor deposition is used mostly to deposit polycrystalline metal thin films. Among the earliest methods is *evaporative deposition*. With this technique, the source material is vaporized in a vacuum chamber (e.g. using a resistive coil or an electron beam) and then condenses at the wafer surface to form a thin solid film. Films obtained by evaporative deposition are highly textured, and with poor step coverage for conformal deposition.

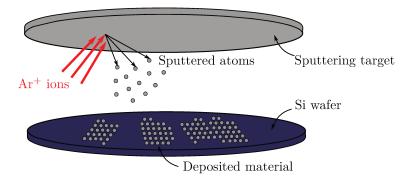

FIGURE I.1: Schematic illustration of thin-film deposition by sputtering.

The most widely used physical vapor deposition (PVD) technique for IC manufacturing is *sputtering* (Figure I.1). The sputtering target, a circular plate covered of source material, is placed in front of the wafer inside a vacuum chamber, thereby forming two parallel electrodes. A gas (typically argon) is then introduced in the chamber while a high voltage is prescribed between the two plates to create a plasma containing positive ions. The sputtering target is maintained at a negative potential, resulting in ion impingement and the ejection of source material away from the plate. The sputtered atoms then form a vapor in the chamber that deposits onto the wafer to form a thin solid film. Due to higher pressure inside the chamber, the latter technique has better step coverage compared to *evaporation*. The obtained films grow without a preferred crystallographic orientation, lead to smaller grain size, and generally contain a larger number of defects and impurities.

#### I.2.1.2 Electrochemical deposition

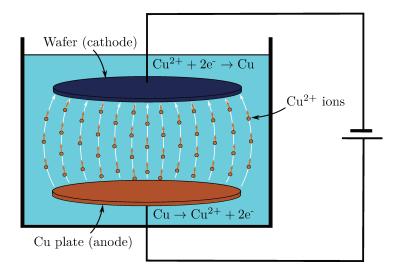

FIGURE I.2: Schematic illustration of thin-film deposition by electroplating.

Metal thin films can also be deposited by *electroplating*, or electrochemical deposition (ECD) (Figure I.2). A plate covered of source material is placed in front of the wafer to form two parallel electrodes. These are immersed in an electrolyte solution containing ions of the metal to be deposited, and connected to a DC current generator. The wafer is maintained at a negative potential to attract the positively charged metal ions. An electrochemical reaction occurs in the electrolytic cell, which turns the ions into atoms. These metal atoms accumulate at the surface of the wafer to form a film of the deposited material. This technique enables to grow thick films, in the range of microns to tens of microns.

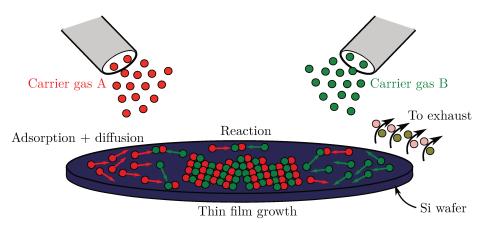

#### I.2.1.3 Chemical vapor deposition

In the semiconductor industry, chemical vapor deposition (CVD) is mostly used to deposit amorphous dielectric thin films. CVD relies on chemical reactions between different carrier gases used to bring all the atoms necessary to form the desired thin film (Figure I.3). The carrier gases are admitted separately into the chamber, where they are adsorbed at the wafer surface. The adatoms and adsorbed molecules then migrate across the wafer surface to react together and grow into a thin film. Adatom mobility is enhanced due to the high temperature inside the chamber. The volatile reaction byproducts on the other hand are desorbed and evacuated out of the reactor. Contrary to sputtering, good film conformality is obtained with this technique.

FIGURE I.3: Schematic illustration of thin-film deposition by CVD.

For some applications where low deposition temperatures are required, reactions between carrier gases can be activated using a plasma. With plasma-enhanced CVD (PECVD), an RF current source is used to induce a plasma in the chamber. This plasma enables reactant dissociation in the carrier gases, thereby promoting film deposition at lower temperatures with high growth rates and good film conformality.

A wide range of extensions have been developed in the last few decades to improve the *gapfill* capability of the CVD even further, for instance using different pressure regimes, e.g. with low-pressure CVD (LPCVD) or sub-atmospheric CVD (SACVD). Another example is high-density plasma CVD (HDPCVD), for which in addition to plasma enhancement the surface is bombarded by argon ions to remove the excess material accumulated in the corners<sup>1</sup>, thereby leading to better sidewall coverage for high-aspect-ratio features.

<sup>&</sup>lt;sup>1</sup>Indeed, film deposition around a high-aspect-ratio cavity may lead to accumulation and bridging of the excess material, eventually causing the formation of a void inside the gap to be filled.

#### I.2.2 Lithography

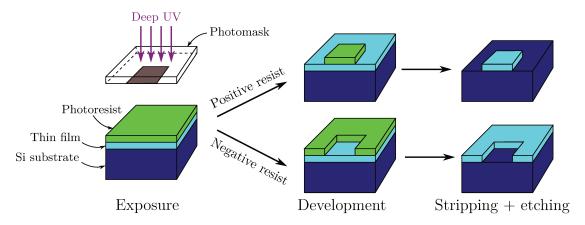

To fabricate an electronic circuit on the Si substrate, the wafer surface must be processed selectively so that a desired pattern can be formed. This is achieved using a photolithography process. The pattern is first imprinted on a photosensitive resin coating (*photoresist*) using UV light transmitted through the *photomask*, a quartz plate containing opaque chromium patterns (Figure I.4).

FIGURE I.4: Schematic principle of the photolithography process for layer patterning.

First, liquid photoresist is spin-coated onto the substrate and cured at about 90  $^{\circ}$ C for solvent evaporation. The wafer is then exposed to UV light through a lens system. In the exposed regions, the photoresist is chemically altered:

- either the resist is polymerized by UV exposure, making subsequent dissolution more difficult in the exposed regions (negative resist),

- or a stabilizing additive is introduced in the resist to prevent dissolution, and this additive breaks down under the action of UV light to make subsequent dissolution easier in the exposed regions (positive resist).

The removal of the exposed photoresist is referred to as the development step. It enables subsequent processing in the patterned regions exclusively, while the rest of the surface is protected under the remaining resin. Upon completion of this subsequent process step, the unexposed photoresist can be removed (or *stripped*) chemically or physically<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>For instance, using an oxygen plasma

#### I.2.3 Etching

In many instances during the fabrication of an ICs, it is necessary to selectively remove material, for instance to expose the Si substrate for dopant implantation, or to form trenches to fabricate metal interconnects. In either case, a photolithography step is carried out following which the wafer is coated with a patterned layer of photoresist. There are several ways to transfer this pattern to the underlying layer(s):

- wet etching A straightforward method is to dip the wafer in an appropriate etching solution, e.g. buffered hydrofluoric acid for  $SiO_2$  [11]. This approach enables selective etching, i.e. only the layer to be removed is dissolved in the etching solution.

- **dry etching** With this method (also called reactive-ion etching), the wafer is placed in a plasma containing a suitable gas, which reacts with the material to be removed while the energetic ions in the plasma collide with the surface. The formed reaction products are thereby etched off, increasing the chemical reactivity of the underlying material [12].

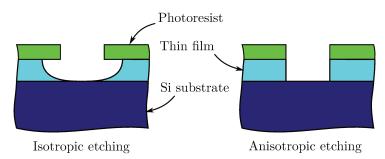

FIGURE I.5: Schematic illustration of the difference between isotropic and anisotropic behavior, obtained by wet and dry etching (respectively).

Wet etching is isotropic, i.e. material removal occurs not only in the vertical direction, but also across the sides of the cavities to be etched (Figure I.5). As a result, the obtained feature size is actually larger compared to the exposed region on the photoresist. For that reason, wet etching is primarily used to remove blanket films on the wafer.

For reactive-ion etching however, the ions able to reach the layer through the patterned photoresist are preferentially those with vertical trajectories. Therefore, anisotropic etching behavior is obtained, with etched cavities having almost vertical sides (Figure I.5). However, despite this advantage, dry etching has generally poorer material selectivity: at the end of the etching process, ions continue to bombard the underlying material<sup>1</sup>.

$<sup>^{1}</sup>$ To avoid this, a method referred to as end-point detection is used. The end of the etching process is inferred from the detection by optical emission spectroscopy of a change in the chemical composition of the volatile reaction products etched away by ion impact.

#### I.2.4 Doping

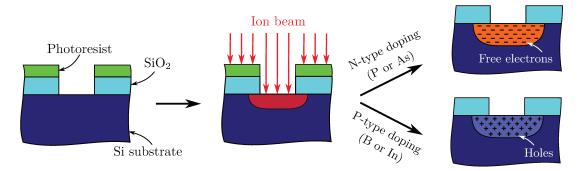

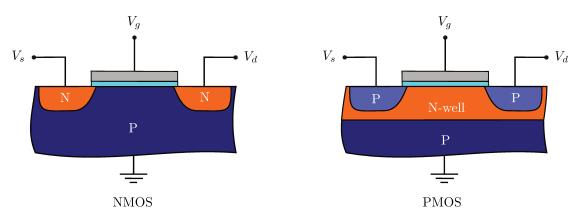

To form semiconductor devices (i.e. electronic components directly embedded onto the wafer), such as the stress sensors studied in Chapter III, the electrical conductivity of the Si substrate must be enhanced in desired locations. This is achieved by the incorporation of specific doping agents introducing free charge carriers into the crystal.

Depending on whether the desired free carriers are electrons or holes<sup>1</sup>, a different type of doping must be used, namely N type or P type (respectively). For the N type, the dopant is an atom with additional electrons compared to Si atoms, while for the P type it is an atom with fewer electrons. The doping atom must be incorporated into Si lattice sites for the free carriers to become available, therefore atoms with an electronic configuration close to that of Si are used. These doping elements are phosphorus or arsenic for N-type doping and boron or indium for P-type doping.

FIGURE I.6: Schematic illustration of the principle of semiconductor doping by ion implantation using a  $SiO_2$  masking layer previously patterned by photolithography.

To introduce these impurities into the Si crystal, the most widely used technique is ion implantation (Figure I.6). With this method, the doping elements are ionized so they can be accelerated towards the wafer at high energies. A photolithography step is always carried out beforehand to protect regions on the wafer where doping is not needed. By scanning the wafer under the ion beam, the dopants are bombarded into the exposed regions of the substrate<sup>2</sup>. By precisely monitoring the energy of the ion beam and implantation duration, a desired implantation dose (i.e. impurity concentration) can be obtained. However, at the end of the doping process the implanted atoms are not all necessarily incorporated to the Si structure. A thermal treatment at high temperatures (900 to  $1200 \,^{\circ}$ C) is thus used to *activate* the dopants, i.e. allow diffusion into lattice sites. Incidentally, this activation anneal also enables to heal the defects introduced in the Si crystal due to ion bombardment. The region at the surface of the substrate with activated dopants is referred to as the *active region*.

The temperature and duration of subsequent annealing steps during IC fabrication must be carefully optimized to avoid undesired changes in the implantation profile<sup>3</sup> due to dopant diffusion.

<sup>&</sup>lt;sup>1</sup>An *electron hole*, or simply *hole*, is an electron vacancy in the valence band of an element, which by convention can be regarded as a positive charge.

<sup>&</sup>lt;sup>2</sup>To neutralize the implanted ions, the wafer is electrically grounded during implantation.

<sup>&</sup>lt;sup>3</sup>Dopant concentration distribution across the thickness of the implanted region.

For this purpose, the quantity of interest is the *thermal budget* (i.e. the total amount of thermal energy transferred to the wafer) prescribed to the IC during the process sequence. In particular, for a 3D-IC assembled by hybrid bonding a thermal anneal is necessary for chip stacking, for which the thermal budget must be optimized (Chapter II).

#### I.2.5 Planarization

In the last thirty years, due to IC miniaturization, more stringent constraints regarding surface planarity of the deposited thin films have become necessary. Indeed, due to ICs becoming more complex, the number of layers deposited onto the substrate has considerably increased, leading cumulatively to larger surface waviness near the end of the fabrication sequence.

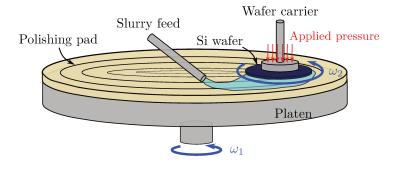

FIGURE I.7: Schematic illustration of surface planarization by CMP.

Chemical-mechanical polishing (CMP), combining chemical etching and mechanical polishing has emerged as the main method for surface planarization of the deposited layers (Figure I.7). The wafer is placed on a rotating carrier and pressed onto a soft pad mounted on a rotating *platen*. Wafer and platen both rotate in the same direction at distinct rotation speeds and thus a relative sliding velocity is prescribed for mechanical polishing. At the same time, a *slurry* comprised of an etching solution and nano-sized abrasive particles (typically silica) is dispensed onto the pad. CMP is a sequential process: the wafer undergoes several polishing steps on different platens, from the most abrasive pad to a buffing pad.

When CMP is carried out on a patterned surface with material heterogeneities, the difference in the abrasion rates may lead to surface topography defects. These defects are discussed further in Chapter II, and their potential detrimental impact on the hybrid bonding process for 3D chip stacking is studied.

#### I.3 Front-end processing: from bare wafer to IC

IC manufacturing is a long and complex task involving hundreds of processing steps, typically resulting in total fabrication times in the order of months. In the semiconductor industry, these processes are commonly divided into two categories, namely front-end (FE) at the beginning of the process sequence, and back-end (BE) at the end<sup>1</sup>. Starting from a bare Si wafer, ICs are fabricated step-by-step by combining (and repeating) the elementary operations previously described: film deposition, photolithography, etching, doping and surface planarization. Using this approach, all of the electronic components making up the IC can be processed (and interconnected) simultaneously at the substrate surface, layer-upon-layer. This method of fabricating ICs is referred to as the *planar process* or *planar technology*, and falls within the front-end process category.

#### I.3.1 Semiconductor devices (front-end-of-line)

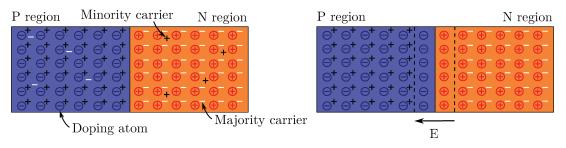

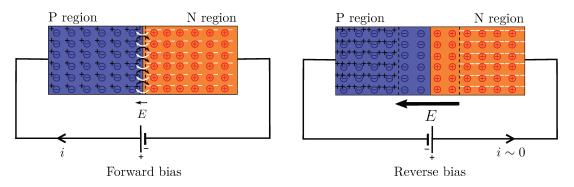

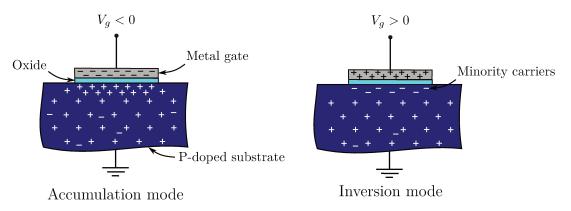

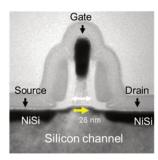

Planar technology enables to fabricate semiconductor devices directly at the wafer surface. The fabrication of these devices is called *front-end-of-line* (FEoL) processing, and by extension this expression is also refers to the part of the IC multilayer stack where those devices are located. In the following paragraphs and in Appendix A, the main semiconductor devices present in a typical image sensor IC are described, such as transistors and pixel sensors. These semiconductor devices rely on the specific electrical properties obtained at the interface between P-type and N-type doped regions, called P-N junctions, described in Appendix A.

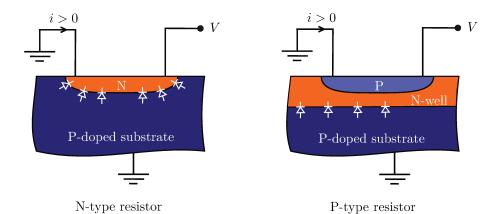

#### I.3.1.1 Si resistors

Resistors can be fabricated directly onto the Si substrate by selectively doping the wafer surface to form an elongated N-type region embedded within the P-type bulk<sup>2</sup>. If an electrical current originally flowing into the metal interconnects is diverted into this N-doped region, a decrease of conductivity is obtained: the N-doped region thus acts as resistor. The current does not flow into the grounded P bulk due to the formation of a depletion region (i.e. a diode) at the P-N junction, as described in Appendix A (Figure I.8).

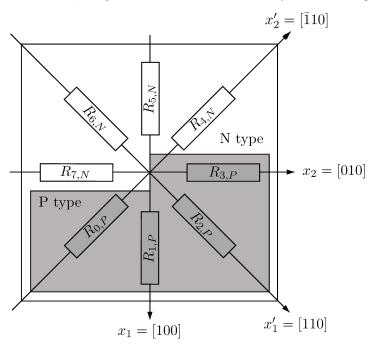

This kind of device is referred to as N-type resistor. However, it is also possible to create P-resistors on the P-doped substrate. This can be achieved by first forming a large N region at the surface of the P bulk, referred to as a *well*, and then forming an elongated P-type region embedded within this N-well. In Chapter III, a stress sensor consisting of an array of such N-type

$<sup>^{1}</sup>$ Quite often, these two categories also indicate different geographical locations for manufacturing, with IC fabrication in front-end plants and IC packaging in back-end plants.

<sup>&</sup>lt;sup>2</sup>Doping agents are already present in bare Si wafers used at the beginning of IC fabrication. The most widely used wafers in the semiconductor industry are P-type substrates. They are incorporated into the melt during the crystal growth process (Czochralski process) to form the silicon ingots from which wafers are then sliced.

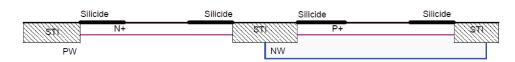

FIGURE I.8: Schematic illustration of the operation of N-type and P-type Si resistors.

and P-type resistors, arranged in a rosette configuration, is used to investigate process-induced stress variations in the active region of the studied 3D image sensor.

#### I.3.1.2 CMOS active pixel sensor

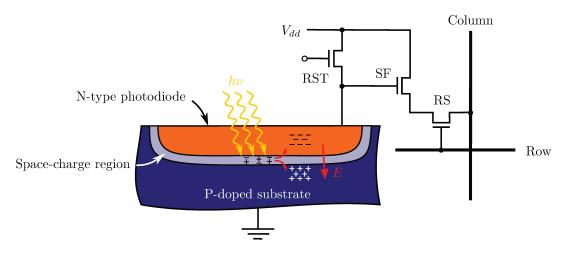

Using a P-N diode and at least three transistors (see Appendix A), a semiconductor device able to convert photons into a digital signal can be fabricated. This type of sensor is referred to as an *active pixel sensor* (APS) (Figure I.9).

The region of the pixel exposed to light is called the photodiode. In its simplest version, it can obtained by implanting an N-well into the P-type bulk to form a P-N junction. The photodiode enables the conversion of incident photons into free charge carriers (*photogeneration*) inside the depletion region at the P-N junction. Photogeneration occurs due to the photoelectric effect, i.e. the generation of an electron-hole pair upon absorption of a sufficiently energetic photon in the semiconductor substrate. To generate an electron-hole pair, the energy of the photon must overcome the bandgap energy<sup>1</sup> of the semiconductor. For silicon at room temperature, this amounts to an energy  $h\nu > E_g = 1.12 \,\text{eV}$ , corresponding to wavelengths below 1100 nm. Silicon is therefore particularly well-suited for image sensing in the range of visible light.

To preserve the collected signal, recombination of the electron-hole pairs generated by photon absorption in the photodiode must be avoided. Fortunately, under the effect of the internal electric field in the depletion region, electron-hole pairs are effectively dissociated: free electrons are stored in the N well, while holes migrate to the P bulk. It can be noted that although it is also possible to use a P photodiode to collect holes instead of electrons, this is generally not the case due to the higher mobility of electrons compared to holes.

<sup>&</sup>lt;sup>1</sup>The bandgap energy is the difference between the minimum energy of the conduction band and the maximum energy of the valence band of the considered element (here, silicon). It corresponds to the minimum energy needed for a valence electron to make the transition to the conduction band and become a free electron. As a free electron is created, a hole appears in the valence band and thus an electron-hole pair is generated. The bandgap energy depends on the material considered and photogeneration can be activated both through light (photon energy) or heat (phonon energy).

FIGURE I.9: Schematic drawing of a CMOS active pixel sensor.

This kind of device is referred to as a CMOS active pixel sensor (APS), since at least three CMOS transistors are included within the pixel in addition to the photodiode (Figure I.9). Their respective functions are (i) to convert the accumulated charges into a voltage and to amplify it (source follower transistor, SF), (ii) to transmit that voltage to the readout circuit (row select transistor, RS) and (iii) to reset the photodiode into reverse bias for charge collection (reset transistor, RST). The photodiode is directly connected to the source terminal of the reset transistor and the gate terminal of the source follower, via the sensing node (SN).

The integration sequence of the generated signal is as follows:

- 1. At the beginning of an integration cycle, the reset transistor is switched on to prescribe a potential to the photodiode. This voltage enables to evacuate all charges previously accumulated due to photogeneration.

- By opening the reset transistor, charge accumulation can start again in the depletion region. The collected signal is converted to a voltage and amplified by the source follower. The row select transistor is used to transmit the amplified signal to the readout circuit.

- 3. Finally, the reset transistor is switched on again to evacuate all charges previously accumulated and the next integration cycle starts.

Pixels are arranged on the IC to form a matrix. The integration procedure, occurring within each pixel, enables the conversion of accumulated charges into a voltage. By varying the integration time, the exposure time can thus be controlled. The resulting analog signal is then sent to the readout circuit. Generally, the pixel matrix is addressed row by row.

The bandgap energy  $E_g$  varies significantly for a strained lattice, as does charge carrier mobility for the CMOS transistors in the pixel. Therefore, a potential adverse effect of mechanical stress on the electro-optical performance of the pixels can be expected [13], which motivates the development of *in situ* stress sensors in the active region of the studied image sensor IC discussed in Chapter III.

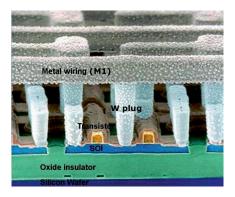

#### I.3.2 Metal-silicon contacts (middle-of-line)

All individual semiconductor devices formed at the wafer surface need to be accessible electrically. This is achieved by fabricating vertical metal plugs embedded in dielectric material (Figure I.10), providing access points to the different terminals of the semiconductor devices, e.g. between a photodiode and its associated transistors. These metal plugs are referred to as *contacts* and the surrounding dielectric matrix is called *pre-metal dielectric (PMD)*.

The pre-metal dielectric layer is generally made of phosphosilicate glass (PSG) (i.e. phosphorusdoped SiO<sub>2</sub>), due to the ability of phosphorus atoms to capture ionic contaminants that could otherwise damage semiconductor devices in the underlying active region [14]. This material is sensitive to humidity however, and it is therefore typically capped by a layer of undoped silicate glass (USG). The typical thickness of the PMD layer is in the 100 nm range. Due to the small lateral dimensions of semiconductor devices, metal plugs are generally high-aspectratio structures. Therefore, the metal deposition process used to fill contact holes etched in the dielectric layer must be sufficiently conformal. For this reason, tungsten is used to fabricate the metal plugs, because historically it is the easiest metal to deposit by CVD [15]. In addition, diffusion into silicon of the metal must be prevented, and thus most low-resistivity metals such as Al or Cu cannot be used. Tungsten is a refractory metal and offers great benefit in that respect. However, it has low adhesion to SiO<sub>2</sub>, and thus the presence of a metal liner (typically TiN) is necessary.

After CVD deposition of the PMD layer, a photolithography step is carried out to etch holes into the layer, which are filled with CVD tungsten. Subsequent chemical-mechanical polishing (CMP) enables to remove the tungsten deposited in excess. This fabrication sequence is sometimes called *middle-of-line* (MOL). Typical dimensions for the tungsten metal plugs are a few 10 nm in diameter for a thickness in the 100 nm range.

FIGURE I.10: Colorized SEM cross-section view showing, from bottom to top, the active region, the tungsten contacts and the first metallization level (M1), with the dielectric material removed (Source: IBM).

#### I.3.3 Metal interconnections (back-end-of-line)

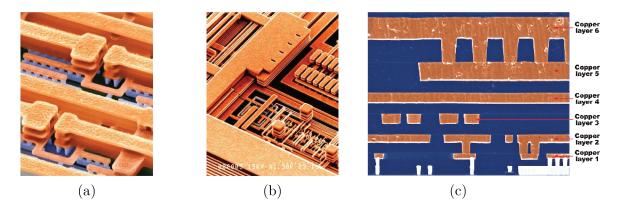

In addition to the vertical contacts described above, a horizontal network of wires is also necessary to interconnect the different semiconductor devices and thereby build a circuit. This is achieved by fabricating on top of the PMD layer a network of metal lines embedded in dielectric material (Figure I.11). These metal lines are referred to as *interconnects* and the dielectric material between them as *intermetal dielectric* (IMD).

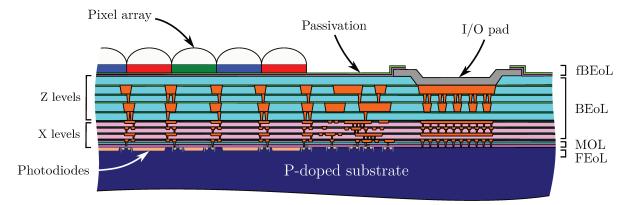

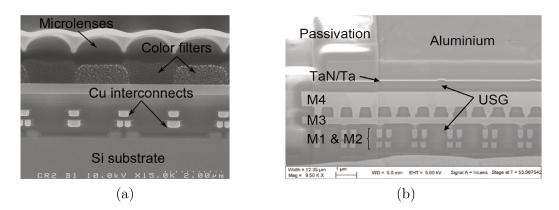

Due to the high density of semiconductor devices at the wafer surface, several tiers are actually necessary for this network of metal lines. Typically, between one and fifteen *metallization levels* (MLs) are processed at the surface of an IC. Altogether, these metallization levels form a stack about 10 µm thick. To interconnect adjacent metallization levels, vertical metal plugs are processed between the horizontal lines. These are referred to as vertical interconnect access, or simply *via*, and the dielectric material between the different metallization levels as *interlayer dielectric* (ILD). For simplicity, metal or via layers are generally referenced as  $M_i$  and  $V_i$ , with *i* denoting the metallization level number, in ascending order from the PMD upwards. The fabrication of these interconnects is called *back-end-of-line* (BEoL) processing, and by extension this expression is also used to refer to the interconnect stack.

The BEoL stack also enables a change in scale between the submicron-scale semiconductor devices and the outside world. It is commonly divided into several regions with increasing layer thickness, line width, spacing and length from the PMD upwards (Figure I.11):

- The lowermost layers are the *X*-levels (local interconnects): this network of thin, fine and short metal lines ensures local interconnection between semiconductor devices.

- Absent in some devices, *Y*-levels (semi-global interconnects) consist of layers of intermediate thickness, line width and density, and are used to join groups of semiconductor devices.

- The uppermost are the *Z*-levels (global interconnects): they contain the thickest metal layers, with wide metal lines enabling long distance communication between different regions on the chip, as well as power/ground distribution.

This interconnection network consists of lines with rectangular cross-section, and generally run along orthogonal directions (i.e. no oblique or curved lines), due to limitations inherent to the planar process (especially photolithography). Typical thickness for the different levels are about 100 nm for an X-level, a few 100 nm for a Y-level and about 1  $\mu$ m for a Z-level. Typical lateral dimensions for the metal lines are in the 0.1-10  $\mu$ m range, and for the via plugs in the 0.01-1  $\mu$ m range.

Interconnects were originally fabricated using aluminum for the lines, tungsten for the vias, and  $SiO_2$  for the dielectric layers. After deposition of an Al layer by PVD, a positive photoresist was used during the lithography step to expose the region between the lines, which were removed by dry etching. The dielectric layer was then deposited by CVD to embed the lines and surface waviness of the deposited layer was suppressed by CMP. However, Al lines lead to significant

FIGURE I.11: Colorized tilted SEM view of (a) local and (b) global metallization levels, and (c) cross-section view of an interconnection stack (Source: IBM).

reliability issues, such as stress voiding and electromigration [16, 17]. These issues were first alleviated using AlCu alloy lines, before the manufacturability of Cu interconnects was demonstrated in 1997 [18]. Cu lines have since progressively been adopted and replaced AlCu alloys in more advanced technology nodes, due to the great benefits of copper in terms of resistivity and electromigration resistance.

Contrary to aluminum, copper cannot be dry-etched to process the lines directly from a blanket film by subtractive etching. To circumvent this issue, a new method referred to as the *damascene process* was developed. After deposition of an etch-stop layer (typically, silicon nitride) and the dielectric layer by PECVD<sup>1</sup>, a negative resist is used during the photolithography step to expose the region corresponding to the lines, which is removed by dry etching. A very thin Cu seed layer is then deposited by PVD, and a thick Cu film is grown by ECD to fill the etched pattern. The excess Cu material (*overburden*) is then removed by CMP. However, contrary to aluminum, copper has poor adhesion with SiO<sub>2</sub> and also easily diffuses into the dielectric layer surrounding the line. Therefore, a thin tantalum nitride/tantalum (TaN/Ta) liner is usually deposited by PVD before the Cu seed layer to act as a diffusion barrier and improve adhesion. After deposition of the thick ECD Cu layer, an annealing step is necessary to enable recrystallization and thereby decrease line resistivity.

Historically, the vias between Al lines had been made from tungsten, due to a strong sensitivity to electromigration with aluminum for these high-aspect-ratio structures. However, the introduction of the damascene process has enabled to fabricate Cu vias in addition to the Cu lines. For that reason, a *dual-damascene process* is actually used<sup>2</sup>, for which both the lines and the vias are processed during the same process step for a given metallization level<sup>3</sup>.

<sup>&</sup>lt;sup>1</sup>PECVD is the preferred deposition method for dielectric materials in the BEoL due to its low deposition temperatures. Indeed, a great number of layers need to be deposited to form the interconnect stack. Reducing the deposition temperature for these layers enables to alleviate thermal budget constraints.

<sup>&</sup>lt;sup>2</sup>Except for the M1 level resting on the PMD layer

<sup>&</sup>lt;sup>3</sup>Several fabrication sequences exist for the dual-damascene process: (i) trench first, via last, (ii) via first, trench last, (iii) self-aligned.

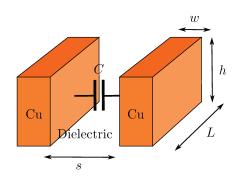

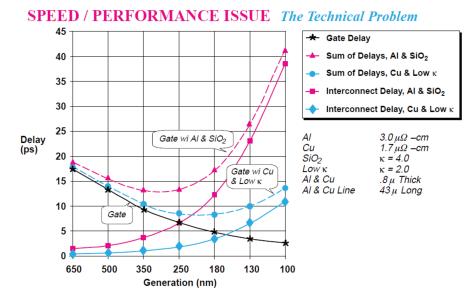

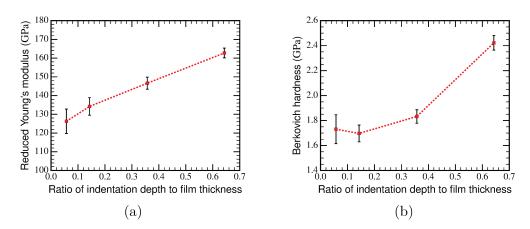

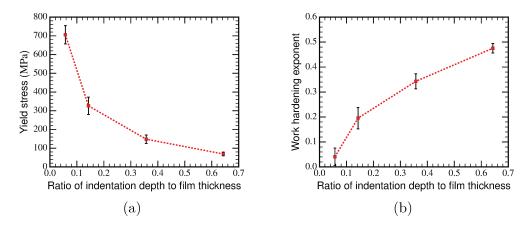

Due to the increase of the number of semiconductor devices at the surface of ICs, finer and denser interconnect structures are necessary, especially for the X levels of the interconnect stack. A direct consequence of interconnect downscaling is the generation of parasitic capacitances between Cu lines (see Section I.5.1). Over time, the contribution of interconnects to signal delay has become significant compared to that of semiconductor devices, resulting in an overall decrease in IC performance. This limitation has led to the introduction of low-permittivity materials (*low-k*<sup>1</sup>) for the X and Y levels instead of conventional USG ( $\kappa = 4$ ). Notable examples include fluorosilicate glass (FSG,  $\kappa = 3.7$ ), i.e. fluorine-doped SiO<sub>2</sub>, or SiOC ( $\kappa = 3$ ), i.e. carbon-doped SiO<sub>2</sub>. It can also be noted that for these levels, silicon nitride etch-stop layers (SiN,  $\kappa = 7$ ) are also typically replaced with a material with lower permittivity, namely C-doped silicon nitride (SiCN,  $\kappa = 5$ ).

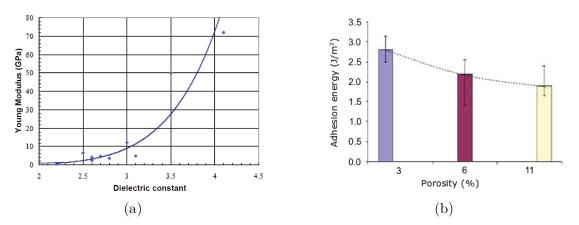

This decrease in the permittivity of dielectric layers has not been without consequences for the mechanical robustness of the interconnect stack. As reported in Figure I.12, low-k dielectrics are brittle materials with low elastic modulus and poor adhesion properties. This makes the fine X-levels more prone to cracking and delamination. More recently, *ultra-low-k (ULK)* dielectrics (SiOC:H,  $\kappa = 2.7$ ) have been developed using porous low-k for further permittivity reduction, thus resulting in even weaker mechanical properties.

FIGURE I.12: Graphs illustrating (a) the decrease in the Young's modulus of low-k and ultralow-k dielectric materials [19], and (b) the influence of ultra-low-k dielectric porosity on the adhesion energy of a SiOCH/USG interface [20].

#### I.3.4 Surface capping (far-back-end-of-line)

At the end of the BEoL processing, a three-dimensional network of Cu lines has been fabricated, interconnecting the different semiconductor devices. A change of scale has also been achieved, from fine local interconnects (X levels) to global interconnects (Z levels), enabling electrical access to these devices for power supply and grounding. However, the largest metal lines in the Z levels are still at most only a few microns wide. Therefore, aluminum plates are formed at the surface of the IC to act as the input/outputs (IOs) of the electronic circuit (Figure I.13 and

<sup>&</sup>lt;sup>1</sup>Here, the letter  $\kappa$  or k is used to denote the permittivity of the dielectric material.

I.14). These IO pads have dimensions on the order of a hundred microns, much more suitable for electrical probing or IC connection onto a substrate. This is achieved by depositing an Al layer at the surface of the IC by PVD, and then forming the Al pads by subtractive etching.

In addition, a passivation stack is deposited onto the IC surface to provide mechanical and chemical protection from the external environment (Figure I.13). A phosphosilicate glass (PSG) layer is first deposited at the wafer surface by PECVD, due to the ability of phosphorus atoms to trap ionic contaminants [14]. Since PSG is sensitive to humidity however, an additional undoped silicate glass (USG) layer is deposited by PECVD. This passivation stack, very similar to the PMD layer used to protect the active region, has a thickness on the order of one micron. To provide electrical access to the IO pads, the passivation stack is then etched above the Al plates, in a step called *passivation opening*. At the end of the front-end process sequence, a final anneal of the IC is carried out to passivate defects and dangling bonds in the active region.

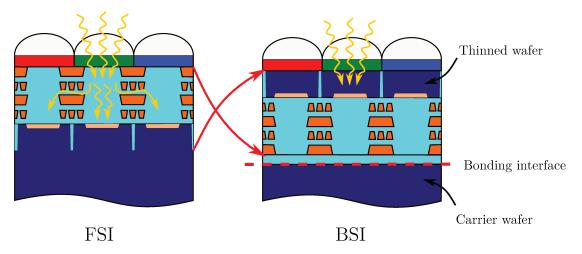

#### I.3.5 Pixel array

To guide the incident light signal to the active pixel sensors, arrays of color filters and microlenses are processed at the surface of the IC, above the pixel matrix (Figure I.13 and I.14). The color filter array consists of red, green and blue regions, forming  $2 \times 2$  unit cell repeated all over the pixel matrix. In the majority of cases a Bayer pattern is used, consisting of a RGGB (red-greengreen-blue)<sup>1</sup> cell. This is achieved by depositing pigmented resins which are then developed to form the desired pattern, by successive lithography steps, first for the green cells and then the blue and red cells. An organic layer is deposited onto the color filter array to planarize the surface before forming the microlens matrix. A resin layer is then deposited, from which the microlenses are etched and then melted during an annealing step to obtain a spherical shape.

FIGURE I.13: Schematic cross-section of an image sensor (FSI integration).

The most straightforward approach to fabricate image sensors is with the color filter array and microlenses matrix deposited on the frontside of the IC, a configuration referred to as *frontside-illuminated (FSI)*. For FSI integration, the incoming light must therefore be able to travel

$<sup>^{1}</sup>$ The green color is repeated due to a peak of sensitivity of the human eye to those wavelengths, thus requiring maximum signal for this color.

FIGURE I.14: a) FIB/SEM cross-section view of a FSI 1.75 µm-pitch image sensor [21], and b) FIB/SEM cross-section view of an IO pad of the 120 nm process node [22].

through the BEoL stack to reach the pixels in the active region. This leads to strong constraints on interconnection layout, due to the requirement for a transparent dielectric-only stack above the photodiodes. Although interconnections can be moved to the periphery of the pixels, a nonnegligible fraction of the incident light is still reflected on the metal lines, leading to crosstalk between adjacent pixels associated with different colors [23].

FIGURE I.15: Schematic illustration of the difference between FSI and BSI image sensors.

In the late 2000s, a new technology was introduced, namely backside-illuminated (BSI) image sensors, which has gained much importance in recent years [23] and in particular is mandatory for the 3D integrated image sensor studied in this work. For BSI integration, the colors filters and microlenses are deposited on the backside of the CMOS image sensor (Figure I.15). First, the frontside of the processed wafer is bonded<sup>1</sup> to a bare Si substrate. After thinning of the processed wafer by backgrinding (see Section I.4.1), color filters and the microlens matrix are formed on the backside. In this configuration, the screening effect of the interconnects is avoided, enabling

<sup>&</sup>lt;sup>1</sup>The process used to attach the two wafers is called *direct bonding*. It relies on the molecular bonding phenomenon occurring between sufficiently flat and smooth surfaces placed in close proximity, due to surface interaction forces. At the end of the BEoL process, a blanket  $SiO_2$  film is first deposited on top of the interconnect stack, which is then subjected to extensive surface preparation by CMP to reach the stringent planarity requirements for molecular bonding. Finally, the bonded assembly is annealed to increase the bonding energy. Molecular bonding is described in more detail in Chapter II.

a significant increase of the optical performances, while at the same time relaxing constraints on BEoL design [23].

In this section, the "front-end" part of the fabrication sequence for the studied image sensor has been presented. In Chapter IV, an approach based on Si piezoresistive stress sensors is proposed to evaluate the mechanical stress induced by these processing steps in the active region of the image sensor. In addition, the contribution of chip packaging to the mechanical stress in the active region will also be investigated. In the following section, the processing steps corresponding to chip packaging, i.e. the "back-end" part of the fabrication sequence, are described.

#### I.4 Back-end processing: from IC to packaged chip

After completion of the front-end process sequence, an array of ICs has been formed at the surface of the Si substrate. After electrical testing at the wafer level, functional ICs must then be extracted from the wafer to be encapsulated in a supporting case, referred to as a *package*. The role of the package is to protect the die from the external environment (e.g. contamination, shocks) and to act as an electrical interface for direct use in external circuits. The associated process steps fall into the *back-end* (BE) processing category.

#### I.4.1 Thinning

With a thickness of 775 µm for a diameter of 300 mm, Si wafers used for IC manufacturing provide sufficient mechanical stability throughout the process sequence, e.g. for wafer handling or during various annealing steps. However, this thickness range is generally too large for compact electronic products, such as hand-held and portable devices. Therefore, the backside of processed wafers is typically thinned down to between 400 to 50 µm, depending on the application.

This is achieved using a multi-step grinding process, called *backgrinding* or simply *wafer thinning*. About 90% of the initial thickness is removed by coarse mechanical grinding first, while for the remaining thickness a polishing process and/or chemical etching is used. Indeed, coarse grinding leaves scratches on the wafer backside, potentially detrimental for IC mechanical robustness in the subsequent process steps or product life, e.g. under bending loads.

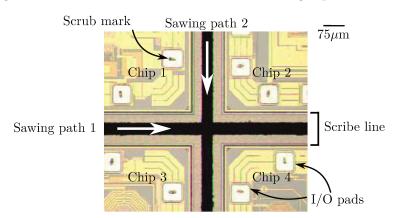

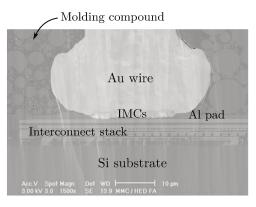

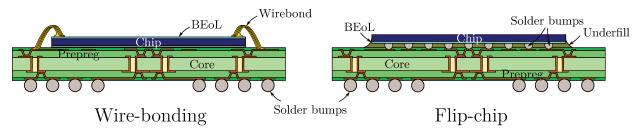

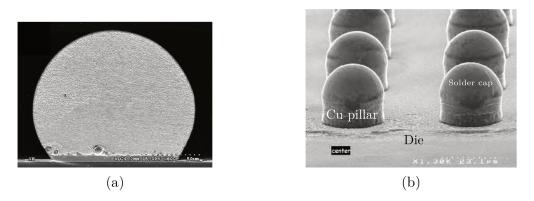

### I.4.2 Singulation