## Development of a CMOS pixel sensor with on-chip artificial neural networks

Ruiguang Zhao

#### ▶ To cite this version:

Ruiguang Zhao. Development of a CMOS pixel sensor with on-chip artificial neural networks. High Energy Physics - Experiment [hep-ex]. Université de Strasbourg, 2019. English. NNT: 2019STRAE050. tel-02517257

### HAL Id: tel-02517257 https://theses.hal.science/tel-02517257

Submitted on 24 Mar 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

**UNIVERSITÉ DE STRASBOURG**

### ÉCOLE DOCTORALE Physique et Chimie-Physique

### Institut pluridisciplinaire Hubert Curien (IPHC) - UMR 7178

## **Ruiguang ZHAO**

soutenue le : 20 Décembre 2019

pour obtenir le grade de : **Docteur de l'université de Strasbourg** Discipline/ Spécialité : Électronique, Microélectronique, Photonique

## Development of a CMOS pixel sensor with on-chip artificial neural networks

| THÈSE dirigée par :<br>M. HU Yann           | Professeur, Université de Strasbourg            |

|---------------------------------------------|-------------------------------------------------|

| RAPPORTEURS :<br>M. DE LA TAILLE Christophe | Directeur, Laboratoire OMEGA                    |

| M. BERRY François                           | Professeur, Institut PASCAL                     |

| AUTRES MEMBRES DU JURY :                    |                                                 |

| M. PRIGENT Michel                           | Professeur, Institut XLIM                       |

| Mme. COURTIN Sandrine                       | Professeur, Université de Strasbourg            |

| M. BESSON Auguste                           | Maître de Conférences, Université de Strasbourg |

## Contents

| Contents    | I                            |

|-------------|------------------------------|

| Acknowle    | edgementsV                   |

| List of Fig | guresVII                     |

| List of Ta  | blesXI                       |

| Résumé e    | n FrançaisXIII               |

| Introduct   | ionXXIII                     |

| 1 Inter     | national Linear Collider1    |

| 1.1 I       | LC Project1                  |

| 1.1.1       | Physics Programs of the ILC2 |

| 1.1.2       | ILC Layout4                  |

| 1.2 I       | LC Experimental Conditions5  |

| 1.2.1       | Beam Structure               |

| 1.2.2       | Beam Background5             |

| 1.3 I       | nternational Large Detector6 |

| 1.3.1       | Vertex Detector7             |

| 1.3.2       | Silicon Tracking Part11      |

| 1.3.3       | Time Projection Chamber11    |

| 1.3.4       | Calorimeter System12         |

| 1.3.5       | Muon System12                |

| 1.3.6       | Coil and Yoke System12       |

| 1.4 N       | Aotivation12                 |

|       | 1.4   | .1      | Challenges for Track Reconstruction        | 12 |

|-------|-------|---------|--------------------------------------------|----|

|       | 1.4.2 |         | Trajectory of Charged Particles            | 14 |

| 1.4.3 |       | .3      | Principle for Particle Recognition         | 17 |

|       | 1.5   | Sur     | nmary                                      | 18 |

|       | 1.6   | Bib     | liography                                  | 19 |

| 2     | Sei   | micol   | nductor Detectors                          | 23 |

|       | 2.1   | Car     | riers Generation                           | 24 |

|       | 2.1   | .1      | Carriers Generated by Photons              | 24 |

|       | 2.1   | .2      | Carriers Generation by Charged Particles   | 25 |

|       | 2.2   | Car     | riers Transport                            | 26 |

|       | 2.2   | 2.1     | Drift                                      | 26 |

|       | 2.2   | 2.2     | Diffusion                                  | 26 |

|       | 2.3   | P-N     | Junction                                   | 27 |

|       | 2.3   | .1      | Forward Bias                               | 28 |

|       | 2.3   | 5.2     | Reverse Bias                               | 28 |

|       | 2.4   | Me      | tal-Oxide-Semiconductor                    | 29 |

|       | 2.5   | Sili    | con Detector Types                         | 30 |

|       | 2.5   | 5.1     | Strip Detector                             | 30 |

|       | 2.5   | 5.2     | CCD                                        | 32 |

|       | 2.5   | 5.3     | Hybrid Pixel Sensor                        | 33 |

|       | 2.5   | 5.4     | DEPFET Sensor                              | 34 |

|       | 2.5   | 5.5     | Monolithic Active Pixel Sensor             | 34 |

|       | 2.5   | 5.6     | Conclusions                                | 36 |

|       | 2.6   | Sur     | nmary                                      | 38 |

|       | 2.7   | Bib     | liography                                  | 39 |

| 3     | Ar    | tificia | al Neural Networks for Pattern Recognition | 43 |

|       | 3.1   | Patt    | tern Recognition                           | 43 |

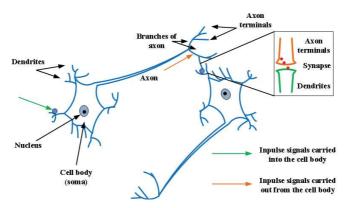

|       | 3.2   | Bio     | logical and Artificial Neuron              | 45 |

|       | 3.2   | 2.1     | Biological Neurons                         | 45 |

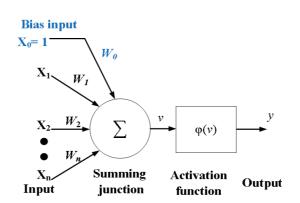

|       | 3.2   | 2.2     | Artificial Neuron                          | 46 |

|       | 3.2   | 2.3     | Activation Function                        | 47 |

|       | 3.3   | Тур     | bes of Artificial Neural Networks          | 49 |

|       | 3.3   | 5.1     | Multi-Layer Perceptron (MLP)               | 50 |

|       | 3.4   | Fea     | ture Extraction                            | 51 |

|   | 3.5 ANN Supervised Learning |      |                                                 |             |

|---|-----------------------------|------|-------------------------------------------------|-------------|

|   | 3.5.1 BP Algorithm          |      | 53                                              |             |

|   | 3.6                         | AN   | IN in HEP                                       | 57          |

|   | 3.7                         | Cha  | allenges for ANN Implementation                 | 59          |

|   | 3.8                         | Sui  | nmary                                           | 60          |

|   | 3.9                         | Bib  | bliography                                      | 61          |

| 4 | FP                          | GA ] | Implementation of ANN for Reconstructing Incide | nt Angles65 |

|   | 4.1                         | Ray  | w Data Acquisition System                       | 66          |

|   | 4.1                         | .1   | CMOS Pixel Sensor                               | 67          |

|   | 4.1                         | .2   | 2 Rotations Support                             |             |

|   | 4.1                         | .3   | Readout Chain                                   | 73          |

|   | 4.2                         | Imj  | plementations in the FPGA                       | 74          |

|   | 4.2                         | 2.1  | Interface to Read in Raw Data                   | 76          |

|   | 4.2                         | 2.2  | Cluster Search                                  | 79          |

|   | 4.2                         | 3    | Data Format Conversion                          | 86          |

|   | 4.2                         | .4   | Feature Extraction                              |             |

|   | 4.2                         | 5    | Normalized Features                             | 93          |

|   | 4.2                         | 6    | ANN Implementation                              | 93          |

|   | 4.2                         | 2.7  | DeNormalized Module                             | 96          |

|   | 4.2                         | 8    | Interface to Output                             | 97          |

|   | 4.3                         | Tes  | t results                                       |             |

|   | 4.3                         | .1   | Analysis and Discussion                         | 100         |

|   | 4.4                         | Sui  | nmary                                           | 102         |

|   | 4.5                         | Bib  | bliography                                      |             |

| 5 | An                          | On-  | chip Algorithm for Cluster Search               |             |

|   | 5.1                         | Mo   | tivation                                        | 105         |

|   | 5.2                         | Alg  | gorithm for Cluster Search                      | 106         |

|   | 5.2                         | .1   | Algorithm for One Column                        | 107         |

|   | 5.2                         | 2.2  | Steps for a Cluster                             | 110         |

|   | 5.2                         | 3    | Supplementary Explanation                       | 112         |

|   | 5.3                         | Sin  | nulation Results                                |             |

|   | 5.3                         | .1   | Cluster Windows                                 |             |

|   | 5.3                         | .2   | Seed Thresholds                                 | 117         |

|   | 5.3                         | .3   | Algorithm in the FPGA VS. Algorithm Proposed    | 118         |

| 6 | Cor  | nclus | sions and Perspectives                             |     |

|---|------|-------|----------------------------------------------------|-----|

|   | 5.7  | Bib   | liography                                          |     |

|   | 5.6  | Sun   | nmary                                              | 132 |

|   | 5.5. | .4    | Synthesized Result of the 64-column Implementation | 130 |

|   | 5.5. | .3    | Simulation of the 256-column Implementation        | 129 |

|   | 5.5. | .2    | Timing                                             | 127 |

|   | 5.5. | .1    | Implementation of the 64-column Algorithm          | 124 |

|   | 5.5  | Alg   | orithm Implementation                              | 124 |

|   | 5.4. | .3    | Overlap Parts                                      | 123 |

|   | 5.4. | .2    | Separated Parts                                    | 122 |

|   | 5.4. | .1    | Large Clusters                                     | 120 |

|   | 5.4  | Dise  | cussion                                            | 120 |

## Acknowledgements

I would like to thank China Scholarship Council (CSC) for the financial support during my doctoral study at University of Strasbourg, France and Institut Pluridisciplinaire Hubert Curien (IPHC), CNRS.

This thesis was made possible by the support of many individuals during my past four years in France. I would like to express my sincere gratitude to my supervisor Prof. Yann HU and Marc WINTER, the leader of the CMOS-ILC research group, for offering me the opportunity to work in IPHC. Their guidance has been helpful during my research and for writing this thesis. I sincerely appreciate Dr. Auguste BESSON for his guidance and fruitful suggestions throughout my doctoral study, the analysis of the simulation result, and providing the corrections and suggestions for this thesis.

I am grateful to Dr. Christine HU-GUO, the director of the microelectronic group, for giving me insightful guidance for my design and providing exhaustive suggestions for my publications and posters.

I would like to thank Prof. Michel PAINDAVOINE, in Electronics, Signal and Image Processing of Burgundy University, for communication and guidance at the beginning of my thesis. I would like to thank Luis alejandro PEREZ PEREZ and Mathieu GOFFE for their help in the whole process of the raw data acquisition and the ANN training. I am grateful to Kimmo JAASKELAINEN for his help in the FPGA system design. I would like to thank Claude COLLEDANI and Guy DOZIERE for providing help and offering encouragements during my doctoral period.

I would also like to thank all my colleagues in IPHC: Jerome BAUDOT, Frederic MOREL, Abdelkader HIMMI, Gregory BERTOLONE, Isabelle VALIN, Maciej KACHEL, Gilles CLAUS, Mathieu SPECHT, Christian ILLINGER, Andrei

DOROKHOV, Pham Thanh HUNG and Yu ZHANG for their kind help and technical support in my work.

I would like to express my respect to doctoral candidates, Julian HEYMES and Yue ZHAO, of our group. We got together to share ideas, discussed processes and analysed results.

I am so appreciated to my friends Jiahui FAN, Siyu LU who gave me faithful supports during the whole stage of my thesis.

Last but not least, I would like to thank my parents for raising me and making me be surrounded by unconditional support, understanding and love. I am very grateful to my future girlfriend, thanks for her absence during my doctoral period and did not hurt my heart.

## **List of Figures**

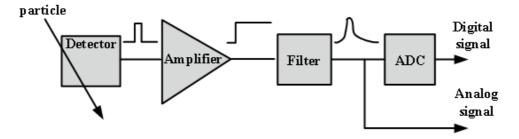

| Figure 2.1: Typical semiconductor detector system                                                                          |

|----------------------------------------------------------------------------------------------------------------------------|

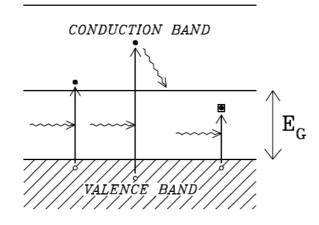

| Figure 2.2: Generation of electrons and holes by absorption of photons, the energy loss=                                   |

| Eg, >Eg, and < Eg [5]                                                                                                      |

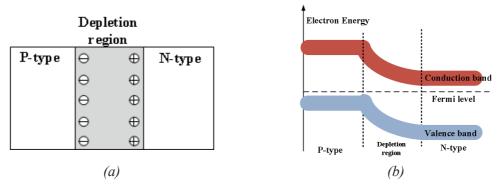

| Figure 2.3: P-N junction (a) Depletion region (b) Energy band diagram                                                      |

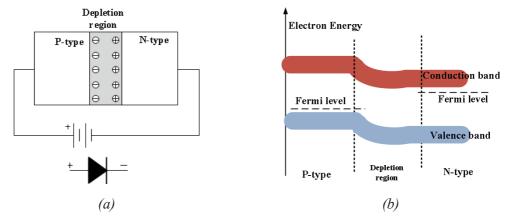

| Figure 2.4: P-N junction under forward bias (a) Depletion region (b) Energy band diagram.28                                |

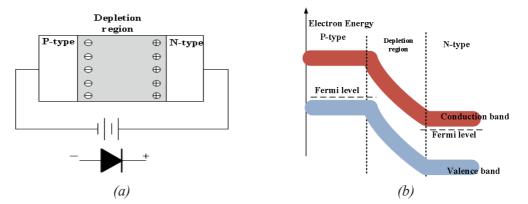

| Figure 2.5: P-N junction under reverse bias (a) Depletion region (b) Energy band diagram. 28                               |

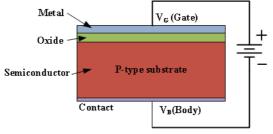

| Figure 2.6: N-type Metal-Oxide-Semiconductor structure                                                                     |

| Figure 2.7: An n-type MOS under accumulation, depletion and inversion conditions [10]29                                    |

| Figure 2.8: Single-sided strip detector (a) DC coupled strip detector (b) AC coupled strip                                 |

| detector [13]                                                                                                              |

| Figure 2.9: Operation principle of a double-sided strip detector [17]                                                      |

| Figure 2.10: Timing diagram of voltage schemes to transport charge through a three-phase                                   |

| CCD                                                                                                                        |

| Figure 2.11: A simplified schematic diagram of a single pixel in a hybrid silicon detector, it is                          |

| composed of a sensor part and a readout electronics part [24]                                                              |

| Figure 2.12: Schematic layout of the DEPFET [27]                                                                           |

| Figure 2.13: Schematic of the first-generation MAPS structure                                                              |

| Figure 2.14: Schematic of the second-generation MAPS structure                                                             |

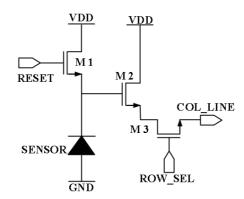

| Figure 2.15: Typical in-pixel readout circuit [30]                                                                         |

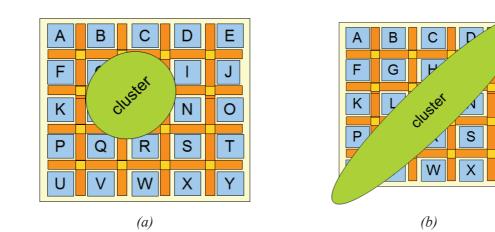

| Figure 3.1: Examples of cluster shapes (a) Cluster shape generated by charged particles from                               |

| the physics event (b) Cluster shape generated by charged a charged particle from the beam                                  |

| background                                                                                                                 |

| Figure 3.2: Connections between two biological neurons                                                                     |

| Figure 3.3: Computational model of artificial neurons                                                                      |

| Figure 3.4: McCulloch-Pitts model of an artificial neuron                                                                  |

| Figure 3.5: Sigmoid activation functions                                                                                   |

| Figure 3.6: Taxonomy of feedforward and feedback network architectures [13]                                                |

| Figure 3.7: Connection architectures of Multi-Layer Perceptron                                                             |

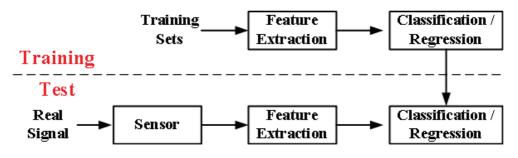

| Figure 3.8: Training and test phase [25].52                                                                                |

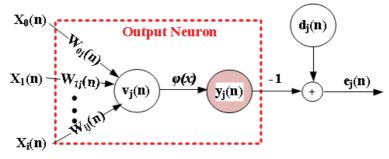

| Figure 3.9: Signal-flow graph of output neuron j                                                                           |

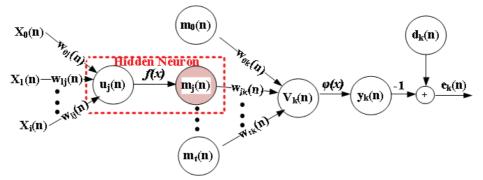

| Figure 3.10: Signal-flow graph of hidden neuron j                                                                          |

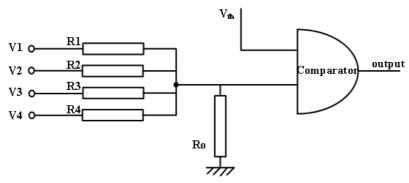

| Figure 3.11: Basic coincidence electric circuit.    58                                                                     |

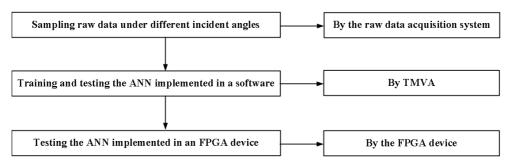

| Figure 4.1: Main procedures of the offline methodology. The training and the test process in                               |

| TMVA have been accomplished by my colleague Luis alejandro PEREZ PEREZ                                                     |

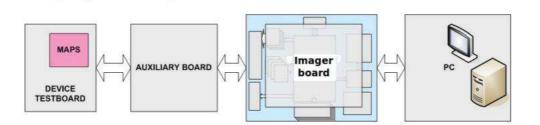

| Figure 4.2: Schematic diagram of the raw data acquisition system                                                           |

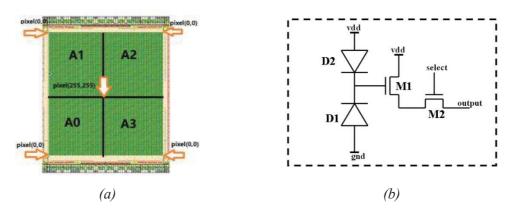

| Figure 4.3: CMOS pixel sensor MIMOSA 18 (a) Layout of MIMOSA 18 (b) The pixel                                              |

| structure of the MIMOSA18 [3]                                                                                              |

| Figure 4.4: Schematic of the 2 rotations support                                                                           |

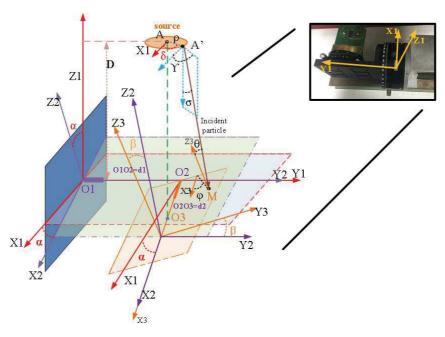

| <b>Figure 4.5:</b> Simulation result of the correlation between incident angle $\varphi$ , $\theta$ and $\alpha$ , $\beta$ |

| Figure 4.6: Schematic diagram of the MIMOSA 18 readout chain [4]73                                                         |

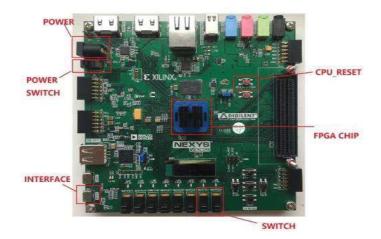

| Figure 4.7: FPGA development board (Nexys Video Artix-7 FPGA) used in our study 74                                         |

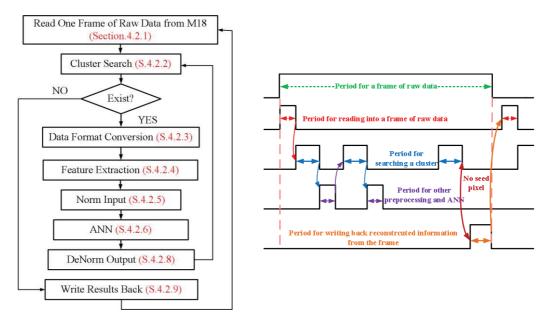

| Figure 4.8: Main procedures and timing in the FPGA device                                                                  |

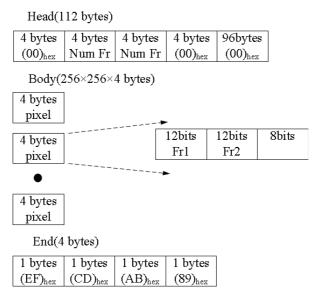

| Figure 4.9: Frame format stored in a binary file (256×256 pixels)                                      | 77       |

|--------------------------------------------------------------------------------------------------------|----------|

| Figure 4.10: Timing waveform to read in raw data of an example from PC to the FPGA d                   | evice.   |

|                                                                                                        | 79       |

| Figure 4.11: Incident angles of charged particles.                                                     | 80       |

| Figure 4.12: Algorithm for cluster search implemented in the FPGA device.                              | 81       |

| Figure 4.13: Steps of searching neighbour pixels around seed pixel.                                    | 82       |

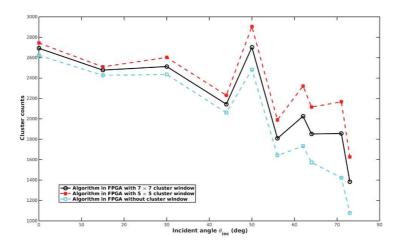

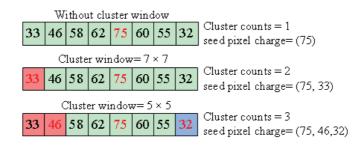

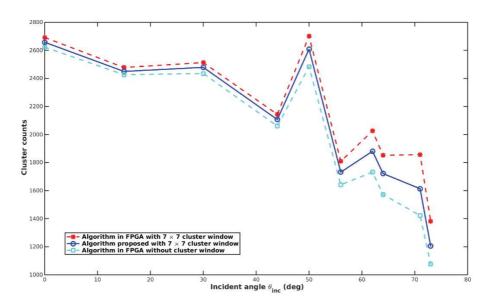

| Figure 4.14: Cluster counts found by algorithms with different cluster windows                         | 84       |

| Figure 4.15: Cluster counts of an elongated cluster found by the three algorithms                      | 85       |

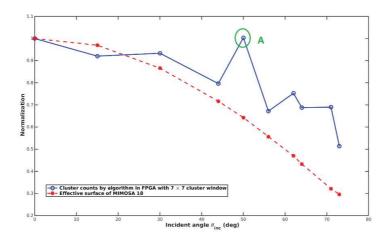

| Figure 4.16: Simulation of cluster counts and effective surface.                                       | 85       |

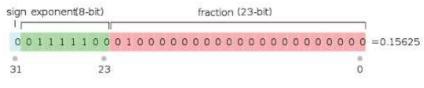

| Figure 4.17: Format of Single-precision floating-point [10]                                            | 86       |

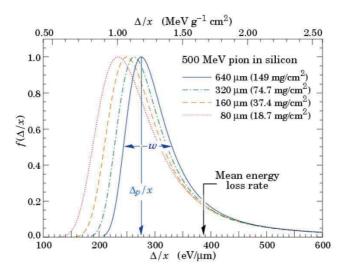

| Figure 4.18: Stopping power for positive muons in cupper Straggling functions in silice                | on for   |

| 500MeV pions, normalized to unity at the most probable value $\Delta p/x$ [12]                         | 88       |

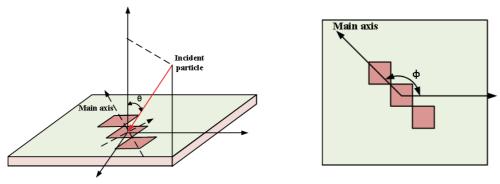

| Figure 4.19: The main axis of a cluster.                                                               | 88       |

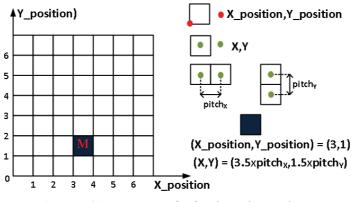

| Figure 4.20: Position of a fired pixel in a cluster.                                                   | 90       |

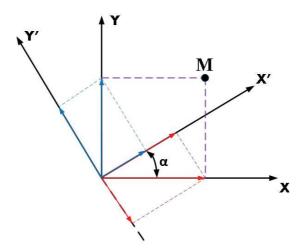

| Figure 4.21: Correlation between two coordinate systems                                                | 91       |

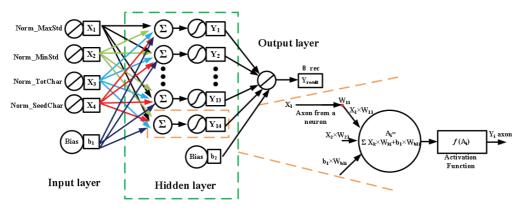

| Figure 4.22: Structure of the artificial neural network.                                               | 93       |

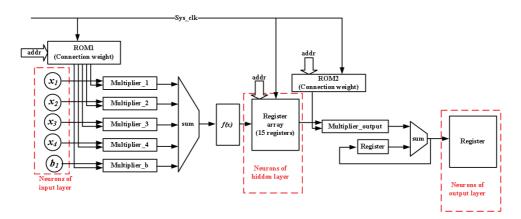

| Figure 4.23: Digital circuit of the artificial neural network.                                         | 95       |

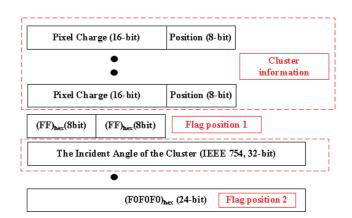

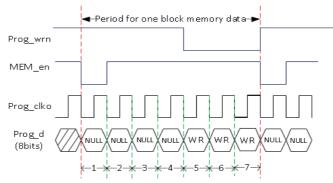

| Figure 4.24: Reconstructed information format of a cluster                                             | 97       |

| Figure 4.25: Timing of transporting the output result of one memory cell.                              | 98       |

| Figure 4.26: Reconstructed results of a frame of raw data (a) The content of reconstru                 | ructed   |

| results (b) First cluster shape (c) Second cluster shape                                               | 99       |

| Figure 4.27: Difference between the mean value of reconstructed angles and the incident a              | angle.   |

|                                                                                                        | 100      |

| Figure 4.28: Distribution of reconstructed angles $\theta_{rec}$ versus incident angles $\theta_{inc}$ | 101      |

| Figure 5.1: Definition of a seed pixel in a cluster                                                    | 107      |

| Figure 5.2: Flowchart of the algorithm proposed.                                                       | 108      |

| Figure 5.3: Comparison between the data [3] and the max_value register                                 | 109      |

| Figure 5.4: Comparison between the column seed pixel and the neighbour max_value reg                   | gisters. |

|                                                                                                        | 109      |

| Figure 5.5: Information of an example cluster.                                                         | 110      |

| Figure 5.6: Processing steps of the example cluster.                                                   | 111      |

| Figure 5.7: Two "seed pixels" in the same column, pixel A is the seed pixel, pixel B is a p            | oart of  |

| the cluster                                                                                            |          |

| Figure 5.8: Two "seed pixels" in the same row, pixel A is the seed pixel, pixel B is a part            | of the   |

| cluster                                                                                                | 114      |

| Figure 5.9: Simulation results of cluster counts found by algorithms proposed in this cl               | napter   |

| with different cluster windows (7×7 and 5×5 cluster window)                                            | 116      |

| Figure 5.10: Simulation results of the percentage of lost cluster counts between algor                 |          |

| with the $7 \times 7$ and the $5 \times 5$ cluster window                                              |          |

| Figure 5.11: Simulation results of cluster counts by algorithms with different seed thresh             |          |

|                                                                                                        |          |

| Figure 5.12: Simulation results of cluster counts found by the algorithm proposed                      | 1 VS.    |

## **List of Tables**

| Table 1-1: Major physics processes to be studied by the ILC [17]                                       | 3     |

|--------------------------------------------------------------------------------------------------------|-------|

| Table 1-2: Parameter a and b for detectors.                                                            | 9     |

| Table 1-3: Parameters of the design composed of three layers of double-sided ladders [26]              | . 10  |

| Table 1-4: Minimum transverse momentum of a particle to arrive different layers (R <sub>layer</sub> is | ; the |

| radius of the vertex detector and R is the radius of the particle trajectory)                          | . 15  |

| Table 2-1: Advantages and disadvantages of these detector technologies [6]                             | . 37  |

| <b>Table 4-1:</b> The setting of the angle $\theta$ , $\varphi$ , and $\alpha$ , $\beta$               | . 73  |

| Table 5-1: Simulation results of the occupied surface and power consumption of the 64-colu             | umn   |

| mplementation                                                                                          | 130   |

## Résumé en Français

#### A. Introduction

Le modèle standard de la physique des particules est un cadre théorique utilisé pour décrire les particules fondamentales constituant la matière ordinaire et les forces fondamentales. Les expériences de physique des hautes énergies (HEP) sont conçues pour rechercher des particules fondamentales via des collisions parmi une grande quantité de particules de haute énergie. Divers détecteurs sont équipés autour du point d'interaction pour détecter et enregistrer les informations relatives aux collisions. L'ILC (International Linear Collider) est un projet d'accélérateur linéaire de particules proposé pour les expériences HEP, en complément du LHC (Large Hadron Collider) au CERN. En raison de leur courte durée de vie, de l'ordre de plusieurs picosecondes, les quarks lourds doivent être reconnus par les trajectoires partant du vertex de la décroissance secondaire. Le détecteur de vertex (VTX) sera situé près du point d'interaction.

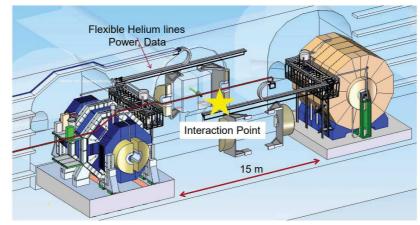

Dans les expériences HEP, différents types de détecteurs à semi-conducteurs ont été utilisés pour la détection et la mesure de la position du passage des particules. Les capteurs à pixels CMOS (CPS) également appelés capteurs monolithiques à pixels actifs (MAPS) et proposés par des chercheurs de l'IPHC-Strasbourg (Institut Pluridisciplinaire Hubert Curien), intègrent sur un même substrat l'électronique pour la détection et la lecture des signaux. Les CPS constituent un condidali naturel pour l'équipement du VTX, car ils offrent un très bon compromis entre la granularité, le budget de matière, la tolérance au rayonnement et la vitesse de lecture. Ils ont été utilisés pour la jouvence du détecteur PiXeL (PXL) de l'expérience STAR au RHIC et sont actuellement en phase de production pour la mise à jour de l'ITS (Inner Tracking System) de l'expérience ALICE-LHC. Comme le montre la figure 1, Le point d'interaction est entouré de deux détecteurs , (International Grand Detector (ILD) et Silicon Detector (SiD)), qui fonctionnent selon un schéma push-pull pour partager la même luminosité.

Figure 1: International Grand Detector (ILD) et Silicon Detector (SiD).

Dans le détecteur de vertex de l'ILC, la simulation Monte-Carlo montre qu'un nombre élevé d'impacts supplémentaires seront générés par des électrons résultant de processus liés au bruit de fond des faisceaux. Leur impulsion se trouve typiquement dans la gamme de 10-100 MeV/c, et est généralement à celle des particules issues d'événements associés à des processus physiques.

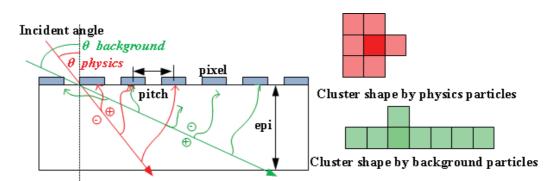

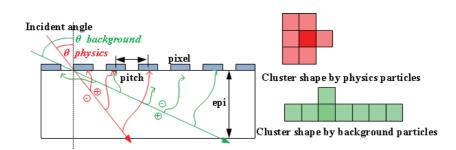

Sous l'effet du champ magnétique dans le détecteur, les électrons provenant du bruit de fond, en raison de leur faible impulsion, traversent les détecteurs avec un grand angle d'incidence par rapport à la normale au plan des détecteurs. Les paires électrons-trous, environ ~80 e-h/µm, sont créées par le processus d'ionisation lorsque les particules chargées traversent la couche épitaxiale. Les électrons sont collectés par la diode de collection implantée dans chaque pixel. Les amas de pixels (clusters) générés par les électrons issus du bruit de fond présentent des formes plutôt allongés comme le montre la figure 2. En considérant les réseaux neuronaux artificiels (ANNs) qui ont été largement utilisés dans le domaine de la reconnaissance de motifs, notre groupe à l'IPHC a proposé d'explorer le concept d'un capteur à pixels CMOS avec des ANNs intégrés pour marquer et supprimer les pixels touchés (hits) générés par ces électrons.

*Figure 2:* Les formes de cluster générées par des particules du processus physique VS. l'arrière-plan de faisceau.

Au cours de ma thèse de doctorat, je me suis concentré sur l'étude d'un capteur à pixels CMOS avec des ANNs intégrés portant sur les aspects suivants :

- I. L'implémentation de modules de prétraitement et d'un ANN dans un composant FPGA pour l'étude de faisabilité ;

- II. Un algorithme pour la recherche de clusters, qui fait partie des modules de prétraitement, a été proposé en vue d'être intégré dans la conception de l'ASIC (Application-Specific Integrated Circuit).

#### **B.** Travail Doctoral

#### 1) L'implémentation dans un FPGA

Pour concevoir le capteur à pixels CMOS avec des réseaux neuronaux artificiels intégrés, la première étape est l'étude de faisabilité qui consiste à comparer la mise en œuvre de l'ANN dans le FPGA à celui mise en œuvre dans un software. Les deux implémentations sont exploitées par une méthode offline, ce qui signifie que les données brutes utilisées sont acquises par un système indépendant.

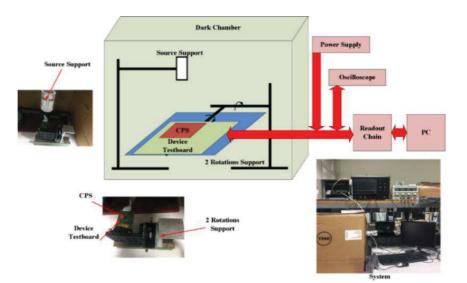

Le système d'acquisition de données brutes a été mis en place pour recueillir des données brutes à partir d'un capteur existant, MIMOSA 18, illuminé par une source  $\beta^-$  de <sup>90</sup>Sr. Un support à 2 rotations est utilisé pour placer le CPS. Dans le cas où la source serait fixe, l'angle  $\theta$  d'incidence des particules chargées peut être choisi en ajustant les angles entre le support et le plan de référence.

Dans la procédure d'apprentissage effectuée par le logiciel appelé Toolkit for Multivariate Data Analysis (TMVA), une grande quantité de données brutes a été recueillie pour chaque angle  $\theta$  d'incidence donné (10 au total) afin de former les poids de l'ANN.

Pour l'implémentation de l'ANN dans le FPGA, j'ai déterminé d'abord les entrées de l'ANN en utilisant des modules de prétraitement. Ensuite, j'ai implémenté ces modules de prétraitement et l'ANN dans une carte de développement NEXYS VIDEO FPGA en utilisant le langage de description matérielle. La procédure de test a été accomplie dans le FPGA. 500 trames de données brutes ont été échantillonnées pour chaque angle d'incidence donné afin de tester l'ANN. Les données brutes ont été introduites dans le FPGA puis traitées par CDS (Correlated Double Sampling) et des valeurs de pixel de 12 bits sont générées.

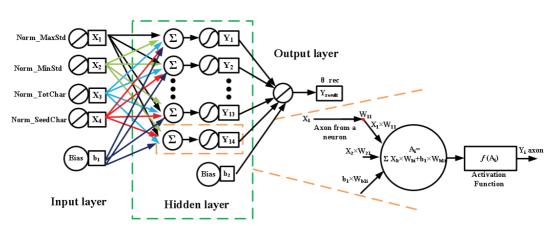

#### a. Modules de prétraitement

Les modules de prétraitement contiennent principalement la recherche de clusters et l'extraction de paramètres. Le module de recherche de clusters est utilisé pour trouver les pixels de départ et localiser les clusters dans la trame des valeurs de pixels. Les modules d'extraction de fonctionnalités sont utilisés pour produire des paramètres caractérisant un cluster. Quatre paramètres sont définis : la charge totale d'un cluster, la charge d'un pixel de départ, les écarts-types maximum et minimum. Le module MCA (Main Component Analysis) fait partie de l'extraction des fonctionnalités implémenté dans le FPGA et est utilisé pour calculer les écarts-types maximum et minimum.

Figure 3: L'ANN implémentée dans le FPGA.

Ces quatre paramètres sont normalisés puis introduits dans l'ANN pour reconstruire l'angle d'incidence en fonction des poids de l'ANN. La structure de l'ANN est illustrée sur la figure 3. Elle se compose de la couche d'entrée, de la couche cachée

et de la couche de sortie. La couche d'entrée est composée de 4 neurones d'entrée et d'1 neurone de biais. La couche cachée qui vient après celle d'entrée a 14 neurones de calcul et 1 neurone de biais. Le nombre de neurones de la couche cachée est déterminé par la procédure d'apprentissage dans le software, en prenant en compte un équilibre entre la complexité et les performances de la structure de l'ANN. La fonction d'activation utilisée dans l'ANN est une tangente hyperbolique.

##

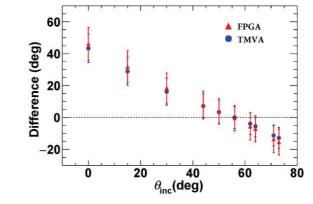

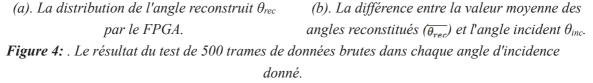

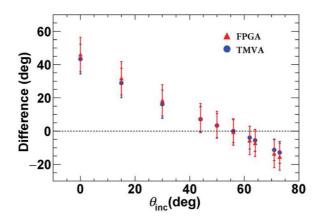

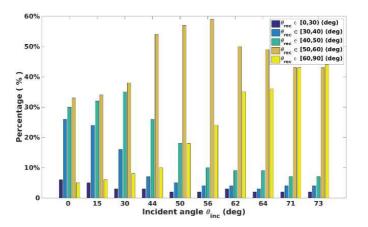

Dans la procédure de test, j'ai enregistré et analysé les angles d'incidence reconstruits. La figure 4(a) présente la distribution des angles reconstruits ( $\theta_{rec}$ ). Au fure et à mesure que l'angle d'incidence ( $\theta_{inc}$ ) augmente, le pourcentage d'angles reconstruits ( $\theta_{rec}$ ) entre 60 et 90 degrés augmente alors que le pourcentage d'angles reconstruits ( $\theta_{rec}$ ) entre 30 et 50 degrés diminue. Compte tenu de l'application spécifique du détecteur, la gamme d'angles reconstruits d'intérêt est comprise entre 50 à 75 degrés. Tout d'abord, les formes de clusters générées par des particules d'angles d'incidence inférieurs à 50 degrés ne varient évidemment pas ou très peu. De plus, ces angles d'incidence peuvent être directement reconstruites à partir des informations des hits données par une échelle double-face (double-sided ladder). D'autre part, en raison de la limitation de la fenêtre 7×7, les entrées ANN extraites des clusters présentent des caractéristiques similaires si l'angle d'incidence est supérieur à 78 degrés.

La figure 4(b) représente la différence « D », voir dans la formule (1), entre la valeur moyenne des angles reconstruits ( $\overline{\theta_{rec}}$ ) et l'angle d'incidence ( $\theta_{inc}$ ); notons que

les résultats reconstruits par le FPGA sont présentés en rouge et ceux reconstruits par le logiciel TMVA en bleu. On remarque que les angles reconstruits par les deux méthodes ont la même valeur moyenne, ce qui valide l'étude de faisabilité. Cependant, ils ne coïncident pas complètement en raison de la différence dans la précision des données entre le hardware et le software.

$$D = \overline{\theta_{rec}} - \theta_{inc} = \frac{1}{n} \sum_{i=1}^{n} (\theta_{rec_i}) - \theta_{inc} .$$

(1)

De plus, les différences entre  $\overline{\theta_{rec}}$  et  $\theta_{inc}$ , que ce soient pour le FPGA ou pour le TMVA, n'ont pas encore atteint un niveau de précision permettant de prédire l'angle d'incidence réel car la structure de l'ANN et la procédure de formation doivent encore être optimisées. Idéalement, la différence entre  $\overline{\theta_{rec}}$  et l'angle d'incidence ( $\theta_{inc}$ ) devrait se situer près de l'axe X (y=0).

Même si l'ANN n'a pas permis une reconstruction très précise, comme indiqué, les résultats reconstruits présentent clairement la même tendance que la variété d'angles d'incidence. En outre, la preuve du principe que les particules laissent une "signature" qui dépend de l'angle d'incidence a été établie.

#### 2) Un algorithme sur l'ASIC pour la recherche de cluster:

Le module de recherche de cluster implémenté dans le FPGA ne peut pas être transplanté directement dans la conception ASIC. En premier lieu, un grand nombre de mémoires serait nécessaire pour stocker une trame entière de valeurs de pixels; en second lieu, beaucoup de ressource calcul et de temps seraient nécessaires pour détecter les pixels voisins. J'ai proposé propose un algorithme pour la recherche de cluster qui peut être intégré dans le capteur à pixels CMOS et collecter des clusters en temps réel.

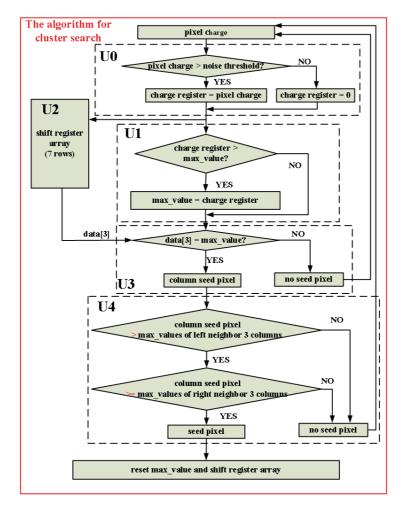

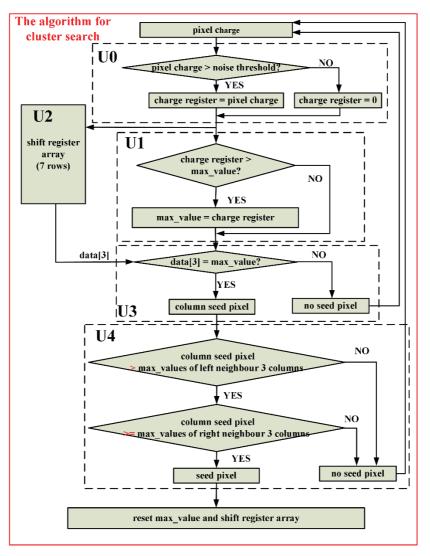

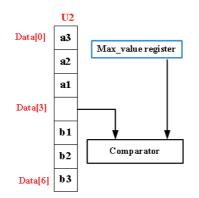

#### a. Algorithm

Au lieu de rechercher des pixels de départ dans une matrice pixel par pixel, l'algorithme recherche un pixel de départ en temps réel dans le processus de lecture de la valeur de pixel ligne par ligne. Le pixel de départ est admis en comparant les pixels situés au-dessus et en dessous de celui-ci et les pixels les plus grands situés dans les colonnes gauche et droite d'une certaine plage de fenêtres. La procédure de l'algorithme est illustrée à la figure 5.

Figure 5: La description de la procédure de l'algorithme.

#### **b.** Simulation

J'ai élaboré l'algorithme en code C et l'ai simulé. 500 trames de données brutes pour chaque angle d'incidence donné sont utilisées pour tester ces algorithmes. Le résultat montre que l'algorithme atteint le même niveau de comptage des clusters que les autres algorithmes, y compris celui implémenté dans le FPGA.

#### c. Implémentation

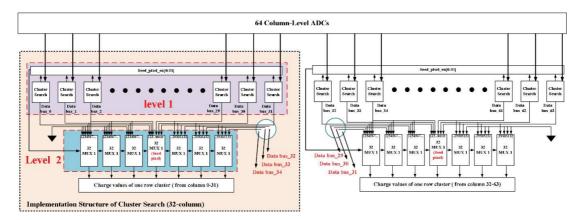

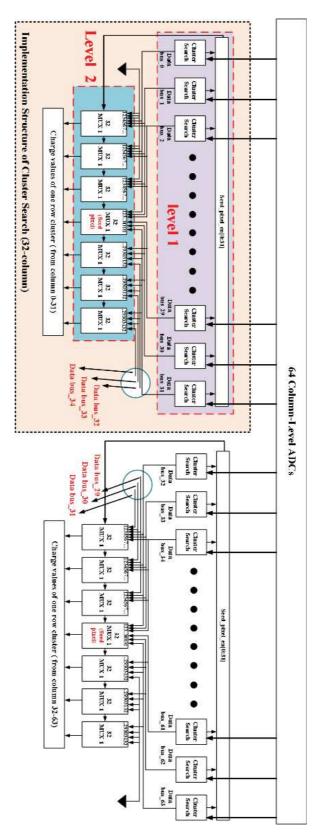

La mise en oeuvre de l'algorithme est basée sur une matrice à modulo  $2^{N}$ -colonnes. La figure 6 montre un exemple de deux modules de 32 colonnes (N=5). Les entrées de l'implémentation sont les sorties des 64 ADC de colonne. Le niveau 1 se compose de 32 unités, chacune implémentant l'algorithme de recherche de cluster. Le niveau 2 a sept (pour la fenêtre de 7×7) multiplexeurs 32-1. Le nombre de multiplexeurs est déterminé par la taille de la fenêtre dans l'algorithme.

Figure 6: Structure de l'algorithme implémenté dans une matrice à 64 colonnes.

J'ai implémenté la structure à 64 colonnes avec différents paramètres et effectué la synthèse de ces implémentations en ciblant la technologie CMOS TowerJazz 0,18  $\mu$ m. Il n'y a pas de différence significative entre les implémentations dans une matrice à modulo de 16 colonnes (N=4), 32-colonnes (N=5) et 64 colonnes (N=6) en termes de surface occupée et de puissance dissipée. Toutefois, compte tenu de l'extraction des fonctionnalités et du module ANN qui suivent la mise en œuvre de la recherche de cluster, une surface occupée et une dissipation de puissances accrues sont nécessaires si le modulo de 16 colonnes est utilisé. Ces deux paramètres d'évaluation peuvent être diminués en utilisant la fenêtre de 5×5 au lieu de celle de 7×7. Ceux-ci pourraient encore être améliorés avec une horloge à basse fréquence ou un ADC de basse résolution. Si l'on choisit la technologie CMOS 65 nm, la densité d'intégration augmente impliquant une diminution de la surface occupée et de la puissance consommée. Si l'on utilise un substrat présentant une couche épitaxiale de haute résistivité, une fenêtre de cluster plus petite peut alors être utilisée car les formes de cluster générées par les particules sont réduites.

#### C.R&D

Sur la base des recherches de la thèse, le concept d'un capteur à pixels CMOS avec des ANNs intégrés sera étudié plus avant en mettent l'accent sursous les deux aspects suivants :

#### Optimiser l'ANN pour améliorer la précision de reconstruction:

L'architecture ANN doit être optimisée, telle que le nombre de neurones d'entrée. Plusieurs fonctionnalités peuvent être introduites pour présenter un cluster. L'ANN pourrait recevoir en entrée davantage de données brutes pour optimiser les poids afin d'accroître la précision de la reconstruction.

## Développer des modules fonctionnels sur puce pour réaliser la conception matérielle complète

Une solution pour diminuer la dissipation de puissance de cette conception sera d'optimiser le système de contrôle grâce à la technique dite de Power Gating qui permet de couper l'alimentation des modules non utilisés. Pour la couche épitaxiale à haute résistivité, la consommation d'énergie et les surfaces occupées du module seront réduites grâce à l'application d'une petite fenêtre en clusters ( $5 \times 5$ ). En plus, un algorithme sera proposé pour l'extraction des paramètres des clusters et intégré dans l'ASIC.

Si la technologie CMOS 65 nm est utilisee à l'avenir, la surface occupée sera réduite car une densité de circuit plus élevée est fournie; une réduction significative de la consommation d'énergie pourra être obtenue en raison de la faible source de courant. La technologie d'intégration 3D pourrait également être appliquée pour intégrer des ANN dans le capteur àde pixels CMOS. La matrice de pixels et les modules de traitement numérique (recherche de cluster, extraction de caractéristiques et ANN) pourraient alors être séparés en différents niveaux.

## Introduction

High Energy Physics (HEP) experiments are established to extend and improve the understanding of the universe. In machines of HEP experiments, physics particles are accelerated and then taken into collisions. Various detectors equipped are used to record and measure the products of the collisions. The International Linear Collider (ILC) as a complementary experiment to the Large Hadron Collider (LHC) has been proposed. The current program of the ILC for a 125 GeV Higgs boson will be processed at a centre-of-mass energy of 250 GeV. The International Large Detector (ILD) and the Silicon Detector(SiD) are two detector concepts that will be installed around the interaction point and operated in a push-pull scheme to share the same luminosity. Vertex detectors are located at the most inner part of a detector to measure the primary interaction vertex and secondary vertices from decay particles under cooperation from other tracking detectors. The vertex detector of the ILD consists of a cylindrical concentric multi-layer structure to achieve an excellent spatial point resolution. On the vertex detector, a large number of hits will be generated by electrons coming from the beam background. These extra hits will increase the data flow and reduce the bandwidth of the system. The momentum of these electrons coming from the beam background typically lie in the range of 10-100 MeV/c, which is lower than that of particles coming from physics events. Due to the effect of multiple scattering, the reconstruction of tracks generated by low momentum particles is significantly degraded.

In order to tag and remove the extra hits generated by background particles, this thesis aims to make contributions to the development of a CMOS pixel sensor with on-chip artificial neural networks.

Electron-hole pairs about ~80 e-h/ $\mu$ m are created by the ionization process when a charged particle passes through the epitaxial layer of CMOS pixel sensors. Because of diffusion, electrons generated are collected by two or more independent pixels that constitute a charge cluster which expresses hit information. Under the effect of the magnetic field in the detector, electrons from the beam background, owing to low momenta, will cross the vertex detector with a large incident angle. Clusters generated by these electrons (large incident angles) present rather elongated shapes.

CMOS pixel sensors (CPS), also named Monolithic Active Pixel Sensors (MAPS) are monolithic devices that integrate signal sensing and readout electronics on the same substrate. They offer an attractive balance among granularity, material budget, radiation tolerance and readout speed. CMOS pixel sensors have been used in the PiXeL detector (PXL) upgrade of the STAR experiment at RHIC and now are being built for the upgrades of the Inner Tracking System (ITS) of the ALICE-LHC experiment.

Artificial Neural Networks (ANNs) are computational modules that are inspired by the biological neural network. An ANN consists of processing units and connections between these units. It has been proved that ANNs are suitable for pattern recognition in a wide variety of field.

In this thesis, we study the feasibility of integrating ANNs within CPS to reconstruct incident angles of particles. In addition, an algorithm for cluster search is proposed to integrate into the CPS for real-time preprocessing.

The thesis is organized as follows,

- In chapter 1, ILC physics processes and layout are introduced briefly. Then, major experimental conditions including beam structure and beam background are presented. ILD, especially the vertex detector part, is presented. Finally, due to challenges existing for multi-layer vertex detector targeting at low momentum particles, the motivation of a CMOS pixel sensor with on-chip artificial neural networks is provided. The trajectory of charged particles under the effect of the magnetic field is projected on both the transverse and parallel plane respectively and described.

- In chapter 2, the pinciple of carriers generation and transport in semiconductors are introduced. Then, structures and bias modes of P-N junctions and Metal-Oxide-Semiconductors are expressed. Lastly, several types of silicon detectors are presented and compared.

- In chapter 3, pattern recognition is introduced firstly. The biological and

artificial neuron structure and principle are explained. Then, a multi-layer perceptron structure is presented. Next, the feature extraction procedure and supervised learning procedure of ANN is outlined. ANN' applications in the HEP are presented.

- In chapter 4, the feasibility study of the CMOS pixel sensor with on-chip ANNs, which is achieved by the off-line method, is described in detail. Firstly, a raw data acquisition system, including CMOS pixel sensor, 2 rotations support and readout china is illustrated. Then, the entire design implemented in a Field Programmable Gate Array (FPGA) development board is introduced in detail, including the cluster search module, the feature extraction module and the ANN structure. Lastly, the reconstruction results of incident angles by the ANN are compared and analysed.

- In chapter 5, an on-chip algorithm for cluster search is proposed and presented. Firstly, the motivation for the algorithm is given. Secondly, the algorithm is illustrated in detail, including the principle description and detail step demonstration. Then, simulation results are presented. Next, the discussion of the algorithm is provided targeting at three cases of the cluster shape. Finally, the implementation of the algorithm is expressed and the synthesized result of the implementation is analysed.

- In conclusions, the results obtained in this thesis are summarized. In the end, perspectives for the CPS integrated with ANNs are presented, including an in-pixel algorithm for cluster search and an structure for feature extraction.

## **1 International Linear Collider**

The ILC was proposed for the High Energy Physics (HEP) and encouraged by requirements on the precision measurement of the Higgs Boson. The International Linear Collider (ILC) is introduced briefly in the chapter, and the development motivation of a CMOS Pixel Sensor (CPS) with on-chip Artificial Neural Networks (ANNs) is also illustrated. Firstly, physics programs and the baseline of the ILC are presented. Secondly, ILC experimental conditions and the International Large Detector (ILD) are illustrated. The chapter ends with a description of the motivation for developing a CMOS pixel sensor with on-chip ANNs, that is tagging and removing hits generated by charged particles coming from the beam background based on the cluster shapes.

### **1.1 ILC Project**

Everything in the universe is found to be made from fundamental particles. A lot of scientists are devoted to experimental and theoretical efforts, in order to explore the nature of fundamental particles. The Standard Model (SM) is a theoretical framework, which is proposed to explain the principle of fundamental particles constituents of ordinary matter and related forces (including electromagnetic, weak, and strong interactions, excepting the gravitational force). The current Standard Model was finalized in the early 1970s, which has explained almost all results of HEP experiments to date. For instance, the model has forecast the existence of quarks, the top quark, and the tau neutrino and been confirmed. The Standard Model has become established as a

well-tested physics theory [1][2].

HEP experiments are designed to research fundamental particles via collisions and conversion among a large amount of high-energy particles. In machines, two beams of particles are moved in opposite directions and accelerated, then brought into collisions at the interaction point. Various detectors are equipped around the interaction point to detect and record information of collisions [3][4].

In the past, a large number of high energy physics experiments and equipment have been designed and established by physicists [5]. In 2012, a particle with a mass of about 125GeV was discovered by the ATLAS and CMS Collaborations at the Large Hadron Collider (LHC) which is located at Geneva Switzerland [6]. Many properties of the particle are in accordance with the postulated Higgs boson of the Standard Model. Details of the Higgs boson and the presence or not of other anticipated new particles need to be studied to complete the Standard Model framework. More precise measurements of the Higgs boson can be achieved by lepton colliders which provide the well-defined initial state of collisions and clean background level [7][8][9][10].

In 2001, a common conclusion was proposed by all three regional organizations (ACFA in Asia, HEPAP in North America, and ECFA in Europe) of the HEP field: The next major project in the HEP would be an electron-positron linear collider with a centre-of-mass energy of 500 GeV named International Linear Collider [11][12]. In autumn 2012, the Japanese high-energy physics community proposed to locate the ILC in Japan. In 2013, after the discovery of the Higgs boson, the Technical Design Report (TDR) for the ILC accelerator was published. The machine was designed to achieve a centre-of-mass energy of 500 GeV [13][14].

According to the recommendation from the Japan Association of High Energy Physicists (JAHEP) [15], the initial program of the ILC for a 125 GeV Higgs boson would be started with a centre-of-mass energy of 250 GeV [7]. The ILC project is divided into three phases, the preparation phase (2019/20-2022/2023), the construction phase (foreseen from 2023) and the commissioning phase (foreseen 2031-2032) [16].

#### **1.1.1 Physics Programs of the ILC**

Major physics processes to be studied at various centre-of-mass energies (from 90 GeV to 1000 GeV) in the ILC are shown in table 1-1, Standard Model reactions and physics goals are presented.

| Energy               | Reaction                                           | Physics goal                     |

|----------------------|----------------------------------------------------|----------------------------------|

| 91 GeV               | $e^+e^- \rightarrow Z$                             | Ultra-precision electroweak      |

| 160 GeV              | $e^+e^- \rightarrow WW$                            | Ultra-precision W mass           |

| 250 GeV              | $e^+e^- \rightarrow Zh$                            | Precision Higgs couplings        |

|                      | $e^+e^- \rightarrow t \overline{t}$                | Top quark mass and couplings     |

| 350-400 GeV          | $e^+e^- \rightarrow WW$                            | Precision W couplings            |

| (Upgrade)            | $e^+e^- \rightarrow v \overline{v} h$              | Precision Higgs couplings        |

|                      | $e^+e^- \rightarrow f\overline{f}$                 | Precision search for Z'          |

|                      | $e^+e^- \rightarrow t t h$                         | Higgs coupling to top            |

| 500 GeV<br>(Upgrade) | $e^+e^- \rightarrow Zhh$                           | Higgs self-coupling              |

| (Opgrade)            | $e^+e^- \rightarrow \overline{x} \overline{x}$     | Search for supersymmetry         |

|                      | $e^+e^- \rightarrow AH, H^+H^-$                    | Search for extended Higgs states |

|                      | $e^+e^- \rightarrow v \overline{v} hh$             | Higgs self-coupling              |

| 700-1000 GeV         | $e^+e^- \rightarrow v \overline{v} VV$             | Composite Higgs sector           |

| (Upgrade)            | $e^+e^- \rightarrow v \overline{v} t \overline{t}$ | Composite Higgs and top          |

|                      | $e^+e^- \rightarrow \overline{t} \overline{t} *$   | Search for supersymmetry         |

Table 1-1: Major physics processes to be studied by the ILC [17].

In the ILC, electrons and their antiparticles (positrons) are accelerated and collided at high energy. The physics process of the ILC at a centre-of-mass energy of 250 GeV is the reaction  $e^+ e^- \rightarrow Zh$ . The current program of the ILC (250 GeV) will focus on high-precision and model-independent measurements of the Higgs boson coupling. In addition, it will search for direct new physics in exotic Higgs decays and in pair-production of weakly interacting particles, even exploration of beyond the Standard Model physics.

In the future, the ILC will be upgraded for raising the centre-of-mass energy to 500 GeV even 1 TeV. With the raising of the centre-of-mass energy, the ILC can be used to take precision studies of the top quark and measurement of the top Yukawa coupling, to determine the strength of the Higgs boson's nonlinear self-interaction and to search for new particles.

#### 1.1.2 ILC Layout

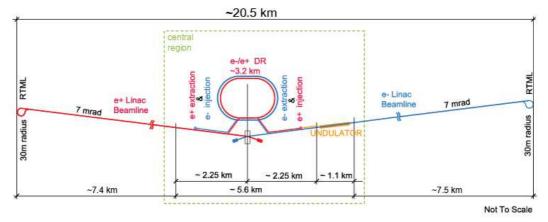

Figure 1.1: Schematic layout of the ILC in the 250 GeV staged configuration [18].

The schematic layout of the ILC in the current 250 GeV configuration is shown in figure 1.1. It is composed of two linear accelerators that face each other, stretching approximately 20.5 kilometres in length. Main parts of the ILC system are expressed as [7]:

- Electrons (e-) and Positrons (e+) Sources. They are designed to produce 5 GeV beam pulses.

- 2. Damping Ring (DR). There are two oval DRs housing in a common tunnel, operating at a beam energy of 5 GeV. Each oval DR has 3.2 km circumference. They are used to accept electron and positron beams with large emittances and produce the low-emittance beams, to dampen the incoming beam jitter to provide highly stable beams and to delay bunches from the source.

- 3. Main Linac. Two main linacs are used to accelerate beams from 5 GeV to the maximum 125 GeV. Each main linac is comprised of two parts. The first part is a two-stage bunch compressor system. Beams are accelerated to 15 GeV in the second stage and the bunch length is reduced from 6 mm to 0.33 mm. The second part following the two-stage bunch compressor is the main linac which is about 6 km.

- 4. Ring To Main Linac (RTML). It is the connection part between the DR and the entrance of the main linac. It is used to transport of the beams from the DR to upstream ends of the main linac, collimate the beam halo generated in the DR.

- 5. Beam Delivery System (BDS). Two BDSs are used to transport and focus beams from two main linacs to the interaction point, then take beams into

collisions. Each BDS is 2254 m long from the end of the main linac to the interaction point.

### **1.2 ILC Experimental Conditions**

Major experimental conditions of the ILC are introduced in the section, including the beam structure and the beam background. Experimental conditions determine some requirements for design of the detector.

# Bunch Structure 1 train = 1312 bunches

#### 1.2.1 Beam Structure

Figure 1.2: Beam structure of the ILC.

As presented in figure 1.2, the beam structure of the ILC is composed of trains at a frequency of 5 Hz (5 trains/second). Each train maintains about 727  $\mu$ s constituted by 1312 bunches. A bunch is separated from the other by ~554 ns. Between two trains there is a period of ~199 ms named beamless time [7][13].

The beam structure is related to the design of detectors in the ILC. Average power consumption of detectors can be reduced by switching off during beamless time which occupies about 99% period. The known interval between every two bunches and trains makes a possible to achieve detectors without triggers. The read-out strategy and sequence are can be implemented between two bunches or after a train [19].

### 1.2.2 Beam Background

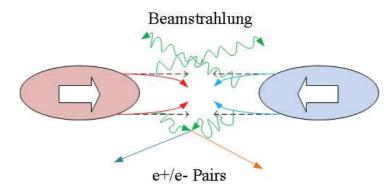

Beamstrahlung is the most important background in the ILC which is created via the bunch interacting with the electromagnetic field of another bunch. In the approach procedure of electron and positron bunches which have strong electric fields, as the small size of bunches indicates that they possess a very high space charge. As shown in figure 1.3, under the effect of the electromagnetic field of bunches, two beams from opposite directions do not point to each other directly, while towards the centre of the oncoming bunch, which is named the pinch effect. Beamstrahlung photons are generated by the beam-beam interaction to radiate the energy [20][21]. Electron-positron pairs with low momenta are released around the interaction point by beamstrahlung photons, which makes a major contribution to the machine-induced background [22][23].

*Figure 1.3:* Illustration of the pinch effect and generation of beamstrahlung photons in bunch collisions.

Low momentum electrons and positrons produced by beamstrahlung photons hit on detectors and make an influence on physics measurements. Momenta of these particles typical lie in the range of 10-100 MeV/c [19]. These background particles are from the interaction region, forward region and even the detector region.

#### **1.3 International Large Detector**

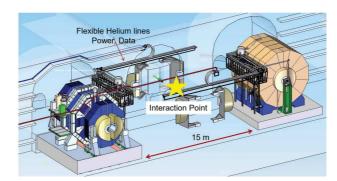

High precision detectors will be equipped in the ILC to provide excellent vertexing and tracking capabilities. Two concepts of detectors, the Silicon Detector (SiD) and the ILD, are developed. The two detectors are swapped into the interaction point within the scheme named "push-pull", to achieve the sharing of the luminosity [17][24], as shown in figure 1.4.

Figure 1.4: Two detectors and the "push-pull" mode [25].

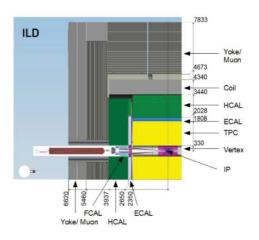

The ILD is designed as a multi-purpose detector concept, which has been optimised on the respect of precision. As shown in figure 1.5, the concept schematic is composed of a vertex detector, a hybrid main tracking system, including a silicon tracking part and a Time Projection Chamber (TPC), a calorimeter system and the outer detector including a muon system and a coil and yoke system.

Figure 1.5: Quadrant view of the ILD detector concept. Dimensions are in mm [26].

#### **1.3.1 Vertex Detector**

The vertex detector is used to measure primary interaction vertices and secondary vertices from decay particles. It is located in the most inner layer around the interaction point of the ILD. For the physics program of the ILC, the vertex detector will play important role on flavour tagging, displaced vertex charge determination and tracking capability for the low momentum particles that cannot reach the main tracking system. The vertex detector is designed based on the ILC experimental conditions and some physics constraints (spatial resolution and material budget, etc.)

#### **Impact Parameter Resolution**

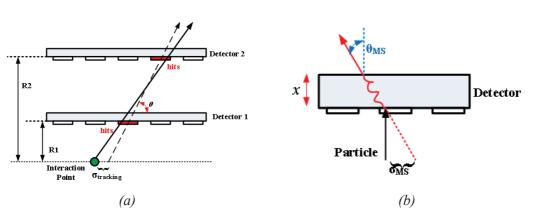

The performance of spatial resolution can be presented by the impact parameter resolution, which is written as [19]

$$\sigma_d = \sigma_{tracking} \oplus \sigma_{MS} = a \oplus \frac{b}{p \times \sin^2 \theta}, \quad (1-1)$$

where

*p* is the particle momentum.

$\theta$  is the polar angle with respect to the beam axis.

As shown in figure 1.6(a), when a charged particle traverses the vertex detector including two layers of detectors (Detector 1 and Detector 2), the reconstructed track has a discrepancy with the real track ( $\sigma_{tracking}$ ).  $\sigma_{tracking}$  is related to the detector geometry (R1 and R2) and the spatial resolution ( $\sigma$ 1 and  $\sigma$ 2,  $\sigma$ 1 =  $\frac{Pixel \, pitch \, of \, vertex \, detector \, 1}{\sqrt{12}}$ ). As shown in formula (1-2),  $\sigma_{tracking}$  achieves the best precision with small values of radii and spatial resolutions.

$\sigma_{tracking} = a = \frac{R1\sigma 1 \oplus R2\sigma 2}{R2-R1}.$  (1-2)

*Figure 1.6: Impact parameter resolution (a) Finite single point resolution (b) Multiple scattering.*

As shown in figure 1.6(b), for a single detector, when a charged particle traverses the detector, the particle undergoes small-angle deflections ( $\theta_{MS}$ ).  $\sigma_{MS}$  is the error of the impact parameter due to the multiple scattering effect. Parameter *b* depends on the distance of the first detector to the interaction point and the material budget (x/X0),

<sup>1</sup>  $x \oplus y = \sqrt{x^2 + y^2}$

where X0 is the radiation length of the scattering medium.

$$b = R1 \times 13.6 \ (MeV) \times \sqrt{\frac{x}{X0}} \times \left[1 + 0.038 \ln\left(\frac{x}{X0}\right)\right] \qquad (1-3)$$

Some examples of parameter *a* and *b* in formula (1-1) for other experiments are shown in table 1-2. Parameter *a* and *b* are set as  $\leq 5 \ (\mu m)$  and  $\leq 10 \ (\mu m \cdot \text{GeV})$  for the ILD.

|         | <i>a</i> (µm) | b (μm·GeV) |

|---------|---------------|------------|

| LEP     | 25            | 70         |

| SLD     | 8             | 33         |

| LHC     | 12            | 70         |

| RHIC-II | 13            | 19         |

| ILD     | ≤5            | ≤10        |

Table 1-2: Parameter a and b for detectors.

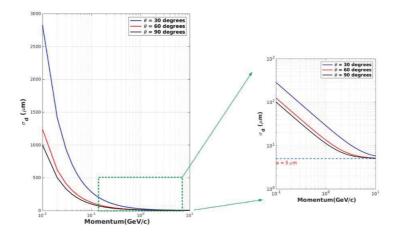

The impact parameter resolution of ILD ( $a=5 \ \mu m$  and  $b=10 \ \mu m \cdot GeV$ ) is simulated according to the formula (1-1). As shown in figure 1.7, the polar angle ( $\theta$ ) is fixed (30, 60, 90 degrees), the impact parameter resolution increases as the momentum of the charged particle decreases. The track generated by a low momentum charged particle will make larger deflection than that by a high momentum charged particle.

Figure 1.7: Impact parameter resolution as a function of the particle momentum.

#### Requirements

In order to meet experimental conditions and the impact parameter resolution of the ILC, requirements for the ILD are as follows:

- > Read-out time  $\sim$ 2-9 µs

- > Spatial resolution:  $\leq 3 \mu m$  (corresponding to a pitch of  $\sim 17 \mu m$ );

- ➤ Material budget: O(0.15% X<sub>0</sub>/layer);

- > A first layer located at a radius of  $\sim 1.6$  cm;

- > Occupancy: ~ 5 part/cm<sup>2</sup>/BX.

- > Radiation hardness: O(100kRad) and  $O(1 \times 10^{11}n_{eq(1Mev)})$  /year (layer 1).

- ▶ Power dispation:  $\sim 50 \text{ mW} / \text{cm}^2$ .

#### Geometries

Figure 1.8: Vertex detector scheme of the ILD.

The vertex detector scheme (figure 1.8) of the ILD consists of three double-sided ladders which are equipped by CMOS pixel sensors on both sides (~ 2 mm apart) [27]. Radii of thee ladders range from 16 mm to 60 mm, Z position ranges from 62.5 mm to 125 mm, as presented in table 1-3. Six pieces of position information of a charged particle which traverses the detector are recorded and measured.

Table 1-3: Parameters of the design composed of three layers of double-sided ladders [26].

| Barrel   | layer  | R <sub>layer</sub> (mm) | Z (mm) |

|----------|--------|-------------------------|--------|

| Ladder 1 | Layer1 | 16                      | 62.5   |

|          | Layer2 | 18                      | 62.5   |

| Ladder 2 | Layer3 | 37                      | 125    |

|          | Layer4 | 39                      | 125    |

| Ladder 3 | Layer5 | 58                      | 125    |

|          | Layer6 | 60                      | 125    |

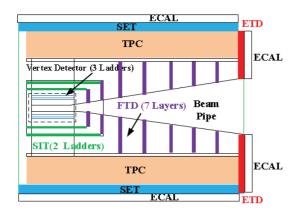

## **1.3.2 Silicon Tracking Part**

The silicon tracking part is a complement component of the main tracking system for the track reconstruction capability. It is made up of four components to measure particles' momenta, including the Silicon Inner Tracker (SIT), the Silicon External Tracker (SET), the Forward Tracking Detector (FTD) and the Endcap Tracking Detector (ETD).

Figure 1.9: ILD schemes of the silicon tracking system.

As shown in figure 1.9, the SIT and the SET are barrel components. The SIT is positioned between the vertex detector and the TPC, and constituted by 2 double layers of CMOS pixels sensors. The SET is located between the TPC and the Electromagnetic CALorimeter (ECAL, see figure 1.5), it is composed of 2 layers of silicon strip detectors. The FTD consists of 7 tracking disks that are positioned between the beam pipe and the TPC, the first two disks which are closed to the vertex detector are pixel detectors and the other five disks are silicon strip detectors. The ETD is located between the TPC end plate and the ECAL, providing a precise point for tracks that go into the endcap [26][28].

## **1.3.3 Time Projection Chamber**

The Time Projection Chamber (TPC) is a central component of the main tracking system. It is about 4.6 m in length, from 33 cm to 180 cm in radii. The TPC is optimised for 3-dimensional point resolution (better than 100  $\mu$ m in  $r\varphi$ , and about 1 mm in Z) which provides large accuracy for the reconstruction. For charged particles with momenta above 100 MeV, the tracking efficiency up to nearly 100% simulated realistically with full backgrounds. The TPC providing particle identification

capabilities by the specific energy loss (dE/dx).

#### **1.3.4 Calorimeter System**

Calorimeters are used to measure the energy of a particle. In the particle flow approach, all particles in an event are reconstructed individually. The calorimeter system for ILD consists of a nearly cylindrical barrel calorimeter and two large end cap calorimeters. Each calorimeter is composed of the ECAL and the Hadronic CALorimeter (HCAL), which is designed to identify photons and neutral hadrons respectively and measure their energy.

#### 1.3.5 Muon System

The muon system is used to identify muons in the ILD by some measurement stations outside the solenoid coil. It is implemented by square tiles of  $30 \times 30 \text{ mm}^2$  and a thickness of 10 mm, with the Silicon PhotoMultiplier (SiPM) readout.

## 1.3.6 Coil and Yoke System

A large volume superconduction coil surrounding calorimeters is used to supply the magnetic field for a nominal 3.5 T and maximum 4 T solenoidal central field. The iron yoke surrounding the coil is used to identify muons and catch tails of hadronic showers. It returns the flux of the magnetic and reduces the outside stray fields.

# **1.4 Motivation**

There are a large amount of hits generated by charged particles coming from the beam background (low momentum). Our group in the IPHC proposed to integrate the Artificial Neural Network into CMOS pixel sensor to tag and remove hits generated by these particles. The motivation of the concept is described in the section.

#### **1.4.1 Challenges for Track Reconstruction**

For the ILC program at the centre-of-mass energy of 250 GeV, data rate

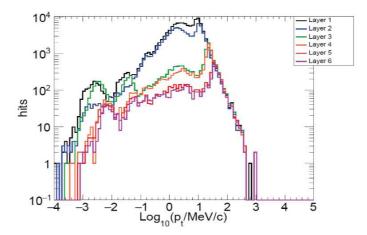

requirement for the vertex detector is ~3 Gbits/s with the safety factor of 3, which is ~30%-50% data flow of the total system. A large fraction of the data flow is related to hits generated by particles coming from the beam background. As simulation result shown in figure 1.10,  $10^4$  hits are generated on the layer 1 of the vertex detector by particles with momenta of 10 MeV/c. Particles from the beam background have typical lower momenta (~10-100 MeV/c) [19] than particles coming from the physics process.

Figure 1.10: Beam background features simulation [29].

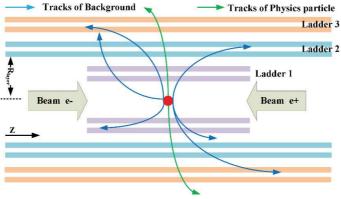

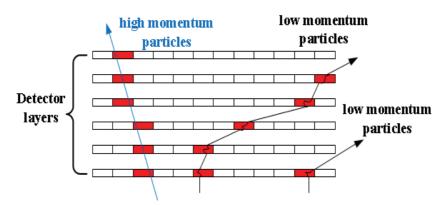

Track reconstruction for low-momentum particles is challenging. Due to the multiple scattering effect, particles with low momenta make obvious deflections when they are traversing a layer of the detector leading to the failure of reconstruction. In figure 1.11, hits and tracks of different momentum particles in a 6-layer detector are presented and compared. Firstly, these deflections formed by low momentum particles produce many segments of different layers, which cannot be merged. Secondly, low momentum particles creating large deflections on the track may hit only one layer of the detector (just a single hit), resulting in the lack of information for reconstruction.

*Figure 1.11:* Schematic diagram of tracks generated by particles, one is created by a particle with high momentum (blue) and others are created by particles with low momenta.

## 1.4.2 Trajectory of Charged Particles

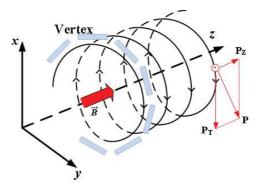

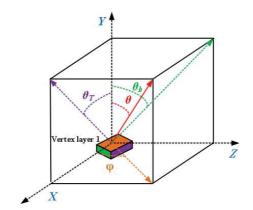

In detectors of the ILC, under the effect of the magnetic field, charged particles move along the helix trajectory. The helix trajectory is shown in figure 1.12. *Vertex* represents the vertex detector of the ILD, *z* presents the beam direction, the momentum (P) of the particle is decomposed into the transverse momentum  $(P_T)$  and the momentum along the *Z*-axis  $(P_Z)$ .

Figure 1.12: Helix trajectory of charged particles under the effect of the magnetic field.

The trajectory is projected on both the transverse and parallel plane respectively to illustrate and analyse.

#### **Trajectory Projected on Transverse Plane**

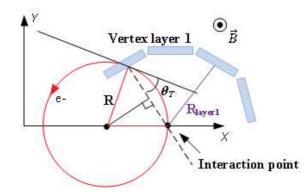

As indicated in figure 1.13, the trajectory of an electron (*e*-) is projected on the transverse plane (plane *xy*) and presents a circle movement. The electron hits on the vertex detector and the incident angle projected is named  $\theta_T$ .

Figure 1.13: Trajectory projection of a charged particle on the transverse plane.

The centripetal force of the electron is supplied by the Lorentz force:

$$qvB = \gamma m \frac{v^2}{R},\qquad(1-4)$$

Where

- *v* is the speed of the electron.

- *B* is the magnetic field perpendicular to the direction of the electron, measured in *Tesla*.

- q is the electron charge.

- *m* is the rest mass of the electron.

- $\gamma$  is a constant value.

- *R* is the radius of the trajectory measured in meter.

According to formula (1-4), the momentum of the electron in the magnetic field is expressed as

$$P = \gamma m v = q B R$$

,  $\left( units: kg \cdot \frac{m}{s} \right).$   $(1-5)$

Applying unit conversion to the formula (1-5), the transverse momentum is

$$P_T \approx 0.3 \times B[T] \times R[m], \ \left(units : \frac{GeV}{c}\right), \qquad (1-6)$$

According to formula (1-6), the minimum transverse momentum required for an electron to arrive at different layers is as follows (without the influence of energy loss and scattering in the trajectory and B = 3.5 T):

*Table 1-4: Minimum transverse momentum of a particle to arrive different layers (* $R_{layer}$  *is the radius of the vertex detector and R is the radius of the particle trajectory).*

| Layer | R <sub>layer</sub> (mm) | R(mm) | P <sub>T</sub> (MeV/c) |

|-------|-------------------------|-------|------------------------|

| 1     | 16                      | 8     | 8.4                    |

| 2     | 18                      | 9     | 9.5                    |

| 3     | 37                      | 19.5  | 19.5                   |

| 4     | 39                      | 19.5  | 20.5                   |

| 5     | 58                      | 29    | 30.5                   |

| 6     | 60                      | 30    | 31.5                   |

In figure 1.13, incident angle  $\theta_{T}$  is the angle between the tangent line at the hit point and the normal line of the vertex detector, calculated as

$$\theta_T = \frac{\pi}{2} - \arccos\left(\frac{R_{layer1}}{2 \times R}\right) = \frac{\pi}{2} - \arccos\left(\frac{0.3 \times B \times R_{layer1}}{2 \times P_T}\right), \quad (1-7)$$

where

$R_{layer1}$  is the radius of the first layer vertex detector, which is 16mm [26].

According to formula (1-7),  $\theta_T$  as a function of the transverse momentum is plotted in figure 1.14.  $\theta_T$  decreases as the transverse momentum of the particle increases. Particles from the beam background (typical 10-100 MeV/c) [19] possess larger incident angles than particles from the physics event due to low momenta.

*Figure 1.14:* Incident angle  $\theta_T$  as a function of the particle transverse momentum ( $P_T$ ).

#### **Trajectory Projected on Parallel Plane**

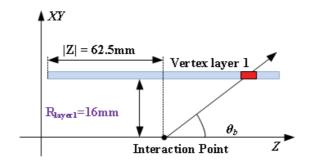

In figure 1.15, the trajectory of the electron projected on a parallel plane, where Z-axis represents the beam line, *Vertex layer 1* presents the location of the ladder 1 whose |Z| is 62.5 mm [26],  $b_e$  is the angle between the trajectory and Z-axis,

$$\theta_b = \arctan\left(\frac{R_{layer1}}{x}\right),$$

(1-8)

where

x is the distance along the Z-axis from the interaction point to the hit location.

Figure 1.15: Trajectory projection of a charged particle on the parallel plane.

Minimum angle  $b_e$  that can generate a hit on the vertex detector is 14.36 degrees, calculated as

$$\theta_{bmin} = \arctan\left(\frac{R_{layer1}}{|z|}\right) = \arctan\left(\frac{16}{62.5}\right) = 14.36 \ (deg). \qquad (1-9)$$

## **1.4.3 Principle for Particle Recognition**

Considering the artificial neural network successfully applied in many fields of pattern recognition, our group in the IPHC proposed a CMOS pixel sensor with artificial neural networks to identify and remove hits generated by particles from the beam background for reducing the bandwidth (maximum rate of data transfer) of the data stream and improving tracking capability.

Figure 1.16: Schematic diagram of an incident angle on the vertex detector.

As shown in figure 1.16, angle  $\theta_b$  and  $\theta_T$  is the projection of the incident angle ( $\theta$ ) on two planes respectively. Under the situation that  $\theta_b$  has a fixed value, the incident angle ( $\theta$ ) increases as the particle transverse momentum decreases (P<sub>T</sub>). Particles from the beam background (typical lower momenta) possess larger incident angles into the vertex detector than those of particles from physics events.

*Figure 1.17: Cluster shapes generated by particles from the physics process and particles from the beam background.*

When a charged particle passing through the epitaxial layer of the CPS vertex detector, electron-hole pairs are created by the ionization process about typical ~80 e-h/ $\mu$ m. Electrons are collected by the diode in each pixel. If the hit is at nearby the border of pixels, electrons would be collected by two or more independent pixels. These independent pixels constitute a charge cluster which expresses hit information. Especially with the decrease in the size of the pixel geometry, the charge-sharing effect becomes more obvious and important [30][31][32]. In figure 1.17, the larger incident angle of a background particle leads to producing an elongated cluster shape. The difference in clusters generated by the two particles makes it possible to tag and remove hits generated by background particles using artificial neural networks.

# **1.5 Summary**

The ILC project and the motivation of a CMOS pixel sensor with on-chip artificial neural networks are introduced in the chapter. In the ILC, a large amount of hits are generated by particles coming from the beam background which have low momenta. Due to the multiple scattering, tracks make large deflections for these particles, leading to the failure on the track reconstruction. Our group propose a CPS with on-chip ANNs to tag and remove hits generated by these particles. Under the effect of the magnetic field, particles with low momenta produce large incident angles on the vertex detector and create elongated cluster shapes. An ANN is implemented to reconstruct the incident angle and tag the hit.

The principle and technology of semiconductor detector will be introduced in the next chapter.

# 1.6 Bibliography

- [1]. https://home.cern/science/physics/standard-model

- [2]. Brau, James, Yasuhiro Okada, and Nicholas Walker. "Ilc reference design report volume 1-executive summary." arXiv preprint arXiv:0712.1950 (2007).

- [3]. Edwards, Donald A., and Michael J. Syphers. *An introduction to the physics of high energy accelerators*. John Wiley & Sons, 2008.

- [4]. Wille, Klaus. *The physics of particle accelerators: an introduction*. Clarendon Press, 2000.

- [5]. https://ilchome.web.cern.ch/ilc/project

- [6]. https://home.cern/science/accelerators/large-hadron-collider

- [7]. Bambade, Philip, et al. "The International Linear Collider: A Global Project." *arXiv* preprint arXiv:1903.01629 (2019).

- [8]. Barish, Barry, and James E. Brau. "The International Linear Collider." *International Journal of Modern Physics A* 28.27 (2013): 1330039.

- [9]. Behnke, Ties. "The international linear collider." *Fortschritte der Physik* 58.7-9 (2010): 622-627.

- [10]. Adams, T., et al. "Terascale physics opportunities at a high statistics, high energy neutrino scattering experiment: nuSOnG." *International Journal of Modern Physics A* 24.04 (2009): 671-717.

- [11]. Loew, Gregory A. "Report from the international linear collider technical review committee." *Proceedings of the 2003 Particle Accelerator Conference*. Vol. 1. IEEE, 2003.

- [12]. Loew, Gregory. International Linear Collider Technical Review Committee: Second Report, 2003. No. SLAC-R-606. Stanford Linear Accelerator Center, Menlo Park, CA (US), 2003.

- [13]. Adolphsen, Chris. *The International Linear Collider Technical Design Report-Volume 3. II: Accelerator Baseline Design.* No. arXiv: 1306.6328; ILC-REPORT-2013-040; ANL-HEP-TR-13-20; BNL-100603-2013-IR; IRFU-13-59; CERN-ATS-2013-037; COCKCROFT-13-10; CLNS-13-2085; DESY-13-062; FERMILAB-TM-2554; IHEP-AC-ILC-2013-001; INFN-13-04-LNF; JAI-2013-001; JINR-E9-2013-35; JLAB-R-2013-01; KEK-REPORT-2013-1; KNU-CHEP-ILC-2013-1; LLNL-TR-635539; SLAC-R-1004; ILC-HIGRADE-REPORT-2013-03. Argonne National Lab.(ANL),

Argonne, IL (United States); Thomas Jefferson National Accelerator Facility (TJNAF), Newport News, VA (United States); Brookhaven National Laboratory (BNL), Upton, NY (United States); SLAC National Accelerator Lab., Menlo Park, CA (United States); Fermi National Accelerator Lab.(FNAL), Batavia, IL (United States), 2013.

- [14]. Adolphsen, Chris. The International Linear Collider Technical Design Report-Volume 3.

I: Accelerator\& in the Technical Design Phase. No. arXiv: 1306.6353;

ILC-REPORT-2013-040; ANL-HEP-TR-13-20; BNL-100603-2013-IR; IRFU-13-59;

CERN-ATS-2013-037; COCKCROFT-13-10; CLNS-13-2085; DESY-13-062;

FERMILAB-TM-2554; IHEP-AC-ILC-2013-001; INFN-13-04-LNF; JAI-2013-001;

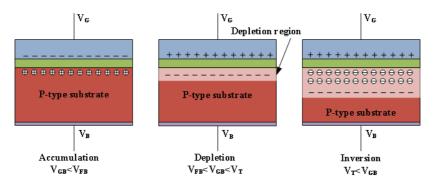

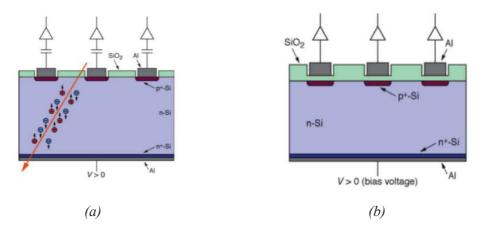

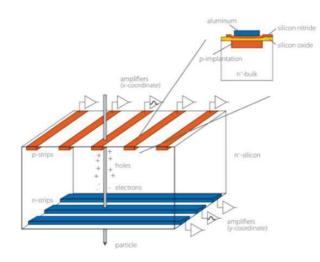

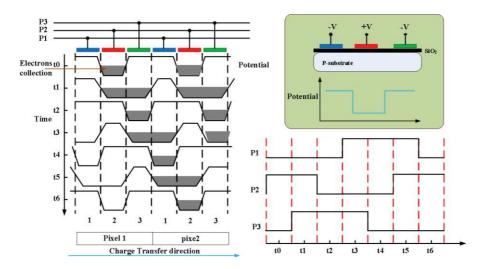

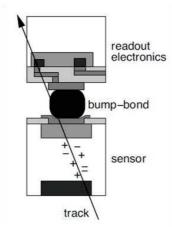

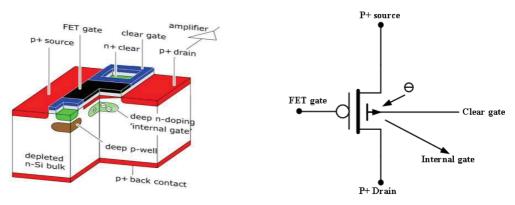

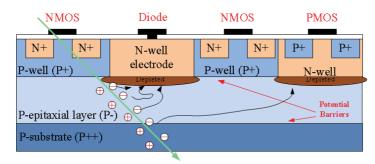

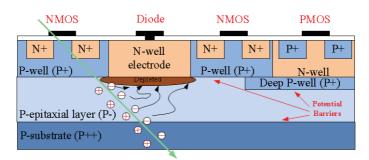

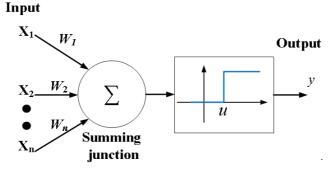

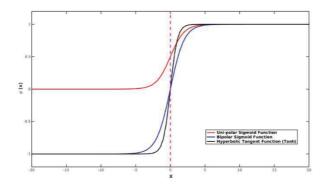

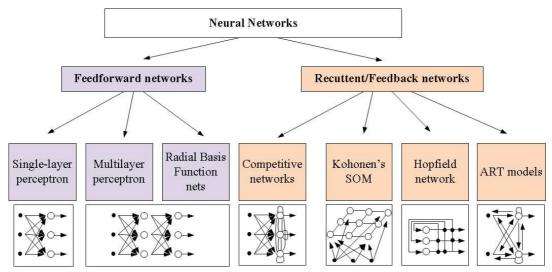

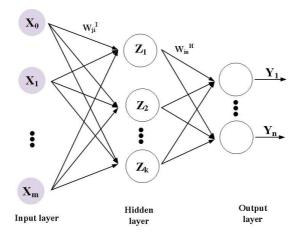

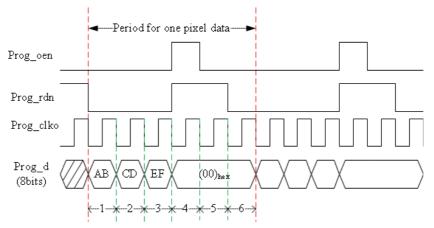

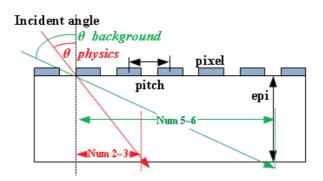

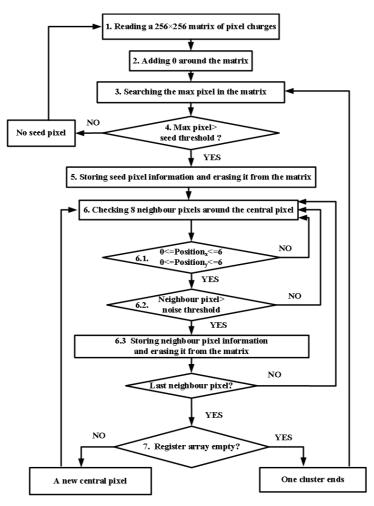

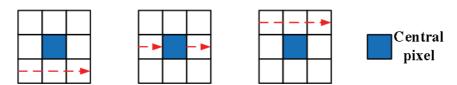

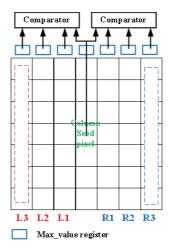

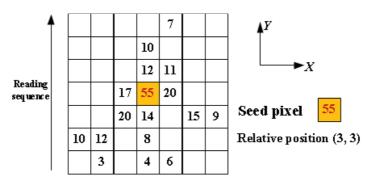

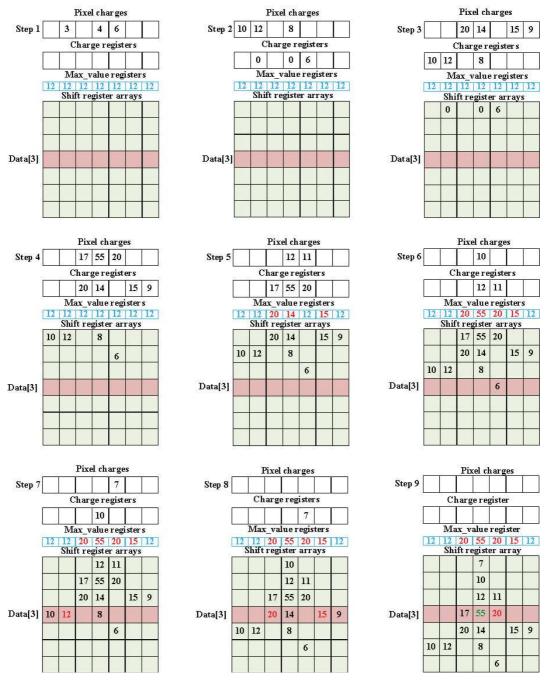

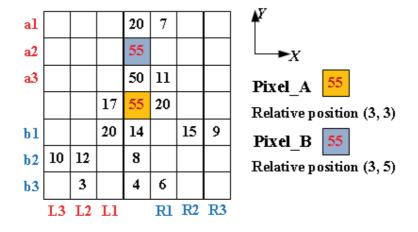

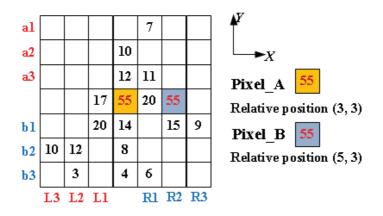

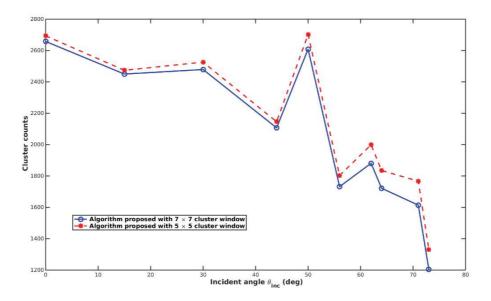

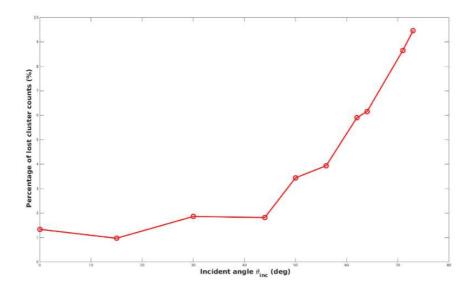

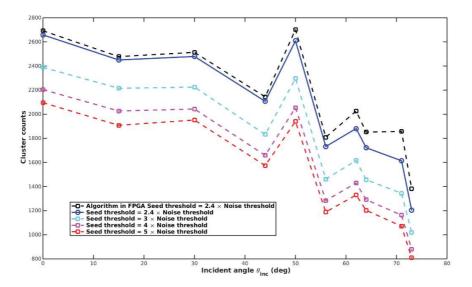

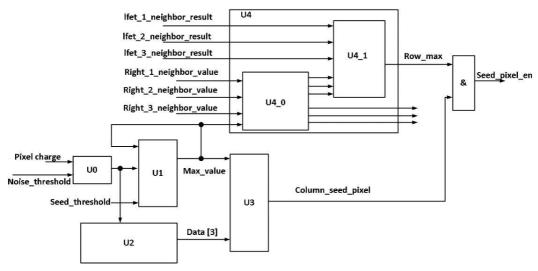

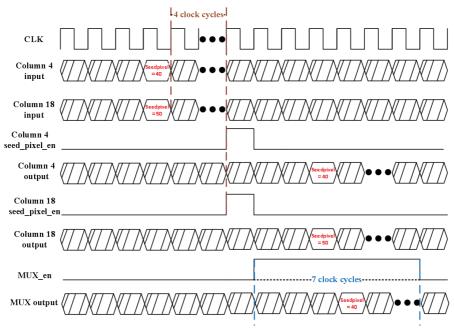

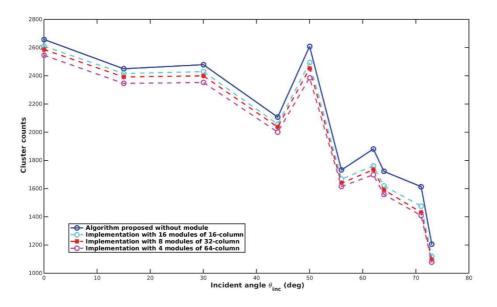

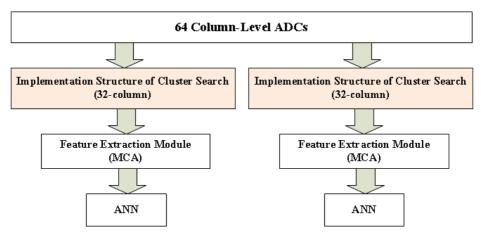

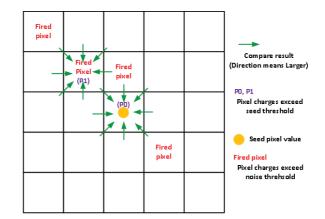

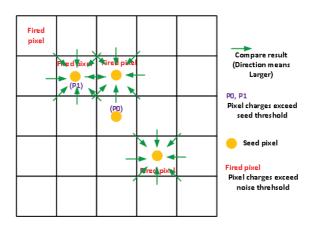

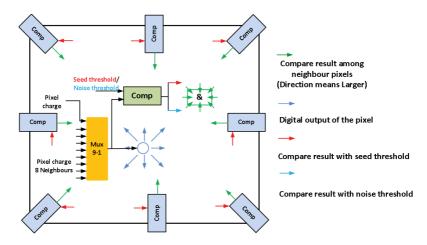

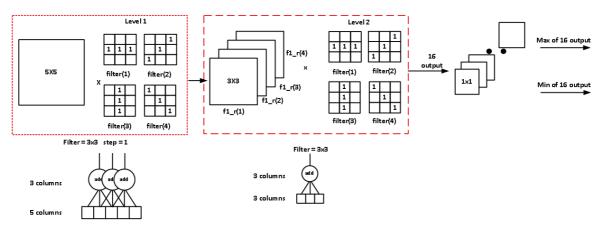

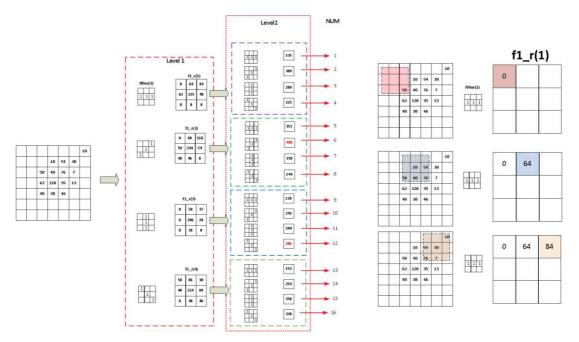

JINR-E9-2013-35; JLAB-R-2013-01; KEK-REPORT-2013-1; KNU-CHEP-ILC-2013-1;