### Fault Tolerance and Reliability for Partially Connected 3D Networks-on-Chip

Alexandre Augusto da Penha Coelho

#### ► To cite this version:

Alexandre Augusto da Penha Coelho. Fault Tolerance and Reliability for Partially Connected 3D Networks-on-Chip. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2019. English. NNT: 2019GREAT054. tel-02523770

### HAL Id: tel-02523770 https://theses.hal.science/tel-02523770

Submitted on 29 Mar 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Communauté UNIVERSITÉ Grenoble Alpes

### THÈSE

Pour obtenir le grade de

#### DOCTEUR DE LA COMMUNAUTÉ UNIVERSITÉ GRENOBLE ALPES

Spécialité : Nano Électronique & Nano Technologies

Arrêté ministériel : 25 mai 2016

Présentée par

### Alexandre Augusto da PENHA COELHO

Thèse dirigée par **Raoul VELAZCO** et codirigée par **Nacer-Eddine ZERGAINOH**

préparée au sein du Laboratoire Techniques de l'Informatique et de la Microélectronique pour l'Architecture des systèmes intégrés dans l'École Doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

# Tolérance aux fautes et fiabilité pour les réseaux sur puce 3D partiellement connectés

# Fault Tolerance and Reliability for Partially Connected 3D Networks-on-Chip

Thèse soutenue publiquement le **25 Octobre 2019**, devant le jury composé de :

Monsieur Raoul VELAZCO Directeur de Recherche, CNRS Délégation Alpes , Directeur de thèse Monsieur Nacer-Eddine ZERGAINOH Maître de Conférences, Université Grenoble Alpes, Co-Directeur de thèse Madame Lirida NAVINER Professeur, Telecom ParisTech, Président du jury Monsieur Gilles SASSATELLI Directeur de Recherche, CNRS Délégation Occitanie Est, Rapporteur Monsieur Amer BAGHDADI Professeur, IMT Atlantique Bretagne-Pays de la Loire, Rapporteur

Dear Lord, thank you for giving me the strength and the conviction to complete the task you entrusted to me. Thank you for guiding me straight and true through the many obstacles in my path. And for keeping me resolute when all around seemed lost. Thank you for your protection and your many signs along the way. Thank you for the friends I made during my PhD. And thank you for finally allowing me to finish this thesis, I am so very tired. I fought the good fight, I finished the race, I kept the faith.

- Adapted from "Book of Eli Movie"

To Cristina, Aline, Linus and Alexia

### Acknowledgement

I would like to express my sincere gratitude to my advisors Dr. Raoul Velazco and Dr. Nacer-Eddine Zergainoh, who gave me the chance to work with them and guided me through this harsh road. Their guidance undoubtedly helped me to improve my research and mitigate all the insecurities a Ph.D. student may have. I want to express my special thanks to Prof. Lirida Naviner, Dr. Gilles Sassatelli, and Prof. Amer Baghdadi, who accepted being part of my examining board. Their valuable and constructive feedback went a long way towards improving the quality of this manuscript and the dissertation defense.

I want(would like to) to thank the Brazilian National Council for Scientific and Technological Development (CNPq Brazil) for their financial support.

I would like to thank all the staff of TIMA Laboratory, EEATS, and CIME Nanotech, who somehow always managed to help me with countless issues. I would like to name a few friends whose collaboration impacted decisively in the result of this work: Amir Charif, Juan Fraire, Miguel Solinas, Matheus Garay, Rodrigo Possamai, Thiago Leite, Renato Feitoza, David Saraiva, and Jasmina Karajanov (italki). Their feedbacks and friendship were essential for the final result of this work.

I would like to thank some people that were important in my decision to do a Ph.D.: Sobral, Helano, Cortez, Jardel, and Jarbas. Thank you guys very much for supporting and encouraging me during this arduous journey. (arduous journey)

I would like to extend great thanks to my dear Vozinha, to whom I dedicate this thesis. I am grateful for her teaching, love, kindness, and affection. I also express my gratitude to my mother-in-law Lais. Her passion, love, and dedication to taking care of my children are incredible. Without her support, I could not finish this thesis.

I would like to thank my loved ones, from whom I had to stay apart since I decided to move to France. My sisters Karine, Isabel, Rebeca, and my niece and nephews Ana Mel, Carlos, Arthur, and João Gabriel. Furthermore, I would like to thank my Dad for introducing me to the road of computers and electronics at an early age, and also for teaching me to think critically.

I would like to thank my beloved wife, Aline, for loving me as I am, for all these happy years of marriage, and her support and inspiration during the development of this thesis. Thank you again for your motivation, encouragement, and patience. I love you so much. Also, I want to thank my children, Linus and Alexia, for being my inspiration, for their love, tenderness, and

for their smiles that have decorated my life.

Finally, I would especially like to thank my Mother for everything she did for me. She was the best Mother I could ever have imagined having. This work could not have been done without her love. Thanks for teaching me to dream and for always believing in me, even when I do not believe in myself. Mother, you are eternally my inspiration. I miss you so much. I would change everything to spend more time with you...

# **Table of Contents**

| strac | t                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xvii                                                                                                 |

|-------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| sumé  |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xix                                                                                                  |

| INT   | <b>FROD</b>                                                           | UCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                    |

| Intro | oduction                                                              | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3                                                                                                    |

| 1.1   | Contril                                                               | oution I: Fault-Tolerant Solutions for 3D Networks-on-Chips                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                                    |

|       | 1.1.1                                                                 | Strategies to deal with soft-errors in 3D-NoCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7                                                                                                    |

|       | 1.1.2                                                                 | The FL-RuNS Fault-Tolerant Routing Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                                                                                                    |

| 1.2   | Contril                                                               | oution II: Automated Fault Injection Tools for HDL Based Design                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8                                                                                                    |

|       | 1.2.1                                                                 | NETFI-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                                                                                                   |

|       | 1.2.2                                                                 | NoCFI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                   |

|       |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13<br>15                                                                                             |

|       |                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15                                                                                                   |

|       |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16                                                                                                   |

|       |                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                                                                   |

|       | 2.3.1                                                                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19                                                                                                   |

|       | 2.3.2                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21                                                                                                   |

|       | 2.3.3                                                                 | Routing Computation Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23                                                                                                   |

| 2.4   | Resilie                                                               | nt Route Computation Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25                                                                                                   |

|       | 2.4.1                                                                 | Detection: Double Sampling and Custom VC Allocator                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                                                                   |

|       | 2.4.2                                                                 | Detection: Custom VC Allocator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26                                                                                                   |

|       | 2.4.3                                                                 | Detection: Fault Detection Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27                                                                                                   |

|       | 2.4.4                                                                 | Correction: Rerouting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27                                                                                                   |

| 2.5   | Fault-I                                                               | njection Experimental Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28                                                                                                   |

|       | sumé<br>IN7<br>Intro<br>1.1<br>1.2<br>TH<br>A So<br>2.1<br>2.2<br>2.3 | Introduction         1.1       Contribution         1.1       1.1.1         1.1.2       1.2         1.2       Contribution         1.2       Contribution         1.2       Contribution         1.2       Contribution         1.2       Contribution         1.2       Introduction         2.1       Introduction         2.1       Introduction         2.3       3D-No         2.3.1       2.3.2         2.3.3       2.4         Resilie       2.4.1         2.4.2       2.4.3         2.4.3       2.4.4 | sumé INTRODUCTION Introduction 1.1 Contribution I: Fault-Tolerant Solutions for 3D Networks-on-Chips |

|    | 2.6  | Evalua          | ation And Analysis                                           | 30       |

|----|------|-----------------|--------------------------------------------------------------|----------|

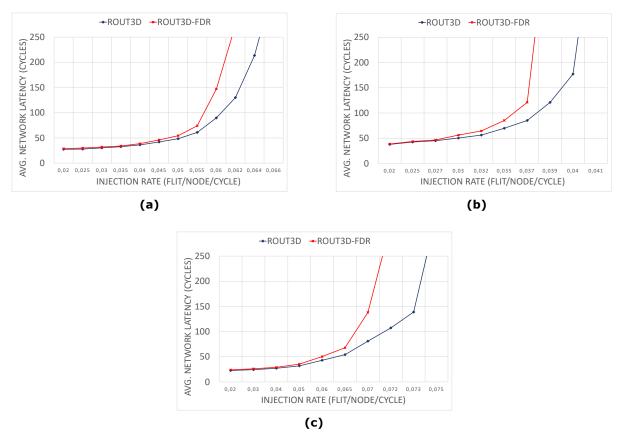

|    |      | 2.6.1           | Latency Results                                              | 30       |

|    |      | 2.6.2           | Hardware Synthesis Results                                   | 31       |

|    | 2.7  | Conclu          | usion                                                        | 32       |

| 3  | FL-] | RuNS:           | A High Performance and Runtime Fault-Tolerant Routing Scheme | 35       |

|    | 3.1  | Introd          | uction                                                       | 35       |

|    | 3.2  | State-o         | of-the-art                                                   | 37       |

|    | 3.3  | First-L         | Last Baseline Architecture                                   | 38       |

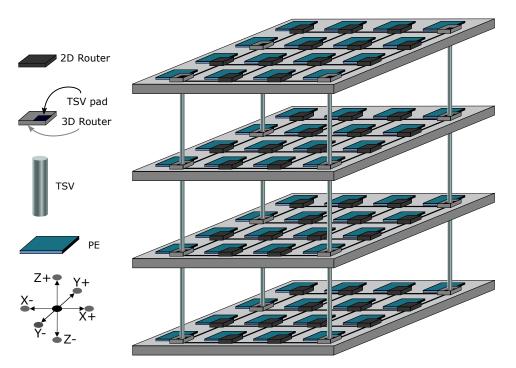

|    |      | 3.3.1           | 3D-NoC Topology                                              | 39       |

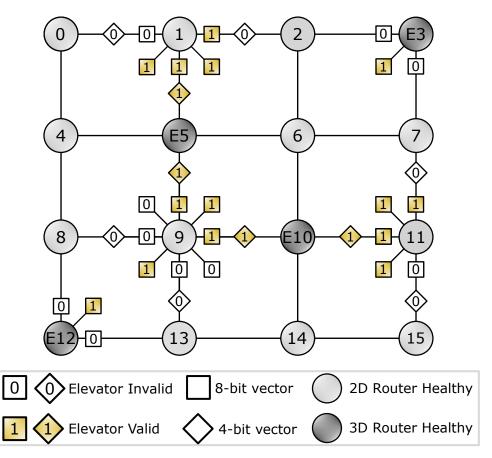

|    |      | 3.3.2           | Locating Healthy Elevators                                   | 39       |

|    |      | 3.3.3           | First-Last: The baseline algorithm                           | 40       |

|    | 3.4  | FL-Ru           | NS Routing Schemes                                           | 42       |

|    |      | 3.4.1           | Propagating Faulty Elevators                                 | 42       |

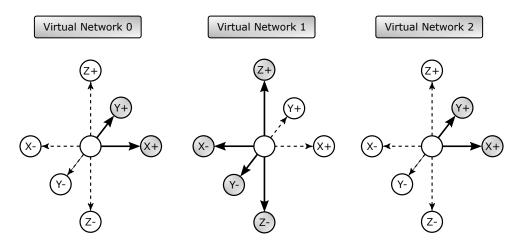

|    |      | 3.4.2           | 1-Flit-Dedicated Virtual Channels                            | 43       |

|    |      | 3.4.3           | Proposed Routing Algorithm                                   | 45       |

|    |      | 3.4.4           | Deadlock-freedom                                             | 51       |

|    | 3.5  | Simula          | ation Results and Discussion                                 | 51       |

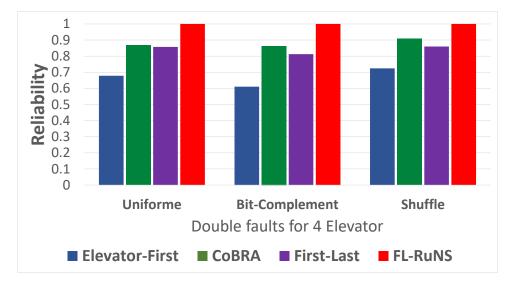

|    |      | 3.5.1           | Performance and reliability analysis under a 4x4x4 mesh      | 52       |

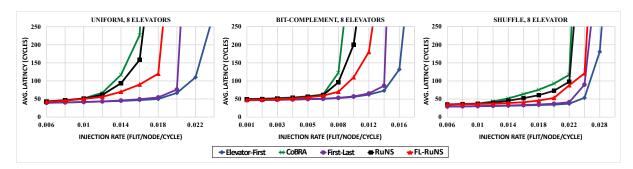

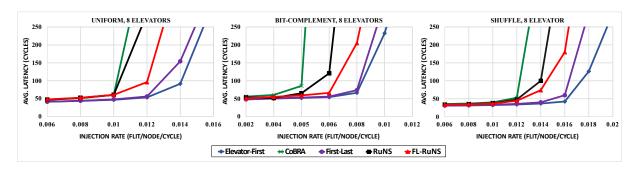

|    |      | 3.5.2           | Performance and reliability analysis under a 8x8x4 mesh      | 55       |

|    |      | 3.5.3           | Hardware synthesis analysis                                  | 56       |

|    | 3.6  | Conclu          |                                                              | 57       |

|    |      |                 |                                                              |          |

| II | ΙΤ   | OOLS            | S FOR FAULT INJECTION IN HDL DESIGN                          | 59       |

| 4  | NET  | FFI <b>3.</b> / | A Framework to Fault Injection in HDL-Based Design           | 61       |

| -  | 4.1  |                 |                                                              | 61       |

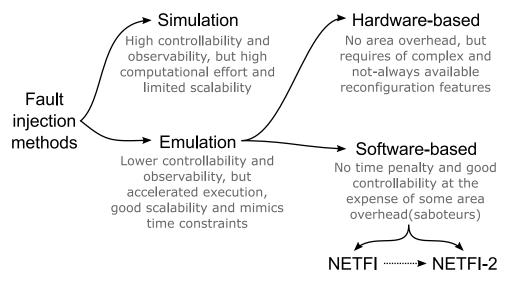

|    | 4.2  |                 | of-the-art                                                   | 62       |

|    | 4.2  | 4.2.1           |                                                              | 63       |

|    |      | 4.2.1           | Hardware-based Fault Emulation                               | 63       |

|    | 1 2  |                 | Software-based Fault Emulation                               | 64       |

|    | 4.3  |                 | I-2                                                          | -        |

|    |      | 4.3.1           | Methodology                                                  | 65       |

|    |      | 4.3.2           | Architecture                                                 | 68<br>70 |

|    |      | 4.3.3           | LUT Transformation                                           | 70       |

|    |      | 4.3.4           | Evaluation and Validation                                    | 72       |

|    | 4.4  | 2               | In Machine Under Test                                        | 73       |

|    |      | 4.4.1           | BM-slice LUT Transformation                                  | 73       |

|    |      | 4.4.2           | Fault-Injection Campaign                                     | 75       |

|    |                                      | 4.4.3    | Result Analysis                              | . 77  |  |

|----|--------------------------------------|----------|----------------------------------------------|-------|--|

|    |                                      | 4.4.4    | Discussion                                   | . 78  |  |

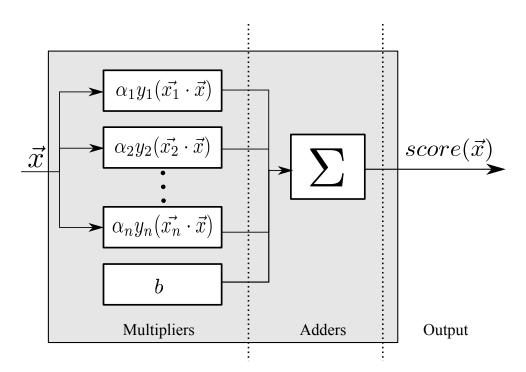

|    | 4.5                                  | Suppor   | rt Vector Machine Under Test                 | . 80  |  |

|    |                                      | 4.5.1    | Support Vector Machine background            | . 80  |  |

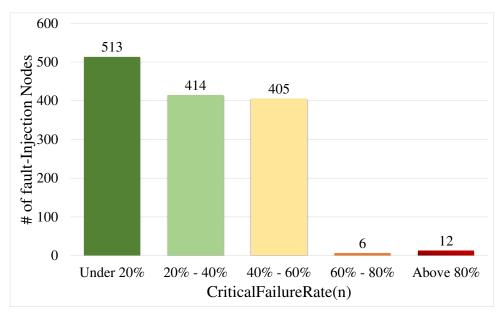

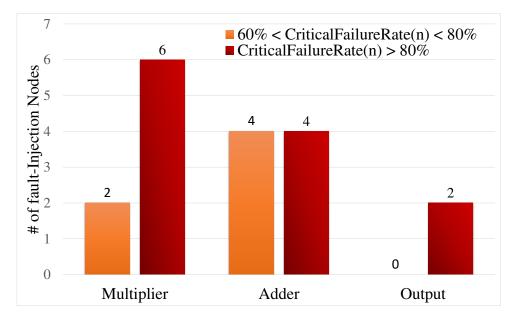

|    |                                      | 4.5.2    | Set of input vectors                         | . 82  |  |

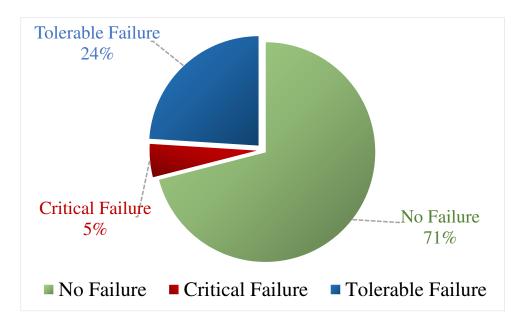

|    |                                      | 4.5.3    | Results of the Fault Emulation Campaign      | . 83  |  |

|    | 4.6                                  | Radiat   | ion Test Experiment and Results              | . 85  |  |

|    |                                      | 4.6.1    | Radiation test set-up                        | . 85  |  |

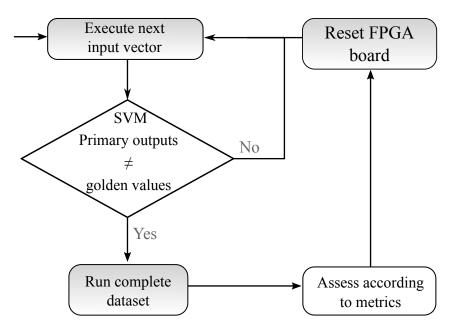

|    |                                      | 4.6.2    | Radiation test method                        | . 87  |  |

|    |                                      | 4.6.3    | Assessment of radiation test results         | . 87  |  |

|    | 4.7                                  | Conclu   | usion                                        | . 89  |  |

| 5  | NoC                                  | CFI: A N | Networks-On-Chip Fault Injection Methodology | 91    |  |

|    | 5.1                                  | Introdu  | uction                                       | . 91  |  |

|    | 5.2                                  | State-o  | of-the-art                                   | . 92  |  |

|    | 5.3                                  | 2D-No    | C Architecture Background                    | . 94  |  |

|    | 5.4                                  | The Ef   | ffects of Soft-Errors in 2D-Routers          | . 95  |  |

|    | 5.5                                  | NoCFI    | Ι                                            | . 97  |  |

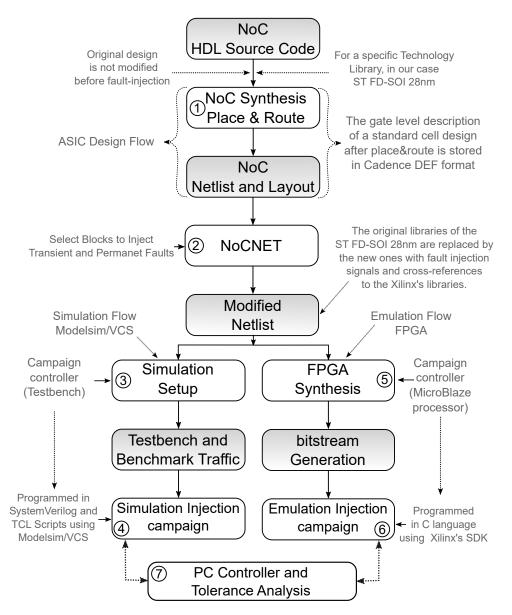

|    |                                      | 5.5.1    | Methodology                                  | . 97  |  |

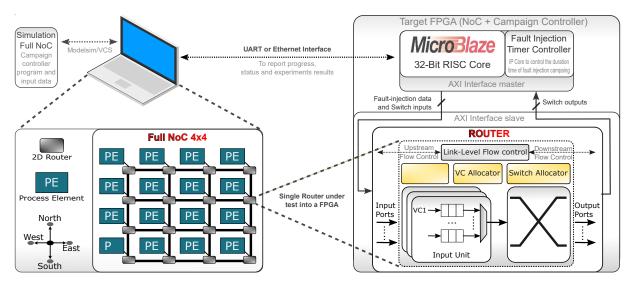

|    |                                      | 5.5.2    | NoCFI Architecture                           | . 101 |  |

|    |                                      | 5.5.3    | The Fault Injection Process                  | . 102 |  |

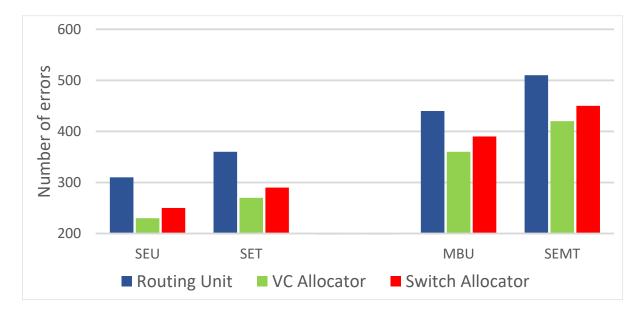

|    | 5.6                                  | Evalua   | ation and Validation                         | . 103 |  |

|    | 5.7                                  | Conclu   | usion                                        | . 104 |  |

| IV | C C                                  | ONCI     | LUSIONS                                      | 105   |  |

| 6  | Con                                  | clusions | s and Perspectives                           | 107   |  |

|    | 6.1                                  | Conclu   | usions                                       | . 107 |  |

|    | 6.2                                  | Future   | Directions                                   | . 109 |  |

| Bi | Bibliography of Author's Publication |          |                                              |       |  |

| Re | eferences 127                        |          |                                              |       |  |

# **List of Figures**

| 1.1  | Evolution of the System-On-Chip intra-chip communication architecture from           |    |

|------|--------------------------------------------------------------------------------------|----|

|      | (a) the bus architecture to (b) the two-dimensional Networks-on-Chip, and fi-        |    |

|      | nally to (c) the three-dimensional Networks-on-Chip                                  | 5  |

| 1.2  | Types of failures in a three-dimensional Networks-on-Chip architectures from [45].   | 6  |

| 1.3  | Radiation strike causing transistor disruption.                                      | 9  |

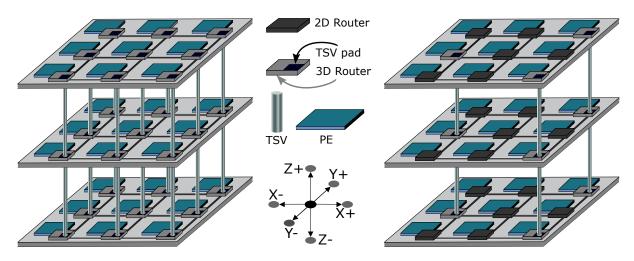

| 2.1  | Three-dimensional Networks-on-Chip (a) fully connected and (b) partially con-        |    |

|      | nected                                                                               | 18 |

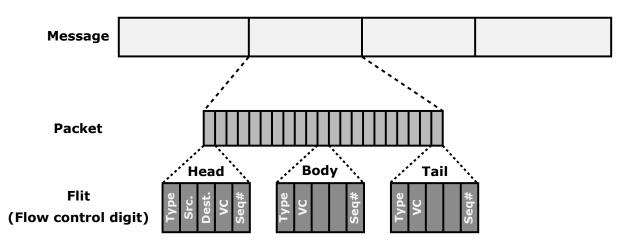

| 2.2  | Packets and Flits definition                                                         | 19 |

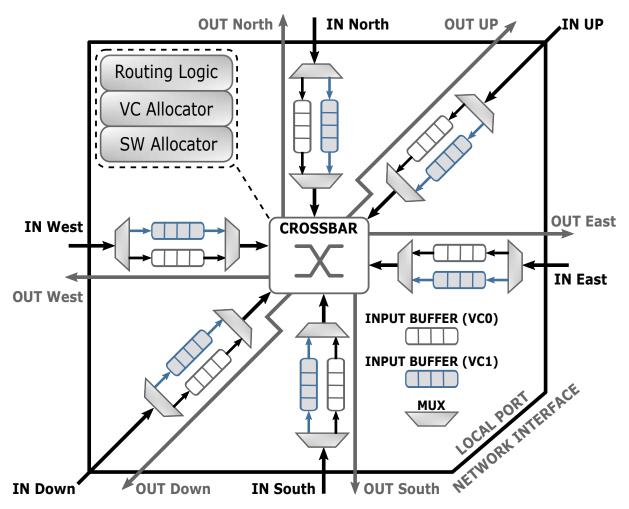

| 2.3  | 3D-router architecture with double virtual channels for each direction               | 20 |

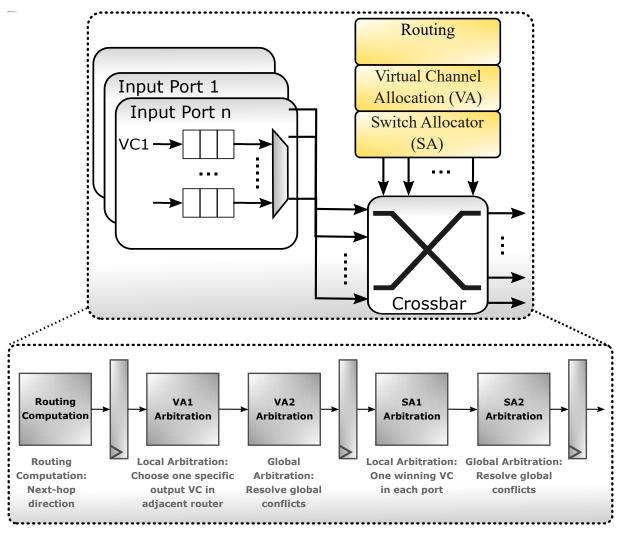

| 2.4  | Generic Router architecture with pipeline                                            | 21 |

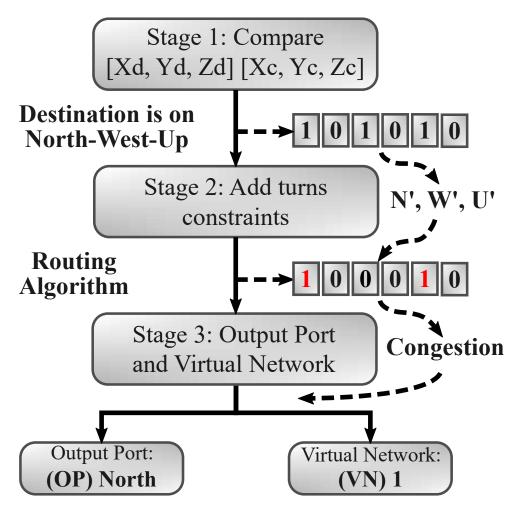

| 2.5  | An example of the three stages of the routing computation unit                       | 24 |

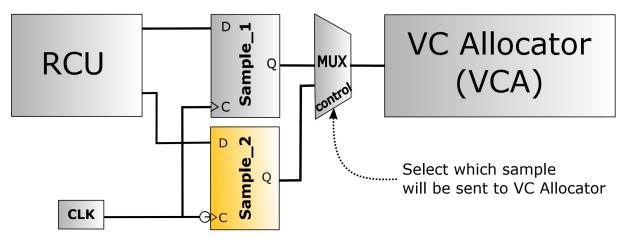

| 2.6  | A Double-Sampling implementation                                                     | 26 |

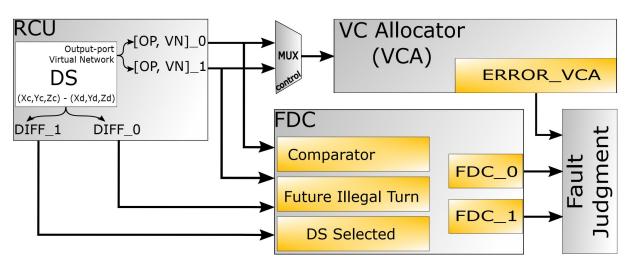

| 2.7  | Fault detection Circuit - FDC.                                                       | 27 |

| 2.8  | A Rerouting Scheme implementation.                                                   | 28 |

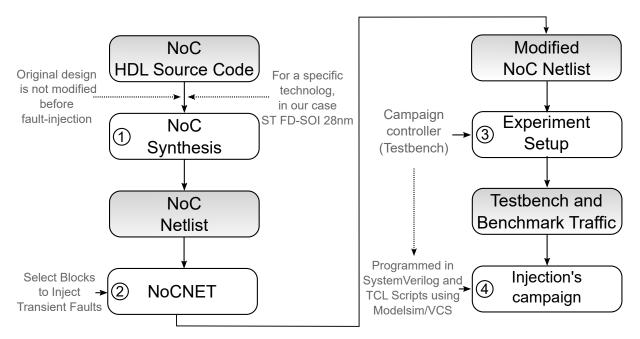

| 2.9  | Fault injection methodology                                                          | 29 |

| 2.10 | Latency of ROUT3D-FDR and baseline ROUT3D under (a) uniform traffic, (b)             |    |

|      | bit complement traffic and (c) shuffle traffic                                       | 31 |

| 3.1  | 3D-NoC architecture vertically and partially connected                               | 36 |

| 3.2  | Elevator configurable bits for initially operation with all healthy elevators        | 39 |

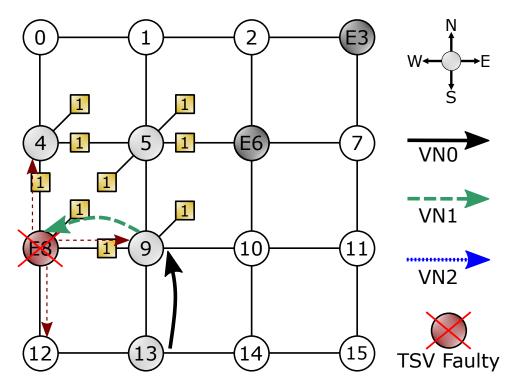

| 3.3  | Virtual Network decomposition for First-Last [15].                                   | 40 |

| 3.4  | An example where the packet cannot reach a healthy elevator using VN1. Here,         |    |

|      | the packet must be dropped since there is not another elevator at negative direc-    |    |

|      | tion from elevator E8                                                                | 41 |

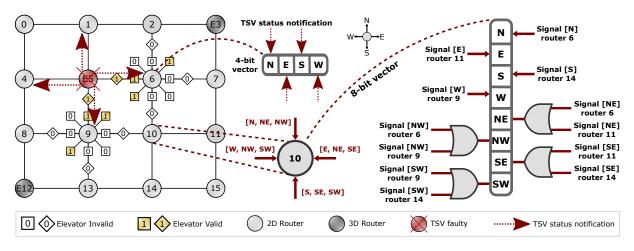

| 3.5  | TSV status propagation through rows and columns with the reconfiguration             |    |

|      | scheme for 4-bit and 8-bit vectors (12-bit)                                          | 43 |

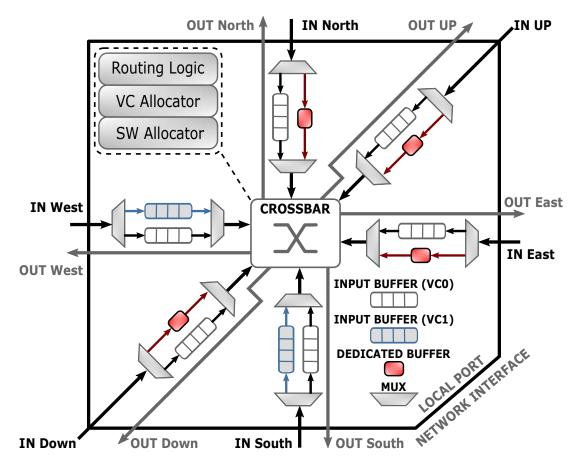

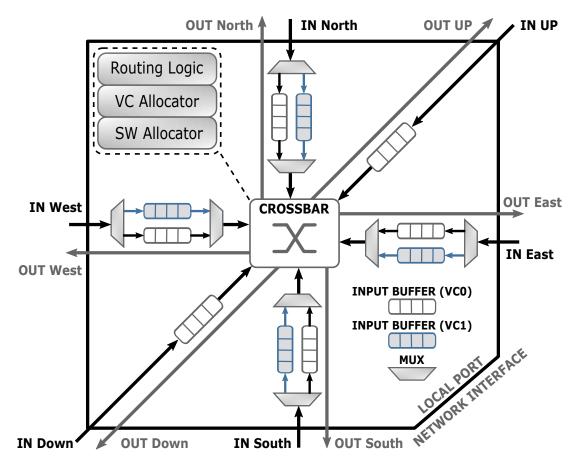

| 3.6  | Architecture of FL-RuNS with 1-flit-dedicated virtual channel. The 1-flit-dedicated  |    |

|      | virtual channel (1-flit Fifo Buffer) is used as alternative virtual channels after a |    |

|      | runtime failures in vertical connecxion.                                             | 44 |

| 3.7  | Elevator-First architecture with distributed buffers. All its buffers are used only |    |

|------|-------------------------------------------------------------------------------------|----|

|      | as a mechanism to avoid deadlock.                                                   | 45 |

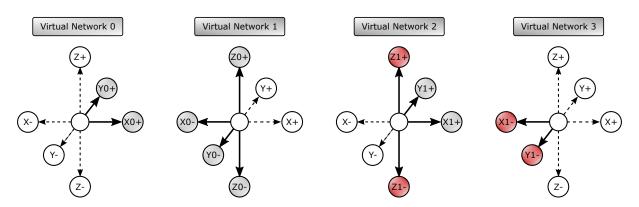

| 3.8  | Decomposition of Virtual Network for FL-RuNS. The 1-Flit-Dedicated virtual          |    |

|      | channels are represented in red: Z1+, Z1-, X1-, and Y1                              | 46 |

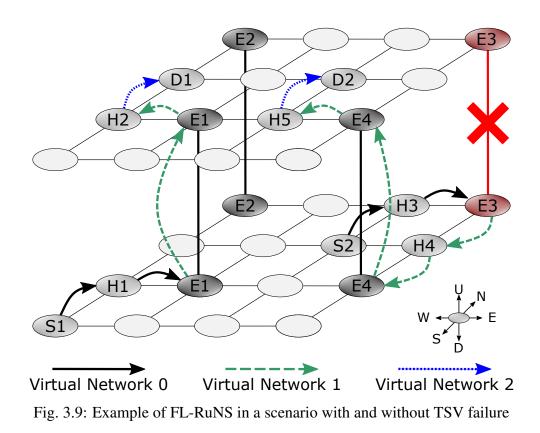

| 3.9  | Example of FL-RuNS in a scenario with and without TSV failure                       | 48 |

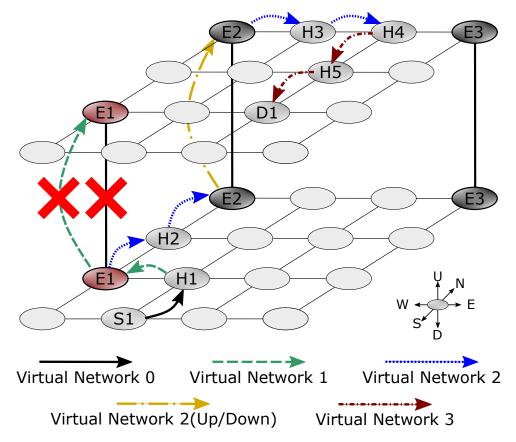

| 3.10 | Example of FL-RuNS using the 1-flit-dedicated virtual channel to rerouting          |    |

|      | packets toward a healthy elevator.                                                  | 49 |

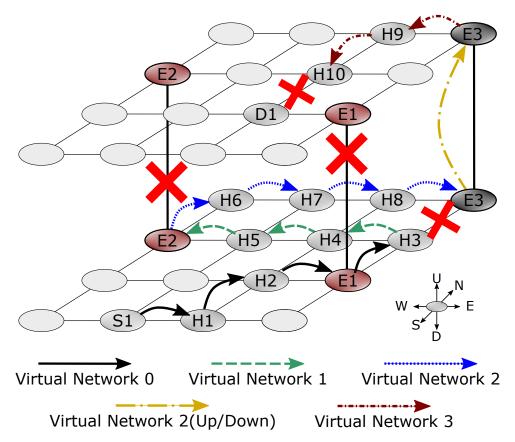

| 3.11 | Example of FL-RuNS in a fault scenario which cannot guarantee packet delivery.      | 50 |

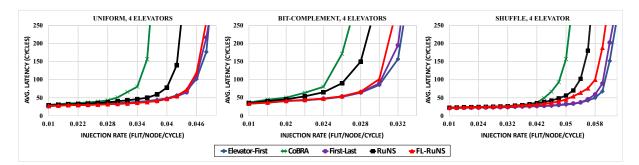

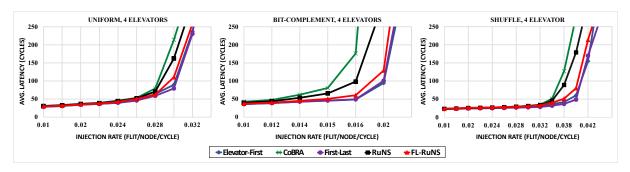

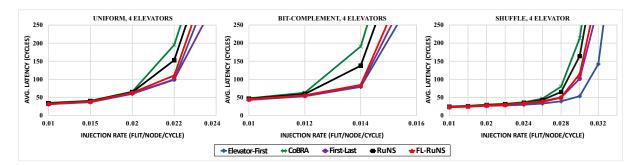

| 3.12 | Average packet latency for an 4x4x4 NoC without fault injection                     | 53 |

| 3.13 | Average packet latency for an 4x4x4 NoC with single fault injection                 | 53 |

| 3.14 | Average packet latency for an 4x4x4 NoC with double fault injection                 | 53 |

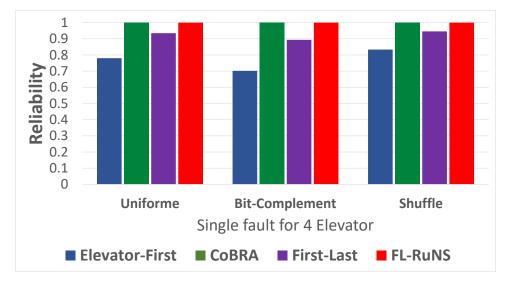

| 3.15 | Reliability under single fault for 4 TSVs                                           | 54 |

| 3.16 | Reliability under double faults for 4 TSVs                                          | 54 |

| 3.17 | Average packet latency for an 8x8x4 NoC without fault injection                     | 55 |

| 3.18 | Average packet latency for an 8x8x4 NoC with double fault injection                 | 55 |

| 4.1  | Fault injection methods classification                                              | 64 |

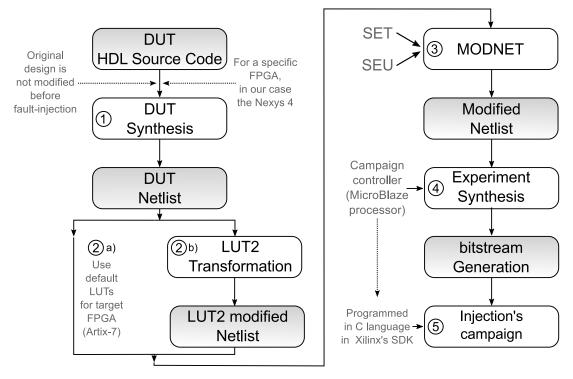

| 4.2  | NETFI-2 methodology                                                                 | 65 |

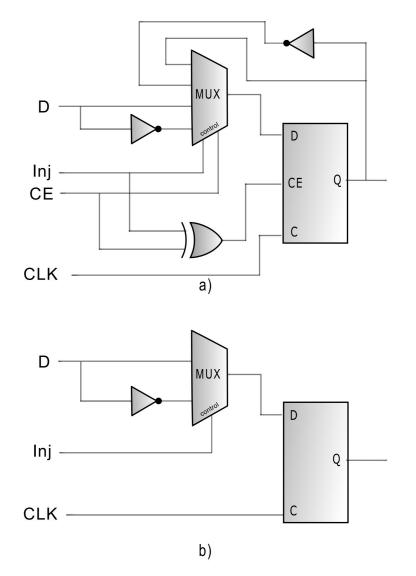

| 4.3  | Modification of flip-flops with enable signal in a) and without enable signal in    |    |

|      | b) [73]                                                                             | 67 |

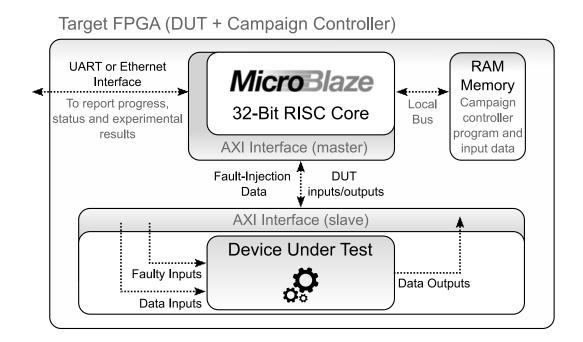

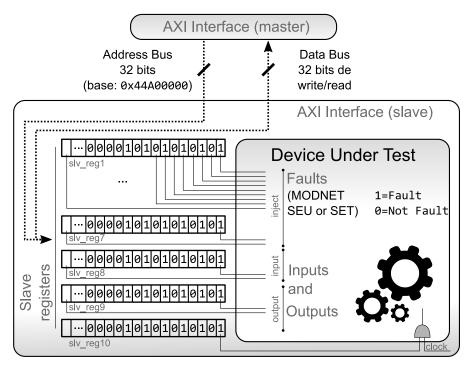

| 4.4  | NETFI-2 architecture                                                                | 68 |

| 4.5  | Interface with CUT                                                                  | 69 |

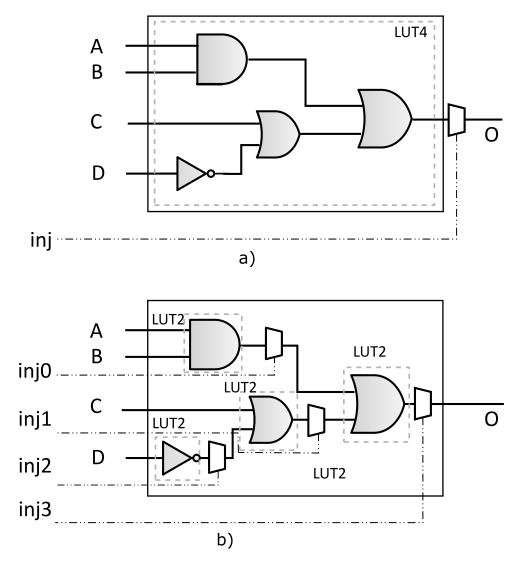

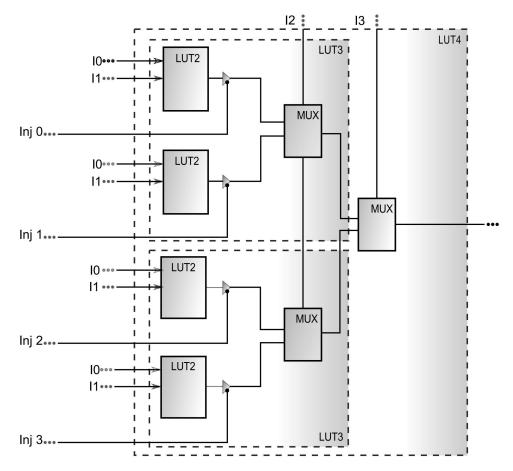

| 4.6  | Example circuit a) based on a LUT4 and b) based on LUT2s                            | 70 |

| 4.7  | Implementing a LUT4 with four LUT2s and three multiplexers or two LUT3s             |    |

|      | and two multiplexers                                                                | 71 |

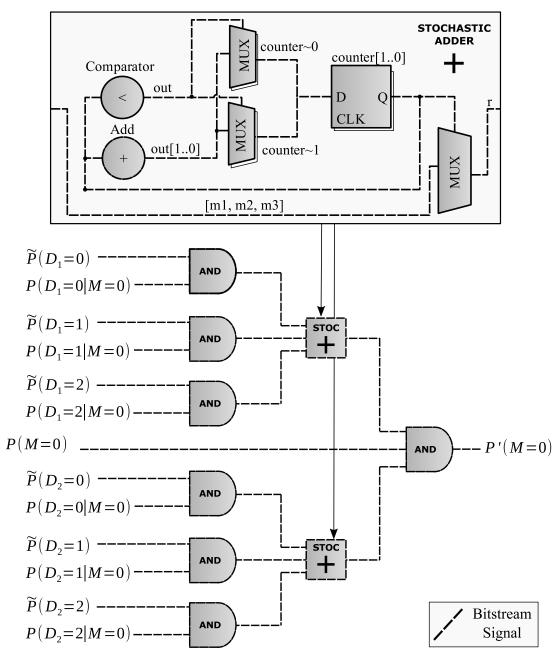

| 4.8  | BM Slice - Hardware implementation                                                  | 74 |

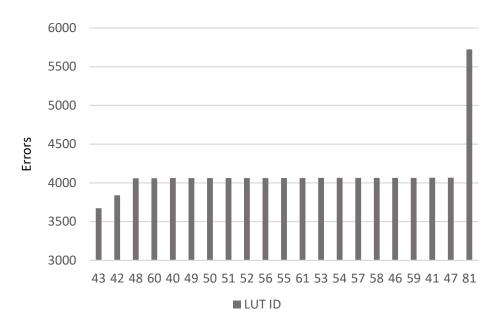

| 4.9  | LUTs of BM-slice (of sizes 4, 5 and 6) where the highest amount of errors were      |    |

|      | observed                                                                            | 79 |

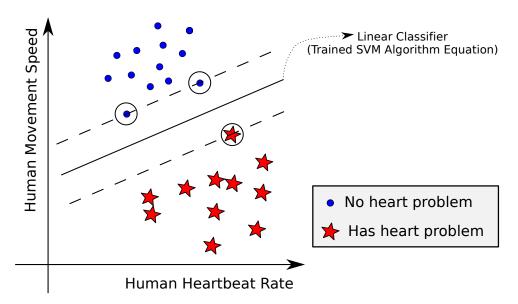

| 4.10 | An SVM algorithm equation (linear classifier) trained to classify the heartbeat     |    |

|      | condition. The horizontal axis represents the human heartbeat rate, while the       |    |

|      | vertical axis represents the human movement speed                                   | 81 |

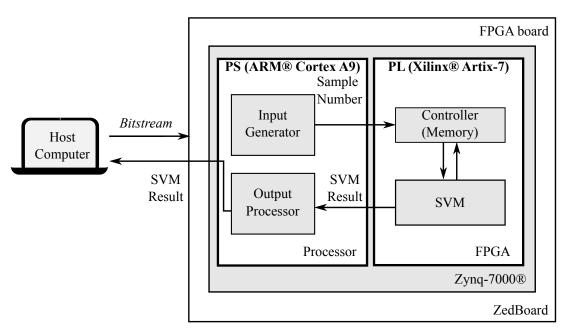

| 4.11 | Overview of the hardware-implemented SVM architecture design                        | 82 |

| 4.12 | Histogram of the critical failure rate of the injection nodes on the SVM archi-     |    |

|      | tecture as given by Equation 4.2                                                    | 84 |

| 4.13 | Histogram representing the correlation among the most critical failure rate nodes   |    |

|      | and their position relative to the the SVM's circuitry implemented in a FPGA.       | 85 |

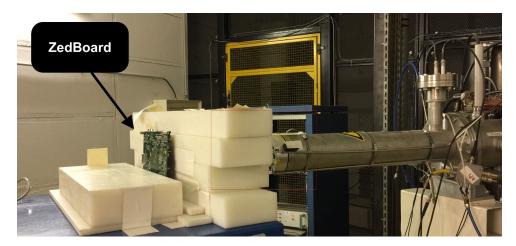

| 4.14 | FPGA board installed at the GENEPi2 accelerator neutron facility                    | 86 |

| 4.15 | Zynq-7000 set-up under radiation test                                               | 86 |

| 4.16 | Method used on the radiation test                                                   | 87 |

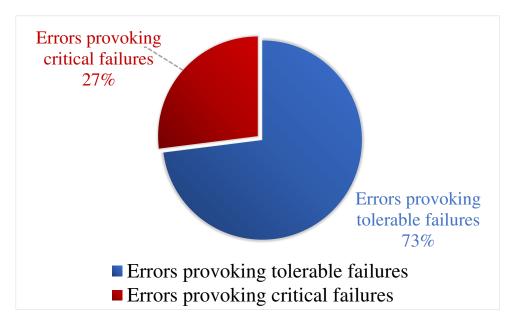

| 4.17 | Percentage of failures that have been provoked by 11 neutron radiation-induced  |     |

|------|---------------------------------------------------------------------------------|-----|

|      | errors                                                                          | 88  |

| 4.18 | Percentage of neutron radiation-induced errors that provoked 1650 tolerable and |     |

|      | critical failures                                                               | 89  |

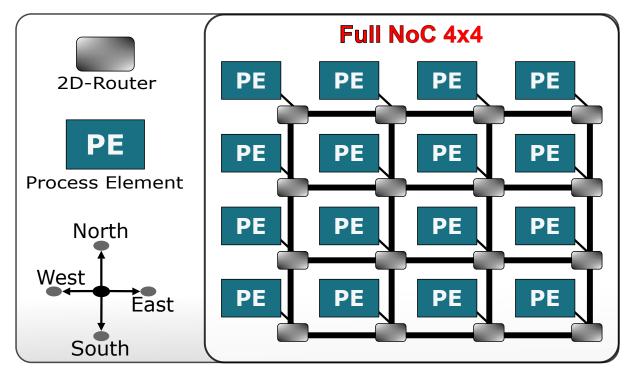

| 5.1  | A 4x4 two-dimensional Networks-on-Chip                                          | 95  |

| 5.2  | A 4-stage 2D-Router pipeline                                                    | 96  |

| 5.3  | NoCFI work-flow methodology                                                     | 98  |

| 5.4  | Block diagram of the NoCFI architecture                                         | 101 |

| 5.5  | The amount of errors observed in the Router after a fault injection campaign    |     |

|      | with one fault (SEU/SET) and two faults (MBU/SEMT)                              | 103 |

## **List of Tables**

| 2.1 | Area and Power results for ROUT3D, ROUT3D-TMR, and ROUT3D-FDR                | 32  |

|-----|------------------------------------------------------------------------------|-----|

| 2.2 | Maximum Operating Frequency for ROUT3D, ROUT3D-TMR, and ROUT3D-              |     |

|     | FDR                                                                          | 32  |

| 3.1 | Area synthesis results                                                       | 56  |

| 3.2 | Power synthesis results                                                      | 57  |

| 4.1 | Detail of resource utilization in the FPGA                                   | 75  |

| 4.2 | Extra signals presented in BM-slice                                          | 76  |

| 4.3 | Fault Injection Campaign Results                                             | 78  |

| 4.4 | Resource utilization of the PL (Artix-7)                                     | 83  |

| 5.1 | Emulation time comparing the fault injection campaign between FPGA-emulation |     |

|     | and Gate-level Simulation.                                                   | 104 |

### Abstract

Networks-on-Chip (NoC) have emerged as a viable solution for the communication challenges in highly complex systems-on-chip. The NoC architecture paradigm, based on a modular packet-switched mechanism, can address many of the on-chip communication challenges such as wiring complexity, communication latency, and bandwidth. Furthermore, the combined benefits of 3D IC and NoC schemes provide the possibility of designing a high-performance system in a limited chip area. The major advantages of Three-Dimensional Networks-on-Chip (3D-NoCs) are a considerable reduction in the average wire length and wire delay, resulting in lower power consumption and higher performance. However, 3D-NoCs suffer from some reliability issues such as the process variability of 3D-IC manufacturing. In particular, the low yield of vertical connection significantly impacts the design of three-dimensional die stacks with a large number of Through Silicon Vias. Equally concerning, advances in integrated circuit manufacturing technologies are resulting in a potential increase in their sensitivity to the effects of radiation present in the environment in which they will operate. In the past, this issue was exclusively related to space applications, while nowadays it must be taken into account for any application operating in the Earth's atmosphere whose errors can have critical consequences. In fact, the increasing number of transient faults has become, in recent years, a major concern in the design of critical System-on-Chip. As a result, the evaluation of the sensitivity of circuits and applications to events caused by energetic particles present in the real environment is a major concern that needs to be addressed. So, this thesis presents contributions in two important areas of reliability research:

- In the design and implementation of deadlock-free fault-tolerant routing schemes for the emerging three-dimensional Networks-on-Chips.

- In the design of fault injection frameworks able to emulate single and multiple transient faults in the HDL-based circuits.

The first part of this thesis addresses the issues of transient and permanent faults in the architecture of 3D-NoCs and introduces a new resilient routing computation unit as well as a new runtime fault-tolerant routing scheme. A novel resilient mechanism is introduced in order to tolerate transient faults occurring in the route computation unit (RCU), which is the most important logical element in NoC routers. Failures in the RCU can provoke misrouting, which may lead to severe effects such as deadlocks or packet loss, corrupting the operation of the entire chip. By combining a reliable fault detection circuit leveraging circuit-level double-sampling, with a cost-effective rerouting mechanism, we develop a full fault-tolerance solution that can efficiently detect and correct such fatal errors before the affected packets leave the router. To validate the proposed solution, we also have introduced a novel method for simulation-based fault-injection based on NoC's gate-level netlist. Experimental results obtained from a vertically-partially-connected 3D Network-on-Chip indicate that our solution can provide a high level of reliability in the presence of errors, at the expense of low area and power overhead.

The first part of this thesis also describes a novel fault-tolerant routing scheme for verticallypartially-connected 3D Networks-on-Chip called FL-RuNS, constructed using our previous routing algorithm First-Last as baseline. Thanks to an asymmetric distribution of virtual channels, our fault-tolerant routing scheme can guarantee 100% packet delivery under an unconstrained set of runtime and permanent vertical link failures. This scheme requires a very low number of asymmetric virtual channels to achieve booth deadlock-freedom and reliability. Also, FL-RuNS uses a runtime mechanism to dynamically and progressively reconfigure the network without any packet loss. Simulation results demonstrate the effectiveness of our approach in terms of performance and reliability when compared with the state-of-the-art routing algorithm. Furthermore, the hardware synthesis performed using a commercial 28nm technology library shows a reasonable area and power overhead with respect to the non-fault-tolerant baseline.

With the aim to emulate the radiation effects on new systems-on-chip designs, the second part of this thesis addresses the fault injection methodologies by introducing two frameworks named NETFI-2 (Netlist Fault Injection) and NoCFI (Networks-on-Chip Fault Injection). NETFI-2 is a fault injection methodology able to emulate transient faults such as Single Event Upsets (SEU) and Single Event Transient (SET) in a HDL-based (Hardware Description Language) design. NETFI-2 was constructed using as baseline an existing fault injection framework developed in the TIMA Laboratory. NETFI-2 allows injecting SEUs and SETs from a single FPGA without external controllers, while allowing to choose the combinational logic granularity to better emulate SETs. Extensive experiments performed on two appealing case studies are presented to demonstrate NETFI-2 features and advantages. Finally, in the last part of this work, we present NoCFI as a novel methodology to inject multiple faults such as MBUs and SEMT in a Networks-on-Chip architecture. NoCFI combines ASIC-design-flow, in order to extract layout information, and FPGA-design-flow to emulate multiple transient faults. In order to validate the NoCFI's methodology, a two-dimensional NoC was used as a study case.

*Keywords:* Three-dimensional Networks-on-Chip, Soft-errors, Fault-tolerant routing algorithm, transient and permanent faults

### Résumé

Les réseaux sur puce (NoC) sont apparus comme une solution viable aux problèmes de communication dans les systèmes sur puce très complexes (SoC). Le paradigme de l'architecture NoC, basé sur un mécanisme modulaire de commutation par paquets, peut répondre à de nombreux défis de communication sur puce tels que la complexité du câblage, la latence des communications et la bande passante. De plus, les avantages combinés des schémas 3D IC et NoC offrent la possibilité de concevoir un système haute performance dans une zone de puce limitée. Les principaux avantages des réseaux tridimensionnels sur puce (3D-NoCs) sont une réduction considérable de la longueur moyenne des fils et du temps de propagation des fils, ce qui se traduit par une consommation d'énergie moindre et des performances supérieures. Cependant, les NoCs 3D souffrent de certains problèmes de fiabilité tels que la variabilité des processus de fabrication 3D-IC. En particulier, le faible rendement de la connexion verticale a un impact significatif sur la conception des piles de matrices tridimensionnelles avec un grand nombre de trous traversants en silicium. De même, les progrès des technologies de fabrication de circuits intégrés entraînent une augmentation potentielle de leur sensibilité aux effets des rayonnements présents dans l'environnement dans lequel ils vont fonctionner. Dans le passé, cette question était exclusivement liée aux applications spatiales, alors qu'aujourd'hui elle doit être prise en compte pour toute application opérant dans l'atmosphère terrestre dont les erreurs peuvent avoir des conséquences critiques. En fait, le nombre croissant de défaillances transitoires est devenu, ces dernières années, une préoccupation majeure dans la conception des systèmes sur puce critiques. Par conséquent, l'évaluation de la sensibilité des circuits et des applications aux événements causés par les particules énergétiques présentes dans l'environnement réel est une préoccupation majeure à laquelle il faut répondre. Cette thèse présente donc des contributions dans deux domaines importants de la recherche sur la fiabilité :

- Dans la conception et la mise en œuvre de schémas de routage à tolérance de pannes sans blocage pour les réseaux sur puce tridimensionnels émergents.

- Dans la conception de cadres d'injection de fautes capables d'émuler des fautes transitoires simples et multiples dans les circuits à base de HDL.

La première partie de cette thèse aborde les problèmes des défauts transitoires et permanents dans l'architecture des NoCs 3D et présente une nouvelle unité de calcul de routage résiliente

ainsi qu'un nouveau schéma de routage tolérant aux défauts d'exécution. Un nouveau mécanisme résilient est introduit afin de tolérer les défauts transitoires se produisant dans l'unité de calcul de route (RCU), qui est l'élément logique le plus important dans les routeurs NoC. Les défaillances de la télécommande peuvent provoquer des erreurs d'acheminement, ce qui peut entraîner des effets graves tels que des blocages ou la perte de paquets, corrompant le fonctionnement de la puce entière. En combinant un circuit de détection de défauts fiable à double échantillonnage au niveau du circuit et un mécanisme de réacheminement économique, nous développons une solution complète de tolérance aux fautes qui peut détecter et corriger efficacement ces erreurs fatales avant que les paquets affectés ne quittent le routeur. Pour valider la solution proposée, nous avons également introduit une nouvelle méthode d'injection de défaillances basée sur la simulation basée sur la liste de réseau au niveau de la porte de NoC. Les résultats expérimentaux obtenus à partir d'un réseau sur puce 3D à connexion verticale partielle indiquent que notre solution peut fournir un haut niveau de fiabilité en présence d'erreurs, au détriment d'une faible surface et d'une surcharge électrique.

La première partie de cette thèse décrit également un nouveau schéma de routage tolérant aux pannes pour les réseaux 3D connectés verticalement sur puce, appelé FL-RuNS, construit en utilisant notre algorithme de routage précédent First-Last comme référence. Grâce à une distribution asymétrique des canaux virtuels, notre système de routage tolérant aux pannes peut garantir une livraison de paquets à 100% dans le cadre d'un ensemble illimité de temps d'exécution et de pannes permanentes des liaisons verticales. Ce système nécessite un très faible nombre de canaux virtuels asymétriques pour garantir la liberté et la fiabilité des cabines dans l'impasse. De plus, FL-RuNS utilise un mécanisme d'exécution pour reconfigurer dynamiquement et progressivement le réseau sans perte de paquets. Les résultats de la simulation démontrent l'efficacité de notre approche en termes de performance et de fiabilité par rapport à l'algorithme de routage le plus moderne. De plus, la synthèse matérielle effectuée à l'aide d'une bibliothèque technologique commerciale de 28nm montre une surface et une surcharge électrique raisonnables par rapport à la référence non tolérante aux pannes.

Dans le but d'émuler les effets du rayonnement sur les nouvelles conceptions de systèmes sur puce, la deuxième partie de cette thèse aborde les méthodologies d'injection de fautes en introduisant deux frameworks nommés NETFI-2 (Netlist Fault Injection) et NoCFI (Networkson-Chip Fault Injection). NETFI-2 est une méthodologie d'injection de fautes capable d'émuler les fautes transitoires telles que les perturbations d'événement unique (Single Event Upsets -SEU) et les transitoires d'événement unique (Single Event Transient - SET) dans une conception basée sur HDL (Hardware Description Language). NETFI-2 a été construit en utilisant comme référence un cadre d'injection de fautes existant développé dans le laboratoire TIMA. NETFI-2 permet d'injecter des SEU et des SETs à partir d'un seul FPGA sans contrôleurs externes, tout en permettant de choisir la granularité logique combinatoire pour mieux émuler les SETs. Des expériences approfondies réalisées sur deux études de cas attrayantes sont présentées pour démontrer les caractéristiques et les avantages de la NETFI-2. Enfin, dans la dernière partie de ce travail, nous présentons NoCFI comme une nouvelle méthodologie pour injecter des défauts multiples tels que les MBU et SEMT dans une architecture de réseaux sur puce. NoCFI combine ASIC-design-flow, afin d'extraire les informations de layout, et FPGA-design-flow pour émuler plusieurs défauts transitoires. Afin de valider la méthodologie du NoCFI, un NoC bidimensionnel a été utilisé comme cas d'étude.

*Keywords:* Réseaux tridimensionnels sur puce, erreurs logicielles, algorithme de routage tolérant aux pannes, pannes transitoires et permanentes

# Part I INTRODUCTION

## Chapter 1

### Introduction

The continuous advances in semiconductor technologies make possible to integrate billions of gates into a single chip [11]. The availability of such abundant resources have enabled designers to fabricate chips with tens or hundreds of Processing Elements (PE) blocks on a single chip, resulting in the conception of Multiprocessor System-on-Chips (MPSoC). For a MPSoCs on such massive scale, connectivity is a major concern, and inefficient/unreliable interconnects can severely limit performance. For example, MPSoCs architectures with two or four cores typically use the traditional on-chip bus communication between cores. However, as the number of cores on a chip increases, the communication between the cores plays a crucial role in its performance. Due to the bus's lack of scalability, Networks-on-Chip (NoCs) design has emerged as a scalable on-chip interconnection network that can efficiently handle the strict communication requirements between cores on a chip. It has happened thanks to the ability of NoCs supporting simultaneous communication between multiple pairs of cores.

On the other hand, while the same technological evolution to nanometric scaling process has its benefits in terms of delay, area, and power consumption, it is known to pose some serious reliability concerns. It means that circuits in nanoscale era are more sensitive to failures caused at the manufacturing process, due to process variations, or even simply being exposed to harsh environments, such as space. Despite the sensitivity and some reliability concerns, a careful fault-tolerant design still promises to achieve reliable systems from both MPSoCs and NoCs architectures. And, of course, the development of a new fault-tolerant design calls for evaluation and validation of these mechanisms at an early design stage. In other words, to cope with permanent and transient faults, designers need to be able to evaluate their impact, implement suitable error mitigation techniques, and validate the results.

However, the analysis of permanent and transient faults in the MPSoCs and NoCs architectures is not as trivial as it may seem. It is due to the fact that these failures must be investigated when the circuit is in operation (i.e., on-the-fly) which may lead the circuit to an unpredictable behavior. Also, some failures caused by multiple-cell upset (MCU), multiple-bit upsets (MBU), and single-event multiple transient (SEMT) that were not considered in the older technology, due to its inherent ability to mask these failures, are now a major concern that needs to be addressed in the new MPSoCs and NoCs architectures.

One of the most popular techniques to evaluate the reliability of digital circuits is to submit those circuits to a radiation test campaign under a large particle flow [31]. However, these campaigns are very expensive and are usually performed on the final physical implementation of the circuit. Consequently, the sensitive parts of the circuits which require mitigation can only be detected after the radiation campaign. It may result in re-working project phases, in new manufacturing processes, and in new radiation campaigns that increase the budget of the project as well as its time-to-market. So, a solution for this problem is to verify if the circuits satisfy fault tolerance requirements during its project phases instead of only in its final prototype. With this in mind, *Simulation-based* and *Emulated-based* fault injection are two widely adopted methods to analyze the effects of transient faults in (Hardware Description Language) HDL-based design [94] already in its initial project phases. Also, new tools to test and validate multiple bits upset taking adjacent cell into account are necessary to better understand the behavior of the circuit under permanent and transient faults.

Emerging technology such as Systems-on-Chip design based on machine learning is being increasingly implemented in integrated circuits instead of only in a software application. Also, MLSoCs (Machine Learning Systems-on-Chip) have been employed in critical applications due to their capacity to predict errors and learn from their own decisions. Those two features, learning and predicting, have motivated the use of this type of algorithm in many other applications such as medical diagnostics [7], robot intelligence [53], and geoscience/aerospace domain [62]. But, MLSoCs suffer from the same reliability issues as all standard digital circuits, which means that they also must be evaluated in the context of reliability.

In summary, the study of new fault-tolerant solutions for both SoCs and NoCs is mandatory in the nanoscale era. Also, new high-accuracy fault injection approaches able to evaluate and validate the effects of permanent and transient faults in the future SoC/NoC design are essential. The reliability issues presented above motivated us to propose in this thesis contributions in two crucial areas of microelectronic research:

- In design and implementation of deadlock-free fault-tolerant routing scheme for the emerging three-dimensional Networks-on-Chips.

- In design of fault injection frameworks able to emulate single and multiple transient faults in the HDL-based circuits.

All contributions of this thesis are summarized in the remainder of this Section.

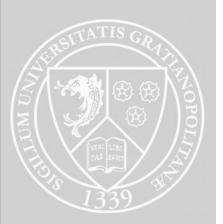

Fig. 1.1: Evolution of the System-On-Chip intra-chip communication architecture from (a) the bus architecture to (b) the two-dimensional Networks-on-Chip, and finally to (c) the three-dimensional Networks-on-Chip.

### 1.1 Contribution I: Fault-Tolerant Solutions for 3D Networkson-Chips

Traditionally, System-on-Chip (SoC) designers employ buses or hierarchical bus structures to interconnect Processing Elements (PE) blocks [42]. However, as chip integration grows, the global bus-based interconnection has become a bottleneck for future high-performance SoC designs [33]. To overcome this limitation, Networks-on-Chip has emerged as a promising infrastructure for on-chip communication due to its scalability, high bandwidth, better throughput, and lower power consumption [98]. However, wire delay and power consumption increase significantly by the usage of global interconnections in Two-Dimensional Integrated Circuit (2D-IC) designs. In other words, the restricted floor-planning choices of 2D-IC designs limit the

Fig. 1.2: Types of failures in a three-dimensional Networks-on-Chip architectures from [45].

potential performance of two-dimensional Networks-on-Chip (2D-NoC) architecture [50, 78]. In order to extend 2D-IC capabilities, multiple layers of active devices are integrated using vertical high-speed interconnection in a three-dimensional integrated circuit (3D-IC) architecture [35]. This approach permits the use of three-dimensional Networks-on-Chip (3D-NoC) as a communication infrastructure that reduces the interconnection lengths and improves the overall performance. Figure 1.1 shows the evolution of the on-chip interconnection from bus-based to three-dimensional Networks-on-Chip.

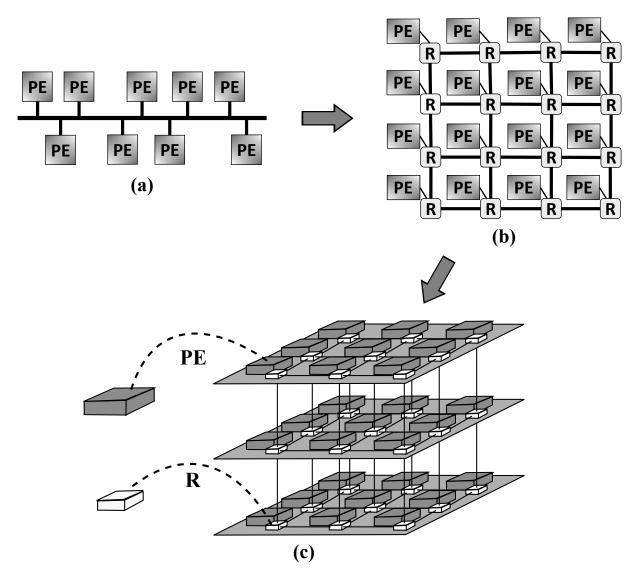

The need for reliability assessment in order to figure out the underlying process variation of NoC architecture has become more critical as CMOS technology continues to shrink. Figure 1.2 summarizes the potential faults, affecting the performance of 3D-NoC design and divides them into subcategories [45]. In this thesis, our contributions for 3D-NoC architecture are mainly focused on the fault-tolerant solutions to mitigate the **SEE impacts** and **TSV issues**. The first part of this thesis focuses on:

- Investigating the effects of transient faults in the sequential and combinational logic of 3D-NoC's routers. New fault-tolerant solutions that can mitigate these effects of transient faults in the control logic of the 3D-NoC's routers are introduced.

- Improving the reliability of the 3D-NoCs when transient and/or permanent failures occur in the vertical links. To this end, we propose online-fault-tolerant schemes that permit the continued operation of the network in the presence of failures in booth manufacture and execution time.

- Proposing fault-tolerant techniques for 3D-NoCs architecture that can be feasible in terms

of hardware employing the ASIC design flow. It means that all solutions and mechanisms introduced throughout this thesis are implemented and synthesized. Also, in order to make a fair comparison in terms of hardware overhead, all our contributions, as well as the existent state-of-the-art architectures, were synthesized using the 28nm design kit from ST-Microelectronics.

In this context, in Chapter 2, we introduce some strategies to tolerate soft-errors in the Routing Computation Unit (RCU). Then in Chapter 3, we propose a runtime and reconfigurable routing scheme able to tolerate transient and permanent faults in the vertical connections of the 3D-NoC. It is worth mentioning that the proposed solutions avoid dropping packets while the 3D-NoC is being recovered from failures.

#### 1.1.1 Strategies to deal with soft-errors in 3D-NoCs

The increasing complexity of 3D-NoC routers, the continuous miniaturization of silicon technology, the lower operating voltages, and the higher operating frequencies have made the 3D-NoC increasingly vulnerable to soft errors. In particular, transient faults occurring in the route computation unit (RCU) can provoke misrouting, as packets may be directed to the wrong output port. This may lead to severe effects such as deadlocks or packet loss that can corrupt the operation of the entire chip. It is therefore mandatory to provide some level of protection against routing errors. So, in Chapter 2, we have proposed some fault-tolerant solutions to mitigate the effects of transient faults in the RCU. In other words, a full fault-tolerance solution that can efficiently **detect** and then **correct** fatal errors in the RCU before the affected packets leave the router is described and validated. The main contributions of Chapter 2 are summarized below:

- We have introduced a reliable fault detection circuit which works in parallel with pipeline of the control path of the NoCs without incurring any path delay.

- We have proposed a fault detection strategy based on the concept of double-sampling.

- We have proposed a solution for recovering from faults based on a cost-effective rerouting mechanism. In other words, when the failures provoke errors that cannot be masked by the double-sampling techniques, the RCU must recompute the packet to avoid deadlock as well as packet loss.

- we have validated our fault-tolerant solutions by means of a novel simulation-based faultinjection methodology which is based on the NoC's gate-level netlist.

To provide the reader with a better understanding of the on-chip interconnection networks, a brief overview of three-dimensional networks-on-Chip architecture is described in Section 2.3 Some parts of this work was published in [25].

#### 1.1.2 The FL-RuNS Fault-Tolerant Routing Scheme

Since three-dimensional Networks-on-Chip (3D-NoC) have been accepted as an effective solution to the scalability and latency issues in modern complex System-On-Chips, Through-Silicon Via (TSV) has been usually adopted as a viable technology enabling vertical connection among NoC layers. However, TSV-based architectures typically exhibit high vulnerability to transient and permanent faults, calling for robust routing solutions capable of sustaining operation under unpredictable failure patterns. Those issues motivated us to propose a complete fault-tolerant routing scheme named FL-RuNS that guarantees 100% packet delivery under an unconstrained set of runtime and permanent vertical link failures. So, in Chapter 3, we explore, for the first time, a fault-tolerant scheme for assigning TSVs to routers both offline and during runtime phase. The contributions in this domain can be summarized as follows:

- We have introduced a fault-tolerant scheme that requires a very low number of virtual channels to achieve booth deadlock-freedom and reliability. Our methodology is based on an asymmetric use of virtual channels instead of the usual symmetry approach. The idea is to provide a tradeoff among a fault-tolerant scheme, hardware overhead, and high throughput.

- we have proposed a runtime mechanism to dynamically and progressively reconfigure the network without any packet loss. It means that when faults are detected in the vertical connection, the network can be reconfigured online without stopping the operation of the network and/or dropping packets.

- we have validated the effectiveness of our approach in terms of performance and reliability using simulation and comparing its results with the state-of-the-art routing algorithm. Also, the hardware synthesis performed on our approach shows a reasonable area and power overhead compared to the non-fault-tolerant baseline.

A preliminary version of the FL-RuNS routing scheme was published in [28] and [24]

### 1.2 Contribution II: Automated Fault Injection Tools for HDL Based Design

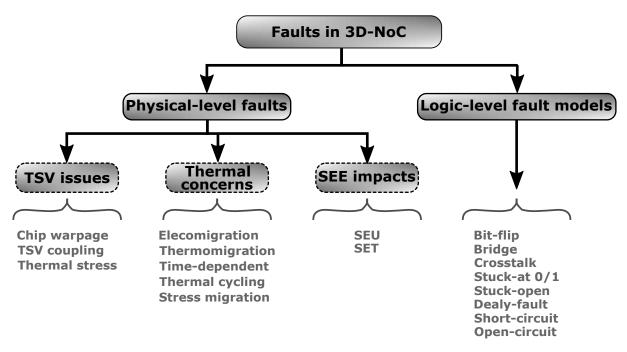

Radiation on integrated circuits can cause a wide variety of effects. As shown in Figure 1.3, a single energetic particle (neutron, proton, heavy ion or alpha particle) when interacting with the semiconductor material can produce a destructive or non-destructive event. Among them, nonpermanent single-event effects (SEEs), also known as soft-errors, have the potential for inducing the highest failure rate of all other reliability mechanism combined [40, 56, 71]. The most importants SEEs of this type are single-event upset (SEU) and the single-event transient

Fig. 1.3: Radiation strike causing transistor disruption.

(SET). So, radiation environment and their effects must be taken into account early enough in the design cycle for any application devoted to operating in the Earth's atmosphere of which a fault may have critical consequences. As a result, the demand for new tools able to test emerging circuits already in their project phase has been growing in the last years. In particular, there has been an increasing demand for tools that can emulate SEUs and SETs with high accuracy in the circuits under test (CUT) with a minimum modification in the CUT's structure.

Fault injection is a well-known technique to evaluate the sensitivity of integrated circuits to the effects of radiation. For this reason, fault injection has been a research topic for decades [94, 95] and has been classified in two main categories: Simulation-based and Emulation-based fault injection methodologies. Simulation-based approaches use a digital simulator to execute HDL-based design and perform fault injections models. On the other hand, emulation-based approaches are normally based on FPGAs, where both the emulation of the circuit under test (CUT) as well as the fault injection campaign are performed.

In the second part of this thesis, we propose two fault injection frameworks to study the effects of transient faults in the HDL-based circuits. In the first framework presented in Chapter 4, an existing emulation-based methodology called NETFI [73] is extended, updated and improved under the name of NETFI-2. NETFI-2 can emulate the effects of SEU and SET in a CUT using only a single FPGA. Also, NETFI-2 permits an inject faults approach without modifying the source code of the CUT to model the faulty behavior. In the second framework presented in Chapter 5, we have proposed a fault injection methodology named NoCFI. NoCFI is a hybrid fault-injection framework that allows emulating multiple faults such as MBUs and

SEMTs taking adjacent cells into account. In other words, NoCFI makes use of the layout information of the circuit under test to emulate the effects of multiple failures in their neighboring cells. Furthermore, NoCFI is a simulation-based and emulation-based fault injection methodology which means that it can be used to inject faults in both HDL-simulators and FPGAs-based architectures.

#### 1.2.1 NETFI-2

In Chapter 4, we introduce the NETFI-2 fault injection methodology. NETFI-2 allows for unique hardware resources a highly efficient fault injection campaign as well as a very accurate error rate estimation. This is achieved by a dedicated embedded campaign controller in charge of injecting SEUs and SETs in sequential and combinatorial blocks with configurable granularity. Because of its configurable granularity, NETFI-2 can determine which specific component is responsible for each error observed in the output of the CUT.

So, in Chapter 4 the following contributions were made:

- we have introduced a new version of our old fault injection method. This new version is more friendly to use and also presents more accuracy in terms of radiation-effects emulation.

- The whole fault injection campaign can be done using only one FPGA. It means that both the controller of the fault injection campaign as well as the CUT are prototyped inside the same FPGA.

- We have analyzed the effects of transient faults in the emerging stochastic computer technology such as Bayesian Machine (BM) and Support Vector Machine (SVM). Moreover, a real radiation beam campaign was performed in the SVM architecture. This campaign was conducted using a proton accelerator from GENEPI2 [118], and its results were compared with the ones provided by our fault injection tool.

To the best of our knowledge, this is the first work that presents a comprehensive analysis of the effects of radiation on the stochastic computer circuits. Some parts of this work were published in [26, 27, 110].

#### 1.2.2 NoCFI

Although we have introduced a generic fault injection methodology in Chapter 4, that method does not take into consideration some issues relevant for the study of the effects of radiation on integrated circuits. So, in Chapter 5, we are more specific and propose a method to emulate soft-errors in NoCs named NoCFI (Network-on-Chip Fault Injection). This method supports

the emulation of single faults as well as multiple faults by taking cell adjacency into account. It is possible because NoCFI combines booth ASIC-based and FPGA-based flows to inject faults. The idea is simple. First, NoCFI performs place&route for the NoC under test in order to provide netlist and layout information. Then, NoCFI manipulates the gate netlist provided by the ASIC design flow and inserts additional circuits (i.e., saboteur) in the gate netlist. Finally, NoCFI uses the modified gate netlist as input for the FPGA design flow to emulate multiple faults in the Networks-on-Chip.

In summary:

- We have proposed a methodology that can be used to identify vulnerable cells nodes in the NoC's design and allow the classification of placement strategies of fault tolerant ASIC designs.

- We have developed a tool to manipulate the netlist provided by the place&router and translate it to a netlist that can be used by the FPGA design flow.

- We have presented a hybrid methodology that can be used as simulation-based and/or emulation-based taking into account the layout position of the NoC's cells.

- We have used a generic 5-stage pipeline 2D-NoC (Two-Dimensional Networks-on-Chip) in order to evaluate our methodology.

A preliminary version of the NoCFI was published in [29].

#### 1. Introduction

## Part II

# THREE-DIMENSIONAL NETWORKS-ON-CHIP

# Chapter 2

# A Soft-error Resilient Route Computation Unit

## 2.1 Introduction

One of the biggest concerns raised by the VLSI community regarding recent and future Networkson-Chip (NoCs) designs is the continuous decrease in feature size and its impact on reliability. In fact, as the feature sizes of integrated circuits decrease aggressively, combinational logic becomes more susceptible to transient faults [85]. Specifically, *soft-errors* provoked by defects, radiation particles, or cross-talk noise, were generally masked and thus disregarded in older technology. However, as operating voltages become lower and clocking frequency increases, the design of integrated circuits with technology node below  $0.25\mu m$  requires of particular attention to soft-error effects [108]. Indeed, NoC routers are not the exception since they have several combinational logic elements. In fact, the probability of the occurrence of a soft-error is higher in 3D-NoC routers which are more complex than 2D-NoC routers because of the increasing number of connecting ports. Therefore, the study of 3D-NoC routers reliability towards softerrors becomes mandatory for future large-scale integration of dependable System-on-Chips (SoC).

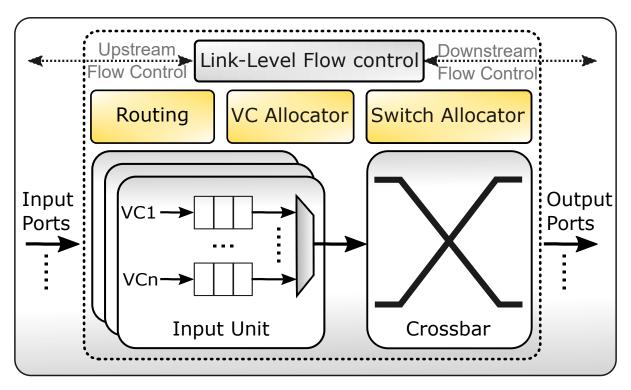

Components inside a NoC router are typically structured into two interacting modules, the *control path* and the *data path* [59]. Soft-errors occurring in the data path can affect the data encoded in the packet. Fortunately, this type of fault is easy to detect and correct through existing error detecting and error correcting codes [125]. By contrast, faults in the control path are harder to detect and correct, and may leave the network in an inconsistent state, ultimately causing the entire chip to fail.

One of the most critical component in the NoC's control path is the Route Computation Unit (RCU), as it is the one responsible for selecting the next output port (i.e. direction) that a packet must take at every hop. Also, most recent proposal in the area of NoCs favor the use of adaptive routing for fault-tolerance, load balancing, etc., requiring more sophisticated routing

decisions [18, 103]. This makes the Route Computation Unit significantly more complex, which can be expected to increase its vulnerability to soft errors. If the RCU fails, packets may be forwarded to wrong outbound ports (i.e., *misrouting*) eventually leading to deadlocks (cyclic dependencies between packets) or packet loss. It is therefore mandatory to provide some level of protection against routing errors.

In this chapter, we propose to enhance the reliability of 3D-NoCs by detecting and correcting errors provoked by transient faults in the RCU. The primary characteristic of our method is the ability to reliably and quickly *detect* misrouting based on a combination of fault tolerance techniques. Those techniques are called double-sampling and complementary illegal turn detection method. And they are combined into a specific hardware unit called *fault detection circuit*, which can make decisions in order to recover from faults. The second characteristic of our method is the ability to *correct* misrouting either by the reuse of the route computation samples provided by double-sampling or by directly rerouting the in-transit packet. In order to validate the robustness of the proposed solution, we have used a method to simulate transient faults using NoC's gate-level netlist. This method of fault injection is presented in more details in Chapter 5. Finally, a thorough evaluation on a partially vertically connected 3D-NoC is performed to demonstrate the increased resiliency, and to estimate the area and power overhead of the proposed fault-tolerant routing computation unit architecture.

#### 2.2 State-of-the-art

Previous works have used *spatial redundancy* (i.e., execute parallel routing calculations) to deal with faults provoked by soft errors in NoCs. For example, the authors in [30] proposed the BulletProof router that employs N-modular redundancy (NMR) techniques to provide fault tolerance. The work in [127] proposed a fault-resilient routing unit for NoCs based on of a single and simplified redundant computation unit operating side-by-side with the RCU. While the RCU supports a fully adaptive routing algorithm, the redundant unit only supports limited paths, but it is only activated when errors are detected. In general, spatial redundancy approaches are expensive, as they require more silicon area than the baseline router.

Another approach to fault tolerance in NoCs is based on *temporal redundancy* (i.e., repeat routing calculations). Authors in [34] applied temporal redundancy in fully-connected 3D-NoCs. The authors in [60, 128] propose a mechanism to detect faults based on illegal turns in the chosen packet path. The fault detection is done at the neighboring routers which repeat a simplified route computation using input parameters provided by the previous router. If the selected direction is valid, the packet handling process continues, if not, either a new route is calculated or the packet is dropped. In general, temporal redundancy solutions incur in increased packet processing time.

Hybrid spatial and temporal approaches were also explored. For example, authors in [22]

proposed to borrow RCUs from neighboring input ports in the NoC router. In this case, three different route computations are performed for each new packet, to then compare the resulting values in order to detect possible faults. Some of these calculations might happen in parallel (spatial redundancy) or in serial (temporal redundancy) depending on the router load. Indeed, since all arriving packets need to wait for two other RCUs to be available, this method can add significant delay in networks with heavy traffic load.

Packet retransmission techniques were also proposed to trigger recalculations when necessary. In [89], the authors proposed a mechanism to detect and recover from transient faults through the analysis of the requested output port. When the RCU request an invalid output port, the router triggers a new routing computation to correct the error (i.e., rerouting). If the fault cannot be detected, the next router in the path will detect the fault and send a negativeacknowledgement (NACK) message to the previous router unit asking for recalculation and retransmission. In a similar approach, the FoReVer framework [88] presents a method to detect and recover lost, duplicated, and misrouted packets from routing errors. Since FoReVer is based on End-to-End detection and recovery, dealing with soft errors requires retransmission of the whole packet. In general, retransmission-based recovery mechanisms require additional retransmission buffers.