## Non-Foster circuits applied to Full-Duplex systems

Saadou Al Mokdad

#### ▶ To cite this version:

Saadou Al Mokdad. Non-Foster circuits applied to Full-Duplex systems. Electronics. Université de Bretagne occidentale - Brest; Université Libanaise, 2020. English. NNT: 2020BRES0009. tel-02524398v2

## HAL Id: tel-02524398 https://theses.hal.science/tel-02524398v2

Submitted on 20 May 2020

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# THESE DE DOCTORAT DE

L'UNIVERSITE

DE BRETAGNE OCCIDENTALE

ET

L'UNIVERSITE LIBANAISE

ECOLE DOCTORALE N° 601

Mathématiques et Sciences et Technologies

de l'Information et de la Communication

Spécialité: Electronique

Par

## Saadou ALMOKDAD

« Non-Foster Circuits Applied to Full-duplex Systems »

Thèse présentée et soutenue à Brest, le 28 janvier 2020 Unité de recherche : Lab-STICC

#### Rapporteurs avant soutenance :

Mohamed ISMAIL Professeur à la Wayne State Université

Elias RACHID Professeur à l'Ecole Supérieure d'Ingénieurs de Beyrouth

#### **Composition du Jury:**

Président du Jury : Sobhi ABOU CHAHINE Professeur à l'Université Arabe de Beyrouth

Mohamed ISMAIL Maître de conférences HDR, UBO, Lab-STICC

Elias RACHID Professeur, Université Libanaise

Dir. de thèse : André PERENNEC Professeur à la Wayne State Université

Co-dir. de thèse : Sawsan SADEK Professeur à l'Ecole Supérieure d'Ingénieurs de Beyrouth

Co-encadrant : Marc LE ROY Maître de conférences, UBO, Lab-STICC

Invité(s):

Raafat LABABIDI

Enseignant-chercheur, ENSTA Bretagne, Lab-STICC

Ingénieur de recherche, ENSTA Bretagne, Lab-STICC

Emanuel RADOI Ingenieur de recherche, ENSTA Bretagne, Lab-STICC

Professeur, Université de Bretagne Occidentale, Lab-STICC

### Acknowledgments

I would like to sincerely express my gratitude to Professor Sawsan Sadek for her guidance and support during my thesis.

I would also like to thank Dr. Marc Le Roy, André Pérennec, Denis Le Jeune, and Raafat Lababidi for their time and efforts. I have had a rewarding learning experience and I deeply appreciate their willingness to share their insight and to be available to help me all the time.

I also have to thank the members of my PhD committee, in first place, Professors Mohamed Ismail and Elias Rachid for agreeing to report on my work and Professor Sobhi Abou Chahine for the PhD reviewing, and Professor Emanuel Radoi for accepting the invitation of being a member of my jury.

I would like to thank my friends and my entire family, particularly my mother for her endless love, support and encouragement.

Lastly, I would like to thank God, I am so grateful for all that I have is because of him.

# **Summary**

| ACKNOWLEDGMENTS                                               | I   |

|---------------------------------------------------------------|-----|

| SUMMARY                                                       | II  |

| TABLE OF FIGURES                                              | V   |

| LIST OF TABLES                                                | XII |

| GENERAL INTRODUCTION                                          | 1   |

| CHAPTER 1                                                     | 3   |

| 1. INTRODUCTION                                               | 3   |

| 1.2 DUPLEXING TECHNIQUE IN MODERN WIRELESS LINKS              | 4   |

| 1.2.1 TIME DIVISION DUPLEX (TDD)                              | 4   |

| 1.2.2 FREQUENCY DIVISION DUPLEX (FDD)                         | 4   |

| 1.2.3 OTHER DUPLEXING/MULTIPLEXING TRANSMISSION TECHNIQUES    | 5   |

| 1.3 ADVANTAGES AND DISADVANTAGES OF FULL-DUPLEX TECHNIQUE     | 6   |

| 1.4 SOURCES OF SELF-INTERFERENCE                              | 7   |

| 1.5 FD REQUIREMENTS                                           | 8   |

| 1.5.1 PASSIVE SELF-INTERFERENCE SUPPRESSION                   | 11  |

| 1.5.2 ANALOG SELF-INTERFERENCE CANCELLATION                   | 11  |

| 1.5.3 DIGITAL SELF-INTERFERENCE CANCELLATION                  | 12  |

| 1.6 DISTORTION AND NOISE ISSUES IN FD                         | 13  |

| 1.7 PROPOSED TOPOLOGIES FOR SI CANCELLATION                   | 15  |

| 1.8 ANTENNA SPECIFICATIONS FOR A COMPACT FD SYSTEM            | 18  |

| 1.9 MOTIVATION, OBJECTIVES AND PROPOSED TOPOLOGY              | 19  |

| 1.10 ORGANIZATION OF THE THESIS                               | 20  |

| 1.12 REFERENCE                                                | 21  |

| CHAPTER 2                                                     | 23  |

| 2.1 INTRODUCTION TO FOSTER AND NON-FOSTER ELEMENTS            | 23  |

| 2.3 NIC AND NII BASICS.                                       | 24  |

| 2.4 TOPOLOGIES OF NIC                                         | 26  |

| 2.5 OTHER NON-FOSTER TOPOLOGIES                               | 27  |

| 2.5.1 NIC BASED ON AMPLIFIERS                                 | 27  |

| 2.5.2 NIC BASED ON A TRANSFORMER                              | 28  |

| 2.5.3 NON-FOSTER CIRCUITS BASED ON A NEGATIVE GROUP DELAY NGD | 28  |

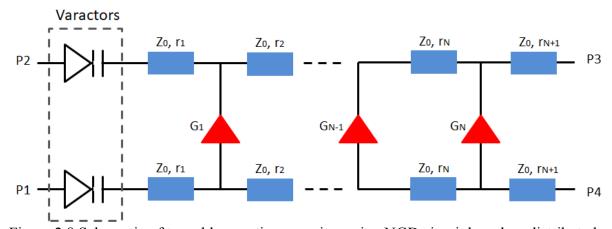

| 2.5.4 NON-FOSTERS BASED ON DISTRIBUTED AMPLIFIER              | 29  |

| 2.7 NICS CHOSEN CIRCUIT                                       | 30  |

| 2.7.1 CASE R <sub>0</sub> INFINITE:                           | 31  |

| 2.7.2 CASE R <sub>0</sub> IS FINITE                           | 32  |

| 2.8 STABILITY WITHIN NICS                                     | 33  |

| 2.9 LINVILL ANALYSIS LIMITATION                                         | 35    |

|-------------------------------------------------------------------------|-------|

| 2.10 CONCLUSION                                                         | 36    |

| 2.11 REFERENCES                                                         | 37    |

| CHAPTER 3                                                               | 39    |

| 3.1 PHASE SHIFTER                                                       | 39    |

| 3.2 TYPES OF PHASE SHIFTERS                                             | 40    |

| 3.2.1 ACTIVE AND PASSIVE PS                                             | 40    |

| 3.2.2 MECHANICAL OR ELECTRONIC PHASE SHIFTERS                           | 41    |

| 3.2.4 FIXED OR ADJUSTABLE PHASE SHIFTERS                                | 41    |

| 3.2.3 DIGITAL OR ANALOG TUNABLE PHASE SHIFTERS                          | 42    |

| 3.2.5 RECIPROCAL OR NONRECIPROCAL PHASE SHIFTERS                        | 43    |

| 3.2.6 Pure Phase Shifters                                               | 43    |

| 3.3 1 <sup>ST</sup> DESIGN OF PS TUNABLE AROUND 180° USING NF CIRCUIT   | 44    |

| 3.3.1 Proposed Topology                                                 | 45    |

| 3.3.2 NF CAPACITANCE DESIGN AND MINIMIZATION OF RESIDUAL RESISTIVE PART | г. 45 |

| 3.3.3 IMPROVED REDUCTION OF RESISTIVE PART OF NF CAPACITANCE AT         | THE   |

| S-PARAMETERS LEVEL                                                      | 48    |

| 3.3.4 ACTIVE TUNABLE PURE PHASE SHIFTER SIMULATION RESULTS              | 50    |

| 3.4 STABILITY STUDY                                                     | 51    |

| 3.4.1 STABILITY STUDY BASED ON NDF                                      | 51    |

| 3.4.2 STABILITY STUDY: INFLUENCE OF DC BIAS                             | 54    |

| 3.4.3 STABILITY STUDY: INFLUENCE OF TRANSMISSION LINE                   | 56    |

| 3.5 DESIGN OF NON-FOSTER COMPONENTS USING TRANSISTOR WITH I             | LOW   |

| TRANSITION FREQUENCY                                                    | 58    |

| 3.5.1 MEASURED RESULTS                                                  | 60    |

| 3.5.1.1 Prototype 1                                                     | 60    |

| 3.5.1.2 Prototype 2                                                     | 61    |

| 3.5.1.3 Prototype 3                                                     | 64    |

| 3.5.2 2 <sup>nd</sup> Design of Tunable PS                              | 68    |

| 3.6 CONCLUSION                                                          | 71    |

| 3.7 PERSPECTIVES ON PS                                                  | 72    |

| 3.8 REFERENCES                                                          | 73    |

| CHAPTER 4                                                               | 75    |

| 4.1 INTRODUCTION                                                        | 75    |

| 4.1.1 DEFINITION OF AN ESA                                              | 75    |

| 4.1.2 Typical Applications of ESAs                                      | 76    |

| 4.1.3 CHARACTERISTIC IMPEDANCE OF ESA                                   | 76    |

| 4.1.4 FUNDAMENTAL PARAMETERS OF ESA                                     | 78    |

| 4.1.4.1 Quality factor Q                                                | 78   |

|-------------------------------------------------------------------------|------|

| 4.1.4.2 Bandwidth                                                       | 79   |

| 4.1.4.3 Gain-Bandwidth Limitation of Lossless Passive Matching Networks | 80   |

| 4.2 ACTIVE CIRCUITS APPLIED TO IMPEDANCE MATCHING                       | 82   |

| 4.3 METHODOLOGY OF COMBINED NON-FOSTER AND PASSIVE BROAD                | BAND |

| MATCHING NETWORKS                                                       | 83   |

| 4.3.1 CONVENTIONAL MONOPOLE ANTENNA                                     | 83   |

| 4.3.2 FIRST MATCHING TOPOLOGY: NF-PASSIVE-ANTENNA                       | 85   |

| 4.3.3 SECOND MATCHING TOPOLOGY: PASSIVE-NF-ANTENNA                      | 89   |

| 4.3.4 PROPOSED MATCHING TOPOLOGY: PASSIVE-NF-PASSIVE-ANTENNA            | 91   |

| 4.3.5 TOPOLOGIES COMPARISON AND DISCUSSION                              | 93   |

| 4.4 DESIGN OF A FULL-DUPLEX FRONT-END DEDICATED TO CLOSE                | AND  |

| ELECTRICALLY SMALL ANTENNAS (ESA) BY USING NF CIRCUITS                  | 96   |

| 4.4.1 FULL DUPLEX APPROACH USING PASSIVE ELEMENTS                       | 96   |

| 4.4.1.1 Analysis of topologies                                          | 98   |

| 4.4.1.2 Simulations and Measured Results                                | 99   |

| 4.4.2 FULL DUPLEX TOPOLOGY USING NON-FOSTER ELEMENTS                    | 102  |

| 4.4.2.1 Non-Foster matching of one monopole antenna                     | 102  |

| 4.4.2.2 Non-Foster Matching and decoupling                              | 108  |

| 4.4.2.3 Combining Two Levels of Self-Interference Cancellation          | 111  |

| 4.5 CONCLUSION                                                          | 113  |

| 4.6 REFERENCES                                                          | 115  |

| CHAPTER 5                                                               | 117  |

| APPENDICES                                                              | 119  |

| APPENDIX A                                                              | 119  |

| APPENDIX B                                                              | 121  |

| APPENDIX C                                                              | 124  |

| APPENDIX D                                                              | 129  |

| COMMUNICATIONS AND PUBLICATIONS                                         | 132  |

# **Table of Figures**

| FIGURE 1.1 TRANSMISSION MODES                                                       |

|-------------------------------------------------------------------------------------|

| FIGURE 1.2 COMPARISON BETWEEN TDD, FDD, AND FD IN TERM OF UPLOADING AND             |

| DOWNLOADING DATA IN FREQUENCY AND TIME DOMAIN                                       |

| FIGURE 1.3 VARIOUS LEVELS IN THE TX AND THE RX CHAIN TO GET SI CANCELLATION         |

| FIGURE 1.4 ILLUSTRATION OF REQUIRED LEVELS AND DISTRIBUTION OF SI CANCELLATION9     |

| FIGURE 1.5 DIFFERENT SECTIONS OF SIC                                                |

| FIGURE 1.6 BLOCK DIAGRAM OF ANALOG RF SELF-INTERFERENCE CANCELLATION                |

| FIGURE 1.7 BLOCK DIAGRAM OF DIGITAL BASEBAND SELF-INTERFERENCE CANCELLATION 13      |

| FIGURE 1.8 WHAT THE RADIO IS EXPECTED TO TRANSMIT (A), WHAT IS ACTUALLY TRANSMITTED |

| (B)                                                                                 |

| FIGURE 1.9 ANTENNA SEPARATION                                                       |

| FIGURE 1.10 ANTENNA PLACEMENT                                                       |

| FIGURE 1.11 MIDU TOPOLOGY                                                           |

| FIGURE 1.12 ELECTRIC BALANCE TOPOLOGY                                               |

| FIGURE 1.13 TOPOLOGY TO REDUCE SI IN A COMPACT FD FRONT-END                         |

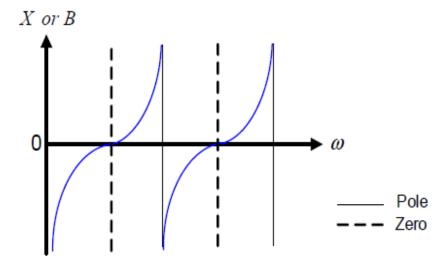

| FIGURE 2.1 REACTANCE OR SUSCEPTANCE OF FOSTER ELEMENT ALONG FREQUENCY AXIS 23       |

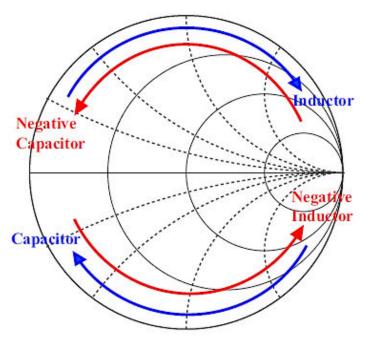

| FIGURE 2.2 REFLECTION COEFFICIENT OF FOSTER AND NF ELEMENTS ON SMITH CHART 24       |

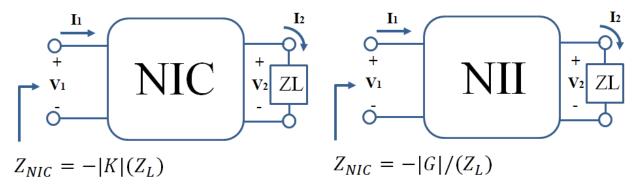

| FIGURE 2.3 SCHEME OF NIC (A), AND NII (B) TWO-PORT NETWORKS                         |

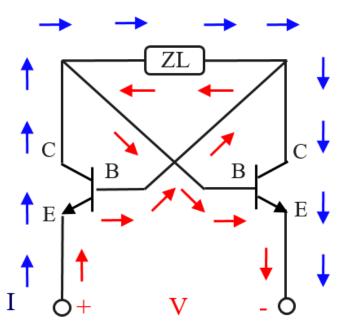

| FIGURE 2.4 BASIC NIC TOPOLOGY SHOWING VOLTAGE FLOW (RED ARROWS) AND CURRENT         |

| FLOW (BLUE ARROWS) 25                                                               |

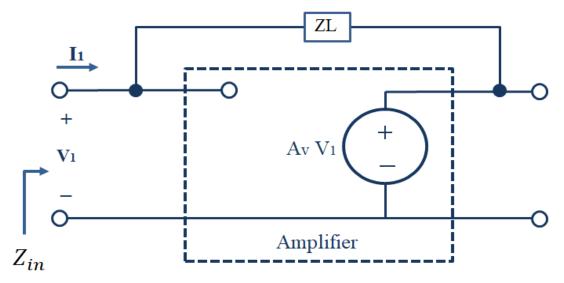

| FIGURE 2.5 AMPLIFIER BASED NIC                                                      |

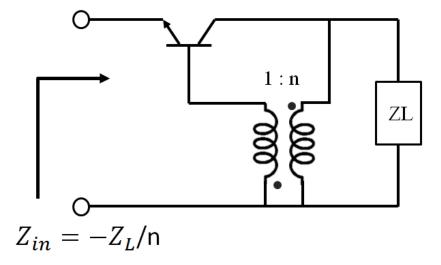

| FIGURE 2.6 TRANSFORMER BASED NIC                                                    |

| Figure 2.7 (a) Series and parallel RLC resonators used for optioning NGD. (B        |

| COMBINATION OF SERIES AND PARALLEL RLC RESONATORS FOR WIDEBAND NGI                  |

| RESPONSE29                                                                          |

| FIGURE 2.8 SCHEMATIC OF TUNABLE NEGATIVE CAPACITOR USING NGD CIRCUIT BASED ON         |

|---------------------------------------------------------------------------------------|

| DISTRIBUTED AMPLIFIER                                                                 |

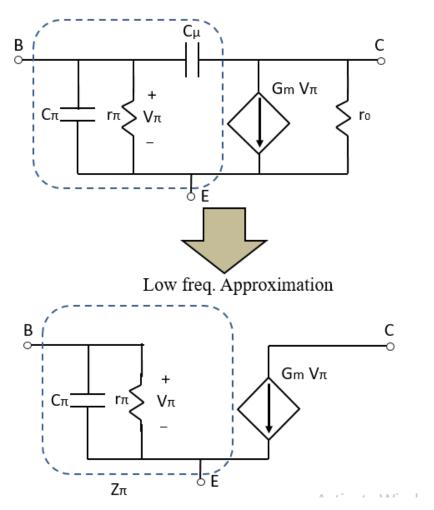

| FIGURE 2.9 SMALL SIGNAL II-MODEL REPRESENTATION OF BJT TRANSISTOR                     |

| FIGURE 2.10 NIC OPEN CIRCUIT STABLE (OCS) TOPOLOGY                                    |

| Figure 2.11 NIC Open Circuit Stable (OCS) topology where $\ensuremath{r_0}$ is Finite |

| FIGURE 2.12 GENERAL TOPOLOGY OF NIC WITH STABILITY CONDITIONS                         |

| FIGURE 2.13 IDEAL NIC DIAGRAM PRESENTING REFERENCE PLAN FOR (A) OPEN-CIRCUIT AND (B)  |

| SHORT-CIRCUIT STABILITY CONDITION                                                     |

| FIGURE 3.1 TWO-PORT NETWORK SCHEMATIC OF A PHASE SHIFTER                              |

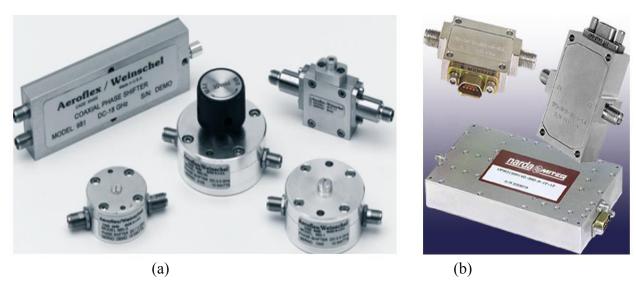

| Figure 3.2 Example on Mechanical Phase Shifters [15] (a), and Electrical Phase        |

| Shifters [16] (b)                                                                     |

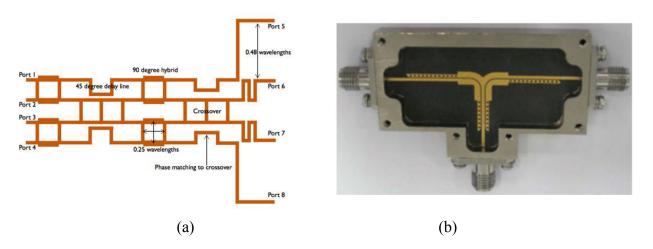

| FIGURE 3.3 BUTLER MATRIX (A), PHASE INVERTER (B)                                      |

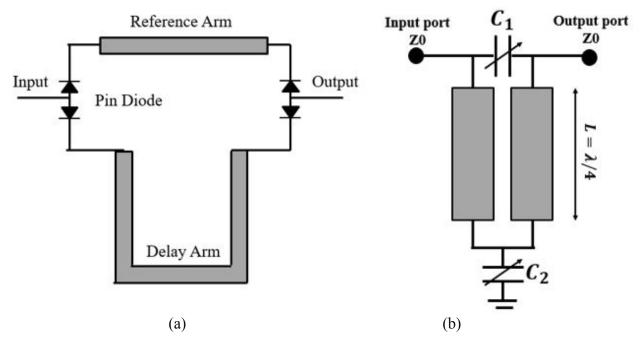

| FIGURE 3.4 DIGITAL PHASE SHIFTER (A), ANALOG PHASE SHIFTER (B)                        |

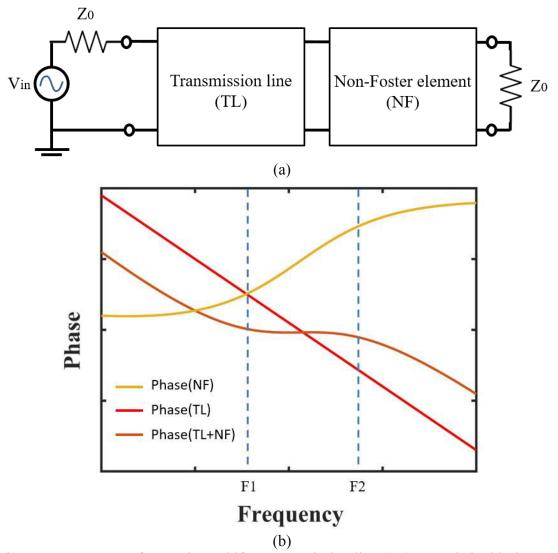

| FIGURE 3.5 STRUCTURE OF PURE PHASE SHIFTER: TRANSMISSION LINE (TL) CASCADED WITH THE  |

| Non-Foster (NF) element (a), ideal behavior of their pure phase response (b) 43       |

| FIGURE 3.6 PROPOSED PHASE SHIFTER TOPOLOGY                                            |

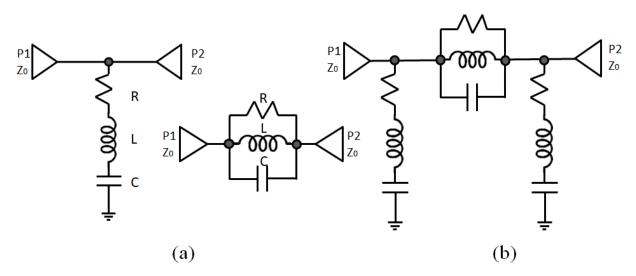

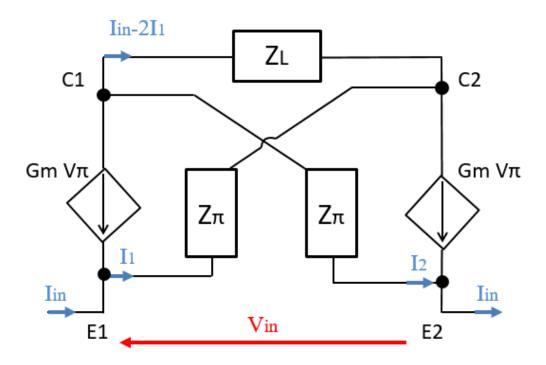

| Figure 3.7 Even-mode equivalent circuit (a), Odd-mode equivalent circuit (b) 45       |

| FIGURE 3.8 EQUIVALENT XCP CIRCUIT MODEL WITH OUTPUT AT SOURCE (A), AND WITH OUTPUT    |

| AT DRAIN (B)                                                                          |

| FIGURE 3.9 CASCADING SOURCE AND DRAIN TOPOLOGY TO GET -1PF                            |

| FIGURE 3.10 XCP INPUT IMPEDANCE (IMAGINARY AND REAL PARTS) FOR OUTPUT AT SOURCE       |

| AND DRAIN COMPARED TO A NEGATIVE CAPACITANCE OF – 2PF                                 |

| Figure 3.11 Real part of the cascaded NF topology and the modified one (a), image     |

| OF MODIFIED CASCADE TOPOLOGY COMPARED TO -1PF (B)                                     |

| FIGURE 3.12 MODIFIED SOURCE XCP TOPOLOGY                                              |

| FIGURE 3.13 SCHEMATIC OF THE MODIFIED CASCADED NF TOPOLOGY                            |

| FIGURE 3.14 THE COMPLETE CIRCUIT STRUCTURE OF THE ACTIVE PHASE SHIFTER                    | 50       |

|-------------------------------------------------------------------------------------------|----------|

| FIGURE 3.15 PS REFLECTION AND TRANSMISSION COEFFICIENTS (A), PHASE VARIATION USING        | ЗΑ       |

| Varactor (b)                                                                              | 51       |

| FIGURE 3.16 PHASE SHIFTER TOPOLOGY WITH SUSPECTED NODES                                   | 52       |

| FIGURE 3.17 NDF of the Phase Shifter                                                      | 52       |

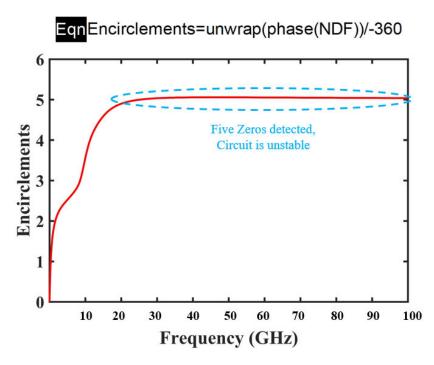

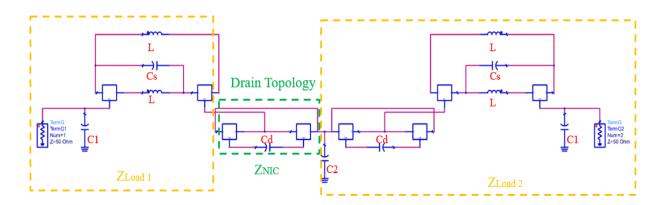

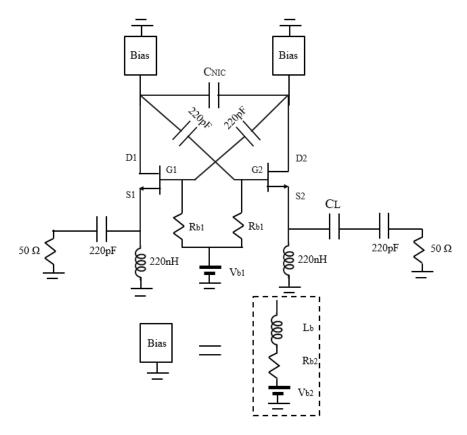

| FIGURE 3.18 NUMBER OF ENCIRCLEMENT OF NDF AROUND THE ORIGIN                               | 53       |

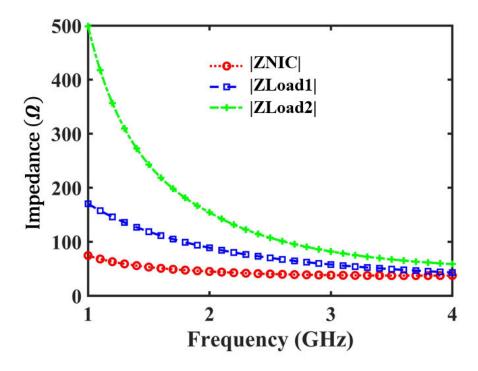

| FIGURE 3.19 DRAIN TOPOLOGY IMPEDANCE AND ITS LOAD IMPEDANCE                               | 53       |

| FIGURE 3.20 DRAIN TOPOLOGY IMPEDANCE COMPARED TO LOAD IMPEDANCE                           | 54       |

| FIGURE 3.21 BIAS NETWORK FOR SOURCE TOPOLOGY                                              | 55       |

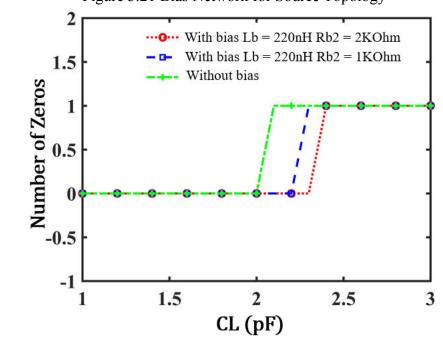

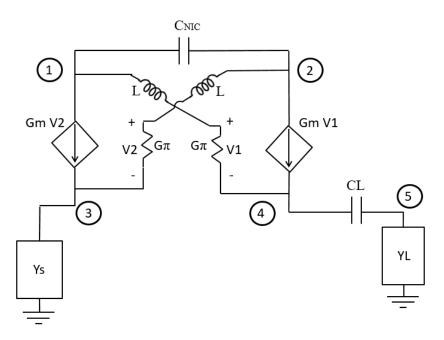

| Figure 3.22 Number of Zeros of NDF according to value of $C_{\text{L}}$                   | 55       |

| Figure 3.23 Source Topology with Inductors L to mimic interconnect lines                  | 56       |

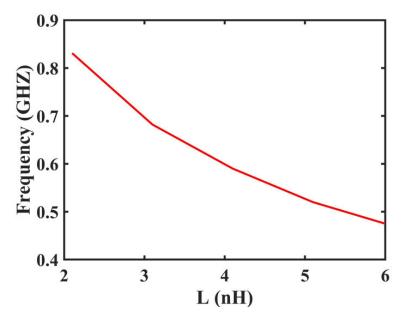

| FIGURE 3.24 OSCILLATION FREQUENCY AS A FUNCTION OF INDUCTANCE VALUE                       | 57       |

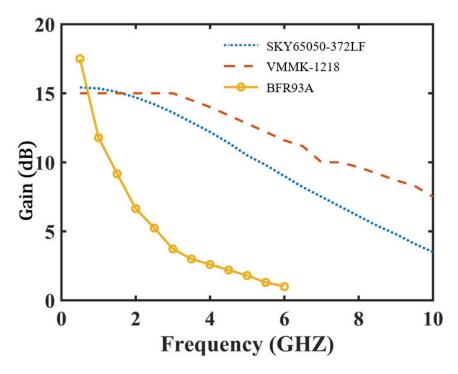

| FIGURE 3.25 TRANSISTORS GAIN VS FREQUENCY COMPARISON                                      | 59       |

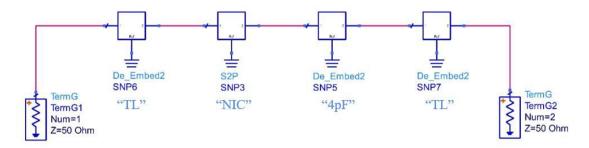

| Figure 3.26 De-embedding in ADS                                                           | 59       |

| FIGURE 3.27 NIC STRUCTURE WITH AVAGO VMMK-1218 FET STRUCTURE (A), BUILT VI                | EW       |

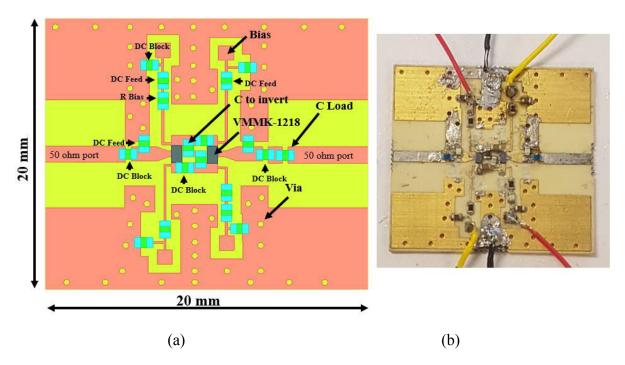

| (B)                                                                                       | 60       |

| FIGURE 3.28 SPECTRUM OF OSCILLATING NIC WITH AVAGO VMMK-1218 PHEMT                        | 60       |

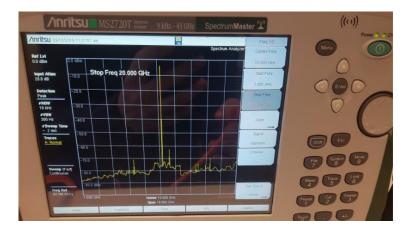

| FIGURE 3.29 NIC STRUCTURE: (A) TOP VIEW, (B) PERSPECTIVE VIEW, (C) BUILT VIEW             | 61       |

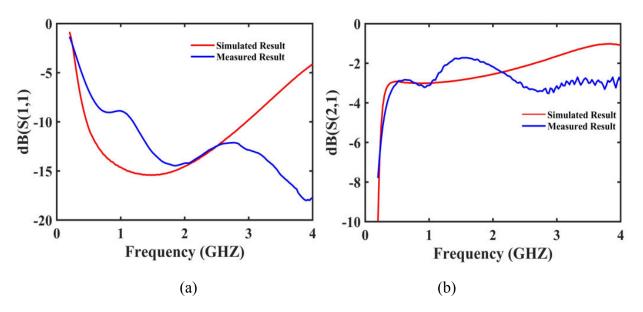

| Figure 3.30 Comparison between Measured and Simulated Result of loaded NIC $\scriptstyle$ | 62       |

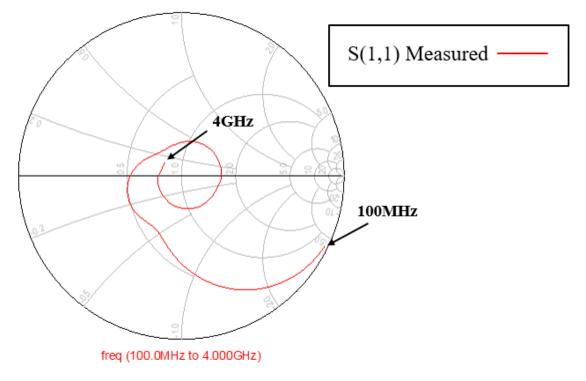

| FIGURE 3.31 MEASURED RETURN LOSS ON SMITH CHART OF LOADED NIC LAYOUT                      | 62       |

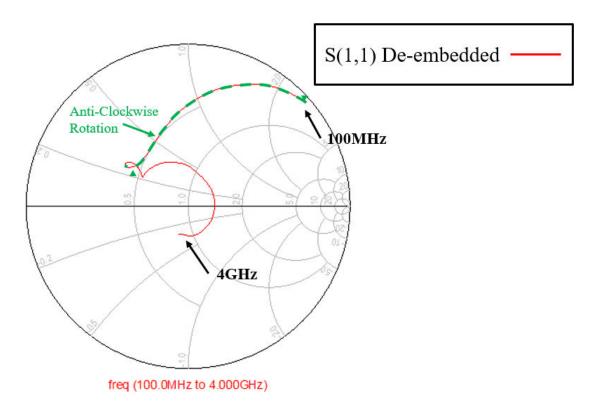

| FIGURE 3.32 DE-EMBEDDED MEASURED RETURN LOSS ON SMITH CHART OF NIC                        | 63       |

|                                                                                           |          |

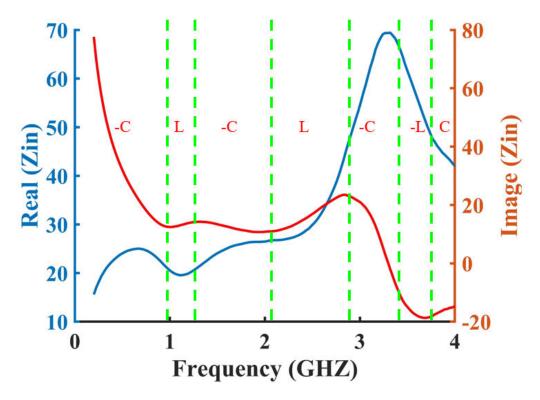

| FIGURE 3.33 DE-EMBEDDED REACTANCE OF THE NIC                                              | 63       |

| FIGURE 3.33 DE-EMBEDDED REACTANCE OF THE NIC                                              |          |

|                                                                                           | 64       |

| FIGURE 3.34 THE CAPACITANCE AND INDUCTANCE OF THE DE-EMBEDDED NIC                         | 64<br>65 |

| FIGURE 3.38 DE-EMBEDDED REACTANCE OF THE BFR93A NIC                                             |

|-------------------------------------------------------------------------------------------------|

| FIGURE 3.39 THE CAPACITANCE AND INDUCTANCE OF THE DE-EMBEDDED BFR93A NIC 67                     |

| FIGURE 3.40 THE CAPACITANCE AND INDUCTANCE OF THE DE-EMBEDDED NIC                               |

| FIGURE 3.41 2 <sup>ND</sup> PS REFLECTION AND TRANSMISSION COEFFICIENTS (A), AND PHASE          |

| TRANSMISSION (B)                                                                                |

| FIGURE 3.42 NDF of the 2 <sup>ND</sup> Phase Shifter                                            |

| FIGURE 3.43 NUMBER OF ENCIRCLEMENT OF NDF AROUND THE ORIGIN FOR THE 2 <sup>ND</sup> PS 69       |

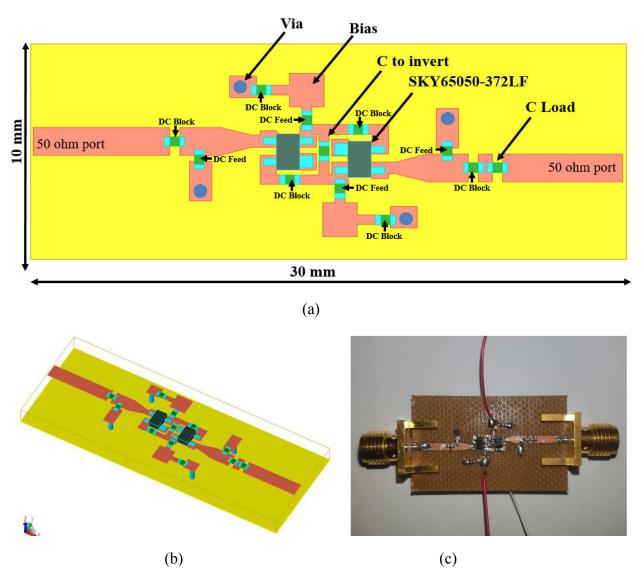

| FIGURE 3.44 2 <sup>ND</sup> PS STRUCTURE: (A) TOP VIEW, (B) PERSPECTIVE VIEW, (C) BUILT VIEW 70 |

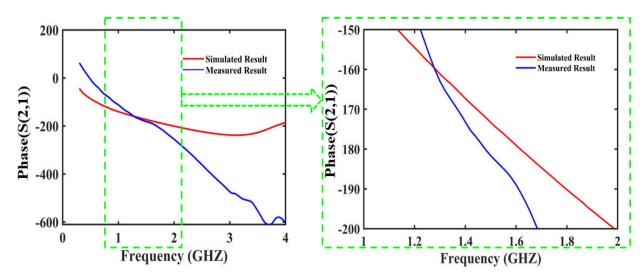

| FIGURE 3.45 COMPARISON BETWEEN MEASURED AND SIMULATED RESULTS FOR 2 <sup>ND</sup> PS            |

| Figure 3.46 Comparison between Measured and Simulated Results for the                           |

| TRANSMISSION PHASE OF THE 2 <sup>ND</sup> PS                                                    |

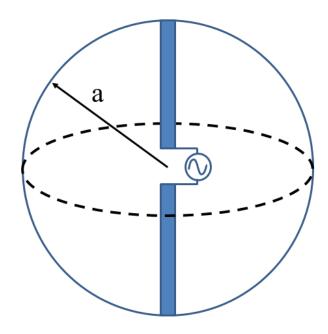

| FIGURE 4.1 A DIPOLE ANTENNA CIRCUMSCRIBED BY A SPHERE WITH RADIUS A                             |

| Figure 4.2 Some example of ESA used in everyday life system such as (a) garage                  |

| KEYLESS DOOR OPENER [3], (B) VEHICULAR MULTIFUNCTION ANTENNA [4], (C) A RFID TAG                |

| ANTENNA [5]                                                                                     |

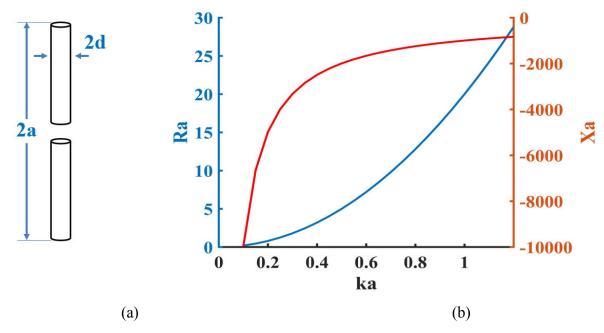

| FIGURE 4.3 SMALL ELECTRIC DIPOLE (A), IMPEDANCE ZA AS FUNCTION OF SIZE FACTOR KA (B             |

| [7]                                                                                             |

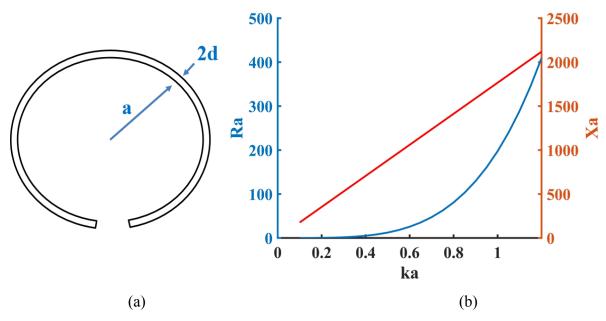

| Figure 4.4 Single turn small loop antenna (a), resistive and reactive response of               |

| SMALL LOOP WITH $A/D = 100$                                                                     |

| Figure 4.5 Comparison between 1 stage L-network and 2 stage L-network on C                      |

| FACTOR (A), THE EFFECT OF Q FACTOR ON BANDWIDTH (B)                                             |

| FIGURE 4.6 PORT LOSSLESS MATCHING NETWORK FOR A SERIES PASSIVE RC                               |

| FIGURE 4.7 A POSSIBLE REFLECTION COEFFICIENT RESPONSE WITH A 2-PORT MATCHING                    |

| NETWORK FOR A SERIES PASSIVE RC [15]                                                            |

| Figure 4.8 Comparison between (a) passive and (b) active matching for an ESA                    |

| REPRESENTED AS A SERIES CAPACITOR                                                               |

| FIGURE 4.9 ANTENNA SCHEMATIC AND RETURN LOSS                                    |

|---------------------------------------------------------------------------------|

| FIGURE 4.10 ANTENNA IMPEDANCE (REAL AND IMAGINARY) PARTS                        |

| FIGURE 4.11 MAXIMUM ACHIEVABLE ANTENNA RADIATION EFFICIENCY                     |

| Figure 4.12 Antenna matching on Smith Chart                                     |

| FIGURE 4.13 RESISTANCE CIRCLES ON SMITH CHART                                   |

| Figure 4.14 Antenna with Passive transformer (a), antenna with NF-Passiv        |

| MATCHING (B)                                                                    |

| FIGURE 4.15 ANTENNA MATCHING STEPS ON SMITH CHART                               |

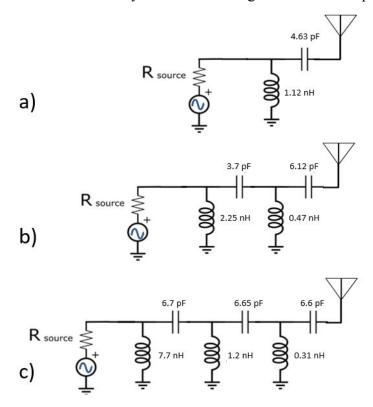

| Figure 4.16 (a) One stage L passive matching (b) two stages L matching (c) thre |

| STAGES L MATCHING                                                               |

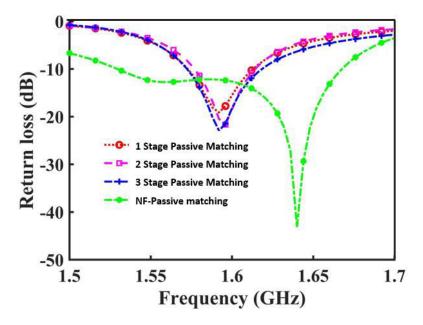

| FIGURE 4.17 MULTI-STAGE L-NETWORKS VS NF AND PASSIVE MATCHING                   |

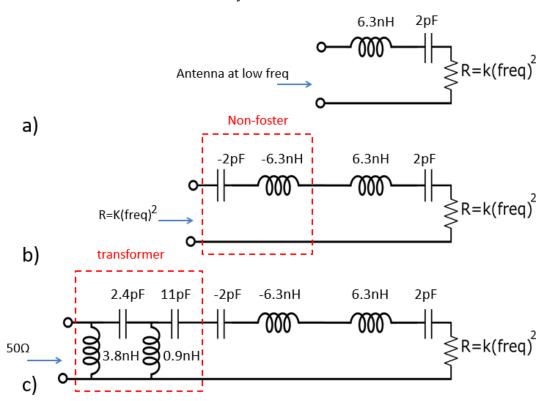

| FIGURE 4.18 ANTENNA MODEL AT LOW FREQUENCY (A), NF REACTIVE PART COMPENSATION   |

| (B), COMPLETE MATCHING (C)                                                      |

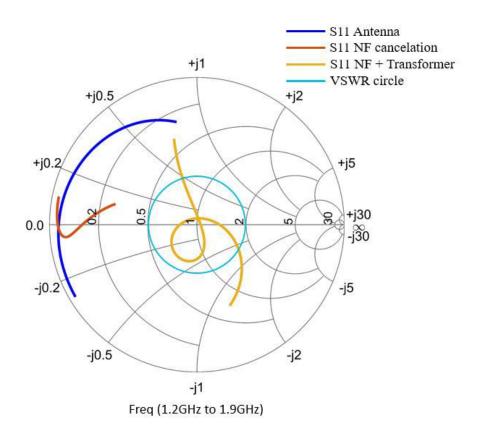

| FIGURE 4.19 STEP BY STEP MATCHING ON SMITH CHART                                |

| Figure 4.20 Passive-NF matching                                                 |

| Figure 4.21 Illustration of the Step-by-Step matching using the 3rd topology (a |

| Passive matching, (B) Non-Foster matching, (C) Passive transformer9             |

| FIGURE 4.22 STEP-BY-STEP WIDEBAND MATCHING FOR THE 3RD TOPOLOGY                 |

| Figure 4.23 Comparison between the three topologies                             |

| FIGURE 4.24 COMPARISON BETWEEN QUALITY FACTORS OF THE THREE TOPOLOGIES          |

| FIGURE 4.25 INCIDENT AND REFLECTED WAVES AT THE MATCHING CIRCUIT ACCESSES94     |

| Figure 4.26 Comparison of TTC for the three topologies                          |

| FIGURE 4.27 EFFICIENCY OF THE SYSTEM                                            |

| FIGURE 4.28 PROPOSED FULL-DUPLEX SYSTEM                                         |

| FIGURE 4.29 RETURN AND INSERTION LOSS BETWEEN TWO CLOSELY SEPARATED ANTENNAS 9  |

| FIGURE 4.30 SCHEMATIC OF TWO CLOSELY SPACED MONOPOLES AS PROPOSED IN [22] (A),   |

|----------------------------------------------------------------------------------|

| MODIFIED TOPOLOGY (B)97                                                          |

| Figure 4.31 two-port network representation of reference topology (a), and       |

| MODIFIED ONE (B)99                                                               |

| Figure 4.32 even odd mode representation of reference topology (a), and modified |

| ONE (B)99                                                                        |

| FIGURE 4.33 MANUFACTURED STRUCTURE OF REFERENCE TOPOLOGY (A), AND MODIFIED ONE   |

| (B)100                                                                           |

| Figure 4.34 Manufactured structure of reference topology at 2.3 GHz (a), and     |

| MODIFIED ONE AT 2.3 GHz (B), REFERENCE TOPOLOGY AT 1.6 GHz (C), AND MODIFIED ONE |

| AT 1.6 GHz (D)                                                                   |

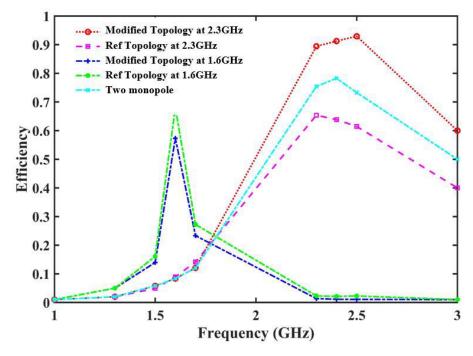

| FIGURE 4.35 SIMULATED EFFICIENCY OF THE FIVE CONFIGURATIONS                      |

| FIGURE 4.36 REALIZED GAIN COMPARISON BETWEEN TWO MONOPOLE, REFERENCE TOPOLOGY,   |

| AND MODIFIED ONE AT 1.6 GHz (A), AND 2.3 GHz (B)                                 |

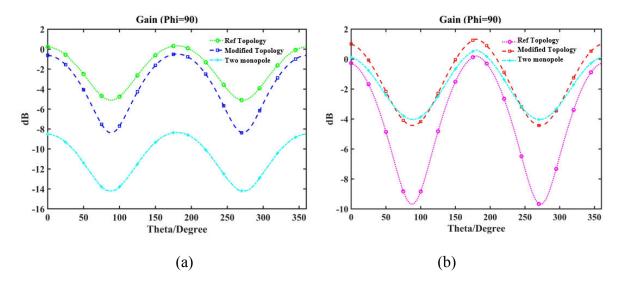

| FIGURE 4.37 SCHEMATIC OF NON-FOSTER CIRCUIT WITH ANTENNA SHOWING THE CURRENT     |

| PATH (A), THE CORRESPONDING LAYOUT (B), AND THE PHOTO OF THE FABRICATED ONE (C)  |

|                                                                                  |

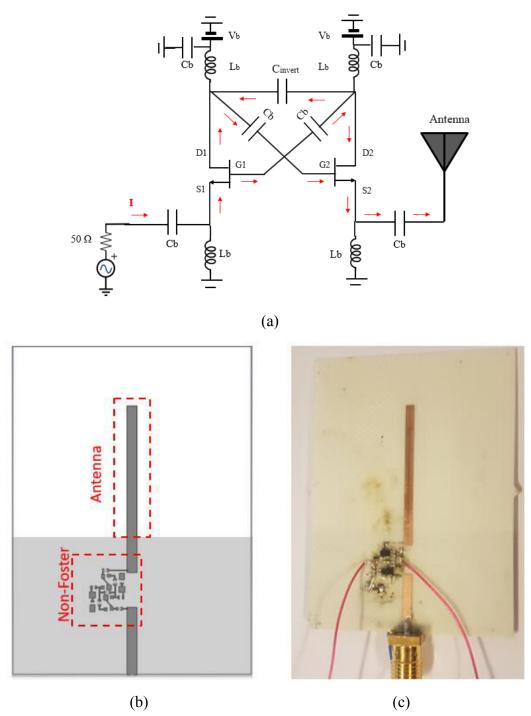

| Figure 4.38 Surface current distribution at 1.6GHz (a) geometry of non-foster    |

| CIRCUIT AND ANTENNA WITH ALL THE ASSOCIATED ELEMENTS (B)                         |

| FIGURE 4.39 COMPARISON BETWEEN SIMULATED AND MEASURED RETURN LOSS OF A MONOPOLE  |

| ANTENNA MATCHED BY NF CIRCUIT                                                    |

| Figure 4.40 Comparison between antenna with/without NF matching for Imaginary    |

| PART (A), AND REAL PART (B)                                                      |

| FIGURE 4.41 EFFICIENCY COMPARISON OF ANTENNA WITH/WITHOUT NF MATCHING            |

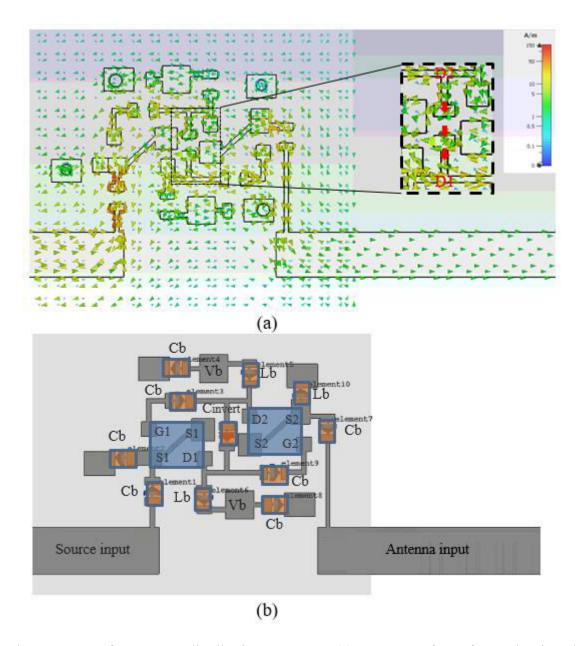

| Figure 4.42 combined passive and NF matching first topology (a), second topology |

| (B), FABRICATED FIRST TOPOLOGY (C), AND FABRICATED SECOND TOPOLOGY (D)           |

| FIGURE 4.43 SCHEMATIC OF COMBINED PASSIVE AND NF MATCHING, TOPOLOGY 1 (A), AND     |

|------------------------------------------------------------------------------------|

| TOPOLOGY 2 (B)                                                                     |

| Figure 4.44 Comparison between NF matching and combined passive and NF             |

| MATCHING                                                                           |

| Figure 4.45 Simulated vs Measured Result of Passive NF matching of topology one    |

| (A), AND TOPOLOGY TWO (B)                                                          |

| Figure 4.46 Two monopole antennas Matching and Decoupling using NF circuits (a),   |

| AND MATCHING USING NF CIRCUIT AND DECOUPLING USING PASSIVE CIRCUIT (B) 109         |

| Figure 4.47 Two port network representation (a), even-odd mode representation (b)  |

| 110                                                                                |

| FIGURE 4.48 SIMULATED RETURN AND INSERTION LOSS OF NF MATCHING AND DECOUPLING (A), |

| NF MATCHING AND PASSIVE DECOUPLING (B)                                             |

| FIGURE 4.49 PROPOSED FD TOPOLOGY (A), WITH IDEAL ELEMENTS (B)                      |

| FIGURE 4.50 SIMULATED RETURN AND INSERTION LOSS OF IDEAL FD SYSTEM                 |

| Figure 4.51 Comparison between simulated return and insertion loss with ideal      |

| ONES 112                                                                           |

# **List of Tables**

| TABLE 1.1 COMPARISON BETWEEN HD AND FD                                            |

|-----------------------------------------------------------------------------------|

| Table 1.2 Rough estimation of SI cancellation requirements to enable FD in 4G and |

| WI-FI                                                                             |

| TABLE 1.3 SUMMARY OF THE FOUR TOPOLOGIES                                          |

| TABLE 2.1 IMPEDANCE CONVERTER AND INVERTER PARAMETERS                             |

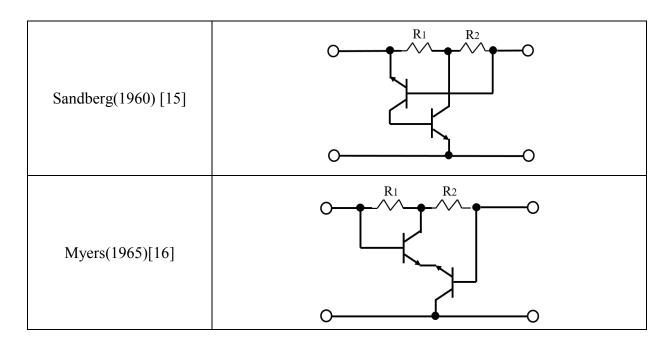

| TABLE 2.2 COLLECTION OF NIC TOPOLOGIES                                            |

| TABLE 3.1 PARAMETRIC STUDY ON INDUCTOR AND FREQUENCY OF OSCILLATIONS              |

| TABLE 3.2 COMPONENTS USED IN THE IMPLEMENTED NIC                                  |

| TABLE 3.3 COMPONENTS USED IN THE IMPLEMENTED NIC USING BFR93A                     |

| Table 3.4 Components used in the implemented PS using SKY transistor              |

| TABLE 4.1 BANDWIDTH COMPARISON BETWEEN DIFFERENT MATCHING TOPOLOGIES              |

| TABLE 4.2 COMPONENT VALUES FOR EACH TOPOLOGY                                      |

| TABLE 4.3 COMPONENT VALUES USED IN BOTH TOPOLOGIES OF COMBINED PASSIVE AND NF     |

| MATCHING                                                                          |

| Table 4.4 Components values from calculation used in both Matching and            |

| DECOUPLING TOPOLOGIES                                                             |

### **General Introduction**

This PhD study is made in the context of a co-tutelle work between the Lebanese university and Université de Bretagne Occidentale (UBO, Brest). At UBO, this PhD is hosted at Lab-STICC laboratory (UMR CNRS 6285) in the MOM department (Microwave, Optoelectronics and materials) in the DIM Team (Dispositifs et Interfaces Multiphysiques). The field of investigation of DIM team is wide and the design of devices and systems in RF and Microwave domain is the federative element of the team that brings original solutions in various domains: telecommunications, sea, defense and health.

The main goal of this work consists in achieving a wireless Full-Duplex (FD) system where the user can transmit and receive signal using the same frequency at the same time. Our aim is to build this FD in the context of small electronic devices (e.g. IoT, 5G...). In addition, many standards and frequency bands are emerging currently, which lead us to focus on a wide operating bandwidth.

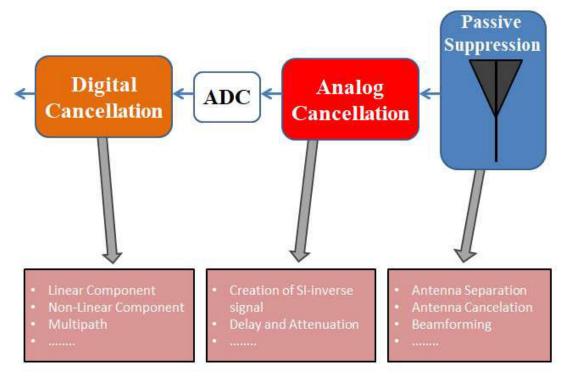

In wireless Full-Duplex system, the main issue is the self-interference (SI) that occurs between the transmitter chain and the receiver chain. The SI cancellation (SIC) architecture is usually divided into three main parts: decoupling or isolation at the antenna level (often called passive decoupling), analog cancellation (either in RF or in baseband) and digital cancellation. This thesis is dedicated to SIC at the antenna and analog levels in order to achieve a high isolation level (at least 40dB) between the transmitter chain and the receiver chain.

In the context of wireless Full-Duplex for wireless small devices, the most restricting constraint comes from the limited space, which is very tricky upon antenna design. Indeed, ideally the antenna should be single and small. However, none of single antenna full-duplex system is able to emit and receive following the same direction, which is mandatory for our system. Moreover, most Full-Duplex systems that include SIC system at the antenna level rely on wave cancellation at RX antenna and thus require at least three antennas.

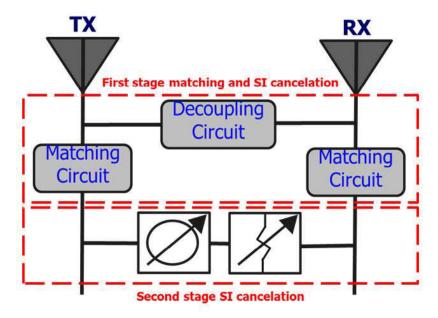

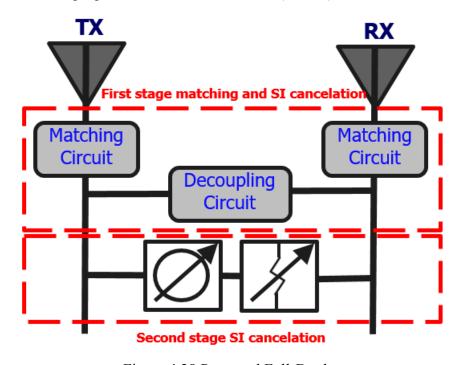

Analyzing state-of-the-art on FD wireless system is thus of prime interest to bring out the pros and cons of the most relevant systems for our application. The four main topologies are compared in chapter I and are identified to be narrow band and difficult to transpose to our context. Therefore, we put forward a FD topology that consists of the first two stages of SIC (i.e. antenna decoupling/isolation and analog cancellation). The first stage consists in matching and decoupling the two antennas in order to widen the frequency bandwidth of FD and offers a first level of SIC. The second one requires a tunable phase shifter (slightly tunable around 180°) associated with an attenuator. By combining these two stages together, we expect to achieve a high isolation level between the transmitter chain and the receiver chain over a wide frequency range.

Our redefined goals are therefore to build up the first stage of SIC (i.e. matching and decoupling network) and to design a variable PS that is going to be used in the second stage of SIC.

Since our goal is dedicated for small electronic devices (e.g. IoT ...), miniaturized antenna are thus required. One way to miniaturize an antenna is to shift down its operating frequency band. Such antennas are known as ESA (Electrically Small Antenna). Classical passive matching networks can do this but only over a narrow band due to a gain-bandwidth limitation. Indeed, in order to widen the bandwidth of our antenna we could introduce losses into the system, which in terms would lower the antenna gain. Thus for a wider high gain

band result, we suggest to use non-Foster matching circuit (i.e. that use negative capacitances and inductances). Chapter II will present a state-of-the-art of the different kinds of non-Foster circuits. Among them, XCP circuits (cross-coupled pair of transistors) seem a priori more likely to get wider frequency response than other techniques. In addition, we propose to study the behavior of NF circuit (i.e. how it works) in details through analysis and synthesis equations in order to understand the negative behavior of the system and to identify the most significant associated parasitic effects. Finally, Normalized determinate function (NDF) technique that seems to be the most relevant technique for XCP stability analysis will be described and will be used in order to test the stability of our circuits under study.

In Chapter III, a Phase Shifter (PS) topology based on NF circuit is introduced. The phase shifter offers a 180° phase shift potentially tunable (theoretically pure phase value, i.e. a flat phase in transmission) between its two ports and requires the use of negative capacitance. We will present a thorough study of the PS topology, including equations and expected ideal performance. The PS design performance greatly depends on the quality of the negative capacitance, which is difficult to keep ideal over a wide frequency band. Thus, we will present and test experimentally different configurations and improvements in the design of XCP circuits in order to improve the purity of the non-Foster element. Moreover, the stability method described in chapter II will be used to verify the reliability of this key element of the PS but also of this PhD work. Several parameters are likely to be tricky when working above 1GHz with XCP circuits. At least, three of them should be particularly supervised: i) the residual real part of XCP circuit, ii) interconnect lines and iii) the transition frequency of the selected transistor. The first one should influence the PS performance whereas the two others could bring stability issues.

In chapter IV, our goal focuses at last on the design of the wireless compact FD system. The relevance and performance of the proposed topology will be studied by considering a system based on two closely separated planar monopole antenna. All studies and techniques explored and validated in previous chapters will be implemented here to move towards this goal. Thereby, non-Foster circuits will be used to match the antennas in a wide frequency band much lower than their initial resonance frequency (i.e. antennas are then considered as electrically small antenna (ESA)) and also to decouple the antennas in order to get a first level of SIC. Prior to that, the definition of ESAs and their limitations using only passive element for matching will be recalled. A methodology study will be carried out in order to find the best way to match the antenna in order to have a wideband high gain performance. Almost at all steps (i.e. matching, decoupling), analysis equations will be given and the results obtained by using actual non-Foster components will be compared in simulation and experimentally to those from passive networks. Moreover the efficiency of the whole systems (passive and NF) will be quantified and compared. We will also put forward some improvements in the NF decoupling architecture.

Lastly, we will combine the two stages of SIC together (i.e. at the antenna level and by using PS and attenuator). As a first step, we will identify the maximum achievable SIC level by using ideal elements that will serve as a reference while implementing our actual NF components. A discussion will be given to identify the origin of any differences between the ideal response and the obtained one.

Finally, some conclusions will be drawn and some prospects will be suggested to go beyond the potential limitations of our compact FD system.

## Chapter 1

## **Full Duplex Overview**

#### 1. Introduction

The evolution of the mobile cellular and wireless networks has led to increased global network traffic [1]. The increase of smart devices (e.g., smart phones, and Internet of Things (IoT) devices) and the race for 5G drives toward finding a solution for air interface enhancements to use the radio resources more efficiently. Future 5G objective is to provide capabilities for very high data rates, very low latency, high reliability, and the possibility to handle intense device densities, in both cost and energy efficient manner [2]. Moreover, 5G and IoT are strongly related as 5G, due to its highly flexible architecture, is intended to offer a unified communication platform for the IoT and thus to potentially be a catalyst for IoT growth and vice versa.

In that context, Full-duplex (FD), i.e. transmitting and receiving simultaneously in the same frequency band, has received significant attention in both academia and industry [3], [4]. Several efforts are now underway to use FD technology in future cellular 5G standards [5] and in IoT [6].

FD wireless transmission is considered as an encouraging method for future wireless systems as it handles many key issues spectral efficiency. Nevertheless, this FD approach places strong requirements to the transceiver implementation due to self-interference (SI) phenomena (i.e. the transmitter signal is leaking into its own receiver signal). But if it is successfully handled, it will provide significant improvements to wireless systems [7]. Enabling wireless devices to operate in FD mode will lead to doubling their spectral efficiency in terms of transmitted bits per second per Hz. FD system can improve collision avoidance/detection mechanism, reduce air interface delays in networks, and improve the secrecy performance of the system [8].

FD wireless technique has been already used in the 1960's with FD radars [9] with a approach named "feed-through nulling". A high level of isolation was experienced but the system was very bulky, heavy and expensive which avoid such implementations in spatial and terrestrial wireless communication systems like cellular mobile. In relay configurations, Full Duplex systems have been used in some special cases such as high gain cell enhancer but they required a high physical separation and isolation between the receiver and transmitter more likely to be feasible in a relay context; moreover these systems had to face out some severe restrictions on the transmitter output power [10].

However, interest in using FD for the future evolution of wireless systems has significantly increased in the past few years due to some actual and reliable implementations. Potential use cases proposed for FD include relaying, microwave backhaul links, mesh networks, cognitive radio, access points/base stations and mobile systems [11], [12]. Short-range systems (e.g., Pico-cells in mobile wireless systems and Wi-Fi systems) are especially feasible operation environments for FD because the SI requirements are much more relaxed in these environments compared to large cell systems.

### 1.2 Duplexing Technique in Modern Wireless Links

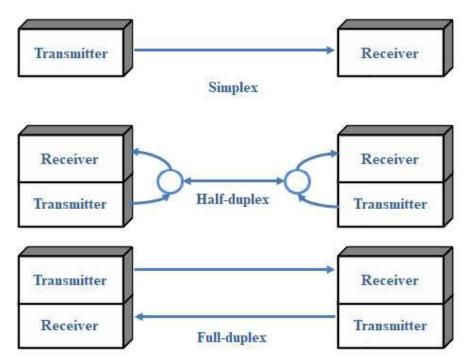

Globally, wired and wireless communication can be either simplex or duplex. A simplex communication is a one-way communication. On the other hand, a duplex communication is a two-way communication, where both nodes can communicate with each other in both forward and reverse directions. Duplex systems are presented in two forms: Half-Duplex (HD) and Full-Duplex communication FD. Figure 1.1 shows the three communication techniques: Simplex, Half-Duplex and Full-Duplex. Most current communication terminals operate in HD mode, separating the transmission and reception in either time or frequency domain. Wireless HD is a bidirectional transmission, which is mainly based on two orthogonal channels using time (i.e., Time Division Duplex (TDD)), or frequency (i.e., Frequency Division Duplex (FDD)) dimensions, in order to offer a separation between the transmitted and received signals. These methods are described in the following sections.

Figure 1.1 Transmission modes

#### 1.2.1 Time Division Duplex (TDD)

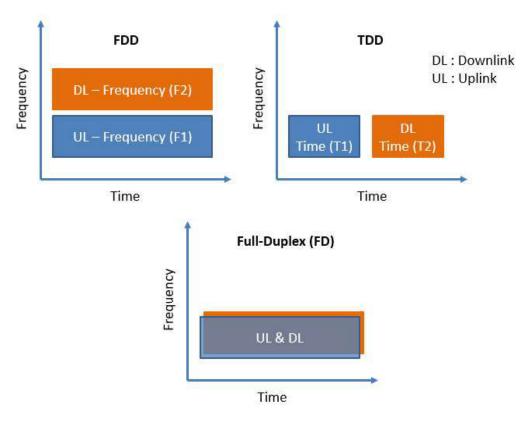

TDD uses a single frequency band for transmitting and receiving. This method uses the same frequency band by assigning different time slots to transmit and receive information. For example, uplink is transmitted at time 'T1' instance and downlink is transmitted at time 'T2'. Both uplink and downlink transmissions will take place at same RF carrier frequency [13]. The information to be transmitted can be voice, video, or computer data in serial binary format.

#### 1.2.2 Frequency Division Duplex (FDD)

In FDD, both uplink and downlink transmissions will be assigned two separate frequencies Fc<sub>1</sub> and Fc<sub>2</sub> respectively. Both utilize same time slot 'T' for transmission. FDD uses more frequency spectrum resources, generally at least twice the spectrum needed by

TDD. However, it does not suffer from discontinuous transmission encountered using TDD. Despite that, in both TDD and FDD the available communication resources are not efficiently utilized. Both TDD and FDD are two spectrum usage techniques used for mobile communication networks such as mobile Wimax, LTE, etc.

#### 1.2.3 Other Duplexing/Multiplexing Transmission Techniques

Other duplexing and multiplexing techniques can be combined with TDD and FDD classical techniques, such as orthogonal frequency division multiplexing access OFDMA, which uses a large number of frequency carriers orthogonal to each other (i.e. the peak of each carrier starts at the null of its neighbor carrier). CDMA (Code division multiple access CDMA) is another duplexing technique that allows numerous signals to occupy a single transmission channel, where each signal has its own code. So only a receiver whose frequency response is programmed with the same code can intercept it. Both OFDMA and CDMA use multiple frequencies for communications thus more frequency spectrum resources are required; moreover, both are utilized in FDD or TDD mode.

In order to enhance the efficiency of wireless and mobile communications, it is relevant to transmit and receive simultaneously in the same frequency band and simultaneously, which is leading to Full-Duplex technique. Indeed, FD uses the same frequency and same time slot for both uplink and downlink which overcomes both TDD and FDD in term of efficient usage of link resource [13]. Figure 1.2 shows FD technique compared to both TDD and FDD in terms of upload and download data.

Figure 1.2 Comparison between TDD, FDD, and FD in term of uploading and downloading data in frequency and time domain

### 1.3 Advantages and Disadvantages of Full-Duplex technique

FD has several advantages, but also exposes weaknesses compared to HD. For example, due to a double throughput gain, an FD node has to process twice as many packets as an HD node due to its simultaneous transmission and reception. The advantages and disadvantages of FD are summarized below.

#### Advantages of FD:

- Throughput gain: As compared to HD, FD has nearly doubles the throughput gain of HD. But none of the existed FD techniques experimentally attained the theoretical doubling throughput gain, because the wireless system always suffer from signal to noise ratio (SNR) loss due to the high self-interference (SI) problems, which is caused by the large power difference between the transmitted signal and the received signal of interest arriving from a remote antenna (TA) [14]. In fact, strong SI may decrease the SNR of FD to fall below that of the HD systems, which in this case destroys the interest of using FD.

- Solving the hidden terminal problem: The problem of hidden terminals can be solved using FD. Let us consider a scenario of multiple nodes having data in their buffer for direct transmission and reception from a common access point (AP). If a node starts transmitting its data to the AP and the AP simultaneously starts transmitting data back to this node, the other nodes will hear the transmissions from the AP and delay their transmissions to avoid collisions. By using FD, the node will not delay its transmission because FD uses the same link to transmit and receive data.

- Reducing congestion: link congestion occurs when a link is carrying more data than it can handle. This might lead to package lost. However, with the aid of FD, a node is capable of both transmitting and receiving simultaneously; hence, the network throughput approaches the single link capacity, while simultaneously benefitting from the spatial diversity gain.

- Reducing the end-to-end delay: as compared to the conventional store-and-forward technique employed in HD, FD is capable of forwarding and receiving package at same time, which reduces the end-to-end delay between the two remote nodes.

#### Disadvantages of the FD:

- SI: Using the FD technique, the power of the transmitted signal is higher than that of the received signal, and back reflected signals also affect the received signal, hence, the interference imposed upon the received signal would consequently degrades the FD throughput gains.

- A higher buffer size: a sufficiently large buffer size compare to HD is required for enabling the packets to be forwarded (that would otherwise have been discarded due to queue overflow).

The advantages and disadvantages of FD compared to HD are summarized in Table 1.1. In practical implementations, the decision as to whether adopting the FD or the HD depends on several factors, such as the system throughput gain required, the SI cancellation capability, and the affordable hardware/software complexity, etc. Among the mentioned factors, the SI signal significantly constrains the advantages of the FD techniques and would be the key limiting factor in developing FD systems.

Table 1.1 Comparison between HD and FD

| Content                   | HD       | FD                                   |

|---------------------------|----------|--------------------------------------|

| Throughput Gain           | Lower    | Higher (in theory is 2 x that of HD) |

| Hidden Terminal Collision | Suffered | None                                 |

| Congestion                | Higher   | Lower                                |

| End-to-end Delay          | Higher   | Lower                                |

| Self-Interference         | None     | High                                 |

| Queuing Size              | Smaller  | Larger                               |

SI degrades the receiver (RX) performances unless it is cancelled out (ideally to noise floor level). The total SI cancellation depends on the system scenario and should reach more than 100dB in some applications, particularly those with long distance wireless links. To solve this challenge, the SI reduction needs to be implemented in multiple stages across the FD transmitter (TX) chain. The implementation of the FD is limited by the capability of the radio transceivers to be able to provide a high SI cancellation level. To overcome this problem, an implemented method should prevent the transmitted signal from leaking back to its own receiver and to cancel any SI from the receiver path using knowledge of the transmitter signal. These methods should be implemented along the TX chain, including digital chain, analog chain, and at the antenna level. More details about SI are developed in the following sections.

#### 1.4 Sources of Self-Interference

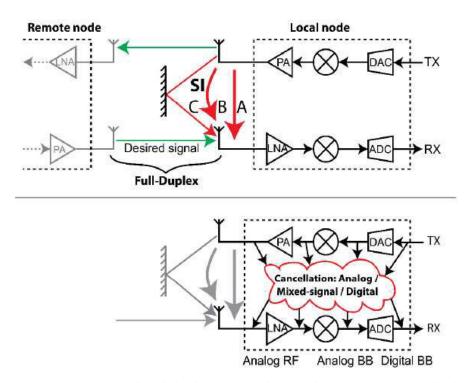

Potential use cases for FD transmission in wireless networks are short-range radio connections, such as in future 5G small indoor or outdoor radio cells (e.g., femto or picocells), device-to-device connections, transmission in mesh networks, etc. The main target in all cases is to improve spectral efficiency beyond legacy HD. Depending on the system scenario, the transmitted power level may range from 80dB to 120dB higher than the receiver noise-floor level, implying that the total SI cancellation should be at least on the same order. Figure 1.3, shows a FD link with a local and remote TX chain. Each chain has one antenna to transmit and another one to receive signal. We can notice three main sources of SI that limit the proper reception of the signal coming from the remote node by the local RX. First, leakage occur on-board (type A). Such direct cross talk is predominant in dense integration. Second, line-of-sight leakage between the two antennas may also occur (type B). This SI is reduced by implementing antenna with specific polarizations or radiation patterns or by isolating between the two antennas. Finally, TX signals can be reflected from nearby objects back into the receiver (type C). Such multipath reflection results in frequency-dependent SI and is particularly challenging in numerous multipath channels, mainly Non-line-of-sight (NLOS) path, encountered in indoor environment.

Figure 1.3 Various levels in the TX and the RX chain to get SI cancellation

Most of the SI cancellation techniques rely on copying a reference signal from the TX chain and subtracting it after modification (i.e. attenuation and phase shifting) in the RX chain. Figure 1.3 provides all possible places in the transmitter and receiver chain where we can apply SI cancellation methods. The RF/analog and antenna solutions focus on canceling the SI from direct cross talk and line-of-sight leakage (type A and B), while the digital solutions cancelation is introduced to suppress the residual SI below or close to the receiver noise floor thanks to adaptive algorithms and covering also the SI due to multi-path reflection.

## 1.5 FD Requirements

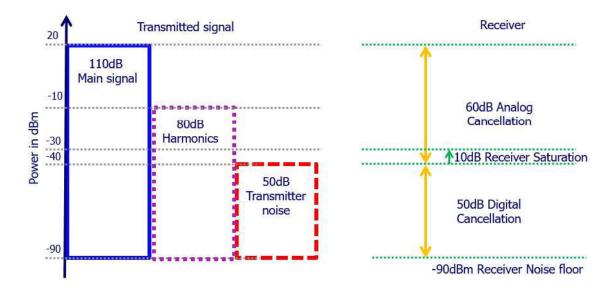

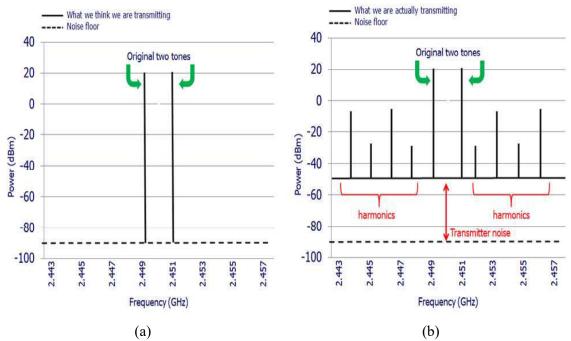

To implement FD, SI needs to be cancelled enough so that its power is reduced to the same level as the receiver noise floor. There is no point in canceling beyond that level since we will not see any benefits. Considering a scenario where the main signal is being transmitted at 20dBm (100mW) and having a noise floor level around -90dBm, then SI is then calculated as 20 - (-90) = 110dB above the receiver noise floor. The transmitter noise is around 50dB above the receiver noise floor, and the nonlinear harmonic components are 80dB above the noise floor as shown in Figure 1.4. Note that these numbers are consistent with other RF measurement studies reported in [15] for standard Wi-Fi. Moreover, if SI is not sufficiently cancelled, then any residual SI will act as noise or jammer to the received signal and degrades SNR. For instance, if the received signal SNR without FD is 25dB but after using FD it is reduced to 5dB due to 20dB residual SI. This is worse than using the original HD link with 25dB SNR and it is better in this case to turn off FD.

Figure 1.4 Illustration of required levels and distribution of SI cancellation

There are four main ideas from the above analysis:

- 1) Most FD system need to provide around 110dB of SI cancellation to reduce it to the receiver noise floor.

- 2) Transmitter noise is by definition random noise, which cannot be cancelled by any algorithm. The better way to cancel transmitter noise is to copy the TX signal in the analog/RF domain section and cancel it there.

- 3) A final constraint is that if the SI signal is above the analog to digital converter (ADC) full scale range, this leads to the saturation of the RX chains. Assume a 12 bits ADC resolution is used in Wi-Fi systems, in practice it is necessary to leave 2 bits of margin (i.e. a 12 bits ADC should be used as a 10 bits ADC to reduce quantization noise). We have a theoretical 60dB of dynamic range, which implies that the strongest signal level that can be present on the input to the radio relative to the receiver noise floor is -90dB + 60dB = -30dB, beyond this level the receiver will go into saturation.

To sum up, most FD design needs to provide at least 110dB of linear cancellation that can only be achieved by combining multiple levels of SIC, e.g. 60dB of analog cancellation and 50dB of digital cancellation as seen in Figure 1.4. Furthermore, Table 1.2 [16], [18] presents the amount of SI cancellation required to enable FD operations in several technologies for both 4G and Wi-Fi. Despite that, if by any chance the analog and digital cancellations suffer from some performance degradations due to hardware imperfections, their combined cancellation may not be enough. To solve this problem a method called passive suppression [19] is also invoked to reduce the SI by increasing the pass loss between the transmitting and receiving antenna of the FD node (Figure 1.5). In the following sections, we will address some methods to perform passive suppression, digital and analog cancelation of SI.

Figure 1.5 Different sections of SIC

Table 1.2 Rough estimation of SI cancellation requirements to enable FD in 4G and Wi-Fi

| Generations     | Technologies / Access<br>Technology                                                                                      | Channel<br>Bandwidth   | Transmit power | Noise<br>power | Required SI cancellation |

|-----------------|--------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|----------------|--------------------------|

| 4G              | Long Term Evolution Advanced (LTE-A) (Orthogonal / Single Carrier Frequency Division Multiple Access) (OFDMA / SC-FDMA)  | 20 MHz                 | 46 dBm         | -101 dBm       | 147 dB                   |

| Mobile<br>WiMAX | Worldwide Interoperability for Microwave Access (WIMAX) (Scalable Orthogonal Frequency Division Multiple Access (SOFDMA) | 10 MHz                 | 44 dBm         | -106 dBm       | 150 dB                   |

| Wi-Fi           | 802.11ac - Gigabit Wi-Fi<br>(nicknamed 5G Wi-Fi)                                                                         | 20, 40, 80,<br>160 MHz |                | -90 dBm        | 110 dB                   |

|                 | 802.11ad - Wireless<br>Gigabit (Microwave Wi-<br>Fi)                                                                     | 2 GHz                  | 20 dBm         | -81 dBm        | 101 dB                   |

|                 | 802.11af – White-Fi                                                                                                      | 5, 10, 20,<br>40 MHz   |                | -98 dBm        | 118 dB                   |

#### 1.5.1 Passive Self-Interference Suppression

Passive or "antenna level" SI suppression is defined as the attenuation of the SI signal done by the path loss effect due to the physical separation and/or isolation between the TX and RX of the same node [4].

First, by reducing the electromagnetic coupling between the TX and RX at the antenna level, the power of SI can be reduced as it arrives to the receiving antenna. Numerous methods of passive SI suppression exist [20], [21]. For example, passive suppression can also depend on beamforming techniques by directing the lobes of TX and RX antennas in different directions [20], which also reduce the SI between the two antenna. This means that the system can emit and receive simultaneously in the same frequency band but not in the same direction, i.e. a complete FD wireless link is not allowed between two nodes. In a multi antenna system, the polarization decoupling technique enables the TX and RX antennas to operate with the help of orthogonal (e.g. horizontal and vertical) polarizations to reduce their coupling [21].

#### 1.5.2 Analog Self-Interference Cancellation

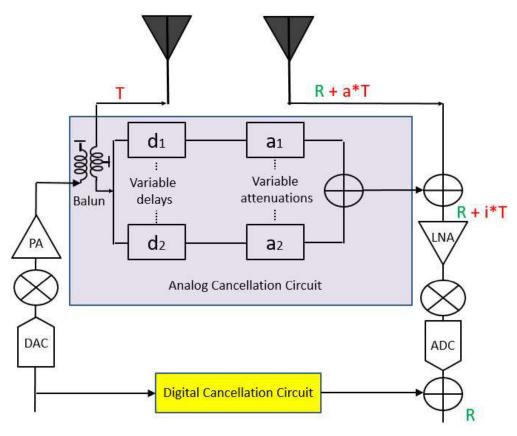

The principle of most analog cancellation techniques can be summarized as follows: in order to sufficiently reduce the SI power, a copy of the radio signal is required to create a reference signal corresponding to a perfect replica of the SI signal. Combining the created replica with the SI signals is in theory capable of perfect SI cancellation [22]. Analog cancellation can take place either at the RF or at the analog baseband stage [23] or at both stages.

At RF level, analog cancellation can be realized by executing the following two steps:

- Creation of SI-inverse signal: Basically, SI inversion can be implemented by an FD radio upon simply inverting a signal by inverting its phase. A balanced/unbalanced (Balun) transformer, which is a common component in RF, can be utilized for perfectly (in theory) converting between an input signal and its inverse at all time.

- Delay and attenuation adjustment: Since the signal is transmitted over the either, then it will surely experiences both attenuation and delay in all practical scenarios, hence an identical attenuation and delay has to be applied to the inverted SI as seen in Figure 1.6.

Nevertheless, subtracting the SI from the received signal by simply depending on the SI-inversion technique remains a challenge in practical systems, because the FD radio only knows the "clean" digital representation of the baseband signal, rather than its processed counterpart transmitted over the air. As discussed briefly in the upcoming section, digital SI cancellation is thus required to complete the Passive, analog and/or RF SIC level.

Figure 1.6 Block diagram of Analog RF self-interference cancellation

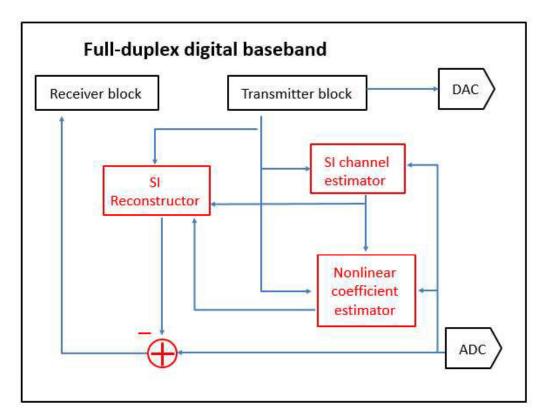

#### 1.5.3 Digital Self-Interference Cancellation

Digital cancellation by definition operates in the digital domain and exploits the knowledge of the interfering signal in order to cancel it after the received signal has been quantized by the ADC [24]. To achieve this, the transmitter send first a reference signal to the receiver, which is used to estimate the linear and non-linear distortion in phase and magnitude experienced by the SI signal (mostly in the channel and analog/RF components). It allows building a copy of the actual residual SI to digitally subtract it. Coherent SI-detection can also be employed to recover the SI by correlating the received signal with the clean regenerated SI-inversion-based reference signal, which is available at the output of the FD transmitter. This technique then requires the receiver to estimate both the delay and phase shift between the transmitted and the received signals, relying on techniques such as the correlation peak-based algorithm for subtracting the SI signal. Consequently, the linearity and nonlinearity of the system component of the leakage channel must be accurately characterized for the sake of high SI cancellation in the digital domain, Figure 1.7 shows an example of block diagrams in digital baseband self-interference cancellation.

Figure 1.7 Block diagram of digital baseband self-interference cancellation

In conclusion, these three methods (i.e. antenna level, analog and digital SIC) are necessary for a FD system in order to achieve a high SI cancellation between the TX chain and the RX chain [11].

#### 1.6 Distortion and noise issues in FD

Researchers at Stanford [22] and other groups in industry and academia [25] have proposed proof-of-concept designs to build FD system. It can be noticed that designing FD generally focuses first on SI cancellation at the antenna level mainly for two reasons. First, as the power difference between the transmitted and received signal is maximal, SI might cause a high risk of saturation of the receiver. Moreover, using directly the actual TX signal close to the antenna as a reference is preferable since it contains most information regarding any TX imperfections such as TX-generated noise and distortion that the signal has experienced. If, for example, the TX reference would be copied before the power amplifier (PA), then the PA nonlinearities would not be canceled out. Many designs have made significant progress on the SI cancellation problem [26]. However, some designs show 85dB of cancellation in simulation, which leaves about 25dB of residual SI (if 110 of SIC is expected as in Figure 1.4) and therefore reduces the SNR. To see the throughput benefits with these FD designs, the HD SNR of the link has to be extremely high (45dB or higher), i.e. the two nodes should be separated by not more than 5m to see such high SNRs. Outside this range, it would be better to turn off FD and use only the HD mode. However, these designs were intended for lowpower and narrow-band wireless links, as ZigBee where 85dB of SI cancellation is sufficient for FD. Wi-Fi is far more demanding in terms of both bandwidth as well as cancellation level.

Indeed, the reader might ask: why achieving wireless FD is still so challenging. After all, the sender knows the signal being transmitted, subtracting it should be easy to implement), but in fact, the RX antenna does not know exactly what has been actually emitted. What it does know is the "clean" digital representation of the signal in baseband. Varying near-field environment (e.g. a person holding the device) constantly changes the magnitude and phase of type A and B SI (Figure 1.3), which requires an adaptive solution. When the signal is converted to analog and up-converted to the right carrier frequency, the TX signal will looks different from its baseband form. Analog components in the TX chain alter the signal in both linear and non-linear ways, impairments and added noise (e.g., from PA) will also affect the signal. Moreover, small inaccuracy (e.g., oscillator might be tuned slightly off their oscillation frequency) will also shift the transmitted signal characteristics away from the expected SI. In fact, the transmitted signal is a combination of nonlinear function of the ideal transmitted signal along with unknown noise. Unsurprisingly, naively subtracting a "known" version of the TX signal without considering for all these analog distortions does not work.

RF front-end is not simply a black box that takes the digital signal, converts it to analog, up-converts it to the carrier frequency and sends it. In fact, this abstraction turns out to be incorrect. Radios distort the signal being transmitted. These distortions can be divided into three major categories:

- 1) Linear Components: these distortions on the modulated signal (e.g. 2 tones as in Figure 1.8.a) are due to attenuation and reflections from the environment. These are linear components because they can be written as a linear combination of delayed copies of the main two tones.

- 2) Non-Linear Components: these distortions are created from inside the circuit, because the circuit takes in an input signal x and create an output signal that contains non-linear cubic and higher order terms such as x<sup>3</sup>, x<sup>5</sup>. These higher order signals have significant frequency content close to the transmitted frequencies that correspond to all the harmonics that correspond to signal distortions, as seen in Figure 1.8.b.

- 3) Transmitter Noise: a radio will always have noise, for a typical WiFi radio the noise power level is of about -90dB (1 picowatt) [15]). This extra noise is generated from high power components in the transmitter chain such as Power Amplifier. The authors in [26] referred to as broadband noise. Figure 1.8 shows what the radio is expected to transmit (a), and what is actually transmitted (b).

Figure 1.8 what the radio is expected to transmit (a), what is actually transmitted (b)

### 1.7 Proposed topologies for SI cancellation

Many designs have been proposed recently to implement FD wireless systems. All focus on achieving a high SI cancellation: some designs are based on SI canceling transceiver front-end structure [27]. Other designs are based on dual-polarized micro-strip patch antenna structures, complemented with an active analog cancellation network [28]. Other designs are based on an electrical balance duplexer circuit, which connects with a single port antenna [29]. The most significant ones are detailed below:

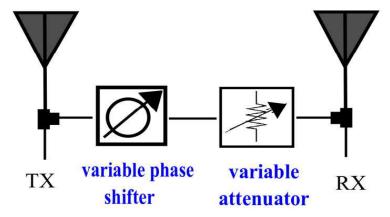

1) Antenna separation: This design is based on a variable phase shifter and a variable attenuator that are added between the two antennas (Figure 1.9). This path intends to provide a 180° phase difference and an identical signal level of the SI transmitted signal coupled at the receiver, in order to cancel it up at the receiver antenna [30]. In [30], a cancellation of about 33dB is achieved over a 100MHz bandwidth. The two antennas are separated from each other by a distance much greater than λ/2 in order to reduce the coupling level (direct SI) between TX and RX. On the other hand, this distance is not preferable for compact devices especially at lower operating frequency where the wavelength will be large.

Figure 1.9 Antenna separation

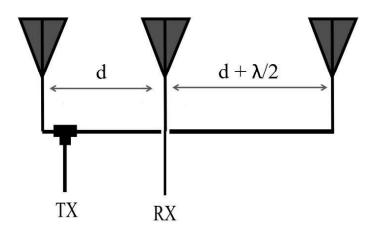

2) Antenna placement: Two TX and one RX antennas are structured in a way to force the TX signals to cancel each other at the receiver position (Figure 1.10). The first antenna is set at a distance d from the receiver and the second antenna is at distance d + λ/2 from the receiver (λ is the wavelength of the operational frequency). As a result, there will be a 180° phase difference between them, which results in a destructive interference at the RX level. In theory, a null is created at the position of the RX if the leakage power magnitude level from the pair of TXs are identical which is impossible to obtain in practical implementation. Thus, this method can only reduce the SI from about 30dB and with the help of digital cancelation it can reach 60dB at least but remains intrinsically narrowband [30].

Figure 1.10 Antenna placement

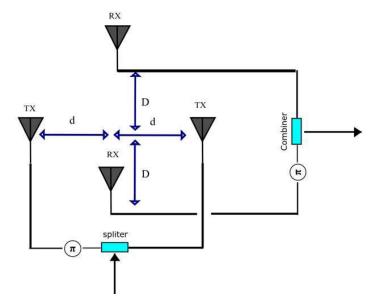

3) MIDU topology: In MIDU (Enabling MIMO Full-Duplex) project, a symmetric placement of antenna is used to cancel SI in a FD system [31]. Antenna cancellation technique is duplicated at both transmit and receive stages. The two identical transmit antennas are separated by a distance d and transmit at the same time but with opposite phase; thus, for the receiver antenna, the potential null point will be located on the perpendicular bisector of the line connecting the two transmitter antennas Figure 1.11. The same principle is applied at the receiver stage and can potentially eliminate the need of other forms of analog cancellation, thereby avoiding the need for delays and variable attenuator. In [31], the overall isolation is about 45dB over a bandwidth of 625 KHz. It should be pointed out that the radiation patterns of TX antennas shows a null on RX antenna axis and identically for RX antenna pattern on TX axis. This technique is potentially more wideband than the second one.

Figure 1.11 MIDU topology

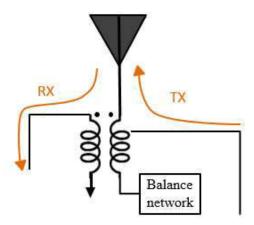

4) **Electric Balance topology:** This technique uses only one antenna to transmit and receive simultaneously at the same time, which is an advantage for compact devices. The RF circuit is made up of a transformer and a balance network which is a tunable load impedance (Figure 1.12), virtually isolating the receiver from the transmitter [29]. In [29], this technique offers around 47dB of isolation over a narrow bandwidth about 229MHz.

Figure 1.12 Electric Balance topology

Table 1.3 summarizes the four topologies advantages and disadvantages. These topologies are mainly suitable to actively boost the isolation between TX and RX branches. Indeed, in practice they can provide isolation by 30dB - 47dB before reflections (NLOS: Non-Line-Of-Sight paths) become the dominant SI. A complementary digital SI canceller with flexible and adaptive algorithm is then more suited to get rid of these NLOS reflections.

Table 1.3 Summary of the four topologies

| Techniques            | Isolation | Advantages                                                                                                                                                        | Disadvantages                                                                                                                                                                                 |  |

|-----------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Antenna<br>separation | 33dB      | <ul> <li>TX and RX are widely separated which increase the path loss between them offering a good isolation</li> <li>Suitable for narrowband scenarios</li> </ul> | Requires manual tuning and therefore do not adapt to the environmental changes                                                                                                                |  |

| Antenna<br>placement  | 30dB      | Easy to implement                                                                                                                                                 | <ul> <li>Requires 3 antennas; extra cost</li> <li>Suffers from amplitude mismatch</li> <li>Very narrowband</li> </ul>                                                                         |  |

| MIDU                  | 45dB      | <ul> <li>Suitable for narrowband scenarios</li> <li>Offer higher cancellation level between TX and RX</li> <li>Provides extra RF chain</li> </ul>                 | <ul> <li>Requires at least 4 antennas; extra cost</li> <li>Suffers from amplitude mismatch</li> <li>Requires manual tuning and therefore do not adapt to the environmental changes</li> </ul> |  |

| Electric<br>Balance   | 47dB      | <ul> <li>Uses one antenna</li> <li>Suitable for small compact<br/>devices</li> <li>Not constrained by<br/>separation distance</li> </ul>                          | Requires manual tuning     Suffers from non-linear distortions which limits isolation bandwidth                                                                                               |  |

## 1.8 Antenna specifications for a compact FD system

The future communication generation (5G) and the strong demand for multi-function or multi-standard devices call for the use of wide-band/multi-band antennas. In Internet of Things (IoT), M2M (Machine to Machine) and medical sensors, antennas need to be implemented in small devices to ensure the interaction between the sensors and their environment and to allow a widespread use.

Thus, antennas are required to be small, compact and low-cost. Although the need for wide-band small antennas is spreading, the design and the matching of Small Antennas (SA) or Electrically Small antennas (ESA) is not an easy task especially in wide and low frequency band applications. Indeed, SAs famously suffer from high quality factor Q value since there is a high reactive energy stored in their near field and a small real power is propagated in their far field [32]. In other words, SA and ESA are intensely reactive, which results in a poor efficiency-bandwidth trade-off when using passive impedance matching [33]. This limit can be overcome by adding active elements, such as non-Foster Circuits (NFC) to the antenna's matching circuit, which are characterized by their negative reactance [33].

We suggest exploring in this PhD the study and design of NF circuits, which will serve as key components to achieve a high SI cancellation between two SAs in order to realize a compact full-duplex system. The Non-Foster circuits will be implemented at different levels of the front-end and a dedicated front-end topology is put forward in the following section.

### 1.9 Motivation, Objectives and Proposed topology

FD is an emerging subject that has attracted many researchers' interest through the past few years as it can play important role in the coming future 5G communications and IoT devices. However, there exist many challenges for deploying FD, the main one is the high SI cancellation between the TX chain and the RX chain. It was found out that for communication systems, we need around 110dB of SI cancellation, and this cancellation can only be achieved by two levels of SIC at least, i.e., analog and digital cancellation. Analog cancellation focuses on the Radio front-end and can proceed at antenna stage and/or in RF/analog-base band circuits, while digital cancellation is basically an algorithm that deals with all the distortions and noise that the signal faces along the RX chain and in NLOS channels.

Many topologies have been recently studied to achieve FD system, where they can offer around 30dB - 47dB of SI cancellation at the analog/RF stage. The amount of SI cancellation needed depends mainly on the system scenario and application; and since our focus is on small devices (e.g. IoT), the need of compact devices is of prime interest. Then, our goal is to design a compact FD front-end based on two small antennas (TX and RX) working at a low frequency range and if possible over a wide frequency range. In that context, the two antennas have to be small and need to be really close to each other, i.e. much more closer than in previous FD front-end studies. It means that none of the aforementioned approaches is suitable for these tough specifications.

Indeed, the close proximity of the antennas requires a specific decoupling topology where non-Foster circuits may bring some advanced solutions by cancelling or compensating the reactive components that model the antenna coupling. The Non-Foster circuits, through is a dedicated matching network, seem also to be a promising way to shift antenna operating band to low frequency which corresponds to compactness improvement.

Moreover, a 2<sup>nd</sup> stage or complementary SI cancellation circuit is intended to achieve a higher SI cancellation level and we put forward the design of a 180° phase shifter based on non-Foster in that aim.

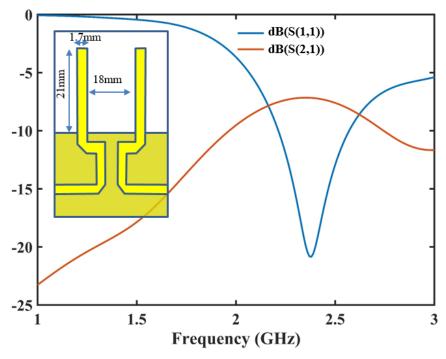

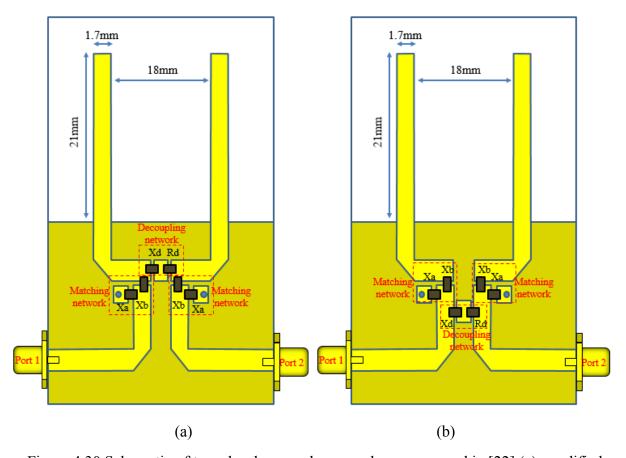

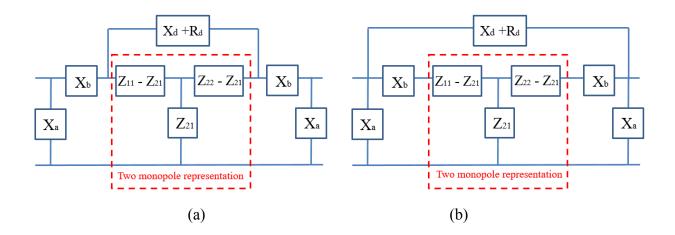

In this thesis, we propose to design and implement a compact FD front-end system following the topology depicted in Figure 1.13. A Non-Foster circuit will be studied first. Then, a phase shifter tunable around 180° over a wide frequency range will implemented by using this NF circuit. A frequency band from 1GHz to 4GHz will be targeted. This tunable phase shifter is dedicated to the second level of SI cancellation (i.e. analog SIC in figure 1.13). This Non-Foster topology will also be used to match and decouple two antennas placed close to each other in order to get the first level of SIC. The antennas will have initial resonance frequencies around 2.3-2.4GHz. The matching and decoupling circuits are intended to allow the antennas to operate at a lower and wider frequency range than their initial operating bandwidth (i.e. at around 1.6GHz), which corresponds to a miniaturization of antennas, namely electrically small antenna (ESA), suitable for compact devices such as IoTs.

We are hoping for our topology to provide at least 45dB of SI interference cancellation, which is at the state-of-the-art level and potentially sufficient for short-range wireless FD system.

Figure 1.13 topology to reduce SI in a compact FD front-end

### 1.10 Organization of the Thesis

In this chapter, a brief introduction of FD, covering up the SI issues between TX chain and RX chain have been proposed. SI cancellation are usually organized following three levels and existing Antenna/RF/analog SI cancellation techniques (i.e. the first two analog SIC levels) have been detailed, compared and discussed prior introducing a new topology based on non-Foster circuits.

The fundamental characteristics of Non-foster circuits will be addressed in Chapter 2, where a literature review on non-Foster, the used topologies, and the main stability issues are all covered.

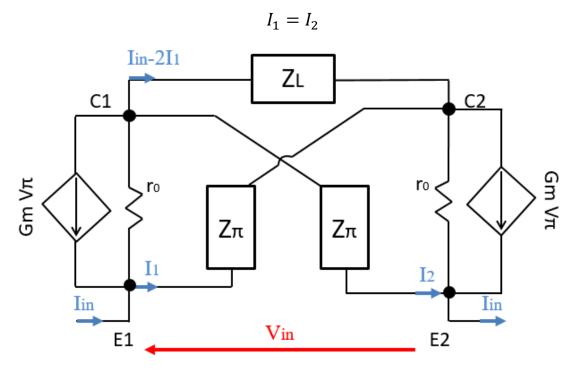

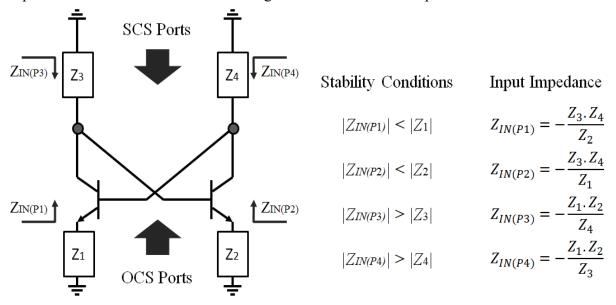

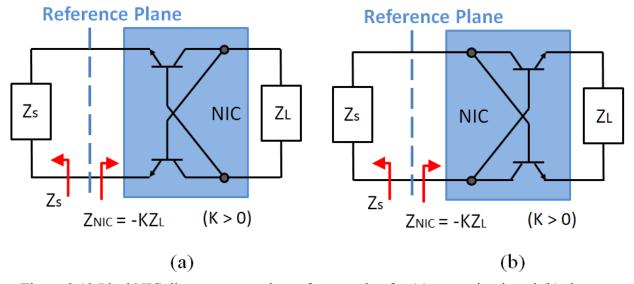

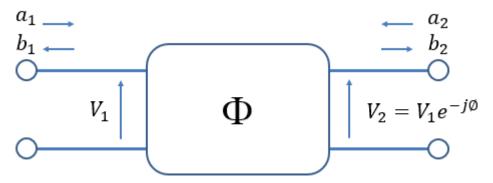

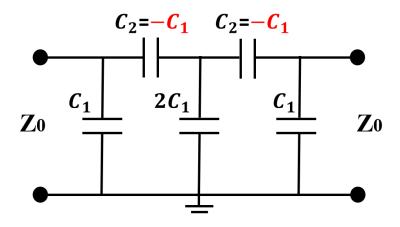

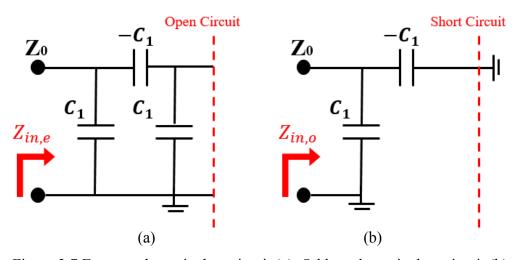

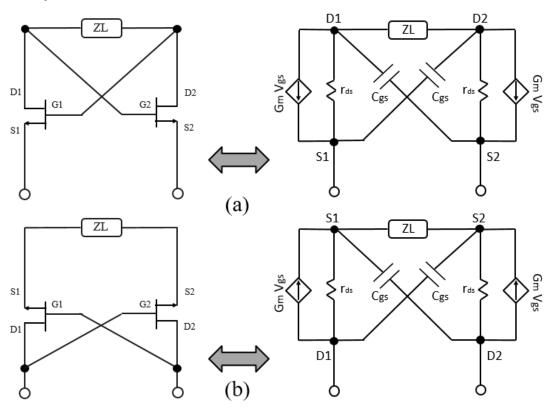

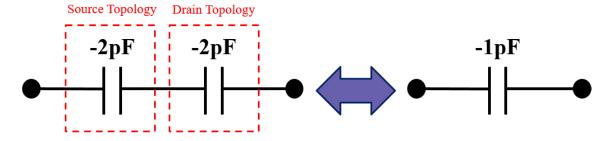

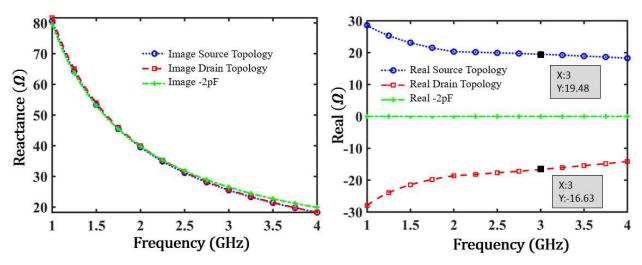

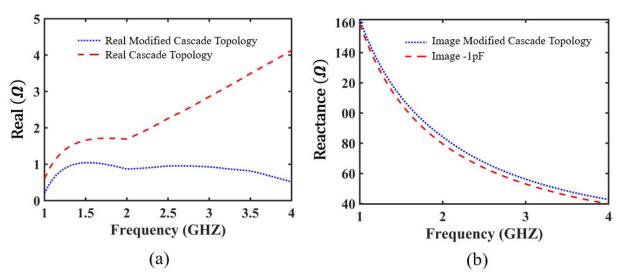

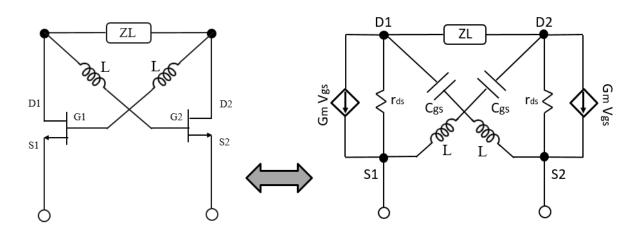

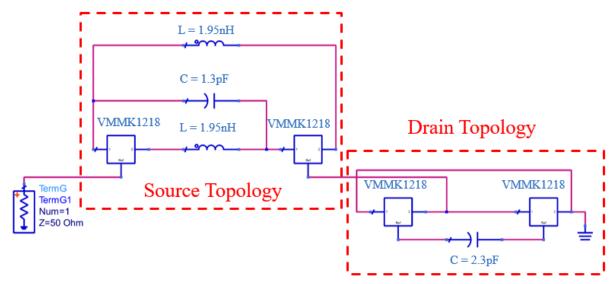

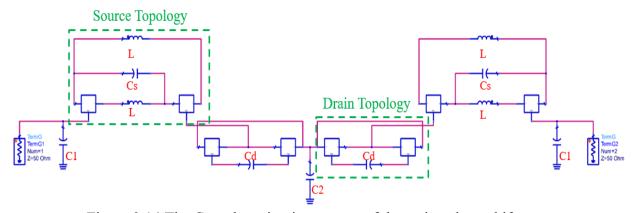

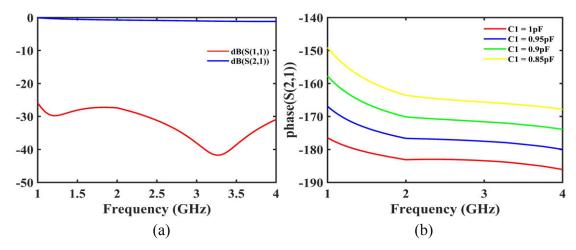

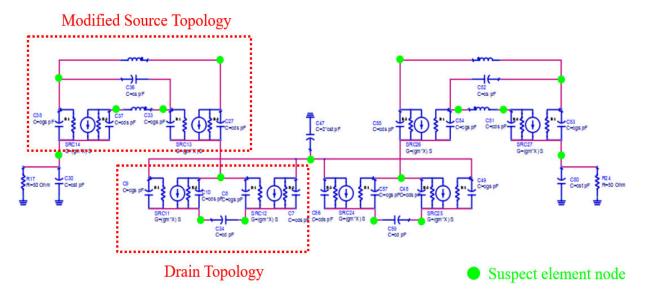

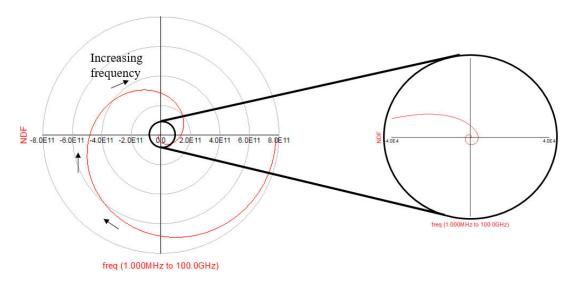

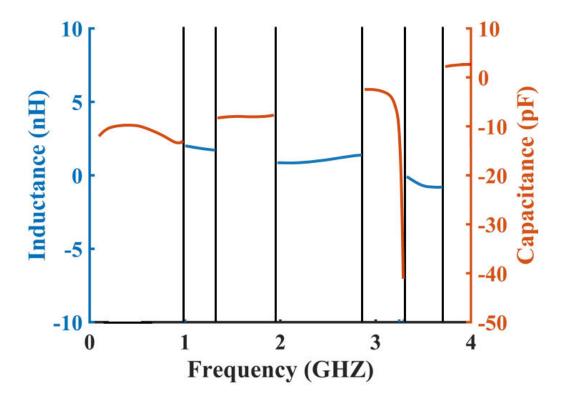

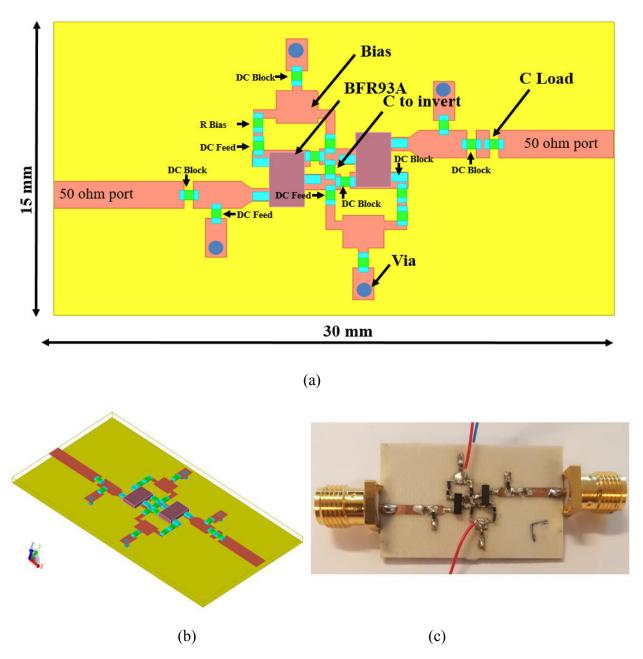

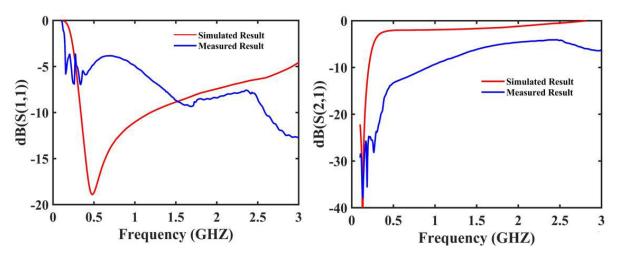

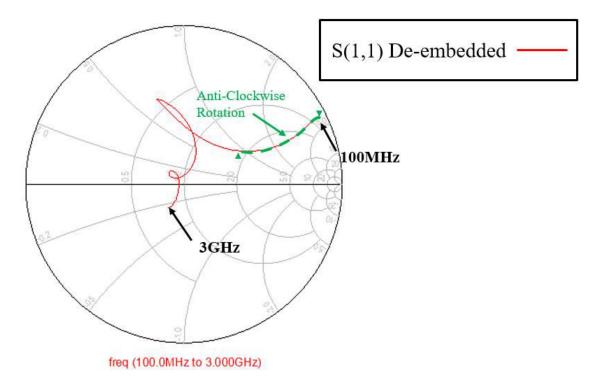

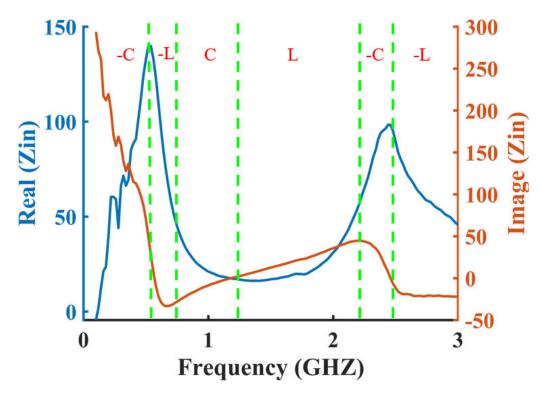

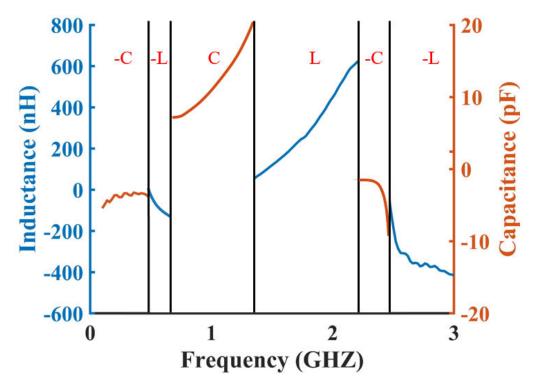

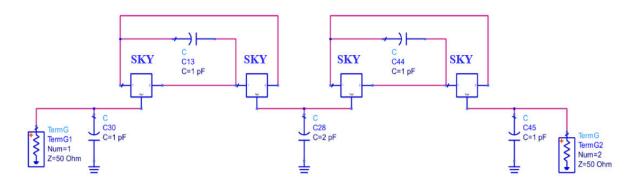

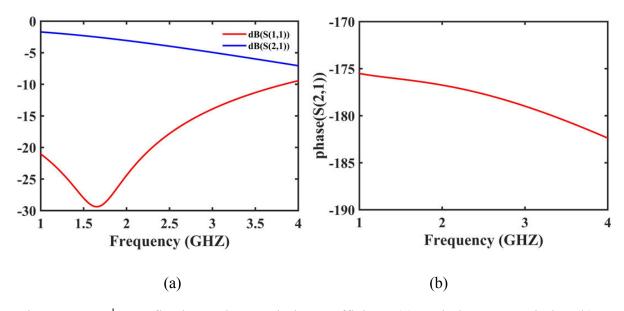

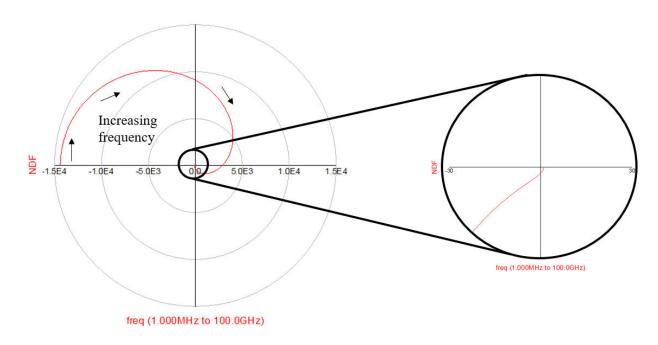

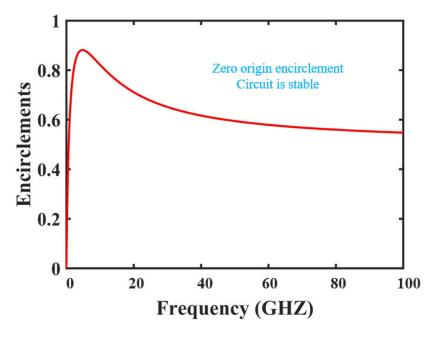

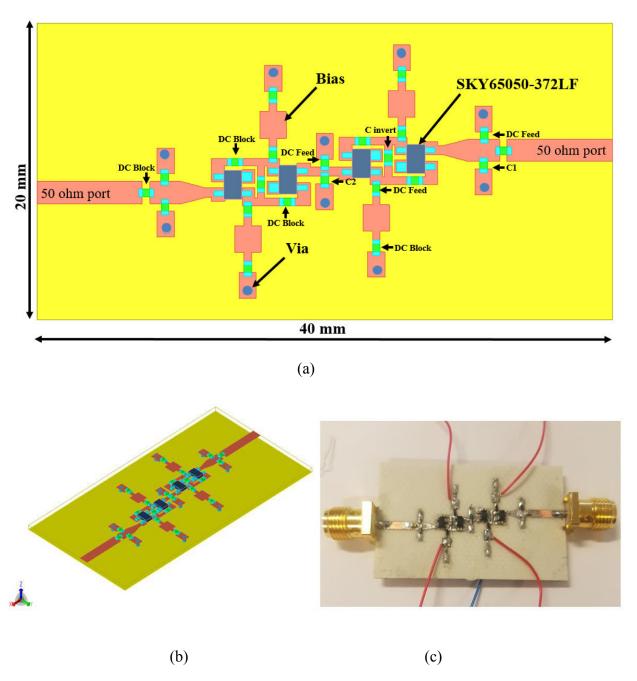

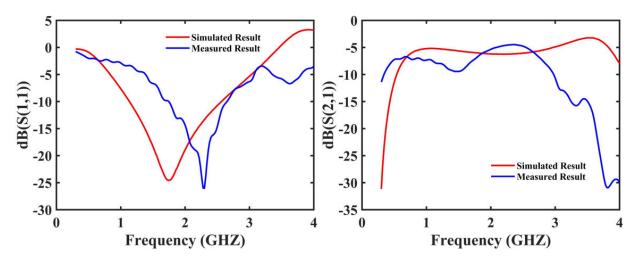

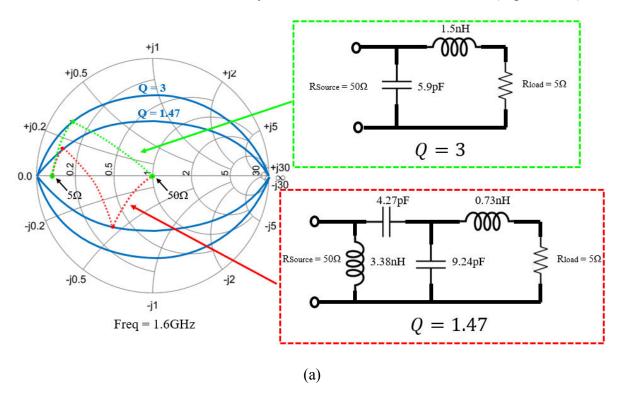

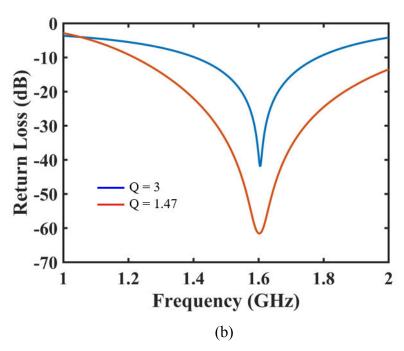

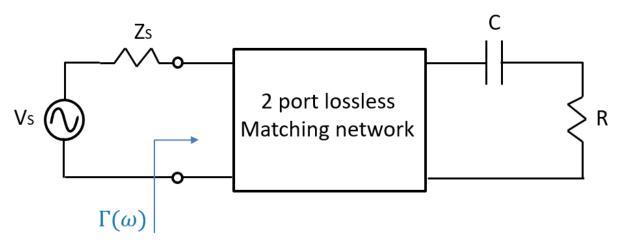

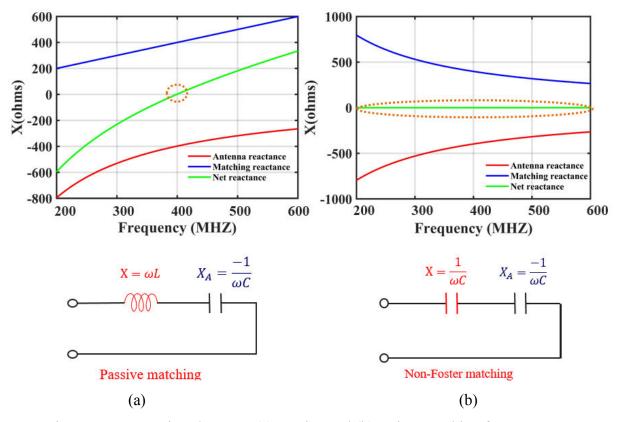

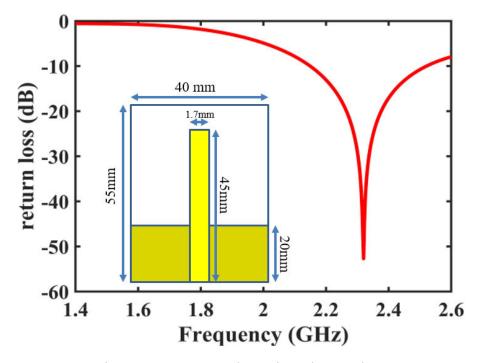

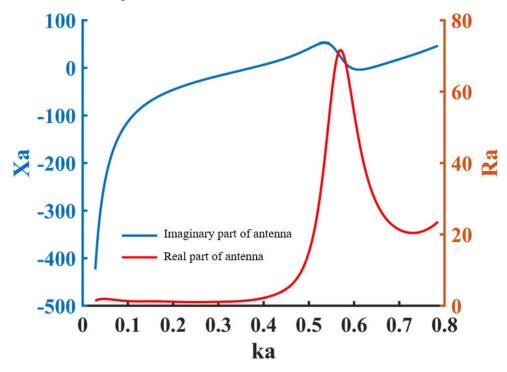

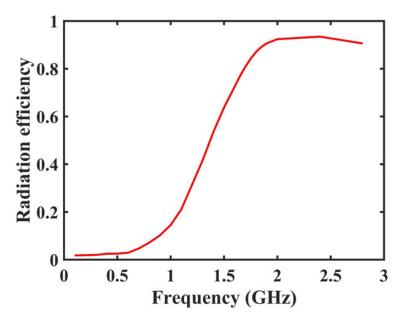

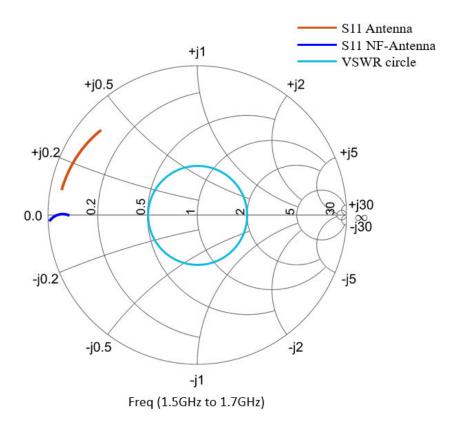

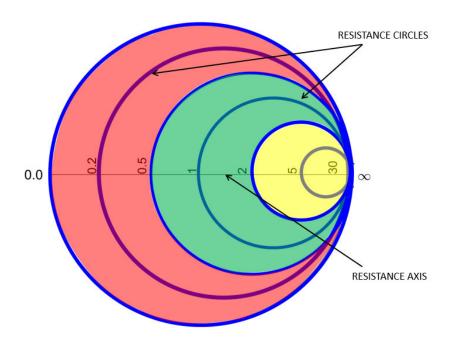

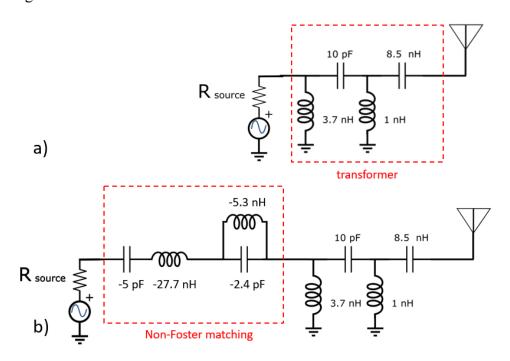

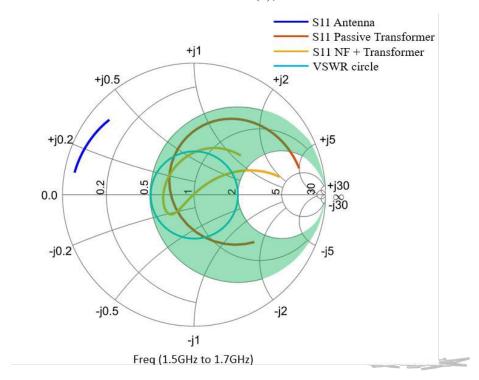

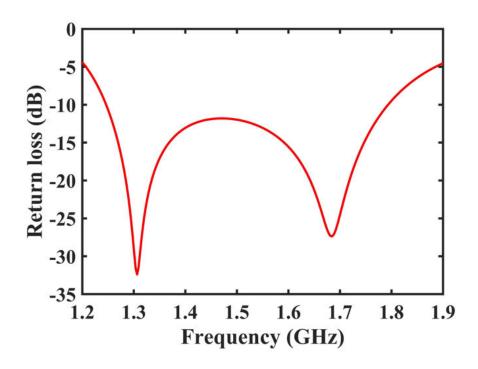

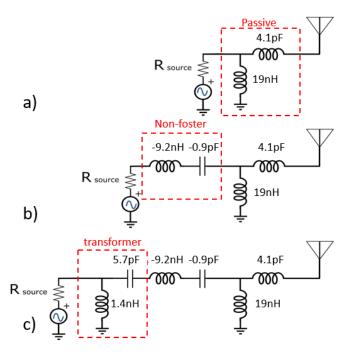

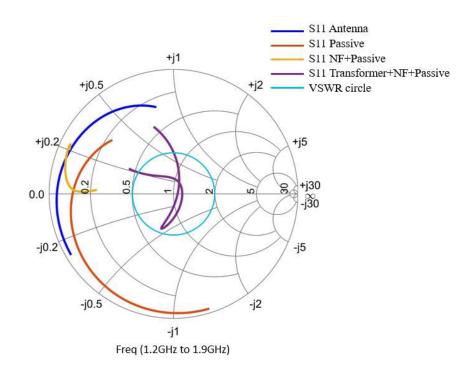

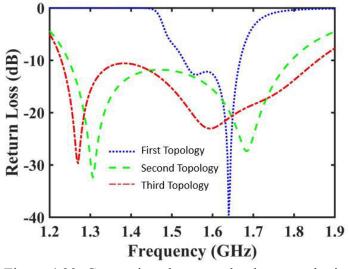

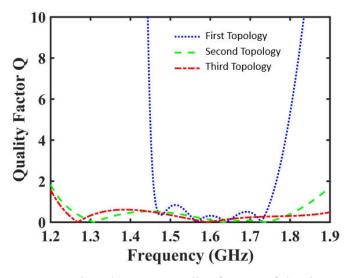

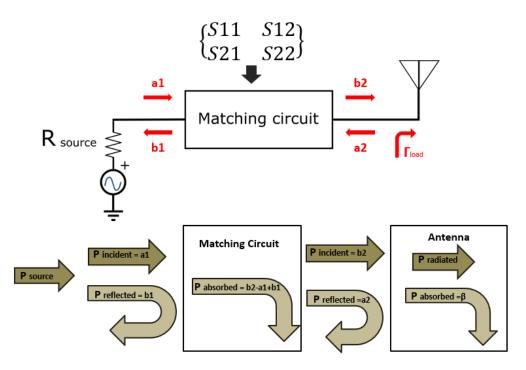

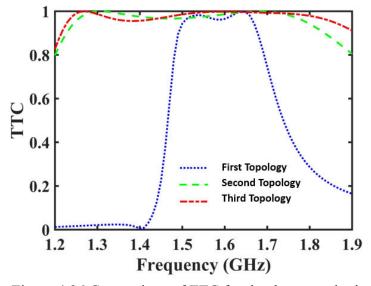

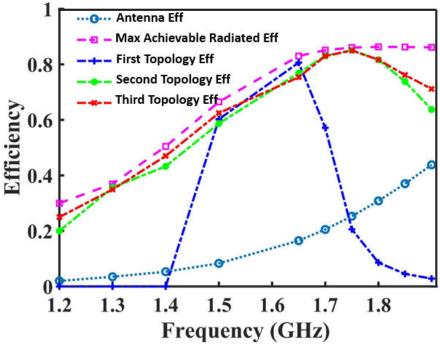

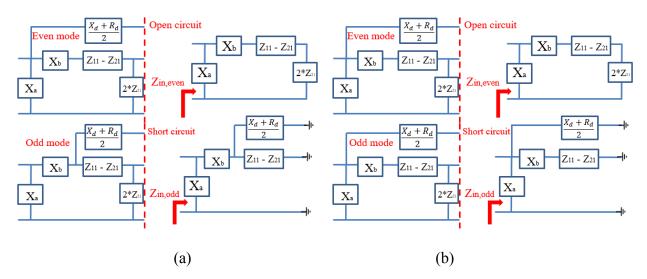

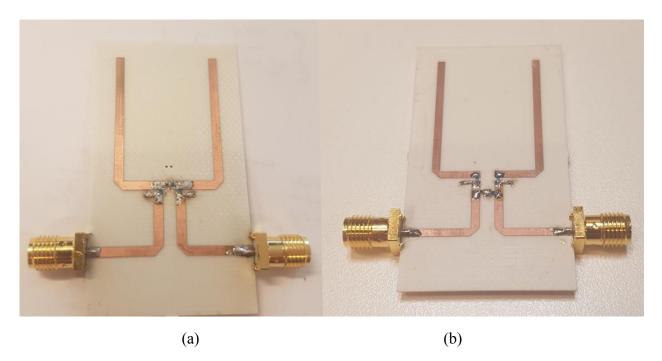

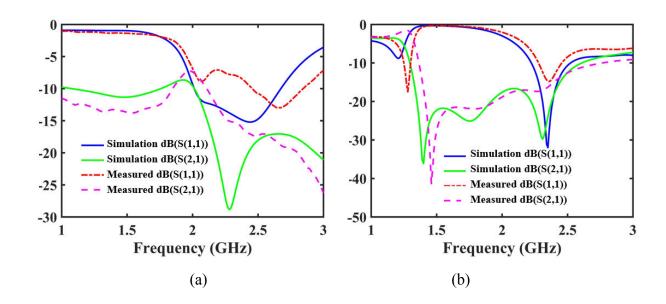

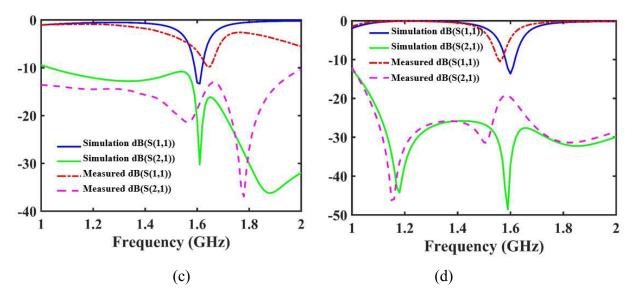

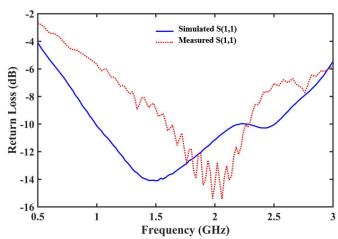

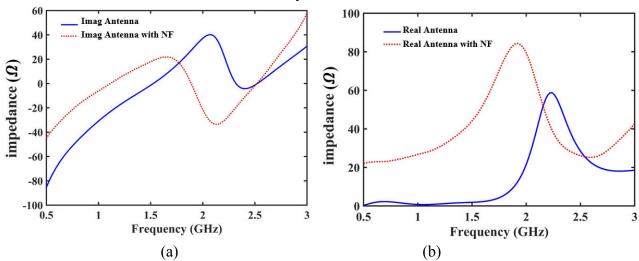

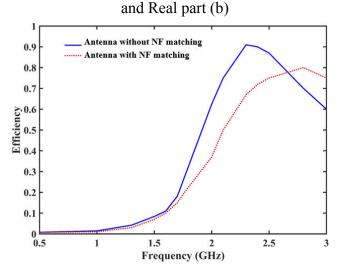

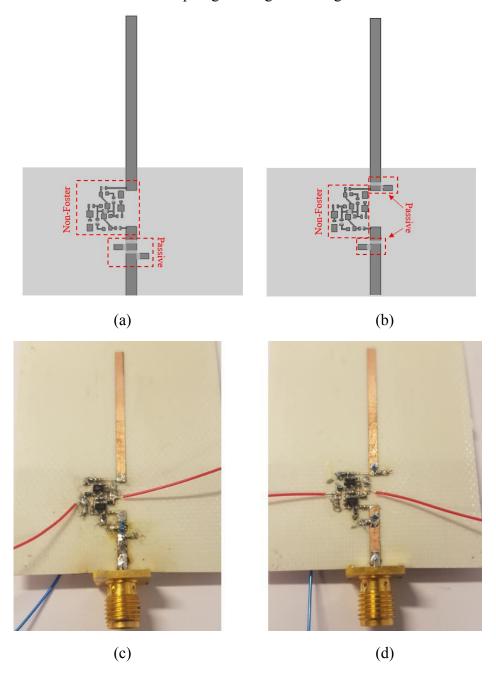

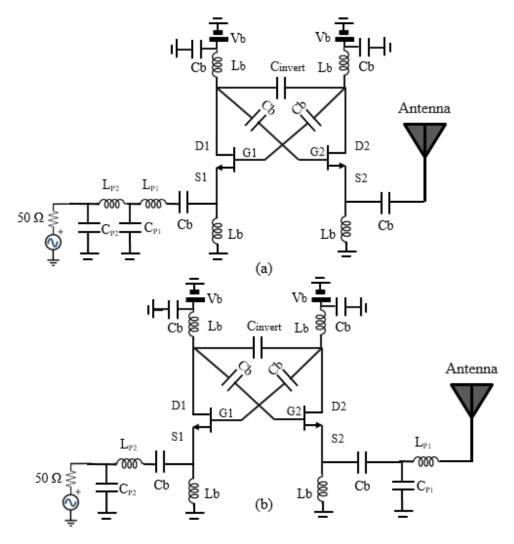

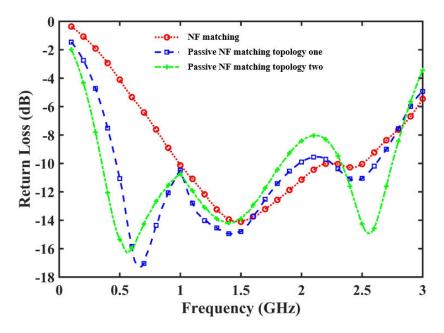

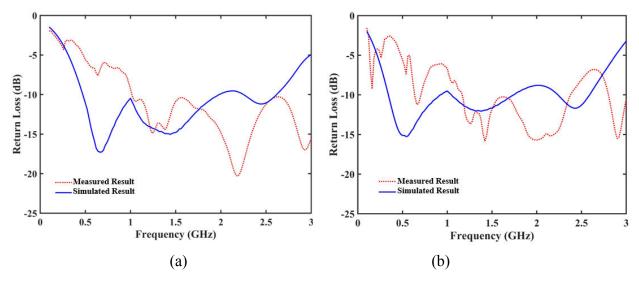

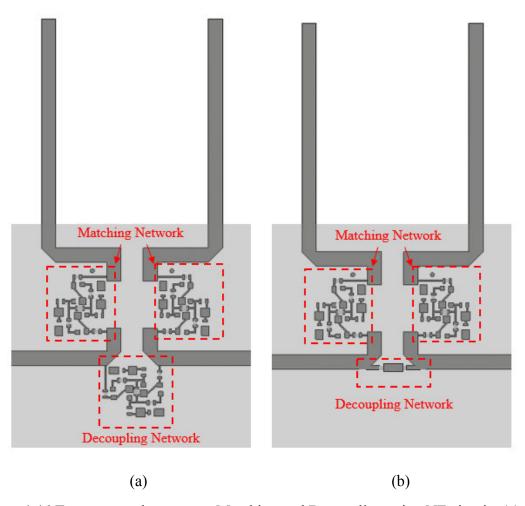

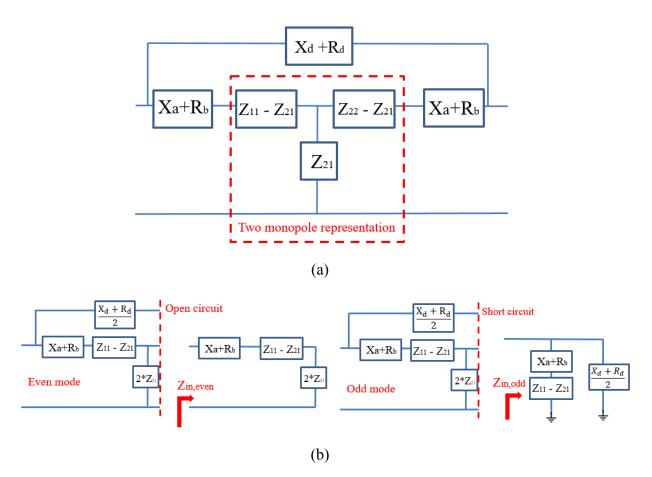

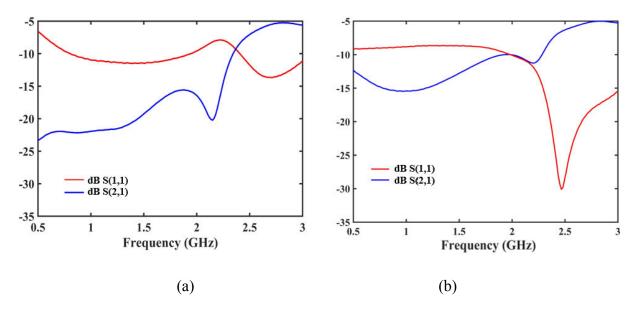

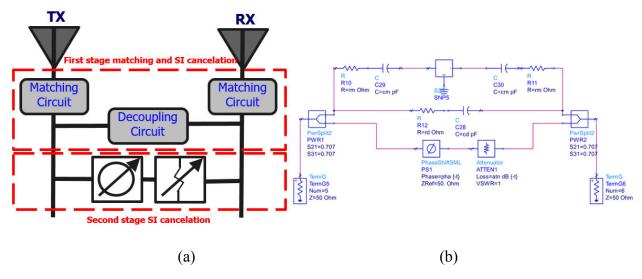

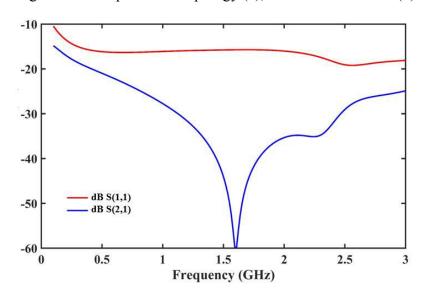

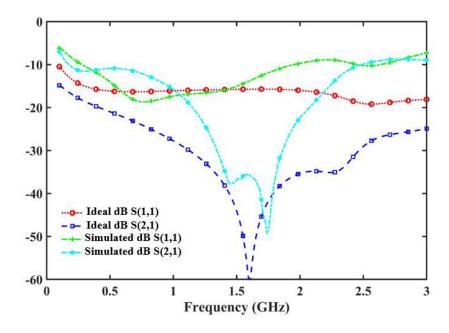

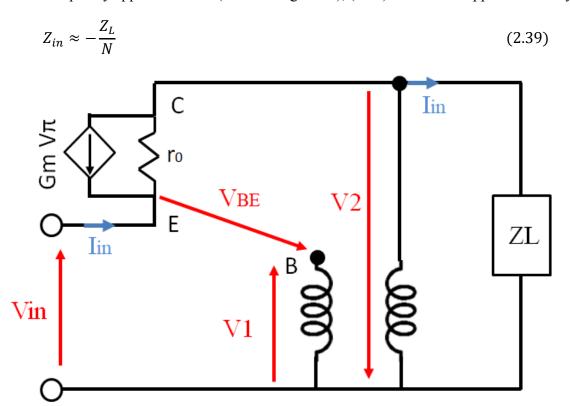

Chapter 3 will deal with the design of a variable phase shifter that is going to be used inside the second stage of FD topology in order to provide a complementary SI cancellation level. NF circuit stability will be thoroughly studied. In addition, we will discussed the difficulties in working with NF circuit due to the parasitic components and will bring and try some ideas to get rid of the main undesired parts.