## Exploring analog-to-information CMOS image sensor design taking advantage on recent advances of compressive sensing for low-power image classification Wissam Benjilali

### ▶ To cite this version:

Wissam Benjilali. Exploring analog-to-information CMOS image sensor design taking advantage on recent advances of compressive sensing for low-power image classification. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2019. English. NNT: 2019GREAT067. tel-02529080

## HAL Id: tel-02529080 https://theses.hal.science/tel-02529080

Submitted on 2 Apr 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## THÈSE

Pour obtenir le grade de

**DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES** Spécialité : NANO ELECTRONIQUE ET NANO TECHNOLOGIES

Arrêté ministériel : 25 mai 2016

Présentée par

### Wissam BENJILALI

Thèse dirigée par **Gilles Sicard**, Ingénieur de recherche, HDR, CEA-LETI, encadré par **William Guicquero**, Ingénieur de recherche, CEA-LETI et co-encadré par **Laurent Jacques**, Professeur, UCLouvain.

préparée au sein du CEA-LETI dans l'école doctorale Electronique, Electrotechnique, Automatique, Traitement du Signal (EEATS)

Etude d'architectures d'imageurs exploitant l'acquisition compressive pour la classification d'images à basse consommation énergétique

Exploring analog-to-information CMOS image sensor design taking advantage of recent advances in compressive sensing for lowpower image classification

Thèse soutenue publiquement le **16 décembre 2019**, devant le jury composé de :

Madame Valérie Perrier Professeur des universités, Grenoble INP, Grenoble, France, Président Monsieur Ricardo Carmona Galan Chercheur, Instituto de Microelectrónica de Sevilla, IMSE-CNM, Séville, Espagne, Rapporteur Monsieur François Berry Professeur des universités, Université Clermont Auvergne, Clermont-Ferrand, France, Rapporteur Monsieur Gianluca Setti Professeur, Politecnico di Torino, Turin, Italie, Examinateur Monsieur Laurent Jacques Professeur, UCLouvain, Louvain-la-Neuve, Belgique, Co-encadrant Monsieur William Guicquero Ingénieur de recherche, CEA-LETI, Grenoble, France, Encadrant Monsieur Gilles Sicard Ingénieur de recherche, HDR, CEA-LETI, Grenoble, France, Directeur

The more I read, the more I acquire, the more certain I am that I know nothing. — Voltaire

To my parents ...

# Acknowledgements

I would like to express my gratitude and thanks to my thesis advisor, William Guicquero, for being the great mentor, guide and collaborator. This thesis would never have seen the light of day without his commitment and availability. I thank him for introducing me to the smart image sensor world, for giving me enough insights and original views to explore multi-disciplinary research axes and for showing me how to methodically achieve, analyze and communicate results. I am also grateful to Laurent Jacques who kindly accepted to be my co-advisor. I thank him for the many remote but fruitful discussions we had during the last two years as well as for his mathematical rigor and theoretical background from whose I have tremendously benefited. My thanks, of course, go also to Gilles Sicard, my thesis director, for being always open and of great support.

I would like to thank Ricardo Carmona Galan and François Berry, my thesis reviewers, for reading the thesis and for their detailed and relevant comments on the manuscript in a relatively short time. I also thank Gianluca Setti, my thesis examiner, and Valérie Perrier, the president of the jury, for the interest they have shown to my work.

I would like to thank all my friends and colleagues from the smart imaging and display lab for adopting me so fast and making me feel at home. Special thanks to Camille, Nicolas, and Yoann, my office mates, for the many interesting discussions, and Yoann for the intuitive explanations of the IC design world. I also want to thank the coffee break team with Amaury, Margot, Simon and Yohan, that I had the pleasure, with the office mates, to host in the "Ph.D. students office". My thanks extend to Arnaud V. and P. for the sparse technical discussions, Laurent A. for his kindness and humor, Laurent M. for the feedbacks on my figures and for blessing them, Bertrand for sharing the stories of his amazing trips, Jean-Alain, the only football supporter of the lab, for the post champions league matchs discussions, and Jean-Pierre and Thomax for their kindness. I am thankful to Fabrice, for accepting me in his team first as an intern and second as a Ph.D. student. It has been a pleasure for me to work in the DACLE department with its great atmosphere and rich technical environment.

I can never forget my good friends in Paris, Lyon and Grenoble for making my stay in France so much more pleasant. They were like a second family to me and were always been there for me.

With all my heart, I thank my parents and my brothers for their constant and endless support.

Grenoble, December 2019

## Abstract

Recent advances in the field of CMOS Image Sensors (CIS) tend to revisit the canonical image acquisition and processing pipeline to enable on-chip advanced image processing applications such as decision making. Despite the tremendous achievements made possible thanks to technology node scaling and 3D integration, designing a CIS architecture with onchip decision making capabilities still a challenging task due to the amount of data to sense and process, as well as the hardware cost to implement state-of-the-art decision making algorithms. In this context, Compressive Sensing (CS) has emerged as an alternative signal acquisition approach to sense the data in a compressed representation. When based on compact devices to on-the-fly generate sensing patterns, CS enables drastic hardware saving through the reduction of Analog to Digital conversions and data off-chip throughput while providing a meaningful information for either signal recovery or signal processing. Traditionally, CS has been exploited in CIS applications for compression tasks coupled with a remote signal recovery algorithm involving high algorithmic complexity. To alleviate this complexity, signal processing on CS provides solid theoretical guarantees to perform signal processing directly on CS measurements without significant performance loss opening as a consequence new ways towards the design of low-power smart sensor nodes.

Built on algorithm and hardware research axes, this thesis illustrates how Compressive Sensing can be exploited to design low-power sensor nodes with efficient on-chip decision making algorithms. After an overview of the fields of Compressive Sensing and Machine Learning with a particular focus on hardware implementations, this thesis presents four main contributions to study efficient sensing schemes and decision making approaches for the design of compact CMOS Image Sensor architectures. First, an analytical study explores the interest of solving basic inference tasks on CS measurements for highly constrained hardware. It aims at finding the most beneficial setting to perform decision making on Compressive Sensing based measurements. Next, a novel sensing scheme for CIS applications is presented. Designed to meet both theoretical and hardware requirements, the proposed sensing model is shown to be suitable for CIS applications addressing both image rendering and on-chip decision making tasks. On the other hand, to deal with on-chip computational complexity involved by standard decision making algorithms, new methods to construct a hierarchical inference tree are explored to reduce MAC (Multiply-ACcumulate) operations related to an on-chip multi-class inference task. This leads to a joint acquisition-processing optimization when combining hierarchical inference with Compressive Sensing. Finally, all the aforementioned contributions are brought together to propose a compact CMOS Image Sensor architecture

enabling on-chip object recognition facilitated by the proposed CS sensing scheme, reducing as a consequence on-chip memory needs. The proposed architecture takes advantage of a pseudo-random data mixing circuit of reduced silicon footprint, an in- $\Sigma\Delta \pm 1$  modulator and a small Digital Signal Processor (DSP) to achieve on-chip inference. In addition to the data dimensionality reduction made possible thanks to CS, several hardware optimizations are presented to fit requirements of future ultra-low power (~  $\mu$ W) CIS design. Typically, through the reduction of CS measurements resolutions as well as digital operations resolutions at the DSP level.

Key words: CMOS Image Sensor, compressive sensing, random permutations, random modulations, Sigma-Delta, machine learning, hierarchical inference, support vector machines, neural networks.

# Résumé

Les avancés récents dans le domaine des capteurs d'image CMOS repose sur la remise en question du schéma classique d'acquisition et de traitement d'images, cela, afin de permettre des traitements avancés sur puce tels que la prise de décision. Malgré les réalisations rendues possibles grâce à l'utilisation des nœuds technologiques avancés et à l'intégration 3D, la conception de capteurs avec des capacités de prise de décision reste une tâche ardue en raison de la quantité de données acquise et à traiter, ainsi que du coût matériel que représente l'implémentation des algorithmes de prise de décisions classiques. Dans ce contexte, l'Acquisition Compressive (AC) semble une approche alternative pour inspecter des données en profitant de la réduction de dimensionnalité. Dans le cas où l'AC exploite des motifs générés à l'aide de structures matérielles compactes ayant un comportement pseudo-aléatoire, il permet une réduction considérable en réduisant les conversions analogique-numérique ainsi que du débit des données collectées, tout en conservant les informations pertinentes intrinsèques afin de permettre à la fois la reconstruction du signal ou bien son traitement dans sa nouvelle forme de représentation. Traditionnellement, l'AC a été exploité dans des applications de capteurs d'image pour des tâches de compression couplées à des algorithmes de reconstruction distants impliquant une complexité algorithmique élevée. Pour relâcher cette complexité, il apparaît dans la littérature des garanties théoriques solides pour effectuer le traitement du signal directement dans le domaine compressé sans perte significative de performance, ce qui constitue donc une nouvelle piste pour concevoir des nœuds de capteurs intelligents à basse consommation énergétique.

Basée sur des axes de recherche traitant de l'algorithmique et de l'implémentation matérielle, cette thèse étudie des voies de développement exploitant l'acquisition compressive pour concevoir des nœuds de capteurs dotés de capacités de prise de décision sur puce à basse consommation énergétique. Après une présentation du contexte matériel et algorithmique lié à l'acquisition compressive et les techniques d'apprentissage machine, la thèse présente quatre contributions principales pour optimiser les schémas d'acquisition du signal et des traitements associés dans le contexte des capteurs d'image CMOS. Dans un premier temps, une étude analytique explore l'intérêt de résoudre des tâches d'inférence à partir des mesures compressées pour des applications à forte contraintes matériels. L'objectif est d'identifier une approche pertinente en terme de complexité matérielle et algorithmique permettant d'implémenter des traitements de prise de décisions à partir de mesures compressées. Ensuite, un nouveau schéma d'acquisition compressive dédié aux applications imageurs CMOS est présenté. Conçu pour répondre à la fois aux exigences théoriques et matérielles, le modèle s'avère être approprié pour les capteurs qui traitent à la fois des tâches de rendu d'image et de prise de décision sur puce. D'autre part, pour réduire la complexité de calcul sur puce impliquée par les algorithmes de prise de décision standard, de nouvelles méthodes de construction d'arbres d'inférence hiérarchique sont explorées afin de réduire les opérations MAC (Multiply-ACcumulate) liées à une tâche d'inférence pour de la classification en classes multiples sur puce. Cela conduit à une optimisation conjointe traitement-acquisition lors de la combinaison de l'inférence hiérarchique avec l'acquisition compressive. Enfin, une architecture compacte d'un capteur d'image embarquant les contributions algorithmiques susmentionnées est présentée permettant la reconnaissance d'objets sur puce à faible empreinte matérielle. L'architecture proposée exploite principalement un mélangeur analogique permettant la permutation pseudo-aléatoire des pixels des lignes sélectionnées dans un mode de lecture en rolling shutter; un convertisseur analogique-numérique Sigma-Delta ( $\Sigma\Delta$ ) incrémental de premier ordre pour implémenter la modulation pseudo-aléatoire, la sommation des pixels mélangés ainsi que la conversion analogique-numérique; et un petit processeur de signal numérique (DSP) pour implémenter la fonction affine de prise de décision. En plus de la réduction de dimension rendu possible grâce à l'AC, différentes optimisations matérielles sont présentées pour répondre aux exigences de la conception des futures capteurs CMOS dits ultra-basse consommation (~  $\mu$ W), à savoir, la réduction de la résolution des mesures compressées extraites ainsi que la résolution des opérations logiques au niveau du DSP.

Mots clefs : Capteur d'image CMOS, acquisition compressive, permutations aléatoires, modulations aléatoires, Sigma-Delta, apprentissage machine, inférence hiérarchique, machines à vecteurs de support, réseaux de neuronnes.

## **Notations**

- x, X denotes a scalar

- $\boldsymbol{x}$  denotes a vector

- X denotes a matrix or a linear operator

- $x_i$  denotes the  $i^{th}$  component of a vector x

- $X_i$  denotes the *i*<sup>th</sup> column of a matrix X

- $X_{ij}$  denotes the entry on the  $i^{th}$  row and  $j^{th}$  column

- $\boldsymbol{x}^{\top}, \boldsymbol{X}^{\top}$  denotes the transpose of a vector  $\boldsymbol{x}$  or a matrix  $\boldsymbol{X}$

- $X^{-1}$  denotes the inverse of a matrix X

- $X^{\dagger}$  denotes the Moore-Penrose pseudoinverse of a matrix X defined as  $X^{\dagger} := (X^{\top}X)^{-1}X^{\top}$

- $\mathbb{N}$  denotes the set of all natural numbers

- $\mathbb{R}$  denotes the set of all real numbers

- [*n*] denotes the set of indices such that  $[n] := \{1, ..., n\}$

- $I_n$  denotes the  $n \times n$  identity matrix

- $\mathbf{1}_n$  denotes a *n*-dimensional vector with all entries equal to one

- $\mathbf{0}_n$  denotes a *n*-dimensional vector with all entries equal to zero

supp(x) denotes the support of a vector  $x \in \mathbb{R}^n$ , such that, supp(x) := { $i \in [n], x_i \neq 0$ }

- sign(x) denotes the sign function that extracts the sign of a scalar x

- |x| denotes the absolute value of a scalar x

- $\|\boldsymbol{x}\|_p$  denotes the  $\ell_p$  norm of a vector  $\boldsymbol{x}$  defined as  $\|\boldsymbol{x}\|_p := (\sum_i |x|^p)^{\frac{1}{p}}$  for  $p \ge 1$

- $\|\boldsymbol{x}\|_0$  denotes the  $\ell_0$  norm of a vector  $\boldsymbol{x}$  defined as the support of  $\boldsymbol{x}$ , *i.e.*,  $\|\boldsymbol{x}\|_0 := \operatorname{supp}(\boldsymbol{x})$

- $\|X\|_F$  denotes the Frobenius norm of a matrix X defined as  $\|X\|_F := \sqrt{\sum_i \sum_j |X_{ij}|^2}$

- $\langle x, y \rangle$  denotes the standard inner product in the Euclidean space between two vectors  $x, y \in \mathbb{R}^n$  defined as  $y^\top x := \sum_{i=1}^n x_i y_i$

- x \* y denotes the convolution between two vectors  $x, y \in \mathbb{R}^n$

- $\boldsymbol{x} \circ \boldsymbol{y}$  denotes the Hadamard product between two vectors  $x, y \in \mathbb{R}^n$

- $X \otimes Y$  denotes the Kronecker product between two matrices

- ${\mathscr C} \ \ {\rm denotes} \ {\rm a} \ {\rm set}$

- $\operatorname{card}(\mathscr{C})$  denotes the cardinality of a set  $\mathscr{C}$ , indicating the number of the elements of the set

- $g(x) = \mathcal{O}(f(x))$  denotes that  $|\frac{f(x)}{g(x)}|$  is bounded as  $x \to \infty$

- $\mathcal{N}(\mu, \sigma^2)$  denotes the Gaussian distribution with mean  $\mu$  and variance  $\sigma^2$

- $\mathscr{U}(a, b)$  denotes the Uniform distribution on the interval [a, b]

# Contents

| Ac | knov             | wledge  | ments                                                    | i    |

|----|------------------|---------|----------------------------------------------------------|------|

| Ał | ostra            | ct (Eng | lish/Français)                                           | iii  |

| No | otatio           | ons     |                                                          | vii  |

| Li | st of            | figures |                                                          | xiii |

| Li | st of            | tables  |                                                          | xvii |

| 1  | Intr             | oducti  | on                                                       | 1    |

| 2  | State Of The Art |         |                                                          |      |

|    | 2.1              | Comp    | pressive Sensing background                              | 8    |

|    |                  | 2.1.1   | An Invitation to Compressive Sensing                     | 8    |

|    |                  | 2.1.2   | Basic Algorithmic Tools                                  | 11   |

|    |                  | 2.1.3   | CS Sensing Matrix Properties                             | 12   |

|    |                  | 2.1.4   | CS Sensing Market                                        | 14   |

|    |                  | 2.1.5   | Signal Processing in CS Domain                           | 16   |

|    |                  | 2.1.6   | CS Hardware Implementations                              | 17   |

|    | 2.2              | Mach    | ine Learning background                                  | 22   |

|    |                  | 2.2.1   | Machine Learning Algorithms Market                       | 22   |

|    |                  | 2.2.2   | Edge AI                                                  | 28   |

|    | 2.3              | Concl   | lusion and discussion                                    | 30   |

| 3  | Infe             | erence  | Tasks On Compressive Measurements                        | 33   |

|    | 3.1              | ML-D    | R Learning Mathematical Background                       | 34   |

|    |                  | 3.1.1   | LDA (Linear Discriminant Analysis)                       | 35   |

|    |                  | 3.1.2   | SVM (Support Vector Machine)                             | 35   |

|    |                  | 3.1.3   | DLSI (Dictionary Learning with Structured Incoherence)   | 36   |

|    | 3.2              | Classi  | fication Combining ML-DR and CS-DR                       | 37   |

|    |                  | 3.2.1   | Approach A: Inference Learned in The CS Domain           | 38   |

|    |                  | 3.2.2   | Approach B: Projection Based Inference                   | 39   |

|    |                  | 3.2.3   | Approach C: Inference in The Reconstructed Signal Domain | 41   |

|    | 3.3              | Embe    | edded Resources Requirements Study                       | 43   |

|   |     | 3.3.1 Approach A: Inference Learned in CS Domain               | 43  |

|---|-----|----------------------------------------------------------------|-----|

|   |     | 3.3.2 Approach B: Projection Based Inference                   | 45  |

|   |     | 3.3.3 Approach C: Inference in The Reconstructed Signal Domain | 45  |

|   |     | 3.3.4 Complexity Analysis                                      | 47  |

|   | 3.4 | Experimental Results                                           | 47  |

|   | 3.5 | Conclusion                                                     | 49  |

| 4 | Ran | dom Permutations and Modulations for Compressive Imaging       | 53  |

|   | 4.1 | Proposed Sensing Scheme                                        | 54  |

|   | 4.2 | CS Properties Verification                                     | 58  |

|   |     | 4.2.1 On The Non-Universality of The Proposed CS Model         | 58  |

|   |     | 4.2.2 Analytical Study                                         | 60  |

|   |     | 4.2.3 Coherence Analysis                                       | 61  |

|   |     | 4.2.4 Compressive Embedding Analysis                           | 64  |

|   | 4.3 | Signal Recovery Using the Proposed Sensing Scheme              | 67  |

|   |     | 4.3.1 Reconstruction of Sparse Signals                         | 67  |

|   |     | 4.3.2 Reconstruction of Compressible Signals                   | 68  |

|   | 4.4 | Inference Using the Proposed Sensing Scheme                    | 72  |

|   | 4.5 | Dedicated Hardware Implementations and Conclusion              | 73  |

| 5 | Hie | archical Decision Making                                       | 75  |

|   | 5.1 | Hierarchical Classification on CS: Key Concepts                | 76  |

|   | 5.2 | Proposed Hierarchical Learning Methods                         | 77  |

|   |     | 5.2.1 Notations                                                | 77  |

|   |     | 5.2.2 Binary SVM                                               | 77  |

|   |     | 5.2.3 Training the Hierarchical Classifier                     | 78  |

|   |     | 5.2.4 Testing the Hierarchical-Based Inference                 | 81  |

|   |     | 5.2.5 Embedded Resources Requirements Analysis                 | 82  |

|   | 5.3 | Simulation Results                                             | 83  |

|   | 5.4 | Conclusion                                                     | 85  |

| 6 | Har | dware implementations                                          | 87  |

|   | 6.1 | Proposed image sensor architecture                             | 88  |

|   |     | 6.1.1 Dedicated PRG for the PRP                                | 89  |

|   |     | 6.1.2 Pseudo Random-Permutations (PRP)                         | 94  |

|   |     | 6.1.3 RMS $\Delta$                                             | 102 |

|   |     | 6.1.4 On-Chip Inference (DSP)                                  | 107 |

|   | 6.2 | Inference with tunable algorithmic complexity                  | 111 |

|   |     | 6.2.1 Notations                                                | 112 |

|   |     | 6.2.2 One-vsall SVM                                            | 112 |

|   |     | 6.2.3 Hierarchical SVM                                         | 113 |

|   |     | 6.2.4 Neural Network                                           | 114 |

|   |     | 6.2.5 Complexity analysis                                      | 114 |

|              | 6.3                   | Simul  | ations and performance optimization | 115 |  |

|--------------|-----------------------|--------|-------------------------------------|-----|--|

|              |                       | 6.3.1  | Background                          | 115 |  |

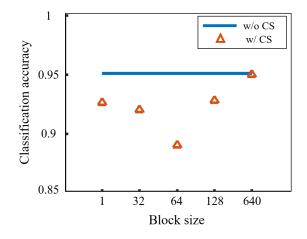

|              |                       | 6.3.2  | PRP optimization                    | 116 |  |

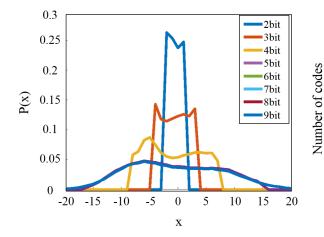

|              |                       | 6.3.3  | RMS $\Delta$ optimization           | 116 |  |

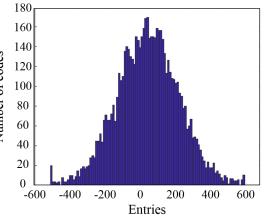

|              |                       | 6.3.4  | DSP optimization                    | 119 |  |

|              |                       | 6.3.5  | Simulation results                  | 121 |  |

|              | 6.4                   | Concl  | usion                               | 122 |  |

| 7            | Con                   | clusio | ns                                  | 125 |  |

| Pu           | Publications & Patent |        |                                     |     |  |

| Bibliography |                       |        |                                     |     |  |

# List of Figures

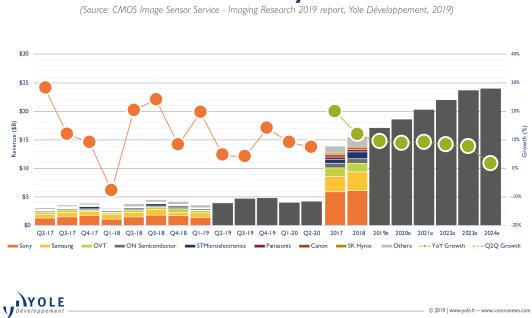

| 1.1 | CIS market dynamics by Yole Développement.                                                                                                                                                                                                             | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

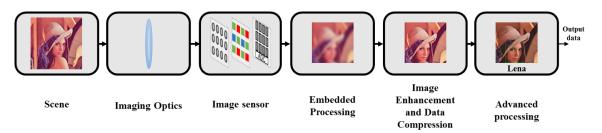

| 1.2 | Imaging system pipeline.                                                                                                                                                                                                                               | 3  |

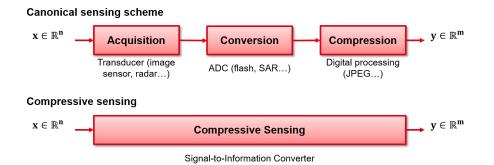

| 2.1 | The canonical compression scheme (top) Compressive Sensing scheme (bottom).                                                                                                                                                                            | 8  |

| 2.2 | An illustration of the rare eclipse problem.                                                                                                                                                                                                           | 16 |

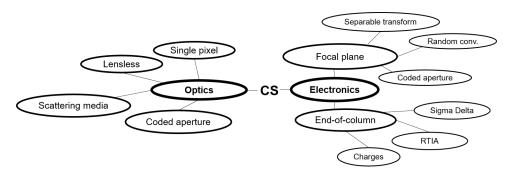

| 2.3 | A mind-map of the main compressive imaging techniques.                                                                                                                                                                                                 | 21 |

| 2.4 | An illustration of the projection in the LDA domain for $C = 3. \ldots \ldots \ldots$                                                                                                                                                                  | 24 |

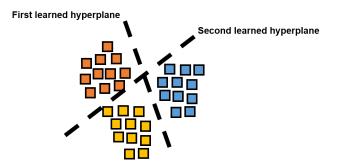

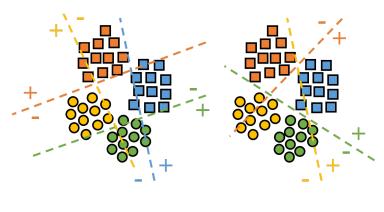

| 2.5 | An illustration of the SVM classifier for $c = 4$ : (a) One-vsall strategy; (b) One-vs                                                                                                                                                                 |    |

|     | one strategy for the blue class.                                                                                                                                                                                                                       | 25 |

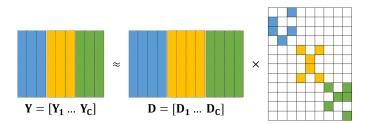

| 2.6 | Structure of the coefficient matrix in a sparse representation.                                                                                                                                                                                        | 26 |

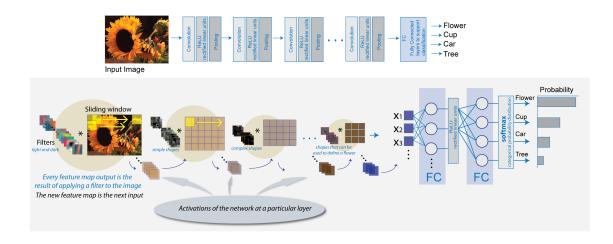

| 2.7 | An illustration of a CNN network from [1].                                                                                                                                                                                                             | 28 |

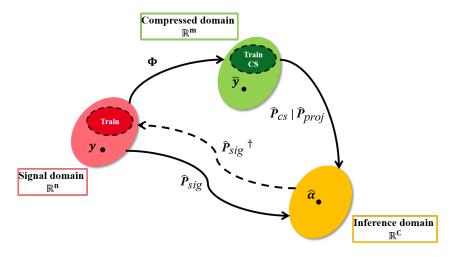

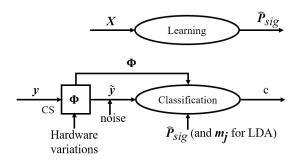

| 3.1 | An illustration of the projections involved by the studied inference approaches.<br>$y$ and $\hat{y}$ are an observed unknown sample and its projection in the CS domain                                                                               |    |

|     | using $\Phi$ respectively; and <i>c</i> is the predicted class of <i>y</i>                                                                                                                                                                             | 37 |

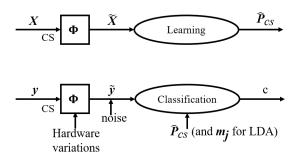

| 3.2 | Schematic description of "inference learned in CS domain" (Approach A). $\ldots$                                                                                                                                                                       | 38 |

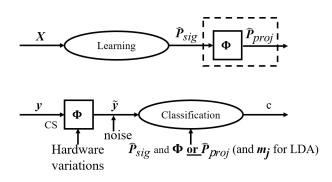

| 3.3 | Schematic description of "projection based inference" (Approach B)                                                                                                                                                                                     | 40 |

| 3.4 | Schematic description of "inference in the reconstructed signal domain" (Ap-                                                                                                                                                                           |    |

|     | proach C)                                                                                                                                                                                                                                              | 42 |

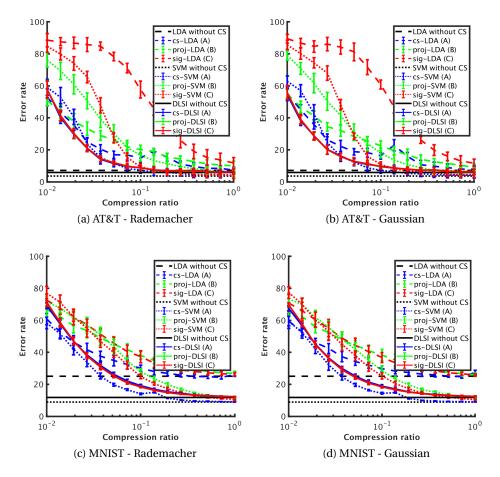

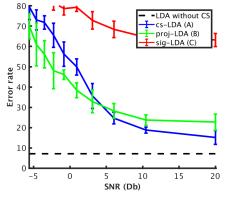

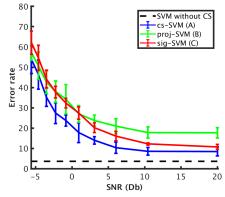

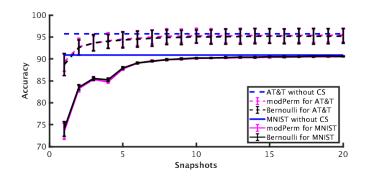

| 3.5 | Inference accuracy for the AT&T and MNIST databases using a Rademacher and Gaussian distributions. We set $n_1 = n_2 = 5$ for AT&T and $n_1 = 5000$ , $n_2 = 1000$ for MNIST. (c) Robustness to additive noise. (d) Robustness to hardware variations. |    |

|     | Blue, green and red lines refer approaches A, B and C respectivelly.                                                                                                                                                                                   | 49 |

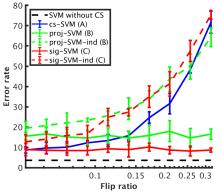

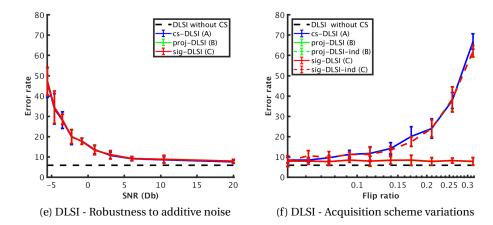

| 3.6 | Robustness to additive noise and hardware alterations for the LDA, SVM and                                                                                                                                                                             |    |

|     | DLSI. Blue, green and red lines refer approaches A, B and C respectivelly                                                                                                                                                                              | 52 |

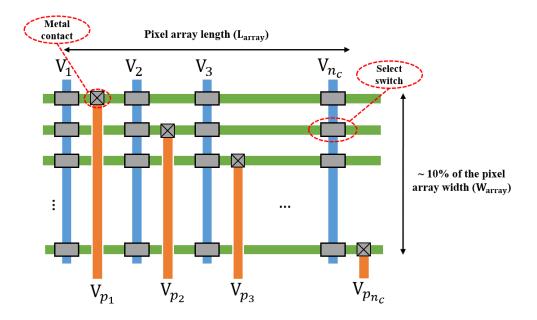

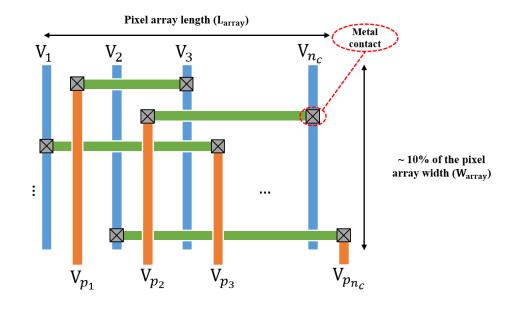

| 4.1 | Schematic 2D representation of the proposed CS sensing scheme for one snap-<br>shot. In particular, all the pixels sharing the same color are readout through to                                                                                       |    |

|     | the same colorized end-of-column circuitry. Each pixel of the matrix <b>U</b> is also                                                                                                                                                                  |    |

|     | being modulated by the factor $\pm 1$                                                                                                                                                                                                                  | 54 |

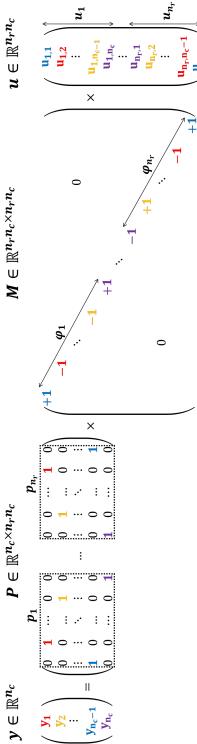

| 4.2 | Matrix representation of the proposed CS sensing scheme for a single snapshot.                                                                                                                                                                         | 57 |

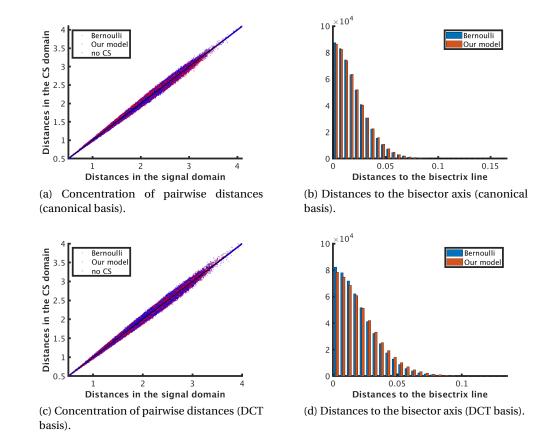

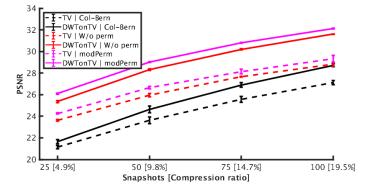

| 4.3        | An analytical proof of the compressive embedding of the proposed sensing scheme in (4.3). (a) shows concentration of pairwise distances of our model and a Bernoulli distribution in the canonical basis around the pairwise distances in the signal domain (bisector axis) for $n = 1024$ , $k = 10$ and $m = 128$ ( $s = 4$ ); (b) report the histogram of distances to the bisector axis of our model and a Bernoulli distribution; (c) and (d) report the extracted plots in the DCT basis. | 60 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

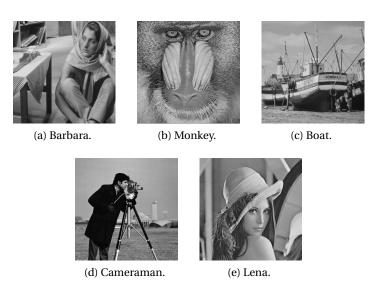

| 4.4<br>4.5 | Testbench for sparse image recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68 |

|            | to a success reconstruction above 40 <i>dB</i> for per-column Bernoulli (Col-Bern), our model without permutations (W/o perm) and our model sensing schemes                                                                                                                                                                                                                                                                                                                                     |    |

| 4.6        | (modPerm) respectivelly                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69 |

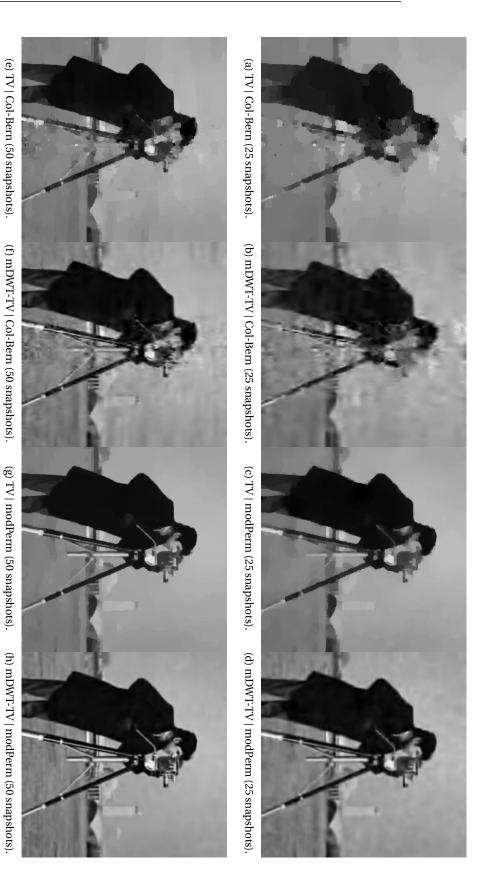

|            | acquisition scheme: (top) 25 snapshots, <i>i.e.</i> , 20.48 compression ratio (bottom)                                                                                                                                                                                                                                                                                                                                                                                                          | 70 |

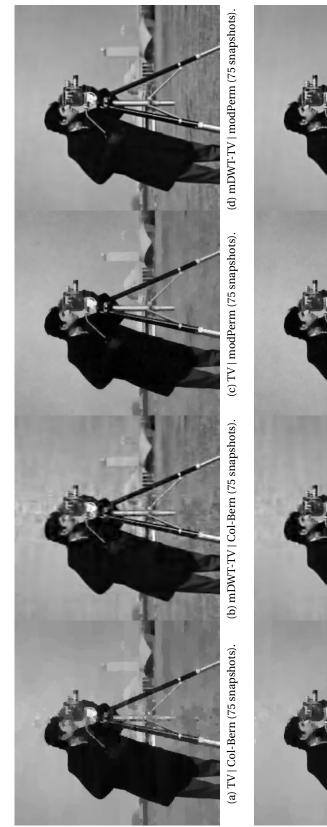

| 4.7        | 50 snapshots, <i>i.e.</i> , 10.24 compression ratio                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70 |

|            | 100 snapshots, <i>i.e.</i> , 5.12 compression ratio                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71 |

| 4.8        | Quality of reconstruction of our sensing model compared to a per-column                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|            | Bernoulli acquisition scheme over 10 batches.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72 |

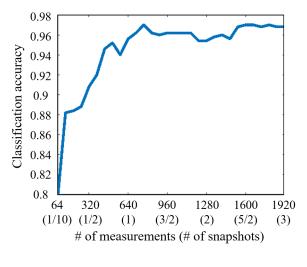

| 4.9        | Classification accuracy for the AT&T and MNIST databases.                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73 |

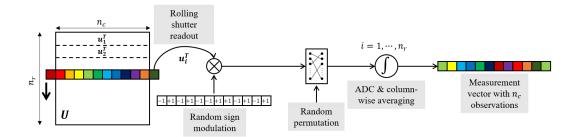

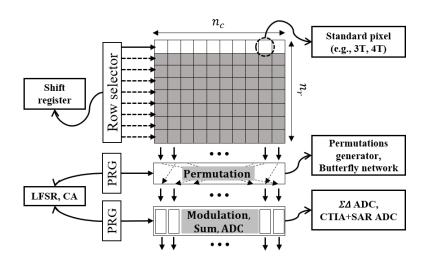

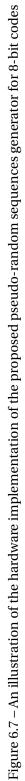

| 4.10       | Top-level architecture of a pseudo-random modulations & permutations com-pressive image sensor.                                                                                                                                                                                                                                                                                                                                                                                                 | 74 |

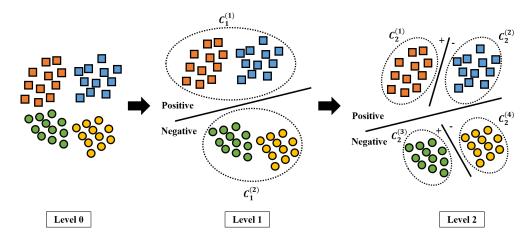

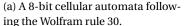

| 5.1        | An illustration of the hierarchical learning. The input multi-class dataset to be classified is presented at Level 0. A first balanced clustering (2 clusters, each associated to the same number of classes) is performed at Level 1, then a binary classifier is trained. This process is repeated for each cluster until the construction of a single-class cluster at each terminal node. Here, $C_i^{(j)}$ represents                                                                      |    |

| - 0        | $j^{th}$ cluster at level $i$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 79 |

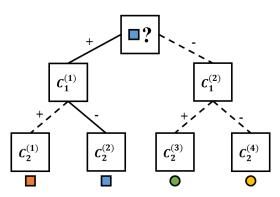

| 5.2        | The inference process in the case of a binary hierarchical tree for an unknown sample (represented by the blue square in this figure).                                                                                                                                                                                                                                                                                                                                                          | 82 |

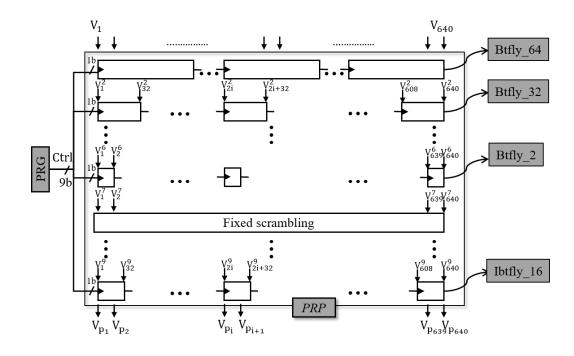

| 6.1        | Image sensor top-level architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 89 |

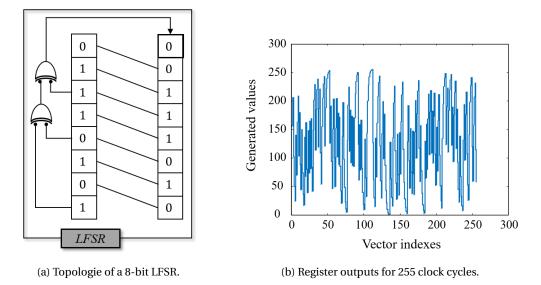

| 6.2        | A 8-bit LFSR: (a) Architecture; (b) Generated outputs                                                                                                                                                                                                                                                                                                                                                                                                                                           | 90 |

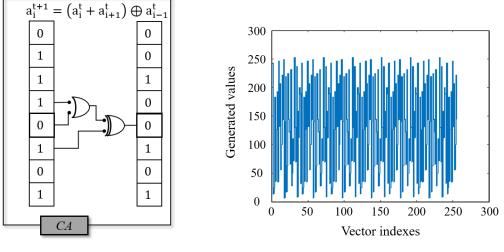

| 6.3        | A 8-bit cellular automata: (a) Architecture; (b) Generated outputs                                                                                                                                                                                                                                                                                                                                                                                                                              | 91 |

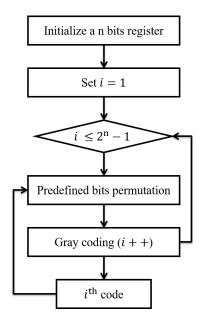

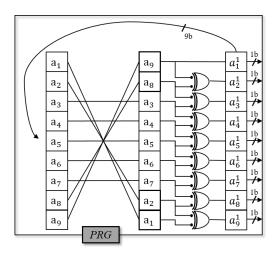

| 6.4        | Process of codes generation performed by the proposed PRG                                                                                                                                                                                                                                                                                                                                                                                                                                       | 92 |

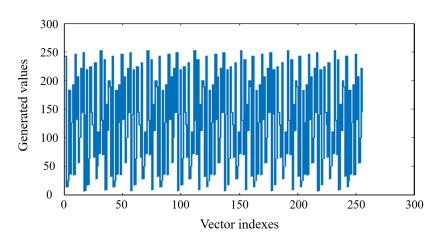

| 6.5        | Register outputs for 255 clock cycles of the proposed codes generator                                                                                                                                                                                                                                                                                                                                                                                                                           | 92 |

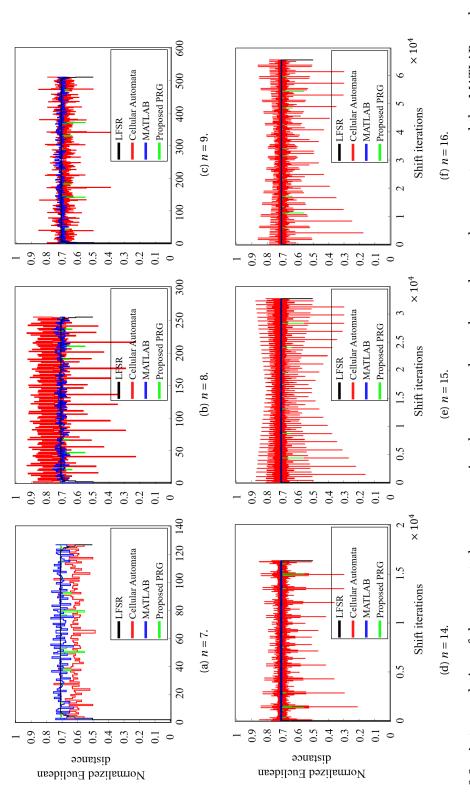

| 6.6        | Autocorrelation of the generated sequence using the proposed pseudo-random codes generator and the MATLAB random permutations algorithm for different                                                                                                                                                                                                                                                                                                                                           |    |

|            | code lengths.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93 |

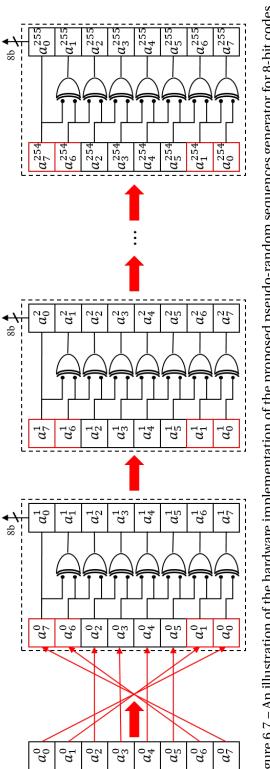

| 6.7        | An illustration of the hardware implementation of the proposed pseudo-random                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|            | sequences generator for 8-bit codes                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 95 |

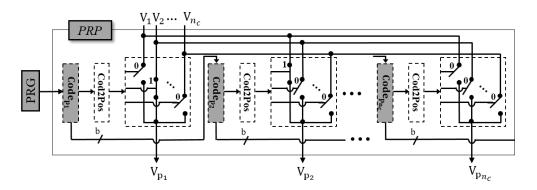

| 6.8        | Fully connected pseudo-random multiplexer based PRP                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96 |

| 6.9  | Analog ransmission gate.                                                                | 96  |

|------|-----------------------------------------------------------------------------------------|-----|

| 6.10 | Equivalent silicon footprint involved by the interconnect wires of the fully con-       |     |

|      | nected pseudo-random multiplexer based PRP                                              | 97  |

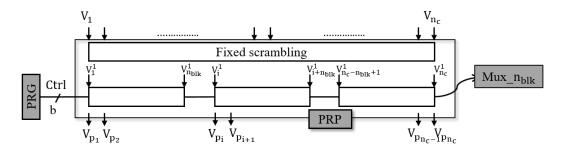

| 6.11 | Block-parallel pseudo-random multiplexer based PRP.                                     | 98  |

| 6.12 | Equivalent silicon footprint involved by the interconnect wires of the fixed scram-     |     |

|      | bling layer.                                                                            | 99  |

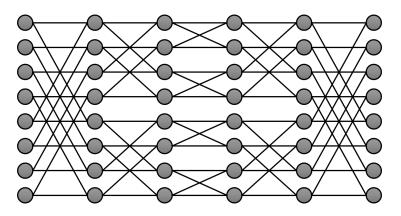

|      | A $8 \times 8$ Beneš network.                                                           | 100 |

| 6.14 | Beneš network based PRP.                                                                | 101 |

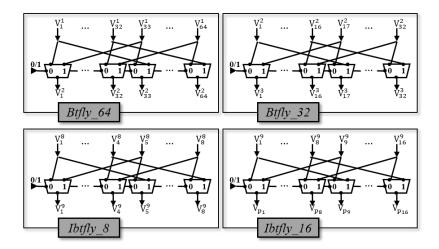

| 6.15 | Various examples of Butterfly circuits.                                                 | 101 |

| 6.16 | A 9-bit PRG.                                                                            | 102 |

| 6.17 | Enumerations of each mapping input/output performed by the PRP for a single             |     |

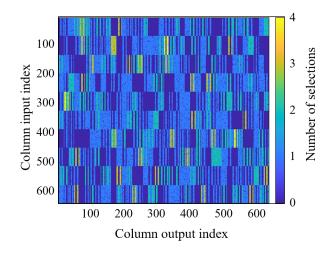

|      | snapshot                                                                                | 103 |

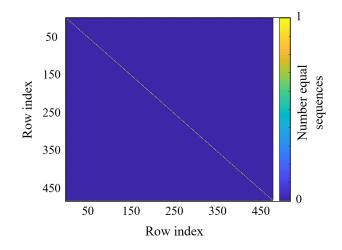

|      | Enumerations of similar generated sequences.                                            | 103 |

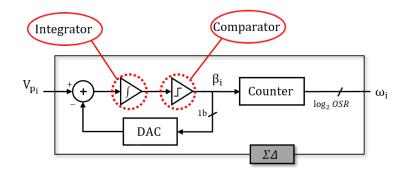

| 6.19 | Incremental $\Sigma\Delta$ ADC                                                          | 104 |

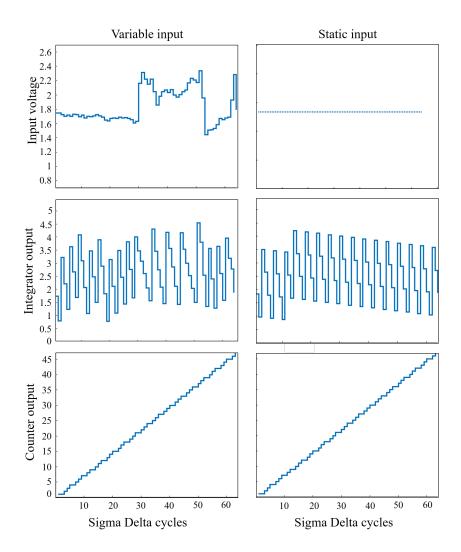

| 6.20 | Averaging and quantization through an incremental $\Sigma\Delta$ ADC. (Top): input sig- |     |

|      | nals; (Middle): integrator output; (Bottom): counter output highlighting the fact       |     |

|      | that the output of the signal and its average is the same                               | 105 |

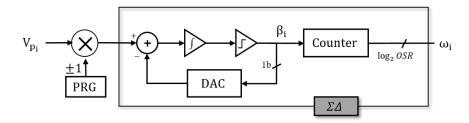

| 6.21 | System level concept of the RMSD                                                        | 105 |

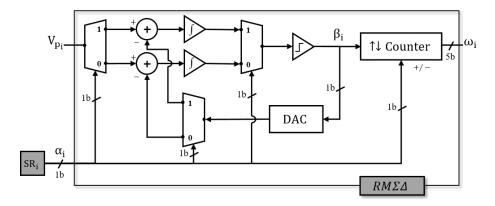

| 6.22 | Double-path integration based RMS $\Delta$ .                                            | 107 |

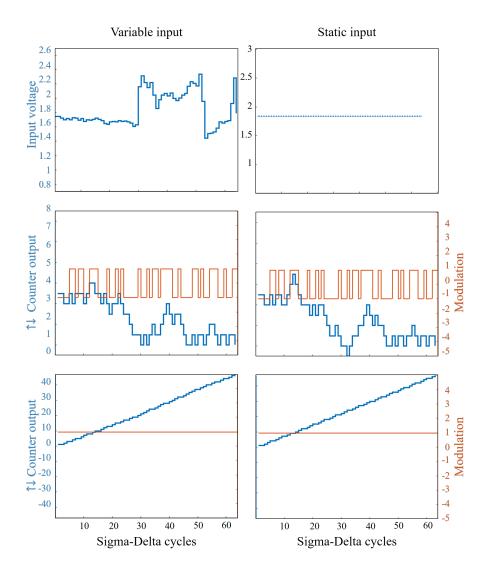

| 6.23 | Evolution of $RM\Sigma\Delta$ counter output with respect to various types of inputs    |     |

|      | demonstrating modulation-averaging operations. (Top): input signals; (Middle):          |     |

|      | counter output of the modulated inputs; (Bottom): counter output without                |     |

|      | modulation of the input signal.                                                         | 108 |

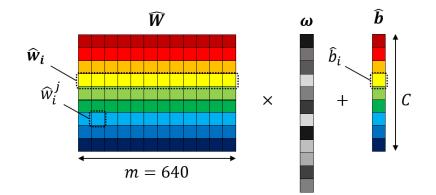

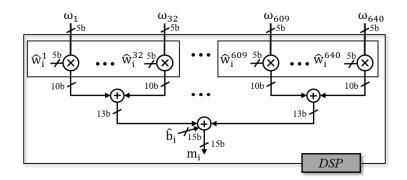

| 6.24 | Schematic representation of the affine function performed by the DSP. $\ldots$ .        | 109 |

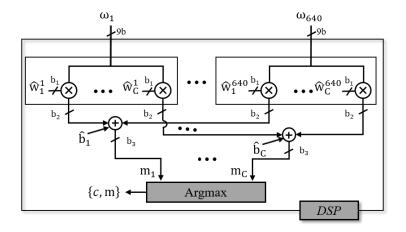

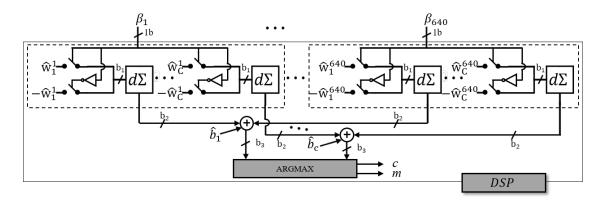

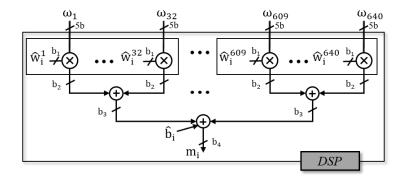

| 6.25 | Parallel DSP                                                                            | 109 |

| 6.26 | Conditional DSP                                                                         | 110 |

| 6.27 | Iterative DSP                                                                           | 110 |

| 6.28 | Three presented approaches, dashed lines represents projector-orthogonal hy-            |     |

|      | perplanes: (a) SVM; (b) Hierarchical SVM; (c) First layer of the proposed neural        |     |

|      | network                                                                                 | 111 |

|      | Iterative Argmax circuit.                                                               | 113 |

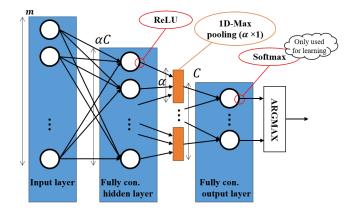

| 6.30 | Topology of the proposed Neural Network.                                                | 114 |

| 6.31 | PRP fixed scrambing.                                                                    | 116 |

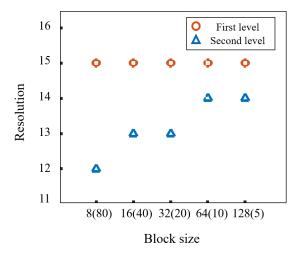

| 6.32 | Performance optimization of the RMSD                                                    | 118 |

| 6.33 | A 5-bit up/down conditional counter ( $\uparrow\downarrow$ counter)                     | 119 |

|      | DSP MAC                                                                                 | 121 |

| 6.35 | Optimized iterative DSP                                                                 | 121 |

| 6.36 | DSP MAC                                                                                 | 122 |

# **List of Tables**

| 3.1 | Embedded resources requirements to perform near sensor decision making for the studied inference approaches (A, B and C) and techniques (LDA, SVM and DLSI). | 51  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | A comparison of embedded resources requirements of hierarchical learning                                                                                     |     |

|     | approach compared to the one-vsall and one-vsone strategies.                                                                                                 | 83  |

| 5.2 | Classification accuracy of our methods compared to one-vsall approach, one-                                                                                  |     |

|     | vsone approach and the K-means based hierarchical learning. *with a Com-                                                                                     |     |

|     | pression Ratio of 25%. **Number of projections to perform at the inference                                                                                   |     |

|     | stage                                                                                                                                                        | 84  |

| 6.1 | Number of MSB and LSB bits to swap in function of the desired code length                                                                                    | 94  |

| 6.2 | Number of possible bits swapping over the $n!$ possible permutations of a $n$ -                                                                              |     |

|     | length register                                                                                                                                              | 94  |

| 6.3 | A comparison of embedded resources requirements of a one-vs.all SVM, hierar-                                                                                 |     |

|     | chical SVM and Neural Network inference strategies.                                                                                                          | 115 |

| 6.4 | GIT-10 SVM recognition accuracy for different levels of description of our archi-                                                                            |     |

|     | tecture. # measurements are reported between parentheses.                                                                                                    | 120 |

| 6.5 | Recognition accuracy for different datasets and infrence strategies using the                                                                                |     |

|     | proposed architecture.                                                                                                                                       | 123 |

## Chapter 1

## Introduction

The last few years have witnessed the tremendous growth of the filed of CMOS Image Sensors (CIS). They are now ubiquitous in many disciplines of science and industry. Driven by consumer electronic products (e.g., mobile phones, tablets, gaming, cameras), the overall CIS market has reached \$15.5 billion in 2018 with 12% Year-on-Year (YoY) growth as reported in Figure 1.1. This dynamic is expected to improve significantly in the next three years with 10% YoY growth as expected by Yole Développement, a market research and strategy consulting company. Yet, emerging applications such as ADAS (Advanced driver-assistance systems), drones and IP cameras could potentially reshape the current CIS landscape pushing the main CIS's players (e.g., Sony, Samsung, OmniVision) to suggest innovative approaches to meet the increasing needs in terms of CIS resolution, dynamic rage, wavelengths and more recently the ability to embed smart on-chip image processing and/or analysis, typically, with the democratization of machine learning tools. As widely discussed in the CIS literature, the current trend moves forward machine vision applications (e.g., object detection/avoidance/tracking, quality control). In such specific tasks, signal processing is essential to extract the most significant and interpretable information. However, designing such systems to handle large-scale data and extract meaningful informations involves considerable amount of computational and hardware resources limiting as a consequence their use for end-user applications. The main challenge consists then in the design of smart low-power compact imagers that seemingly involves to revisit the canonical image acquisition and processing pipeline.

In the conventional image acquisition and processing pipeline (*cf.*, Figure 1.2), sensing and analysing an observed scene is achieved through the following steps [2]. First, the light rays reflected by the observed scene are focused on the image sensor using an imaging lens. The CIS chip is composed of an array of pixels and peripheral circuits. Based on the photoconversion phenomena enabled by each pixel photodiode, the accumulated charge or its equivalent voltage or current value are read out in a rolling shutter fashion (*i.e.*, sequential line scanning) after a certain exposure time. Through this readout scheme, the quality of the sensed image is influenced by technological dispersions as well as pixels response nonuniformity. This

### **CIS market dynamics**

Figure 1.1 – CIS market dynamics by Yole Développement.

nonideality is known formally by the Fixed-Pattern Noise (FPN) and generally modeled as an affine mapping of the pixels values. To handle the offset FPN, a Correlated Double Sampling (CDS) circuit is typically implemented at the end-of-column circuitry [3]. Indeed, the pixel value is readout twice, at the reset and the end of the integration. This way, the pixel value at the reset is subtracted from the one after the integration allowing to suppress the offset PFN induced throughout the acquisition. The CDS output is then amplified and converted into a digital representation using an Analog-to-Digital Converter (ADC) [4]. Furthermore, an on-chip microlens array is typically deposited on top of pixel array to collimate incident light to the photodiode that occupies a percentage of the pixel area known as the fill-factor. On the other hand, to perform color imaging, an on-chip Color Filter Array (CFA) is built above the pixel array to separate colors through a certain pattern (e.g., RGB Bayer filter). To recover a full color image, a demosaicking algorithm is typically used based on color interpolation. Further digital processing can be done, for instance, color correction for image enhancement; and image compression to reduce the amount of data to store or sent to a remote processing station. Finally, to perform scene analysis (e.g., pattern recognition, decision making), State-Of-The-Art (SOTA) machine learning algorithms can be used. However, designing compact machine vision systems with on-chip decision making capabilities will involve high on-chip complexity either at the hardware level (e.g., power consumption, memory needs) or algorithmic one due to digital operations involved by SOTA heavy algorithms. A relevant approach to overcome these limitations consists in exploring alternative signal acquisition schemes allowing to reduce on-chip constraints and perform low-power on-chip decision making processing, for instance, for always-on sensor nodes that trigger signal when detecting specific patterns in the image scene.

Figure 1.2 – Imaging system pipeline.

In the last decade, a new signal acquisition scheme called Compressive Sensing (CS) has emerged as an alternative framework extending the classical Nyquist-Shannon sampling theorem. In the imaging context, CS is generally presented as a Dimensionality Reduction (DR) technique that maps a full-resolution image into a compressed vector. Since the early works in the field of CS, a deep theoretical study has been performed to highlight the interest of CS for sensor node applications. Based on a solid theoretical background, the CS framework provides several tools enabling the design of CS sensing schemes (*i.e.*, structured/non-structured DR operators), effective original signal recovery at the decoder level and finally effective signal processing on CS measurements. Moreover, some initial steps have been proposed to implement CS sensing schemes in the CMOS focal plane pushing forward the design of lowpower sensor nodes. In fact, the main interest of CS is the dimensionality reduction performed in the analog domain leading to a drastic reduction of the amount of A/D conversions which is one of the most energy-hungry component of a CIS, in the absence of embedded digital processing. In addition, the extracted compressed measurements allows to reduce on-chip digital Multiply and Accumulate (MAC) operations related to machine learning algorithms. For these reasons, CS is considered as a powerful sensing scheme for future low-power ( $\mu W$ ) CIS design. In this context, this thesis explores new paths towards the design of smart low-power CIS taking advantage of CS as a preliminary feature extraction stage combined with dedicated machine learning algorithms for cutting-edge applications with on-chip Artificial Intelligence (AI) capabilities.

### Layout of the manuscript

This thesis explores the design of CMOS image sensors taking advantage of CS to alleviate hardware constraints to perform basic on-chip inference tasks. To this end, two complementary parts are exposed. The first one (Chapter 3, 4 and 5), identifies mathematical and algorithmic enablers for efficient on-chip CS and inference problem solving tasks. In the second one (Chapter 6), we study how to efficiently design a compact CIS allowing to extract CS measurements and perform on-chip decision making without major modification of a canonical CIS architecture with well optimized standard pixels taking advantage of industrial-rated pixel

3

optimizations (*e.g.*, fill factor, full well capacity density, reset and read noise) enabling as a consequence various functioning modes (*e.g.*, CS, features extraction, classification, standard high resolution and low noise acquisition). The layout of the manuscript is as follows.

- **Chapter 2** presents an overview of the Compressive Sensing and Machine Learning landscapes. It first introduces key theoretical concepts and fundamentals for the design and study of CS sensing schemes. Next, it provides a non-exhaustive listing of SOTA recovery algorithms and theoretical guarantees for efficient signal processing on compressed measurements without major loss of the processing performance compared to signal processing on original data. SOTA efforts to design CIS devices with on-chip CS are reported with a focus on CMOS implementations highlighting the relevance of each approach regarding concrete applications. On the other hand, an overview of the SOTA of supervised machine learning techniques is presented. We finally highlight the current efforts towards the design of CIS devices with on-chip decision making tasks as well as dedicated System-On-Chip (SOC) for inference problem solving with either algorithmic or hardware optimizations (*e.g.*, binary deep learning accelerators).

- **Chapter 3** studies the interest of solving basic inference tasks on compressed measurements for highly constrained hardware (*e.g.*, always-on ultra low power vision systems). In particular, it tries to find the most beneficial setting to perform on-chip inference tasks on compressed measurements. Based on commonly known randomly generated CS matrices, three approaches to perform the inference on CS are presented for different SOTA machine learning algorithms involving different levels of complexity. The relevance of each approach is evaluated through the accuracy of the inference for real-world inference tasks as well as general considerations of the hardware complexity in terms of computing, memory needs and robustness to some hardware variations for two object recognition applications.

- **Chapter 4** proposes a novel compressive sensing scheme for CIS applications. It is formally generated based on random modulation and permutation matrices enabling the use of pseudo-random generators to extract compressed measurements and, thus, relax hardware constraints to generate the CS matrix. The proposed sensing model being basically designed to meet both theoretical (*i.e.*, stable embedding) and hardware requirements (*i.e.*, power consumption, silicon footprint), is highly suitable for image sensor applications addressing both image rendering and on-chip decision making tasks. The main contributions of this chapter are summarized as follows: we first provide theoretical and analytical analyses of the proposed sensing scheme based on CS theoretical tools to address inference tasks. On the other hand, we provide several numerical experiments to highlight the improvements enabled compared to SOTA CS based CIS architectures.

- **Chapter 5** deals with on-chip computational complexity involved by canonical decision making algorithms. It explores hierarchical learning in order to reduce MAC operations related to an embedded multi-class inference task. It typically introduces new methods to

construct the hierarchical tree in order to train a hierarchical classifier (*i.e.*, a binary decision tree) minimizing as a consequence the number of decision nodes, and thus, the number of binary classifiers to perform at the inference level. Indeed, in the context of limited processing and memory resources, CS is considered as a preliminary feature extraction stage for both training and inference problem solving allowing as a consequence a joint acquisition-processing optimization to meet highly constrained on-chip inference tasks. Finally, several simulation are carried out to show the relevance of the proposed methods for real-world inference tasks in terms of both decision making accuracy and hardware saving.

- **Chapter 6** heart of this thesis, packs conclusions of previous chapters together to define the architecture of a compact compressive CIS with dedicated CS sensing scheme and optimized inference strategies. It studies possible paths to implement the CS sensing scheme proposed in Chapter 3 using passive analog routines and an optimized ADC architecture enabling significant hardware saving. To show the relevance of the proposed architecture for real-world applications, two object recognition tasks are carried out using a dedicated Digital Signal Processing (DSP) architecture adapted to address the first stage of various inference algorithms, compliant with the proposed architecture, and therefore well adapted to the context of highly limited hardware implementations. Although being based on high-level simulations, several levers have been identified to make this implementation hardware-friendly, typically, to reduce the number of clock cycles in an incremental ADC (generally the most power hungry component of a CIS core in the absence of embedded digital processing neglecting IO-ring related power); lower extracted CS measurements resolution; and finally in-sensor memory needs.

- **Chapter 7** summaries, finally, the main contributions of each chapter and discusses possible outlooks and open questions not fully addressed throughout this thesis.

## **Chapter 2**

# **State Of The Art**

The goal of this chapter is to provide an overview of the research area related to this thesis. At the intersection of the fields of microelectronics, signal processing and machine learning, we present in details the elements that are most relevant to apprehend this work and in a nutshell the topics and tools related but not necessary to understand the contributions of this work. In particular, we illustrate how randomness can be exploited to design efficient signal acquisition devices and give enough theoretical guarantees to design algorithms that process random measurements enabling a compact signal acquisition and processing pipeline.

The chapter is divided into two major sections. The first section deals with the theoretical background of Compressive Sensing (CS) and related algorithmic tools, then with the main contributions of the CMOS Image Sensor (CIS) community regarding the design of imaging devices and systems with a particular focus on the compressive imaging schemes State-Of-The-Art (SOTA). The interest and guarantees of signal processing on compressed measurements framework are then presented. This alternative signal processing paradigm (*i.e.*, CS) has emerged as an attractive approach to tackle hardware drawbacks related to highly constrained embedded applications. The second section shifts the focus to the problem of pattern recognition and machine learning. It provides a review of the commonly used machine learning techniques with a particular focus on supervised learning algorithms. It further discusses several hardware contributions to implement SOTA inference techniques, both by analog pre-processing and dedicated digital hardware accelerators. Finally, some initial steps towards compressive sensing based decision making systems are presented and discussed for specific applications.

### 2.1 Compressive Sensing background

### 2.1.1 An Invitation to Compressive Sensing

The last few years have testified a widespread of connected nodes and data specific processing units. The trend for cost-optimized and value-added mixed IC design [5] has made considerable contributions in the world of Internet of Things (IoT) as well as smart sensors [6, 7]. In this context, the amount of data to sense, store and process has grown in leaps and bounds leading to power, multiply-accumulate (MAC) and memory hungry systems. To deal with the complexity bottleneck involved by the data dimensionality, a compression technique is typically introduced in the signal processing pipeline [8]. Several data compression algorithms have been developed to tackle this issue. In particular, transform coding is widely used as a fast and efficient compression technique, and aims typically to find *sparse* or *compressible* representations of the signals of interest in specific bases [9]. Considering a signal  $x \in \mathbb{R}^n$ (e.g., an image with n pixels), the concept of sparse representation allows to express x using a few non-zeros coefficients [10]. Thus, given an orthonormal basis  $\Psi \in \mathbb{R}^{n \times n}$ , x can be approximated by k non-zeros coefficients in  $\Psi$ , *i.e.*,  $\mathbf{x} = \Psi \boldsymbol{\alpha}$ , with  $k = \|\boldsymbol{\alpha}\|_0 = \operatorname{supp}(\boldsymbol{\alpha})$  is the degree of sparsity of x in  $\Psi$ . For compressible signals, the coefficients of x in  $\Psi$  (*i.e.*,  $\alpha$ ) tend rapidly to 0 when sorted by decreasing order of magnitude. Sparse representations are used in many compression standards like MP3, JPEG, JPEG 2000 and MPEG. Hopefully, the sparsity property of the signals also involves a low entropy of the data in the sparse domain, implying a direct possible usage of entropy coders to efficiently perform compression in terms of bitstream. Furthermore, with the rise of advanced CIS technology nodes, several works have focused on implementing near image sensor compression techniques [11, 12]. However, these implementations bring high computational and memory costs mainly related to the transform coding but also to the signal analysis needed for adaptive entropy coding.

On the other hand, Compressive Sensing (CS) has emerged as a powerful hardware-friendly framework for signal acquisition and sensor design based on random measurements. In contrast to the canonical approach where a signal is first sampled with respect to the Nyquist-Shannon theorem, converted to a digital representation using an Analog-to-Digital Converter (ADC) and then compressed using a compression standard (*cf.*, Figure. 2.1), CS proposes to

directly sense the observed signal in a compressed representation promising a large reduction of the hardware-algorithm complexity. Indeed, CS allows to dramatically reduce the amount of A/D conversions and digital operations and thus the power consumption of the signal acquisition and processing pipeline thanks to its signal-independent dimensionality reduction. Based on the works of E. Candès, J. Romberg, T. Tao and D. Donoho [13, 14], CS attests via a set of theoretical results that a sparse or compressible signal can be faithfully recovered from a small set of compressed measurements extracted based on non-adaptive linear projections [15, 16, 17]. However, the major limitations of CS based systems are typically the processing complexity related to the signal recovery compared to the classical approach as well as the generation/storage of the sensing matrix at the sensor side. Mathematically, considering a signal  $\mathbf{x} \in \mathbb{R}^n$ , we can express the CS acquisition scheme to extract *m* compressed measurements as follows

$$\boldsymbol{y} = \boldsymbol{\Phi} \boldsymbol{x},\tag{2.1}$$

where,  $\mathbf{\Phi} \in \mathbb{R}^{m \times n}$  is the sensing matrix enabling a signal-independent dimensionality reduction mapping the signal  $\mathbf{x} \in \mathbb{R}^n$  to a measurement vector  $\mathbf{y} \in \mathbb{R}^m$ , with *m* much smaller than *n* (*m*  $\ll$  *n*).

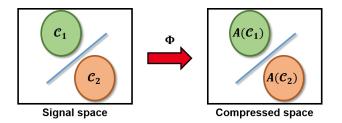

The CS community has been concerned with two main challenges. First, defining the classes of sensing matrices  $\Phi$  enabling a stable embedding property, *i.e.*, preserving the information content of the signal x in the compressed domain. Second, recovering faithfully the original signal x from the compressed vector y. The theory and applications of these two complementary research axes were elegantly developed gathering contributions from different scientific communities(mathematics, computer science, physics ...).

As mentioned above, the concept of sparse representations is traditionally used in lossy image compression to minimize the number of nonzero coefficients in the new basis. In particular, images are sparse in a wide variety of bases (*e.g.*, Discrete Cosine, Wavelets). In the CS context, sparsity is exploited as a prior knowledge to recover the original signal. Indeed, when  $m \ll n$ , recovering  $\mathbf{x}$  from  $\mathbf{y}$  is an ill-posed problem because  $\mathbf{\Phi}$  becomes an overcomplete dictionary instead of a basis. To tackle this issue, the CS theory takes advantage of the *sparsity* of the sensed signals in an *a priori* known basis. Thus, given the sparsity hypothesis of the signal  $\mathbf{x}$  in a sparsity basis  $\mathbf{\Psi}$ , recovering  $\mathbf{x}$  from  $\mathbf{y}$  can be expressed by a non-convex optimization problem aiming at finding the sparsest signal  $\hat{\mathbf{x}}$  such that  $\mathbf{y}$  is very close to  $\mathbf{\Phi}\hat{\mathbf{x}}$ :

$$\hat{\boldsymbol{x}} = \underset{\boldsymbol{x}}{\operatorname{argmin}} \|\boldsymbol{\Psi}^{\top}\boldsymbol{x}\|_{0} \text{ s.t. } \boldsymbol{y} = \boldsymbol{\Phi}\boldsymbol{x}.$$

(2.2)

Unfortunately, it was shown that this optimization problem is NP-hard [18, 19] because of

the  $\ell_0$  norm which is non-convex. However, because of  $\|\Psi^{\top} x\|_q^q$  approaches  $\|\Psi^{\top} x\|_0$  as q > 0 tends to 0 [20, 21], we can approximate (2.2) by

$$\hat{\boldsymbol{x}} = \underset{\boldsymbol{x}}{\operatorname{argmin}} \|\boldsymbol{\Psi}^{\top}\boldsymbol{x}\|_{q} \text{ s.t. } \boldsymbol{y} = \boldsymbol{\Phi}\boldsymbol{x}.$$

(2.3)

In the specific case of q = 1, this relaxation becomes convex and allows therefore to solve a much simpler  $\ell_1$ -minimization problem rather than the  $\ell_0$  problem leading to the following Basis Pursuit (BP):

$$\hat{\boldsymbol{x}} = \underset{\boldsymbol{x}}{\operatorname{argmin}} \|\boldsymbol{\Psi}^{\top}\boldsymbol{x}\|_{1} \text{ s.t. } \boldsymbol{y} = \boldsymbol{\Phi}\boldsymbol{x}.$$

(2.4)

However, the success of exact recovery via BP is achieved with respect to a certain condition expressed by the spasity level. Indeed, the bound defining the sparsity level required to ensure this equivalence is provided by the works of D. Donoho, X. Huo, M. Elad and A. Bruckstein [22, 23, 24]. Furthermore, we can reformulate (2.4) alternatively to extend this optimization problem to a more general  $\ell_1$ -minimization taking measurements error as well as compressible signals into account. In fact, due to sensors nonidealities, noisy measurements can probably be extracted leading to a recovered signal with *m* nonzero components instead of *k*. On the other hand, real-world images are generally compressible rather than sparse with the existence of sparse approximations that approximate them by sparse vectors. Given these considerations, it becomes reasonable to consider the following Basis Pursuit Denoising (BPDN) under the assumption of an Additive white Gaussian noise (AWGN):

$$\hat{\boldsymbol{x}} = \underset{\boldsymbol{x}}{\operatorname{argmin}} \|\boldsymbol{\Psi}^{\top}\boldsymbol{x}\|_{1} \text{ s.t. } \|\boldsymbol{y} - \boldsymbol{\Phi}\boldsymbol{x}\|_{2}^{2} \le \epsilon.$$

(2.5)

Equivalently, (2.5) can be expressed using its augmented Lagrangian form:

$$\hat{\boldsymbol{x}} = \operatorname*{argmin}_{\boldsymbol{x}} \|\boldsymbol{\Psi}^{\top}\boldsymbol{x}\|_{1} + \lambda \|\boldsymbol{y} - \boldsymbol{\Phi}\boldsymbol{x}\|_{2}^{2},$$

(2.6)

where  $\lambda$  is an inner regularization parameter allowing to control the energy of the fidelity term, *i.e.*, the sparsity level on the recovered signal. There exists a wide variety of algorithms to solve the  $\ell_1$ -minimization problems stated in (2.4), (2.5) and (2.6). In the next section we provide a sparse insight about the commonly used methods for sparse signal recovery or

sparse approximation problems.

#### 2.1.2 Basic Algorithmic Tools

Once the CS measurements extracted in the sensor side, a reconstruction algorithm is typically needed to solve the  $\ell_1$ -minimization problems expressed by (2.4) and (2.5). In the CS portfolio, there exists a wide variety of algorithms that guarantee a faithful and efficient signal recovery. Efficiency of these algorithms depends however on the complexity in terms of speed and memory needs as well as the quality of recovery in terms of reconstruction error. Several classifications have been proposed in the literature to group sparse recovery methods under different categories [25, 26, 27]. Here, three major classes are considered to solve sparse approximation problems: recast-based methods, greedy methods and non-convex methods. In the following, we give some elementary materials related to each algorithms class.

### **Recast-based Methods**

Before discussing recast-based methods, we note that in *convex optimization* [28] an optimization problem is generally expressed as:

$$\hat{\boldsymbol{x}} = \operatorname*{argmin}_{\boldsymbol{x}} f_0(\boldsymbol{x}) \text{ s.t. } f_i(\boldsymbol{x}) \le b_i, i \in [n],$$

(2.7)

where  $f_0 : \mathbb{R}^n \to \mathbb{R}$  is called an *objective function*,  $f_i : \mathbb{R}^n \to \mathbb{R}$ ,  $i \in [n]$  are called *constraint functions* and the constants  $b_i$  are called bounds for the constraints. Notice that when  $f_i$ 's are all linear, the problem is called a *linear program*. If  $f_i$ 's are all convex, then the problem is called a *convex optimization problem* and consequently its equivalent augmented Lagrangian as well.

We have mentioned previously that CS signal recovery can be expressed as a convex problem thanks to a convex relaxation leading to the  $\ell_1$ -minimization problem (*i.e.*, equations (2.4) and (2.5)). In addition, it was shown that the problem in (2.4) can be recast as a linear program by introducing slack variables [29]. This way, one can use the classical Dantzig's Simplex method [28] to solve (2.4). However, in the most physical-friendly approach (*i.e.*, BPDN in (2.5)), the signal recovery problem becomes a second-order cone problem, *i.e.*, a problem with quadratic constraint functions. The interior-point methods [30, 31] were among the first methods used to solve sparse approximation problems by convex optimization [32] expressed with a quadratic constrain (*i.e.*, (2.5)). However, although their low complexity, they are less competitive compared to greedy methods, specifically designed for  $\ell_1$ -minimization. Indeed, their performance is insensitive to the sparsity of the reconstructed signals or the value of the regularization parameter (*i.e.*, (2.6)).

#### **Greedy Methods**

A greedy method refers to a step-by-step fashion to recover a sparse signal [33, 34, 35, 36, 37, 38, 39, 40, 41]. This signal recovery selection can advantageously be combined with a thresholding routine leading to a precise tuning of the sparsity level of the estimated signal. In addition, greedy algorithms are known to be simple to implement, fast and applicable to large-datasets. These methods therefore provide strong theoretical guarantees for sparse signal recovery. A non-exhaustive list of the commonly used greedy methods can be found in [42] as well as recovery proofs and algorithms complexity in terms of computation and storage costs.

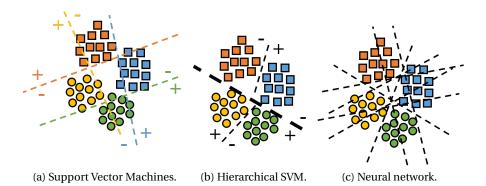

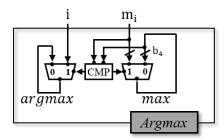

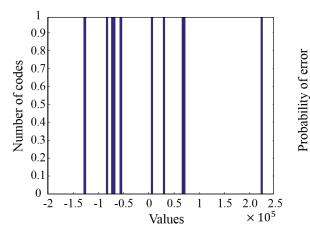

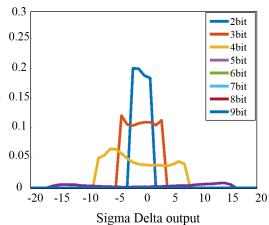

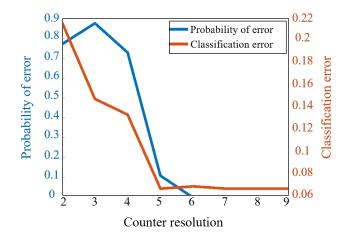

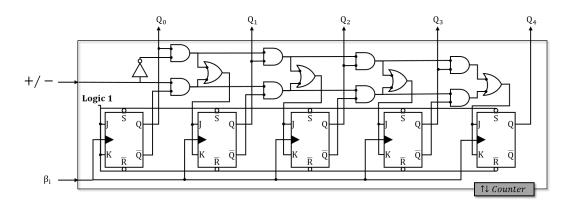

### Non-convex Methods