# Design and Fabrication of 3D Hybrid CMOS/NEM relays technology for energy-efficient electronics

Giulia Usai

#### ▶ To cite this version:

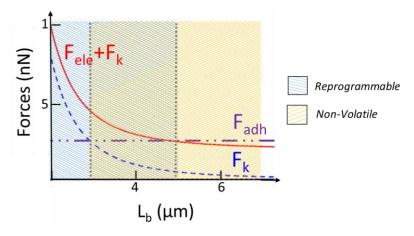

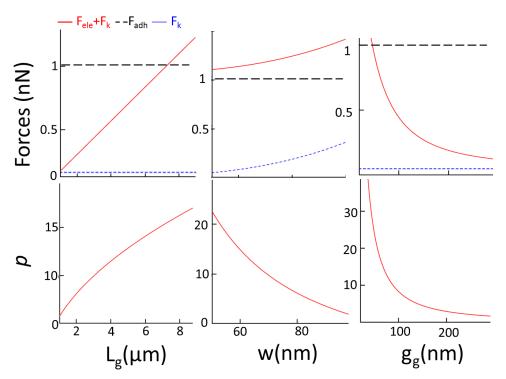

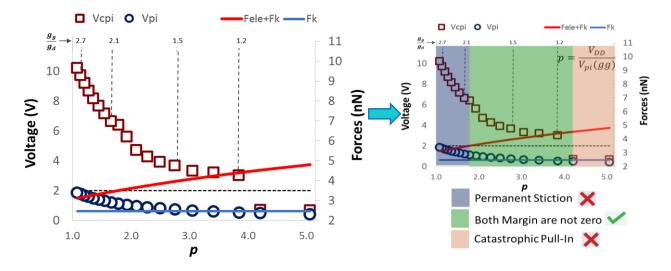

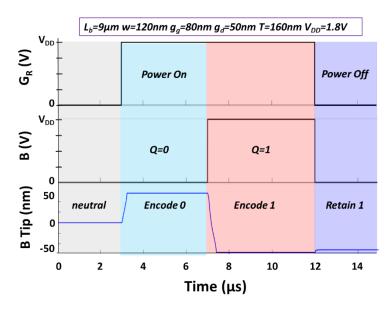

Giulia Usai. Design and Fabrication of 3D Hybrid CMOS/NEM relays technology for energy-efficient electronics. Micro and nanotechnologies/Microelectronics. Université Grenoble Alpes, 2019. English. NNT: 2019 GREAT069. tel-02529390

#### HAL Id: tel-02529390 https://theses.hal.science/tel-02529390

Submitted on 2 Apr 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

#### **THÈSE**

Pour obtenir le grade de

## DOCTEUR DE LA COMMUNAUTE UNIVERSITE GRENOBLE ALPES

Spécialité : Nanoélectronique et Nanotechnologies

Arrêté ministériel : 25 mai 2016

Présentée par

#### Giulia USAI

Thèse dirigée par **Thomas Ernst**, *PhD*, CEA Leti et **Tsu-Jae King Liu**, *PhD*, UC Berkeley

Préparée au sein du Laboratoire d'électronique et de technologie de l'information (CEA-Leti) dans l'École Doctorale électronique, électrotechnique, automatique et traitement du signal EEATS

### Conception et Fabrication hybride 3D monolithique de relais NEMS cointégrés CMOS

Thèse soutenue publiquement le « 5 12 2019 », Devant le jury composé de :

Dr. Laurent, PICHON

Professeur, Université de Rennes 1 (Président)

Dr. Núria, BARNIOL BEUMALA

Professeur, Universitat Autonoma de Barcelona, Espagne (Rapporteur)

Dr. Damien, DELERUYELLE

Professeur, INSA Lyon, (Rapporteur)

Dr. Louis, HUTIN

Ingénieur-Docteur, CEA LETI, Grenoble (Encadrant)

Dr. Thomas, ERNST

Directeur de recherche au CEA-Leti, Grenoble (Directeur de thèse)

Dr. Tsu-Jae, KING LIU

Professeur, UC Berkeley, États-Unis (Co-Directrice de thèse)

A mio Marito Giorgio Palma, Fonte di infinito amore e sostegno.

#### **ABSTRACT**

This manuscript focuses on Nano-Electro-Mechanical (NEM) relays with electrostatic actuation for advanced logic and memory applications. The use of Nano-Electro-Mechanical relays was recently proposed for digital logic circuits in order to overcome the fundamental energy-efficiency limitations that mainstream CMOS technology is currently facing. The cumulated benefits of essentially Zero Off-State current and ultimately abrupt DC switching characteristics enable alleviating the power-performance trade-off as the supply voltage  $V_{DD}$  is reduced. Additionally, for some particular switch designs (e.g. free of dielectric layers), an increased resistance to ionizing radiations is also anticipated, making such components valuable for defense or aerospace applications.

However, NEM relays have intrinsic limitations in terms of integration density, endurance and operation frequency. Therefore, rather than considering them as technology that could replace MOSFETs, we adopt an intermediate approach that consists in using NEM relays as a complement to CMOS circuits (e.g.: buffers, non-volatile elements for SRAM and CAM), which can be fabricated in a 3D cointegration scheme. This approach mitigates the area penalty issue.

The thesis explores the strength and the weakness of NEMS relays and identifies applications for which hybrid NEMS/CMOS circuits are potentially interesting.

This work includes the manufacturing of prototype devices designed to be proof of concept for the identified applications. At first, NV NEM relays design and dimensioning through modeling and simulations was performed. Then NV NEM/CMOS circuits were validated trough simulations. This was followed by the tapeout and the process integration of monolithically co-integrated NEMS above CMOS. After wafer processing the devices were electrically characterized.

This all-inclusive works allows identifying some crucial challenges that NEMS relays still have to face.

#### RESUME

Ce travail de thèse porte sur les relais nano électromécaniques (NEMS en anglais). Afin de surmonter la limite d'efficacité énergétique inhérente à la technologie CMOS, l'utilisation de relais NEMS pour des circuits logiques a été récemment proposée. En effet, les bénéfices cumulés d'un courant nul à l'état bloqué et d'une commutation abrupte permettent d'améliorer le compromis puissance-performance lorsque la tension d'alimentation  $V_{DD}$  est réduite.

Cependant, les relais NEMS sont limités intrinsèquement par leur endurance, leur fréquence de fonctionnement ainsi que par leur faible densité d'intégration. De ce fait, une approche complémentaire basée sur la cointégration entre CMOS et relais (mémoire tampon, éléments non volatile) plutôt qu'un remplacement semble plus pertinent à court terme. Une intégration 3D monolithique permet l'ajout de tels éléments sur la même surface tout en bénéficiant d'une précision d'alignement lithographique. De plus, pour certains dispositifs (ex. sans couche diélectrique), une plus grande immunité aux radiations ionisantes est attendue, ouvrant des perspectives dans les domaines des applications militaires ou spatiales.

En particulier, ce travail de thèse explore les forces et les faiblesses de ces structures et identifie des applications à fort potentiel. Il comprend en outre la conception de prototypes correspondants, depuis leur modélisation et simulation permettant un dimensionnement fonctionnel, le perfectionnement de l'intégration 3D « NEMS sur CMOS », et enfin leurs tests électriques. A la lumière de ces analyses, des recommandations sont fournies pour le développement de circuits hybrides 3D CMOS/NEMS pour la logique et les mémoires avancés.

#### **ACRONYMS**

**AFM** Atomic Force Microscope

**ALD** Atomic Layer **D**eposition

**CBRAM** Conductive Bridge Random Access Memory

CMOS Complementary Metal Oxide Semiconductor

CMP Chemical-Mechanical Polishing

**CPI** Catastrophic Pull-In

**CPU** Central Processing Unit

**BEOL** Back End Of Line

**DIBL** Drain Induced Barrier Lowering

**D**L **D**rain **L**eft

**DR D**rain **R**ight

**DRAM** Dynamic Random Access Memory

**DVS** Dynamic Voltage Scaling

**DUV** Deep Ultra Violet

**EBEAM** Electron **B**EAM

**EOT** Effective Oxide Thickness

FinFET Fin Field Effect Transistor

FEA Finite Element Analysis

FEM Finite Element Method

FEOL Front End Of Line

FeRAM Ferro-electric Random Access Memory

FDSOI Fully Depleted Silicon On Insulator

FPGA Field-Programmable-Gate Arrays

GAA Gate All Around

GND GrouND

**HP High Performance**

IC Integrated Circuit

**Internet Of Things**

ITRS International Technology Roadmap for Semiconductors

LP Low Power

LSP Low Standby Power

LUT Look Up Table

MEMS Micro Electro-Mechanical System

MEOL Middle End Of Line

MOSFET Metal Oxide Semiconductor Field Effect Transistor

ML Match Line

NEMS Nano Electro-Mechanical System

NV Non-Volatile

**NVM** Non-Volatile Memory

OxRAM Oxide Resistive Access Memory

PCM Phase Change Memory

PECVD Plasma-Enhanced Chemical Vapor Deposition

PEALD Plasma Enhanced Atomic Layer Deposition

PI Pull-In

**RIE** Reactive Ion Etching

**RRAM** Resistive Random Access Memory

**RWL** Re-Write Line

**RWLB** Re-Write Line Bar

**SEM** Scanning Electron Microscope

SL Search Line

SN Storage Node

SRAM Static Random Access Memory

SS Subthreshold Swing

STT-RAM Spin Transfer Torque Random Access Memory

SOI Silicon On Insulator

**SPDT** Single Pole Double Throw

**SPM** Scribe line Primary Marks

TCAM Ternary Content-Addressable Memory

TEOS Tetra-Ethyl Ortho-Silicate

#### **ACKNOWLEDGEMENTS**

I would like to thank the jury members, Dr. Laurent Pichon, Dr. Núria Barniol Beumala, Dr. Damien Deleruyelle, for accepting to review my manuscript and for their relevant remarks.

Before starting the thesis, I was young and not at all aware of the huge amount of work, strength, discipline, perseverance that a thesis such as mine required. My internship supervisor, which then became my thesis supervisor (Dr. Louis Hutin) convinced me to embark on this journey.

For this, I would like to thank him. He helped me to push all my limits, allowing me to discover that I was able to grow more and more professionally but also personally. He challenged me every day in becoming always my better self.

I would love to thank Claude Tabone; his sentence: 'Les voies du Seigneur sont impenetrable' became my mantra. Claude with 40 years of experience taught me thousands of fabrications tricks that cannot be learnt from books.

I would love to thank Thomas Ernst, my thesis director. He was very busy, however during my thesis he always could free up some time the time to talk to me and help me. Thank you for listening and giving me useful advices. You taught me that a good thesis work is not done only through research but is also done through time management and smart use of communication skills.

I would love to thank my co-director Tsu Jae King Liu. You are the busiest person I ever met and yet you found time to be part of my thesis. Thank you to showing me that it is possible to be Dean of Engineering at UC Berkeley, Board of Directors of Intel, wonderful teacher and supervisor, woman and mother. Your achievements are amazing, it was a privilege to meet you. I would love to thank the rest of the MADN/MD2N team: Christophe Plantier, Sebastien Hentz, Jose Munoz Gamarra and Emmanuel Roland. Our team was dynamic and fun. Each one of you had experience in different topics, each one of you had different skills and knowledge. Together we rocked (3). I loved our Friday meeting where I learnt how to find the root of a problem, be more precise and mostly to never give up (and I also learnt many useful French expression!). I would love to thank the Jedi council: Alex, Vincent, Julien, Mathilde, Jessy, Yoon Ji, Benoit, Lina, Sotiris, Carlos, Remy, Thomas, and the Padawans: Camila, Daphne, Rony. Thankfully I had you on my journey, I have so many things to say to each one of you that I could write another manuscript. Therefore, I will just say: "Padawans do not give up. The thesis will finish sooner than you expect! May the force be with you". I would love to thank Urmita Sikder and the rest of the Tsu Jae's groups, working with you has enhanced this thesis work and seeing how research is done on the other part of the world has enriched me professionally. I would love to thank Bernard P. Master of Expida. You take wonderful pictures, my switches never looked better [3]!

I would love to thank LICL, LMDK, LCM, DCOS and DACLE labs during my thesis I had the pleasure to interact with many of you.

I would love to thank all my Grenobloise friends with a special thanks to my dance buddy Sana Rachidi.

Thanks to all my long date friends because you are always with me, supporting me and giving me your love even if we live faraway.

Thanks to my family who is always there for me, no matter where I am or what I am doing. I love you so much. You are my heart.

Thanks to my family in law who support me and fills me with affections.

Finally, I am grateful of having the best husband of the world: Giorgio. Thanks for holding me tight when I was feeling down and celebrating with me when I was feeling up.

Thank you to each one of you.

### **CONTENTS**

|   | Abstract                                                            | 3 |

|---|---------------------------------------------------------------------|---|

|   | Résumé                                                              | 4 |

|   | Acronyms                                                            | 5 |

|   | Acknowledgements                                                    | 7 |

|   | Contents                                                            | 3 |

| L | Introduction                                                        | 2 |

|   | 1.1 MOSFET miniaturization: Purpose and limits                      | 3 |

|   | 1.2 Moore's Law                                                     | 3 |

|   | 1.3 The Conventional MOSFET                                         | 4 |

|   | 1.3.1 MOSFET Scaling Limits                                         | 7 |

|   | 1.3.1.1 Performance-Leakage Trade OFF                               | 3 |

|   | 1.4 Memory Hierarchy                                                | 1 |

|   | 1.5 General Review of Beyond CMOS devices                           | 4 |

|   | 1.5.1 Beyond CMOS Logic Devices                                     | 5 |

|   | 1.5.1.1 Tunnel Field Effect Transistors                             | 5 |

|   | 1.5.1.2 Impact Ionization MOSFET IMOS                               | 5 |

|   | 1.5.1.3 Negative Capacitance Field-Effect Transistor (Neg-Cg FET)27 | 7 |

|   | 1.5.2 Beyond CMOS Emerging Non-Volatile Memories                    | ) |

|   | 1.5.2.1 Resistive RAM (RRAM)                                        | ) |

|   | 1.5.2.2 NEMS                                                        | 3 |

|   | 1.5.2.2.1 Electromagnetic                                           | 4 |

|   | 1.5.2.2.2 Electrothermal                                            | 5 |

|   | 1.5.2.2.3 Piezoelectric                                             | 5 |

|   | 1.5.2.2.4 Electrostatic                                             | 7 |

|   | 1.6 Thesis COAL                                                     | a |

| 2 NEMS Relay: State of Art                                          | 41           |

|---------------------------------------------------------------------|--------------|

| 2.1 Introduction                                                    | 42           |

| 2.2 Nanoelectromechanical Switches                                  | 44           |

| 2.2.1 Design                                                        | 44           |

| 2.2.2 NEM Relay Actuation Mechanism                                 | 48           |

| 2.2.3 Materials                                                     | 50           |

| 2.2.3.1 Sacrificial Layer                                           | 50           |

| 2.2.3.2 Structural Layer                                            | 51           |

| 2.2.3.3 Contact and Coating layer                                   | 54           |

| 2.2.3.3.1 Coating Layer                                             | 54           |

| 2.2.4 Metal Interconnection Air Gap for NEM rel<br>Release Process? |              |

| 2.2.4.1 Interconnection stack Air Gap Fabricati                     | on56         |

| 2.2.4.2 Air gap reliability issues                                  | 58           |

| 2.2.4.3 Conclusion                                                  | 59           |

| 2.2.5 Nano-contact                                                  | 59           |

| 2.2.6 Endurance                                                     | 61           |

| 2.2.7 Mechanical Delay                                              | 65           |

| 2.2.8 Scaling limits                                                | 65           |

| 2.2.9 Harsh Environment                                             | 68           |

| 2.3 Target Applications                                             | 70           |

| 2.3.1 Logic NEMS                                                    | 70           |

| 2.3.1.1 Nano-Electro-Mechanical relays for FP                       | GA routing71 |

| 2.3.1.2 Logic NEMS Relay in SRAM                                    | 72           |

| 2.3.2 Non-Volatile NEM relay                                        | 73           |

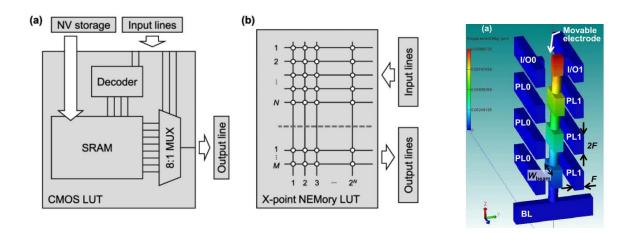

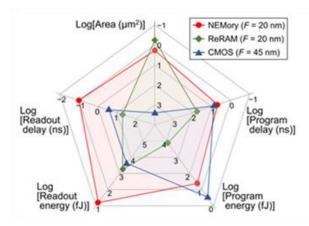

| 2.3.2.1 Look-up Table                                               | 74           |

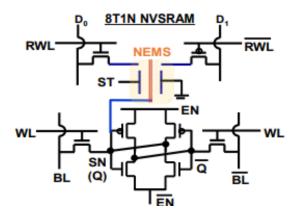

| 2.3.2.2 NV-SRAM                                                     | 76           |

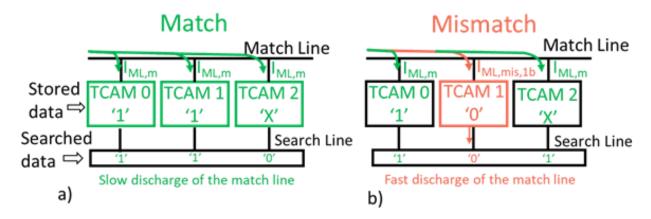

| 2.3.2.3 NV-TCAM                                                           | 77    |

|---------------------------------------------------------------------------|-------|

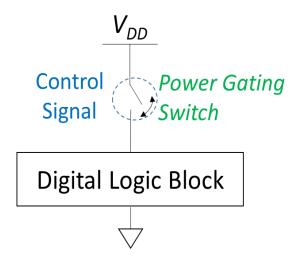

| 2.3.3 Power Gating                                                        | 78    |

| 2.3.4 Remaining Challenges                                                | 80    |

| 2.3.4.1 Challenges for Reducing Relay Size                                | 80    |

| 2.3.4.2 Challenges for Reducing Operating Voltages                        | 81    |

| 2.3.4.3 Challenges for Monolithically NEMS CMOS Integration               | 81    |

| 3 Modeling of NV NEM Relays                                               | 82    |

| 3.1 Design and Modeling of NEM Relays                                     | 83    |

| 3.1.1 Parallel Plate Capacitor Approximation                              | 83    |

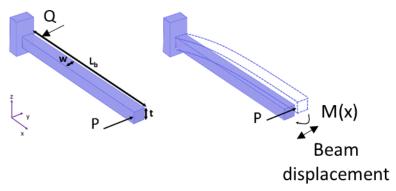

| 3.1.2 Modeling of Mechanical Beam                                         | 87    |

| 3.1.2.1 Stiffness                                                         | 88    |

| 3.1.2.2 Cantilever and Clamped-Clamped Beam Stifness and Resonant Frequer | ncy89 |

| 3.1.3 Mechanical Delay                                                    | 91    |

| 3.2 Working Margin Optimization                                           | 92    |

| 3.2.1 Pull In Voltage Modeling For "Beam" NEM Relay                       | 93    |

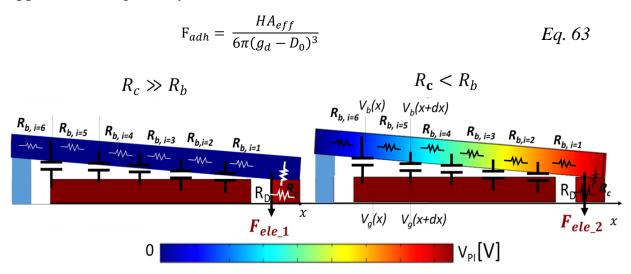

| 3.2.2 Catastrophic Pull In Voltage                                        | 98    |

| 3.2.2.1 Working Margin Optimization Summary                               | 100   |

| 3.3 Design Optimization for Non Volatile NEM Relay                        | 100   |

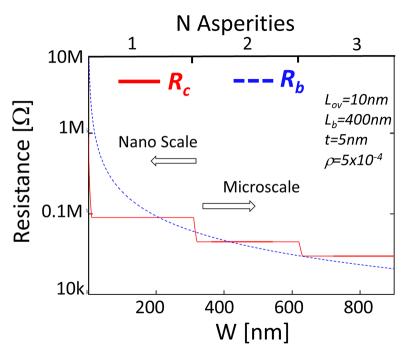

| 3.4 Contact Instability Due to Scalability                                | 106   |

| 3.5 Case Study: NV SRAM                                                   | 112   |

| 3.5.1 6-T SRAM                                                            | 112   |

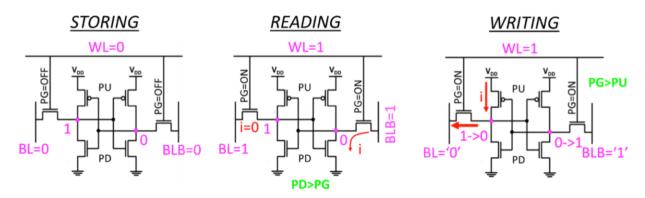

| 3.5.1.1 Storing-Writing-Reading Operations                                | 112   |

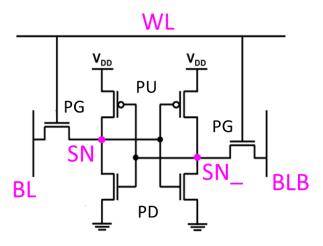

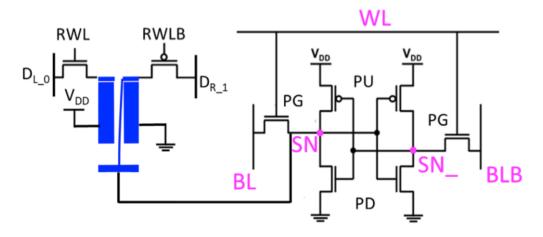

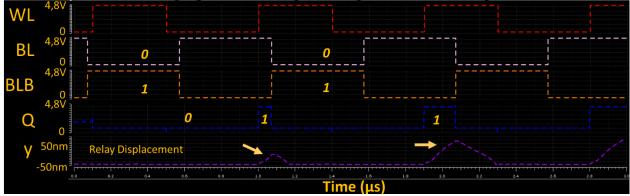

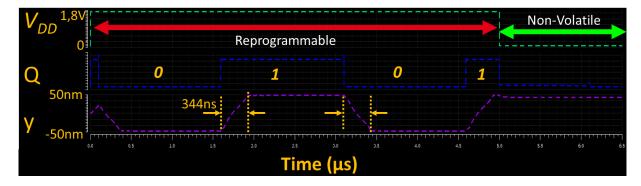

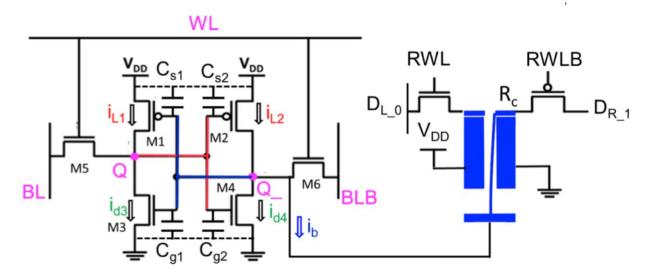

| 3.5.2 1-Relay (R)-8T NoN-Volatile (NV) SRAM                               | 113   |

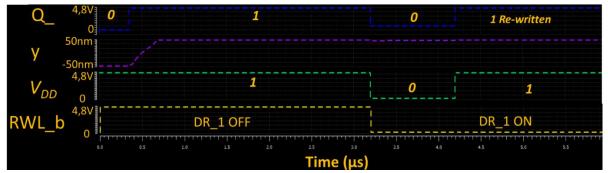

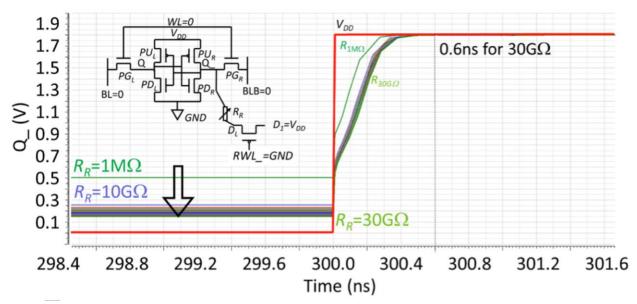

| 3.5.2.1 Re-Writing Operation                                              | 115   |

| 3.6 Conclusion                                                            | 118   |

| 4 Focus On 3D monolithic NEMS/CMOS Cointegration Process Flow             | 120   |

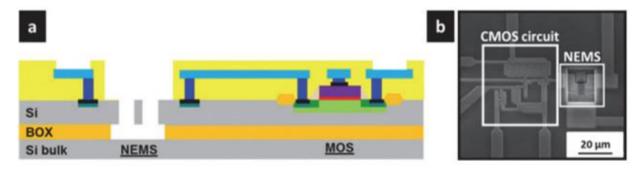

| 4.1 NEMS/CMOS Monolithic Co-Integration                              | 121 |

|----------------------------------------------------------------------|-----|

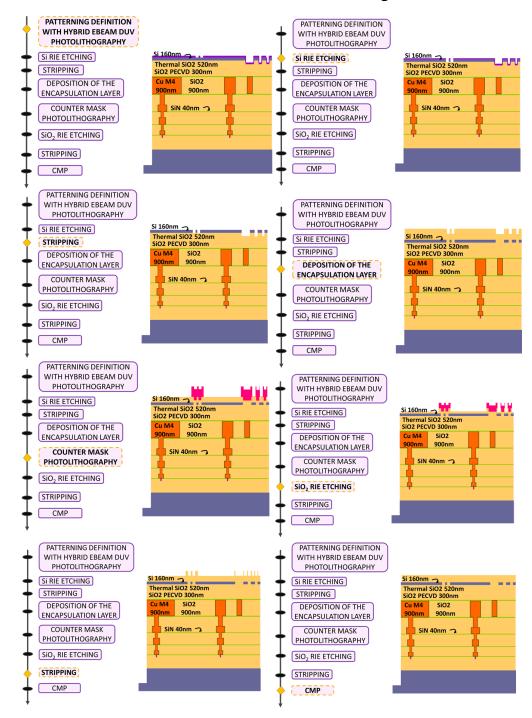

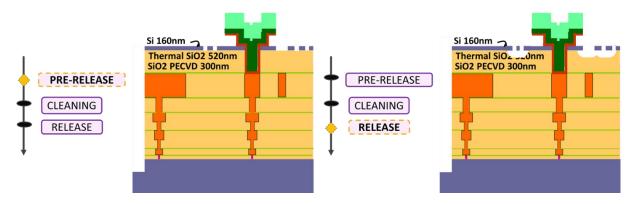

| 4.2 c-Si NEMS ABOVE CMOS: Flow Overview                              | 125 |

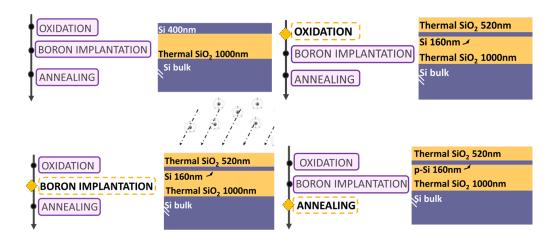

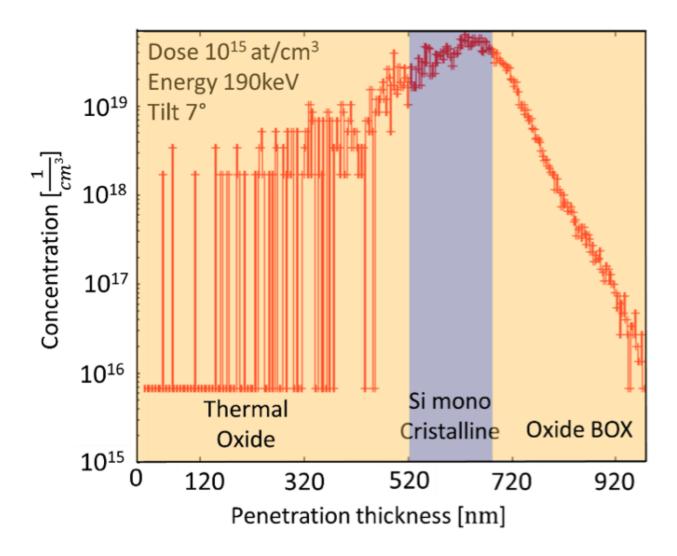

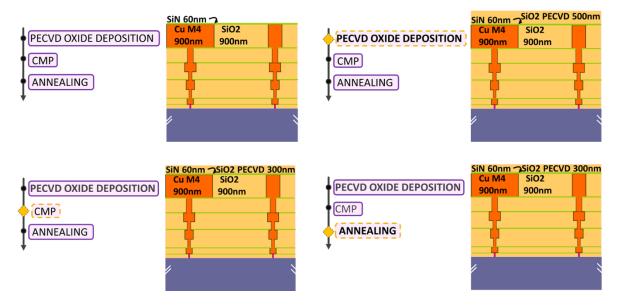

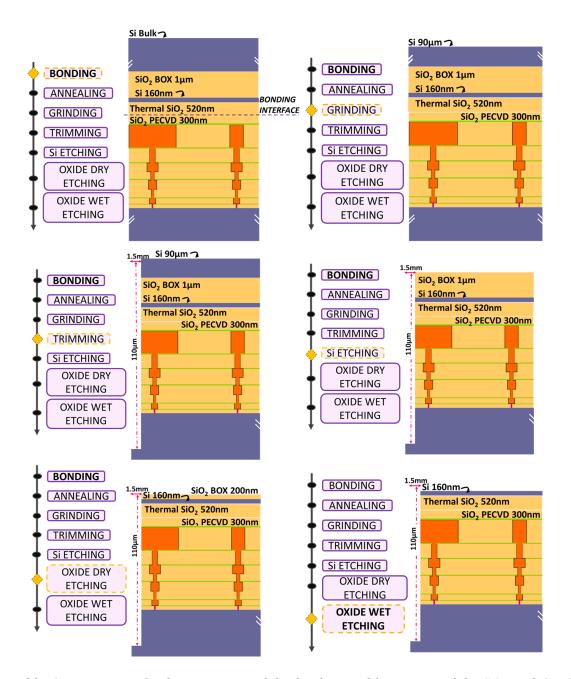

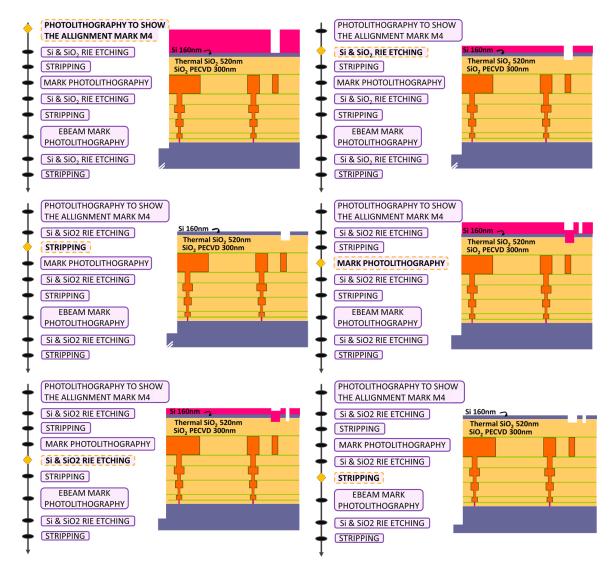

| 4.2.1 Preparation of The SOI Substrate                               | 126 |

| 4.2.2 CMOS Substrate Preparation                                     | 129 |

| 4.2.3 Bonding, Grinding and Trimming                                 | 130 |

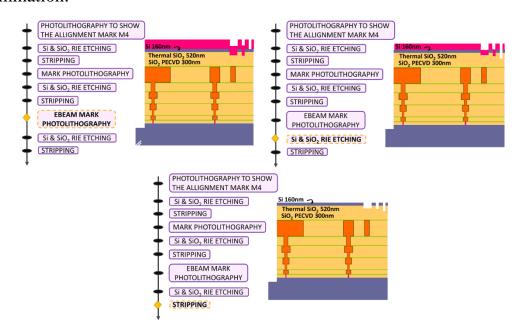

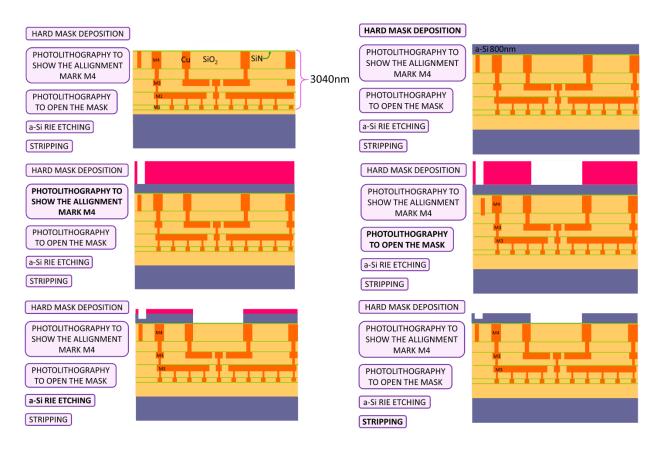

| 4.2.4 NEMS Patterning                                                | 133 |

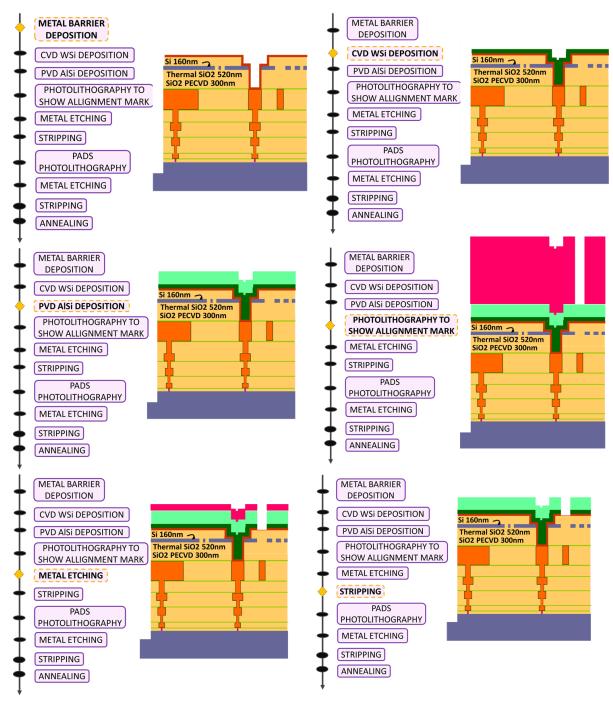

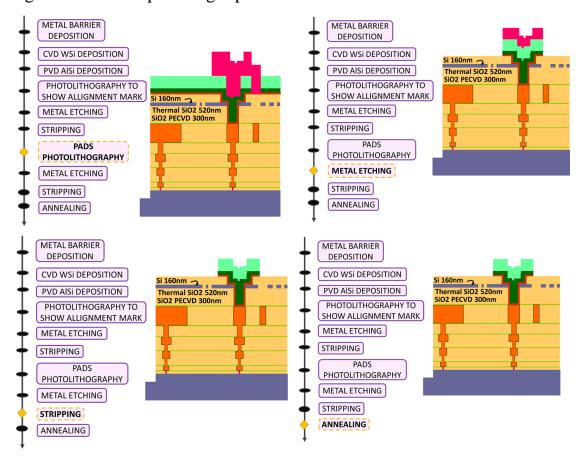

| 4.2.5 Interconnections and Pads Definition                           | 137 |

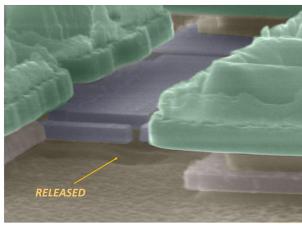

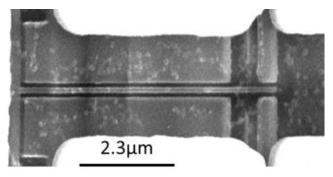

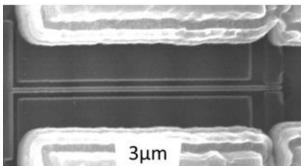

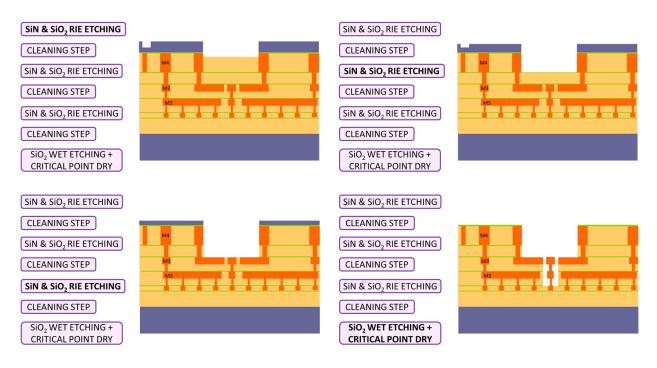

| 4.2.6 Nems Release                                                   | 141 |

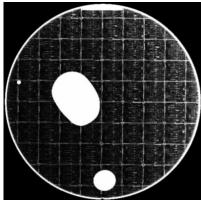

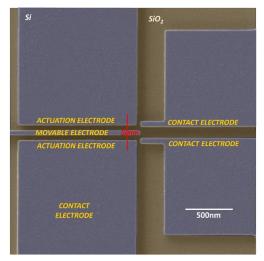

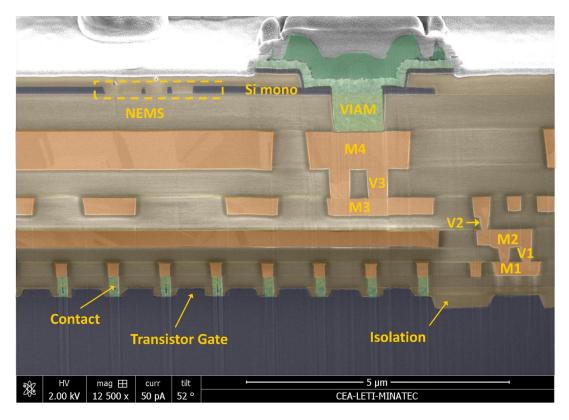

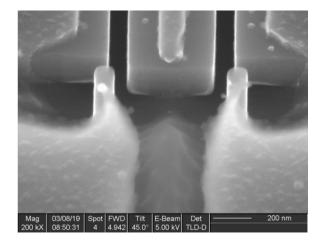

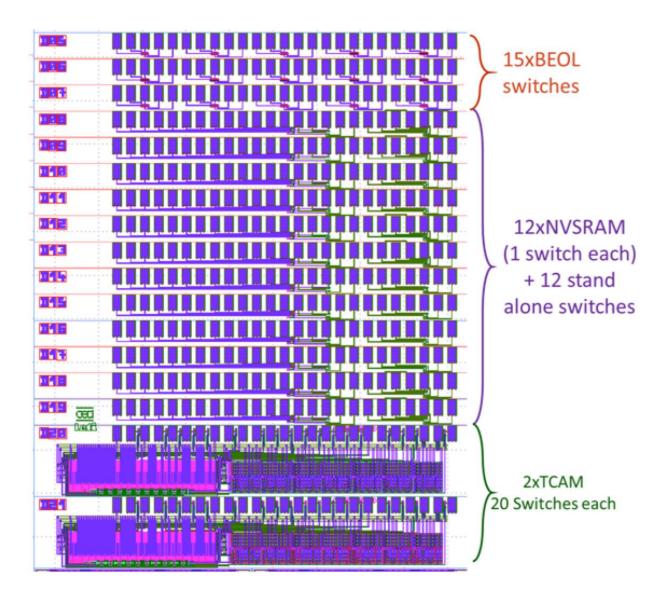

| 4.3 Fabricated Devices                                               | 143 |

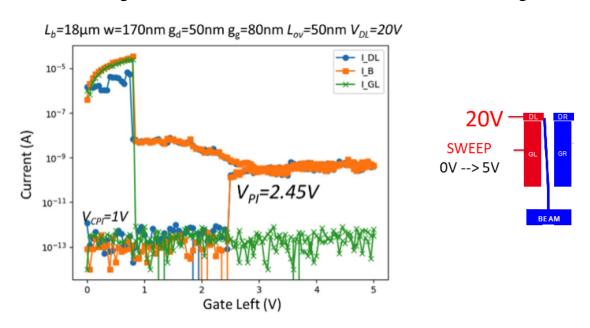

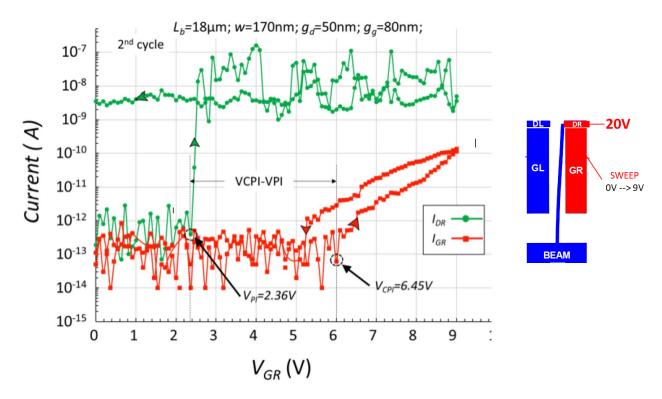

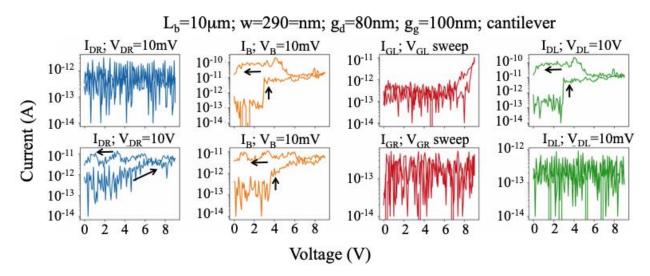

| 4.4 I/V Characterization of Monocrystalline Stand-Alone NEMS relay   | 145 |

| 4.5 Conclusion.                                                      | 149 |

| 5 Conclusions and Perspectives                                       | 150 |

| 5.1 Conclusion.                                                      | 151 |

| 5.2 Perspectives                                                     | 155 |

| 6 ANNEX 1                                                            | 157 |

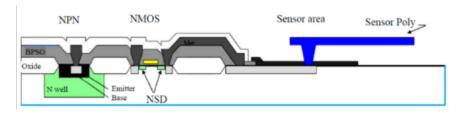

| 6.1 Poly-Si NEMS above CMOS                                          | 158 |

| 6.1.1 I/V Characterization of Polycrystalline Stand-Alone NEMS Relay | 161 |

| 6.1.1.1 DC Characteristic                                            | 163 |

| 6.2 Cu BEOL NEMS                                                     | 164 |

| 6.2.1 Switch Release                                                 | 165 |

| Bibliography                                                         | 170 |

### 1 INTRODUCTION

# 1.1 MOSFET MINIATURIZATION: PURPOSE AND LIMITS

#### 1.2 MOORE'S LAW

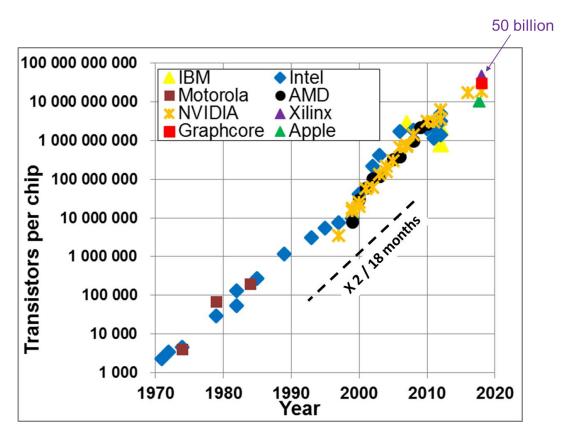

Moore's law [Moore 1965], which has been accepted by general consensus as a roadmap for the semiconductor industry for many decades states that: "The number of active transistors present in a single chip will double every 18 months". Indeed, the number of transistors integrated in a single chip has increased every year owing mainly to technology progress in device miniaturization. One of the messages of Moore's law is that the cost per transistor decreases with each new technology generation. This law also highlights the fact that, for each generation, there is an optimal number of components per integrated circuits that results into a minimum cost. Further increasing the number of components per circuit above that optimal number increases chip area and reduces the process yield (increasing the final cost). Since 1975, the semiconductor industry followed Moore's trends, and miniaturizations allowed to place billions of transistors on a single chip see Fig. 1.

Fig. 1: Plot of transistor count vs year of introductions [Colinge 2016]

Moore's law drove the semiconductor market for at least 52 years. In 1965, there were no fundamental physical limits limiting transistors scaling. Once the transistor size reached the nano scale, however, parasitic effects started to appear, causing performance degradation and increasing device-to-device variability. Therefore, keeping extending Moore's Law requires working on innovation strategies. For example, to increase the channel mobility, strain and new materials such as SiGe have been introduced. The gate stack has been modified and the classical SiO<sub>2</sub>/polysilicon gate stack has been substituted with high-k gate dielectric and metal gate to scale the effective oxide thickness (EOT). To improve the channel control new transistors structures have been proposed (*e.g.* FinFET, Gate All Around (GAA)). Additionally, new device solutions (*i.e.* beyond CMOS devices), new computational methods and new integration methods (*e.g.* 3D monolithic integration) have been suggested to help to keep Moore's law going.

#### 1.3 THE CONVENTIONAL MOSFET

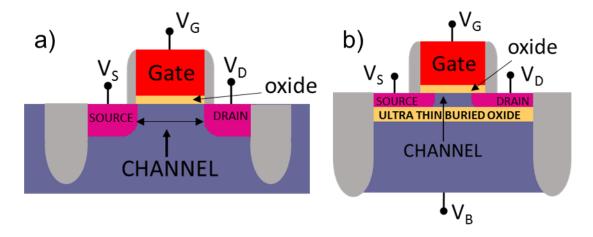

The key component of the integrated circuits, so far, has been the Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) see schematic view in Fig. 2. The MOSFET has four electrodes, the gate, which controls the channel, the body, which connects the semiconductor to ground, the source and the drain. The transistor is called n-type or p-type depending on the dopant type implanted on source and drain, usually opposite to the channel dopant type. An oxide of thickness  $t_{ox}$  separates the gate from the channel region, which has a physical length  $L_G$  and a width w. When a voltage difference  $V_{GS}$  is applied between gate and source, an electric field is created to control and modulate the current density in a channel formed between drain and source. The carriers in the channel can be holes or electrons depending on the transistor type (respectively p-type or n-type).

Fig. 2: Cross sections of MOSFET device a) typical Bulk MOSFET; b) Fully Depleted (FD)-Silicon On Insulator MOSFET with 4 terminals.

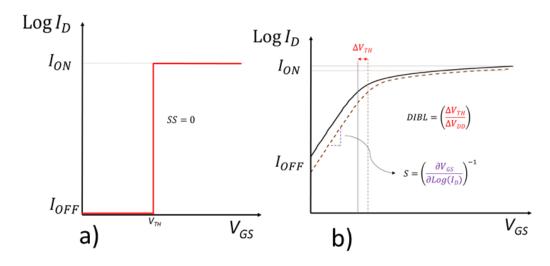

For logic applications, the ideal MOSFET electrical characteristics should be similar to those of the *ideal* switch shown in Fig. 3 a). If the voltage difference applied between source and gate  $V_{GS}$  is smaller than a certain threshold voltage  $V_{TH}$ , no channel is formed and there is no current flow between source and drain ( $I_{OFF}\cong 0$  in a first approximation). Once  $V_{GS}>V_{TH}$  a current path (channel) between source and drain is formed ( $I_{ON}\neq 0$ ). In an ideal switch,  $I_{OFF}=0$  and the resistance of the channel is negligible ( $R_{ON}=0$ ). However, real MOSFETs always present finite  $I_{OFF}$  see Fig. 3 b). This OFF current is called the leakage current. The value of  $I_{OFF}$  depends on the temperature (diffusion current), on short channel effects (*e.g.* DIBL and  $V_{TH}$  shift), on ultra-short channel effects, on direct tunneling and on the junctions quality [CHEN 1987].

Fig. 3: a) Characteristic curve of an ideal switch: the switch presents a steep slope. b) n-MOSFET Characteristic curve, drain current vs.  $V_{GS}$  showing the subthreshold slope and the drain induced barrier lowering

The various MOSFET technologies are benchmarked with some merit factors that are listed below:

| $I_{OFF}$ | Leakage current                                                                        |  |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| $I_D$     | Drain current (corresponding to the saturation current $I_{ON}$ for logic application) |  |  |  |  |  |  |

| DIBL      | IBL Drain-Induced Barrier Lowering                                                     |  |  |  |  |  |  |

| SS        | Subthreshold Swing (S <sup>-1</sup> )                                                  |  |  |  |  |  |  |

The subthreshold swing SS (inverse subthreshold slope) is defined as the change in gate voltage required changing the subthreshold drain current by one decade. In a bulk transistor, it is given by the following expression:

$$SS = \frac{\partial V_g}{\partial \psi_s} x \frac{\partial \psi_s}{\partial log I_{DS}} = m \times n = \frac{kT}{q} ln 10 \times \left(1 + \frac{C_{dep}}{C_{ox}}\right)$$

Eq. 1

Where  $\psi_s$  is the potential at Si/insulator interface, m is called body factor, which depends from  $C_{dep}$  the depletion region capacitance, and  $C_{ox}$  the gate-to-channel (oxide) capacitance in MOSFET,  $m = \frac{kT}{q} \ln 10$ , k is the Boltzmann constant, T is the absolute temperature. In some devices such as SOI transistors of GAA MOSFETs,  $C_{dep}$  is replaced by the capacitance between the channel and ground, which can be much smaller than  $C_{ox}$ , in which case the body factor n can have a value close to 1.

A lower value of SS means that a lower gate voltage swing is required to turn the transistor from the OFF to the ON state (or: to reach  $V_{TH}$  for a given  $I_{OFF}$ ). The subthreshold swing has a theoretical minimum value of 60 mV/dec. for a conventional silicon device, at T=300K [GoDOY 2001].

#### 1.3.1 MOSFET SCALING LIMITS

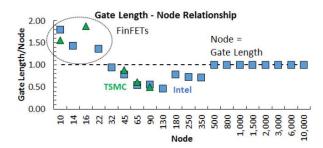

Moore's law reigned for more than 50 years, and each 18 months the semiconductor industry launched a new generation labeled by a technology node (specific manufacturing process and design rules). The technology node numerical value corresponds to the MOSFET gate length  $L_G$  until node 32nm. Nowadays, the node numerical name is chosen with respect marketing strategies and its value does not have to correspond to physical gate length see Fig. 5.

Since 1974, transistor scaling was driven by employing "Dennard scaling rules" that required to maintain a constant electric field in the transistor [DENNARD 1974] see Fig. 4. Those scaling rules allowed to increase transistor performance, and to reduce power consumption while decreasing linearly dimensions and supply voltage. In other words, they allowed maintaining power density constant.

| TABLE I<br>SCALING RESULTS FOR CIRCUIT PERFORMANCE |                |  |  |

|----------------------------------------------------|----------------|--|--|

| Device or Circuit Parameter                        | Scaling Factor |  |  |

| Device dimension $t_{ox}$ , $L$ , $W$              | 1/κ            |  |  |

| Doping concentration $N_a$                         | κ              |  |  |

| Voltage $V$                                        | $1/\kappa$     |  |  |

| Current I                                          | $1/\kappa$     |  |  |

| Capacitance $\epsilon A/t$                         | $1/\kappa$     |  |  |

| Delay time/circuit VC/I                            | $1/\kappa$     |  |  |

| Power dissipation/circuit VI                       | $1/\kappa^2$   |  |  |

| Power density VI/A                                 | 1              |  |  |

Fig. 4: Scaling relationship to maintain power density constant while improving performance. [Dennard 1974]

Fig. 5: Gate length vs technology node showing that scaling the equation gate length=node is no longer valid. [JONES 2017]

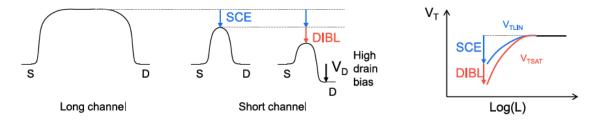

However, as the transistor size reached sub-µm dimensions undesirable effects, such as short channel effects started appearing Fig. 6. The short channel effects appear when the channel length is comparable with the depletion layer width of source and drain junctions, which results in lowering the threshold voltage. Additionally, if a high voltage is applied to the drain the barrier between drain/channel junctions is further reduced (Drain-Induced Barrier Lowering) reducing the electrostatic control of the transistor.

Further, in FDSOI and FinFET technologies, when the channel thickness reaches ~7nm dimensions, quantum effects such as carrier confinement or tunneling start to influence the transistor behavior.

Fig. 6: Schematic showing the short channel effect and the DIBL due to the channel length downsizing figures from [Berthelon 2018]

#### 1.3.1.1 PERFORMANCE-LEAKAGE TRADE OFF

The CMOS power consumption per clock cycle can be divided in two components Eq. 2: Dynamic power consumption (Eq. 3), proportional to activity factor  $\alpha$ , input signal frequency f, load capacitance  $C_{LOAD}$ ; and static power consumption, proportional to leakage current  $I_{leak}$  and supply voltage  $V_{DD}$ . The static power consumption represents the power consumed when the circuit is in standby.

$$P_{consumptions} = P_s + P_{dyn}$$

Eq. 2

$$P_{dyn} = C_{LOAD} * V_{DD}^2 * f_c * \alpha$$

Eq. 3

$$P_{\rm S} = V_{\rm DD} * I_{\rm leak}$$

Eq. 4

For simplifications, we can consider that the *subthreshold leakage* is the only source of leakage (Eq. 5), since it is the main contributor to the MOSFET off-state current  $I_{OFF}$ . This current corresponds to the current measured on the drain when the transistor is OFF ( $V_{gs}$ =0) and  $V_{DS}$ =  $V_{DD}$ .

$$I_{leak} \approx I_0 e^{\frac{-V_{TH}}{SS}}$$

Eq. 5

$I_0$  is the current at threshold  $V_G = V_{TH}$ . Thus, the leakage current  $I_{OFF}$  is limited by the subthreshold swing at given  $V_{TH}$  and  $I_0$ . For a chip with 100 million transistors, the average  $I_{leak}$  of turned-off devices should not exceed a few times 10nA, which corresponds to a total current of 1A and a standby power dissipation of 1 watt if  $V_{DD}$ =1V. In practice, because the subthreshold slope cannot be decreased below 60 mV/dec., the threshold voltage must be kept to values higher than approximately 0.3V at operating temperature [KISHORE, 2013].

Reducing dynamic power consumptions requires reducing  $V_{DD}$ , and while reducing  $V_{DD}$ , to maintain speed and, therefore, a high on current, it is necessary to reduce  $V_{TH}$  together with  $V_{DD}$ .

$$f_{perf} \propto \frac{I_{ON}}{C_{LOAD}} \propto \frac{(V_{DD} - V_{TH})^2}{C_{LOAD}}$$

Eq. 6

However, scaling  $V_{TH}$  results on an exponential increment of leakage, according to Eq. 6, augmenting static power consumption. Hence, decreasing dynamic power consumption increases static power consumption. Therefore, there is a limit in total power dissipated per operation for any CMOS based digital circuit.

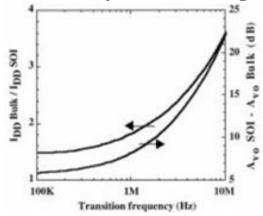

Fig. 7: Example of comparison of simulated total current dissipation and DC open-loop gain performance of the bulk and SOI cascoded CMOS OTAs as a function of the transition frequency. [FLANDRE 1999]

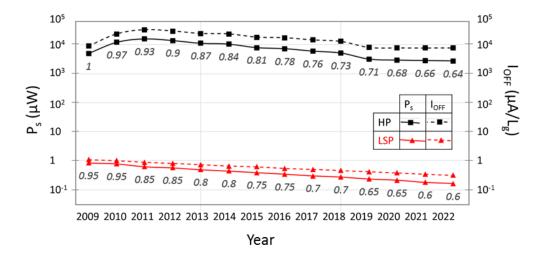

For the reason above, CMOS technology can be found in various flavors. Sorted by leaking/performance trade-offs, *i.e.* CMOS can be optimized for High-Performance (HP), Low Power (LP) and Low Standby Power (LSP) applications (see Fig. 8).

- **Increasing Performance**: *e.g.* for high-performance computing, CPU speed comes at the expense of power consumption.

- **Decreasing Power Consumptions**: application that requires Low Standby Power LSP, are for example mobile, IoT sensors, or Low Operating Power LOP devices, *e.g.* smart phone processors.

Fig. 8: Single device static power consumption ( $P_s$ ) and leakage current VS year for High Performance and Low Standby Power application, data adapted from IRDS 2017 Reports.

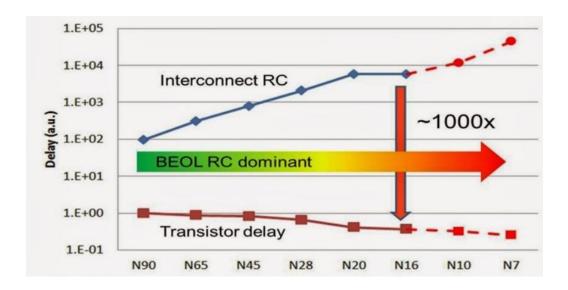

Another problem of scaling is an overall increase of delay at the circuit level (to not be confused by the delay at the device level). Scaling increases the transistor density by reducing physical dimensions; metal line width and thickness is also reduced, but the length of global interconnects is not. As a result, the metal interconnection delay (RC) keeps increasing with scaling and interconnect delay becomes dominant over the gate delay (Fig. 9). Therefore, the global circuit delay is degraded due to the dominance of the capacitance of the metal lines. To address this challenge, copper has replaced aluminum [INFOWORD, 1997] and, to decrease the capacitance coupling between metal lines air gaps are introduced [SHIEH 1998]. However, interconnects delay nowadays, still limits the circuit performance. Monolithic 3D integration processing, such as CoolCube<sup>TM</sup>, can help in reducing the interconnect delay by shortening the overall metal interconnection length. The transistor performance can be maintain using a less aggressive transistor scaling, but the transistor density can be preserved or improved by stacking devices on the top of each other.

Fig. 9: Projection of on-chip electrical interconnect delays with technology scaling [Yeap 2013]

Despite the power challenges presented above, there still are many opportunities to optimize and to extend the life of CMOS for quite some time. However, the minimum energy point in CMOS between active and static energy consumption is obstacle in the way of achieving ultra-low power and energy-efficiency circuits. One way to improve this minimum energy point is to decrease the subthreshold slope of the switching device. Several devices proposed as alternatives have demonstrated a subthreshold swing below 60mV/dec.

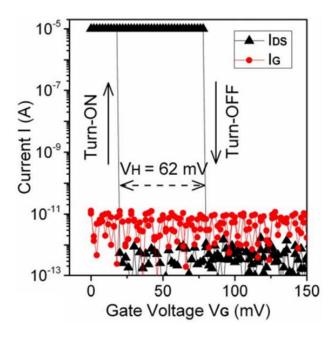

Among these devices, we will focus on nanoelectromechanical relay that shows a competitive energy-efficient technology. NEMS relays exhibit abrupt turn-on/turn-off behavior and can operate at very low voltages ( $e.g. \sim 50 \text{mV}$  [OSOBA 2016]) providing for low dynamic power consumption. NEMS relay also exhibits zero  $I_{OFF}$  (leakage current), which eliminates static power consumption.

#### 1.4 MEMORY HIERARCHY

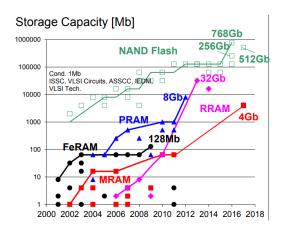

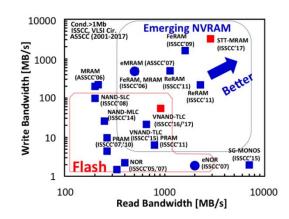

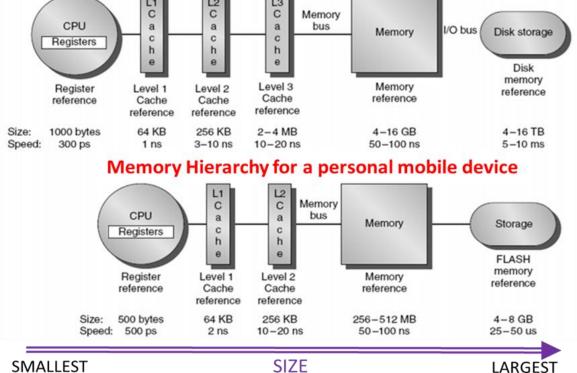

The scaling race has created a large gap between the central process unit CPU access time and speed (<1ns and 10GB/s) and out of CPU memory (e.g. Dynamic Random Access Memory DRAM ~10-30ns, Flash ~1ms). In general, memory improvements have mostly been in terms of data density (Fig. 10), rather than in terms of read/write data bandwidth (transfer rates), as shown in Fig. 11 and accordingly a "memory hierarchy" has been established.

Fig. 10: Memory capacity trend of emerging non-volatile memories from [ISSCC 2017]

Fig. 11: Read/write bandwidth comparison of non-volatile memories [ISSCC 2017]

Fig. 12 shows the memory hierarchy, which is established considering size (bytes), access time and memory type. Designing computers for high performance requires considering the memory restrictions showed by the memory hierarchy, *i.e.* the size and capabilities of each component. CPU are very fast (>2.5GHz) but need to spend much of their time idling, waiting for memory I/O transfers to complete. This bandwidth gap between processor and memories it is known as the Von Neumann bottleneck [BACKUS 1977]. For example, there is a large gap between Flash memories and DRAM. Flash main issues are latency and low write bandwidth, as shown in Fig. 11. In addition, typical endurance parameter for FLASH is about 10<sup>6</sup> cycles whereas DRAM requires 10<sup>15</sup> cycles endurance [PALMA 2013]. Another limitation is the high operating voltage of FLASH memories that is a problem for advanced CMOS node. As result, novel memory candidates are under investigations. With lower latency, higher bandwidth and process compatibility with CMOS technologies.

Fig. 12: Schematics of Memory hierarchy system for server and personal mobile device, adapted from [Silvano 2012]

LARGEST

#### 1.5 GENERAL REVIEW OF BEYOND CMOS DEVICES

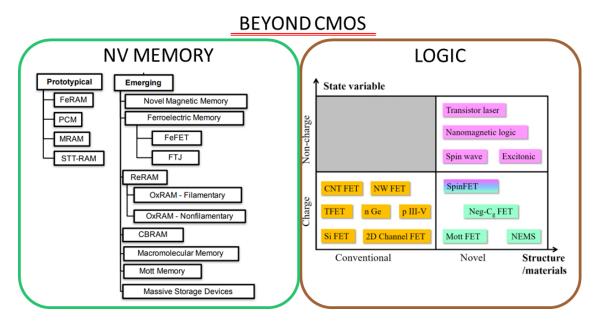

The International Technology Roadmap for Semiconductors 2.0 (ITRS) has identified devices with the potential capability to achieve SS below 60 mV/dec., those devices are in the categories of "Beyond-CMOS" devices [2013 ITRS]. ITRS has also identified nonvolatile memory devices that have high performance and robustness, that are nonvolatile and have a low cost per bit. Some of the beyond CMOS devices and memories are prototypical and some are still under study for both existing and new functions to extend the IC scaling. Beyond CMOS technologies have to increase efficiency, functionality and performance of the integrated circuit. Those devices, to enter on the productions have to fulfill some conditions: firstly, they have to be competitive with the MOSFET or have to introduce new functionality to the MOSFETs circuitry. Secondly, Process fabrication of these steep slope devices must be compatible with the co-integration of MOSFETs and monolithic 3D power scaling.

In Fig. 13 are listed two classes of beyond CMOS devices, the logic and the nonvolatile memory. For logic, one of the major challenges is to reduce the subthreshold swing, in order to reduce the power consumption, targeting ultra-low power applications. For memories, the challenges are that they should be scalable above the current limits of SRAM and Flash, CMOS process flow compatible, and should combines the best features of current memories: non-volatility with high speed and high density.

Fig. 13: Overview of the leading Beyond CMOS memories and logic devices adapt from [IRDS 2017]

#### 1.5.1 BEYOND CMOS LOGIC DEVICES

Ultra-low power applications need devices capable to abruptly switch ON and OFF without spending a great amount of supply voltage. The figure of merit SS gives an immediate information about this capability because it indicates how much voltage is needed to increase the  $I_{ON}$  current one decade (see Eq. 1 for MOSFET). For beyond CMOS devices Eq. 1 is no longer valid, either because of their different structure or because different actuation mechanism and/or current path/emission with respect the MOSFET.

Device such as Tunnel FET and Impact Ionization MOS have a smaller *n* factor than the MOSFET because they are not driven by thermionic emission and they are not limited by Maxwell-Boltzmann distribution. Devices such as negative capacitance Neg-Cg and nanoelectromechanical NEM relays have a very steep slope, with body factor below unity.

However, lowering SS is not enough to be completely competitive with MOSFET, it is also necessary to be competitive in terms of cost and in terms of speed and scaling for a given applications. In the next paragraphs a brief description of beyond CMOS steep slope devices, their operation methods and physics is given.

#### 1.5.1.1 TUNNEL FIELD EFFECT TRANSISTORS

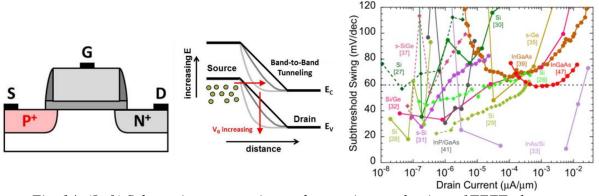

The tunnel Field-Effect Transistor (FET) switch mechanism relies on the modulation of band-to-band tunneling to inject carriers and obtaining an  $I_{ON}$  current. Therefore, TFETs can potentially have a subthreshold swing smaller than 60mV/dec. [REDDICK 1995]. Their physical structure is similar to that of a MOSFET but the source and the drain are differently doped (e.g. in homojunction TFETs the source is N doped for P-TFETs and it is P doped for an N-TFET, see Fig. 14 (left). The TFET lowest measured sub-threshold swings approach 20 mV/decade, however this result is obtained for a narrow range of subthreshold currents [TOMIOKA 2012]. Additionally, in TFETs, low subthreshold slope it is not always accompanied by high ON current comparable to the CMOS  $I_{ON}$ . The highest TFET  $I_{ON}$  current is observed at  $1nA/\mu m$ , but for a SS=60mV/dec. [DEWEY 2011]. Otherwise, for SS<60mV the highest  $I_{ON}$  current is ~0.1nA/ $\mu m$  [LU 2014] see Fig. 14 (right).

Fig. 14: (Left) Schematic cross section and operation mechanism of TFET, the turn on operation is based on gate-voltage modulation of the channel potential with carrier injection through the potential barrier via band to band tunneling [Kim 2012]. (Right) Comprehensive plot showing TFET sub-threshold swing Vs I<sub>D</sub> (drain current) per unit width for TFETs having SS below 60 mV/decade [Lu 2014].

The discrepancy between the measured characteristics and the simulated curves is due to the fact that in the simulation many secondary interface effects are neglected. For example, a typical neglected secondary effects is the trap-assisted tunneling (TAT) which is an interface and temperature dependent effect causing band to band tunneling even when the device is supposed to be off, resulting on generation of currents degrading the subthreshold slope [DIAZ LLORENTE 2018].

#### 1.5.1.2 IMPACT IONIZATION MOSFET IMOS

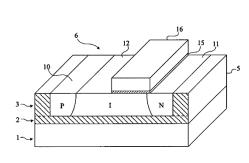

Fig. 15: Schematic cross view of a IMOS-type transistor [Charbuillet 2006]

Fig. 16:  $I_D$  versus  $V_{GS}$  characteristic for an n-channel IMOS and n-MOS [SENG 2012A]

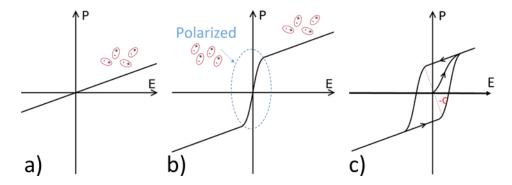

The impact-ionization field effect transistor (IMOS) modulates voltage breakdown of a gated p-i-n structure in order to turn ON and OFF the transistor, using impact ionization and avalanche breakdown [GOPALAKRISHNAN 2002]. The avalanche breakdown is a form of electric current multiplication enabling a steep increase of carrier multiplications (high  $I_{ON}$  current). The avalanche process occurs when the electric field, due to the gate voltage, accelerates source carriers until their energies is sufficient to create mobile or free electron-hole pairs via collisions with bound

electrons of the intrinsic region. Very steep slopes have been demonstrated: on silicon-on-insulator wafers (SOI), using a standard CMOS process, a subthreshold swing of 6mV/dec. and 2 mV/dec. respectively for n and p I-MOS [MAYER 2006]. The challenges are that the avalanche breakdown requires very high electric field leading to high drain bias (~20V) [GOPALAKRISHNAN 2002]. Additionally, IMOS devices are intrinsically slow due to the statistical avalanche charge multiplication process, and speed limitations due to carrier multiplication delay and statistical retardation delay. There is also the problem that the hot carrier injected in the gate dielectric causes a voltage threshold and SS degradation.

## 1.5.1.3 NEGATIVE CAPACITANCE FIELD-EFFECT TRANSISTOR (NEG-CG FET)

The majority of dielectrics have a linear relation between the electric displacement field  $\vec{D}$  and electric field  $\vec{E}$  (Eq. 7), where  $\varepsilon_0$  is the vacuum permittivity and  $\varepsilon_r$  is the relative permittivity. The permittivity is also related to the susceptibility  $\varepsilon_r = (1 + \chi)$  that is the proportional factor between the electric field and polarization density  $\vec{P}$  of individual particles on the material Eq. 8 and Eq. 9. In paraelectric materials, the permittivity is not linear, and it depends on the strength of the electric field as Eq. 9.

$$\vec{D} = \varepsilon_0 \varepsilon_r \vec{E}$$

Eq. 7

$$\vec{D} = \varepsilon_0 (1 + \chi) \vec{E} = \varepsilon_0 \vec{E} + \vec{P}$$

Eq. 8

$$\varepsilon_r = \frac{\vec{P}}{\varepsilon_0 \vec{E}}$$

Eq. 9

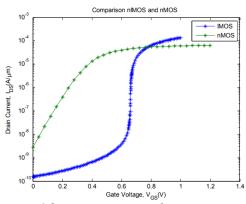

Ferroelectric materials, besides being paraelectric, have an intrinsic or spontaneous nonzero polarization even when no electric field is applied. Applying a strong electric field on the opposite direction can reverse this spontaneous nonzero polarization. The final polarization depends on the value of the previous polarization and on the applied electric field, giving a hysteresis loop. Fig. 17 shows the polarization as a function of the applied electric field, for the case of a linear polarization, paraelectric polarization and ferroelectric polarization, where the permittivity is the slope of the P(E).

Fig. 17: a) Linear Polarization b) Paraelectric Polarization c) Ferroelectric Polarization

Thanks to their behavior, ferroelectric materials can be inserted in the gate stack of MOSFETs, between the gate and the semiconductor channel to create a "negative capacitance" effect [APPLEBY 2014; CATALAN 2015] in order to obtain a subthreshold swing below <60mV/dec. [LEE 2017; Li 2015]. The negative capacitance [SALAHUDDIN 2008] allows one to boost and increase the surface potential for a same voltage applied to the gate, allowing obtaining a subthreshold swing smaller than 60mV/dec. (see Eq. 10), being  $C_{FE}$  the negative ferroelectric capacitance. The fact that the surface potential increases faster than the gate voltage allows creating a large amount of carrier and a higher current compared to the MOSFET.

$$SS = \left(1 + \frac{C_S}{C_{FE}(<0)}\right) \times \frac{kT}{q}$$

Eq. 10

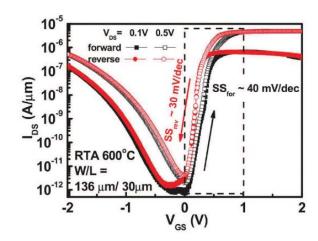

Sub-20-mV/decade Subthreshold Slope have been demonstrated [Ko 2017]. One of the challenges of this negative capacitance transistor is that sometimes the ferroelectric material stays polarized inducing a shift on  $V_{TH}$  and a hysteresis effect in the  $I_D$  vs  $V_G$  curve. Consequently, a big challenge resides in the identification of appropriate materials (oxides and ferroelectrics) for the best swing with minimal hysteresis. Even if recently was reported a small hysteresis window with  $V_{TH}$  shift below 0.1V see Fig. 18. Integrating high-quality single-crystalline ferroelectric oxides on silicon stays a challenge [MIKOLAJICK 2018].

Fig. 18: Transfer characteristics (I<sub>DS</sub> vs V<sub>GS</sub>) of FE-HZO FETs with a hysteresis window <0.1 V for 600°C annealing [Lee 2015].

## 1.5.2 BEYOND CMOS EMERGING NON-VOLATILE MEMORIES

Usually, systems-on-chip for low-power applications separate volatile and nonvolatile memories in two different macros. The nonvolatile macro is made using nonvolatile memories NVMs such as Flash. NVMs generally require a high voltage and have high dynamic power consumption during read/write operations. Usually NVMs are slow and have limited endurance. However, the limited endurance is not a showstopper for the NVs macro. Especially because of the FLASH serial peripheral interface SPI which resulting on sequential access of data, relaxing endurance requirements. The positive aspect of these two macros approach is that NVMs enables to switch off the power supply and to suppress standby power (e.g. in a mobile chip), thereby extending battery life without a loss of data. The negative aspect is the long power off-on time that requires power intensive task caused by the transfer operation between the two macros limiting the battery lifetime. The volatile macro is usually made by Static Random Access Memory SRAM that is the best candidate to achieve high performance with low voltage and high endurance. In fact, SRAM provides on-chip storage, high speed read/write operations and a low minimum supply voltage (e.g. 5.36GHz for 1.115V @7nm [CLINTON, 2018]). Unfortunately, SRAMs are unable to preserve data when the power supply is turned off.

Nowadays, many applications are very data intensive, requiring both real-time and offline manipulation of great amounts of data. Extended battery life and rapid, reliable power on/off operations are very important for mobile applications (*e.g.* smartphone, smartwatch). Most of the time, those applications have relaxed workload, but need a high performance burst right after being powered up. In addition, many wireless electronics or bioelectrical devices and sensor applications

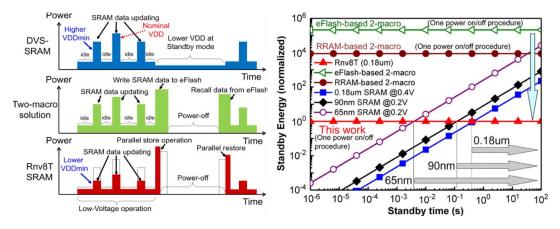

are usually in stand-by or in deep sleep mode and needs to quickly activate to perform few necessary tasks before returning to an inactive state. Dynamic voltage scaling (DVS) is a popular approach to suppress active-mode standby power and dynamic power by adjusting the operating voltage but it does not completely suppress the stand-by-power consumption Fig. 19 left. Moreover, when the standby time is long the standby power becomes significant Fig. 19 right. The two-macro solutions eliminate the need of stand-by power but create the need of additional power to transmit the data.

From here the idea or the necessity to combine high performing SRAM with NVMs having ultra-low standby power, obtaining NV-SRAM. The main idea is to integrate the NV element at the standard cell level, in such a way that the store and restore operation can be done bit-to-bit, which allows lowering store and restore time, memory latency time, and avoiding data retention failure due to powering off the volatile memory.

Fig. 19: (Left) Power consumption of Dynamic voltage scaling SRAM, two macro solutions, and NV resistive SRAM and (Right) Comparison of standby mode energy consumption [Chiu 2012]

Many Beyond CMOS NV memories could be used for NV-SRAMs, such as magnetic spin transfer torque memory (STT-RAM), phase change memories PCM and FeRAM which are prototypical. But there are also emerging beyond CMOS NV memories that need further investigation such as Resistive RAM (RRAM) (*e.g.* Oxide based RAM OxRAM, Conductive Bridging RAM CBRAM) and nanoelectromechanical NEM switches. Example of Resistive NVSRAM cell can be found in [CHIU 2012] and example of RRAM based ternary content addressable memory (TCAM) can be found in [GROSSI 2018]. Within the scope of this thesis, NV NEMS/SRAM and TCAM cells have been investigated and fabricated.

#### 1.5.2.1 RESISTIVE RAM (RRAM)

In general, the term Resistive RAM includes all the memories that are made by two electrodes that sandwich a resistive layer. There are two main families of RRAM:

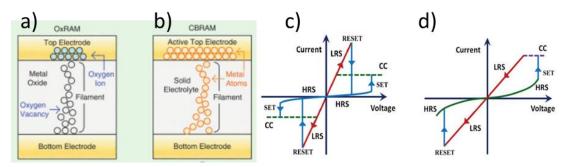

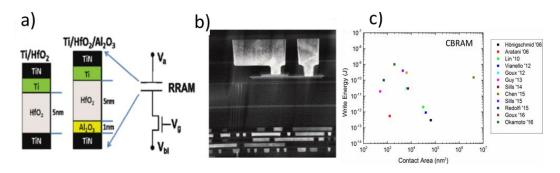

The Oxide RAM (OxRAM) and the Conductive Bridge RAM (CBRAM). OxRAMs are based on filamentary switching made by oxygen vacancies while CBRAM are based on metal ion filamentary switching, as shown in Fig. 20 (left). The standard operating behavior of a RRAM cell is composed of three different states. A highly resistive state, which corresponds to the resistance state just after processing, a low resistive state (LRS) or written state, that occurs once a path between the two electrodes into the resistive layer is created (filament formation) and a high resistive state (HRS) that occurs once the path is dissolved (filament dissolution). The conductive path or conductive filament is created at first with a forming operation at high voltage. RRAM can be also classified by their switching mechanism. In fact, there are two main switching modes: the unipolar and the bipolar modes. The unipolar switching direction depends on the amplitude of the applied voltage but not on its polarity, meaning that SET and RESET can happen on the same polarity. On the contrary, for bipolar switching the SET can only occurs at one polarity of the applied voltage and RESET to the reverse one Fig. 20 (right). OxRAM Bipolar switching can be achieved with 100uA compliance current, after initial forming at ~ 2.8V [AZZAZ 2015]. TaOx and HfOx are the most common switching materials used for OXRAM. For the CBRAM the filament or conductive bridge is usually made by Cu/Ag ions, rather than oxygen filament (e.g. of schematic and TEM cross section of OxRAM in Fig. 21 a) and b)).

Fig. 20: (Left) A schematic RRAM based on oxygen vacancies in the filament in the oxide, referred to as OxRAM (a). RRAM based on metal ions diffusion from active electrode to form conductive bridge in solid electrolyte, referred to as CBRAM b). Adapted From [Yu, 2016]. (Right) Schematic of I-V curves showing the two RRAM modes of operation: (c) Unipolar and d) Bipolar adapt from [Grossi 2016].

Fig. 21: (a) Schematics of the RRAM cells integrated into a 1t1R structure (b) TEM cross section of the cell from [Azzaz 2015] integrated in 28nm CMOS technology. (c) CBRAM Write energy vs Contact area Adapted from [Wong 2018]

This kind of memory needs a selector device to avoid sneak current problems and to give current compliance. In fact, a permanent dielectric breakdown during the Set process could occurs if any current compliant is imposed. A big advantage of Re-RAM technologies is that they have the potential to achieve a  $4F^2$  cell, and they can be stacked in 3D architecture to enhance memory density that positions them very well for scaling. Switching from one state to the other requires 10 ns, and energy roughly on the order of 0.1–5pJ can be assumed for programming. Retention and endurance can vary over a wide range depending on the material choice for the stack. OxRAM endurance is >10<sup>6</sup> with value of high resistance  $10^5 \,\Omega$  and low resistance of  $10^3 \,\Omega$  [AZZAZ 2015]. For the RRAM a trade-off between write energy and retention is necessary, because higher writing energy gives filament robustness. Hence typical writing voltage is around 2V and writing current between  $100\mu$ A- $200\mu$ A for 100ns, obtaining a typical writing energy of 20pJ-40pJ. To read the memory the current is around 1- $10\mu$ A,  $V_G$ ~<2V [Jurczak, 2015], obtaining a typical reading energy of 0.1pJ-1pJ. See Fig. 22 for reference.

|                             |                | A. CBRAM                           | B. OXRAM                          | C. OxRAM - Interface      |

|-----------------------------|----------------|------------------------------------|-----------------------------------|---------------------------|

| Storage Mechanism           |                | Electrochemical filament formation | Valence change filament formation | Change in interface       |

| Feature size F              | Best projected | <5nm [A1]                          | <5nm                              | <10nm [C1, C2]            |

|                             | Demonstrated   | 20 nm (GeSe) [A2]                  | 3 nm [B1]                         | 30nm [C3]                 |

| Cell Area (2D)              | Best projected | 4F <sup>2</sup>                    | $4F^2$                            | 4F <sup>2</sup>           |

|                             | Demonstrated   | 4F <sup>2</sup> [A3]               | 4F <sup>2</sup>                   | $4F^2$                    |

| Read Current                | Best projected | not available                      | not available                     | n/a                       |

| Read Current                | Demonstrated   | 100 pA [A4]                        | ~ 100 pA [B2]                     | 0.1μA [C3]                |

| W/E time                    | Best projected | <1ns                               | <1 ns                             | <10ns [C1, C2]            |

|                             | Demonstrated   | < 1ns [A5]                         | 100ps [B3] 85ps (AlN) [B4]        | 10ns [C1, C2]             |

| Retention Time              | Best projected | >10yr                              | > 10yr                            | 3yr @ 55°C [C2]           |

|                             | Demonstrated   | >10 yr (1000hr 200°C) [A6]         | > 10 yr (50 days @ 250°C) [B5]    | 180 days @ 110°C [C3]     |

| Write Cycles                | Best projected | > 10 <sup>11</sup> [A7]            | >105 @ 240°C (B6)                 | >10 <sup>12</sup> cy [C5] |

|                             | Demonstrated   | 10 <sup>10</sup> [A7]              | 10 <sup>12</sup> [B7], [B8]       | 10 <sup>12</sup> cy [C5]  |

| Write operating voltage (V) | Best projected | <0.5V                              | <1V                               | n/a                       |

|                             | Demonstrated   | 0.4V [A8]                          | 110mV [B9]                        | <3V (pulsed) [C1]         |

| Bond enguating voltage (U)  | Best projected | <0.1V                              | 0.1 V                             | n/a                       |

| Read operating voltage (V)  | Demonstrated   | 0.05V [A9]                         | 0.1                               | 0.1V [C3]                 |

| III                         | Best projected | not available                      | 0.1 fJ [B10]                      | n/a                       |

| Write energy (J/bit)        | Demonstrated   | 0.1-10pJ [A10]                     | 3.8fJ SET, 20fJ RESET [B11]       | <1pJ [C1, C2, C4]         |

Fig. 22: [IRDS 2017] Reports RRAM Demonstrated and projected parameters.

#### 1.5.2.2 **NEMS**

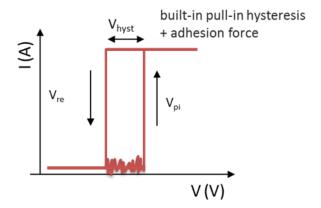

With Nanoscale electromechanical switches (NEMS) it is possible to controls the presence (or absence) of current by making (or breaking) a physical contact between two conductive electrodes. The two electrodes are normally separated by an air gap, allowing achieving virtually "zero" leakage current and abrupt switching. Fig. 23 shows typical I-V curves, where  $V_{PI}$  is the voltage to be applied to pull the movable electrode into the contact electrode and  $V_{PO}$  is the voltage at which the contact is broken. The NEMS typically have a hysteresis that depends on the design, contact material, contact surface and cycling. Because of their steep slope and zero leakage current there is a high level of interest on using NEMS for ultra-low power applications [LIU 2017A; OSOBA 2018; XU 2014A; BEIU 2014].

Fig. 23: Typical I-V transfer characteristic of a NEM switch: source [Qian 2017a]

Various actuation mechanism can be employed for mechanical actuation such as electromagnetic, electrothermal, piezoelectric and electrostatic. For the scope of this thesis only the electrostatic mechanism will be detailed but here a brief explanation of the various mechanism will be given.

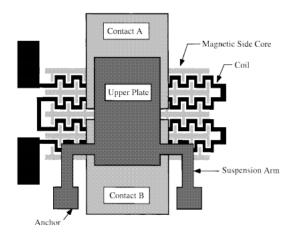

#### 1.5.2.2.1 ELECTROMAGNETIC

An electromagnetic switch uses magnetic force to actuate a movable electrode to make a contact, see example in Fig. 24. The movable electrode in response to the magnetic field moves, and once the magnetic field is removed (or reversed the magnetic polarity), the movable element goes back to its original position (thanks to the restoring spring force. Most of the electromagnetic switches employ external permanent magnet [Wu, 2010], which is a disadvantage because of its incompatibility with CMOS ICs. Otherwise some electromagnetic relays employs micro-coils to create electromagnetic field to move the element [GLICKMAN 2011]. However, this kind of relay is not suitable for low-power applications because the micro-coils requires high static power dissipation [DELEONIBUS 2018].

Fig. 24: Schematic view (left) and photograph (right) of an electromagnetic cantilever microrelay [Taylor 1998]

#### 1.5.2.2.2 ELECTROTHERMAL

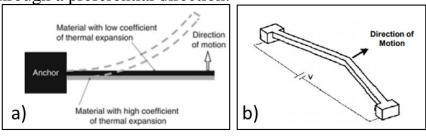

An electrothermal relay actuates through joule heating effect caused by passing current through a conductor and inducing thermal expansion and contraction of a movable element.

The thermal actuator is generally made by a single material [UDESHI 2004], with a specific geometry shape that allows elongation [LI 2010B], rotation [Dellaert, 2015] or bending through a preferential direction.

Fig. 25: Examples of thermal actuator designs, including bimorph (a) [Riethmuller, 1988] (b) geometry-based (V-shaped) [Girbau 2003]

However, such a switch can also be made by stacked layers of different materials, having different expansion coefficients (bimorph). The different thermal expansion between the two layers due to temperature increment results in a bending moment creating vertical displacement. This kind of relay can provide a very large contact force with low voltage; however, the power consumption and the actuation speed are higher than with respect the other types of relay. Examples of electrothermal actuator are represented in Fig. 26 and Fig. 27.

Fig. 26: SEM picture of magnetostatic and electrothermal MEMS switch [Wu 2010]

Fig. 27: SEM pictures of an electrothermal vertical displacement of a micro-mirror [Wu 2008]

#### 1.5.2.2.3 PIEZOELECTRIC

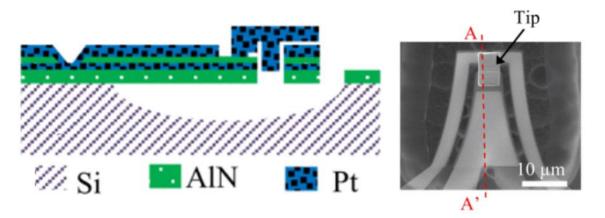

Piezoelectric relays exploit piezoelectricity to achieve amplified deflections to make/break contact. Piezoelectricity is the linear coupling between electric polarization ( $P_{ij}$ ) and strain ( $\epsilon_{ij}$ ) and stress ( $\sigma_{ij}$ ). In Fig. 28 is shown an example of piezoelectric relay.

Fig. 28: Schematic and SEM images of the triple beam NEM piezoelectric switch [Zaghloul, 2013]

The mechanical deformation (induced stress or strain) is obtained while applying a certain electric field. The deflection direction is usually perpendicular to the electric field. The beam deflection amplitude is linearly controlled by the magnitude of the applied electric field across the piezoelectric layers, allowing very low actuation voltages [CHEN 2015]. ~10 mV gate voltage swing, with body bias voltage applied are reached in [Zaghloul, 2013]. The hysteretic switching behavior is only due to contact surface adhesive force, such that the hysteresis voltage can be very small (~8mV). Typical material used for MEM switch applications include ZnO, AlN and lead zirconate titanate (PZT) [Trolier-McKinstry, 2004]. Compared

to electrothermal switches this relay technology offers better switching speed ~1 µs, and lower active power consumption [CHEN 2015]. However, to make them compelling to IC applications, piezoelectric relay should overcome the following challenges. a) Scaling: Lateral dimension scaling to increase device density at the scope of augmentation of functionality per area. Piezoelectric film thickness scaling to achieve low actuation voltage while maintaining low leakage current through the piezoelectric film. b) Maintaining stress uniformity: it is crucial to maintain the same stress profile across many devices and same stress gradient across the multilayer thin film stuck of piezoelectric actuator to achieve a uniform actuation voltage [Deleonibus 2018].

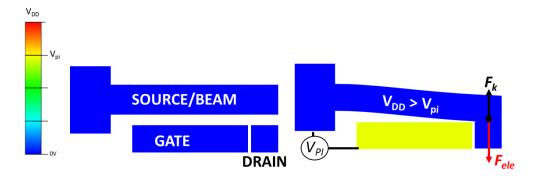

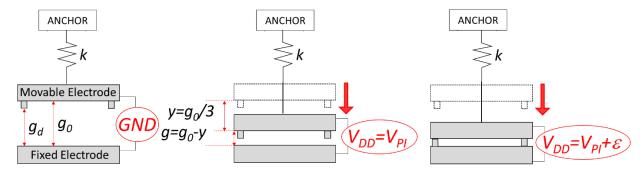

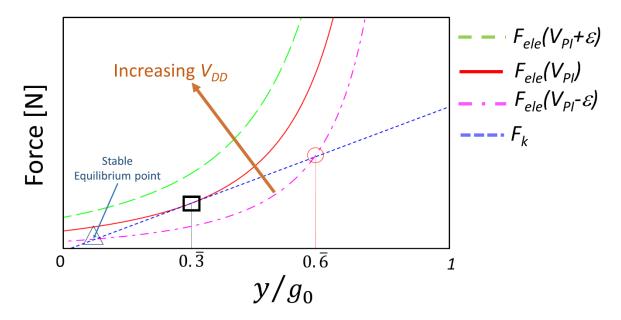

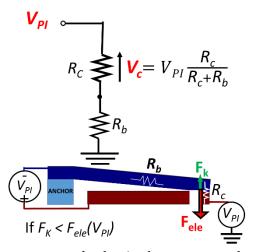

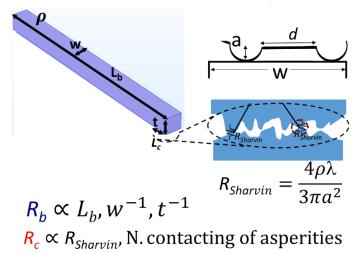

## 1.5.2.2.4 ELECTROSTATIC

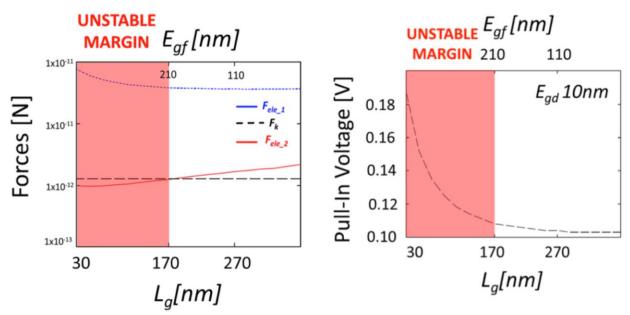

An electrostatic relay actuates thanks to capacitive effects. When a voltage difference between a fixed (gate) and a movable electrode (source) is applied, the charges of opposing polarity create an electrostatic force. By charging and discharging the capacitor, the movable electrode is attracted (by electrostatic force) or pushed away (by elastic force). If the potential value applied to the gate and the source corresponds to the pull in voltage  $V_{PI}$  than the source is able to pull into the contact electrode (drain). Source and drain are normally separated by an air gap, allowing zero off leakage current (zero static power consumption). The electrostatic force is not linearly dependent on the gap between gate and source, while the elastic force is. For this reason, when operating in pull-in mode (i.e. the gap between drain and source is 1/3 the gap between source and gate) electrostatic relay has a built-in hysteresis Fig. 29. In addition to this "built-in" hysteresis in pull-in mode, adhesion forces appear upon contact, counteracting the spring restoring force. This hysteresis is a drawback for logic switches, while it is an advantage for nonvolatile switches, allowing increasing CMOS functionality while adding a memory element to it. Electrostatic switches are the most used for mechanical switches because they can be fabricated above CMOS circuitry. Electrostatic nanorelays can achieve relatively fast switching speed (~100 ns). Moreover, NEMS shows promises for future low-cost, ultra-low-power electronics applications.

Fig. 29: Hysteretic behavior showing the pull in voltage and the release voltage that is always smaller than  $V_{pi}$ .

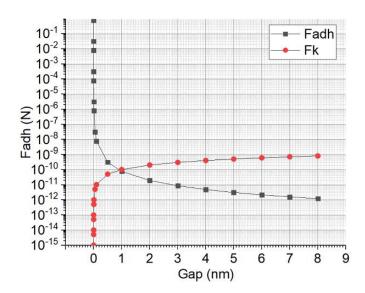

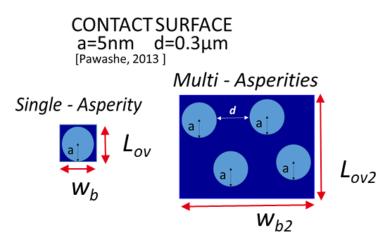

However, some challenges still need to be approached, such as the variability and reliability of the contact surface and consequentially the reliability and magnitude of contact resistance. For digital logic applications, the ON-state resistance ( $R_{ON}$ ) of a relay can be as high as ~10k $\Omega$  without significantly affecting circuit performance [Liu 2012]. For NON-Volatile application, the contact resistance needs to be lower than the resistance given by the CMOS technology (see Chapter 3).

# 1.6 THESIS GOAL

This dissertation aims to address the promises and challenges associated with Non-Volatile NEMS relay electrostatically actuated. It presents the fabrication of monolithically co-integrated NEMS above CMOS technology with the goal of achieving ultra-low power consumptions. The originality of this thesis work resides in exploring the NEMS as nonvolatile element to increase CMOS functionality together with energy efficiency.

The details of the chapters are as follows:

Chapter 2 gives overview of the NEM state-of-art, it introduces mechanical and electrical behavior of NEMS relays. It gives an extensive review of the suitable materials used to fabricate NEM relay device. It investigates about NEM relay challenges such as high and/or variable contact resistance, mechanical delay, and scaling limits. It gives general information about the issues that are still blocking the development of NEM relay technology.

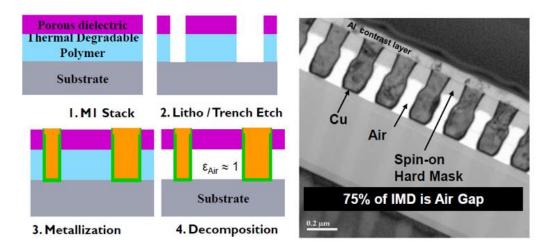

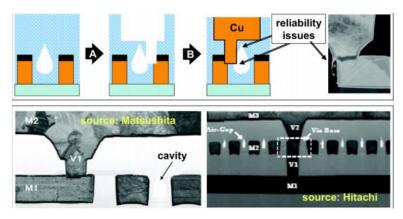

Chapter 3 covers design and modeling for non-volatile NEM relay. In particular, it deals with design studies such as: relay configurations, actuation type, and dimensioning of the relay parameters. The presented study aims at optimizing NEM relays in terms of reliability and performance and it is supported by simulations and modeling. Design strategies are presented in order to obtain a larger working margin that is robust to pull in voltage shift and variation due to cycling and/or pull in voltage variability due to fabrication. The chapter continues with a study that gives design guidelines for Non-Volatile NEM relay. The particularity of this study is that it considers the incertitude of adhesion force value and the possibility of catastrophic pull in (beam contacting the gate), resulting in a more robust approach. In the chapter two parentheses are opened; One to investigate volatile NEM relay scaling in terms of contact stability and contact resistance. The other parenthesis investigates the actual advantages of having air gap in the CMOS interconnections, to simplify the fabrication and release process of NV NEM relay. The chapter end with simulation studies of NV NEM relay implemented with SRAM using MEMS+ plugin for Cadence.

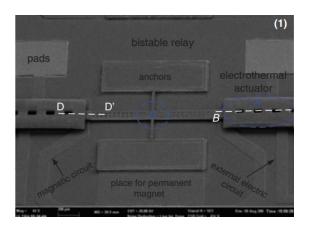

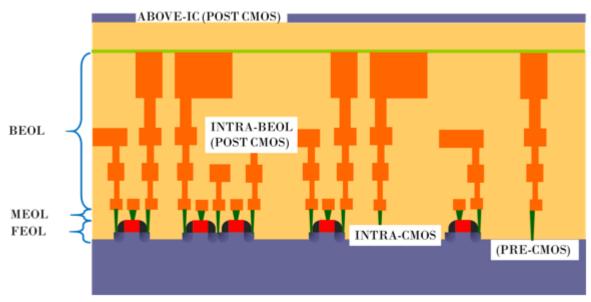

Chapter 4 discusses the fabrication of hybrid NEM/CMOS technology. It explores the feasibility and the interest of the co-integration between CMOS technology and NEM relays using monolithically 3D integration. In particular it presents the process flow to fabricate in-plane actuated relay defined on a mono-crystalline Silicon layer. This fabrication method is obtained by doping and annealing the mono-crystalline Si layer of an SOI wafer, followed by wafer bonding between a commercial CMOS technology wafer with functional circuits and the SOI wafer. The chapter ends with the presentation of electrical results of the fabricated technology.

Chapter 5 summarizes the key results and gives perspective for future research.

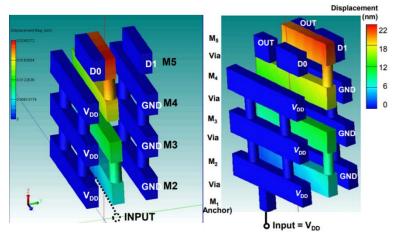

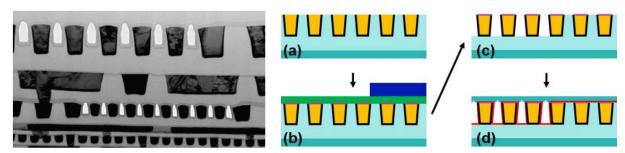

In the annexes two different fabrication approaches for monolithically integration of NEM relay with CMOS are explored: i) NEM relays defined on a polycrystalline Silicon layer above a commercial CMOS technology wafer. ii) Vertical defined NEM relays made by multi-levels of metal interconnections of a commercial CMOS technology wafer (ST 130nm). The first approach is obtained by depositing amorphous silicon p-doped in situ above a CMOS wafer and followed by laser annealing re-crystallization and dopant activation.

2 NEMS RELAY: STATE OF ART

# 2.1 INTRODUCTION

Technological development of Silicon and in general CMOS device fabrication technology has affected positively the development of micro/nano-electro-mechanical system. That is why, Nano-electro-mechanical (NEM) relays have been considered as good candidate for ultra-low power consumption microelectronics applications. From now on, on this manuscript the term NEM relay/switch will refer only to micro/nanoelectromechanical switches that are turned OFF and ON by making and breaking a contact through electrostatic actuations.

Many studies regarding the use of NEMS as logic switches to replace or help MOSFET have been published *e.g.* [KAM 2015]. At the same time, owing to the NEMS relay intrinsic hysteresis NEM switches have also been considered as good candidates for Non-Volatile applications and memory in computing [Xu 2014; Kim 2015; Usai 2017; Qin 2018].

The main opportunities offered by NEM relays are:

- 1) Zero off-state leakage.

- 2) Abrupt switching (ideally zero subthreshold swing).

- 3) Infinite ON/OFF current ratio.

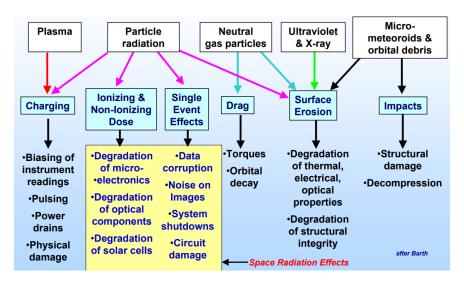

- 4) Ability to operate in harsh environment.

- 5) Non-Volatility depending on the design.

Despite the fact that simulations show low actuation voltages, only few experimental results effectively demonstrated sub 1-V actuation voltages [Zaghloul 2014; Osoba 2016; Qian 2017] exploiting the body-bias technique and adding an anti-adhesion coating. However, the body-bias technique requires the presence of an additional terminal, which increases the overall footprint.

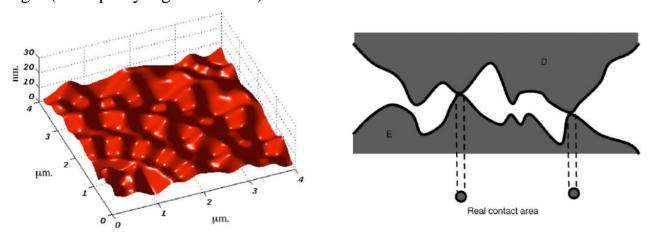

NEMS relay contact stability remains a reliability concern. In fact, over many switching cycles, a progressive alteration of the morphological and chemical properties of the contacting surfaces may cause a drift in the contact resistance and in the adhesion forces [MUHLSTEIN 2001].

The main challenges for NEMS relays that are shared by both logic and memory applications are:

- 1) Achieving low Pull-In voltages to assure low switching power (active power).

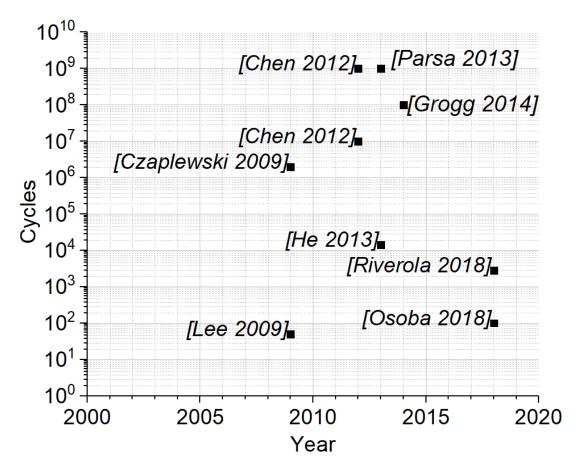

- 2) Improving endurance (cycling) with stable OFF/ON resistance over the life of the switch ( $e.g. \sim 1 \times 10^{14}$  switching cycles for logic application,  $\sim 10 \times 10^3$  for Code macro and  $\sim 10^6$  for data macro and Nonvolatile applications in automotive).

- 3) Fabricating NEMS with CMOS-compatible process, especially in case of hybrid CMOS/NEMS applications.

- 4) Scaling the footprint and the actuation speed (below 10ns).

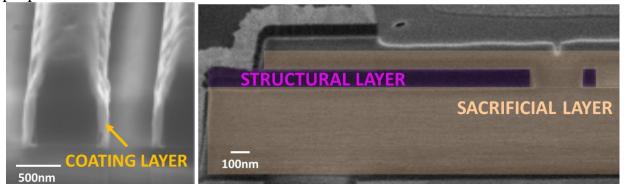

This chapter deals with NEMS relay State of the Art, describing NEMS relay typical design and orientation type and reporting suitable materials for all the NEM switching parts such as: structural layer, sacrificial layer, contact layer.

Contacts propriety will be discussed in 2.2.5, explaining the NEM switching contact domain and contact resistance. Relay endurance, switching speed and scaling will also be approached.

Explanation about the main issues that interfere with reaching high endurance will be given in 2.2.6, additionally with the relay endurance state of the art. Section 2.2.7 and section 2.2.8 will deal with relay mechanical delay and scaling limits.

Section 2.2.9 deals with why Logic NEMS relays are today a good candidate for computing in a harsh environment. In fact, NEMS relays have been successfully tested at up to 500 °C [Lee 2010c]; therefore NEMS relays could be suitable for many applications: e.g. automotive, aerospace, or geothermal exploration. In fact, those applications need a microcontroller that could operate at very high temperatures. MOSFET transistors operating at high temperature are subject to electrical failure due to material electrical properties degradation.

Finally, we will list the applications that so far have been targeted for NEMS relays, highlighting the advantages that NEMS relay will give to those applications.

To study NEMS relays it is necessary to include considerations from various disciplines such as mechanical engineering, material science and integration engineering.

## 2.2 NANOELECTROMECHANICAL SWITCHES

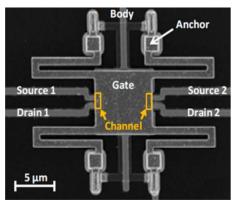

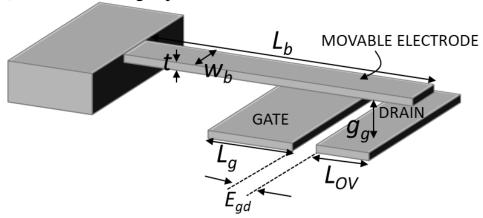

# **2.2.1 DESIGN**

In general, A NEM switch has at least three terminals: The source (input), the drain (output), the gate (actuation terminal) and sometimes the body. The body allows for having a reference potential for actuation besides the source. The source and the drain are separated by an air gap. Some relay designs have more than one electrode intended for the actuation, the source or the drain. Terminology such as "drain", "source", "gate" and "body" is used to make analogies to their MOSFET counterpart [NATHANAEL 2012] see Fig. 30 for reference.

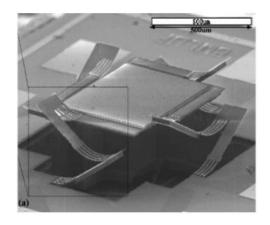

Fig. 30: SEM plan view of a 6T relay (1 Gate, 1 body and 2 sources and 2 drains) of a logic relay [Liu 2012]

The relay design is strongly influenced by the target application. Therefore, its design can vary in terms of number of terminals, structure orientation, actuation direction and fabrication process. Additionally, each research group has its own expertise in relay design. For example, logic relays with cantilever beam designs can be found in [CHONG 2009; JANG 2008] and clamped-clamped beam designs can be found in [CZAPLEWSKI 2009; KAM 2009].

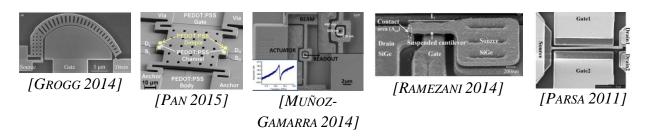

Nanoelectromechanical relay can have a lithographically-defined gap with an actuation area partially defined by deposition (see *e.g.* in Fig. 31): [GROGG 2014; MUÑOZ-GAMARRA 2014; PARSA 2011], or a gap defined by deposition with a lithographically-defined actuation area *e.g.* in Fig. 31: [PAN 2015; RAMEZANI 2014]. Multiple NEM relays structure orientation exists such as lateral, vertical or seesaw (*e.g.* in see Fig. 32).

Fig. 31: Example of various NEM relay design type and structural orientation

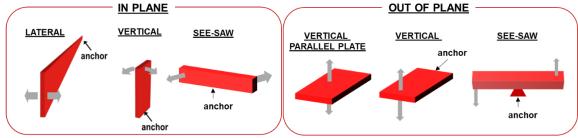

Fig. 32: Options for NEM relay structural orientation; Figure adapted from [Liu 2017a]

Commonly, NEMS relays are vertically (out of plane) or laterally (in plane) actuated. The vertical actuation is when the relay moves or tilts out of the plane of the wafer surface see literature examples Table 1, and lateral actuation is when it moves or tilts in the plane of the wafer surface see literature examples Table 2. In the tables below  $w_b$  is used to indicate the beam width and  $L_b$  the beam length,  $F^2$  is used to indicate the device footprint.

Table 1: Vertical Actuated Relays State of Art:

| REF              | Figure                                         | Terminals | Nominal F <sup>2</sup>                                                                                                        | $V_{DD}$                            | Applications                     |

|------------------|------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------|

| [Do 2013]        | Contact Dimples Actuator                       | 3         | $F^2=9*10^{-12}m^2$ $L_b=18\mu m$ Contact dimple width=500nm                                                                  | 9V                                  | Memory<br>(with vibration reset) |

| [KIM 2011]       | E                                              | 3         | -                                                                                                                             | 66V                                 | Logic (suppressed bouncing)      |

| [NATHANAEL 2012] | Gate Body Source Drain Body Gata               | 4         | F <sup>2</sup> =2.622*10 <sup>-9</sup> m <sup>2</sup> From anchor to anchor vertical =40μm From anchor to anchor lateral=70μm | 8V to 2V<br>(Tuned by<br>body bias) | Logic                            |

| [Joshi 2010]     |                                                | 4         | $L_b$ =5 $\mu$ m                                                                                                              | 4V                                  | Logic                            |

| [LEE 2009A]      | (c) Source Movable electrode  200nm Gate Drain | 3         | F <sup>2</sup> = $4*10-13$ m <sup>2</sup><br>$L_b$ : 700 nm;<br>$w_b*3:200$ nm                                                | 8V                                  | Logic<br>(liquid packaging)      |

Table 2: Lateral Actuated Relays State of Art:

| REF               | Figure                                                                         | Terminals | Nominal F <sup>2</sup>                                                                            | Pull-In | Applications                                   |

|-------------------|--------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------|---------|------------------------------------------------|

| [PARSA 2013]      | Gate Drain  Gate  Gate  Gate                                                   | 5         | $F^2=6*10^{-11} \text{m}^2$ $L_b = 16 \mu \text{m}$ $w_b *6+\text{gap}=600 \text{nm}$             | 7V      | Logic (Platinum coating to improve Resistance) |

| [LEE 2009B]       | S S S S S S S S S S S S S S S S S S S                                          | 5         | $F^2 = 2*10^{-12} \text{m}^2$<br>$L_b = 5 \mu \text{m}$<br>$w_b *6 + \text{gap} = 4 \mu \text{m}$ | -       | Logic (high temperature)                       |

| [CZAPLEWSKI 2009] | 102mm                                                                          | 5         | $F^2=1.6*10^{-12}m^2$ $L_b=4\mu m$ $w_b*6+gap=400nm$                                              | 6V      | Logic<br>(co-integration with<br>CMOS)         |

| [LEE 2010A]       | Drain 2 Drain 1 TiN TiN perimeter beams  Cate 1  Gate 2  Poly Si/TiN  Beam LTO | 5         | F <sup>2</sup> =1*10 <sup>-10</sup> m <sup>2</sup>                                                | 34V     | Logic<br>(Titanium as structural<br>layer)     |

| [LEE 2010C]       | Vss IN OUT                                                                     | 3         | -                                                                                                 | 6V      | Logic (high temperature)                       |

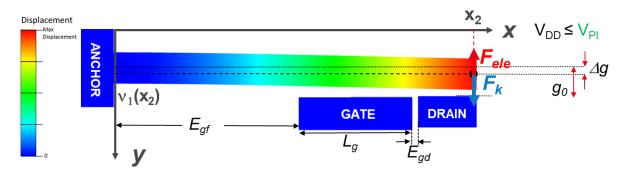

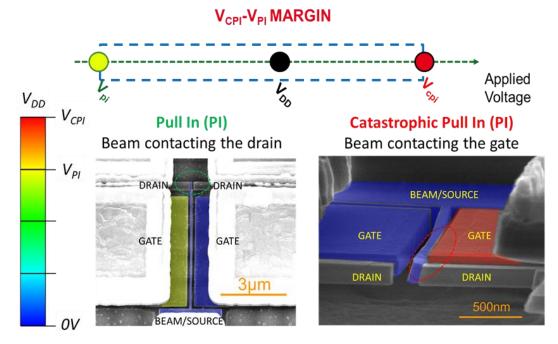

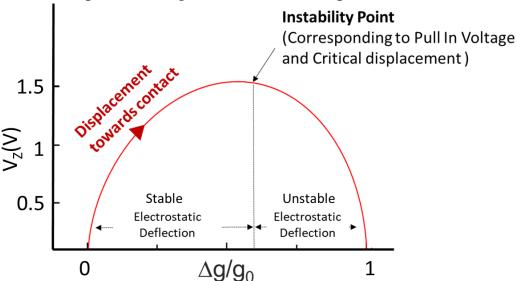

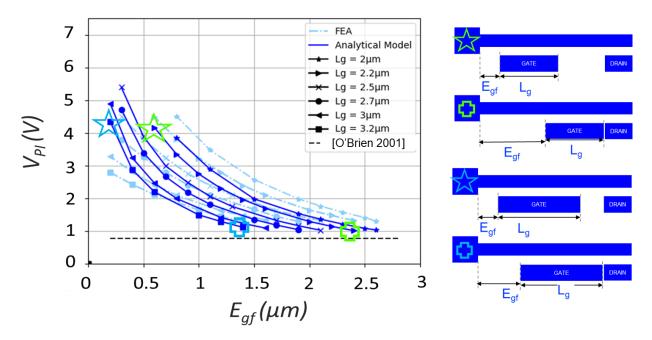

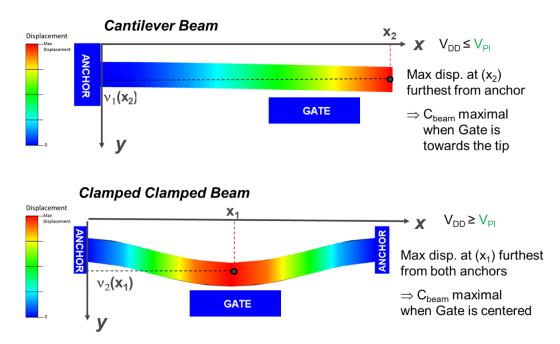

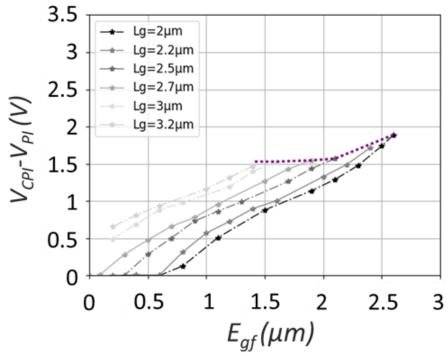

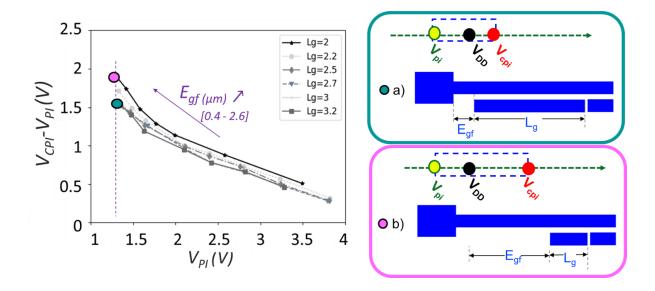

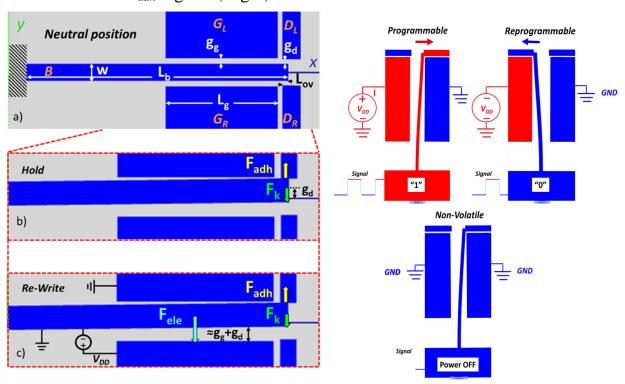

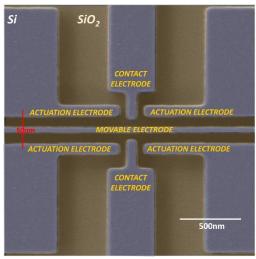

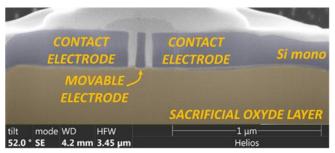

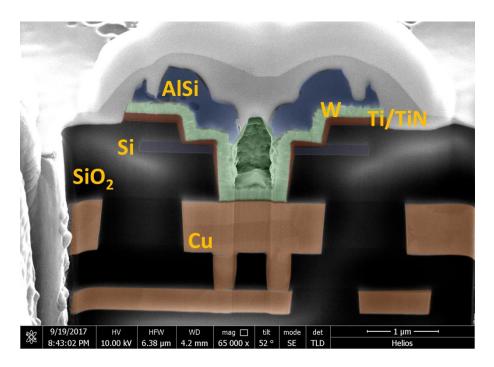

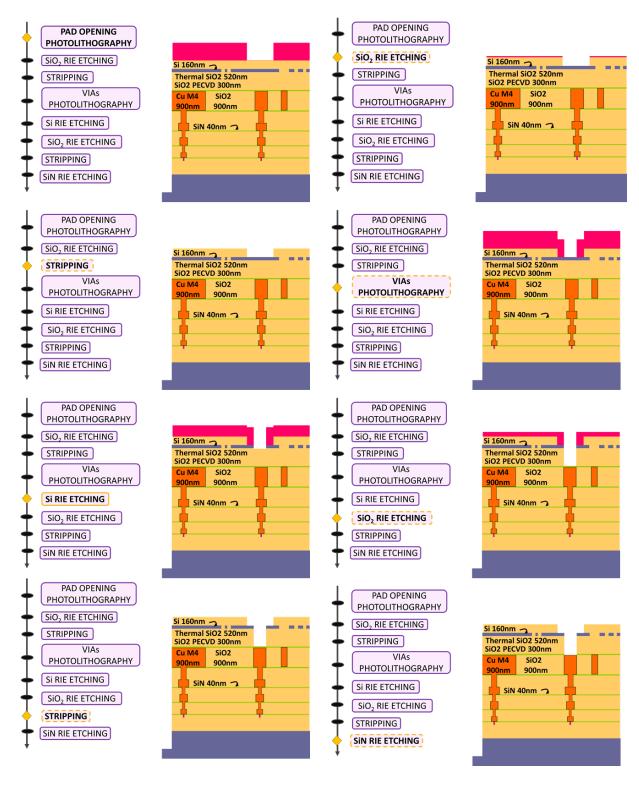

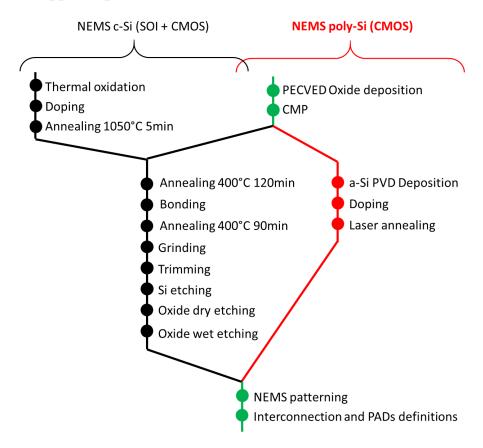

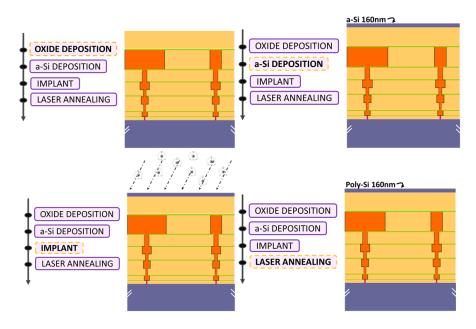

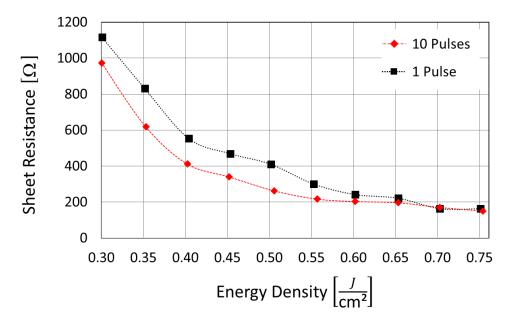

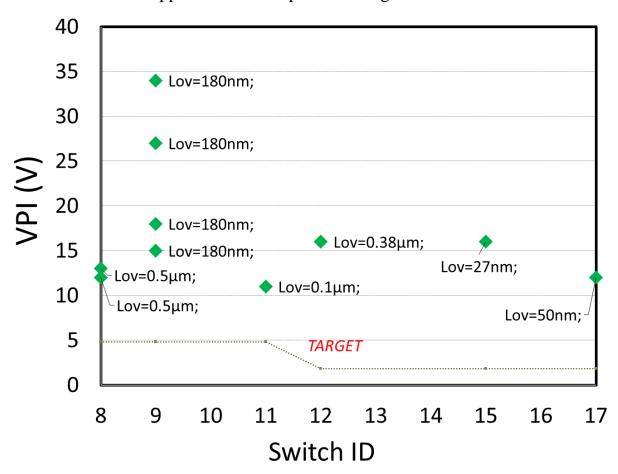

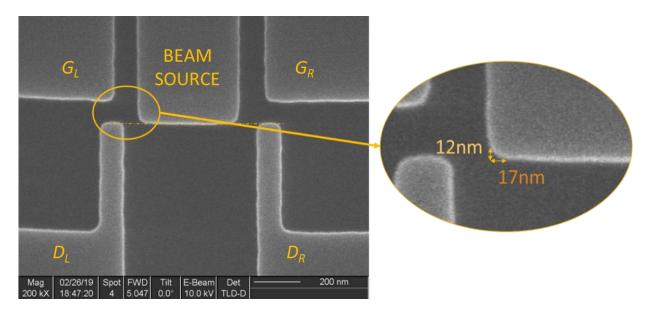

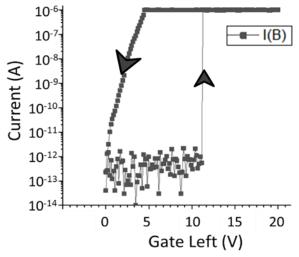

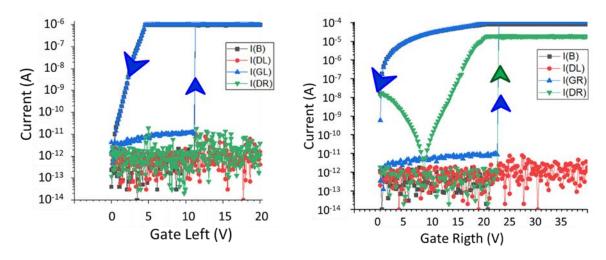

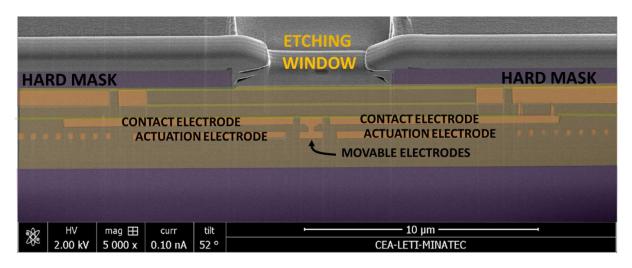

## 2.2.2 NEM RELAY ACTUATION MECHANISM