# Design space exploration of 64-bit arm compute nodes for highly energy effcient Exascale

Joël Wanza Weloli

### ▶ To cite this version:

Joël Wanza Weloli. Design space exploration of 64-bit arm compute nodes for highly energy effcient Exascale. Electronics. Université Côte d'Azur, 2019. English. NNT: 2019AZUR4042 . tel-02530122

## HAL Id: tel-02530122 https://theses.hal.science/tel-02530122

Submitted on 2 Apr 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Ph.D. Thesis

## Modélisation, simulation de différents types d'architectures de noeuds de calcul basés sur l'architecture ARM et optimisés pour le calcul haute-performance

## Design Space Exploration of 64-bit ARM Compute Nodes for Highly Energy Efficient Exascale

## Joël WANZA WELOLI

### LEAT/Bull

A dissertation submitted to the Ecole Doctorale Sciences et Technologies de L'Information et de la Communication (EDSTIC) of the Université Côte d'Azur for the degree of Doctor of Electronic

**Directed by**: Cécile Belleudy and Sébastien Bilavarn

Thesis defense: June 24th 2019

### Members of the Thesis jury:

- Mr. Bertrand Granado, Professor, Sorbonne Université, Examiner

- Mr. Frédéric Petrot, Professor, Université Grenoble Alpes, Examiner

- Mr. Dominique Lavenier, CNRS Research Director, IRISA

- Mr. Elyes Zekri, Dr. Eng., Bull/Atos

- Mr. François Verdier, Professor, Université Côte d'Azur

- Mr. Gabor Dozsa, Dr. Eng., Arm

- Mrs. Cécile Belleudy, Associate Professor, Université Côte d'Azur, Thesis director

- Mr. Sébastien Bilavarn, Associate Professor, Université Côte d'Azur, Thesis co-supervisor

# Design Space Exploration of 64-bit ARM Compute Nodes for Highly Energy Efficient Exascale

Joël Wanza Weloli

Department of Electronic University of Côte d'Azur

This dissertation is submitted for the degree of Doctor of Electronic and Computer Architecture

Laboratoire d'Electronique, Antennes et Télécommunications

2018 - 2019

I would like to dedicate this thesis to my loving parents, especially to my mother Vicky, the first teacher I ever had.

# Declaration

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other University. This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration, except where specifically indicated in the text. This dissertation contains fewer than 65,000 words including appendices, bibliography, footnotes, tables and equations and has less than 150 figures.

Joël Wanza Weloli 2018-2019

# Acknowledgements

Foremost, I would like to express my acknowledgments to my Ph.D advisors Cecile Belleudy and Sébastien Bilavarn for their support and help during my Ph.D study and research. Thank you Cecile for being the first one to believe in my Ph.D project. My sincere gratitude to Sébastien for his patience and helpful guidance in all the time for research and writing of this thesis.

My sincere thanks also go to Sylvie Lesmanne who hired me at Bull for my Ph.D student position in the hardware architecture team. Also, to Said Derradji for being a surefire support within Bull and a continuous mentoring on diverse exciting European projects. I'm very grateful to the different organizations who funded the work of this thesis: Bull, ANRT, European commission via Mont-Blanc 2 and 3 projects, but also the LEAT laboratory for hosting this collaboration.

Last but not the least, I would like to thank my family, friends and close colleagues who supported me throughout during these years. Thank you all for always being there. You all have been a real human inspiration to me. A special dedication to Benoît Welterlen (if you thought I was about to forget you :-) Thank you for having given to me my chance as an intern at Bull.

And the very finally, Thanks a lot to all the jury members.

## Abstract

#### English version:

Title: Design Space Exploration of 64-bit ARM Compute Nodes for Highly Energy Efficient Exascale.

Abstract: This work is part of a family of European projects called Mont-Blanc whose objective is to develop the next generation of Exascale systems. It addresses specifically the issue of energy efficiency, at micro-architectural level first by considering the use of 64-bit Armv8-A based compute nodes and an associated relevant SoC topology, and examine also the runtime aspects with notably the study of power management strategies that can be better suited to the constraints of HPC highly parallel processing. A design space exploration methodology capable of supporting the simulation of large manycore computing clusters is developped and lead to propose, design and evaluate multi-SoC and their associated SoC Coherent Interconnect models (SCI). This approach is then used to define a pre-exascale achitecture allowing to globally reduce the complexity and cost of chip developments without sacrifying performances. The resulting partitioning scheme introduces interesting perspectives at technology level such as the integration of more compute nodes directly on an interposer based System-in-Package (SiP), possibly based on 3D Through Silicon Vias (TSVs) using High Memory Bandwidth (HBM). Energy efficiency is addressed more directly in second instance by studying current power management policies and proposing two strategies to help reducing power while preserving performances. The first one exploits finer application execution knowledge to adjust the frequency of extensive parallel threads and better balance their execution time. The second strategy reduces core frequencies at synchronisation points of jobs to avoid running the cores at full speed while it is not necessary. Experiment results with these strategies, both in simulation and real hardware, show the possibilities offered par this approach to address the strong requirements of Exascale platforms.

#### Version française:

Titre: Modélisation, simulation de différents types d'architectures de nœuds de calcul basés sur l'architecture ARM et optimisés pour le calcul haute-performance. Résumé: Ce travail s'inscrit dans le cadre de la famille de projets Européens Mont-Blanc dont l'objectif est de développer la prochaine génération de systèmes Exascale. Il s'intéresse particulièrement à la question de l'efficacité énergétique, d'abord au niveau micro-architectural en considérant l'utilisation de nœuds de calcul basés sur l'Armv8-A 64-bit associée à une topologie SoC pertinente, puis en examinant les aspects exécutifs notamment par une étude de stratégies de gestion énergétique (power management) mieux adaptées à des contraintes de traitement massivement parallèle. Une méthodologie d'exploration architecturale capable de supporter la simulation de larges clusters de calcul parallèle est définie et exploitée pour proposer, développer et évaluer des modèles multi-SoC et de réseaux de communication associés (SoC Coherent Interconnect, SCI). Cette démarche est ensuite poursuivie pour définir une architecture Exacale permettant de réduire globalement la complexité et les coûts de développement en dégradant le moins possible les performances. Le partitionnement de la puce permet ainsi des possibilités intéressantes au niveau technologique telles que l'intégration de nœuds supplémentaires basée sur des technologies System-in-Package (interposer), ou 3D Through Silicon Vias (TSVs) et High Memory Bandwidth (HBM). En second lieu, les aspects énergétiques sont abordés plus directement par l'étude de politiques de gestion énergétique existantes et en proposant deux stratégies pour permettre réduire la consommation en préservant les performance. La première exploite une perception applicative plus fine pour ajuster la fréquence de nombreuses tâches parallèles et mieux équilibrer leurs temps d'exécution. La seconde stratégie réduit la fréquence des cœurs aux points de synchronisation des tâches pour limiter les fonctionnements inutiles à pleine puissance. Les résultats d'expérimentation obtenus avec ces stratégies, à la fois en simulation et sur plateforme réelle, montrent les possibilités offertes par cette approche pour répondre aux fortes contraintes des plateformes pre-exascale sur le plan énergétique.

# Contents

| Contents          |                    |        |                                                                                                                                                |  |  |  |  |  |  |  |

|-------------------|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| List of Figures x |                    |        |                                                                                                                                                |  |  |  |  |  |  |  |

| Li                | st of              | Tables | xiii                                                                                                                                           |  |  |  |  |  |  |  |

| $\mathbf{Li}$     | st of              | terms  | xv                                                                                                                                             |  |  |  |  |  |  |  |

| Ι                 | $\mathbf{B}$       | ACKO   | ROUND 1                                                                                                                                        |  |  |  |  |  |  |  |

| 1                 | Intr               | oducti | on 2                                                                                                                                           |  |  |  |  |  |  |  |

|                   | 1.1                | Object | vives and Contexts                                                                                                                             |  |  |  |  |  |  |  |

|                   | 1.2                | Thesis | ${\rm contributions}  \ldots  \ldots  \ldots  \ldots  \ldots  3$                                                                               |  |  |  |  |  |  |  |

|                   |                    | 1.2.1  | Main contributions                                                                                                                             |  |  |  |  |  |  |  |

|                   |                    | 1.2.2  | Published papers                                                                                                                               |  |  |  |  |  |  |  |

|                   | 1.3                | Thesis | outlines                                                                                                                                       |  |  |  |  |  |  |  |

| <b>2</b>          | State-of-the-Art 6 |        |                                                                                                                                                |  |  |  |  |  |  |  |

|                   | 2.1                | HPC I  | background                                                                                                                                     |  |  |  |  |  |  |  |

|                   |                    | 2.1.1  | History                                                                                                                                        |  |  |  |  |  |  |  |

|                   |                    | 2.1.2  | Exascale Challenges                                                                                                                            |  |  |  |  |  |  |  |

|                   |                    | 2.1.3  | Applications                                                                                                                                   |  |  |  |  |  |  |  |

|                   | 2.2                | HPC (  | $Compute node architectures \dots \dots$ |  |  |  |  |  |  |  |

|                   |                    | 2.2.1  | Introduction                                                                                                                                   |  |  |  |  |  |  |  |

|                   |                    | 2.2.2  | Intel Xeon E series architecture: Skylake (Haswell) $\ldots \ldots \ldots 17$                                                                  |  |  |  |  |  |  |  |

|                   |                    | 2.2.3  | Intel Xeon Phi Coprocessor architecture: Knights Landing $\ldots 20$                                                                           |  |  |  |  |  |  |  |

|                   |                    | 2.2.4  | Emerging compute node architectures: SunWay 22                                                                                                 |  |  |  |  |  |  |  |

|                   |                    | 2.2.5  | Emerging compute node architectures: Opteron                                                                                                   |  |  |  |  |  |  |  |

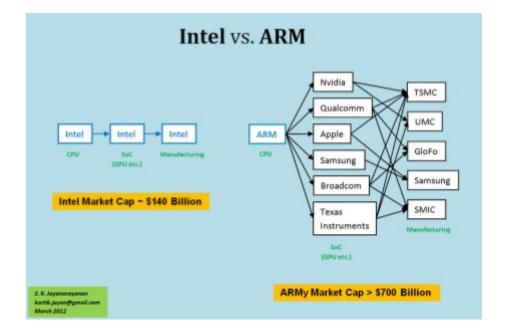

|          |              | 2.2.6                                                         | Arm vs Intel Compute node architecture              | 26                                                                                                                                                                     |

|----------|--------------|---------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

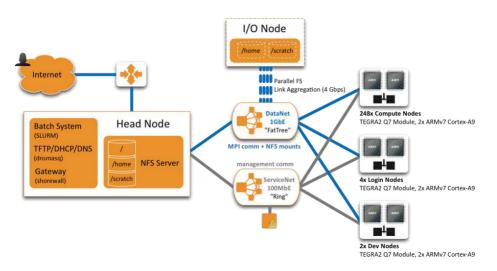

|          |              | 2.2.7                                                         | The first Arm-based HPC Cluster: Tibidabo           | 27                                                                                                                                                                     |

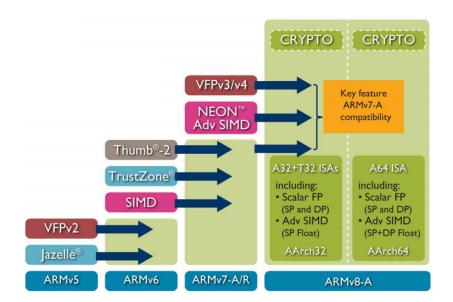

|          | 2.3          | Aarch                                                         | 64 architecture and ARMv8 processors                | 29                                                                                                                                                                     |

|          |              | 2.3.1                                                         | ARMv8 or AArch64 ?                                  | 29                                                                                                                                                                     |

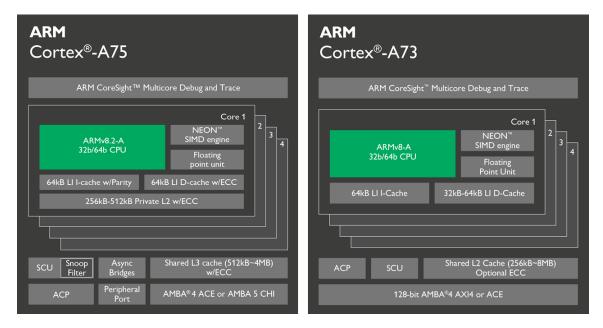

|          |              | 2.3.2                                                         | ARMv8-A processors : Cortex-A75                     | 30                                                                                                                                                                     |

|          |              | 2.3.3                                                         | SVE: Scalable Vector Extension                      | 32                                                                                                                                                                     |

|          | 2.4          | Resear                                                        | rch projects                                        | 33                                                                                                                                                                     |

|          |              | 2.4.1                                                         | Design space exploration methodologies              | 33                                                                                                                                                                     |

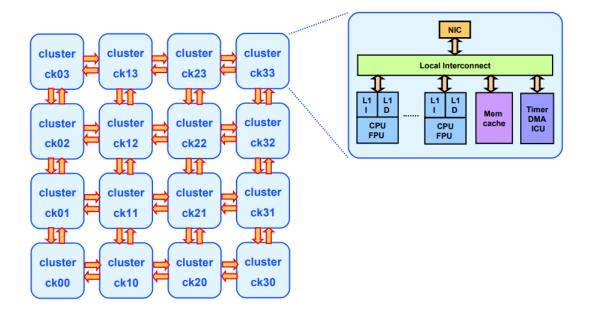

|          |              | 2.4.2                                                         | TSAR Architecture example                           | 34                                                                                                                                                                     |

|          |              | 2.4.3                                                         | Global projects overview                            | 36                                                                                                                                                                     |

|          |              | 2.4.4                                                         | Asian projects                                      | 36                                                                                                                                                                     |

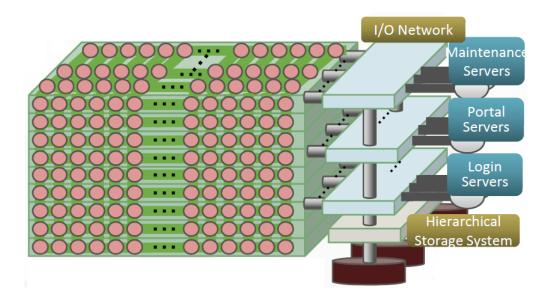

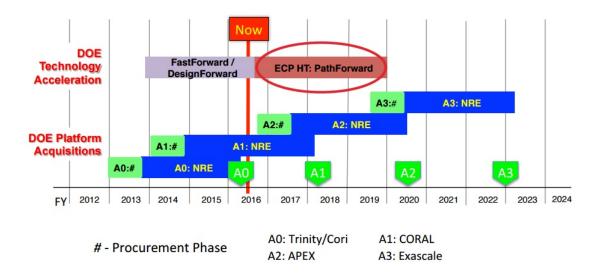

|          |              | 2.4.5                                                         | American project : Exascale Computing Project (ECP) | 38                                                                                                                                                                     |

|          |              | 2.4.6                                                         | European Projects                                   | 39                                                                                                                                                                     |

|          | 2.5          | Conclu                                                        | usion                                               | 40                                                                                                                                                                     |

|          |              |                                                               |                                                     |                                                                                                                                                                        |

| II       | E            | XPE                                                           | RIMENTATION AND ANALYSIS                            | <b>42</b>                                                                                                                                                              |

|          |              |                                                               |                                                     |                                                                                                                                                                        |

| <b>3</b> | Mo           | deling                                                        | and exploration methodology                         | <b>43</b>                                                                                                                                                              |

|          |              | 0                                                             |                                                     |                                                                                                                                                                        |

|          | 3.1          |                                                               | uction                                              | 43                                                                                                                                                                     |

|          | $3.1 \\ 3.2$ | Virtua                                                        | uction                                              | 43<br>44                                                                                                                                                               |

|          |              |                                                               | uction                                              | 43<br>44<br>44                                                                                                                                                         |

|          |              | Virtua                                                        | uction                                              | 43<br>44<br>44<br>44                                                                                                                                                   |

|          |              | Virtua                                                        | uction                                              | 43<br>44<br>44<br>44<br>45                                                                                                                                             |

|          |              | Virtua                                                        | uction                                              | 43<br>44<br>44<br>45<br>48                                                                                                                                             |

|          |              | Virtua                                                        | uction                                              | 43<br>44<br>44<br>45<br>48<br>49                                                                                                                                       |

|          |              | Virtua<br>3.2.1                                               | uction                                              | <ul> <li>43</li> <li>44</li> <li>44</li> <li>45</li> <li>48</li> <li>49</li> <li>50</li> </ul>                                                                         |

|          |              | Virtua<br>3.2.1<br>3.2.2                                      | uction                                              | 43<br>44<br>44<br>45<br>48<br>49<br>50<br>54                                                                                                                           |

|          |              | Virtua<br>3.2.1                                               | uction                                              | 43<br>44<br>44<br>45<br>48<br>49<br>50<br>54<br>57                                                                                                                     |

|          |              | Virtua<br>3.2.1<br>3.2.2                                      | uction                                              | 43<br>44<br>44<br>45<br>48<br>49<br>50<br>54<br>57<br>57                                                                                                               |

|          |              | Virtua<br>3.2.1<br>3.2.2                                      | uction                                              | 43<br>44<br>44<br>45<br>48<br>49<br>50<br>54<br>57                                                                                                                     |

|          |              | Virtua<br>3.2.1<br>3.2.2<br>3.2.3                             | uction                                              | 43<br>44<br>44<br>45<br>48<br>49<br>50<br>54<br>57<br>57                                                                                                               |

|          | 3.2          | Virtua<br>3.2.1<br>3.2.2<br>3.2.3                             | uction                                              | <ul> <li>43</li> <li>44</li> <li>44</li> <li>45</li> <li>48</li> <li>49</li> <li>50</li> <li>54</li> <li>57</li> <li>57</li> <li>57</li> </ul>                         |

|          | 3.2          | Virtua<br>3.2.1<br>3.2.2<br>3.2.3<br>Explor                   | uction                                              | <ul> <li>43</li> <li>44</li> <li>44</li> <li>45</li> <li>48</li> <li>49</li> <li>50</li> <li>54</li> <li>57</li> <li>57</li> <li>57</li> <li>59</li> </ul>             |

|          | 3.2          | Virtua<br>3.2.1<br>3.2.2<br>3.2.3<br>Explor<br>3.3.1          | uction                                              | <ul> <li>43</li> <li>44</li> <li>44</li> <li>45</li> <li>48</li> <li>49</li> <li>50</li> <li>54</li> <li>57</li> <li>57</li> <li>57</li> <li>59</li> <li>59</li> </ul> |

|          | 3.2          | Virtua<br>3.2.1<br>3.2.2<br>3.2.3<br>Explor<br>3.3.1<br>3.3.2 | uction                                              | <ul> <li>43</li> <li>44</li> <li>44</li> <li>45</li> <li>48</li> <li>49</li> <li>50</li> <li>54</li> <li>57</li> <li>57</li> <li>57</li> <li>59</li> <li>60</li> </ul> |

|          |     |         | 3.3.3.3 Memory and cache consistency                                                                |

|----------|-----|---------|-----------------------------------------------------------------------------------------------------|

|          |     |         | 3.3.3.4 Scalability                                                                                 |

|          | 3.4 | Conclu  | usion                                                                                               |

| 4        | Arc | hitectu | ral exploration 68                                                                                  |

|          | 4.1 | Memo    | ry coherency and SoC partitioning                                                                   |

|          | 4.2 | Cache   | coherence protocols                                                                                 |

|          |     | 4.2.1   | Overview                                                                                            |

|          |     | 4.2.2   | Snoop Transaction types                                                                             |

|          |     | 4.2.3   | Directory based filtering                                                                           |

|          |     | 4.2.4   | ARM Coherence Protocols                                                                             |

|          | 4.3 | SoC C   | Coherent Interconnect                                                                               |

|          |     | 4.3.1   | Description                                                                                         |

|          |     | 4.3.2   | SCI Architecture                                                                                    |

|          |     | 4.3.3   | Cache model                                                                                         |

|          |     |         | $4.3.3.1  \text{Cache controller}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |

|          |     |         | 4.3.3.2 Cache Snoop controller                                                                      |

|          |     | 4.3.4   | SCI Snoop Filter model                                                                              |

|          |     | 4.3.5   | SoC Partitionning                                                                                   |

|          |     |         | 4.3.5.1 Partitioning topology overview                                                              |

|          |     |         | 4.3.5.2 Multi-SoC scenarios                                                                         |

|          |     |         | 4.3.5.3 Coherent Proxy extensions                                                                   |

|          | 4.4 | Simula  | ations                                                                                              |

|          |     | 4.4.1   | Directory-based snoop filtering benefits                                                            |

|          |     | 4.4.2   | Partitioning analysis                                                                               |

|          |     | 4.4.3   | Parallel programming efficiency                                                                     |

|          | 4.5 | Conclu  | usion                                                                                               |

| <b>5</b> | Pow | ver ma  | nagement 91                                                                                         |

|          | 5.1 | HPC e   | energy efficiency constraints                                                                       |

|          |     | 5.1.1   | Existing power strategies for HPC                                                                   |

|          |     | 5.1.2   | OS based strategies                                                                                 |

|          |     | 5.1.3   | Energy efficiency improvement                                                                       |

|          | 5.2 | Evalua  | ation of OS power strategies                                                                        |

|          |     | 5.2.1   | Simulation framework                                                                                |

|          |     |         | 5.2.1.1 GEM5                                                                                        |

|          |     |         | 5.2.1.2 Benchmarks                                                                                  |

|              |       |         | 5.2.1.3    | Energy efficiency evaluation                                                                                                      | 96  |

|--------------|-------|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

|              |       | 5.2.2   | Simulati   | on results                                                                                                                        | 96  |

|              | 5.3   | Power   | strategies | s for HPC                                                                                                                         | 100 |

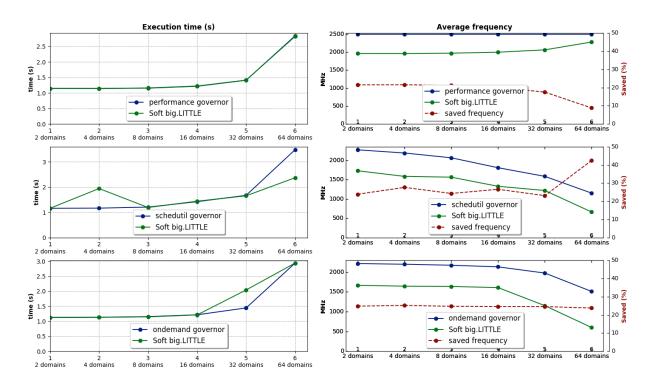

|              |       | 5.3.1   | Soft big.  | LITTLE strategy simulations with GEM5                                                                                             | 100 |

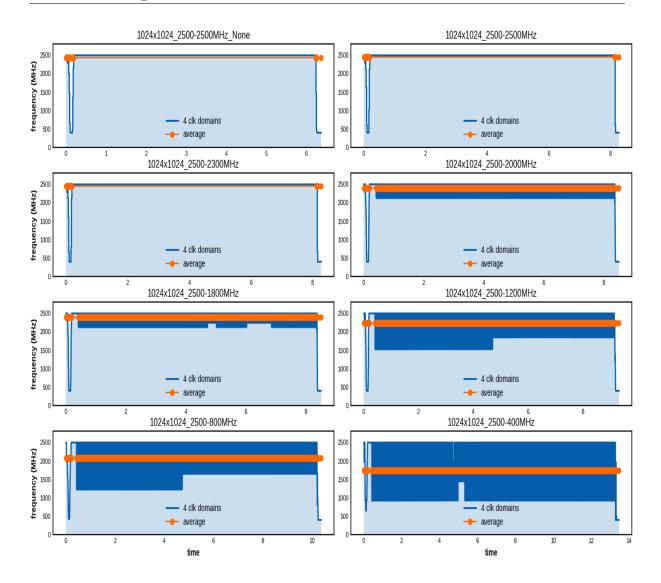

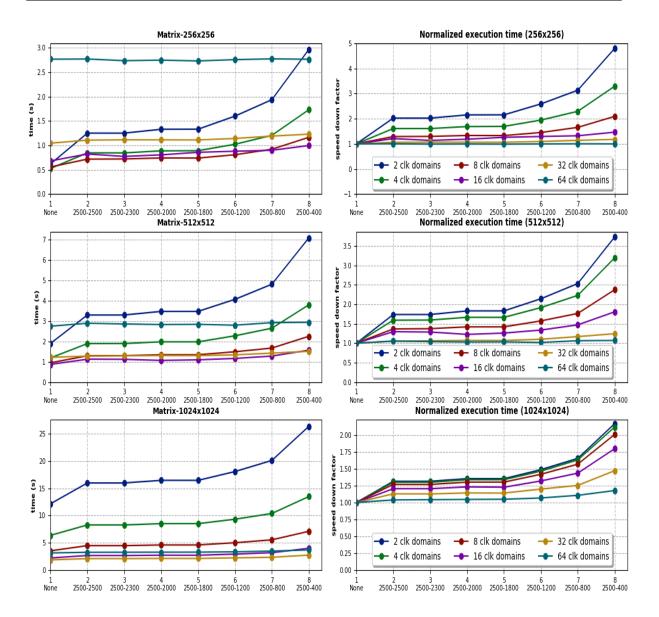

|              |       | 5.3.2   | Blocking   | g point strategy simulations with GEM5                                                                                            | 103 |

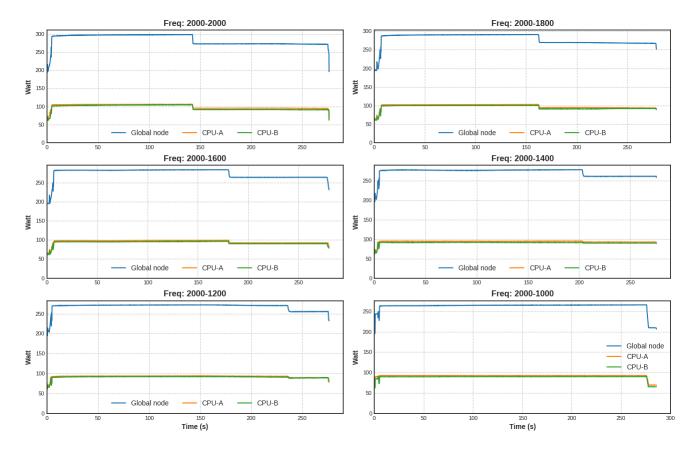

|              | 5.4   | Measu   | rements v  | with Cavium ThunderX2                                                                                                             | 107 |

|              |       | 5.4.1   | Platform   | $a description \dots \dots$ | 107 |

|              |       | 5.4.2   | Soft big.  | LITTLE strategy execution on ThunderX2 $\ldots$                                                                                   | 108 |

|              |       | 5.4.3   | Blocking   | g point strategy execution on ThunderX2 $\ldots$                                                                                  | 111 |

|              | 5.5   | Conclu  | ision      |                                                                                                                                   | 113 |

|              |       |         |            |                                                                                                                                   |     |

| III          | (     | CONC    | CLUSIC     | ONS                                                                                                                               | 114 |

| 6            | Con   | clusior | ns and P   | Perspectives                                                                                                                      | 115 |

| Bił          | oliog | raphy   |            |                                                                                                                                   | 117 |

| $\mathbf{A}$ | Gen   | n5 Rela | ated wor   | rk                                                                                                                                | 126 |

| в            | Gen   | 15 full | system     | stack effort                                                                                                                      | 127 |

# List of Figures

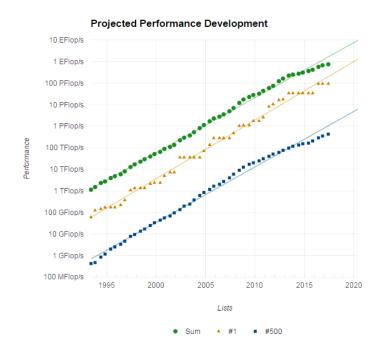

| 2.1  | HPC systems performance projections                                                                | 7  |

|------|----------------------------------------------------------------------------------------------------|----|

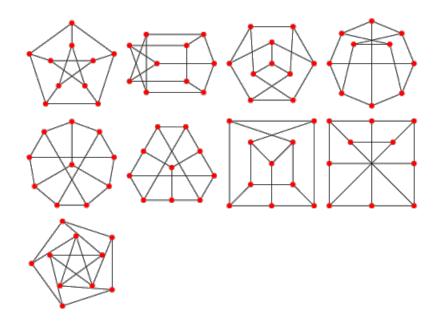

| 2.2  | Petersen Graph (Moore Graph illustration)                                                          | 9  |

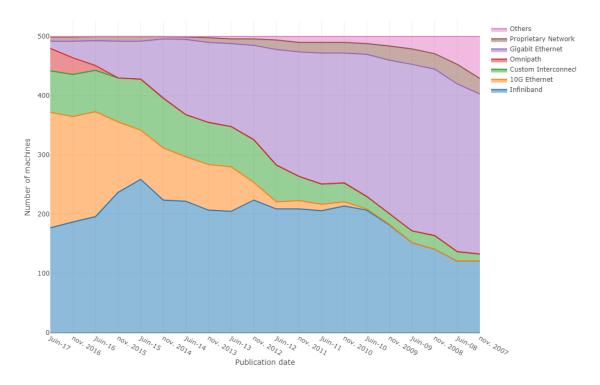

| 2.3  | Interconnect Family in the Top500                                                                  | 10 |

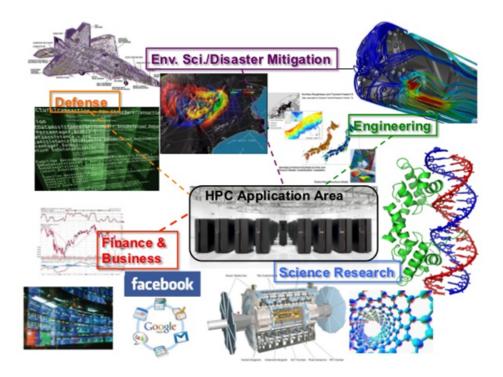

| 2.4  | Non-exhaustive HPC applications                                                                    | 12 |

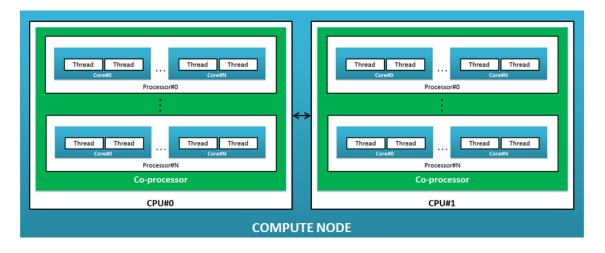

| 2.5  | Imbrication of annotations in a compute node $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 15 |

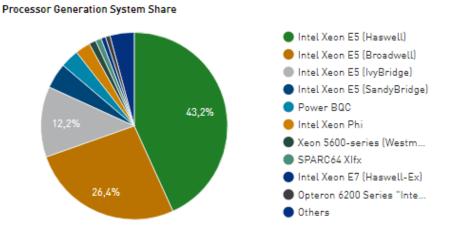

| 2.6  | x86 architectures hegemony in the HPC Top500 [June 2017] $\ldots \ldots$                           | 17 |

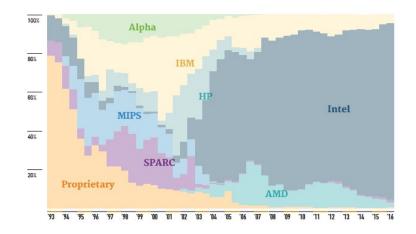

| 2.7  | Intel processors hegemony history in the HPC Top500                                                | 17 |

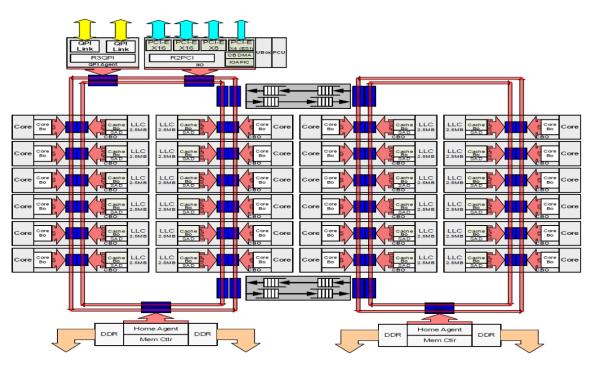

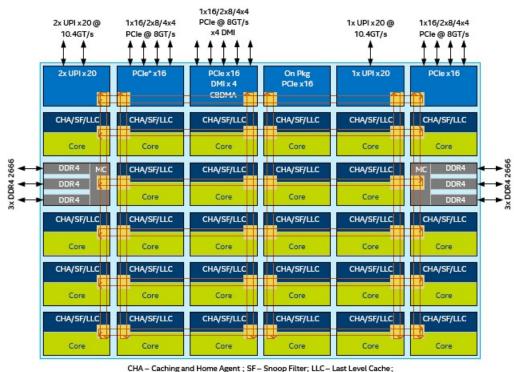

| 2.8  | Haswell EP Architecture block diagram                                                              | 18 |

| 2.9  | Skylake Architecture block diagram                                                                 | 19 |

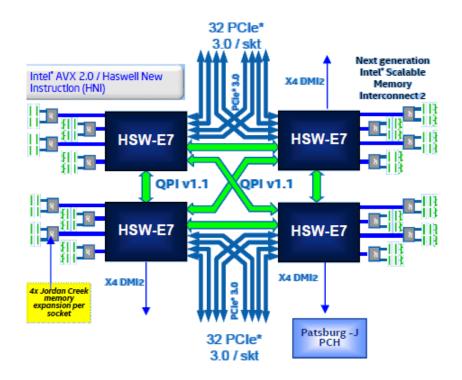

| 2.10 | Haswell based quad-socket platform example                                                         | 20 |

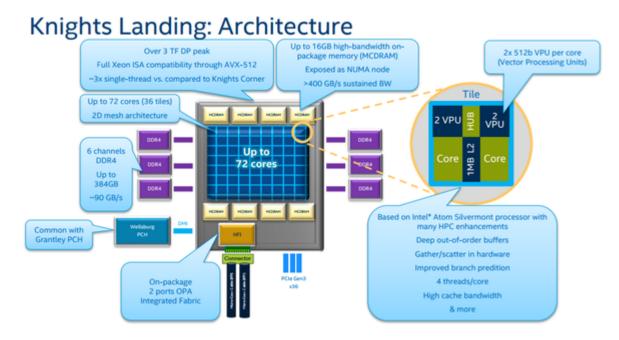

| 2.11 | Knights Landing Architecture block diagram overview                                                | 21 |

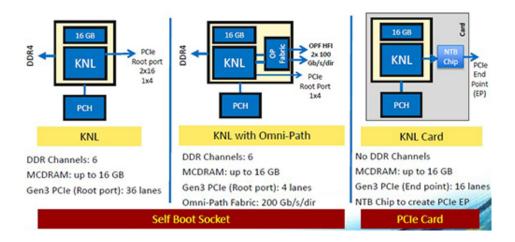

| 2.12 | Knights Landing (KNL) based Chips                                                                  | 22 |

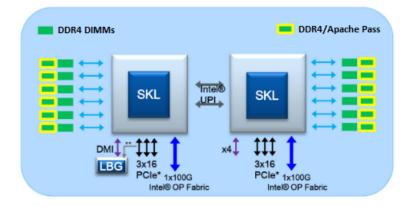

| 2.13 | Purley Platform: bi-socket Storm Lake Integrated with Skylake                                      | 22 |

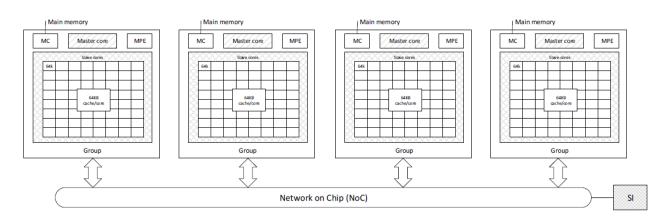

| 2.14 | Sunway SW26010 compute node architecture diagram                                                   | 24 |

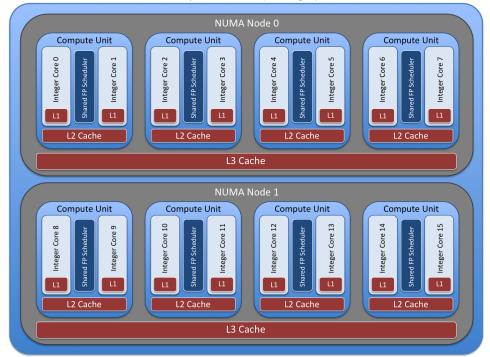

| 2.15 | AMD Opteron                                                                                        | 25 |

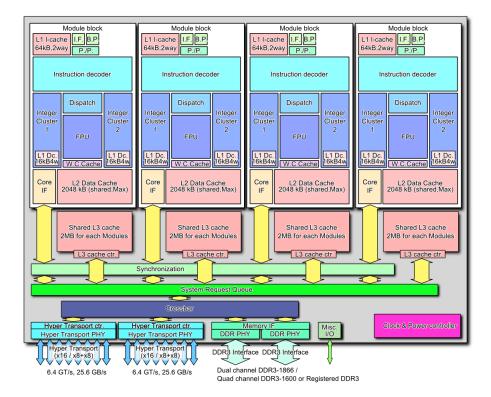

| 2.16 | Internal view                                                                                      | 26 |

| 2.17 | Arm vs INTEL Design flexibility                                                                    | 27 |

| 2.18 | Tibidabo Arm-based Cluster                                                                         | 28 |

| 2.19 | Arm architecture generations                                                                       | 29 |

| 2.20 | The Arm Cortex-A75 processor improvements                                                          | 30 |

| 2.21 | Arm DynamIQ concept overview                                                                       | 31 |

| 2.22 | TSAR Architecture                                                                                  | 35 |

| 2.23 | Post-K Computer Hardware                                                                           | 37 |

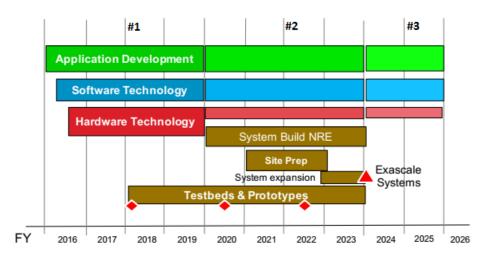

| 2.24 | The US Exascale Computing Project Roadmap                                                          | 38 |

| 2.25 | ECP Timeline                                                                                       | 39 |

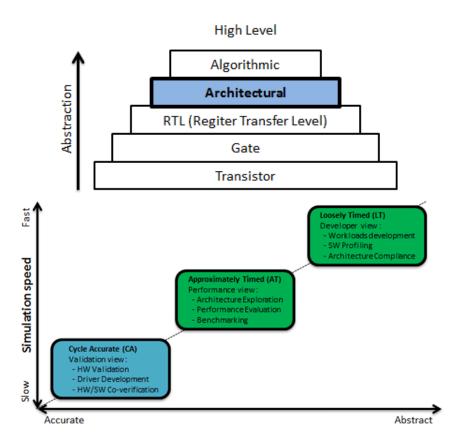

| 3.1  | Modeling levels                                                                                    | 44 |

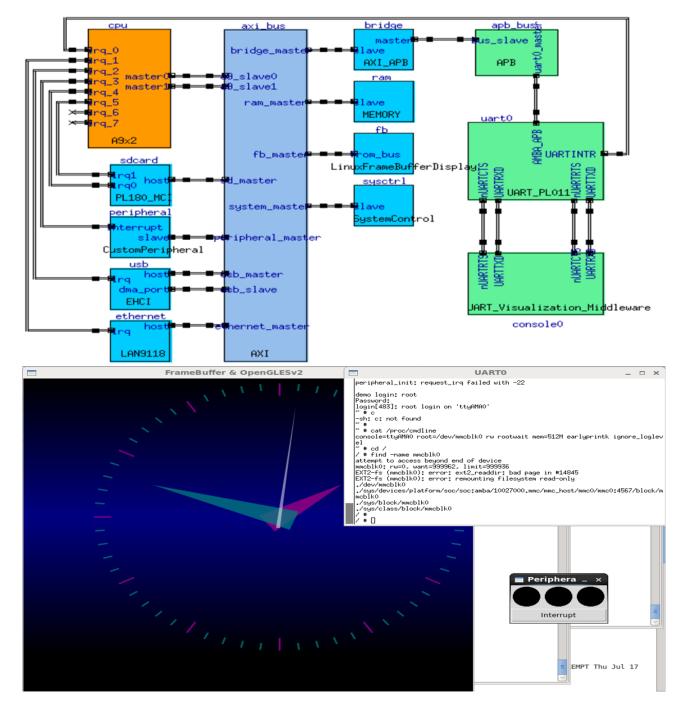

| 3.2  | VISTA modelled platform and output view                                                            | 46 |

| 3.3  | Reference platform for SoC Designer evaluation                                   | 47 |

|------|----------------------------------------------------------------------------------|----|

| 3.4  | Gem5 Medium scale platform                                                       | 49 |

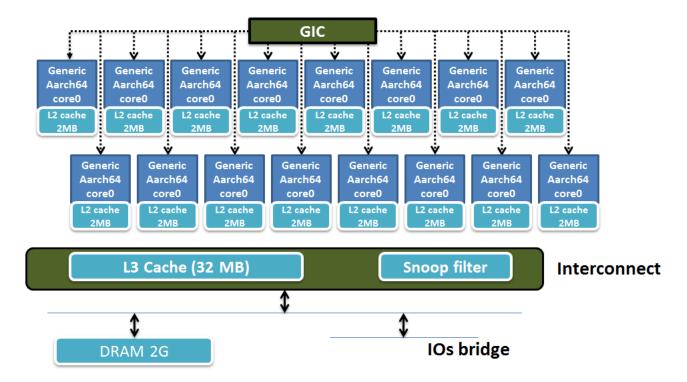

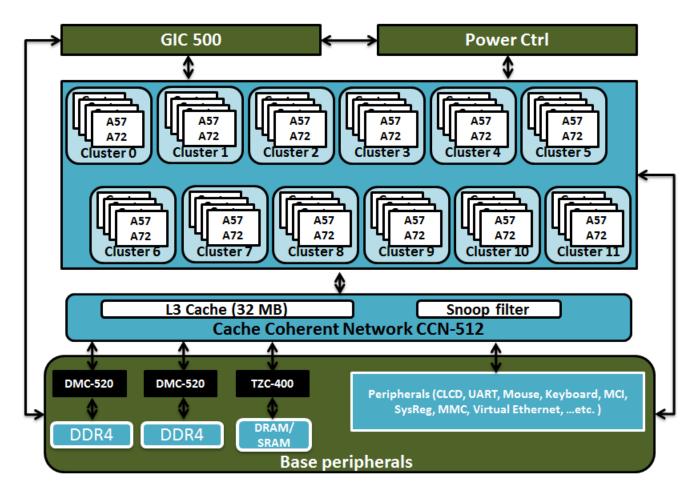

| 3.5  | 48 AFM Cores block diagram                                                       | 51 |

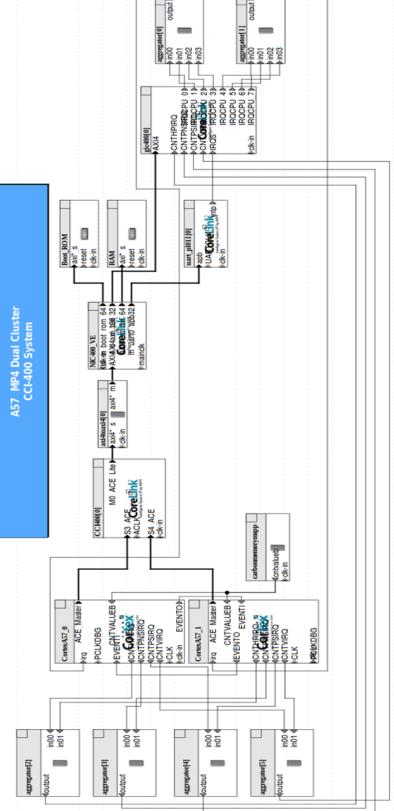

| 3.6  | Platform example based on Cortex-A57 Fast Model                                  | 52 |

| 3.7  | Equivalent VPU based platform                                                    | 52 |

| 3.8  | Dhrystone task graph                                                             | 53 |

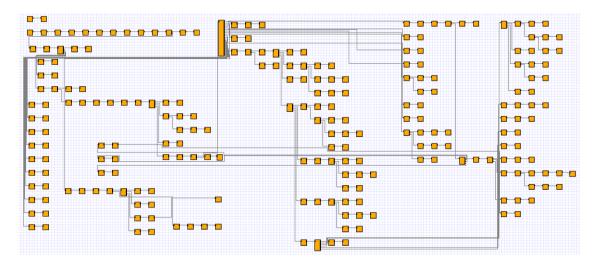

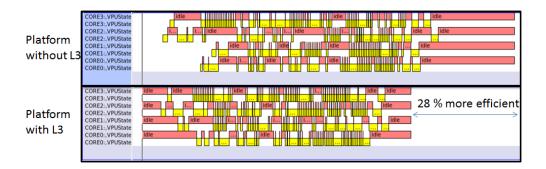

| 3.10 | Task graphs results With vs Without L3 cache                                     | 54 |

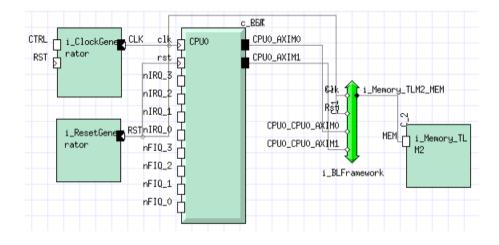

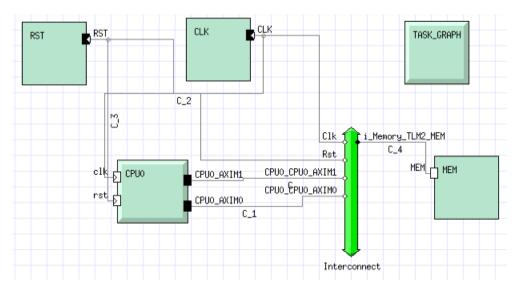

| 3.9  | Simulation outputs: Fast models vs. VPU (Dhrystone benchmark)                    | 54 |

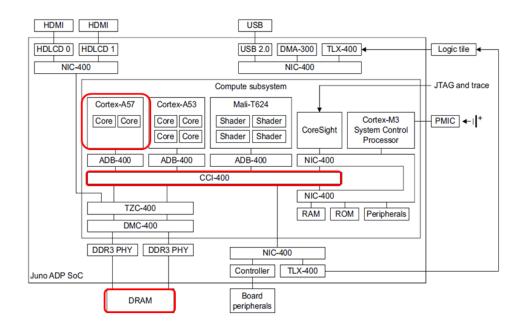

| 3.11 | Juno board diagram                                                               | 55 |

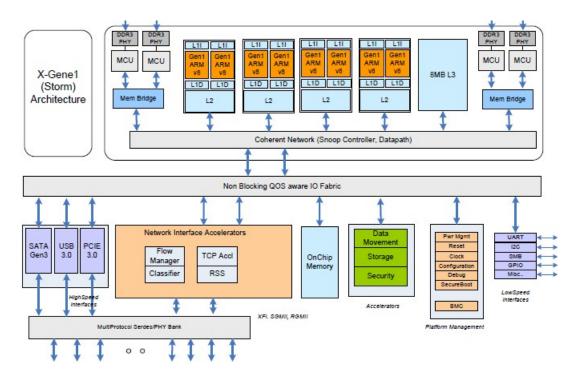

| 3.12 | APM first ARMv8 processor : Xgene1 Storm                                         | 56 |

| 3.13 | AMD Seattle's architecture : Floorplan and block diagram                         | 56 |

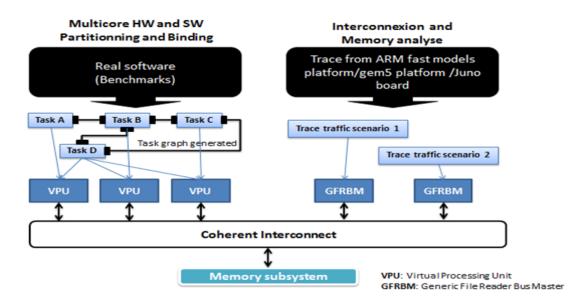

| 3.14 | VPU vs Traffic generator                                                         | 60 |

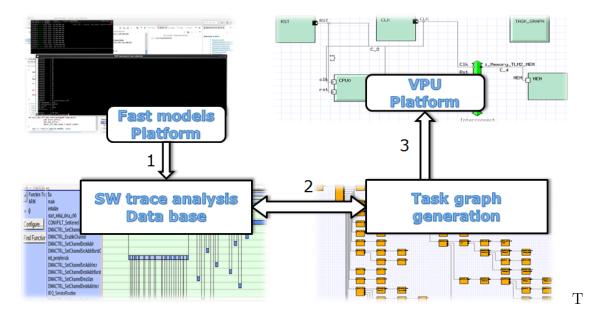

| 3.15 | Global Modeling Methodology                                                      | 61 |

| 3.16 | Extensible VPU platform (Dhrystone benchmark)                                    | 61 |

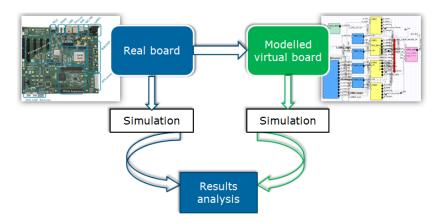

|      | Principle of correlation study                                                   | 62 |

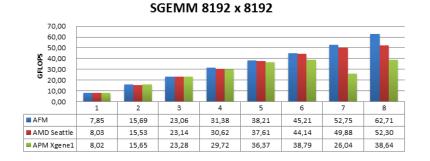

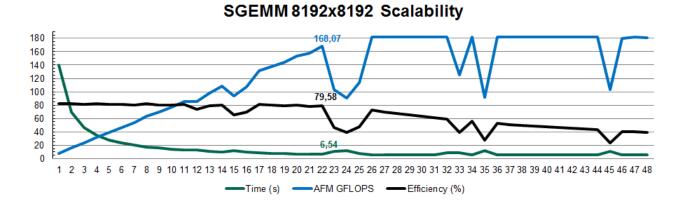

|      | SGEMM GFlops Scalability                                                         | 63 |

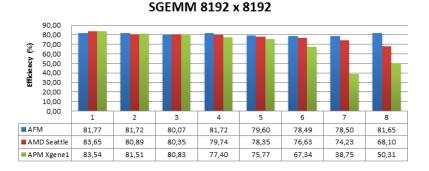

| 3.19 | SGEMM Performance efficiency correlation                                         | 63 |

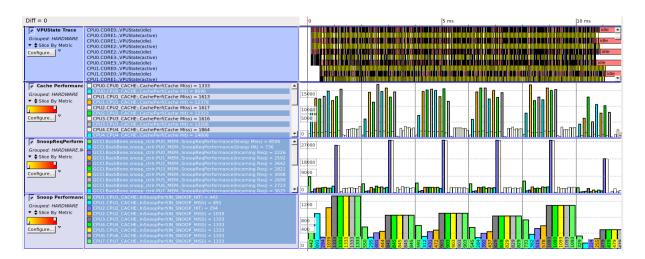

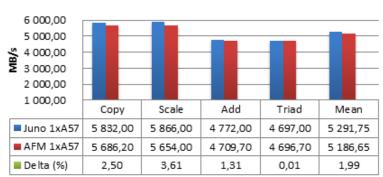

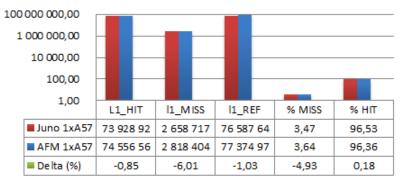

| 3.20 | Arm Juno vs. AFM memory level analysis                                           | 64 |

|      | From 1 to 48 threads scalability                                                 | 65 |

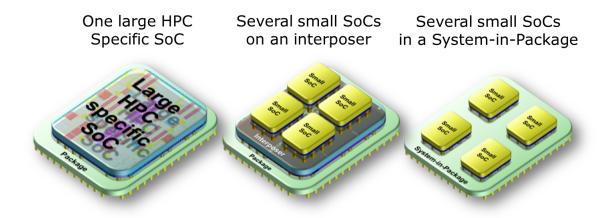

| 4.1  | SoC partitioning scenarios (Mont blanc project)                                  | 68 |

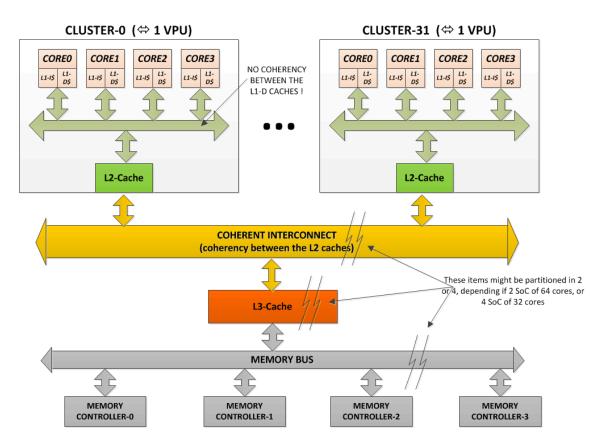

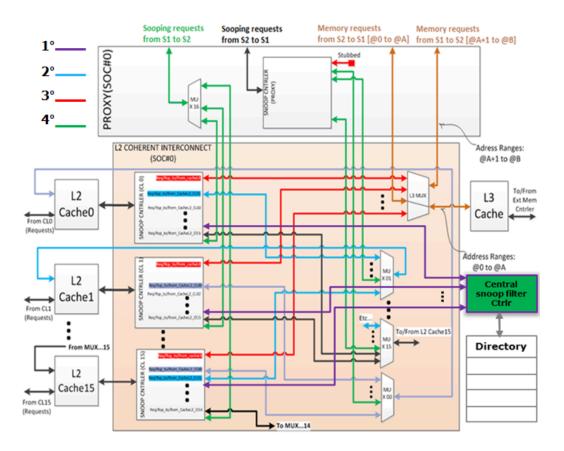

| 4.2  | on-Chip Coherent Interconnect                                                    | 74 |

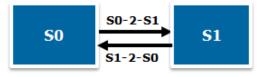

| 4.3  | 2 SoC : simple Chip-toChip topology                                              | 78 |

| 4.4  | Four small SoC : The on-Chip Interconnect partitioning topology alter-           |    |

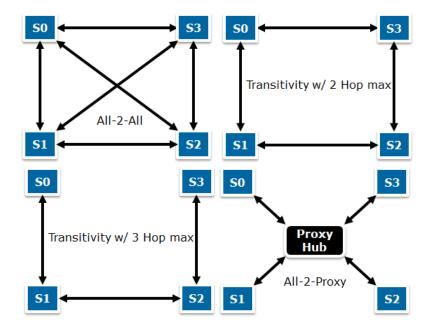

|      | natives                                                                          | 78 |

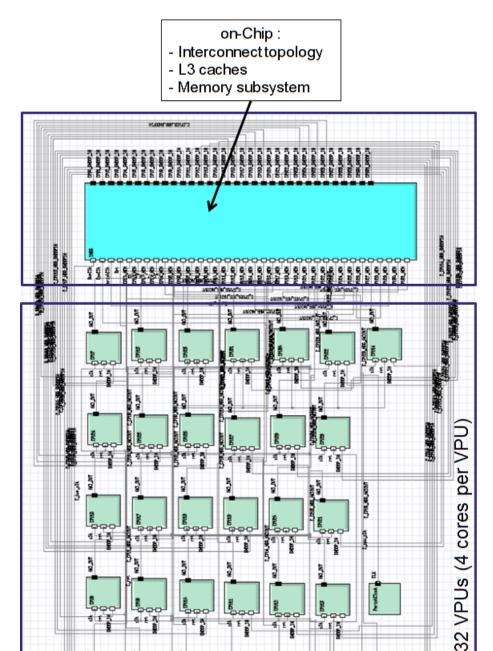

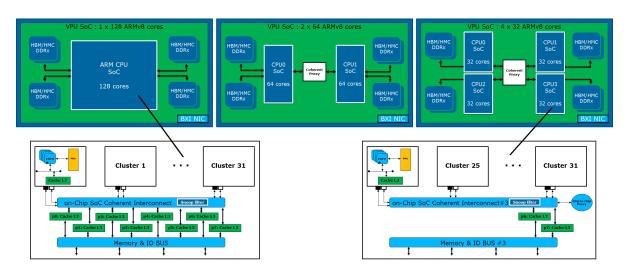

| 4.5  | Large scale ARM based VPU : partitioning scenarios                               | 80 |

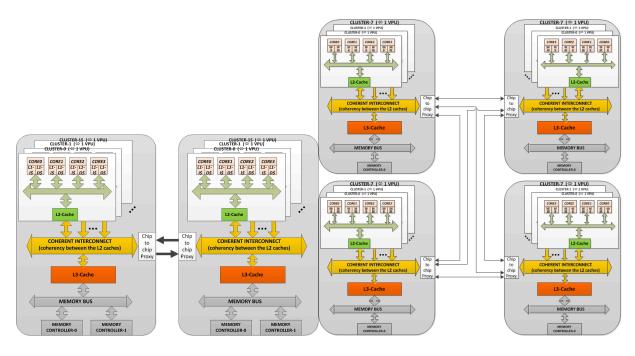

| 4.6  | $2 \times 64$ and $4 \times 32$ SoC partitioning with coherent proxy ports       | 81 |

| 4.7  | Coherent proxy entensions                                                        | 82 |

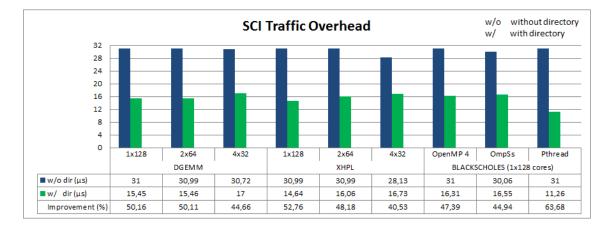

| 4.8  | Number of transactions for different SoC and directory configurations            | 84 |

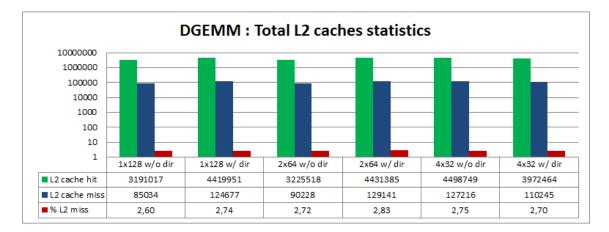

| 4.9  | DGEMM cache statistics                                                           | 84 |

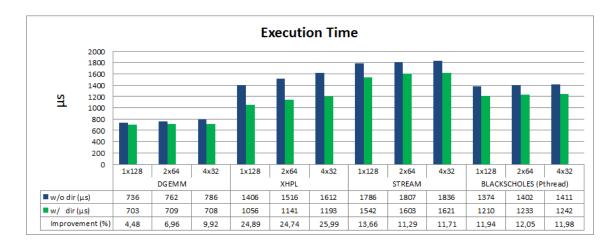

| 4.10 | Benchmark performance for different SoC and directory configurations             | 85 |

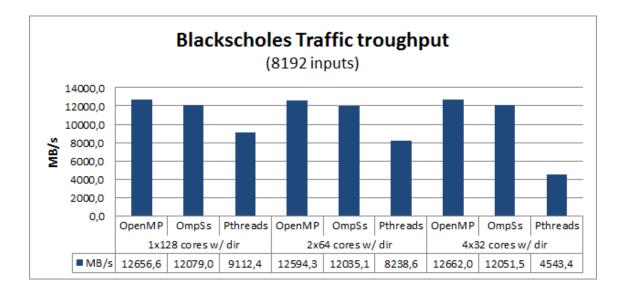

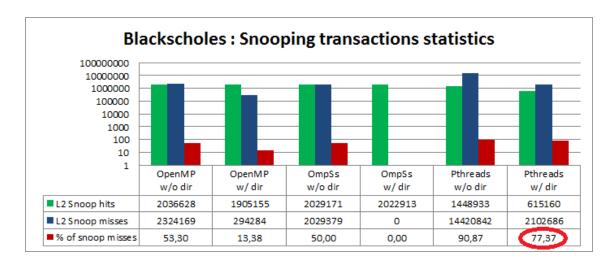

| 4.11 | Impact of programming models on throughput (blackscholes)                        | 87 |

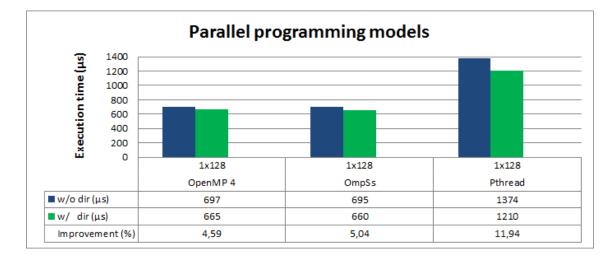

| 4.12 | Impact of programming models on performance (blackscholes, $1 \times 128$ cores) | 88 |

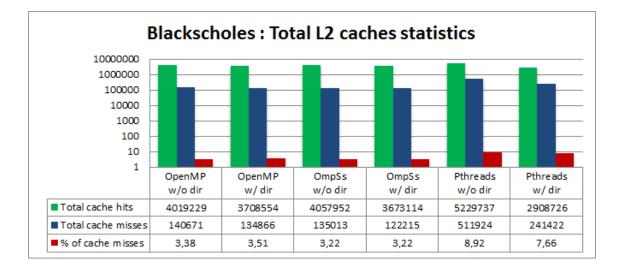

| 4.13 | Impact of programming model on L2 cache misses (black<br>scholes, $1{\times}128$ |    |

|      | cores)                                                                           | 88 |

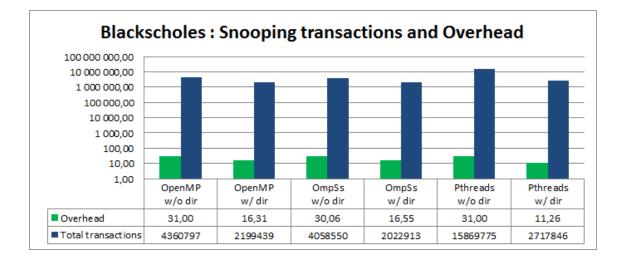

| 4.14 | Impact of programming models on the number of snooping transactions              |    |

|      | and overhead (blackscholes, $1 \times 128$ cores)                                | 89 |

| 4.15 | Snooping traffic statistics (blackscholes, $1 \times 128$ cores)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

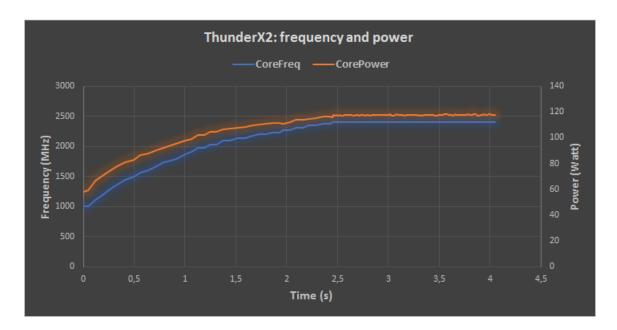

| 5.1  | Frequency and Power on Cavium's ThunderX2 processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

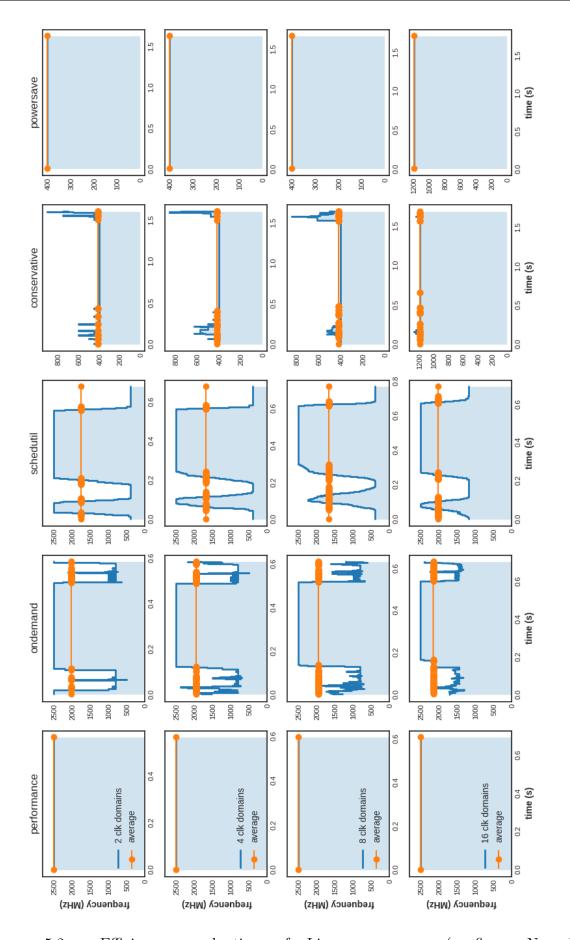

| 5.2  | Efficiency evaluation of Linux governors (config: Nparallel_256x256_matrix_products)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3  | 2parallel_256x256_matrix_products and 2parallel_128x128_matrix_products102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.4  | Soft big.LITTLE strategy scalability $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

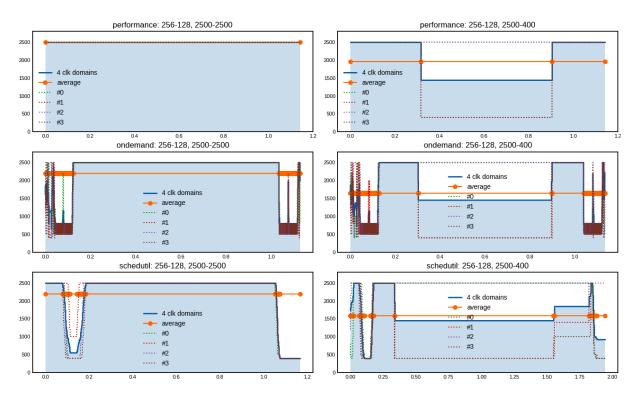

| 5.5  | Before and After blocking point strategy: 4 clock domains $\ldots \ldots \ldots \ldots 105$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.6  | Scaling up Before and After blocking point strategy $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 107$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.7  | $Power \ profiles \ of \ the \ Nparallel\_MxM\_matrix\_products \ on \ Cavium \ Thundrel and the large states \ and \ and\$ |

|      | $\mathrm{der}\mathrm{X2}\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.8  | Nparallel_MxM_matrix_products global power summary $\ldots \ldots \ldots 110$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

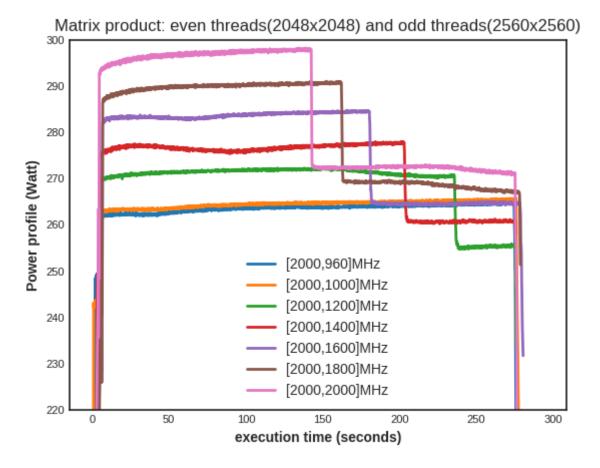

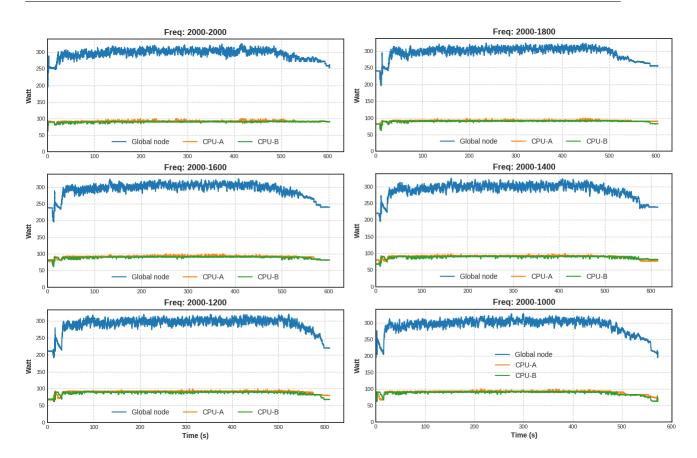

| 5.9  | Power profiles of the distributed_matrix_product_ $10240 \times 10240$ for 1 node111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

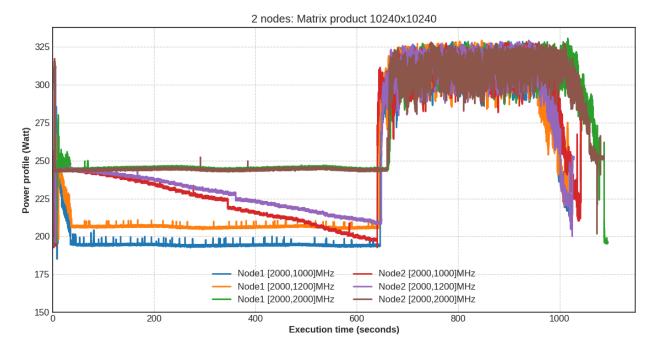

| 5.10 | Power profiles of the distributed_matrix_product_ $10240 \times 10240$ for 2 nodes $112$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# List of Tables

| 2.1 | Continents HPC shared systems                                       | • | • | • | • | 36  |

|-----|---------------------------------------------------------------------|---|---|---|---|-----|

| 4.1 | Cache characteristics in the 128 cores VPU platform $\ldots \ldots$ |   | • |   |   | 75  |

| 5.1 | Execution time and power breakdown for Blocking point strategy      |   |   |   |   | 113 |

# List of terms

#### **Roman Symbols**

- AICS RIKEN Advanced Institute for Computational Science

- API Application Programming interface

- APL ARM Performance Libraries

- ASIP Application-Specific Instruction Set Processors

- ATLAS Automatically Tuned Linear Algebra Software

- CERE Codelet Extractor and REplayer

- CISC Complex Instruction Set Computing

- CMT Cluster Management Tools

- CPE Computer Processing Element

- CPI Cycle Per Instruction

- CSC Cache Snoop Controller

- FFT Fast Fourier Transform

- HAS High level Architecture Specifications

- HBM High Bandwidth Memory

- HPC High Performance Computing

- HPCG High Performance Conjugate Gradients

- IP Intellectual Property, generaly used in this document to designate under license features

- ISA Instruction Set Architecture

- ISA Instruction Set Architectures

- LAPACK Linear Algebra PACKage

- LISA Language Instruction Set Architecture of ARM fast models

- MPE Management Processing Element

- MPI Message Passing Interface

- MPSoC Multi-Processor Systems-on-Chip

- NoC Network-on-chip

- OpenMP Open Multi-Processing

- QPI QuickPath Interconnect

- **RISC** Reduced Instruction Set Computing

- RTL Register-Transfer Level

- SIMD Single Instruction, Multiple Data

- STT Structural Simulation Toolkit

- SVE Scalable Vector Extension

- UPI UltraPath Interconnect

- VPU Virtual Processing Unit

### **Greek Symbols**

HPC High performance Computing

# Part I BACKGROUND

# Chapter 1

# Introduction

The performance of supercomputers has traditionally grown continuously with the advances of Moore's law and parallel processing, while energy efficiency could be considered as a secondary problem. But it quickly became clear that power consumption was the dominant term in the scaling challenges to reach the next level. It is roughly considered that 20 times energy efficiency improvement is required for exascale computing (1018 FLOPS) to cope with the tremendous electrical power and cost incurred by such computational capacity. The idea of using concepts borrowed from embedded technologies has naturally emerged to address this.

First prototypes based on large numbers of low power manycore microprocessors (possibly millions of cores) instead of fast complex cores started to be investigated, putting forward a number of proposals for improvement at node level architecture to meet HPC demands. These works covered a variety of 32-bit RISC cores ranging from Arm Cortex-A8 and Cortex-A9 to more recently Cortex-A15 and Cortex-A7 cores and addressed for example dual and quad core systems based on Arm Cortex-A9 cores.

The different results indicated various processing limitations to meet HPC performance requirements, in terms of double precision floating point arithmetic, 32-bit memory controllers (limiting the address space), ECC memory (e.g. for scientific and financial computing), and fast interconnect (communication intensive applications) and additionally confirmed that the variability in performance and energy could largely be attributed to floating point and SIMD computations, and interactions with the memory subsystem.

Other works which addressed explicit comparison against x86 based systems also pointed out the need for higher levels of performance to meet HPC demands. [4] concludes that the cost advantage of Arm clusters diminishes progressively for computation-intensive applications (i.e. dynamic Web server application, video transcoding), and other works like [8] conducted on Arm Cortex-A8, Cortex-A9, Intel Sandybridge, and an Intel Atom confirmed that Arm and x86 could achieve similar energy efficiency, depending on the suitability of a workload to the micro architectural features at core level. Of the works addressing the feasibility of Arm SoCs based HPC systems, efforts focused widely on single-node performance using micro benchmarks. Fewer studies considered large-scale systems exceeding a few cores even though multinode cluster performance is an essential aspect of future Exascale systems.

Considering further that new generations of cores such as the ARMv8-A ISA support features to improve specifically on HPC workloads (64-bit address space, 64-bit arithmetic, high speed interconnects, fast memory hierarchies), this work is one of the first to describe outcomes of research opened up with these perspectives.

## **1.1** Objectives and Contexts

The different contributions of this work take place in the context of European Exascale research efforts funded by the European Commission under the Horizon 2020 programme. Especially, they are part of the long term family of Mont Blanc 1/2/3 projects investigating Arm based HPC clusters and and their software ecosystem for the realization of densely integrated HPC compute nodes under critical system power constraints. The general philosophy of these approaches is to build on the long experience gained in embedded system technologies to bring processing and power efficiency to the next level. Aspects of this research therefore address centrally the recent 64-bit ARMv8 architecture for power efficiency, but also the unavoidable architectural (parallelism and memory hierarchy), methodological (design space exploration, hardware and software co-development), and runtime (power and resource management) related aspects.

### **1.2** Thesis contributions

### **1.2.1** Main contributions

A first contribution therefore is to describe an evaluation of available tools, models and platforms able to set the foundations of a methodical system level exploration approach for HPC applications scaling up to 128 Arm 64-bit cores and how it was used to examine the relevance of SoC partitioning to limit complexity, cost and power consumption. A second achievement is, based on previous methodology, to deeply explore and evaluate the relevance of chip level partitioning based on the SoC Coherent Interconnect (SCI) developped by Atos Bull for its Exascale interconnect (BXI) technology. Finally, a last part of the study addresses the runtime aspect and investigates specific HPC improvements at power management level to also account for the important amount of power that can be saved additionally at runtime. In addition to this global perspective, the following more specific points are other contributing elements to Exascale research efforts: i) The evaluation of different tools, models and methodologies allowing the design and analysis of large HPC systems possibly made of several compute nodes. ii) The definition of an approach allowing mutli level hardware and software analysis. iii) The design choices description and evaluation of a SoC Coherent Interconnect design. iv) The analysis and evaluation of a directory filtering based cache coherence management protocol in a large multi SoC design context. v) An efficiency analysis of parallel programming models. vi) An investigation of specific power strategies for HPC and their implementation analysis on virtual and real platforms. vii) The potential of specific HPC power strategies to further improve power savings.

### 1.2.2 Published papers

- WELOLI, J. Wanza, BILAVARN, Sébastien, DE VRIES, Maarten, et al. Efficiency modeling and exploration of 64-bit Arm compute nodes for exascale. Microprocessors and Microsystems, 2017, vol. 53, p. 68-80.

- WELOLI, Joël Wanza, BILAVARN, Sébastien, DERRADJI, Said, et al. Efficiency Modeling and Analysis of 64-bit Arm Clusters for HPC. In : 2016 Euromicro Conference on Digital System Design (DSD). IEEE, 2016. p. 342-347.

- WELOLI, Joël Wanza, BILAVARN, Sébastien, DERRADJI, Said, et al. Modélisation et analyse de l'Efficacité de supercalculateurs HPC basés sur l'ISA ARMv8 64-bit. GDR SOC SIP 2016 (Poster).

- Joël Wanza Weloli, Maarten De Vries, Said Derradji, Sébastien Bilavarn, Cecille Belleudy. Platform Architect for HPC ARM-based SoC Design. Synopsys User Group France. June, 2017.

## 1.3 Thesis outlines

The outline of the thesis is to present firstly a detailled discussion of state of the art efforts related to Exascale High Performance Computing (HPC) systems covering the most relevant academic and industry architecture and research projects worlwide. The core of the matter is made in chapters 3, 4 and 5 adressing respectively methodology definition and model evaluations, architectural exploration and analysis, and the investigation of specific HPC power management strategies. Each aspect comes with its own experimentation, result analysis and conclusions that are drawn keeping as close as possible to realistic operation (real platforms, operating system, runtime software, model relevance, benchmarks, etc.) to assess processing and power efficiency improvements as reliably as possible. This will lead finally to a global conclusion in chapter 6 to indicate the key achievements that can be formulated from the different results and several perspectives arising from them.

# Chapter 2

# State-of-the-Art

## 2.1 HPC background